Patents

Literature

3541 results about "Hardware circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

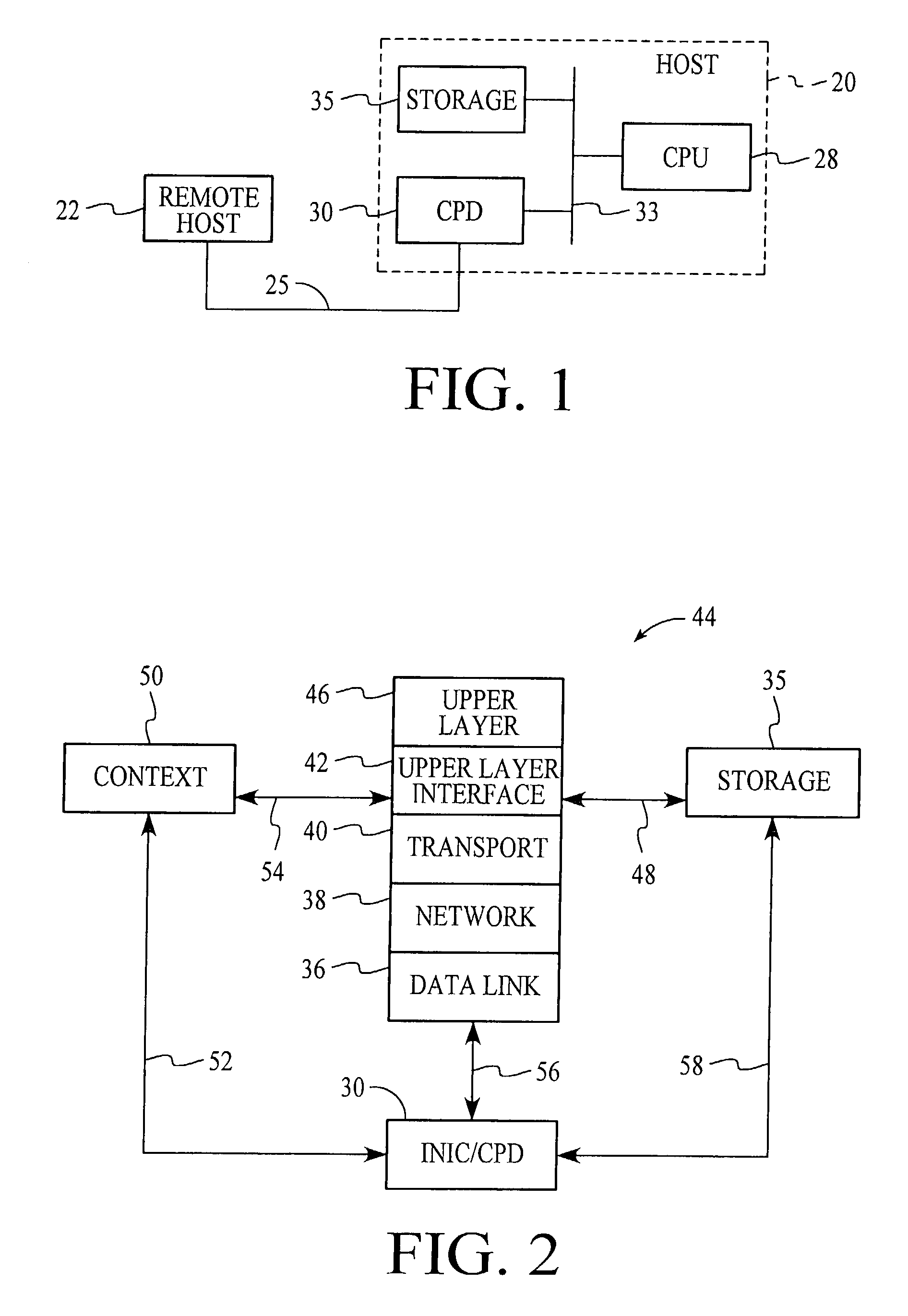

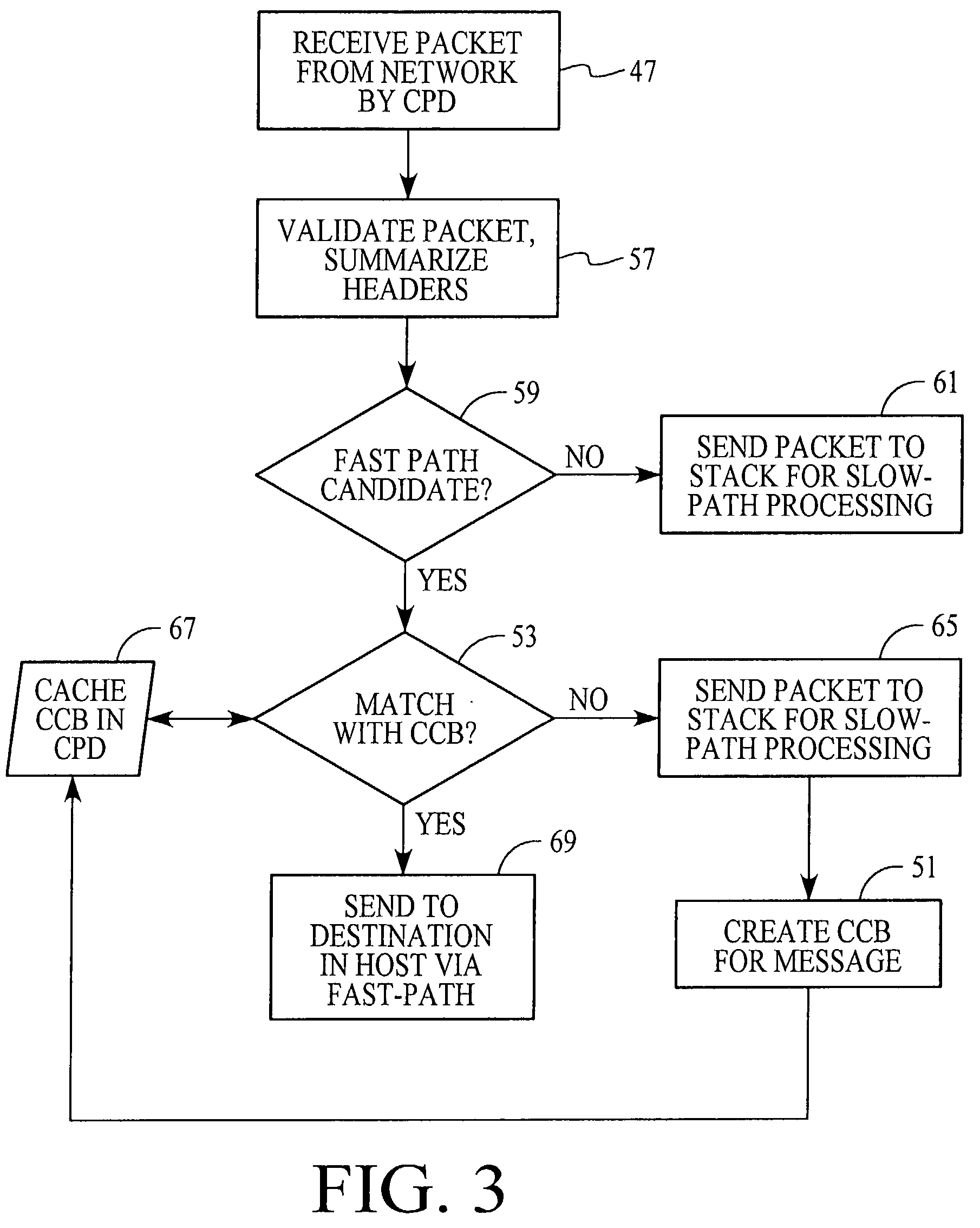

TCP/IP offload network interface device

InactiveUS20020156927A1Negligibly effectMove quicklyMultiple digital computer combinationsNetwork connectionsFast pathGeneral purpose

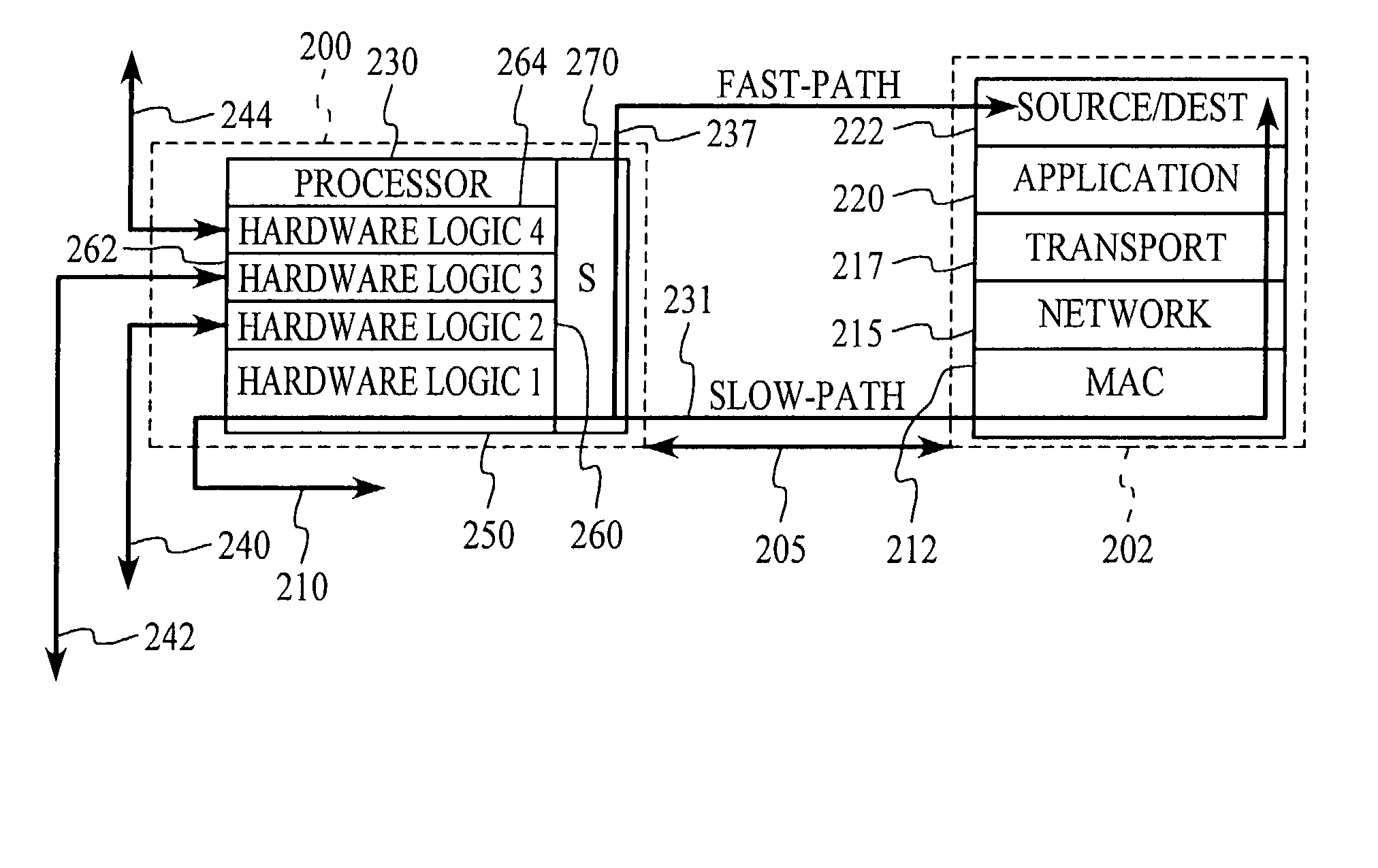

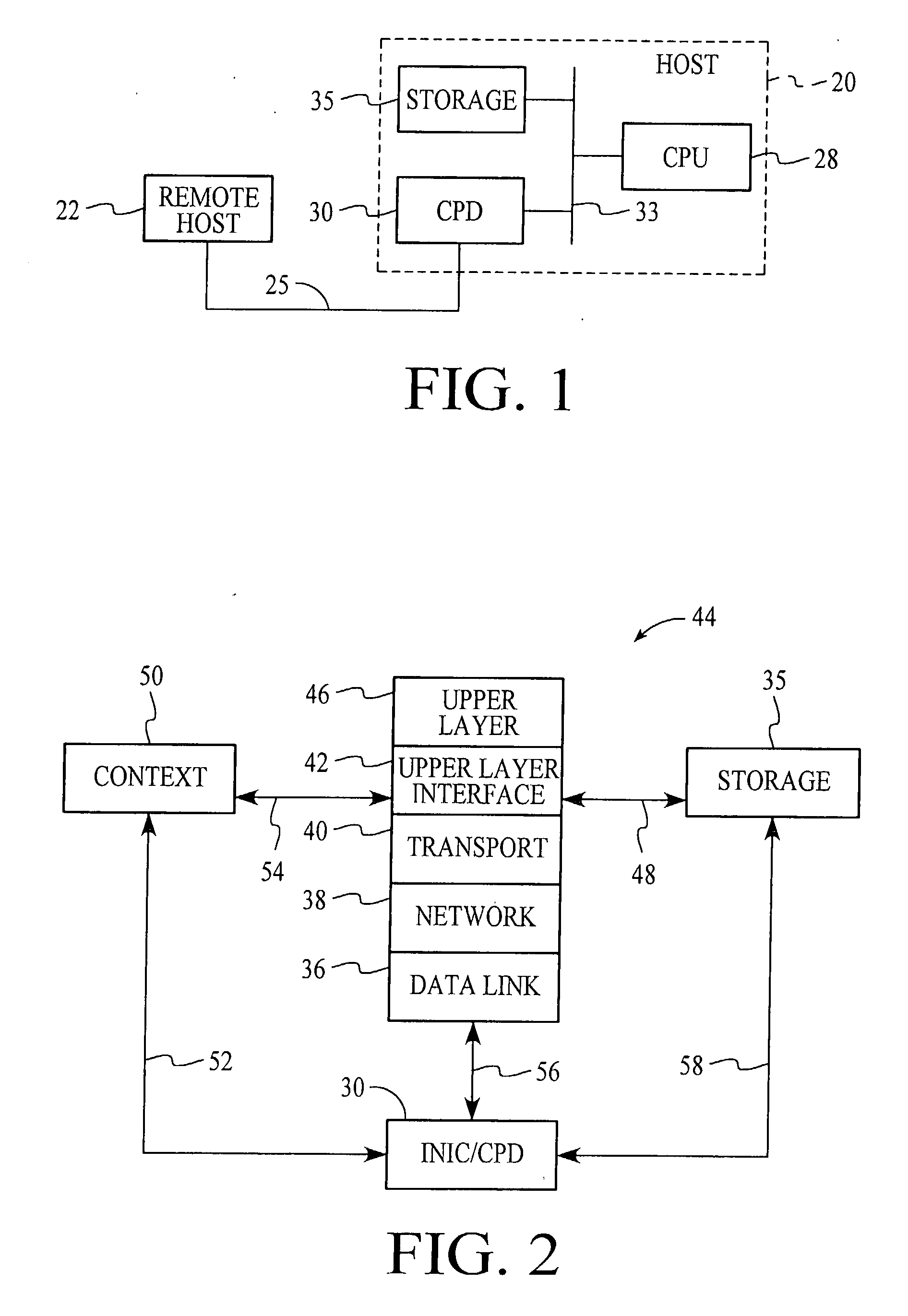

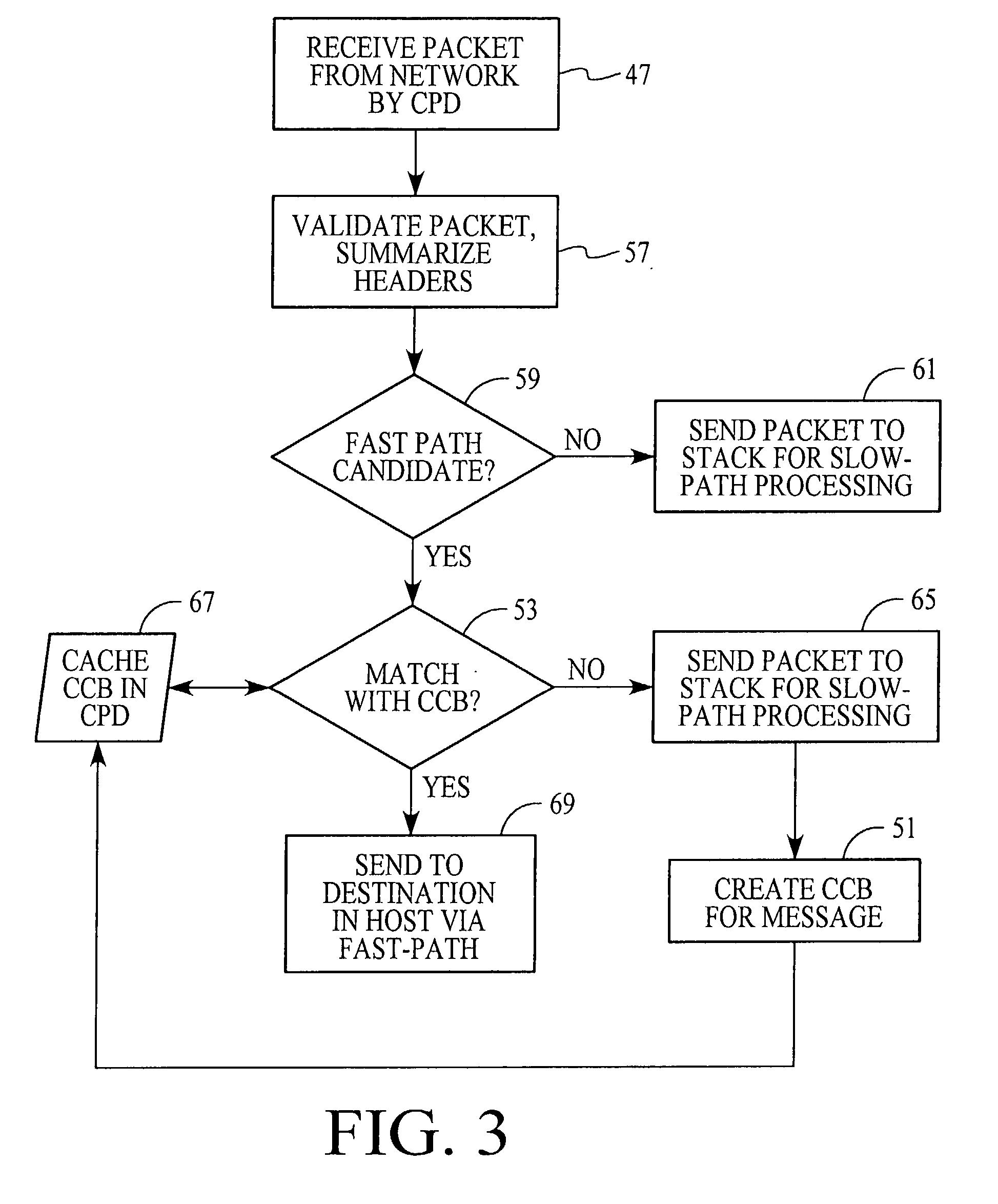

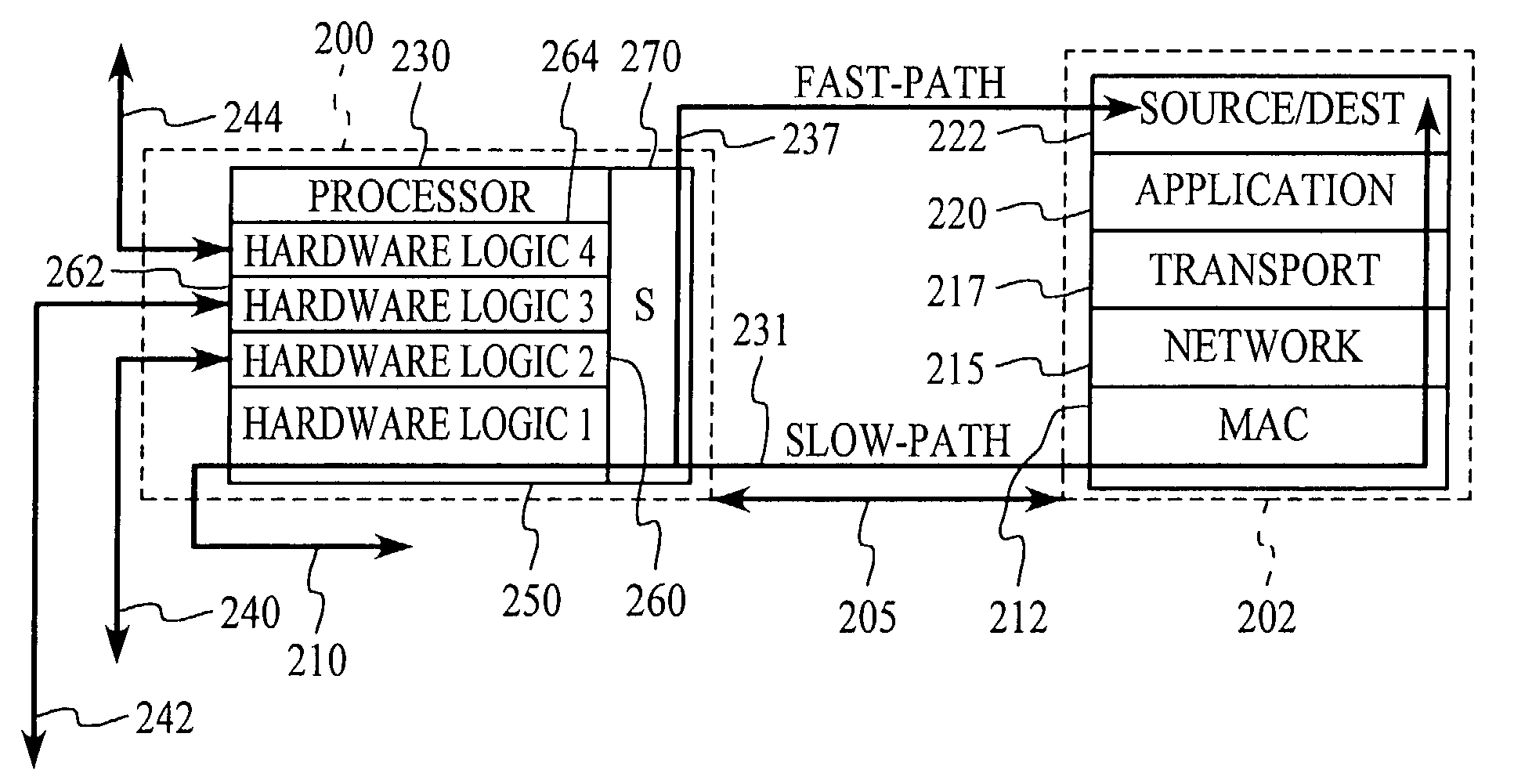

A system for protocol processing in a computer network has a TCP / IP Offload Network Interface Device (TONID) associated with a host computer. The TONID provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The TONID also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the TONID to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the TONID as a communication control block (CCB) that can be passed back to the host for message processing by the host. The TONID contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

TCP/IP offload network interface device

InactiveUS7174393B2Little and no performance benefitMove quicklyMultiple digital computer combinationsData switching networksGeneral purposeFast path

A system for protocol processing in a computer network has a TCP / IP Offload Network Interface Device (TONID) associated with a host computer. The TONID provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The TONID also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the TONID to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the TONID as a communication control block (CCB) that can be passed back to the host for message processing by the host. The TONID contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

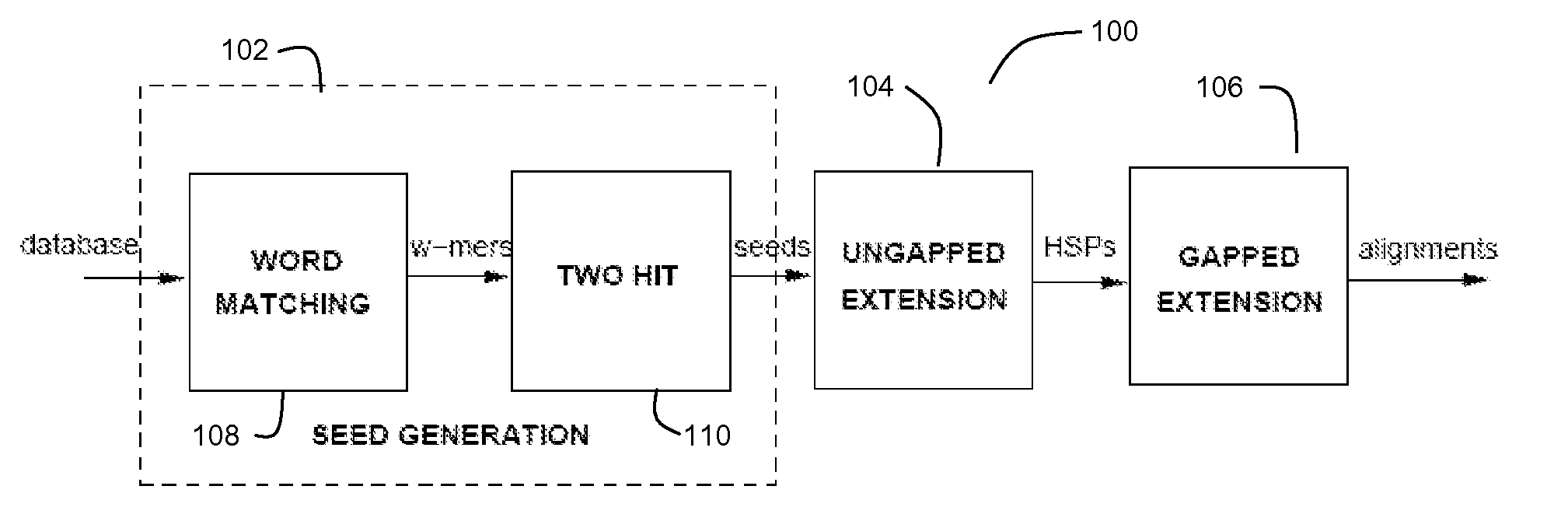

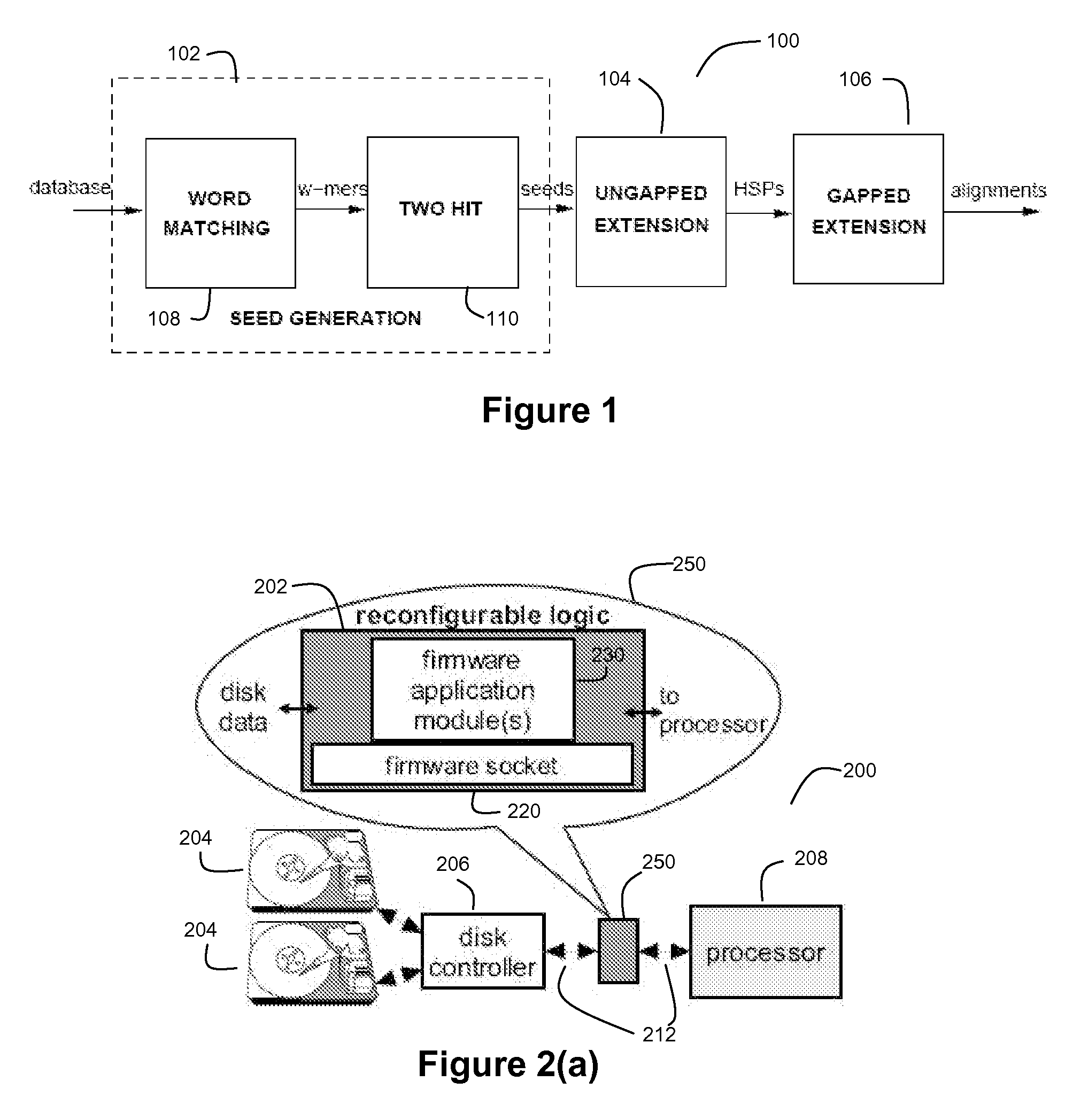

Method and Apparatus for Protein Sequence Alignment Using FPGA Devices

InactiveUS20080086274A1Quick understandingImprove throughputBiological testingSequence analysisAdemetionineHardware implementations

Disclosed herein is a hardware implementation for performing sequence alignment that preferably deploys a seed generation stage, an ungapped extension stage, and at least a portion of a gapped extension stage as a data processing pipeline on at least one hardware logic device. Hardware circuits for the seed generation stage, the ungapped extension stage, and the gapped extension stage are individually disclosed. In a preferred embodiment, the pipeline is arranged for performing BLASTP sequence alignment searching. Also, in a preferred embodiment, the at least one hardware logic device comprises at least one reconfigurable logic device such as an FPGA.

Owner:CHAMBERLAIN ROGER +4

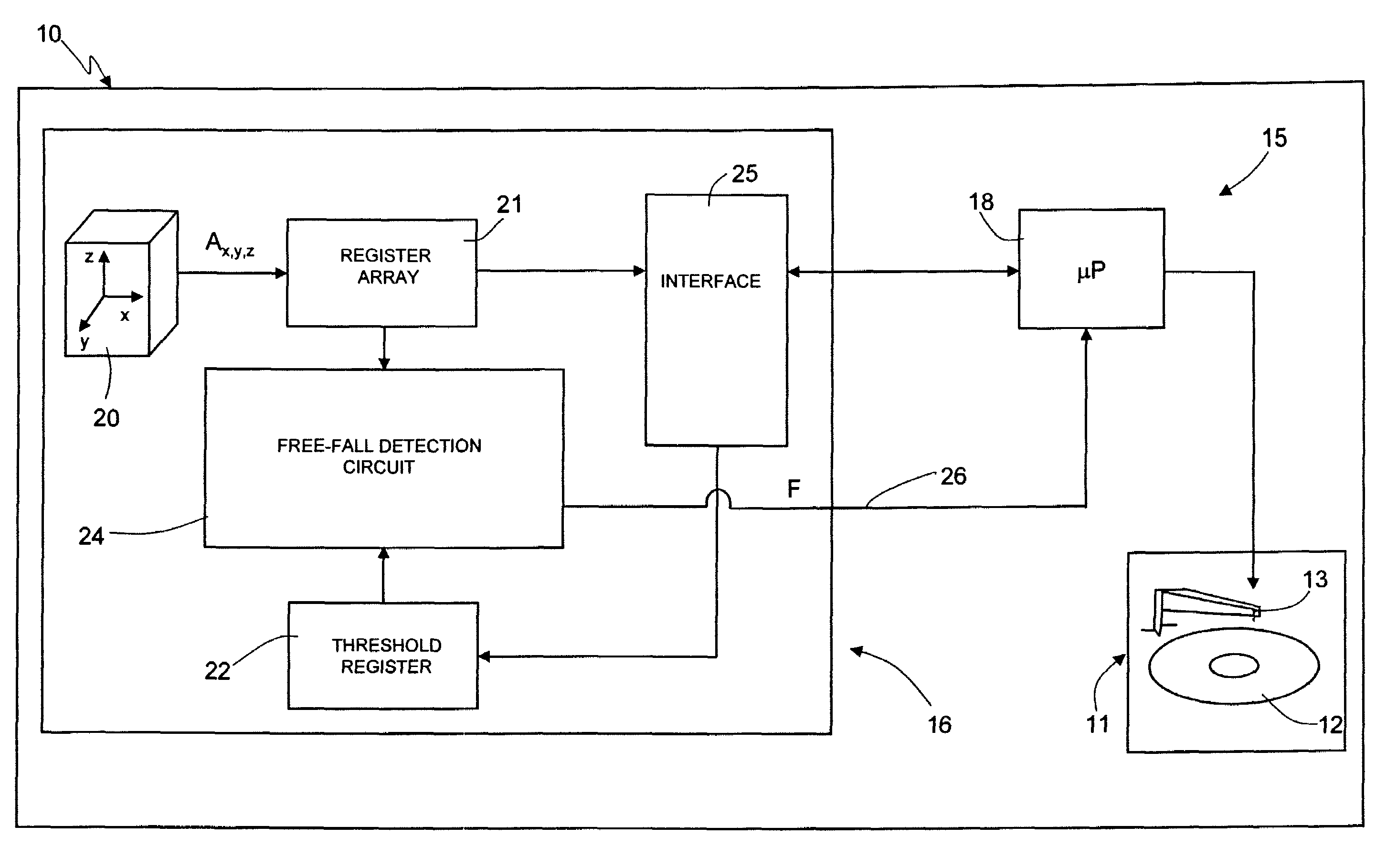

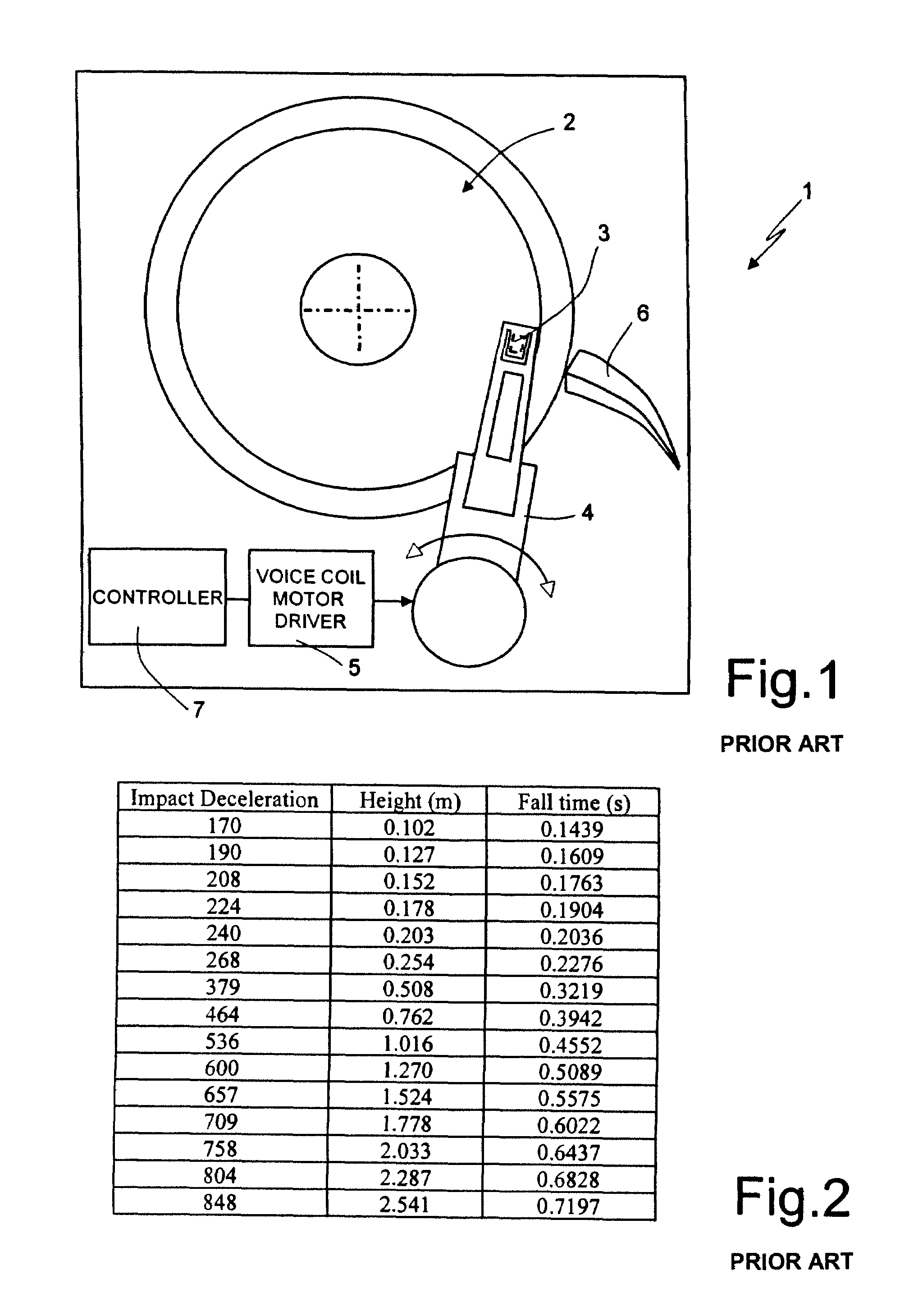

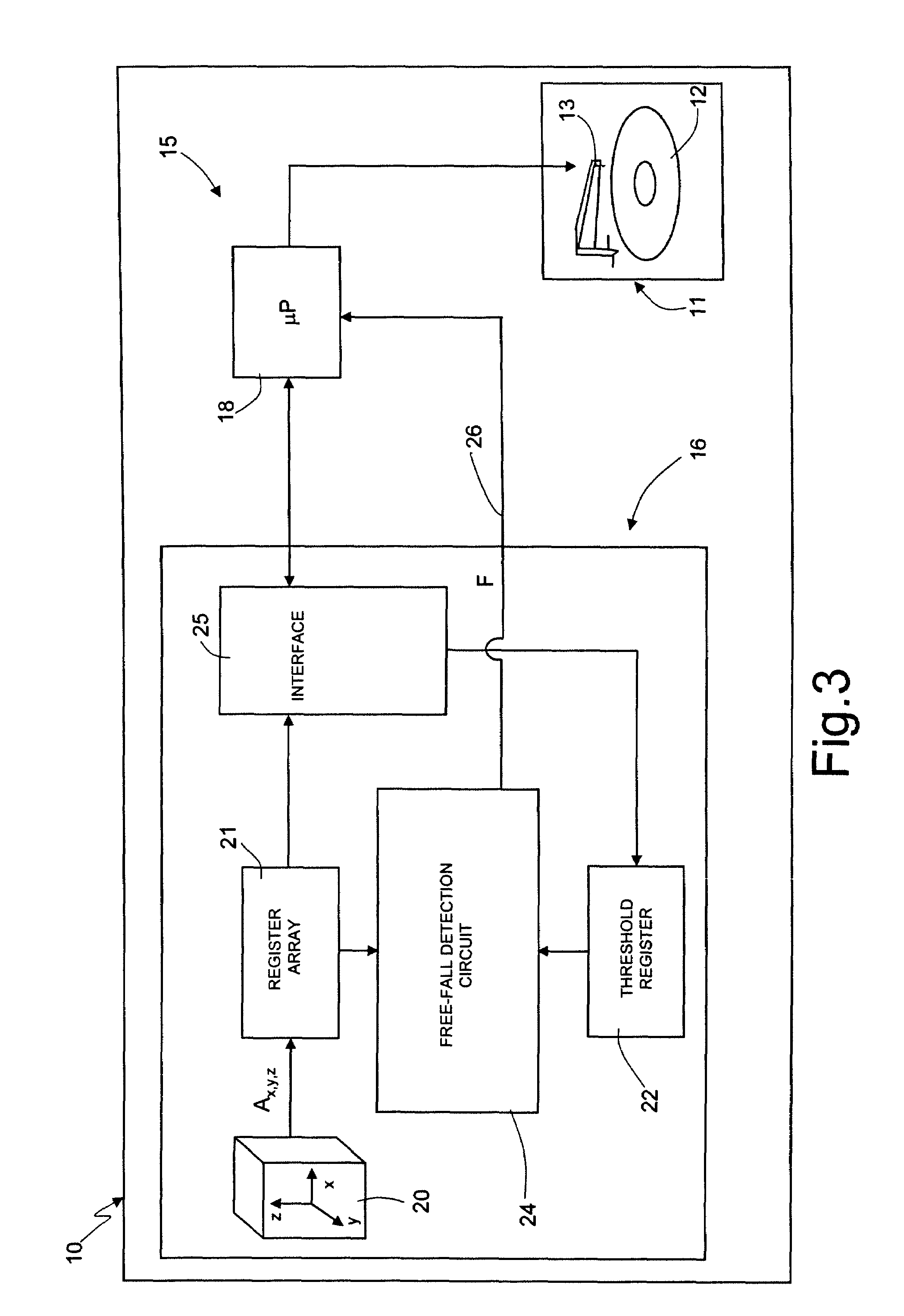

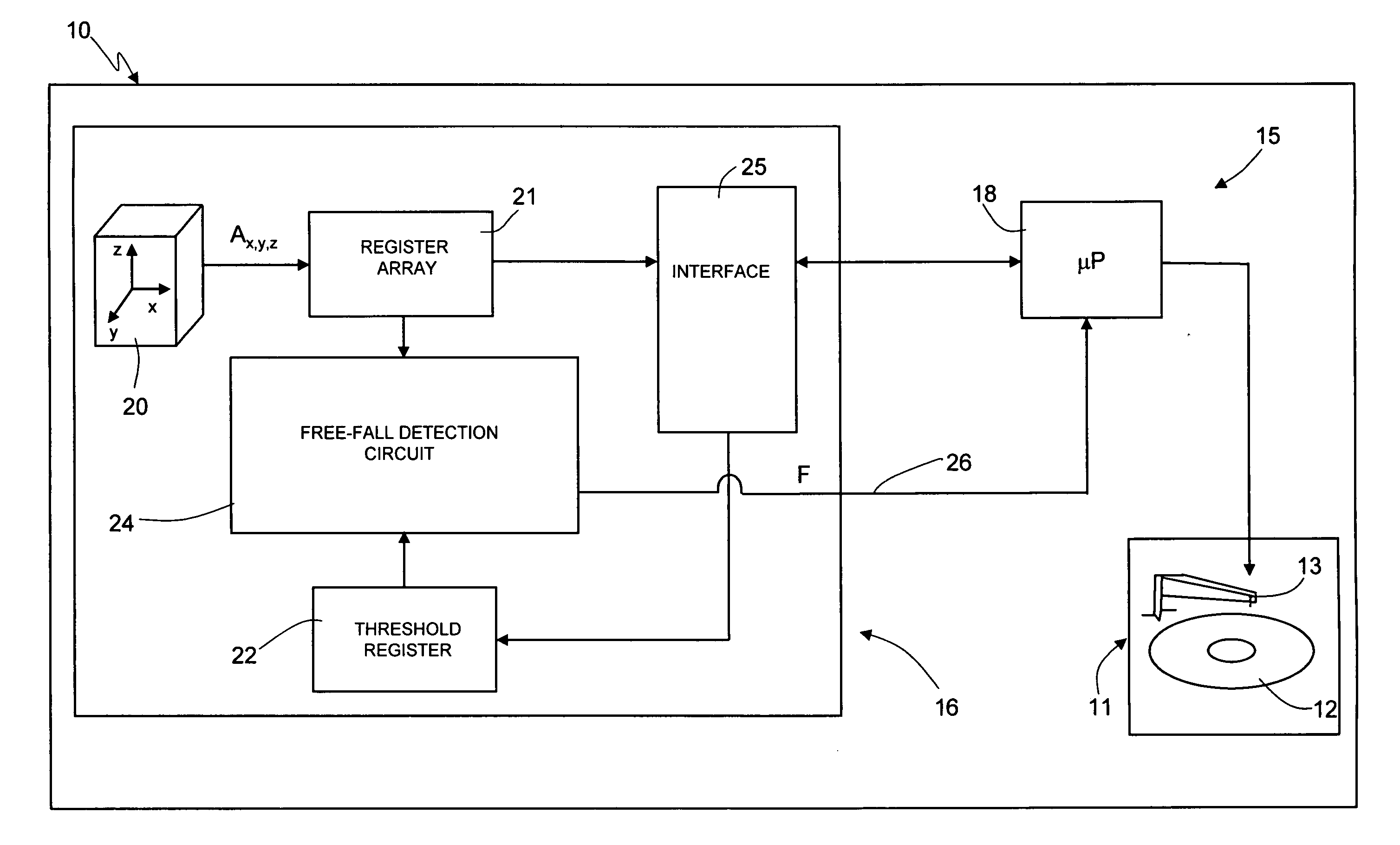

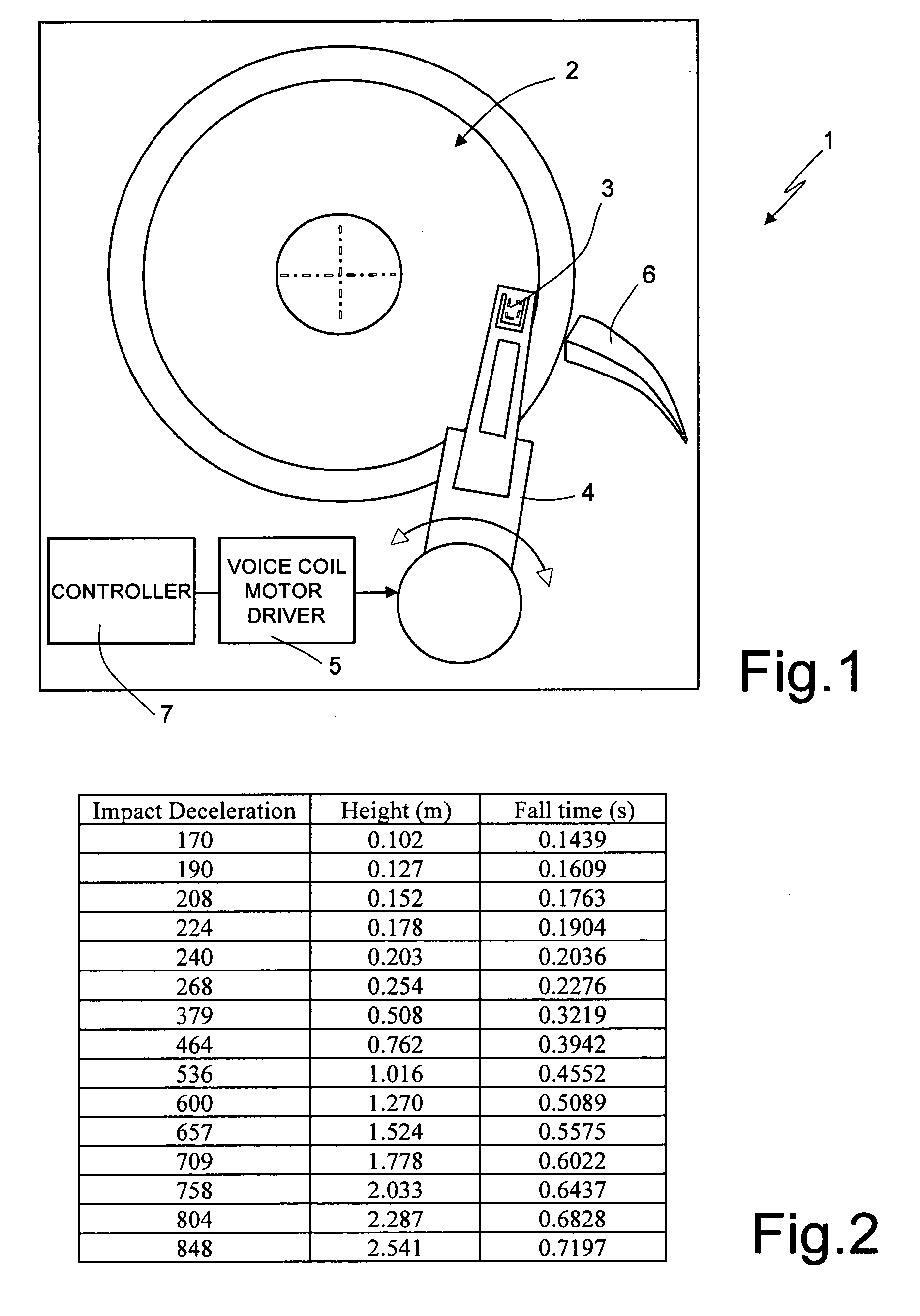

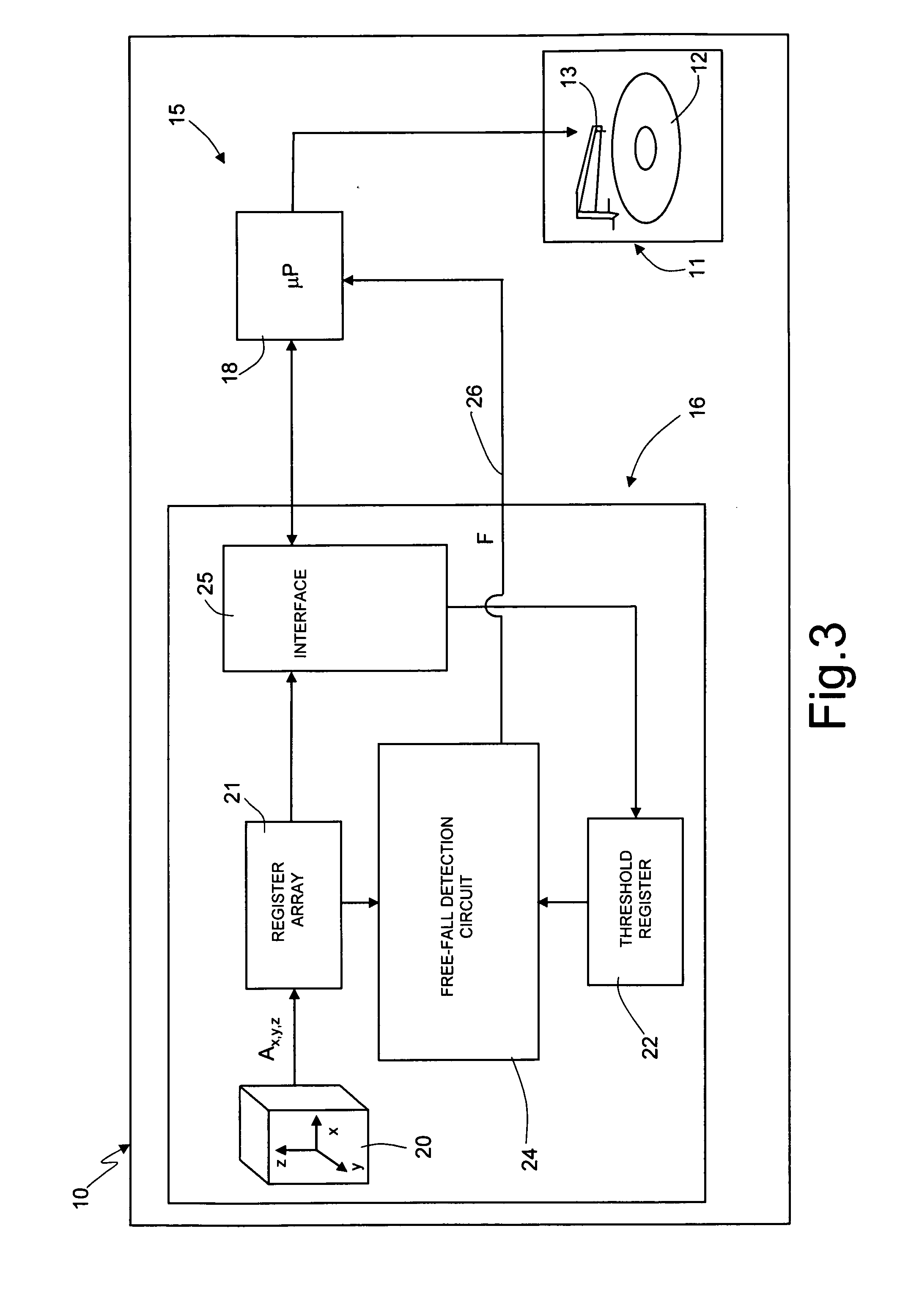

Free-fall detection device and free-fall protection system for a portable electronic apparatus

ActiveUS7450332B2Acceleration measurement using interia forcesDriving/moving recording headsFree fallingEngineering

In an integrated free-fall detection device for a portable apparatus an acceleration sensor generates acceleration signals correlated to the components of the acceleration of the portable apparatus along three detection axes. A dedicated purely hardware circuit connected to the acceleration sensor generates a free-fall detection signal in a continuous way and in real-time. The free-fall detection signal has a first logic value in the event that the acceleration signals are simultaneously lower than a respective acceleration threshold, and is sent to a processor unit of the portable apparatus as an interrupt signal to activate appropriate actions of protection for the portable apparatus. Preferably, the acceleration sensor and the dedicated purely hardware circuit are integrated in a single chip and the acceleration sensor is made as a MEMS.

Owner:STMICROELECTRONICS SRL

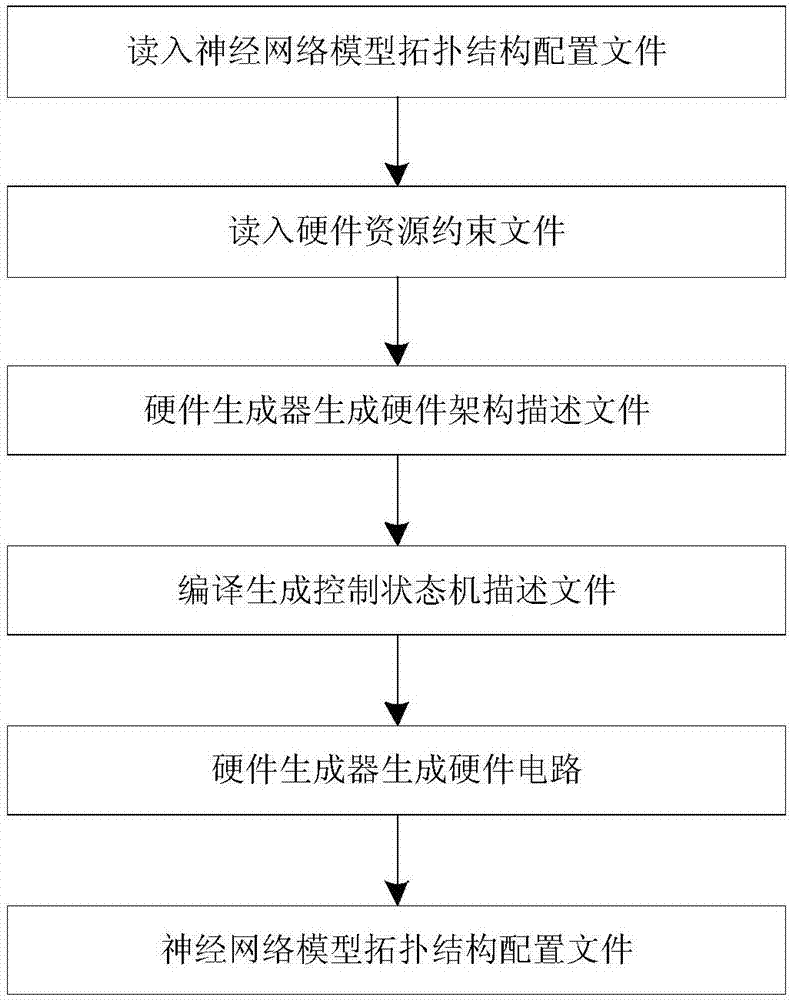

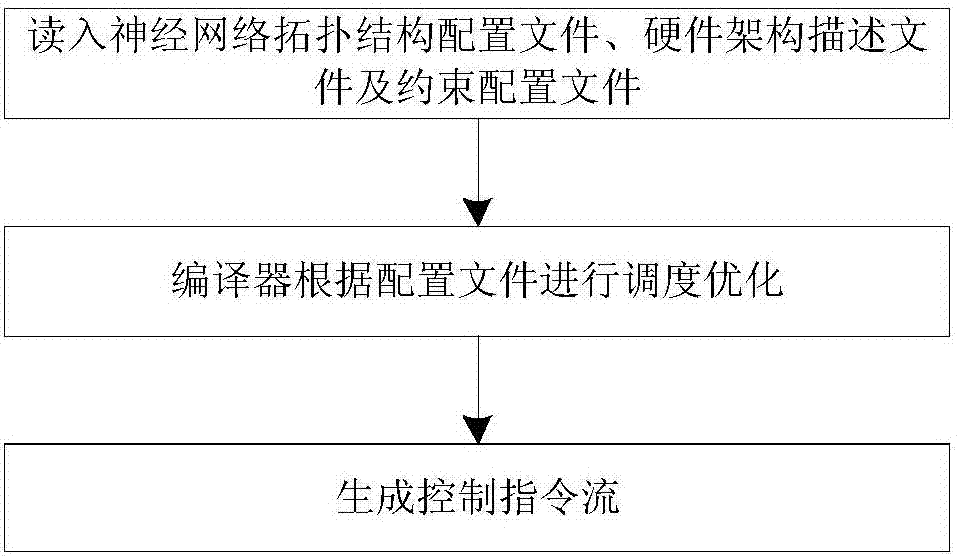

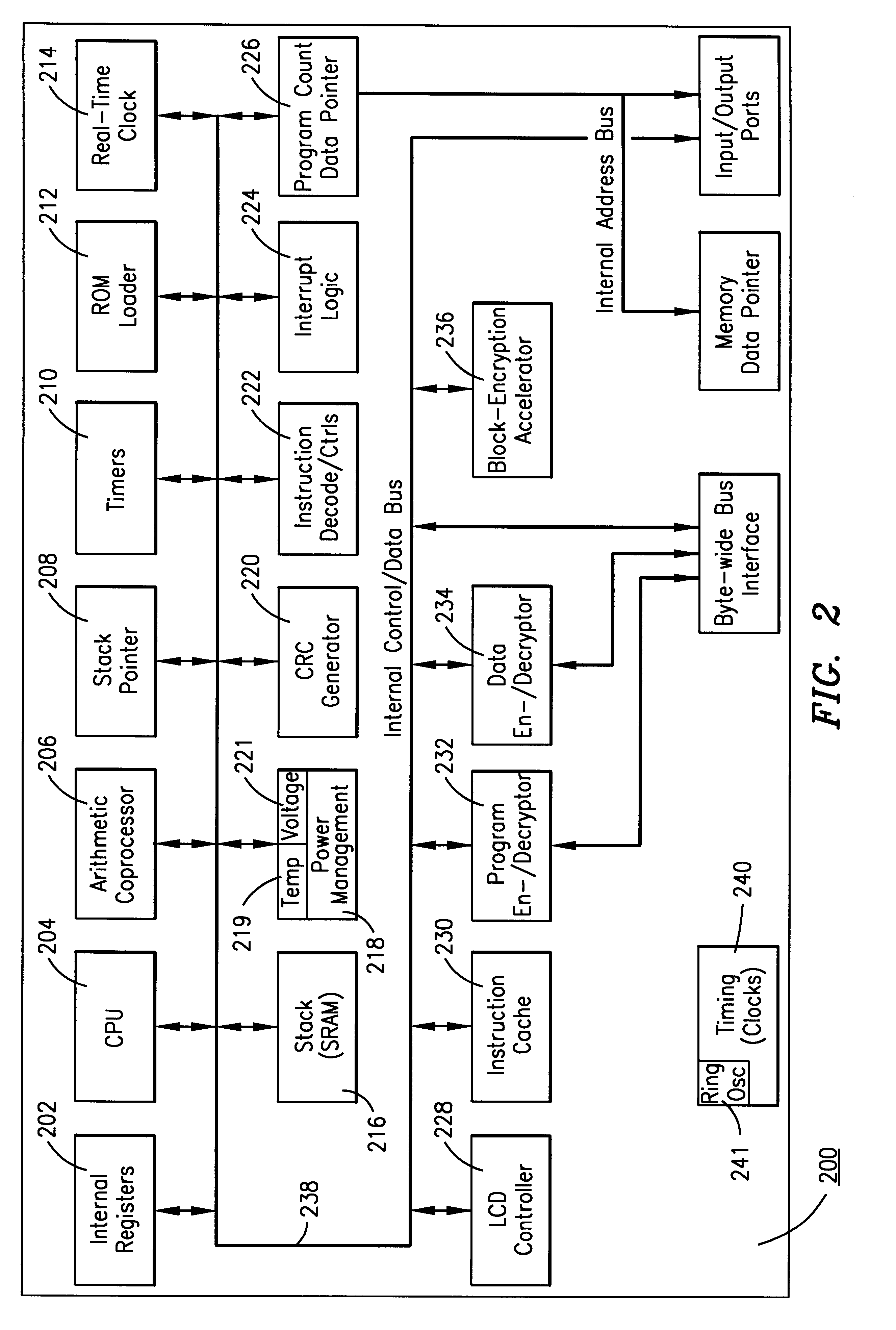

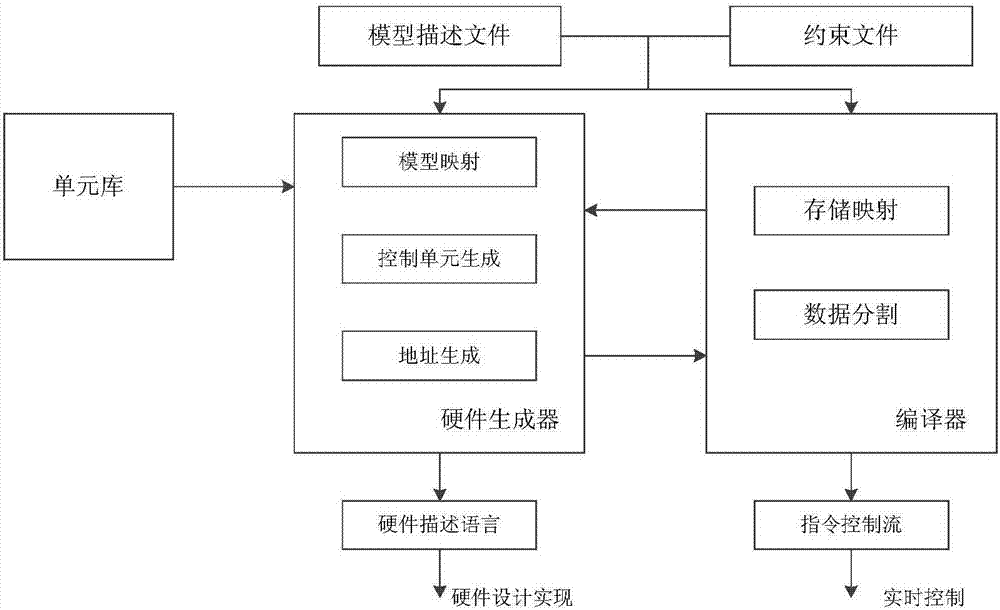

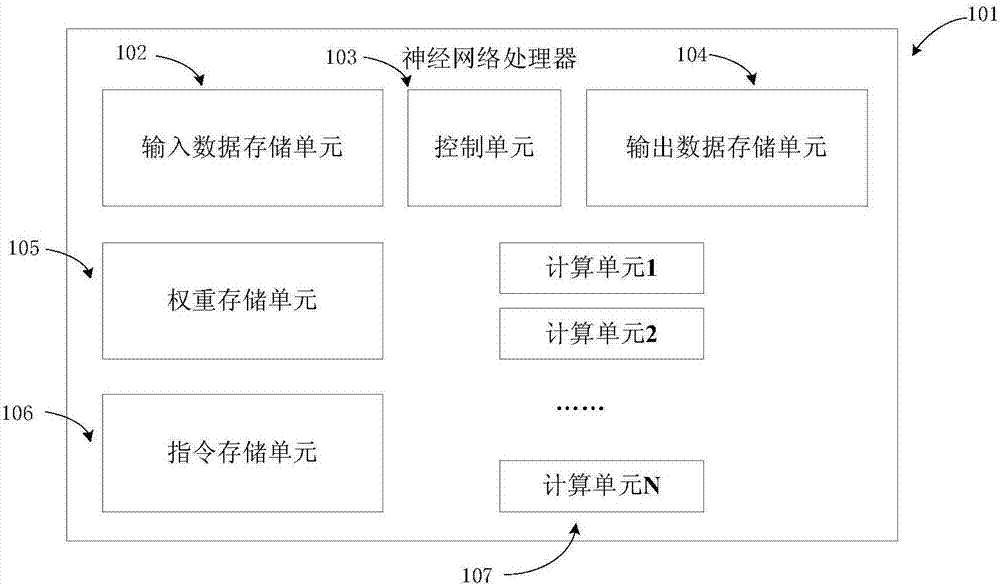

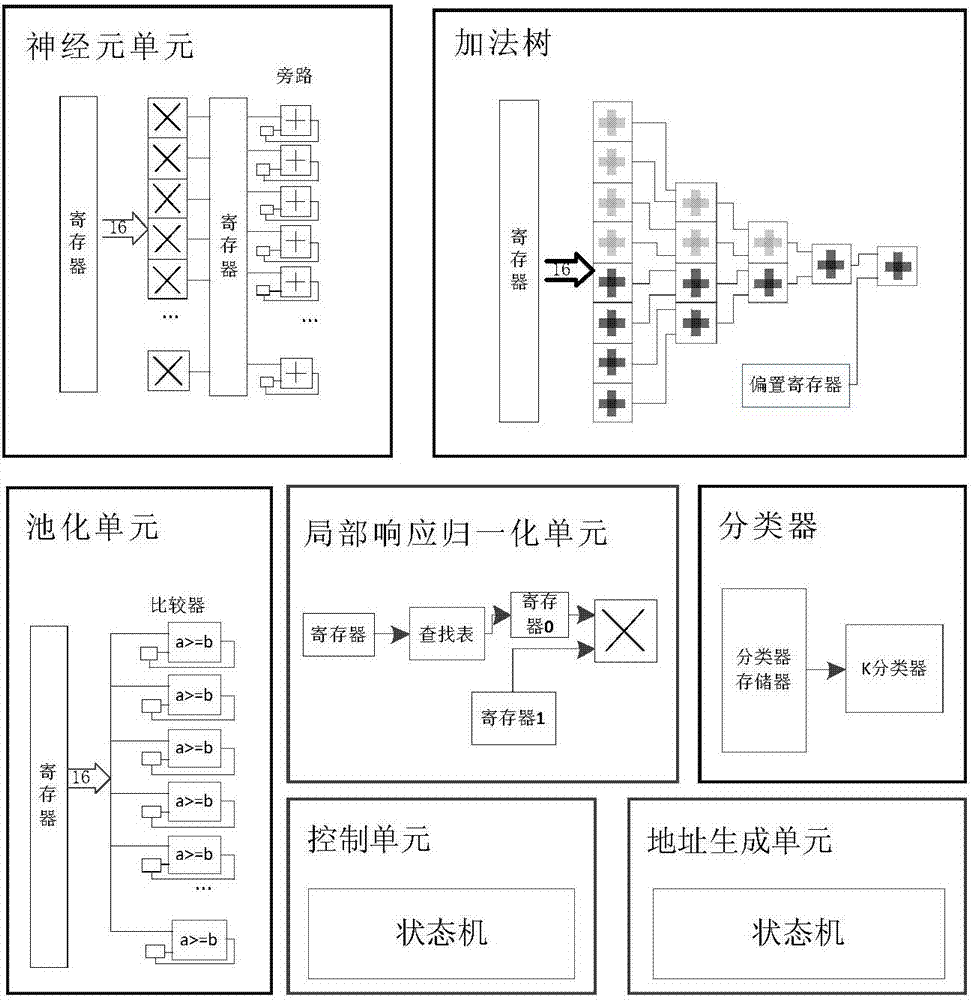

Automated design method, device and optimization method applied for neural network processor

ActiveCN107016175ABiological neural network modelsCAD circuit designComputer architectureHardware architecture

The invention discloses an automated design method, device and optimization method applied for a neural network processor. The method comprises the steps that neural network model topological structure configuration files and hardware resource constraint files are obtained, wherein the hardware resource constraint files comprise target circuit area consumption, target circuit power consumption and target circuit working frequency; a neural network processor hardware architecture is generated according to the neural network model topological structure configuration files and the hardware resource constraint files, and hardware architecture description files are generated; according to a neural network model topological structure, the hardware resource constraint files and the hardware architecture description files, modes of data scheduling, storage and calculation are optimized, and corresponding control description files are generated; according to the hardware architecture description files and the control description files, cell libraries meet the design requirements are found in constructed reusable neural network cell libraries, corresponding control logic and a corresponding hardware circuit description language are generated, and the hardware circuit description language is transformed into a hardware circuit.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

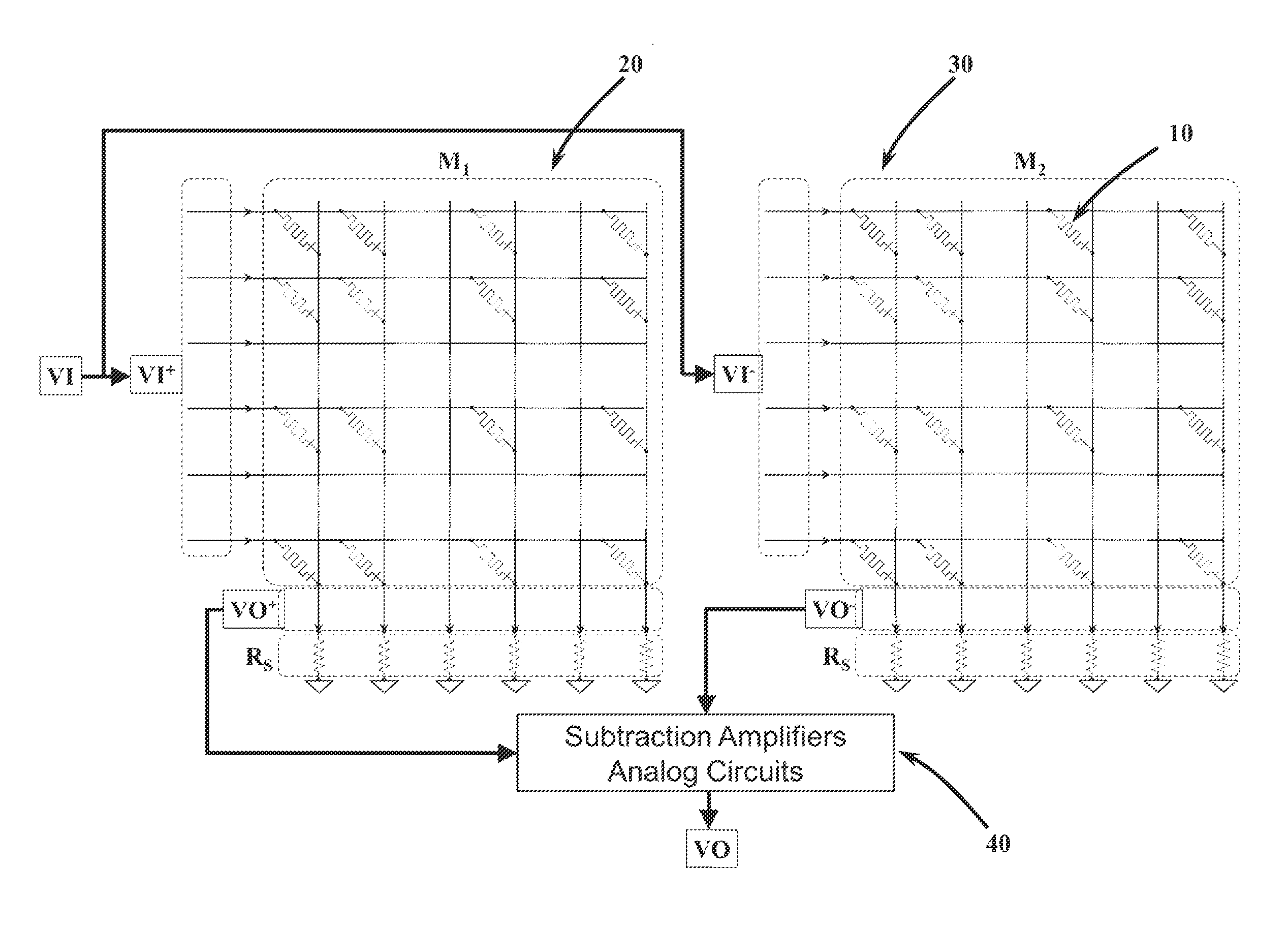

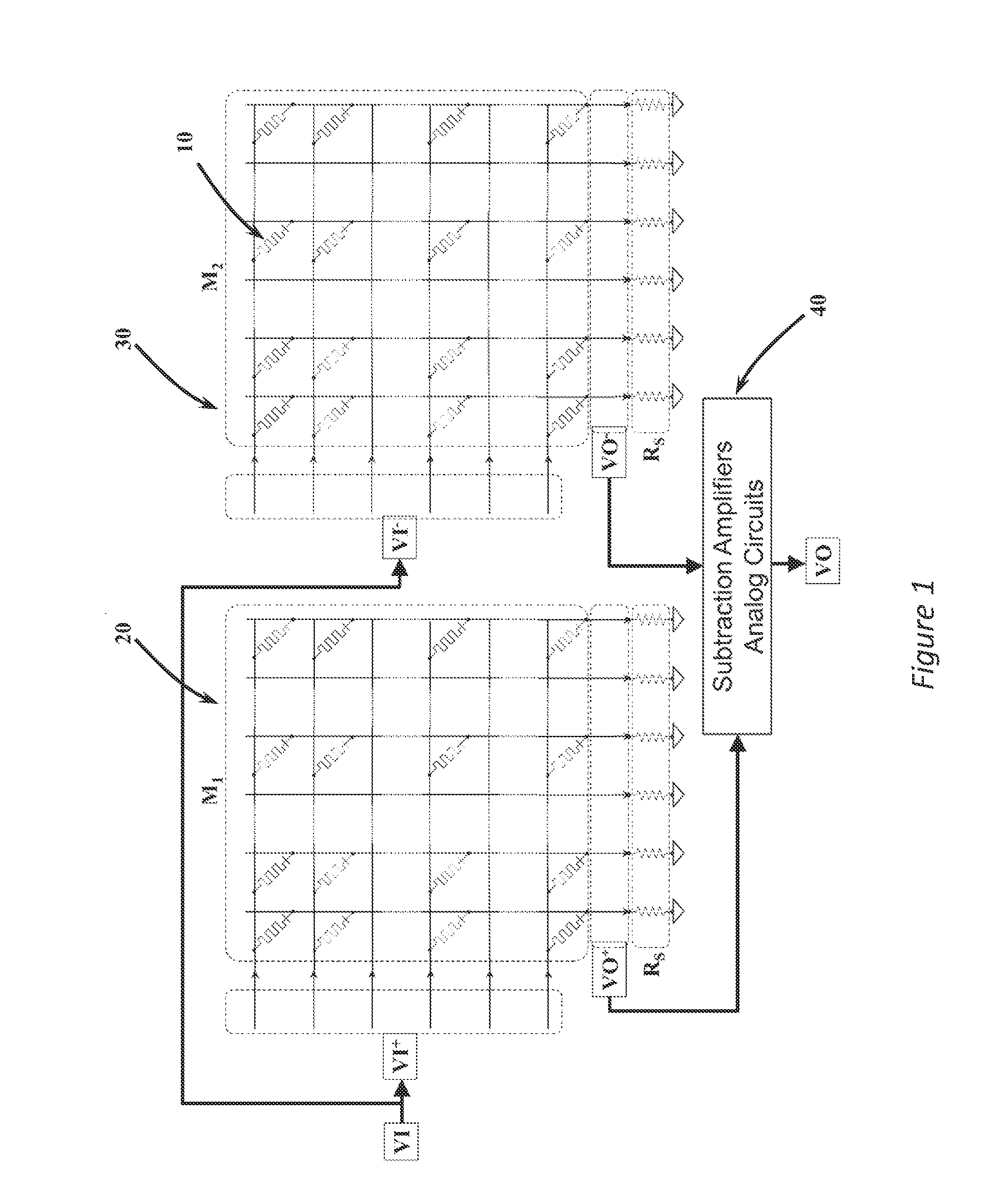

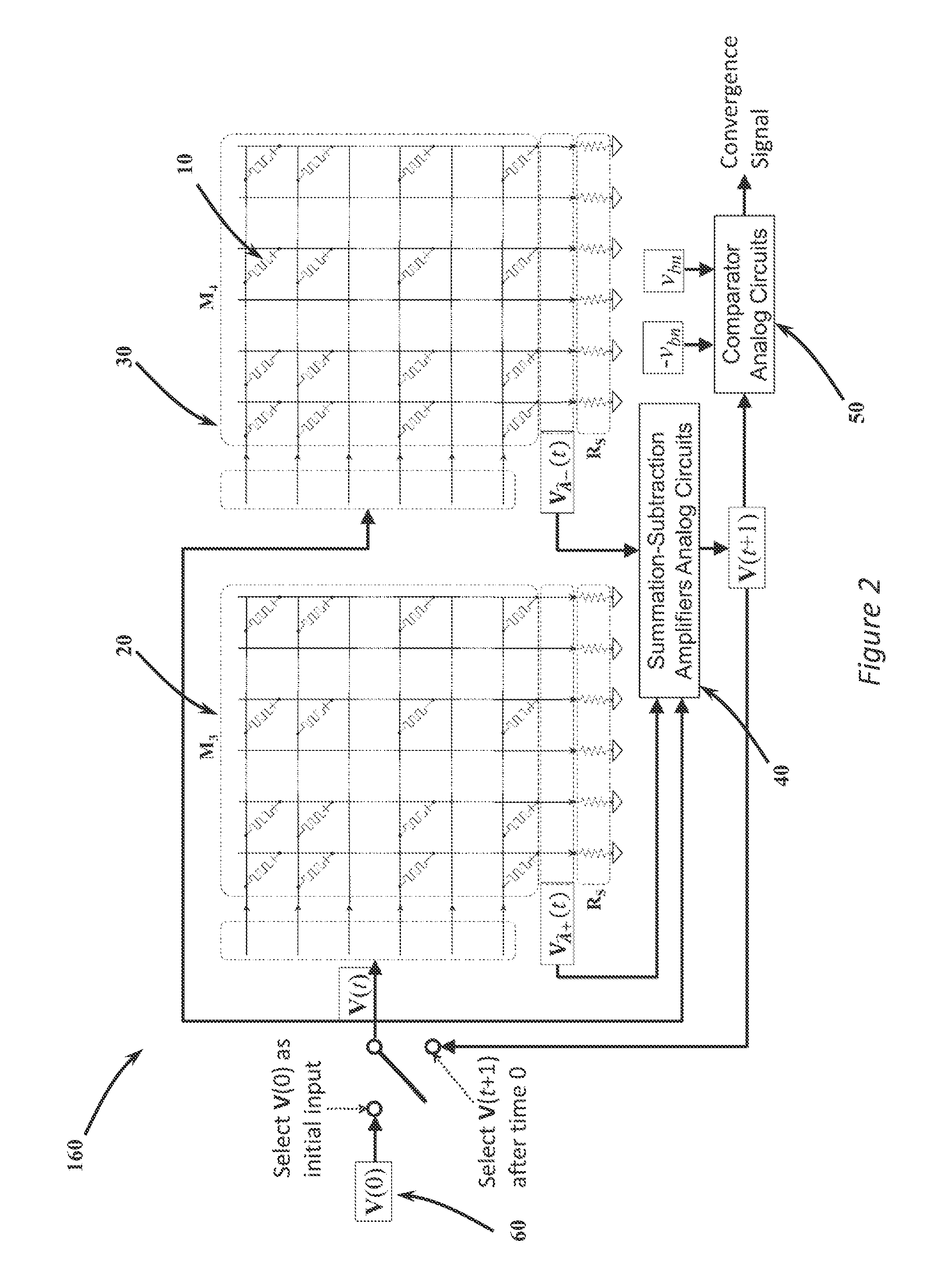

Method and apparatus for performing close-loop programming of resistive memory devices in crossbar array based hardware circuits and systems

ActiveUS20150170025A1Reduce Design ComplexityConvenient and accurateDigital computer detailsDigital storageObservational errorElectrical resistance and conductance

Method and apparatus for performing close-loop programming of resistive memory devices in crossbar array based hardware circuits and systems. Invention provides iterative training of memristor crossbar arrays for neural networks by applying voltages corresponding to selected training patterns. Error is detected and measured as a function of the actual response to the training patterns versus the expected response to the training pattern.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

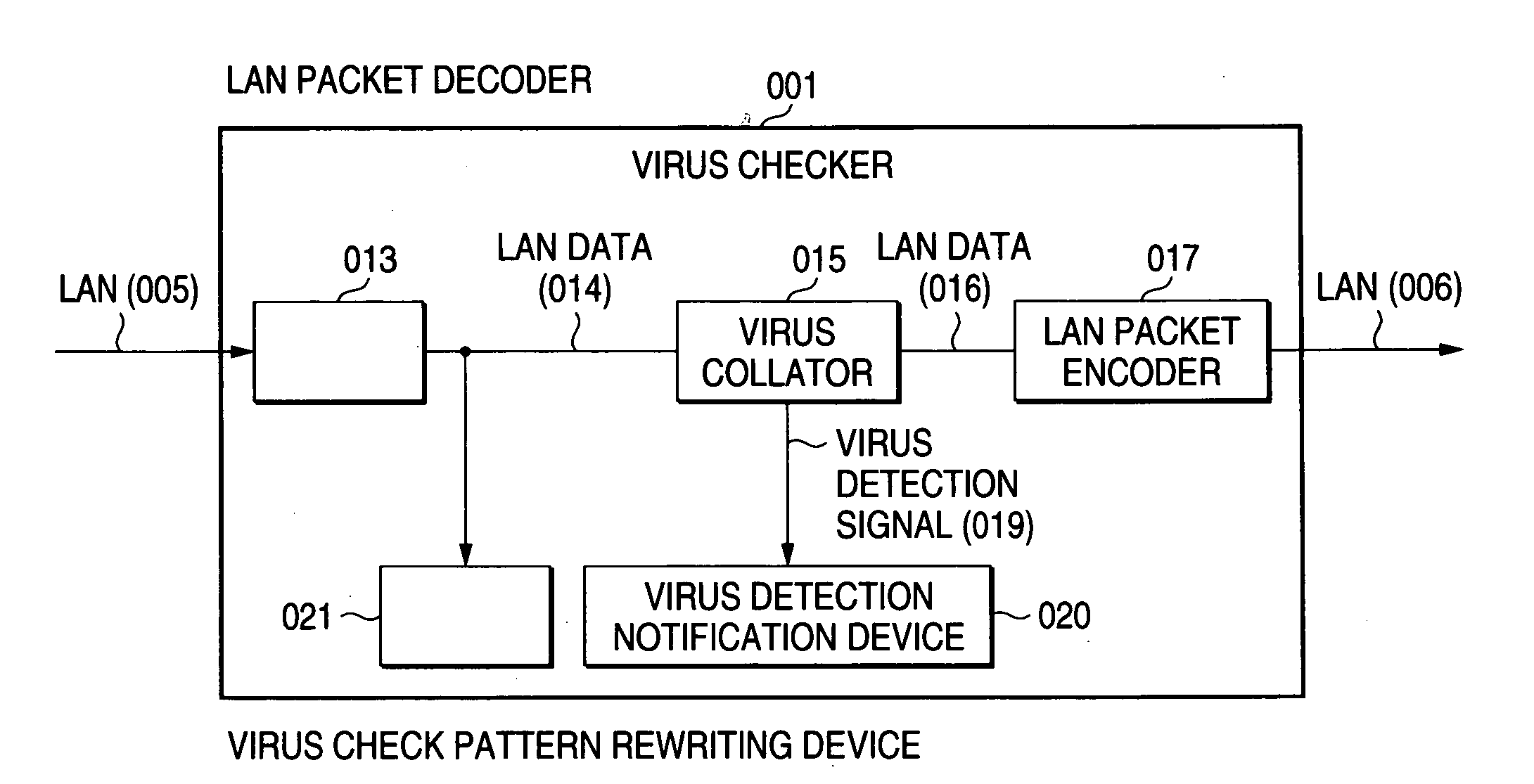

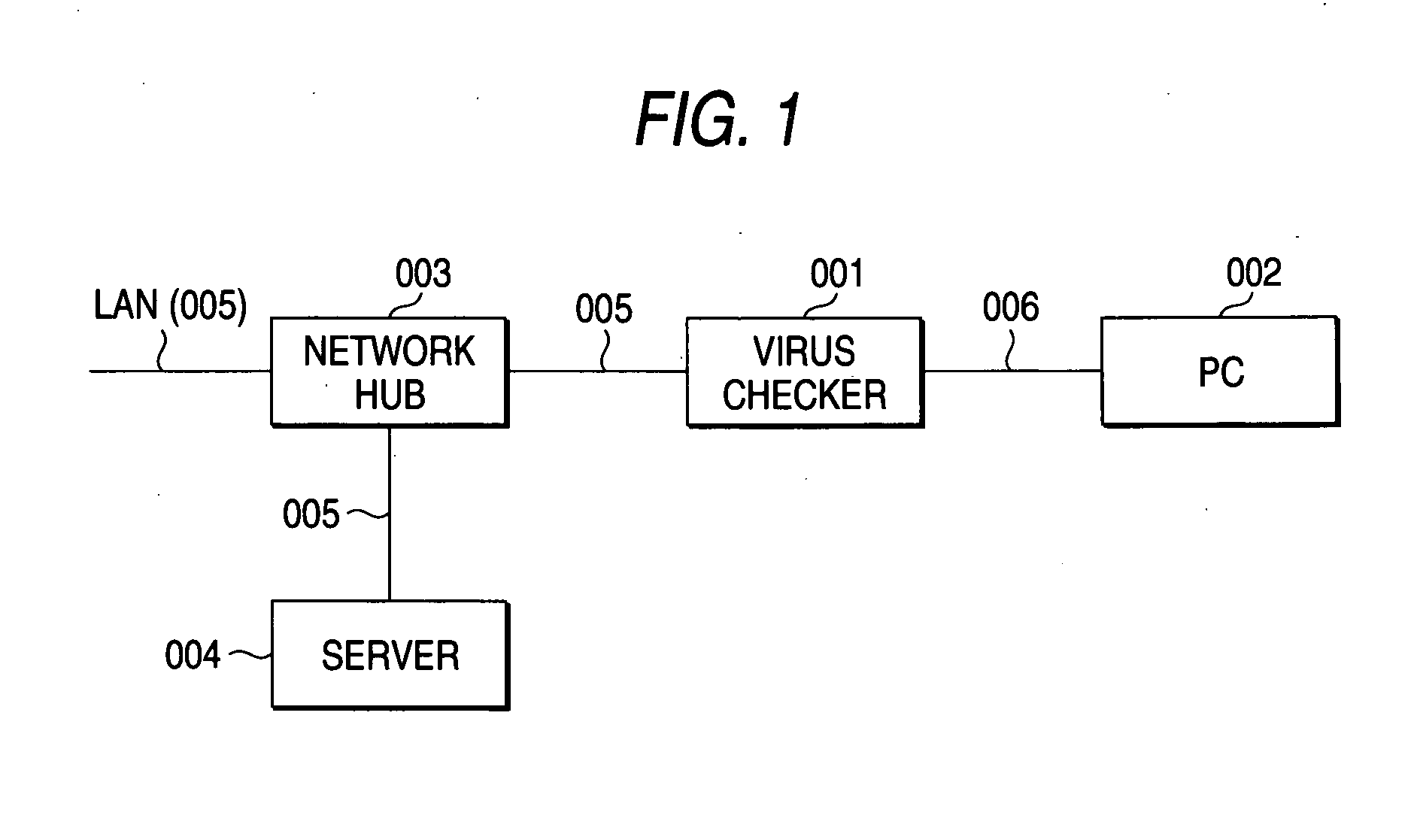

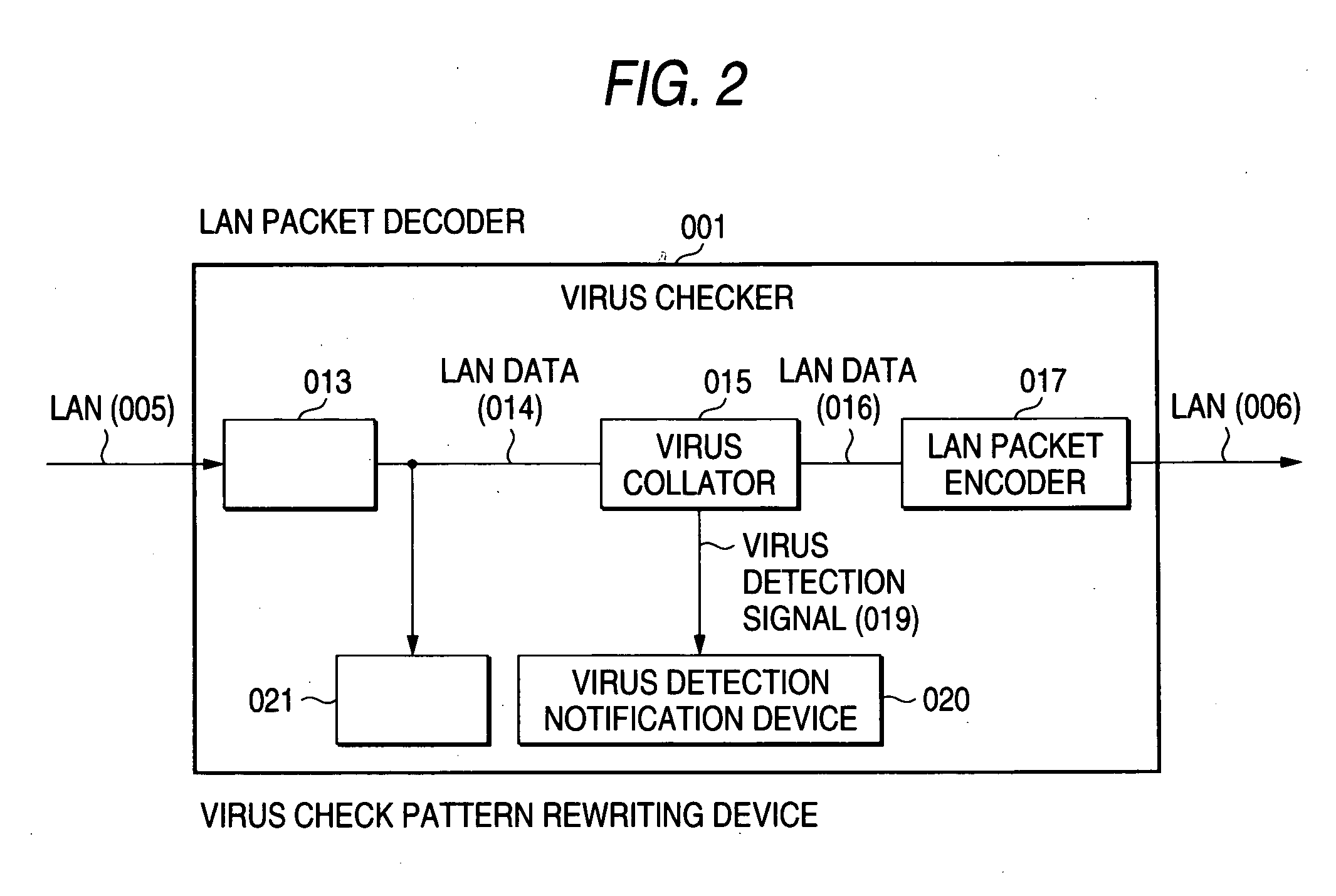

Virus check device and system

InactiveUS20060242686A1High speed machiningSimple processDigital data processing detailsError detection/correctionDigital dataInformation processing

The present invention detects a computer virus at high speed from digital data acquired through a network using hardware in virus monitoring. With the invention, in an information processing terminal 002 capable of communicating with other information processing apparatus through a communication network 005, a virus checking apparatus 001 constructed of a hardware circuit is disposed in the side of an input channel of the network 005 and a virus is checked from input data from the network 005 by the virus checking apparatus 001. In order to change a virus pattern collated with the input data by hardware, the hardware circuit is detachably mounted or a rewritable logic device is used in the hardware circuit. The virus pattern of the logic device can be rewritten by sending virus definition information of a server 004 or control data generated based on this information to the virus checking apparatus 001.

Owner:NAT INST OF ADVANCED IND SCI & TECH

Free-fall detection device and free-fall protection system for a portable electronic apparatus

ActiveUS20060152842A1Acceleration measurement using interia forcesDriving/moving recording headsFree fallingEngineering

In an integrated free-fall detection device for a portable apparatus an acceleration sensor generates acceleration signals correlated to the components of the acceleration of the portable apparatus along three detection axes. A dedicated purely hardware circuit connected to the acceleration sensor generates a free-fall detection signal in a continuous way and in real-time. The free-fall detection signal has a first logic value in the event that the acceleration signals are simultaneously lower than a respective acceleration threshold, and is sent to a processor unit of the portable apparatus as an interrupt signal to activate appropriate actions of protection for the portable apparatus. Preferably, the acceleration sensor and the dedicated purely hardware circuit are integrated in a single chip and the acceleration sensor is made as a MEMS.

Owner:STMICROELECTRONICS SRL

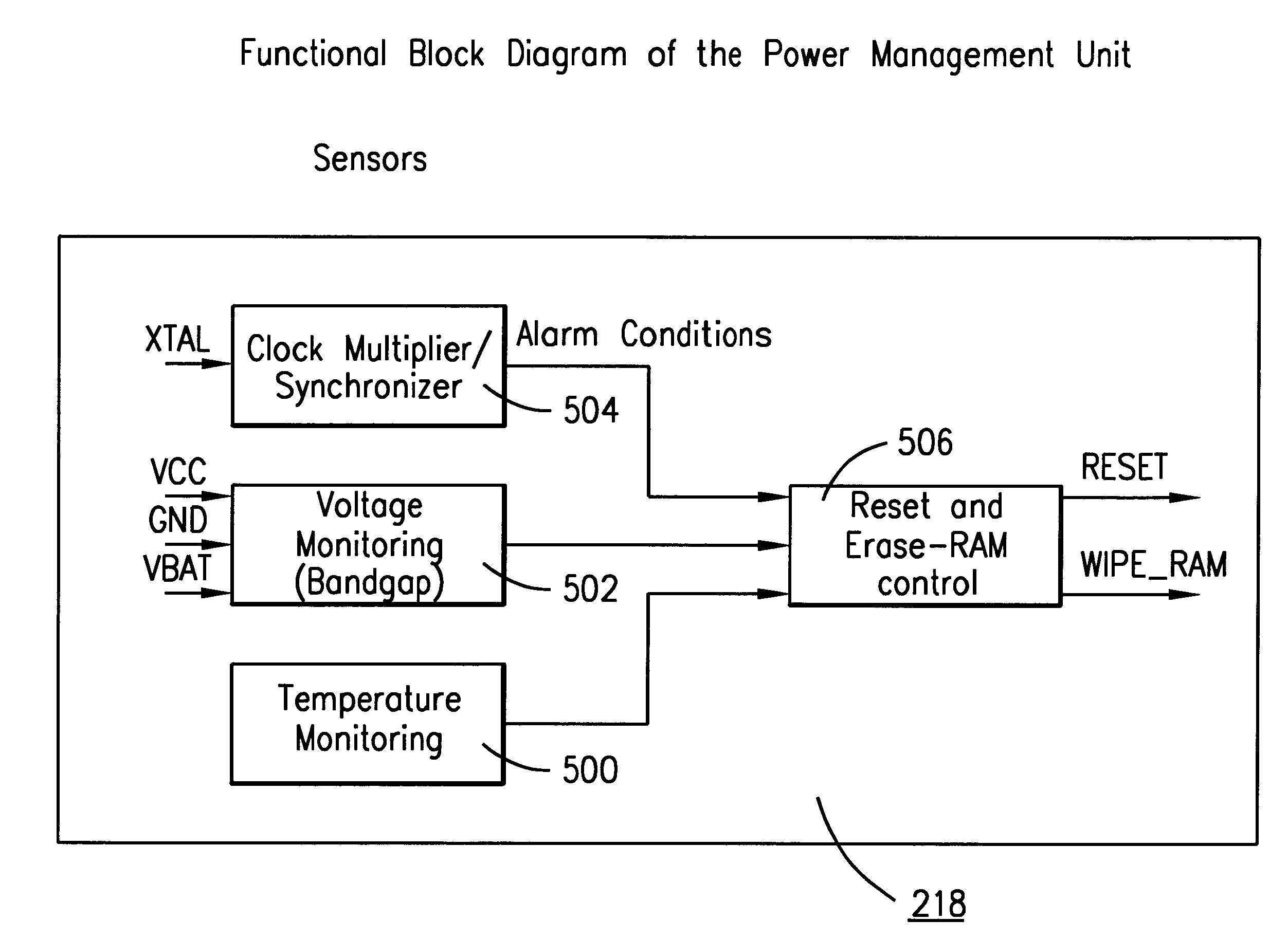

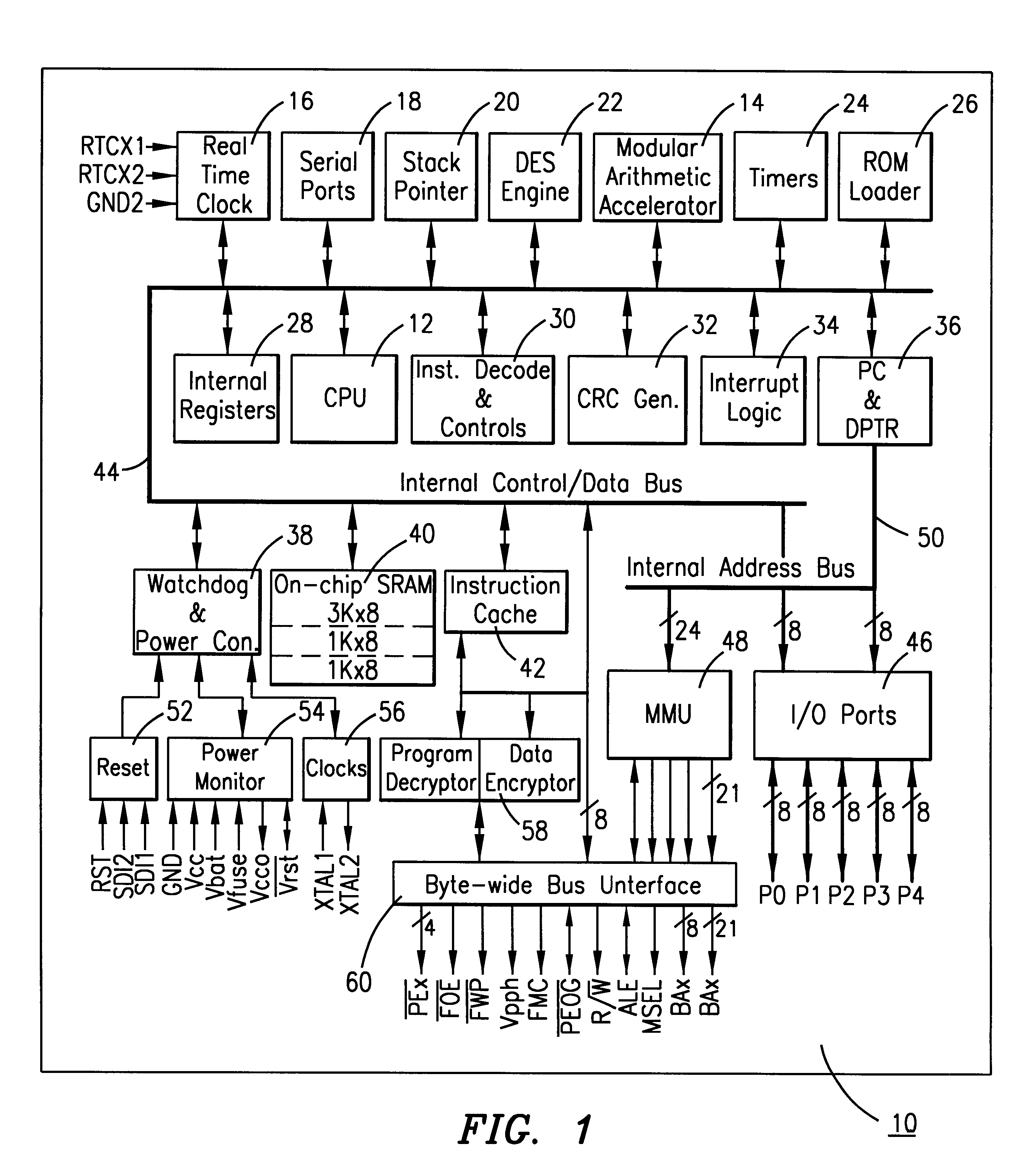

Integrated circuit having hardware circuitry to prevent electrical or thermal stressing of the silicon circuitry

InactiveUS6330668B1Digital data processing detailsAnalogue secracy/subscription systemsElectricityEngineering

An integrated circuit, such as a microprocessor, which incorporates hardware mechanisms to prevent the circuitry from operating outside the proper bounds of design. The hardware circuitry prevents the microprocessor circuitry from being forced to operate at clock speeds that are greater than it is designed for, from operating at temperatures above or below that which it is designed for, and from being forced to operate at voltages that are above or below voltages that the microprocessor is designed to operate at.

Owner:MAXIM INTEGRATED PROD INC

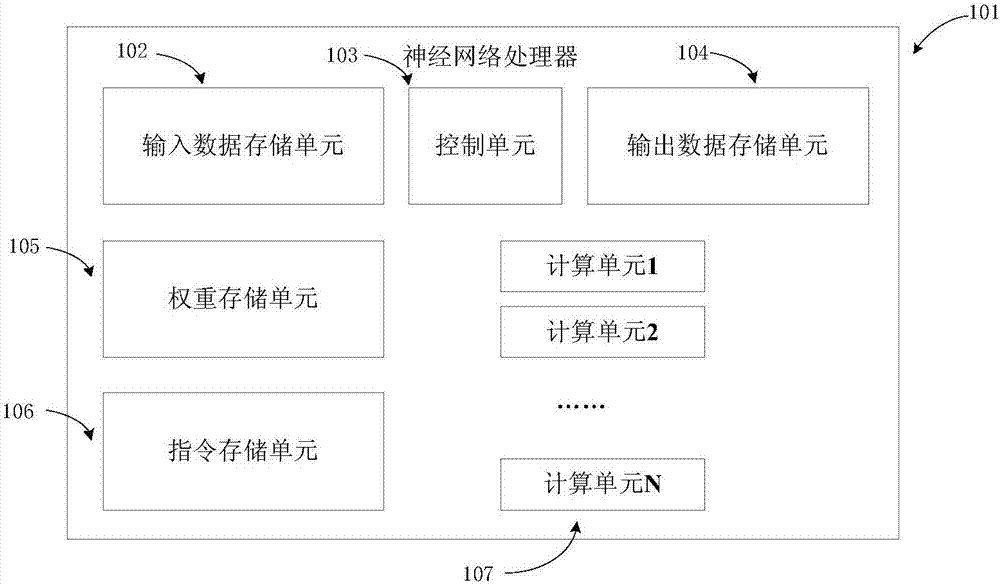

Neural network processor oriented automatic design method, device and optimization method

ActiveCN107103113AAutomate collaborative designShorten the design cycleBiological neural network modelsCAD circuit designNerve networkAlgorithm

The invention provides a neural network processor oriented automatic design method, device and optimization method. The automatic design method includes: a first step, acquiring a neural network model description file and a hardware resource constraint parameter, wherein the hardware resource constraint parameter includes the hardware resource size and the target operation speed; a second step, searching a unit library from an established neural network assembly library according to the neural network model description file and the hardware resource constraint parameter, and generating a hardware description language code corresponding to a neural network processor of the neural network model according to the unit library; and a step 3, converting the hardware description language code into a hardware circuit of the neural network processor.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

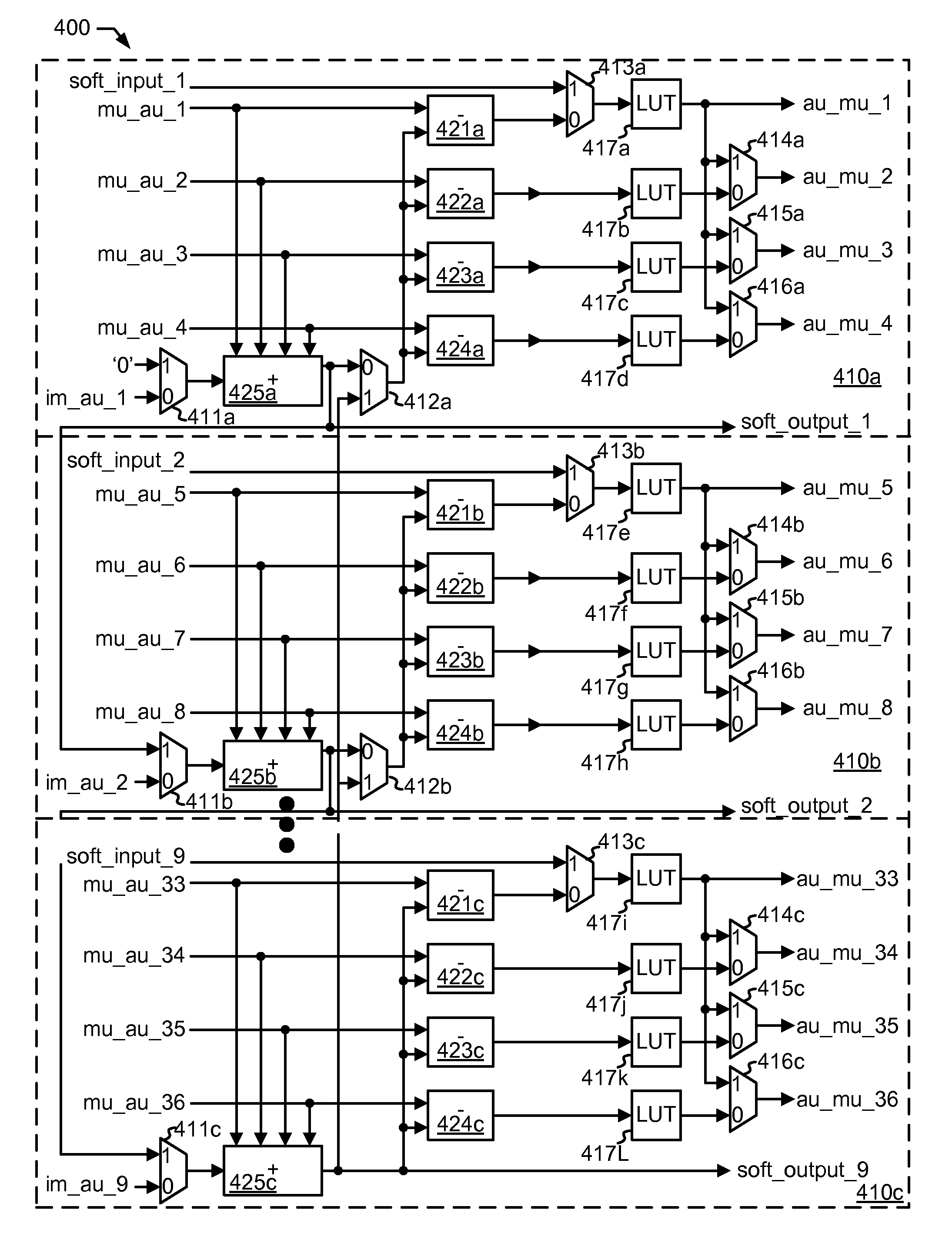

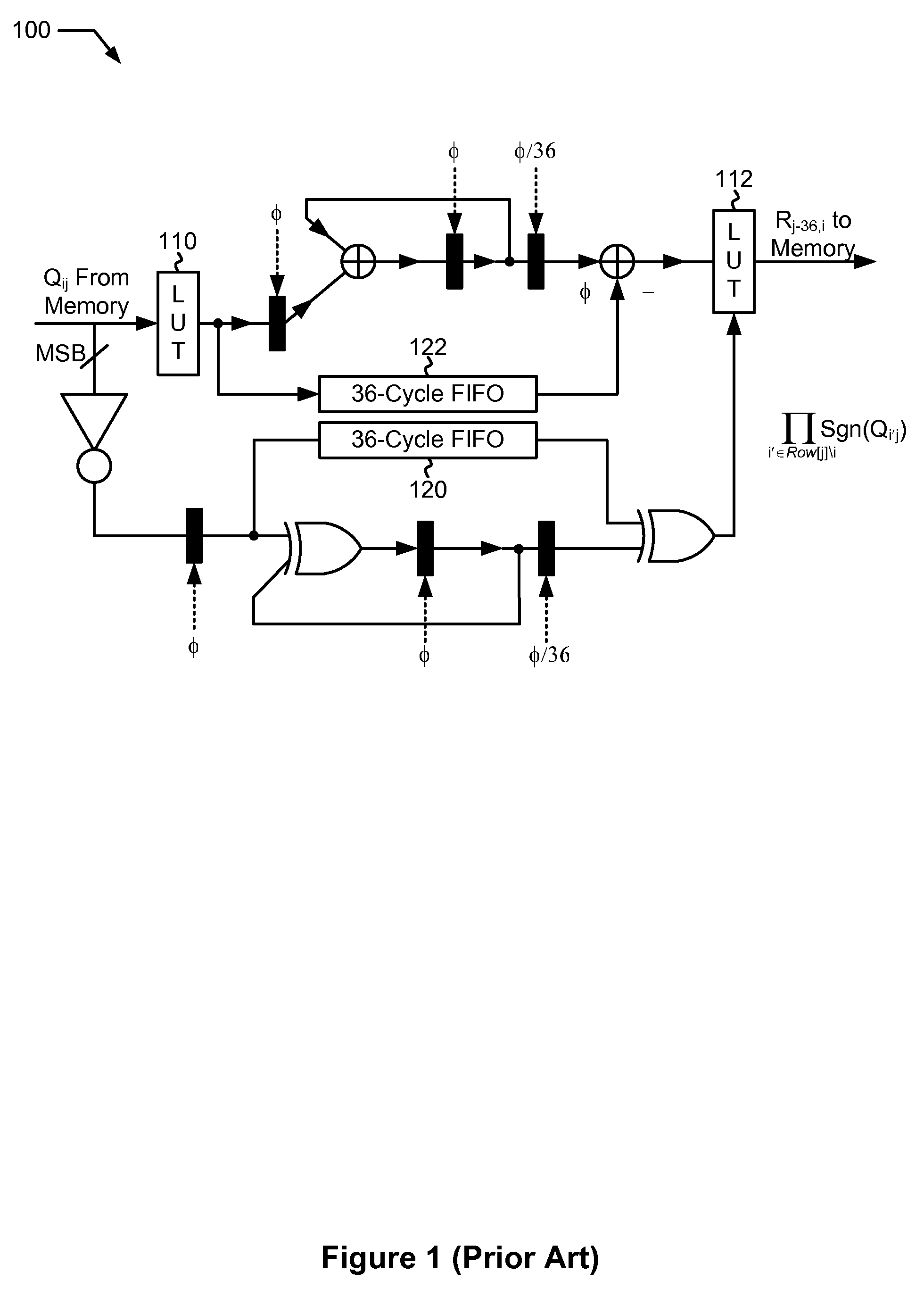

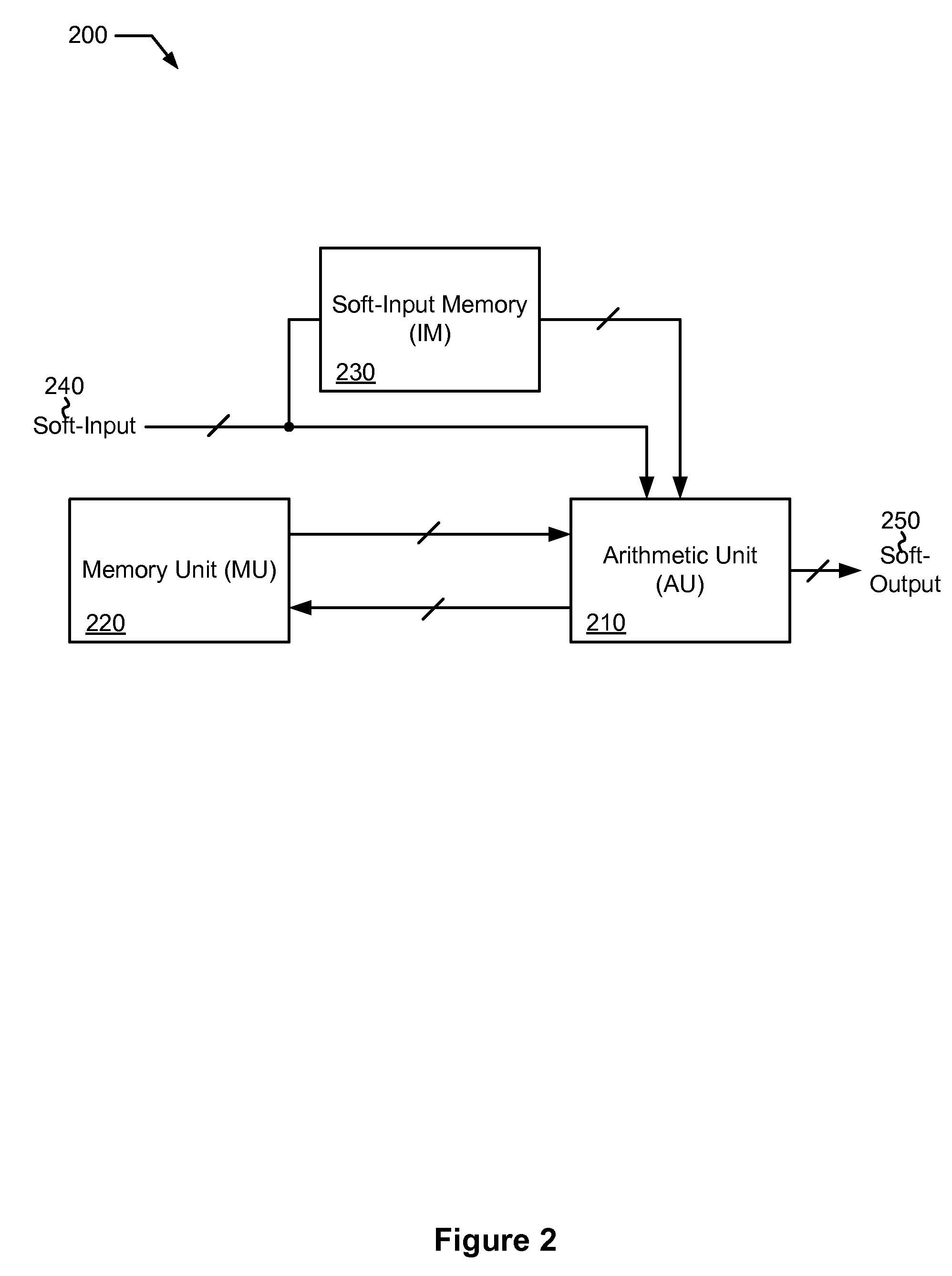

Systems and Methods for Low Cost LDPC Decoding

Various embodiments of the present invention provide systems and circuits that provide for LDPC decoding and / or error correcting. For example, various embodiments of the present invention provide LDPC decoder circuits that include a soft-input memory, a memory unit, and an arithmetic unit. The arithmetic unit includes a hardware circuit that is selectably operable to perform a row update and a column update. In such cases, a substantial portion of the circuitry of the hardware circuit used to perform the row update is re-used to perform the column update.

Owner:AVAGO TECH INT SALES PTE LTD

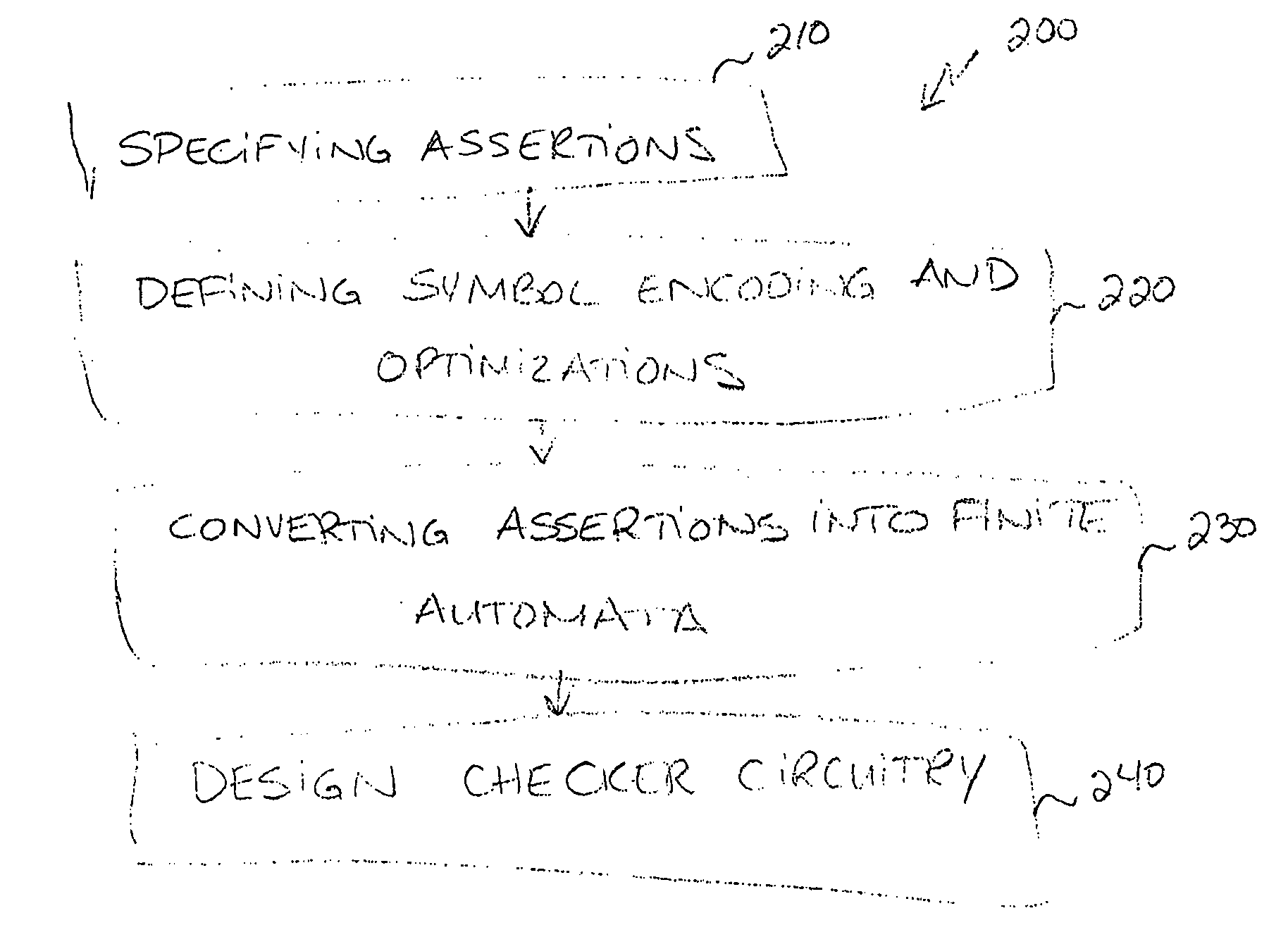

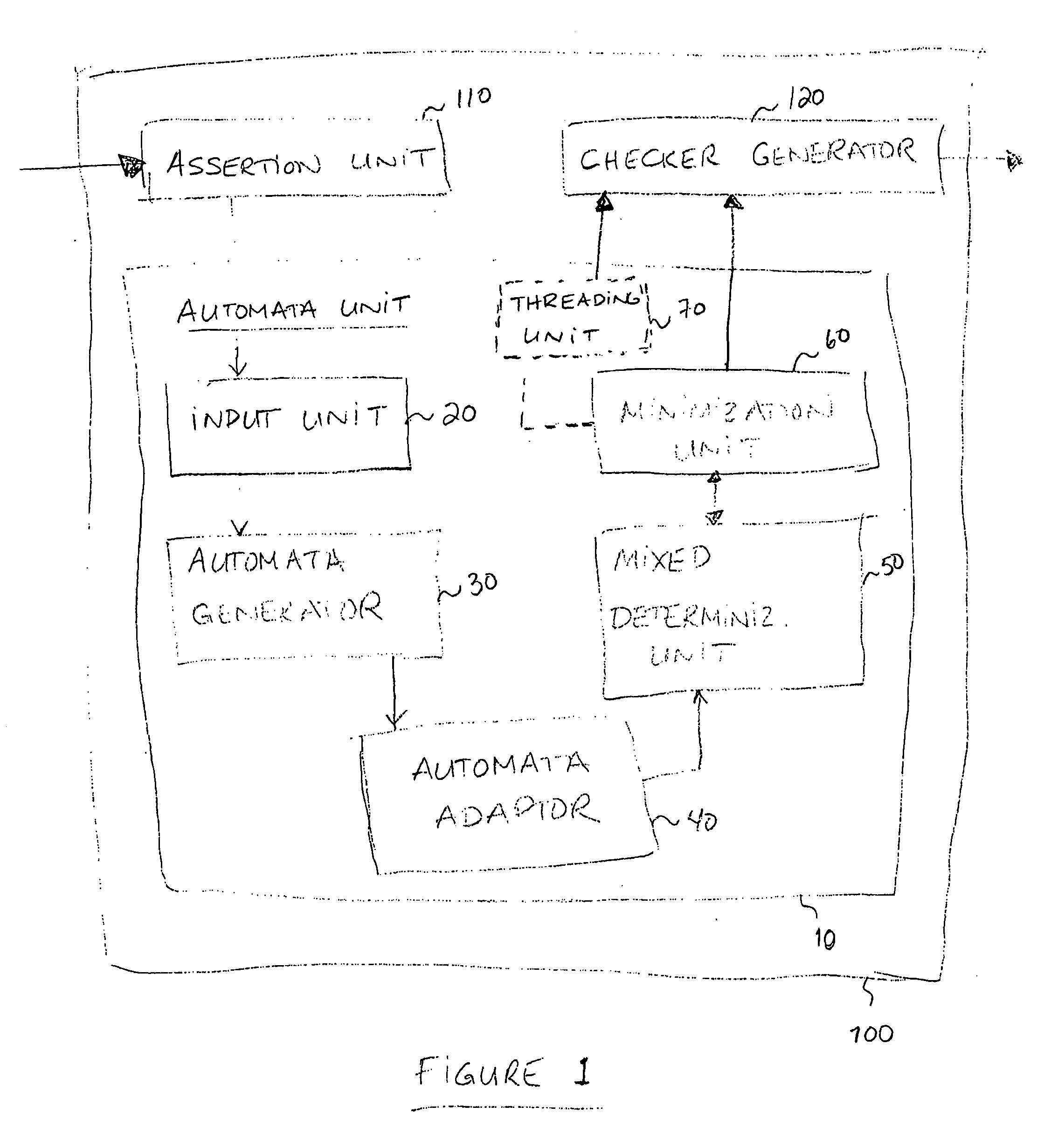

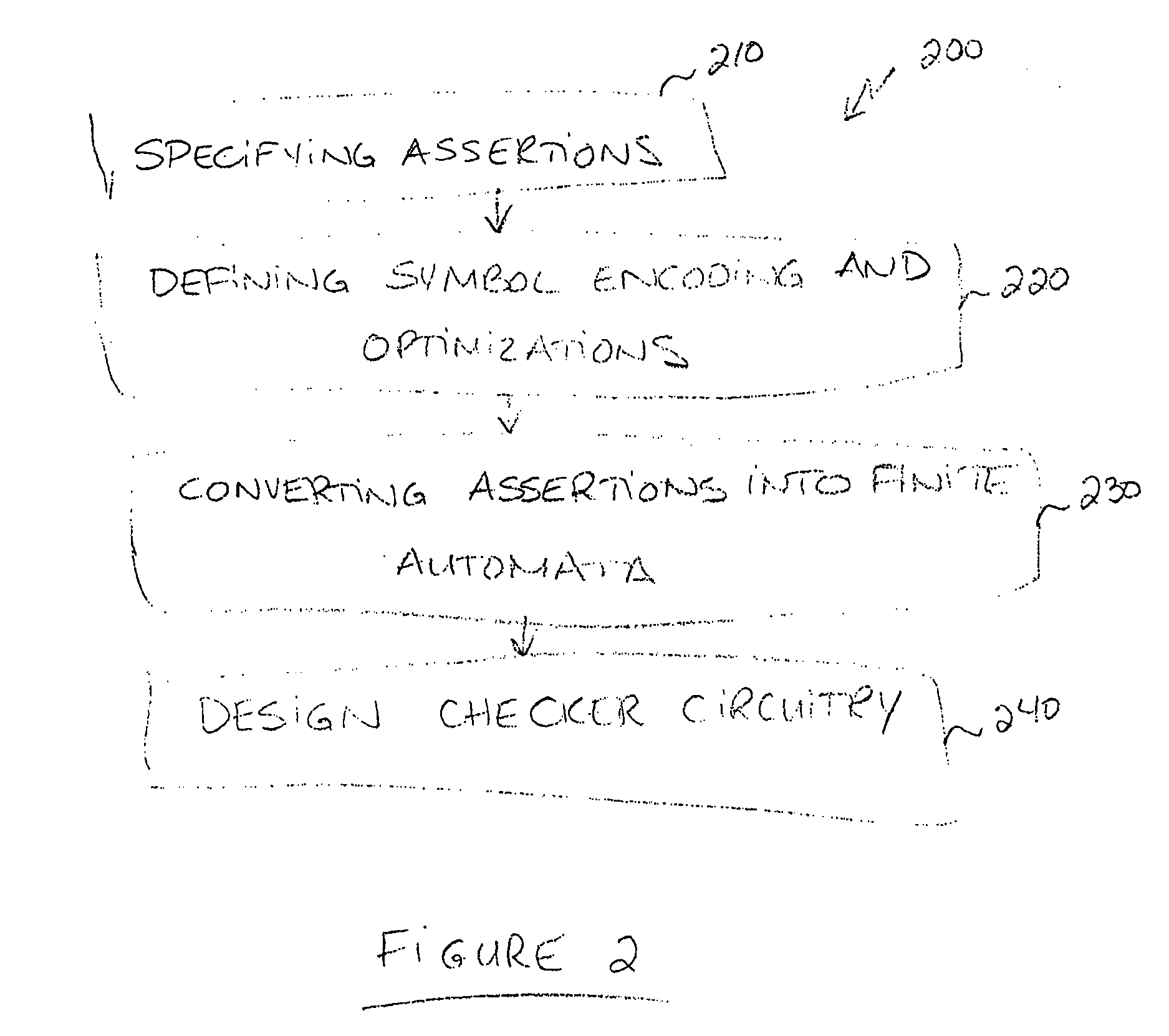

Automata unit, a tool for designing checker circuitry and a method of manufacturing hardware circuitry incorporating checker circuitry

InactiveUS20080082946A1Computer aided designSoftware simulation/interpretation/emulationAutomatonDual layer

The present invention relates to an automata unit, a tool for designing circuitry and / or checker circuitry, and a method for manufacturing hardware circuitry. The automata unit includes an input unit for receiving assertions using Boolean expressions, an automata generator for translating the assertions into automata, and an automata adaptor. The automata generator uses a dual layer symbolic alphabet for representing the assertions, and the automata adaptor adapts automata algorithms so as to support the symbolic alphabet in the generated automata. The tools for designing circuitry and checker circuitry rely on the automata unit, and further include an assertion unit and either a circuit generator or a checker generator.

Owner:MCGILL UNIV

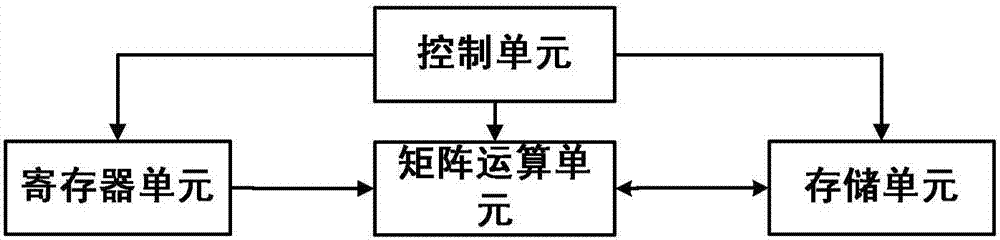

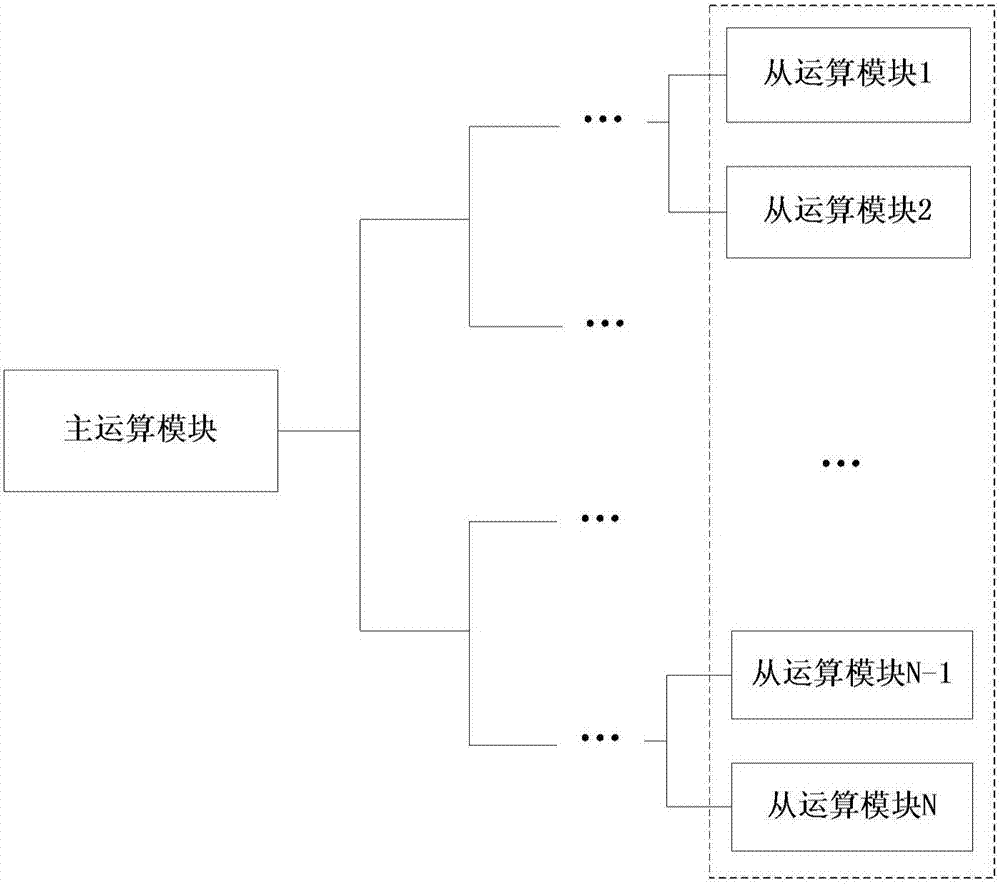

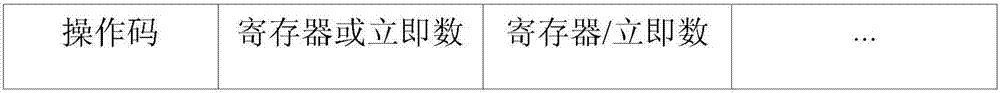

Apparatus and method used for executing matrix multiplication operation

ActiveCN107315574ADigital computer detailsHandling data according to predetermined rulesMatrix multiplicationControl unit

The invention discloses an apparatus and a method used for executing matrix multiplication operation. The apparatus is characterized by comprising a storage unit used for storing matrix data related with a matrix operation instruction, a register unit used for storing scalar data related with the matrix operation instruction, a control unit used for decoding the matrix operation instruction and controlling an operation process of the matrix operation instruction, and a matrix operation unit used for performing the matrix multiplication operation on an input matrix according to the decoded matrix operation instruction, wherein the matrix operation unit is a customized hardware circuit.

Owner:ANHUI CAMBRICON INFORMATION TECH CO LTD

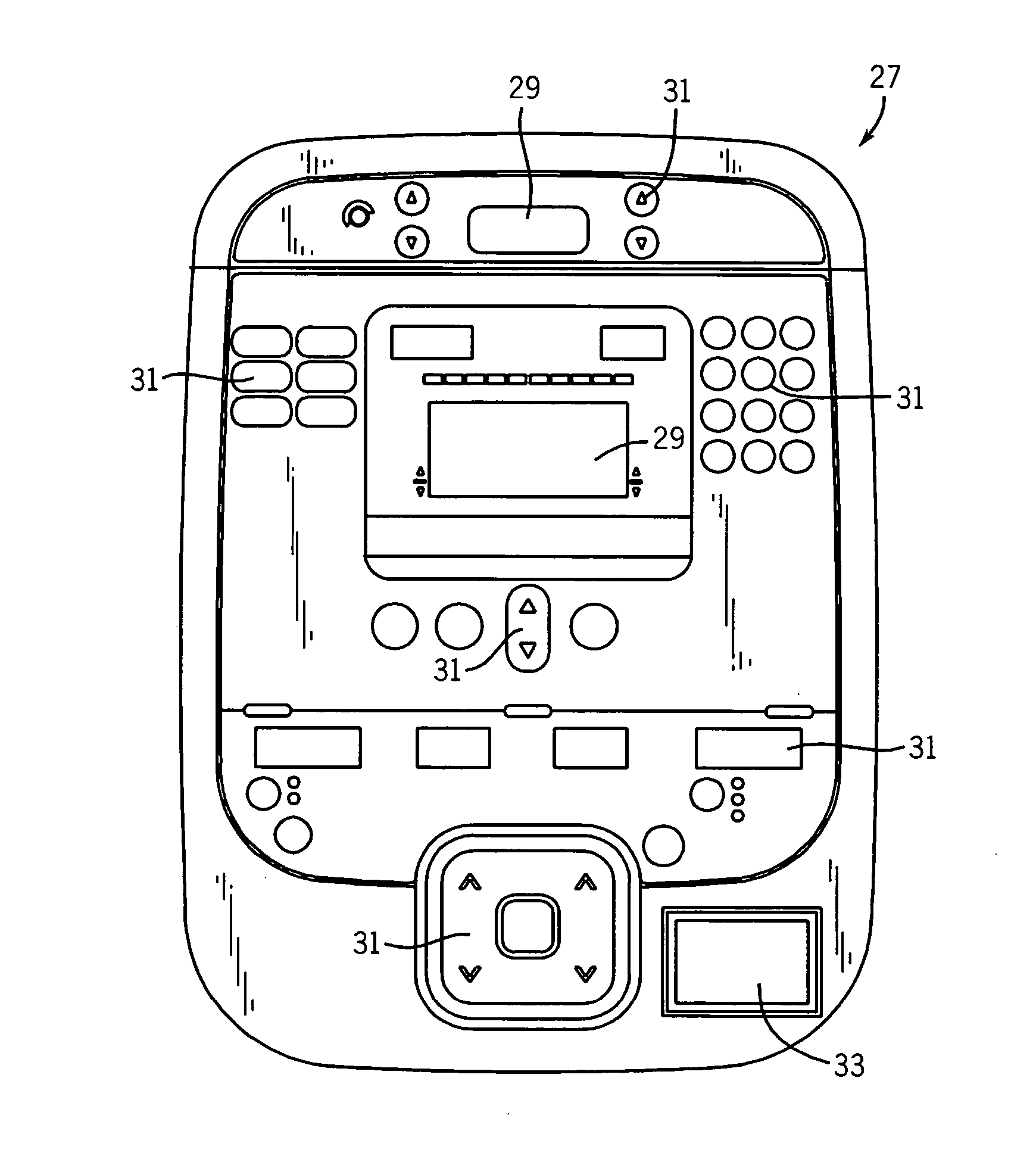

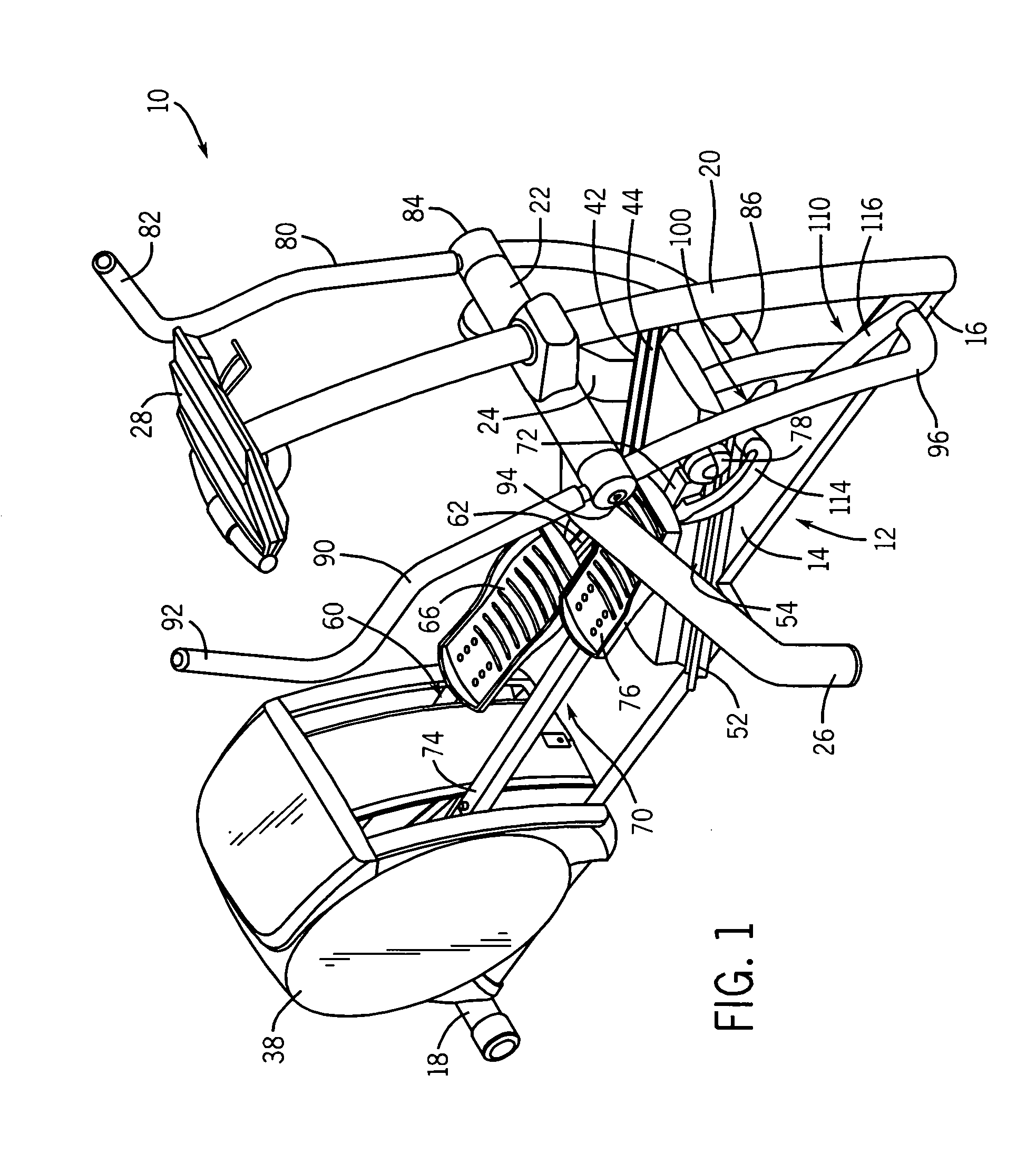

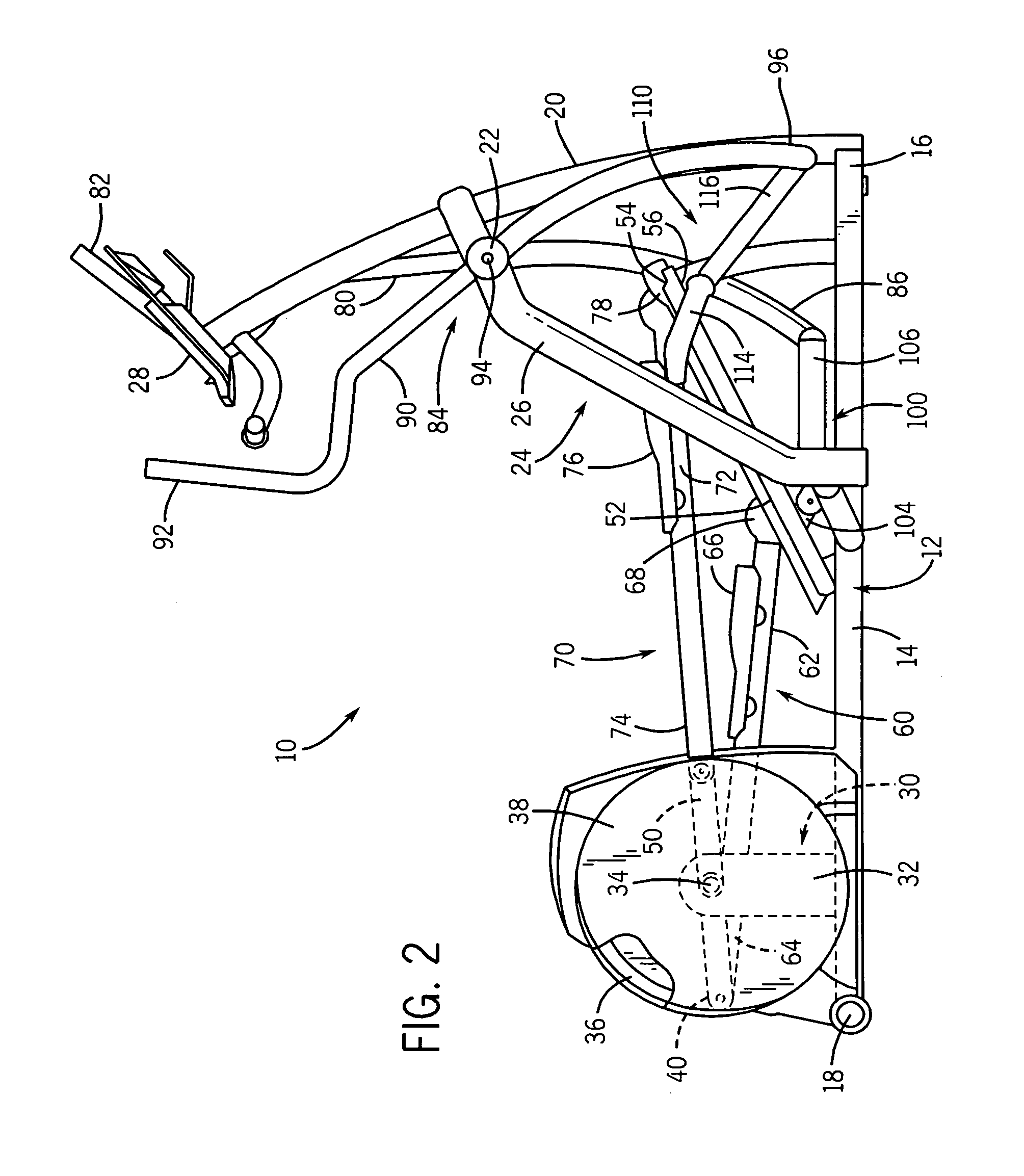

User identification for fitness equipment

InactiveUS20070201727A1Electric signal transmission systemsImage analysisComputer hardwareOperational system

In accordance with the principles of the present invention, an user identification system for a fitness trainer is provided. An operating system architecture for the fitness trainer includes a hardware circuit board, a processor in communication with the hardware circuit board, and memory in communication with the hardware circuit board and the processor. A biometric capture mechanism in communication with the processor and the memory.

Owner:PRECOR

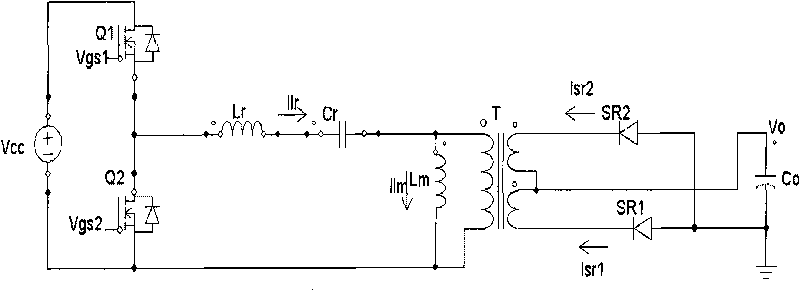

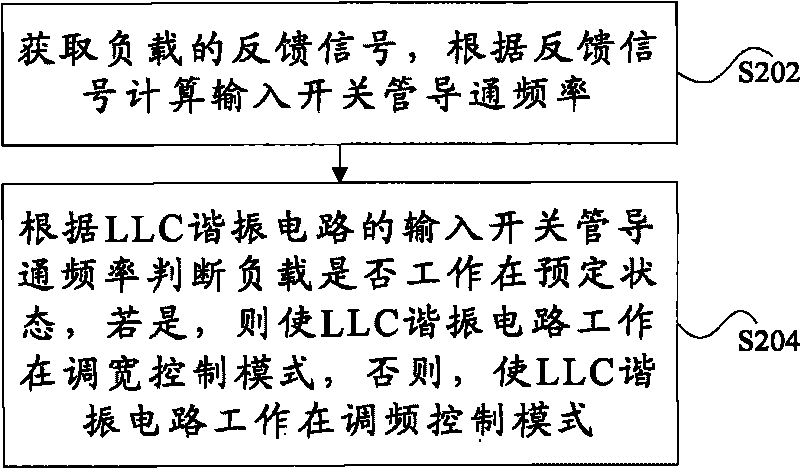

LLC resonant converter control method, synchronous rectification control method and device

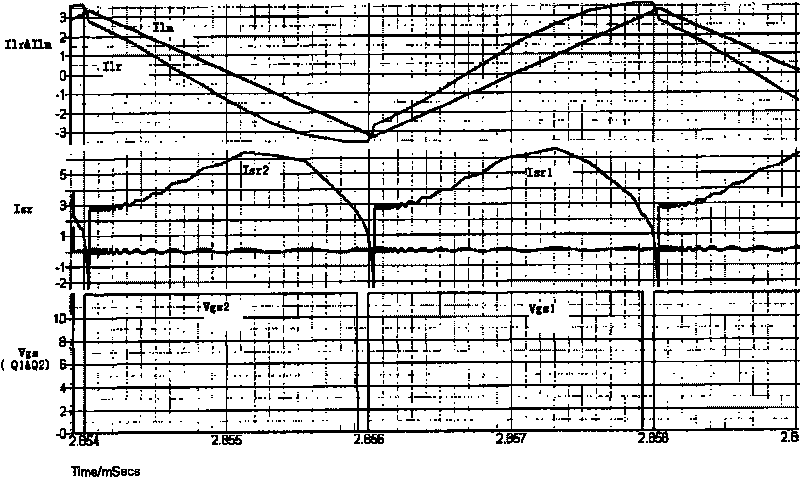

InactiveCN101707440AReduce lossFix stability issuesEfficient power electronics conversionDc-dc conversionResonant converterFrequency modulation

The invention discloses an LLC resonant converter control method, synchronous rectification control method and device, wherein the LLC resonant converter control method comprises the steps of: judging whether a load works in a preset state or not according to the connection frequency of an input switching tube of an LLC resonant circuit; if the load works in the preset state, enabling the LLC resonant circuit to work in a width modulation mode, and otherwise, enabling the LLC resonant circuit to work in a frequency modulation mode, wherein the preset state comprises a light load state or no-load state. The invention realizes the voltage stabilization under the condition of light load or no-load of the LLC resonant circuit, lowers the circuit loss, effectively simplifies a peripheral hardware circuit, and is more reliable in use compared with the prior art.

Owner:ZTE CORP

Method and device for implementing entropy decoder based on H.264

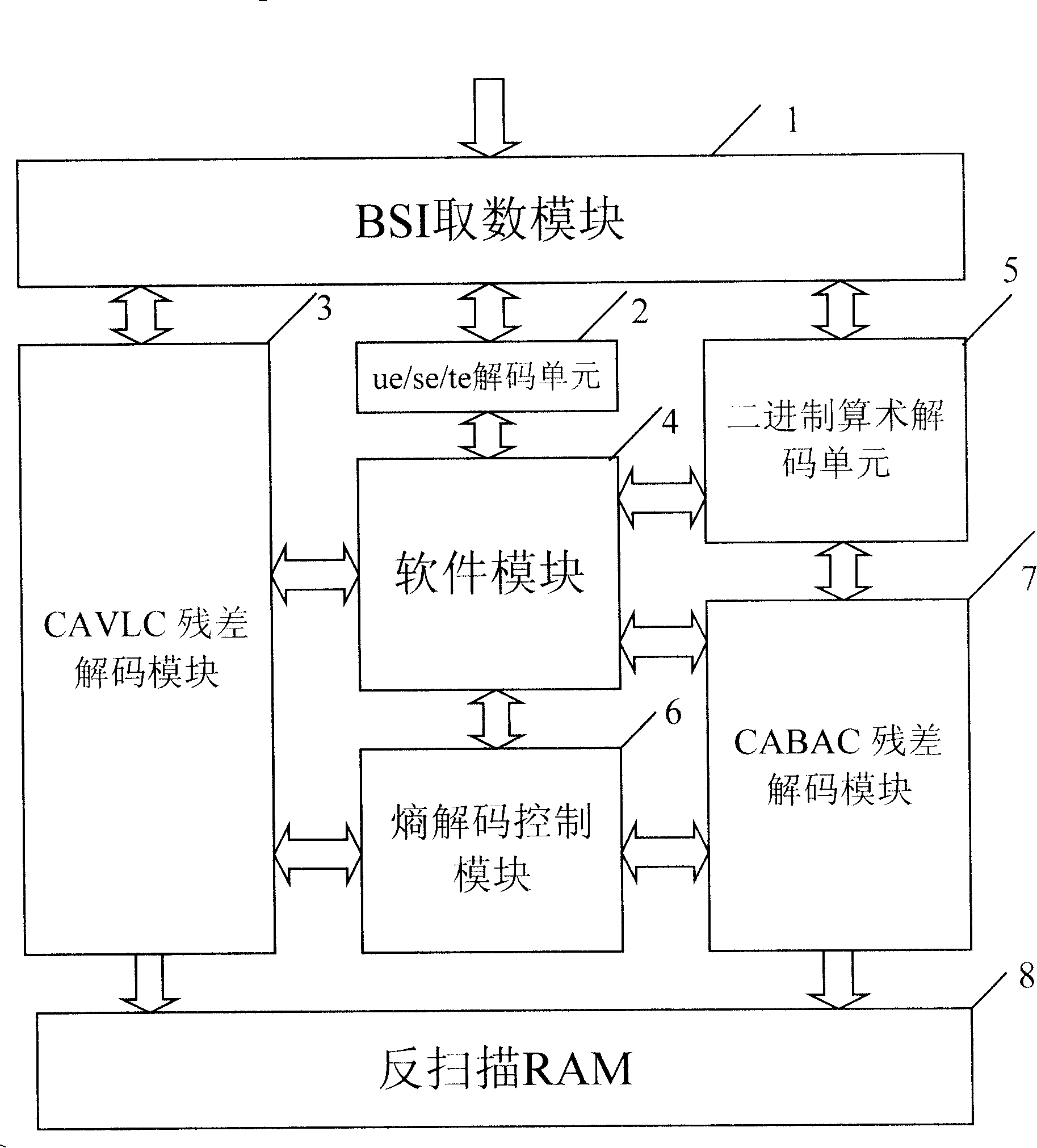

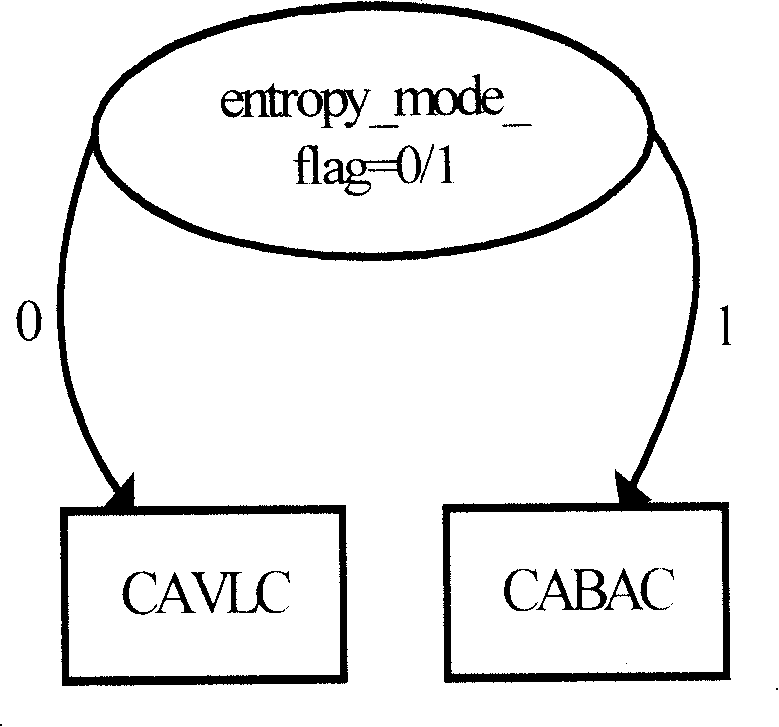

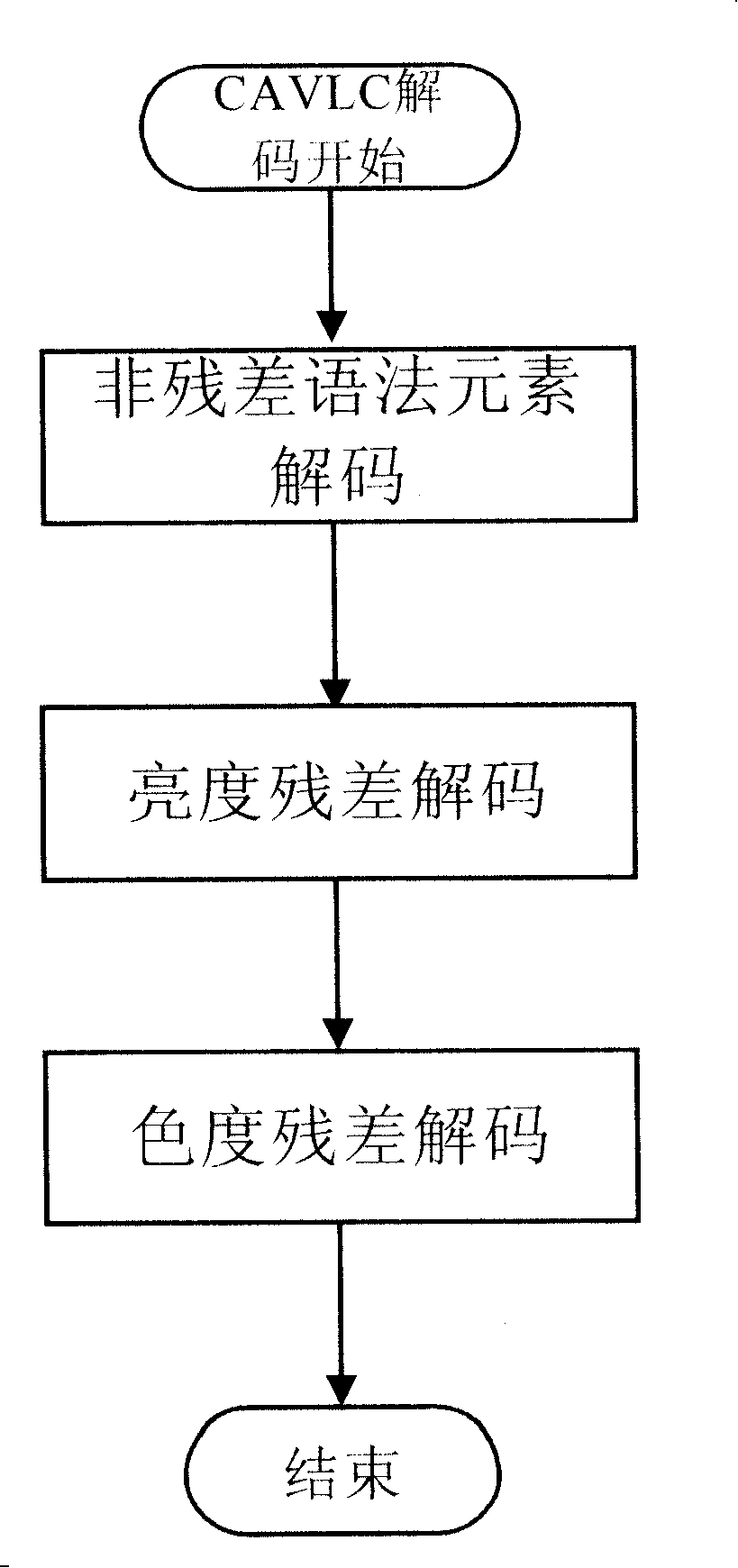

InactiveCN101198051AIncrease the difficultyImplement decodingTelevision systemsDigital video signal modificationComputation complexitySoftware modules

The invention discloses a method for decoding entropy coding residual data and so on which is specially used in an H.264 decoding MAE and a device. Because the method of the invention adopts collaborative work of software and hardware, parts which occupy a large number of resources during the decoding process are realized by means of a software method. The software program method is that: by the means of utilizing an embedded cpu to replace hardware circuits for operation, structural complexity and computation complexity are greatly reduced under the precondition that reliable decoding efficiency and decoding quality of an entropy decoder are guaranteed to be obtained, thereby the contradiction between structure and efficiency is effectively solved and decoding of CAVLC and CABAC entropy coding bit streams is smoothly realized. The entropy decoder comprises a BSI access module, a ue / se / te decoding unit, a CAVLC residual decoding module, a software module, a binary arithmetic decoding unit, an entropy decoding control module, a CABAC residual decoding module and an anti-sweep RAM.

Owner:ARKMICRO TECH

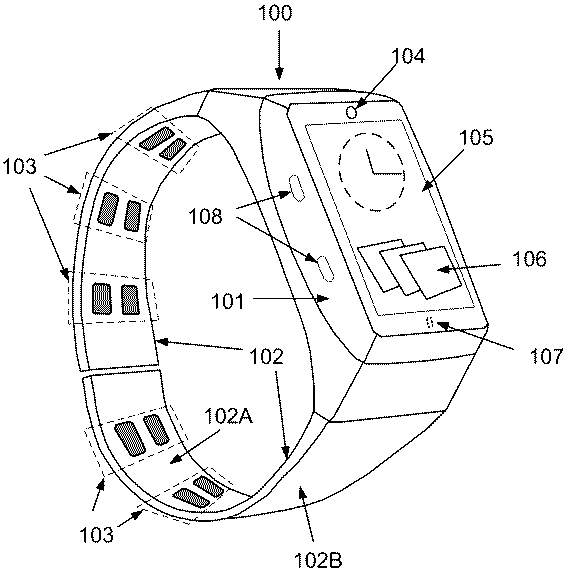

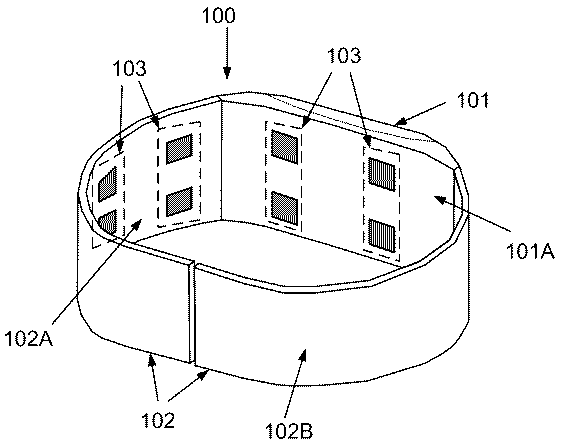

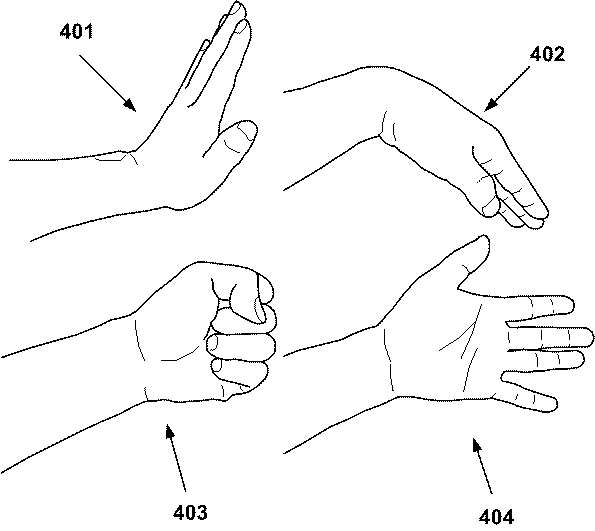

Gesture recognition scheme of smart watch based on arm electromyography

ActiveCN103558918AIncrease valueInput/output for user-computer interactionMechanical clocksUser inputData operations

A smart watch is small and exquisite, and has very high data operation and processing capacity; the disadvantages and the advantages of the smart watch are obvious; compared with a smart mobile phone, a display screen is small in size, so that the smart watch has great limitation in information display and user input, and is not high in practicability; and compared with the smart mobile phone or other electronic equipment, the smart watch clings to skin of a user, so that the smart watch has great advantages in detecting and utilizing life biological information of the user by adding a biological inductor. According to a scheme, a gesture recognition technology based on arm electromyography is added to the smart watch, software fully uses the signal and data processing capacity of the watch, and limited hardware circuits are increased, so that the smart watch can be controlled conveniently by a gesture, the smart watch can be changed into a universal gesture recognition controller by mounting a gesture application program, the practicability and a value of the smart watch are improved and increased greatly, and seamless integration of two technologies is realized.

Owner:SHANGHAI OYMOTION INFORMATION TECH

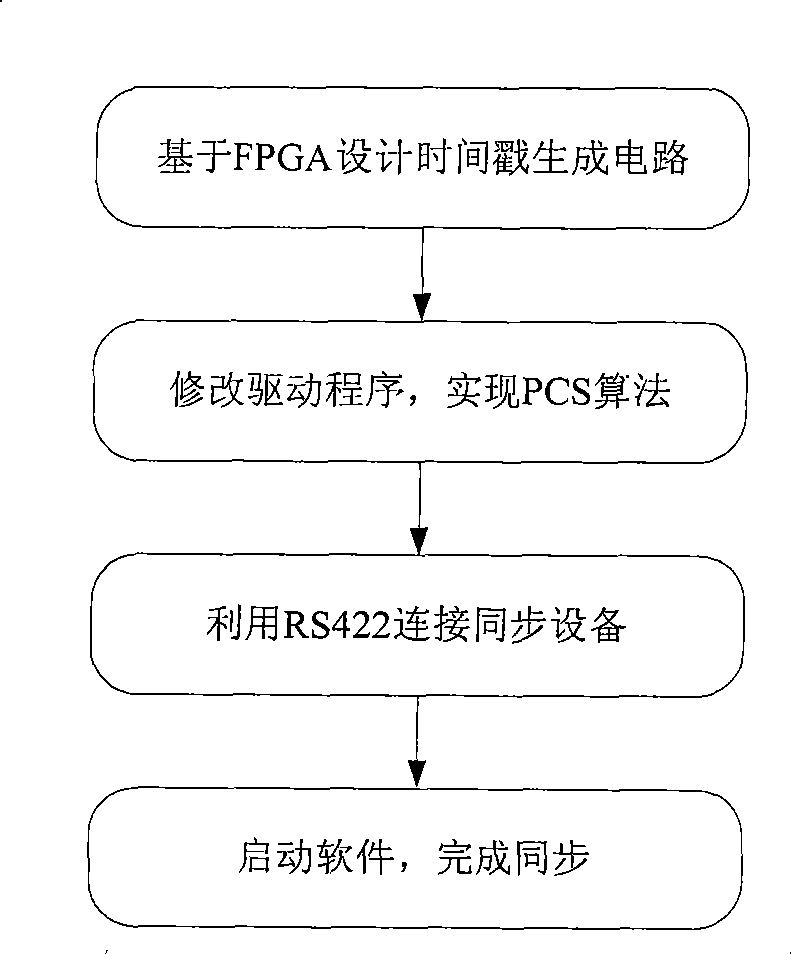

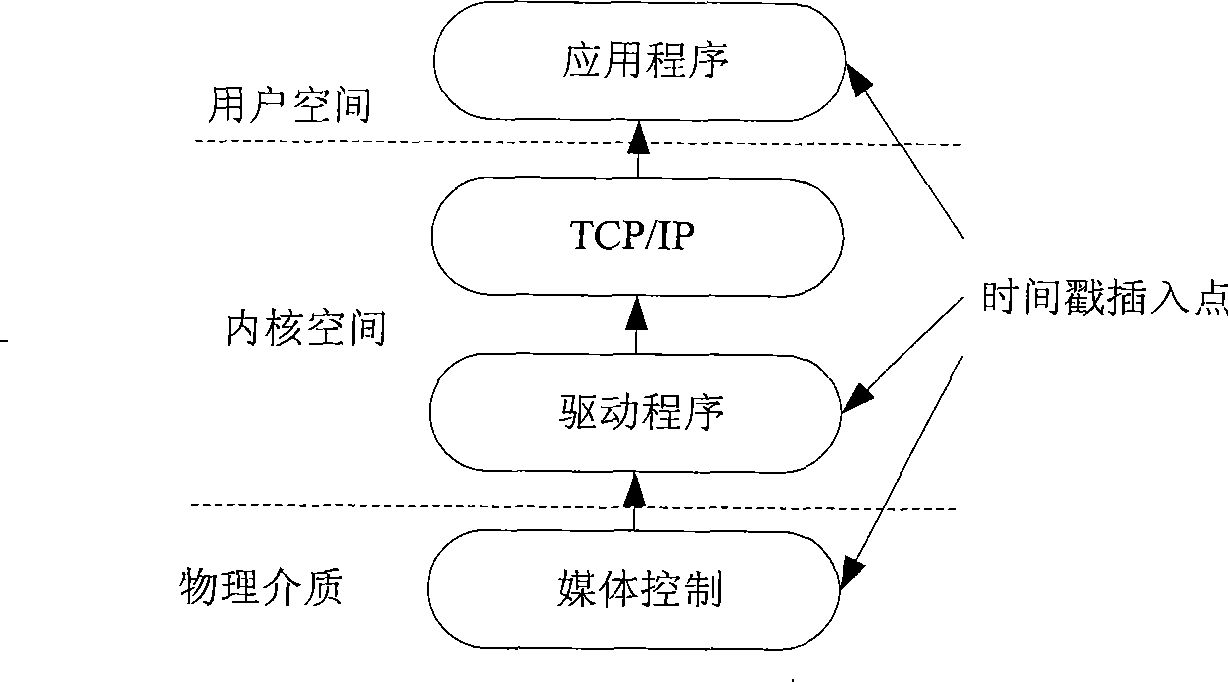

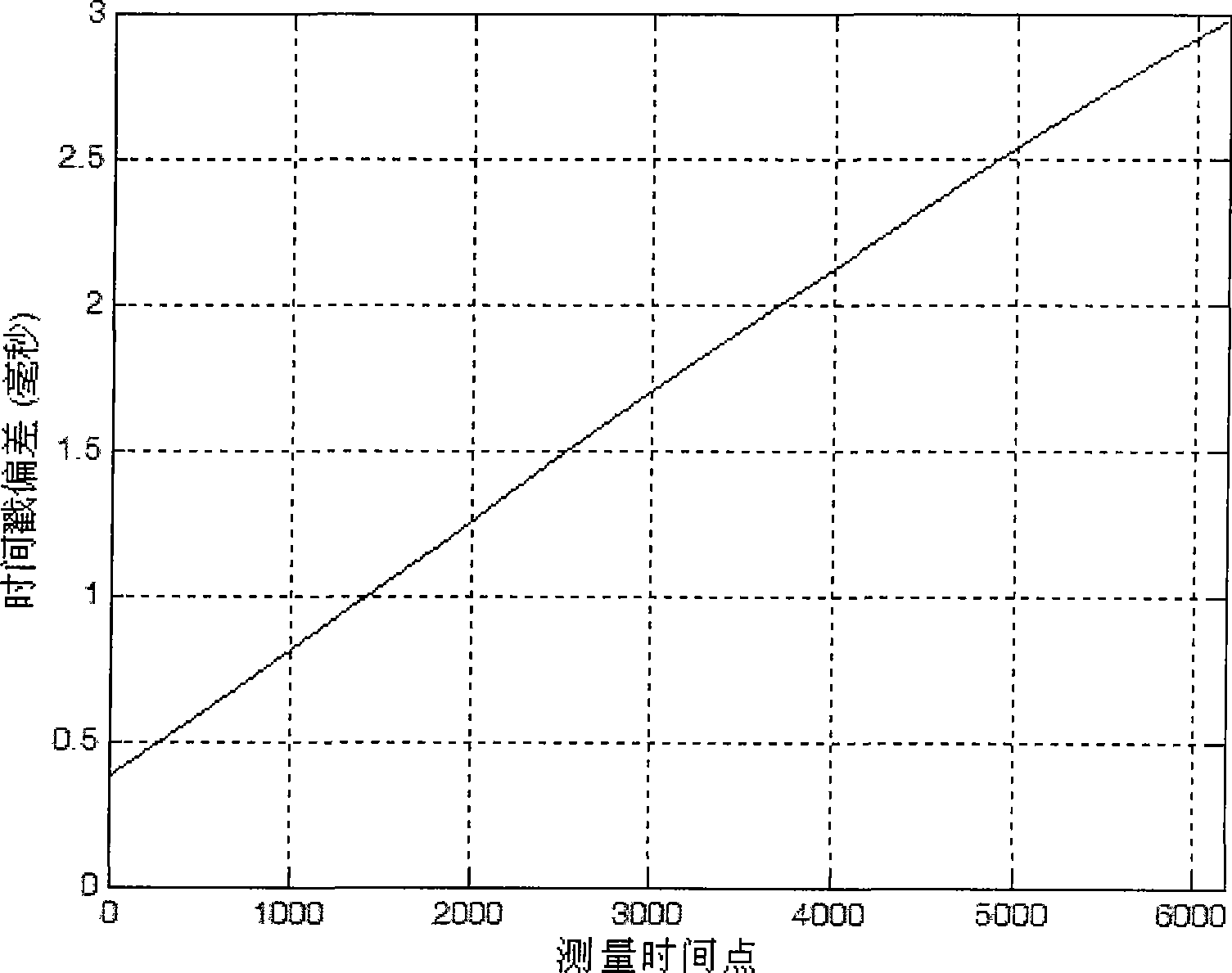

Highly precised time synchronization device, system and method for computer network

InactiveCN101388741AHigh precisionEliminate cache latencyTime-division multiplexTimestampComputer network performance

The invention provides a high-accuracy time synchronizing apparatus, a method and a system for testing the computer network performance, monitoring system and network simulation, which comprises the following steps: utilizing a hardware circuit to realize a timestamp generating circuit, moving a timestamp recording position to a physical chain circuit layer, removing impact of the cache delay in the timestamp of a common software and impact caused by interrupting the response time delay, and realizing the accurate clock synchronization of each measuring node through the prediction-based time synchronous algorithm (Prediction-based Clock Synchronization,PCS). The apparatus improves the accuracy of the timestamp, can guarantee the error of the synchronous timestamp of each measured node notto exceed 100ns, and can reach the accuracy which is equal to adopting GPS synchronization, and the realization is simple and the cost is low.

Owner:SHANGHAI YINGLIAN SOMATOSENSORY INTELLIGENT TECH CO LTD

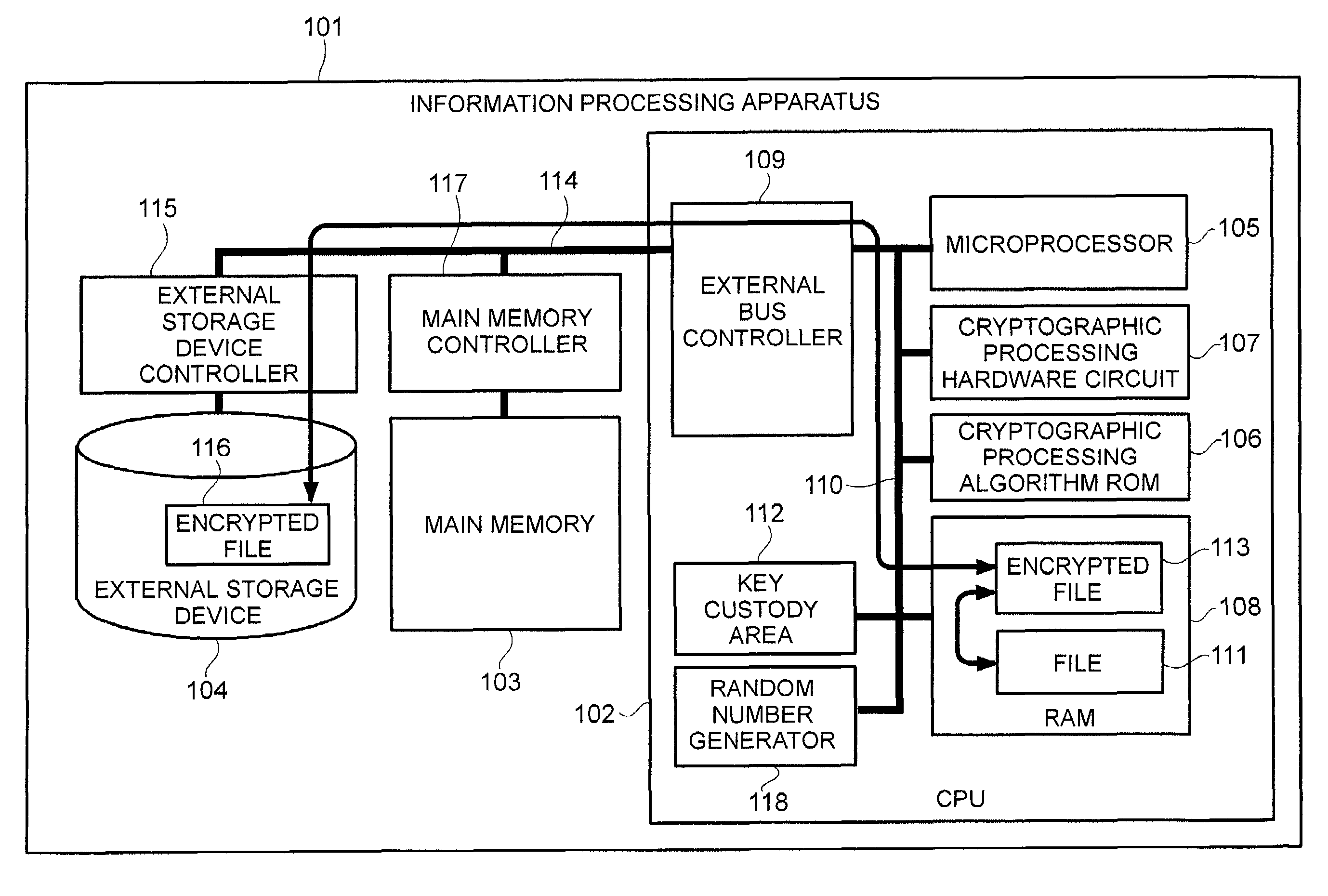

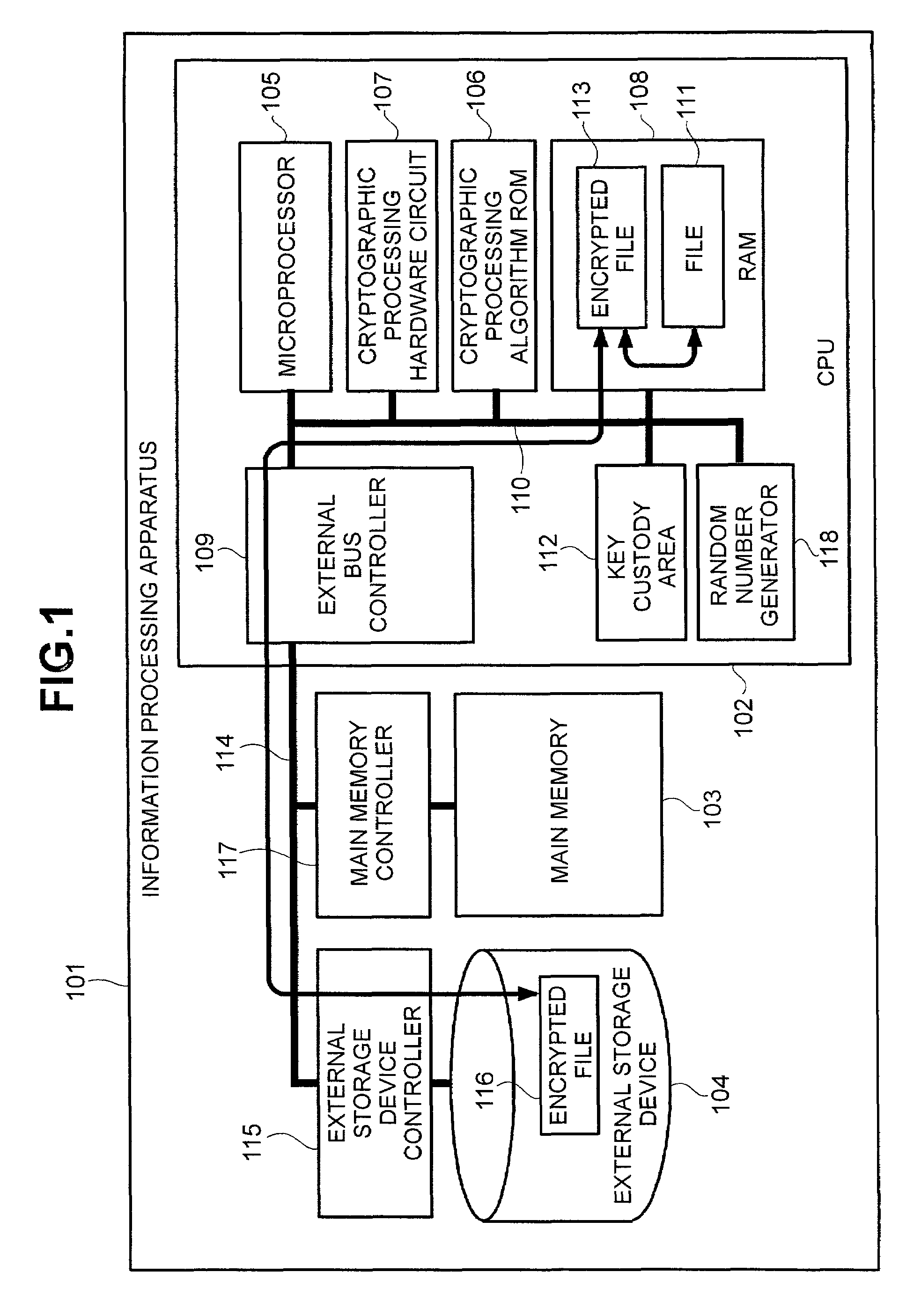

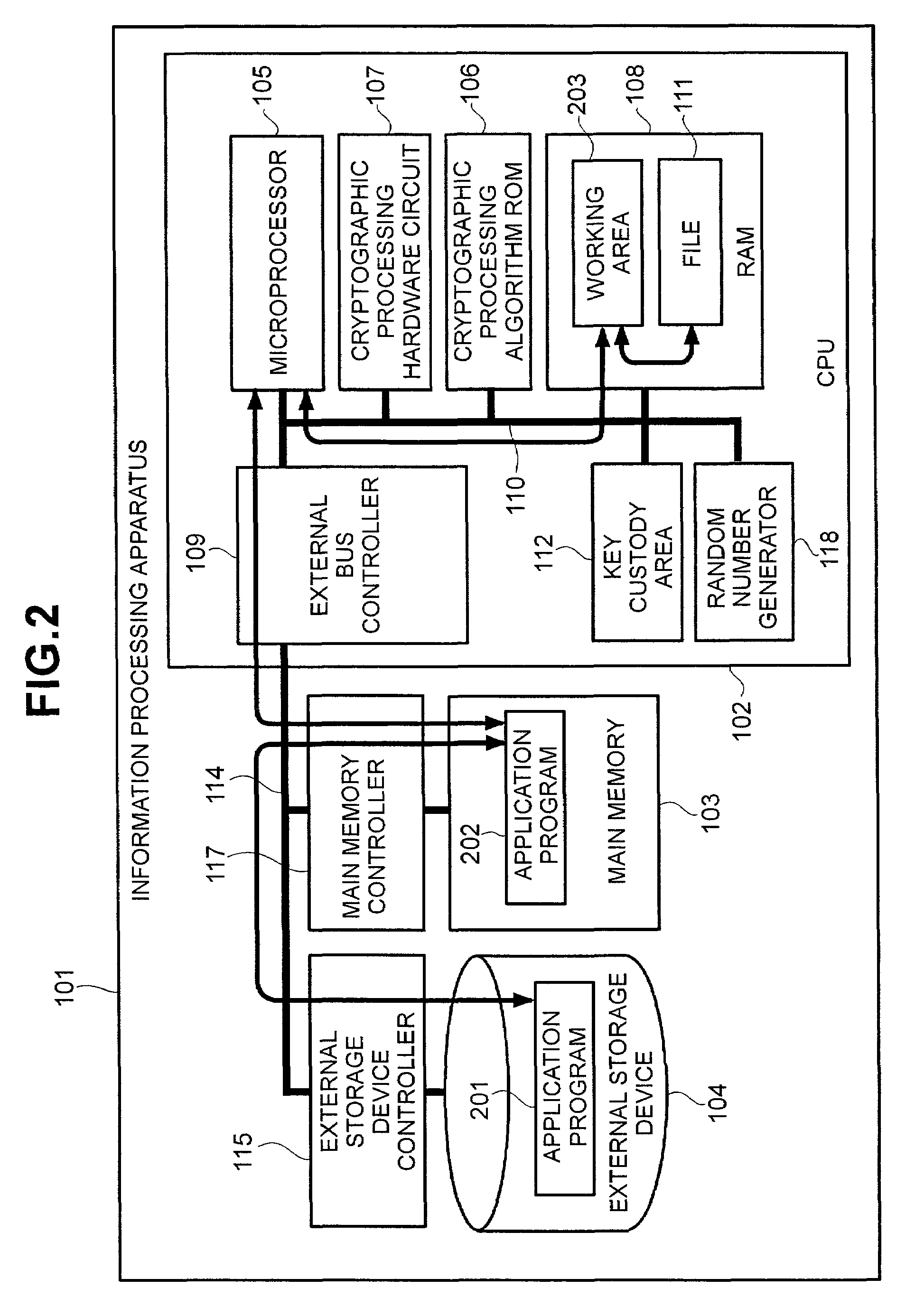

Information processing apparatus

InactiveUS7082539B1Memory loss protectionUnauthorized memory use protectionInformation processingSemiconductor chip

Since a conventional information processing apparatus includes a plurality of semiconductor devices, there is a problem that sensitive information may reside on a system bus in the apparatus or a semiconductor memory device serving as main memory therein. To obviate this problem, each information processing apparatus has a CPU which includes a microprocessor, a cryptographic processing algorithm ROM, a cryptographic processing hardware circuit, a RAM, a key custody area, and an external bus controller, which are all integrated on a single semiconductor chip. Thus, encryption / decryption processing is carried out only in the CPU, and internal operations of the CPU are made non-analyzable from an external signal of the CPU.

Owner:HITACHI LTD

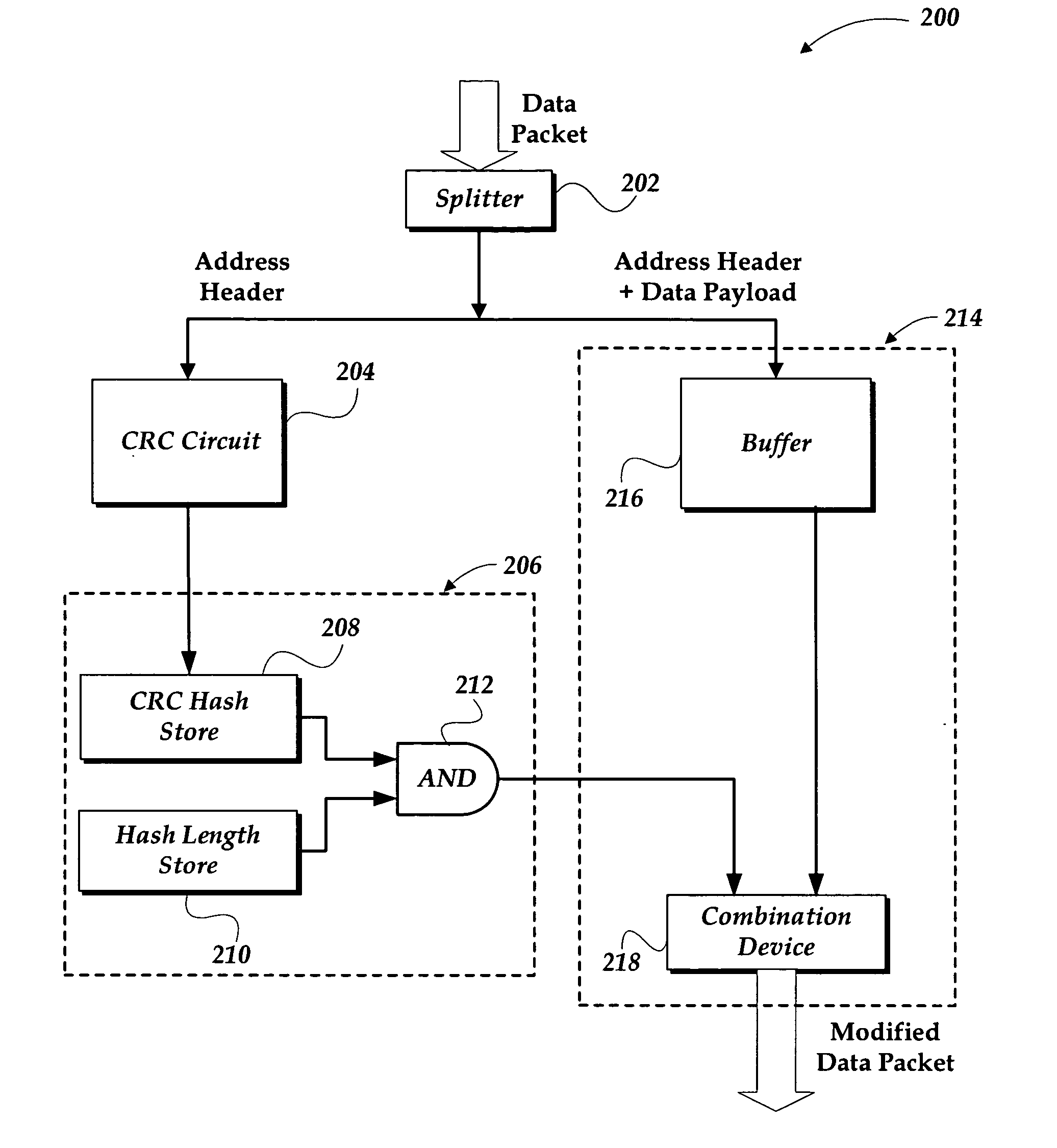

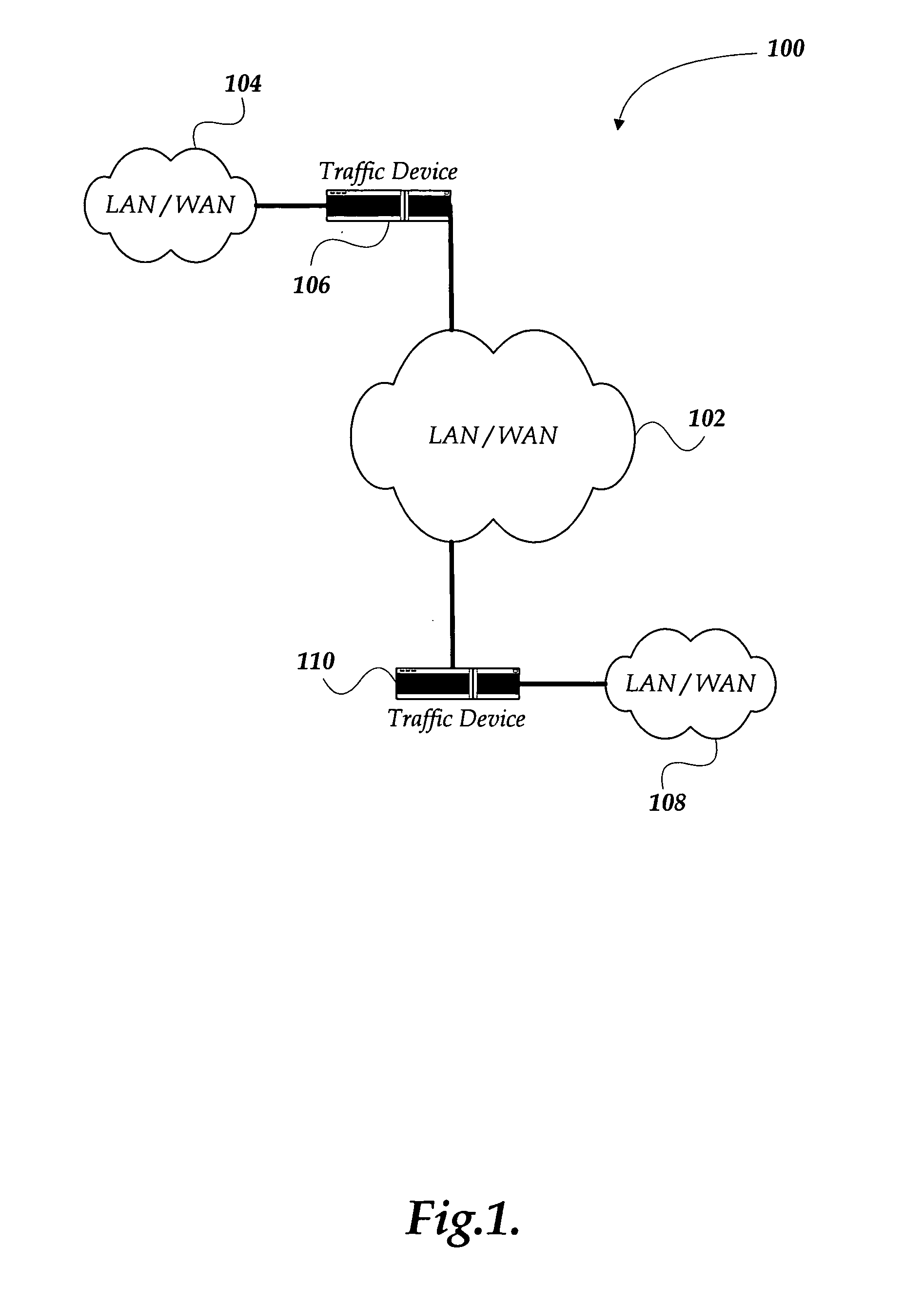

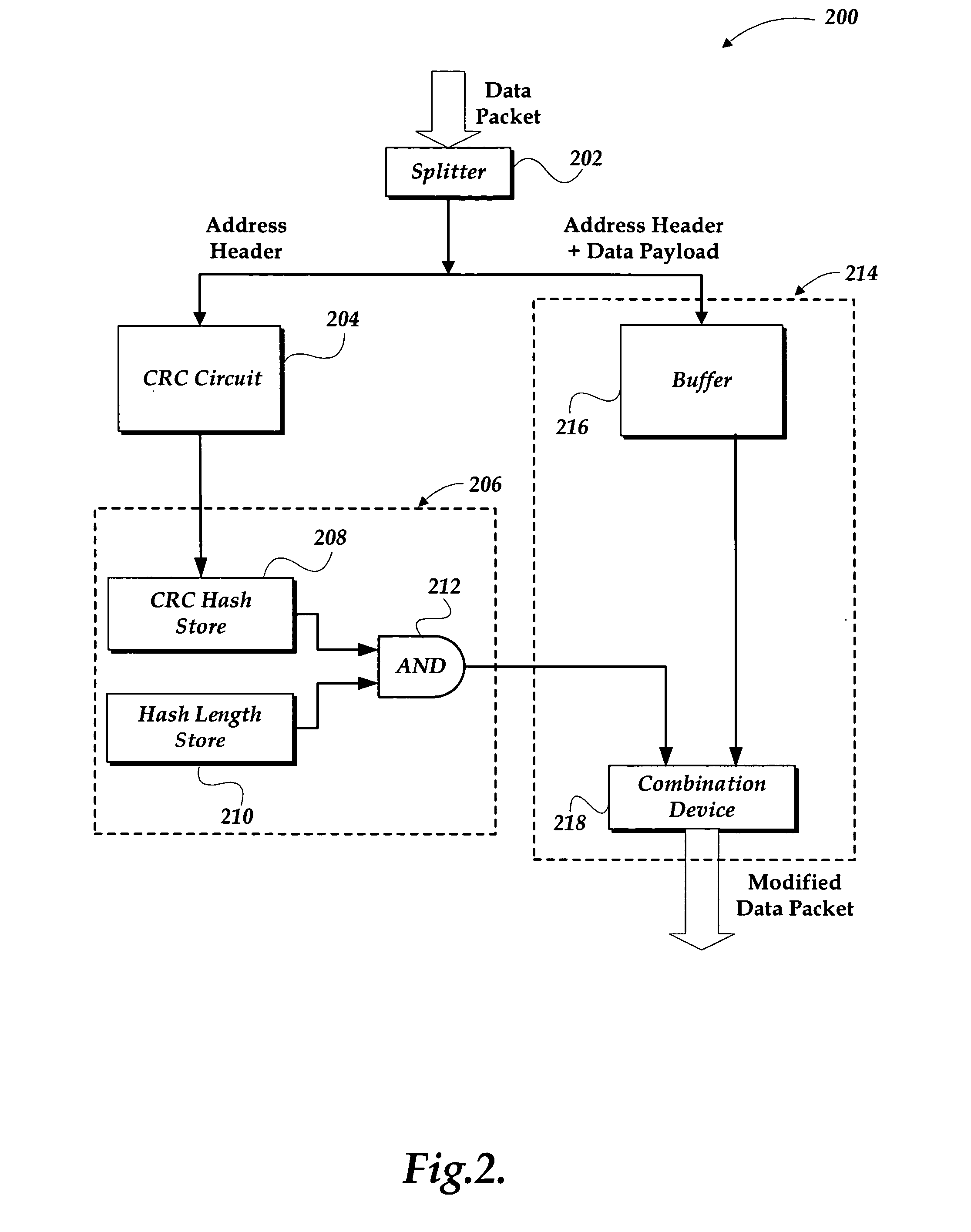

Method and apparatus for managing network traffic using cyclical redundancy check hash functions

Methods, apparatus and systems are directed to managing network traffic using a variable length Cyclical Redundancy Check (CRC) index to hash an address header. The invention copies an address header of a data packet to a CRC generator. A CRC index is determined based, in part, on the address header. A subset of bits is determined from the CRC index based, in part, on a predetermined bit mask. The address header and the data payload are then combined with the subset of bits from the CRC index. The modified data packet is subsequently forwarded over a network. In one embodiment, the invention is implemented on a hardware circuit residing on a traffic device.

Owner:NOKIA CORP

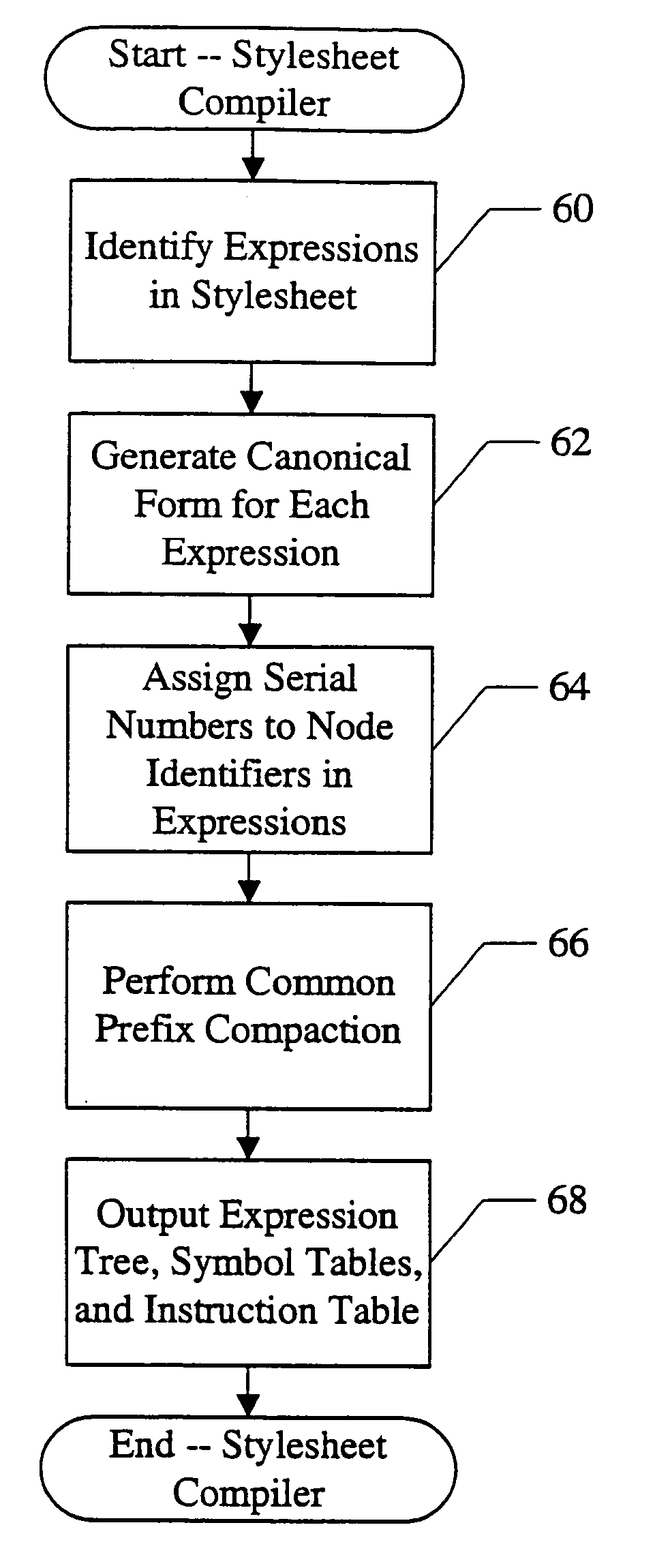

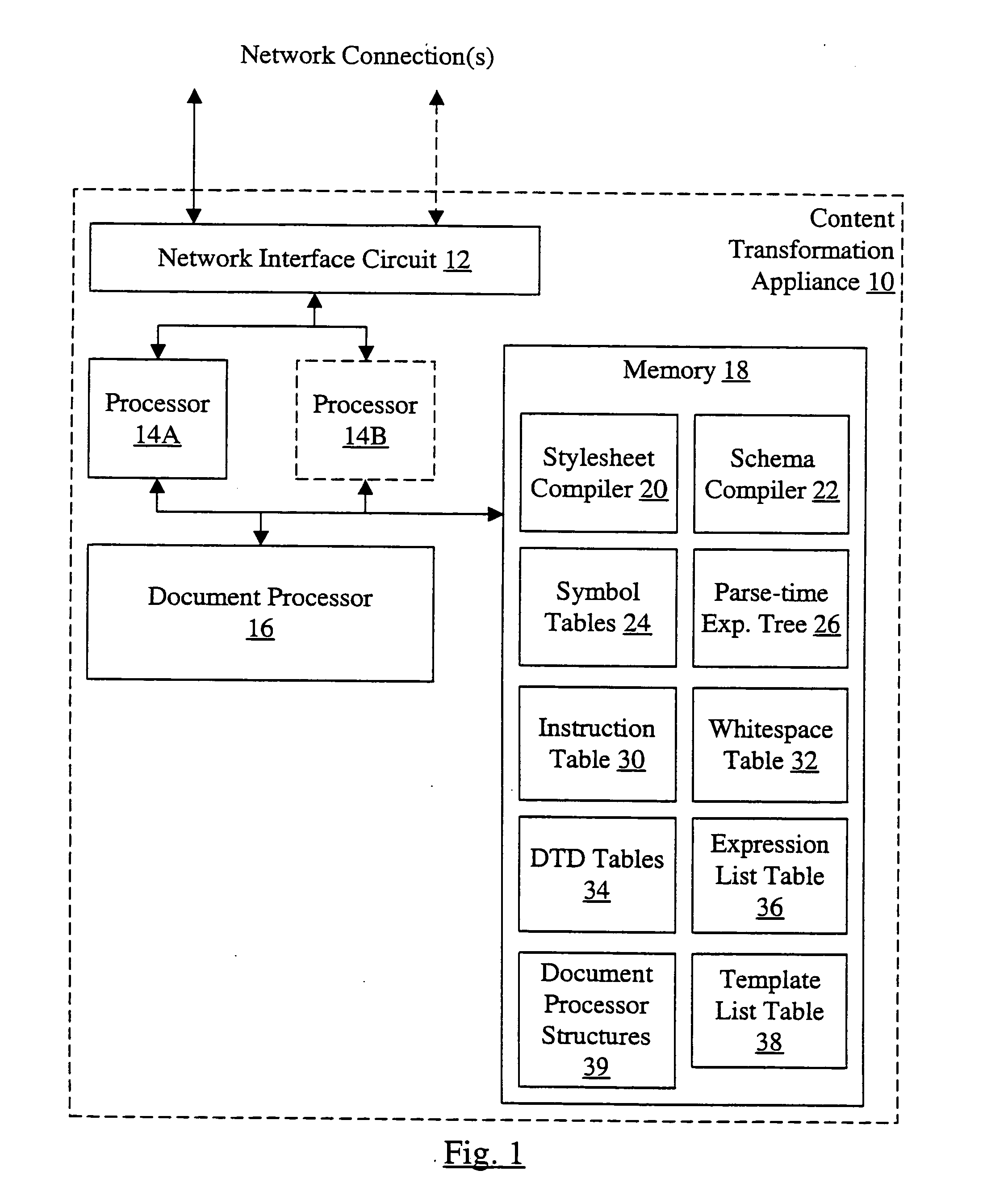

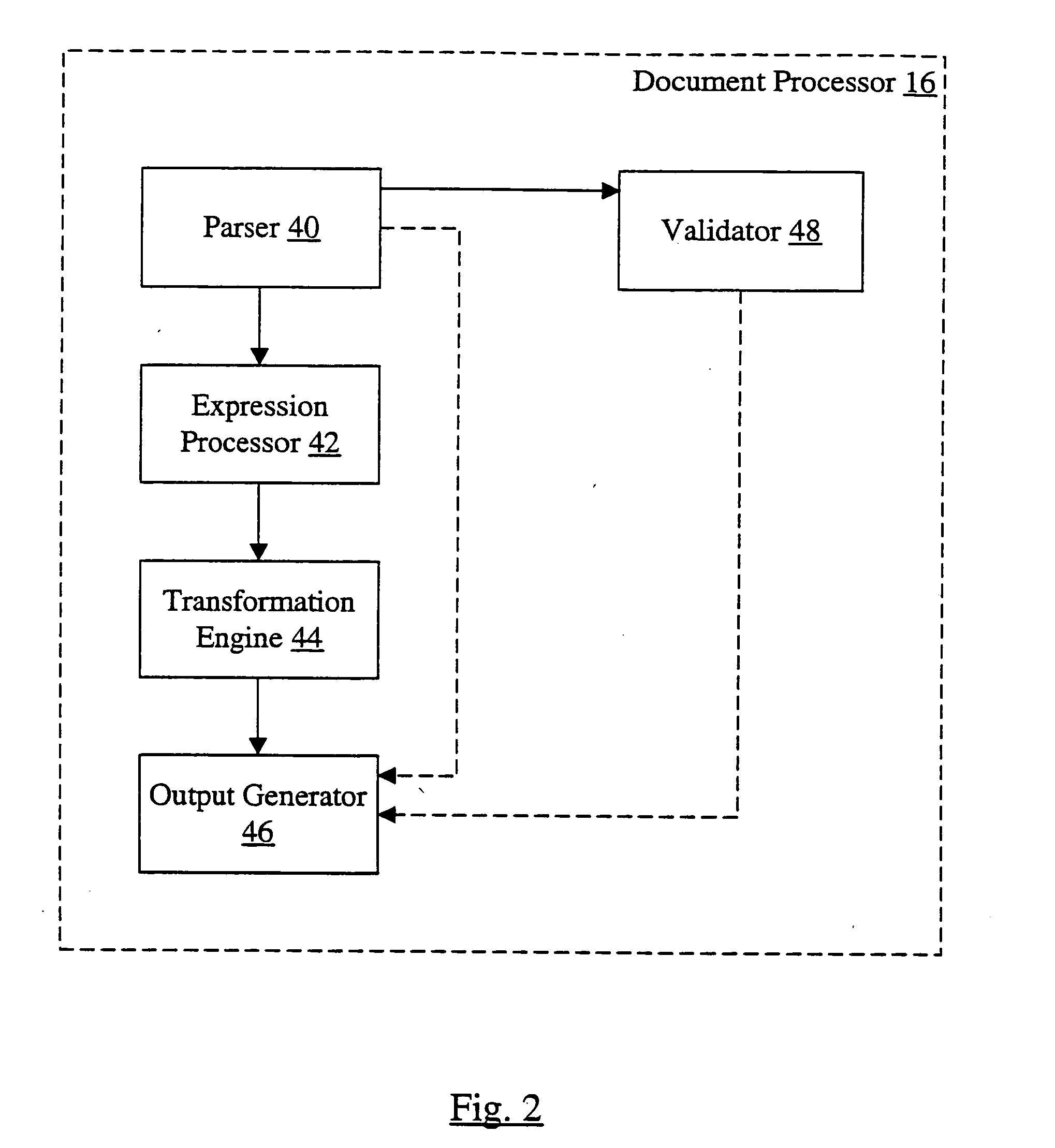

Hardware/software partition for high performance structured data transformation

ActiveUS20050091589A1Data processing applicationsNatural language data processingTheoretical computer scienceDocument preparation

Owner:INTEL CORP

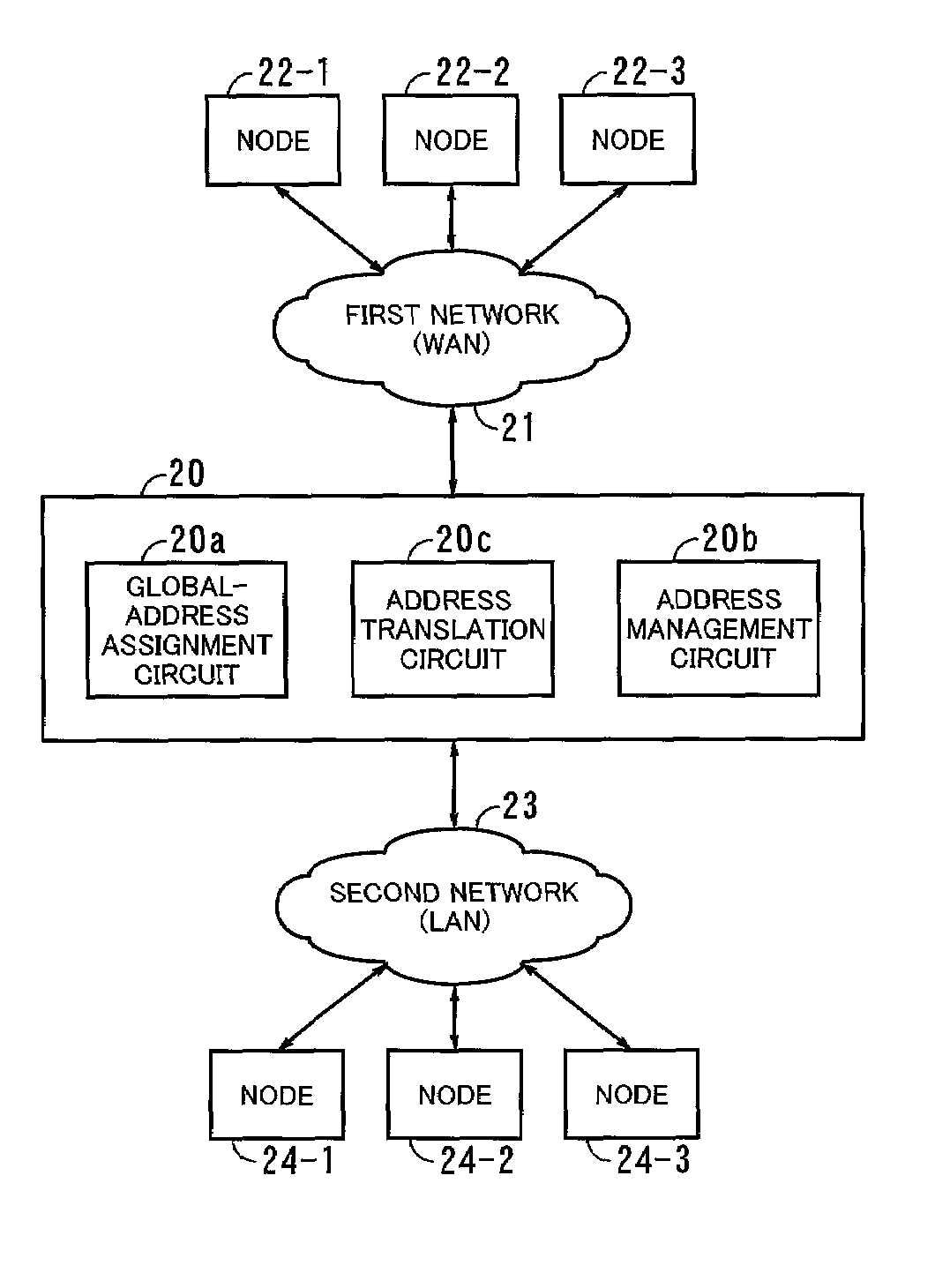

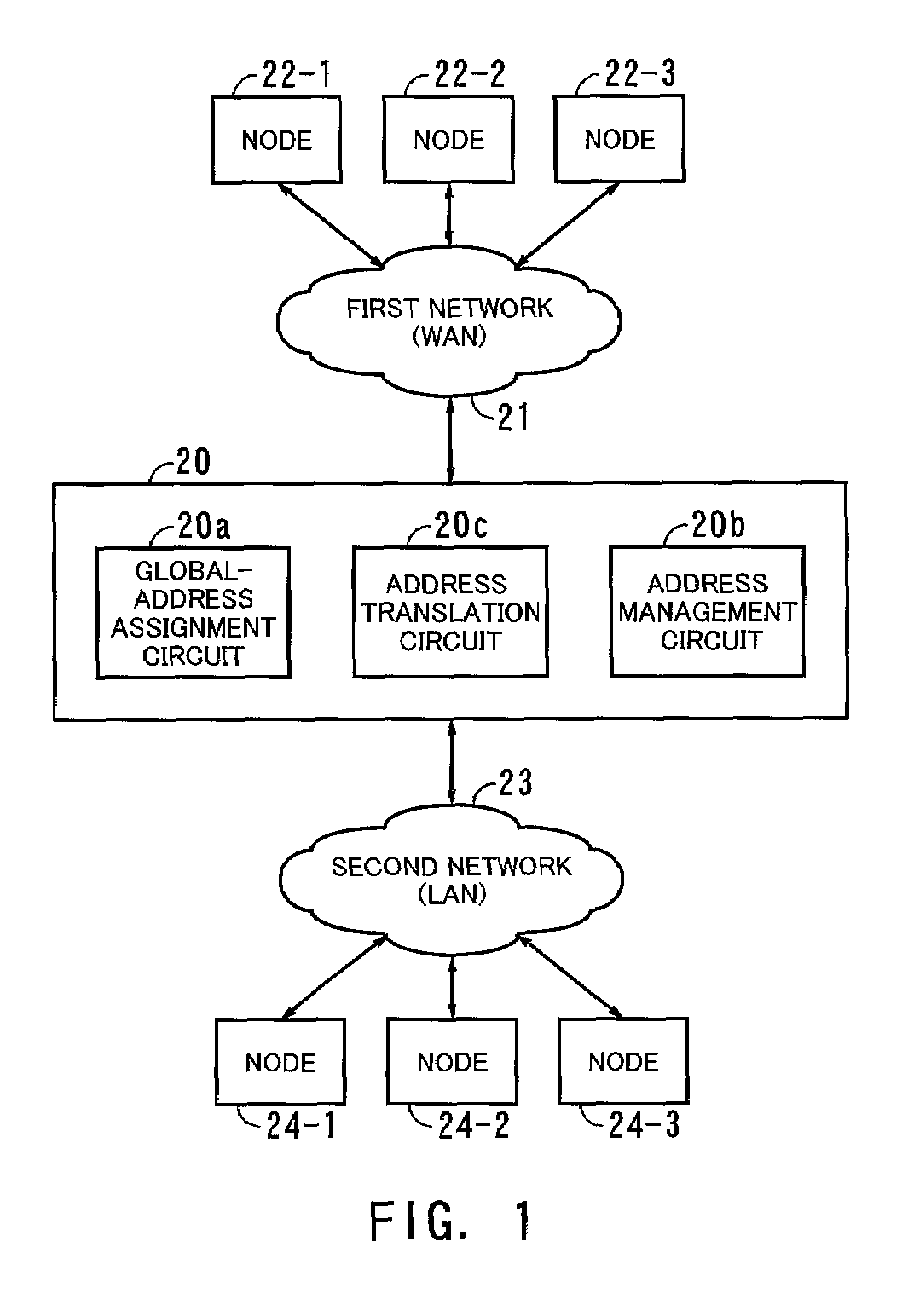

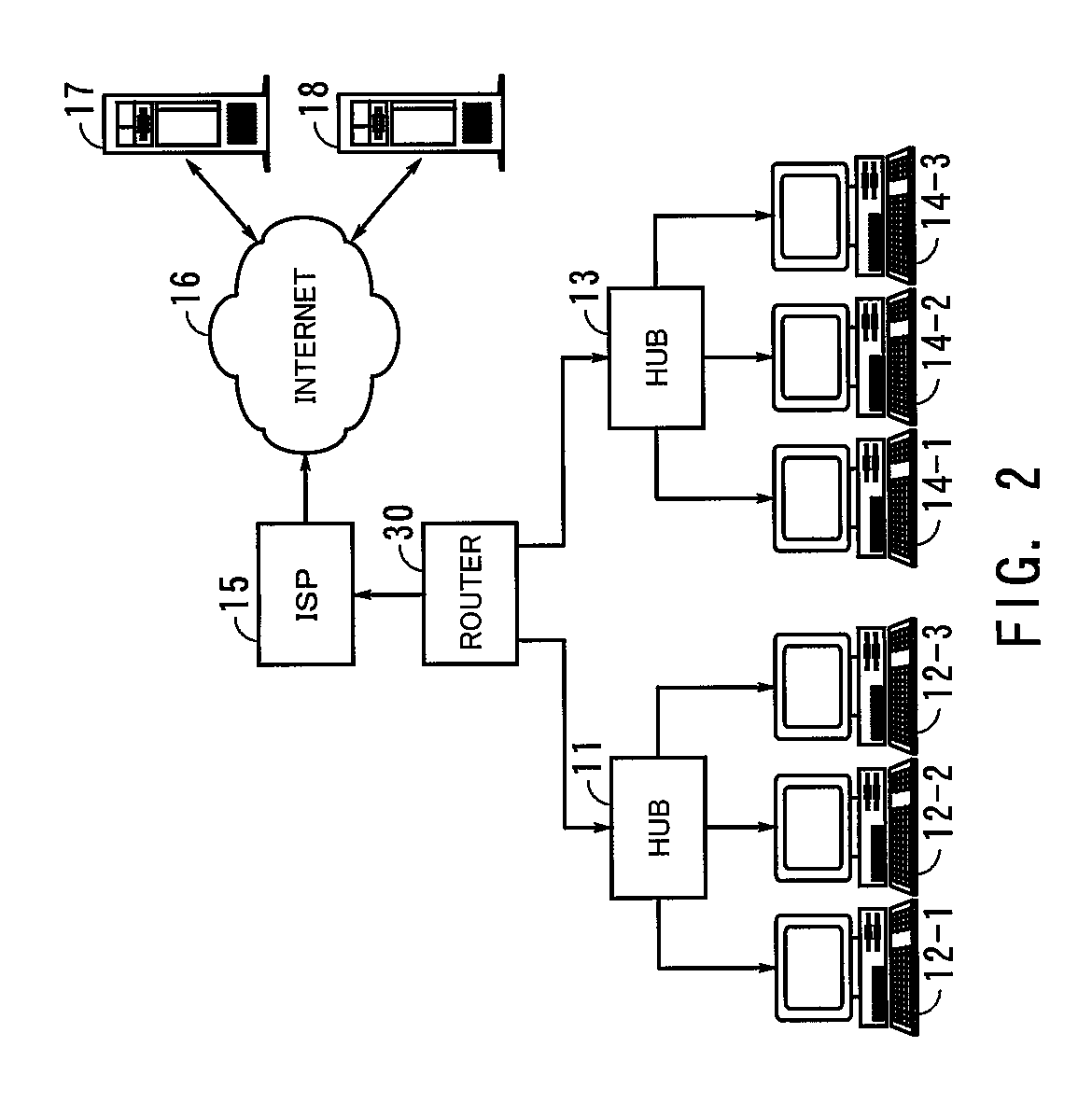

Packet transfer apparatus having network address translation circuit which enables high-speed address translation during packet reception processing

ActiveUS7197035B2Low costNo longer performedNetworks interconnectionElectric digital data processingPrivate networkNetwork addressing

In a packet transfer apparatus for transferring packets between first and second networks, a translated network address is assigned to a first node in the first network and having a first private network address when the first packet from the first node is transferred to a second node in the second network, and said translated network address is stored in an address management circuit associated with said first and second network addresses. Thereafter, address translation for realizing an NAT function is performed on subsequent packets transferred between the first and second nodes, by a dedicated hardware circuit and reference to the address management circuit, while performing processing for receiving the packets.

Owner:SOCIONEXT INC

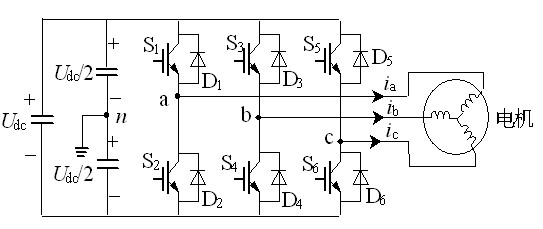

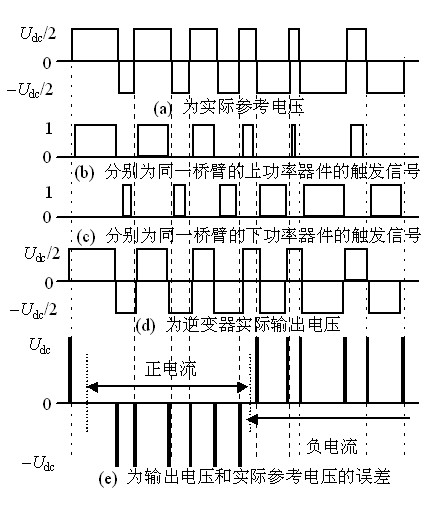

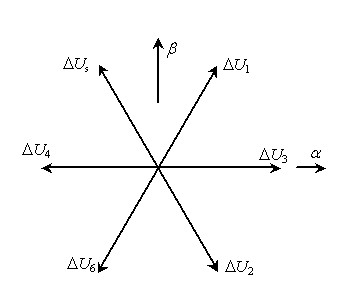

Novel dead-zone effect compensation method of AC servo inverter

InactiveCN102624276AEliminate clampingSmall pulsationElectronic commutation motor controlVector control systemsPower inverterHarmonic

The invention discloses a novel dead-zone effect compensation method of an AC servo inverter. The traditional method is not ideal enough to realize accurate dead-zone compensation, and thus a novel online compensation algorithm is provided aiming at the dead-zone effect of the inverter. The novel online compensation algorithm mainly comprises the four steps of: determining generation of a dead zone of the inverter; determining the relationship between the output voltage of the inverter and the actual reference voltage; determining an error voltage; and providing online compensation. The novel online compensation algorithm can save unnecessary power-on and power-off steps of a switching device, is free from any extra hardware circuit and off-line experiment measurement, has the characteristics of simpleness in implementation, low output waveform harmonic content and the like, well solves the output current pulse of a system at low frequency and effectively eliminates the zero-current clamping phenomenon.

Owner:HANGZHOU DIANZI UNIV

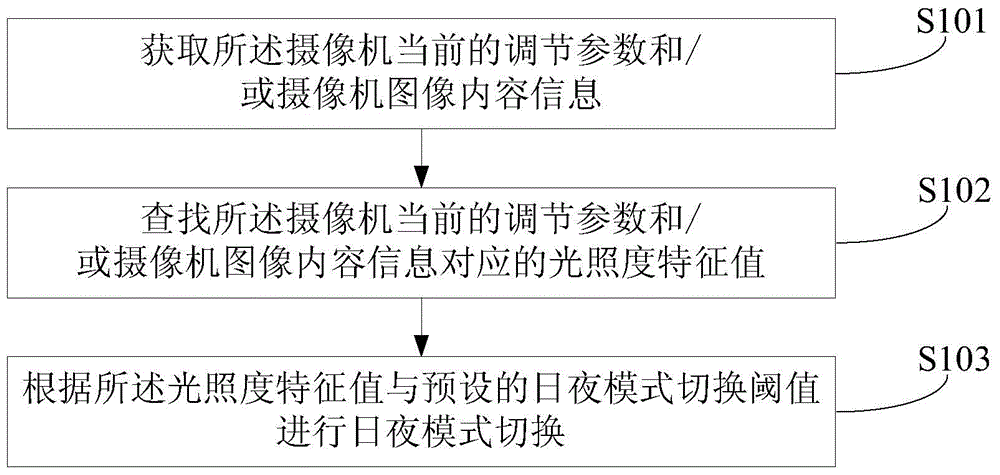

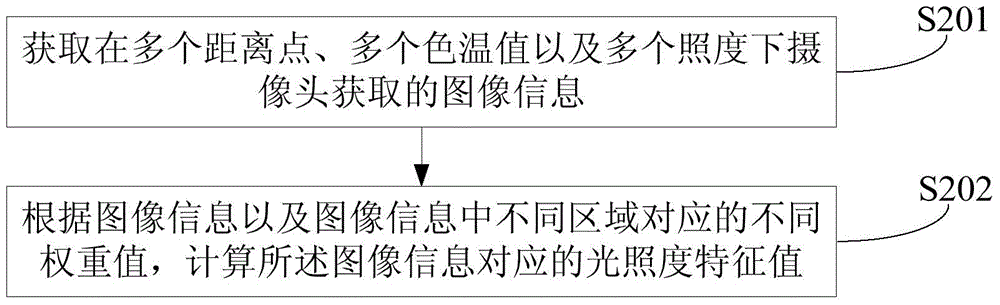

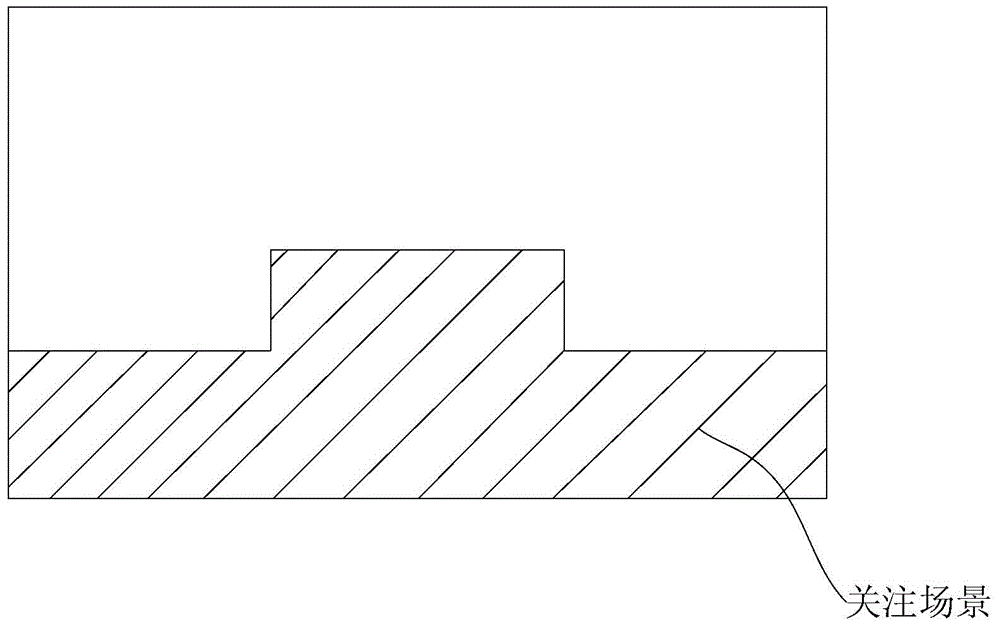

Method and device for switching day and night modes of camera

ActiveCN104580896AOvercoming the inconvenient installation of photosensitive sensorsLow costTelevision system detailsColor television detailsIlluminanceComputer science

The invention is applicable to the field of security and protection, and provides a method and a device for switching day and night modes of a camera. The method comprises steps as follows: acquiring current adjustment parameters of the camera and / or image content information of the camera; finding an illuminance characteristic value corresponding to the current adjustment parameters of the camera and / or the image content information of the camera; switching the day and night modes according to the illuminance characteristic value and a preset day-and-night-mode switching threshold. According to the method and the device, the day and night modes are switched through software monitoring, so that problems that the day and night modes are required to be switched by the aid of hardware circuits and photosensitive components and photosensitive sensors are inconvenient to mount in the prior art are solved, the cost is reduced, no photosensitive sensor is required to be arranged on the camera, and the consistency of product structures is improved.

Owner:SHENZHEN STREAMING VIDEO TECH

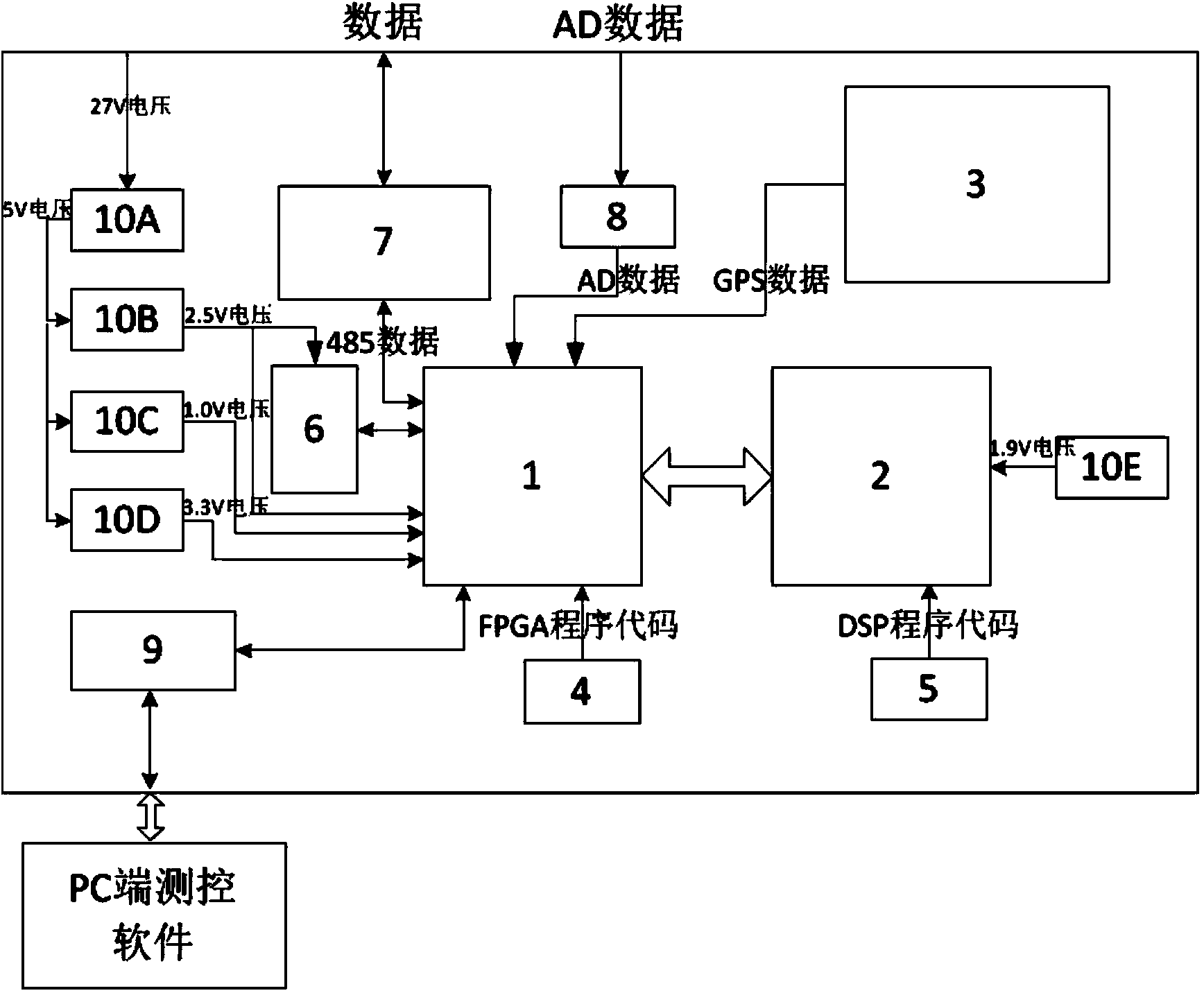

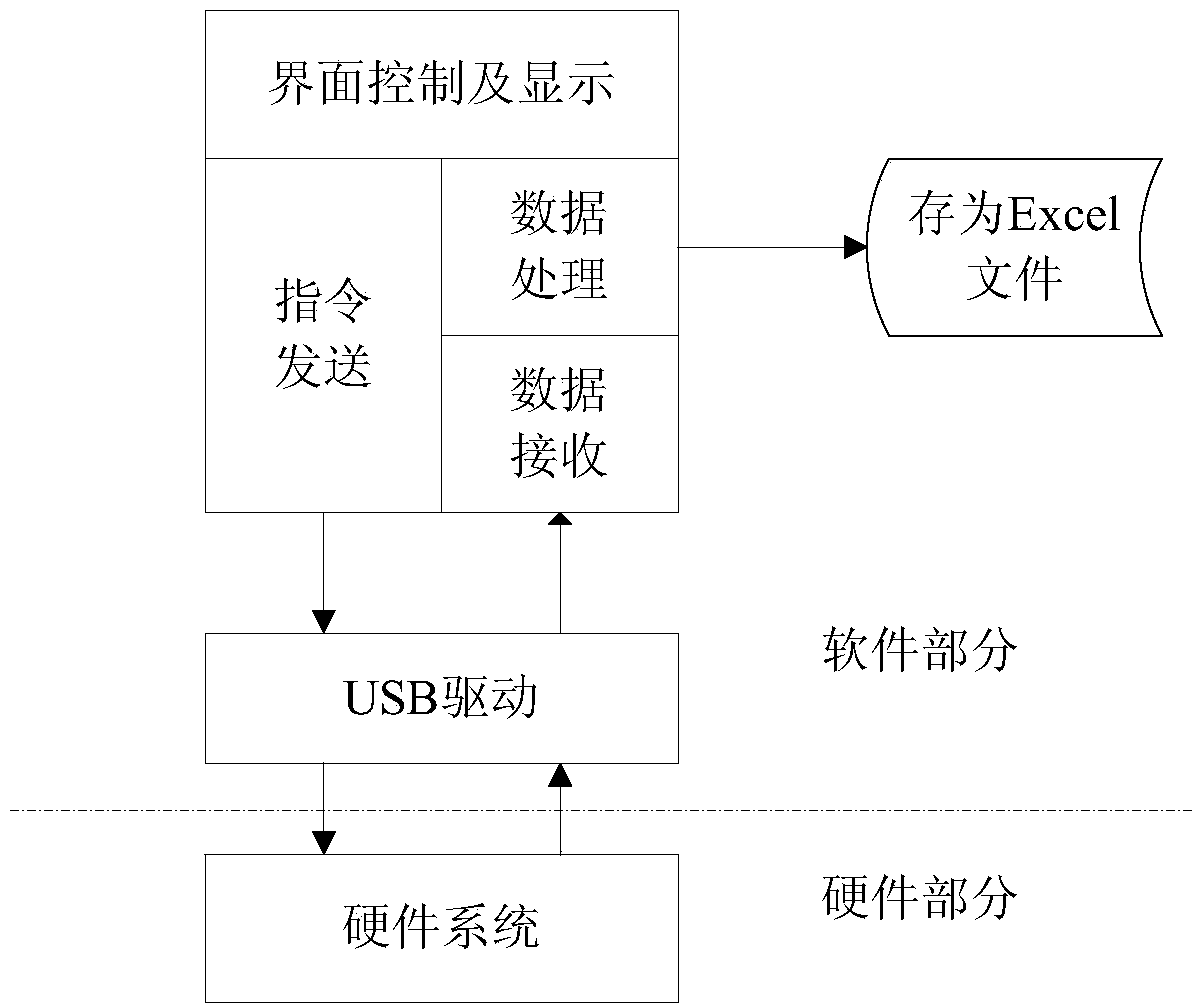

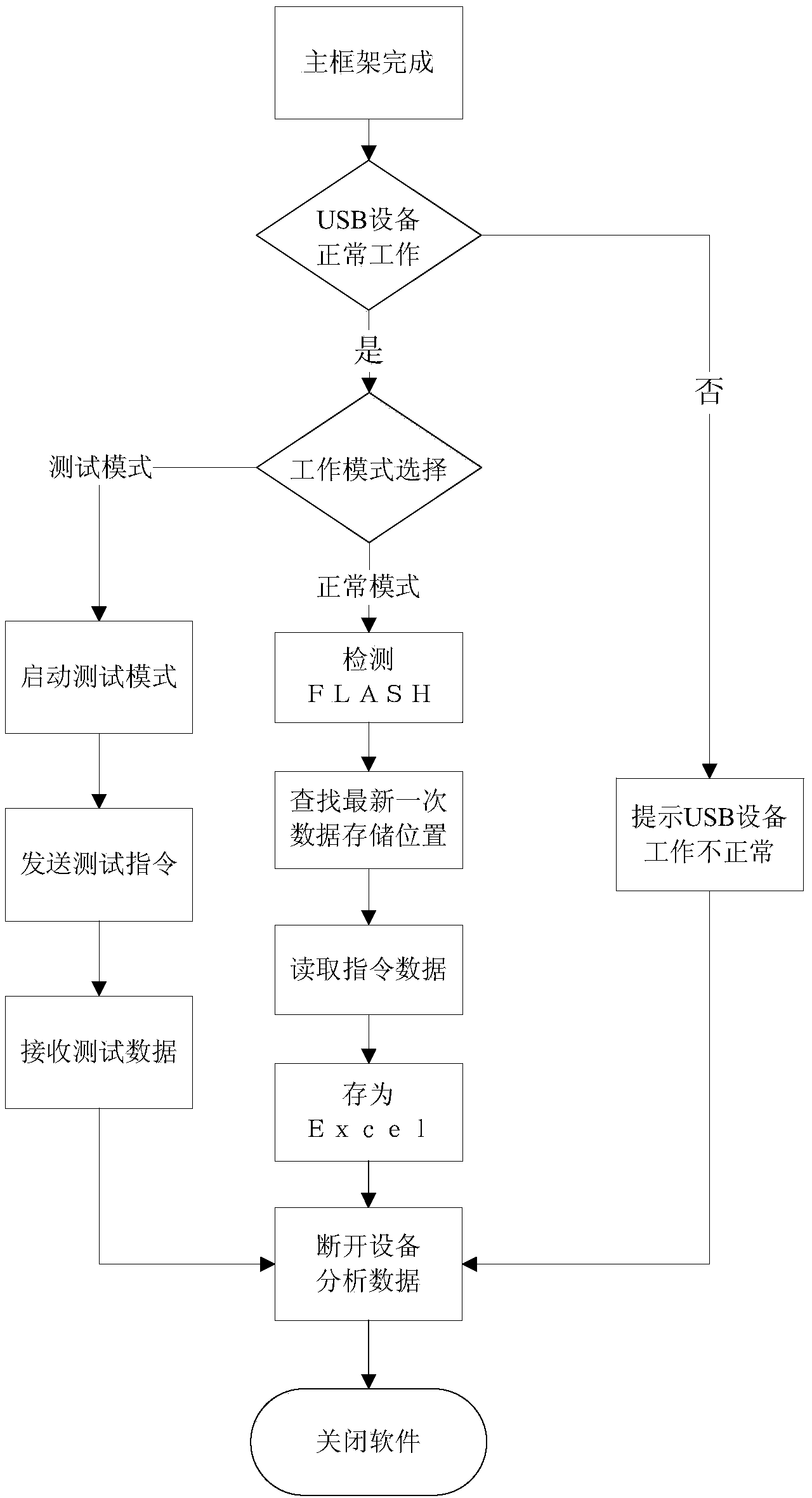

High-speed data recording system based on FPGA+DSP framework and establishment method thereof

ActiveCN103678728AReduce volumeHigh-speed real-time data recordingData acquisition and loggingDsp architectureData acquisition

The invention discloses a high-speed data recording system based on an FPGA+DSP framework. The high-speed data recording system based on the FPGA+DSP framework comprises PC end measurement and control software, an FPGA core control chip, a DSP core control chip, a power supply chip, an FLASH memory chip, a USB communication chip, an HDLC protocol communication chip, an AD chip and a GPS communication daughter board, wherein the FPGA core control chip controls a USB module for PC communication during data uploading, a cache module during communication between the FPGA core control chip and the DSP core control chip, a reading and writing module of the FLASH memory chip, a control module of the GPS communication daughter board and a data sending and receiving module of the HDLC protocol communication chip, the DSP core control chip controls system self-detection in a data transmission and recording mode, an analog quantity data acquisition module and a communication module of the FPGA core control chip, and the power supply chip is connected with all the chips and is used for providing voltage needed by working of the whole system. An establishment method of the high-speed data recording system based on the FPGA+DSP framework comprises five main steps. The high-speed data recording system based on the FPGA+DSP framework has the advantages that a hardware circuit is simple, the size is small, and data can be recorded in real time at a high speed. The high-speed data recording system based on the FPGA+DSP framework can be applied to various systems conveniently.

Owner:杭州雷世科技有限公司

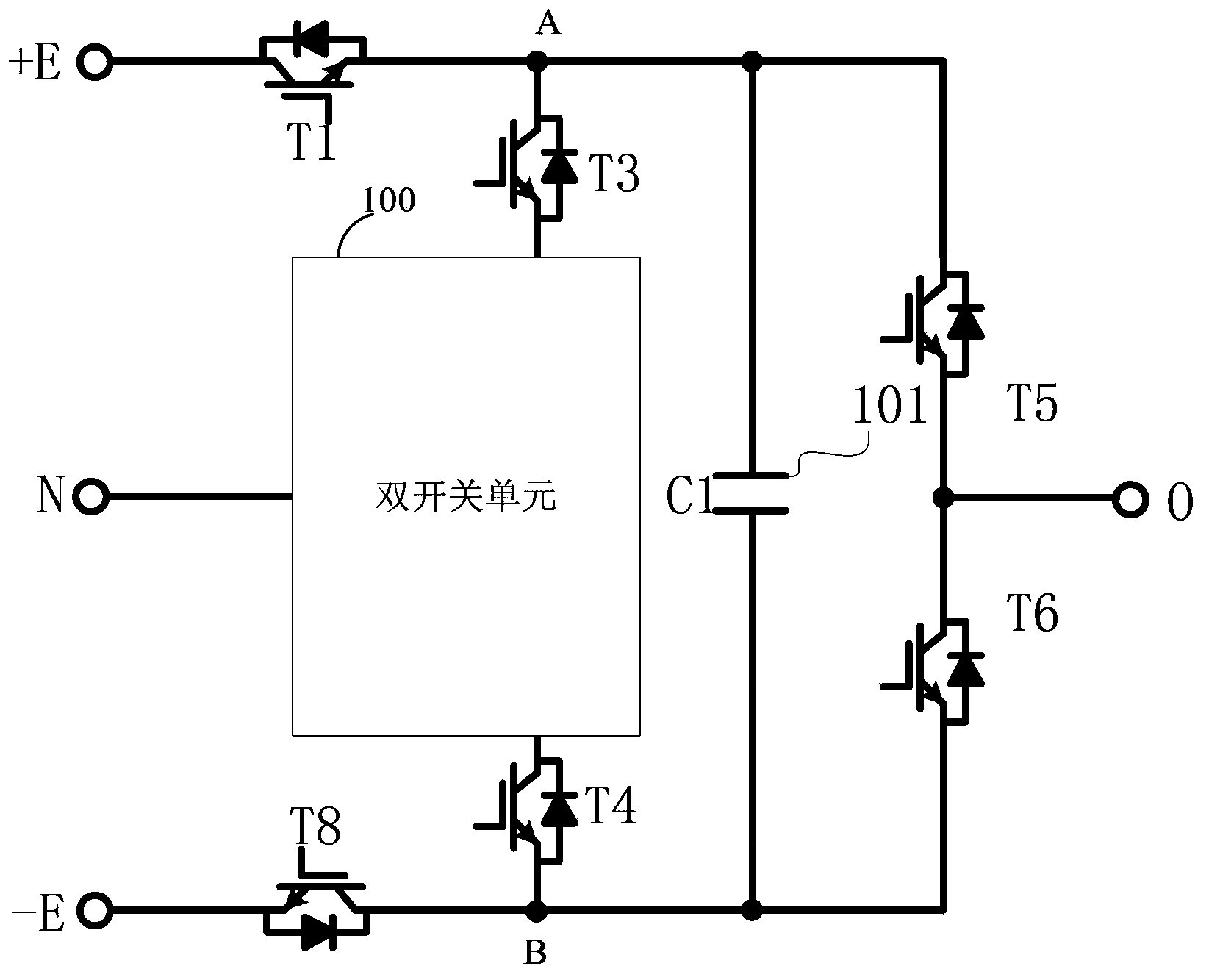

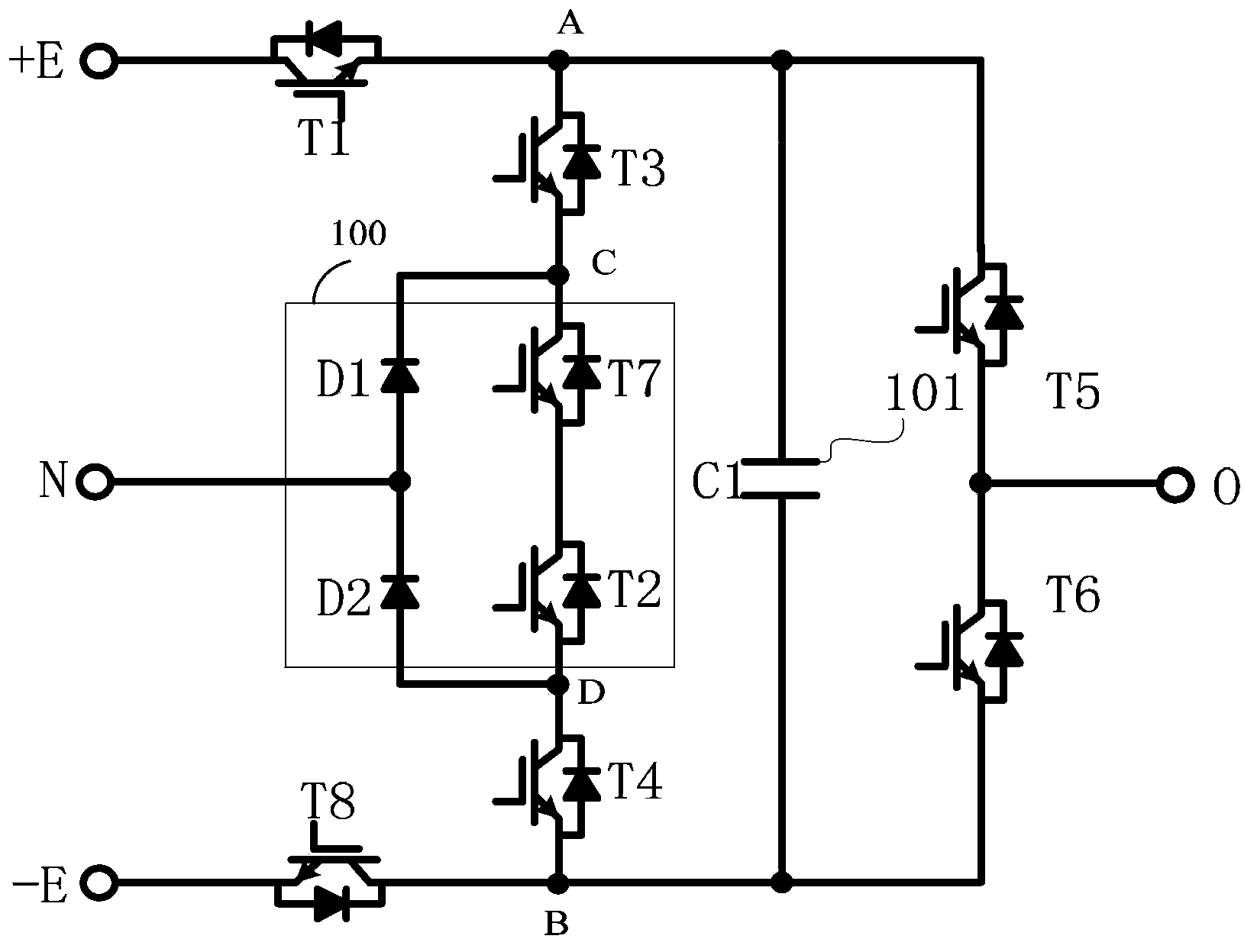

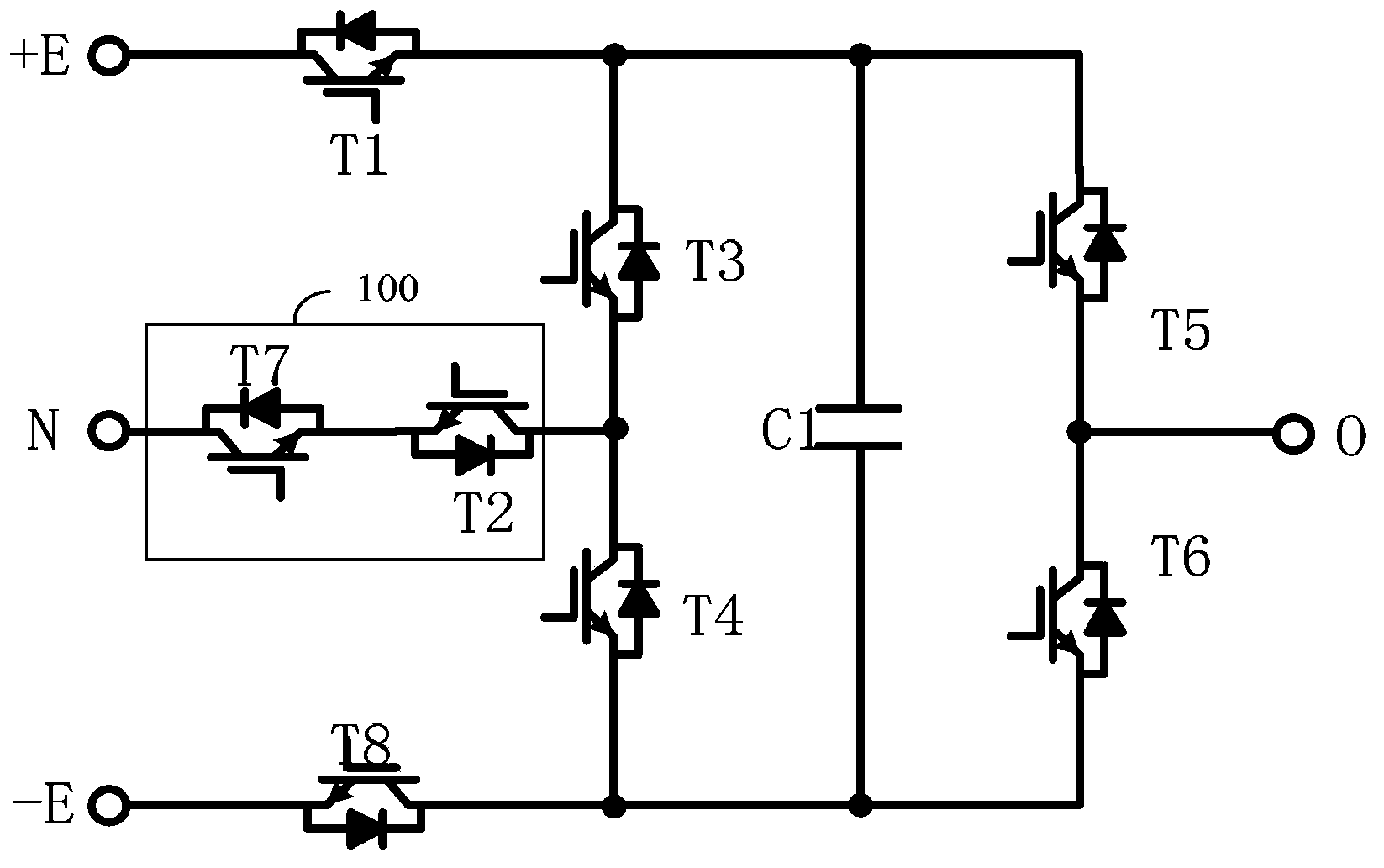

Single-phase five-level topology and inverter

ActiveCN104218832AReduce current harmonic contentReduce hardware costsAc-dc conversionThree levelPower inverter

The invention provides a single-phase five-level topology and an inverter. The single-phase five-level topology comprises a first capacitor, a three-level bridge arm module and four switching tubes, wherein the four switching tubes refer to a first switching tube, a fifth switching tube, a sixth switching tube and an eighth switching tube respectively; each switching tube is reversely connected in parallel with a diode; the three-level bridge arm module comprises two switching tubes and a double-switch unit; the first end of a third switching tube is connected with a first node, and the second end of the third switching tube is connected with a neutral point N through the double-switch unit; and the first end of a fourth switching tube is connected with N through the double-switch unit, and the second end of the fourth switching tube is connected with a second node. Five level states are output, the current harmonic content of a system is reduced, the filter inductance is reduced, the voltage level is raised, the common-mode voltage is restrained, and the running efficiency is increased. Balanced control of capacitor voltage under full power and full modulation can be realized without adding an additional hardware circuit, and the phase output voltage of the system is prevented from degrading from five levels to three levels.

Owner:SUNGROW POWER SUPPLY CO LTD

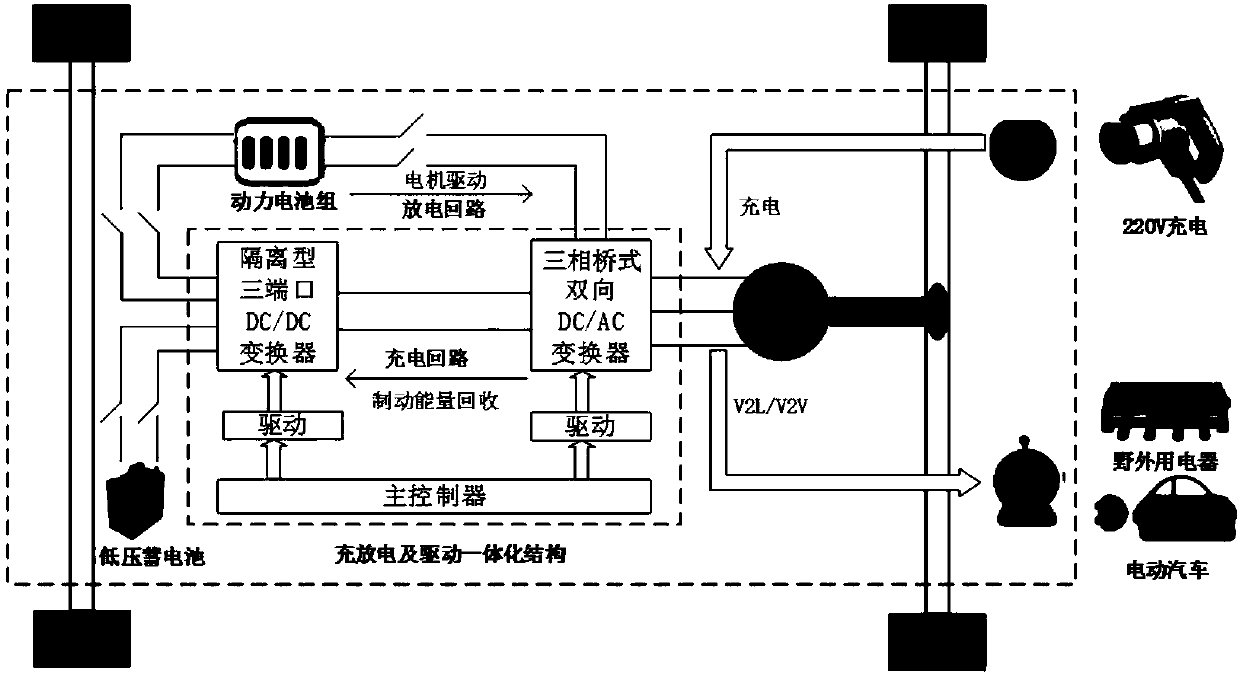

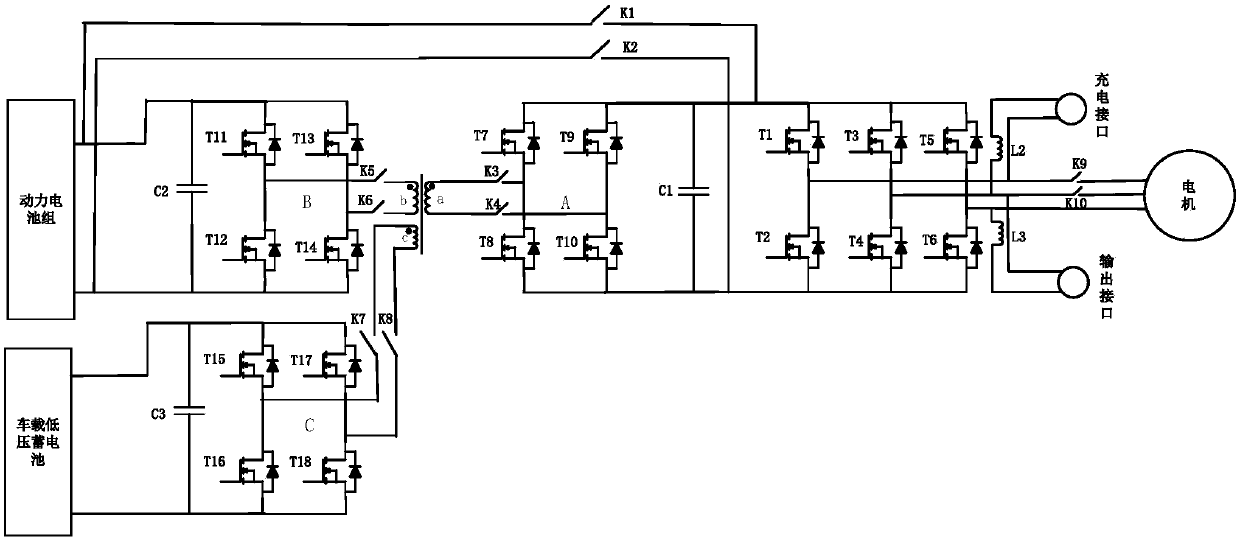

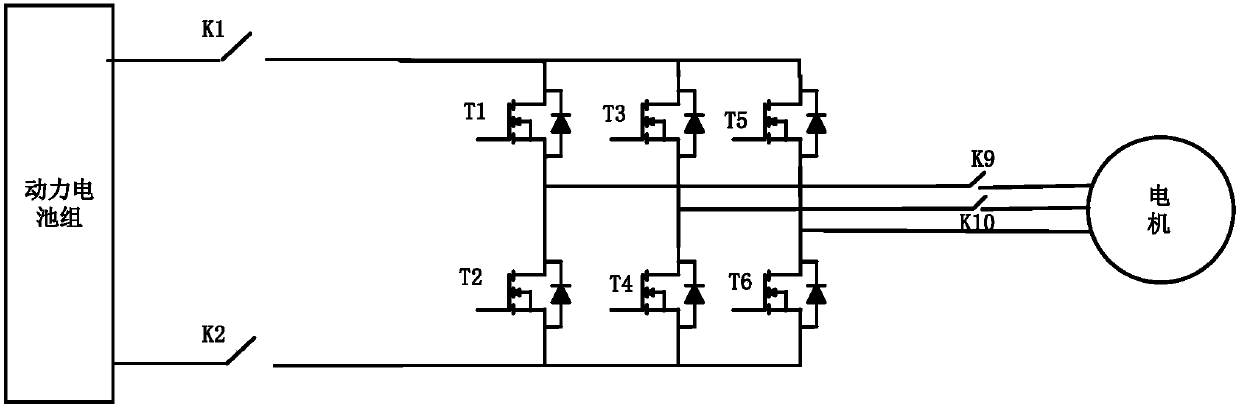

Electric vehicle charging and discharging and motor driving integrated device

ActiveCN107627881AIncrease effective energyImprove work efficiencySpeed controllerElectric machinesLow voltageCharge discharge

The invention discloses an electric vehicle charging and discharging and motor driving integrated device. The device comprises a three-phase bridge type two-way DC / AC converter, an isolated three-portDC / DC converter, a main controller, an integrated device operating mode switching device, a single-phase alternating-current power source input interface device and a single-phase alternating-currentoutput interface. A three-phase inverter for driving a motor in an electric vehicle driving system is subjected to topological reconstruction to form a single-phase rectifier in charging or a single-phase inverter in outward power supplying, so that an integral hardware circuit structure is formed. The three-phase bridge type two-way DC / AC converter, the isolated three-port DC / DC converter, a relay switch and corresponding driving modules are subjected to control switching according to an integral control method in the main controller, so that seamless switching of charging-discharging and driving modes is realized, and braking energy recovery, V2V / V2L and vehicular low-voltage storage battery charging functions are realized. The integrated device has advantages of optimized size, weightreduction, cost saving and reliability improvement.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

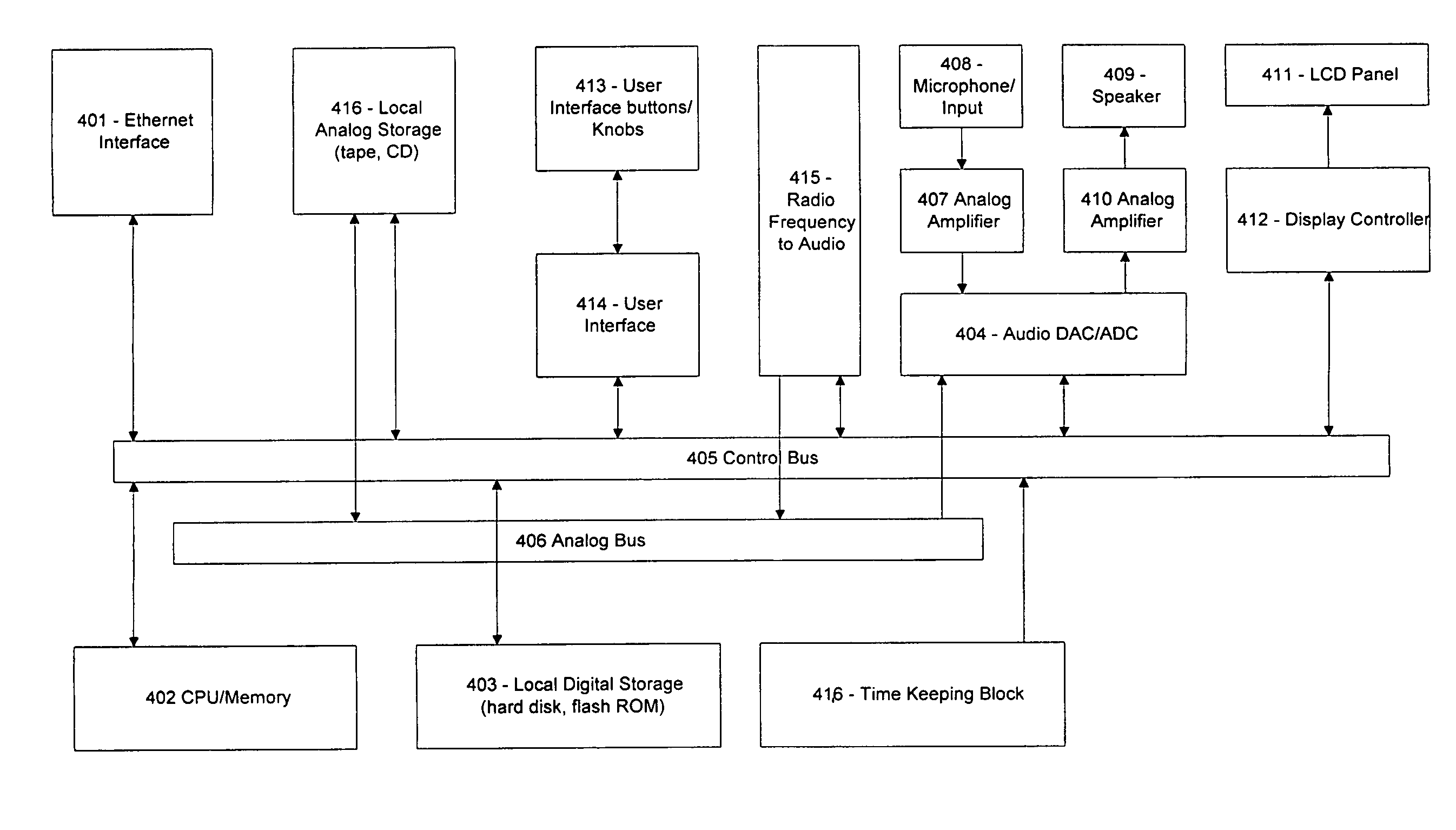

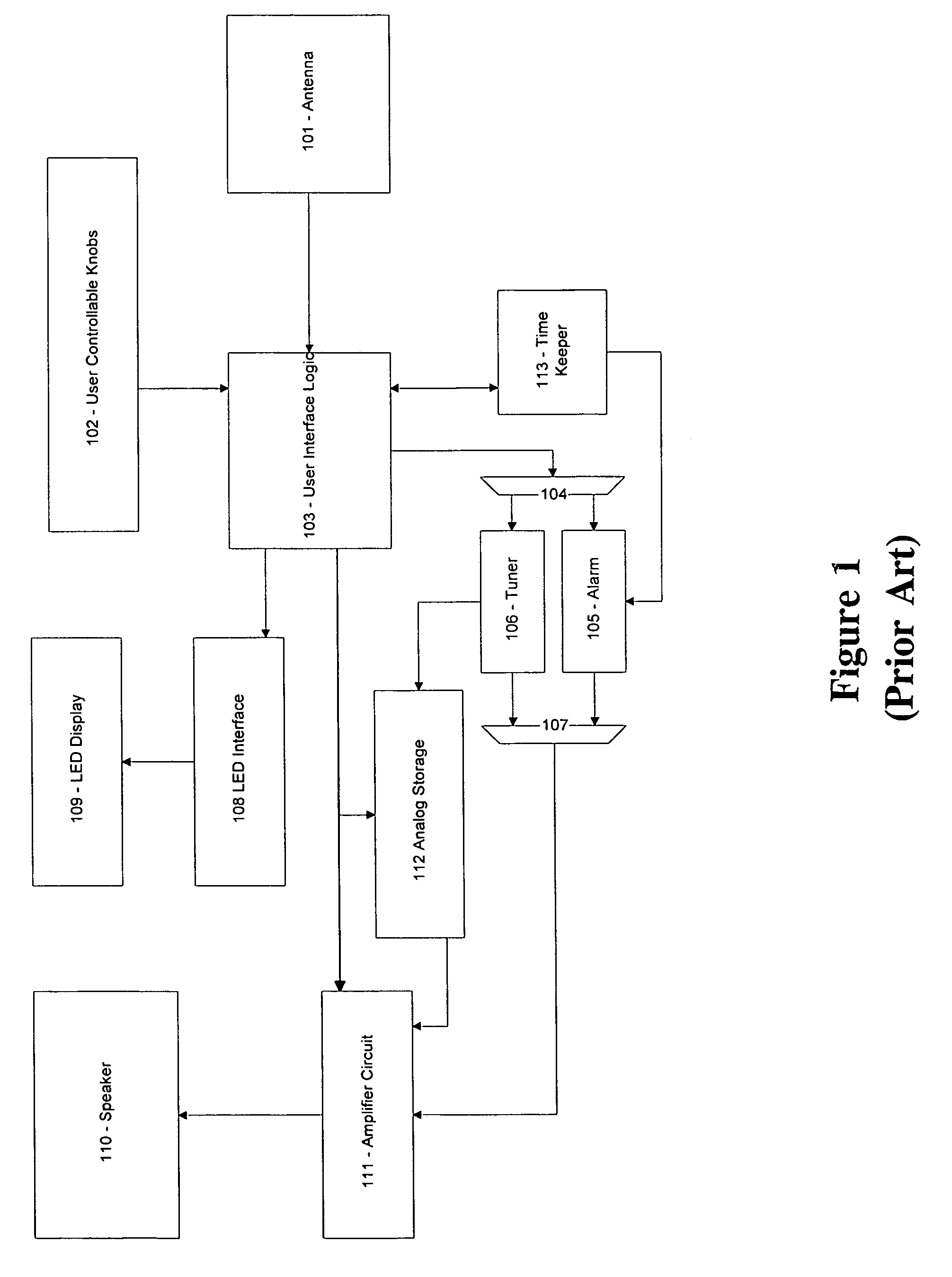

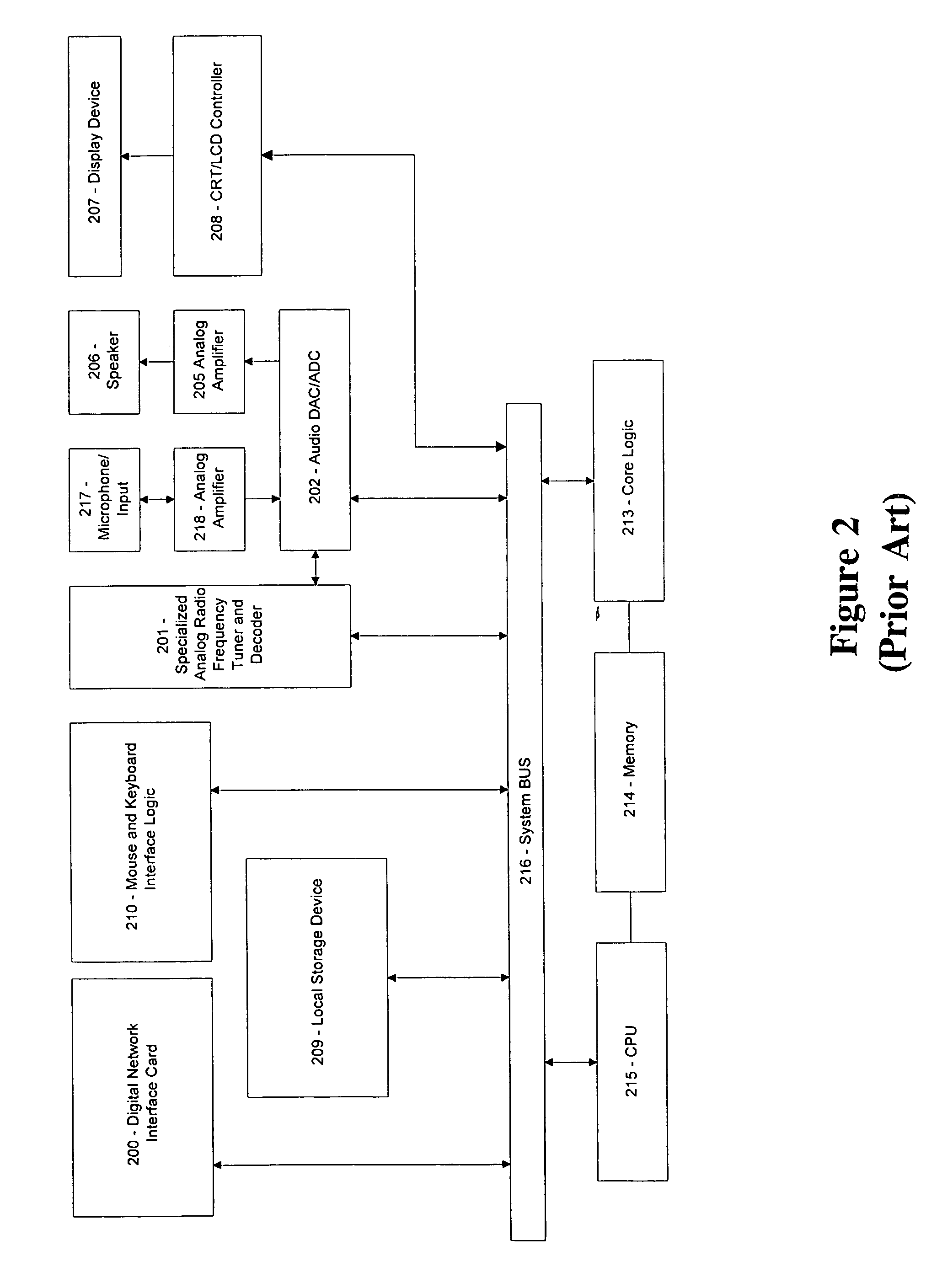

Substantially integrated digital network and broadcast radio method and apparatus

InactiveUS7079807B1Sufficient informationBroadcast-related systemsBroadcast receiving circuitsOutput deviceAnalog-to-digital converter

A multimedia system which substantially integrates analog functions normally found in consumer radios (radio frequency tuner functions, volume functions), and information streams from a digital network in a single design. The system may include an Ethernet interface, central processing unit, memory, local storage device, analog to digital converter, digital to analog converter, audio output speakers, microphone, display controller, liquid crystal display panel, user interface logic, controls for tuning streams, analog and digital radio frequency tuner, and an analog storage device. The system may generate analog signals for audible reproduction. The source of audio signals may be configured in real time by the user. The hardware implementation allows for selection of broadcast radio or digital network streams such that hardware signals indicating which broadcast radio or digital stream to play from are fed to a hardware circuit which determines which stream is sent to an audio output device.

Owner:RADIO INTEGRATION SYST LLC

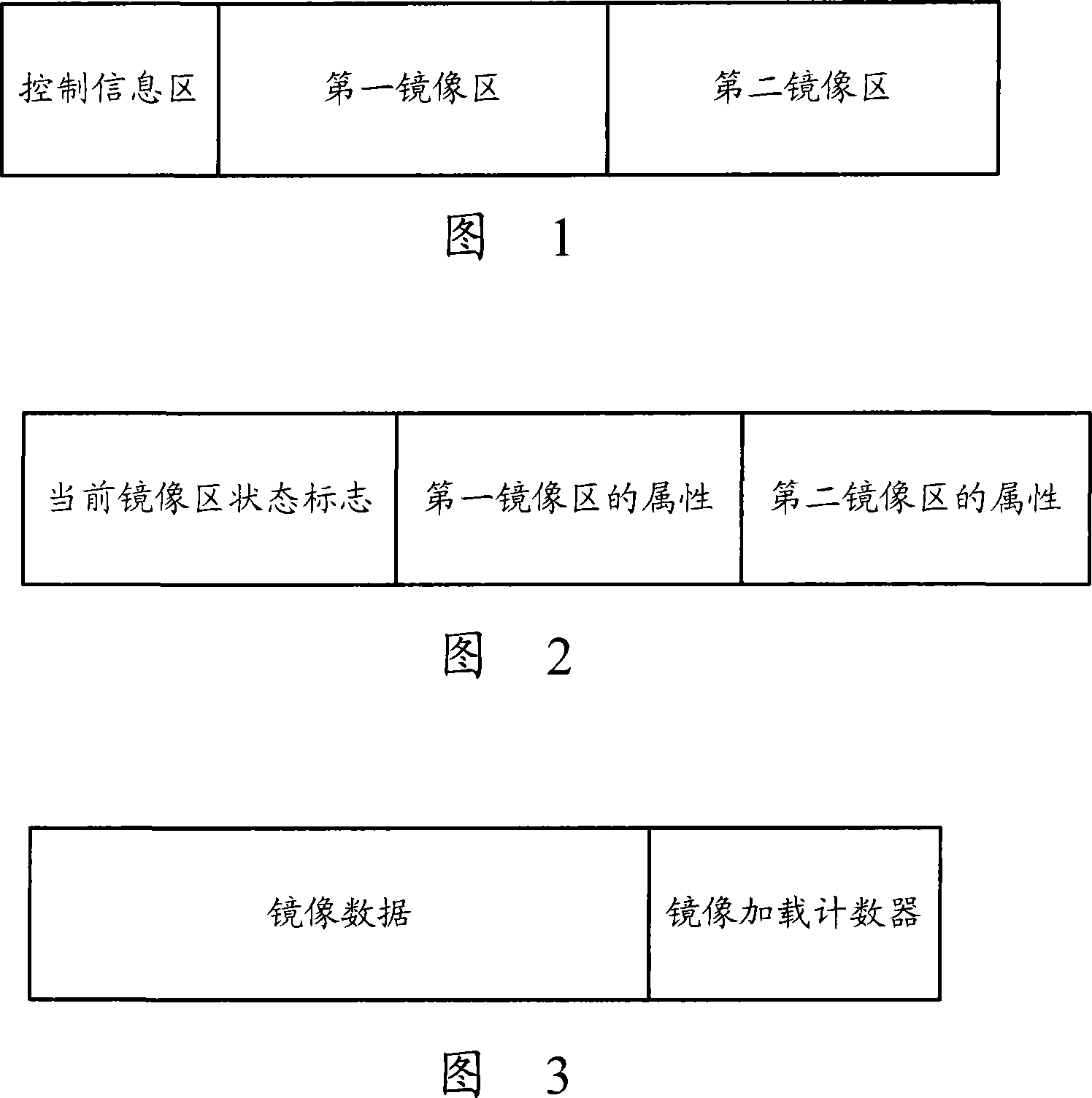

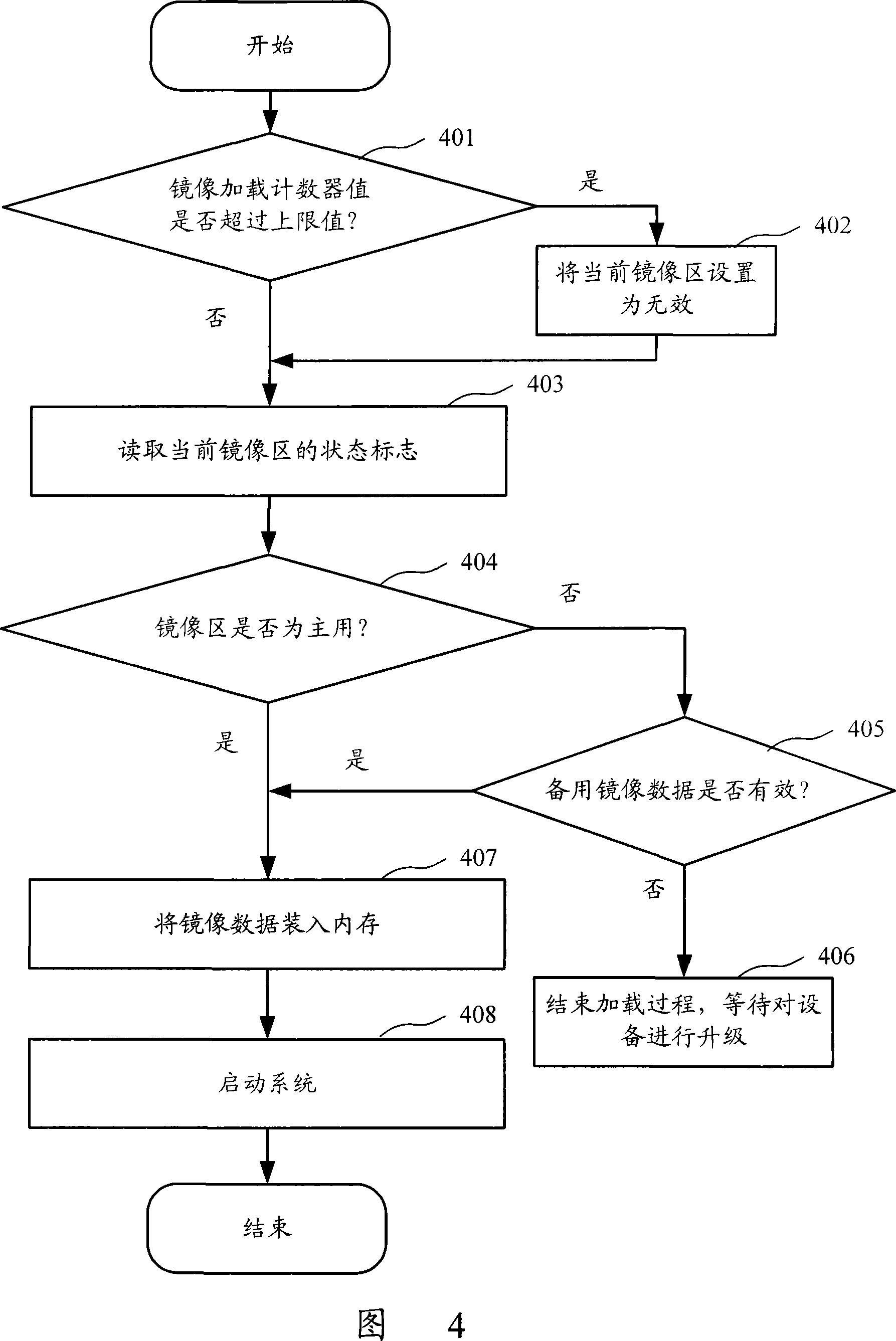

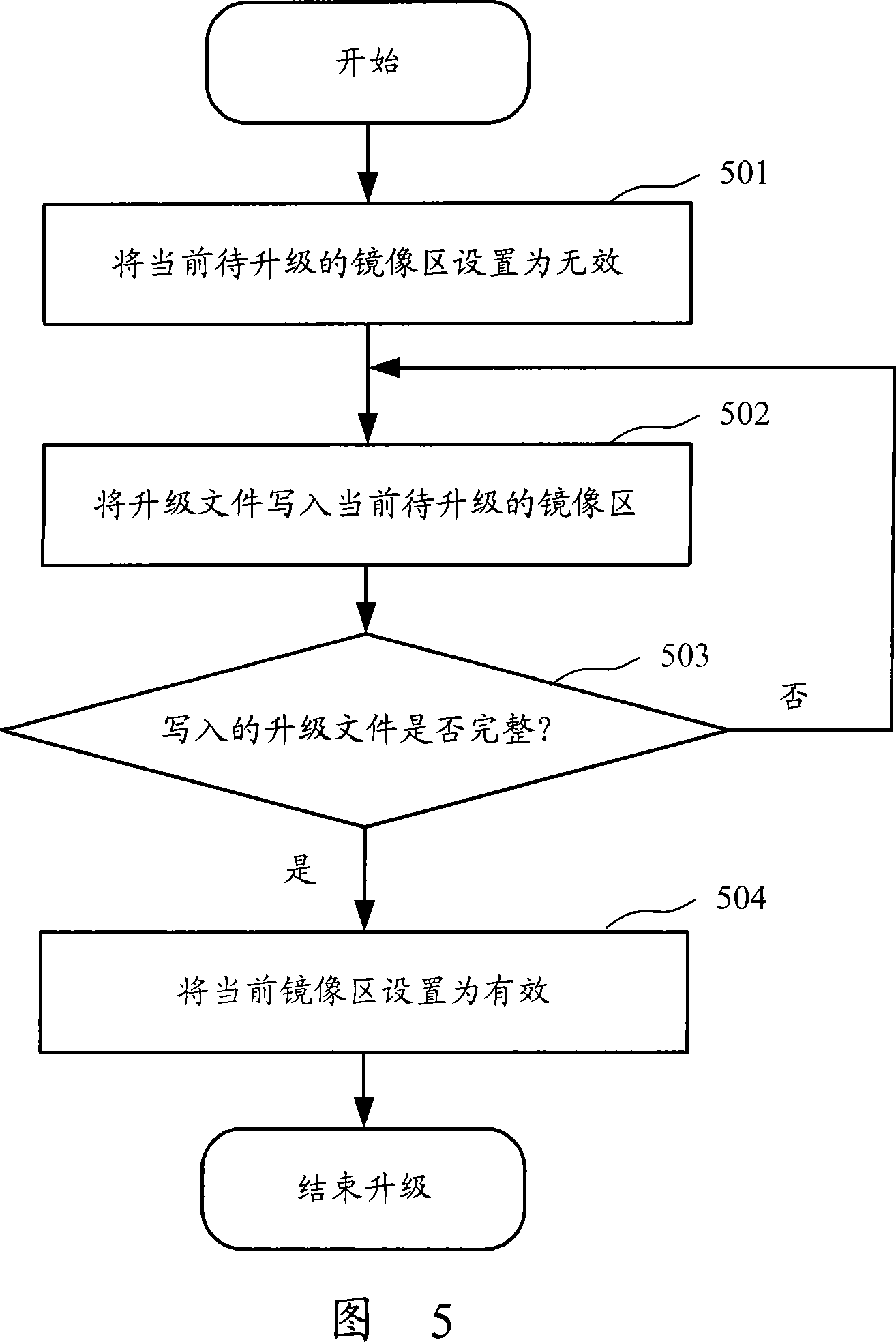

Embedded equipment startup method and software upgrading method

InactiveCN101216772ASimplify complexityLow costProgram loading/initiatingSingle chipSoftware upgrade

The invention discloses a start-up method and a software upgrade method for an embedded device. The method comprises the following steps of: dividing logically the memory space of a single-chip flash chip into a control information section, a first mirror section and a second mirror section backed up mutually with the first mirror section. When the embedded device is started up, the available mirror data in the first mirror section or in the second mirror section can be loaded into the memory and can provide upgrading for the invalid mirror section. The inventive method can simplify the complexity of the hardware circuit design and achieve the safe operating of the single-chip flash memory used in the embedded device and the safe upgrading for the device.

Owner:ZTE CORP

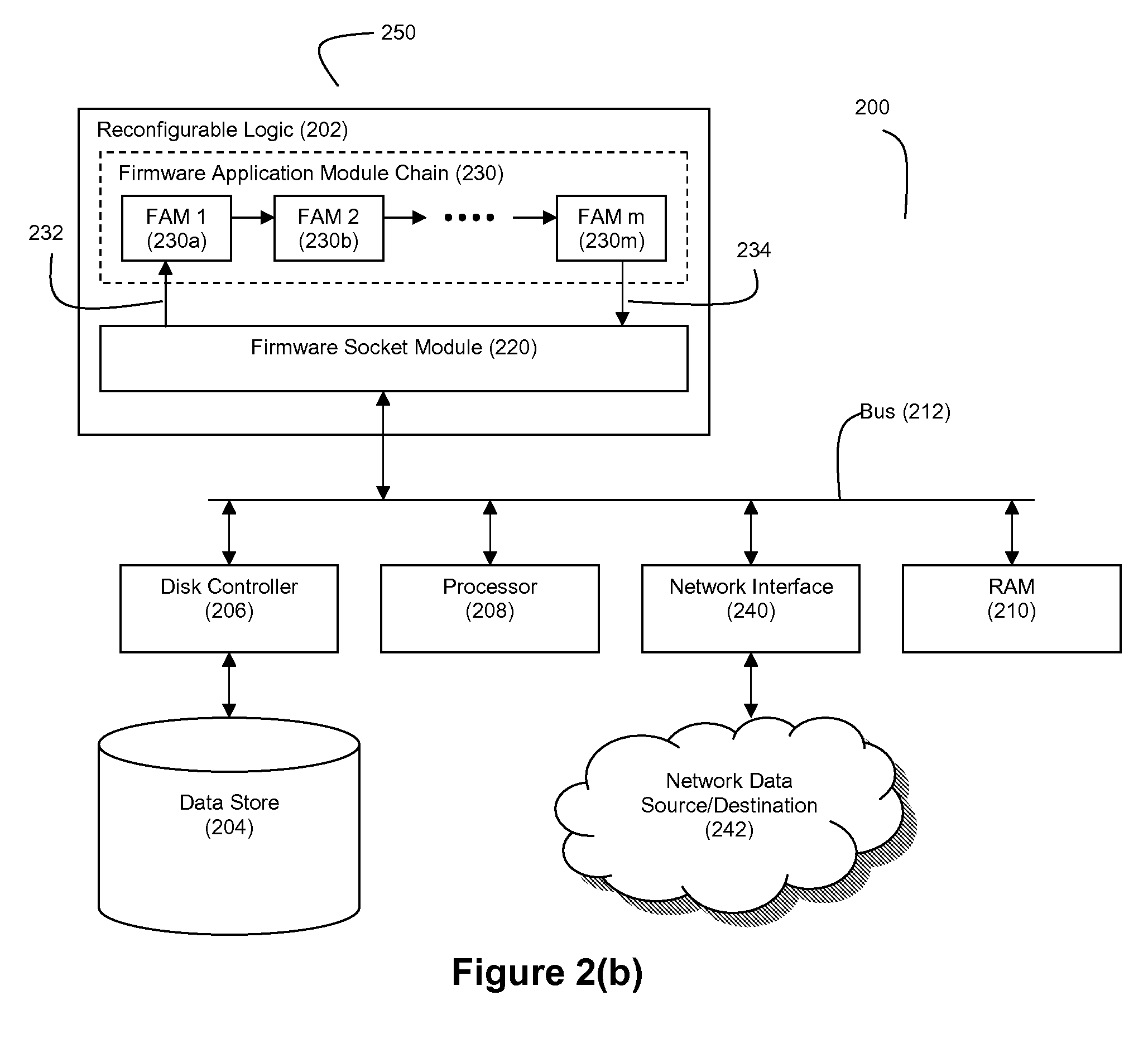

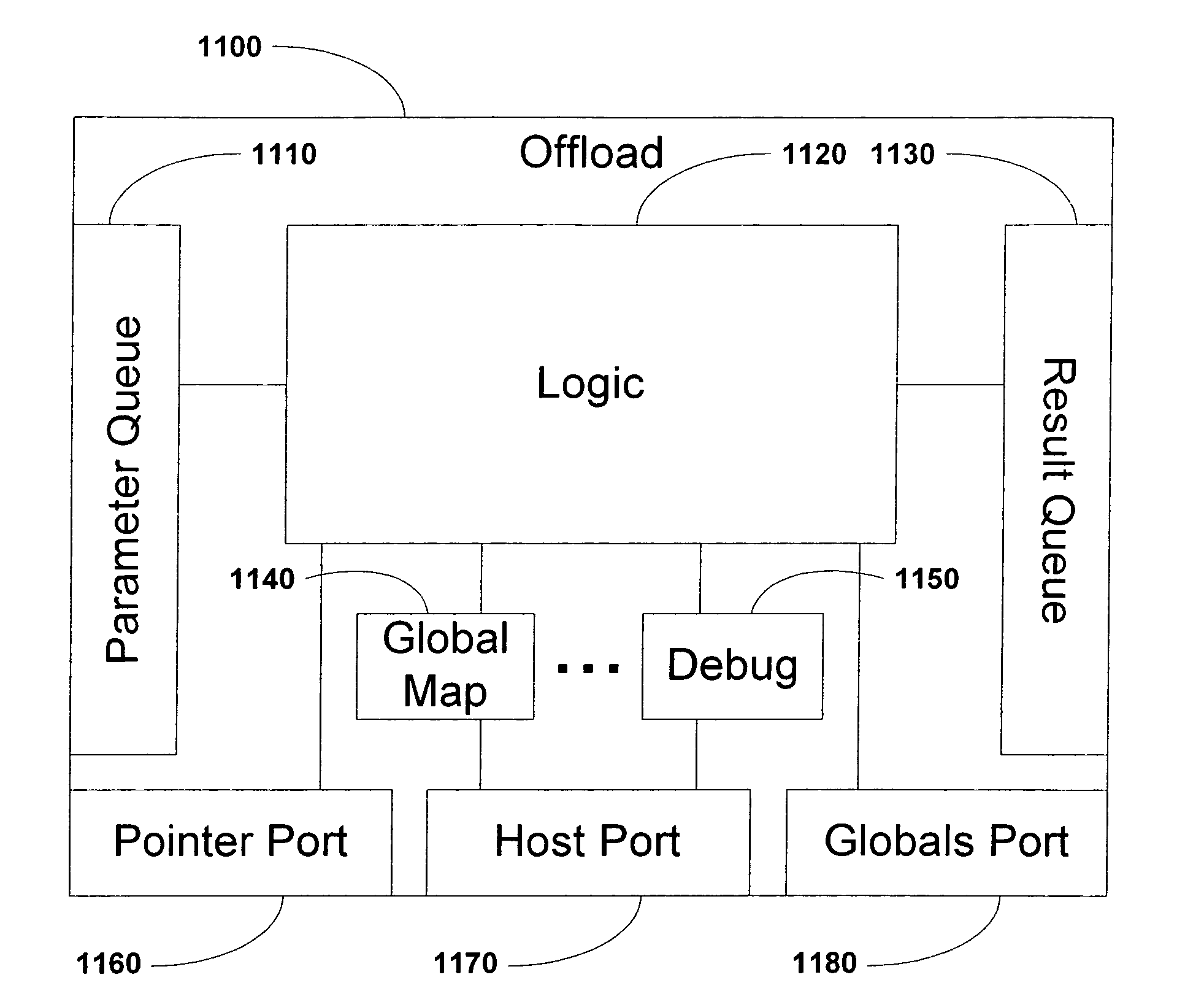

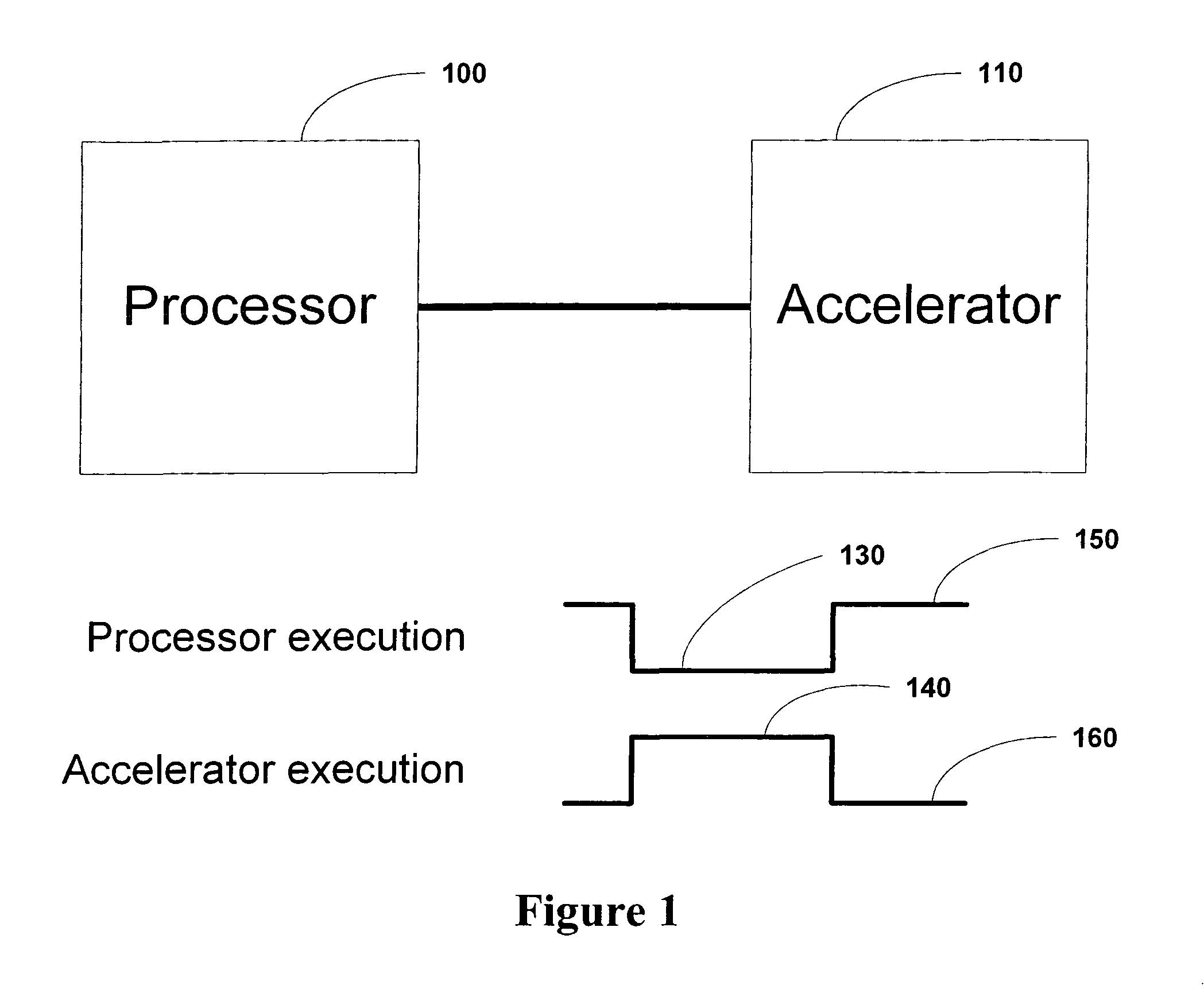

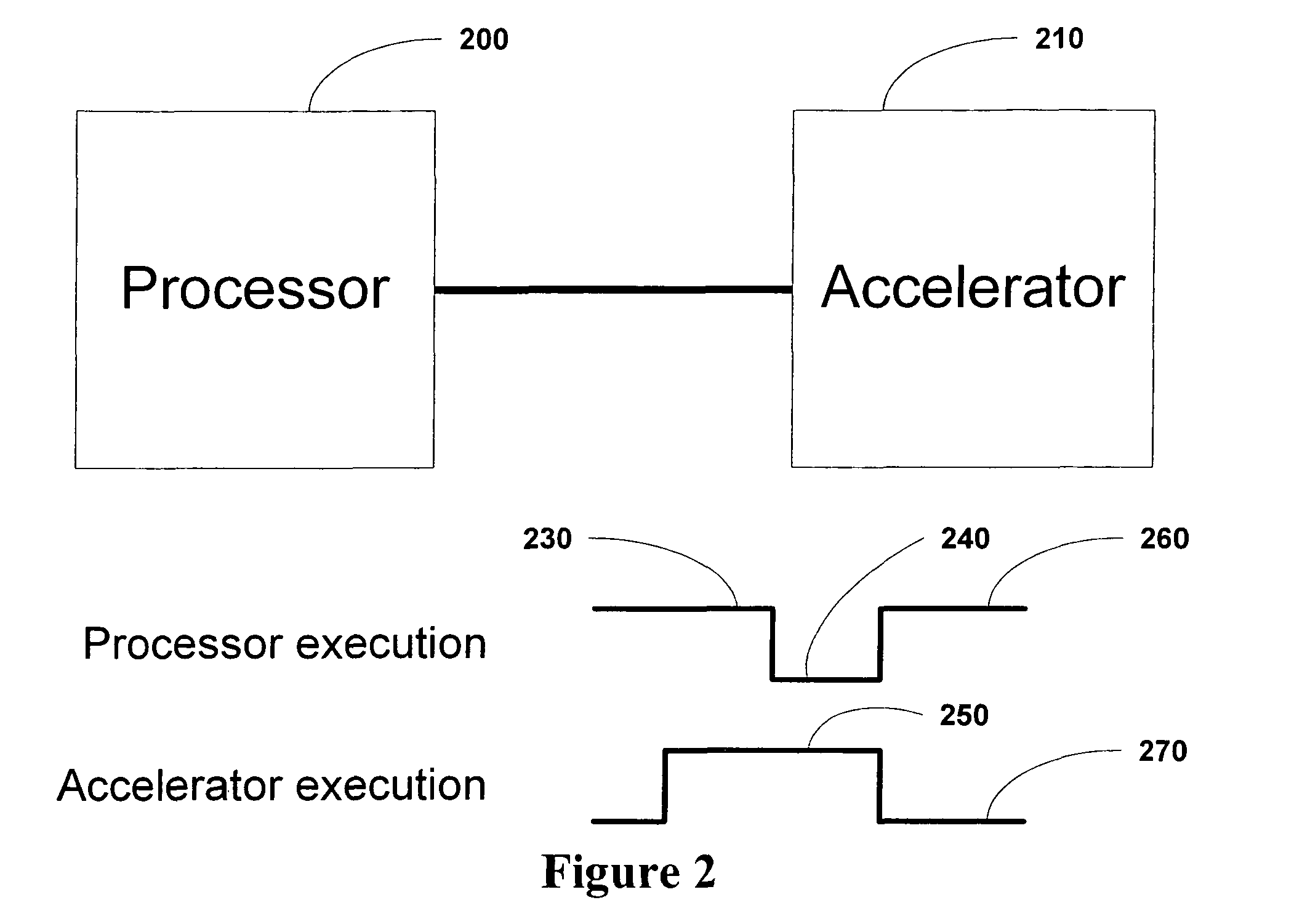

Generating hardware accelerators and processor offloads

ActiveUS8127113B1Interprogram communicationGeneral purpose stored program computerComputer hardwareHardware acceleration

System and method for generating hardware accelerators and processor offloads. System for hardware acceleration. System and method for implementing an asynchronous offload. Method of automatically creating a hardware accelerator. Computerized method for automatically creating a test harness for a hardware accelerator from a software program. System and method for interconnecting hardware accelerators and processors. System and method for interconnecting a processor and a hardware accelerator. Computer implemented method of generating a hardware circuit logic block design for a hardware accelerator automatically from software. Computer program and computer program product stored on tangible media implementing the methods and procedures of the invention.

Owner:SYNOPSYS INC