Patents

Literature

55 results about "Dsp architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

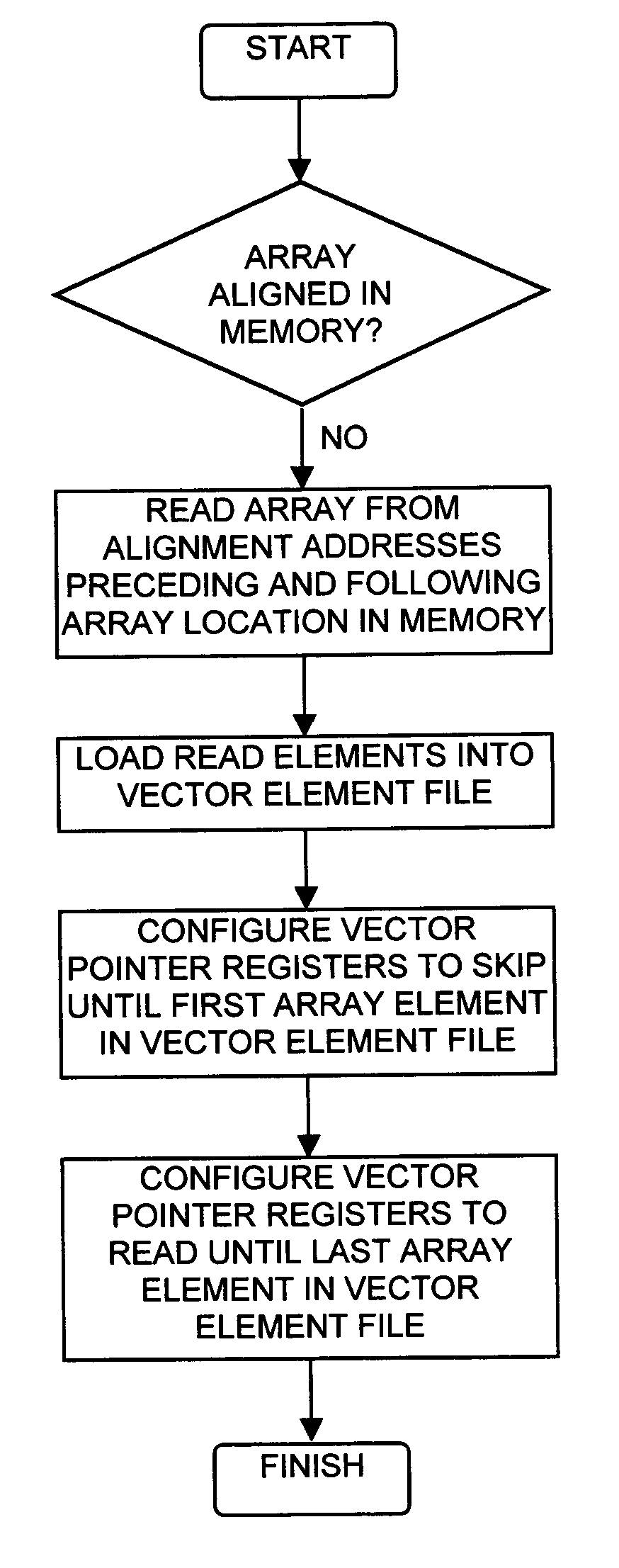

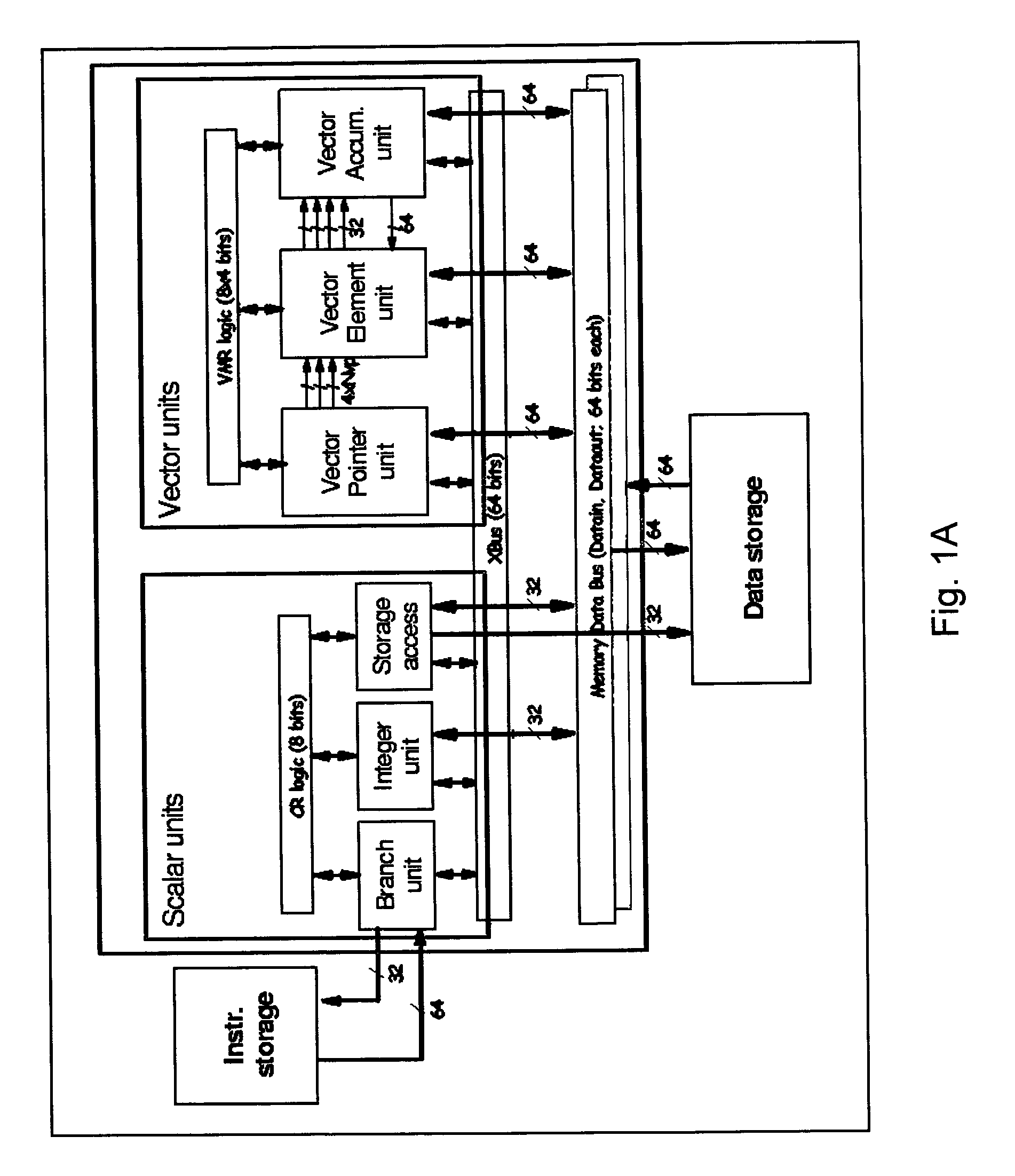

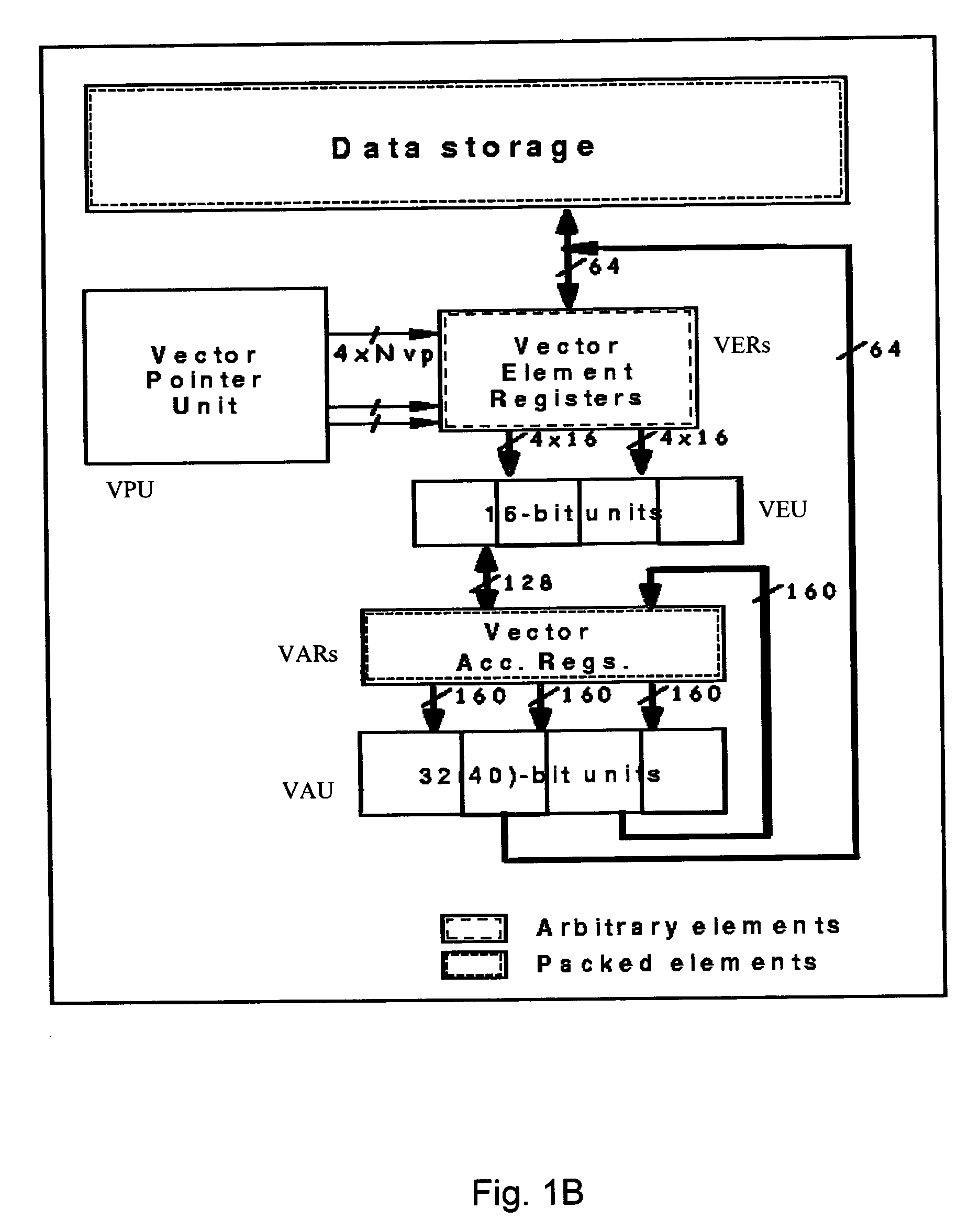

Vectorization in a SIMdD DSP architecture

InactiveUS20050097301A1Simple technologyGeneral purpose stored program computerProgram controlDsp architectureVector element

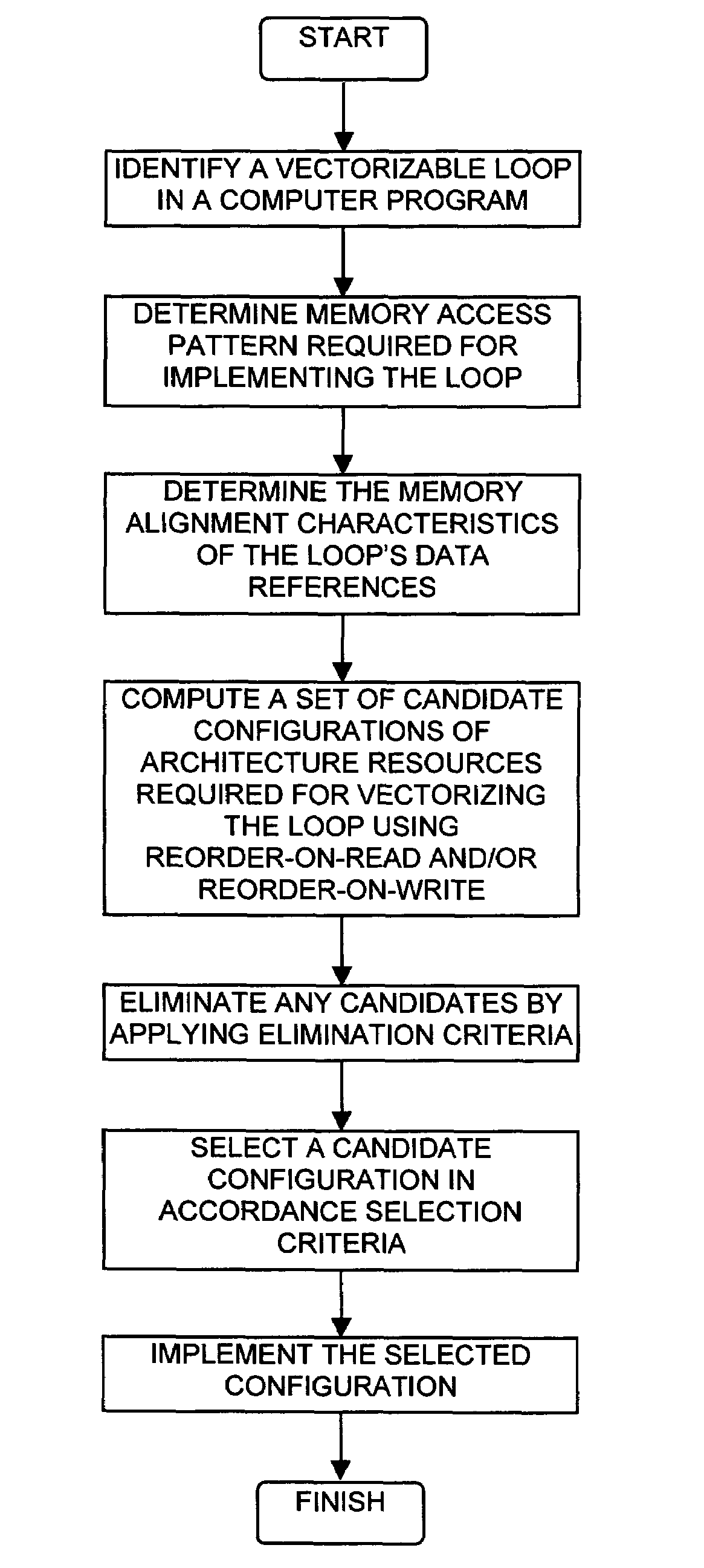

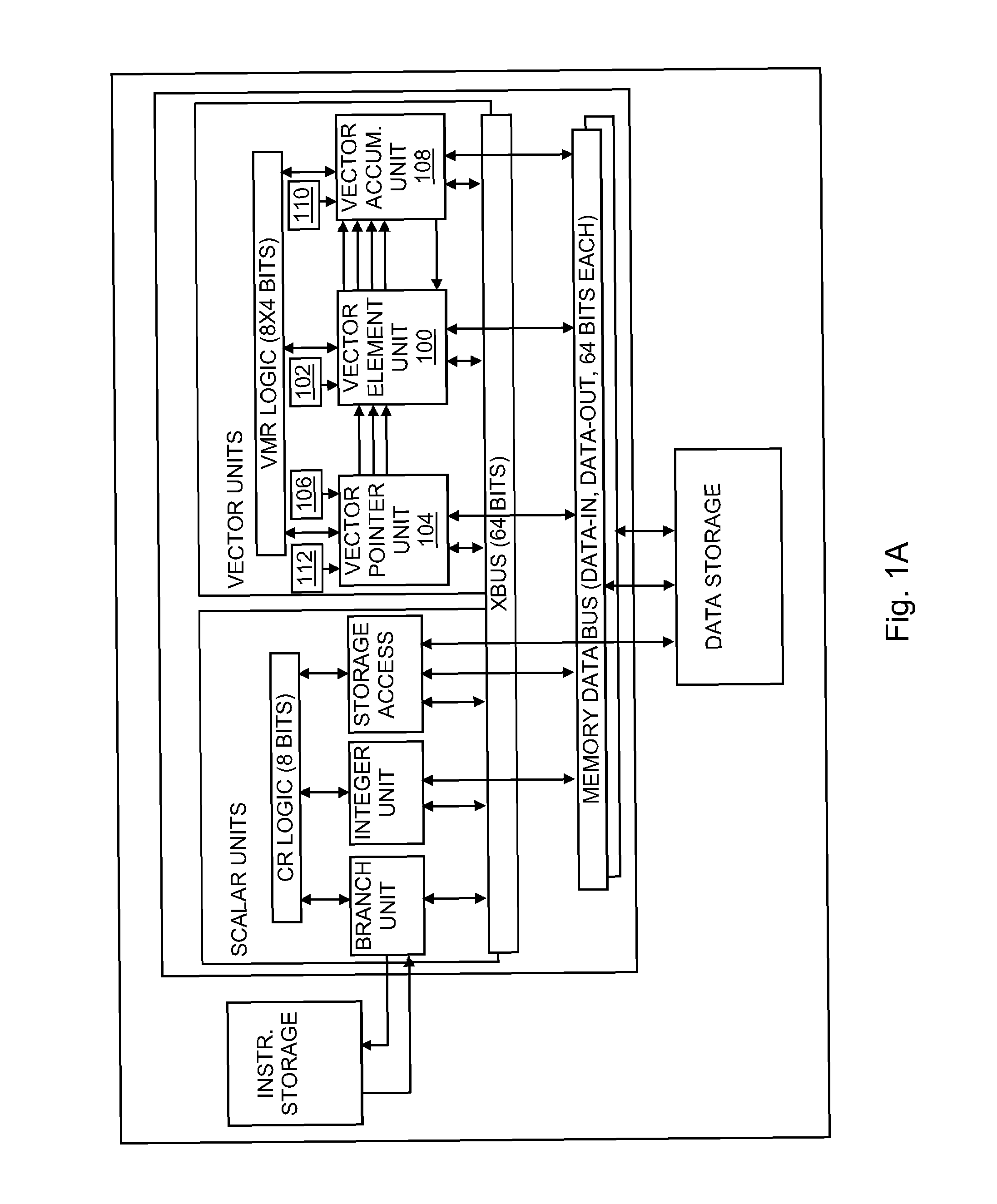

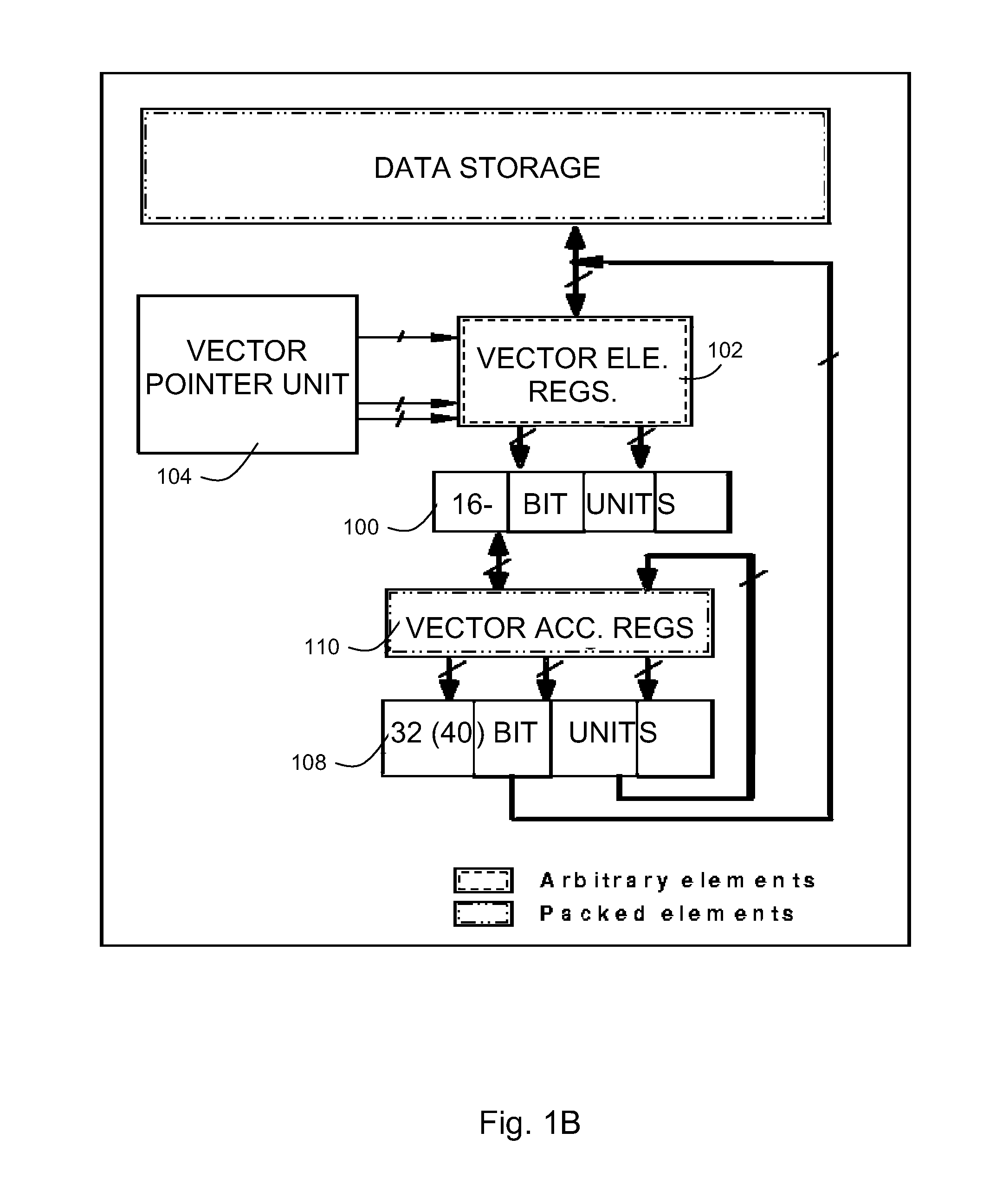

A method for determining vectorization configurations in a computer processor architecture, the method including identifying a vectorizable loop in a computer program, identifying a memory access pattern of data required for implementing the loop in the architecture, computing a set of candidate configurations of resources required for vectorizing the data in the architecture, where the computing step includes configuring a vector pointer register of the architecture in support of either of reorder-on-read use and reorder-on-write use of a vector element file of the architecture, selecting one of the candidates in accordance with predefined selection criteria, and implementing the selected vectorization configuration in the architecture.

Owner:IBM CORP

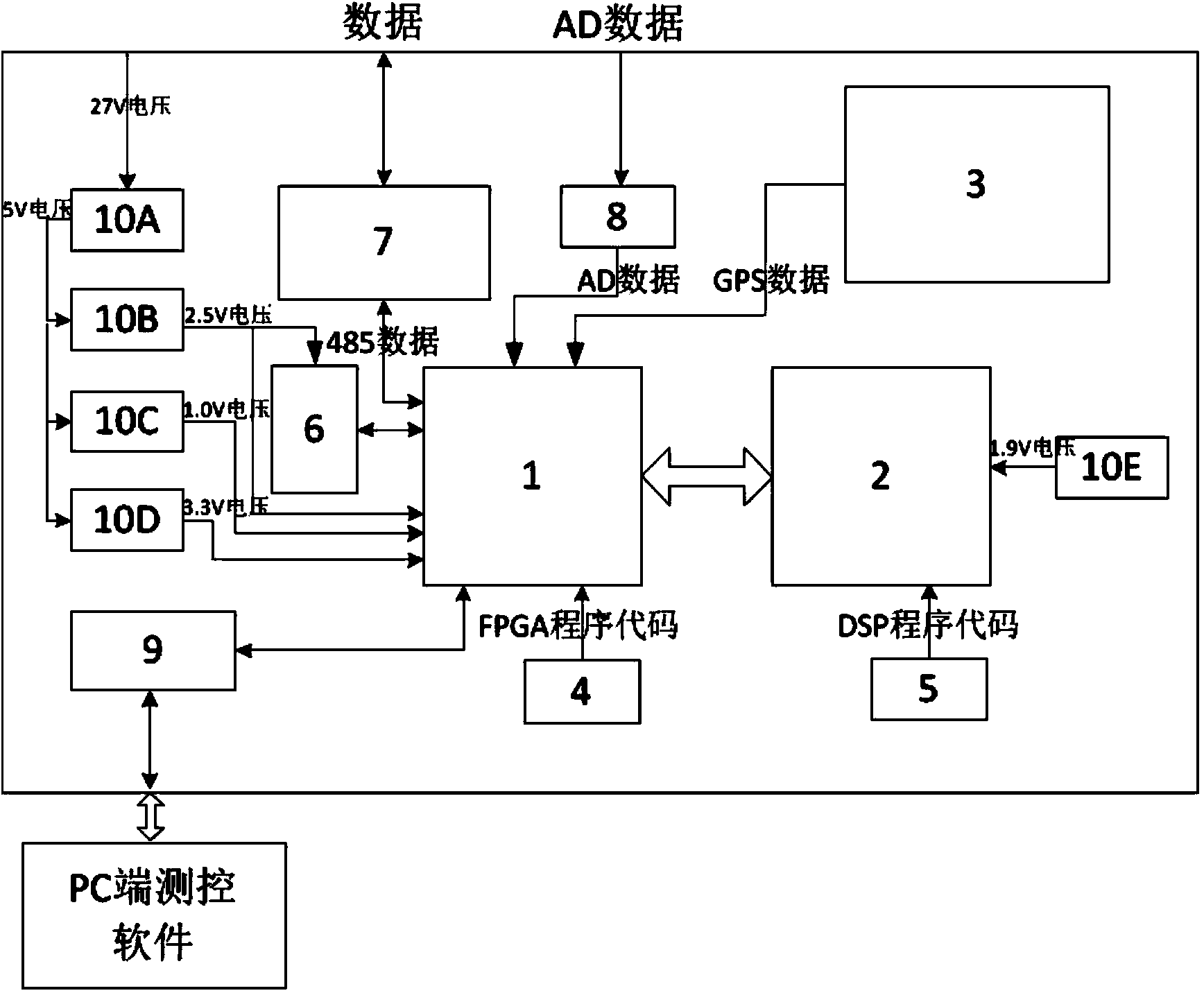

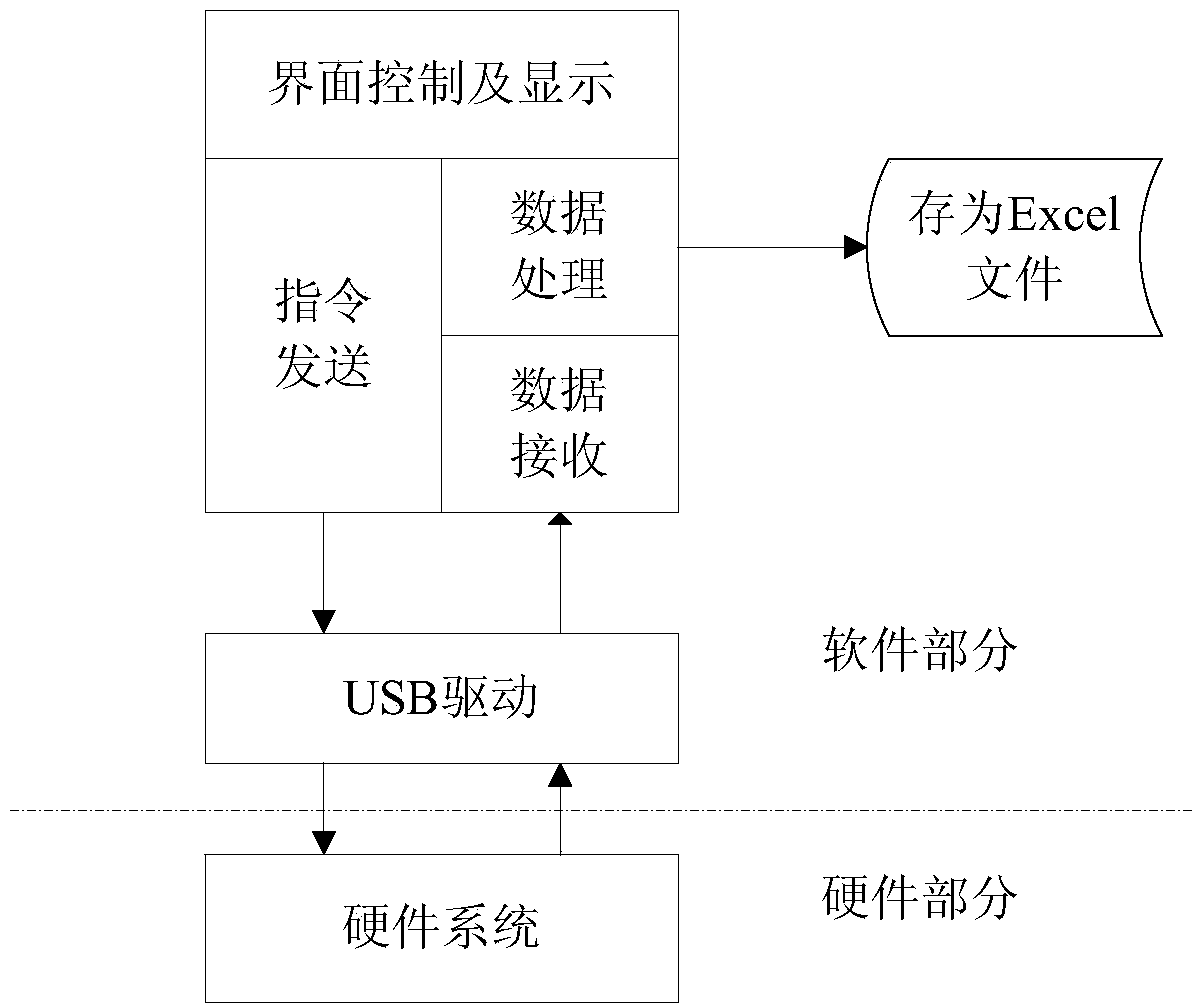

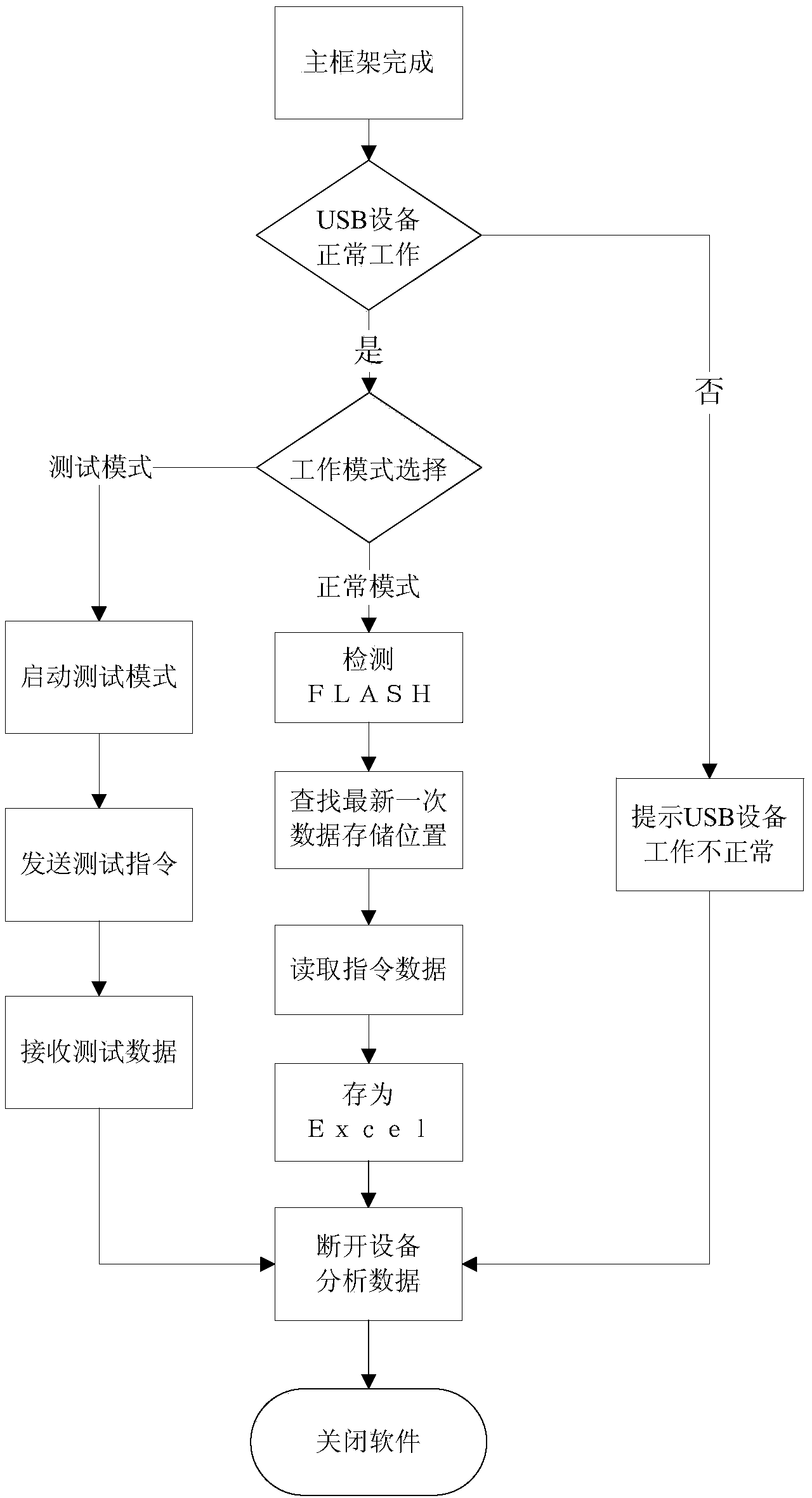

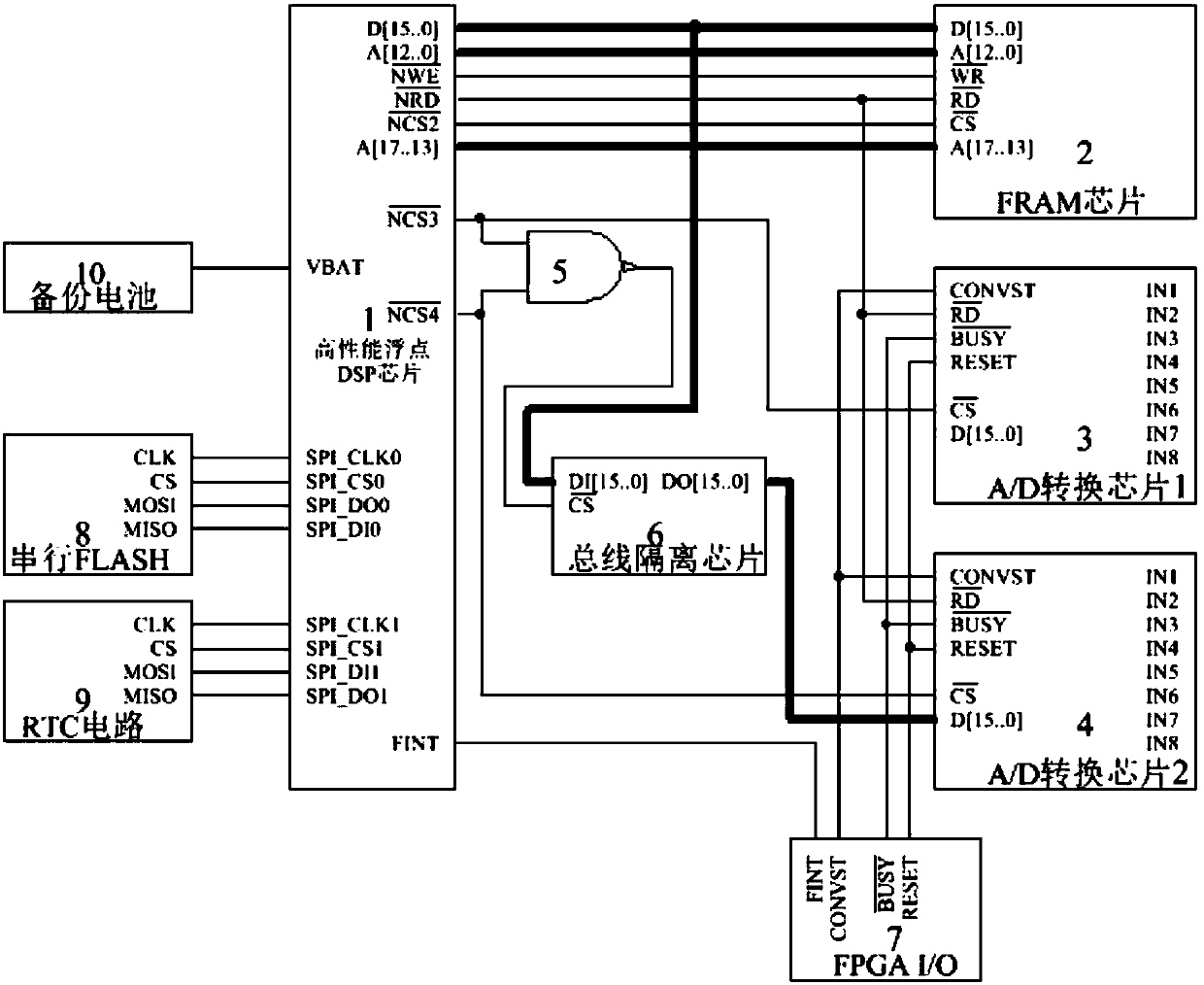

High-speed data recording system based on FPGA+DSP framework and establishment method thereof

ActiveCN103678728AReduce volumeHigh-speed real-time data recordingData acquisition and loggingDsp architectureData acquisition

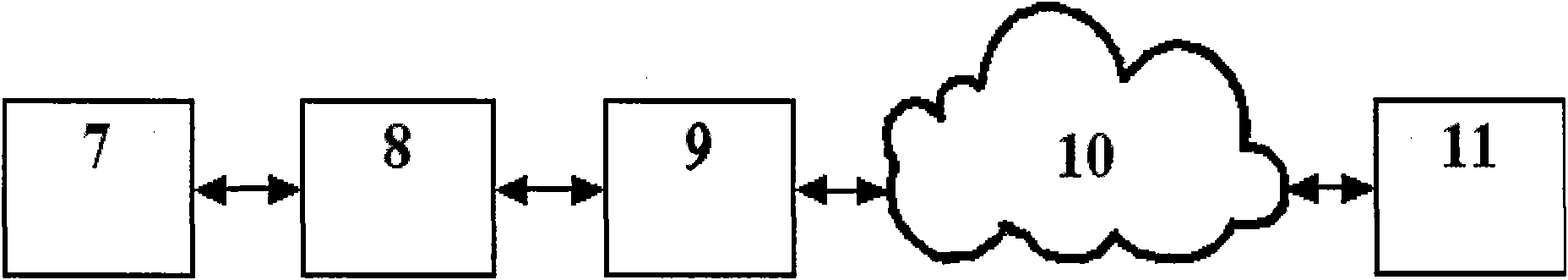

The invention discloses a high-speed data recording system based on an FPGA+DSP framework. The high-speed data recording system based on the FPGA+DSP framework comprises PC end measurement and control software, an FPGA core control chip, a DSP core control chip, a power supply chip, an FLASH memory chip, a USB communication chip, an HDLC protocol communication chip, an AD chip and a GPS communication daughter board, wherein the FPGA core control chip controls a USB module for PC communication during data uploading, a cache module during communication between the FPGA core control chip and the DSP core control chip, a reading and writing module of the FLASH memory chip, a control module of the GPS communication daughter board and a data sending and receiving module of the HDLC protocol communication chip, the DSP core control chip controls system self-detection in a data transmission and recording mode, an analog quantity data acquisition module and a communication module of the FPGA core control chip, and the power supply chip is connected with all the chips and is used for providing voltage needed by working of the whole system. An establishment method of the high-speed data recording system based on the FPGA+DSP framework comprises five main steps. The high-speed data recording system based on the FPGA+DSP framework has the advantages that a hardware circuit is simple, the size is small, and data can be recorded in real time at a high speed. The high-speed data recording system based on the FPGA+DSP framework can be applied to various systems conveniently.

Owner:杭州雷世科技有限公司

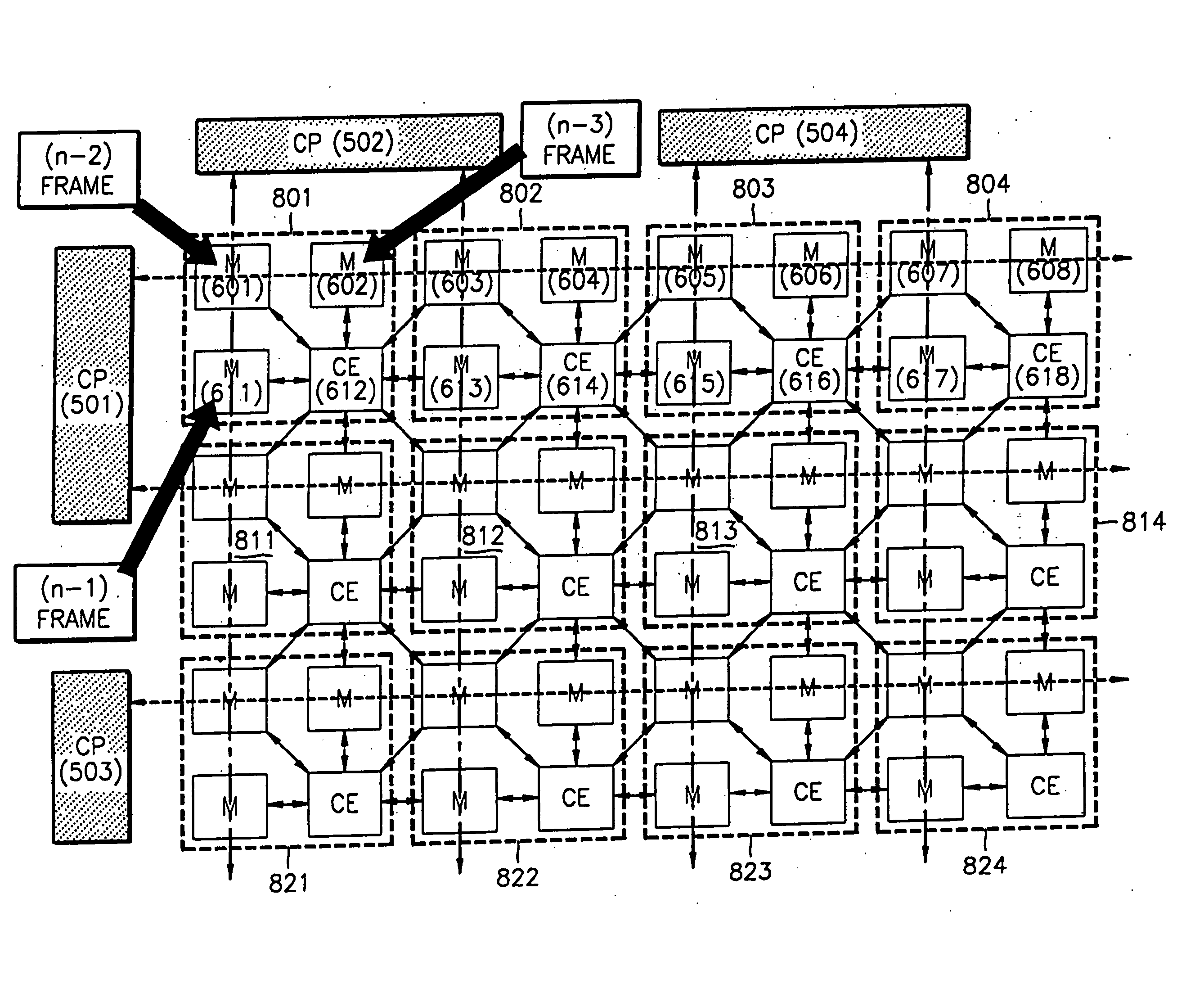

DSP (digital signal processing) architecture with a wide memory bandwidth and a memory mapping method thereof

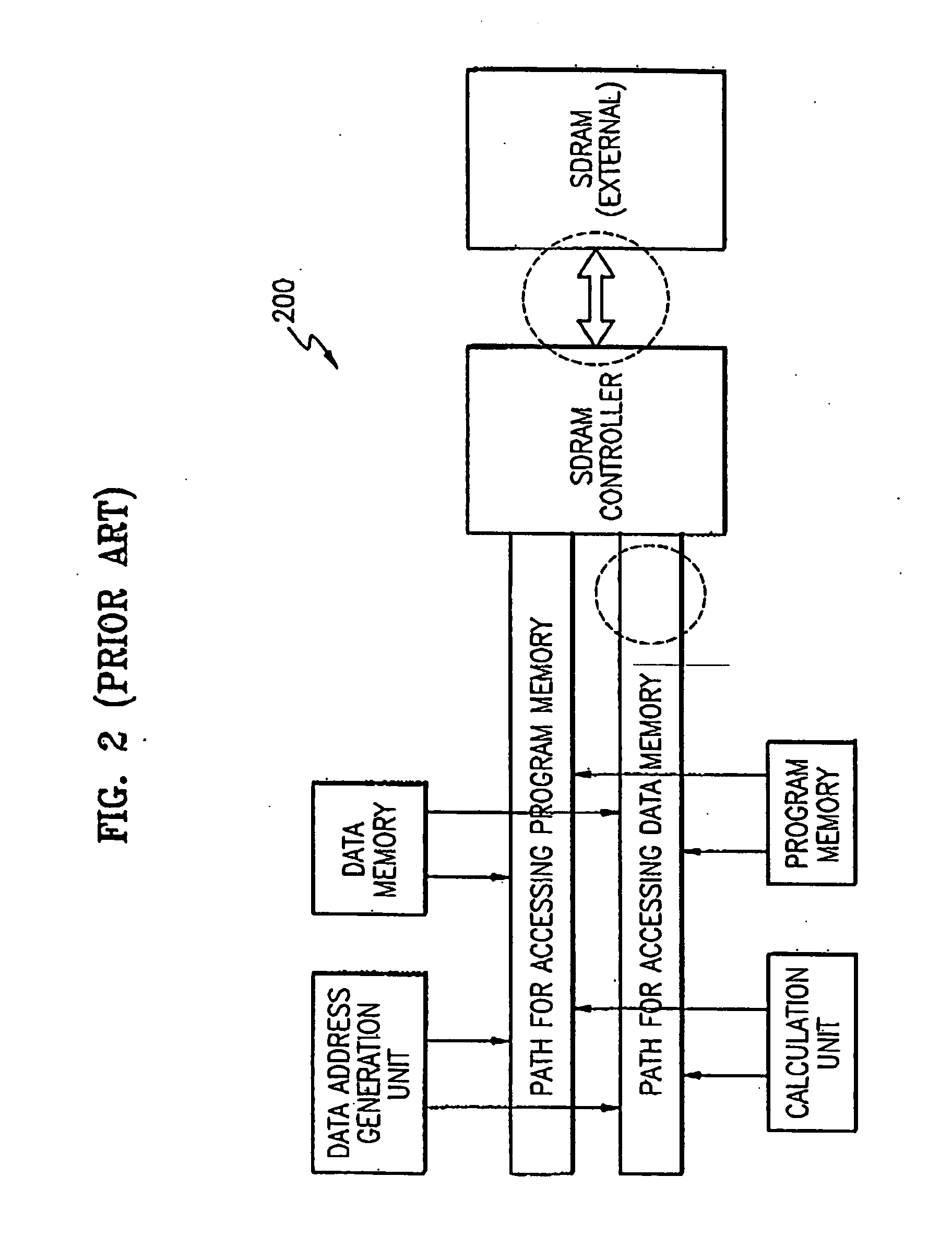

InactiveUS20050083338A1Reduce memory access timeIncrease data rateSingle instruction multiple data multiprocessorsImage data processing detailsDsp architectureComputer architecture

A DSP (Digital Signal Processing) architecture with a wide memory bandwidth and a memory mapping method thereof. The DSP architecture includes: a first communication port; first, second, and third memory devices, which are connected with the first communication port and are arranged in a first row direction of the DSP architecture; a fourth memory device, a calculation element, and a fifth memory device, which are arranged in a second row direction below a first row direction of the DSP architecture; and sixth, seventh, and eighth memory devices, which are connected with the first communication port and arranged in a third row direction of the DSP architecture, wherein the calculation element is connected with the first through the eight memory devices. In the DSP architecture, the calculation element and the first through the eighth memory devices form one arrangement unit, wherein the calculation element is disposed in the center of the arrangement unit, the first through the eighth memory devices are connected to the calculation element, and a plurality of arrangement units are arranged in row directions and column directions of the DSP architecture. Therefore, since a wide data bandwidth is provided between the calculation element of the DSP architecture and the memory devices, it is possible to reduce memory access times when data is processed, and accordingly, to process data with a high data rate, such as a moving image with a high resolution.

Owner:SAMSUNG ELECTRONICS CO LTD

Vectorization in a SIMdD DSP architecture

Owner:INT BUSINESS MASCH CORP

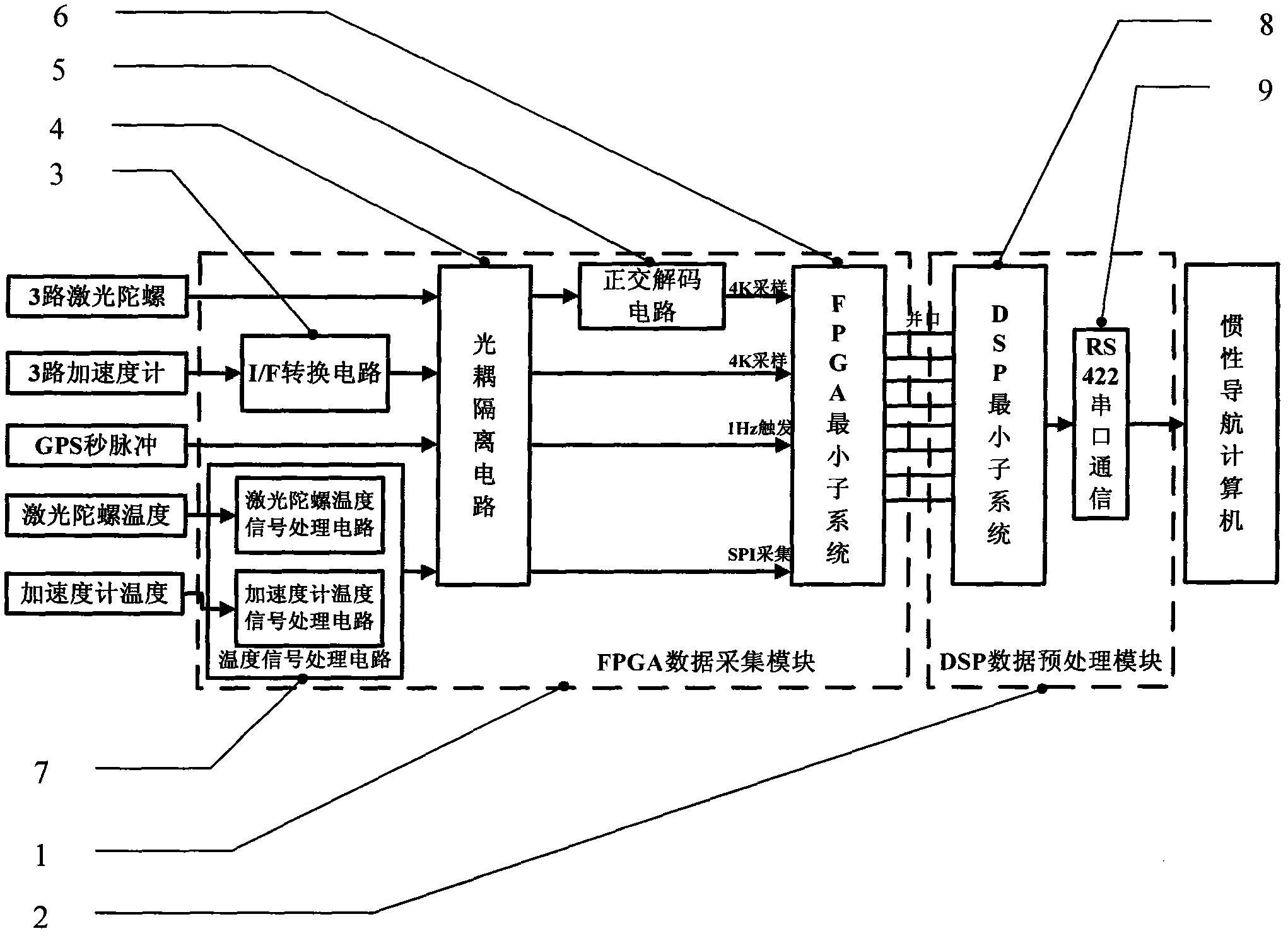

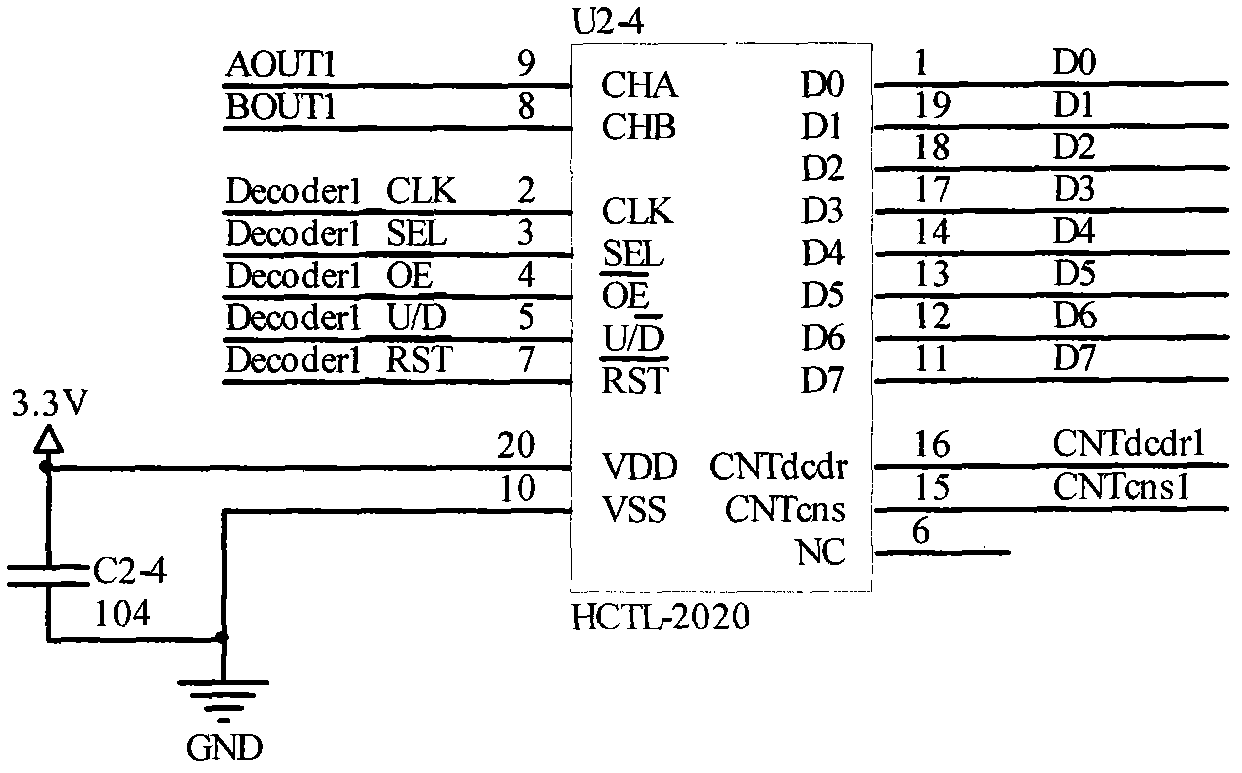

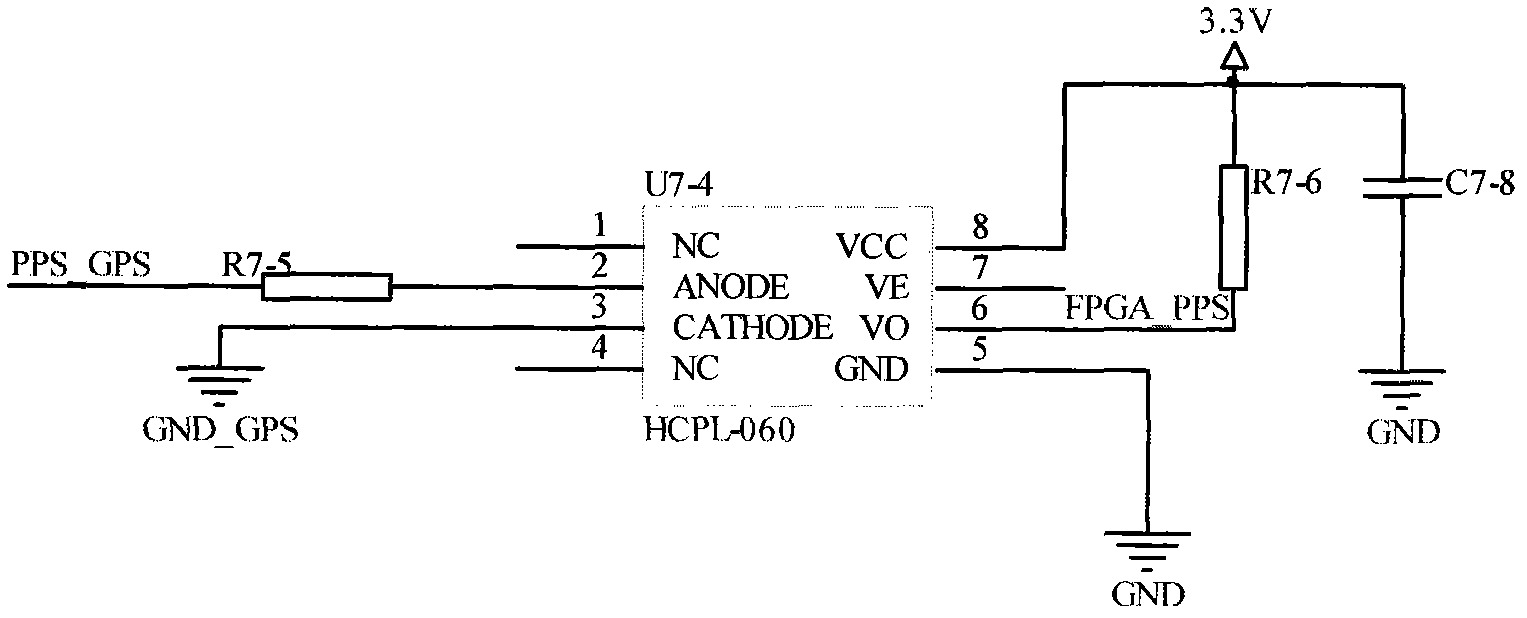

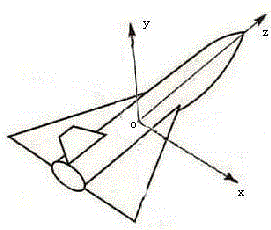

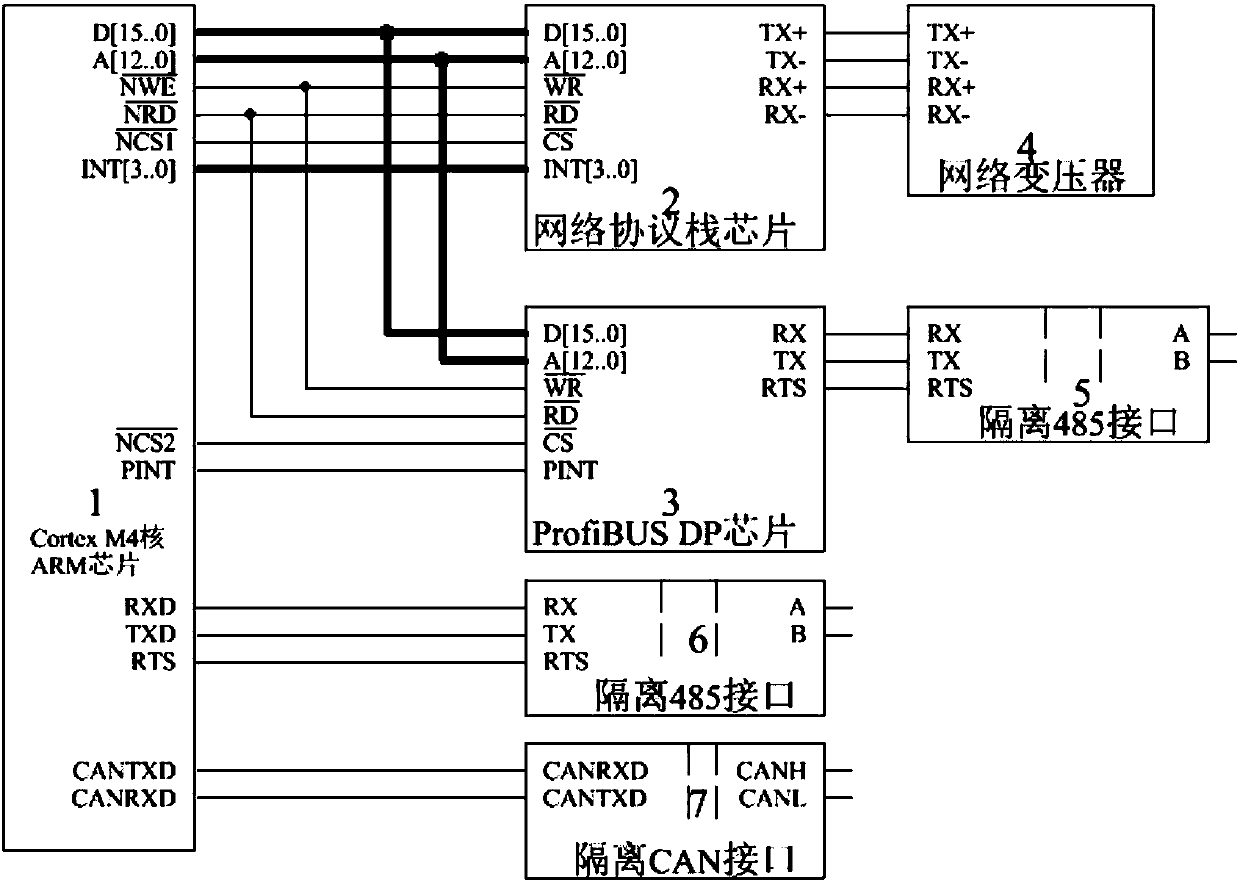

Laser gyro POS (Point of Sales) data acquisition and pre-processing system

InactiveCN102109351AMeet the frequencyHigh precision requirementsNavigation by speed/acceleration measurementsDsp architectureData acquisition

The invention relates to a laser gyro POS data acquisition and pre-processing system which comprises a Field Programmable Gate Array (FPGA) data acquisition module and a Digital Signal Processor (DSP) data pre-processing module. The FPGA data acquisition module realizes the acquisition of laser gyro signal, accelerometer signal and temperature signal and acquires a clock by using the synchronous FPGA data of GPS second pulse. The DSP data pre-processing module reads the laser gyro data, the accelerometer data and the temperature data in the FPGA to pre-process the data and sends the pre-processing result to a navigation computer. The system realizes the integrated design of high-frequency and high-precision laser gyro POS data acquisition and pre-processing system of FPGA / DSP framework; therefore, the power consumption, the volume and the weight of the system are reduced so that the system performance can be greatly improved.

Owner:BEIHANG UNIV

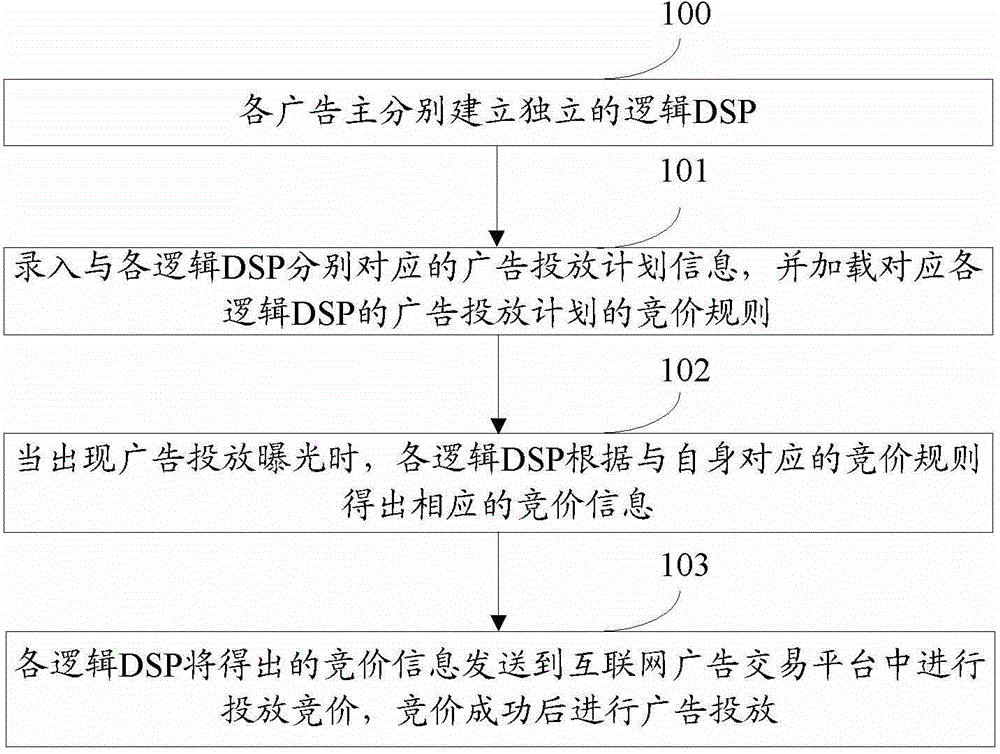

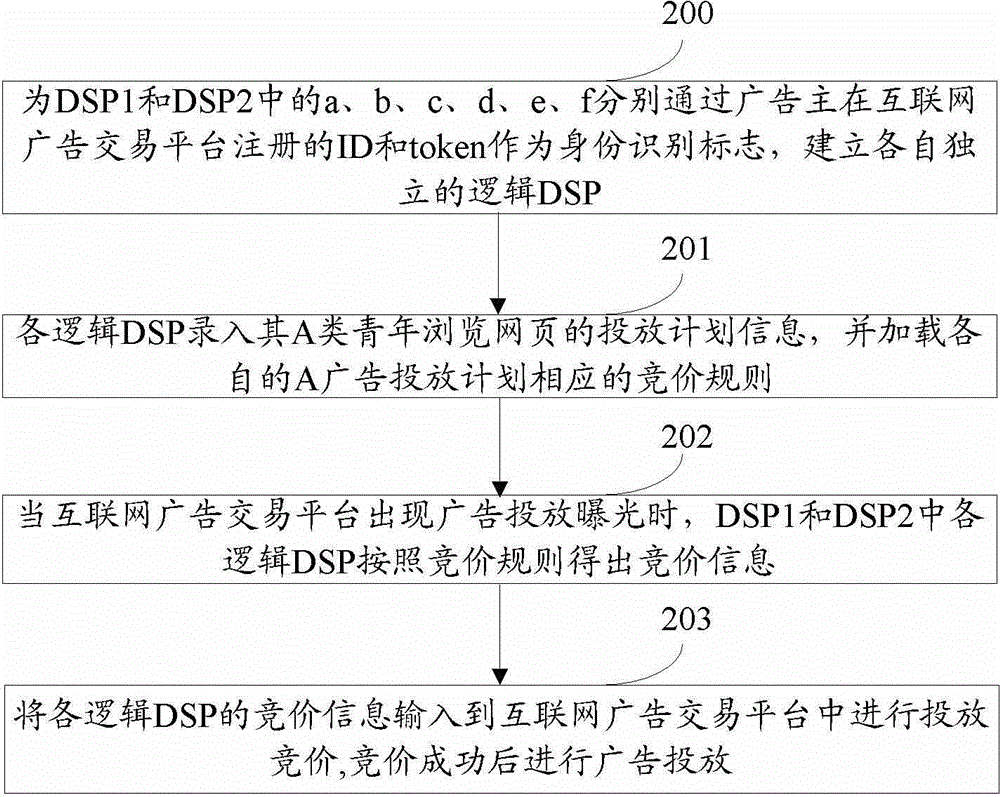

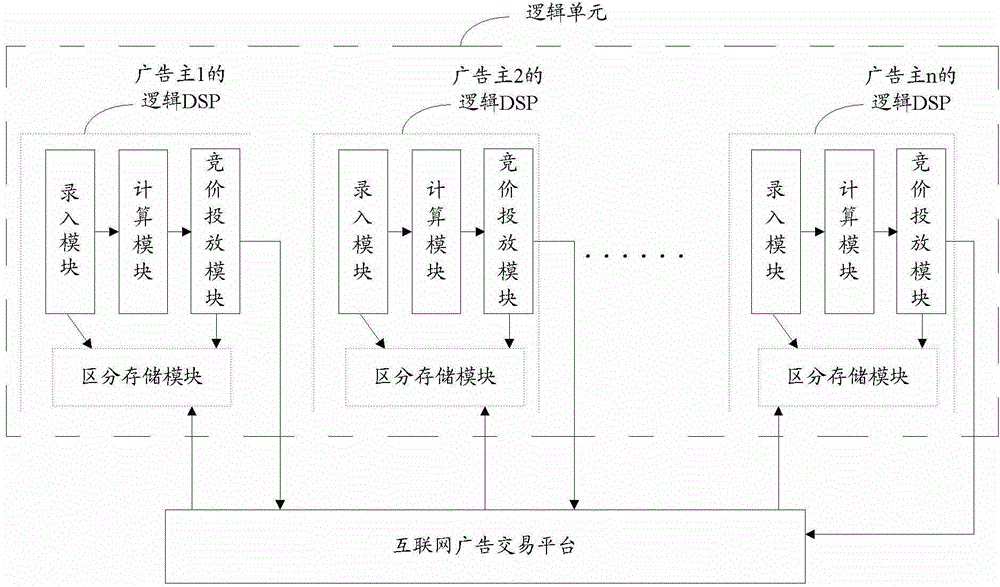

Putting method and device of DSP (demand-side platform) advertisements

ActiveCN104636945AReduce hardwareLow costMarketingSpecial data processing applicationsDsp architectureProgram planning

The invention discloses a putting method of DSP (demand-side platform) advertisements. The method includes the steps: in a same DSP architecture, each advertiser establishes an independent logical DSP; advertisement putting plan information corresponding to the logical DSPs are recorded in, and bidding rules of advertisement putting plans corresponding to the logical DPSs are loaded; if advertisement putting exposure occurs, the logical DSPs acquire corresponding bid information according to the corresponding bidding rules; the logical DPSs transmit the acquired bid information to an internet advertisement trading platform for putting bidding, and advertisement putting is performed after bidding success. The invention further discloses a putting device corresponding to the putting method. By designing the logical DSPs according to the putting method and device, the internet advertisement trading platform is enabled to provide fully fair bidding for all advertisers, and advertisement putting prices are fair and reasonable.

Owner:MIAOZHEN INFORMATION TECH CO LTD

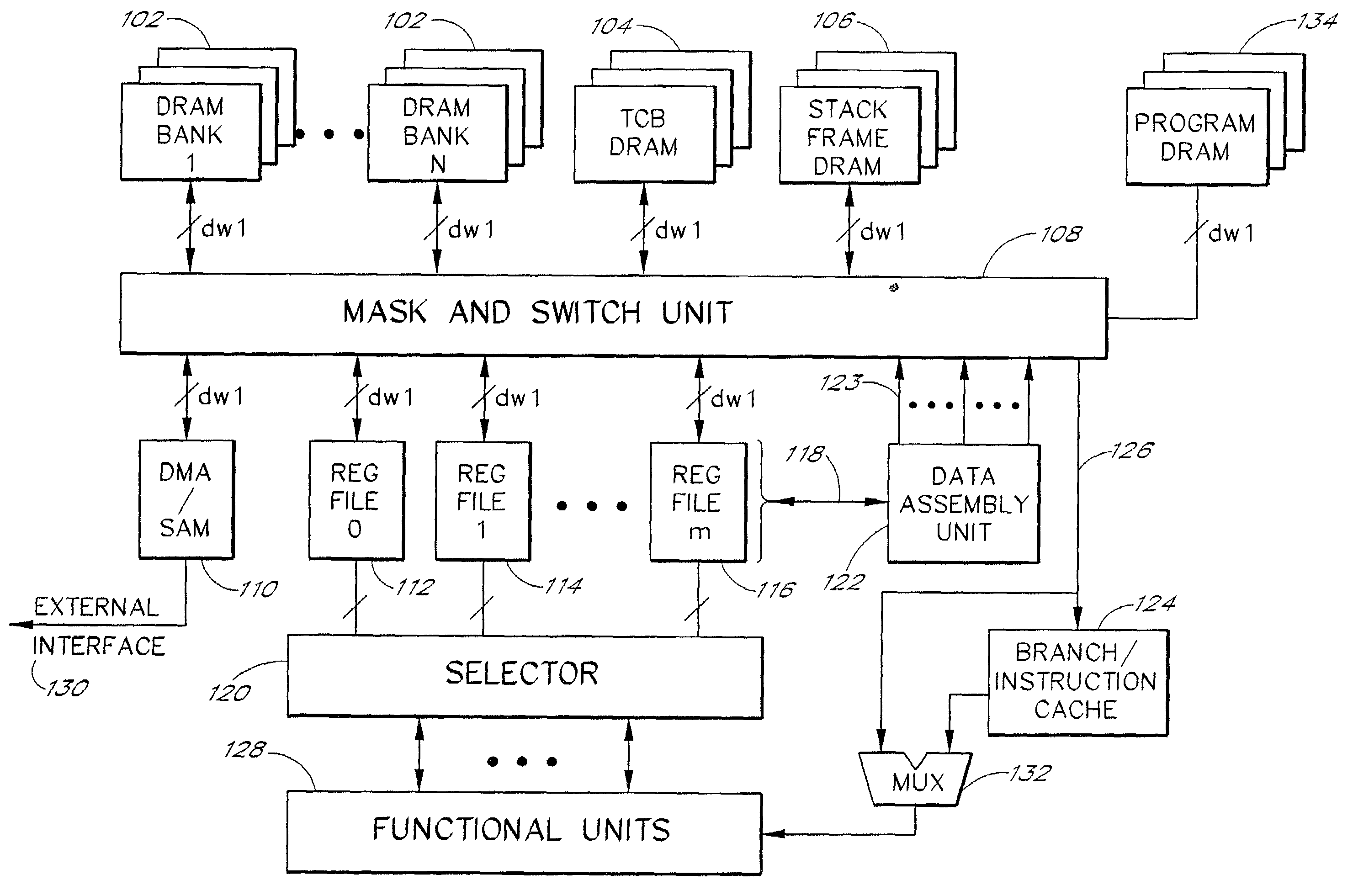

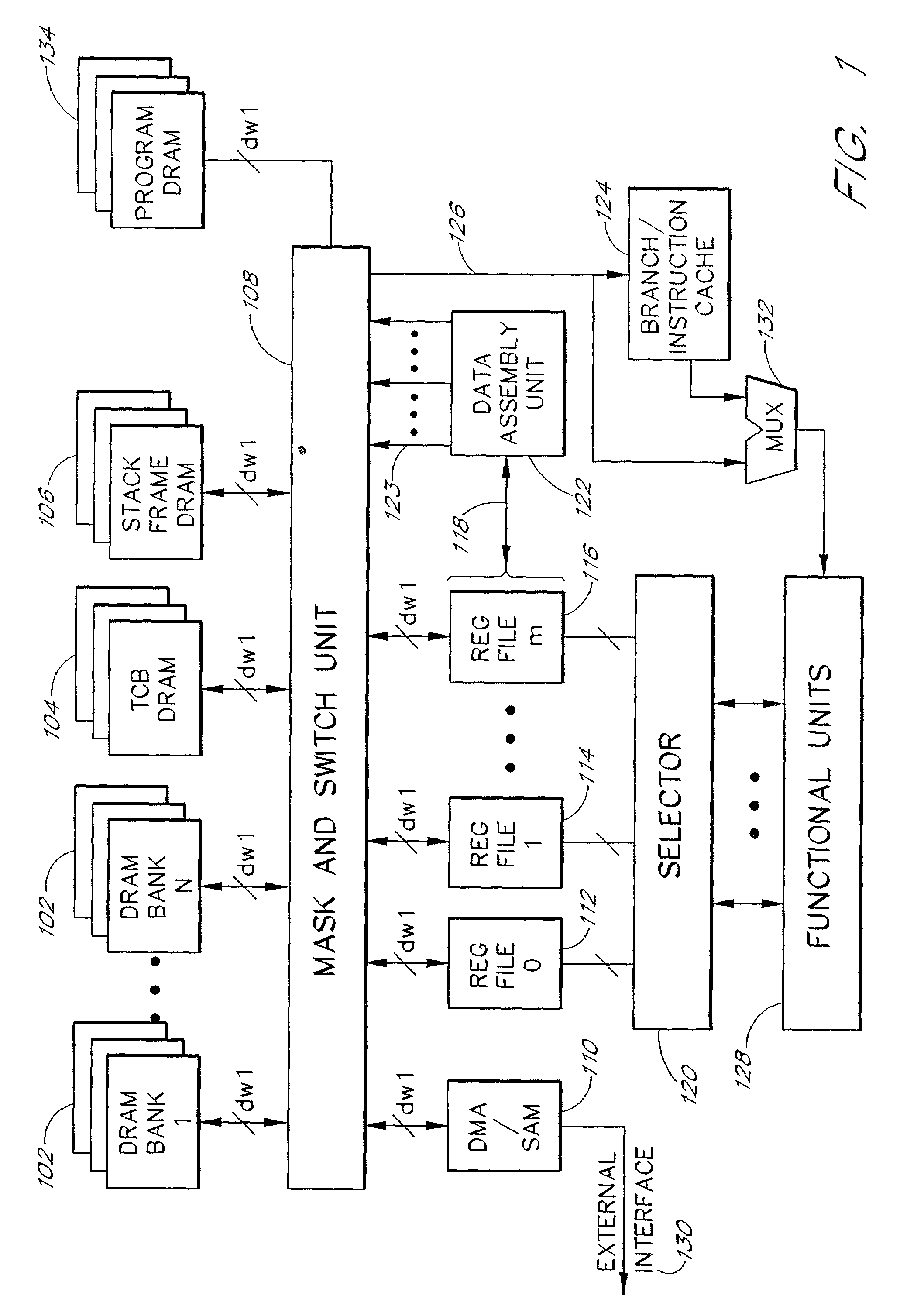

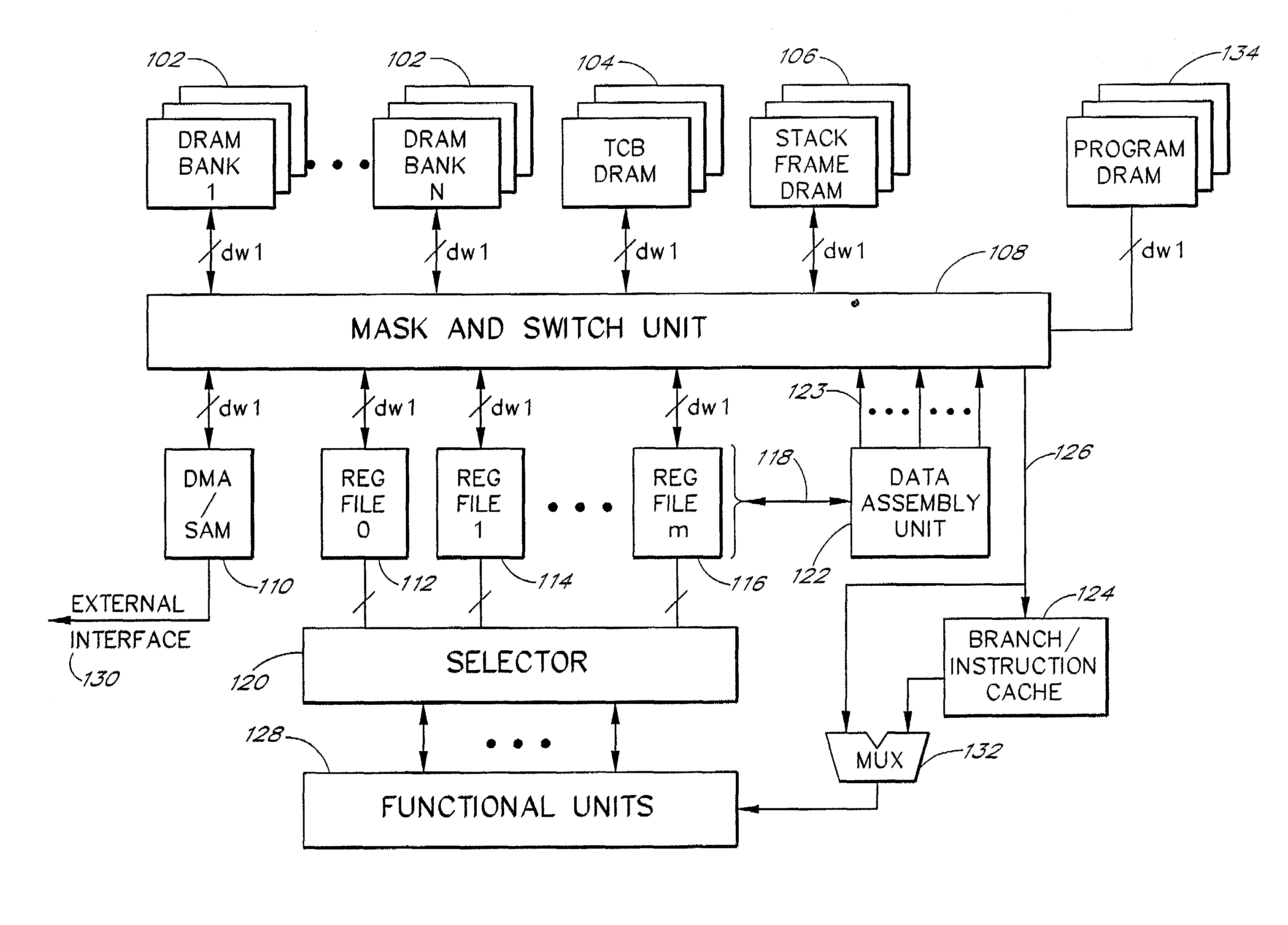

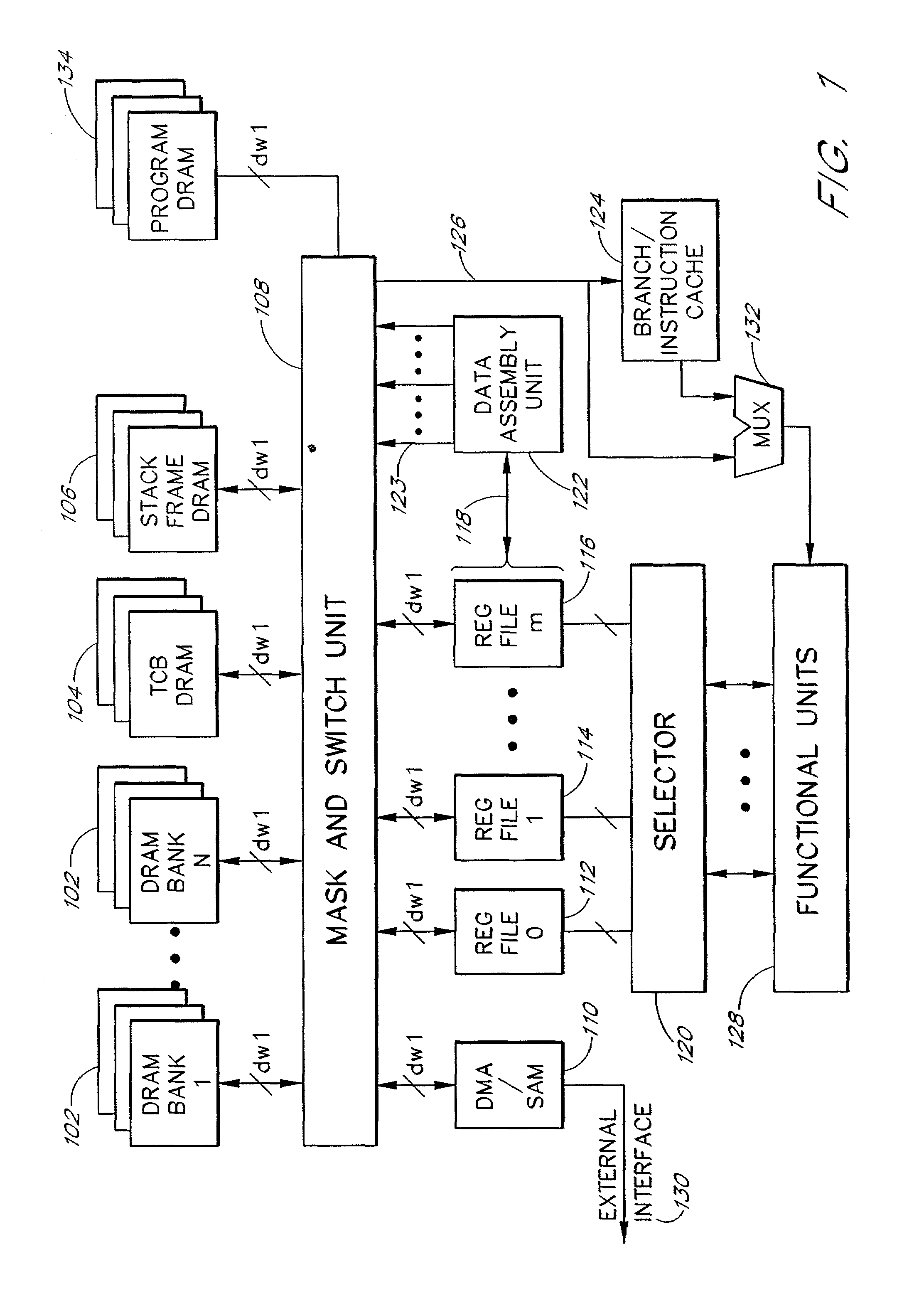

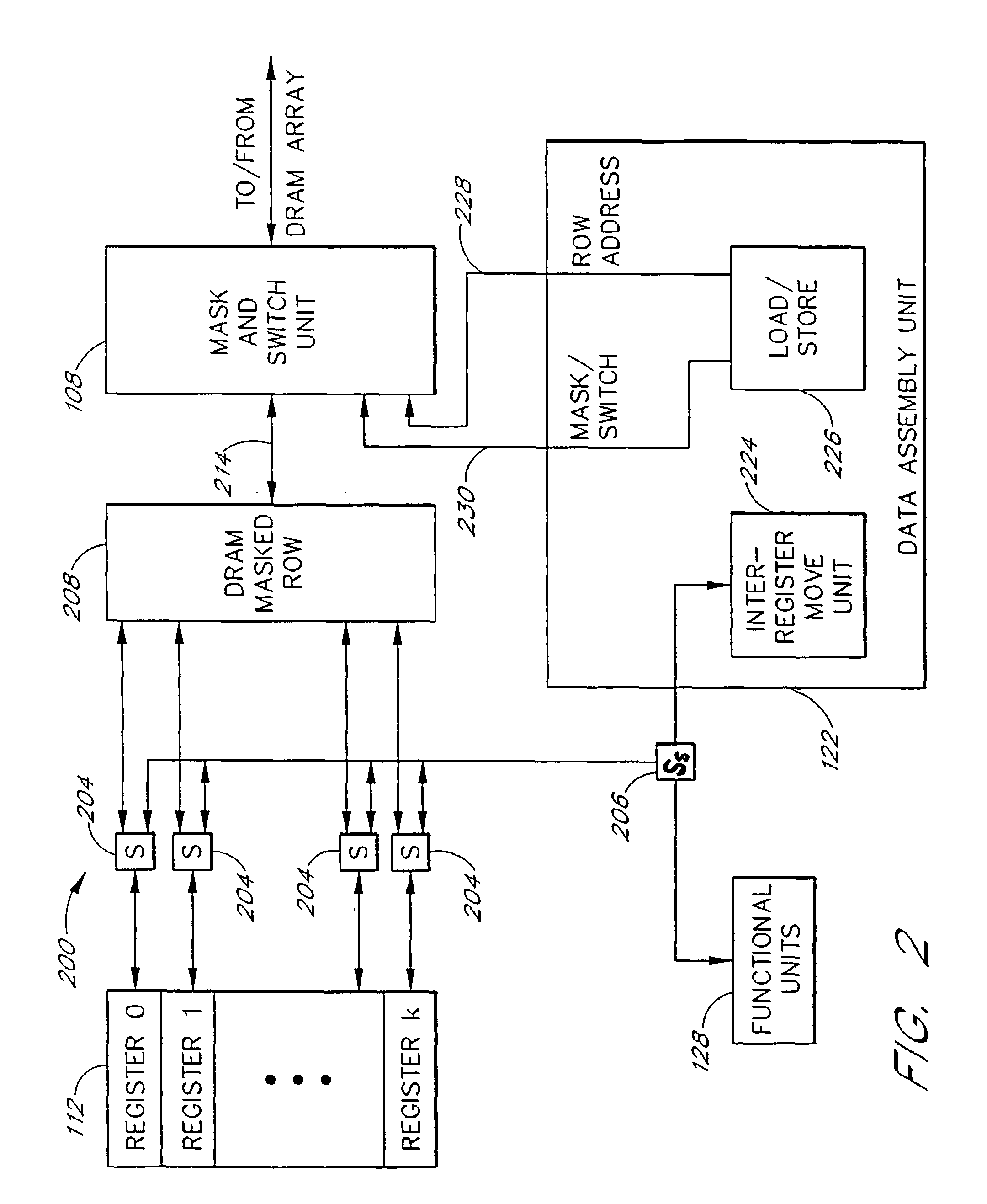

Methods for intelligent caching in an embedded DRAM-DSP architecture

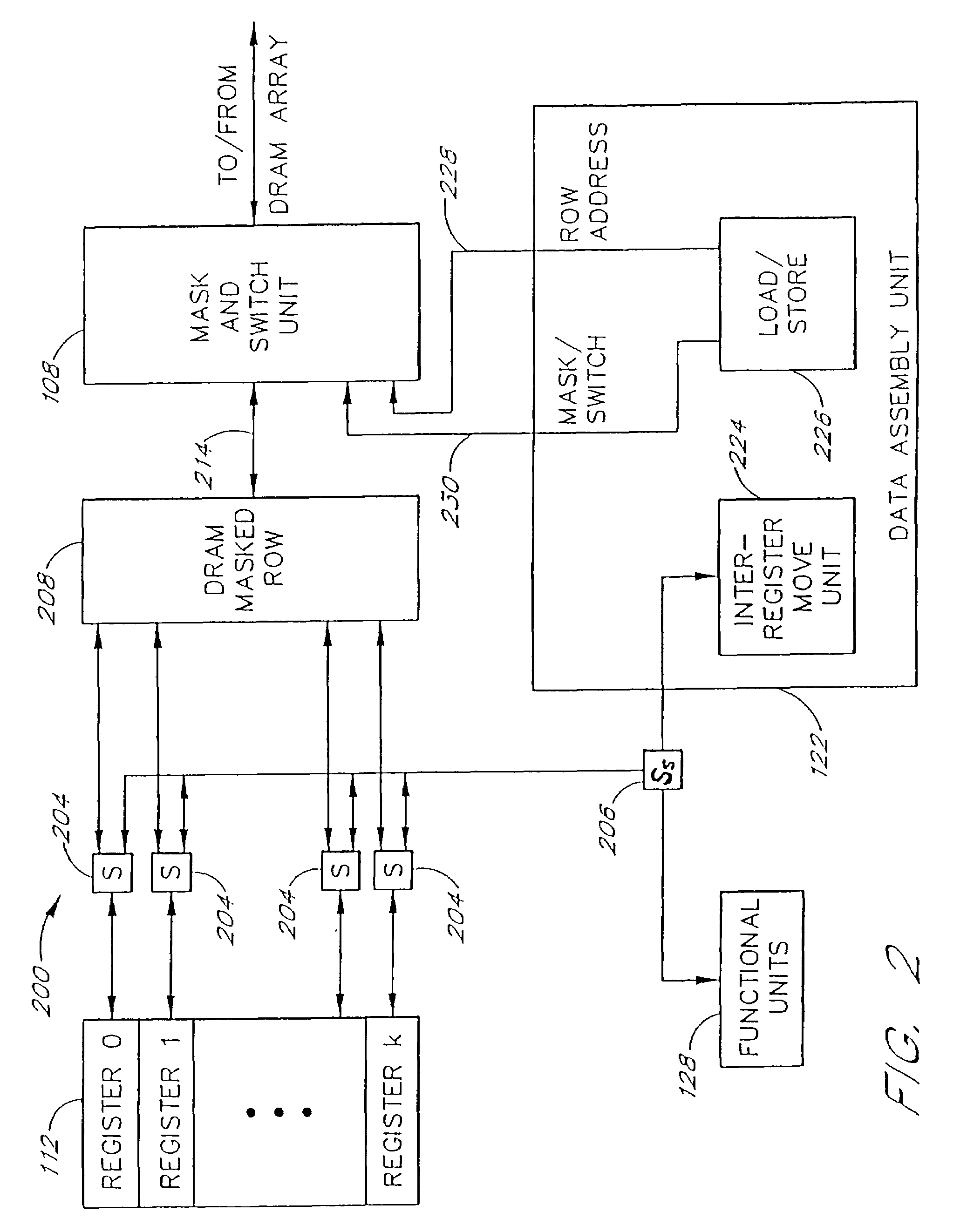

InactiveUS7146489B2Reduce and eliminate wait timeReduce delaysMemory architecture accessing/allocationRegister arrangementsDsp architectureProcessor register

An efficient embedded-DRAM processor architecture and associated methods. In one exemplary embodiment, the architecture includes a DRAM array, a set of register files, set of functional units, and a data assembly unit. The data assembly unit includes a set of row-address registers and is responsive to commands to activate and deactivate DRAM rows and to control the movement of data throughout the system. A pipelined data assembly approach allowing the functional units to perform register-to-register operations, and allowing the data assembly unit to perform all load / store operations using wide data busses. Data masking and switching hardware allows individual data words or groups of words to be transferred between the registers and memory. Other aspects of the invention include a memory and logic structure and an associated method to extract data blocks from memory to accelerate, for example, operations related to image compression and decompression.

Owner:ROUND ROCK RES LLC

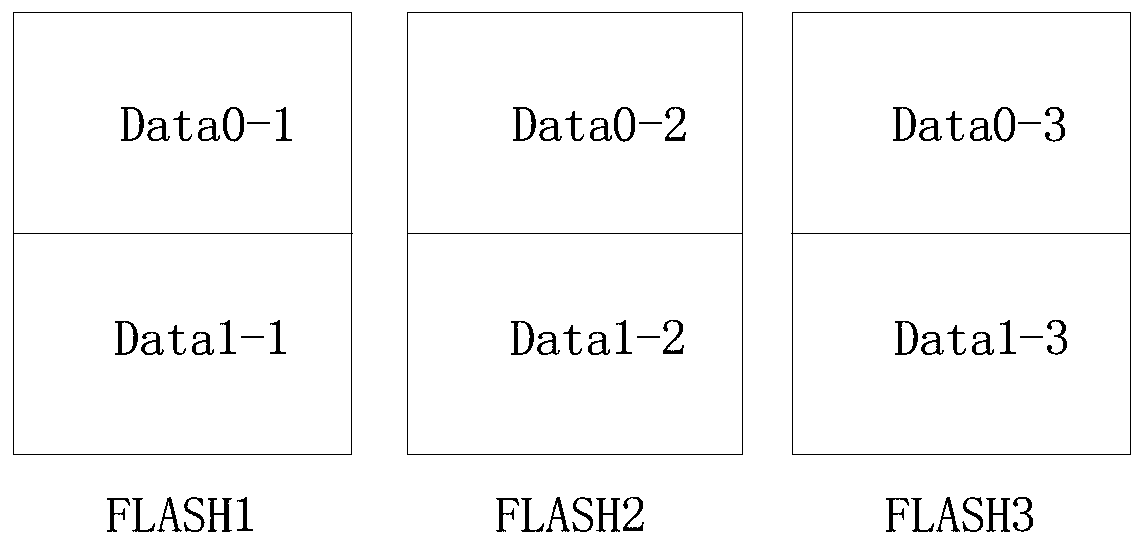

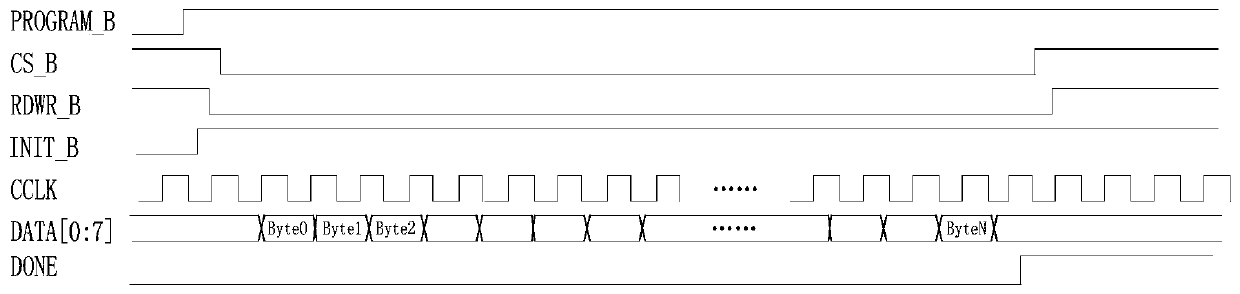

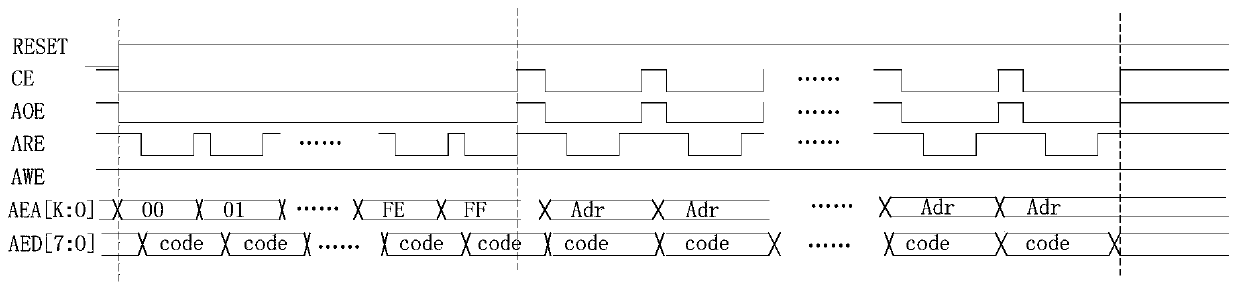

Program on-orbit loading refreshing method based on triple modular redundancy

PendingCN111176908AAvoid bit errorsProperly configure program contentRedundant hardware error correctionEnergy efficient computingDsp architectureDependability

The invention relates to the technical field of satellite loads, in particular to a program on-orbit loading refreshing method based on triple modular redundancy. According to the method, the reliability of on-orbit operation of the space load is remarkably improved, the single-bit overturning phenomenon caused by the space single event phenomenon and the like is avoided to a great extent, and thecontinuous reliability of on-orbit operation of the space load based on the SRAM type FPGA + DSP architecture is improved. The method is simple to implement, and can meet the reliability requirementof long-time on-orbit continuous operation of the space load digital circuit part under the condition of consuming less resources.

Owner:BEIJING RES INST OF TELEMETRY +1

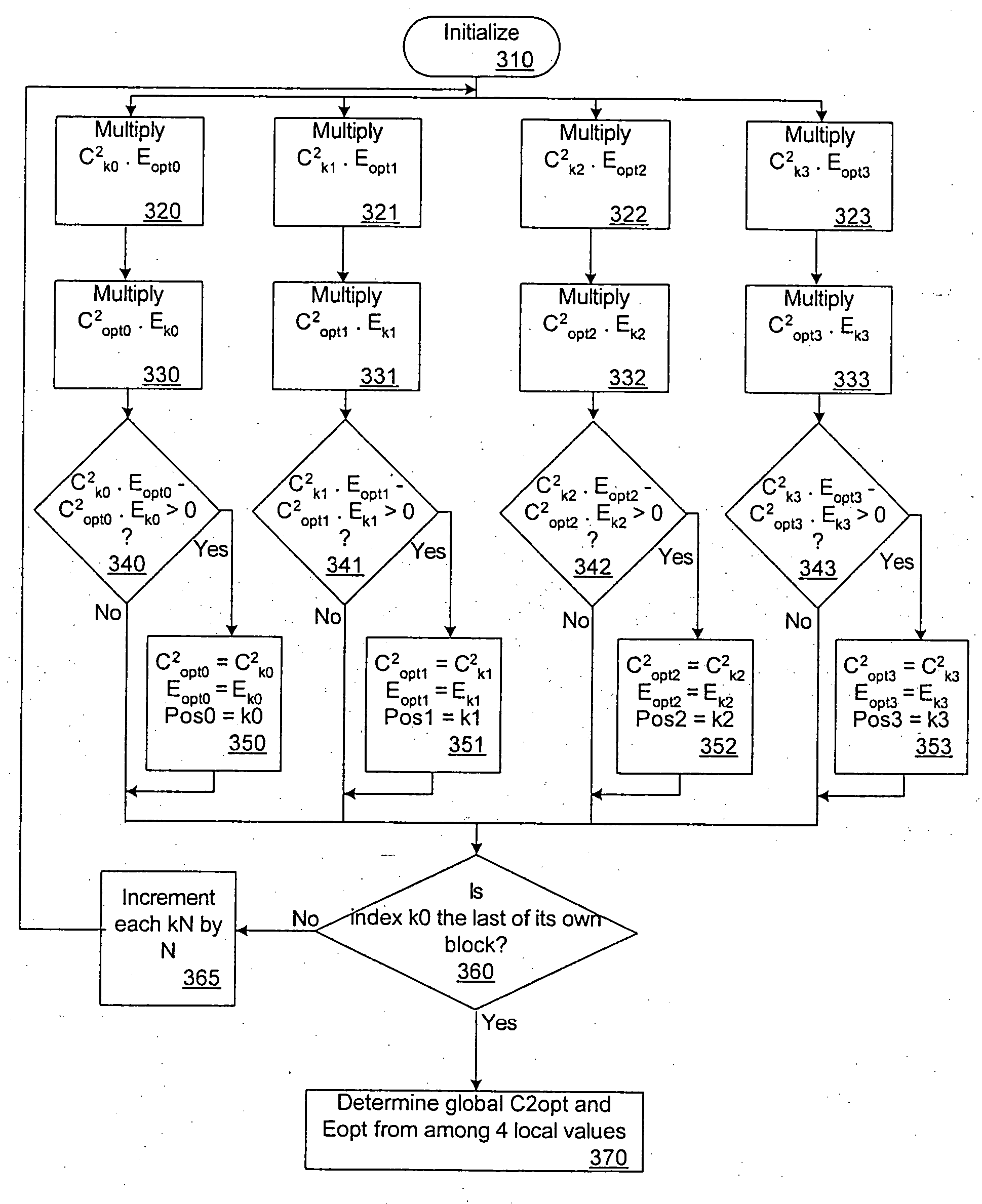

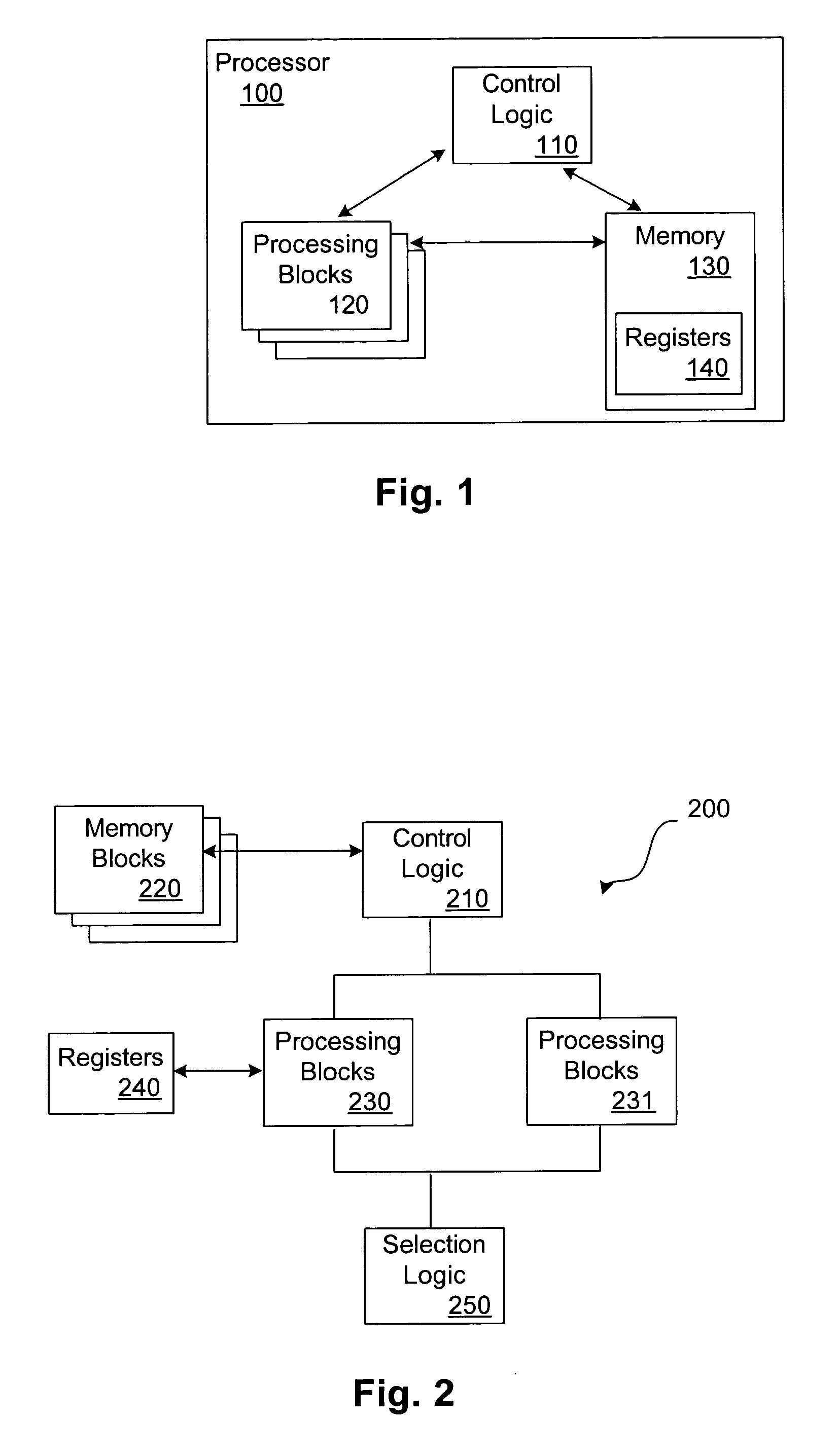

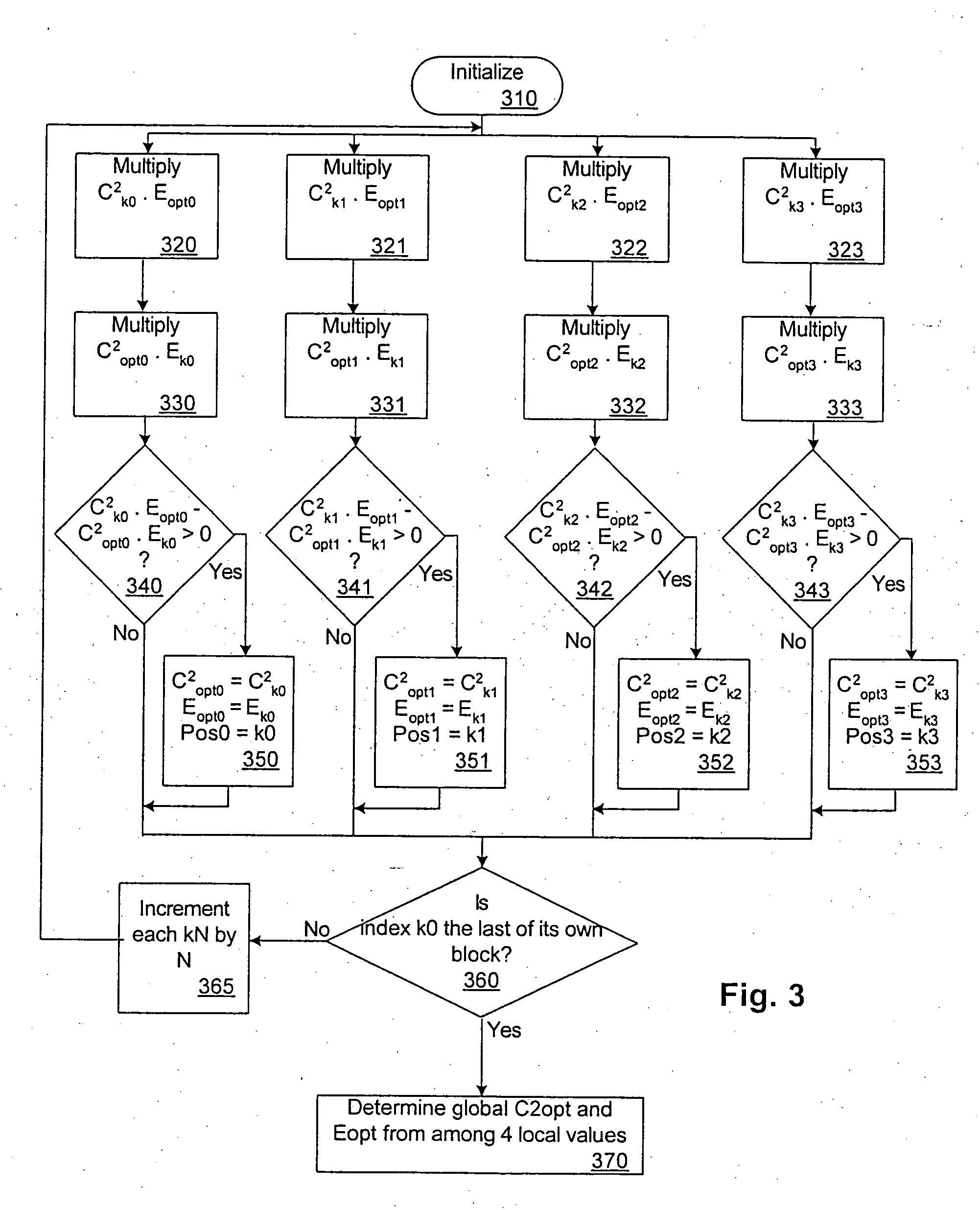

Method for reducing data dependency in codebook searches for multi-ALU DSP architectures

InactiveUS20050050119A1Digital data processing detailsSpeech analysisDsp architectureSequential data

Performing a search of a set of ratios for a maximum or minimum using parallel processing blocks. Various computations related to processing the ratios to determine which is a best value are performed in parallel processing blocks. Splitting the computations into parallel processing paths localizes sequential data dependency by localizing ratio computation and comparison to elements associated with each separate block. After each block determines a local best value, a global best value may be determined.

Owner:INTEL CORP

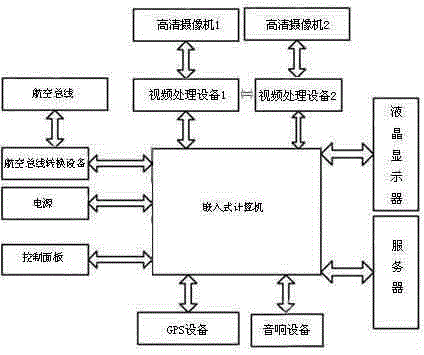

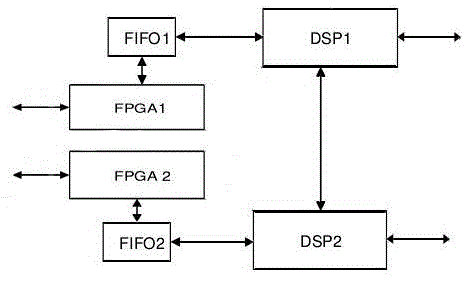

Light airplane comprehensive obstacle avoiding system

InactiveCN104793630AImprove flight safetyImprove securityPosition/course control in three dimensionsDsp architectureAviation

The invention provides a light airplane comprehensive obstacle avoiding system. The light airplane comprehensive obstacle avoiding system comprises data acquisition equipment including aviation bus conversion equipment, GPS (Global Position System) equipment and two high-definition cameras and the like, data processing equipment including two sets of video processing equipment, an embedded type computer, a server and the like, and man-machine interaction equipment including a control panel, sound equipment, a liquid crystal display and the like. The two high-definition cameras are integrated and designed into a nacelle and the optical axes are parallel; and an image plane is parallel or overlapped so that a distance measuring error is reduced. The video processing adopts an FPGA+FIFO+DSP (Field Programmable Gate Array+First-In First-Out-Digital Signal Processor) framework, and a DSP is connected by a high-speed interface. The GPS is fused with a digital map and the like so that known obstacles are avoided. The unknown obstacles are realized by real-time video processing. The server is operated by adopting a website form. The light airplane comprehensive obstacle avoiding system has the advantages that an avionics comprehensive technology, a vision identification technology and a digital map technology are adopted so that a light airplane comprehensive obstacle avoiding function is realized; and the video processing speed is rapid, and the system is economical and intelligent.

Owner:辽宁飞羽航空科技有限公司

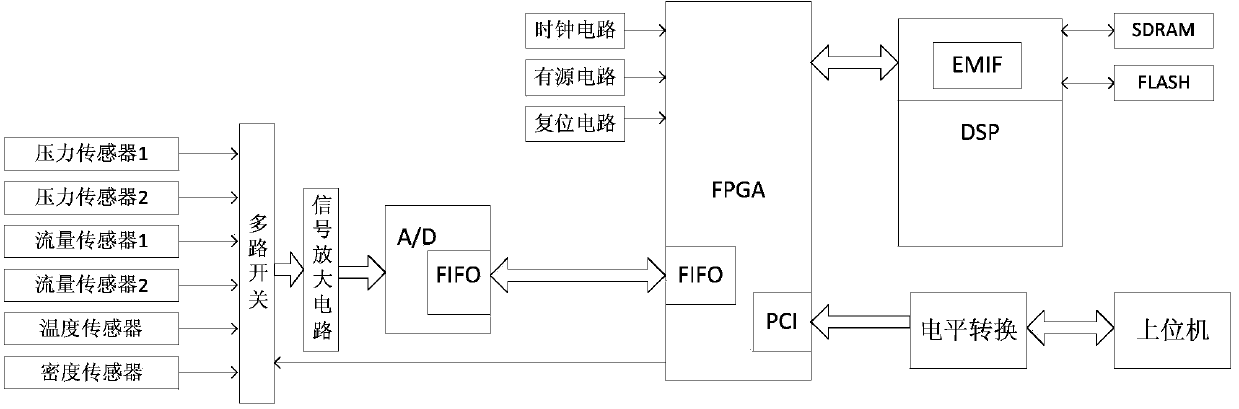

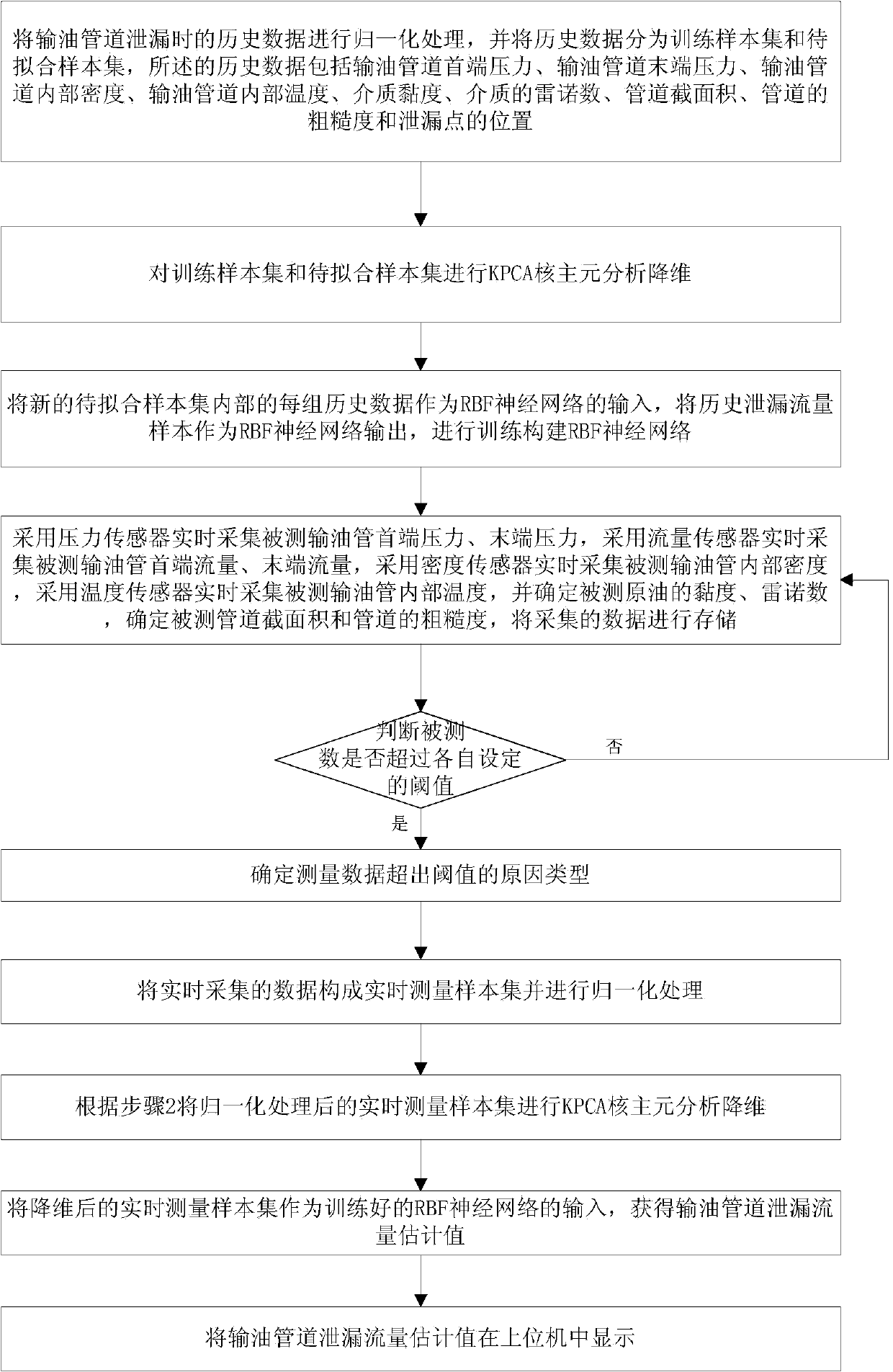

Oil transportation pipeline leakage flow estimating device and method based on KPCA-RBF curve fitting

ActiveCN103994334AImprove real-time performanceReduce development difficultyPipeline systemsKernel principal component analysisDsp architecture

The invention relates to an oil transportation pipeline leakage flow estimating device and method based on KPCA-RBF curve fitting, and belongs to the technical field of oil transportation pipeline detection. According to the estimating method, the dimensionality of data, in which non-linear relationships exist, of an oil transportation pipeline is reduced by using kernel principal component analysis (KPCA), and therefore the number of principal component variables is greatly reduced; the leakage flow is estimated in the mode of KPCA-RBF neural network curve fitting, solution of a high-order equation set is avoided, and accuracy and precision of leakage flow estimation are improved; in addition, information affecting the leakage flow serves as system input, so that the estimating method effectively adapts to the complex and changeful environment, and the practicability of the leakage flow estimating method is improved. An FPGA and DSP architecture is adopted, and compared with a single FPGA system or a single DSP system, an FPGA and DSP system has higher calculation processing capacity; the FPGA and DSP framework simultaneously has the advantages of good real-time performance of an FPGA and low development difficulty of a DSP, shortens a development cycle, reduces technical risks, and is more suitable for real-time data processing, system functions are partitioned clearly, and the overall performance indexes of the system are greatly increased.

Owner:NORTHEASTERN UNIV

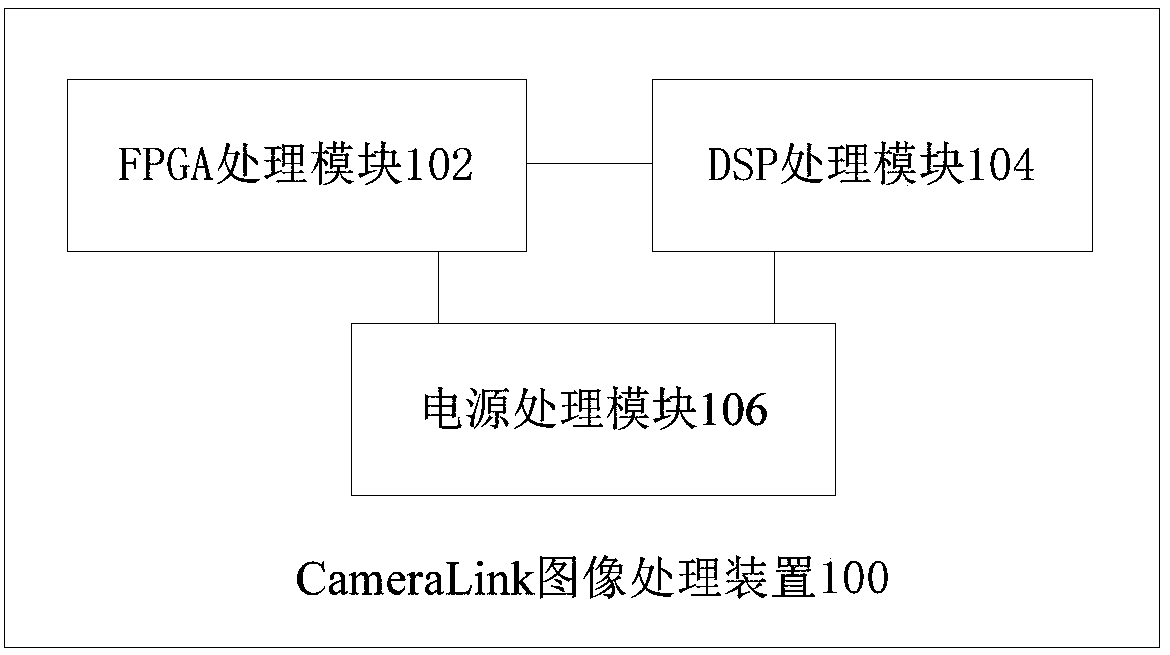

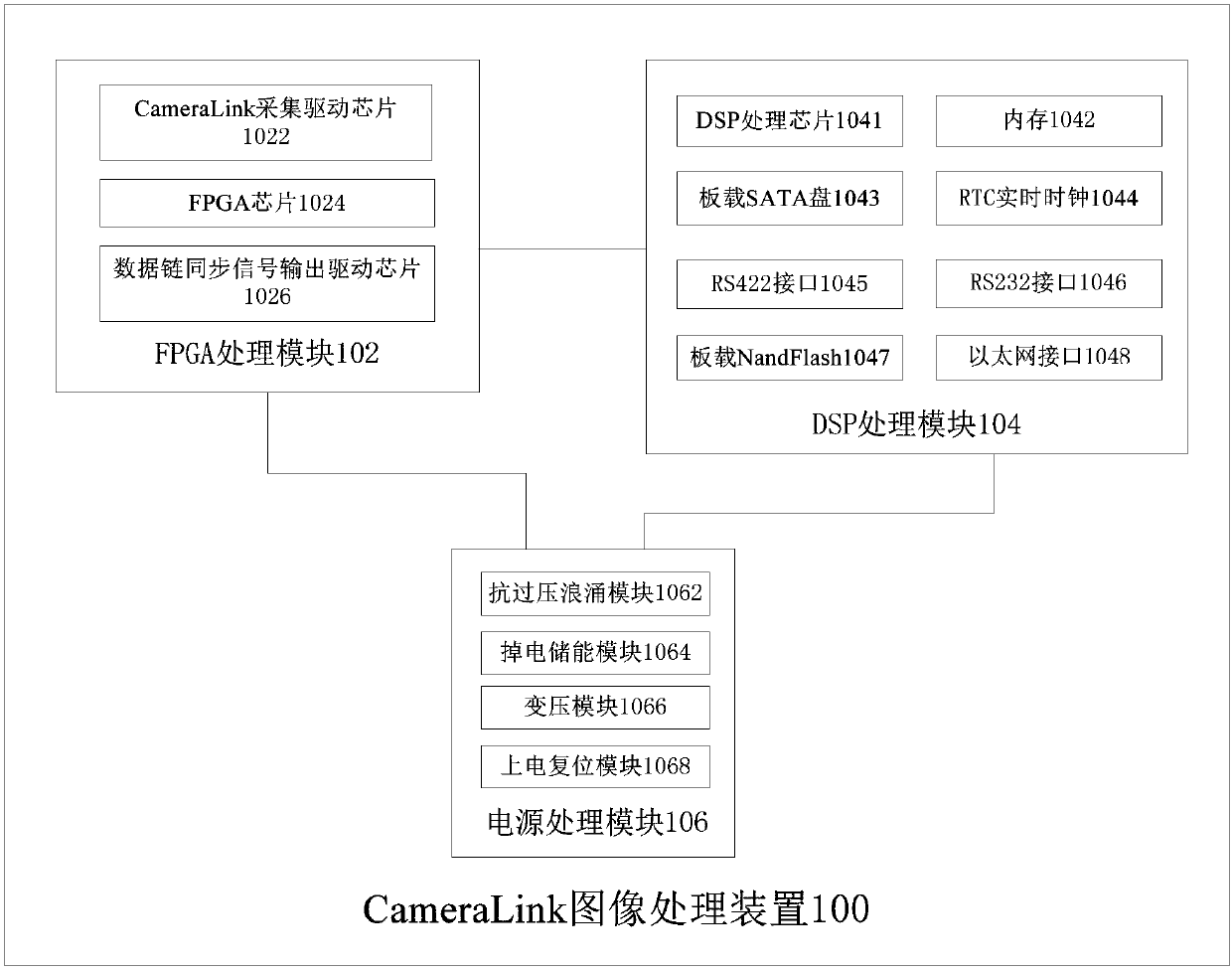

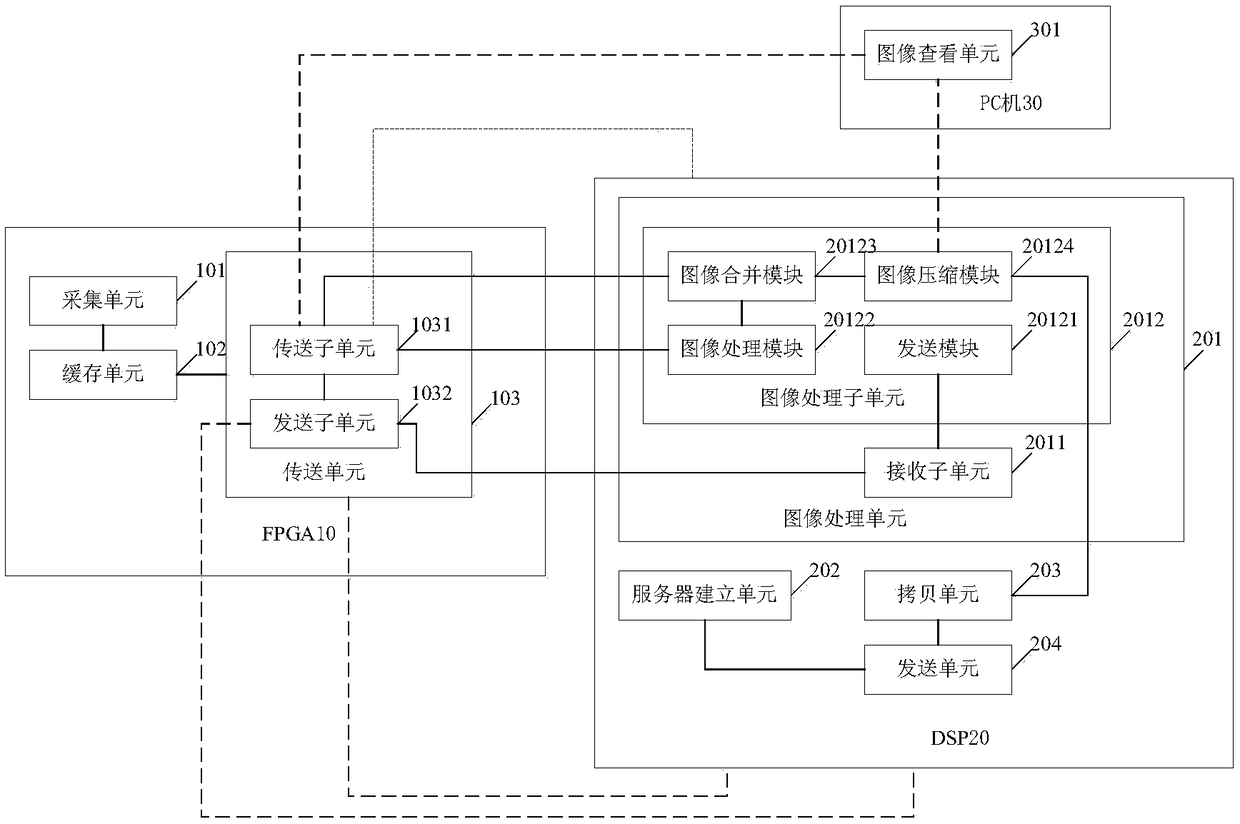

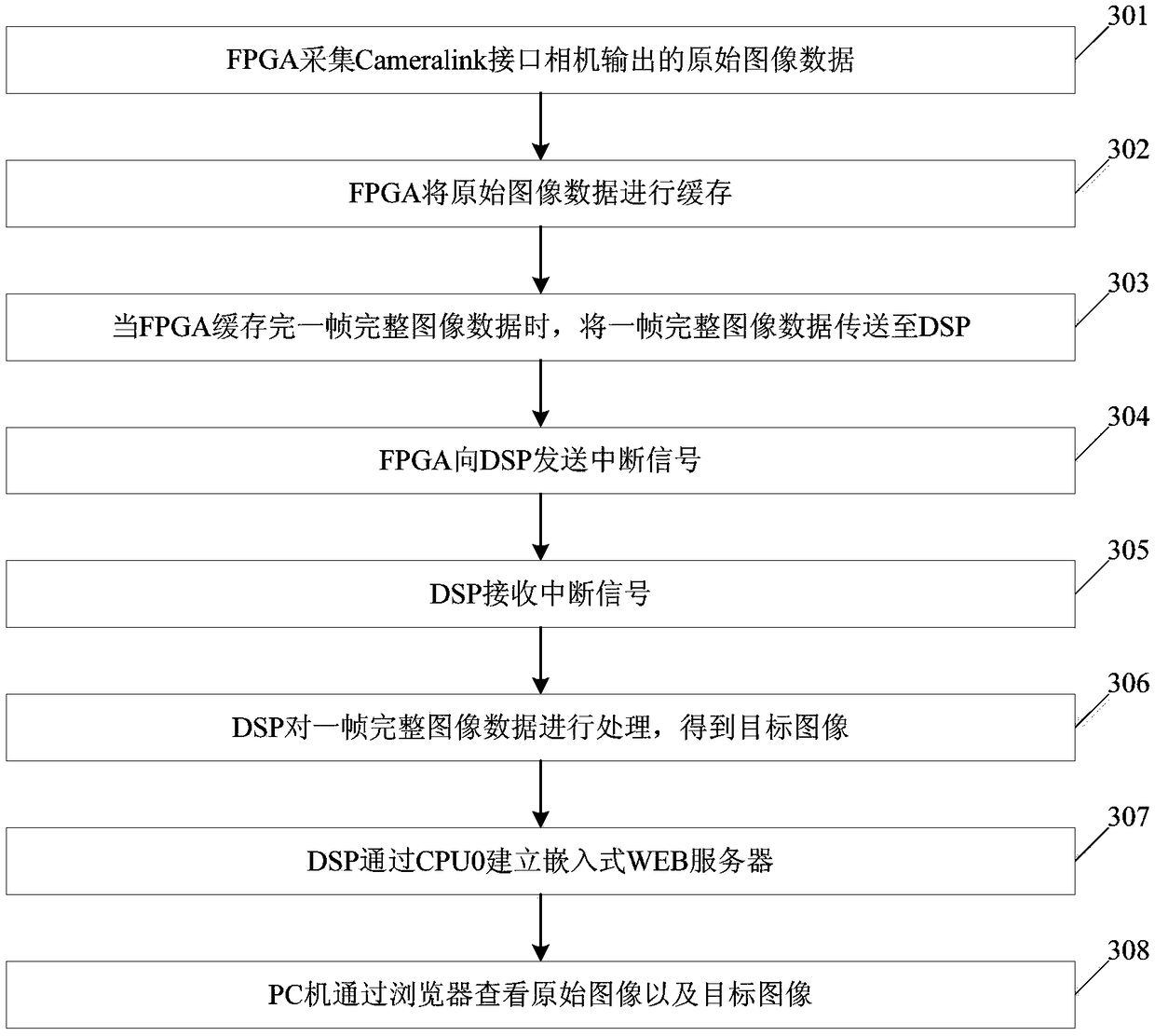

CameraLink image processing device and photoelectric rotating tower

ActiveCN107659784AReduce data bit rateReduce power consumptionTelevision system detailsColor television detailsDsp architectureOn board

The invention provides a CameraLink image processing device and a photoelectric rotating tower, and relates to the technical field of a photoelectric rotating tower. The CameraLink image processing device comprises a FPGA processing module, a DSP processing module and a power supply processing module; and the FPGA processing module acquires a high-definition image in a CameraLink system, convertsgenerated CameraLink data into YUV422 data, sends the YUV422 data to the DSP processing module, receives compressed image data compressed by the DSP processing module and sends the compressed image data to a display control side by a data link, so that the display control side monitors a shooting case of the photoelectric rotating tower in real time. According to the technical scheme provided by the invention, a FPGA and DSP architecture is used, acquired images can be compressed, synchronously transmitted to the data link and synchronously stored in an on-board magnetic disk, snapshot processing on a key region can be implemented, photos are transmitted to the data line in real time, and the CameraLink image processing device and the photoelectric rotating tower can be widely applied in the image recording direction of various on-board, vehicle-mounted and ship-borne photoelectric equipment.

Owner:北京航宇创通技术股份有限公司

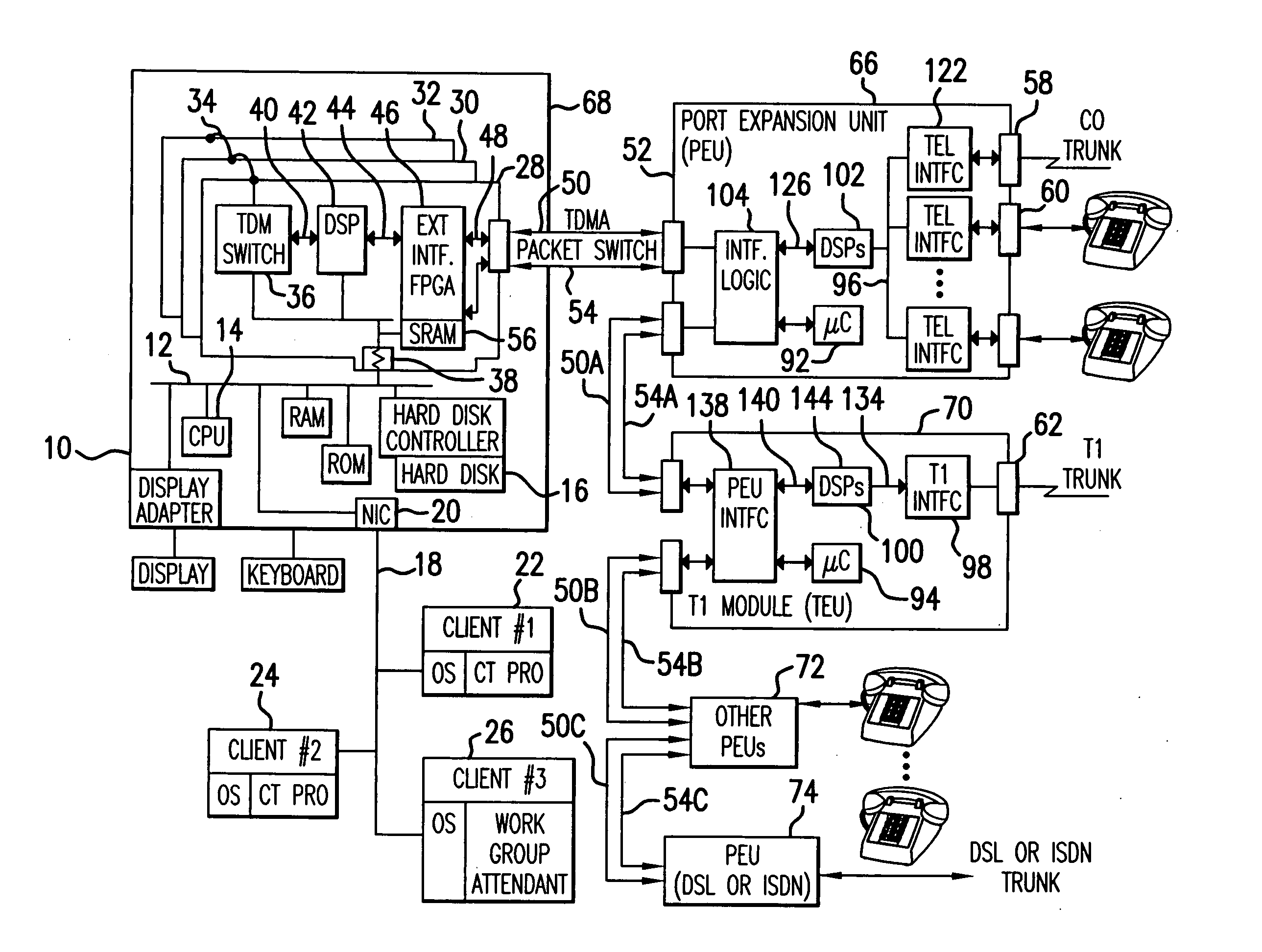

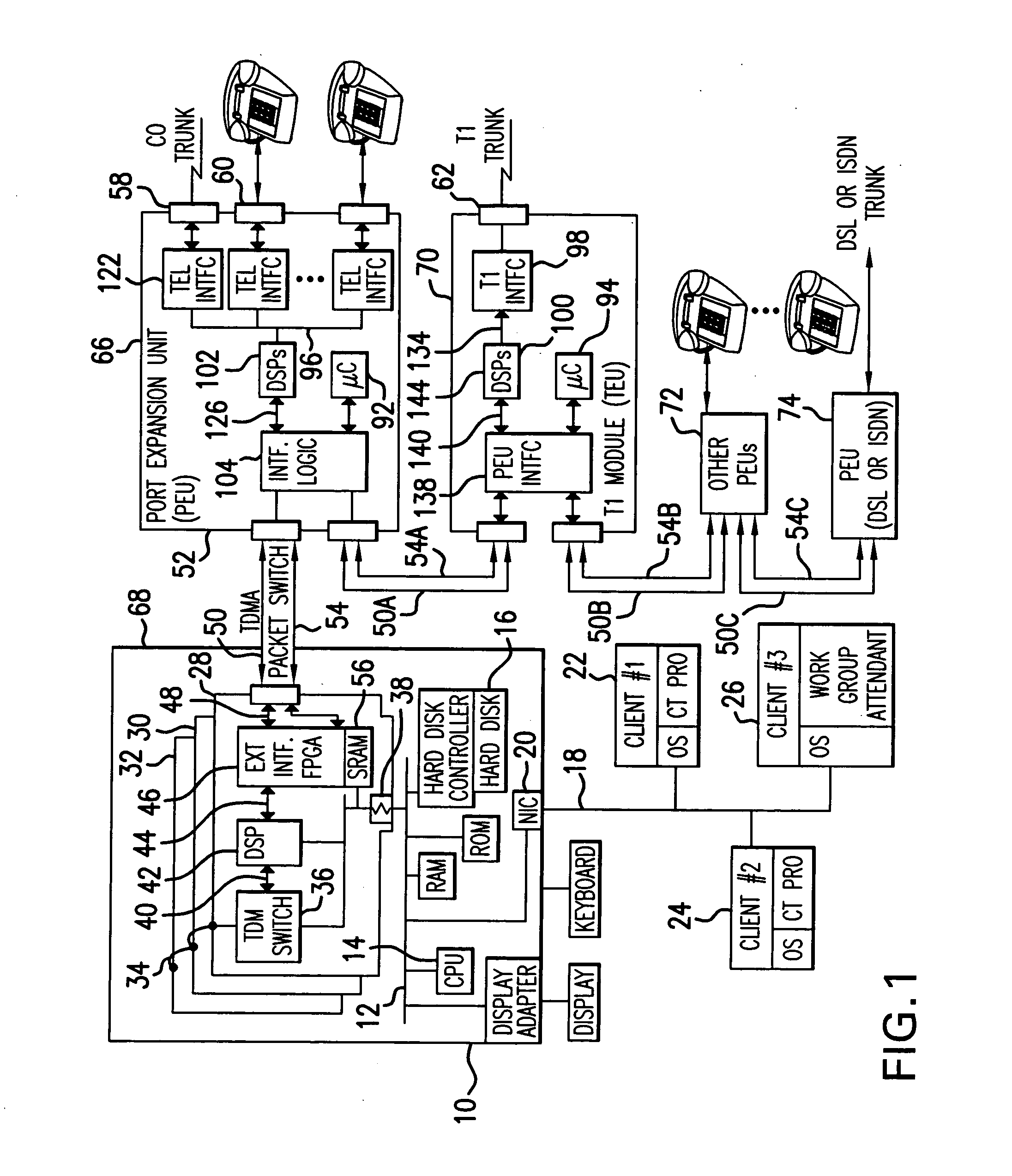

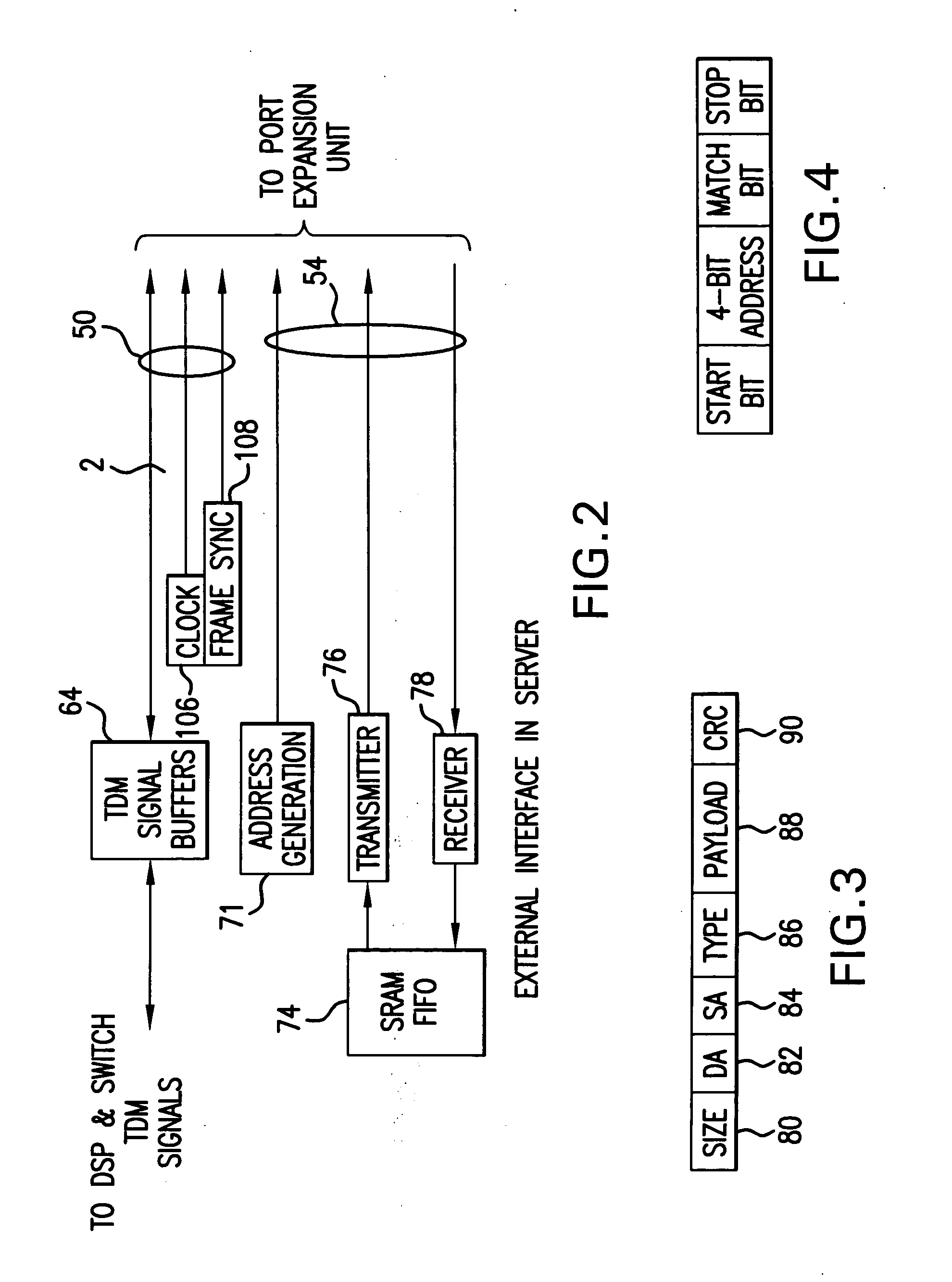

IP packet ready PBX expansion circuit for a conventional personal computer with expandable, distributed DSP architecture

InactiveUS20050030941A1Avoid bottlenecksDigital signal processing capabilitySpecial service for subscribersTime-division multiplexDsp architectureScalable distributed

A personal computer includes a PBX control program and one or more switch cards located in expansion board slots. The one or more switch cards are coupled to one or more port expansion units (PEU), which are coupled to telecommunication lines out to the various extension phones at the customer premises. Each PEU contains its own digital signal processor (DSP) so that distributed digital signal processing may be implemented to avoid any bottlenecks. One master PEU is coupled to a switch card by a time division multiplexed (TDMA) bus as well as a packet switched control bus, and all the other PEUs, if any, are coupled to the master PEU by extensions of the TDMA and packet switched buses. The TDMA bus carries PBX real time conversations while the packet switched bus carries control information, voicemail outbound message data packets, and inbound voicemail data packets.

Owner:INTEL CORP

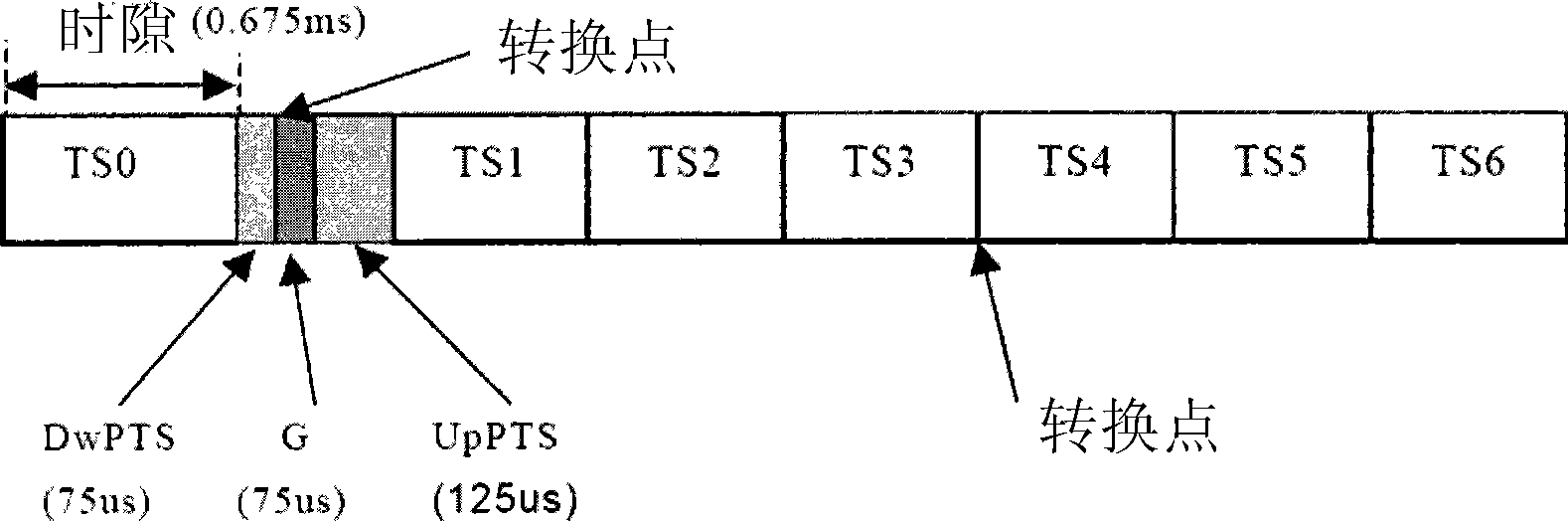

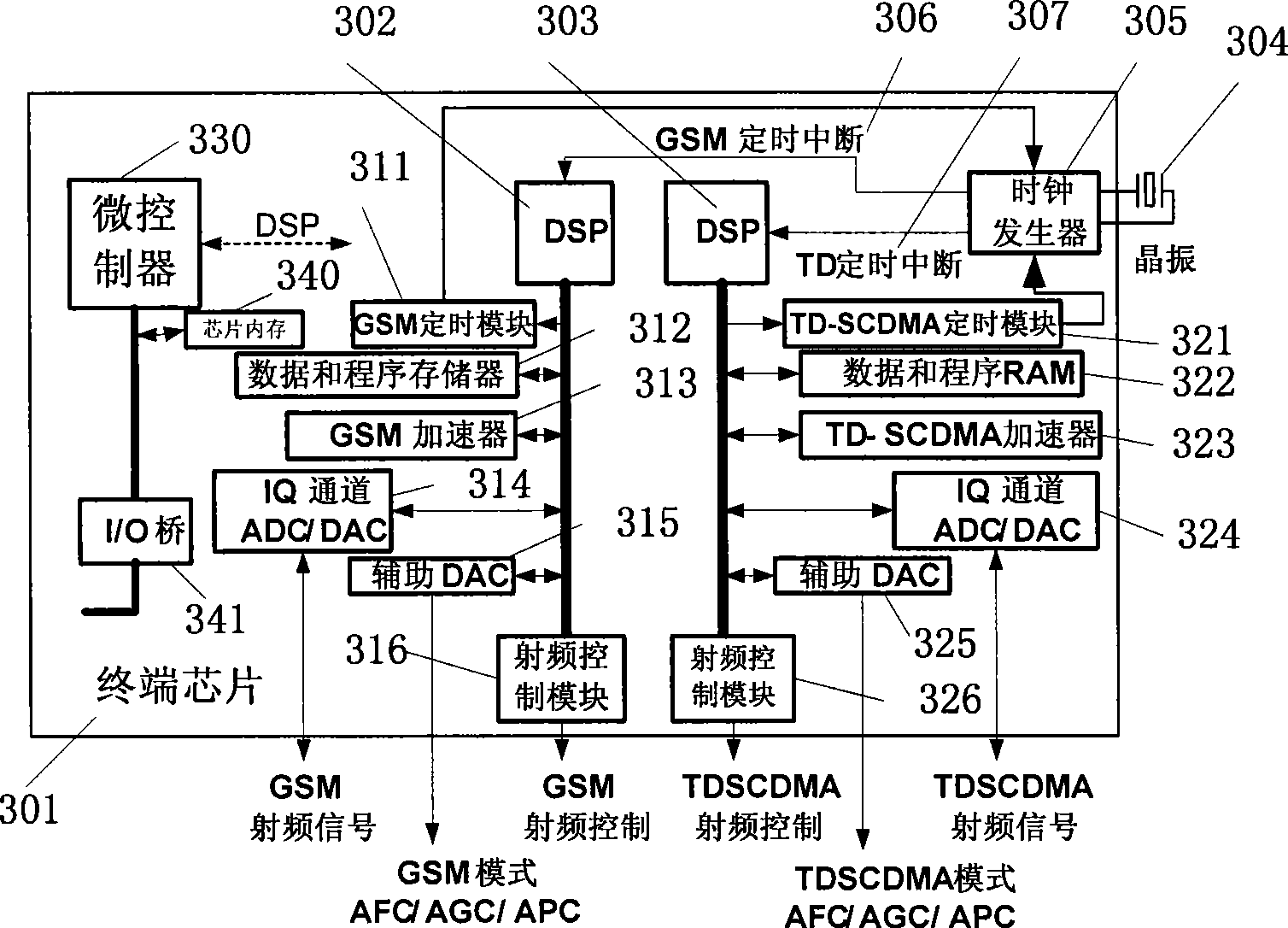

GSM/TD-SCDMA dual-mode terminal chip having single chip and single DSP construction

ActiveCN101400178AReduce areaReduce the totalTransmissionHigh level techniquesDsp architectureDual mode

The present invention discloses a GSM / TD-SCDMA terminal chip of a single-chip single DSP architecture, which realizes the GSM and TD system programs on a single DSP, thereby reducing the chip area and cost, lowering power consumption and improving the performance of interactive systems. The chip includes: a micro-controller; a single clock generator and crystal vibration; and a single DSP chip. The single DSP chip includes a chip control module, responding GSM frame interrupt and TD frame interrupt in time, distributing system resources to the GSM mode and TD-SCDMA mode, controlling the start-up of the GSM and TD-SCDMA radiofrequency signal, and shielding the GSM timer interruption or TD-SCDMA timer interruption for manually controlling network or single mode terminal; a sleeping mode dual affirmation module, detecting that the GSM and TD-SCDMA are all at a sleeping allowing state for allowing the DSP chip to enter into a sleeping mode; a GSM accelerator and a TD-SCDMA accelerator, for performing auxiliary digital signal processing to GSM and TD-SCDMA under the control of a single DSP. The invention can be applied to the mobile communications field.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

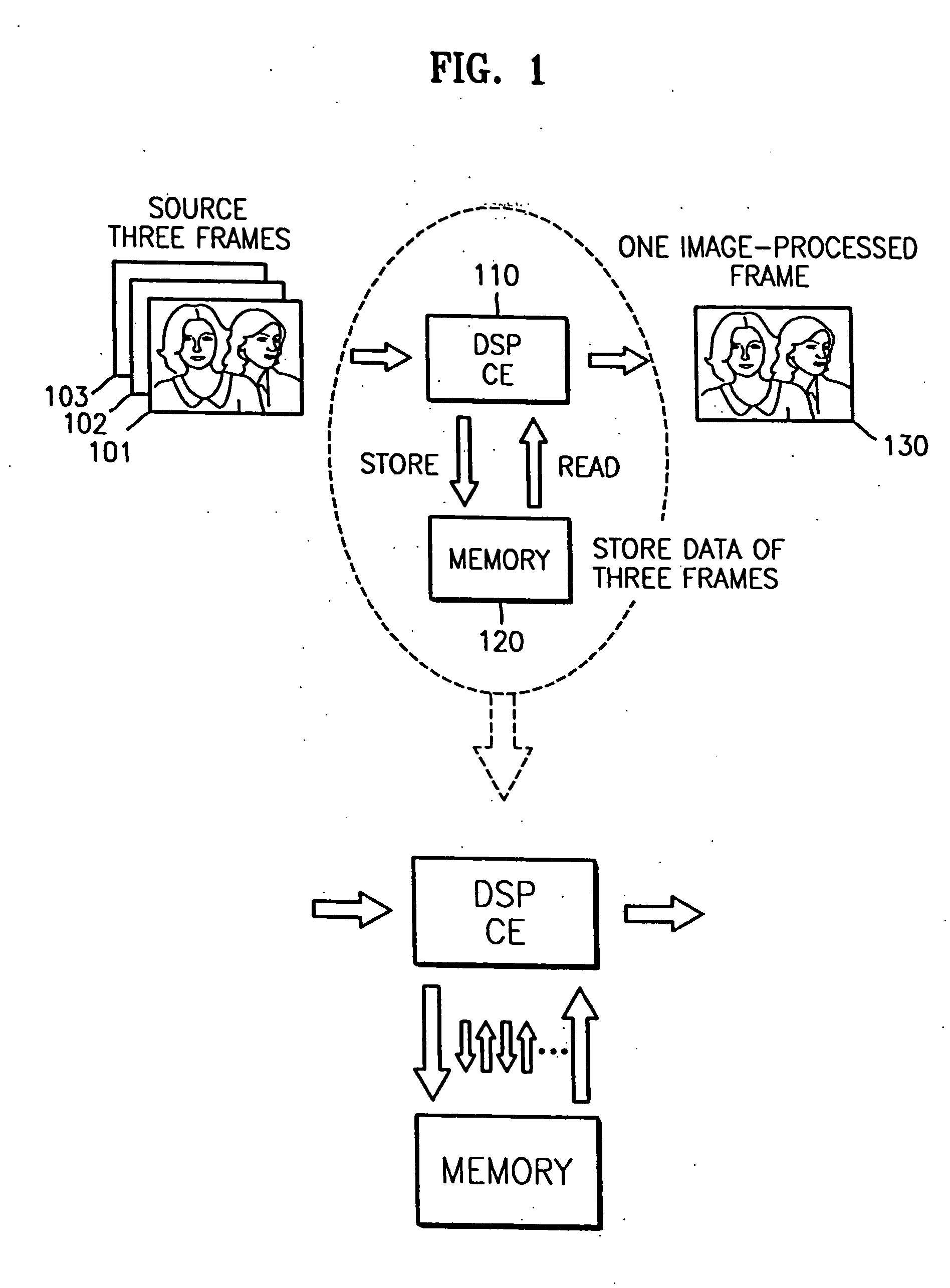

Program controlled embedded-DRAM-DSP architecture and methods

InactiveUS7272703B2Reduce and eliminate wait timeReduce delaysMemory architecture accessing/allocationRegister arrangementsDsp architectureProcessor register

An efficient embedded-DRAM processor architecture and associated methods. In one exemplary embodiment, the architecture includes a DRAM array, a set of register files, set of functional units, and a data assembly unit. The data assembly unit includes a set of row-address registers and is responsive to commands to activate and deactivate DRAM rows and to control the movement of data throughout the system. A pipelined data assembly approach allowing the functional units to perform register-to-register operations, and allowing the data assembly unit to perform all load / store operations using wide data busses. Data masking and switching hardware allows individual data words or groups of words to be transferred between the registers and memory. Other aspects of the invention include a memory and logic structure and an associated method to extract data blocks from memory to accelerate, for example, operations related to image compression and decompression.

Owner:ROUND ROCK RES LLC

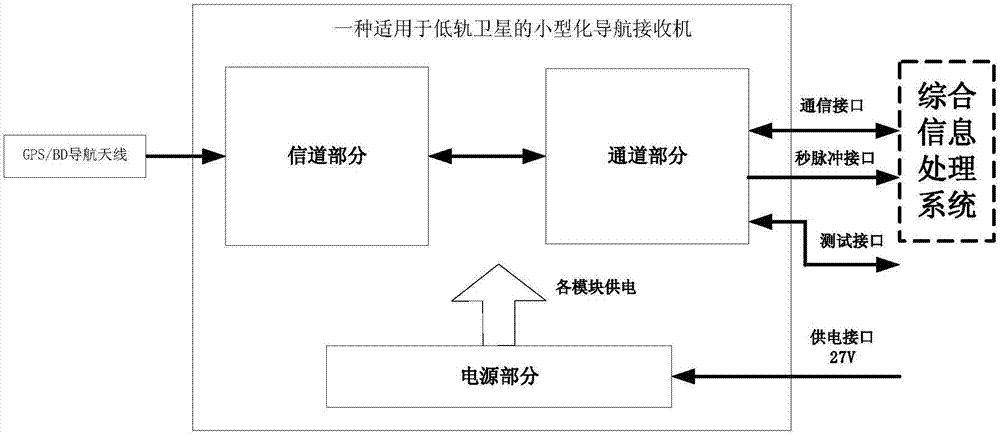

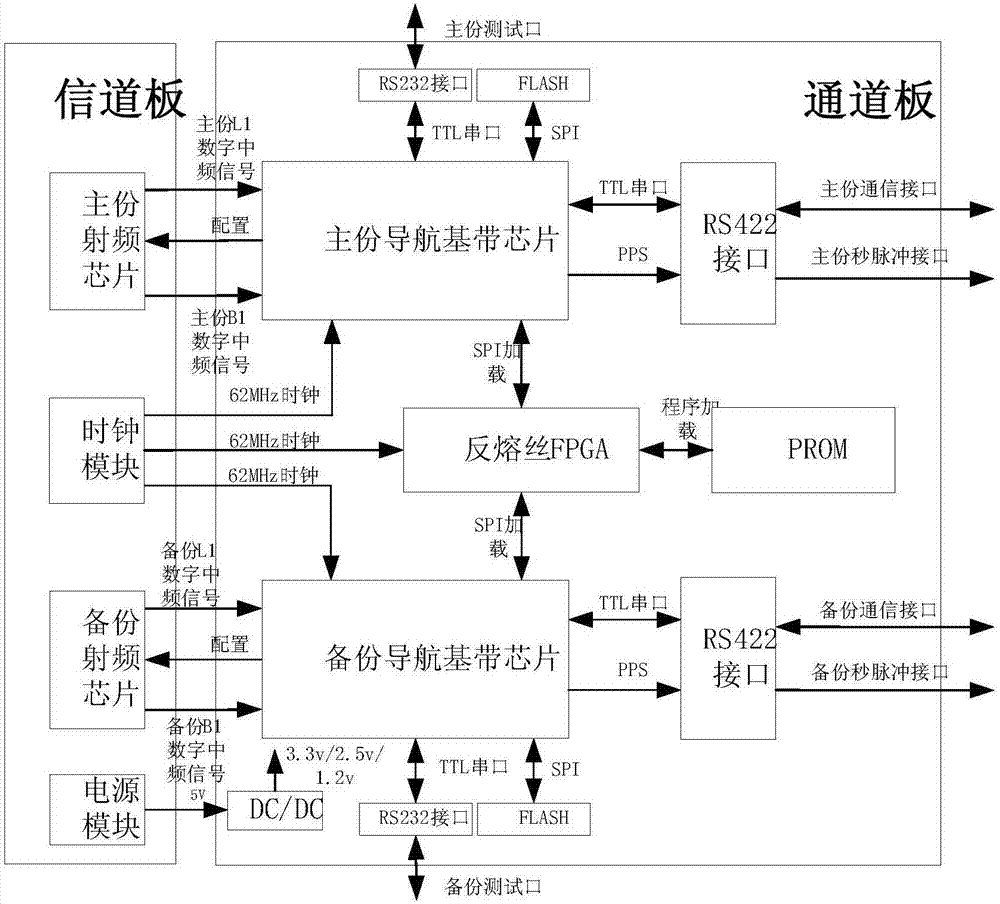

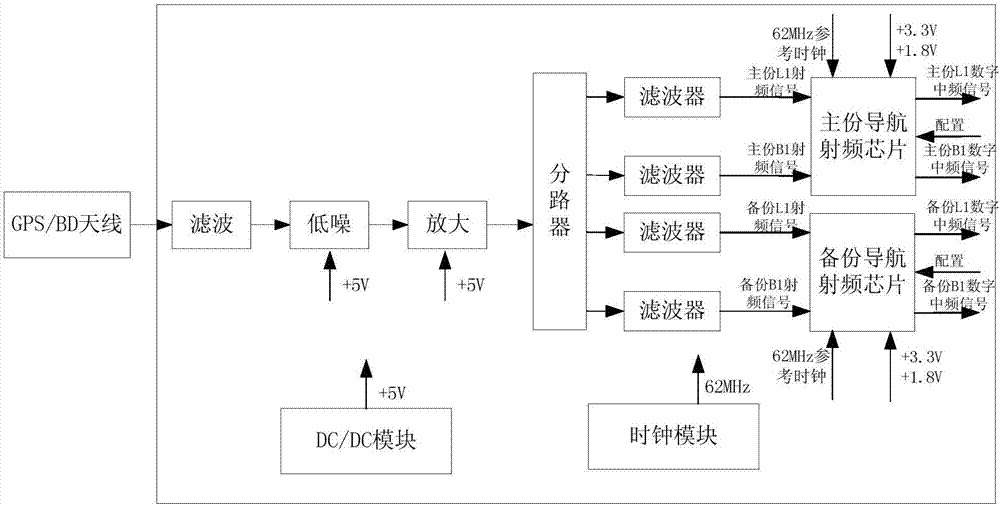

Small navigation receiver applicable to low-earth-orbit satellite

InactiveCN107976694AReduce electromagnetic interferenceImprove receiver sensitivitySatellite radio beaconingDsp architectureCore component

The invention discloses a small navigation receiver applicable to a low-earth-orbit satellite. The small navigation receiver has the advantages that integral design integrating multiple modules such as a channel module and a passage module; the FPGA+DSP architecture of a traditional navigation receiver is broken through, core component's dependence on import is eliminated, a radio frequency chip and base band SoC chip group is applied in an in-orbit manner, and satellite borne navigation production core function chips and domestic design are achieved; a navigation equipment space operation environment is combined with an orbit determination combining dynamics and kinematics to provide a multi-navigation-system real-time orbit determination method, and broadcast ephemeris orbit errors adopta random walk strategy to perform parameterization separation; on the basis of the anti-error estimation principle, extended Kalman filter is used to estimate the optimal motion state of the low-earth-orbit satellite, and spatial information such as high-precision real-time positions and speed is provided for a satellite platform and load; the small navigation receiver is high in reliability, lightweight, especially applicable to small satellite environments and capable of satisfying the requirements of high-reliability, high-integrity and small-size satellite systems.

Owner:BEIJING RES INST OF TELEMETRY +1

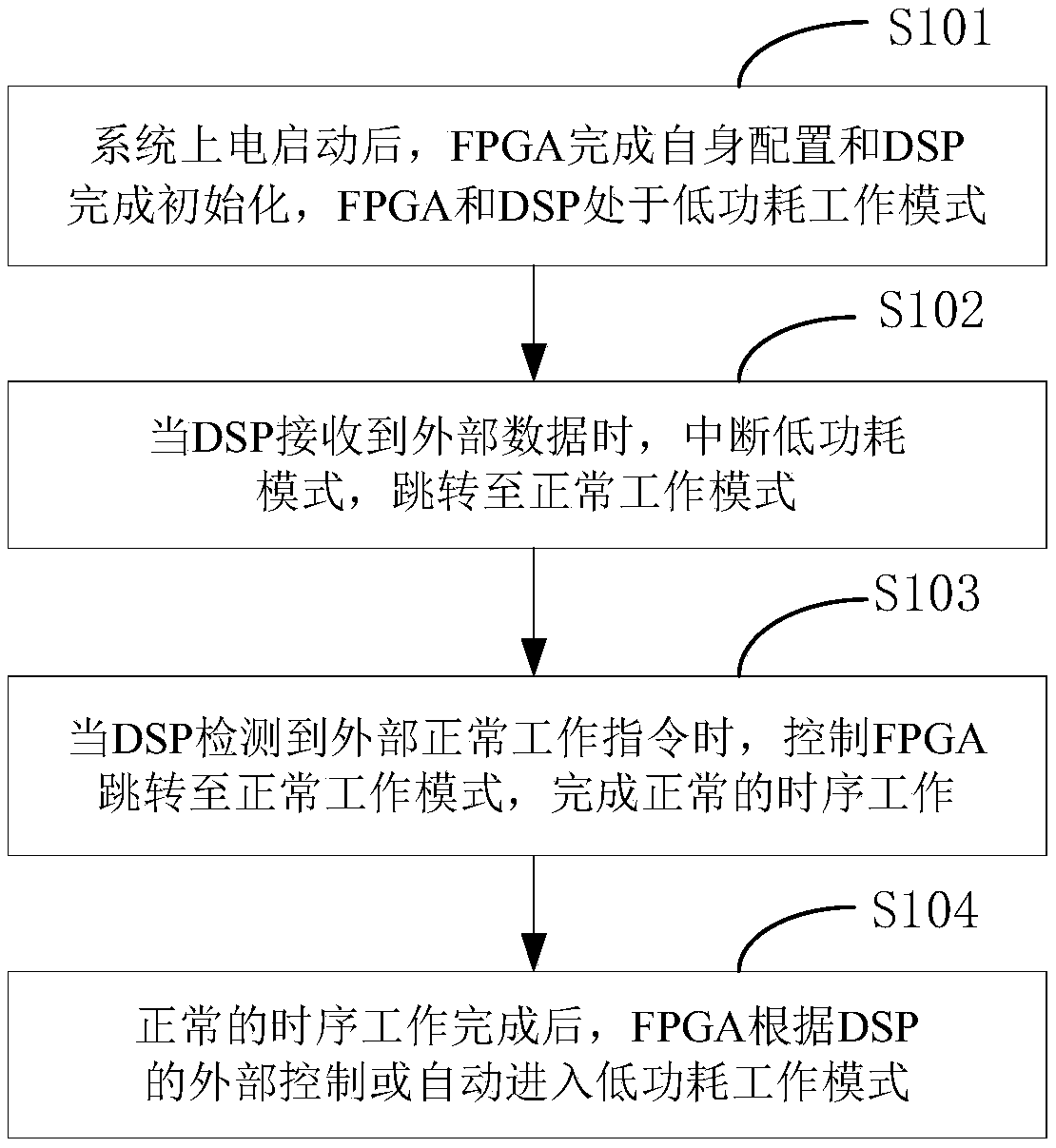

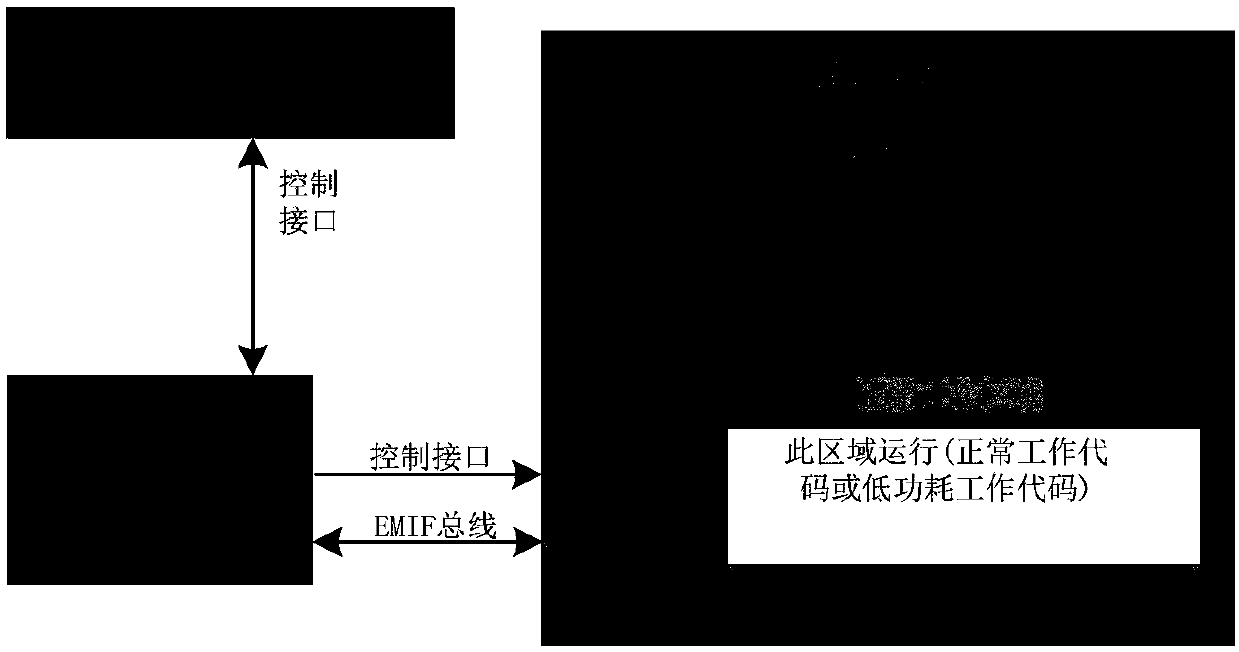

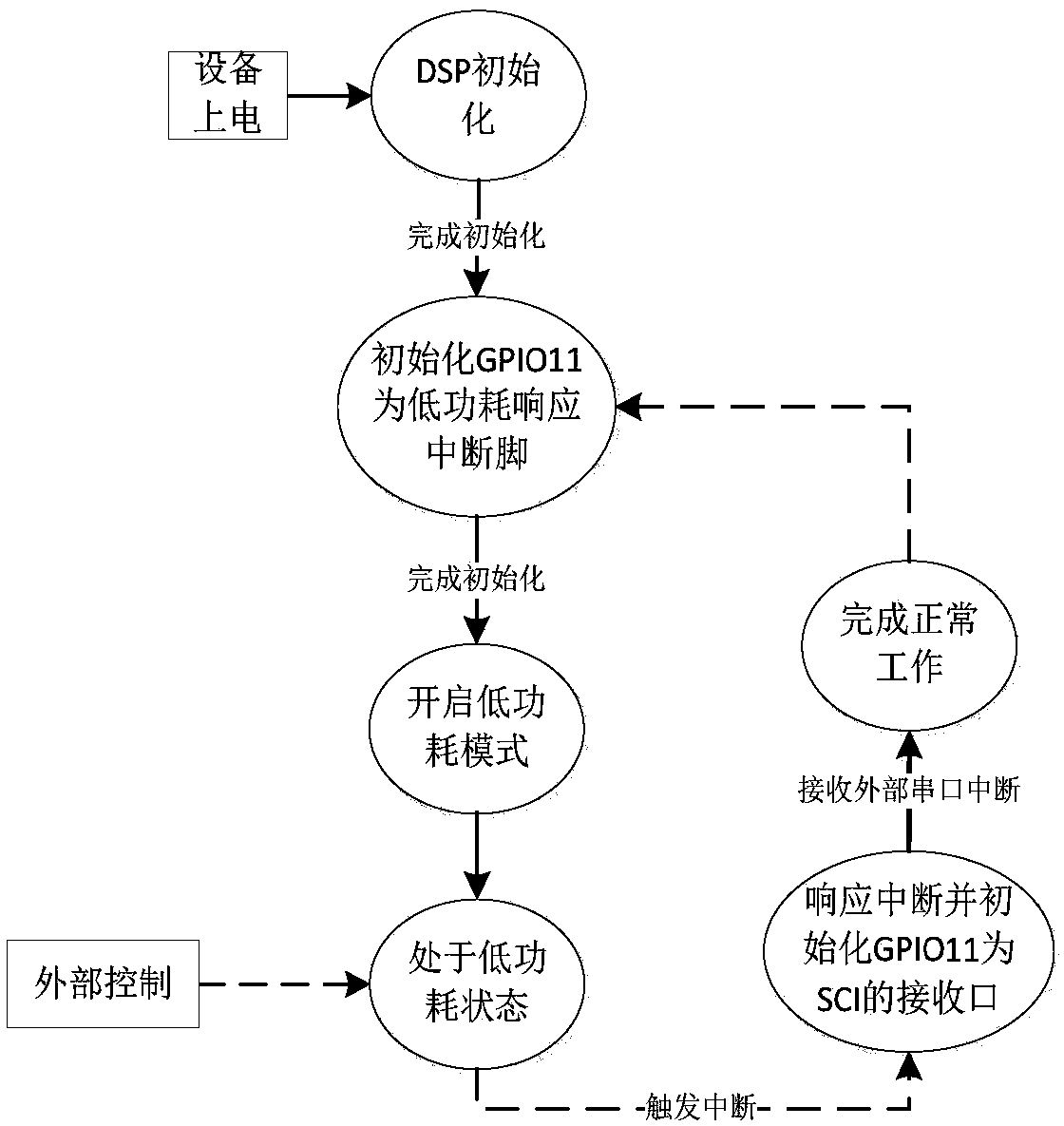

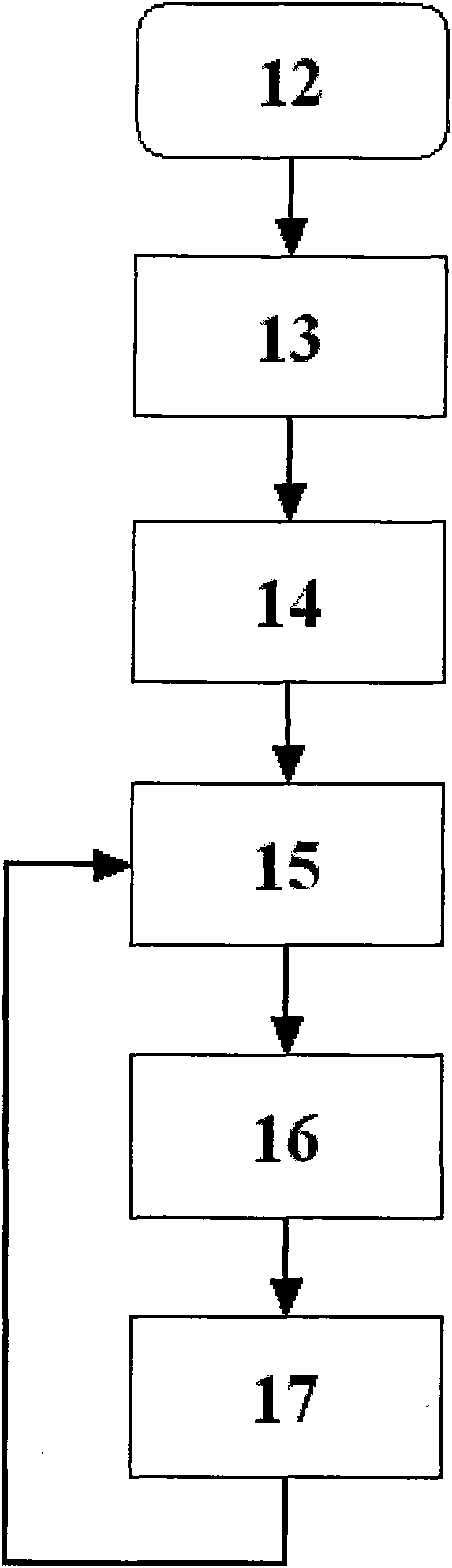

Low-power-consumption processing method based on an FPGA and a DSP architecture

ActiveCN109613970AReduce power consumptionImprove stabilityDigital data processing detailsElectricityDsp architecture

The invention relates to a low-power-consumption processing method based on an FPGA and a DSP architecture, and belongs to the technical field of digital signal processing. The method comprises the following steps that after a system is powered on and started, an FPGA completes self-configuration and DSP initialization, and the FPGA and the DSP are in a low-power-consumption working mode; when theDSP receives the external data, interrupting the low-power-consumption mode, and skipping to a normal working mode; when the DSP detects an external normal working instruction, the FPGA is controlledto jump to a normal working mode, and normal time sequence work is completed; and after the normal time sequence work is finished, the FPGA automatically enters a low-power-consumption working mode according to the external control of the DSP. According to the invention, the problems of unstable work and high consumption of the system caused by high power consumption of the FPGA and the DSP are effectively solved or relieved.

Owner:SICHUAN JIUZHOU ELECTRIC GROUP

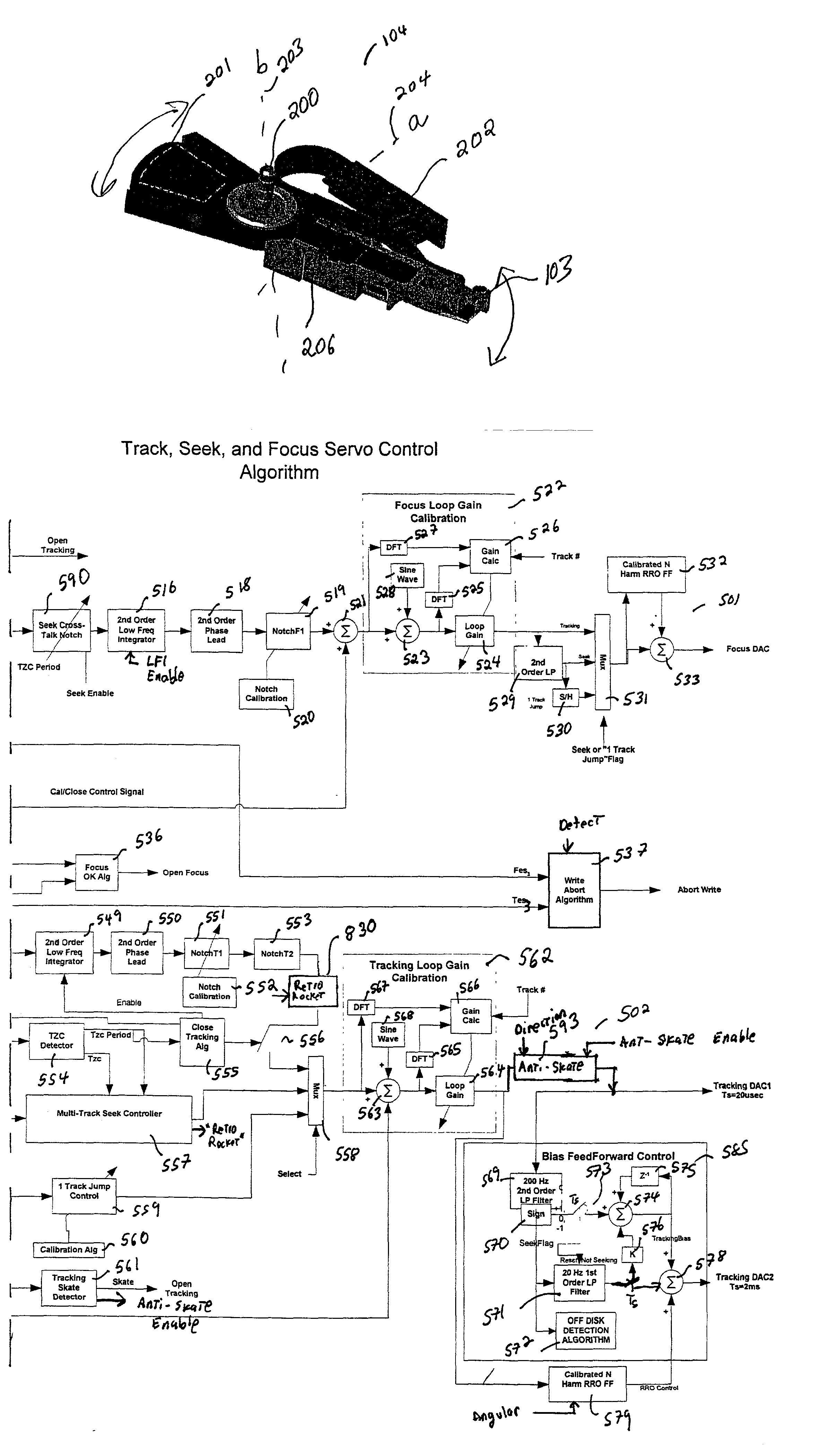

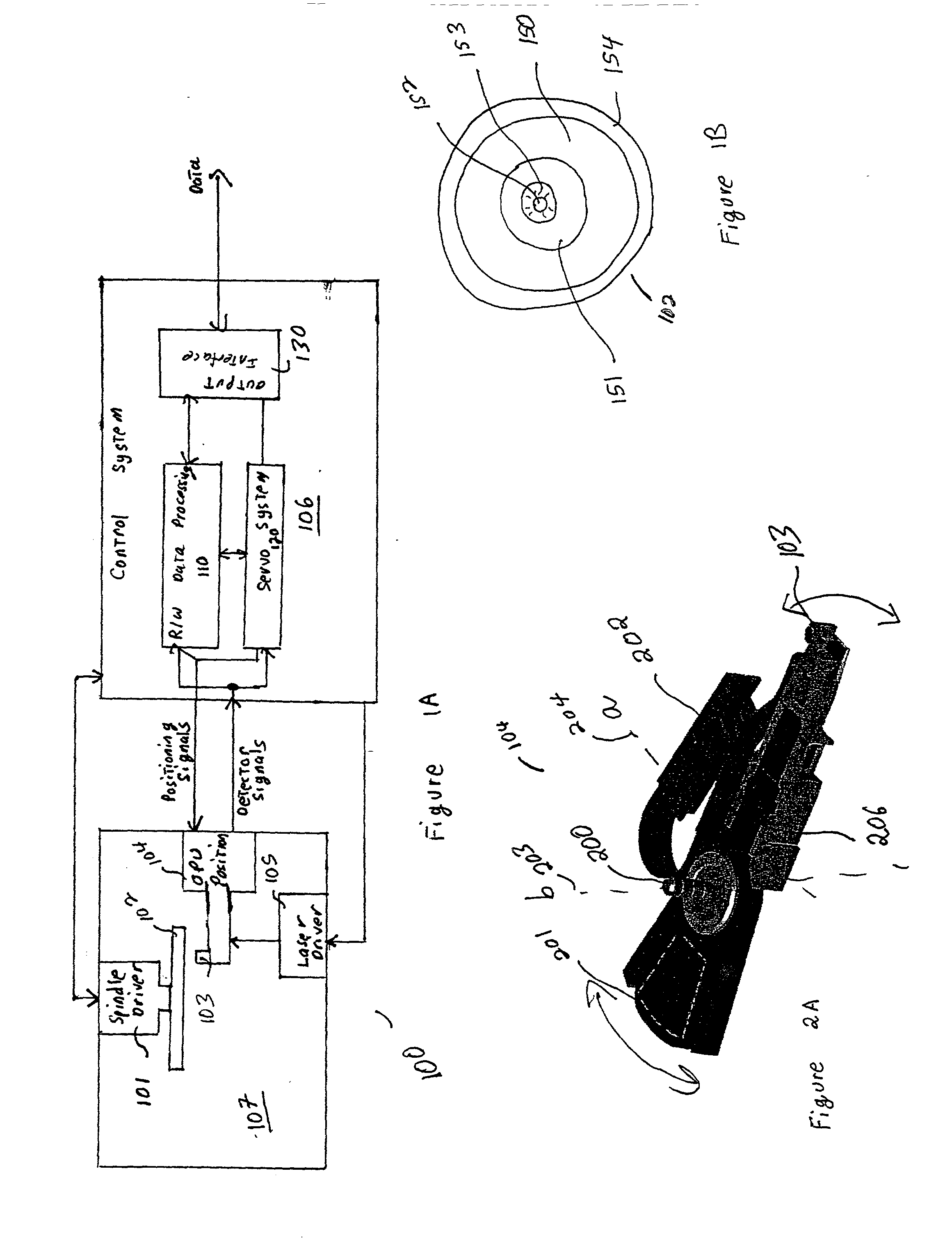

Digital tracking and focus servo system with a DSP architecture

InactiveUS20020097644A1Combination recordingIntegrated optical head arrangementsDsp architectureComputer science

A system with a plurality of servo algorithms executing on a digital signal processor is presented. The digital signal processor receives a sensor interrupt, indicating availability of digitized data from optical sensors, and decides which of a plurality of servo algorithms to service in response to the interrupt. In some embodiments, the plurality of servo algorithms includes a tracking servo algorithm. In some embodiments, the plurality of servo algorithms includes a focus servo algorithm. In some embodiments, multi-track seek operations or one-track jump operations can also be serviced during the interrupt period.

Owner:RPX CORP +1

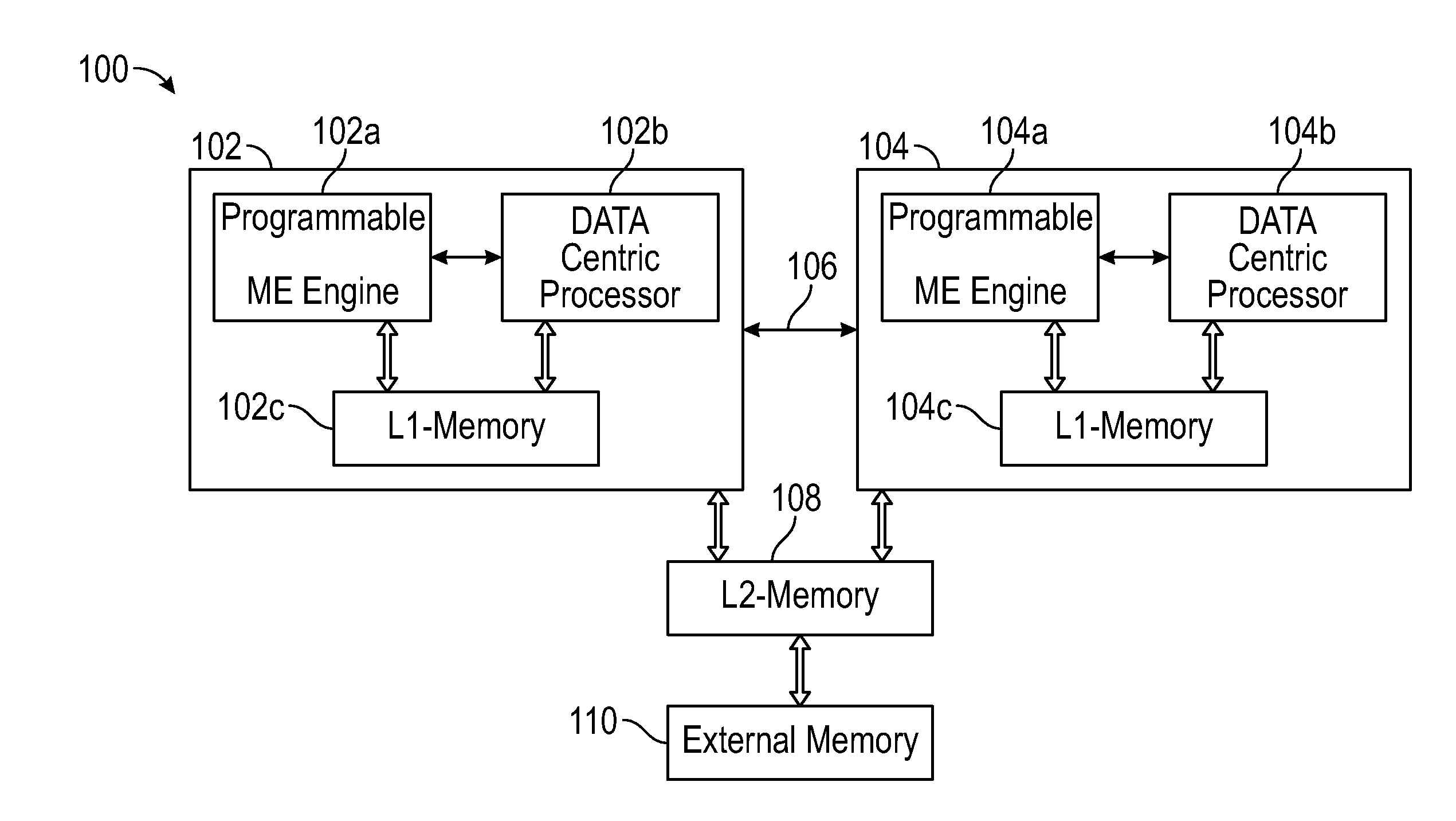

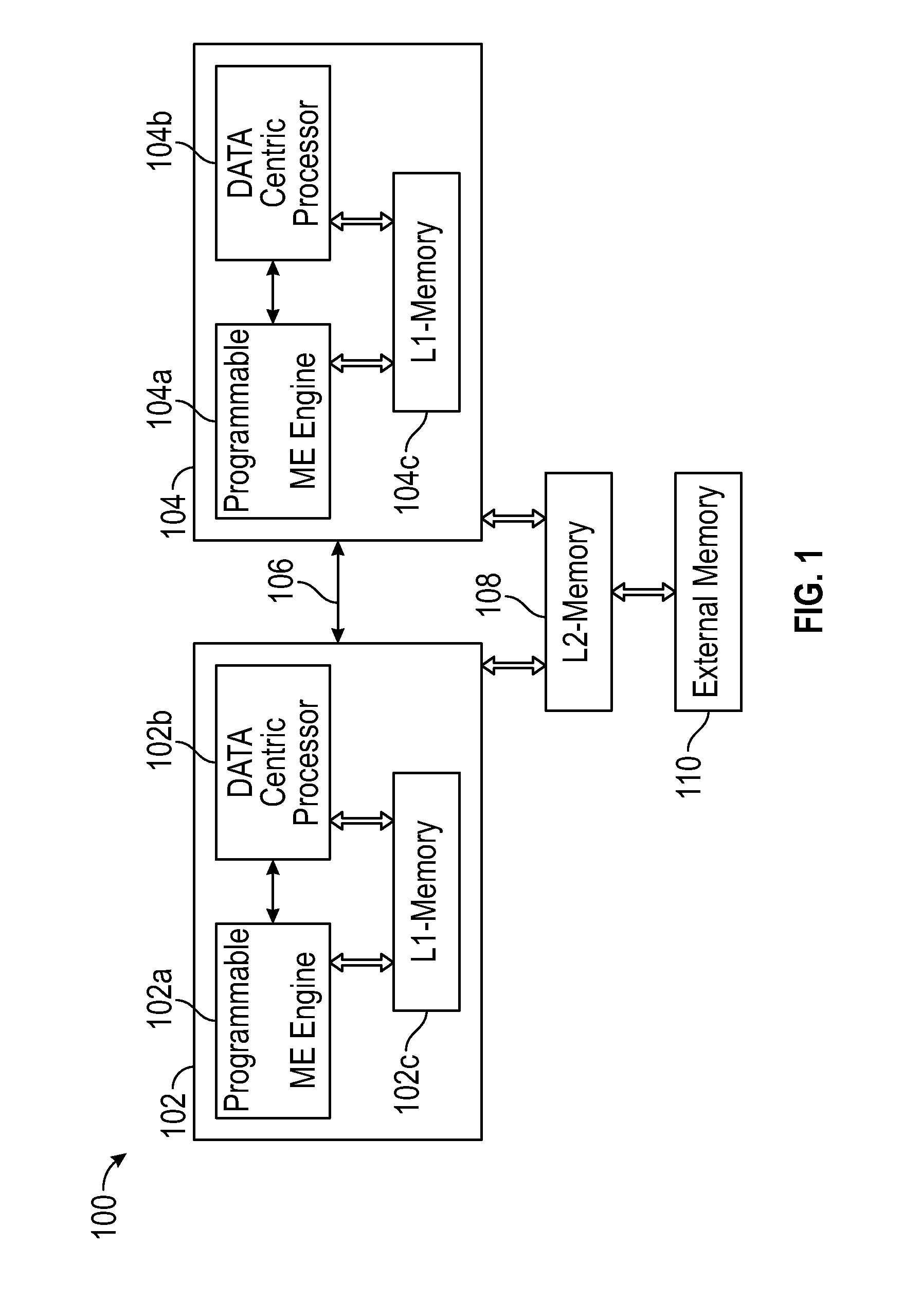

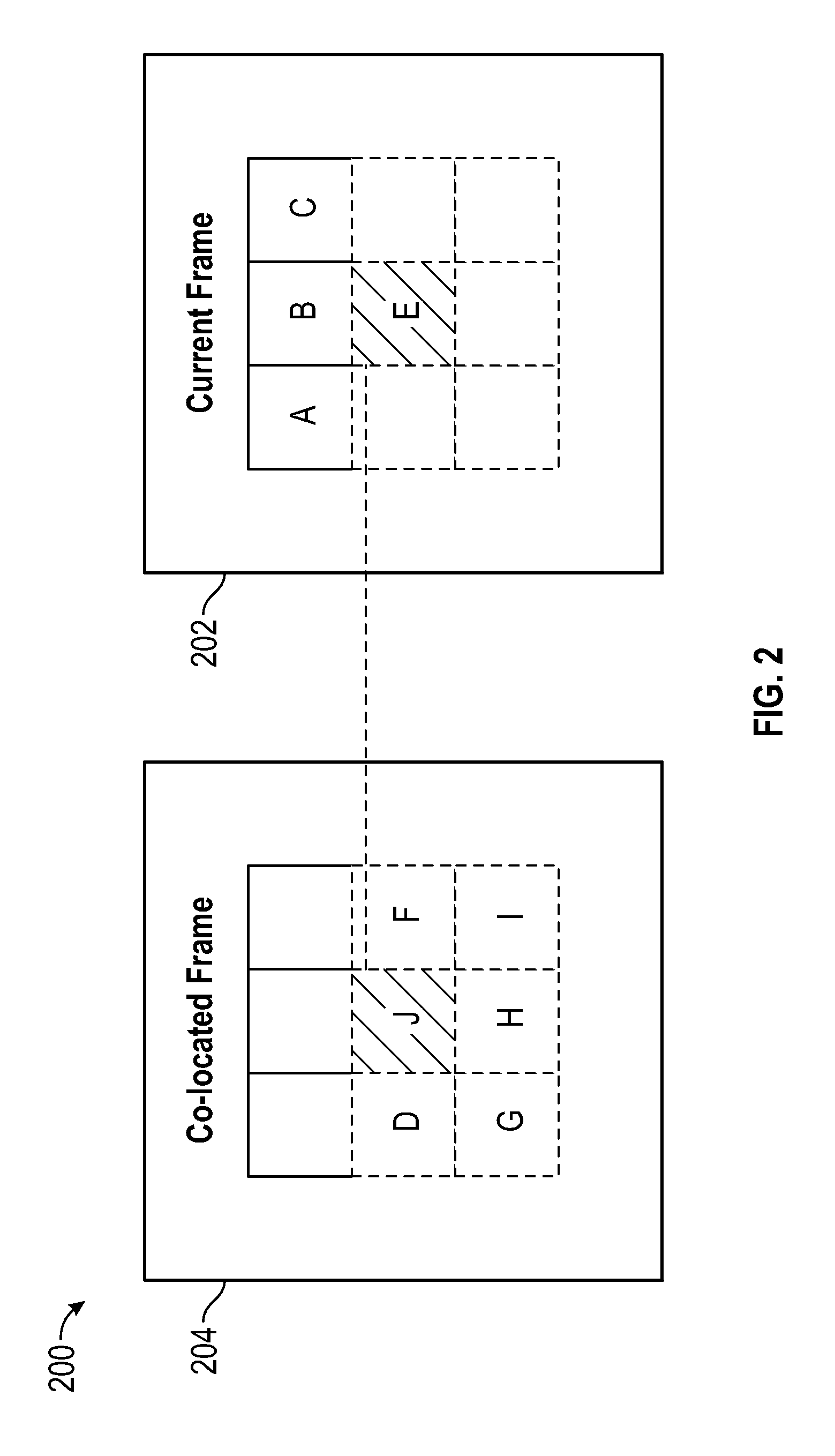

System and method of mapping multiple reference frame motion estimation on multi-core DSP architecture

ActiveUS20150304679A1Color television with pulse code modulationColor television with bandwidth reductionDsp architectureMotion vector

Owner:ALLIUM VITALS

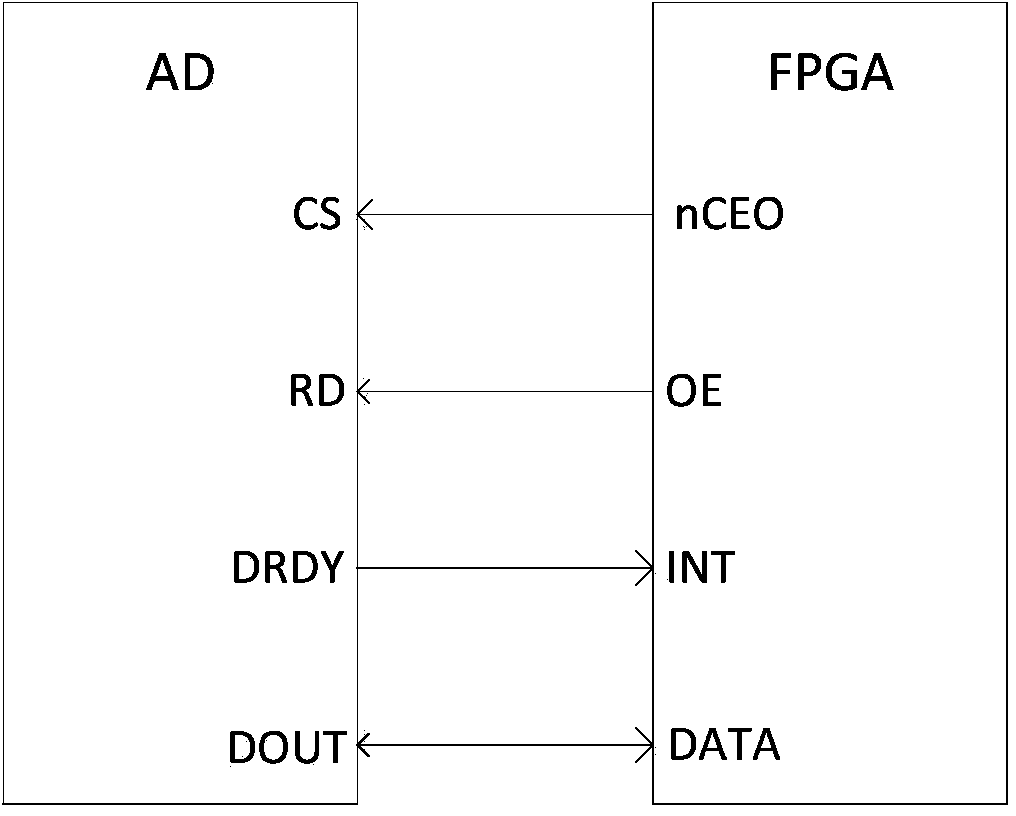

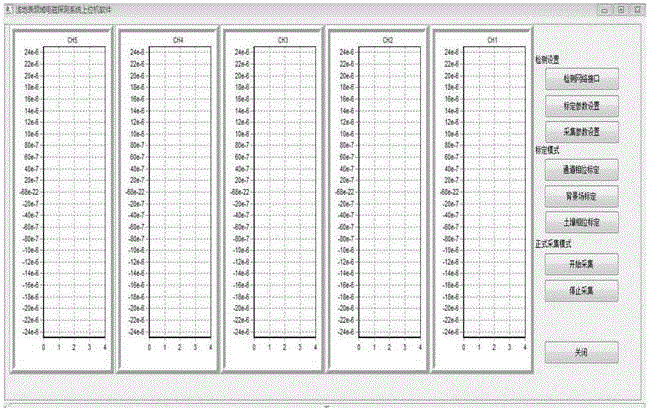

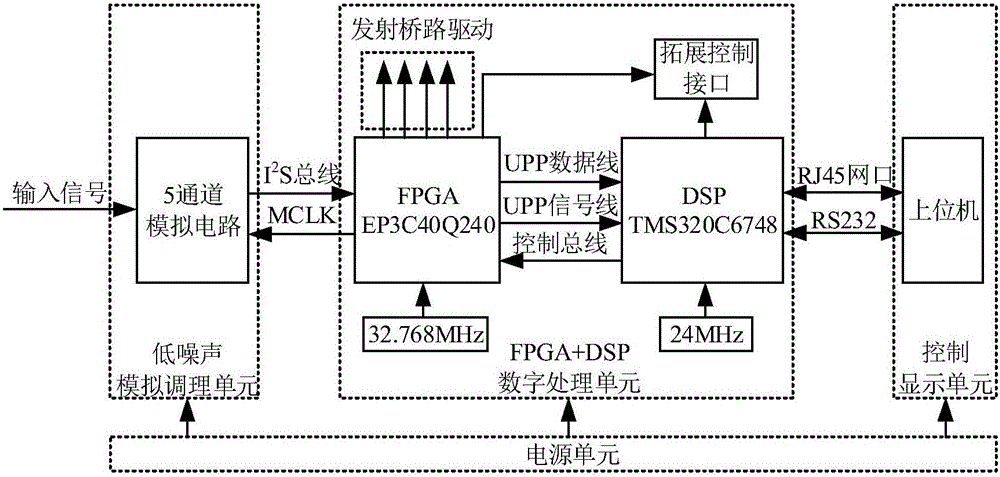

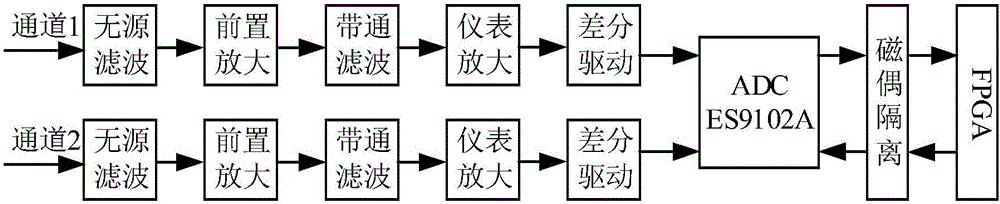

Shallow-earth-surface frequency domain electromagnetic detecting receiving system and data processing method

InactiveCN105785451AEfficient extractionGuaranteed normal transmissionElectric/magnetic detectionAcoustic wave reradiationDsp architectureOperability

The invention relates to a shallow-earth-surface frequency domain electromagnetic detecting receiving system and a data processing method. The shallow-earth-surface frequency domain electromagnetic detecting receiving system is characterized in that a five-channel analog circuit is connected with an upper computer through an FPGA and a DSP; the FPGA is connected with a transmitting bridge circuit and an extended control interface; and the DSP is connected with the extended control interface. The shallow-earth-surface frequency domain electromagnetic detecting receiving system has advantages of simple circuit and relatively small size. An FPGA+DSP architecture is firstly utilized in a shallow-earth-surface frequency domain electromagnetic detecting receiving system field. Compared with the FPGA+(single-chip-microcomputer) architecture of broadband electromagnetic detecting equipment of Jilin University, the FPGA+DSP architecture has an advantage of greatly improving data transmission rate. The data processing equipment is changed from the upper computer to the DSP, thereby settling defects of occupation of large amount of CPU resource and low efficiency in real-time data processing by the upper computer. A high-efficiency data processing algorithm is presented, thereby realizing simple operation, high effectiveness and high operability. The shallow-earth-surface frequency domain electromagnetic detecting receiving system and the data processing method further have advantages of realizing high convenience of the data processing method, reducing processing time and improving operation efficiency. The shallow-earth-surface frequency domain electromagnetic detecting receiving system and the data processing method can be used for shallow-earth-surface electromagnetic detection on metal abnormal members within certain thicknesses.

Owner:JILIN UNIV

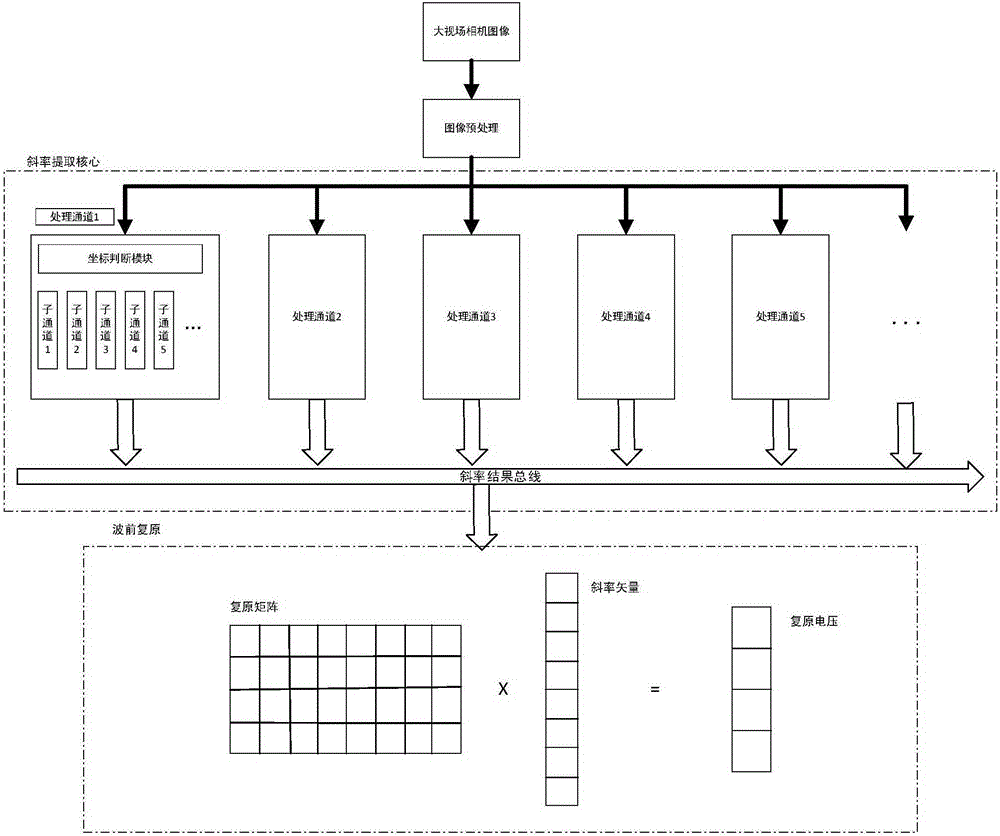

Real-time controller based on multi-visual-line related Shack-Hartmann wavefront sensor

ActiveCN105204405ASolve the problem of inconsistent quantityReduce in quantityProgramme controlComputer controlDsp architectureParallel processing

The invention discloses a real-time controller based on a multi-visual-line related Shack-Hartmann wavefront sensor, particularly relates to a multichannel parallel processing hardware platform architecture which is put forward aiming at the multi-conjugate adaptive optical technique, and is used for detection and reconstruction of wavefront slope in multiple visual line directions within the range of a large field of view. The controller adopts a FPGA and multi-core DSP architecture, and mainly comprises a slope calculation part and a wavefront reconstruction part; as a plurality of subregions need to be divided in each subaperture of the multi-visual-line related Shack-Hartmann wavefront sensor, the platform needs subchannels to be constructed in large channels for slope extraction. The real-time controller is suitable for selecting any amount of subregions from the subaperture of the multi-visual-line related Shack-Hartmann wavefront sensor, therefore the purpose of system upgrading can be achieved by performing repeated structural treatment on the subchannels in the FPGA on the basis of not changing the hardware circuit; besides, the real-time controller has important significance on engineering realization of the multi-conjugate adaptive optical technique.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

Embedded video server based on ARM framework and DSP framework

InactiveCN101651814AImprove reliabilityReduce volumeTwo-way working systemsDsp architectureOperational system

The invention discloses an embedded video server based on an ARM framework and a DSP framework, belonging to the technical field of network video. The embedded video server comprises an ARM9 microprocessor, a TI C6000 DSP chip, a DDR2 SDRAM memory, a Flash memory, an SATA hard disk and a high-speed Ethernet controller, and is characterized in that the ARM9 microprocessor is respectively connectedwith the TI C6000 DSP chip, the DDR2 SDRAM memory, the Flash memory, the SATA hard disk and the high-speed Ethernet controller, and is responsible for operating an operation system and a user program.The invention provides an embedded video server which features reasonable design, high cost performance and good effect, and can be widely used in the following monitoring occasions, such as coal mines, hospitals, schools, road traffic, subdistricts and wine shops and the like; the invention constructs a remote monitoring system, and can prevent the wiring work in traditional monitoring solutions, thus realizing plug and play and reducing the complexity of network configuration.

Owner:SHANDONG UNIV

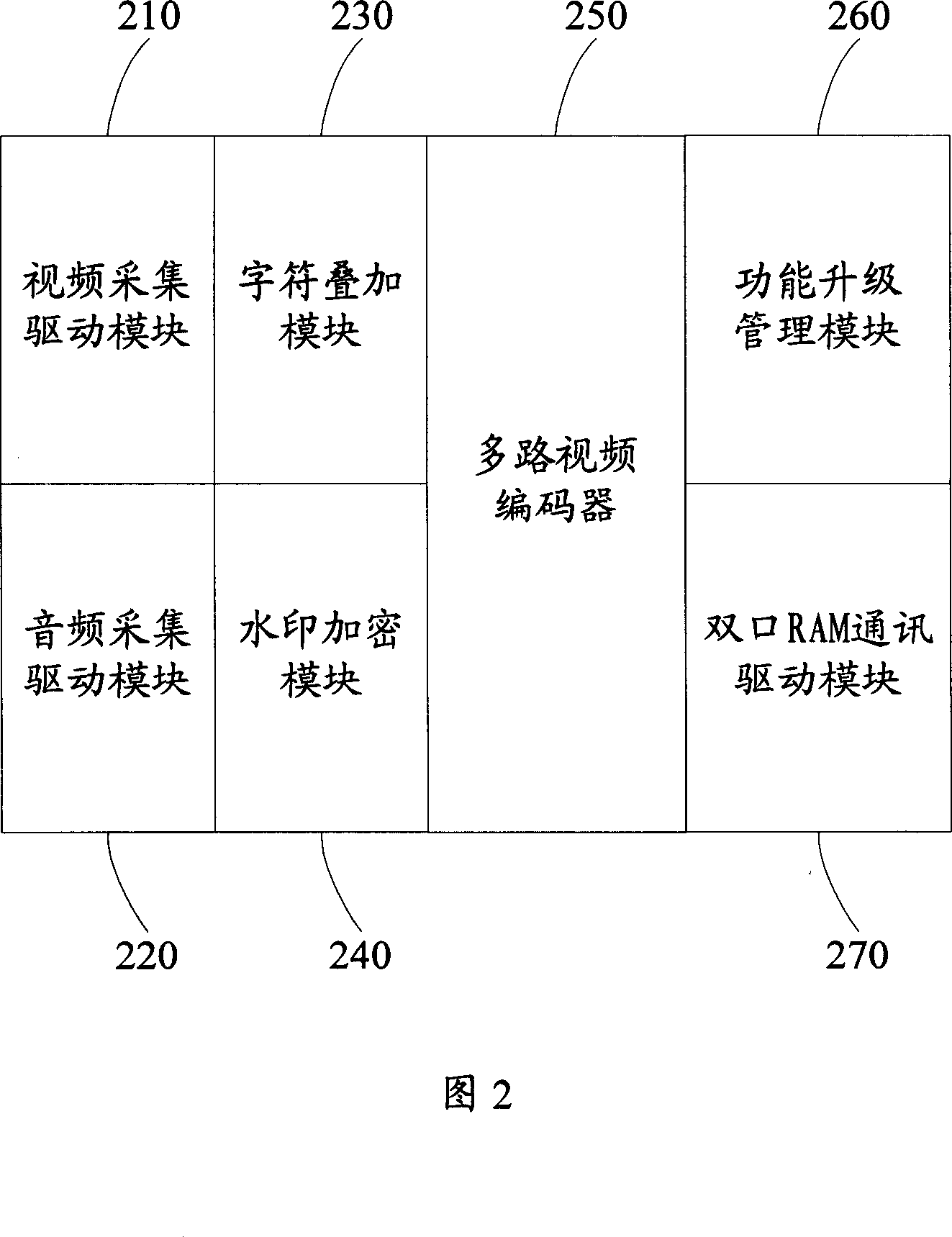

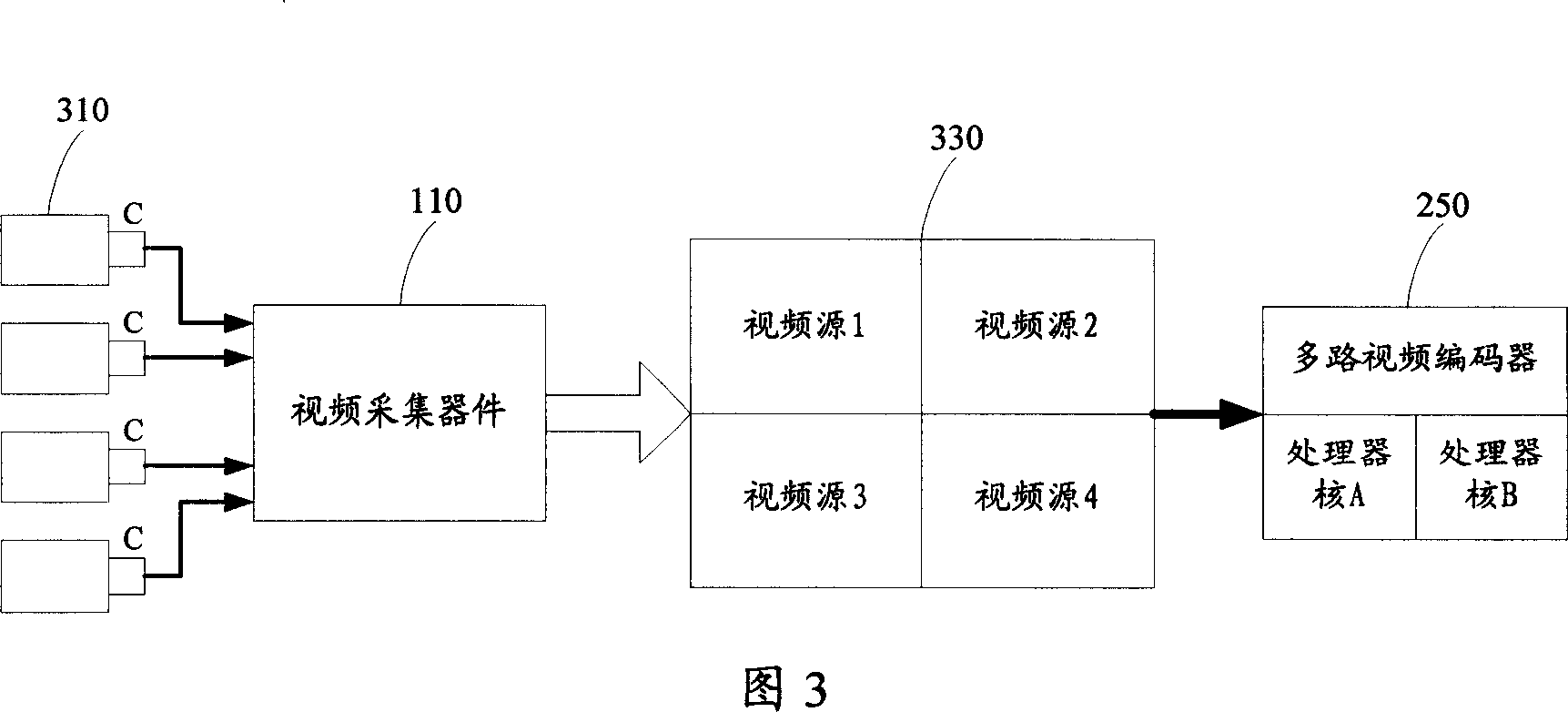

Multichannel video frequency compression system based on single-chip double-nuclear DSP constitution

A multi-path video compression system based on single chip two nuclei DSP structure is prepared as parallel-connecting video collection component and audio collection component to two nuclei DSP processor, connecting SDRAM component and two-port RAM component to system bus of said processor, connecting embedded process wit two nuclei processor through two-port RAM component.

Owner:ZHEJIANG UNIV

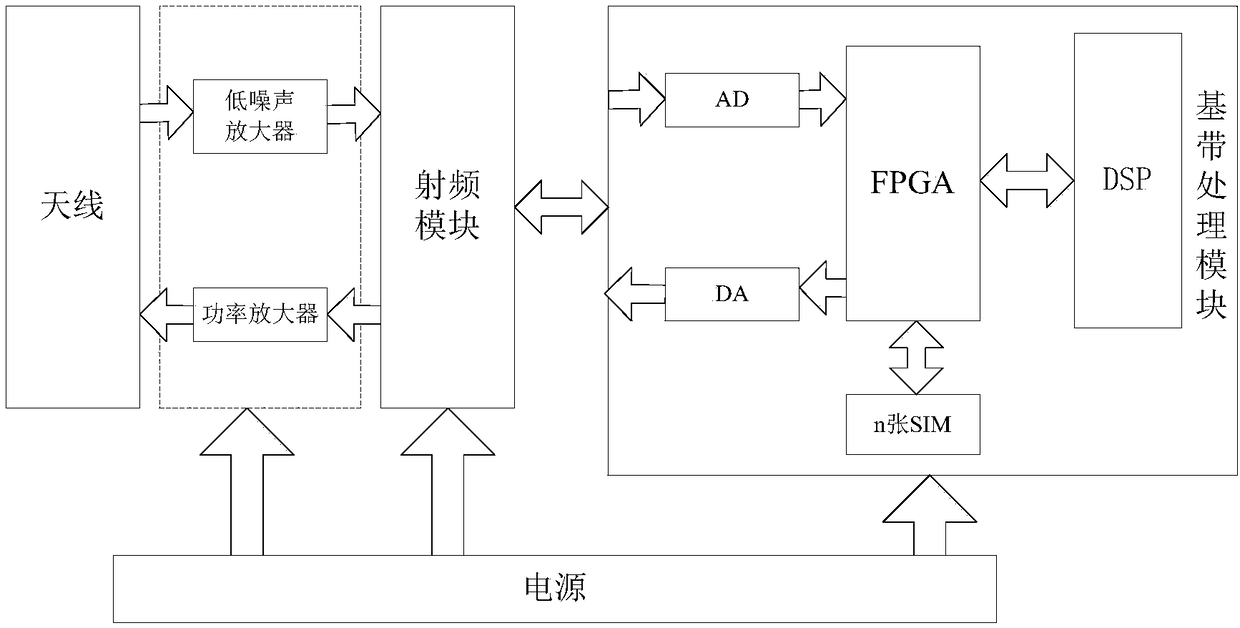

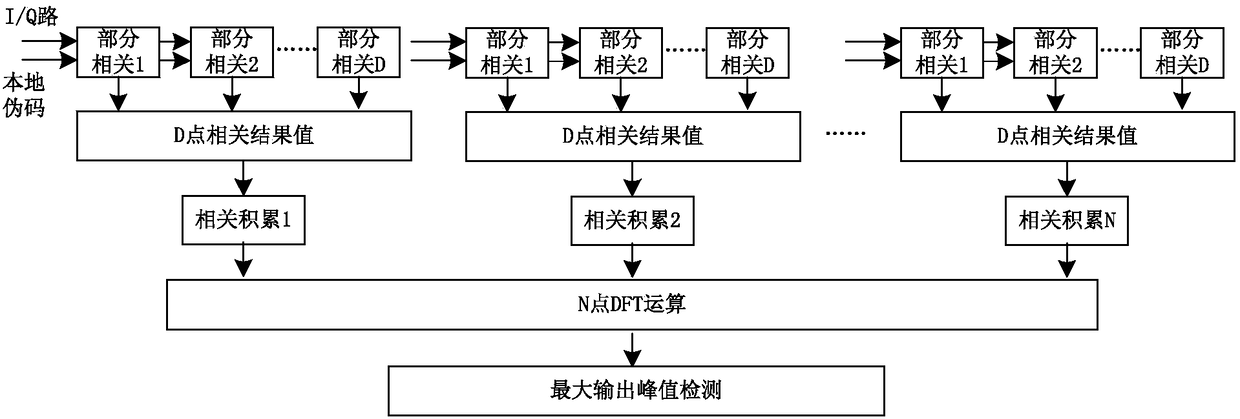

Positioning and notification system for attitude-varying high-dynamic targets

ActiveCN109143285AConducive to miniaturization designPracticalSatellite radio beaconingHigh level techniquesDsp architectureTransceiver

The invention provides a positioning and notification system for attitude-varying high-dynamic targets and belongs to the satellite navigation technology application field. The positioning and notification system includes a transceiver antenna assembly, a low-noise amplifier, a power amplifier, a radio frequency module, a baseband processing module, and a battery module; the transceiver antenna assembly completes RDSS signal transmission, RDSS signal receiving, and RNSS signal receiving; the low-noise amplifier completes the amplification of received RDSS signals and RNSS signals; and the baseband processing module, based on an FPGA+DSP architecture, consists of an RNSS processing module and an RDSS processing module, wherein the RNSS processing module and the RDSS processing module applya PMF-DFT acquisition algorithm. The system of the invention is suitable for position monitoring, searching and the like of the attitude-varying high-dynamic targets, integrates an RNSS navigation andpositioning function and an RDSS short message communication function, and is beneficial to the miniaturization design of the system.

Owner:SPACE STAR TECH CO LTD

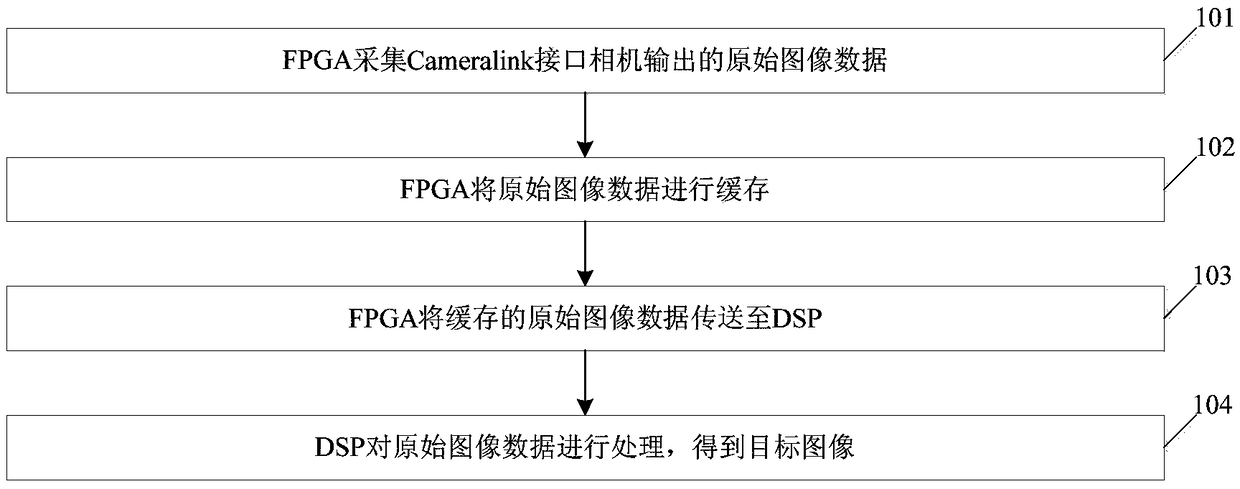

Camera image collecting and processing method and system based on FPGA (Field Programmable Gate Array)+DSP (Digital Signal Processor) architecture

InactiveCN108711135AReduce volumeReduce power consumptionProcessor architectures/configurationTransmissionCamera imageDsp architecture

The invention discloses a camera image collecting and processing method and system based on FPGA (Field Programmable Gate Array)+DSP (Digital Signal Processor) architecture. The method comprises the following steps that: the FPGA collects original image data output by a Cameralink interface camera; the FPGA caches the original image data; the FPGA transmits the cached original image data to the DSP; and the DSP processes the original image data to obtain a target image. Through the method, instantaneity for collecting and processing the image data of the Cameralink interface camera is improved, and in addition, the volume and the power consumption of equipment which processes image data are small.

Owner:广州创龙电子科技有限公司

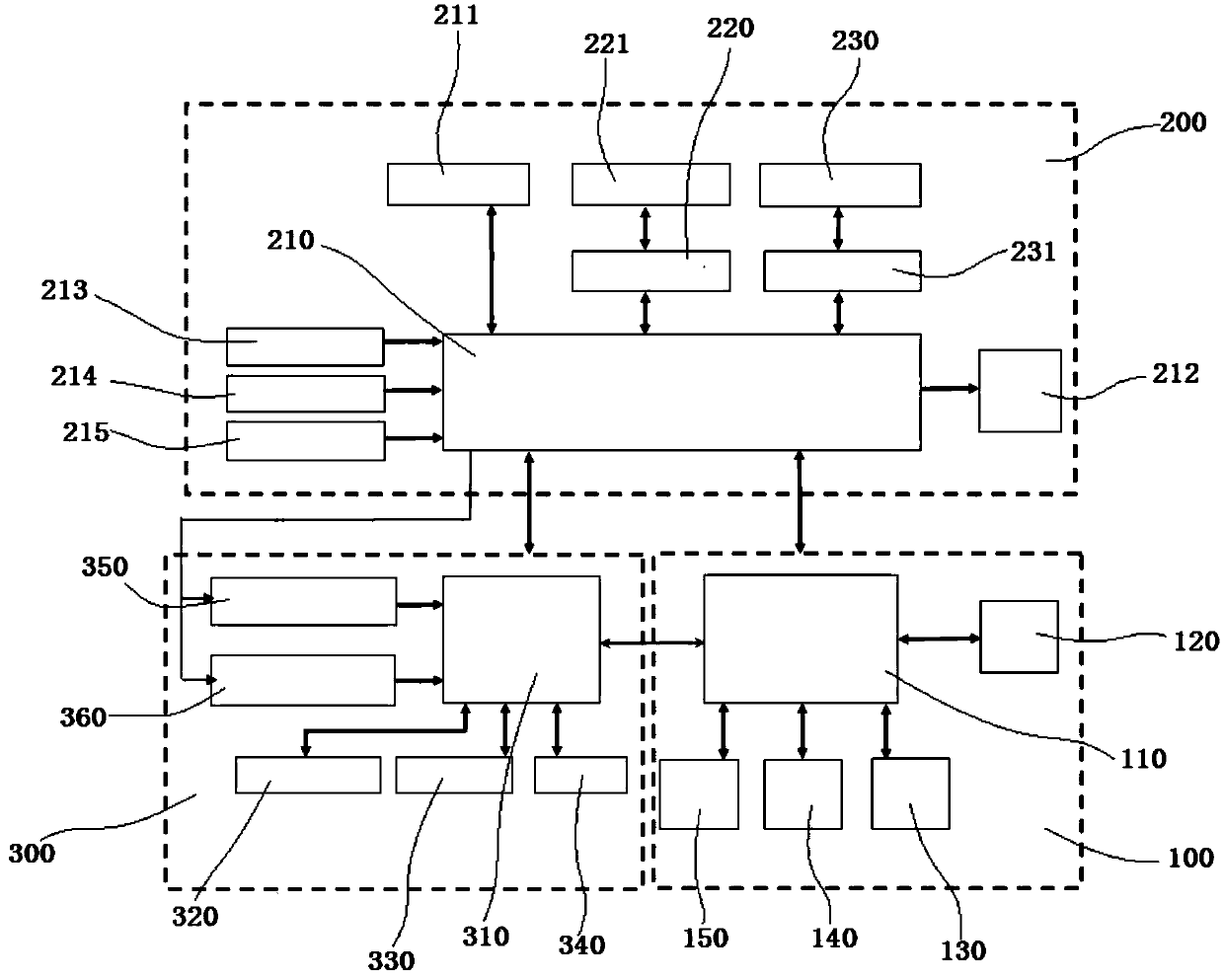

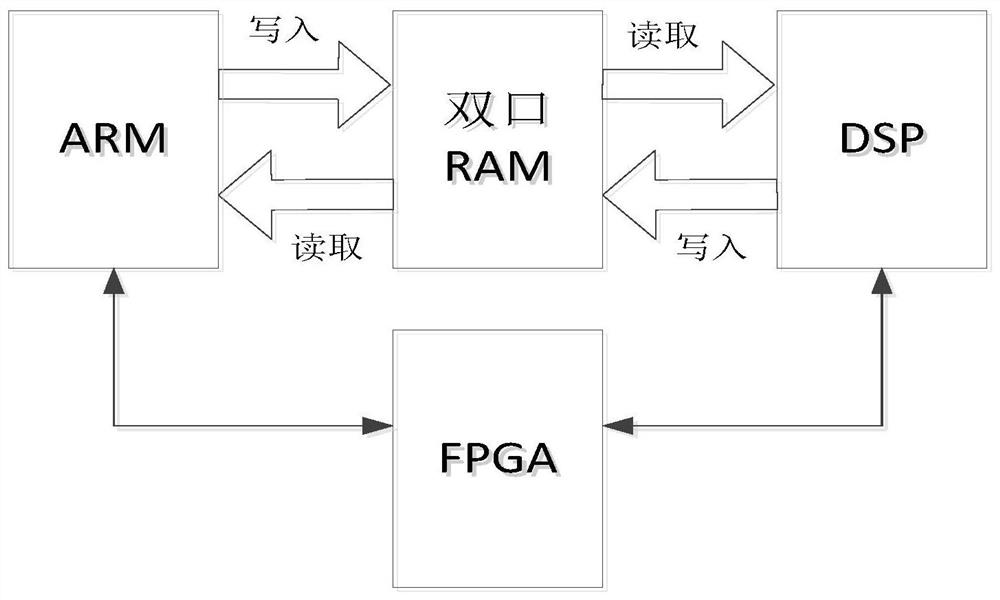

Cascade-type high voltage frequency converter master control system of multiprocessor architecture

PendingCN108052066AFast fault responseEasy to upgradeProgramme control in sequence/logic controllersDsp architectureReal-time data

The invention provides a cascade-type high voltage frequency converter master control system of a multiprocessor architecture. The high voltage frequency converter master control system comprises an ARM circuit unit, an FPGA circuit unit and a DSP circuit unit. The ARM circuit unit and the DSP circuit unit are communicated and carry out real-time data interaction through a dual-port RAM in the FPGA circuit unit. The ARM circuit unit is used for processing external communication and sharing a communication portion function in a high voltage frequency converter. The FPGA circuit unit is used forrealizing high real-time internal processing and fault protection. The DSP circuit unit is used for high voltage frequency conversion algorithm processing. The cascade-type high voltage frequency converter master control system of an ARM+FPGA+DSP architecture possesses characteristics of abundant interfaces, high real-time performance, good expandability and a high anti-interference capability, and various control demands of a cascade-type high voltage frequency converter are satisfied.

Owner:SHANGHAI AUTOWELL POWER ELECTRONICS CO LTD +1

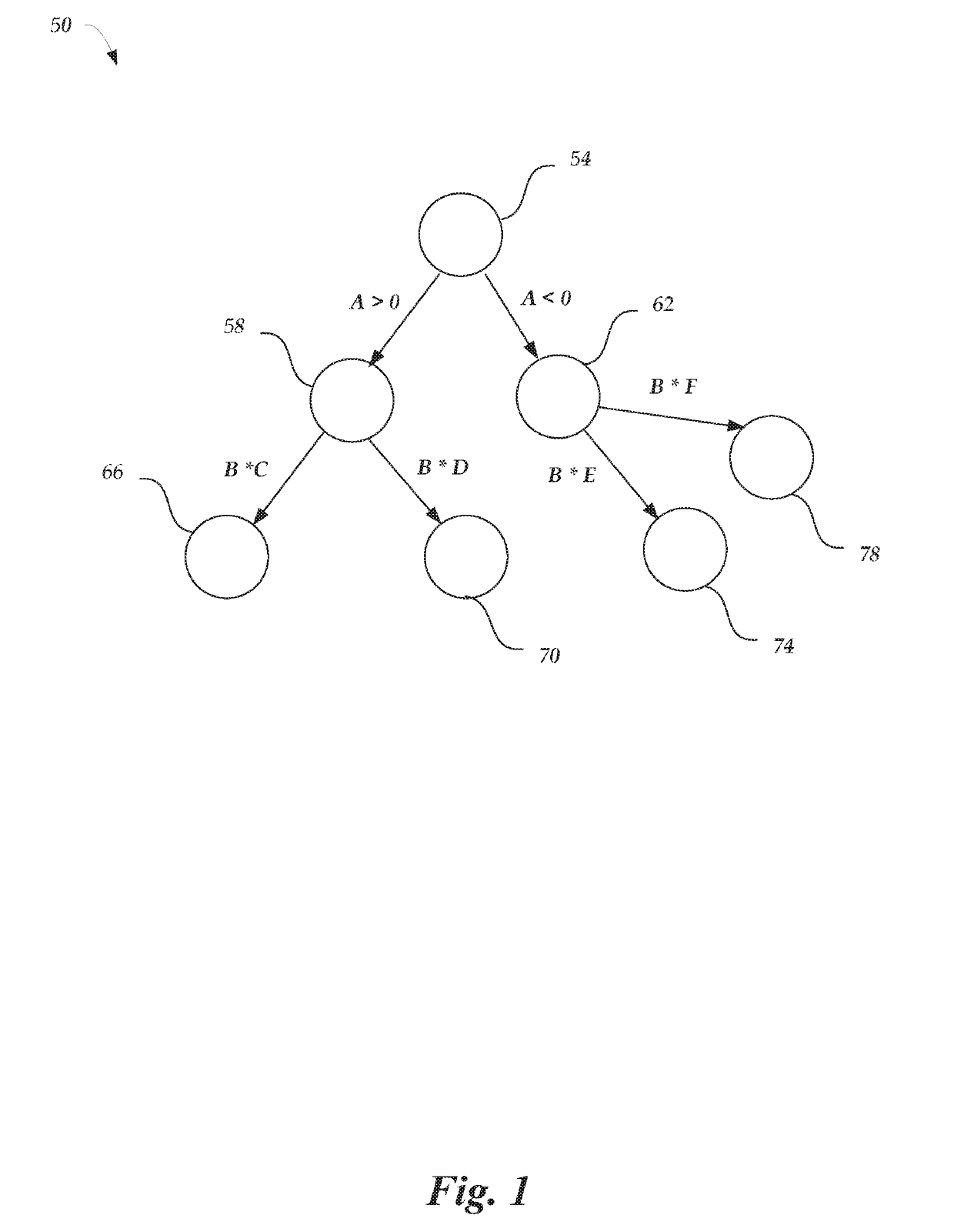

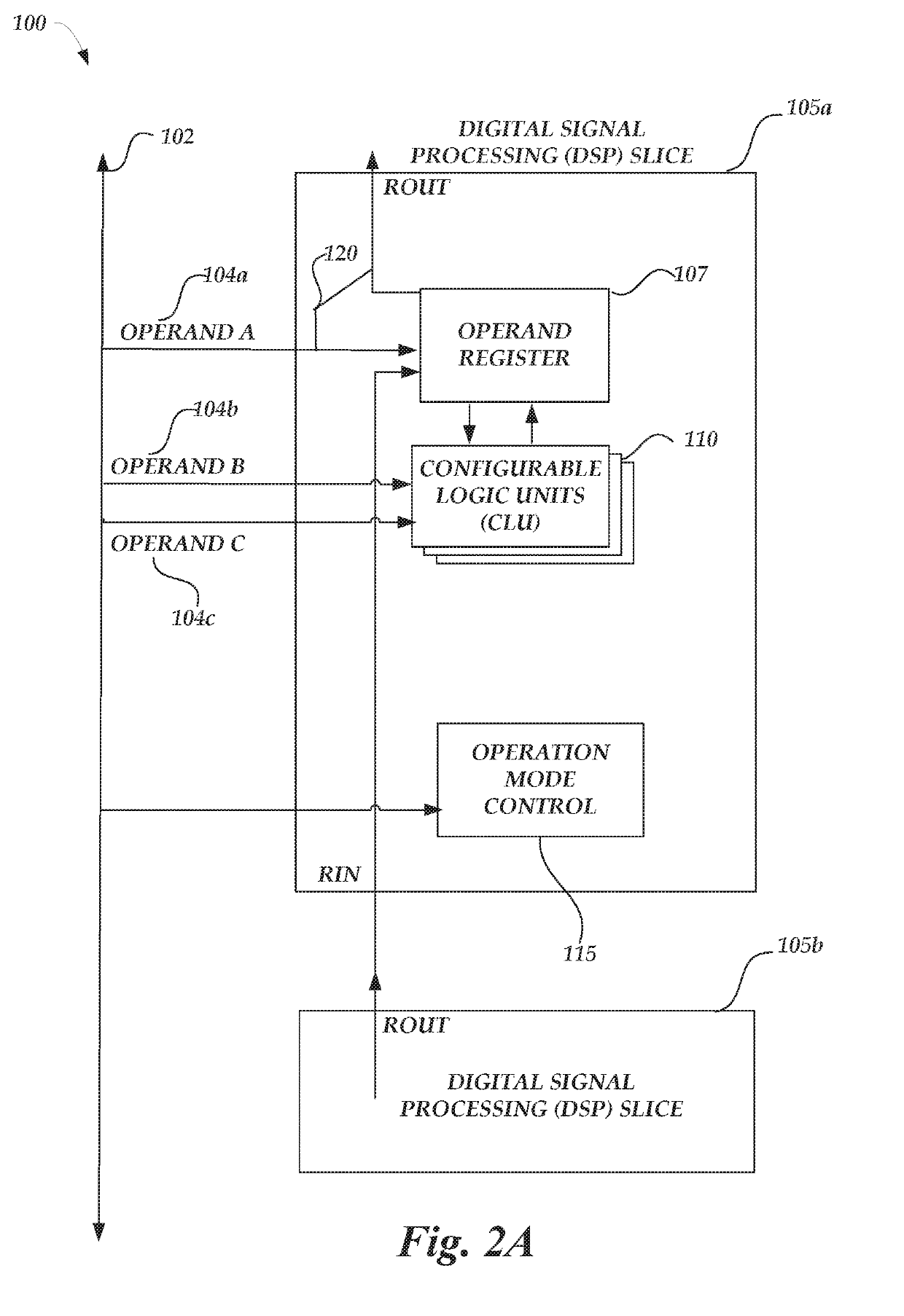

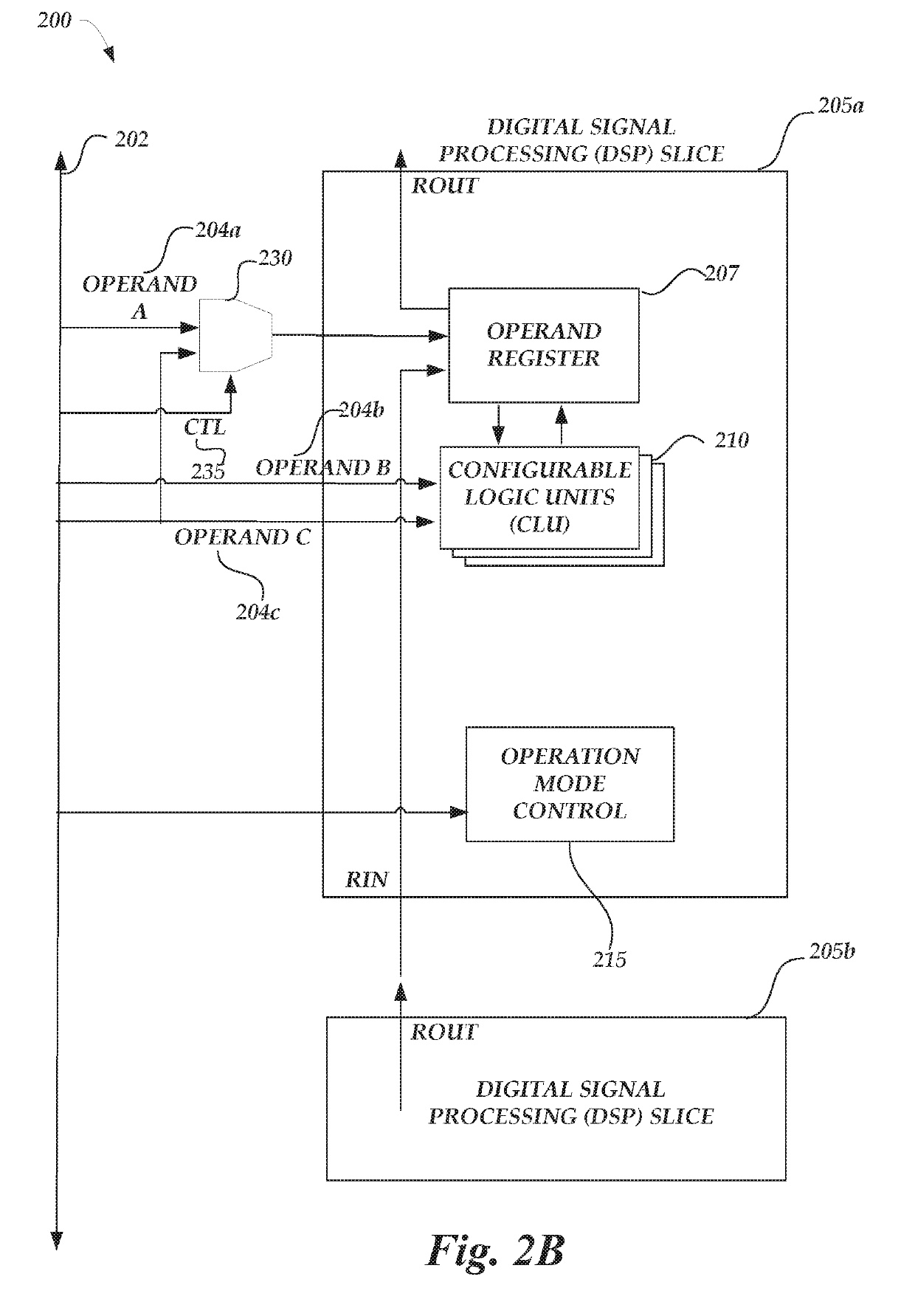

Forwarded operand and machine learning utilizing the same

Apparatuses and methods are disclosed for an FPGA architecture that may improve processing speed and efficiency in processing less complex operands. Some applications may utilize operands that are less complex, such as operands that are 1, 2, or 4 bits, for example. In some examples, the DSP architecture may skip or avoid processing all received operands or may process a common operand more frequently than other operands. An example apparatus may include configurable logic blocks including DSP slices and an interconnected coupling the configurable logic blocks. An operand register of a DSP slice may include an operand input that is coupled to an output of that DSP slice.

Owner:MICRON TECH INC

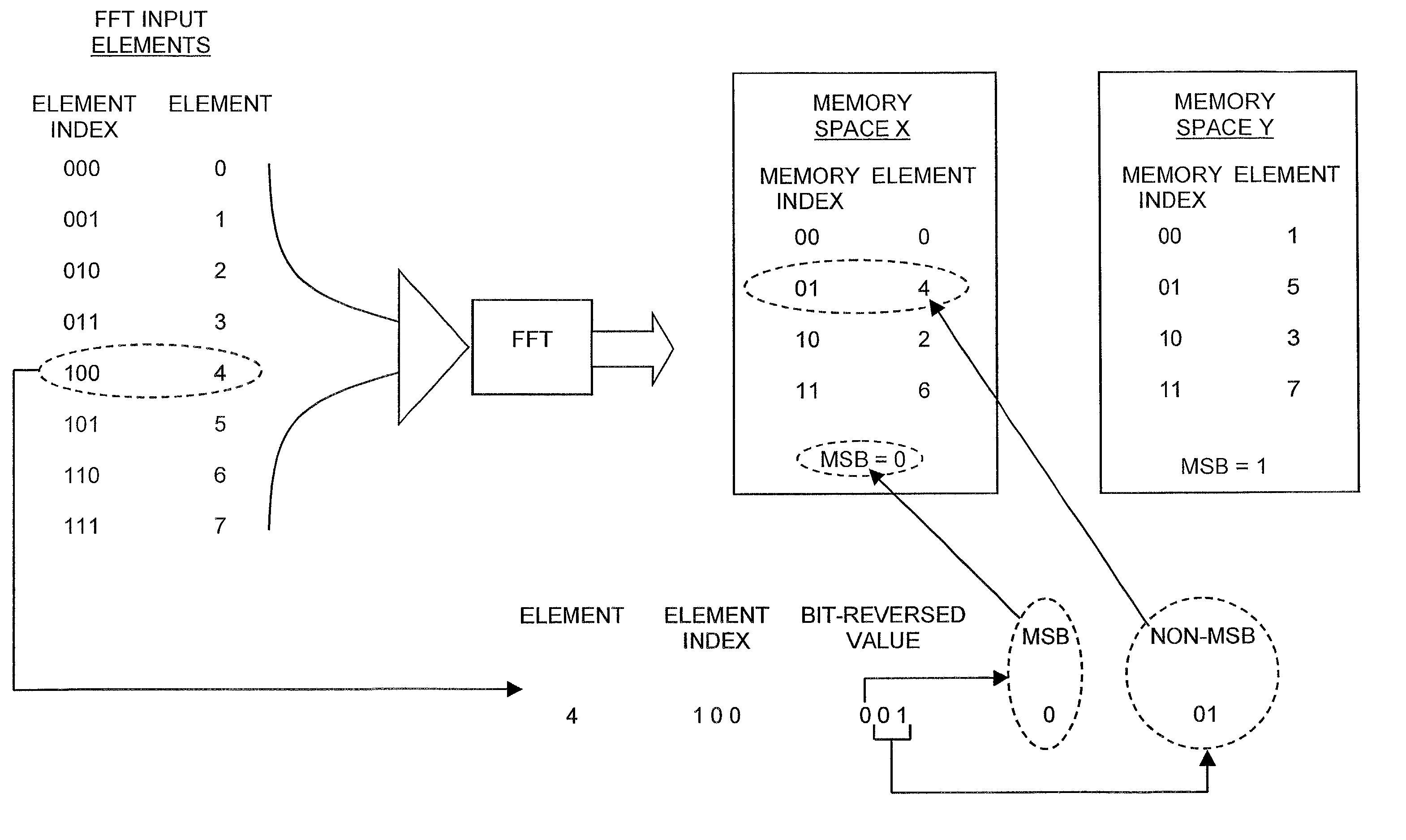

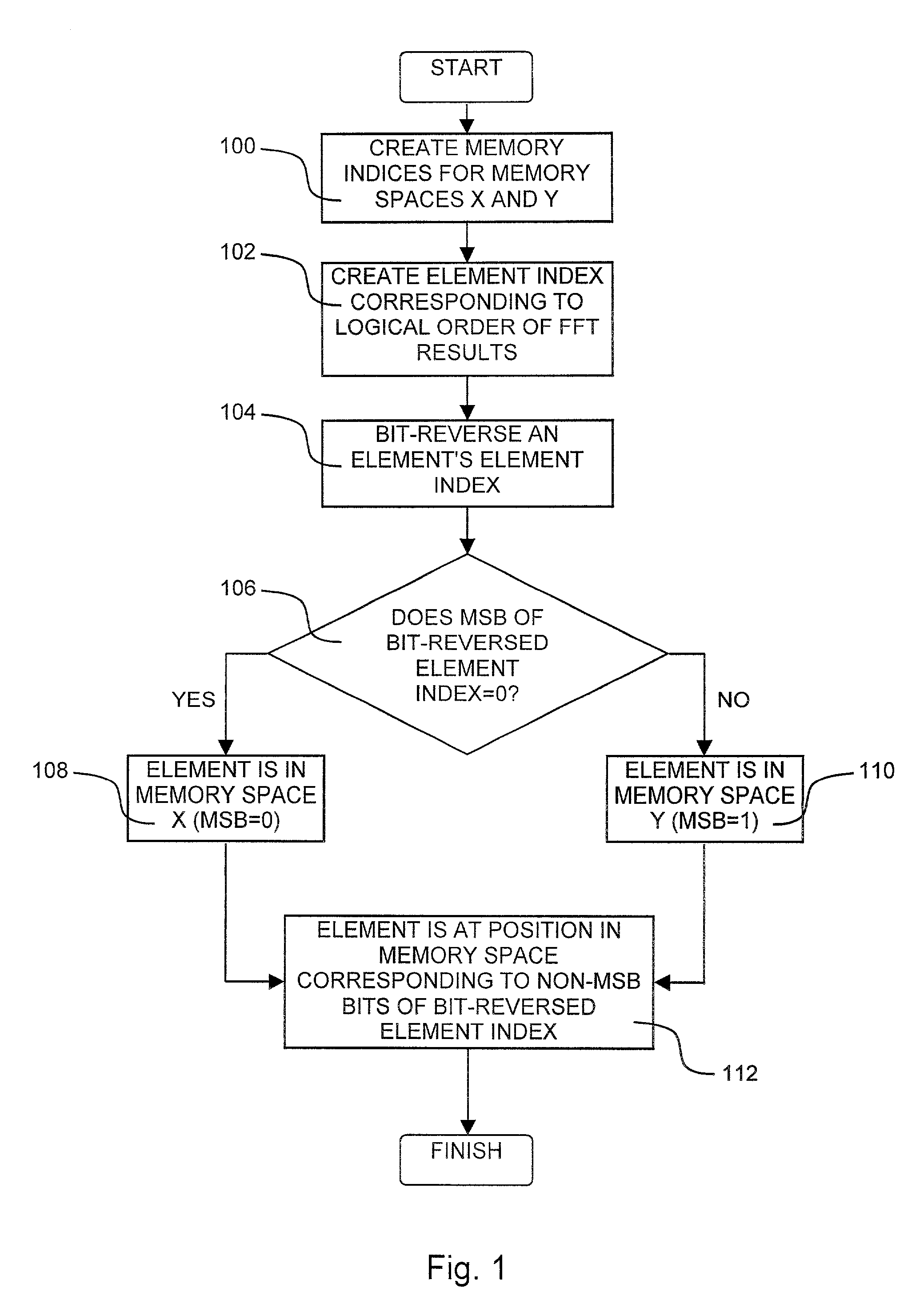

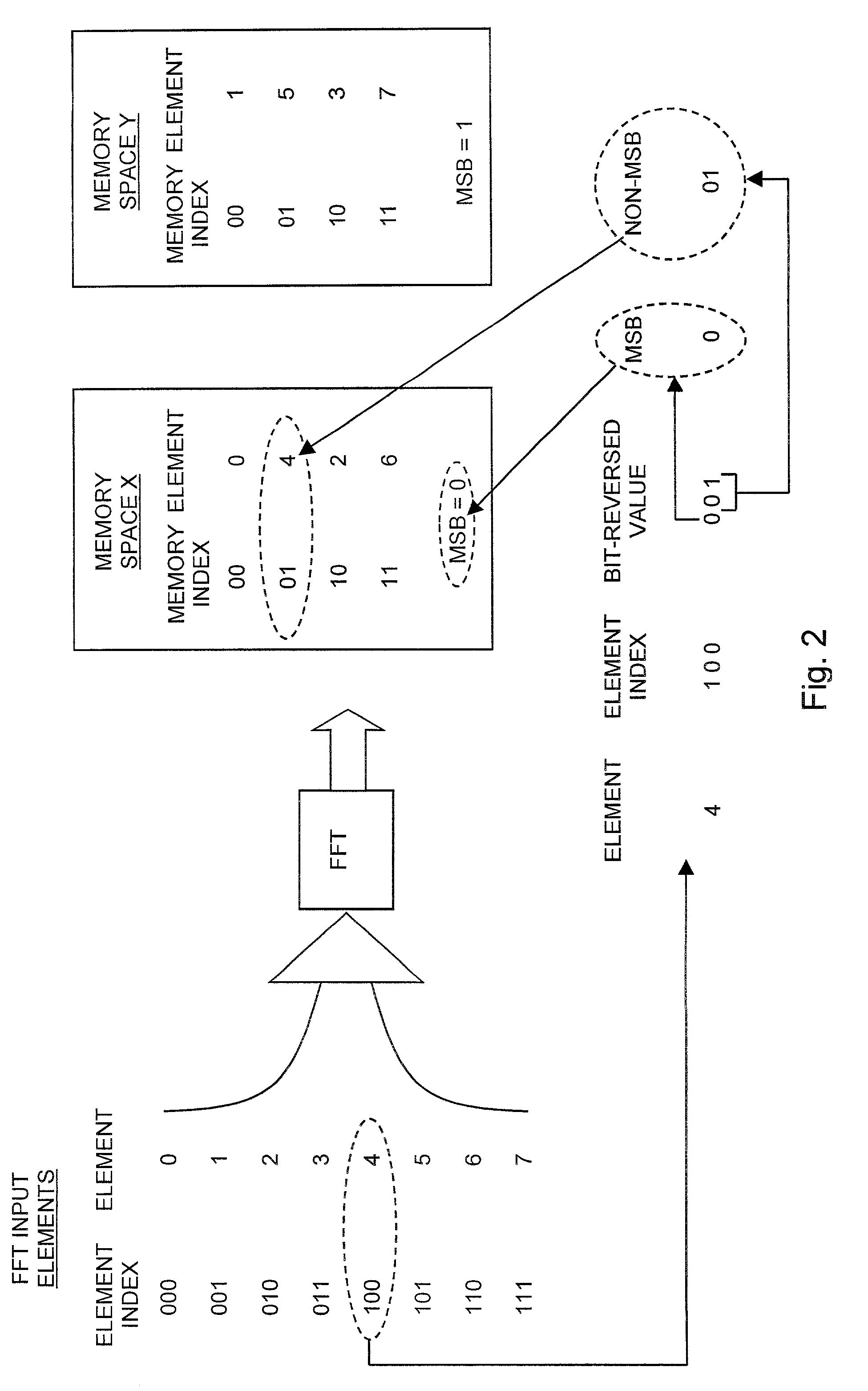

Bit-reversed indexing in a modified harvard DSP architecture

ActiveUS6988117B2Digital computer detailsComplex mathematical operationsDsp architectureParallel computing

Owner:CEVA D S P LTD

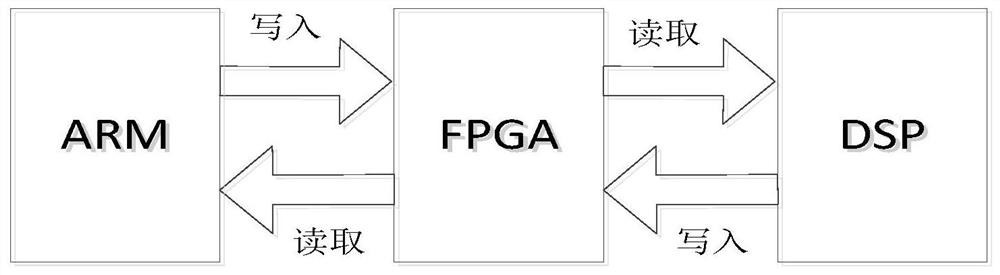

Asynchronous data interaction method and system based on ARM + FPGA + DSP architecture

ActiveCN112147918AReliable transmissionImprove communication efficiencyProgramme controlComputer controlComputer hardwareDsp architecture

The invention discloses an asynchronous data interaction method and system based on an ARM + FPGA + DSP architecture. The method comprises the steps that when an ARM needs to transmit data to a DSP, the ARM packages to-be-transmitted data, writes a packaged data frame into a double-port RAM in an FPGA, and then transmits a write completion signal to the FPGA after packaging is completed; after receiving the write completion signal, the FPGA sends the data frame in the dual-port RAM in the FPGA to the DSP; and the DSP receives the data frame. According to the method and system, the reliabilityand transmission efficiency of data transmission can be improved, the bit error rate of data transmission is reduced, and the user experience is improved.

Owner:CSR ZHUZHOU ELECTRIC LOCOMOTIVE RES INST

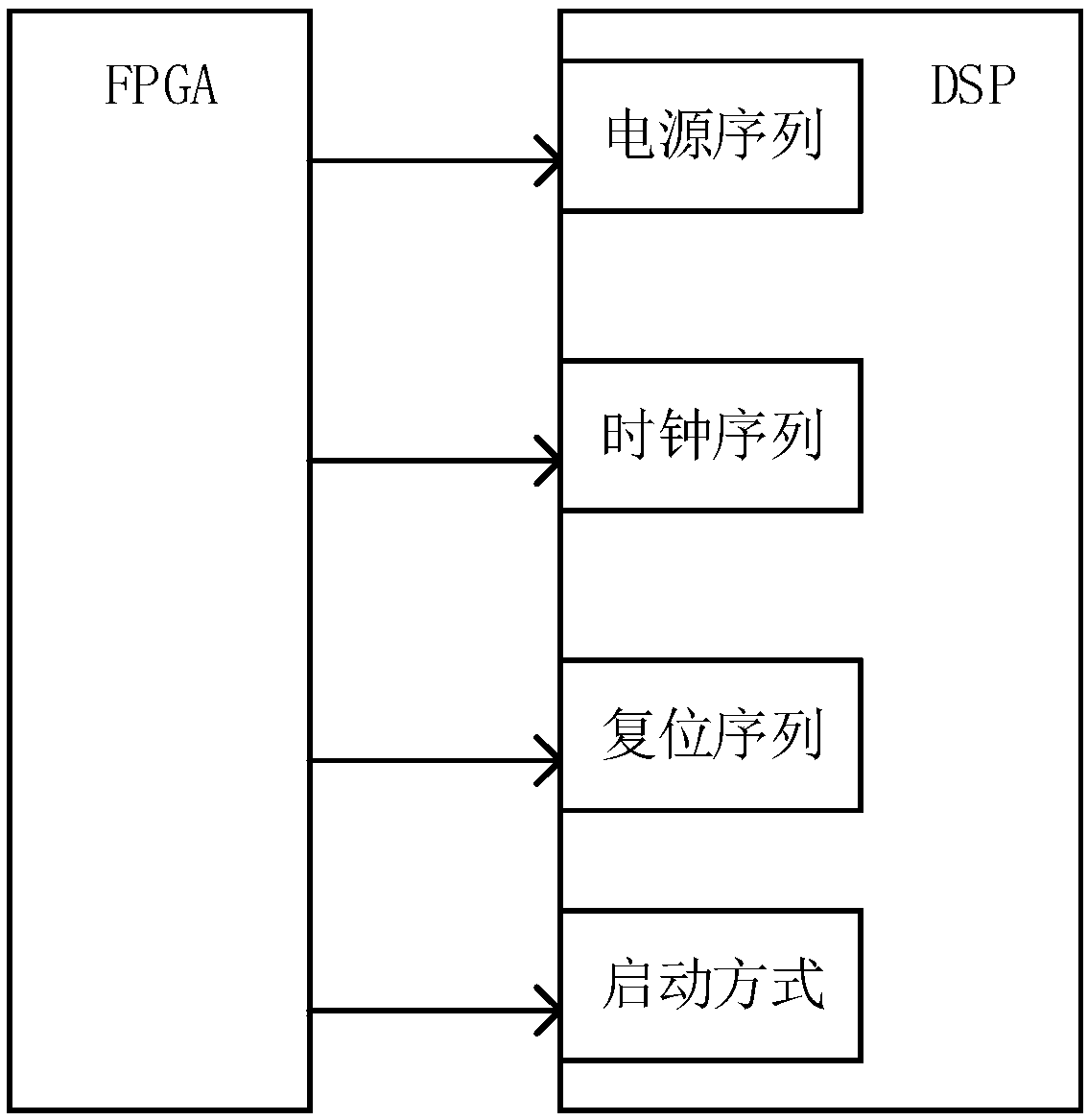

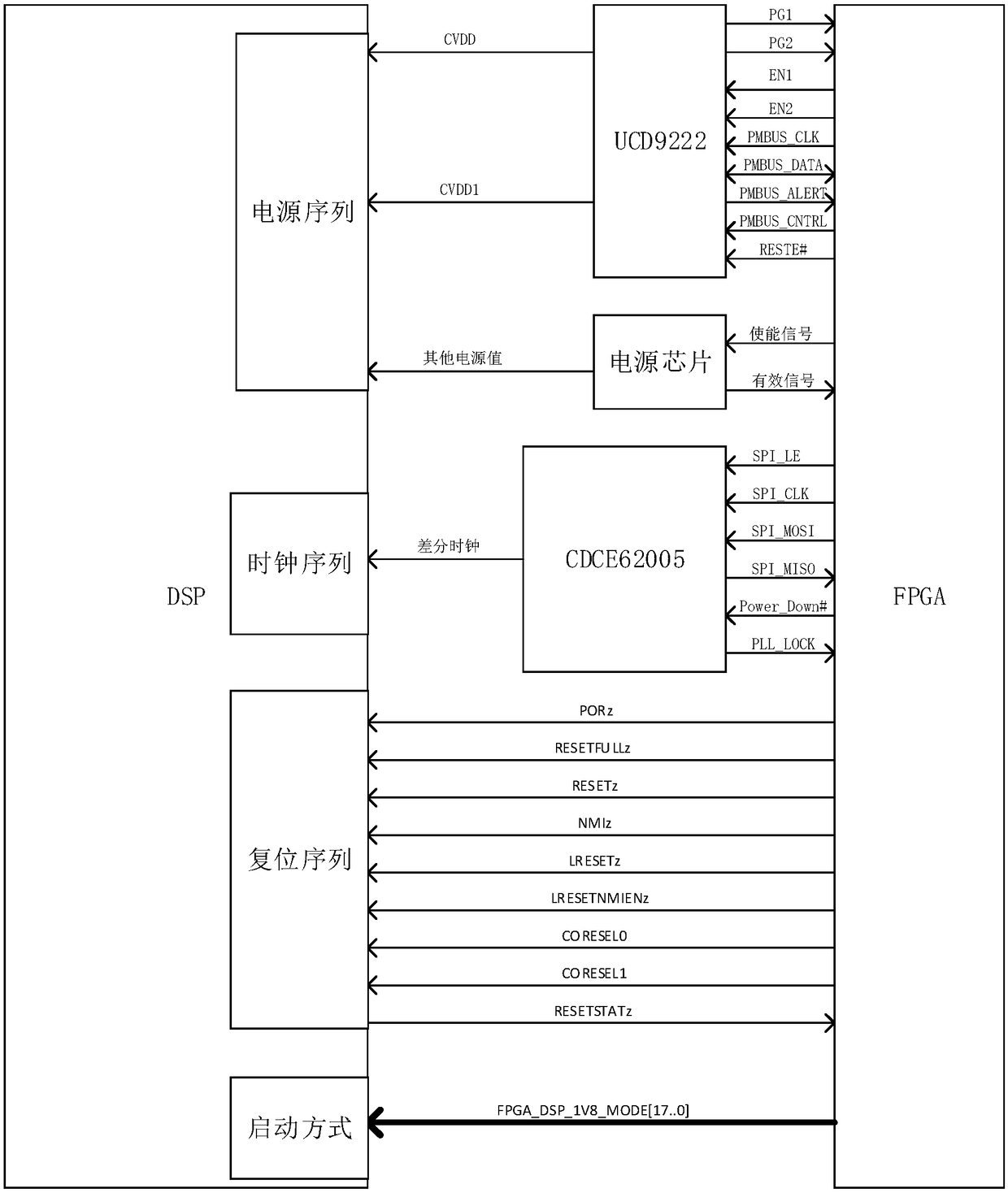

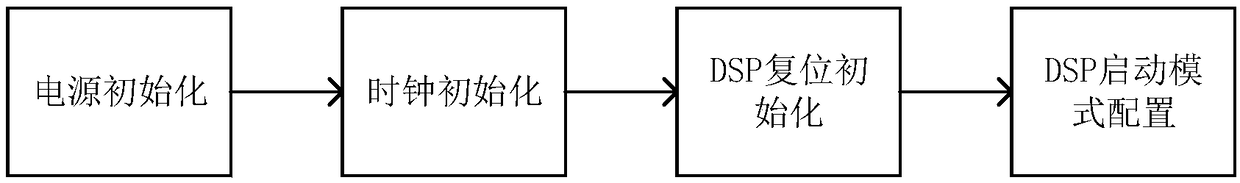

A method of configuring DSP initialization

InactiveCN109324995ASave resourcesEasy to implementDigital computer detailsData resettingDsp architectureComputer science

The invention relates to a method for configuring DSP initialization, which adopts an embedded FPGA + DSP structure, and an FPGA completes the DSP initialization configuration before a DSP works. Themethod comprises the steps of DSP power supply initialization, the clock initialization, the reset initialization and the DSP start-up mode configuration. The method of configuring DSP initializationof the invention adopts the FPGA programmable characteristics, can configure different DSP initialization requirements, can save external hardware resources, and is relatively simple to realize.

Owner:JIANGXI HONGDU AVIATION IND GRP