Patents

Literature

355 results about "Vector element" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Methods for the production of ips cells using non-viral approach

ActiveUS20100003757A1Promote generationExpand the populationGenetically modified cellsVirus peptidesVector elementCell type

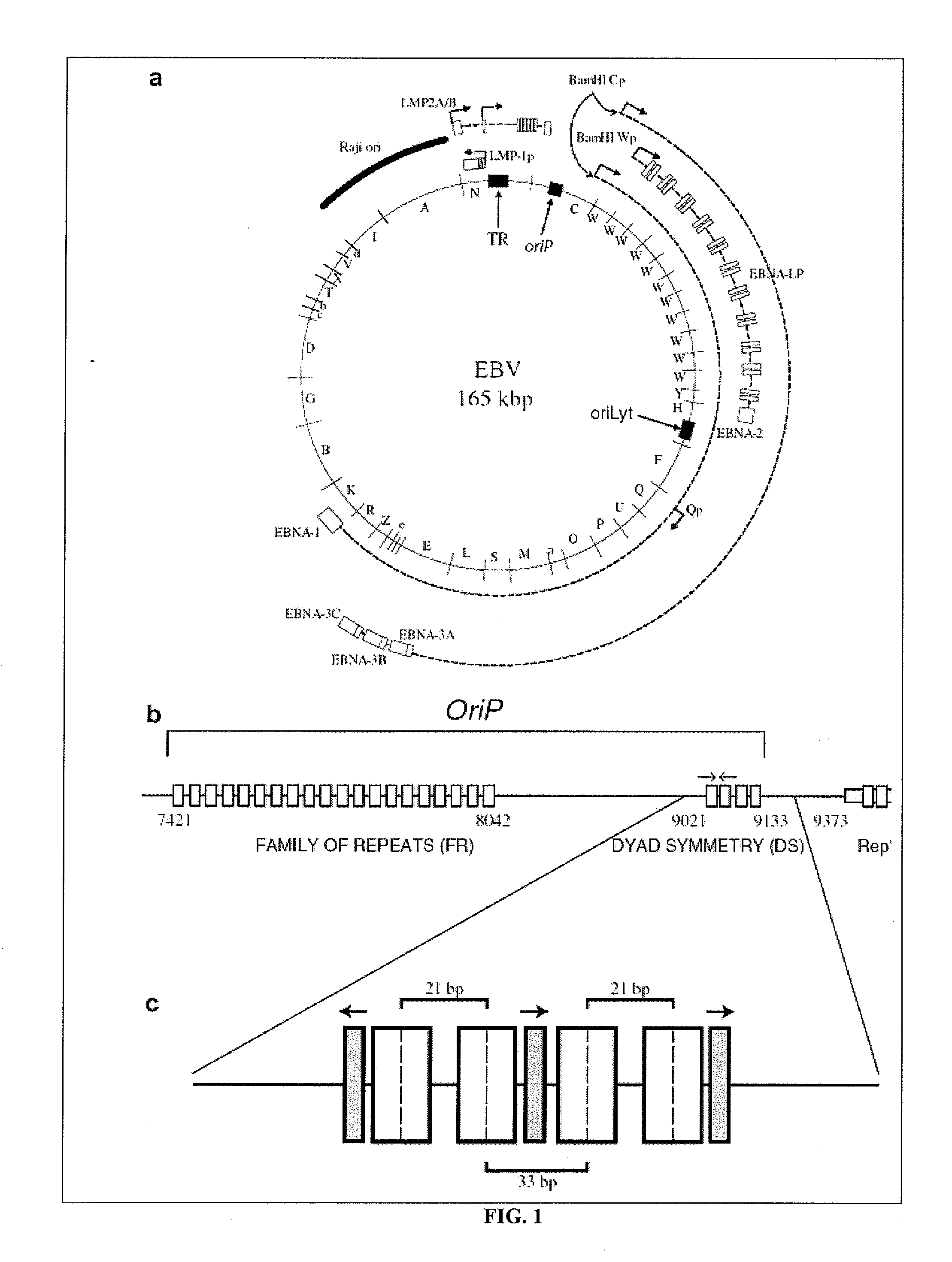

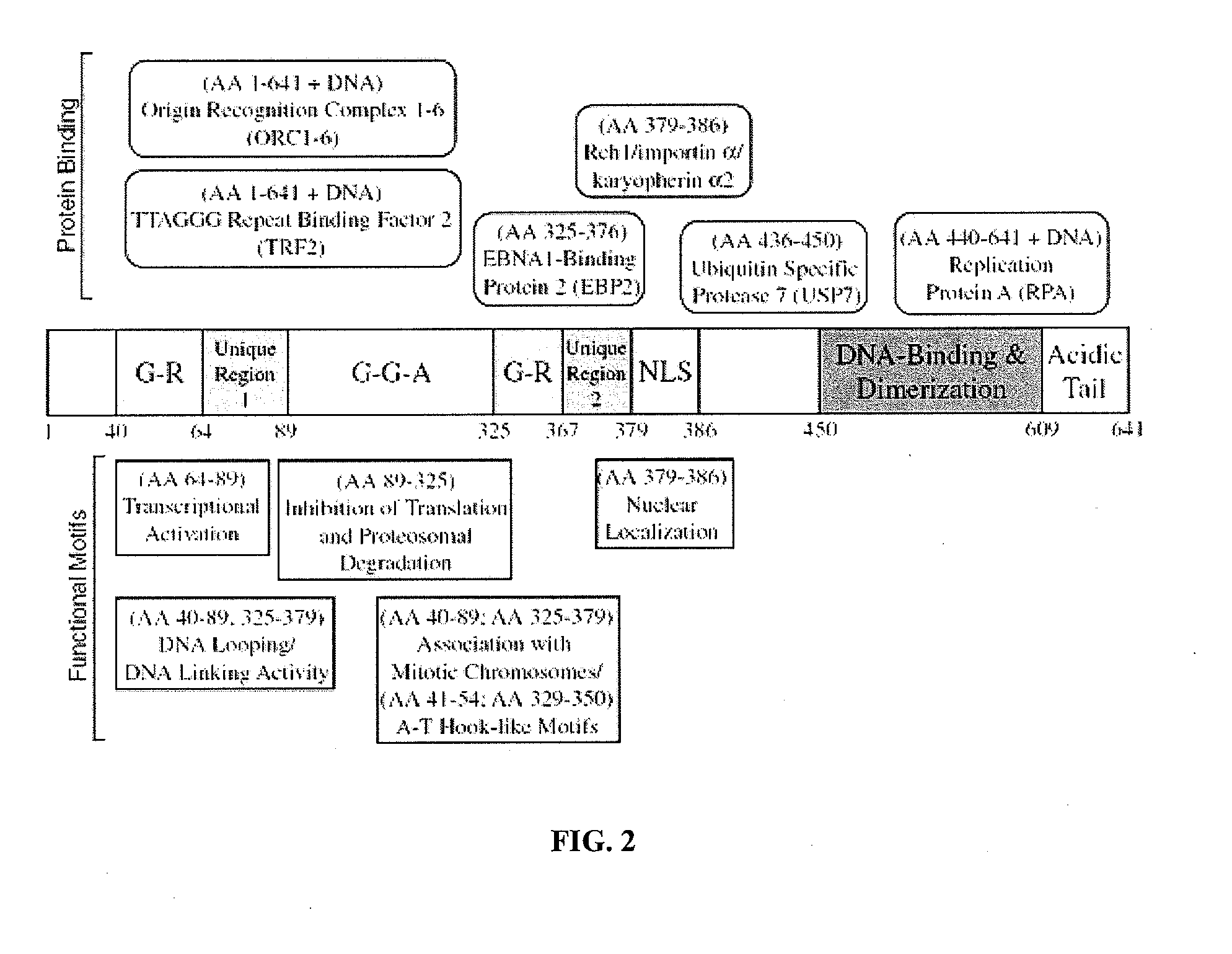

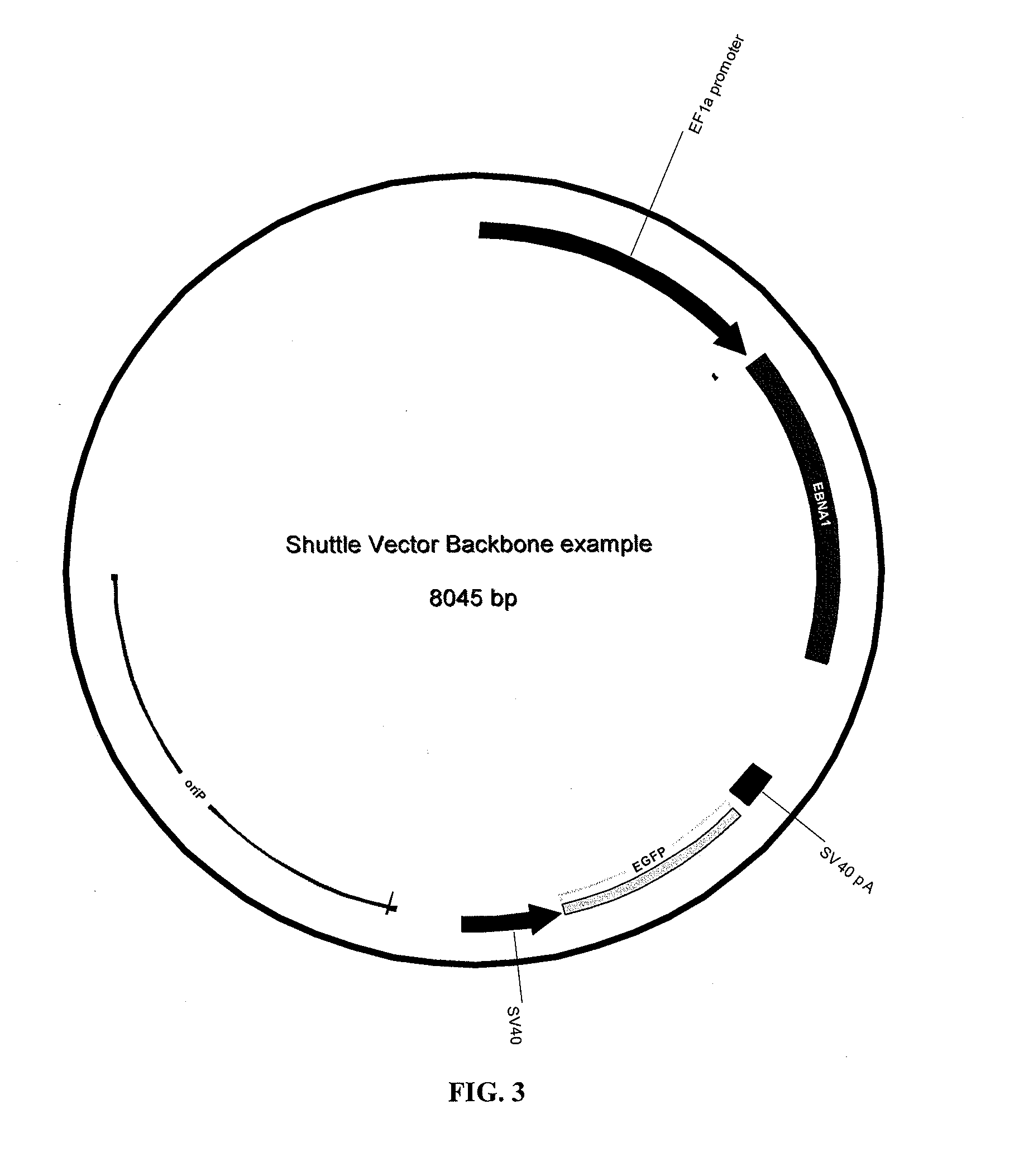

Methods and composition of induction of pluripotent stem cells and other desired cell types are disclosed. For example, in certain aspects methods for generating essentially vector-free induced pluripotent stem cells are described. Furthermore, the invention provides induced pluripotent stem cells and desired cell types essentially free of exogenous vector elements with the episomal expression vectors to express differentiation programming factors.

Owner:FUJIFILM CELLULAR DYNAMICS INC

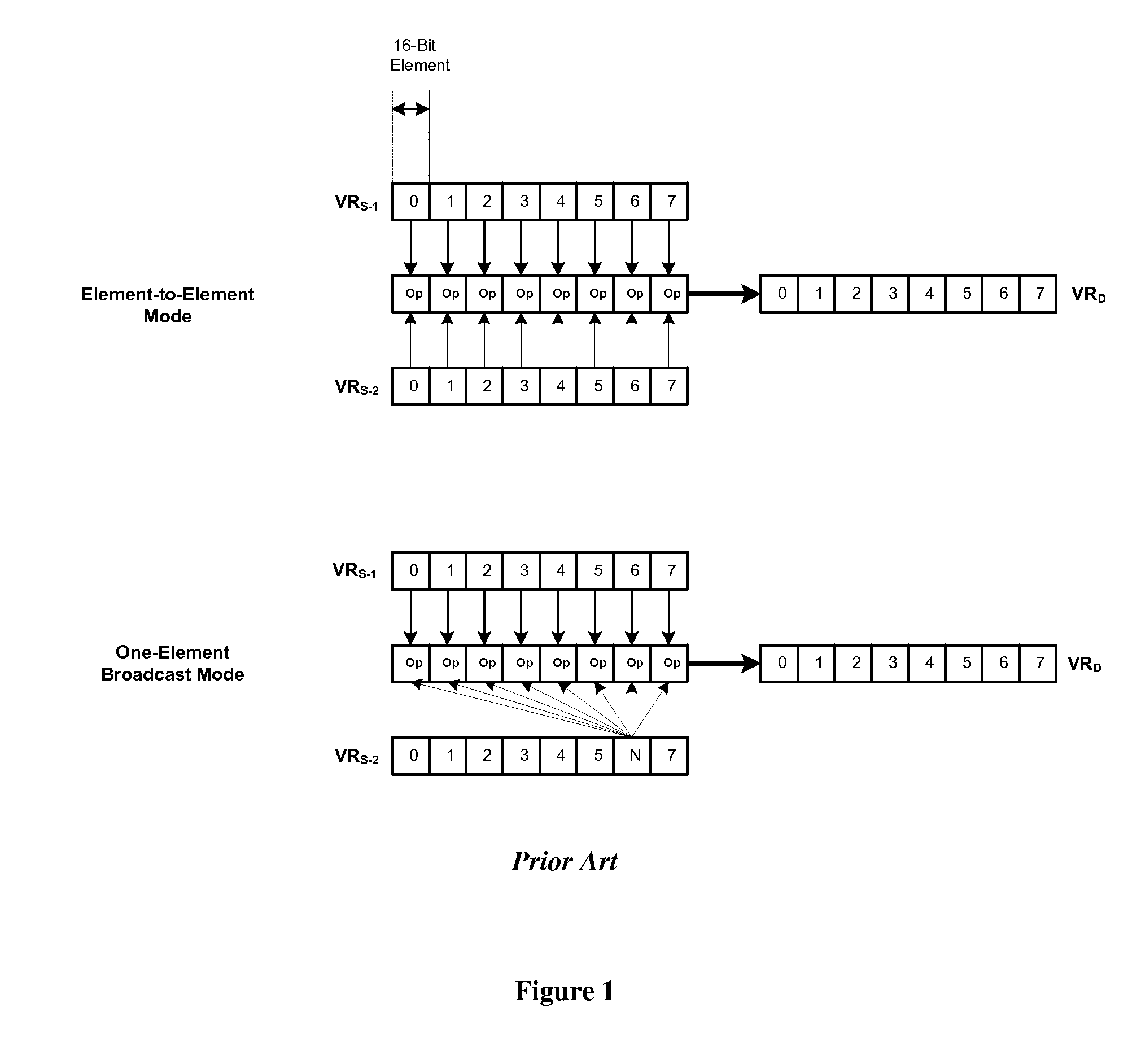

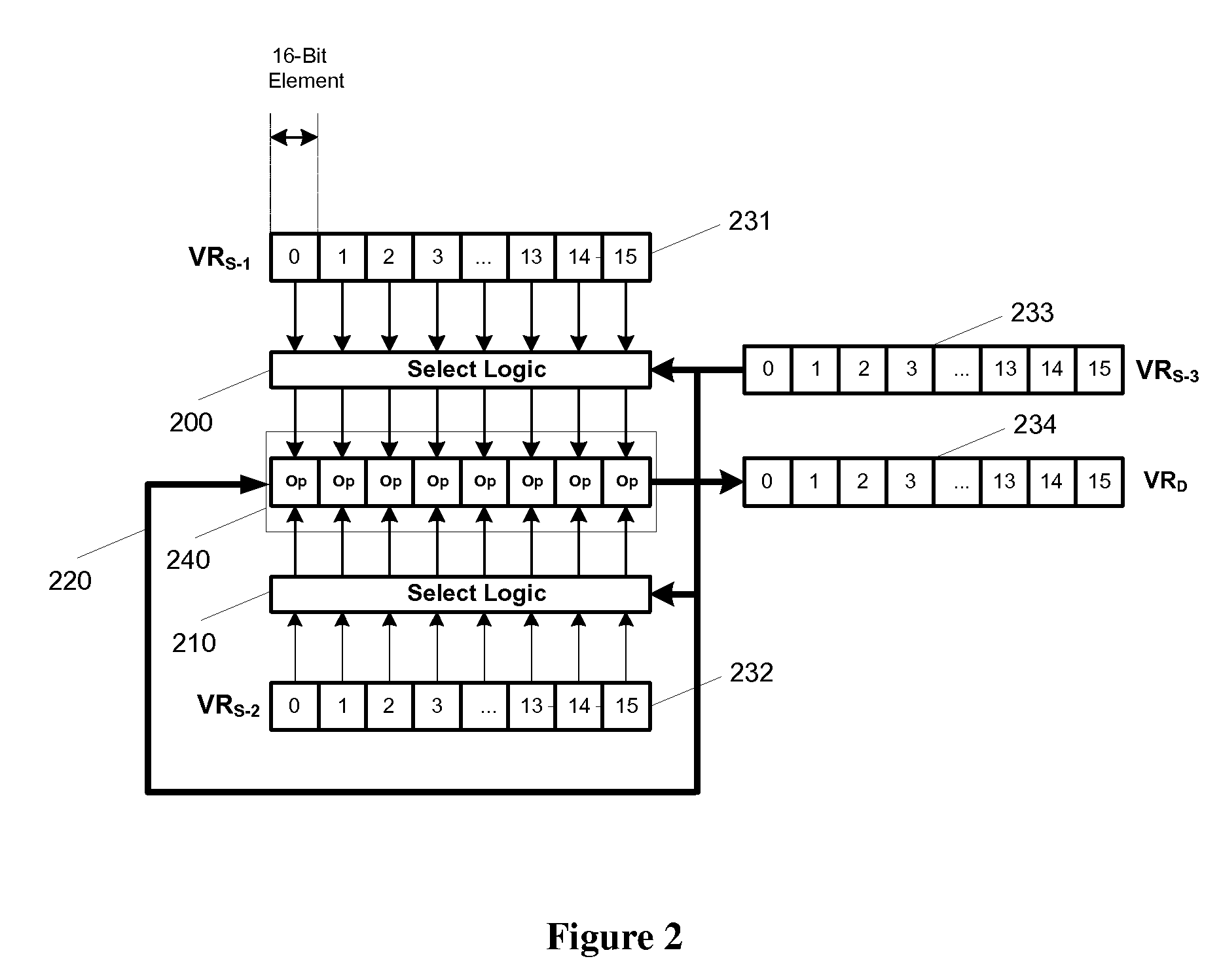

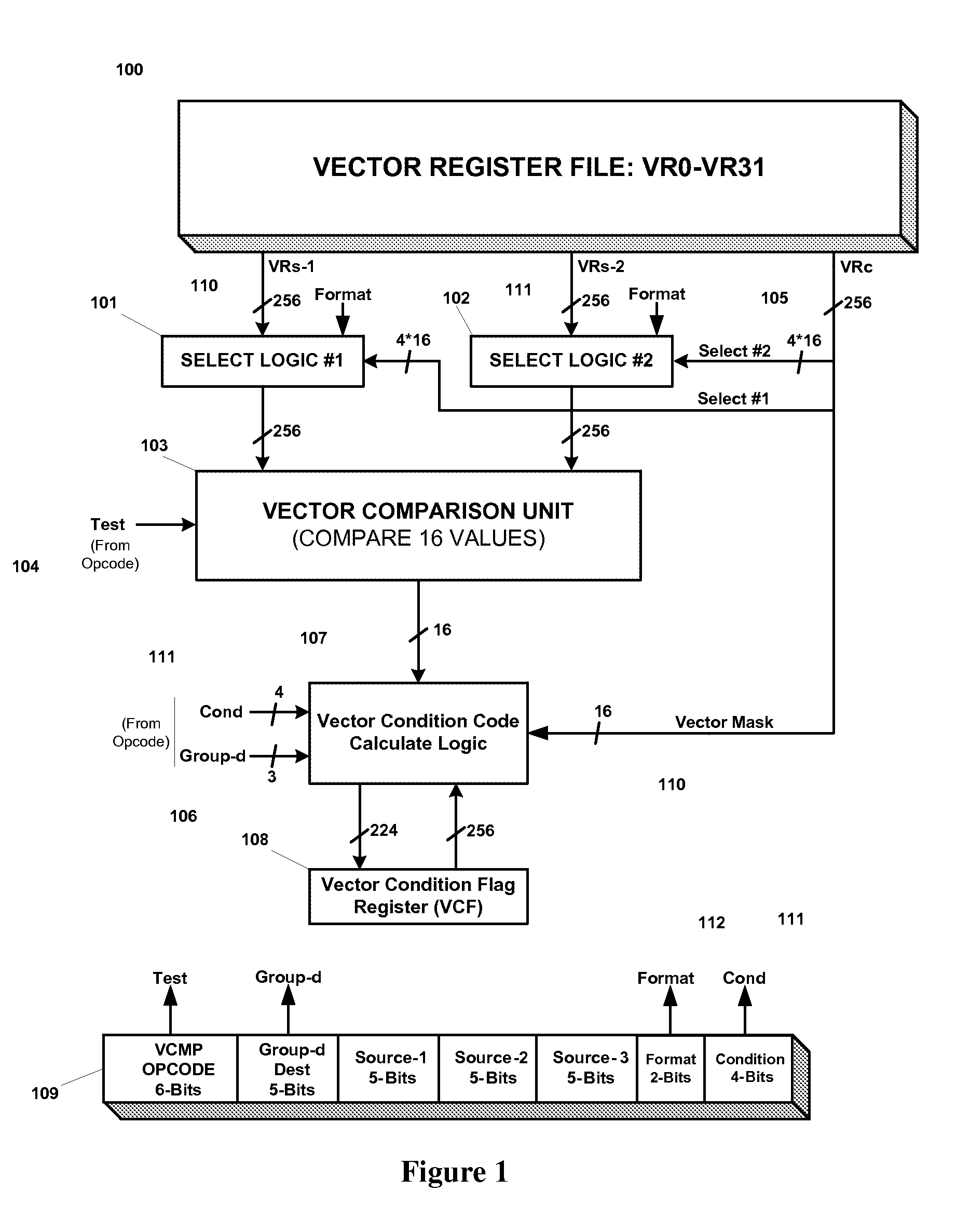

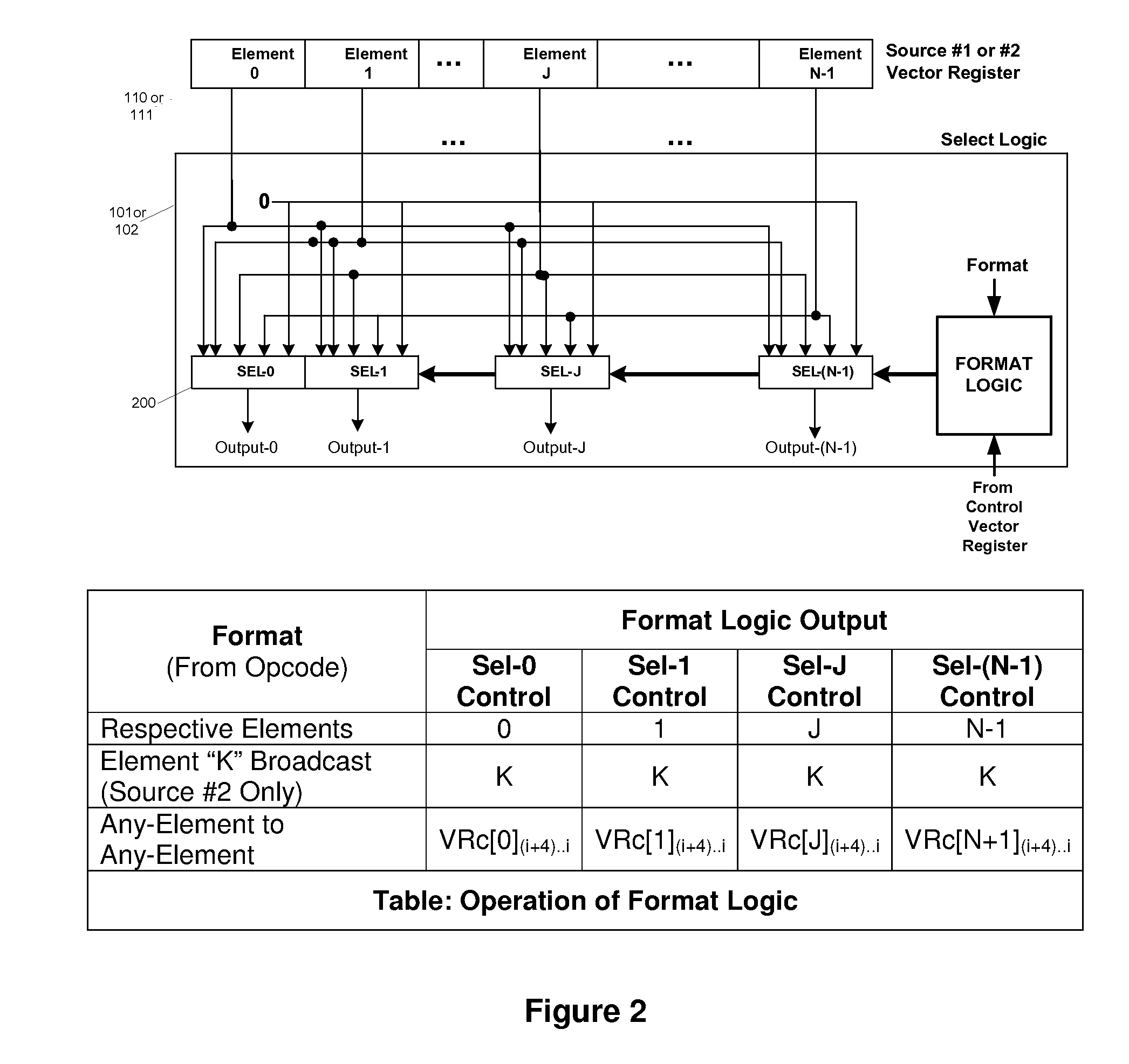

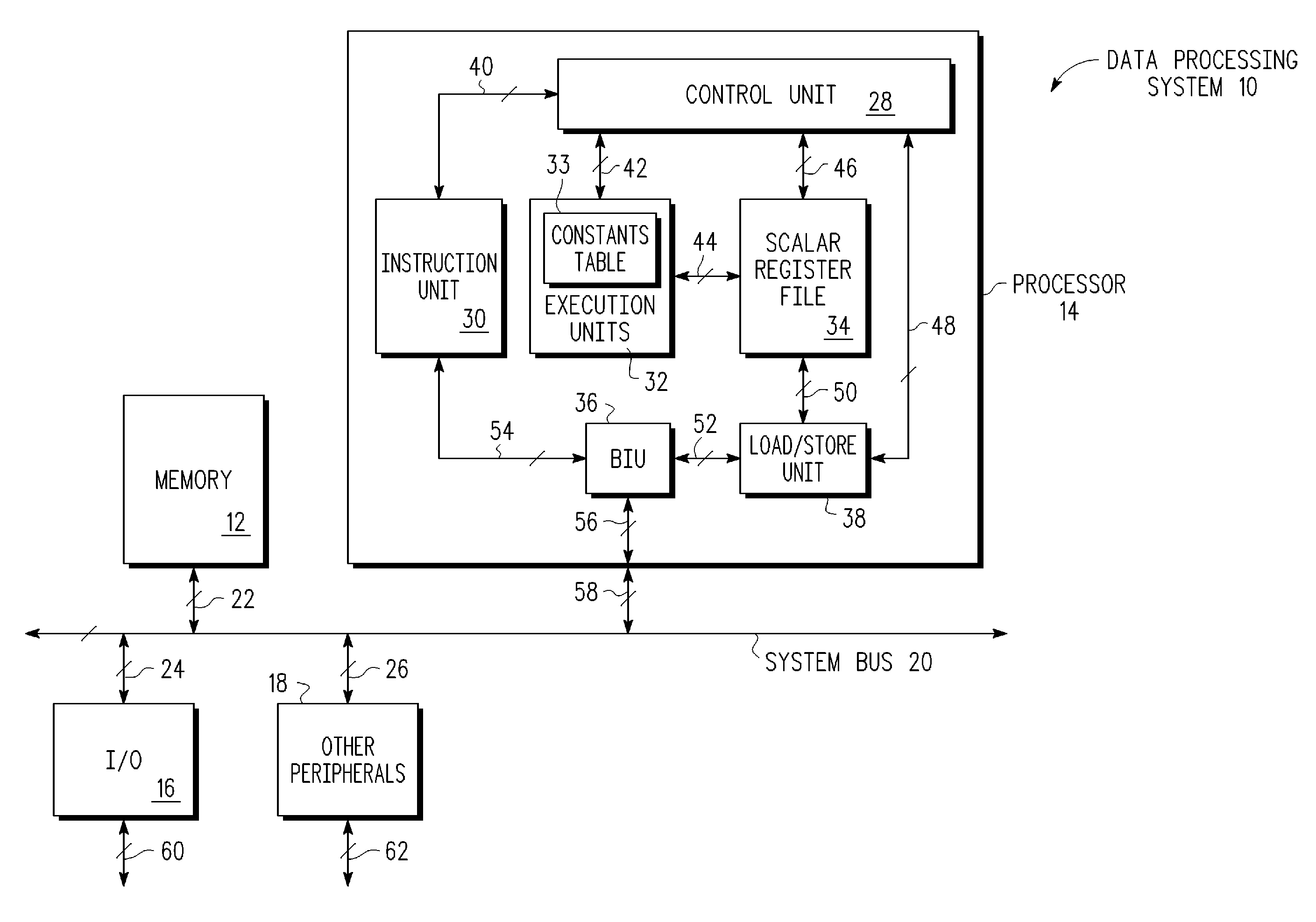

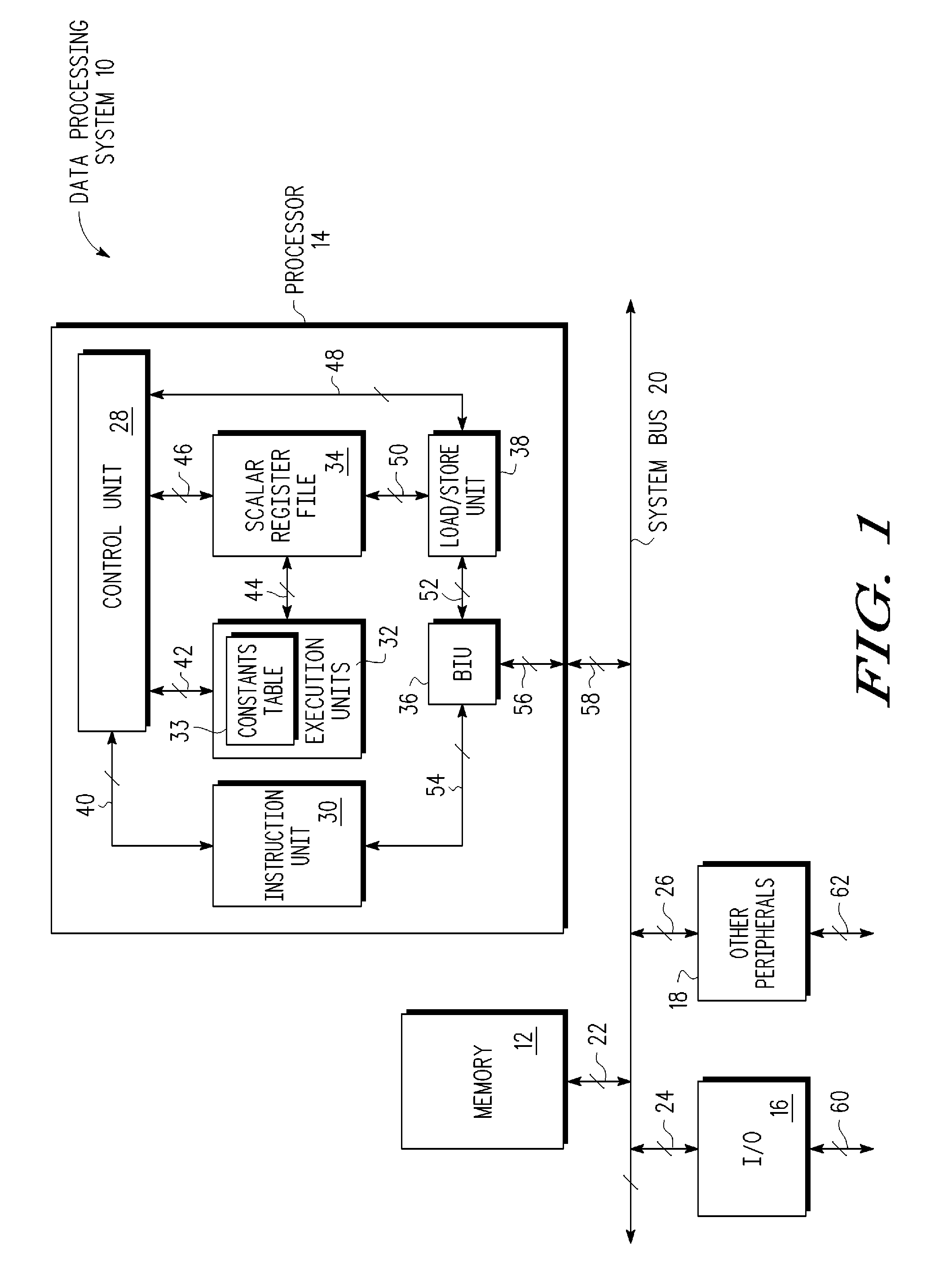

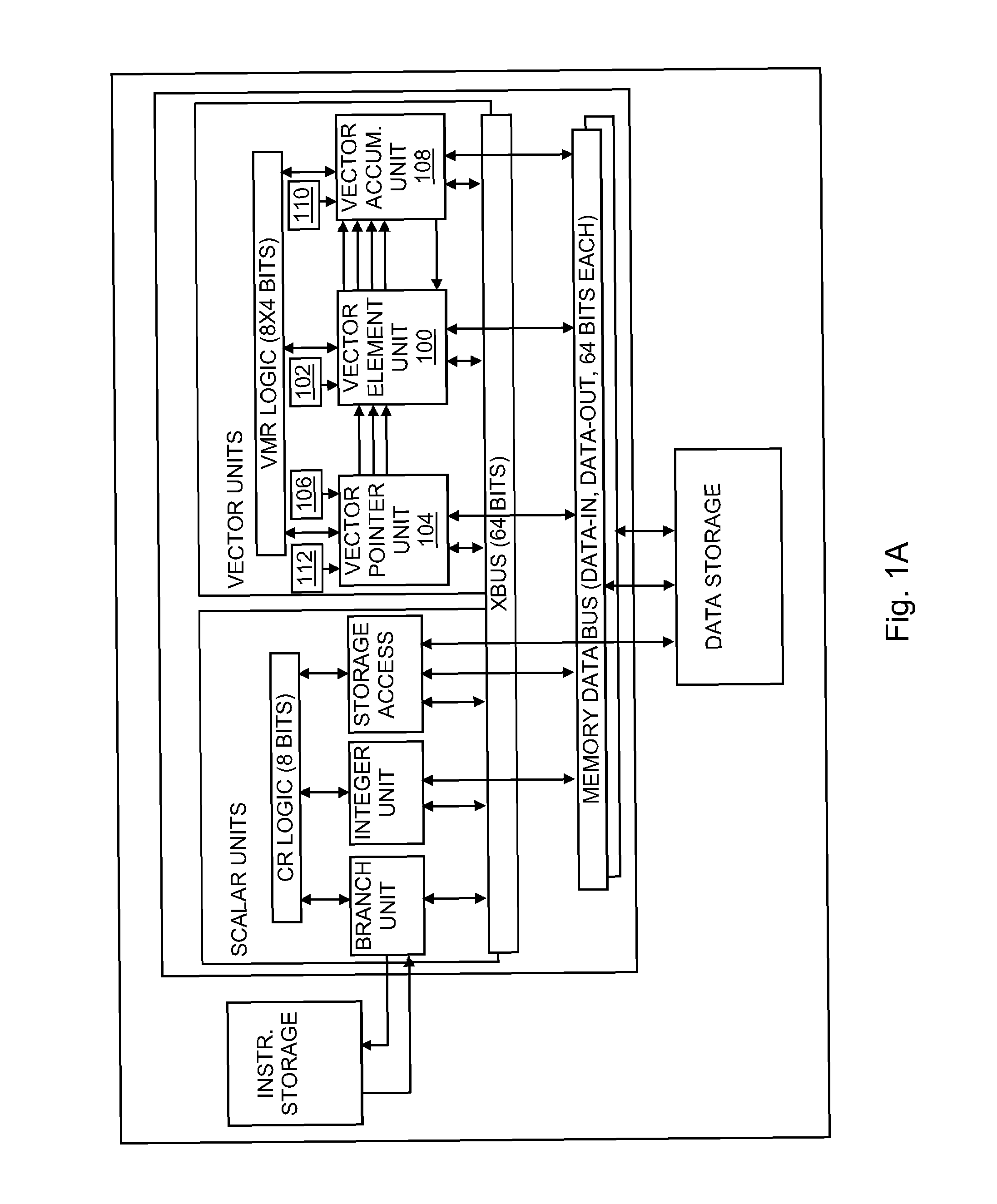

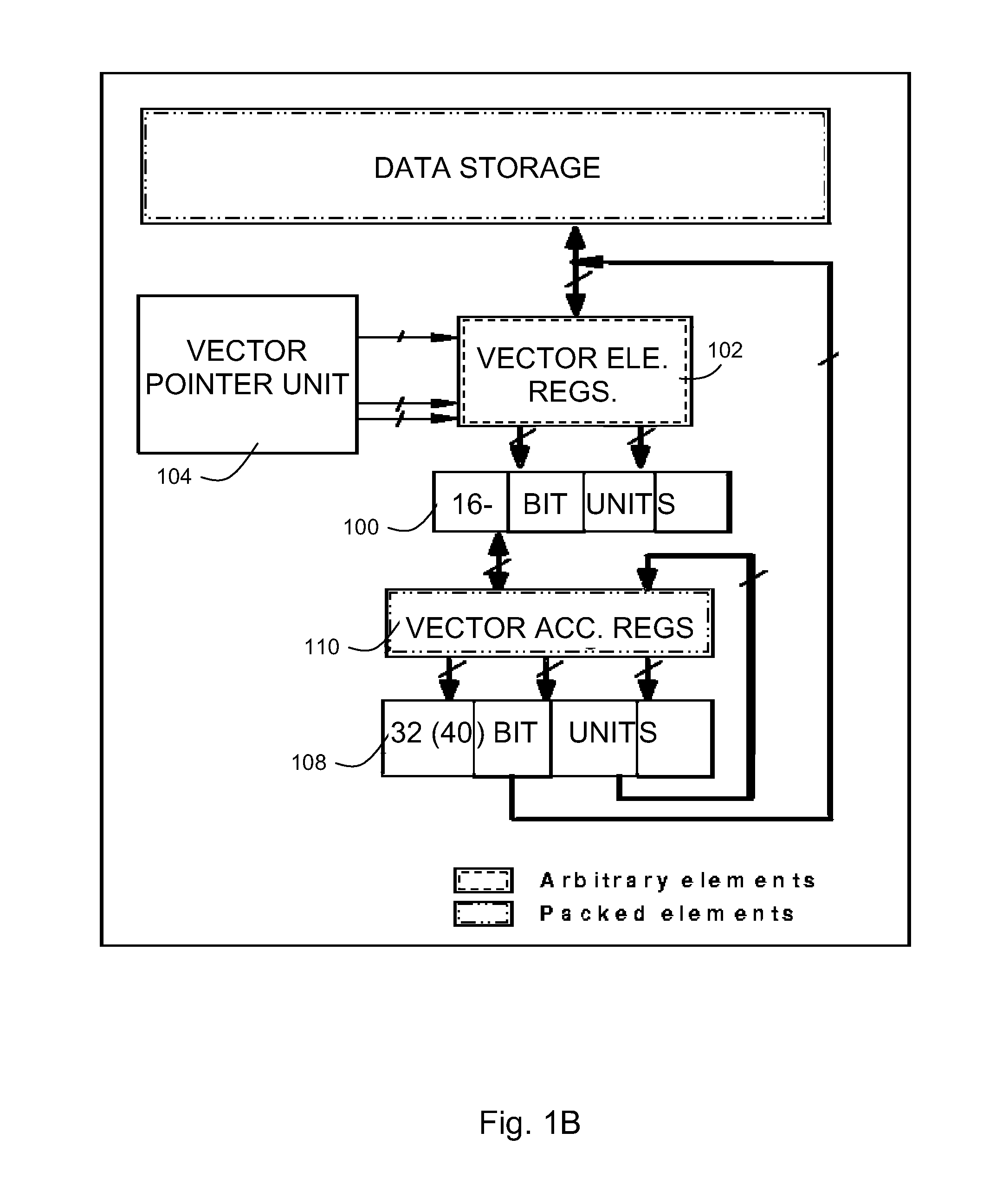

Flexible vector modes of operation for SIMD processor

InactiveUS20100274988A1General purpose stored program computerMachine execution arrangementsComputer architectureVector element

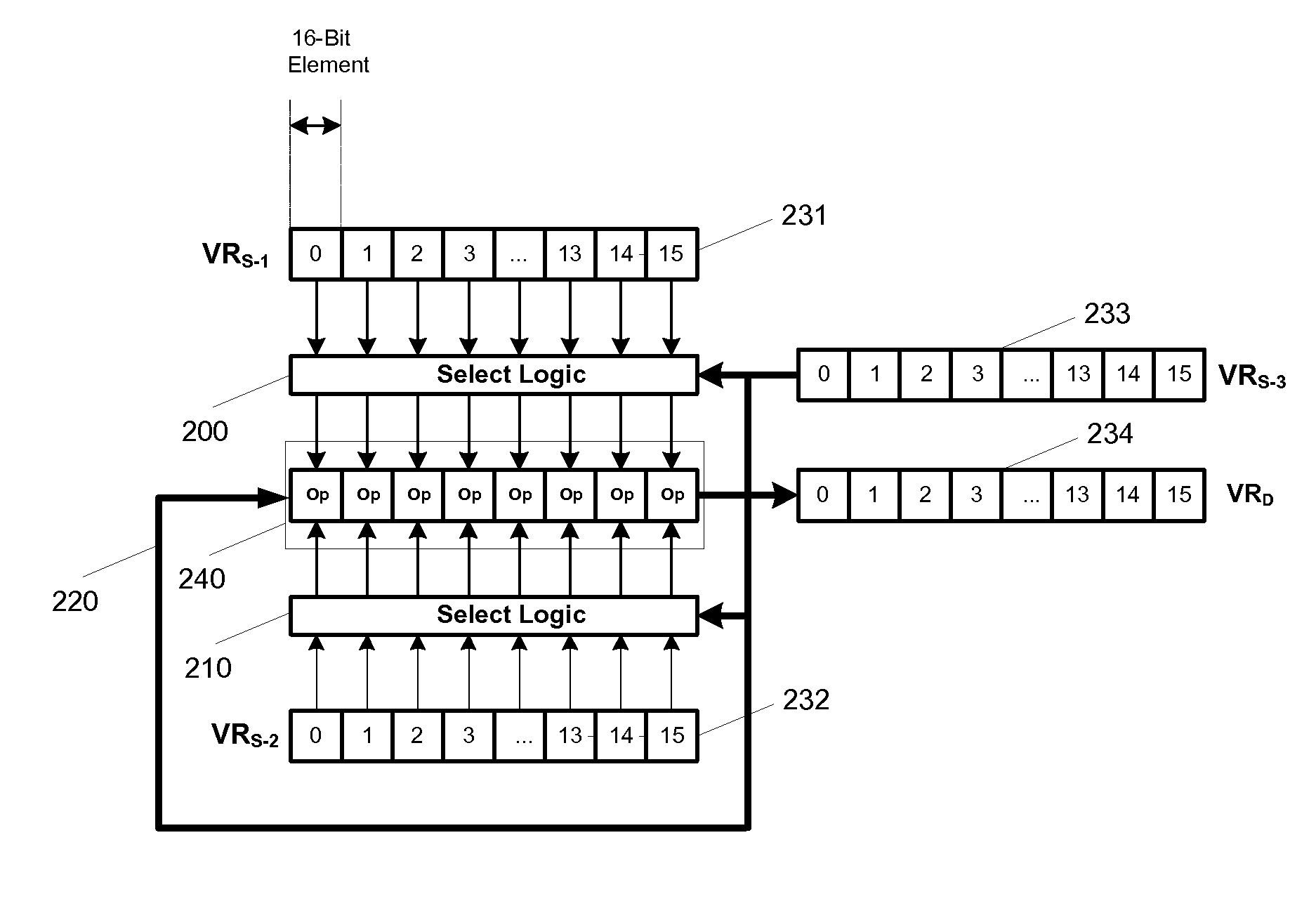

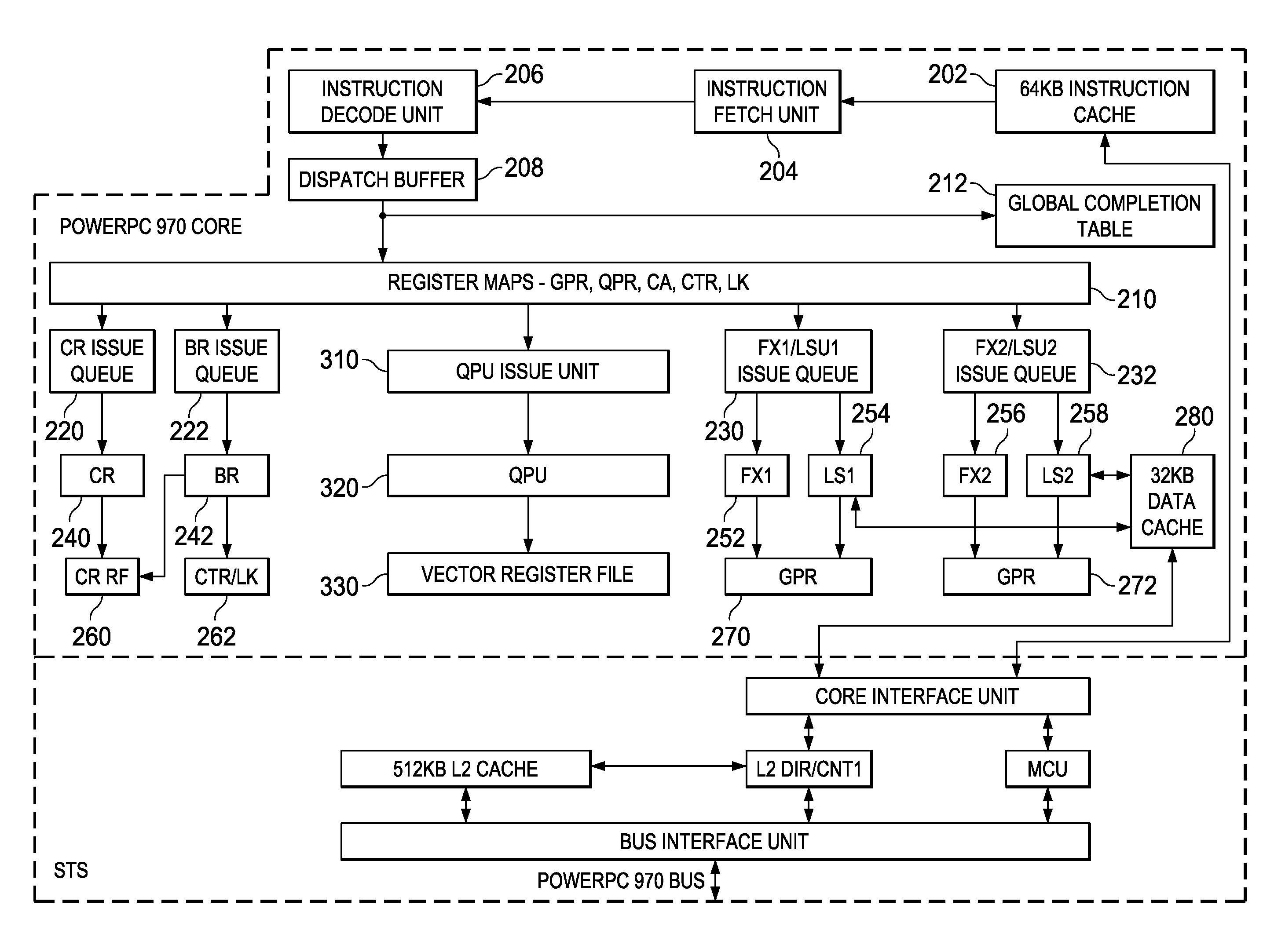

In addition to the usual modes of SIMD processor operation, where corresponding elements of two source vector registers are used as input pairs to be operated upon by the execution unit, or where one element of a source vector register is broadcast for use across the elements of another source vector register, the new system provides several other modes of operation for the elements of one or two source vector registers. Improving upon the time-costly moving of elements for an operation such as DCT, the present invention defines a more general set of modes of vector operations. In one embodiment, these new modes of operation use a third vector register to define how each element of one or both source vector registers are mapped, in order to pair these mapped elements as inputs to a vector execution unit. Furthermore, the decision to write an individual vector element result to a destination vector register, for each individual element produced by the vector execution unit, may be selectively disabled, enabled, or made to depend upon a selectable condition flag or a mask bit.

Owner:MIMAR TIBET

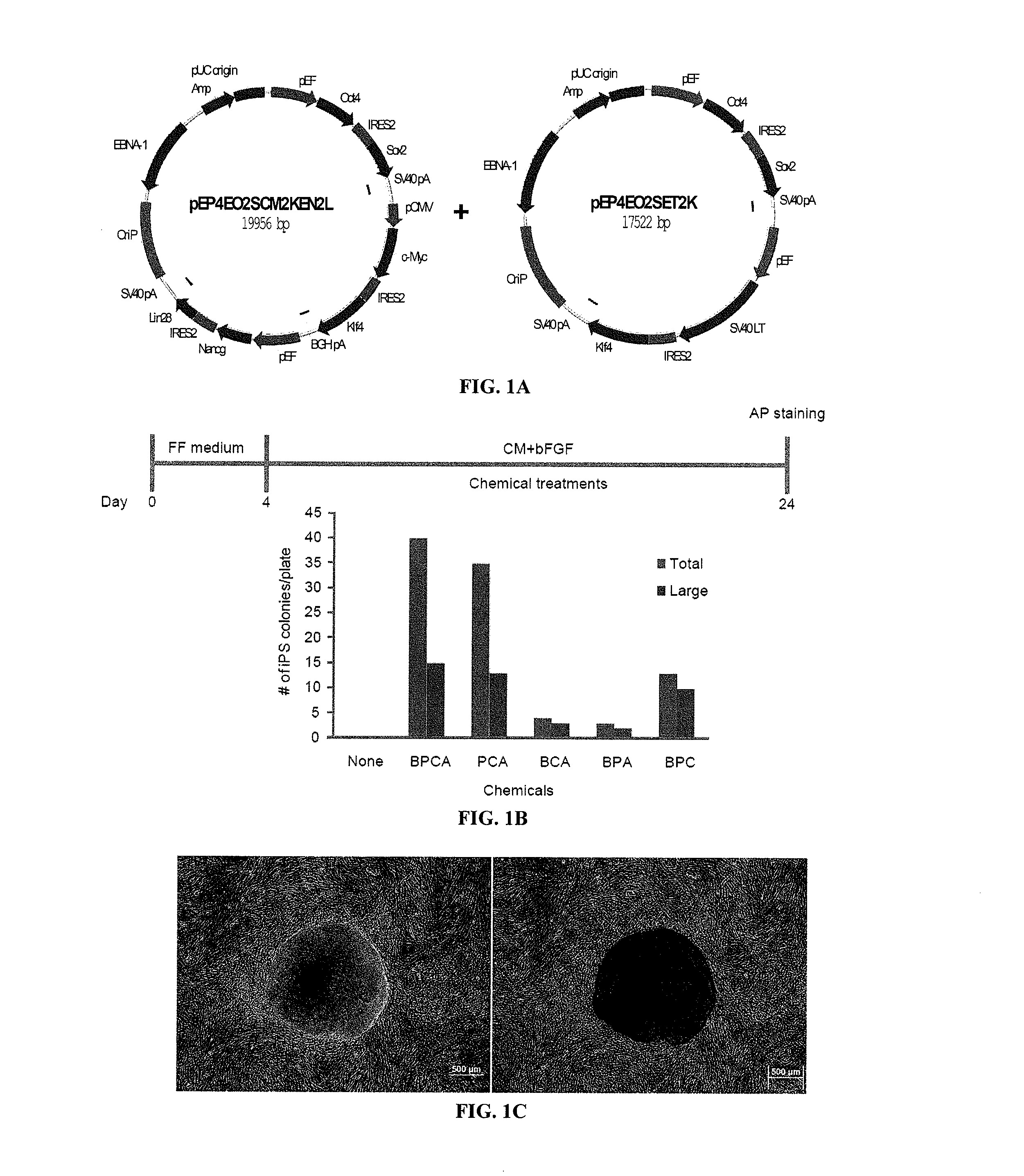

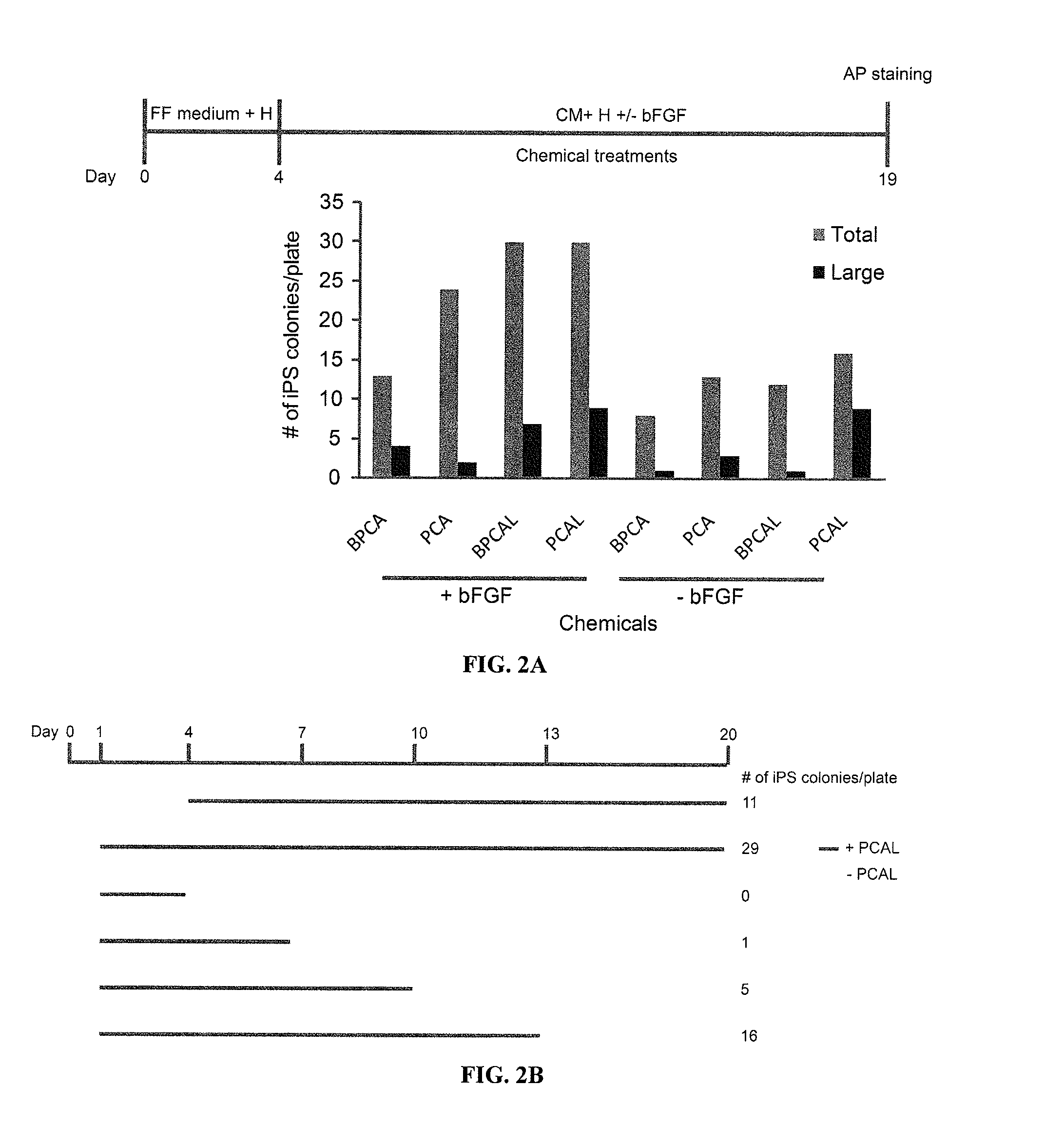

Episomal reprogramming with chemicals

ActiveUS20110104125A1Easy to adaptHigh reprogramming efficiencyBiocideNervous disorderVector elementViral vector

Methods and composition of induction of pluripotent stem cells are disclosed. For example, in certain aspects methods for generating essentially vector-free induced pluripotent stem cells with cell signaling regulators are described. Furthermore, certain aspects of the invention provide novel compositions comprising induced pluripotent stem cells essentially free of exogenous retroviral vector elements in the presence of a medium comprising signaling inhibitors. In certain aspects, feeder-free episomal reprogramming methods may be provided.

Owner:FUJIFILM CELLULAR DYNAMICS INC

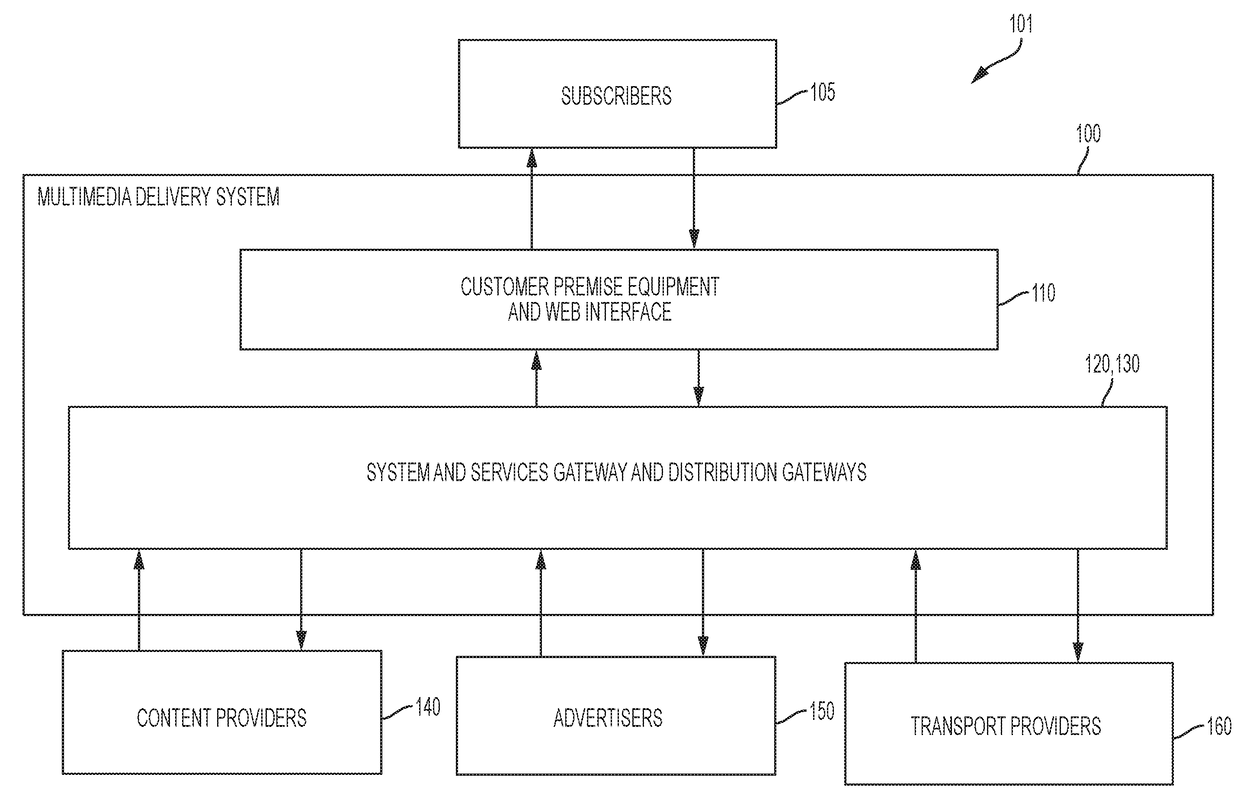

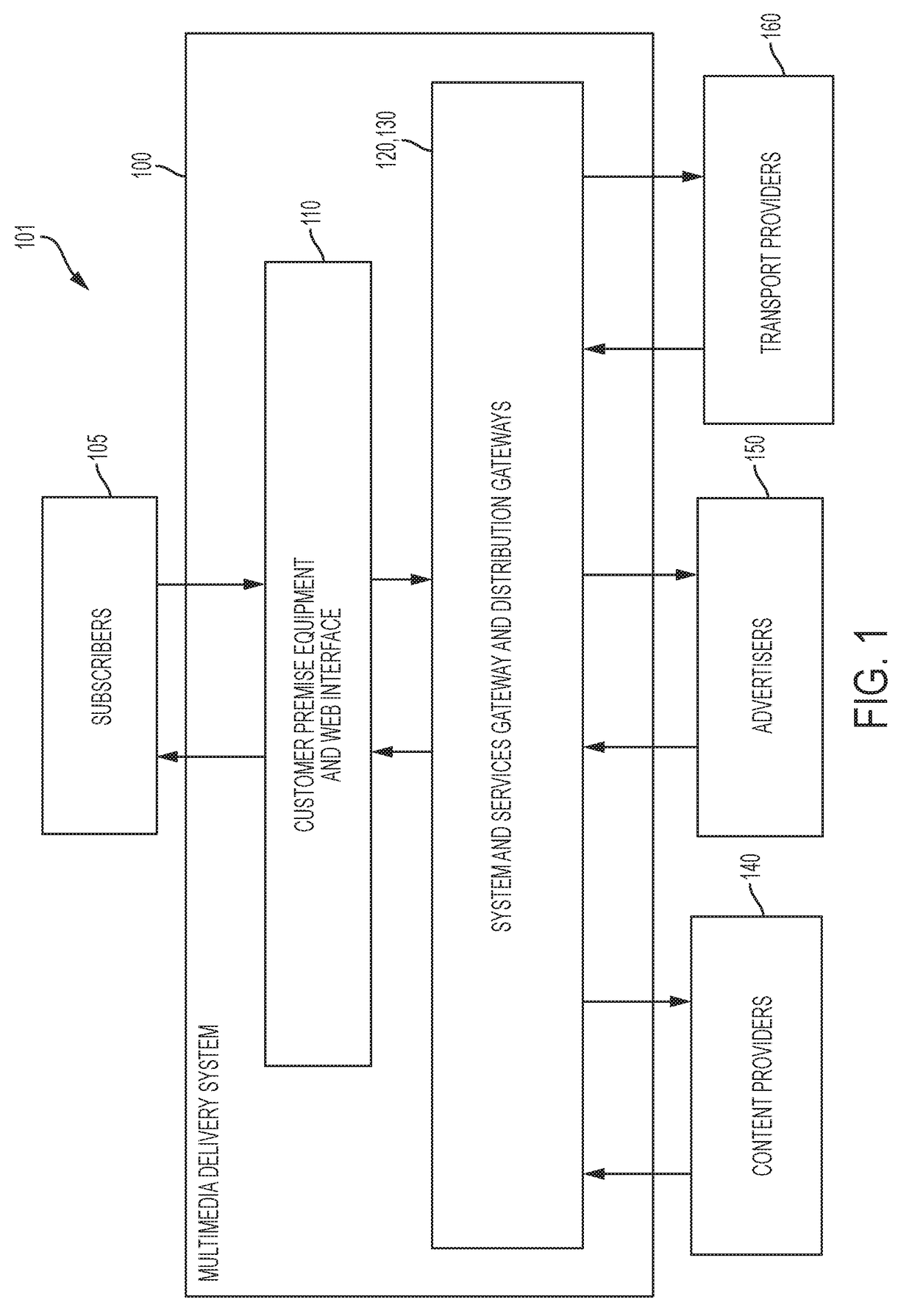

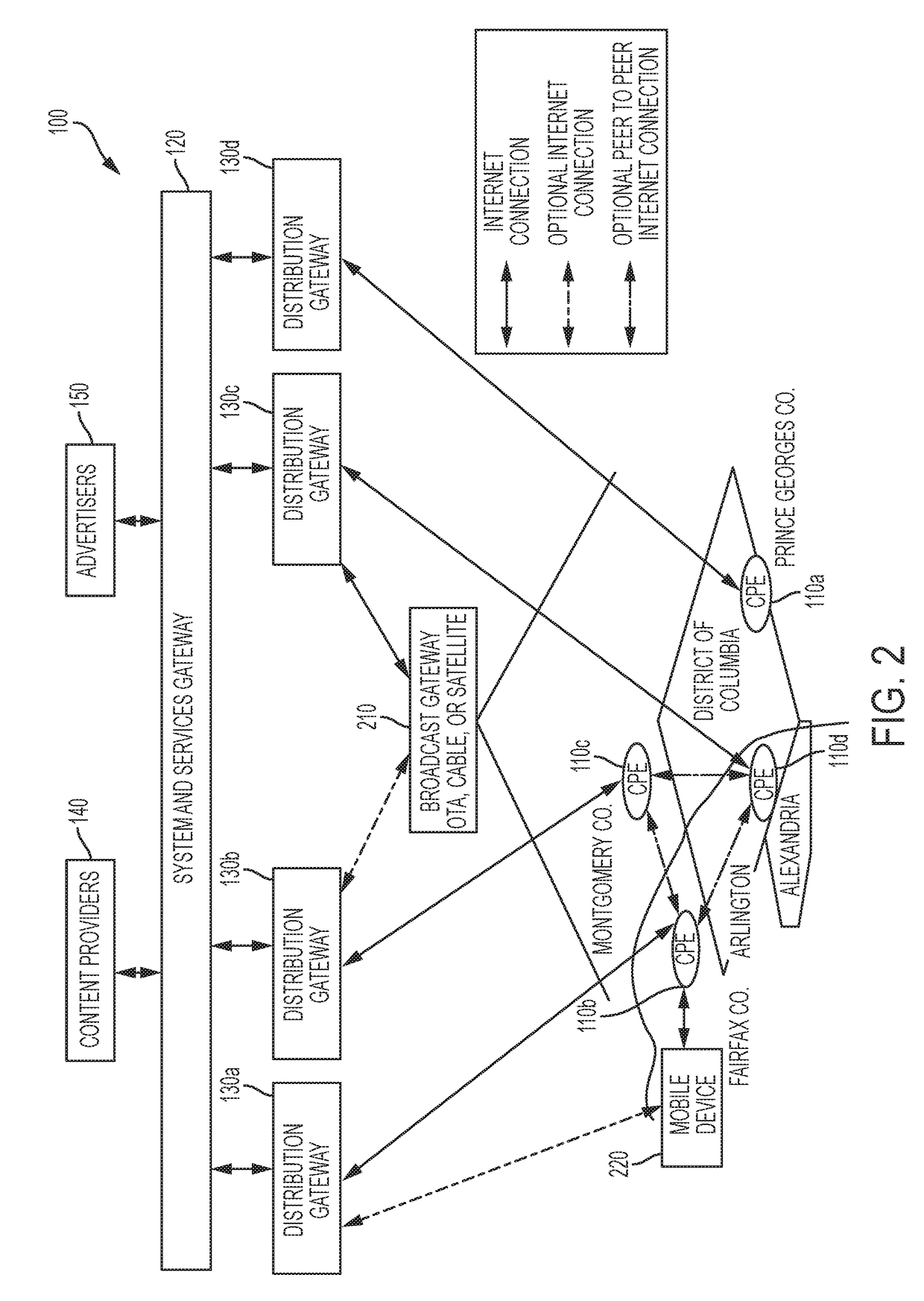

Clustering and adjudication to determine a recommendation of multimedia content

A method and apparatus can include a system processor and a system controller. The system controller can retrieve data from at least one database, the data including information associated with at least one of subscribers, multimedia content, and subscriber interaction with customer premises equipment, and transmit, to a customer premises equipment of a subscriber, a recommendation of multimedia content. The system processor can formulate an input dataset from the retrieved data, perform nonlinear clustering on the input dataset to formulate subscriber and multimedia content clusters having similarities between elements therein, and determine the recommendation of multimedia content based on a metric distance between vector elements of the formulated subscriber and multimedia content clusters and the metric distance crossing a threshold.

Owner:EDGE2020 LLC

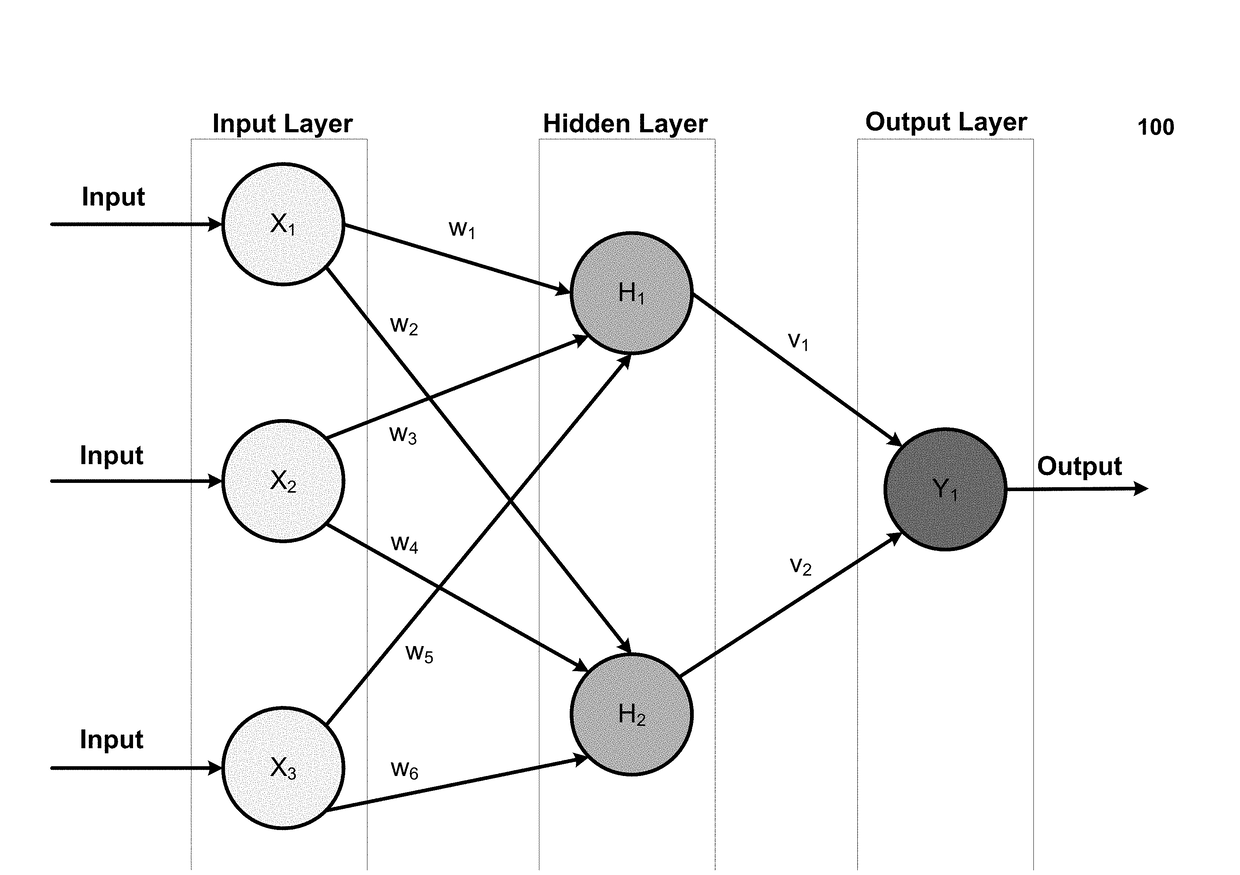

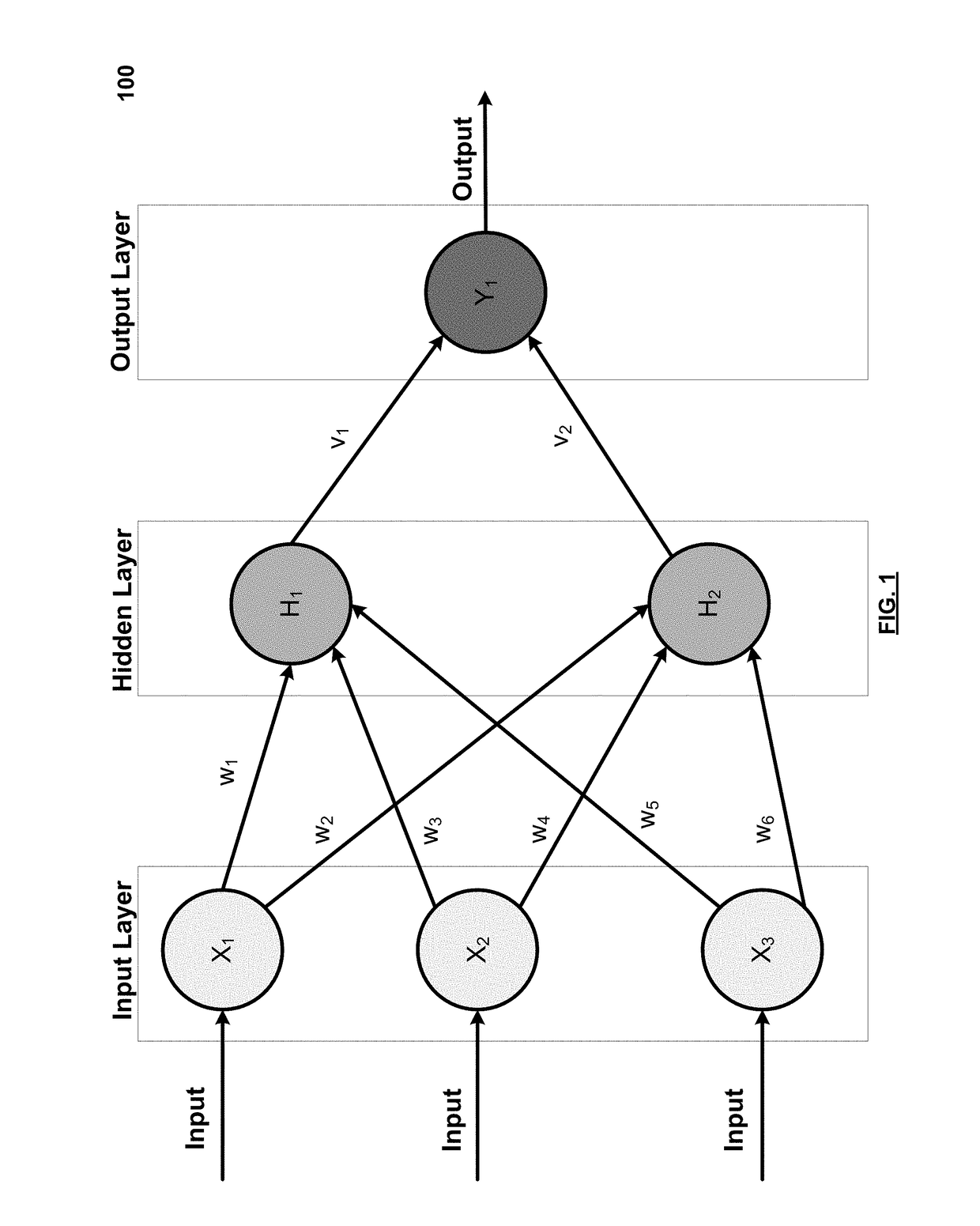

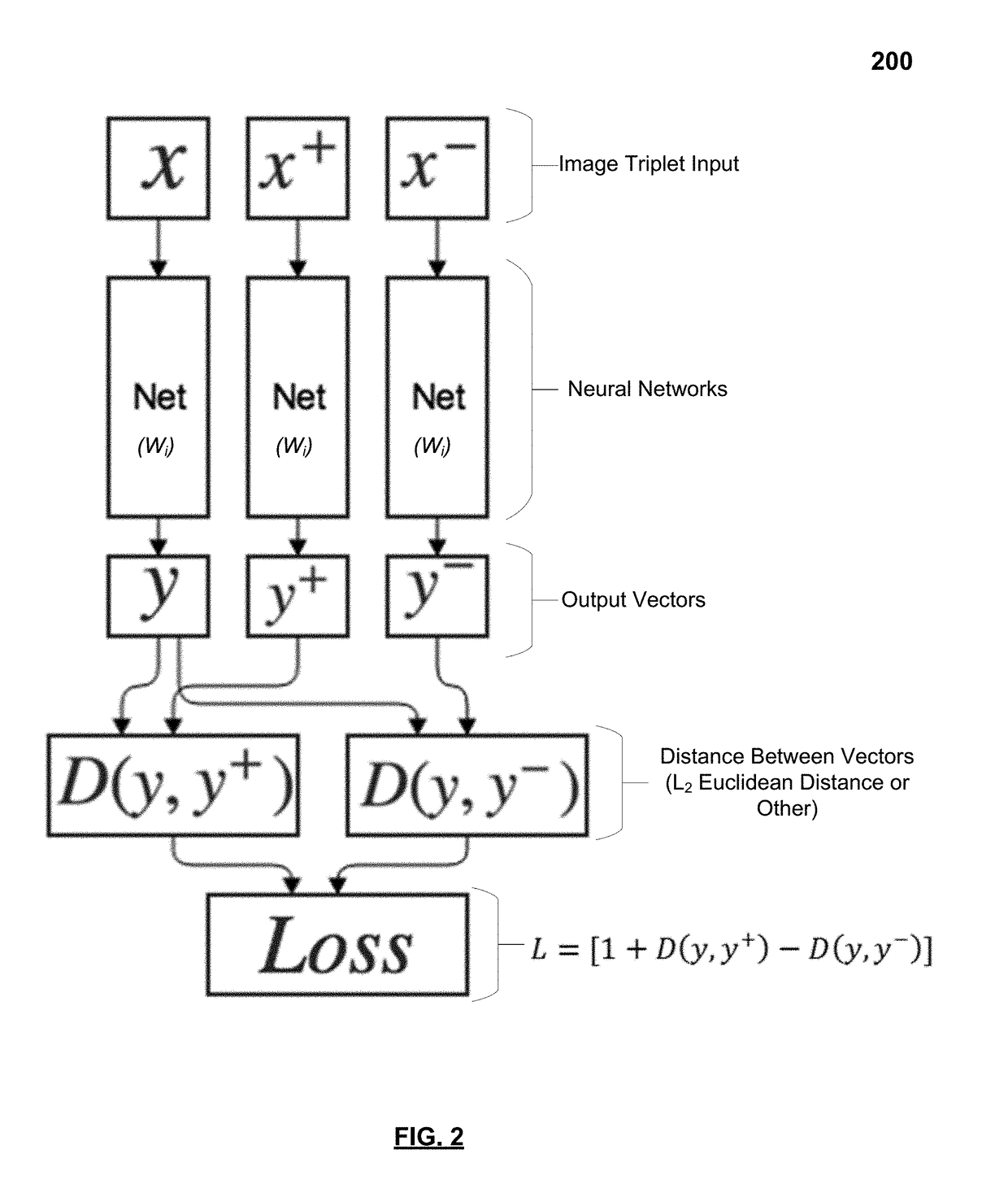

Content embedding using deep metric learning algorithms

ActiveUS20170357896A1Reduce lossesNeural architecturesNeural learning methodsPattern recognitionAlgorithm

The technology disclosed introduces a concept of training a neural network to create an embedding space. The neural network is trained by providing a set of K+2 training documents, each training document being represented by a training vector x, the set including a target document represented by a vector xt, a favored document represented by a vector xs, and K>1 unfavored documents represented by vectors xiu, each of the vectors including input vector elements, passing the vector representing each document set through the neural network to derive an output vectors yt, ys and yiu, each output vector including output vector elements, the neural network including adjustable parameters which dictate an amount of influence imposed on each input vector element to derive each output vector element, adjusting the parameters of the neural network to reduce a loss, which is an average over all of the output vectors yiu of [D(yt,ys)−D(yt,yiu)].

Owner:COGNIZANT TECH SOLUTIONS U S CORP

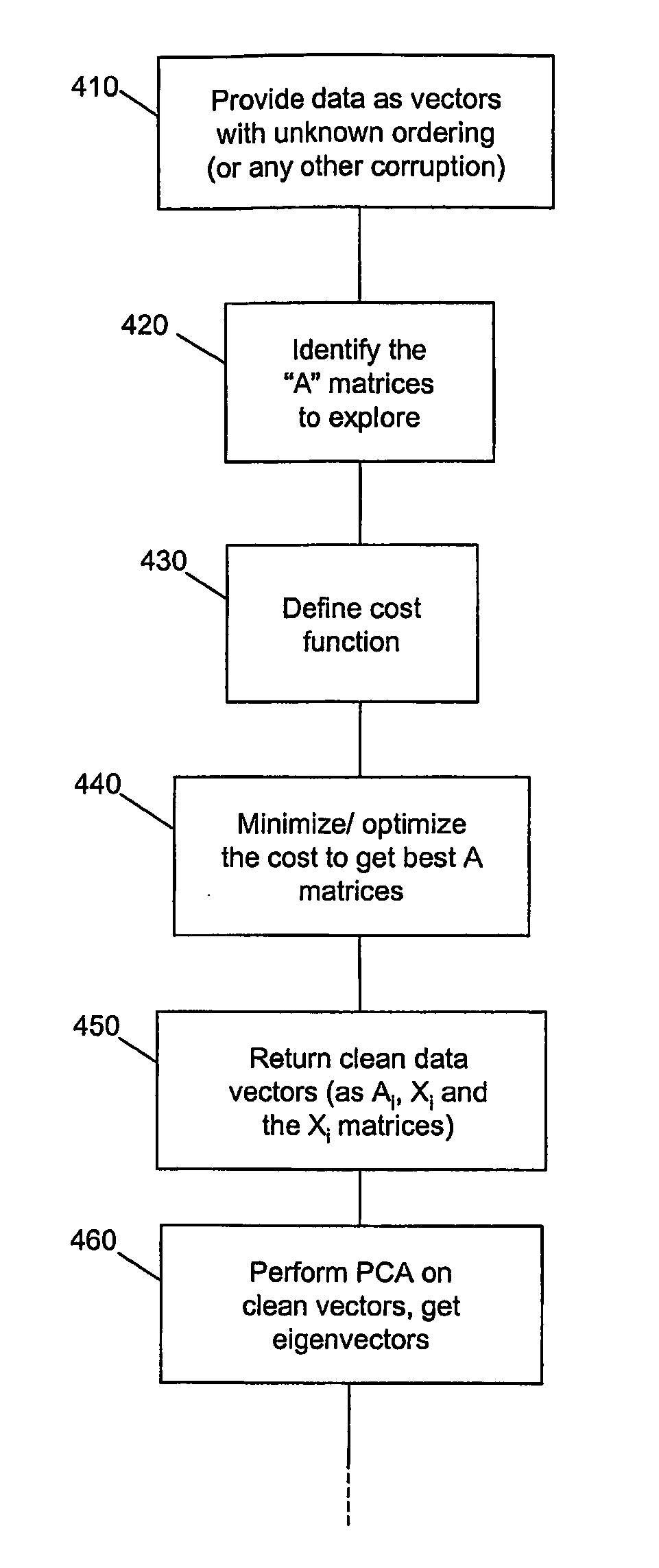

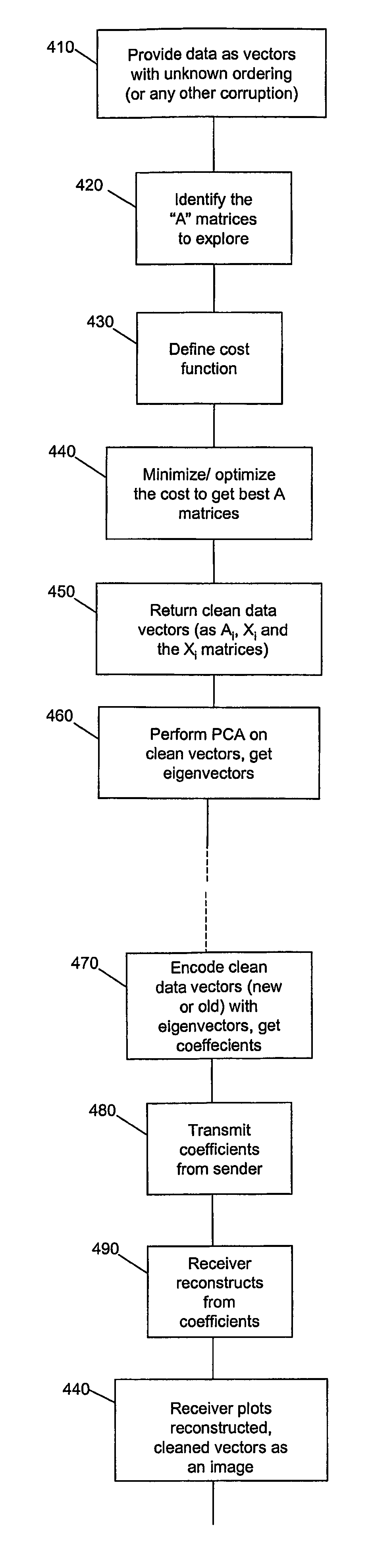

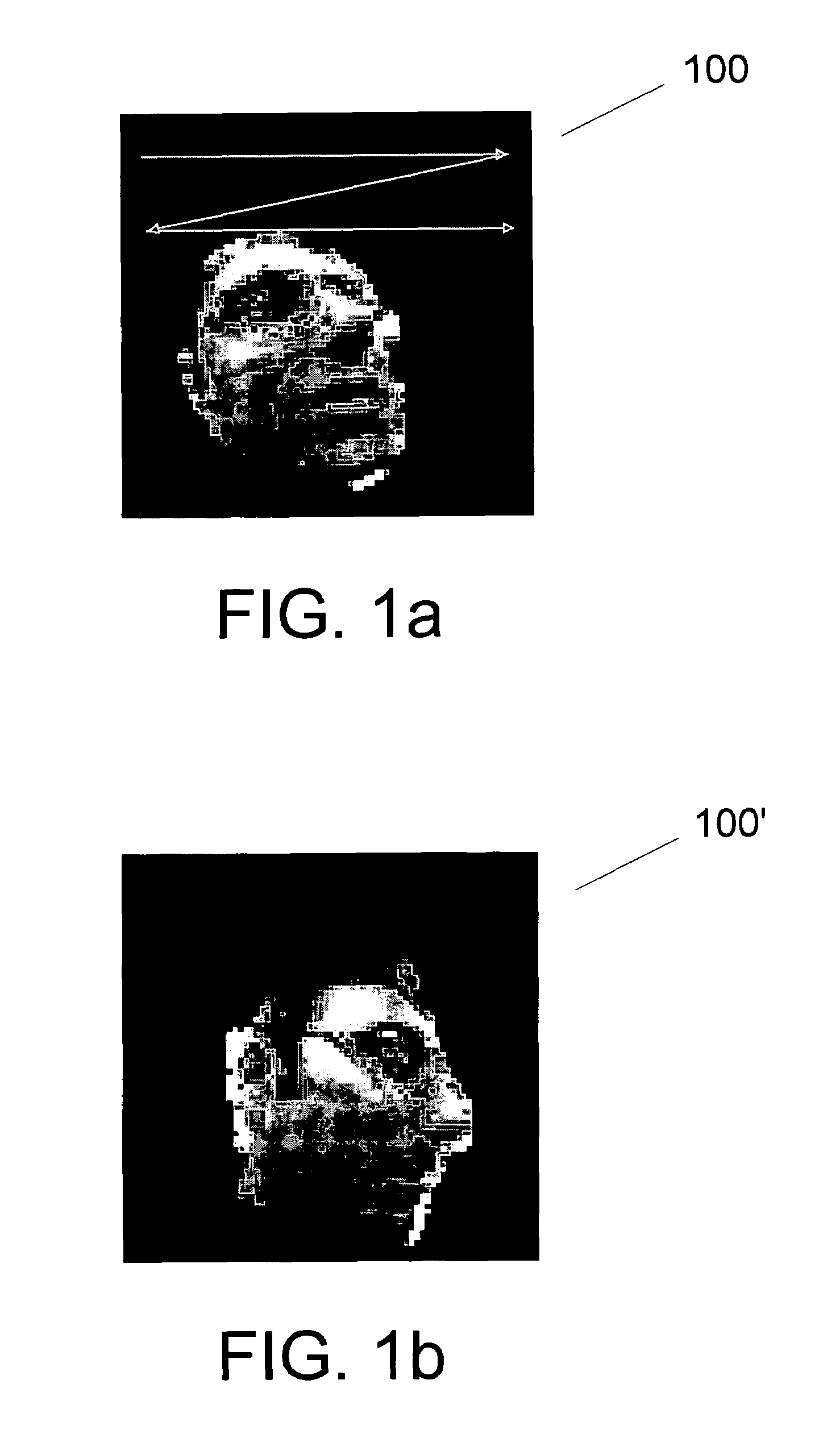

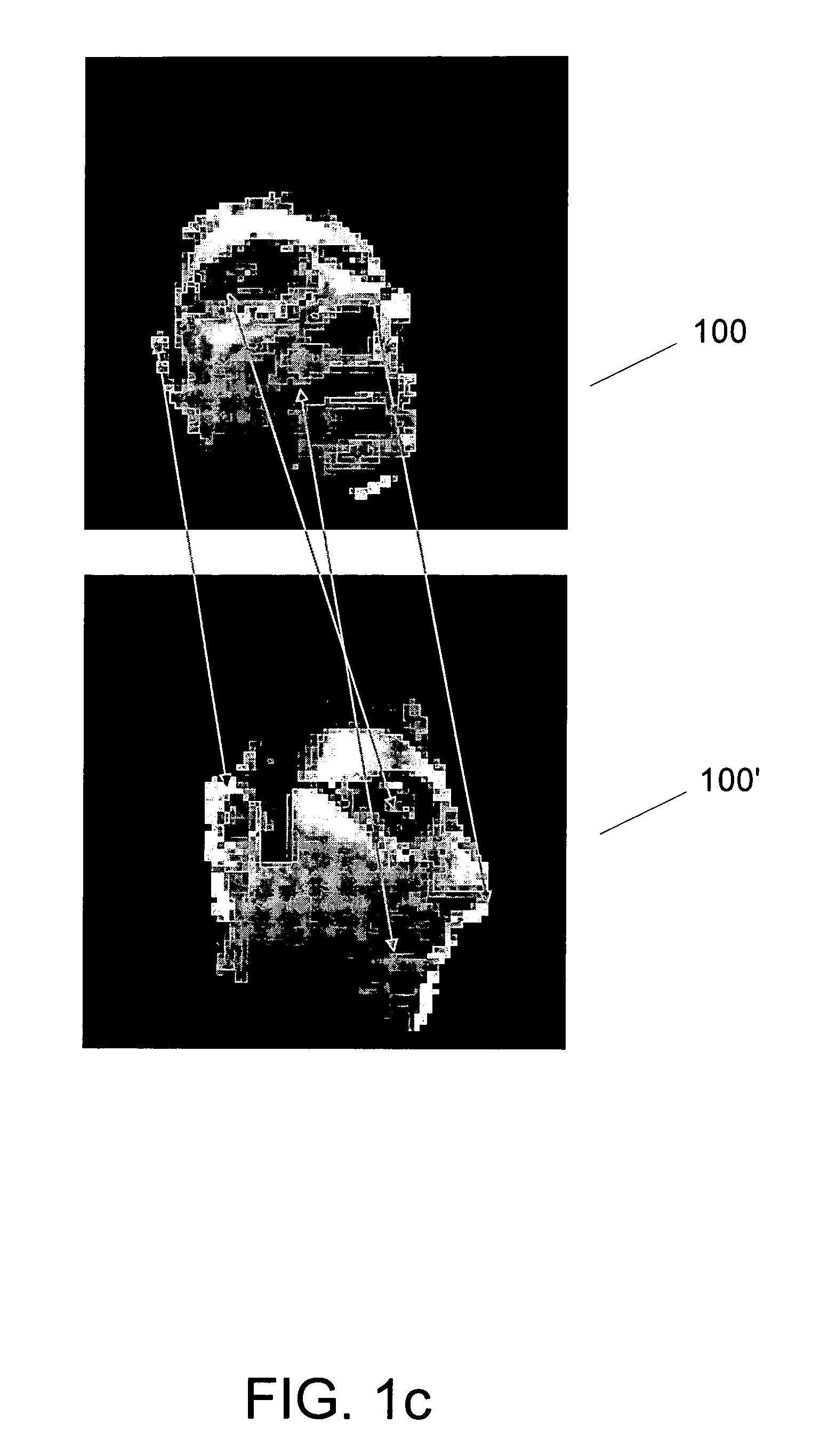

Ordered data compression system and methods

Methods and systems are provided for encoding, transmission and decoding of vectorized input data, for example, video or audio data. A convex invariance learning framework is established for processing input data or a given data type. Each input vector is associated with a variable transformation matrix that acts on the vector to invariantly permute the vector elements. Joint invariance and model learning is performed on a training set of invariantly transformed vectors over a constrained space of transformation matrices using maximum likelihood analysis. The maximum likelihood analysis reduces the data volume to a linear subspace volume in which the training data can be modeled by a reduced number of variables. Principal component analysis is used to identify a set of N eigen vectors that span the linear subspace. The set of N eigenvectors is used a basis set to encode input data and to decode compressed data.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

Vector Predicates for Sub-Word Parallel Operations

InactiveUS20080016320A1General purpose stored program computerProgram controlVector elementControl data

This invention uses vector predicate registers to control conditional execution of instructions for vector elements within a data word. A particular vector predicate registers is addressed via a register index. The state of bits of the vector predicate register controls whether a corresponding sub-word operation is executed or inhibited.

Owner:TEXAS INSTR INC

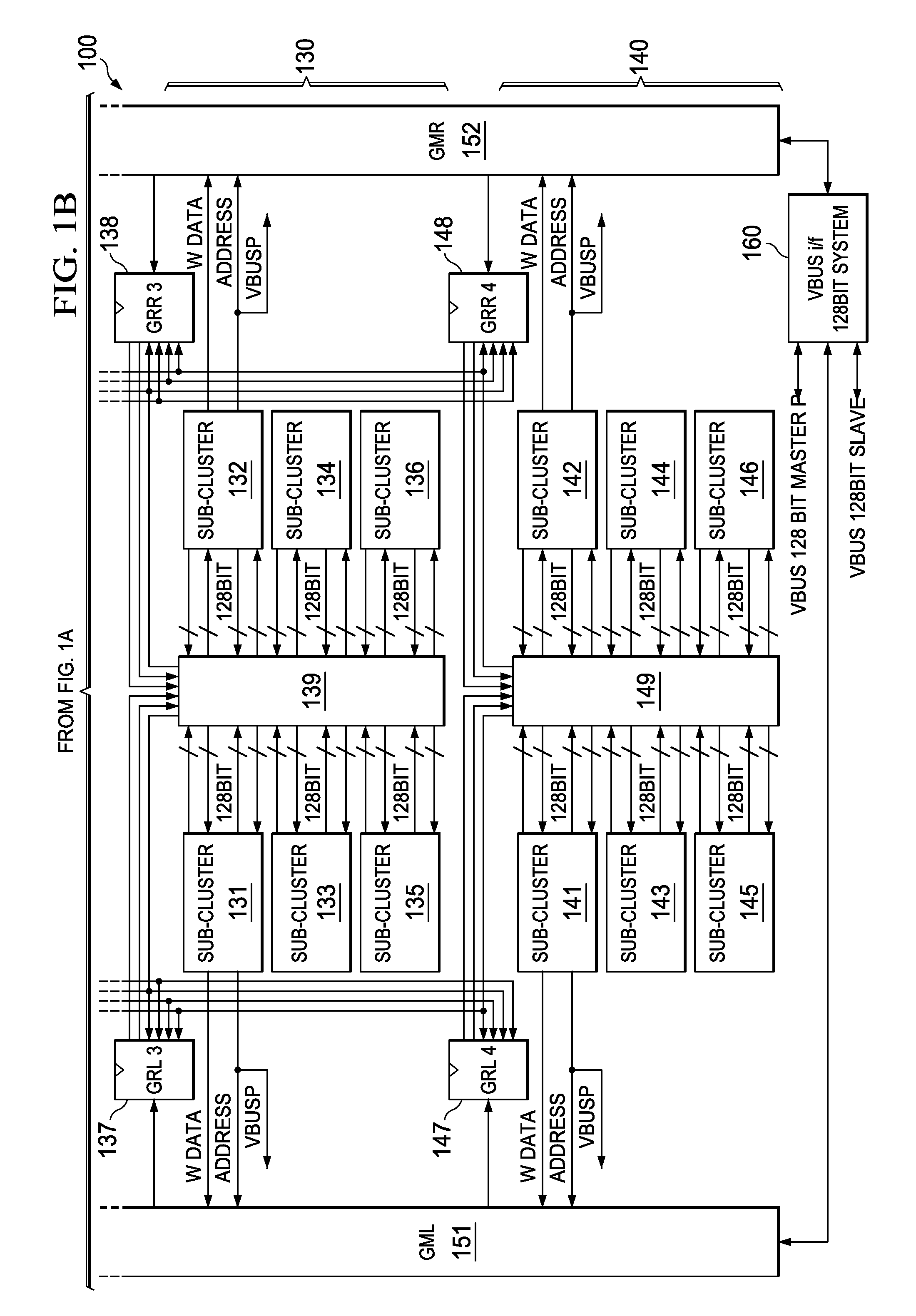

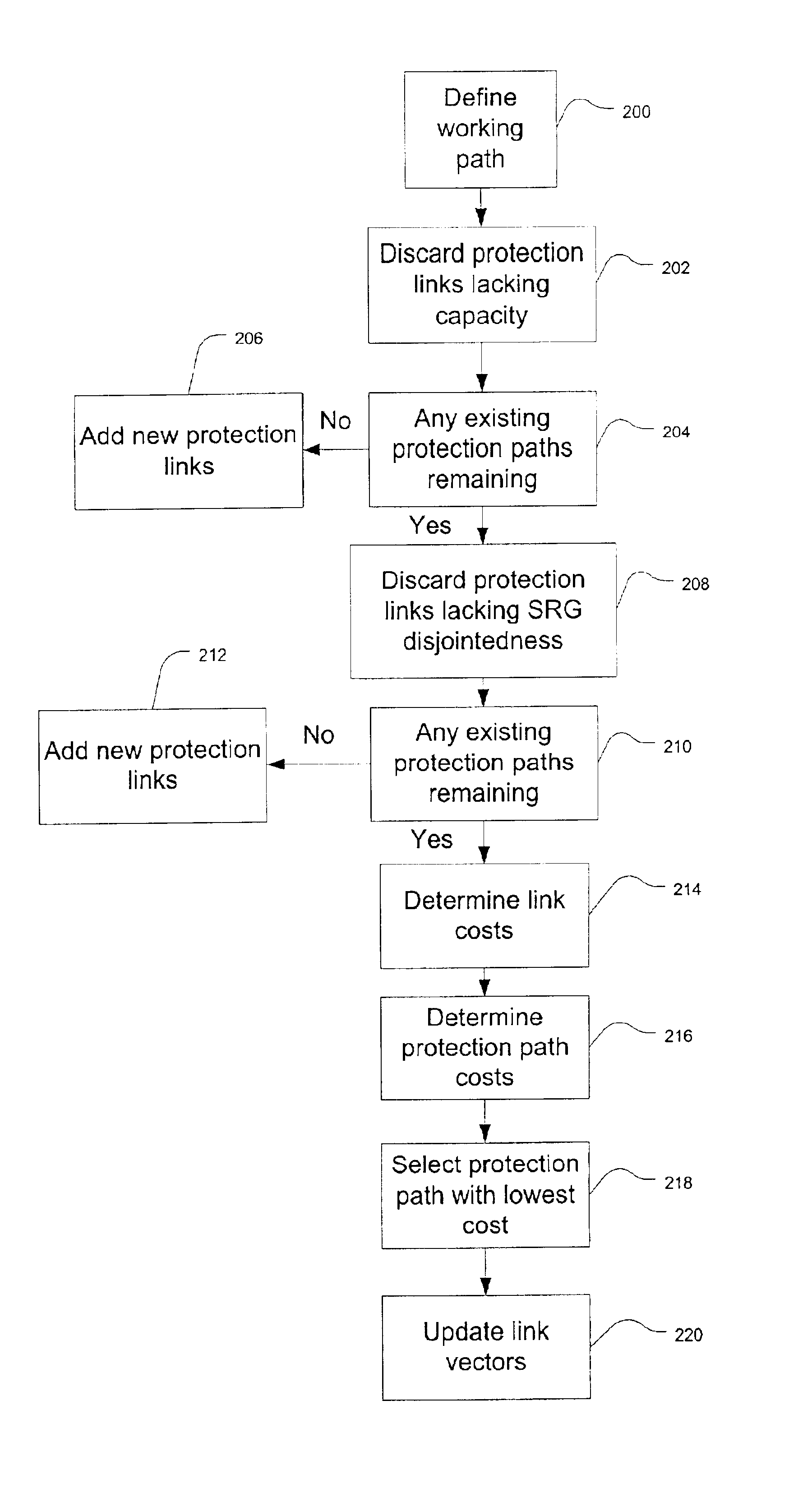

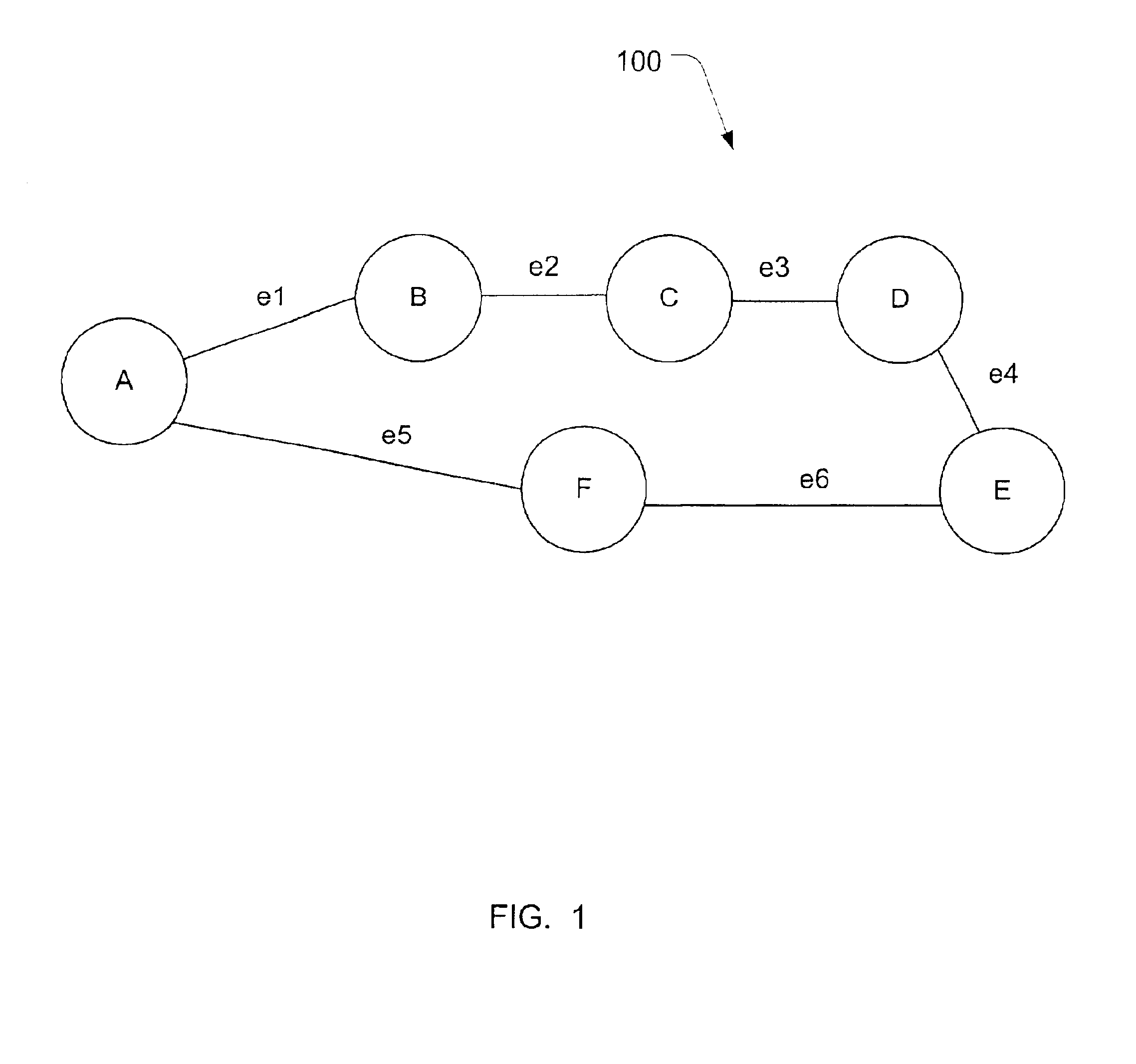

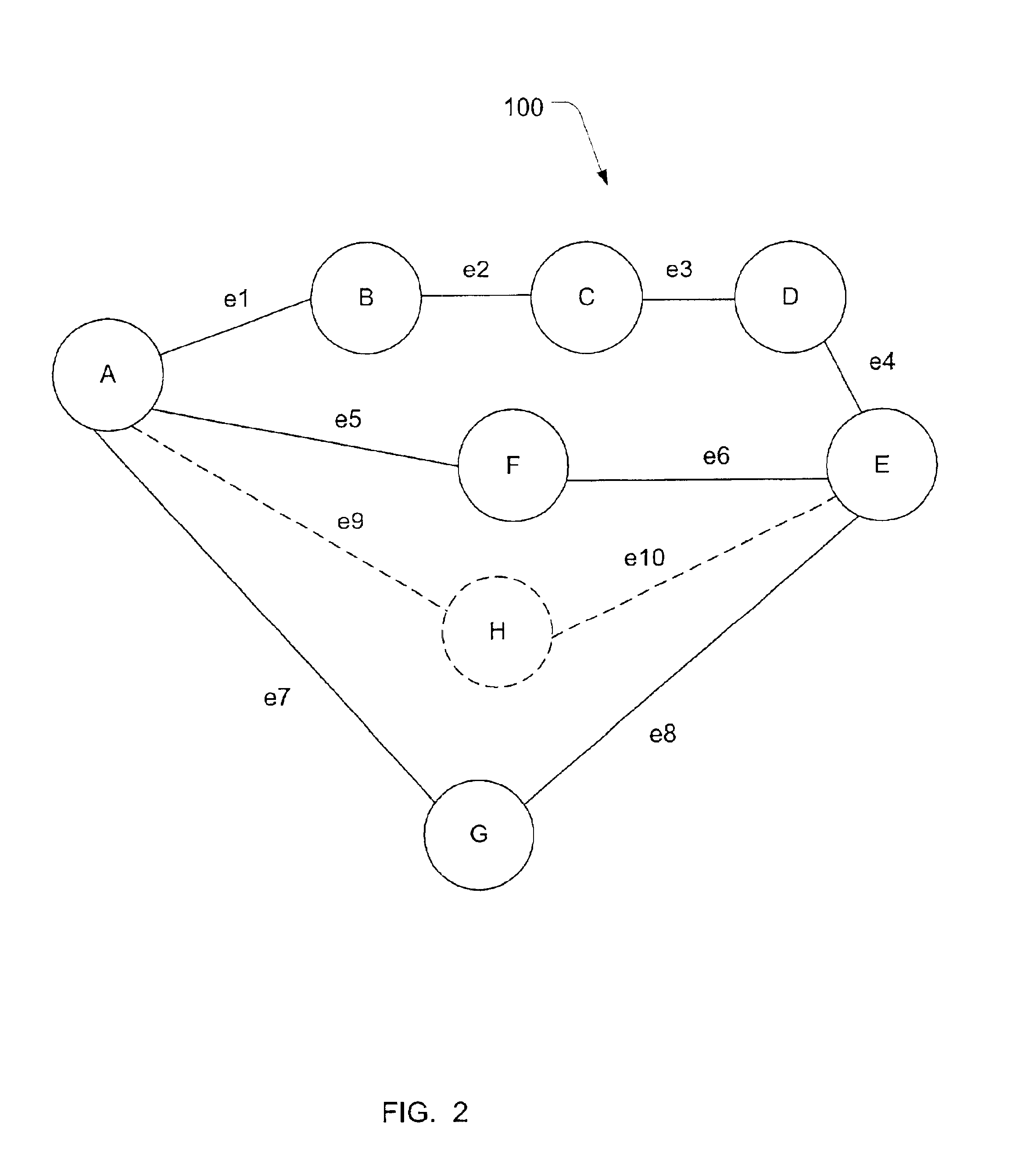

Method and system for allocating protection path resources

An embodiment of the invention is a method of allocating protection path resources including defining a working path and obtaining a link vector for each of a plurality of protection paths. The link vector includes a plurality of link vector elements. A proposed link vector is determined for each of the protection paths. The proposed link vector includes a plurality of proposed link vector elements and is indicative of allocating a respective protection path to the working path. A maximum link vector element is determined and a maximum proposed link vector element is determined. A link cost is determined based on a difference between the maximum proposed link vector element and the maximum link vector element. A path cost is determined for at least two protection paths based on a sum of link costs associated with a respective protection path. One of the at least two protection paths having the minimum path cost is selected to provide protection for the working path.

Owner:CIENA

Efficient implementation of an FIR filter on a general purpose processor

InactiveUS6018755AReduce in quantityEfficient implementationDigital technique networkComplex mathematical operationsFinite impulse responseGeneral purpose

A Finite Impulse Response (FIR) filter is implemented in software on a general purpose processor in a manner which reduces the number of memory accesses as compared to conventional methods. In particular, an efficient implementation for a general purpose processor having a substantial number of registers includes inner and outer loop code which together make memory accesses and KN multiply-accumulates, where L1 is the number of output vector elements computed during each pass through the outer loop and where L2 is the number of taps per output vector element computed during each pass through the inner loop. The efficient implementation exploits L1+2L2 general purpose registers. For an embodiment in which L1=L2=8, inner and outer loop code make memory accesses, which for filter implementations with large numbers of taps, approaches a 4x reduction in the number of memory accesses as compared to conventional methods.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

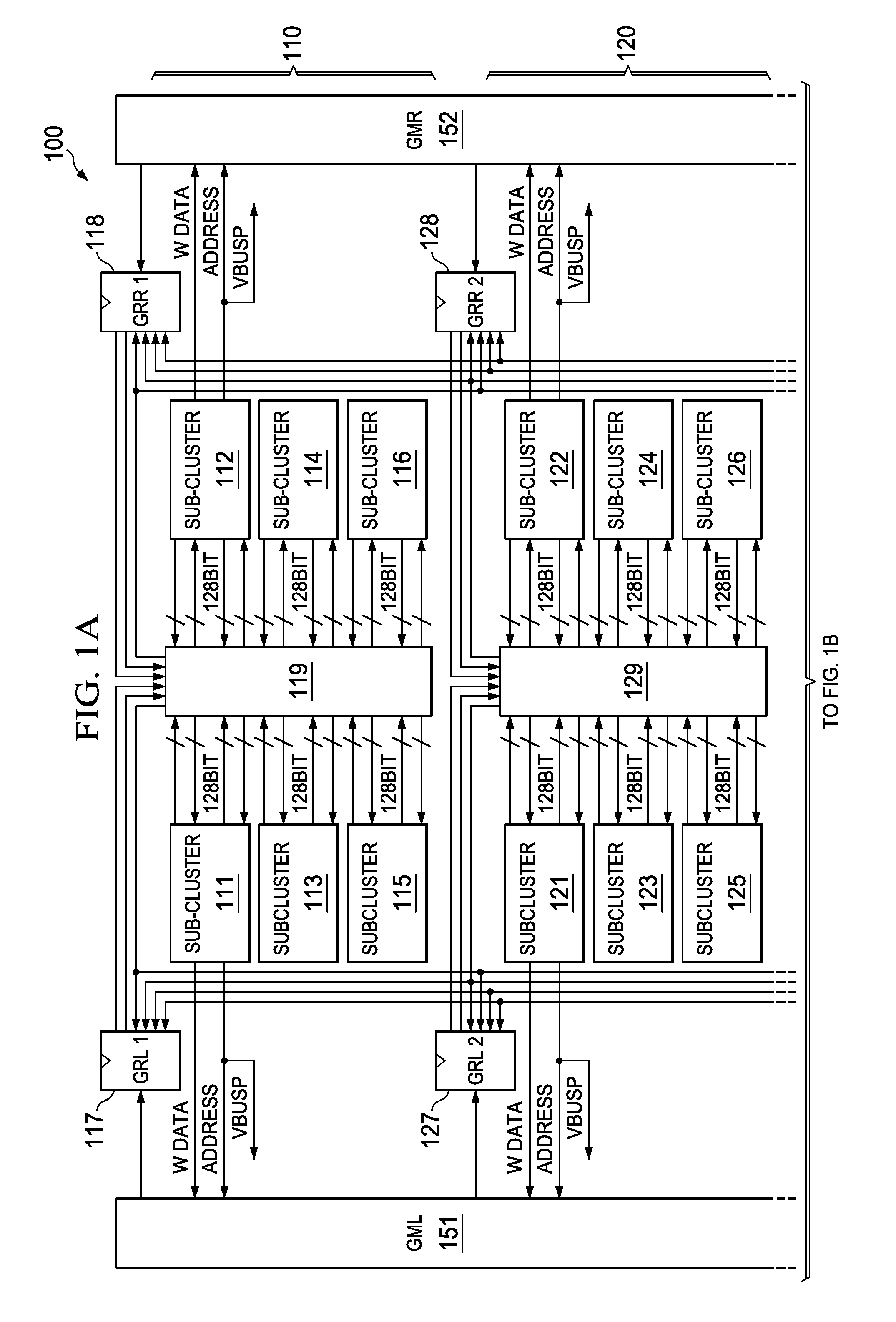

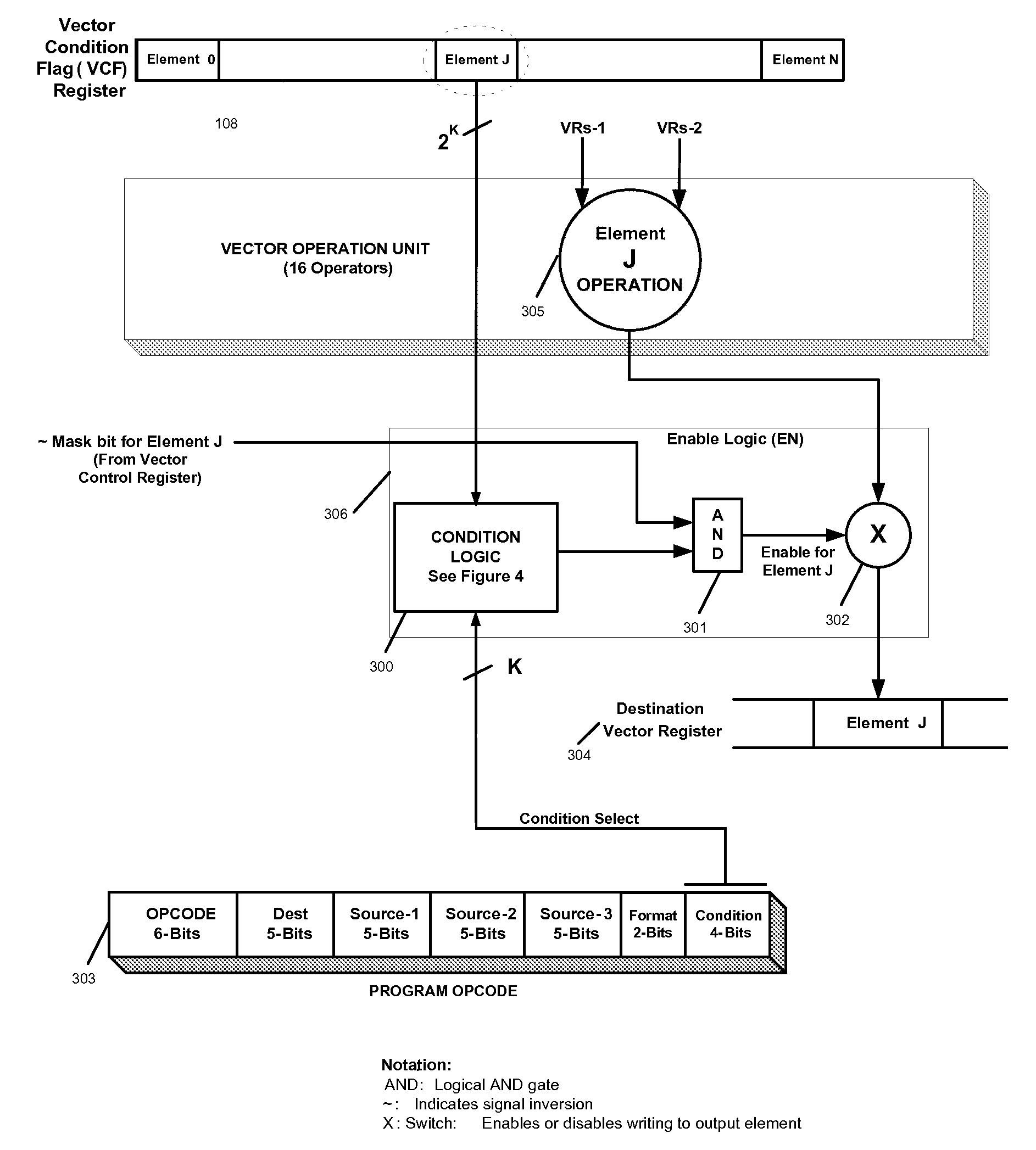

Efficient handling of vector high-level language conditional constructs in a SIMD processor

InactiveUS7793084B1Minimize the numberLow costConditional code generationDigital computer detailsVector elementSimd processing

The present invention provides an efficient method to implement nested if-then-else conditional statements in a SIMD processor, which requires only one vector compare instruction for both if and else parts of the conditional construct. No stack and stack-handling instructions are needed for vector condition codes. Two condition code flag bits representing if and else parts of testing per element provide for nesting of multiple if-then-else. All SIMD instructions are conditional including the vector compare instruction, and this provides a method for aggregating multiple conditions in nested if-then-else statements. M full levels of if-then-else nesting requires (2M−1) nodes or vector test instructions and 2M+1 condition code flags per vector element. Also, capability to compare any element of first source vector register with any element of second source vector is provided.

Owner:CUE BIOTECH

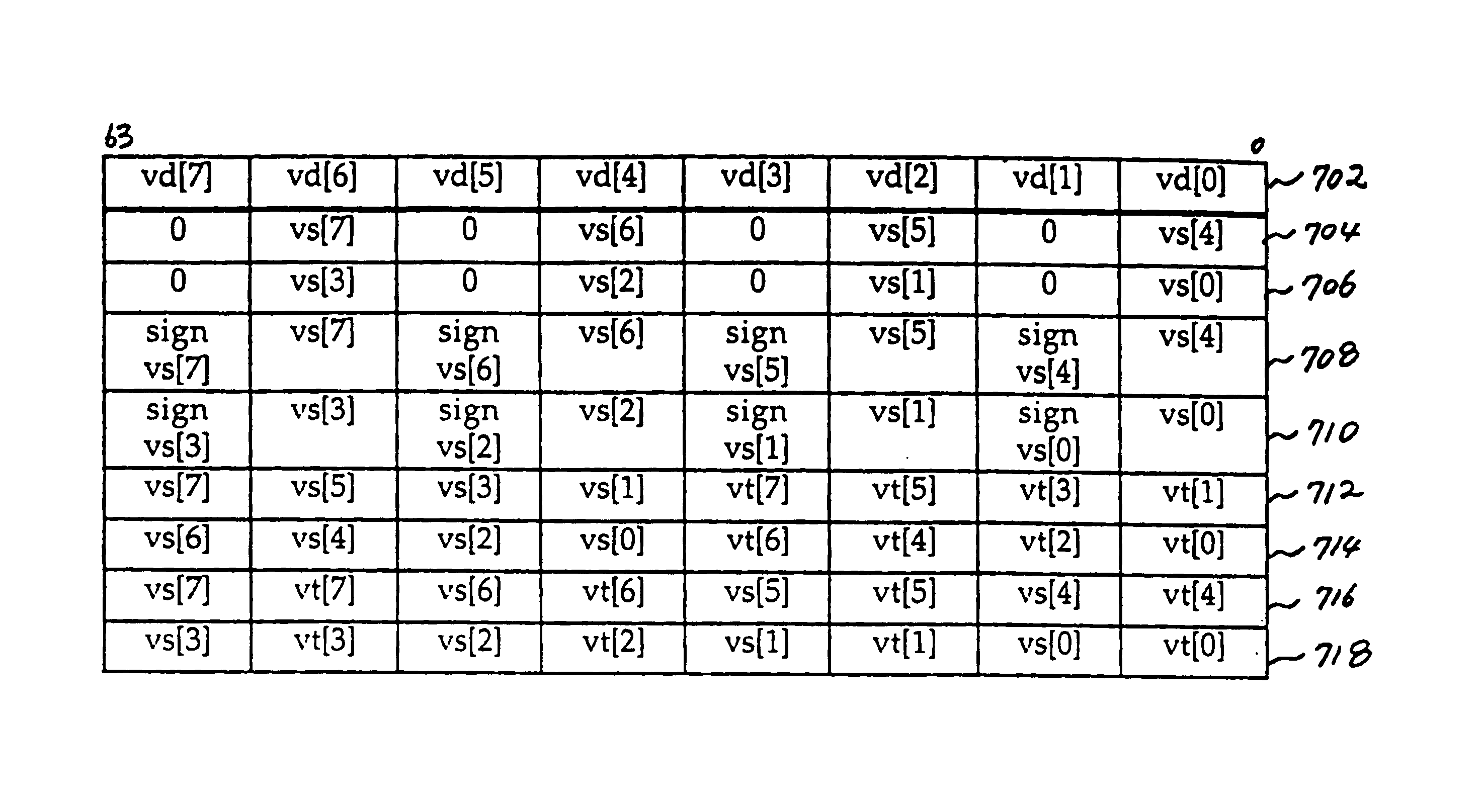

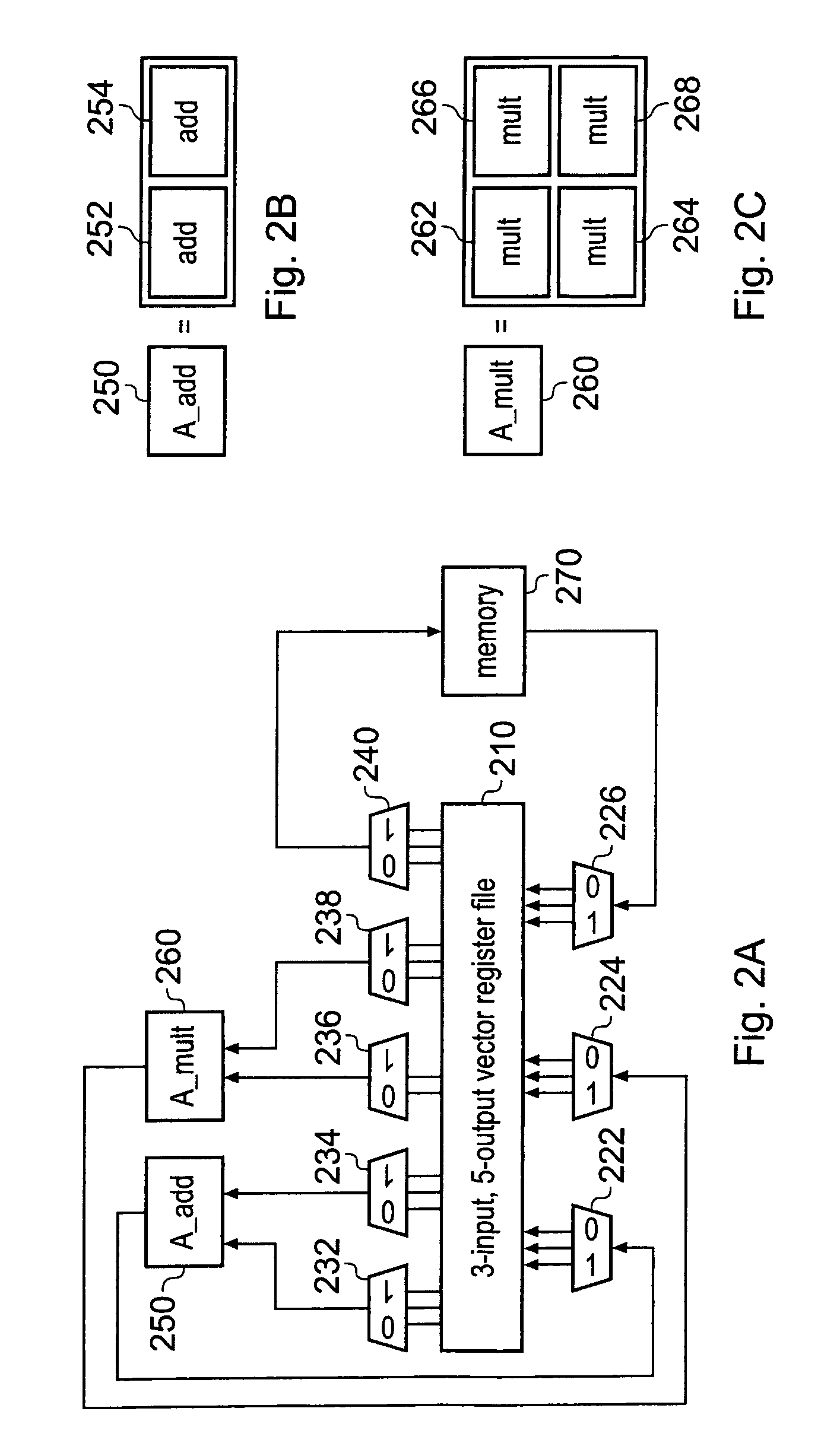

Alignment and ordering of vector elements for single instruction multiple data processing

InactiveUS7197625B1Specific program execution arrangementsMemory systemsProcessor registerVector element

The present invention provides alignment and ordering of vector elements for SIMD processing. In the alignment of vector elements for SIMD processing, one vector is loaded from a memory unit into a first register and another vector is loaded from the memory unit into a second register. The first vector contains a first byte of an aligned vector to be generated. Then, a starting byte specifying the first byte of an aligned vector is determined. Next, a vector is extracted from the first register and the second register beginning from the first bit in the first byte of the first register continuing through the bits in the second register. Finally, the extracted vector is replicated into a third register such that the third register contains a plurality of elements aligned for SIMD processing. In the ordering of vector elements for SIMD processing, a first vector is loaded from a memory unit into a first register and a second vector is loaded from the memory unit into a second register. Then, a subset of elements are selected from the first register and the second register. The elements from the subset are then replicated into the elements in the third register in a particular order suitable for subsequent SIMD vector processing.

Owner:ARM FINANCE OVERSEAS LTD

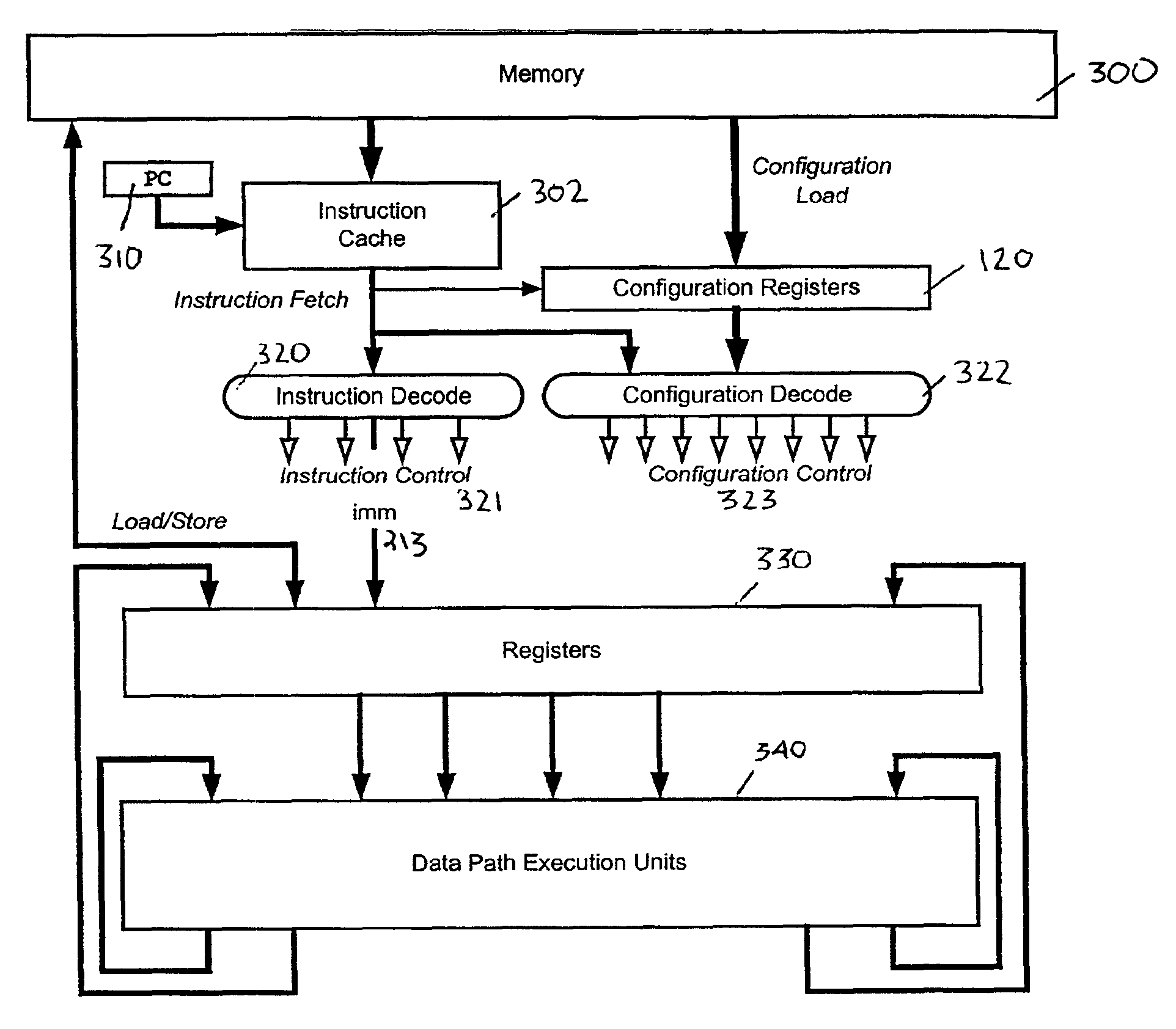

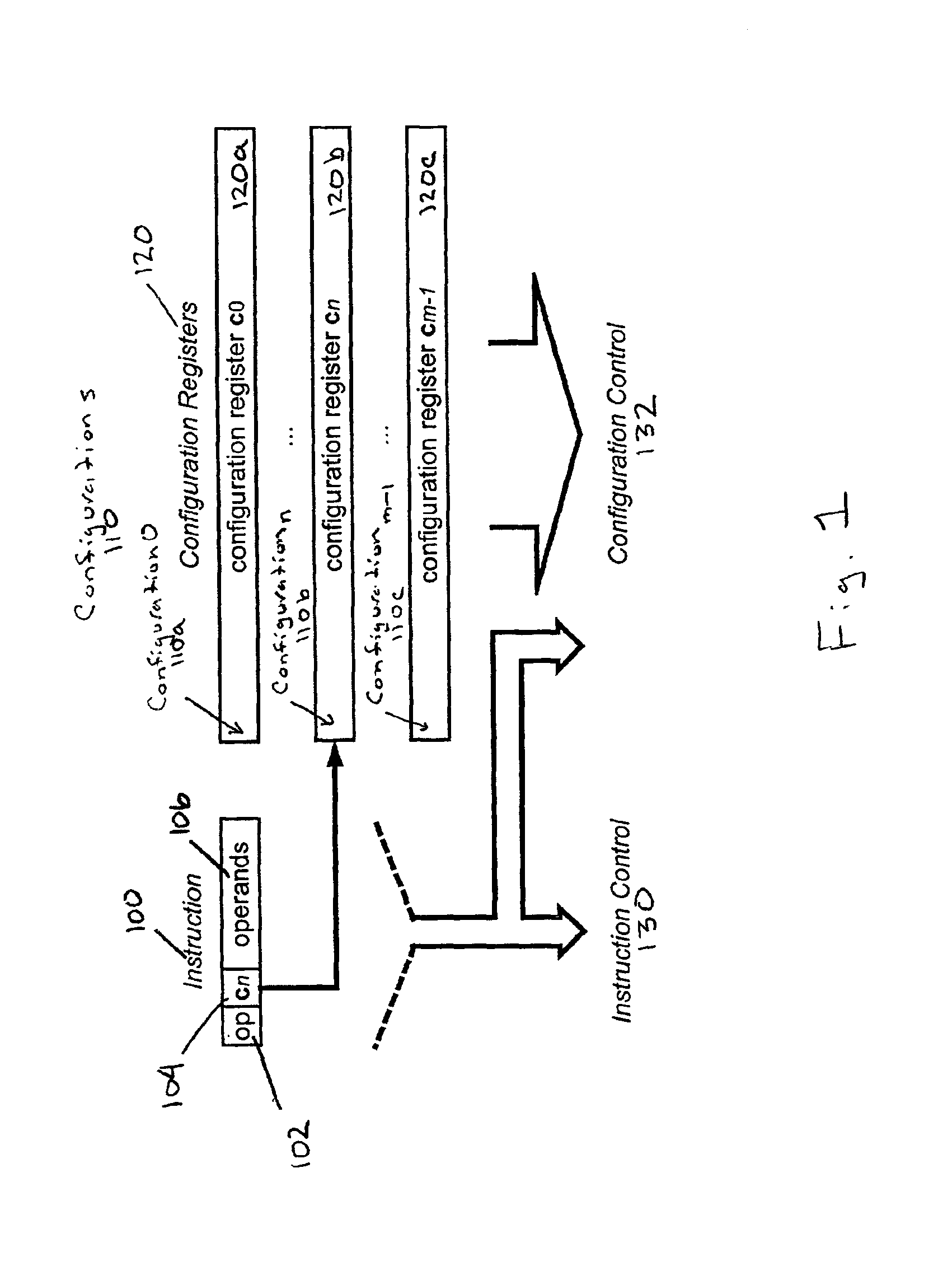

Reconfigurable processing system and method

InactiveUS6959378B2Next instruction address formationArchitecture with single central processing unitProcessor registerData operations

A reconfigurable processing system executes instructions and configurations in parallel. Initially, a first instruction loads configurations into configuration registers. The configuration field of a subsequently fetched instruction selects a configuration register. The instruction controls and controls of the configuration in the selected configuration register are decoded and modified as specified by the instruction. The controls provide data operands to the execution units which process the operands and generate results. Scalar data, vector data, or a combination of scalar and vector data can be processed. The processing is controlled by instructions executed in parallel with configurations invoked by configuration fields within the instructions. Vectors are processed using a vector register file which stores vectors. A vector address unit identifies addresses of vector elements in the vector register file to be processed. For each vector, vector address units provide addresses which stride through each element of each vector.

Owner:AVAGO TECH INT SALES PTE LTD

Floating Point Only Single Instruction Multiple Data Instruction Set Architecture

InactiveUS20100095097A1General purpose stored program computerSpecific program execution arrangementsData processing systemProcessor register

Mechanisms for implementing a floating point only single instruction multiple data instruction set architecture are provided. A processor is provided that comprises an issue unit, an execution unit coupled to the issue unit, and a vector register file coupled to the execution unit. The execution unit has logic that implements a floating point (FP) only single instruction multiple data (SIMD) instruction set architecture (ISA). The floating point vector registers of the vector register file store both scalar and floating point values as vectors having a plurality of vector elements. The processor may be part of a data processing system.

Owner:IBM CORP

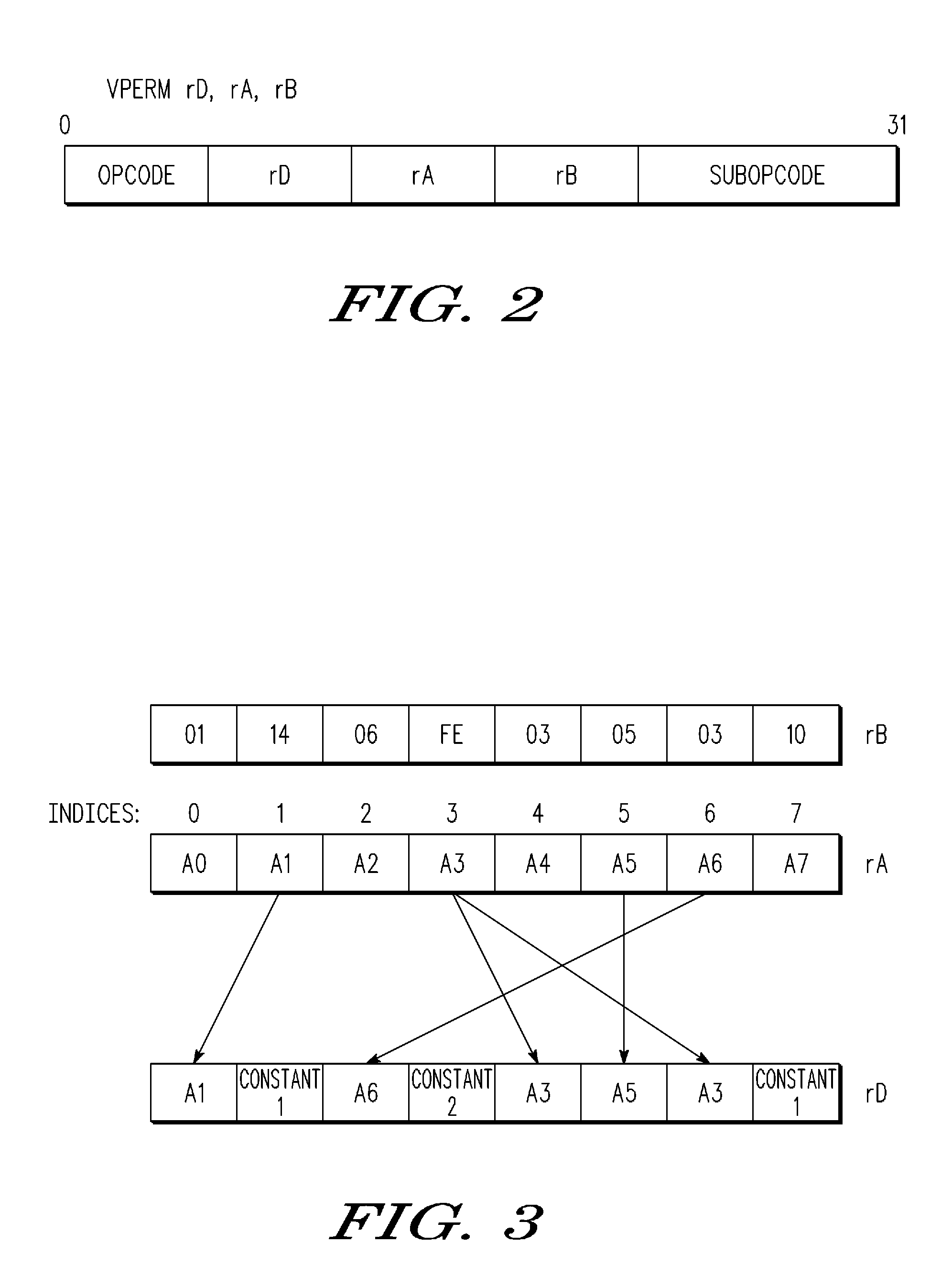

Simd permutations with extended range in a data processor

InactiveUS20090100247A1Instruction analysisProgram control using wired connectionsData processing systemProcessor register

A processor in a data processing system executes a permutation instruction which identifies a first source register, at least one other source register, and a destination register. The first source register stores at least one in-range index value for the at least one other source register and at least one out-of-range index value for the at least one other source register. The at least one other source register stores a plurality of vector element values, wherein each in-range index value indicates which vector element value of the at least one other source register is to be stored into a corresponding vector element of the destination register. Each out-of-range index value is used to indicate which one of at least two predetermined constant values is to be stored into a corresponding vector element of the destination register. Partial table lookups using a permutation instruction shortens the time required to retrieve data.

Owner:NORTH STAR INNOVATIONS

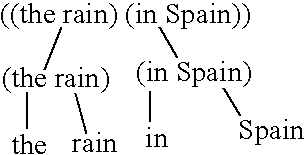

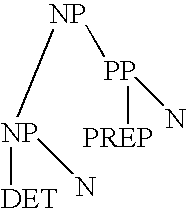

Natural-language processing system using a large corpus

InactiveUS20040024583A1Natural language data processingSpecial data processing applicationsOrder controlSource material

A computer-parsing system based upon using vectors (lists) to represent natural-language elements, providing a robust, distributed way to score grammaticality of an input string by using as a source material a large corpus of natural-language text. The system uses recombining of asymetric associations of syntactically similar strings to form an the vectors. The system uses equivalence lists for your the organization subparts of the string to build equivalence lists for our the province longer strings in an order controlled by the potential these / parse to be scored. The power of recombination of Entries from: vector elements in building longer strings provides a means of representing collocational complexity. Grammaticality scoring is based upon the number and similarity of the vector elements.

Owner:FREEMAN ROBERT J

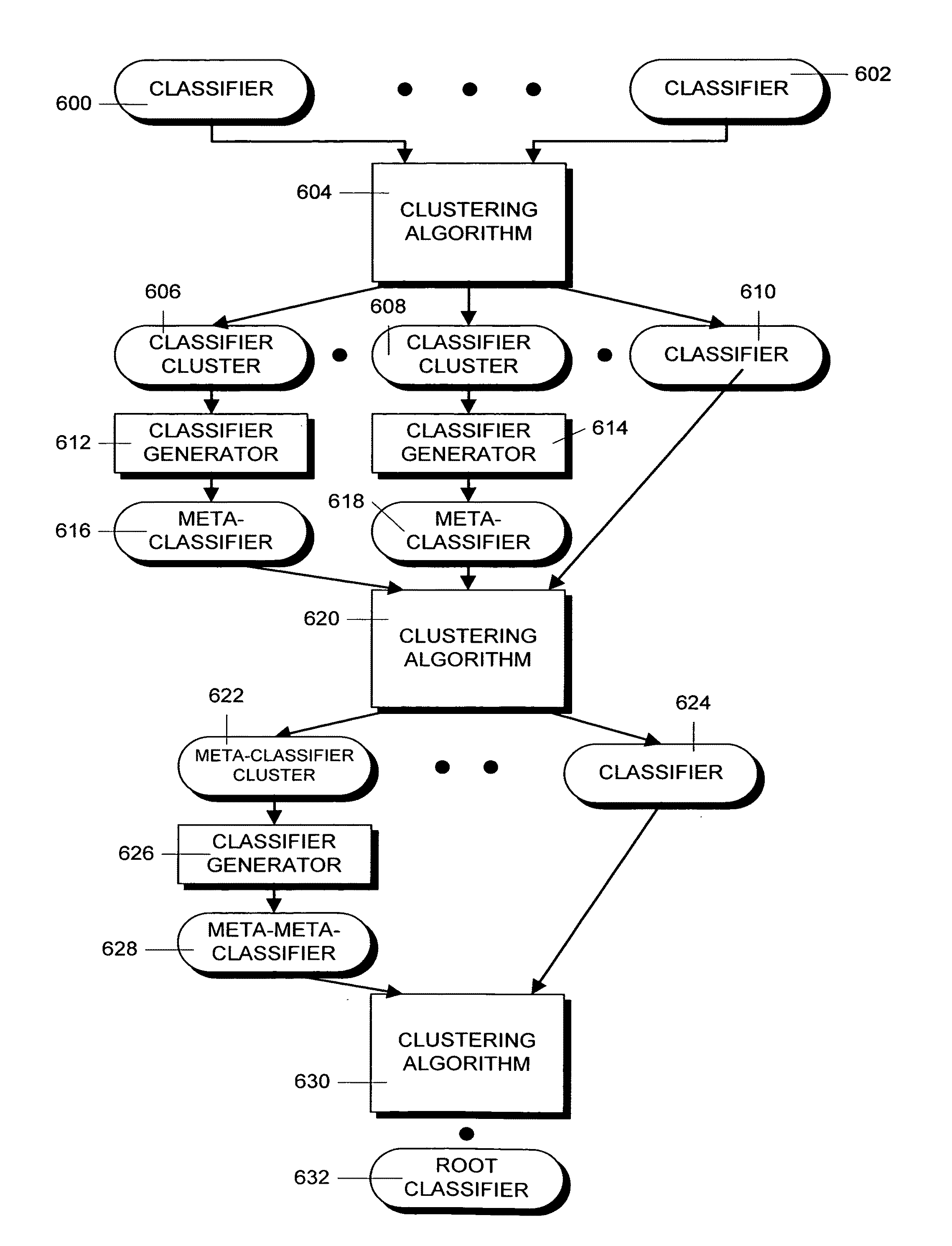

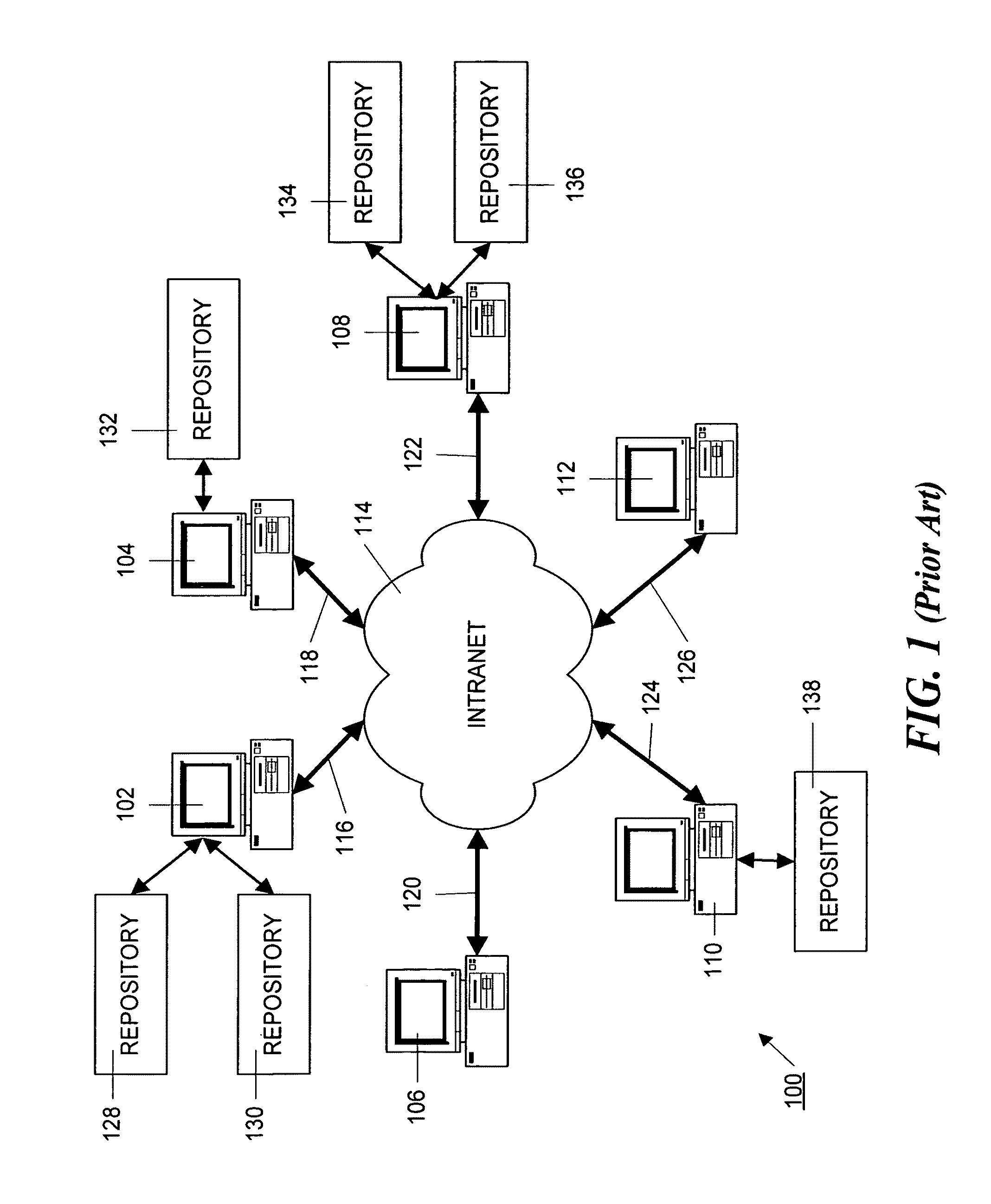

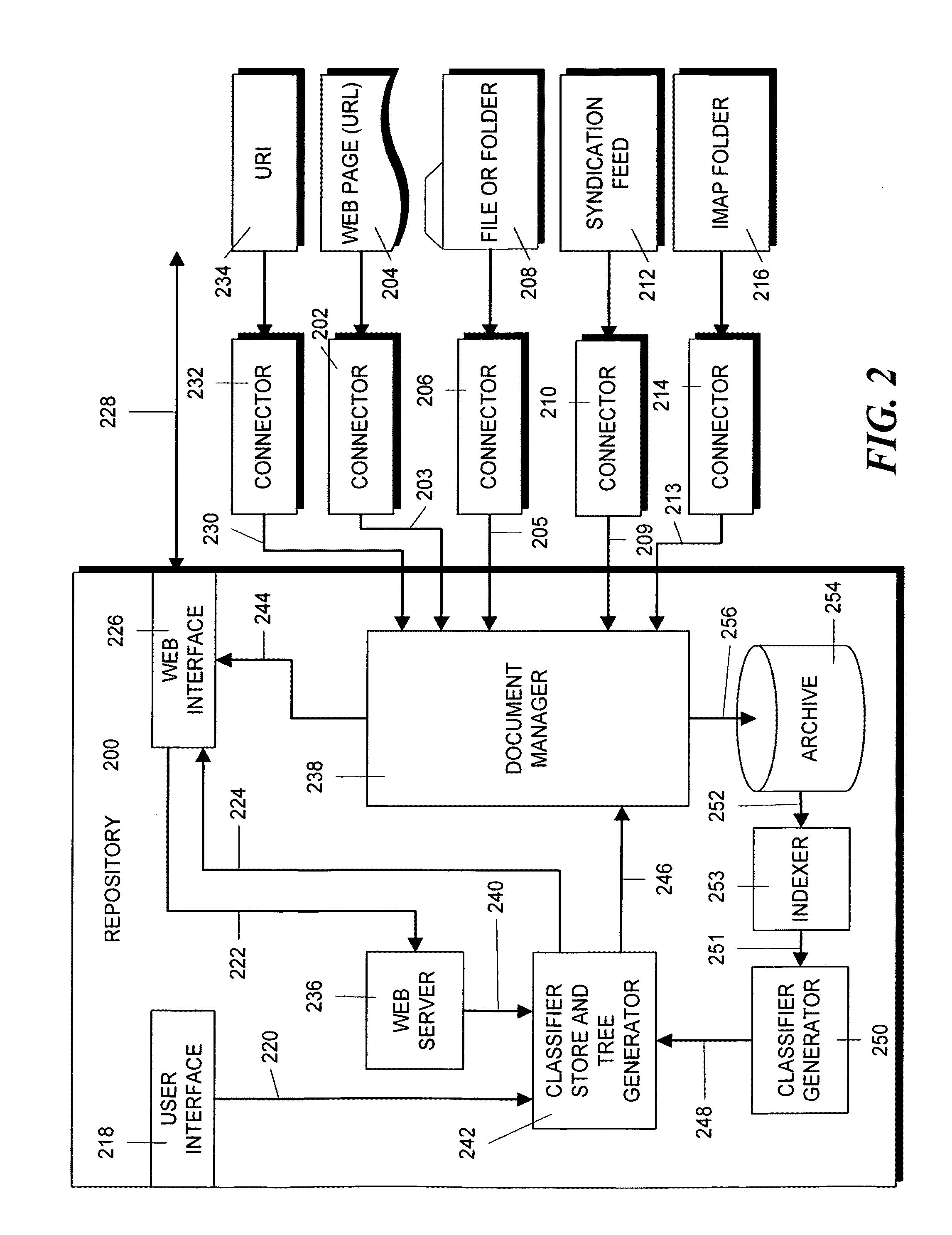

Method and apparatus for searching and resource discovery in a distributed enterprise system

A method for searching and resource discovery in a distributed enterprise (DE), the method including: generating a first classifier for a first repository in the DE; generating a second classifier for a second repository in the DE, where the second classifier has a vector element identifying a location of the second repository; submitting a copy of the second classifier to a web server of the first repository; obtaining a resource at the first repository after submitting the copy of the second classifier; matching the resource to the copy of a second classifier; sending a copy of the resource to the second repository using the vector element; and storing the copy of the resource in the second repository.

Owner:ORACLE INT CORP

Instruction and logic to provide vector compress and rotate functionality

ActiveUS20140122831A1Memory architecture accessing/allocationRegister arrangementsVector elementParallel computing

Instructions and logic provide vector compress and rotate functionality. Some embodiments, responsive to an instruction specifying: a vector source, a mask, a vector destination and destination offset, read the mask, and copy corresponding unmasked vector elements from the vector source to adjacent sequential locations in the vector destination, starting at the vector destination offset location. In some embodiments, the unmasked vector elements from the vector source are copied to adjacent sequential element locations modulo the total number of element locations in the vector destination. In some alternative embodiments, copying stops whenever the vector destination is full, and upon copying an unmasked vector element from the vector source to an adjacent sequential element location in the vector destination, the value of a corresponding field in the mask is changed to a masked value. Alternative embodiments zero elements of the vector destination, in which no element from the vector source is copied.

Owner:INTEL CORP

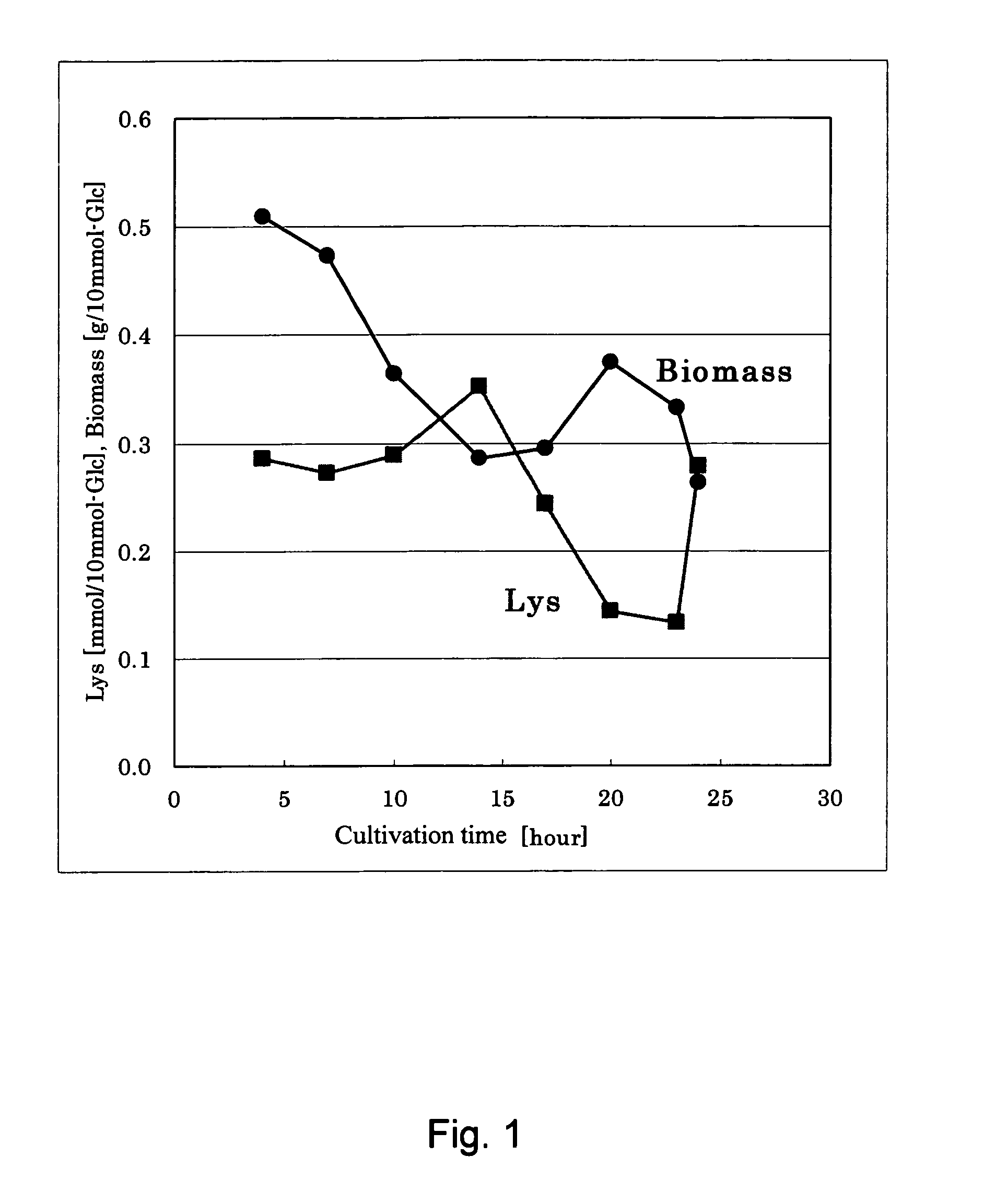

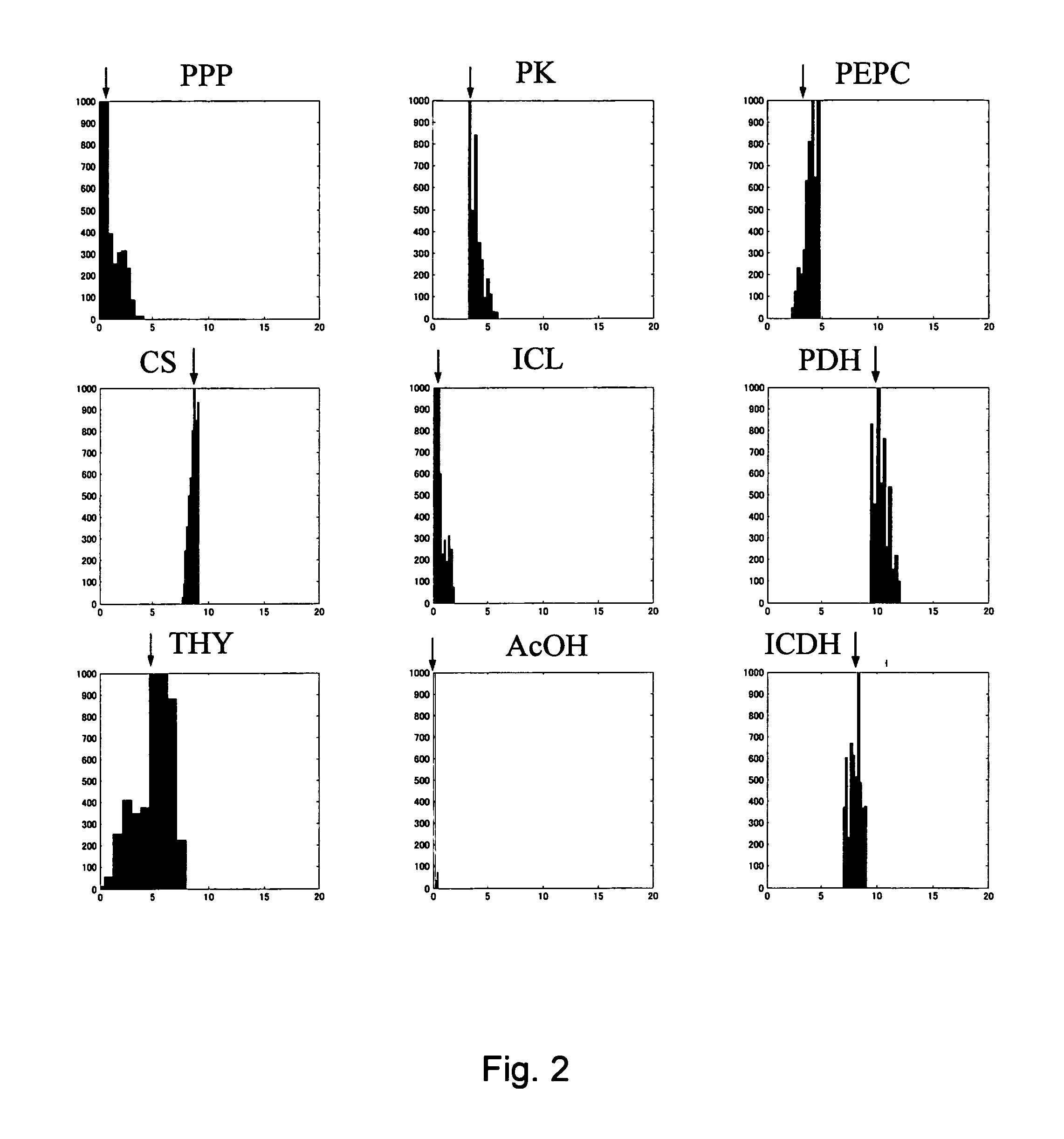

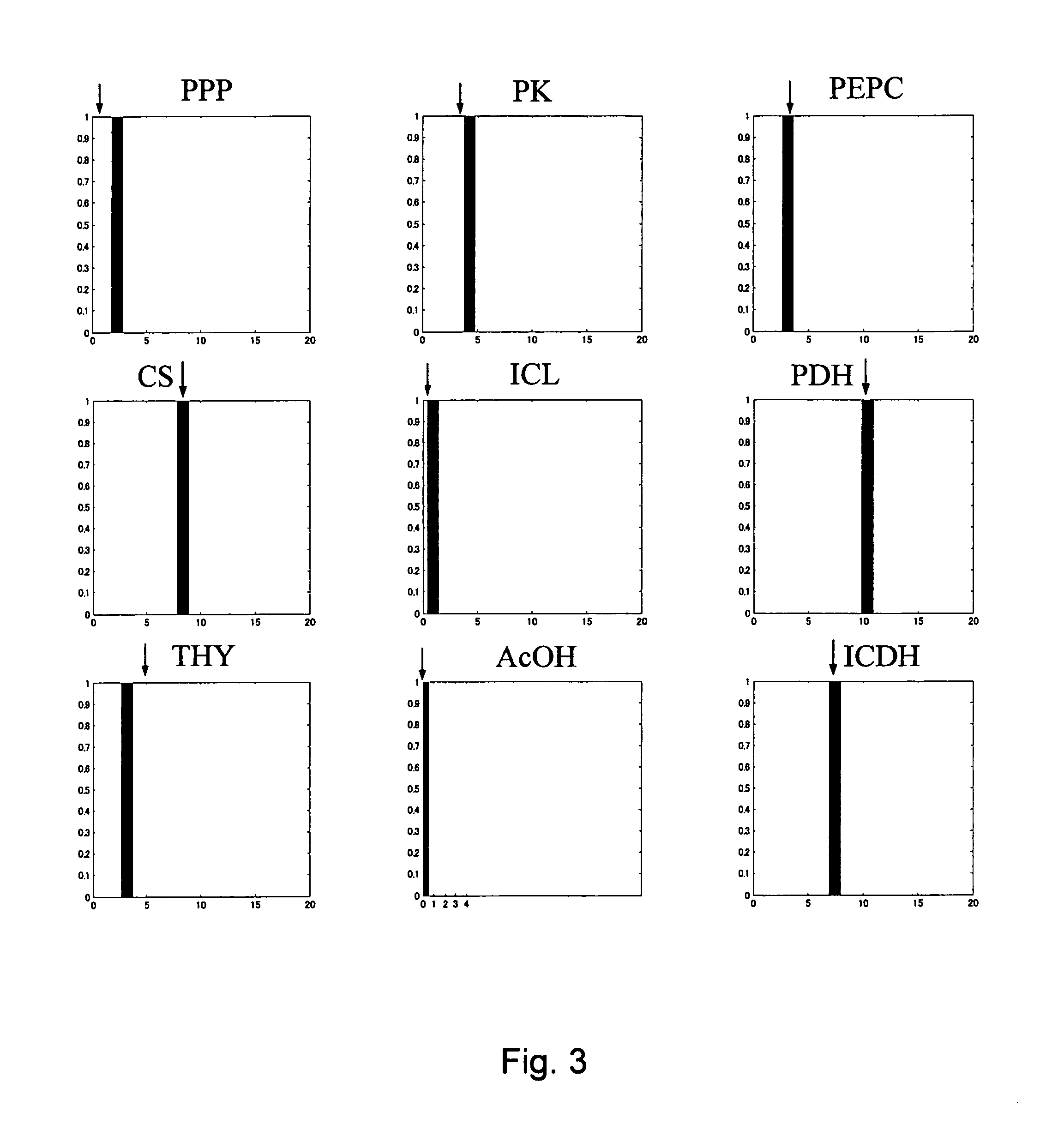

Method for determining metabolic flux

InactiveUS20050221278A1High yieldIncrease productivityData processing applicationsMicrobiological testing/measurementAlgorithmVector element

A method for determining metabolic flux distribution of a cell, which comprises the steps of: 1) creating a stoichiometric matrix based on formulas of biochemical reactions from a substrate to a product, 2) computing a set of vectors of solutions existing in a solution space which the stoichiometric matrix may have, 3) selecting, from the computed set of vectors of solutions, maximum vectors whose vector elements corresponding to respective substances for which input values can be obtained are maximum, and 4) performing linear combination for the selected vectors in accordance with the following equations to obtain a vector representing metabolic flux distribution: Sflux=∑i=1nai·pi·S(i)+∑i=1nbi·qi·A(i)(I)∑i=1nai+∑i=1nbi=1(II)Sflux: Vector representing metabolic flux distribution to be determined, S(i): Vector selected for substance for which inputted value can be obtained, A(i): Adjustment vector, a, b: Coefficients for linear combination (b may be 0), p: Coefficient for obtaining consistency with input value as numerical value, q: Coefficient of adjustment vector.

Owner:AJINOMOTO CO INC

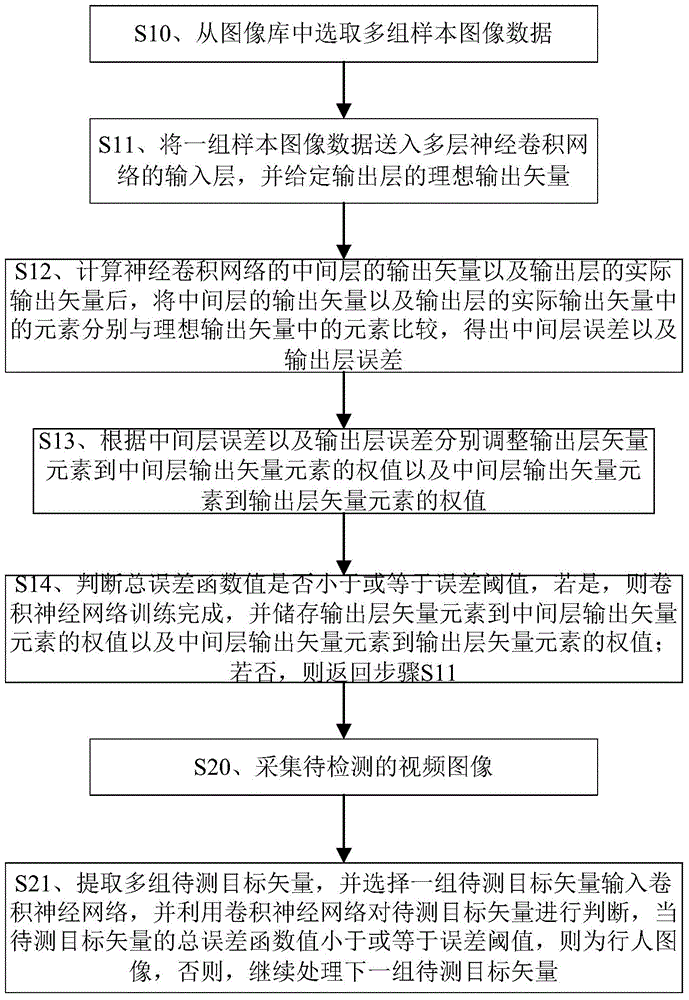

Method and device for pedestrian detection based on depth convolutional network

ActiveCN104063719AImprove detection accuracySimple calculationCharacter and pattern recognitionHigh rateAlgorithm

The invention discloses a method and a device for pedestrian detection based on a depth convolutional network. The method comprises a convolutional neural network training step and a pedestrian detection step. The convolutional neural network training comprises the following steps: S10, a plurality of groups of sample image data are selected from an image library; S11, one group of sample image data is sent to an input layer of a multilayer neural convolutional network; S12, the output vector of an intermediate layer of the neural convolutional network and the actual output vector of an output layer are calculated to obtain the error of the intermediate layer and the error of the output layer; S13, the weight from an output layer vector element to an intermediate layer output vector element and the weight from the intermediate layer output vector element to the output layer vector element are adjusted; and S14, the total error function value is judged, and pedestrians are detected by use of the trained network. The method and the device of the invention have the advantages of better robustness and high rate of detection accuracy.

Owner:SHENZHEN SUNWIN INTELLIGENT CO LTD

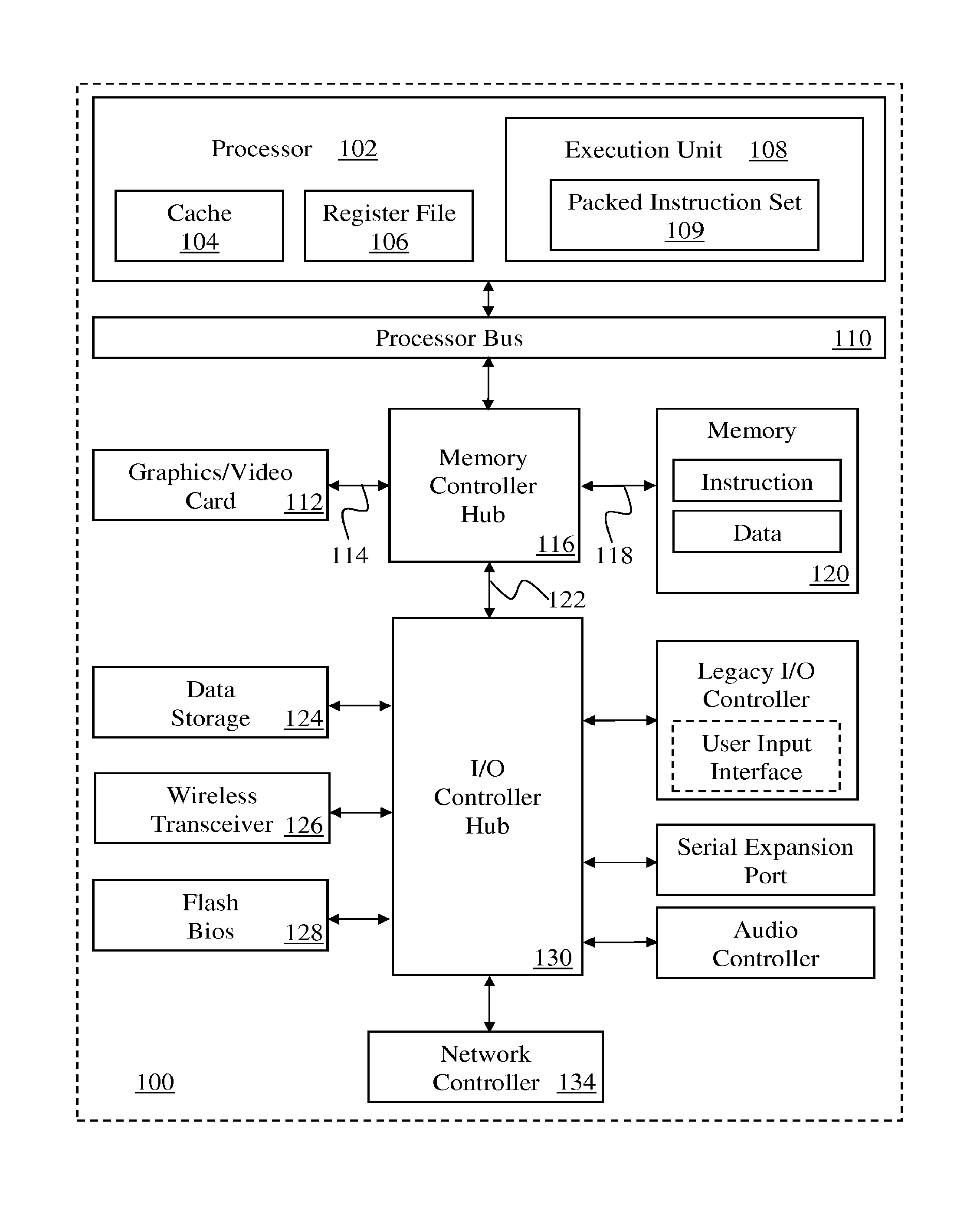

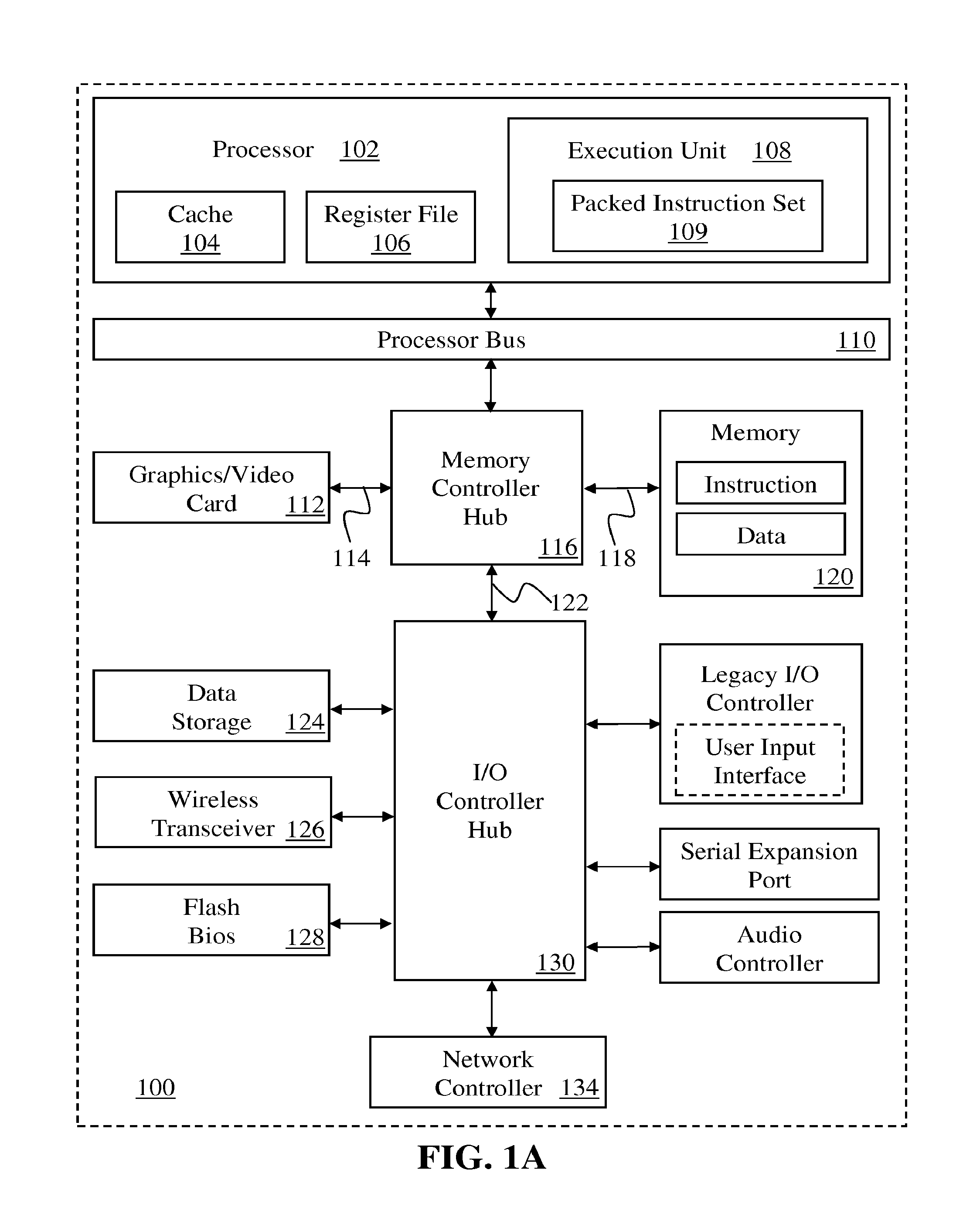

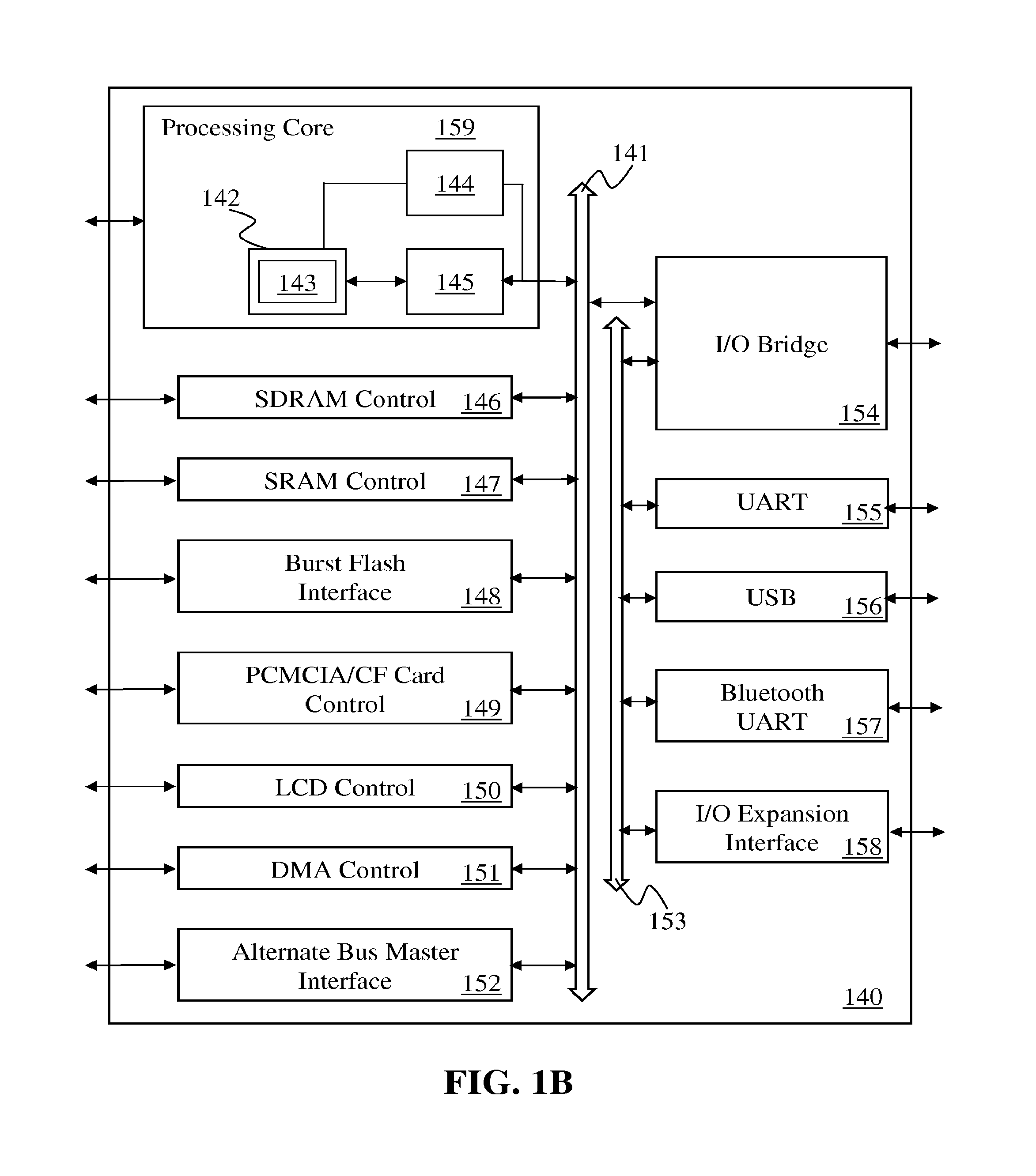

Algebraic single instruction multiple data processing

ActiveUS20070028076A1Affect performanceHigh degreeGeneral purpose stored program computerSpecific program execution arrangementsProgram instructionVector element

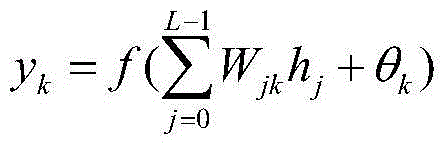

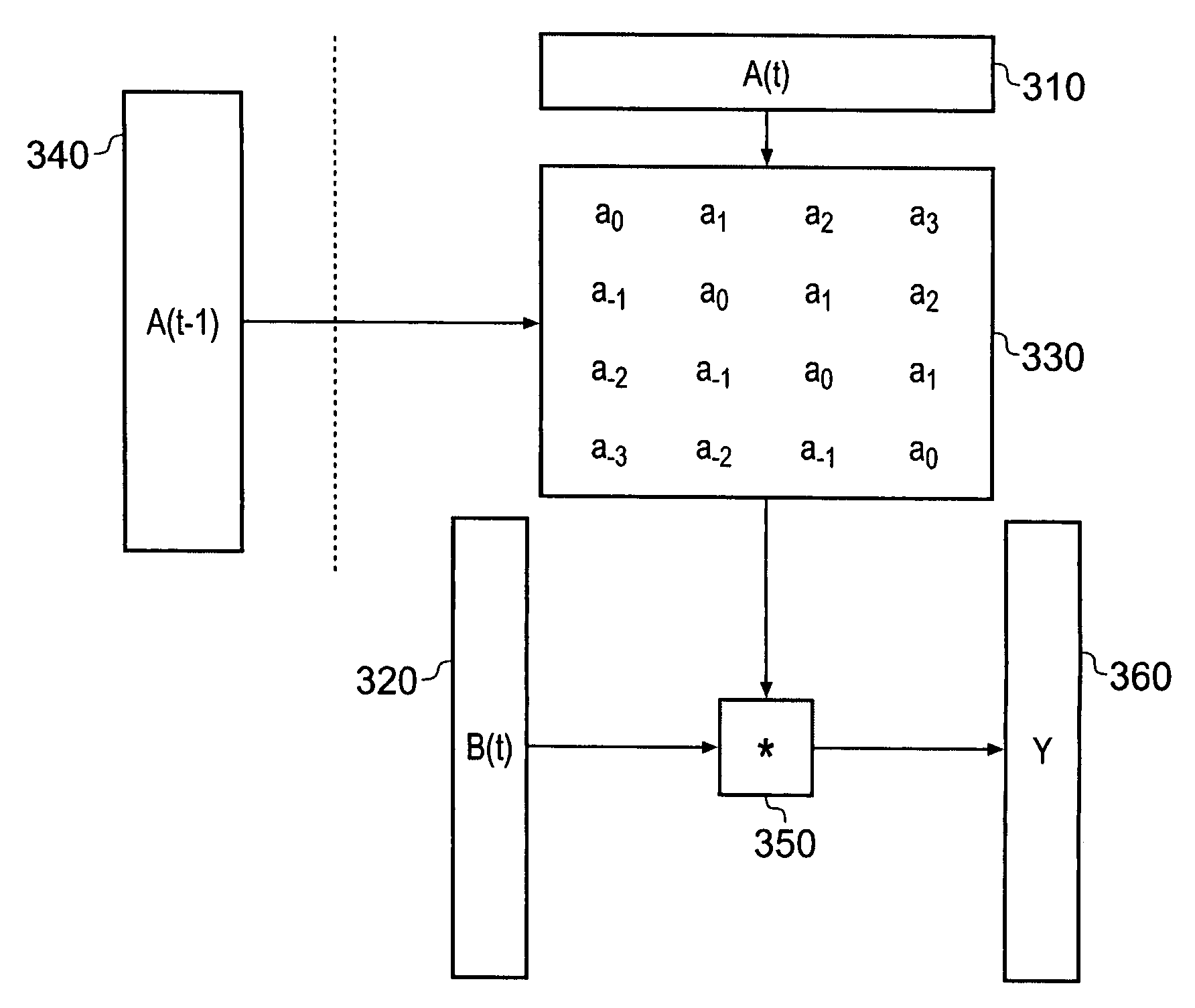

A data processing apparatus comprises data processing logic operable to perform data processing operations specified by program instructions. The data processing logic (140) has a plurality of functional units (142, 144, 146) configured to execute in parallel on data received from a data source. A decoder (130) is responsive to a single program instruction to control the data processing logic (140) to concurrently execute the single program instruction on each of a plurality of vector elements of each of a respective plurality of vector input operands (310, 320) received from the data source using the plurality of functional units (142, 144, 146). During execution of the single program instruction, the plurality of functional units (142, 144, 146) operate as a predetermined group on said plurality of vector elements (310, 320) to perform at least a matrix-vector calculation in which the matrix is a non-identity matrix and entries of the matrix are one of: (i) populated in dependence upon at least one of said vector elements of at least one of the plurality of vector input operands; and (ii) generated within said data processing logic as an explicit function of the single program instruction.

Owner:ARM LTD

Instruction and logic to provide vector blend and permute functionality

ActiveUS20140372727A1General purpose stored program computerConcurrent instruction executionProcessor registerVector element

Vector blend and permute functionality are provided, responsive to instructions specifying: a destination vector register comprising fields to store vector elements, a first vector register, a vector element size, a second vector register, and a third operand. Indices are read from fields in the second register. Each index has a first selector portion and a second selector portion. Corresponding unmasked vector elements are stored to fields of the destination register, wherein each vector element, responsive to the respective first selector portion having a first value, is copied to an intermediate vector from a corresponding data field of the first register, and responsive to the respective first selector portion having a second value, is copied to the intermediate vector from a corresponding data field of the third operand. Then unmasked data fields of the destination are replaced by data fields in the intermediate vector indexed by the corresponding second selector portions.

Owner:INTEL CORP

Vectorization in a SIMdD DSP architecture

InactiveUS20050097301A1Simple technologyGeneral purpose stored program computerProgram controlDsp architectureVector element

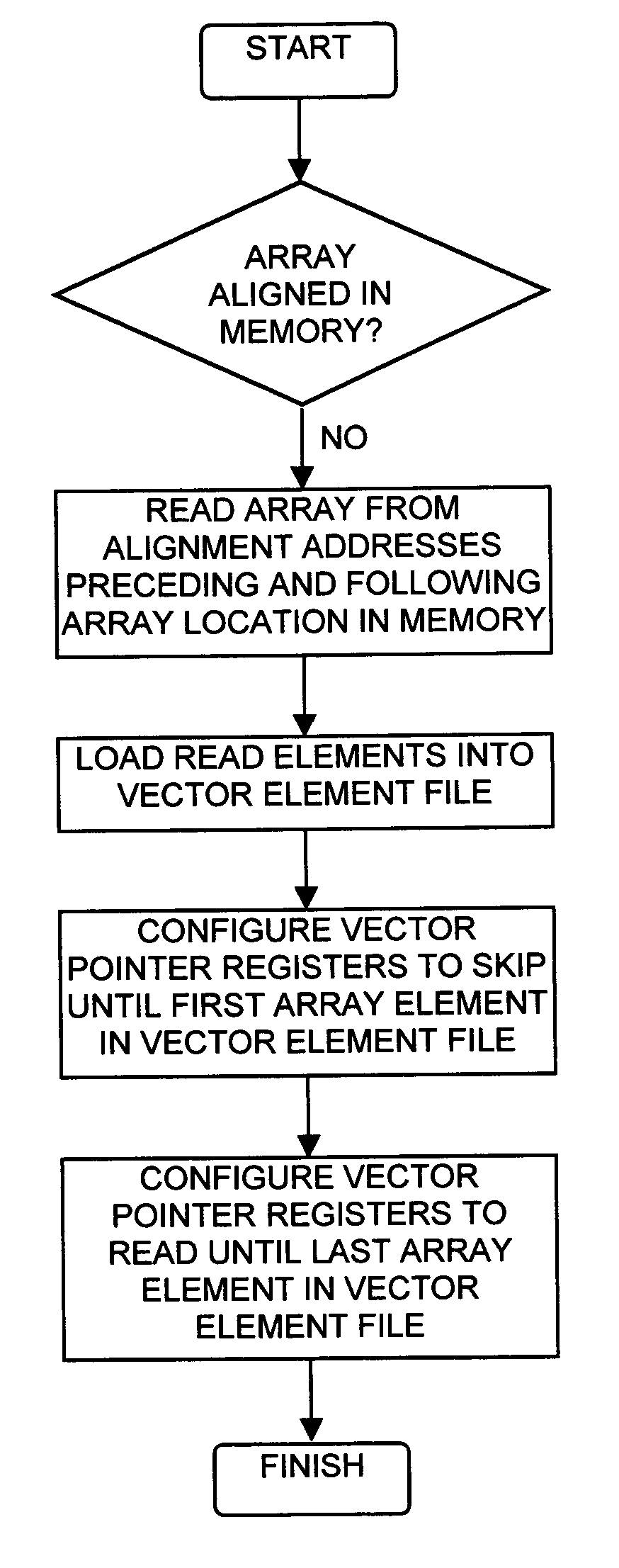

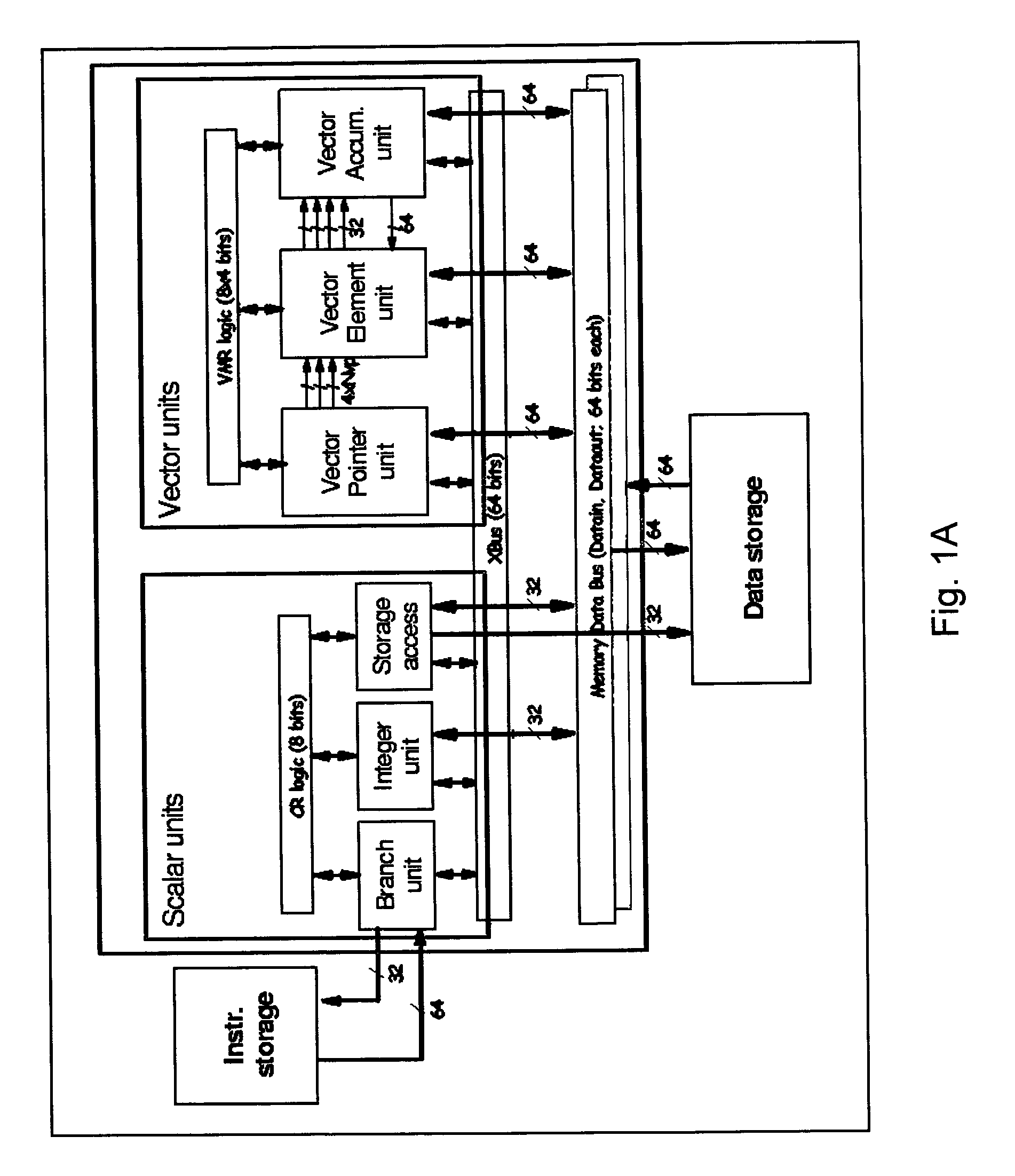

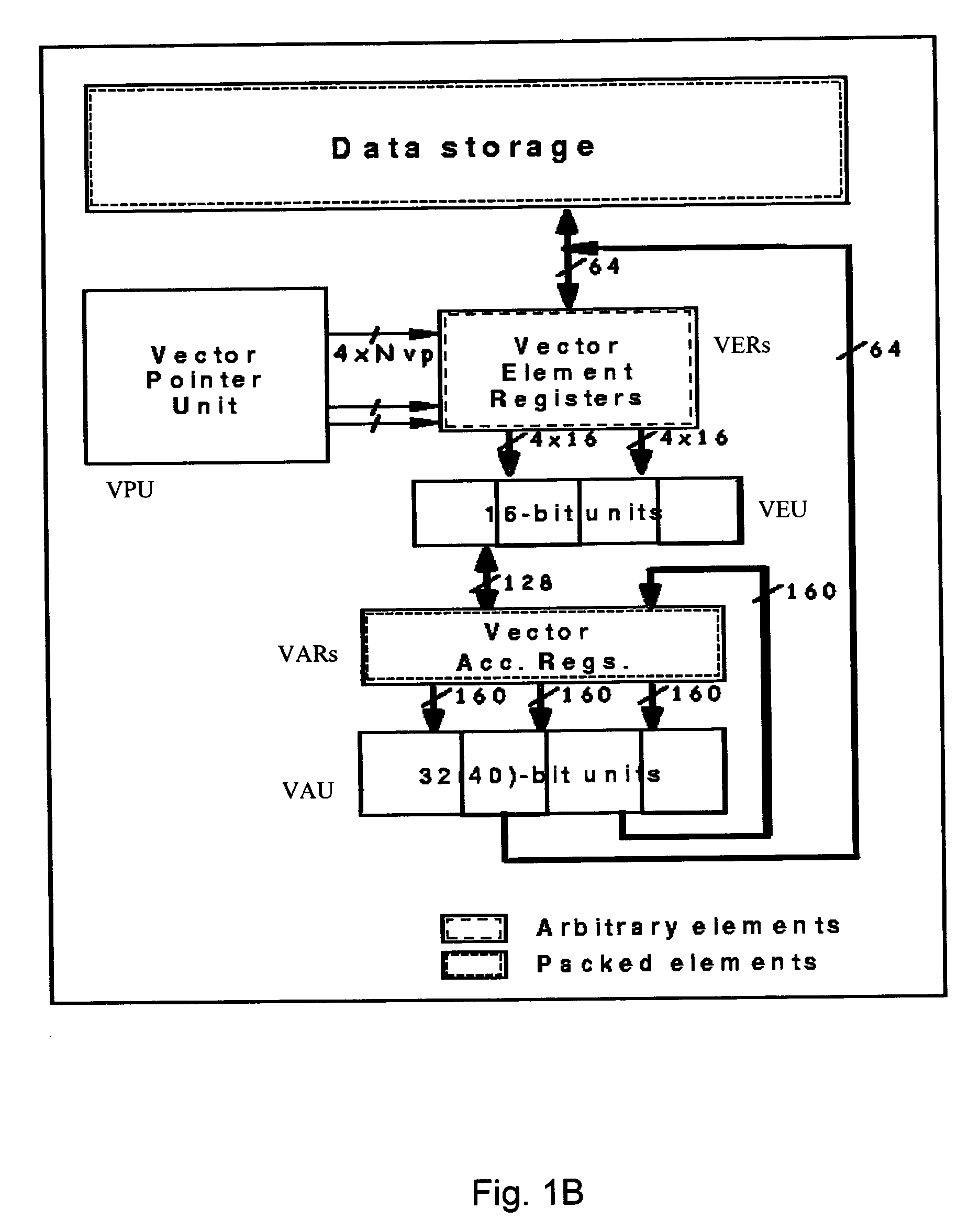

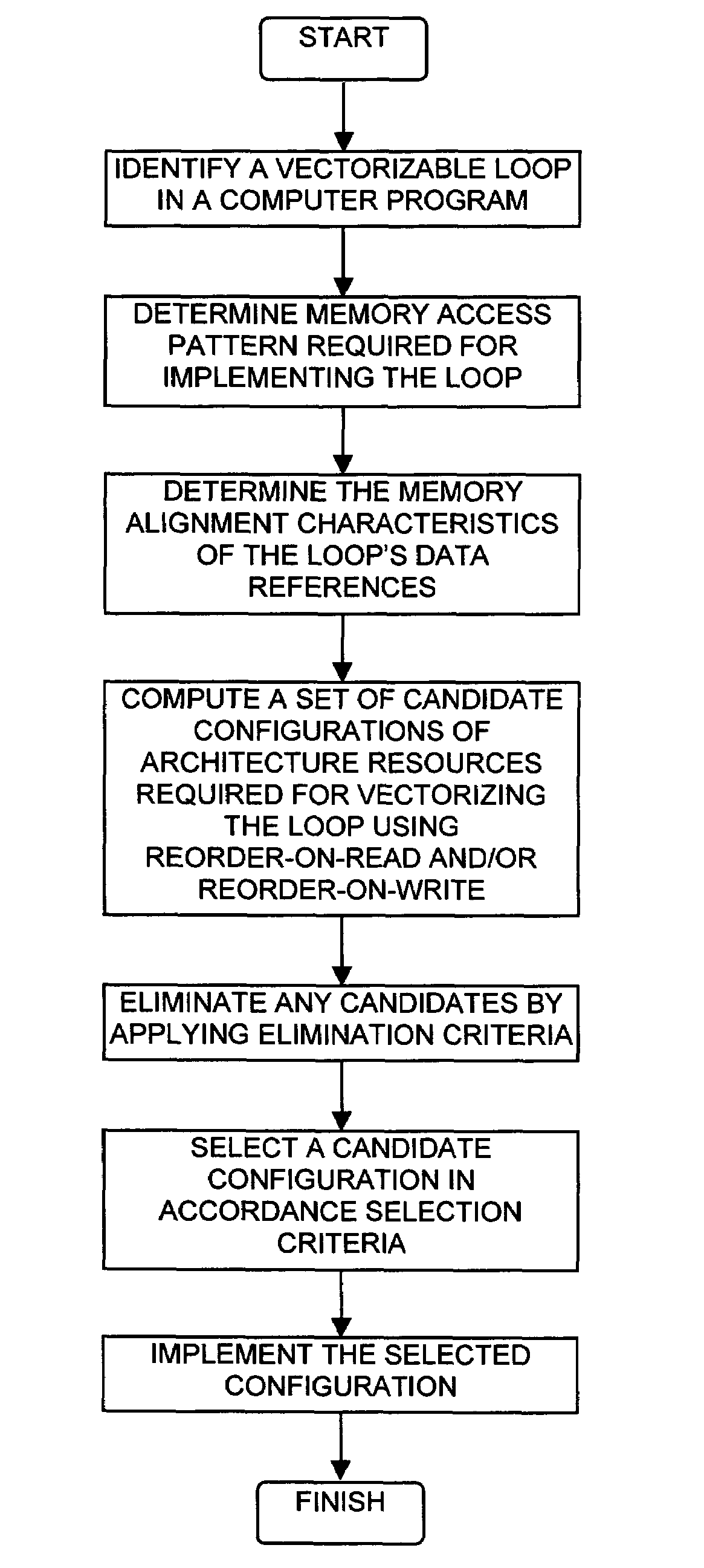

A method for determining vectorization configurations in a computer processor architecture, the method including identifying a vectorizable loop in a computer program, identifying a memory access pattern of data required for implementing the loop in the architecture, computing a set of candidate configurations of resources required for vectorizing the data in the architecture, where the computing step includes configuring a vector pointer register of the architecture in support of either of reorder-on-read use and reorder-on-write use of a vector element file of the architecture, selecting one of the candidates in accordance with predefined selection criteria, and implementing the selected vectorization configuration in the architecture.

Owner:IBM CORP

Vectorization in a SIMdD DSP architecture

Owner:INT BUSINESS MASCH CORP

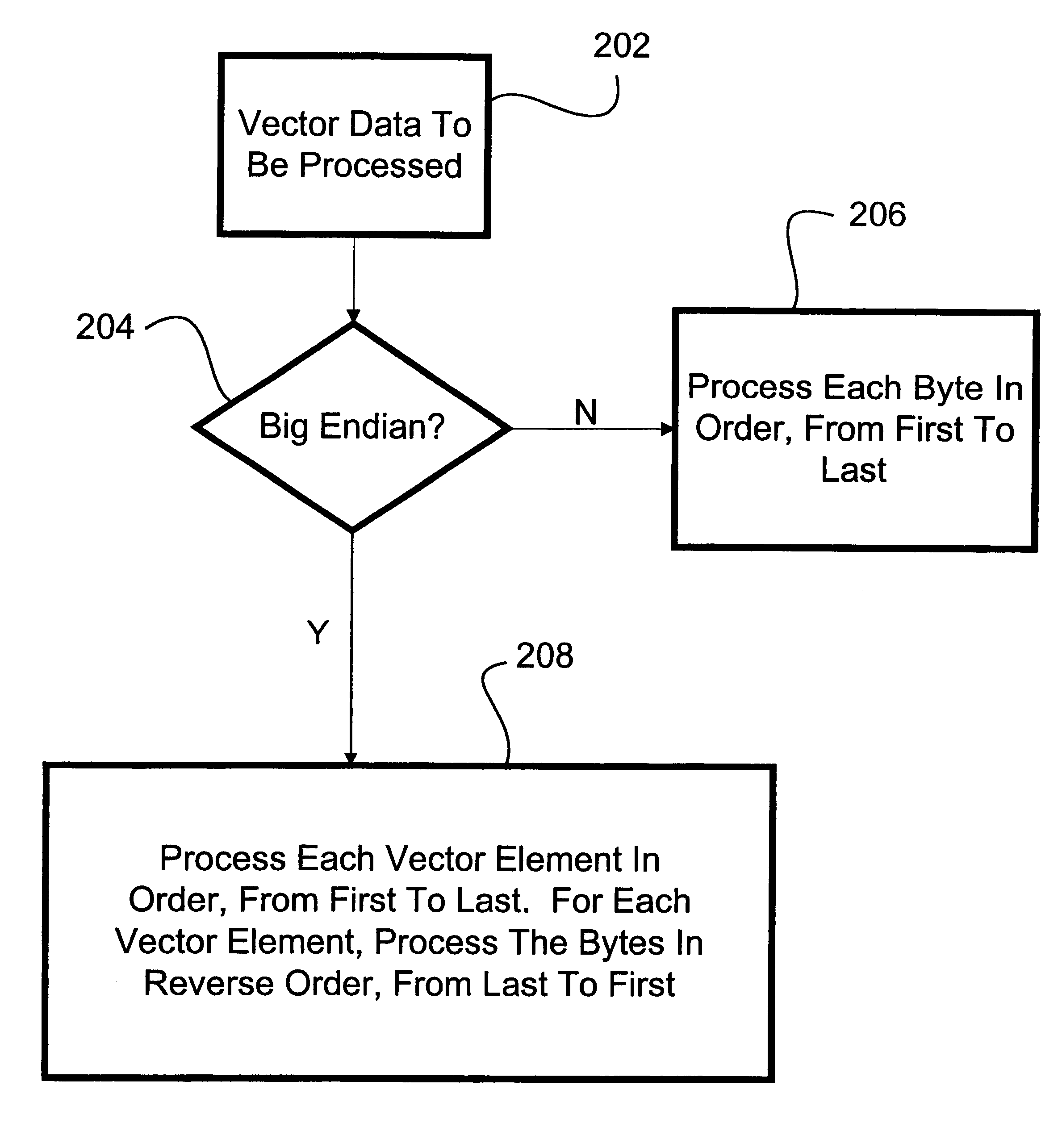

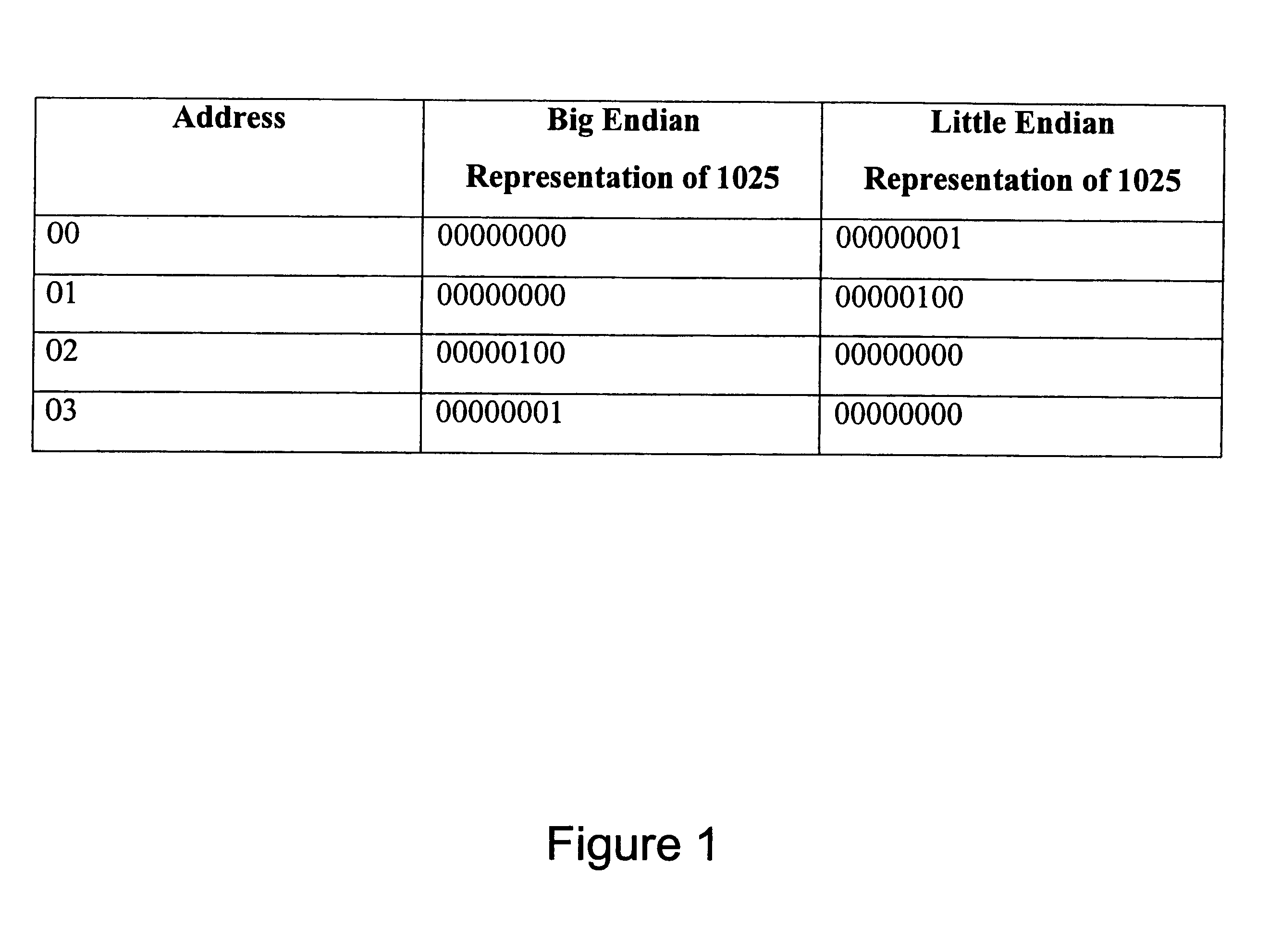

System and method for processing vectorized data

InactiveUS6728874B1Handling data according to predetermined rulesGeneral purpose stored program computerReverse orderVector element

A method and system for correctly processing both big endian and little endian vector data. If the vector has a little endian data order, each piece of data (such as a byte) within the vector is processed in order. If the vector has a big endian data order, each vector element is processed in order, but each piece of data within each vector element is processed in reverse order.

Owner:III HLDG 6

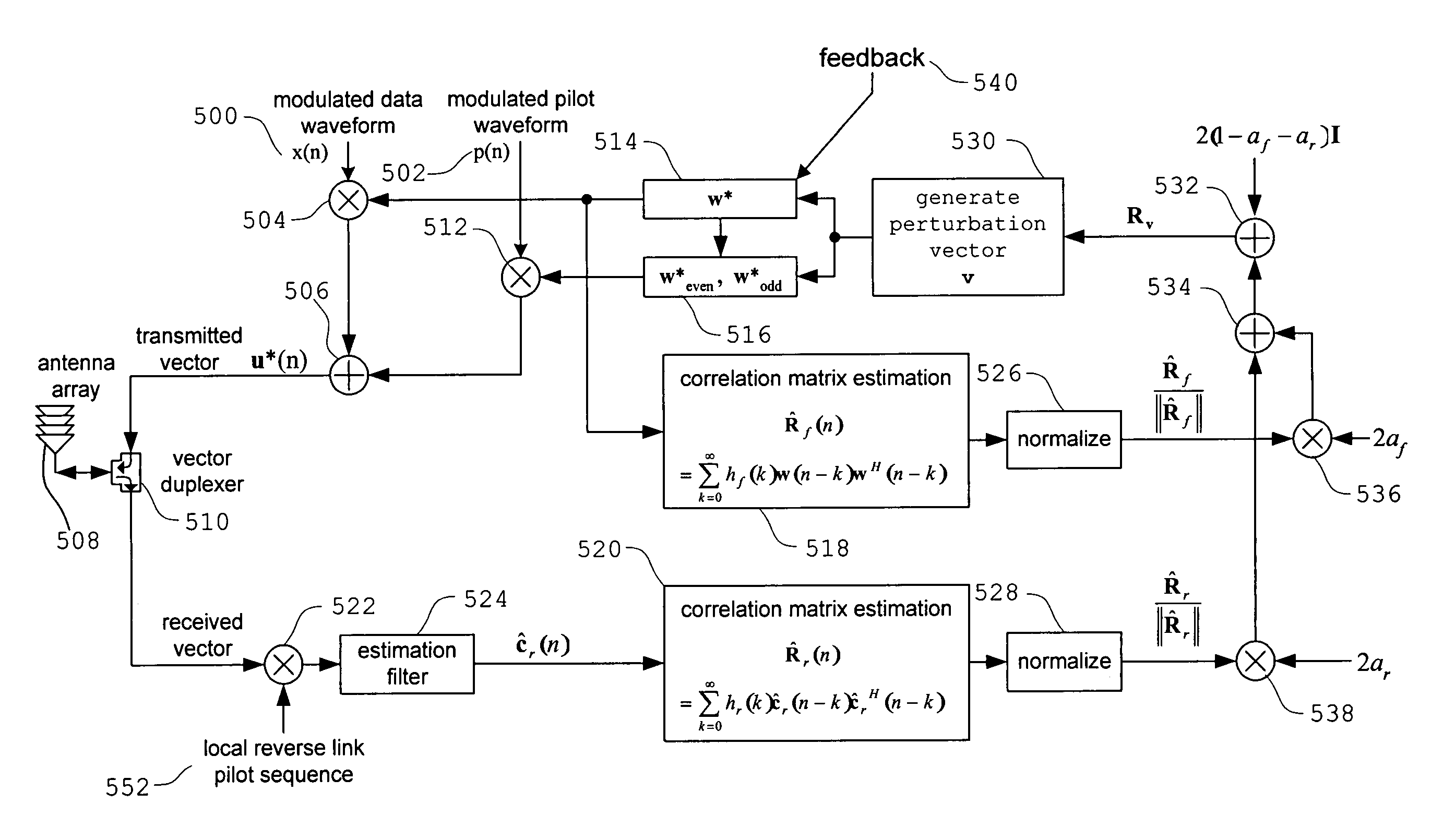

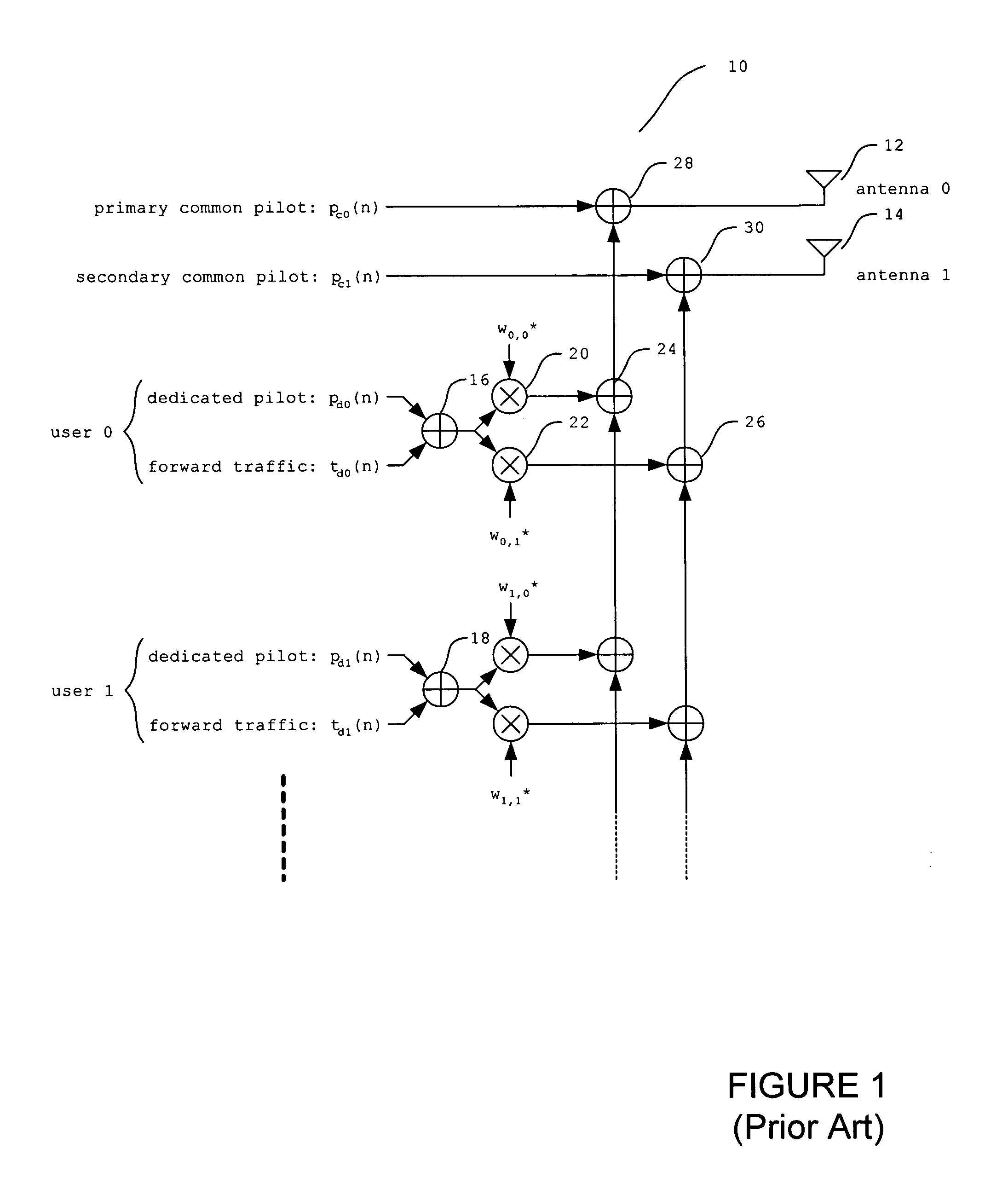

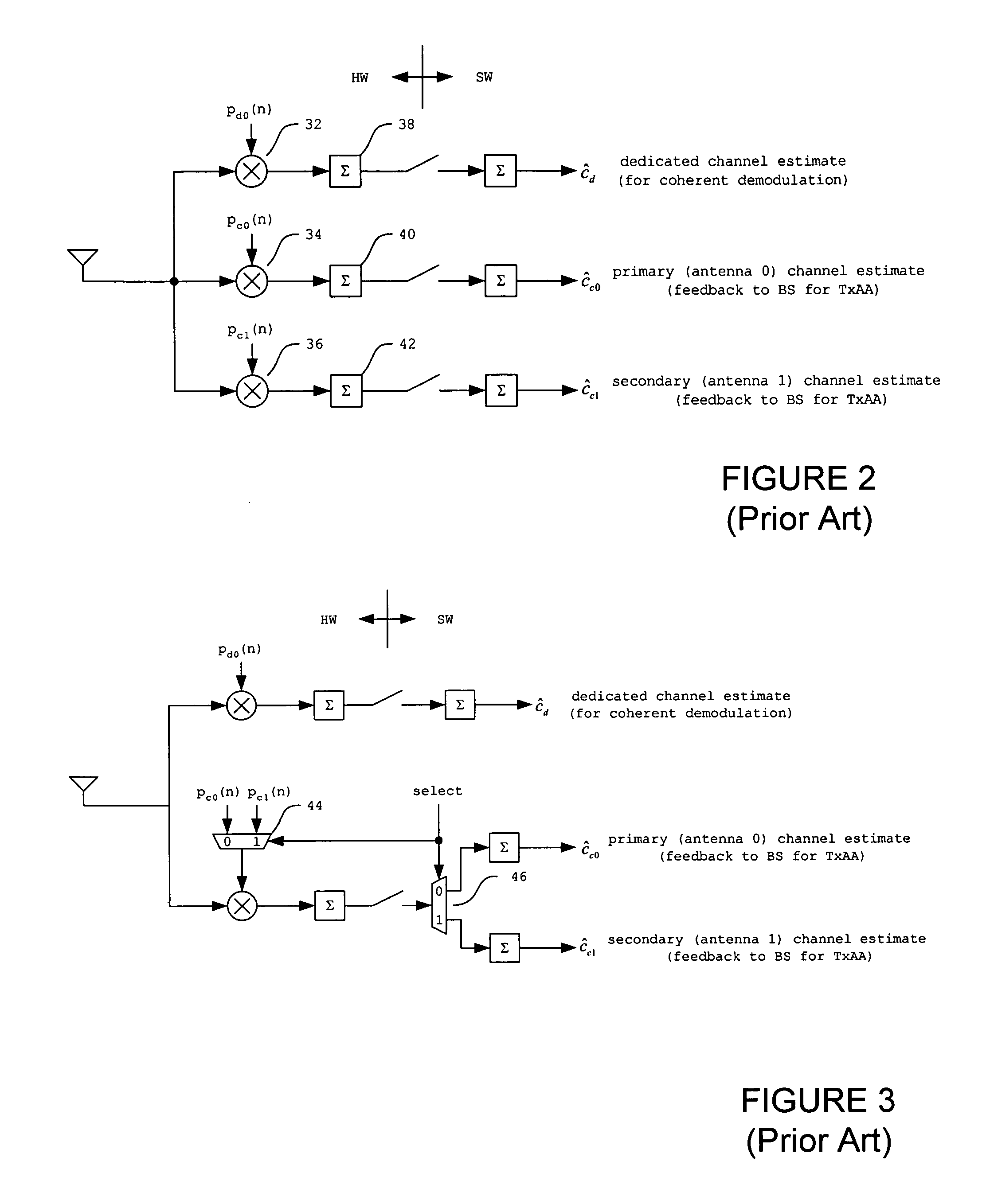

Method and apparatus for improving transmit antenna weight tracking using channel correlations in a wireless communication system

InactiveUS7236538B1Improves weight vector trackingDiversity/multi-antenna systemsError prevention/detection by diversity receptionPhase correlationGradient estimation

A novel method and apparatus for improving transmit antenna weight tracking using channel vector element to element correlations in a wireless communication system is disclosed. The present channel autocorrelation tracking technique utilizes the observation that tracking can be improved when a channel gain vector contains correlated elements. In a first embodiment of the autocorrelation tracking technique, the present invention extracts a coarse gradient estimate by utilizing a perturbation vector autocorrelation matrix estimate and a perturbation autocorrelation matrix to update TxAA weight vectors accordingly. In a second embodiment of the channel autocorrelation tracking technique, the present invention extracts a coarse gradient estimate by utilizing eigendecompositions, perturbation vector autocorrelation matrix estimates, and perturbation autocorrelation matrices to update TxAA weight vectors accordingly. In a third embodiment of the channel autocorrelation tracking technique, the present invention reduces the phase change that can occur at receivers.

Owner:INTEL CORP

Ordered data compression system and methods using principle component analysis

Methods and systems are provided for encoding, transmission and decoding of vectorized input data, for example, video or audio data. A convex invariance learning framework is established for processing input data or a given data type. Each input vector is associated with a variable transformation matrix that acts on the vector to invariantly permute the vector elements. Joint invariance and model learning is performed on a training set of invariantly transformed vectors over a constrained space of transformation matrices using maximum likelihood analysis. The maximum likelihood analysis reduces the data volume to a linear subspace volume in which the training data can be modeled by a reduced number of variables. Principal component analysis is used to identify a set of N eigenvectors that span the linear subspace. The set of N eigenvectors is used a basis set to encode input data and to decode compressed data.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

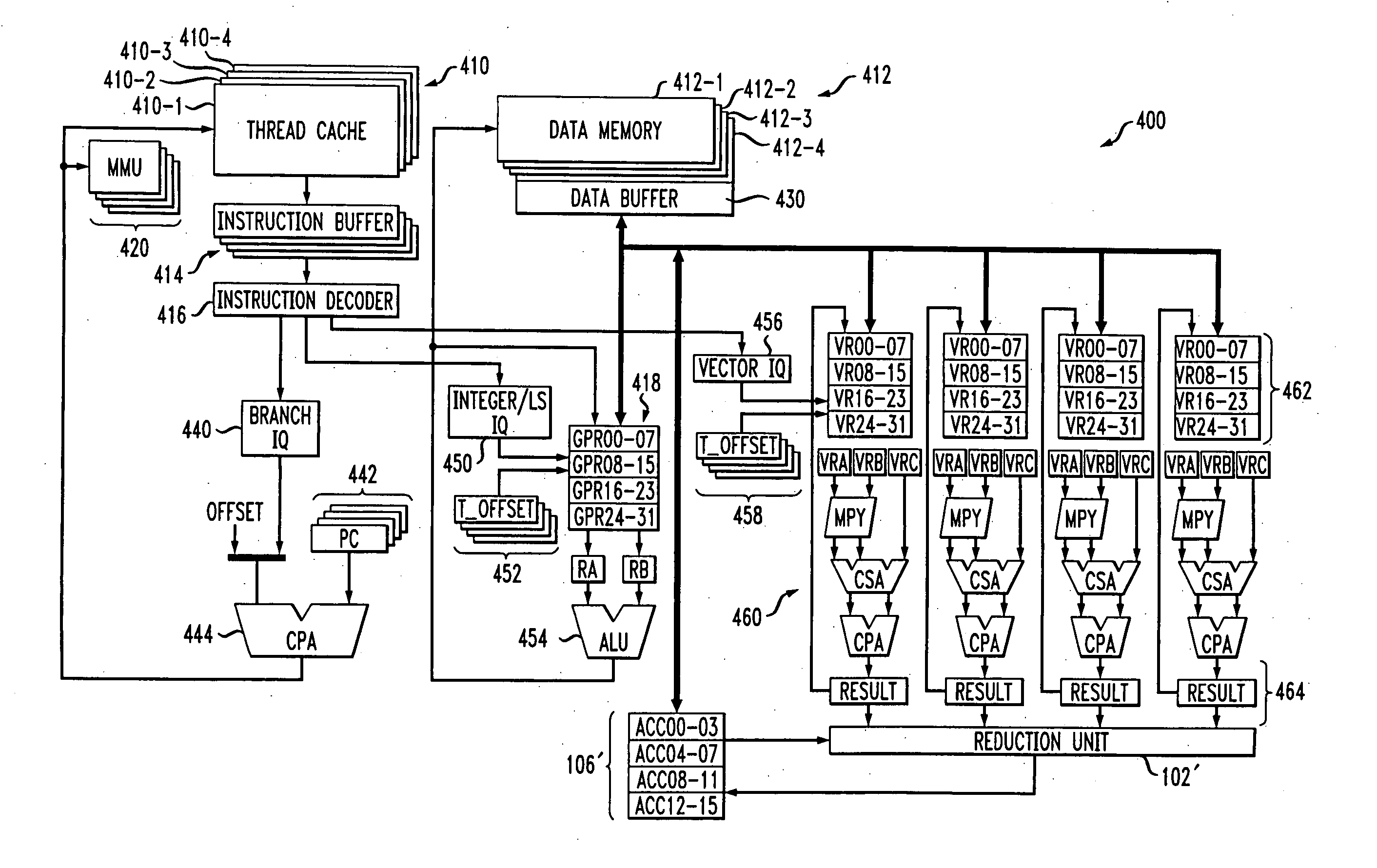

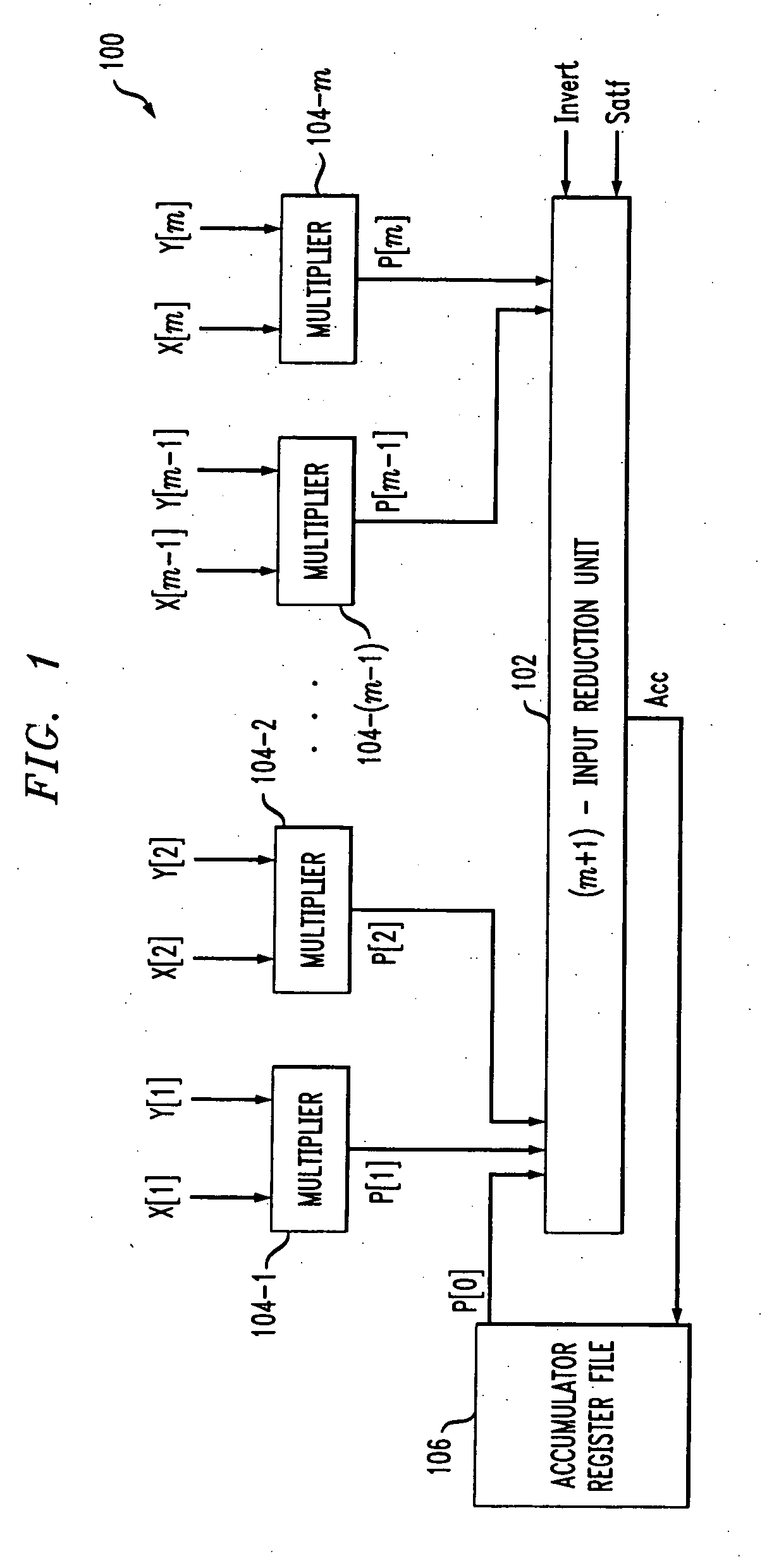

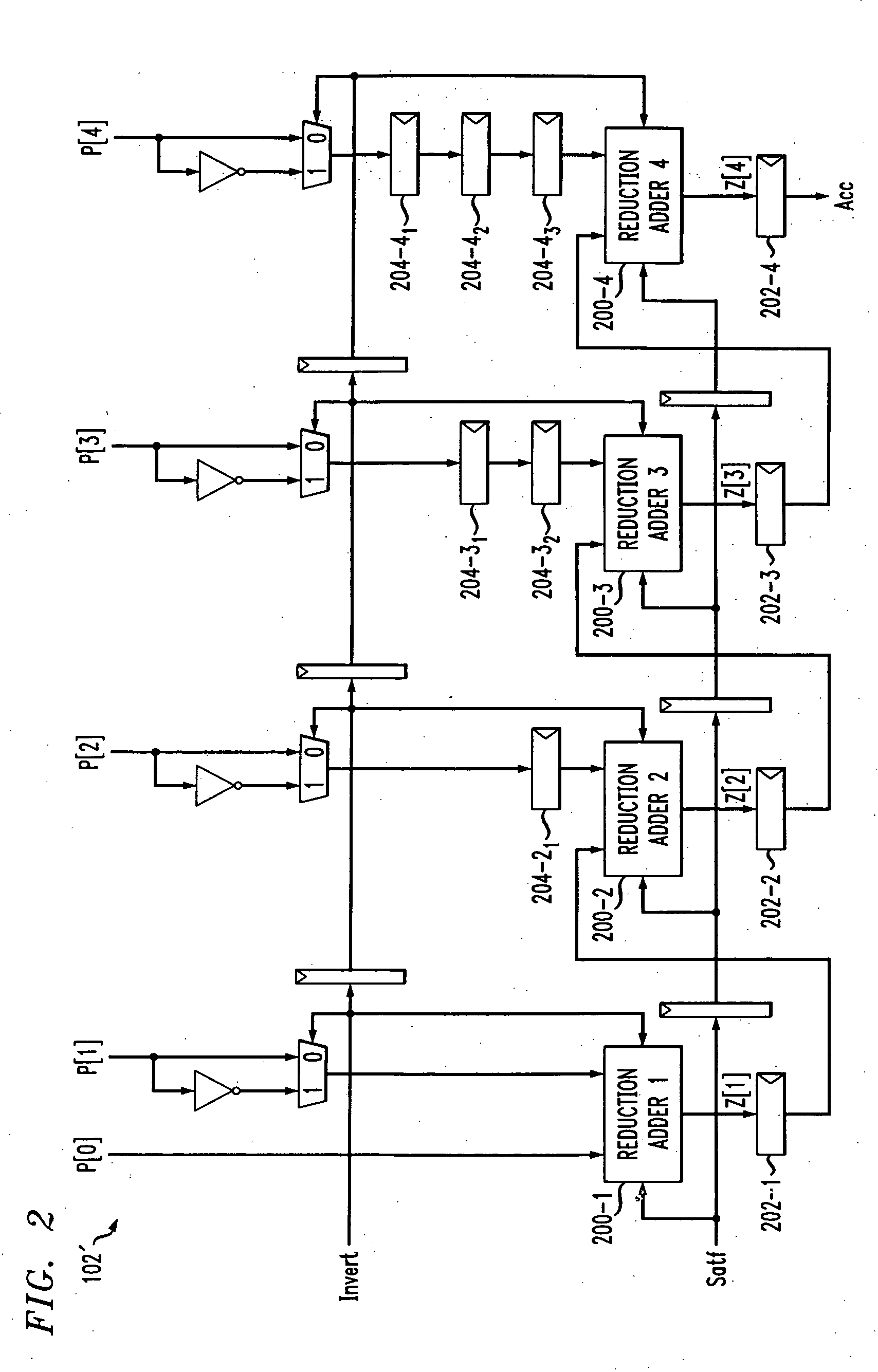

Processor having parallel vector multiply and reduce operations with sequential semantics

ActiveUS20060041610A1Wide rangeReduce stepsComputation using non-contact making devicesDigital computer detailsVector elementParallel computing

A processor comprises a plurality of arithmetic units, an accumulator unit, and a reduction unit coupled between the plurality of arithmetic units and the accumulator unit. The reduction unit receives products of vector elements from the arithmetic units and a first accumulator value from the accumulator unit, and processes the products and the first accumulator value to generate a second accumulator value for delivery to the accumulator unit. The processor implements a plurality of vector multiply and reduce operations having guaranteed sequential semantics, that is, operations which guarantee that the computational result will be the same as that which would be produced using a corresponding sequence of individual instructions.

Owner:QUALCOMM INC

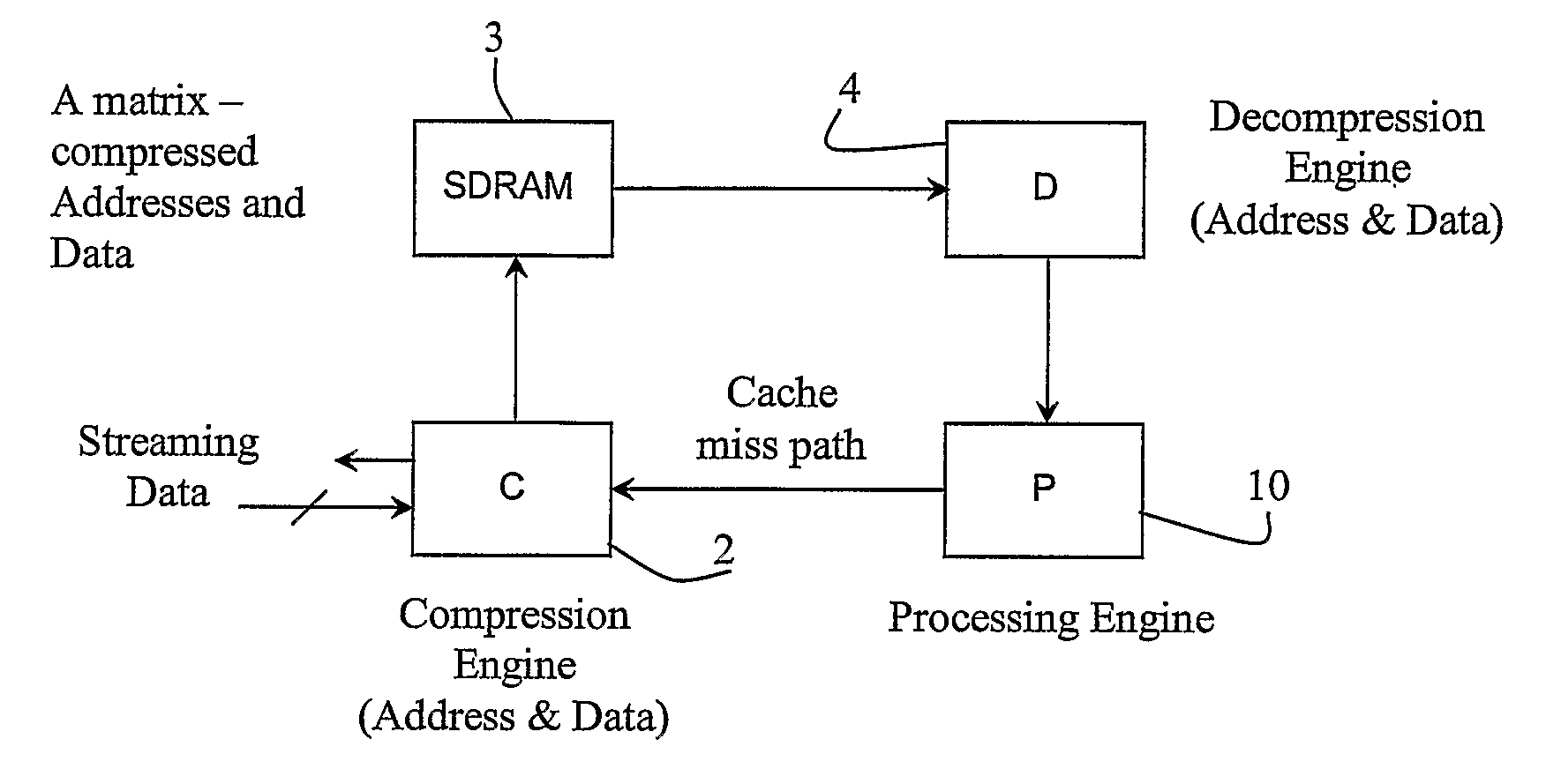

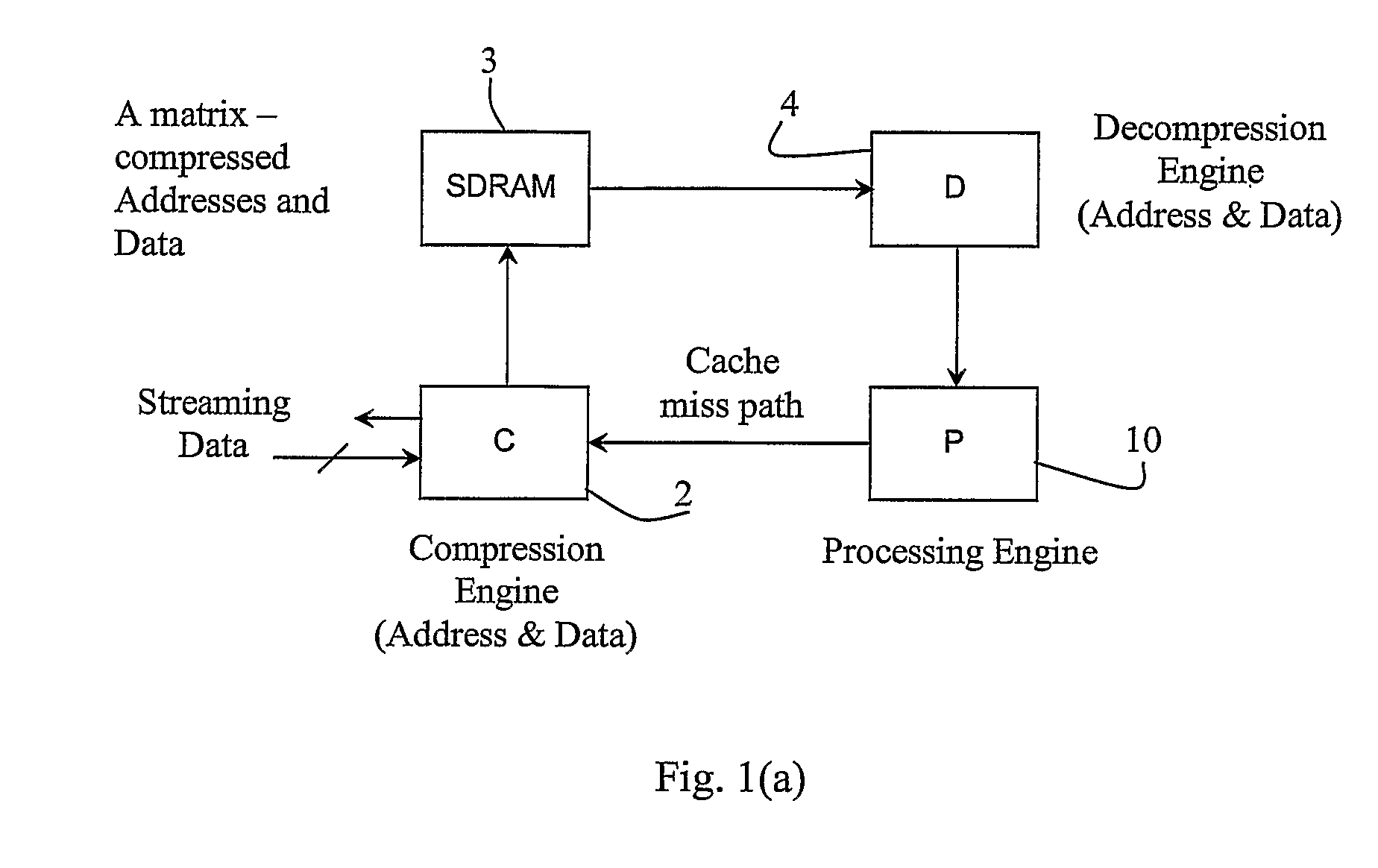

Data processing system and method

InactiveUS20090030960A1Reduce startup timeComputation using non-contact making devicesCode conversionData processing systemVector element

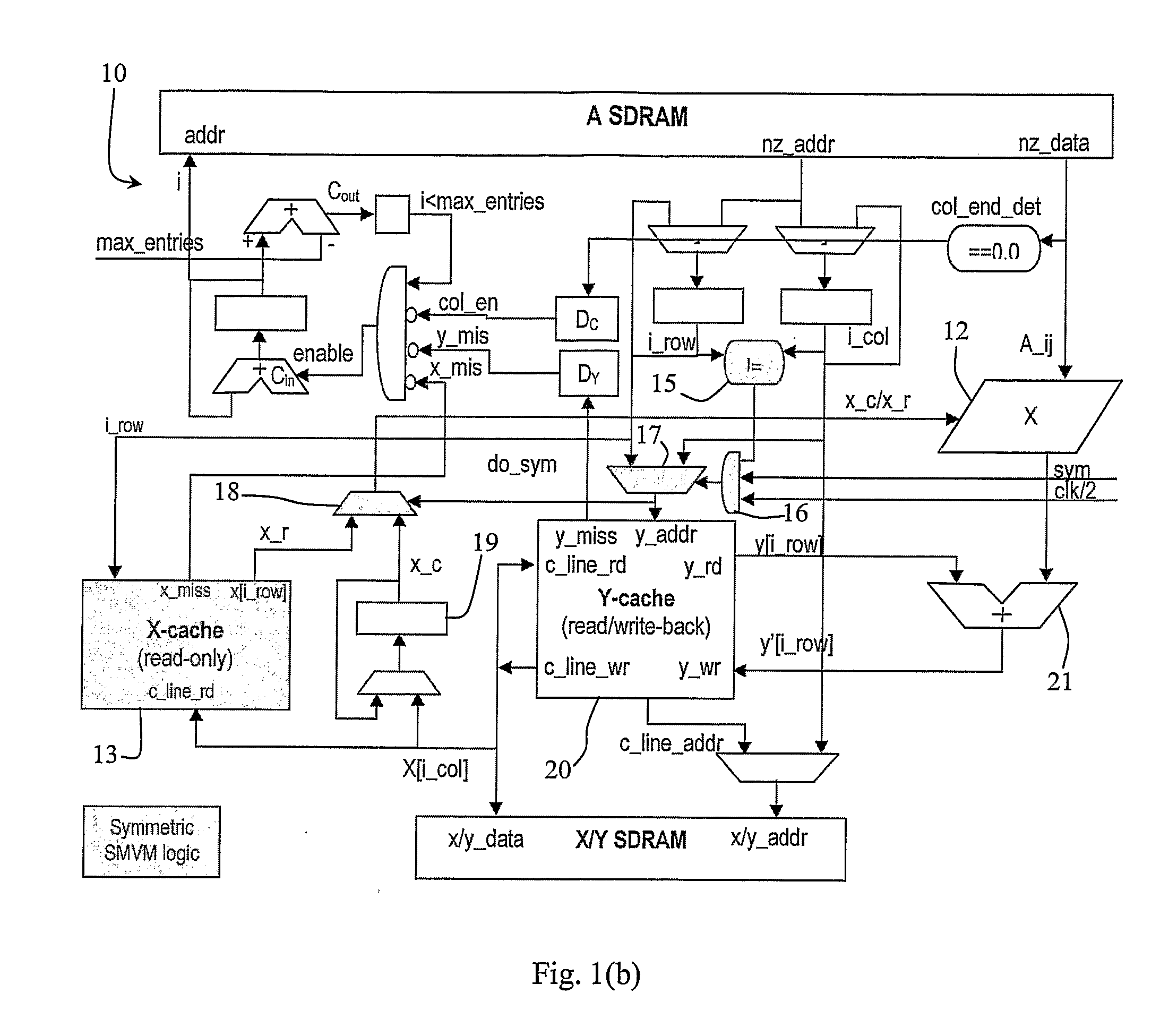

A matrix by vector multiplication processing system (1) comprises a compression engine (2) for receiving and dynamically compressing a stream of elements of a matrix; in which the matrix elements are clustered, and in which the matrix elements are in numerical floating point format, and a memory (SDRAM, 3) for storing the compressed matrix. It also comprises a decompression engine (4) for dynamically decompressing elements retrieved from the memory (3), and a processor (10) for dynamically receiving decompressed elements from the decompression engine (3), and comprising a vector cache (13, 19), and multiplication logic (12, 21) for dynamically multiplying elements of the vector cache with the matrix elements. There is a cache (13) for vector elements to be multiplied by matrix elements to one side of a diagonal, and a separate cache or register (19) for vector elements to be multiplied by matrix elements to the other side of the diagonal. A control mechanism (16, 17, 18) multiplies a single matrix element by a corresponding element in one vector cache and separately by a corresponding element in the other vector cache. The compression engine and the decompression logic are circuits within a single integrated circuit, and the compression engine (2) performs matrix element address compression by generating a relative address for a plurality of clustered elements.

Owner:TRINITY COLLEGE DUBLIN

Floating point only SIMD instruction set architecture including compare, select, Boolean, and alignment operations

InactiveUS7900025B2General purpose stored program computerSpecific program execution arrangementsData processing systemProcessor register

Mechanisms for implementing a floating point only single instruction multiple data instruction set architecture are provided. A processor is provided that comprises an issue unit, an execution unit coupled to the issue unit, and a vector register file coupled to the execution unit. The execution unit has logic that implements a floating point (FP) only single instruction multiple data (SIMD) instruction set architecture (ISA). The floating point vector registers of the vector register file store both scalar and floating point values as vectors having a plurality of vector elements. The processor may be part of a data processing system.

Owner:INT BUSINESS MASCH CORP

Generating and Executing Programs for a Floating Point Single Instruction Multiple Data Instruction Set Architecture

ActiveUS20100095098A1Digital computer detailsSpecific program execution arrangementsVector elementFloating point

Mechanisms for generating and executing programs for a floating point (FP) only single instruction multiple data (SIMD) instruction set architecture (ISA) are provided. A computer program product comprising a computer recordable medium having a computer readable program recorded thereon is provided. The computer readable program, when executed on a computing device, causes the computing device to receive one or more instructions and execute the one or more instructions using logic in an execution unit of the computing device. The logic implements a floating point (FP) only single instruction multiple data (SIMD) instruction set architecture (ISA), based on data stored in a vector register file of the computing device. The vector register file is configured to store both scalar and floating point values as vectors having a plurality of vector elements.

Owner:IBM CORP