Patents

Literature

77 results about "Conditional execution" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Conditionally executed is called a single alternative decision structure because it provides only one alternative path of execution. The action is conditionally executed because it is performed only when a certain condition is true. 2. You need to test a condition and then execute one set of statements if the condition is true.

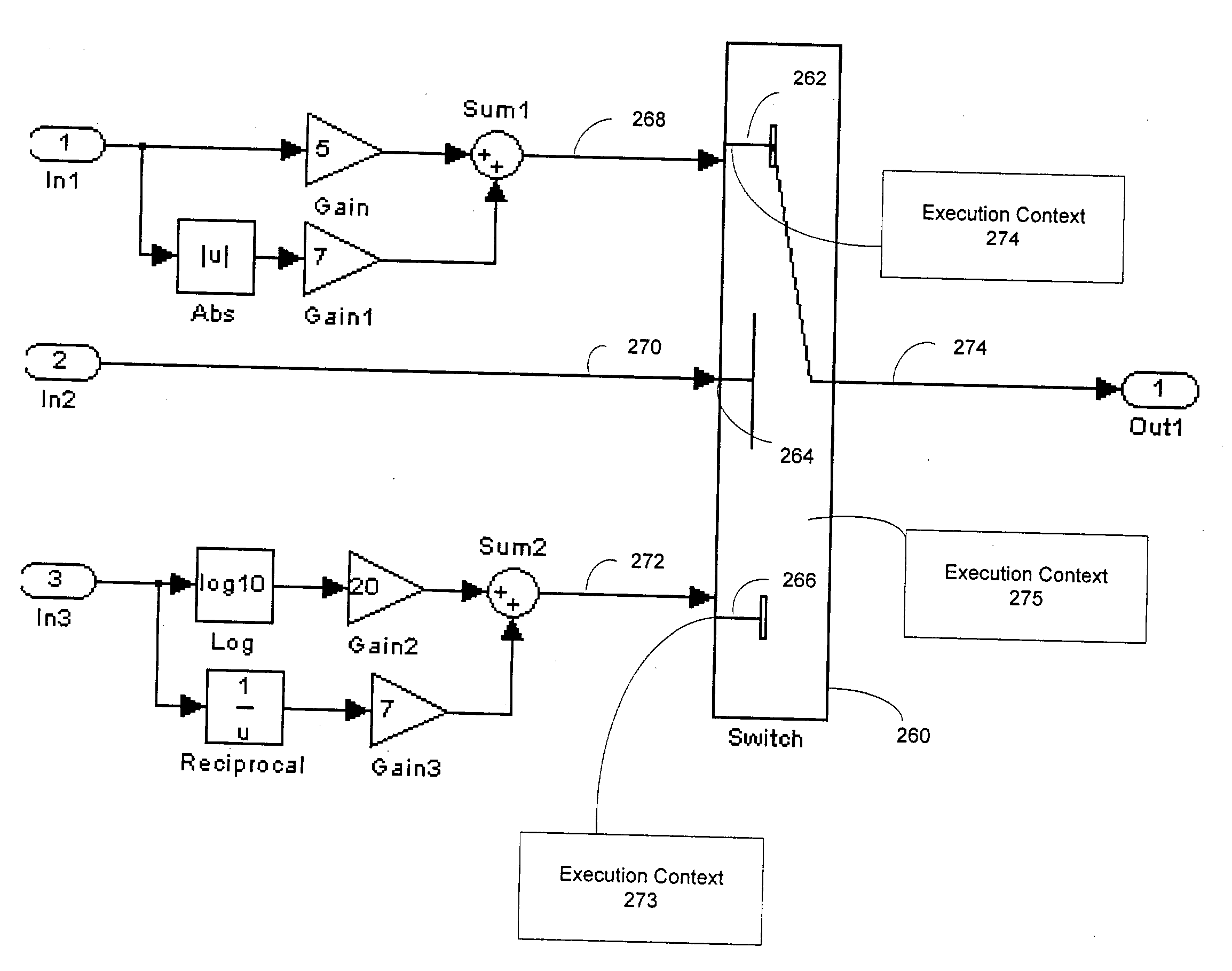

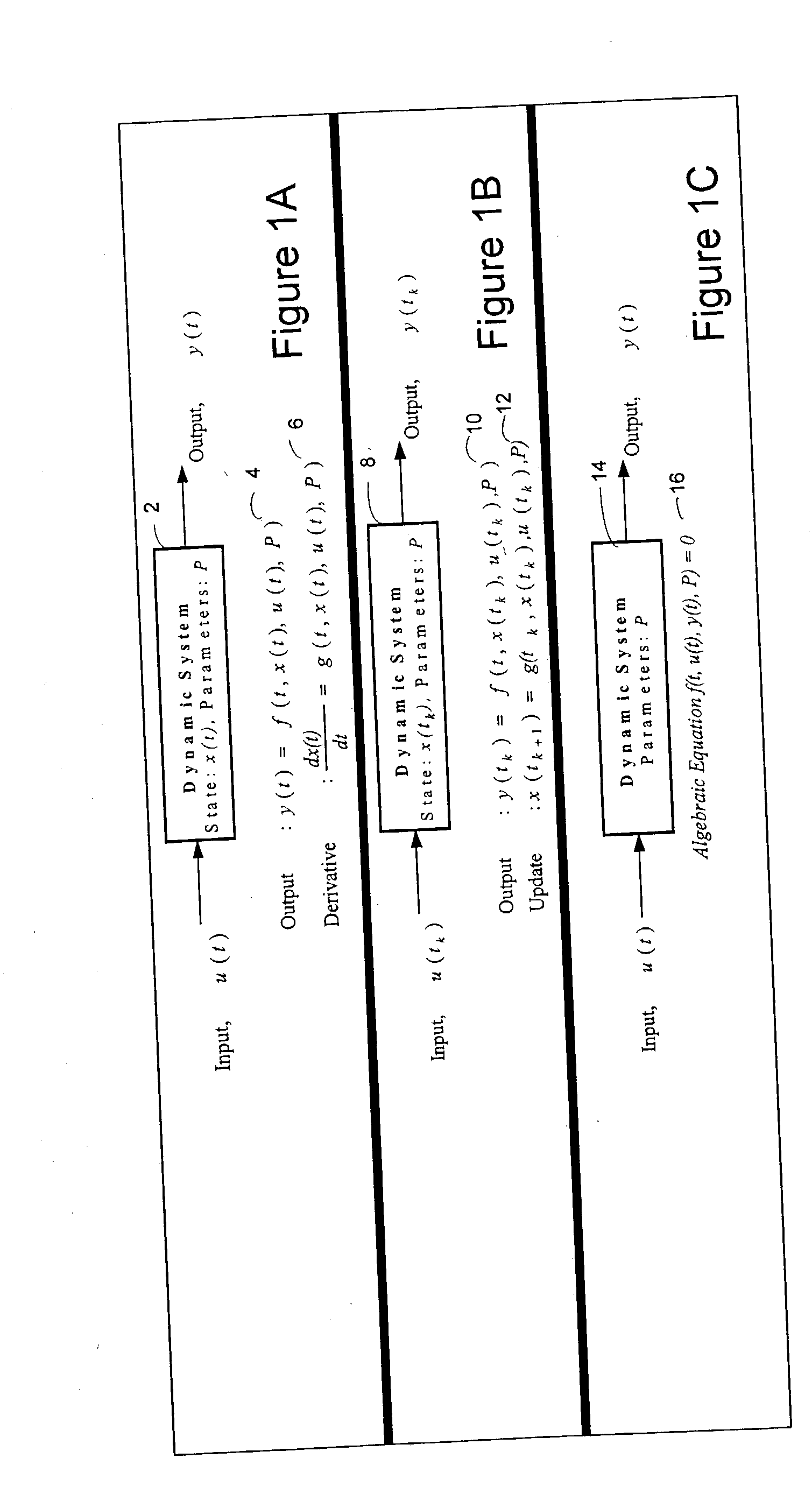

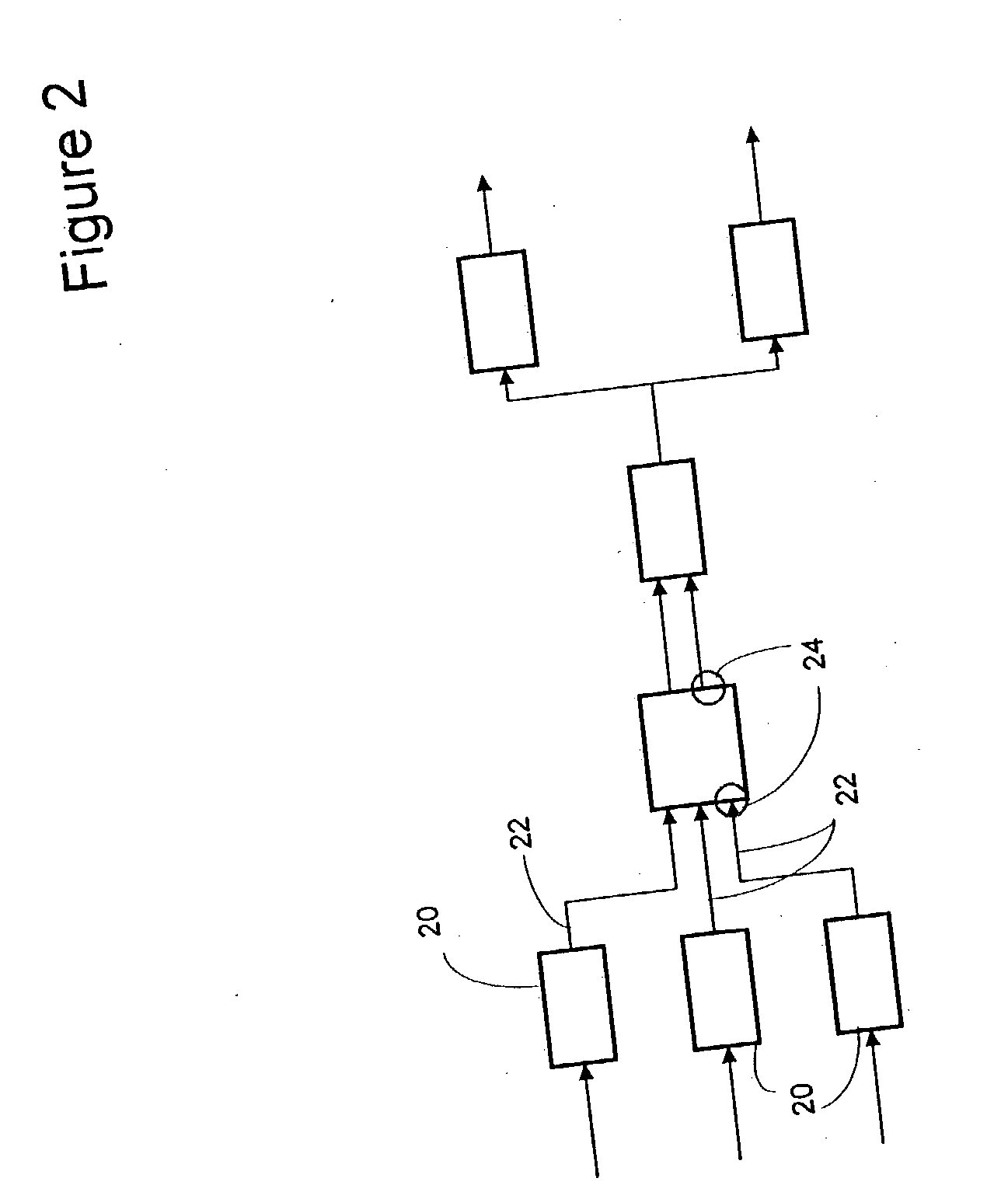

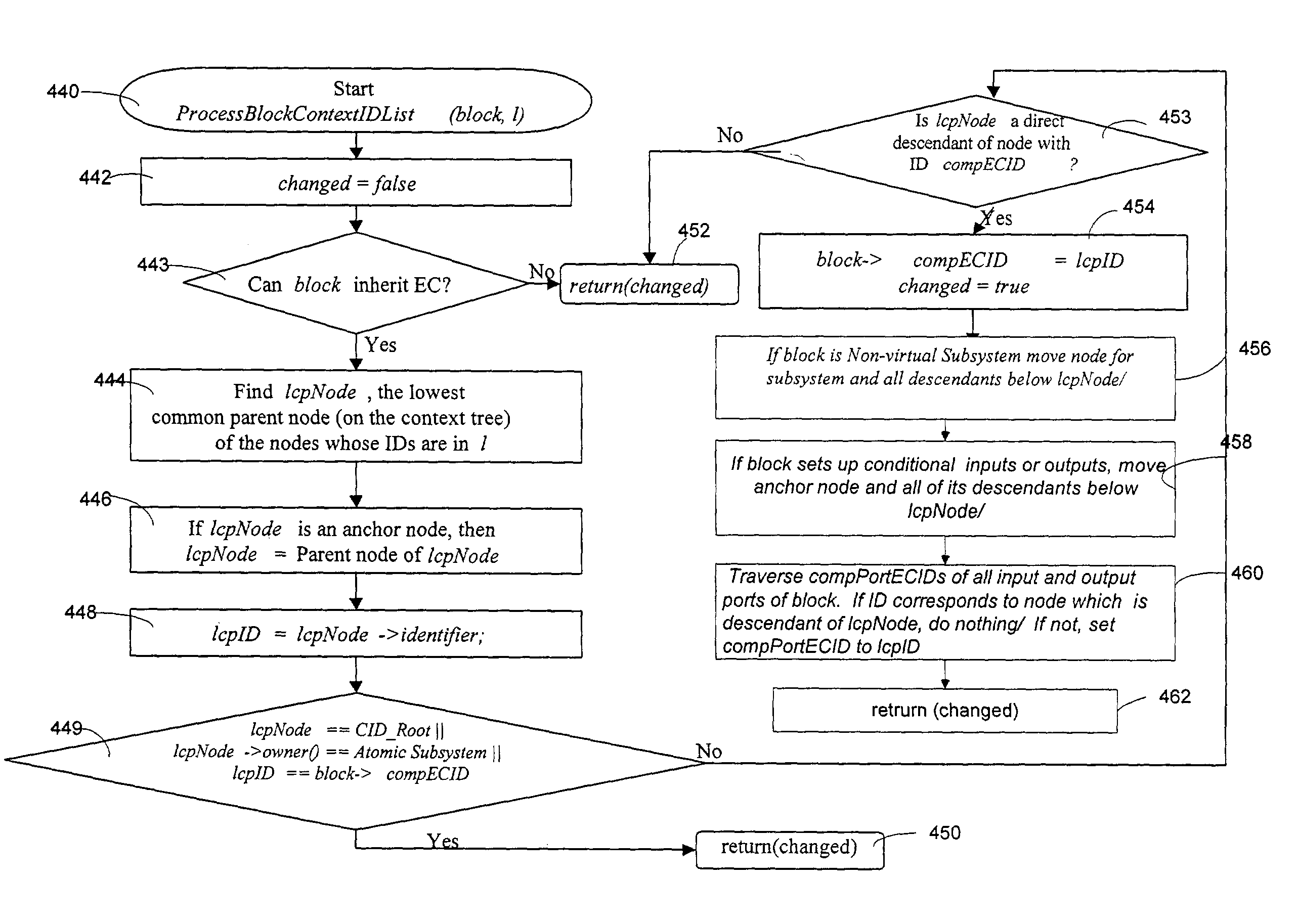

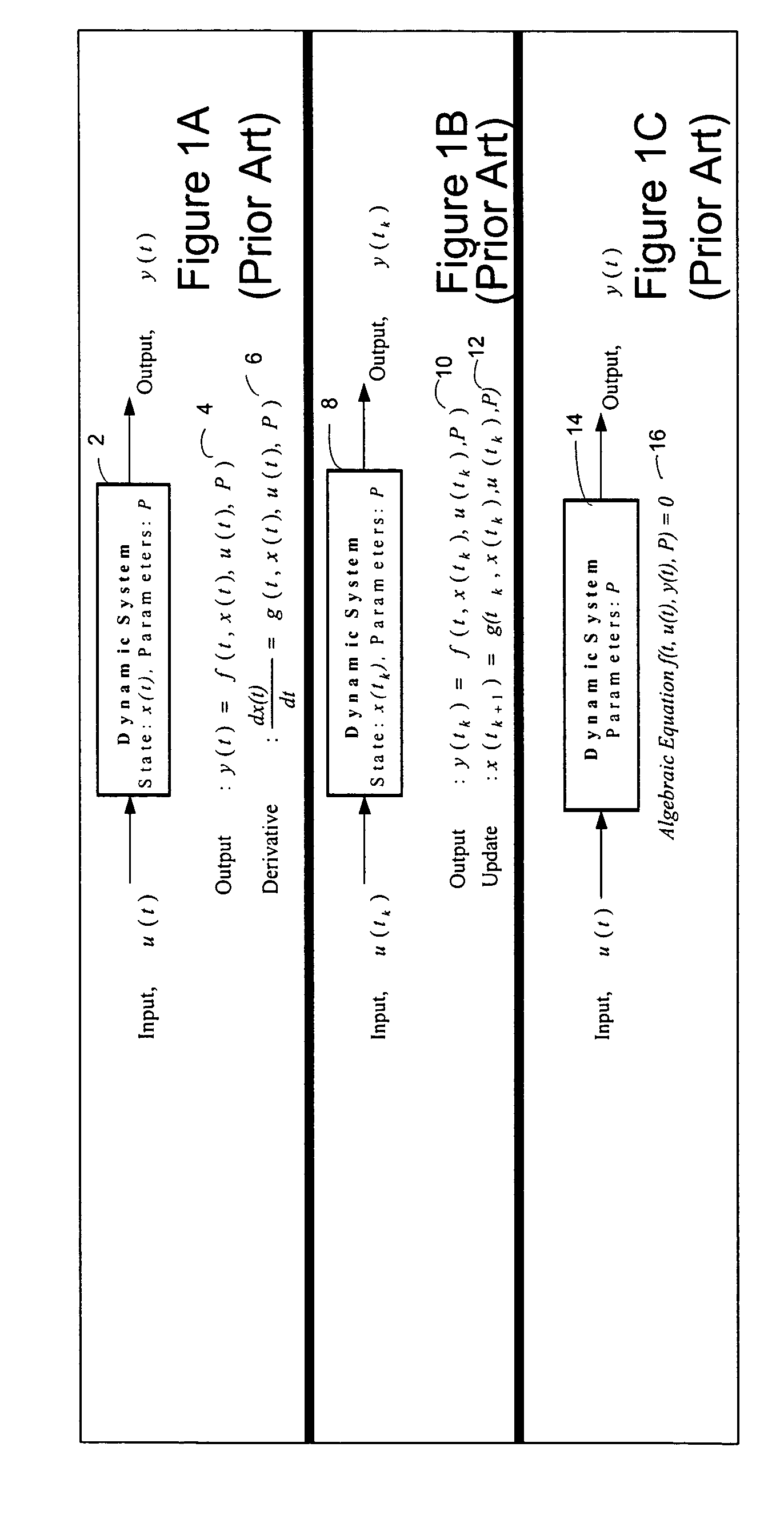

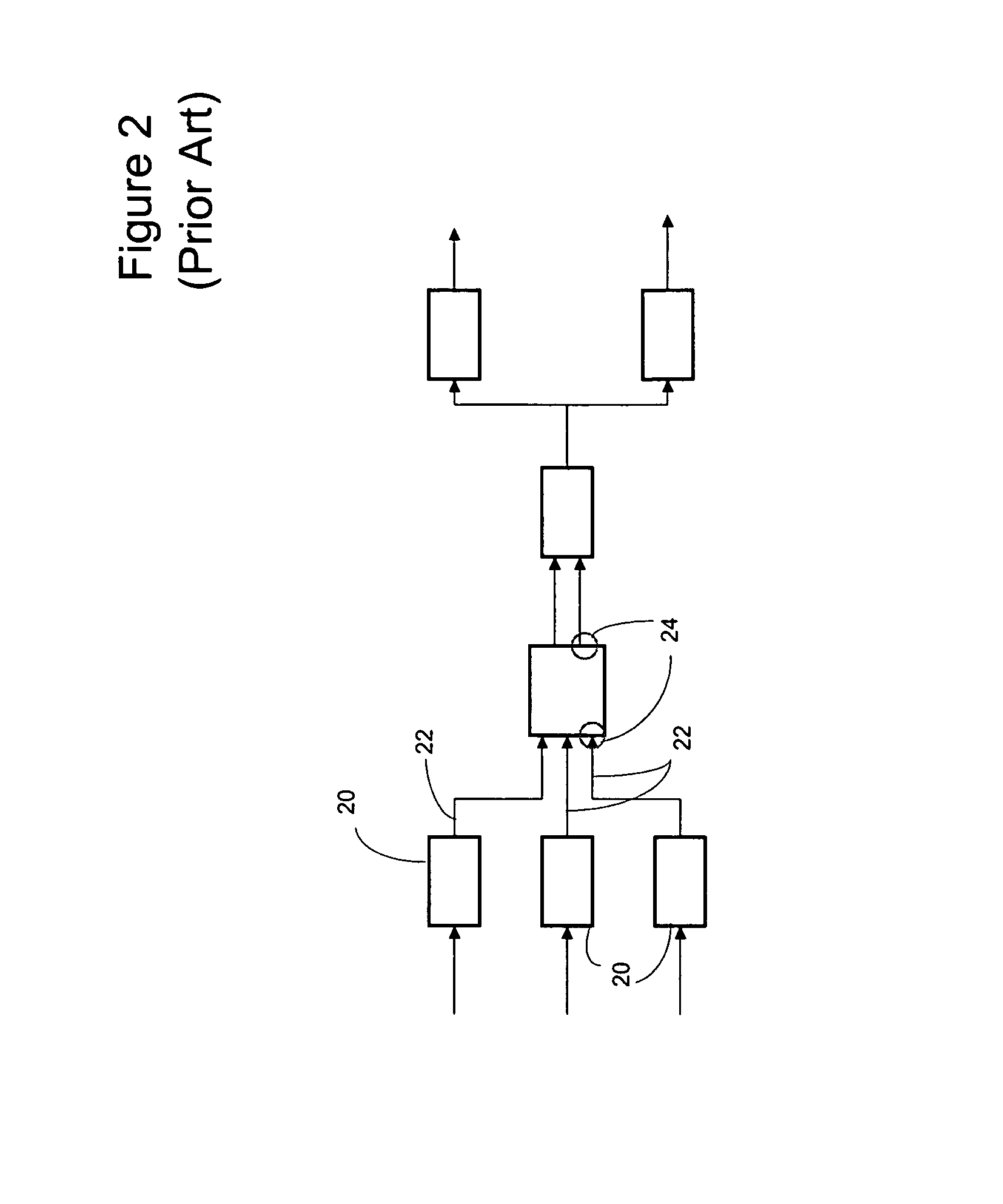

System and method for using execution contexts in block diagram modeling

ActiveUS20040210592A1Digital data processing detailsVisual/graphical programmingPre-conditionModular design

A method of controlling the conditional execution of elements and subsystems in a block diagram is disclosed. Data structures known as Execution Contexts are created and associated with individual block diagram elements and subsystems. The Execution Contexts allow execution of the associated element or subsystem upon satisfaction of a specified pre-condition. The Execution Contexts may be inherited by other elements and subsystems in the block diagram and propagated programmatically throughout the block diagram. The use of the Execution Contexts allows for efficient code generation and block diagram execution, as well as supporting modular design concepts.

Owner:THE MATHWORKS INC

System and method for using execution contexts in block diagram modeling

ActiveUS7809545B2Program control using stored programsDigital data processing detailsPre-conditionTheoretical computer science

A method of controlling the conditional execution of elements and subsystems in a block diagram is disclosed. Data structures known as Execution Contexts are created and associated with individual block diagram elements and subsystems. The Execution Contexts allow execution of the associated element or subsystem upon satisfaction of a specified pre-condition. The Execution Contexts may be inherited by other elements and subsystems in the block diagram and propagated programmatically throughout the block diagram. The use of the Execution Contexts allows for efficient code generation and block diagram execution, as well as supporting modular design concepts.

Owner:THE MATHWORKS INC

Vector Predicates for Sub-Word Parallel Operations

InactiveUS20080016320A1General purpose stored program computerProgram controlVector elementControl data

This invention uses vector predicate registers to control conditional execution of instructions for vector elements within a data word. A particular vector predicate registers is addressed via a register index. The state of bits of the vector predicate register controls whether a corresponding sub-word operation is executed or inhibited.

Owner:TEXAS INSTR INC

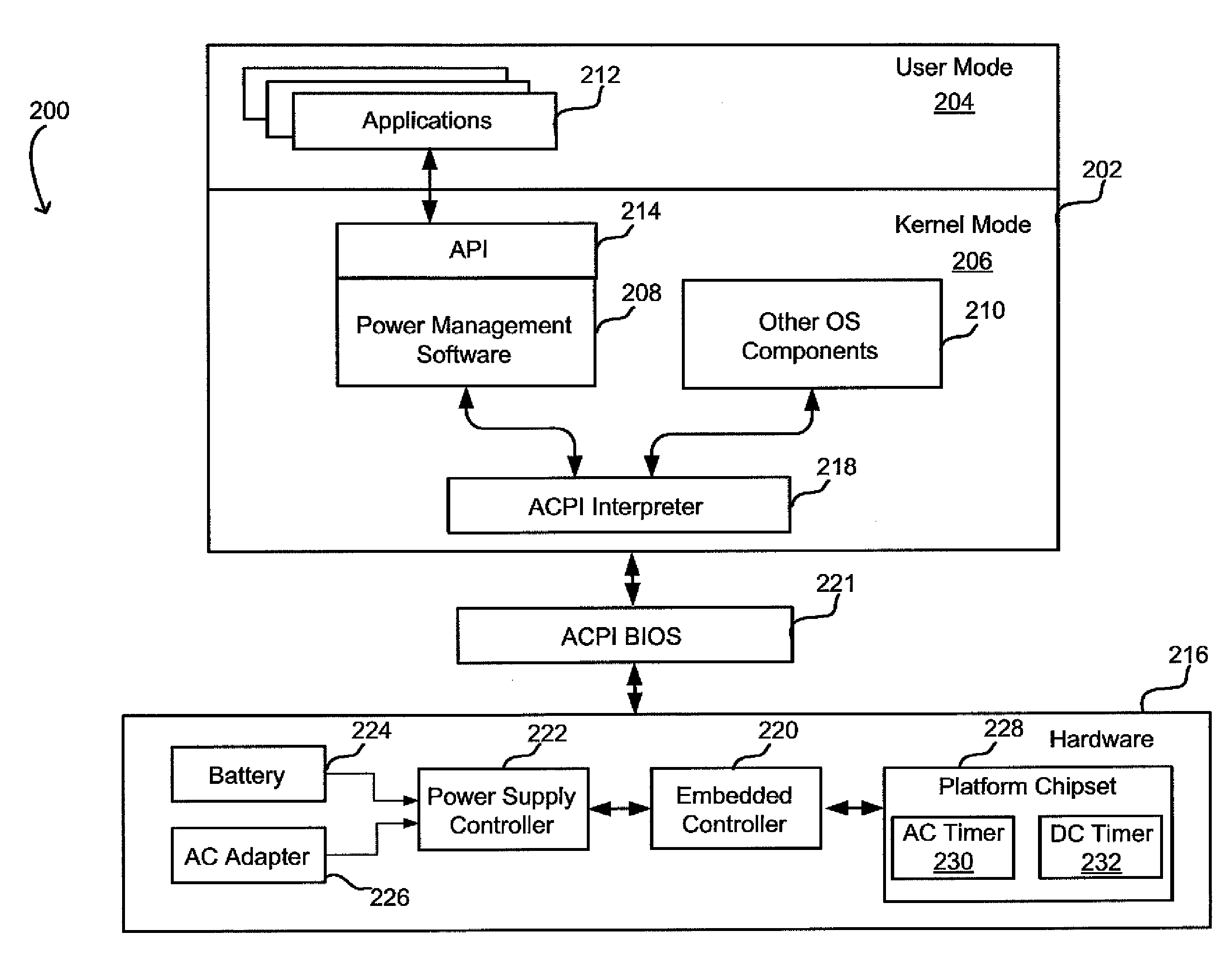

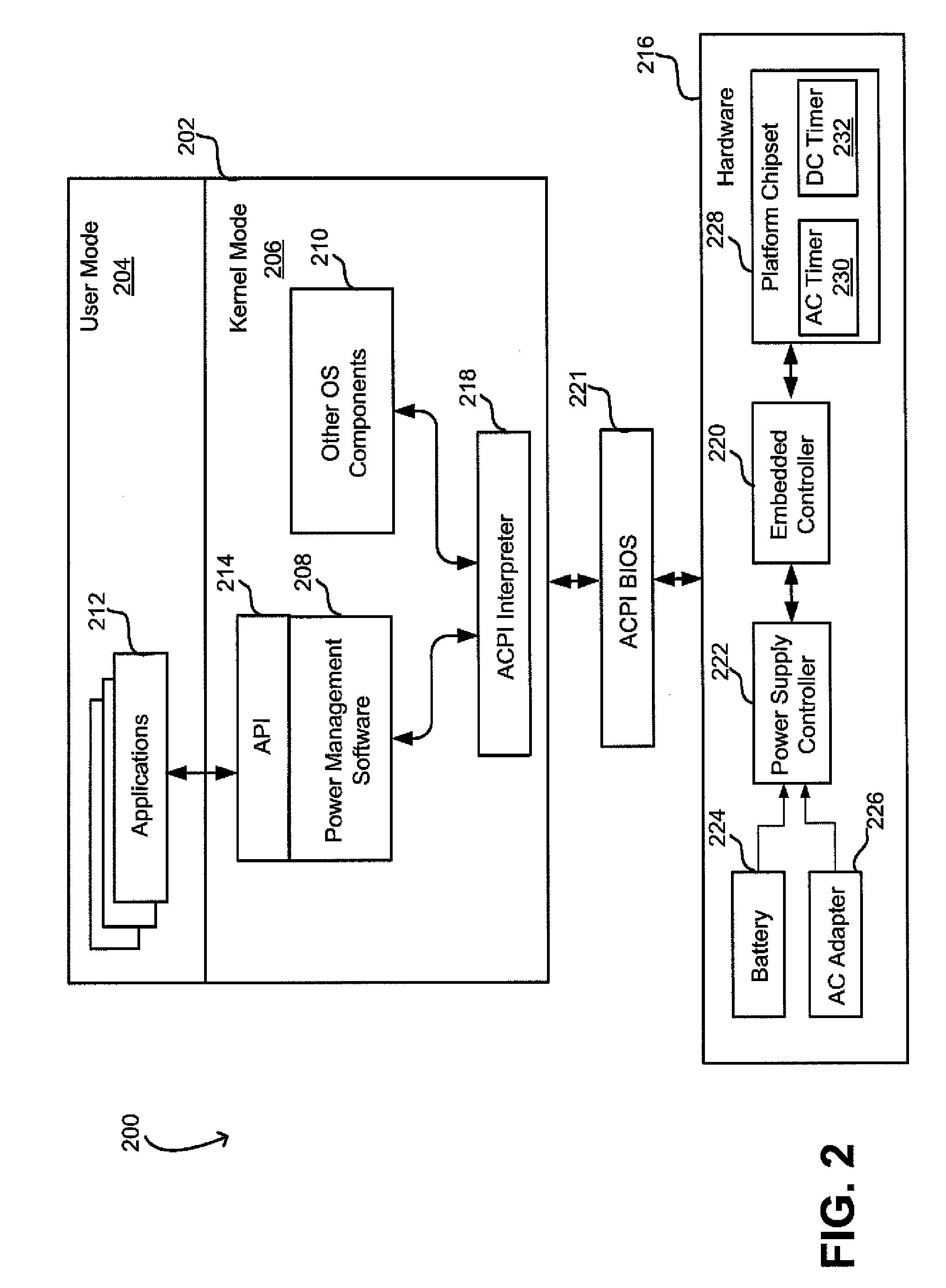

Power state dependent wake-up alarm

ActiveUS20100153765A1Easy to operateDifferent wake-up behaviorDigital data processing detailsHardware monitoringState dependentOperational system

A method of operating a computing device to allow events to be conditionally executed based on a power state of the device at the time of execution of the events. Conditional execution may be implemented using multiple timers, each associated with a power state. A timer such as an “AC timer” or a “DC timer” associated with a respective power state may be used to wake up the device when, upon expiration, or time-out, of the timer, a current power state of the device and the power state associated with the timer match. An Advanced Configuration Power Interface (ACPI) may be employed to abstract implementation of the timers from underlying hardware of the device. The operating system and software applications may request establishing wake-up behavior of the device as commands to program conditional events, which may then be translated into commands to embedded controller to set the timers.

Owner:MICROSOFT TECH LICENSING LLC

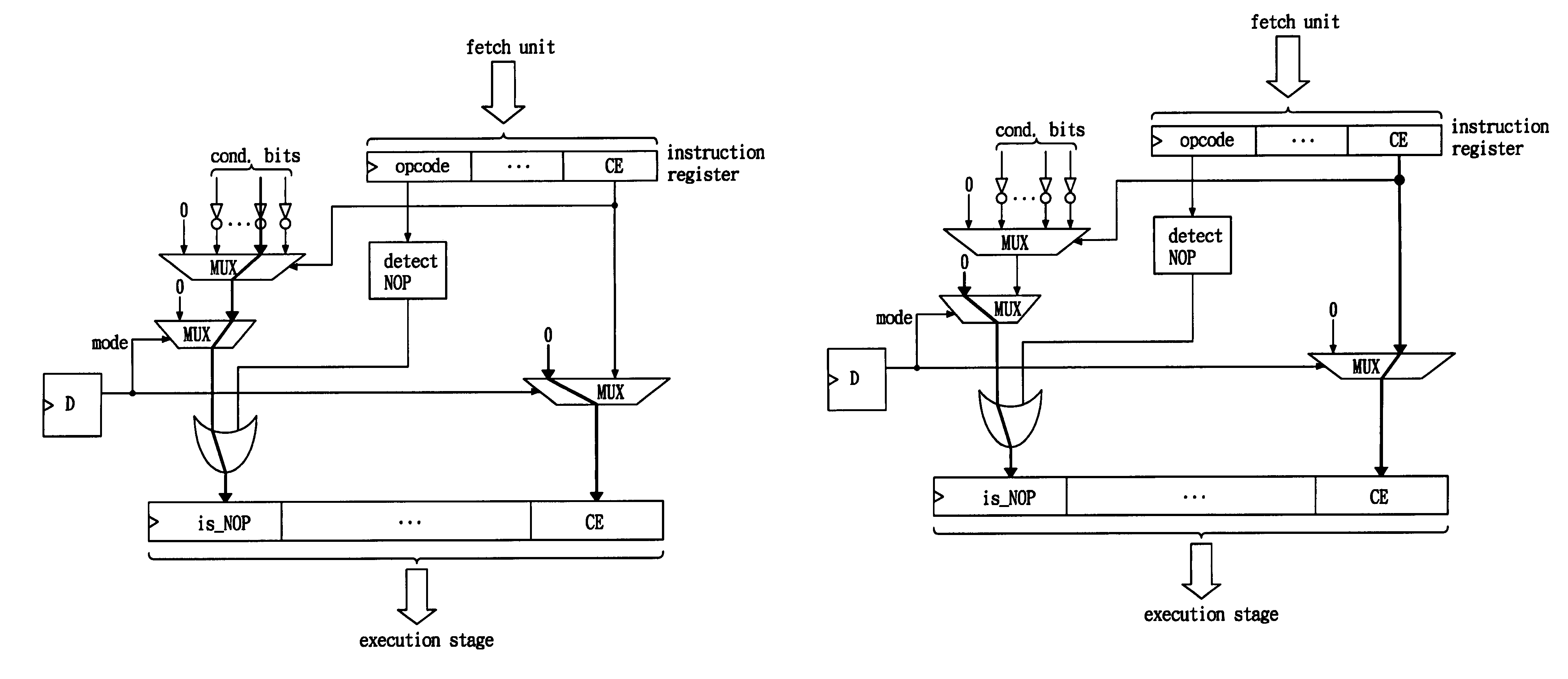

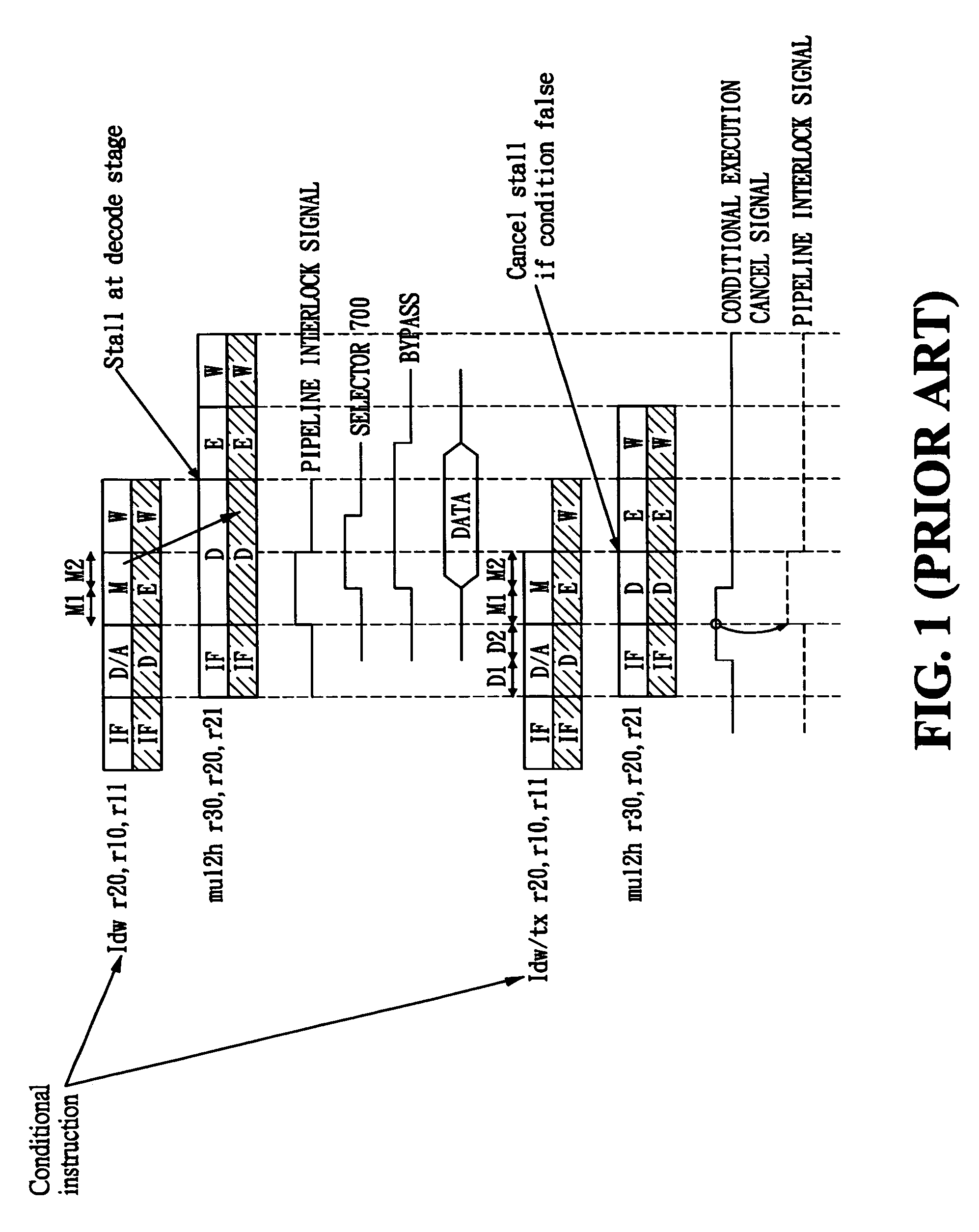

Apparatus and method for switchable conditional execution in a VLIW processor

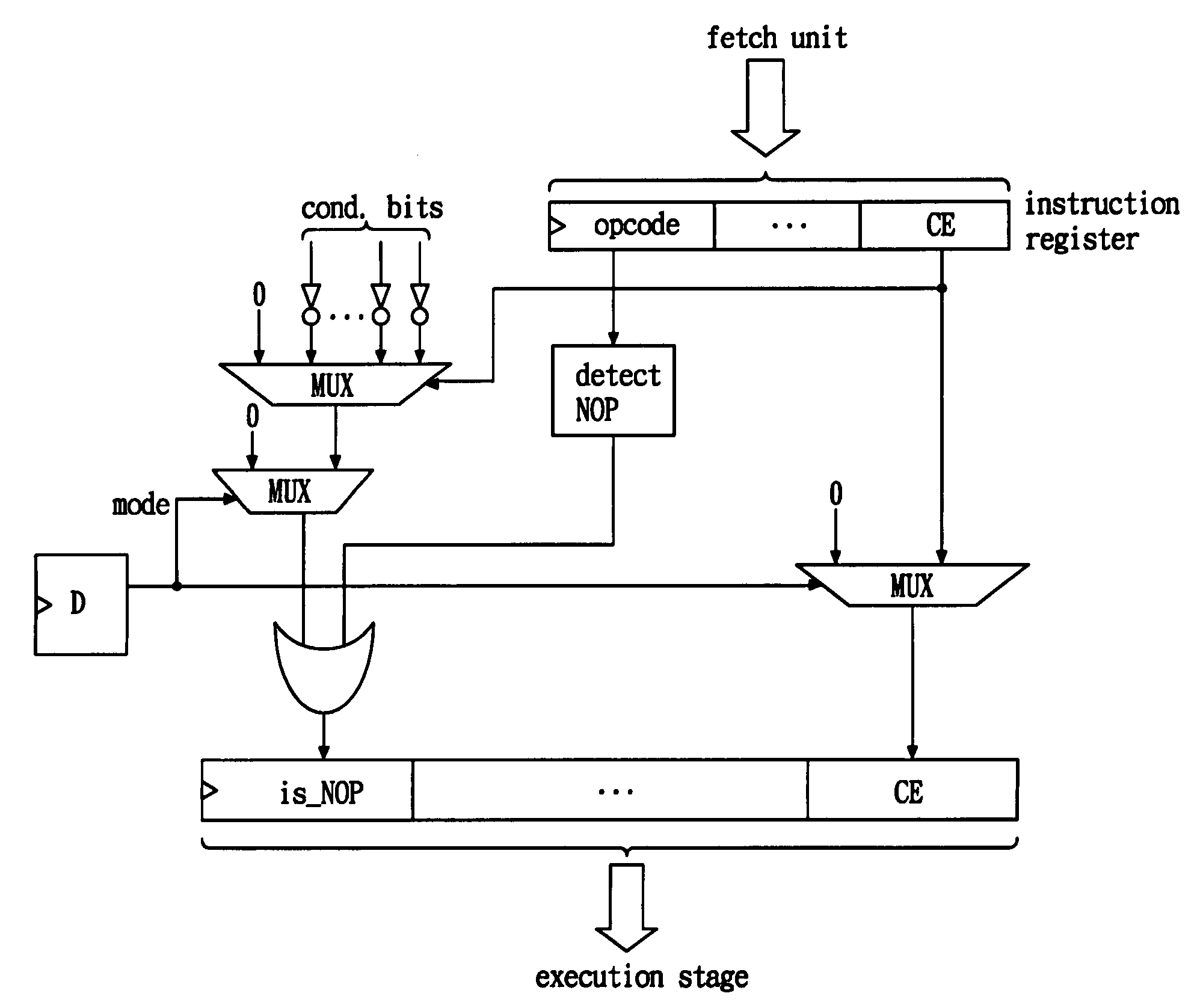

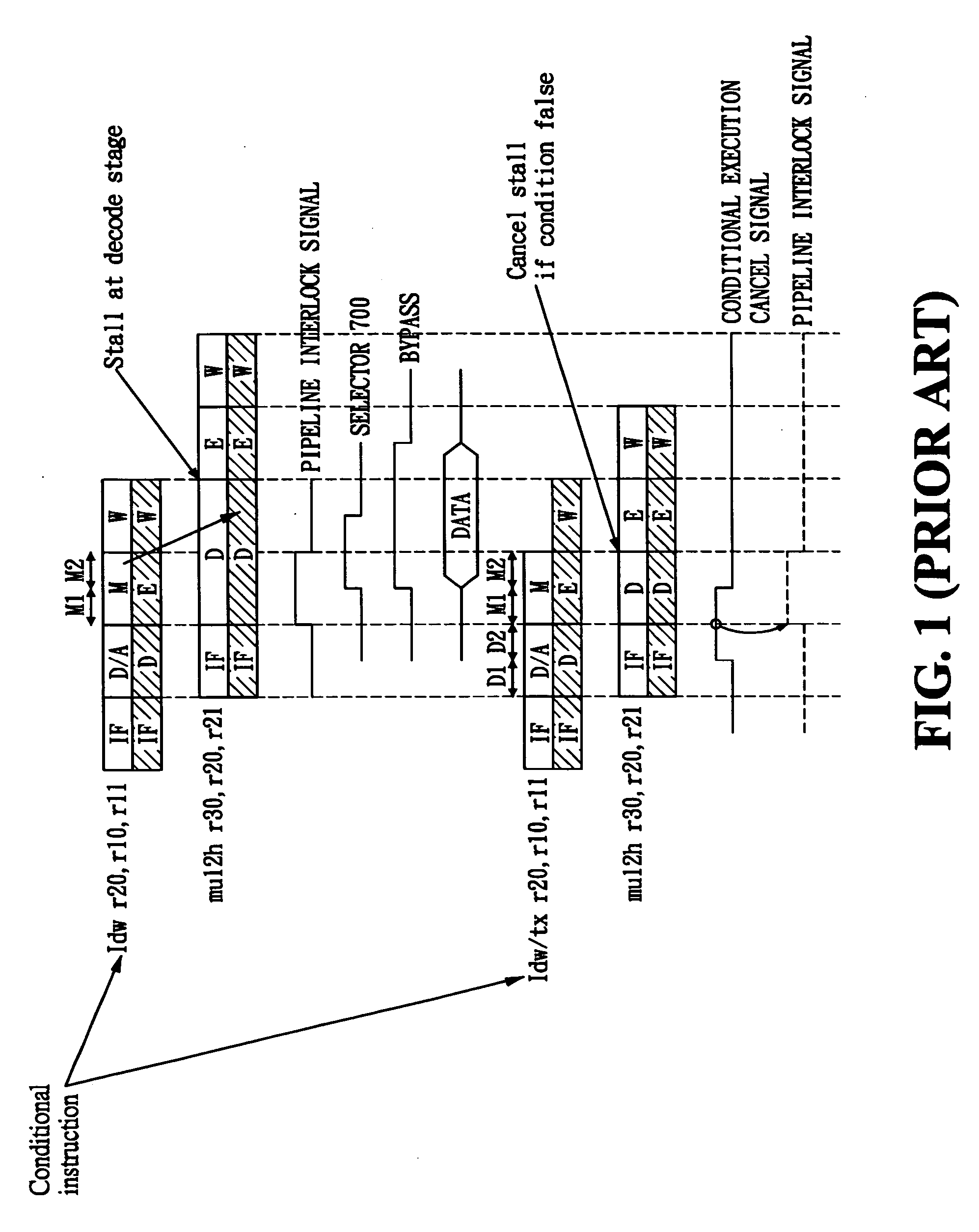

ActiveUS20060288195A1Reduce hardware complexitySave energy consumptionDigital computer detailsSpecific program execution arrangementsConditional executionDecodes

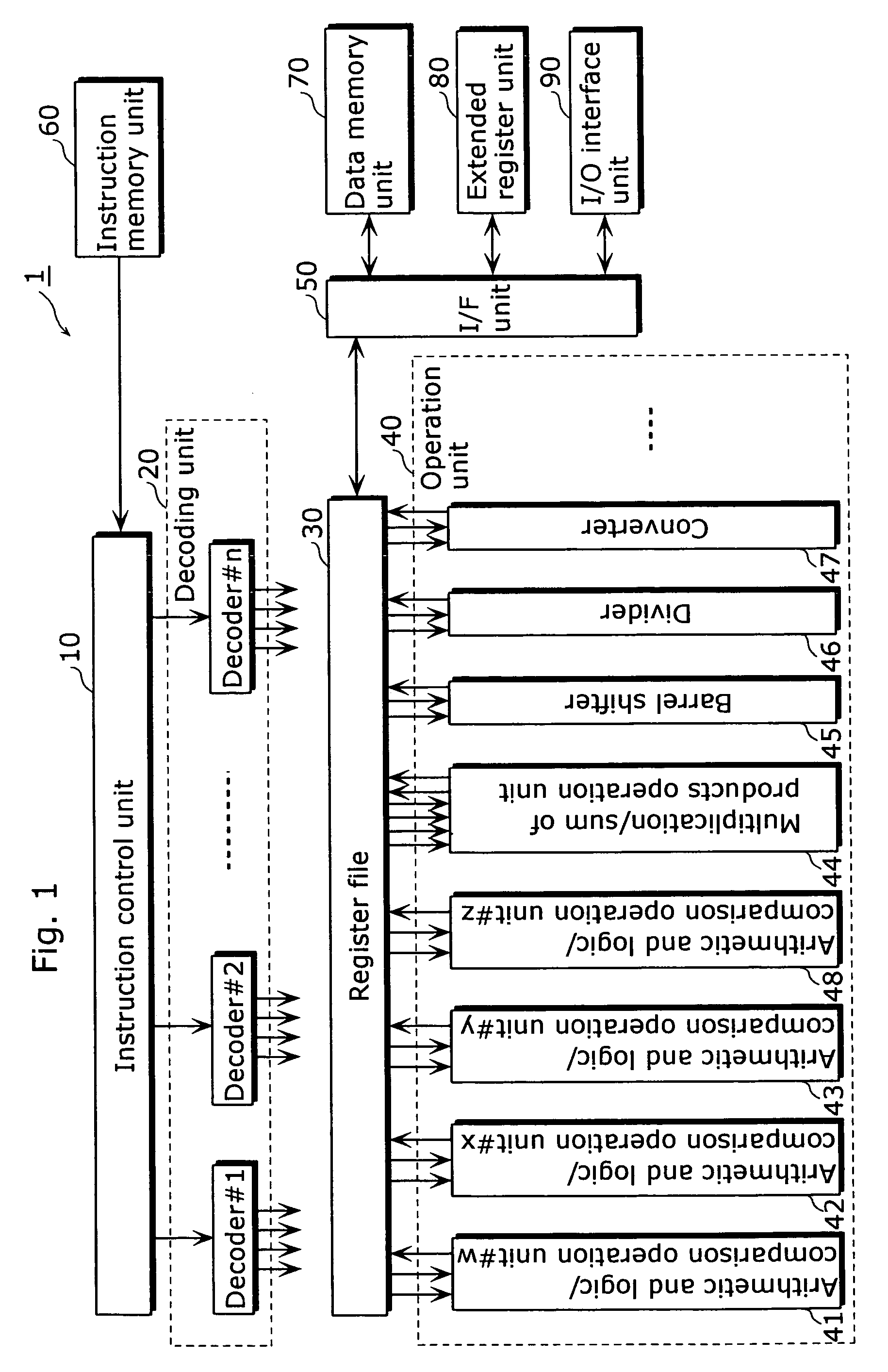

An apparatus for switchable conditional execution in a VLIW processor is provided, comprising one or more decoders, one or more ALU with control units, and a register file. The decoders loads and decodes said instructions from a fetch unit for decoding and sending the decoded instructions to the ALU with control units for execution. The register file stores and forwards the results on result buses to the decoders. The execution of a VLIW instruction includes a fetch stage, a decode stage, plural execution stages and a write-back stage. The invention has the features of approximate ASIC timing by conditional write-back with the compiler support for the conditional write-back, condition resolved just before write-back., software selective conditional issue and conditional write-back modes, and without hardware interlock / dependence checking for the VLIW processor.

Owner:IND TECH RES INST

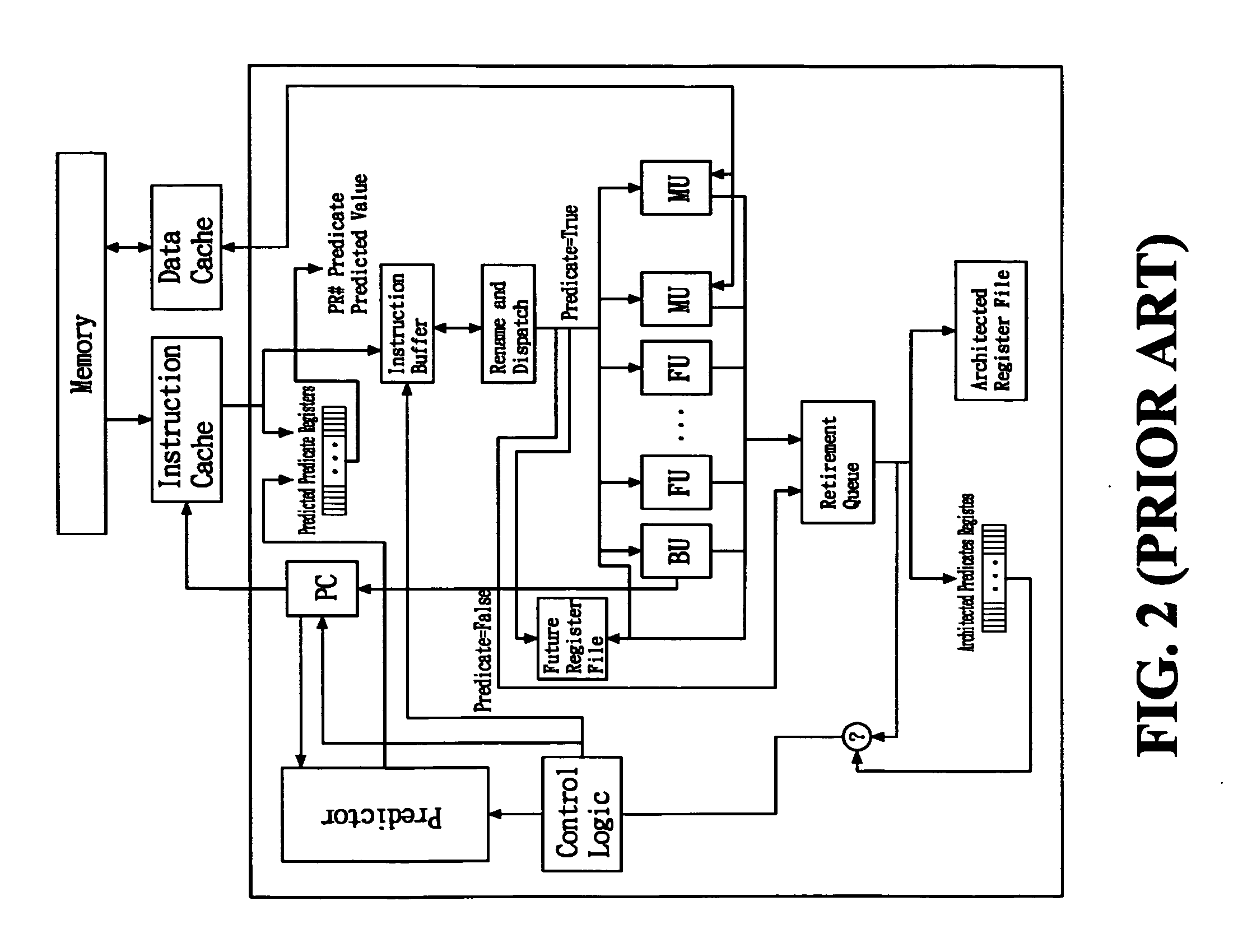

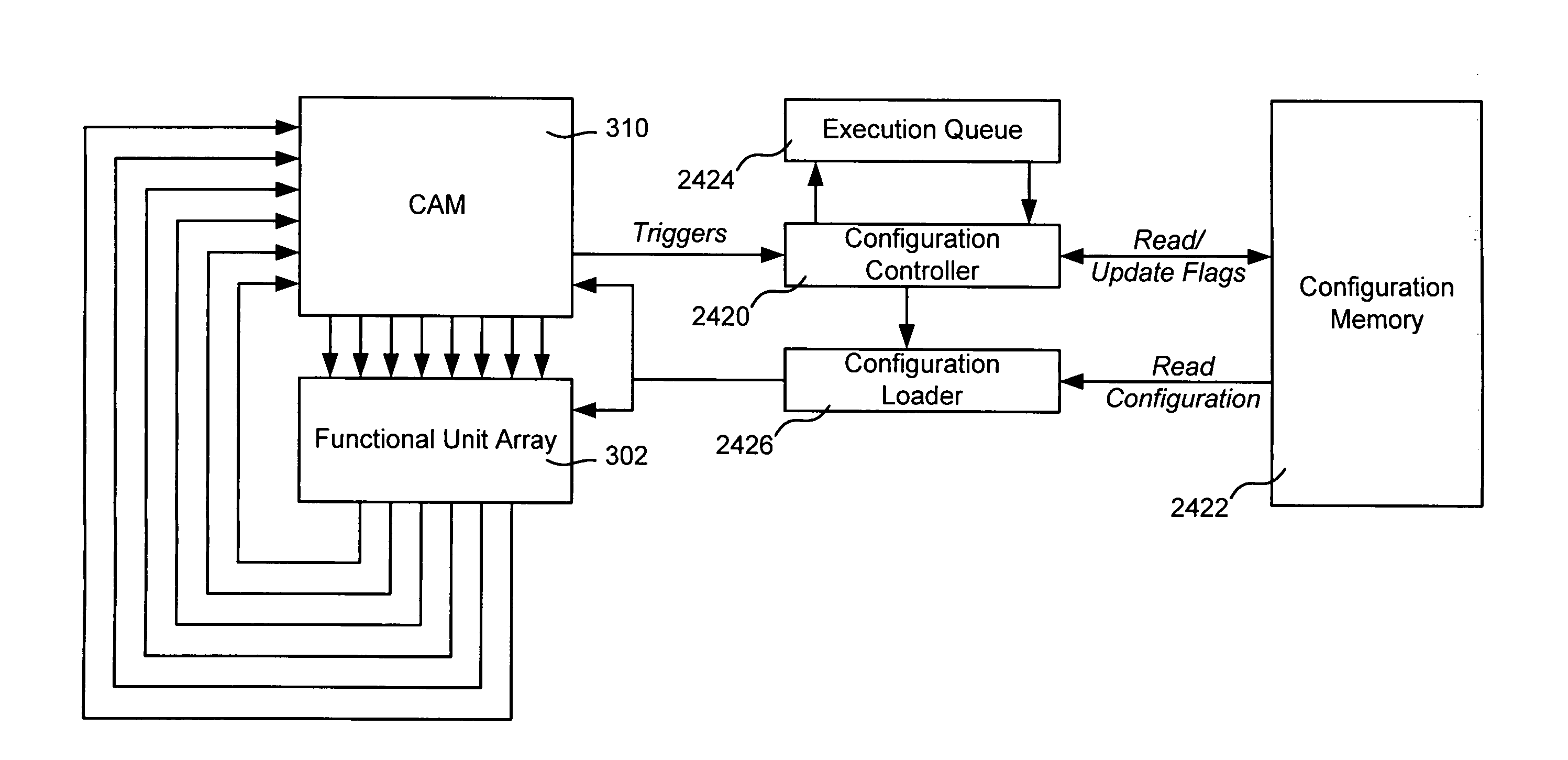

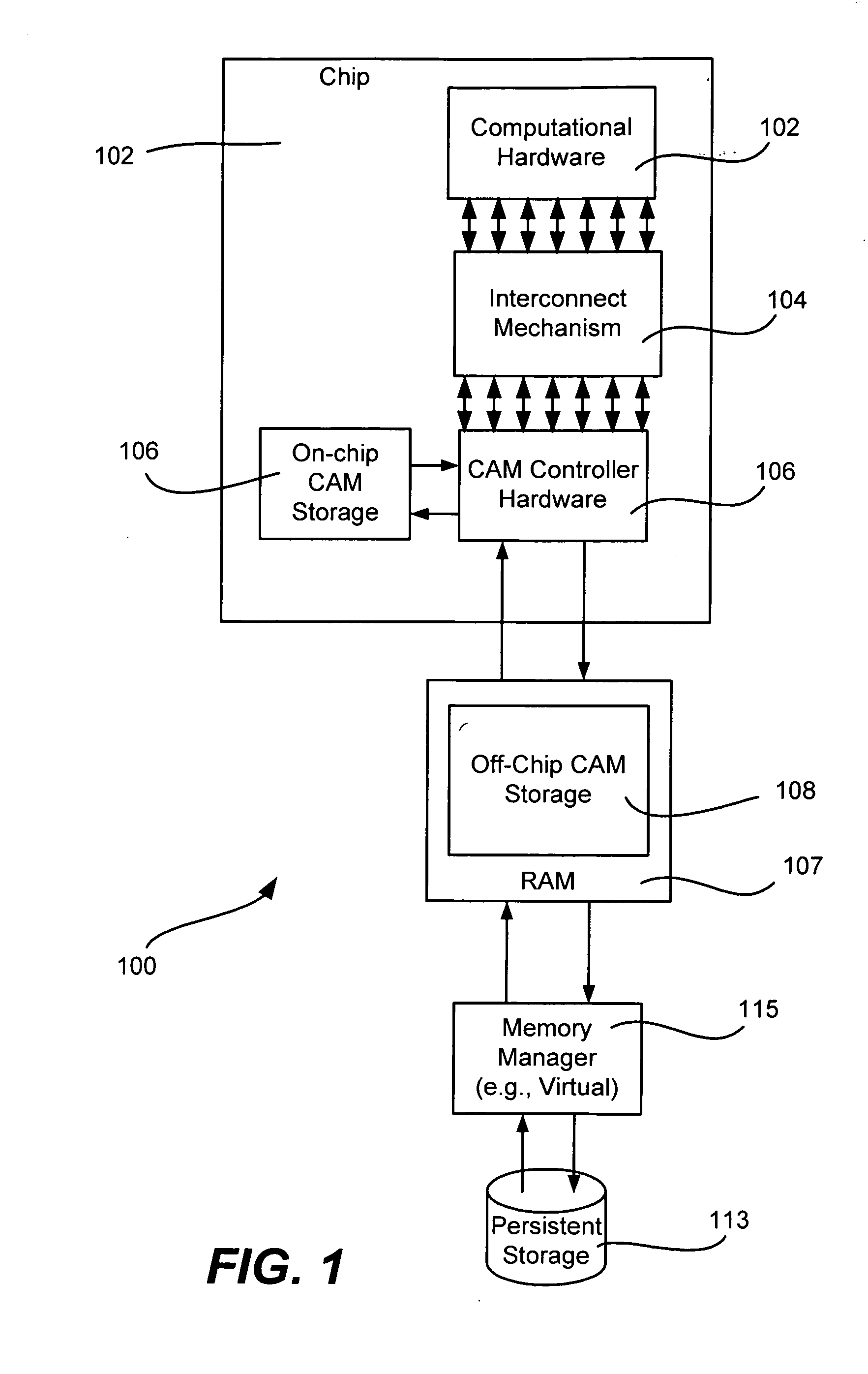

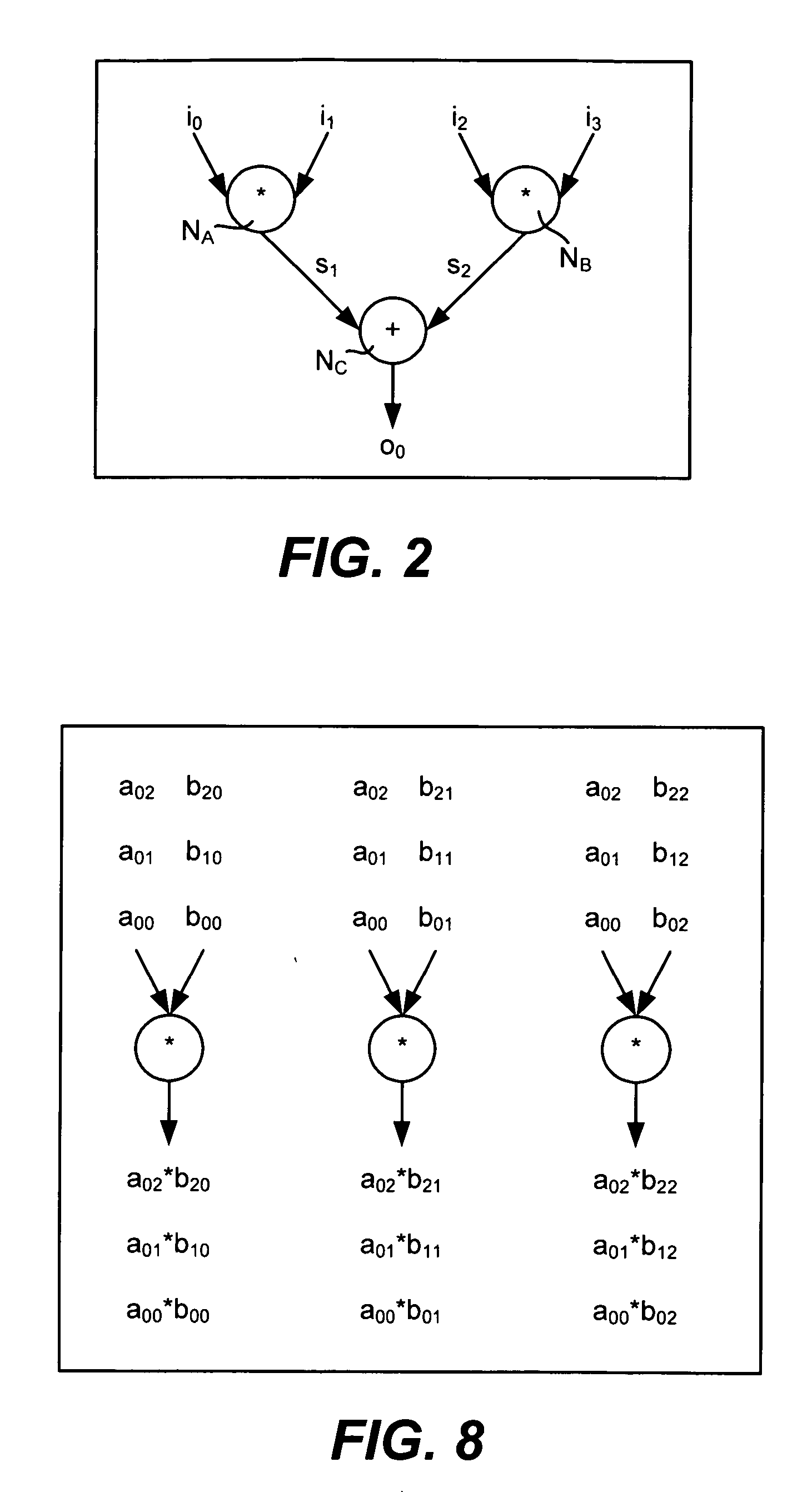

Conditional execution via content addressable memory and parallel computing execution model

ActiveUS20060277392A1Improve performanceOptimize calculation speedProgram control using stored programsDigital data processing detailsConcurrent computationWhile loop

The use of a configuration-based execution model in conjunction with a content addressable memory (CAM) architecture provides a mechanism that enables performance of a number of computing concepts, including conditional execution, (e.g., If-Then statements and while loops), function calls and recursion. If-then and while loops are implemented by using a CAM feature that emits only complete operand sets from the CAM for processing; different seed operands are generated for different conditional evaluation results, and that seed operand is matched with computed data to for an if-then branch or upon exiting a while loop. As a result, downstream operators retrieve only completed operands. Function calls and recursion are handled by using a return tag as an operand along with function parameter data into the input tag space of a function. A recursive function is split into two halves, a pre-recursive half and a post-recursive half that executes after pre-recursive calls.

Owner:MICROSOFT TECH LICENSING LLC

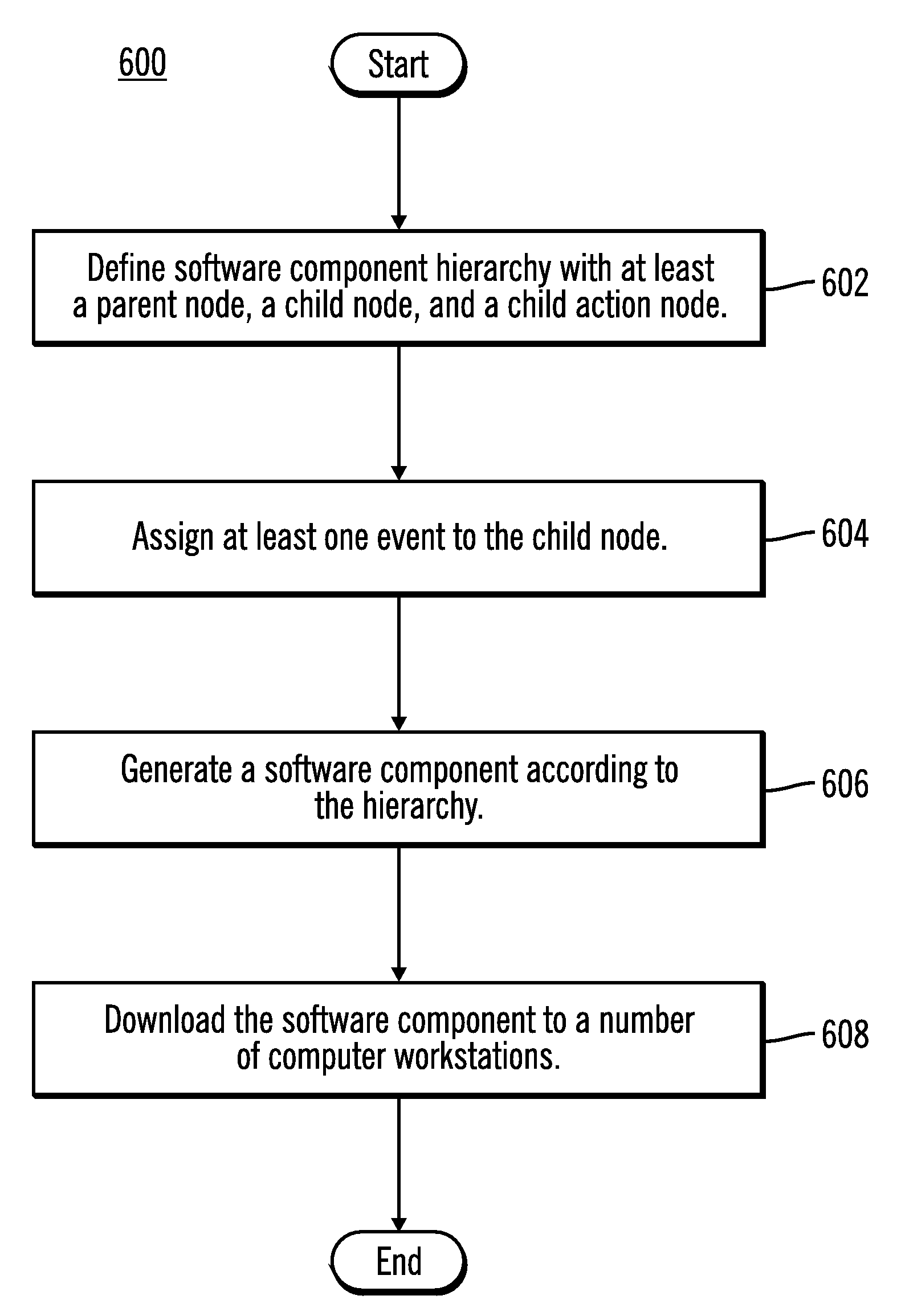

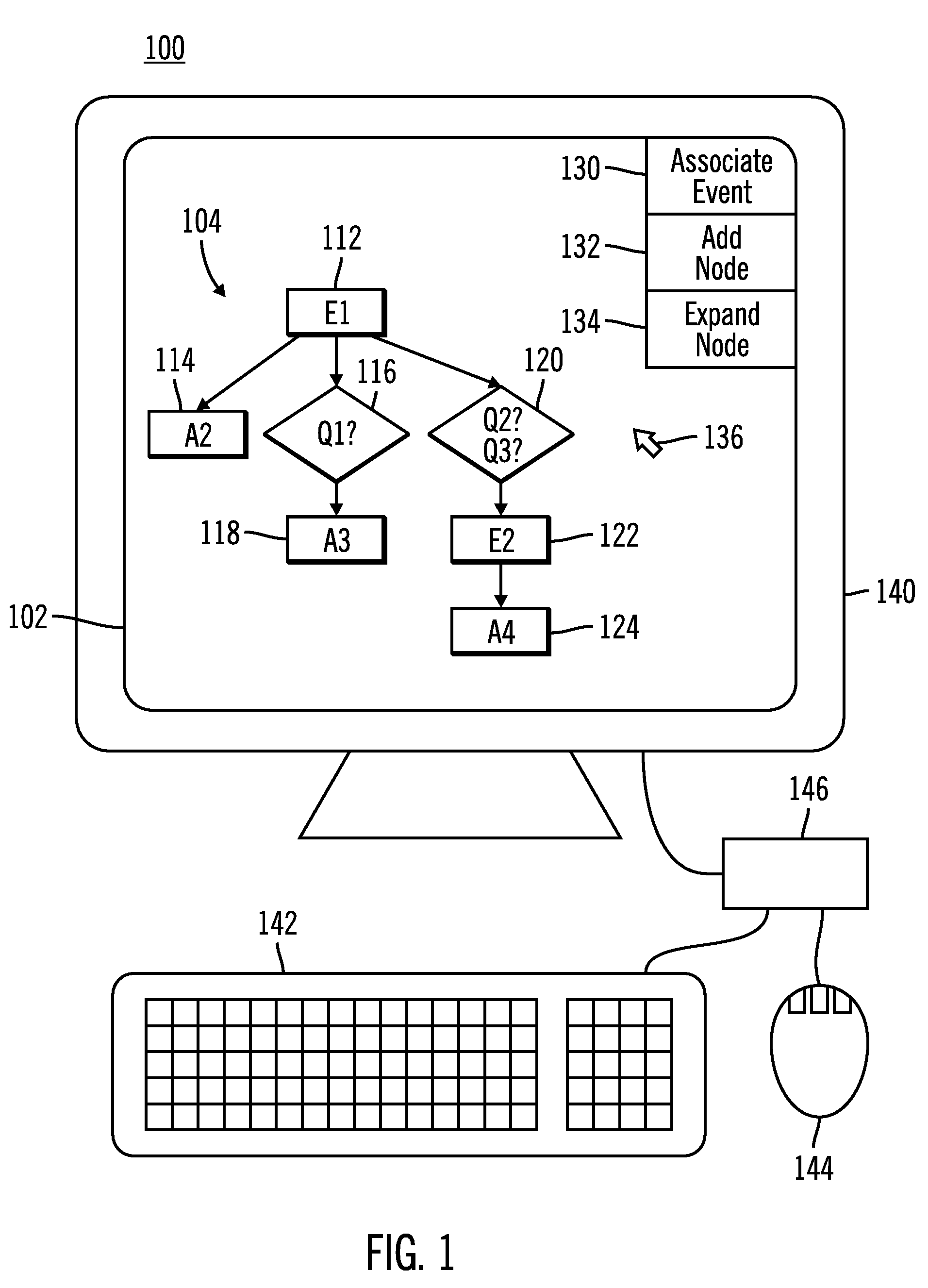

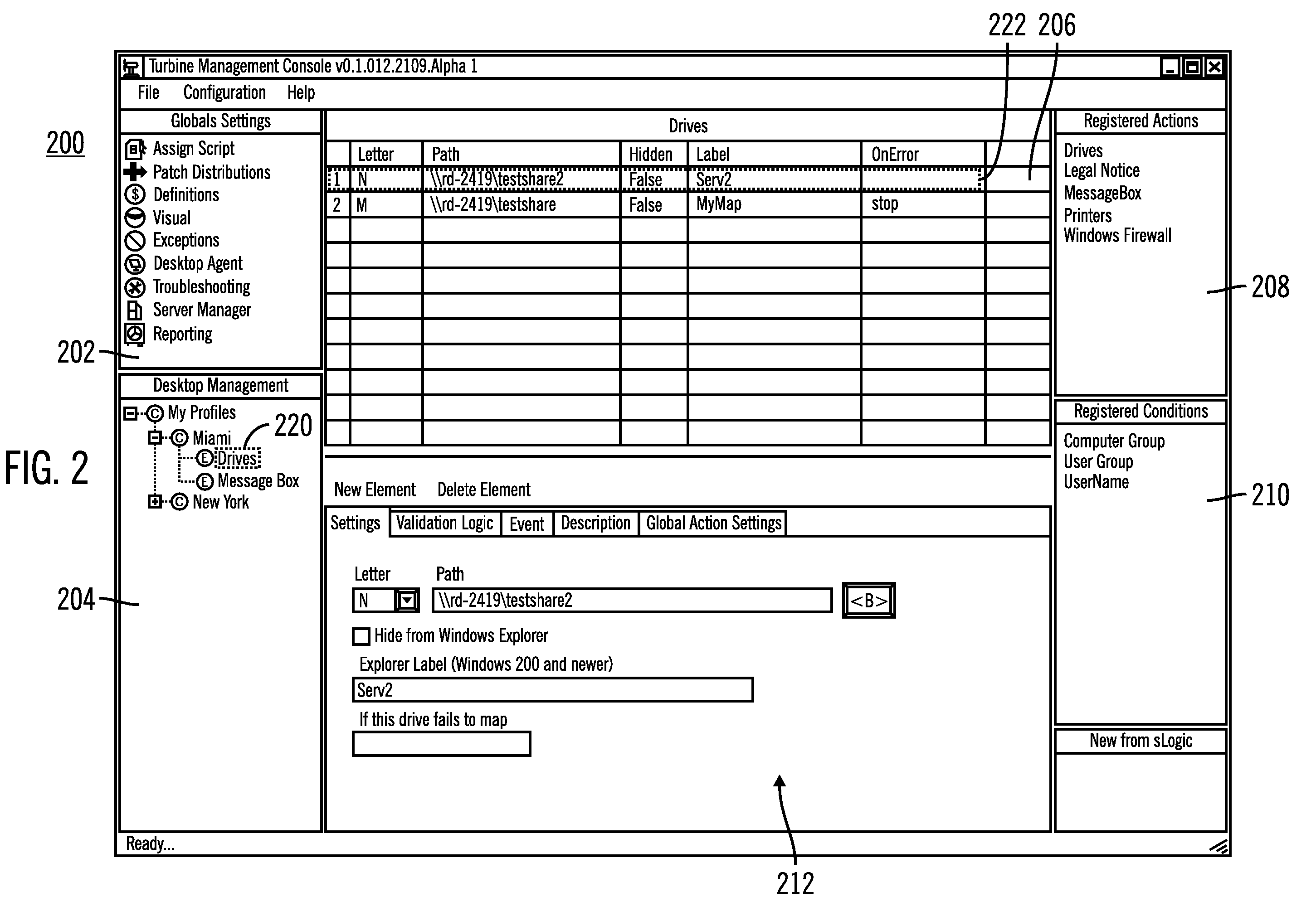

Hierarchical modular software packages and associated development tool

ActiveUS20080016505A1Visual/graphical programmingProgram loading/initiatingSoftware development processGraphics

A hierarchical modular software development tool provides a graphical user interface to allow development of hierarchical module software components. The software development tool allows graphical creation of a software component processing hierarchy and then generates a software component using this specified processing hierarchy. The packages developed using this tool are able to include event modules that allow sub-branches of the software component processing hierarchy to be executed without requiring processing of modules of the software component hierarchy that precede the event nodes. Further nodes that are able to be included in the processing hierarchy include action nodes, that contain operational software, and conditional nodes that allow condition testing and conditional execution of processing branches.

Owner:QUEST SOFTWARE INC

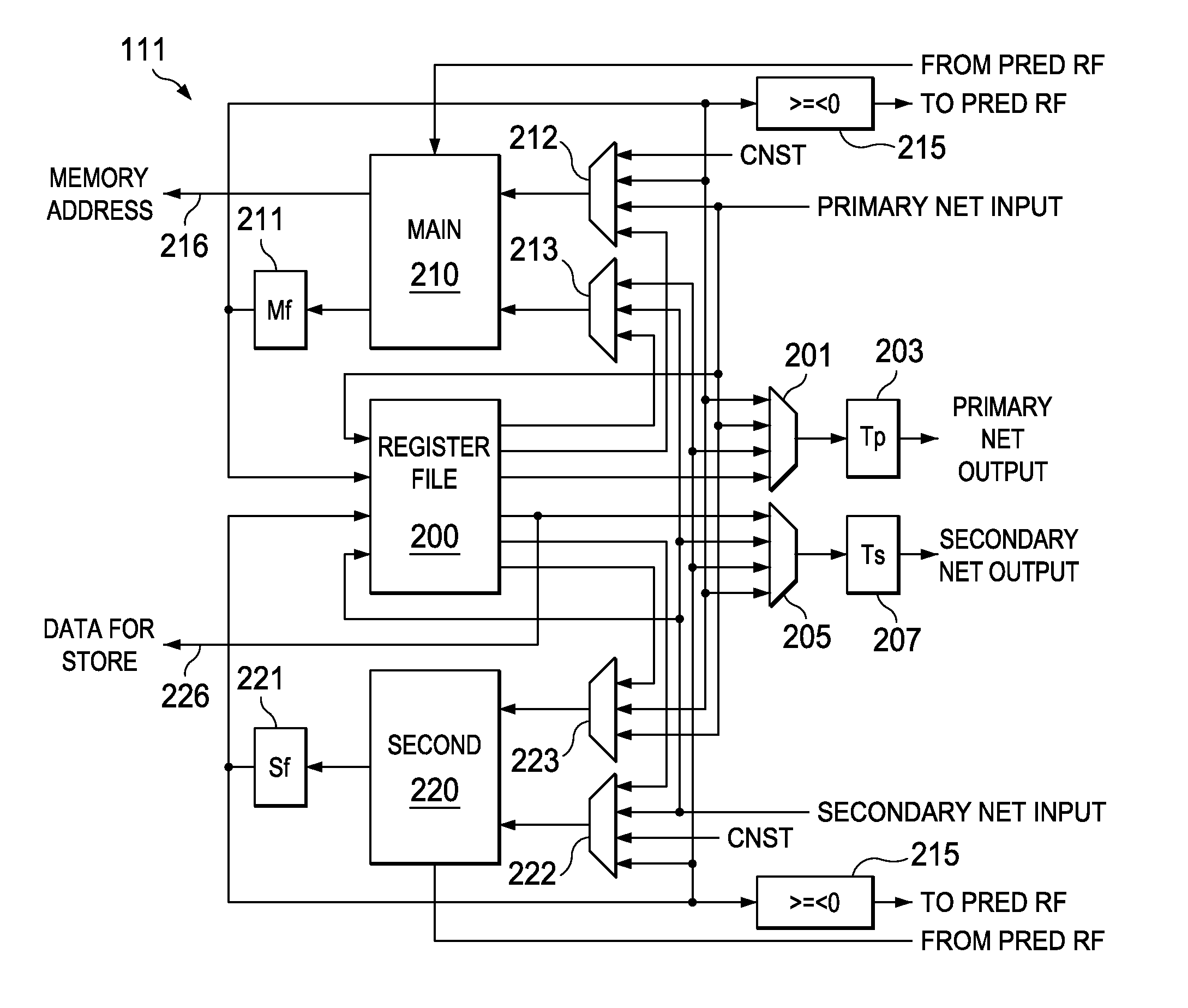

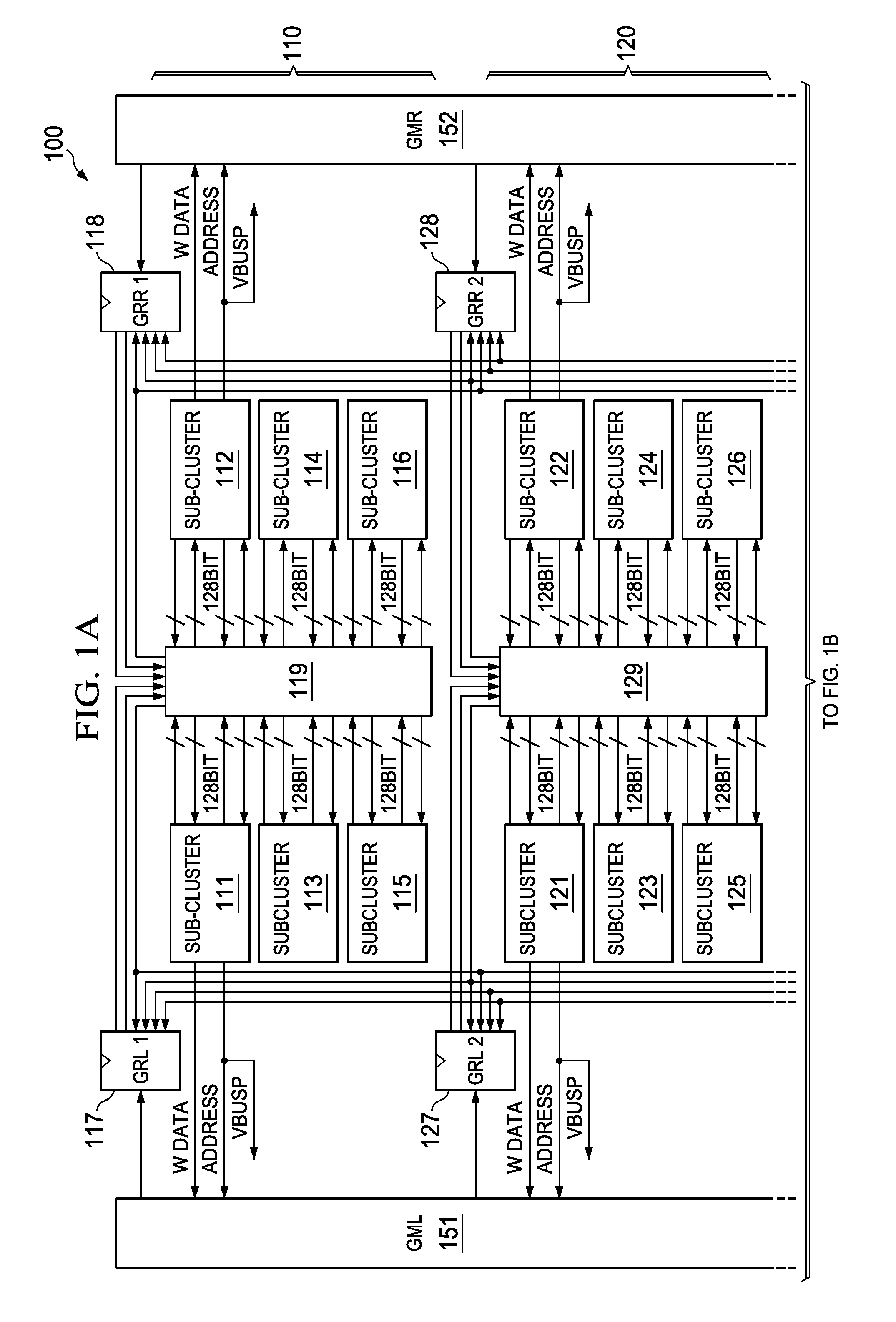

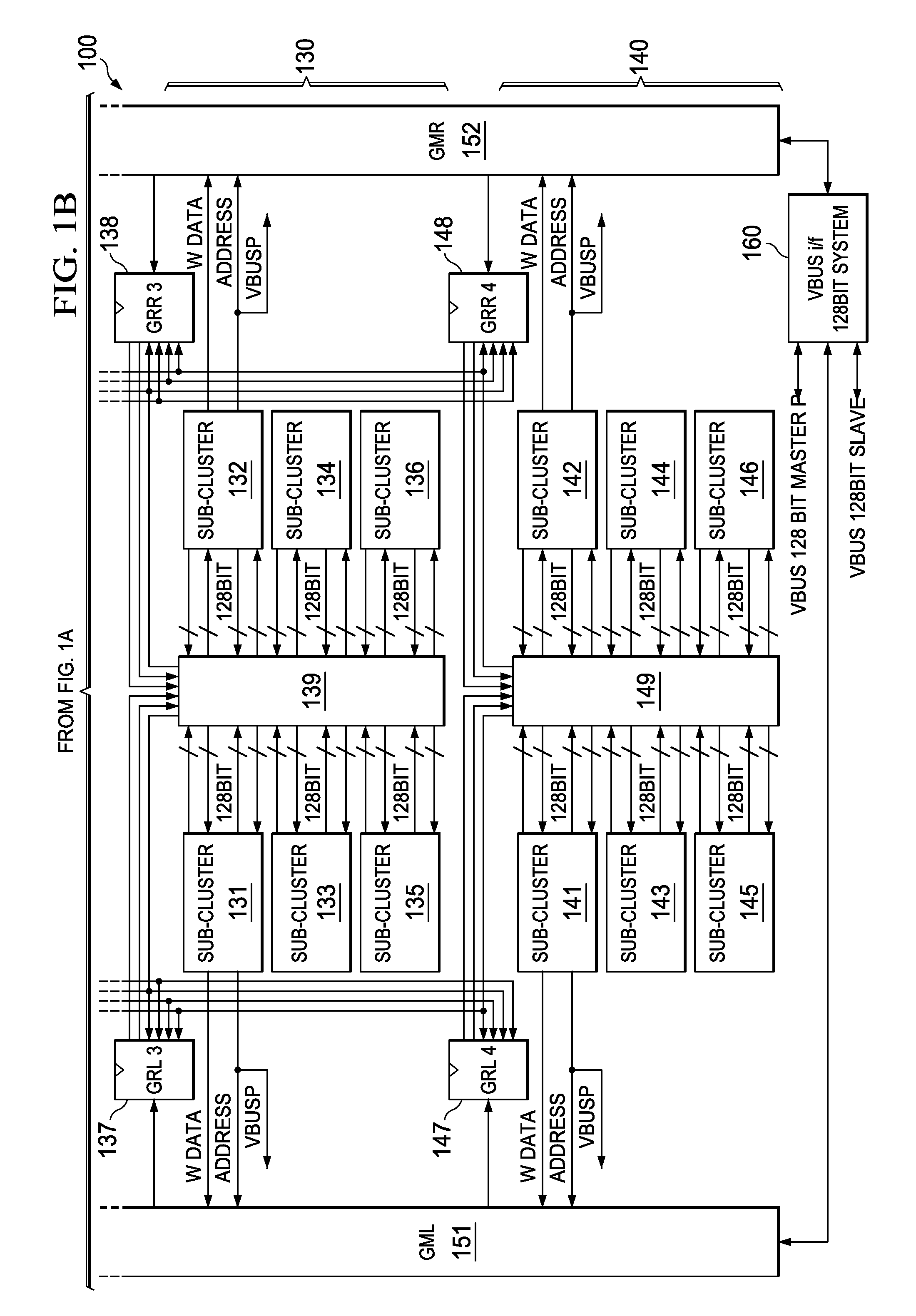

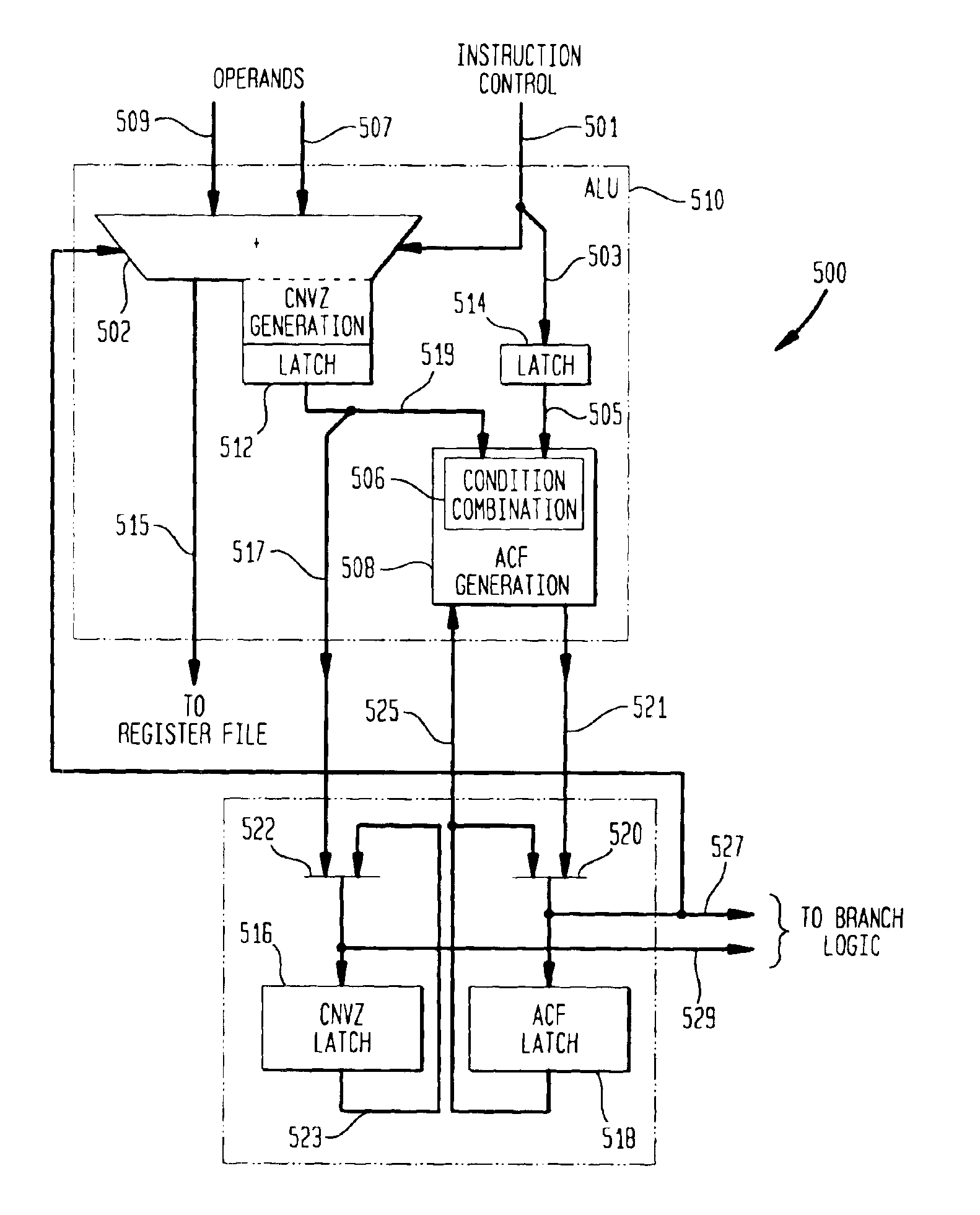

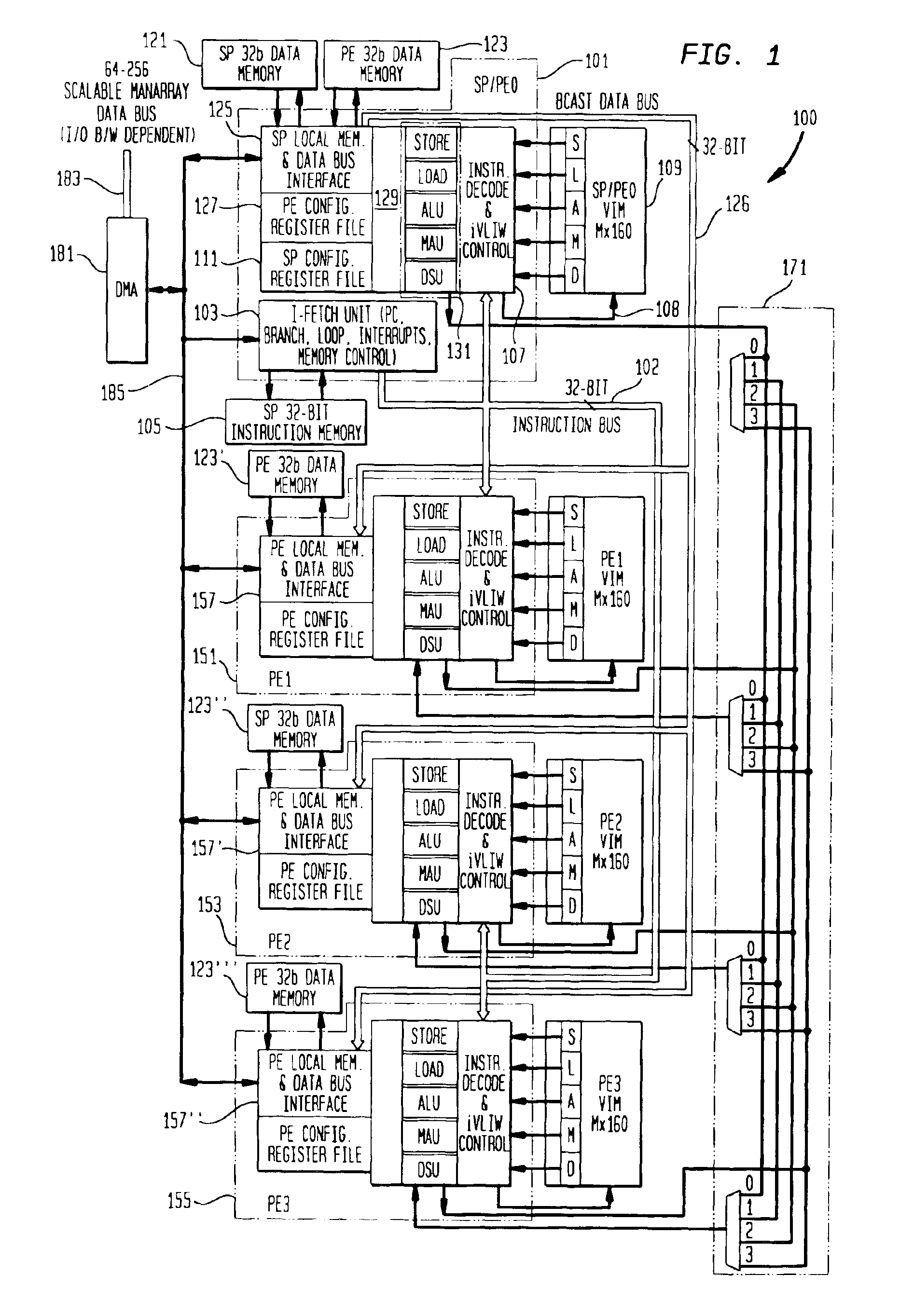

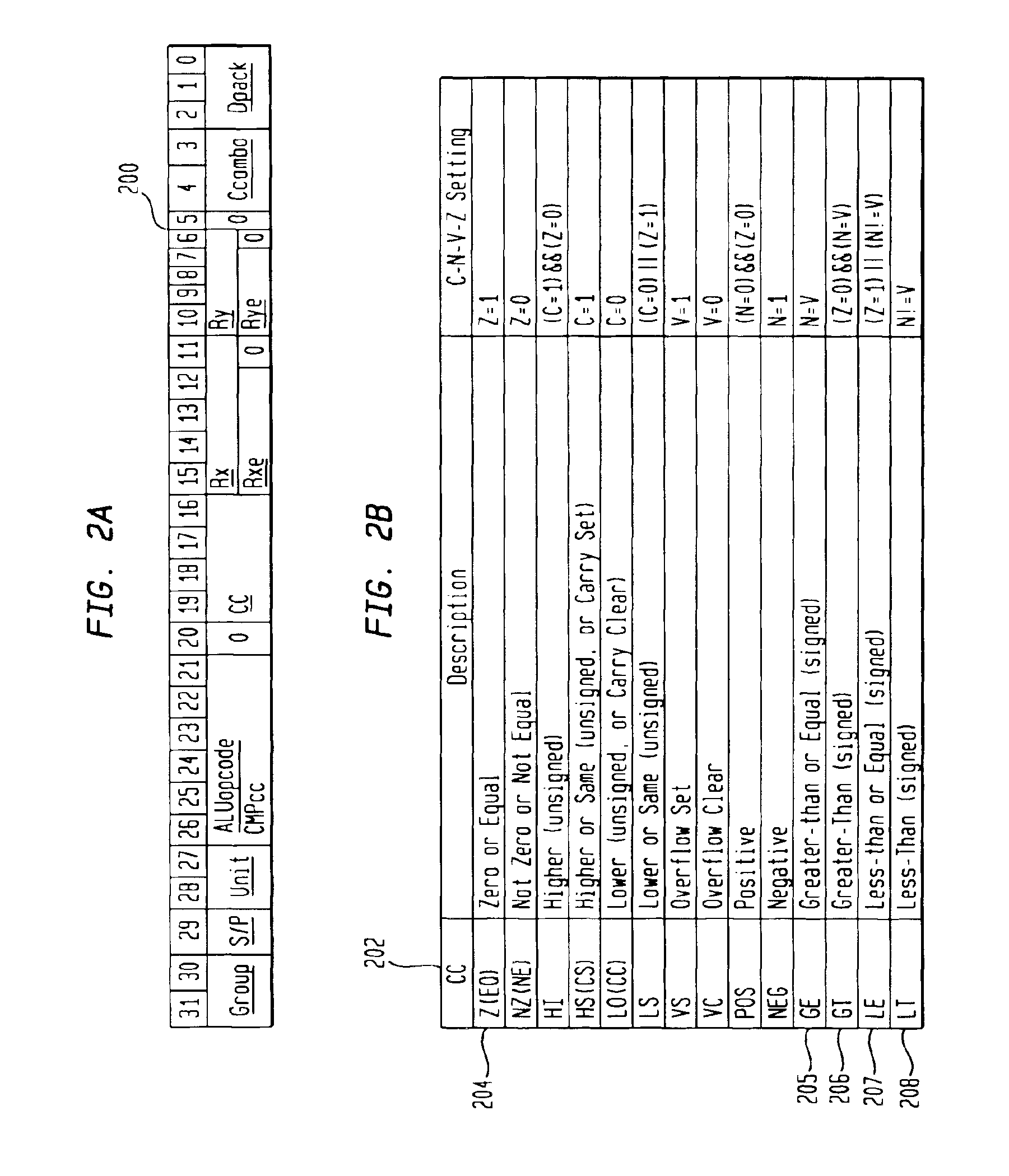

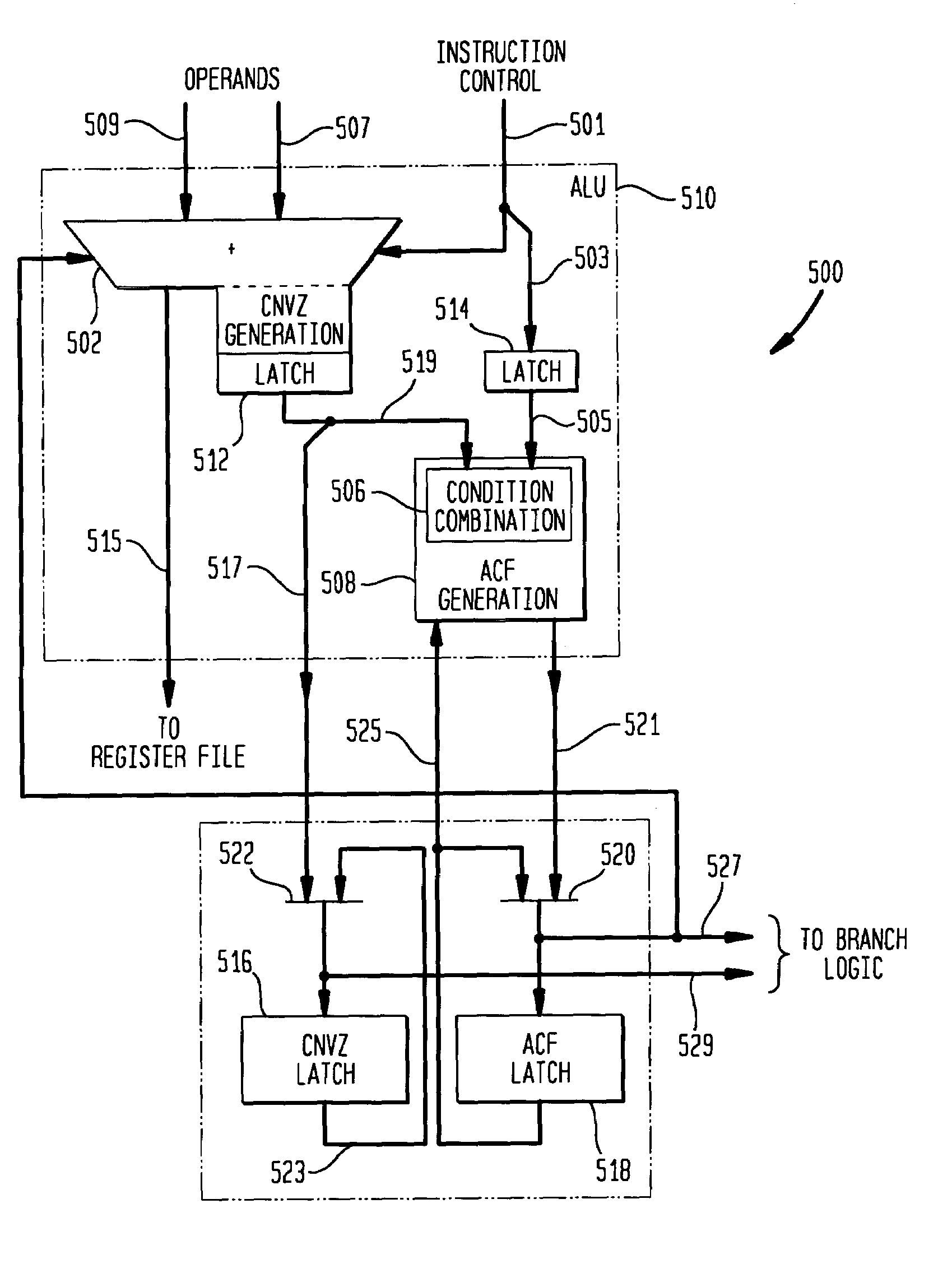

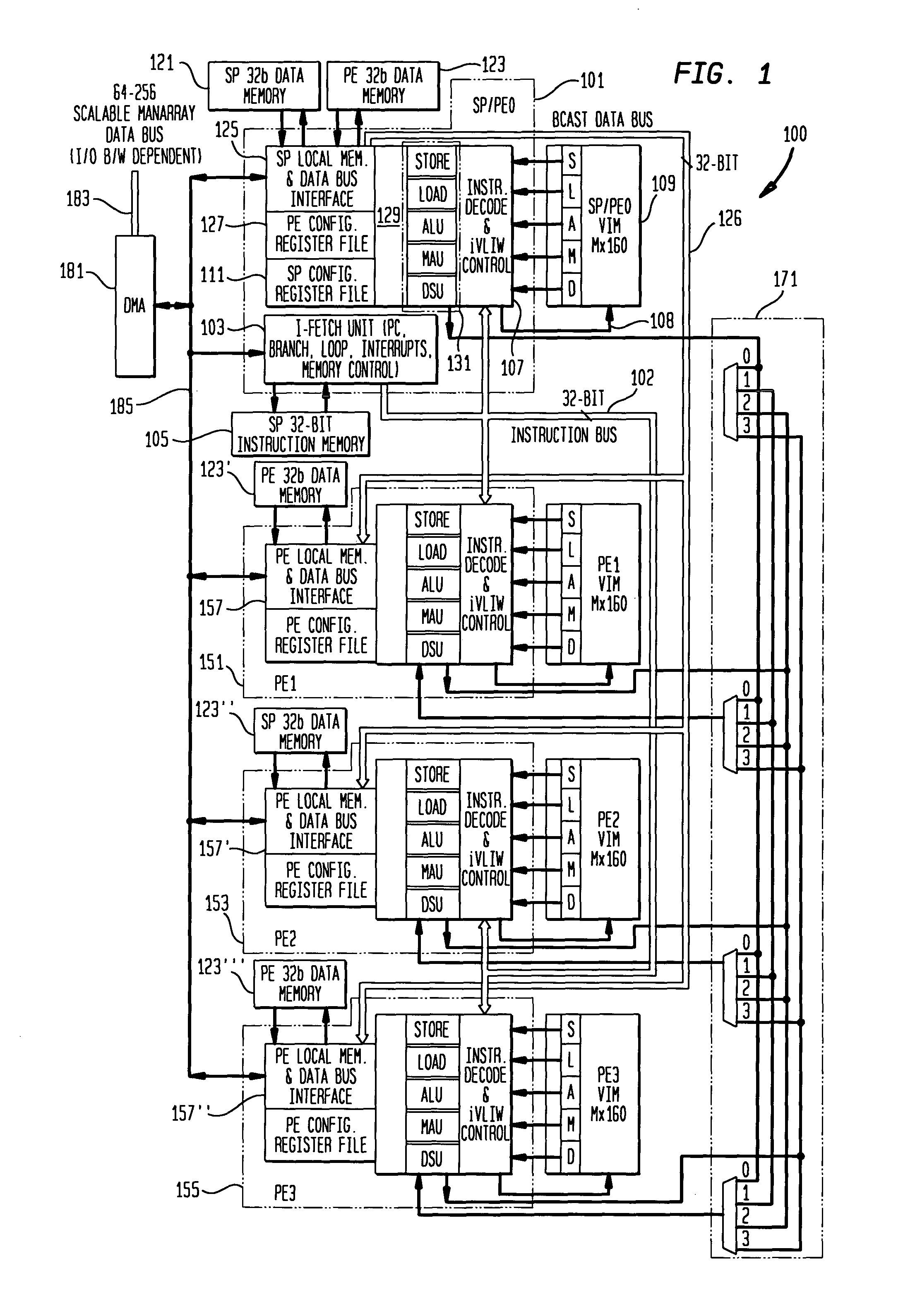

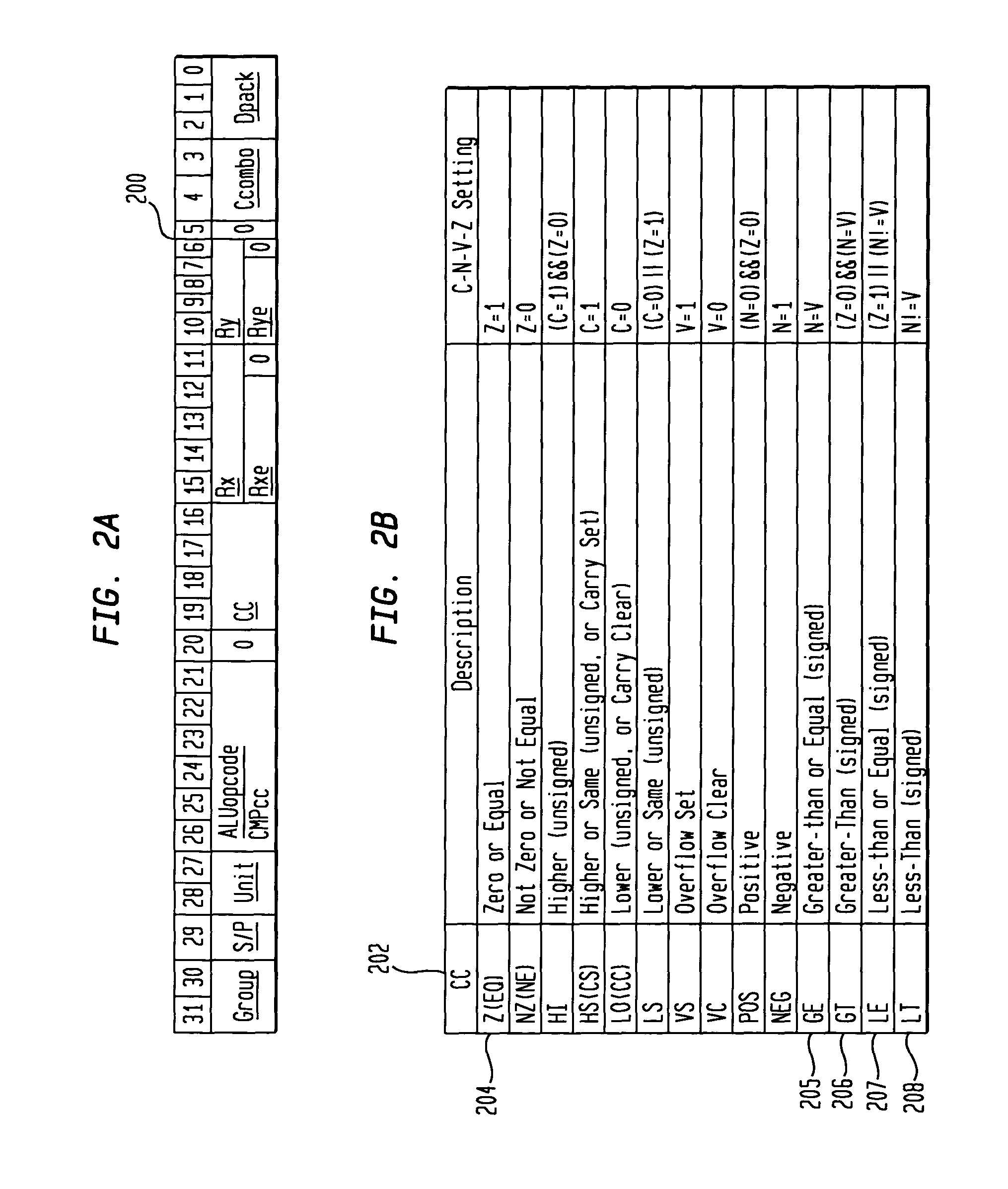

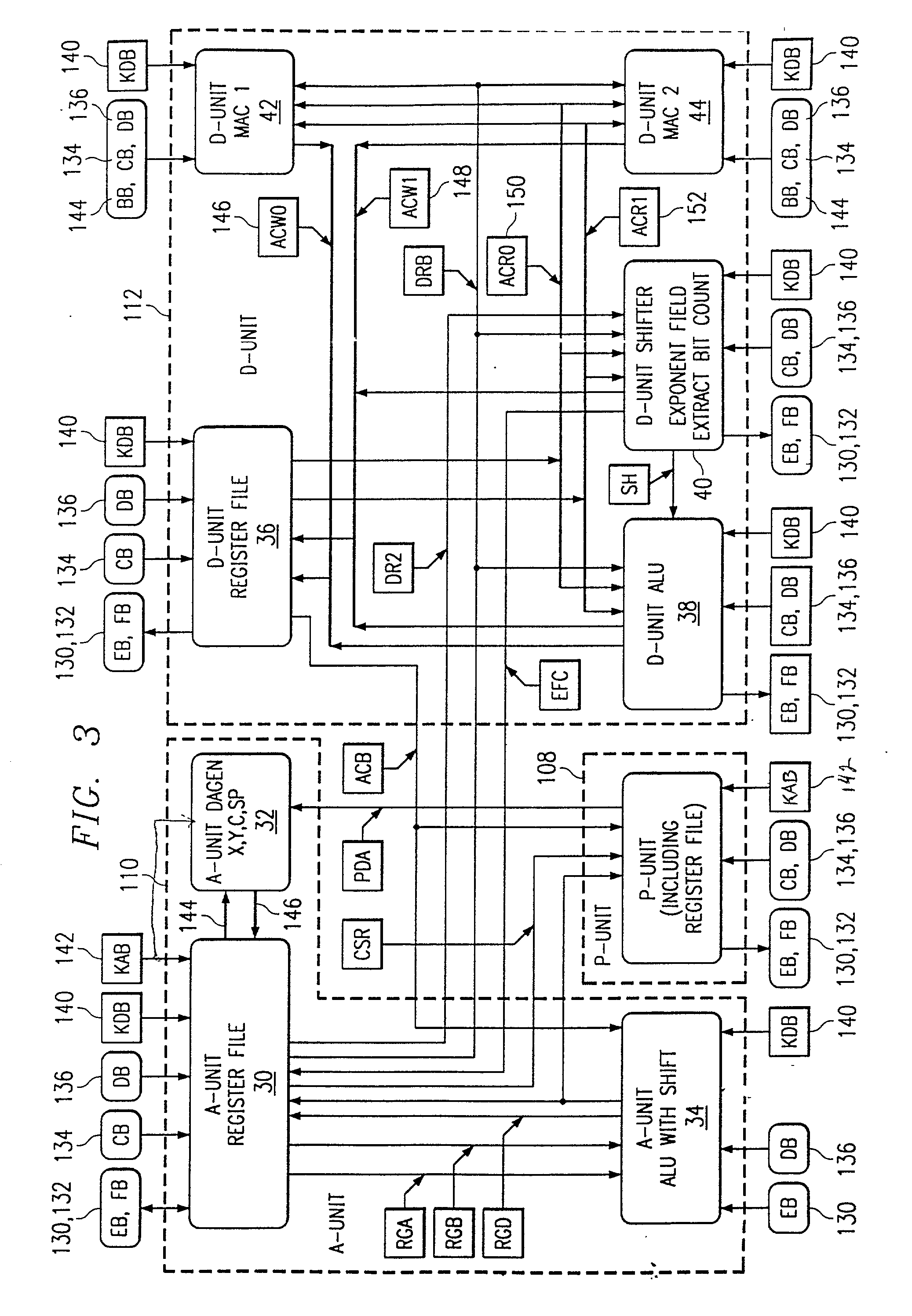

Methods and apparatus to support conditional execution in a VLIW-based array processor with subword execution

InactiveUS6954842B2Not affectFacilitate communicationSingle instruction multiple data multiprocessorsConditional code generationCommunication interfaceGeneral purpose

General purpose flags (ACFs) are defined and encoded utilizing a hierarchical one-, two- or three-bit encoding. Each added bit provides a superset of the previous functionality. With condition combination, a sequential series of conditional branches based on complex conditions may be avoided and complex conditions can then be used for conditional execution. ACF generation and use can be specified by the programmer. By varying the number of flags affected, conditional operation parallelism can be widely varied, for example, from mono-processing to octal-processing in VLIW execution, and across an array of processing elements (PE)s. Multiple PEs can generate condition information at the same time with the programmer being able to specify a conditional execution in one processor based upon a condition generated in a different processor using the communications interface between the processing elements to transfer the conditions. Each processor in a multiple processor array may independently have different units conditionally operate based upon their ACFs.

Owner:ALTERA CORP

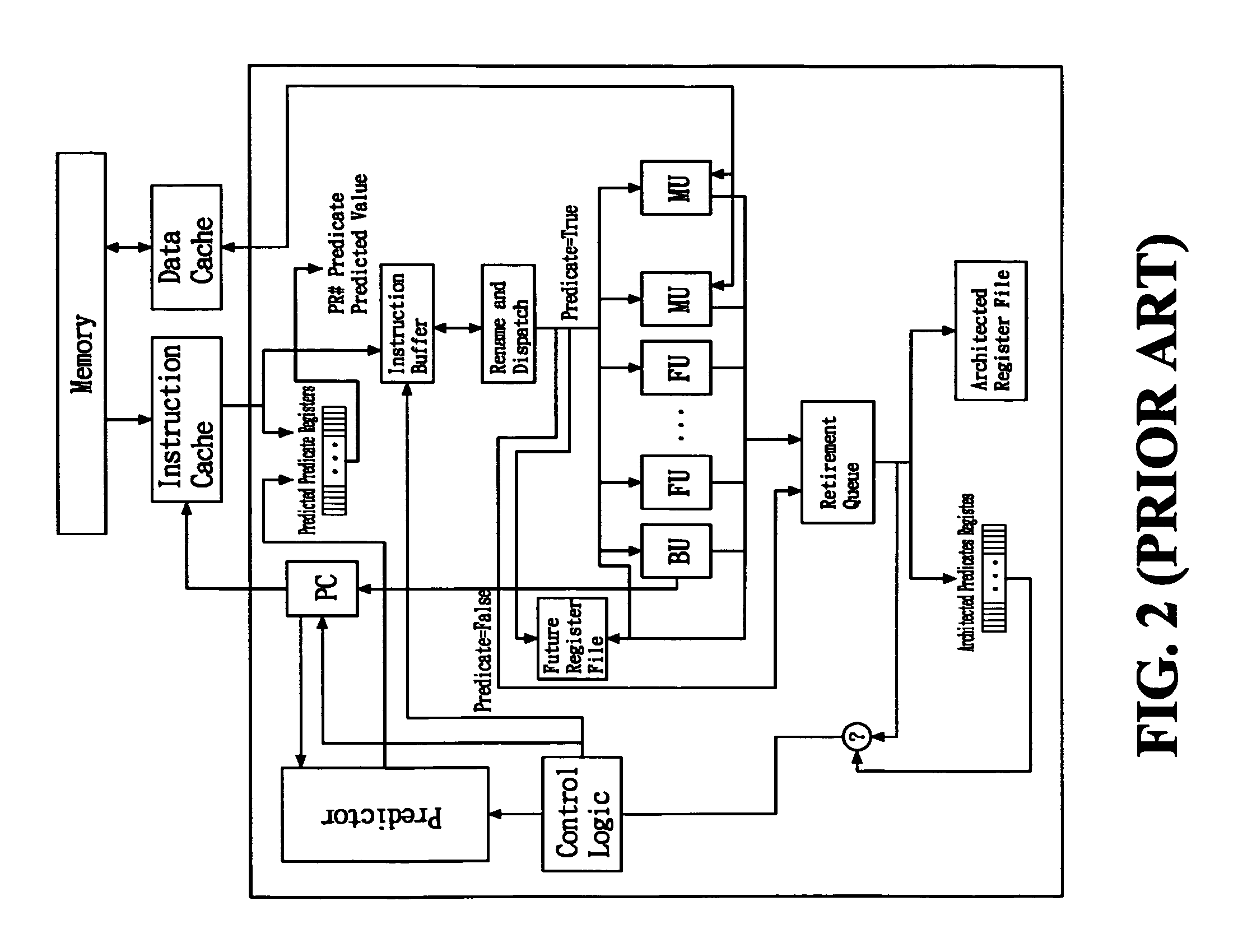

System and method for cooperative execution of multiple branching instructions in a processor

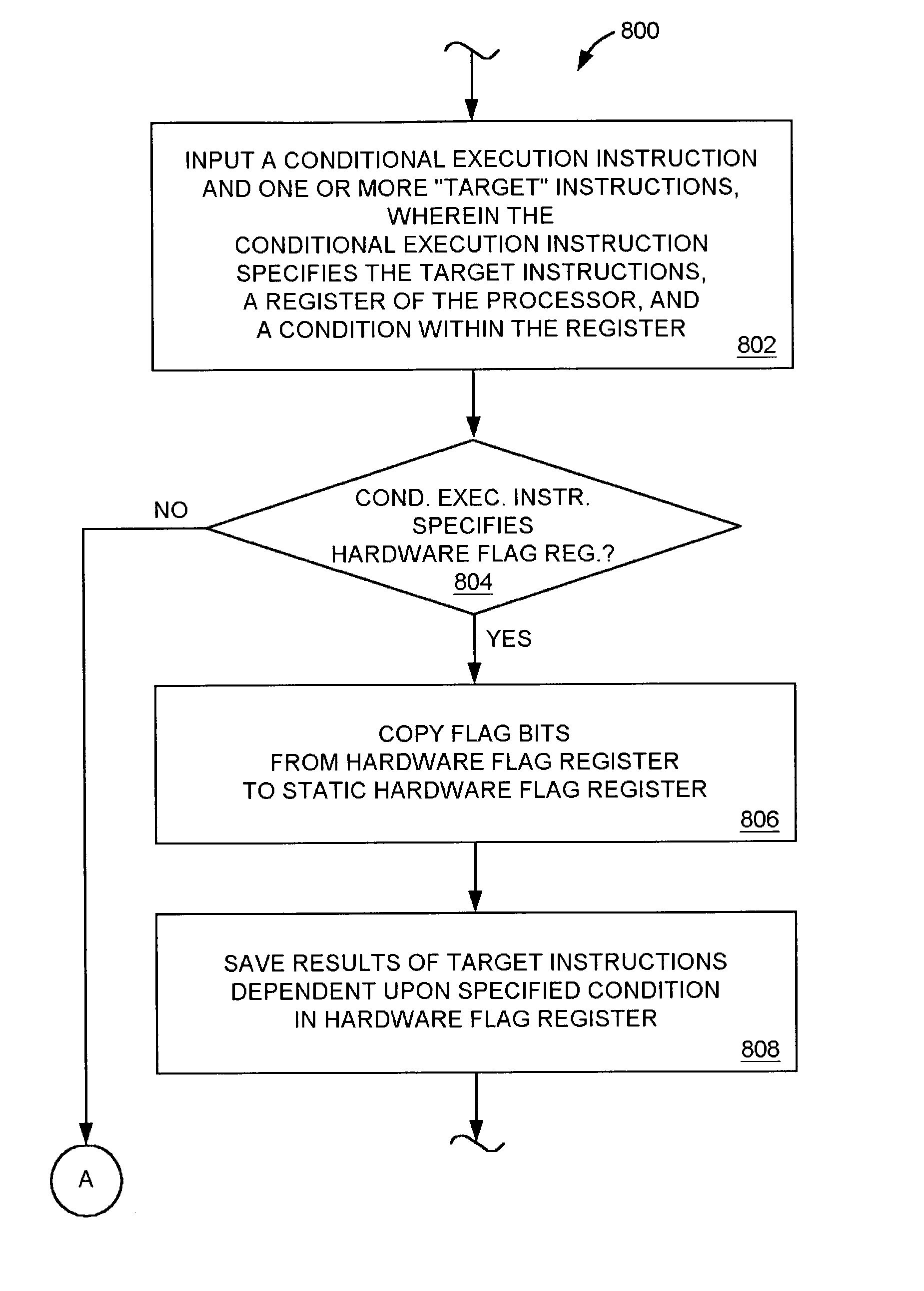

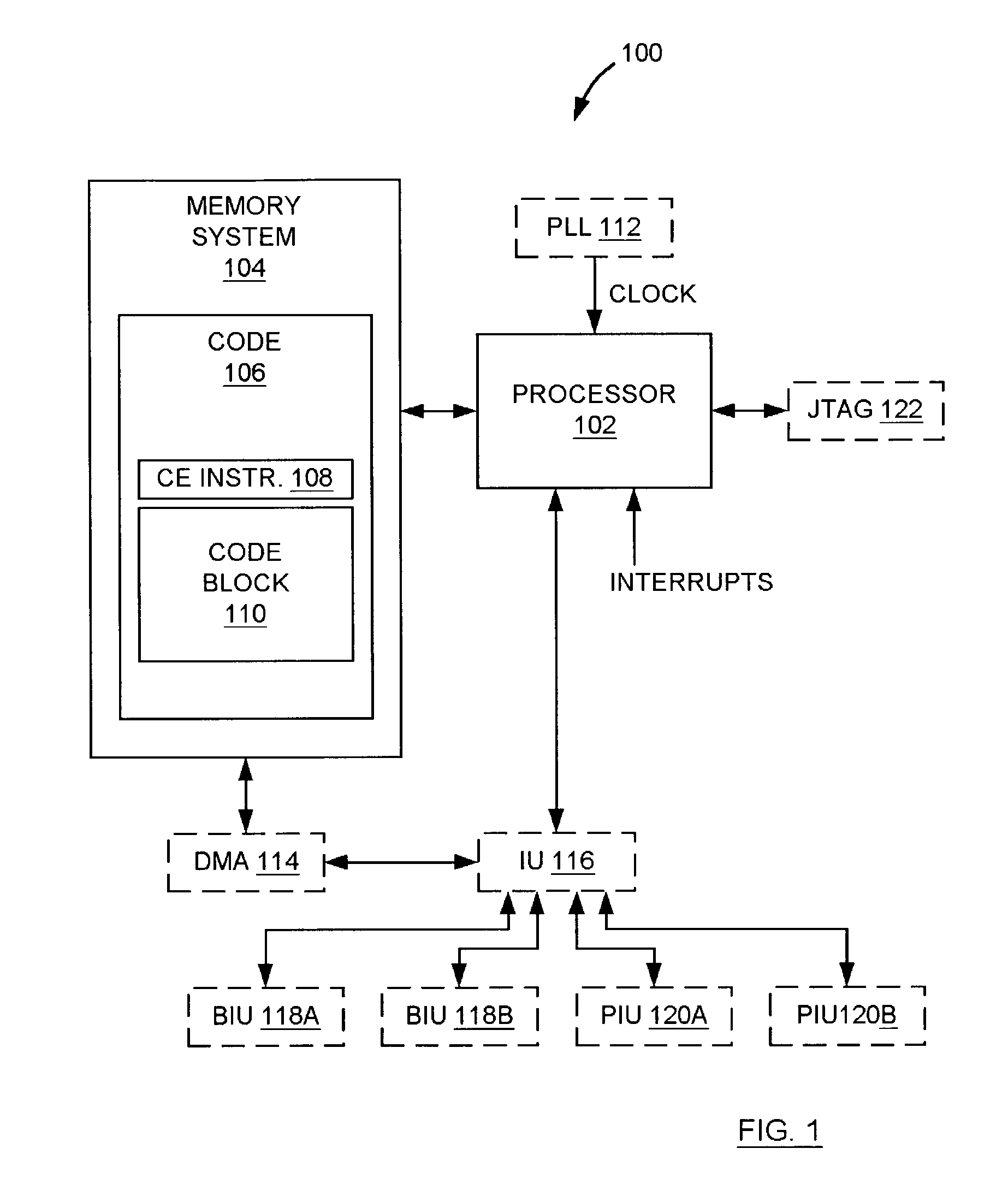

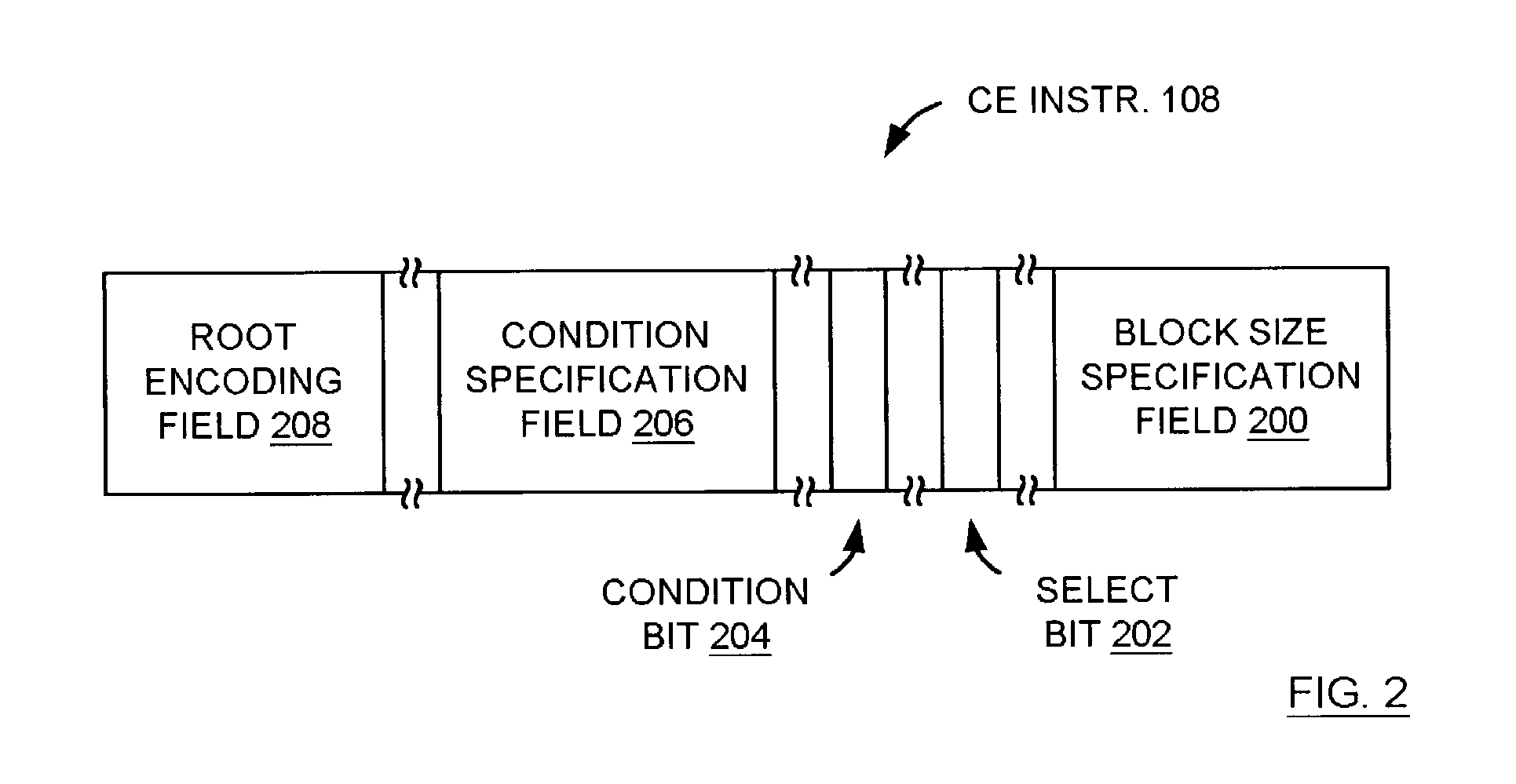

ActiveUS7299343B2Conditional code generationDigital computer detailsProcessor registerConditional execution

A system for conditionally executing an instruction depending on a previously existing condition. The system disclosed is configured to handle conditional execution instructions typically specifying at least one target instruction, a processor register, and a condition within the register. The system saves a result of each of the target instructions dependent upon the existence of the condition in the specified register during execution of the conditional execution instruction. When the conditional execution instruction specifies a first flag register, the system copies the flag bits in the first flag register to a corresponding second flag register, and saves a result of each of the target instructions dependent upon the specified condition in the first flag register during execution of the conditional execution instruction. A subsequent conditional execution instruction may then specify a condition in the second flag register in order to conditionally execute target instructions based on a previously existing condition.

Owner:VERISILICON HLDGCO LTD

Methods and apparatus to support conditional execution in a VLIW-based array processor with subword execution

InactiveUS7010668B2Minimization requirementsFacilitate communicationSingle instruction multiple data multiprocessorsConditional code generationCommunication interfaceGeneral purpose

General purpose flags (ACFs) are defined and encoded utilizing a hierarchical one-, two- or three-bit encoding. Each added bit provides a superset of the previous functionality. With condition combination, a sequential series of conditional branches based on complex conditions may be avoided and complex conditions can then be used for conditional execution. ACF generation and use can be specified by the programmer. By varying the number of flags affected, conditional operation parallelism can be widely varied, for example, from mono-processing to octal-processing in VLIW execution, and across an array of processing elements (PE)s. Multiple PEs can generate condition information at the same time with the programmer being able to specify a conditional execution in one processor based upon a condition generated in a different processor using the communications interface between the processing elements to transfer the conditions. Each processor in a multiple processor array may independently have different units conditionally operate based upon their ACFs.

Owner:ALTERA CORP

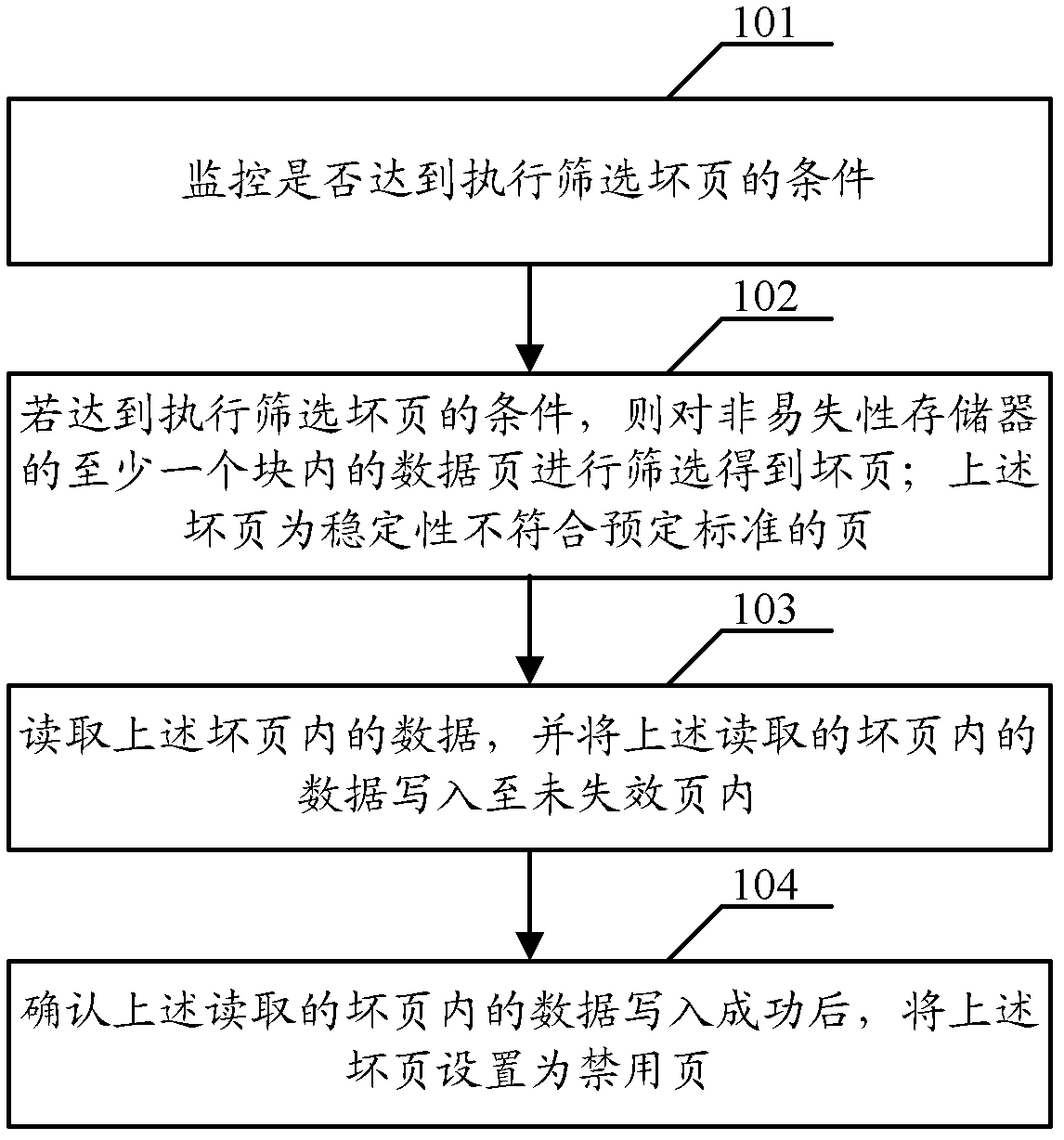

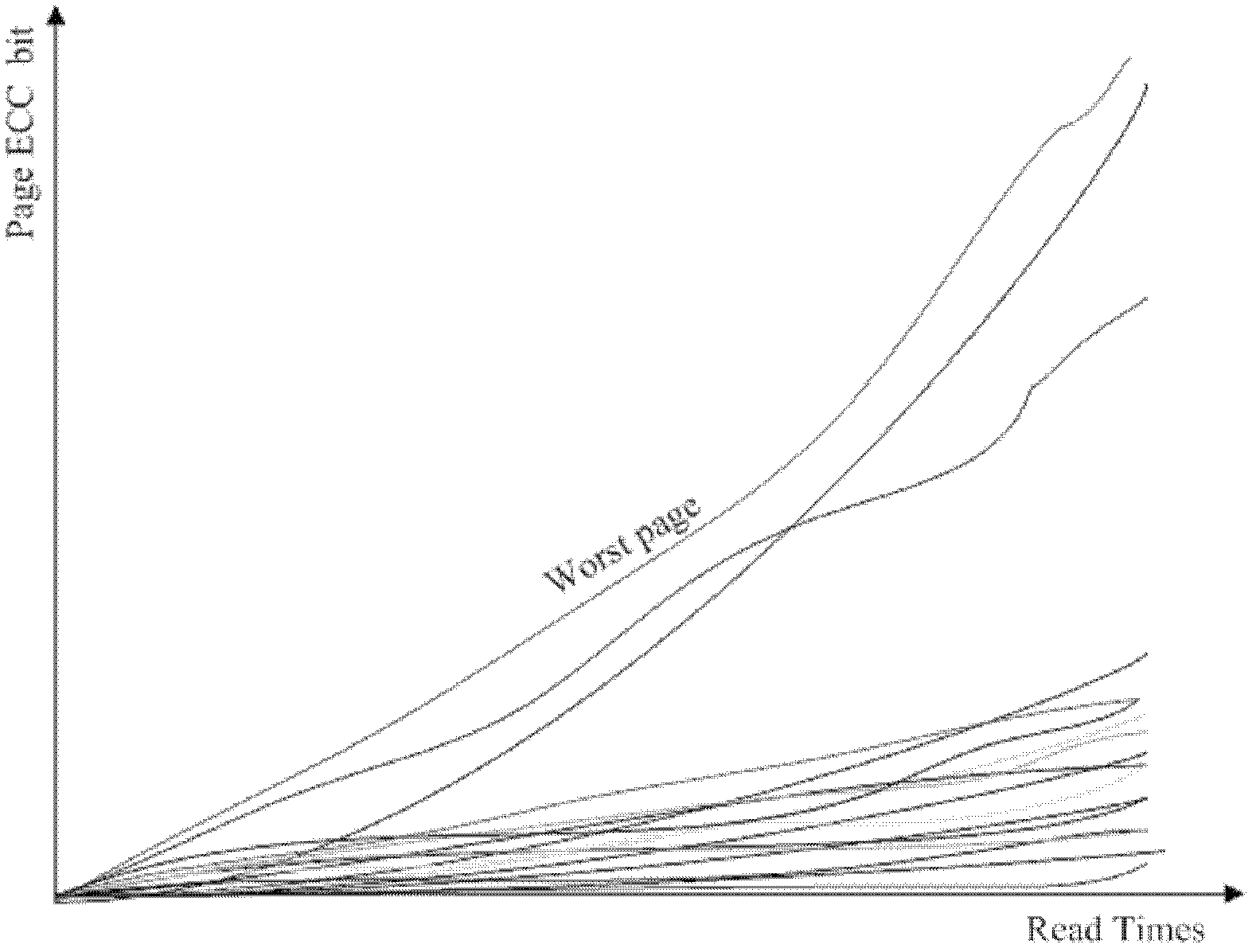

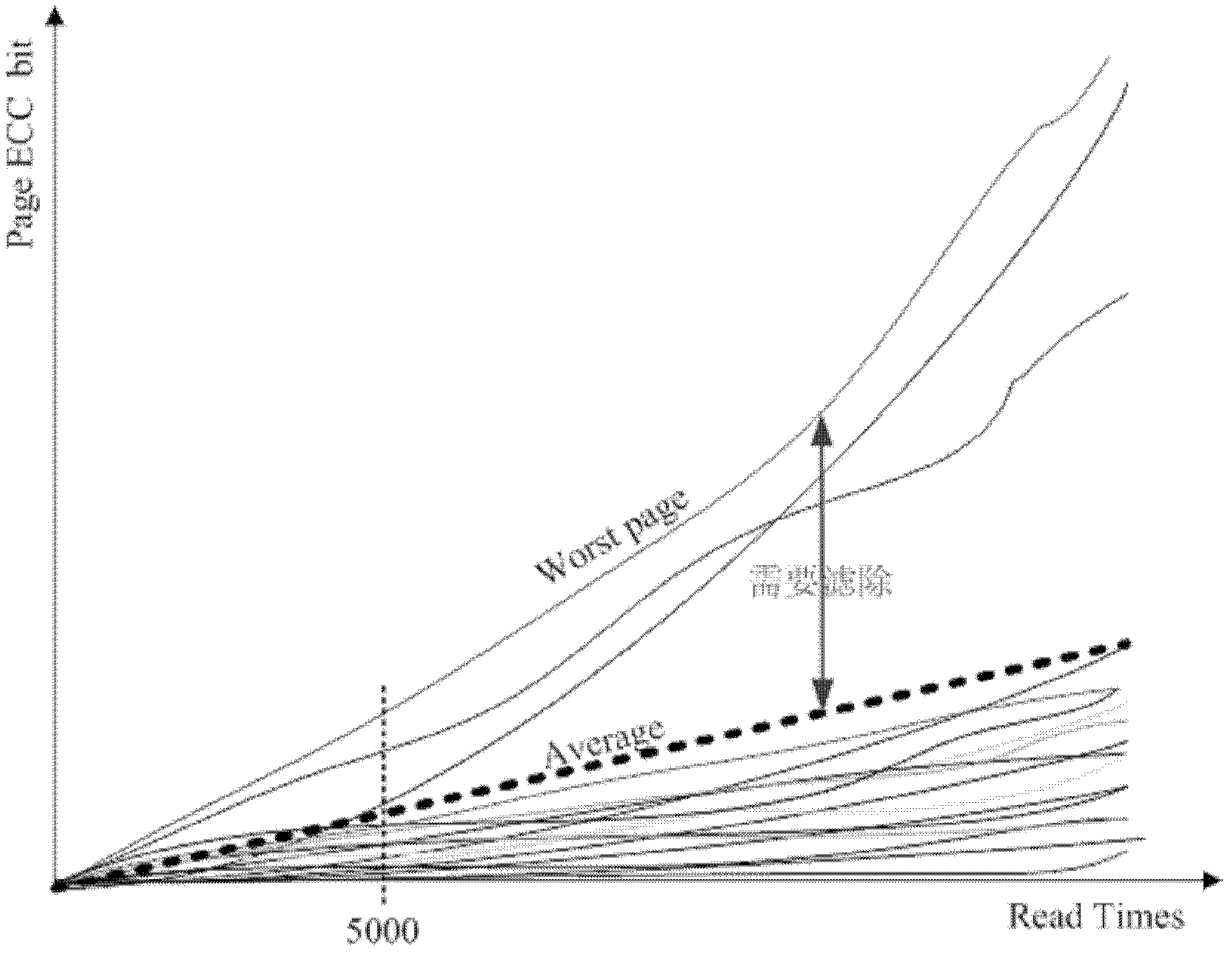

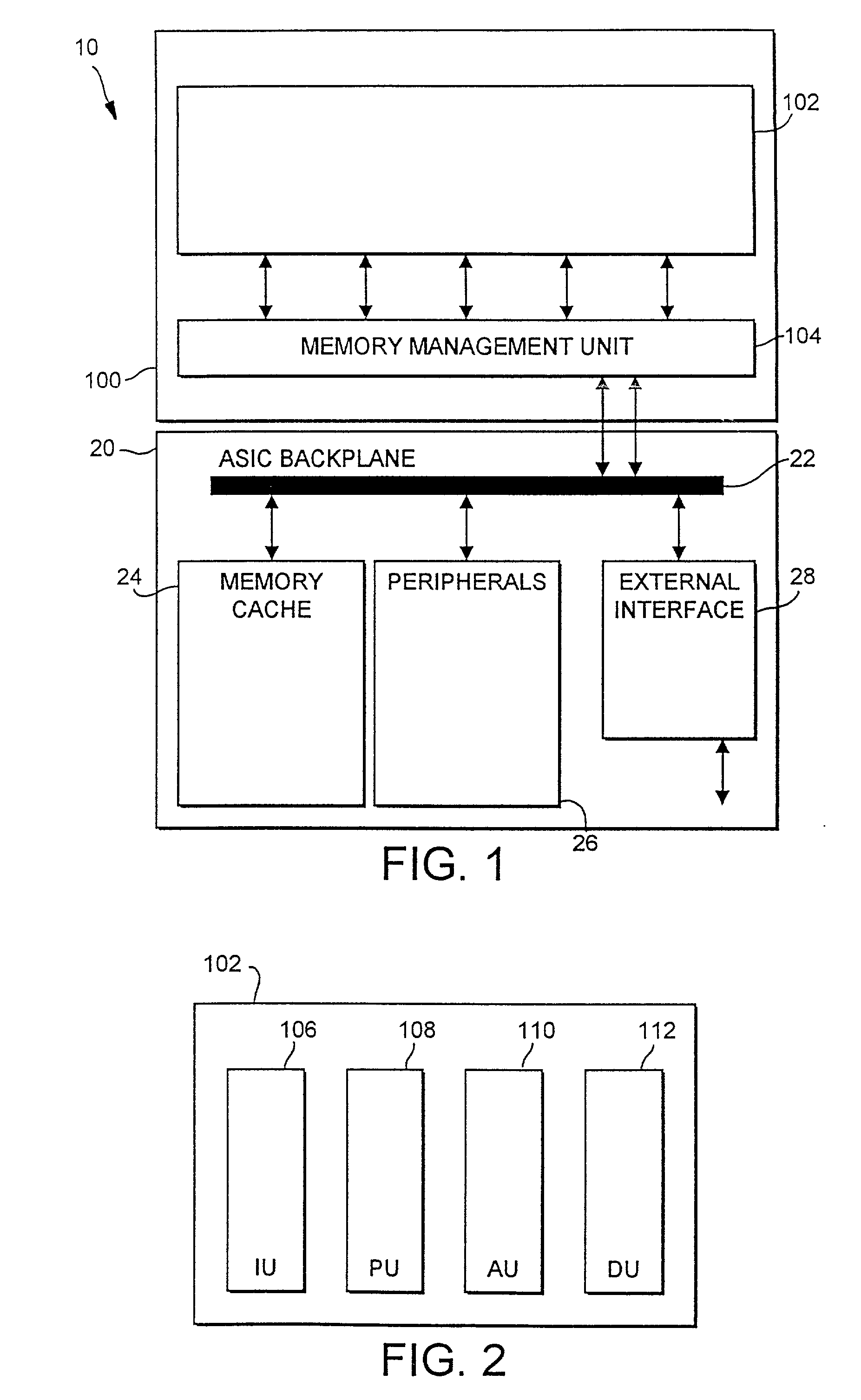

A memory management method and device

InactiveCN102298543AGuaranteed speedExtend your lifeRedundant data error correctionConditional executionMemory management unit

The embodiment of the present invention discloses a memory management method and device, wherein the implementation of the method includes: monitoring whether the condition for screening bad pages is met; if the condition for performing bad page screening is met, at least one block of the non-volatile memory The bad page is obtained by screening the data pages in the bad page; the bad page is a page whose stability does not meet the predetermined standard; the data in the bad page is read, and the data in the bad page read is written to an unused In the invalid page; after confirming that the data in the read bad page is successfully written, set the bad page as a disabled page. The solution for managing the pages of the nonvolatile memory in the embodiment of the present invention is universal, and improves the reliability of the nonvolatile memory on the premise of ensuring the speed of the nonvolatile memory.

Owner:HUAWEI TECH CO LTD

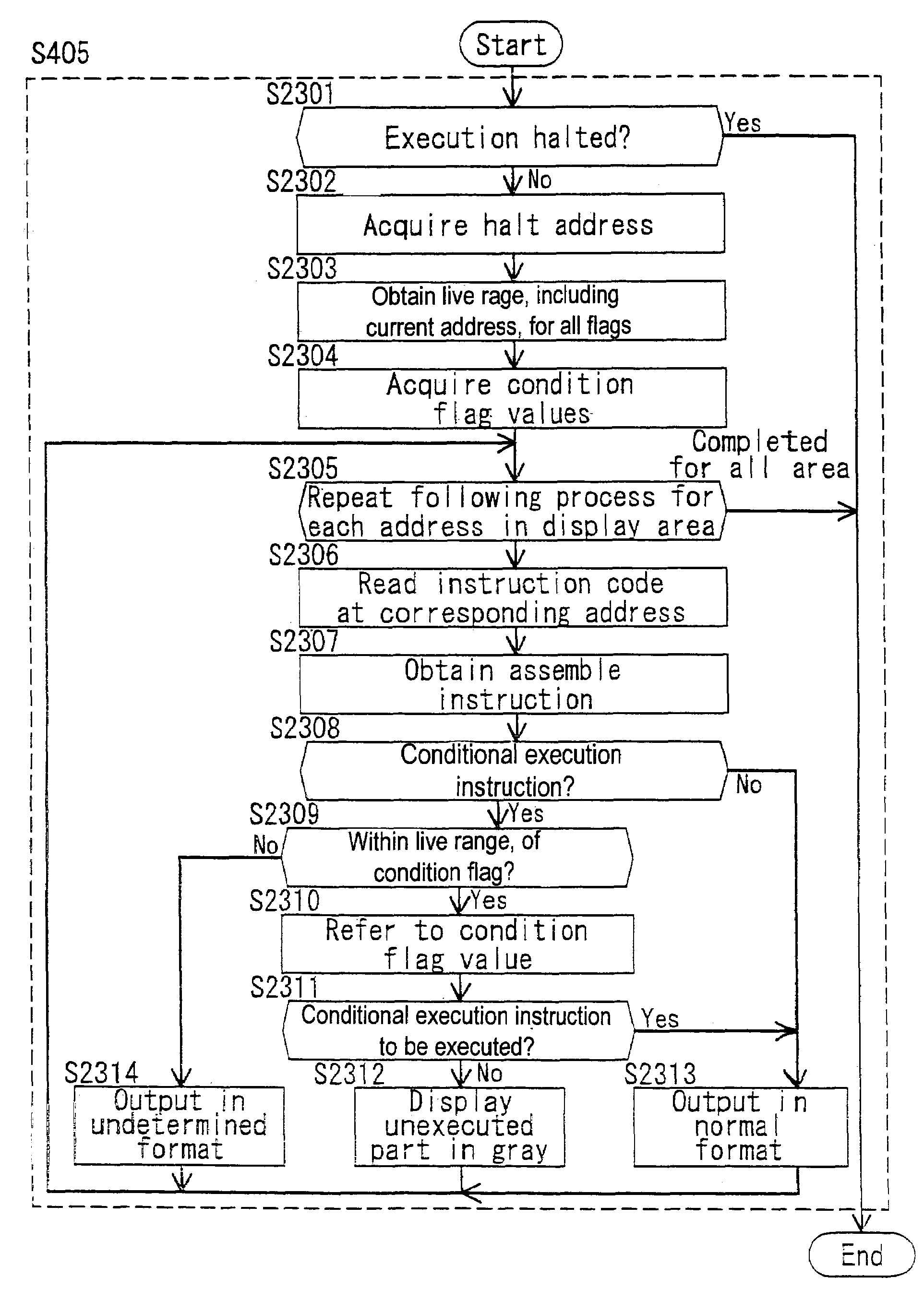

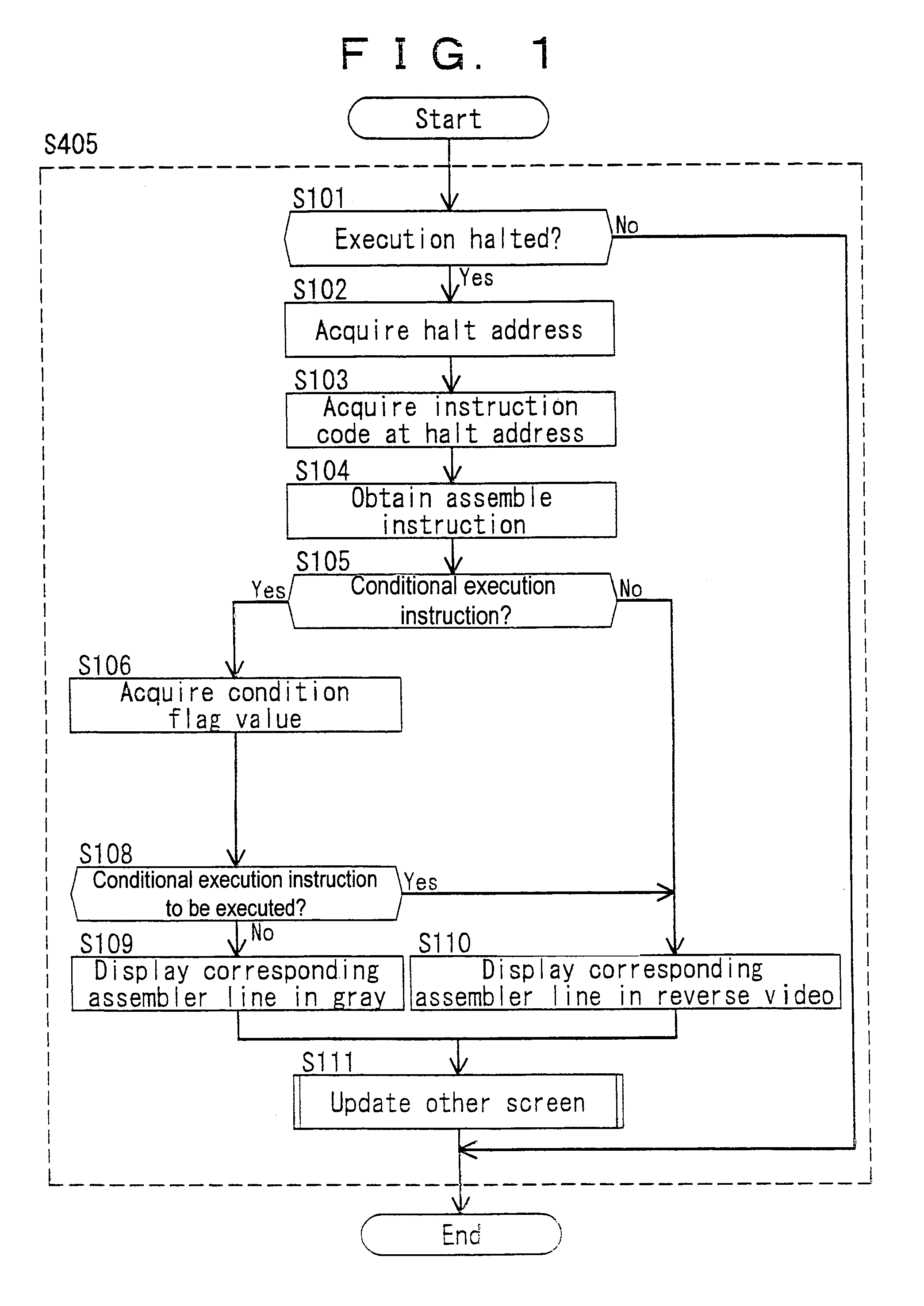

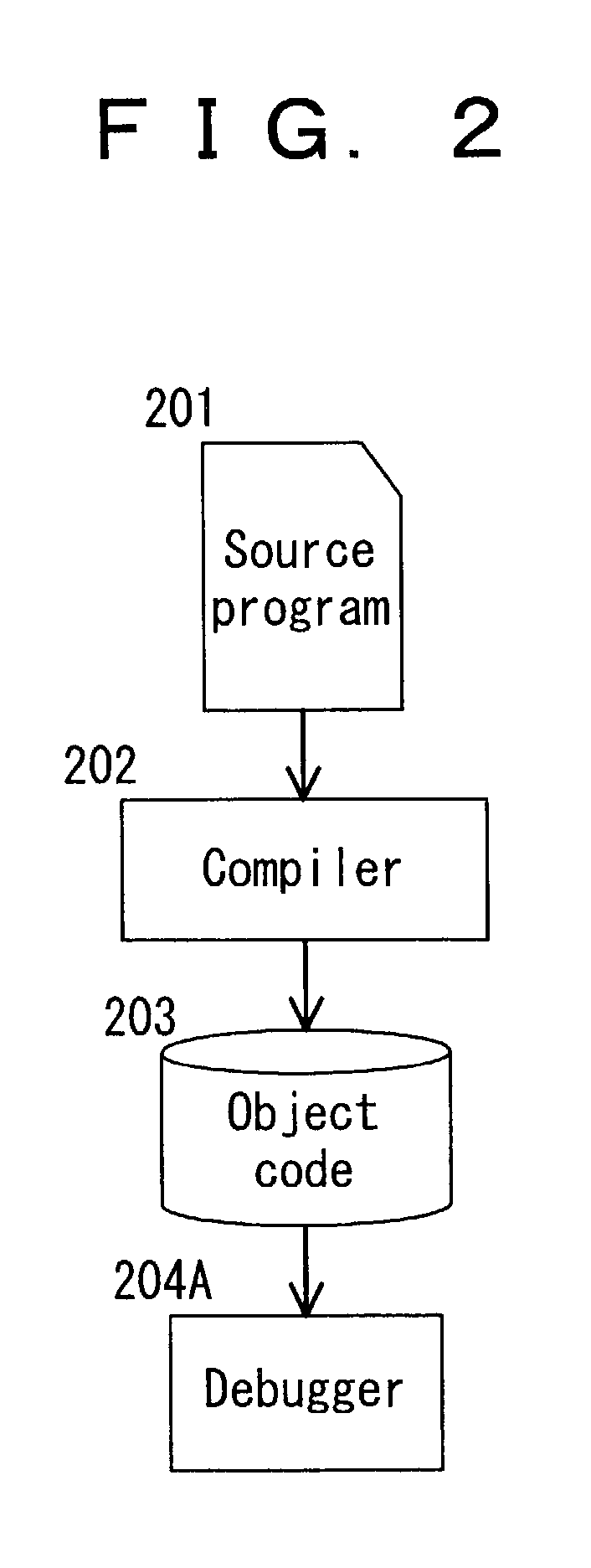

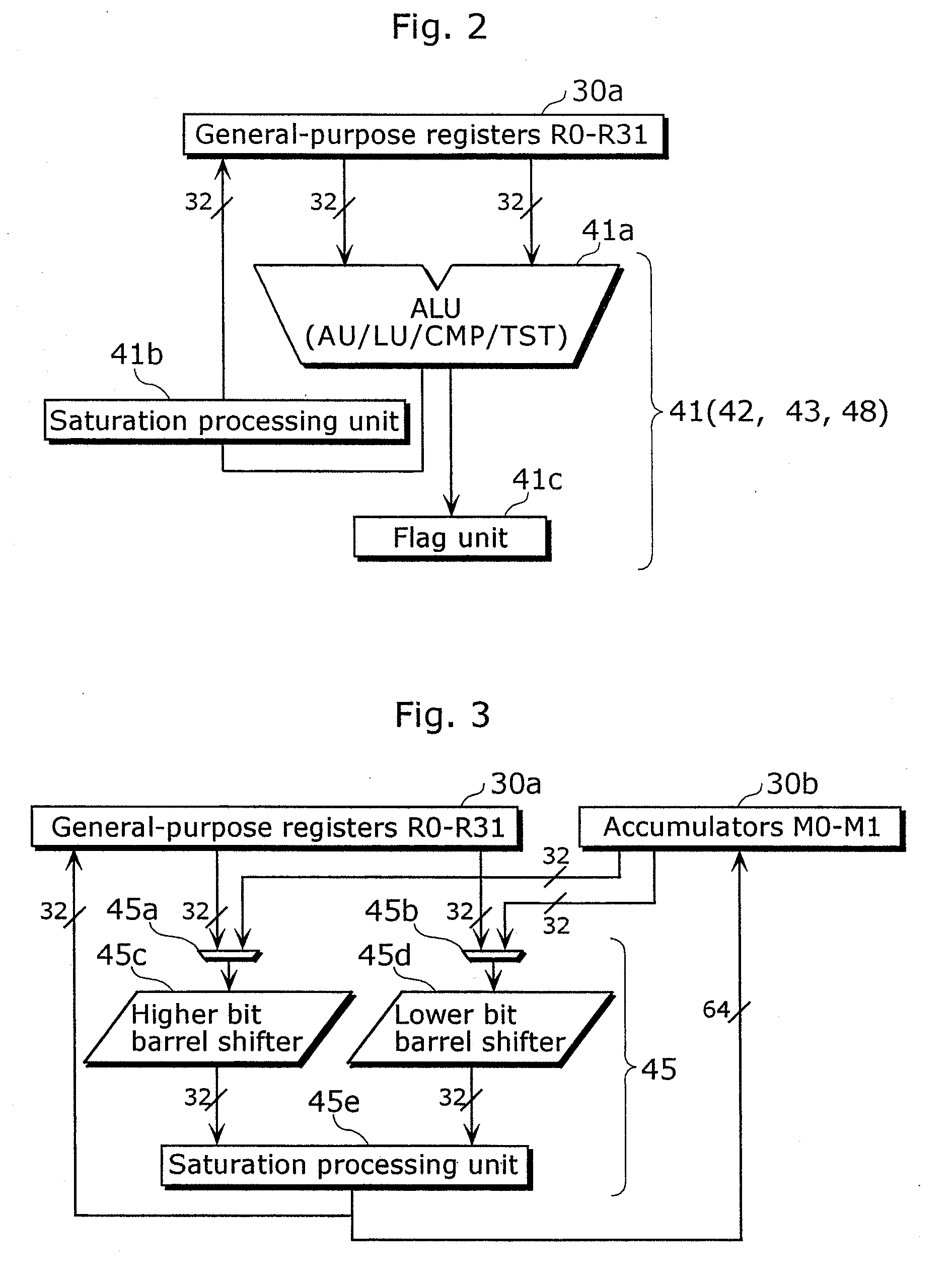

Software debugger and software development support system for microcomputer operable to execute conditional execution instruction

InactiveUS7266809B2Simple to executeSoftware testing/debuggingSpecific program execution arrangementsMicrocomputerSoftware engineering

A software debugger tangibly embodied on a computer readable medium may display a microcomputer program being debugged so that a halt address at which the execution of the program is caused to halt can be distinguished from other addresses. When performing step-by-step execution of the program, a determination is made whether an instruction at the halt address is a predicate execution instruction or not. If the instruction is a predicate execution instruction, a condition flag value for the instruction is acquired. Based on the condition flag value, a determination is made whether the predicate execution instruction is to be executed or not. Then, the instruction at the halt address is displayed on a screen by changing a display method according to the result of the determination.

Owner:PANASONIC CORP

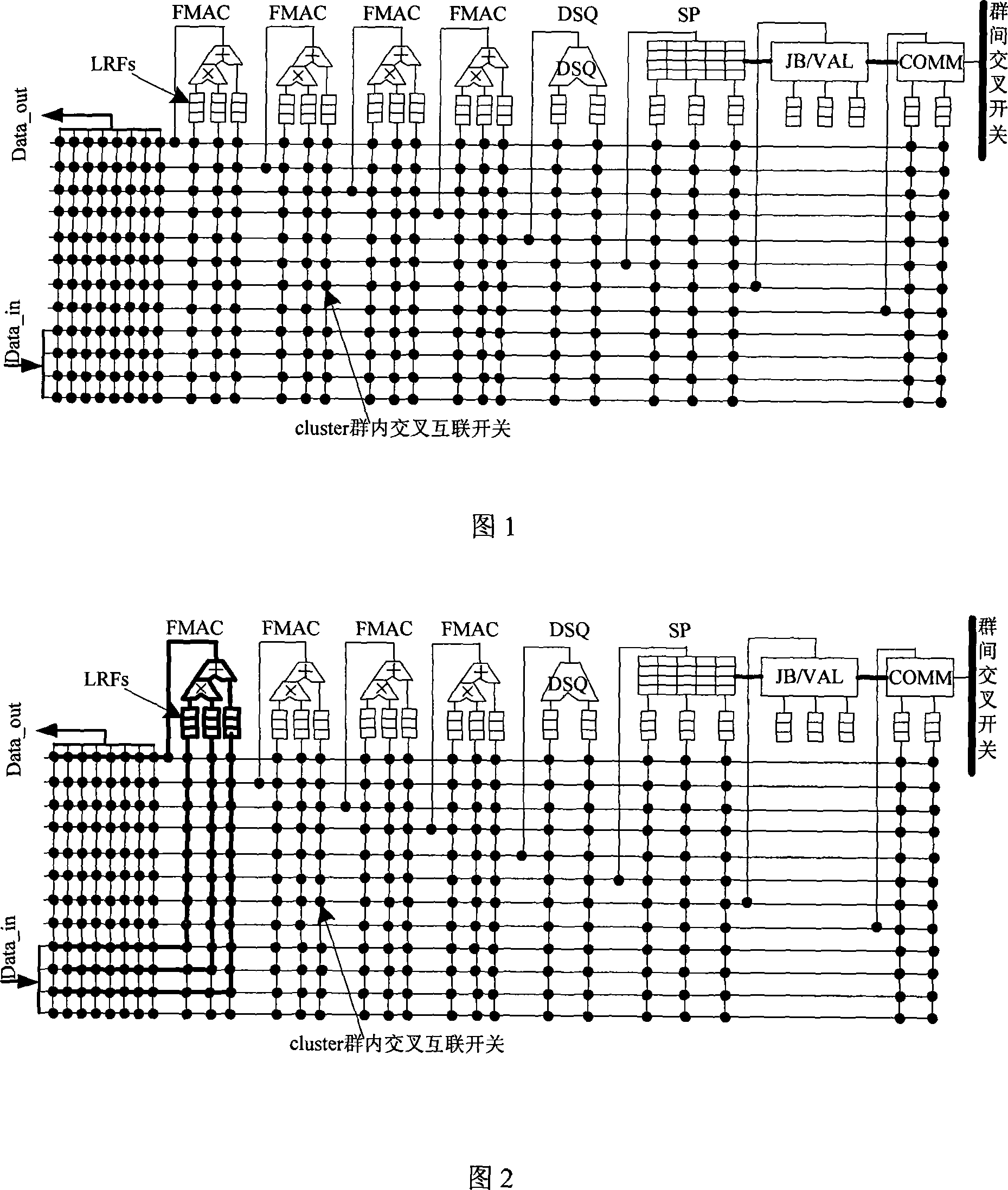

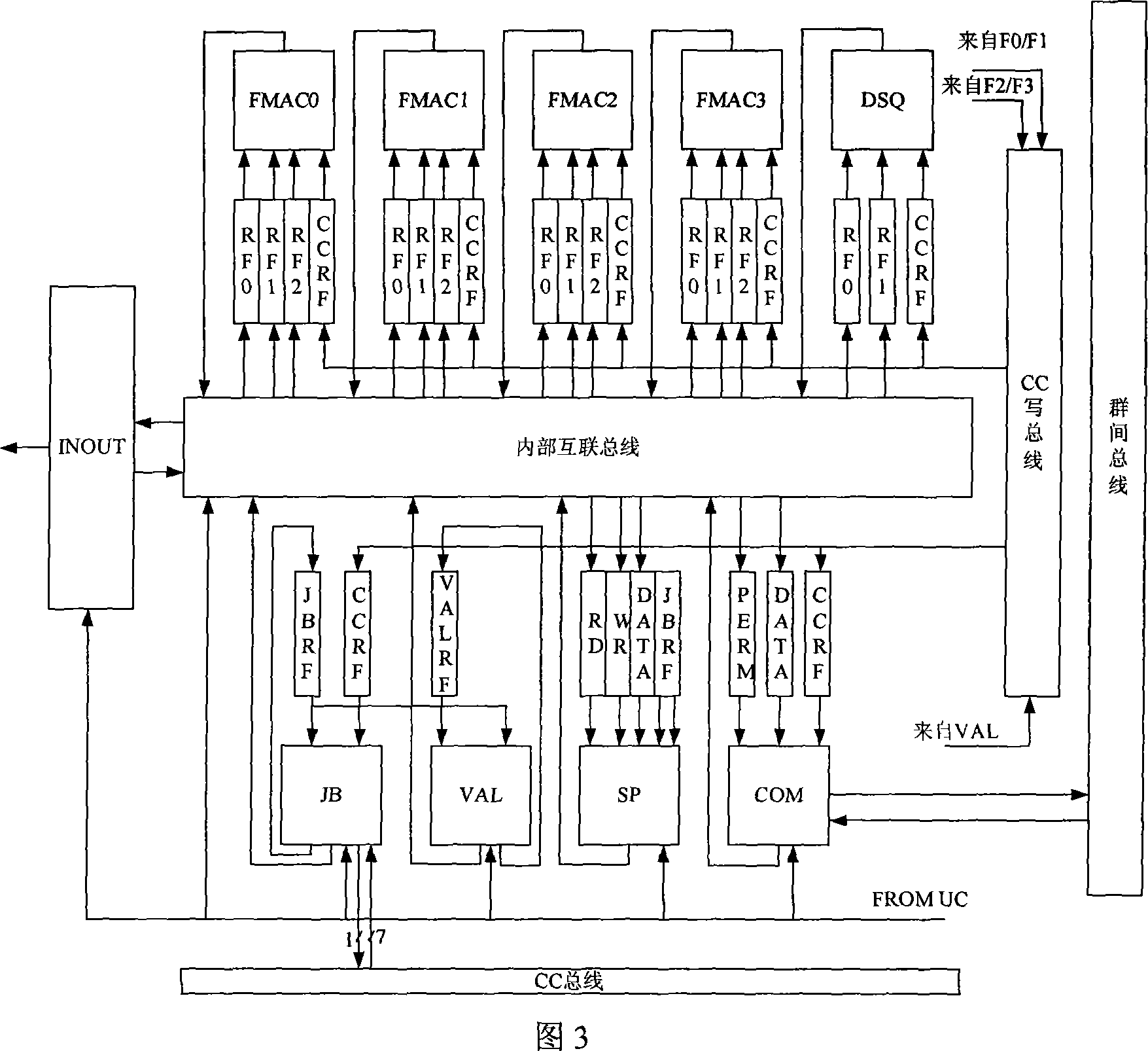

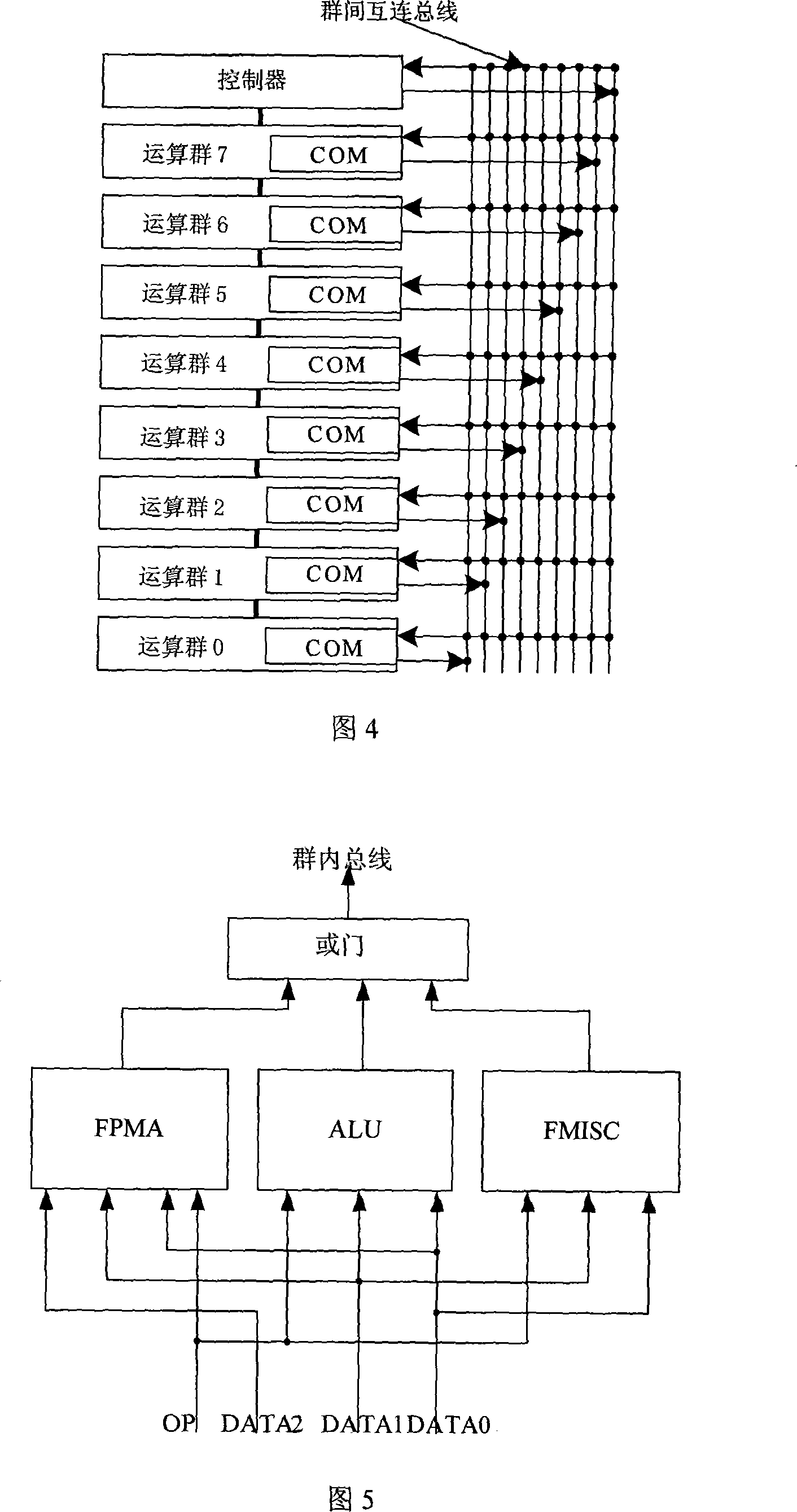

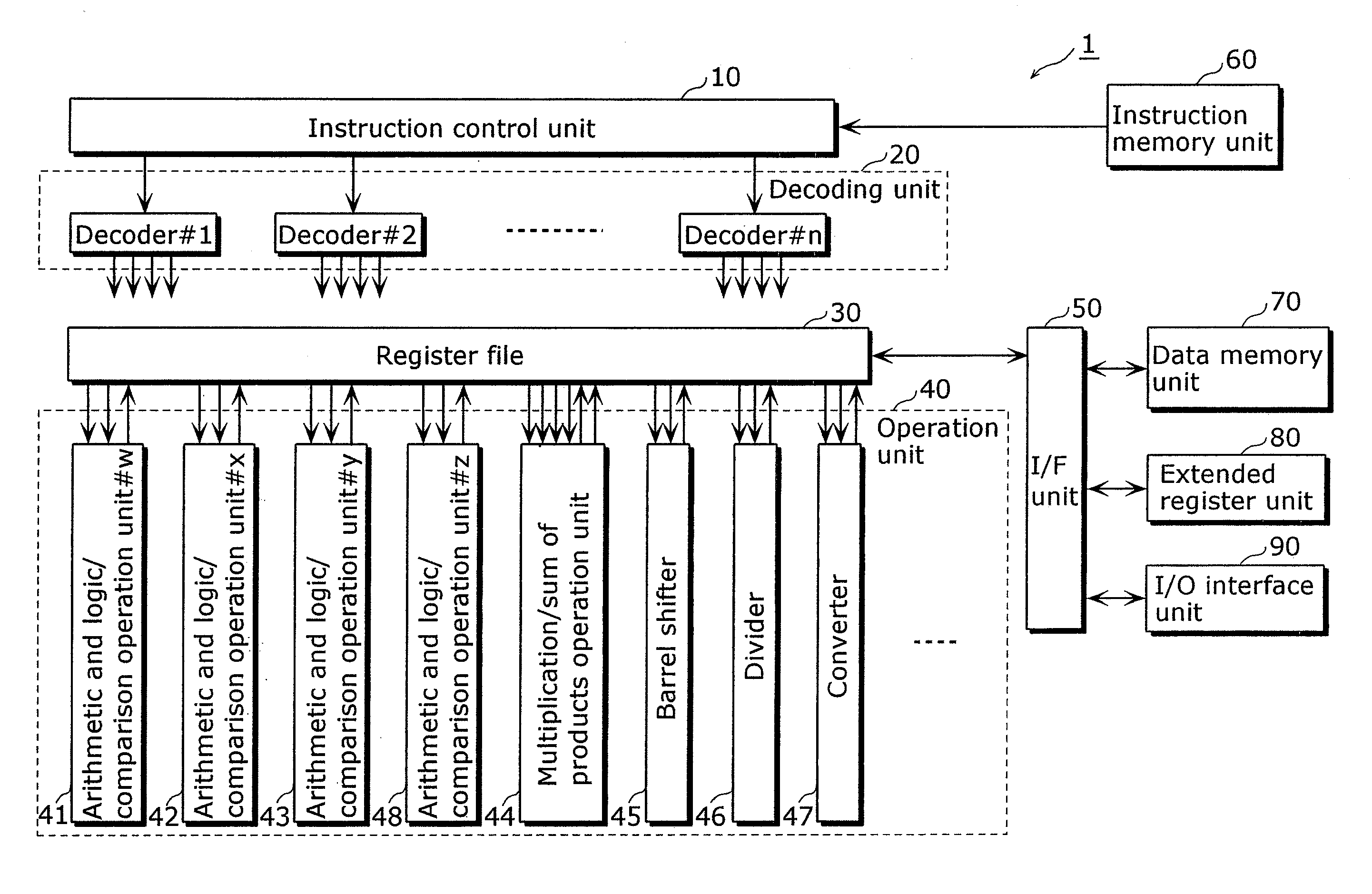

64 bit floating-point integer amalgamated arithmetic group capable of supporting local register and conditional execution

InactiveCN101021832AExtended Data WidthWide data widthArchitecture with multiple processing unitsInstruction memoryFloating point

The invention discloses a 64-bit floating-point integer-fusion operation group which support partial deposit and conditional execution. It includes one or more 64-bit floating point / integer-fusion arithmetic unit, conditional execution unit, component interconnect structure and control unit. The computing unit is connected with conditional execution unit by interconnect structure which also is used to transfer data among units. The storage address of operation group is made up of several independent address spaces, and the local operations can indirectly visiting each address space by unified controller. There are specialized instruction register to storage compiled order. The controller send the compiled instruction to each function unit of the corresponded computing group at the same time when the program running, then each group receive instructions and run it by SIMD and storage the result in the same LRF or output.

Owner:NAT UNIV OF DEFENSE TECH

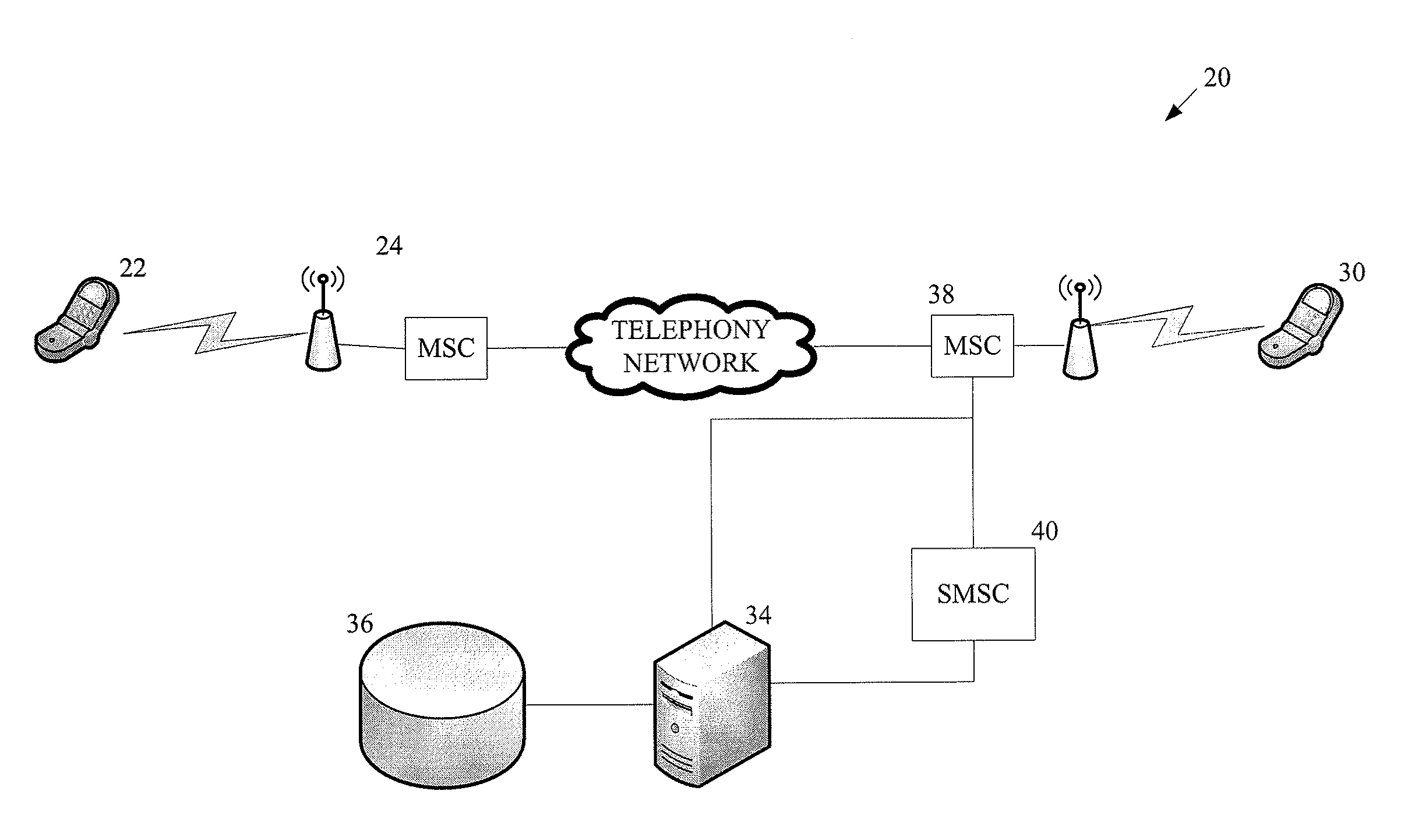

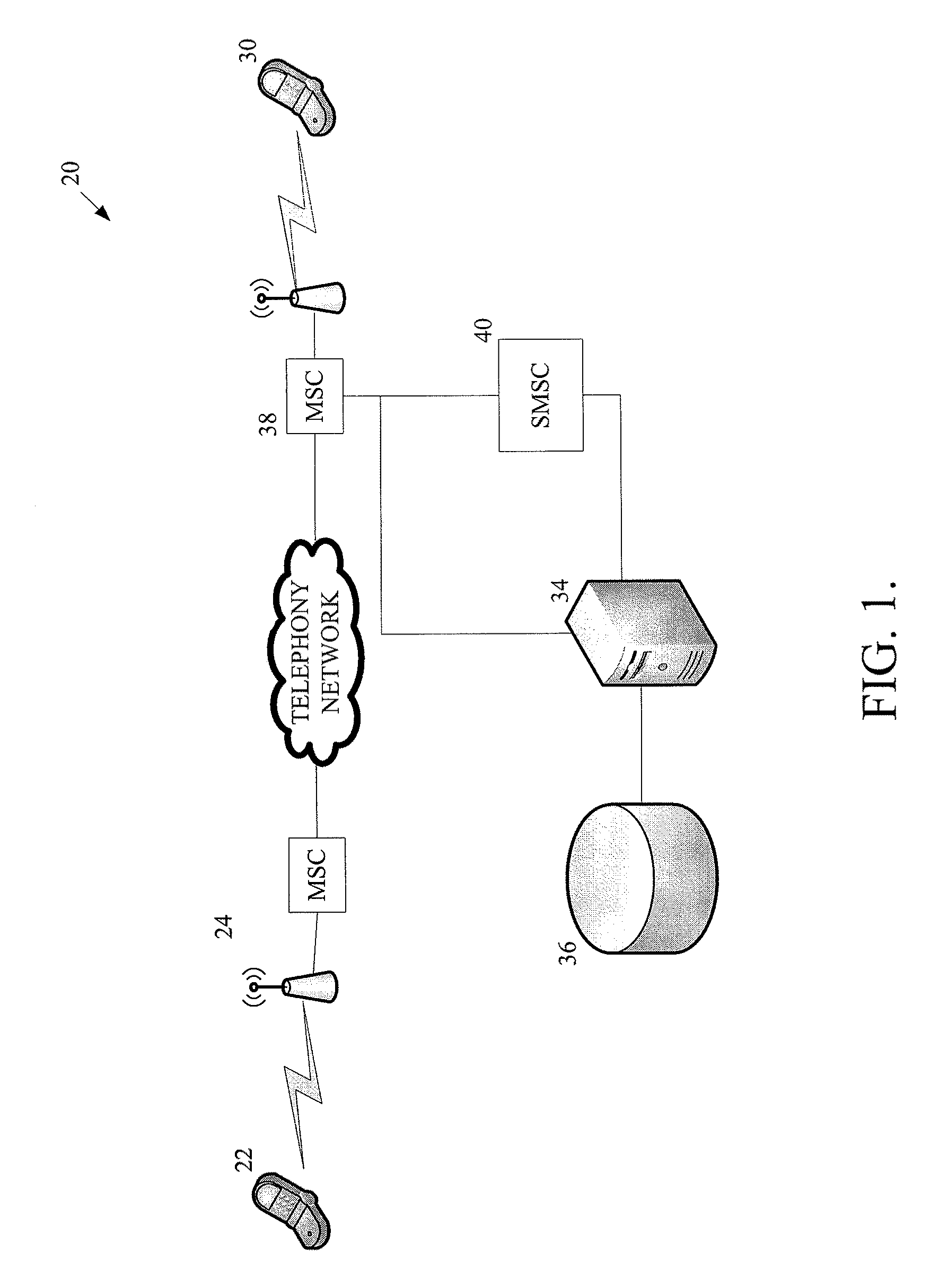

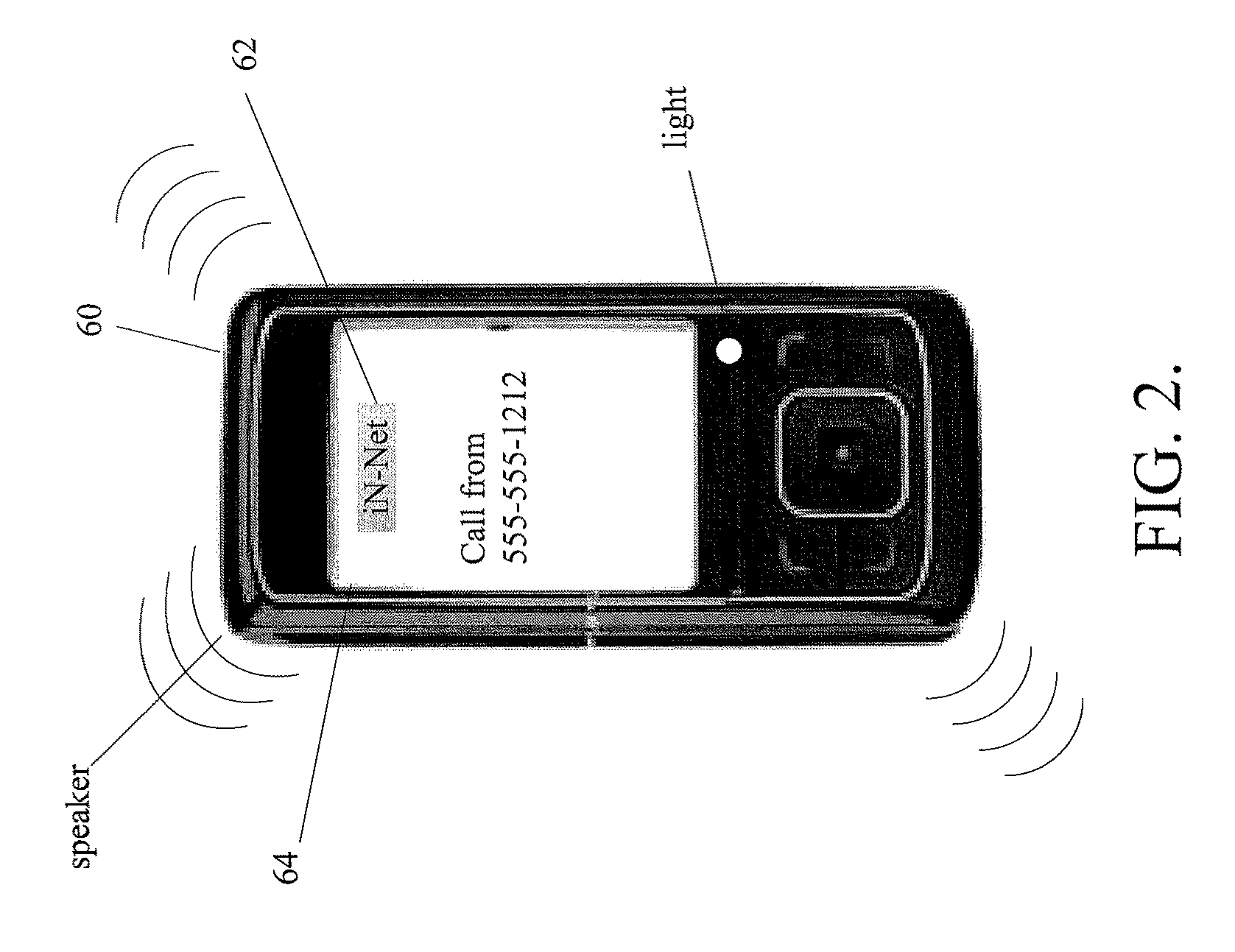

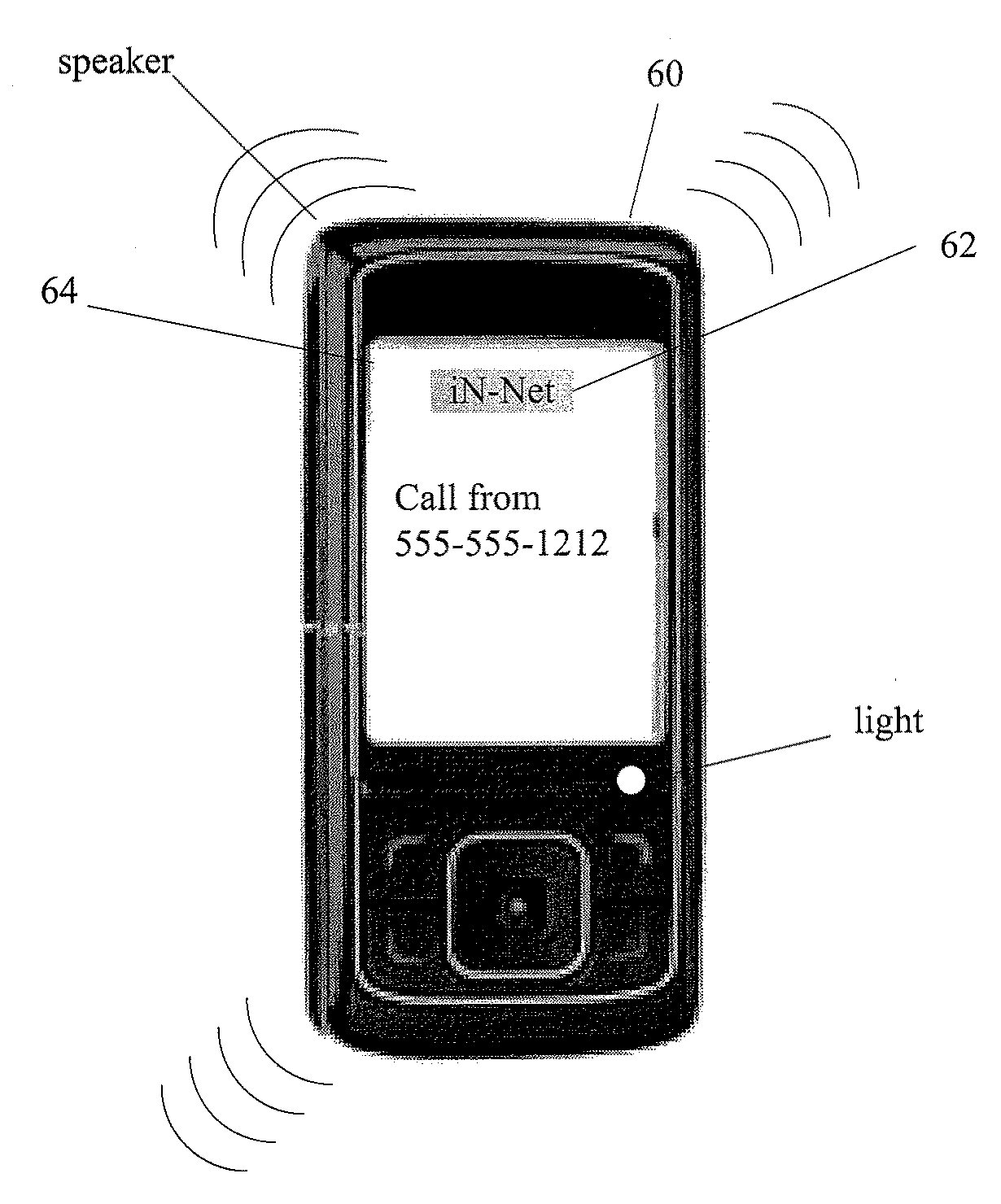

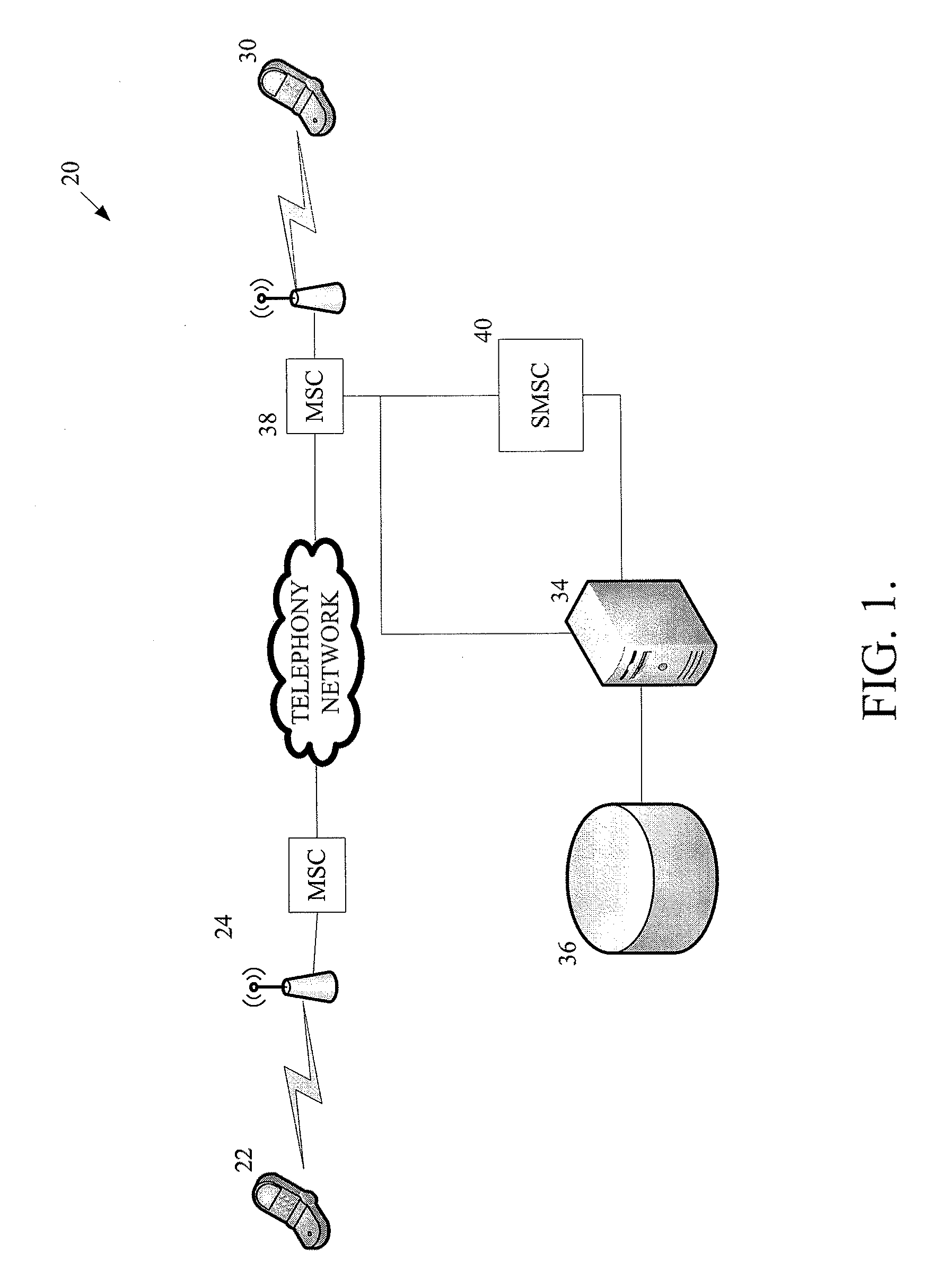

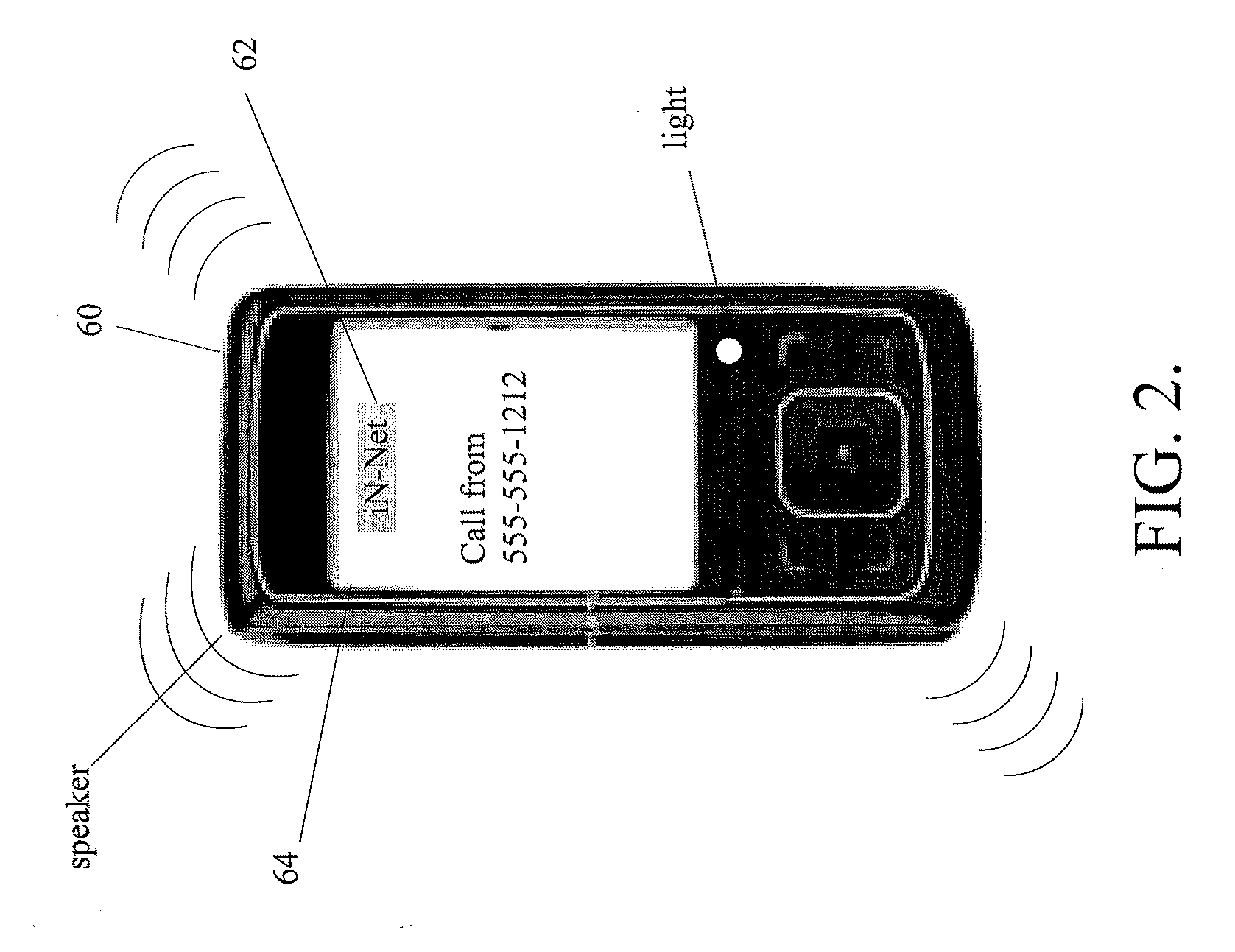

System and method for determination of network and conditional execution of applications and promotions

ActiveUS8160555B2Low costReduced serviceAccounting/billing servicesSpecial service for subscribersProgram planningConditional execution

System and method for determining whether an incoming call originates from inside or outside of a mobile carriers network. An example system performs a GTT (global title translation) on an incoming number to determine the hosting carrier of any mobile phone number. After the result of the matching determination is made, a message is generated and sent to a caller associated with the call page. The generated message includes any of directory information associated with the subscriber, information associated with cost savings or comparisons associated with in-network calling, information regarding promotions for calling plans, mobile devices or device upgrades, requests to join a network, requests to join a social call plan, information regarding instant savings or call rebates, offers for online services or software, offers for reduced cost or free phone service in exchange for adoption of a predefined product or entering into a social network group.

Owner:CEQUINT INC

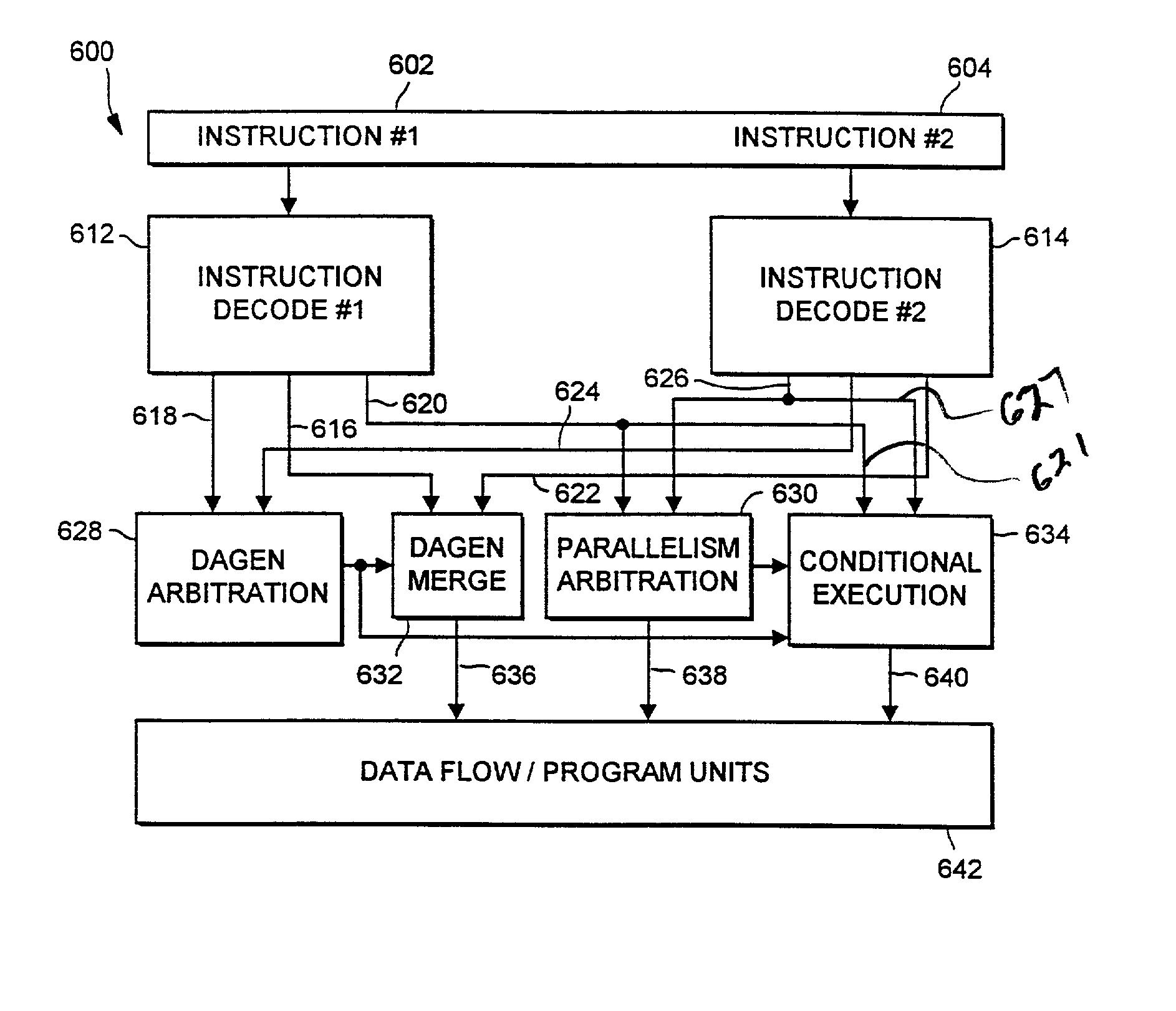

A processor with apparatus for verifying instruction parallelism

InactiveUS20030074543A1Handling data according to predetermined rulesGeneral purpose stored program computerControl powerControl signal

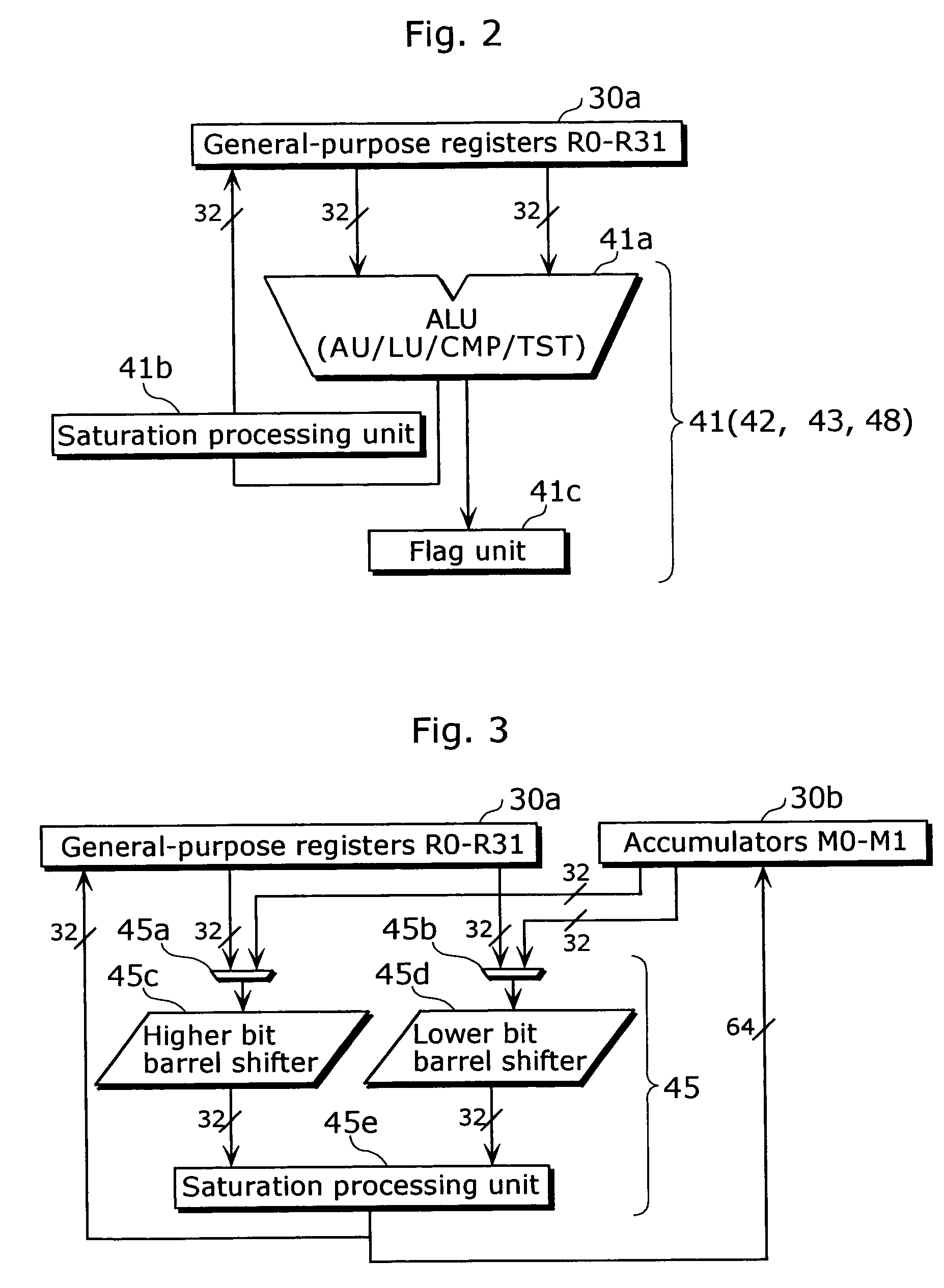

A processing engine 10 for executing instructions in parallel comprises an instruction buffer 600 for holding at least two instructions, with the first instruction 602 in a first position and the second instruction 604 in a second position. A first decoder 612 provides decoding of the first instruction and generates first control signals. The first control signals include first resource control signals, first address generation control signals, and a first validity signal indicative of the validity of the first instruction in the first position. A second decoder 614 provides decoding of the second instruction and generates second control signals. The second control signals include second resource control signals, second address generation control signals, and a second validity signal indicative of the validity of the second instruction in the second position. Arbitration and merge logic 628, 630 is provided for arbitrating between the first and second control signals and for merging the first and second control signals for controlling power of execution of the instructions in accordance with a set of parallelism rules. A conditional execution unit 634 is responsive to false condition signals from the arbitration and merge logic to inhibit or modify the effect of the control signals. The parallelism rules provide for efficient instruction execution, and the avoidance of resource conflicts.

Owner:TEXAS INSTR INC

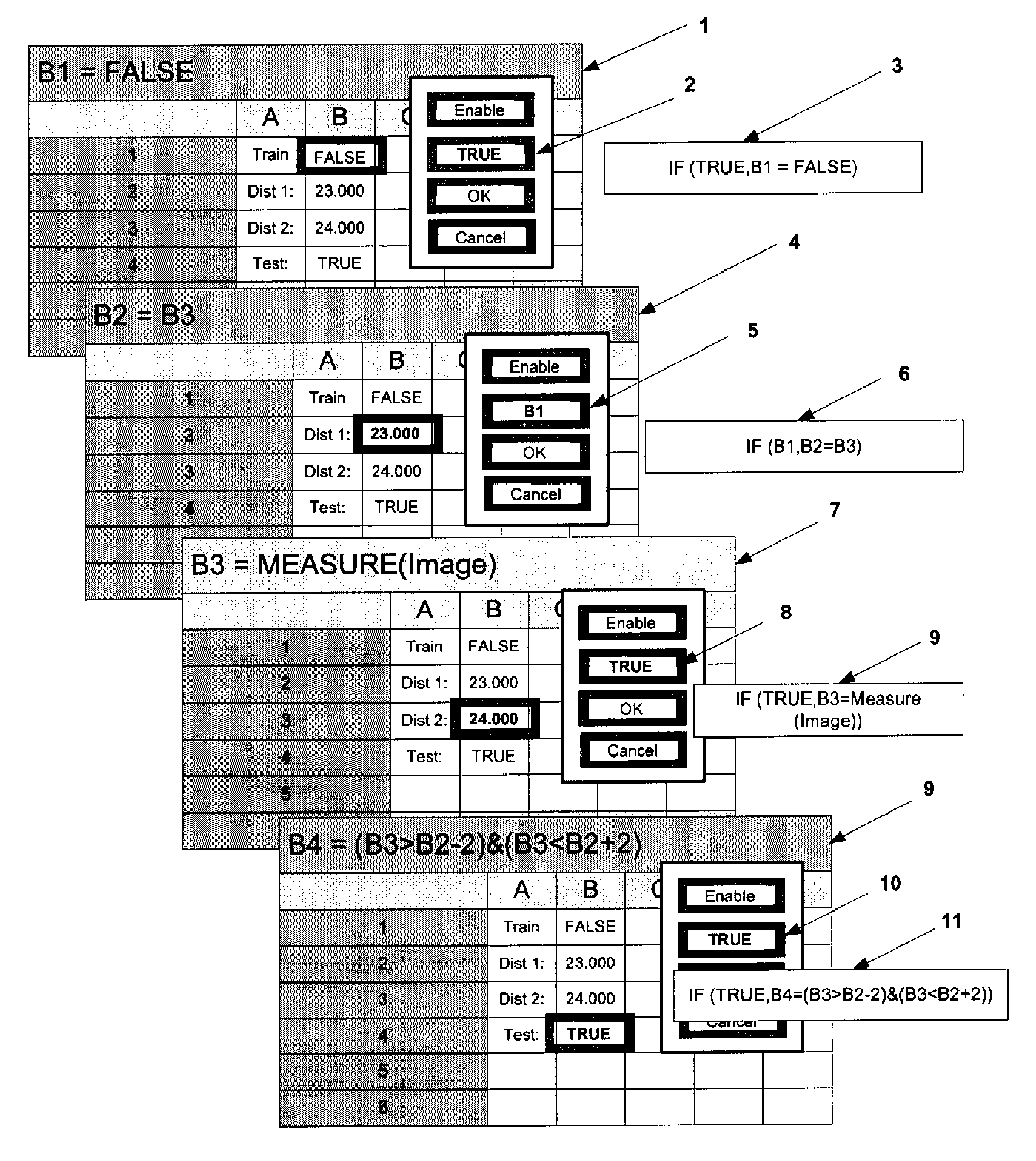

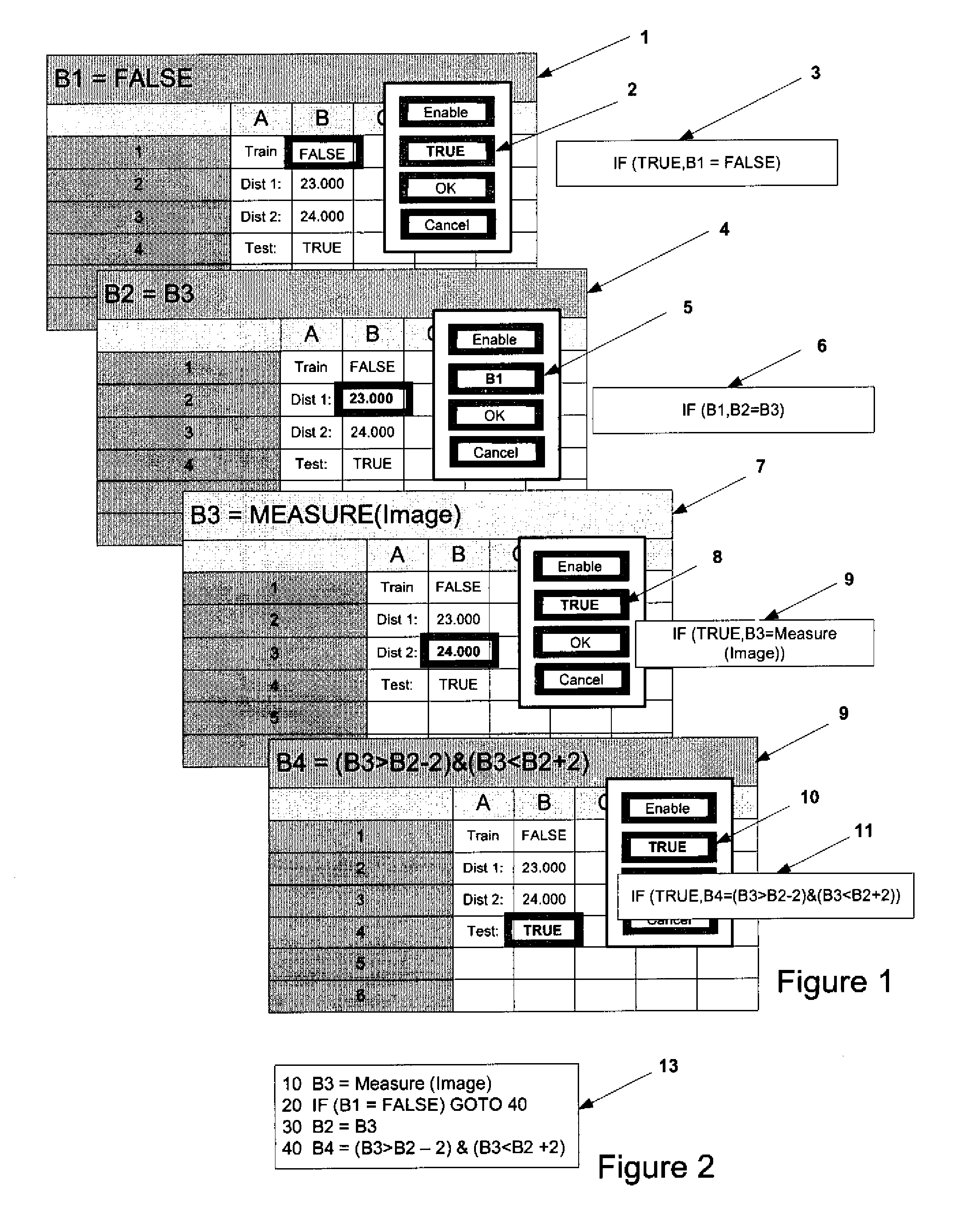

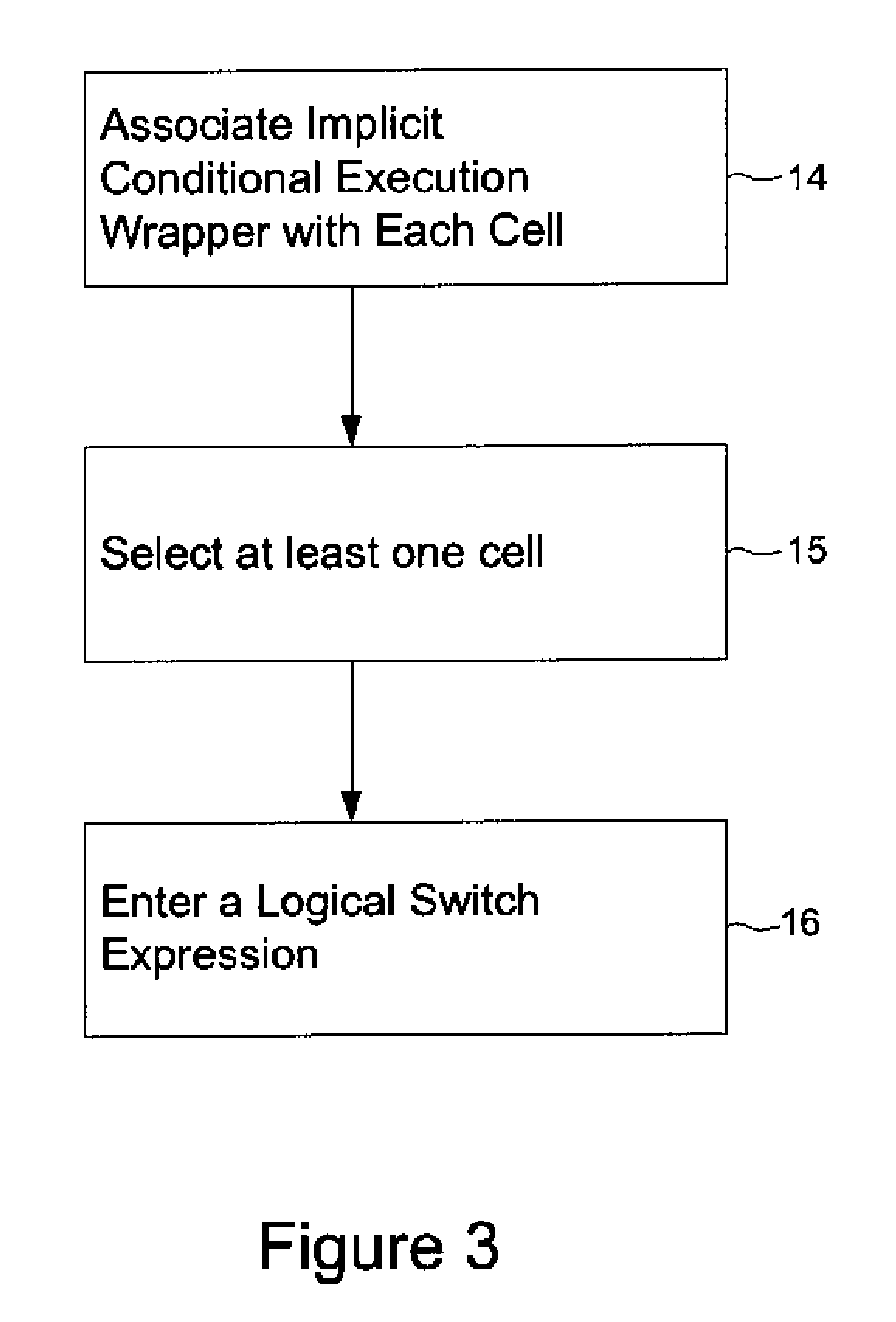

Conditional Cell Execution in Electronic Spreadsheets

InactiveUS20110035652A1Efficiently and elegantly extendedSoftware engineeringText processingConditional expressionConditional execution

An improved electronic spreadsheet is provided for applications requiring conditional expression execution behavior. Each cell having an executable expression is cooperative with an implicit conditional execution wrapper. The execution of each cellular expression is implicitly conditioned on the state of an individually assigned logical switch expression. The improved electronic spreadsheet also includes a user interface by which a user can assign logical switch expressions to a cell, or to a range of cells. The improved electronic spreadsheet facilitates the use of spreadsheets for wider range of applications than was possible with conventional electronic spreadsheets.

Owner:MCGARRY JOHN

Processor and compiler for decoding an instruction and executing the decoded instruction with conditional execution flags

InactiveUS7380112B2Increase speedReduce the amount of powerSoftware engineeringDigital computer detailsCompilerConditional execution

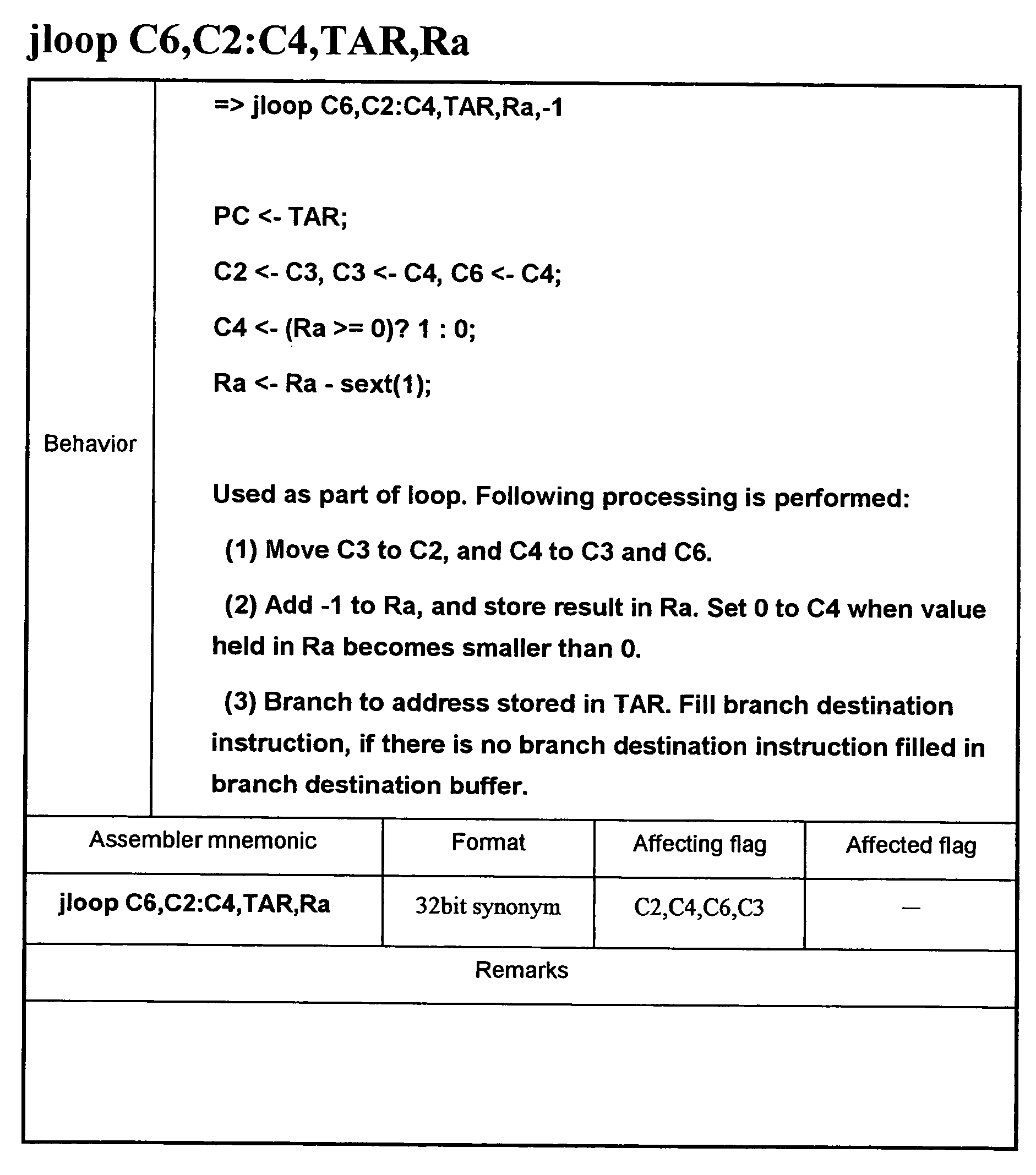

The present invention provides a processor which has a small-scale circuit and is capable of executing loop processing at a high speed while consuming a small amount of power. When the processor decodes an instruction “jloop C6,C1:C4,TAR,Ra”, the processor (i) sets a conditional flag C4 to 0 when the value of a register Ra is smaller than 0, (ii) moves the value of a conditional flag C2 to a conditional flag C1, moves the value of a conditional flag C3 to the conditional flag C2, and moves the value of the conditional flag C4 to the conditional flags C3 and C6, (iii) adds −1 to the register Ra and stores the result into the register Ra, and (iv) branches to an address specified by a branch register (TAR). When not filled with a branch target instruction, the jump buffer will be filled with a branch target instruction.

Owner:PANASONIC CORP

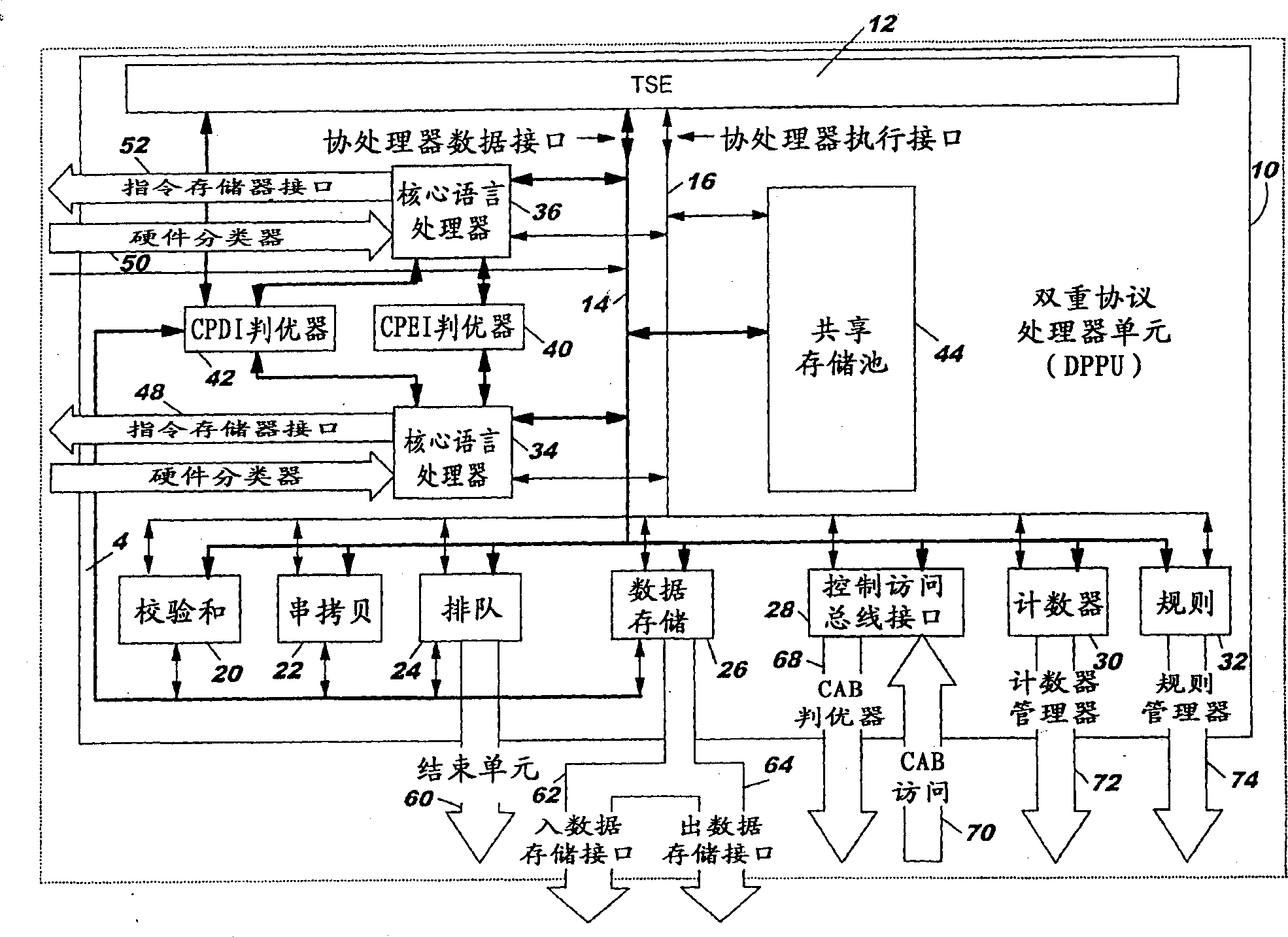

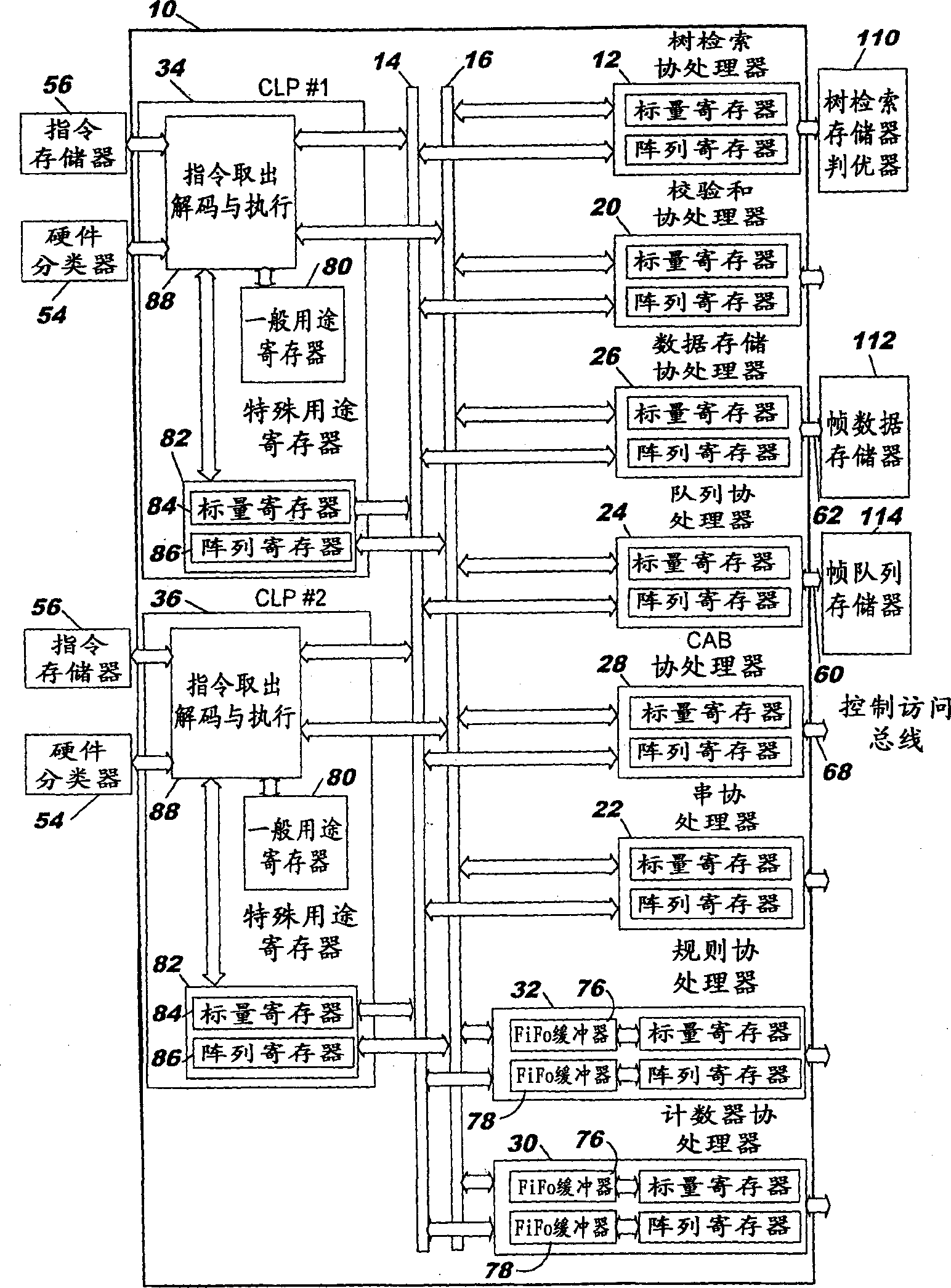

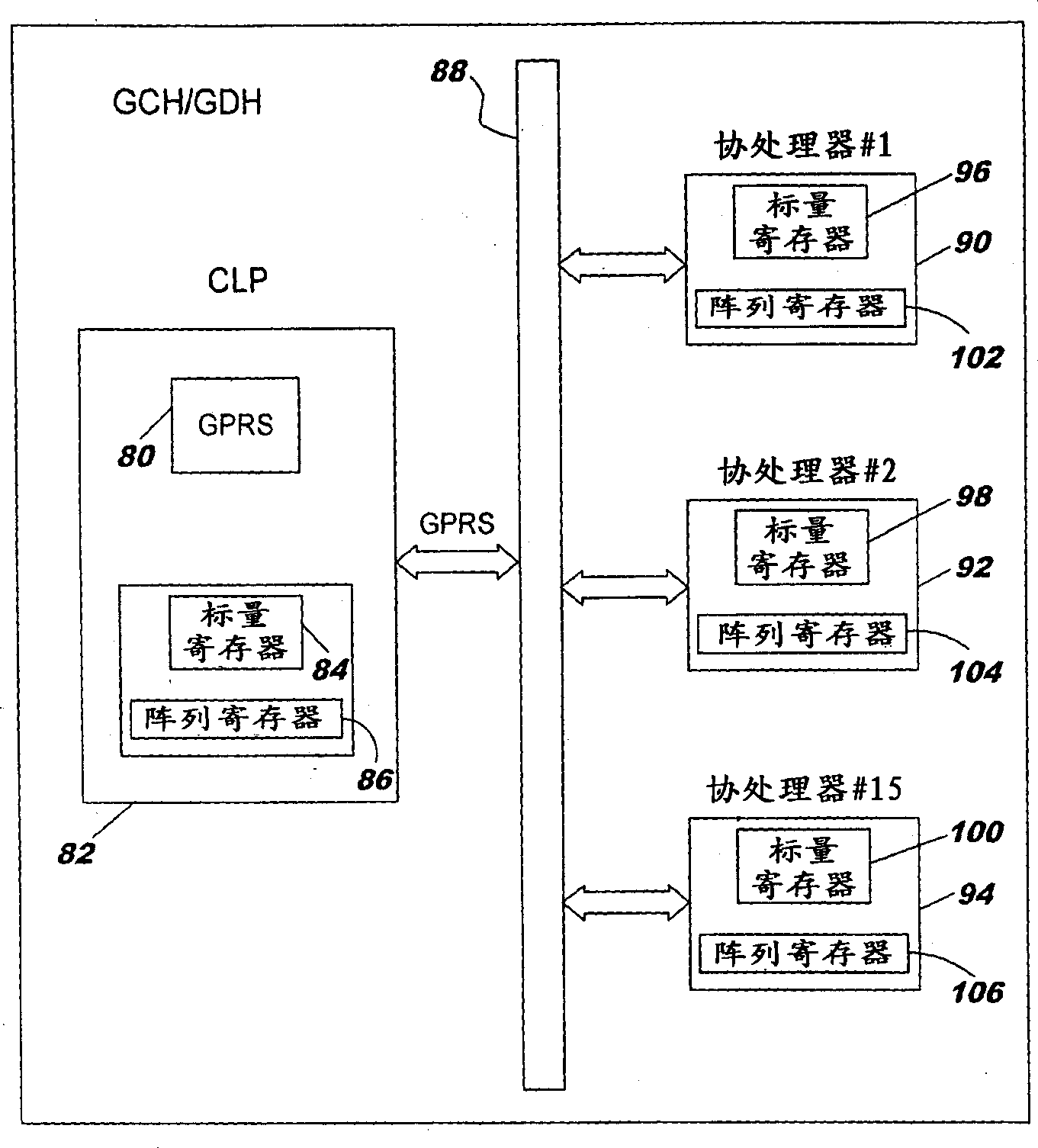

Coprocessor with multiple logic interface

InactiveCN1342940AMultiprogramming arrangementsConcurrent instruction executionOperating instructionCoprocessor

An embedded processor complex contains multiple protocol processor units (PPUs). Each unit includes at least one, and preferably two independently functioning core language processors (CLPs). Each CLP supports dual threads thread which interact through logical coprocessor execution or data interfaces with a plurality of special purpose coprocessors that serve each PPU. Operating instructions enable the PPU to identify long and short latency events and to control and shift priority for thread execution based on this identification. The instructions also enable the conditional execution of specific coprocessor operations upon the occurrence or non occurrence of certain specified events.

Owner:IBM CORP

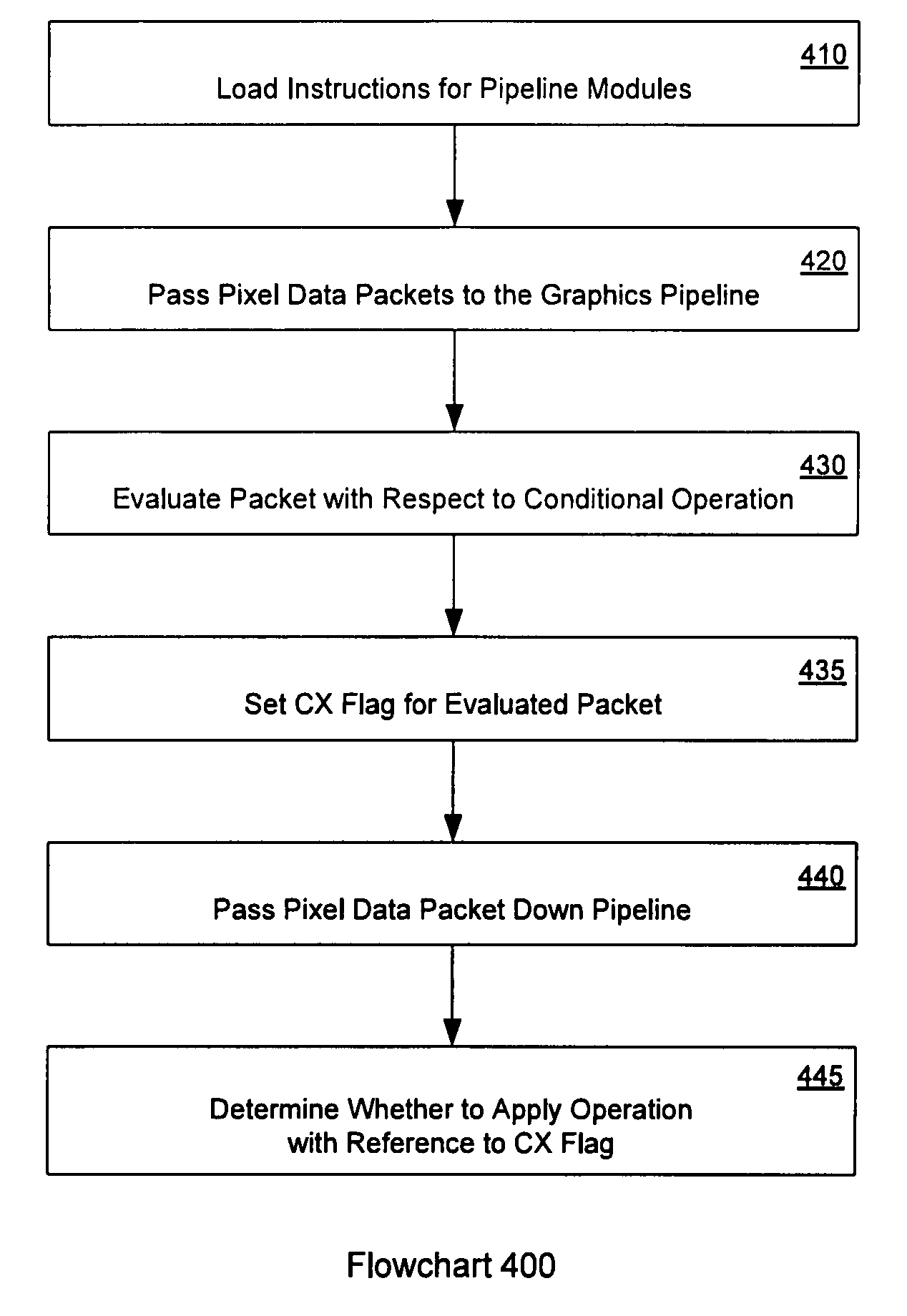

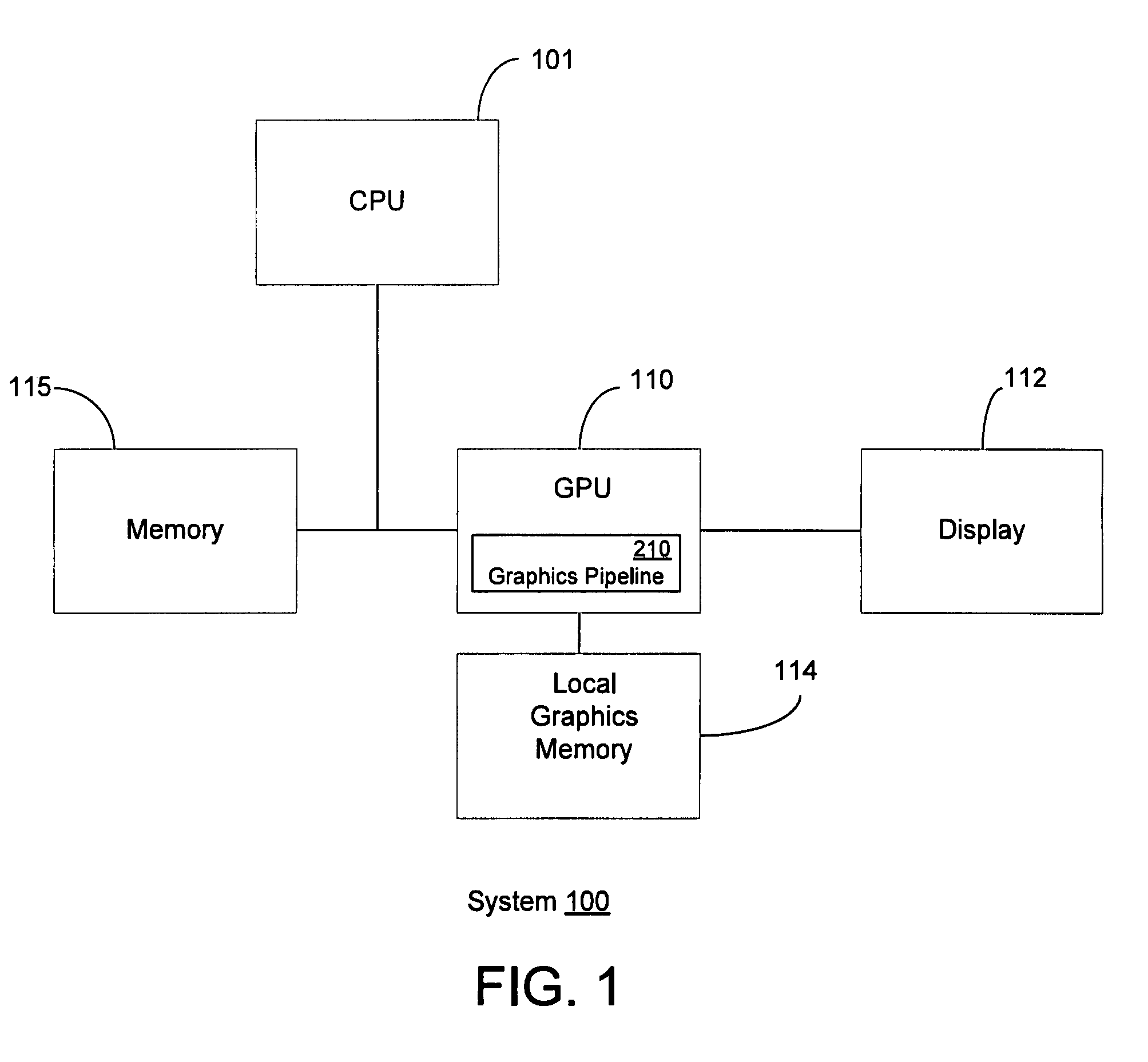

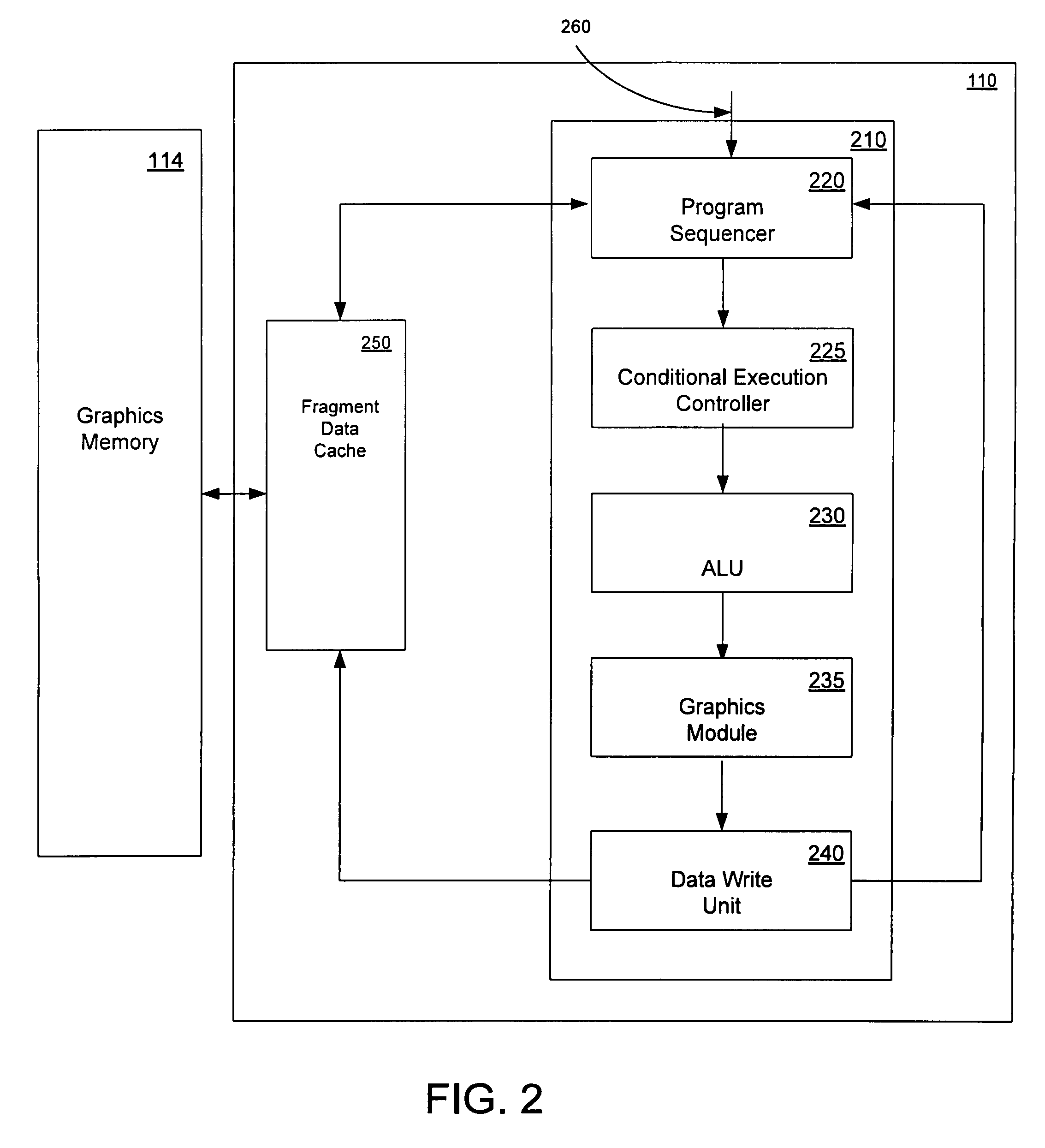

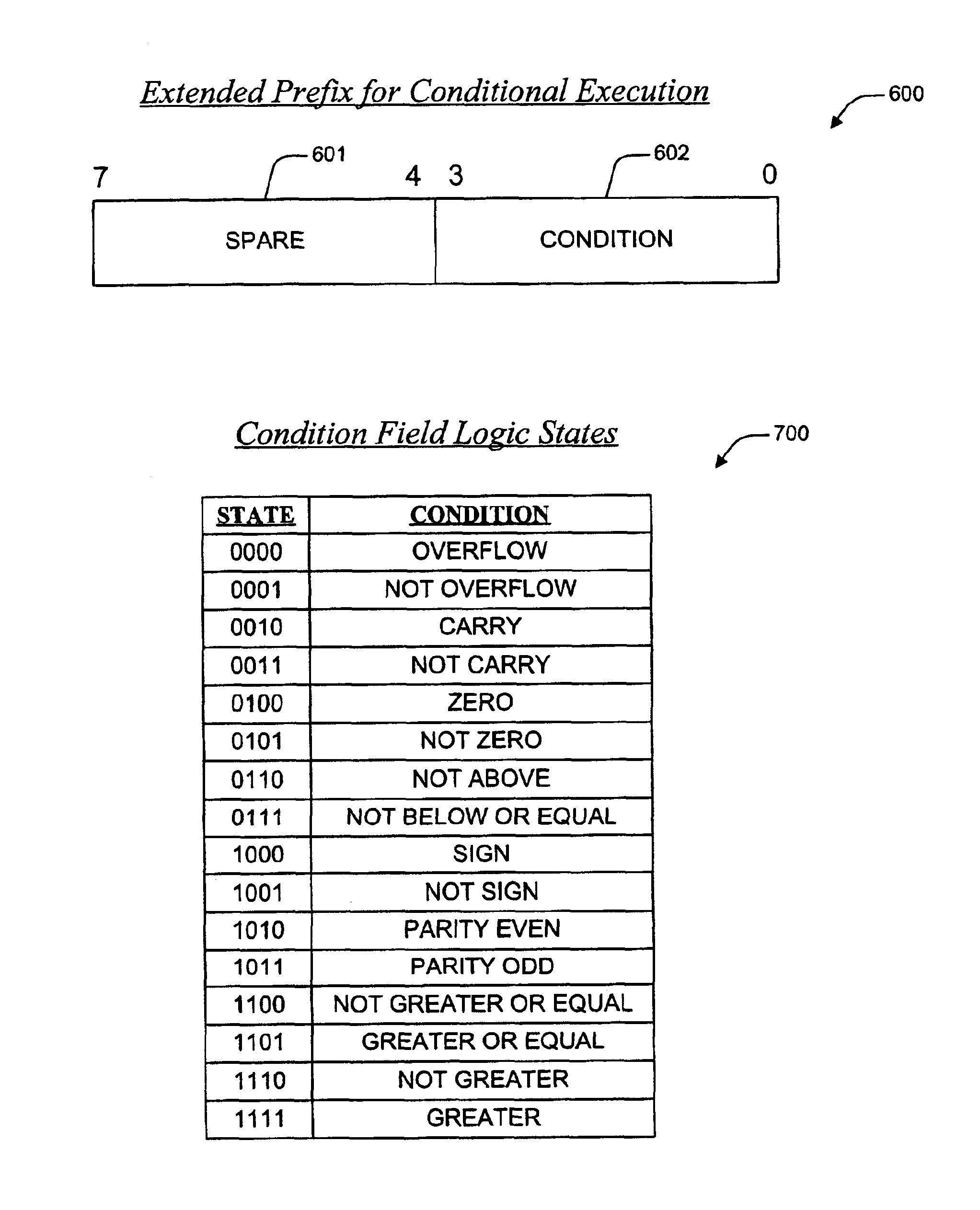

Conditional execution flag in graphics applications

Detailed herein are approaches to enabling conditional execution of instructions in a graphics pipeline. In one embodiment, a method of conditional execution controller operation is detailed. The method involves configuring the conditional execution controller to evaluate conditional test. A pixel data packet is received into the conditional execution controller, and evaluated, with reference to the conditional test. A conditional execution flag, associated with the pixel data packet, is set, to indicate whether a conditional operation should be performed on the pixel data packet.

Owner:NVIDIA CORP

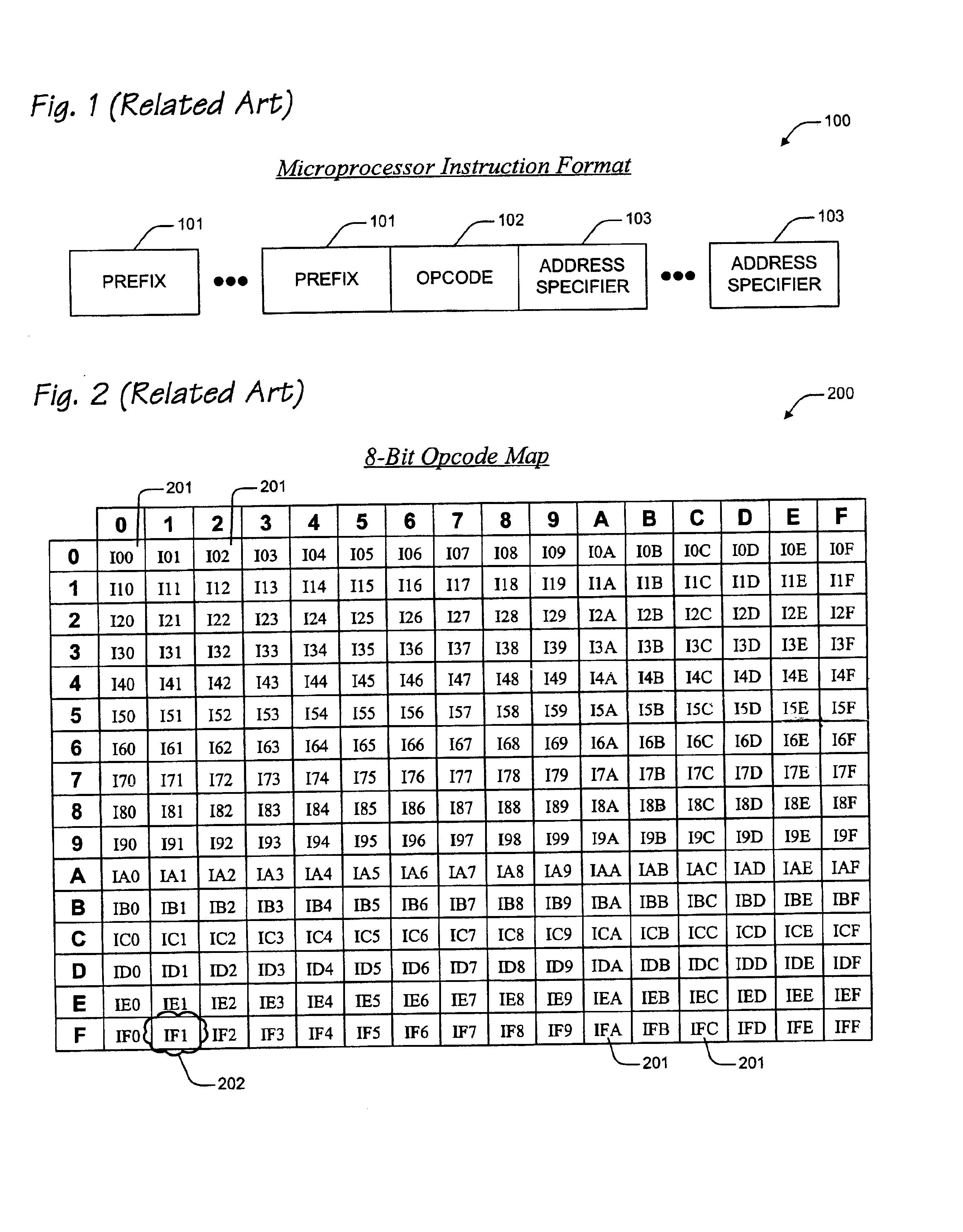

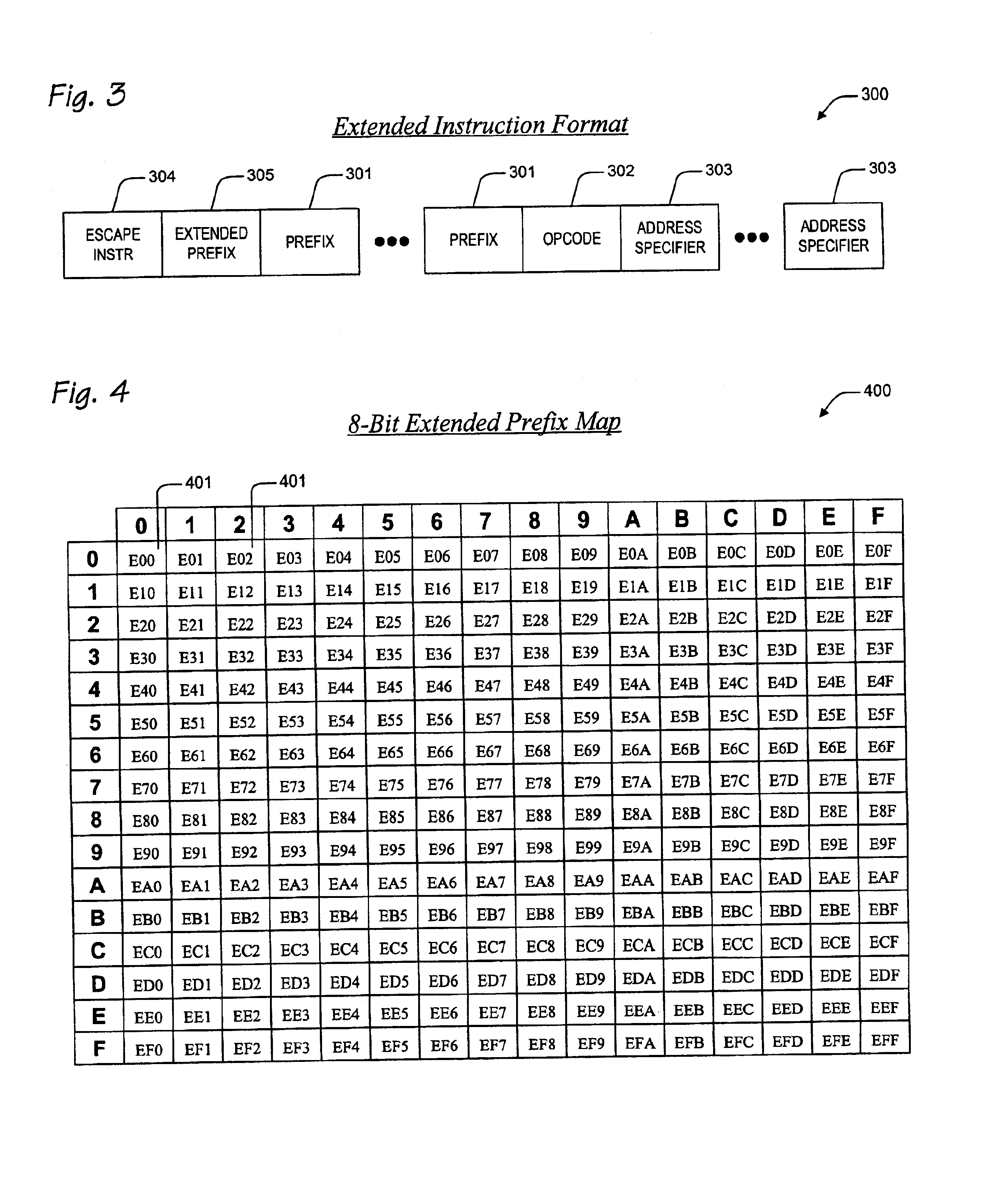

Apparatus and method for conditional instruction execution

ActiveUS7155598B2Preventing executionGood techniqueDigital computer detailsConcurrent instruction executionConditional executionInstruction set

A conditional execution apparatus in a microprocessor is provided. The conditional execution apparatus includes translation logic and extended execution logic. The translation logic translates an extended instruction into corresponding micro instructions. The extended instruction has and extended prefix and an extended prefix tag. The extended prefix specifies a condition, where execution of an operation prescribed by the extended instruction depends upon realization of the condition. The extended prefix tag indicates the extended prefix, where the extended prefix tag is an otherwise architecturally specified opcode within an instruction set for the microprocessor. The extended execution logic is coupled to the translation logic. The extended execution logic receives the corresponding micro instructions, and evaluates the condition. If the condition is not realized, then the extended execution logic precludes execution of the operation.

Owner:IP FIRST +1

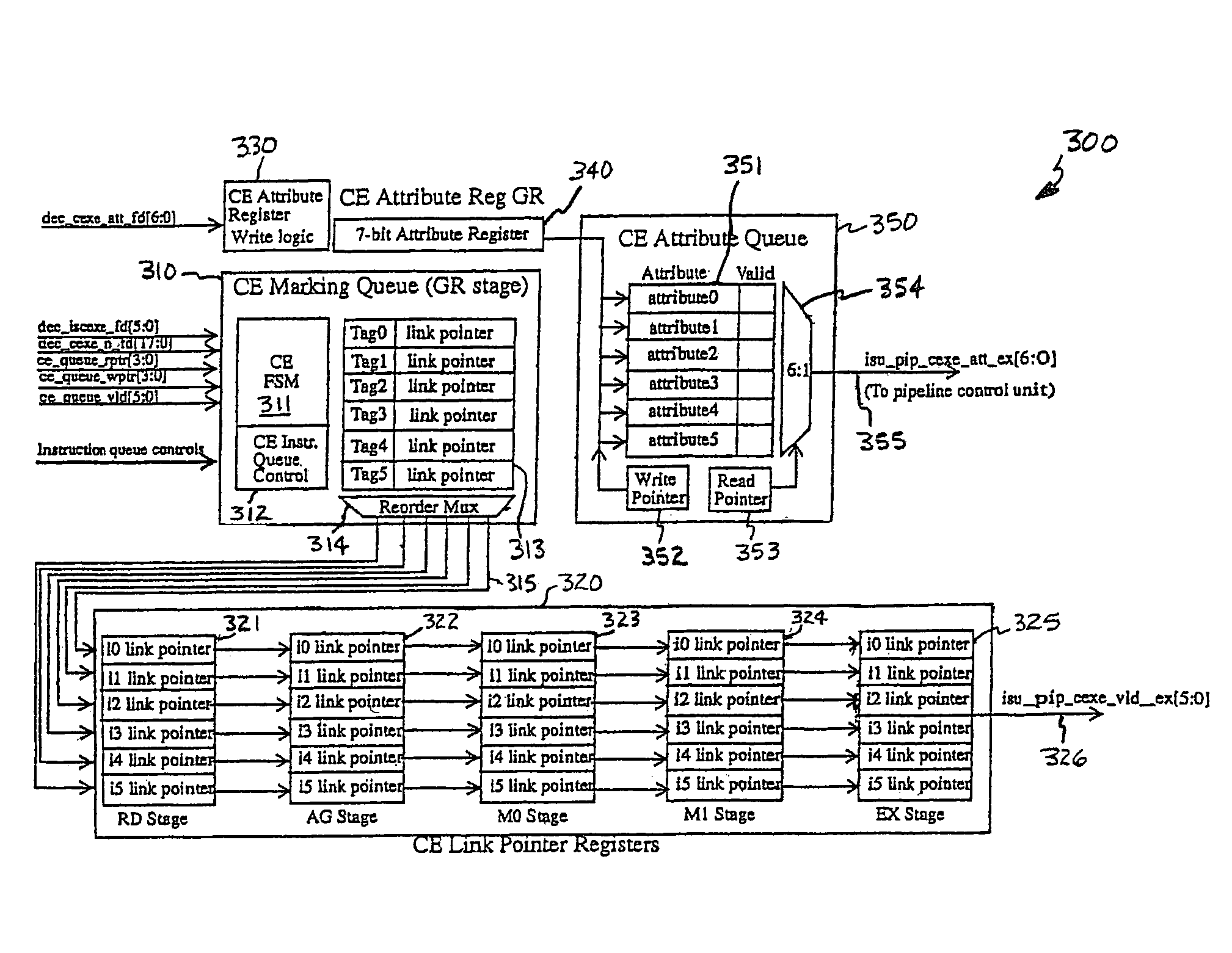

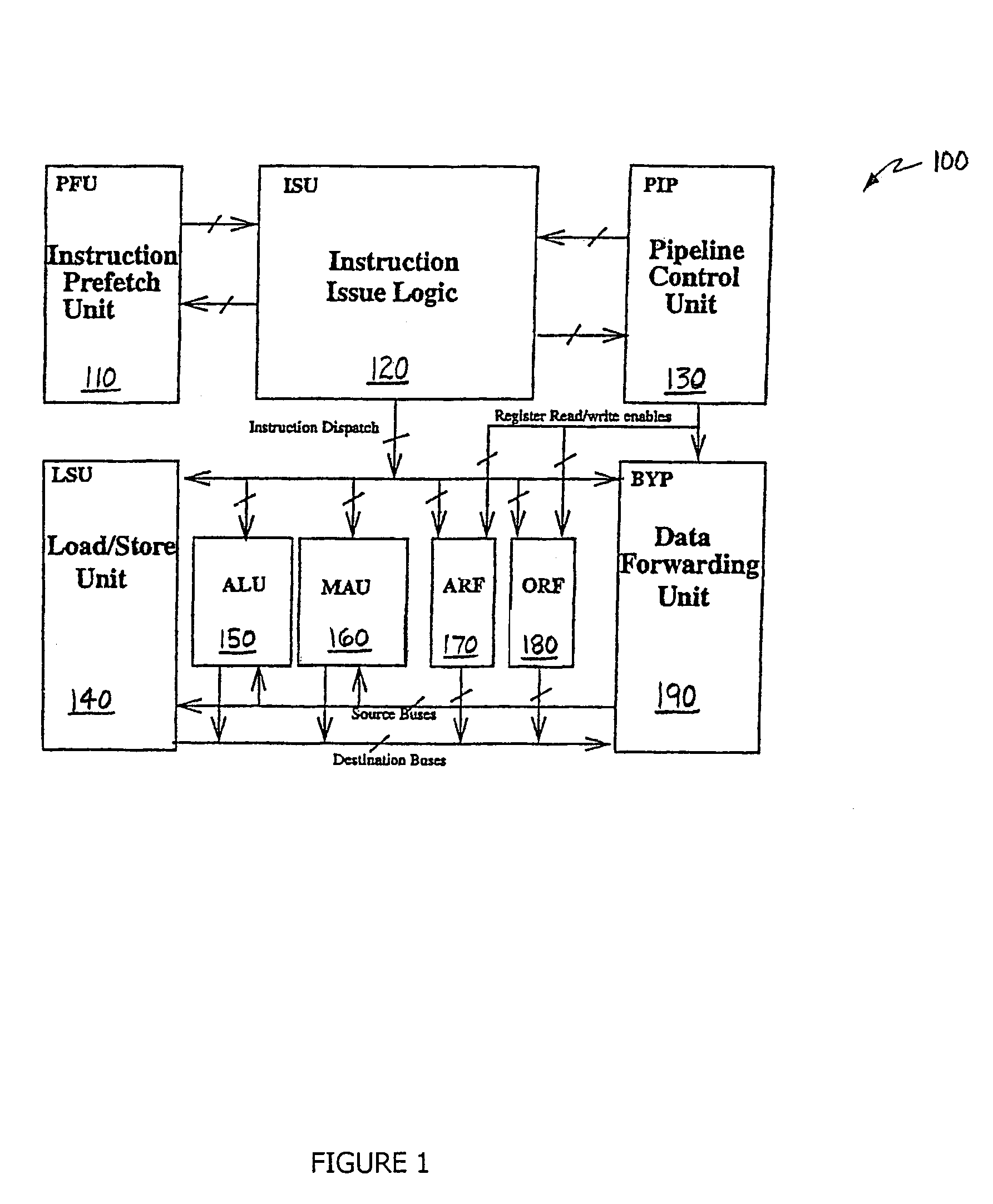

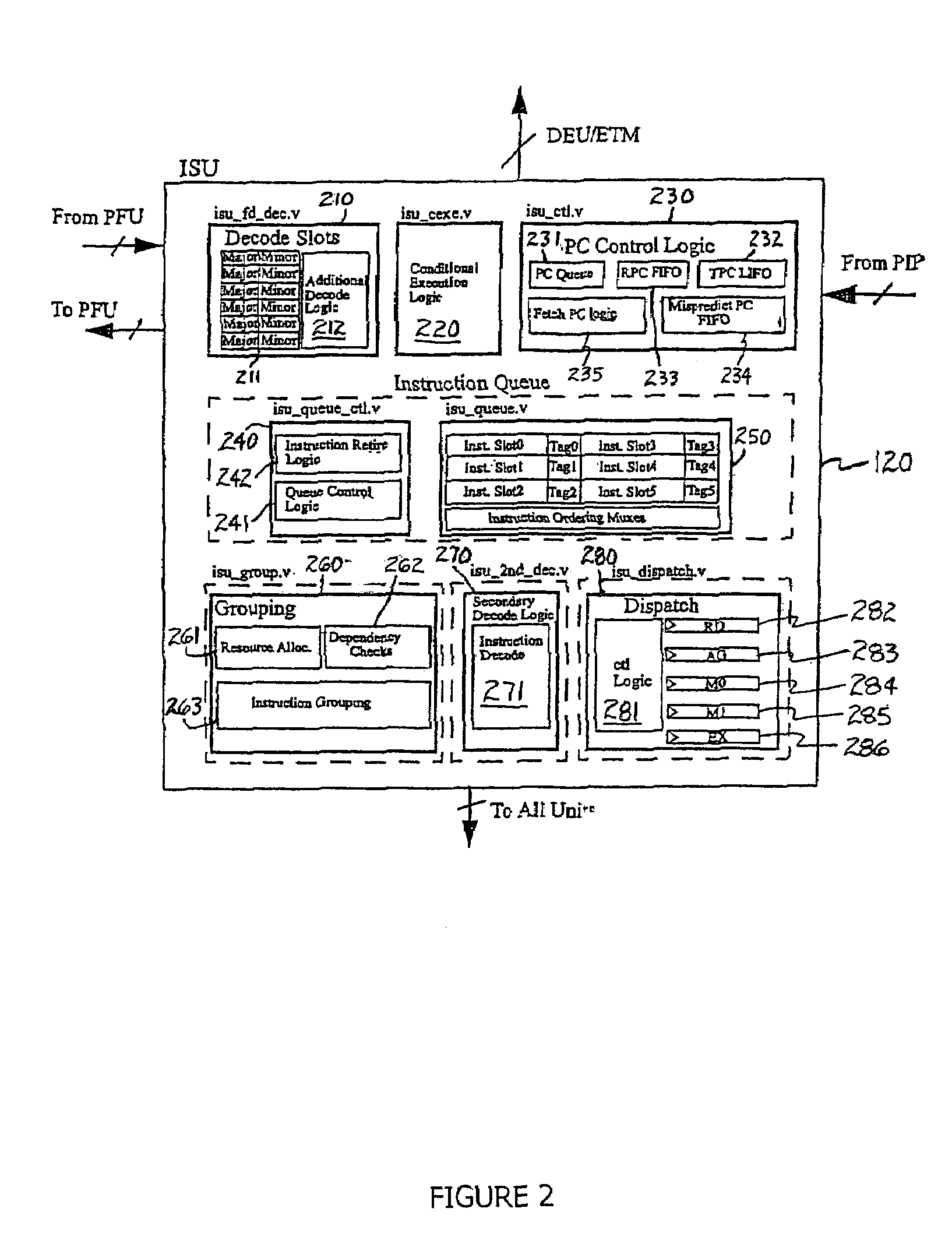

Conditional link pointer register sets marking the beginning and end of a conditional instruction block where each set corresponds to a single stage of a pipeline that moves link pointers through each corresponding register of said register sets as instructions move through the pipeline

InactiveUS7251721B1Save powerGeneral purpose stored program computerSpecific program execution arrangementsSingle stageProcessor register

For use in a wide-issue processor, a mechanism for, and method of, conditionally executing instructions and a digital signal processor (DSP) incorporating the mechanism or the method. In one embodiment, the mechanism includes: (1) a conditional execution block state machine that tags and generates link pointers for instructions located in a conditional execution block and (2) conditional link pointer registers, associated with stages in a pipeline of the processor, that contain and cause the link pointers to move therethrough as the instructions located in the conditional execution block move through the stages.

Owner:VERISILICON HLDGCO LTD

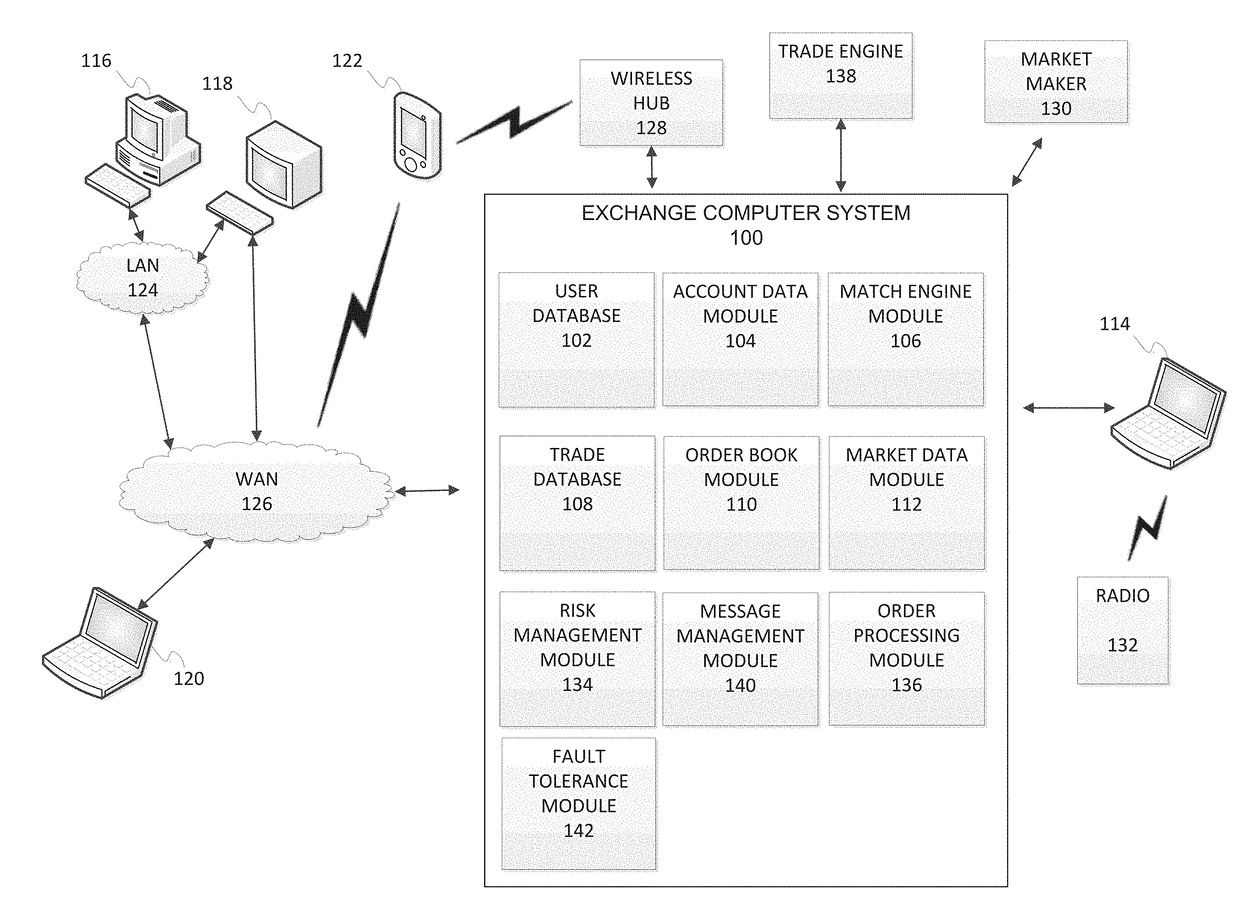

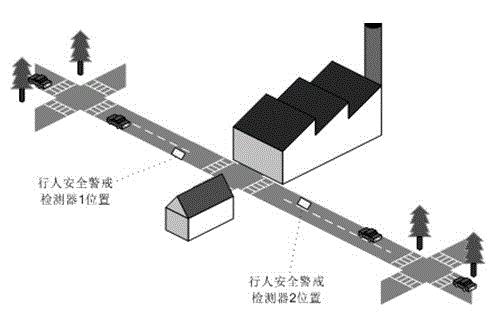

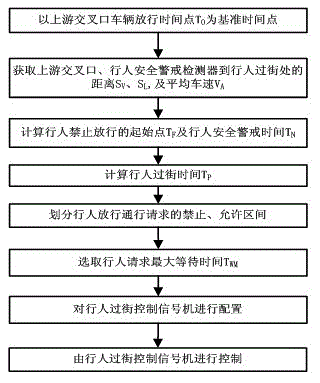

Execution of co-dependent transactions in a transaction processing system

Systems and methods are disclosed for ensuring execution of multiple inter-dependent transactions in an electronic data transaction processing system in which a plurality of data items are transacted by one or more hardware matching processors associated therewith that match a combined electronic data transaction request comprising a conditional execution instruction and a plurality of component electronic data transaction request messages, each for transaction of a different data item of the plurality of data items.

Owner:CHICAGO MERCANTILE EXCHANGE

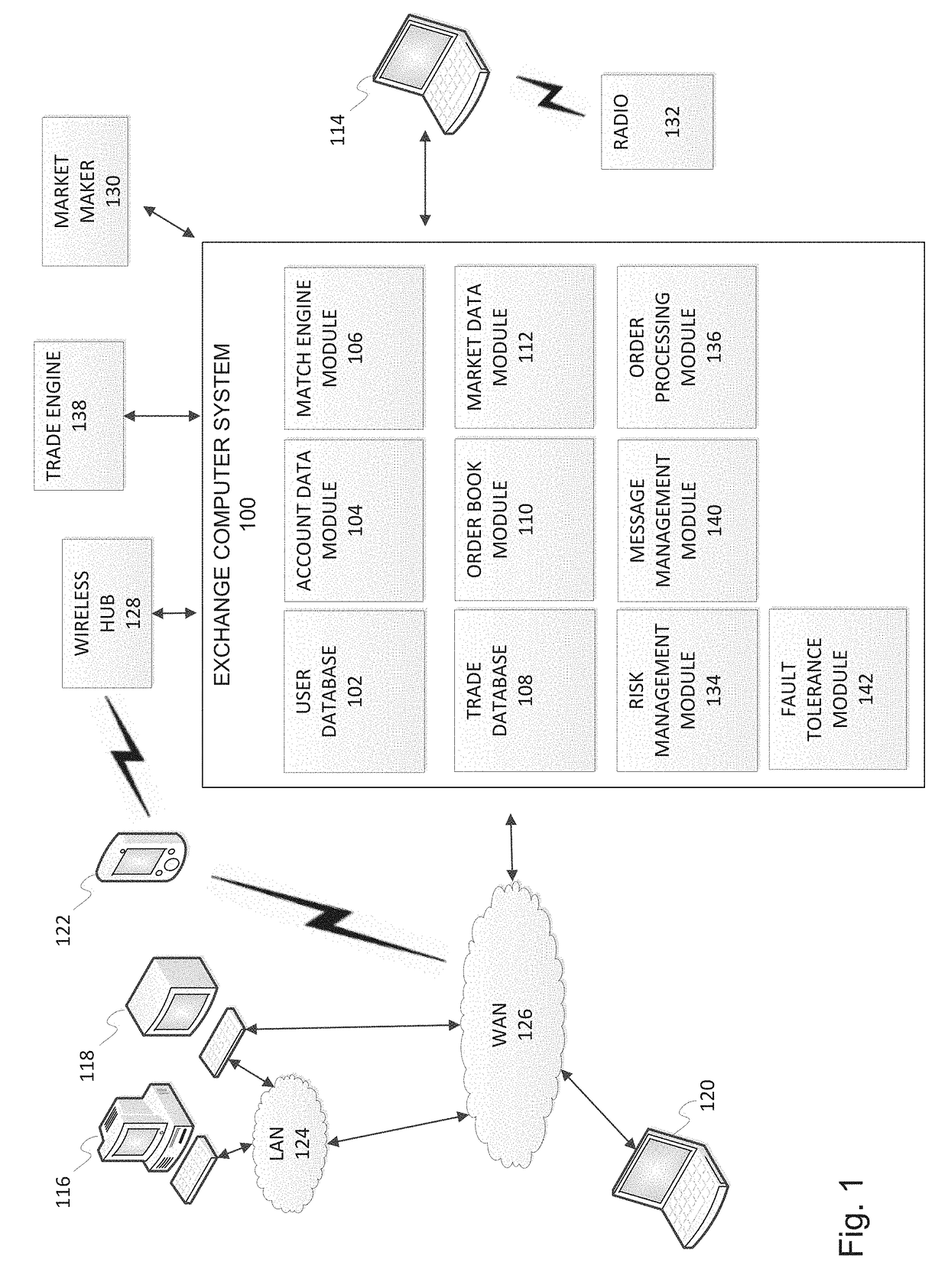

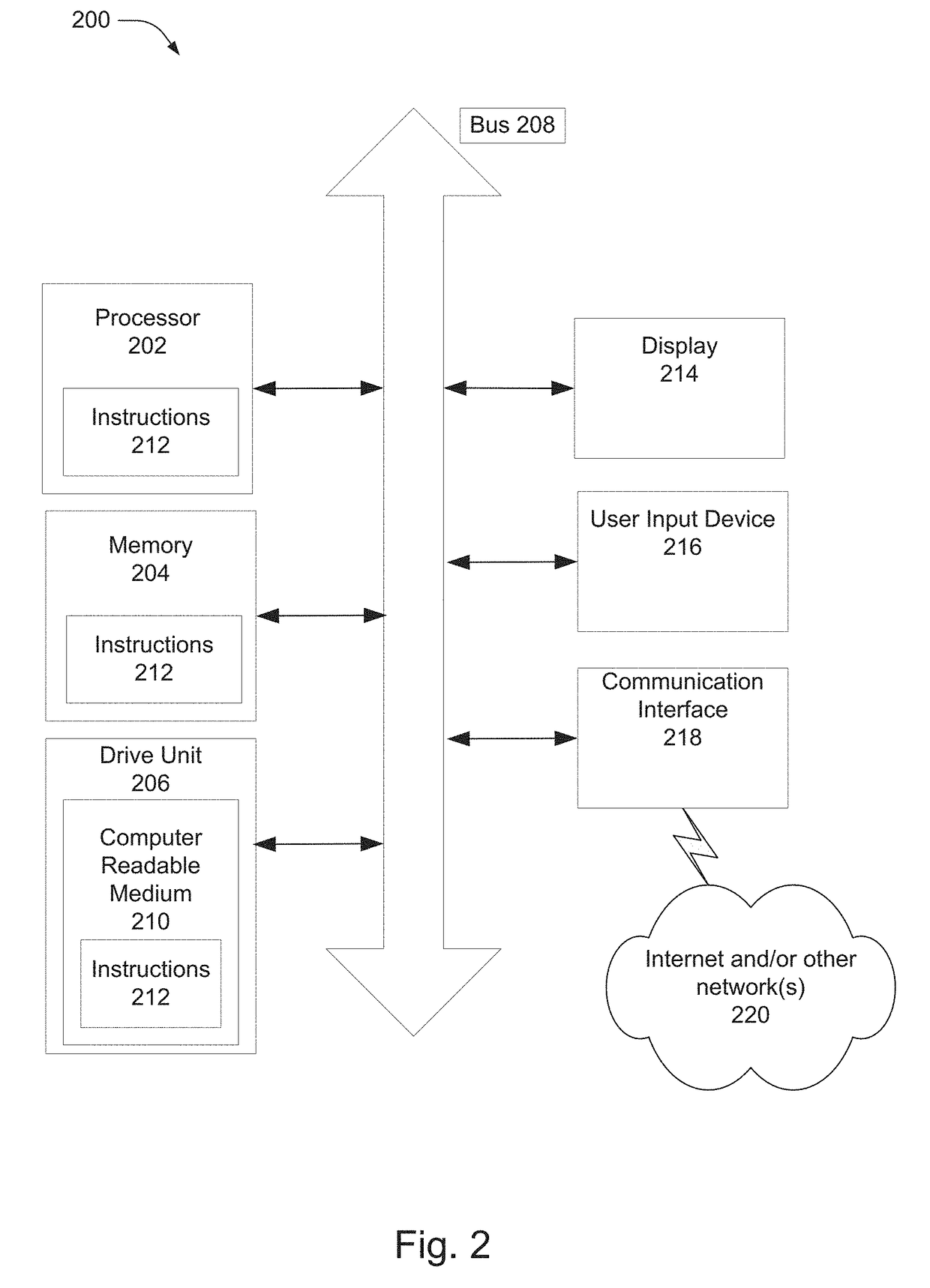

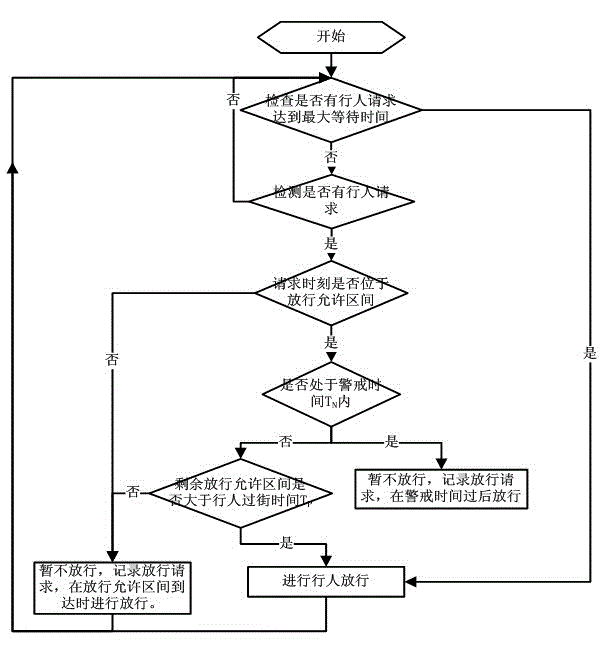

Road segment pedestrian crossing controlling method based on vehicles on upstream and vehicles on downstream coordinated

ActiveCN103065476AEnsure safe crossingGuaranteed right of wayControlling traffic signalsEngineeringConditional execution

The invention discloses a road segment pedestrian crossing controlling method based on vehicles on upstream and vehicles on downstream coordinated. According to the road segment pedestrian crossing controlling method based on the vehicles on the upstream and the vehicles on the downstream coordinated, firstly judging whether present time in within a crossing allowing range when a pedestrian sends out a request, if the present time is within the crossing allowing range, the request of the pedestrian is executed in a conditioned mode after the judging of guiding time and the longest waiting time TWM of the pedestrian, if the resent time is not within the crossing allowing range, the request of the pedestrian can not be executed immediately and can be executed until the request is in the crossing allowing range, and if the request of the pedestrian reaches to the longest waiting time TWM, the pedestrian is allowed to cross immediately. According to the road segment pedestrian crossing controlling method based on the vehicles on the upstream and the vehicles on the downstream coordinated, coordinating effect of the vehicles on the upstream and the vehicles on the downstream is prevented from being destroyed, safe travelling of pedestrians and timely responsiveness of the request are completely considered, intelligent controlling degree of roads is improved, and positive effect on order and smooth releasing of urban vehicles is achieved.

Owner:QINGDAO HISENSE TRANS TECH

Apparatus and method for switchable conditional execution in a VLIW processor

ActiveUS7412591B2Reduce hardware complexitySave energy consumptionGeneral purpose stored program computerSpecific program execution arrangementsProcessor registerConditional execution

Owner:IND TECH RES INST

System and method for conditional execution of applications and promotions

ActiveUS20100261460A1Low costReduced serviceAccounting/billing servicesSpecial service for subscribersToll-Free Telephone NumberConditional execution

System and method for determining whether an incoming call originates from inside or outside of a mobile carriers network. An example system performs a GTT (global title translation) on an incoming number to determine the hosting carrier of any mobile phone number. After the result of the matching determination is made, a message is generated and sent to a caller associated with the call page. The generated message includes any of directory information associated with the subscriber, information associated with cost savings or comparisons associated with in-network calling, information regarding promotions for calling plans, mobile devices or device upgrades, requests to join a network, requests to join a social call plan, information regarding instant savings or call rebates, offers for online services or software, offers for reduced cost or free phone service in exchange for adoption of a predefined product or entering into a social network group.

Owner:CEQUINT INC

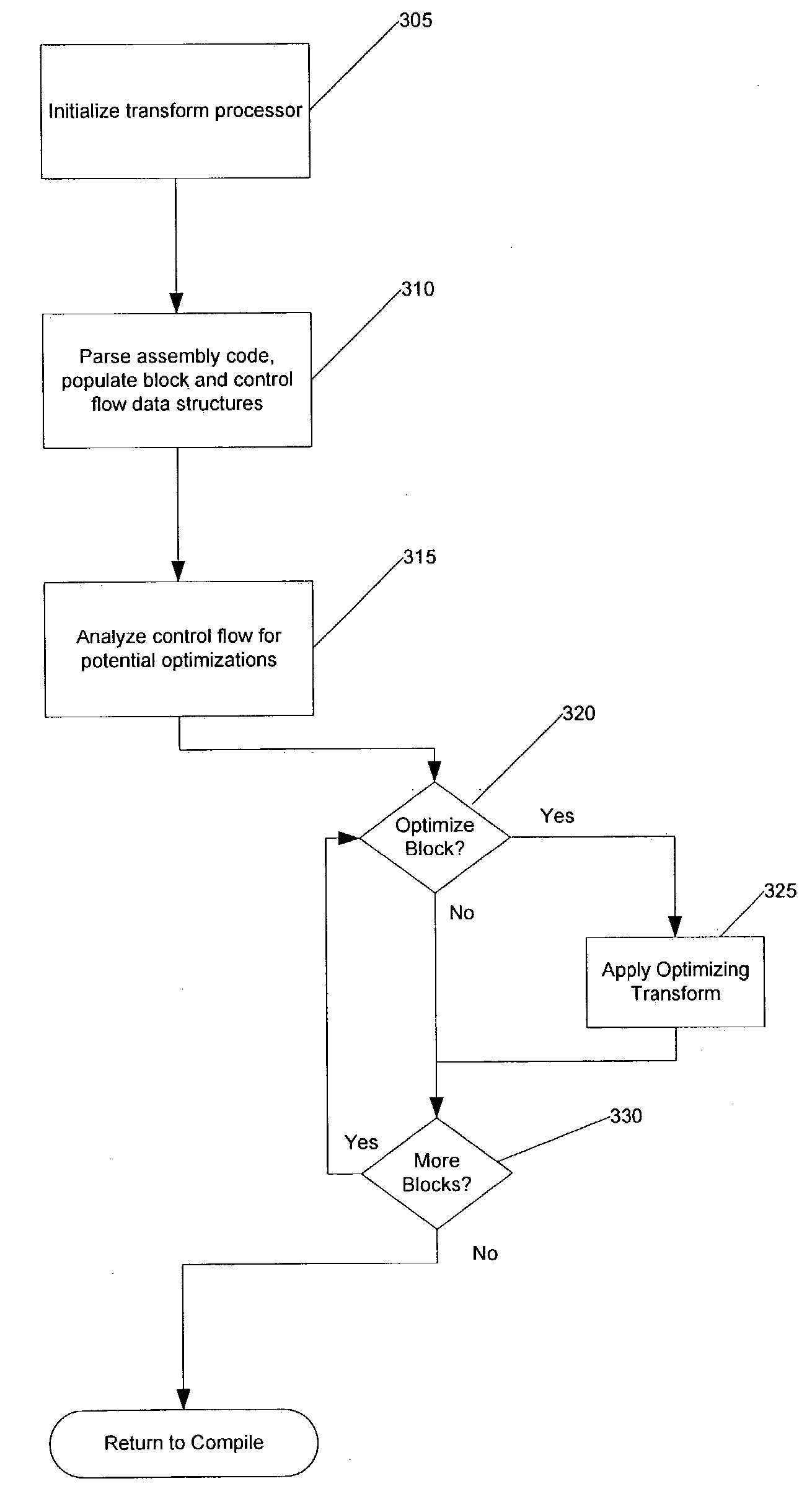

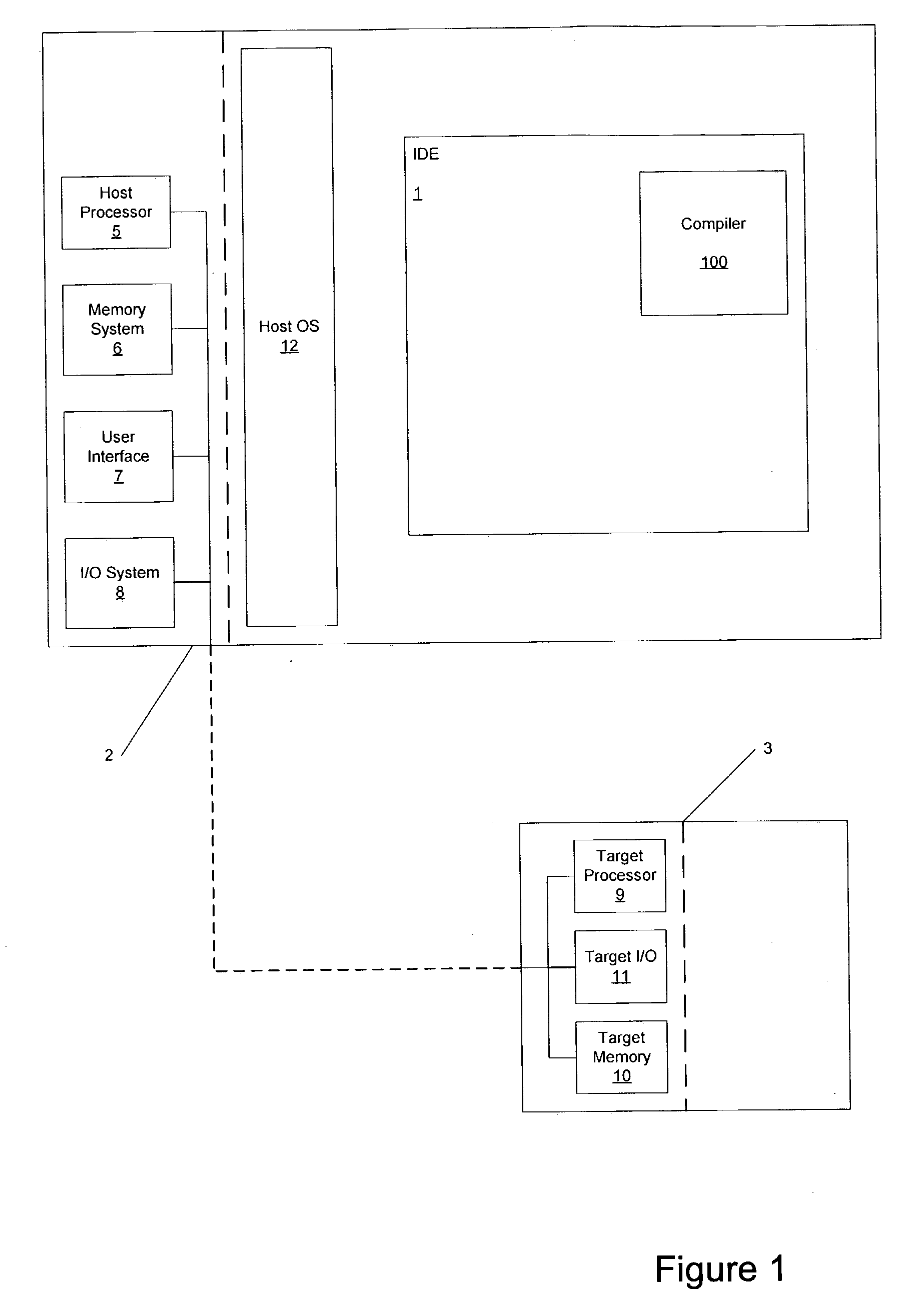

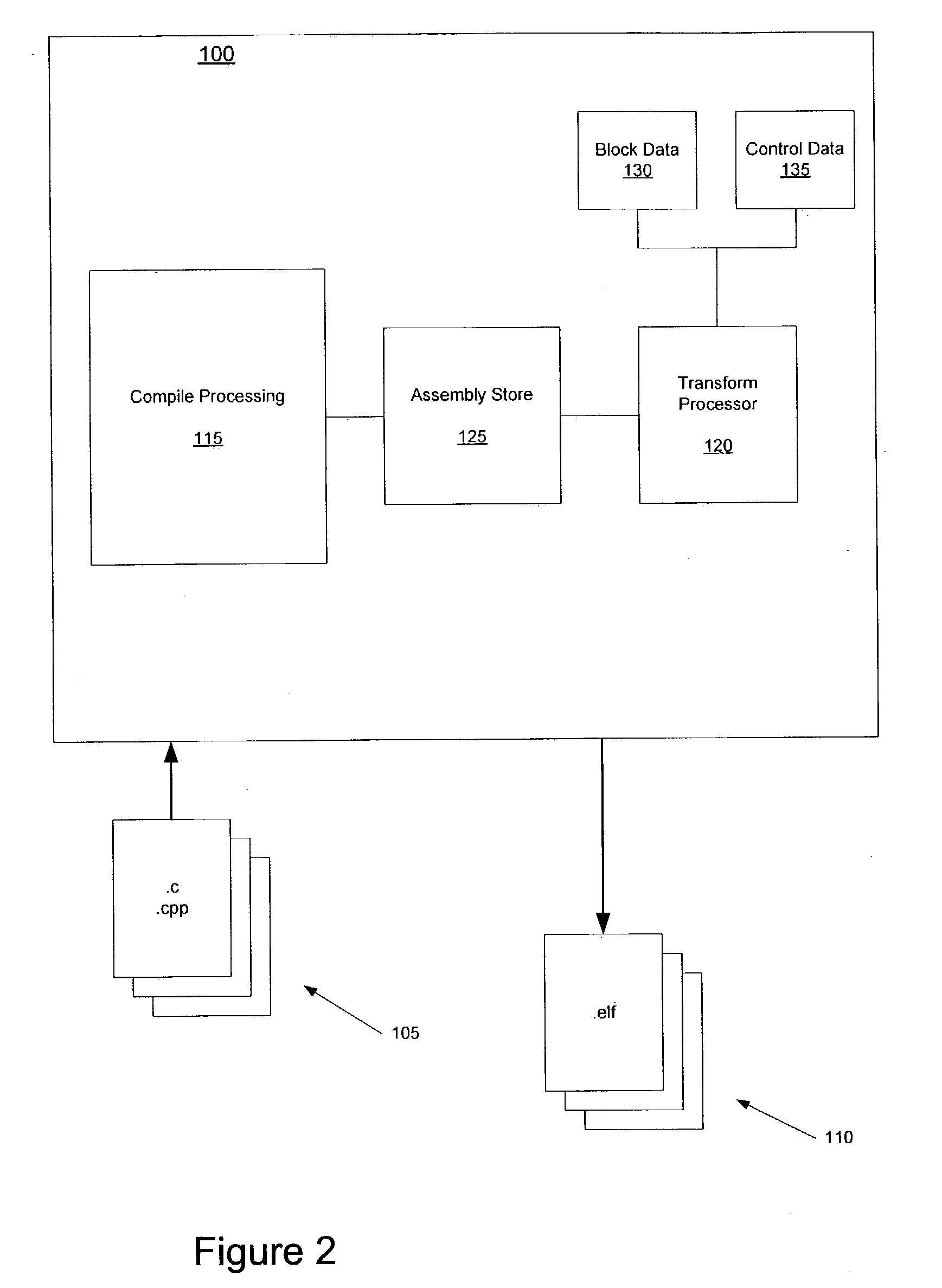

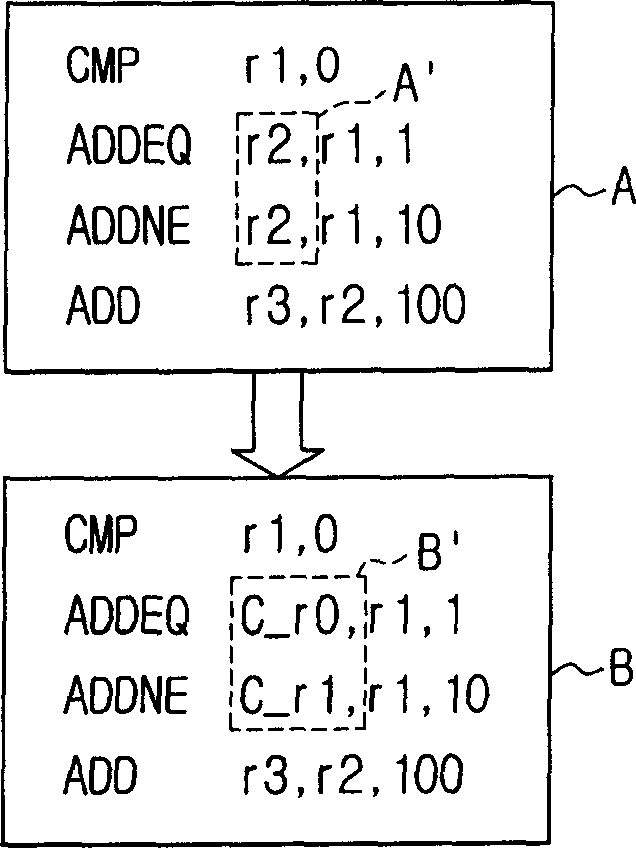

System and method for transformation of assembly code for conditional execution

A method and system may be implemented, according to a preferred embodiment of the present invention, to permit transformation of software to use conditional execution instructions. According to the preferred embodiment, a system and method is provided to transform machine instructions (for example, machine instructions generated by a source code compiler) to make use of the conditional execution features of a processor. The preferred embodiment thus reduces code size and better utilizes the instruction pipeline and cache.

Owner:WIND RIVER SYSTEMS

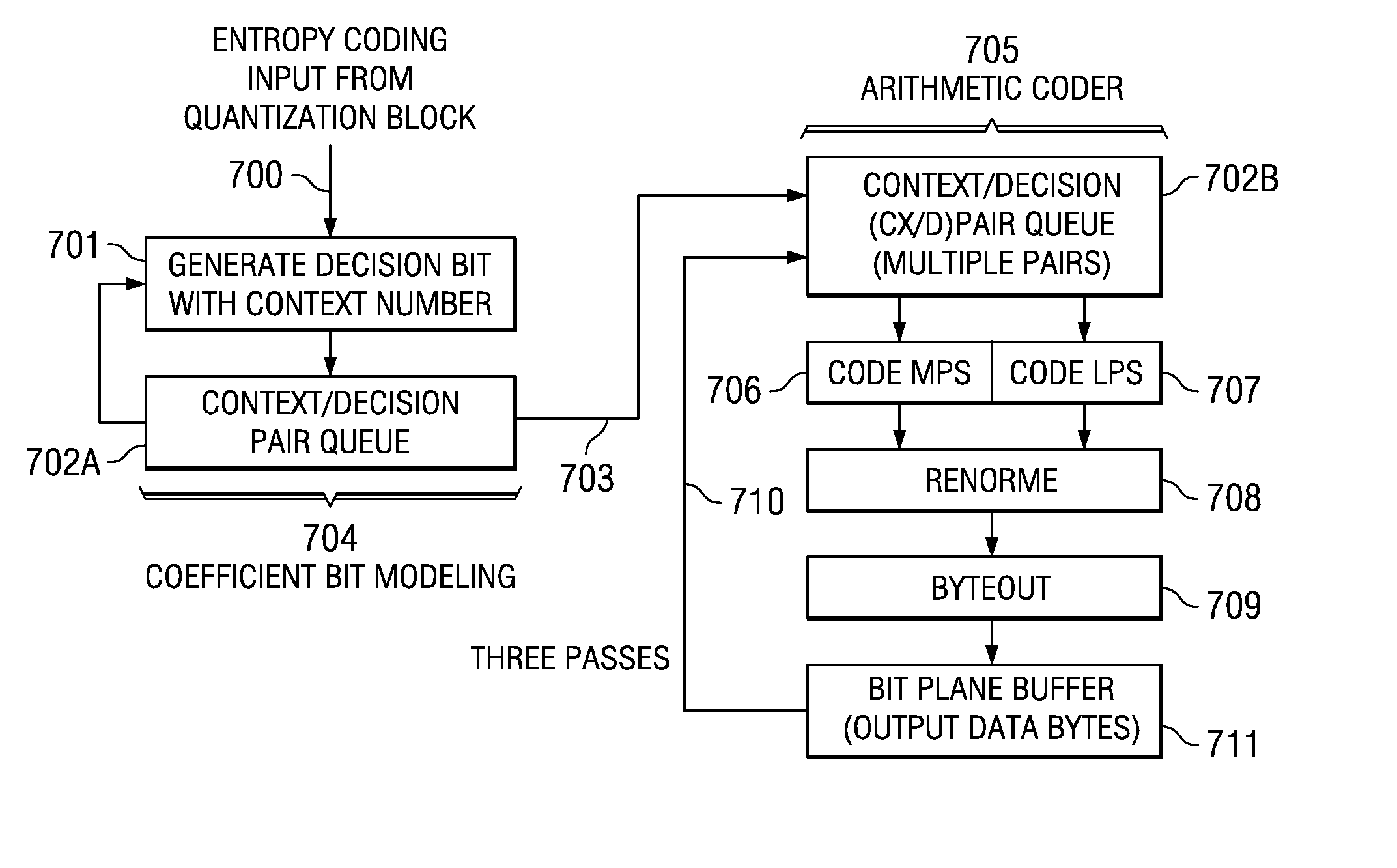

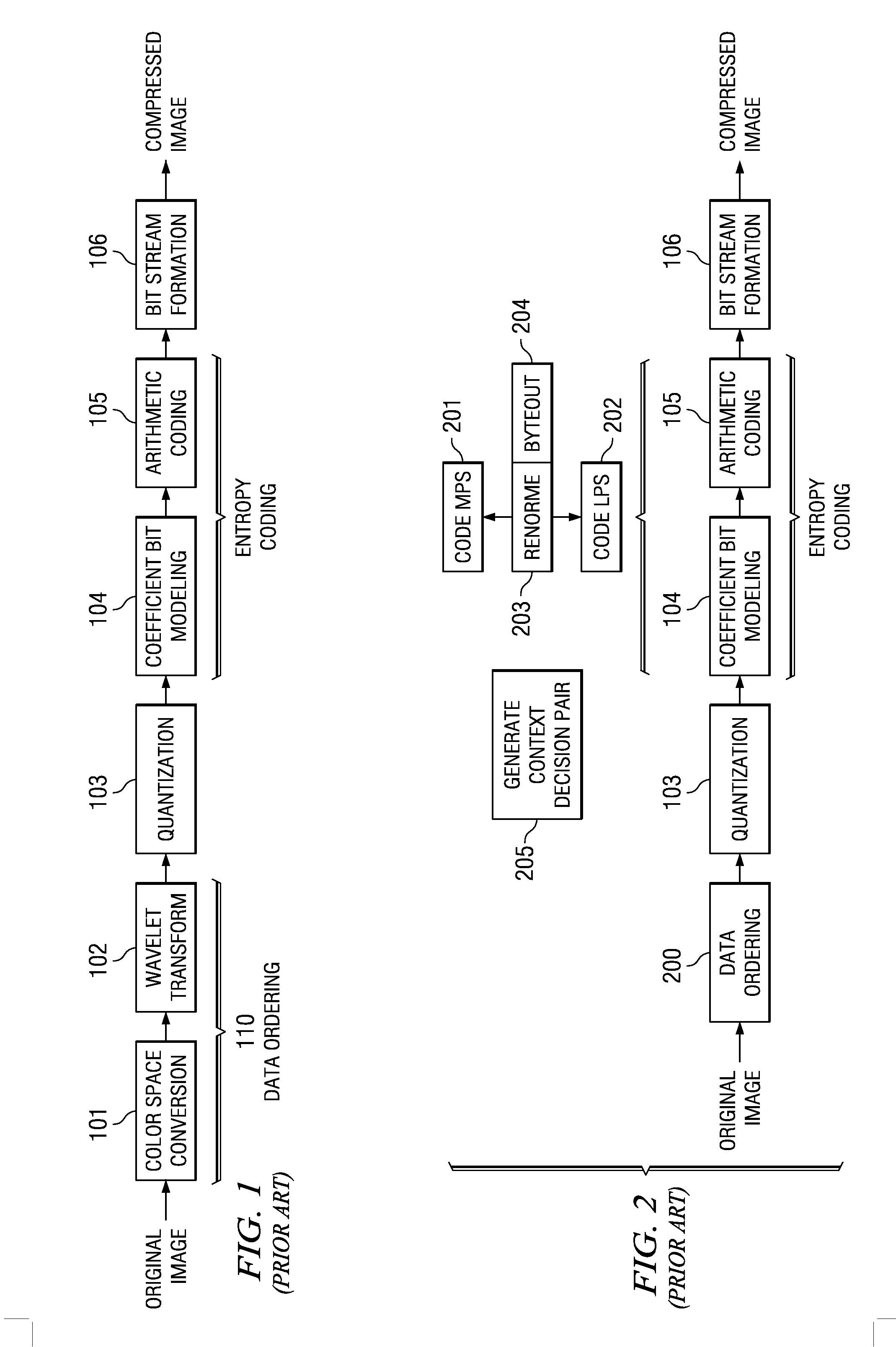

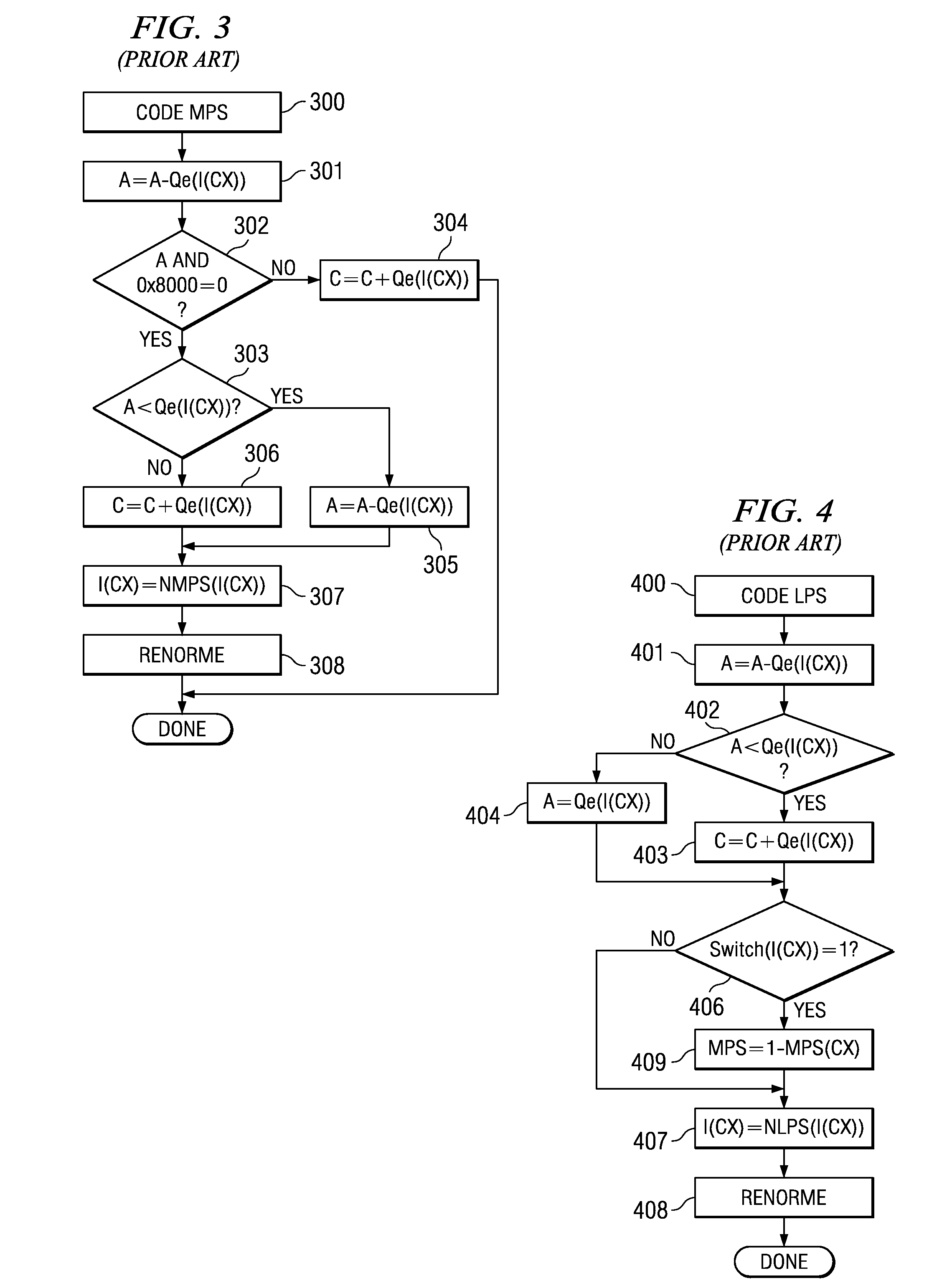

Method for Optimizing Software Implementations of the JPEG2000 Binary Arithmetic Encoder

InactiveUS20080118169A1Eliminating memory dependenciesCode conversionCharacter and pattern recognitionConditional executionArithmetic encoder

This invention is a JPEG2000 arithmetic encoder with improvements to conventional JPEG2000 encoder implementations. This invention decouples co-efficient bit modeling from arithmetic encoding, eliminates the RENORME while loop through least most bit detection, decouples encoding from BYTEOUT, exploits parallelism across conditional execution paths, uses look-up table storage and packing of context state data and eliminates memory dependencies through direct register forwarding.

Owner:TEXAS INSTR INC

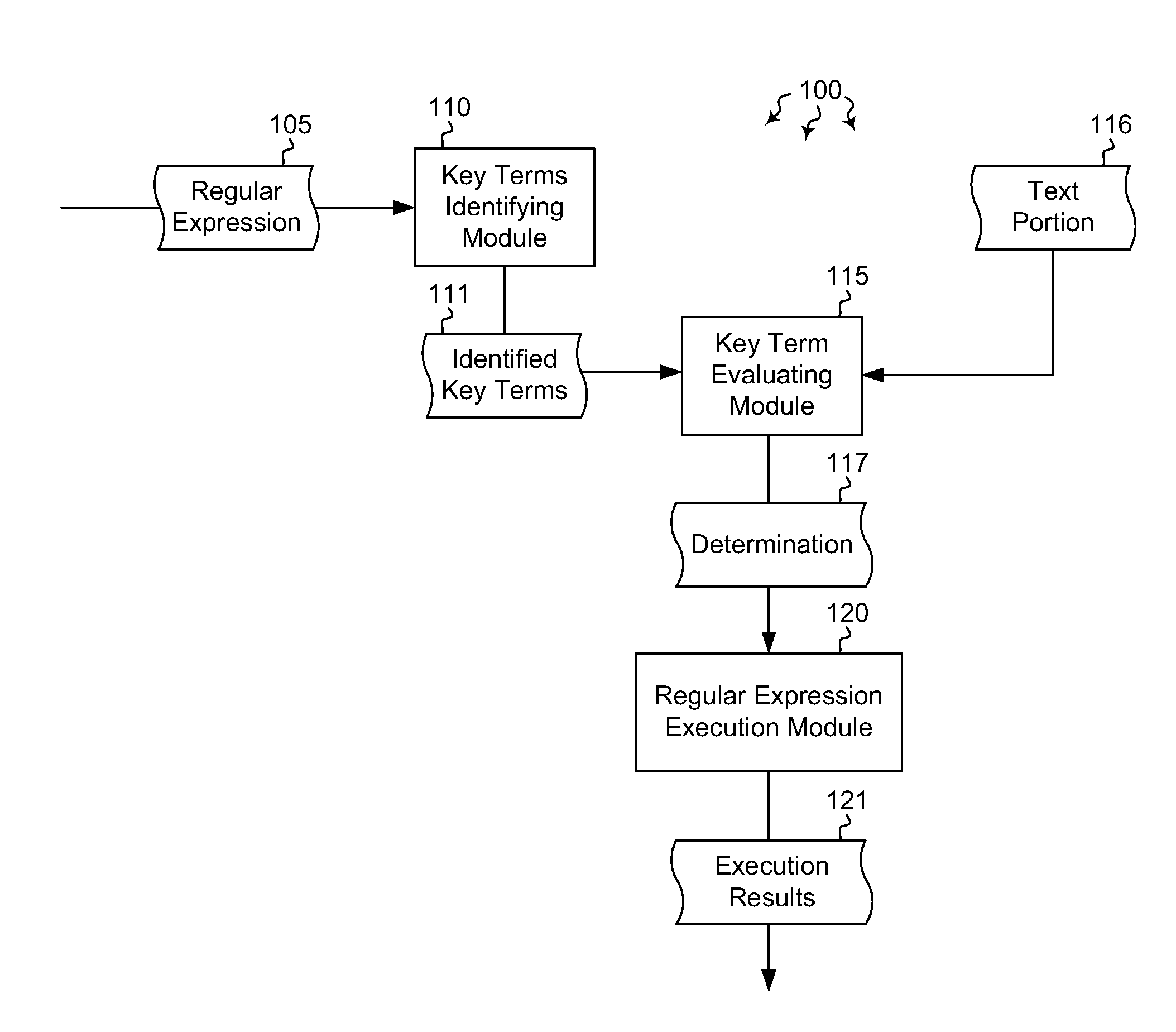

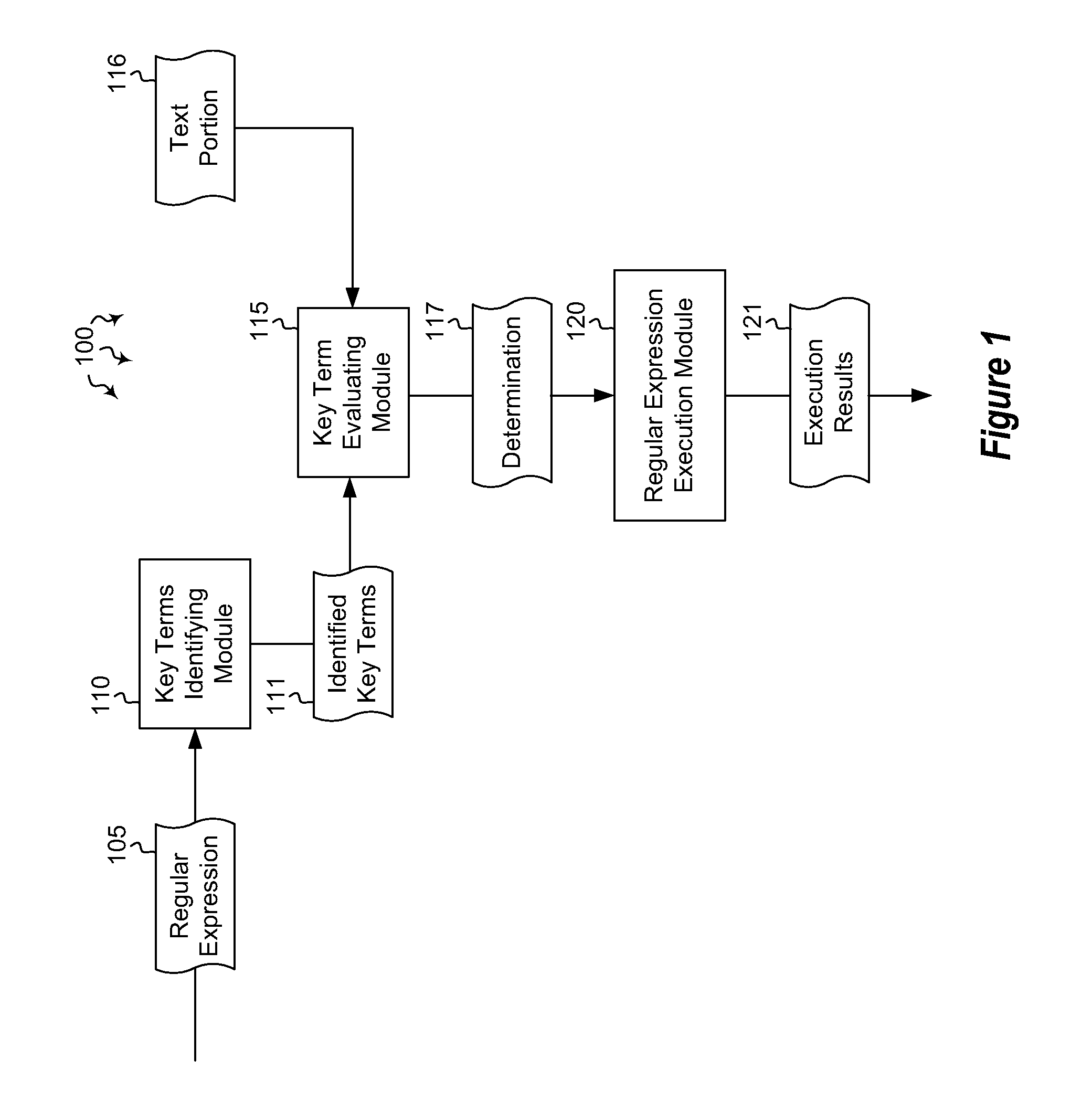

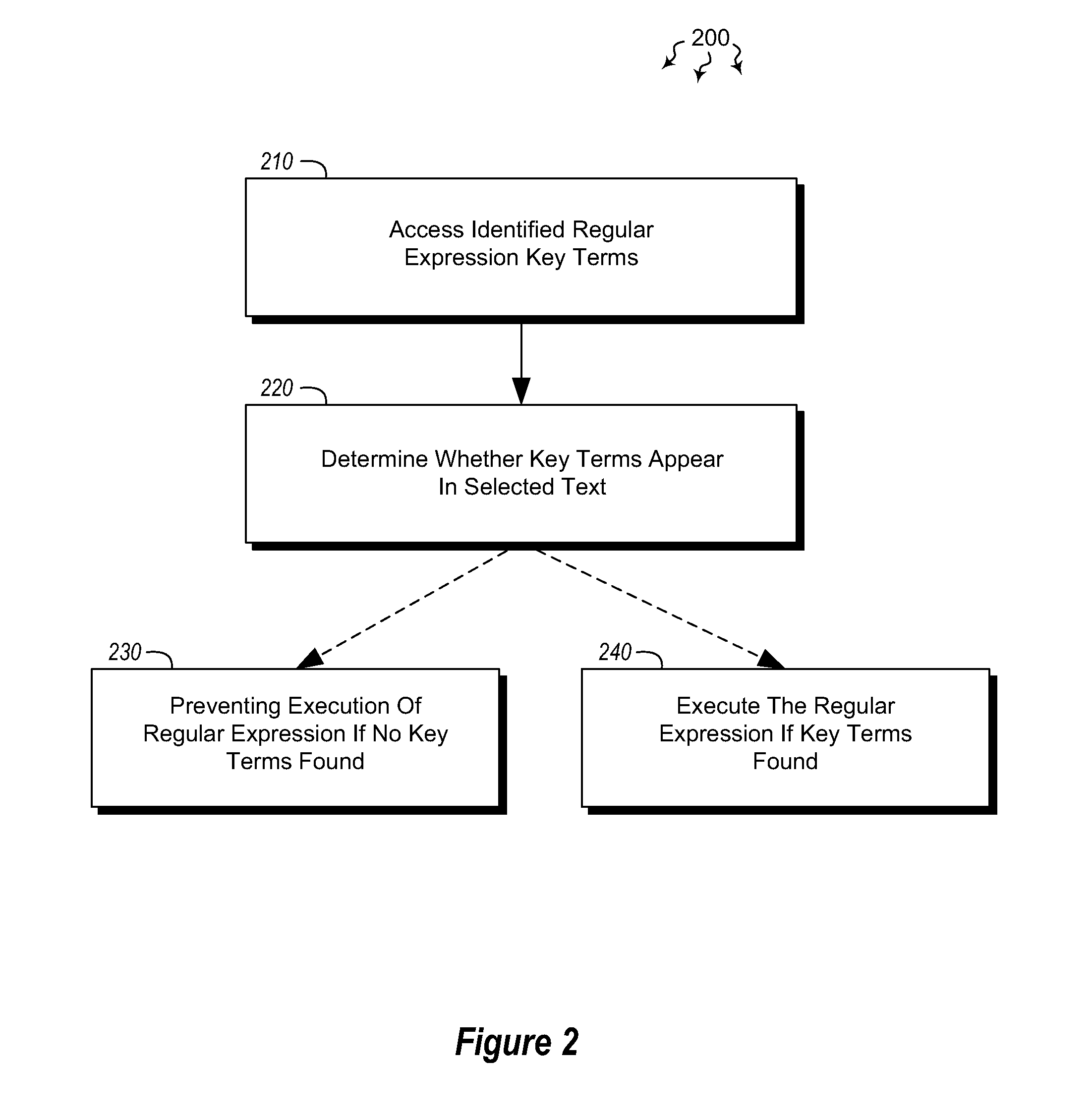

Conditional execution of regular expressions

InactiveUS20120110003A1High expressionPreventing executionDigital data information retrievalDigital data processing detailsKey termsTheoretical computer science

Embodiments directed to conditionally executing regular expressions and to simplifying regular expressions by canonicalizing regular expression terms. In an embodiment, a computer system accesses identified regular expression key terms that are to appear in a selected portion of text. The regular expression key terms are identified from terms in a selected regular expression. The computer system determines whether the identified regular expression key terms appear in the selected portion of text. The computer system also, upon determining that none of the identified regular expression key terms appears in the selected portion of text, prevents execution of the regular expression. Upon determining that at least one of the identified regular expression key terms appears in the selected portion of text, the computer system executes the regular expression.

Owner:MICROSOFT TECH LICENSING LLC

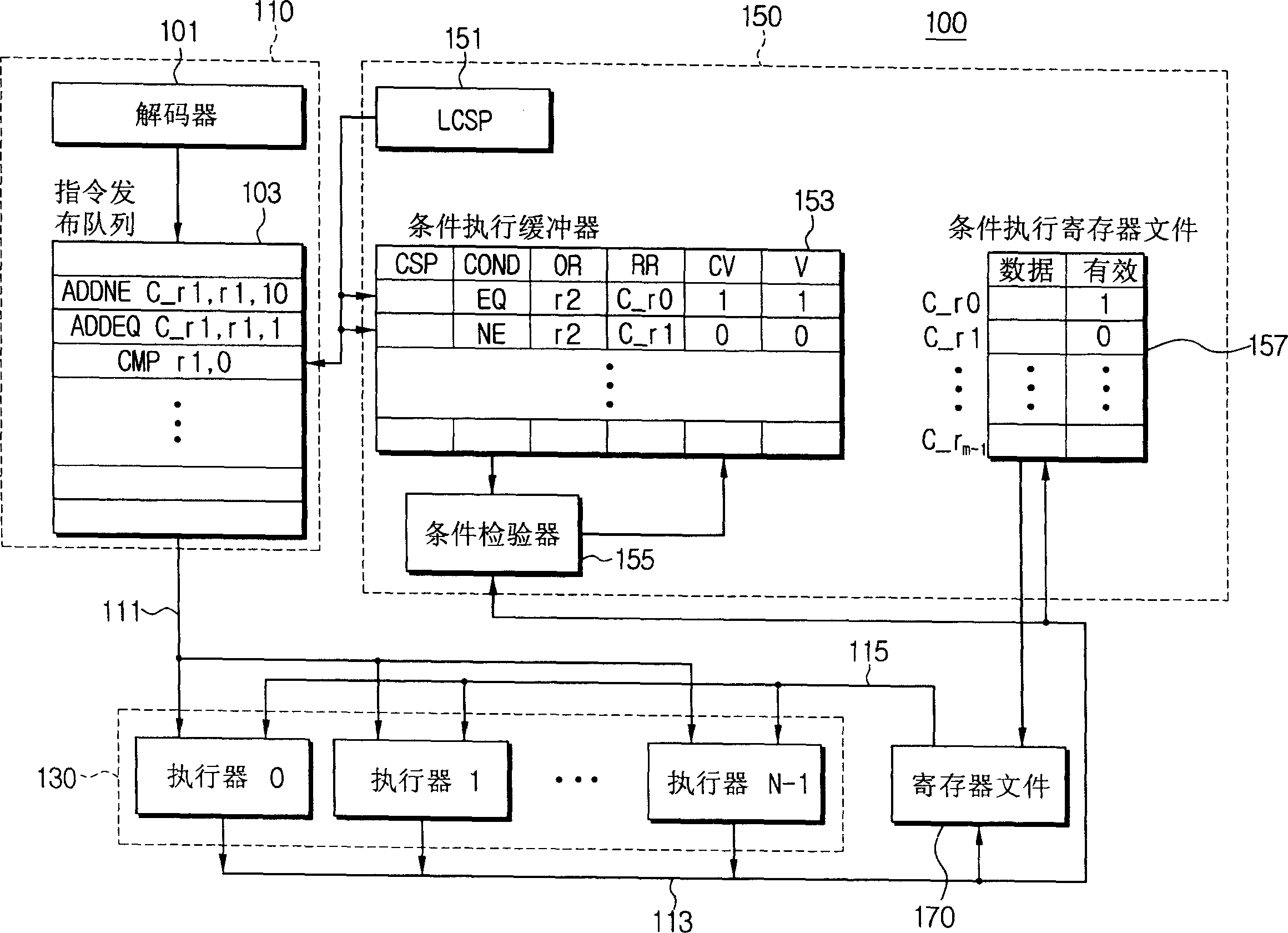

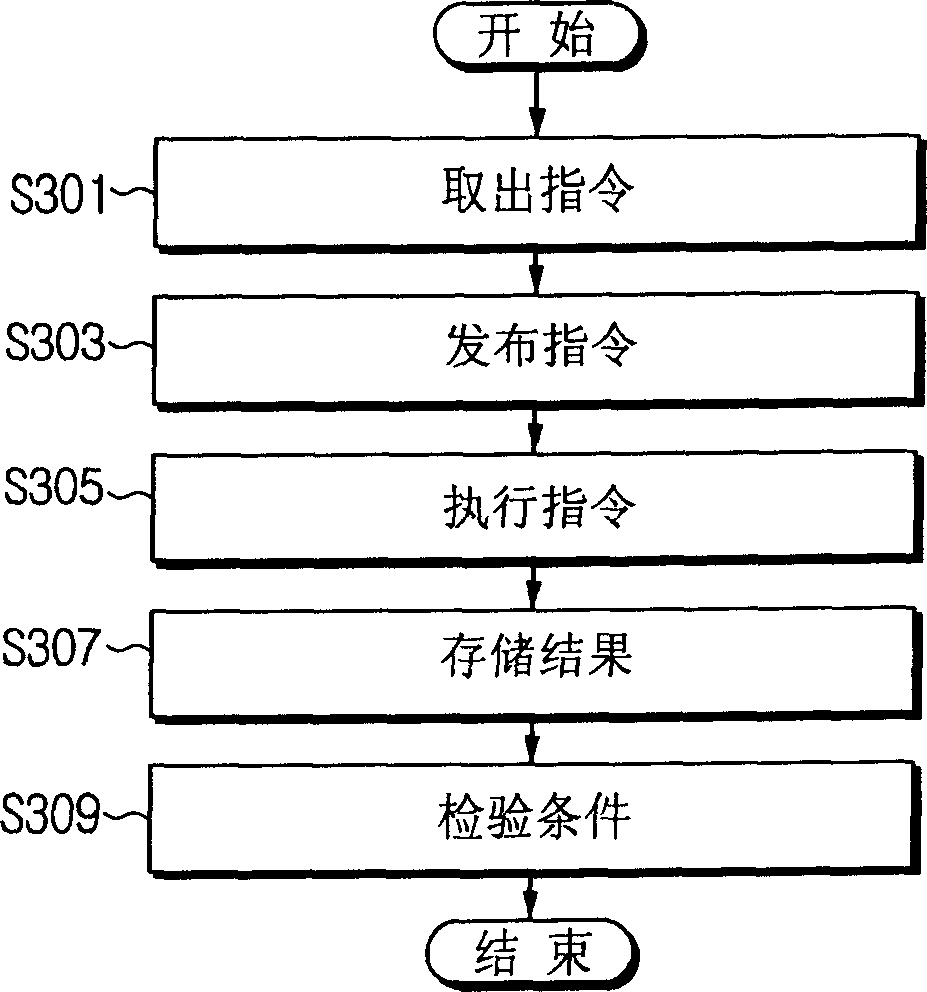

Hardware and executing method for condition commands in disorder

A hardware device for executing conditional instructions out-of-order and the execution method. An architecture is provided, enabling the hardware device such as a processor supporting the conditional instruction and a computer system to execute the instruction out-of-order. To this end, a conditional execution buffer is provided, and a register of a destination operand of the conditional instruction is renamed to another register. Hence, the hardware device using the conditional instruction can carry out the out-of-order execution, and the execution speed of the hardware device can be greatly improved.

Owner:SAMSUNG ELECTRONICS CO LTD

Processor and compiler for decoding an instruction and executing the instruction with conditional execution flags

InactiveUS20080209407A1Increase speedReduce the amount requiredSoftware engineeringNext instruction address formationConditional executionScaling circuits

The present invention provides a processor which has a small-scale circuit and is capable of executing loop processing at a high speed while consuming a small amount of power. When the processor decodes an instruction “jloop C6,C1:C4,TAR,Ra”, the processor (i) sets a conditional flag C4 to 0 when the value of a register Ra is smaller than 0, (ii) moves the value of a conditional flag C2 to a conditional flag C1, moves the value of a conditional flag C3 to the conditional flag C2, and moves the value of the conditional flag C4 to the conditional flags C3 and C6, (iii) adds −1 to the register Ra and stores the result into the register Ra, and (iv) branches to an address specified by a branch register (TAR). When not filled with a branch target instruction, the jump buffer will be filled with a branch target instruction.

Owner:OKABAYASHI HAZUKI +3