Coprocessor with multiple logic interface

A technology of coprocessor and protocol processor, applied in the architecture with a single central processing unit, architecture with multiple processing units, electrical digital data processing, etc., can solve problems affecting system performance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

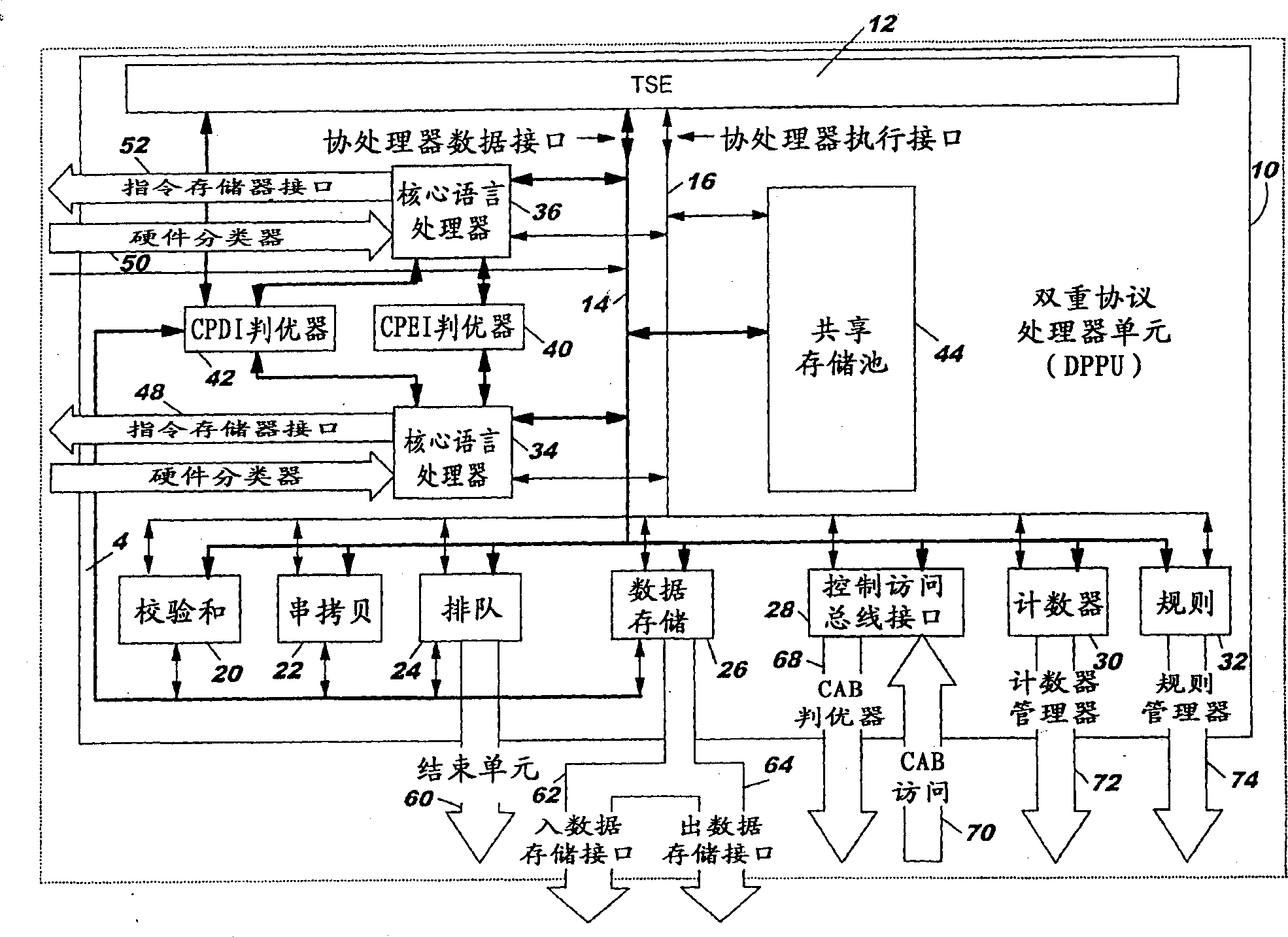

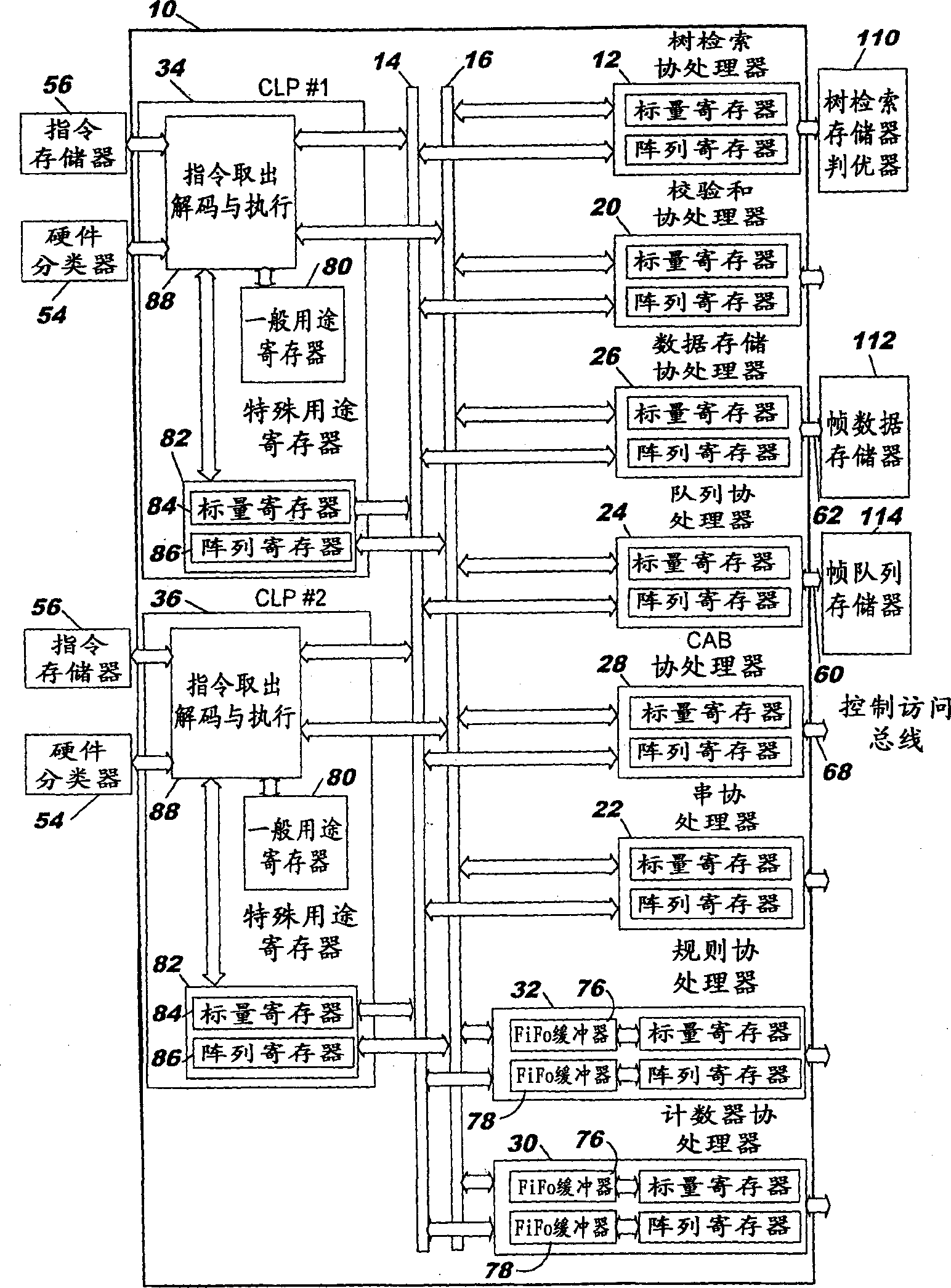

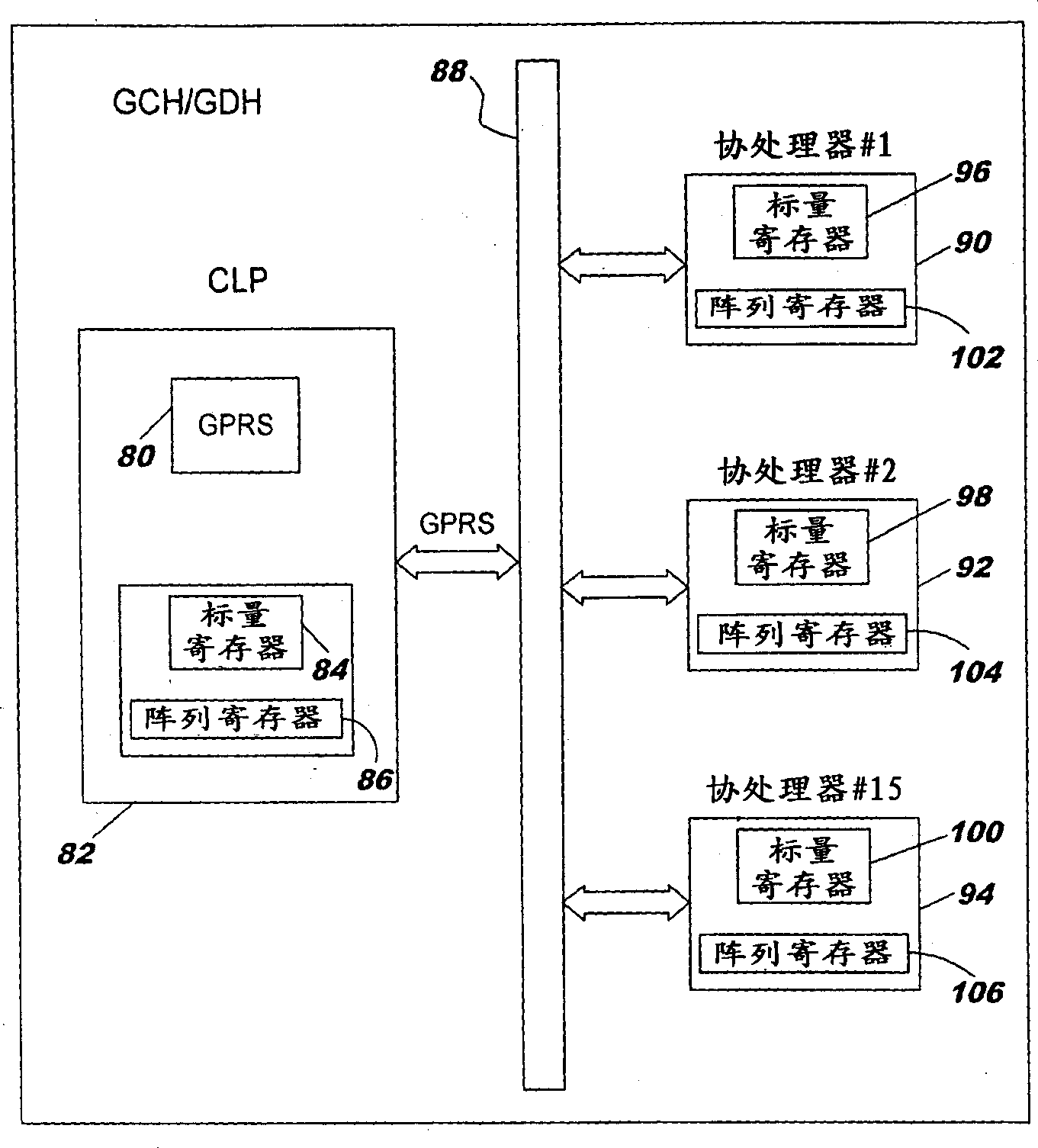

[0015] The present invention will be described in terms of an embedded processor complex providing and controlling the programming capabilities of a network processor. A combined implementation typically includes eight main processing units or protocol processor units (PPUs) working with hardware accelerators to support high-speed mode lookup, data manipulation, internal chip management functions, frame parsing, and data Prefetching. Each PPU comprises the following structural components: two CLPs; at least one, and preferably several dedicated and / or shared coprocessor units and an interface between the main processing unit and each coprocessor unit.

[0016] Each coprocessor unit can perform specific network tasks. The main processing unit executes a series of instructions in a stored program. Each co-processor unit is responsive to the main processing unit and adapted to perform specific tasks effectively under the control of the main processing unit. The interface betwe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More