Patents

Literature

263 results about "Instruction register" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

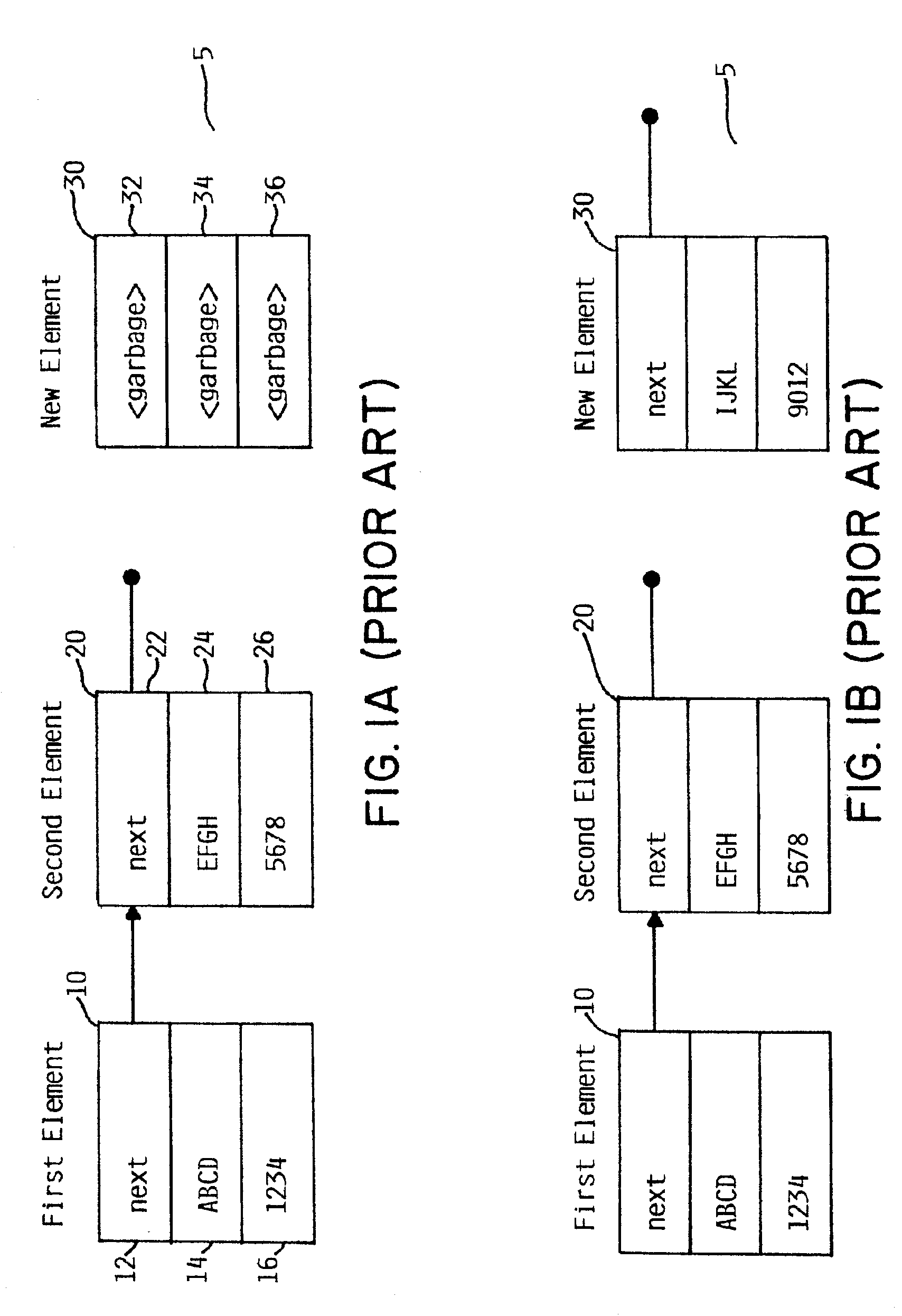

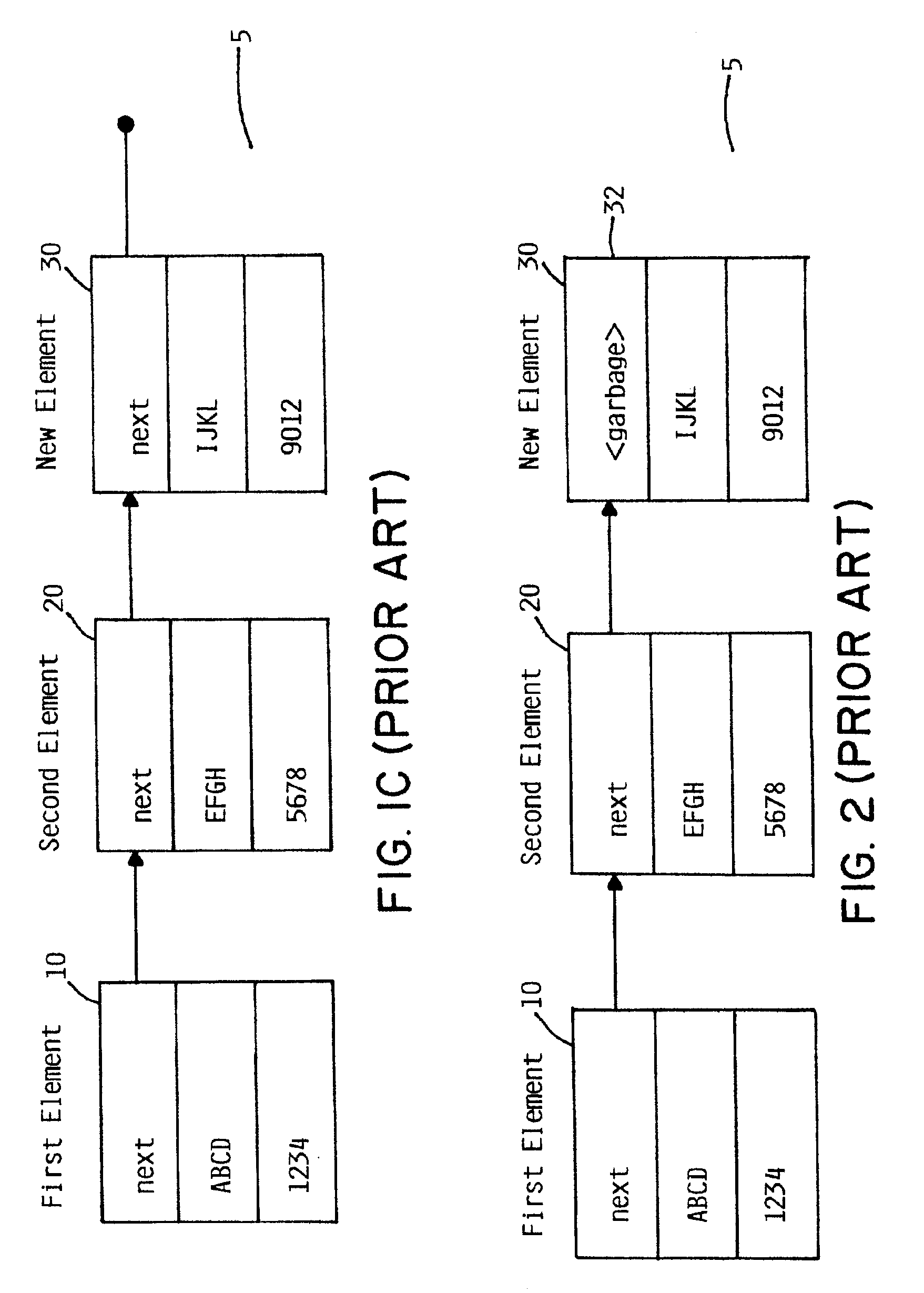

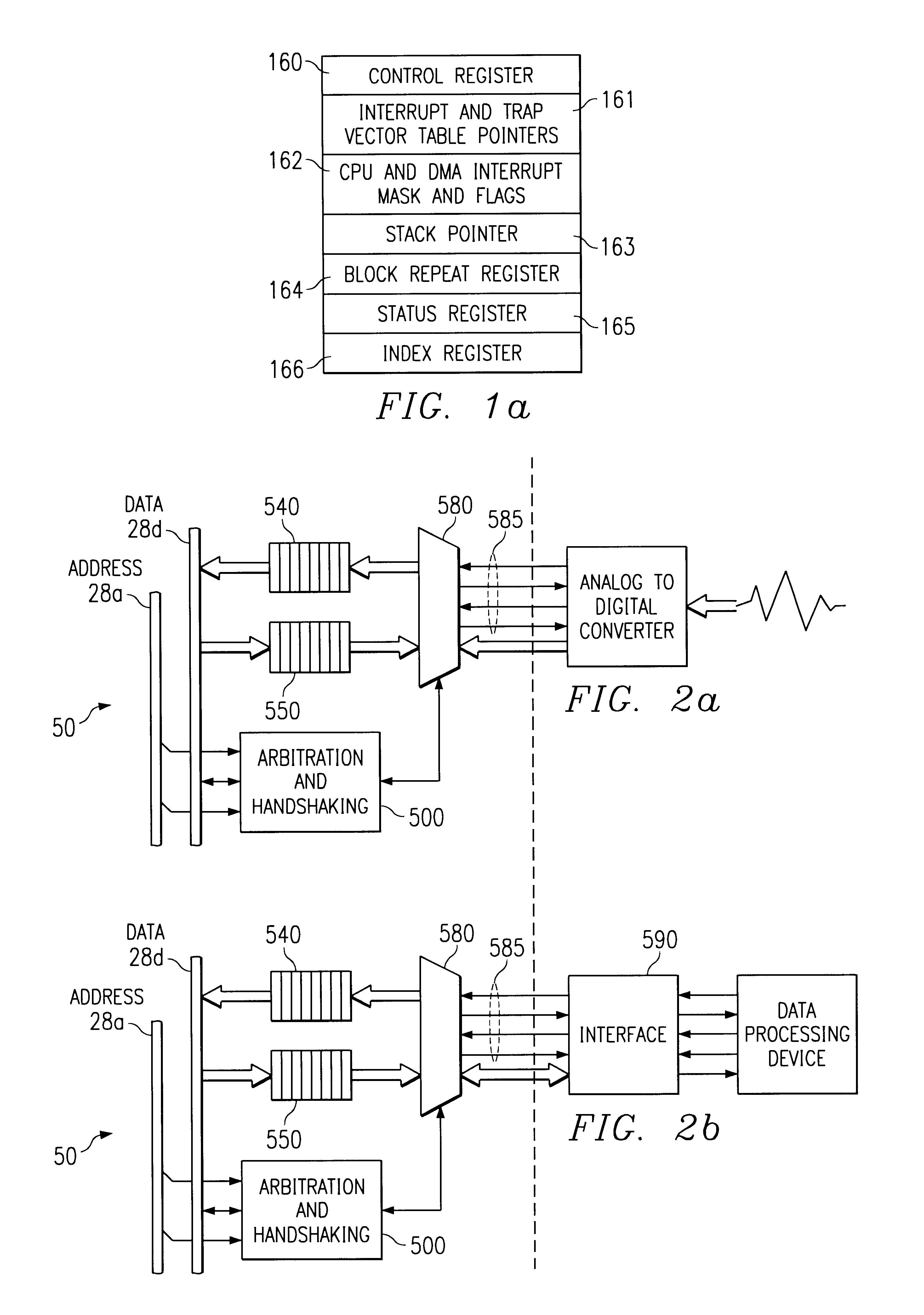

In computing, the instruction register (IR) or current instruction register (CIR) is the part of a CPU's control unit that holds the instruction currently being executed or decoded. In simple processors, each instruction to be executed is loaded into the instruction register, which holds it while it is decoded, prepared and ultimately executed, which can take several steps.

High performance microprocessor having variable speed system clock

InactiveUS6598148B1Improve performanceWithout sacrificing microprocessor speedRandom number generatorsInstruction analysisComputer architectureStatic random-access memory

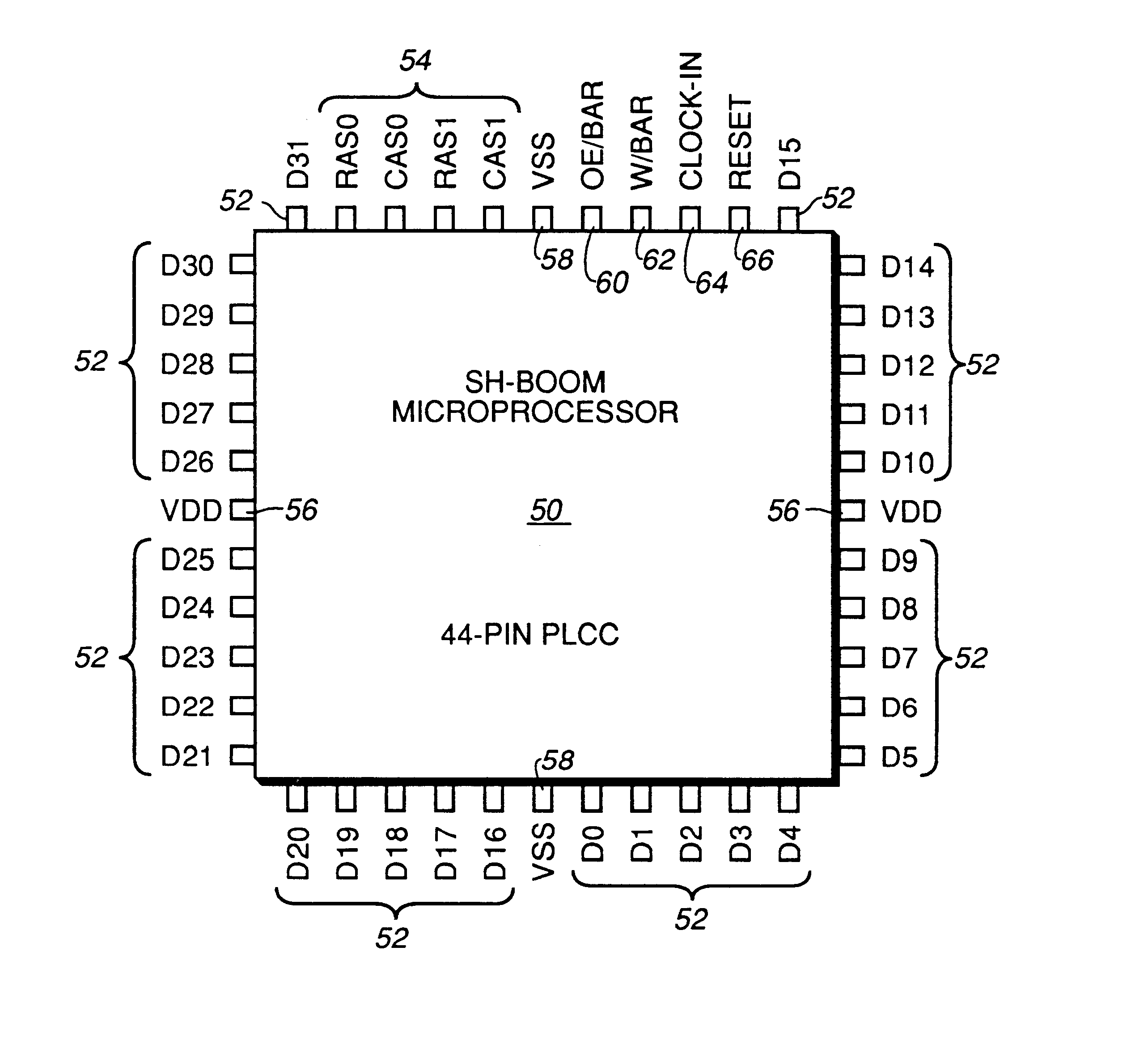

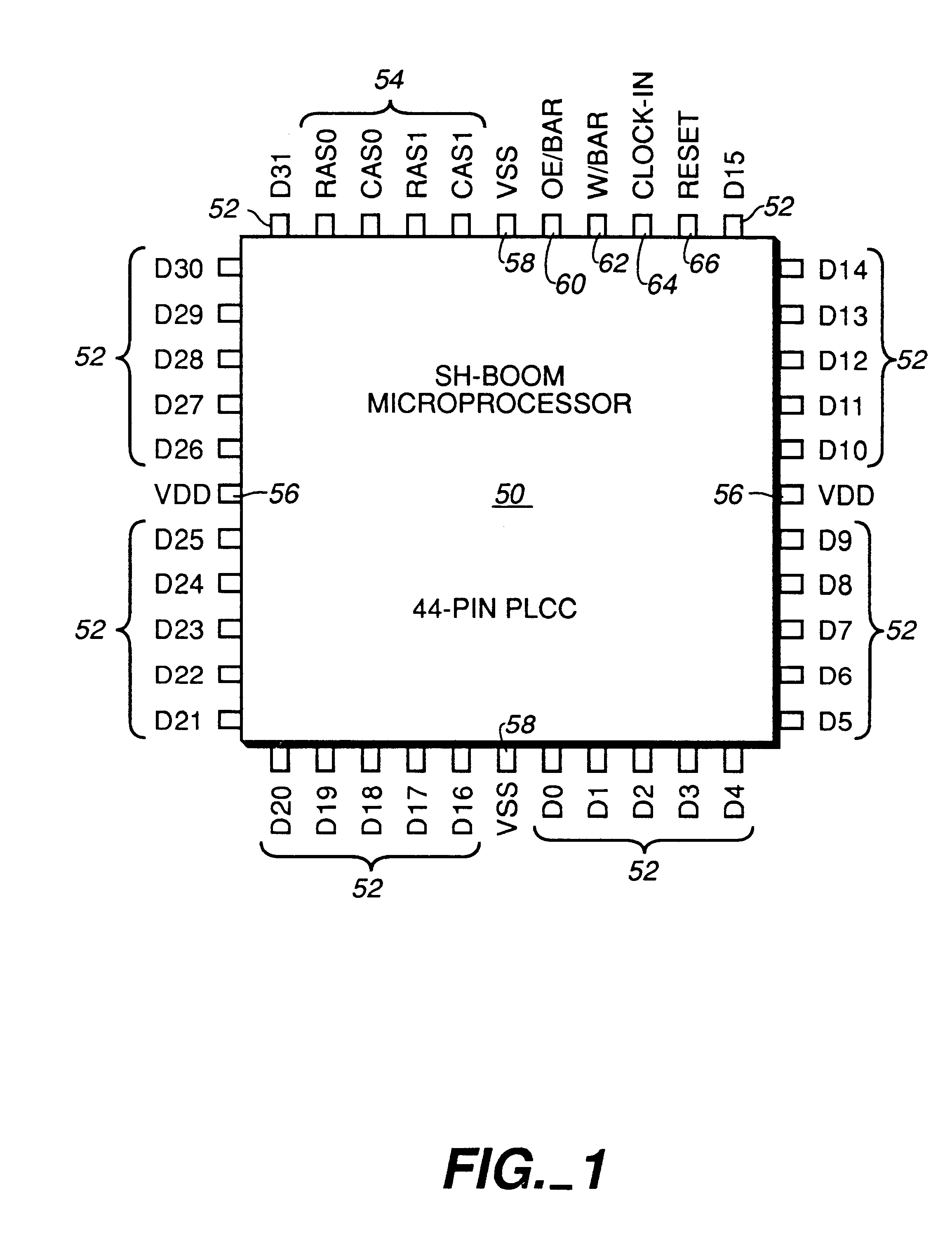

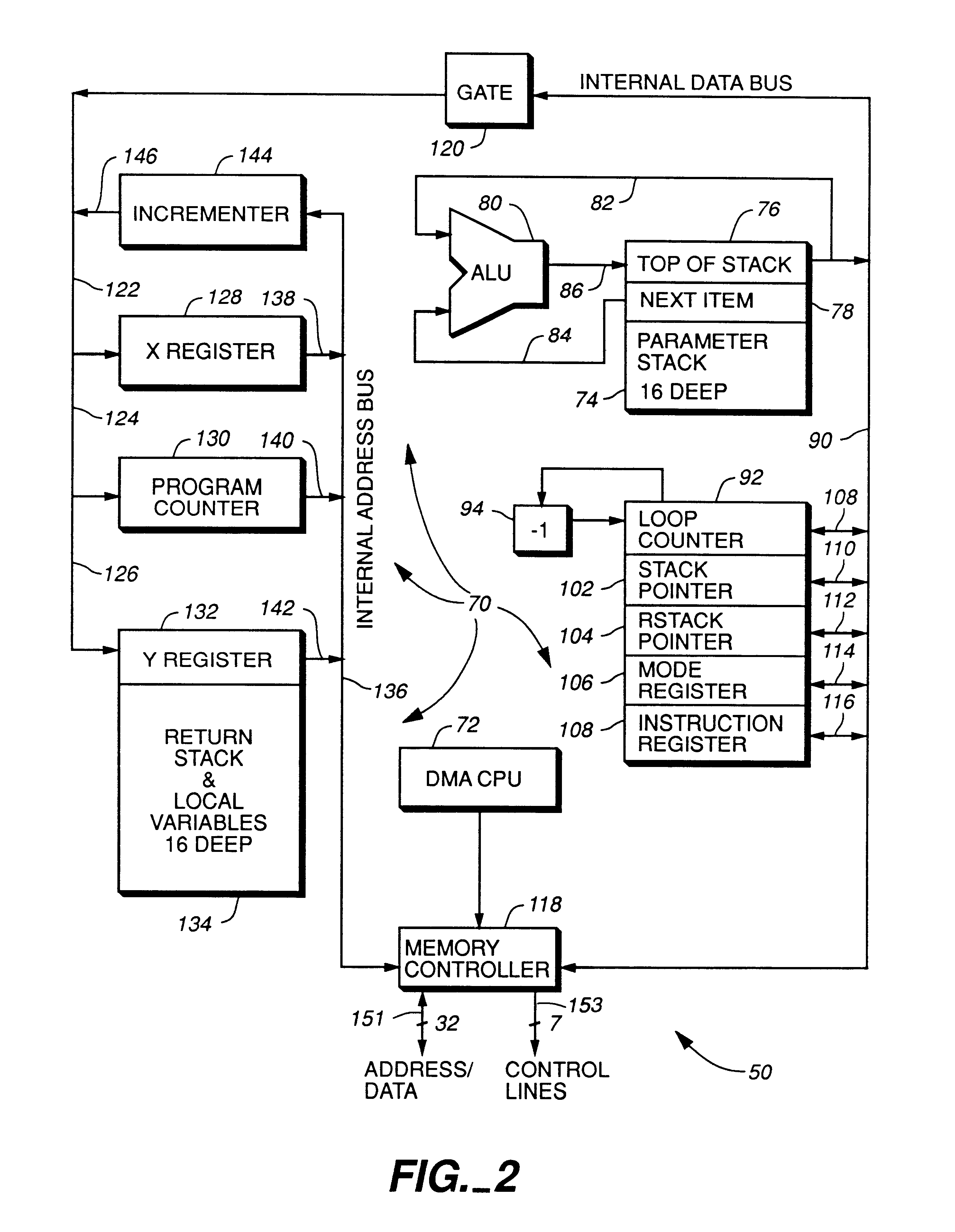

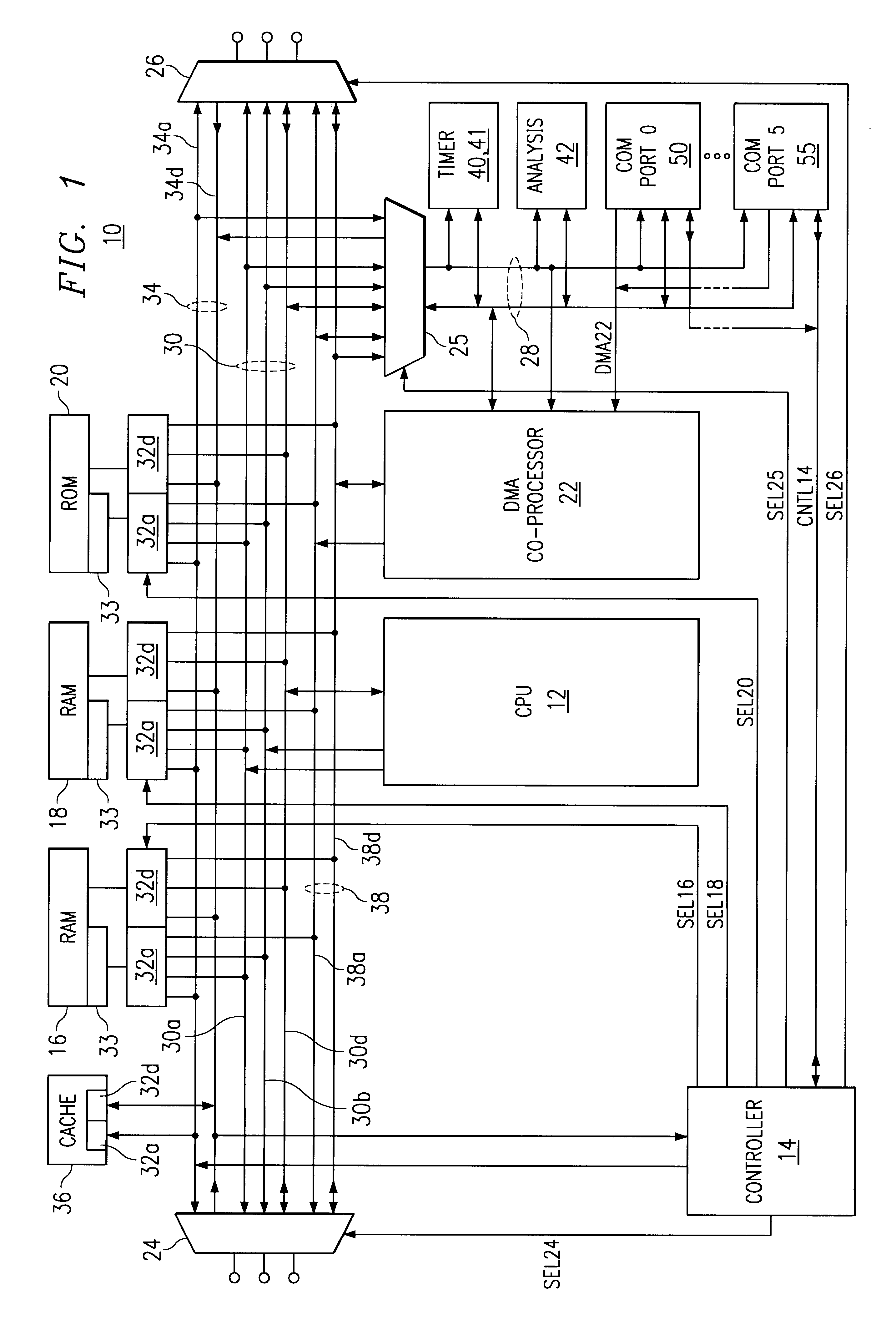

A microprocessor integrated circuit including a processing unit disposed upon an integrated circuit substrate is disclosed herein. The processing unit is designed to operate in accordance with a predefined sequence of program instructions stored within an instruction register. A memory, capable of storing information provided by the processing unit and occupying a larger area of the integrated circuit substrate than the processing unit, is also provided within the microprocessor integrated circuit. The memory may be implemented using, for example dynamic or static random-access memory. A variable output frequency system clock, such as generated by a ring oscillator, is also disposed on the integrated circuit substrate.

Owner:MOORE CHARLES H TTE UTD 03 21 2006 THE EQUINOX TRUST

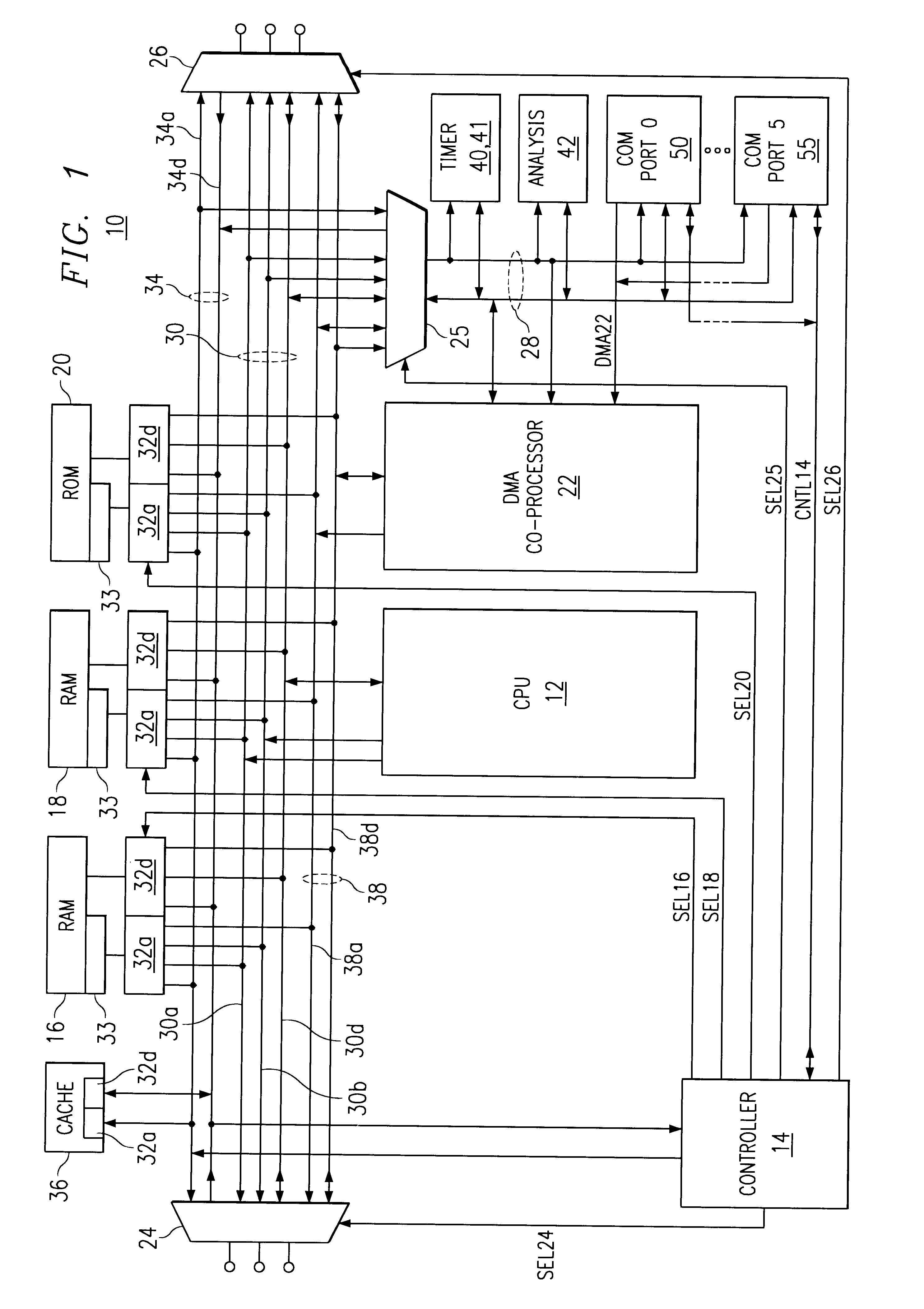

Single-chip microcomputer using adjustable timing to fetch data from an external memory

InactiveUS6125431AIncrease costEasy to operateMemory adressing/allocation/relocationProgram controlMicrocontrollerInternal memory

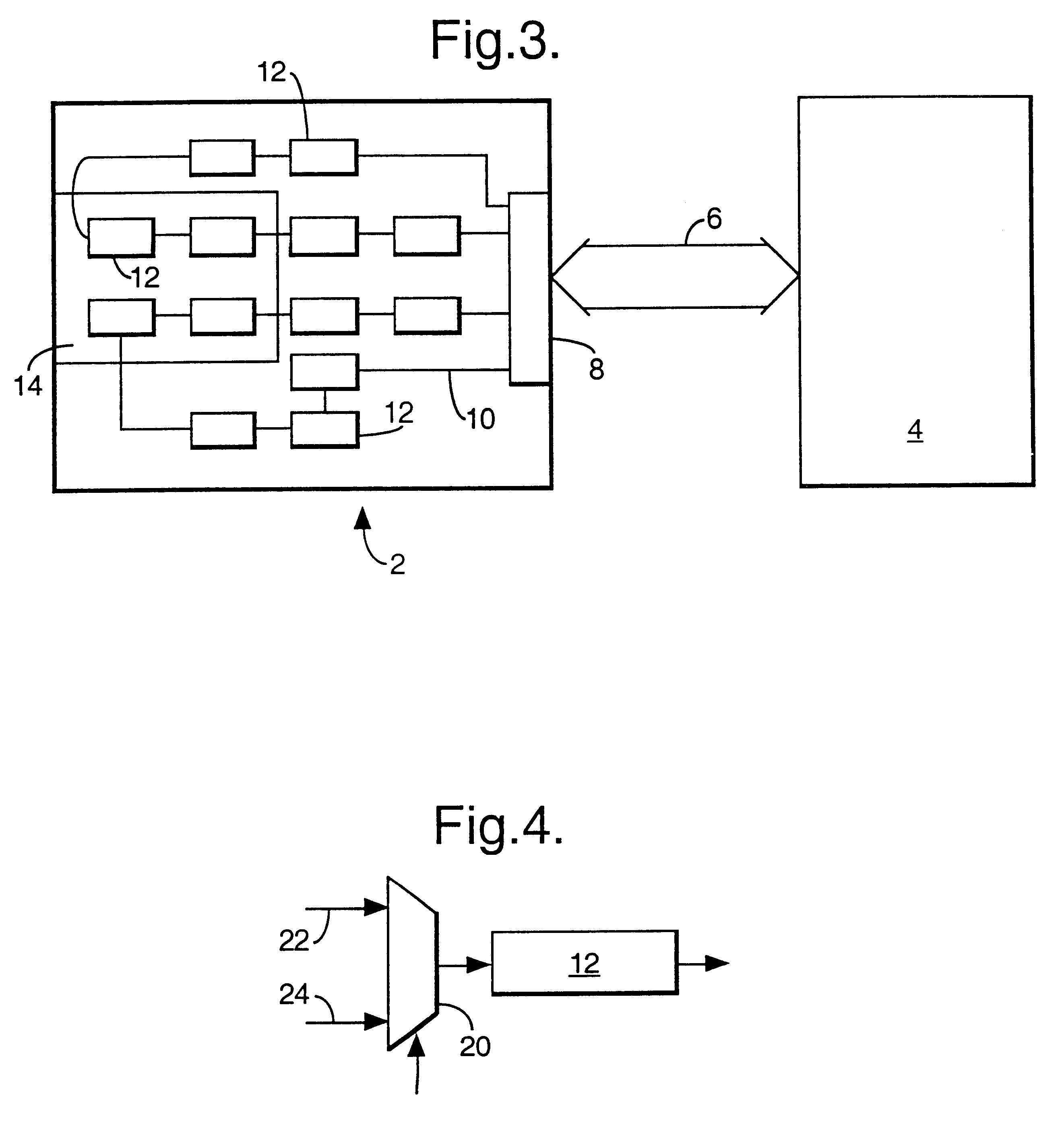

It is an object of the present invention to provide a one-chip microcomputer which permits the access time for an external memory to be equal to that for an internal memory. The one-chip microcomputer 10 includes an internal ROM 11, control circuit 12, output terminals 13, input terminals 14, control circuit 15, selector 16, instruction register 17, delay circuit 18, and fetch control signal select gate 19. For selection of the external ROM 30, a control arrangement 20 and a delay circuit 18 are employed in one embodiment to adjust the time at which ROM data is fetched by the instruction register 17, based on the delay time for accessing the external ROM 30.

Owner:LAPIS SEMICON CO LTD

Software implementation of synchronous memory barriers

InactiveUS6996812B2Program synchronisationDigital computer detailsProcessor registerInter-processor interrupt

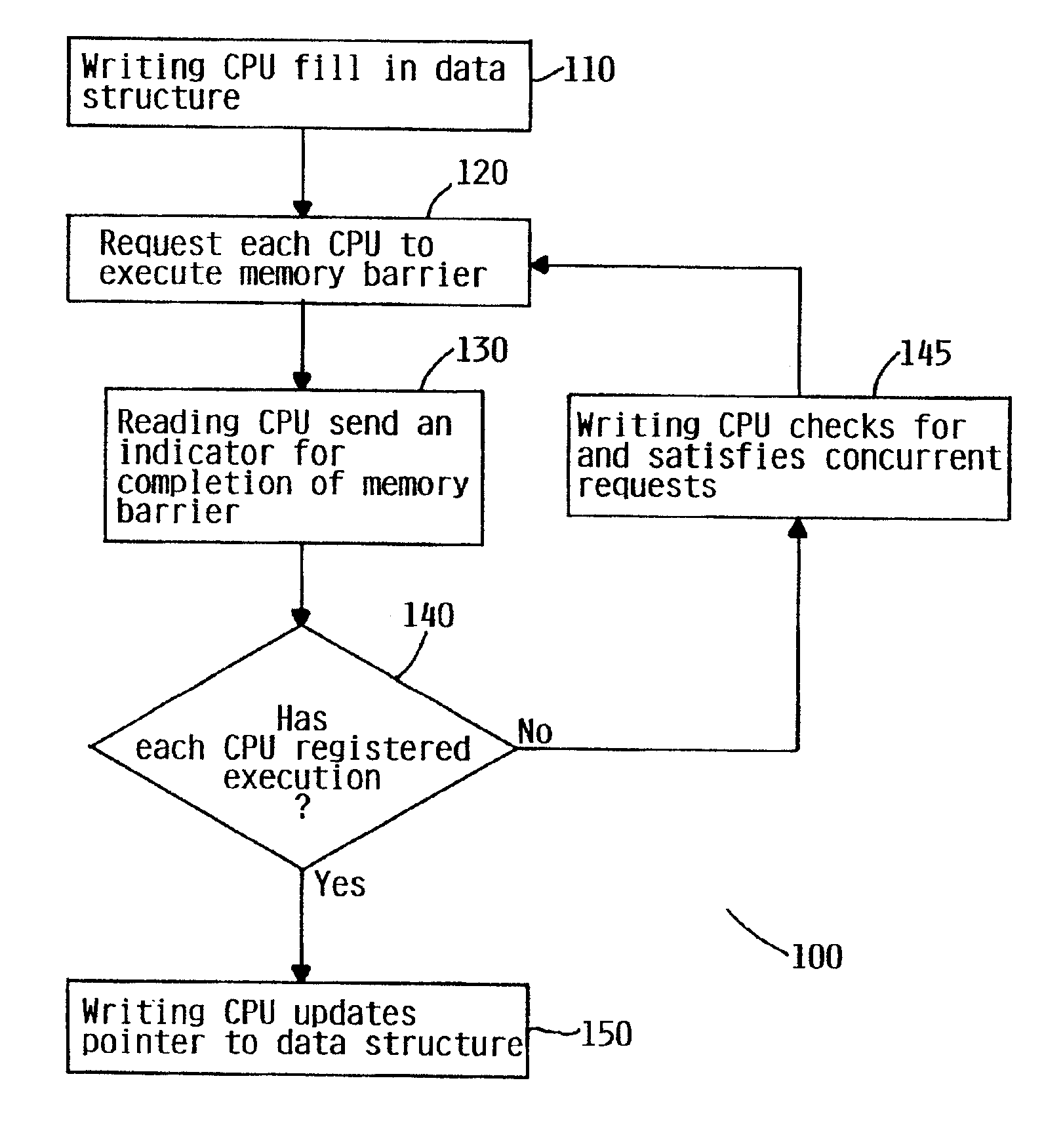

Selectively emulating sequential consistency in software improves efficiency in a multiprocessing computing environment. A writing CPU uses a high priority inter-processor interrupt to force each CPU in the system to execute a memory barrier. This step invalidates old data in the system. Each CPU that has executed a memory barrier instruction registers completion and sends an indicator to a memory location to indicate completion of the memory barrier instruction. Prior to updating the data, the writing CPU must check the register to ensure completion of the memory barrier execution by each CPU. The register may be in the form of an array, a bitmask, or a combining tree, or a comparable structure. This step ensures that all invalidates are removed from the system and that deadlock between two competing CPUs is avoided. Following validation that each CPU has executed the memory barrier instruction, the writing CPU may update the pointer to the data structure.

Owner:IBM CORP

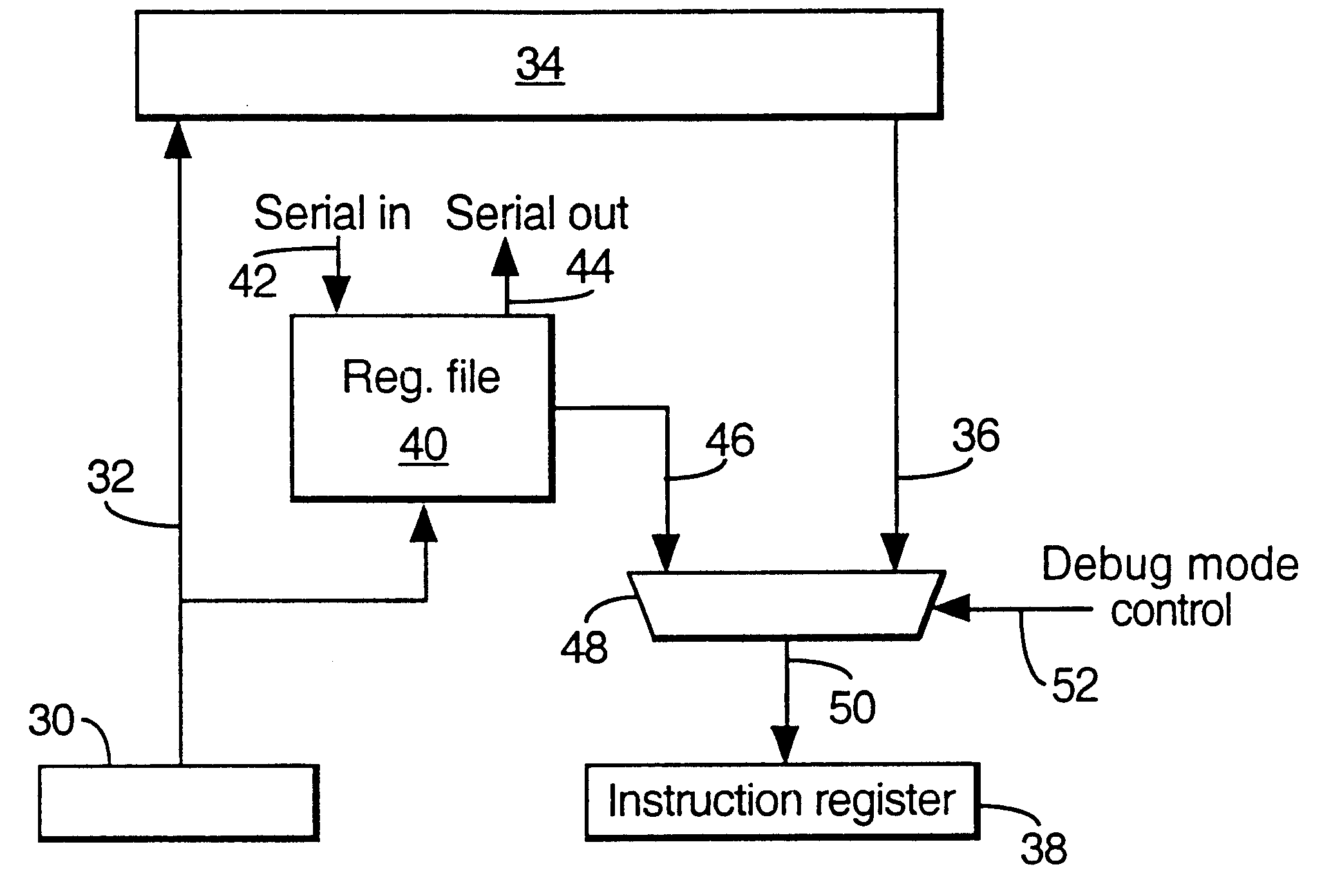

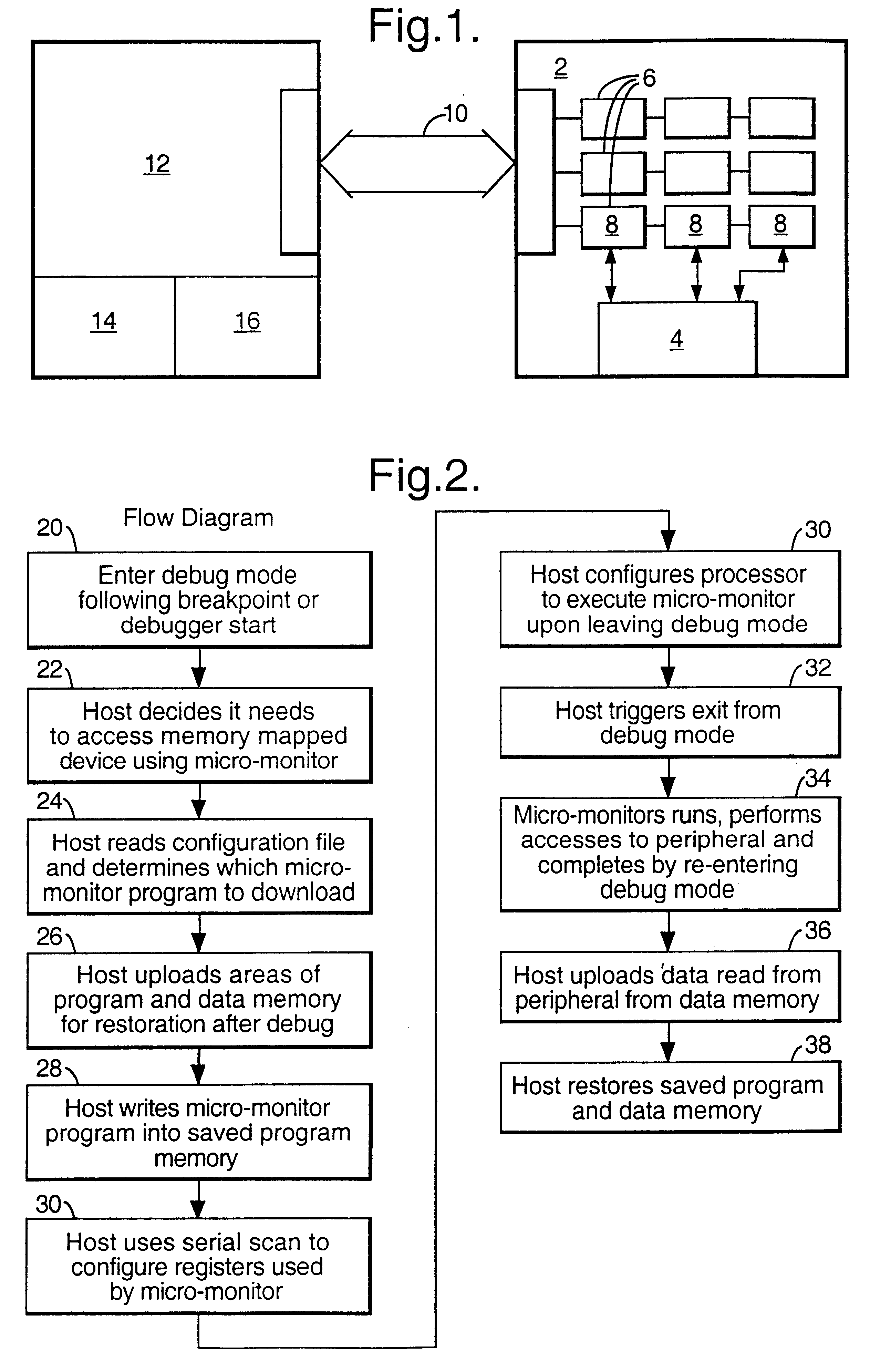

Microprocessor development systems

InactiveUS6574590B1Difficult to useSimple memory accessElectronic circuit testingDigital computer detailsEmbedded applicationsTime delays

A procedure and processor are disclosed for avoiding lengthy delays in debug procedures during access by a memory mapped peripheral device. The processor includes in-circuit emulation means comprising one or more scan chains or serially connected registers for access by an external host computer system. The procedure comprises:a) the host computer system carrying out a debug procedure via said scan chains, and selectively interrupting such debug procedure for access to a peripheral memory mapped device;b) the host computer system writing into an area or memory of the processor a program for reading and / or writing data at a specified memory location; andc) the host computer system causing said processor to run said program, and then to return to said debug procedure.In another aspect, in order to permit small debugging programs to run, in serial scan in circuit emulation processes, on a processor in a deeply embedded application where no program RAM is provided, the processor includes one or more chains of serially connected registers coupled to interface means for access by an external host to enable a serial scan procedure to be carried out, one such chain including a set of serially coupled registers for storing one or more processor instructions read into a set of registers through the interface means, and the processor including address means, for addressing program memory, coupled to said set of registers for addressing the set of registers, and means for reading the processor instructions in the set of registers to an instruction resister of the processor.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

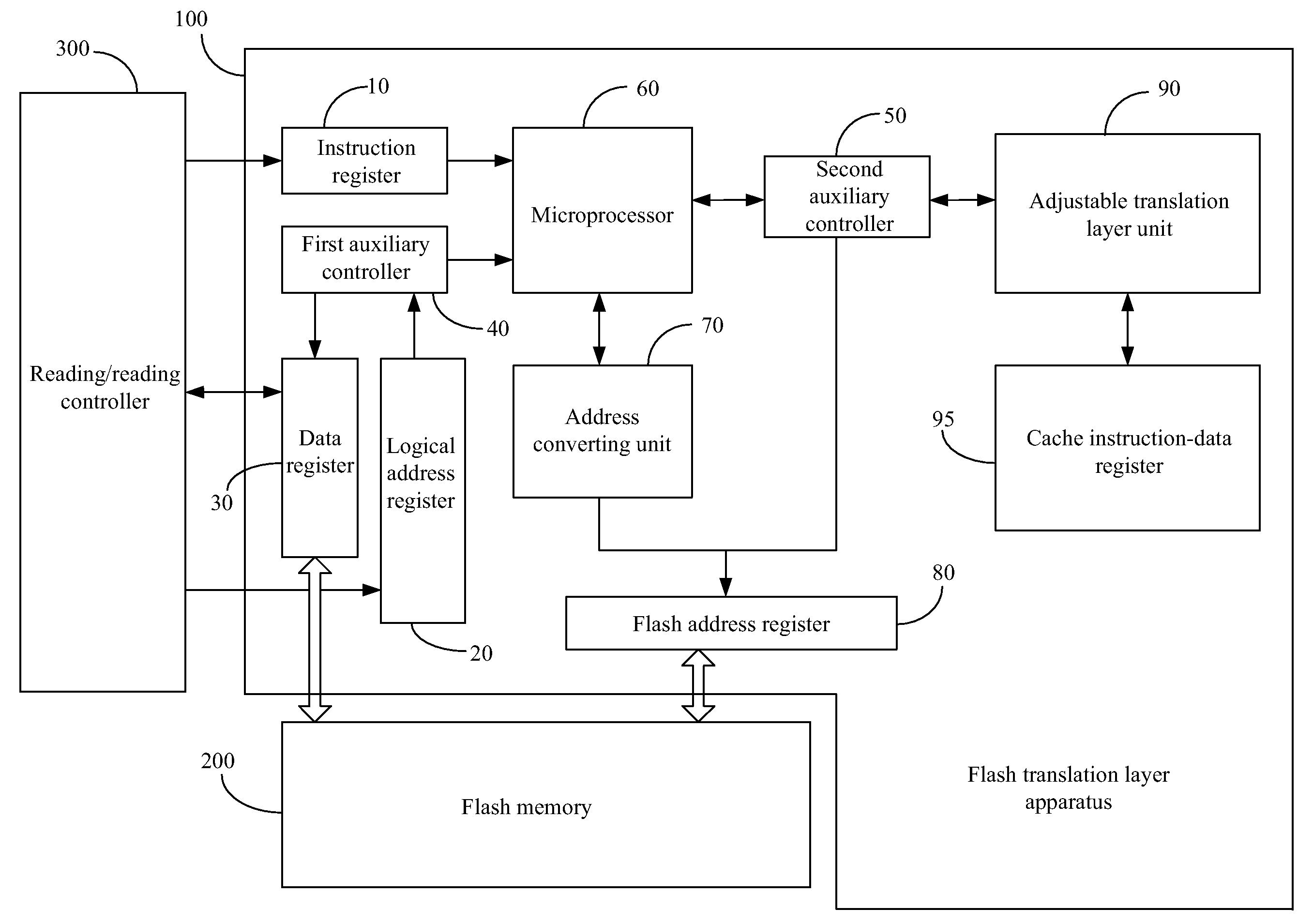

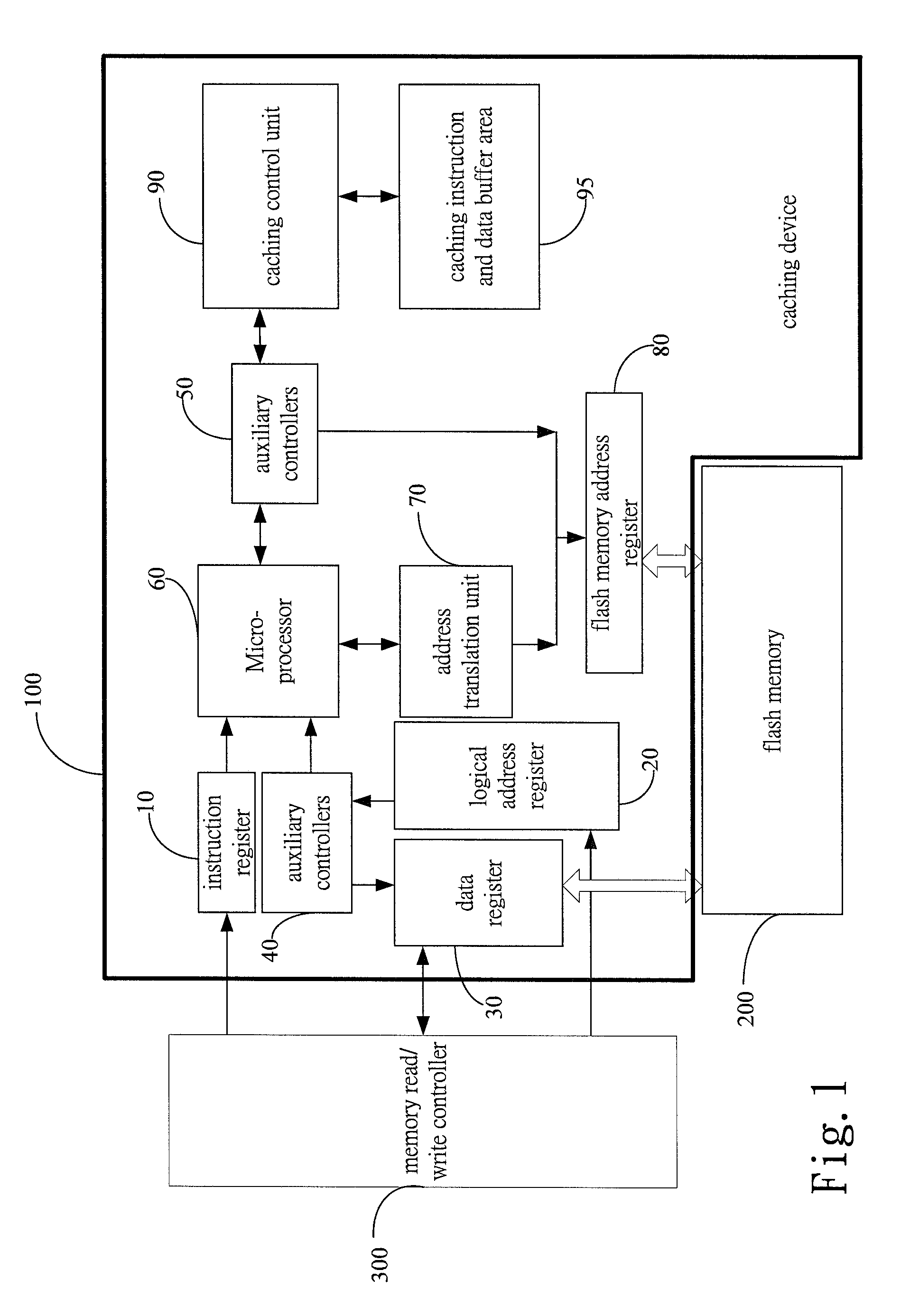

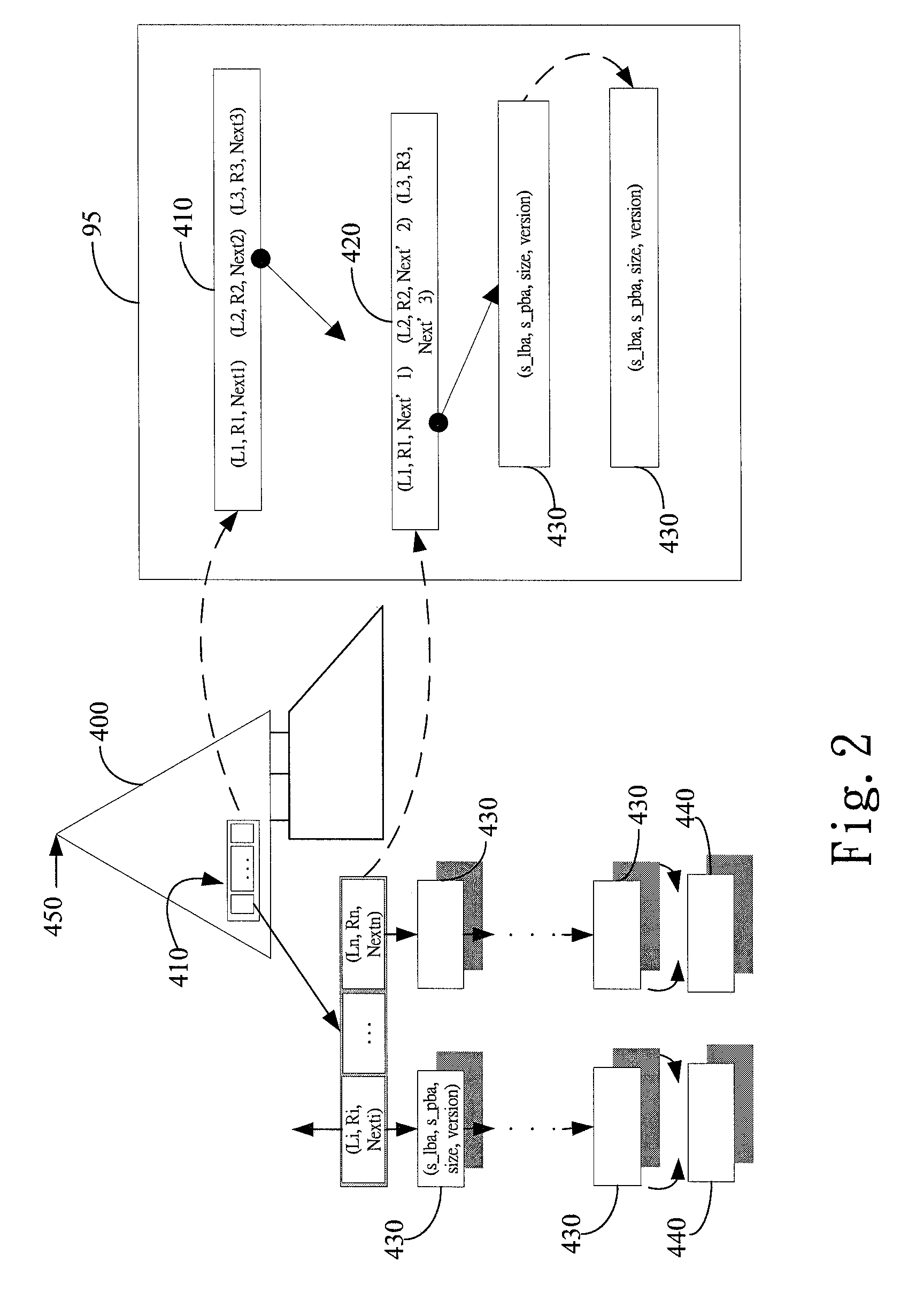

Flash translation layer apparatus

ActiveUS20080183955A1Reduce spacingReduce occurrenceMemory architecture accessing/allocationMemory systemsTranslation tableData harvesting

A flash translation layer apparatus is disclosed. The flash translation layer apparatus coupled to a flash memory and a reading and writing controller, respectively. The flash translation layer apparatus includes an instruction register, a logical address register, a data register, a first auxiliary controller, a microprocessor, an address converting unit, a second auxiliary controller, a flash address register and an adjustable translation layer unit. Furthermore, the adjustable translation layer unit regards the block as a unit for a coarse-grained address translation table and regards the pages as a unit for a fine-grained address translation table, respectively. Therefore, the present invention can provide capabilities of reducing the spaces and the times of a null data collection procedure and increasing the efficiency when a logical address corresponds to a physical address.

Owner:GENESYS LOGIC INC

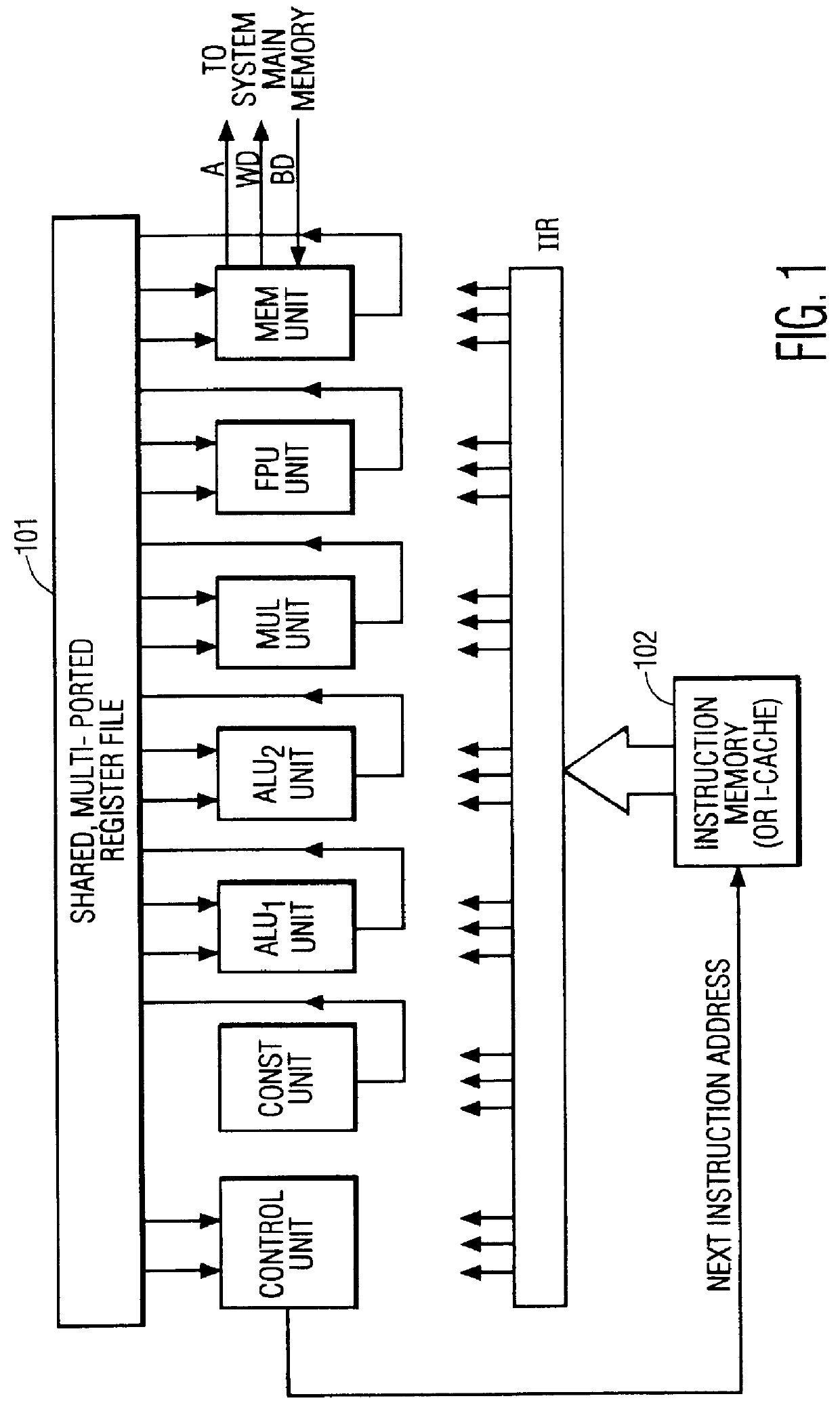

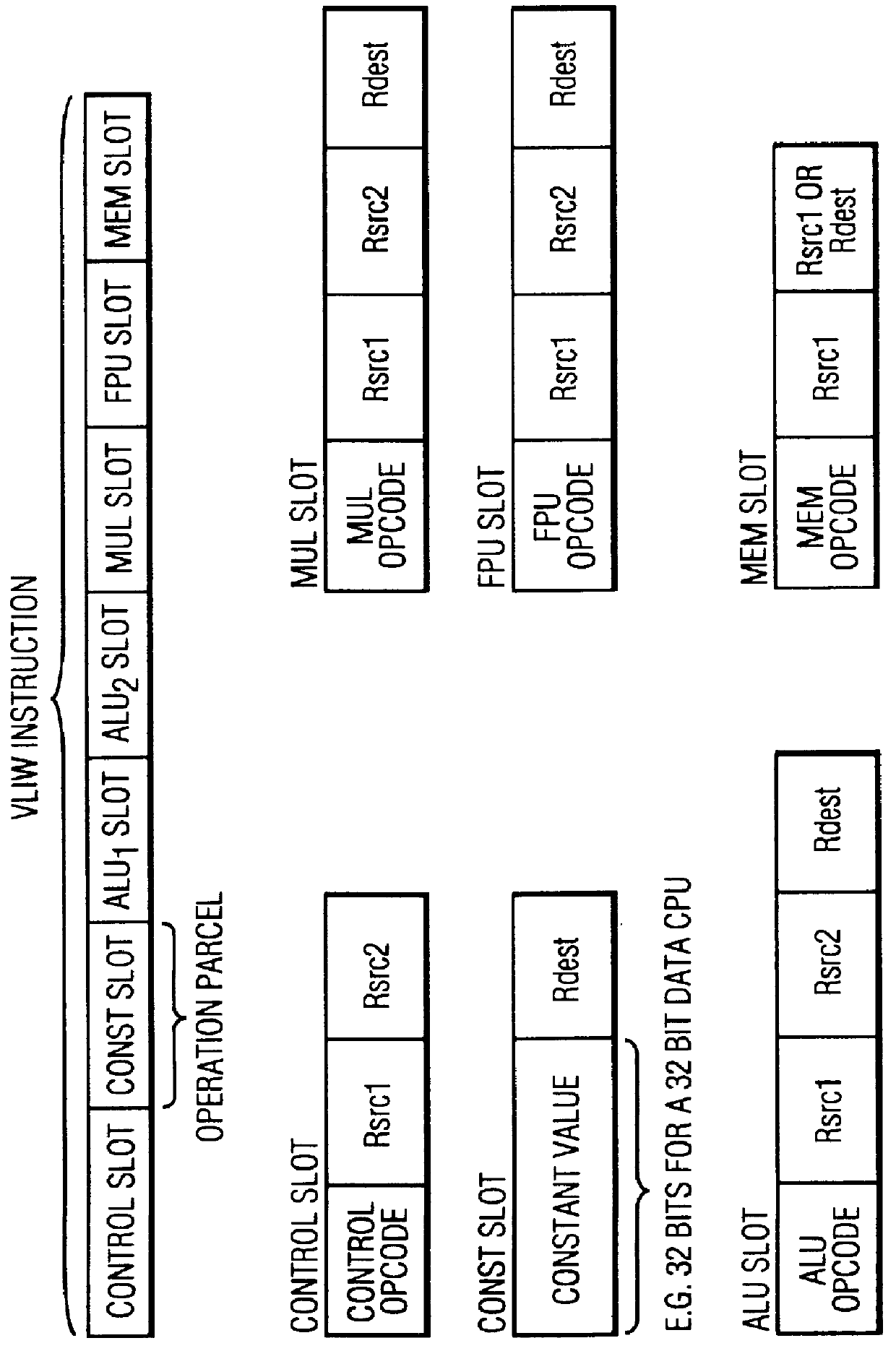

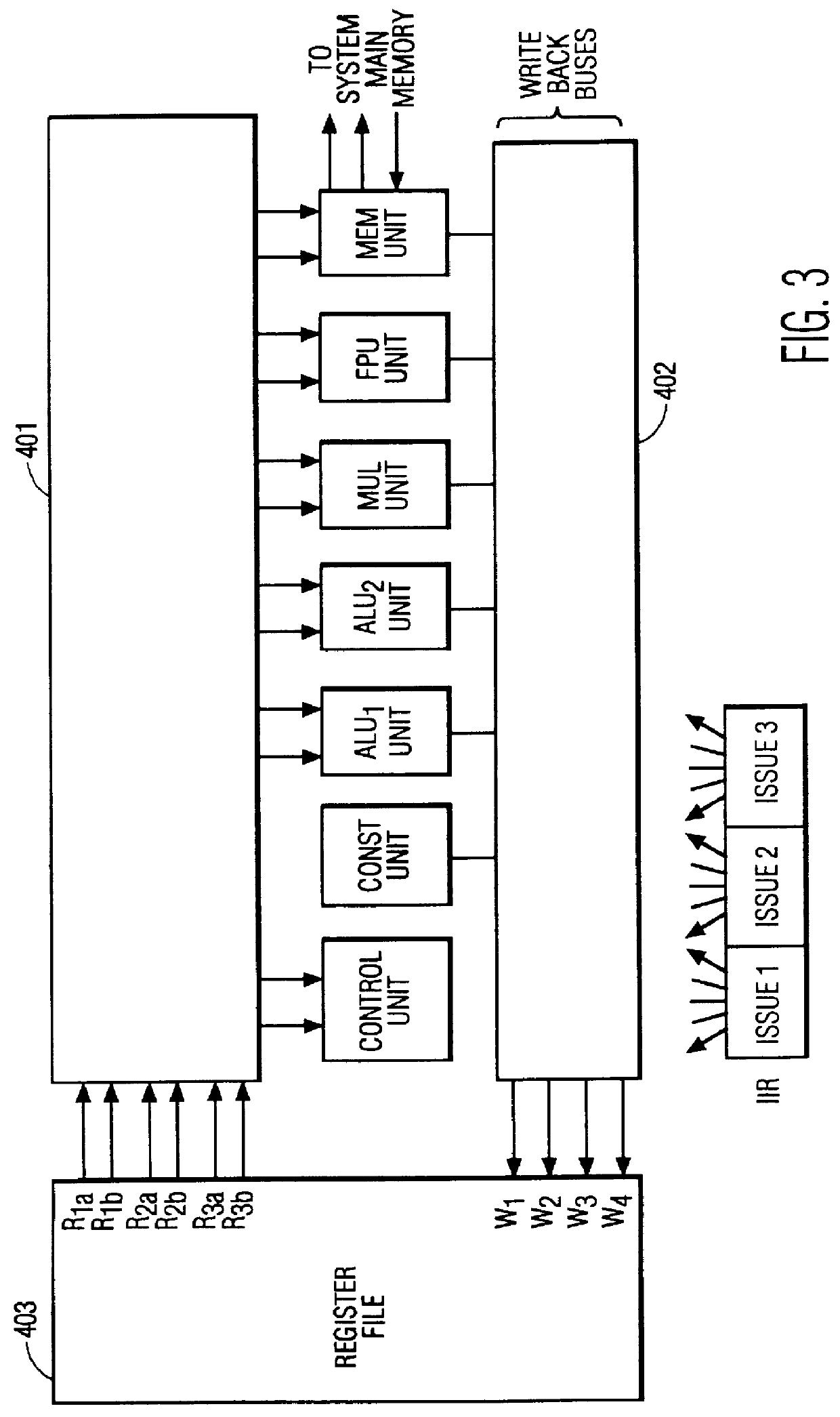

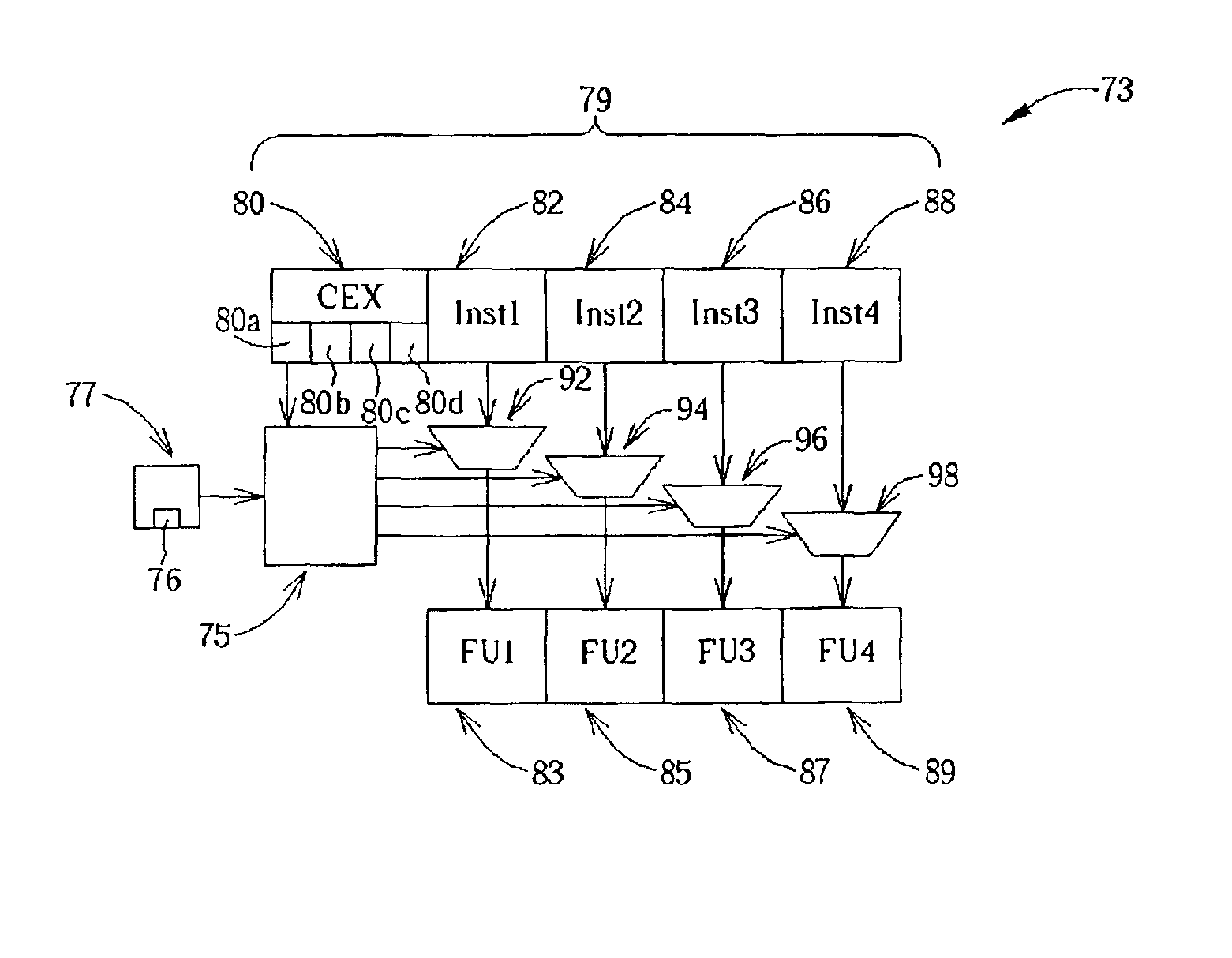

VLIW processor with less instruction issue slots than functional units

InactiveUS6122722AImproved cost-efficiencyRegister arrangementsGeneral purpose stored program computerComputer architectureProcessor register

Owner:FOOTHILLS IP LLC

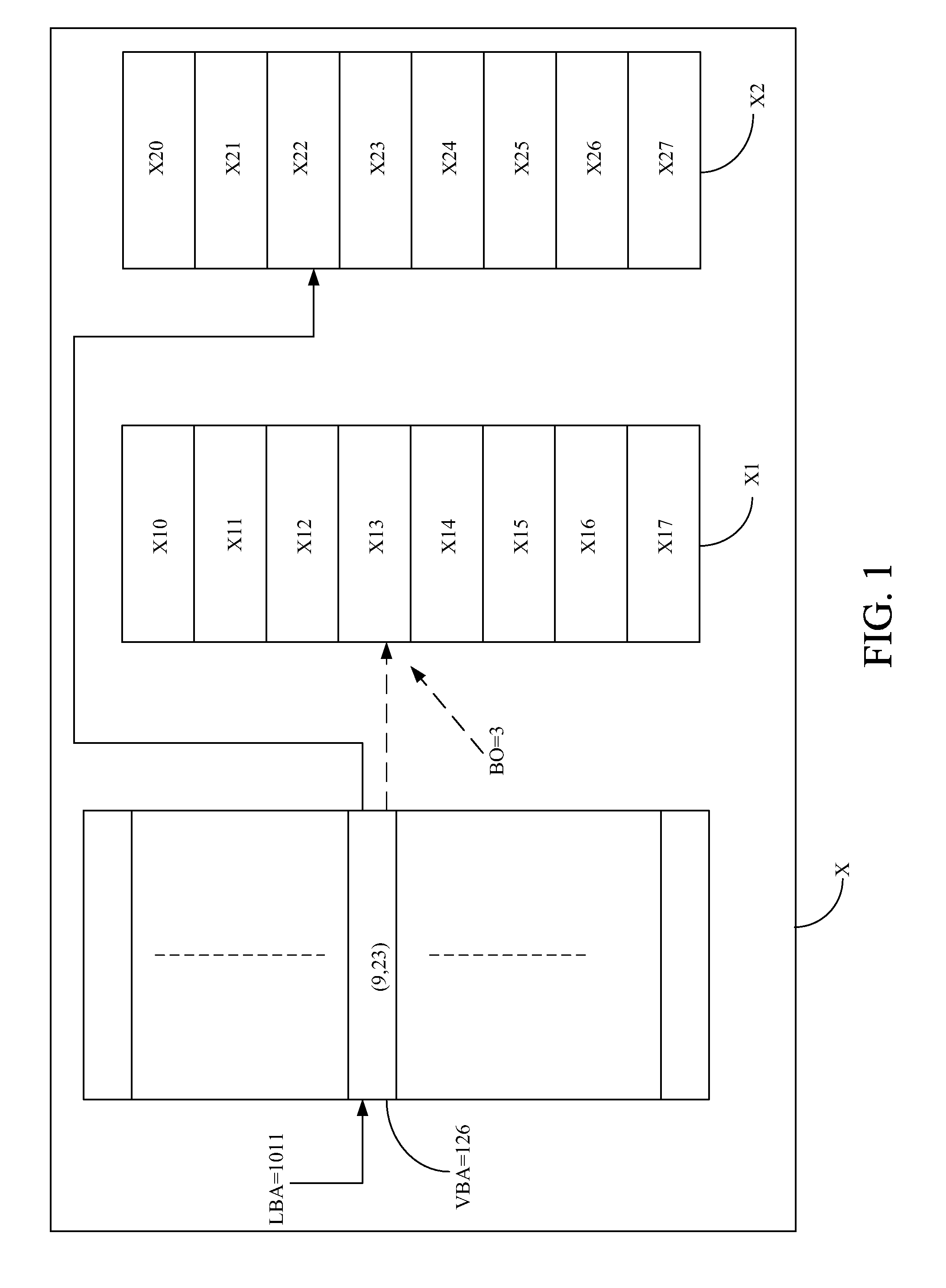

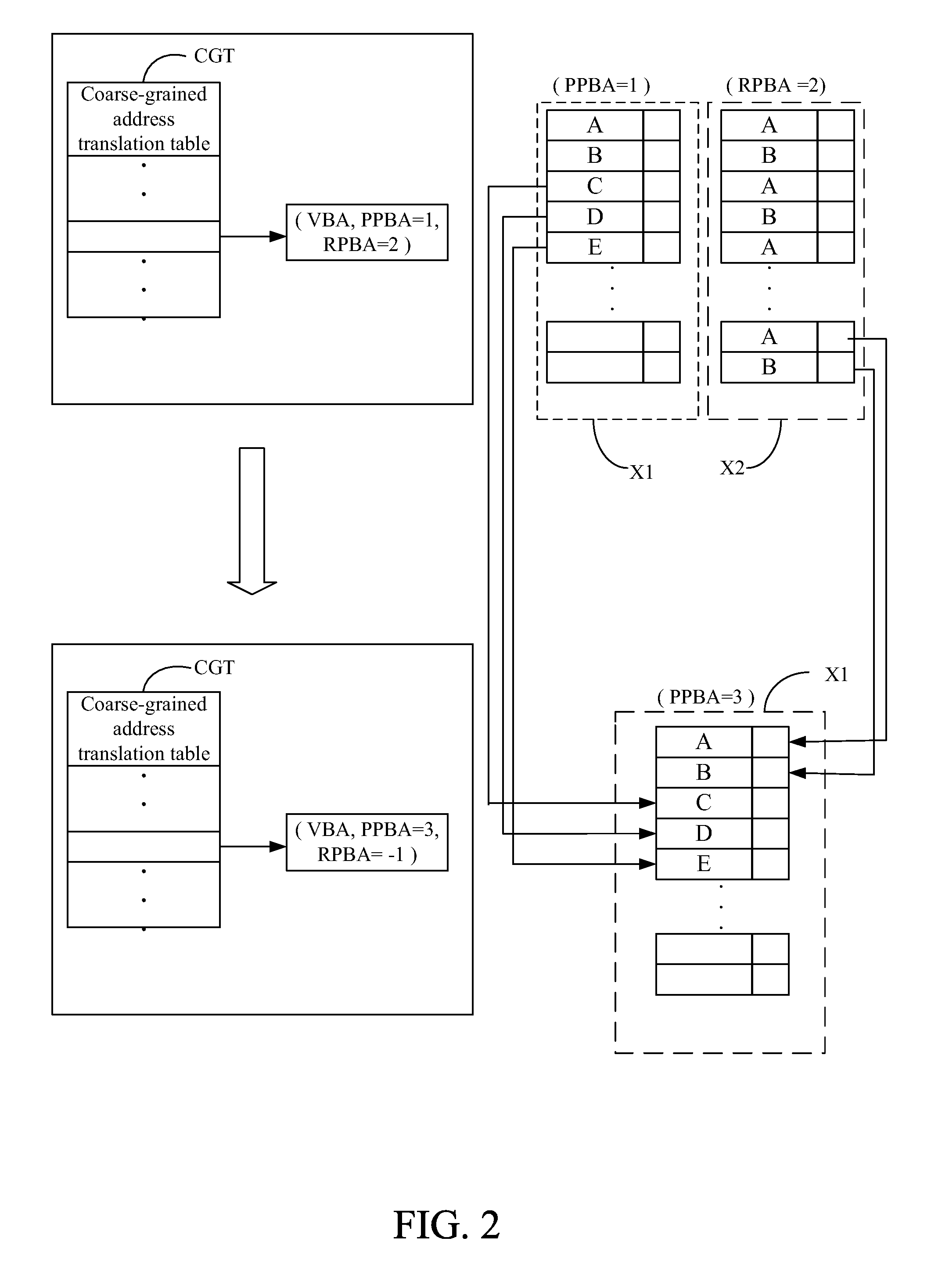

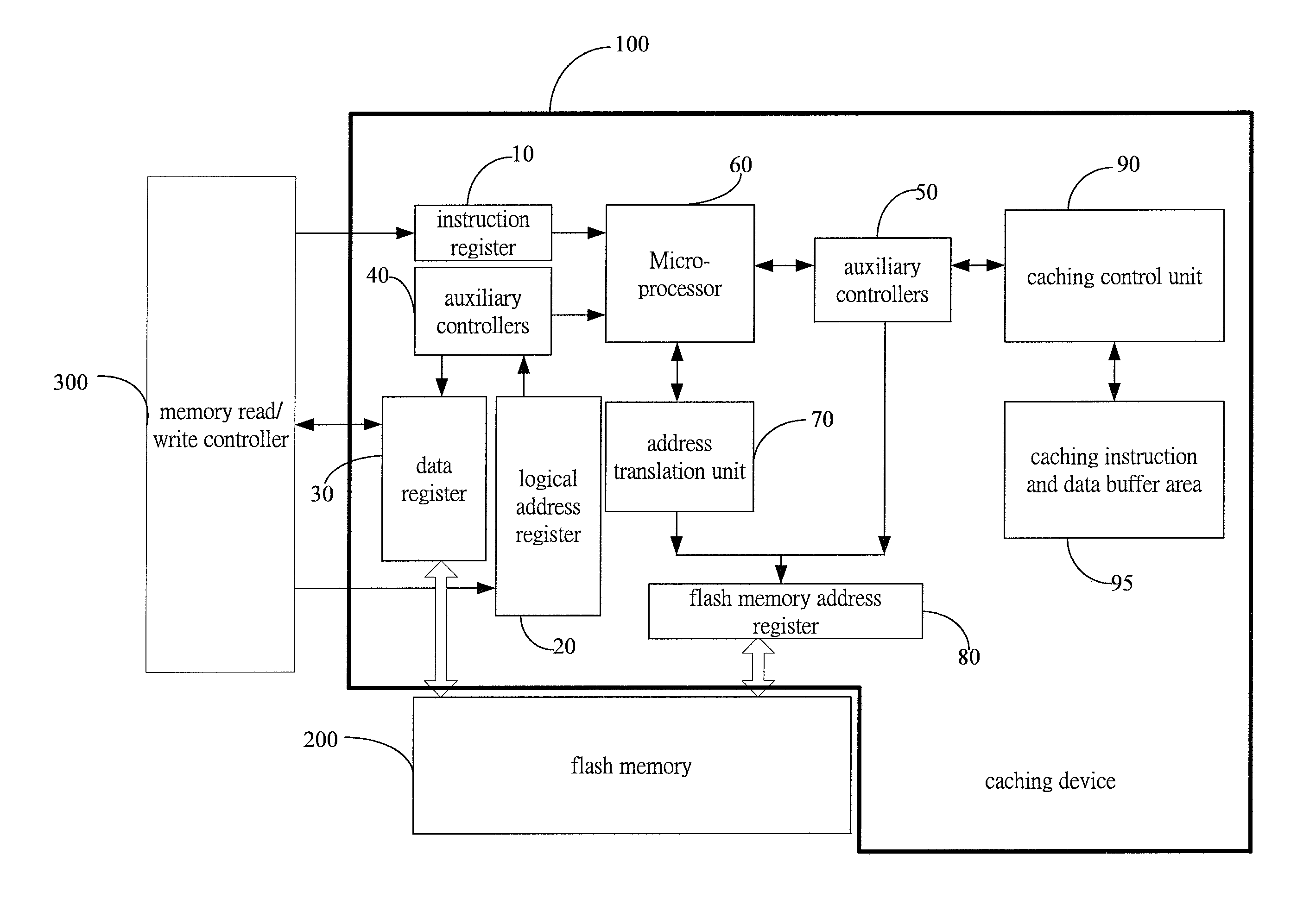

Caching device for NAND flash translation layer

ActiveUS20080162792A1Improve efficiencyImprove read and write access speedMemory architecture accessing/allocationMemory adressing/allocation/relocationInstruction registerData buffer

A caching device is positioned between a memory read / write controller and a flash memory, which contains an instruction register, a logical address register, a data register, a pair of auxiliary controllers, a microprocessor, an address translation unit, a flash memory address register, a caching control unit, and a caching instruction and data buffer area. Among them, the microprocessor is the core of the caching device responsible not only for the reading and writing the flash memory but also for the caching operation for logical and physical address translation. The caching control unit is a programmable device containing the instruction and data for caching the logical and physical address mapping. The caching instruction and data buffer area temporarily stores the caching instruction and data used by the caching control unit.

Owner:GENESYS LOGIC INC

Devices, systems and methods for conditional instructions

A data processing device includes a circuit having status conditions wherein a particular set of the status conditions can occur in operation of the circuit. An instruction register operates to hold a branch instruction conditional on a particular set of the status conditions. A decoder is connected to the instruction register and the circuit. A program counter is coupled to the decoder wherein the decoder is operable to enter a branch address into the program counter in response to the branch instruction when the particular set of the status conditions of the circuit are present. Other data processing devices, systems and methods are also disclosed.

Owner:BOUTAUD FREDERIC +1

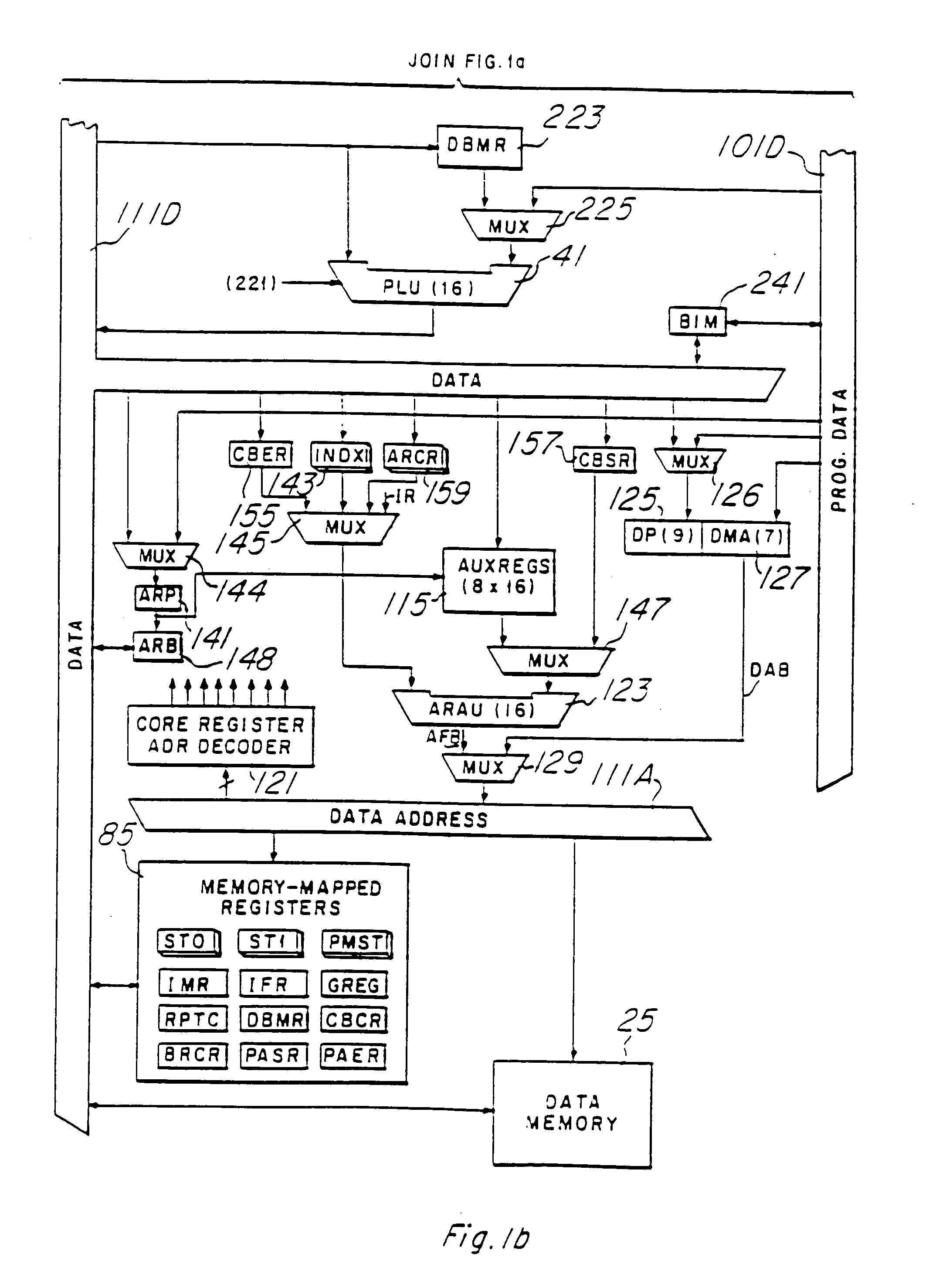

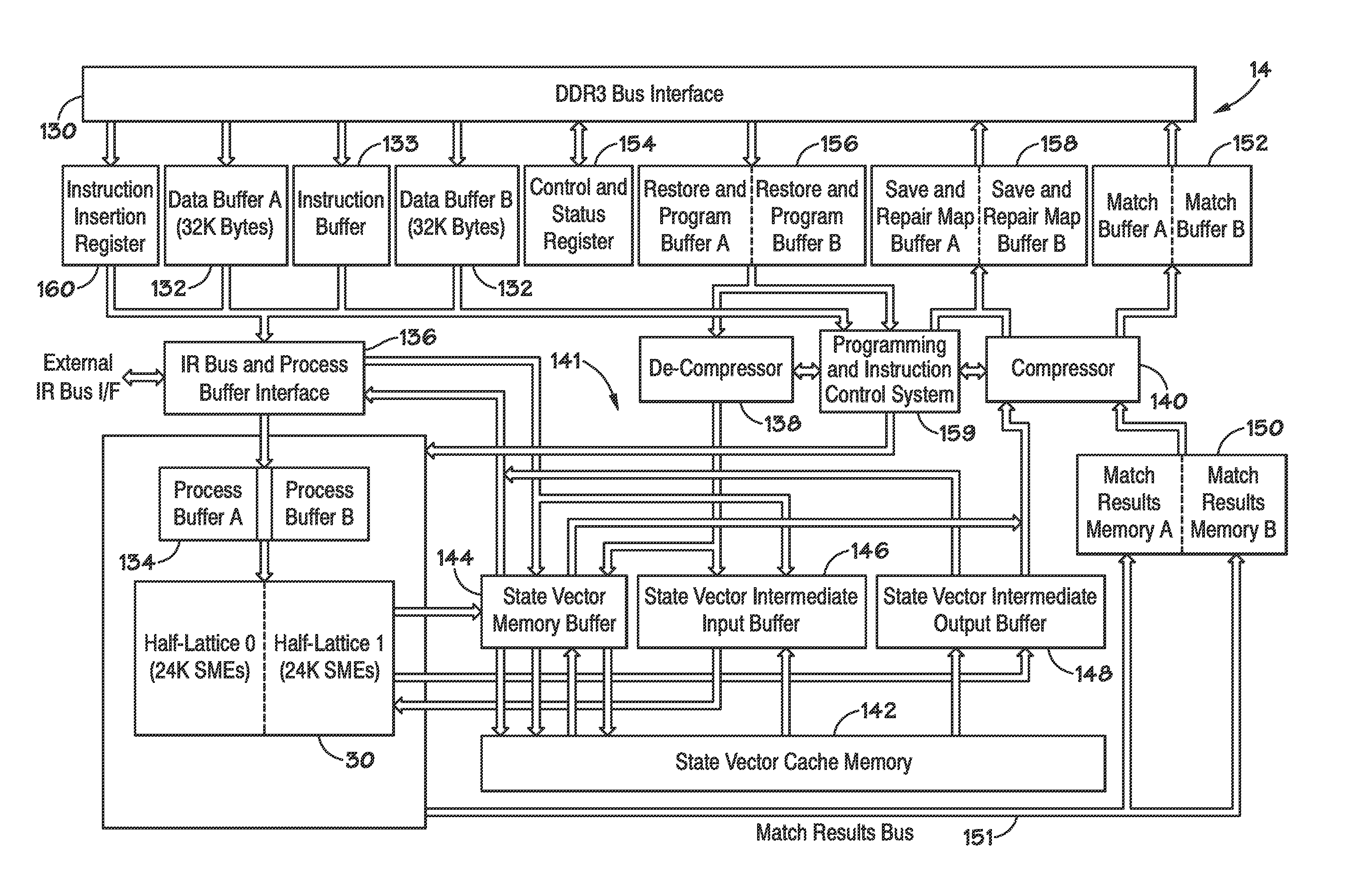

Instruction insertion in state machine engines

State machine engines are disclosed, including those having an instruction insertion register. One such instruction insertion register may provide an initialization instruction, such as to prepare a state machine engine for data analysis. An instruction insertion register may also provide an instruction in an attempt to resolve an error that occurs during operation of a state machine engine. An instruction insertion register may also be used to debug a state machine engine, such as after the state machine experiences a fatal error.

Owner:MICRON TECH INC

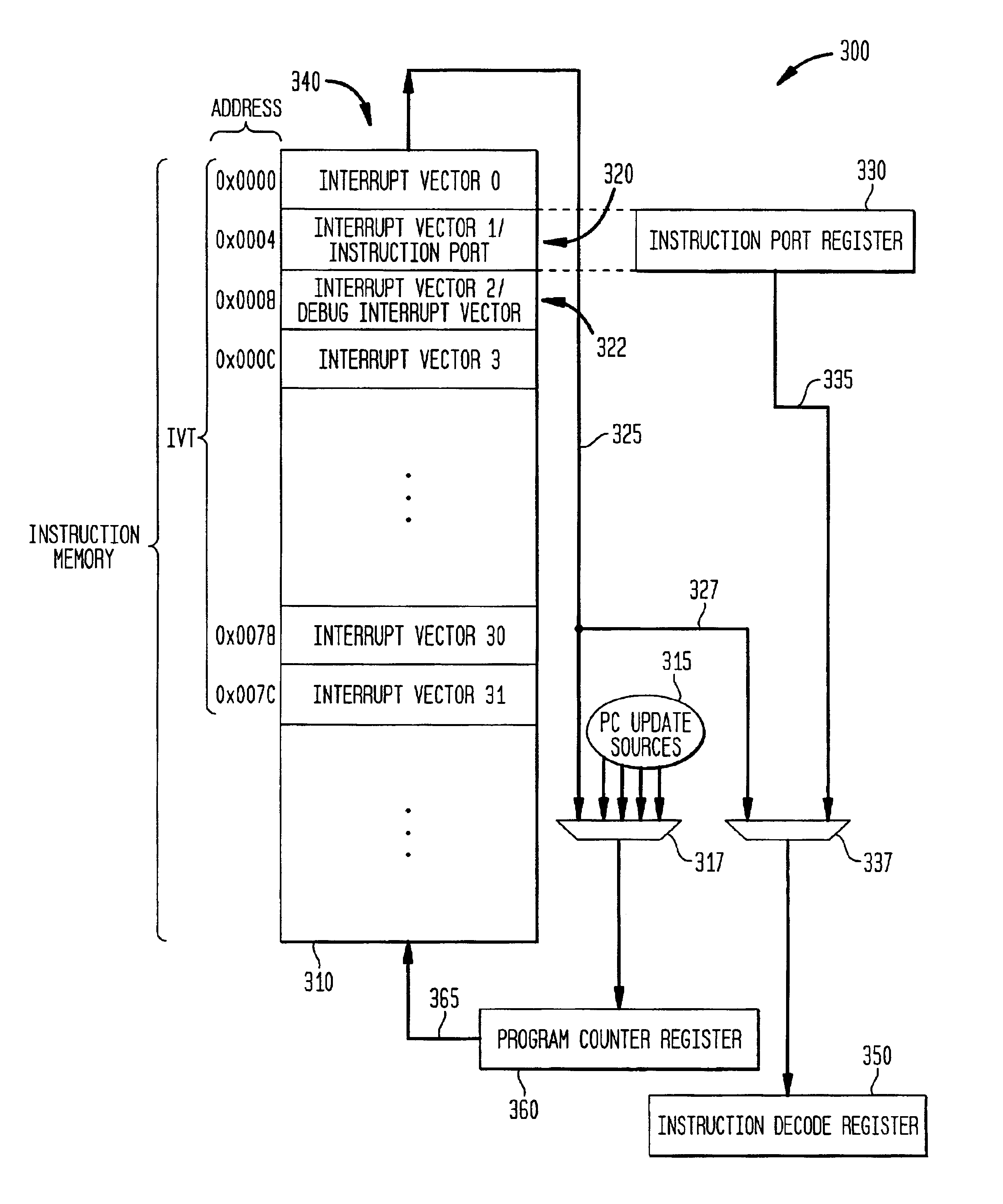

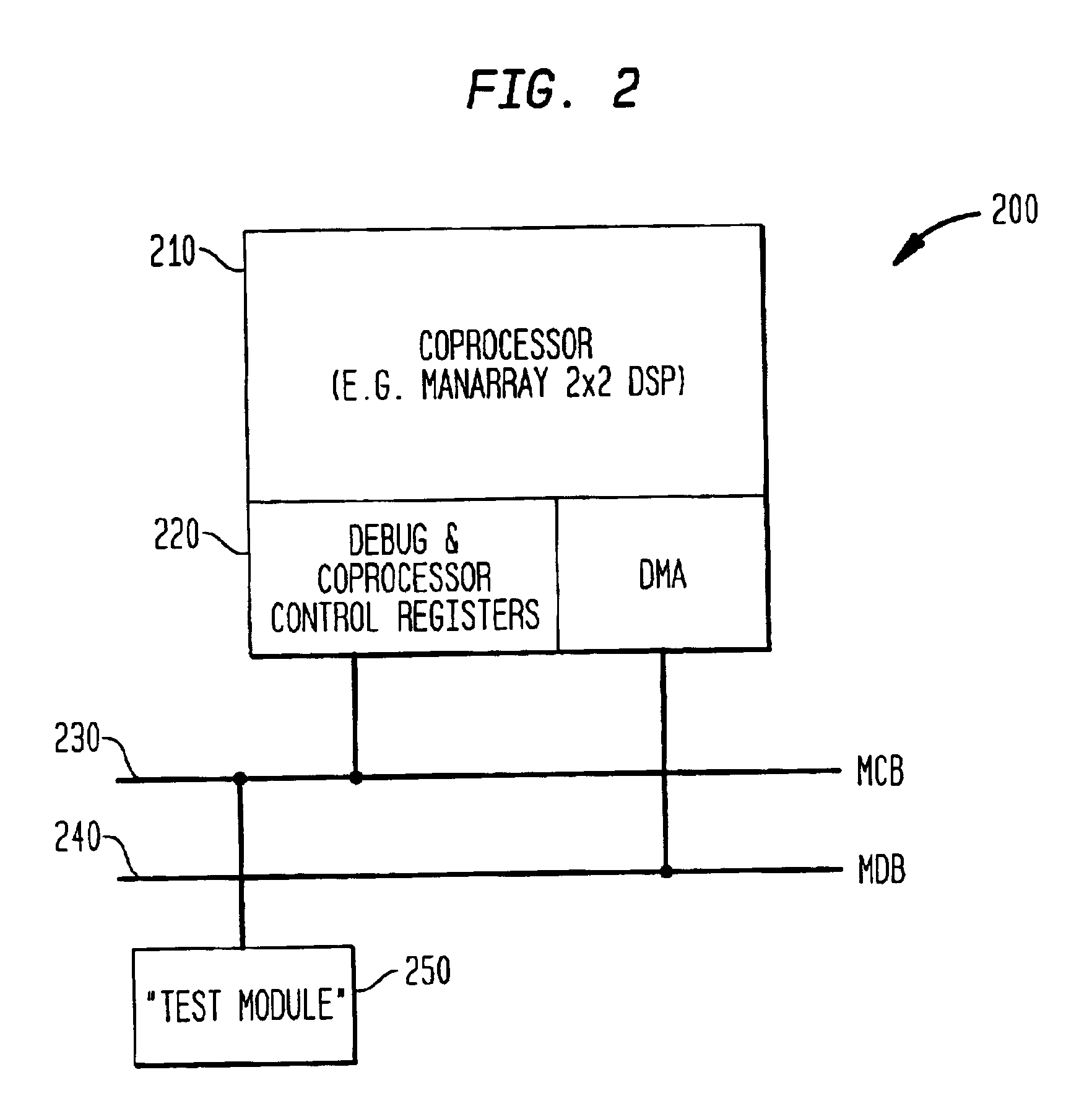

Control processor dynamically loading shadow instruction register associated with memory entry of coprocessor in flexible coupling mode

A method and system are described which provide flexible coupling between a coprocessor and a control processor. The system includes a coprocessor and a system control bus connecting the coprocessor with the control processor. The coprocessor has two modes of access. In the first mode of access, the coprocessor retrieves an instruction stored in instruction memory and, in the second mode of access, the coprocessor retrieves an instruction from the control processor. The system control bus provides a path for loading an instruction to the coprocessor's shadow instruction register. The coprocessor, upon retrieving an entry in its instruction memory associated with the shadow instruction resigter, determines whether to load the instruction as an address in its program counter or to load the contents of the shadow instruction register into the instruction decode register.

Owner:ALTERA CORP

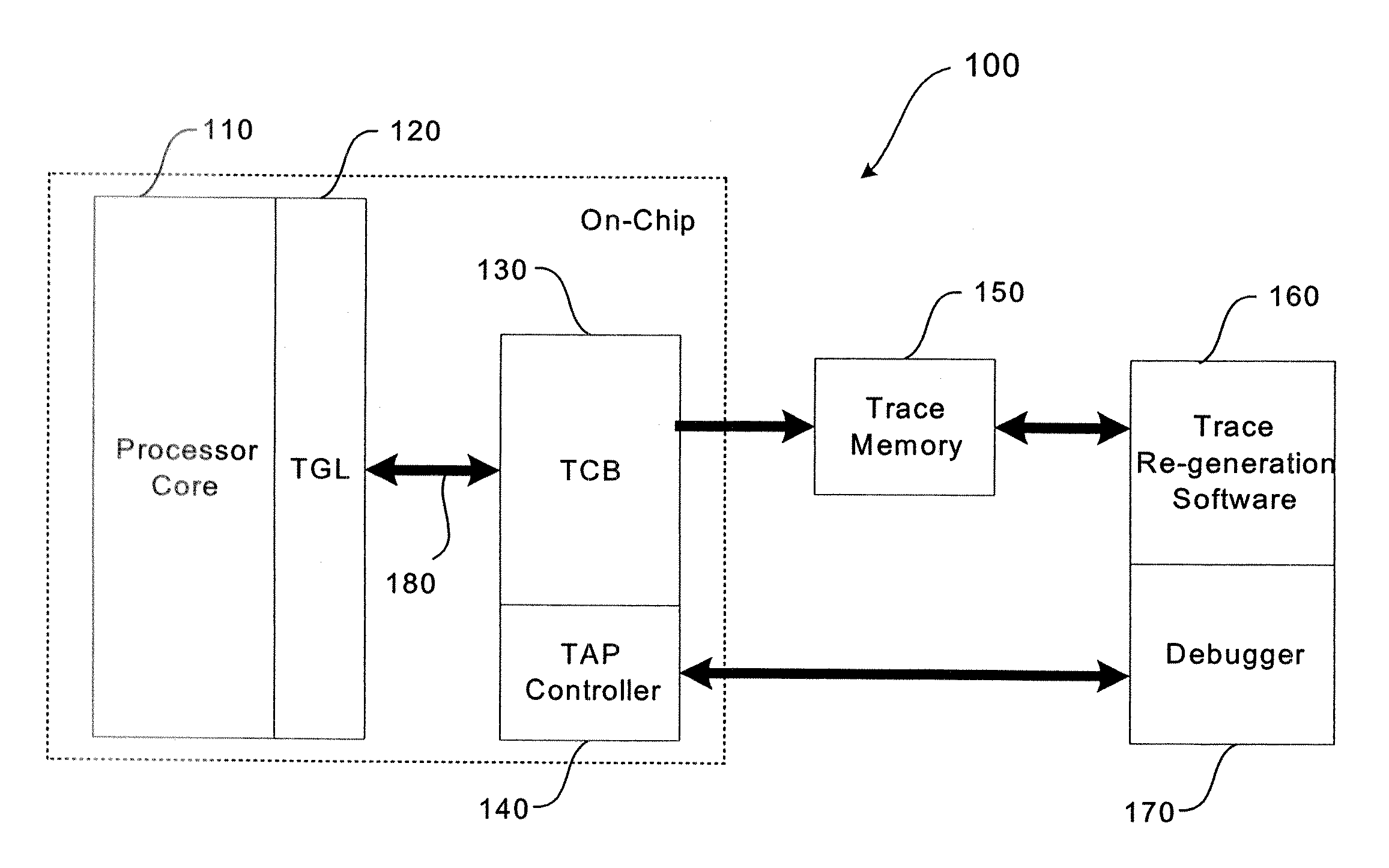

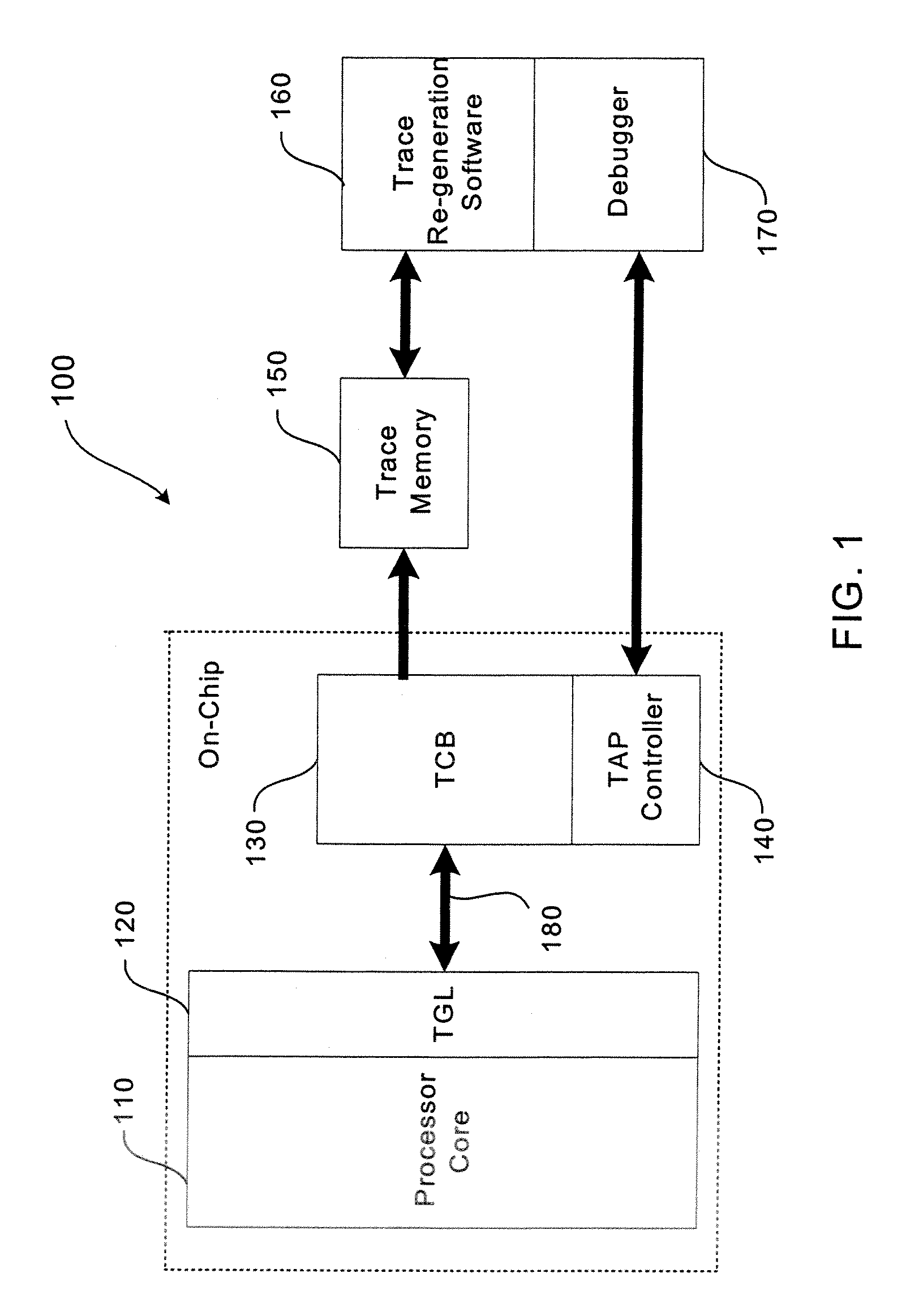

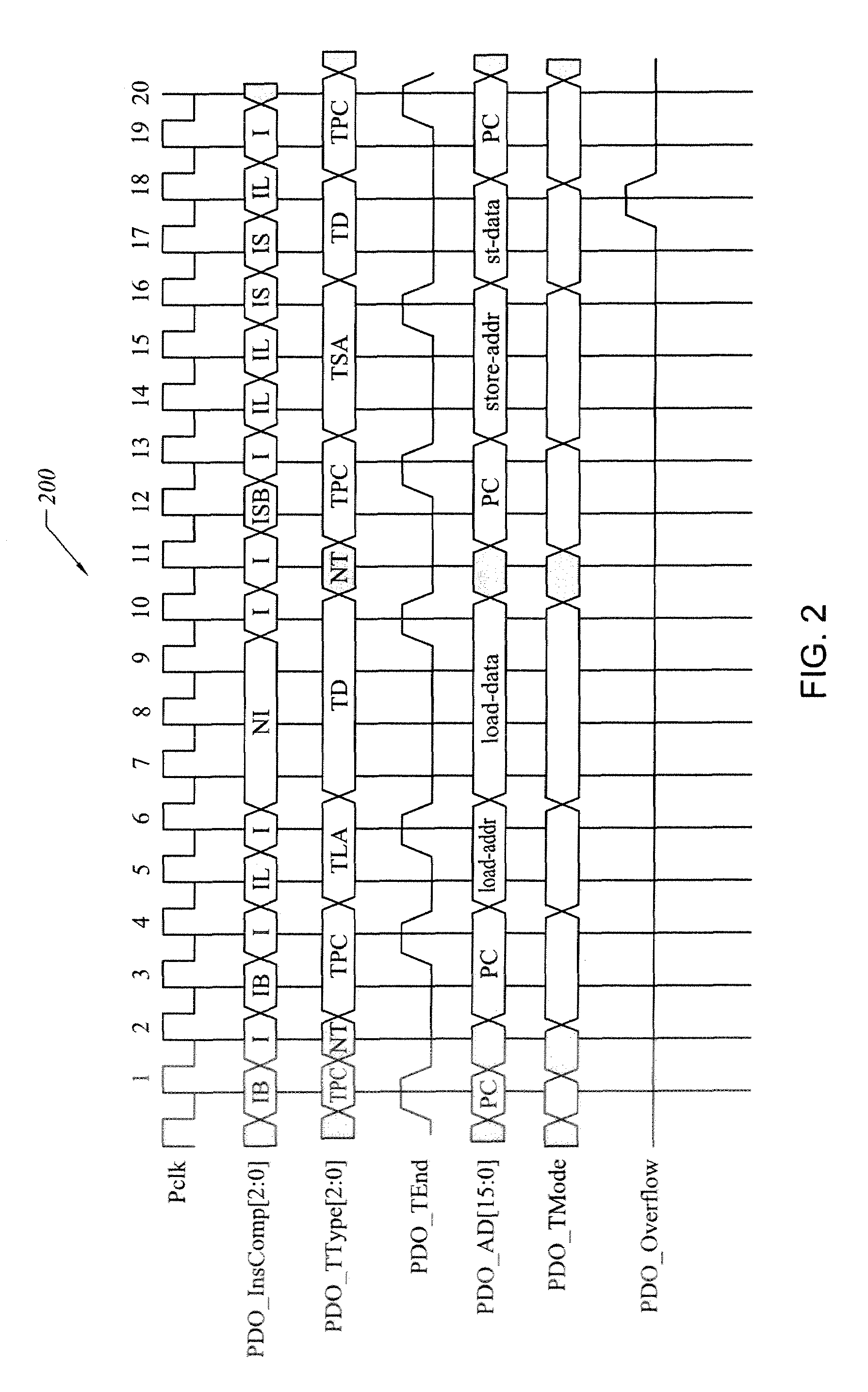

Distributed tap controller

InactiveUS7231551B1Electronic circuit testingError detection/correctionShift registerProcessor register

A system accessible by a test access port controller via a test access port interface includes a data register. The data register is selectable based on an instruction register signal in the test access port interface. The instruction register signal is derived form an instruction register in the test access port controller. A shift register is connected to a data input and a data output in the test access port interface and to the data register. The operation of the shift register is controlled based on an indication of a state of a test access port controller state machine that is received over the test access port interface.

Owner:ARM FINANCE OVERSEAS LTD

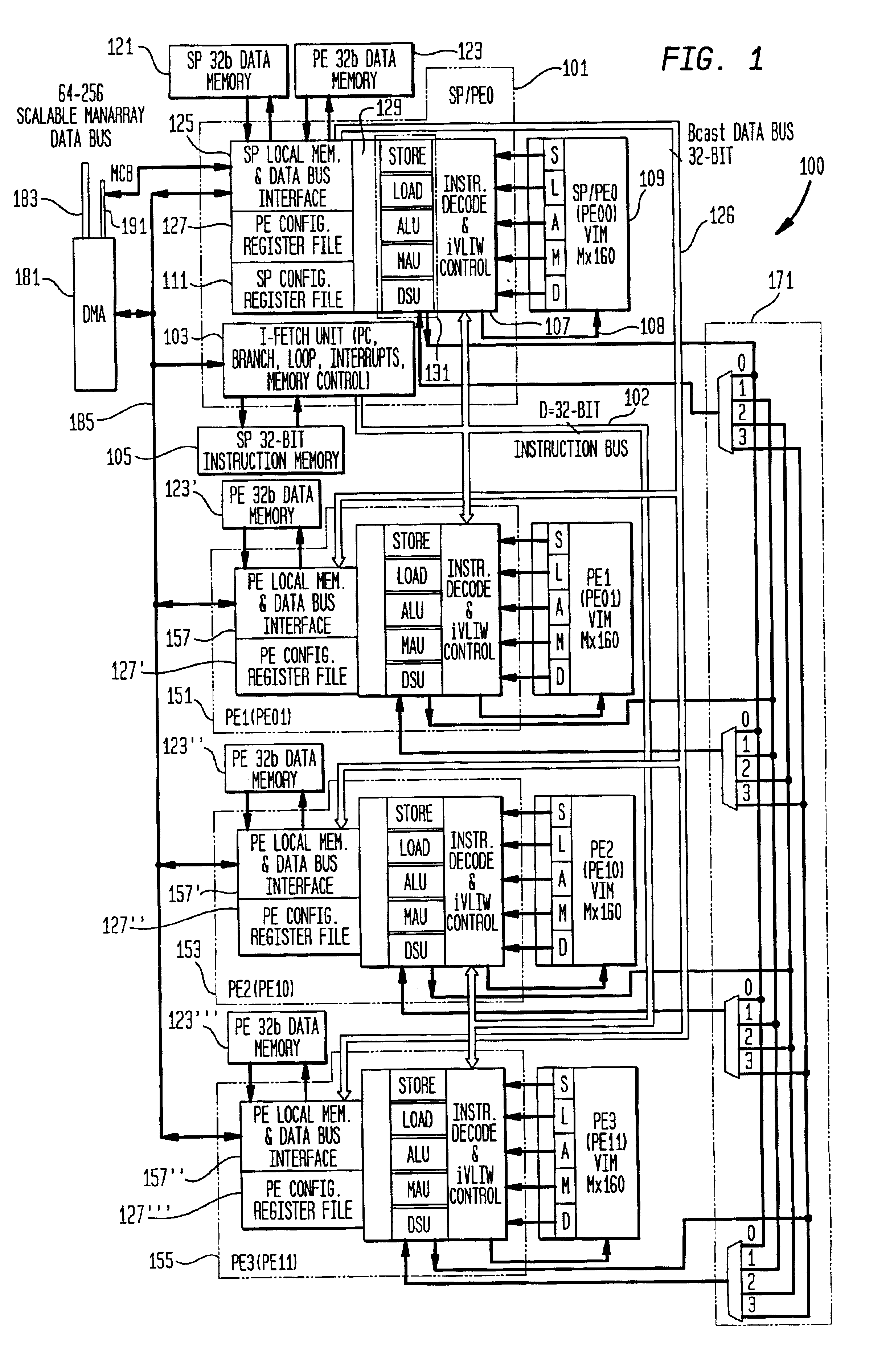

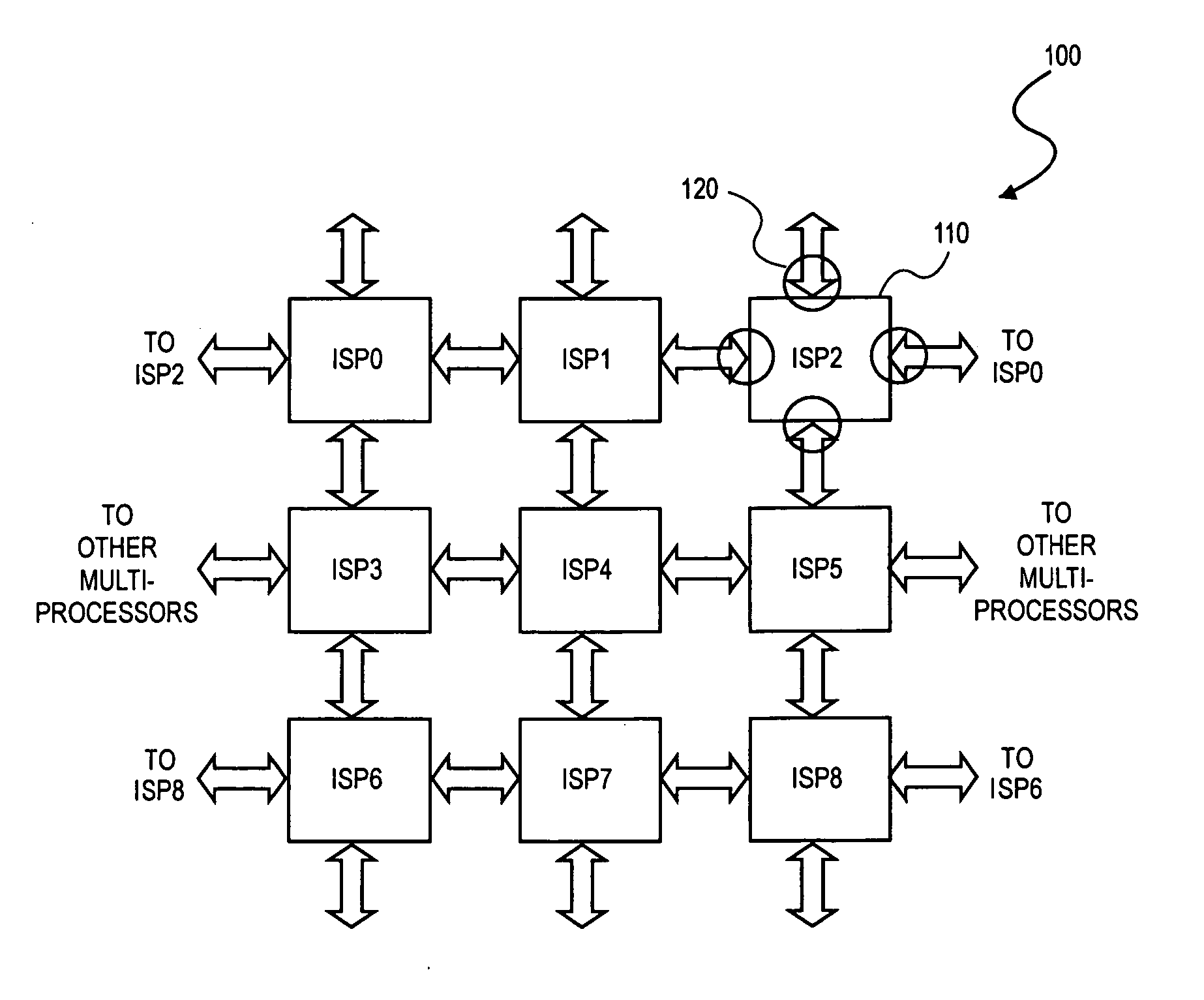

Method and apparatus for multiprocessor debug support

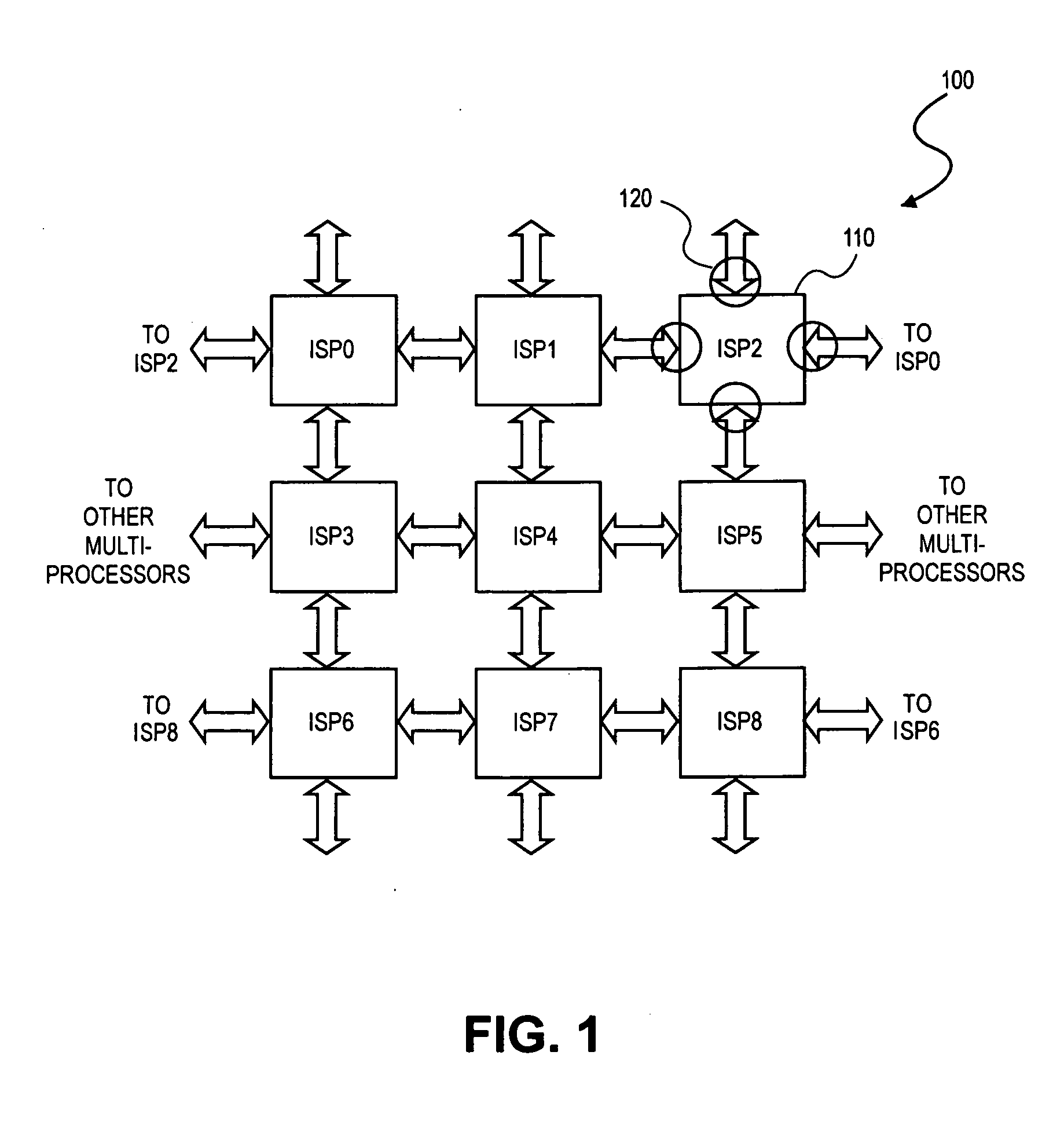

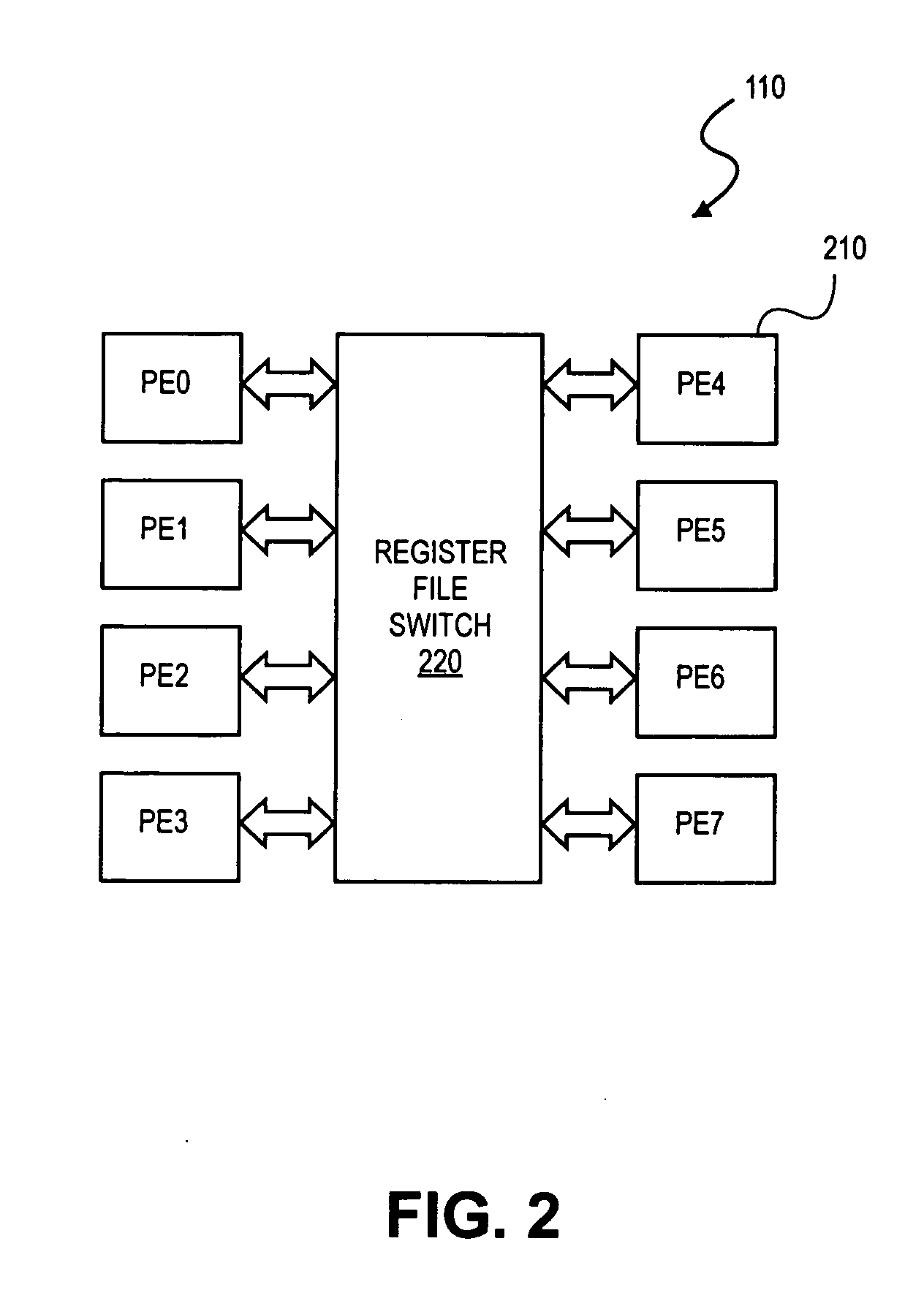

A device having at least one processor connected a controller and a memory; where the controller to execute a debug process. The debug process attaches a breakpoint bit field to each instruction. A system having image signal processors (ISPs), each ISP including processor elements (PEs). The ISPs include a debug instruction register connected to a first mux element. An instruction memory is connected to an instruction register. A decoder is connected to the instruction register. An execution unit is connected to the decoder. A debug executive unit is connected to the instruction memory, and a second mux element is connected to the execution unit and local registers. The decoder decodes a breakpoint bit field of each instruction.

Owner:INTEL CORP

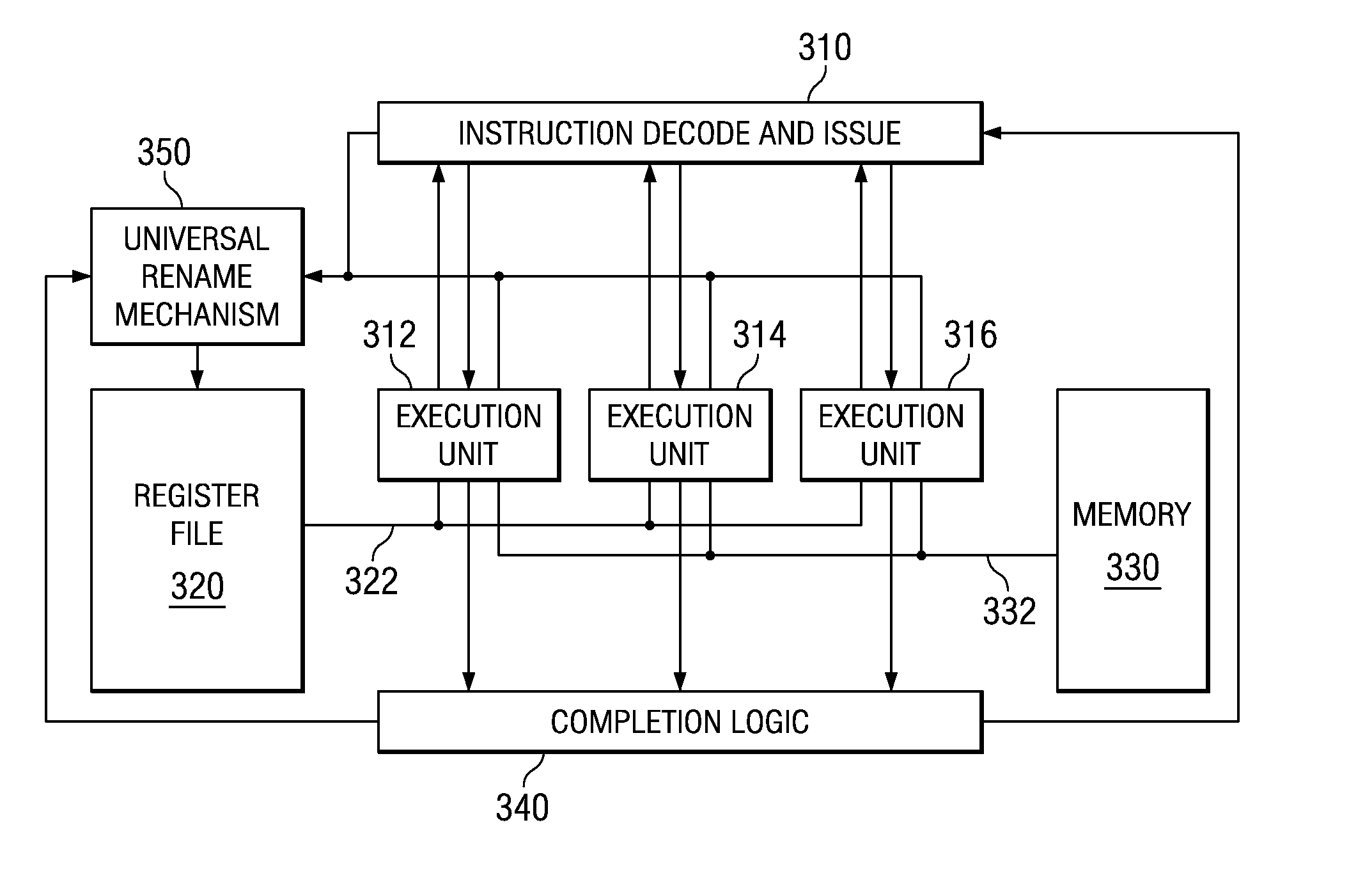

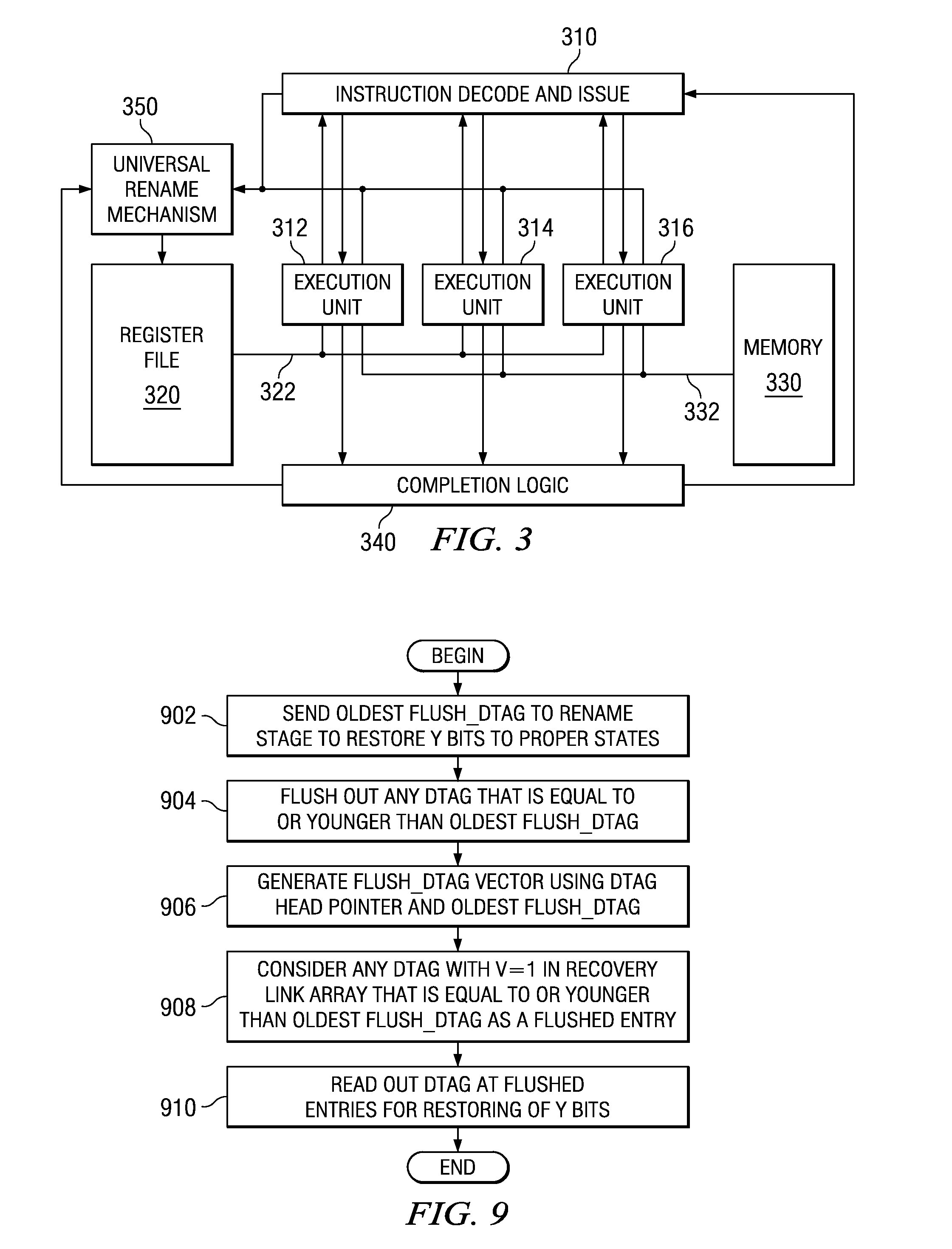

Universal Register Rename Mechanism for Targets of Different Instruction Types in a Microprocessor

InactiveUS20080263321A1Increase powerGeneral purpose stored program computerProgram controlGeneral purposeParallel computing

A unified register rename mechanism for targets of different instruction types is provided in a microprocessor. The universal rename mechanism renames destinations of different instruction types using a single rename structure. Thus, an instruction that is updating a floating point register (FPR) can be renamed along with an instruction that is updating a general purpose register (GPR) or vector multimedia extensions (VMX) instructions register (VR) using the same rename structure because the number of architected states for GPR is the same as the number of architected states for FPR and VR. Each destination tag (DTAG) is assigned to one destination. A floating point instruction may be assigned to a DTAG, and then a fixed point instruction may be assigned to the next DTAG and so forth. With a universal rename mechanism, significant silicon and power can be saved by having only one rename structure for all instruction types.

Owner:IBM CORP

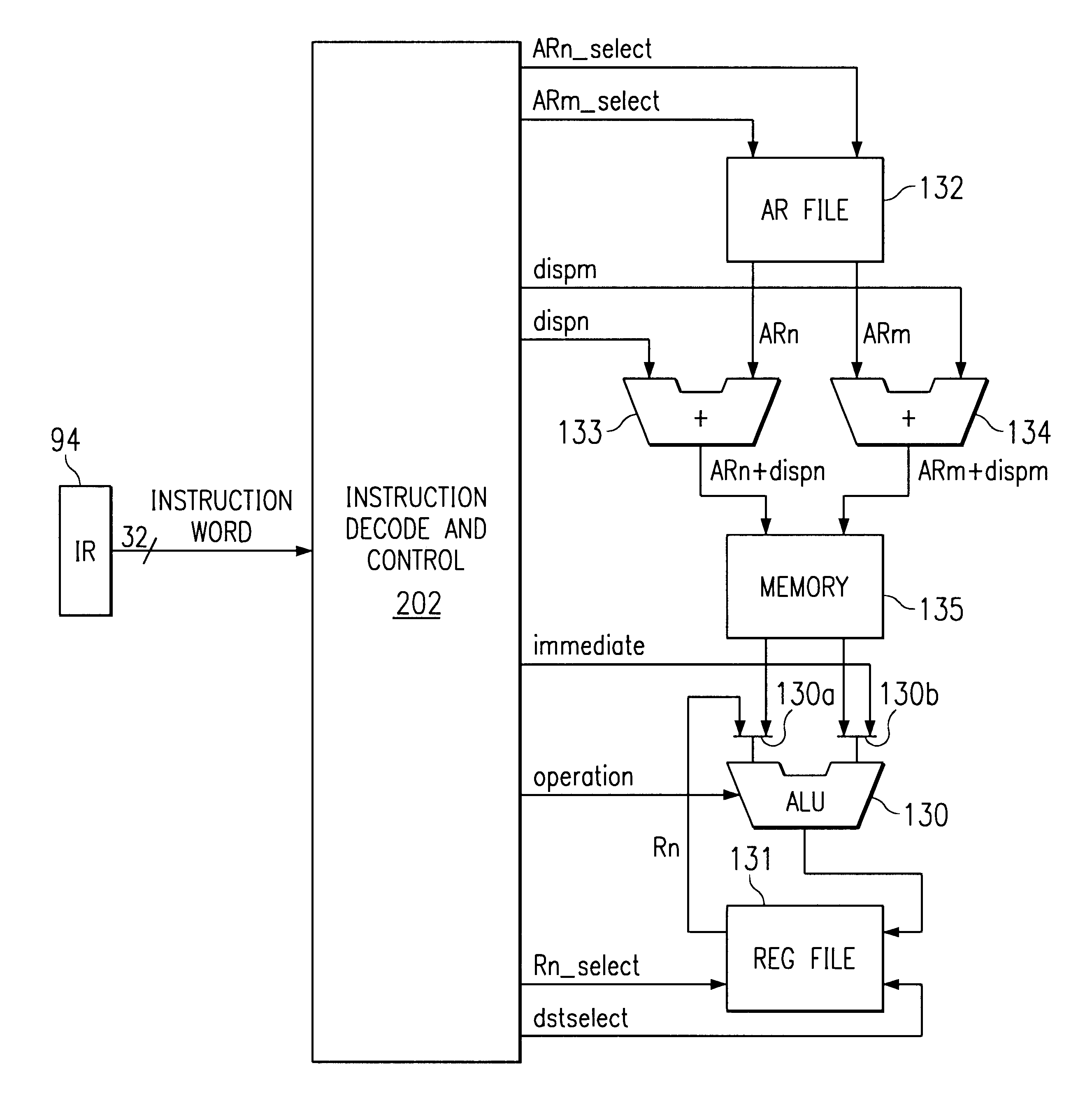

Processing devices with improved addressing capabilities systems and methods

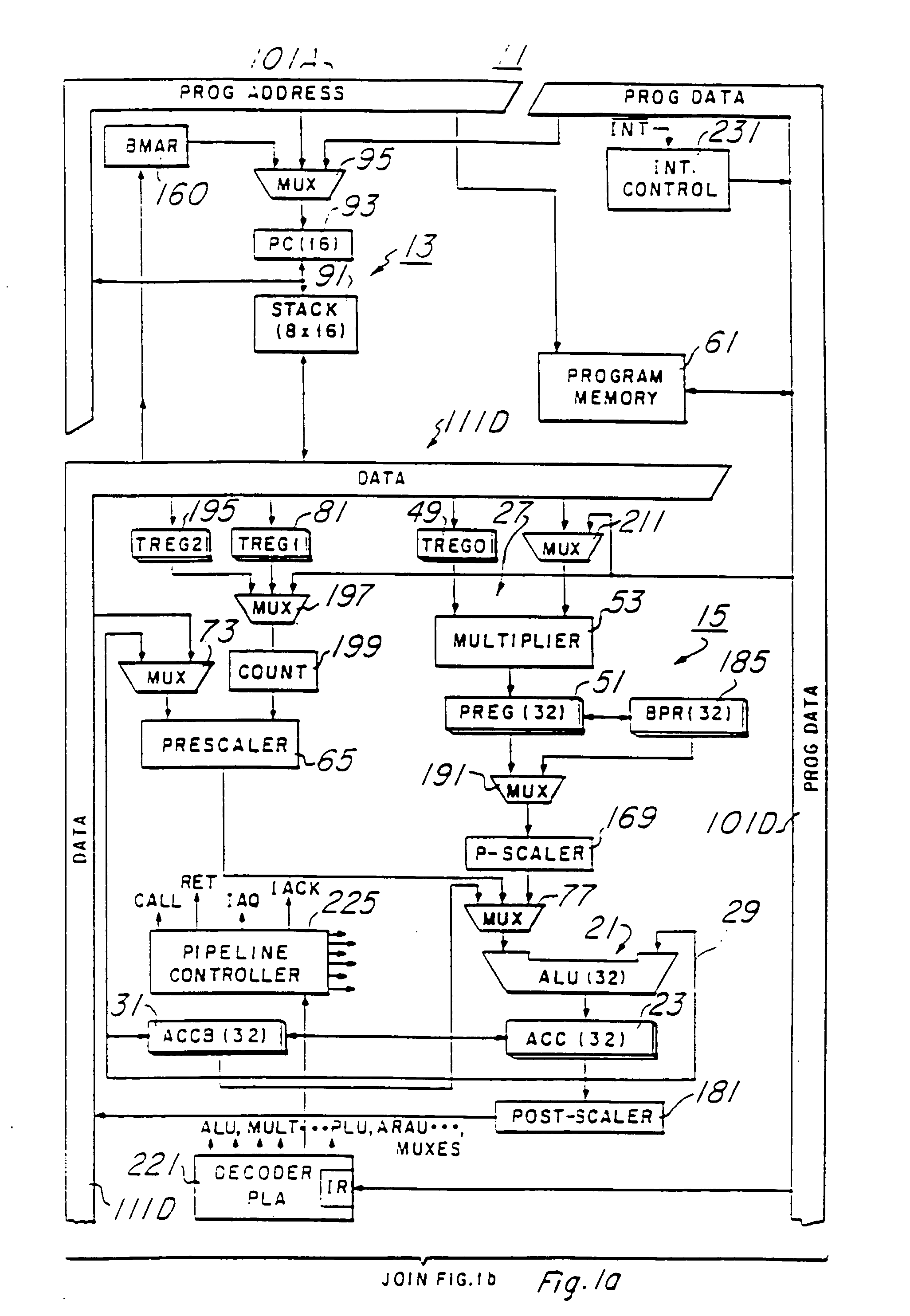

InactiveUS6625719B2Instruction analysisNext instruction address formationArithmetic logic unitProgram instruction

Owner:TEXAS INSTR INC

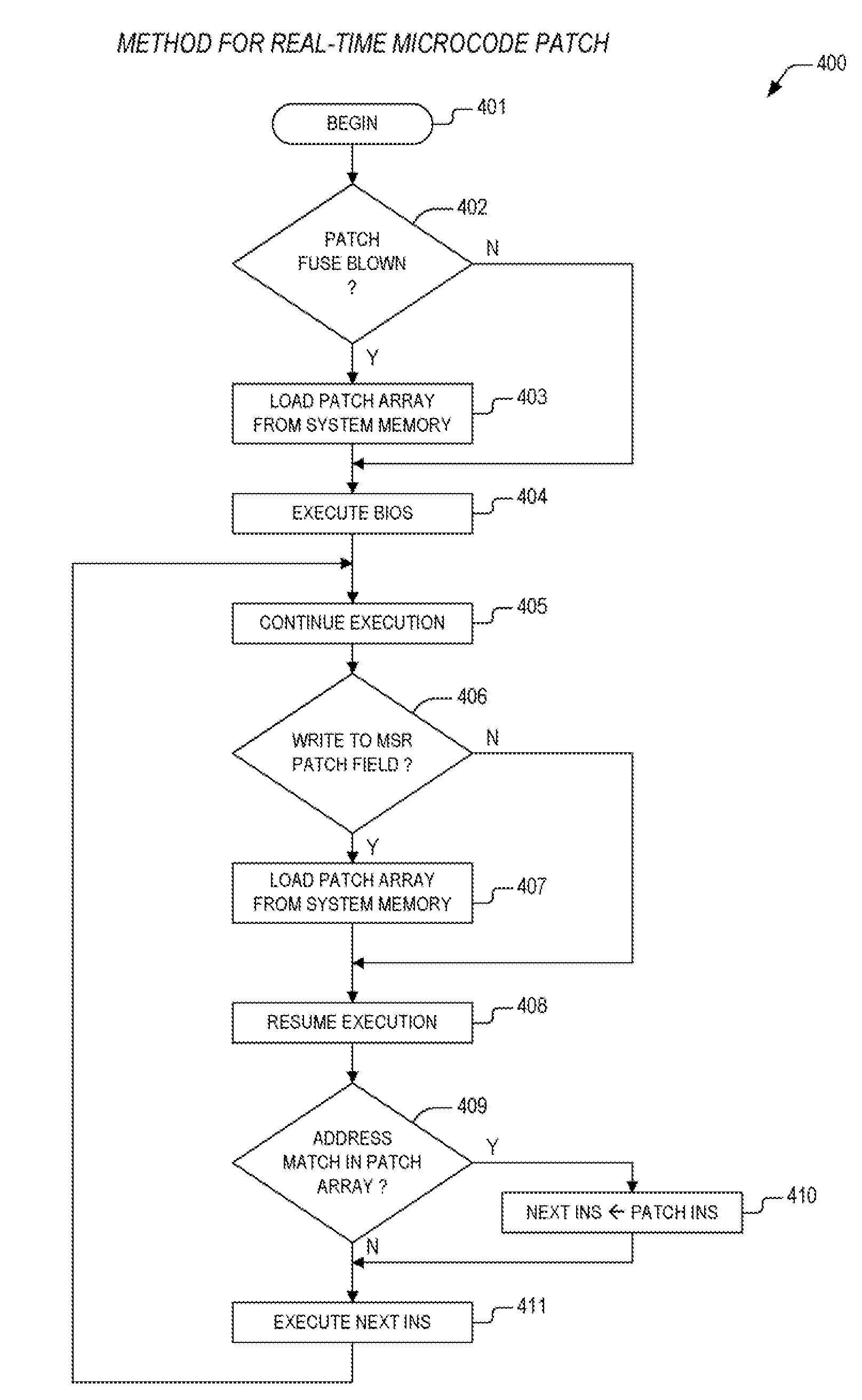

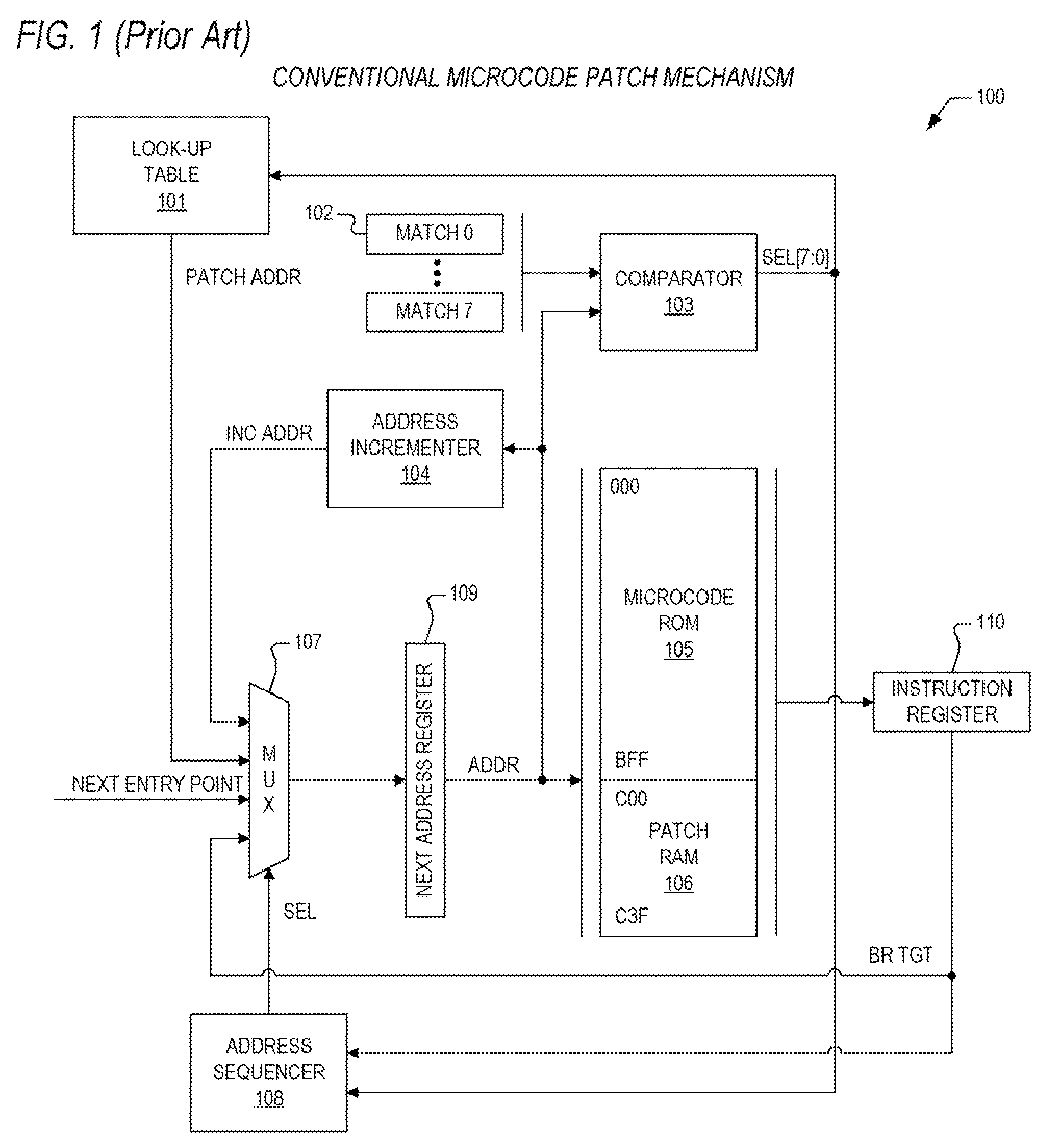

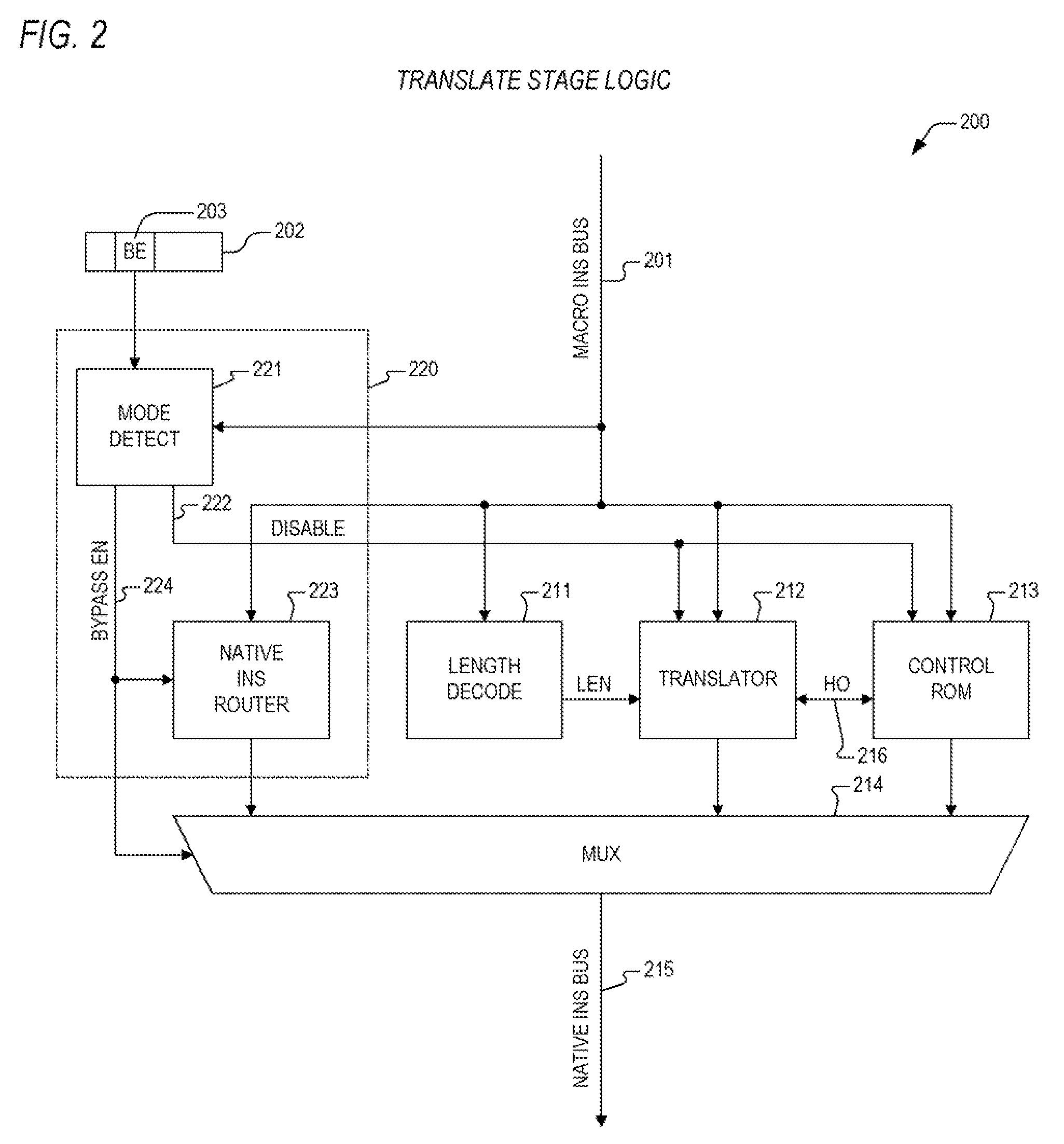

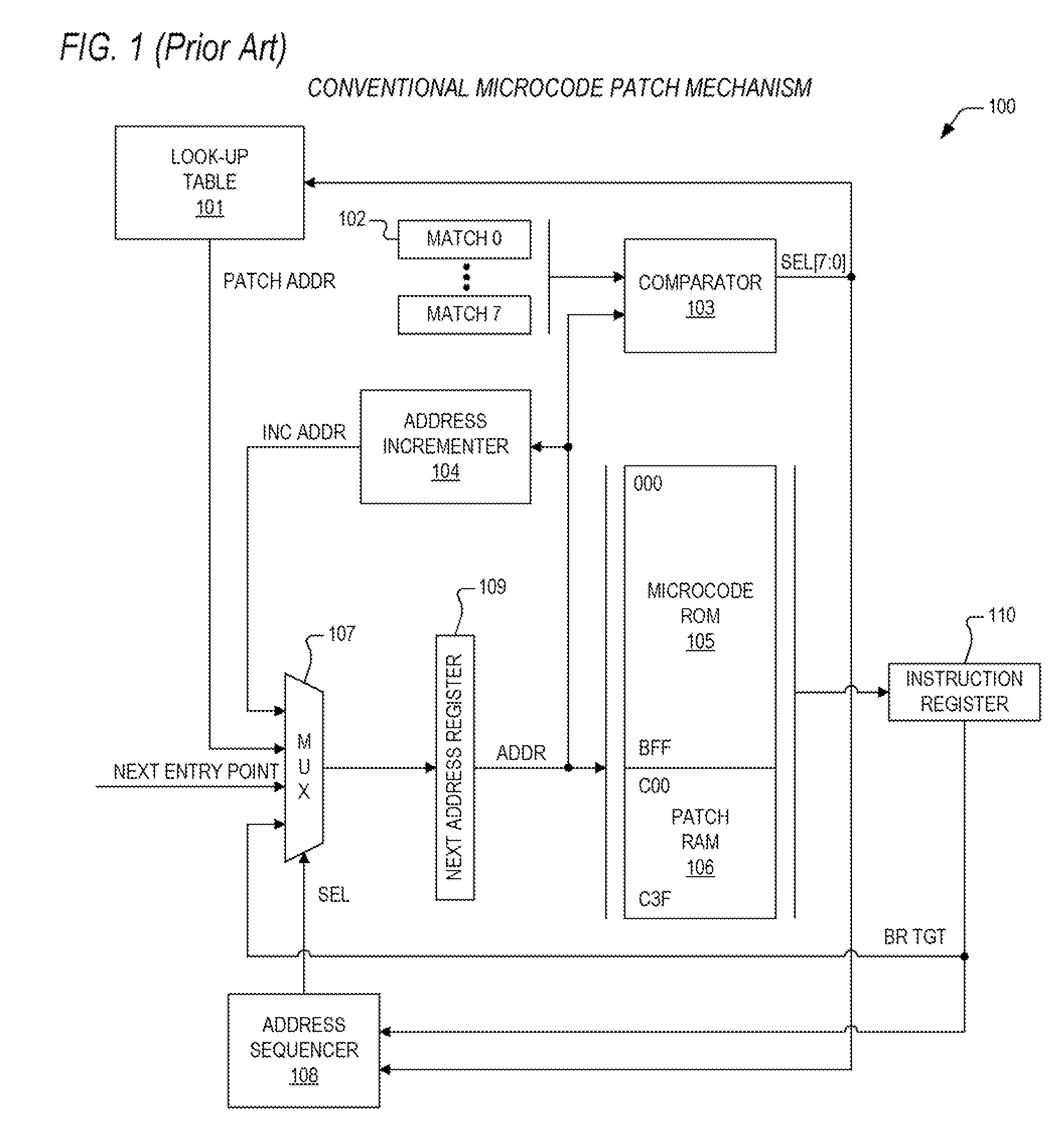

Apparatus and method for real-time microcode patch

InactiveUS20090031121A1Flexible and fastInstruction analysisDigital computer detailsPatch arrayOperating system

An apparatus for performing microcode patches that is both fast and flexible. In one embodiment, an apparatus for performing a real-time microcode patch is provided. The apparatus includes a patch array and a mux. The patch array receives a microcode ROM address and determines that the microcode ROM address matches one of a plurality of entries within the patch array. When the microcode ROM address matches, the patch array outputs a corresponding patch instruction and to assert a hit signal. The mux receives the patch instruction from the patch array and a micro instruction corresponding to the microcode ROM address from a microcode ROM. The mux provides the micro instruction or the corresponding patch instruction to an instruction register based upon the state of the hit signal.

Owner:VIA TECH INC

VLIW processor with write control unit for allowing less write buses than functional units

InactiveUS6044451AImproved cost-efficiencyRegister arrangementsGeneral purpose stored program computerProcessor registerUnit cost

Owner:FOOTHILLS IP LLC

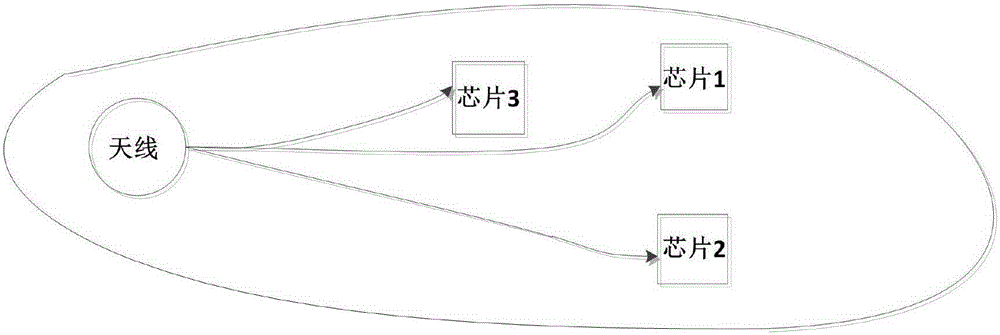

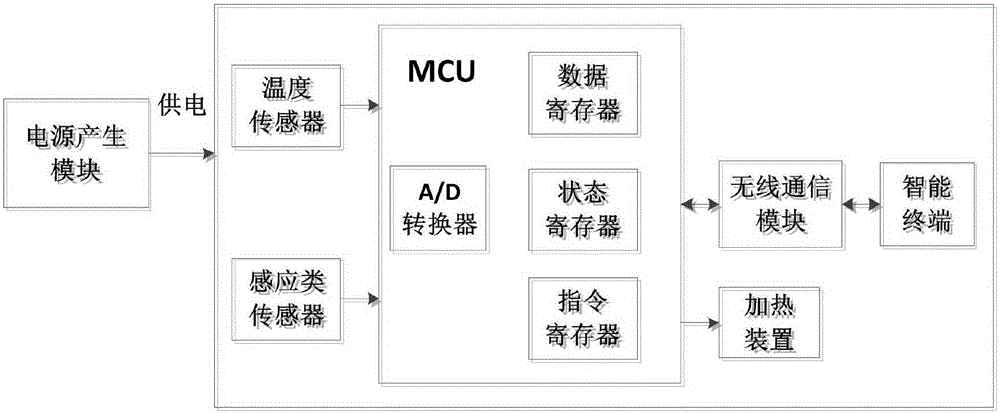

Intelligent insole with wireless charging function and capable of monitoring heart rate and regulating temperature

InactiveCN105192995AReduce volumeImprove applicabilityInsolesAuxillary controllers with auxillary heating devicesProcessor registerComputer module

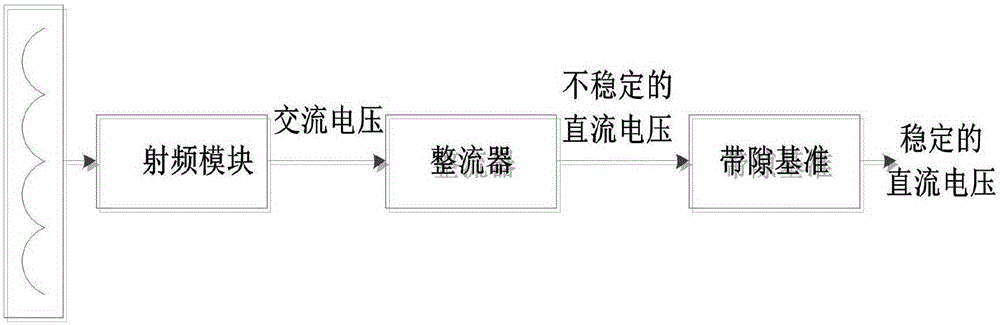

The invention provides an intelligent insole with a wireless charging function and capable of monitoring the heart rate and regulating the temperature. The intelligent insole comprises an insole body and an integrated chip. The integrated chip is arranged in the insole body. A temperature sensor module, a physiological parameter induction-type sensor module, a wireless communication module, an MCU module and a power generation module are included in the integrated chip. An antenna is arranged outside the integrated chip for wireless charging. The temperature sensor module is used for monitoring the temperature of a foot bottom. The induction-type sensor module can monitor change of the heart rate in real time. The MCU module serves as the core of the chip, and a central processing unit (CPU) is used for processing various data. The power generation module converts signal energy into stable direct-current voltages to provide a power supply. Heating operation is conducted through an instruction fed back by an instruction register in the MCU module, and a coil antenna at the rear end of the intelligent insole can receive wireless signals generated by an intelligent terminal. Through matching of the modules, the functions of the entire intelligent insole can be achieved.

Owner:BEIJING UNIV OF TECH

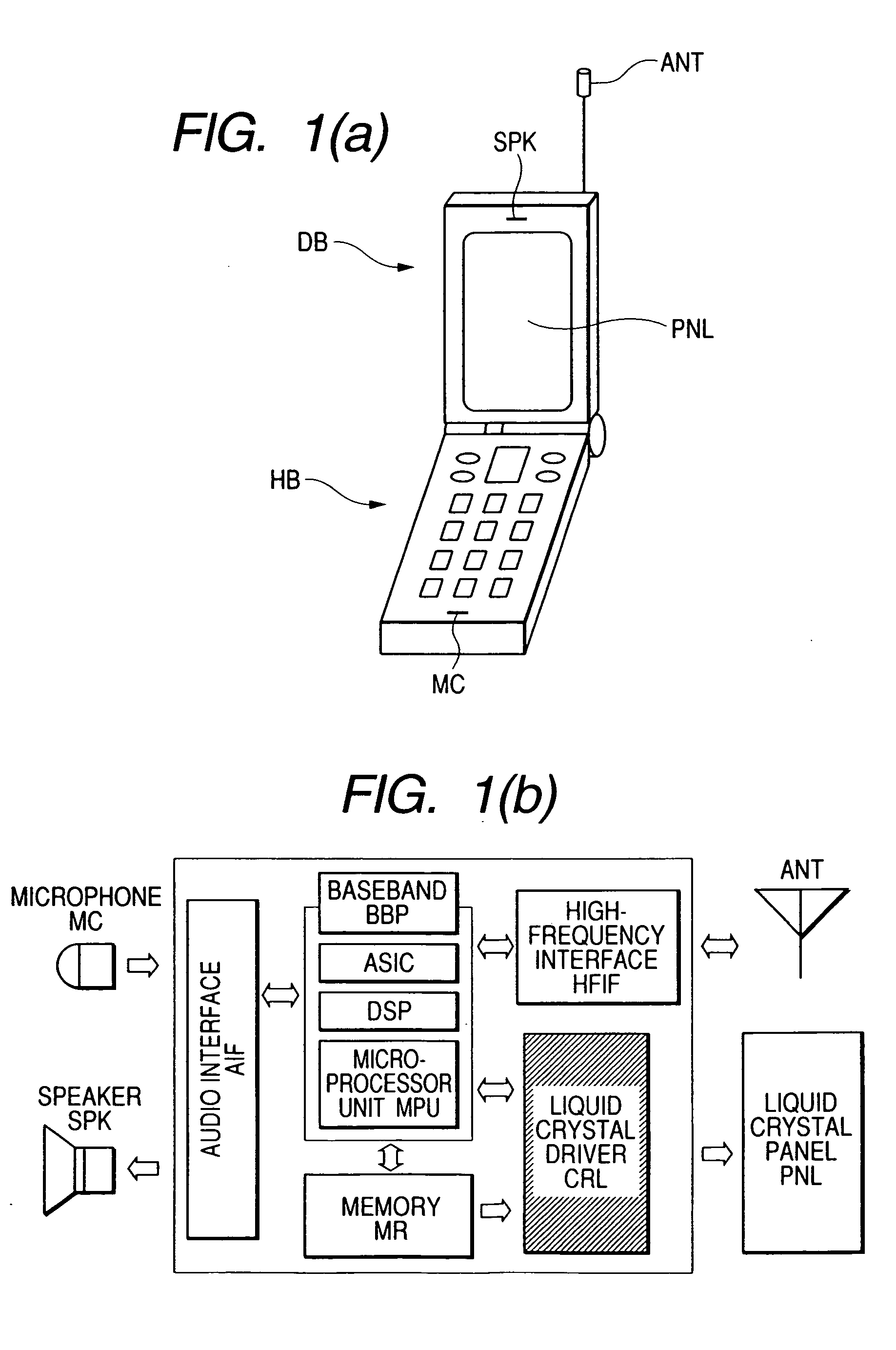

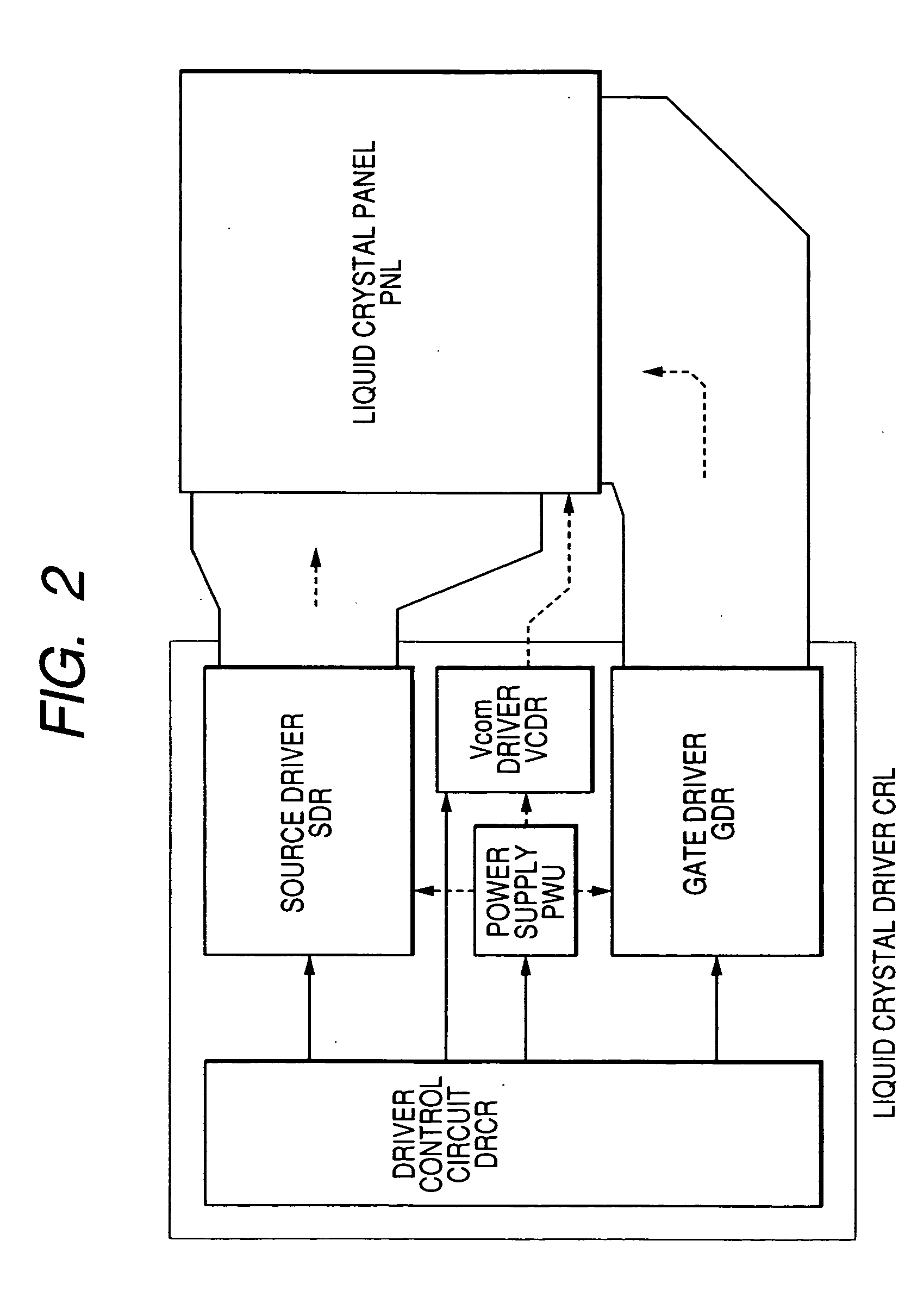

Display drive control device, for which drive method, electronics device and semiconductor integrated circuit

ActiveUS20050017965A1Easy to changeReduce system loadVolume/mass flow measurementCathode-ray tube indicatorsProcessor registerDisplay device

It is aimed at being capable of easily changing a power supply startup procedure and complying with various display devices. A power supply circuit is provided between an instruction register of a liquid crystal driver and a power supply unit. The power supply unit is not directly supplied with a setting value registered to the instruction register from a microprocessor unit. The microprocessor unit writes setting values to the instruction register without need for the time axis. To turn on the power, the time is measured inside the power supply sequencer. Set values are sequentially input to the power supply unit. The instruction register should be also capable of registering an input timing.

Owner:SYNAPTICS JAPAN GK

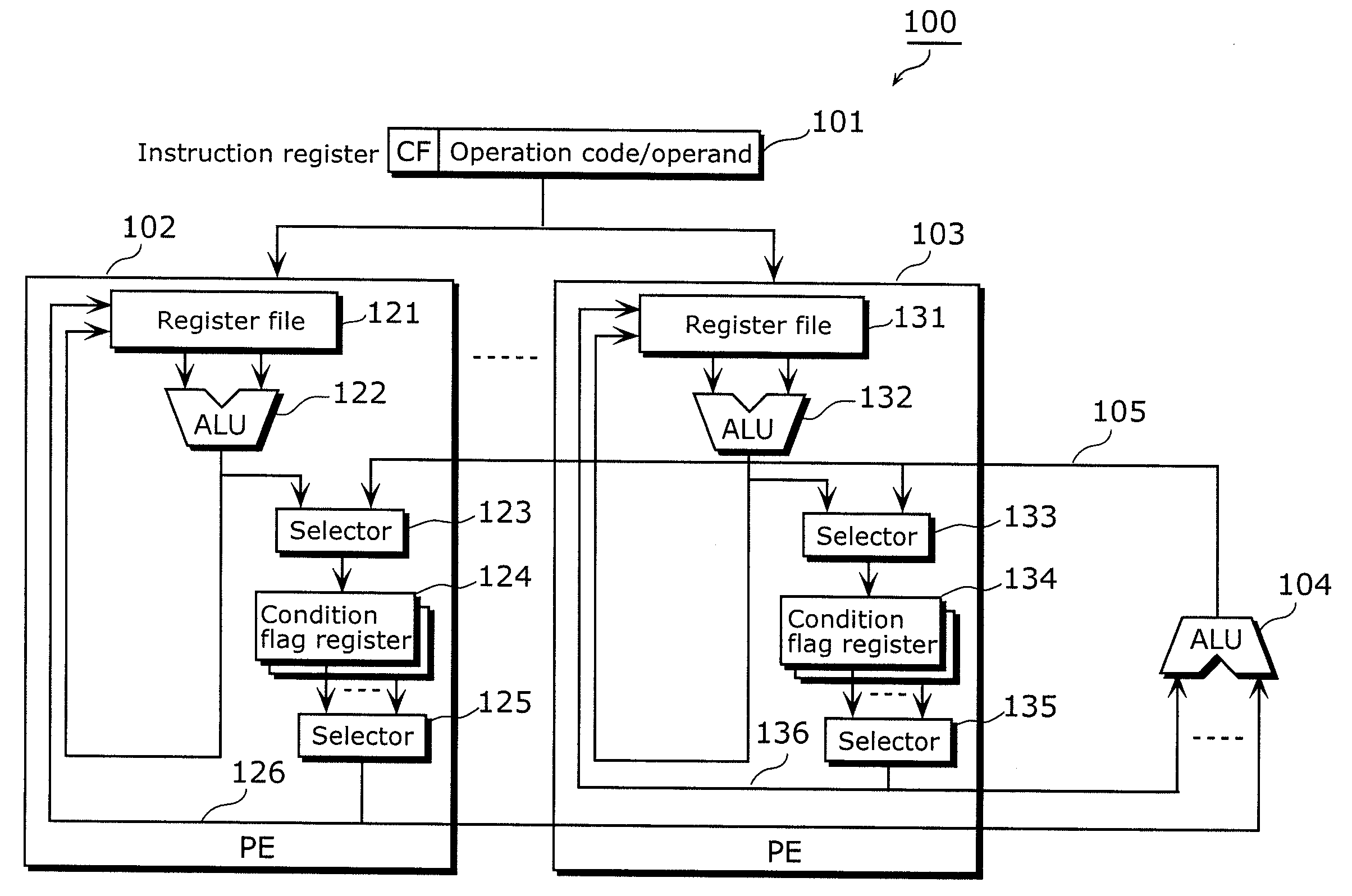

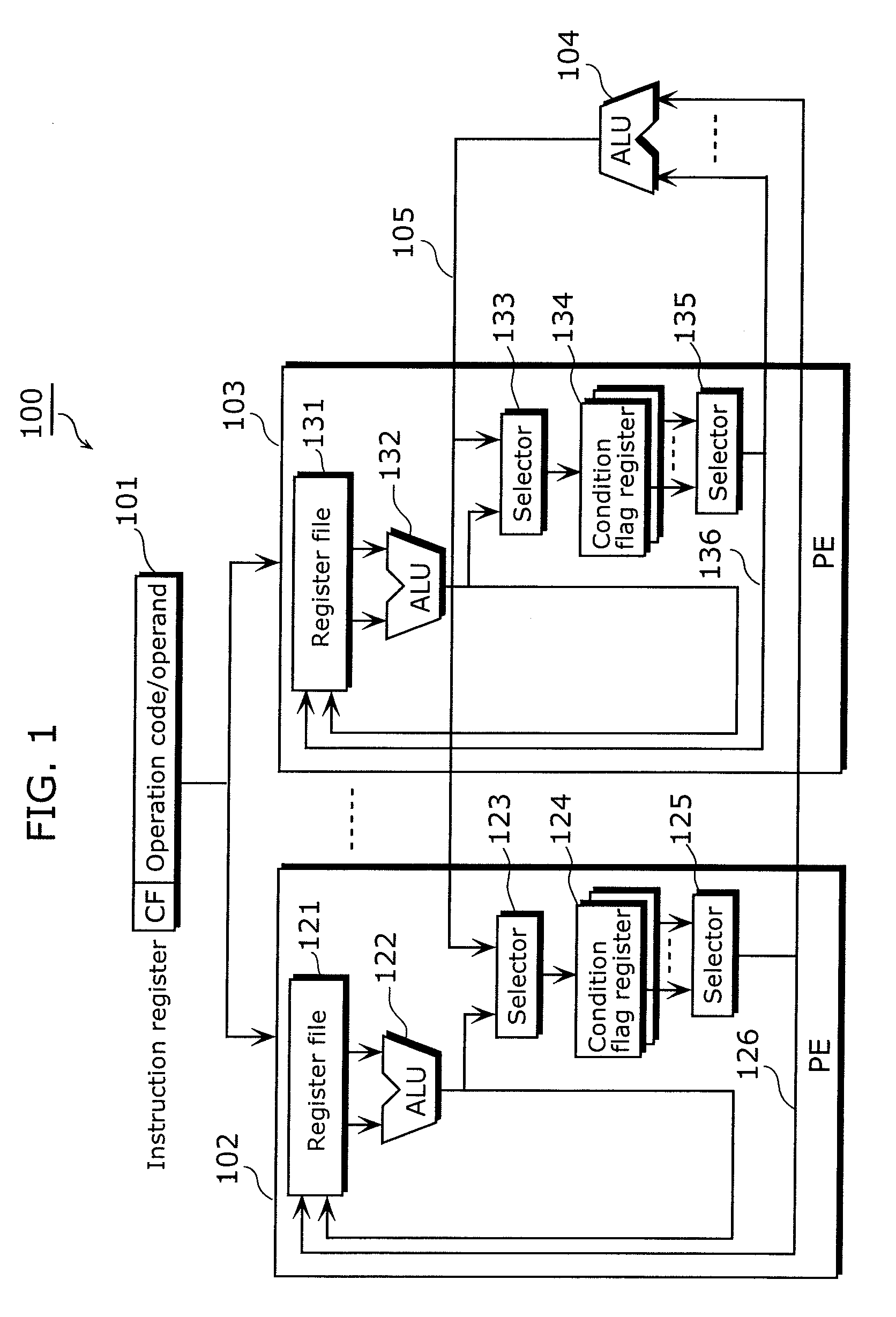

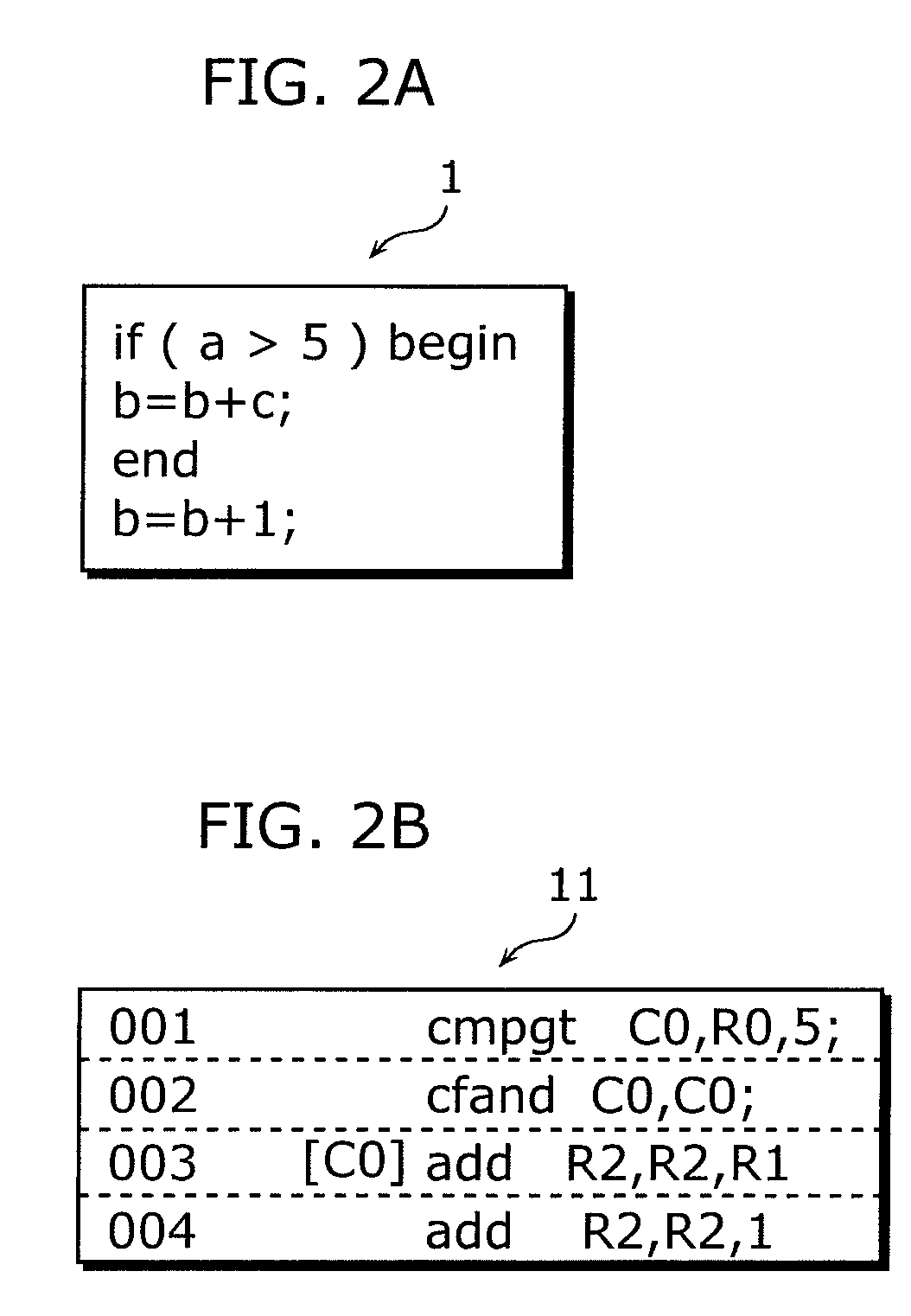

Arithmetic processing apparatus

ActiveUS20090228691A1Performance of was minimizedReduce generationConditional code generationGeneral purpose stored program computerLogical operationsProcessing element

An arithmetic processing apparatus capable of performing an arithmetic operation for generating a condition flag commonly referred to by using a condition flag generated on an arithmetic operation unit basis in as few steps as possible is provided. The arithmetic processing apparatus, which processes multiple data in parallel based on single instruction, includes: processing elements capable of performing a common arithmetic operation based on the evaluation result of the instruction stored in the instruction register; and a condition flag arithmetic operation unit capable of performing one of the logical operation and the comparison operation on the condition flag retained in each processing element, transferring the operation result to each processing element, and updating the condition flag based on the operation result.

Owner:SOCIONEXT INC

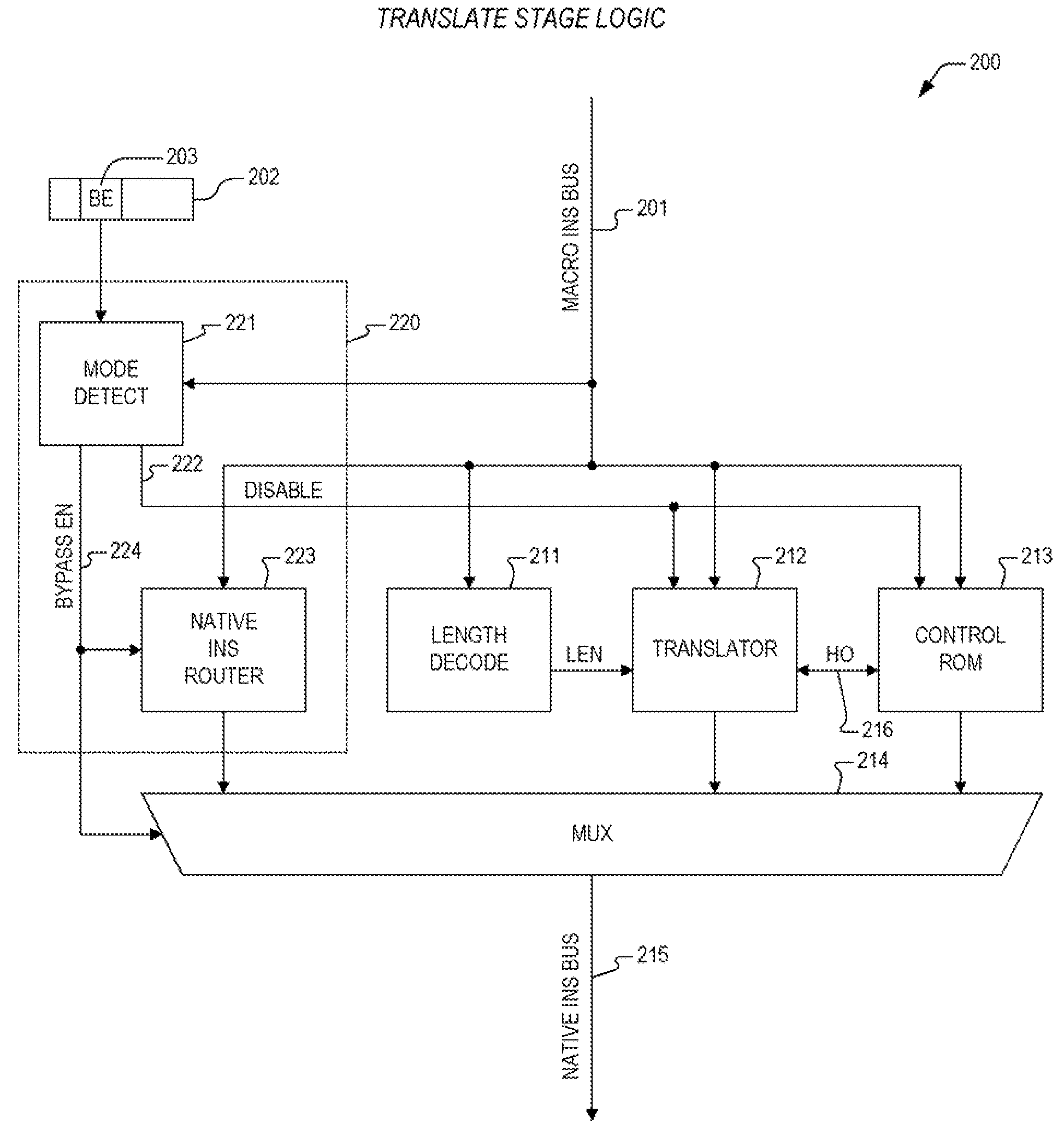

Apparatus and method for fast one-to-many microcode patch

A microcode patch apparatus including a patch array, a mux, and a RAM. The patch array receives a microcode ROM address and determines that the microcode ROM address matches one of a plurality of entries within the patch array. The patch array outputs a corresponding branch instruction and asserts a hit signal. The branch instruction prescribes a microcode branch target address. The mux receives the branch instruction from the patch array and a micro instruction corresponding to the microcode ROM address from a microcode ROM. The mux provides the micro instruction or the corresponding branch instruction to an instruction register based upon the state of the hit signal. The RAM stores a plurality of patch instructions that are to be executed in place of the micro instruction. The first one of the plurality of patch instructions is stored at a location in the RAM corresponding to the microcode branch target address.

Owner:VIA TECH INC

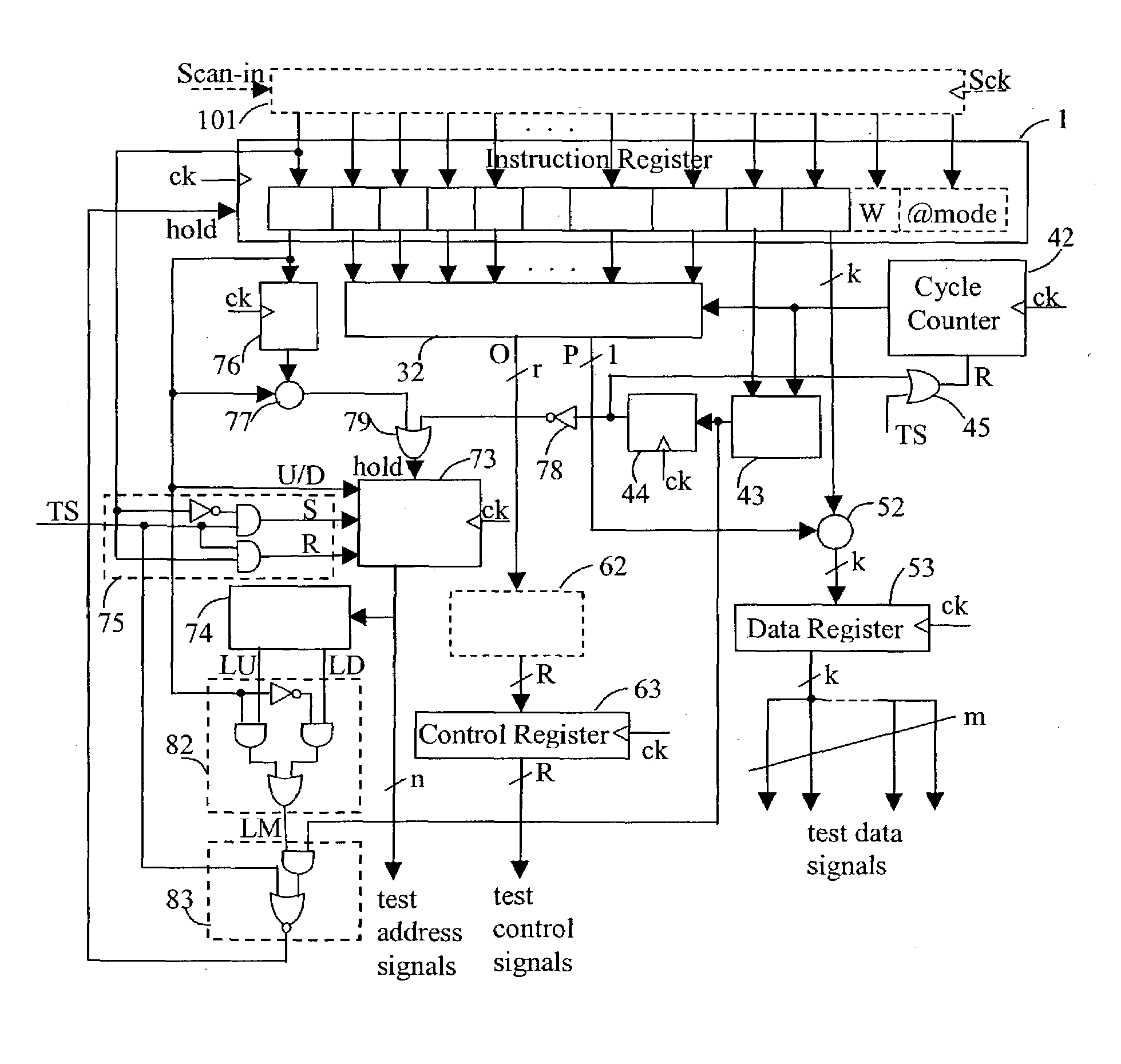

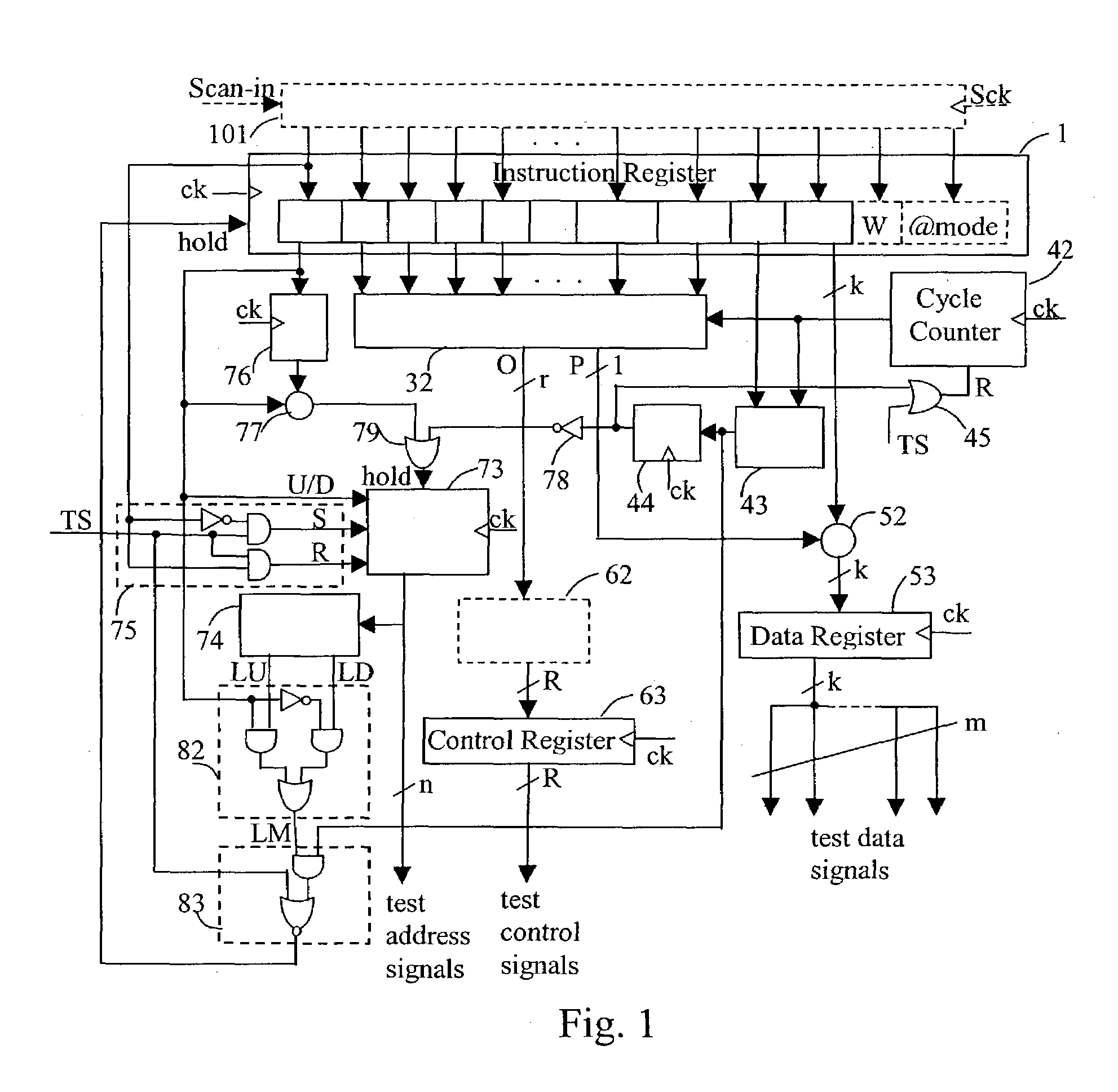

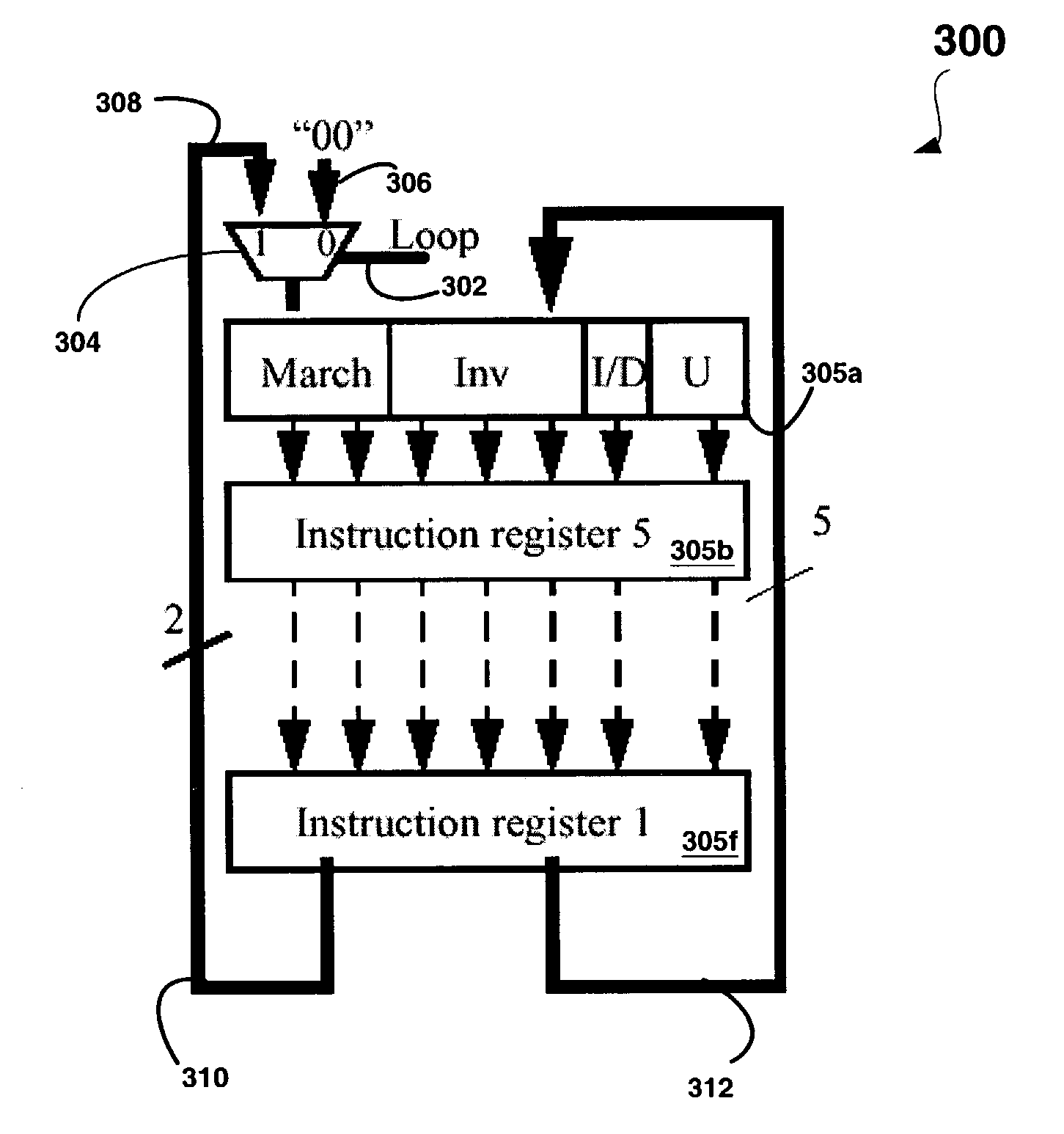

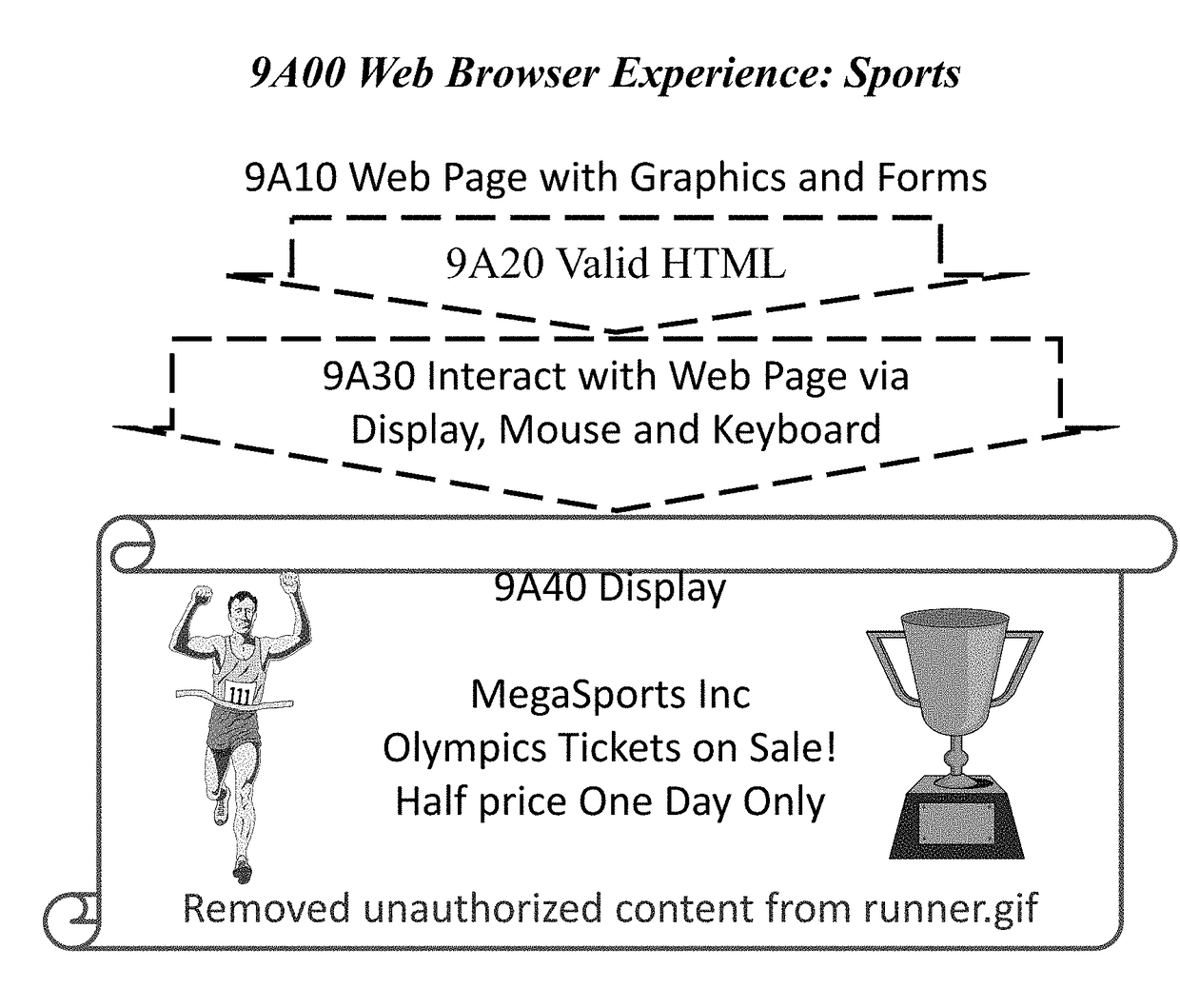

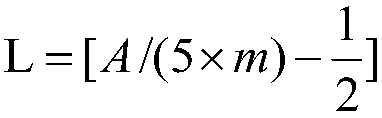

Programmable test for memories

A programmable built in self test, BIST, system for testing a memory, comprises an instruction register formed in the same chip as the memory; a circuit for loading the register by successive instructions, each instruction comprising at least one address control field, a first number (m) of operation fields, a number-of-operations field specifying a second number t+1, with t+1≦m; a circuit controlled by the address control field to determine successive addresses; and a cycle controller for executing, for each successive address, the second number (t+1) of successive operations, each of which is determined by one of the t+1 first operation fields.

Owner:SYNOPSYS INC

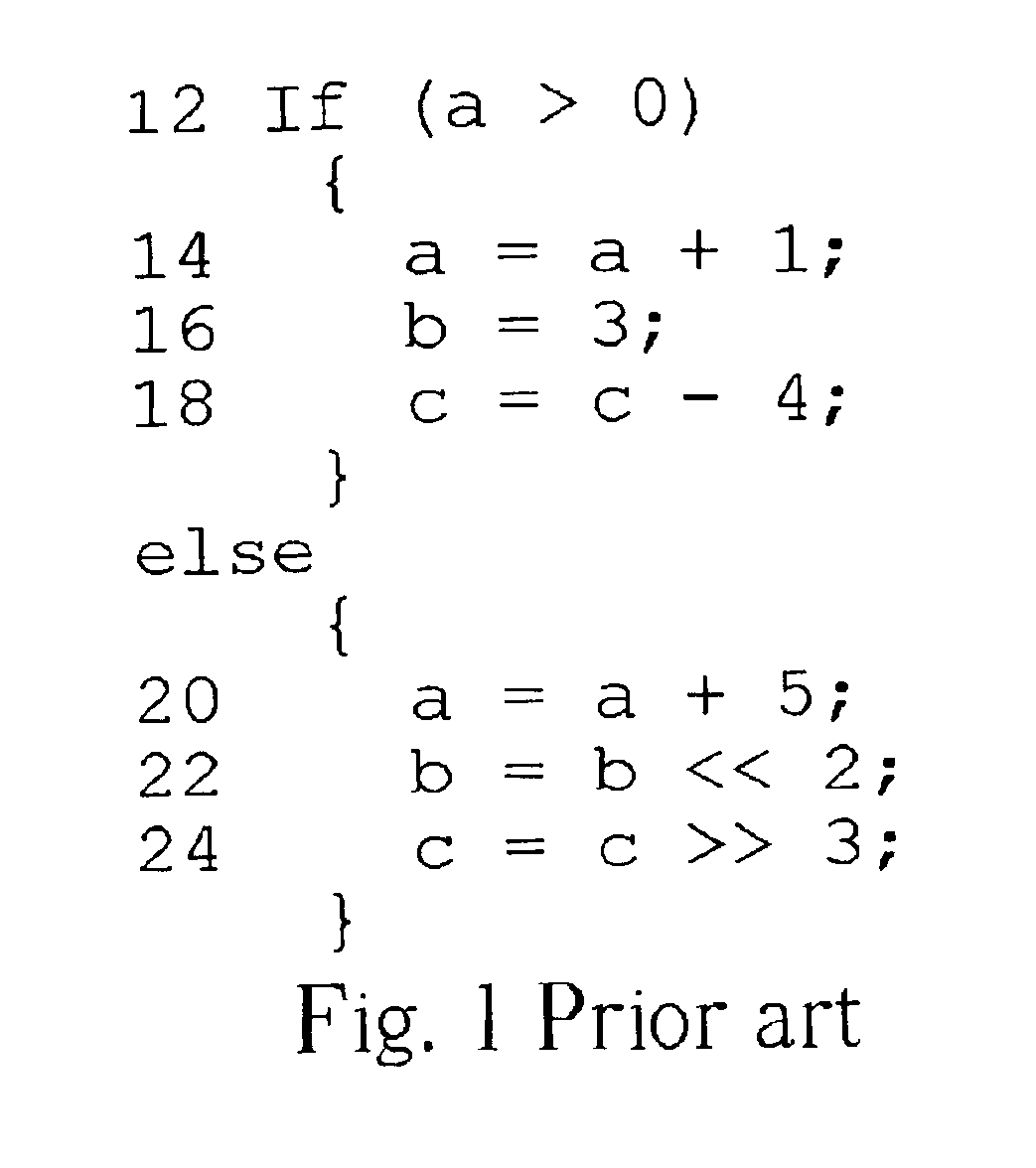

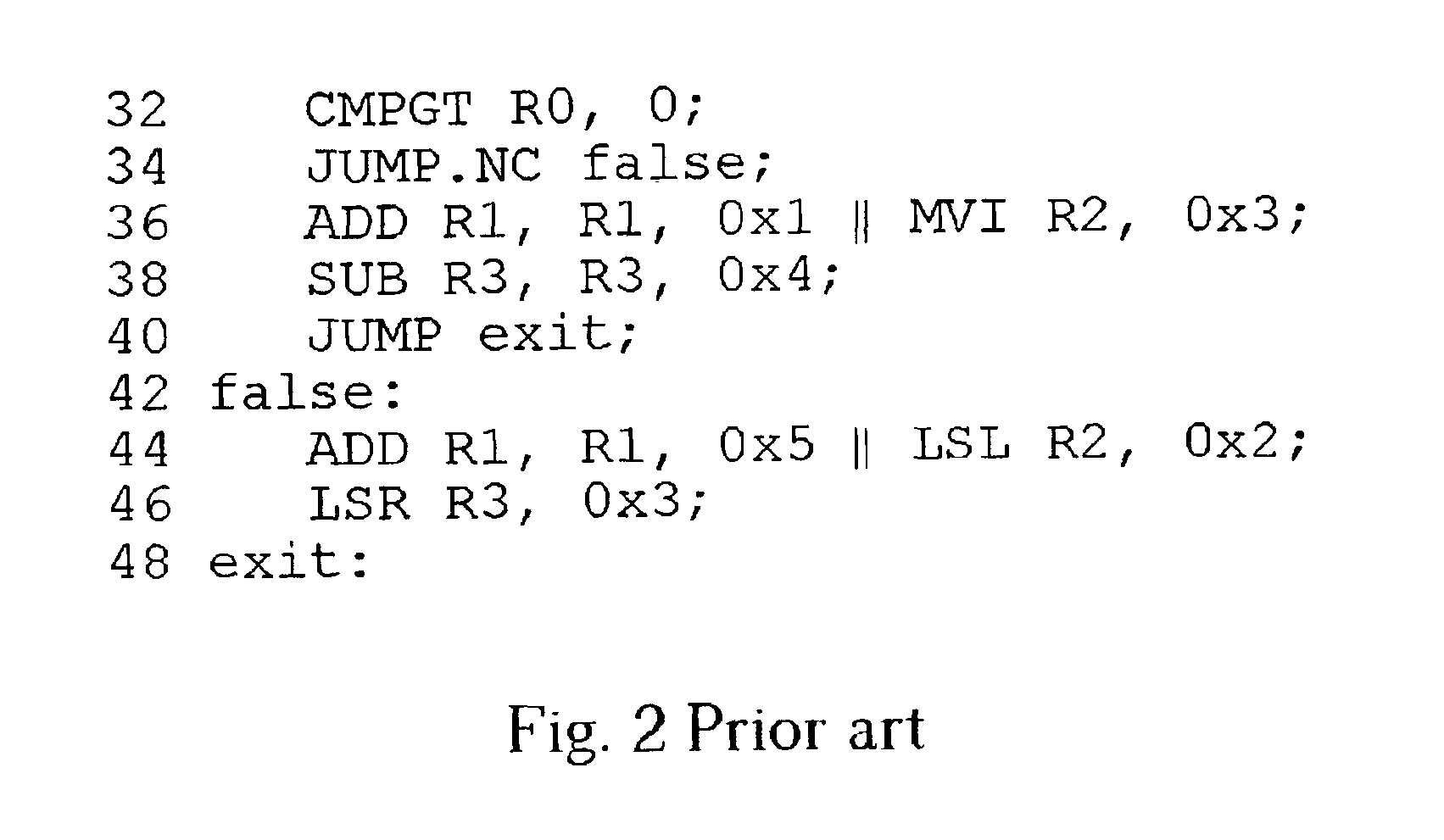

Controlling VLIW instruction operations supply to functional units using switches based on condition head field

InactiveUS6865662B2Reduce in quantityReduce delaysInstruction analysisGeneral purpose stored program computerMultiple criteriaOperand

A VLIW processor for executing a sequence of very long instruction words having a plurality of operations to be executed in parallel. The VLIW processor has a plurality of functional units for parallel execution of the operations specified by the VLIW, an instruction register for holding the VLIW, and a condition flag for indicating the results of a comparison operation. The VLIW includes a conditional head and a plurality of slots, each slot including an operational code and any related operands. The conditional head has a plurality of conditional indicators, each conditional indicator uniquely corresponding to one operation and specifying a condition in which the operation is to be executed if the indicated condition exists. A control circuit is connected to the instruction register and the functional units to deliver the operation from the instruction register to the corresponding functional unit for execution when the condition exists.

Owner:NOVATEK MICROELECTRONICS CORP

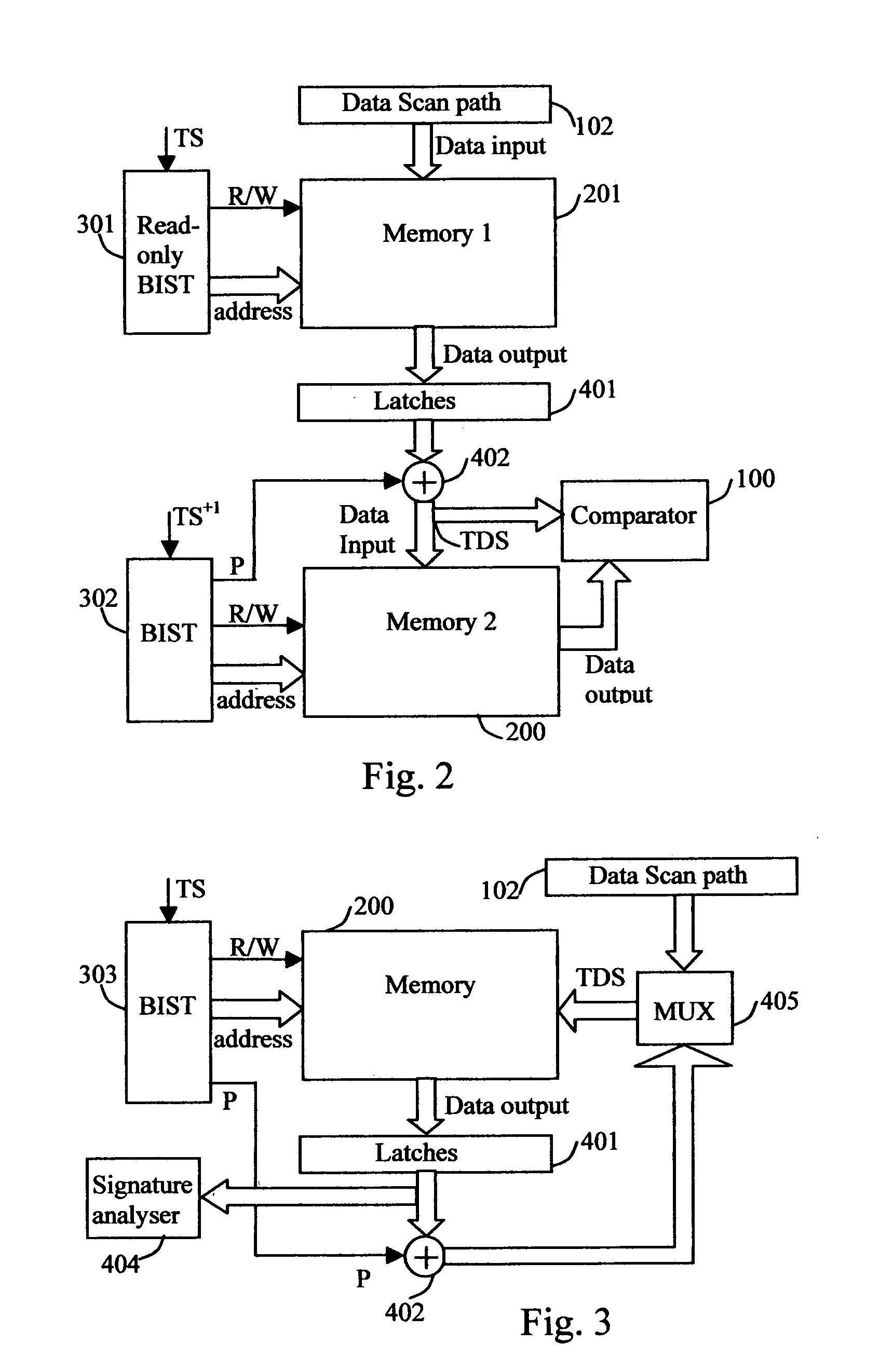

Built-in self-test (BIST) of memory interconnect

ActiveUS7096393B2Efficiently provideElectronic circuit testingStatic storageExternal storageMemory controller

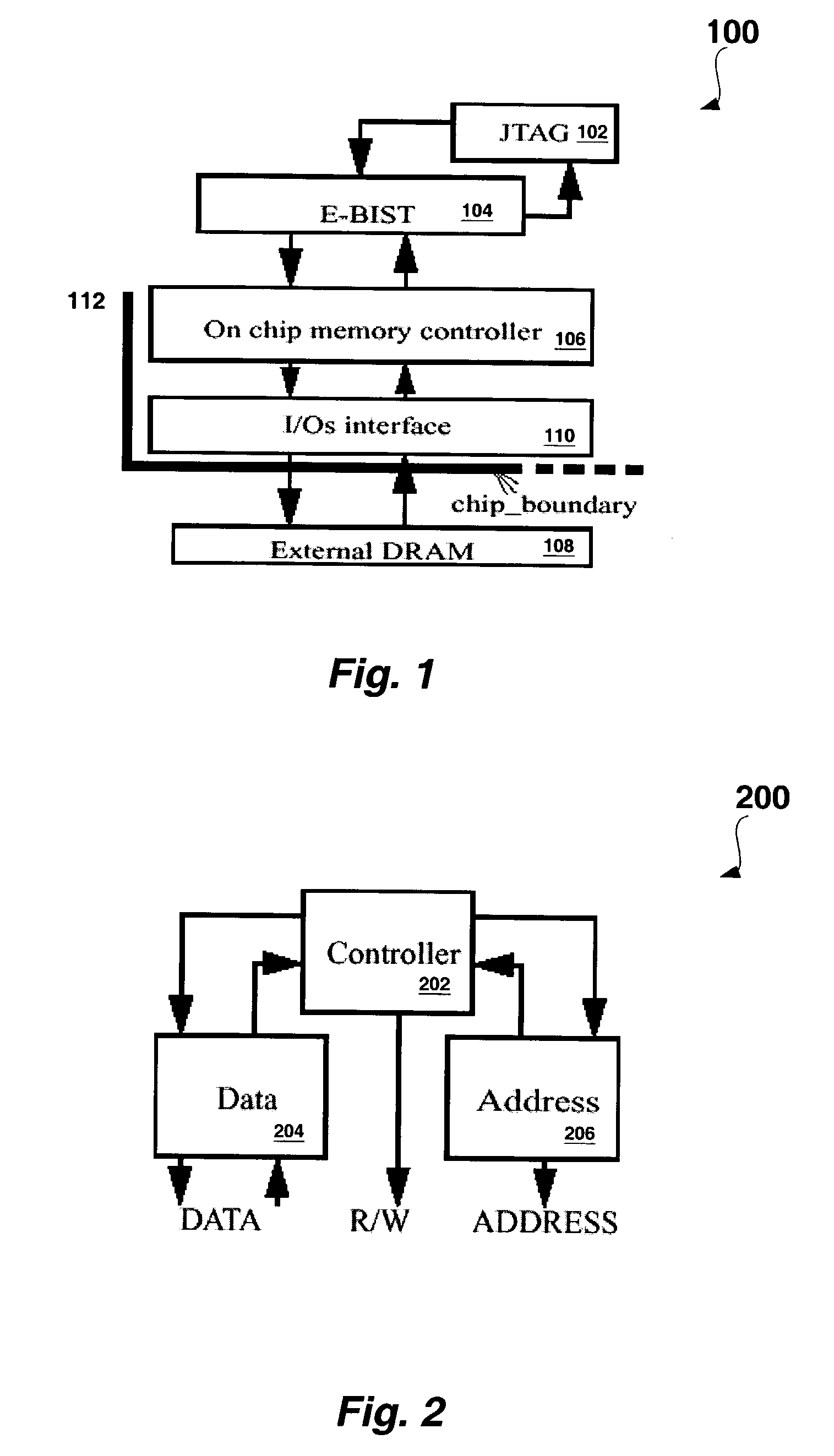

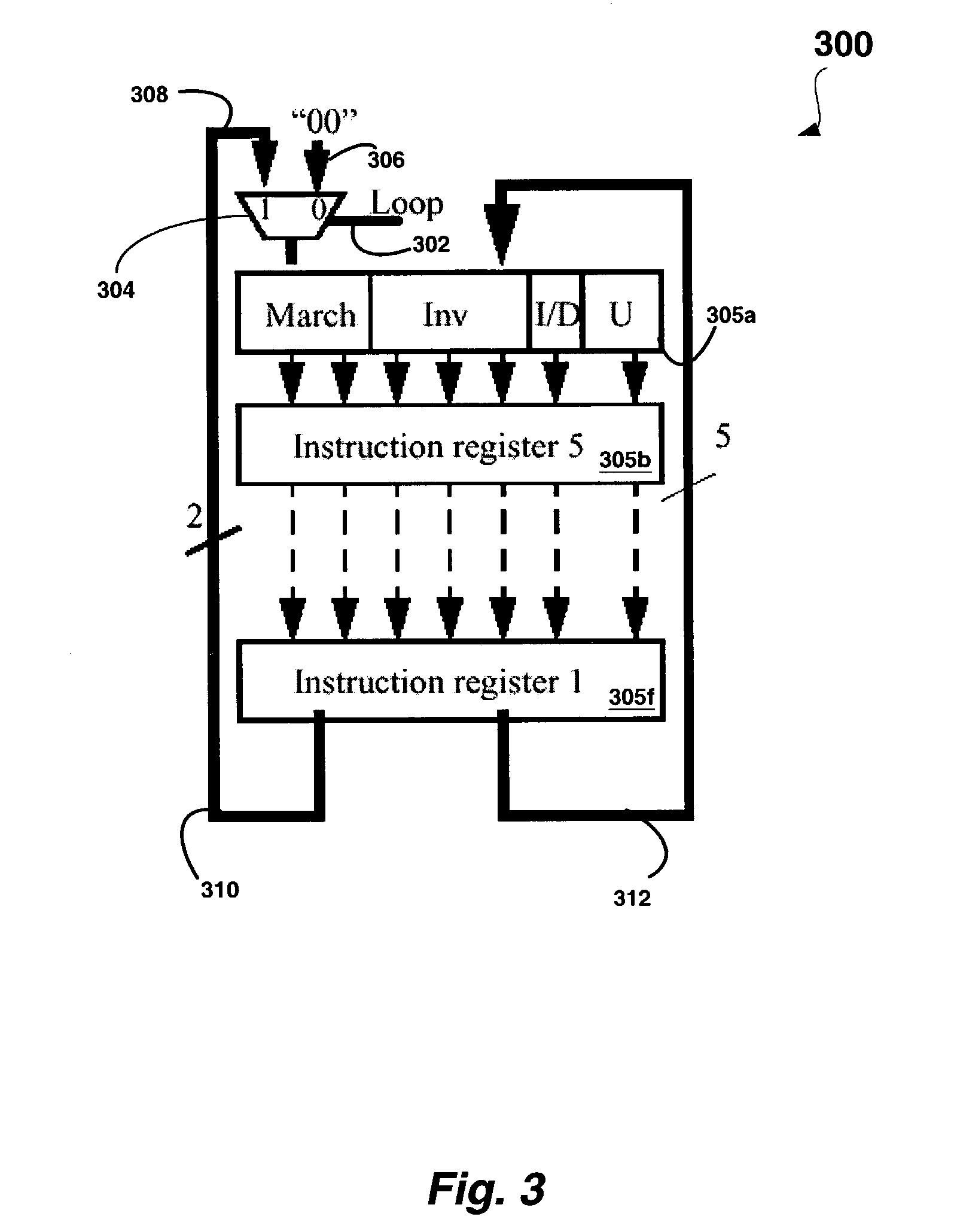

Disclosed are novel methods and apparatus for efficiently providing instruction-based BIST of memory interconnects. In an embodiment of the present invention, a method of testing a memory interconnect between an external memory module and a chip is disclosed. The method includes: providing an on-chip memory controller coupled to the external memory module, the on-chip memory controller sending and receiving data to and from the external memory module; providing an on-chip built-in self-test (BIST) module coupled to the on-chip memory controller, the BIST module including an instruction register to store a plurality of instructions; testing the external memory module; and once the external memory module has successfully passed the testing, utilizing the external memory module in testing the memory interconnect.

Owner:ORACLE INT CORP

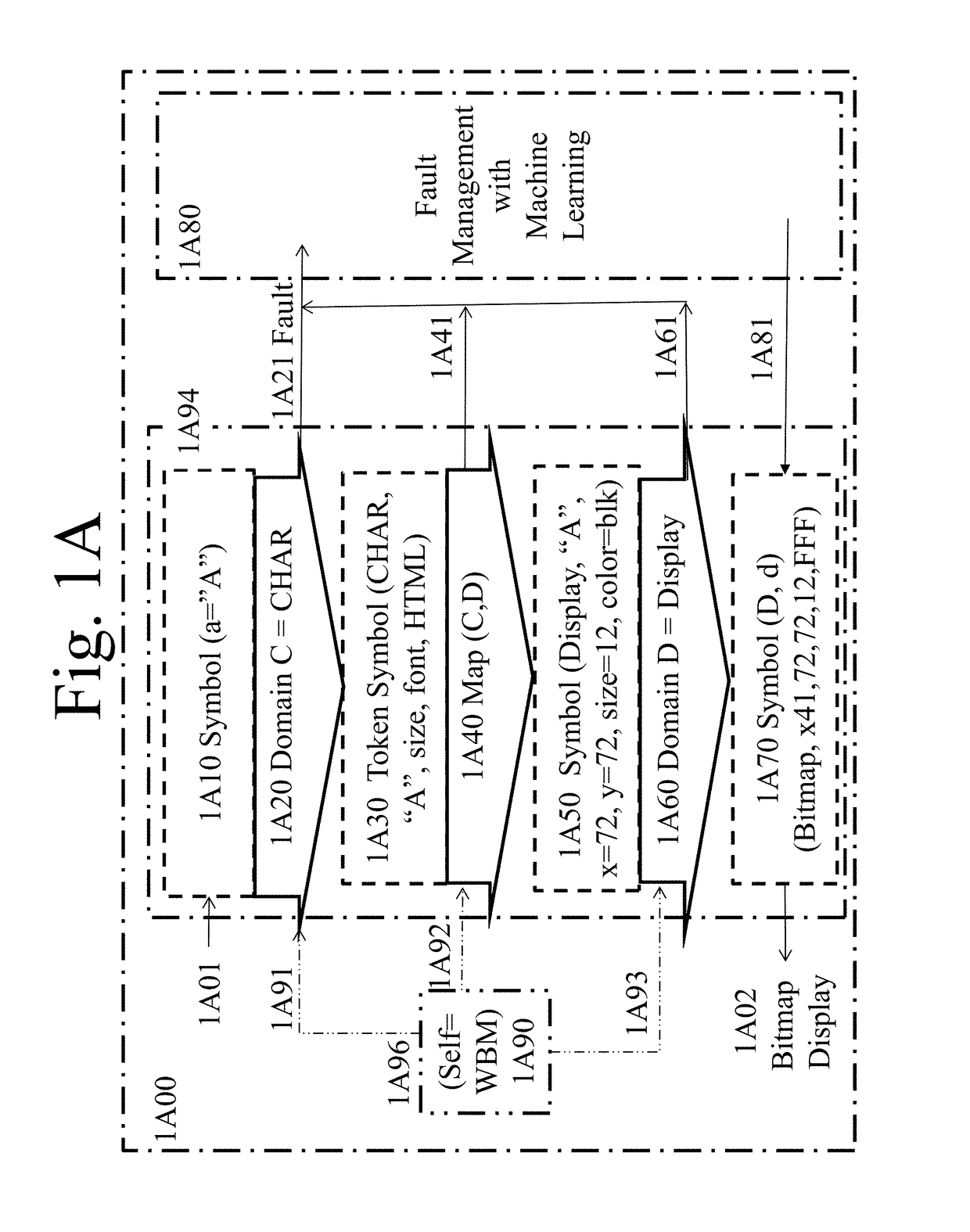

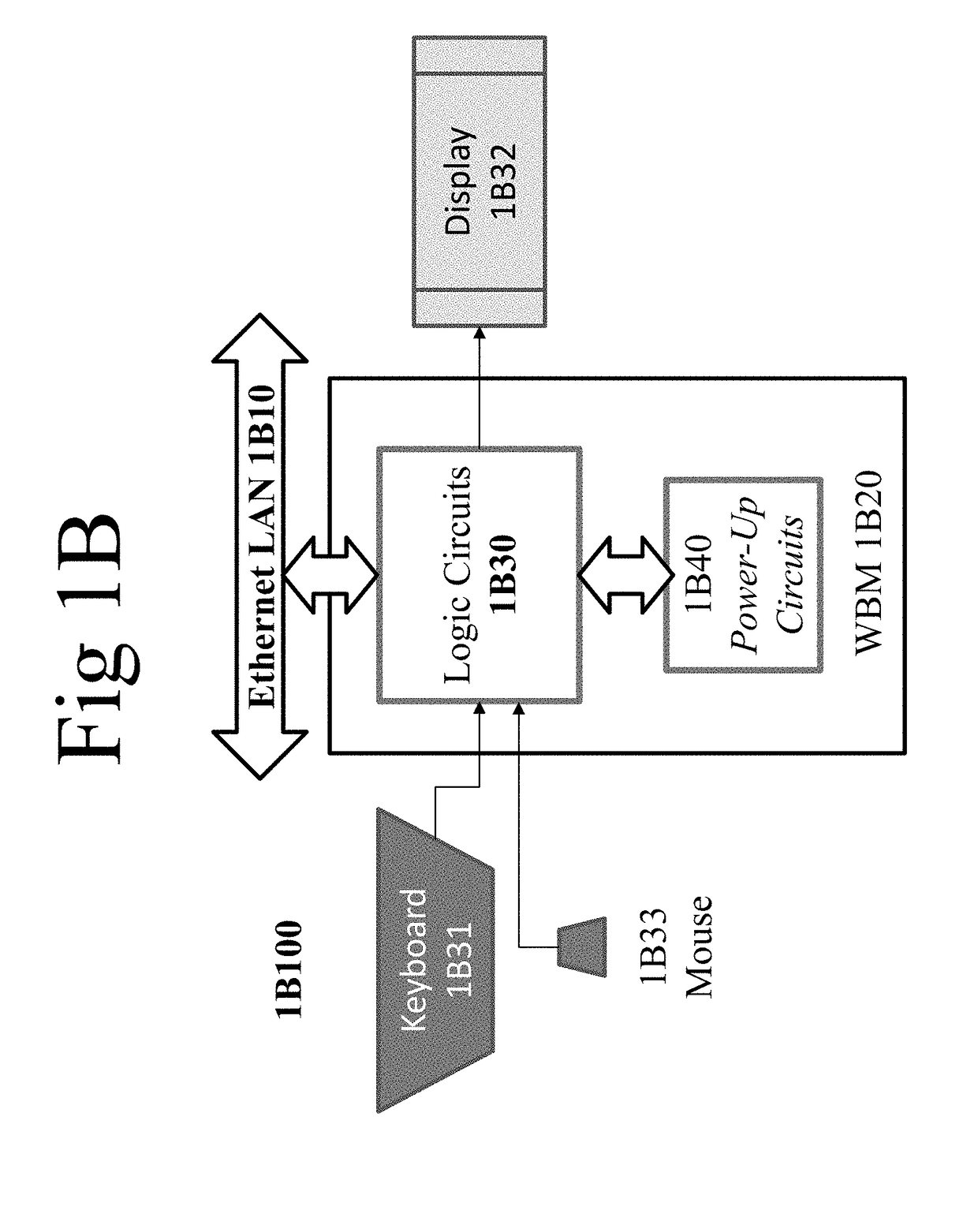

Domain-Specific Hardwired Web Browser Machine

ActiveUS20180052999A1Internal/peripheral component protectionPlatform integrity maintainanceAnti virusOperational system

A domain-specific hardwired symbolic web browser machine is described that processes information via the hardwired mapping of symbols from one or more domains onto other such domains, computing and communicating with improved security and reduced power consumption because it has no CPU, no Random Access Memory (RAM), no instruction registers, no Instruction Set Architecture (ISA), no operating system (OS) and no applications programming. The machine provides web browser functionality including, for example, the display of web pages. In some embodiments, the machine has no unconstrained RAM into which malware may insert itself and needs no anti-virus software.

Owner:HACKPROOF TECH

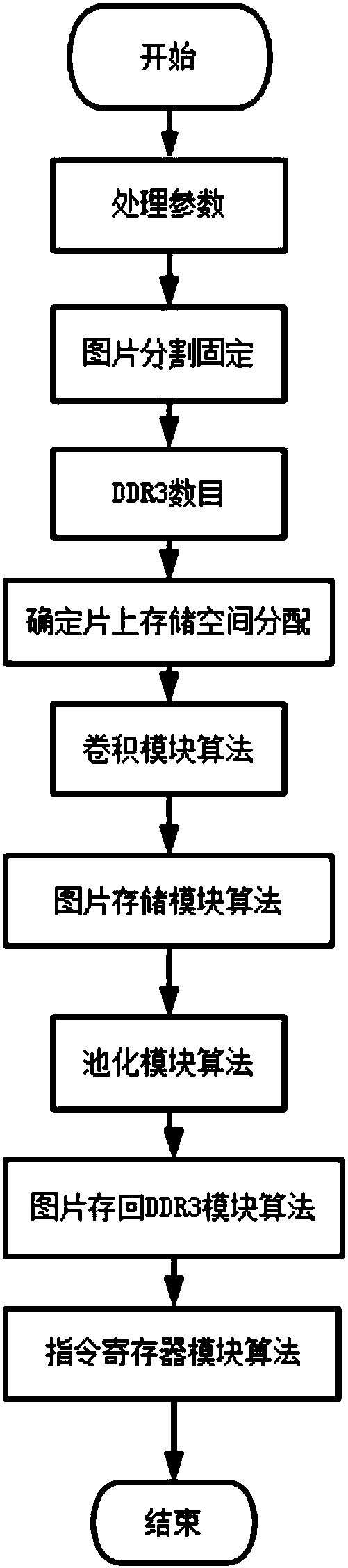

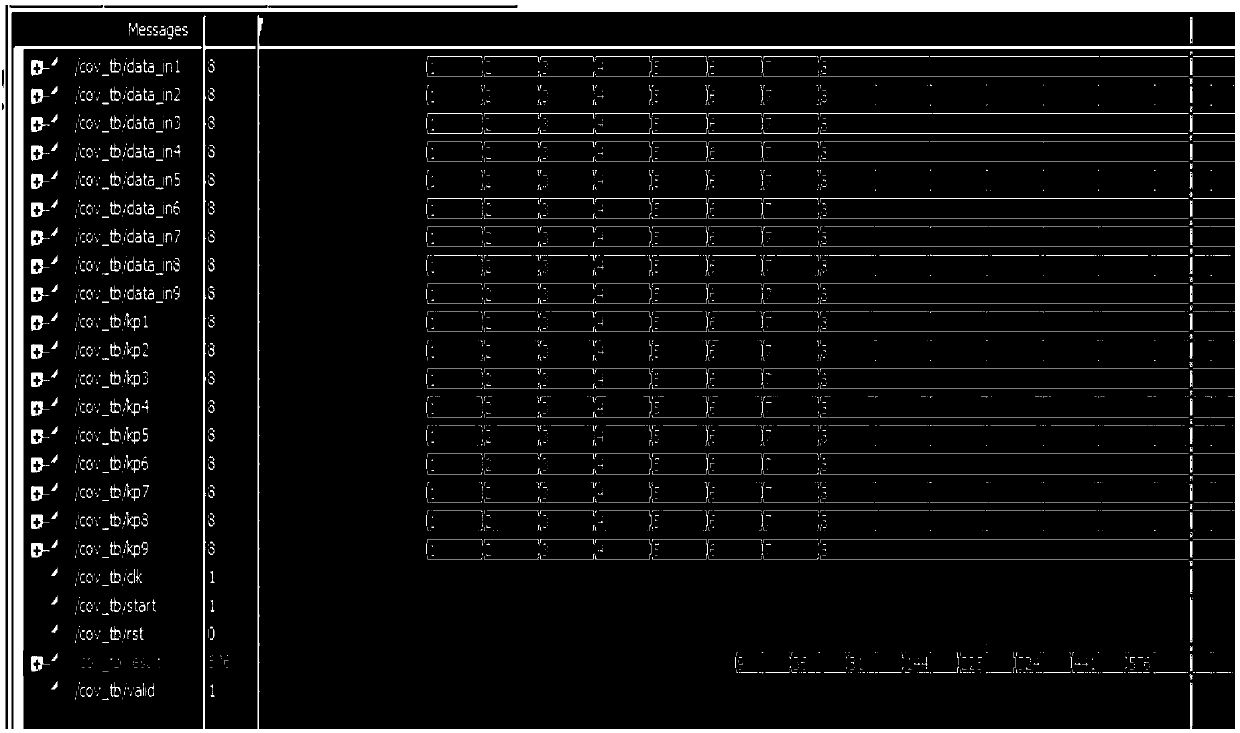

Image processing method based on FPGA accelerated convolution neural network framework

ActiveCN108154229AAccelerate the effectConvolution calculation is uninterruptedNeural architecturesPhysical realisationResource utilizationInstruction register

The invention discloses a image processing method based on an FPGA accelerated convolution neural network framework, which mainly solves the problems of low resource utilization rate and slow speed ofthe prior art. The plan comprises the following steps of:1) calculating a picture division fixed value according to the designed picture parameter and the FPGA resource parameter; 2) determining theDDR3 number according to the picture fixed value and distributing the block ram resource; 3) constructing a convolution neural network framework according to 1) and 2), wherein the framework comprisesa picture storage module, a picture data distribution module, a convolution module, a pool module, a picture storage back DDR3 module and an instruction register group; 4) obtaining a control instruction from the instruction register set through a handshake signal and interacts with each other, and processing the picture data according to the control instruction. The invention improves the resource utilization and acceleration effect through the FPGA-accelerated convolutional neural network framework, and can be used for image classification, target recognition, speech recognition and naturallanguage processing.

Owner:XIDIAN UNIV

Processor integrated circuit

InactiveUS6411984B1Instruction analysisNext instruction address formationArithmetic logic unitProgram instruction

A data processing device comprising a storage circuit accessible by assertion of addresses, an arithmetic logic unit connected to the storage circuit operative to perform an arithmetic operation on data received by the arithmetic unit. Further included is an address register for storing an initial address word indicative of a storage circuit address. An instruction decode and control unit, connected to the storage circuit and having an instruction register operative to hold a program instruction is operative to decode the program instruction into control signals to control the operations of the data processing device and location codes to control data transfers according to predetermined sections of the program instruction wherein at least one of the sections includes a location section selecting the address register and a displacement section containing address data. Further included is an address generating unit connected to the storage circuit, the instruction register, and the address register responsive to the control signals from the instruction decode and control unit combining the initial address word from the address register and the address data from the displacement section to generate a storage circuit address. Other devices, systems and methods are also disclosed.

Owner:TEXAS INSTR INC

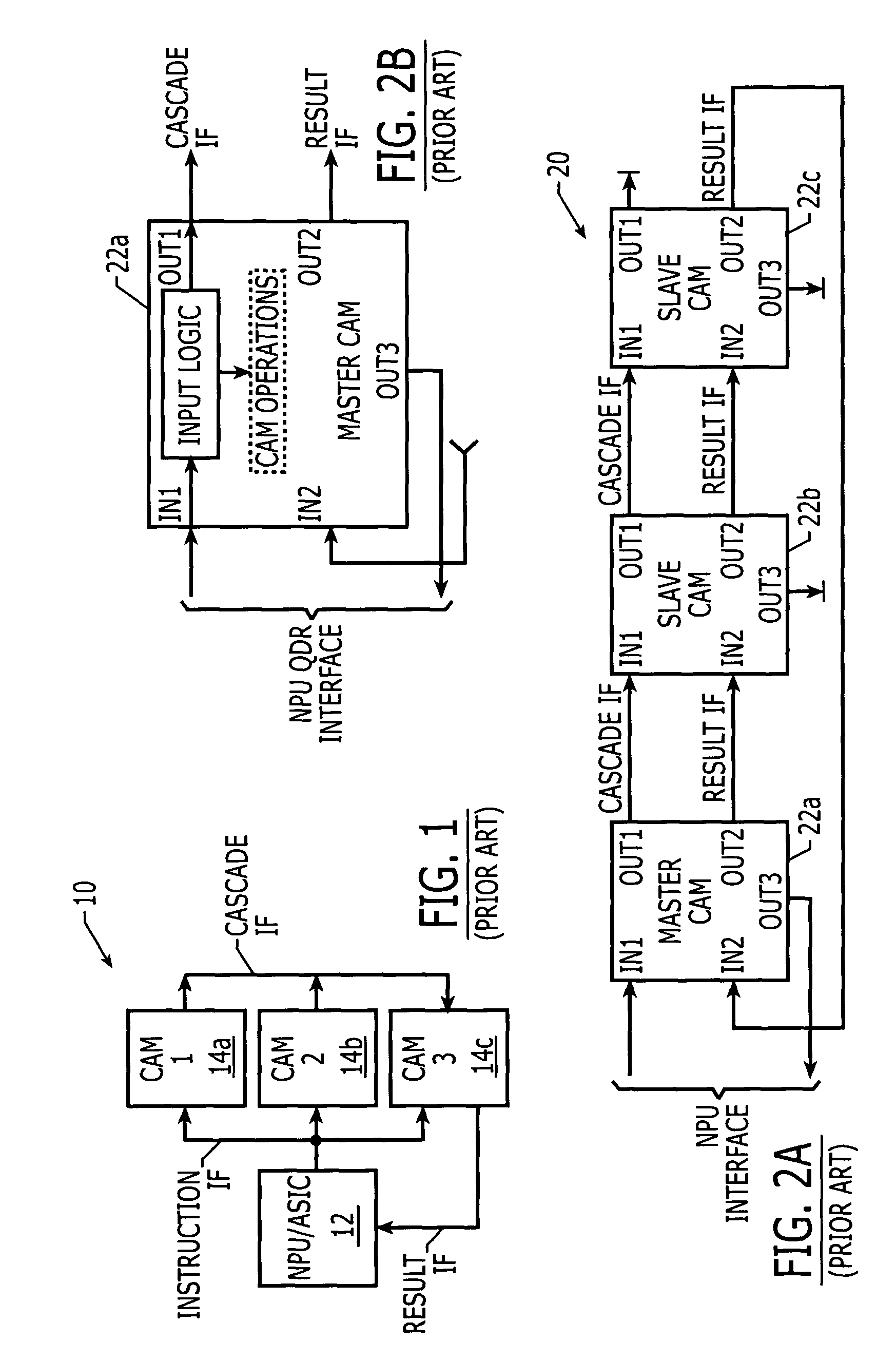

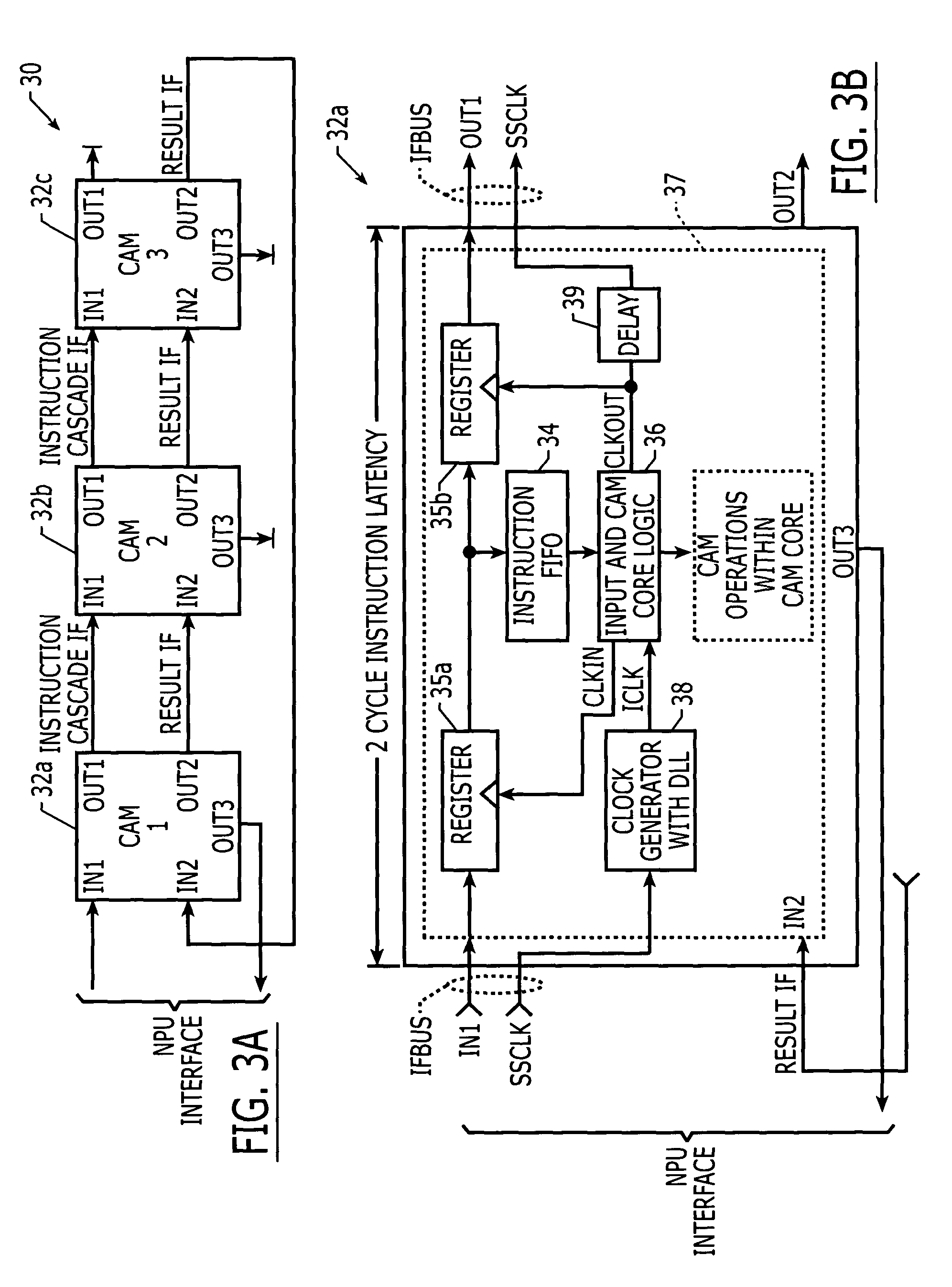

Content addressable memory (CAM) devices that support distributed CAM control and methods of operating same

ActiveUS7058757B1Easy to operateDigital data information retrievalMemory adressing/allocation/relocationProcessor registerParallel computing

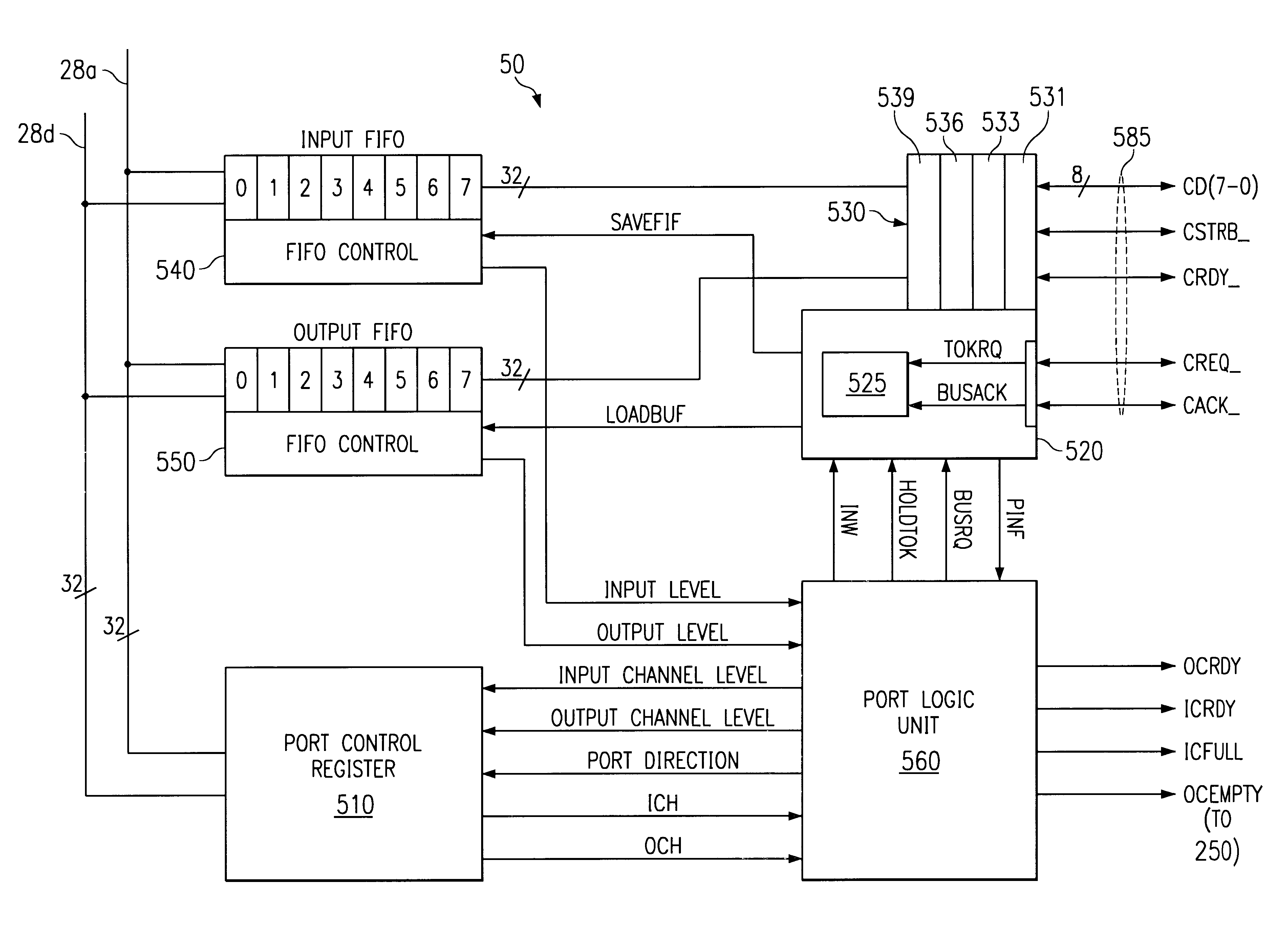

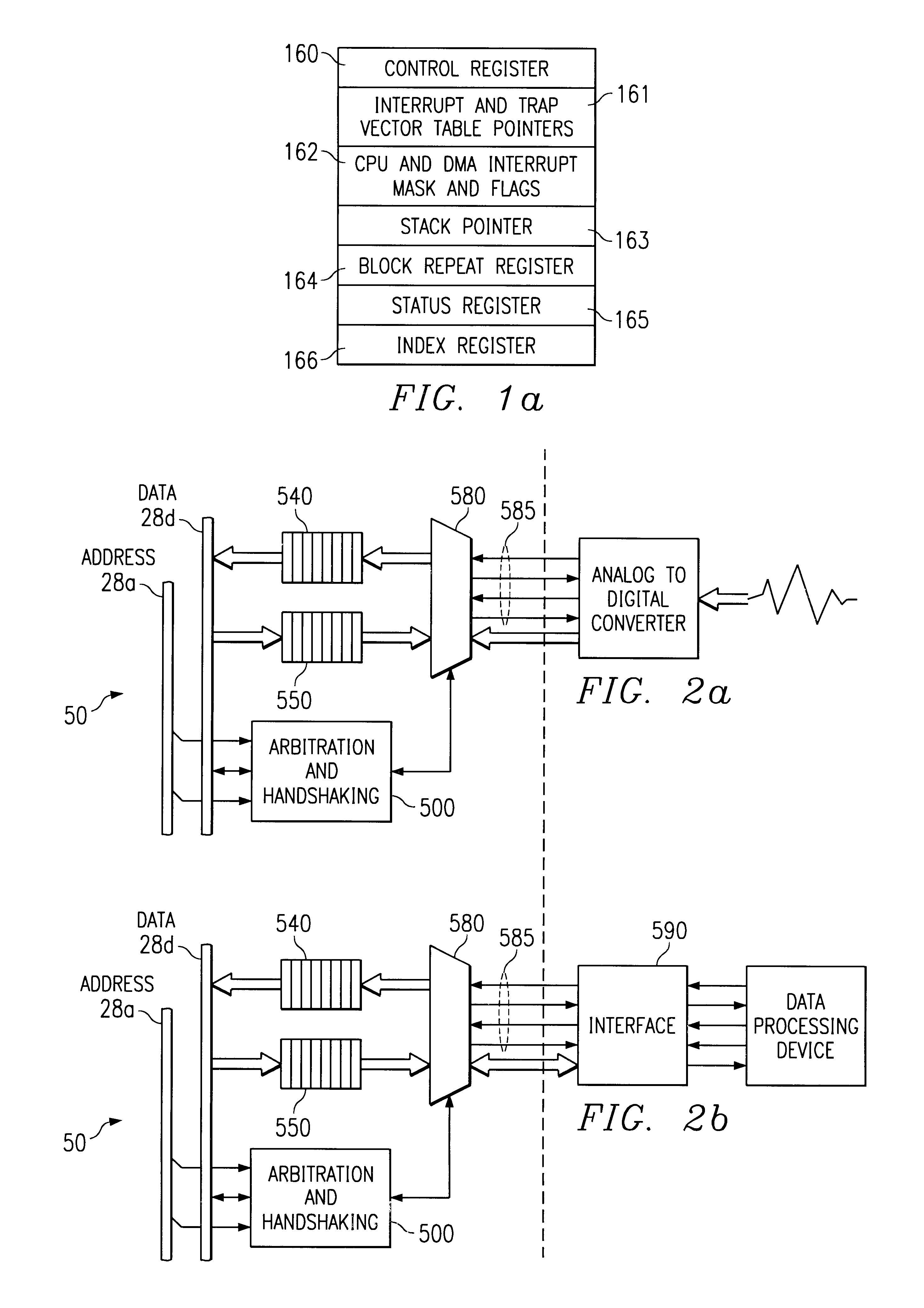

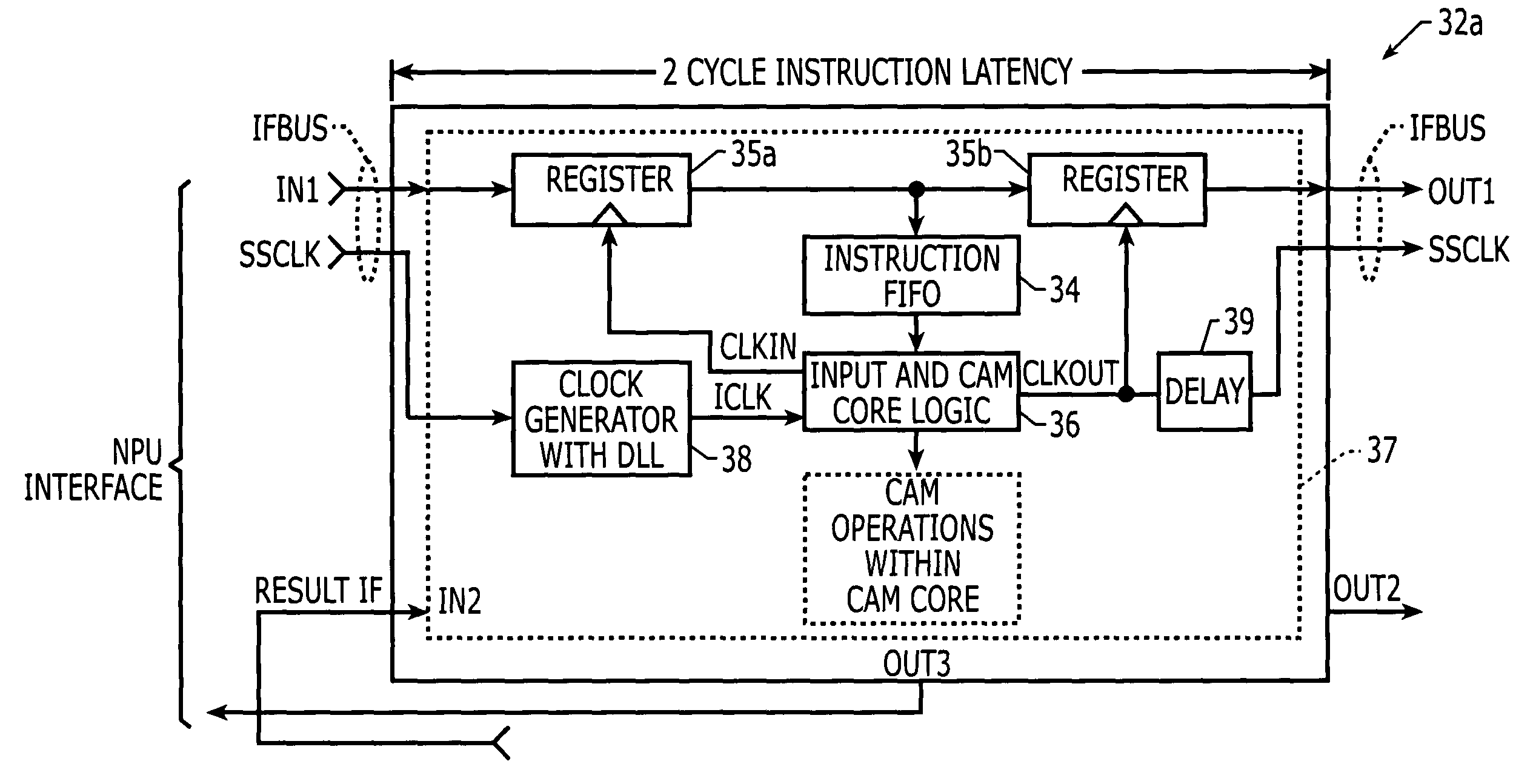

Content addressable memory (CAM) devices include CAM logic that is configured to pass an instruction received at an instruction input port to an instruction output port without inspection or alteration. This enables the CAM devices to be operated as equivalent devices within a cascaded chain of CAM devices that collectively form multiple databases within a lookup engine having distributed CAM control. This CAM logic may include an input instruction register that is configured to latch the instruction received at the instruction input port and an output instruction register that is configured to latch the instruction received from the input instruction register. This CAM logic may also include an instruction FIFO that is configured to buffer instructions received from the input instruction register. A method of performing a learn operation in a cascaded chain of CAM devices may include writing a search key associated with a database into a selected one of the cascaded chain of CAM devices, in response to evaluating whether an NFA table in the selected one of the cascaded chain of CAM devices has a valid NFA address for the search key. Then, following the write operation, an operation may be performed to search each of the CAM devices in the cascaded chain to identify an address of a highest priority invalid entry in a CAM device that retains at least a portion of the database.

Owner:AVAGO TECH INT SALES PTE LTD

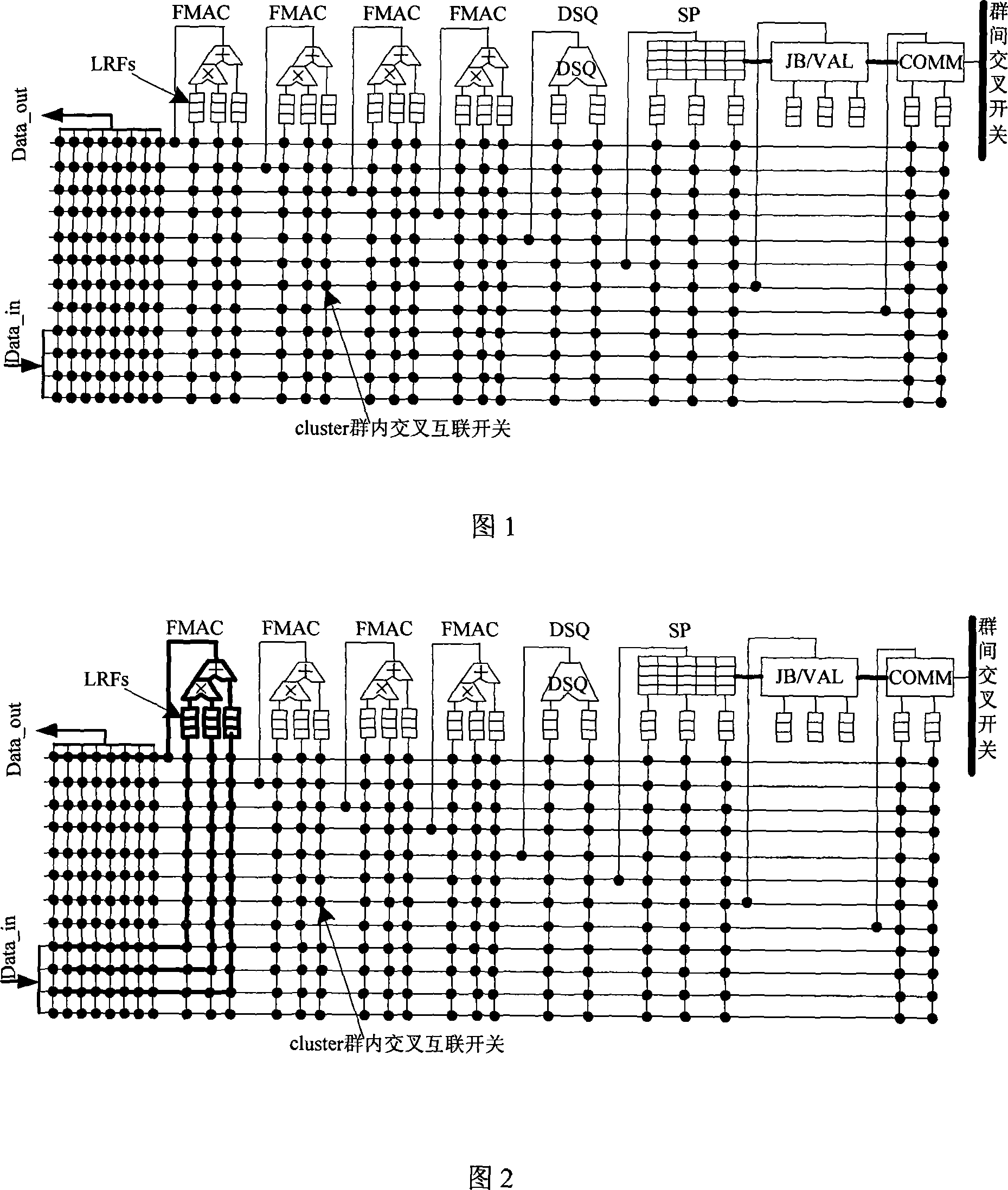

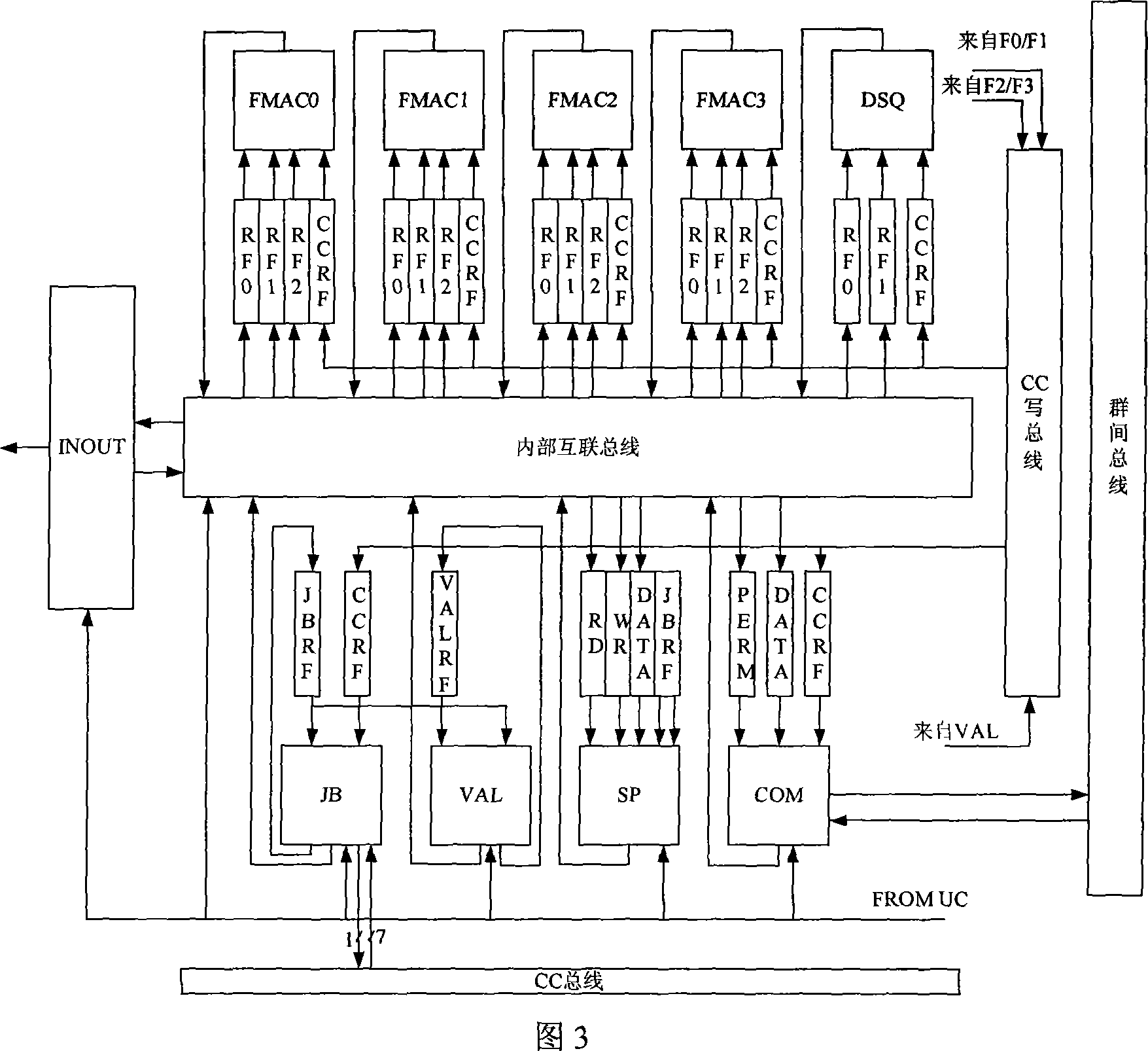

64 bit floating-point integer amalgamated arithmetic group capable of supporting local register and conditional execution

InactiveCN101021832AExtended Data WidthWide data widthArchitecture with multiple processing unitsInstruction memoryFloating point

The invention discloses a 64-bit floating-point integer-fusion operation group which support partial deposit and conditional execution. It includes one or more 64-bit floating point / integer-fusion arithmetic unit, conditional execution unit, component interconnect structure and control unit. The computing unit is connected with conditional execution unit by interconnect structure which also is used to transfer data among units. The storage address of operation group is made up of several independent address spaces, and the local operations can indirectly visiting each address space by unified controller. There are specialized instruction register to storage compiled order. The controller send the compiled instruction to each function unit of the corresponded computing group at the same time when the program running, then each group receive instructions and run it by SIMD and storage the result in the same LRF or output.

Owner:NAT UNIV OF DEFENSE TECH

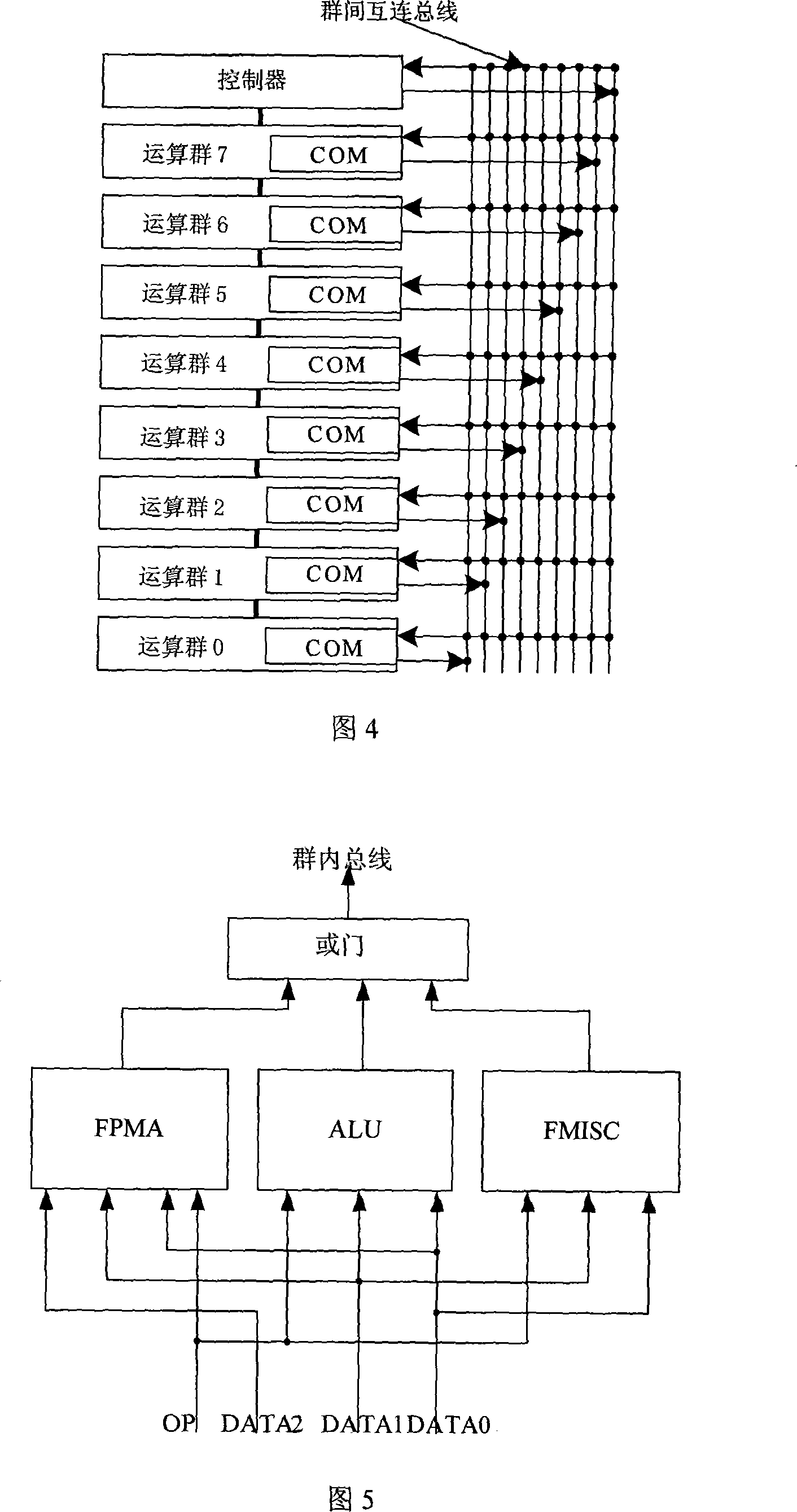

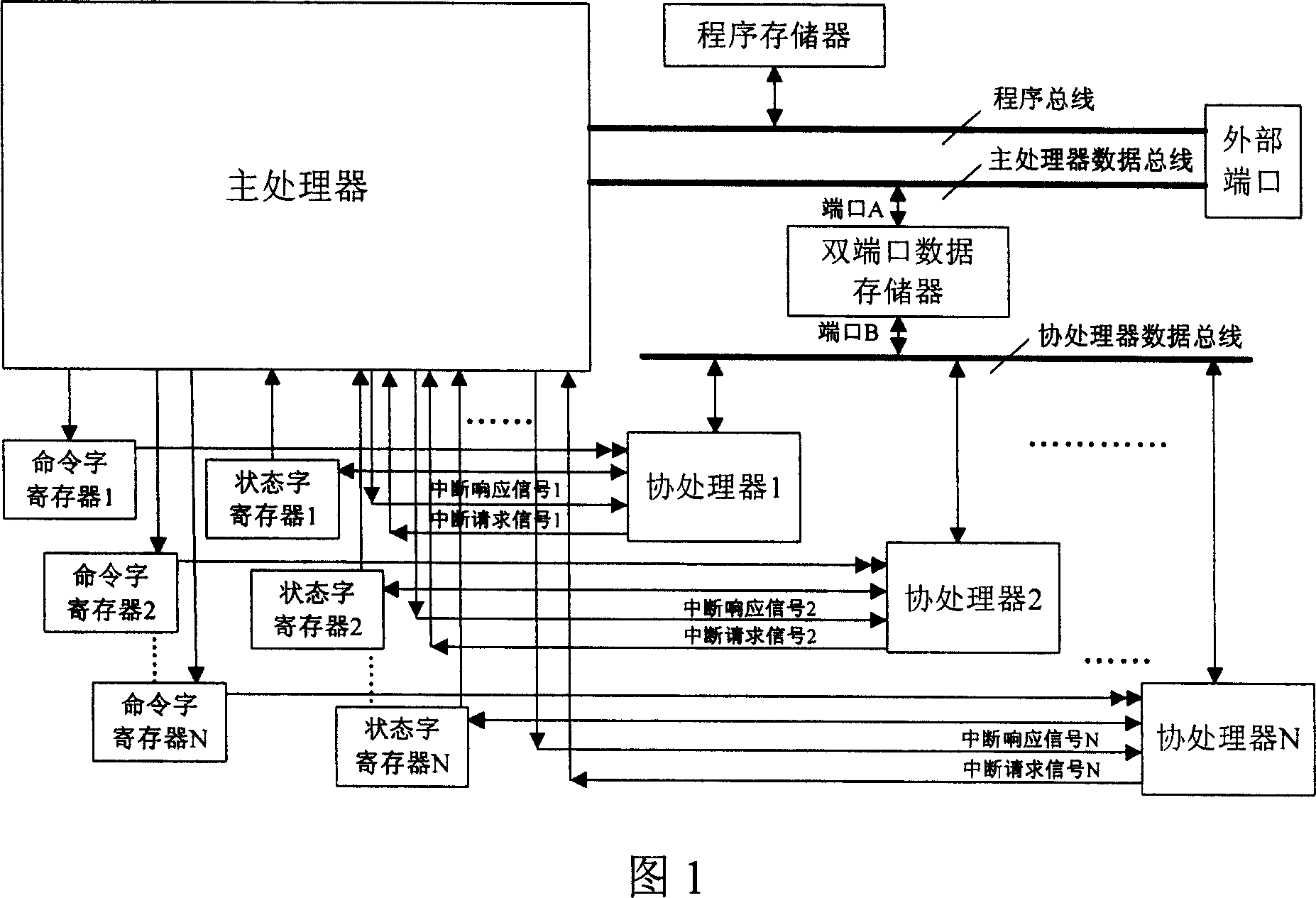

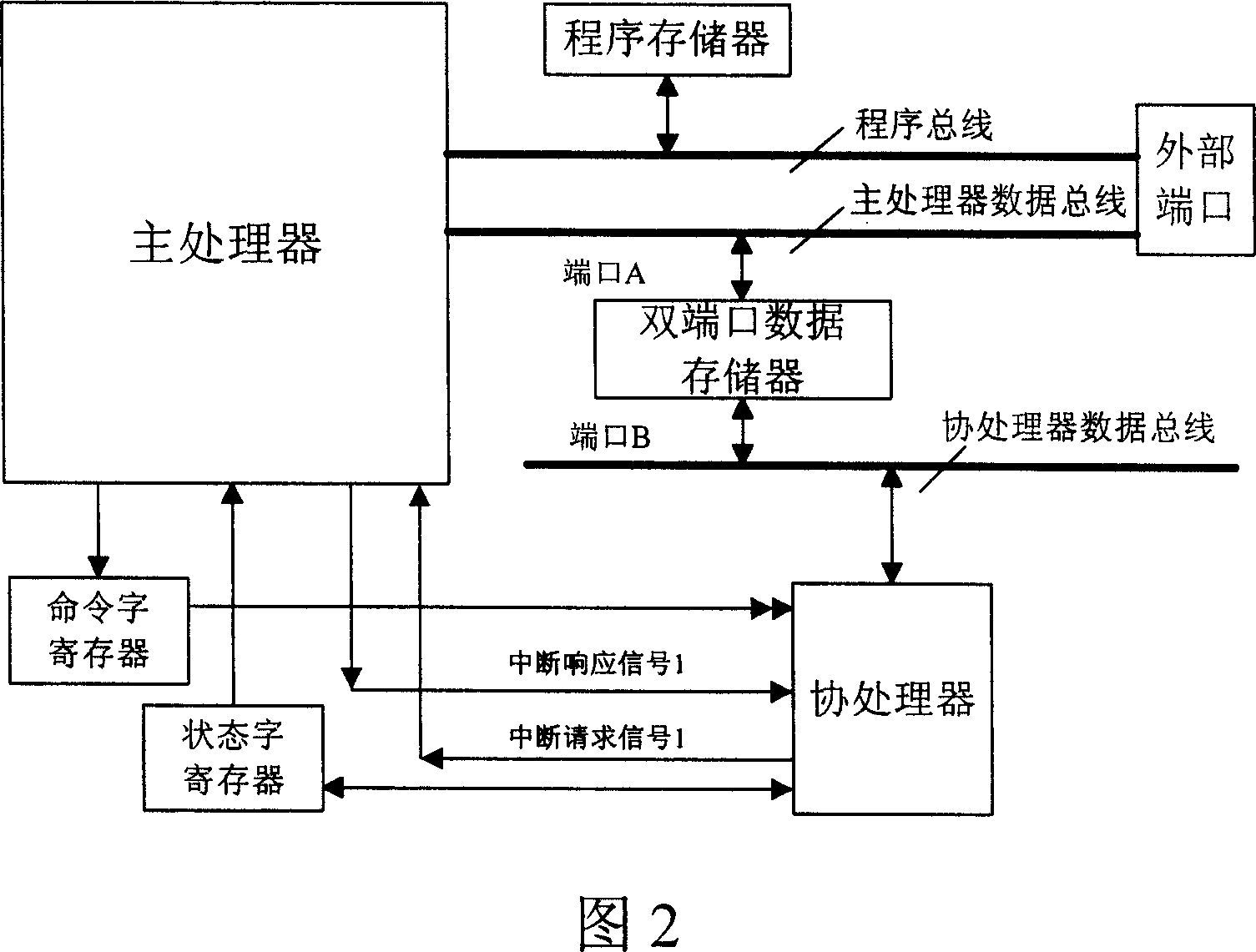

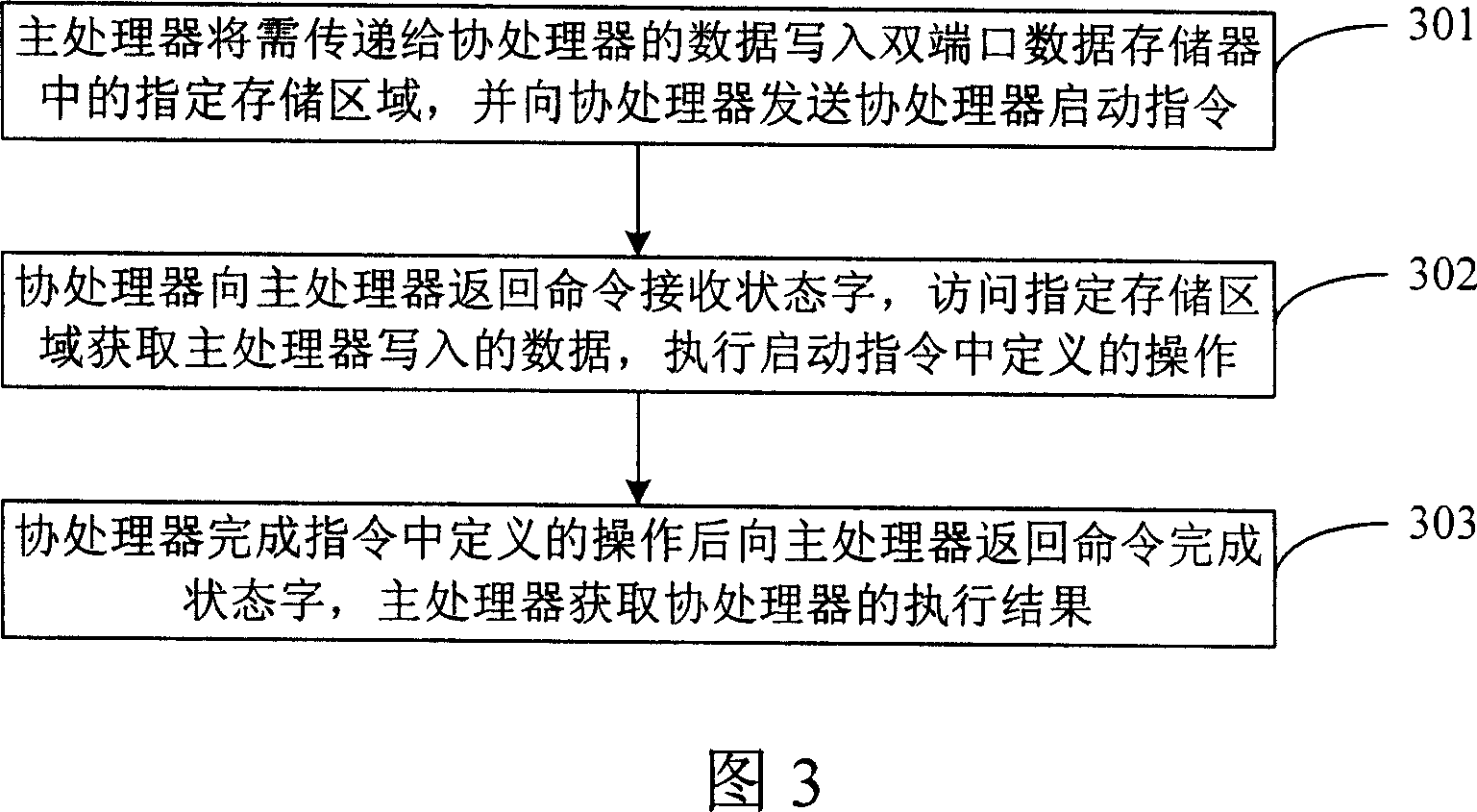

System and method for realizing interconnect between main processor and coprocessor interface

InactiveCN101097559AImprove compatibilityFlexible designElectric digital data processingCompletion StatusComputer architecture

The invention discloses a kind of system to realize connection between main processor and coprocessor, which includes main processor, at least one coprocessor, dual-port data memory, data bus of main processor, data bus of coprocessor, at least one instruction register, and at least one state register. The invention also discloses a kind of method to realize connection between main processor and coprocessor, and it includes: A. the main processor writes the data which will be transmitted to coprocessor in the indicated storage region of dual-port data memory, and sends starting command to coprocessor; B. the coprocessor receives the starting instruction and returns the state character of receiving instruction, and accesses the indicated storage section to get the data written by main processor, and runs the operation defined in starting instruction; C. when the coprocessor finishes the operation, it returns the status character of finishing command to main processor, and the main processor gets the result of coprocessor.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

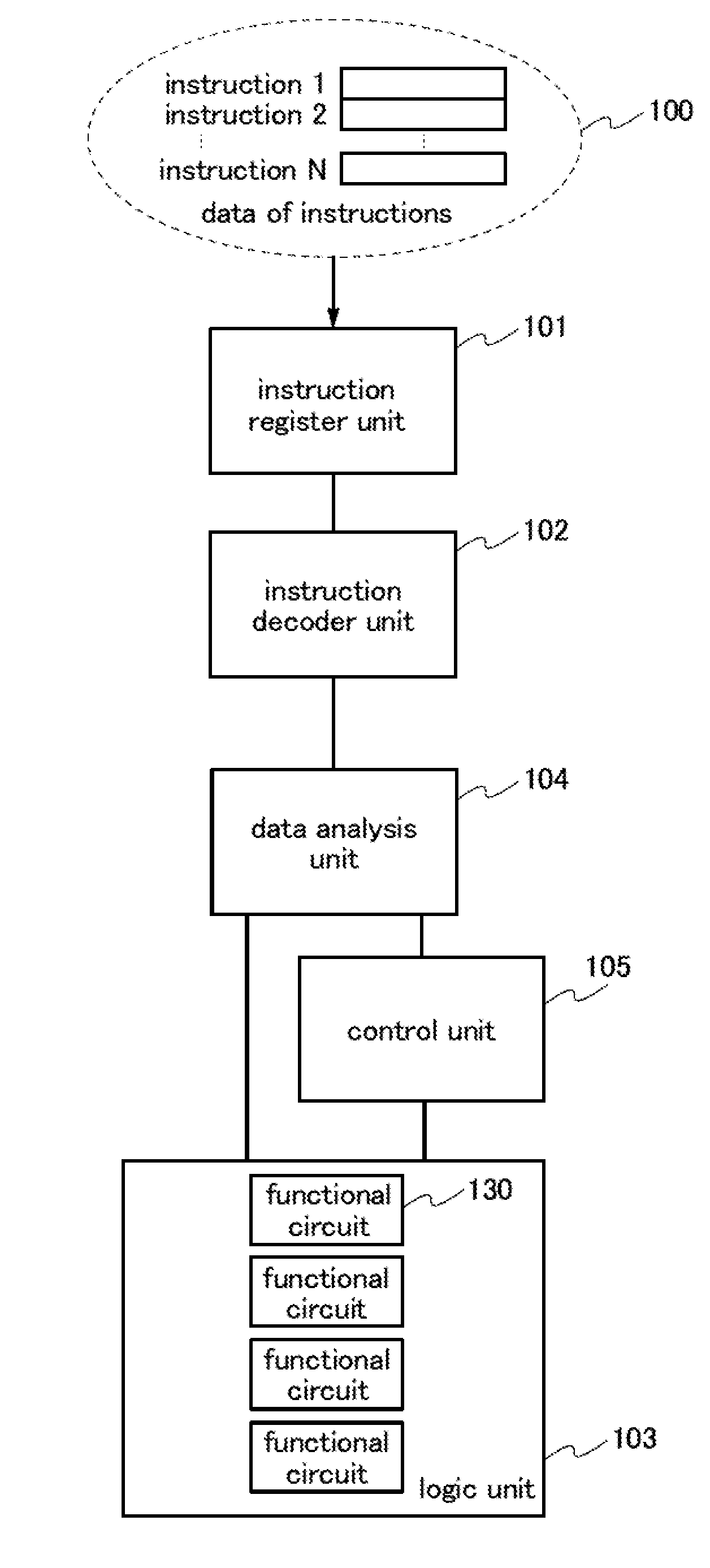

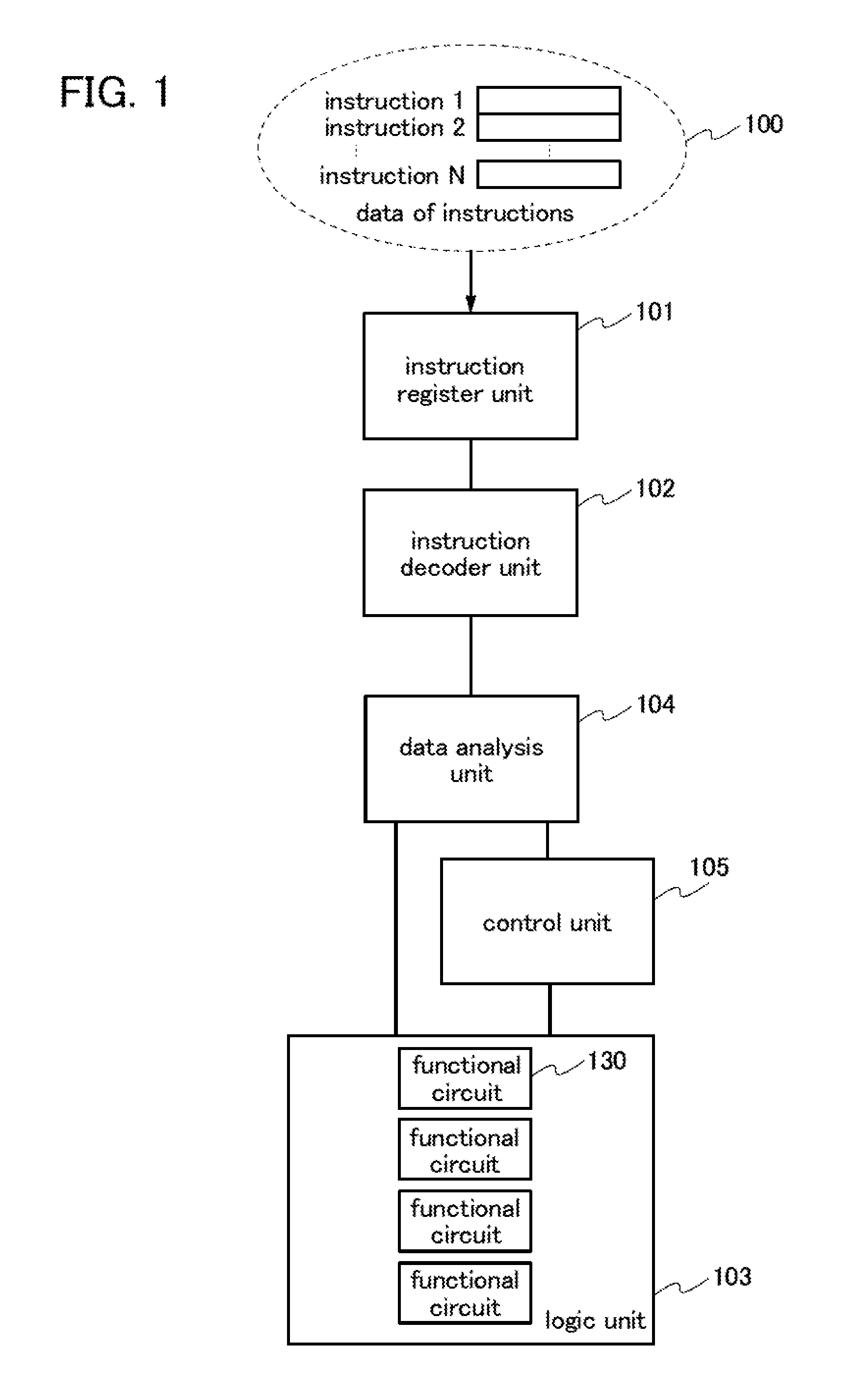

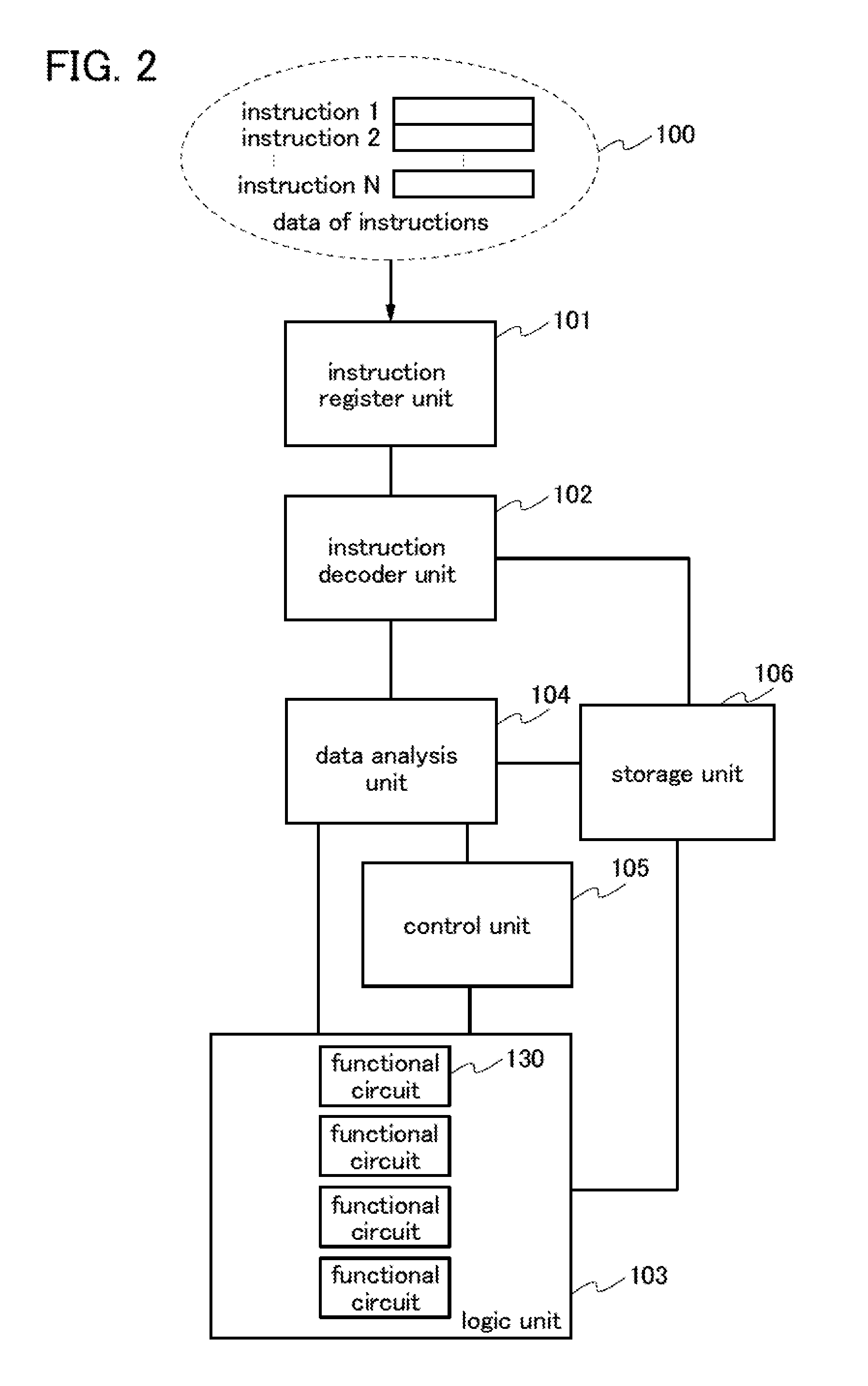

Processor and electronic device

InactiveUS20130262896A1Reduce power consumptionEnergy efficient ICTPower supply for data processingControl signalLogic cell

Power consumption is reduced. A processor includes an instruction register unit in which data of a plurality of instructions is fetched; an instruction decoder unit in which each of the plurality of instructions is translated; a logic unit including a functional circuit which is supplied with a clock signal and a power source voltage, supplied with a data signal including the translated data of the instructions, and operates in accordance with the supplied data of the instructions; a data analysis unit in which the translated data is analyzed so as to calculate a non-operating period of the functional circuit, and a control signal is generated; and a control unit which controls the supply of the clock signal or both the clock signal and the power source voltage to the functional circuit in accordance with the control signal.

Owner:SEMICON ENERGY LAB CO LTD