Image processing method based on FPGA accelerated convolution neural network framework

A convolutional neural network and image processing technology, applied in the field of convolutional neural network implementation, can solve the problems of increased FPGA computing time, lack of convolutional neural network algorithm optimization, and inability to fully utilize FPGA computing resources to achieve transmission efficiency , The effect of maximizing transmission efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

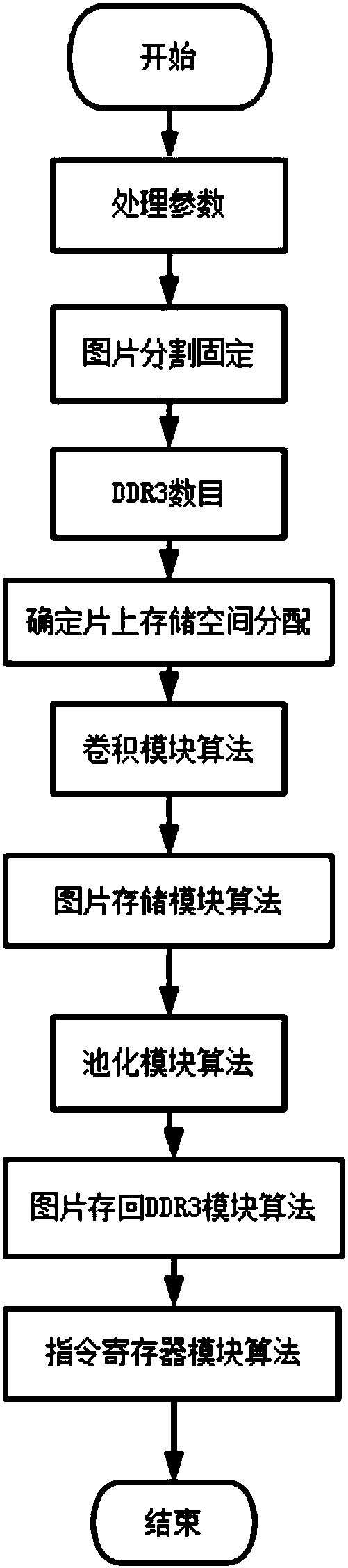

[0037] The embodiments and effects of the present invention will be described in detail below in conjunction with the accompanying drawings;

[0038] Step 1, process parameters.

[0039] 1.1) Read the picture and FPGA board resource parameters input by the user. The FPGA parameters include: picture size N, total block ram resource S sum , synchronous dynamic dynamic random access memory DDR3 number P and calculation function chip DSP number A;

[0040] 1.2) Design parameters, including: FPGA operation frequency f, convolution kernel size m, convolution layer number J, channel number T, pooling layer number C, activation function layer number E, multi-classification function softmax layer number G, softmax layer input number I in , softmax layer output number I out , fully connected layers Q, pooling function and activation function;

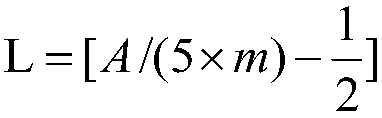

[0041] 1.3) The computer calculates the size value set X of each layer of pictures according to the read parameter values, the maximum numbe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More