Patents

Literature

182 results about "Computer design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

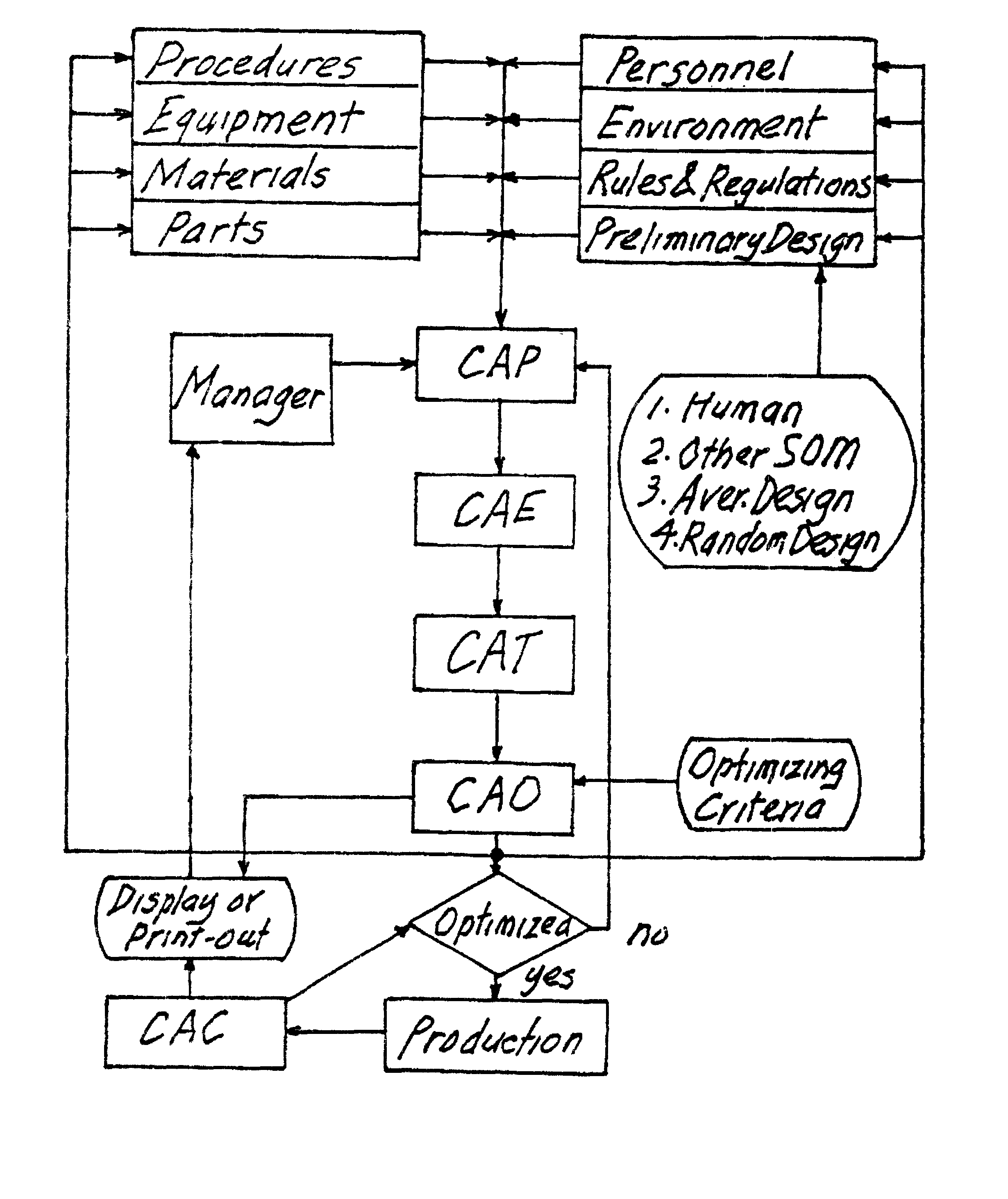

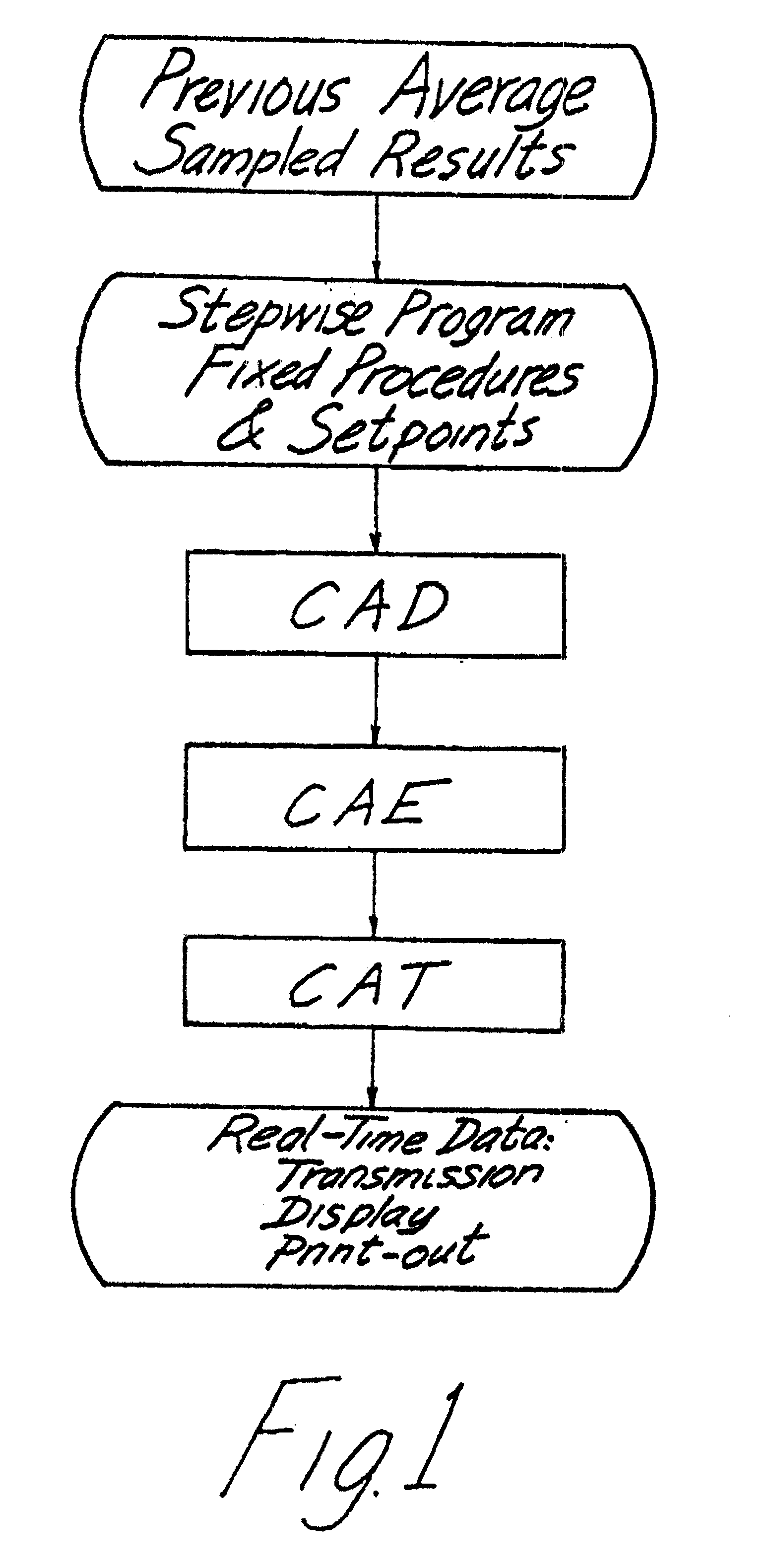

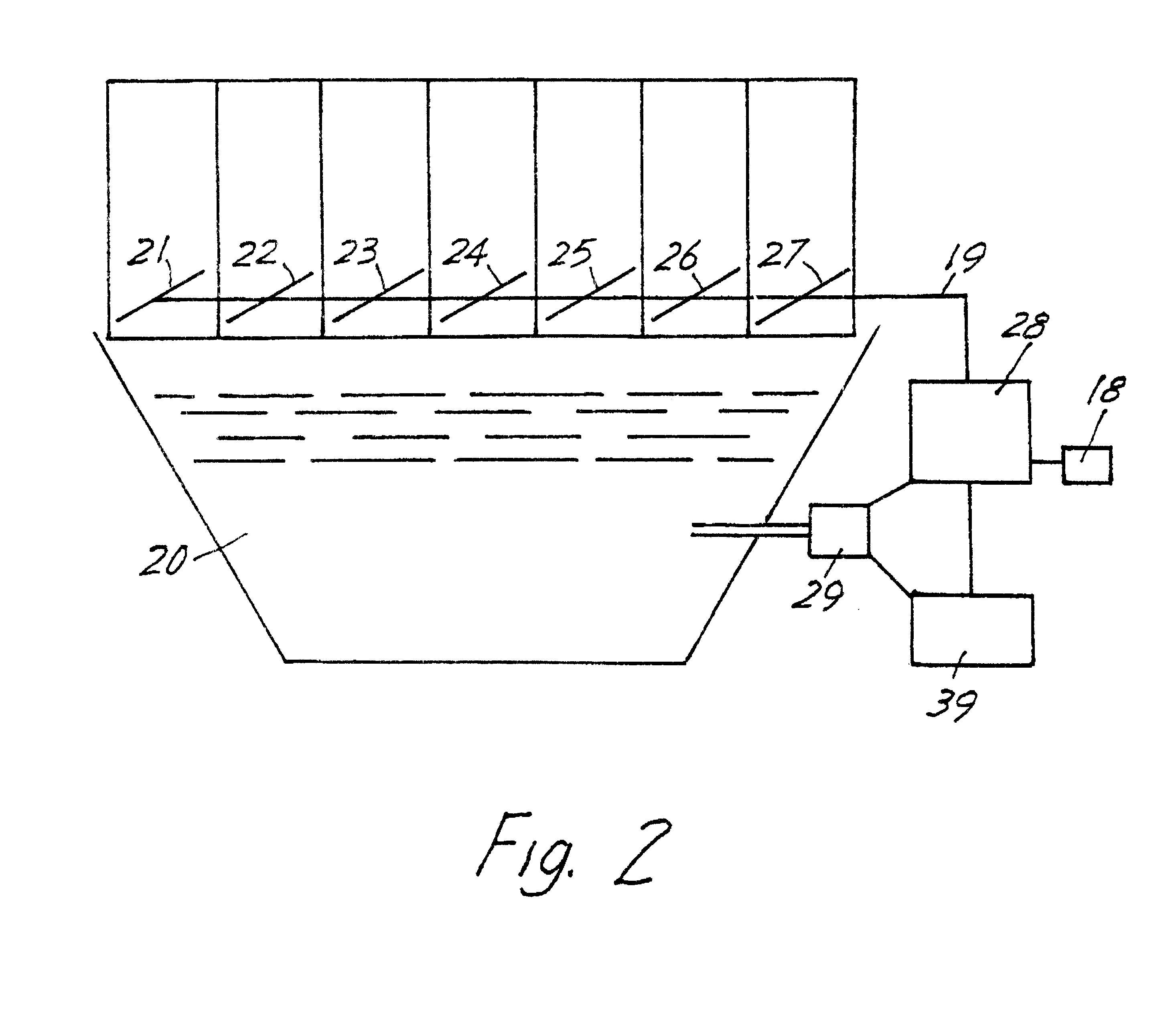

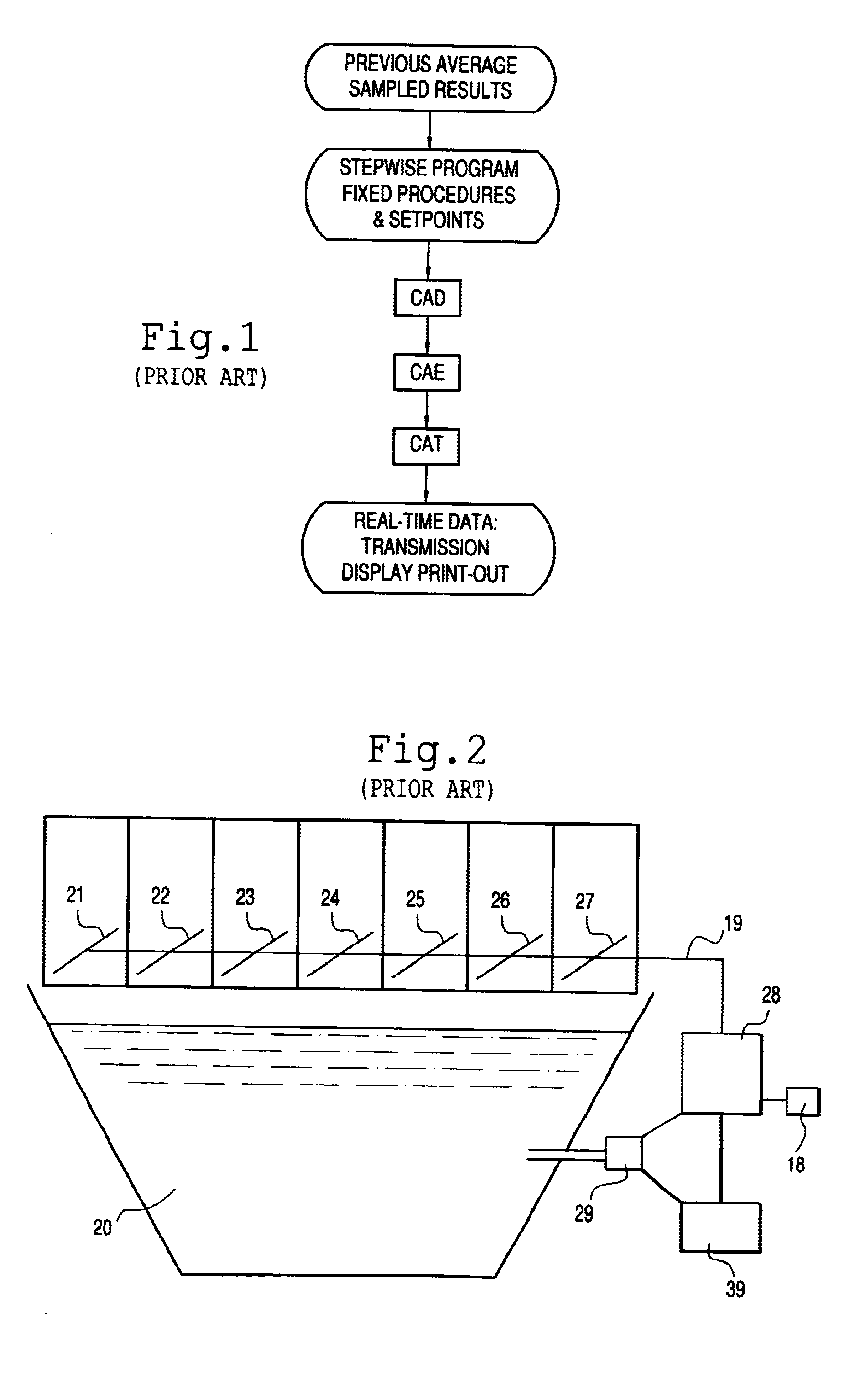

Self-optimization with interactions

A method for computer-generating interaction-specific knowledge base for rapidly improving or optimizing a performance of an object comprises performing, according to computer-designed test matrices, at least several automatic experimental cycles on selected control variables. In at least one of the automatic experimental cycles after the first the computer plans a new test matrix designed to minimize or remove at least one expected two-variable interaction from a main effect of a designated control variable. A machine operating according to the method is also available.

Owner:LI FAMILY HLDG

Self-optimizing method and machine

A method for computer-generating interaction-specific knowledge base for rapidly improving or optimizing a performance of an object comprises performing, according to computer-designed test matrices, at least several automatic experimental cycles on selected control variables. In at least one of the automatic experimental cycles after the first the computer plans a new test matrix designed to minimize or remove at least one expected two-variable interaction from a main effect of a designated control variable. A machine operating according to the method is also available.

Owner:LI FAMILY HLDG

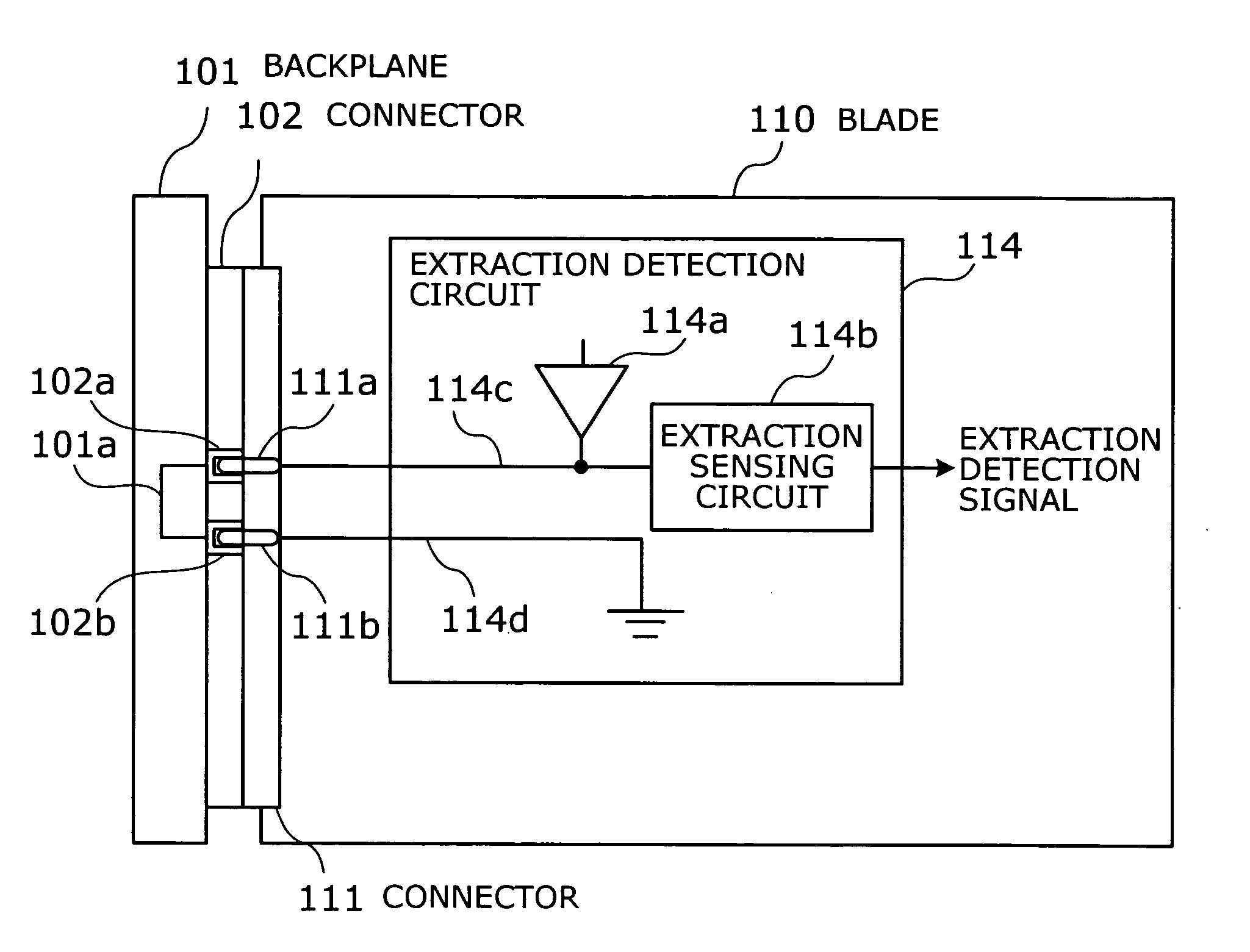

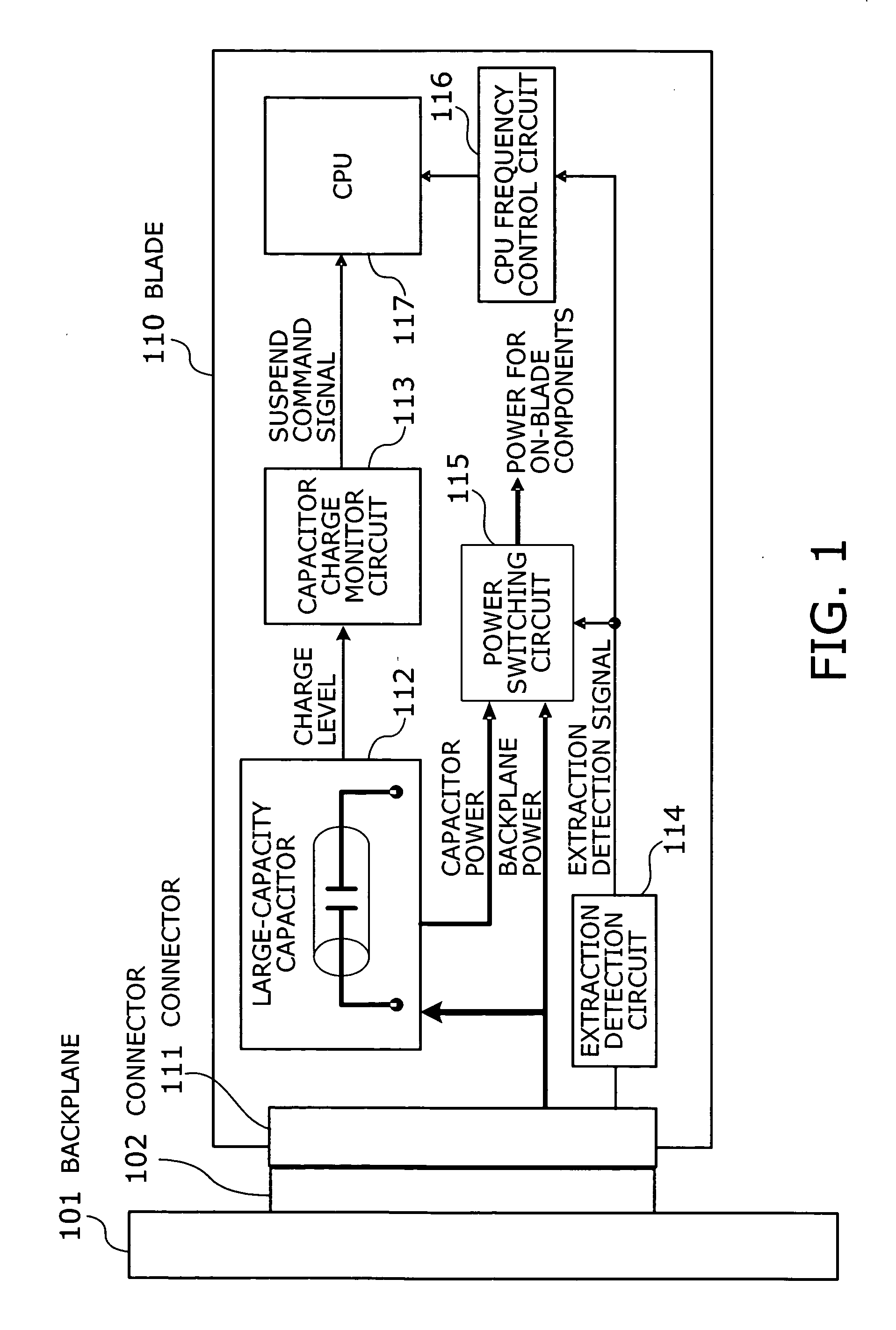

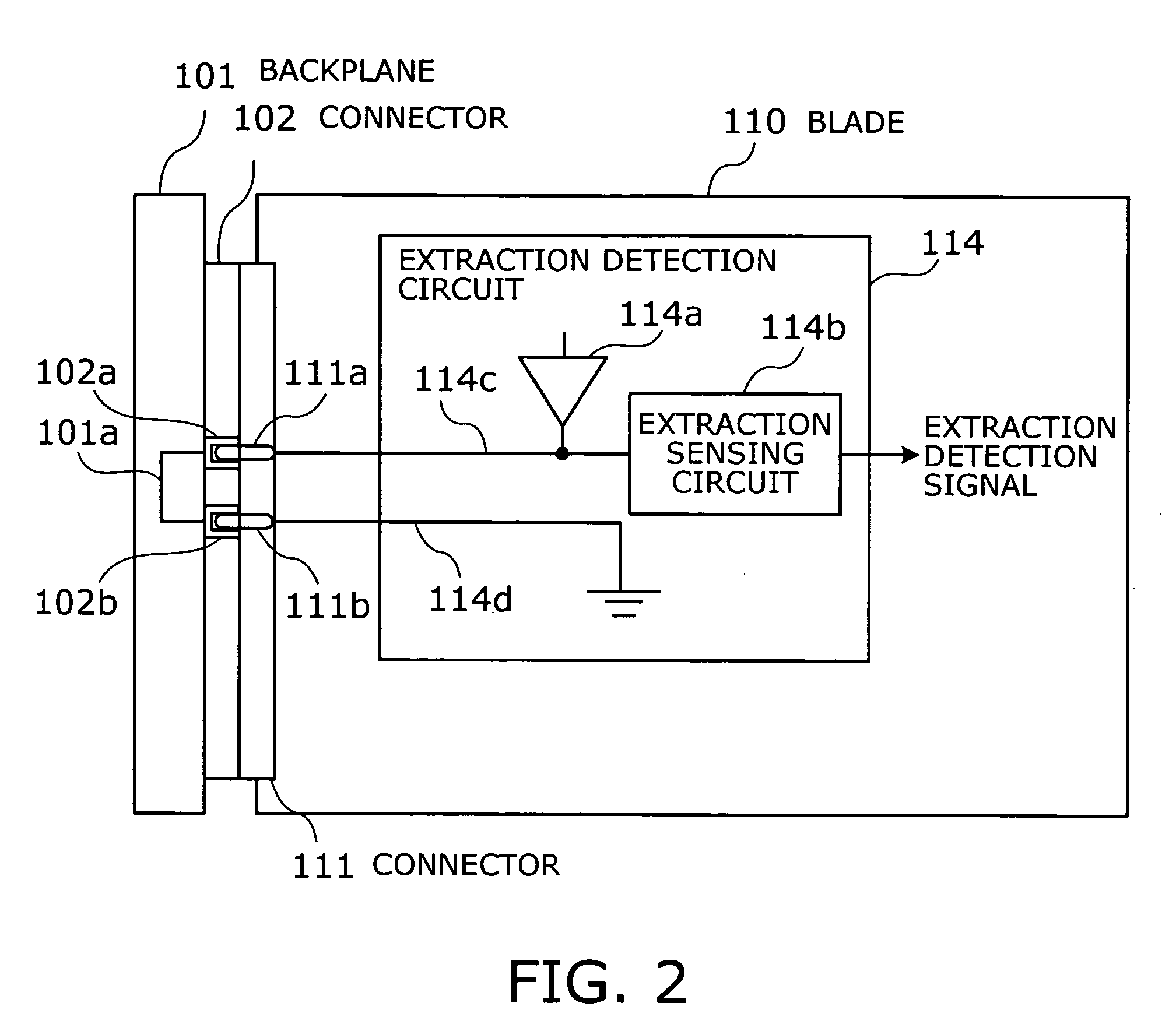

Blade computer with power backup capacitor, and blade management device and program therefor

InactiveUS20060212636A1Avoid service interruptionDigital data processing detailsComputer designElectric power

A blade computer designed to avoid disruption of client service even when it is extracted accidentally from the chassis. Each blade computer on a blade server system has a maintenance-free, large-capacity capacitor, which is charged with backplane power. When the blade computer is extracted from the backplane, that event is detected by an extraction detection circuit on the blade computer itself. The extraction event triggers a power switching circuit so that the electric power in the large-capacity capacitor will be supplied to the blade circuits. In addition, a CPU frequency control circuit reduces the operating frequency of CPU. The CPU continues ongoing data processing tasks at a lower operating frequency than its maximum limit, consuming the charge in the large-capacity capacitor.

Owner:FUJITSU LTD

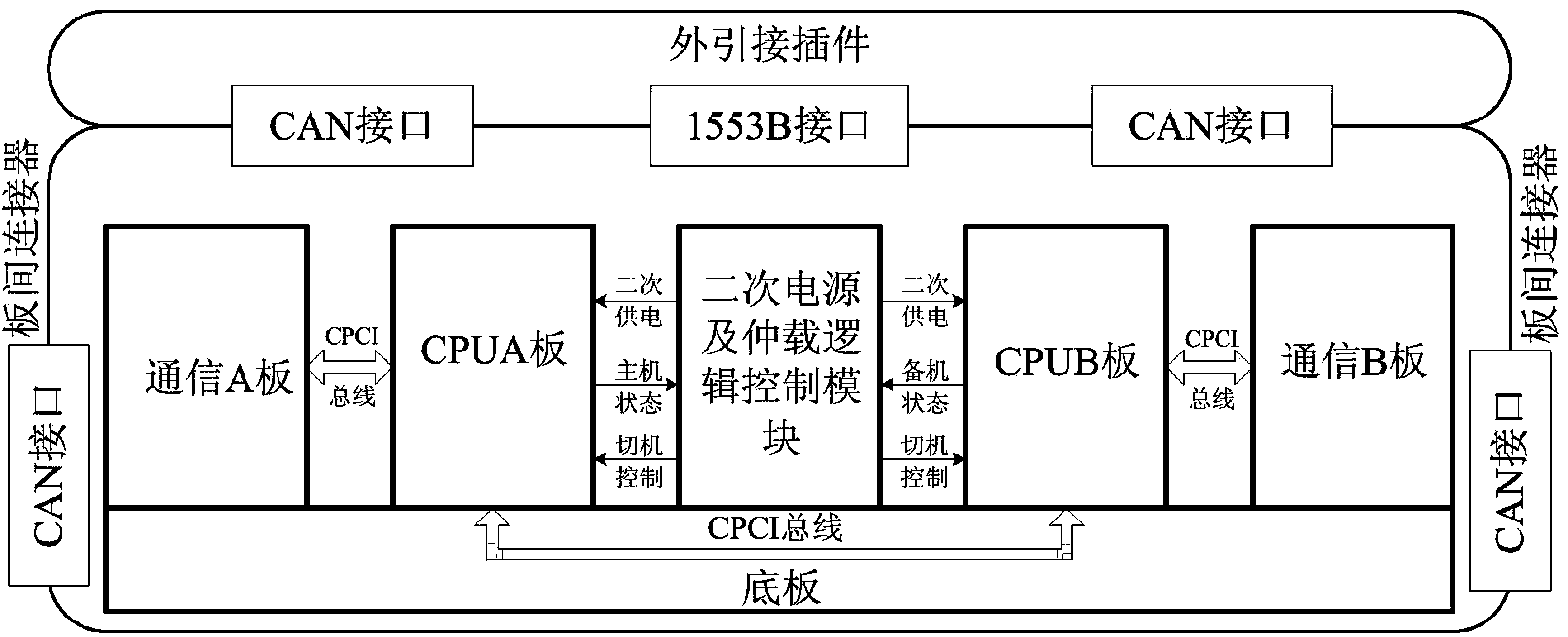

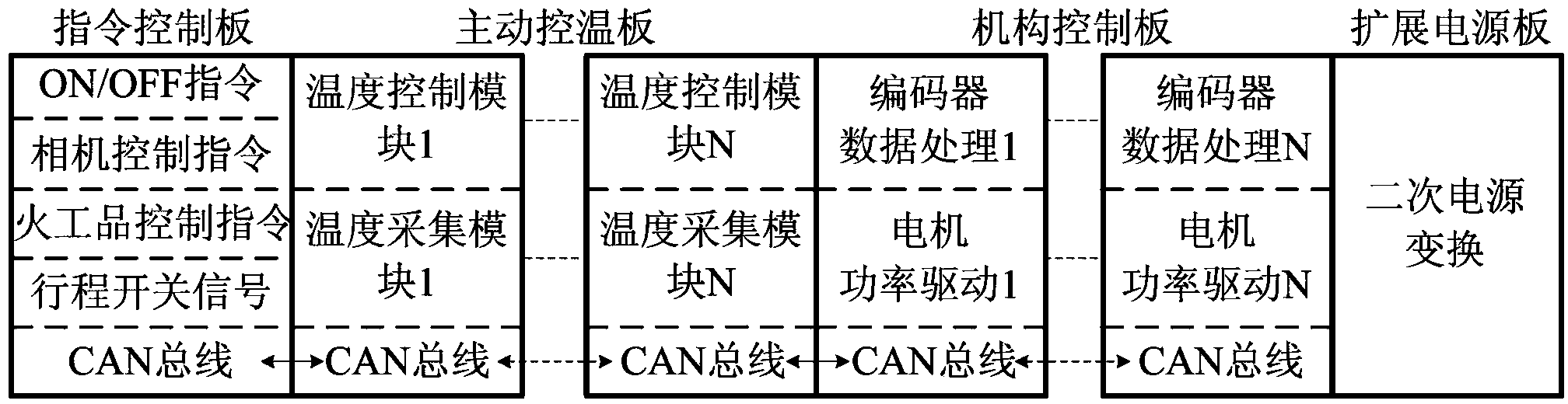

Comprehensive management system for platform and load integrated satellite

InactiveCN104015939ARealize managementReduce in quantityProgramme controlComputer controlAviationResource utilization

The invention provides a comprehensive management system for a platform and load integrated satellite and relates to the technical field of aerospace aviation. The problems that the resource use rate is low and extendibility can not be achieved due to the fact that a distributed type satellite-borne computer design method is adopted in an existing satellite electronic system are solved. The comprehensive management system for the platform and load integrated satellite comprises an integrated comprehensive control unit and a standard function extension unit. The standard function extension unit is interconnected with the integrated comprehensive control unit through an external CAN bus. The integrated comprehensive control unit is composed of a comprehensive management module, a communication interface module, a secondary power source and an arbitration logic control module. The standard function extension unit comprises an order control panel, an active temperature control panel and a mechanism control panel. According to the comprehensive management system, resources are integrated, the number of single machines and elements is reduced, orders are integrated, the order types and forwarding links are reduced, telemetering is integrated, redundant telemetering is reduced so that the bandwidth can be increased, functions are integrated, test links and test procedures are reduced, performance is integrated, and the size, the weight and power consumption of equipment are reduced.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

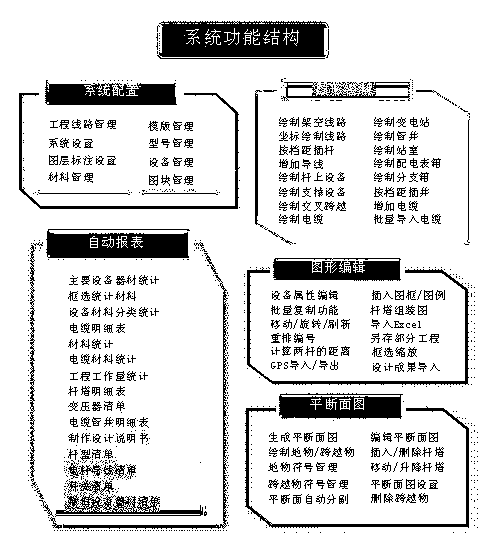

Computer design method of standard distribution network line

ActiveCN102999671ARealize the designPrecise designSpecial data processing applicationsGraphicsEnterprise resource planning

The invention discloses a computer design method of a standard distribution network line. The computer design method of the standard distribution network line comprises the steps of drawing construction diagrams of overhead power distribution lines and cable lines according to distribution line design requirements and a standard diagram, accurately counting materials required by a project, and automatically generating various kinds of report forms. According to the computer design method of the standard distribution network line, the ERP (Enterprise Resource Planning) material entering process can be greatly optimized, and moreover, a preliminary budget of the material part can be automatically embedded into a rural network project preliminary budget template, and the differences between the construction diagram and an as-constructed diagram are analyzed to generate a material balance sheet after the construction diagram and the as-constructed diagram are accomplished, so that a data support is provided for the material recovery, the project auditing and the construction cost, the project materials can be managed and controlled, and create favorable conditions are created for the fixed-assets management, the base data management and the distribution network operation and maintenance management of the post-stage project.

Owner:XUYI POWER SUPPLY OF JIANGSU ELECTRIC POWER +2

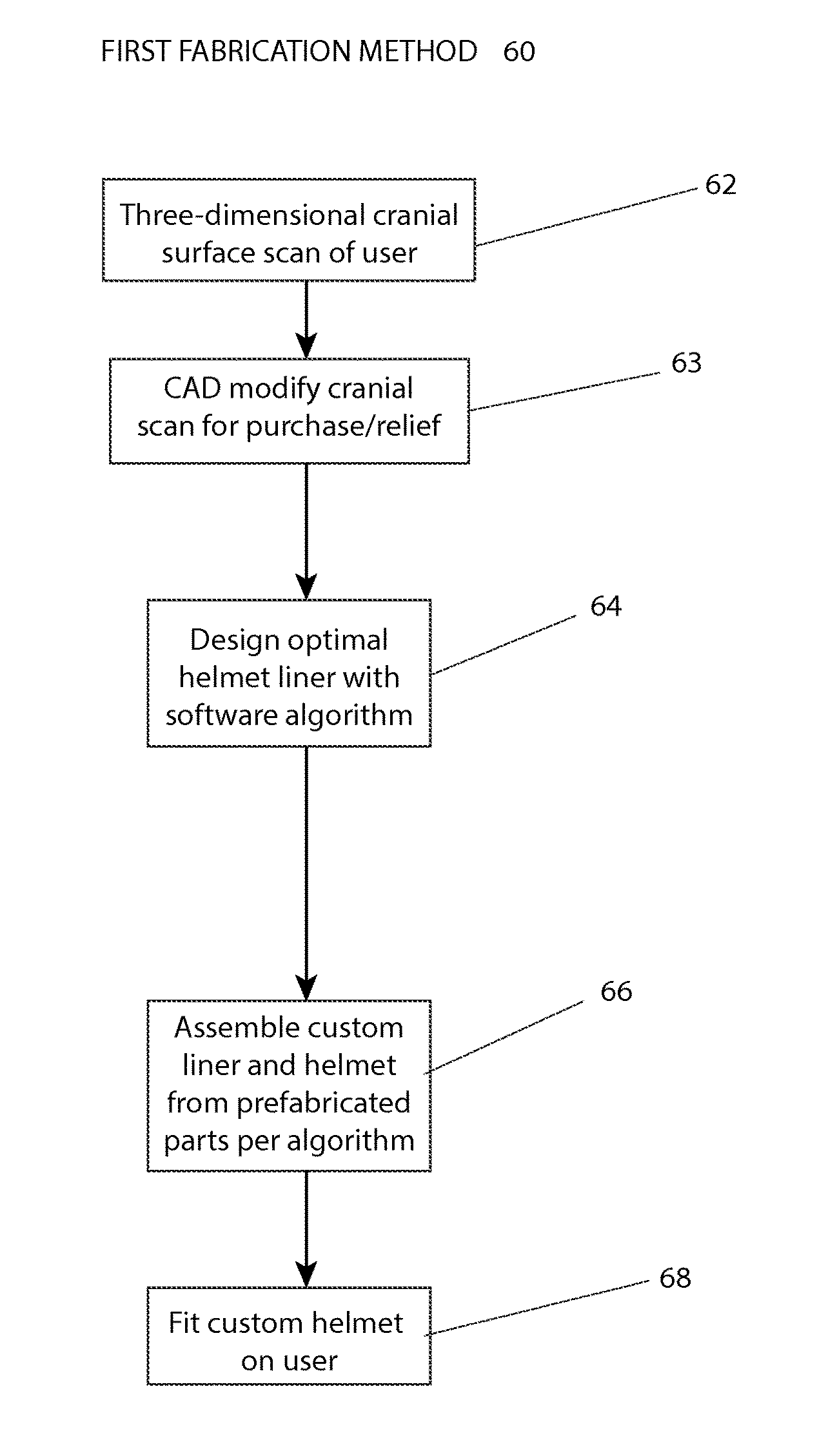

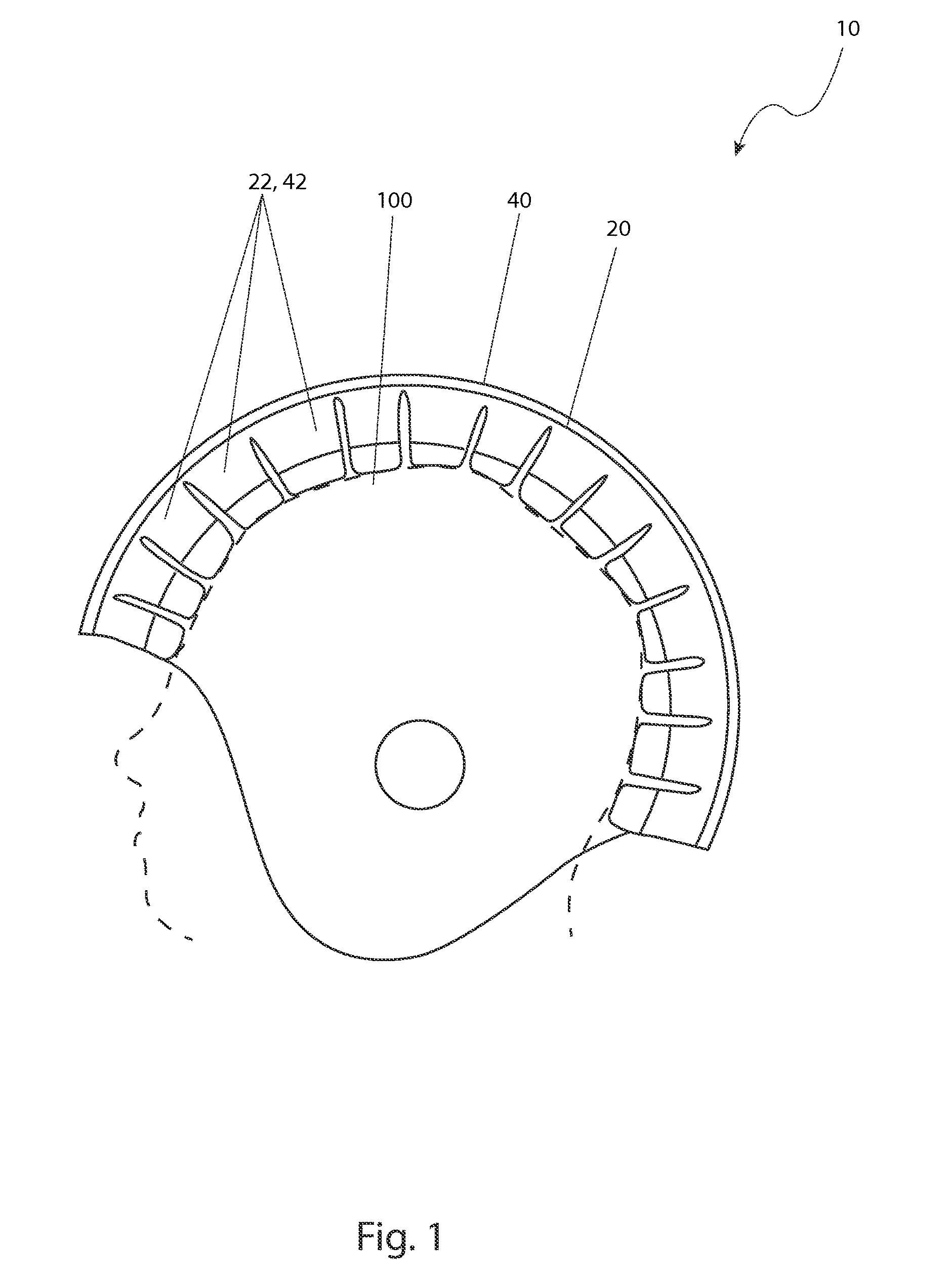

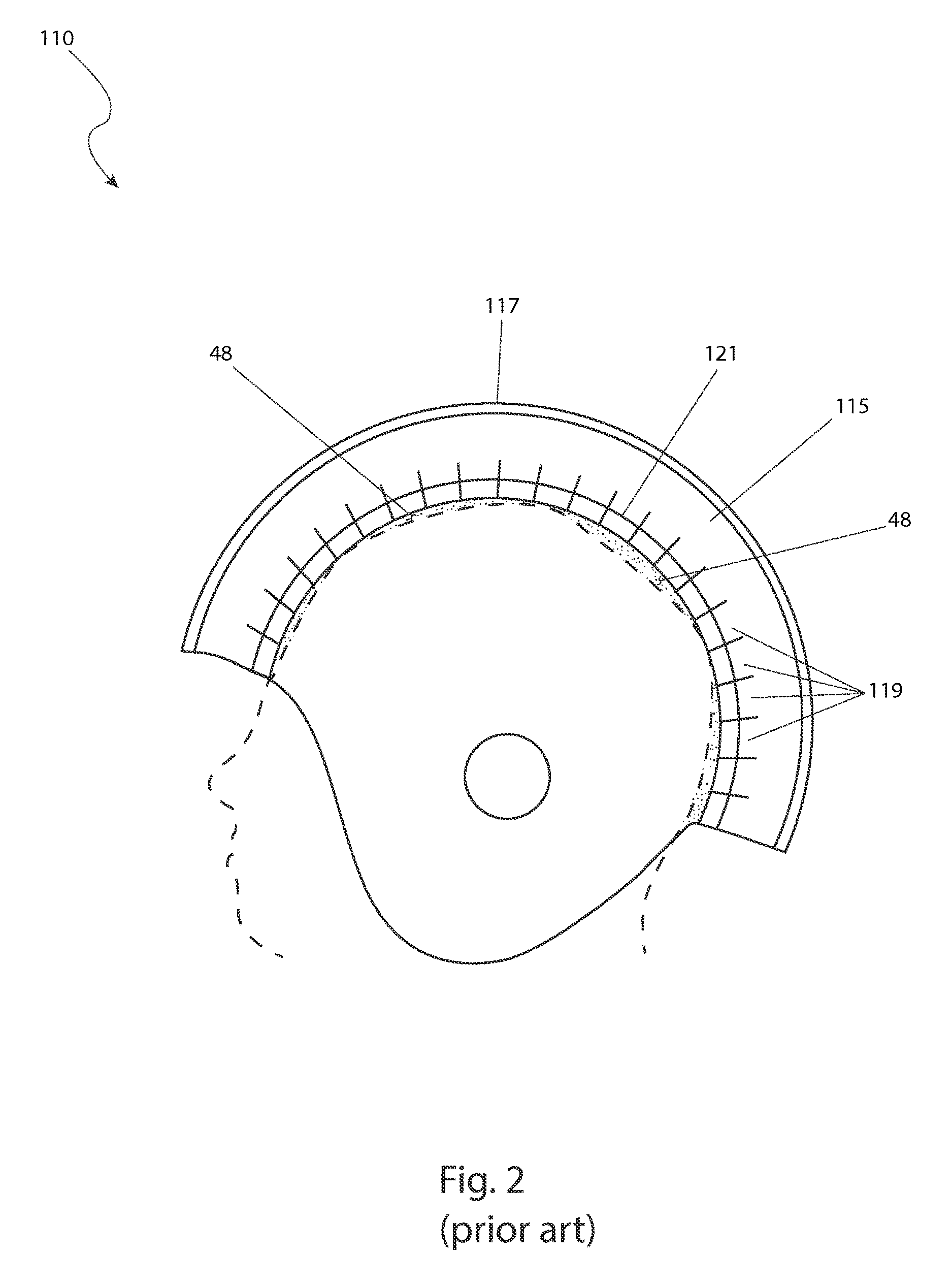

Method for customizing and manufacturing a composite helmet liner

InactiveUS9545127B1Reduction and elimination of air gapEnhanced surface pressure distributionHelmetsHelmet coversComputer Aided DesignThree-dimensional space

A method for producing a customized helmet including a computer designed composite helmet liner to be incorporated into existing and new helmet designs is provided by scanning a user's cranial region, creating a computer rendering surface model of the scan, modifying the surface model using computer aided design software, overlaying and aligning an outer helmet shell model onto the modified cranial model to define the custom liner three-dimensional space to configure the composite liner with a software algorithm including shock absorbing segments having optimal sizes, shapes, and materials, fabricating the liner in a heat sealing process to include an optional encapsulating or serial air bladder, and assembling the liner and outer helmet shell together.

Owner:SANDIFER ALAN T

Double-faced jacquard weaving technology

The invention provides a double-faced jacquard weaving technology. A double-needle spaced fabric adopts computer-designed jacquard patterns and is woven by adopting seven guide bars, and the guide bar GB1, the guide bar GB2, the jacquard guide bar JB3.1, the jacquard guide bar JB3.2, the jacquard guide bar JB4.1, the jacquard guide bar JB4.2 and the guide bar GB5 are sequentially arranged from a front needle bed to a back needle bed. The double-faced jacquard weaving technology specifically comprises the following steps that 1, the guide bar GB1 is fully threaded to serve as a first layer of yarn to be laid to form loops on the front needle bed and used for forming the surface layer of the double-needle spaced fabric; 2, the guide bar GB2 is fully threaded to serve as a second layer of yarn to be alternated to form loops to form spaced yarn for connecting the surface layer with the bottom layer; 3, the guide bar GB5 is fully threaded to serve as a fifth layer of yarn to be laid to form loops on the back needle bed and used for forming the bottom layer of the double-needle spaced fabric. The double-needle spaced fabric made through the double-faced jacquard weaving technology is clear in pattern hierarchy and has the good stereoscopic effect in visual sense; meanwhile, the production procedures are simplified, and the cost is greatly saved.

Owner:SINCETECH FUJIAN TECH CO LTD

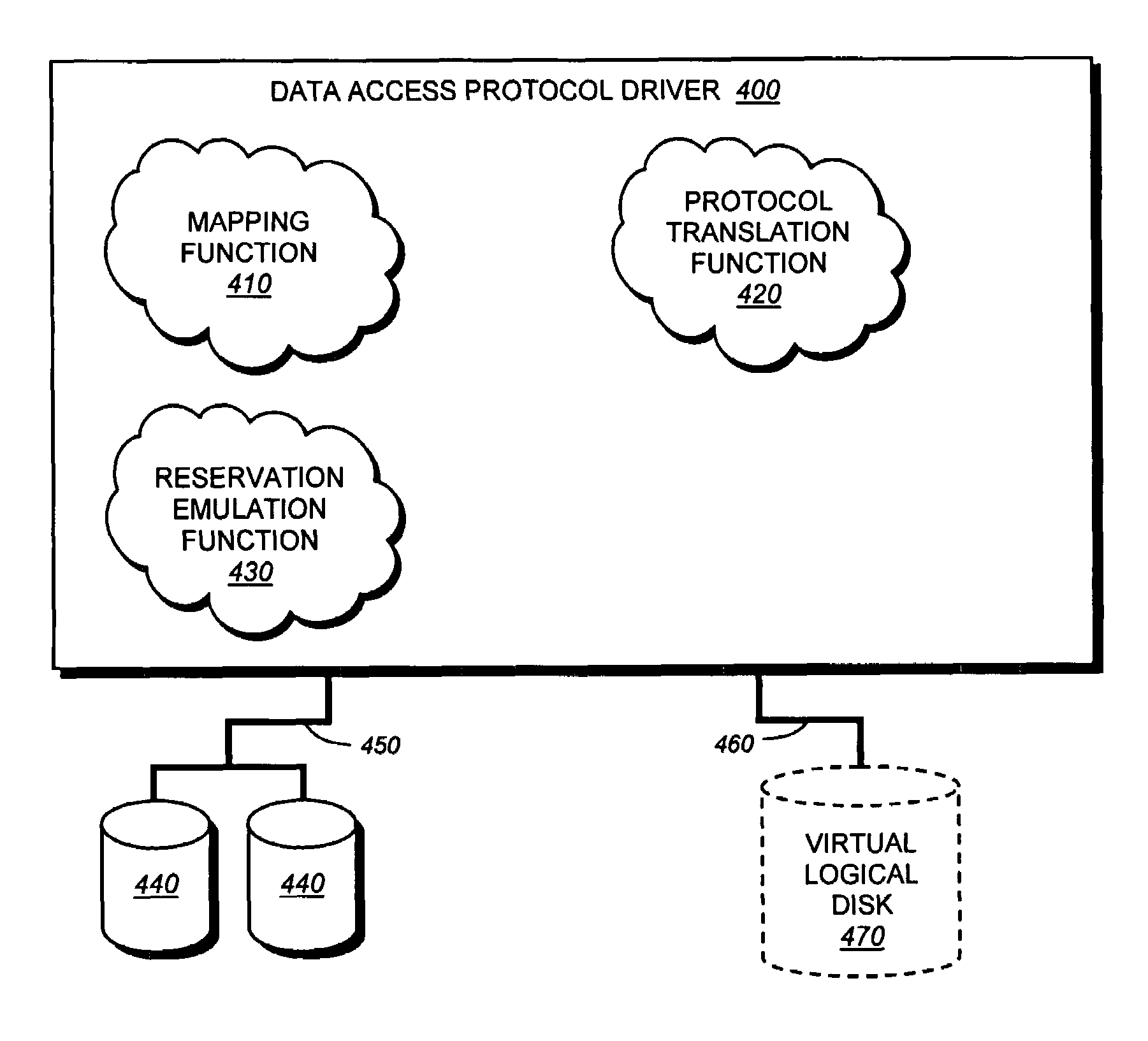

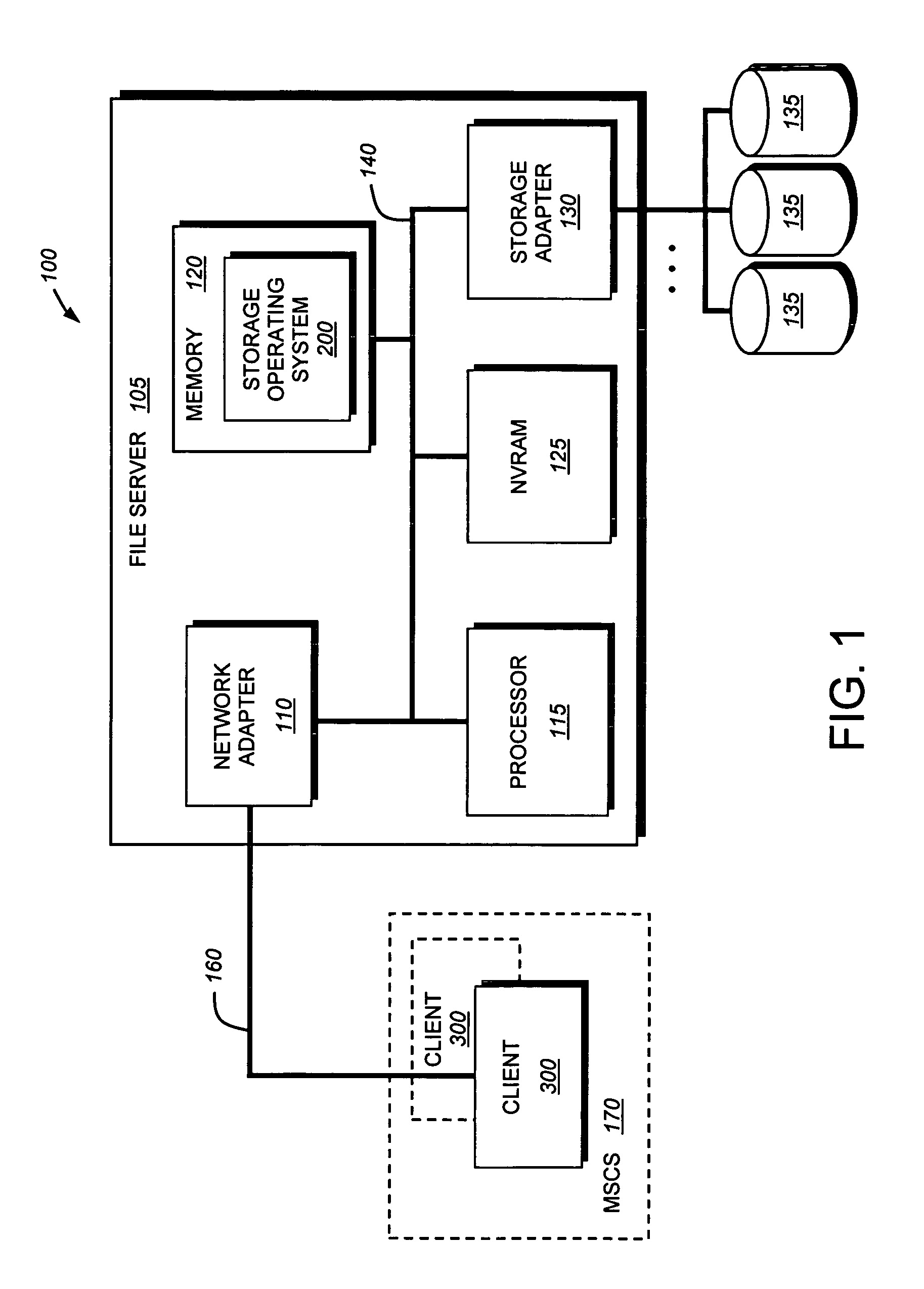

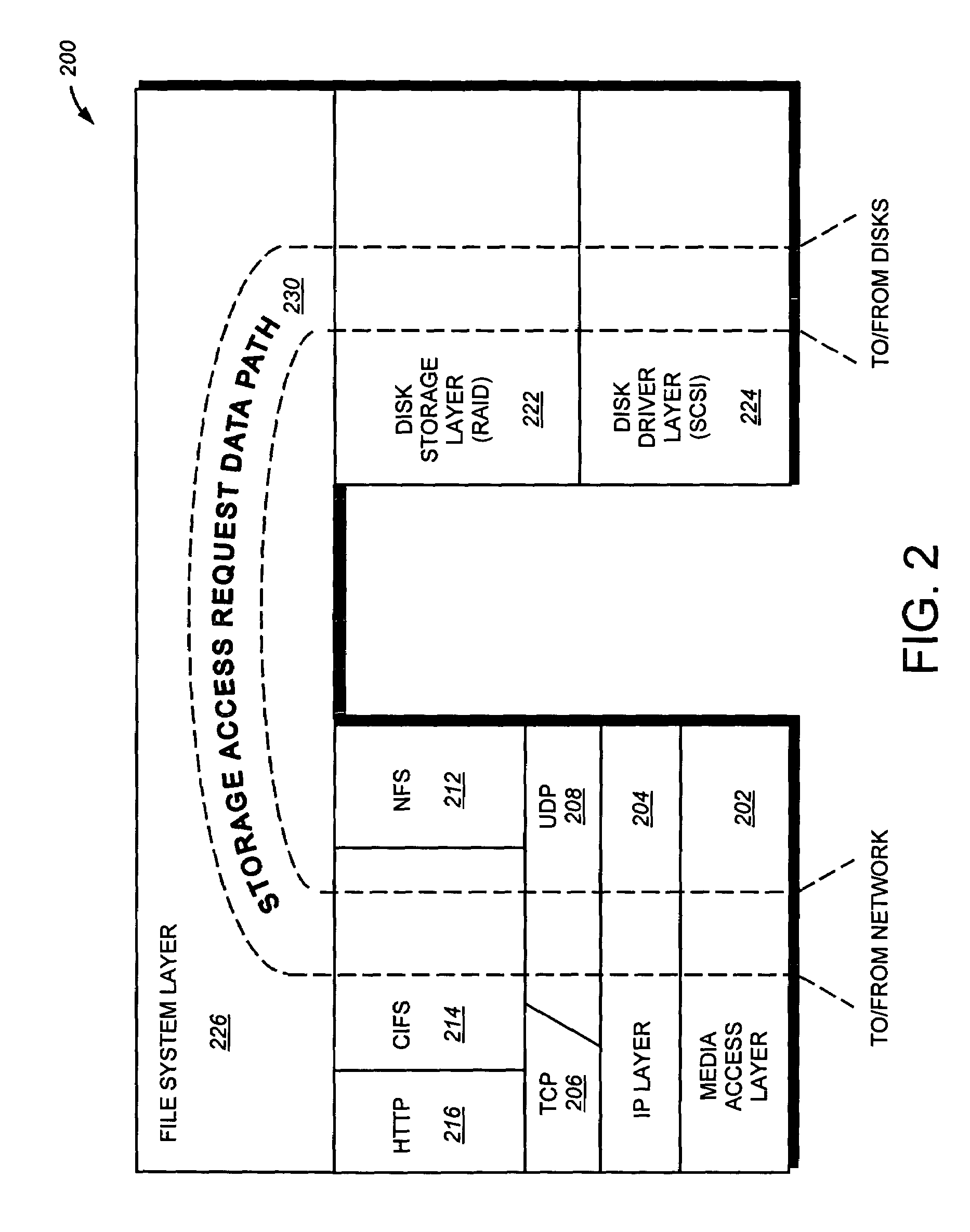

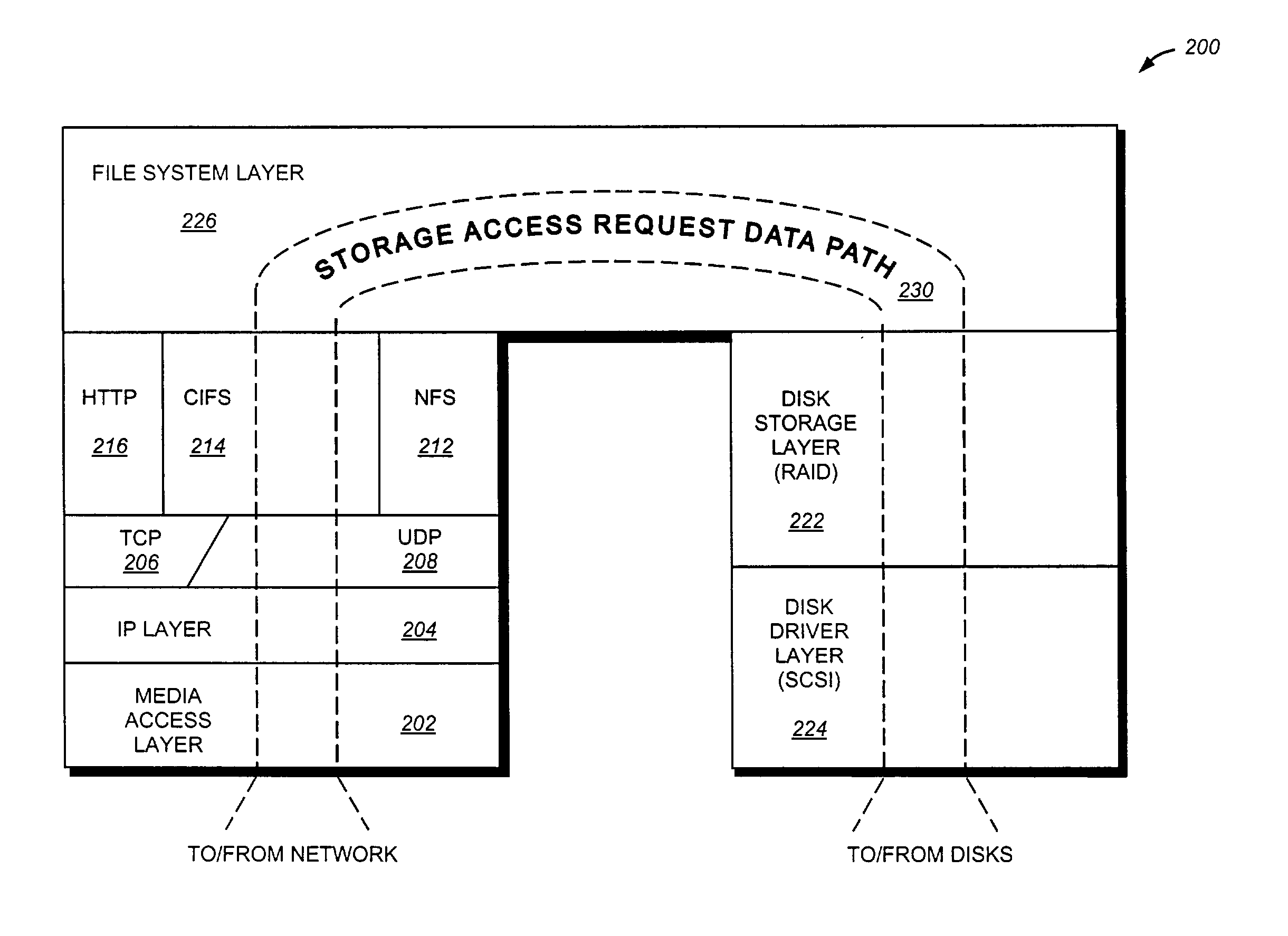

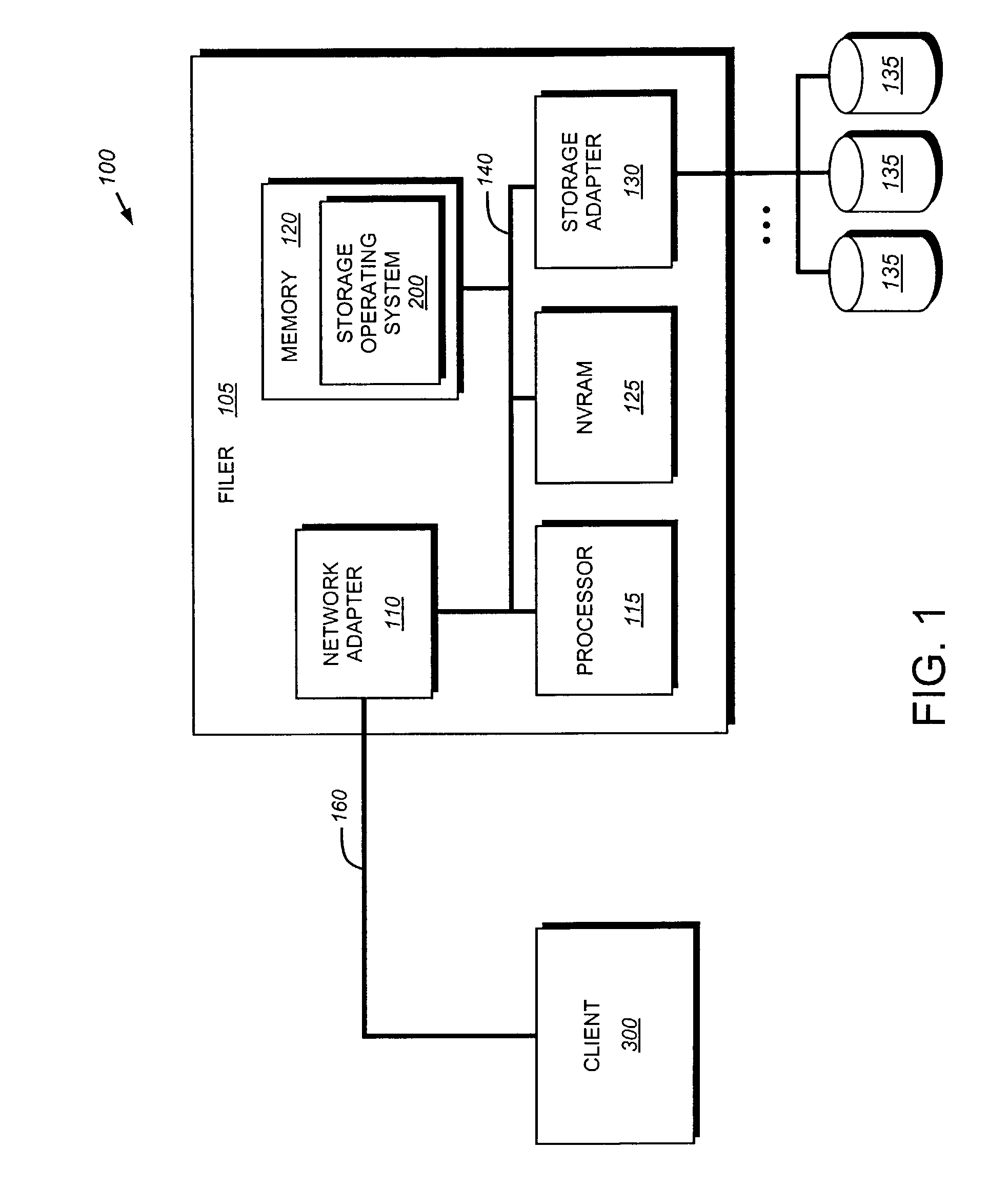

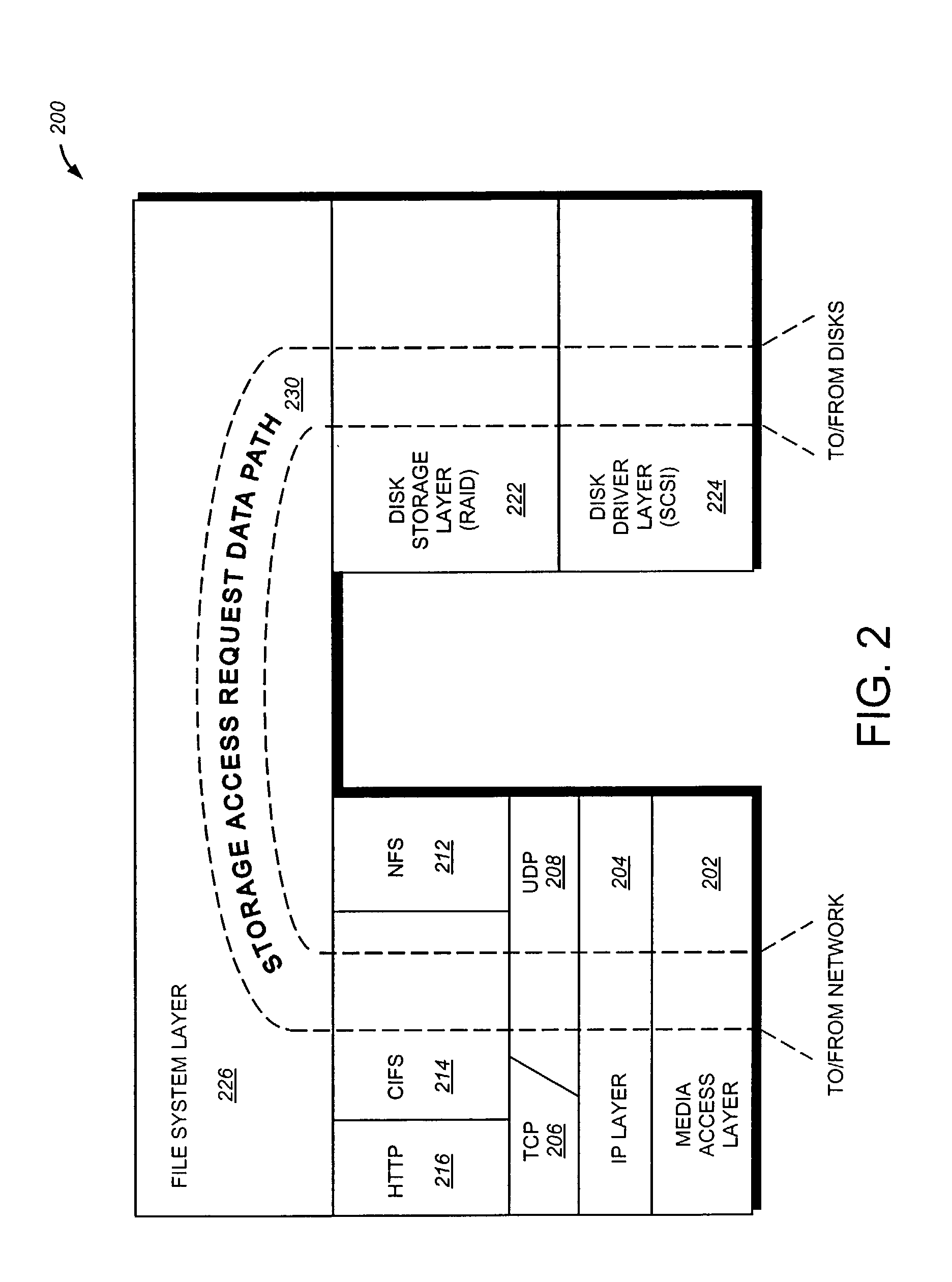

System and method for emulating SCSI reservations using network file access protocols

ActiveUS7711539B1Digital data processing detailsMultiple digital computer combinationsSCSIOperational system

A system and method for emulating SCSI reservations using network file access protocols is provided. The system and method enable applications or operating systems on a networked computer designed to utilize SCSI reservations on only locally attached storage to also access networked data storage. The emulation occurs transparently to higher levels of operating systems or applications so that the applications or operating systems which are designed to only access locally attached storage may be enabled to access networked storage.

Owner:NETWORK APPLIANCE INC

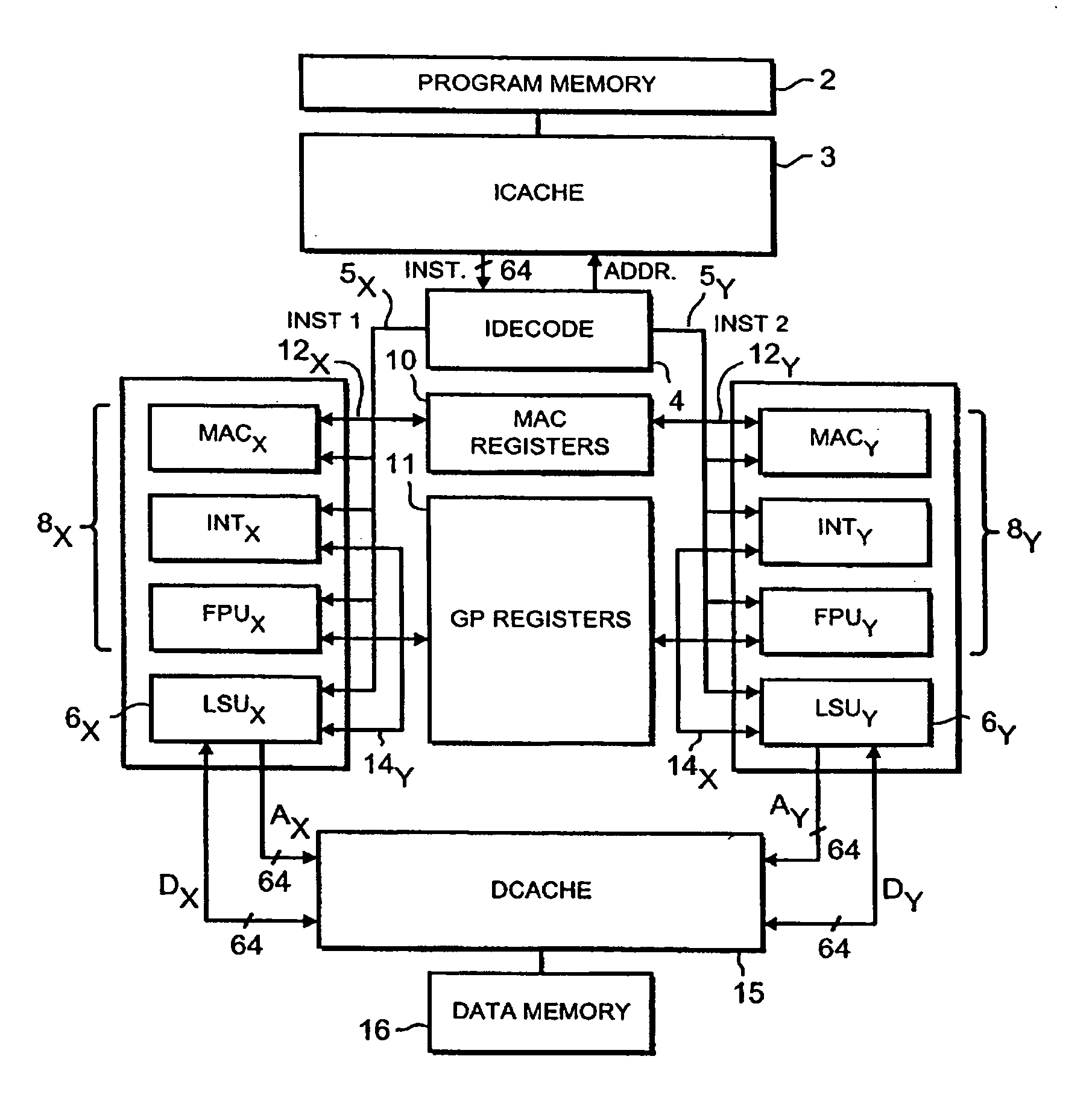

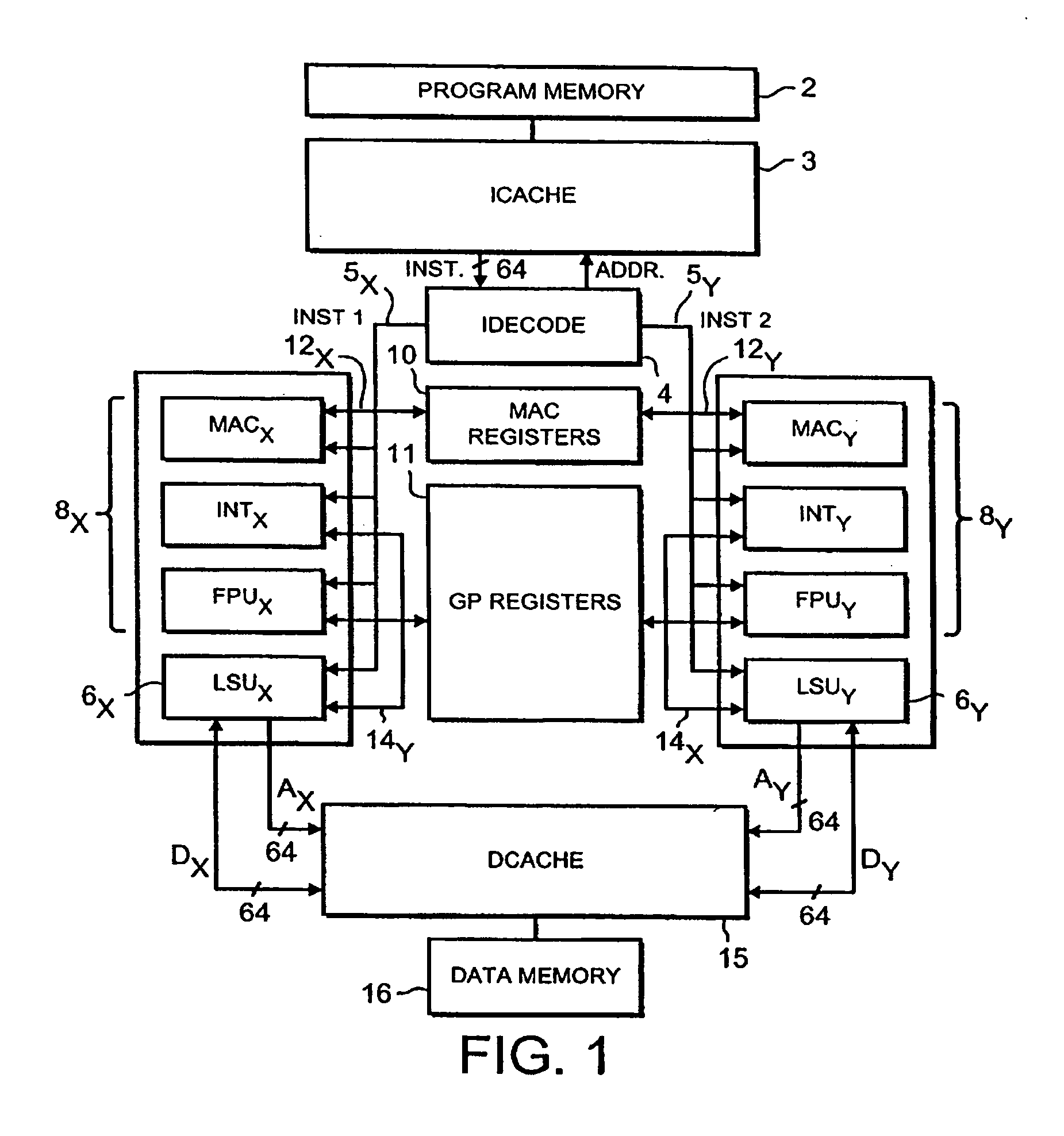

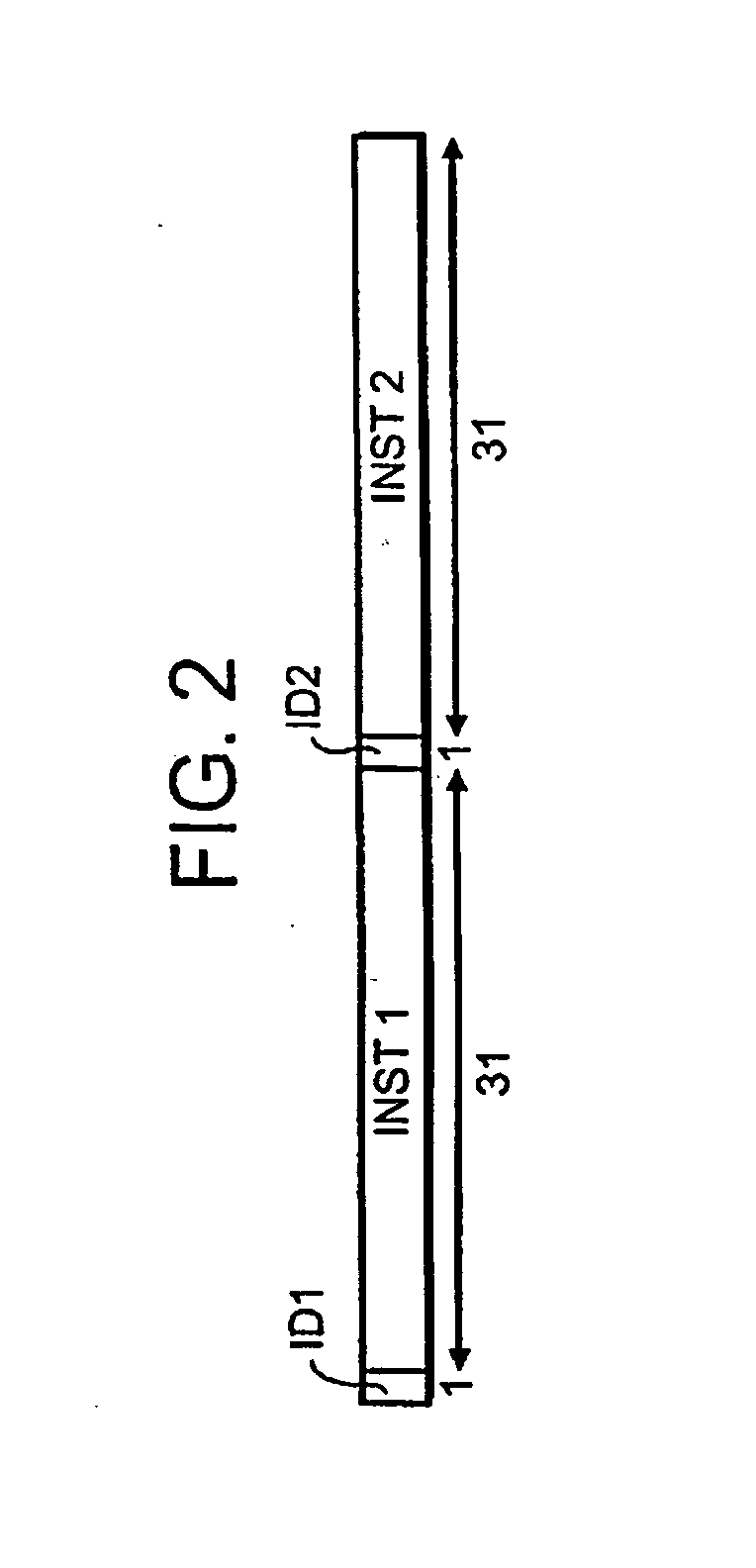

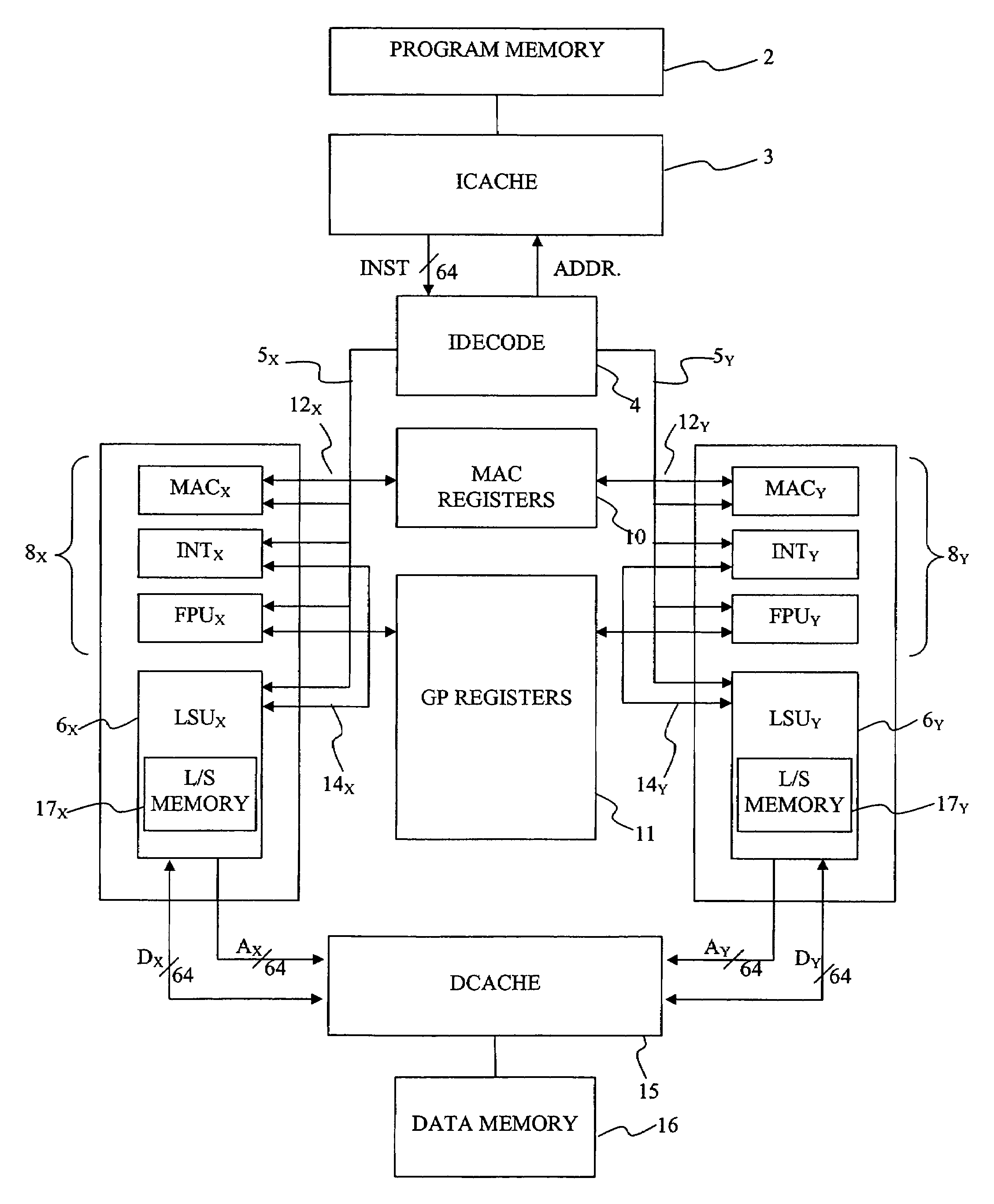

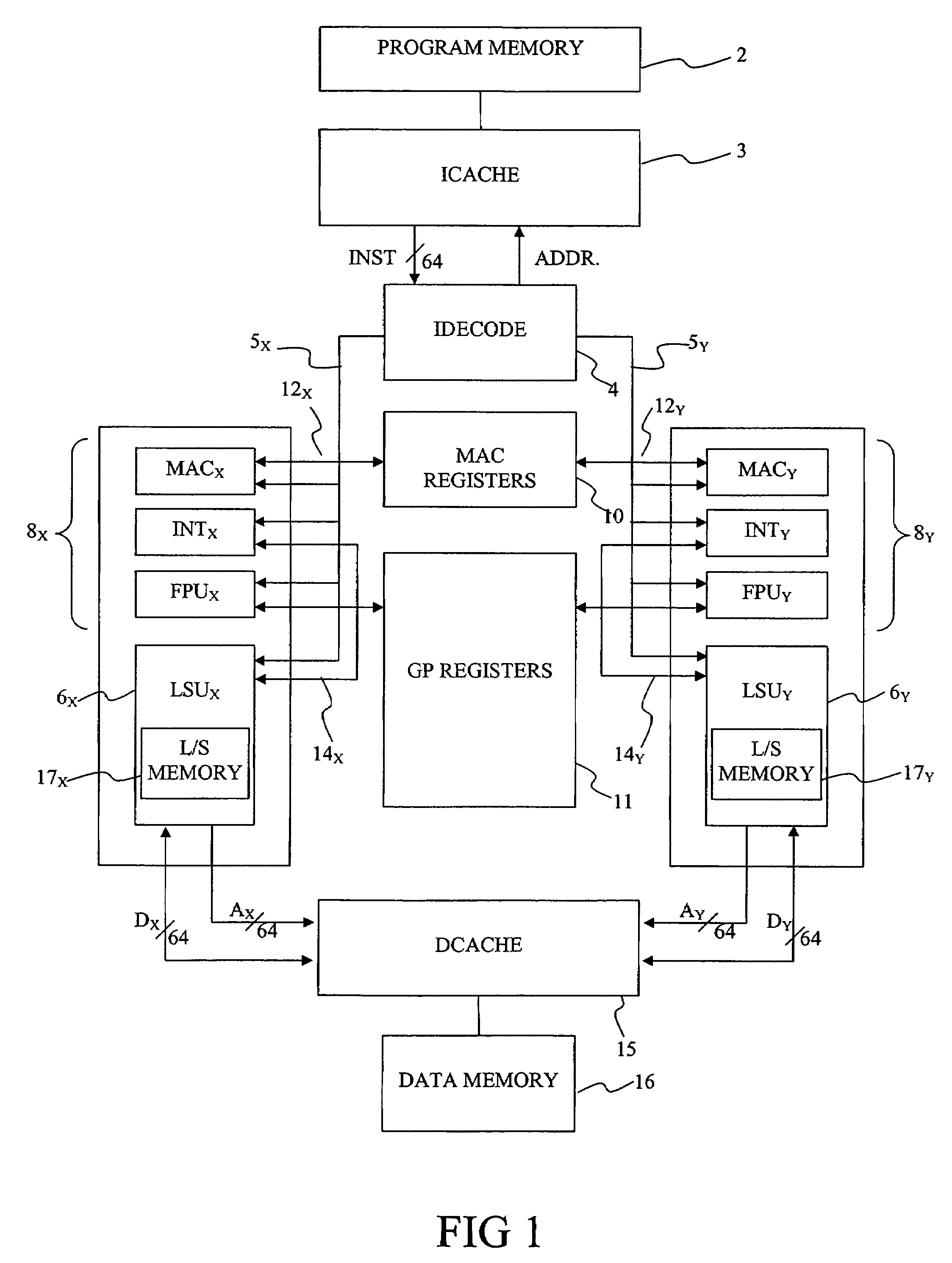

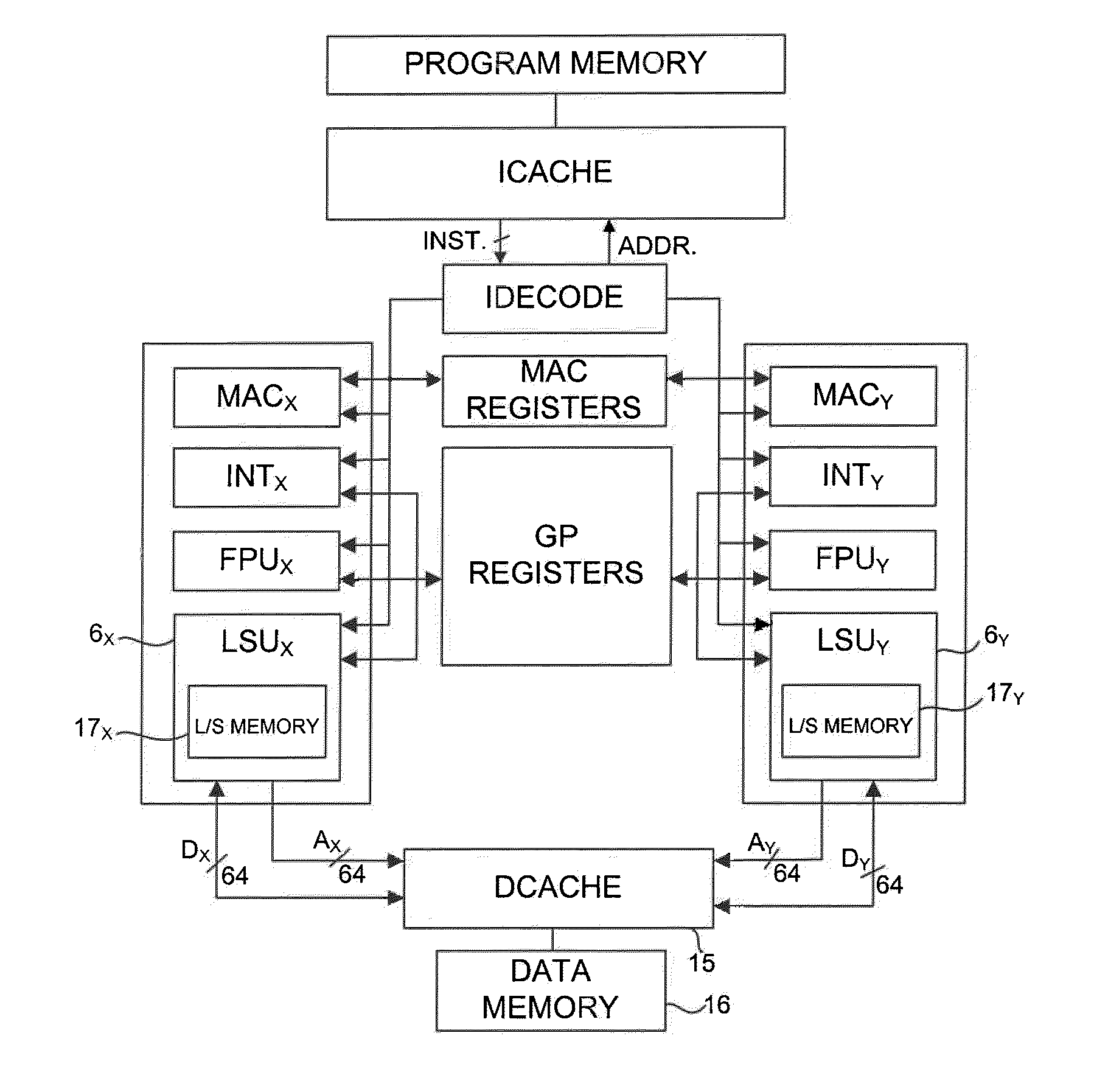

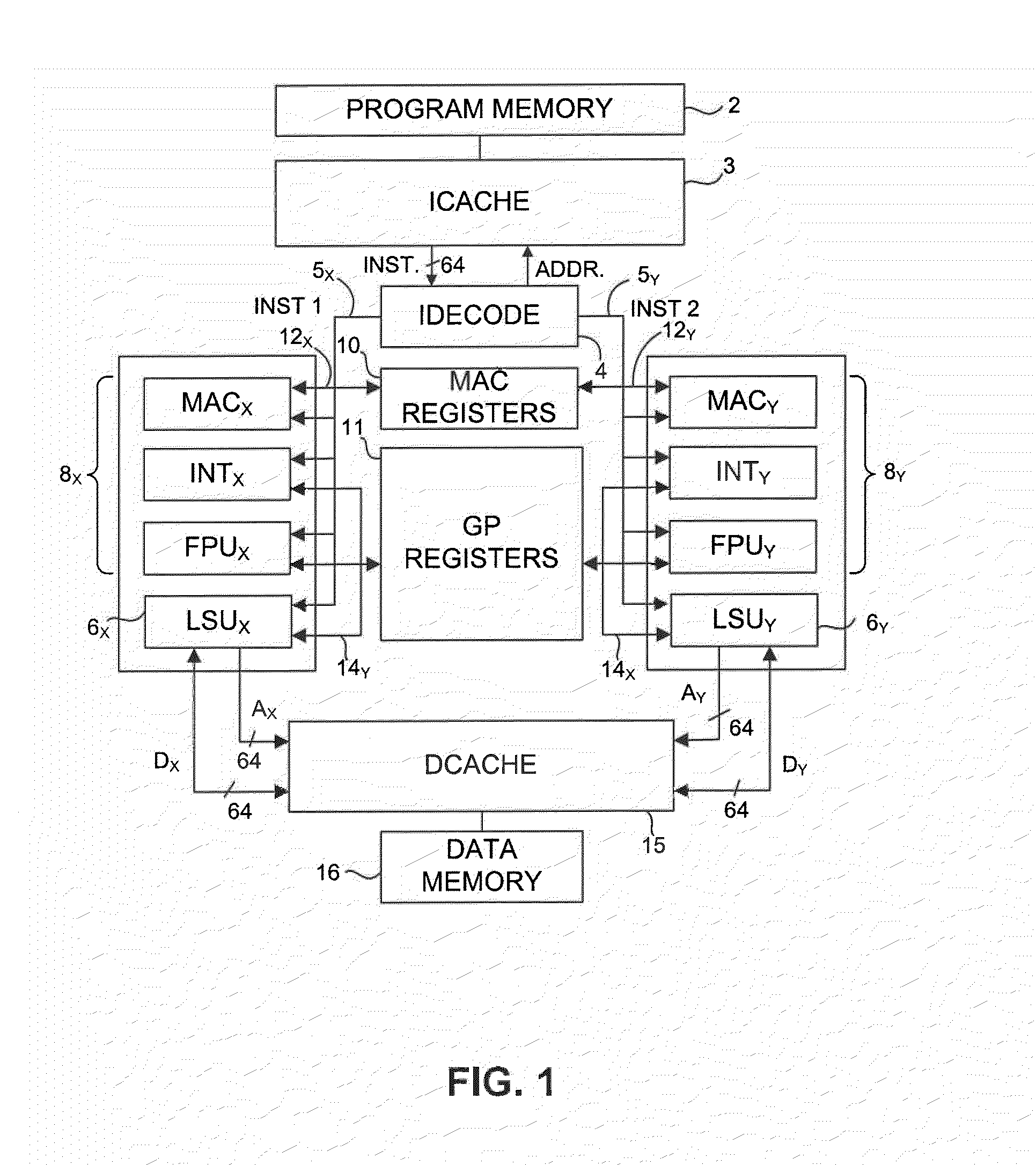

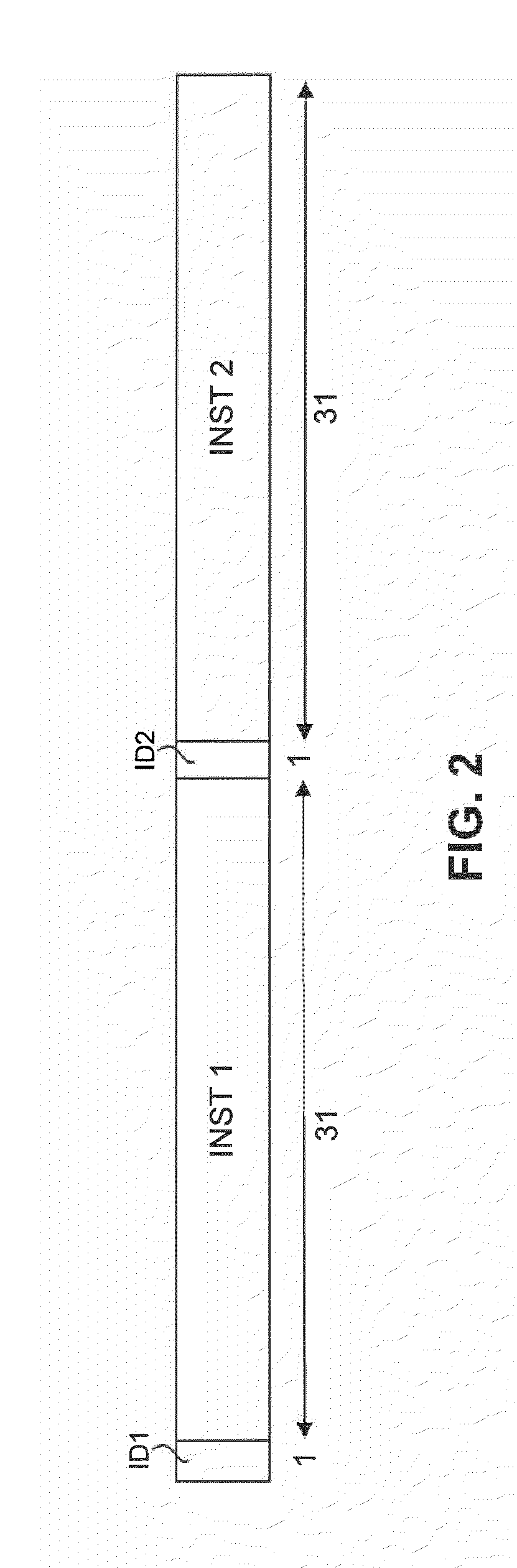

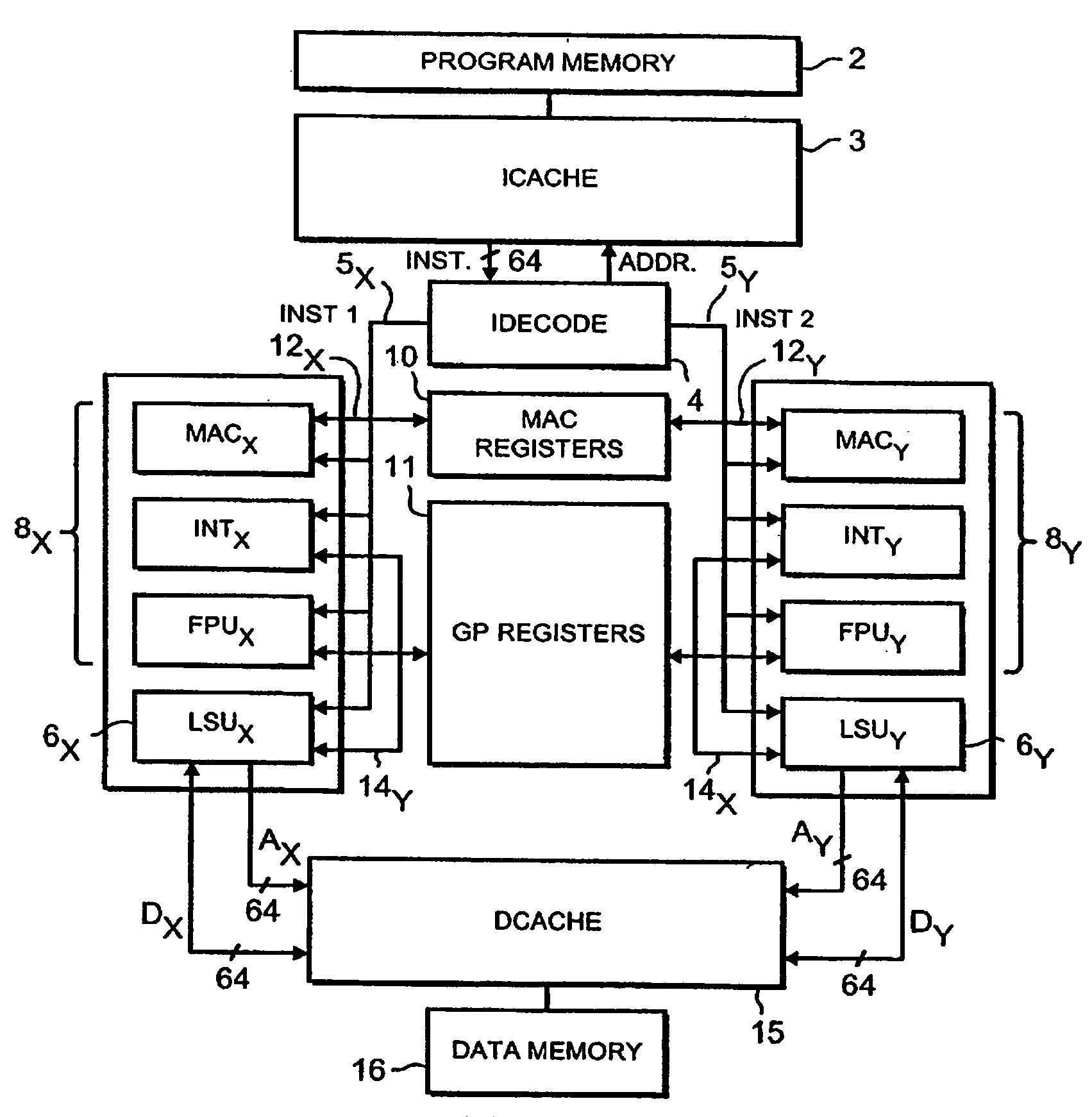

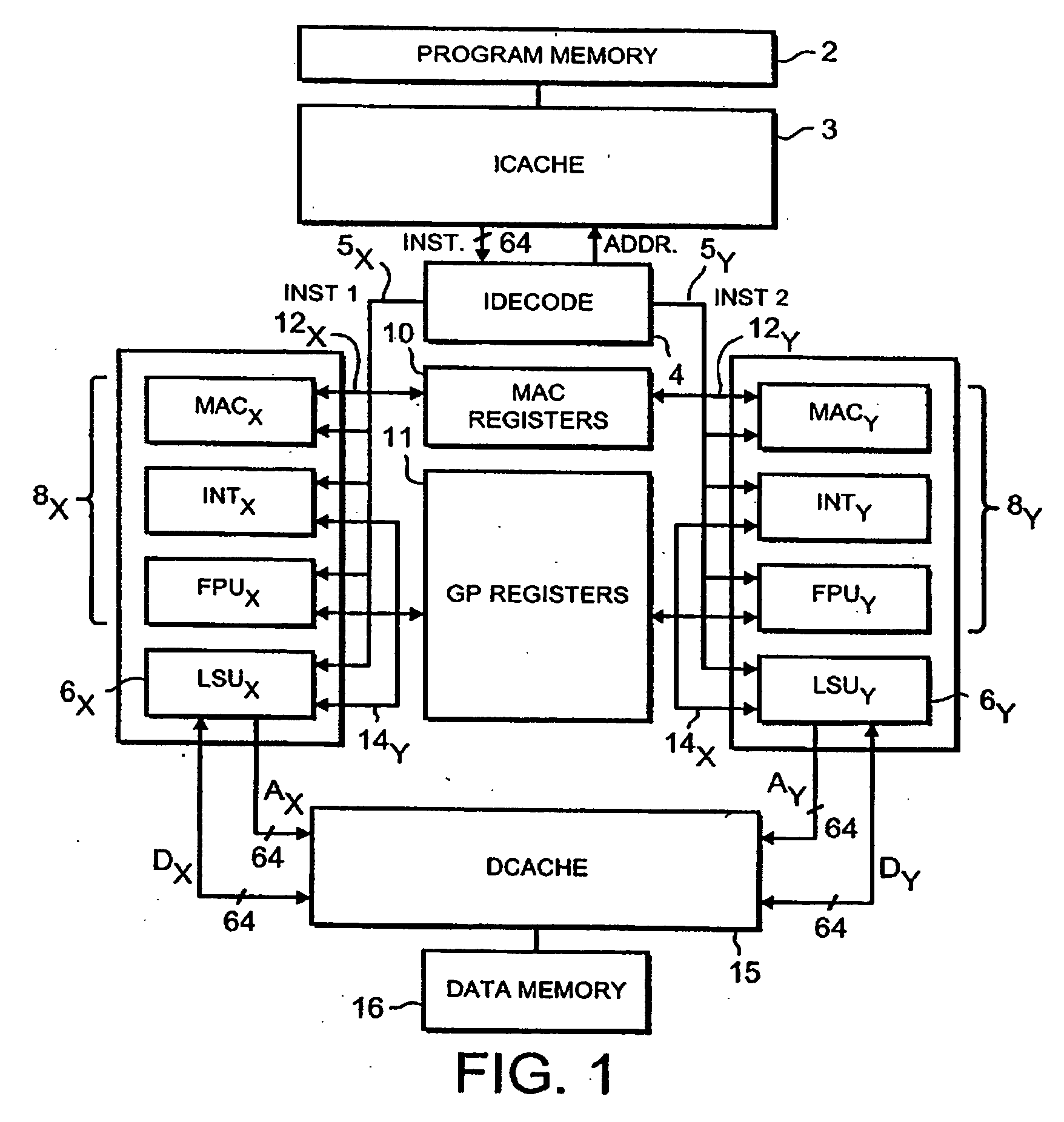

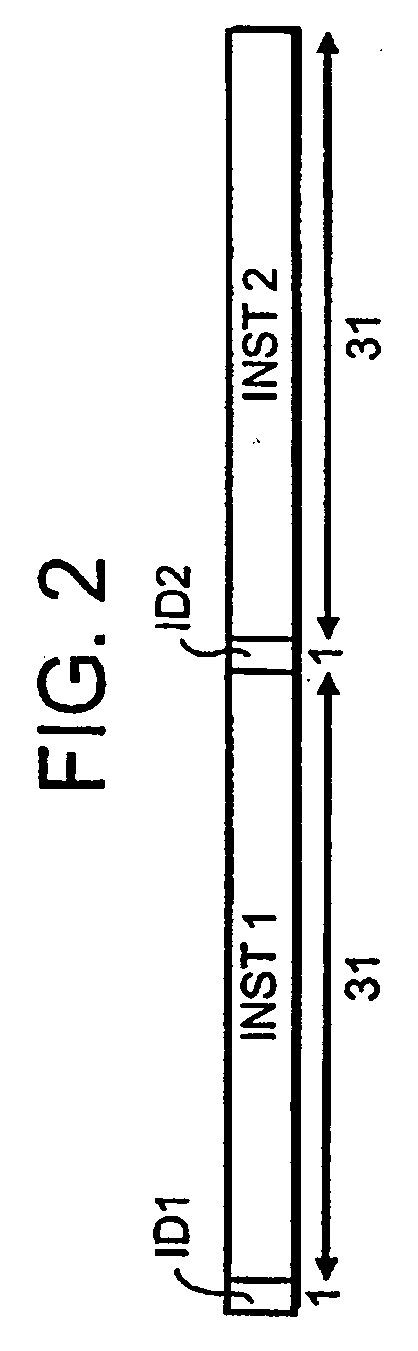

Microprocessor with integrated high speed memory

InactiveUS20050273576A1Improve efficiencyGood benefitMemory adressing/allocation/relocationGeneral purpose stored program computerHigh speed memoryData information

The present invention relates to the field of (micro)computer design and architecture, and in particular to microarchitecture associated with moving data values between a (micro)processor and memory components. Particularly, the present invention relates to a computer system with an processor architecture in which register addresses are generated with more than one execution channel controlled by one central processing unit with at least one load / store unit for loading and storing data objects, and at least one cache memory associated to the processor holding data objects accessed by the processor, wherein said processor's load / store unit contains a high speed memory directly interfacing said load / store unit to the cache and directly accessible by the cache memory for implementing scatter and gather operations. The present invention improves the performance of architectures with dual ported microprocessor implementations comprising two execution pipelines capable of two load / store data transactions per cycle. By including a high speed memory inside the load / store unit, the processor is directly interfaced from its load / store units to the caches and efficiency gains are achieved by reusing the data information already present in the high speed memory structure of the load / store unit.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

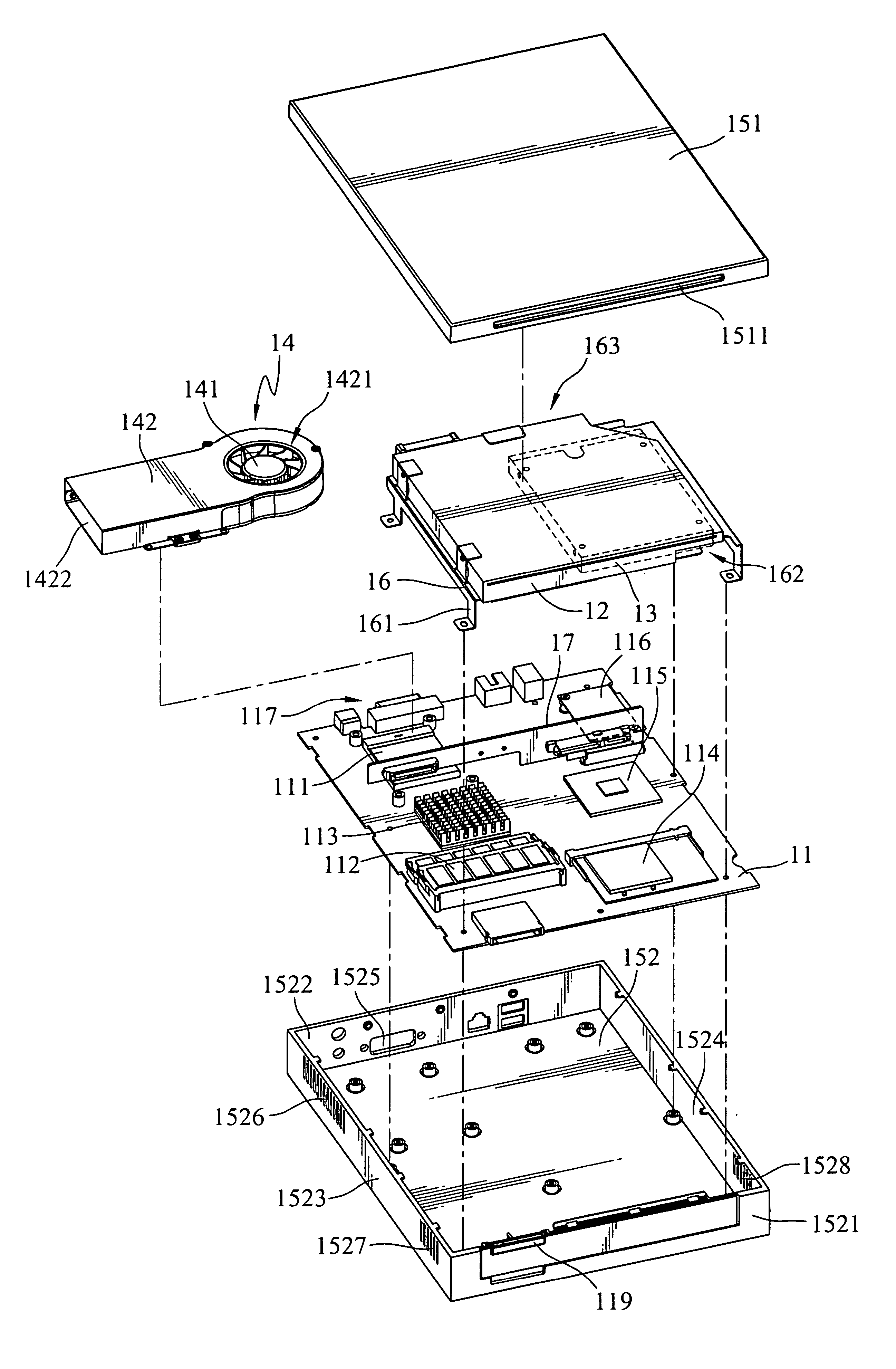

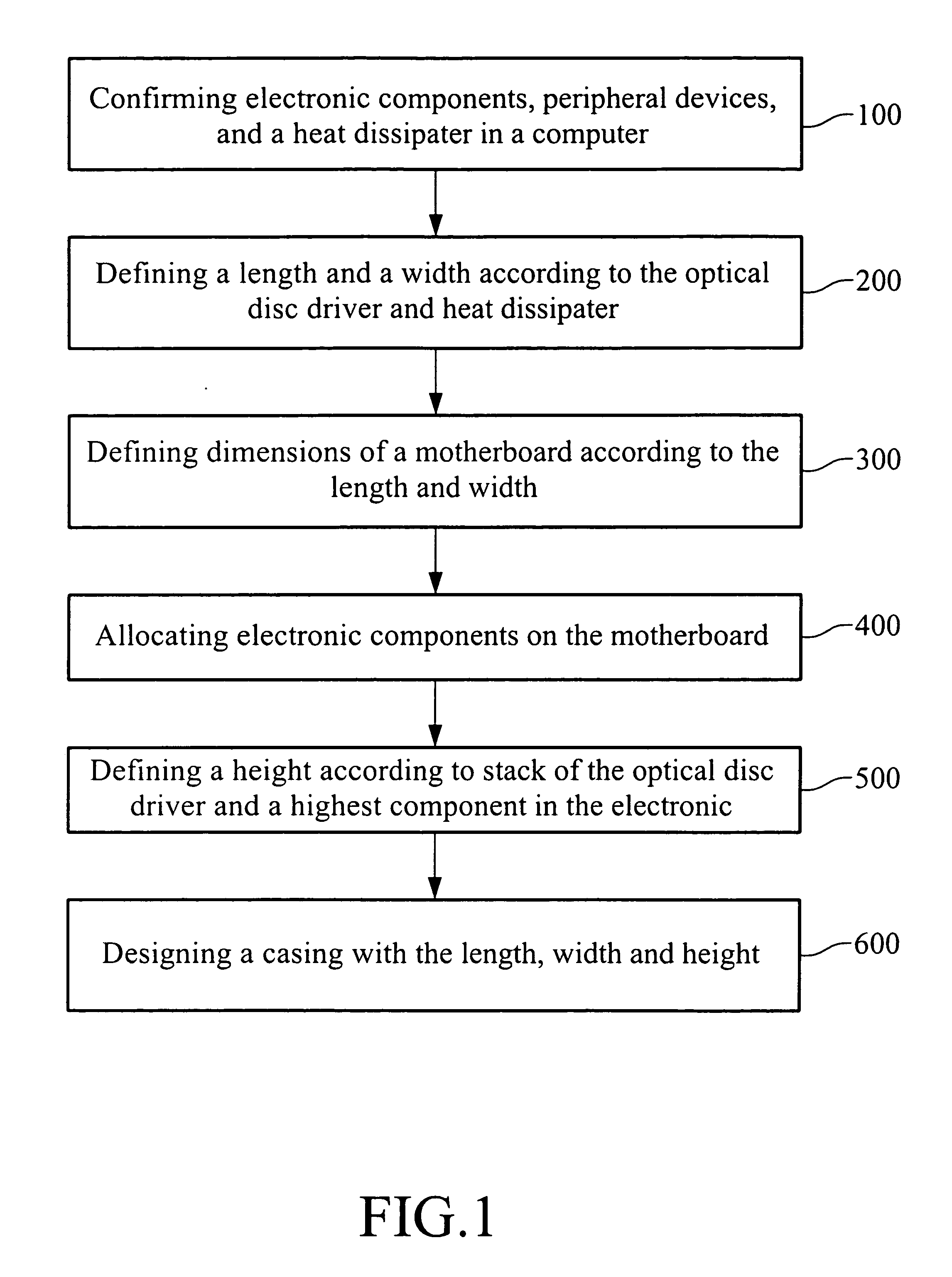

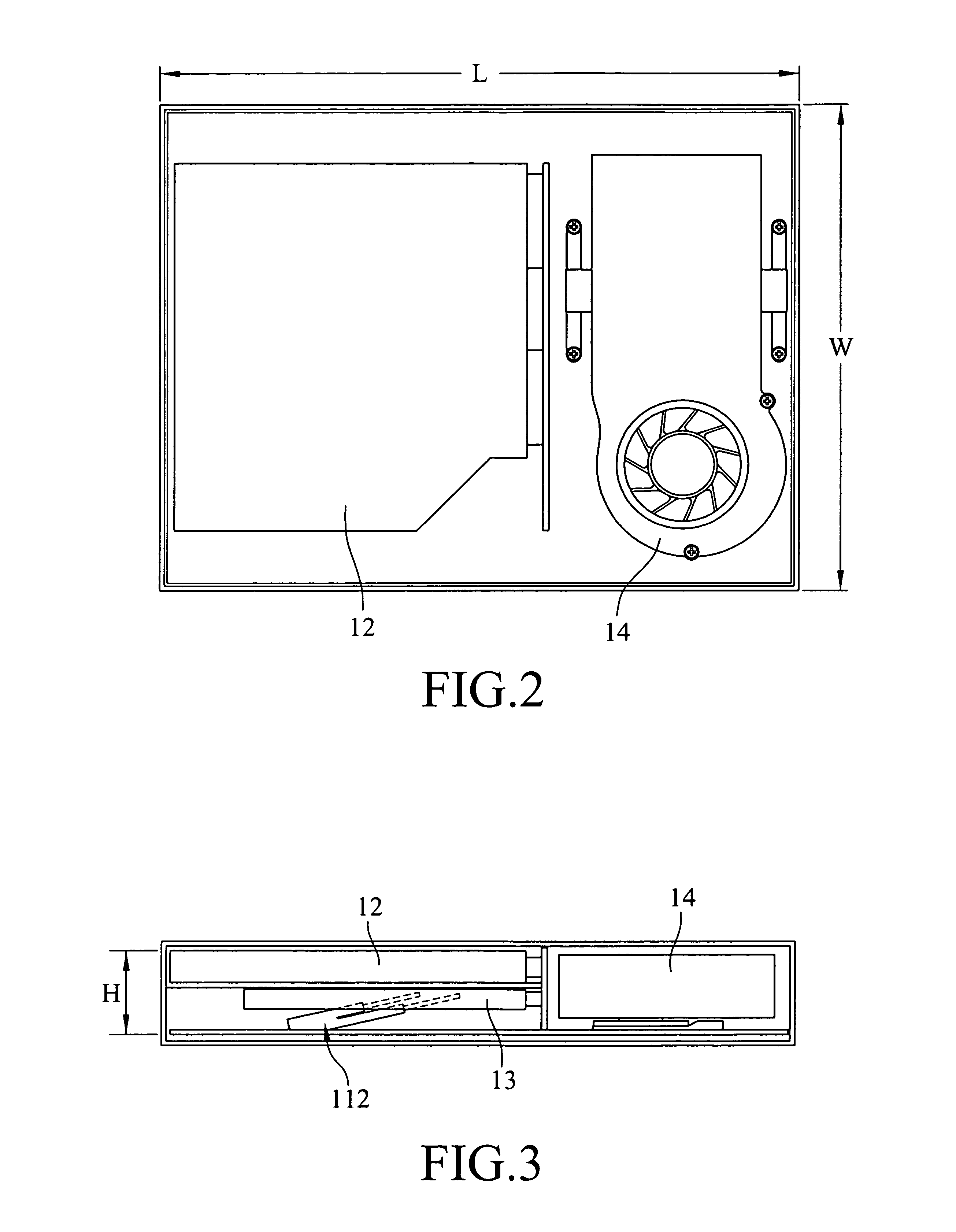

Method of determining minimal dimension of computer and computer designed though the method

InactiveUS20070076369A1Minimal sizeReduce usageDigital processing power distributionCooling/ventilation/heating modificationsEngineeringPersonal computer

A method to determine the minimal dimension of a personal computer and a personal computer constructed through the method are provided An optical disc driver and a heat dissipater are laid aside to define a length and a width of the computer. Then, define the size of a motherboard according to the length and width. The highest electronic component allocated on the motherboard and the optical disc driver are stacked up to define a height. Allocate electronic components on the motherboard and arranging the motherboard, optical disc driver and heat dissipater into a casing with the length, width and height to obtain the minimal dimension of the computer.

Owner:FIRST INTERNATIONAL COMPUTER

Microprocessor with high speed memory integrated in load/store unit to efficiently perform scatter and gather operations

InactiveUS7216218B2Improve efficiencyGood benefitMemory adressing/allocation/relocationConcurrent instruction executionHigh speed memoryProcessor register

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

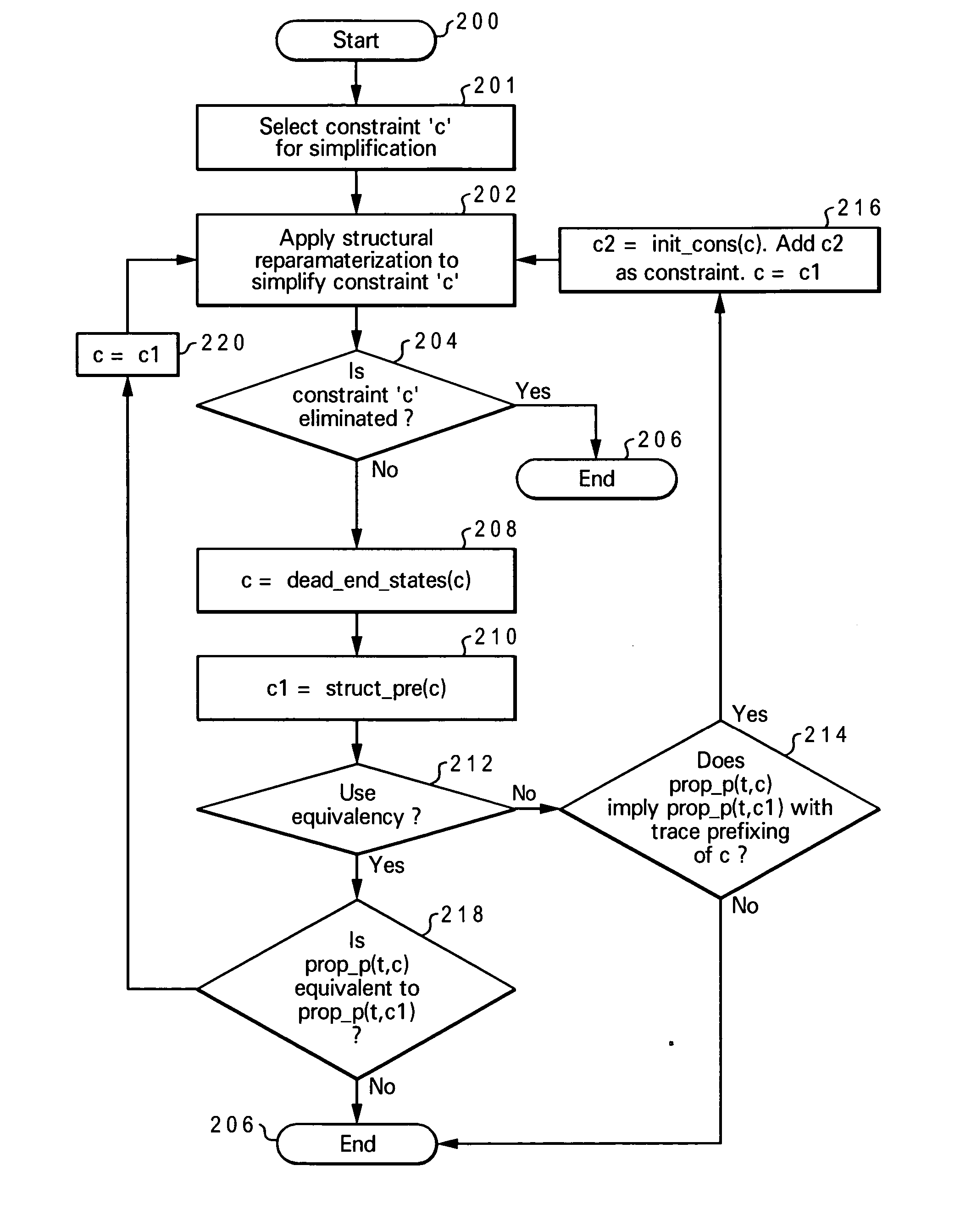

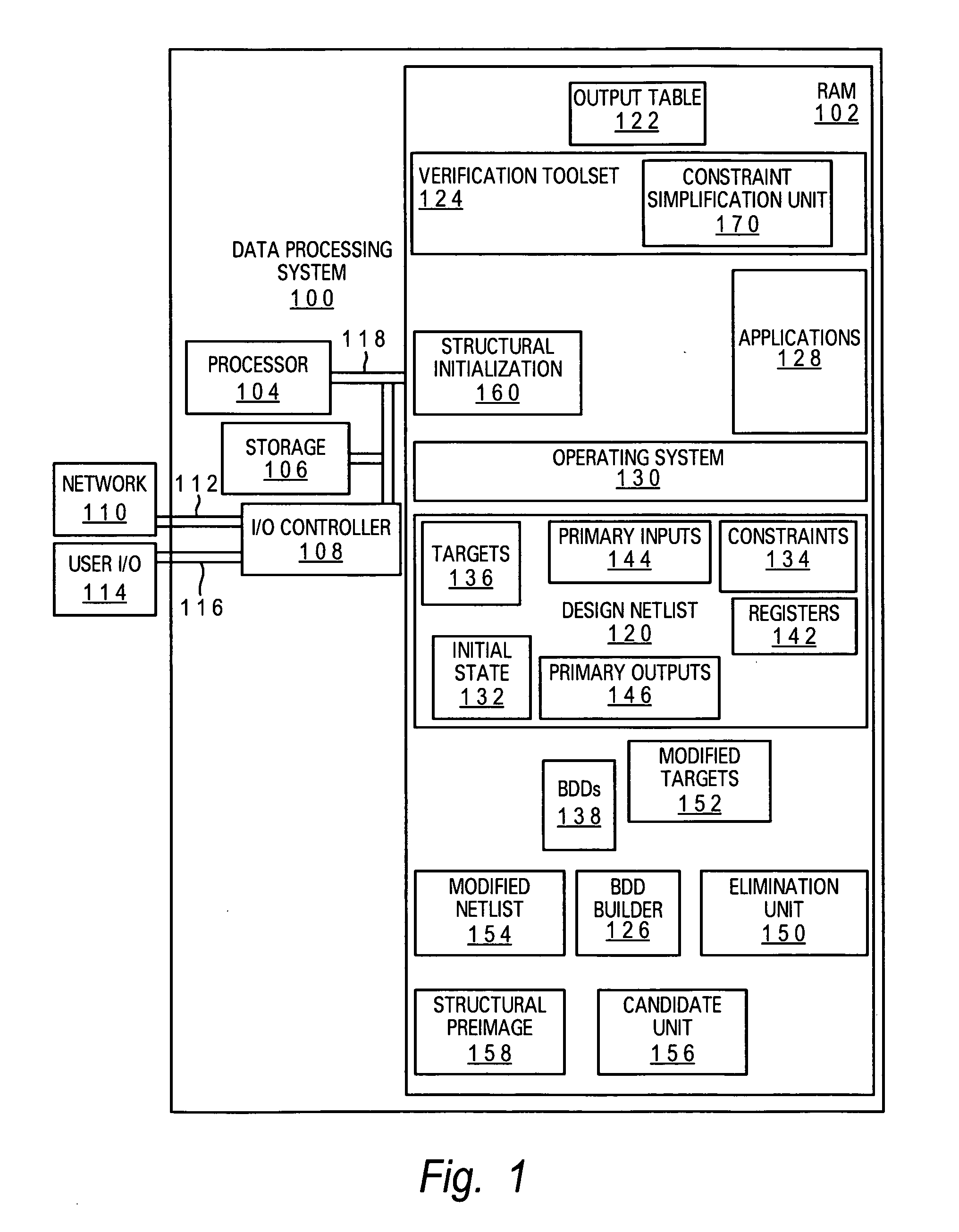

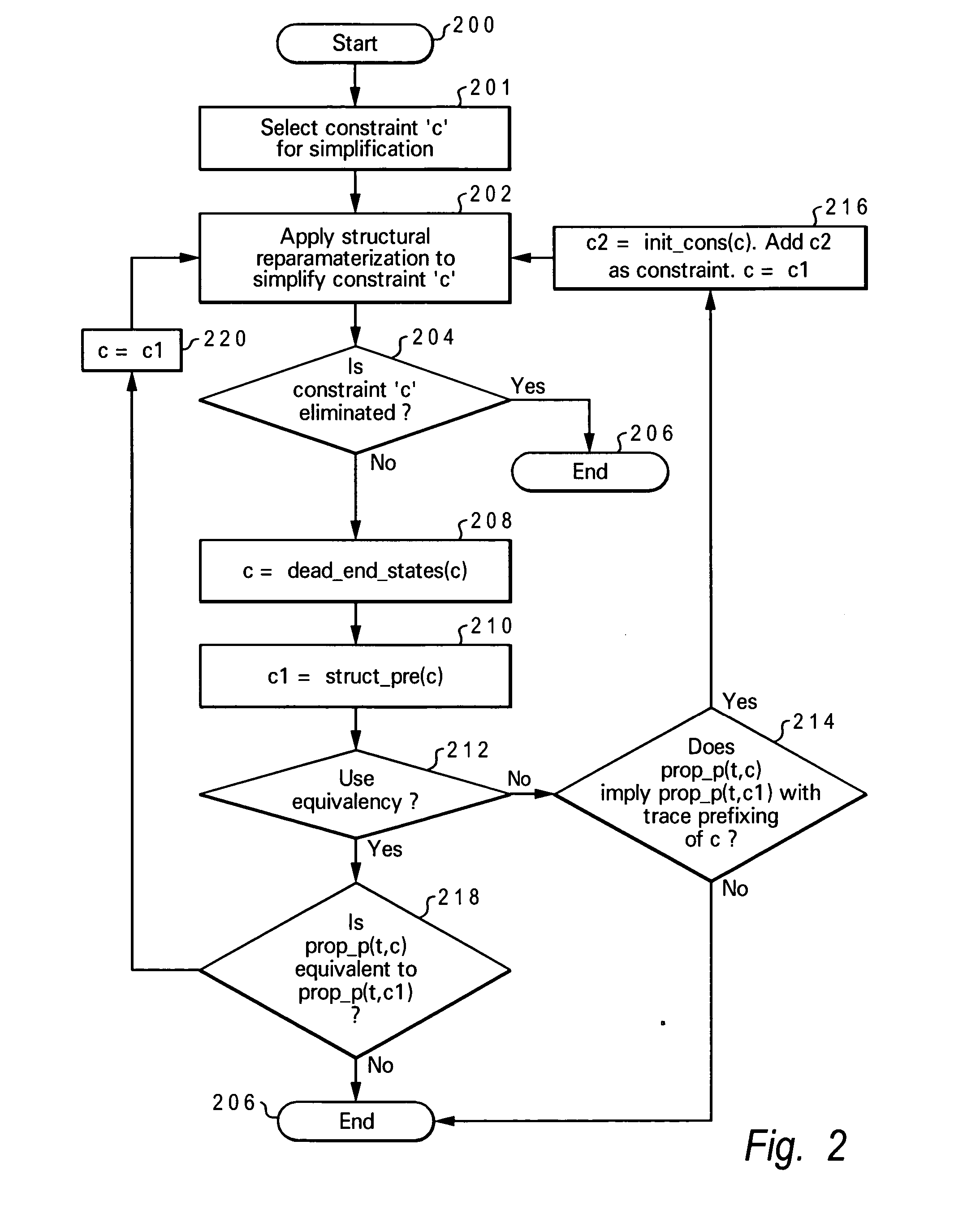

Method and System for Performing Heuristic Constraint Simplification

InactiveUS20080066034A1Computer aided designSoftware simulation/interpretation/emulationTheoretical computer scienceComputer design

A method for performing verification is disclosed. The method includes selecting a first computer-design constraint for simplification and applying structural reparamaterization to simplify the first computer-design constraint. In response to determining that the first computer-design constraint is not eliminated, the first computer-design constraint is set equal to a dead-end state of the constraint. A structural preimage of the first computer-design constraint is created, in response to determining that a combination of a target and the dead-end state of the first computer-design constraint is equal to a combination of the target and the structural preimage of the first computer-design constraint, the first computer-design constraint is set equal to the structural preimage.

Owner:GLOBALFOUNDRIES INC

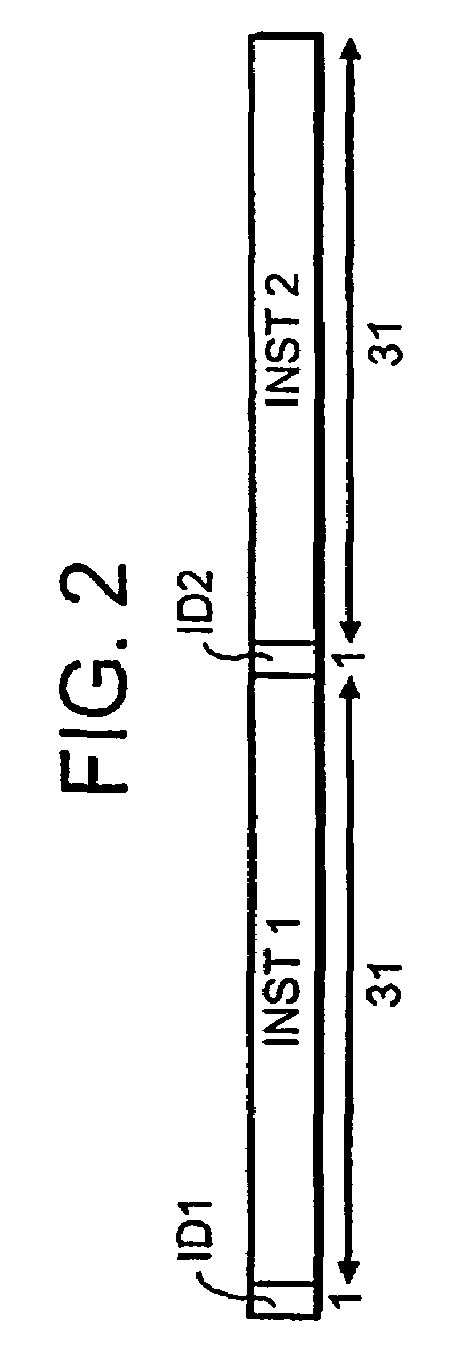

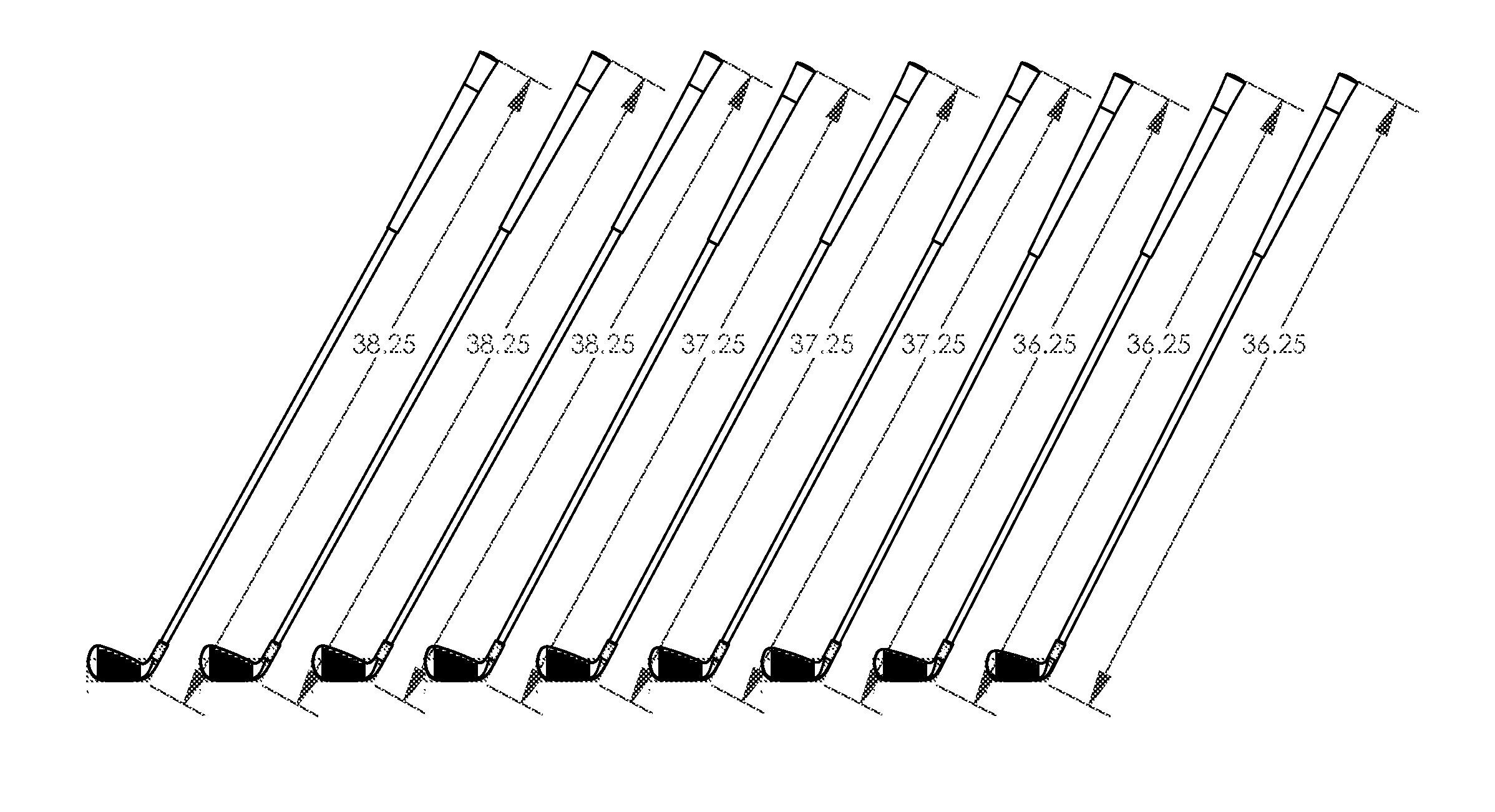

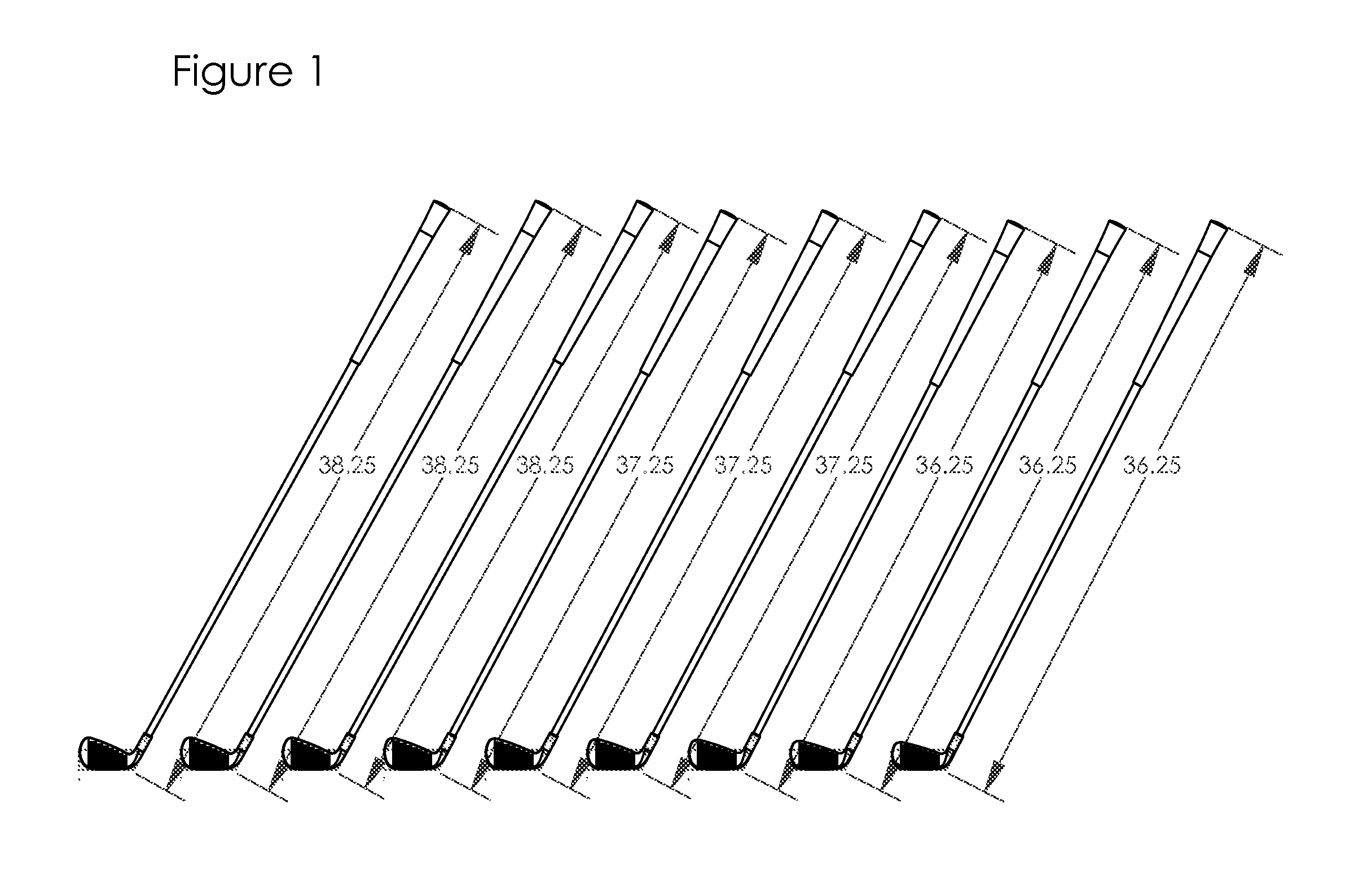

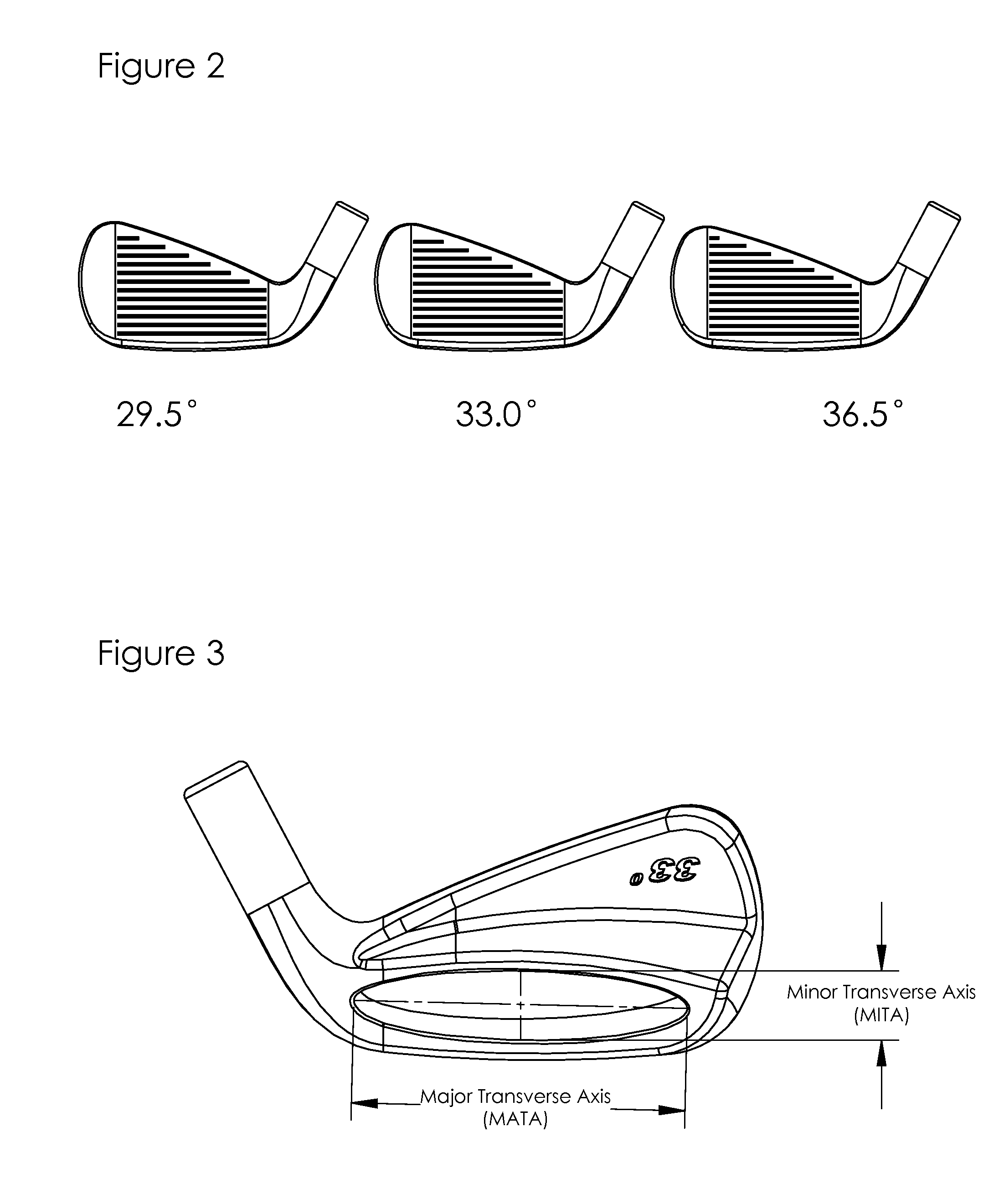

Balanced set of iron type golf clubs

Owner:LYTLE MICHAEL F

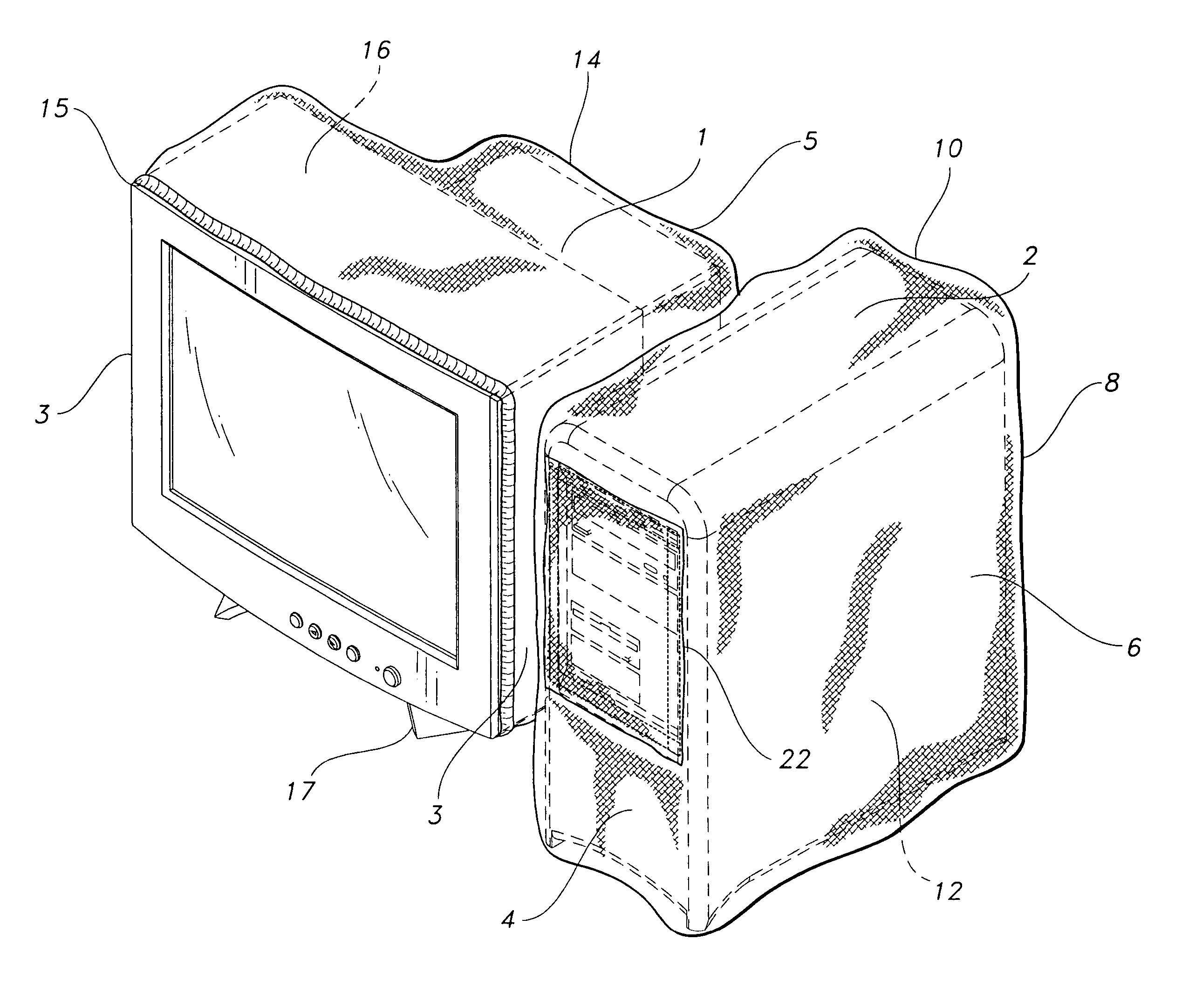

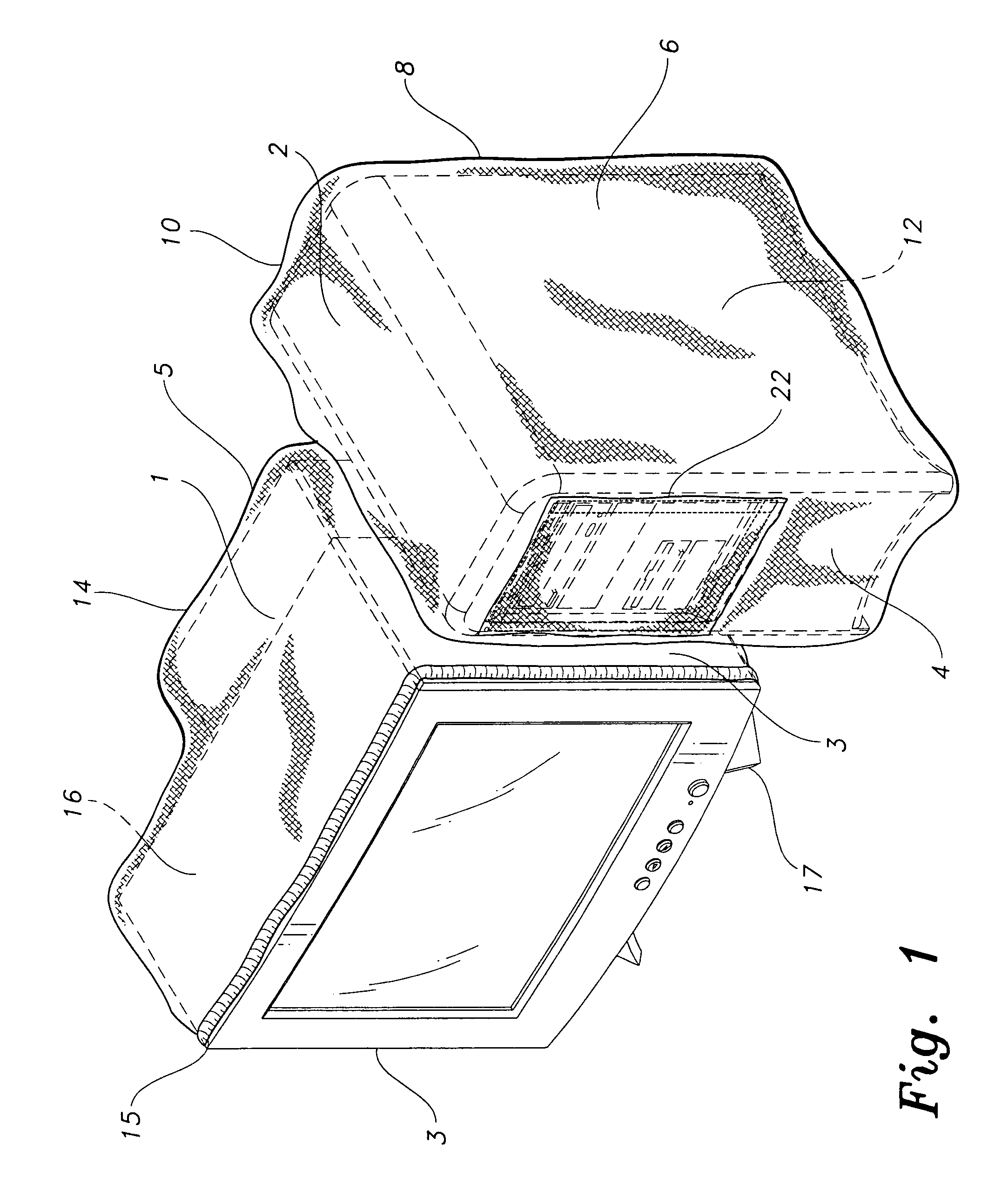

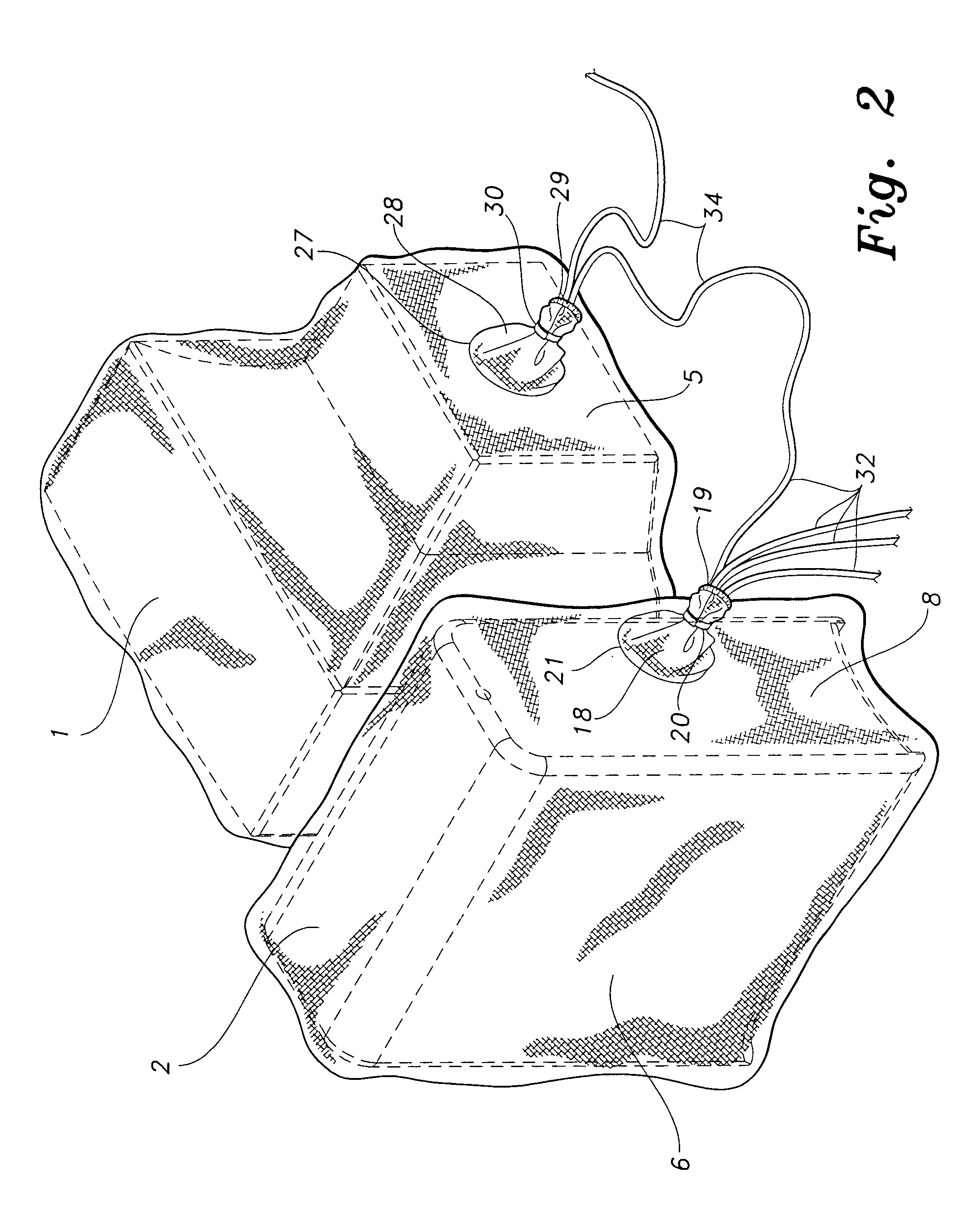

Computer cover

The computer cover is a specially constructed cover for computers adapted to cover the entire computer case or monitor, including the vents and fans. The cover is constructed using a durable polyester material containing a plurality of uniform micron openings. The material may be treated with a hydrophobic process. The resulting material is water repellant, yet filters out dust and debris without detrimentally hindering airflow. The computer cover has a sleeve for wire and port protection in the rear of the computer and a flap positioned to allow access to the computer disk drives. The sleeve has a strap for tightening the sleeve around the wires. The flap, when closed, completely seals and protects the disk drives.

Owner:TRAUGH RICHARD

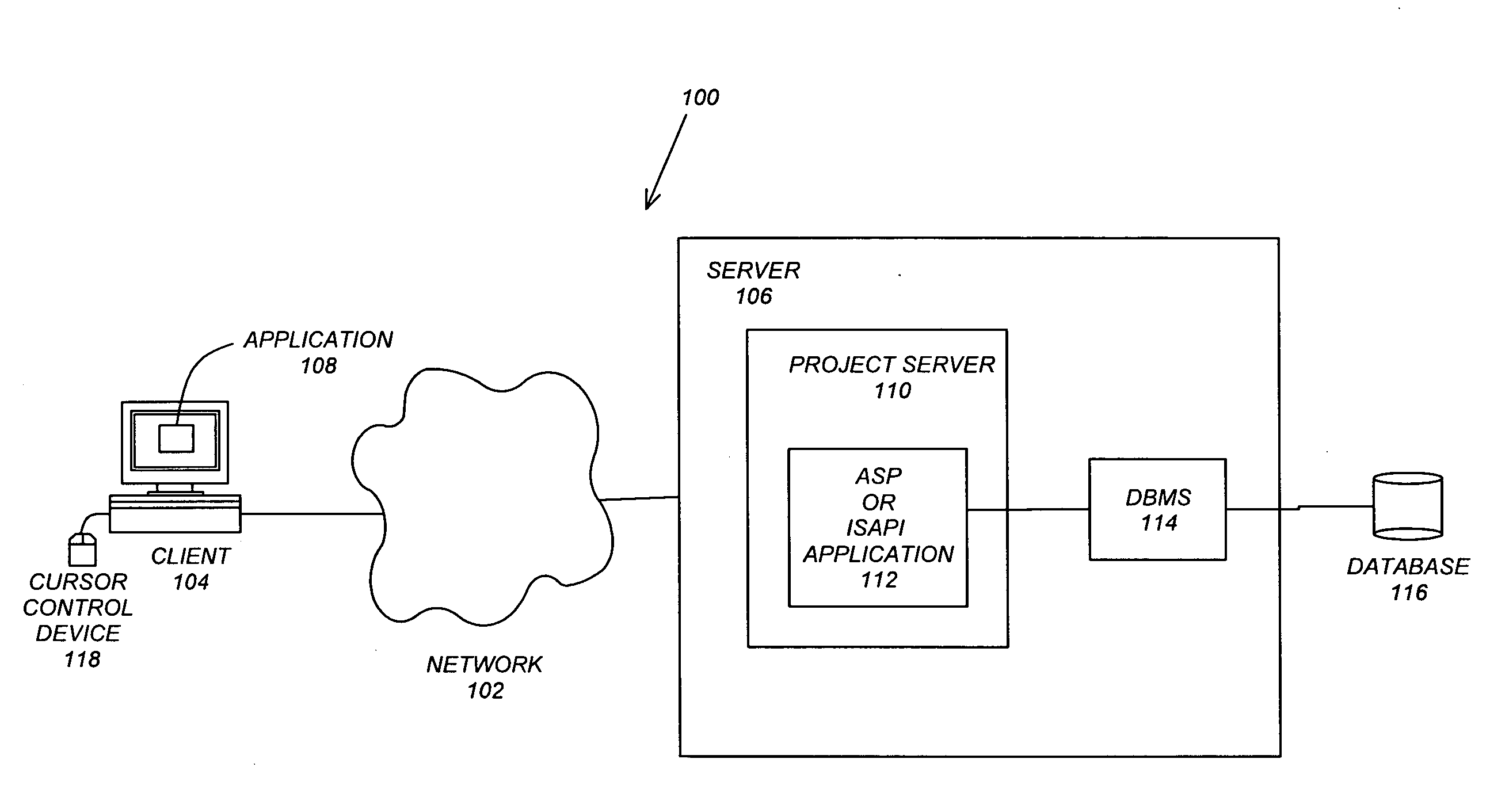

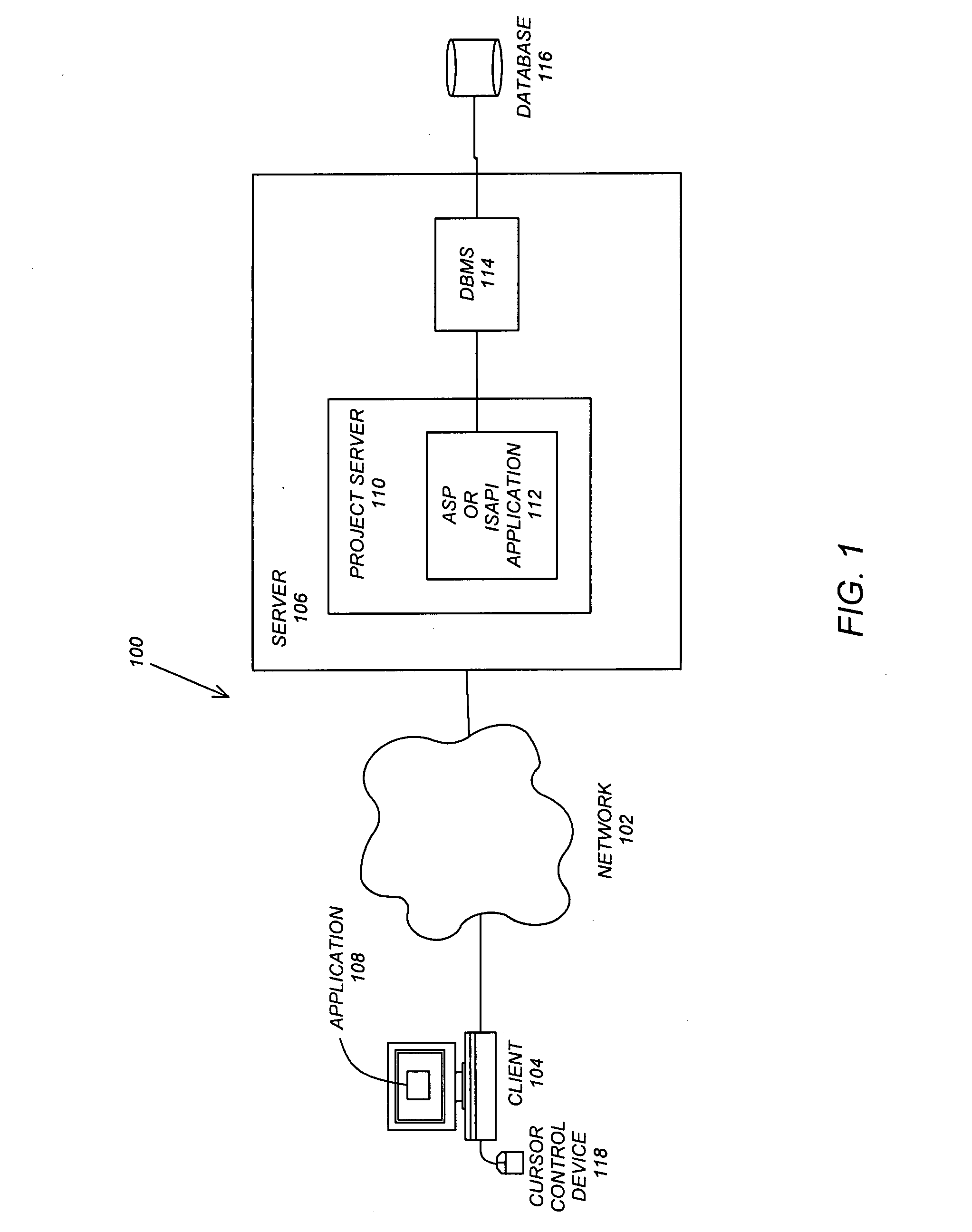

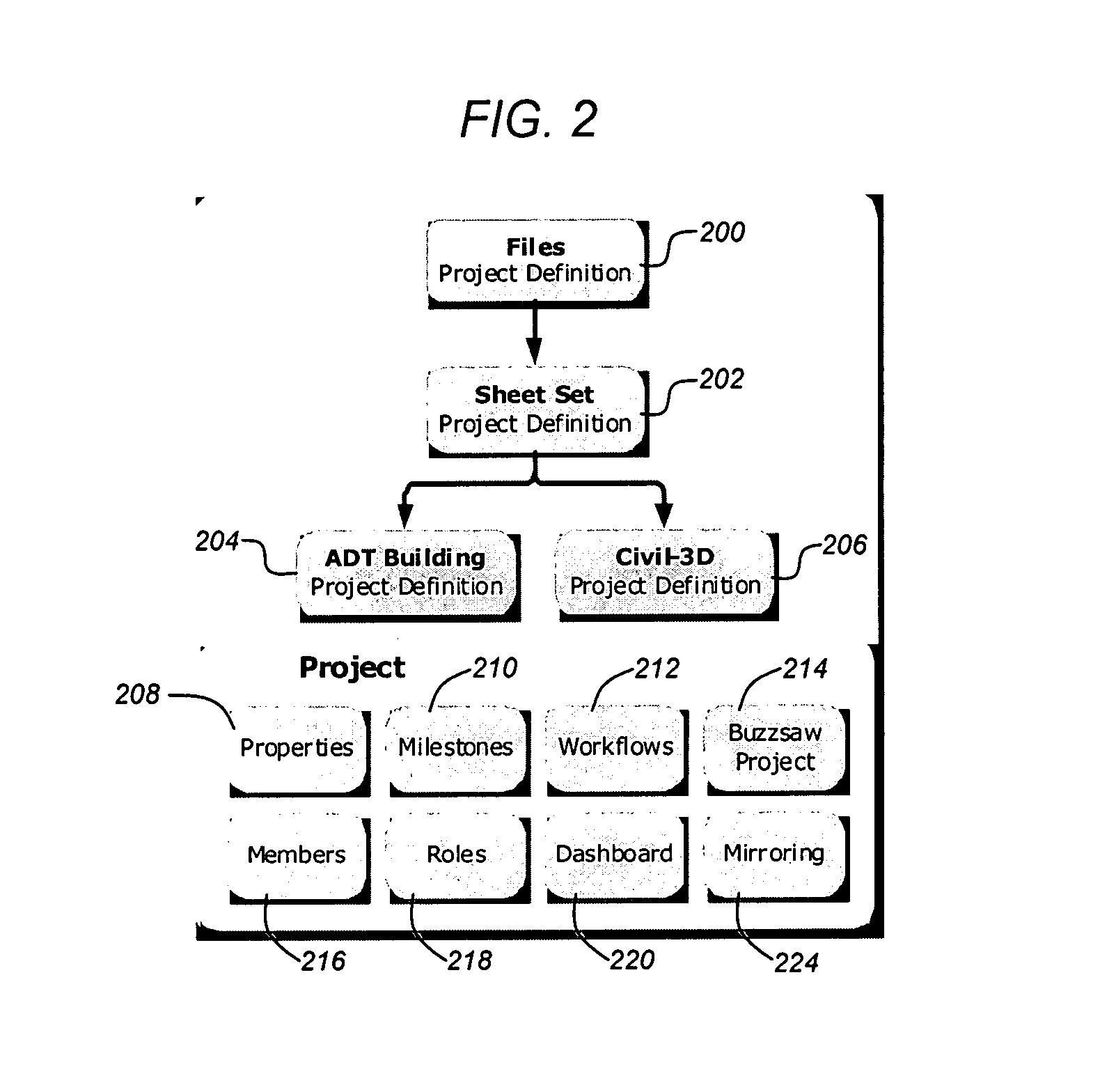

Amalgamation of data models across multiple applications

InactiveUS20080234987A1Digital computer detailsCAD network environmentSoftware engineeringApplication specific

A method, apparatus, and article of manufacture provide the ability to synchronize project data models across multiple computer applications. A first computer design application in a first client computer obtains files that provide a first application project definition specific to the first computer design application. A first application specific conversion application converts, on the first client computer, the first application project definition into a unified project definition that is utilized by a server application. The unified project definition is transmitted to the server application that stores the definition and synchronizes it with additional computer design applications.

Owner:AUTODESK INC

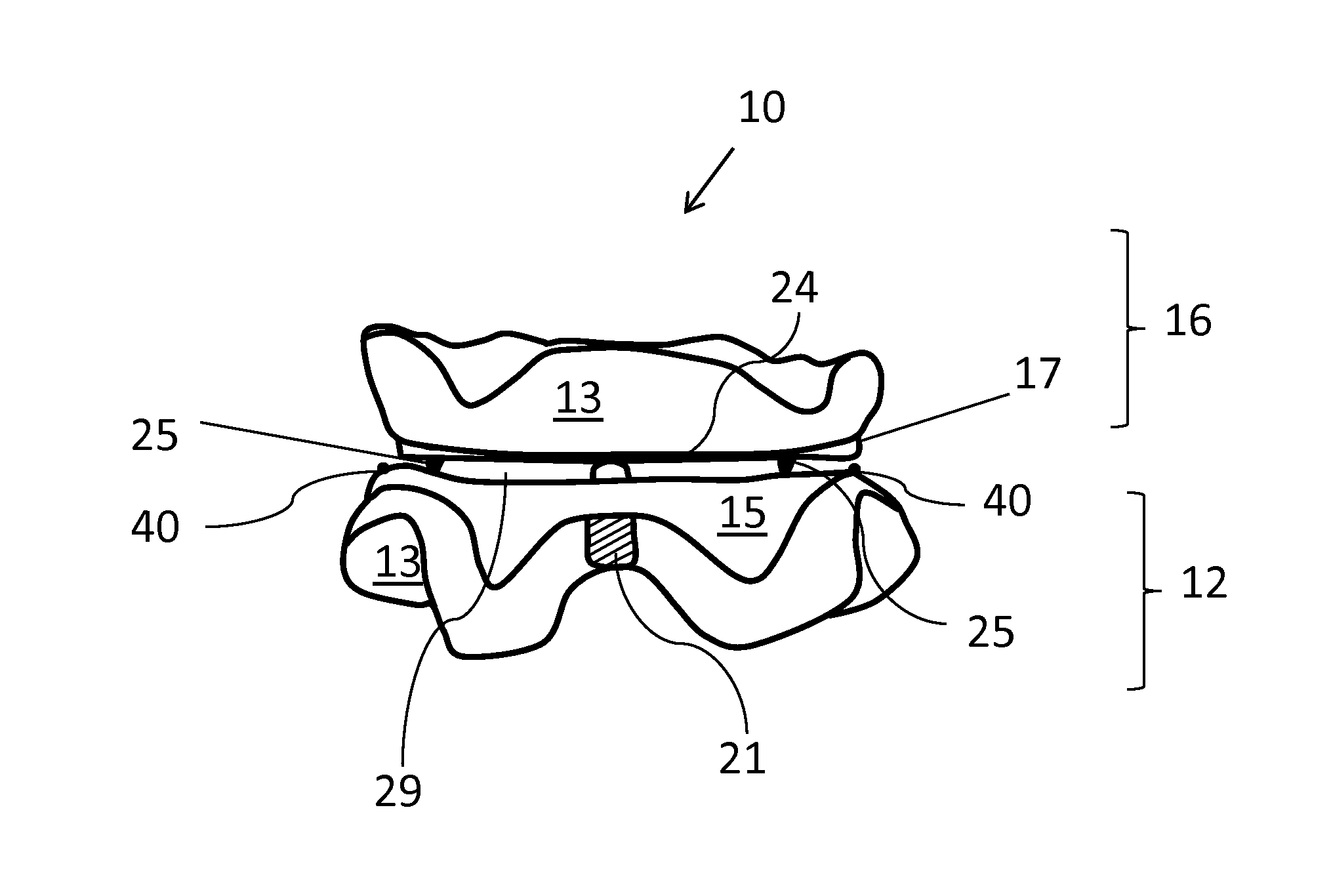

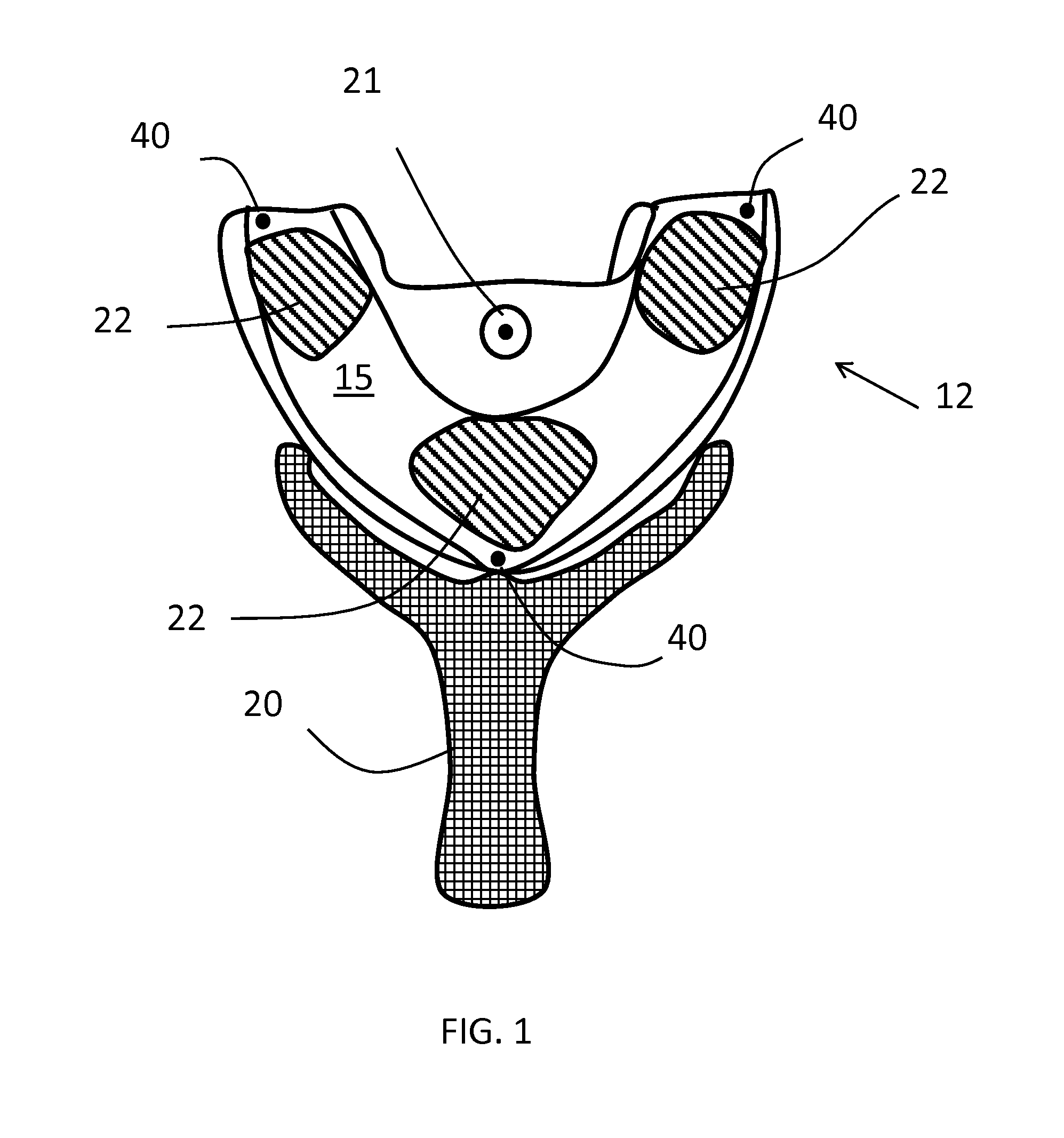

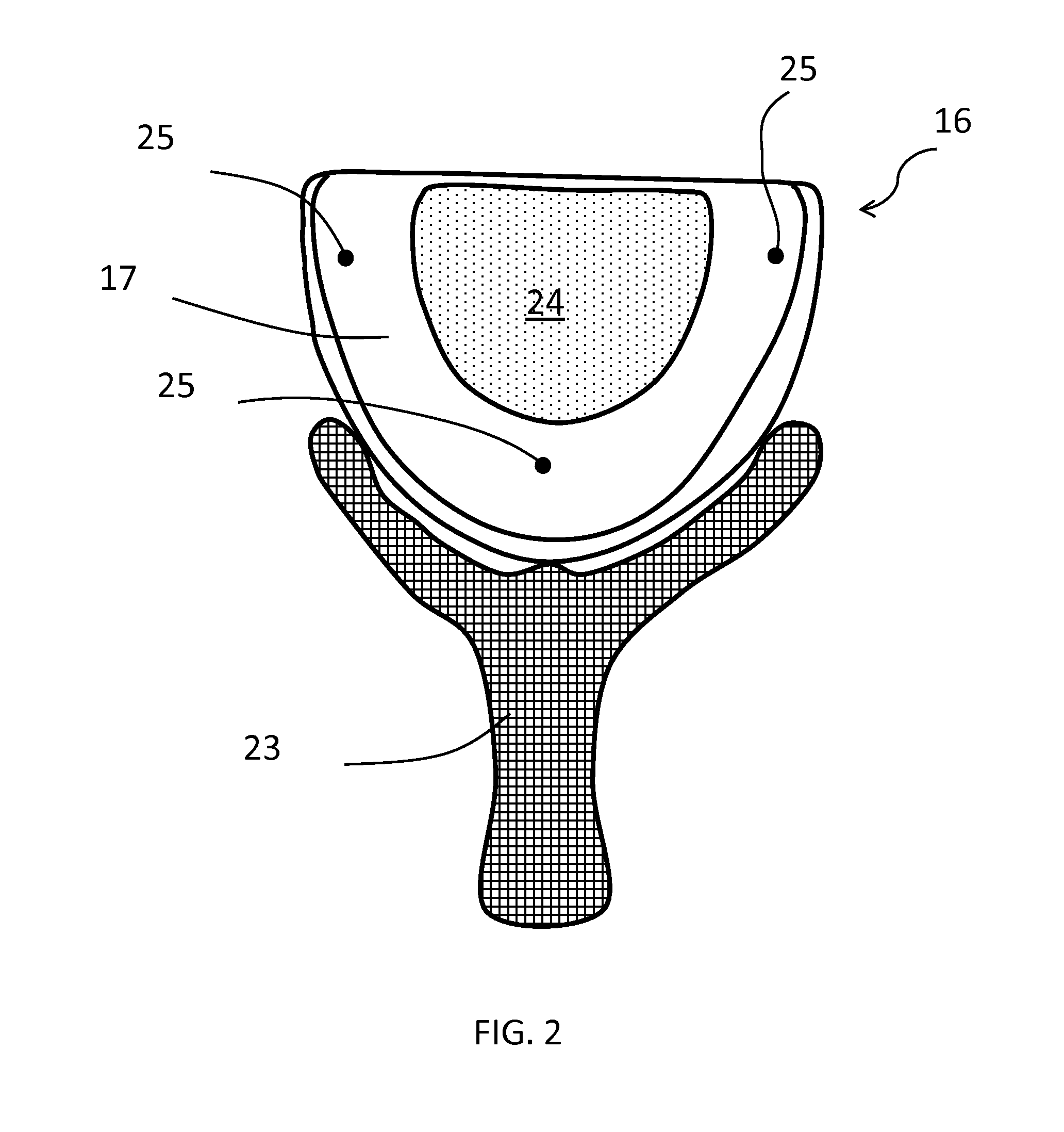

Intra Oral Dental Motion Recording Device and Method for the Digital Diagnosis, Computer Design and Manufacture of Dental Devices

An intra oral dental device and method for recording the 3D envelope of motion of a patient and translating the recording into digital information used to diagnose, computer design and manufacture dental restorations. The dental device is comprised of upper and lower tracing members having tracing pins on one member and complementary recording material on the other. The method includes forming a set of intra oral gothic arch tracings to define the 3D envelope of motion, converting the tracings to a digital data set reproducing the motion, and using the data to create a virtual model of the patient and the jaw motion. The data is used to mill articulator housings to reproduce jaw motion, to virtually position and shape virtual teeth in conformity with the patient's jaw motion, and to mill the completed dental prosthesis insuring teeth contacting surfaces are in harmony with the patient's jaw motion.

Owner:SCHMITT STEPHEN MICHAEL

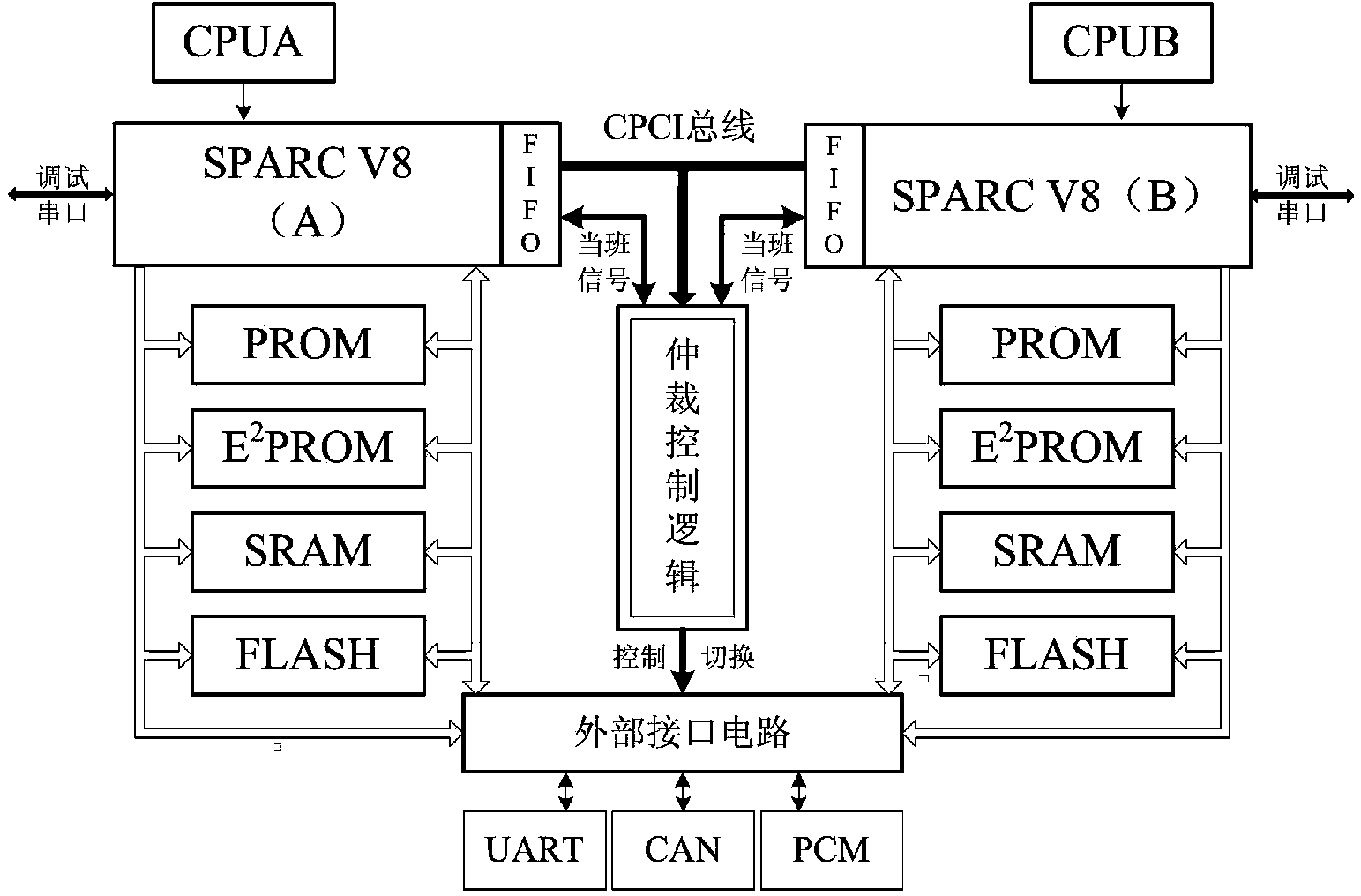

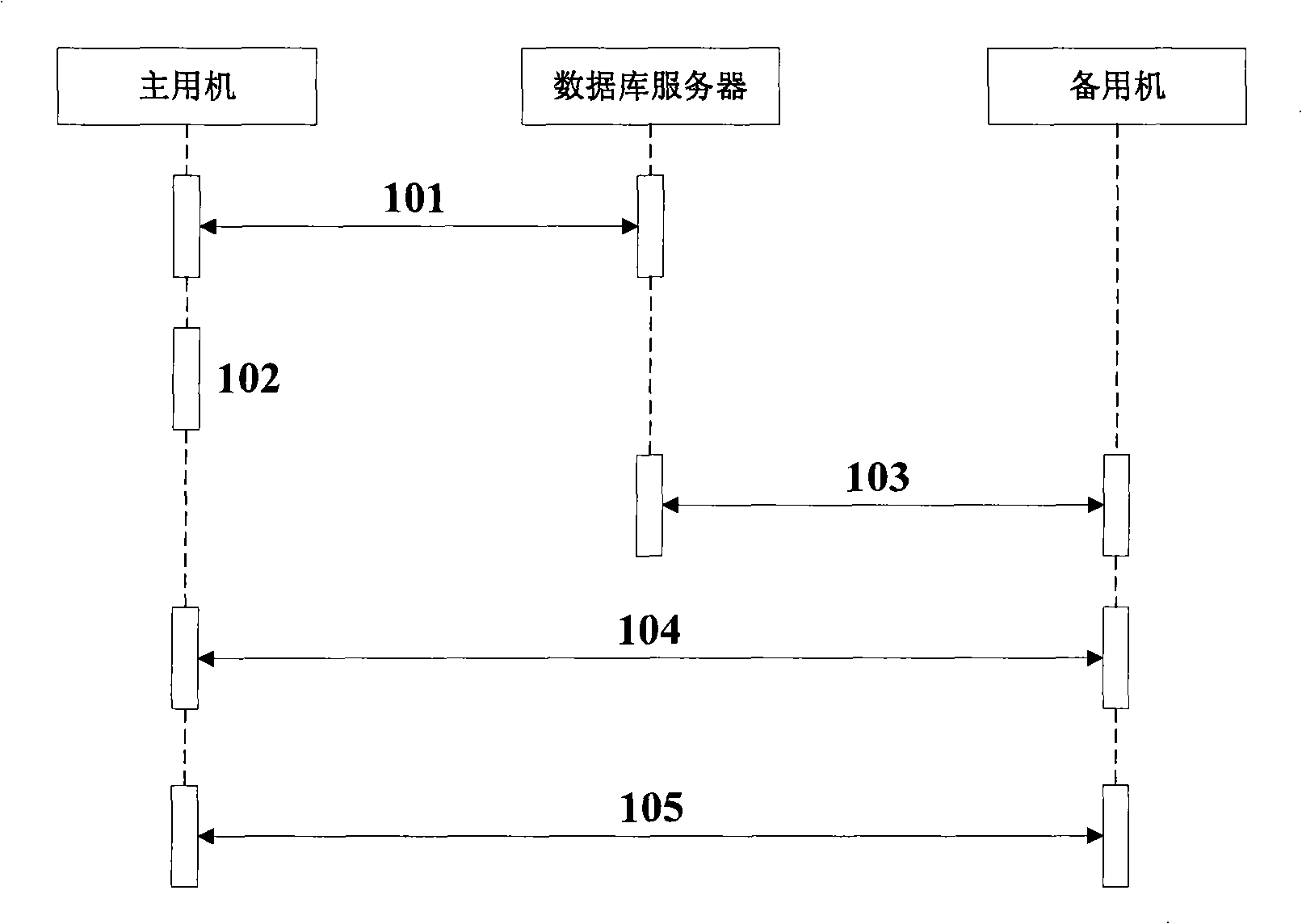

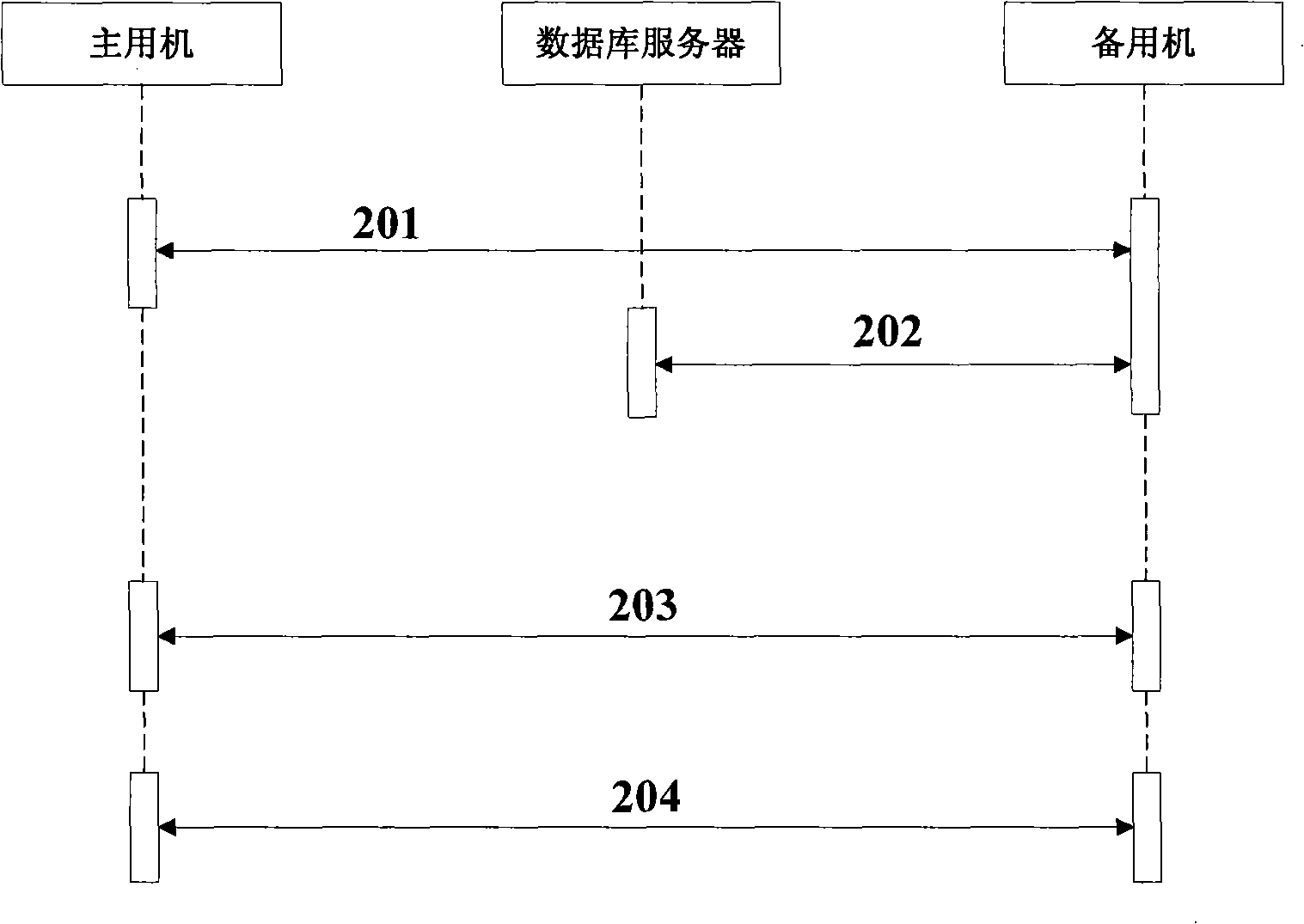

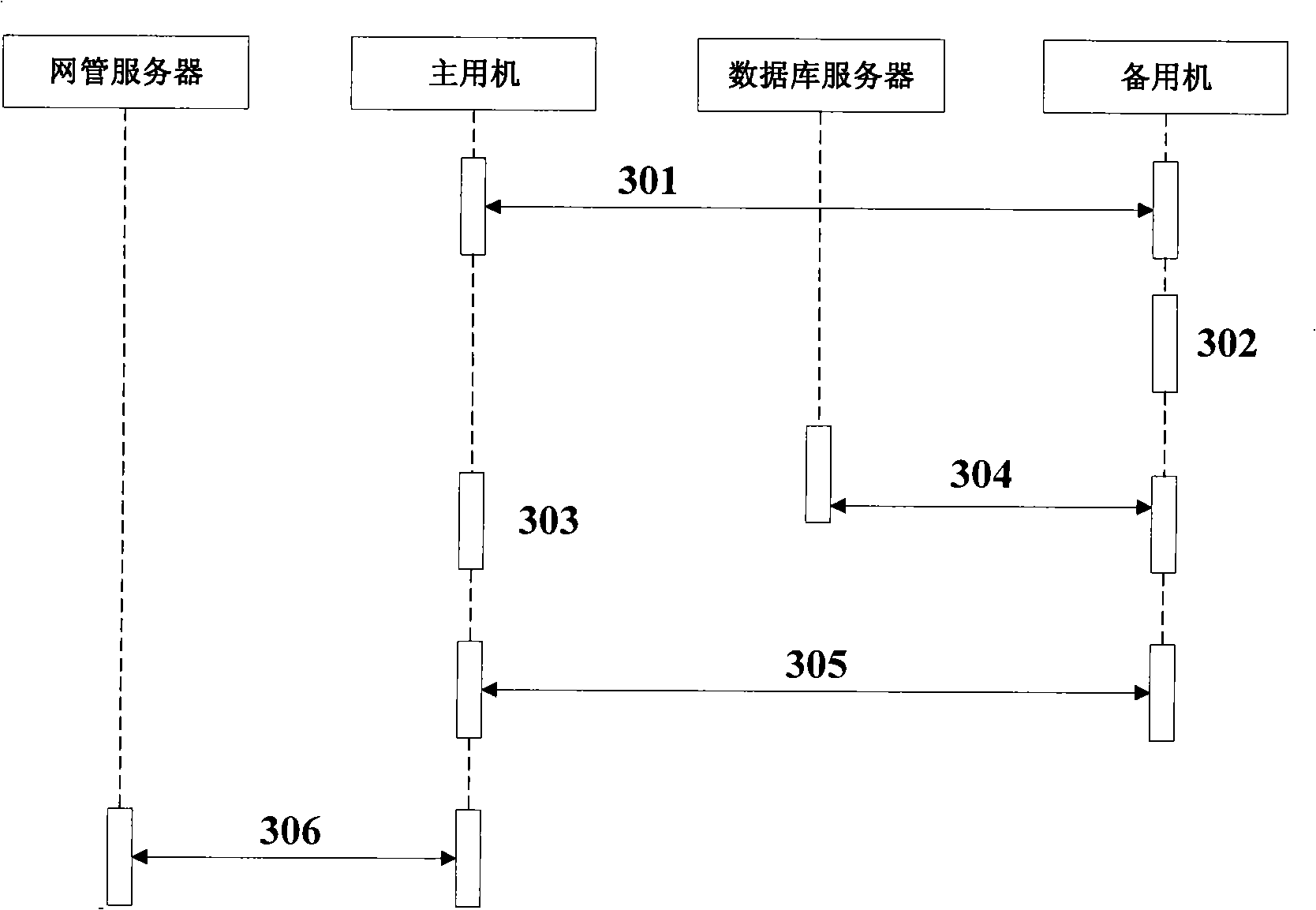

Double machine switching method and system

ActiveCN101340272AOvercoming the need for dual-machine data synchronizationOvercome consistencyError preventionData synchronizationComputer design

The invention discloses a dual-computer switching method and a system thereof, wherein, the method comprises the following steps: public data of a main computer and a standby computer is put in a share database; a database table is preset in the database; the database table has two records which represent running state of the main computer and the standby computer respectively; the records in thedatabase table are checked according to a preset cycle to confirm the running state of the two computers, and the two computers are automatically switched according to the running state recorded in the database table. The method and the system overcome the problem that the data is synchronous and inconsistency in traditional dual-computer design technology; and a hardware DOG card is not needed any more, thus saving investment.

Owner:ZTE CORP

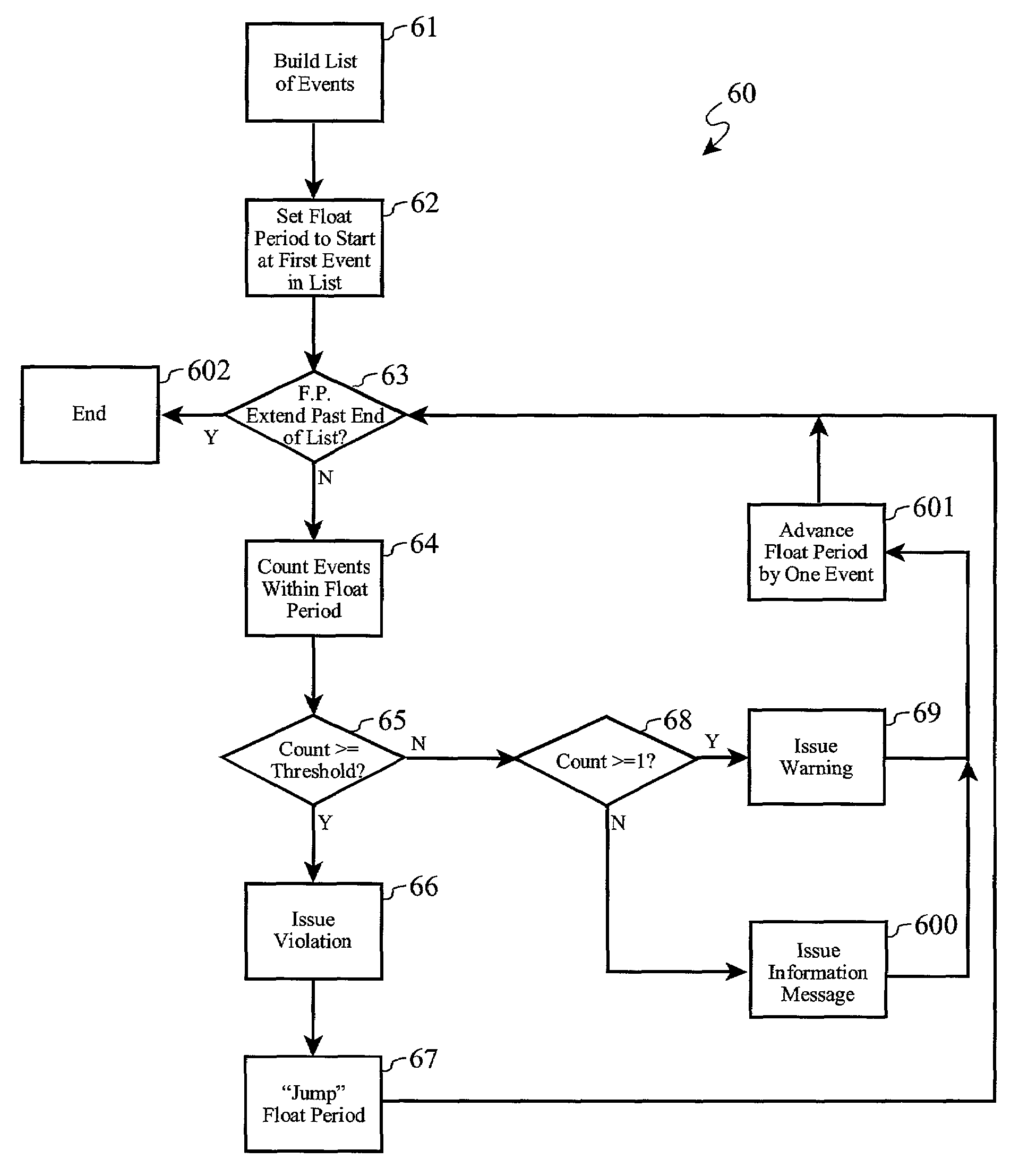

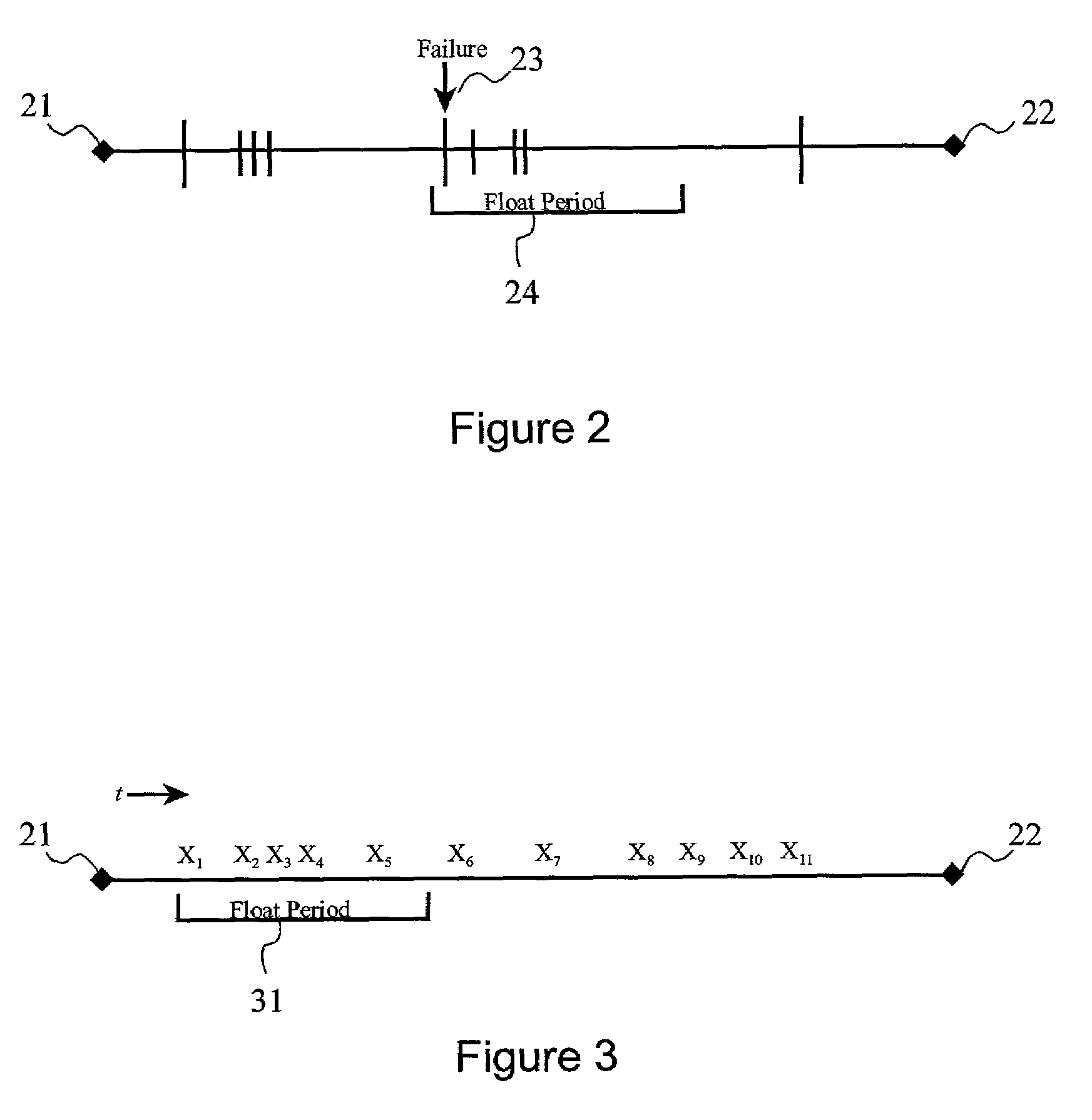

Host-based systematic attack detection tool

ActiveUS6993790B2Attack is still possibleMemory loss protectionDigital data processing detailsComputer designTime frame

A vulnerability checking tool for a host computer designed to examine security logs of attempted logins and revocations, to detect systematic attacks of a wide variety, and to generate a report file that can be examined for information concerning these types of events. Host computer files which contain data regarding attempted accesses and logins are used to create an event list based upon event criteria. The list is evaluated using a “floating period” time frame which advances by single event steps while no violation is detected within a particular floating period, and which advances by “jumps” when violations are detected in a time period so as to reduce the possibility of “over reporting” violations related to the same set of events.

Owner:TREND MICRO INC

Method and system for performing heuristic constraint simplification

InactiveUS20070067746A1Computer aided designSoftware simulation/interpretation/emulationTheoretical computer scienceComputer design

A method for performing verification is disclosed. The method includes selecting a first computer-design constraint for simplification and applying structural reparamaterization to simplify the first computer-design constraint. In response to determining that the first computer-design constraint is not eliminated, the first computer-design constraint is set equal to a dead-end state of the constraint. A structural preimage of the first computer-design constraint is created, in response to determining that a combination of a target and the dead-end state of the first computer-design constraint is equal to a combination of the target and the structural preimage of the first computer-design constraint, the first computer-design constraint is set equal to the structural preimage.

Owner:GLOBALFOUNDRIES INC

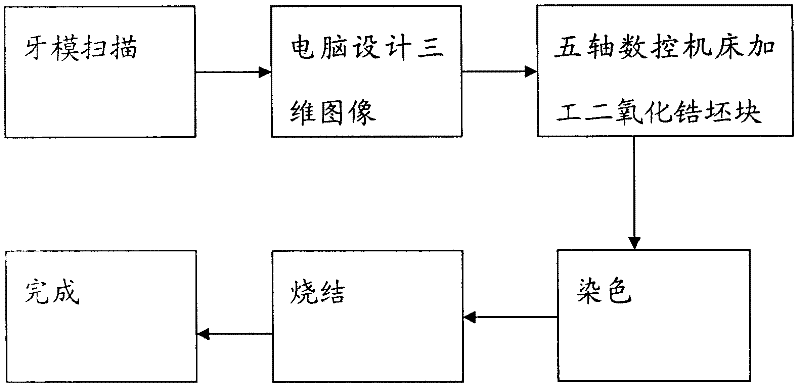

Preparation method of zirconium dioxide false tooth

InactiveCN102579147AImproving the cosmetic restoration of teethQuality improvementDental prostheticsNumerical controlDentures

The invention relates to the field of false teeth and in particular relates to a preparation method of a zirconium dioxide false tooth. The preparation method comprises the following steps: scanning a tooth model via a three-dimensional scanner, transmitting data to a computer, designing through the computer, further transmitting the well designed data to a five-axis numerical control machine tool, completing tooth processing treatment through the five-axis numerical control machine tool, taking out a product, then performing dyeing, and further placing into a sintering furnace for sintering. Compared with the prior art, according to the preparation method disclosed by the invention, a manual false tooth manufacturing process is fundamentally changed, and traditional waxing, casting, porcelain coating and porcelain turning are replaced by computer design and digital processing; and the process steps are simplified, the digital processing precision is improved, a zirconium dioxide all porcelain crown which can not completed by the manual process can be realized, and the tooth esthetical restoration means of a clinician and the quality of the false tooth can be improved.

Owner:深圳市金悠然科技有限公司

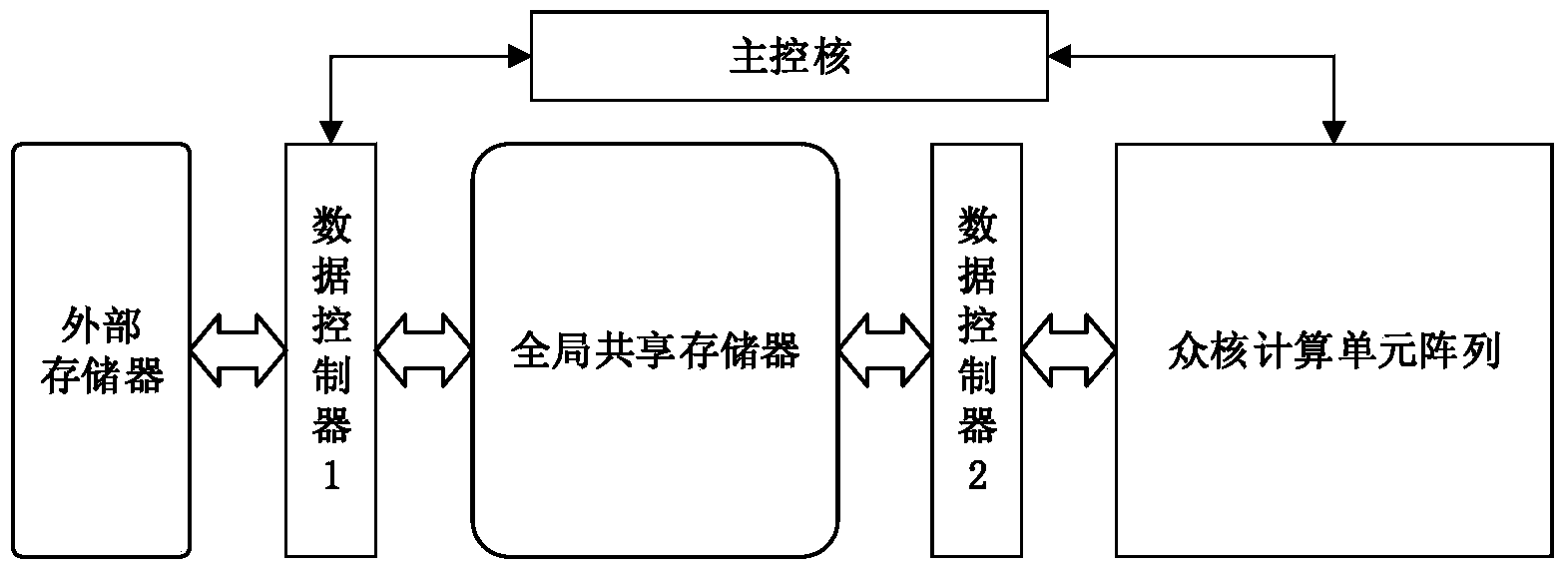

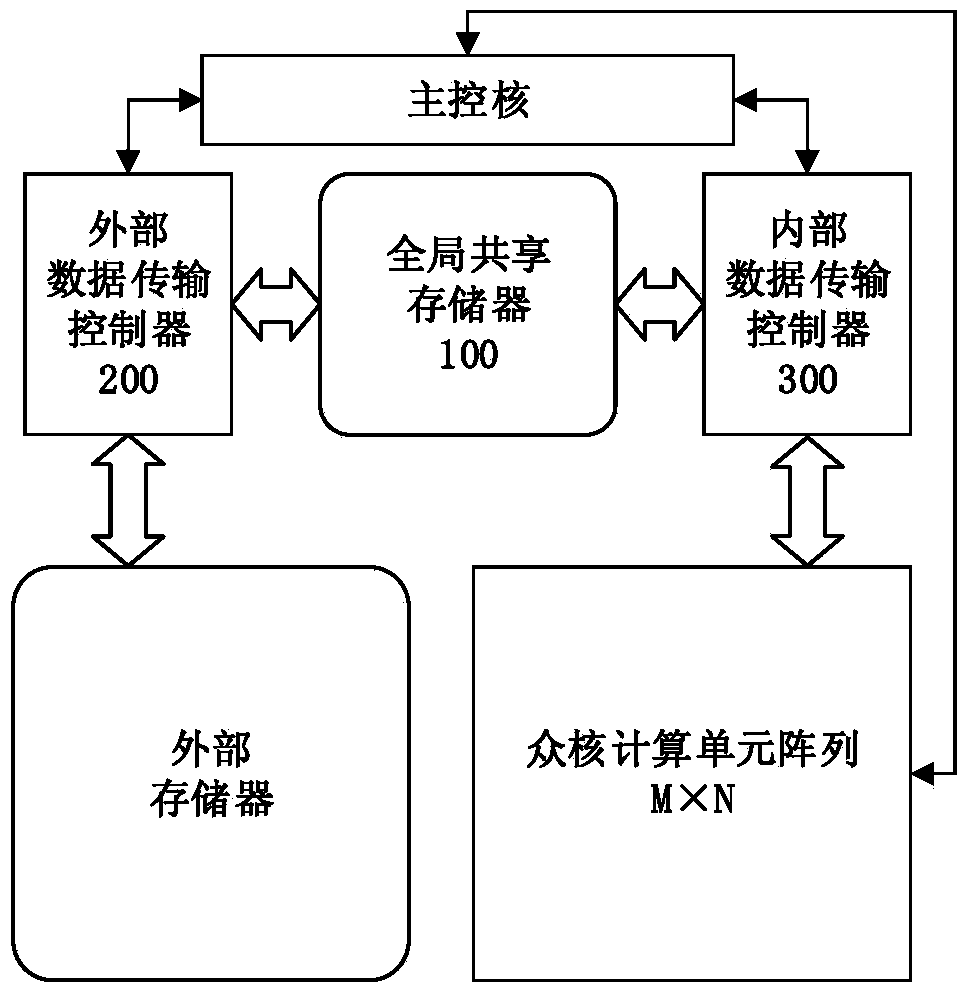

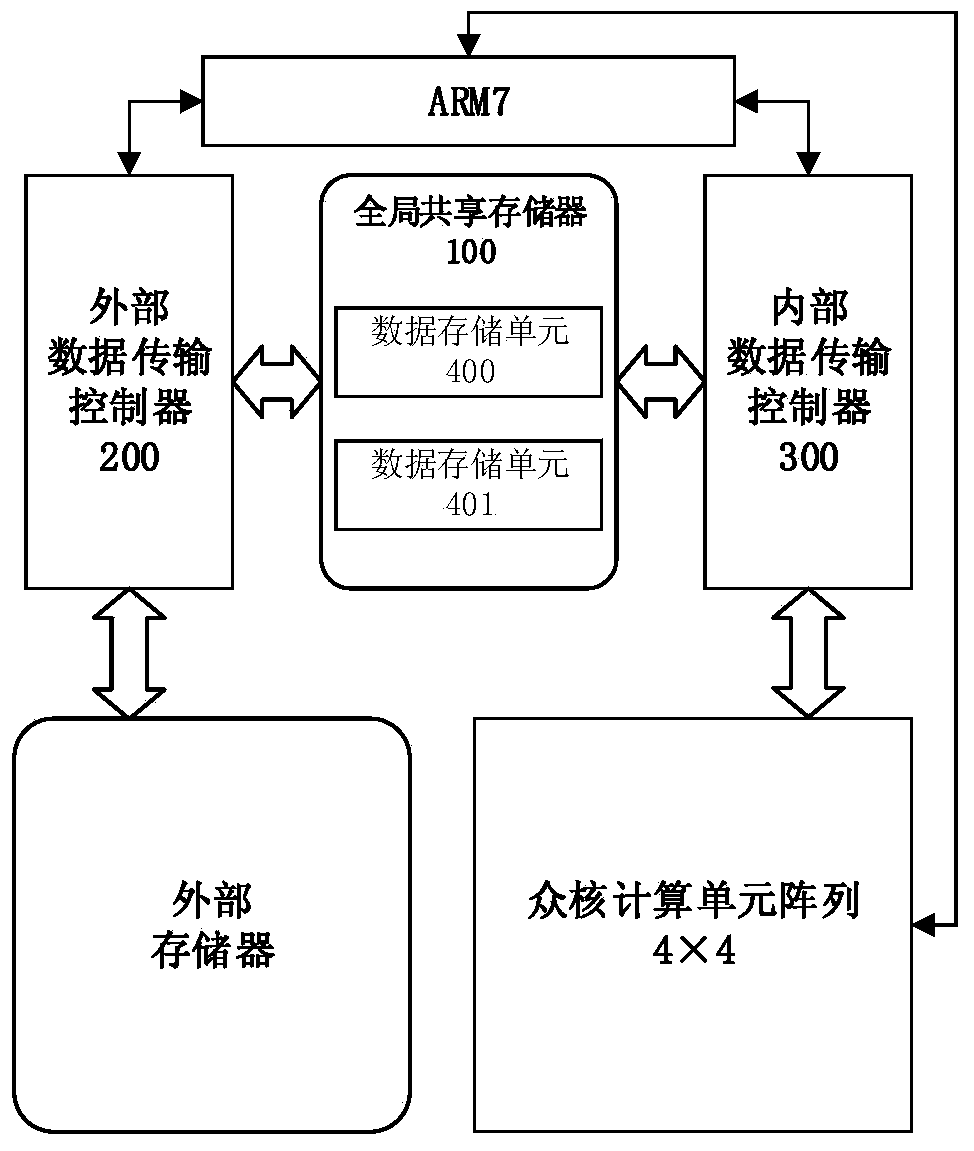

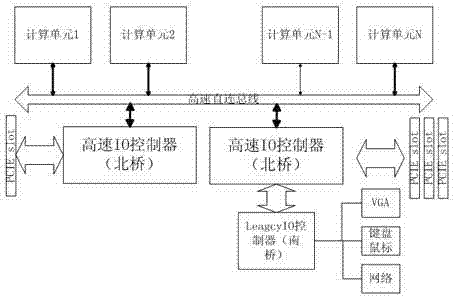

Data storage structure and data access method for multiple core processing system

ActiveCN104317770AImprove data storage efficiencyImprove transmission efficiencyDigital computer detailsElectric digital data processingAccess methodExternal data

The invention relates to the technical field of computers, aims to solve the problem that according to a multiple core processor, the data storage delay is large, the transmitting efficiency is low, and the multiple core calculating unit array parallel calculating efficiency cannot be improved continuously and provides a data storage structure for the multiple core processing system and a data access method for the data storage structure of the multiple core processor. The accessing and storing costs of the multiple core processing system can be reduced, and the accessing and storing efficiency is improved, and the parallel calculating efficiency of the multiple core processor can be improved. Thus, according to the technical scheme, the data storage structure for the multiple core processing system comprises a global shared memory, a foreign data transmission controller and an internal data transmission controller. The data storage structure and the data access method for the multiple core processing system are mainly applied to computer design and manufacture.

Owner:TIANJIN SAIXIANG TECH

System and method for mapping block-based file operations to file level protocols

ActiveUS7584279B1Multiple digital computer combinationsTransmissionOperational systemApplication software

A system and method for mapping block-based file operations to file-level protocols is provided. The system and method enable applications on a networked computer designed to exclusively access only locally-attached storage to also access networked data storage. The mapping occurs transparently to higher levels of operating systems or applications so that applications which are designed to only access locally-attached storage may be enabled to access networked storage.

Owner:NETWORK APPLIANCE INC

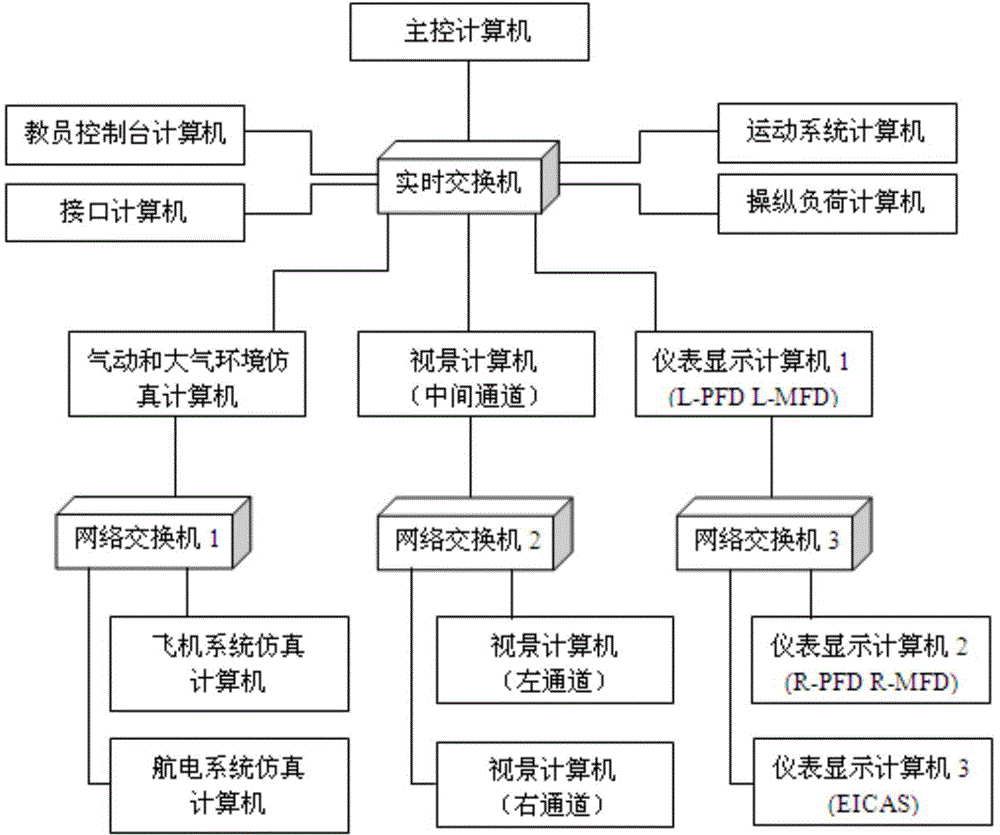

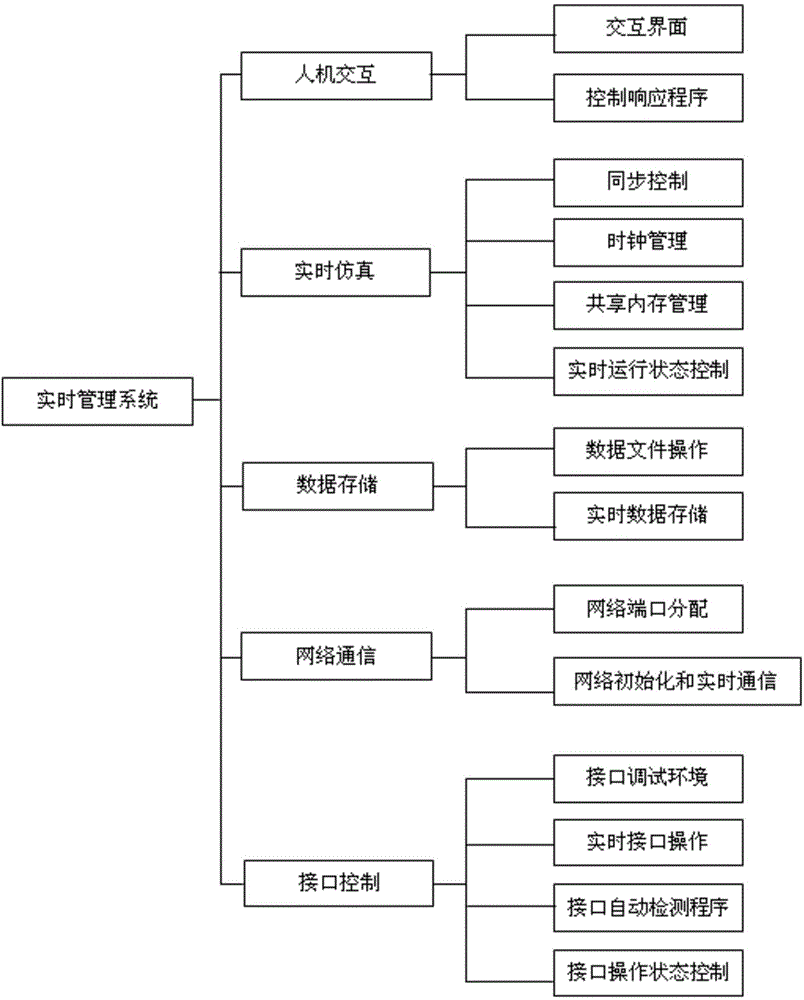

Parallel computation and distribution control method for flight simulation system

InactiveCN104599547AImprove operational efficiencyReduce the impactCosmonautic condition simulationsData processing applicationsComputer designVisual system

The invention discloses a parallel computation and distribution control method for a flight simulation system. The flight simulation system comprises a main control node, a simulation computation node, an instrument display node, an instructor console node, a visual system node, a motion system node, an operation loading system node and an interface node; by means of reflective memory real-time network accessing, the simulation computation node, the instrument display node and the visual system node form a two-level network through a gigabit Ethernet; by means of parallel computation, the computations of the simulation system, instructor console system, multi-channel visual system, operation loading system and motion system are implemented, computers executing different tasks are scheduled comprehensively through the distribution control technology, and the uniformed scheduling of the systems are implemented through synchronous clock computation and data information sharing. The entire computer cost is reduced, the entire computer design risks are reduced, and an important role is played for improving the scalability and fault processing capability of the system.

Owner:冯岩

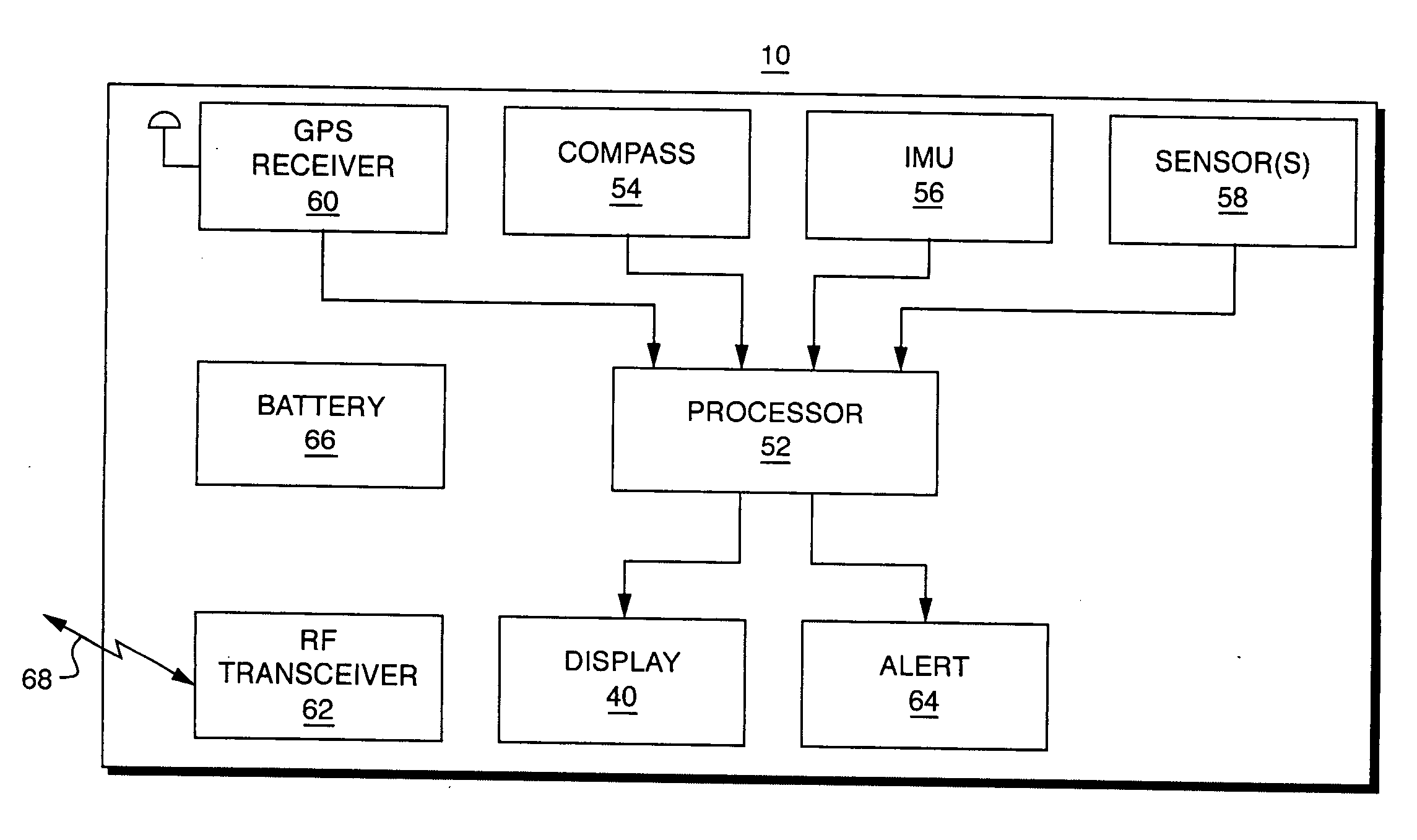

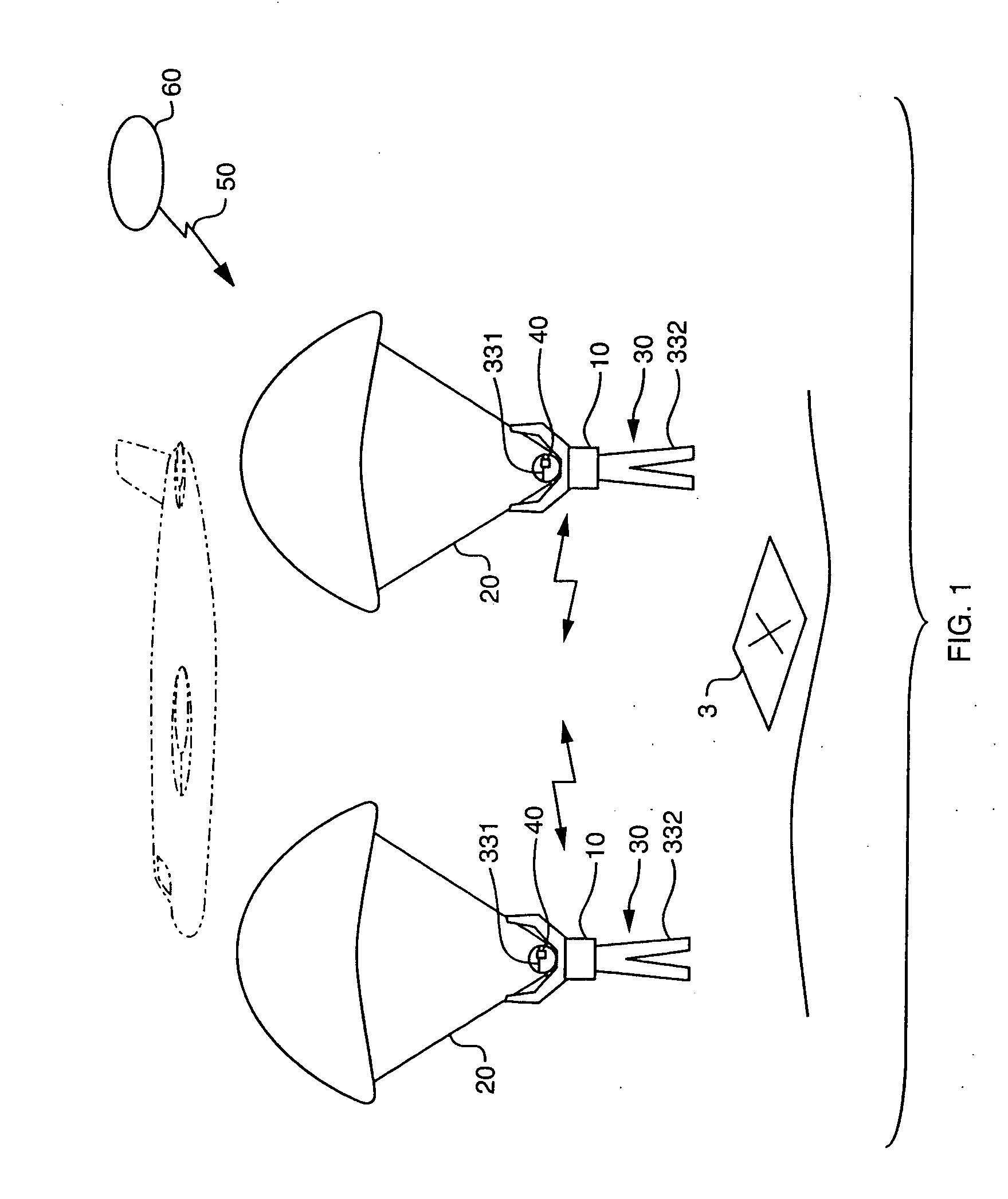

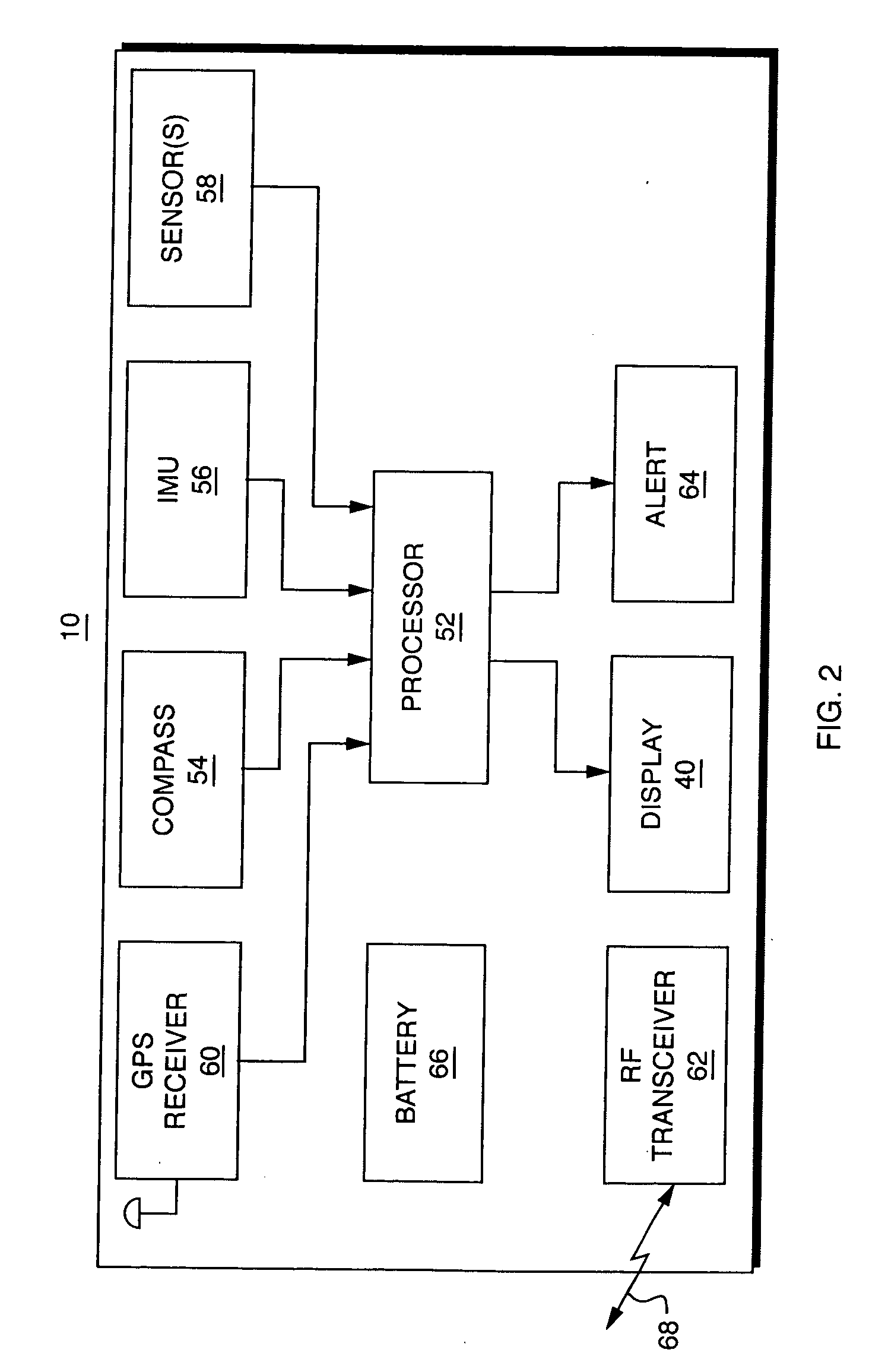

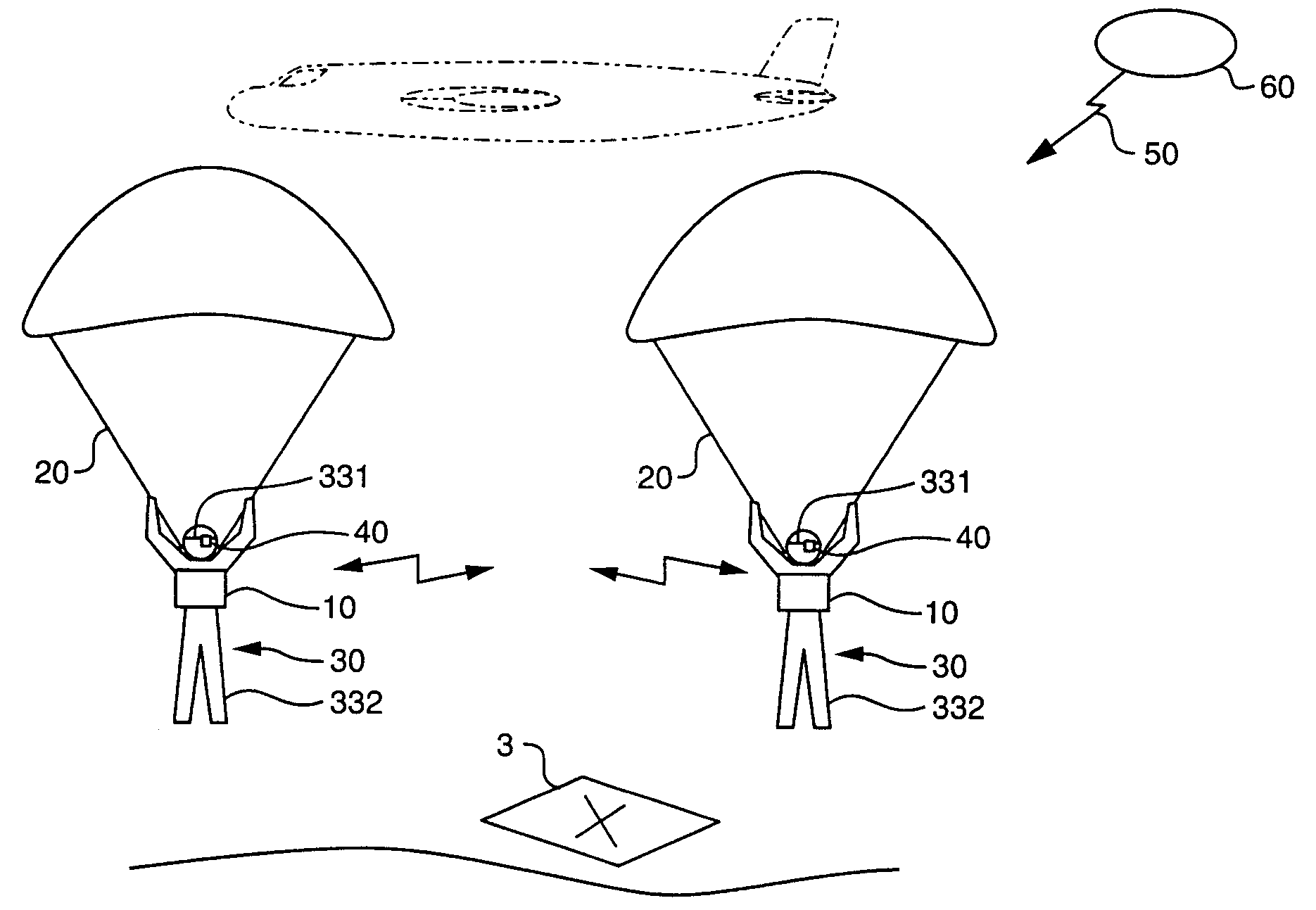

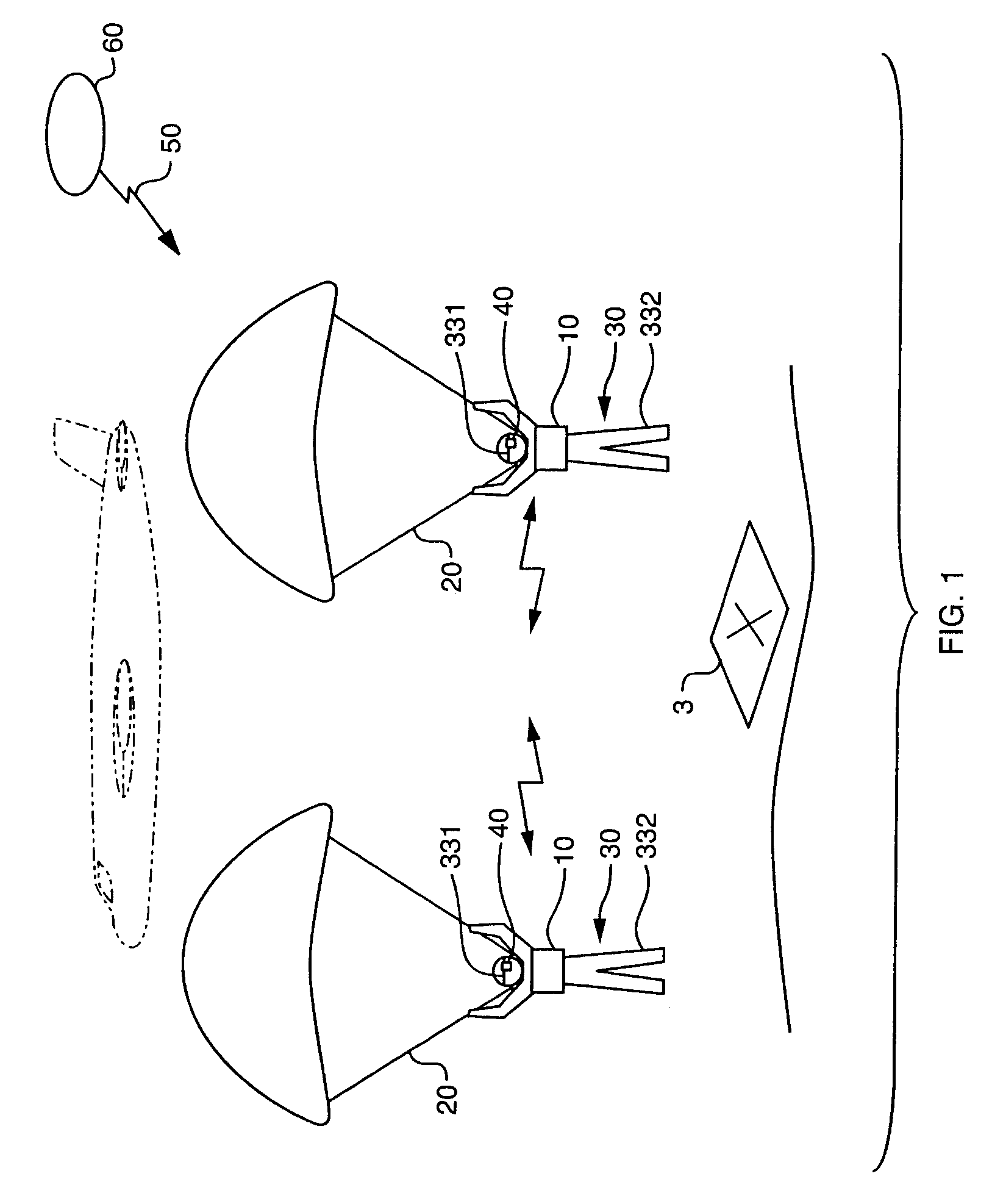

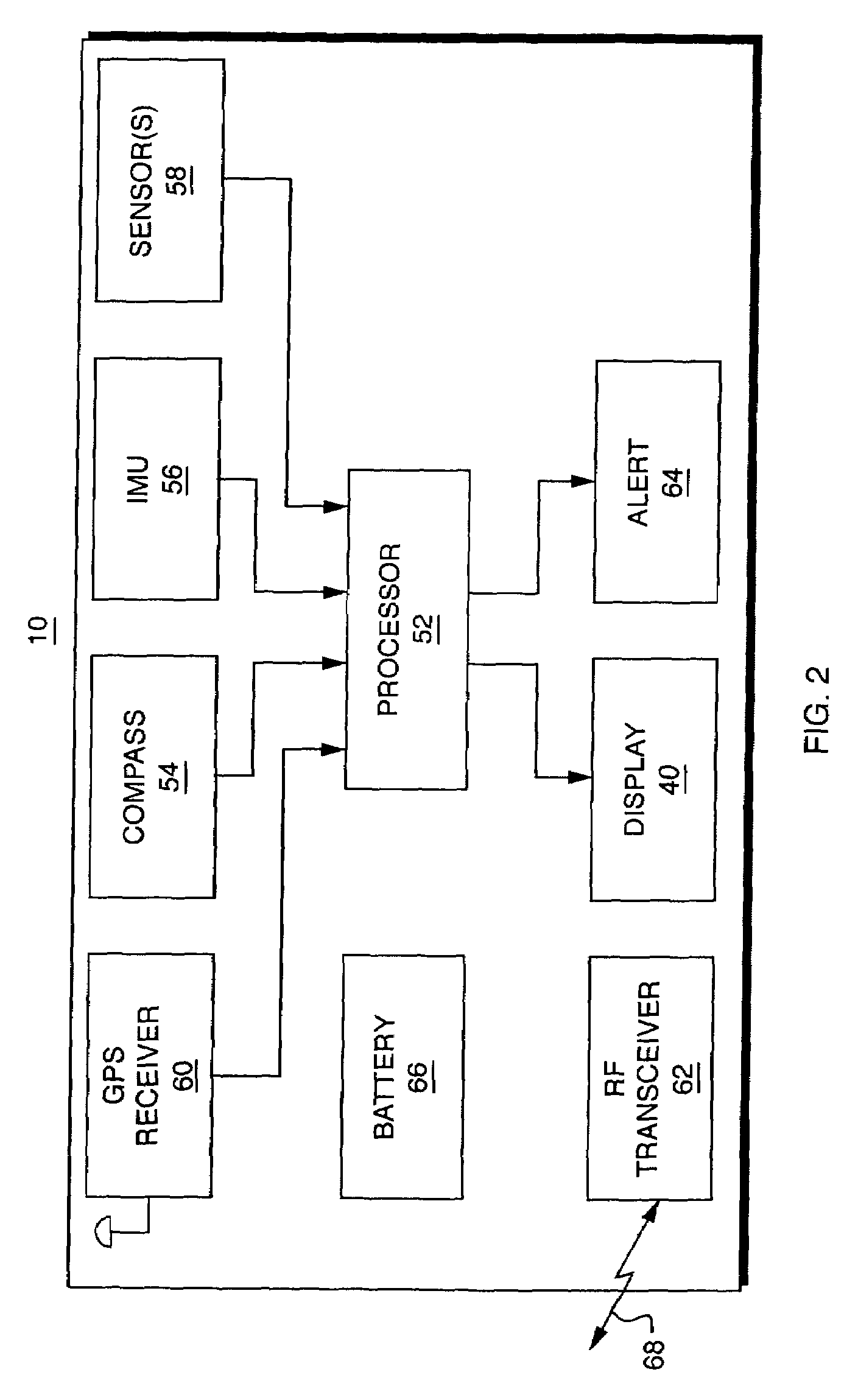

High altitude parachute navigation flight computer

InactiveUS20070233382A1Navigational calculation instrumentsDigital data processing detailsFlight computerComputer design

A navigational computer design for high altitude and other similar navigational needs includes a processor, which receives as input signals from navigational and navigational related sensors such as a GPS, compass, inertial measurement unit and sensors. Processor utilizes the navigational information to provide a display to the user indicating present navigational positional information as well is providing a flight path to follow to the target. The navigational computer includes a device that enables it to operate in a peer-to-peer network with other similar navigational computers such that during use, users may track one another. Once on the ground, the navigational computer may be used to continue navigation.

Owner:ATAIR AEROSPACE

Microprocessor with integrated high speed memory

InactiveUS20110040939A1Data managementQuick managementMemory adressing/allocation/relocationConcurrent instruction executionComputer architectureHigh speed memory

The present invention relates to the field of (micro)computer design and architecture, and in particular to microarchitecture associated with moving data values between a (micro)processor and memory components. Particularly, the present invention relates to a computer system with an processor architecture in which register addresses are generated with more than one execution channel controlled by one central processing unit with at least one load / store unit for loading and storing data objects, and at least one cache memory associated to the processor holding data objects accessed by the processor, wherein said processor's load / store unit contains a high speed memory directly interfacing said load / store unit to the cache. The present invention improves the of architectures with dual ported microprocessor implementations comprising two execution pipelines capable of two load / store data transactions per cycle. By including a cache memory inside the load / store unit, the processor is directly interfaced from its load / store units to the caches. Thus, the present invention accelerates data accesses and transactions from and to the load / store units of the processor and the data cache memory.

Owner:AVAGO TECH INT SALES PTE LTD

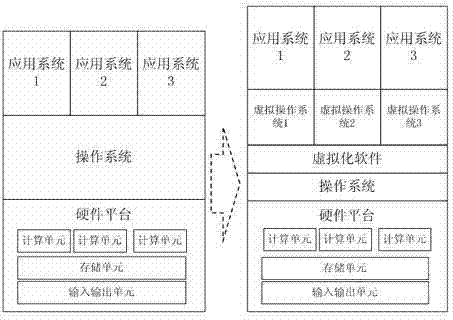

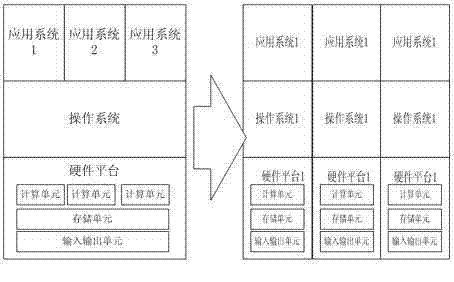

Parallel multiprocessor computer design method

ActiveCN102521209ARealize Physical SegmentationAchieve couplingArchitecture with multiple processing unitsCouplingParallel computing

The invention provides a parallel multiprocessor computer design method. The design method comprises the step of partitioning a plurality of processors and IO resources of a computer system on the physical layer to partition one multiprocessor computer system into a plurality of independent multiprocessor systems, wherein the partitioned computer systems can be coupled to one integrated computer system. Therefore, the method can fully partition and allocate computation resources, storage resources and IO resources of the computer according to traffic loads and traffic types, thereby achieving optimized configuration of the system resources. By providing a set of partition control logic and corresponding hardware circuit support, the method can also achieve physical partitioning or coupling of a NUMA (non-uniform memory access) multiprocessor computer system, like a plurality of computer systems completely independent from each other.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

High altitude parachute navigation flight computer

InactiveUS7302340B2Navigational calculation instrumentsDigital data processing detailsFlight computerComputer design

A navigational computer design for high altitude and other similar navigational needs includes a processor, which receives as input signals from navigational and navigational related sensors such as a GPS, compass, inertial measurement unit and sensors. Processor utilizes the navigational information to provide a display to the user indicating present navigational positional information as well is providing a flight path to follow to the target. The navigational computer includes a device that enables it to operate in a peer-to-peer network with other similar navigational computers such that during use, users may track one another. Once on the ground, the navigational computer may be used to continue navigation.

Owner:ATAIR AEROSPACE

Package type heat exchanger computer design method

InactiveCN1588379AImprove reusabilityHigh degree of visualizationSpecial data processing applicationsComputer Aided DesignShell and tube heat exchanger

The present invention is the computer-aided design method of shell-and-tube heat exchanger, and belongs to the field of cooling and air conditioning technology and computer-aided design technology. The computer-aided design process includes first establishing water pump data base; subsequent establishing of physical property parameter calculation module, heat exchanger design calculation module and I / One module; compiling the codes of the modules in C++ language; designing the interfaces of the modules and establishing DLL file calling interface program with VB language; inputting the required work state parameters and structural parameters into input module; calling DLL file for iterative calculation; and outputting the calculation result to the output module and automatically drawing. The present invention combines VB language for compiling simple interface and C++ language for high speed and high precision operation, and has low cost and high design efficiency.

Owner:SHANGHAI JIAO TONG UNIV

Microprocessor with integrated high speed memory

InactiveUS20050273577A1Data managementQuick managementGeneral purpose stored program computerConcurrent instruction executionHigh speed memoryParallel computing

The present invention relates to the field of (micro)computer design and architecture, and in particular to microarchitecture associated with moving data values between a (micro)processor and memory components. Particularly, the present invention relates to a computer system with an processor architecture in which register addresses are generated with more than one execution channel controlled by one central processing unit with at least one load / store unit for loading and storing data objects, and at least one cache memory associated to the processor holding data objects accessed by the processor, wherein said processor's load / store unit contains a high speed memory directly interfacing said load / store unit to the cache. The present invention improves the of architectures with dual ported microprocessor implementations comprising two execution pipelines capable of two load / store data transactions per cycle. By including a cache memory inside the load / store unit, the processor is directly interfaced from its load / store units to the caches. Thus, the present invention accelerates data accesses and transactions from and to the load / store units of the processor and the data cache memory.

Owner:AVAGO TECH INT SALES PTE LTD

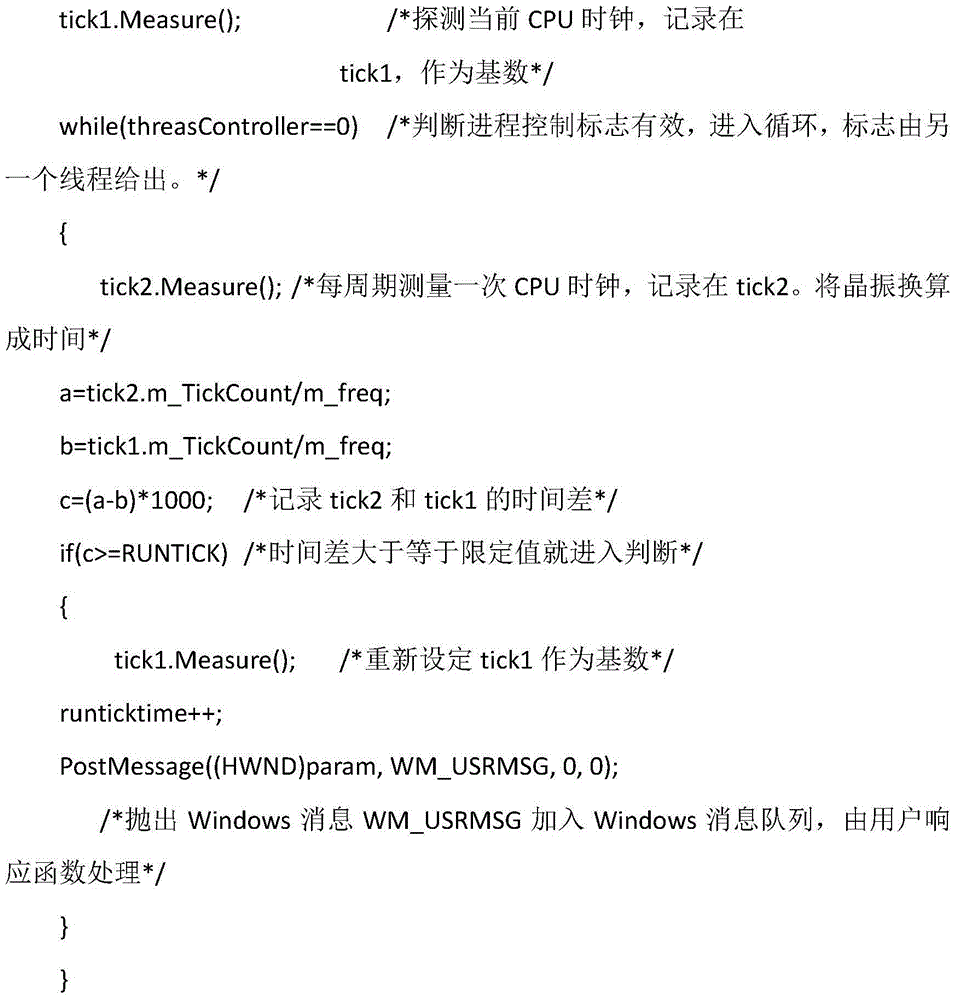

Designing method for computer CPU anti-interference

InactiveCN1677363AMonitor interference in real timeEasy resetSoftware testing/debuggingProgram tracingProcessor register

The invention relates to a designing method for anti-interference property of computer CPU, comprising adding program tracking address register (PTAR), program tracking flag register (PTFR) and program interference flag register (PIFR) and additionally adding three select two counter (CPC), three select two instruction register (ICR) and adding nonscreened interruption (NSI). And a computer designed by this method can both effectively monitor program counter (PC) interference and instruction interference and records the interference interruption point and restoration interruption of the program, therefore provided with the characters of stronger anti-interference property, more accurate and reliable interference judgment, more effective failure treatment as well as real-time property, repairability and scientificalness.

Owner:XIAN UNIV OF SCI & TECH