Parallel multiprocessor computer design method

A multi-processor and design method technology, applied in the computer field, can solve problems such as host failure and low operating efficiency, and achieve high computing efficiency and availability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

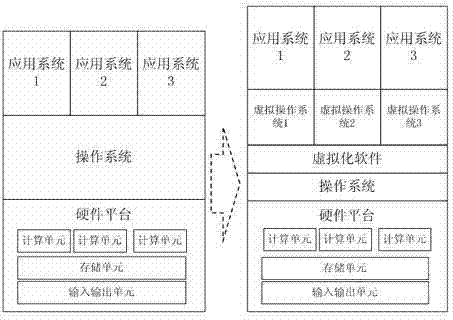

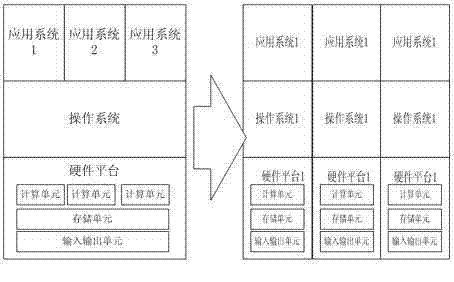

[0038] The design method of the parallel multiprocessor computer of the present invention proposes a new computer architecture based on NUMA, and provides a method for partitioning a multiprocessor computer. Users can set computer partitions by themselves according to business needs. The divided partitions are completely independent physically.

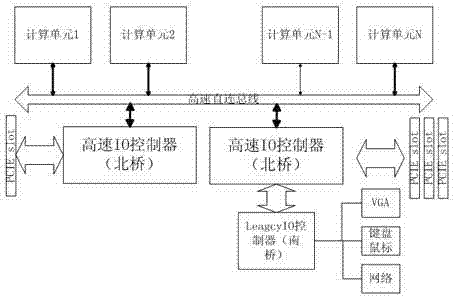

[0039] The physical units of the system's architecture include NUMA-based computing units (including processors and associated memory units), multiple high-speed IO controllers (North Bridge), multiple LeagcyIO controllers (South Bridge), independently controllable Power system, FPGA-based partition logic control unit, multiple system management units.

[0040] The usual NUMA architecture is as follows:

[0041] The logic unit includes: processor direct connection bus configuration logic, reset, timing and power control logic, Leagcy-nonLeagcy configuration logic, partition setting logic, processor and partition presence detection lo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More