Patents

Literature

23770 results about "Design methods" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Design methods are procedures, techniques, aids, or tools for designing. They offer a number of different kinds of activities that a designer might use within an overall design process. Conventional procedures of design, such as drawing, can be regarded as design methods, but since the 1950s new procedures have been developed that are more usually grouped together under the name of "design methods". What design methods have in common is that they "are attempts to make public the hitherto private thinking of designers; to externalise the design process".

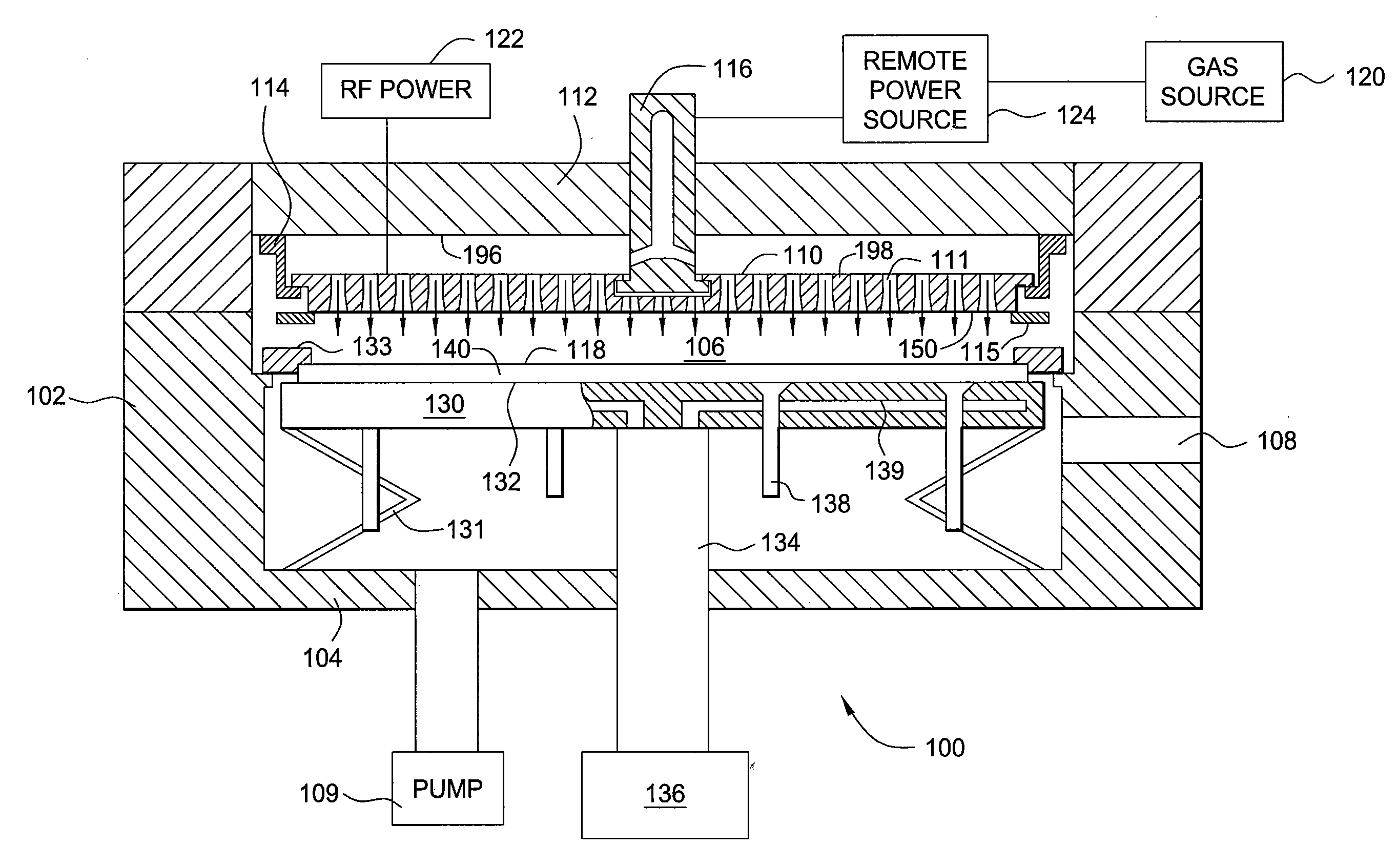

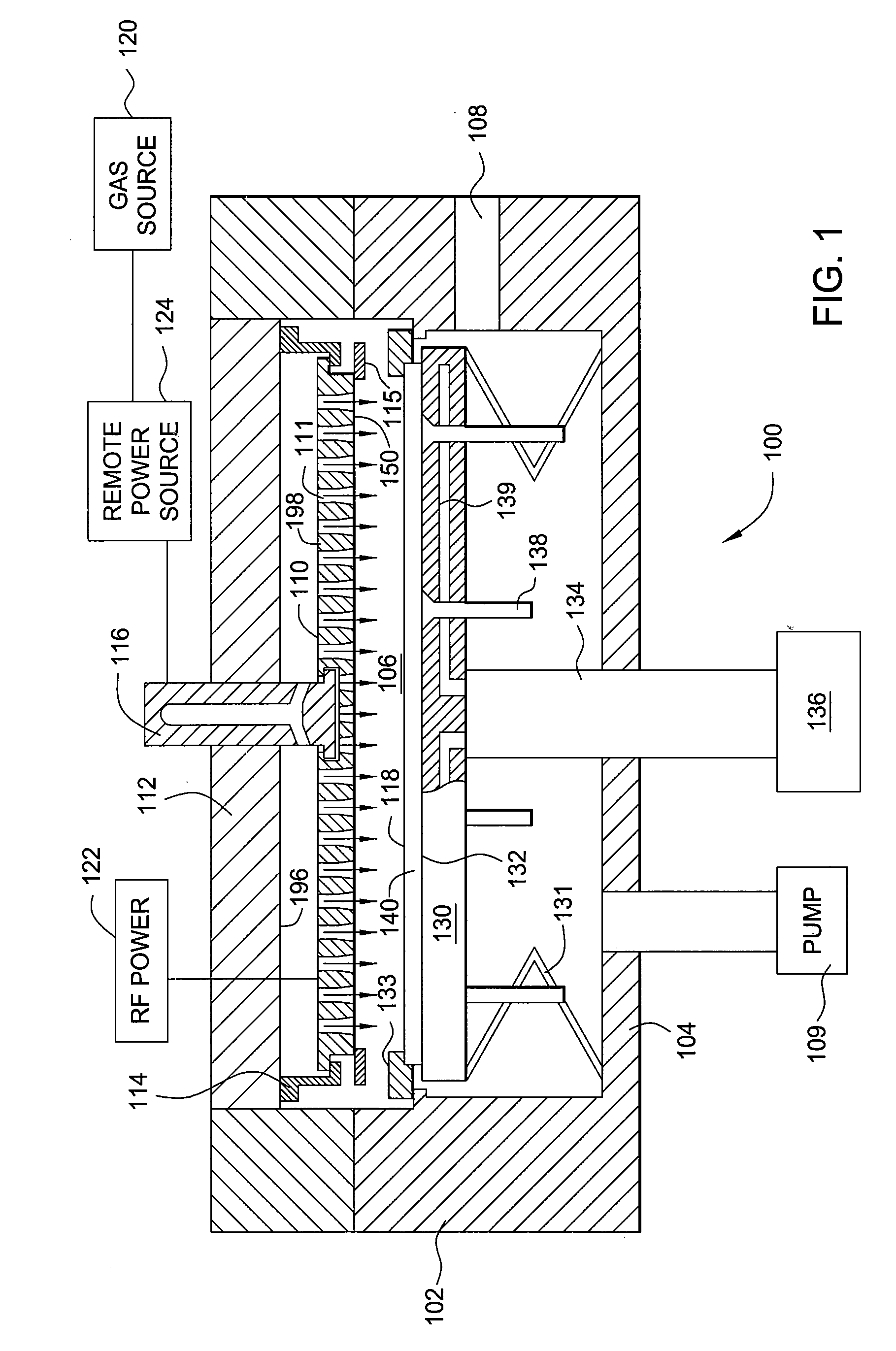

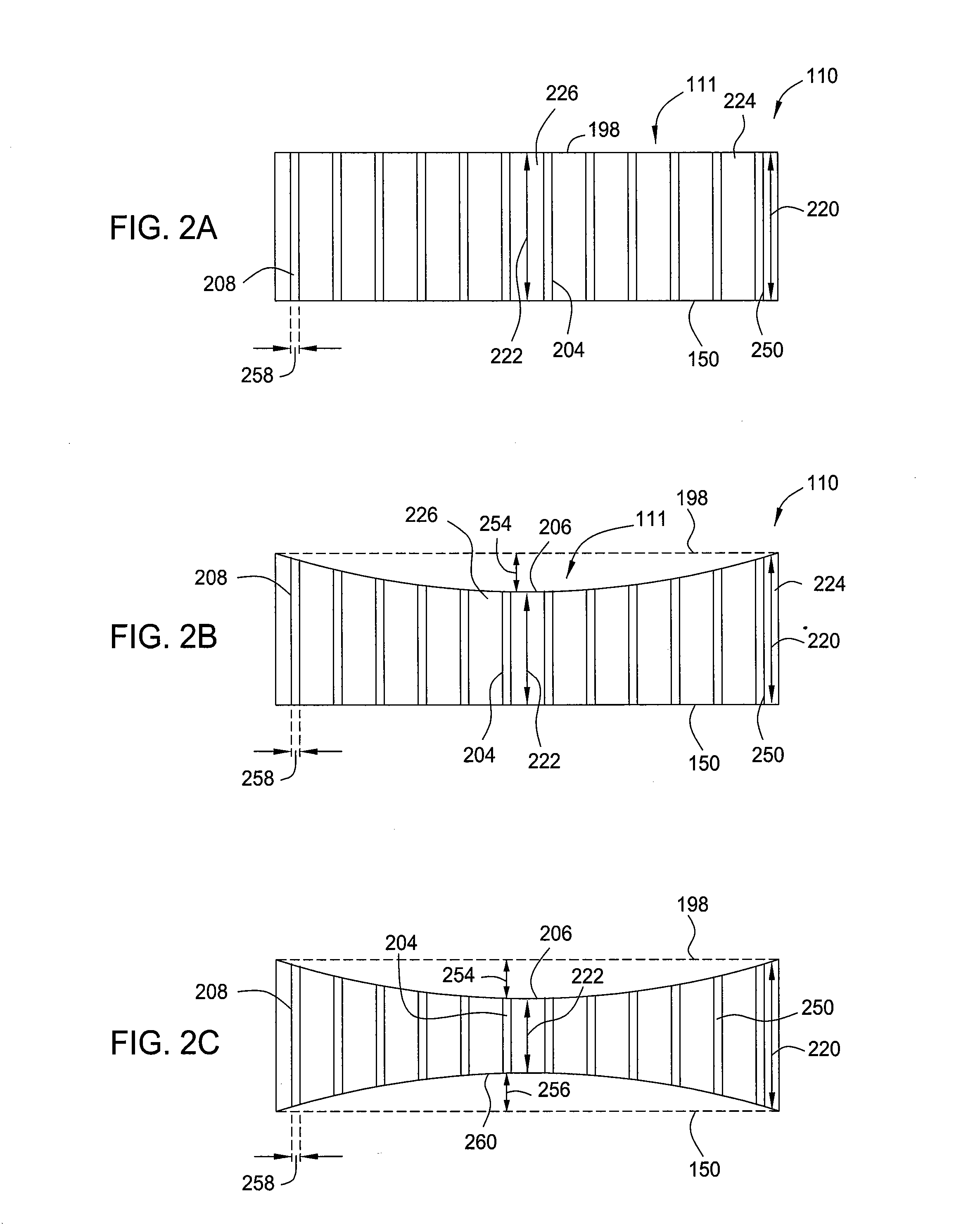

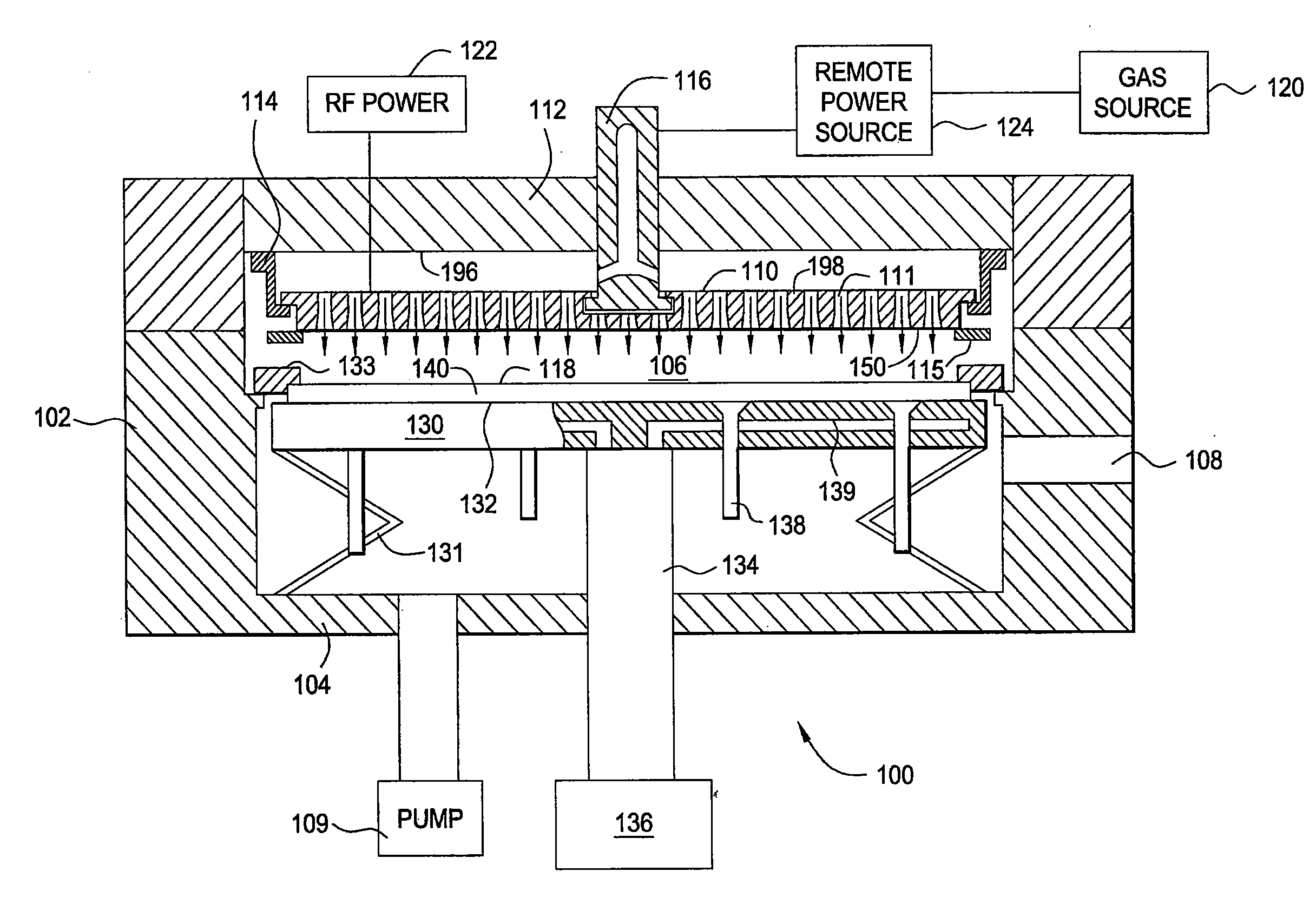

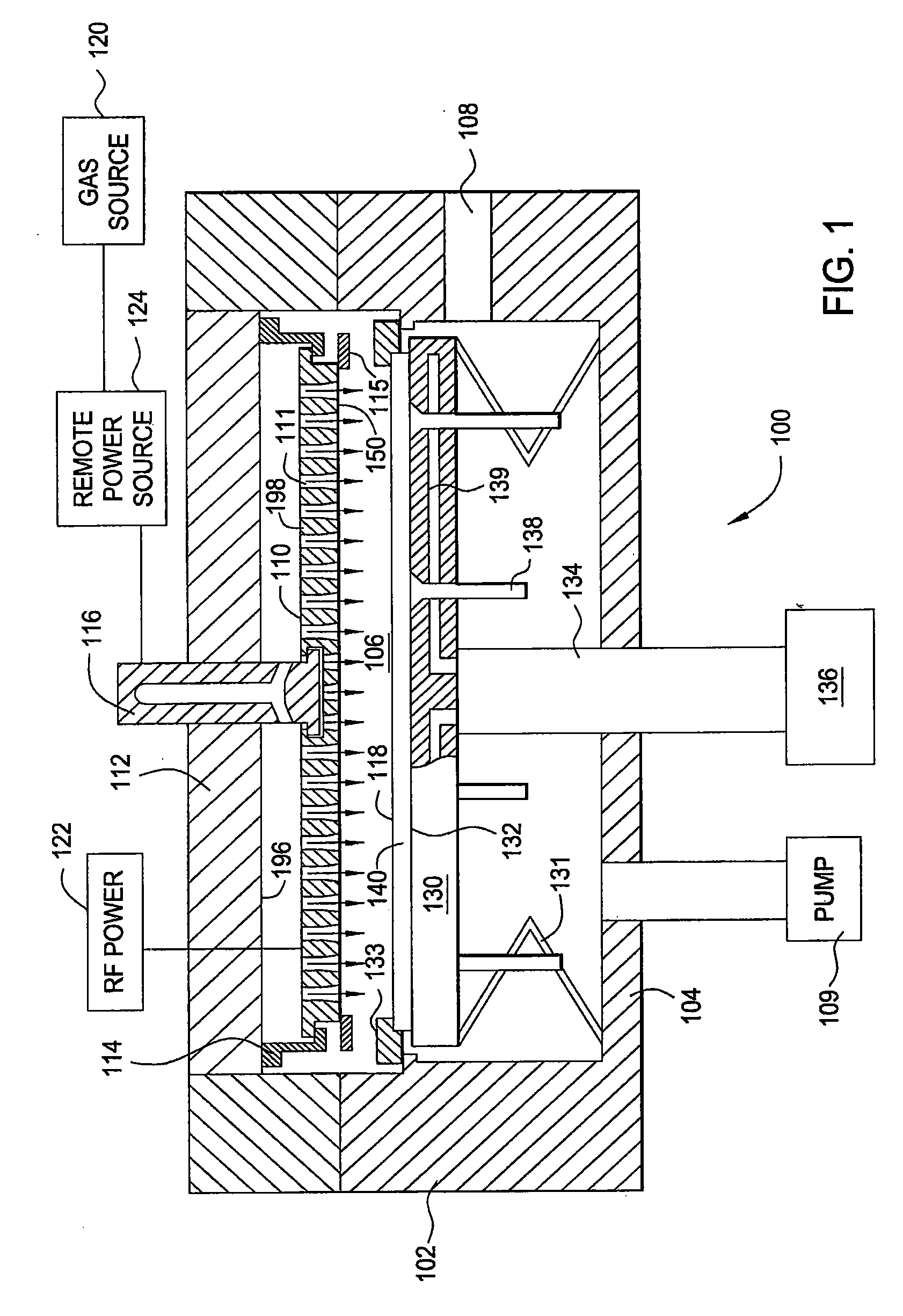

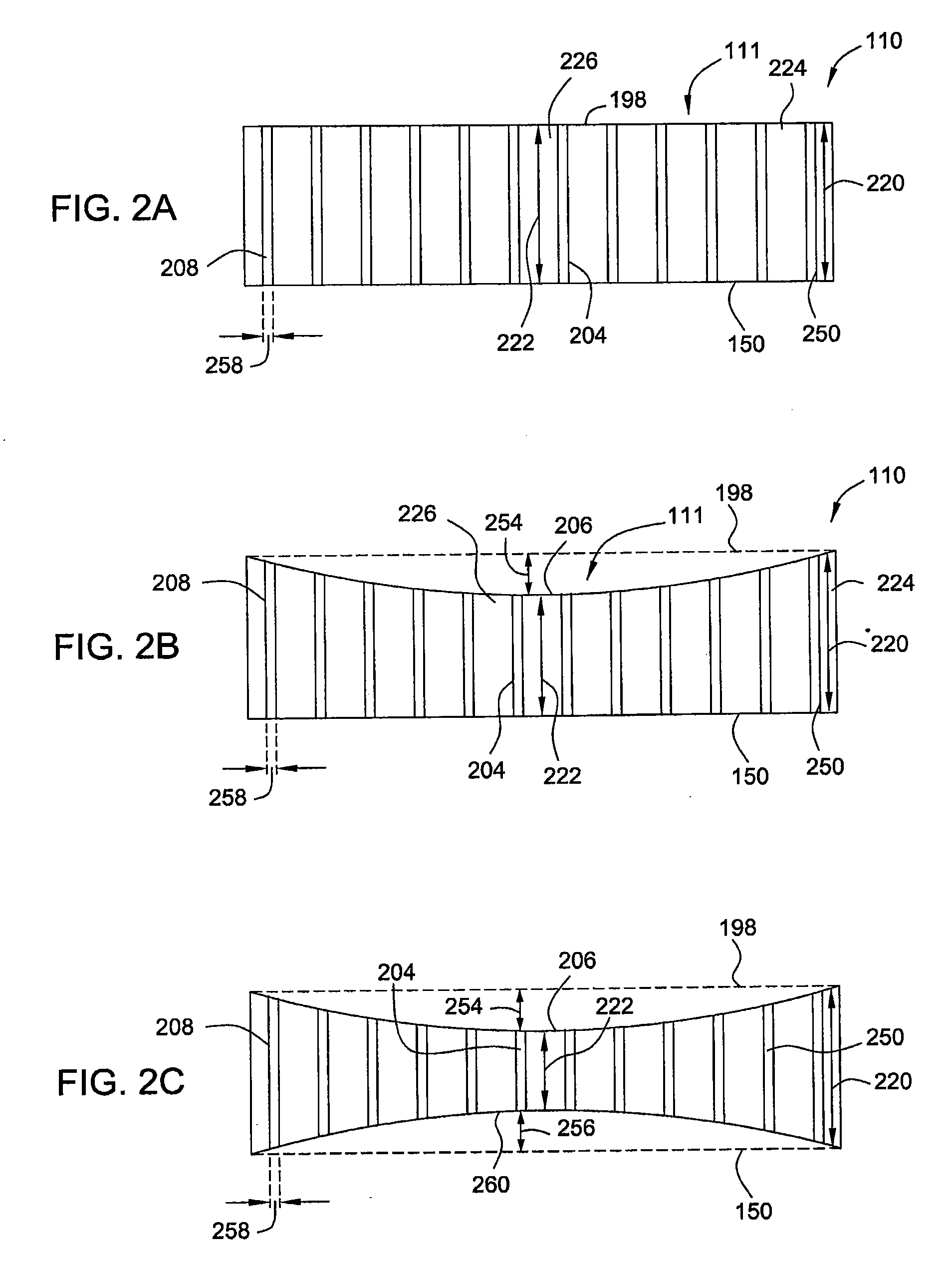

Methods and apparatus for depositing a uniform silicon film with flow gradient designs

Methods and apparatus having a flow gradient created from a gas distribution plate are provided. In one embodiment, the method and apparatus are particularly useful for, but not limited to, depositing a silicon film for solar cell applications. The apparatus for depositing a uniform film for solar cell applications includes a processing chamber, and a quadrilateral gas distribution plate disposed in the processing chamber and having at least four corners separated by four sides. The gas distribution plate further includes a first plurality of chokes formed through the gas distribution plate, the first plurality of chokes located in the corners, and a second plurality of chokes formed through the gas distribution plate, the second plurality of chokes located along the sides of the gas distribution plate between the corner regions, wherein the first plurality of chokes have a greater flow resistance than that of the second plurality of chokes.

Owner:APPLIED MATERIALS INC

Methods and apparatus for depositing a uniform silicon film with flow gradient designs

InactiveUS20090000551A1Electric discharge tubesChemical vapor deposition coatingEngineeringSolar cell

Methods and apparatus having a flow gradient created from a gas distribution plate are provided. In one embodiment, the method and apparatus are particularly useful for, but not limited to, depositing a silicon film for solar cell applications. The apparatus for depositing a uniform film for solar cell applications includes a processing chamber, and a quadrilateral gas distribution plate disposed in the processing chamber and having at least four corners separated by four sides. The gas distribution plate further includes a first plurality of chokes formed through the gas distribution plate, the first plurality of chokes located in the corners, and a second plurality of chokes formed through the gas distribution plate, the second plurality of chokes located along the sides of the gas distribution plate between the corner regions, wherein the first plurality of chokes have a greater flow resistance than that of the second plurality of chokes.

Owner:APPLIED MATERIALS INC

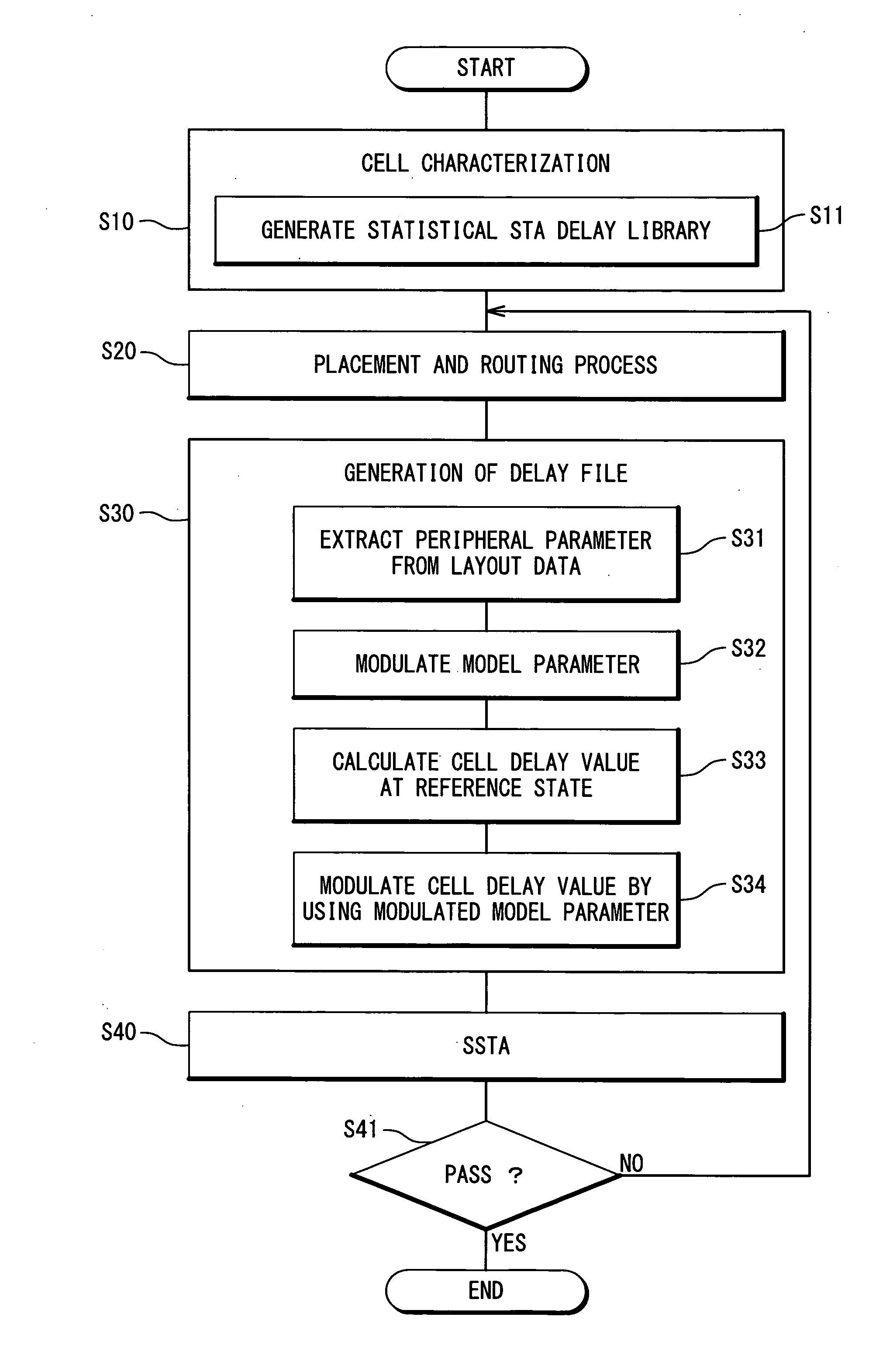

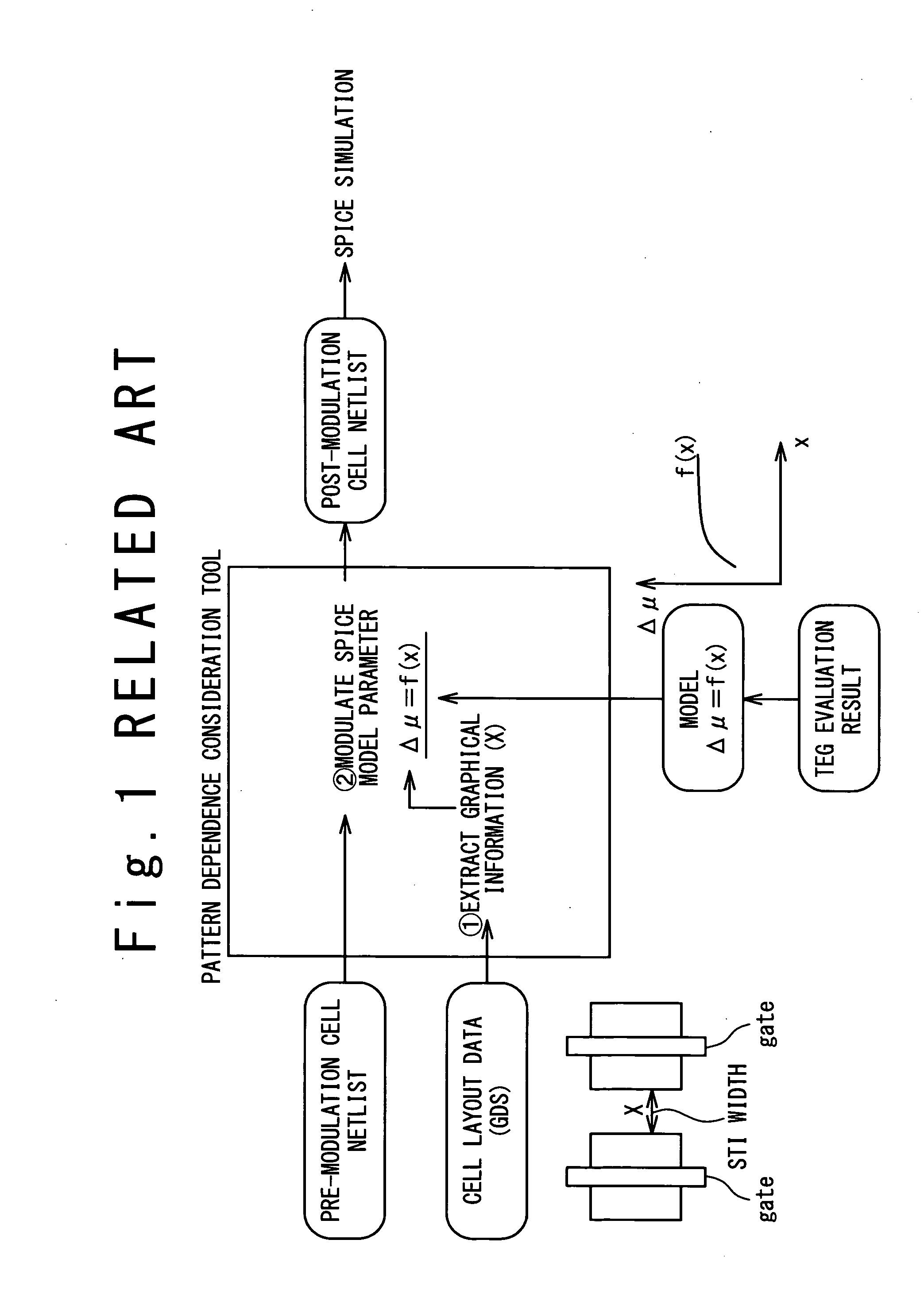

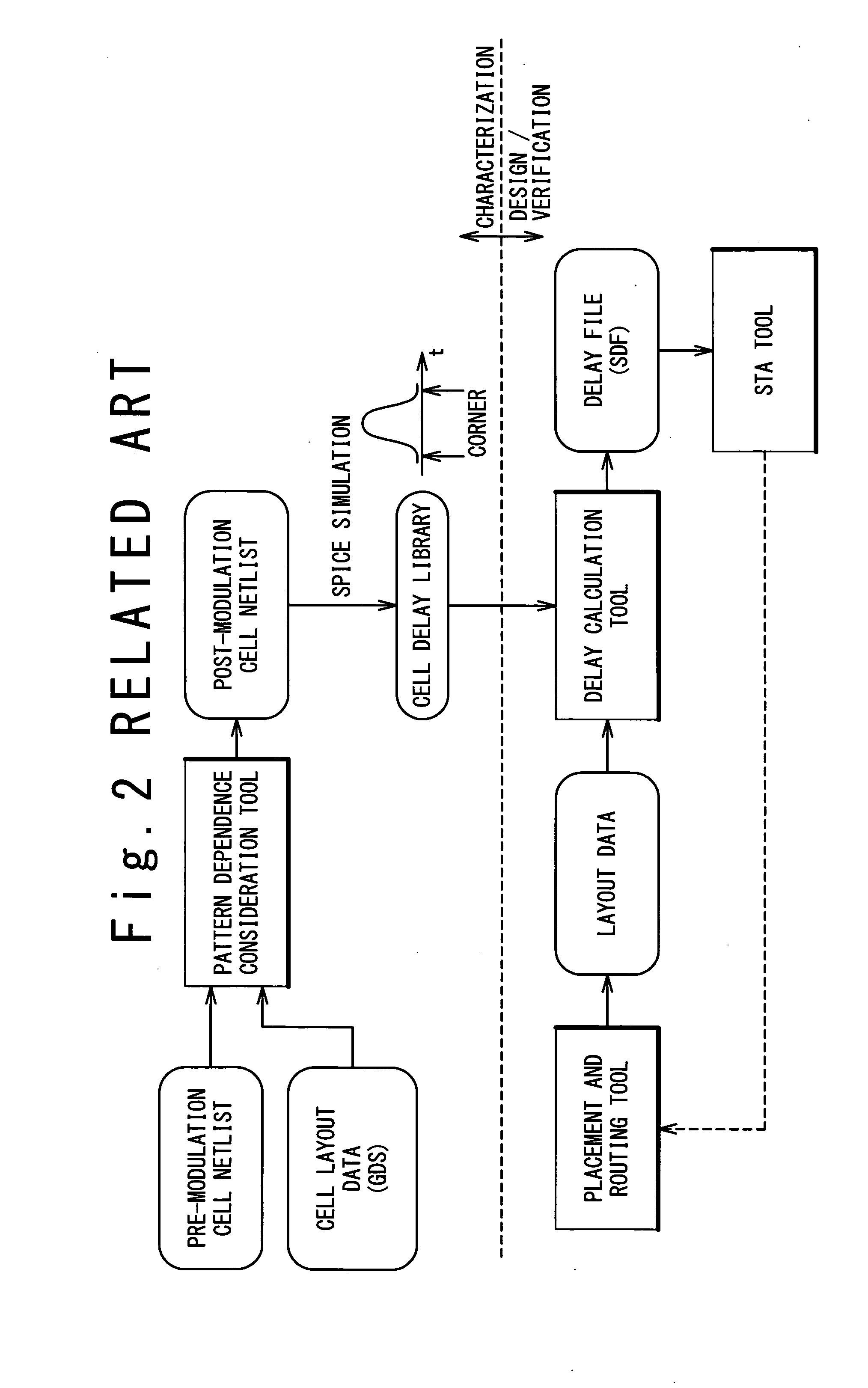

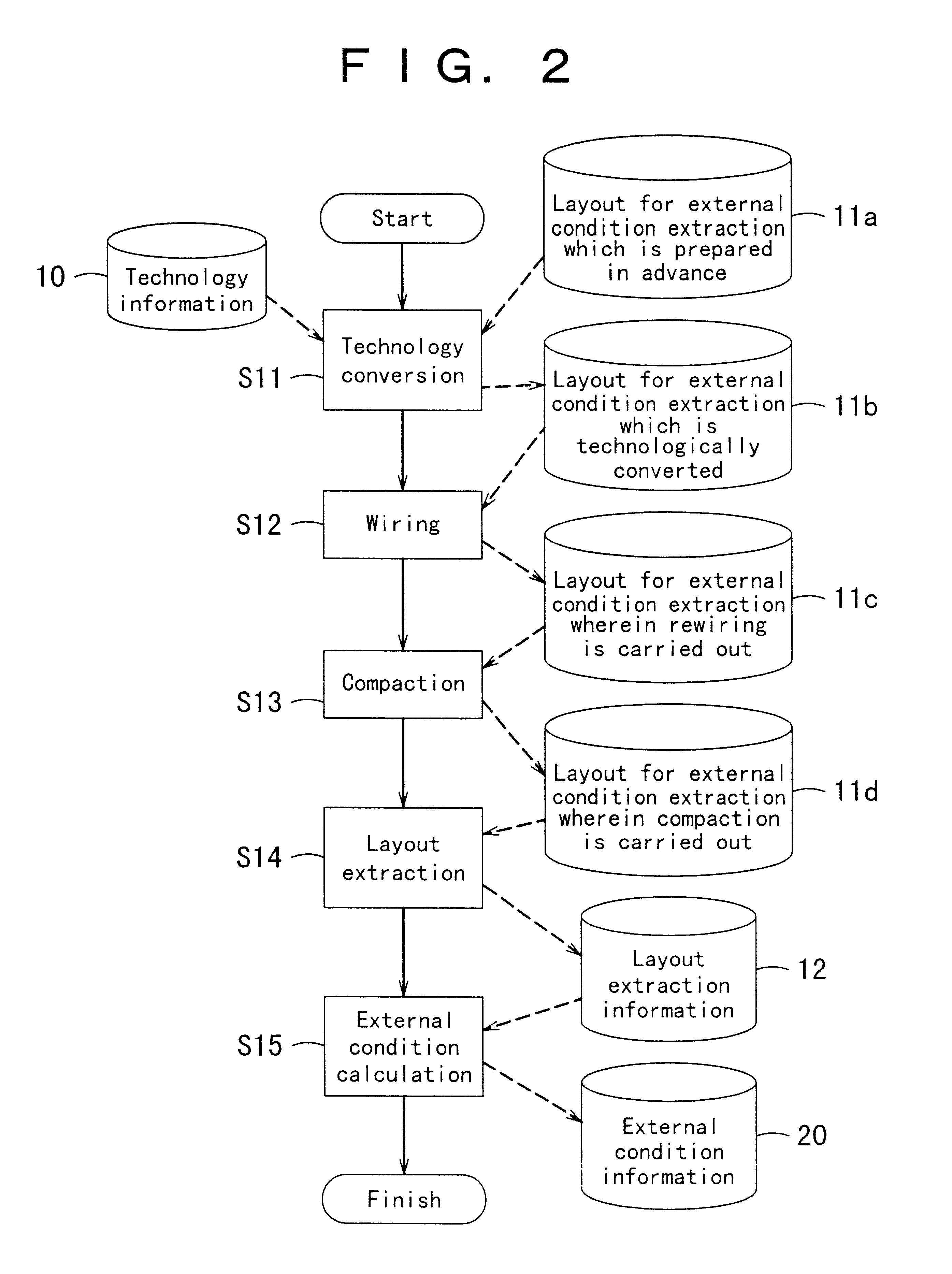

Method and program for designing semiconductor integrated circuit

InactiveUS20090024974A1Increase in design/verification TAT can be preventedHigh delay accuracyCAD circuit designSoftware simulation/interpretation/emulationModel parametersCell based

A design method for an LSI includes: generating a delay library for use in a statistical STA, wherein the delay library provides a delay function that expresses a cell delay value as a function of model parameters of a transistor; generating a layout data; and calculating a delay value of a target cell based on the delay library and the layout data. The calculating includes: referring to the layout data to extract a parameter specifying a layout pattern around a target transistor; modulating model parameters of the target transistor such that the characteristics corresponding to the extracted parameter is obtained in a circuit simulation; calculating, by using the delay function, a reference delay value of the target cell; and calculating, by using the delay function and the modulation amount of the model parameter, a delay variation from the reference delay value depending on the modulation amount.

Owner:RENESAS ELECTRONICS CORP

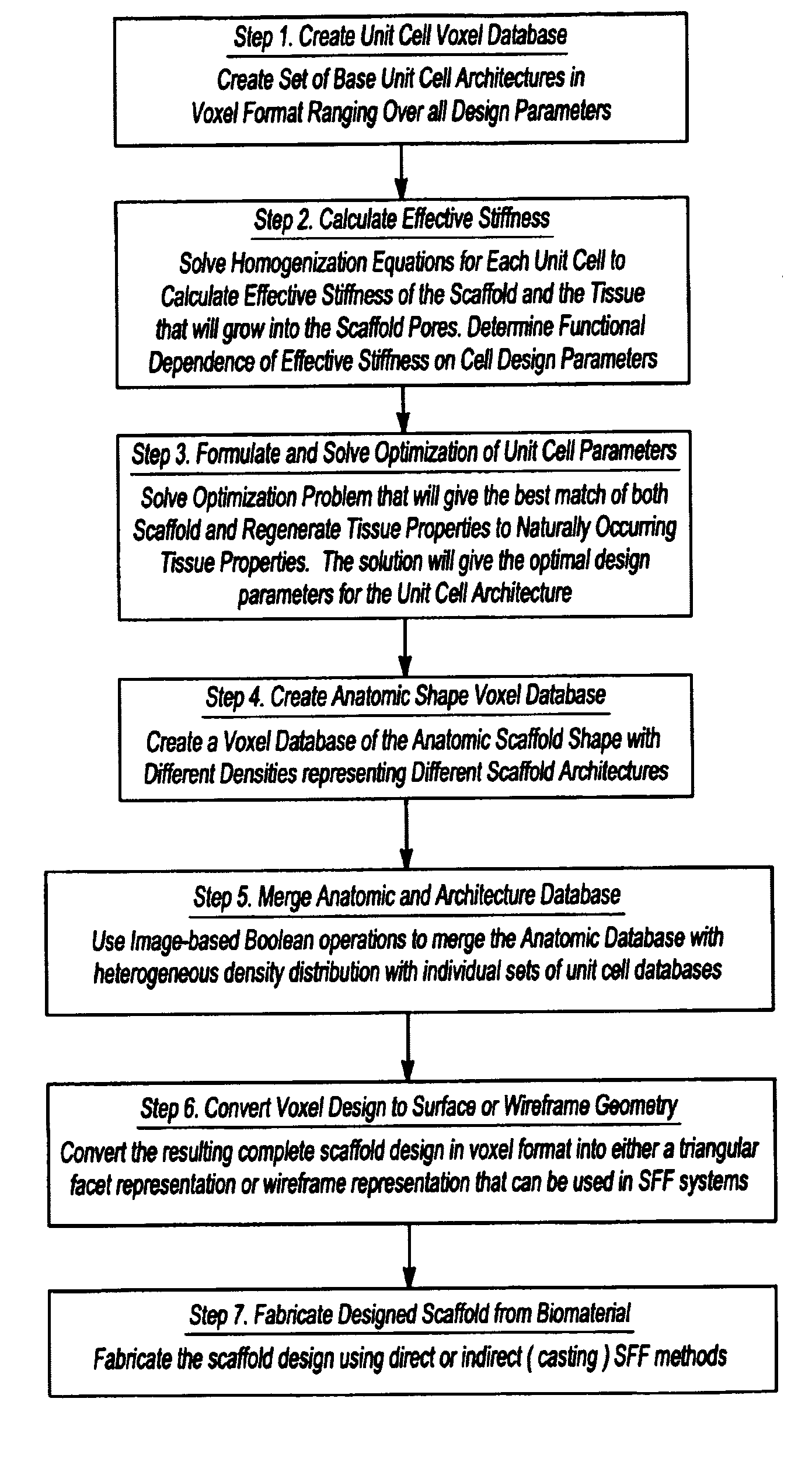

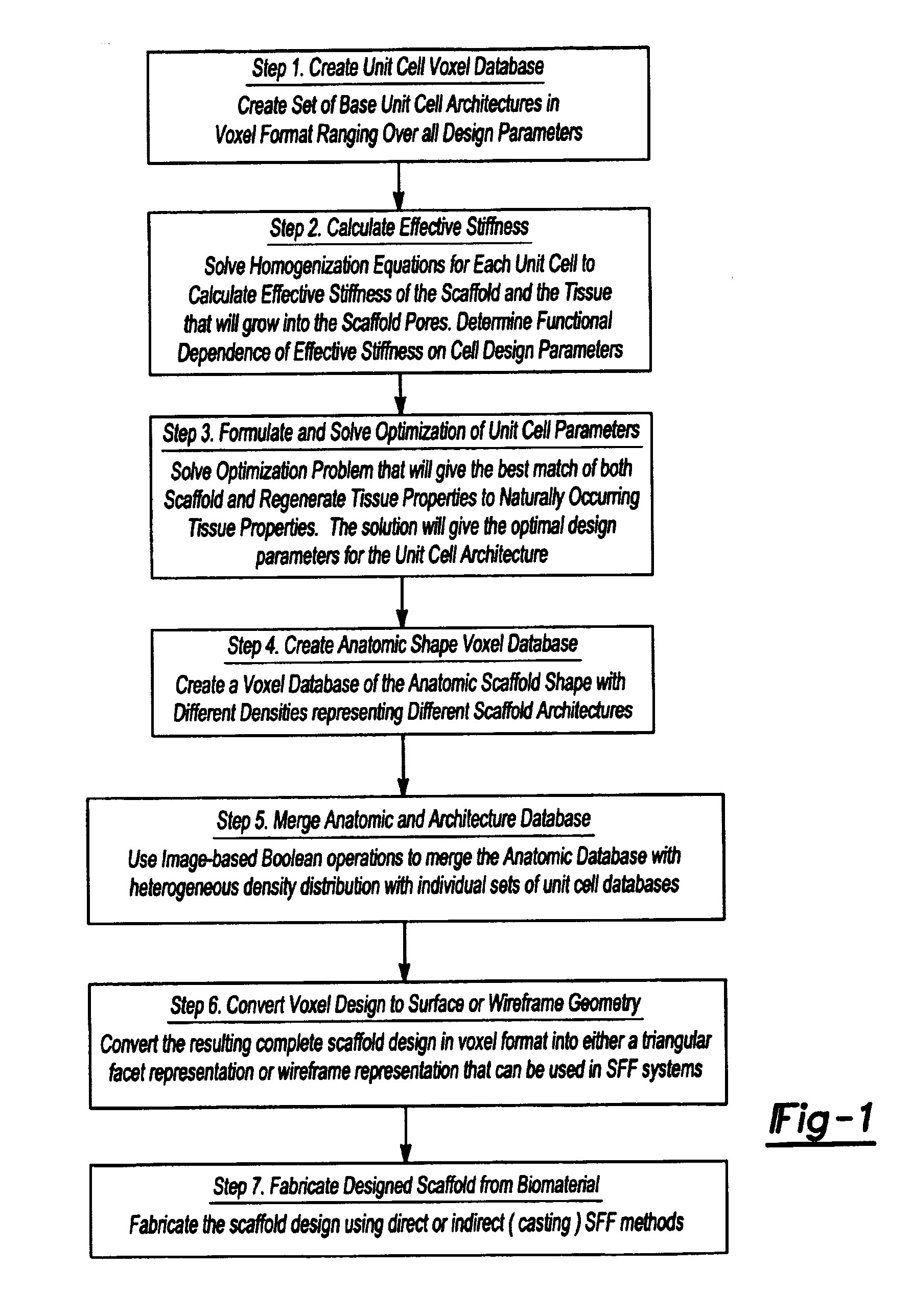

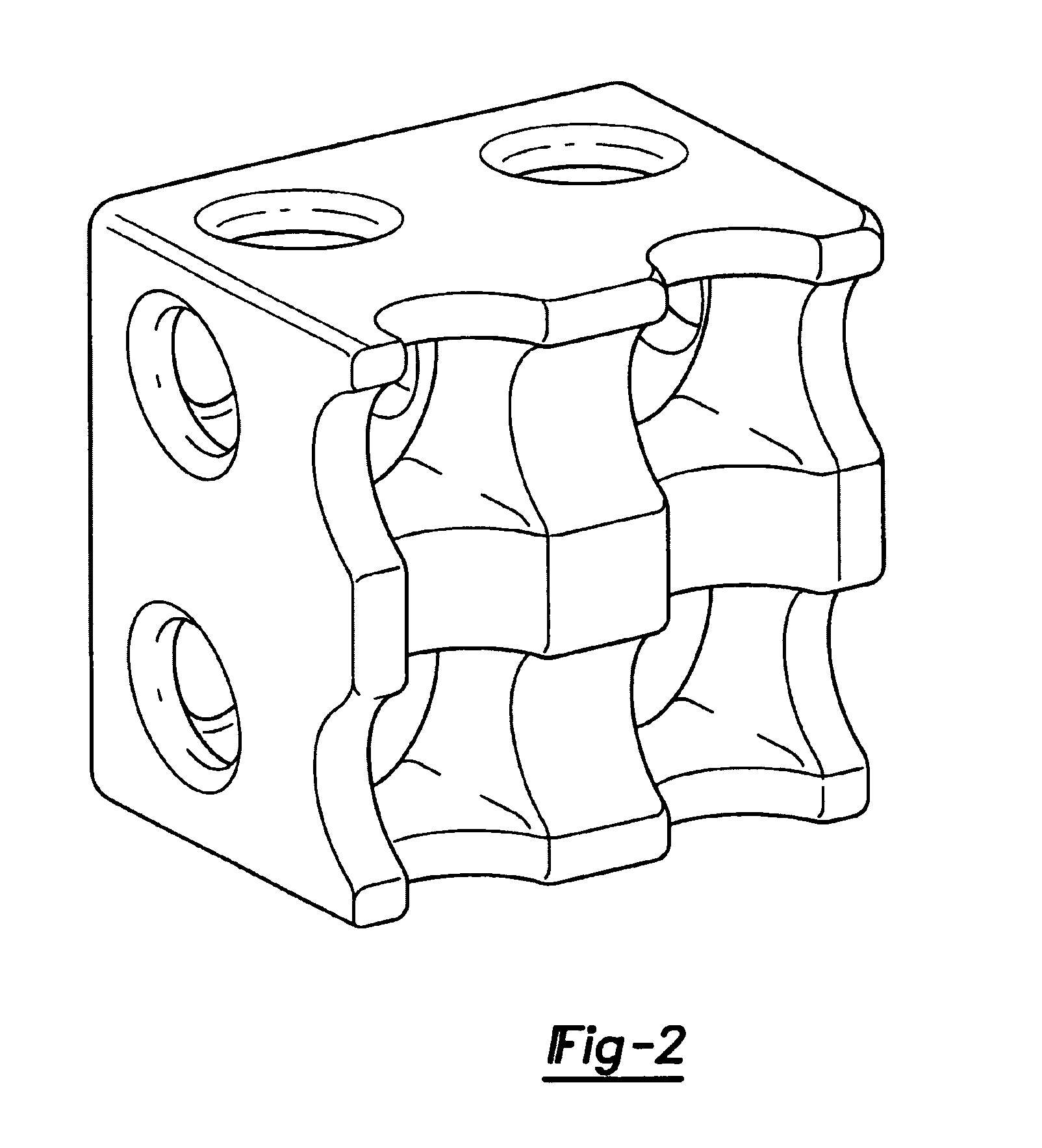

Design methodology for tissue engineering scaffolds and biomaterial implants

A design methodology is provided for creating biomaterial scaffolds optimized for in vivo function with any 3D anatomic shape. The method creates all designs using voxel based design techniques. It also provides for optimization of implant and scaffold microstructure to best match functional and biofactor delivery (including cells, genes and proteins) requirements. The voxel based design techniques readily allow combination of any scaffold or implant microstructure database with any complex 3D anatomic shape created by CT or MRI scanners. These designs can be readily converted to formats for layered manufacturing or casting.

Owner:HOLLISTER SCOTT J +2

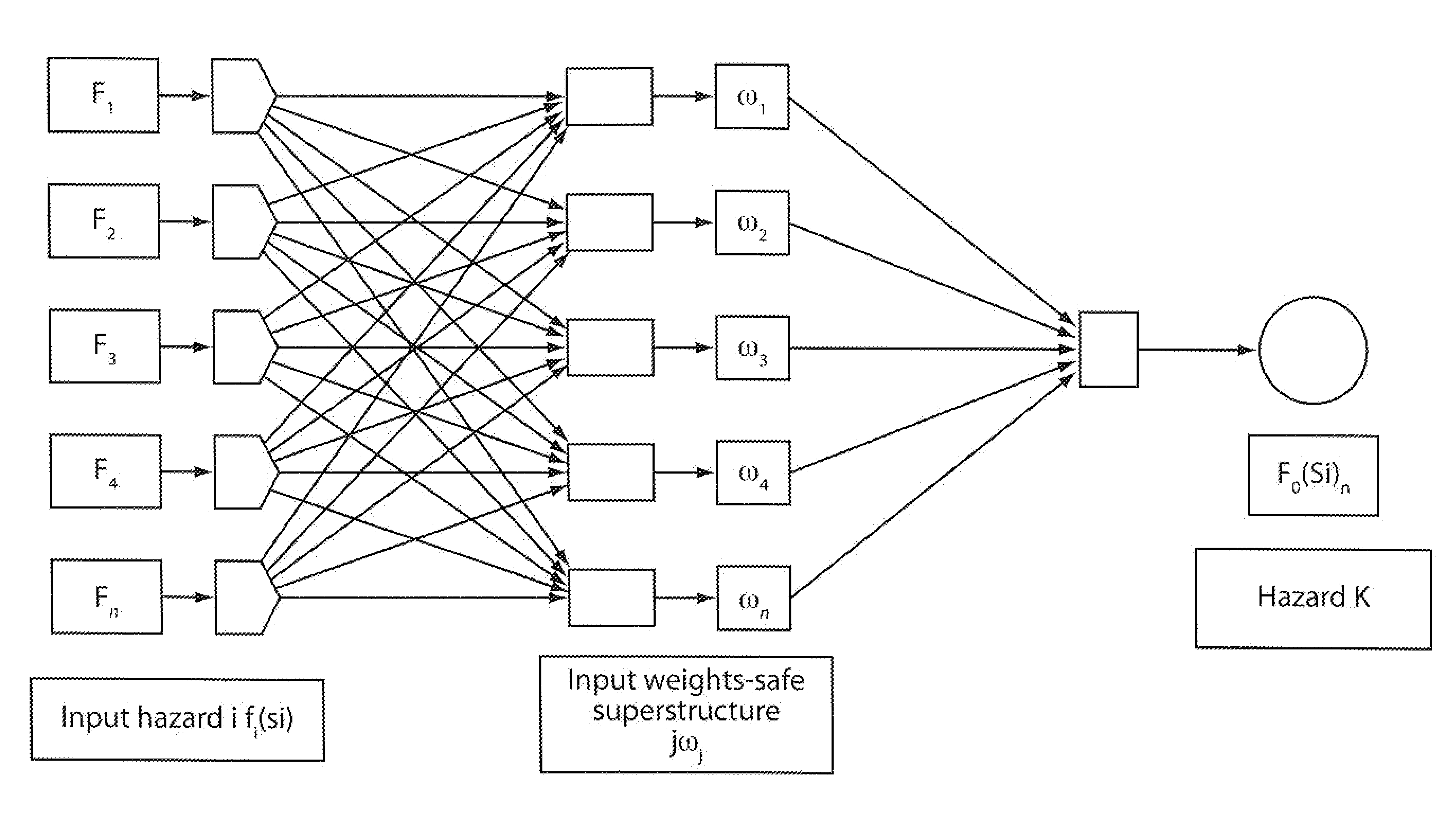

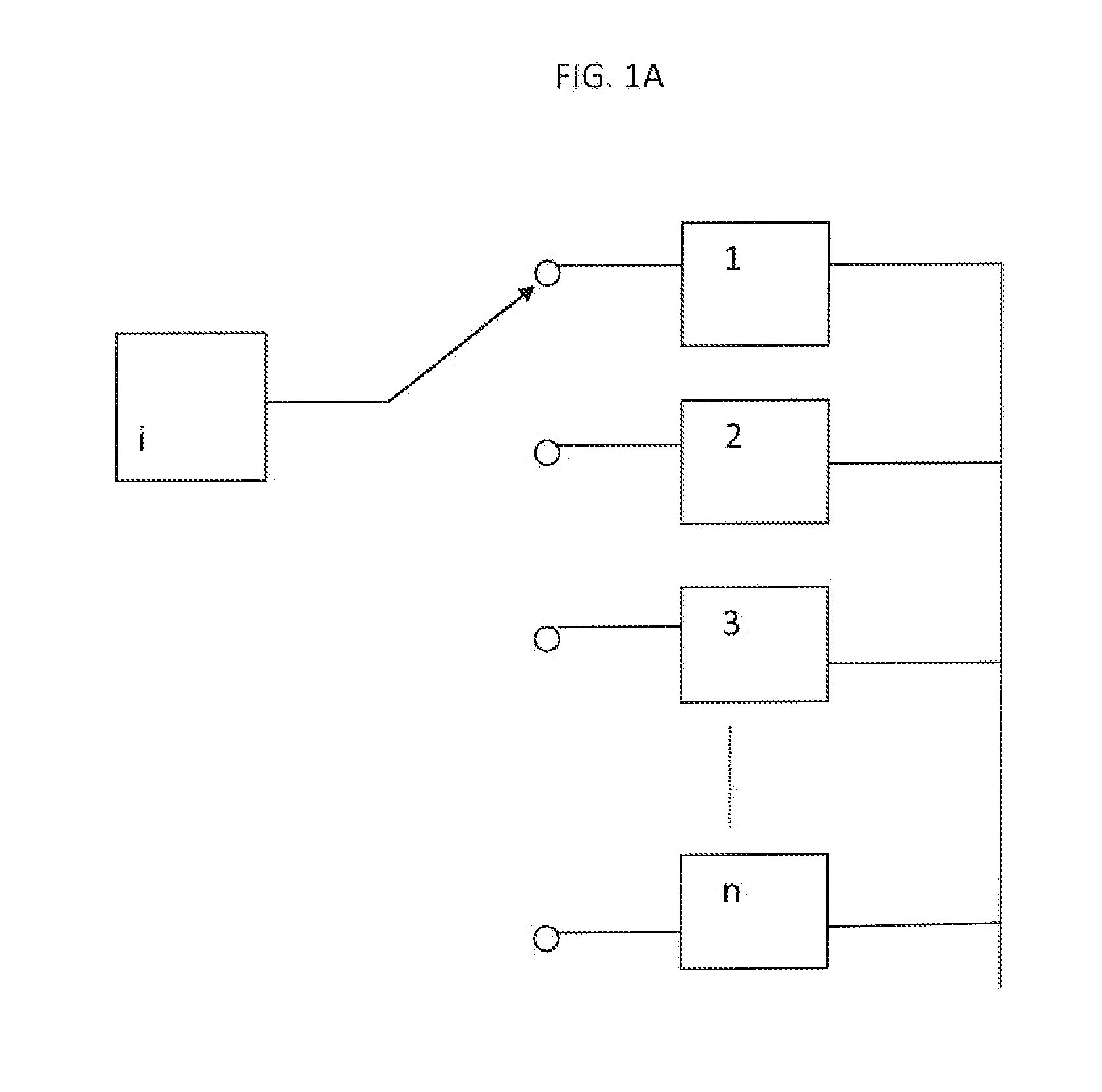

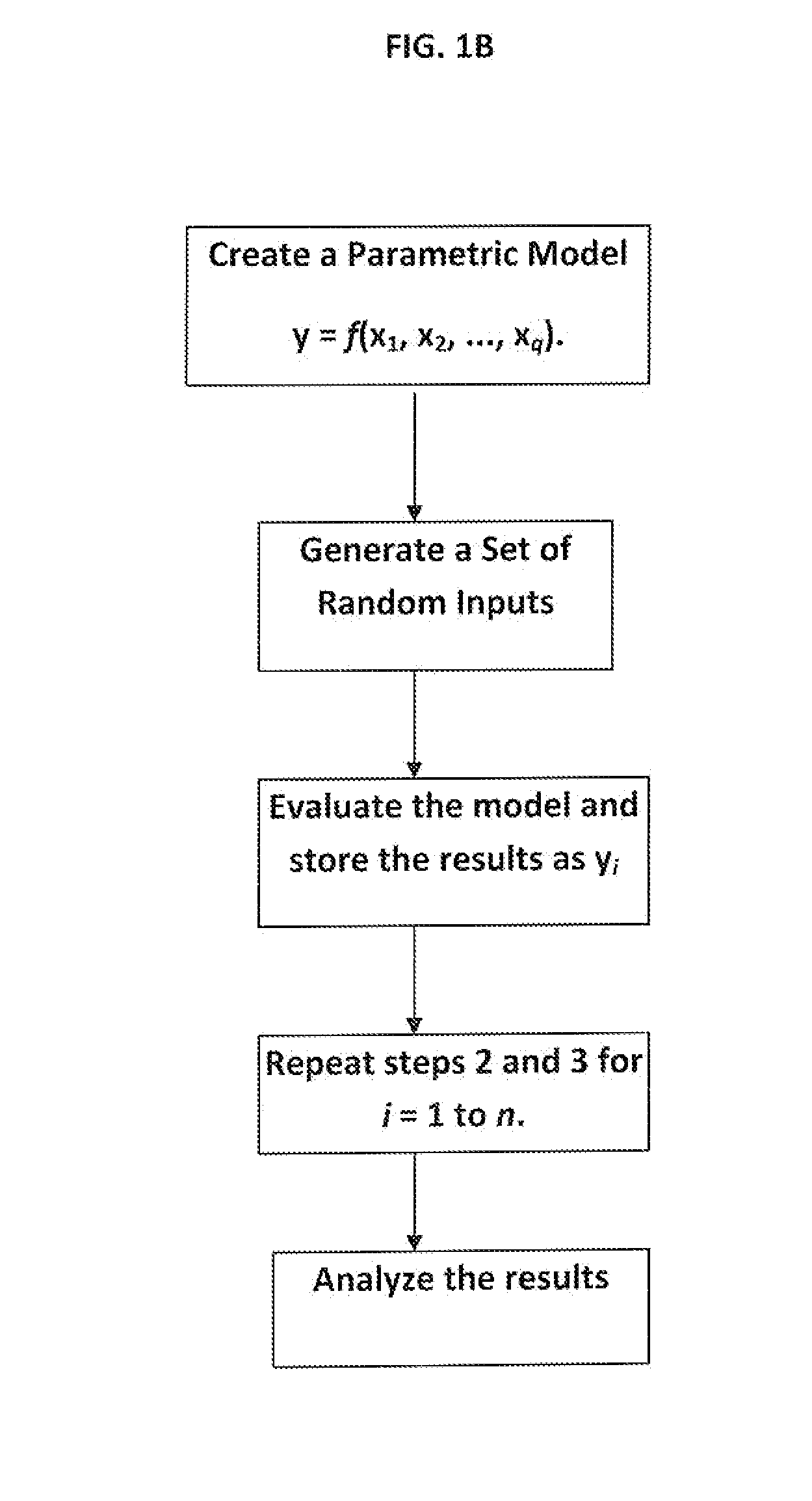

Design of computer based risk and safety management system of complex production and multifunctional process facilities-application to fpso's

InactiveUS20120317058A1Strong robust attributeStrong robust attributesDigital computer detailsFuzzy logic based systemsProcess systemsNerve network

A method for predicting risk and designing safety management systems of complex production and process systems which has been applied to an FPSO System operating in deep waters. The methods for the design were derived from the inclusion of a weight index in a fuzzy class belief variable in the risk model to assign the relative numerical value or importance a safety device or system has contain a risk hazards within the barrier. The weights index distributes the relative importance of risk events in series or parallel in several interactive risk and safety device systems. The fault tree, the FMECA and the Bow Tie now contains weights in fizzy belief class for implementing safety management programs critical to the process systems. The techniques uses the results of neural networks derived from fuzzy belief systems of weight index to implement the safety design systems thereby limiting use of experienced procedures and benchmarks. The weight index incorporate Safety Factors sets SFri {0, 0.1, 0.2 . . . 1}, and Markov Chain Network to allow the possibility of evaluating the impact of different risks or reliability of multifunctional systems in transient state process. The application of this technique and results of simulation to typical FPSO / Riser systems has been discussed in this invention.

Owner:ABHULIMEN KINGSLEY E

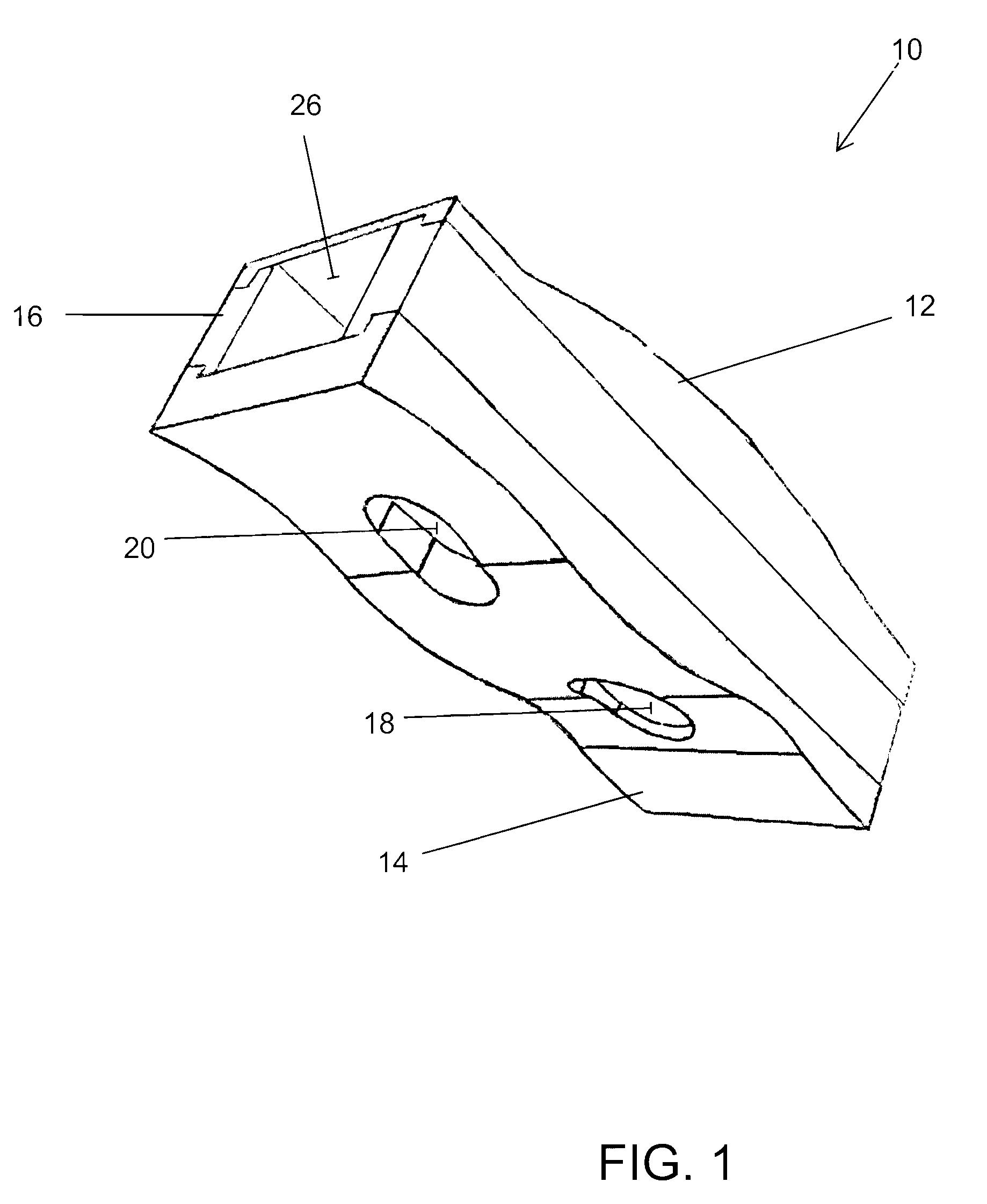

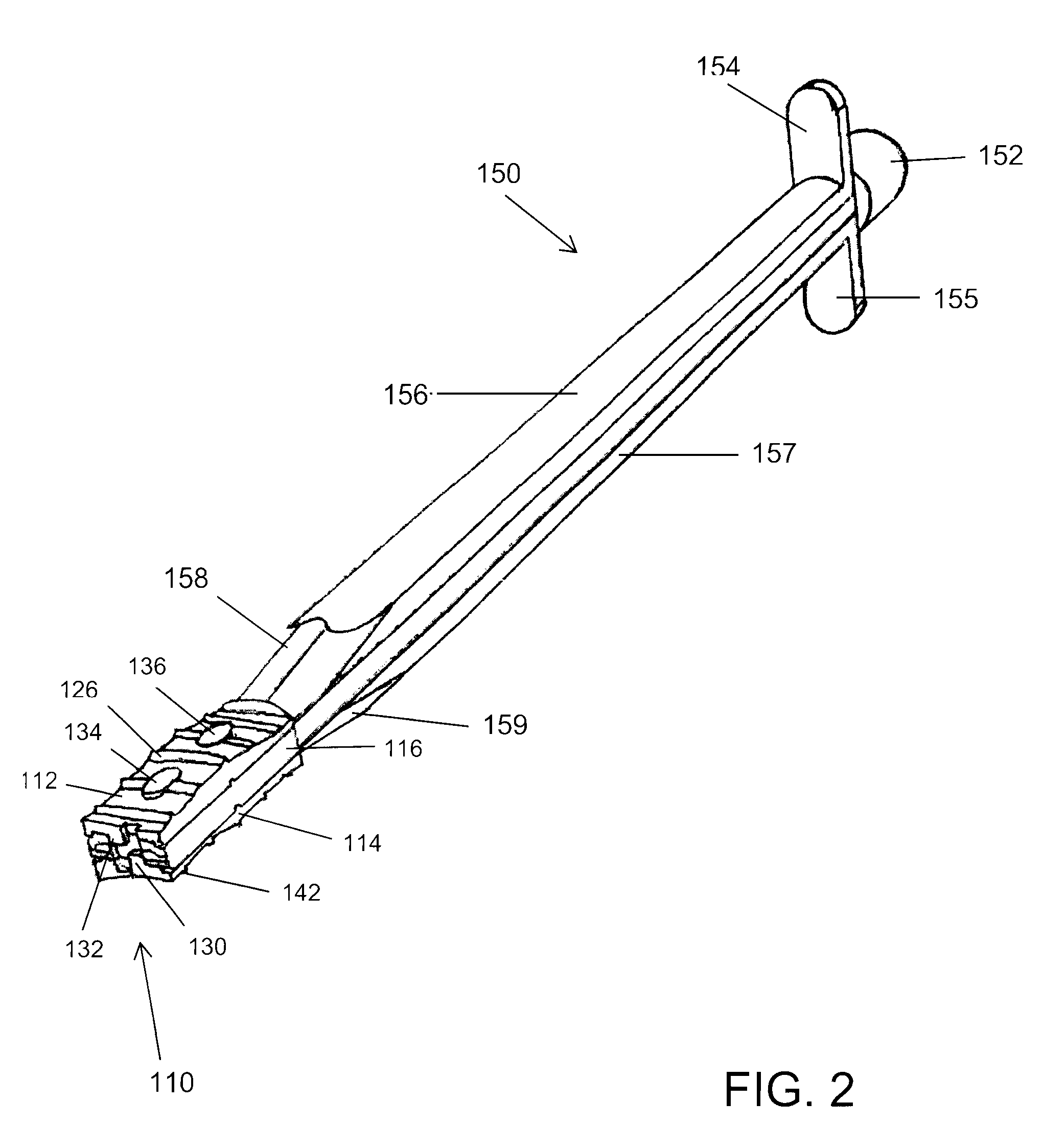

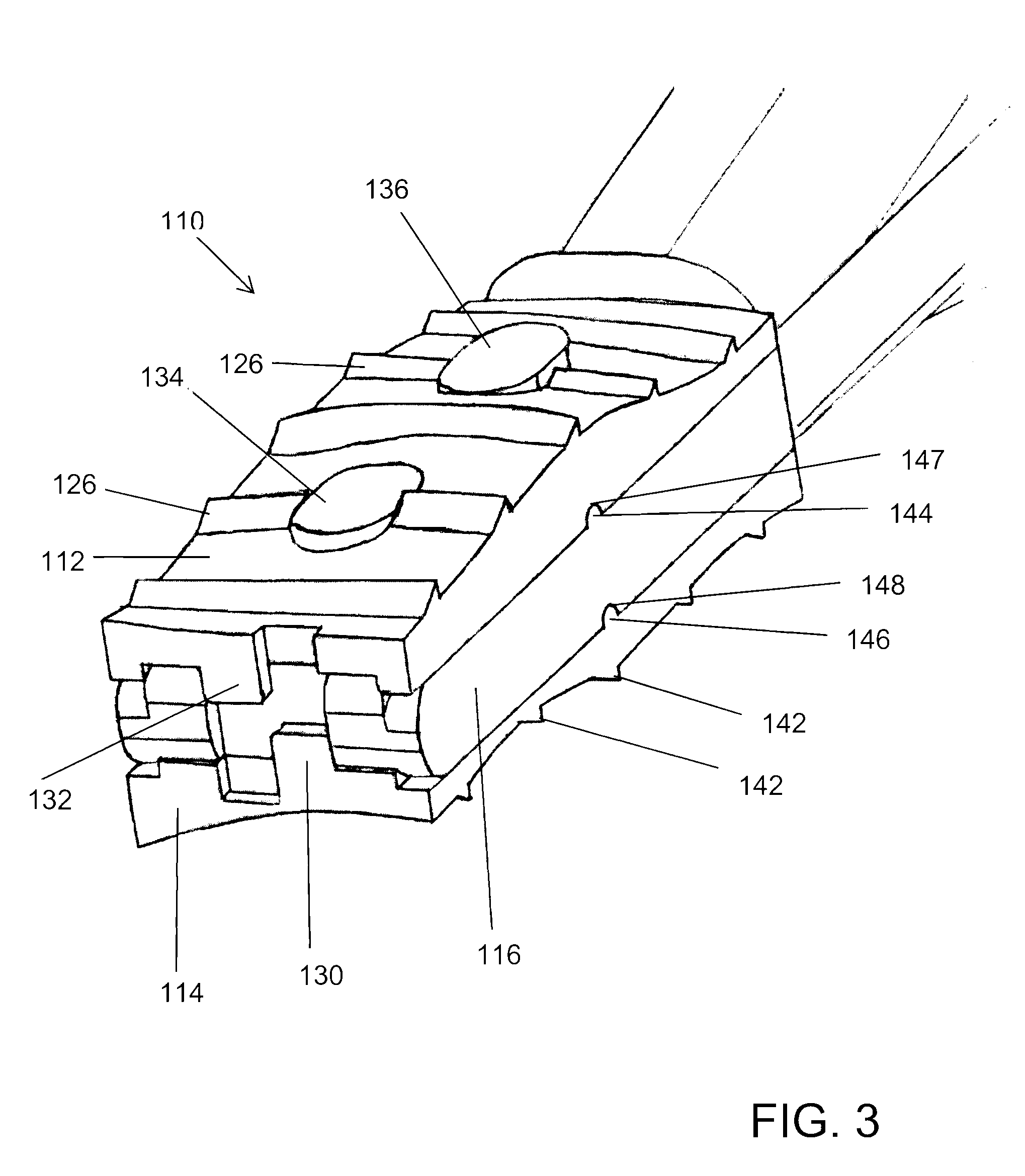

Spinal Fusion Cage, Method of Design, and Method of Use

InactiveUS20070043442A1Prevent backward movementInternal osteosythesisJoint implantsEngineeringSurgical implant

A fusion cage of the present invention includes a first housing portion, a second housing portion, and an insert portion adapted to be received therebetween, wherein the geometry of the fusion cage corresponds substantially to the geometry of a void into which the fusion cage is to be inserted. Also described is a novel tool for insertion of a fusion cage and a novel method for designing a fusion cage or other surgical implant for filling a void identified within a patient.

Owner:ABERNATHIE DENNIS LEE +1

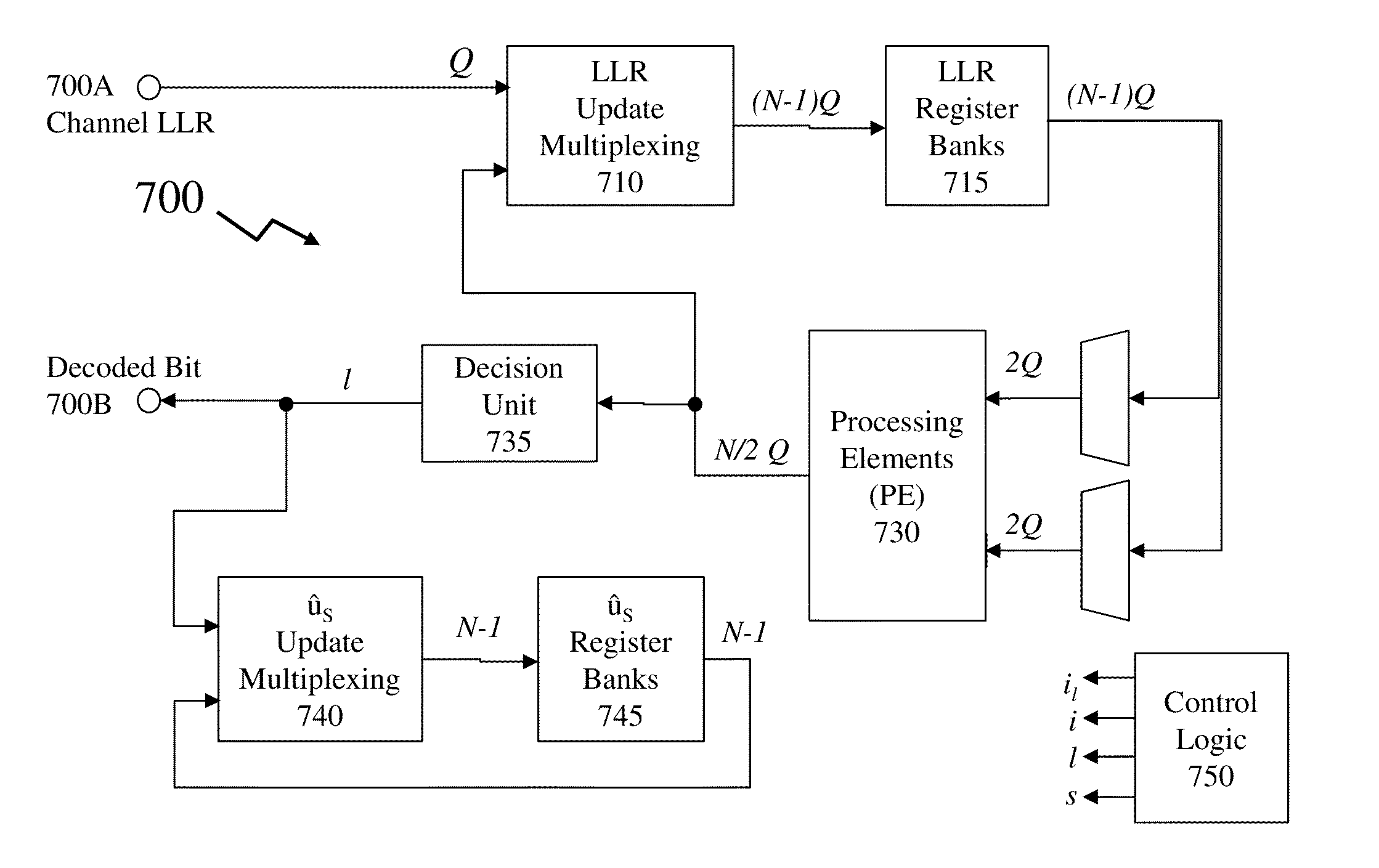

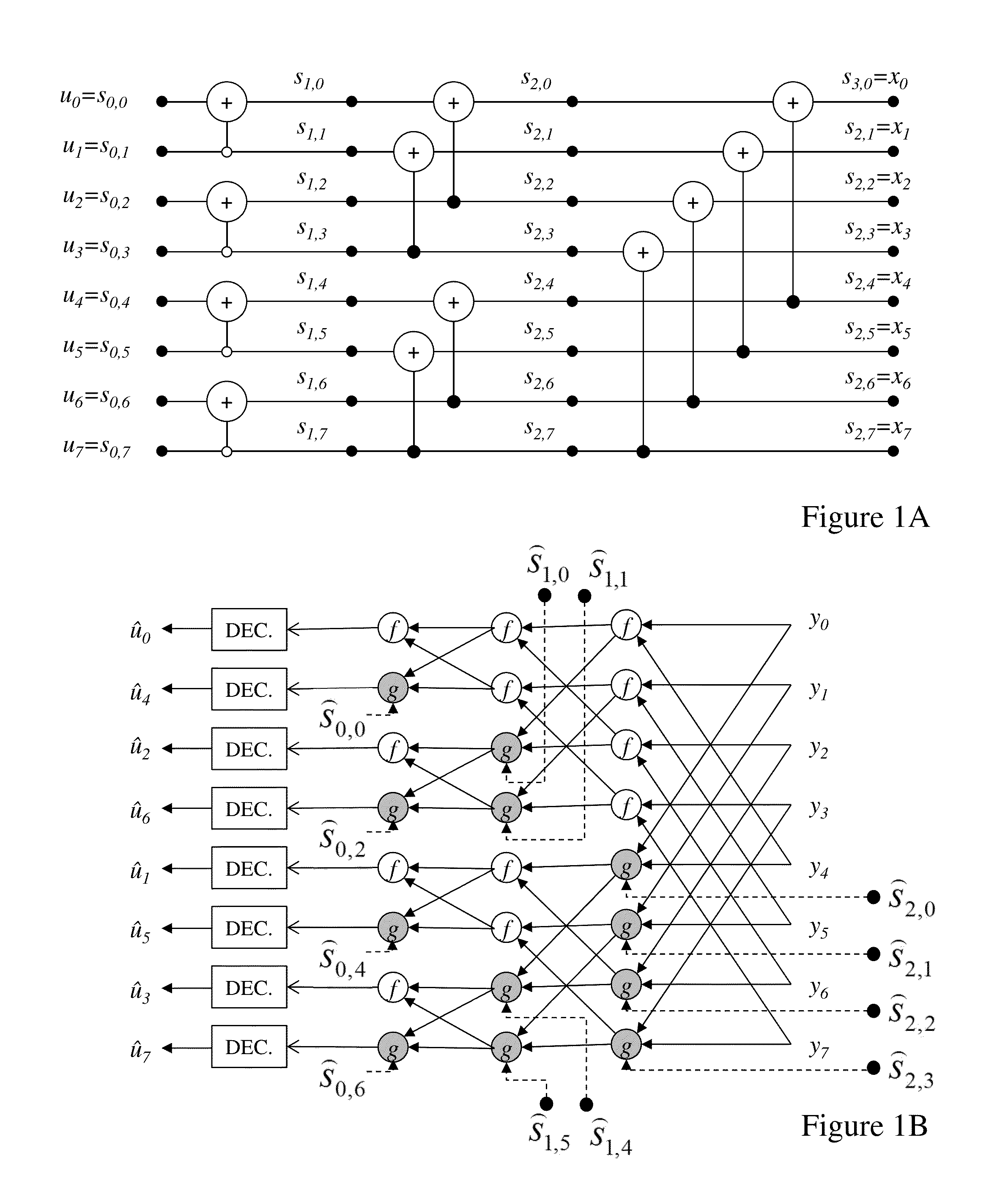

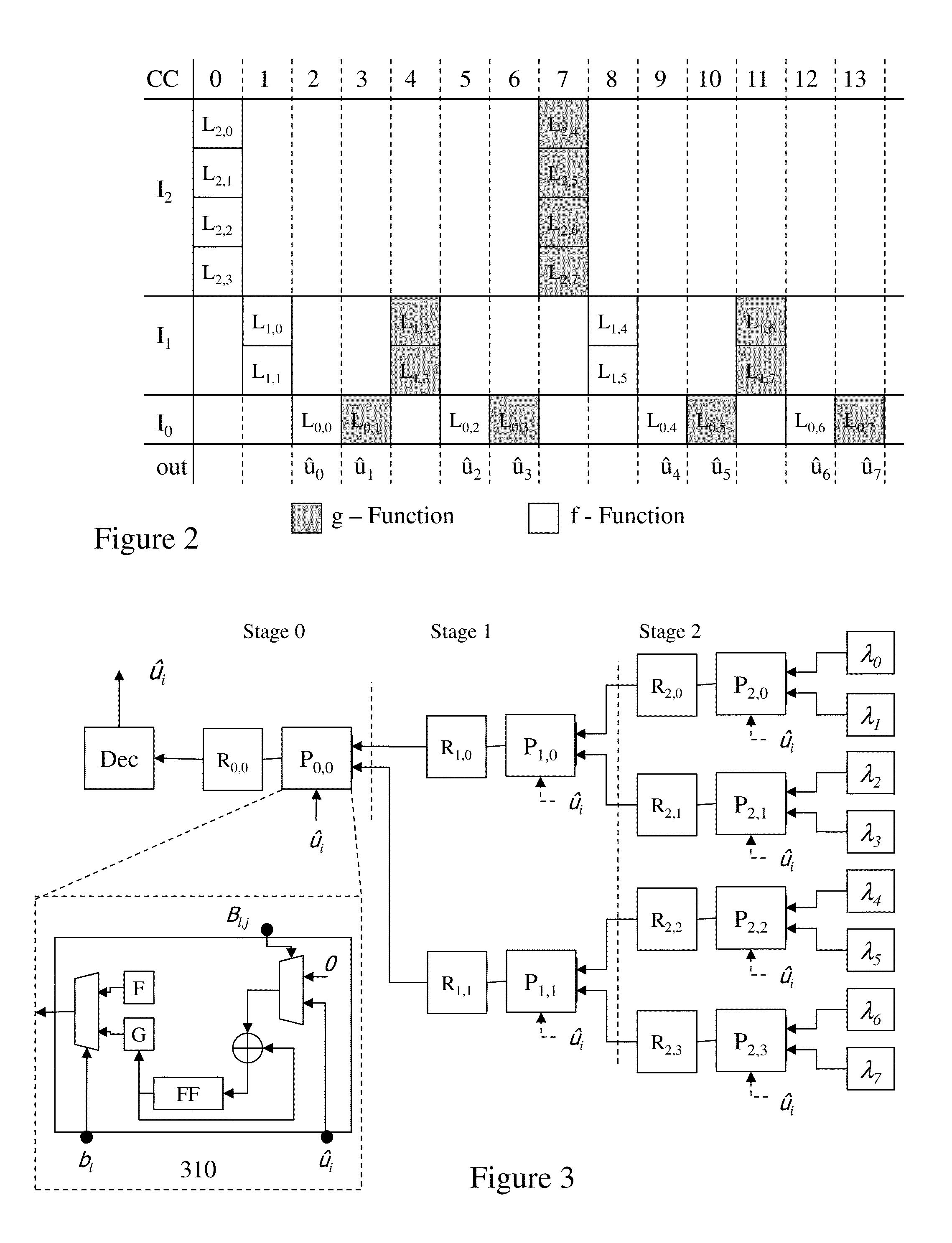

Methods and Systems for Decoding Polar Codes

ActiveUS20130117344A1Improve performanceMitigate such drawbackCode conversionError correction/detection using linear codesProcessing elementHardware implementations

Coding within noisy communications channels is essential but a theoretical maximum rate defines the rate at which information can be reliably transmitted on this noisy channel. Capacity-achieving codes with an explicit construction eluded researchers until polar codes were proposed. However, whilst asymptotically reaching channel capacity these require increasing code lengths, and hence increasingly complex hardware implementations. It would be beneficial to address architectures and decoding processes to reduce polar code decoder complexity both in terms of the number of processing elements required, but also the number of memory elements and the number of steps required to decode a codeword. Beneficially architectures and design methodologies established by the inventors address such issues whilst reducing overall complexity as well as providing methodologies for adjusting decoder design based upon requirements including, but not limited to, cost (e.g. through die area) and speed (e.g. through latency, number of cycles, number of elements etc).

Owner:THE ROYAL INSTITUTION FOR THE ADVANCEMENT OF TECH MCGILL UNIV +1

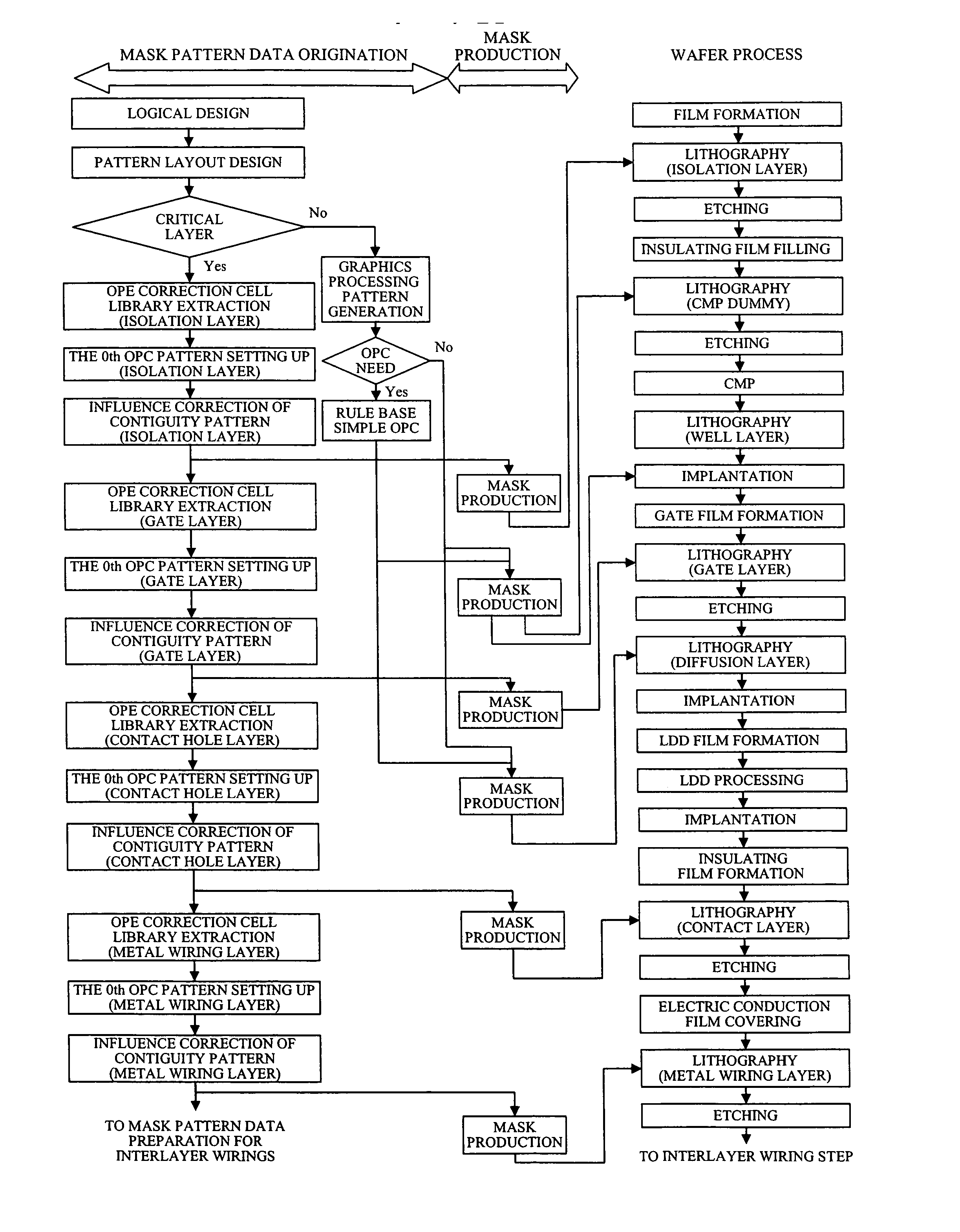

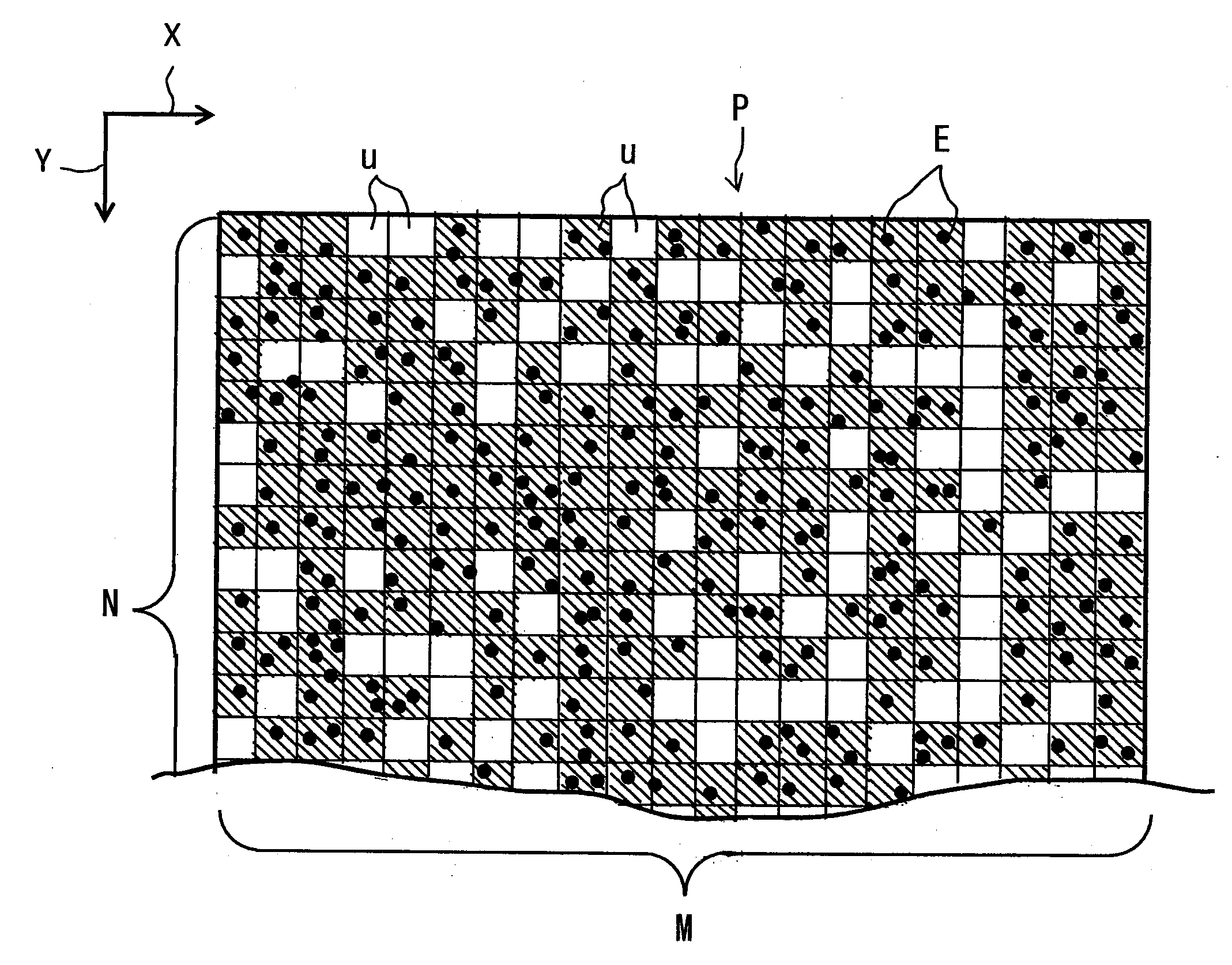

Mask pattern design method and manufacturing method of semiconductor device

InactiveUS20070074145A1Extended processing timeLower manufacturing requirementsOriginals for photomechanical treatmentSpecial data processing applicationsDevice materialSemiconductor chip

To a cell library pattern which makes the basic constitution of a semiconductor circuit pattern, OPC processing is performed beforehand, and a semiconductor chip is produced using this cell library pattern. Since it is influenced by the pattern of the cell arranged to the circumference and the pattern arranged around other cells at this time, correction processing (optimization processing) is performed. The part of this correction processing is a portion in which a pattern faces between cell boundaries in the inside of the region specified from the cell boundary, and proximity effect correction is performed by making the width, the length, and the position of this portion into variables. Or proximity effect correction is performed by making a polygon into a variable. Or sizing is done and proximity effect correction is performed.

Owner:RENESAS TECH CORP

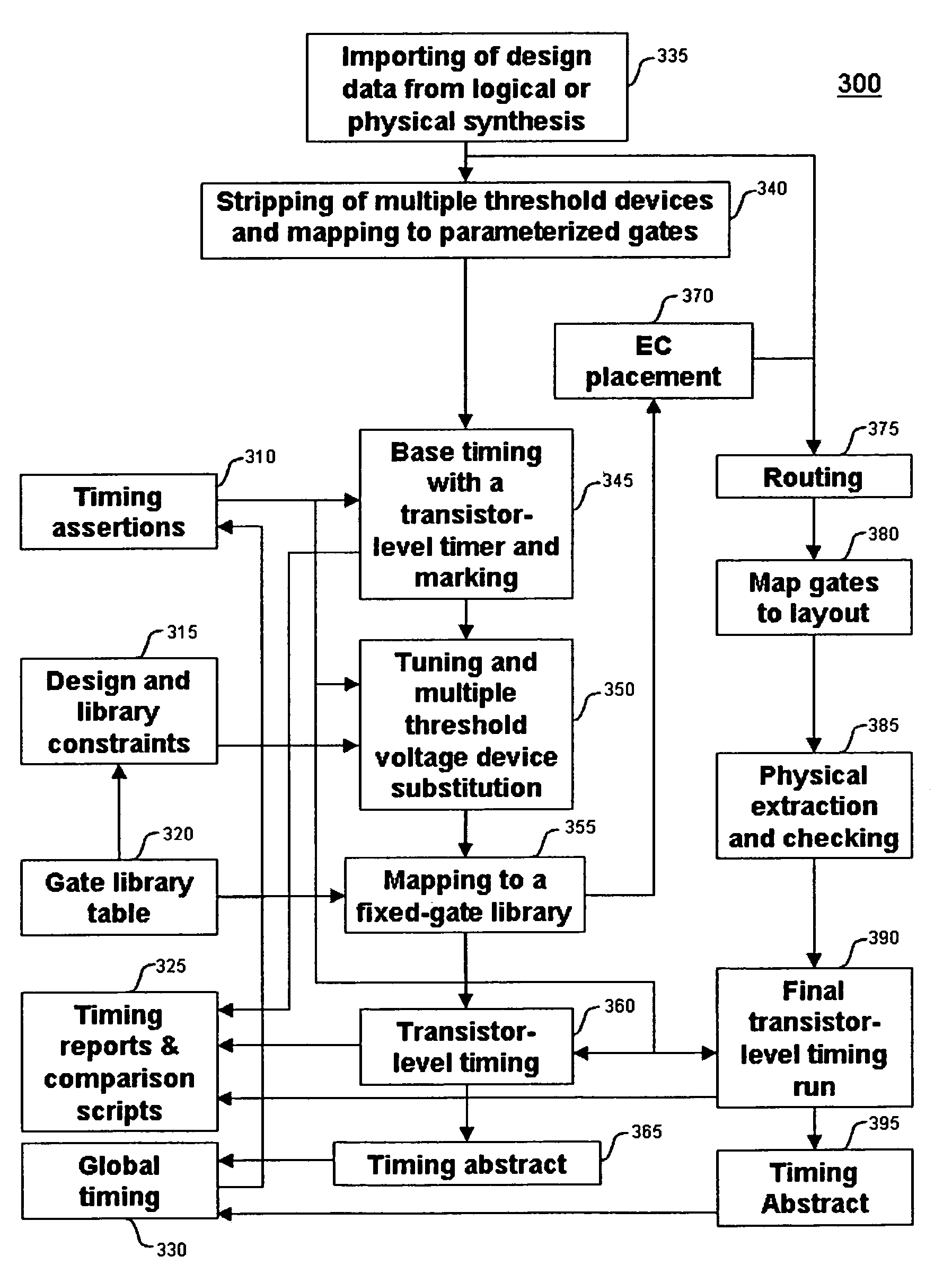

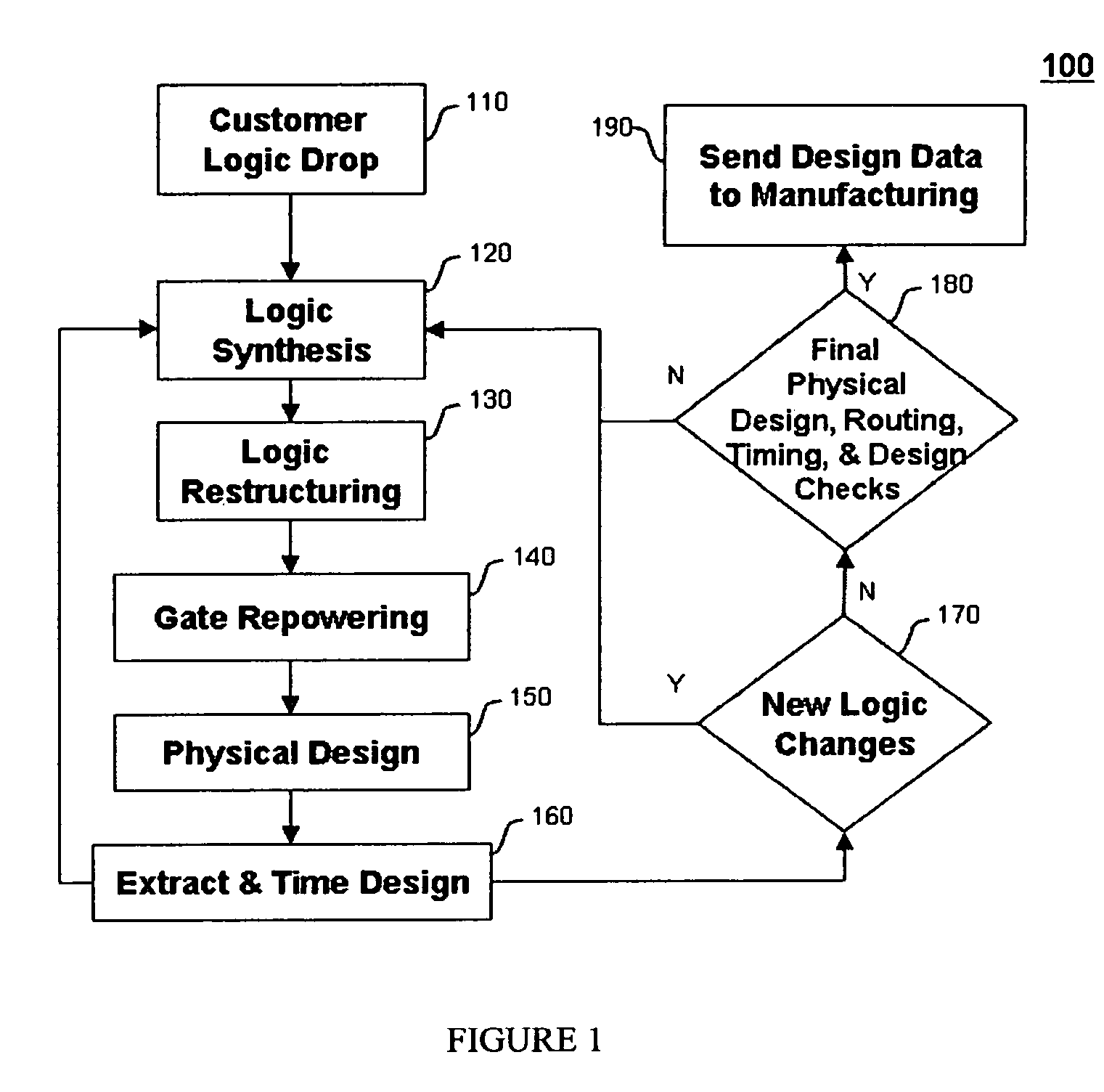

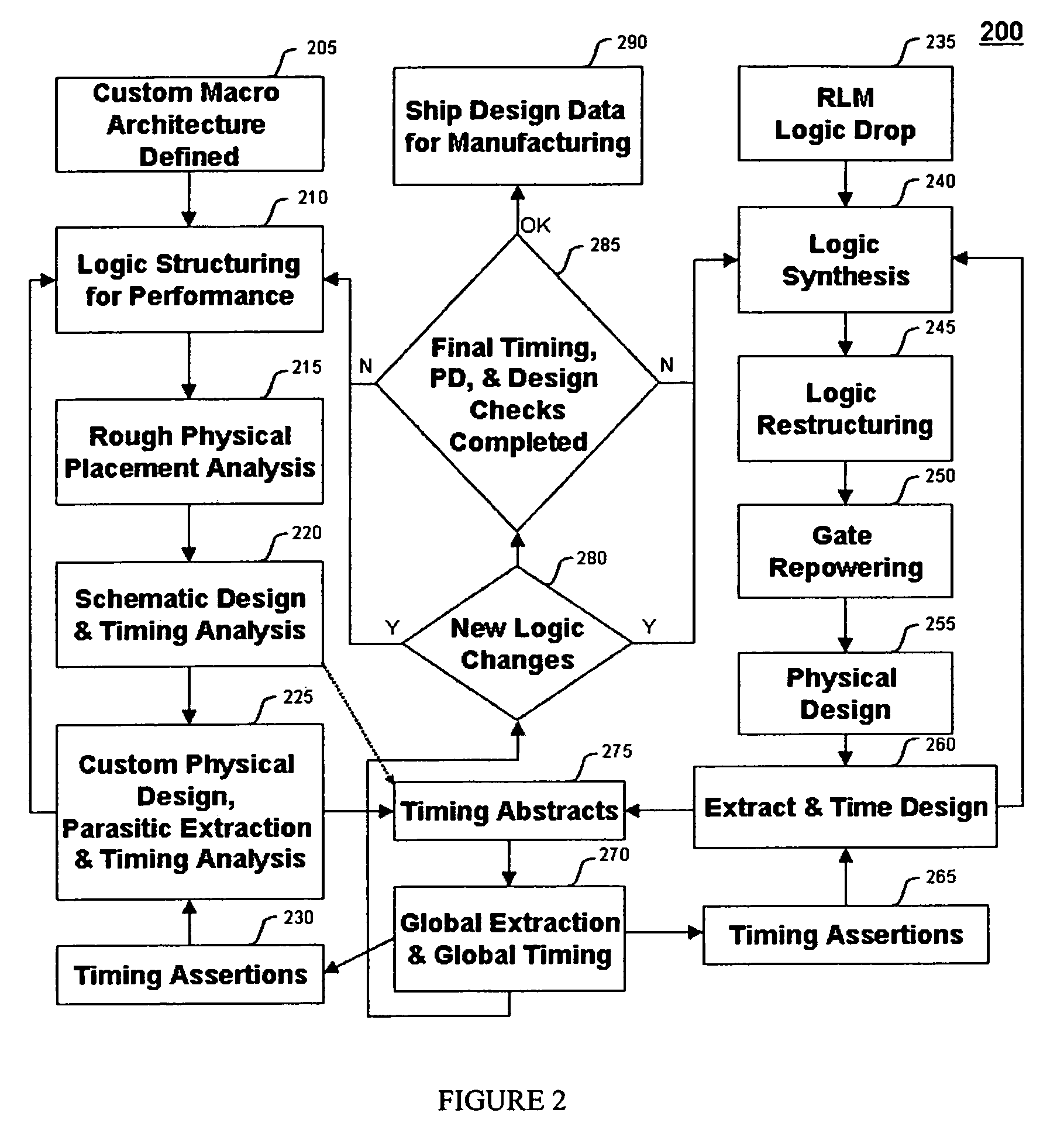

Method for tuning a digital design for synthesized random logic circuit macros in a continuous design space with optional insertion of multiple threshold voltage devices

InactiveUS7093208B2Efficient and effective methodologyError minimizationDigital storageComputer aided designContinuous designCritical section

A Digital Design Method which may be automated is for obtaining timing closure in the design of large, complex, high-performance digital integrated circuits. The methodincludes the use of a tuner on random logic macros that adjusts transistor sizes in a continuous domain. To accommodate this tuning, logic gates are mapped to parameterized cells for the tuning and then back to fixed gates after the tuning. Tuning is constrained in such a way as to minimize “binning errors” when the design is mapped back to fixed cells. Further, the critical sections of the circuit are marked in order to make the optimization more effective and to fit within the problem-size constraints of the tuner. A specially formulated objective function is employed during the tuning to promote faster global timing convergence, despite possibly incorrect initial timing budgets. The specially formulated objective function targets all paths that are failing timing, with appropriate weighting, rather than just targeting the most critical path. Finally, the addition of multiple threshold voltage gates allows for increased performance while limiting leakage power.

Owner:GLOBALFOUNDRIES INC

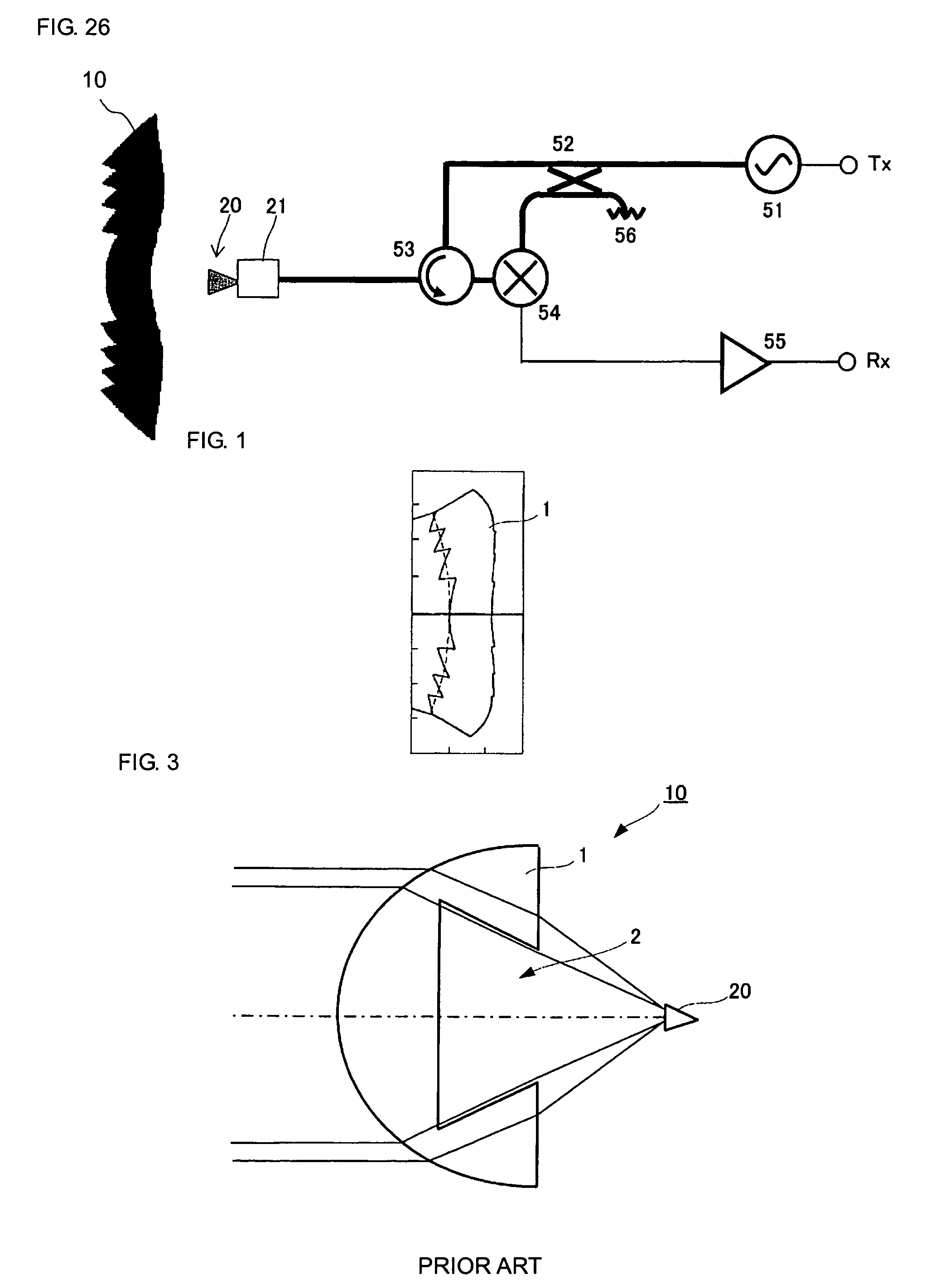

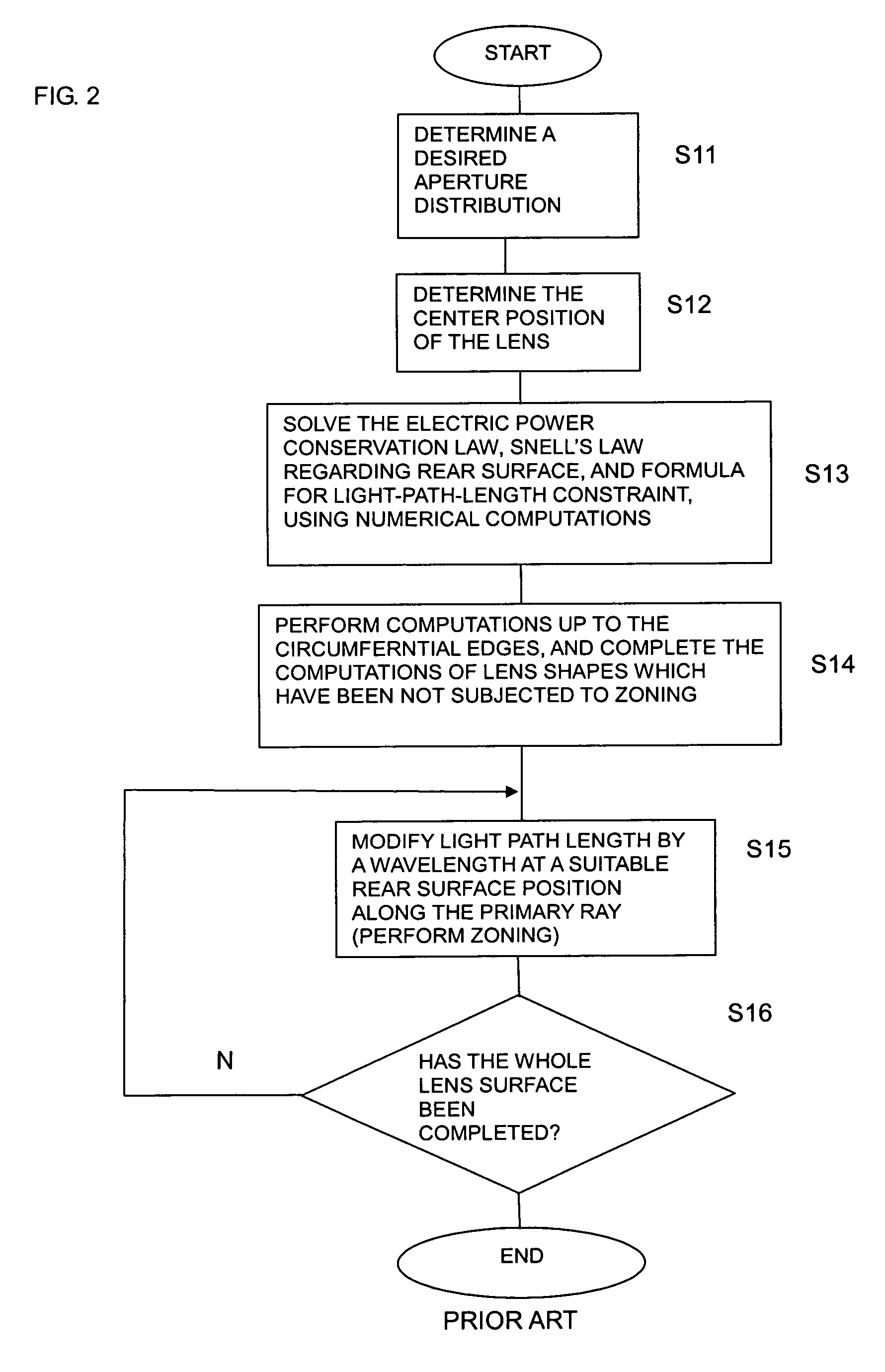

Dielectric lens, dielectric lens device, design method of dielectric lens, manufacturing method and transceiving equipment of dielectric lens

InactiveUS7355560B2Reduce weight and sizeEliminate the problemAntennasPath lengthSimultaneous equations

A design process first determines a desired aperture distribution, then converts the electric power conservation law, Snell's law on the rear face side of a dielectric lens, and the formula representing light-path-length constraint, into simultaneous equations, and computes the shapes of the surface and rear face of the dielectric lens depending on the azimuthal angle θ of a primary ray from the focal point of the dielectric lens to the rear face of the dielectric lens, and then reduces the light path length in the formula showing light-path-length constraint by an integral multiple of the wavelength when the coordinates on the surface of the dielectric lens reach a predetermined restriction thickness position. A dielectric lens is designed by sequentially changing the lazimuthal angle θ from its initial value, and also repeating the second and third steps. Thus, downsizing and quantification is realized by zoning while keeping antenna properties at the time of constituting a dielectric lens antenna in a good condition.

Owner:MURATA MFG CO LTD

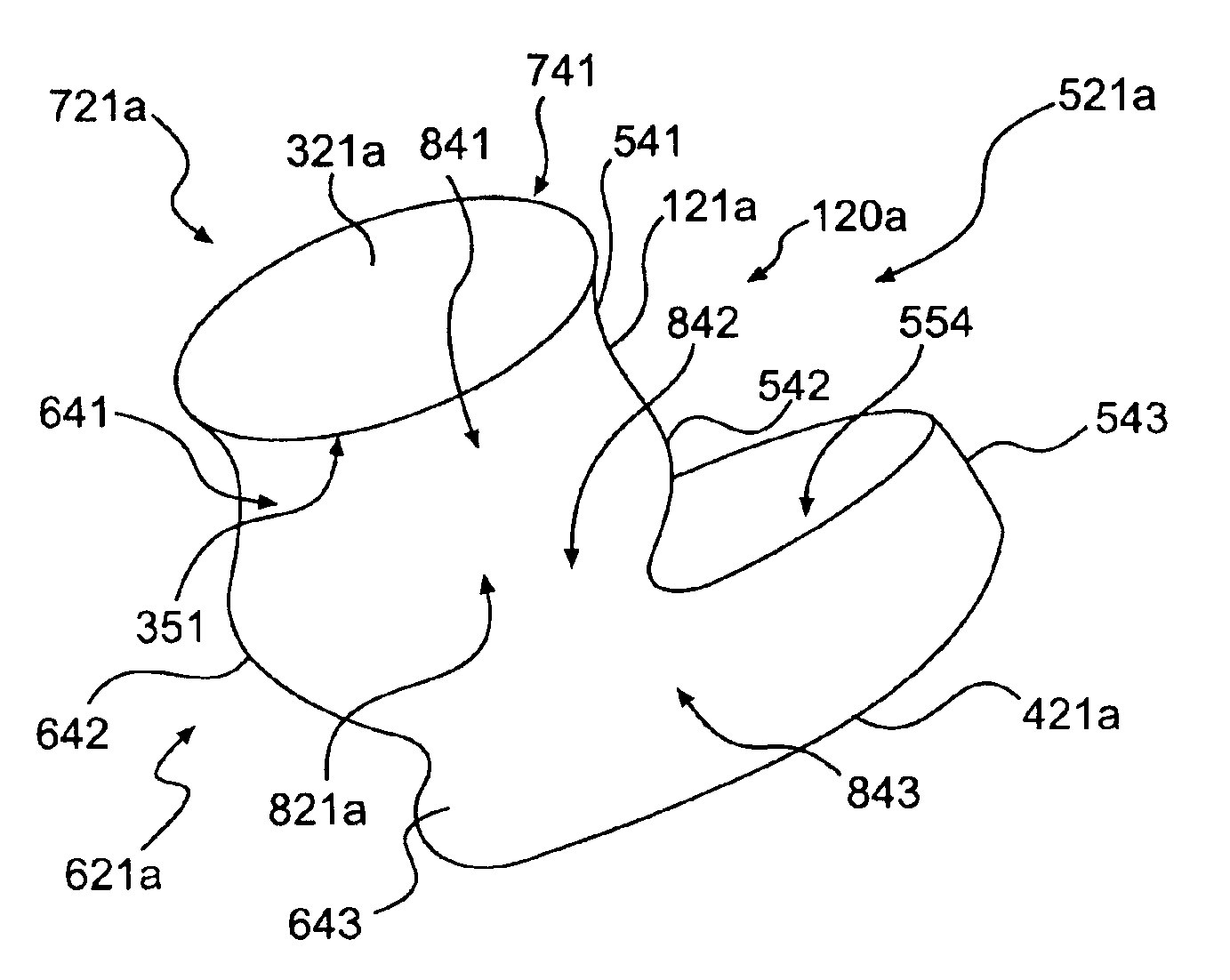

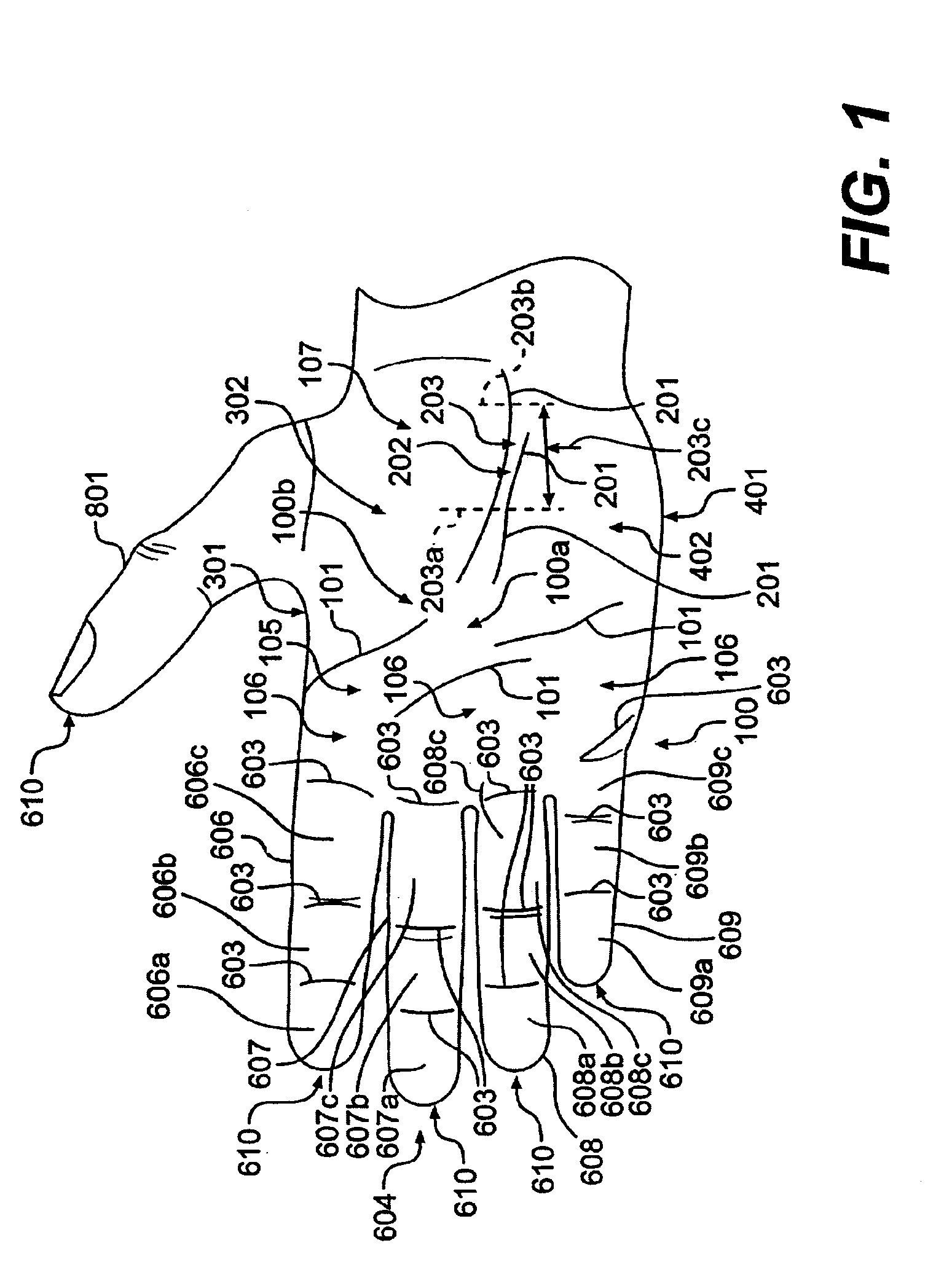

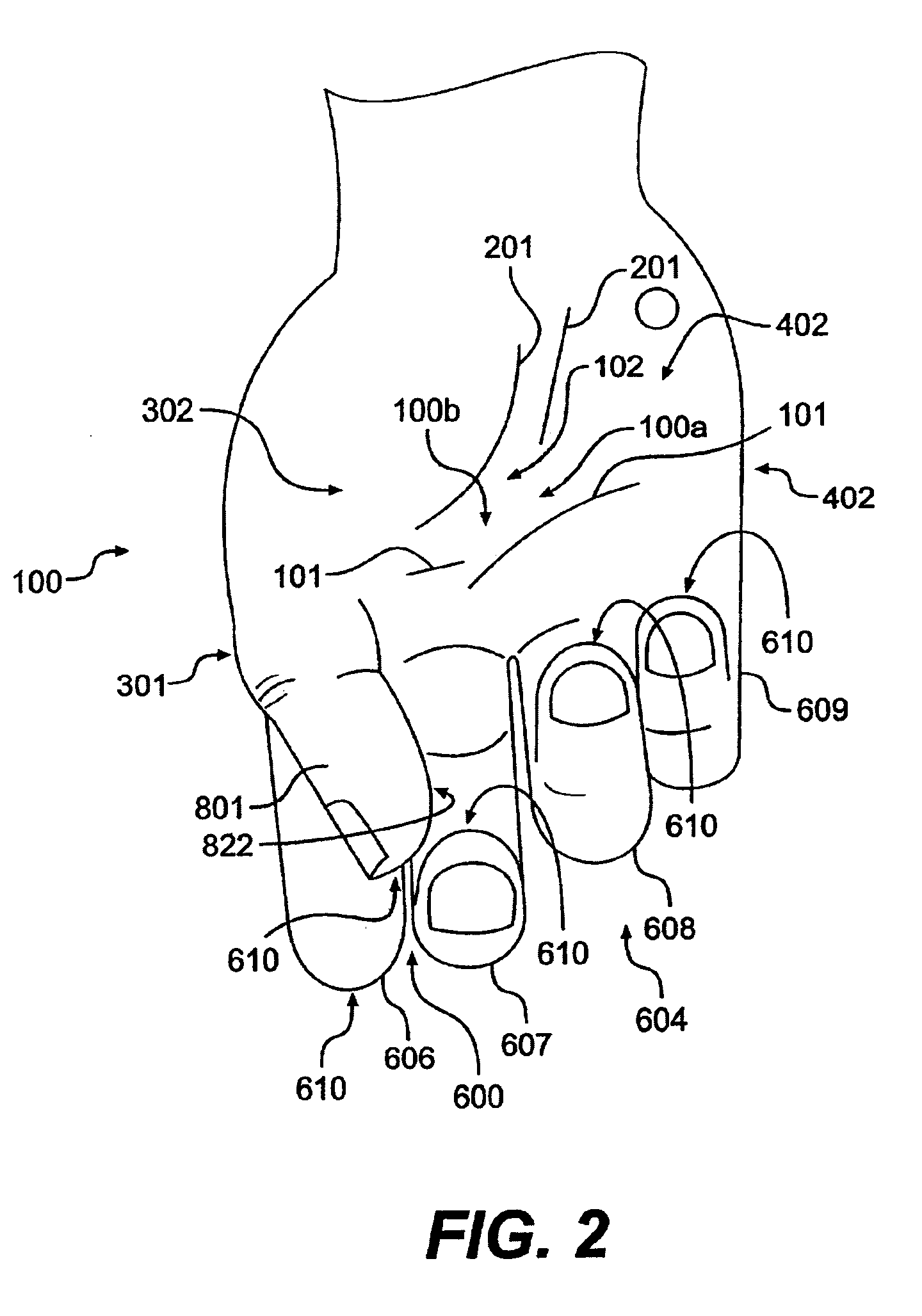

Handle/grip and method for designing the like

The present invention provides a design method and apparatus for a handle or grip providing a shape and structure that fills various regions of the hand except a region in an area over the underlying carpal tunnel. Such design method and apparatus provides for various supports and handles for use by a hand. In particular, the apparatus includes a generally boot-shaped body or portions thereof. The body or body portions include a radial section, an ulnar section and middle section. Furthermore the body has a distal (frontal) finger side, proximal (back) side, palmar side and a thumb side. The body also has radial and ulnar sides. These portions are shaped to engage the various corresponding regions of the inner surface of the hand. These sections and sides forming the body can be divided and used separately for individual applications of the present invention.

Owner:TILLIM STEPHEN L

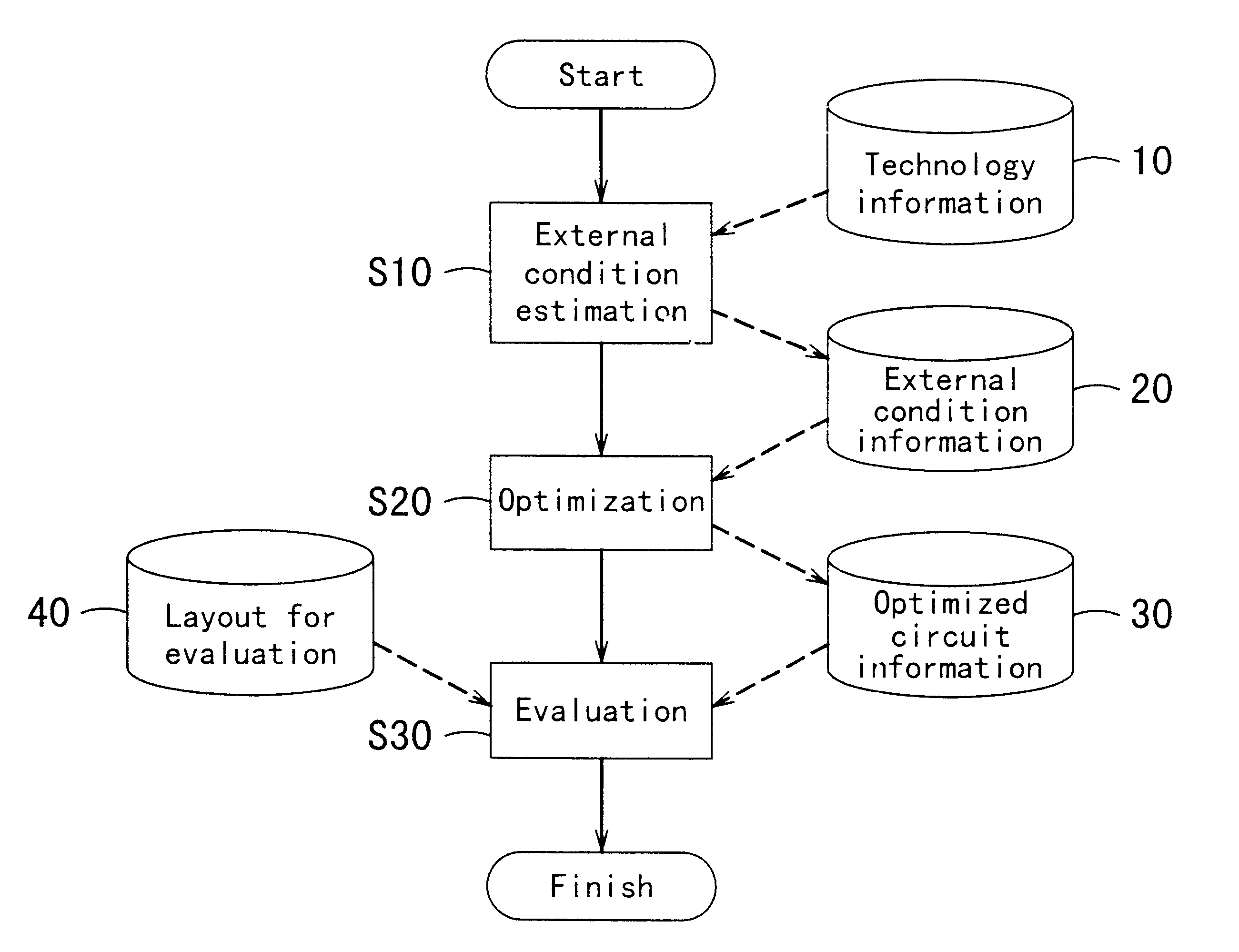

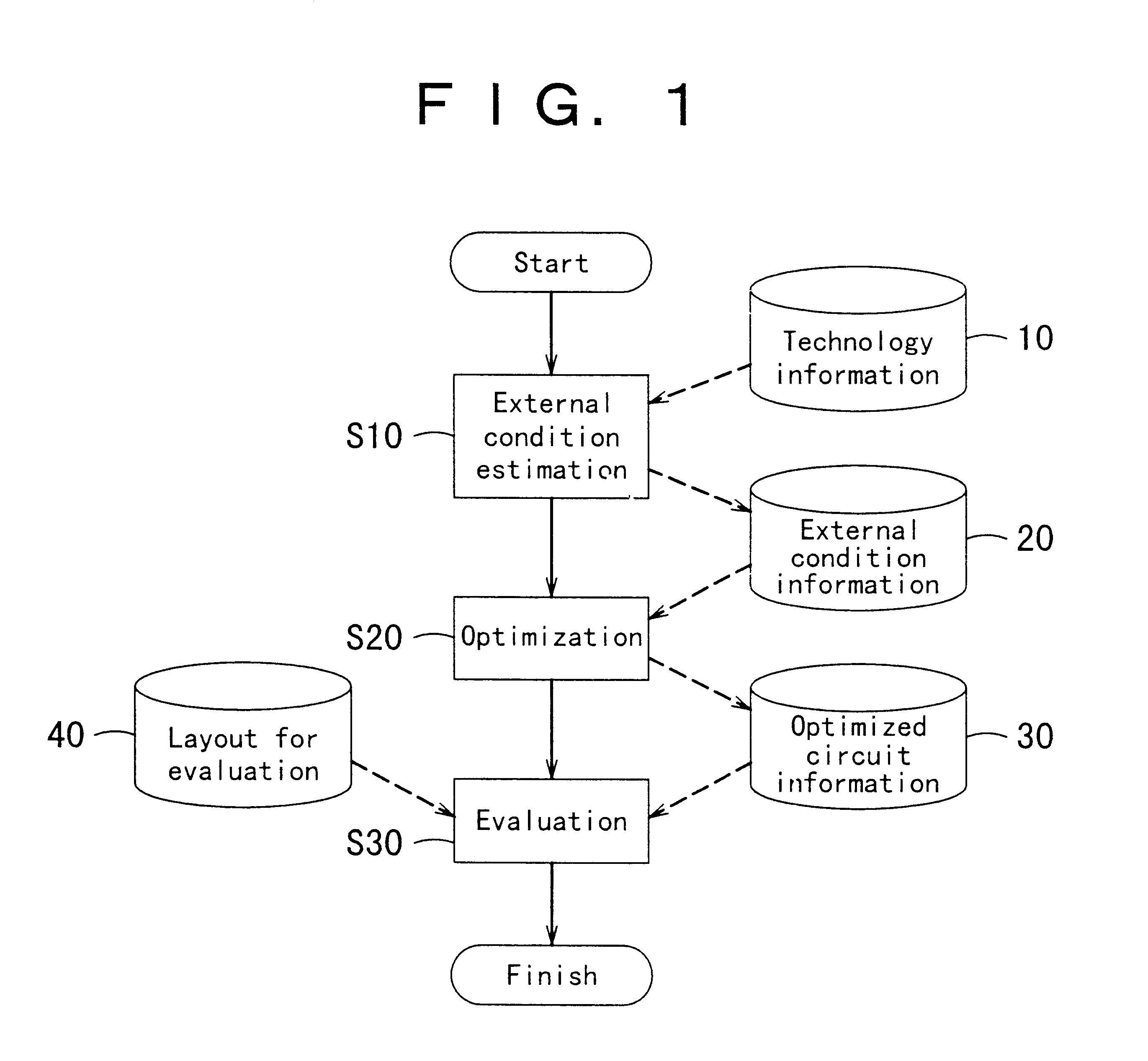

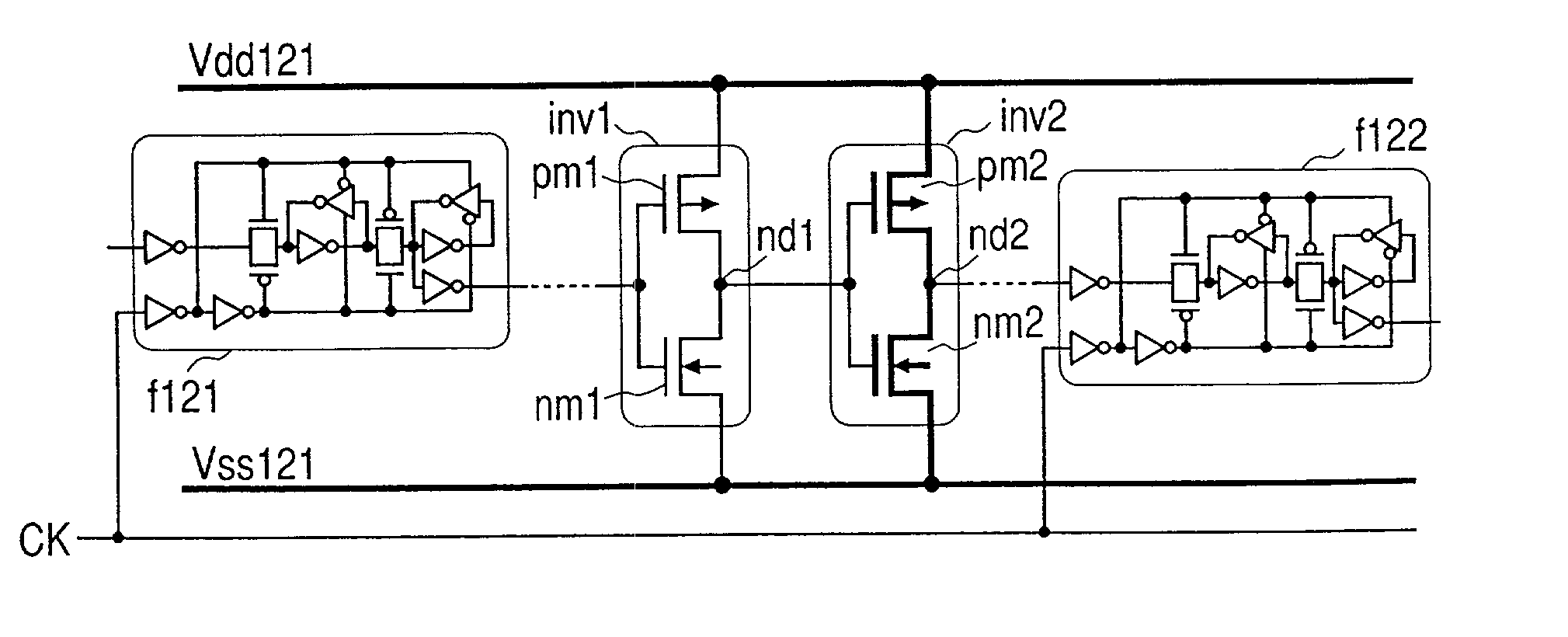

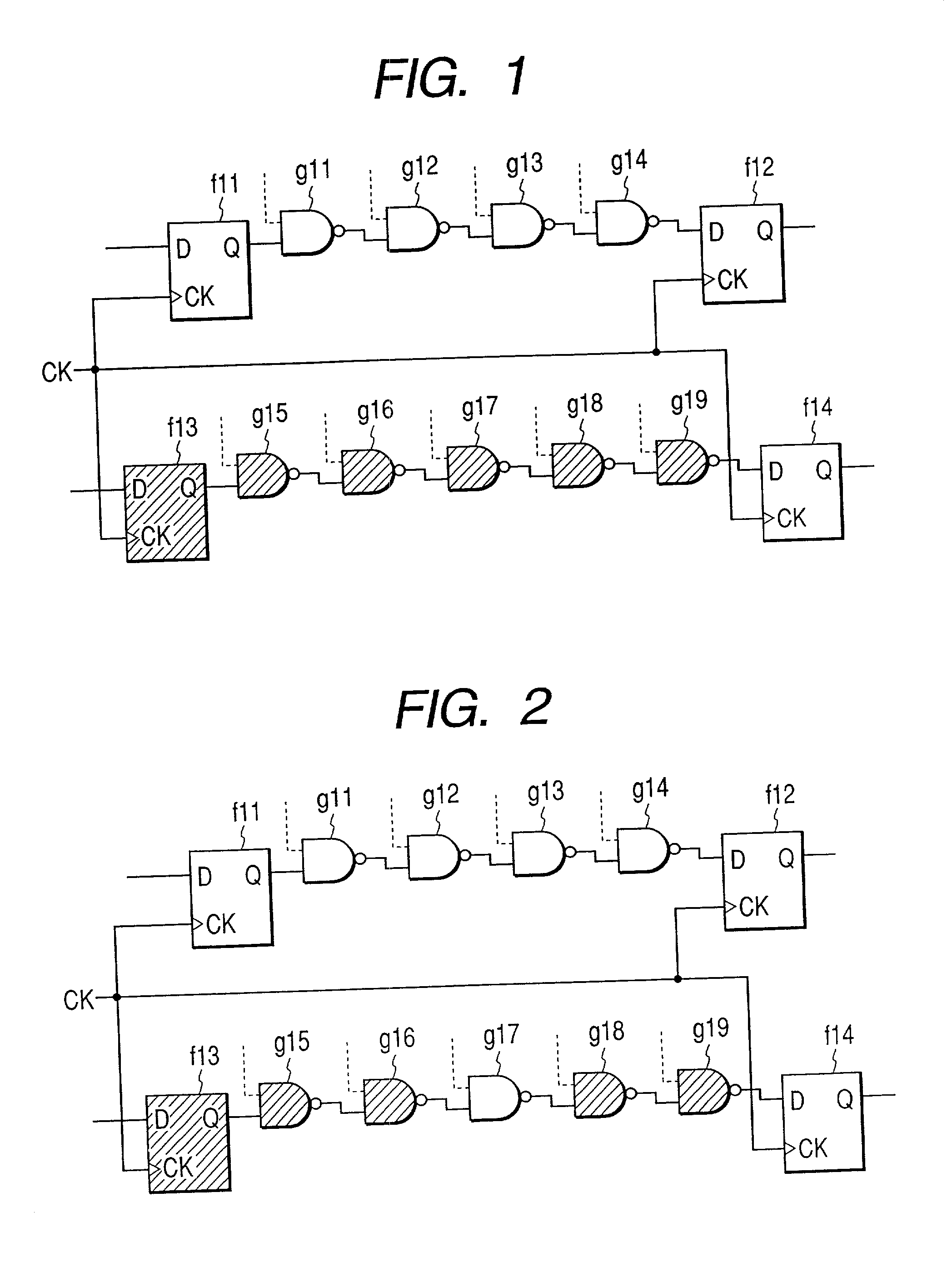

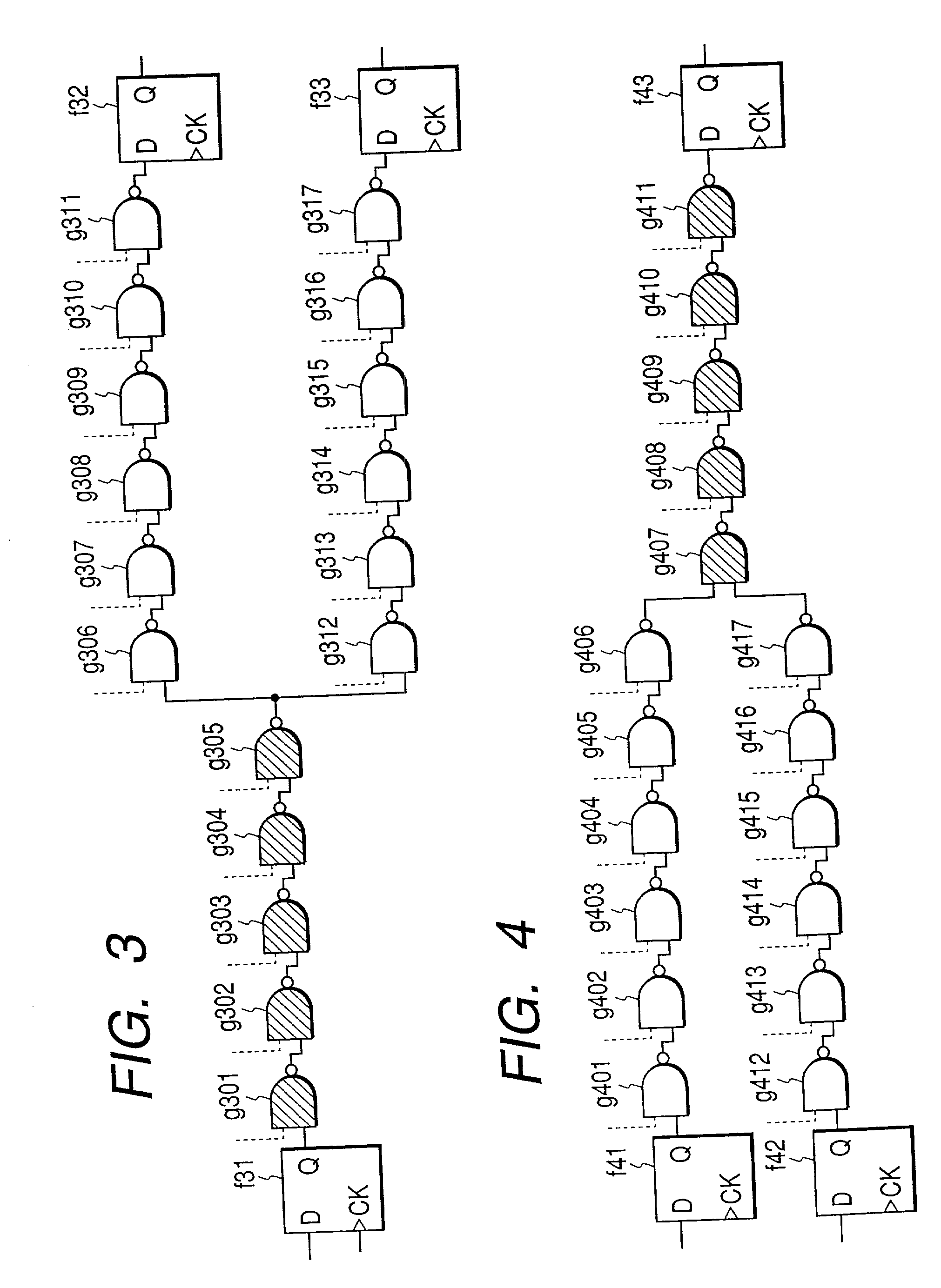

Method for design of partial circuit

InactiveUS6553544B2Easily and precisely estimateAvoid difficult choicesCAD circuit designSoftware simulation/interpretation/emulationEngineeringDesign objective

There is no conventional method for precisely estimating under what external conditions each partial circuit, such as a library cell, is utilized in an actual integrated circuit at the time of designing the partial circuit. Therefore, by estimating the external conditions of a partial circuit when used in an integrated circuit so that the partial circuit is designed in accordance with the external conditions, the partial circuit having optimal performance for the external conditions can be designed. The step of external condition estimation can be formed so as to include the technology conversion step which technologically converts the layout for external condition extraction, that is prepared in advance, based on the technology information of an integrated circuit, which is the design objective; the layout extraction step of extracting layout extraction information which is external information influencing the operation of the partial circuit from the layout for external condition extraction that has been technologically converted; and the external condition calculation step of calculating external conditions of the partial circuit from the layout extraction information. In addition, by simply replacing the designed partial circuit with a partial circuit of a circuit for evaluation, the evaluation of the designed partial circuit can be easily carried out.

Owner:PANASONIC CORP

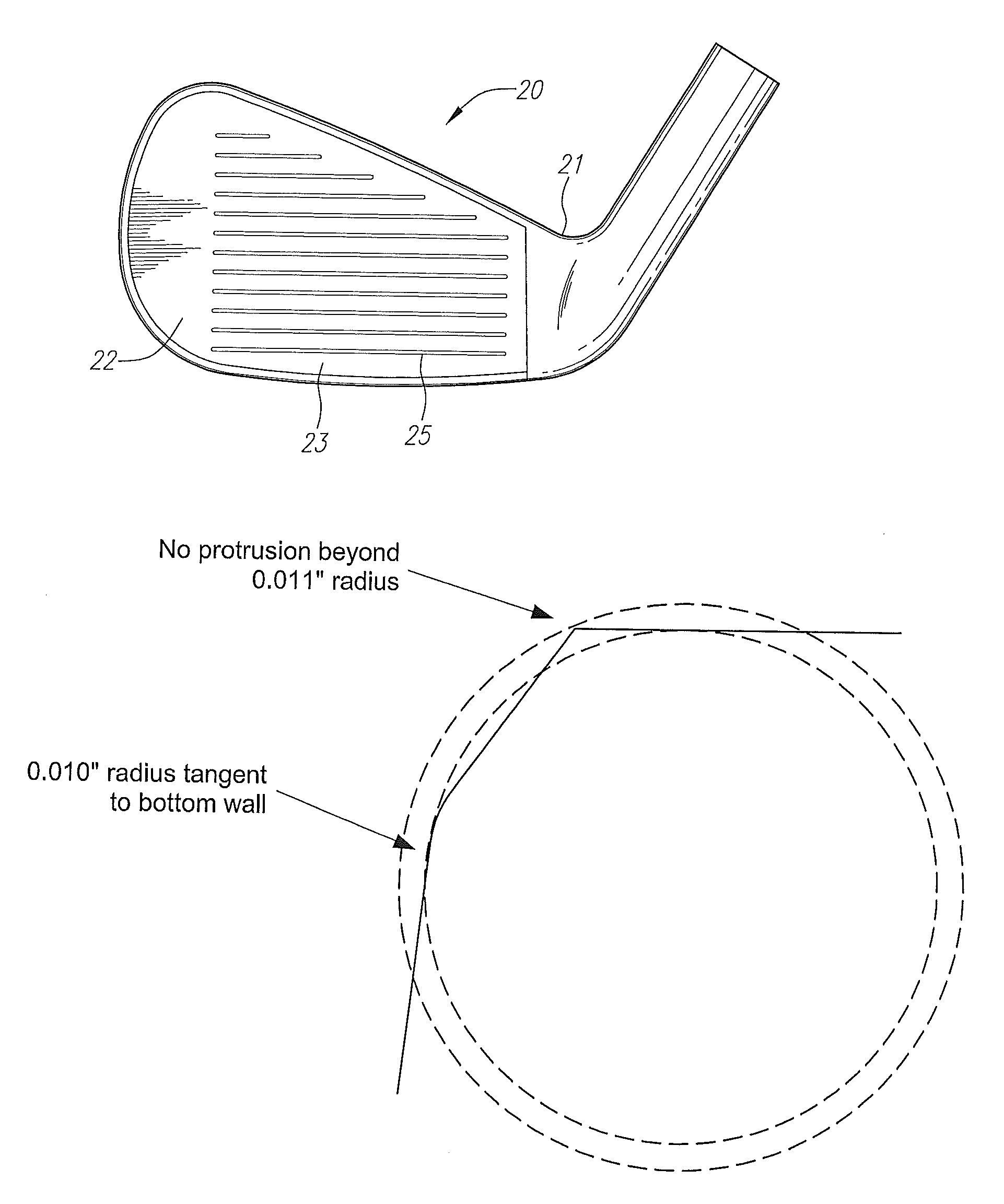

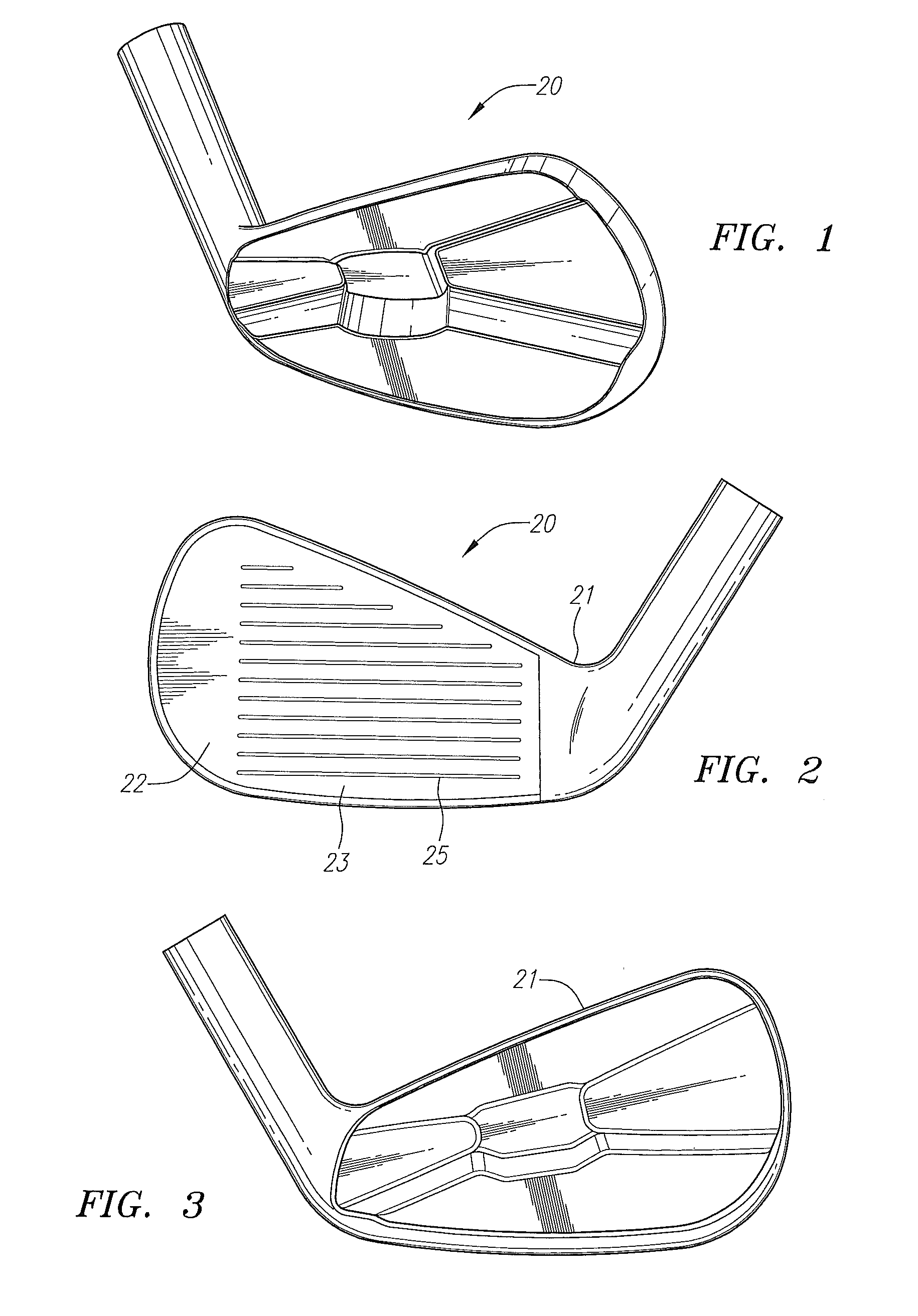

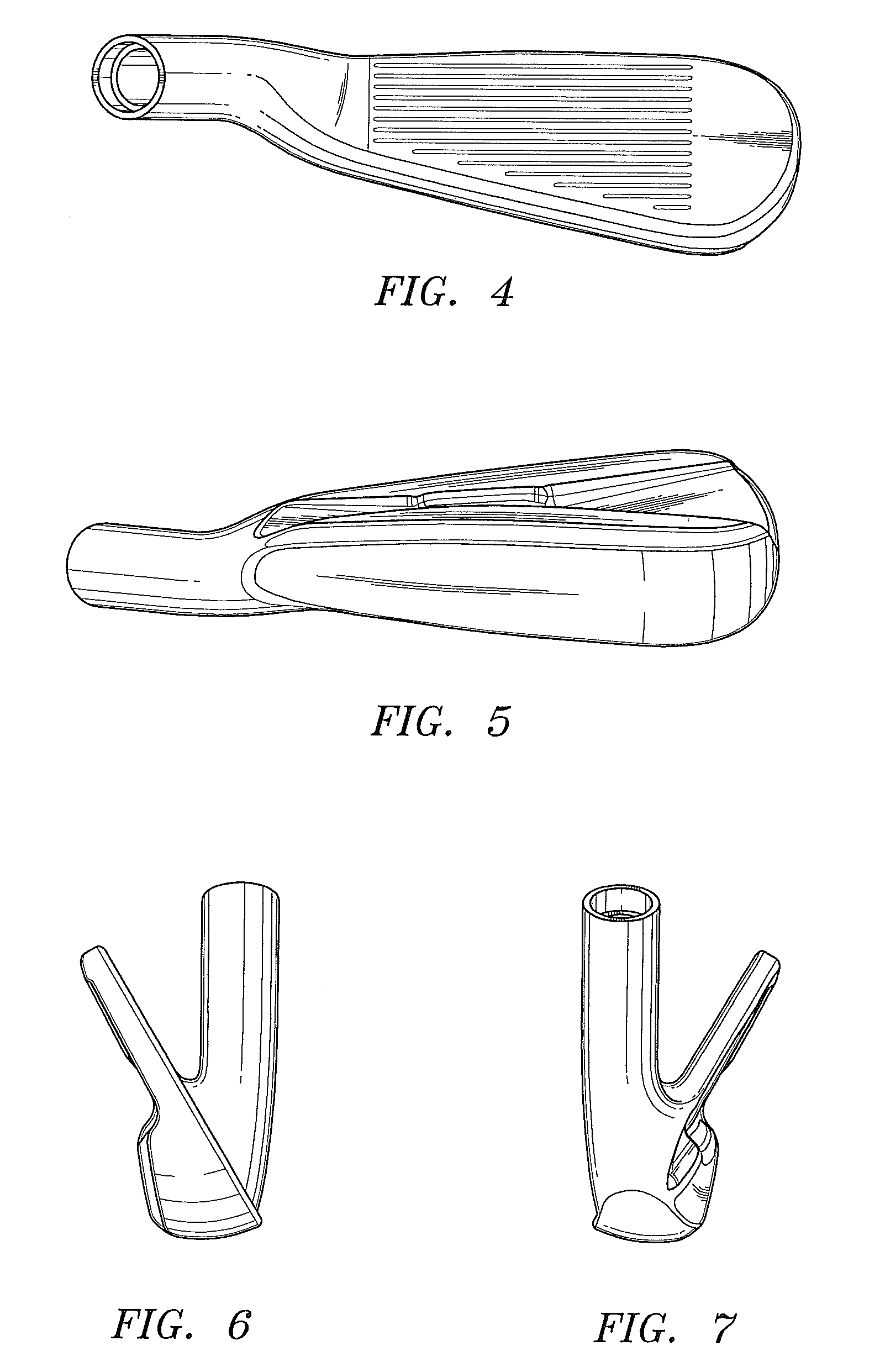

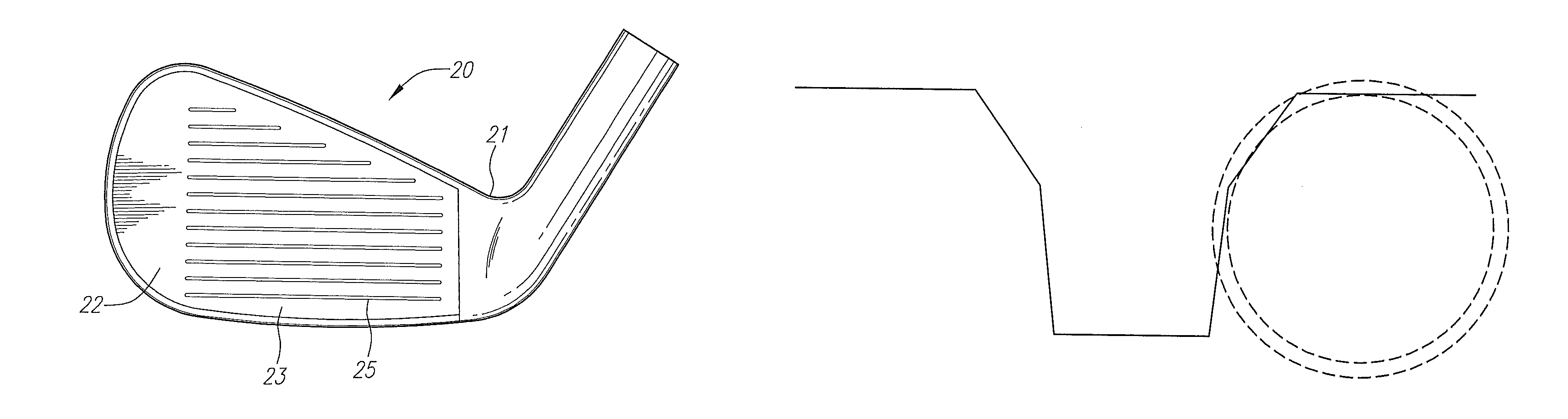

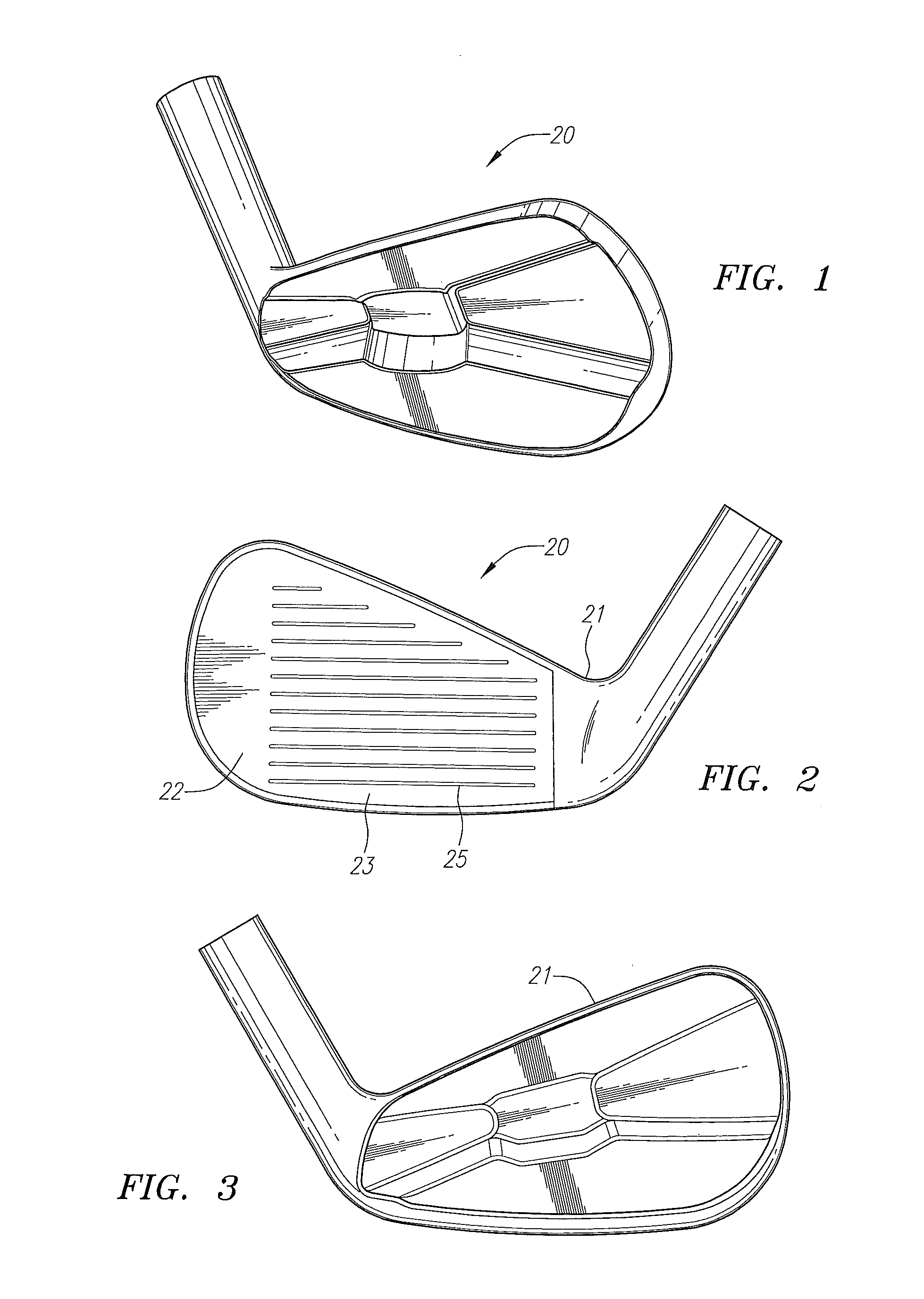

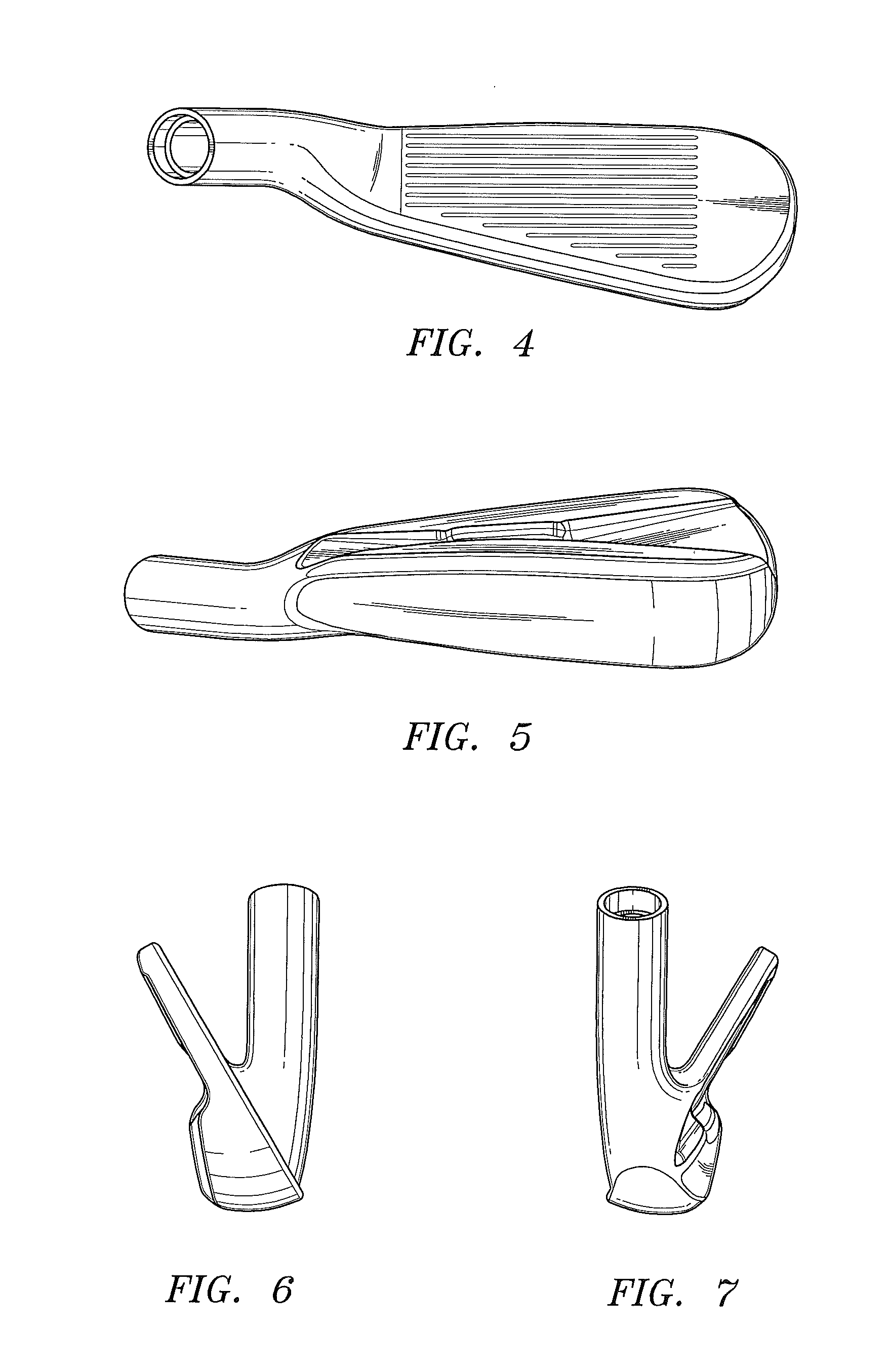

Iron-type golf club head with groove profile in ceramic face

The present invention provides a method of manufacture and design such that very small detail features can be produced within the groove profile on an iron or wedge. The advantage in being able to do this is that spin will be enhanced for a variety of shot types and conditions when striking a golf ball with cover composed of a urethane-based material.

Owner:TOPGOLF CALLAWAY BRANDS CORP

Iron-type golf club head with groove profile in ceramic face

The present invention provides a method of manufacture and design such that very small detail features can be produced within the groove profile on an iron or wedge. The advantage in being able to do this is that spin will be enhanced for a variety of shot types and conditions when striking a golf ball with cover composed of a urethane-based material.

Owner:TOPGOLF CALLAWAY BRANDS CORP

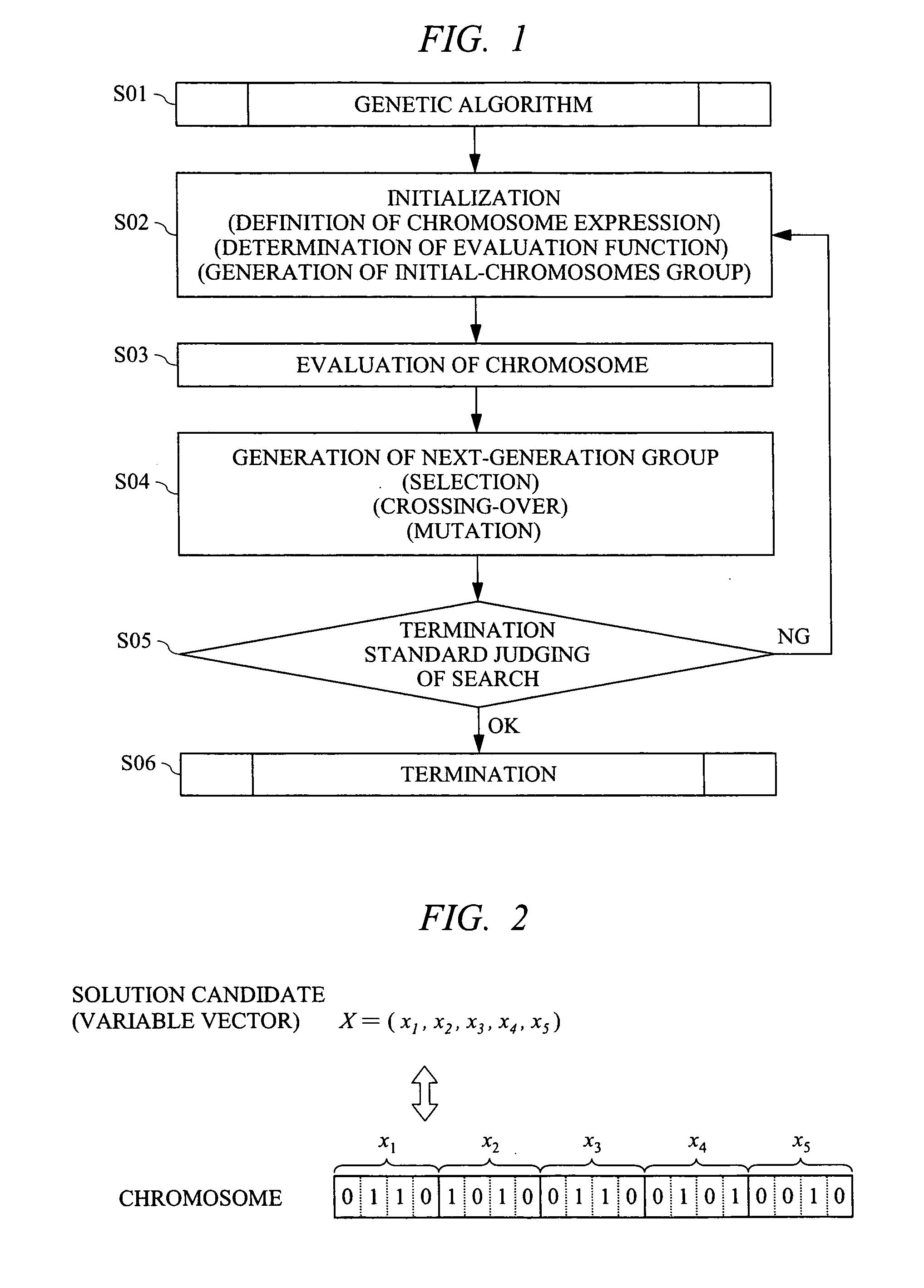

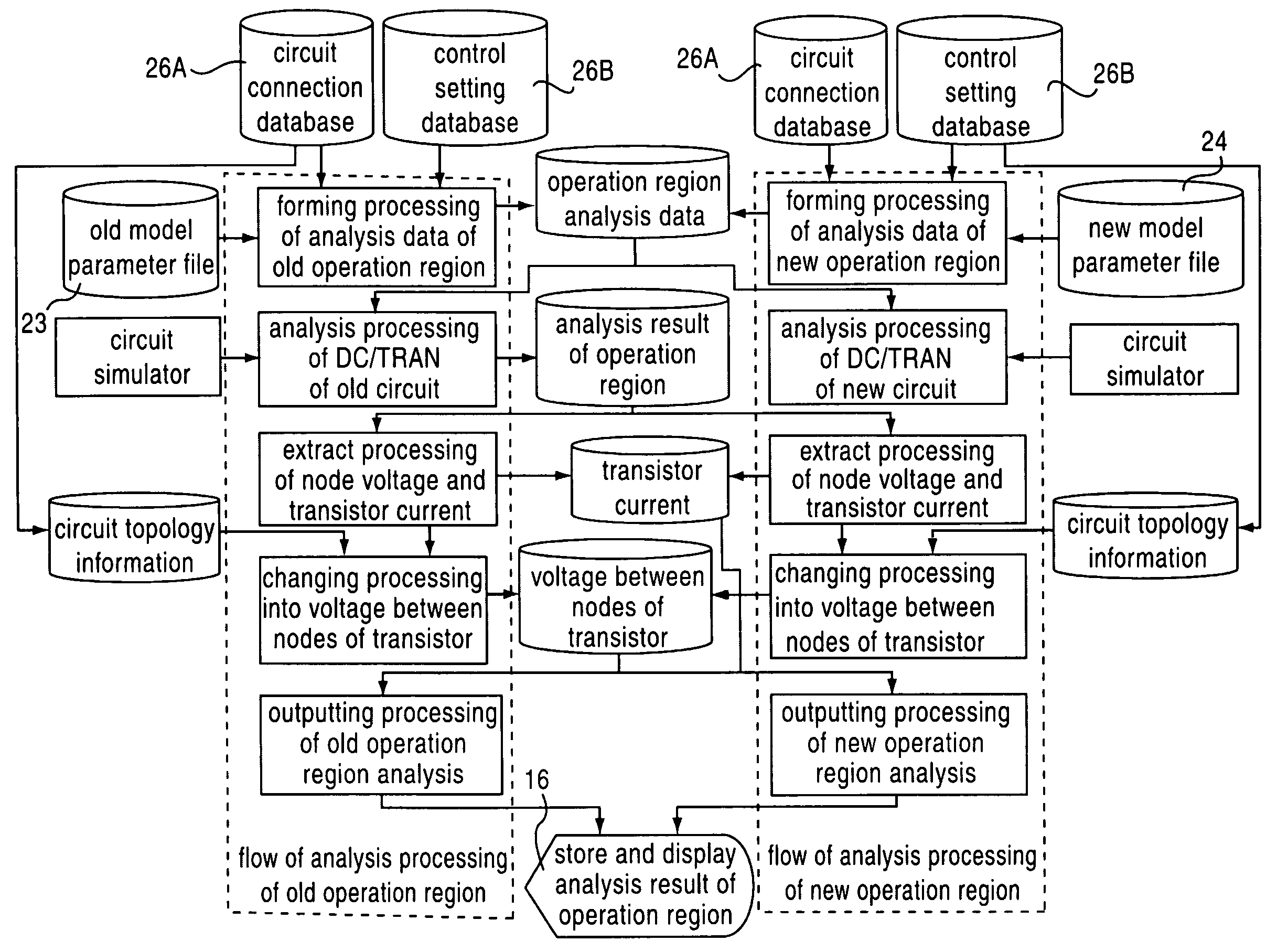

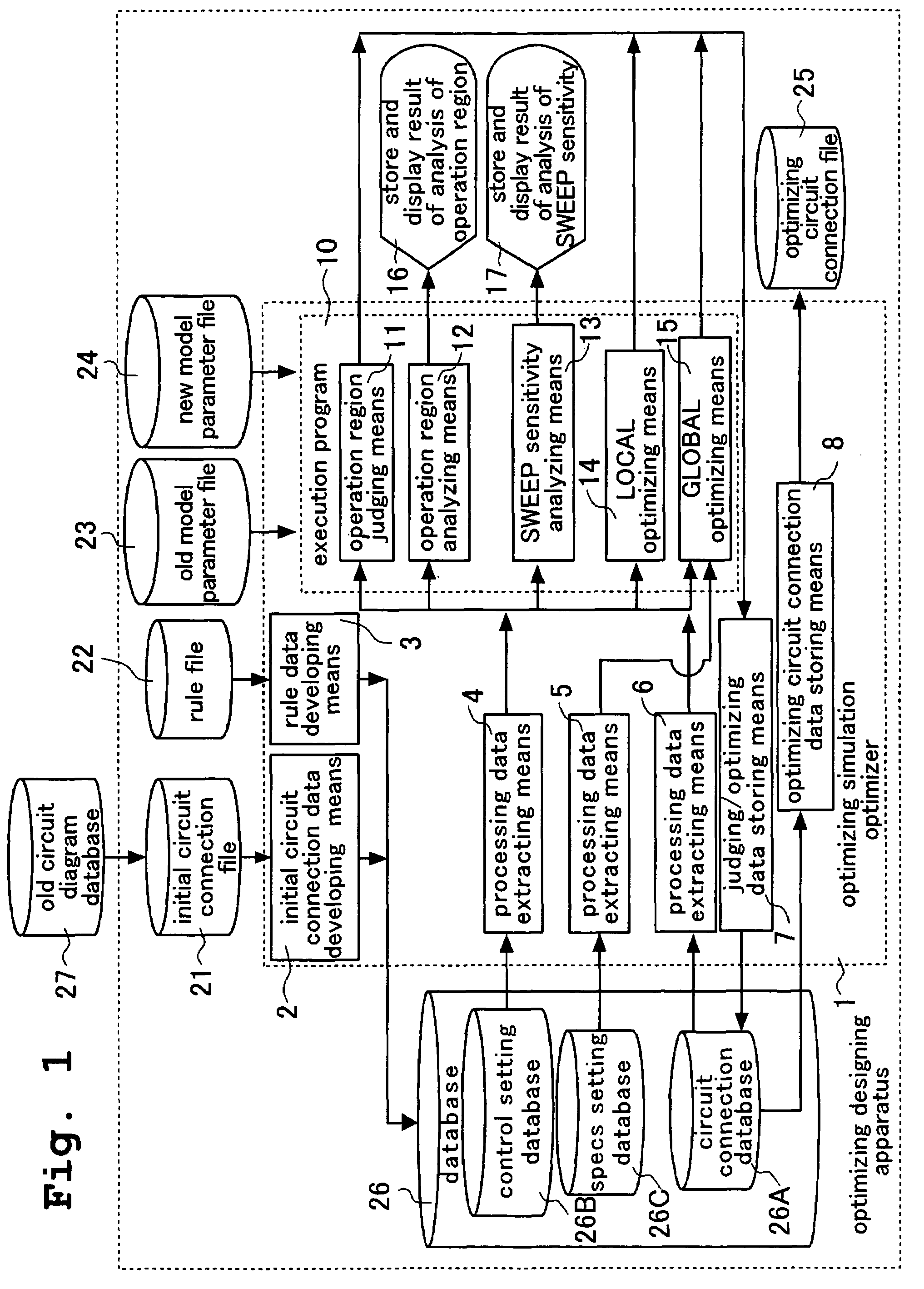

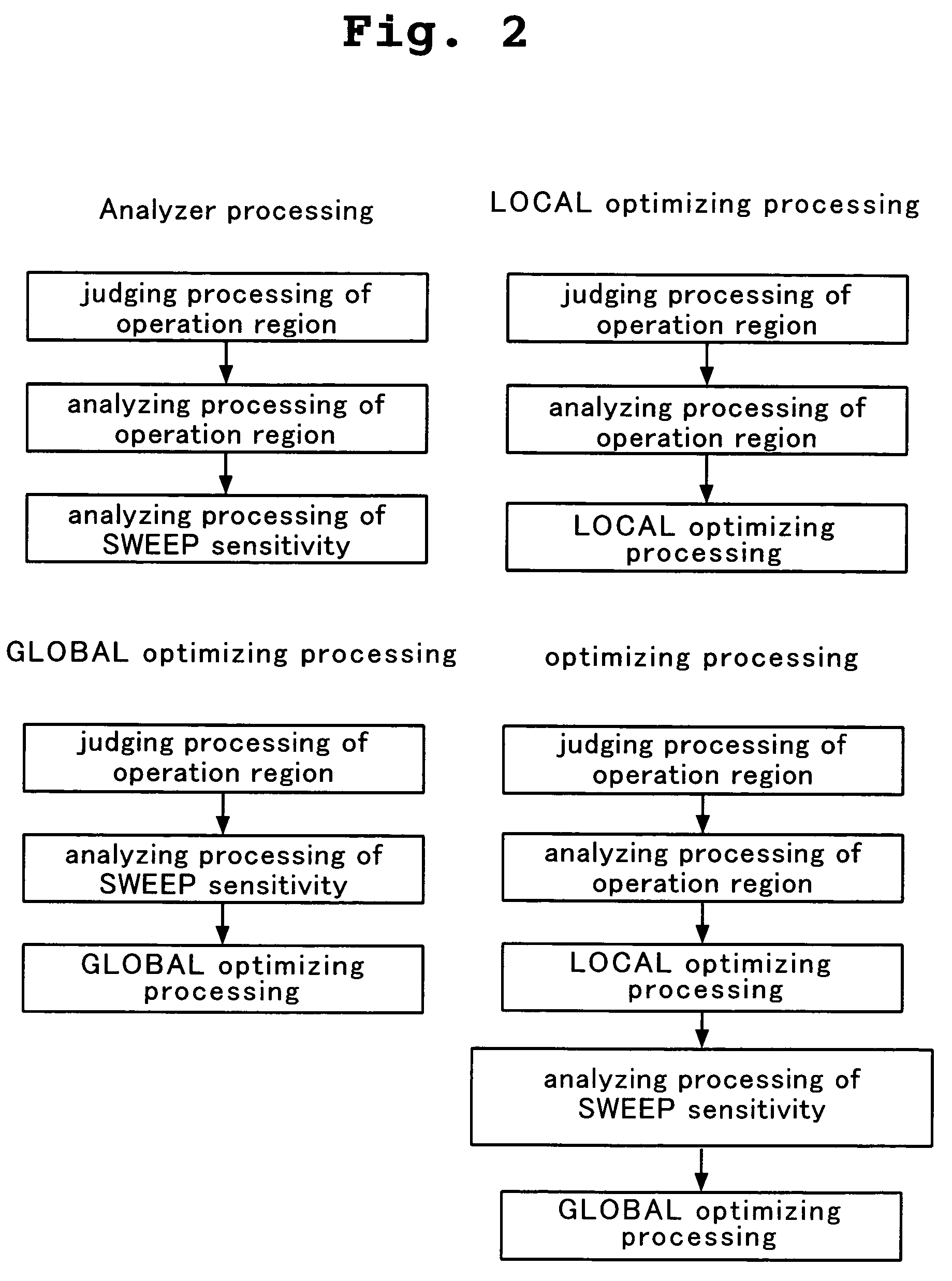

Optimizing designing apparatus of integrated circuit, optimizing designing method of integrated circuit, and storing medium in which program for carrying out optimizing designing method of integrated circuit is stored

ActiveUS7155685B2Easy to carryAnalogue computers for electric apparatusSemiconductor/solid-state device manufacturingLinear regionRegion analysis

It is an object of the present invention to provide a method, an apparatus and a program having high optimization precision and capable of obtaining an answer required by a designer in a short time by combining optimization between individual transistors and optimization as the entire circuit, or by appropriately combining judgment of an operation region, an analysis of the operation region and a SWEEP sensitivity analysis when the optimization is carried out. An optimizing designing apparatus of an integrated circuit for designing a circuit, comprises operation region judging means for adjusting an operation region (linear region, saturation region) of the circuit, operation region analysis means for displaying liner characteristics (Ids-Vgs characteristics) of the circuit and saturation characteristics (Ids-Vds characteristics) of the circuit, and SWEEP sensitivity analysis means for displaying variation in output characteristics of the circuit.

Owner:ABLIC INC

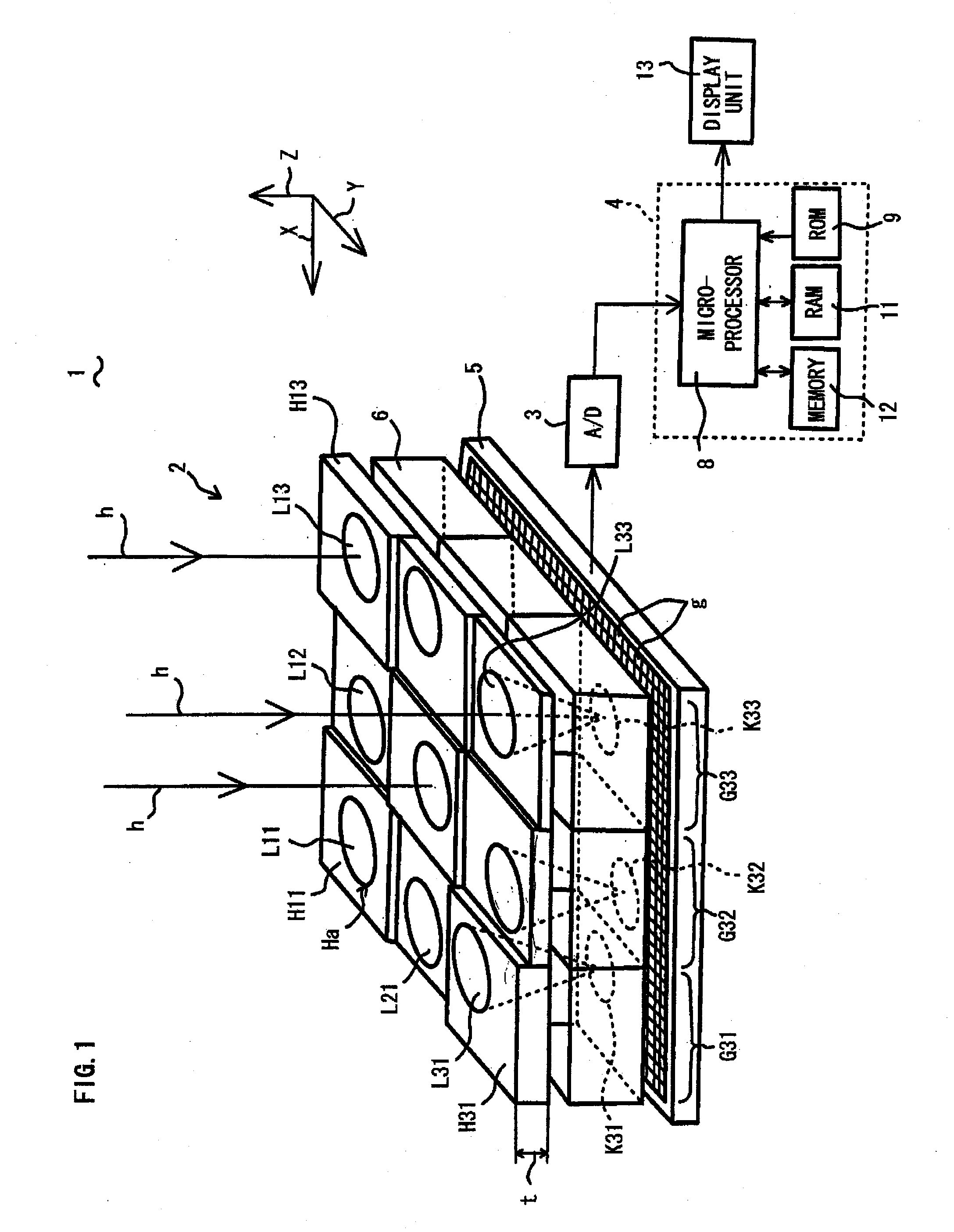

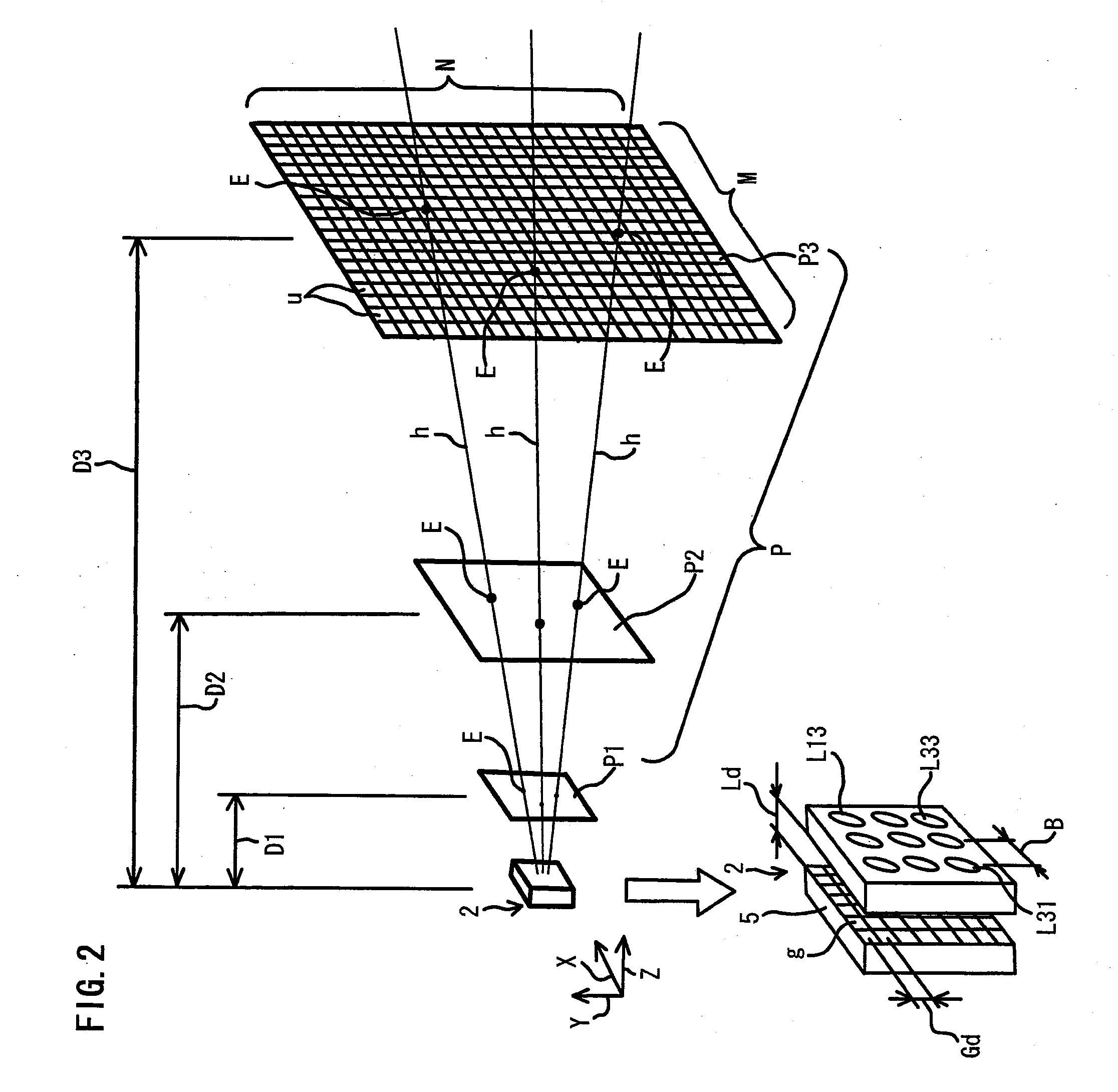

Optical Condition Design Method for a Compound-Eye Imaging Device

InactiveUS20100053600A1Cutting portionHigh definitionTelevision system detailsSolid-state devicesObservation pointHigh definition

An imaginary object plane is set in front of an imaging device body (plane setting step). A part of optical conditions of optical lenses are changed as variables, and positions of points (pixel observation points) on the imaginary object plane where lights coming from pixels of a solid-state imaging element and back-projected through the optical lenses are calculated (pixel observation point calculating step). The dispersion in position of the calculated pixel observation points is evaluated (evaluating step). Finally, a set of values of the variables giving maximum evaluated dispersion of the calculated pixel observation points is determined as optimum optical condition of the optical lenses (condition determining step). This reduces the number of pixels which image the same portions of the target object, making it possible to reduce portions of the same image information in multiple unit images, and to stably obtain a reconstructed image having a high definition.

Owner:FUNAI ELECTRIC CO LTD +1

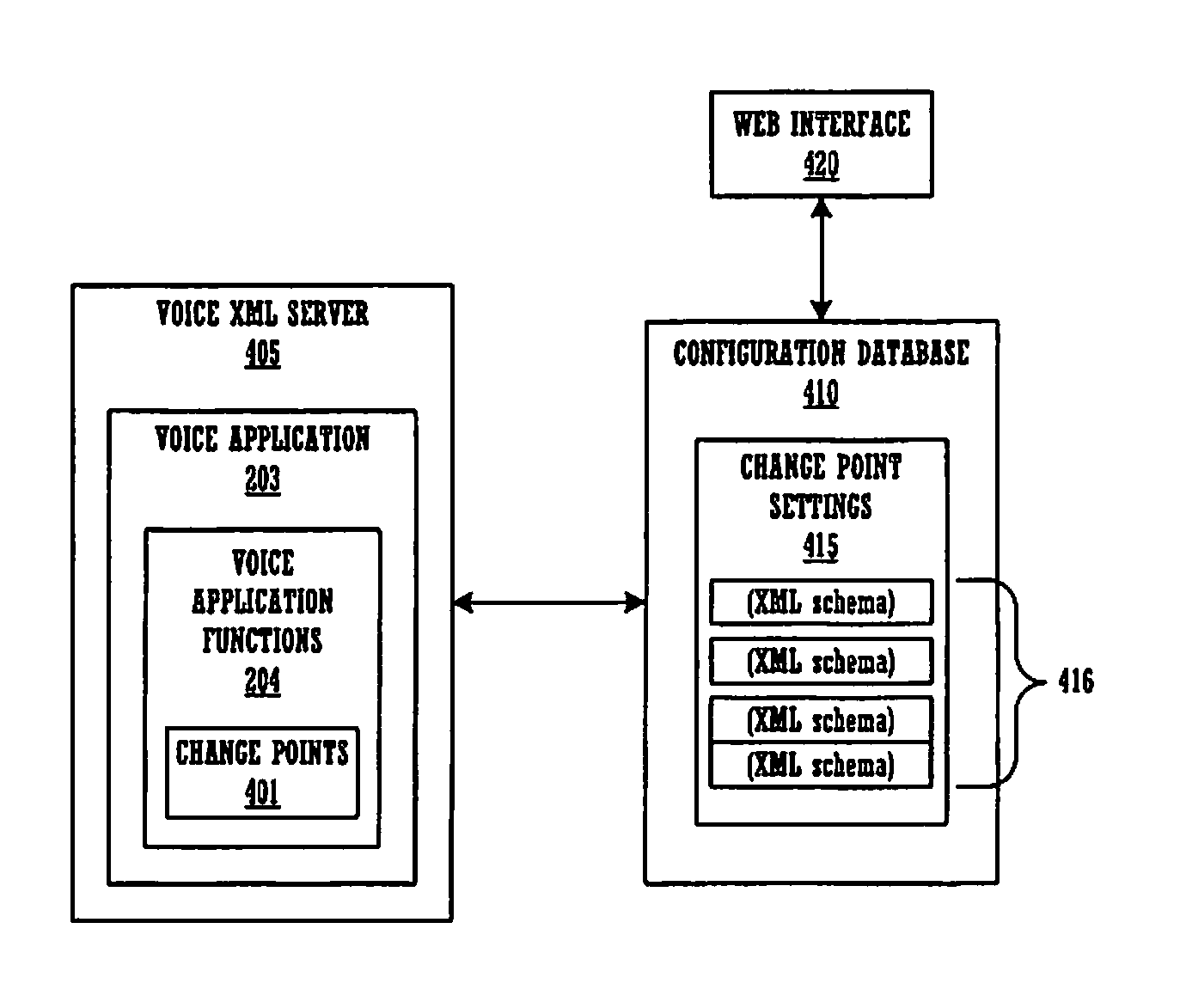

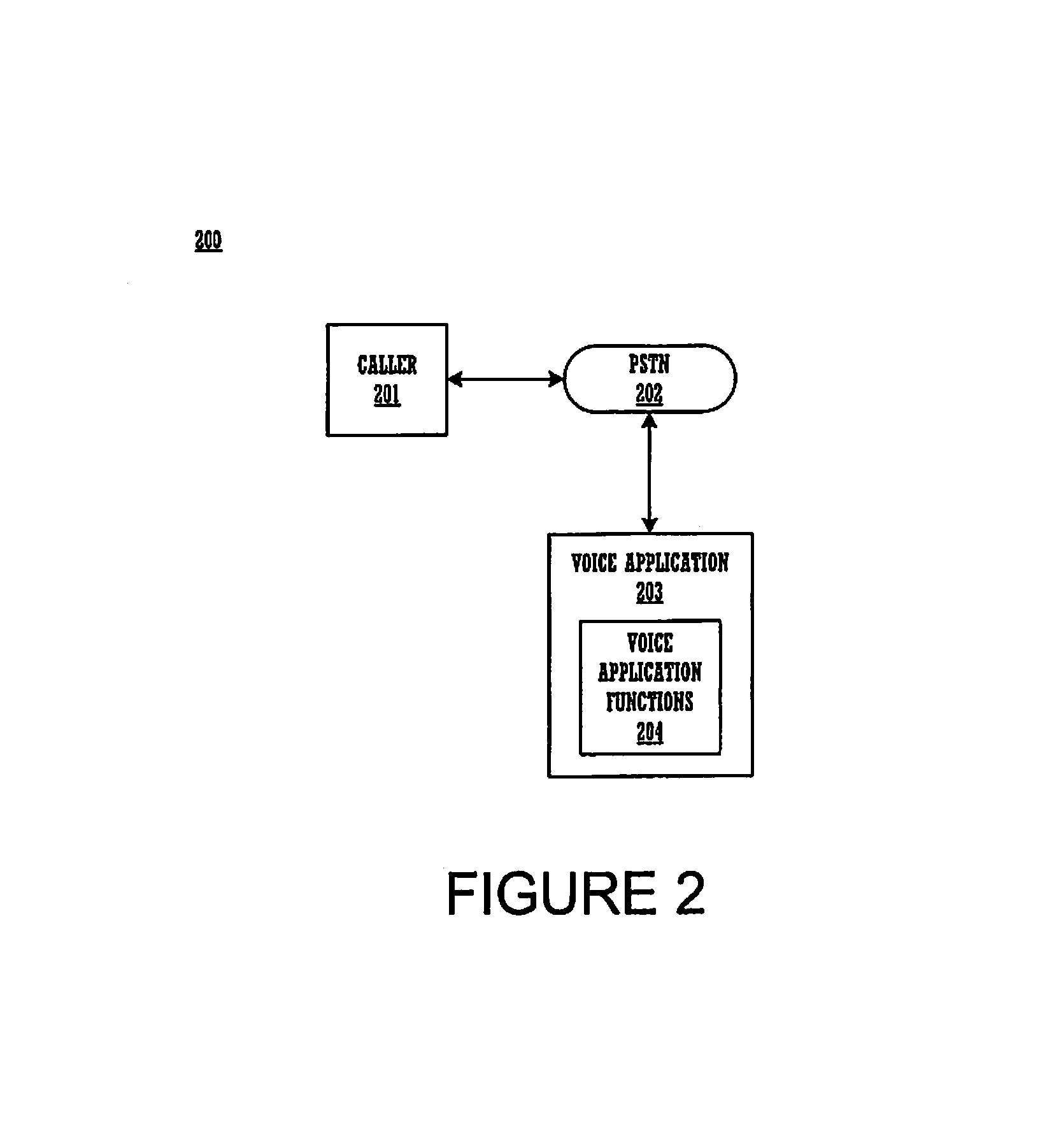

Method and system for design for run-time control of voice XML applications

ActiveUS7672295B1Efficiently and rapidly adaptEasy and rapid adaptationAutomatic call-answering/message-recording/conversation-recordingManual exchangesComputer hardwareSpeech applications

A method and system for implementing run-time control over voice application behavior. The method includes identifying a plurality of control point locations within a given voice application and a plurality of corresponding required responses to the control points. A design-for-control methodology is used to instrument the control points of voice application. A control agent is configured with web-based controls to manage the control points. The control points are used to alter the voice application's behavior during run-time.

Owner:MICROSOFT TECH LICENSING LLC

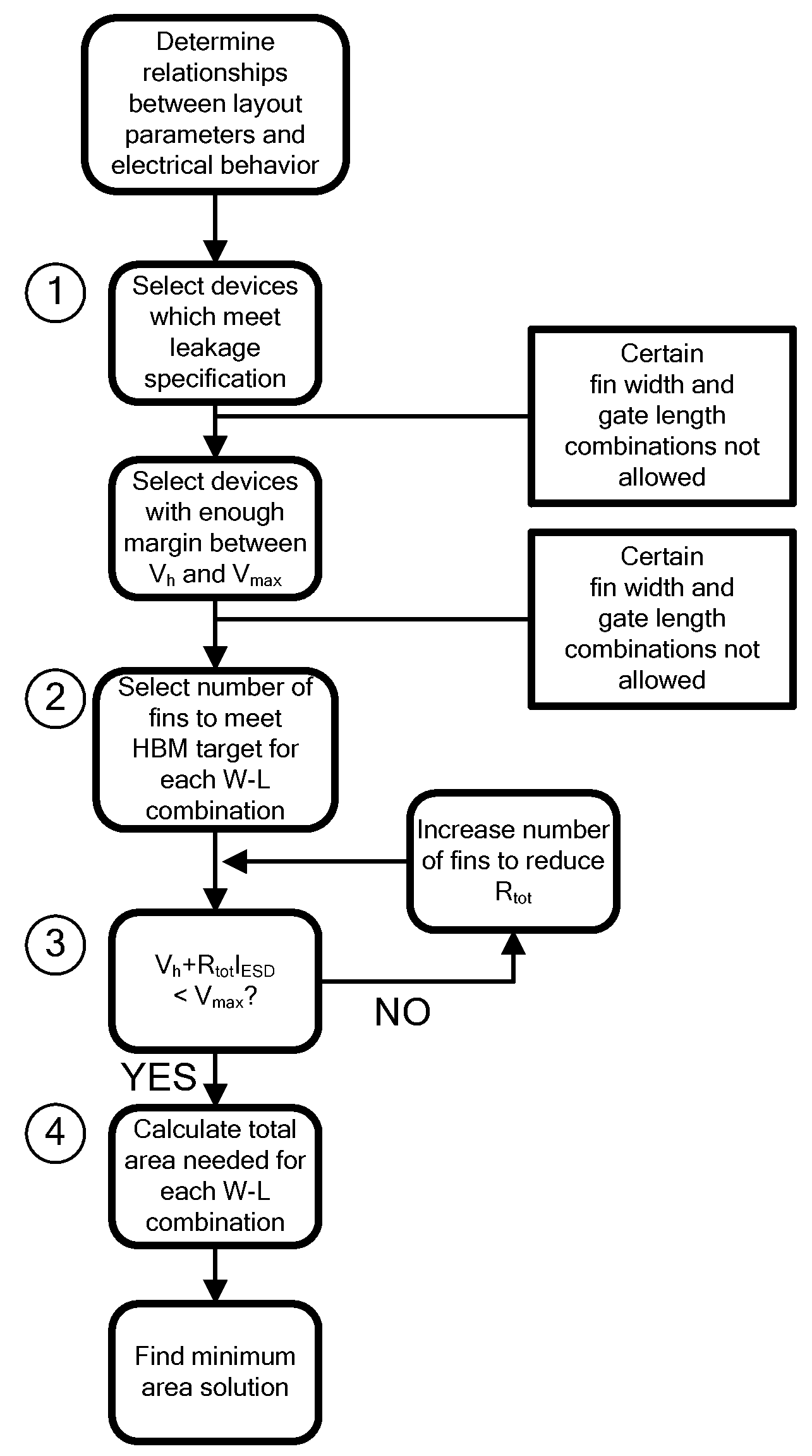

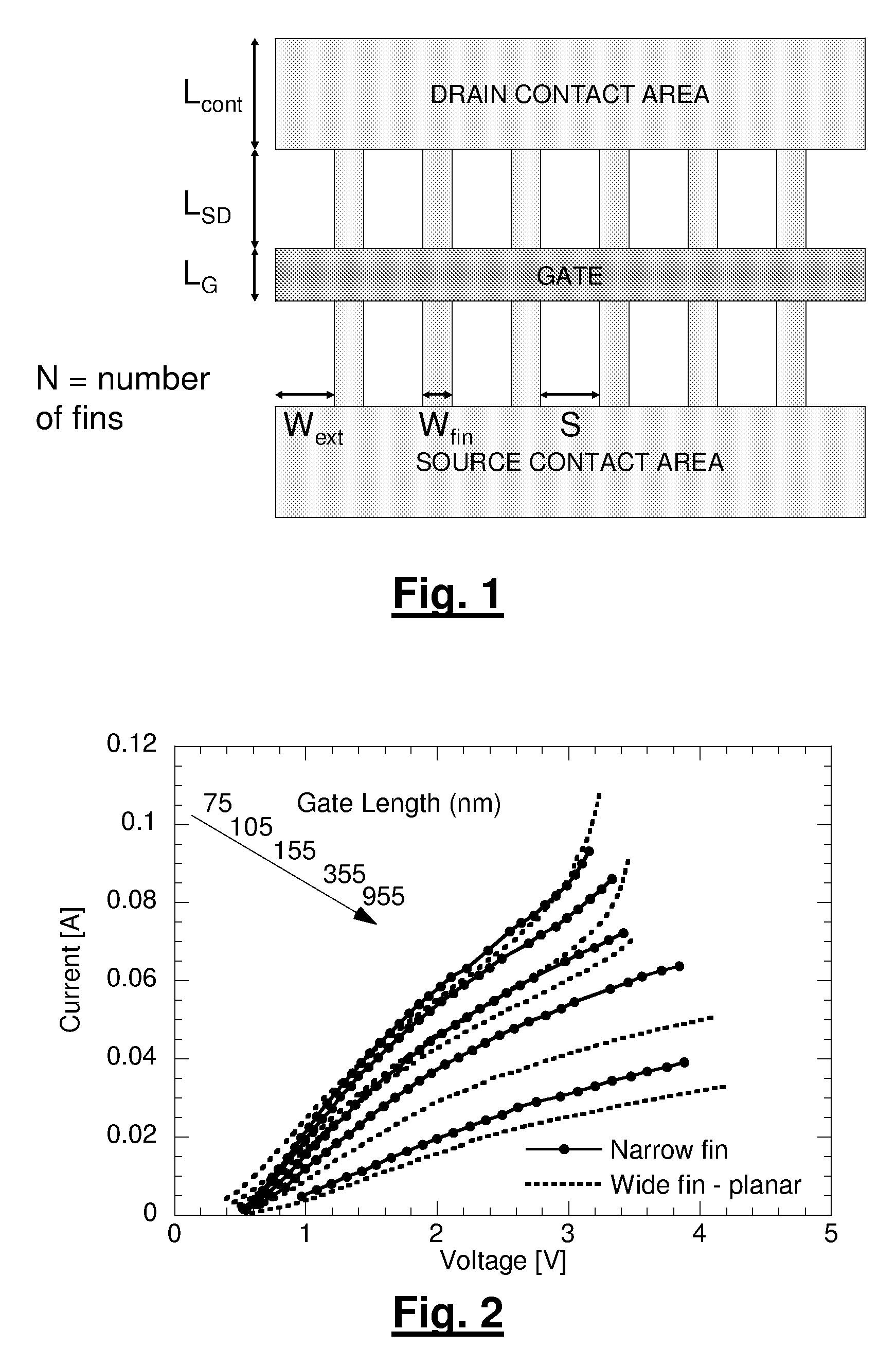

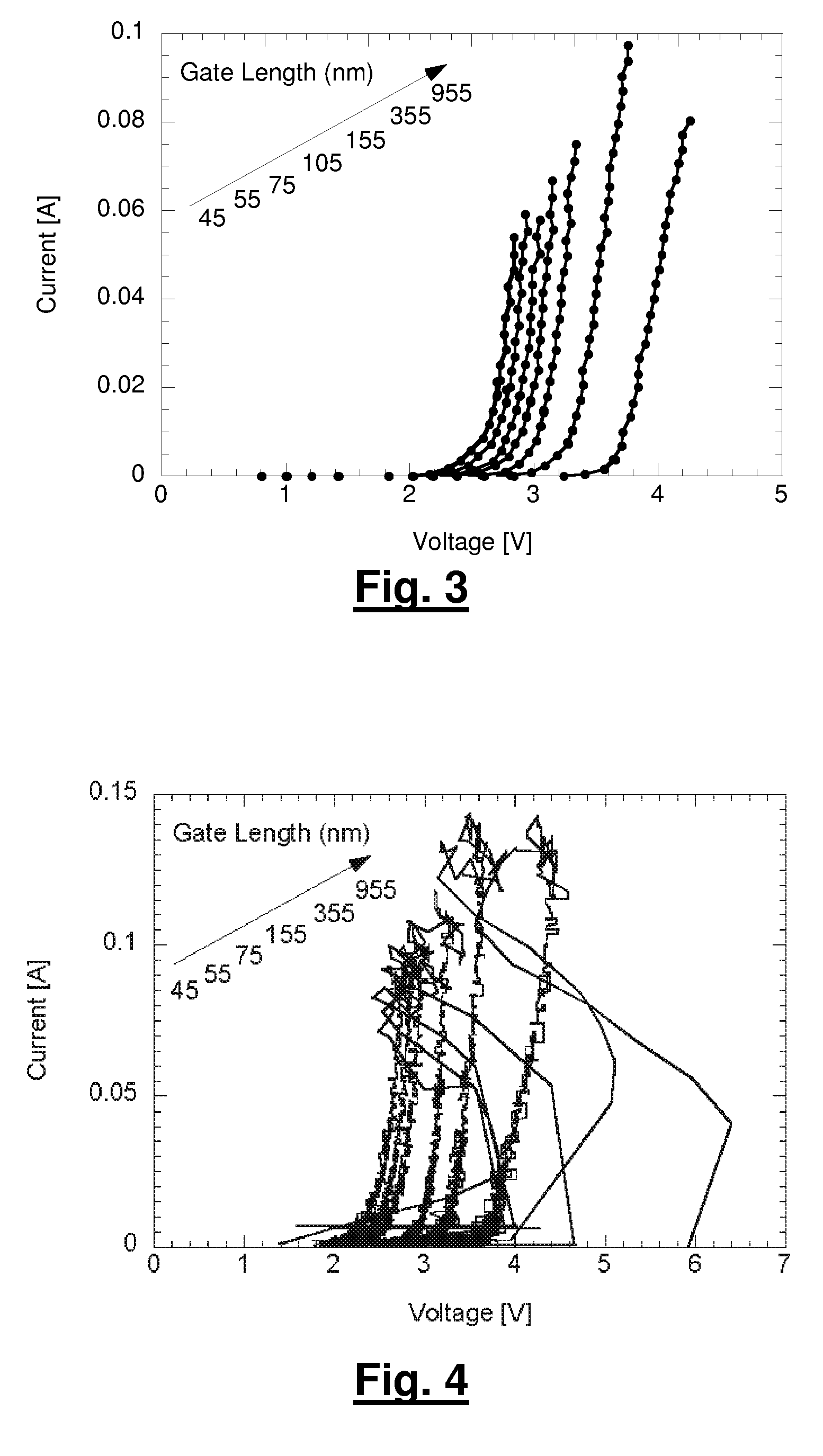

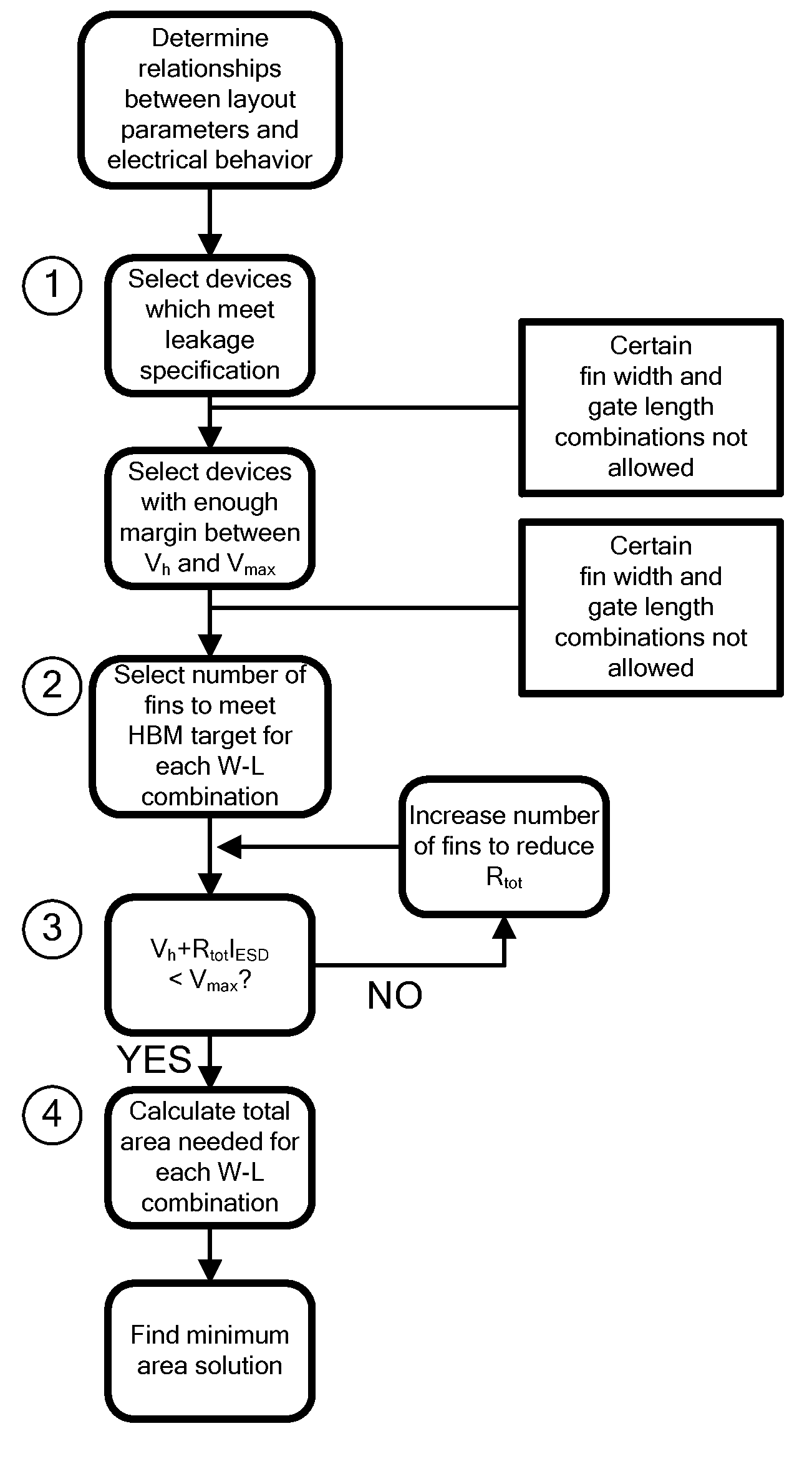

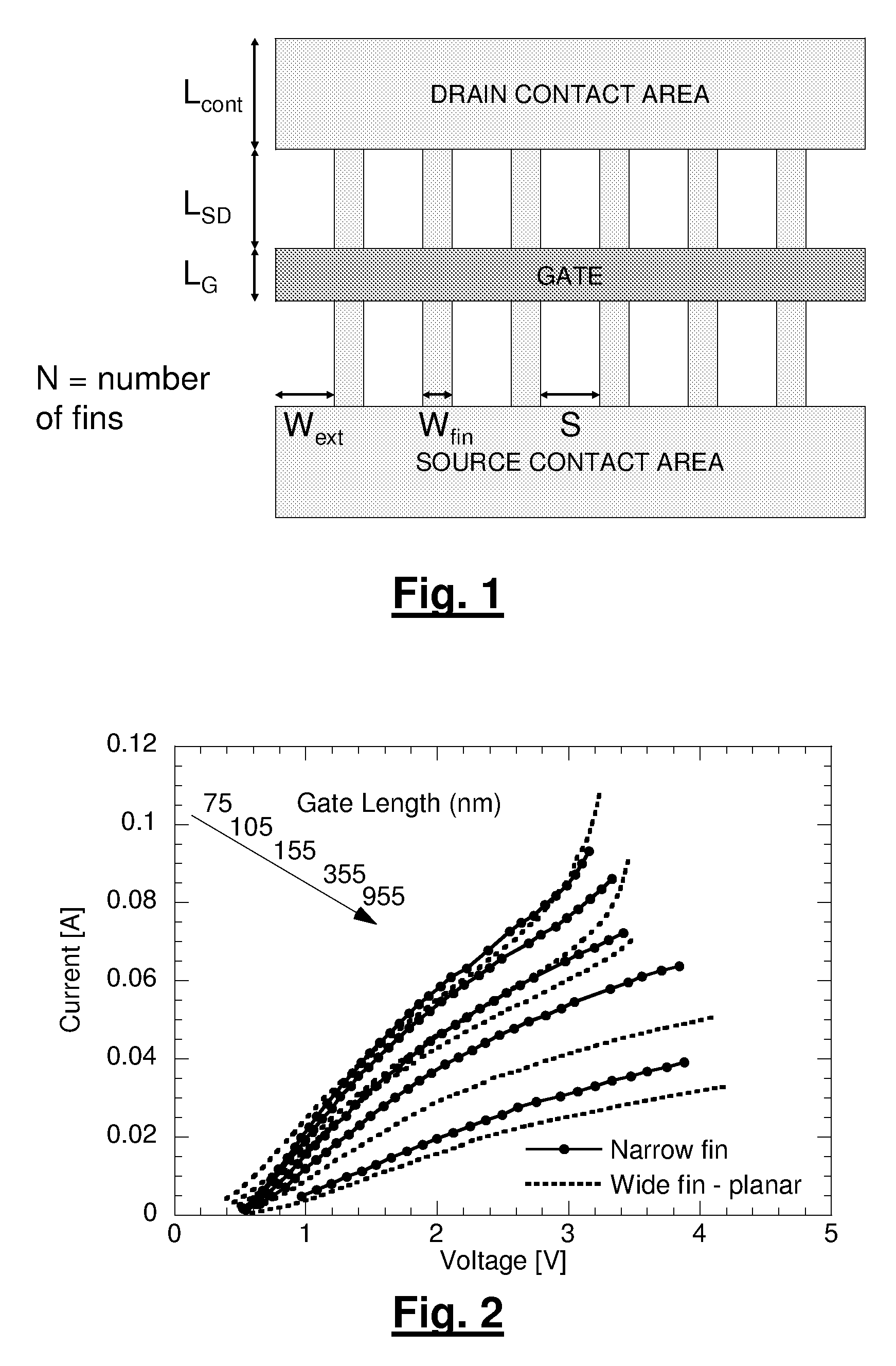

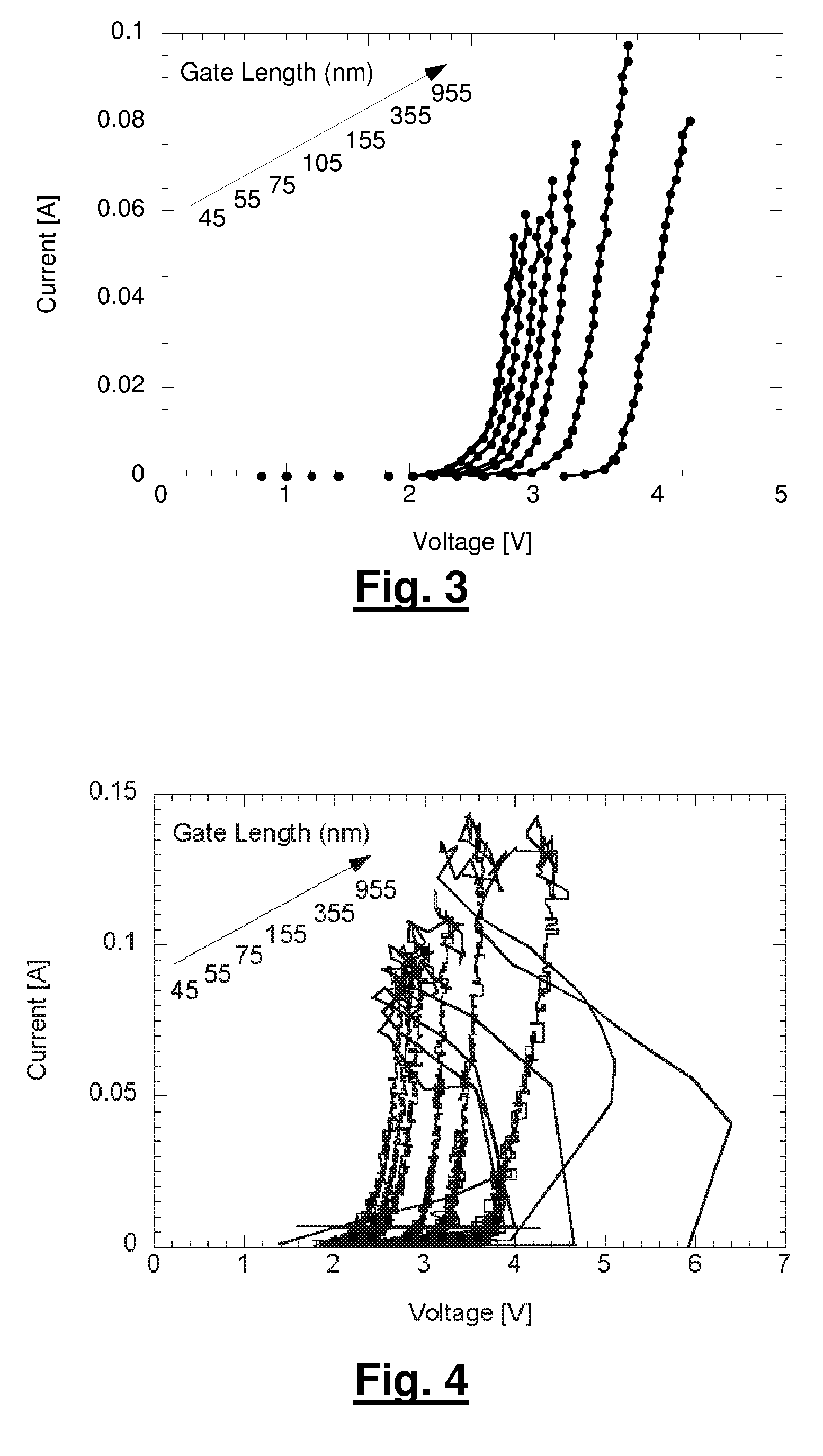

Design Methodology for MuGFET ESD Protection Devices

InactiveUS20090280582A1Easy to optimizePromote resultsSemiconductor/solid-state device testing/measurementSolid-state devicesManufacturing technologyEngineering

A method for manufacturing a MuGFET ESD protection device having a given layout by means of a given manufacturing process, the method comprising selecting multiple interdependent layout and process parameters of which a first set are fixed by said manufacturing process and a second set are variable, selecting multiple combinations of possible layout and process parameter values which meet predetermined ESD constraints; determining an optimum value for at least one other parameter in view of a predetermined design target apart from the predetermined ESD constraints; determining values for fin width (Wfin), gate length (LG) and number of fins (N) on the basis of the optimum value; and manufacturing said MuGFET ESD protection device using the given manufacturing and process values.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Design methodology for MuGFET ESD protection devices

InactiveUS7923266B2Promote resultsSemiconductor/solid-state device testing/measurementSolid-state devicesManufacturing technologyEngineering

A method for manufacturing a MuGFET ESD protection device having a given layout by means of a given manufacturing process, the method comprising selecting multiple interdependent layout and process parameters of which a first set are fixed by said manufacturing process and a second set are variable, selecting multiple combinations of possible layout and process parameter values which meet predetermined ESD constraints; determining an optimum value for at least one other parameter in view of a predetermined design target apart from the predetermined ESD constraints; determining values for fin width (Wfin), gate length (LG) and number of fins (N) on the basis of the optimum value; and manufacturing said MuGFET ESD protection device using the given manufacturing and process values.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

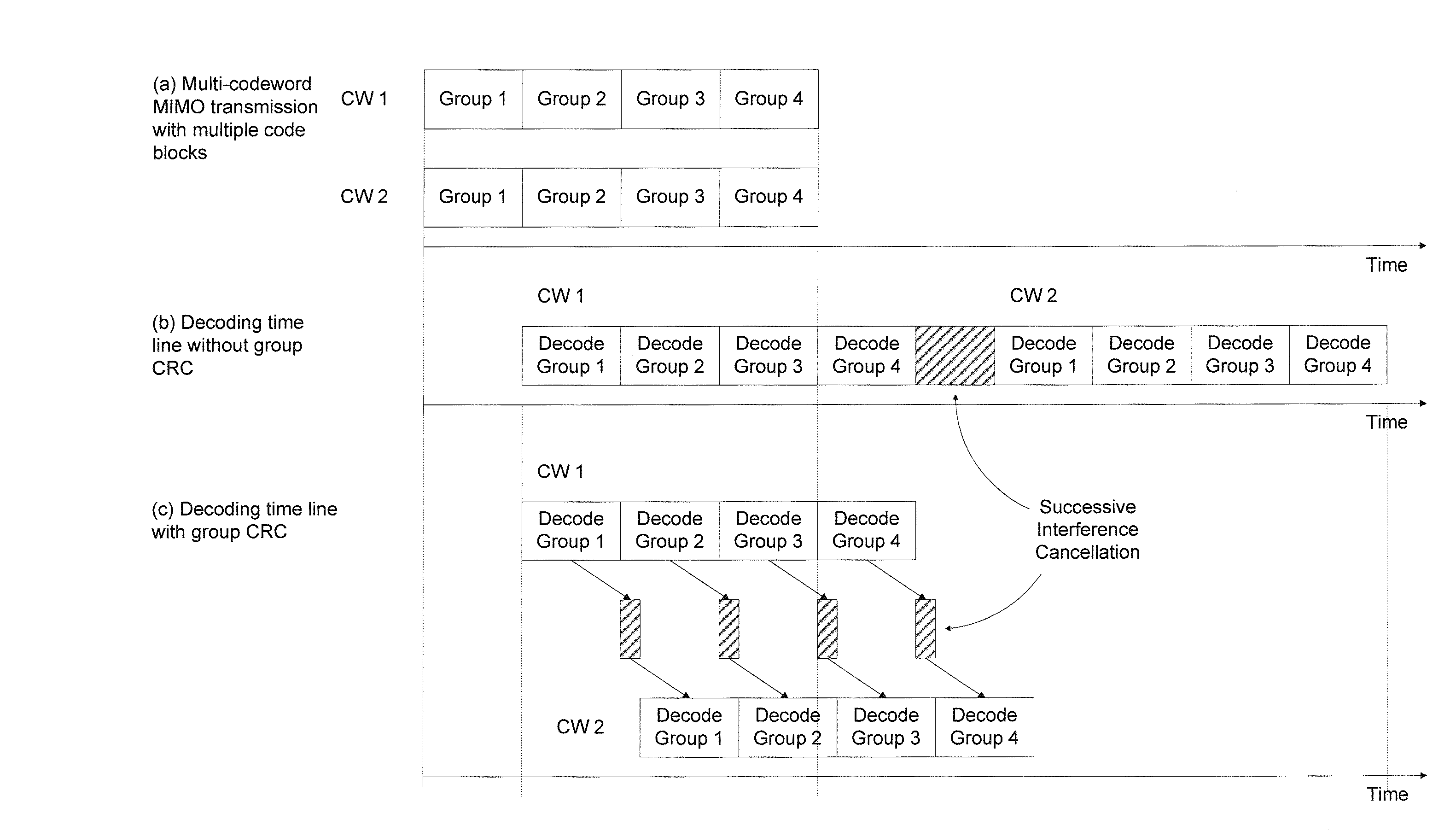

Methods and apparatus to improve performance and enable fast decoding of transmissions with multiple code blocks

ActiveUS20080225965A1Data representation error detection/correctionError preventionCoding blockResource element

Owner:SAMSUNG ELECTRONICS CO LTD

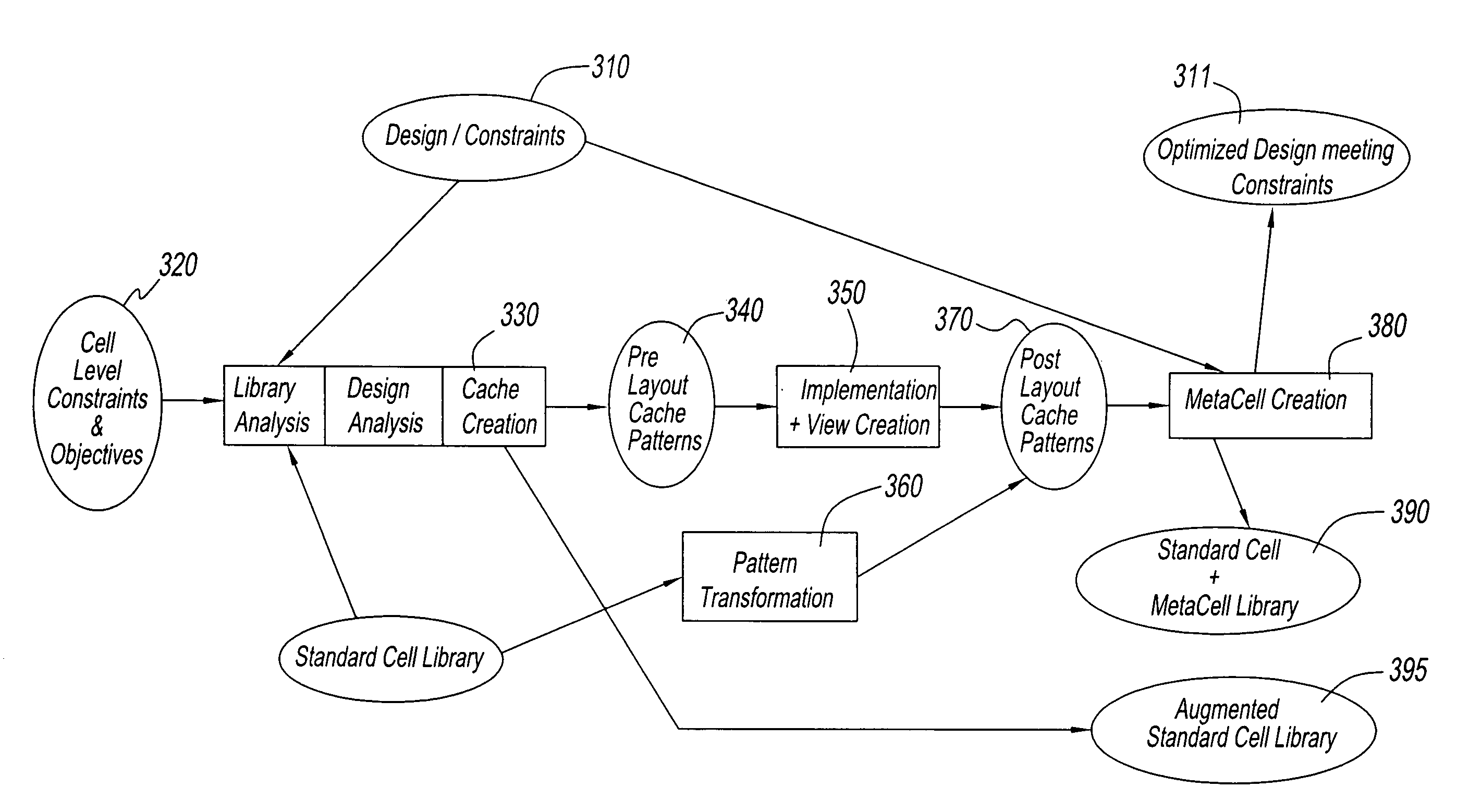

Method of IC design optimization via creation of design-specific cells from post-layout patterns

ActiveUS20080127000A1Increase diversityQuality improvementComputer aided designSoftware simulation/interpretation/emulationClosed loopEngineering

A closed-loop IC design optimization process by automatically or manually creating design-specific cells with desired characteristics (e.g., performance, area, power, noise, etc.), which will be then implemented as a standard cell (also known hereafter as metacell), from a set of post-layout patterns. A post-layout pattern represents a part or whole of a standard cell and contains information regarding the pattern including, but not limited to, layout, timing, area, power and noise. As the metacells are created from post-layout patterns, the inaccuracies of prior dynamic library techniques are easily avoided. Such metacells, being design-specific, are optimized to satisfy the constraints imposed by the design context, thus bringing the powerful design-specific customization to standard cell-based design methodology.

Owner:ALPHAWAVE SEMI INC

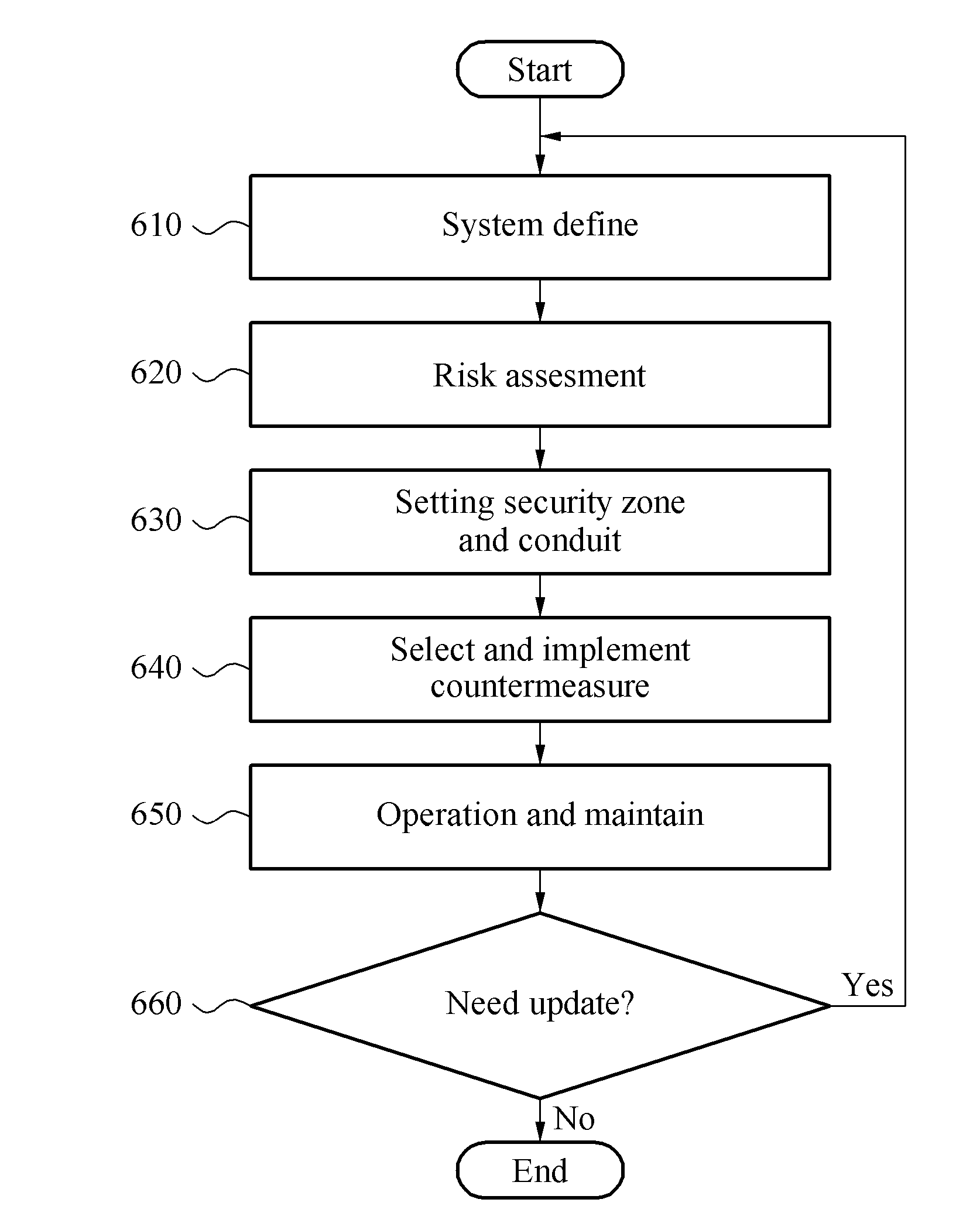

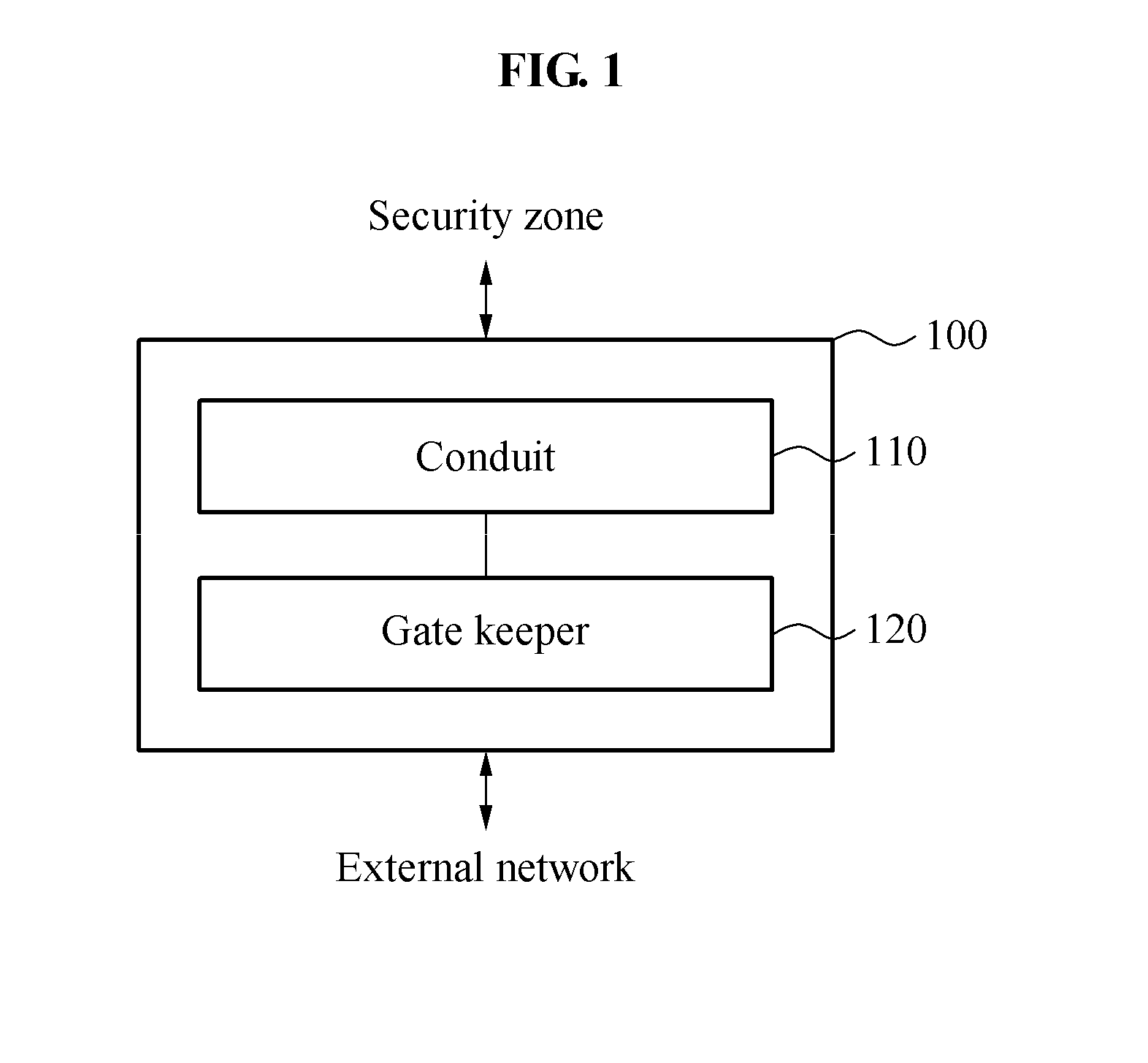

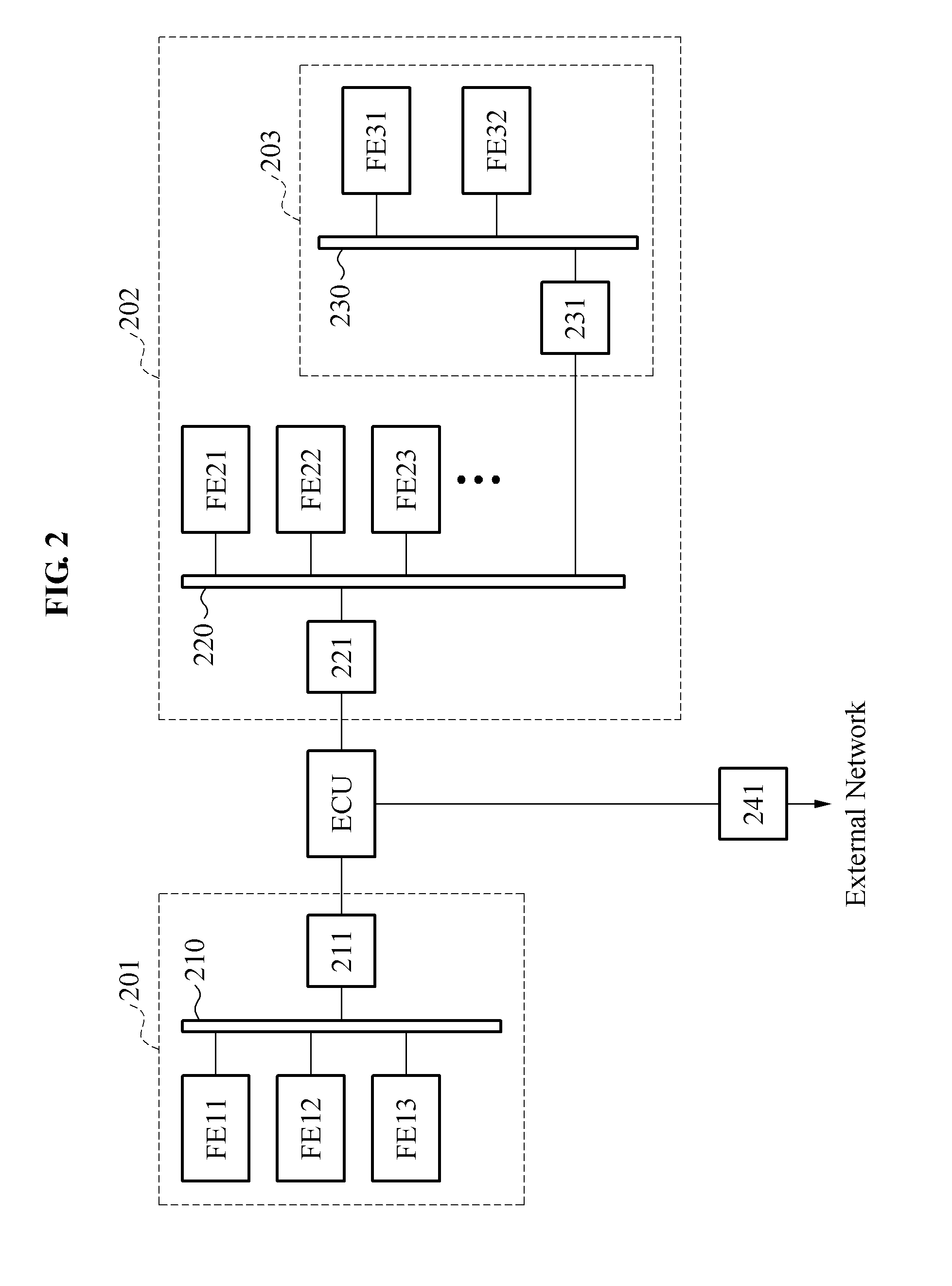

Vehicle security network device and design method therefor

ActiveUS20160255154A1Semiconductor/solid-state device detailsAnti-theft devicesRisk levelCountermeasure

A security system capable of preventing a security attack / threat on a vehicle network is provided. At least one security zone is set by using a risk level which is evaluated for a plurality of vehicle functional elements. In addition, a security countermeasure corresponding to the risk level of the security zone can be provided to a conduit of the security zone so as to perform gate keeping.

Owner:ICTK

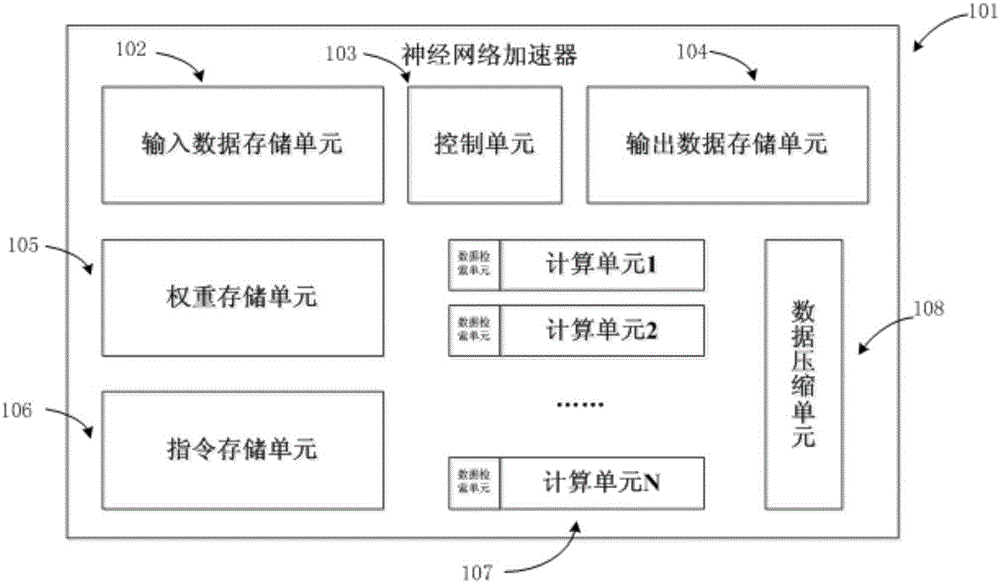

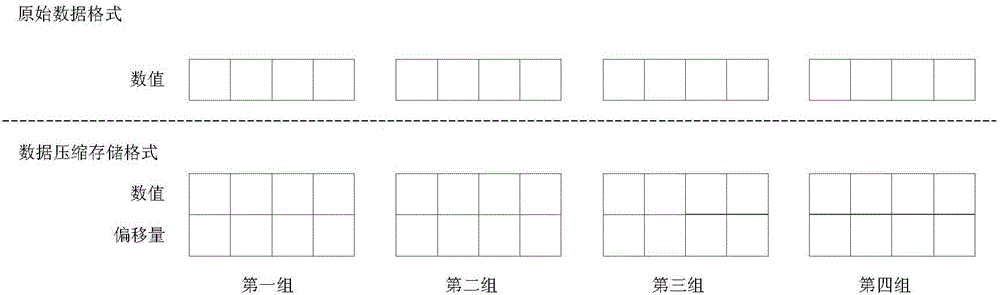

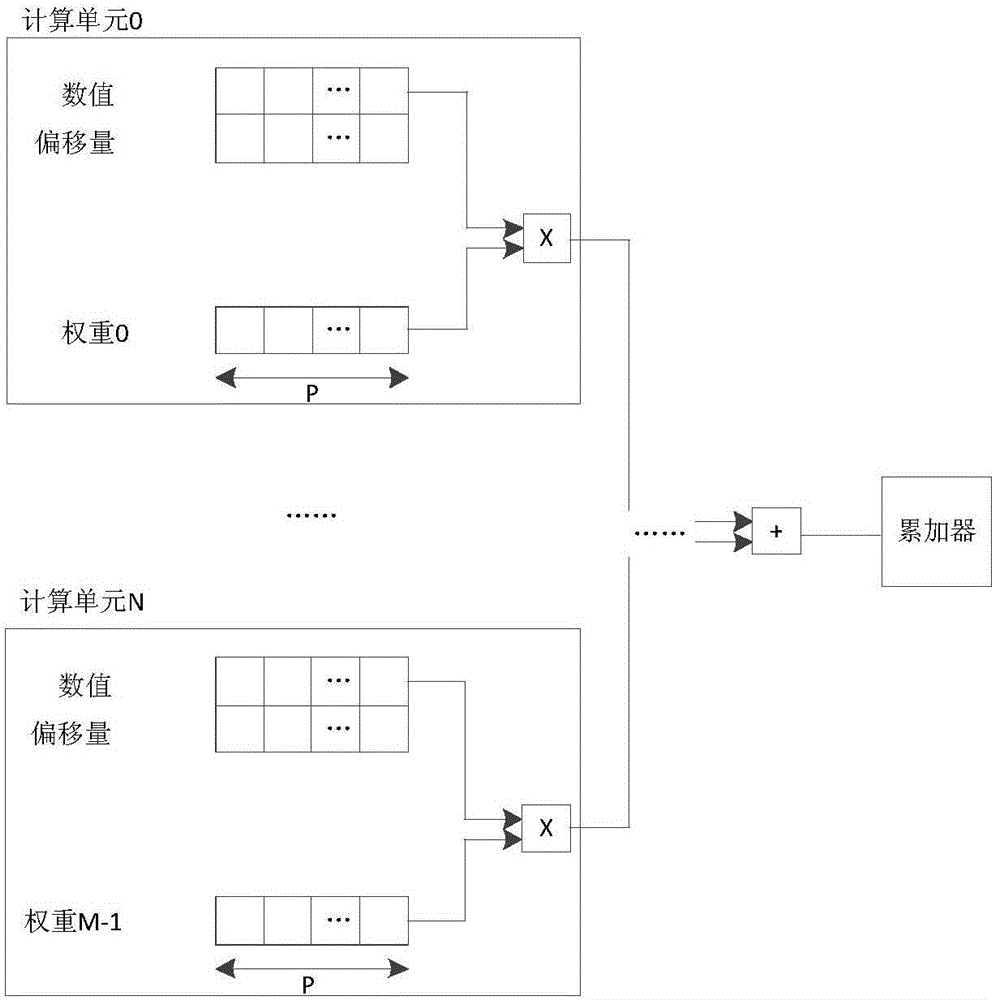

Neutral network processor based on data compression, design method and chip

ActiveCN106447034AIncrease computing speedImprove computing efficiencyPhysical realisationEnergy efficient computingOperating instructionData compression

The invention provides a neutral network processor based on data compression, a design method and a chip. The processor comprises at least one storage unit used for storing operating instructions and data participating in calculation, at least one storage unit controller used for controlling the storage unit, at least one calculation unit used for executing calculation of a neutral network, a control unit connected with the storage unit controllers and the calculation units and used for acquiring instructions stored by the storage unit through the storage unit controllers and analyzing the instructions to control the calculation units, and at least one data compression unit used for compressing data participating in calculation according to a data compression storage format. Each data compression unit is connected with the corresponding calculation unit. Occupancy of data resources in the neutral network processor is reduced, the operating rate is increased, and energy efficiency is improved.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

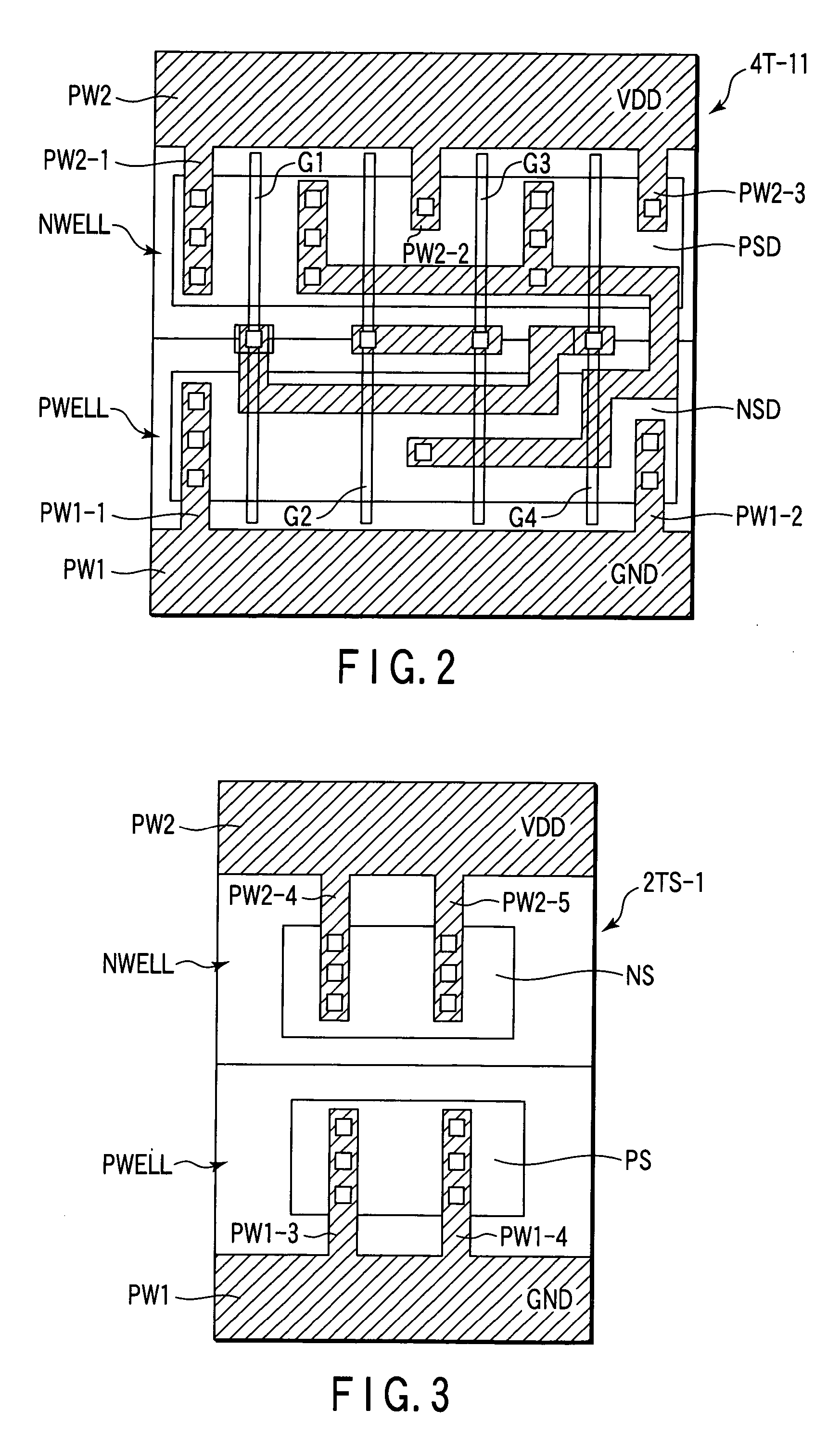

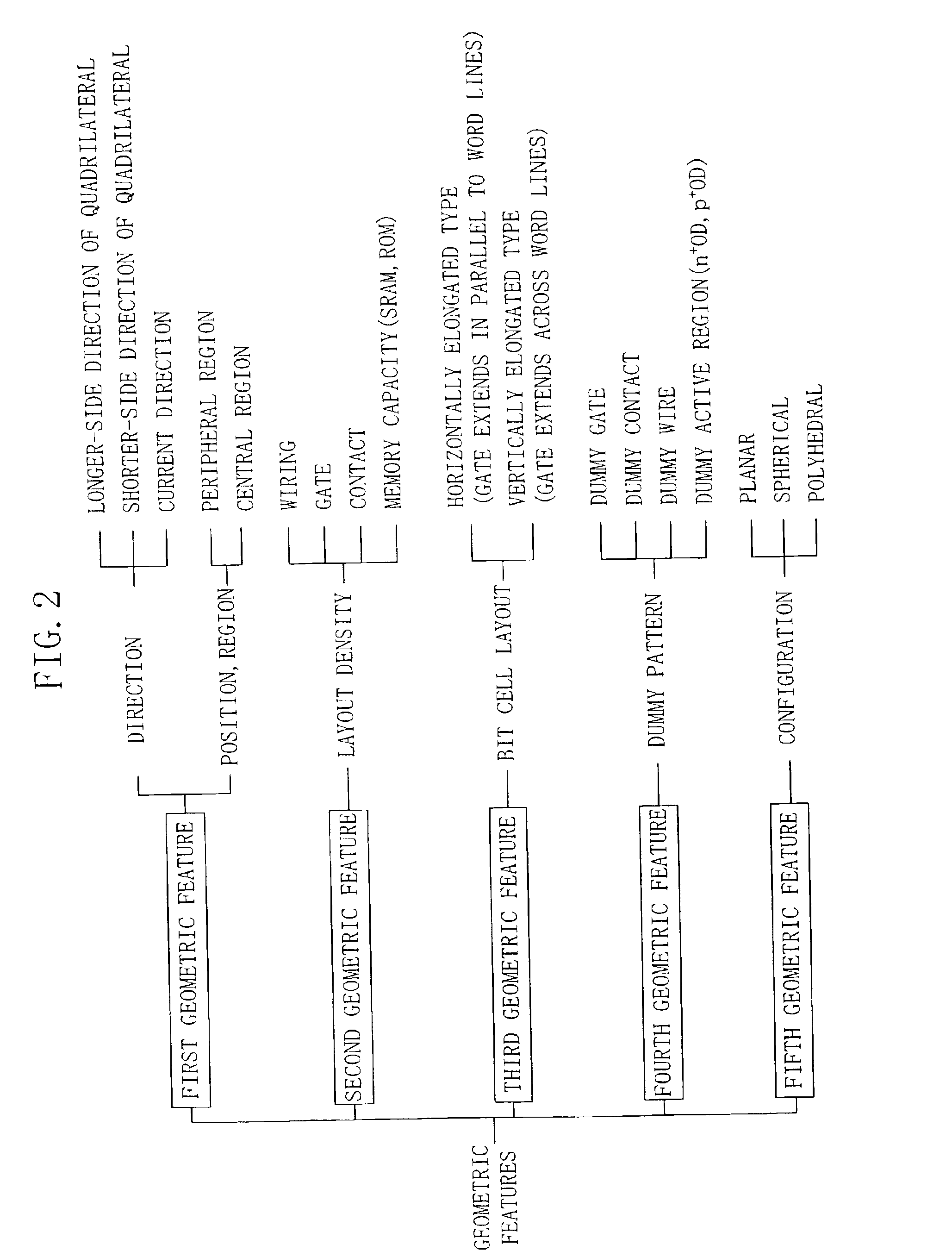

Semiconductor integrated circuit device, storage medium on which cell library is stored and designing method for semiconductor integrated circuit

InactiveUS20020079927A1Power reduction in field effect transistorsSolid-state devicesMOSFETDrain current

Owner:RENESAS ELECTRONICS CORP

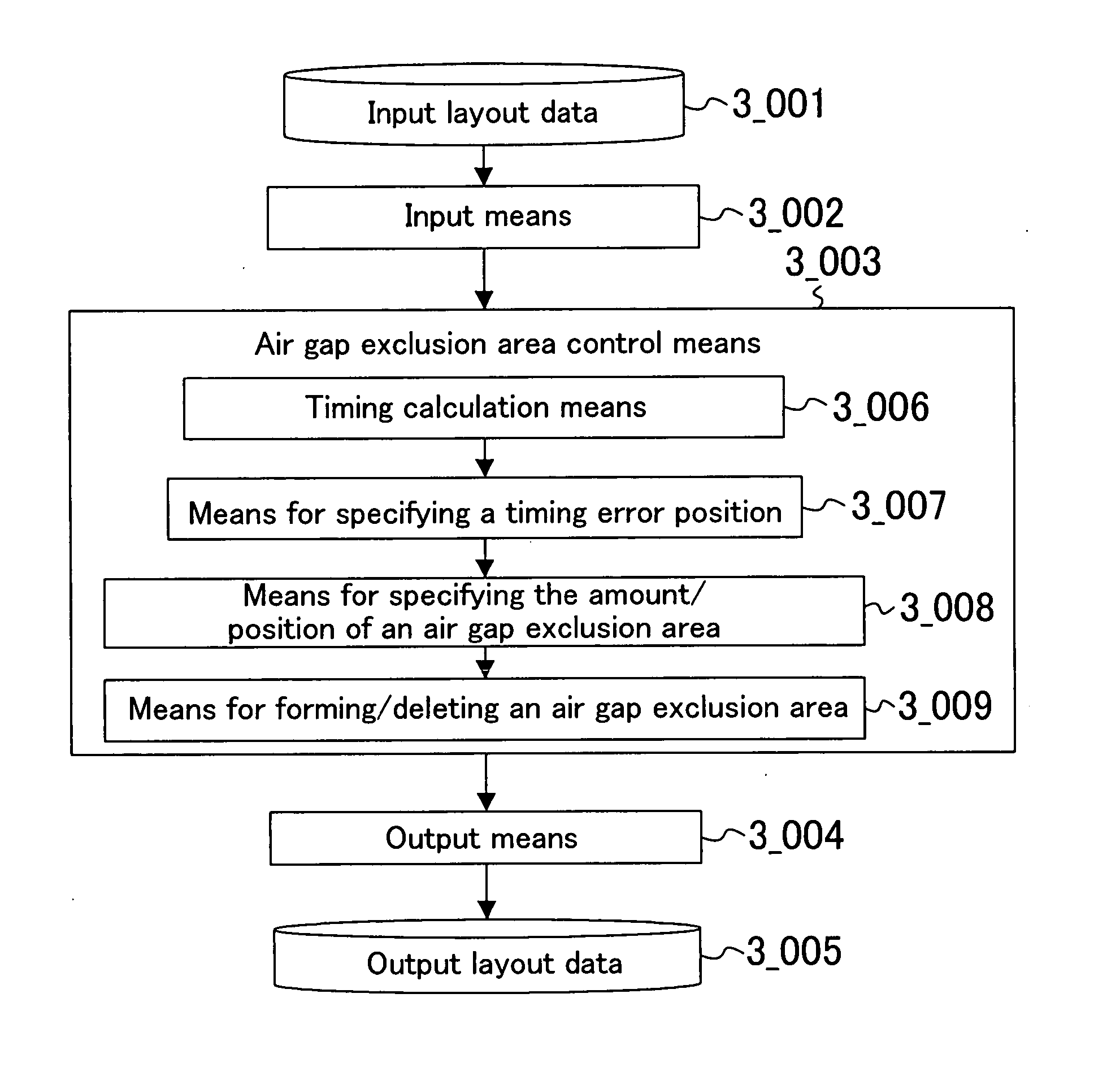

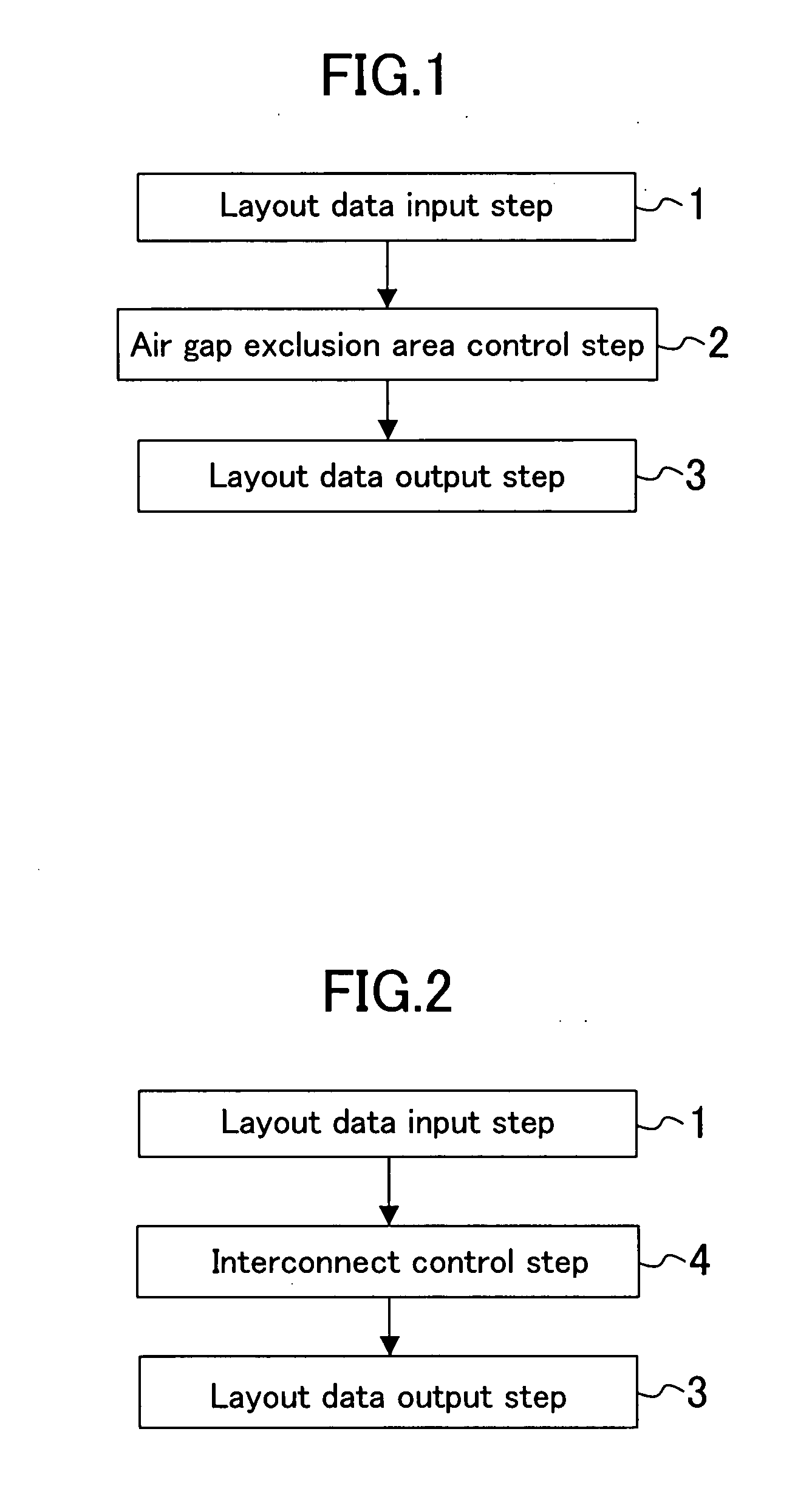

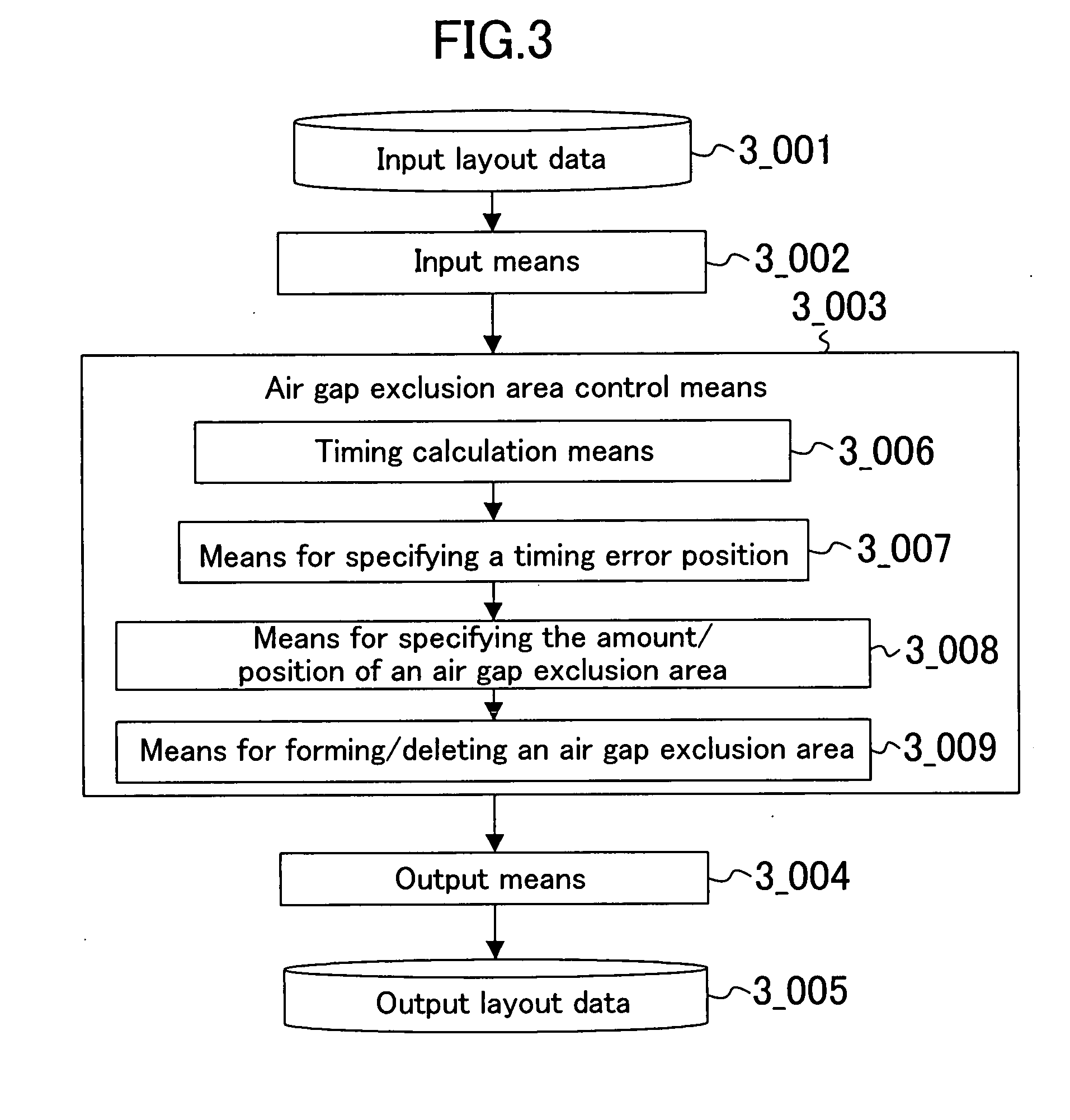

Interconnect structure of semiconductor integrated circuit, and design method and device therefor

ActiveUS20080097641A1Reduce parasitic capacitanceShort timeSemiconductor/solid-state device detailsSolid-state devicesEngineeringDesign methods

A method for designing an interconnect structure of an interconnect layer in a semiconductor integrated circuit device includes the steps of: (a) inputting layout data of the semiconductor integrated circuit device; (b) controlling an air gap exclusion area based interconnects in the layout data; and (c) outputting layout data including the air gap exclusion area determined in the step (b).

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

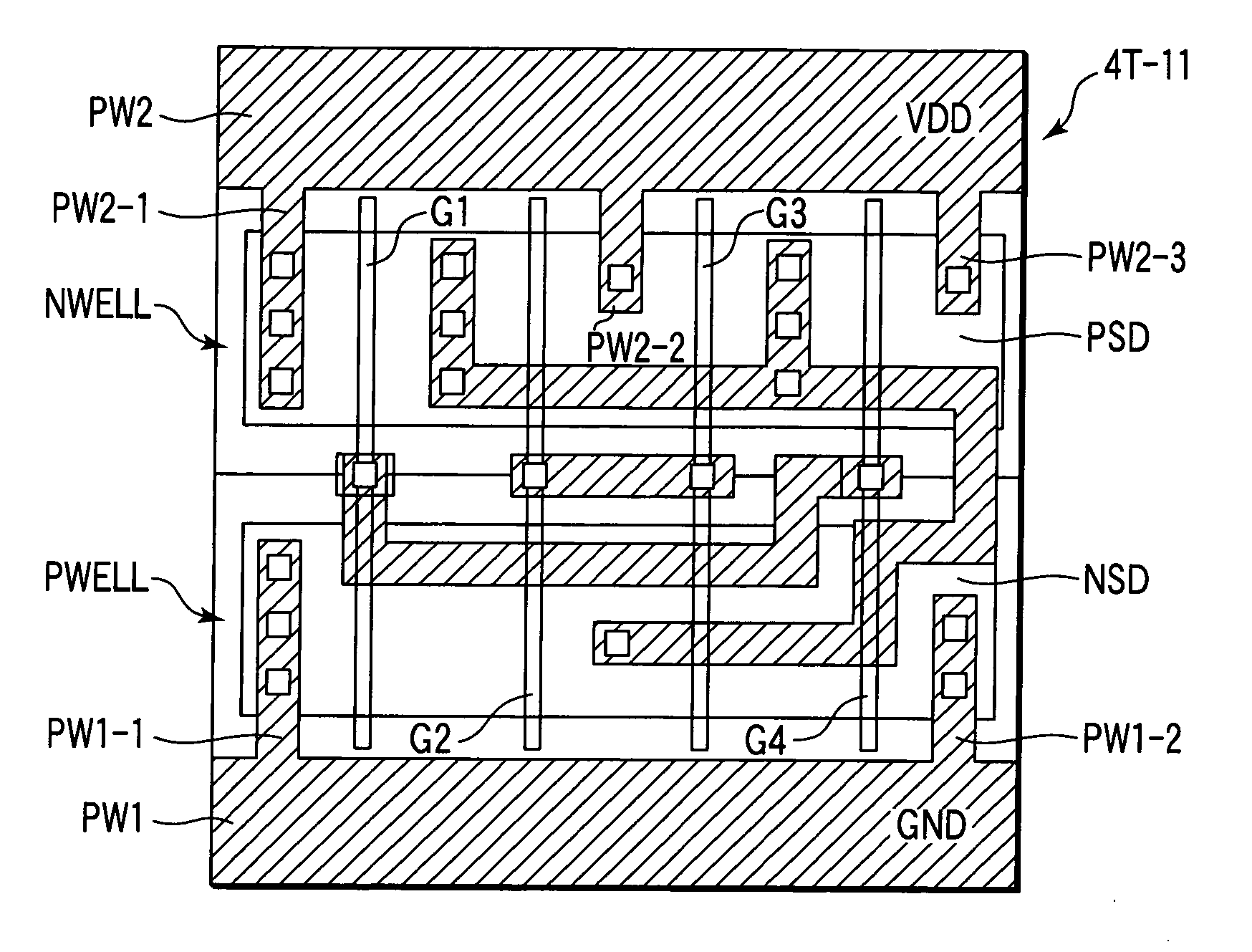

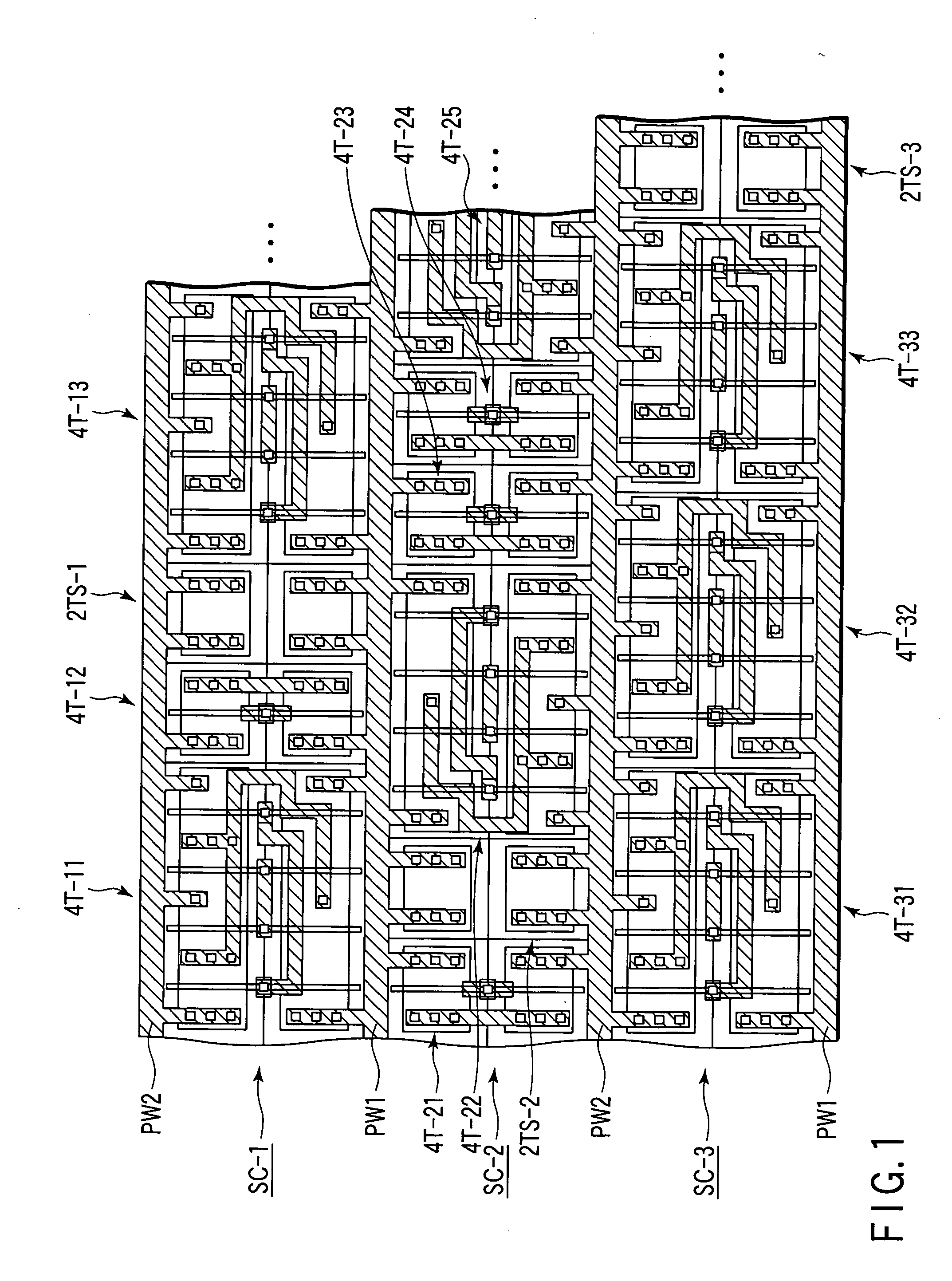

Semiconductor integrated circuit device formed by automatic layout wiring by use of standard cells and design method of fixing its well potential

InactiveUS20060131609A1Semiconductor/solid-state device detailsSolid-state devicesDevice formEngineering

A standard cell is read from a library and automatic layout wiring is performed, thereby configuring a circuit. Next, each cell column in the configured circuit is searched for an empty region. In the empty region in the cell column searched for, a spacer cell or a filler cell is placed. At this time, using the spacer cell or filler cell, the well potential of the standard cells in the cell column is fixed.

Owner:KK TOSHIBA

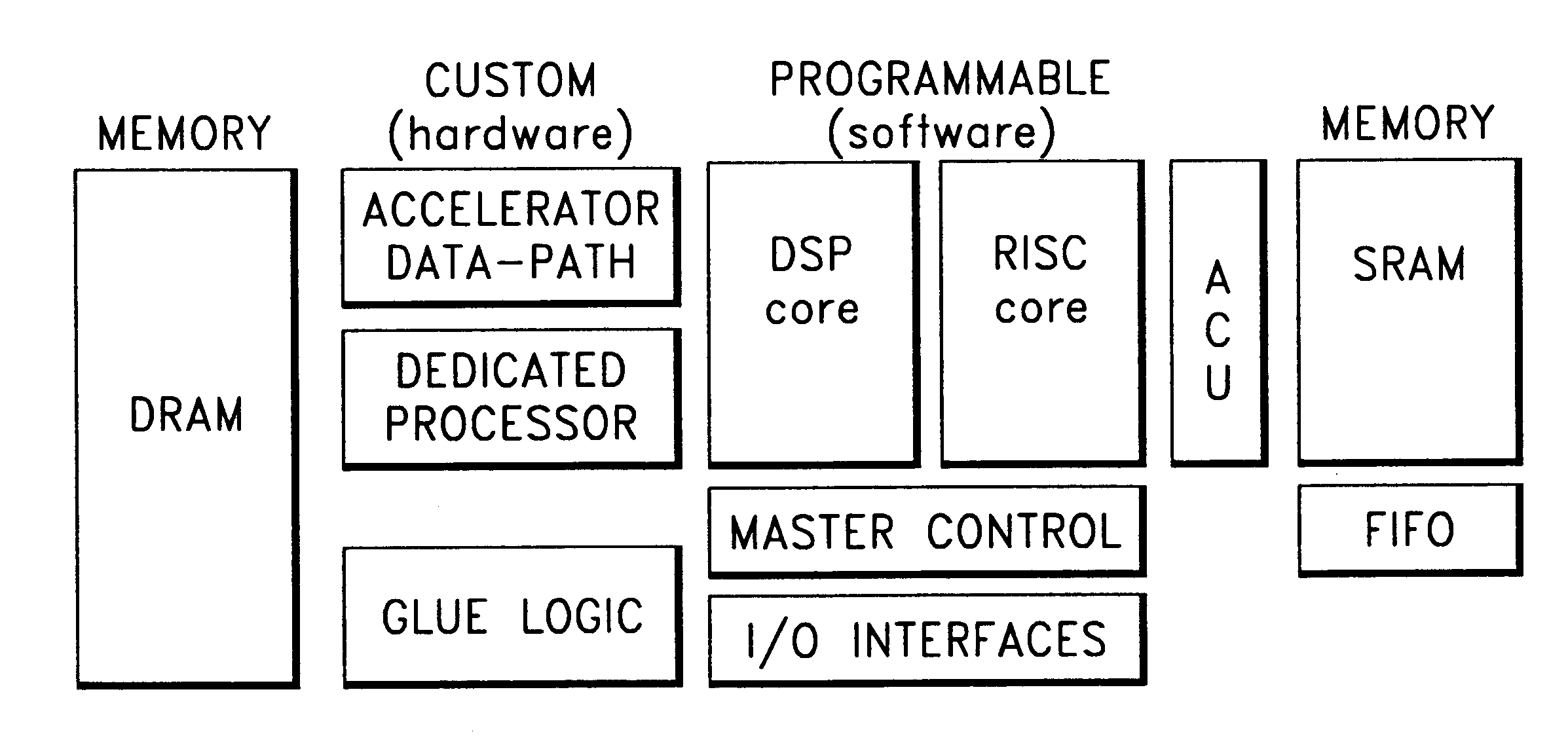

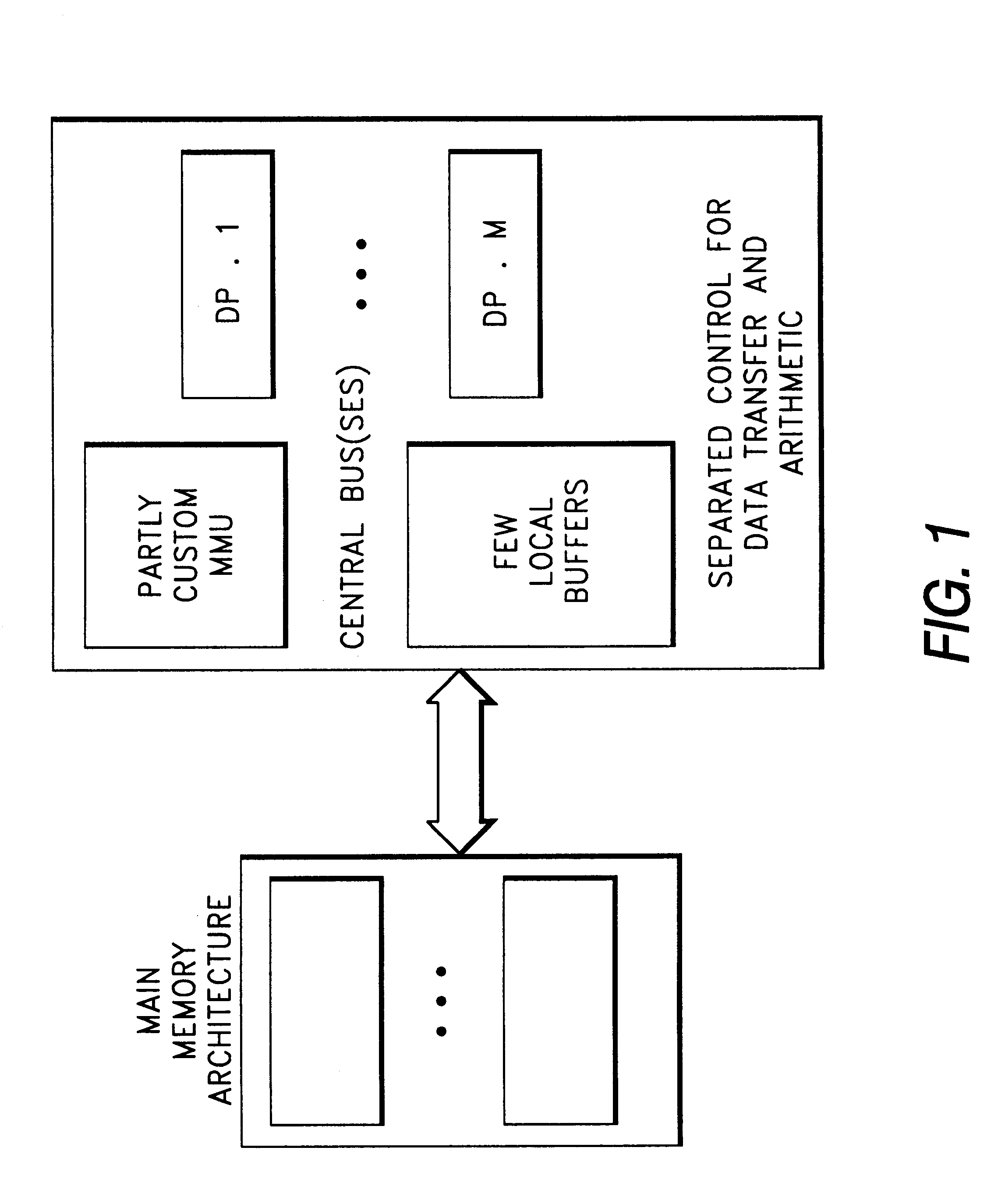

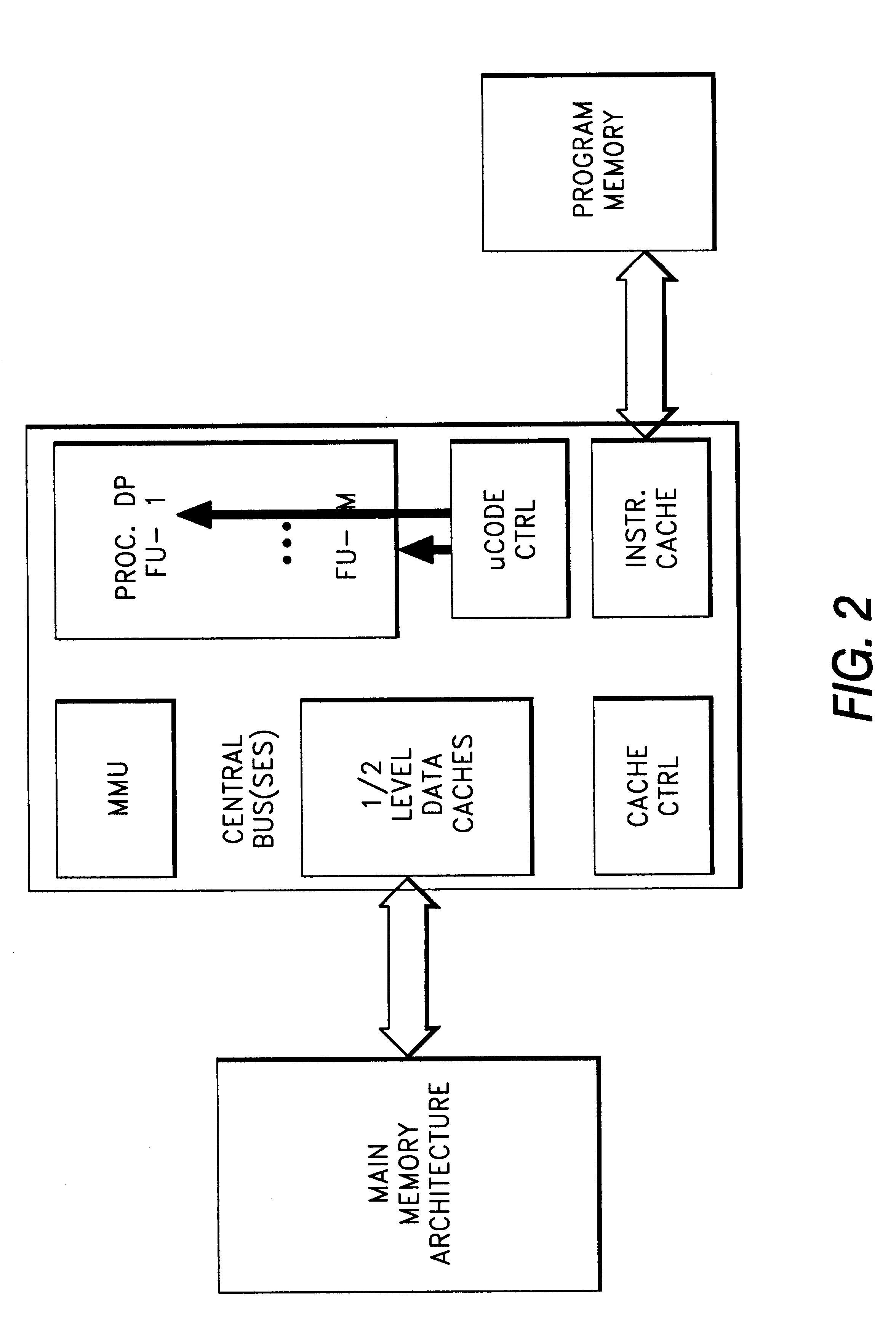

Power-and speed-efficient data storage/transfer architecture models and design methodologies for programmable or reusable multi-media processors

InactiveUS6223274B1Reduce decreaseStay flexibleEnergy efficient ICTMemory adressing/allocation/relocationParallel computingData memory

A programmable processing engine and a method of operating the same is described, the processing engine including a customized processor, a flexible processor and a data store commonly sharable between the two processors. The customized processor normally executes a sequence of a plurality of pre-customized routines, usually for which it has been optimized. To provide some flexibility for design changes and optimizations, a controller for monitoring the customized processor during execution of routines is provided to select one of a set of pre-customized processing interruption points and for switching context from the customized processor to the flexible processor at the interruption point. The customized processor can then be switched off and the flexible processor carries out a modified routine. By using sharable a data store, the context switch can be chosen at a time when all relevant data is in the sharable data store. This means that the flexible processor can pick up the modified processing cleanly. After the modified processing the flexible processor writes back new data into the data store and the customized processor can continue processing either where it left off or may skip a certain number of cycles as instructed by the flexible processor, before beginning processing of the new data.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

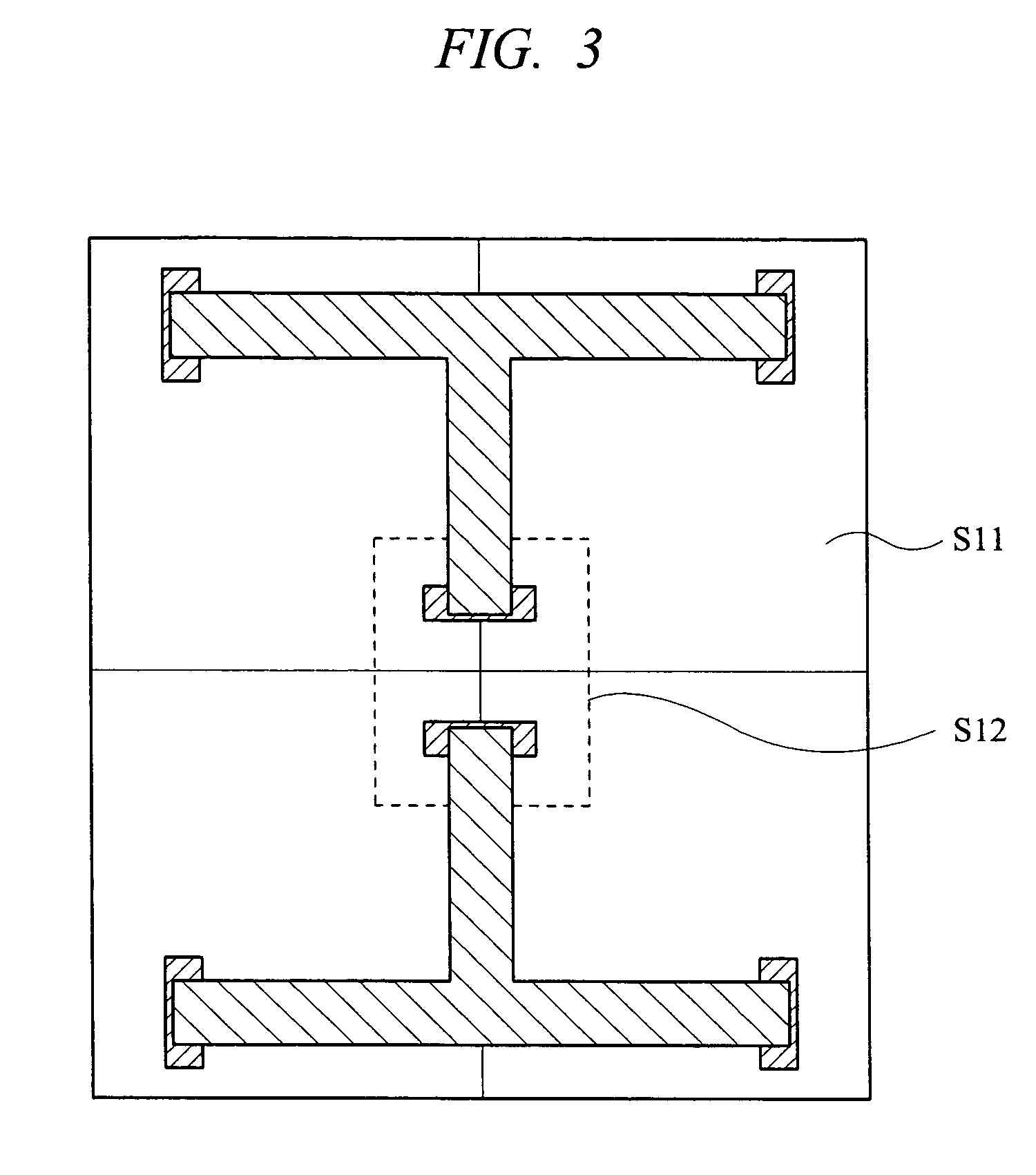

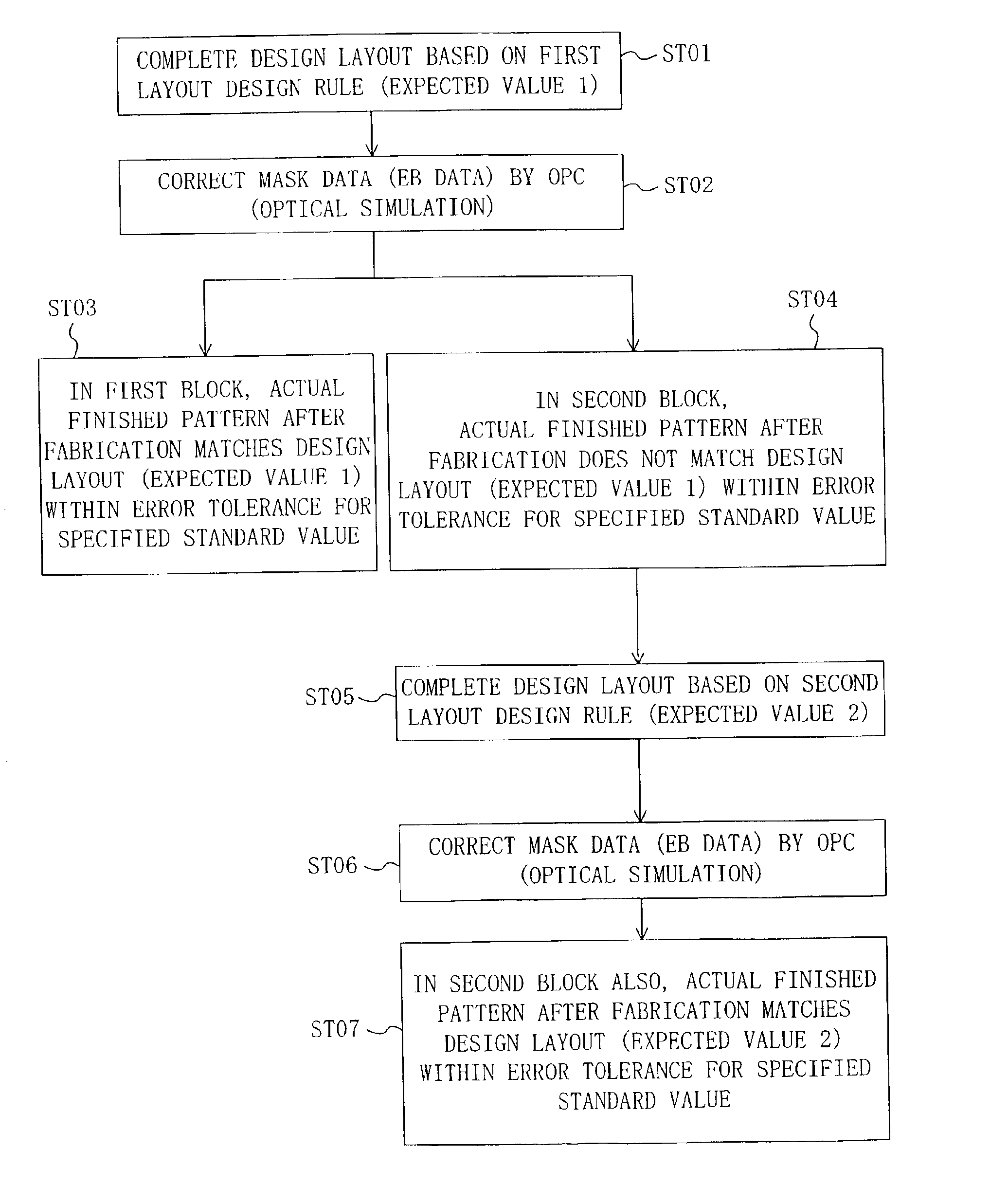

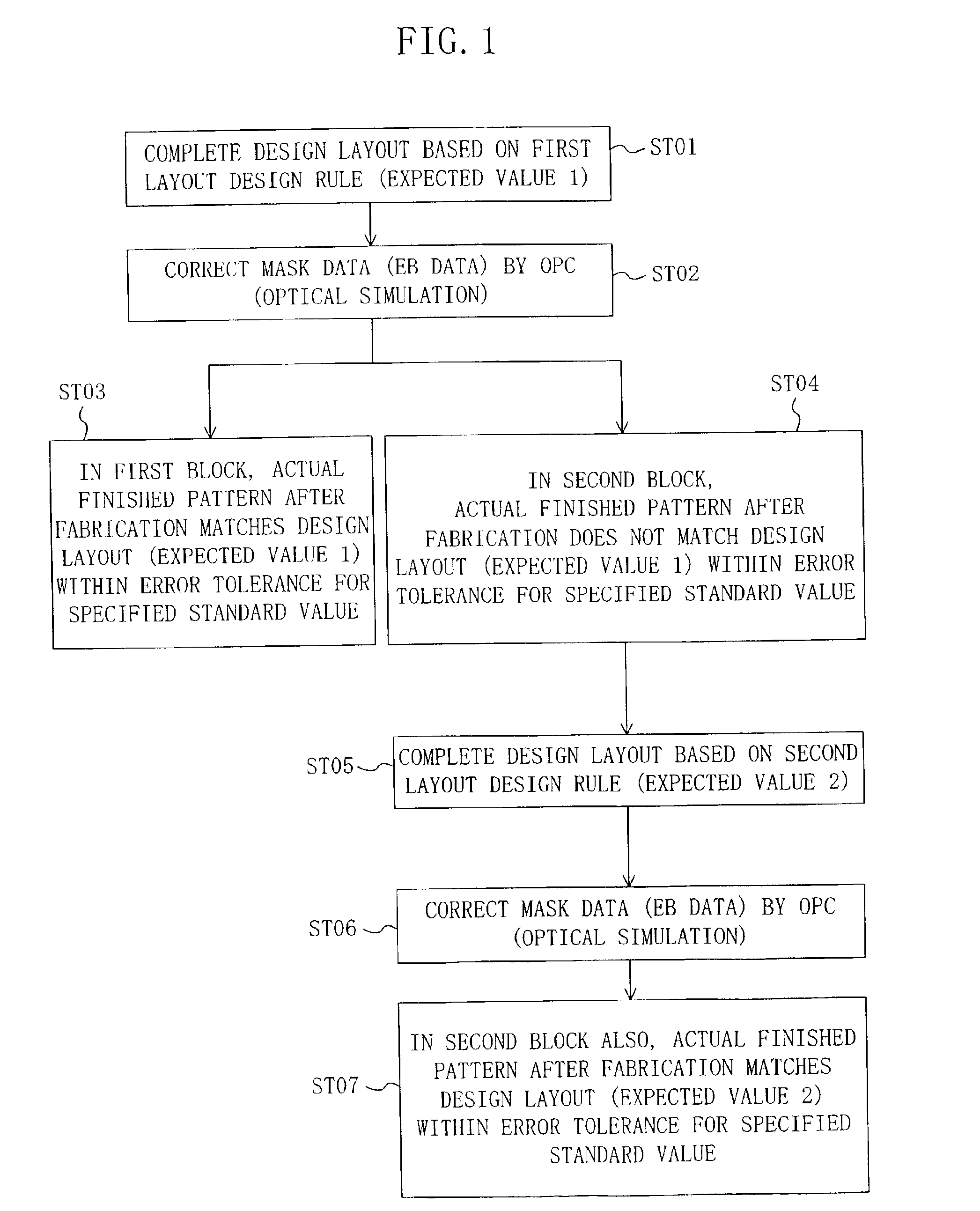

Semiconductor integrated circuit device and method for designing the same

InactiveUS6871338B2Miniaturization is ensuredSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorDesign methods

A method for designing a semiconductor integrated circuit device, the method has the steps of producing, for a plurality of placement regions on each of which a design pattern is to be placed, first layout data having a first expected value based on a first layout design rule, producing, if a difference between the first expected data and an expected finished size after fabrication of the first layout data falls within an error tolerance for a standard value, first OPC data by correcting the first layout data, producing, if the plurality of placement regions include an out-of-tolerance region for which the first OPC data falling within the error tolerance cannot be produced, second layout data having a second expected value for the out-of-tolerance region based on a second layout design rule, producing second OPC data by correcting the second layout data such that an expected finished size after fabrication of the second layout data falls within the error tolerance for the standard value, and producing mask data by using the first OPC data and the second OPC data.

Owner:PANASONIC CORP

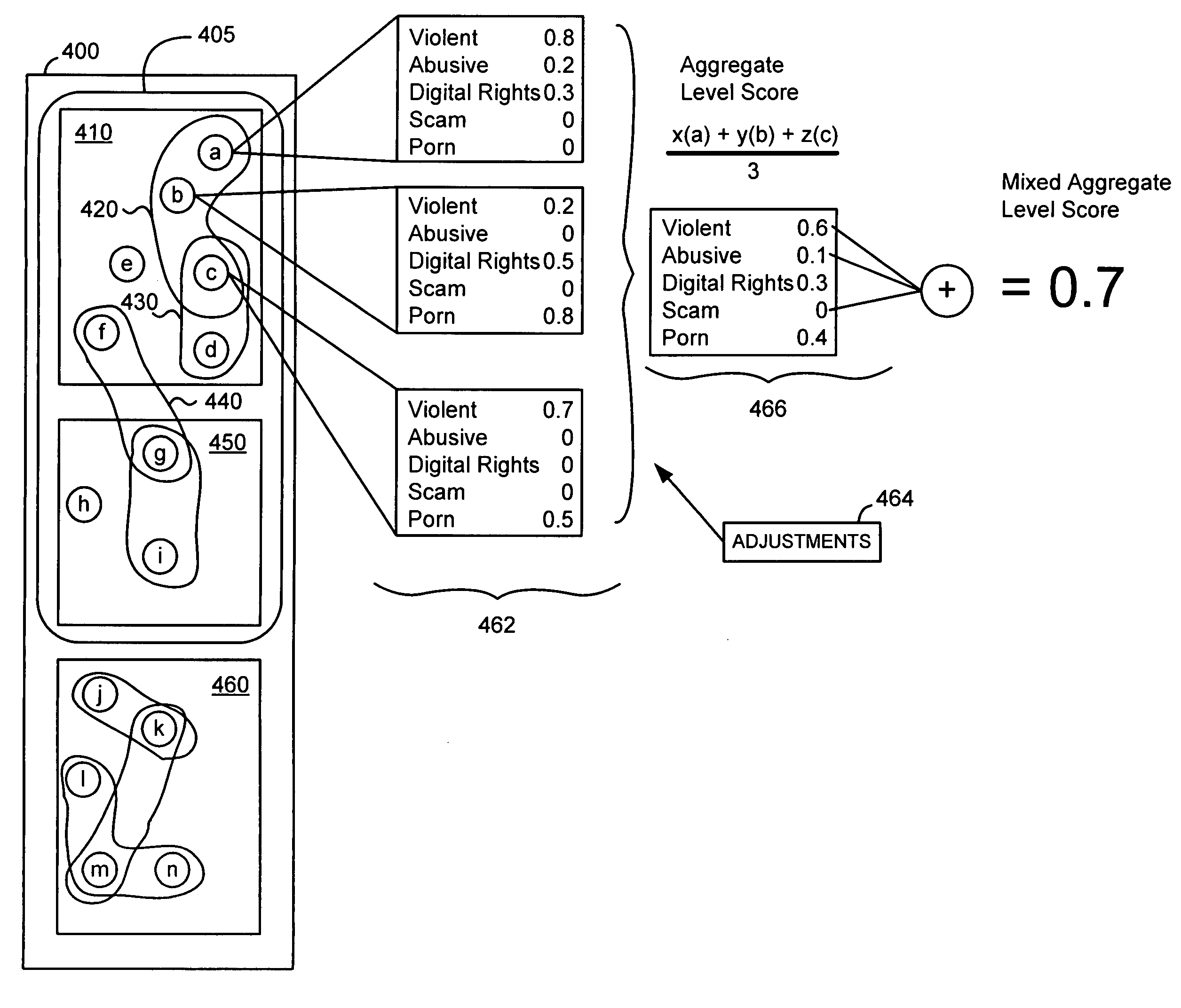

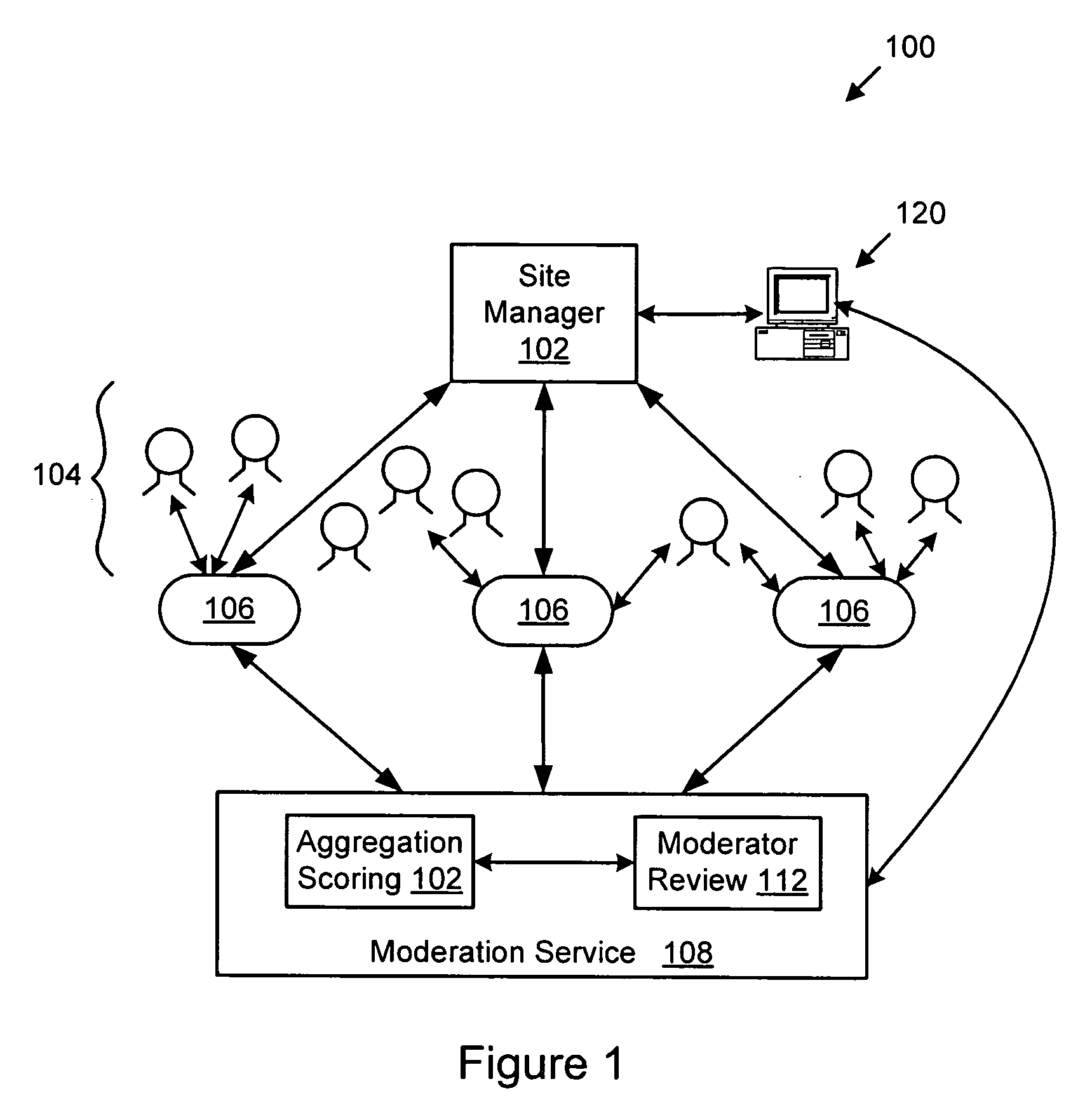

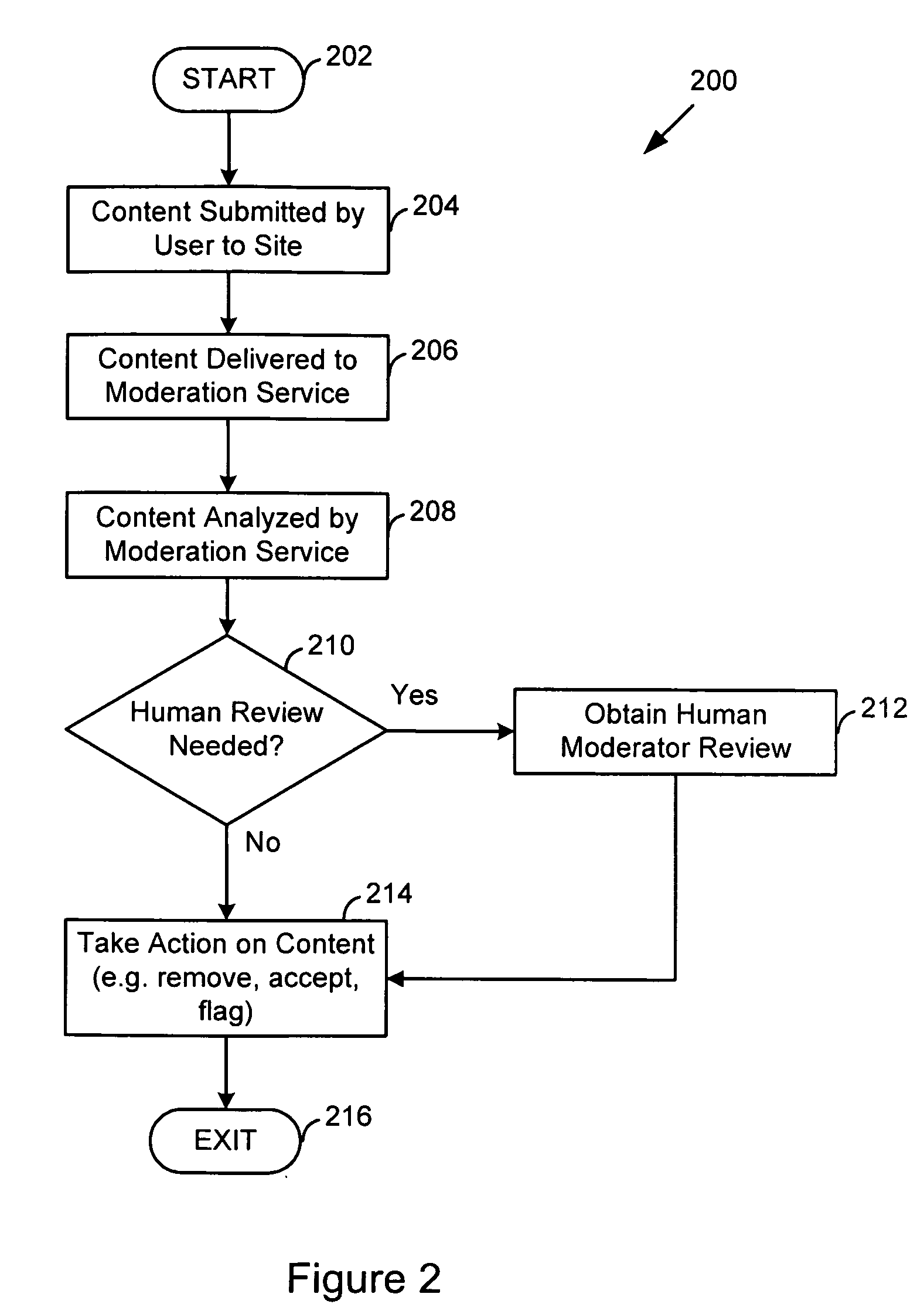

Classification of digital content by using aggregate scoring

ActiveUS20090177670A1Effective reviewEffective filteringDigital computer detailsCharacter and pattern recognitionWeb siteDigital content

Aggregate scoring is used to help classify digital content such as content uploaded to multi-user websites (e.g., social networking websites). In one embodiment, specific categories are used that relate to a social implication of content. For example, text, images, audio or other data formats can provide communication perceived to fall into categories such as violent, abusive, rights management, pornographic or other types of communication. The categories are used to provide a raw score to items in various groupings of a site's content. Where items are related to other items such as by organizational, social, legal, data-driven, design methods, or by other principles or definitions, the related items' raw scores are aggregated to achieve a score for a particular grouping of items that reflects, at least in part, scores from two or more of the related items.

Owner:KHOROS LLC

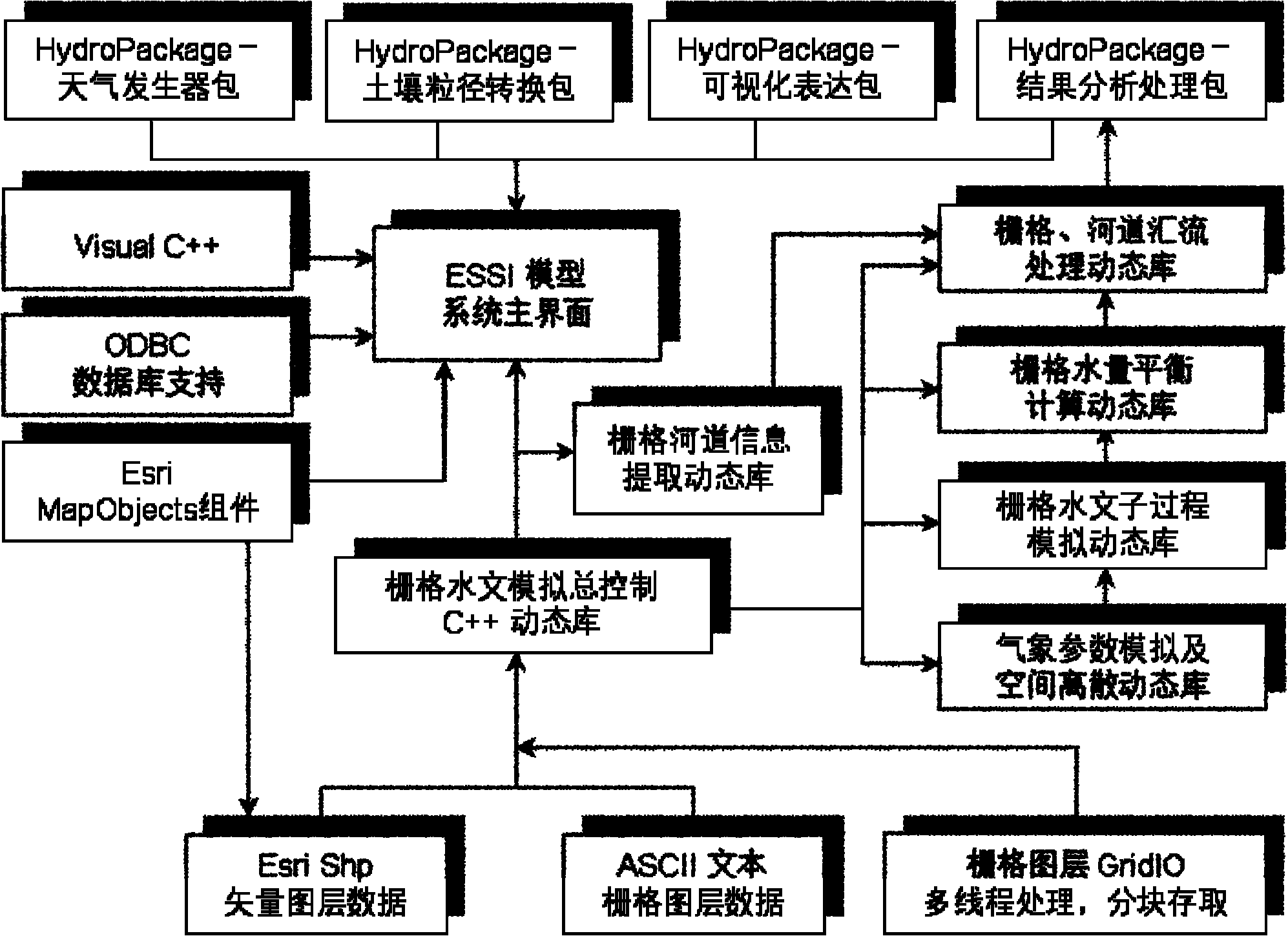

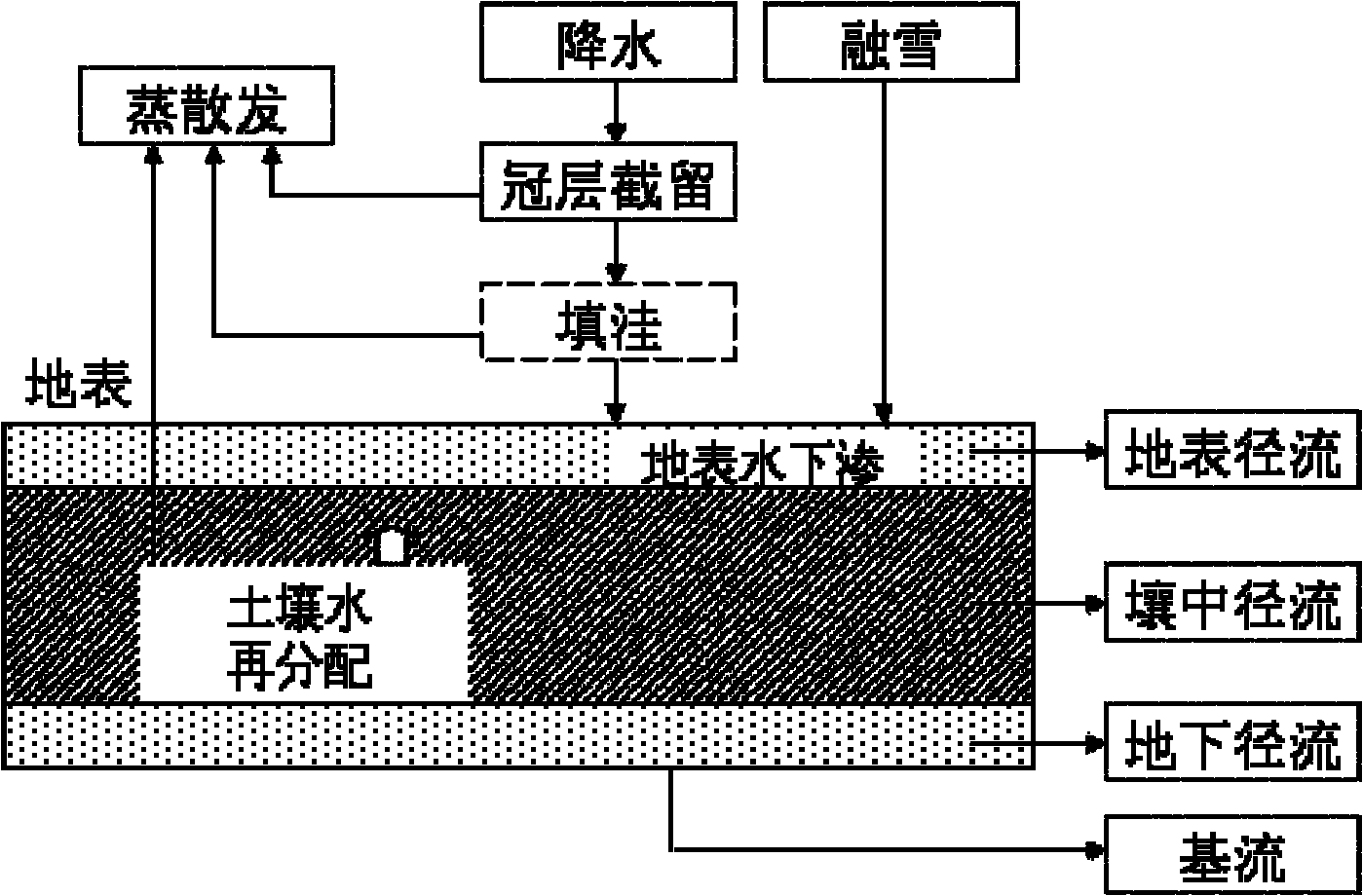

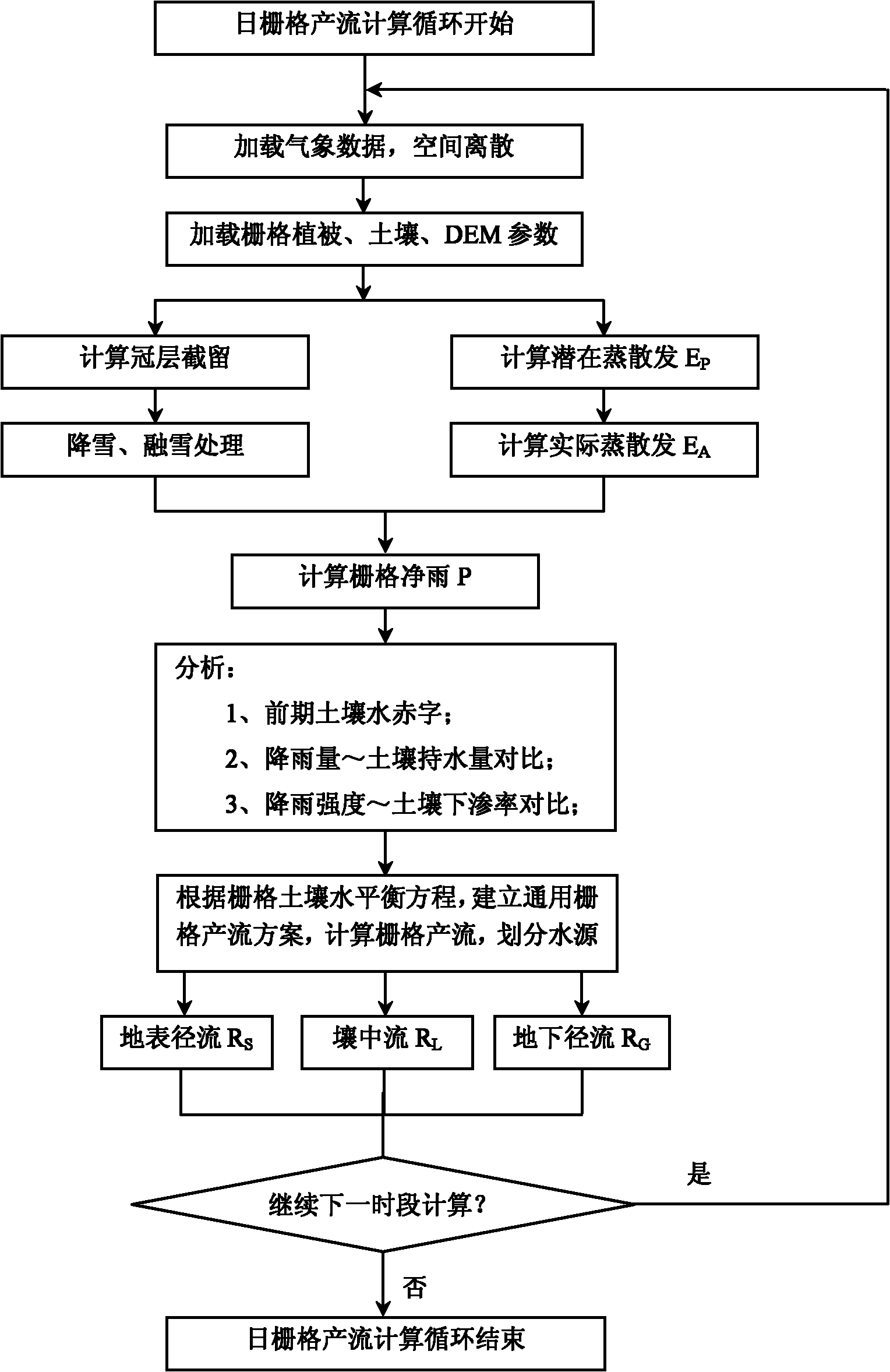

Design method for distributed hydrological model by using grid as analog unit

InactiveCN102034001AImprove scalabilityImprove execution efficiencyClimate change adaptationSpecial data processing applicationsAridRainfall runoff

The invention discloses a design method for a distributed hydrological model by using a grid as an analog unit, which is called as ESSI for short. The design method comprises the following steps of: obtainment of a distributed parameter: converting vector data into grid data; generalization of a watershed hydrological process: establishing a universal runoff generating type for the grid; design of a runoff generating process: respectively computing the water-quantity distributing condition of each part according to different prior-period soil water conditions; design of a flow collecting process: respectively designing a Muskingum-Cunge method, a delay algorithm and a riverway segmentation Muskingum method for the flow collecting process computation of the model under different conditions; and model development and integration. The invention not only can finish the watershed hydrological process simulation at an arid region and a humid region, but also can realize the short-term flood forecast and the long-term rainfall-runoff process simulation and prediction of a watershed by using modularization and integration ideas as means, thereby providing scientific reference bases for deeply learning about the physical mechanism of water circulation by people, reducing the drought and water-logging disasters and reasonably developing and utilizing water resources.

Owner:NANJING UNIV