Optimizing designing apparatus of integrated circuit, optimizing designing method of integrated circuit, and storing medium in which program for carrying out optimizing designing method of integrated circuit is stored

a technology of integrated circuits and designing apparatuses, applied in the field of optimizing designing apparatus of integrated circuits, optimizing designing methods of integrated circuits, and storing media, can solve the problems of inability to obtain designer requirements, inability to optimize circuit characteristics, and time-consuming optimization of circuits, so as to facilitate global optimization, facilitate optimization, and facilitate optimization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0064]An optimizing designing apparatus of an integrated circuit according to an embodiment of the present invention will be explained.

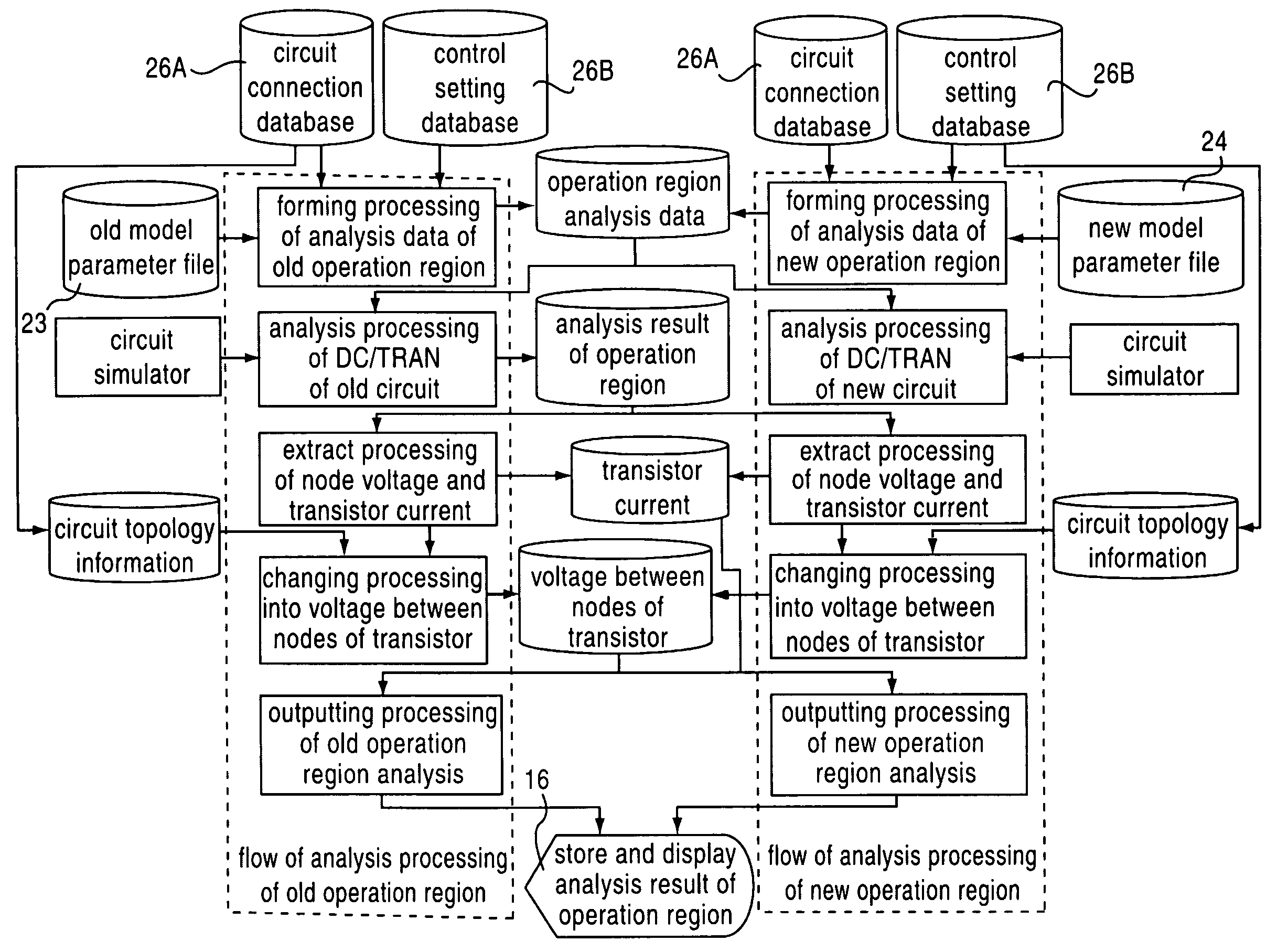

[0065]FIG. 1 is a block diagram showing the entire configuration of the optimizing designing apparatus of the integrated circuit according to the embodiment.

[0066]The optimizing designing apparatus of the integrated circuit according to the embodiment designs an optimizing circuit (second circuit) which is a new circuit having the same function as that of an initial circuit (first circuit) which is an old circuit when producing process or physical specification of a semiconductor is changed. The optimizing designing apparatus includes an optimizing simulation optimizer 1 which is an optimizing designing program and data storing means.

[0067]The data storing means comprises an initial circuit connection file 21, a rule file 22, an old model (first circuit) parameter file 23, a new model (second circuit) parameter file 24, an optimizing circuit (second ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More