Patents

Literature

130 results about "Time to market" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In commerce, time to market (TTM) is the length of time it takes from a product being conceived until its being available for sale. TTM is important in industries where products are outmoded quickly. A common assumption is that TTM matters most for first-of-a-kind products, but actually the leader often has the luxury of time, while the clock is clearly running for the followers.

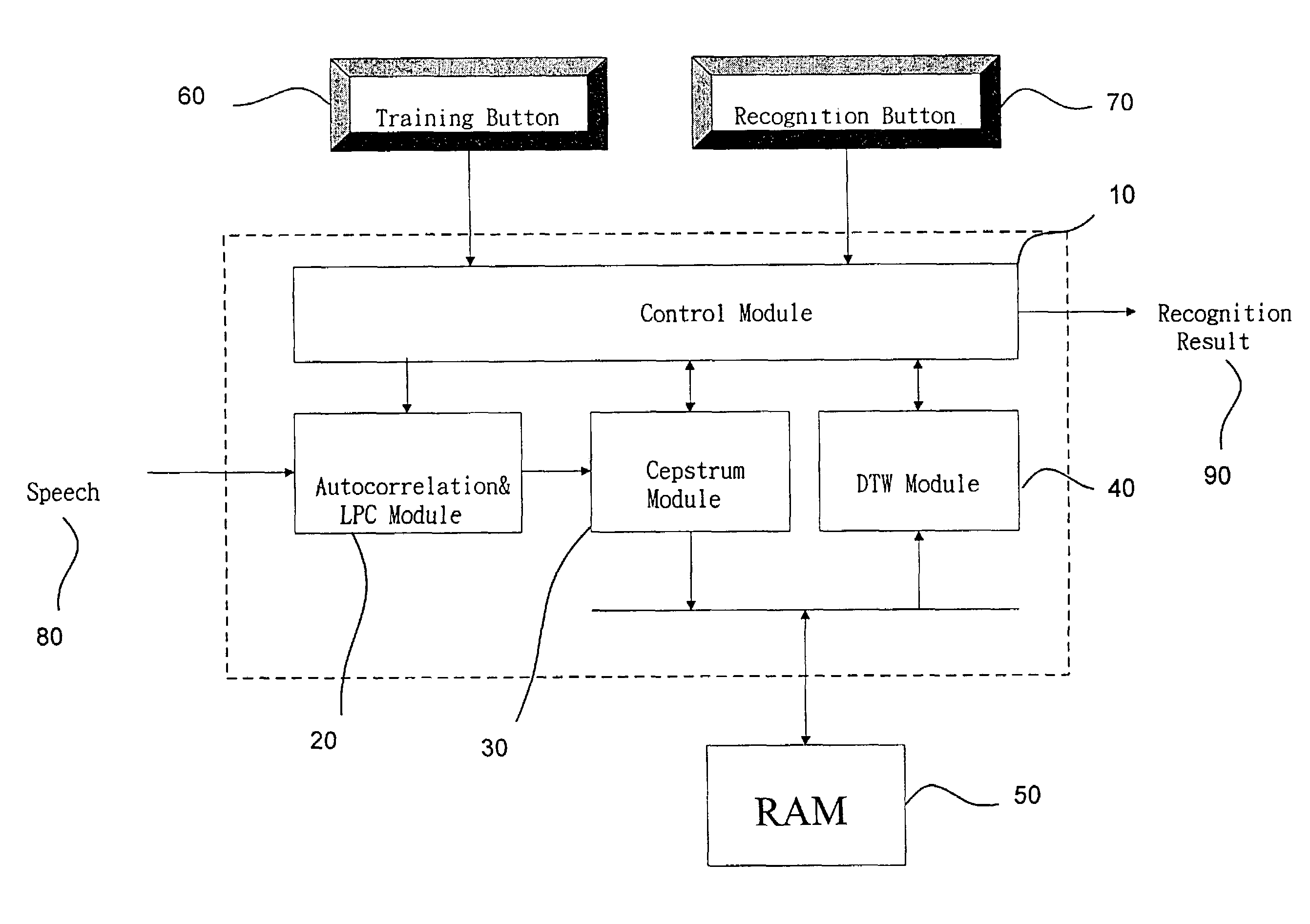

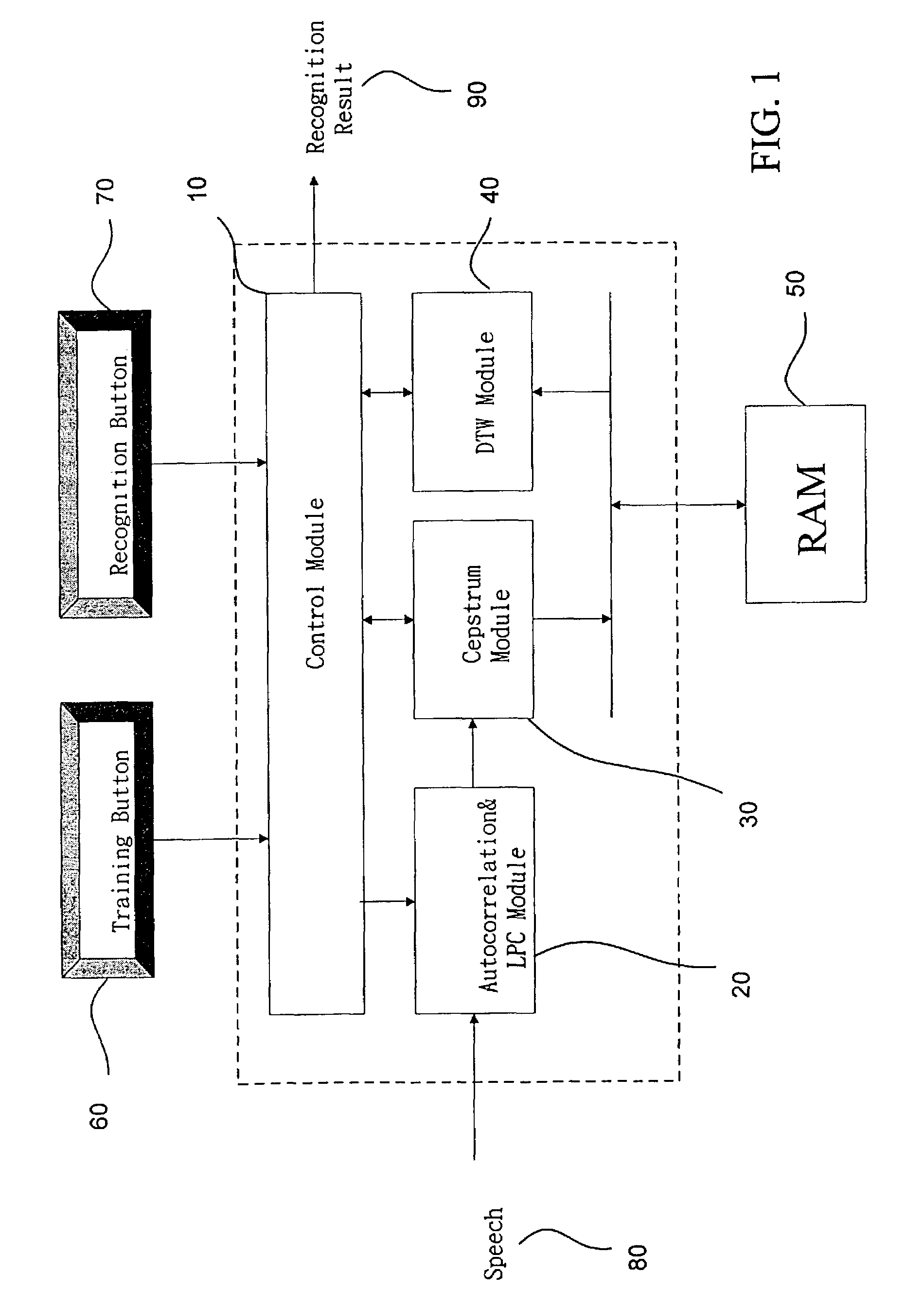

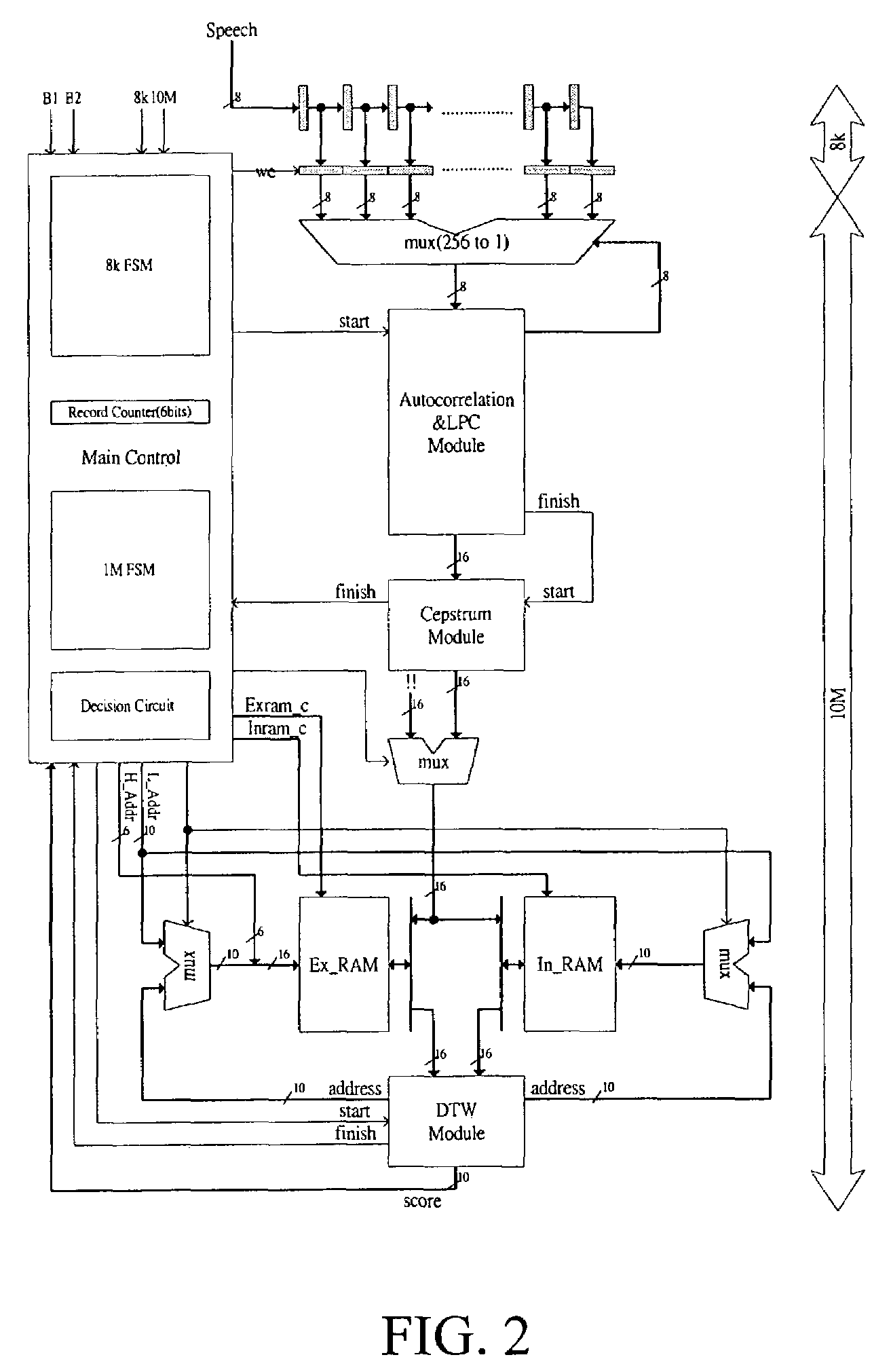

Speech recognition system

InactiveUS7266496B2Improve execution speedLow costSpeech recognitionLinearityLinear prediction coefficient

The present invention discloses a complete speech recognition system having a training button and a recognition button, and the whole system uses the application specific integrated circuit (ASIC) architecture for the design, and also uses the modular design to divide the speech processing into 4 modules: system control module, autocorrelation and linear predictive coefficient module, cepstrum module, and DTW recognition module. Each module forms an intellectual product (IP) component by itself. Each IP component can work with various products and application requirements for the design reuse to greatly shorten the time to market.

Owner:NAT CHENG KUNG UNIV

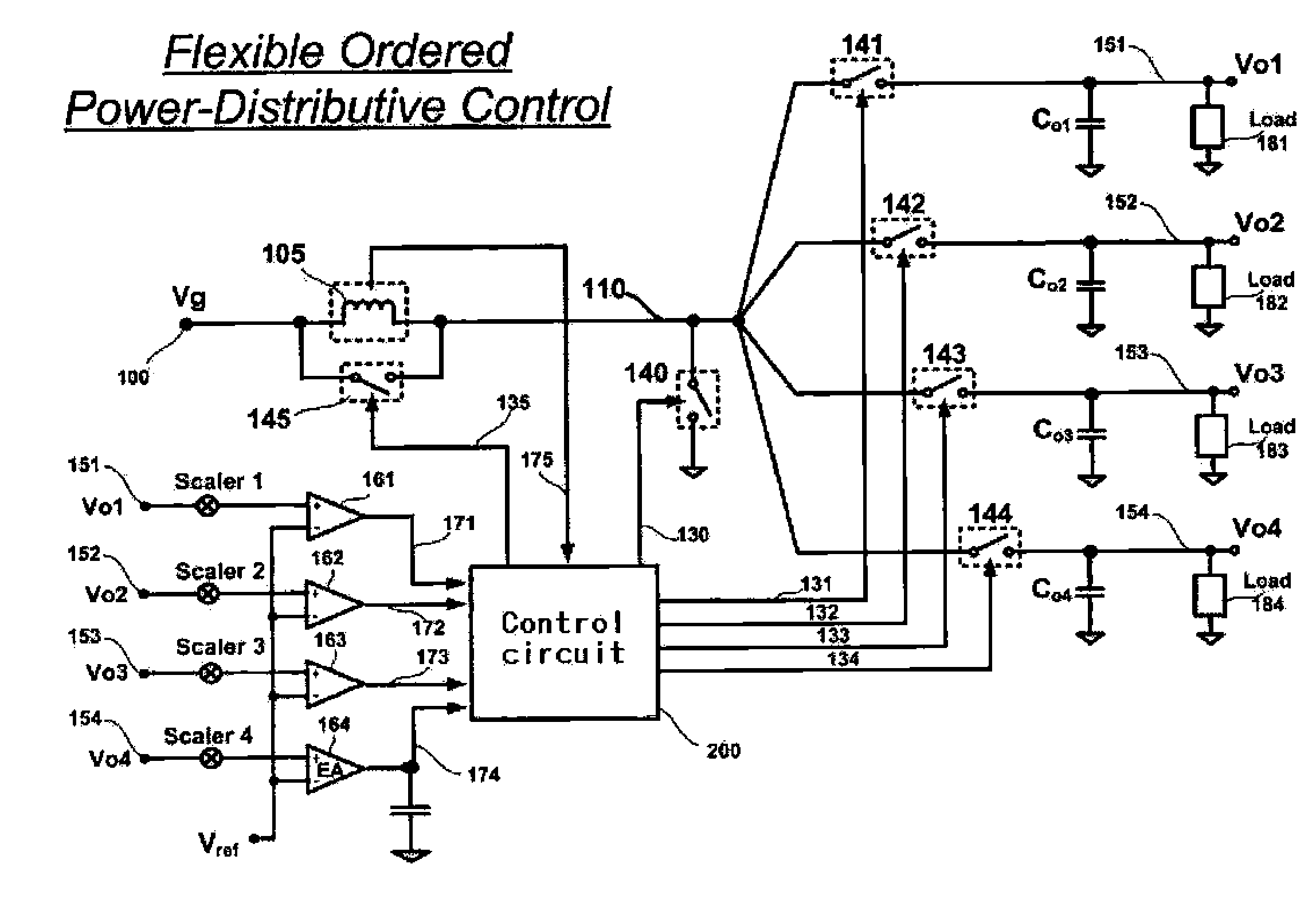

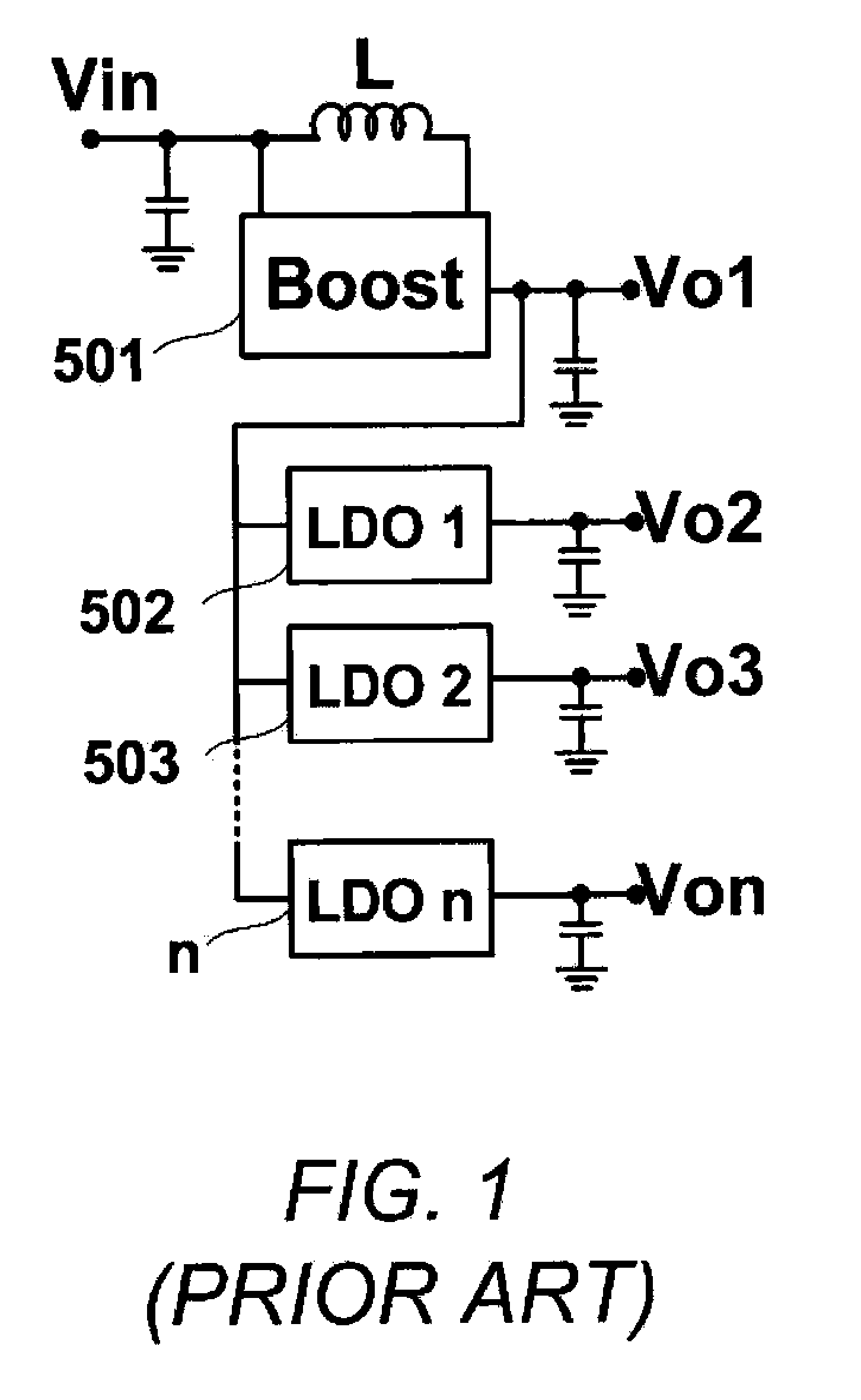

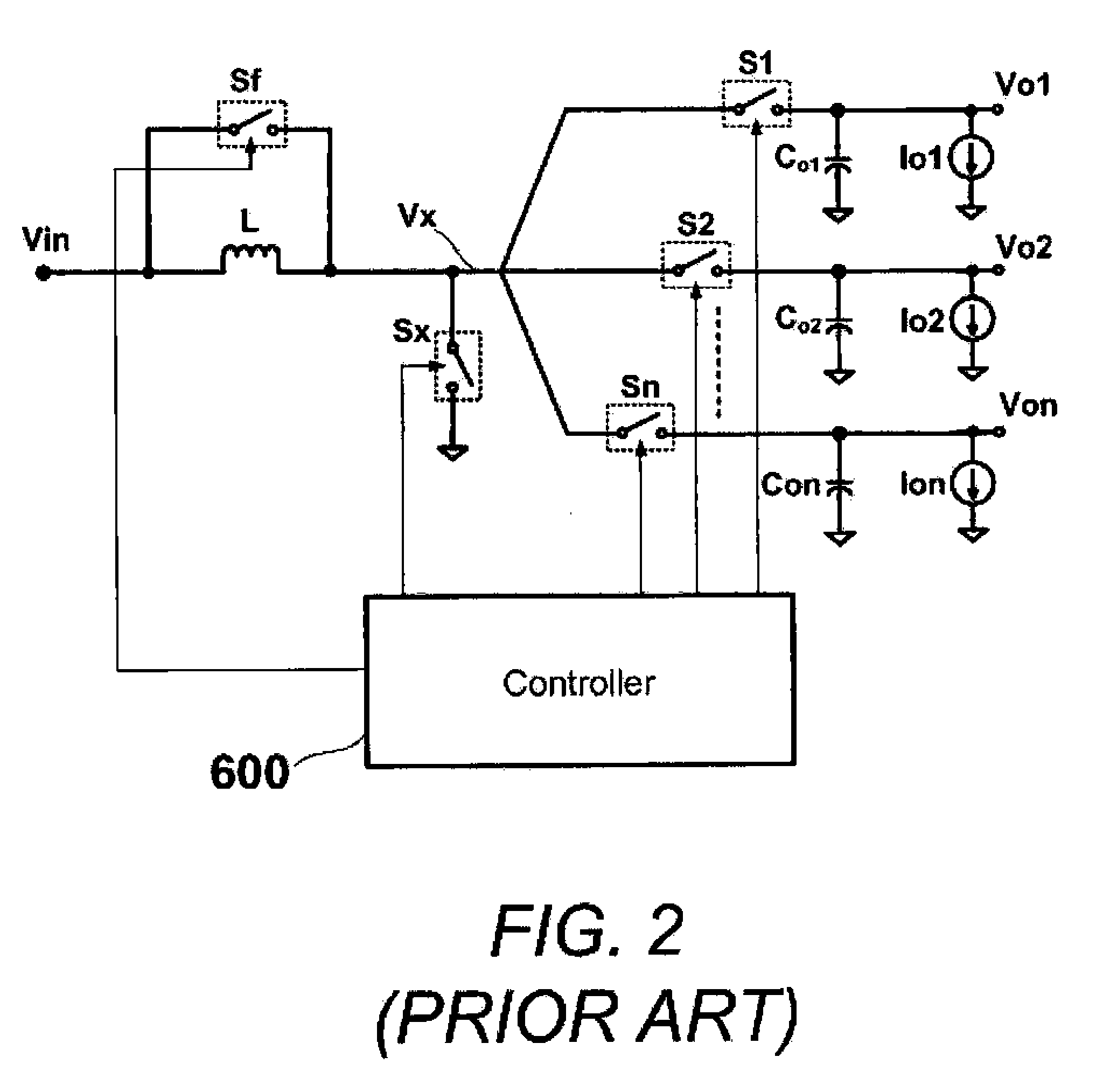

Multiple-Output DC-DC Converter

The invention relates to a DC / DC converter design. The converter requires only one single inductor to draw energy from one input source and distribute it to more than one outputs, employing Flexible-Order Power-Distributive Control (FOPDC). It include a single inductor, a number of power switches, comparators, only one error amplifier, a detecting circuit and a control block to regulate outputs. This converter can correctly regulate multiple outputs with fast transient response, low cross regulation, and effective switching frequency for each output. It can work in both discontinuous conduction mode (DCM) and continuous conduction mode (CCM). Moreover, with FOPDC, future output extension is simple, making a shorter time-to-market process for next versions of the converter. The design can be applied to different types of DC-DC converter.

Owner:JDA TECH

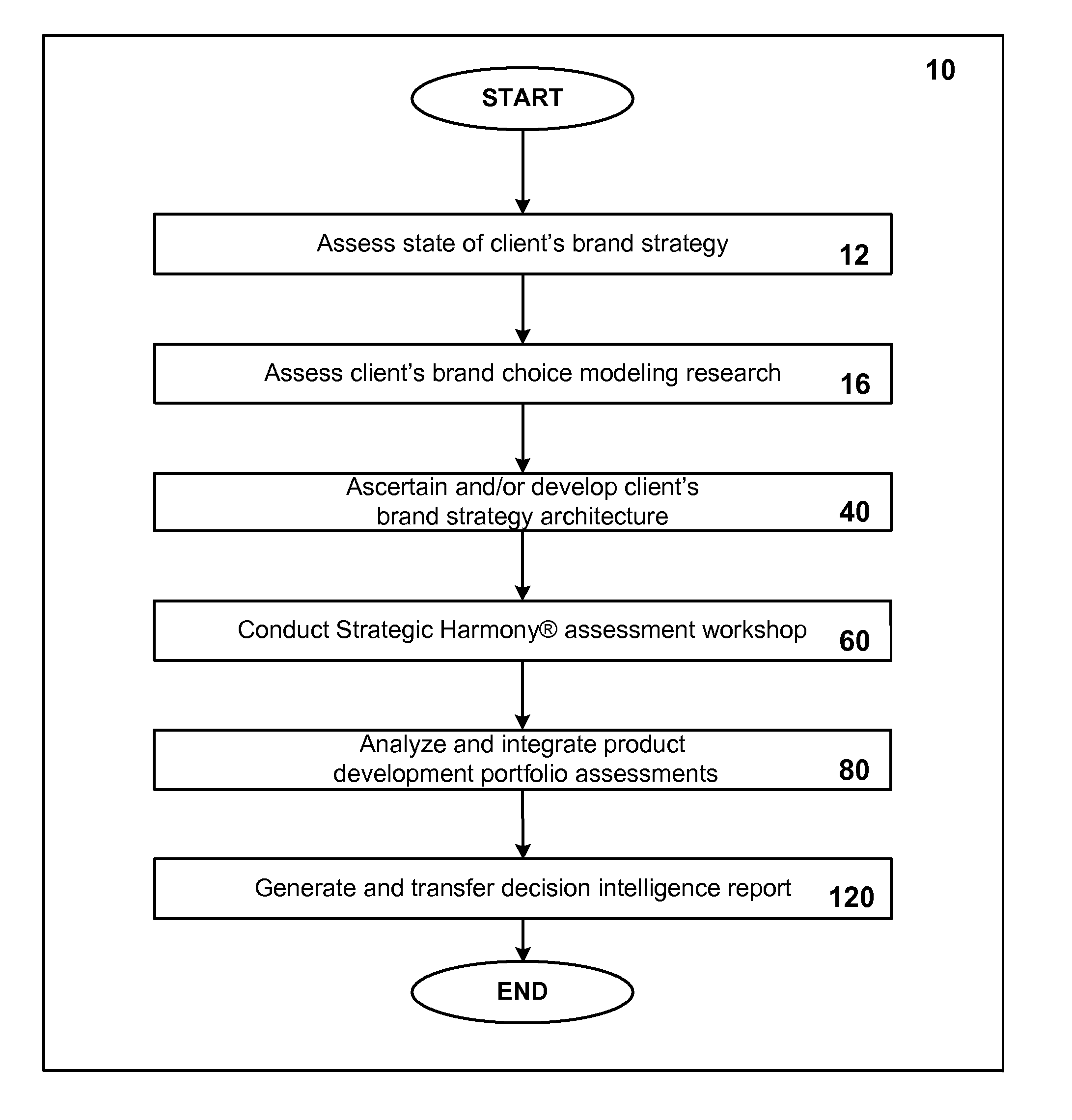

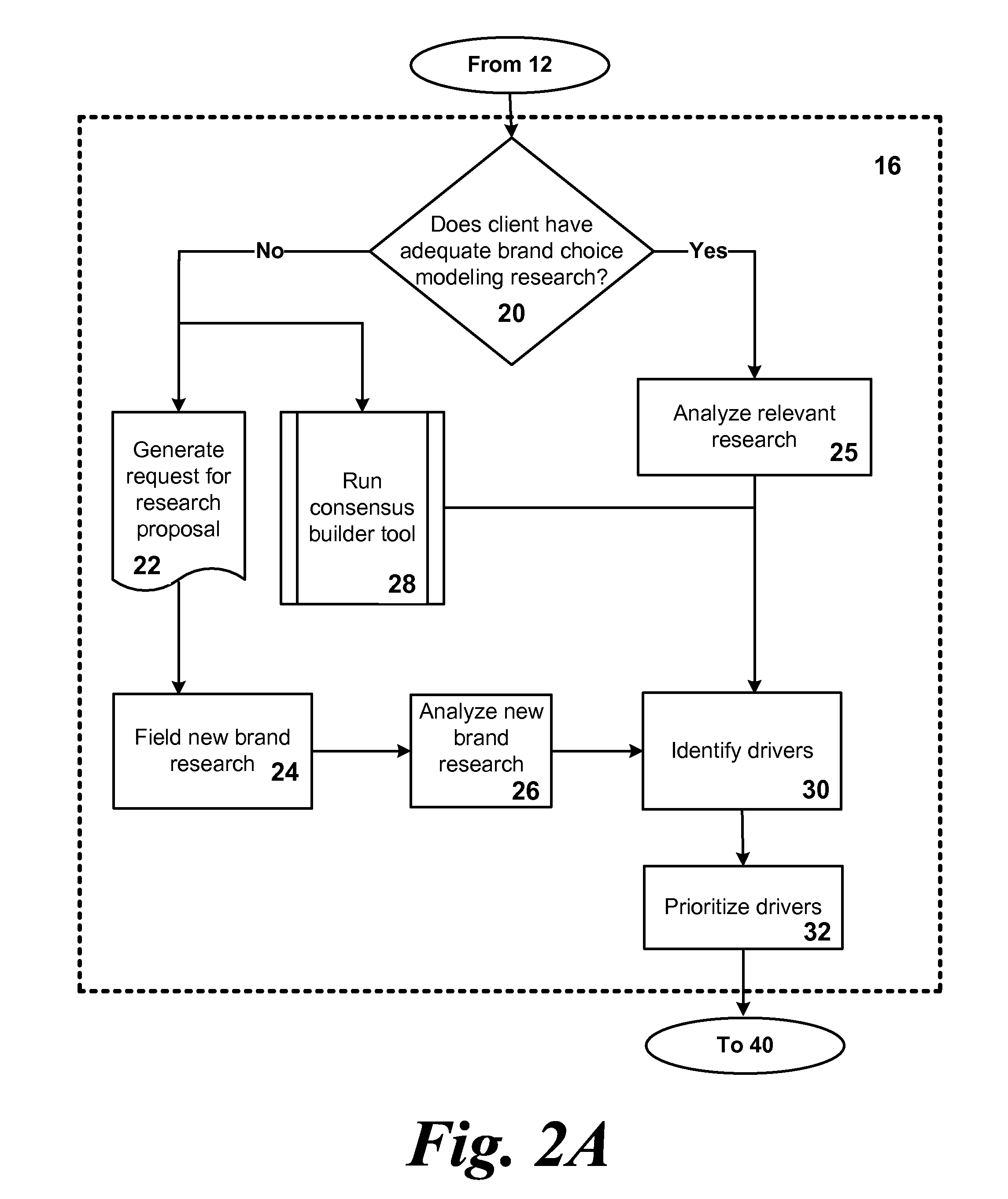

System and method for optimizing product development portfolios and integrating product strategy with brand strategy

InactiveUS20070192170A1Shorten the time to marketImprove business performanceFinanceResourcesTime to marketService composition

A business and software method to cost-effectively optimize product and / or service development portfolios, to reduce time to market, and to better integrate and align product or service strategy with brand strategy. The business and software method includes defining in detail the product and service attributes that characterize the ideal customer experience, categorizing the attributes, assigning a numerical value of importance to the attributes, and applying those values to statistical analysis of each assessed product development initiative in terms of alignment with ideal experience and potential competitive impact relative to the resources and risks required to bring each initiative to market. A prioritization for product development resource allocation is developed based upon these analyses. The prioritization is presented in the form of decision intelligence tools for an organization to use and reach informed judgments concerning resource allocation to develop, maintain, or optimize a given product or service portfolio. The decision intelligence tools serve to improve business performance, increase market impact, and build brand equity for products and services of a given organization by improving alignment between what the organization promises customers and what it actually delivers.

Owner:CRISTOL STEVEN M

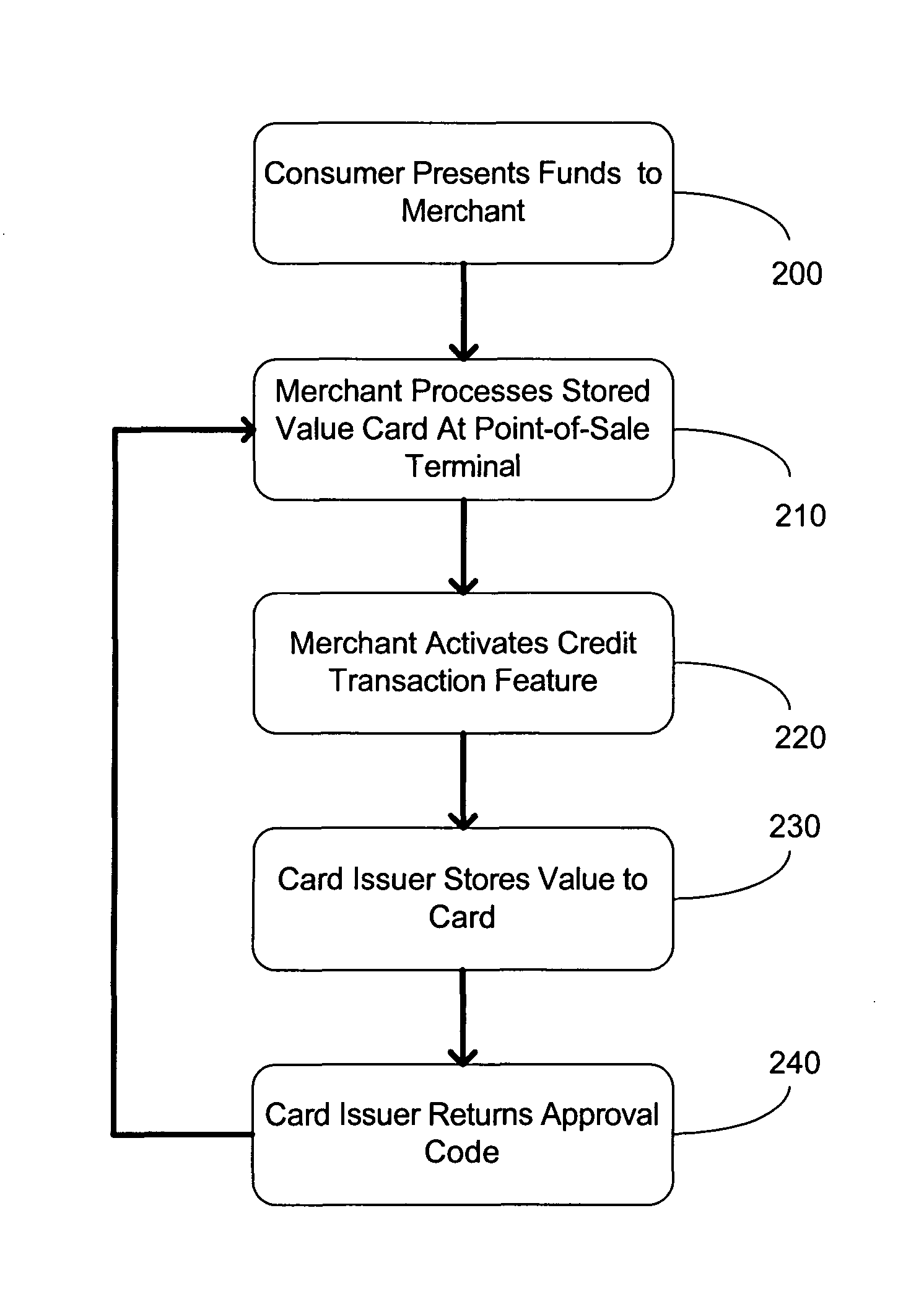

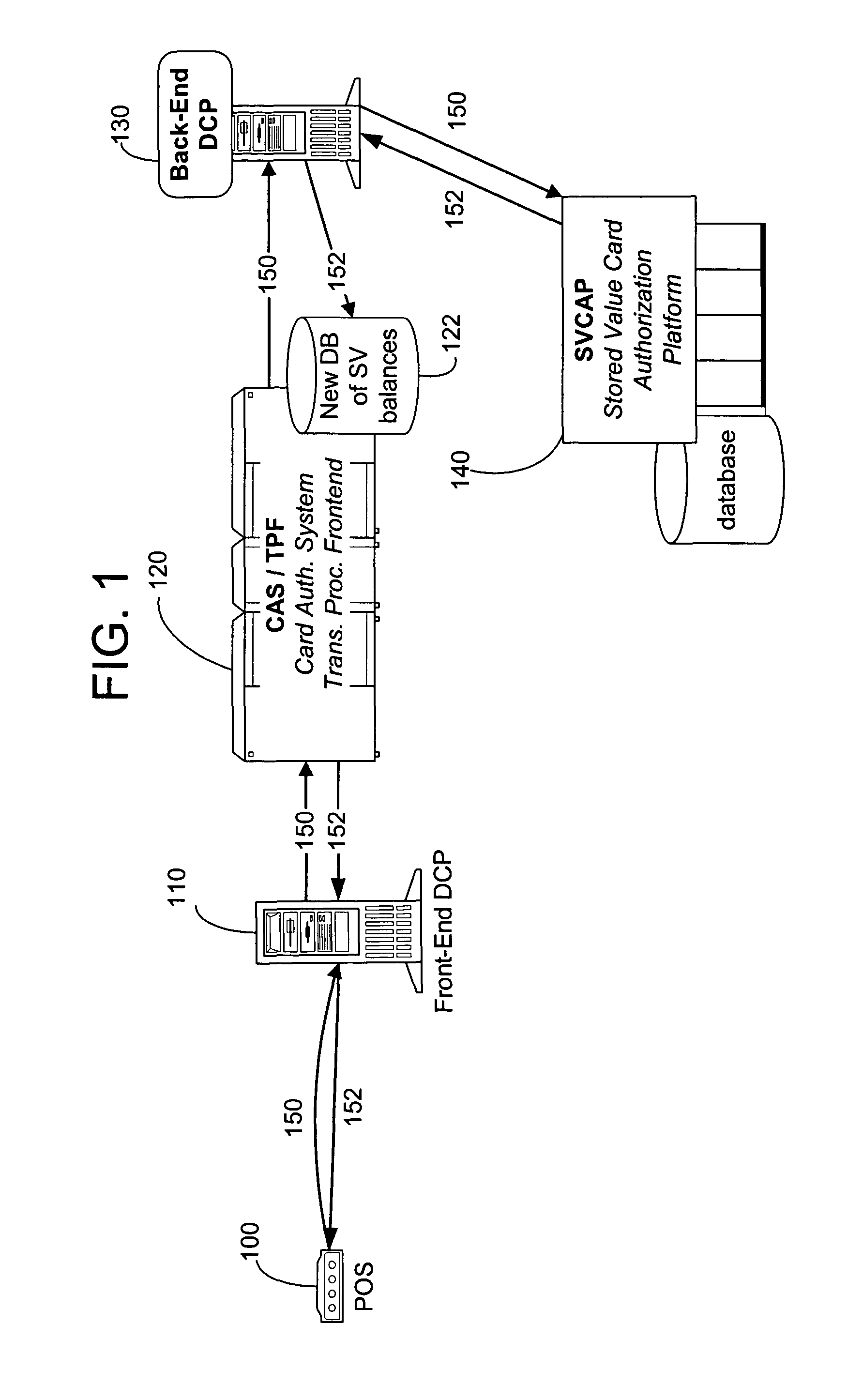

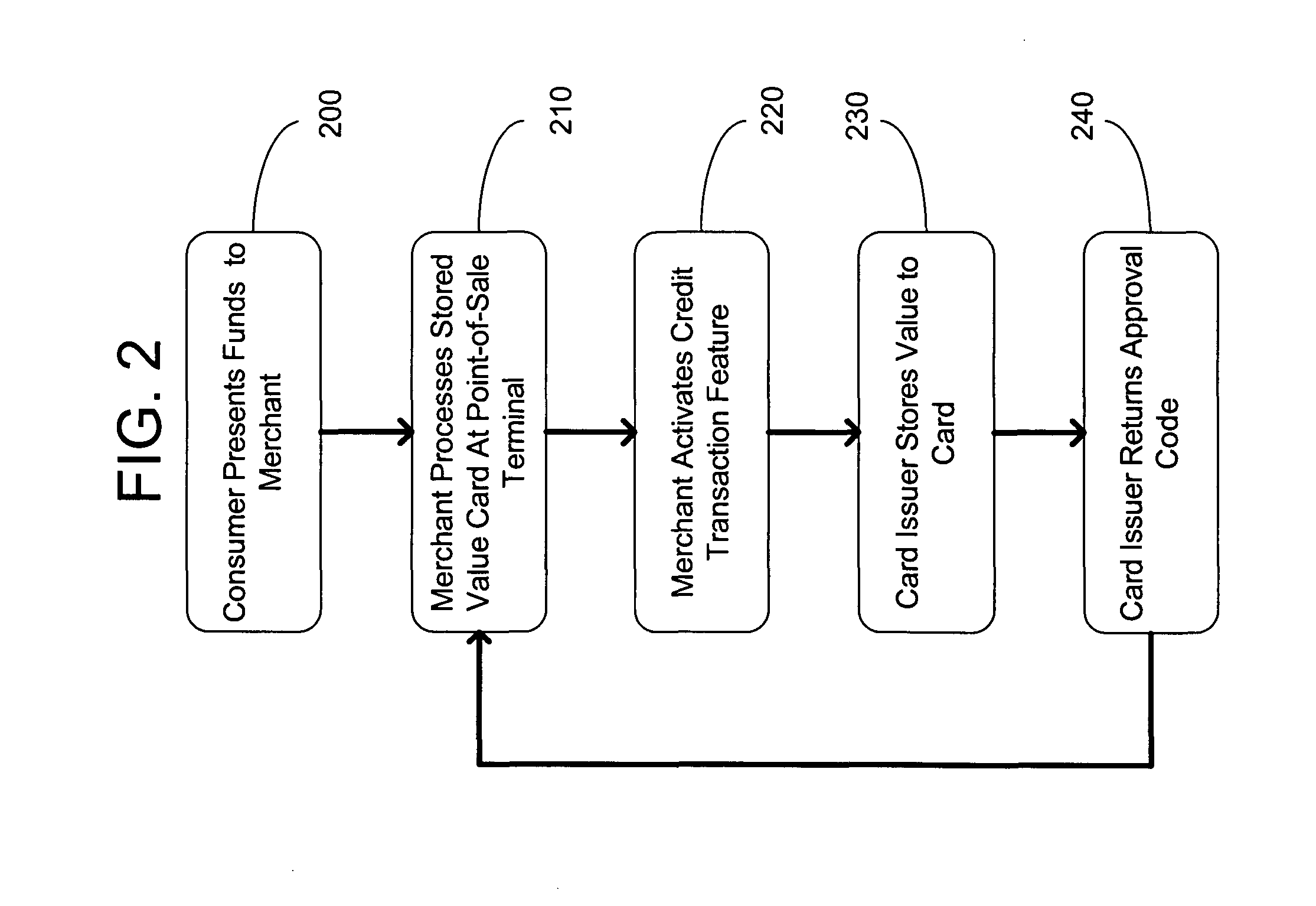

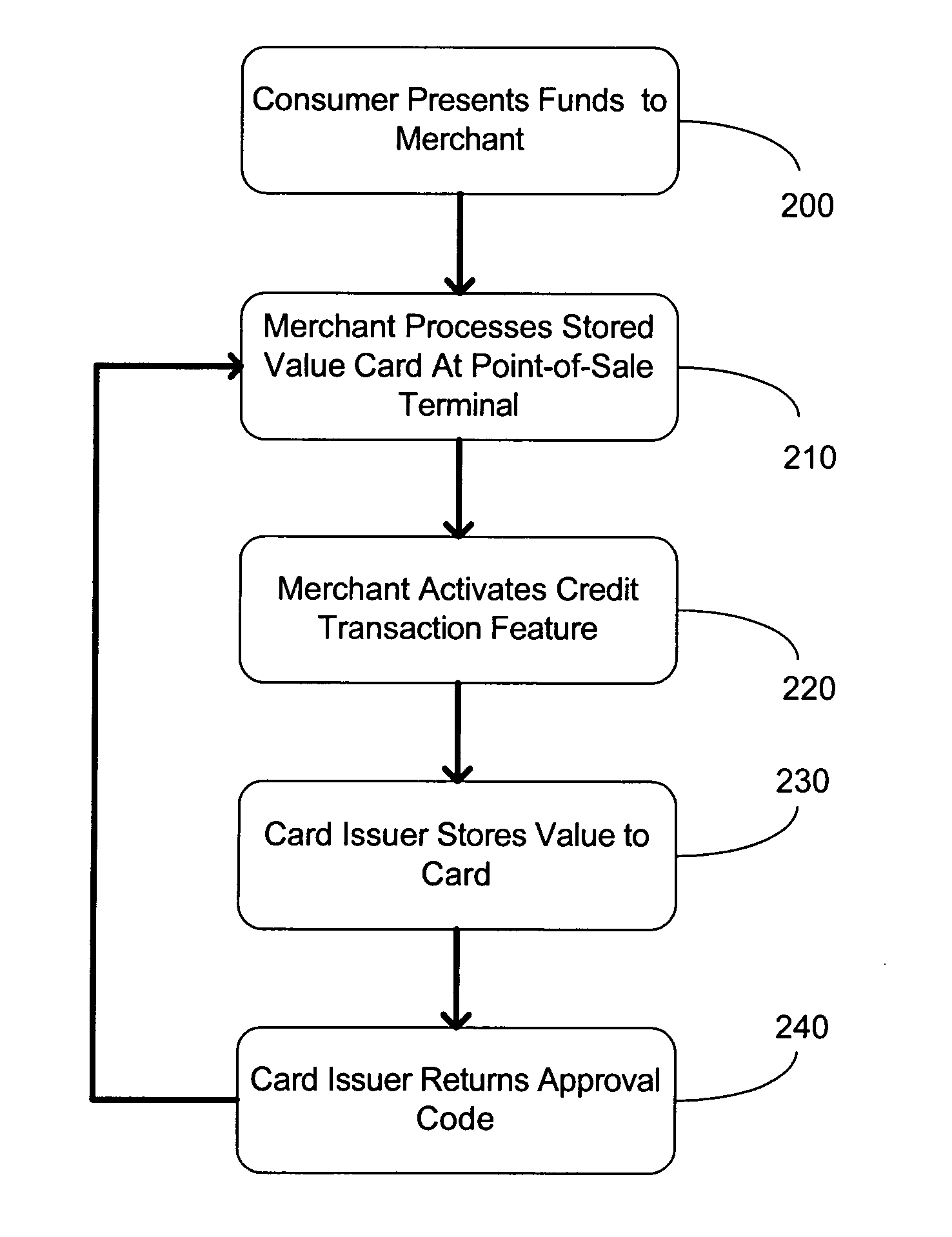

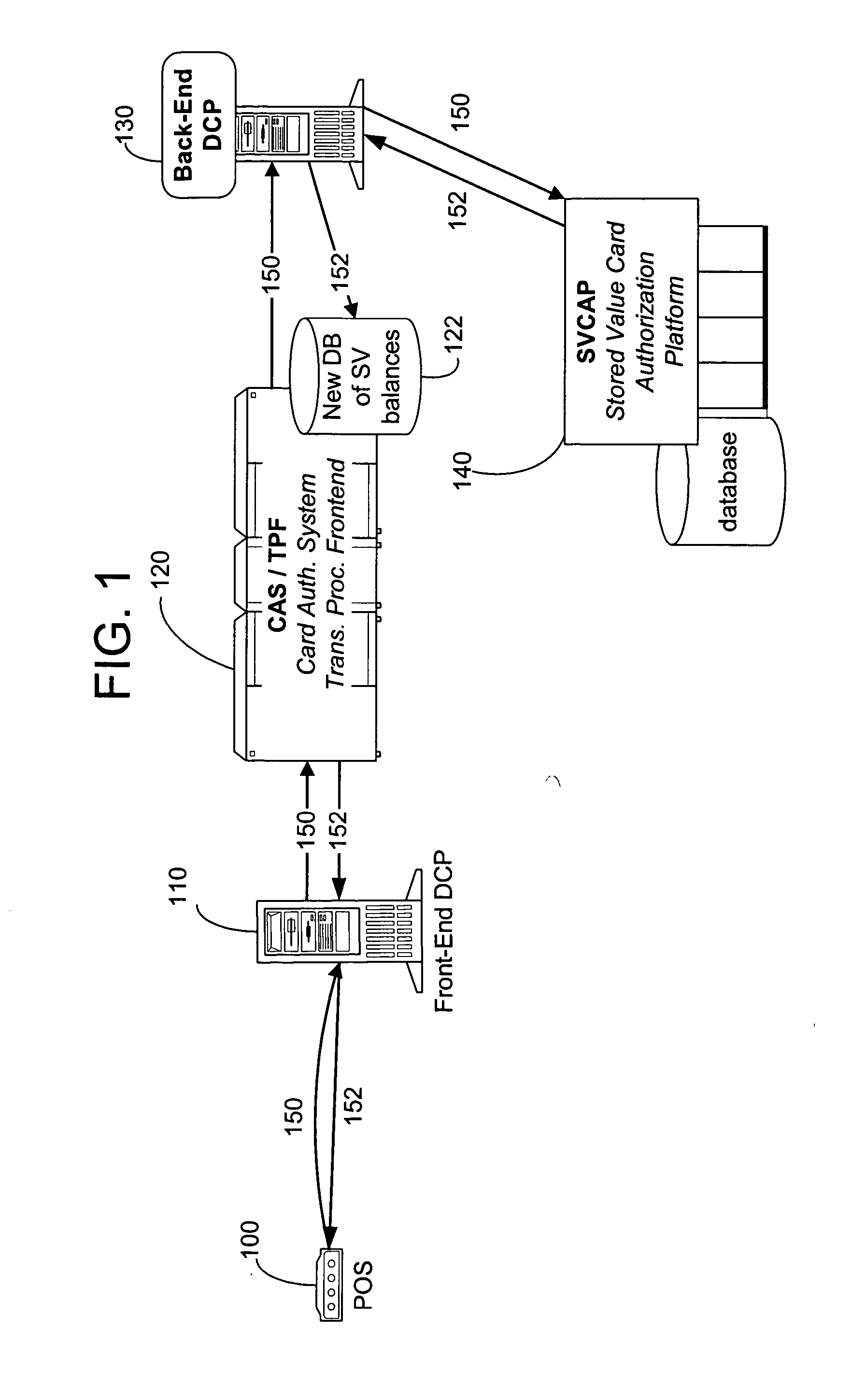

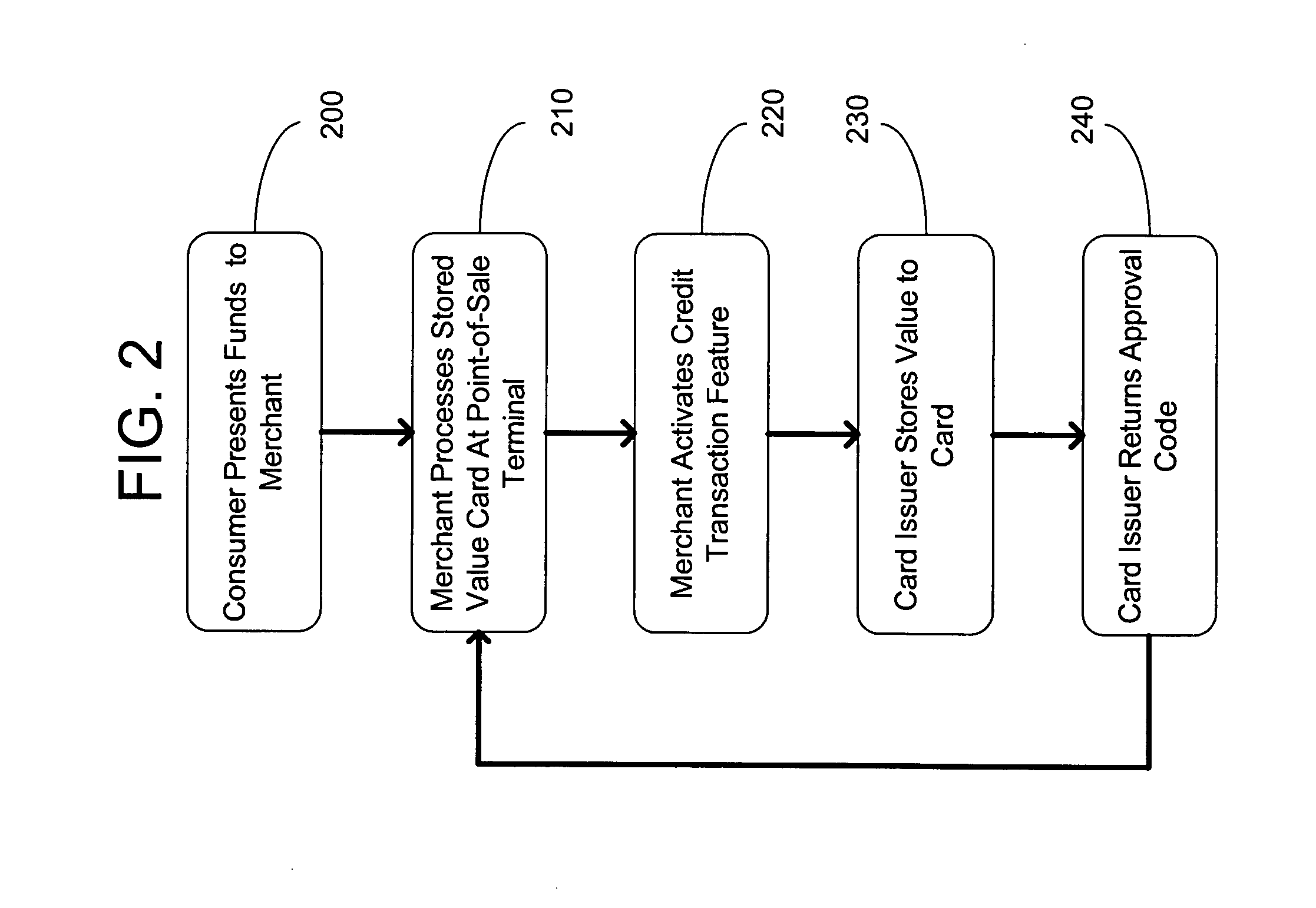

System and method for activating or changing the status of an account associated with a prepaid card

InactiveUS8595074B2Complete banking machinesHand manipulated computer devicesTime to marketDebit card

A system and method for activating and funding prepaid cards at the point of sale by making innovative use of existing point-of-sale devices and existing credit / debit card acceptance networks and processes. The invention obviates the need to implement new / different technology at point-of-sale terminals that are widely used at retail outlets. This invention makes use of the existing credit and charge card systems and processes, including industry standard message formats, to settle funds and fees between the seller and the issuer of the prepaid card, thus further reducing the expense and time-to-market for product distribution.

Owner:LIBERTY PEAK VENTURES LLC

System and method for activating or changing the status of an account associated with a prepaid card

InactiveUS20050027655A1Complete banking machinesHand manipulated computer devicesTime to marketDebit card

A system and method for activating and funding prepaid cards at the point of sale by making innovative use of existing point-of-sale devices and existing credit / debit card acceptance networks and processes. The invention obviates the need to implement new / different technology at point-of-sale terminals that are widely used at retail outlets. This invention makes use of the existing credit and charge card systems and processes, including industry standard message formats, to settle funds and fees between the seller and the issuer of the prepaid card, thus further reducing the expense and time-to-market for product distribution.

Owner:LIBERTY PEAK VENTURES LLC

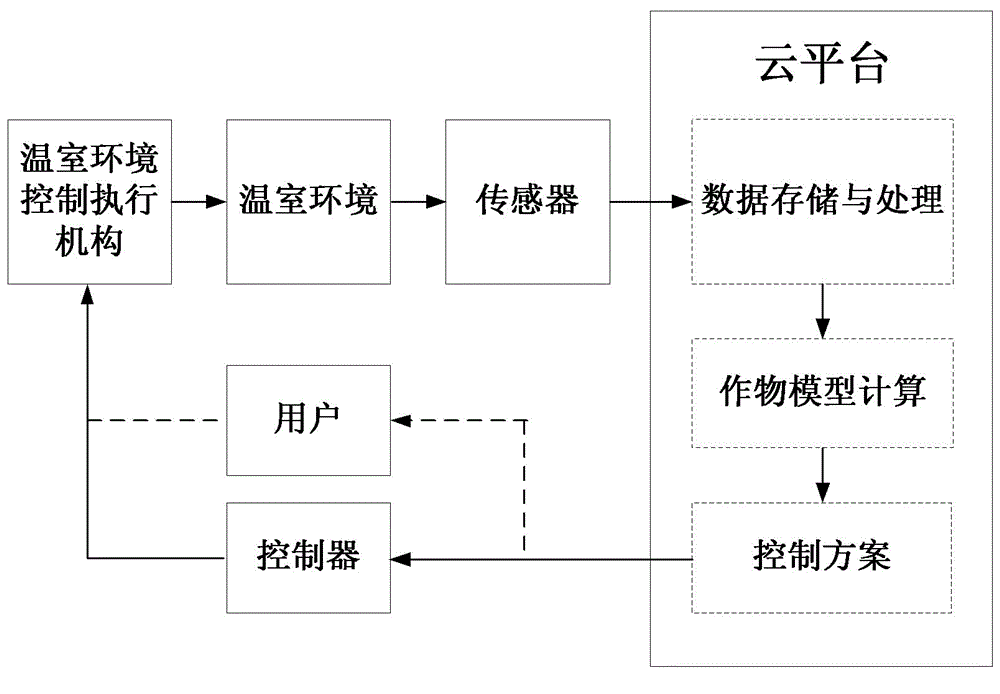

System and method for regulating and controlling greenhouse environment based on Internet of Things and cloud computing technology

ActiveCN104656617AContributes to intelligenceFacilitates automaticityMeasurement devicesTransmissionTime to marketGreenhouse

The invention discloses a system and a method for regulating and controlling a greenhouse environment based on Internet of Things and cloud computing technology. The system comprises a greenhouse environment sensor module, an environmental data transmission module, a cloud platform server module, a greenhouse environment control module and a greenhouse environment executing mechanism. The regulation and control for the environment are combined with the requirements of crops, but are not in single threshold control, so that the greenhouse environment control is more accurate; by utilizing automatically monitored environmental data, the complicated modeling process about crop-environment interaction is avoided, and the environment is directly regarded as input; by utilizing a crop model, the harvesting time to market and yield of the crops can be predicted; the system is significant for improving the intelligence and automaticity of greenhouse management and improving the economic benefit of greenhouse growth.

Owner:QINGDAO ACADEMY OF INTELLIGENT IND

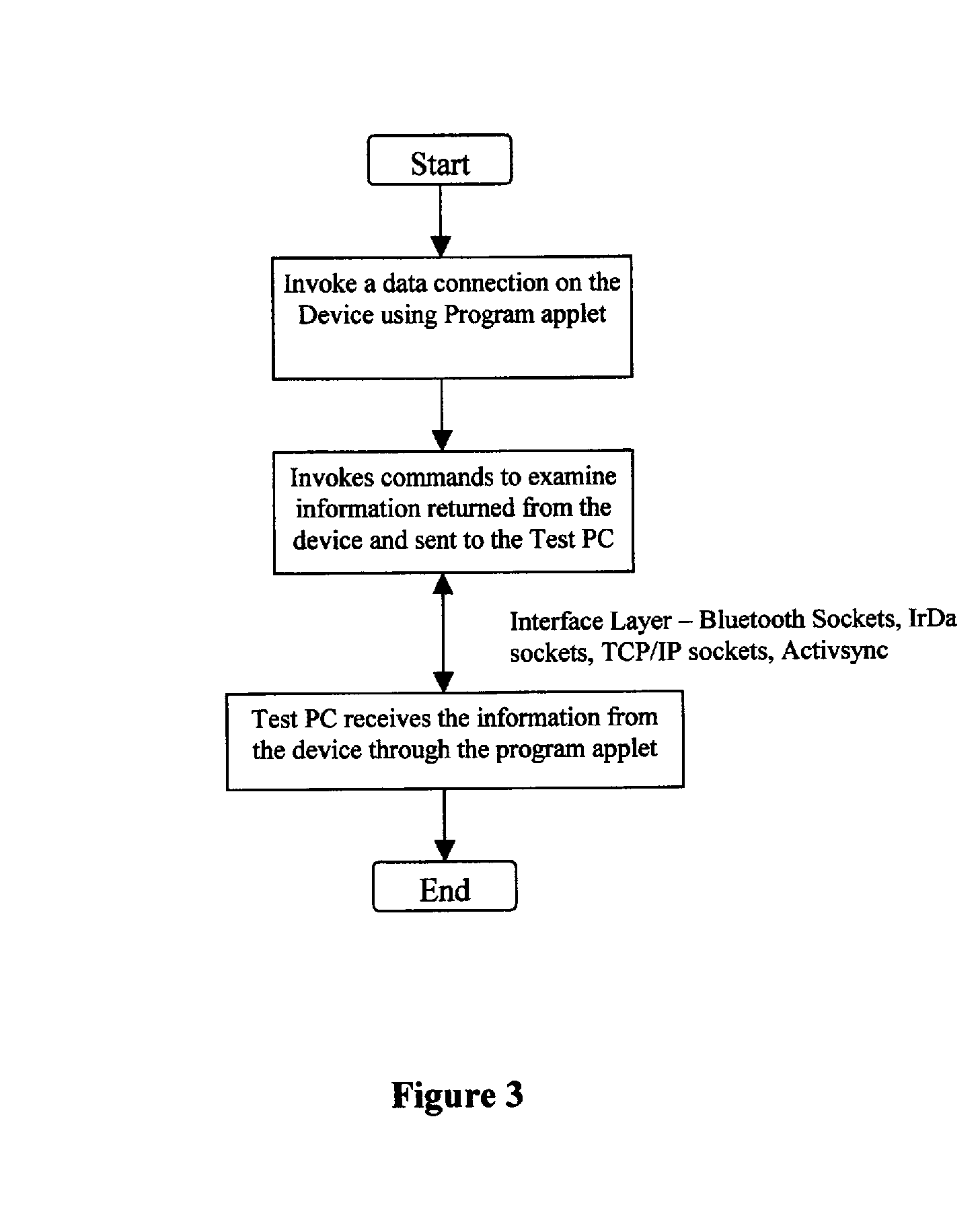

Mobile device throughput testing

InactiveUS20120300649A1Error preventionFrequency-division multiplex detailsComputer hardwareTime to market

The instant invention is a program applet that can be loaded onto mobile devices and directly interfaces with the operating system and automated test scripts. The program applet is capable of initiating the required transfer and will provide information regarding the progress of the transfer such that a test client can properly calculate the data throughput rates. The result is a minimization of time-to-market for test and measurement tools using software architecture that simplify and speed-up development and maintenance of test and measurement tools by removing awareness of complexity of external hardware dependencies from the actual test and measurement software code, and placing dependencies management to carefully defined components that could be reused and shared between multiple test and measurement software tools and systems at once.

Owner:W2BI

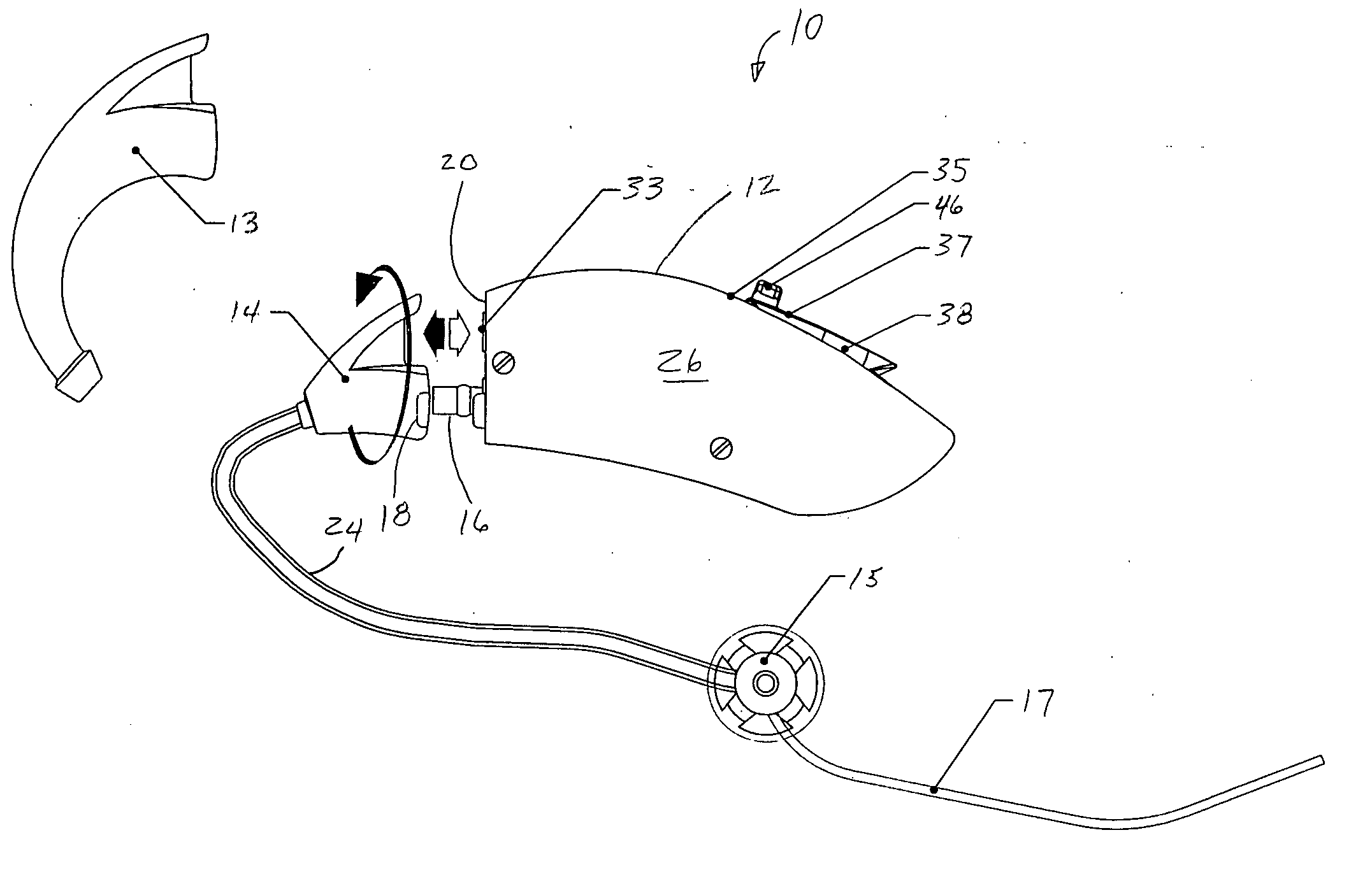

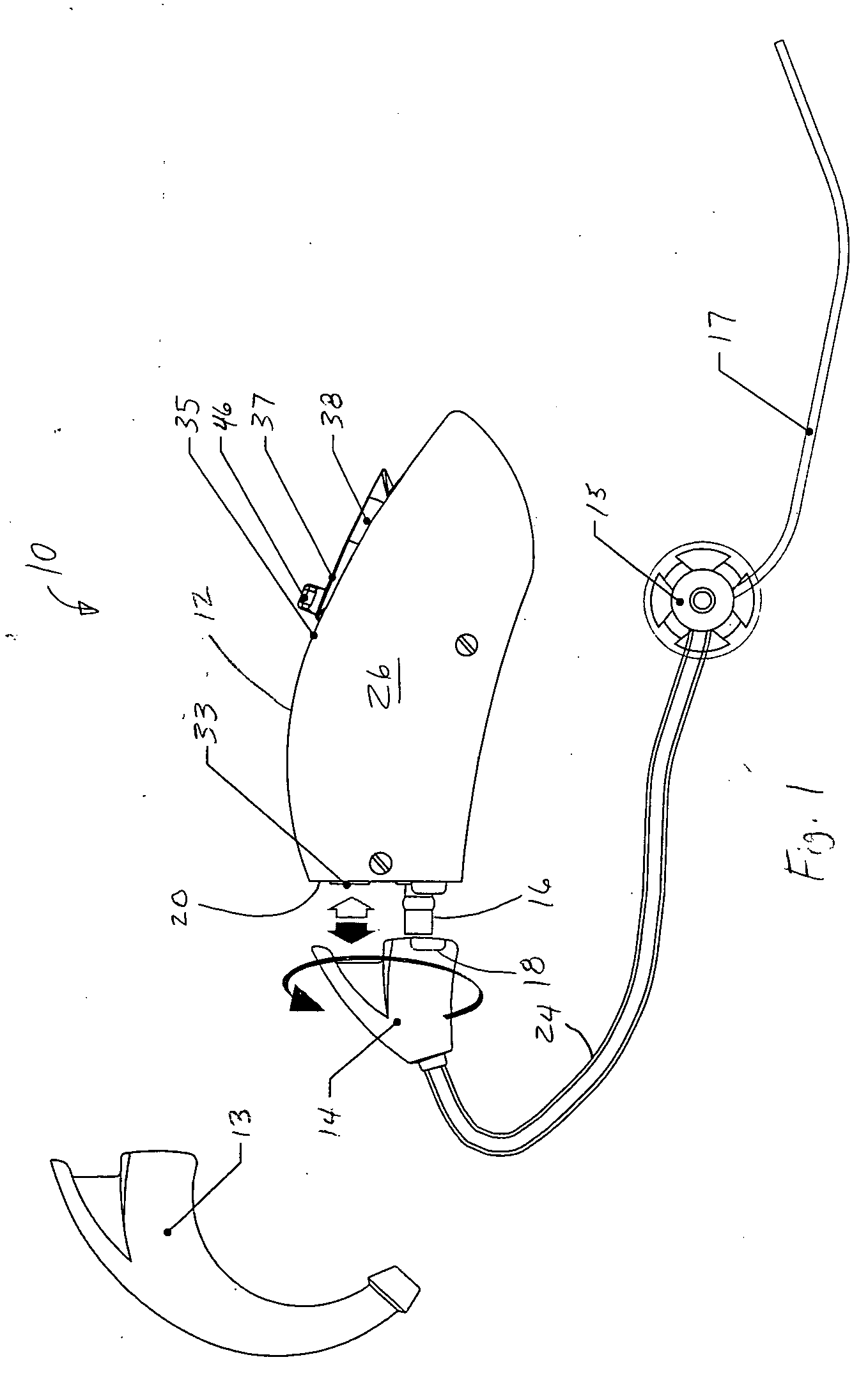

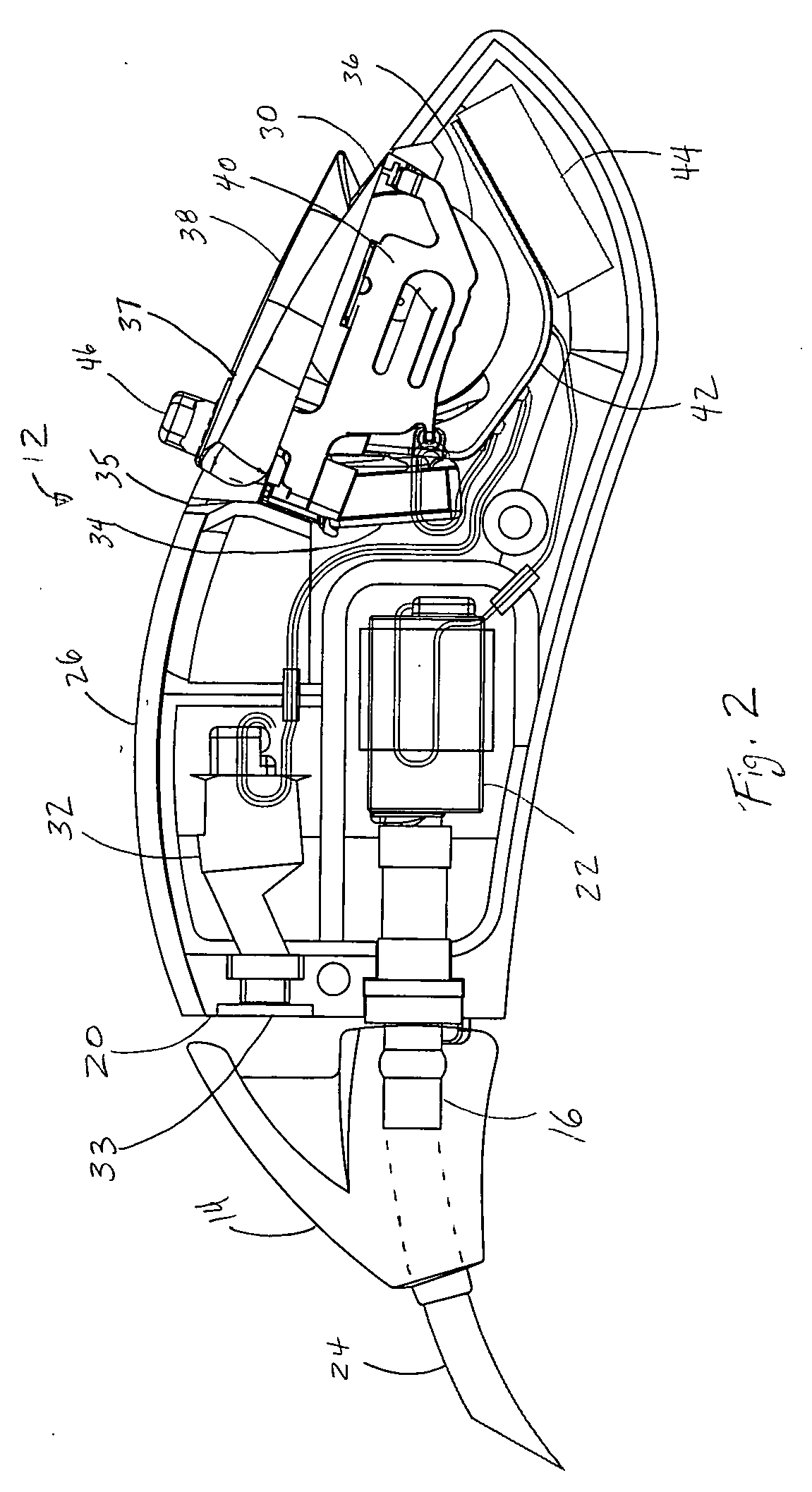

BTE hearing aid component and hearing aid comprising same

InactiveUS20060171550A1MicrophonesBehind the ear hearing aidsSignal conditioning circuitsTime to market

A behind-the-ear hearing aid component employs a multi-functional module easily replaced to enhance repairability and time to market. The multi-functional module is removably secured to a case that carries a microphone, a programming system that receives and stores one or more hearing aid programs, an optional selector for selecting one of a plurality of hearing aid programs, a signal conditioning circuit for conditioning the microphone signal according to a hearing aid program to produce a conditioned microphone signal, and a battery for powering the hearing aid component. A receiver converts the conditioned microphone signal to conditioned sound that is output to an external sound conductor, such as an earhook or tube and tip, which conducts the conditioned sound to an ear of the user.

Owner:AUDINA HEARING INSTR

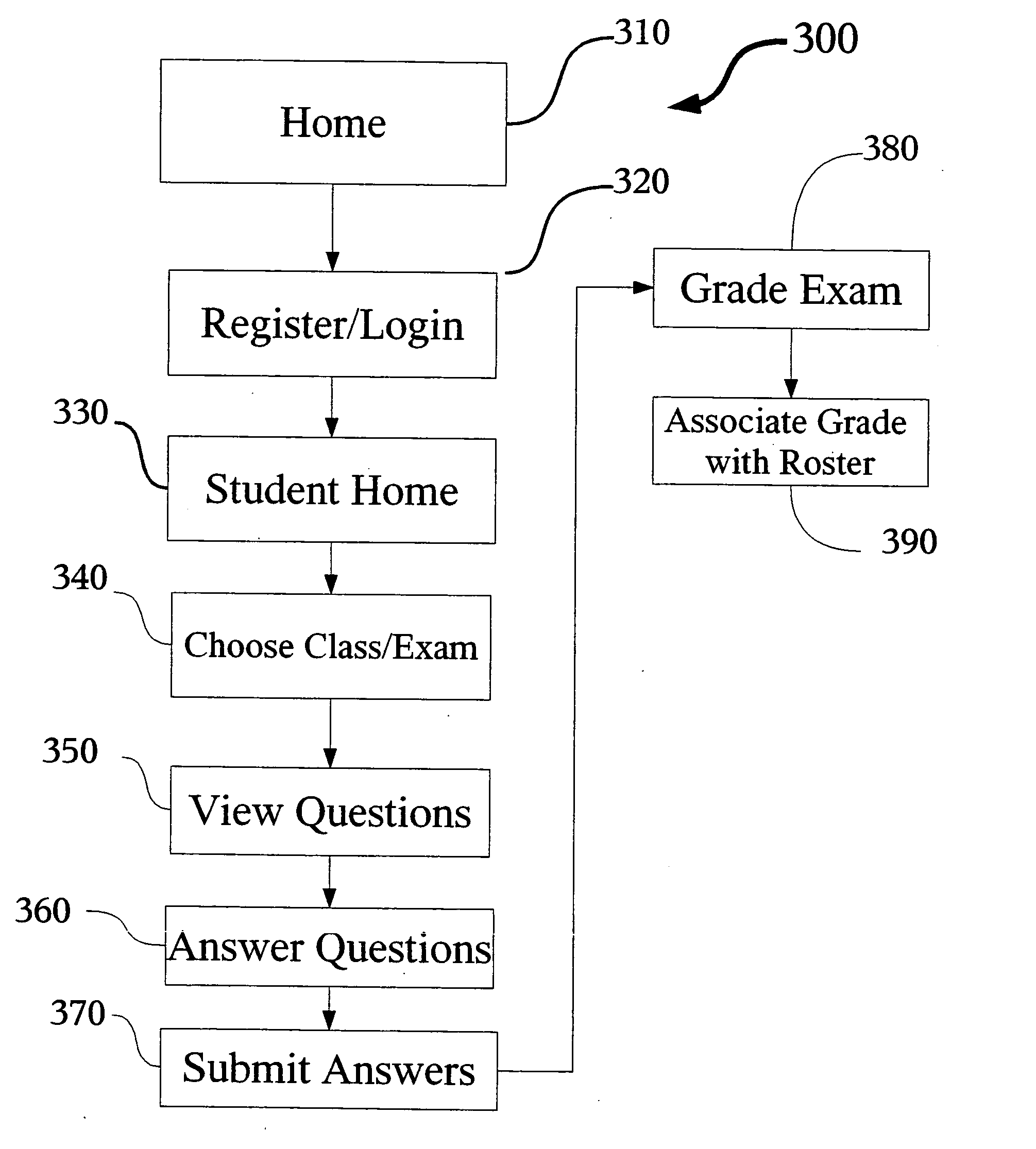

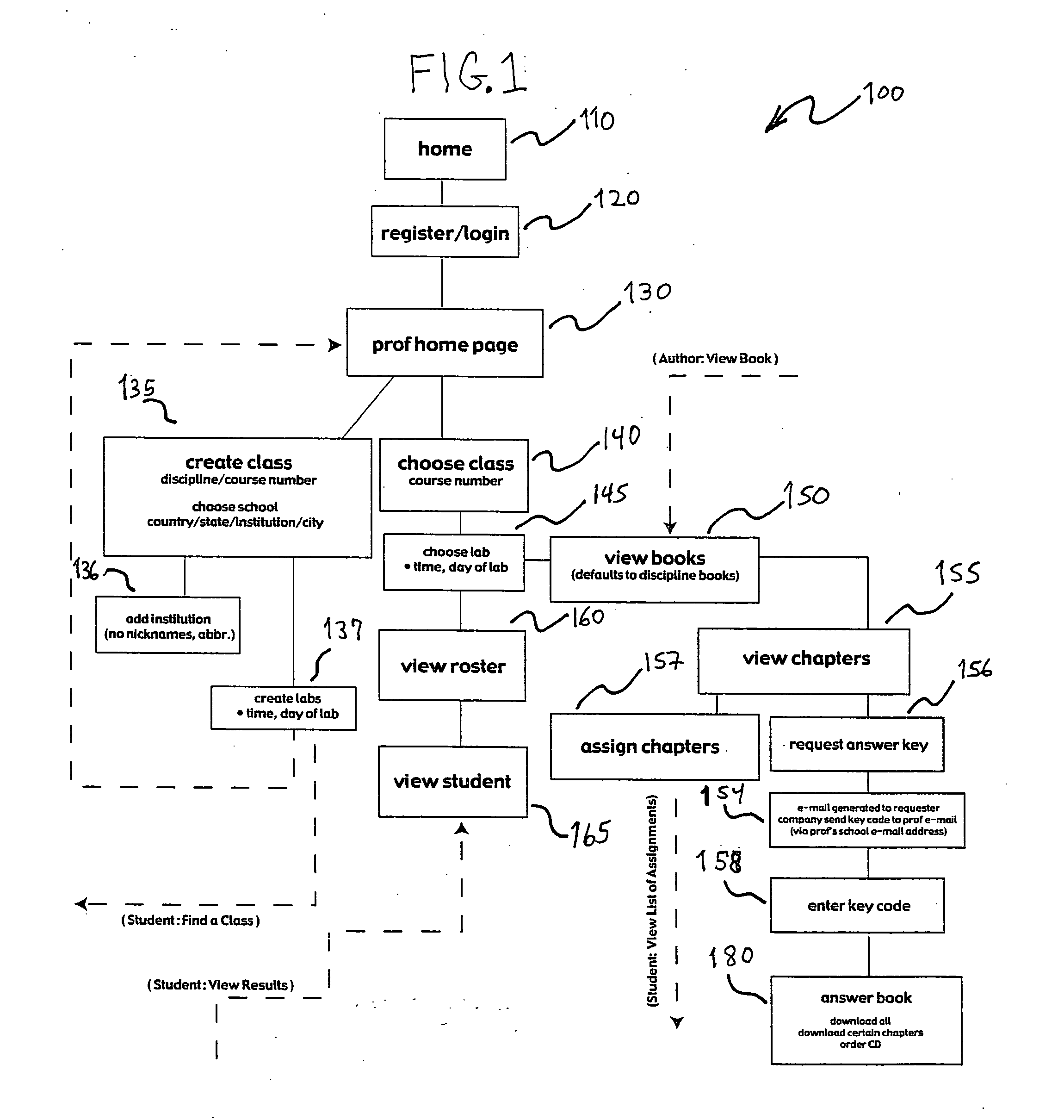

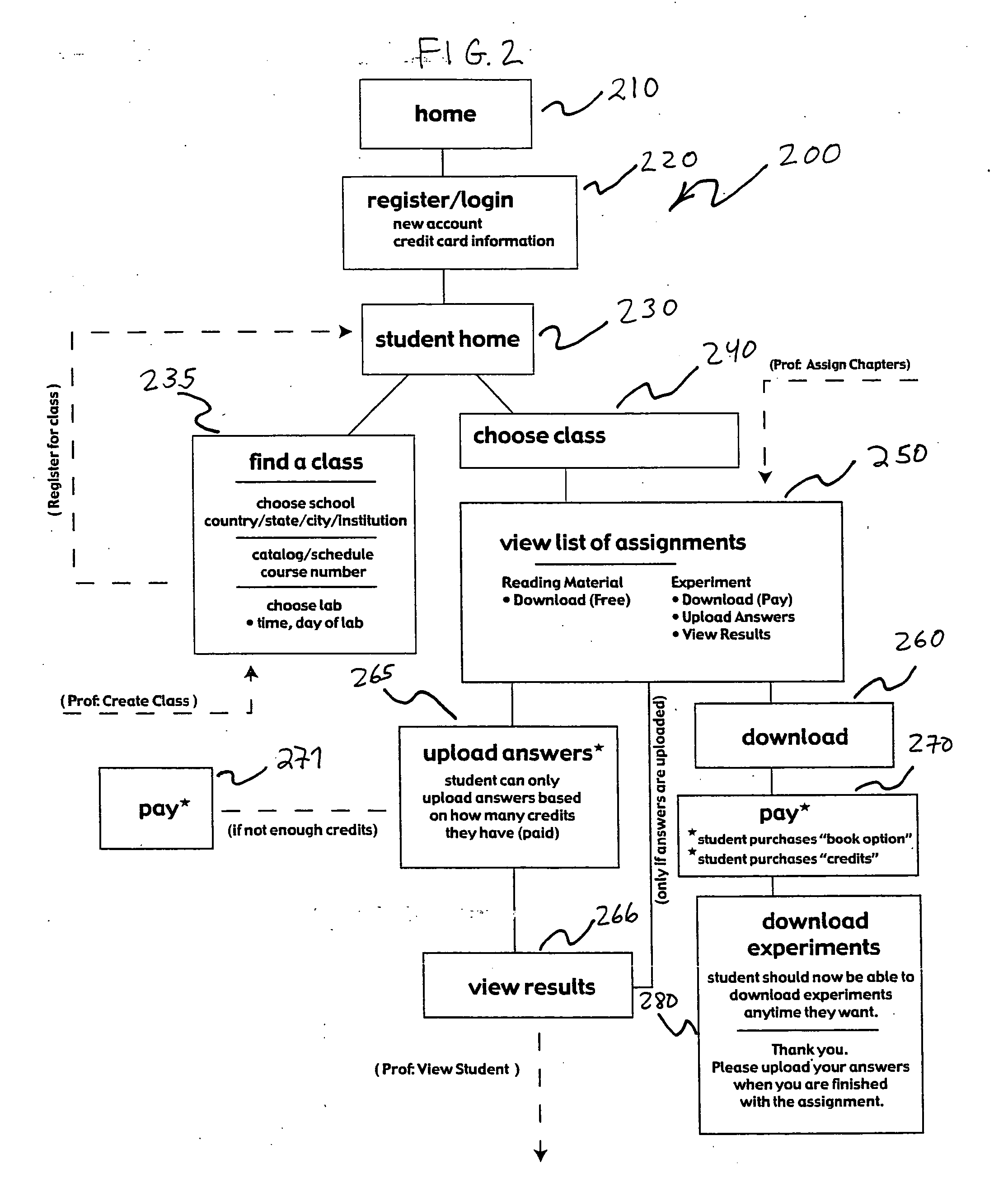

Method of publication and distribution of instructional materials

A method has been developed for the electronic creation and distribution of customized educational materials. An educator compiles a customized text from a catalog of available materials. The customized text is then indexed in an electronic database where it is available for purchase in an electronic format by students. Copyright infringement is discouraged by providing the educator the option of electronic testing and grading such that only students that actually purchase the educational materials are eligible to receive a grade in the class. The custom textbook is easily changed or updated to correct errors without the publisher incurring traditional printing and distribution costs, while simultaneously reducing the time to market for new editions of materials.

Owner:STUDENTS CHOICE LLC

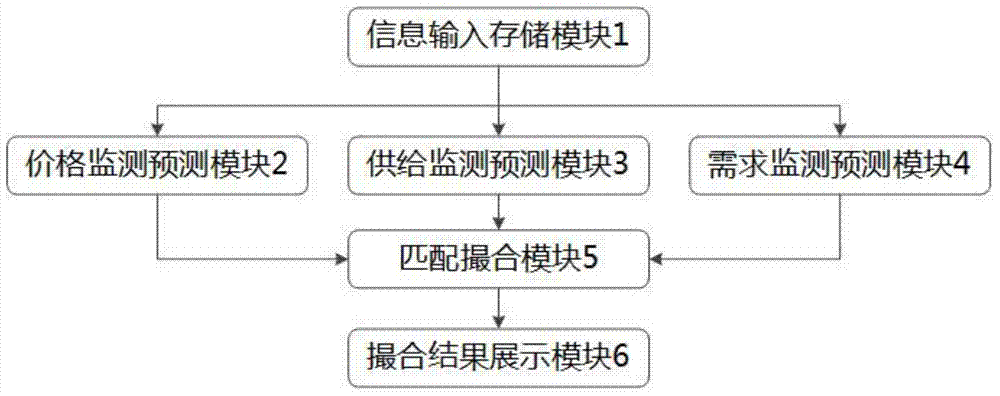

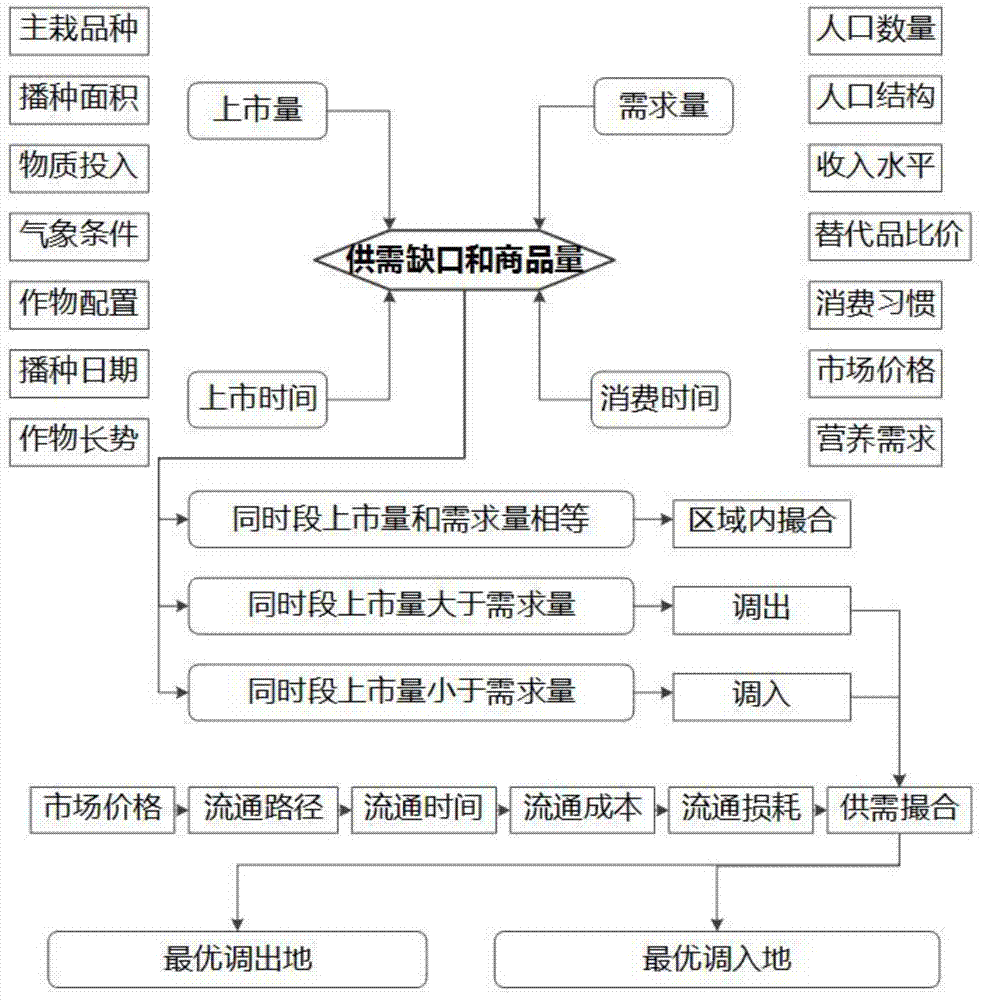

Agricultural product supply and demand matching system and method

The invention belongs to the field of agricultural product circulation intelligentization, and discloses an agricultural product supply and demand matching system and method. Methods such as model prediction, production monitoring and network information grabbing are used to predict the time to market and the market volume of agricultural products in all regions in advance; the demand for consumption of the agricultural products in all regions is predicted according to aspects such as population, an income level and a consumption habit in advance; market prices of the agricultural products can be judged through a big data technique from aspects such as monitoring data and network data, and supply and demand matching of the agricultural products is conducted in advance according to factors such as marketing periods of the agricultural products, preservation time, transportation preservation conditions and producing and marketing region prices. The matching and schedule arrangement of main agricultural products in the nation can be achieved in advance, a producing and marketing matching scheme which is highest in benefit can be custom-made for a producer and a customer, the best purchasing region is selected for the customer, the best marketing region is selected for the producer, so that the optimized producing and marketing matching and the lowest risk can be achieved.

Owner:AGRI INFORMATION INST OF CAS

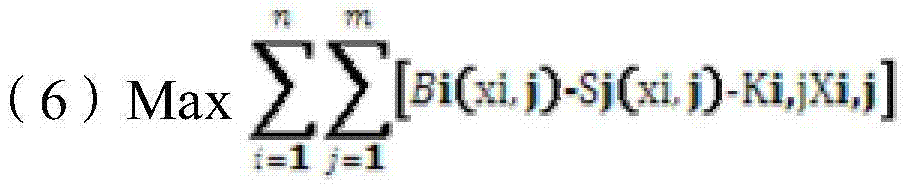

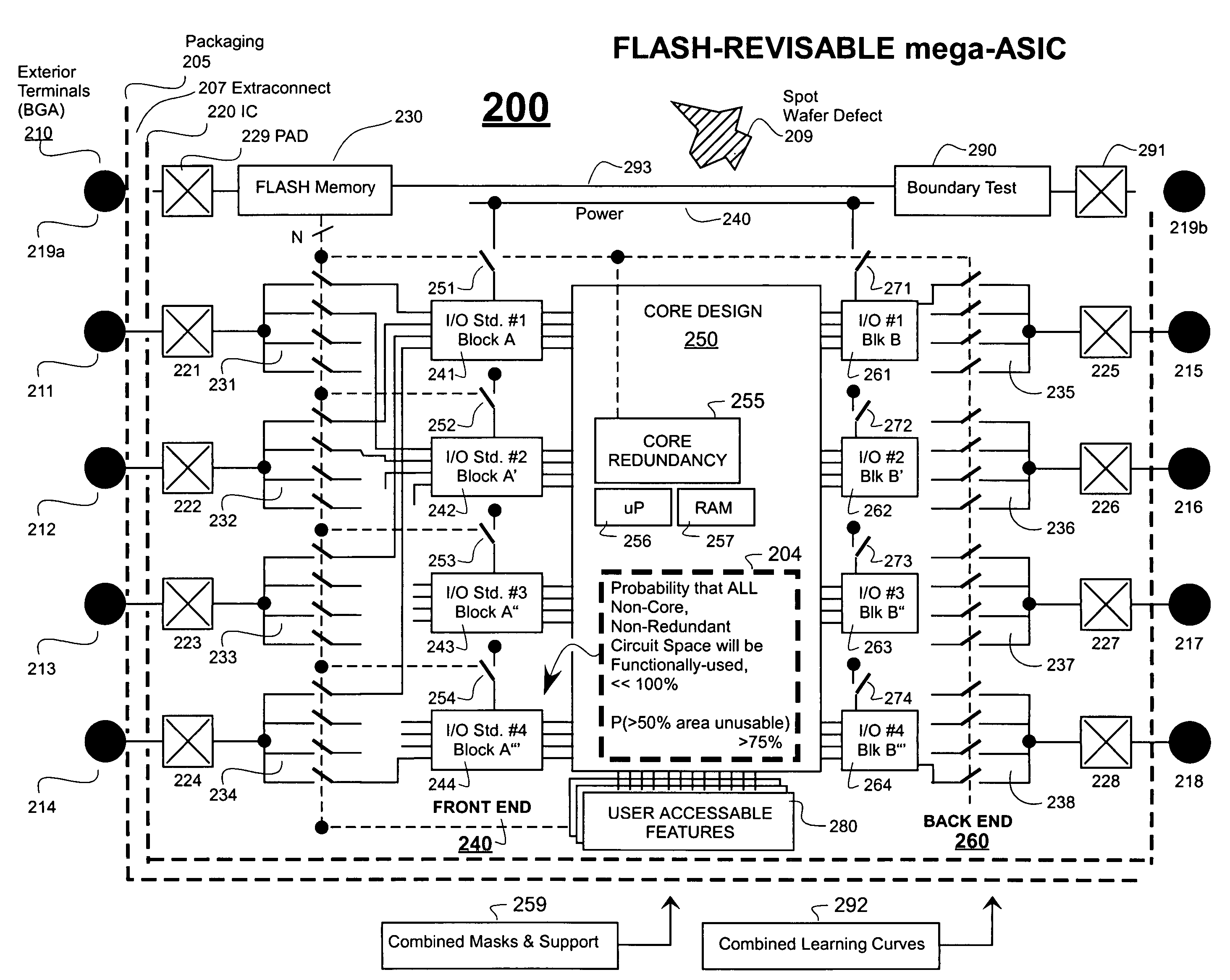

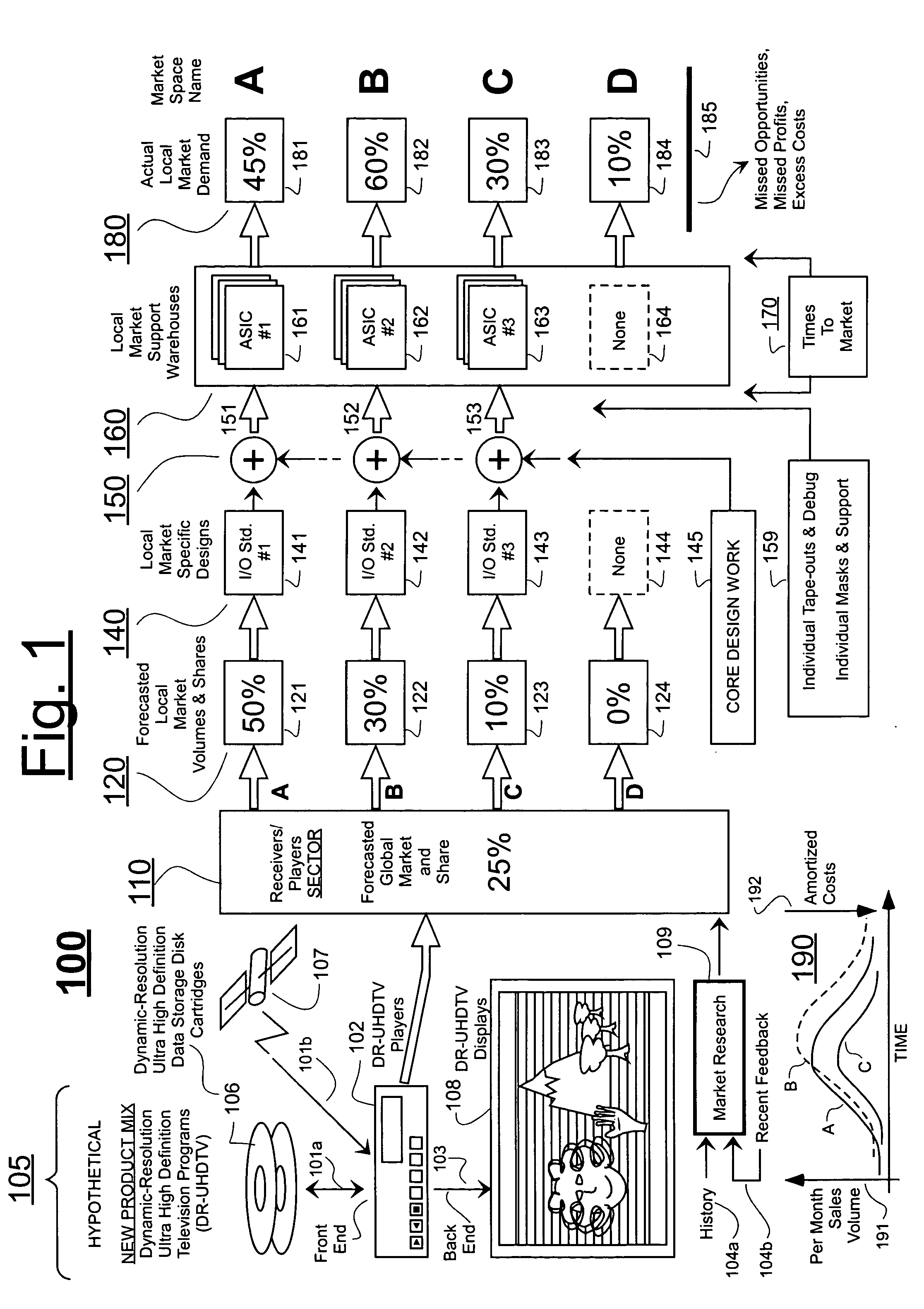

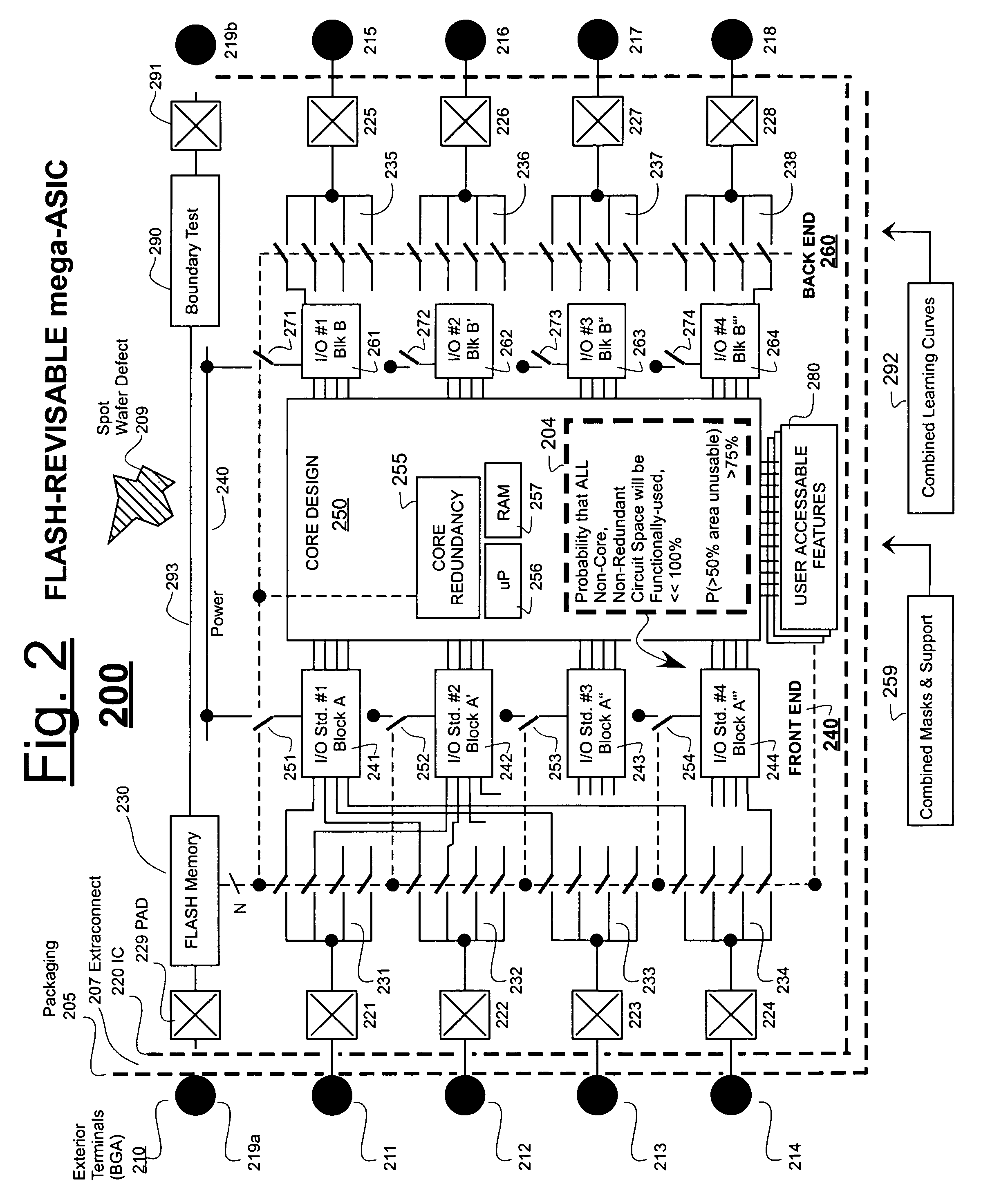

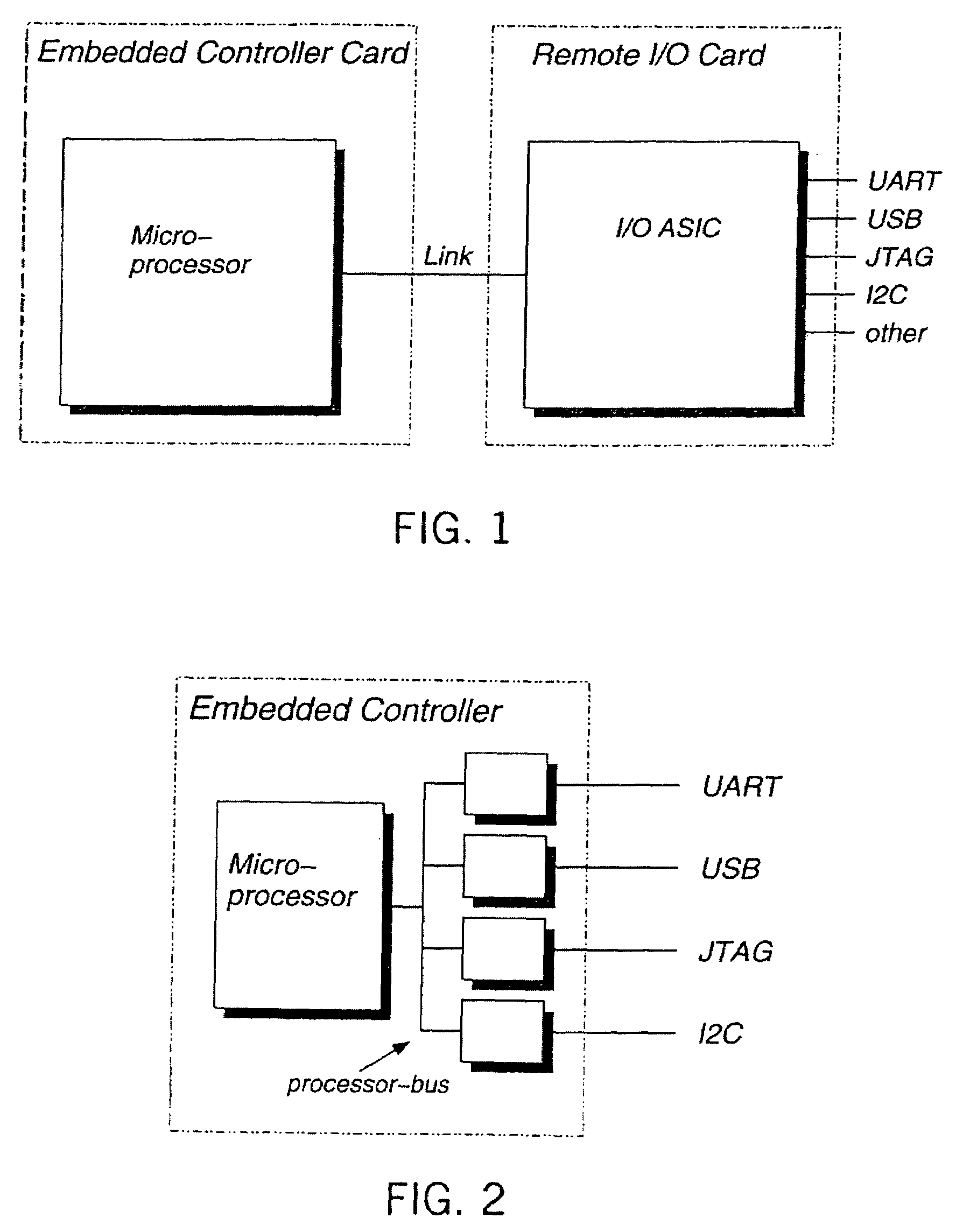

ASICs having more features than generally usable at one time and methods of use

ActiveUS20060080631A1Shorten the time to marketOffset drawbackSolid-state devicesCAD circuit designTime to marketInventory management

More ASIC functionality is crammed into a chip (or chip set) than can probably or definitely be operative at one time when the chip is packaged and inserted into a broader circuit. The excessive ASIC functionality is chosen to cope with different market development probabilities in a host of different market spaces (e.g., in different countries where different interoperability standards are chosen) and a subset of the excessive ASIC functionality is programmably activated in each market space after manufacture. Customer behavior can be fickle. If market trends evolve towards demand for functionality #2 instead of an originally, more expected, functionality #1, the mass produced of the crammed chip (or chip set) is not out of necessarily out of luck. If the mass produced had enough foresight to cram in functionality #2 as well as functionality #1, the producer can programmably activate #2, and deactivate #1 as market demand suddenly shifts in a given market space. In one embodiment, a mega-ASIC with excessive ASIC functionality crammed into it, has a universal core as well as plurality of programmably selectable ASIC function blocks. The ASIC function blocks are programmably activatable and de-activatable so that a mass produced can quickly respond to shifting market demands, thus addresses both time to market and product life issues. The invention allows a small chip designer to simultaneously address more than one market or customer space with one ASIC chip thereby reducing the design cost per product design. By selectively activating the excessive and selectable ASIC functionalities, the small ASIC chip designer can appear to sport different features for different customers and different markets at different times with just one chip, thus he can aggregate the demand of different customers and different markets to achieve economies of scale, and of inventory management and control.

Owner:SHEYU GROUP

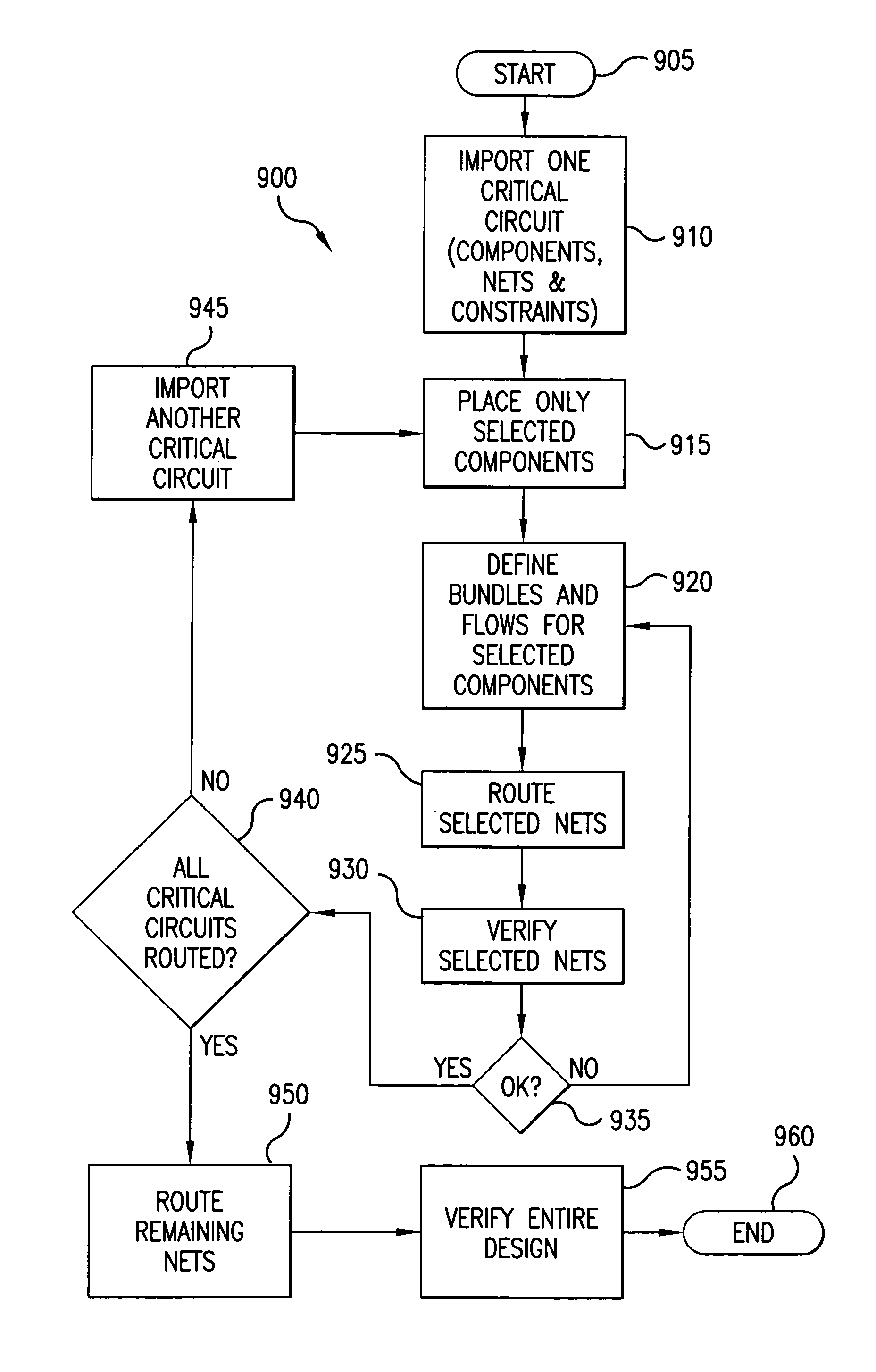

User-guided autorouting

ActiveUS7536665B1Computer aided designSpecial data processing applicationsTime to marketComputer science

A mechanism is provided for the user to define a circuit design intent or strategy in the form of data that is stored with the design database. An autorouter then uses this guidance from the user to create a plan for routing the design. The user can then modify their guidance to the router until the results for the plan are acceptable. Using the planned flow, the autorouter can complete the design, creating detailed paths including etch segments and vias. Allowing such interaction with an autorouter significantly reduces the routing time and hence time-to-market.

Owner:CADENCE DESIGN SYST INC

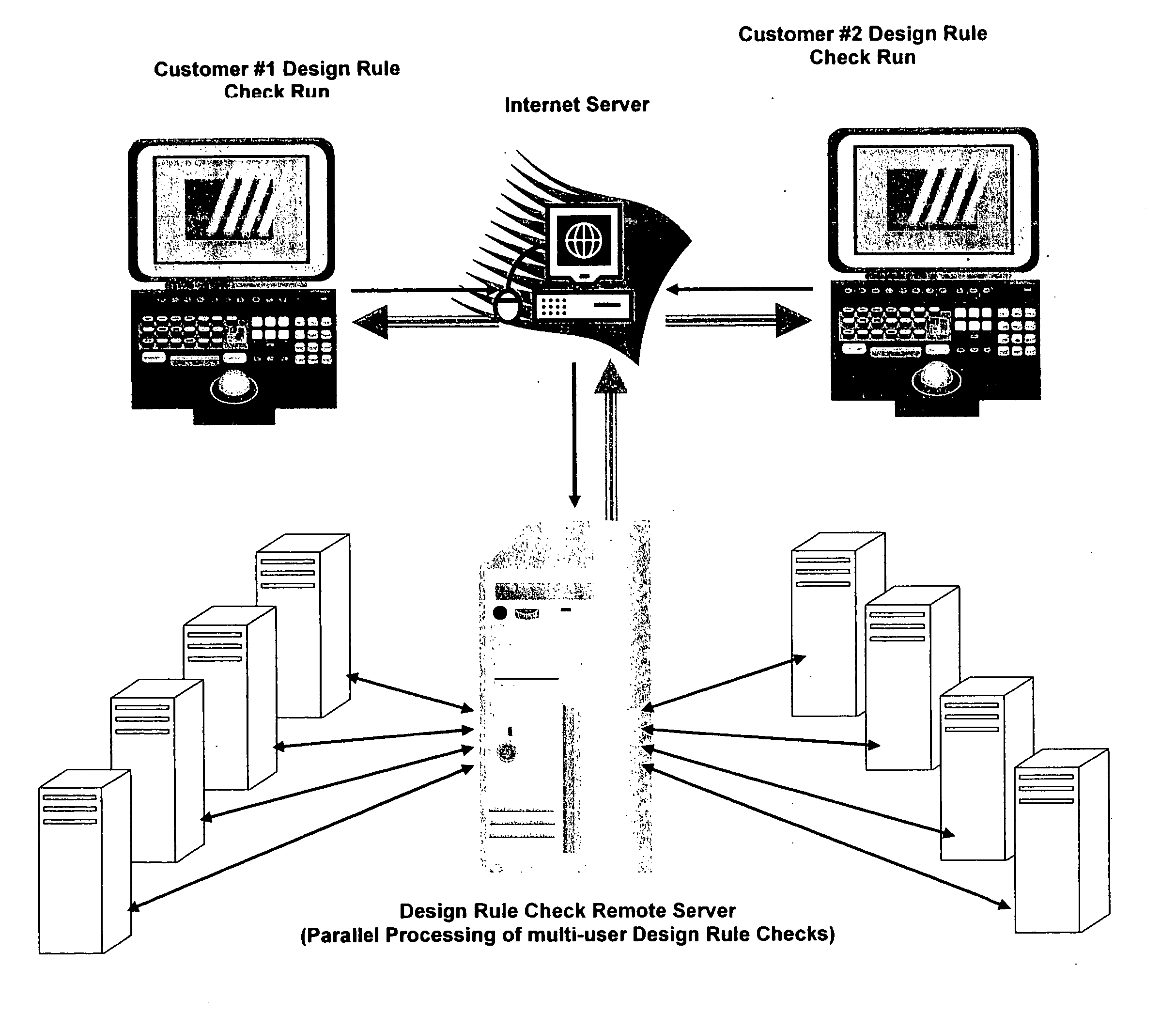

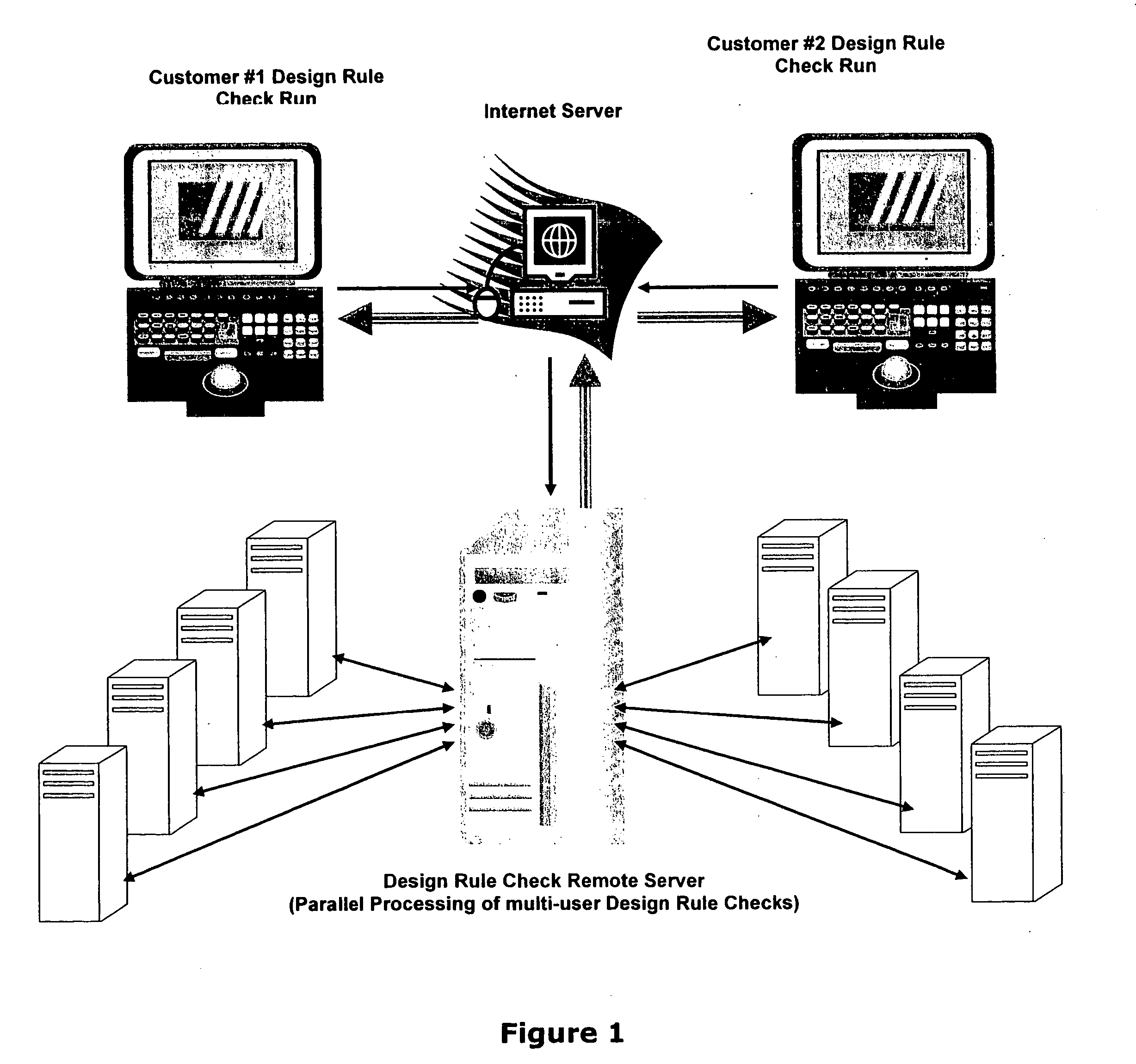

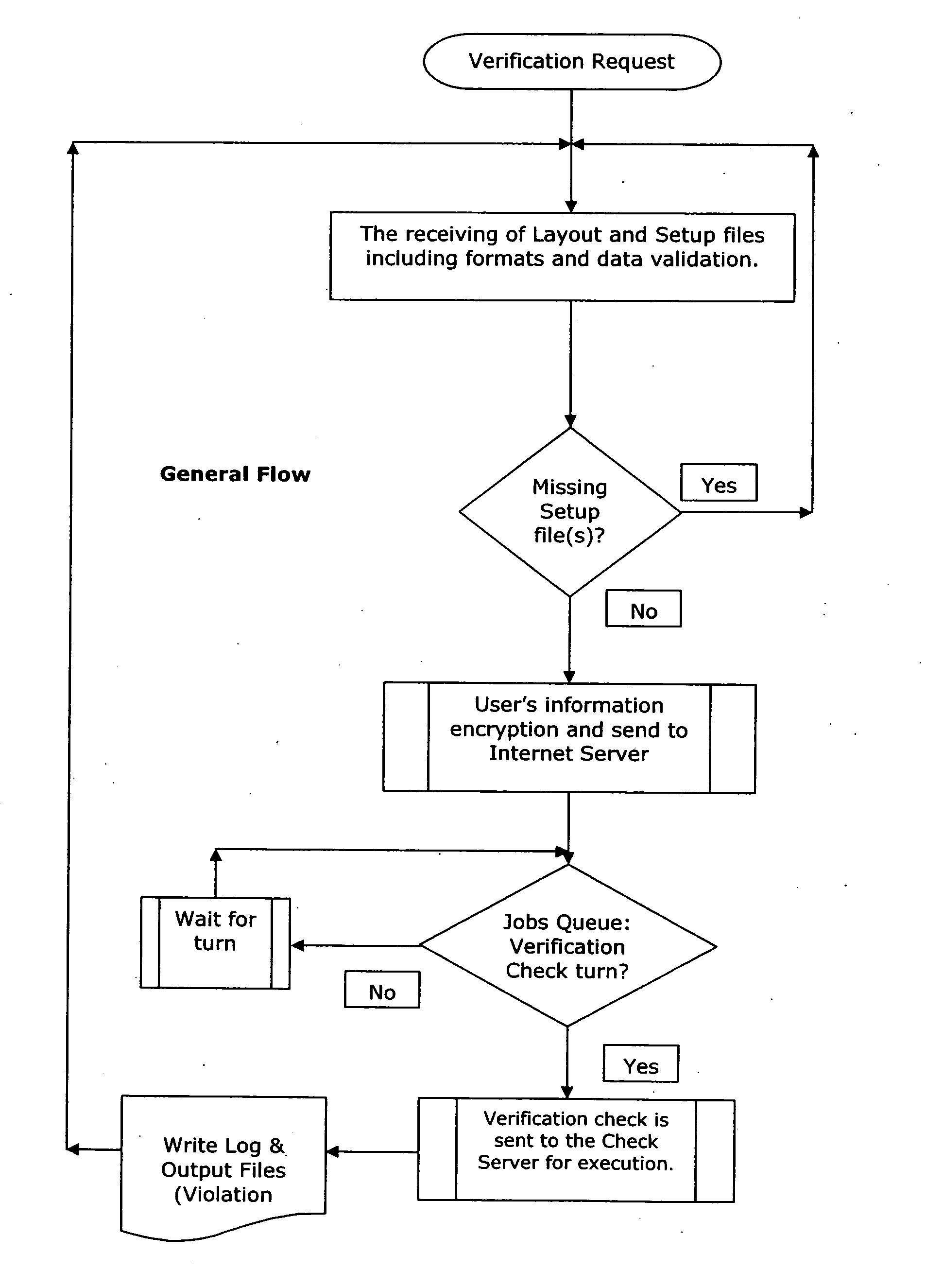

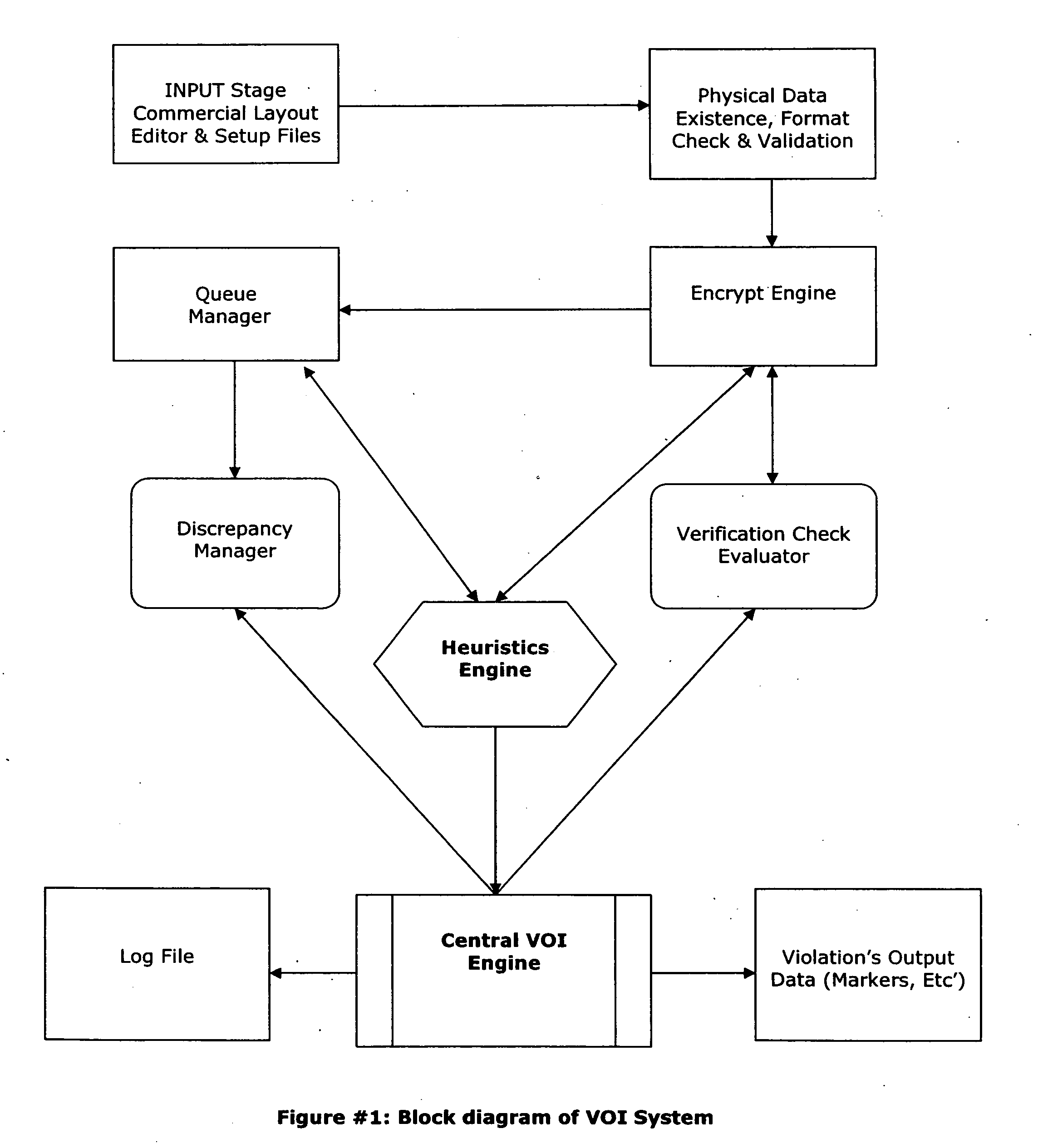

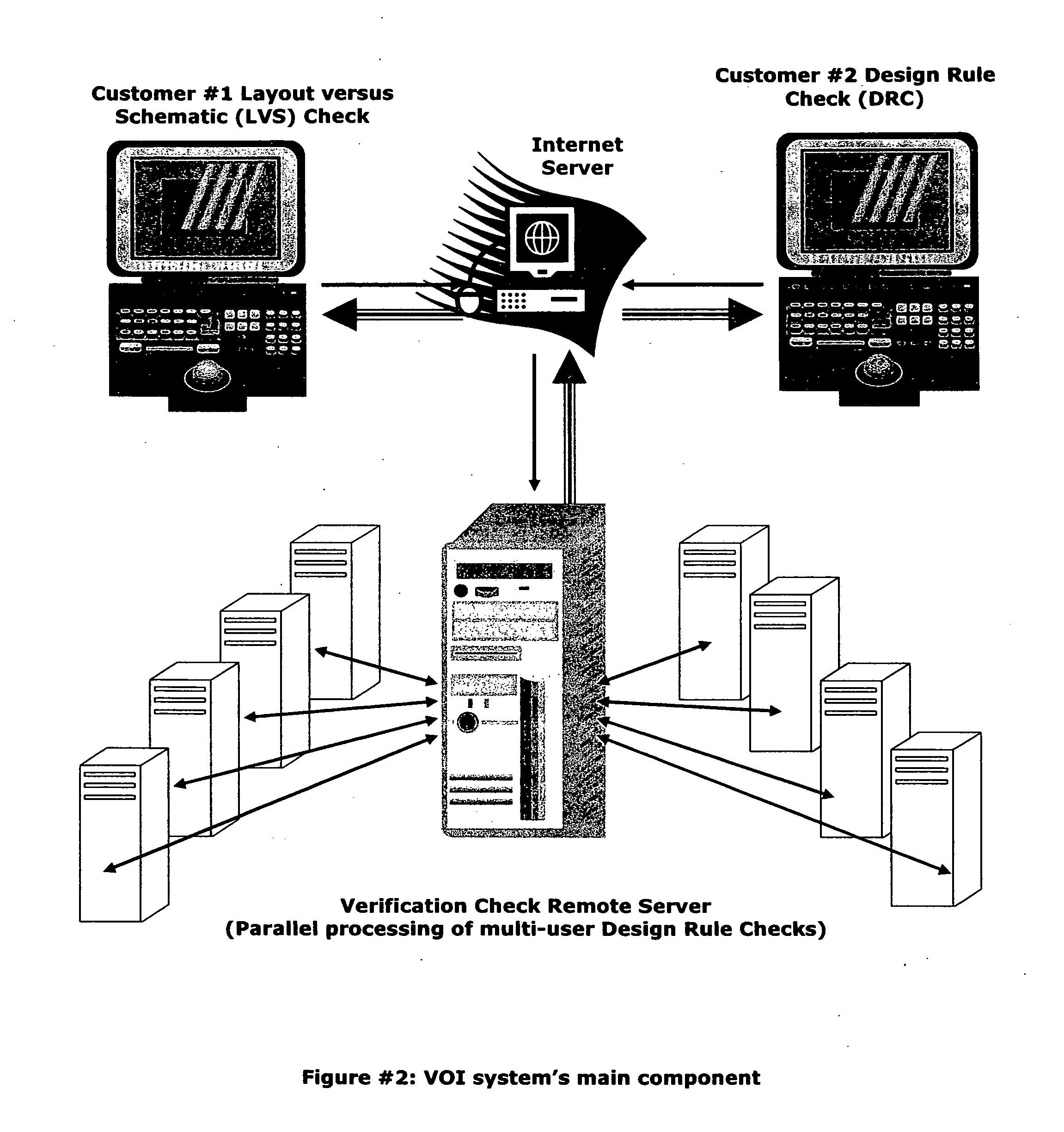

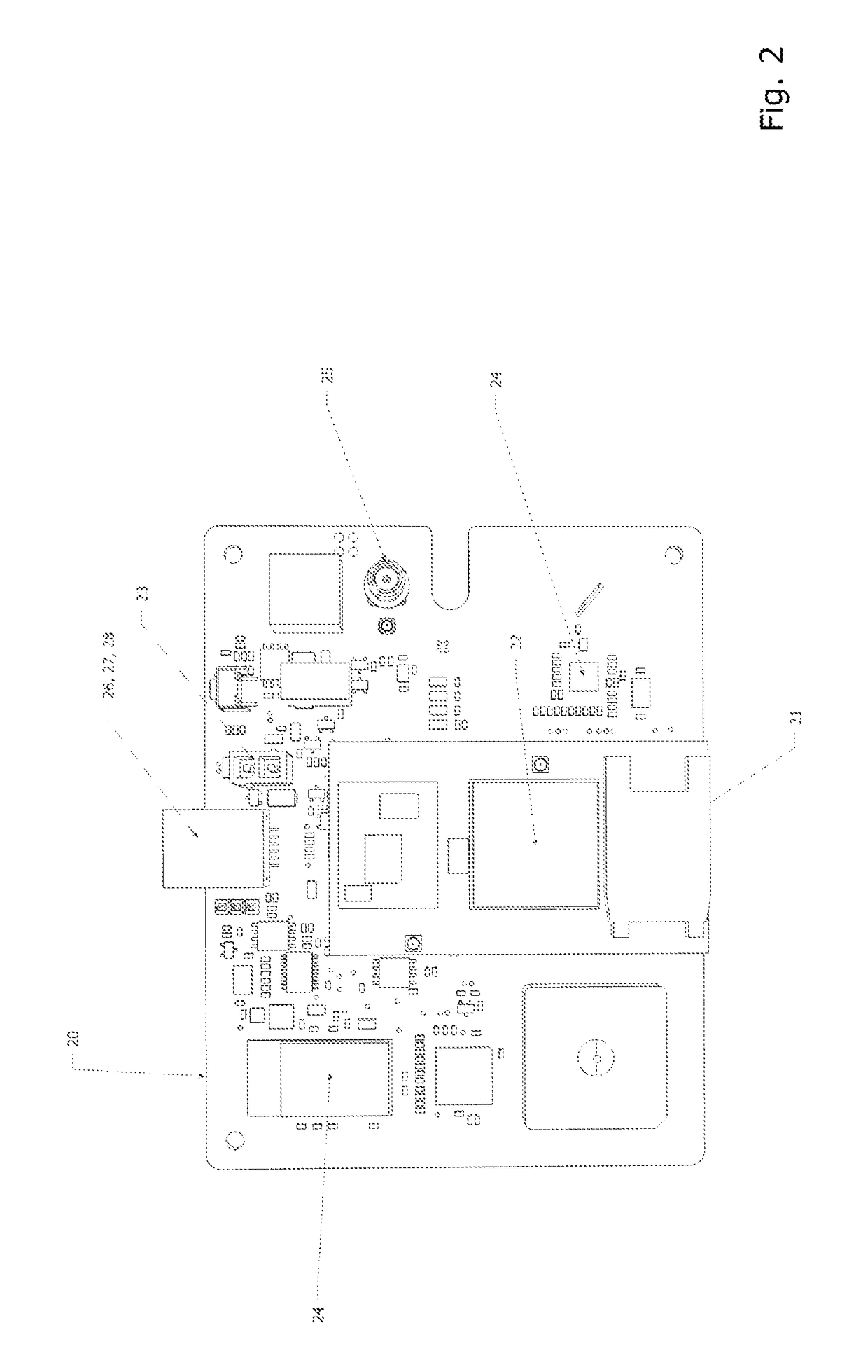

Design rule violations check (DRC) of IC's (integrated circuits) mask layout database, via the internet method and computer software

InactiveUS20060253813A1Fast resultsLow costComputer aided designSpecial data processing applicationsGuidelineSoftware design

This paper describes method and EDA (Electronic Data Automation) computer software invention for design rule violations check of mask layout database (integrated circuits layout) via the internet. The technique takes advantage of a unique algorithm to analyze the mask layout database to find mask layout polygons that are less than the minimum design rules (distances) that are determined by the fabrication process. The computer program then creates an output file that marks all design rule violations location and type. The input of the tool is a mask layout database (i.e.: layout block / s) that is made manually by a mask design specialist or automatically by automatic IC layout tools. The output of the software tool is a guideline mechanism and file to mark all design rule violations for correction. This markers file can be loaded into any industry's standard IC mask layout database editor for viewing and correction. The software performs on individual mask layout blocks and / or on hierarchical structure of mask layout blocks. The system also checks mask layout database incrementally, means only blocks that have been changed are checked. The system is activated via the internet using secured protocol. In order to reduce the cost of DRC (design rule check) computer program, corporations may log in to a main server to submit complete DRC (Design Rule Check) run. User point reference files at a local location (User's local computer) and setup all parameters on a web based interface. The system collects all local information and run a complete design rule check locally or on remote server. The system offer a web based control panel to execute all necessary setups for submitting design rule check over the internet using any secured internet browser like MS Explorer and Netscape. The system offers the option to run on a local machine (user's computer) or on the main server over the internet. The system also offers a PDA (Personal Digital Assistant) interface to launch DRC runs via industry's standard PDA's. The procedure is fully secured by 128 bit security protocol. The system supports existing industry standard rule decks like: Mentor's Calibre, Cadence's Assura and Synopsys's Hercules. All design rules can be easily imported from these rule decks to be used by DRC program on the main server. All necessary files including mask layout GDSII (or GSIII) file and technology file are securely encrypted using 128 bit protocol and send to the remote server. These files are decrypted on the remote computer and submitted for design rule check. The main remote server is distributing the task among other computer system for advanced parallel processing to achieve fast results. All results log files are encrypted using 128 bit security protocol and available for download by the user. In case of local design rule check the results files are available on the user's local machine. This approach eliminates the purchase of a full local license and enables affordable price for small and medium size chip design firms. This fact significantly reduces integrated circuits design cost and time to market factor for chip design corporations, enabling faster deliveries to their end customers.

Owner:MICROLOGIC DESIGN AUTOMATION

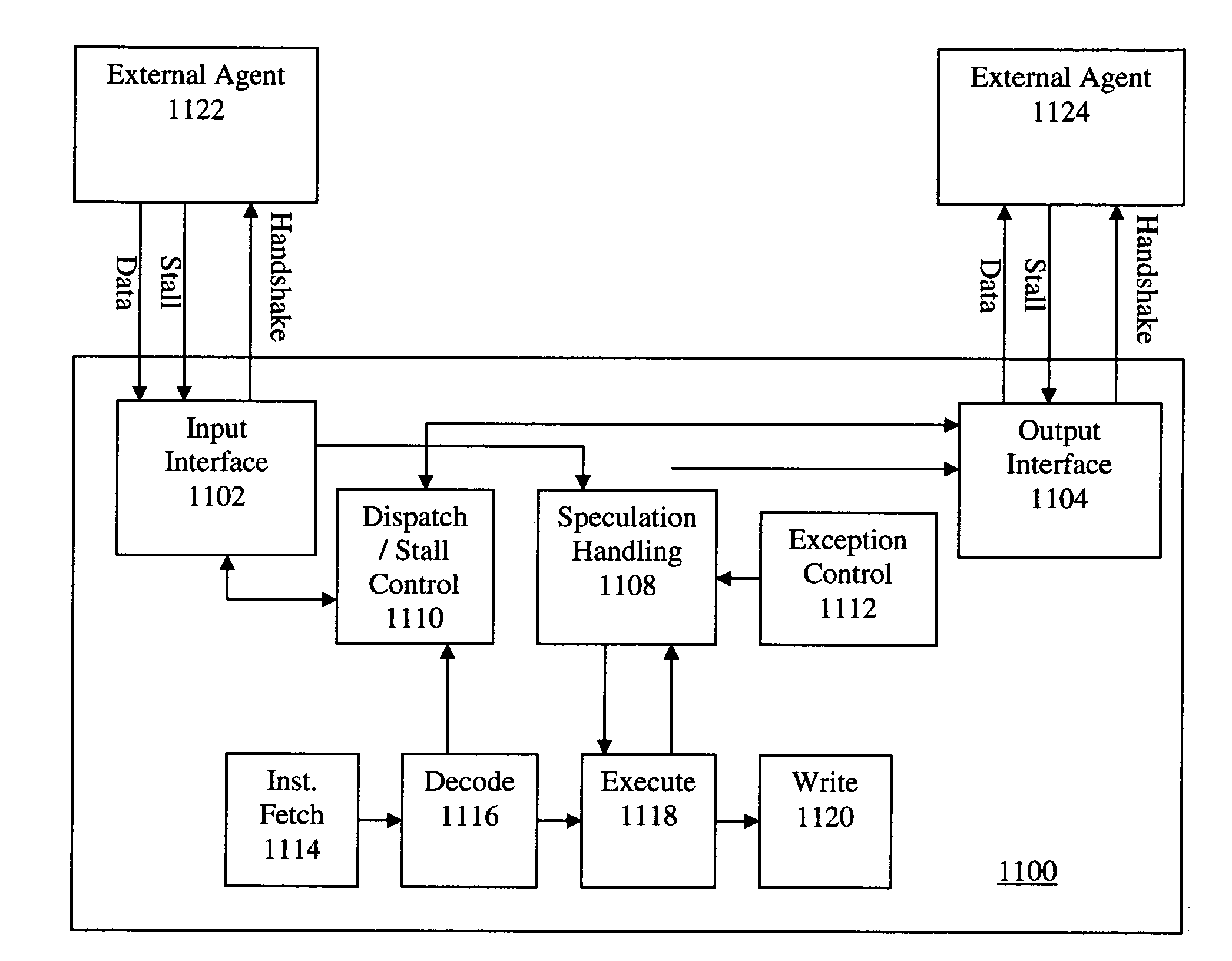

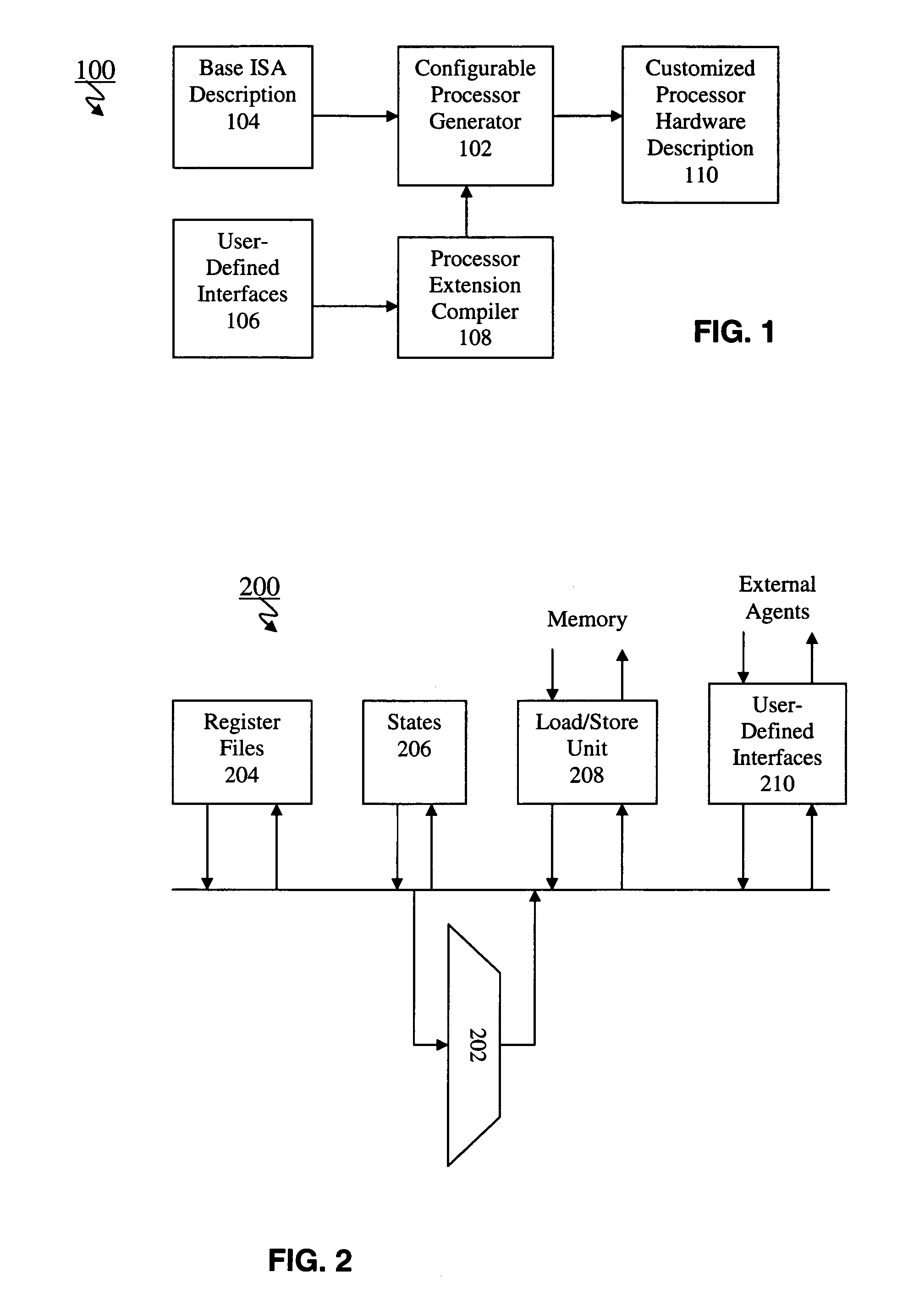

Method and apparatus for providing user-defined interfaces for a configurable processor

ActiveUS7664928B1High bandwidthImprove performanceGeneral purpose stored program computerProgram controlTime to marketComputer architecture

A technique that improves both processor performance and associated data bandwidth through user-defined interfaces that can be added to a configurable and extensible microprocessor core. These interfaces can be used to communicate status or control information and to achieve synchronization between the processor and any external device including other processors. These interfaces can also be used to achieve data transfer at the rate of one data element per interface in every clock cycle. This technique makes it possible to design multiprocessor SOC systems with high-speed data transfer between processors without using the memory subsystem. Such a system and design methodology offers a complete shift from the standard bus-based architecture and allows designers to treat processors more like true computational units, so that designers can more effectively utilize programmable solutions rather than design dedicated hardware. This can have dramatic effects not only in the performance and bandwidth achieved by designs, but also in the time to market and reuse of such designs.

Owner:TENSILICA

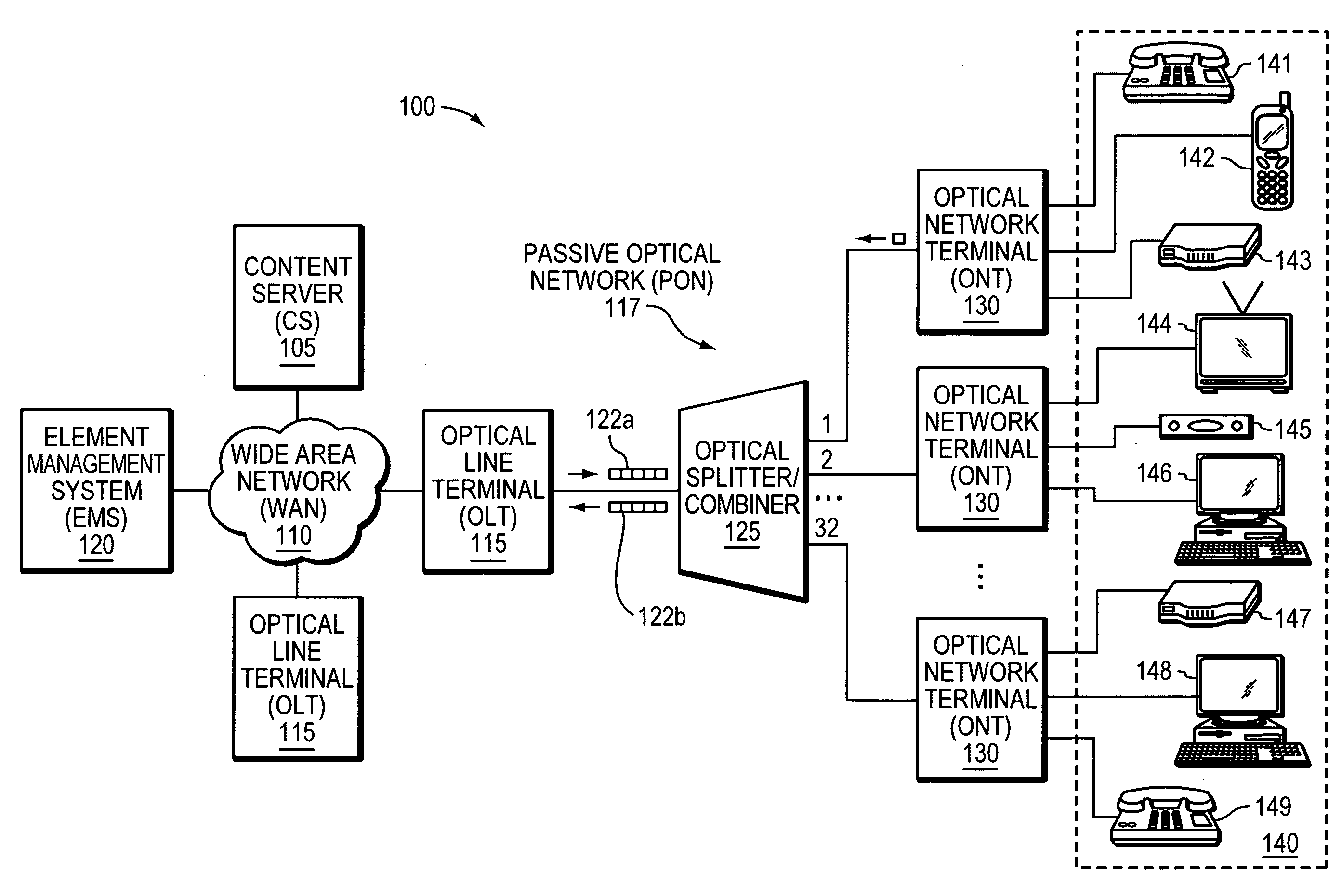

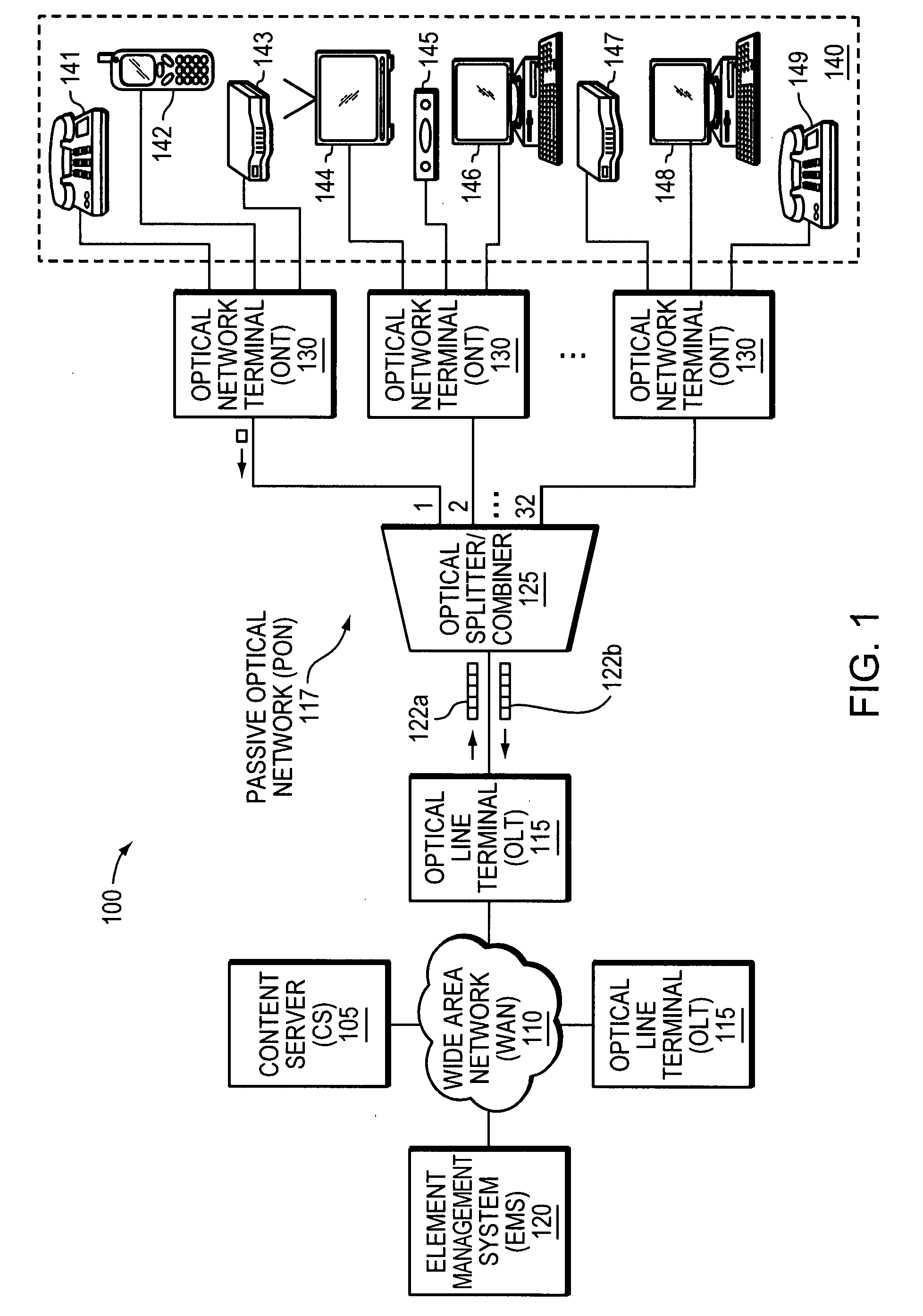

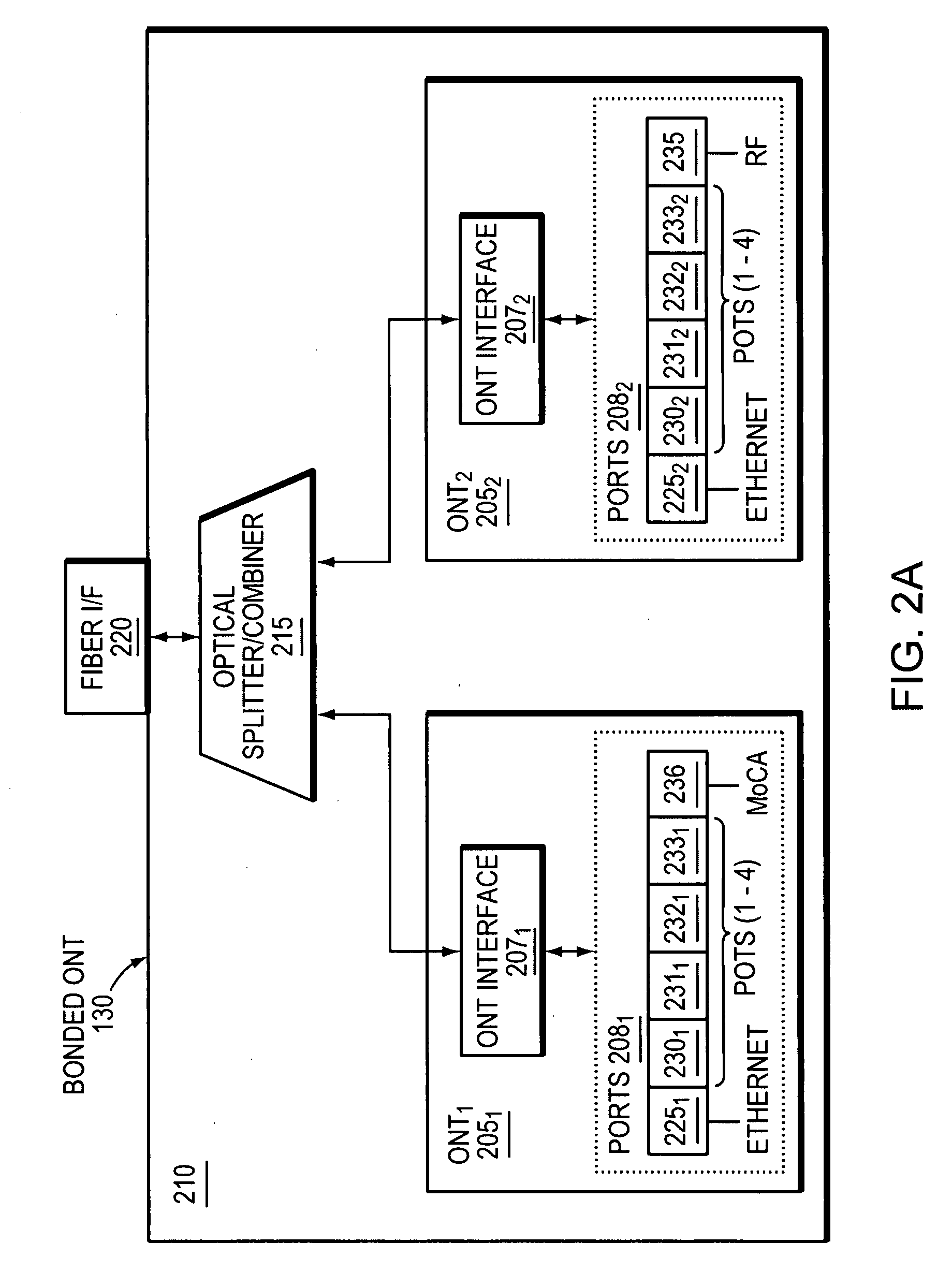

Method and apparatus to provide bonded optical network devices

InactiveUS20090041460A1Multiplex system selection arrangementsOptical multiplexNetwork terminationLogical combination

An apparatus and corresponding method for a bonded Optical Network Terminals (ONT) enhances throughput, redundancy and user-port flexibility by Passive Optical Network (PON) services, such as Gigabit-capable (GPON), Broadband PON (BPON), Ethernet PON (EPON) and future PON services, by mechanically or logically externally managing a plurality of individual ONTs as a single bonded ONT while maintaining individual internal management. Further, multiple OLTs may communicate with the same ONT, thereby increasing throughput and providing redundancy. For manufacturers, user-port flexibility reduces time-to-market for unique products to meet specific user needs. That is, different applications may require multiple ONTs to be managed as a single device, yet provide the port counts from various ONTs. For service providers, mechanical or logical combination(s) of ONTs allows management from a user perspective, providing an opportunity for servicing a single device, improving accounting, billing, inventory, etc.

Owner:TELLABS VIENNA

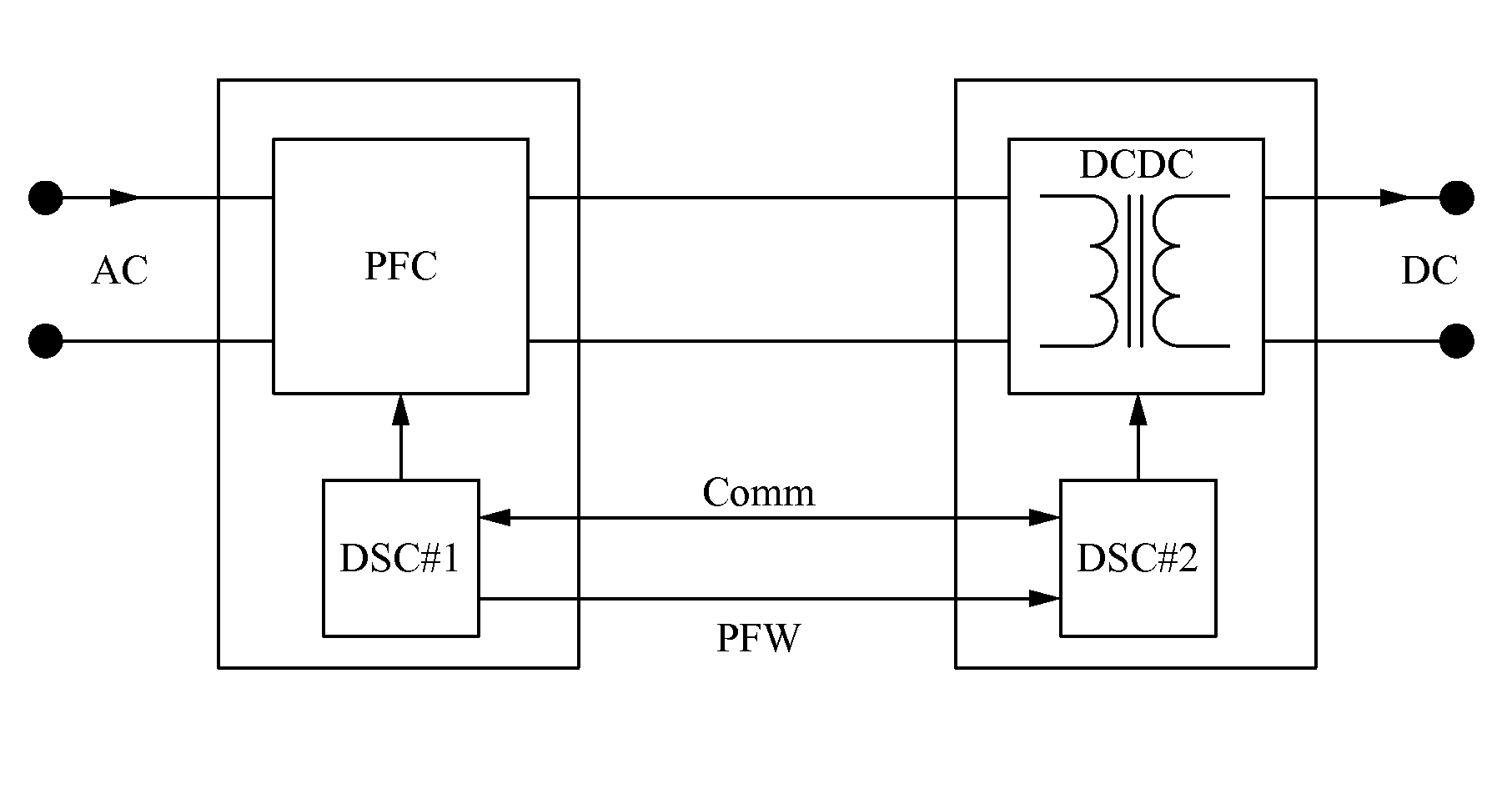

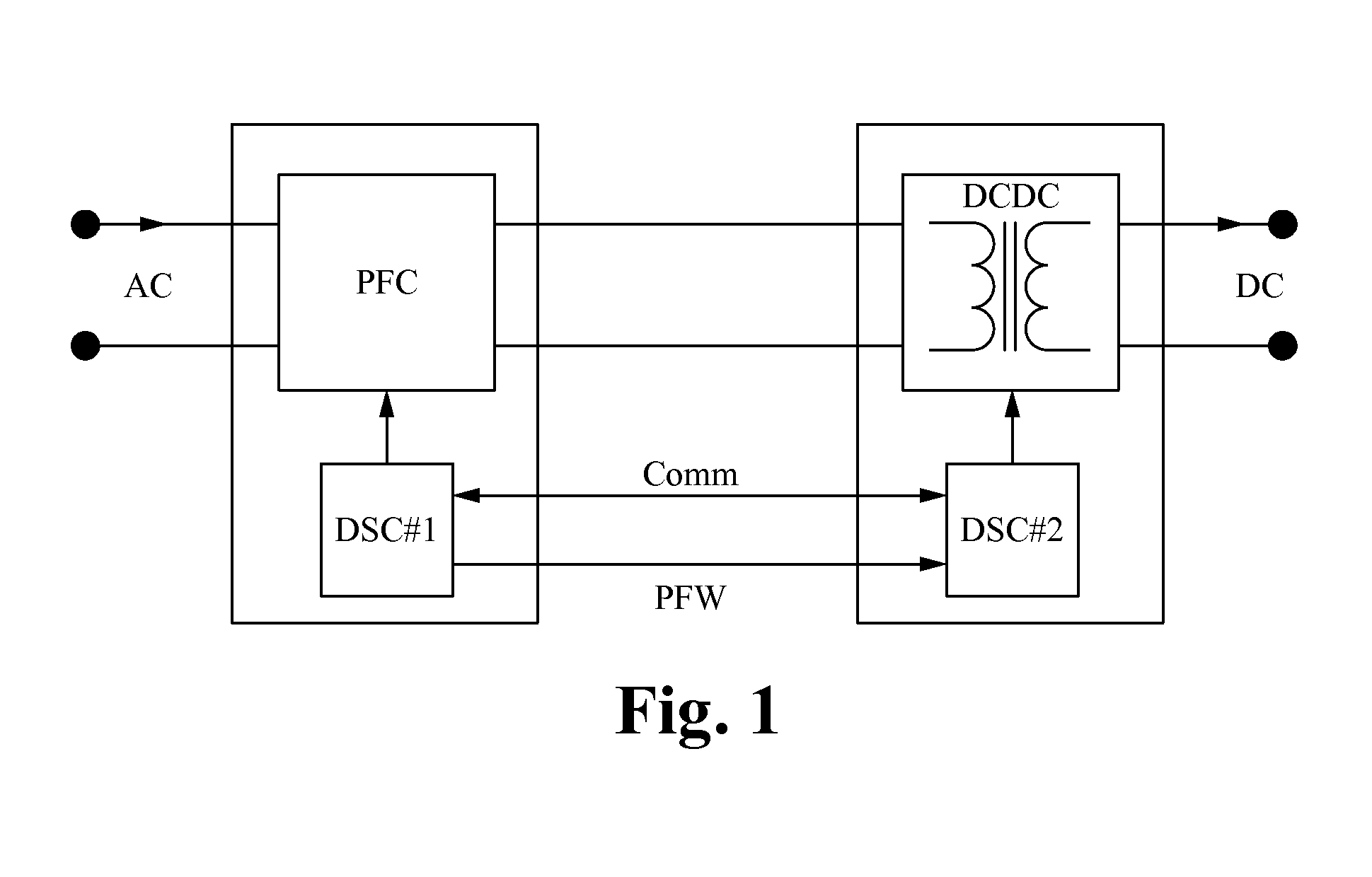

Adaptive digital control of power factor correction front end

ActiveUS8654553B1Simplified digital control loop designOptimizes PFC front-end performanceAc-dc conversion without reversalEfficient power electronics conversionEngineeringLoop design

A method is directed to providing adaptive digital control for the PFC front-end of a switching mode power supply. The method uses an evaluation model to adjust control loop parameters of a control algorithm used by a controller on the primary side of the power supply. The method performs a series of step adjustments of the control loop parameter values to determine optimized values. In some implementations, the method determines and compares the line current THD corresponding to different control loop parameter values. The method provides simplified digital control loop design, optimizes PFC front-end performance, improves system efficiency by decreasing harmonic ripples, and reduces labor cost and time to market due to shorter research and development phase. System performance optimization is fully adaptive adjusted for changes in operating conditions due to, for example, environmental and temperature variations.

Owner:FLEXTRONICS AP LLC

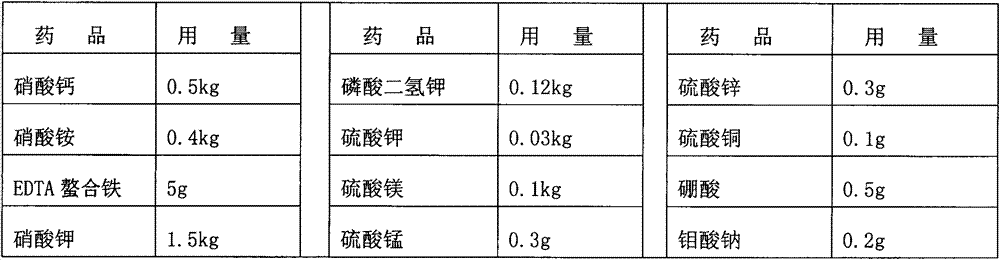

High-yield planting method of broccoli

InactiveCN106171351AHigh activityQuality improvementCalcareous fertilisersSeed and root treatmentTime to marketSeedling

The invention discloses a high-yield planting method of broccoli. The planting method comprises the following steps of (1) treating seeds; (2) preparing a seedling culturing substrate; (3) sowing the seeds; (4) performing seedling hardening treatment; (5) performing seedling field planting; and (6) performing management after field planting. According to the planting method disclosed by the invention, factors including managing seed quality, seedling quality, seedling hardening manner, fertilizer and water after field management in the planting process of the broccoli, are reasonably collocated and optimized, and under the comprehensive action of the steps, the yield per mu of the broccoli is increased by 30% or above, the whole planting benefits are increased by 40% or above, the quality and the nutrient value of the planted broccoli are well perfected, the content of flavonoids in the broccoli is increased by 40-45%, the content of Ca and Mg Elements is increased by 50-55%, and the time to market of the broccoli is advanced by about 8 days, so that the market competitiveness is further improved.

Owner:固镇县华丰农业有限公司

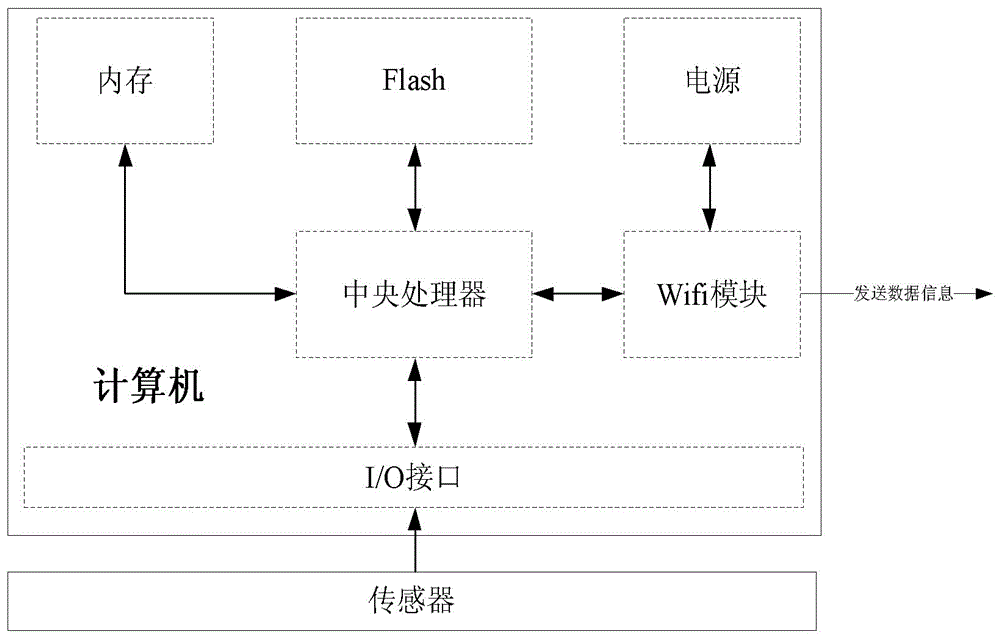

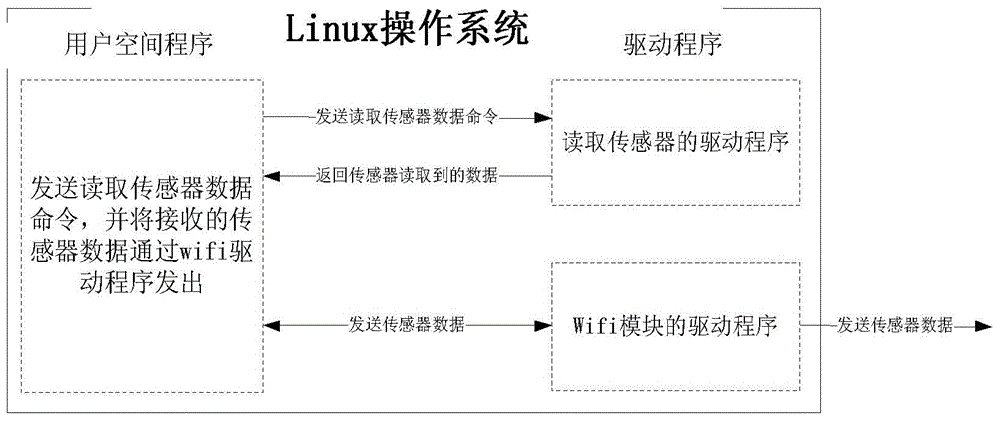

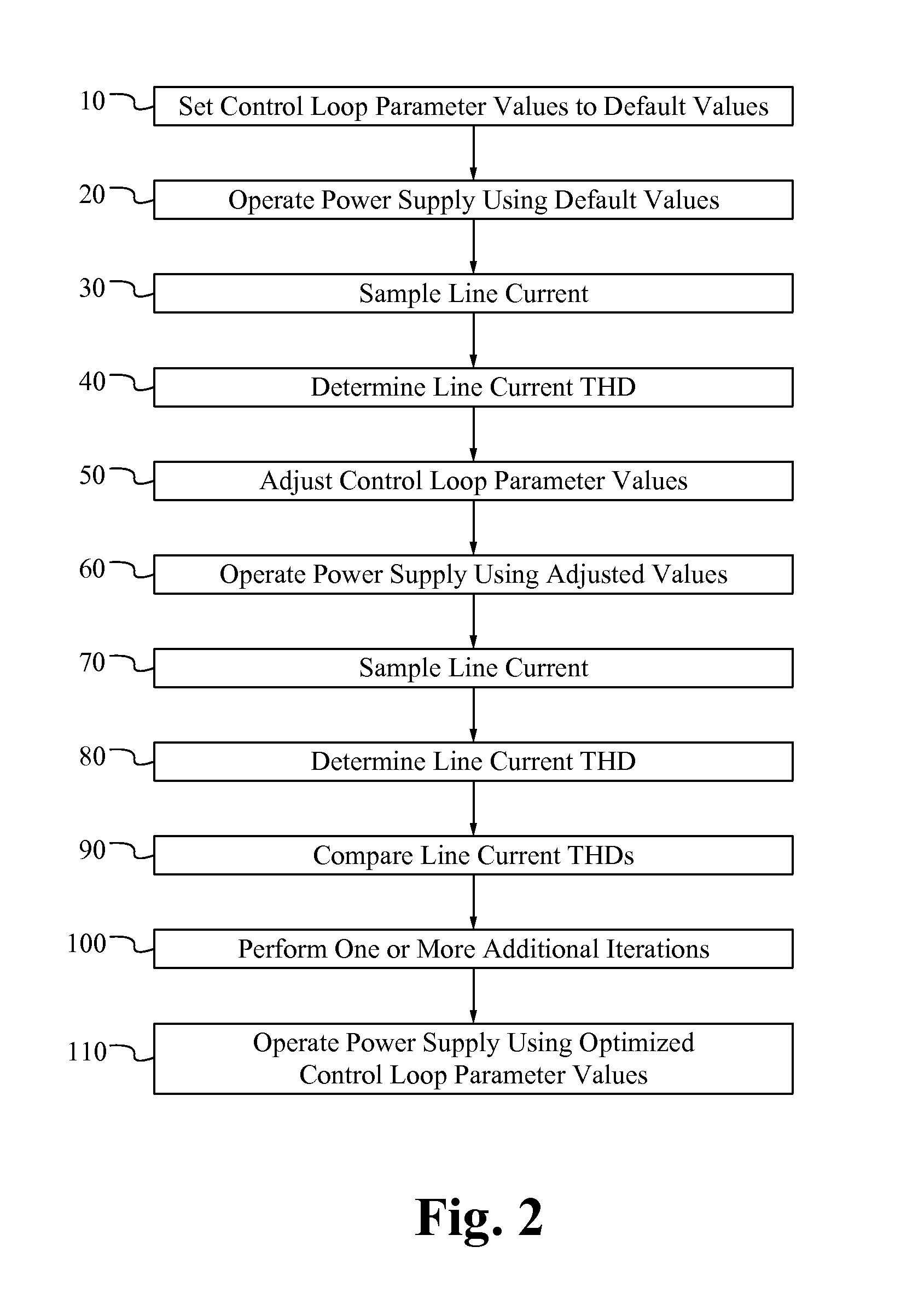

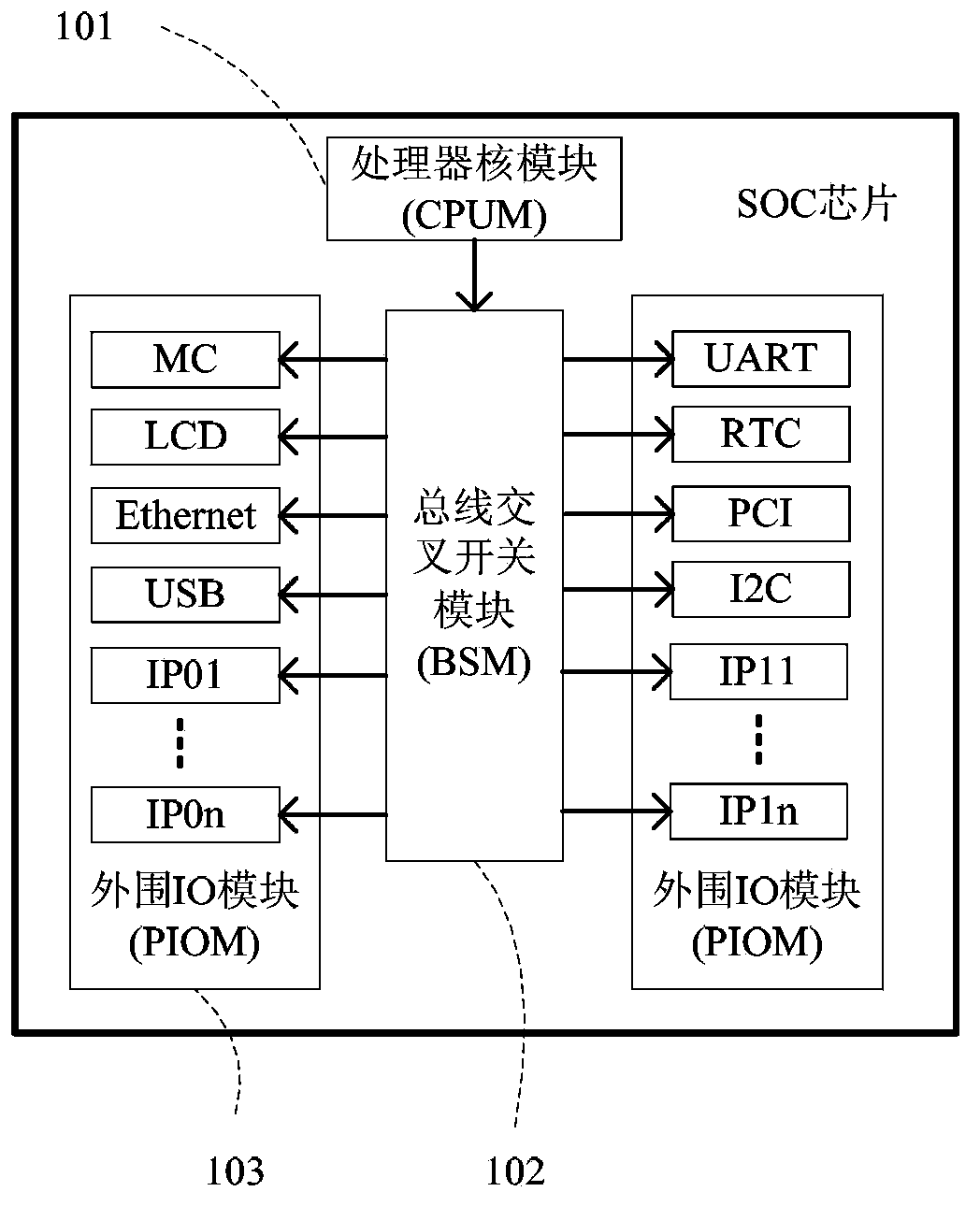

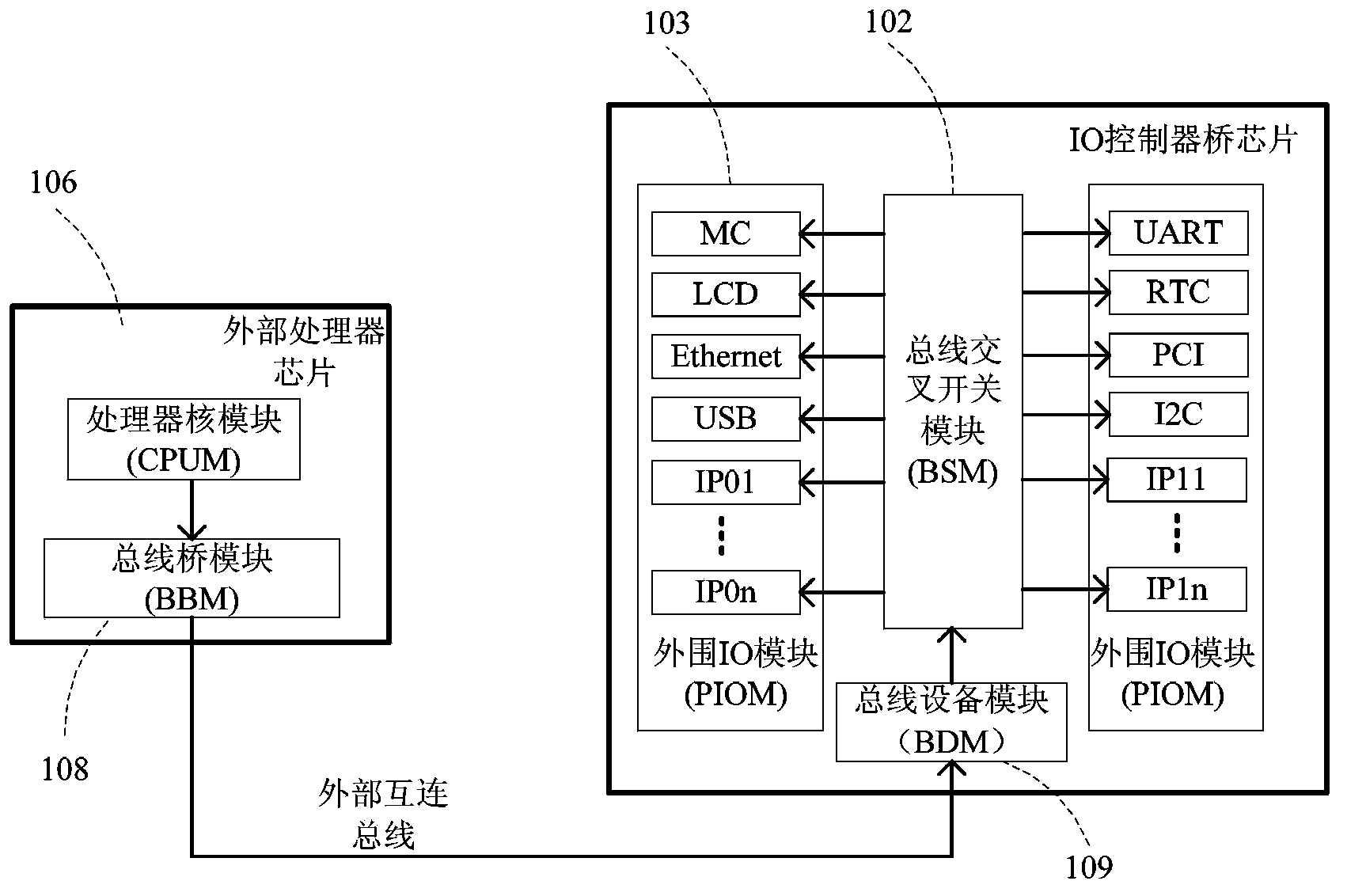

Single SOC chip and multi-working mode multiplexing method of single SOC chip

The invention relates to a single SOC (System On Chip) chip and a multi-working mode multiplexing method of the single SOC chip. The single SOC chip comprises a central processor core module and a peripheral IO module and further comprises a mode control module, a function enabling module, a bus crossbar switch module, an external interconnection bus module, a pin control module and an auxiliary functional module. The mode control module is used for controlling the working modes of the single SOC chip, and the working modes of the single SOC chip comprise a central processor core IP (Intellectual Property) test chip mode, an SOC chip mode and an IO controller bridge chip mode. The function enabling module is used for selecting functional modules needing to be starting up or shutting down. The bus crossbar switch module is used for selecting the address space mapping manners of the functional modules; the external interconnection bus module is used for determining whether the single SOC chip works in the bridge mode or the device mode. The pin control module is used for controlling the IO pin of the single SOC chip to be connected to a signal bus in the single SOC chip. The auxiliary functional module is used for turning on / off the clock and power supply of the functional modules. According to the invention, a manufacturer of the single SOC chip only needs to design one type of tape-out chip to meet three application requirements of the market. Therefore, the frequency of the tape-out chip design is reduced from three times to once, the research and development cycle and the time to market of the conventional single SOC chips are shortened, and the research and development risk and cost of the conventional single SOC chip are lowered.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

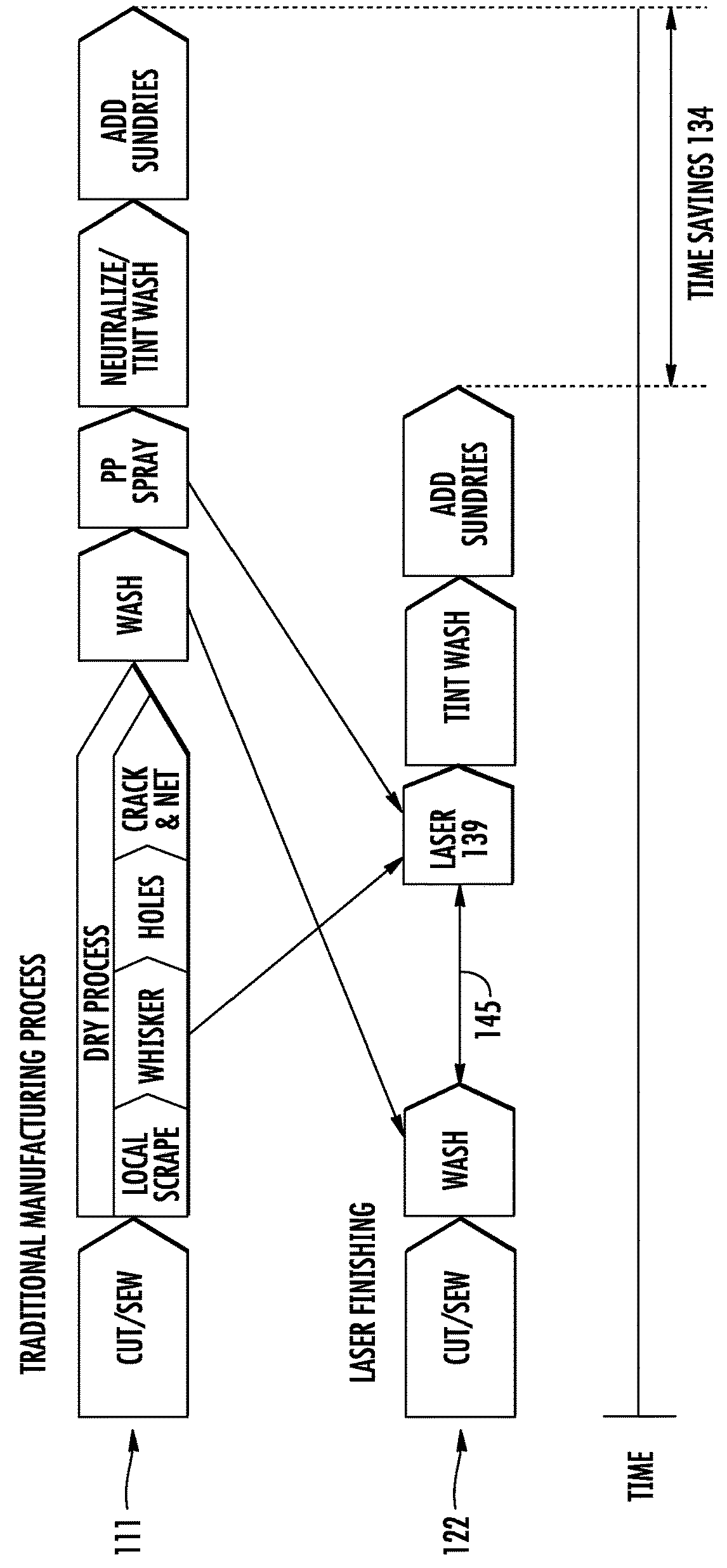

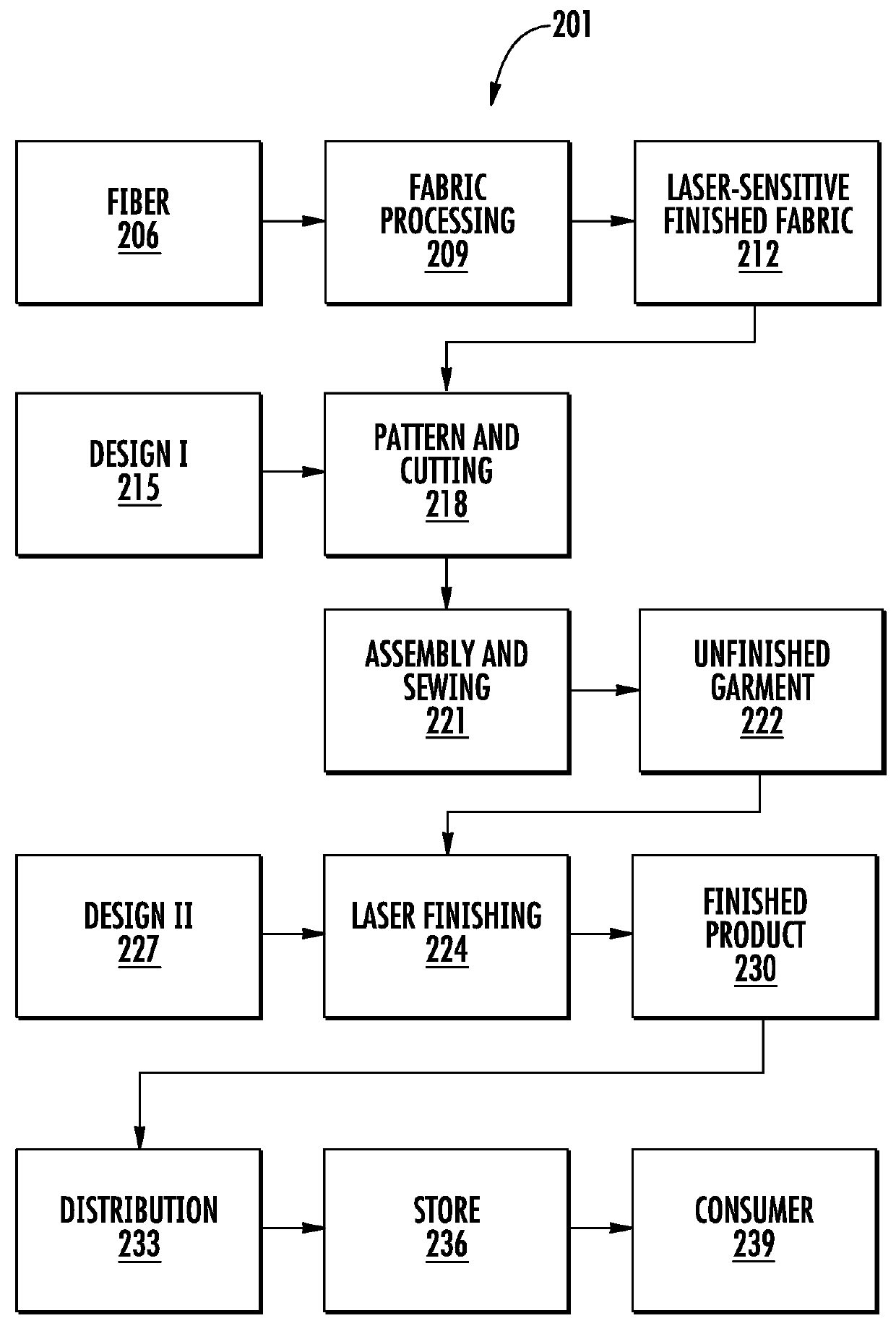

Using Fabric Templates to Obtain Multiple Finishes by Laser Finishing

ActiveUS20180165736A1Reduce finishing costsLow costPattern makingSewing apparatusLost salesTime to market

Laser finishing of apparel products allows an operating model that reduces finishing cost, lowers carrying costs, increases productivity, shortens time to market, be more reactive to trends, reduce product constraints, reduces lost sales and dilution, and more. Improved aspects include design, development, planning, merchandising, selling, making, and delivering. The model uses fabric templates, each of which can be used to produce a multitude of laser finishes. Operational efficiency is improved.

Owner:LEVI STRAUSS & CO

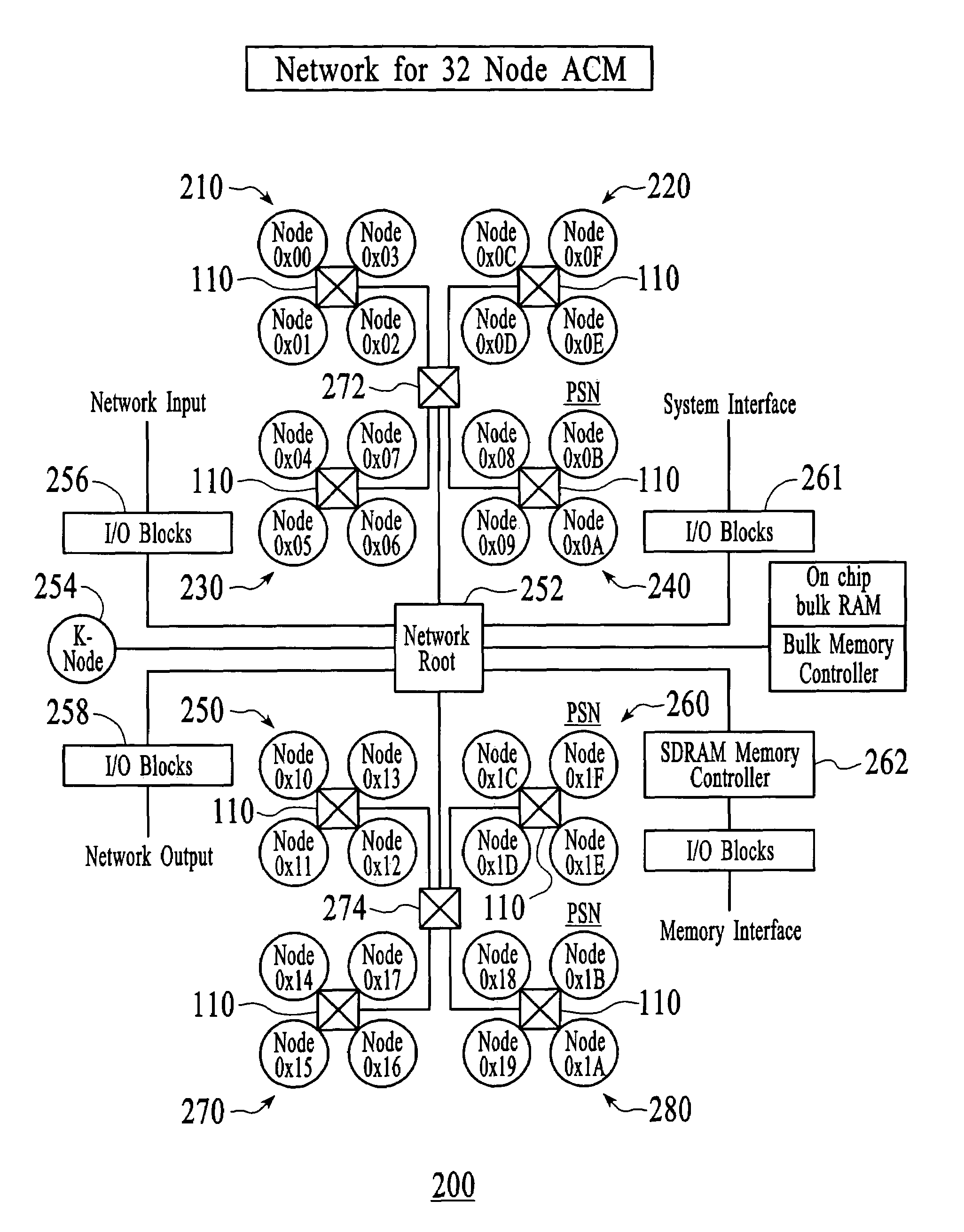

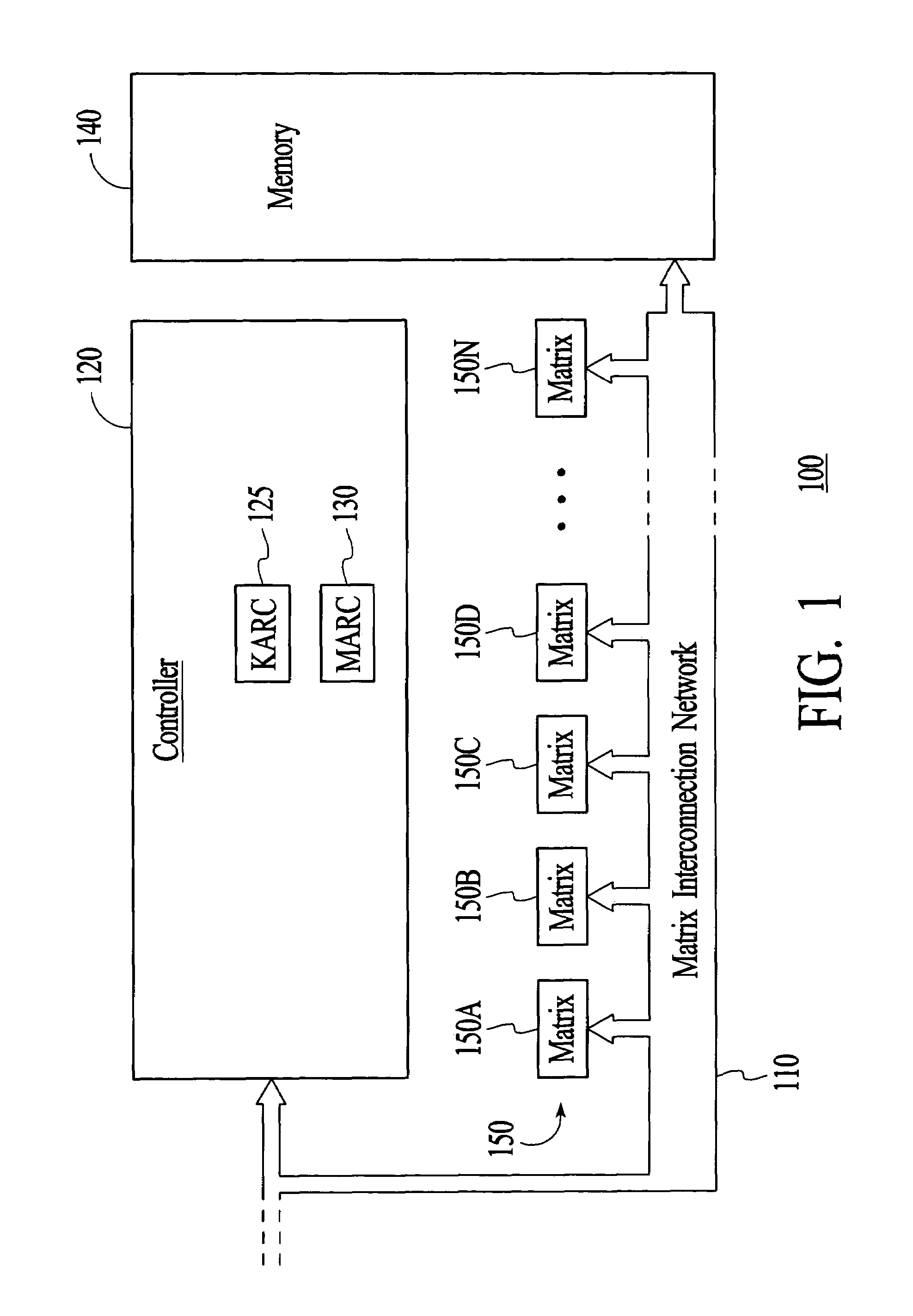

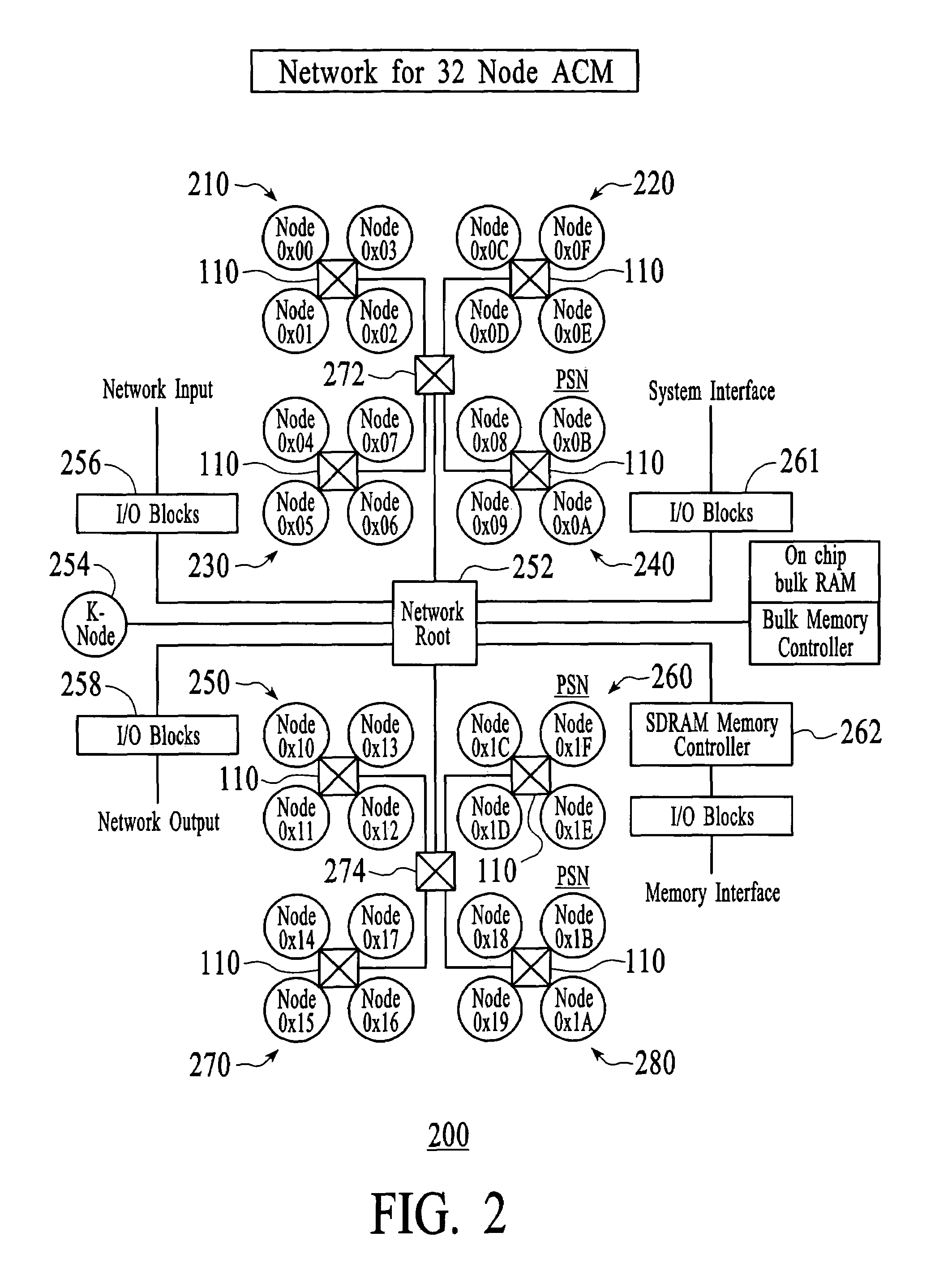

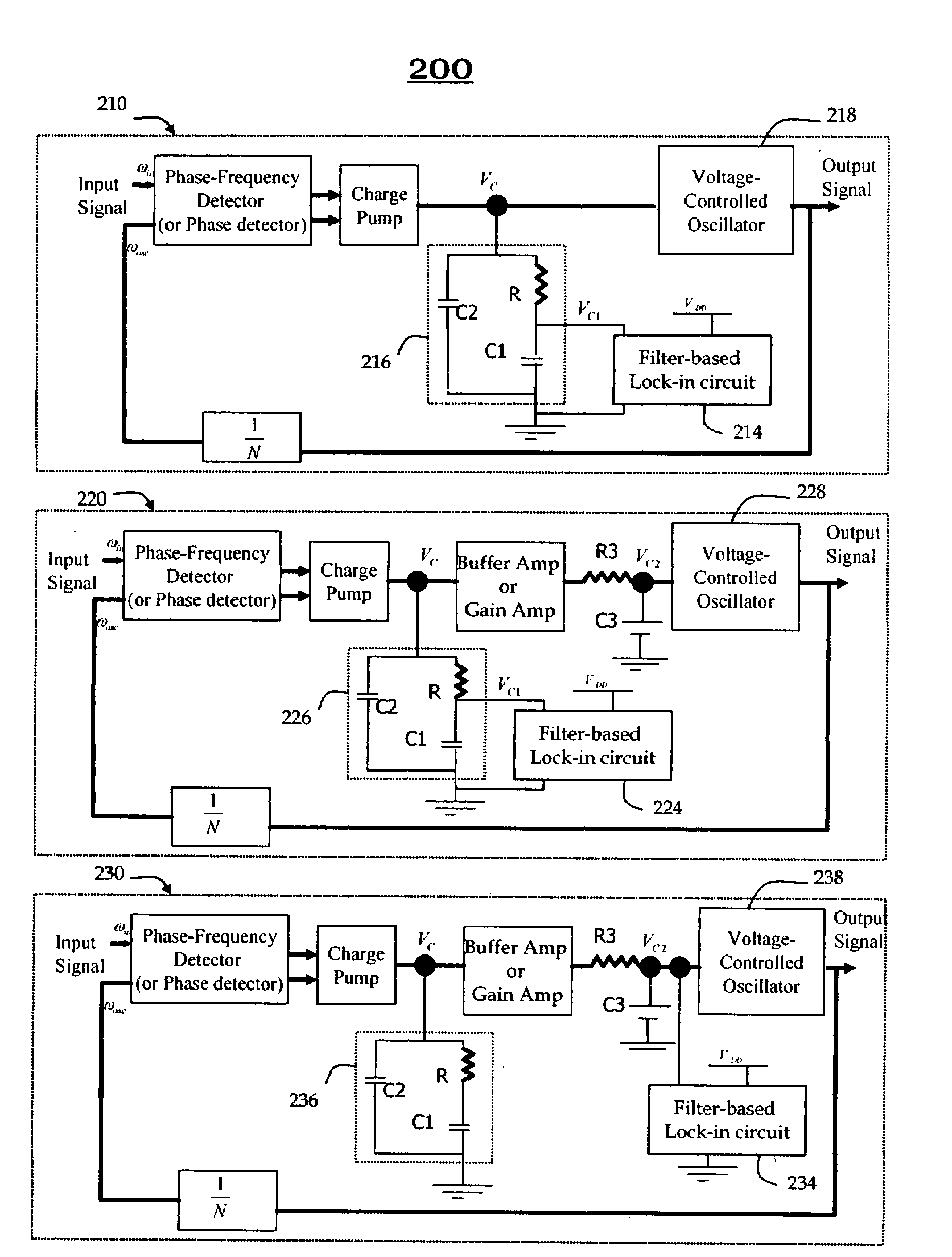

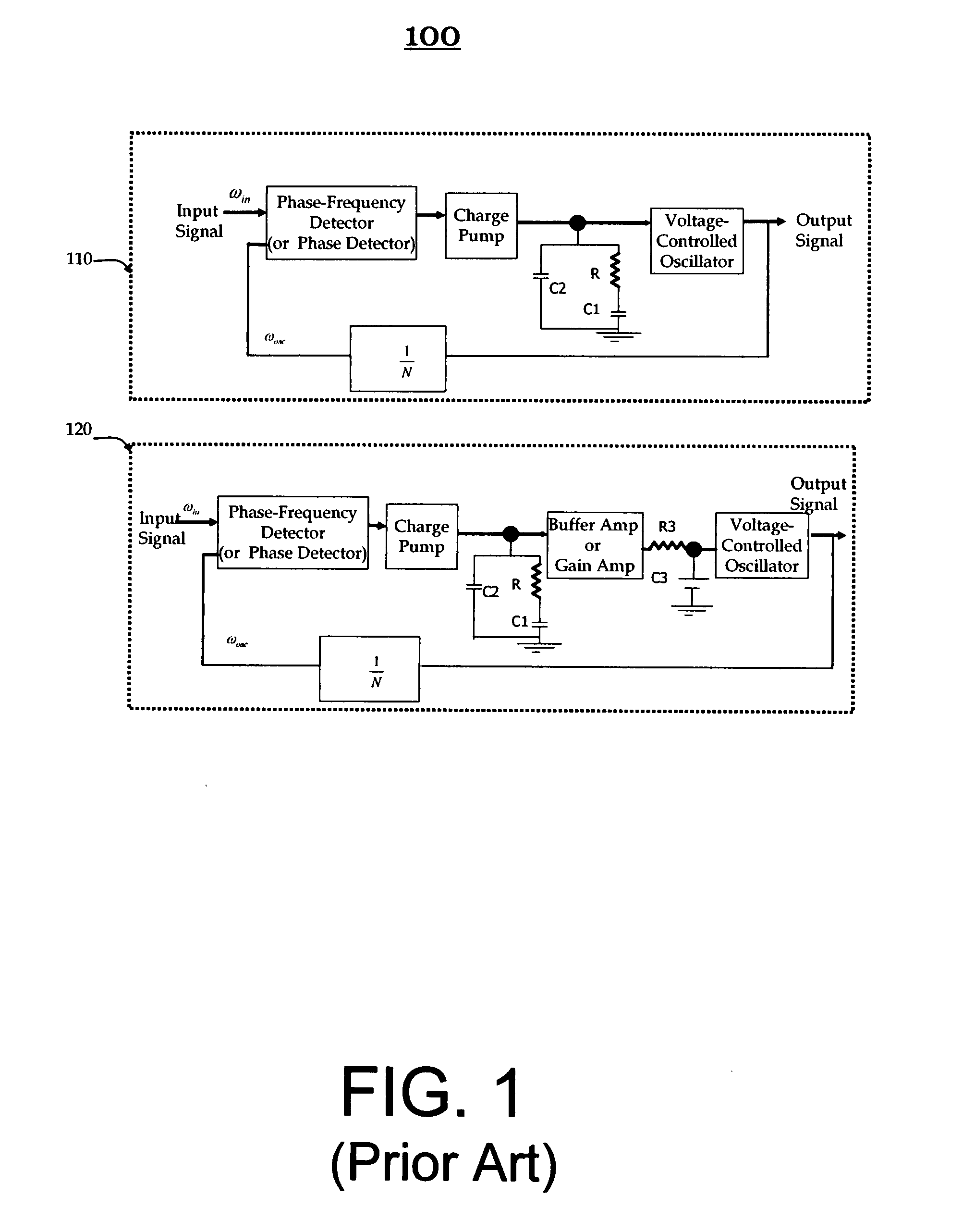

Method and system for reducing the time-to-market concerns for embedded system design

InactiveUS7620678B1Shorten the timeGeneral purpose stored program computerElectric digital data processingTime to marketPersonalization

Aspects for reducing the time-to-market concerns for embedded system design are described. The aspects include providing an infrastructure to support a plurality of heterogeneous processing nodes as a reconfigurable network. Further included is utilizing the infrastructure to customize at least one of the heterogeneous processing nodes according to individualized design needs to achieve a desired embedded system signal processing engine.

Owner:NVIDIA CORP

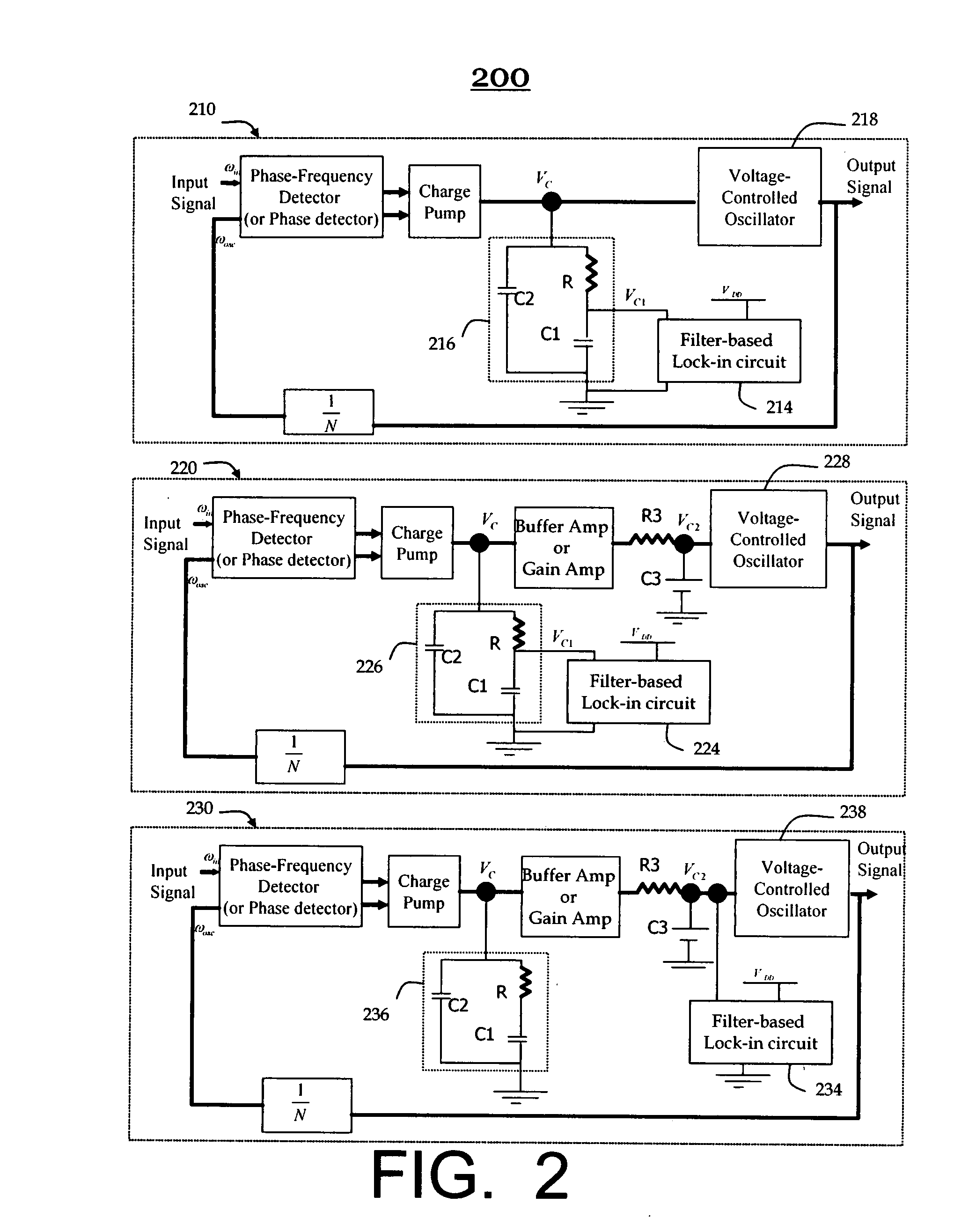

Filter-based lock-in circuits for PLL and fast system startup

InactiveUS20080297263A1Fast lock-in timeSerious problemPulse automatic controlTime to marketSystem testing

All embodiments of the present invention basically include an upper transistor and a lower transistor connected in series between a power supply and ground. The upper transistor and the lower transistor have a shared source (or drain) terminal which becomes a single bidirectional node. They further comprise a sensing gate and a logic gate. The sensing inverter has a function of sensing a voltage at the single bidirectional node and comparing it with an input transition voltage since an input terminal of the sensing inverter is connected to the single bidirectional node. An initial voltage at the single bidirectional node of the filter-based lock-in circuit is almost the same as the input transition voltage of the sensing inverter, where the input transition voltage is an input voltage which causes an output voltage to be VDD / 2. Consequently, all embodiments of the present invention provide a fast lock-in time performance and achieve a drastic improvement in system startup time, system latency time, system simulation time, system test time, cost, and time to market

Owner:SMART SEMICON LLC +3

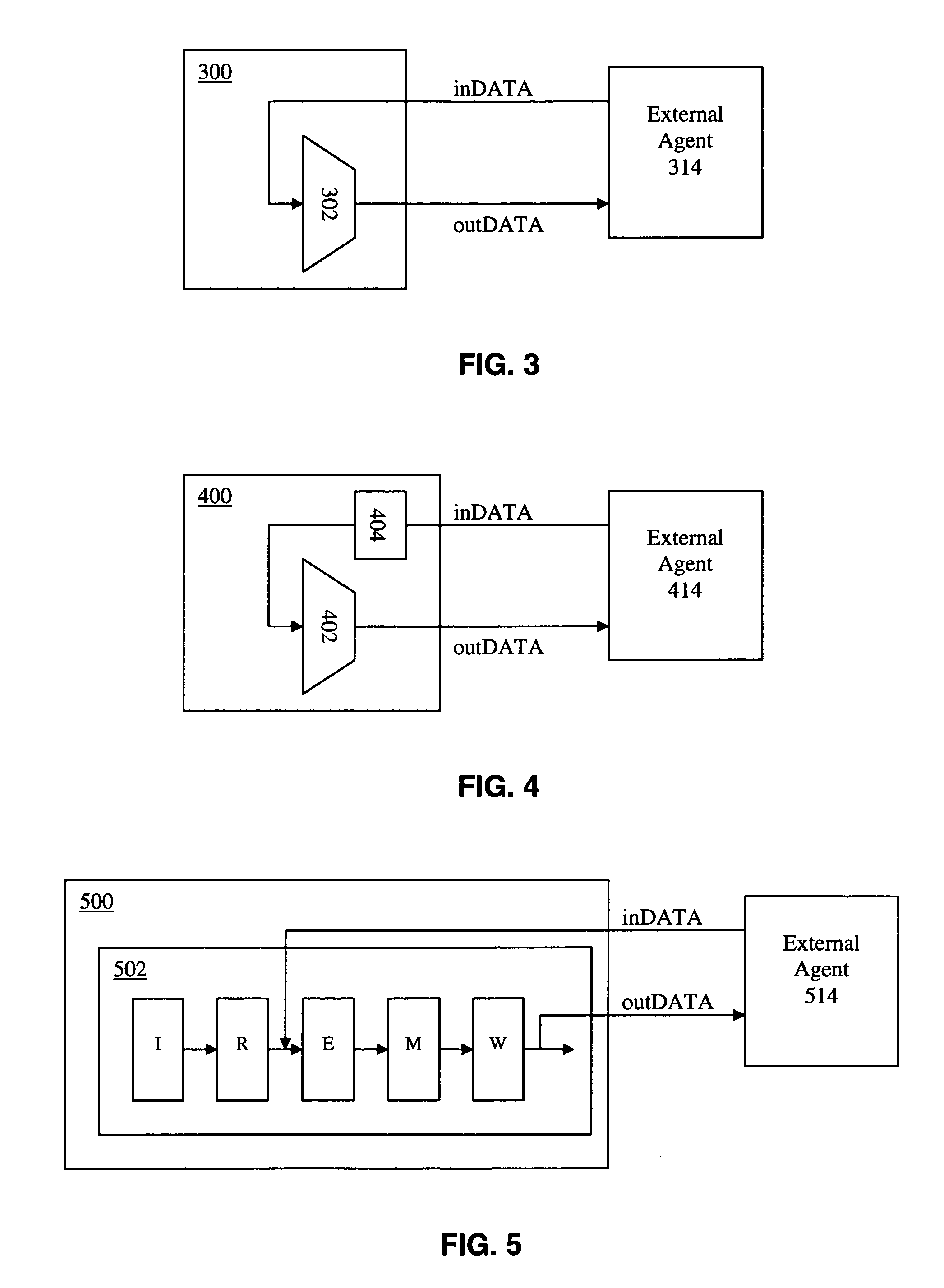

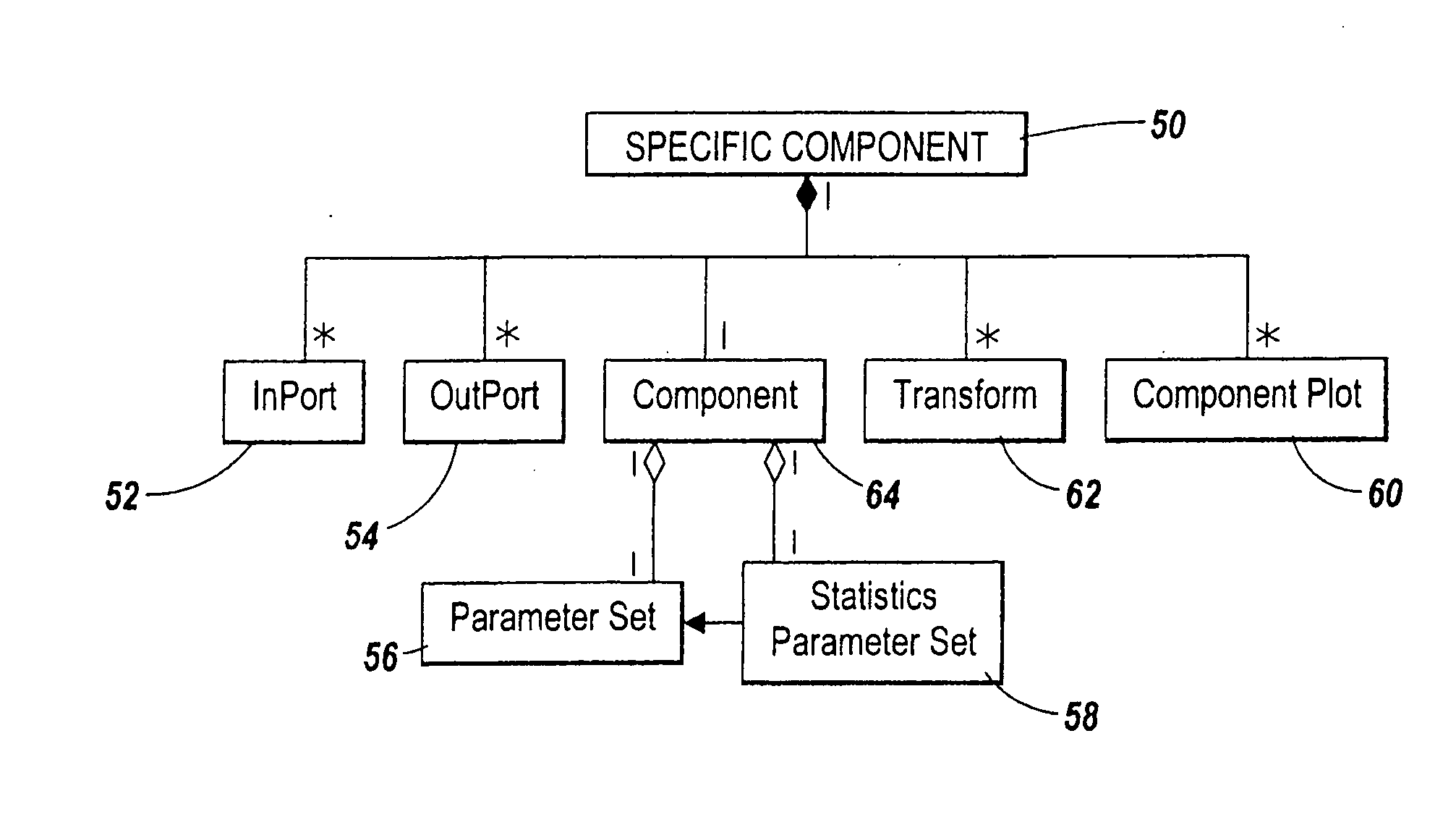

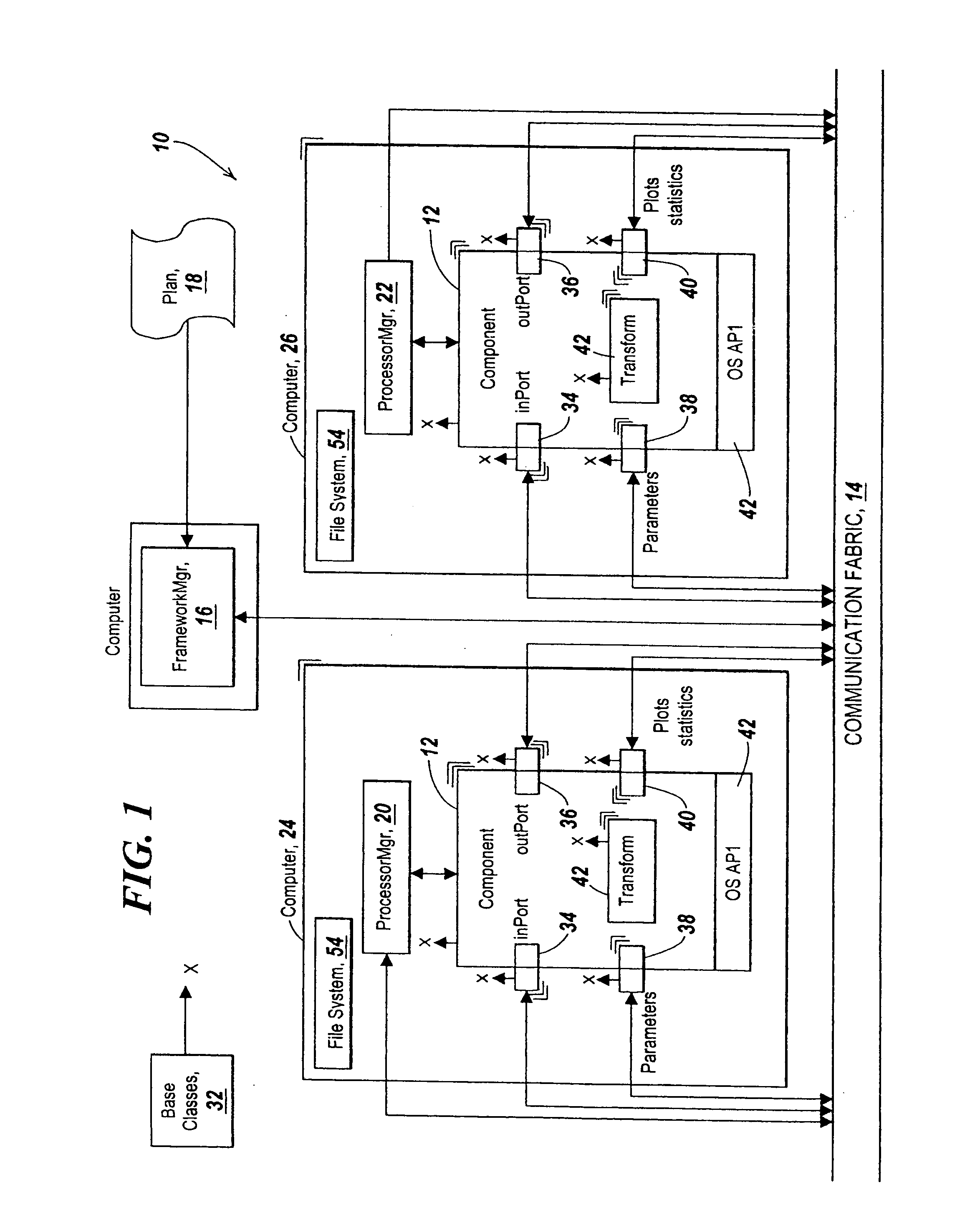

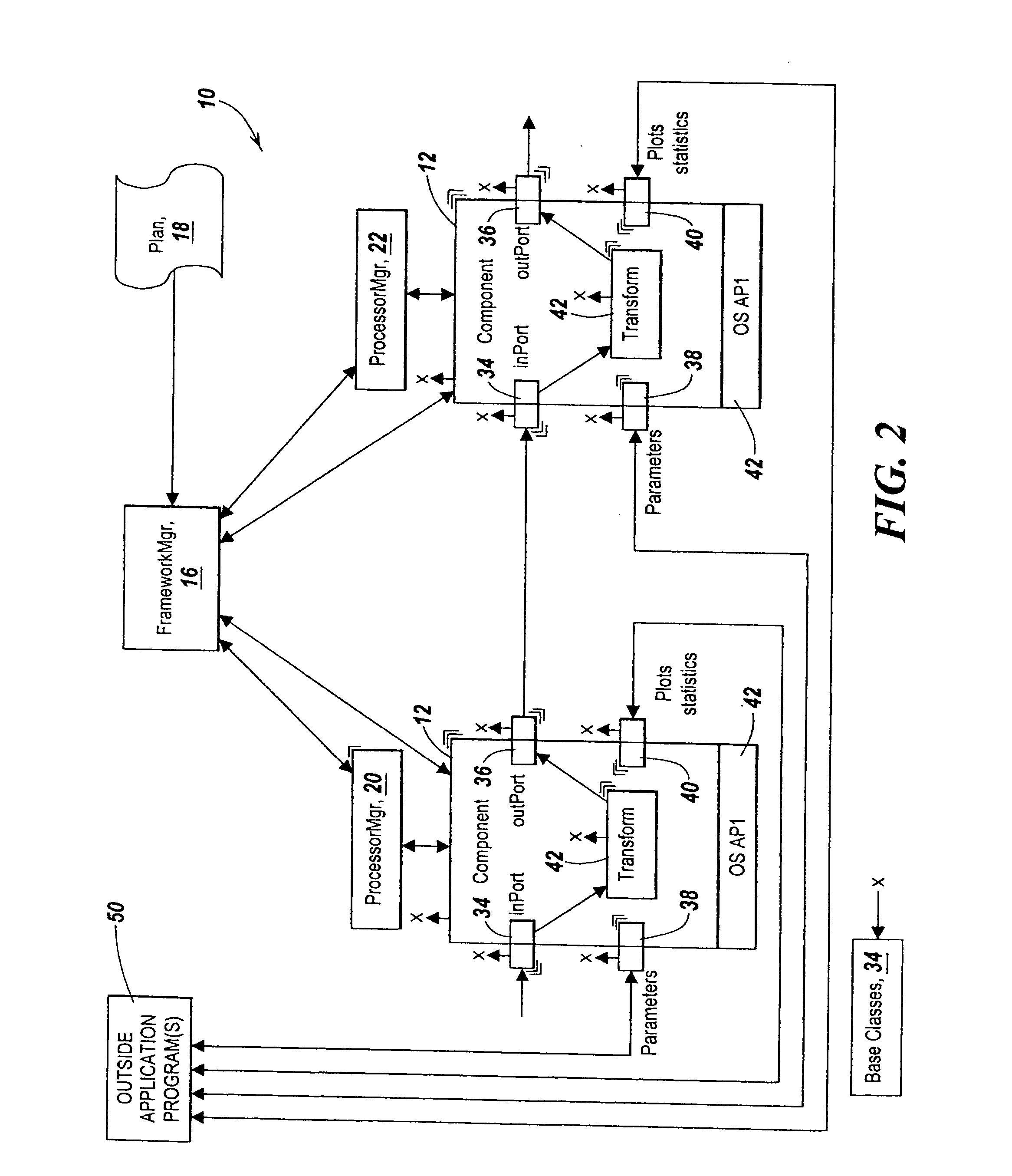

Object-oriented component and framework architecture for signal processing

ActiveUS20050193366A1Reduce decreasePermit reuseDigital computer detailsProgram loading/initiatingBase classSoftware engineering

A reconfigurable distributed signal processing system uses an object-oriented component-framework architecture in which the system permits large-scale software reuse. This is accomplished by the use of a framework and a number of reusable, reconfigurable software components that are hardware independent. The components communicate over a data fabric using open published APIs over one or more data communications mechanisms. Interchangeable software components are used that perform the signal processing. Interchangeability is assured by each component meeting a required interface in which the component inherits the required interface elements from component base classes. This use of inheritance to assure interface compliance also reduces the programming work required for developing a component. Most importantly, the interchangeable components are reconfigurable into various systems at runtime, as defined by a Plan. A Plan is a schematic of the configuration of the various components to be used to solve a particular signal processing problem which includes the list of components, what computer each component is to execute on, how the components are interconnected, and the initial parameter values of the components. The system functionality and capability can be reconfigured at runtime based on a Plan read by a software element of the framework, the Framework Manager. Moreover, the source code for the components is platform independent. The system is able to use heterogeneous commercial off-the-shelf hardware to minimize equipment costs and lower non-recurring engineering costs as well. The system uses the object-oriented programming and software development to reduce time to market and to ensure program success while at the same time exploiting a standard development methodology.

Owner:CALLAHAN CELLULAR L L C

Intensive cultivation and fattening technology of Chinese mitten crab

InactiveCN102283145AAccelerate time to marketDeliciousClimate change adaptationPisciculture and aquariaTime to marketSarcocheilichthys sinensis

The intensified cultivation and fattening technology of Chinese mitten crabs involves aquaculture technology, and is characterized in that: the adult crabs of Chinese mitten crabs that have moulted for the last time are selected as breeding and fattening objects, and the male and female are separated and put into fattening ponds respectively. After the crab enters the fattening period, it is mainly in the stage of fattening and gaining weight. The combination of plant-based concentrate feed and animal-based bait is fed once in the morning and evening, and the daily feeding amount generally accounts for 3-4% of the body weight of the mitten crab. Invention of Chinese mitten crabs through intensive cultivation, due to the plump fat and muscle filling, has enough energy to make the fattened Chinese mitten crabs pass the overwintering stage until April-May of the next year, so that through strengthening measures and corresponding supporting technologies, it can The market time of Chinese mitten crabs is greatly extended, and the balanced listing of Chinese mitten crabs is basically achieved, and Chinese mitten crabs with plump fat, muscle filling and delicious taste can be obtained, and the quality of Chinese mitten crabs can be improved in a short period of time. Get high benefits in a short time.

Owner:芜湖旺龙渔业有限责任公司

Oral Administration of Electrolyzed Water for Treatment and Prevention of PEDv in Swine, Swine Herds and Swine Confinements

ActiveUS20140287065A1The process is fast and efficientShorten the durationBiocideAnimal repellantsTime to marketOral medication

Pigs infected with PEDv often die due to dehydration caused by diarrhea. Those that survive do not reach market weight as scheduled resulting in costs to the producer. The invention includes providing electrolyzed water either as treatment for infected animals or as a prophylactic against symptom severity in uninfected animals. The electrolyzed water is used as a substitute for or as a solution with regular drinking water. Duration of symptoms for infected pigs is markedly lessened; severity of symptoms is also reduced providing a much higher survival rate. Time to market is less negatively affected for surviving pigs than those untreated, and weight at scheduled time for sale is also less effected translating into positive financial results over those expected for untreated herds.

Owner:AG ODOR CONTROL

Integrated circuits verification checks of mask layout database, via the internet method and computer software

InactiveUS20080127028A1Fast resultsLow costComputer aided designSpecial data processing applicationsTime to marketComputer architecture

A system and method for integrated circuits verification checks of mask layout database, via the internet are disclosed. The method includes the submission of mask layout database for a specific verification check, over the internet to a main server. All required setup files are also submitted over the internet to the main server. The results are sent to the user upon check completion via email. The system includes a web based control panel interface to submit and execute all necessary setups and checks types for integrated circuit mask layout database over the internet using secured protocol, implemented within commercial internet browser. The system also offers a PDA (Personal Digital Assistant) interface to launch verification checks via the internet. This approach eliminates the purchase of a full local license and enables affordable prices for small and medium size chip design firms. This fact significantly reduces integrated circuits design cost and time to market factor for chip design corporations, enabling faster deliveries to their end customers.

Owner:MICROLOGIC DESIGN AUTOMATION

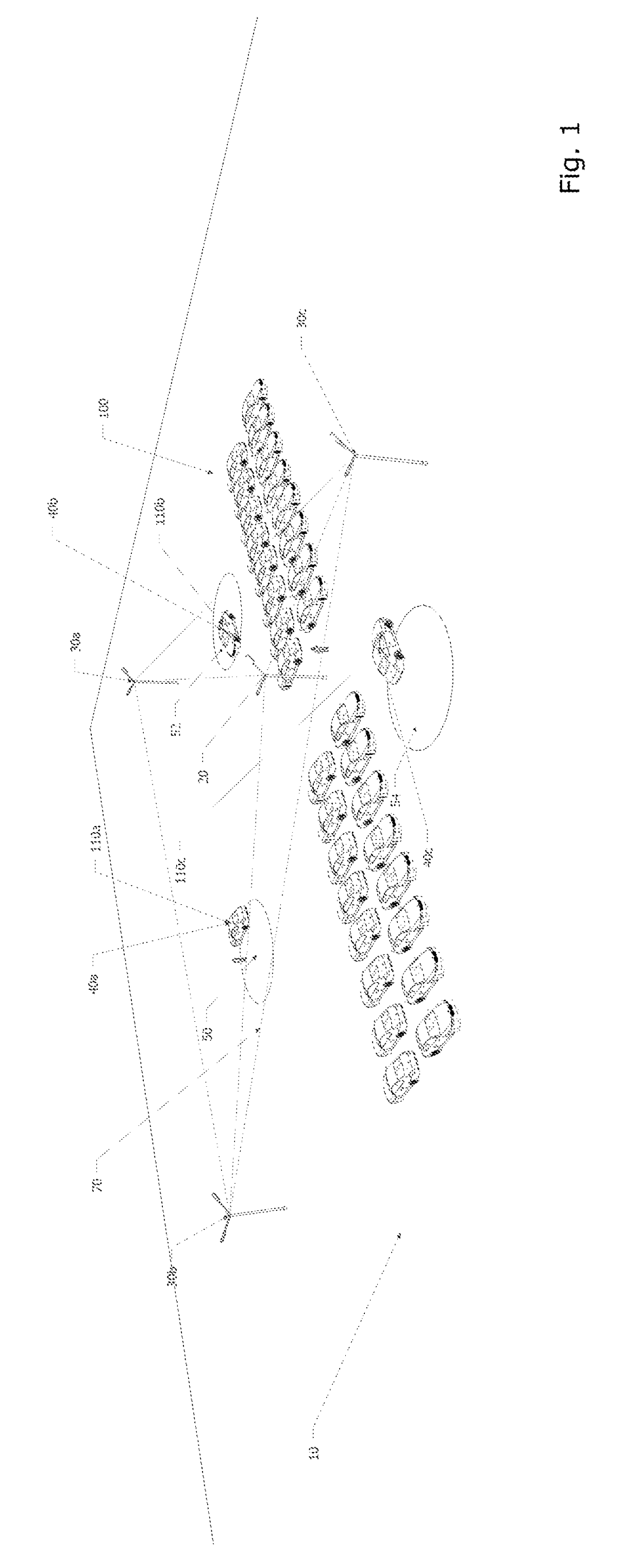

Retail automotive dealership inventory tracking, reconciliation and workflow system

InactiveUS20170357934A1Precise positioningQuantity minimizationLogisticsRecord carriers used with machinesTime to marketEngineering

The present invention provides vehicle dealerships with an UWB enabled smart tag that is installed on the vehicle's windshield. The smart tag broadcasts its location via UWB on a predetermined schedule or as a response to movement. The smart tags location is determined by UWB anchors which use MLAT to localize the tag. The present invention allows dealership personnel to more accurately mange their inventory. The present invention allows banks and lending institutions to more accurately ascertain physical location of vehicles that are floor planed. The present invention results in lower total cost of operations for the dealership. The present invention takes the practices of a timely accurate physical inventory reconciliation puts them into real-time perpetuity of the dealership's operations. The present invention reduces time to market by automating the workflow of vehicles at a dealership.

Owner:CP HANDHELD TECH LLC

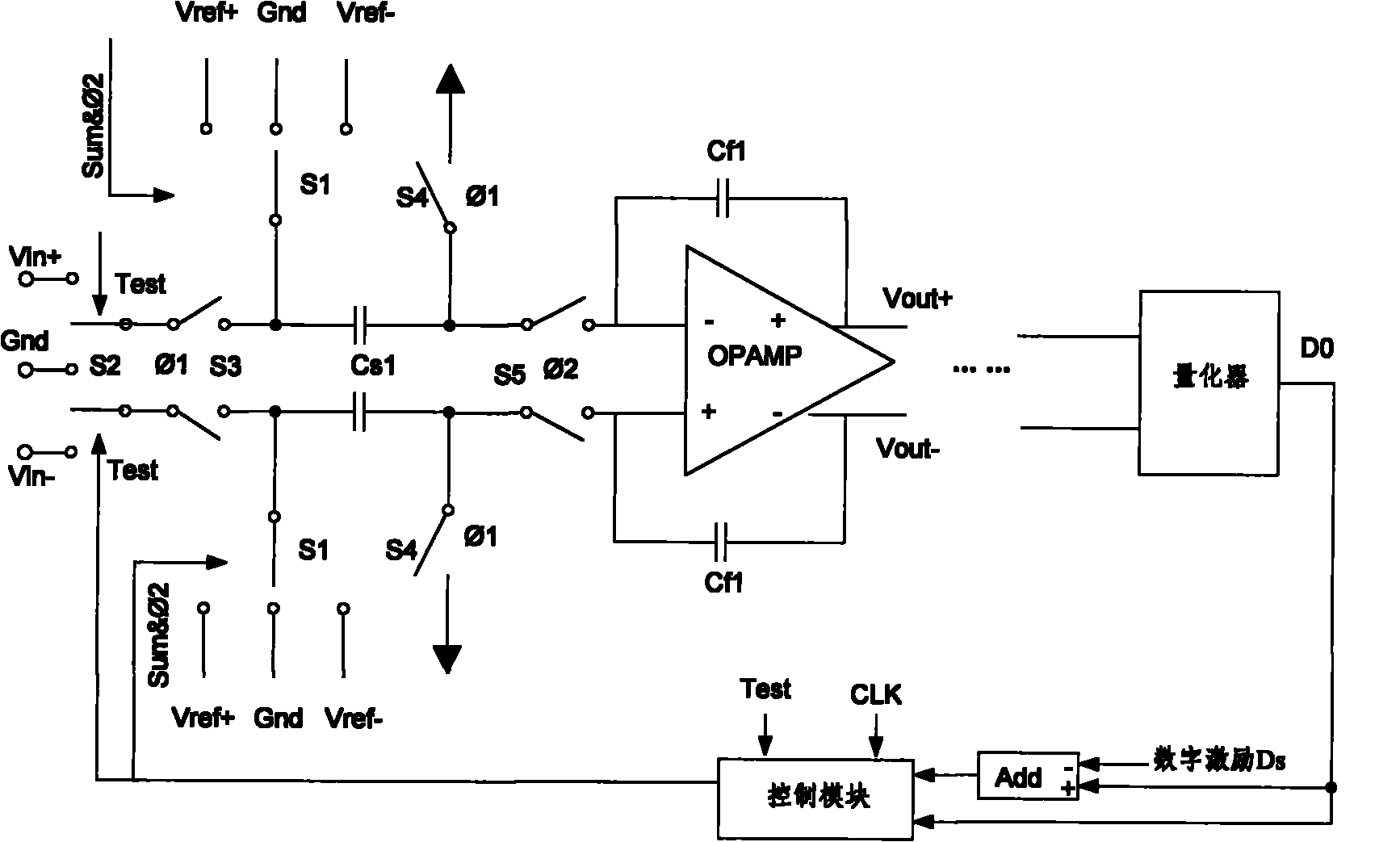

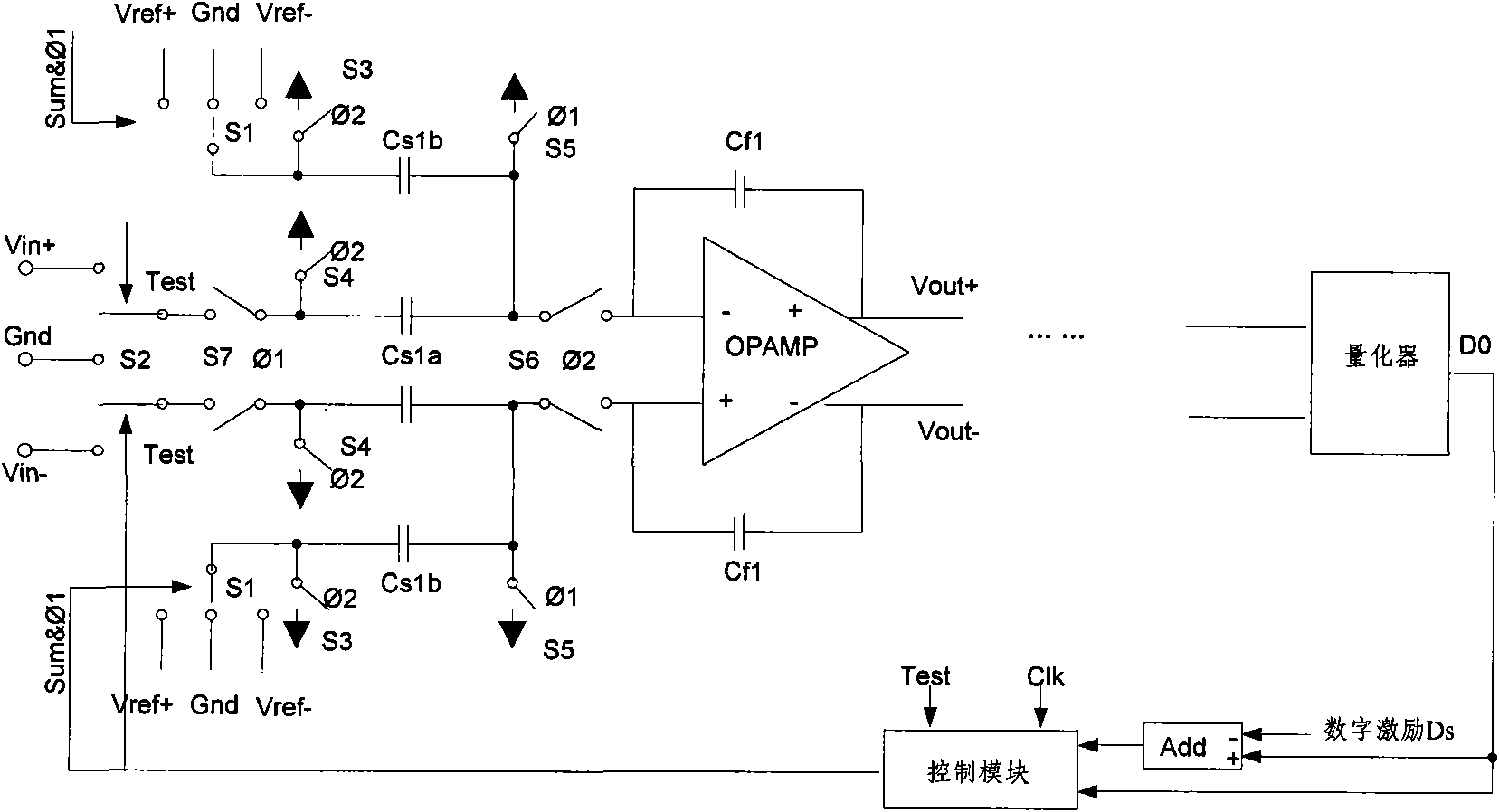

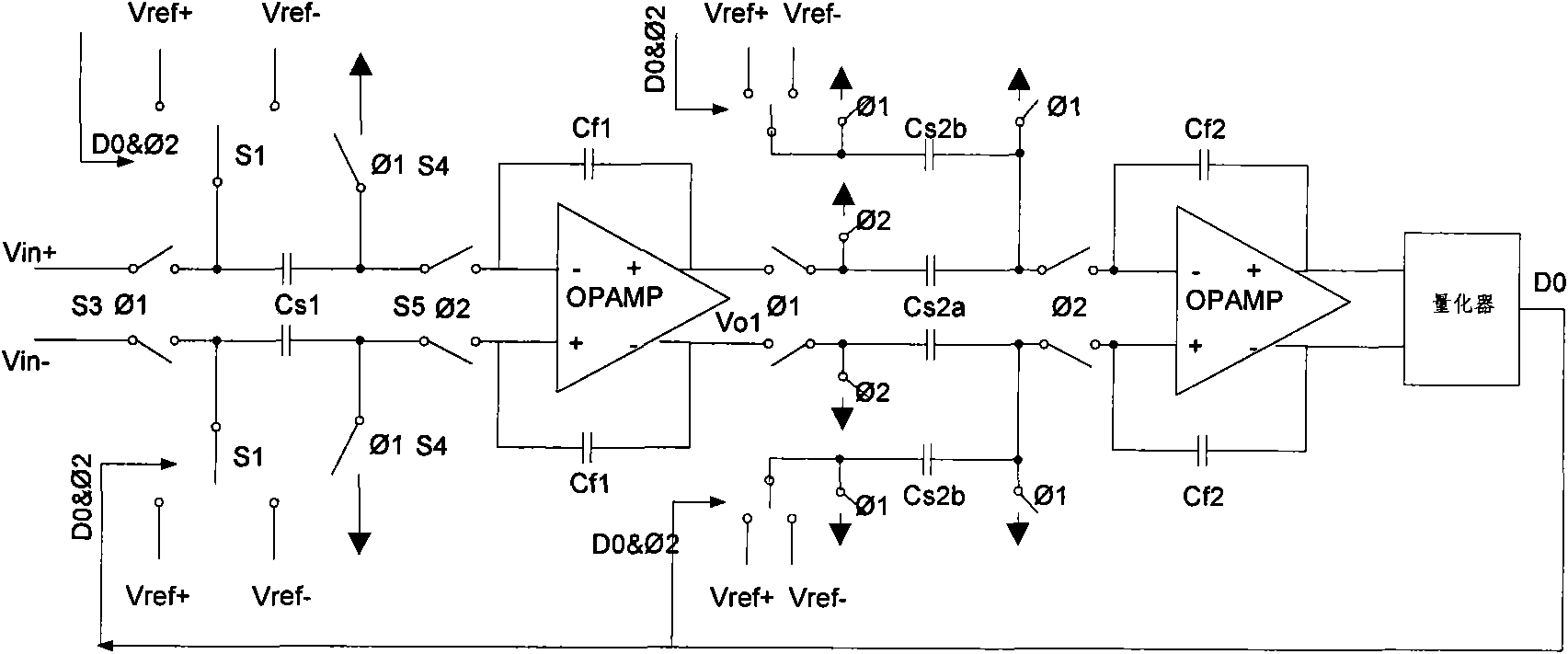

Design for testability circuit and method for full digital switched capacitor sigma-delta modulator

InactiveCN101783687AReduce testing costsShort test timeElectrical testingDelta modulationTime to marketCapacitance

The invention relates to a design for testability method for full digital switched capacitor sigma-delta modulator (DFT), comprising the following steps: modifying according the structure of the designed sigma-delta modulator to be measured, and connecting the original input end to Gnd when testing; multiplexing one feedback DAC contained in the sigma-delta modulator to be measured, and reconfiguring the feedback DAC to three output levels Vref+, Gnd and Vref-; deciding the output of the feedback DAC according to the difference of quantizer digital output (D0) and applied digital drive (Ds), and detecting the performance of the sigma-delta modulator to be measured through analyzing digital drive and quantizer digital output. The invention further provides a corresponding DFT circuit. The technical scheme of the invention provides a full digital switched capacitor sigma-delta modulator DFT method without using expensive analog driving source testing modulator, thereby having at-speed testing ability with very low testing cost and very short testing time and is capable of efficiently reducing time-to-market time of products.

Owner:PEKING UNIV +1

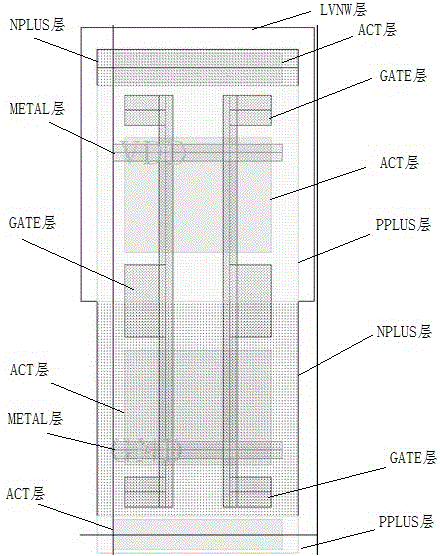

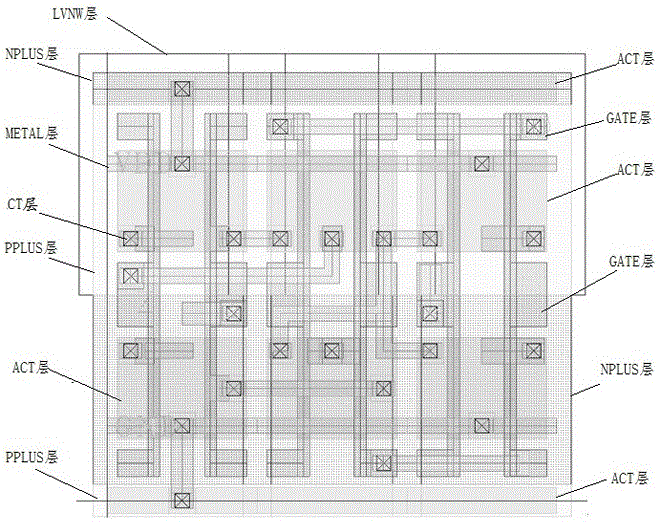

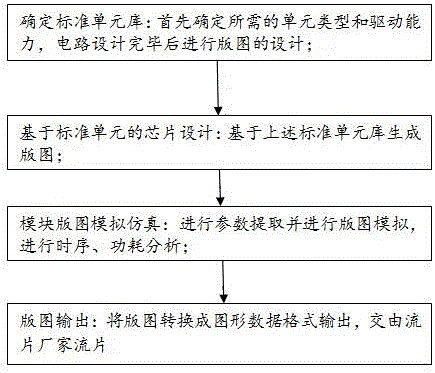

Basic cell, standard cell, standard cell library, back-end full-custom design method and chip

ActiveCN106339532AImprove placement and routing efficiencyImprove design efficiencyCAD circuit designSpecial data processing applicationsTime to marketComputer architecture

The invention discloses a basic cell, standard cell, standard cell library and back-end full-custom design method and a chip manufactured based on the method, and belongs to the technical field of integrated circuit layout designs. The basic cell disclosed by the invention at least comprises GATE layers, ACT layers, an LVNW layer, NPULS layers and PPLUS layers as well as a CT layer and a METAL layer which are all in regular shapes; the regular shapes of the GATE layers, the ACT layers, the LVNW layer, the NPULS layers and the PPLUS layers all need to meet process design rules. The layout of the standard cell comprises M basic cells in different Metal wiring manners, and M is a nonzero integer. The standard cell library comprises a plurality of the standard cells with different functions. The back-end full-custom design method of the invention comprises the following steps: determining the standard cell library, designing the chip based on the standard cell, carrying out analog simulation on a module layout and outputting the layout. The chip realized by adopting the back-end full-custom layout design method is more regular and standard in design to greatly optimize the layout design and improve the layout and processing efficiency so as to shorten the product time to market.

Owner:HANGZHOU CHIPJET TECH

Industrialized production method of minitype rosa chinensis potted flowers

The invention discloses an industrialized production method of minitype rosa chinensis potted flowers. The industrialized production method of the minitype rosa chinensis potted flowers comprises the following steps of (1) preparation of the potted flowers; (2) preparation of production facilities; (3) preparation of three-dimensional cultivation frames; and (4) cultivation of the potted flowers. According to the industrialized production method of the minitype rosa chinensis potted flowers, production of the minitype rosa chinensis potted flowers which are high in ornamental value is achieved after a time of 35 days to 40 days in winter, each pot of the minitype rosa chinensis potted flowers is provided with more than 6 blooming branches, and each minitype rosa chinensis potted flower is full-grown and balanced, influence of weather variation on the production of the minitype rosa chinensis potted flowers is removed, due to the fact that a three-dimensional cultivation mode is adopted, a using rate of equipment is high, and due to the fact that the minitype rosa chinensis potted flowers are large in sales volume and high in price, economic benefit is remarkable. The industrialized production method of the minitype rosa chinensis potted flowers has the advantages of being simple in production condition, easy to operate, high in profit, easy to popularize and apply, and the like. Control of a flowering stage and production arrangement can be carried out according to time to market of the minitype rosa chinensis potted flowers, and the industrialized production method of the minitype rosa chinensis potted flowers has large practical application value in lunar new year flower production of the new year's day and a spring festival.

Owner:JIANGSU ACAD OF FORESTRY

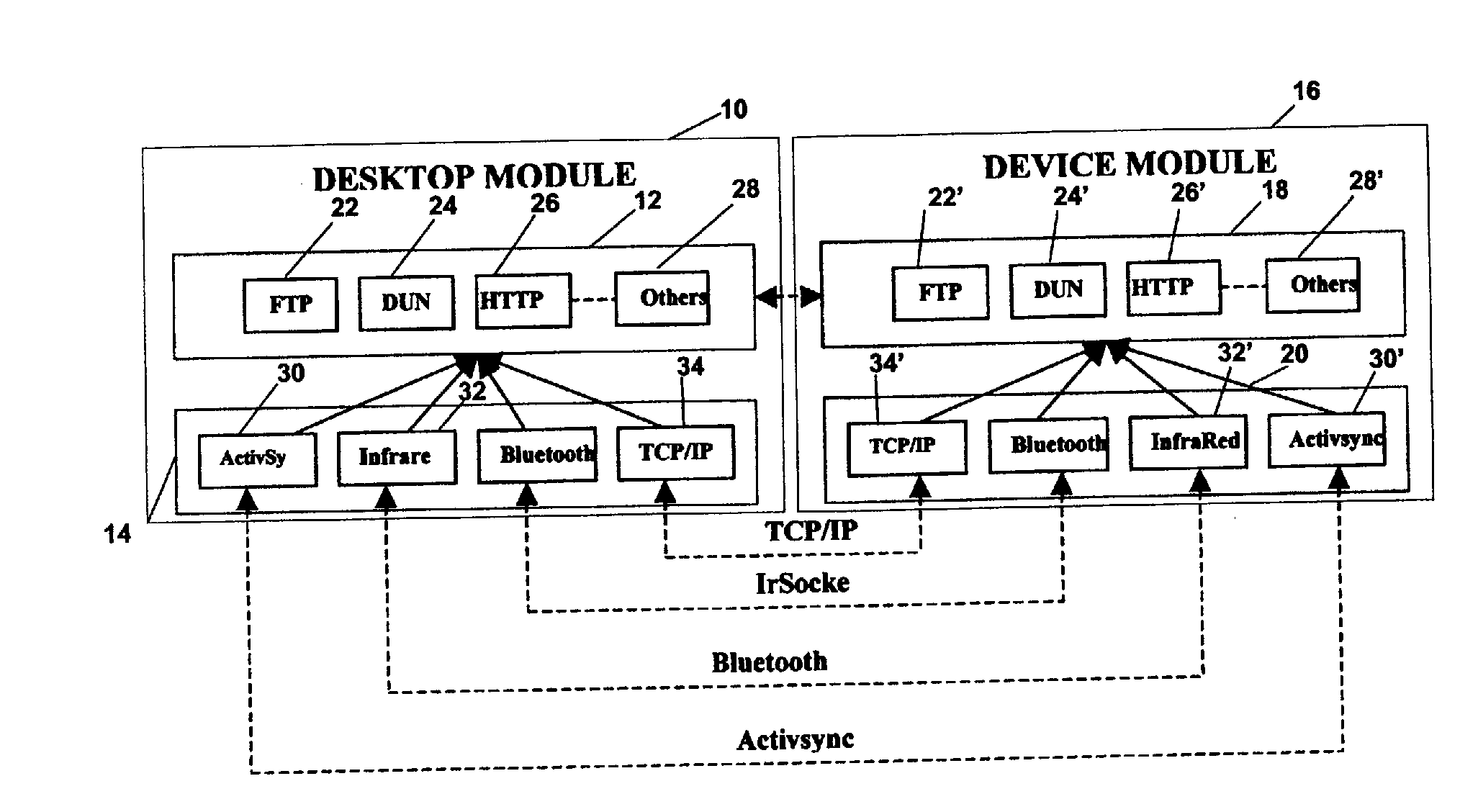

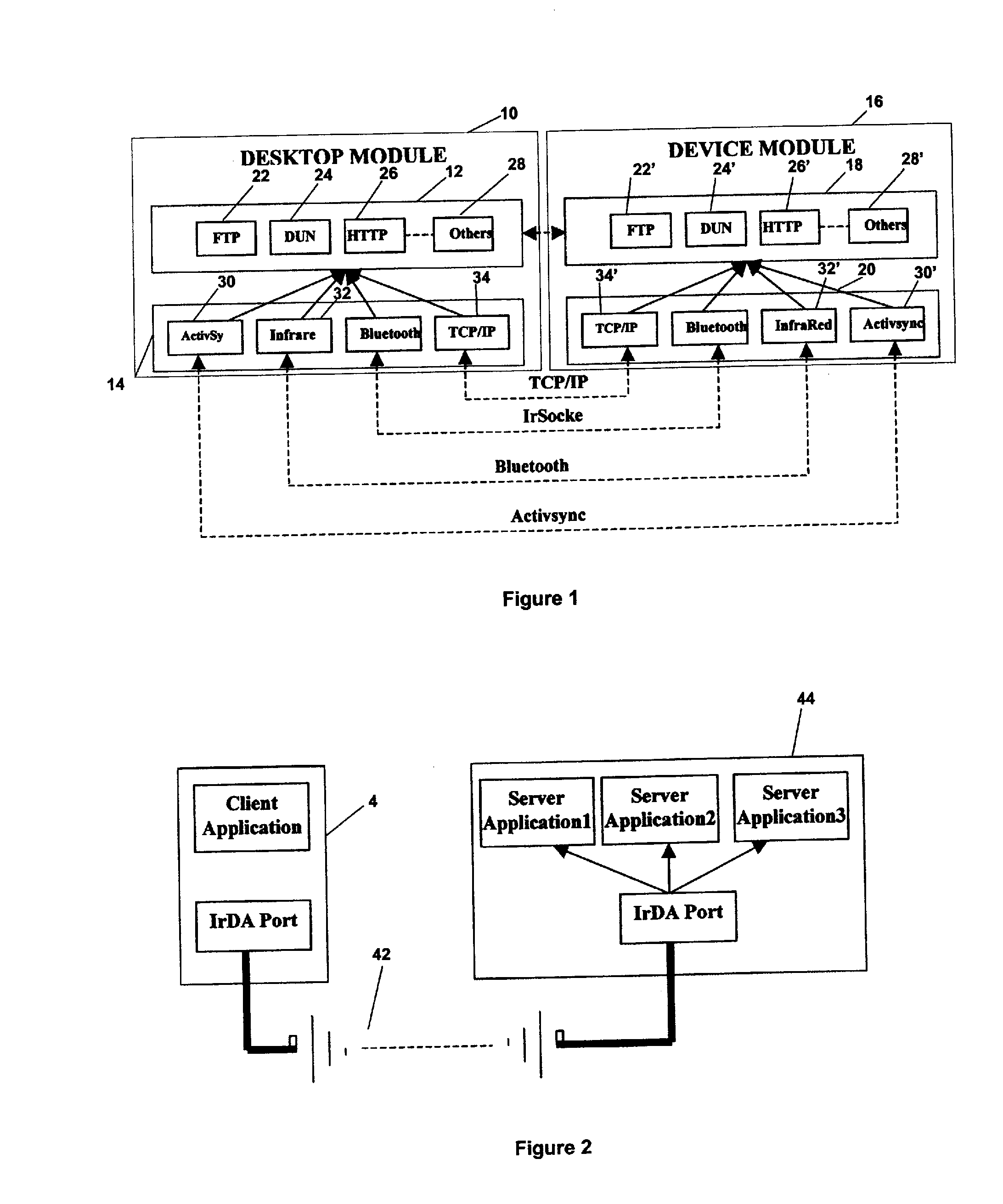

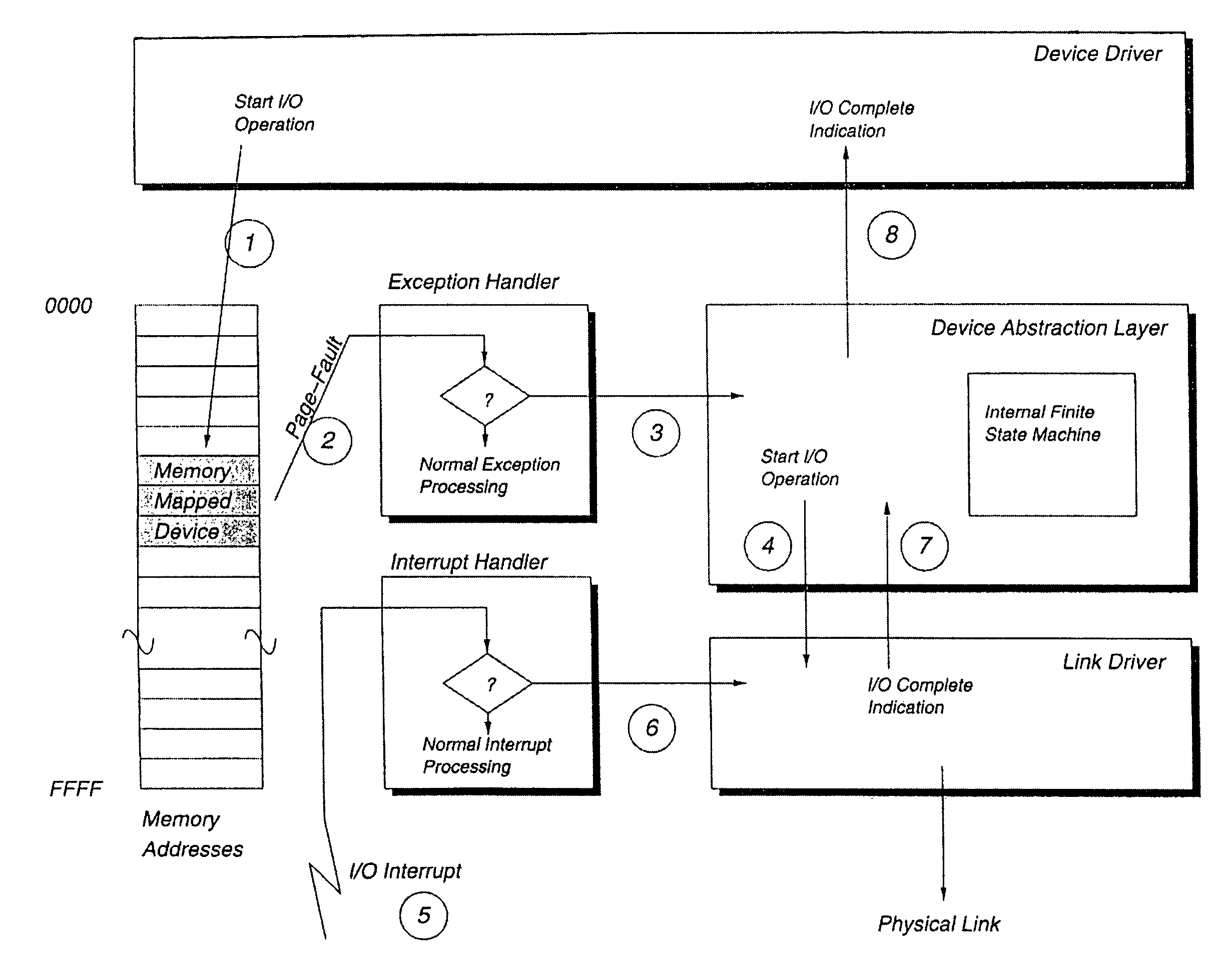

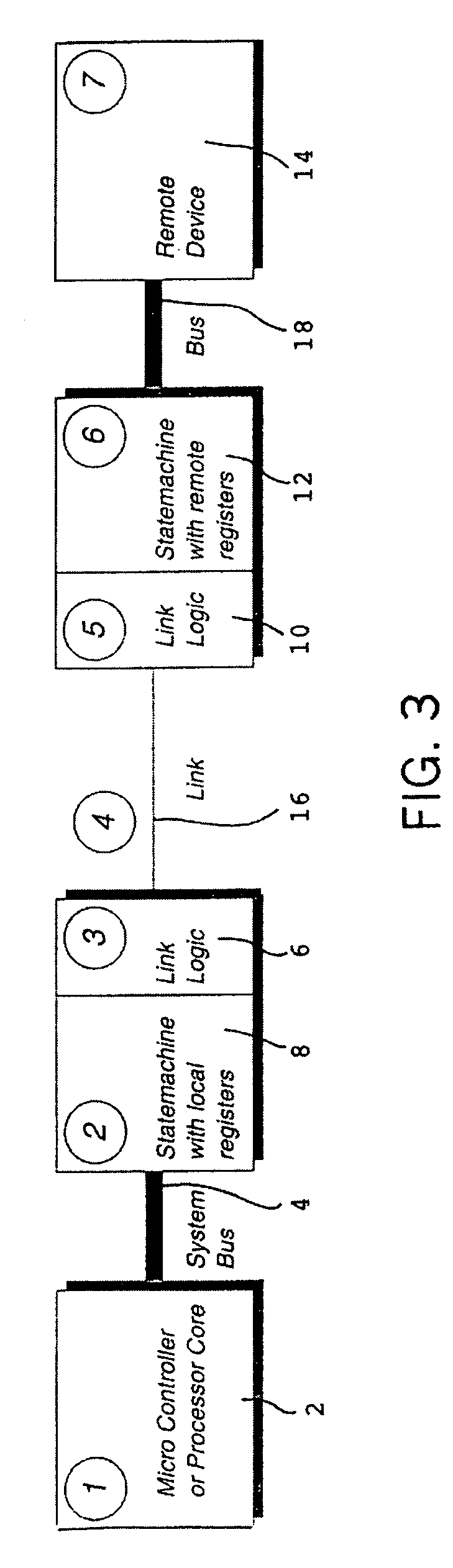

Method and system for efficient access to remote I/O functions in embedded control environments

InactiveUS7076575B2Less programming effortReduce effortMultiprogramming arrangementsProgram loading/initiatingMemory addressTime to market

A method for accessing I / O devices in embedded control environments is provided, wherein said I / O devices are remotely attached to an embedded microprocessor. By mapping said I / O devices' resources to said microprocessor's address or memory address space, existing device drivers can be reused and the time-to-market capability is greatly improved.

Owner:IBM CORP