Single SOC chip and multi-working mode multiplexing method of single SOC chip

A working mode and chip technology, applied in the fields of instruments, electrical digital data processing, etc., can solve the problems of not being able to close the SOC chip, the SOC chip cannot be configured, and the on-chip interconnection bus configuration connection, etc., to reduce research and development risks and costs, The effect of shortening R&D cycle and time-to-market of chips

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

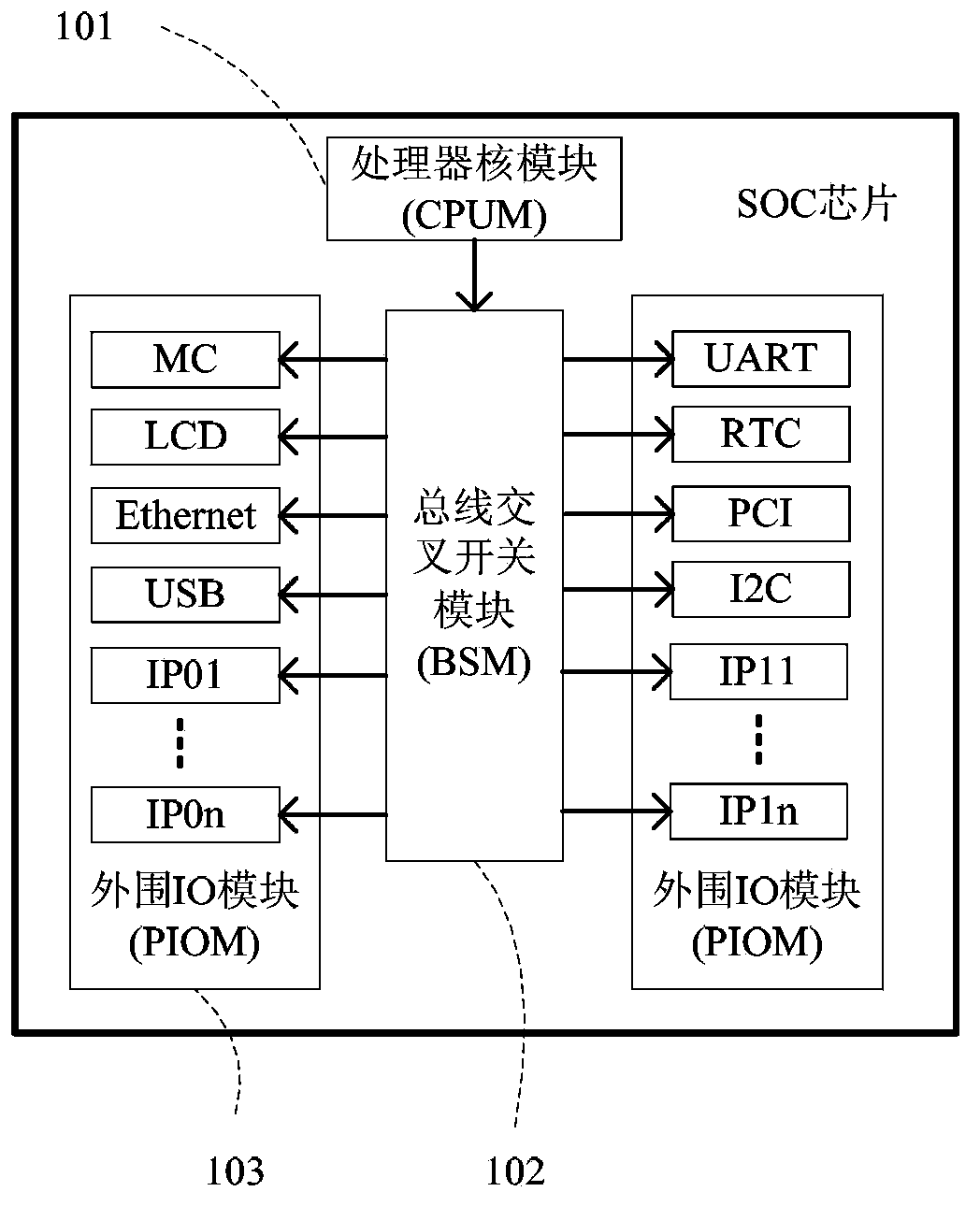

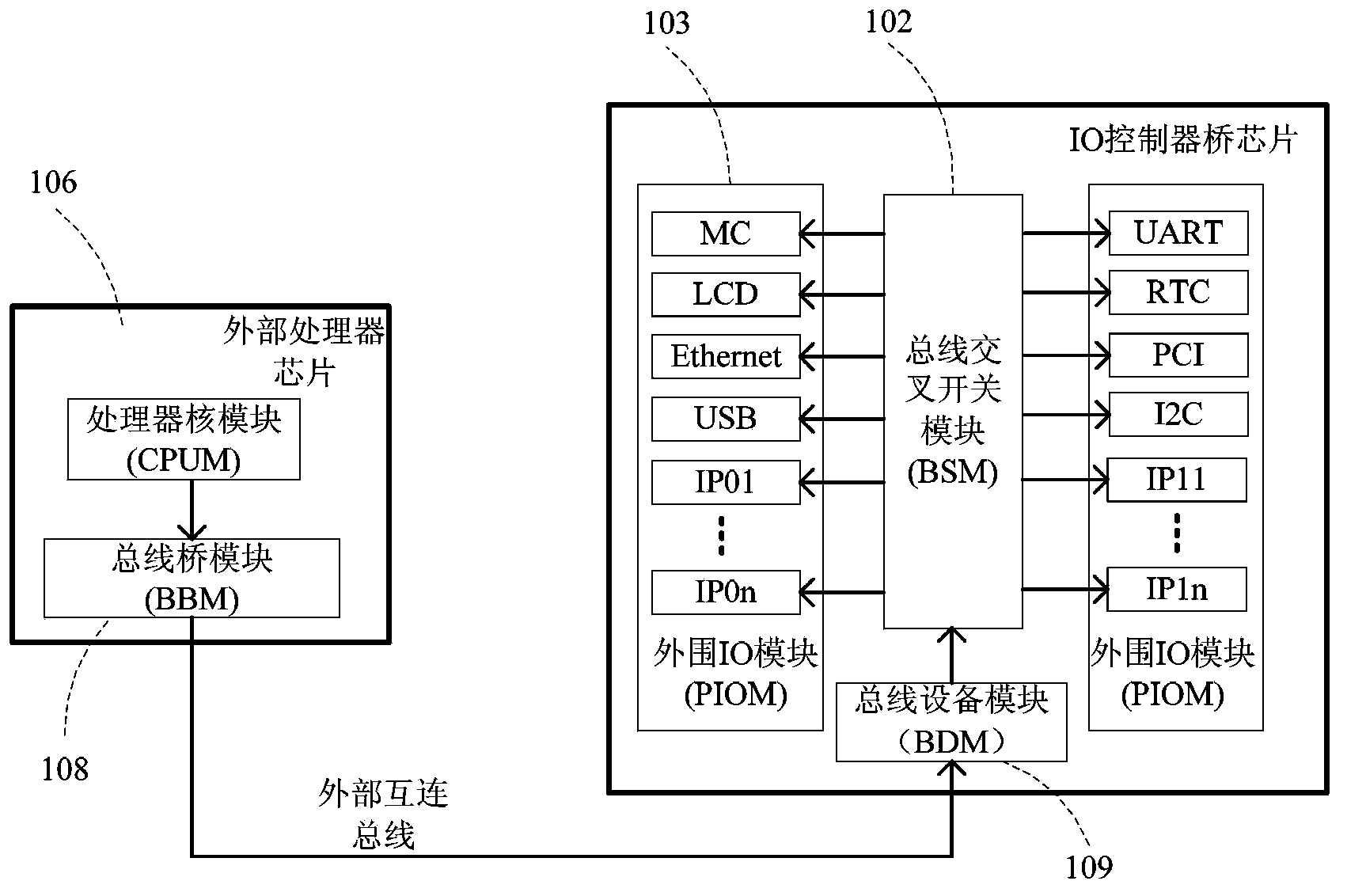

[0044] The multi-mode single SOC chip disclosed by the present invention includes a processor core module (CPUM), a mode control module (MCM), a function enabling module (FEM), a bus crossbar switch module (BSM), a pin control module (PCM), External Interconnect Bus Module (EIBM), Peripheral IO Module (PIOM), Auxiliary Function Module (AFM).

[0045] in,

[0046] 1. Processor core module (CPUM): used to interpret instructions and process data.

[0047] The CPUM of the chip is the computing and control core of the entire chip. Generally, the CPU is composed of an arithmetic unit, a controller, registers, and a bus that realizes the data, control, and status of their connections.

[0048] 2. Mode control module (MCM): used to control the working mode of the chip.

[0049] During the power-on reset period of the chip, the MCM sends control signals to the function enable module, the bus crossbar switch module, the pin control module, and the external interconnection bus module a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More