Design for testability circuit and method for full digital switched capacitor sigma-delta modulator

A technology for switching capacitors and designing circuits, applied in analog/digital conversion calibration/testing, delta modulation, instruments, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

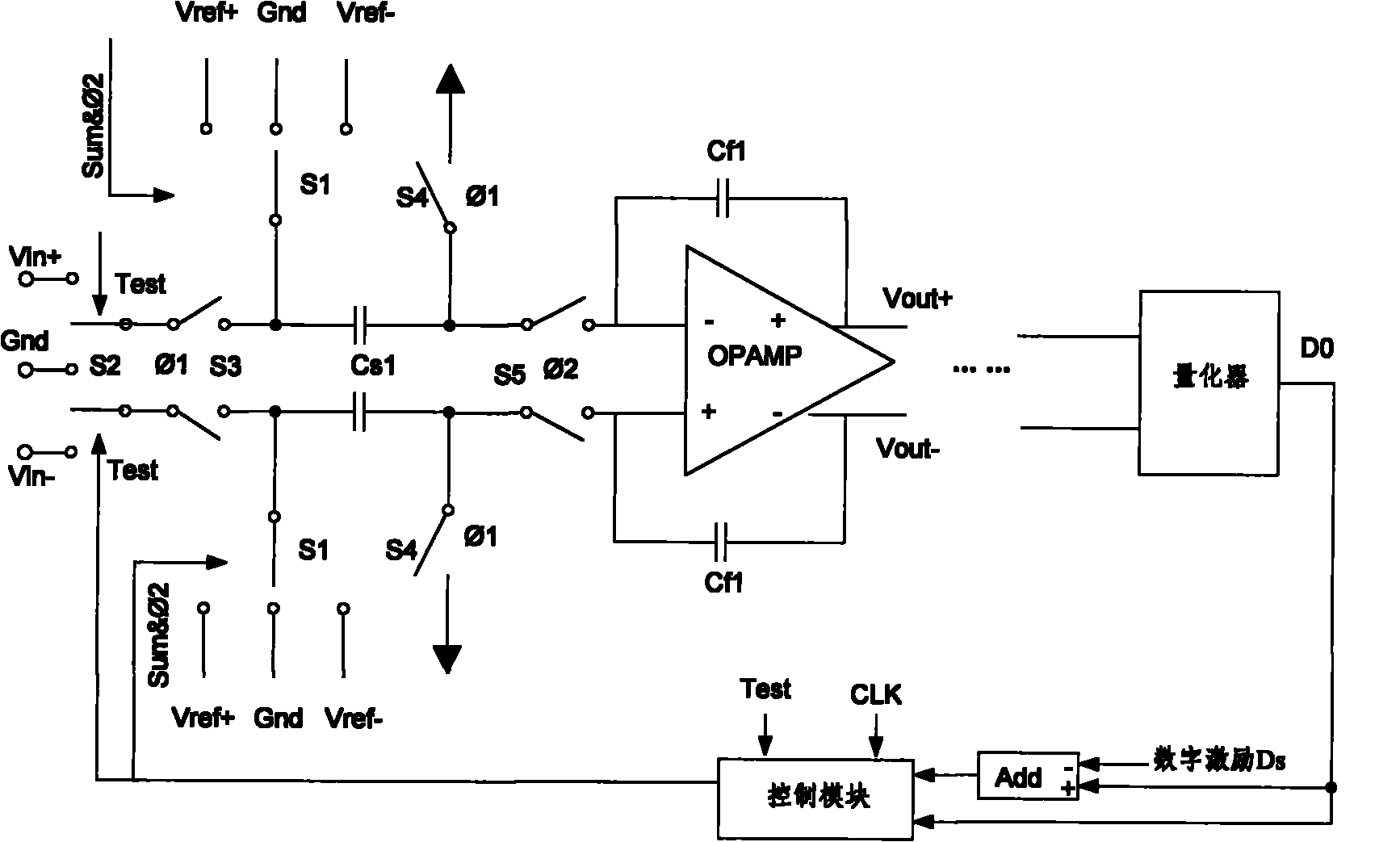

Embodiment 1

[0045] The circuit feature of the common capacitor mode is that the input sampling capacitor and the DAC feedback capacitor are the same capacitor. The modified circuit using the DFT design of the present invention is as follows: figure 1 shown. The original first-stage integrator includes four groups of switches S1, S3, S4, and S5, capacitors Cs1, Cf1, and an operational amplifier OPAMP. The original integrator used a differential input structure, including Vin+ and Vin-; differential output, including Vout+ and Vout-. The original reference levels are Vref+ and Vref-. and It is a two-phase non-overlapping clock. The DFT method provided by the present invention modifies the first-stage integrator, and other integrator structures and operation timing remain unchanged. The modified first-stage integrator adds a switch S2, the switch S1 is modified from a two-way switch to a three-way switch, and a GND input terminal and a GND reference voltage are added. At the same tim...

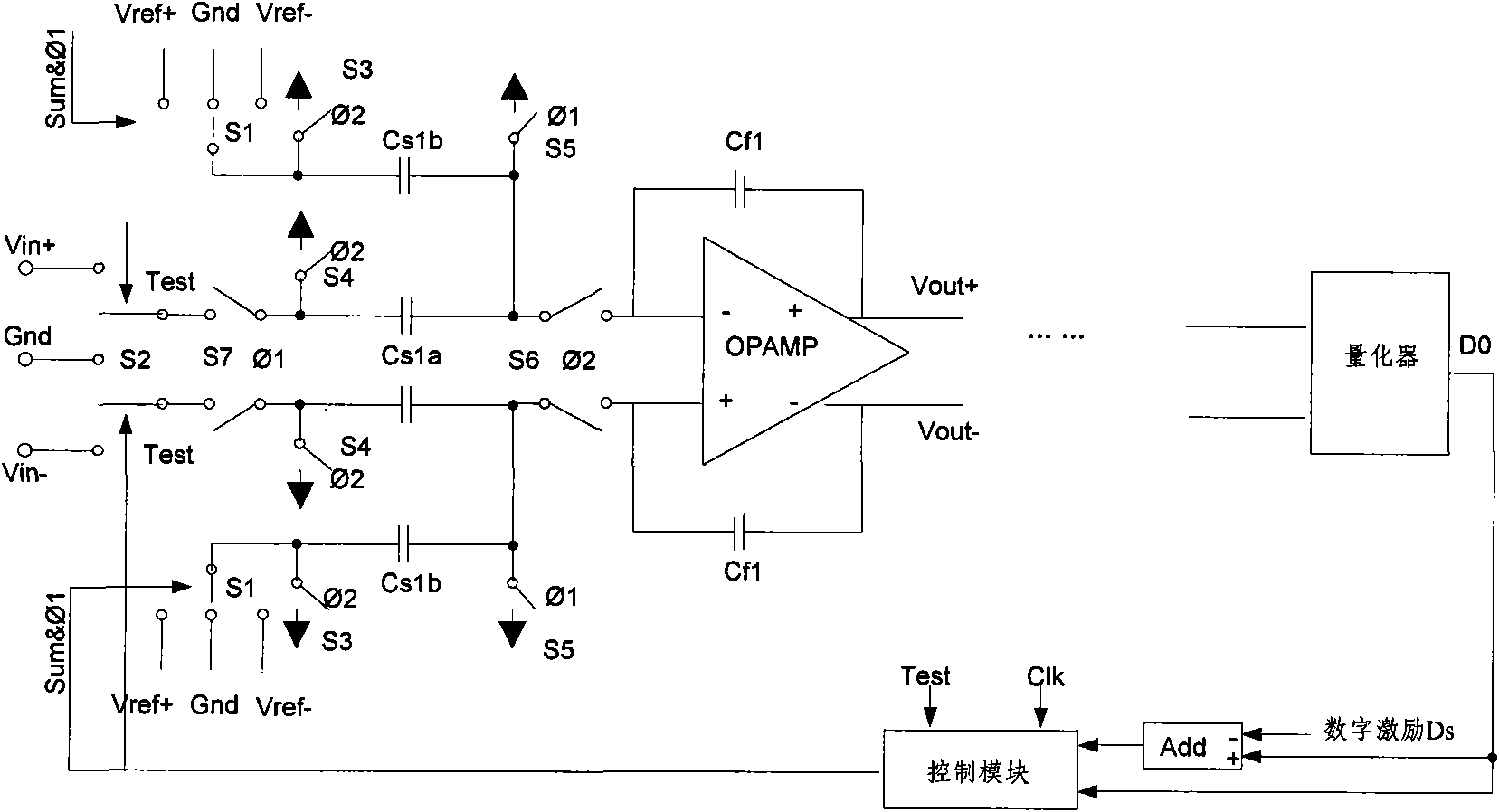

Embodiment 2

[0047] The circuit feature of the dual-capacitor mode is that the input capacitor and the DAC feedback capacitor are two capacitors. The modified circuit using the DFT design of the present invention is as follows: figure 2 shown. The original first-stage integrator includes six groups of switches S1, S3, S4, S5, S6, and S7, capacitors Cs1a, Cs1b, Cf1, and an operational amplifier OPAMP. The original integrator used a differential input structure, including Vin+ and Vin-; differential output, including Vout+ and Vout-. The original reference levels are Vref+ and Vref-. and It is a two-phase non-overlapping clock. The DFT method provided by the present invention modifies the first-stage integrator, and keeps other integrator structures and operation sequences unchanged. The modified first-stage integrator adds a switch S2, the switch S1 is modified from a two-way switch to a three-way switch, and a GND input terminal and a GND reference voltage are added. At the same t...

Embodiment 3

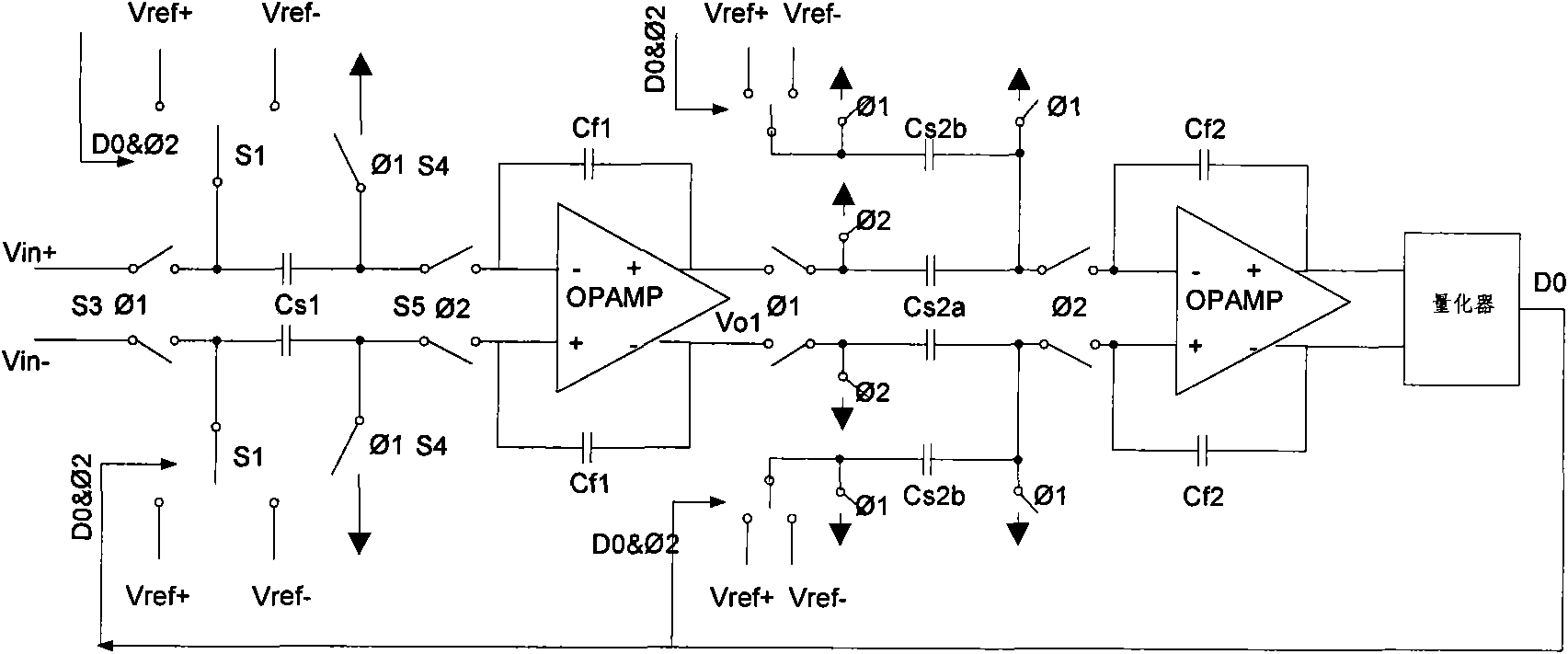

[0051] The present invention is further described below by taking a second-order common capacitance sigma-delta modulator as an example.

[0052] First design a sigma-delta modulator that meets the requirements, such as image 3 shown. The designed first-stage integrator operation timing is: In the clock phase, switches S3 and S4 are closed, and S1 and S5 are open; In the clock phase, switch S5 is closed, S3 and S4 are open, when D0=1, S1 is connected to Vref+, and when D0=-1, S1 is connected to Vref-.

[0053] Figure 4 for image 3 , using the second-order sigma-delta modulator after adding the DFT module in the present invention. relative to image 3 , the modified parts include: adding switch S2 to control the input terminal; changing switch S1 from a two-way switch to a three-way switch; adding a Gnd option to the input signal; adding a Gnd option to the reference level; adding a mode selection signal Test ; Added a control module; added a digital adder module Ad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More