Patents

Literature

743 results about "Delta modulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A delta modulation (DM or Δ-modulation) is an analog-to-digital and digital-to-analog signal conversion technique used for transmission of voice information where quality is not of primary importance. DM is the simplest form of differential pulse-code modulation (DPCM) where the difference between successive samples are encoded into n-bit data streams. In delta modulation, the transmitted data are reduced to a 1-bit data stream. Its main features are...

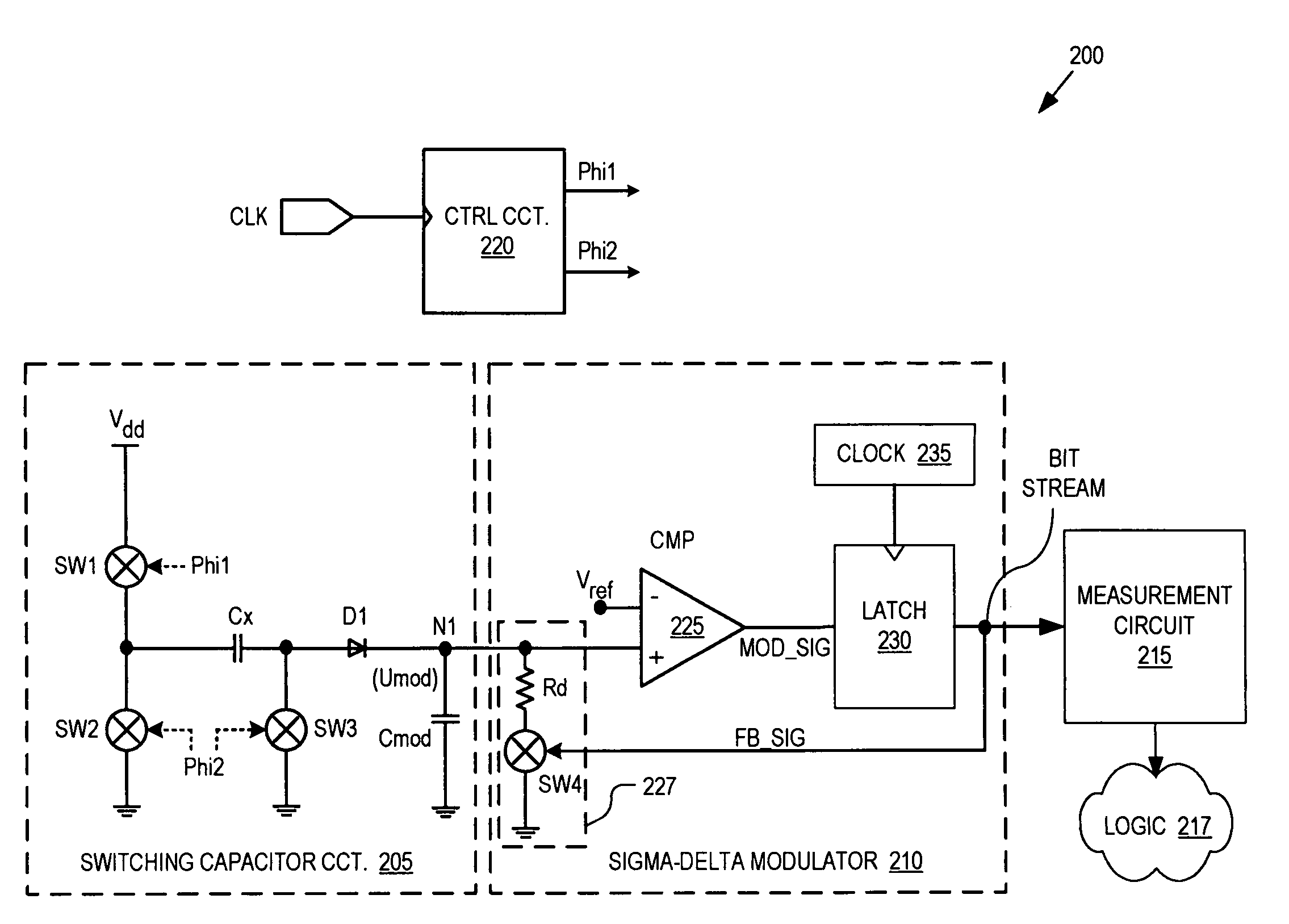

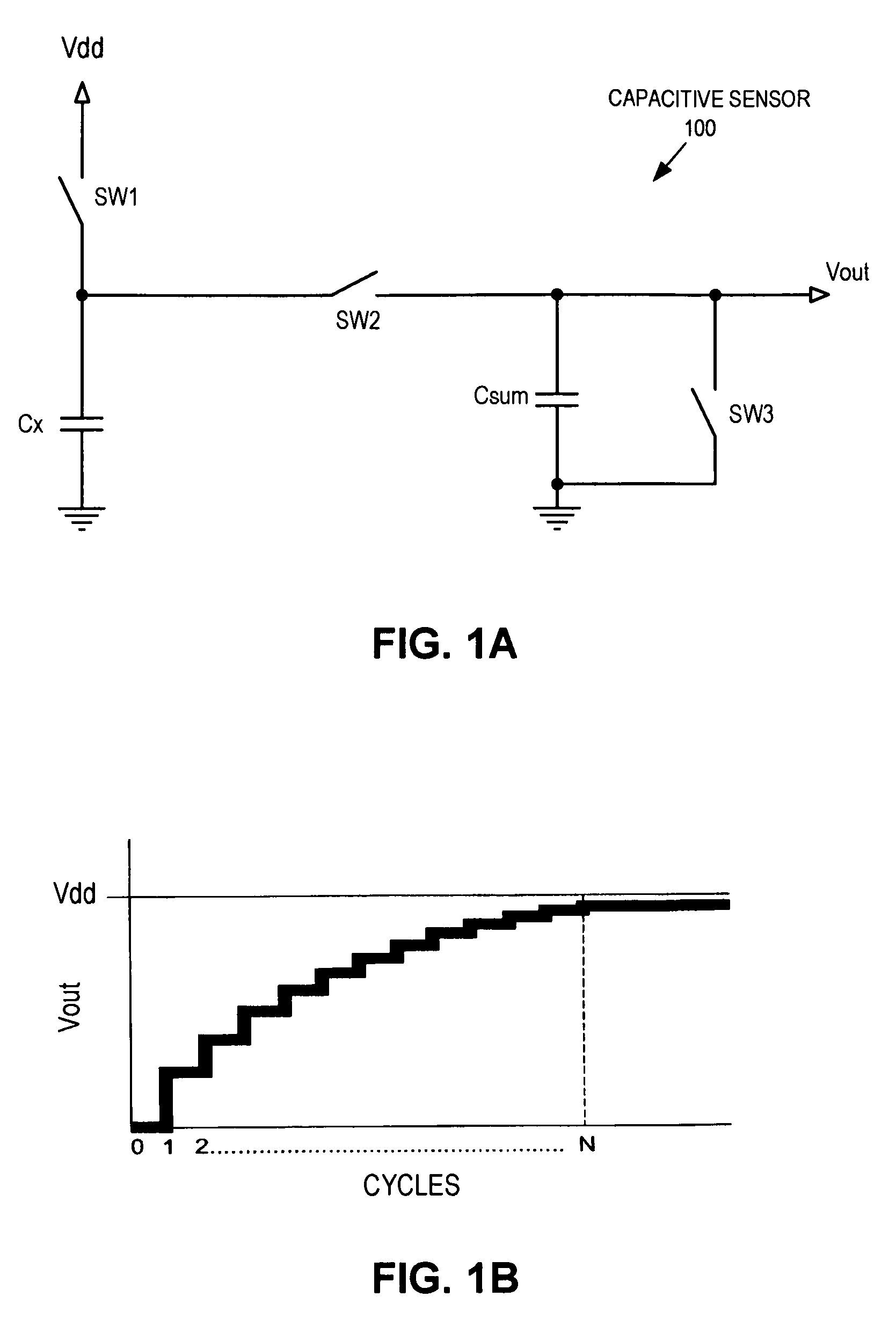

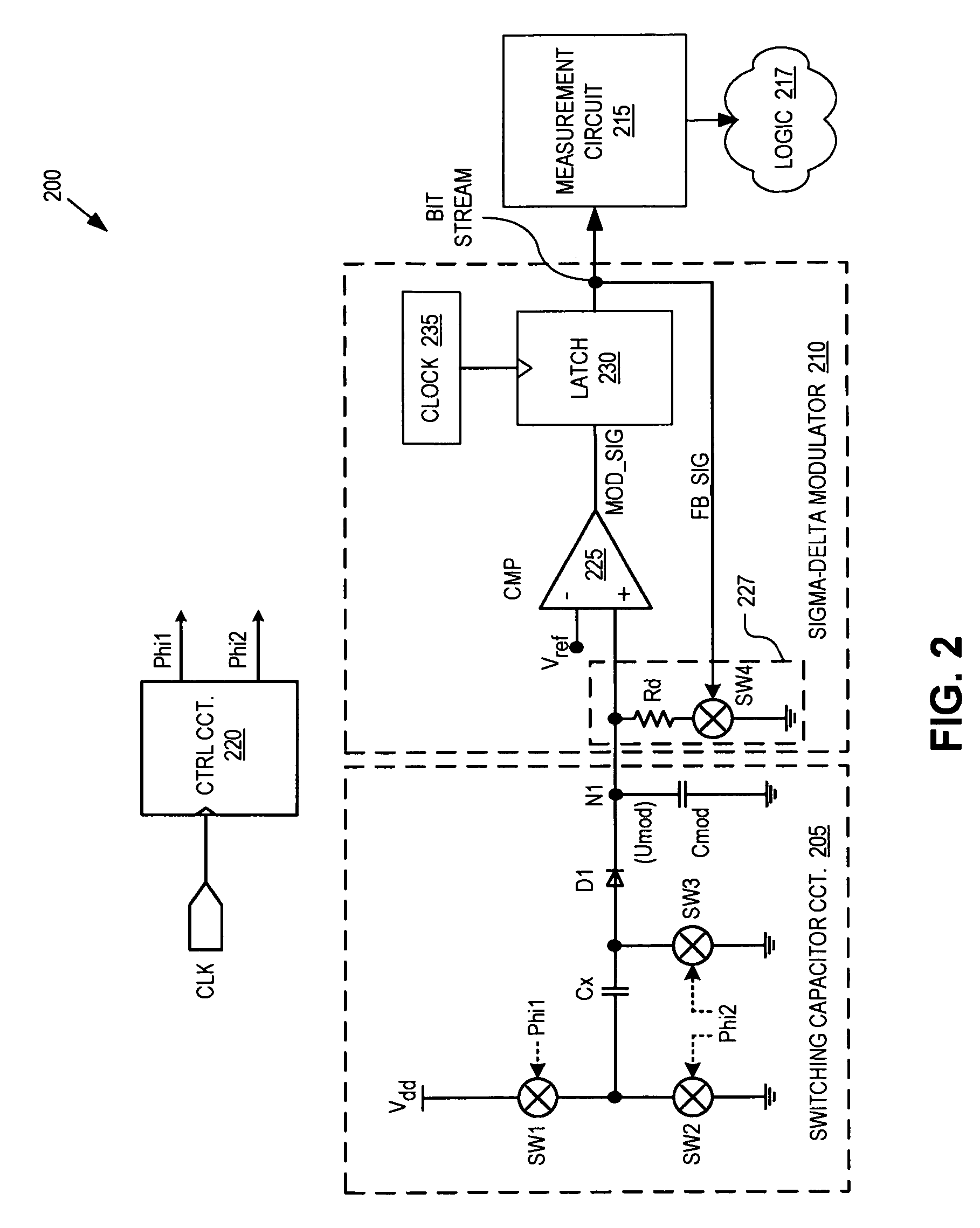

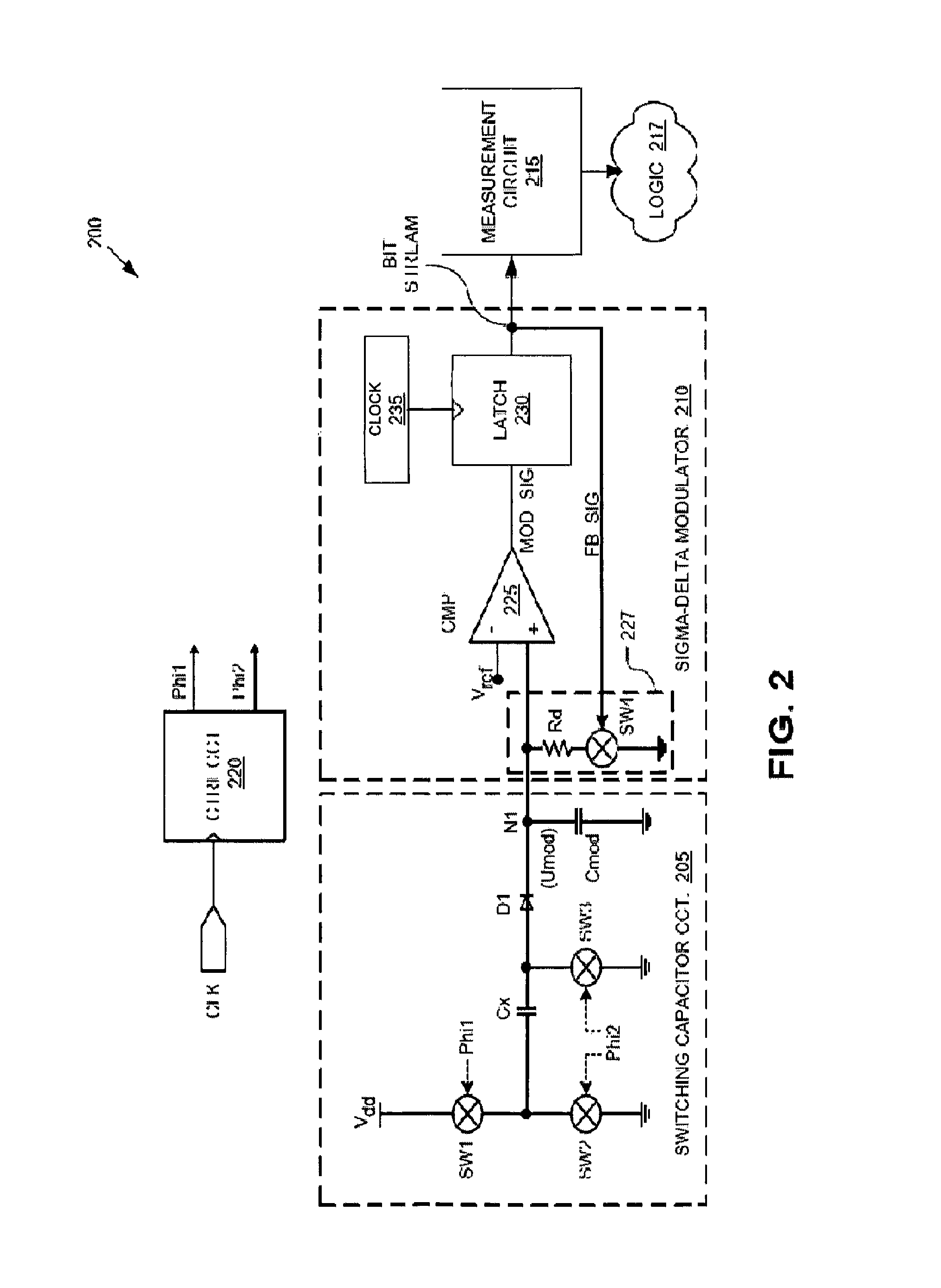

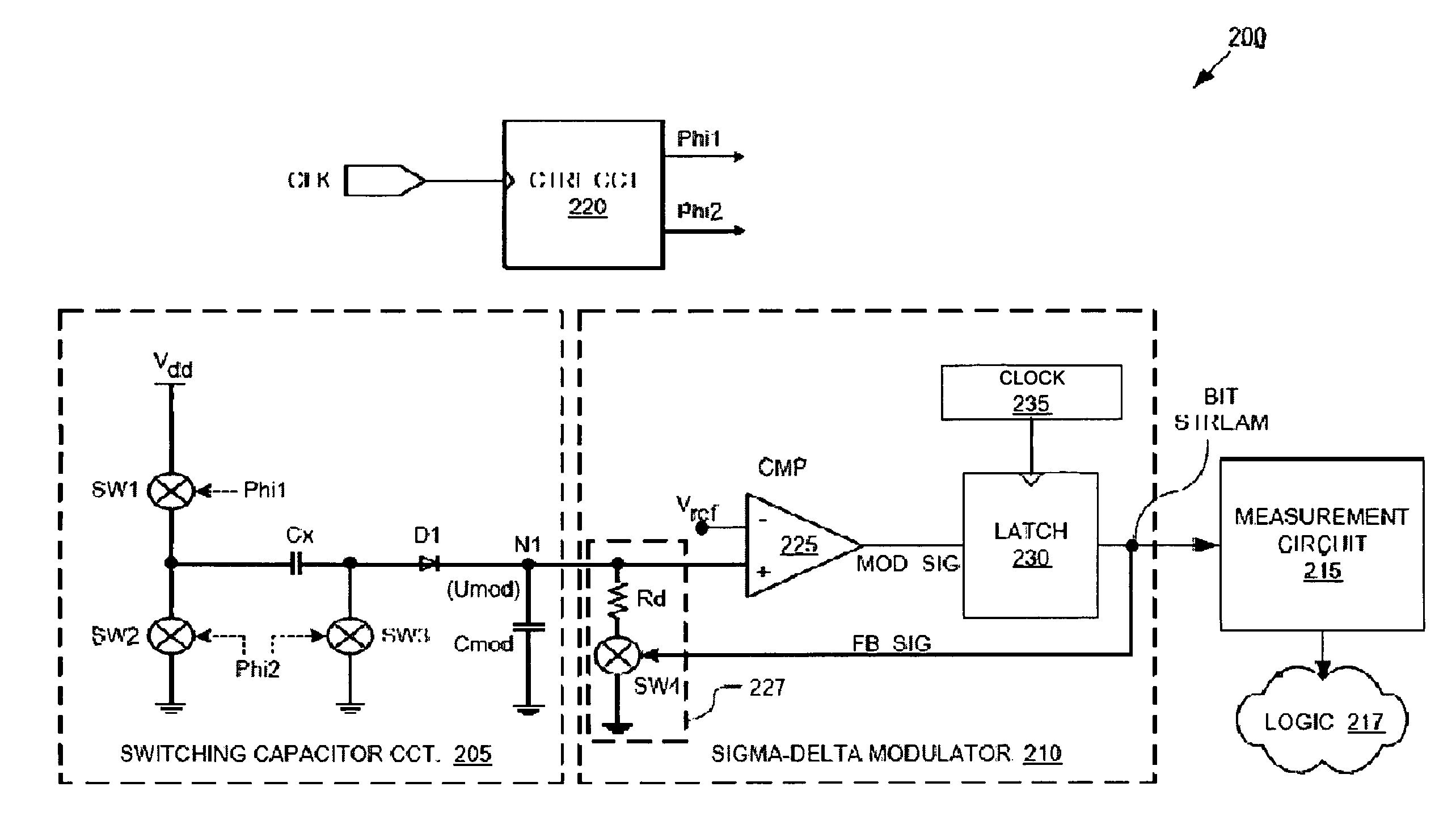

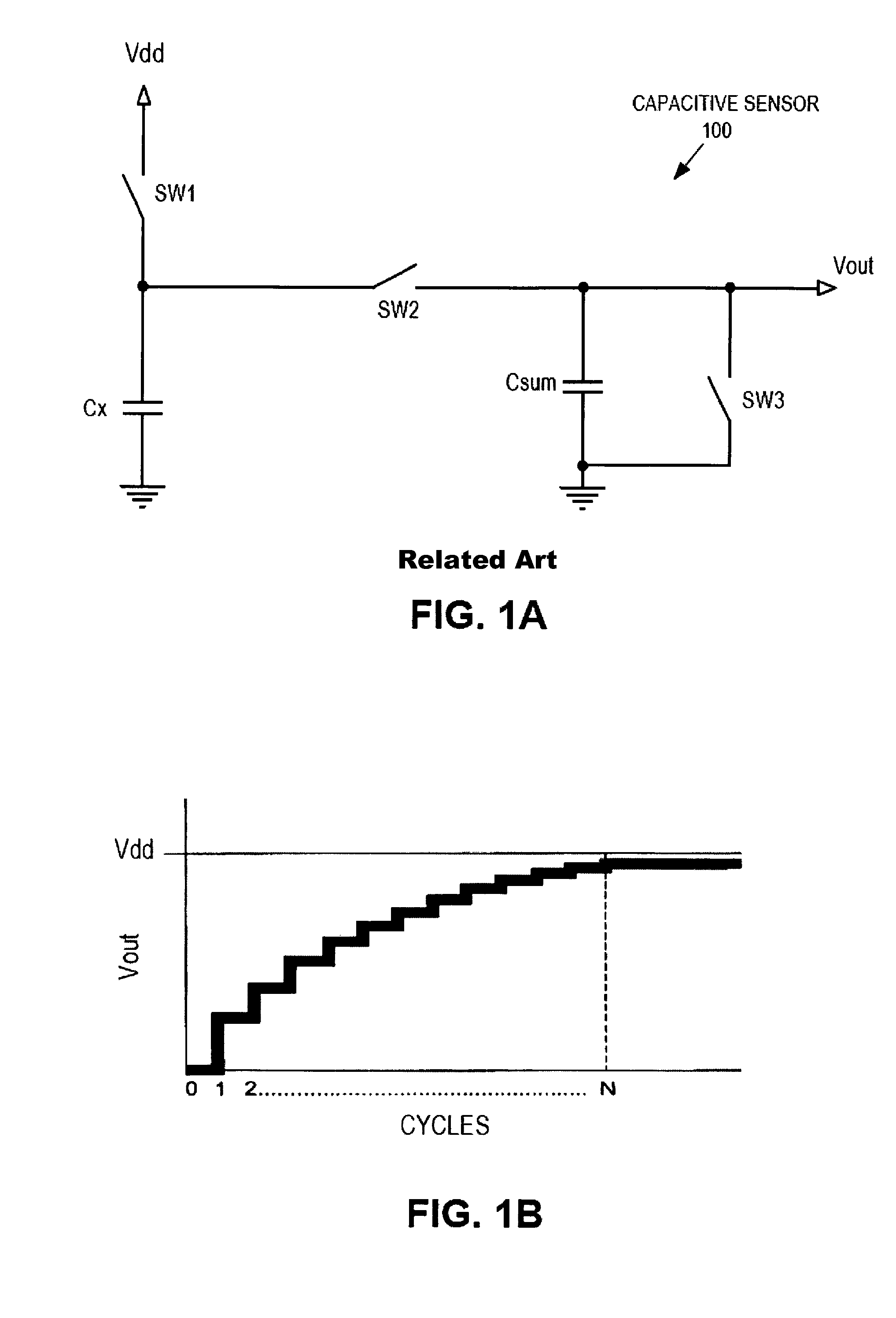

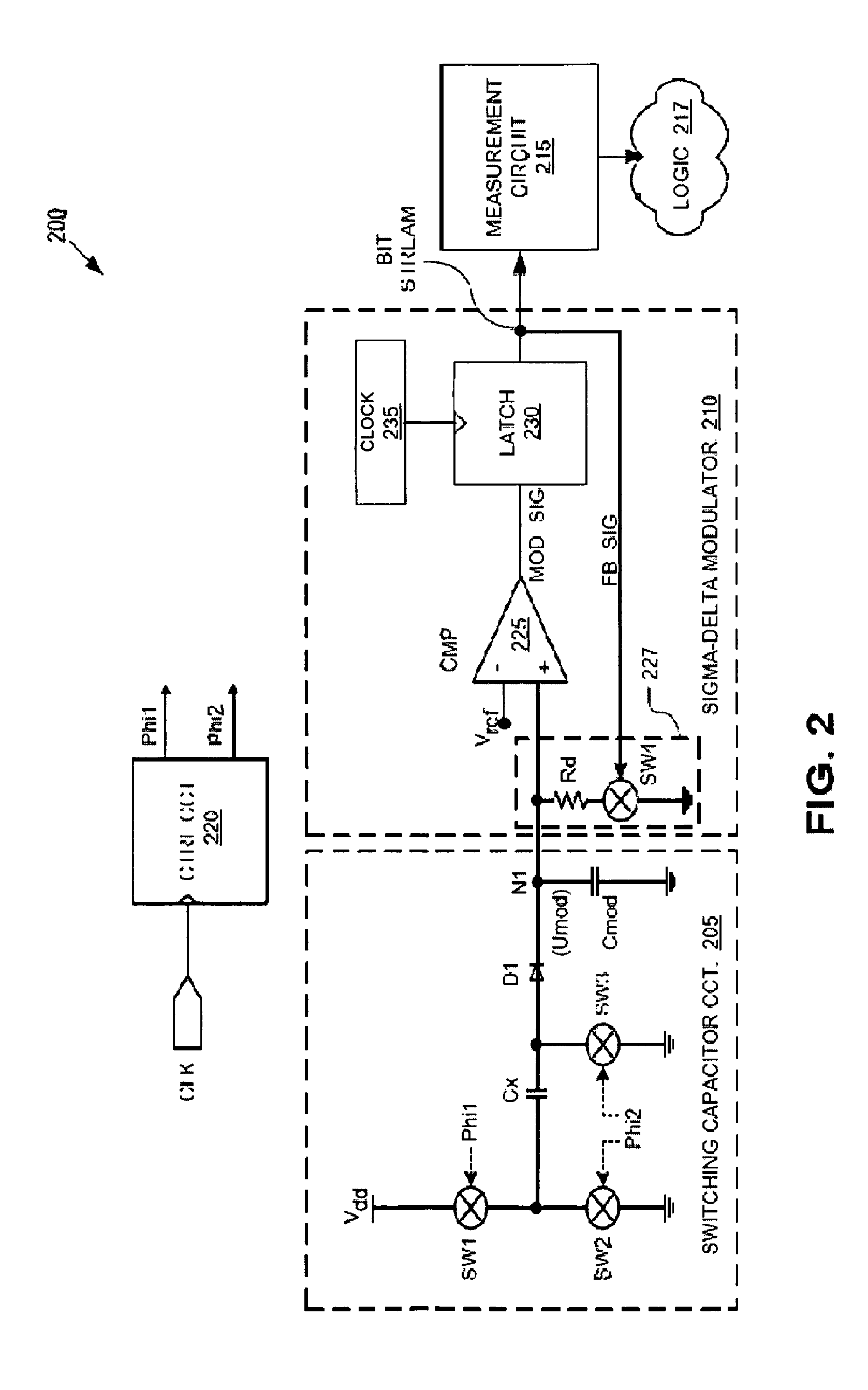

Capacitive field sensor with sigma-delta modulator

A capacitive sensor includes a switching capacitor circuit, a comparator, and a charge dissipation circuit. The switching capacitor circuit reciprocally couples a sensing capacitor in series with a modulation capacitor during a first switching phase and discharges the sensing capacitor during a second switching phase. The comparator is coupled to compare a voltage potential on the modulation capacitor to a reference and to generate a modulation signal in response. The charge dissipation circuit is coupled to the modulation capacitor to selectively discharge the modulation capacitor in response to the modulation signal.

Owner:CYPRESS SEMICON CORP

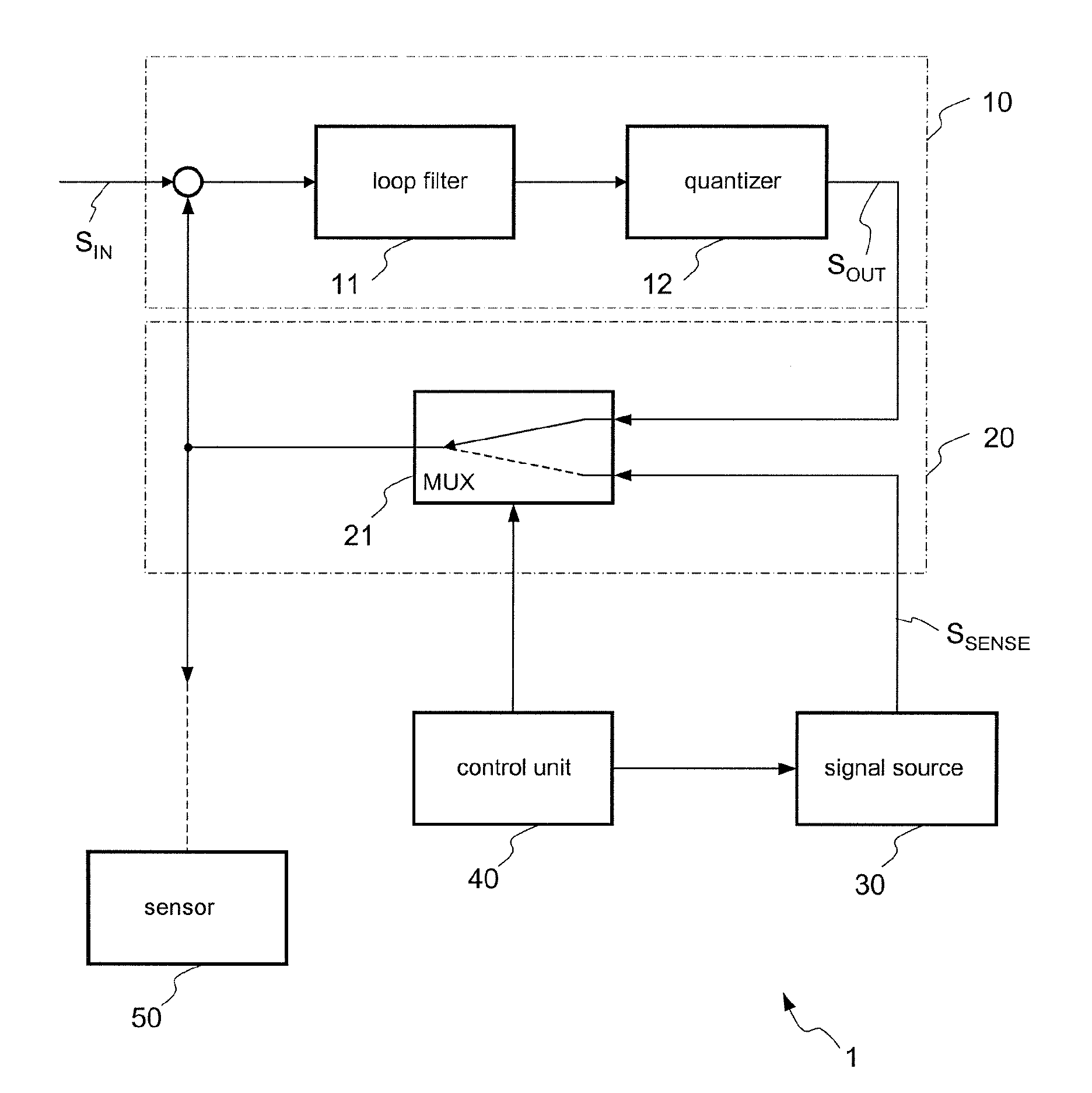

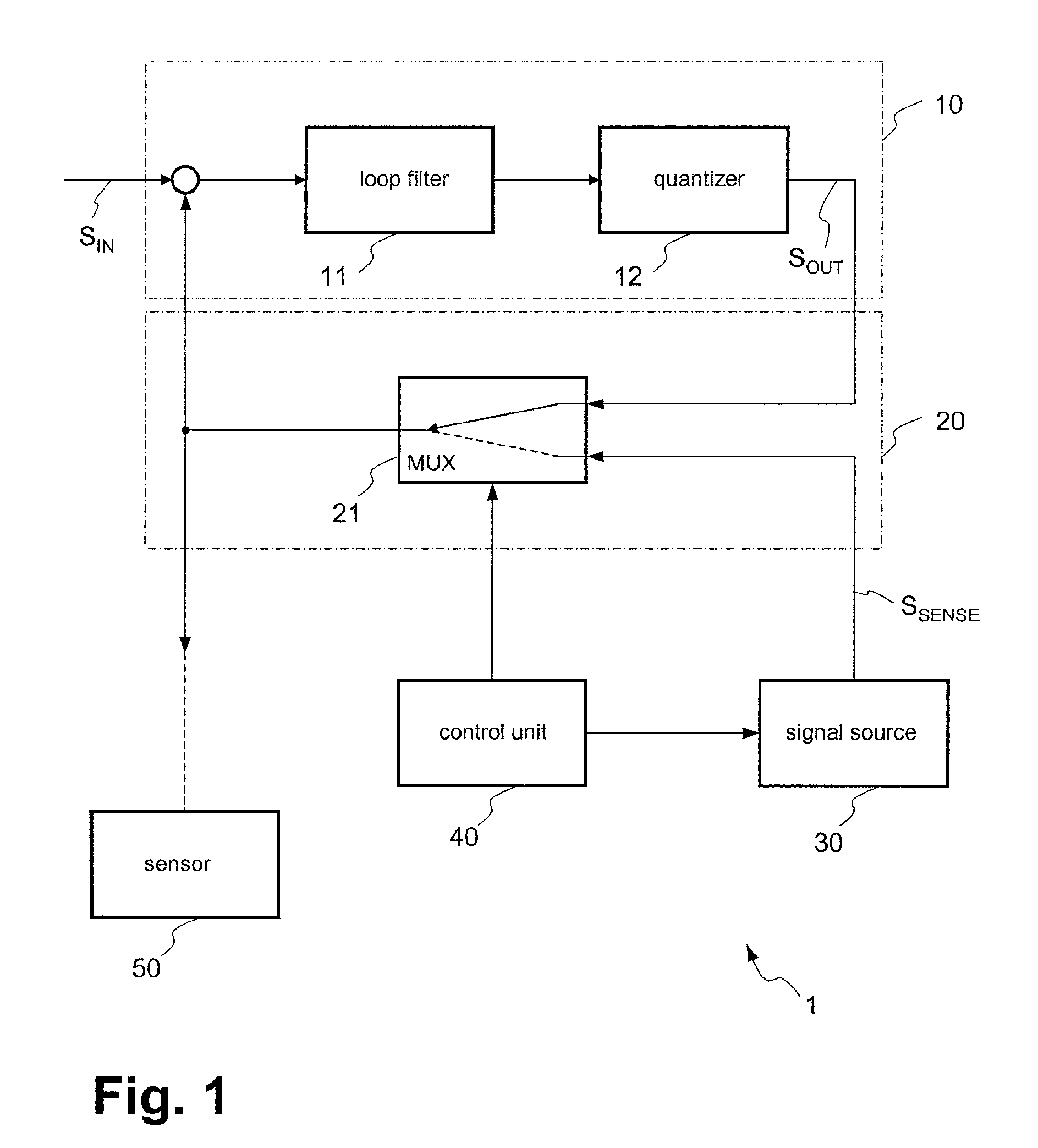

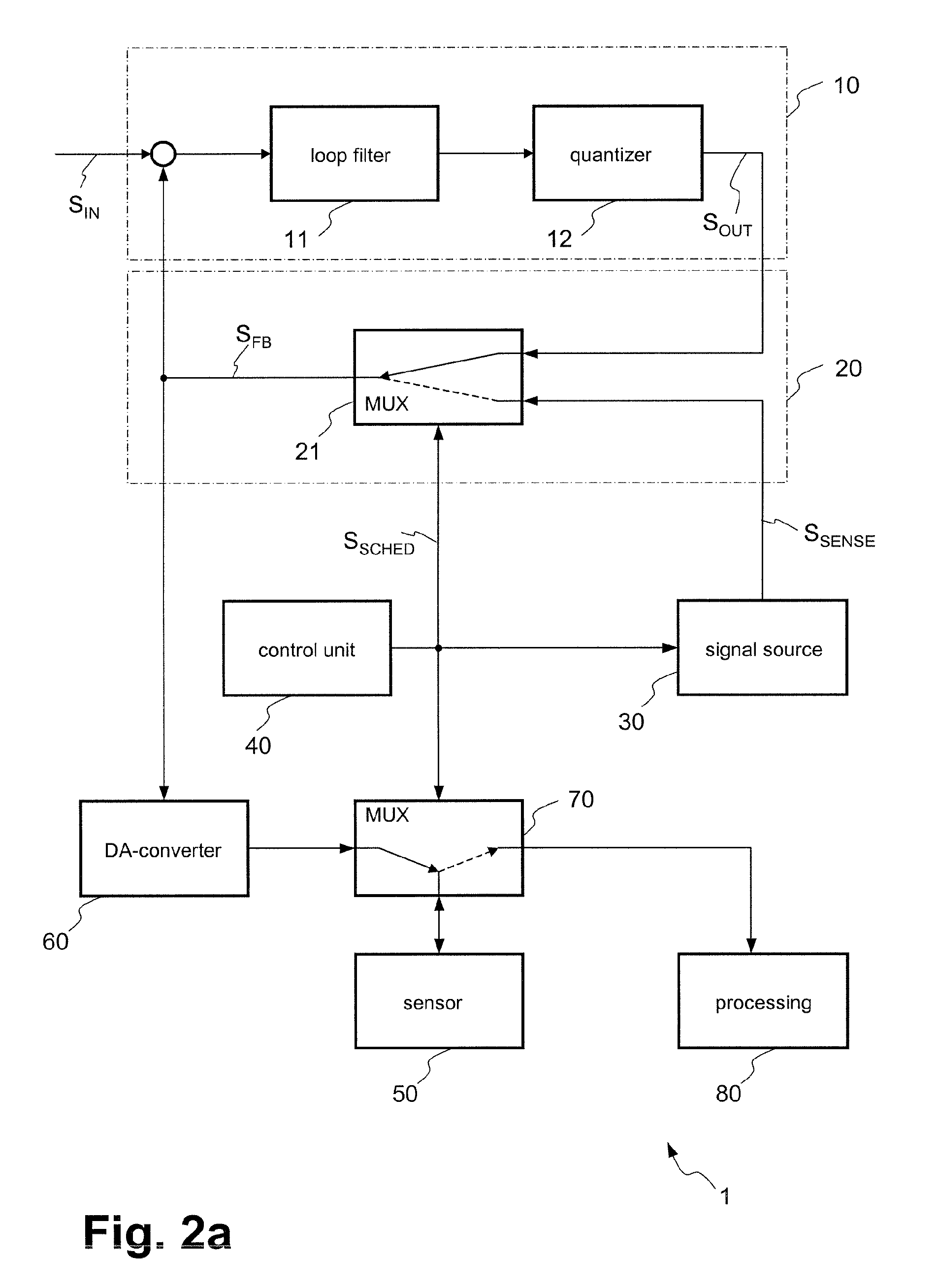

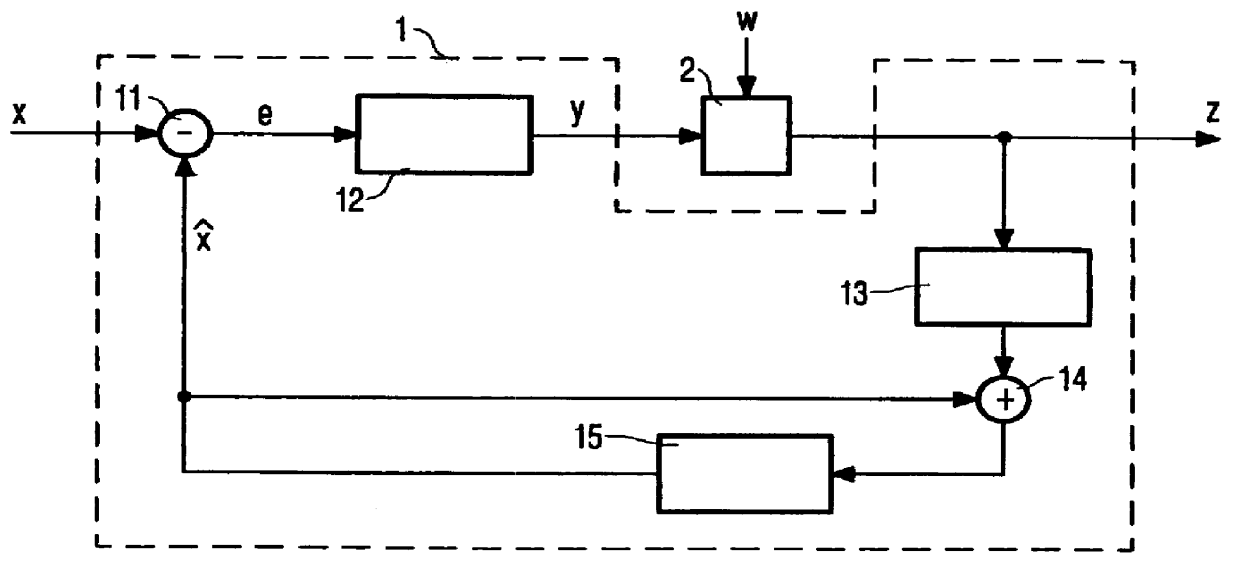

Sigma-delta modulator for operating sensors

InactiveUS7528755B2Electric signal transmission systemsAcceleration measurement using interia forcesLoop filterControl signal

A sigma-delta modulator can be used for actuating a sensor element. The sigma delta modulator includes: a forward branch to which an input signal is fed at an input and which includes a loop filter, a quantizer and an output for providing an output signal. A feedback branch is configured to feed back the output signal of the forward branch at least temporarily to the input of the forward branch. A signal source is configured to generate a readout signal which corresponds to the voltage profile at the sensor element during a measuring process. A control unit is configured to generate a control signal dependent on which either the output signal of the forward branch or the readout signal of the signal source is fed back to the input of the forward branch.

Owner:INFINEON TECH AG

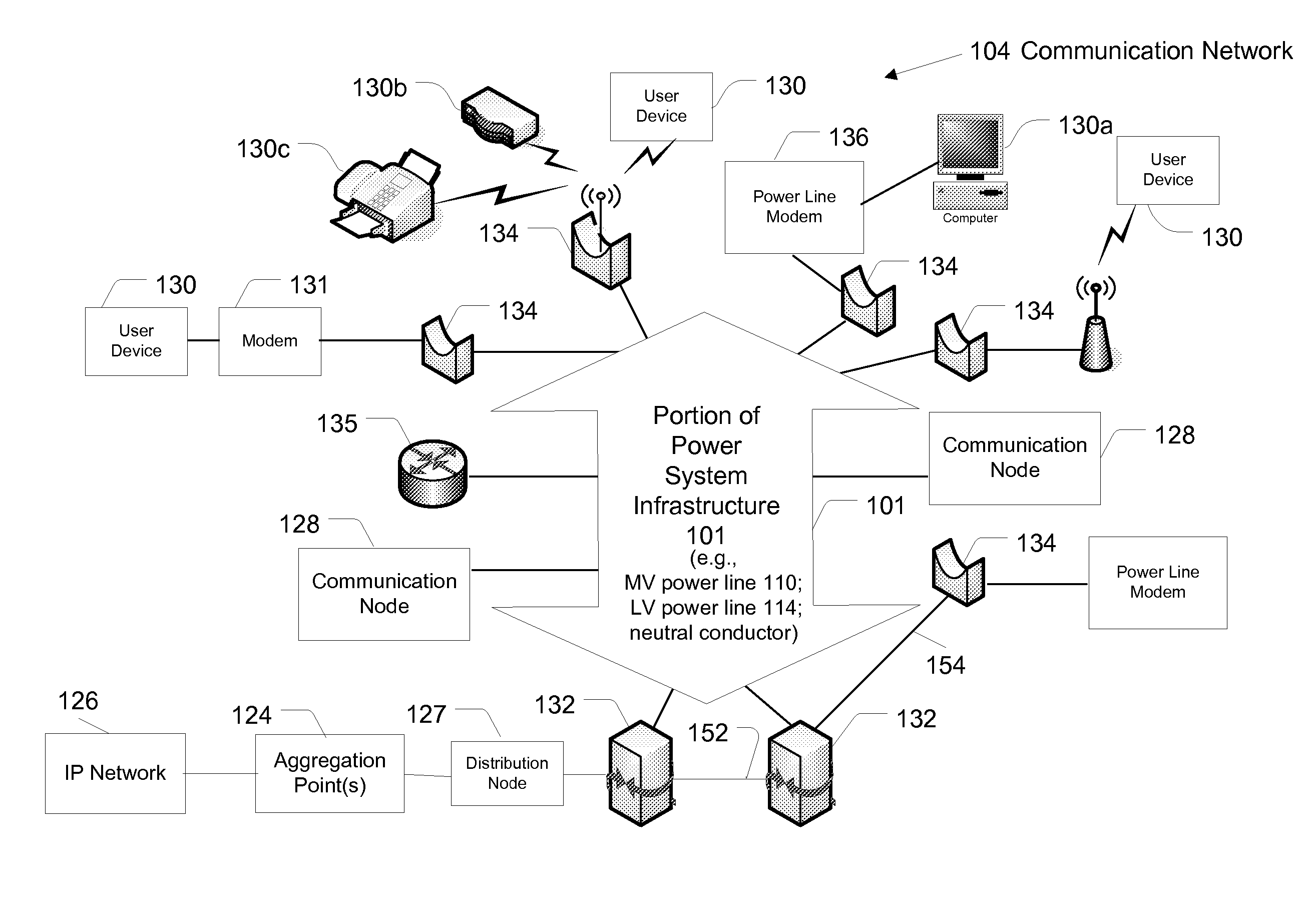

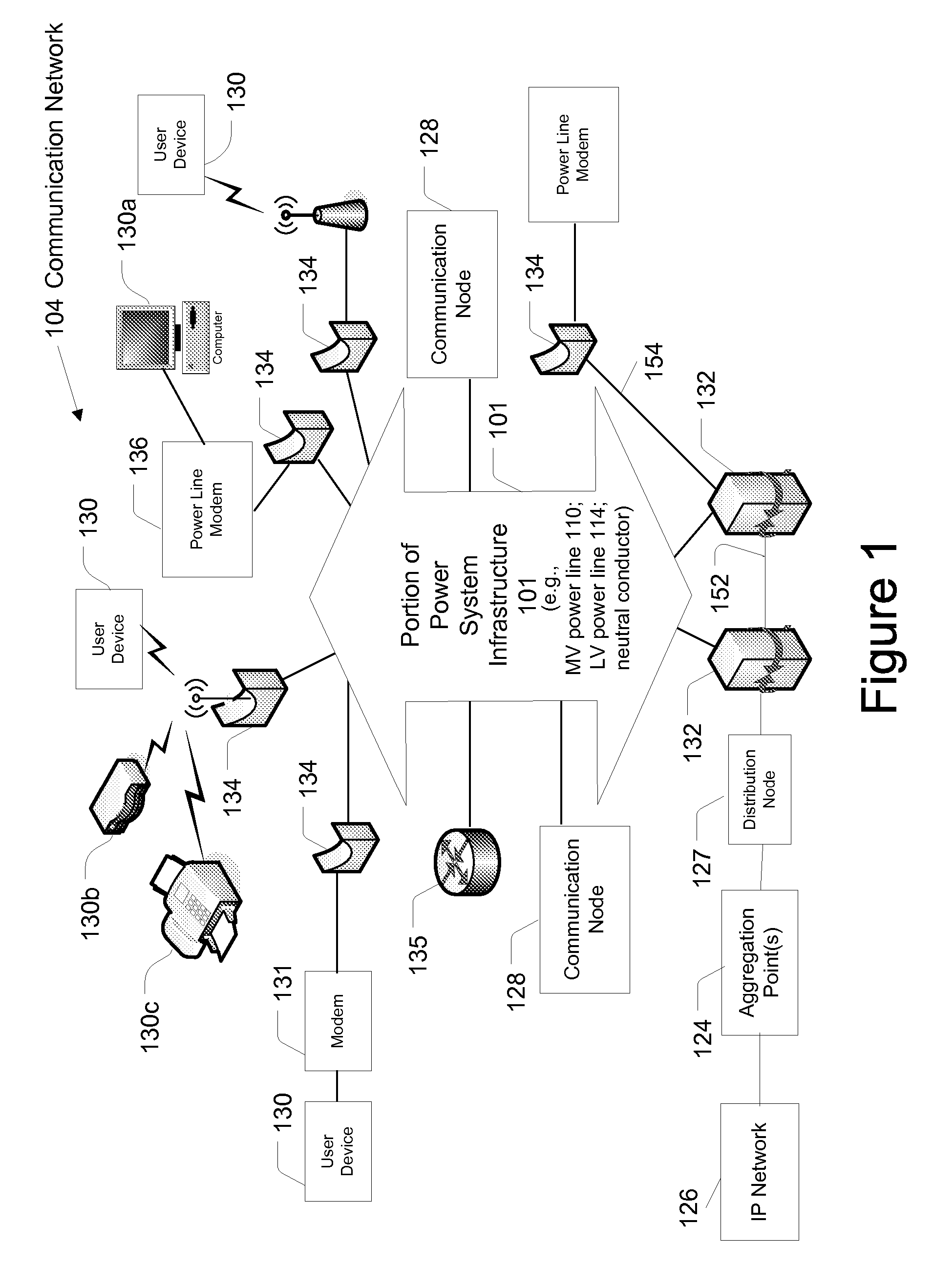

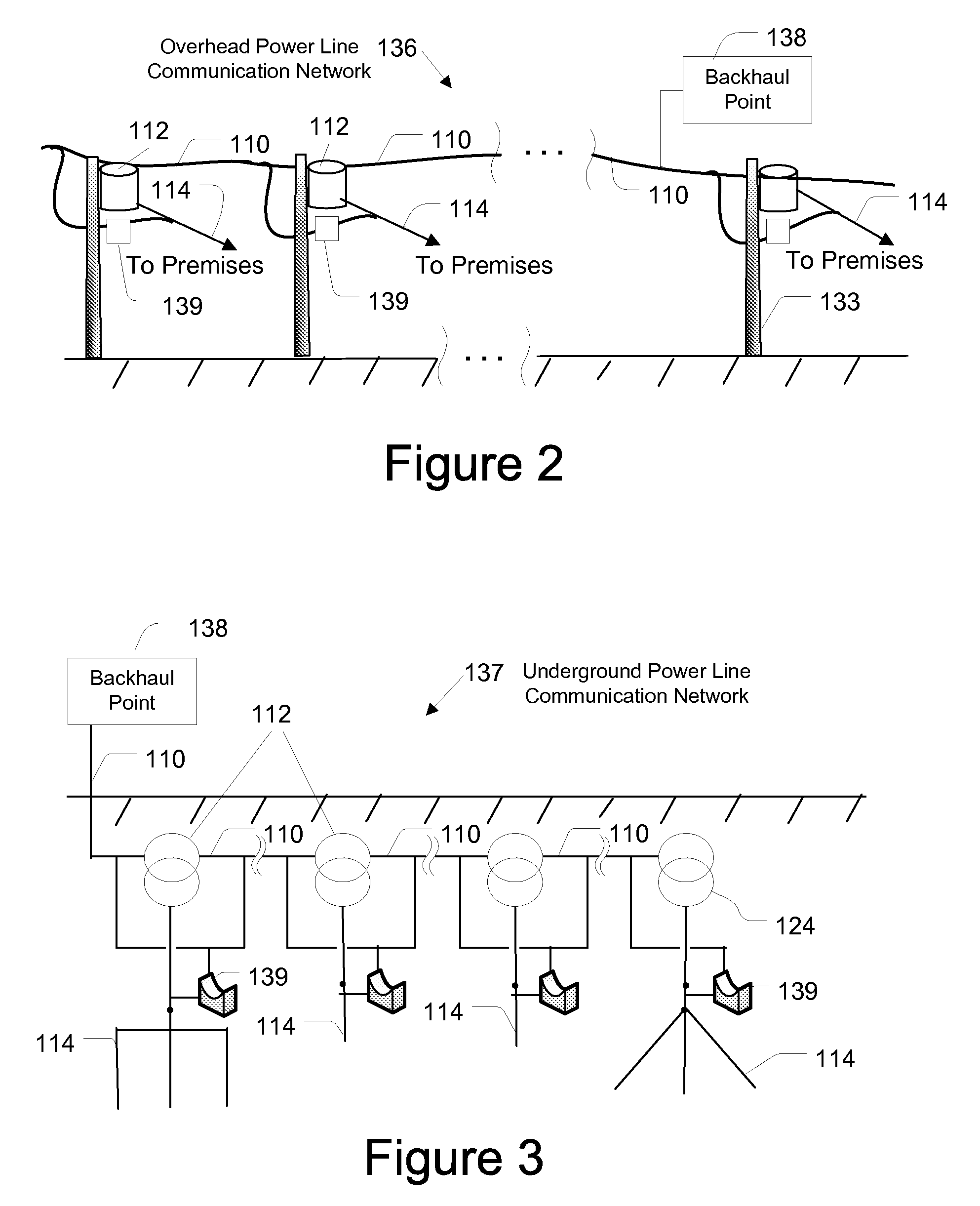

Power Line Communication Device and Method

InactiveUS20070002772A1Error preventionFrequency-division multiplex detailsModem deviceTransmitted power

A power line communication device for communicating data signals over a power line is provided. One example embodiment comprises a conditioning circuit configured to be coupled to the power line and a modem communicatively coupled to the conditioning circuitry to transmit and receive data signals over the power line via the conditioning circuitry. The modem may be configured to transmit and receive orthogonal frequency division multiplexed data signals that comprise a plurality of sub-carriers, wherein the modem is adapted to vary the transmit power for each of a plurality of subsets of the plurality of sub-carriers from substantially zero power to a plurality of increments above zero power. The modem also may be adapted to transmit and receive data signals with the transmit power for each of a plurality of subsets of the plurality of sub-carriers being different and to transmit and receive using a different modulation scheme at different sub-carriers.

Owner:CURRENT TECH

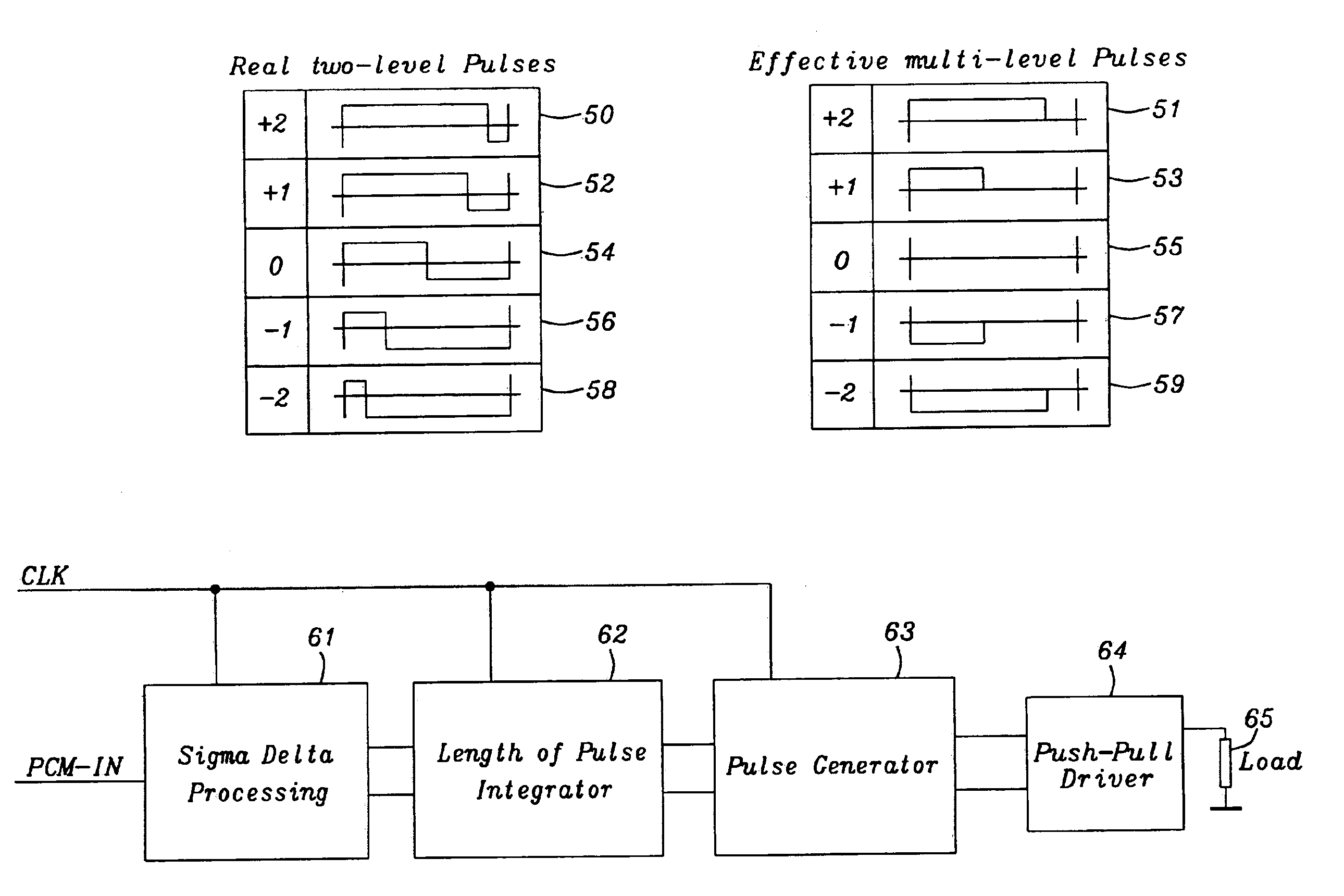

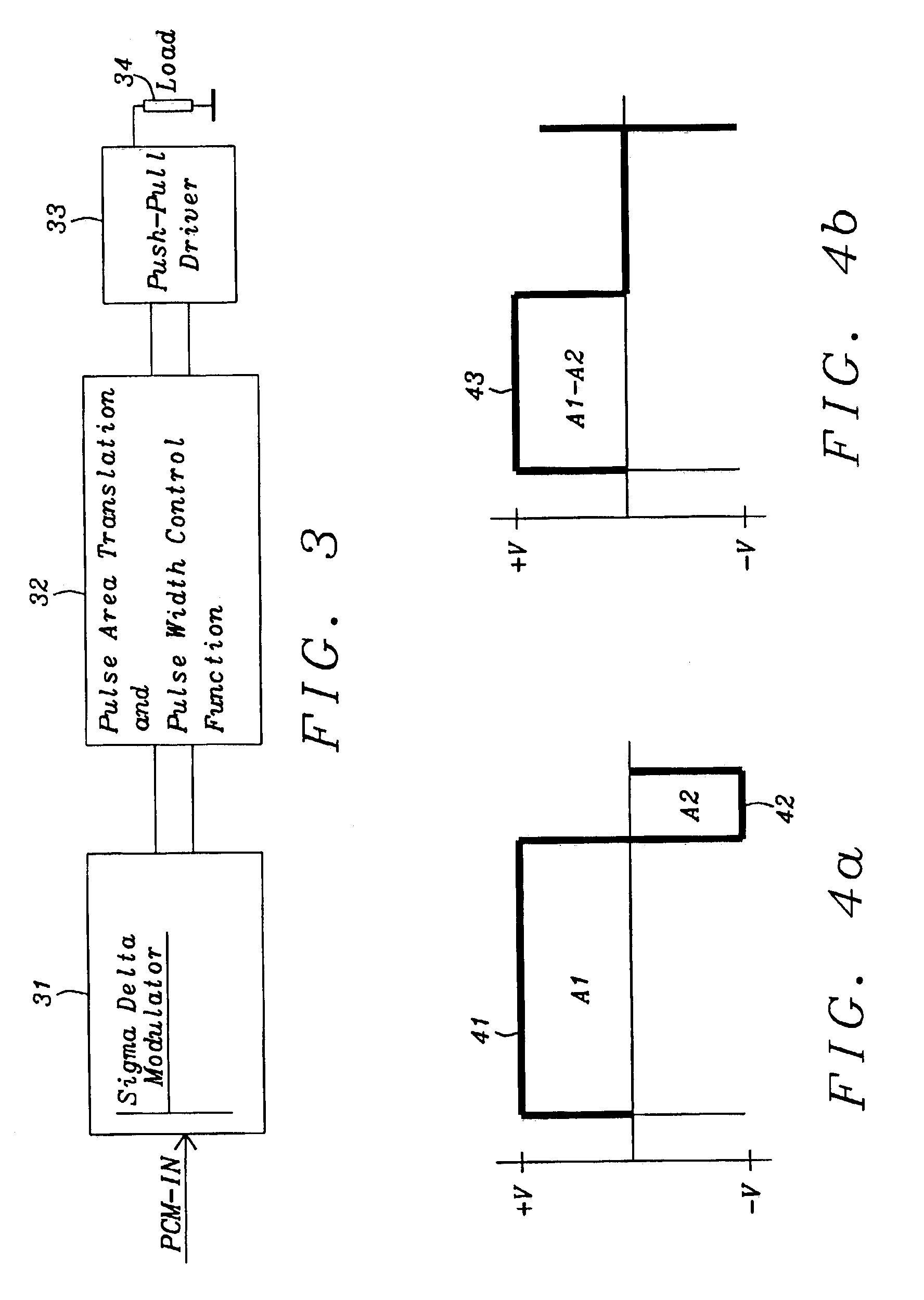

Multi-level Class-D amplifier by means of 2 physical layers

InactiveUS6842070B2Good quality output signalReduce electromagnetic interferencePush-pull amplifiersPhase-splittersSignal qualityClass-D amplifier

Introduce a pulse length control mechanism to generate virtual multi-level output pulses for a Class-D Amplifier, which has only 2 physical output levels. Typically a Sigma-Delta-Modulator converts the input signal into high frequency low bit rate. The disclosed invention adds functions to transform the SDM signal into pulses with equivalent multi-level time-voltage areas and adds a pulse-length-control mechanism to produce various output pulse patterns, where the summations of the positive and negative pulses, within one sampling period, result in time-voltage area values, corresponding to 3 or more digital levels. Thus the invention produces higher signal quality at lower sampling rates.

Owner:DIALOG SEMICONDUCTOR GMBH

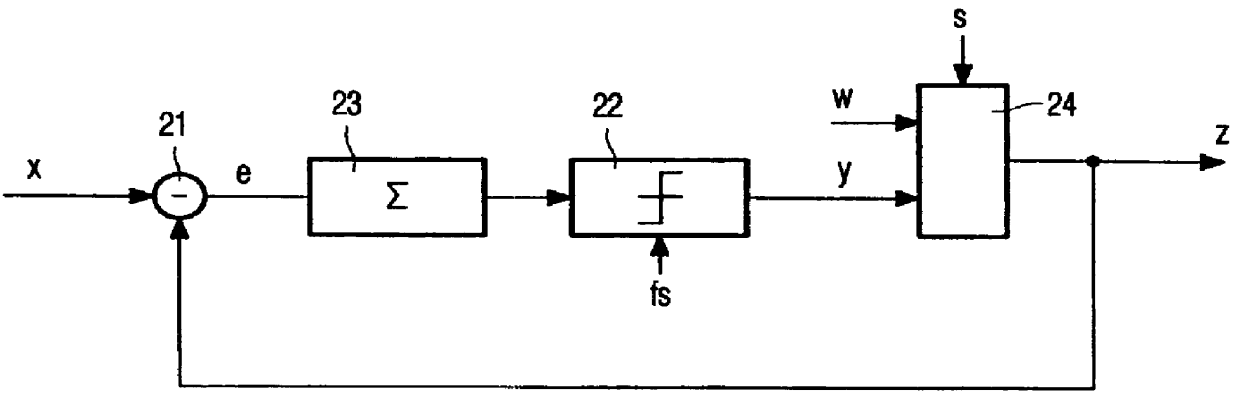

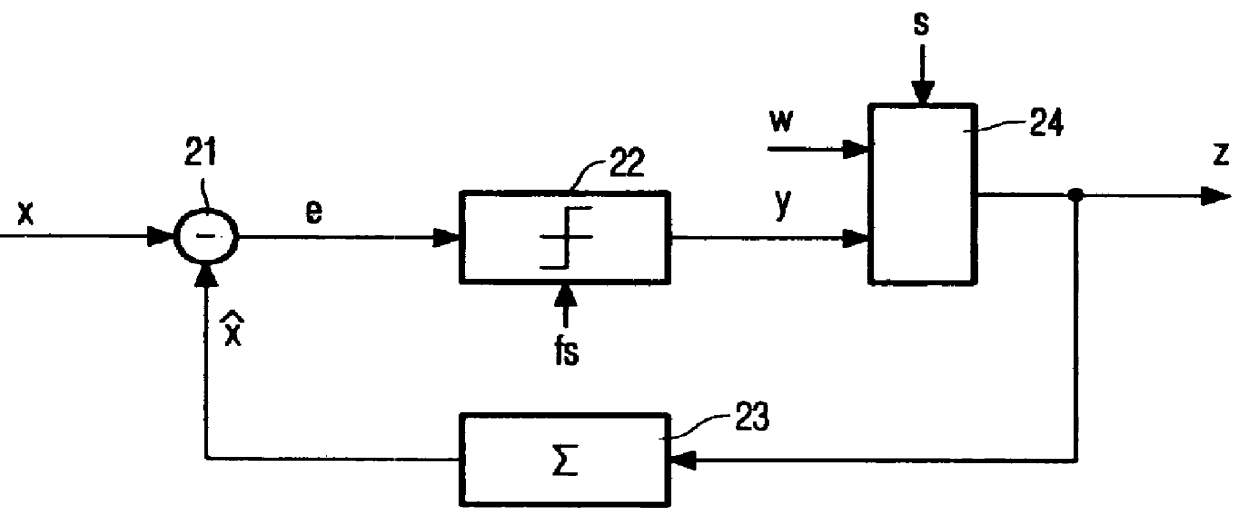

Embedding supplemental data in an encoded signal, such as audio / video watermarks

InactiveUS6157330AReplicaImprove signal-to-noise ratioAnalogue conversionRecord information storageSignal-to-noise ratio (imaging)Watermark method

Method of embedding watermarks in a signal encoded by an encoder having a feedback loop, for example, a sigma-delta modulator (21,22,23). A digital watermark pattern (w) is embedded in the signal (z) by modifying selected samples (for example, replacing every 100th bit) of the encoded signal (y) by samples of the watermark pattern. The circuit (24) for modifying the samples is located inside the loop of the encoder. The effect of watermarking is thus compensated in subsequent encoding steps and the signal-to-noise ratio is only slightly affected.

Owner:U S PHILIPS CORP

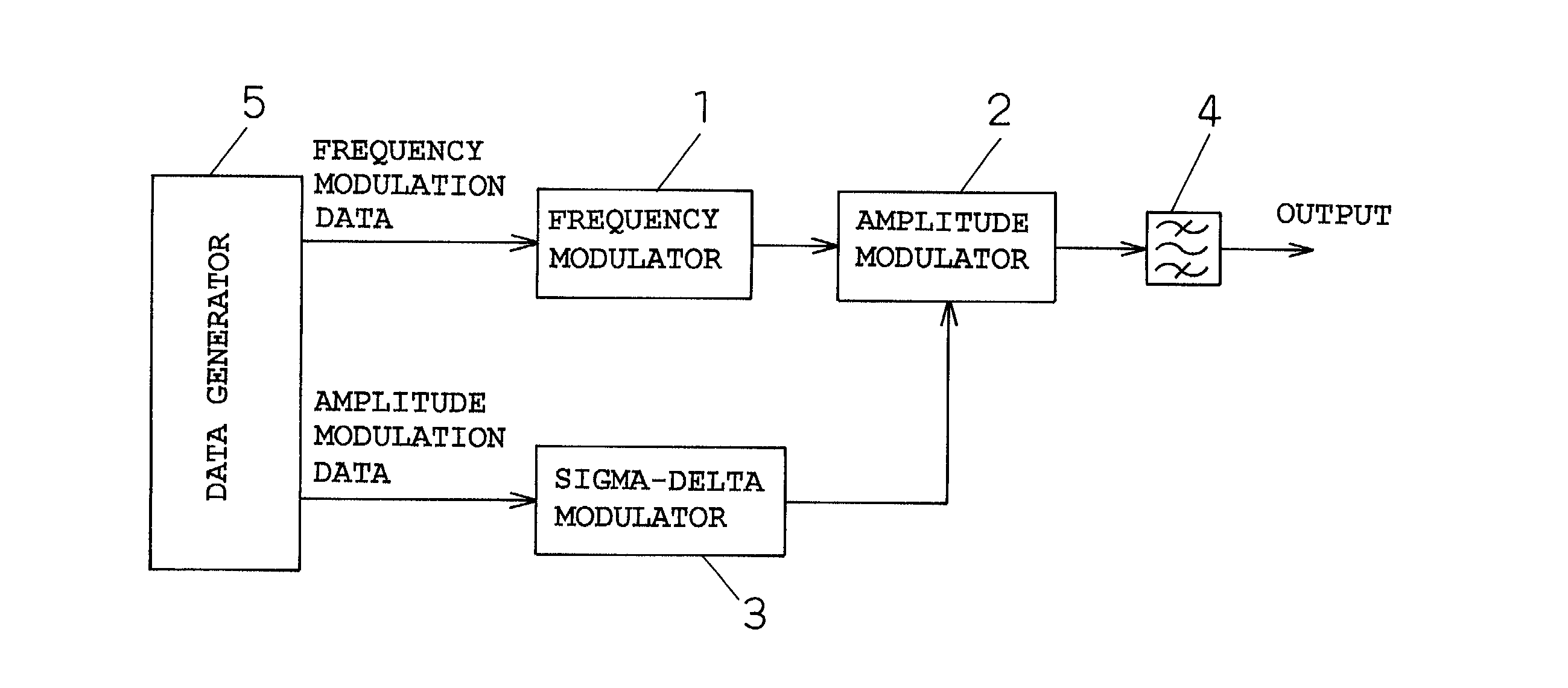

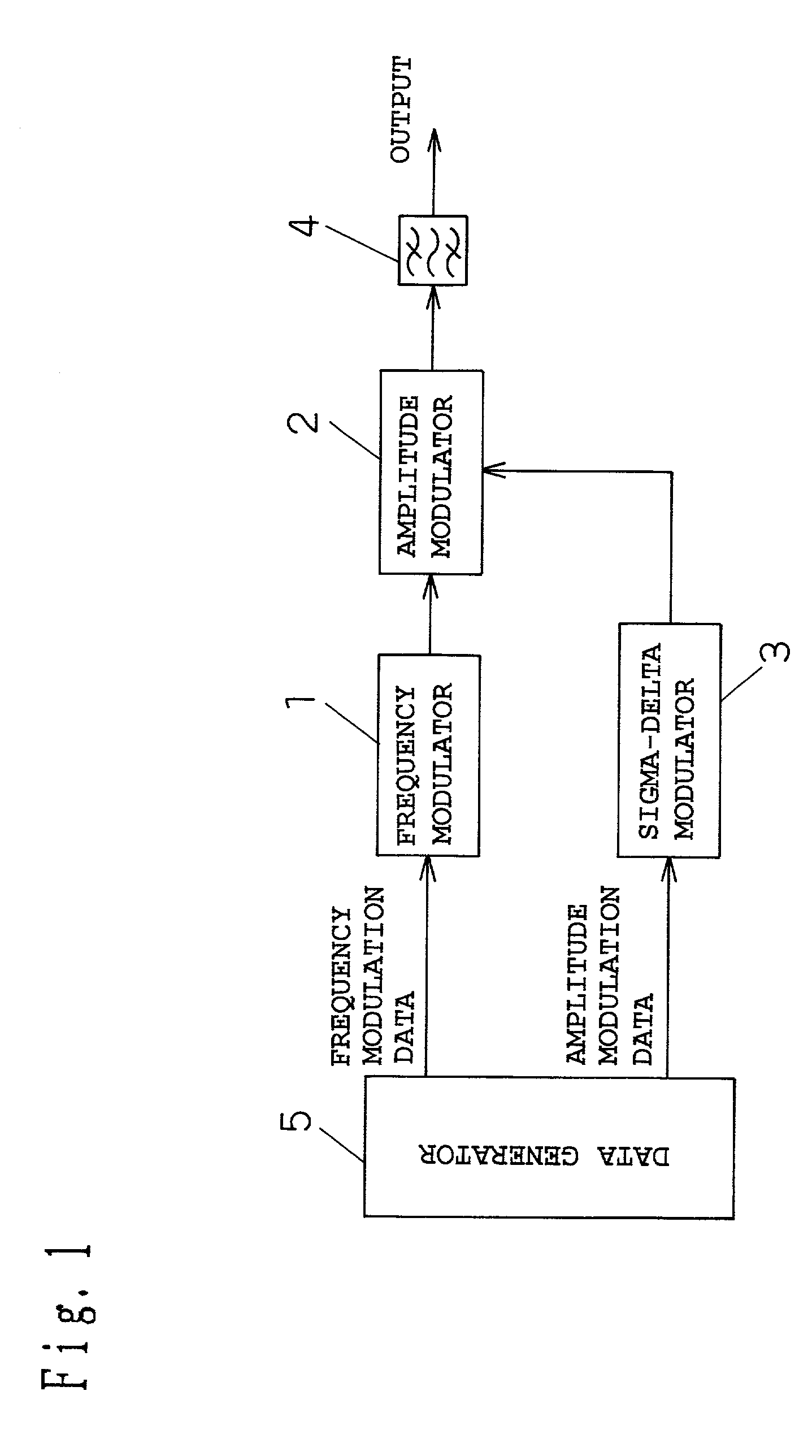

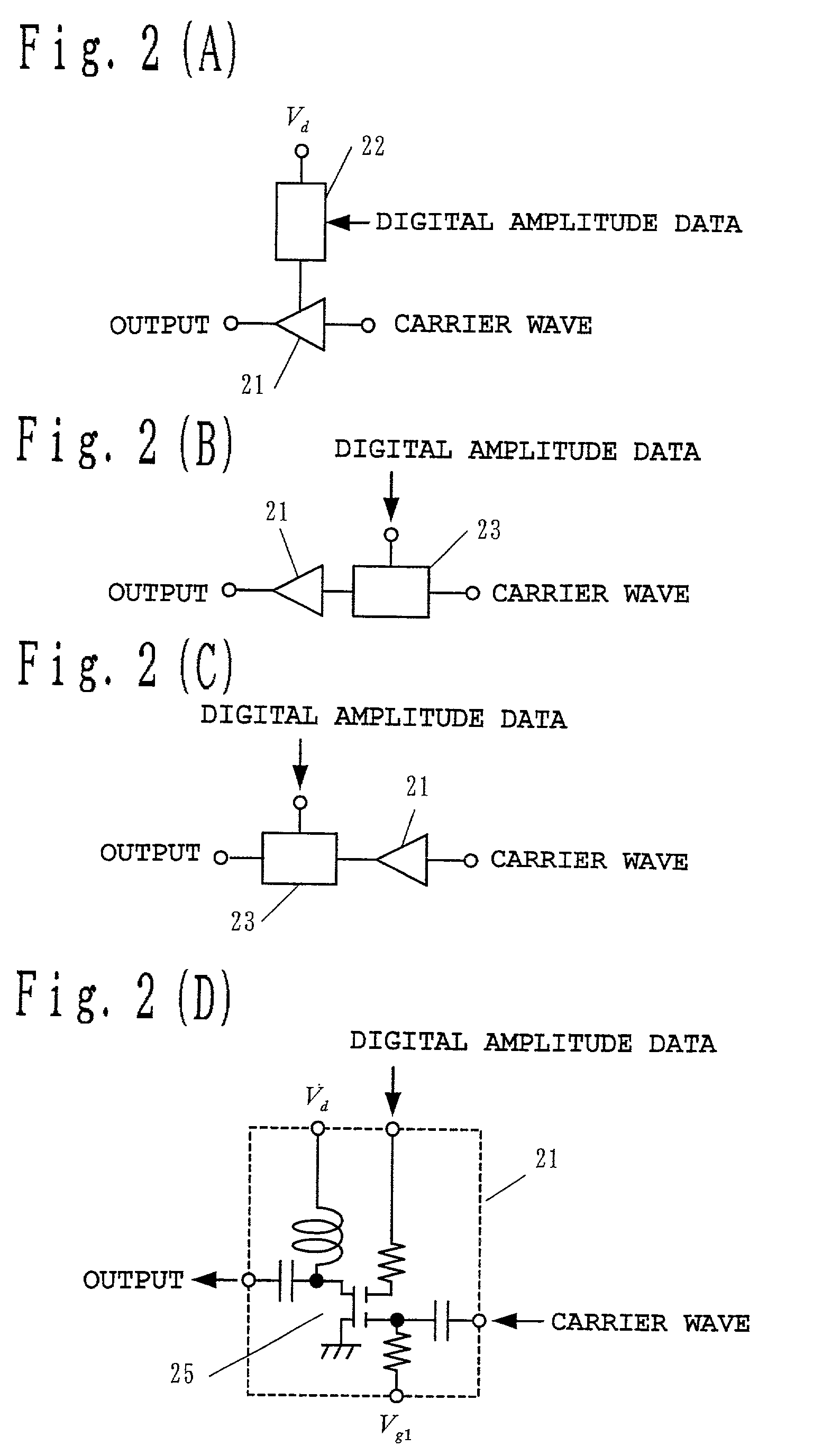

Transmitting circuit apparatus and method

ActiveUS7013090B2Improve linearityHigh transmission output power efficiencyResonant long antennasPower amplifiersCarrier signalGreek letter sigma

A transmitting circuit apparatus hasa frequency modulator that performs frequency modulation of a carrier wave with frequency modulation data and outputs the frequency-modulated carrier wave;a sigma-delta modulator which performs sigma delta modulation of amplitude modulation data; andan amplitude modulator that performs amplitude modulation of the frequency-modulated carrier wave with an output signal of the sigma-delta modulator and outputs the amplitude-modulated carrier wave.

Owner:PANASONIC CORP

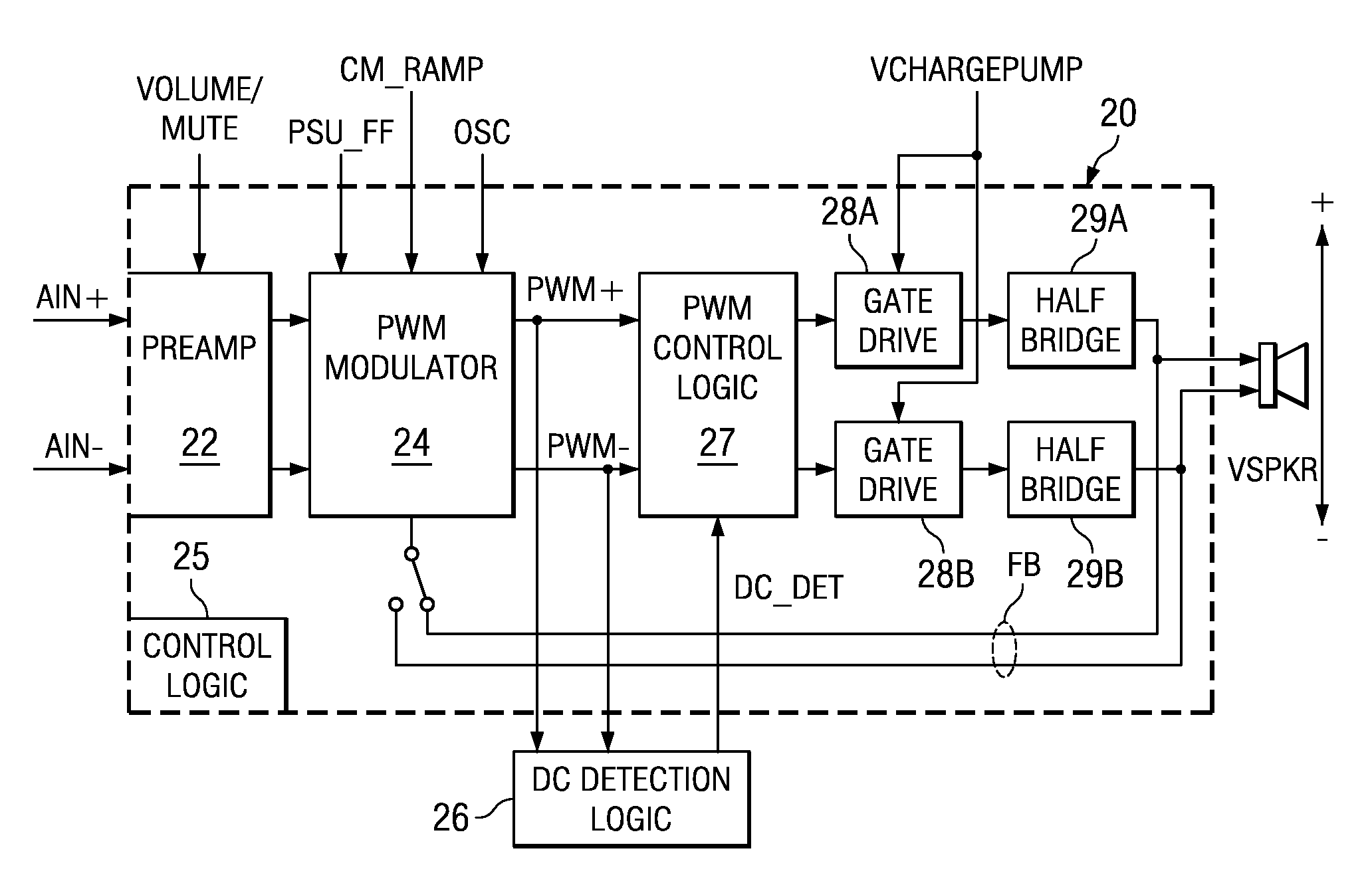

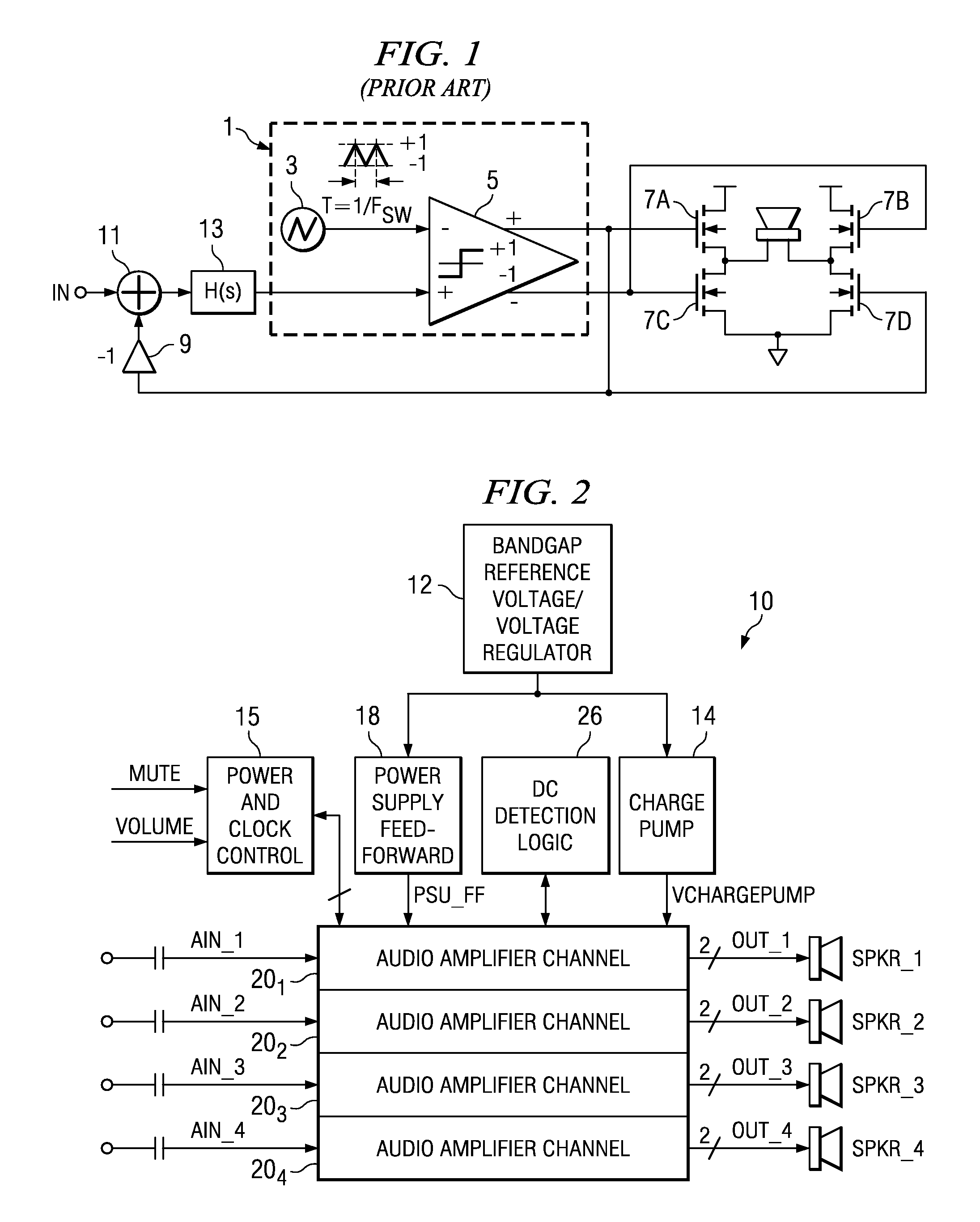

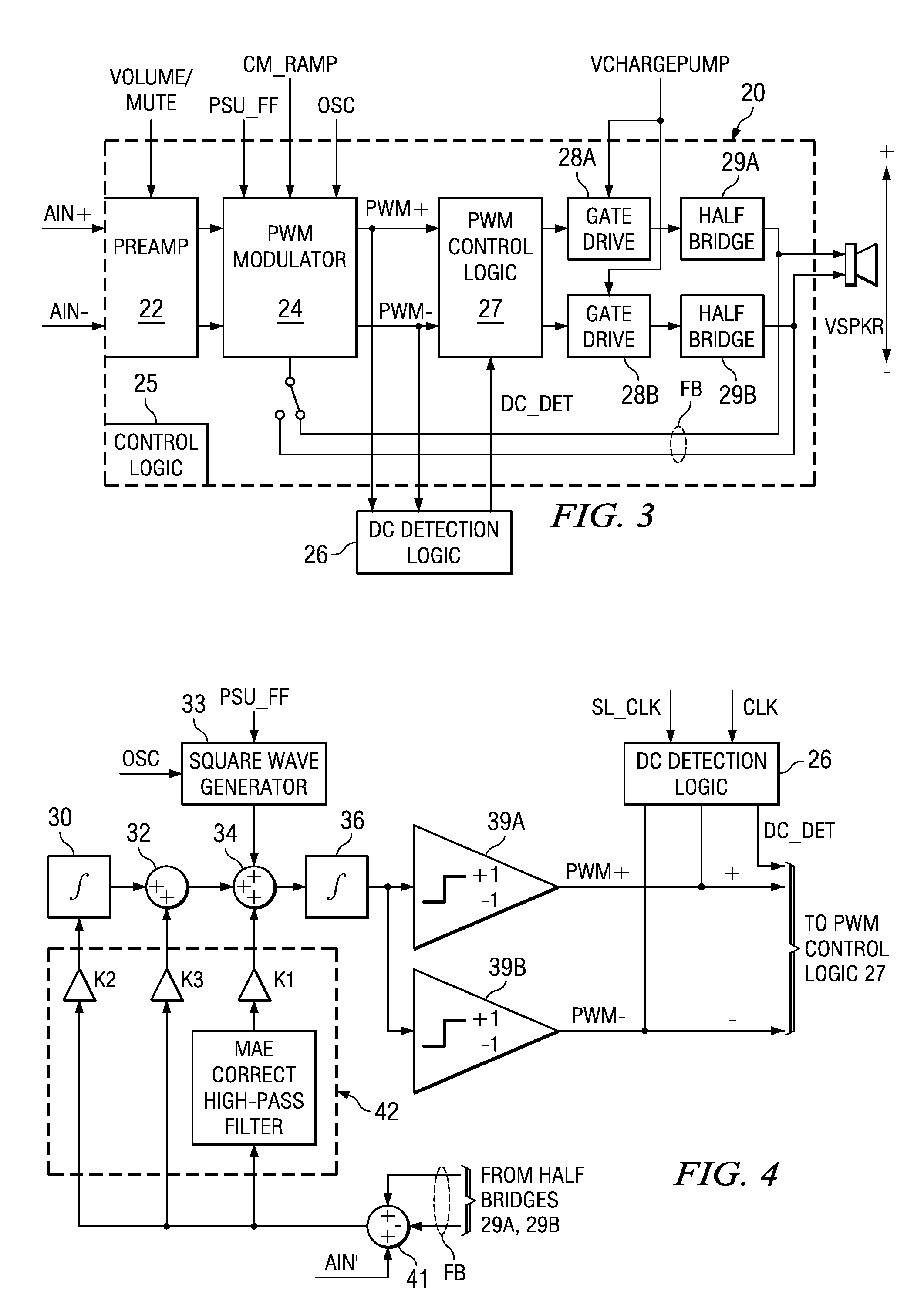

Detection of DC output levels from a class D amplifier

ActiveUS7078964B2Simple analog portionLow cutoff frequencyDuration/width modulated pulse demodulationPulse duration/width modulationUnsafe conditionAudio power amplifier

Owner:TEXAS INSTR INC

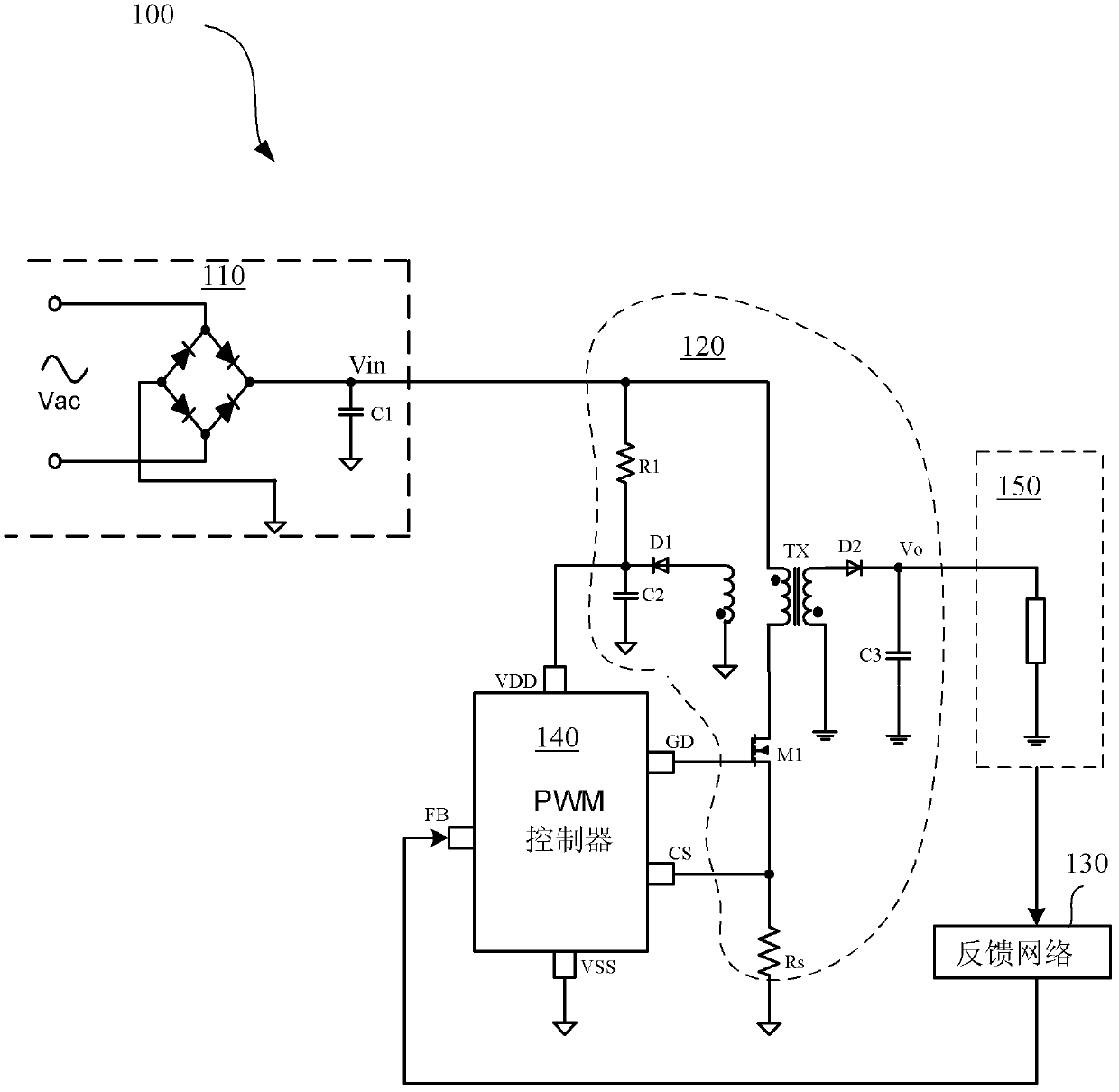

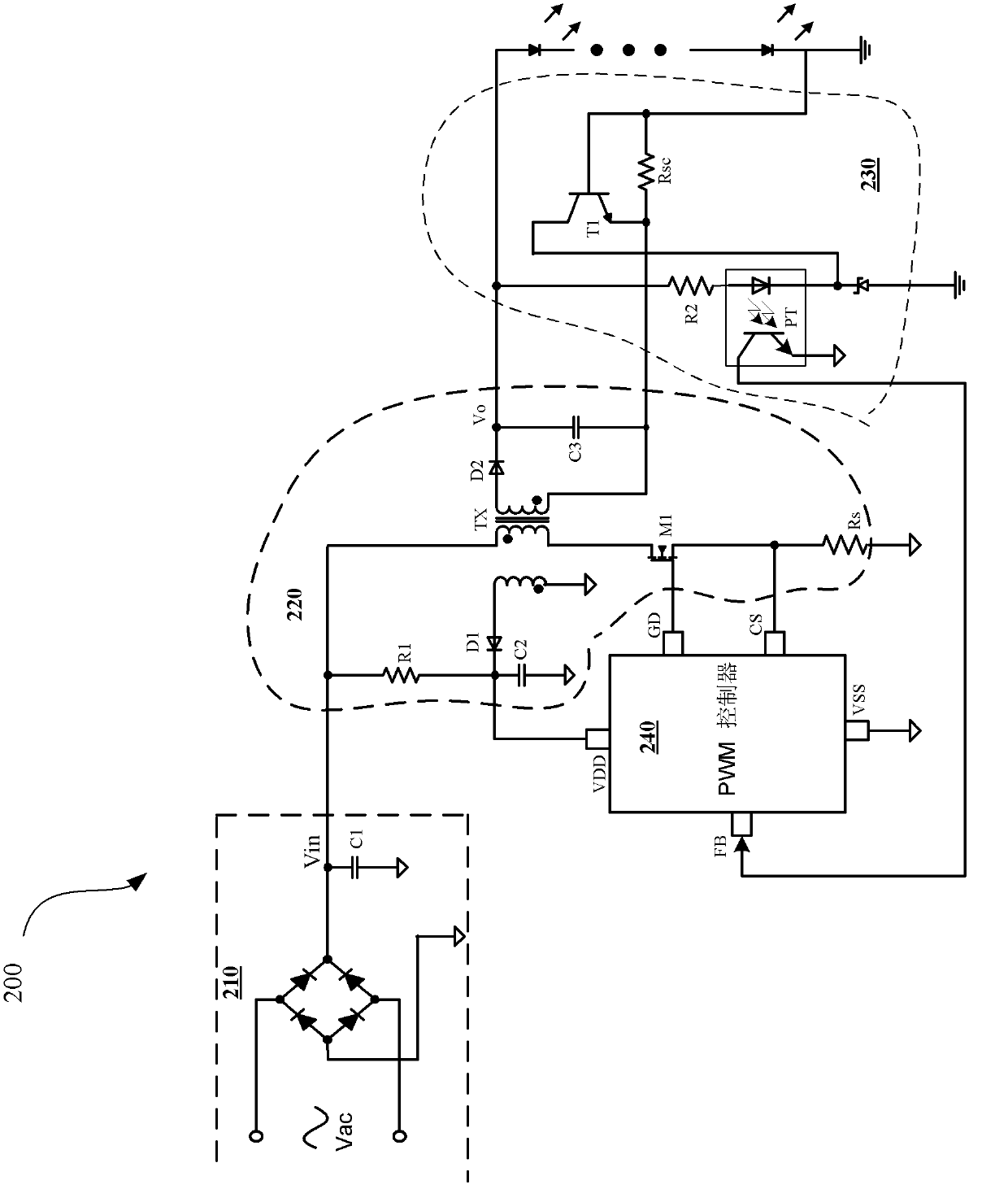

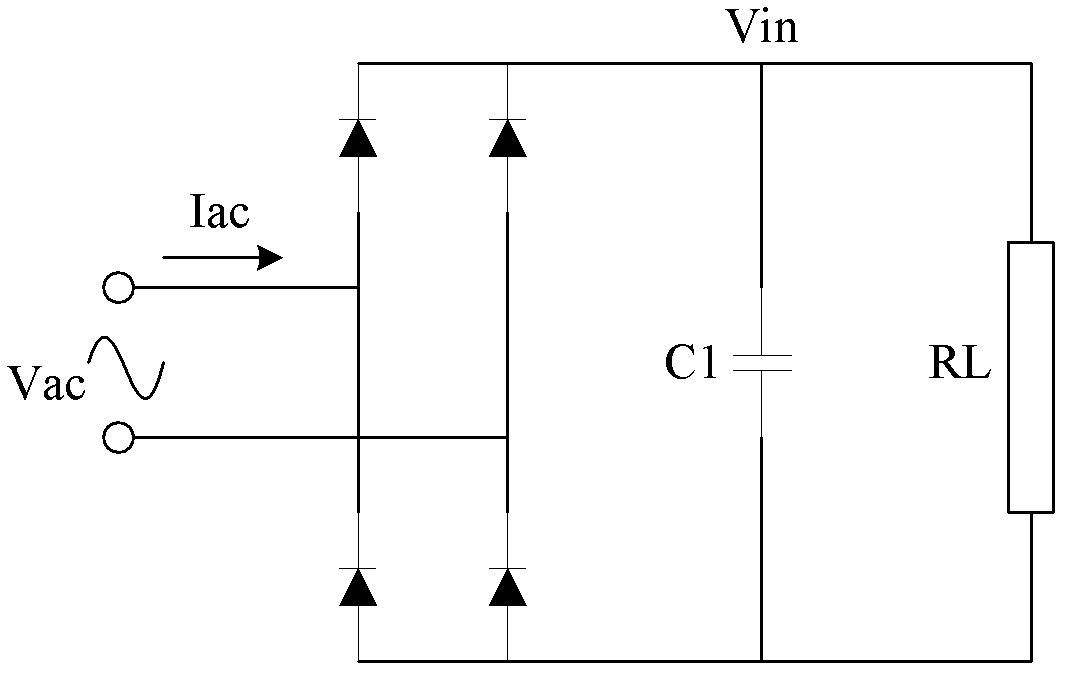

Power-factor correction constant current controller and control method

ActiveCN103296904AImprove efficiencyImprove conversion efficiencyEfficient power electronics conversionAc-dc conversionControl signalPeak value

The invention relates to a PFC constant current controller and a control method of the PFC constant current controller. Unlike the traditional mode of additionally adding a PFC circuit besides a PWM controller, the PFC constant current controller integrates a single-stage PFC circuit and the PWM controller. The PFC constant current controller comprises a peak value sampling device, a feedback signal detector, a sigma delta modulator, a digital signal processor, a digital to analog converter, a comparator, a PWM generator and a power switch driver. The PFC constant current controller can obtain sampled signals of current output by a flyback switching power supply system, and the sampled signals serve as feedback signals to generate a constant-current control signal to be used for controlling averagely-output current. Therefore, the averagely-output currents are limited within a preset reference value, and accordingly the target of constant-current control is achieved.

Owner:SHANGHAI BRIGHT POWER SEMICONDUCTOR CO LTD

Method for reducing DAC resolution in multi-bit sigma delta analog-to digital converter (ADC)

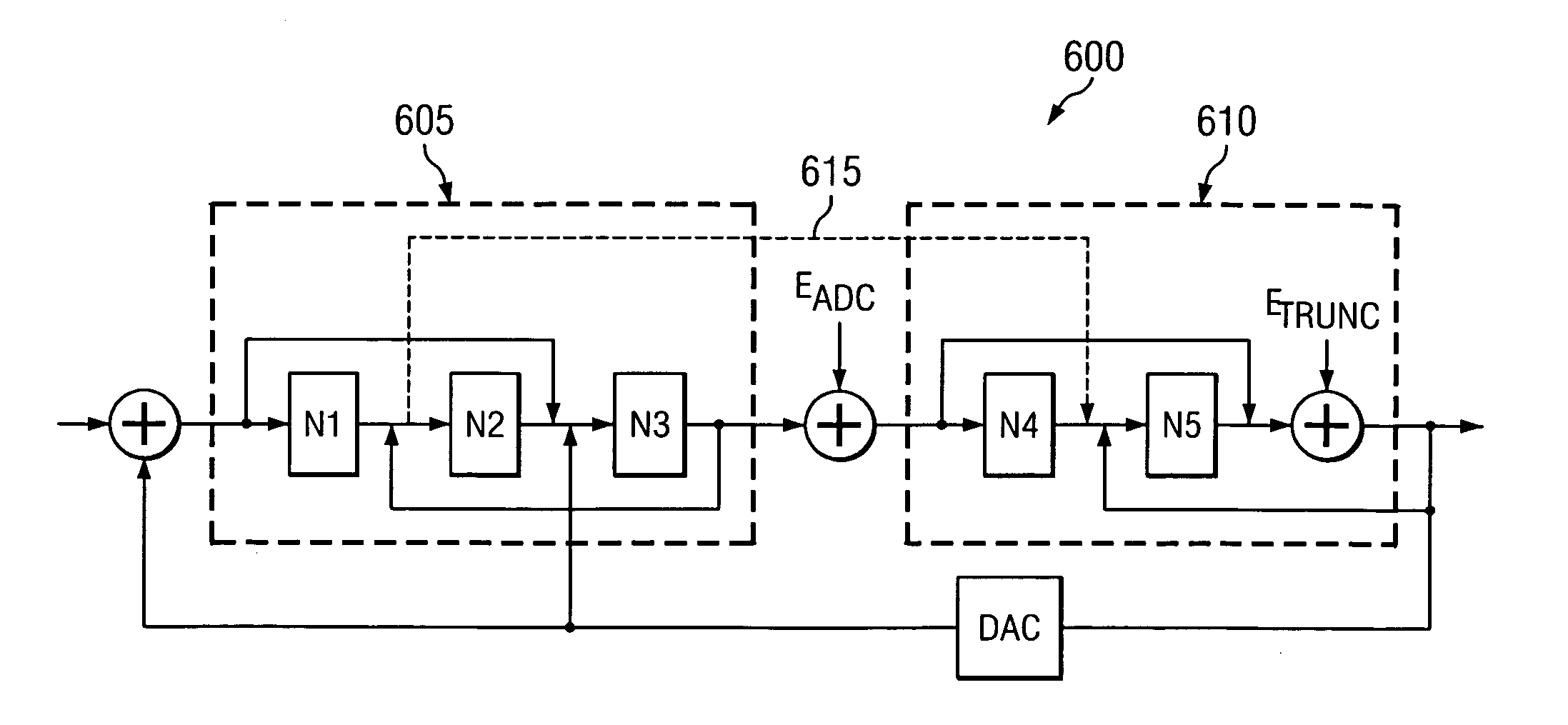

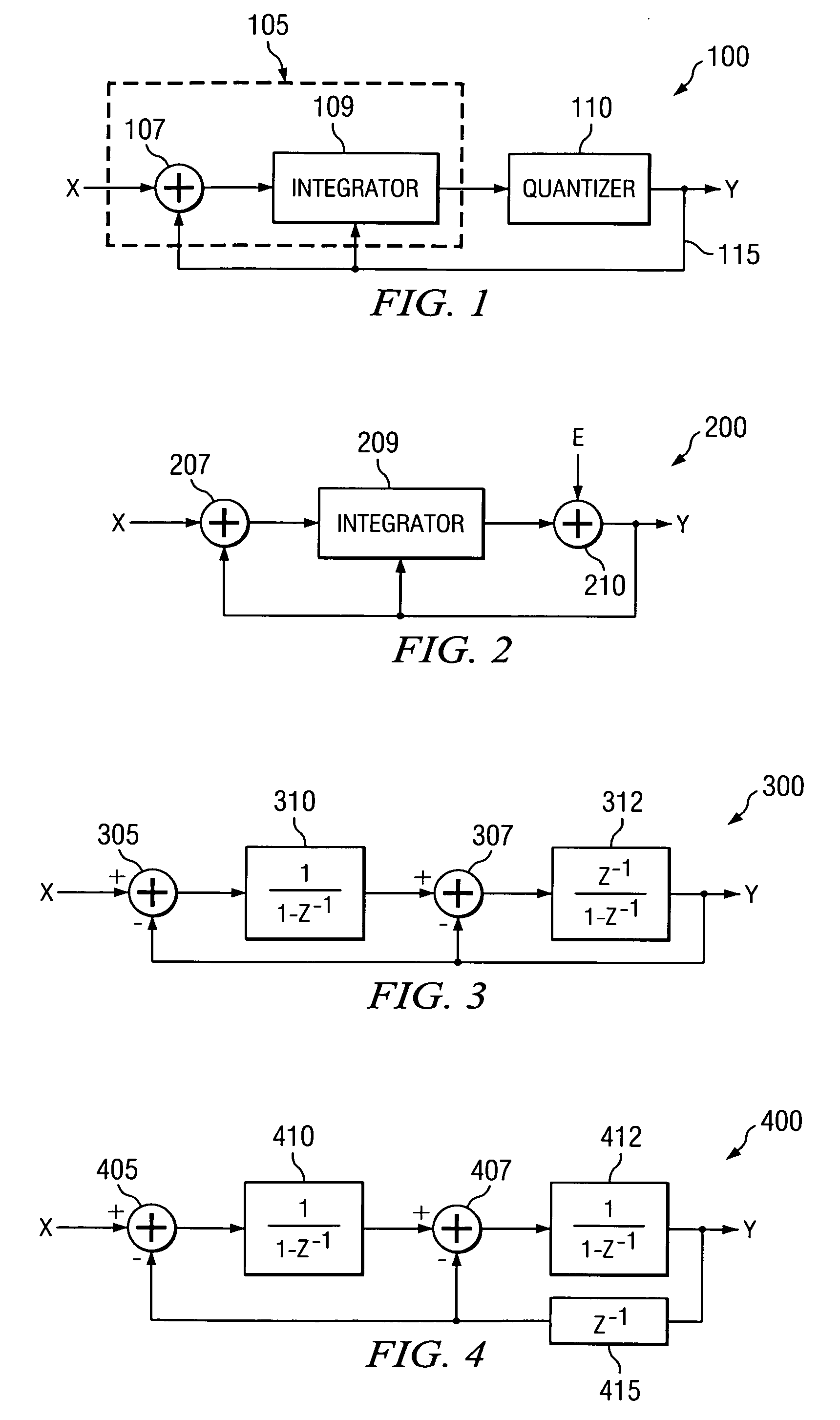

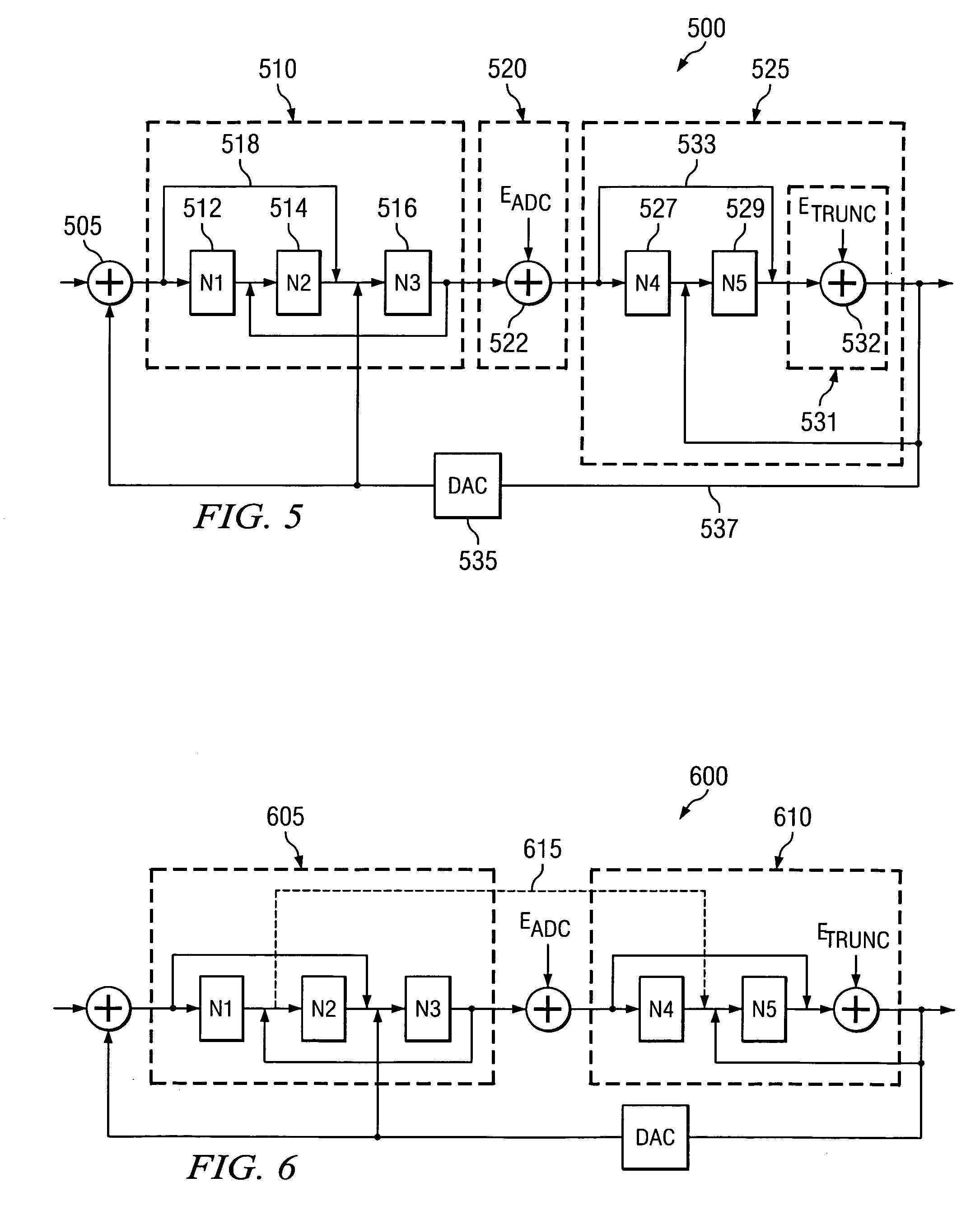

A method for reducing the resolution of a digital-to-analog converter in a multi-bit sigma-delta ADC is described. With the addition of digital sigma-delta modulators in the feedback path of a sigma-delta ADC, the truncation errors between the digital word output of the multi-bit sigma-delta ADC to the DAC input can be shaped to higher order than that of the quantization error. Thus, the DAC resolution can be reduced and the implementation of DEM for multi-bit DAC can be avoided. A preferred embodiment comprises selecting an outermost feedback loop in a sigma-delta ADC that has not been replaced and replacing it with a circuit with an equivalent transfer function. The circuit can be further enhanced with an additional term if the order of the noise shaping of the circuit is less than the order of the noise shaping of the sigma-delta ADC.

Owner:TEXAS INSTR INC

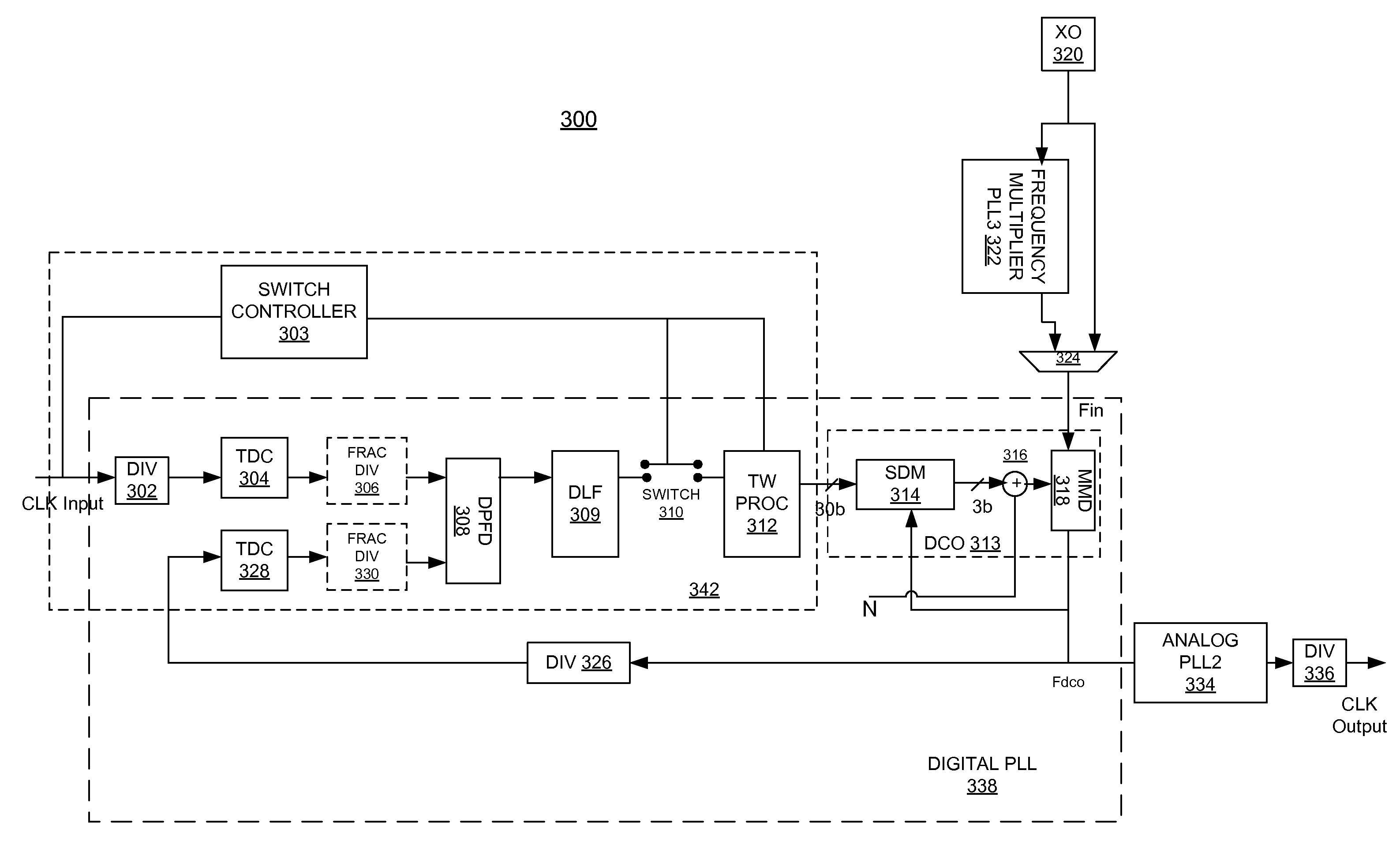

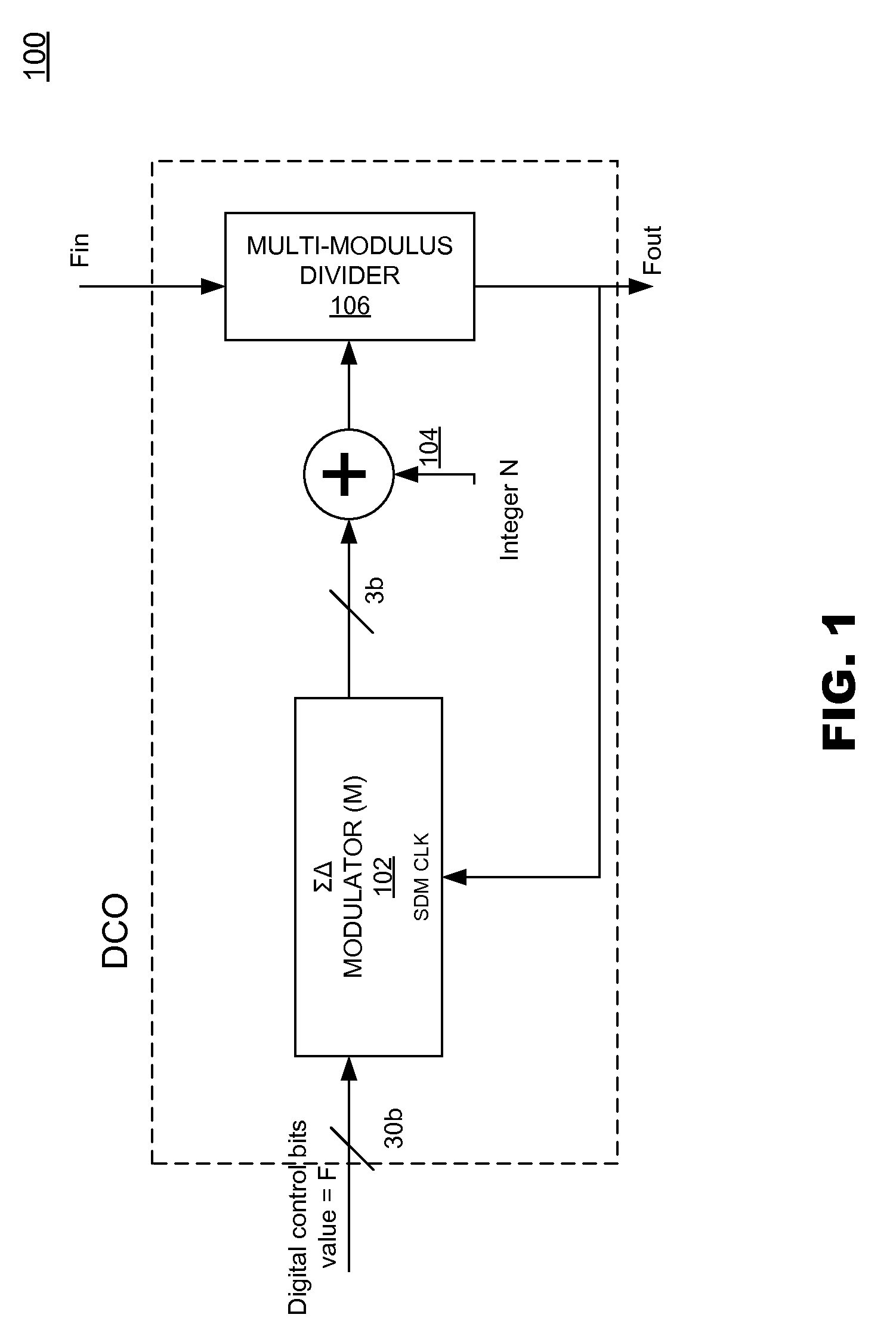

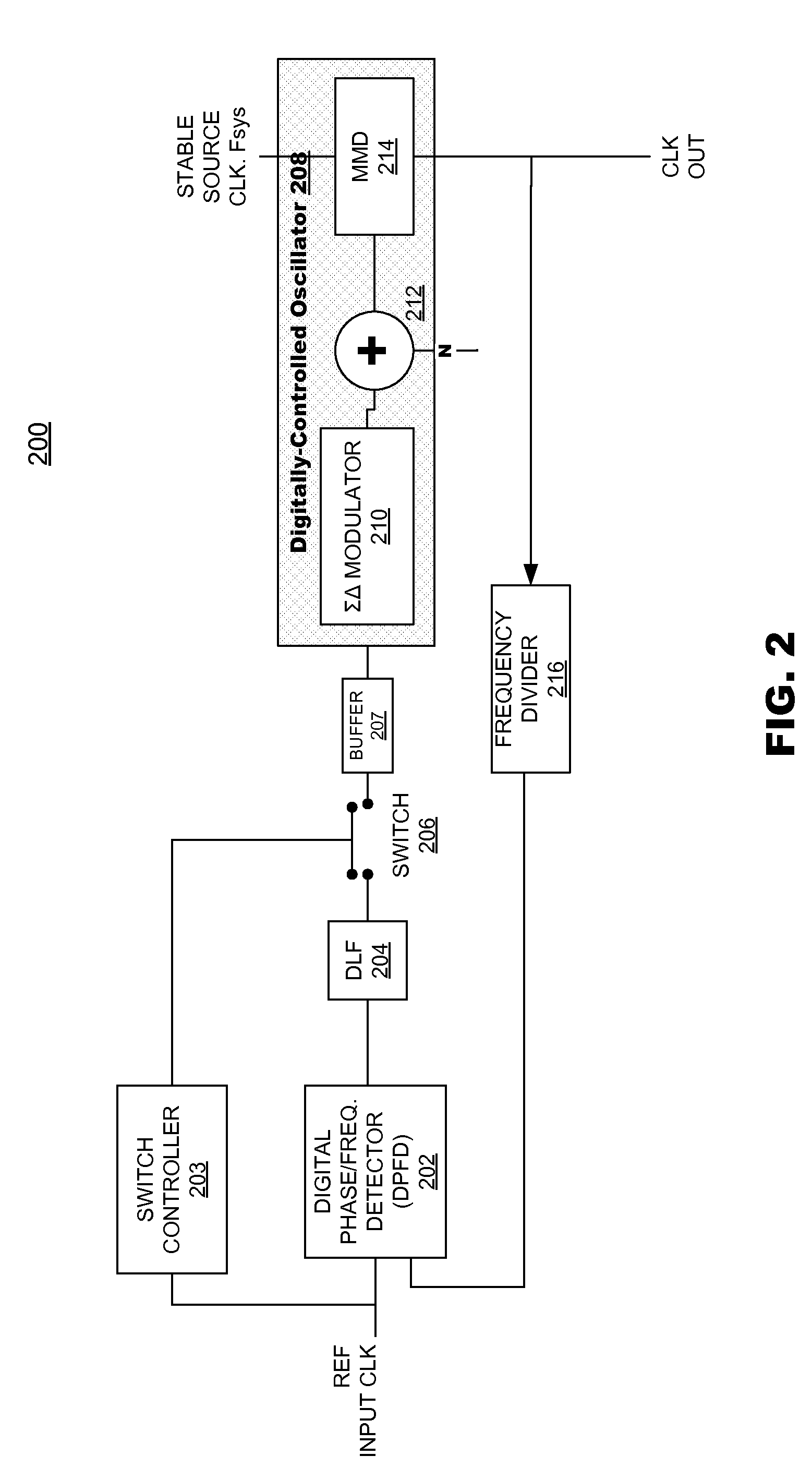

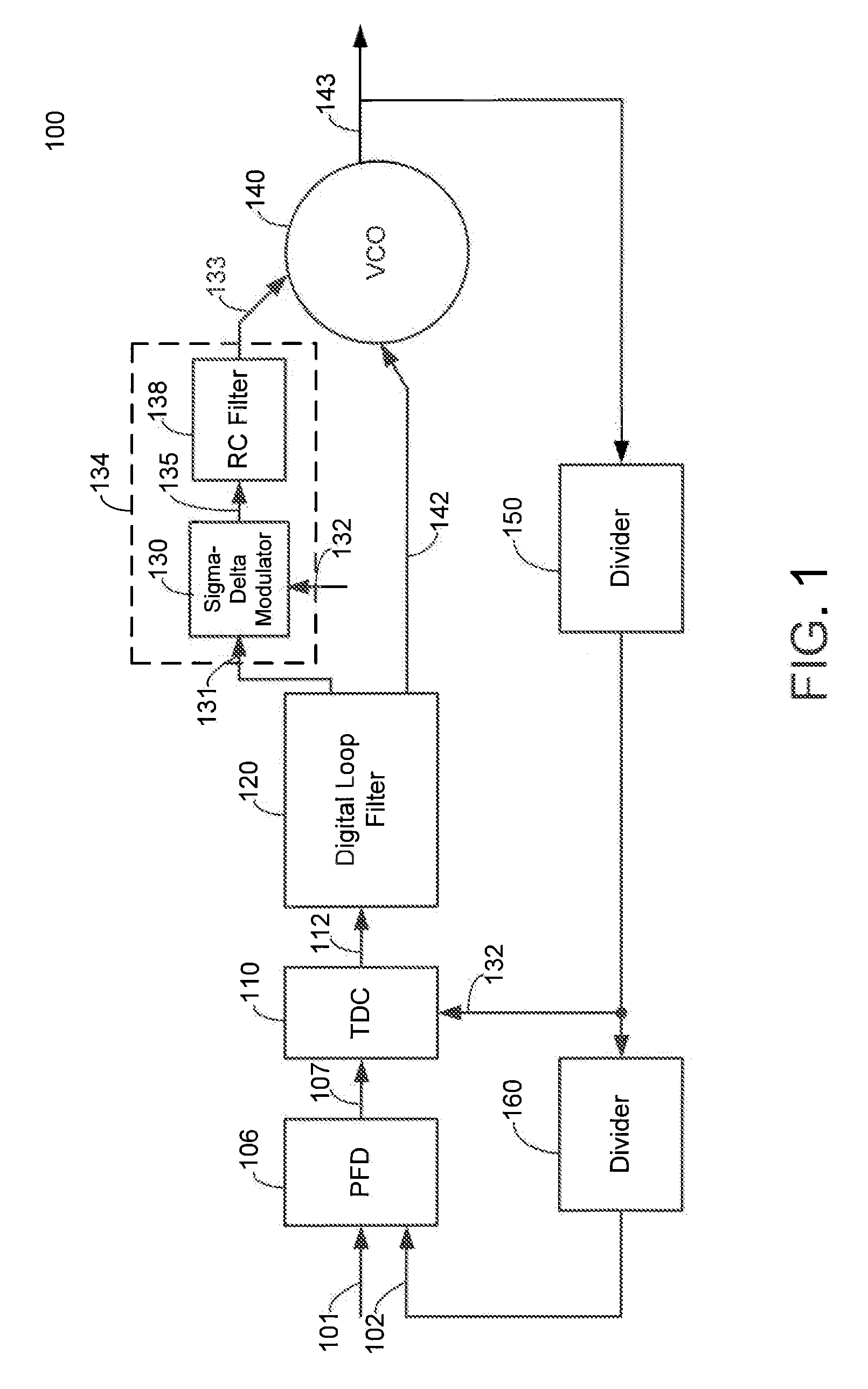

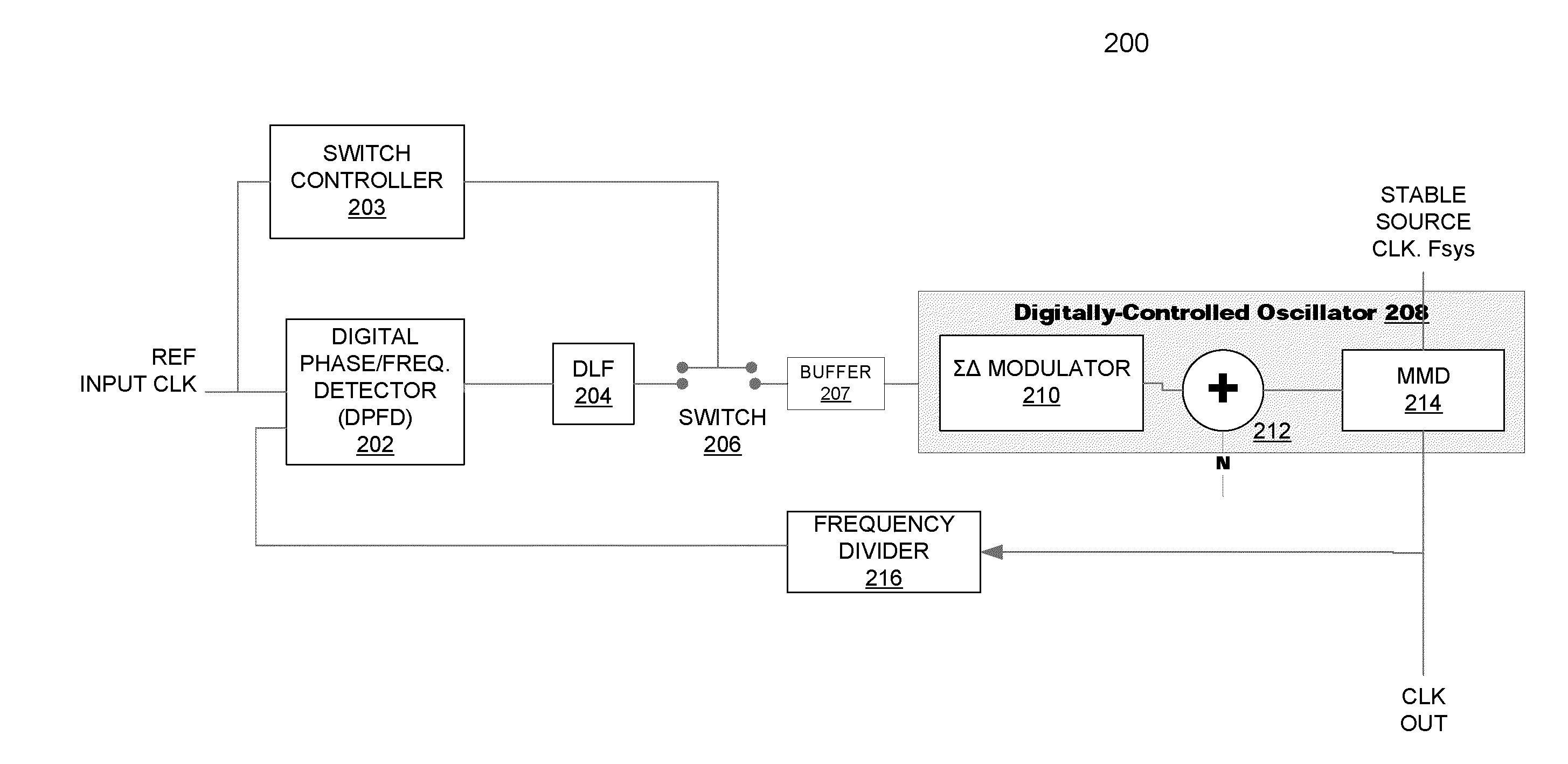

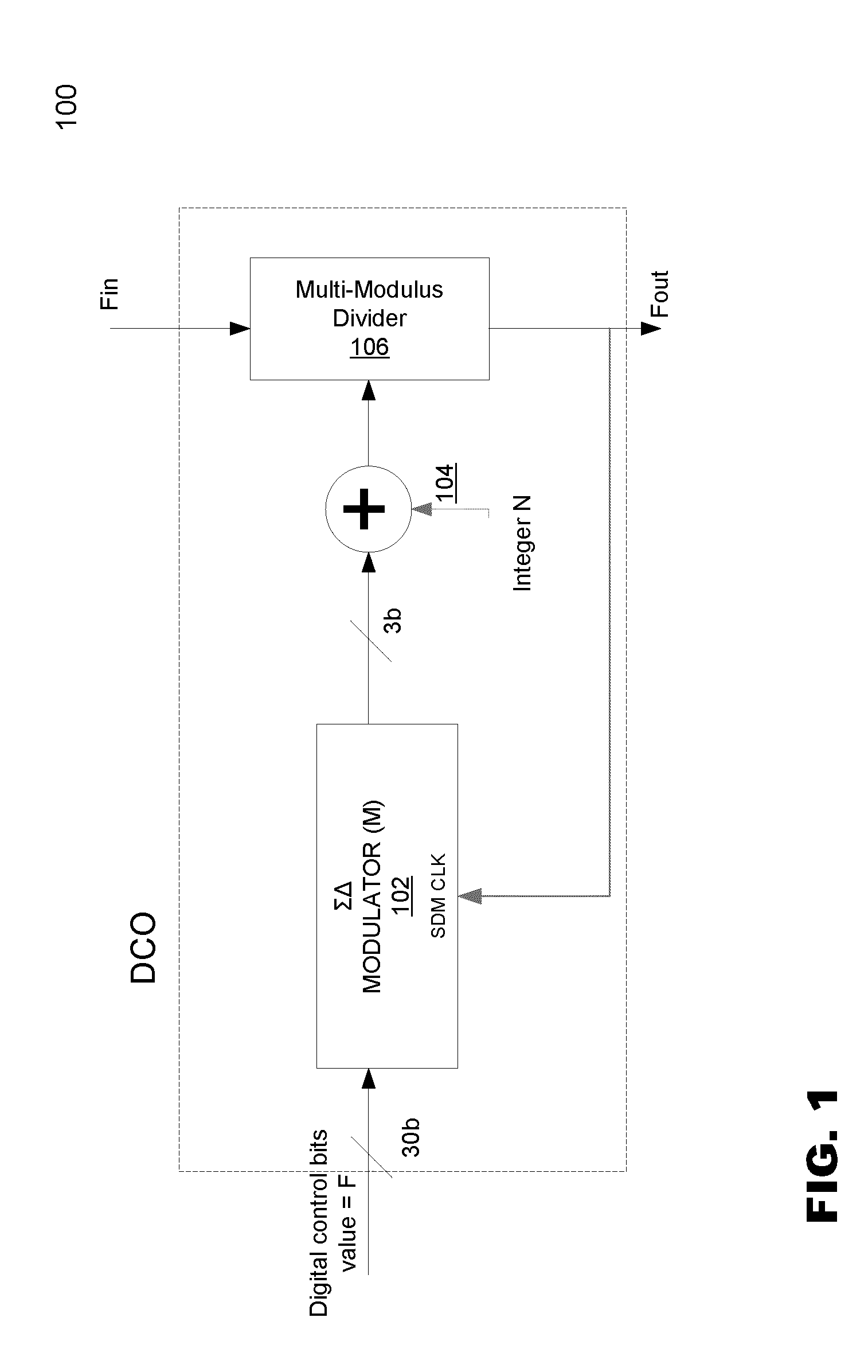

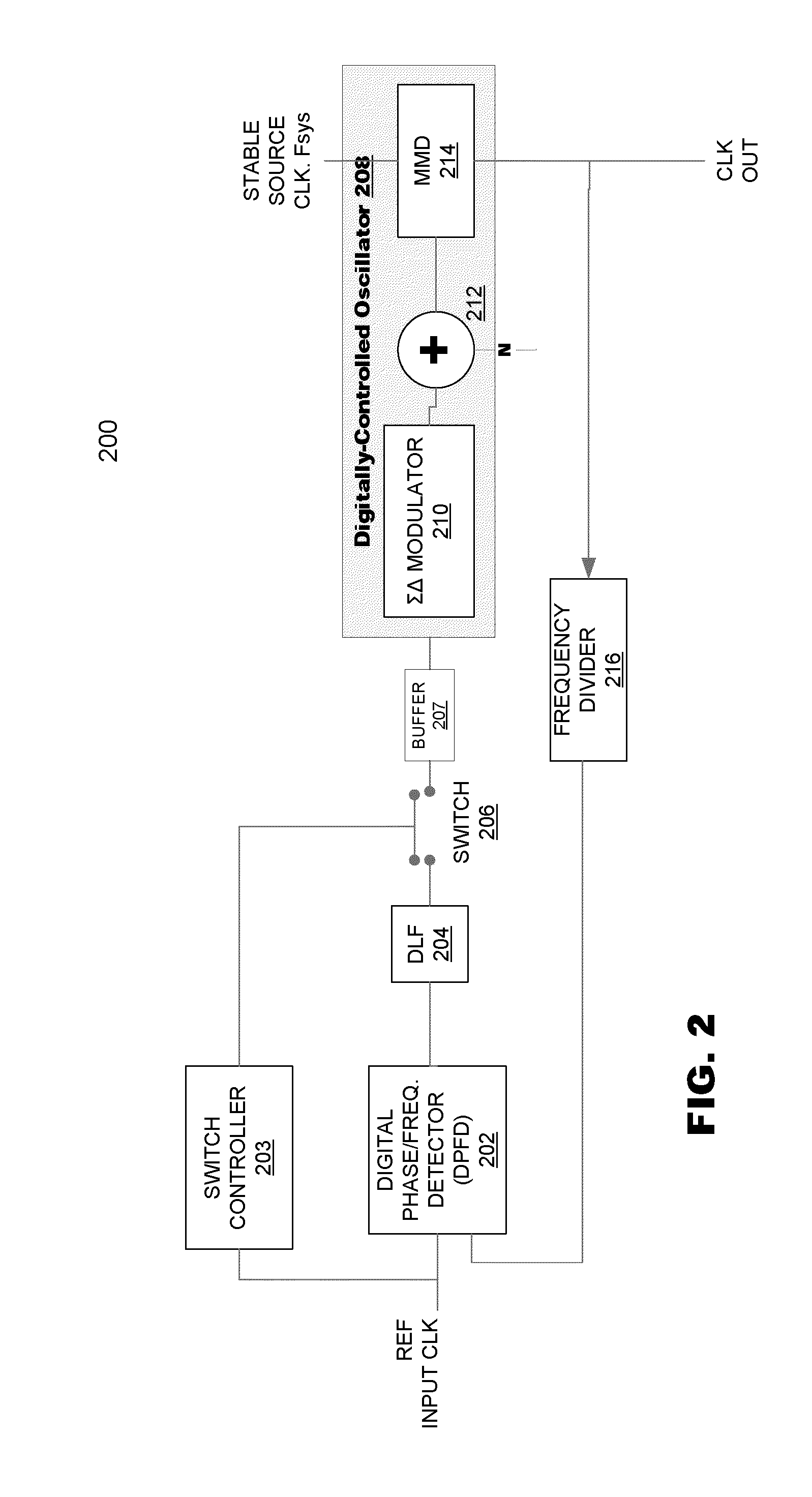

Digital Phase-Locked Loop Clock System

A clock system includes a digital phase / frequency detector (DPFD), a buffer, a digitally-controlled oscillator (DCO) including a sigma-delta modulator (SDM), an adder, a first frequency divider. The DPFD may have a first input for a reference input clock and a second input for a feedback signal, and outputting a difference signal representing a phase and / or frequency difference between the reference input clock and the feedback signal. The buffer may be coupled to the DPFD for accumulating the difference signal over time. The sigma-delta modulator (SDM) may have a control input coupled to the buffer. The adder may have inputs coupled to the (SDM) and a source of an integer control word. The first frequency divider may have an input for a clock signal and a control input coupled to the adder, the DCO generating an output clock signal having an average frequency representing a frequency of the input clock signal divided by (N+F / M), wherein N is determined by the integer control word and F / M is determined by an output of the SDM. The system clock also may include a phase-locked loop (PLL) including a phase / frequency detector that has a first input coupled to the output of the DCO and a second input that is phase-locked to the first input, and a second frequency divider coupled from the second input of the PLL to the second input of the DPFD.

Owner:ANALOG DEVICES INC

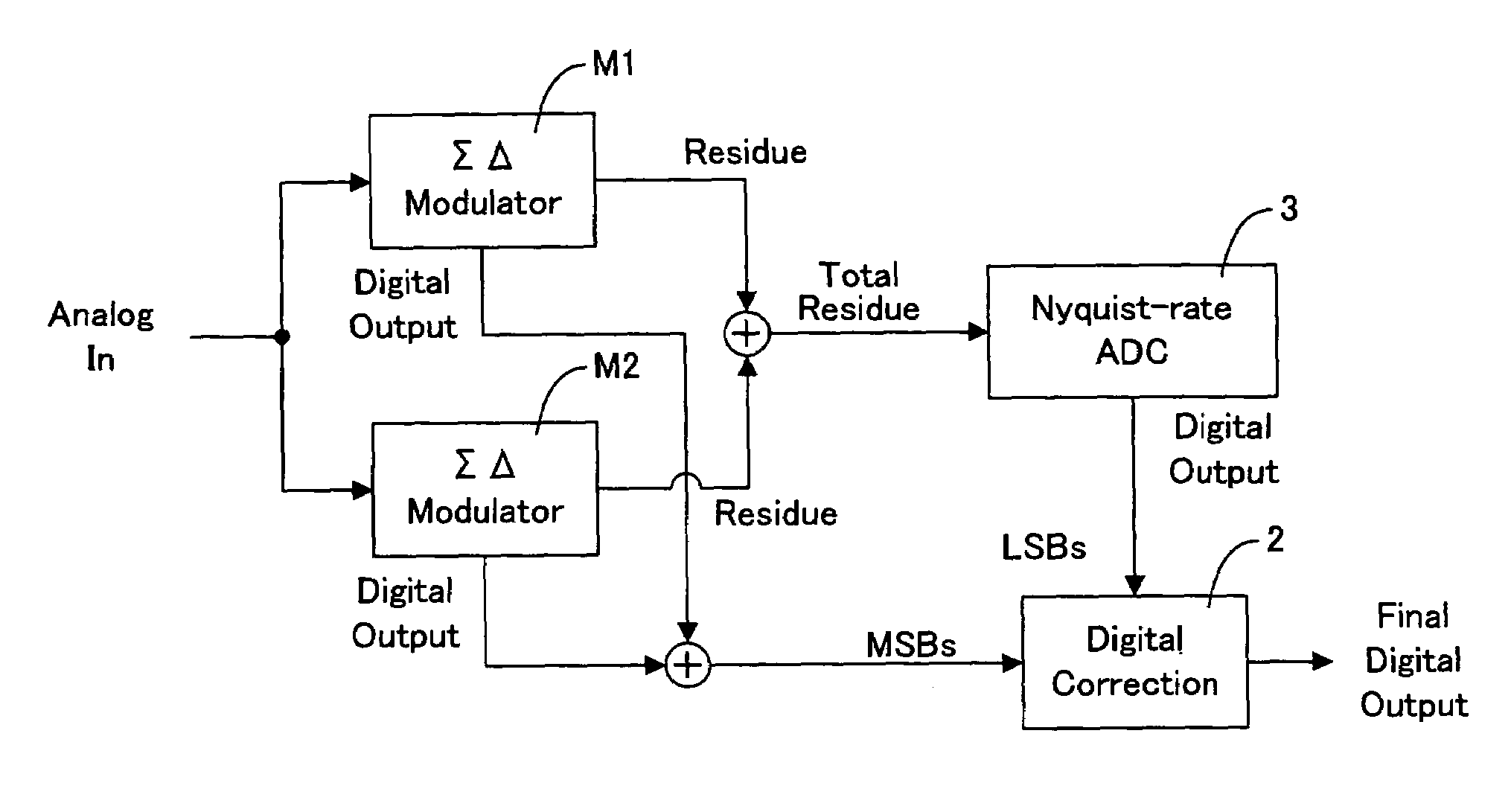

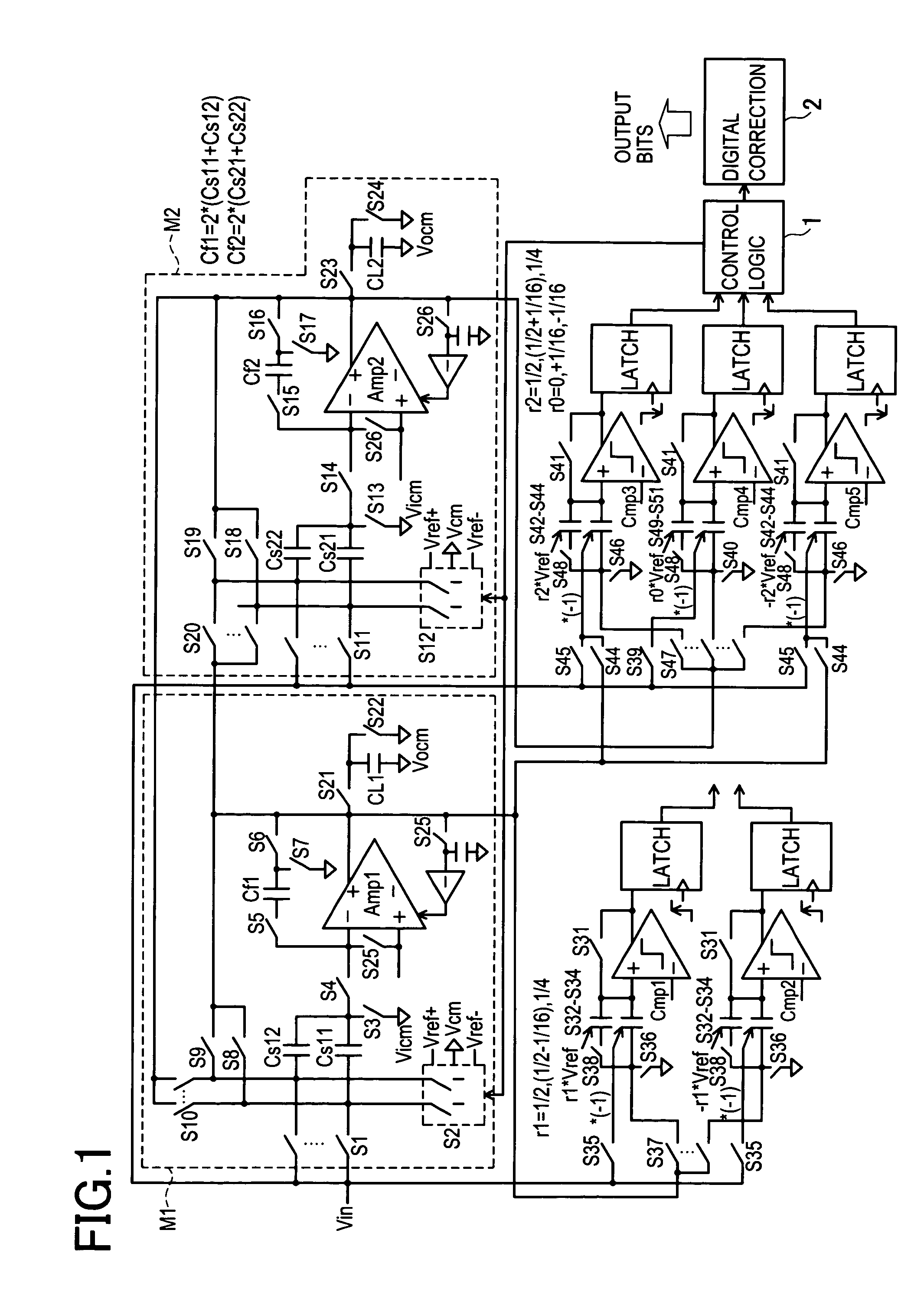

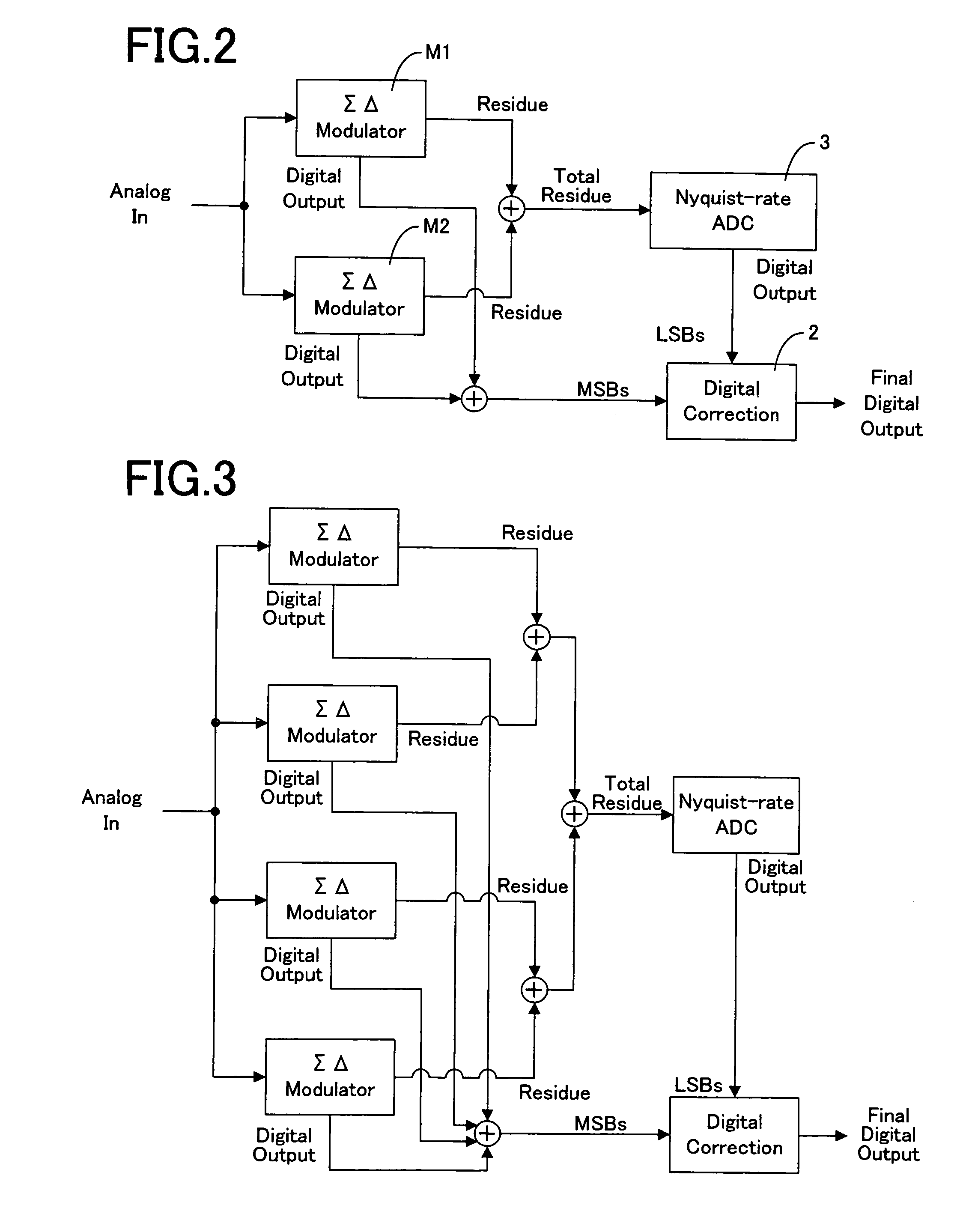

Parallel oversampling algorithmic A/D converter and method of using the same

ActiveUS7289054B1Reduce investmentIncrease speedElectric signal transmission systemsDelta modulationIntegratorBuck converter

Each of plural sigma-delta modulators having a sampling capacitor, an integrator, and a quantizer are connected to each other in parallel. Each of the sigma-delta modulators conducts parallel oversampling in which an analog input signal is sampled by a sampling capacitor, and the sampling result is quantized by the integrator and the quantizer. Then, the quantized values of the sigma-delta modulators are added to obtain MSBs, the residue values of the integrators after quantizing in the respective sigma-delta modulators are added, and the addition result of the residue values is converted analog-to-digital to obtain LSBs.

Owner:TOYOTA JIDOSHA KK

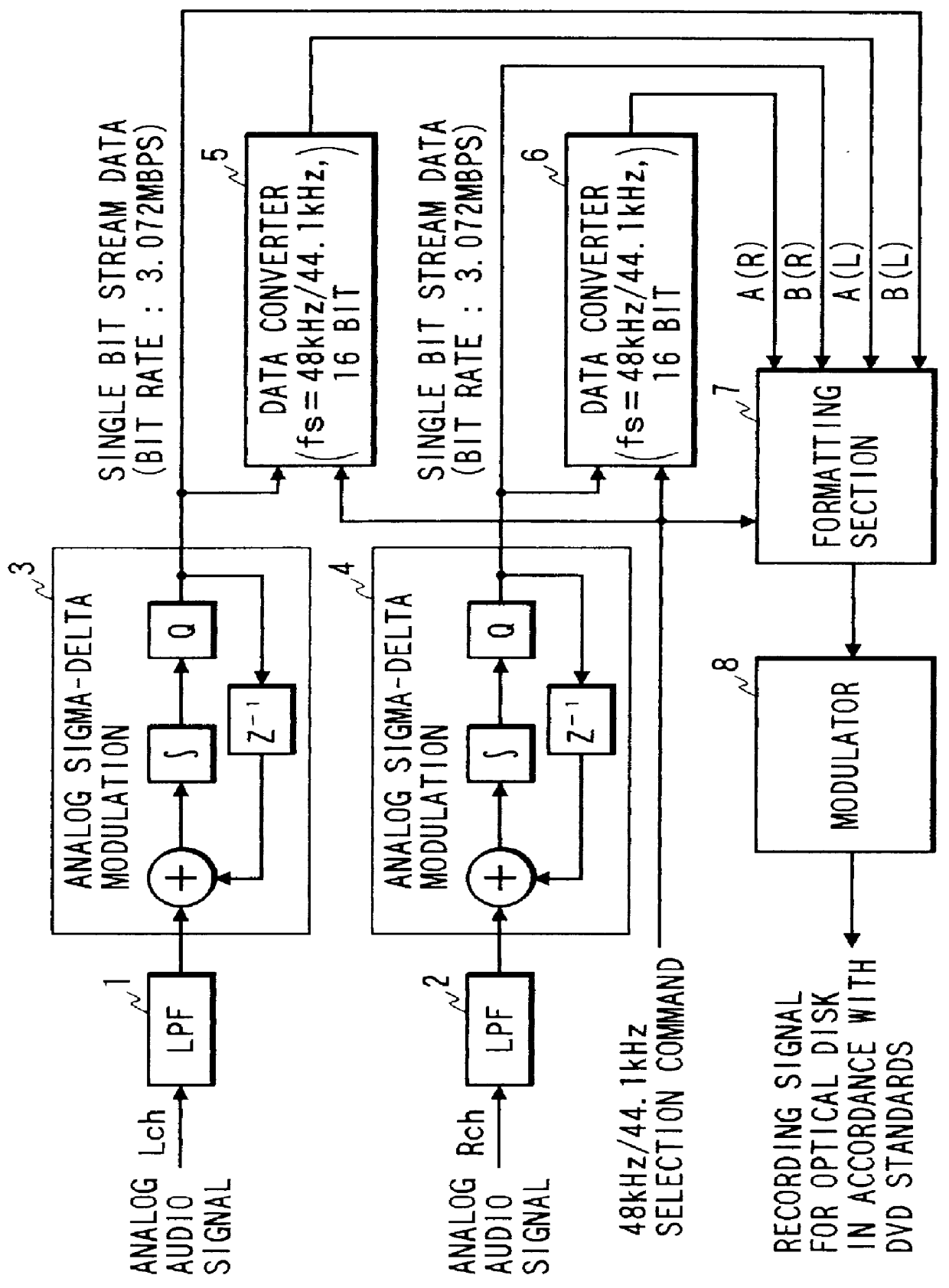

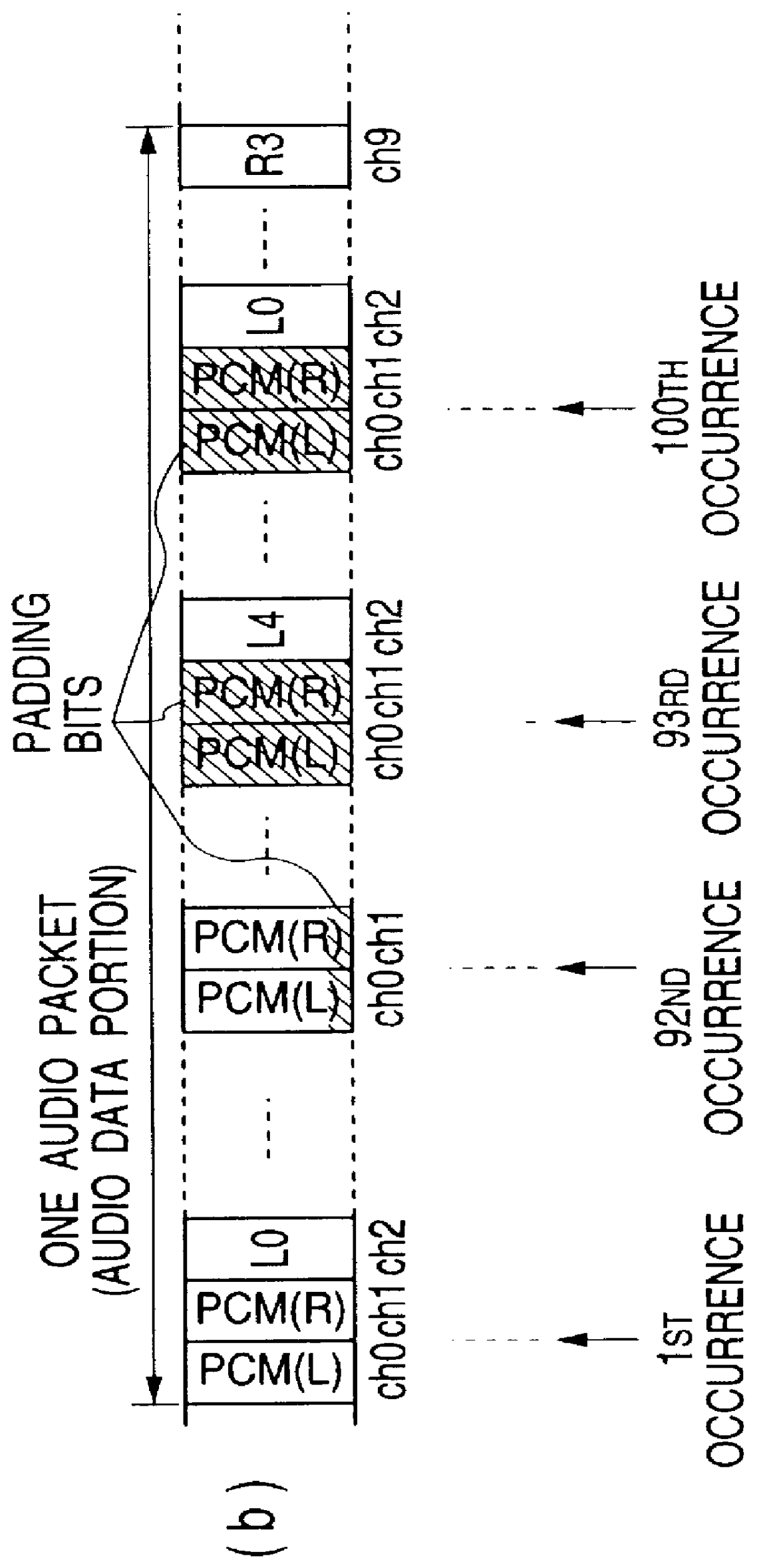

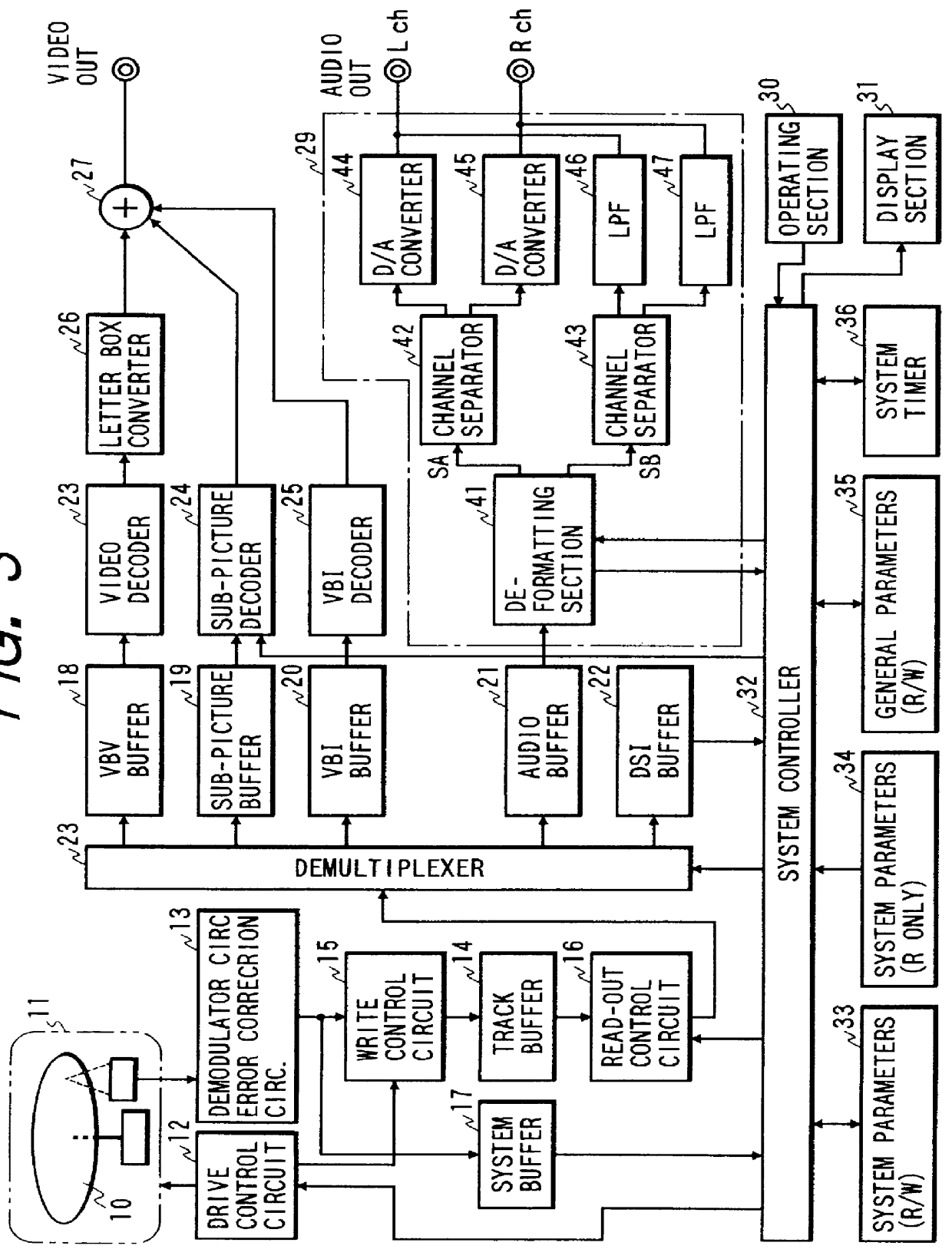

DVD-compatible optical recording disk conveying audio signals encoded both as PCM data and as single bit stream data generated by sigma-delta modulation, and encoder apparatus and decoder apparatus for same

An optical recording disk has audio signals recorded as data encoded in accordance with DVD specifications, both as PCM data and as single bit stream data that are generated by sigma-delta modulation, thereby providing both the improved audio reproduction capability of single bit stream data and also compatibility with existing types of DVD playback apparatus. Data are recorded using proposed new DVD stream modes, having 10 data channels, 48 kHz PCM sampling frequency and 16 or 20 bits / sample, with the ratio (2:8) of data channel capacities allocated to the PCM data and single bit stream data being made identical to the ratio of the respective bit rates at which the PCM data and single bit stream data are generated.

Owner:RAKUTEN INC

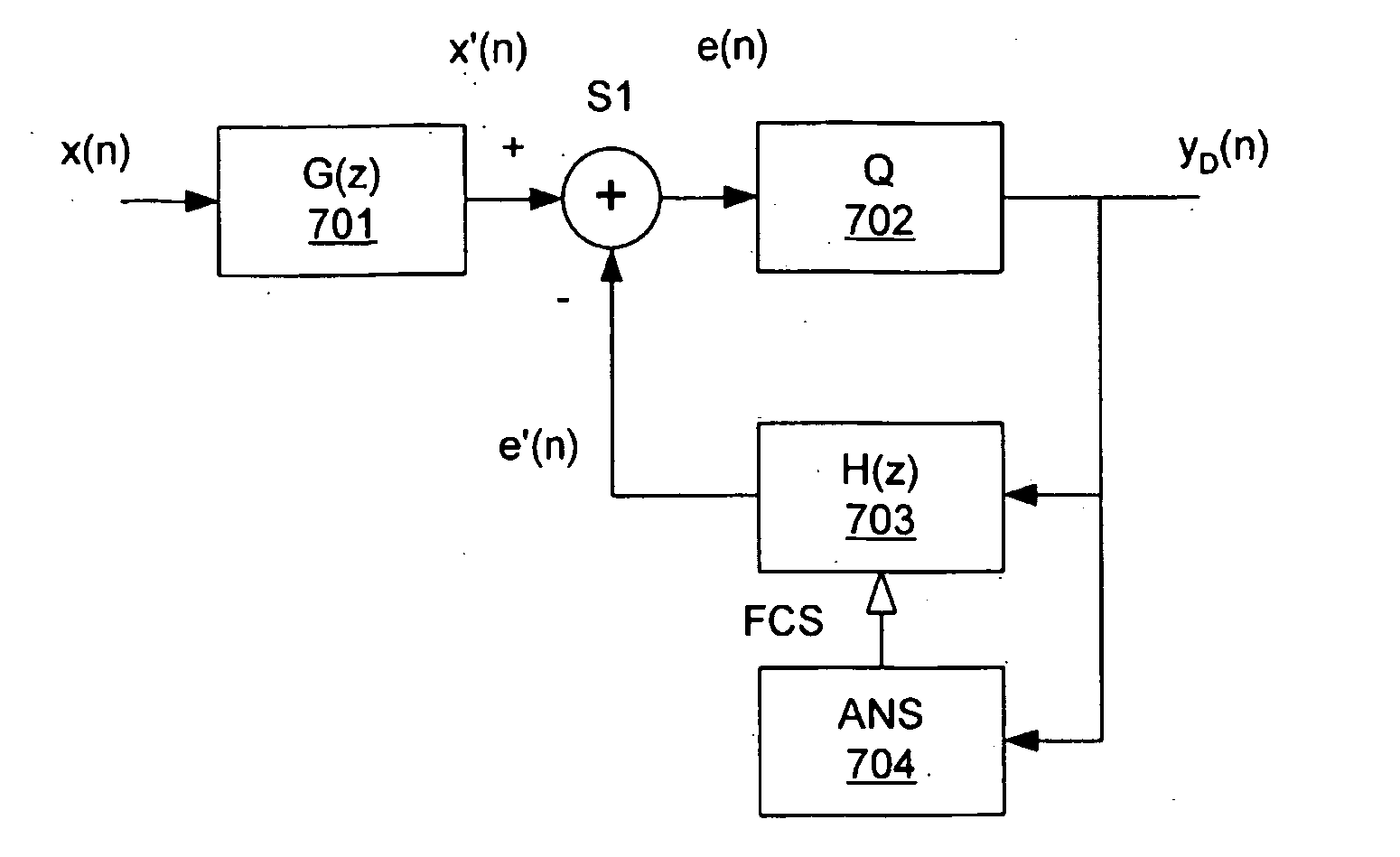

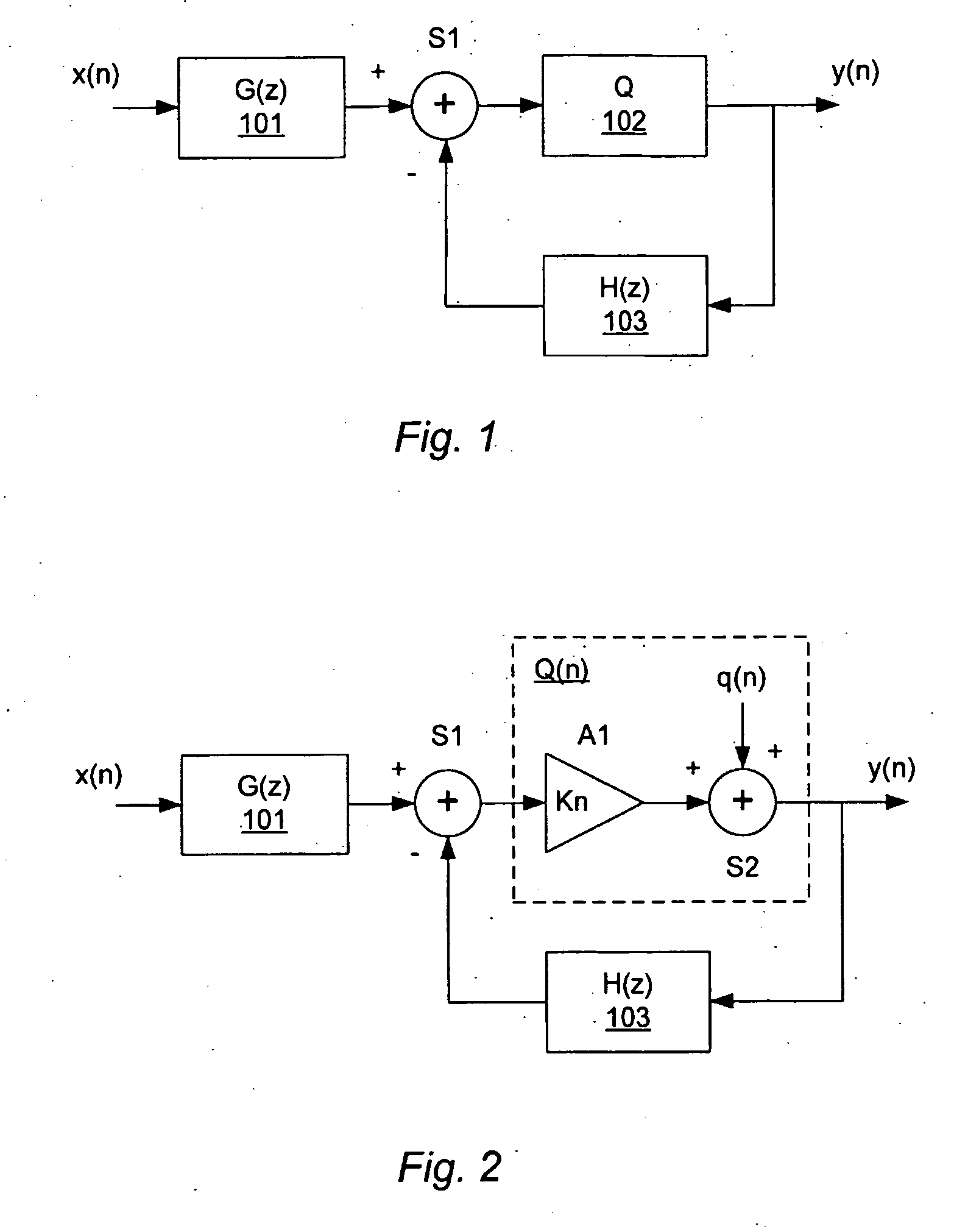

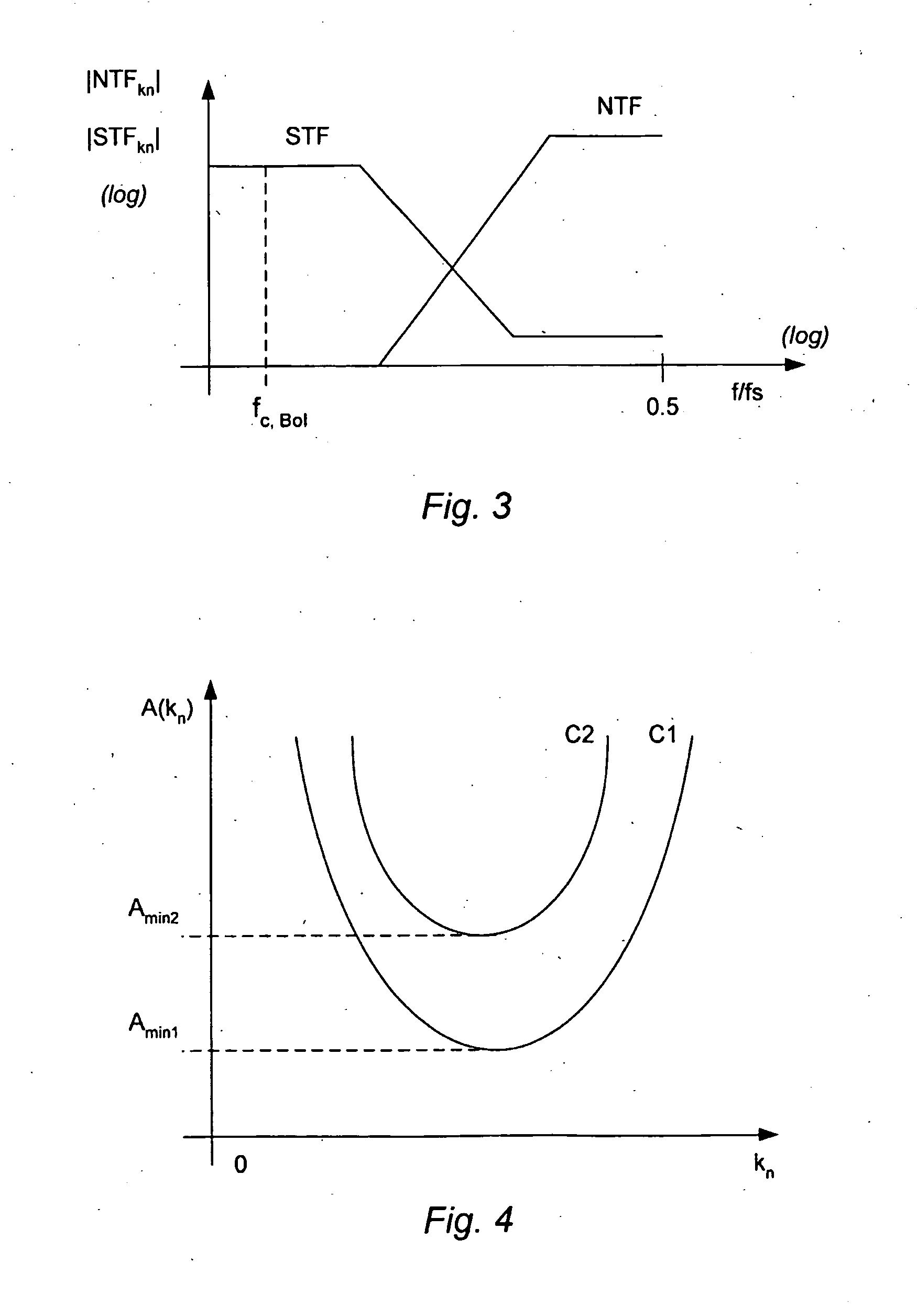

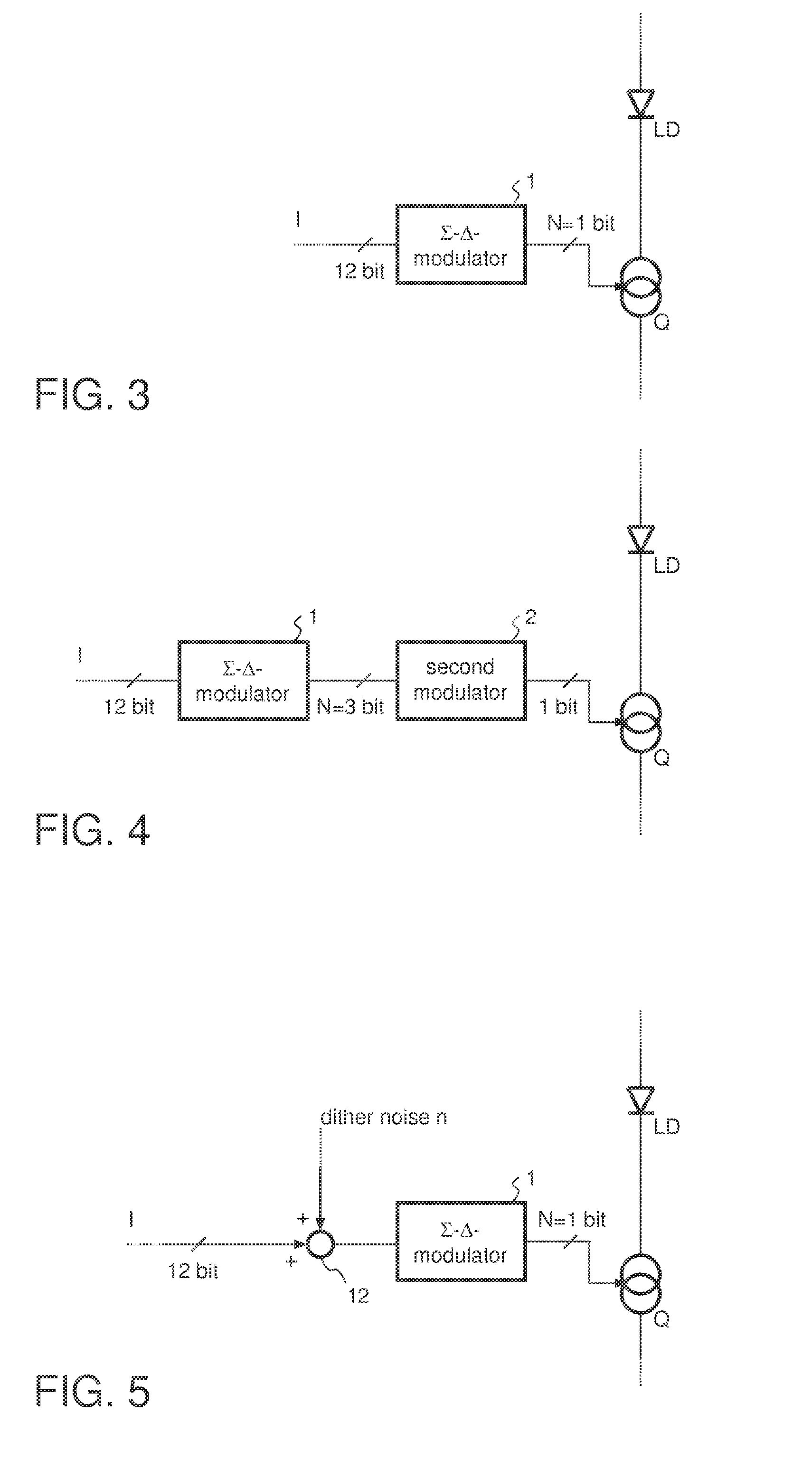

Sigma delta modulator

ActiveUS20090066549A1More freedomStable maintenanceDelta modulationDifferential modulationSignal transfer functionGreek letter sigma

A method of controlling a sigma delta modulator with a loop which establishes a signal transfer function, STF, and a quantization noise transfer function, NTF, of the sigma delta modulator, wherein the sigma delta modulator receives an input signal, x(n), and provides a modulated output signal, y(n) in response to the input signal. The method is characterized in comprising the step of controlling the sigma delta modulator to change the quantization noise transfer function, NTF, in response to a signal feature, A(n), which is correlated with the input signal.

Owner:ANALOG DEVICES INC

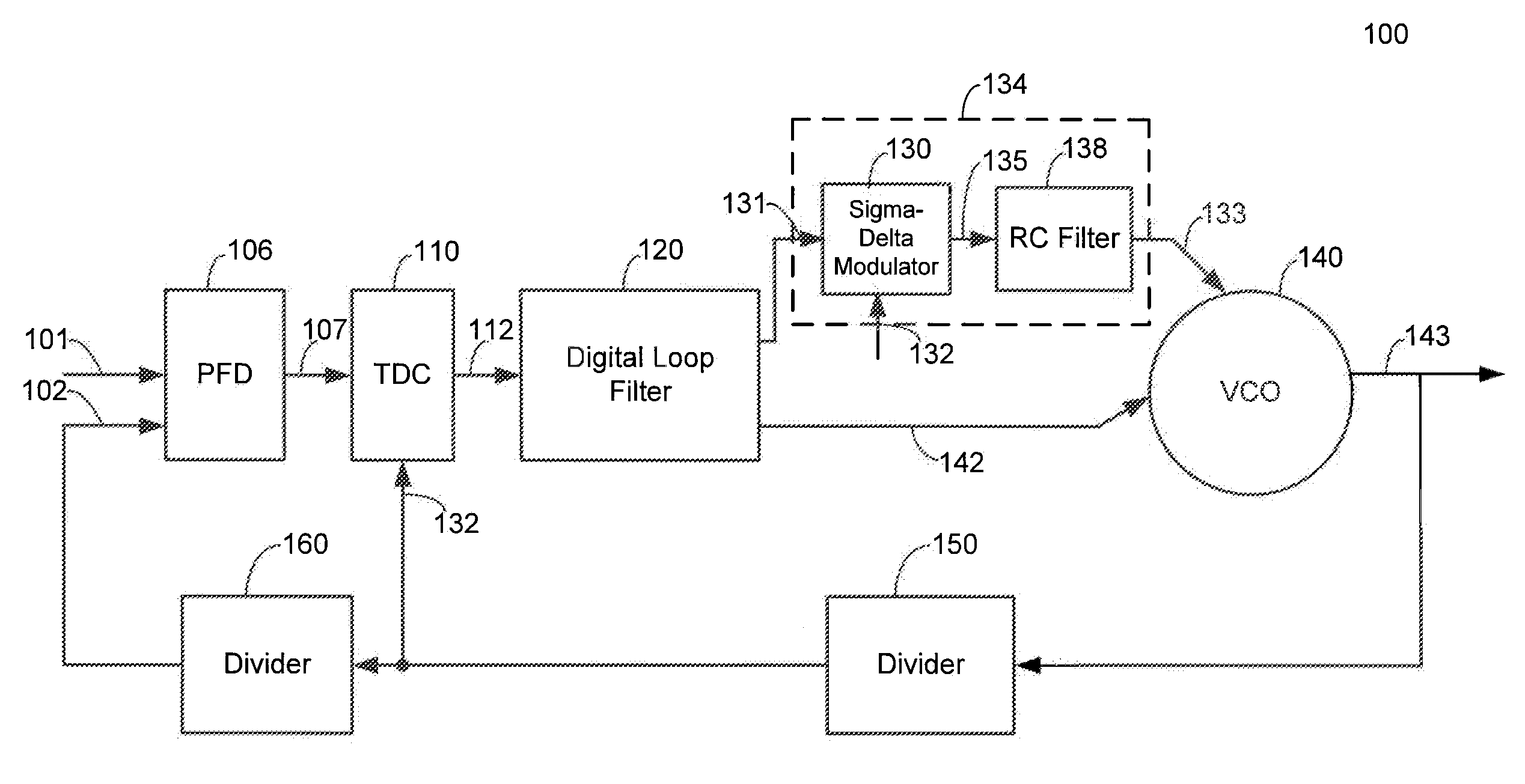

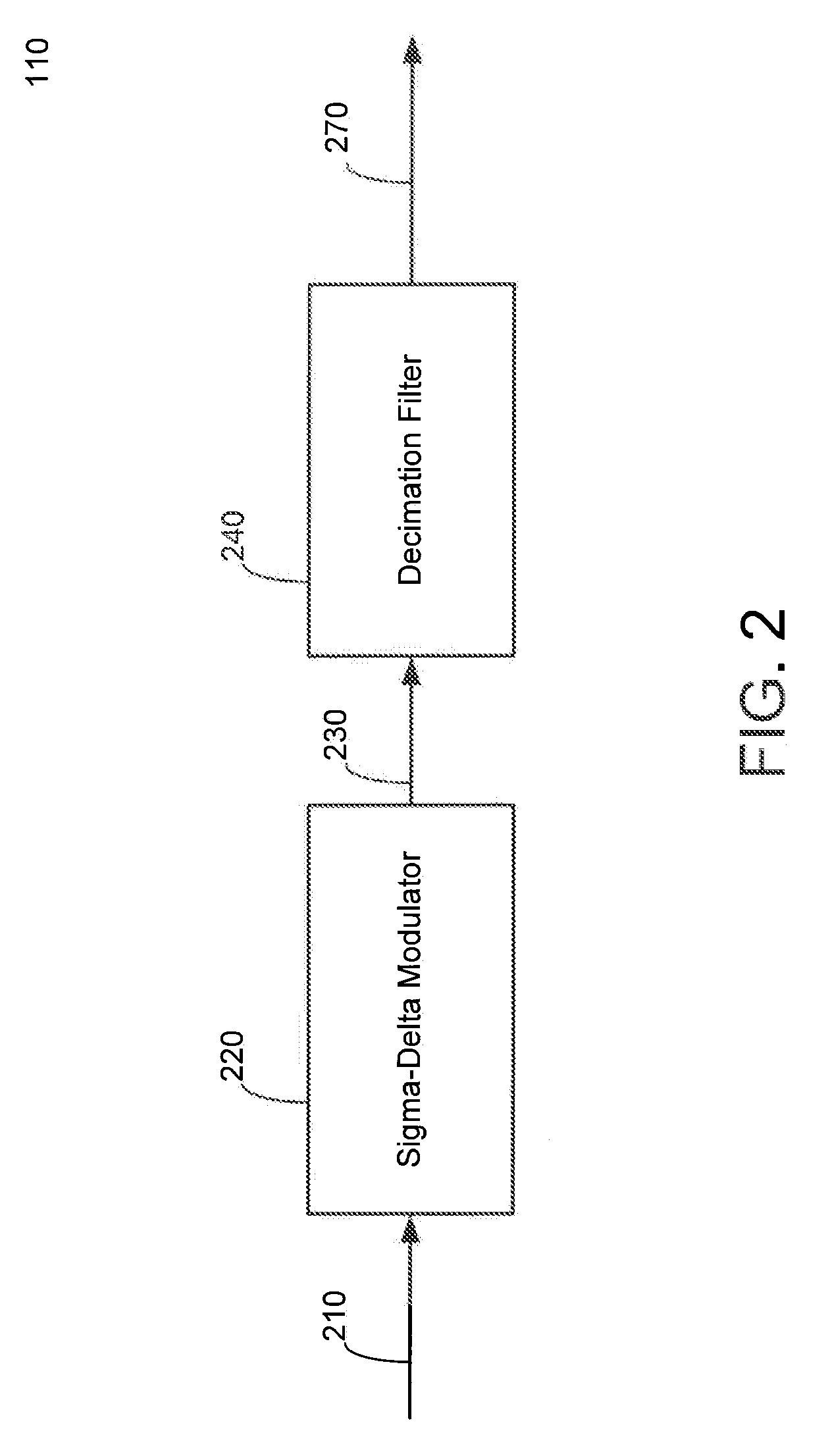

Systems, Circuits, and Methods for a Sigma-Delta Based Time to Digital Converter

ActiveUS20130257494A1Electric signal transmission systemsPulse automatic controlIntegratorEngineering

Systems, methods, and circuits provide a time to digital converter comprising a sigma-delta modulator. The sigma-delta based time to digital converter may receive an analog signal representing a phase error between a reference clock signal and a feedback clock signal and generate a digital signal representing the phase error. The sigma-delta modulator may comprise a subtractor, an integrator, a feedback path, and a quantizer. The subtractor may receive the analog signal and subtract a feedback signal from the analog signal and the integrator may integrate the output of the subtractor. The sigma-delta modulator may accumulate a voltage or a charge over a capacitor as pulses are received from the analog signal and after a number of clock cycles, the capacitor may be discharged to generate a pulse in an output signal.

Owner:AVAGO TECH INT SALES PTE LTD

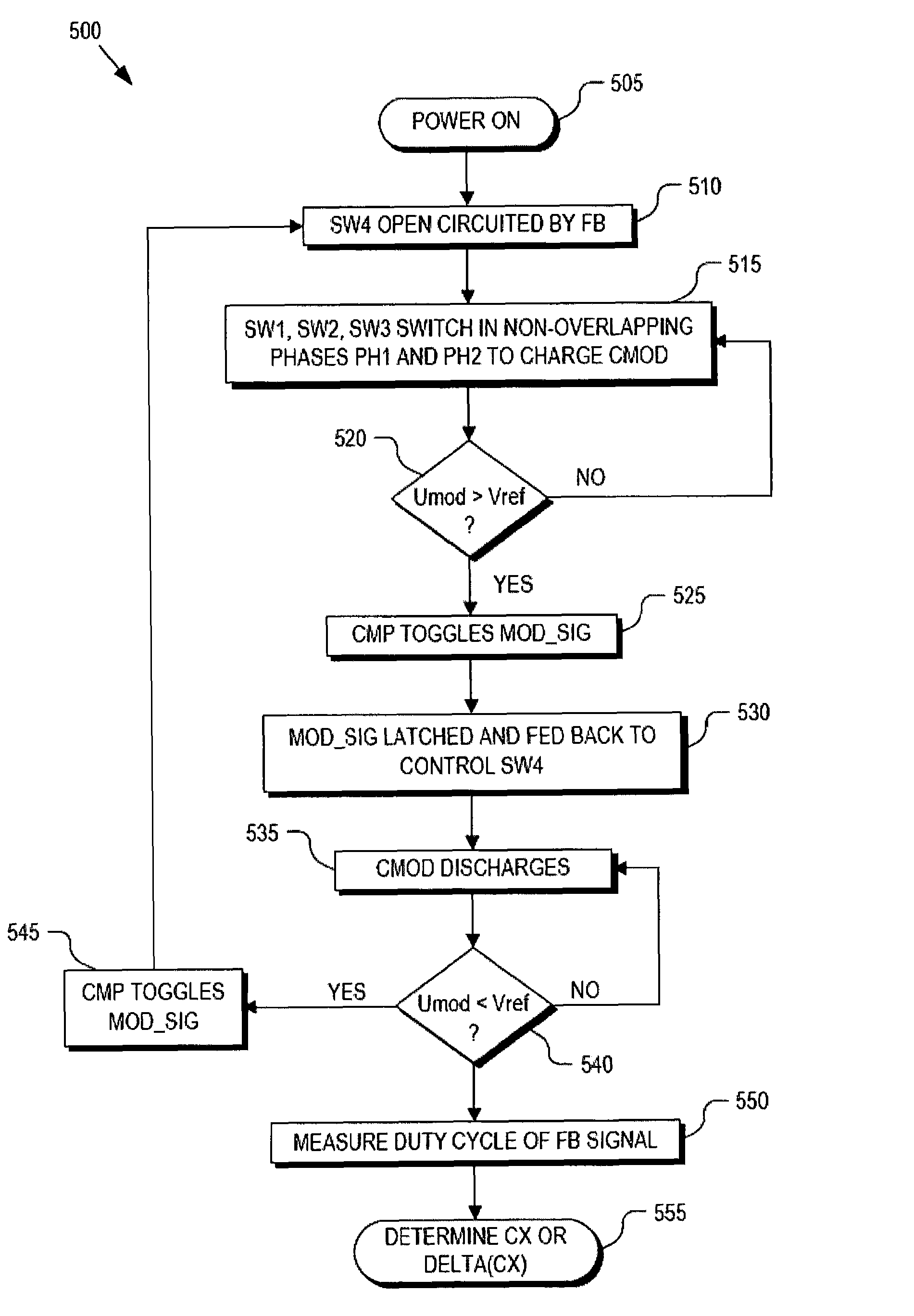

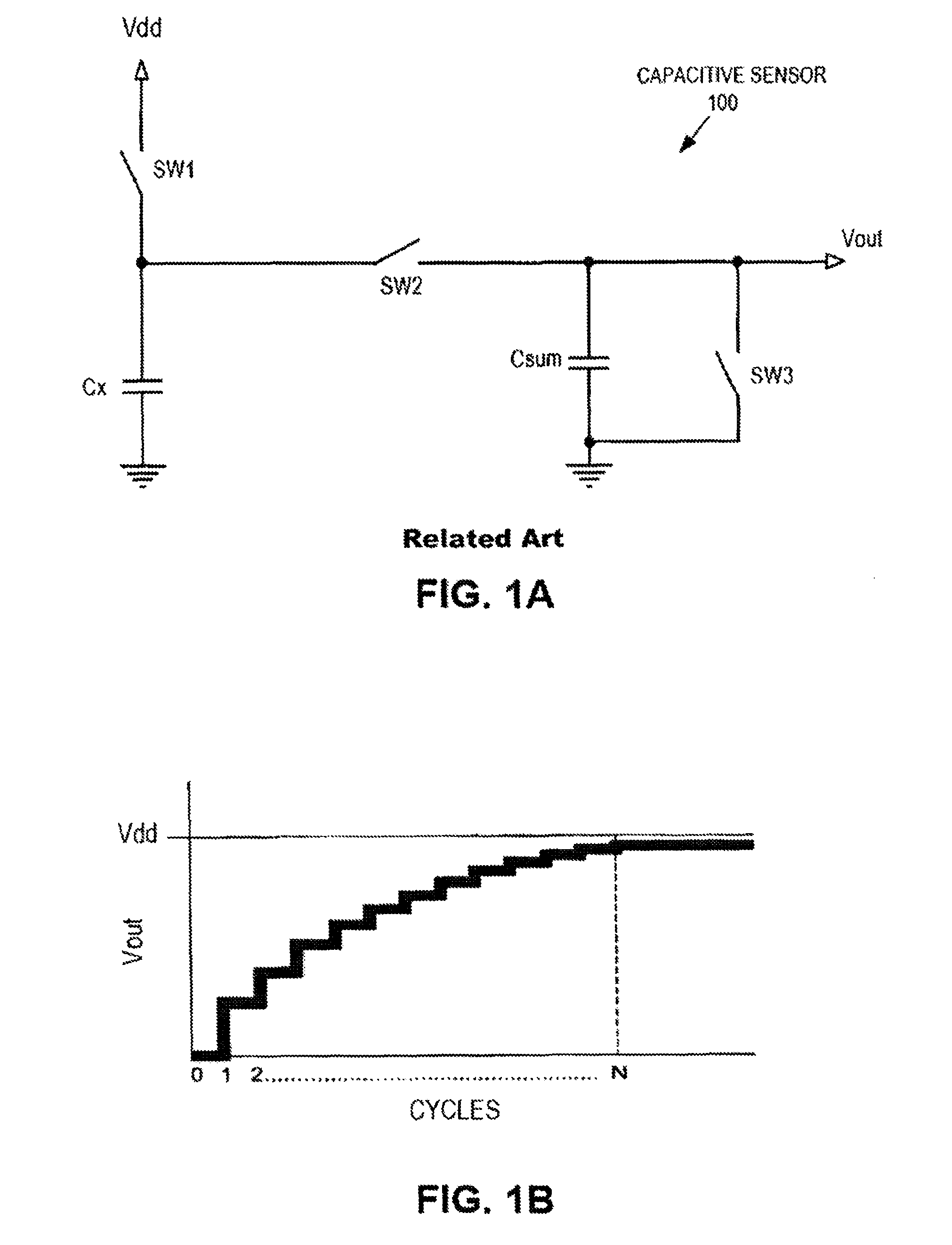

Capacitive field sensor with sigma-delta modulator

A capacitive sensor includes a switching capacitor circuit, a comparator, and a charge dissipation circuit. The switching capacitor circuit reciprocally couples a sensing capacitor in series with a modulation capacitor during a first switching phase and discharges the sensing capacitor during a second switching phase. The comparator is coupled to compare a voltage potential on the modulation capacitor to a reference and to generate a modulation signal in response. The charge dissipation circuit is coupled to the modulation capacitor to selectively discharge the modulation capacitor in response to the modulation signal.

Owner:CYPRESS SEMICON CORP

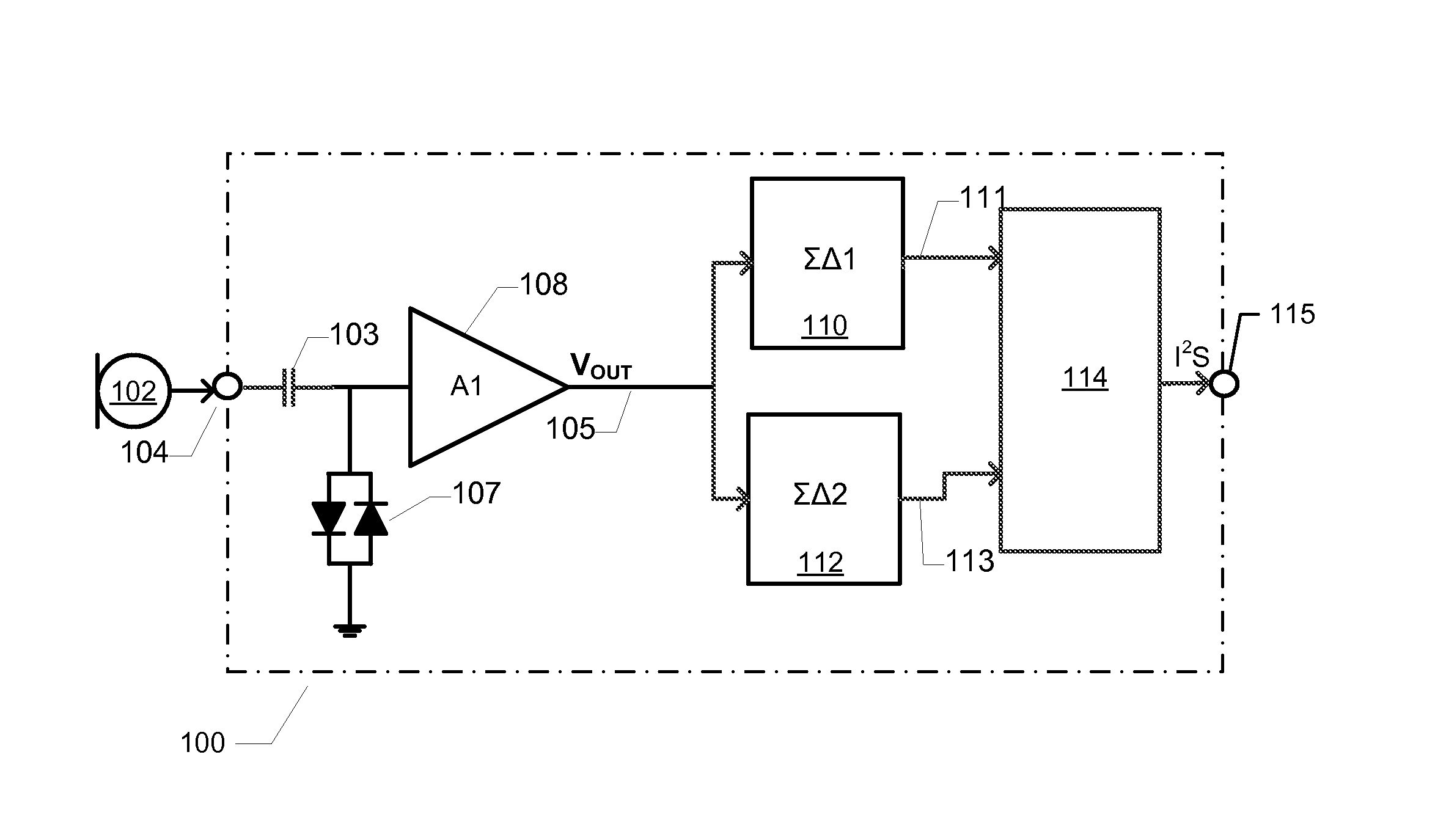

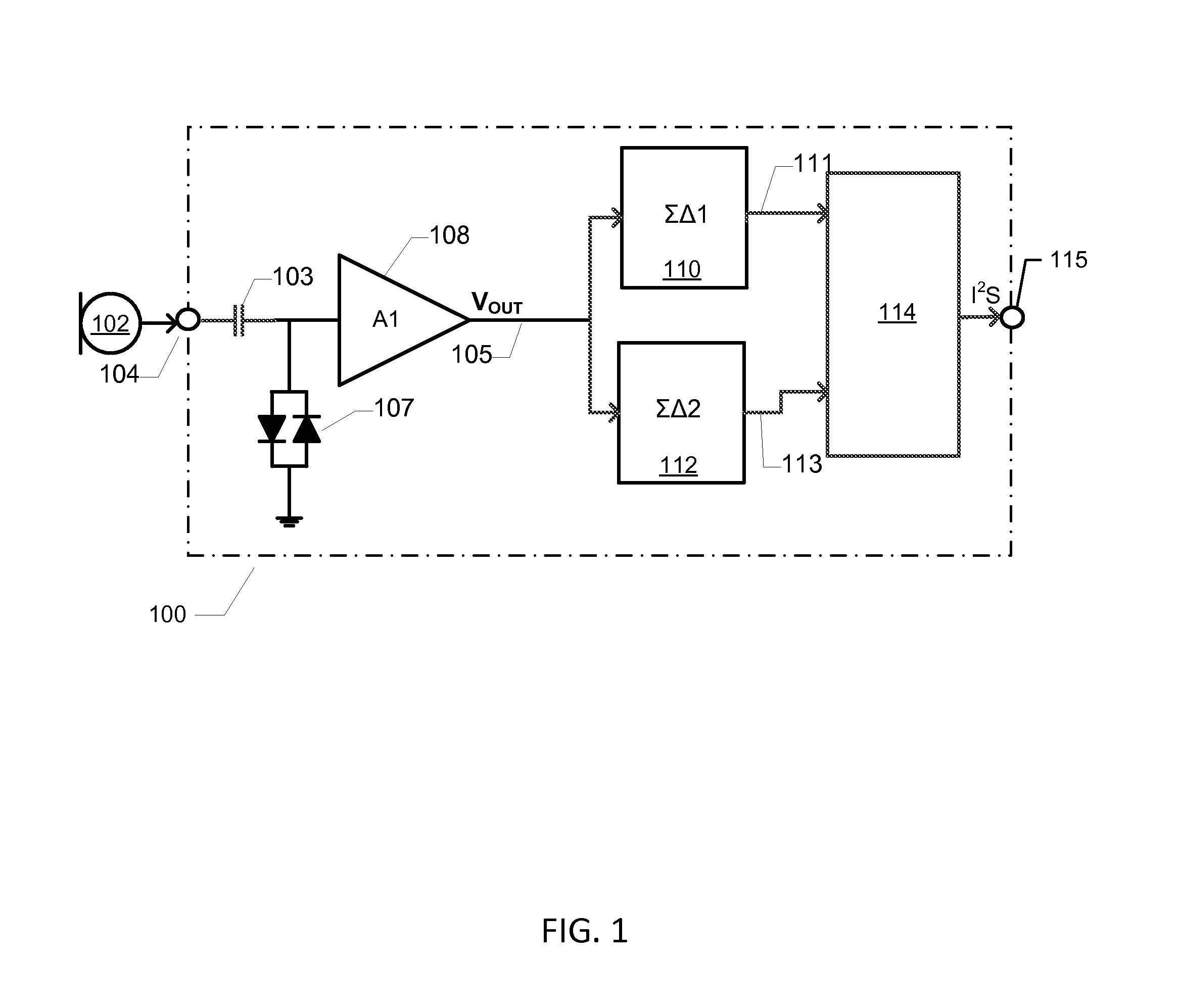

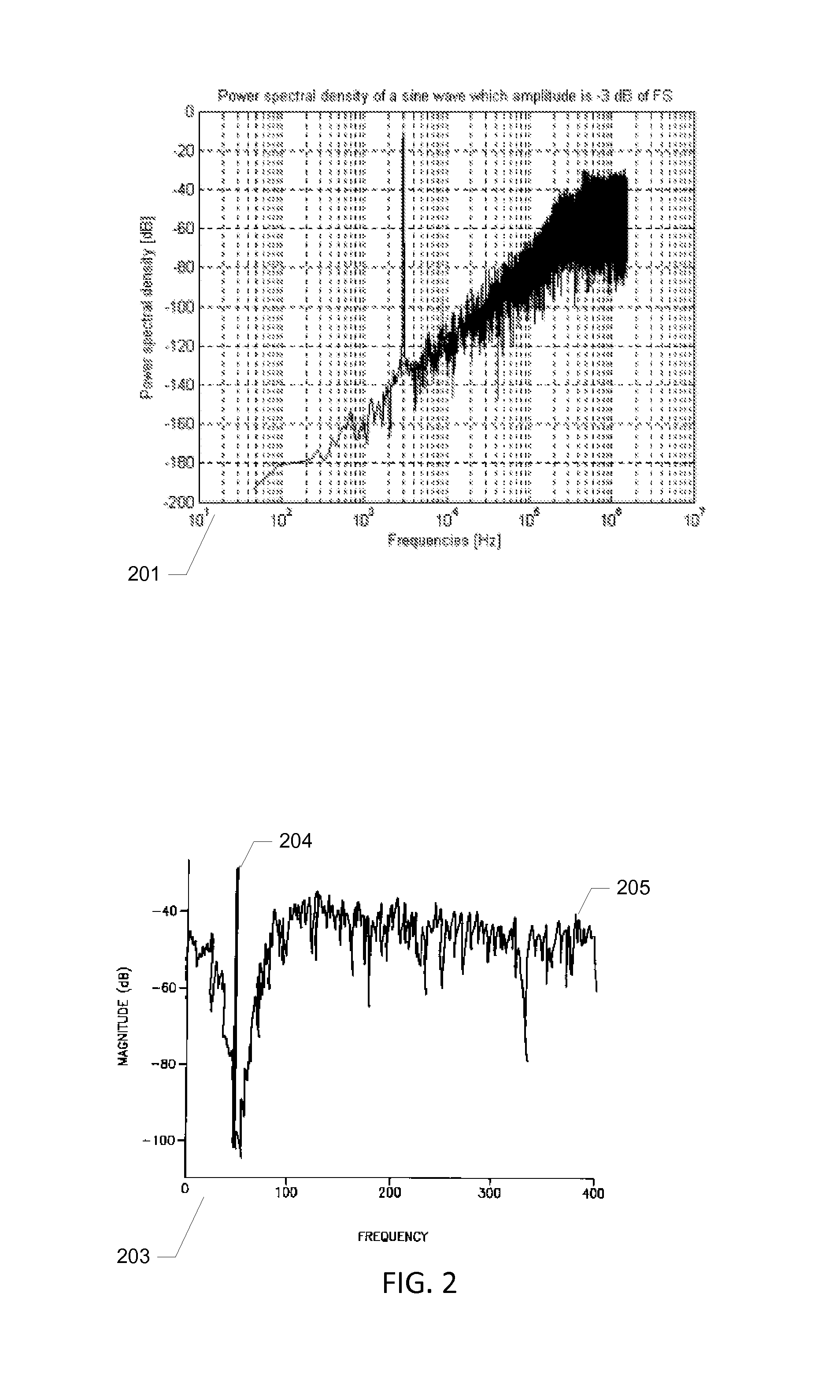

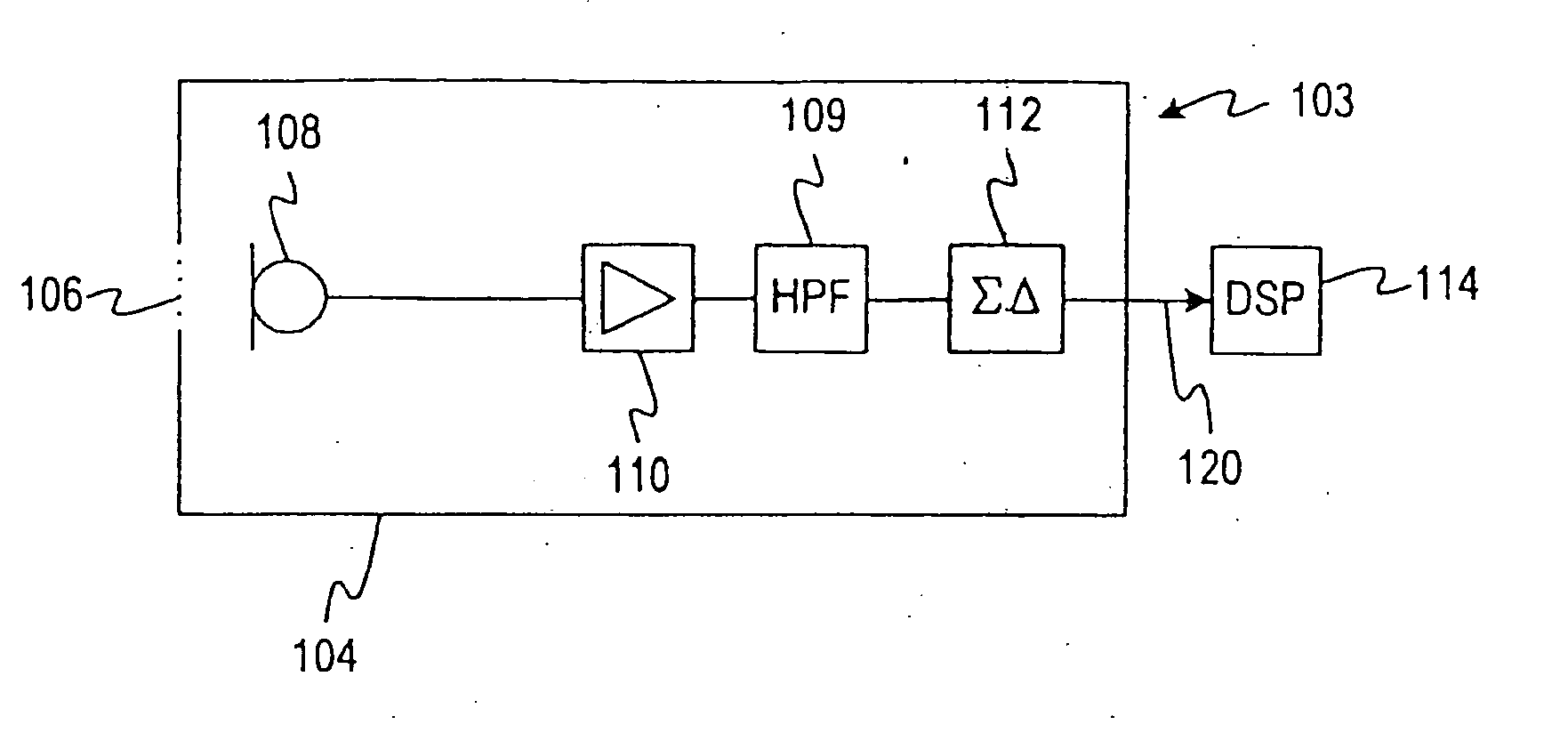

Transducer amplification circuit

ActiveUS20150281836A1Accurate representationImprove responseAmplifier modifications to reduce non-linear distortionSemiconductor electrostatic transducersSonificationTransducer

A transducer amplification circuit may include a preamplifier circuit with a signal input receiving a transducer signal to provide an amplified transducer signal comprising audible frequency components and ultrasonic frequency components. The transducer amplification circuit may include a first sigma-delta modulator configured to sample and quantize the amplified transducer signal to generate a first digital transducer signal comprising a first quantization noise signal. The first sigma-delta modulator may include a first noise transfer function having a high pass response in at least a portion of an audible frequency range to push the quantization noise signal to ultrasonic frequencies. A second sigma-delta modulator is configured to sample and quantize the amplified transducer signal to generate a second digital transducer signal comprising a second quantization noise signal. The second sigma-delta modulator may include a second noise transfer function with a magnitude minimum placed at the ultrasonic frequencies.

Owner:ANALOG DEVICES INT UNLTD

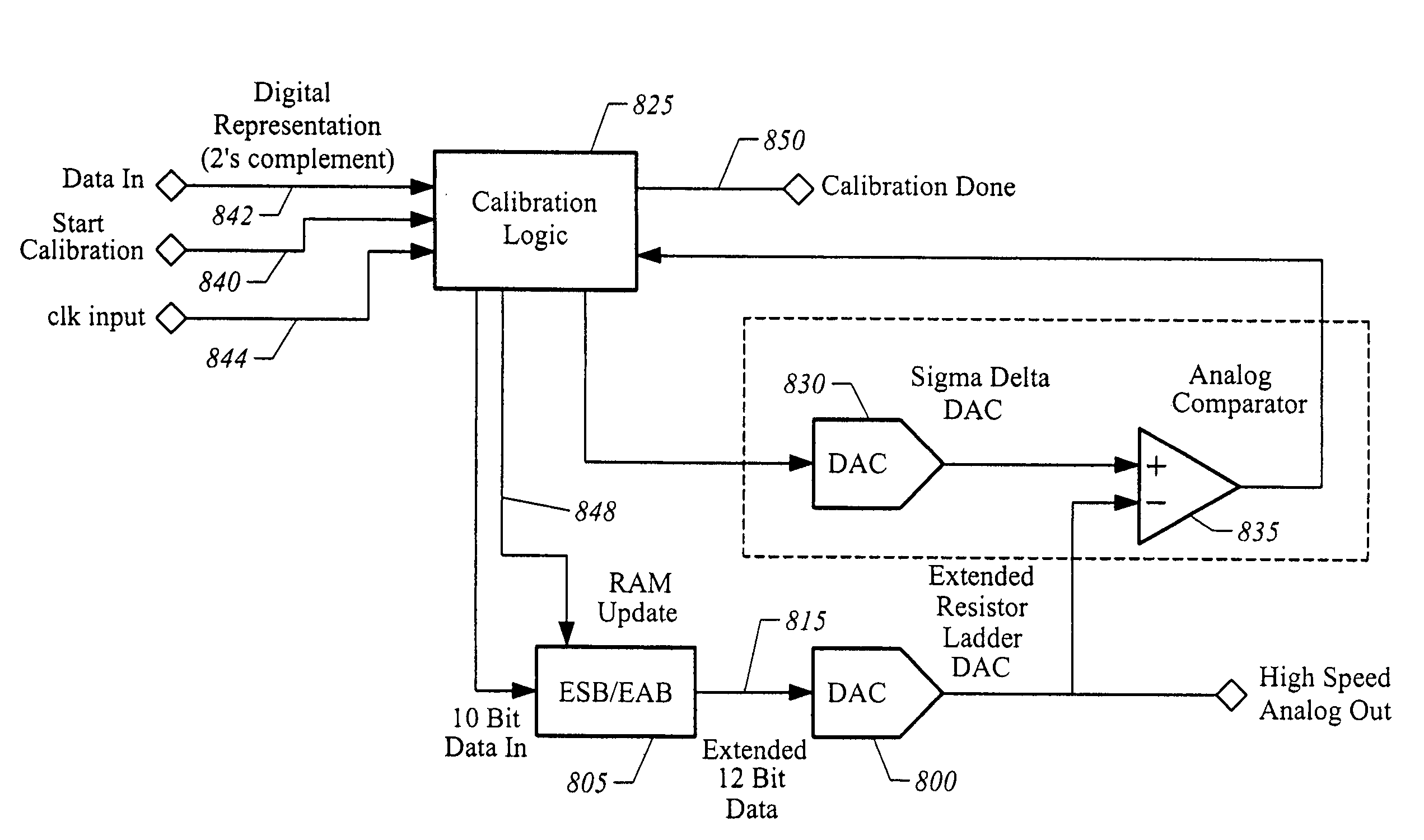

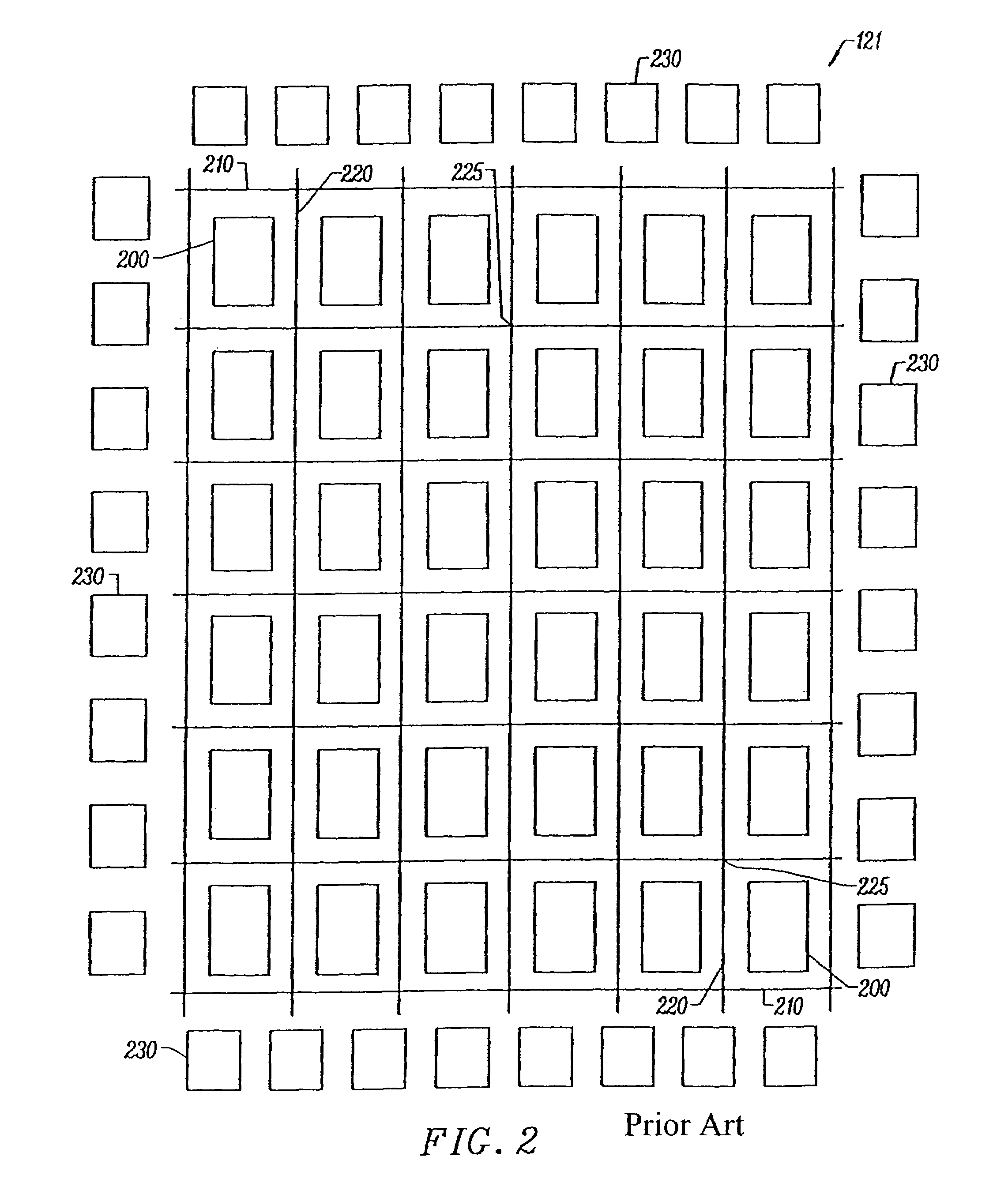

Analog-to-digital converter for programmable logic

InactiveUS6956512B1Electric signal transmission systemsResistance/reactance/impedenceProgrammable logic deviceLogic cell

Digital-to-analog and analog-to-digital conversion are implemented in or using programmable logic. The DAC and ADC circuits may be hardwired in a programmable logic integrated circuit or may be implemented using an intellectual property (IP) core. The IP core would be a series of bits to configure the logic cells and other programmable logic of an integrated circuit to include one or more DACs or ADC, or both on the same integrated circuit. The DAC may be a sigma-delta-modulator-based implementation or a resistor-ladder-based implementation.

Owner:ALTERA CORP

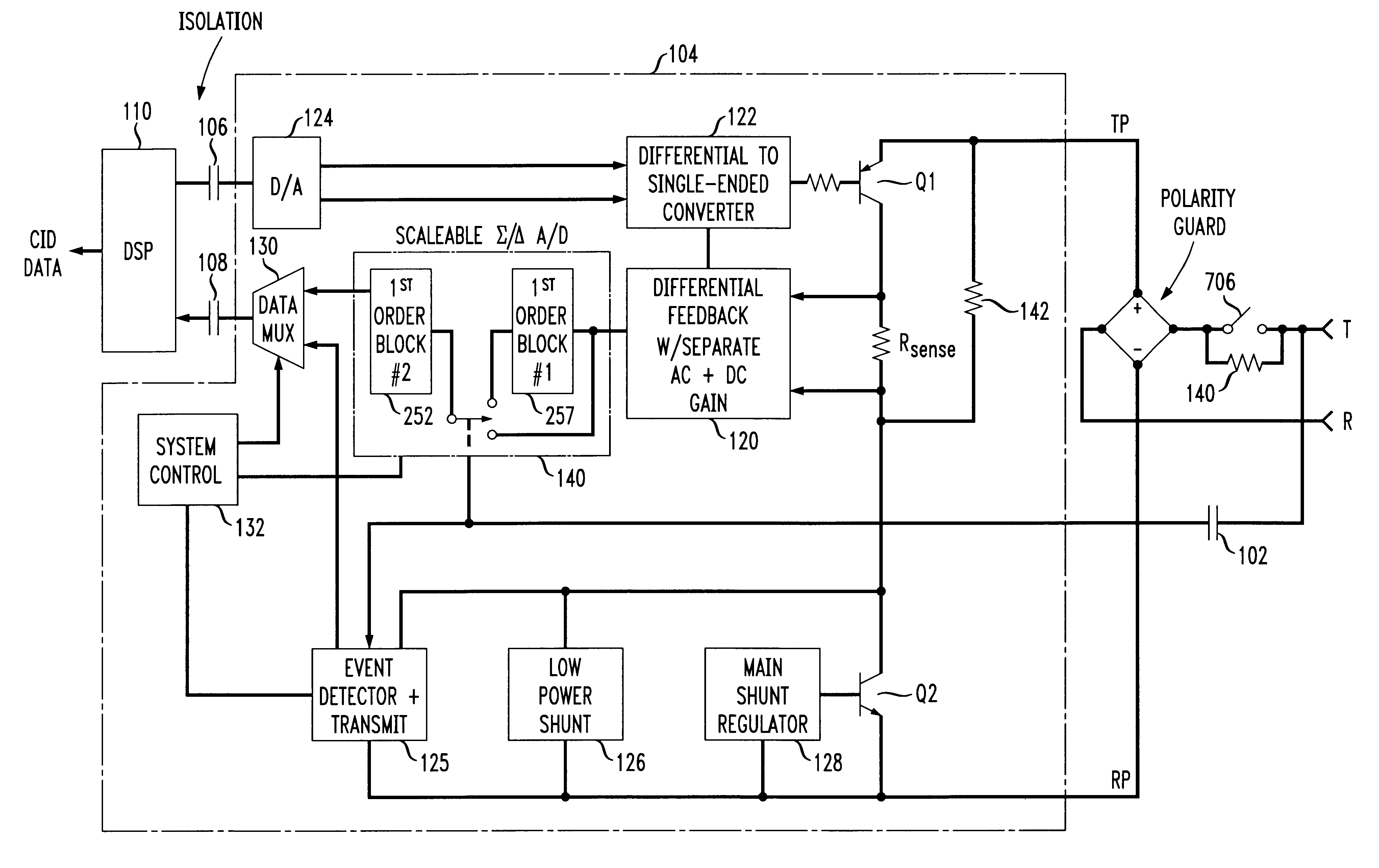

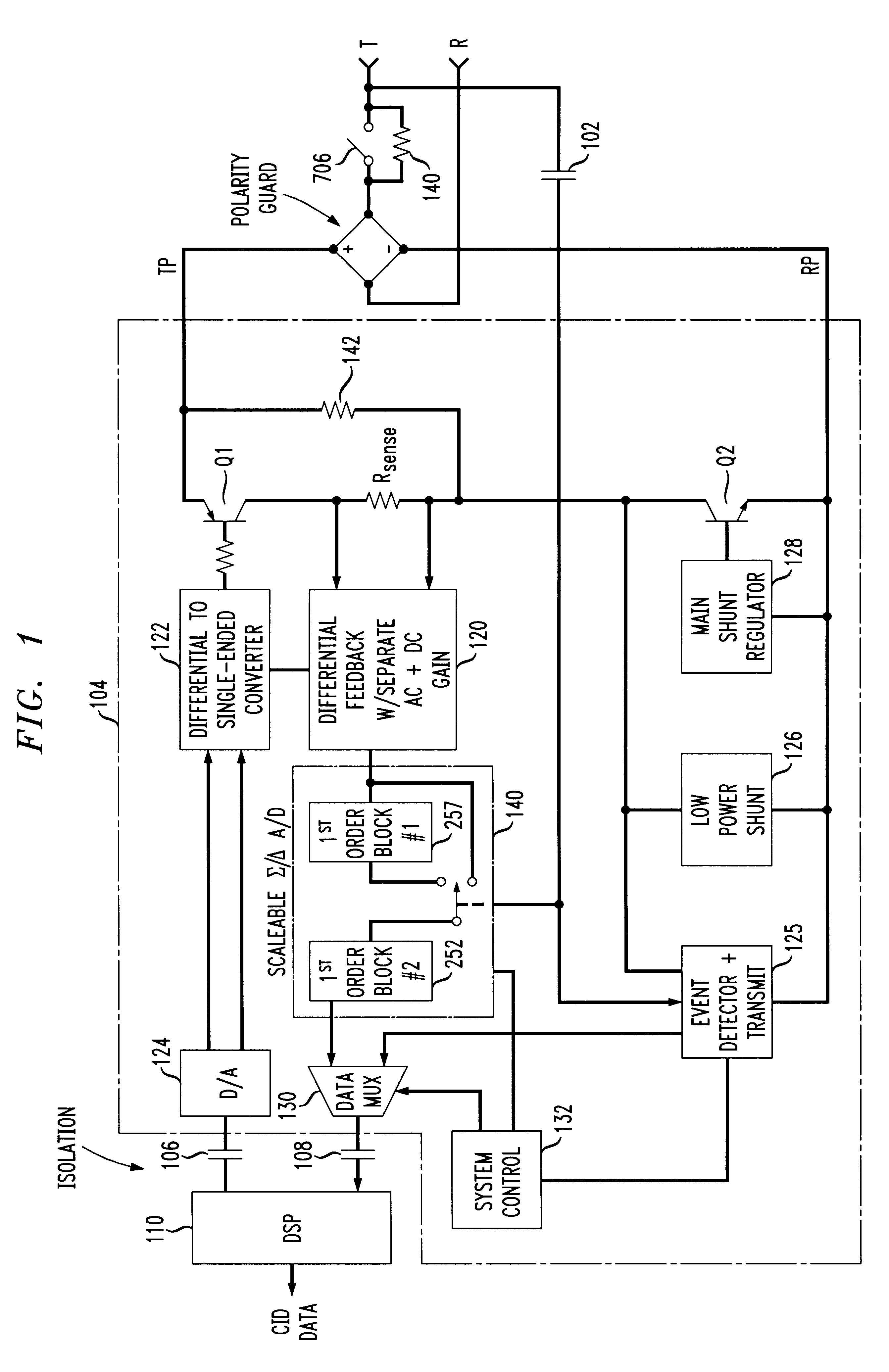

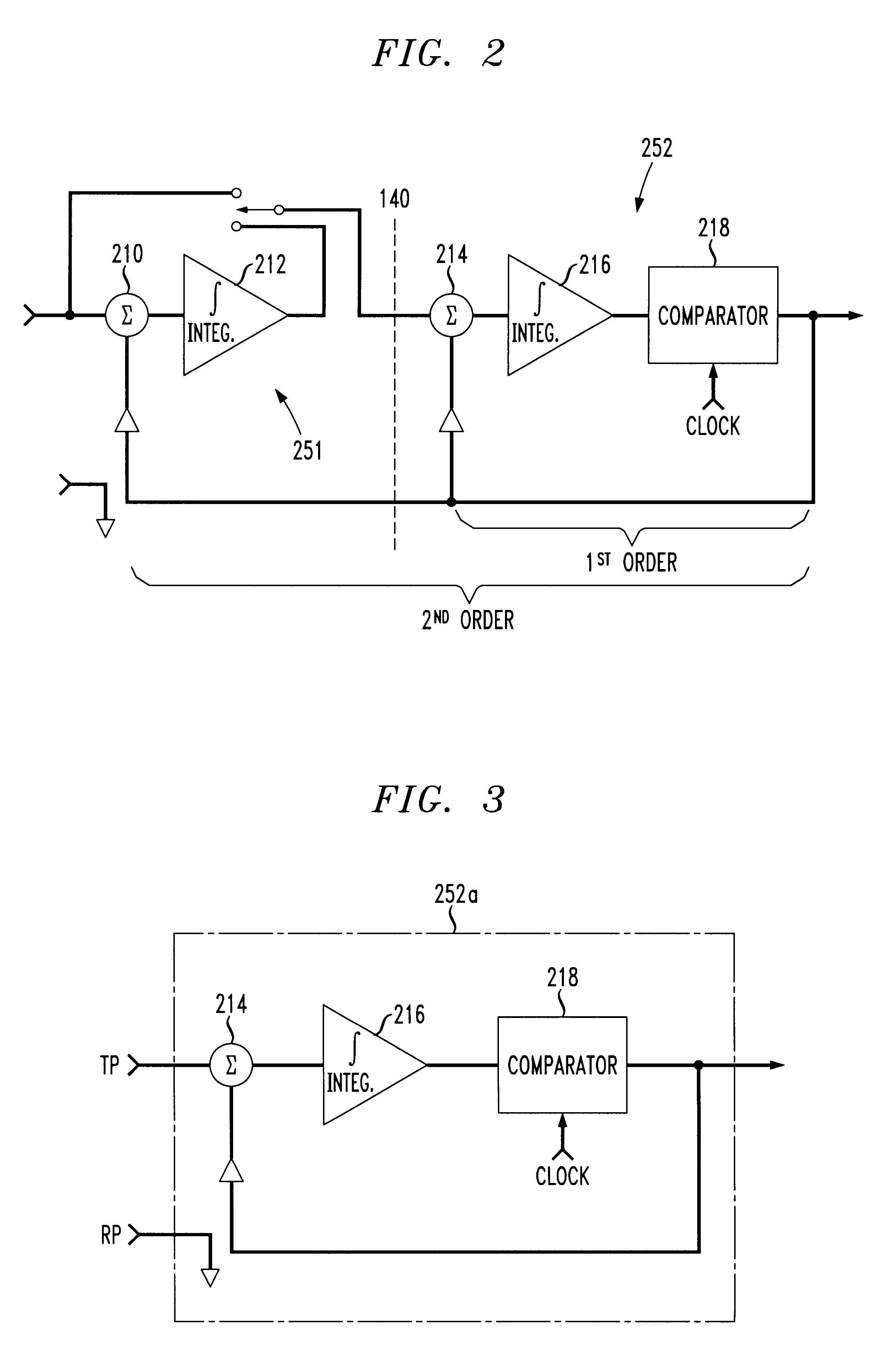

Call related information reception using sigma/delta modulation

InactiveUS6205219B1Interconnection arrangementsUnauthorised/fraudulent call preventionGreek letter sigmaDigitization

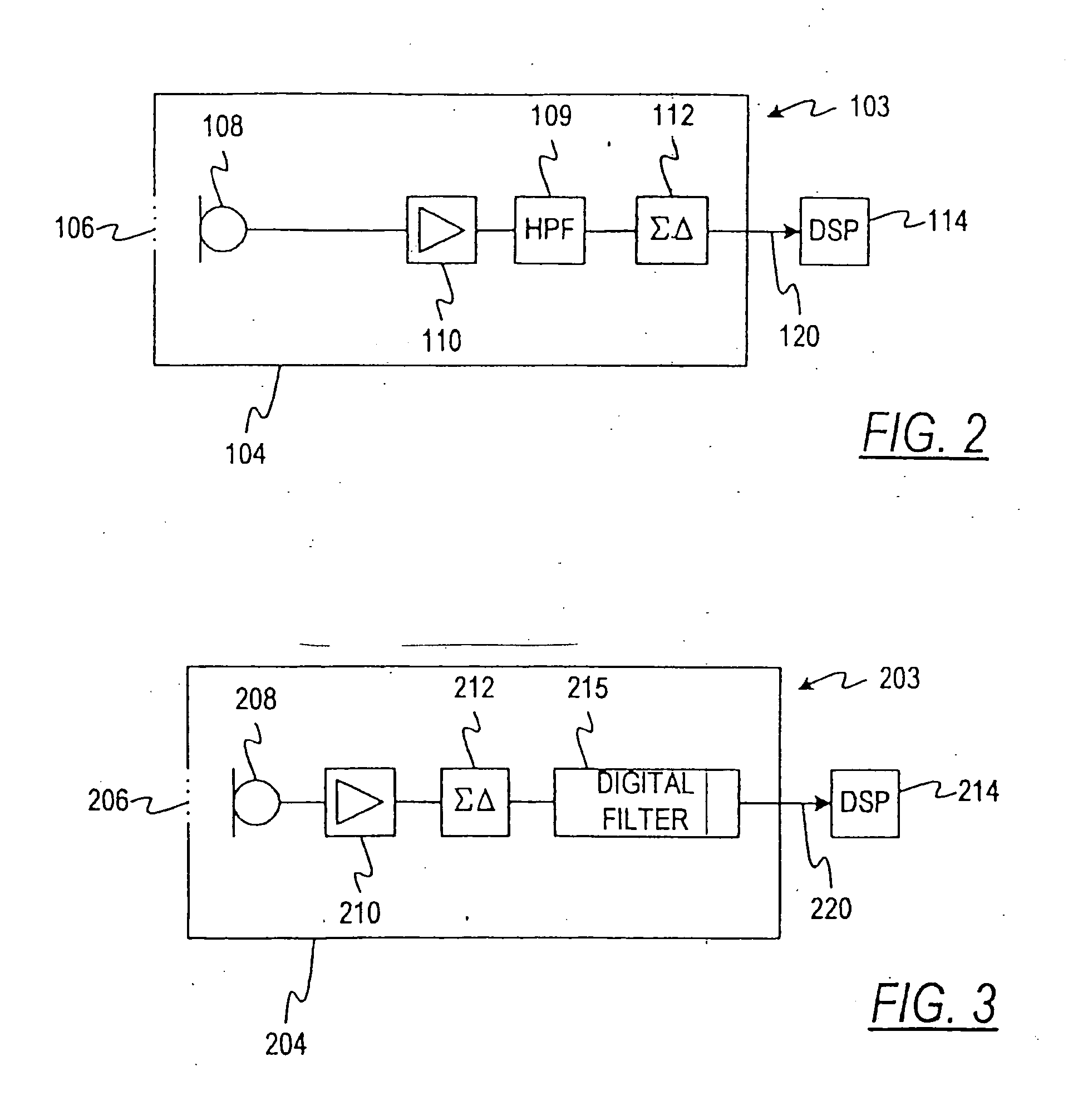

A method and apparatus to receive and demodulate call related information, e.g., Caller ID information, in an audio codec placed on the line side and powered by current drawn from the telephone line. The audio codec includes a 1st order SIGMA / DELTA A / D converter to digitize the signal from the telephone line with SIGMA / DELTA modulation. The 1st order SIGMA / DELTA A / D converter may be a scaleable component capable of alternative operation in a 2nd order. The SIGMA / DELTA encoded digitized signal is digitally processed by a DSP including an amplifier module, a digital filter, a limit / slice module, and an FSK decoder to receive and output the call related information. Placement of the audio codec on the line side and the scaleable SIGMA / DELTA A / D converter provides significantly reduced power requirements for the audio codec, thus allowing operation from power derived from the telephone line. In another embodiment, to further reduce power consumption of the audio codec, the 1st order SIGMA / DELTA A / D converter is sampled at a slower rate than is conventional, e.g., by first dividing or otherwise providing a slower sampling clock.

Owner:LUCENT TECH INC +1

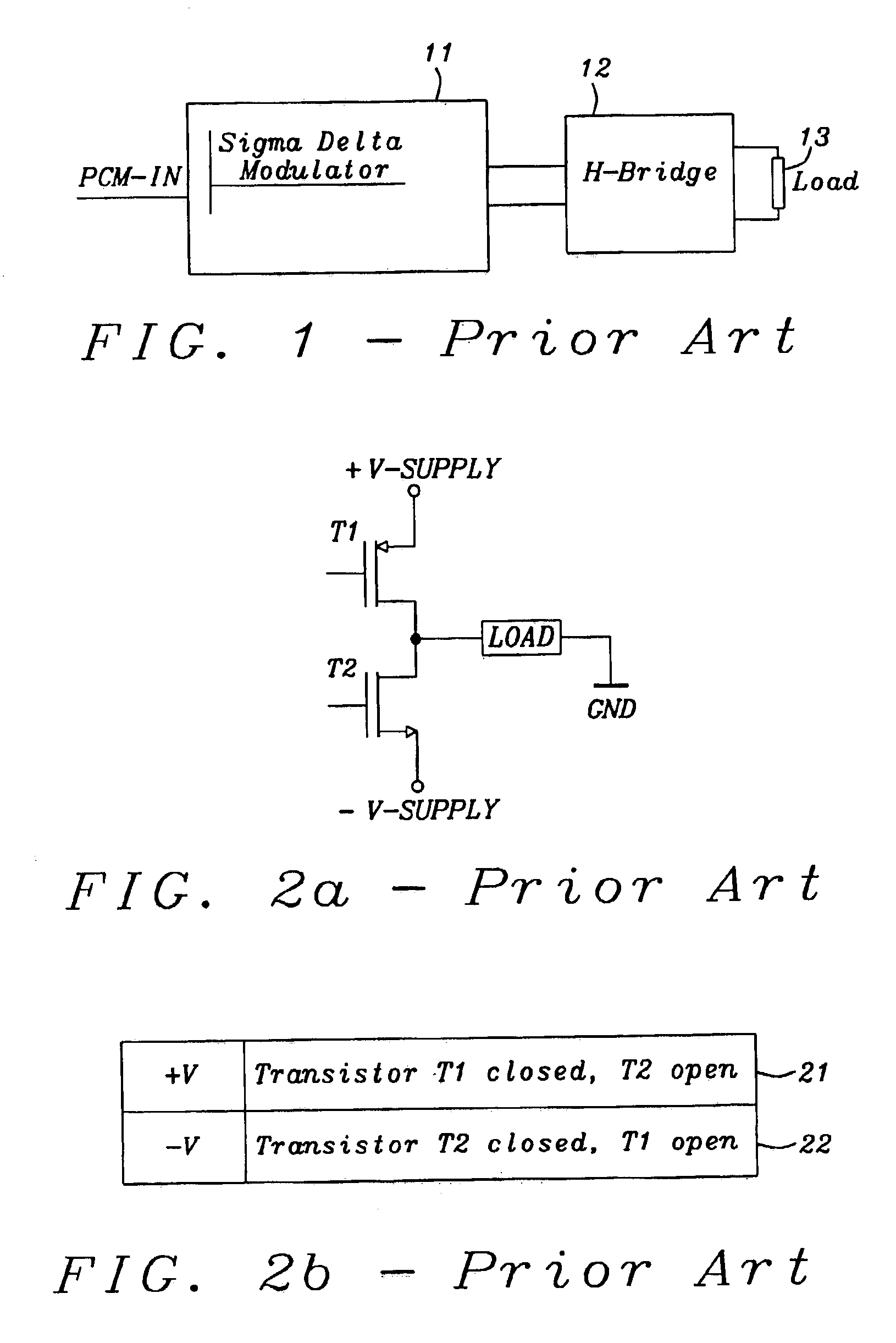

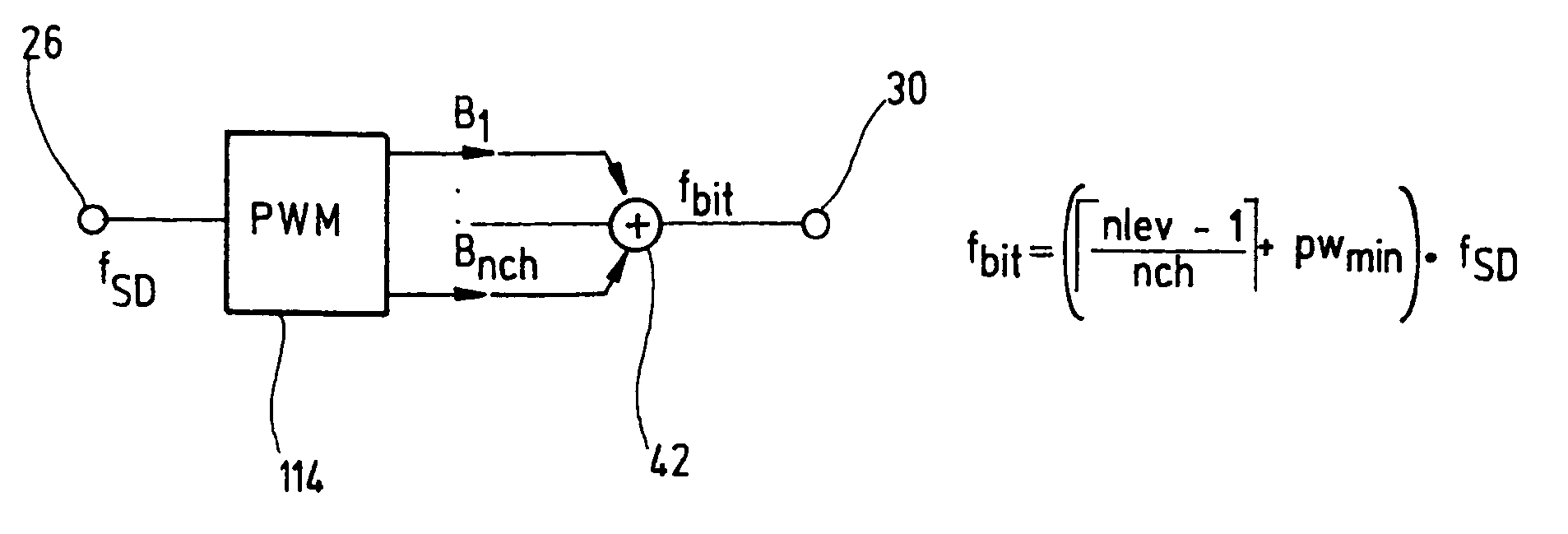

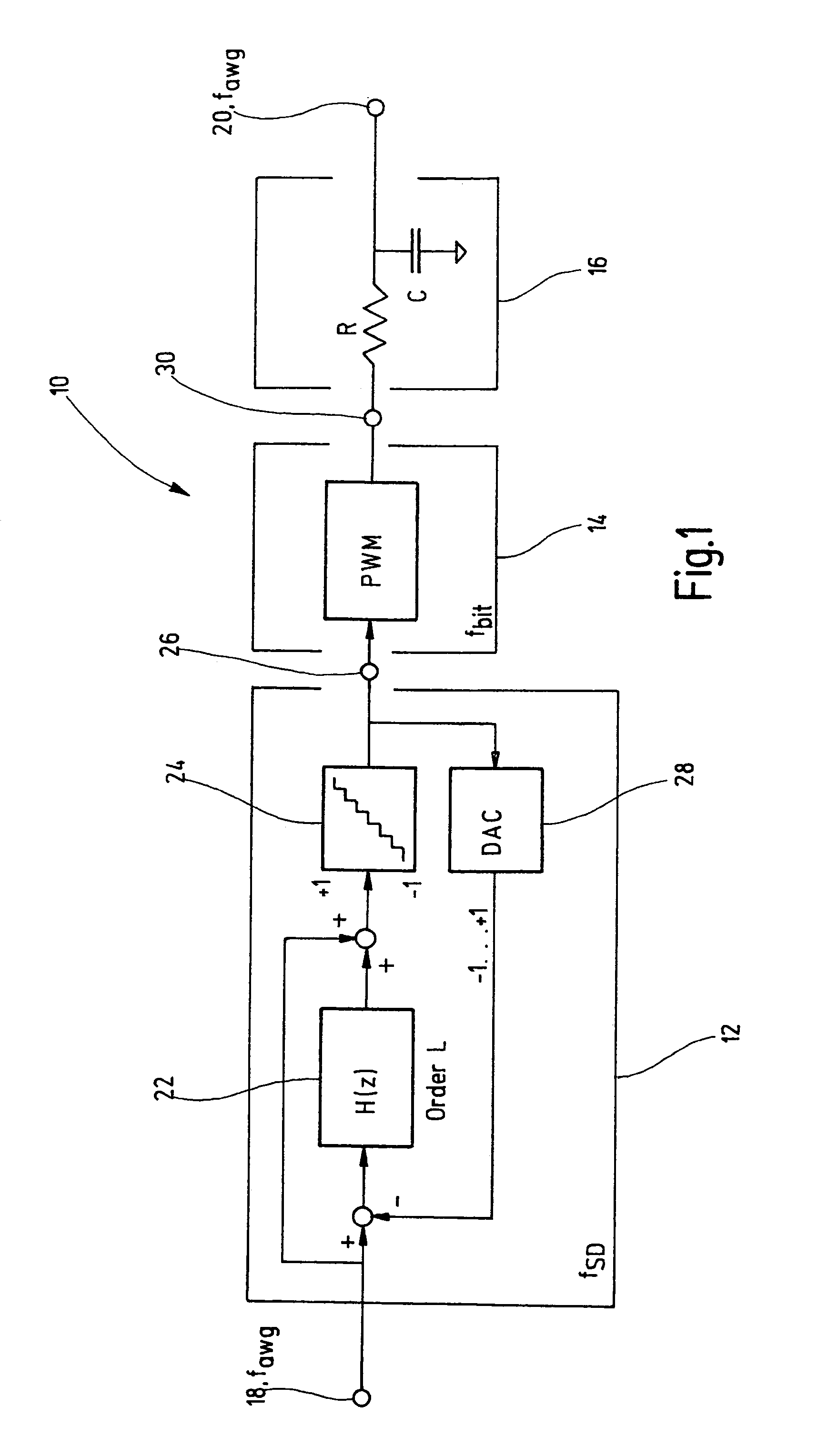

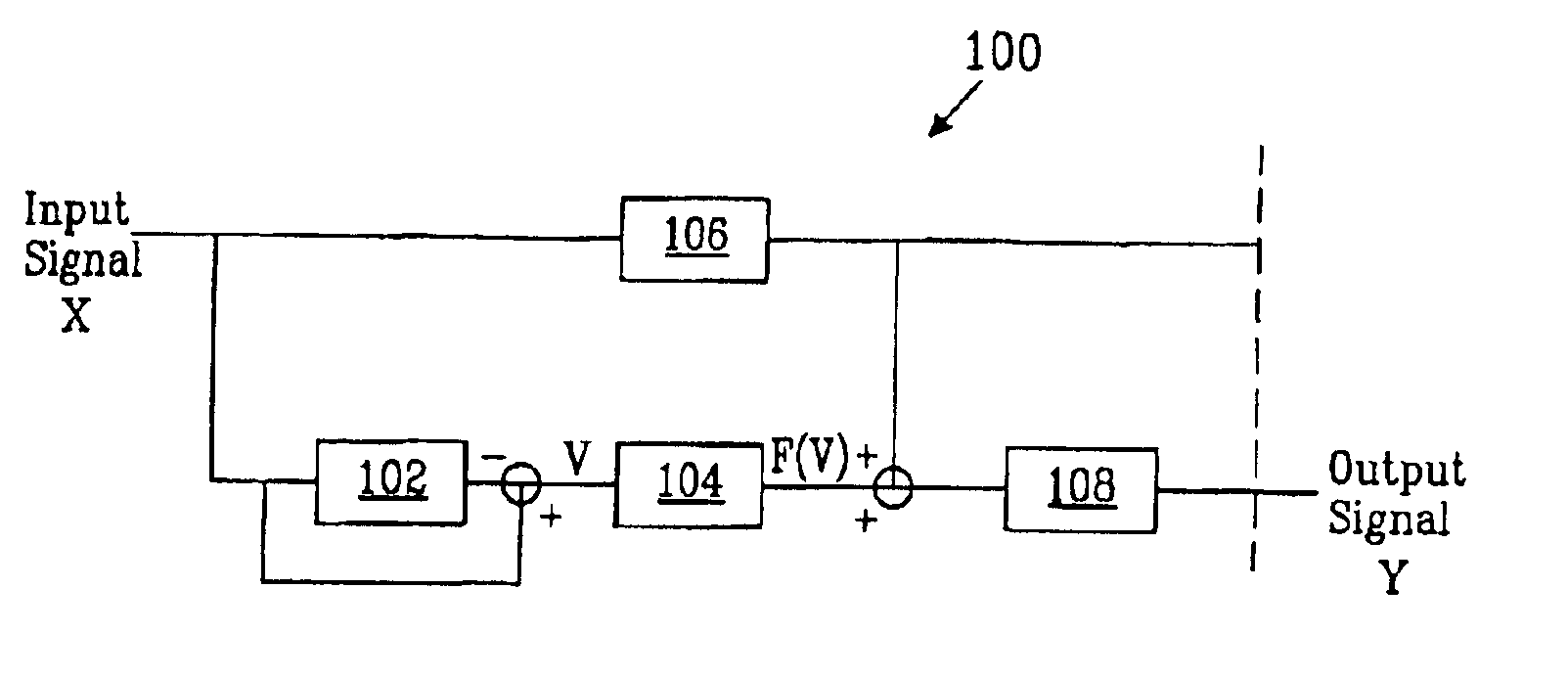

Sigma-delta modulator with PWM output

ActiveUS6972704B2Optimize timingHigh frequency ATE bit rateElectric signal transmission systemsDigital circuit testingQuantum electrodynamicsSigma delta modulation

The present invention relates to a method for providing an improved generated arbitrary waveform using a sigma-delta modulator with pulse width modulation, said method comprising the steps of sigma-delta modulation of said generated arbitrary waveform, and pulse width modulation of the output signal of said sigma-delta modulator, introducing a minimum pulse width (pwmin) during said pulse width modulation.

Owner:ADVANTEST CORP

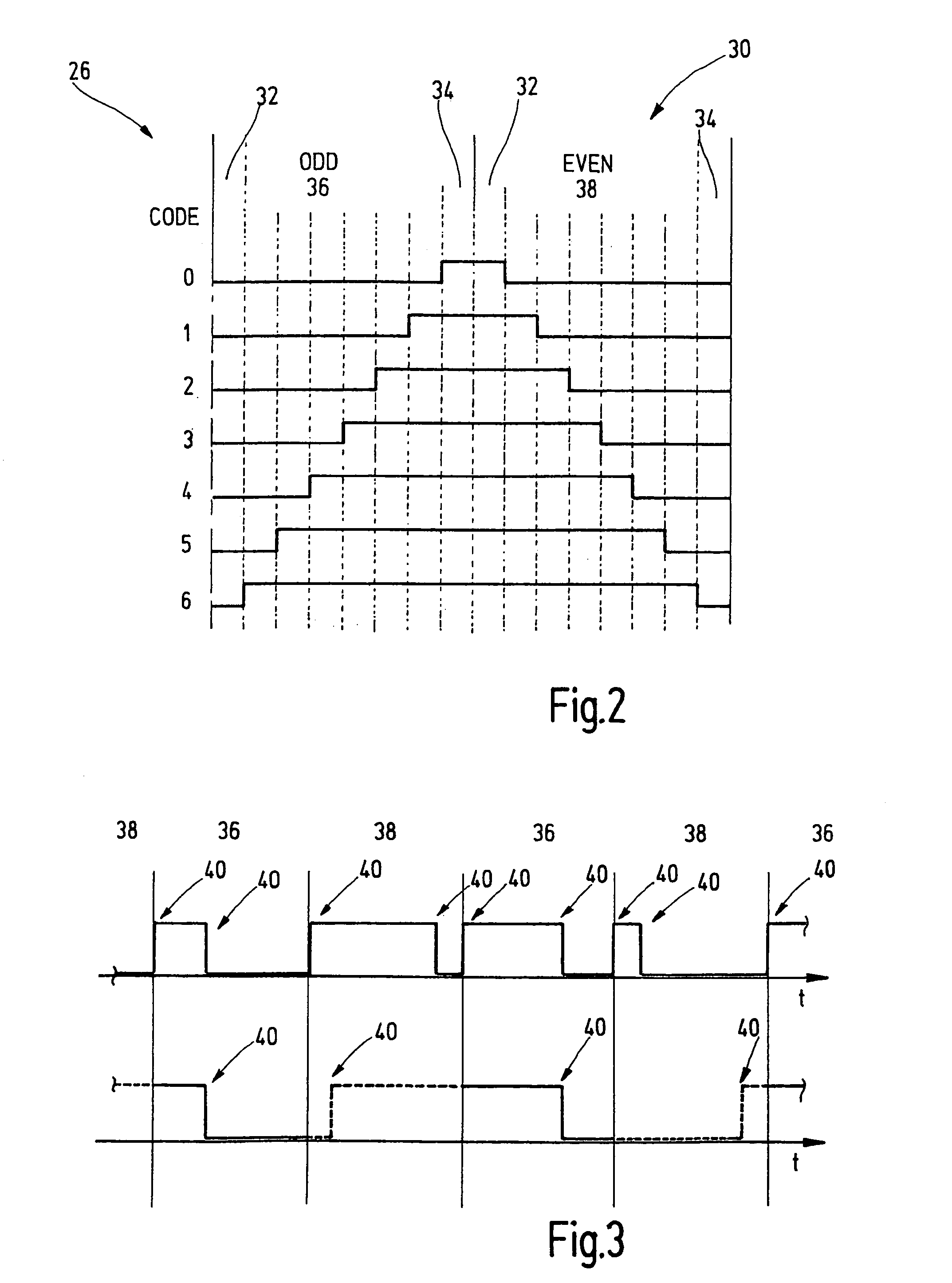

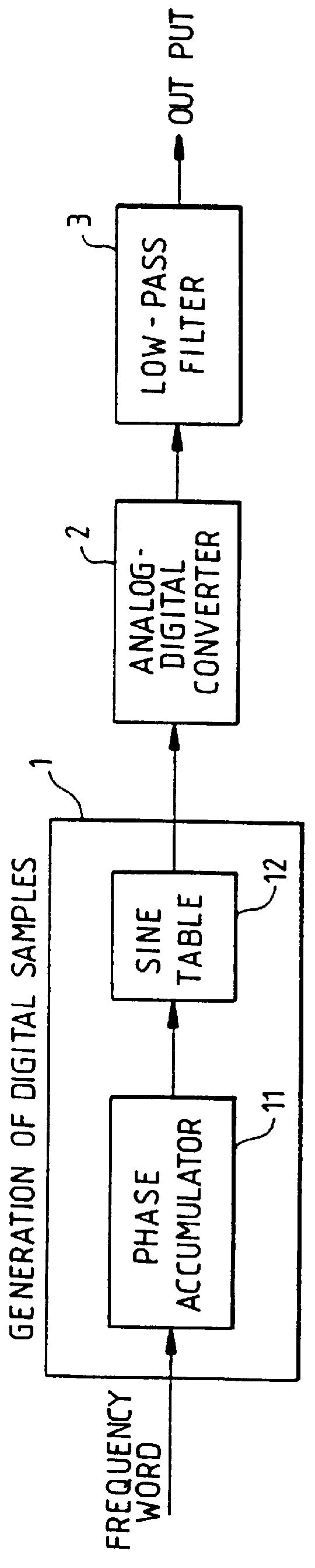

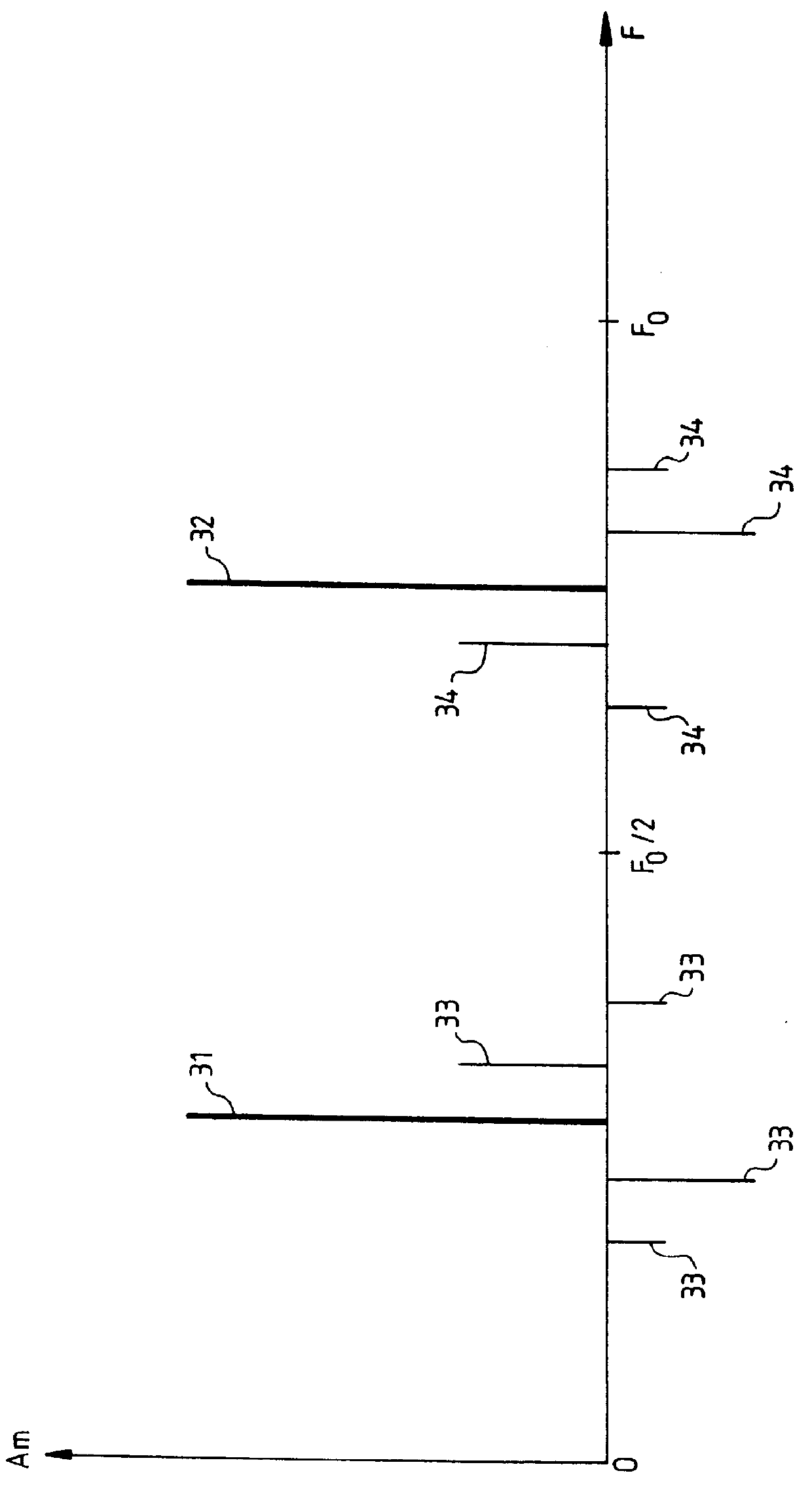

Device for the generation of analog signals through digital-analog converters, especially for direct digital synthesis

InactiveUS6075474AElectric signal transmission systemsAnalogue conversionDigital analog converterLeast significant bit

A device for the generation of analog signals by means of analog-digital converters comprises a block for the generation of words encoded on N bits and an analog-digital converter whose input is encoded on M bits, M being smaller than N. The device furthermore comprises a sigma-delta modulator, at the output of the first block, the bus being separated into M most significant bits reserved for the input of the analog-digital converter and N-M least significant bits that enter the sigma-delta modulator, the output of this modulator being an M-bit bus that is added to the M output bits of the word generation block by digital addition means, M being smaller than N.

Owner:THOMSON CSF SA

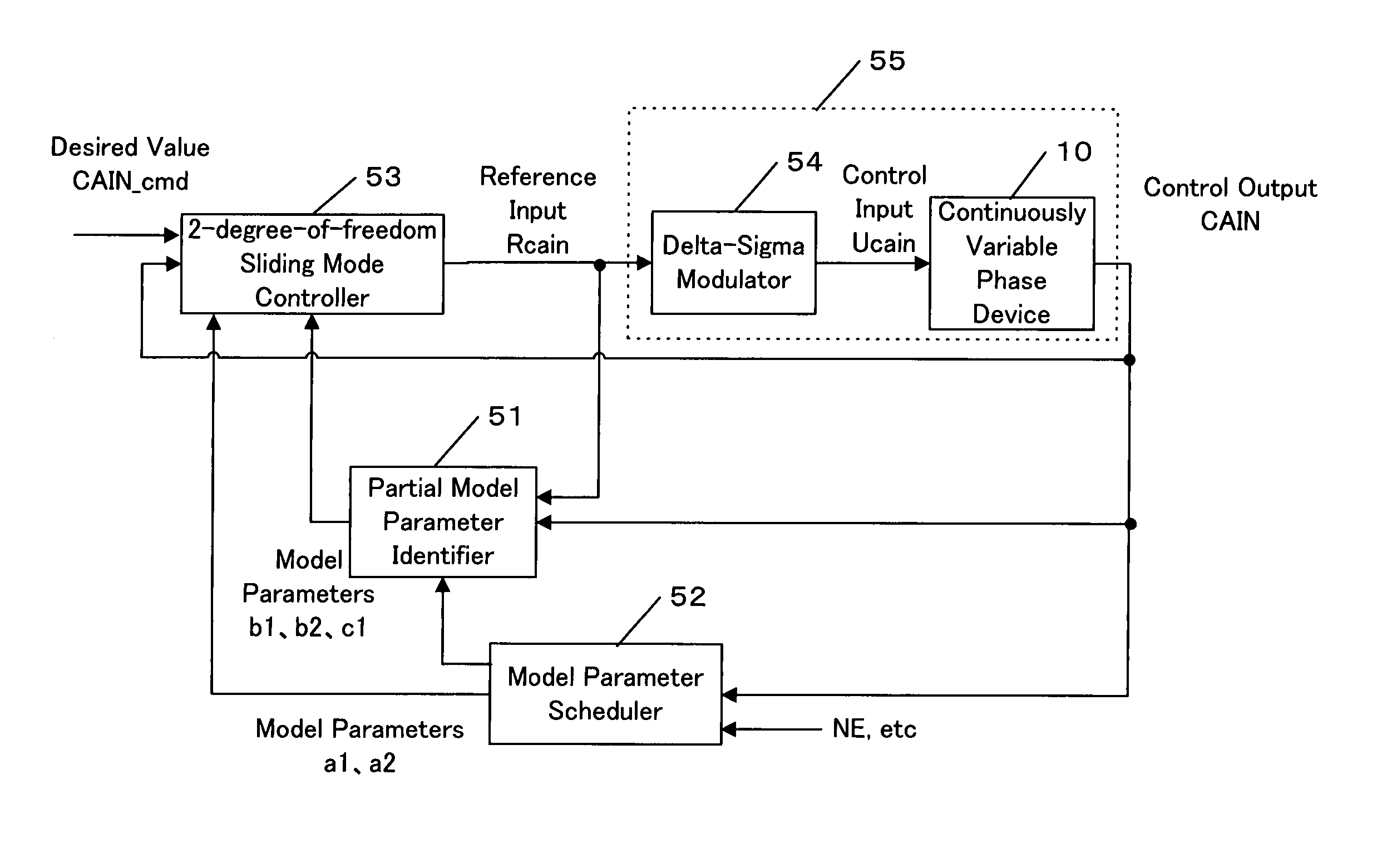

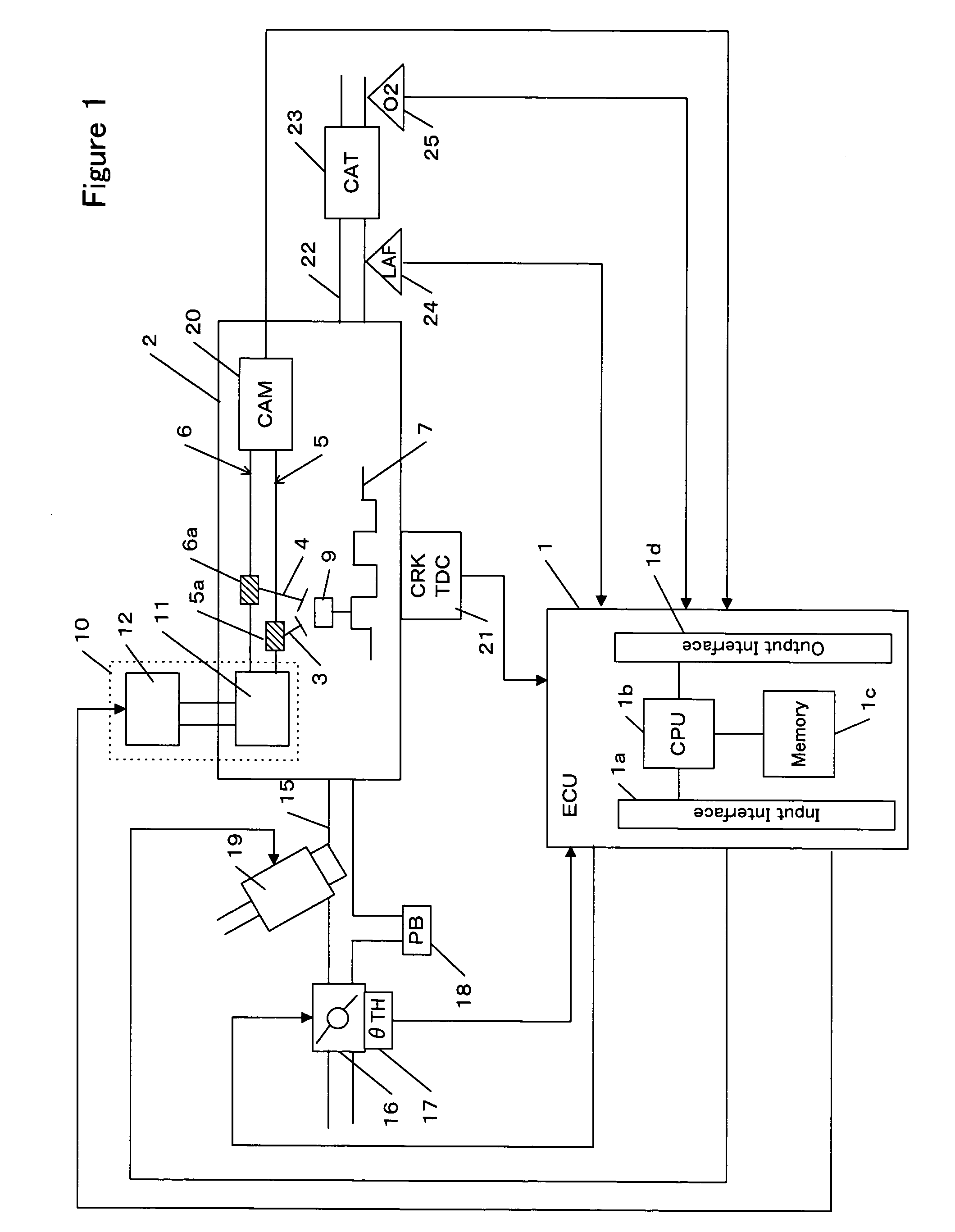

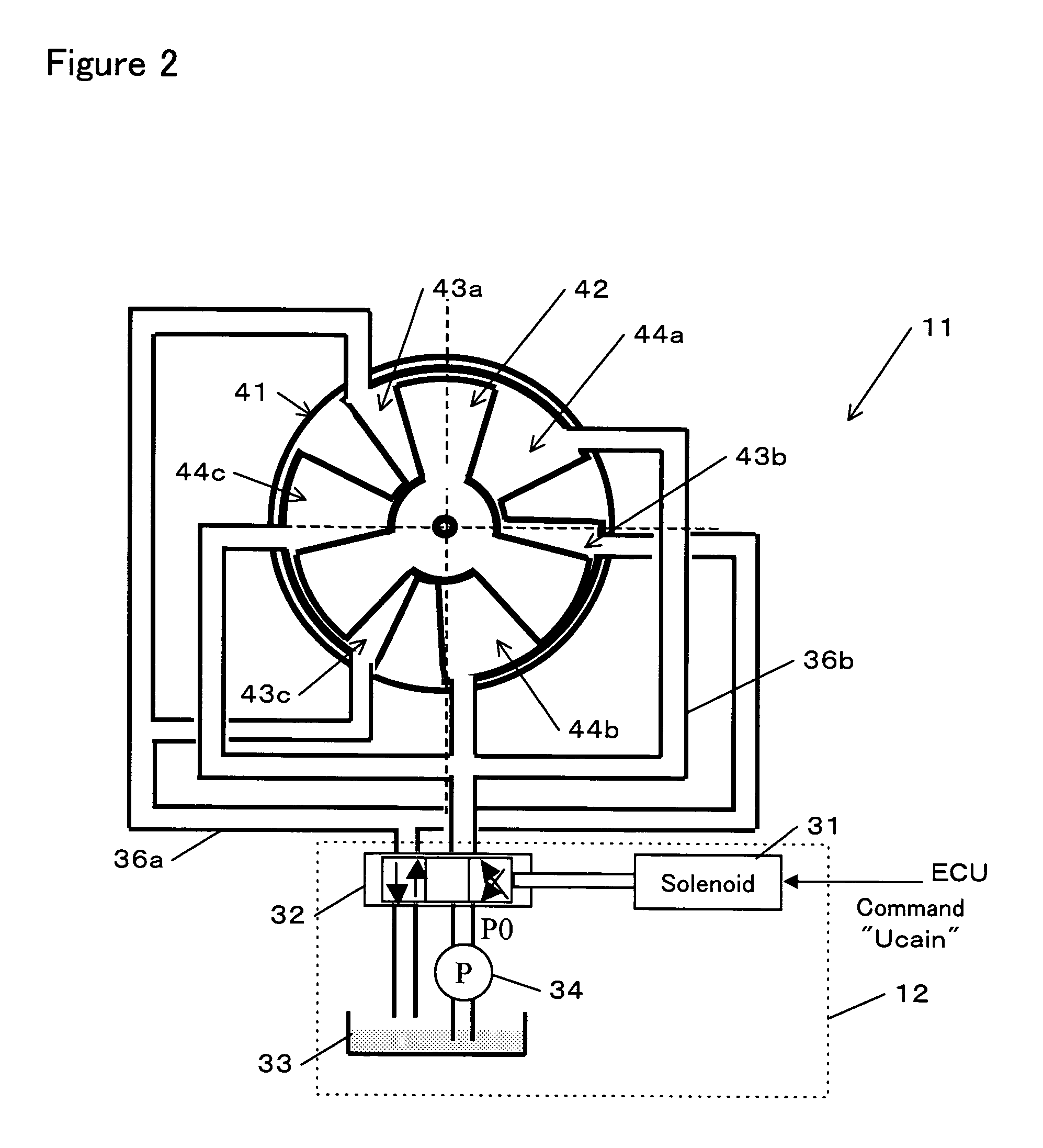

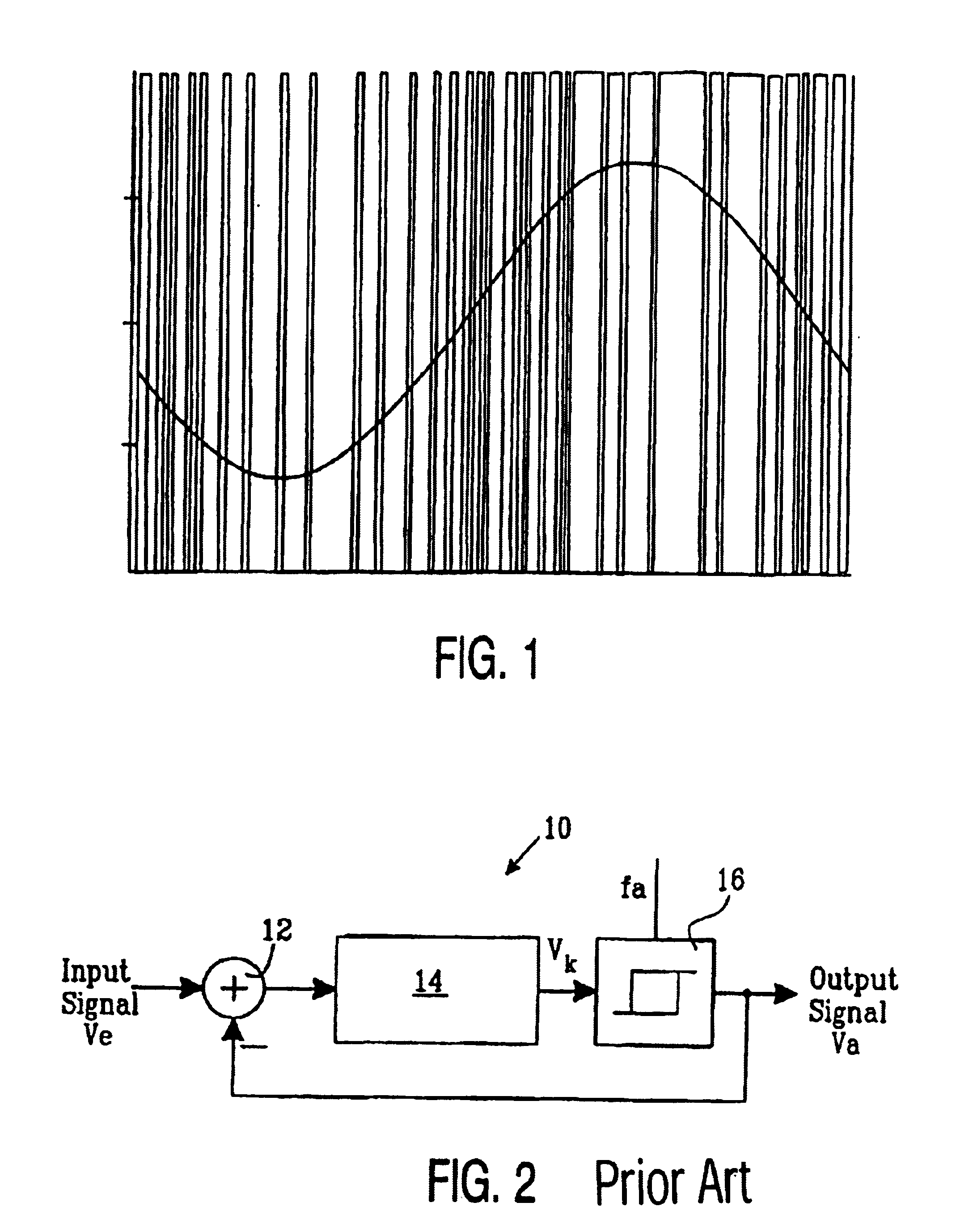

Control apparatus for controlling a plant by using a delta-sigma modulation

InactiveUS7058501B2Avoid vibrationSubstance reductionAnalogue computers for vehiclesHand manipulated computer devicesControl engineeringModel parameters

A control apparatus for controlling an object that is modeled using at least one model parameter is provided. The control apparatus comprises an identifier, a controller and a modulator. The identifier identifies the model parameter. The controller is coupled to the identifier and uses the model parameter to determine a reference input so that an output of the object converges to a desired value. The modulator is coupled to the controller and applies any one of a delta-sigma modulation algorithm, a sigma-delta modulation algorithm and a delta modulation algorithm to the reference input to determine an input into the object. The model parameter is identified based on the output of the object and the reference input. Since the identifier determines the model parameter based on the reference input, the model parameters is prevented from vibrating.

Owner:HONDA MOTOR CO LTD

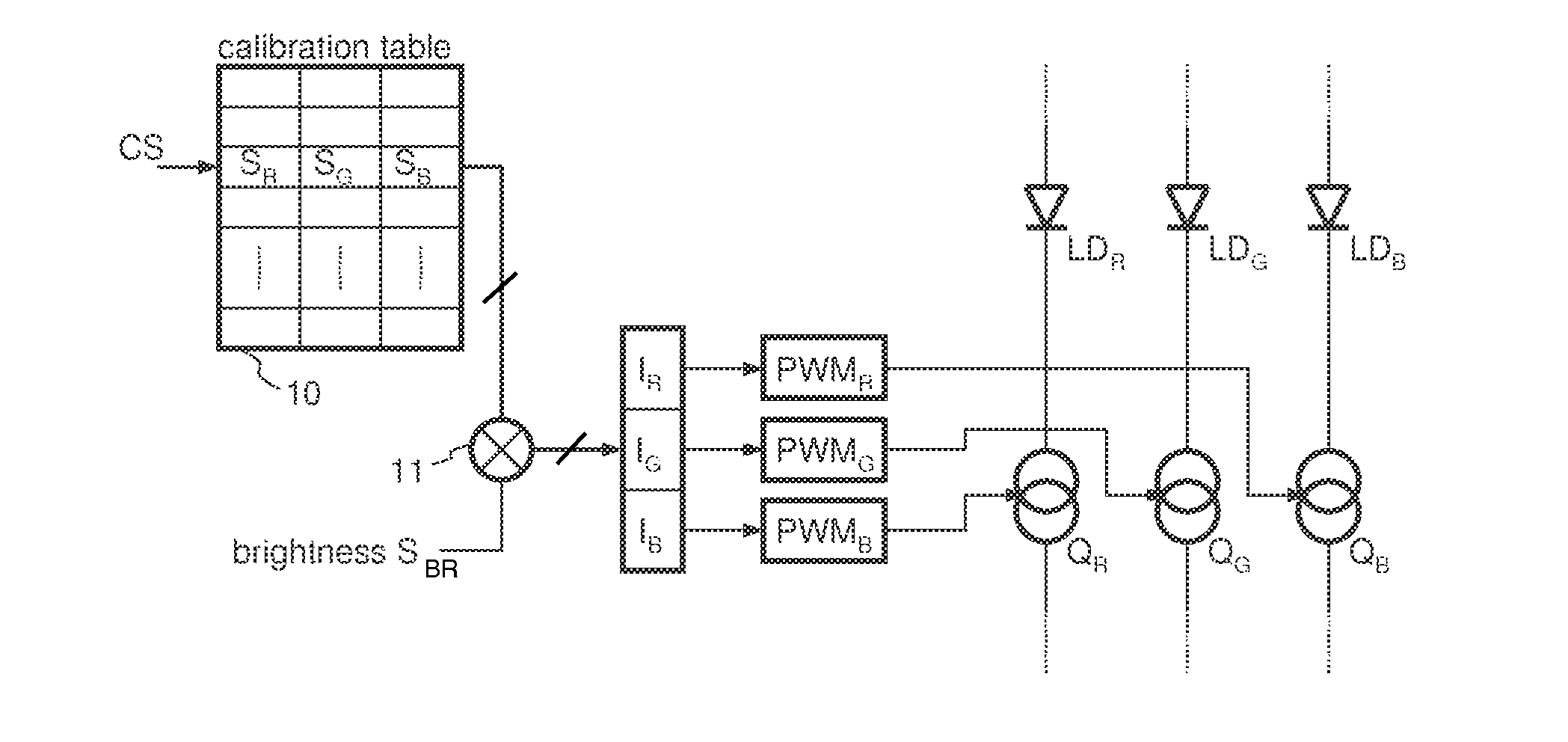

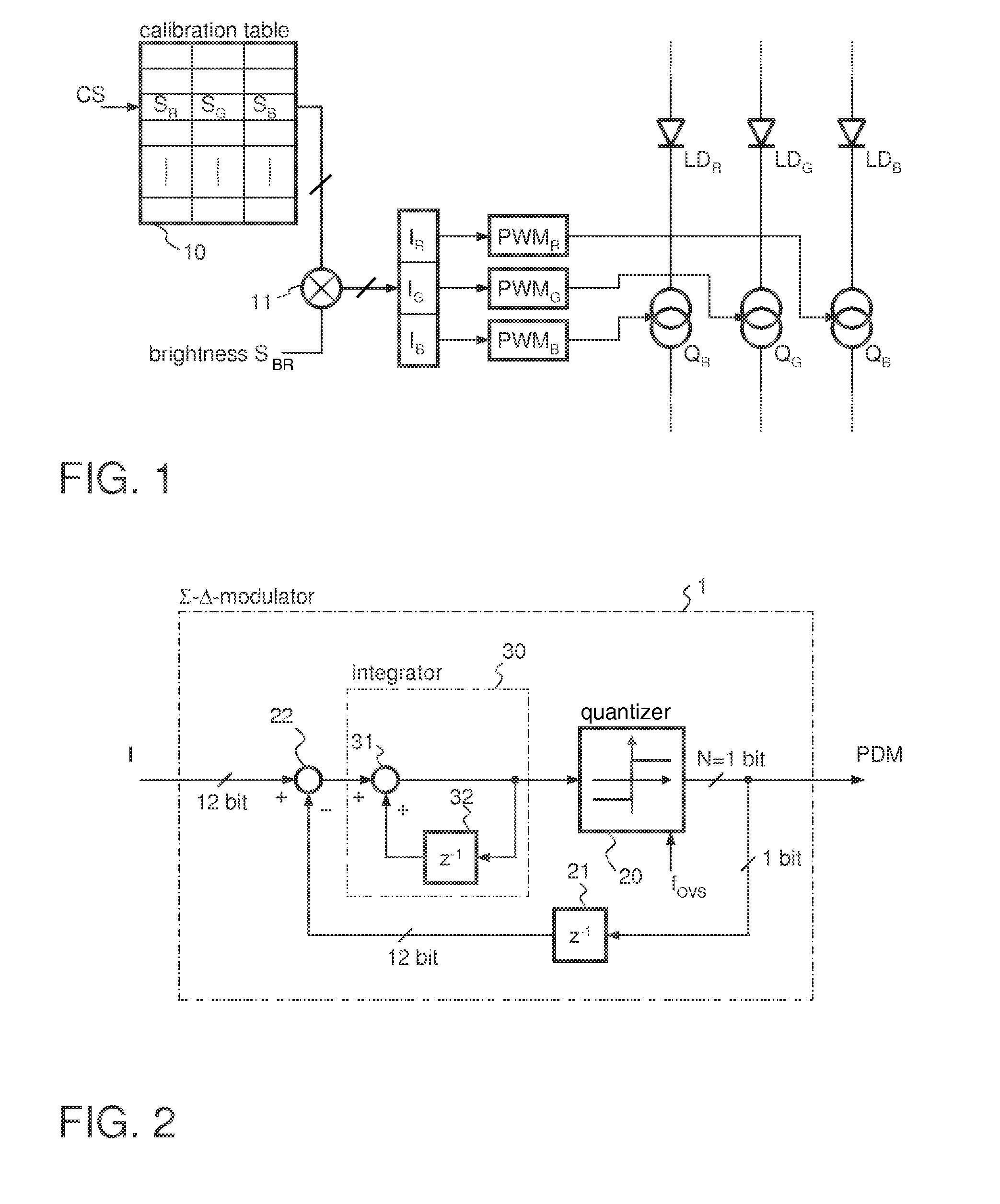

Sigma delta current source and LED driver

A circuit arrangement includes a first light emitting diode and a second light emitting diode emitting light of different colors arranged adjacent to each other for additive color mixing. A first and second controllable current sources are connected to the first and second light emitting diode, respectively, such that the load currents of the light emitting diodes depend on respective control signals received by the current sources. First and second sigma-delta modulators are connected to the first and second light emitting diodes, respectively, and provide bit-streams as control signals to the current sources. The mean value of each bit-stream corresponds to the value of an input signal of the respective sigma-delta modulator.

Owner:INFINEON TECH AUSTRIA AG

Sigma-delta modulation

InactiveUS6975257B2Reduce distortion problemsReduce errorsAnalogue/digital conversionElectric signal transmission systemsEngineeringDistortion

Sigma-delta modulation is provided, comprising feeding an input signal to a first SDM, subtracting the output of the first SDM from the input signal, filtering the output of the subtracting to obtain a filtered signal, delaying the input signal, adding the filtered signal to the delayed signal, feeding the output of the adder to a second SDM and providing the output of the second SDM. The first SDM in combination with the subtracting and filtering delivers a correction signal which, by adding it to the input signal, reduces the distortion in the second SDM, which second SDM performs in fact the sigma-delta modulation of the device.

Owner:KONINK PHILIPS ELECTRONICS NV

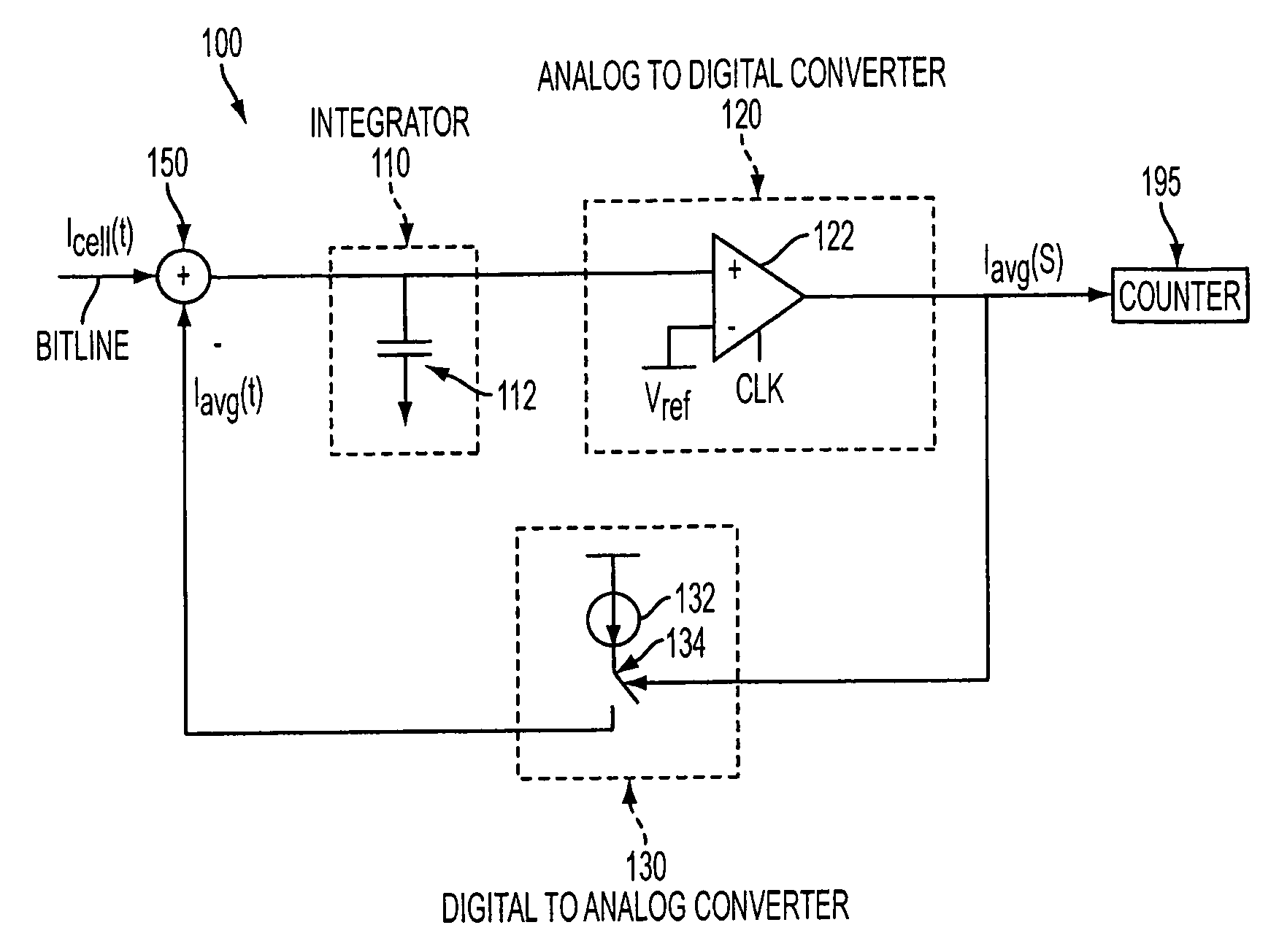

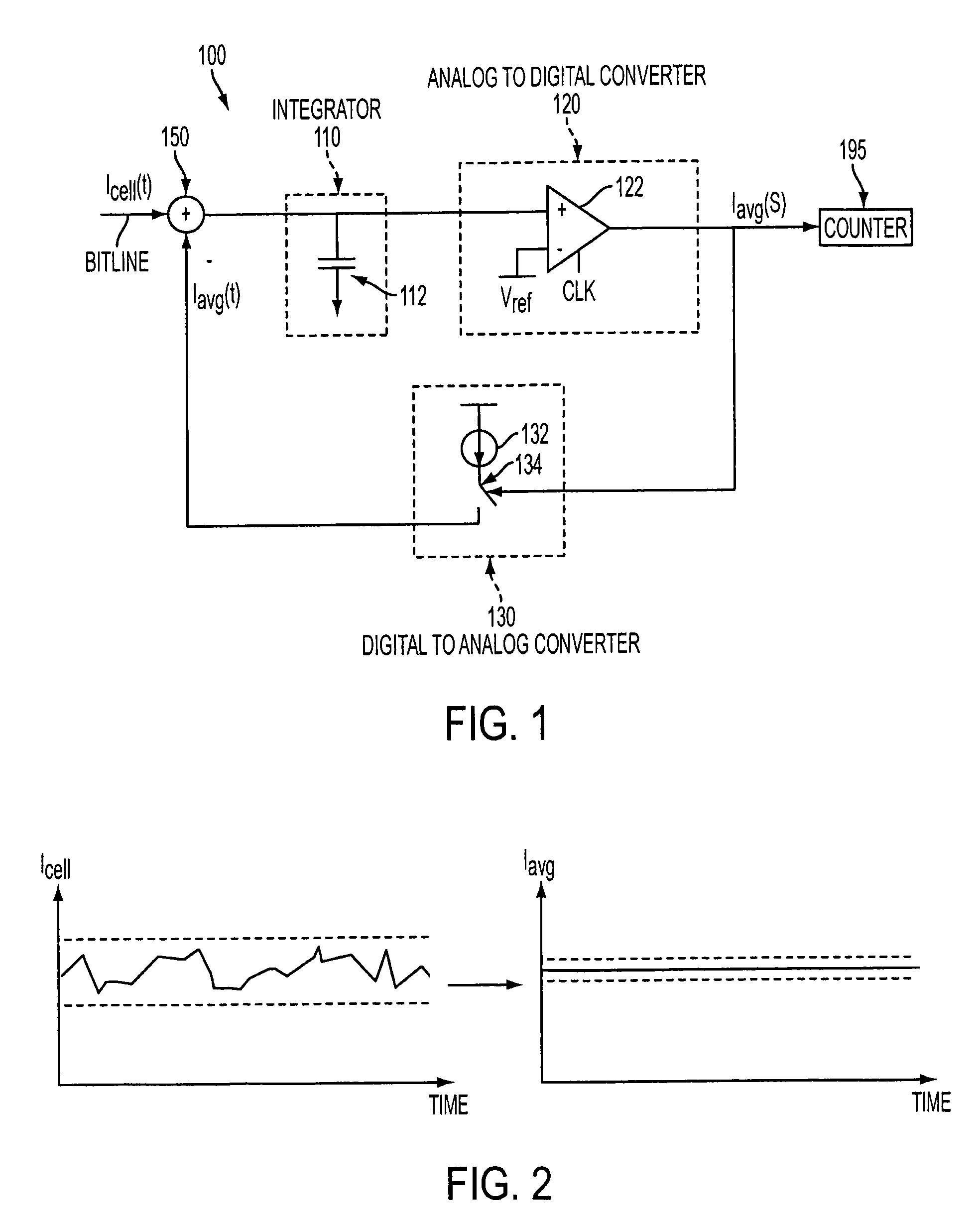

Method and apparatus for sensing flash memory using delta sigma modulation

ActiveUS7366021B2Accurate inductionHigh circuitryRead-only memoriesDigital storageIntegratorAverage current

Owner:MICRON TECH INC

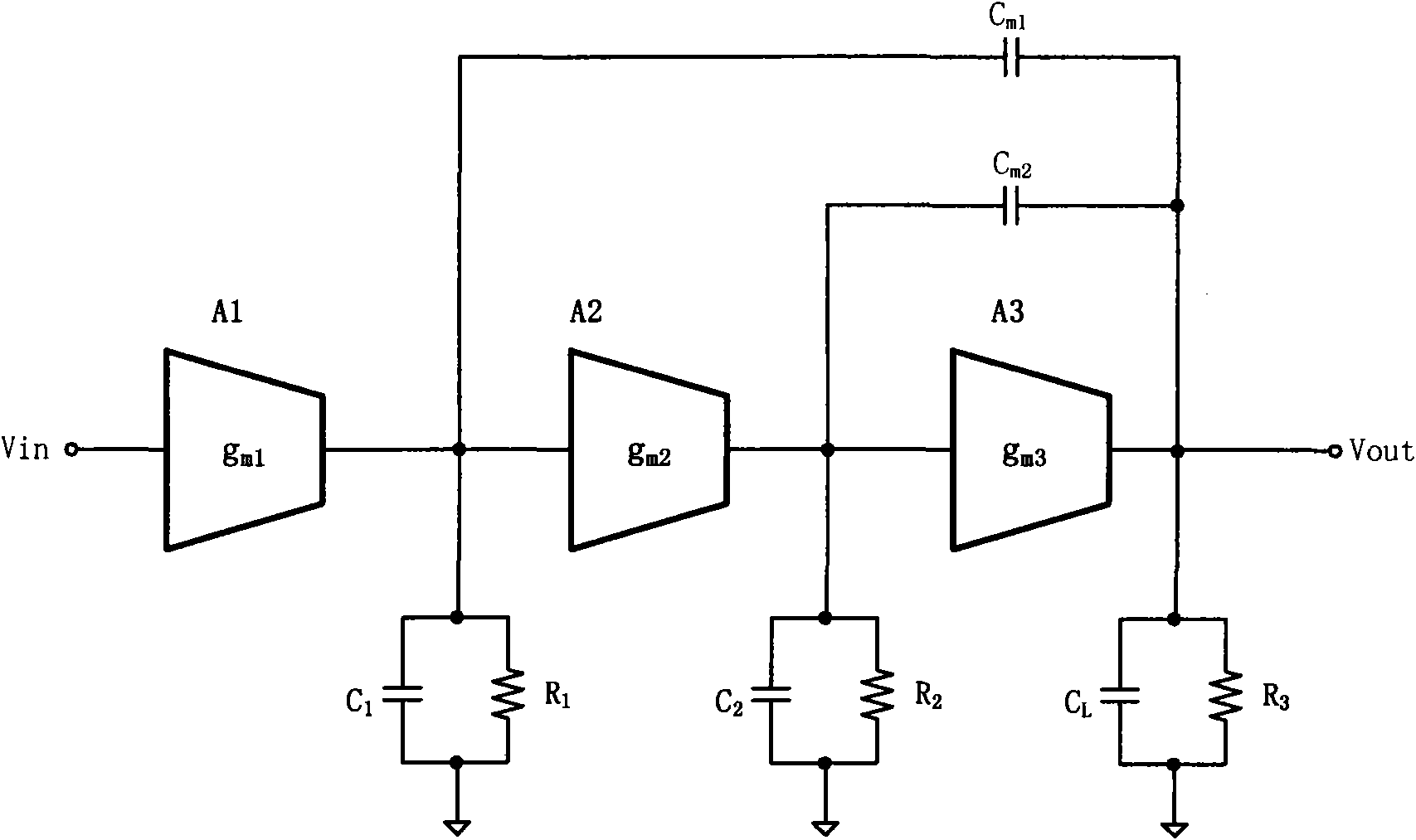

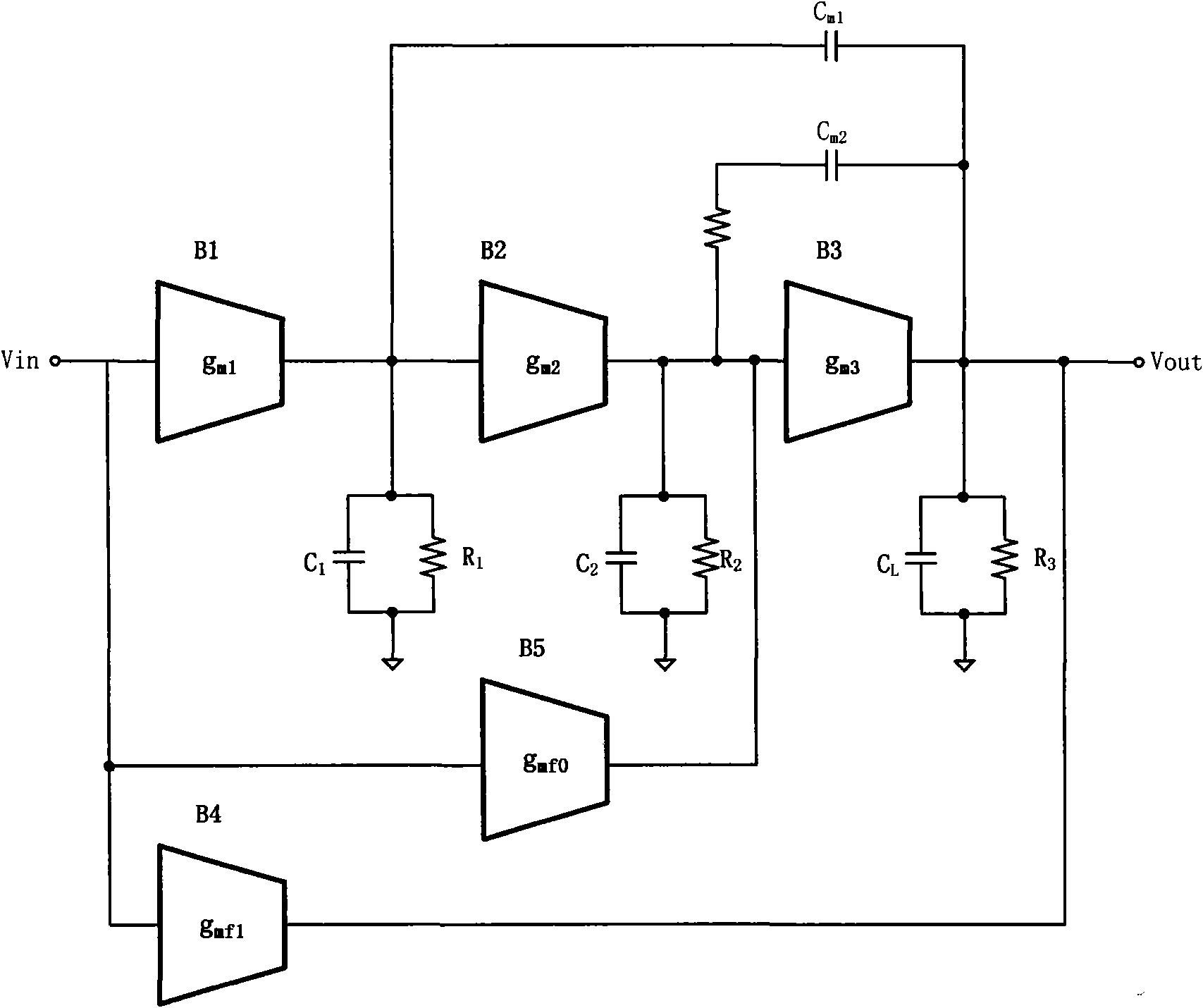

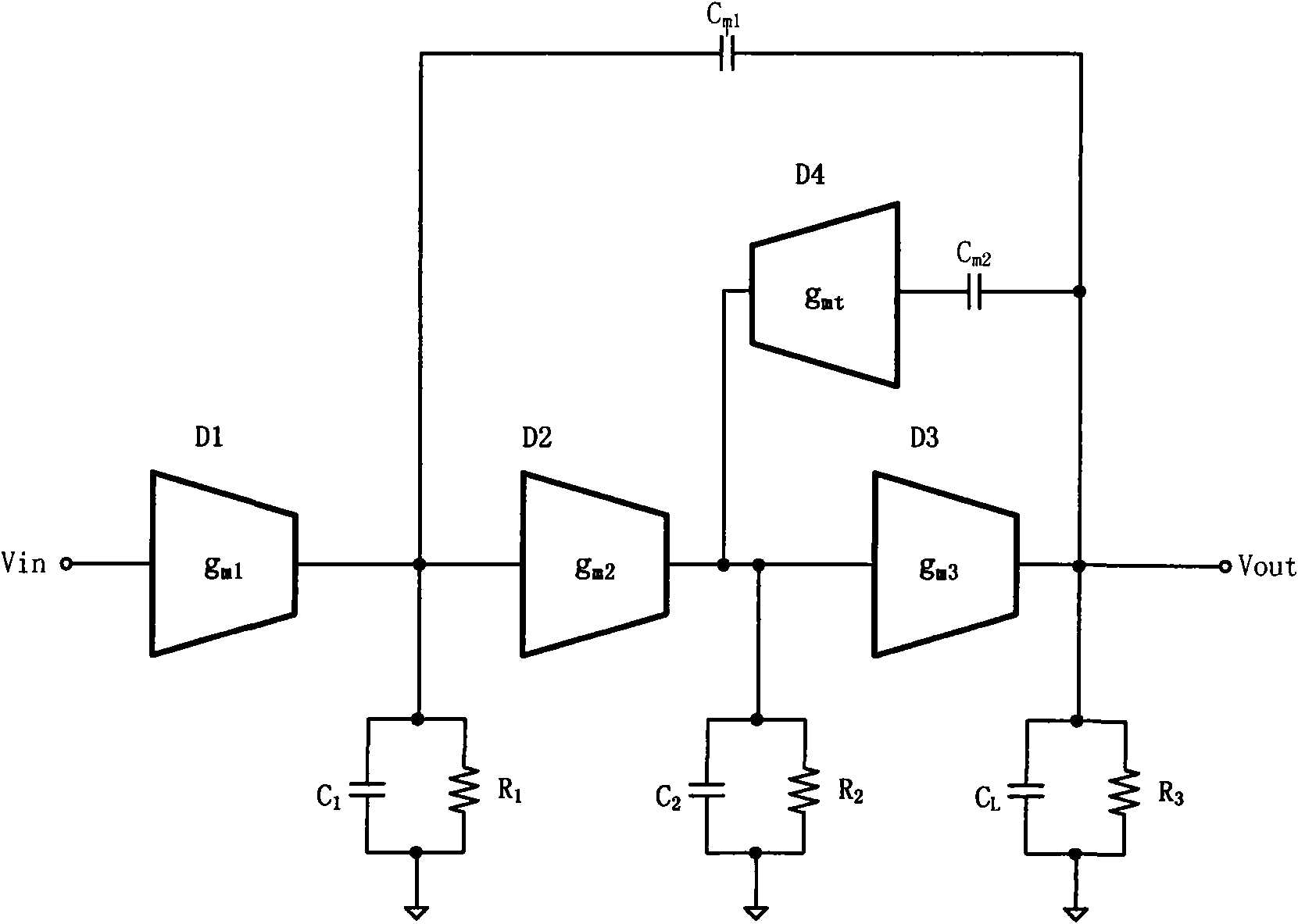

High-bandwidth low-power consumption frequency-compensation three-stage operational amplifier

InactiveCN101917169AGood compensationIncrease separation resistanceEnergy efficient ICTAmplifier modifications to raise efficiencyLoad circuitWireless communication protocol

The invention belongs to the technical field of analog IC (Integrated Circuit) design, in particular to a high-bandwidth low-power consumption frequency-compensation three-stage operational amplifier. The amplifier comprises an input stage, a second stage, an output stage, a common mode feedback stage, a comprehension circuit, an internal feedforward circuit, wherein the second stage is connectedwith the input stage, the output stage is connected with the second stage and used for amplifying a signal output by the second stage and driving an external load circuit, the common mode feedback stage extracts the common mode level of the differential output stage and stabilizes the common mode level, the comprehension circuit comprises a traditional trsanscondutance comprehension circuit, a miller comprehension circuit and a resistor for separating a high-frequency zero pole, and the internal feedforward circuit is used for comprehending an internal additional pole and forming a push-pull circuit together with the output stage to reduce static power consumption. The three-stage operational amplifier realizes high gain, high bandwidth and high stability under the condition of little DC power consumption and can be used in a high-speed analog-digital conversion circuit, such as a sigma-delta modulator suitable for the bandwidth of an LTE (Line Terminator Equipment) wireless communication protocol.

Owner:FUDAN UNIV

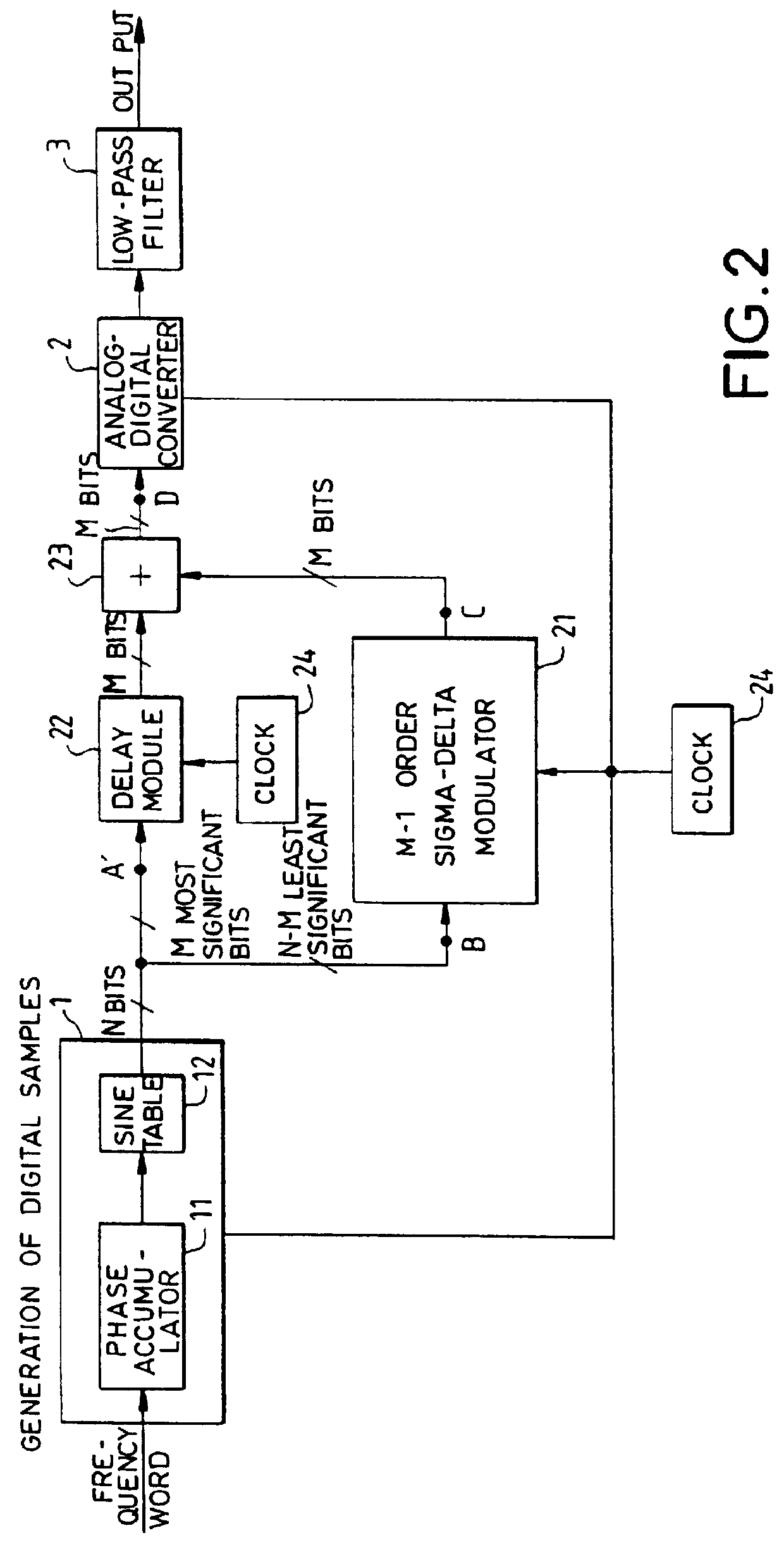

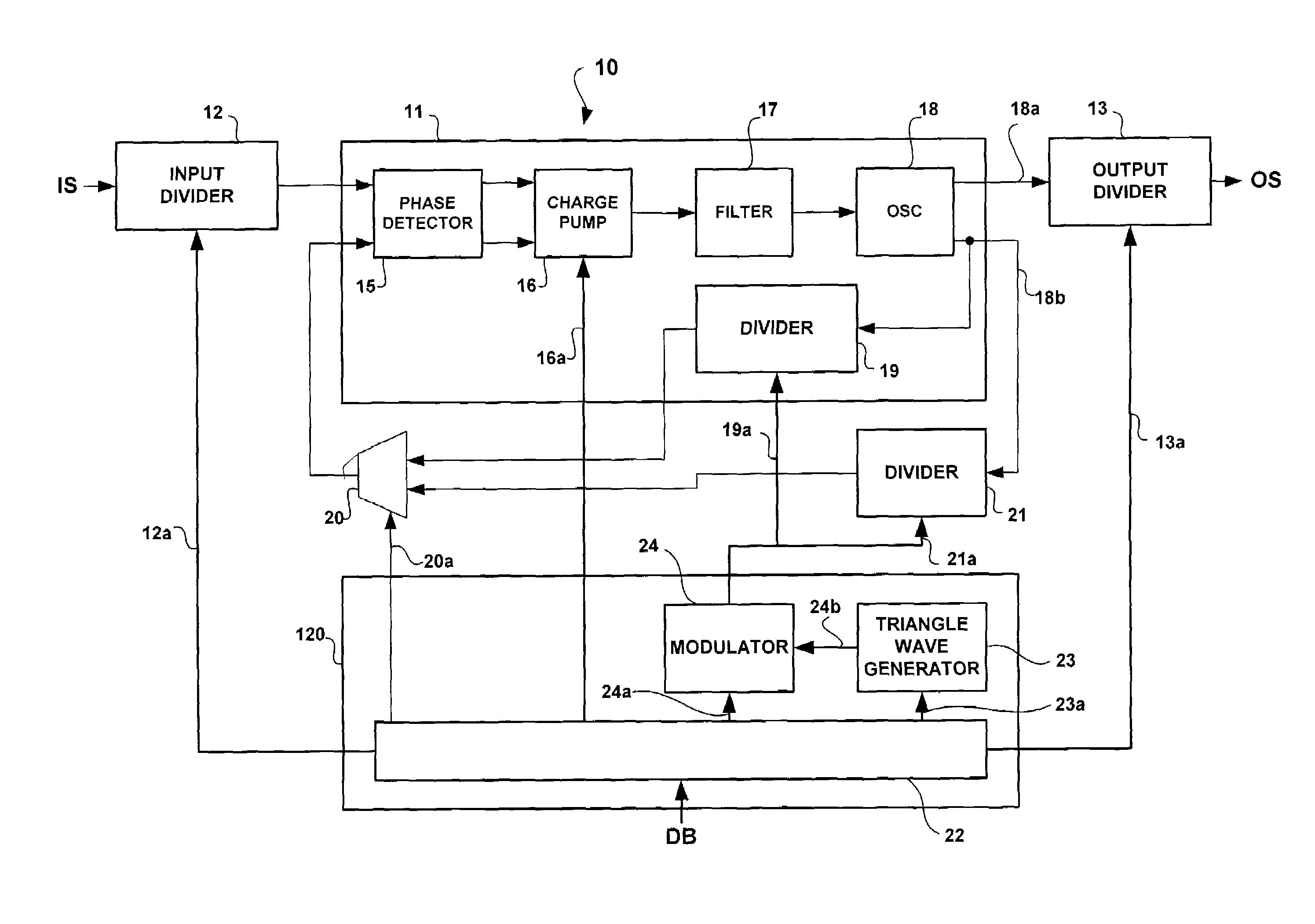

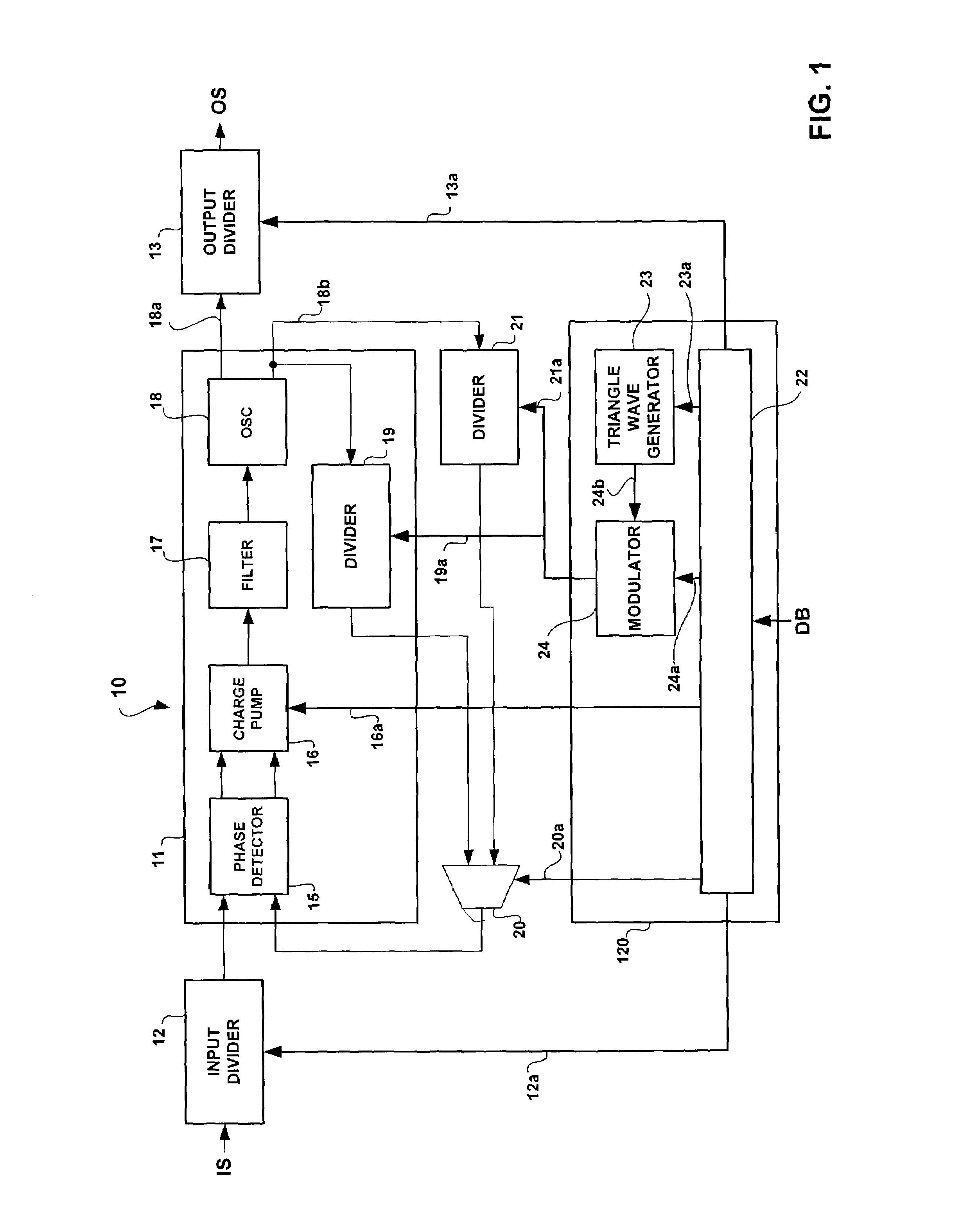

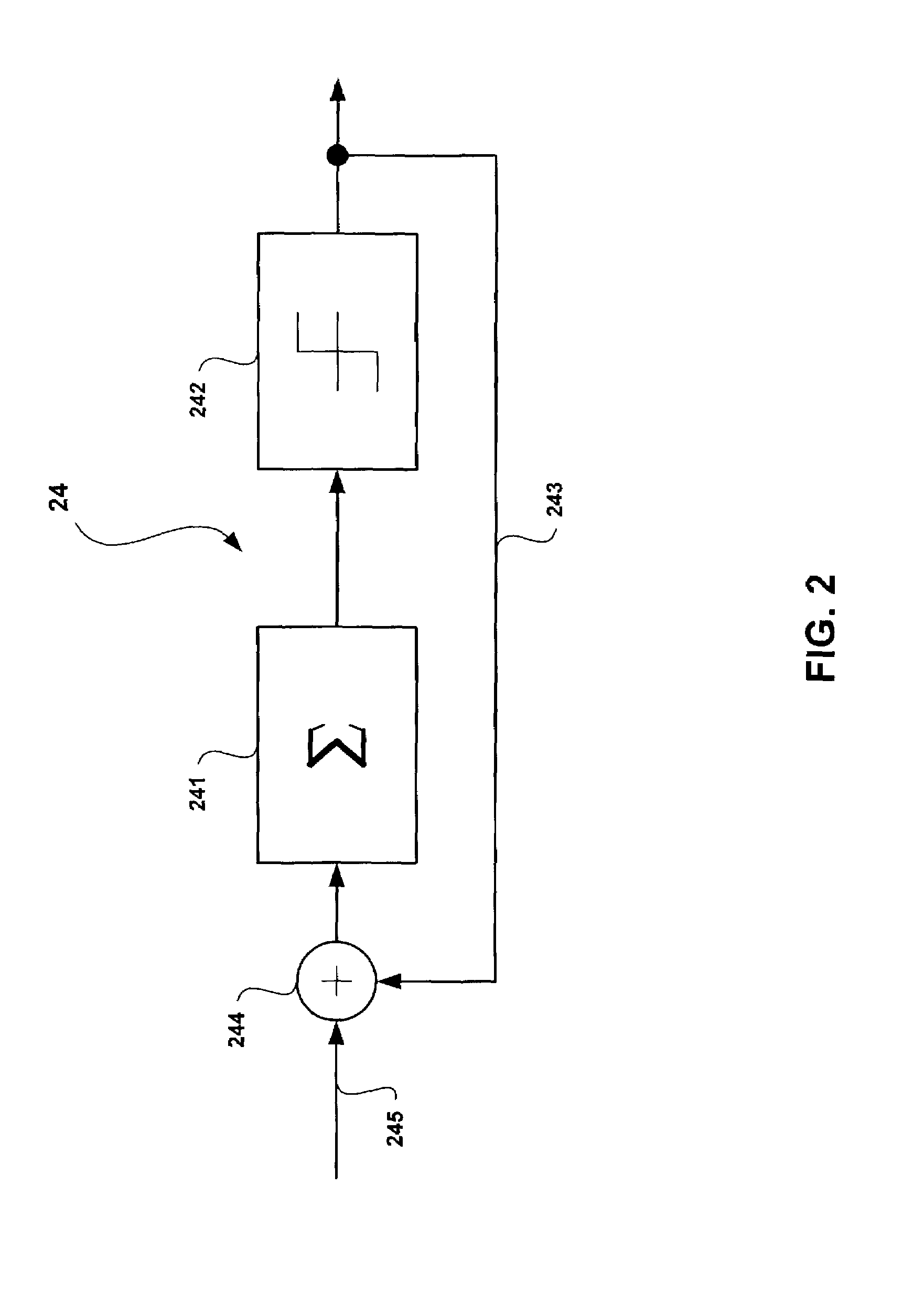

Process for generating a variable frequency signal, for instance for spreading the spectrum of a clock signal, and device therefor

ActiveUS7079616B2The result is validAvoid the needPulse automatic controlTransmissionPhase detectorElectronic systems

The use of a PLL including a phase detector responsive to the phase difference between an input signal and a feedback signal and which pilots an oscillator in function of this difference, is envisaged. The PLL also includes a feedback path that is responsive to the signal generated by the oscillator and which generates said feedback signal via at least one divider with a variable division ratio. The division ratio of said divider is modulated via a sigma-delta modulator, the input of which is fed with a triangular-wave modulating signal. The preferred application is that of a spread spectrum clock generator (SSCG) for digital electronic systems.

Owner:STMICROELECTRONICS SRL

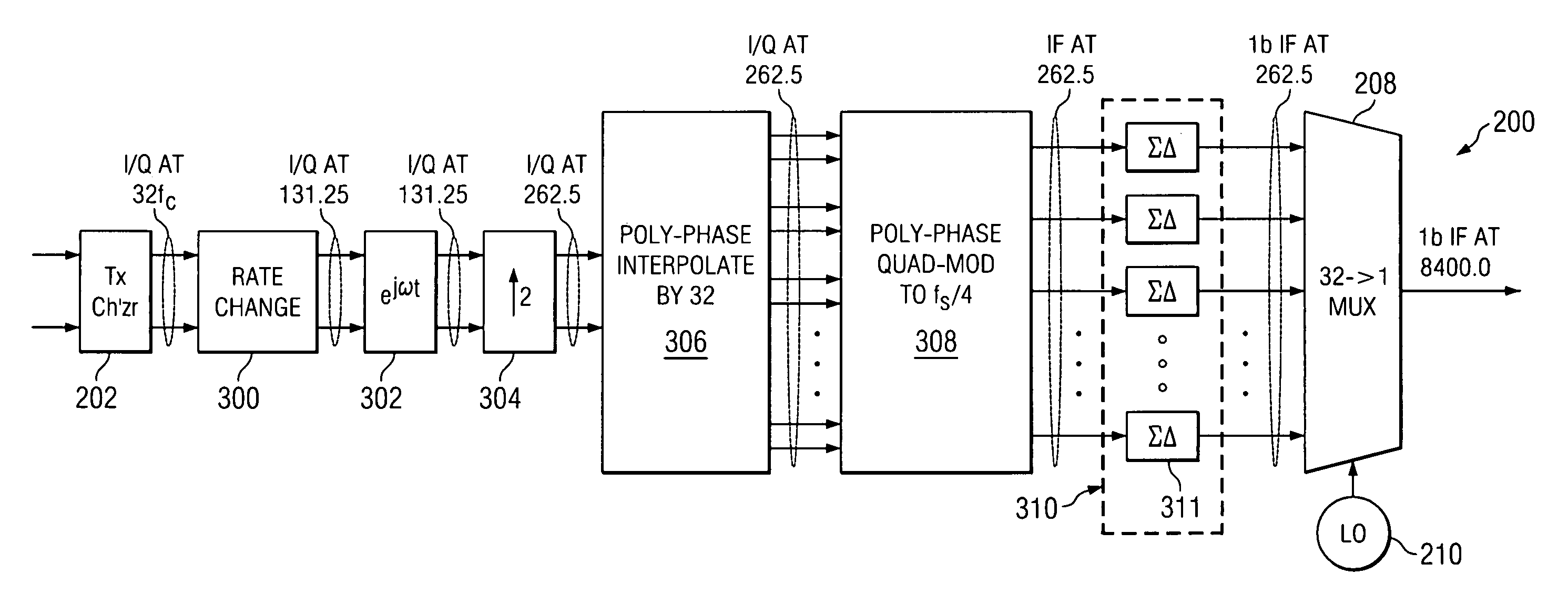

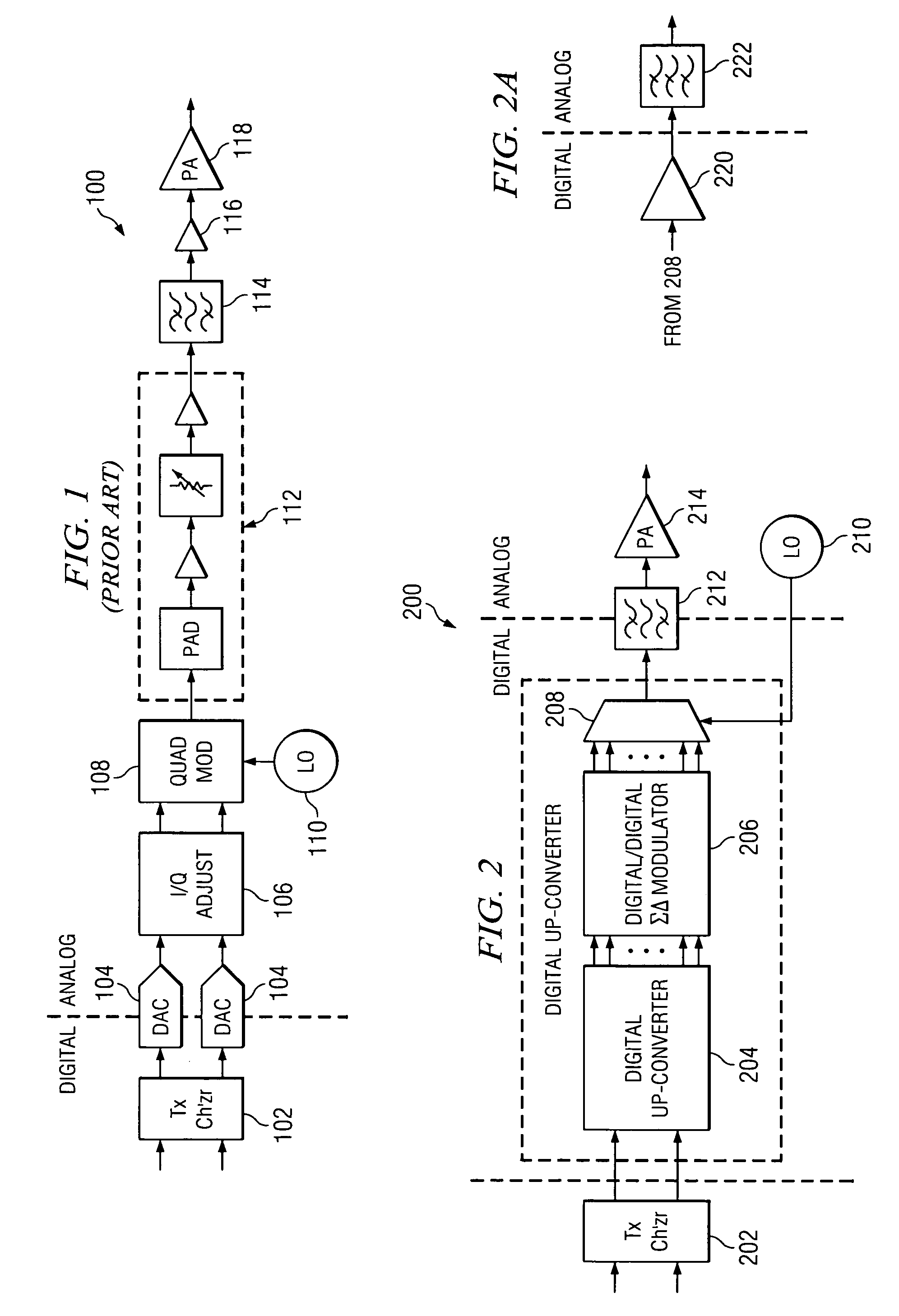

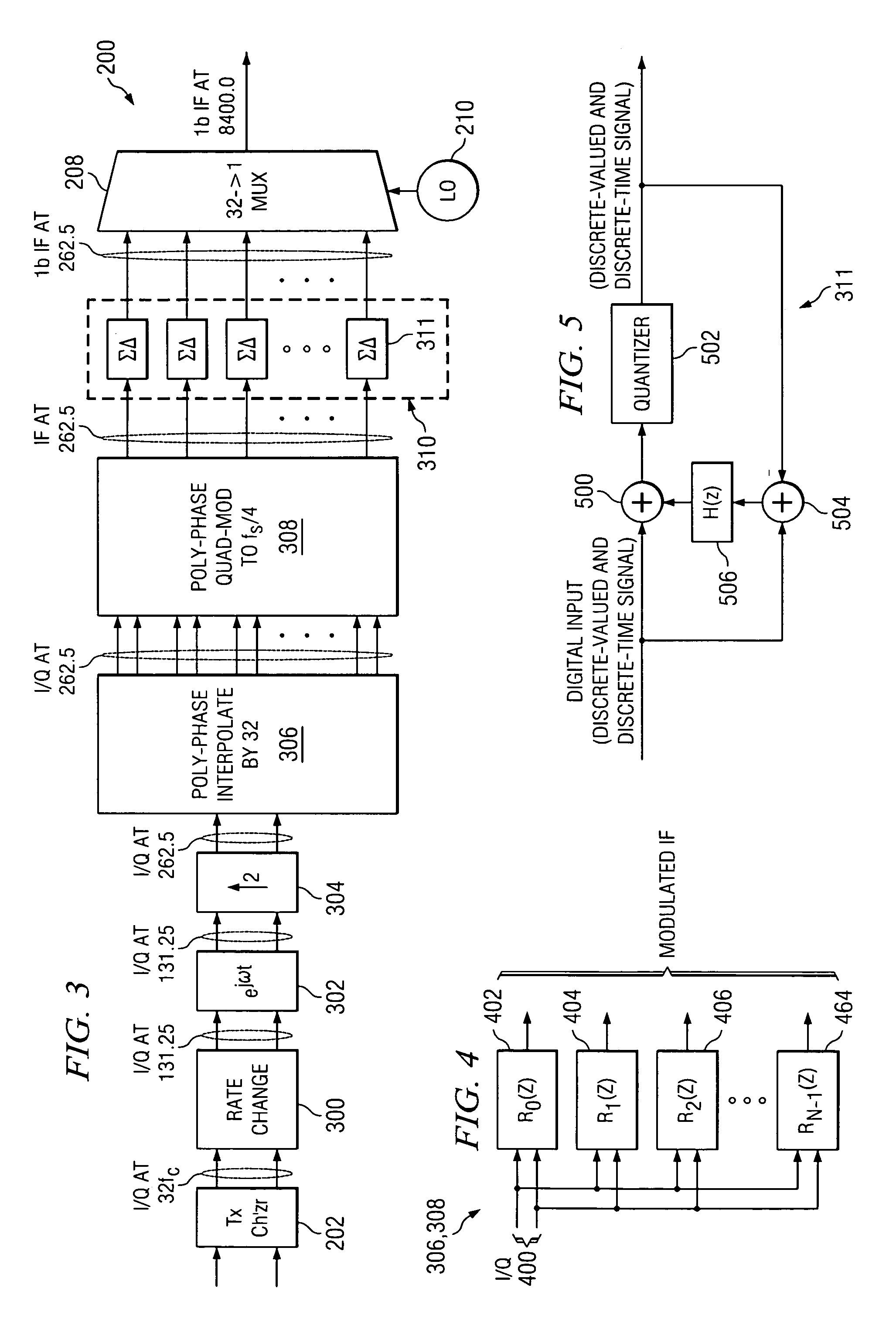

Digital transmitter and method

A transmitter and method is provided for digitally upconverting a baseband digital signal to a modulated intermediate frequency (IF) digital signal and sigma-delta modulating the IF digital signal. The baseband digital signal is split into N phases, as can be accomplished using a polyphase interpolation technique (polyphase filter), and modulated. The modulated N phases are not recombined and each phase is further modulated, as can be accomplished using a digital-to-digital sigma-delta modulator that generates digital output signals at the same rate. A high speed digital multiplexer multiplexes the digital output signals into a single bit stream at a higher rate for subsequent power amplification and RF transmission.

Owner:MICROSOFT TECH LICENSING LLC

Digital phase-locked loop clock system

A clock system includes a digital phase / frequency detector (DPFD), a buffer, a digitally-controlled oscillator (DCO) including a sigma-delta modulator (SDM), an adder, a first frequency divider. The DPFD may have a first input for a reference input clock, a second input for a feedback signal, the DPFD generating an output representing a difference between the reference input clock and the feedback signal. The buffer may be coupled to the DPFD for accumulating the difference signal over time. The sigma-delta modulator (SDM) may have a control input coupled to the buffer. The adder may have inputs coupled to the (SDM) and a source of an integer control word. The first frequency divider may have an input for a clock signal and a control input coupled to the adder, the DCO generating an output clock signal having an average frequency representing a frequency of the input clock signal divided by (N+F / M), wherein N is determined by the integer control word and F / M is determined by an output of the SDM. The system clock also may include a second frequency divider coupled to the DCO output clock signal outputting the feedback signal to the DPFD.

Owner:ANALOG DEVICES INC

Capacitive field sensor with sigma-delta modulator

A capacitive sensor includes a switching capacitor circuit, a comparator, and a charge dissipation circuit. The switching capacitor circuit reciprocally couples a sensing capacitor in series with a modulation capacitor during a first switching phase and discharges the sensing capacitor during a second switching phase. The comparator is coupled to compare a voltage potential on the modulation capacitor to a reference and to generate a modulation signal in response. The charge dissipation circuit is coupled to the modulation capacitor to selectively discharge the modulation capacitor in response to the modulation signal.

Owner:CYPRESS SEMICON CORP

Microphone unit with internal A/D converter

InactiveUS20110096945A1Improve interchangeabilityEasily substitutedElectrostatic transducer microphonesAmplifiersĆuk converterEngineering

Owner:TDK CORPARATION