High-bandwidth low-power consumption frequency-compensation three-stage operational amplifier

An operational amplifier, frequency compensation technology, applied in differential amplifiers, improved amplifiers to expand bandwidth, DC-coupled DC amplifiers, etc., can solve problems affecting amplifier stability, obstacles, etc., to improve phase margin, increase slew rate , to improve the effect of compensation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be described in detail below in conjunction with the accompanying drawings and examples.

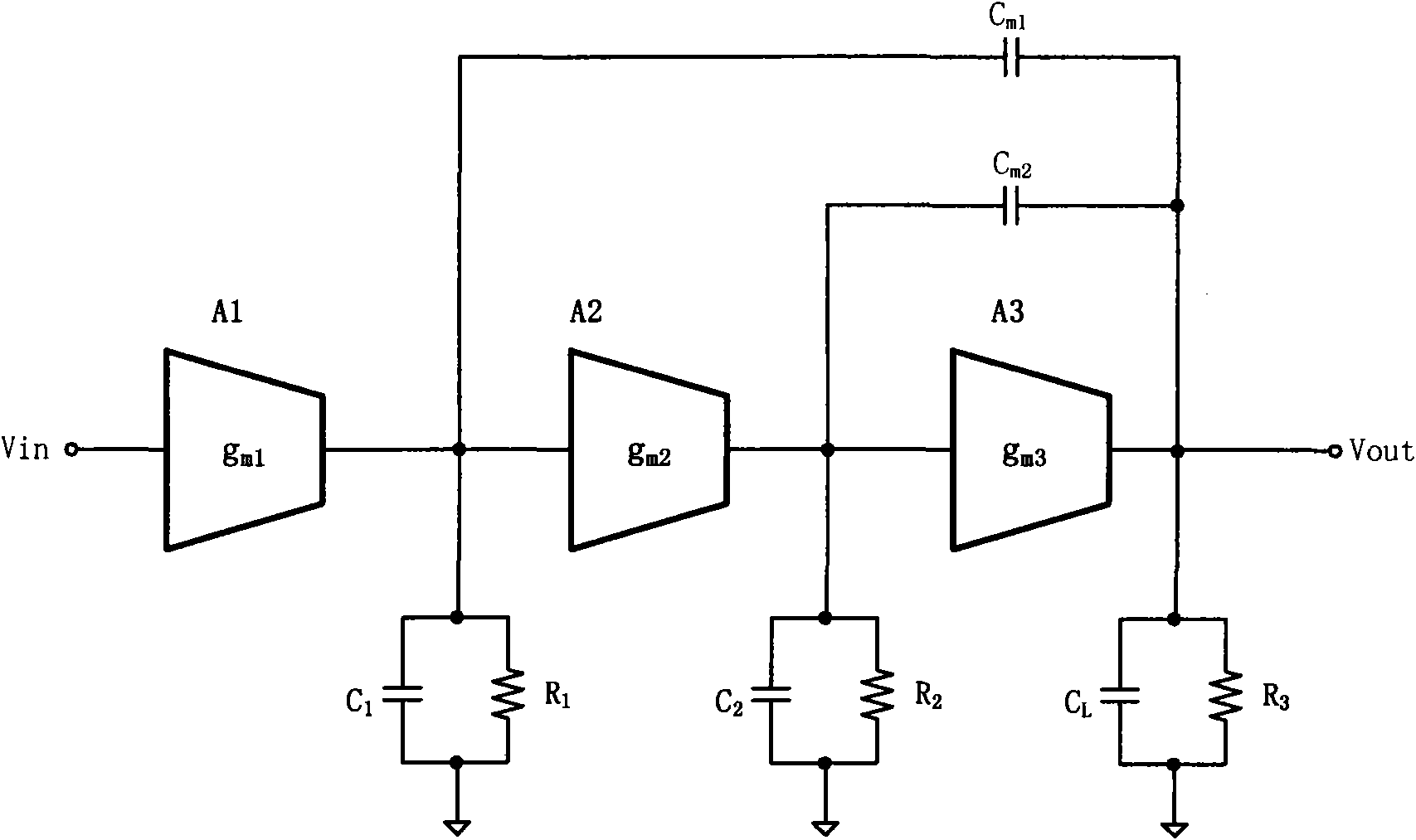

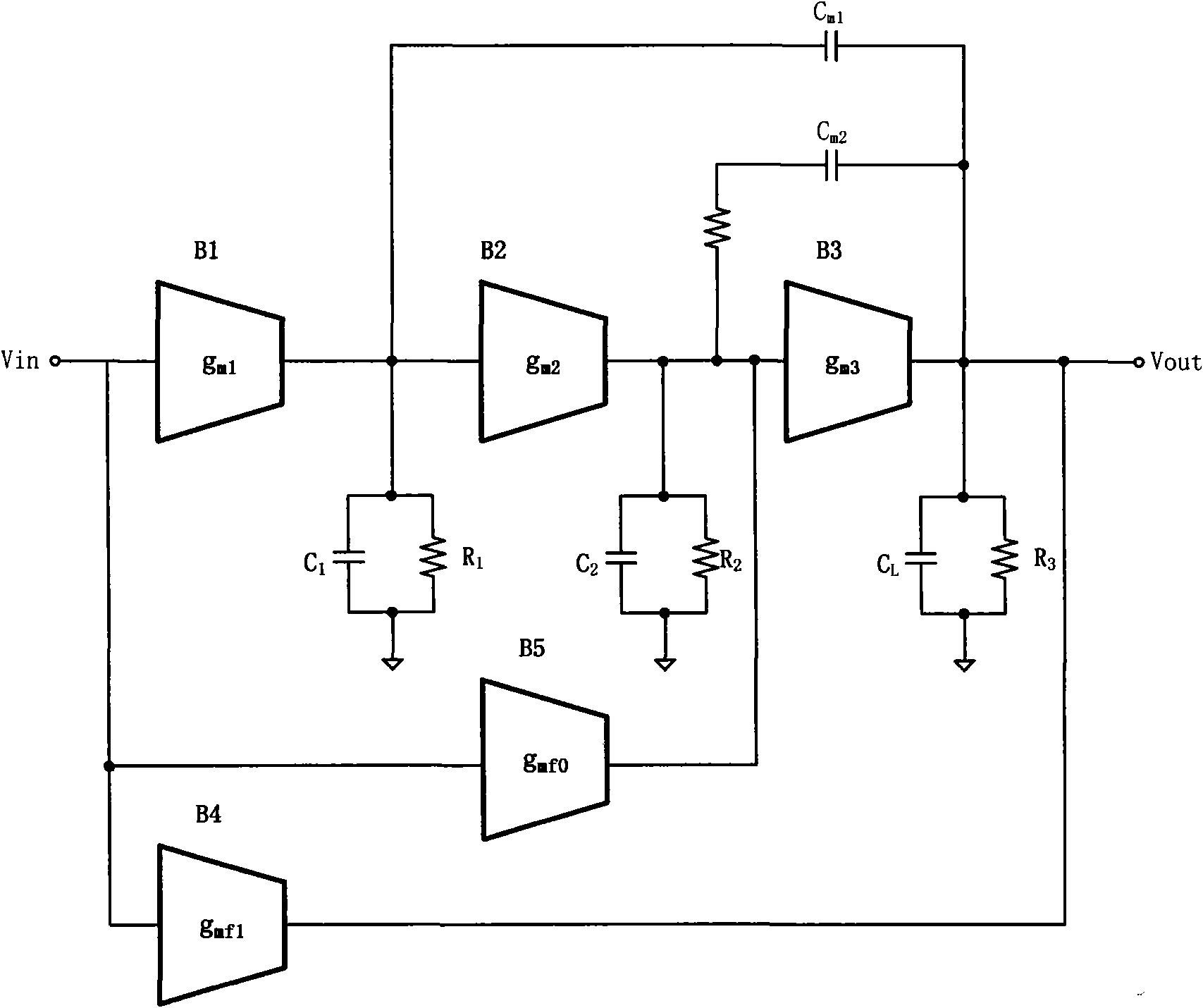

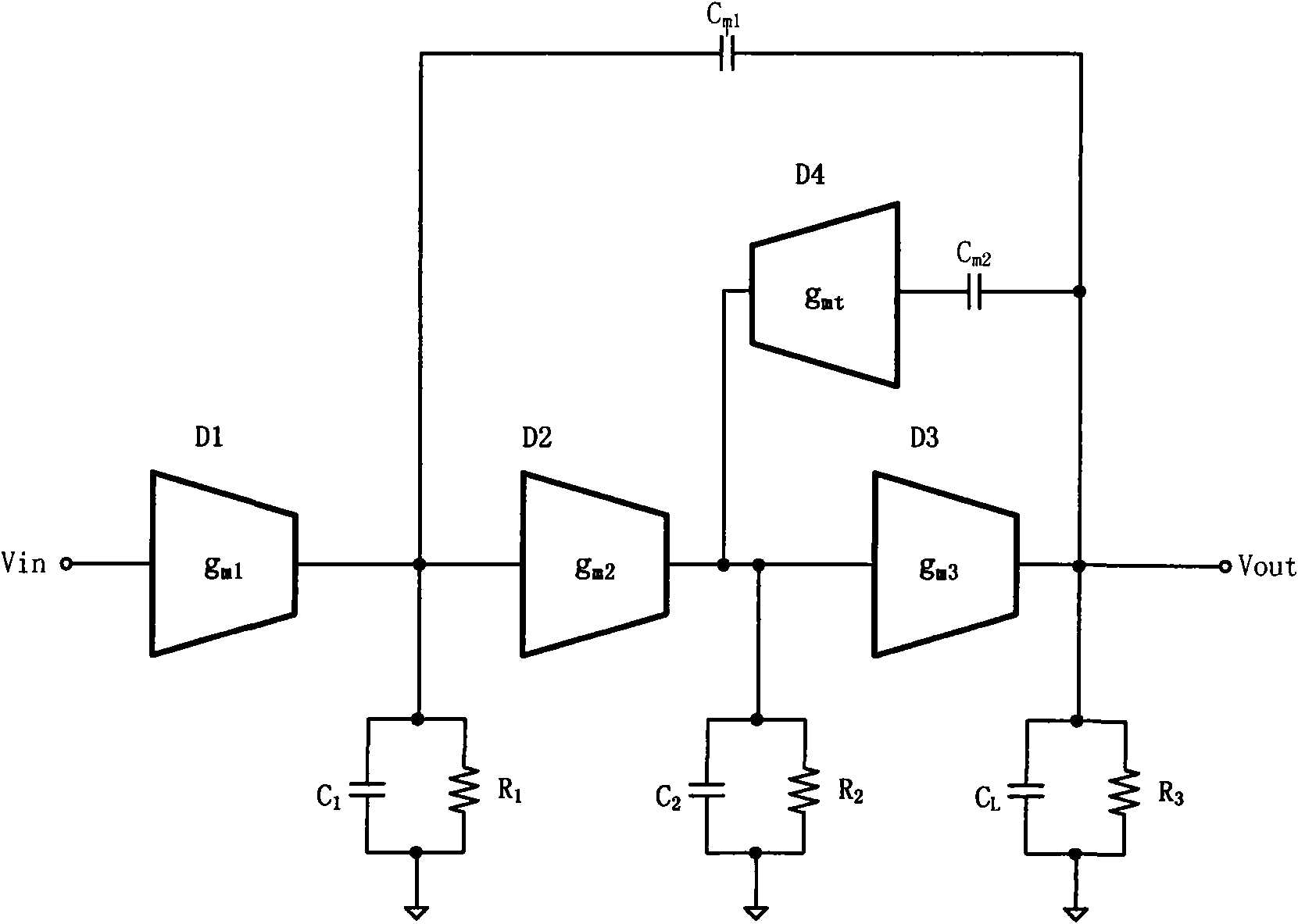

[0039] Figure 4 It is a structural block diagram of a three-stage frequency compensation operational amplifier of the present invention, and the three-stage amplifier includes a first-stage amplifier N1, a second-stage amplifier N2, and a third-stage amplifier N3. The transconductances of these three stages of amplifiers are g m1 , g m2 and g m3 , the output resistances are R 1 , R 2 and R 3 , the lumped output capacitance is C 1 、C 2 and C 3 , the load capacitance is C L . Transconductance stage N4 and feed-forward transconductance stage N5, their transconductances are g mt and g mf . Miller Compensation Capacitor C m1 Across the output terminal of N3 and the high-frequency zero-pole separation resistor R s between. High-frequency zero-pole separation resistor R s across the output of N1 and the Miller compensation capacitor C m1 betw...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More