Patents

Literature

87results about How to "Increase slew rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

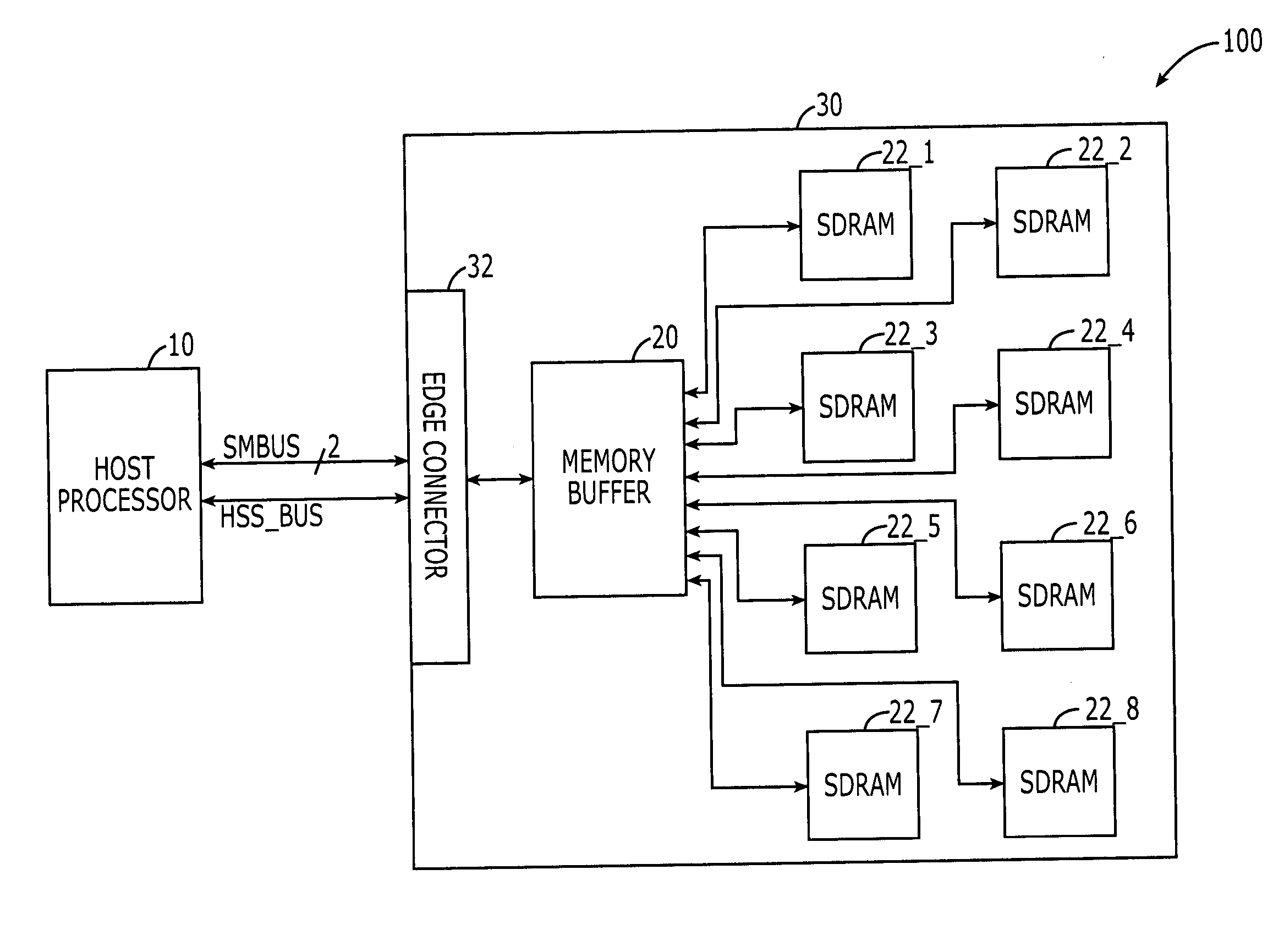

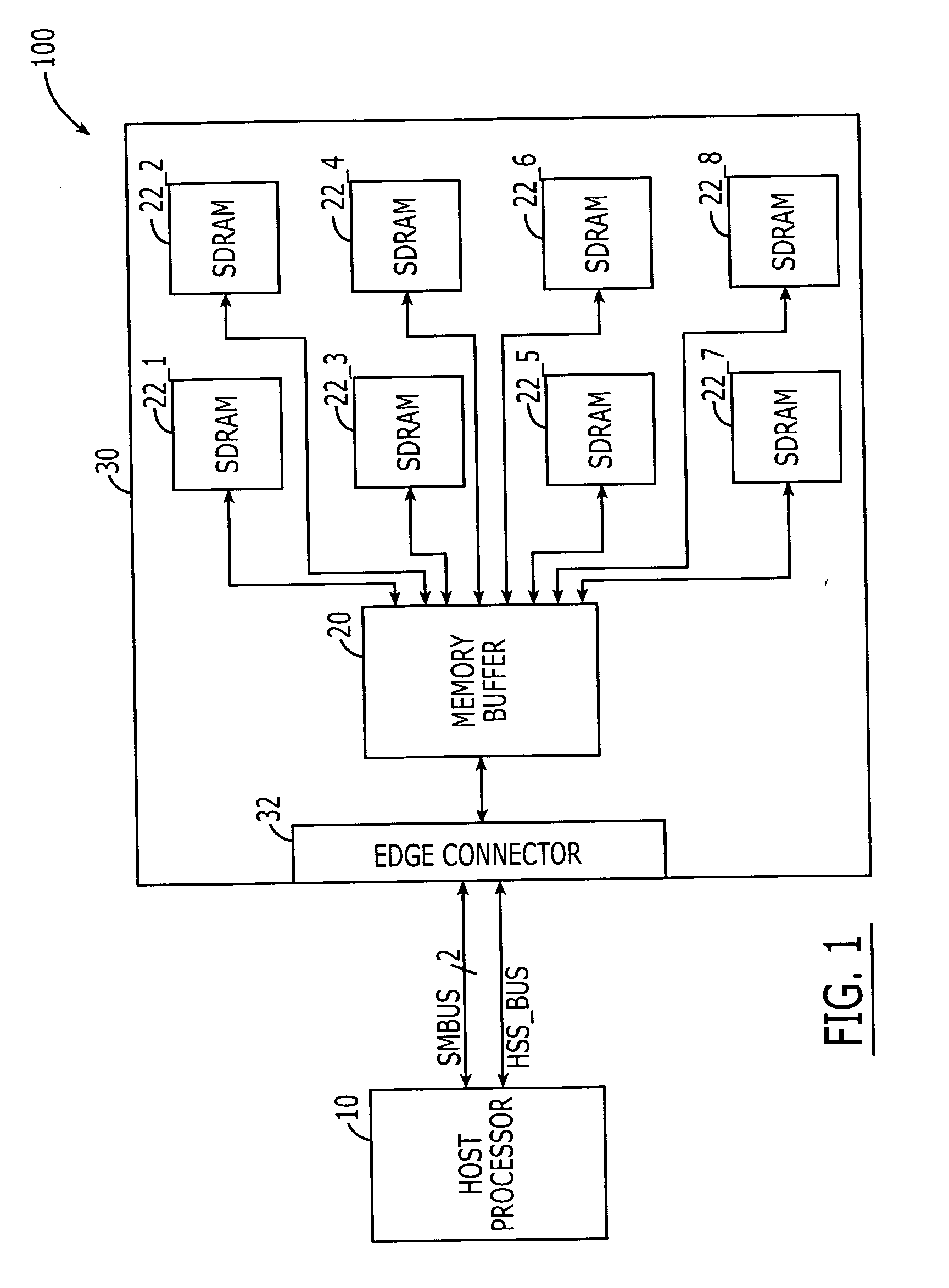

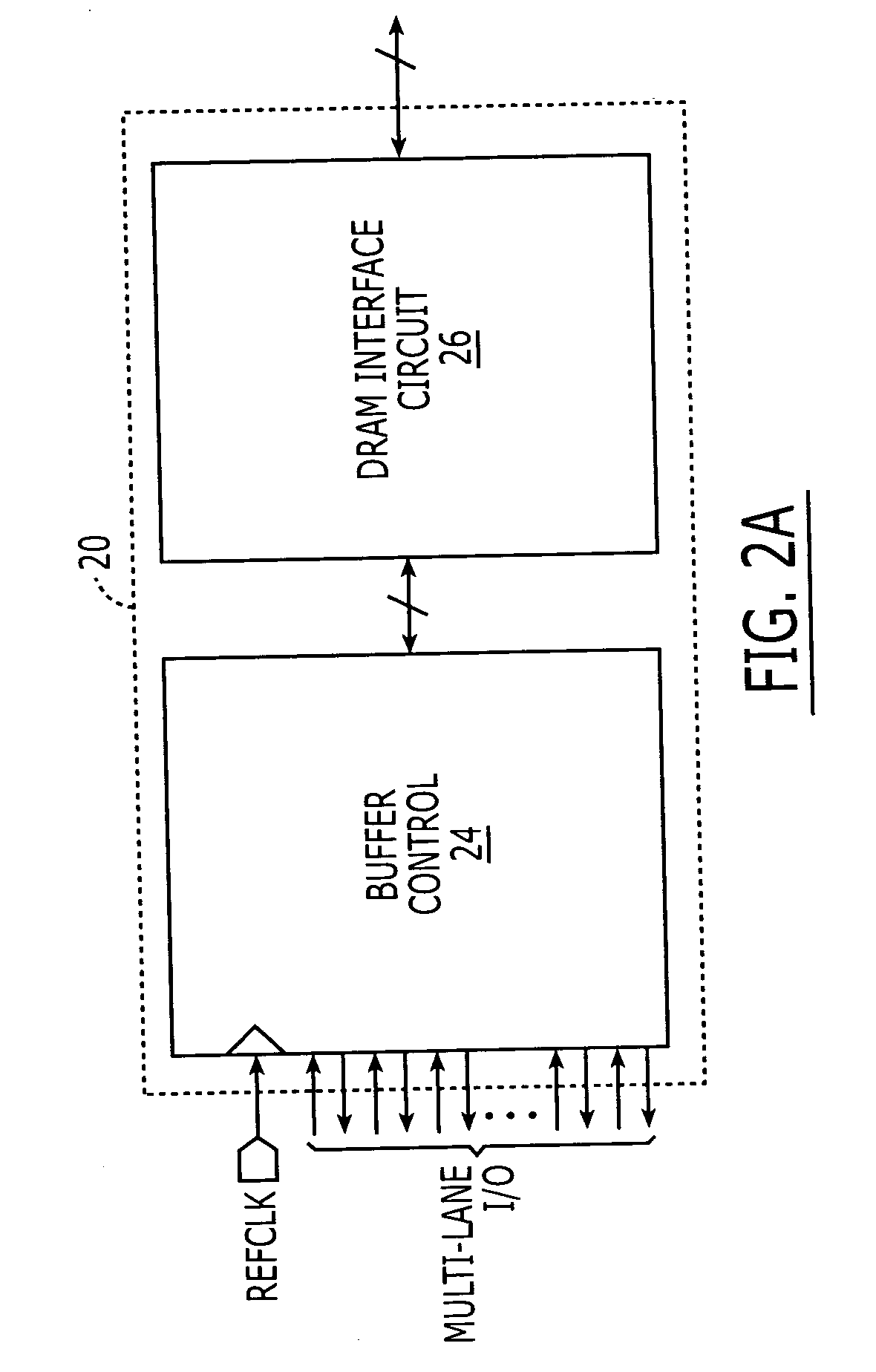

DRAM interface circuits having enhanced skew, slew rate and impedance control

Fully-buffered dual in-line memory modules (FB-DIMM) include advanced memory buffers (AMBs) having enhanced skew, slew rate and output impedance control. The AMB includes user accessible registers that can be programmed to carefully control the edge placement (or phase) of signals generated from the AMB to multiple DRAMs on the module. This control of edge placement, which may be performed independently for each group of signals: clock (CLK, CLK#), command (RAS, CAS, WE), address (including bank address), data (DQ) and data strobe (DQS), provides 360 degrees of control (or one period). This means that any group of signals can be moved independently by one complete period relatively to any other group.

Owner:INTEGRATED DEVICE TECH INC

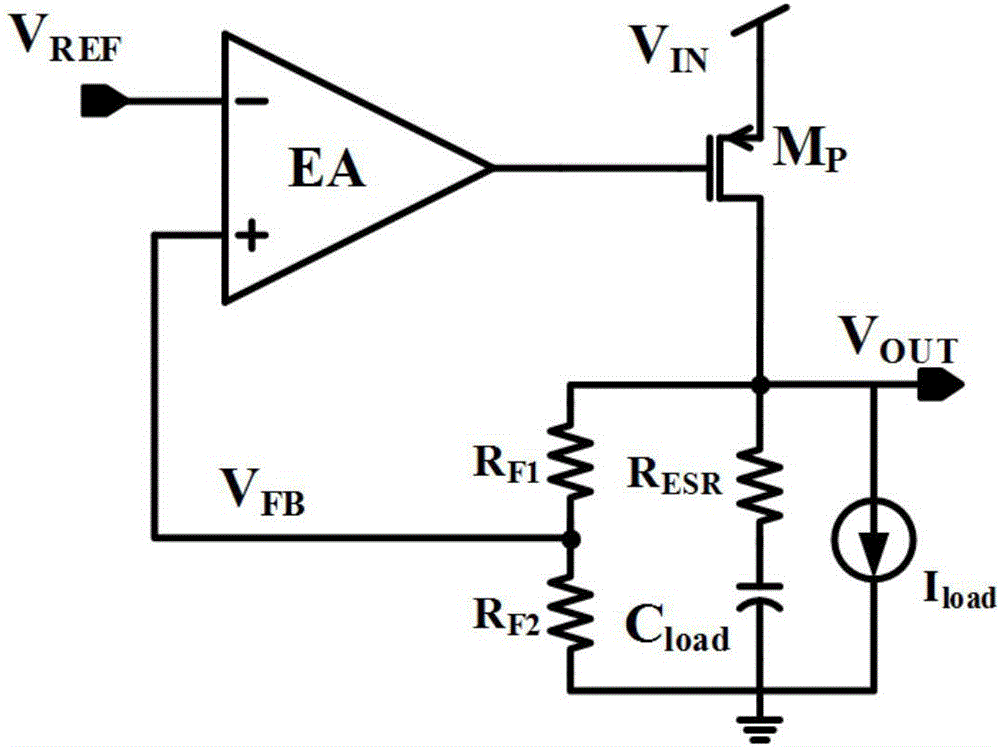

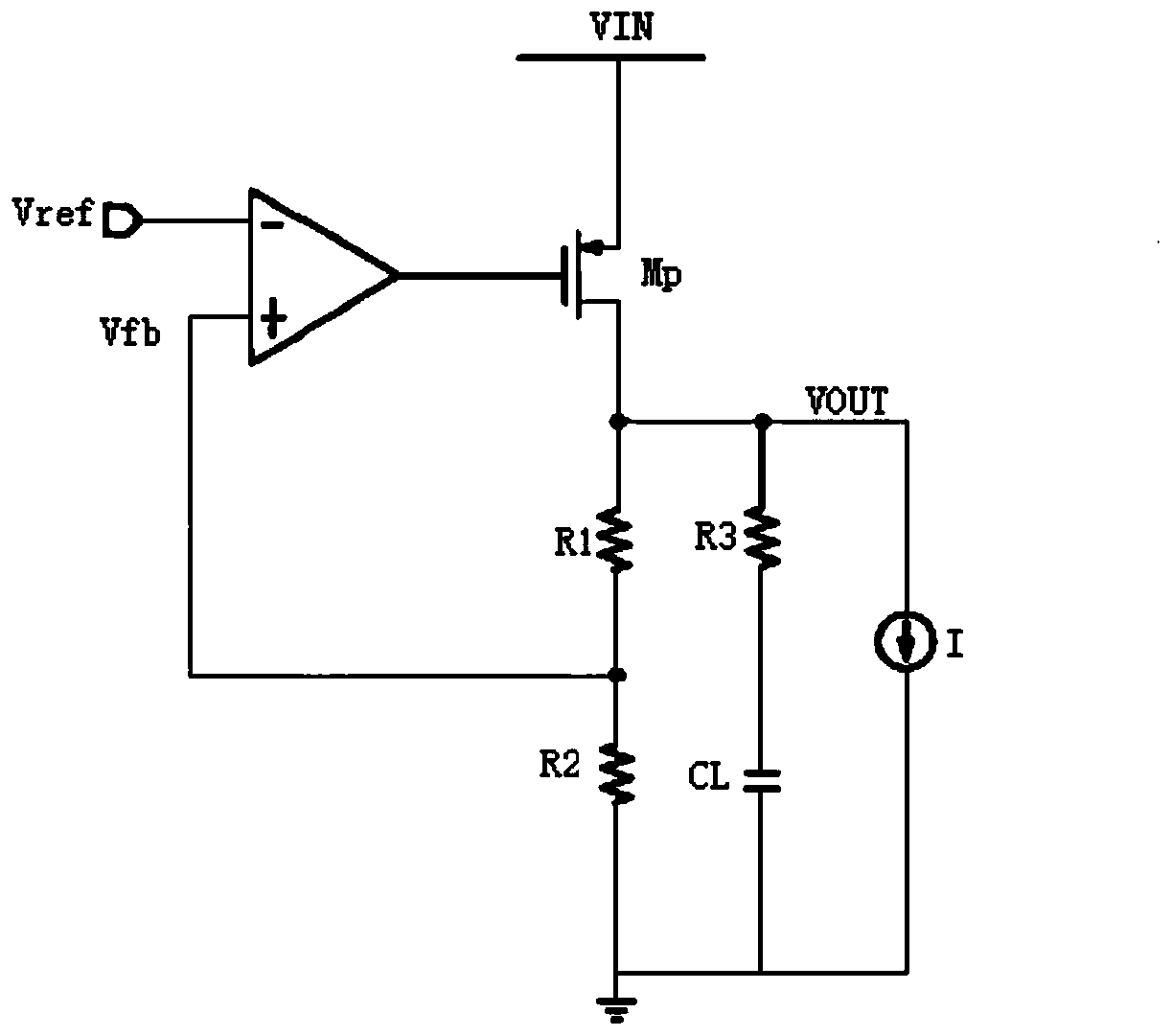

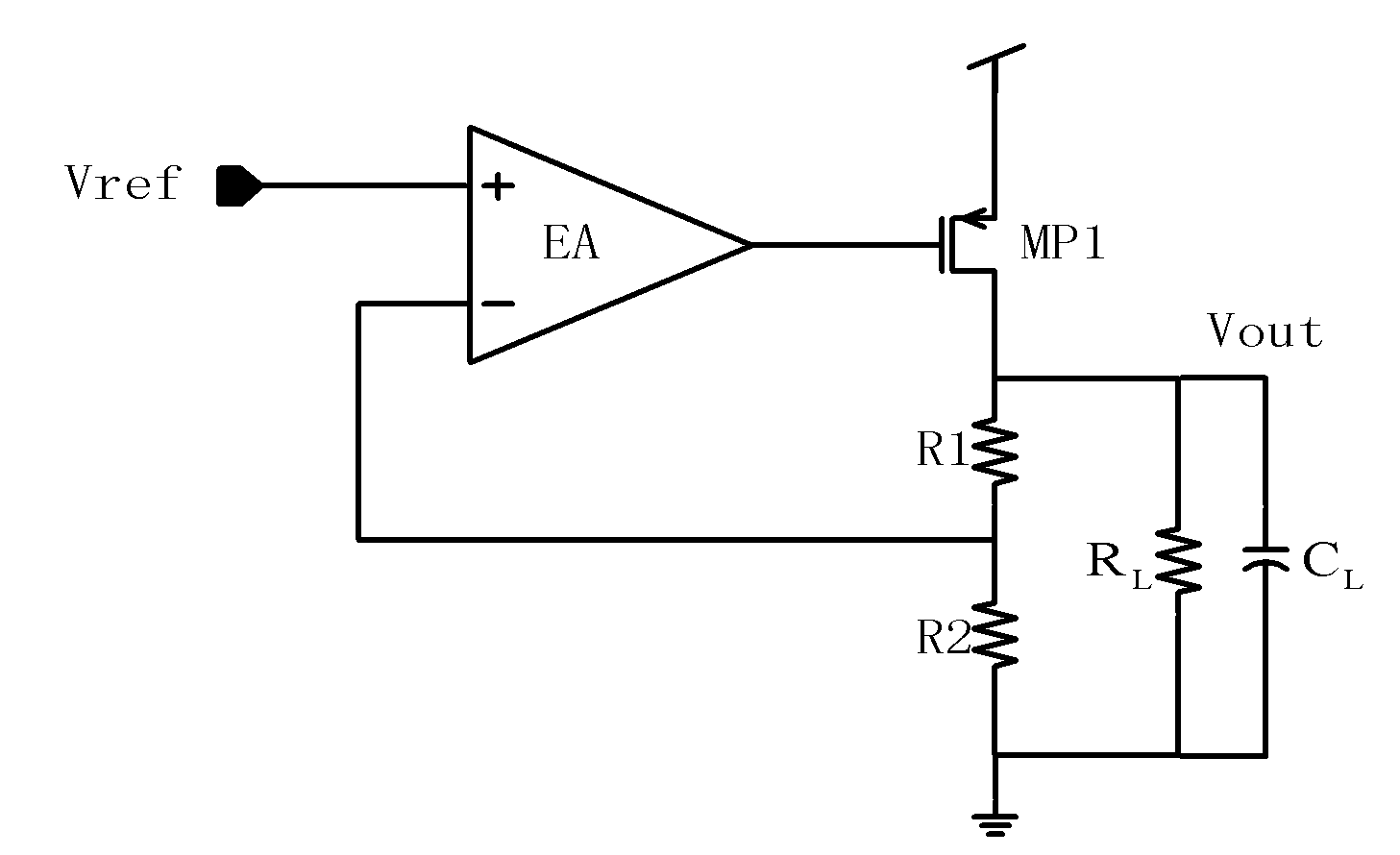

Low dropout linear voltage regulator

InactiveCN102385408AIncrease slew rateHigh bandwidthElectric variable regulationLinear regulatorCapacitance

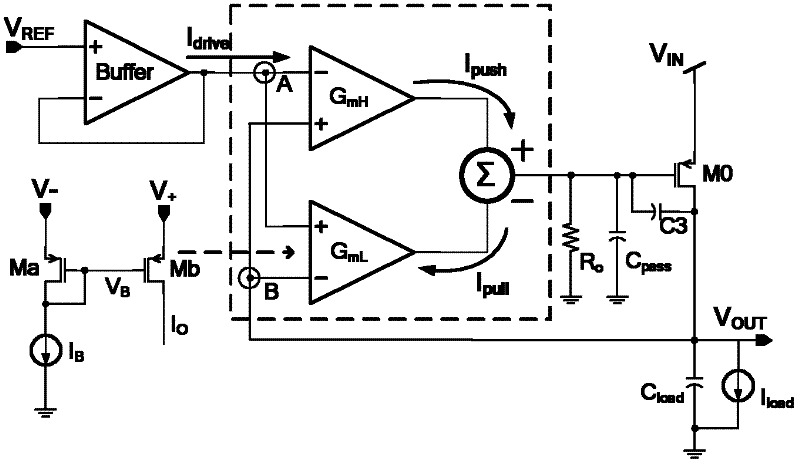

The invention, belonging to the technical field of power supply management, discloses a low dropout linear voltage regulator, which comprises a power tube, a buffer, a first transconductance amplifier, a second transconductance amplifier, a current subtractor and a Miller compensation capacitor. The low dropout linear voltage regulator can remarkably increase slew rate and bandwidth of a common grid type error amplifier and enlarge the scope of the input common-mode voltage by three techniques of adaptive current bias, the current subtractor and capacitance coupling type dynamic charge and discharge, so that transient response speed of the linear voltage regulator is greatly increased and amplitude of the output voltage peak is reduced, meanwhile, good stability of a loop circuit is ensured.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

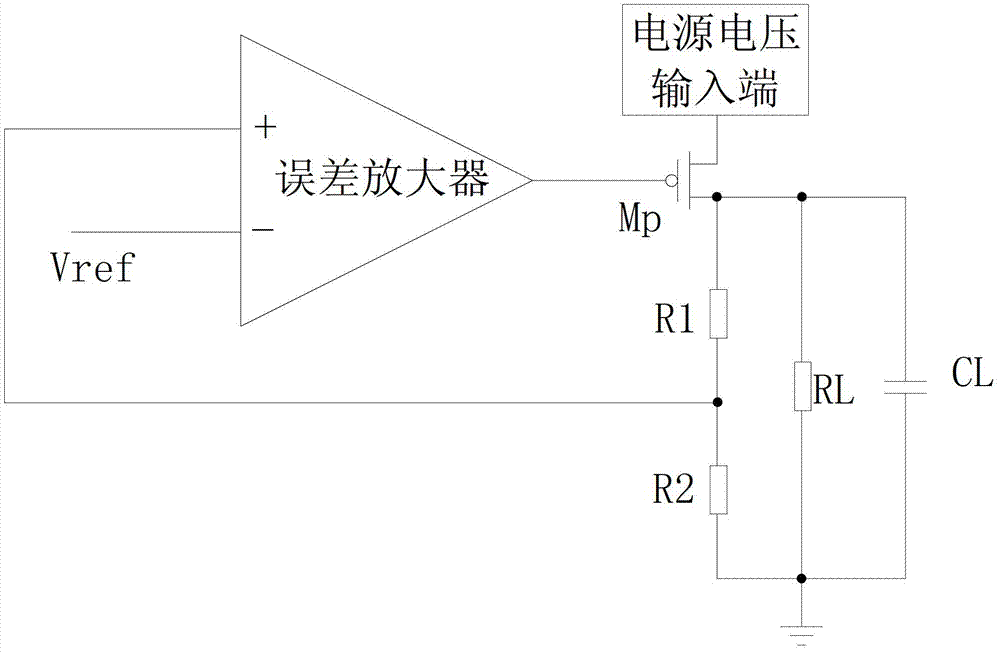

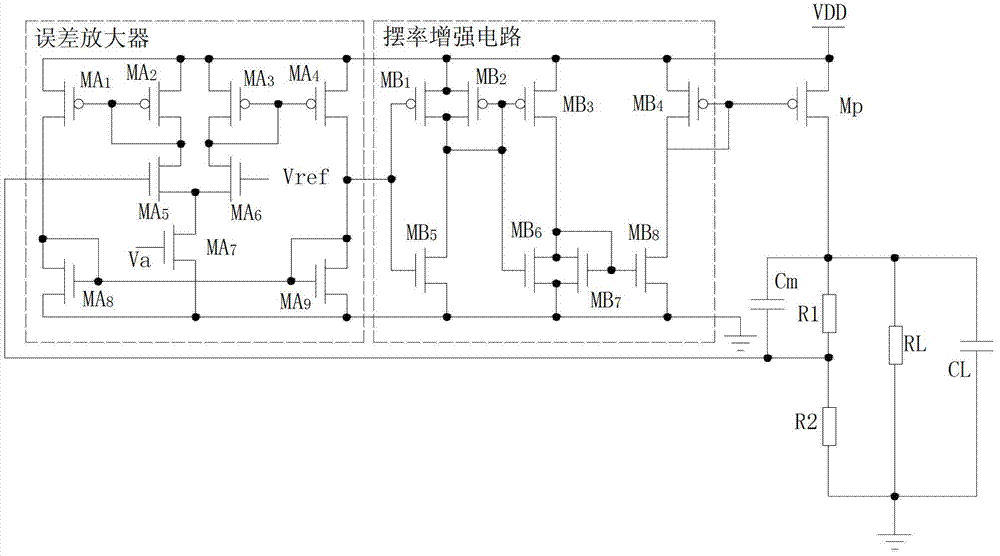

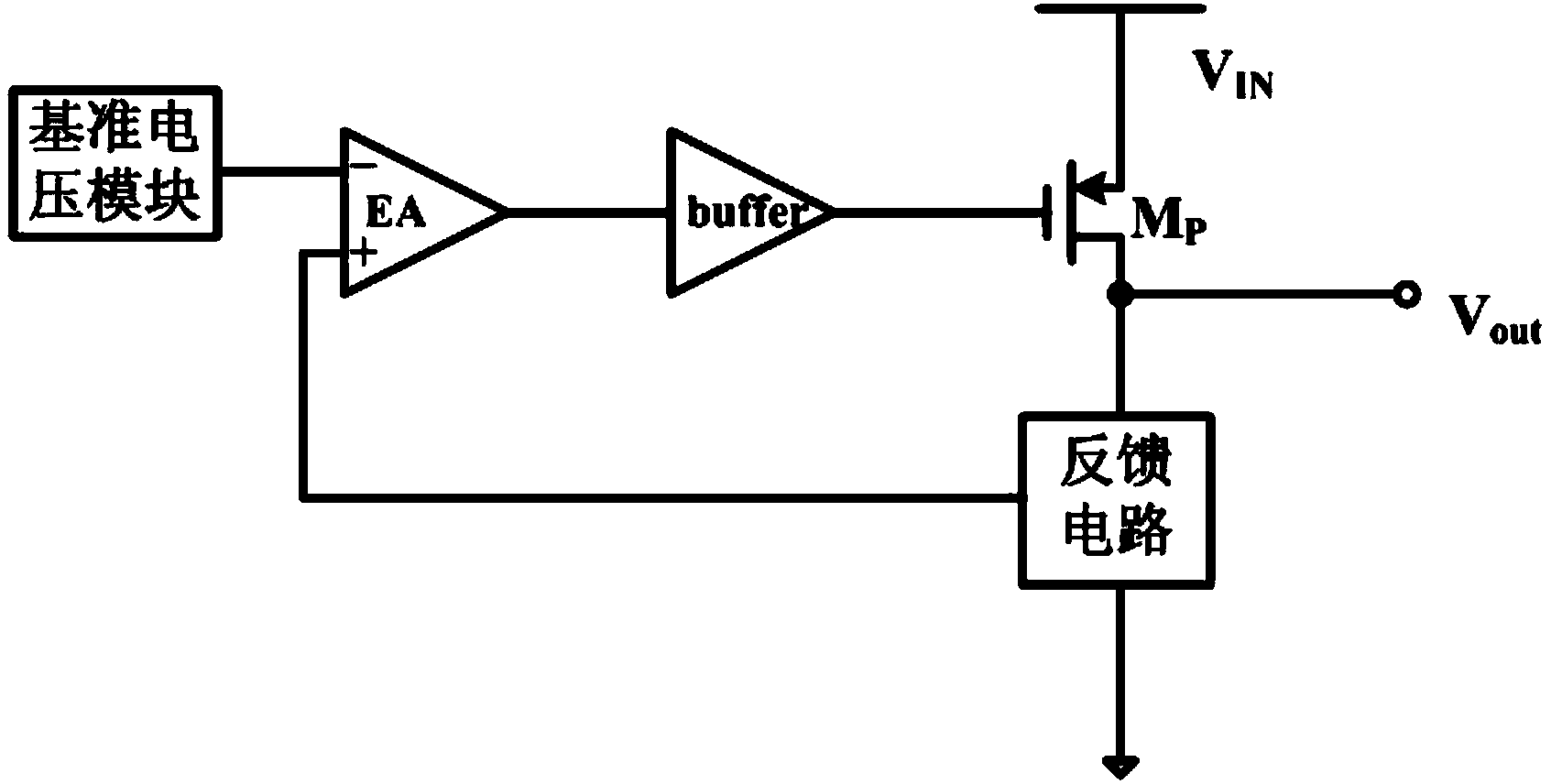

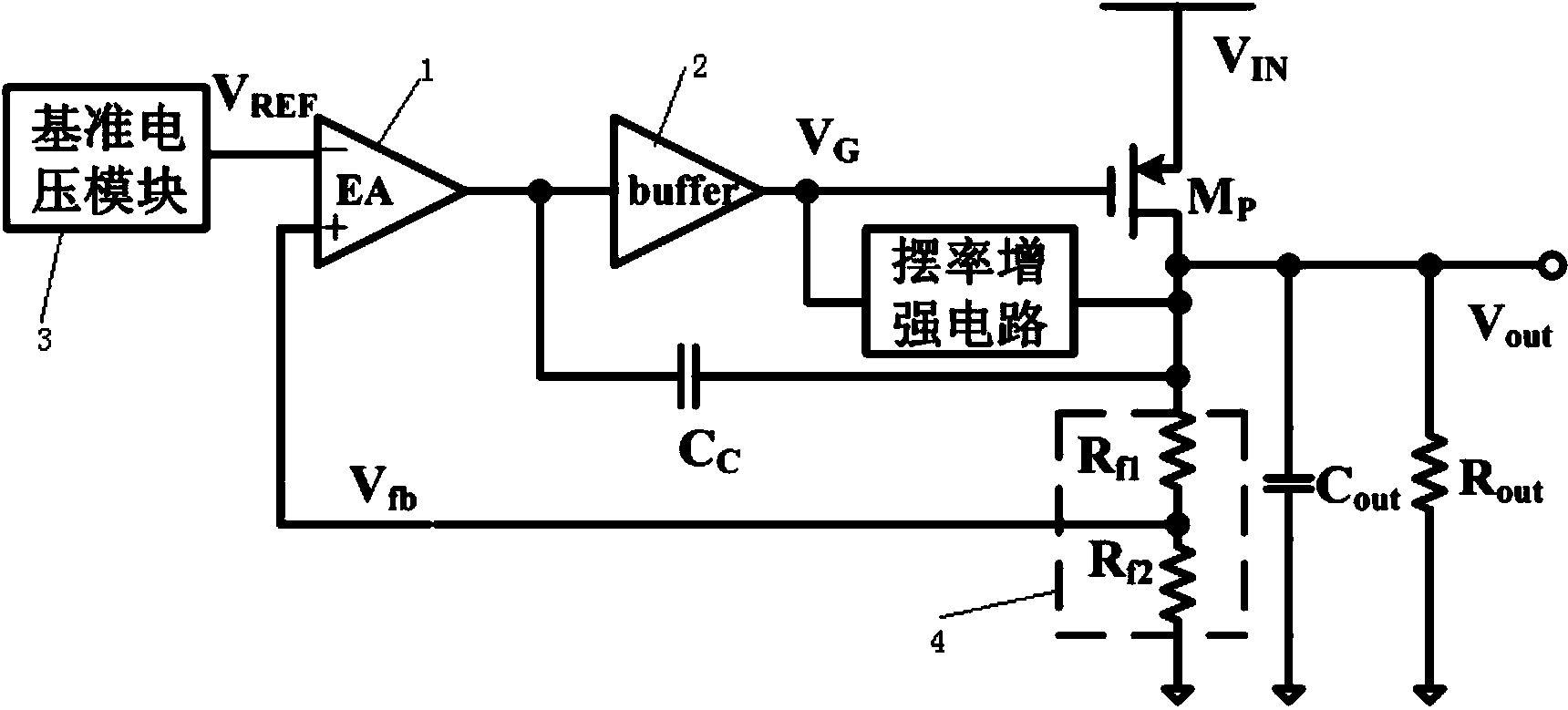

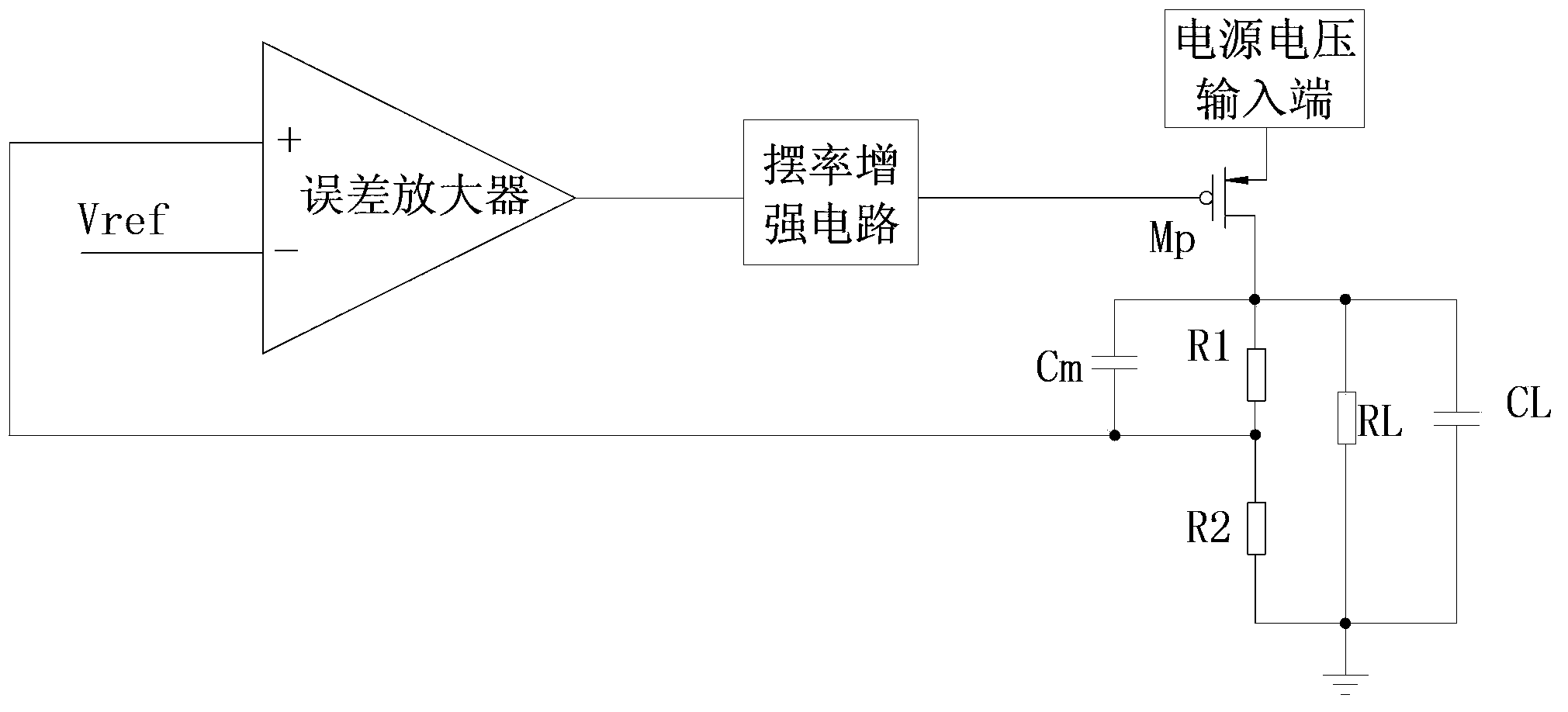

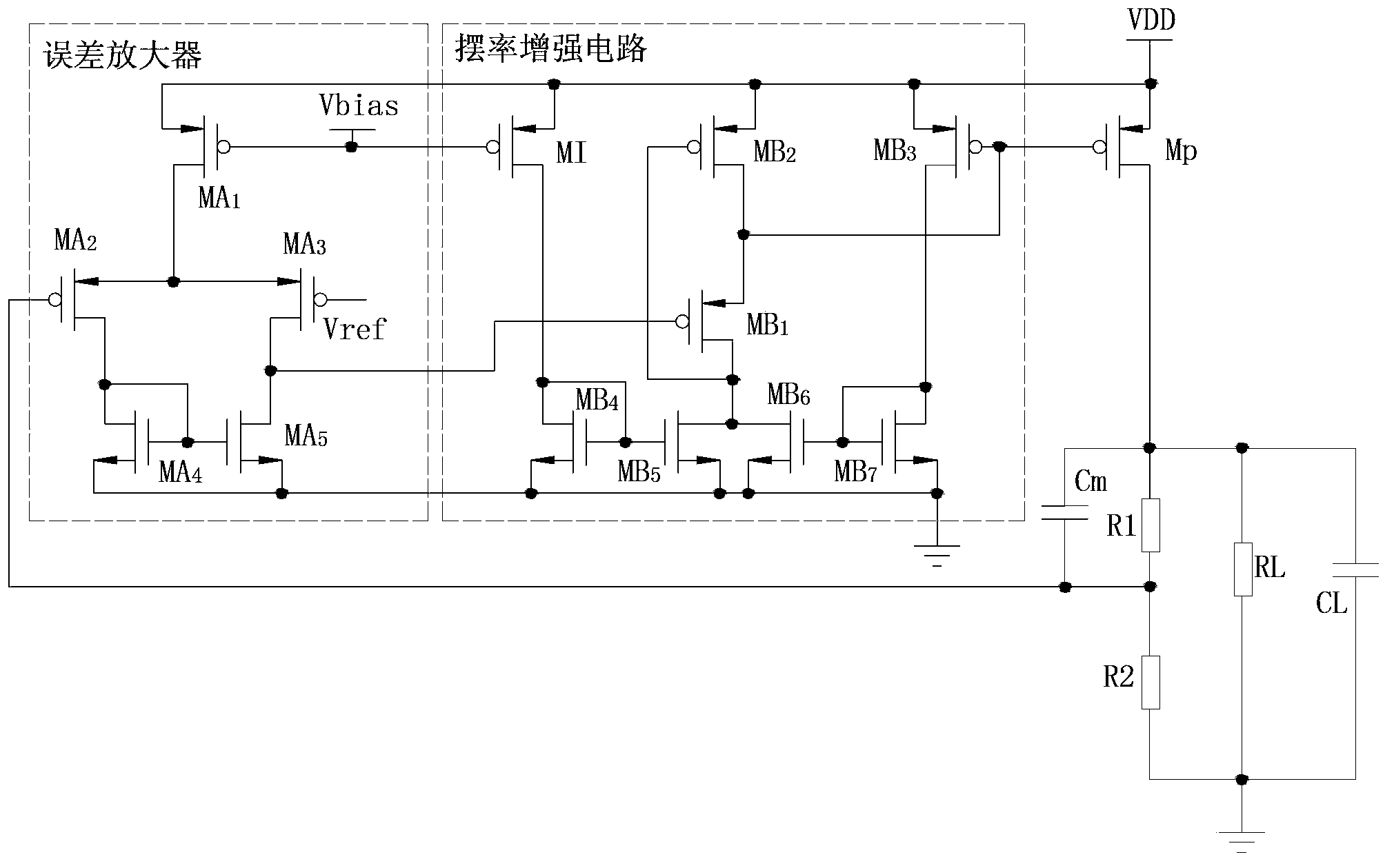

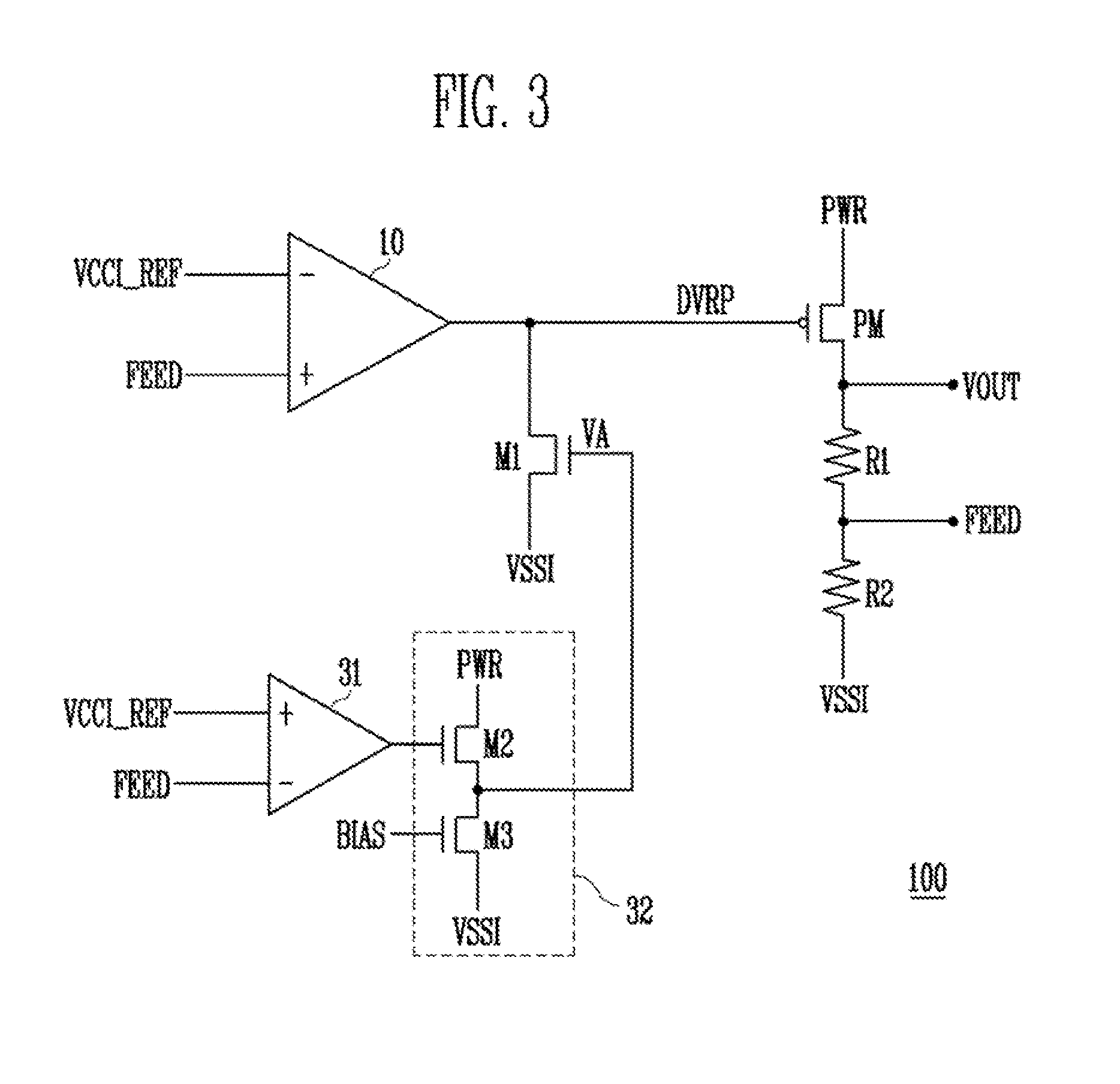

High-PSR (high power supply rejection) low-dropout regulator with slew rate enhancement circuit integrated thereto

ActiveCN103399607AIncrease slew rateImprove transient responseElectric variable regulationCircuit complexityCapacitance

The invention relates to power management technologies, solves the problem that generally voltage spike in output voltage is overcome for the existing low-dropout regulator at the costs of increased circuit complexity, decreased load capacity, increased output voltage noise and the like, and provides a High-PSR (high power supply rejection) low-dropout regulator with a slew rate enhancement circuit integrated thereto. According to the scheme, the regulator compared to the existing LDO regulators has the advantages that the slew rate enhancement circuit and a compensation capacitor are added, the positive phase input end of an error amplifier is connected with a reference voltage source, the negative phase input end of the error amplifier is connected with a resistance feedback circuit, the output end of the error amplifier is connected with the input end of the slew rate enhancement circuit, the output end of the slew rate enhancement circuit is connected with a gate of a pass transistor, one end of the compensation capacitor is connected with the negative phase input end of the error amplifier, and the other end of the compensation capacitor is connected with the output end of the error amplifier. The high-PSR low-dropout regulator has the advantages that transient response is enhanced and the scheme is applied to low-dropout regulators.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

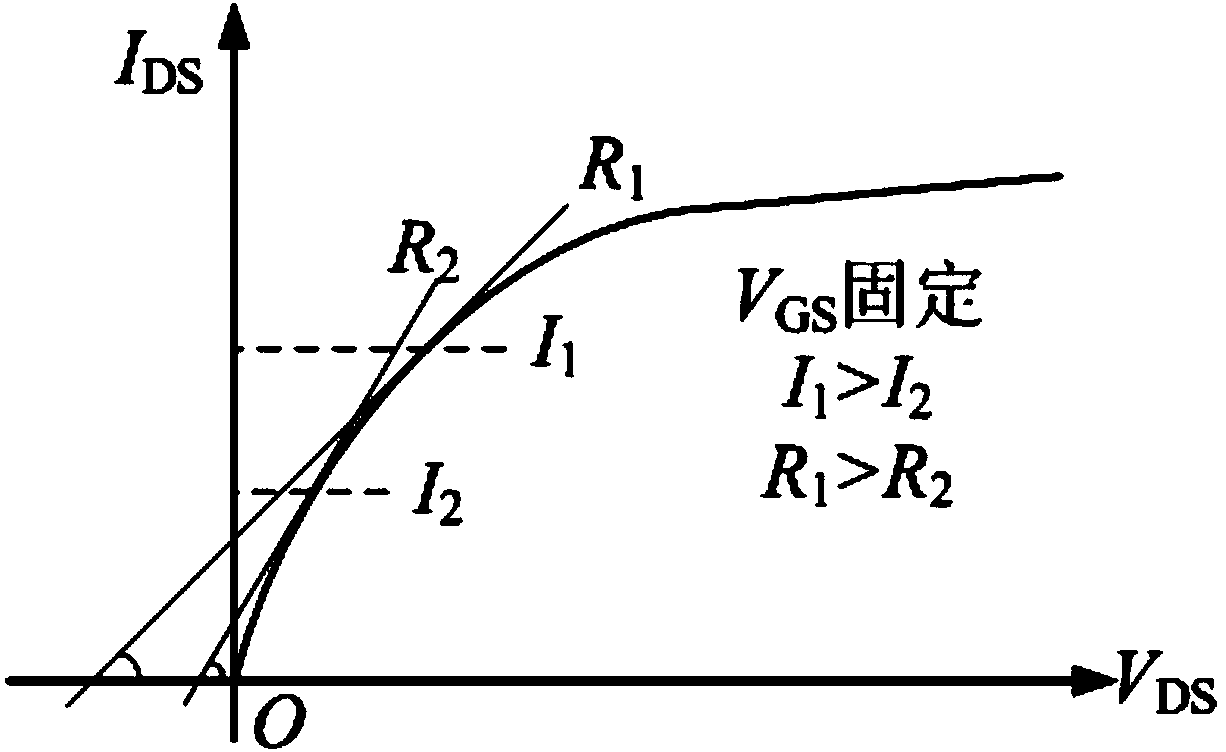

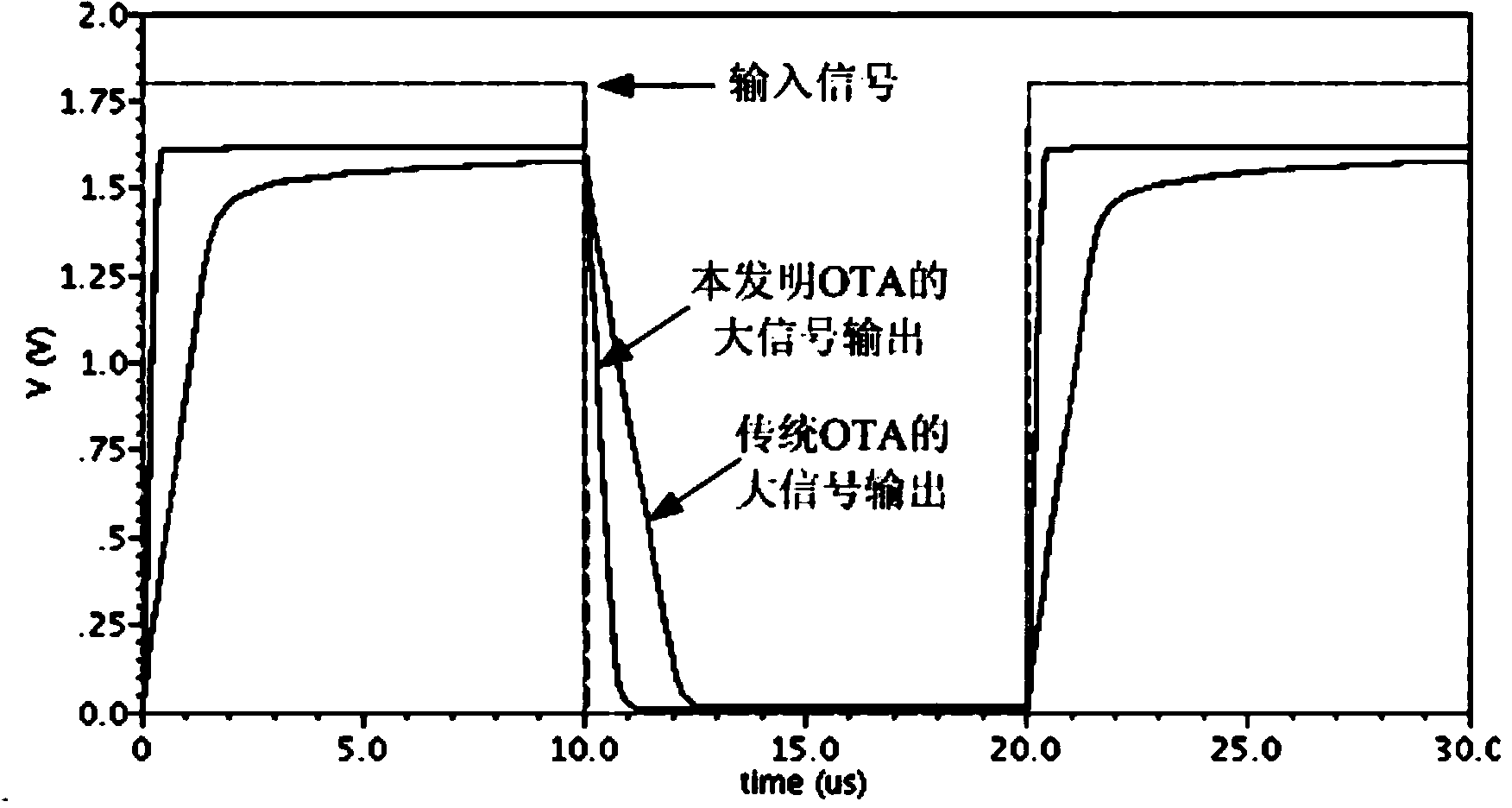

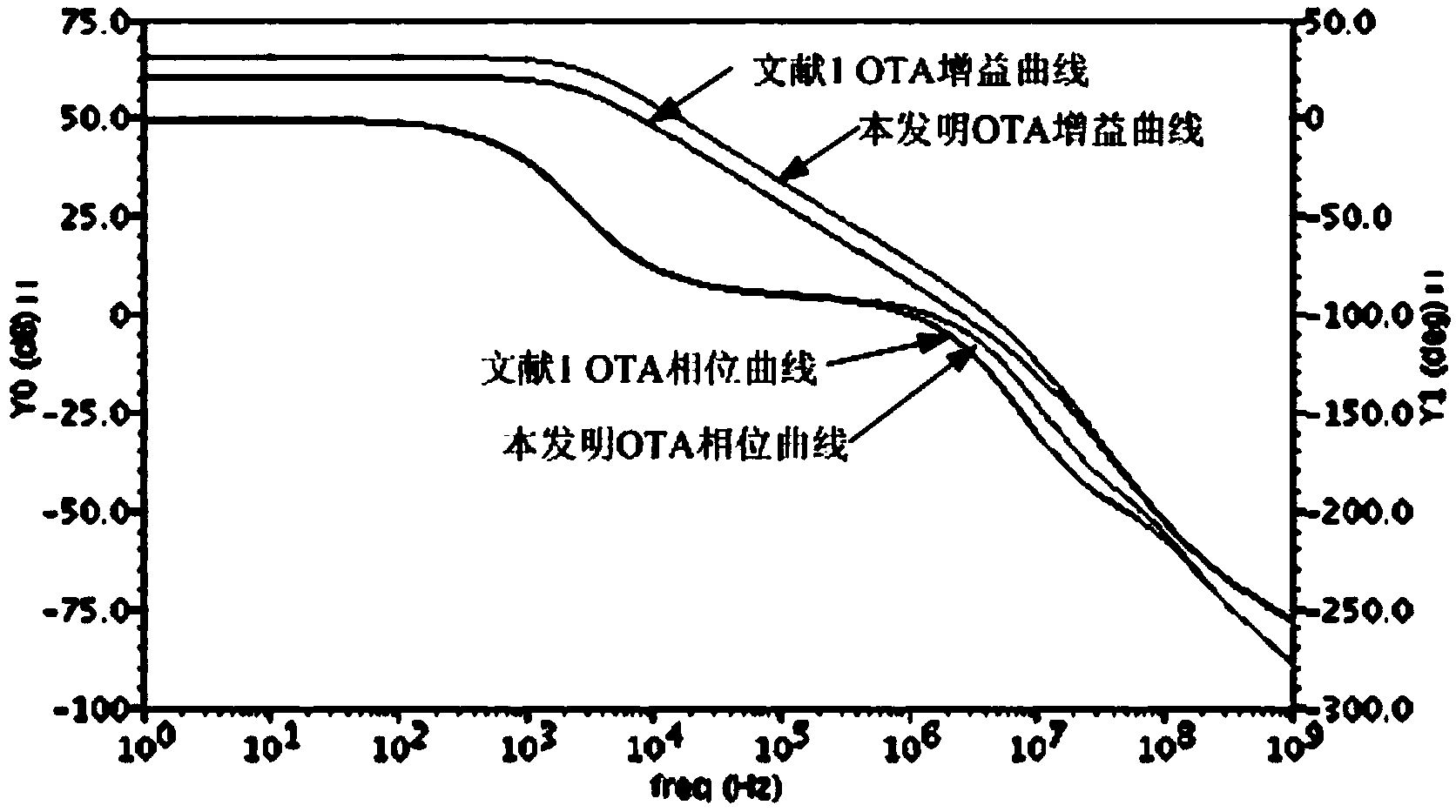

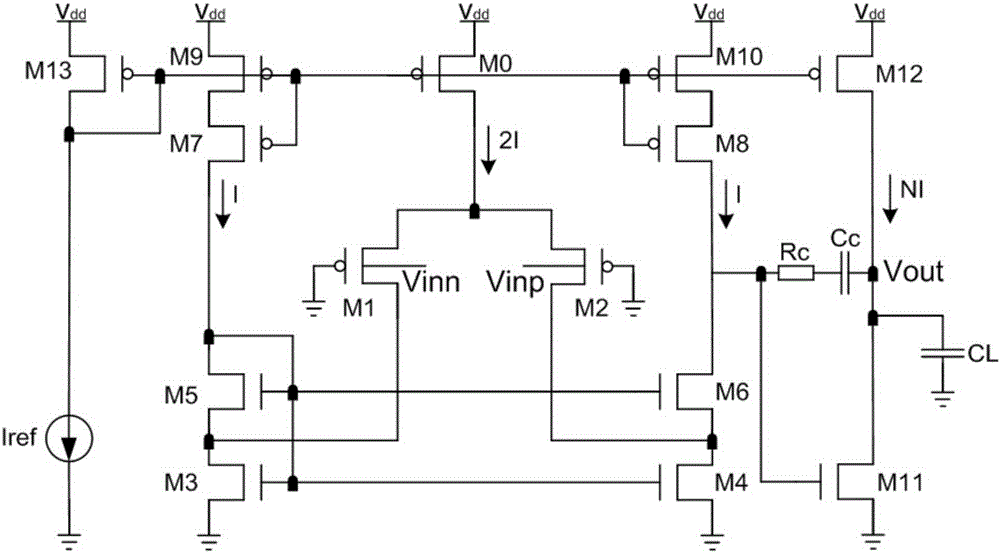

Gain and slew rate enhancement type amplifier

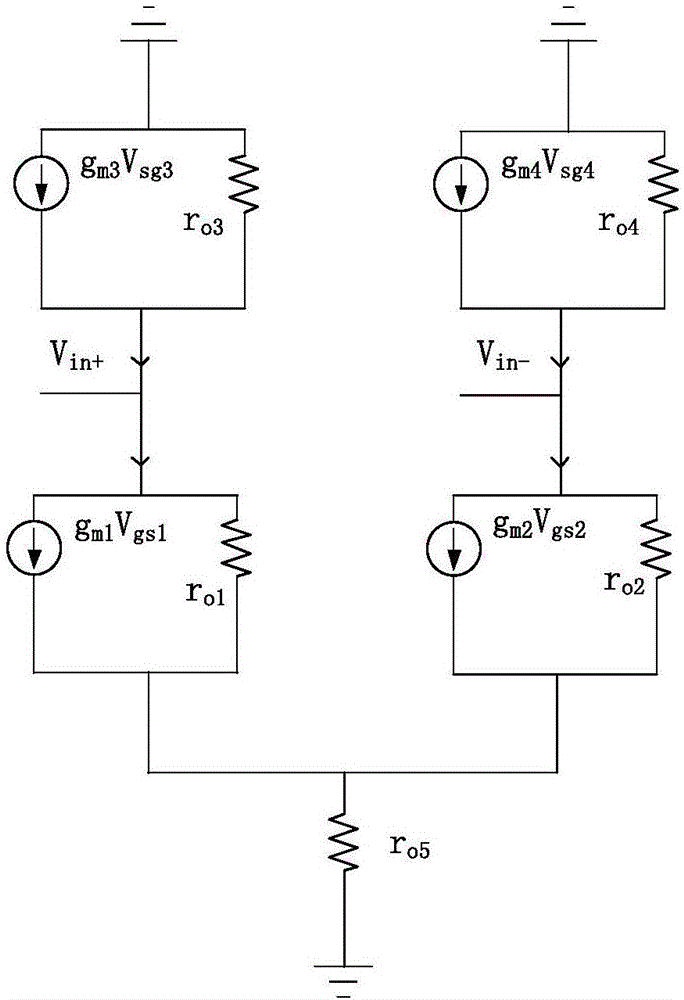

ActiveCN103457553AHigh gainHigh bandwidthDifferential amplifiersAmplifier modifications to extend bandwidthSwitched capacitorBand width

The invention relates to a gain and slew rate enhancement type amplifier, which is realized by a current mirror type operational transconductance amplifier (OTA). The gain and slew rate enhancement type amplifier consists of a differential input stage unit and a double-end to single-end unit. The amplifier disclosed by the invention adopts a mode of adding current control variable resistors to optimize a current mirror structure, and a circuit can obtain higher voltage gain and bandwidth under the situation of the same static power consumption. During big-signal inputting, a higher slew rate can be obtained. According to the gain and slew rate enhancement type amplifier disclosed by the invention, by only adding four current control variable resistors, the circuit slew rate is improved to 4.8V / mu s from 0.88V / mu s and the band width is improved to 4.3MHz from 2.54MHz on the premise that the amplifier keeps the same power consumption. The circuit disclosed by the invention can be widely applied to the circuit fields such as a switched capacitor circuit, a data converter and a mixed signal system on chip.

Owner:NO 24 RES INST OF CETC

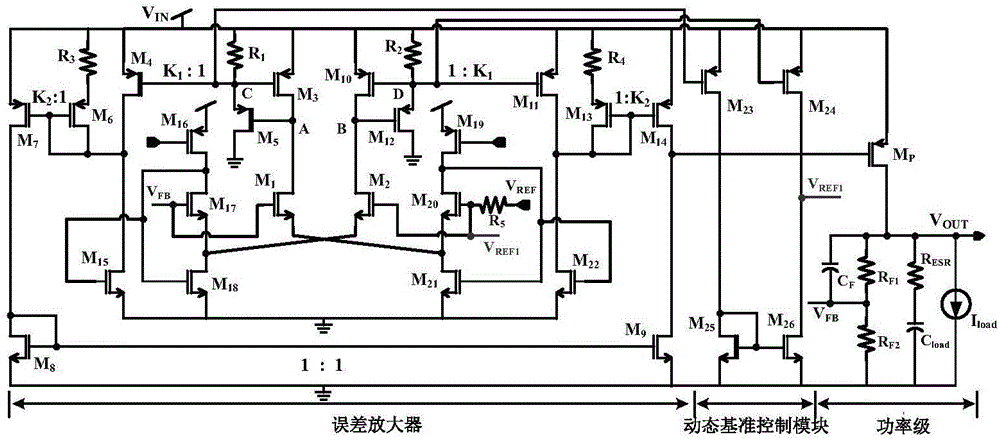

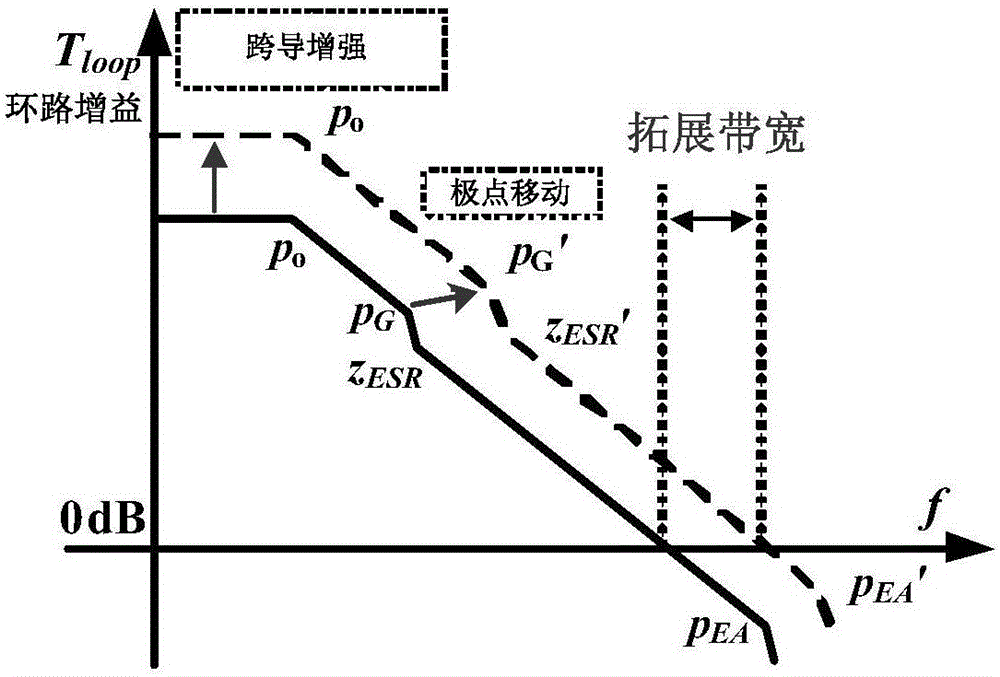

Low dropout linear regulator using super transconductance structure

InactiveCN106774614AExpand EA bandwidthIncrease slew rateAmplifier with semiconductor-devices/discharge-tubesElectric variable regulationLinear regulatorAudio power amplifier

The invention discloses a low dropout linear regulator using a super transconductance structure, and belongs to the technical field of power source management. The super transconductance structure, and belongs to the technical field of power source management. The super transconductance structure refers to a circuit structure that a voltage signal is transformed into a current signal, and the current signal is amplified in an extremely big proportion; an error amplifier EA adopts the super transconductance structure, differential input of the error amplifier EA feeds back a difference value between a voltage feedback VFB and a voltage dynamic reference VREF1 for a sample and transforms the difference value into a small signal current, and the small signal current is amplified by K1-fold through a first grade current mirror, and is then amplified by K2-fold through a second grade current mirror to be used for regulating the grid of a compensating pipe MP. The error amplifier EA with the super transconductance structure is adopted to widen the bandwidth of the error amplifier EA, besides, an SR current of an output end of the error amplifier EA during load transient variation is increased through a dynamic biasing technology and a dynamic reference control technology, and thus the purposes of increasing the slew rate of the error amplifier and strengthening the transient response are achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

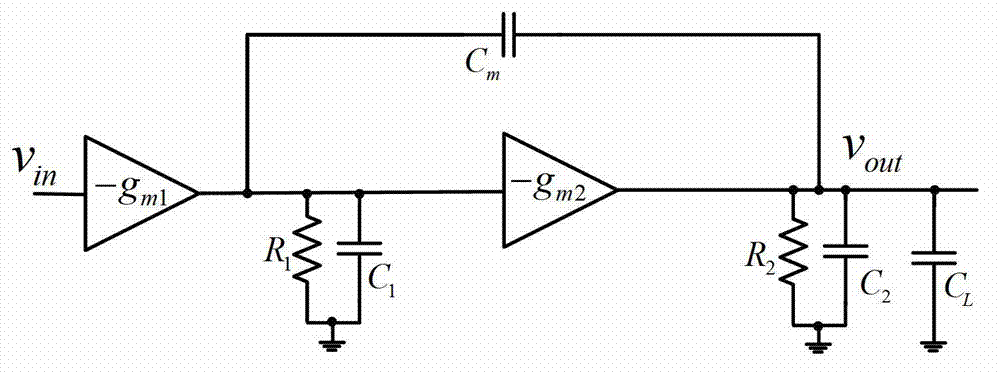

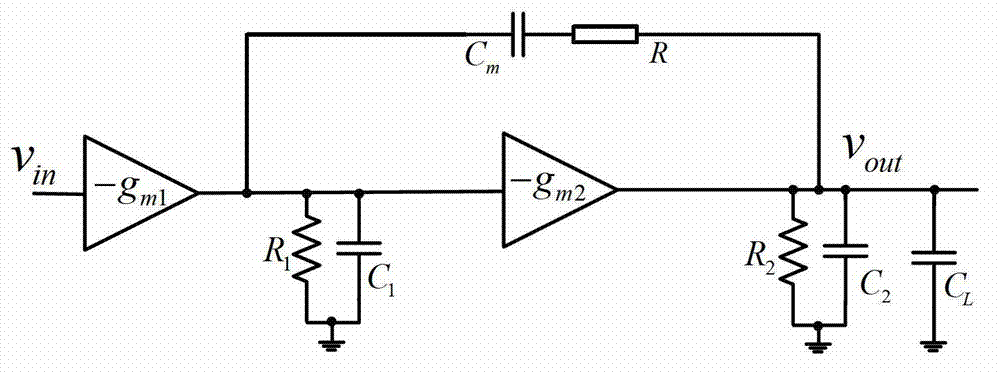

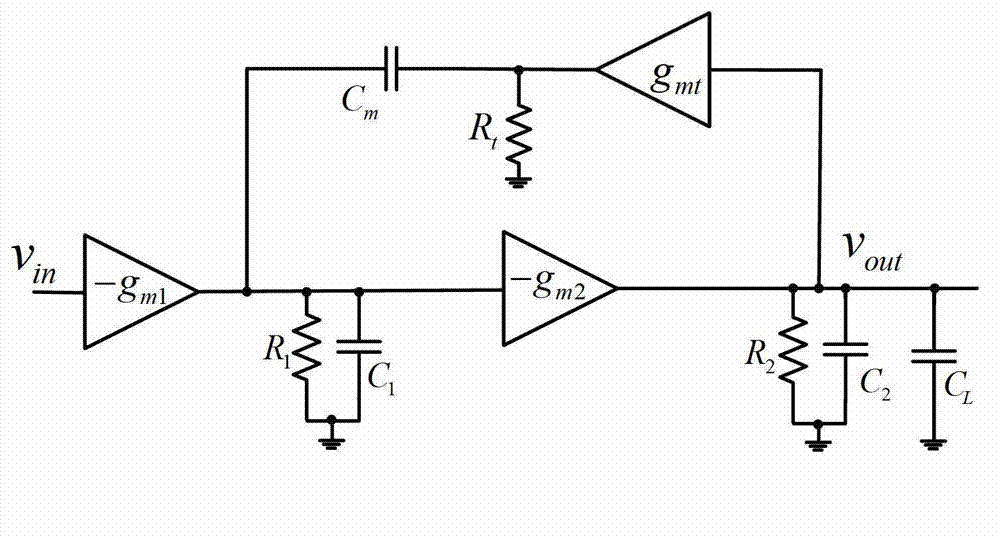

Split compensation two-stage operational amplifier based on inverter input structure

InactiveCN103199807AInhibition effectOffset the impactDifferential amplifiersAmplifier modifications to extend bandwidthCapacitanceFrequency compensation

The invention belongs to the technical field of electronics and relates to the frequency compensation technology of operational amplifiers in analog integrated circuits. The split compensation two-stage operational amplifier comprises a two-stage operational amplifier. A first-stage operational amplifier is composed of N-channel metal oxide semiconductor (NMOS) tubes (M1N, M2N, M3 and M4) and P-channel metal oxide semiconductor (PMOS) tubes (M1P, M2P and M0). A second-stage operational amplifier is composed of a PMOS tube M5P and an NMOS tube M5N. A traditional Miller capacitor is divided into a Cm1 portion and a Cm2 portion to finish frequency compensation of the operational amplifier. A first frequency compensation capacitor Cm1 is connected with the position between the output end of the first operational amplifier and the output end of the whole two-stage operational amplifier. A second frequency compensation capacitor Cm2 is connected with the position between a connection point of a source of the NMOS tube M2N and a drain of the NMOS tube M4 in the first-stage operational amplifier and the output end of the whole two-stage operational amplifier. The split compensation two-stage operational amplifier has strong robustness and higher unit grain bandwidth and output slew rate due to the fact that non-dominant poles and stray parameter are not related.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

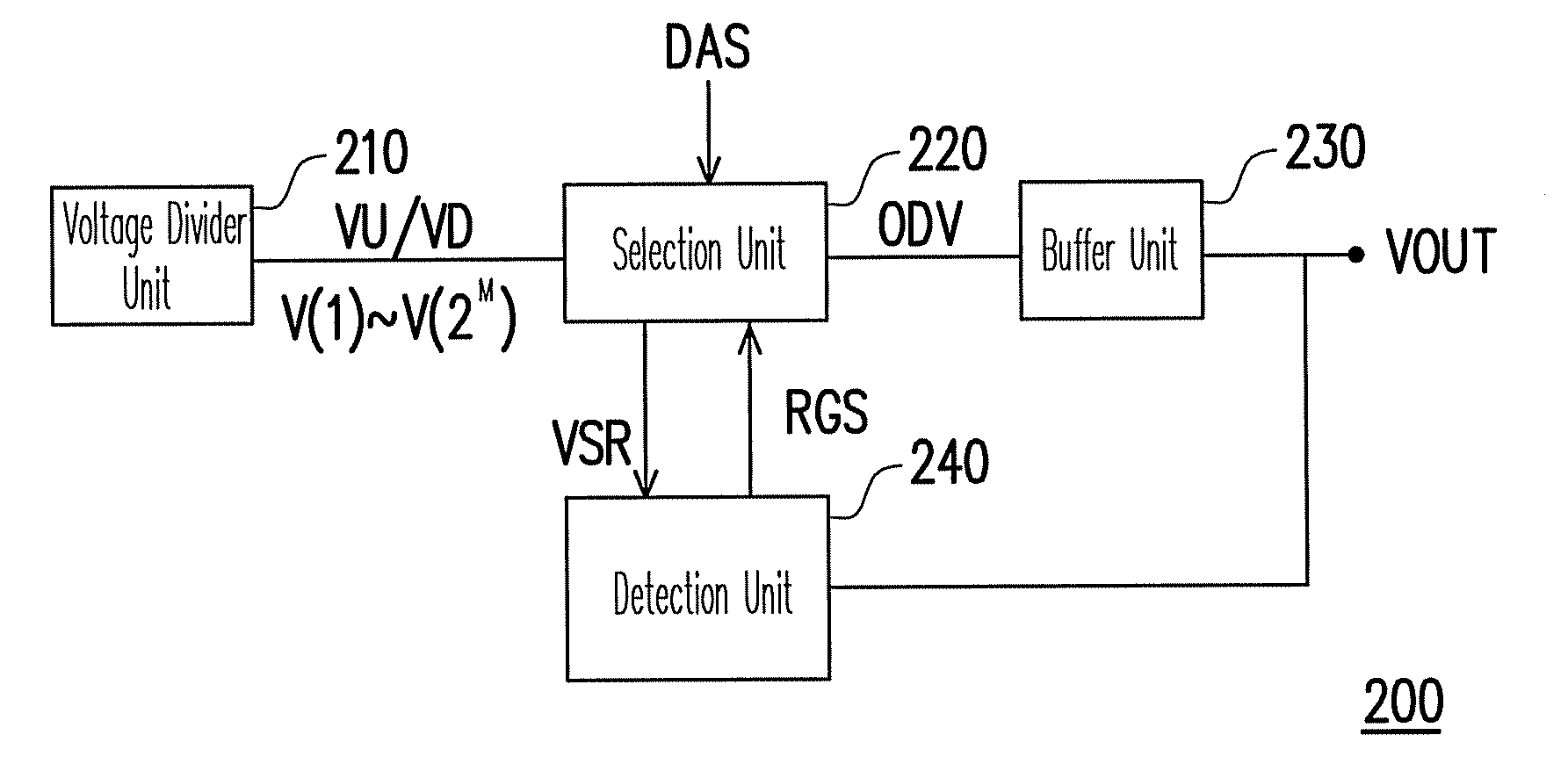

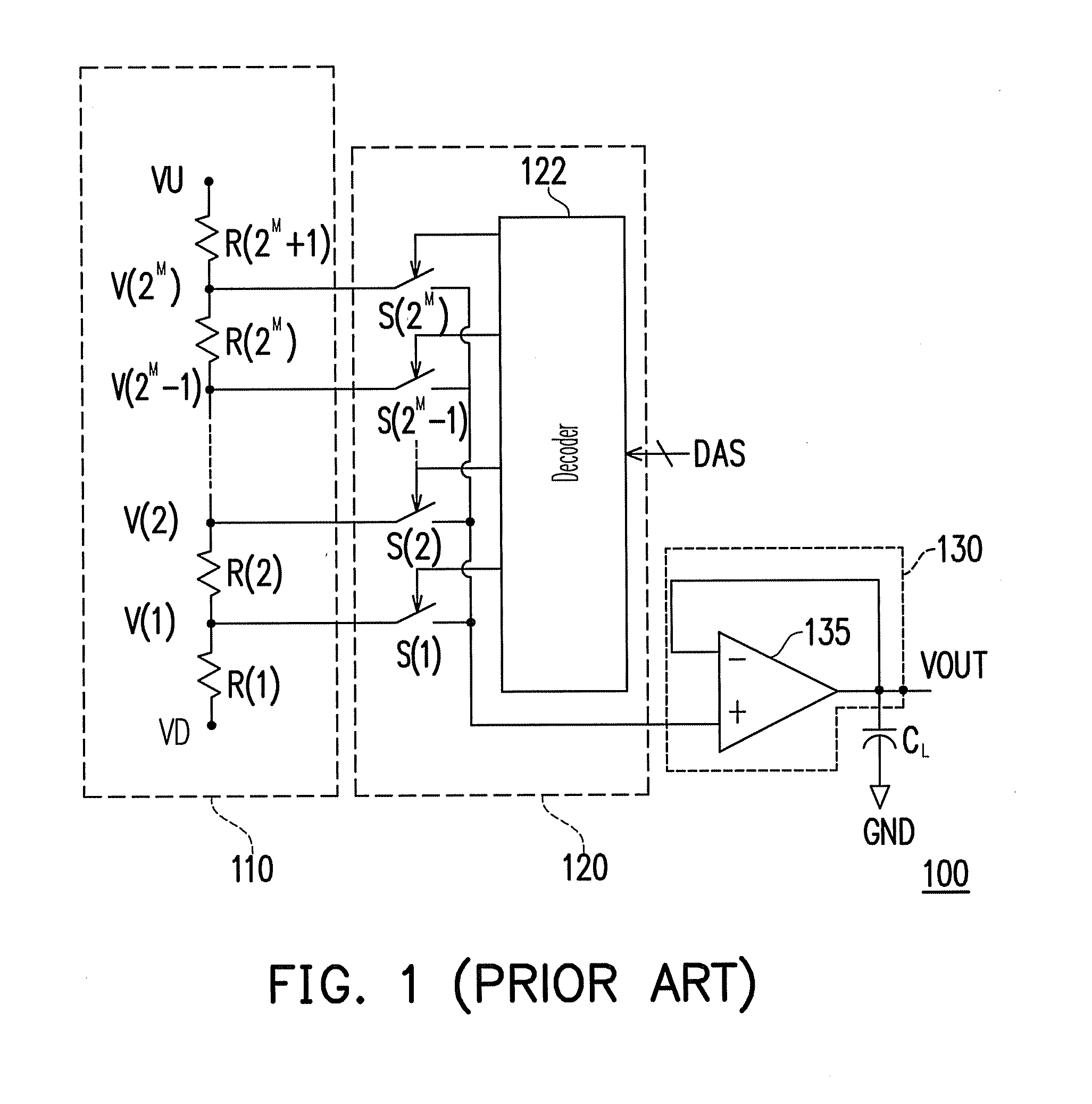

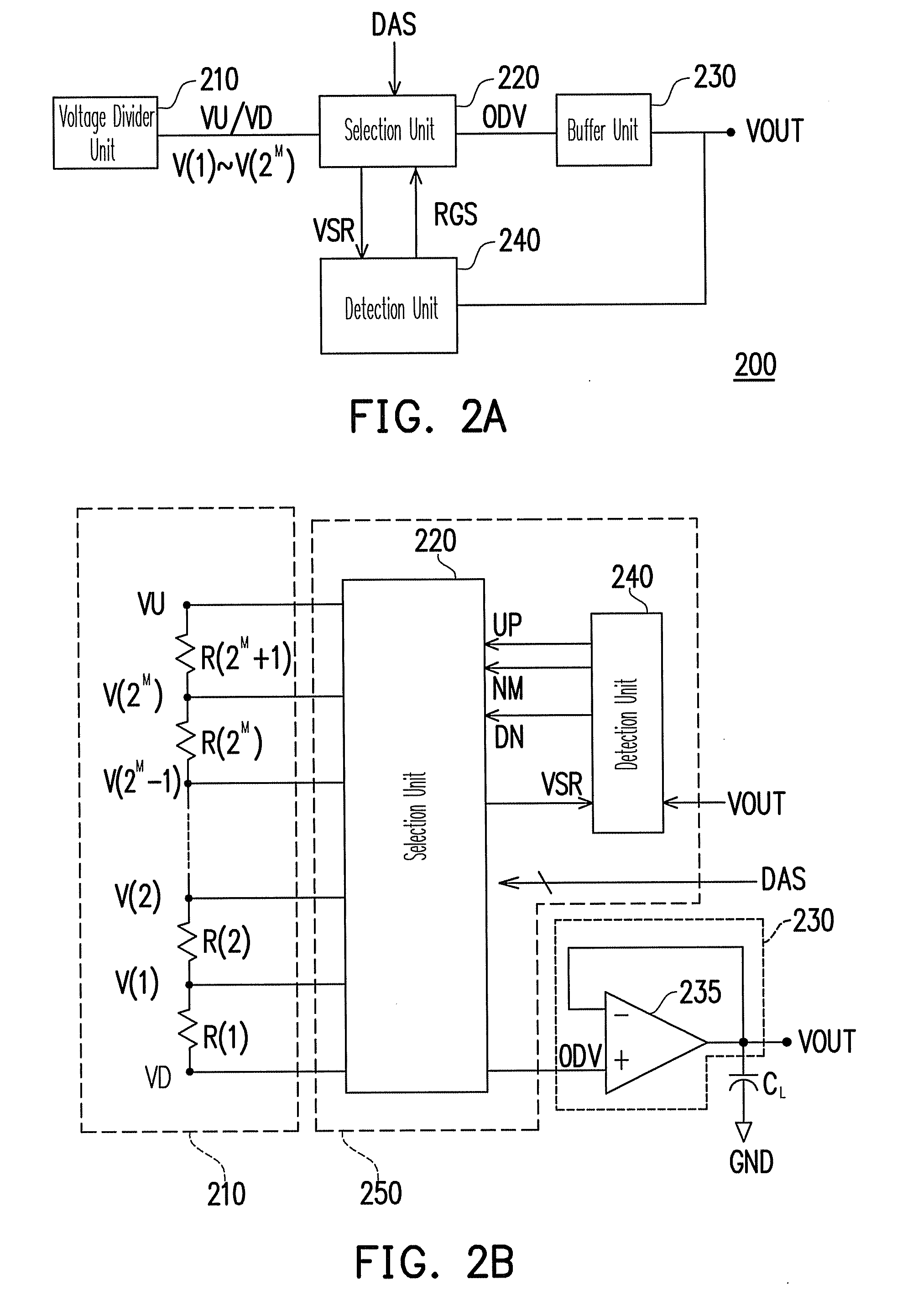

Overdrive digital-to-analog converter, source driver and method thereof

InactiveUS20080055137A1Increase conversion rateImprove conversion speedElectric signal transmission systemsDigital-analogue convertorsVoltage referenceEngineering

An overdrive digital-to-analog converter (DAC), a source driver, and a method thereof are provided. The DAC comprises a voltage divider unit, a selection unit, a buffer unit, and a detection unit. The voltage divider unit provides a plurality of reference voltages. The detection unit outputs a regulation signal according to a comparison result between a specific reference signal corresponding to an input digital signal and an output voltage output from the buffer unit. The selection unit regulates an overdrive voltage input to the buffer unit according to the regulation signal and the input digital signal. Accordingly, the output voltage of the buffer unit is changed quickly, and the conversion speed of the DAC is improved.

Owner:NOVATEK MICROELECTRONICS CORP

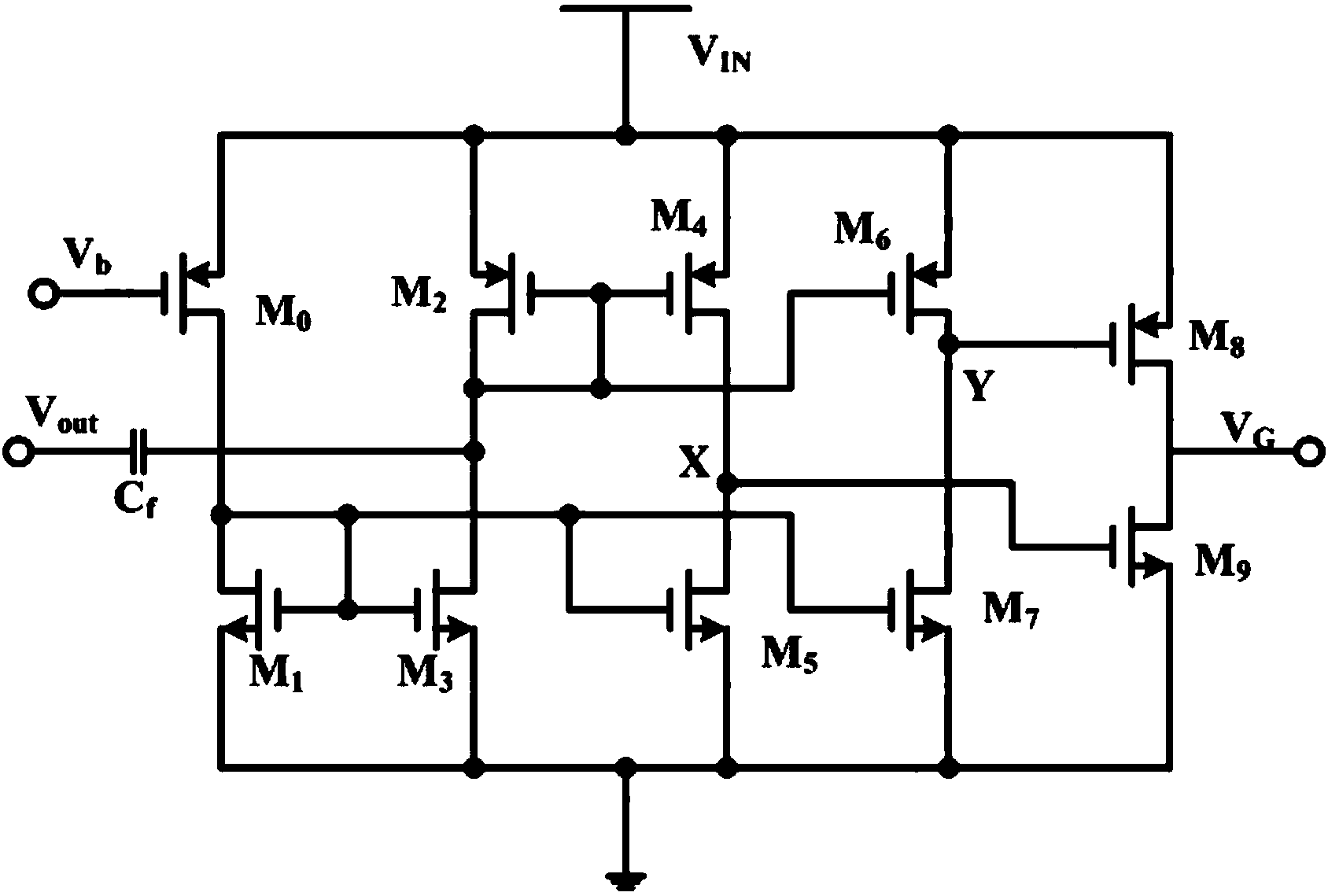

Slew rate enhancement circuit applicable to LDO regulators (low dropout regulators)

InactiveCN103760943AImprove output accuracyIncrease slew rateElectric variable regulationEngineeringCapacitor

The invention discloses a slew rate enhancement circuit applicable to LDO regulators (low dropout regulators). The slew rate enhancement circuit comprises PMOS (P-channel Metal Oxide Semiconductor) transistors M0, M2, M4, M6 and M8, NMOS (N-channel Metal Oxide Semiconductor) transistors M1, M3, M5, M7 and M9, a bias current source I0, and a capacitor Cf. On the premise of not significantly increasing static power consumption, when LDO load of an LDO regulator, which the slew rate enhancement circuit is integrated to, jumps, changes in output end voltage can be quickly detected and a gate of a power regulating tube is transiently regulated; accordingly, the slew rate of voltage in the gate of the power regulating tube is greatly increased, and transient response of the LDO circuit is improved.

Owner:HEFEI UNIV OF TECH

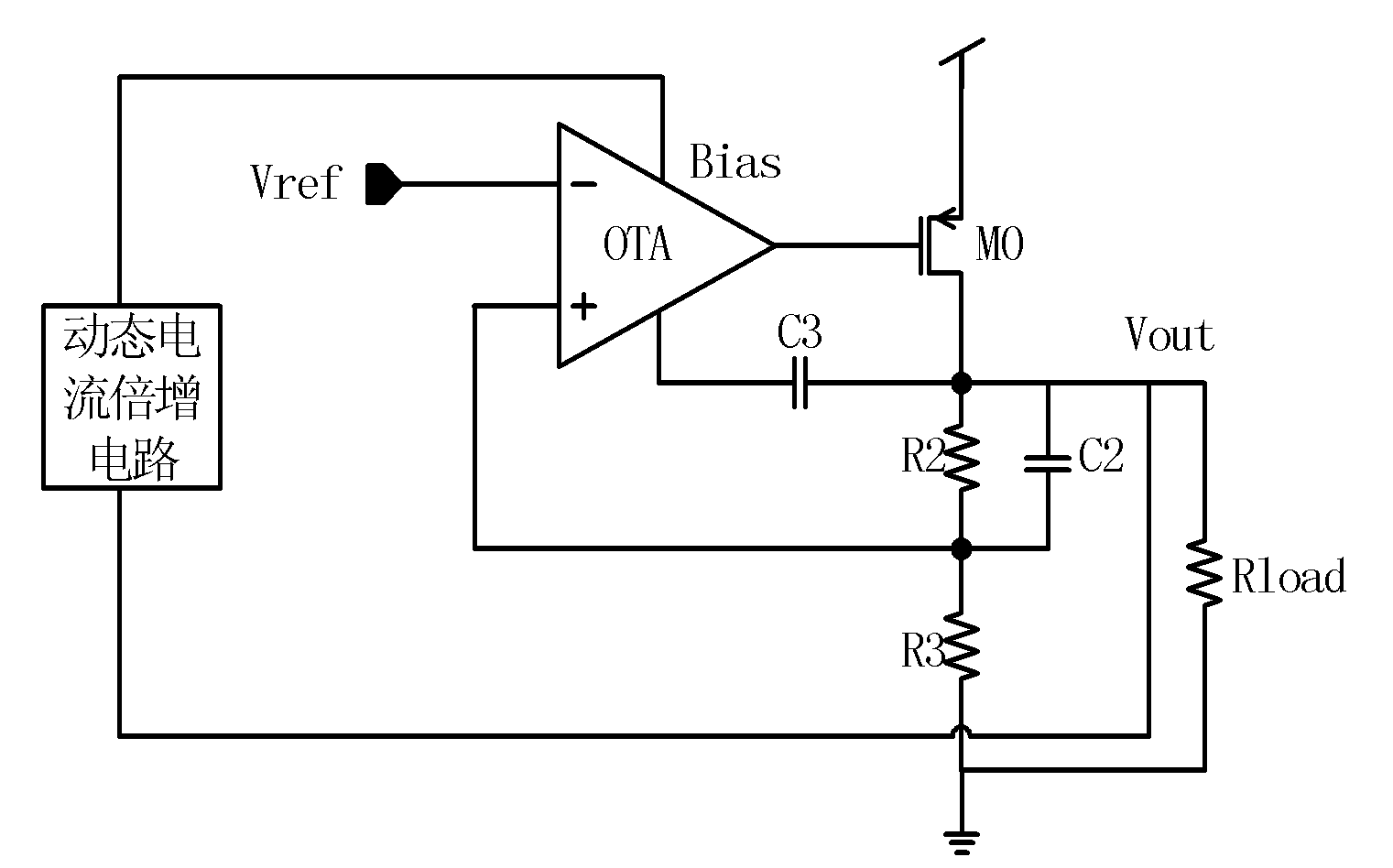

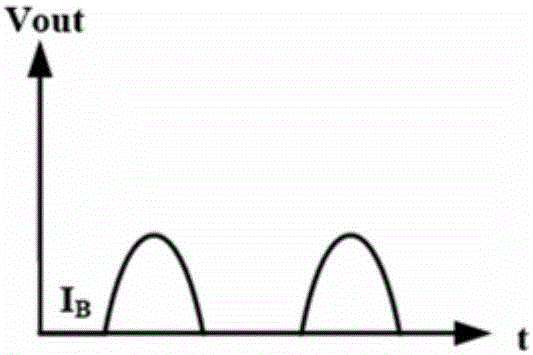

Fast transient response circuit applied to LDO

PendingCN109116905AIncreased bandwidth and slew rateImprove response speedElectric variable regulationCapacitanceSlew rate

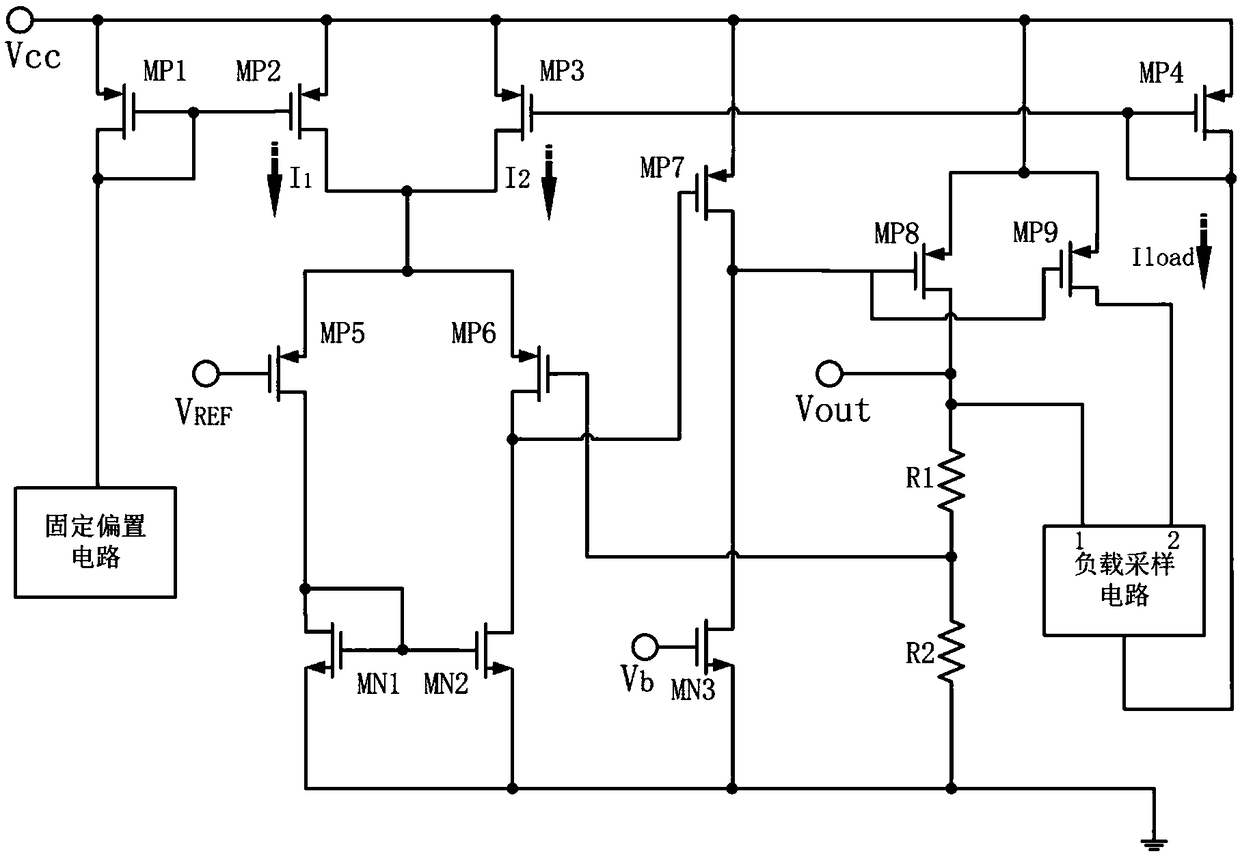

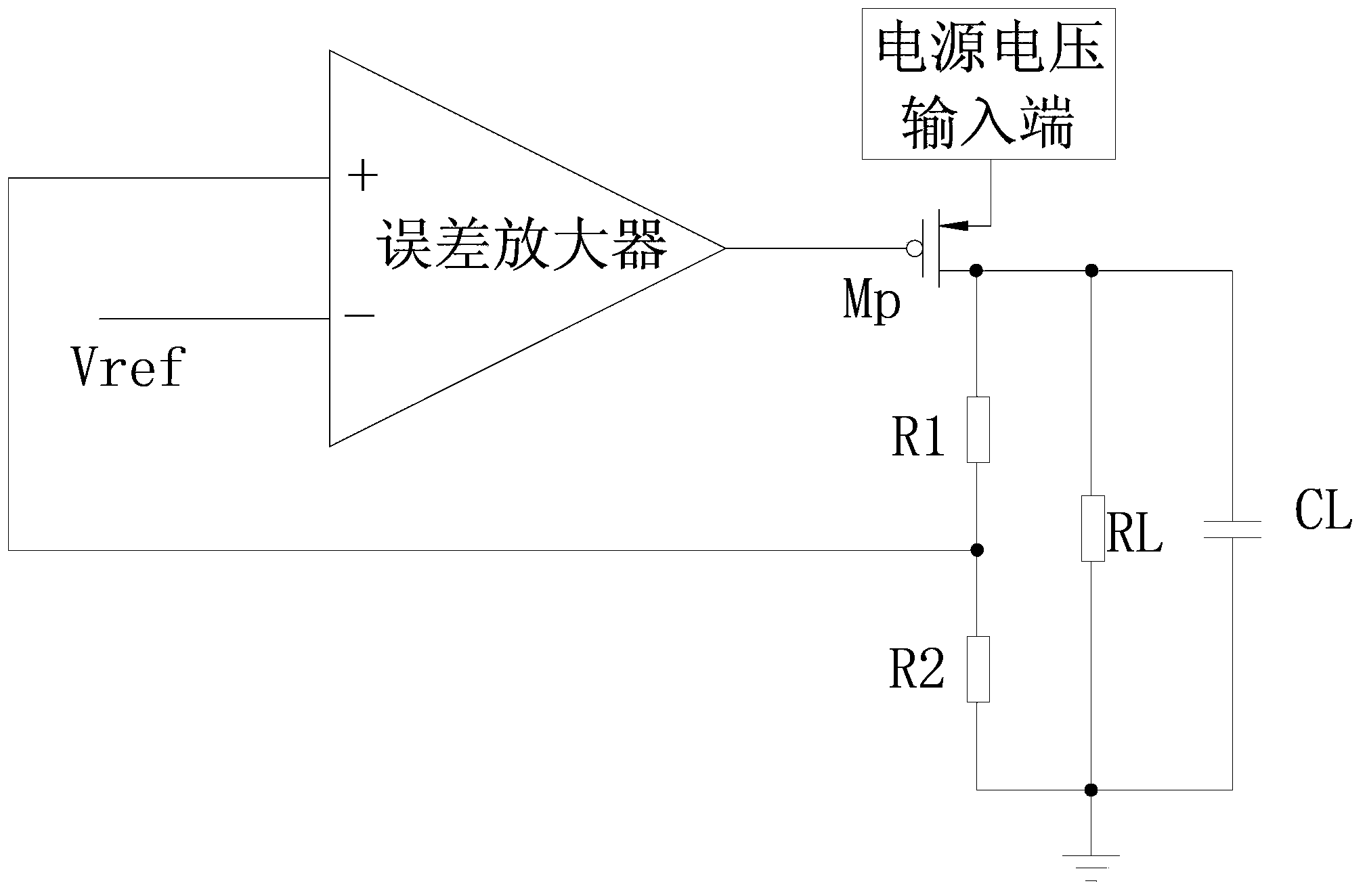

The invention provides a fast transient response circuit applied to an LDO (low-dropout linear voltage stabilizer). An LDO circuit without out-of-chip bulk capacitor is adopted, the fast transient response capacity of the LDO can be enhanced by improving an internal circuit of the LDO, and other performances of the circuit cannot be weakened. The tail current of EA is divided into two parts: one part adopts fixed current bias, and the other part adopts the current from output load sampling; the static current of a chip cannot be increased in the circuit, and the response speed of the loop is also increased along with the increase of the bandwidth and the slew rate of the loop when the load is suddenly increased.

Owner:拓尔微电子股份有限公司

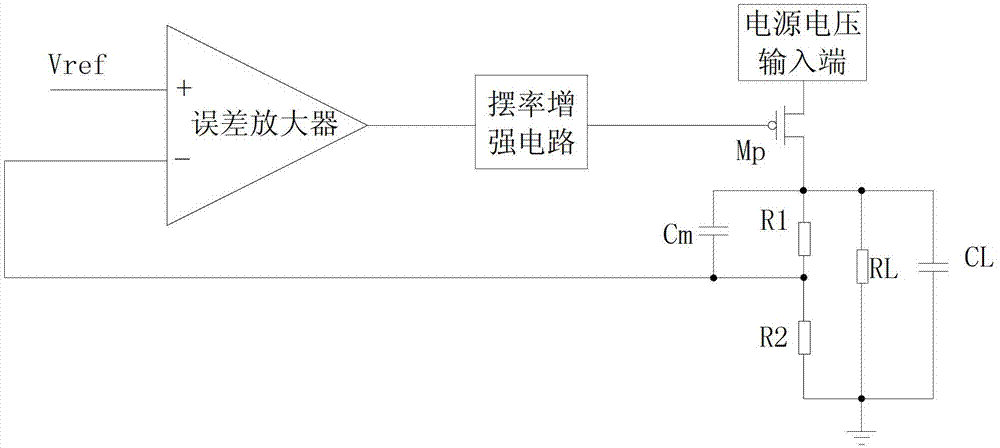

Low dropout regulator (LDO) integrated with slew rate intensifier circuit

ActiveCN103399608AImprove transient responseIncrease slew rateElectric variable regulationCircuit complexityCapacitance

The invention relates to a power supply management technology, solves the problem that the output voltage spike of a conventional low dropout regulator is solved through increasing the circuit complexity, reducing the load capacity and increasing the output voltage, and provides a low dropout regulator (LDO) integrated with slew rate intensifier circuit. The technical scheme adopted by the invention is summarized as follows: compared with a conventional LDO, a slew rate intensifier circuit and a compensation capacitor are additionally arranged, the negative phase input end of an error amplifier is connected with a reference voltage source, the positive phase input end of the error amplifier is connected with a resistance feedback circuit, and the output end of the error amplifier is connected with the input end of the slew rate intensifier circuit; the output end of the slew rate intensifier circuit is connected with a grid electrode of a compensating pipe; one end of the compensation capacitor is connected with the positive phase input end of the error amplifier, and the other end of the compensation capacitor is connected with the output end. The LDO integrated with the slew rate intensifier circuit has the benefit that the transient response is improved, and is applicable to the low dropout regulator.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

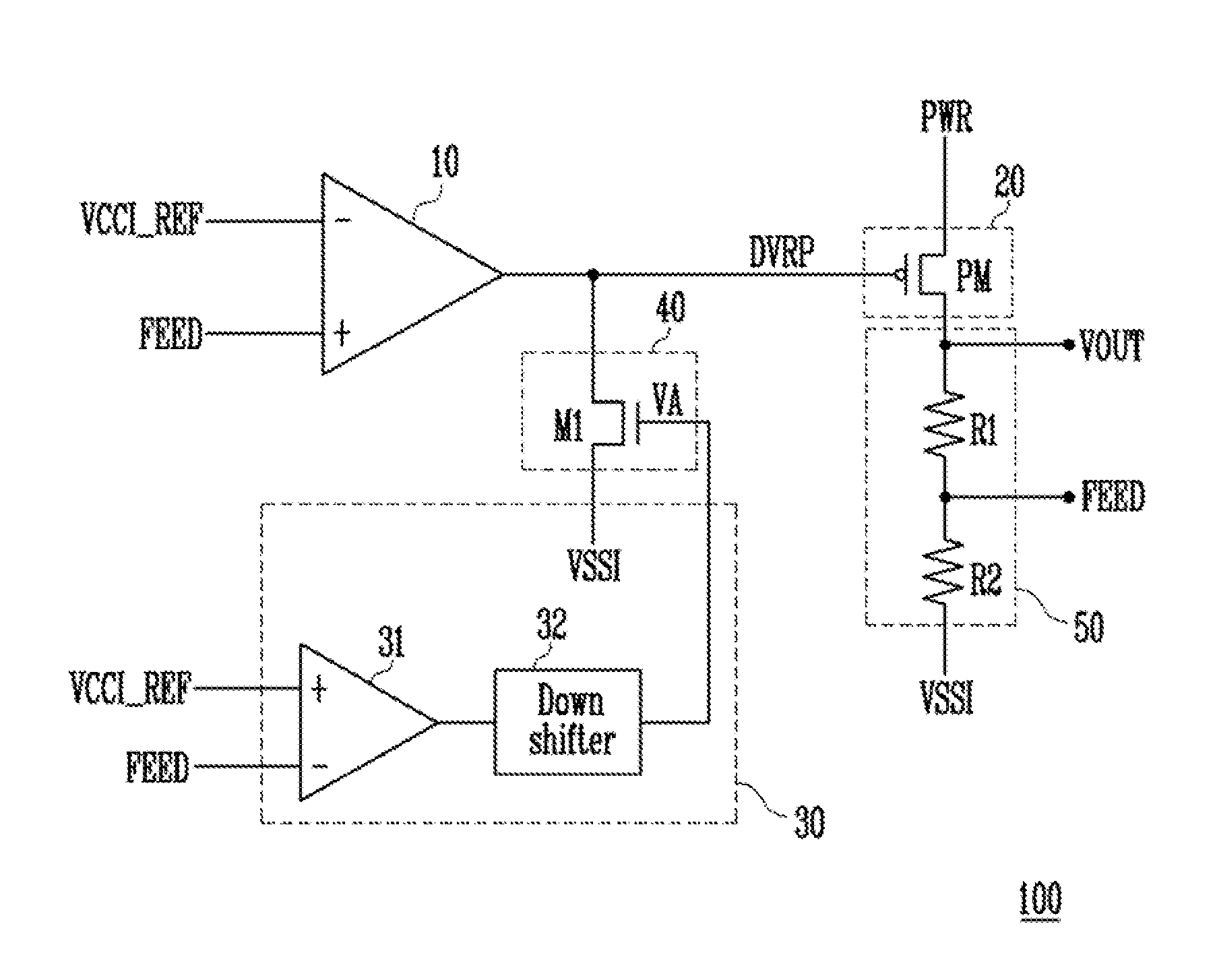

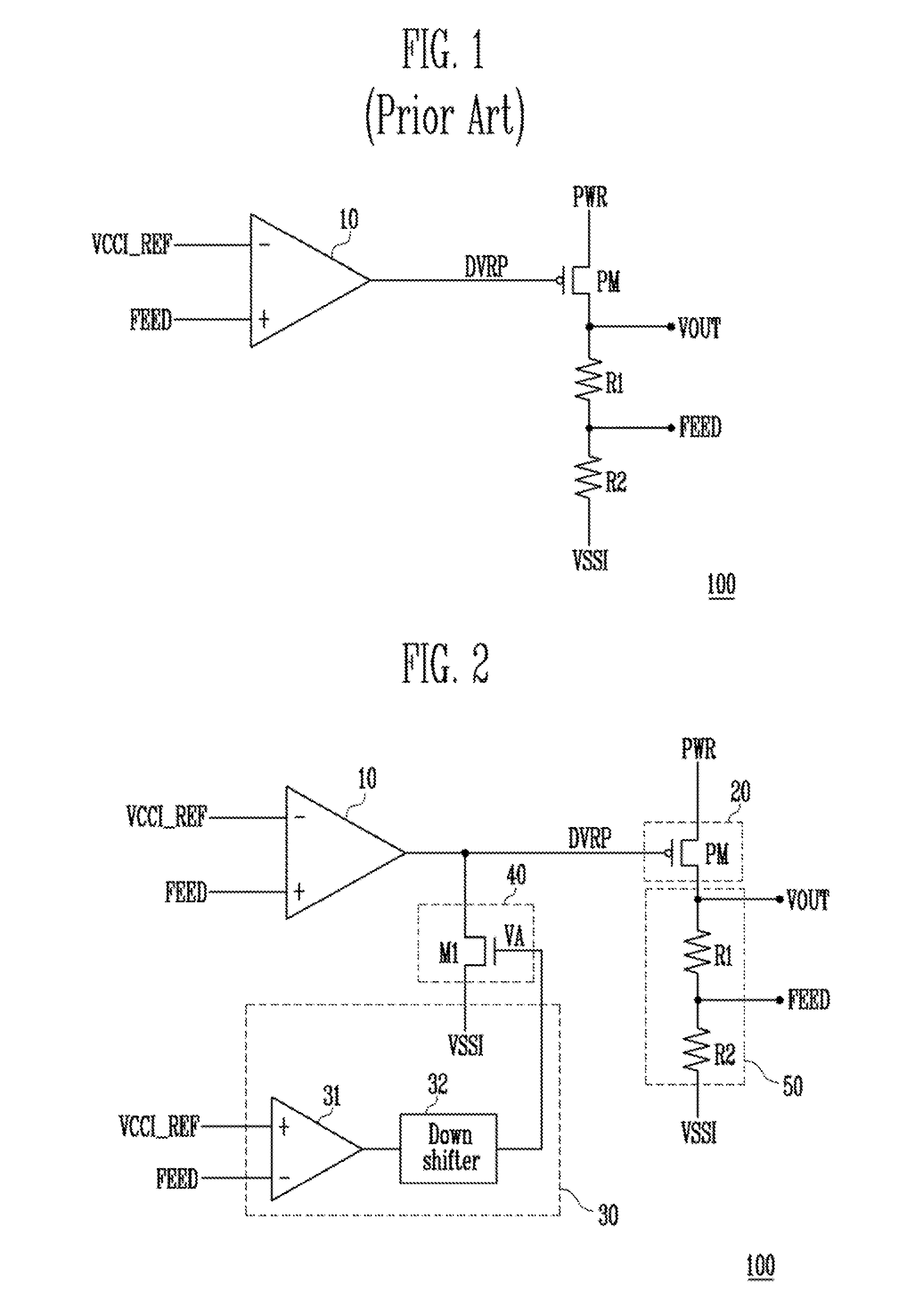

Regulator with enhanced slew rate

ActiveUS20160349777A1High bandwidthIncrease slew rateMultiple input and output pulse circuitsAmplifiers with impedence circuitsPower flowAudio power amplifier

A regulator includes a first operational amplifier configured to receive a reference voltage and a feedback voltage and to output a node voltage based on a difference of the feedback voltage and the reference voltage; a first switch unit configured to receive the node voltage and to supply a recover current based on the node voltage; an output unit configured to output an output voltage and the feedback voltage according to a supply of the recover current; a comparison unit configured to receive the reference voltage and a feedback voltage and to sense a voltage drop of the output voltage; and a second switch unit configured to discharge the first switch unit according to the difference of the reference voltage and the feedback voltage.

Owner:SK HYNIX INC

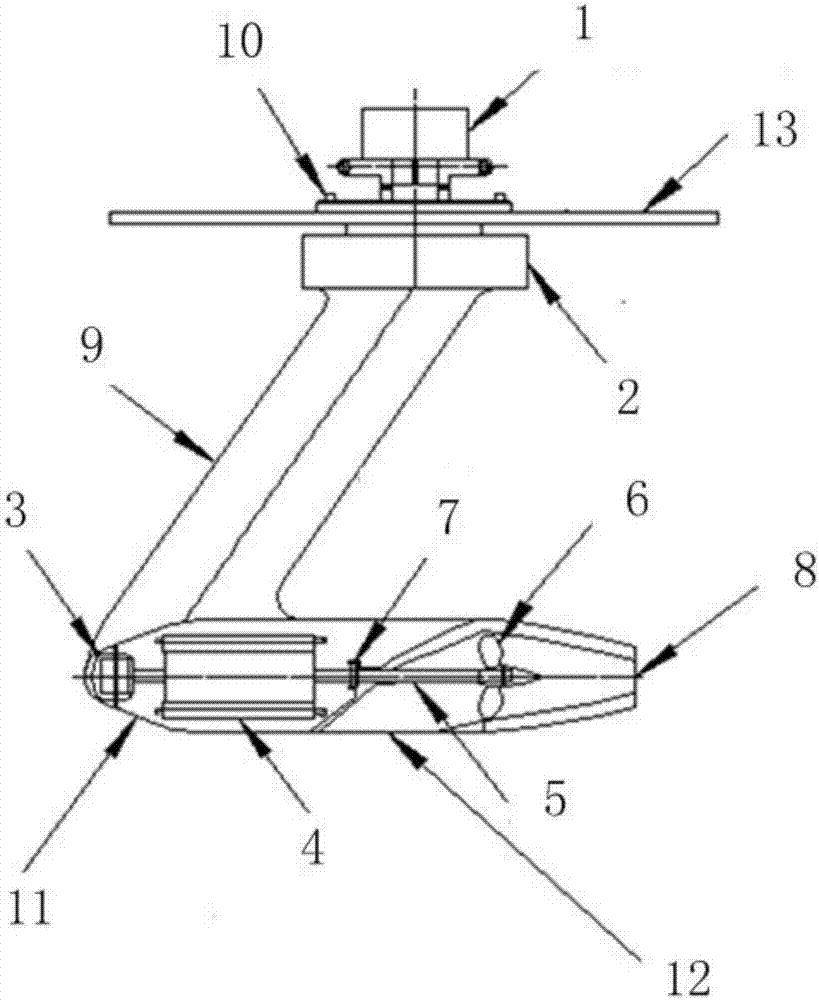

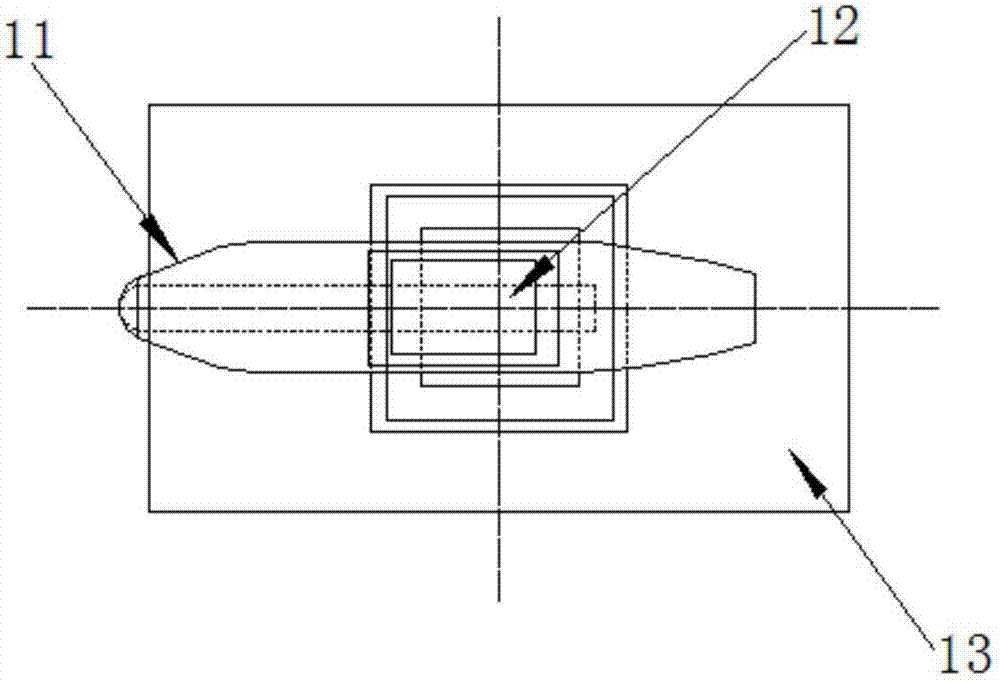

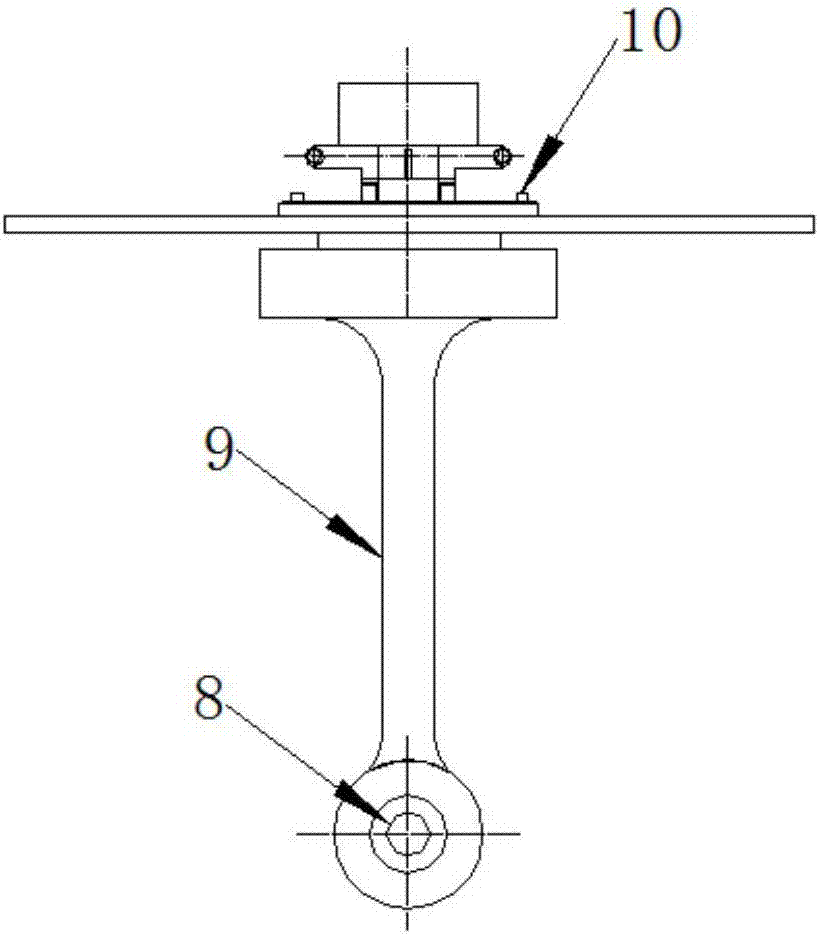

Pod-type water spraying propeller

InactiveCN107244405AStrong anti-cavitation abilityReduce vibrationPropulsive elementsPump-jetPropulsive efficiency

The invention provides a pod-type water jet propulsion unit, which comprises an installation platform, a pod propeller bracket arranged at the lower end of the installation platform, a pod propeller cabin body arranged at the lower end of the pod propeller bracket, a pod propeller cabin body arranged at the pod propulsion The motor base in the cabin body, the motor installed on the motor base, the transmission shaft connected to the output end of the motor, the water jet propulsion pump installed on the transmission axis, the lower end of the pod propeller cabin is provided with an inlet, a side A spout is provided, a flow channel is formed between the inlet and the spout, and the spout is set facing the water jet propulsion pump, and the upper end of the installation platform is provided with a data transmitter and a hydraulic steering device. The present invention is on the basis of maintaining the advantages of the original water jet propeller, adding the bracket, cabin body, electric propulsion system and steering device of the pod propeller, thereby reducing the complicated mechanical transmission mechanism and reversing device of the water jet propeller, further The propulsion efficiency and operational performance of the thrusters are improved, the noise is reduced and the stealth performance is enhanced.

Owner:HARBIN ENG UNIV

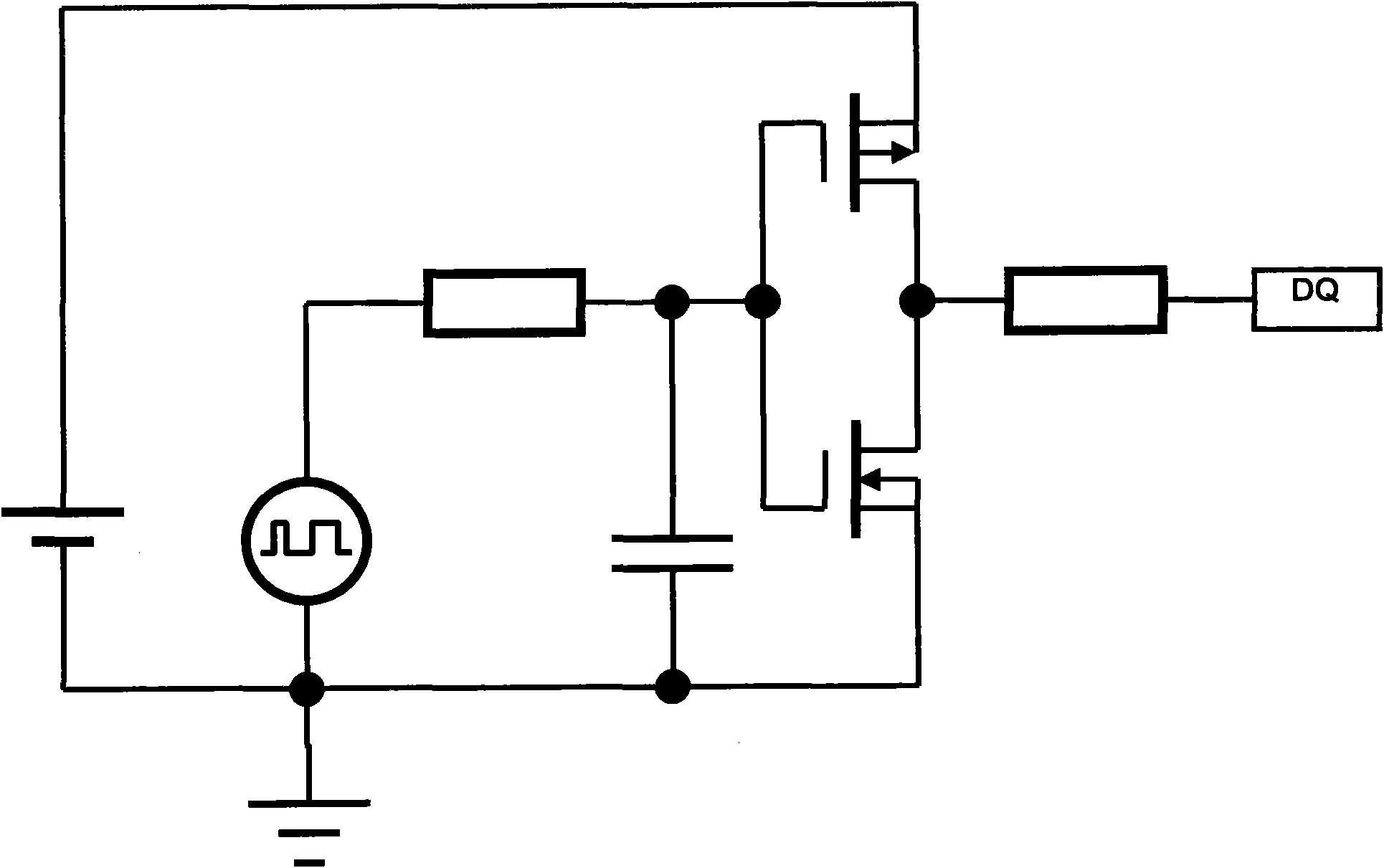

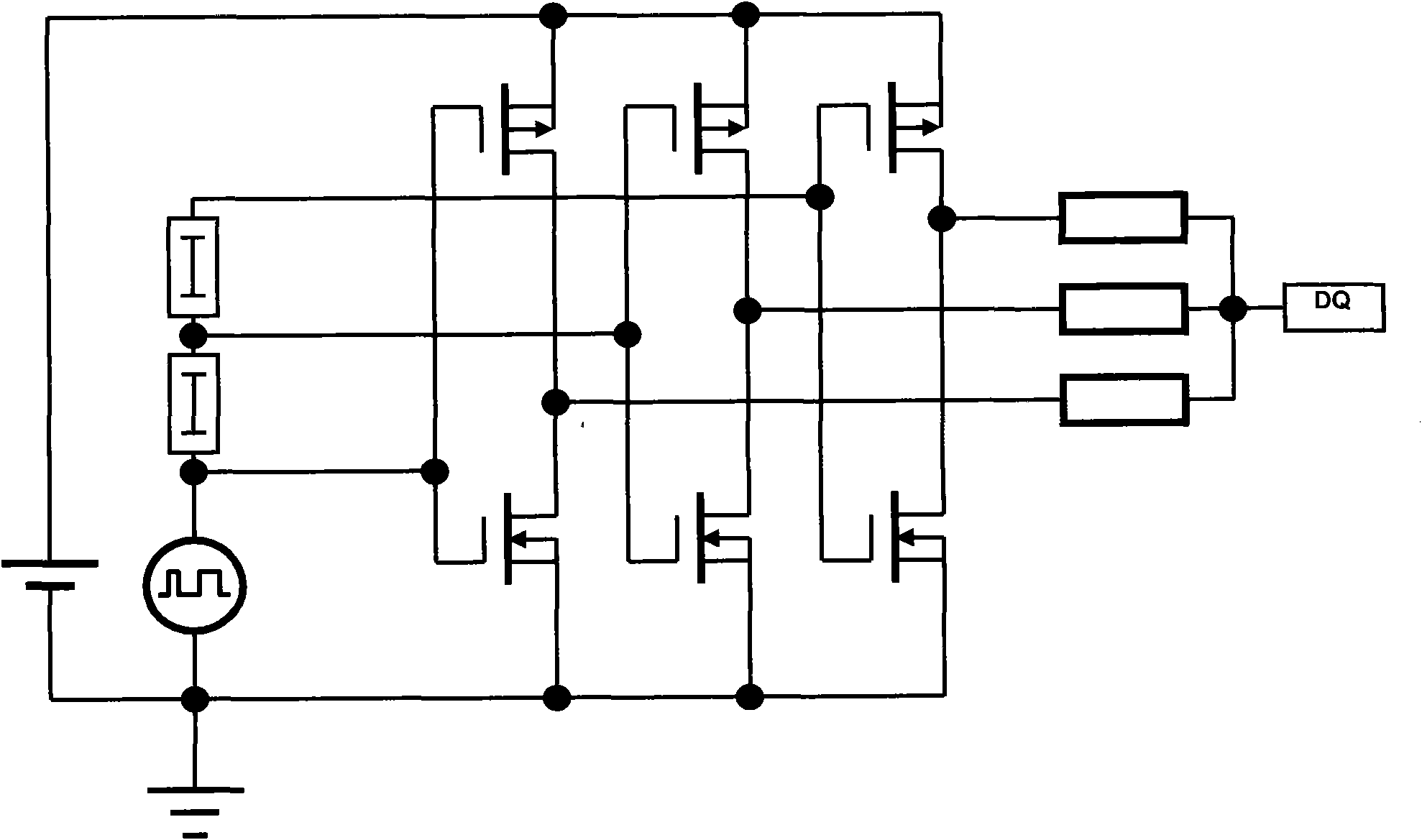

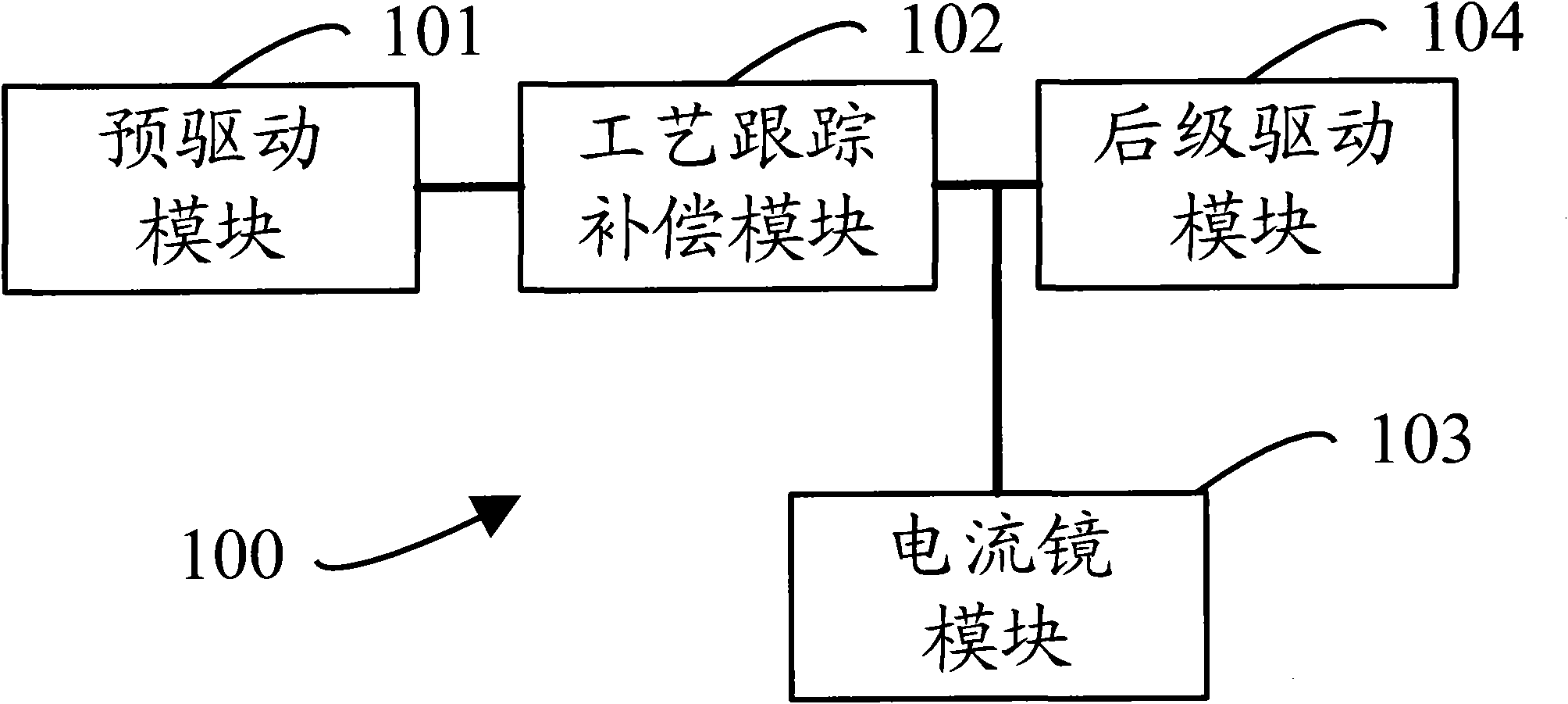

Slew rate control device and method

ActiveCN102034540AReduce power consumptionEasy to controlReliability increasing modificationsRead-only memoriesEngineeringProcess conditions

The invention provides a slew rate control device and method. The slew rate control device comprises a pre-driving module, a process tracking and compensating module, a current mirror module and a post-driving module, wherein the pre-driving module is used for applying a pre-driving voltage on the process tracking and compensating module, the process tracking and compensating module is used for compensating the slew rate according to the process condition of the post-driving module under the control of the pre-driving voltage, the current mirror module is used for keeping the rates of charging and discharging the post-driving module, and the post-driving module is used for generating an output voltage and feeding the output voltage to the pre-driving module to generate the pre-driving voltage. By utilizing the slew rate control device and method provided by the invention, the slew rate can be controlled better, and the influence of the input voltage and temperature on the slew rate can be avoided without the increasing of the circuit area.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

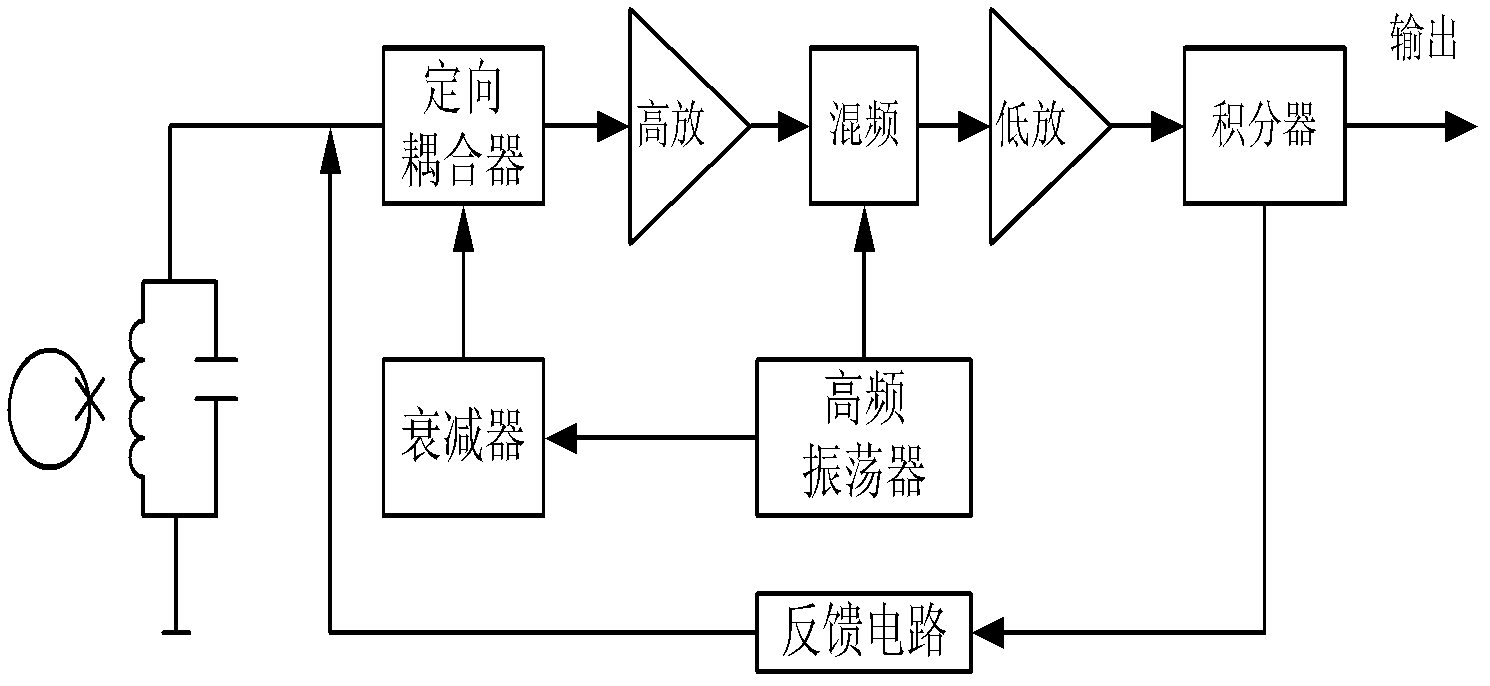

High temperature superconducting magnetic field weakening measurement sensor

InactiveCN102288999AIncrease slew rateHigh sensitivityMagnetic field measurement using superconductive devicesElectric/magnetic detectionLow noiseIntegrator

The invention relates to a high-temperature superconductivity weak magnetic measuring transducer. The high-temperature superconductivity weak magnetic measuring transducer provided by the invention comprises a high-temperature superconductivity device and a phase-locked closed-loop circuit, wherein the phase-locked closed-loop circuit comprises a directional coupler, a high-frequency amplifier, amixer, a low-frequency amplifier, a high-frequency oscillator, a radio frequency signal attenuator, an integrator and a feedback Circuit, wherein the output of the high-temperature superconductivity device is transmitted to the high-frequency amplifier through the directional coupler; the high-frequency amplifier, the mixer, the low-frequency amplifier and the integrator are sequentially connected in series; the output of the high-frequency oscillator is divided into two paths, wherein one path is connected with the input of the mixer and the other path is connected with the directional coupler after being attenuated by the radio frequency signal attenuator; and the output of the integrator is fed back to the directional coupler through the feedback circuit. The high-temperature superconductivity weak magnetic measuring transducer provided by the invention has the advantages of high slew rate, low noise, high sensitivity, high stability and high interference resistance and meets the requirements for measuring a weak magnetic field by utilizing a geophysical electromagnetic method.

Owner:中国地质科学院地球物理地球化学勘查研究所

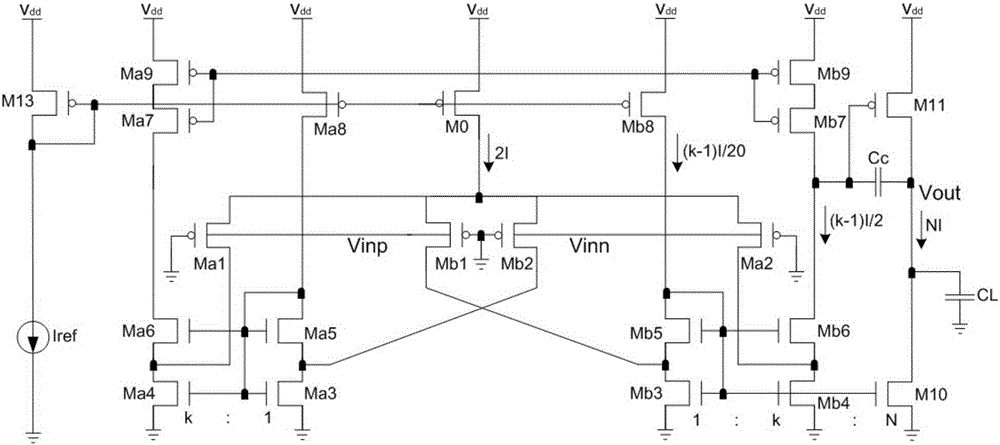

Low-voltage folded cascode transconductance amplifier

ActiveCN105227142AIncrease slew rateHigh speedAmplifier modifications to reduce temperature/voltage variationDifferential amplifiersLow voltageProtein secondary structure

The invention discloses a low-voltage folded cascode transconductance amplifier, comprising an input stage structure, a first stage load structure, a constant current source structure and a second stage structure, wherein the input stage structure comprises PMOS input tubes Ma1 / Ma2 / Mb1 / Mb2 and NMOS input tubes Mna1 / Mna2 / Mnb1 / Mnb2. According to the low-voltage folded cascode transconductance amplifier disclosed by the invention, the input tubes Mna1, Mna2, Mnb1 and Mnb2 are added to effectively inhibit adverse effects generated on the functions and performance of the entire circuit when substrate parasitic transistors of the PMOS input tubes Ma1, Ma2, Mb1 and Mb2 are turned on.

Owner:CHONGQING GIGACHIP TECH CO LTD

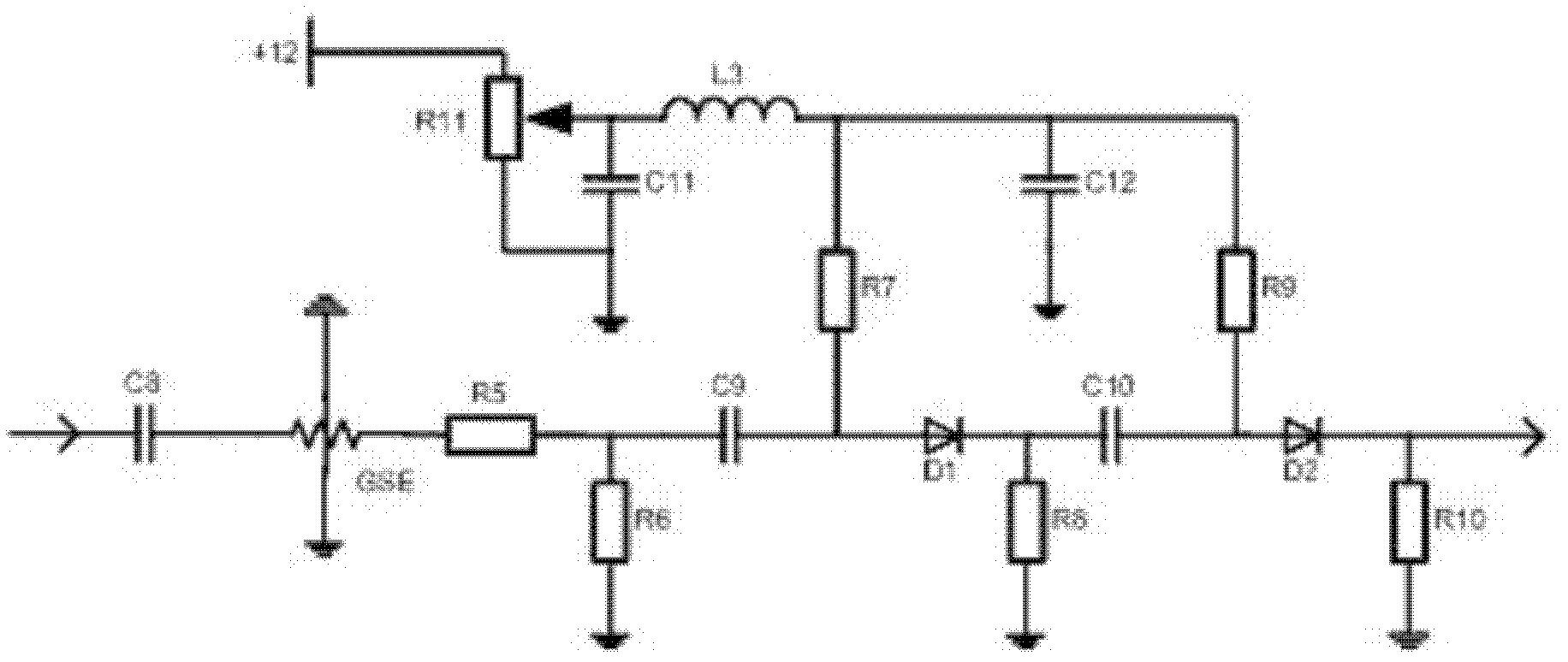

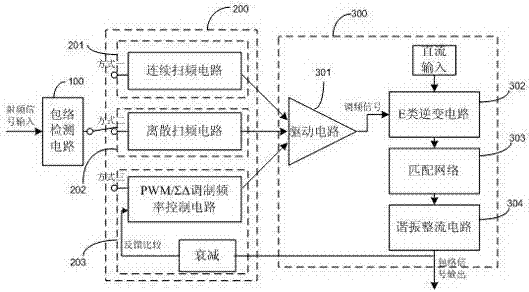

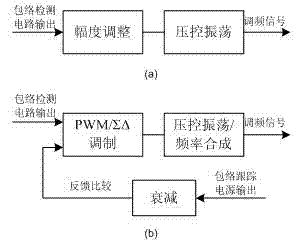

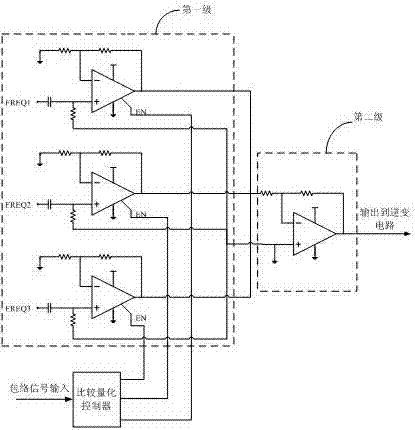

Envelope tracking power supply based on class-E DC (direct current)-DC converter

InactiveCN102868305AHigh precision trackingImprove efficiencyDc-dc conversionElectric variable regulationDriver circuitDc dc converter

The invention provides an envelope tracking power supply based on a class-E DC (direct current)-DC converter. The envelope tracking power supply comprises an envelope detection circuit, a frequency conversion control circuit and a class-E DC-DC converter, wherein the class-E DC-DC converter consists of a drive circuit, a class-E inverting circuit, a matching network and a resonant rectification circuit. According to the envelope tracking power supply, signal envelop is obtained through envelop detection, then the conversion from the envelop to frequency is carried out, and the output power of the class-E DC-DC converter is controlled through continuous frequency scanning or discrete frequency scanning, so that the tracking on the original signal envelop of output voltage is realized. Because the class-E DC-DC converter has high efficiency near the center frequency of the class-E DC-DC converter, works at a high frequency range, and has large slew rate, the envelope tracking power supply disclosed by the invention has the characteristics of high efficiency, high tracking precision and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

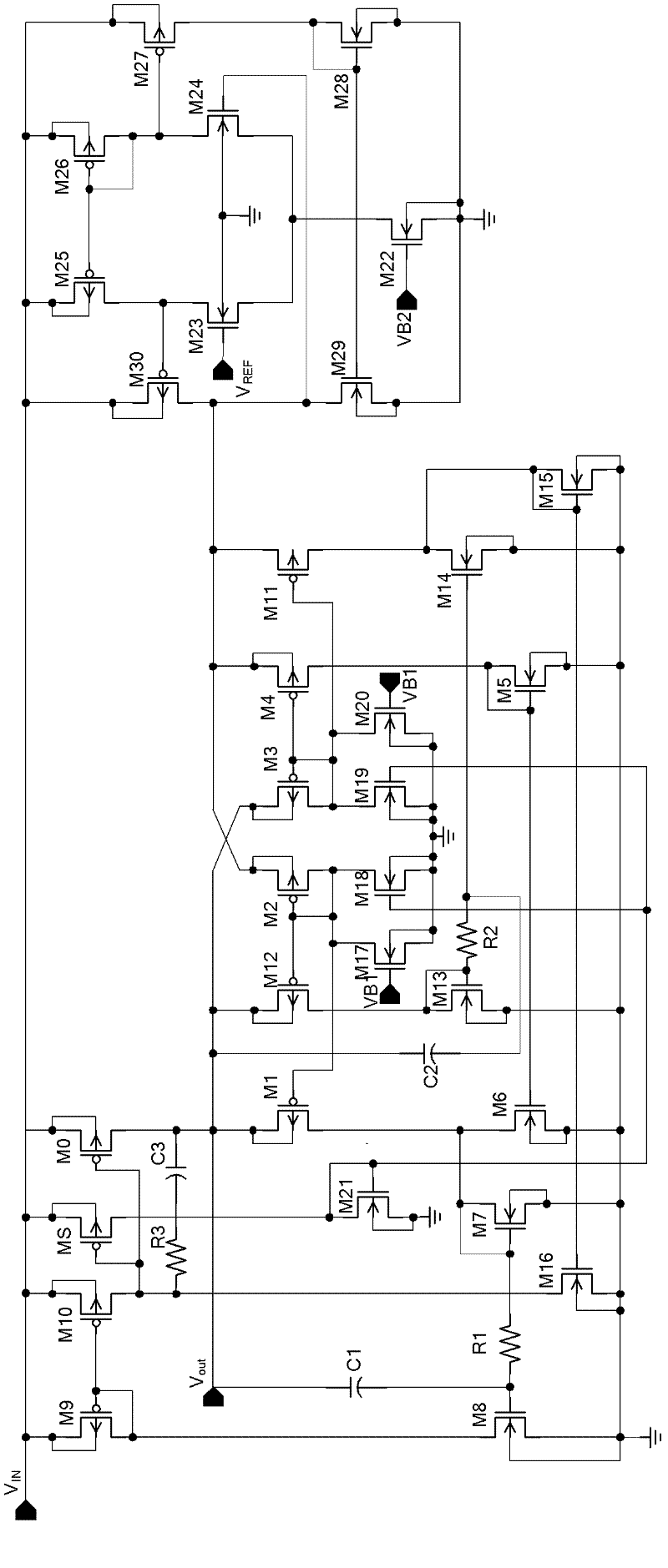

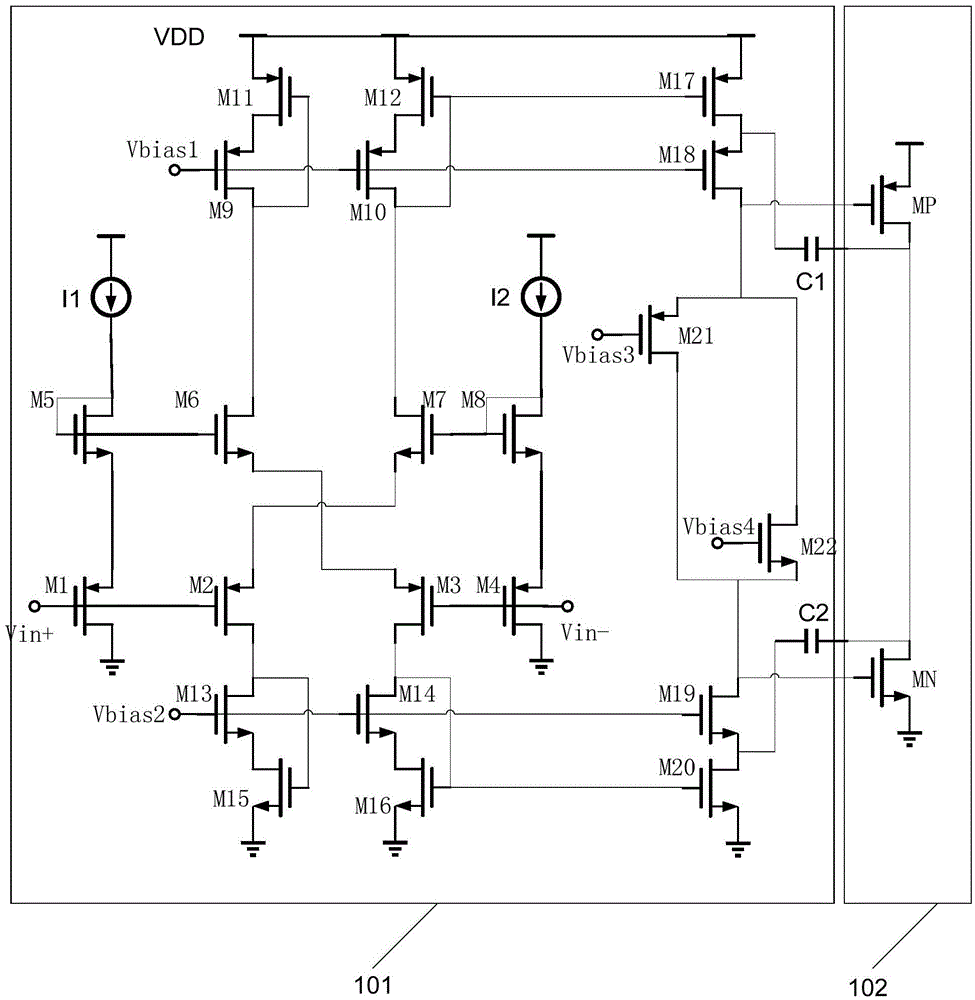

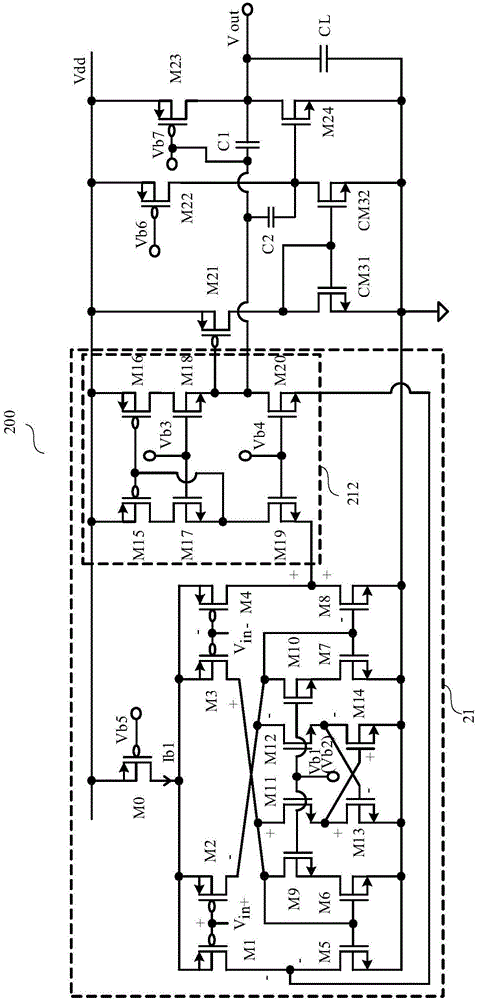

Operational amplifier circuit, operational amplifier and envelope follower power supply

ActiveCN104467714AIncrease slew rateAmplifier modifications to raise efficiencyDifferential amplifiersPower flowAudio power amplifier

The invention discloses an operational amplifier circuit which comprises a first level and a second level. The first level comprises 22 MOS transistors from the first MOS transistor to the twenty-second MOS transistor, a first current source, a second current source, a first capacitor and a second capacitor. The second level comprises a PMOS transistor and an NMOS transistor, wherein the drain electrode of the PMOS transistor and the drain electrode of the NMOS transistor are connected. The input level of an operational amplifier is of a cross coupling pair structure, a load of a cross coupling pair is a cascode current mirror so that an I-V curve of the operational amplifier can have an expansion character instead of an amplitude limiting character of a common differential pair, and therefore a high slew rate can also be obtained under the condition of low static current.

Owner:SOI MICRO CO LTD

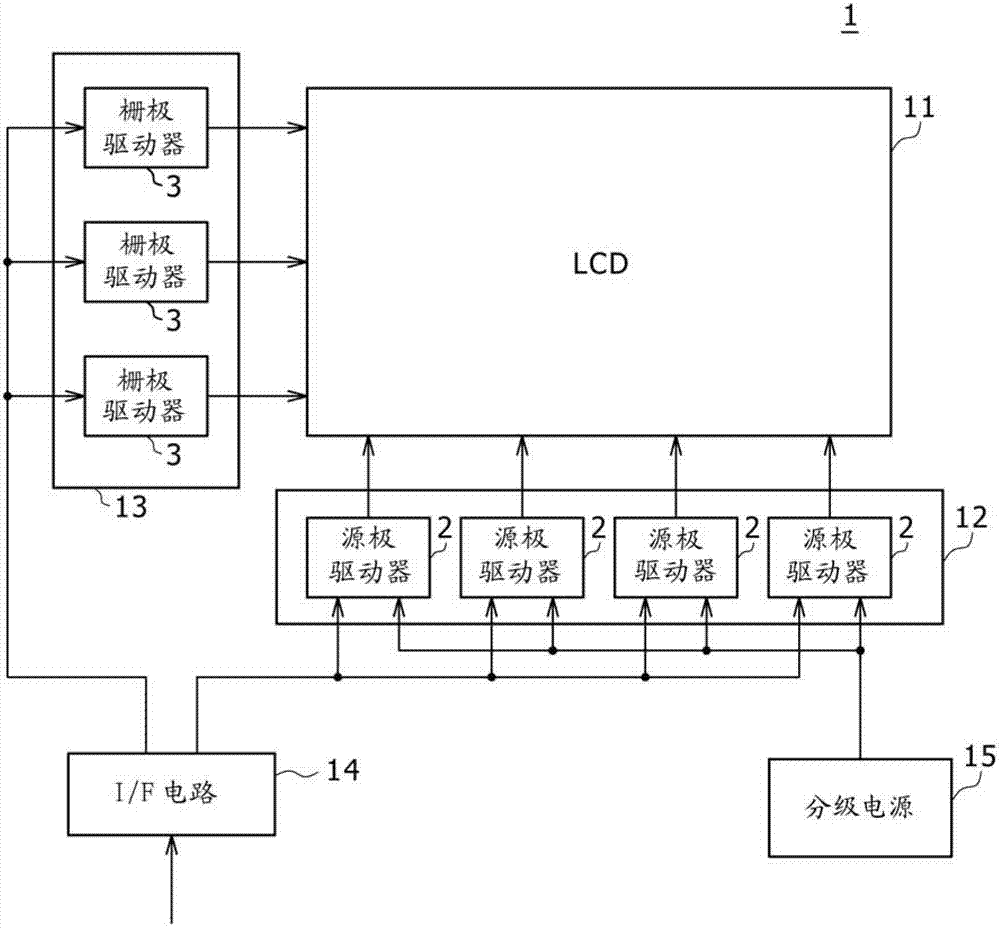

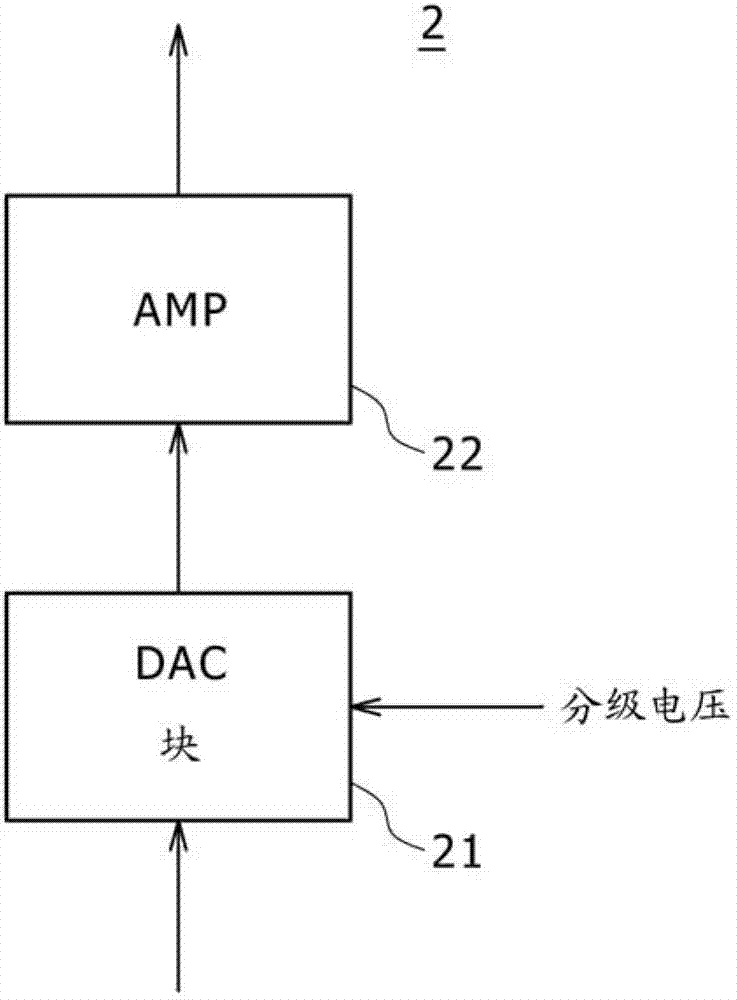

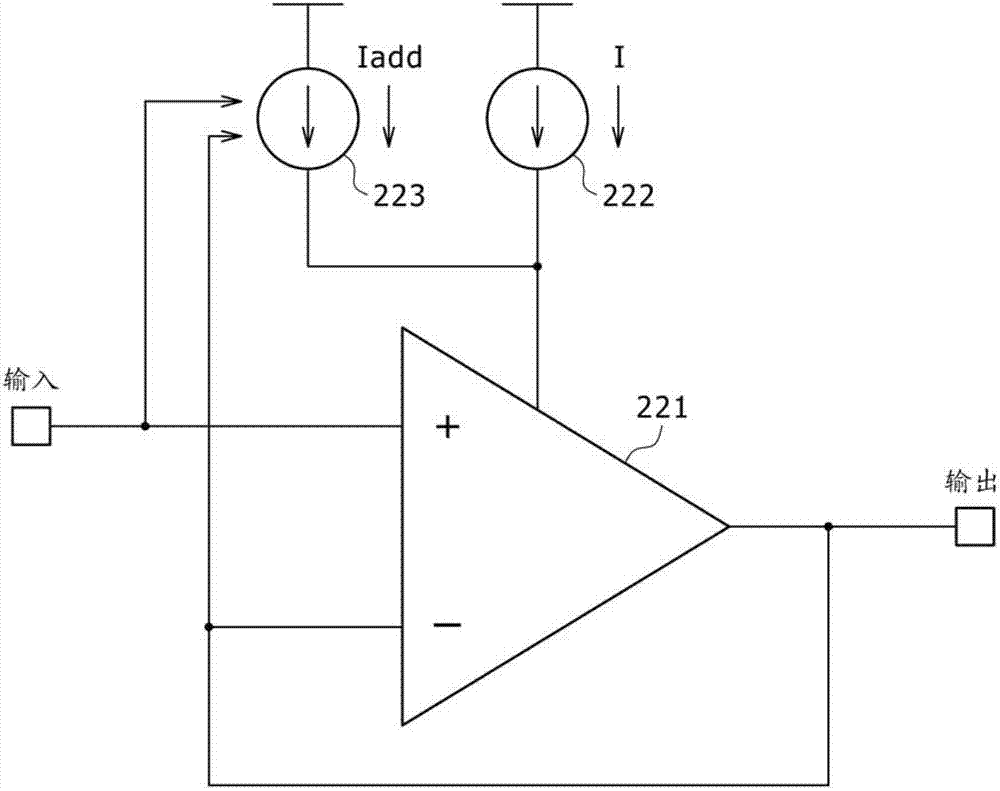

Amplifier, liquid crystal displaying driving circuit and liquid crystal display apparatus

InactiveCN102881267ASuppress power consumptionIncrease slew rateStatic indicating devicesDifferential amplifiersAudio power amplifierLiquid-crystal display

Disclosed herein is an amplifier including a voltage follower circuit having differential input terminals and an output terminal fed back to a first one of the differential input terminals, the voltage follower circuit being configured to amplify an input signal inputted to a second one of the differential input terminals and output the amplified signal from the output terminal; a first current source configured to supply a predetermined current to the voltage follower circuit; and a second current source configured to supply current to the voltage follower circuit when a potential difference between the second one of the differential input terminals and the output terminal is equal to or higher than a predetermined value.

Owner:SONY CORP

Clock driver circuit

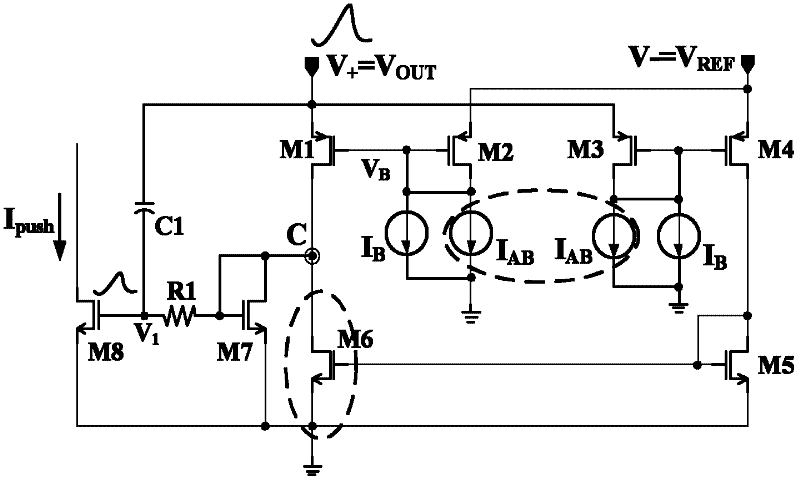

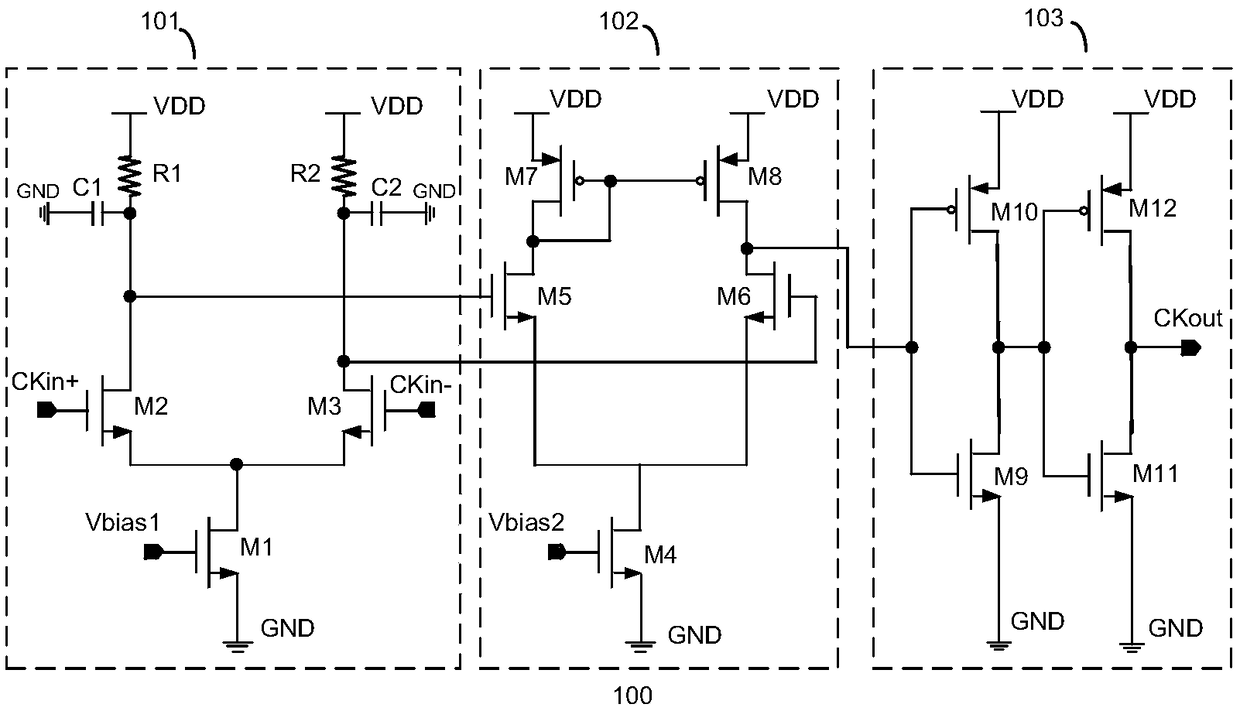

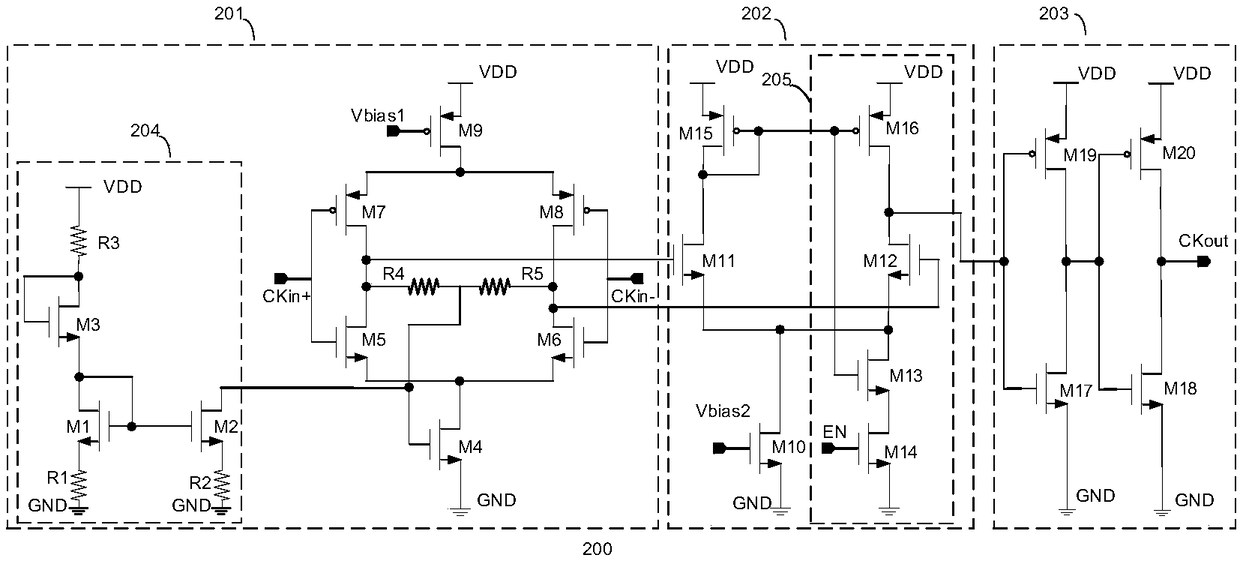

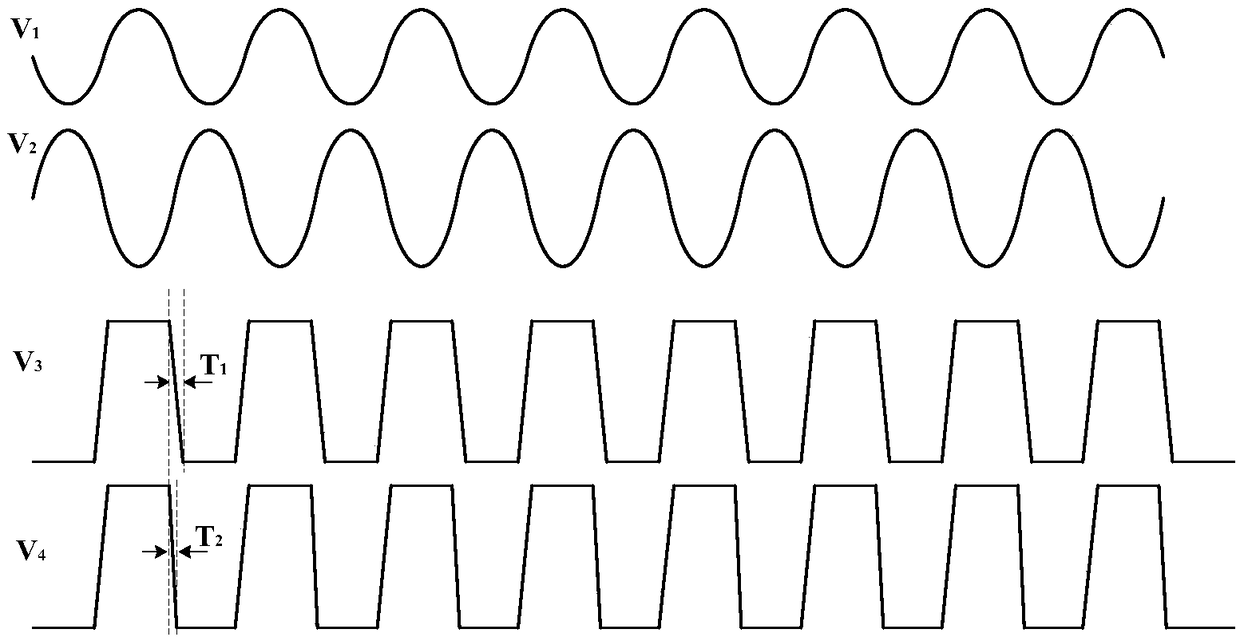

ActiveCN109120243AWide rangeIncrease slew rateAmplifier combinationsElectric pulse generatorPush pullEngineering

The invention provides a clock driver circuit. The clock driver circuit comprises successively connected input stage, double-end-to-single-end stage and driving output stage, wherein the input stage includes differential amplifiers which are the load for each other and a common mode negative feedback loop; the differential amplifiers access differential clock signals for amplification to generatea common mode voltage; the common mode feedback loop is connected to the output ends of the differential amplifiers for stabilizing the output amplitude of the common mode voltage; the double-end-to-single-end stage converts a differential sinusoidal clock signal outputted by the double-end common mode voltage into a single-end square wave clock signal; and the driving output stage includes a multi-stage-cascaded push-pull inverter, so as to increase the driving capability of the square wave clock signal. The clock driver circuit adopts differential amplifiers which are the load for each other, and any one of the two differential amplifiers acts as the load for the other, thus expanding the amplitude range of the input stage, has the capability of inhaling and supplying a large current, and improves the slew rate, so that the clock driver circuit can receive input clock signals with large amplitude and high speed.

Owner:中电科芯片技术(集团)有限公司

Transconductance amplifier adopting signal attenuation technology and method

PendingCN106411273AImprove anti-interference abilityReduce consumptionAmplifier modifications to reduce non-linear distortionDifferential amplifiersUltrasound attenuationAudio power amplifier

The invention relates to a transconductance amplifier adopting the signal attenuation technology and a method. The transconductance amplifier comprises differential input-stage input voltages Vin+ and Vin-, and differential input currents are generated. Power voltage VDD is accessed to a signal attenuation circuit, signal attenuation is carried out on the differential input currents, and a current attenuation signal is generated. The power voltage VDD has access to a bias current source, communication is carried out according to the current attenuation signal, and bias currents are output to a first current mirror and a second current mirror. The first current mirror and the second current mirror both copy the bias currents, and copied currents are generated to be transmitted to a third current mirror. The unity-gain bandwidth is increased through the third current mirror, gain amplification is carried out on the copied currents, and an amplifying signal Iout is output. Compared with the prior art, the influence between input and output voltages is low, no additional pole is introduced, and high linearity, high gain and high-precision amplification are achieved.

Owner:GUANGXI NORMAL UNIV

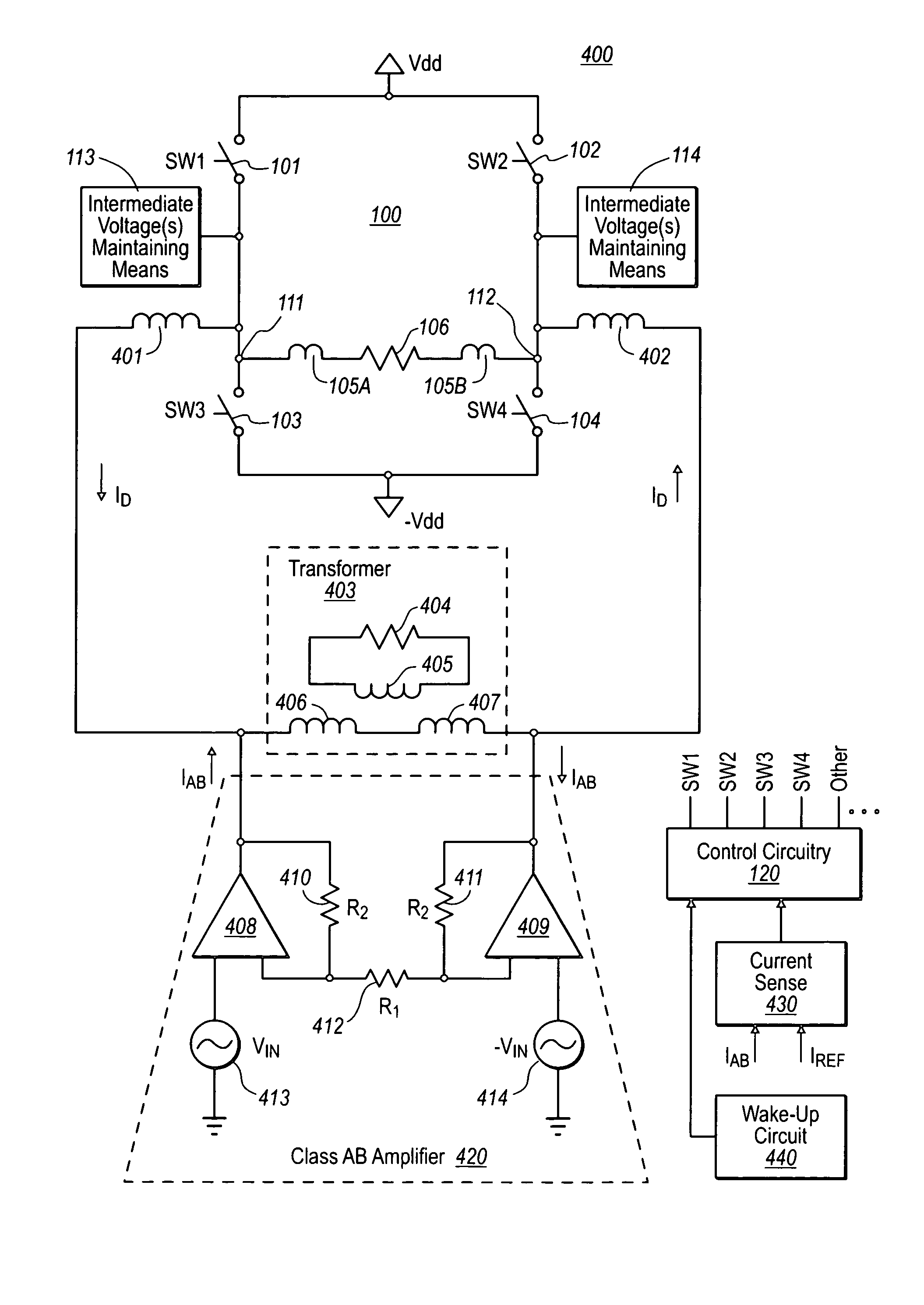

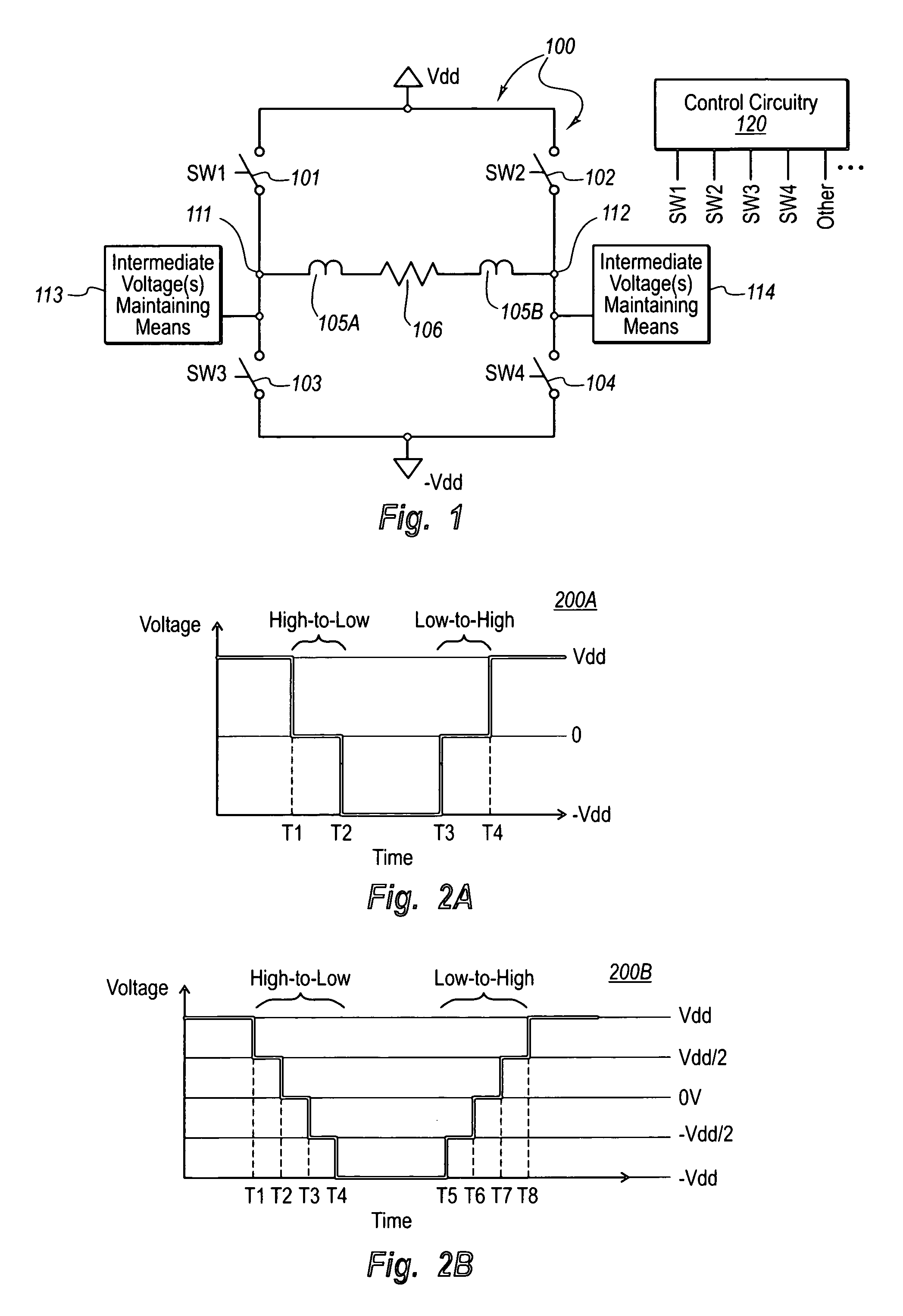

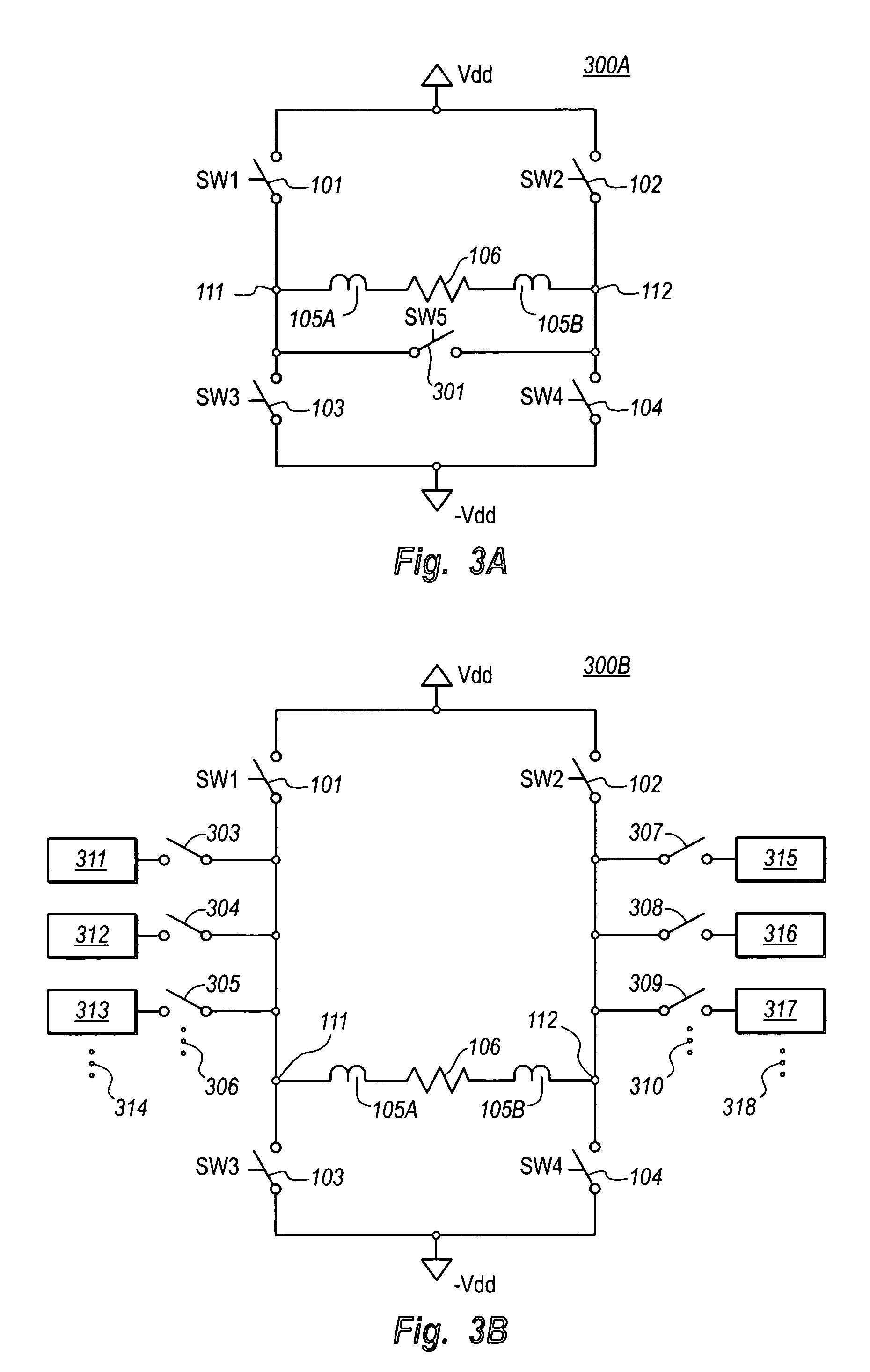

H-bridge utilizing intermediate switching phase(s)

ActiveUS7279973B1Reduce power consumptionReduce any undesirable impactNegative-feedback-circuit arrangementsAmplifier modifications to raise efficiencySignal onLow voltage

An H-bridge circuit capable of performing switching using one or more intermediate voltage phases each held for a period of time in the midst of the switching operation. This reduces power dissipation associated with the switching operation, while only using one set of high / low voltage supplies. The H-bridge may be used to provide current via an inductor to a load. A class AB amplifier may be placed in parallel with the H-bridge to provide supplemental correcting current to the load to allow the combination to act as an efficient and accurate signal driver. Furthermore, the use of intermediate voltages in the H bridge allows for increased slew rates for any given operation frequency, and allows for the driving of a given signal on the load using a lower operational frequency.

Owner:AMI SEMICON BELGIUM

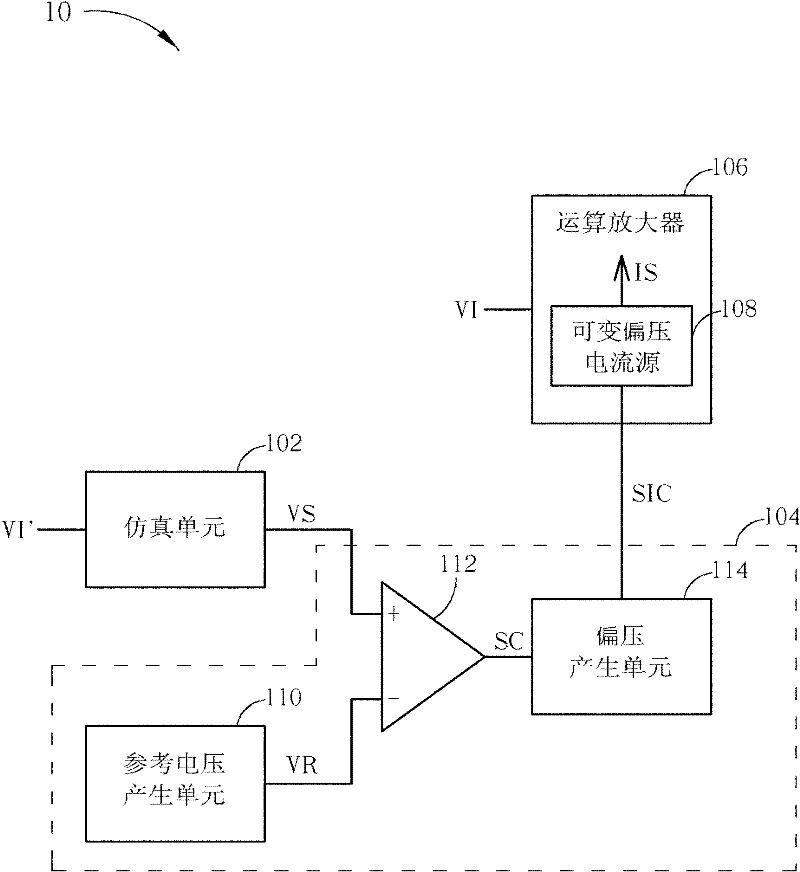

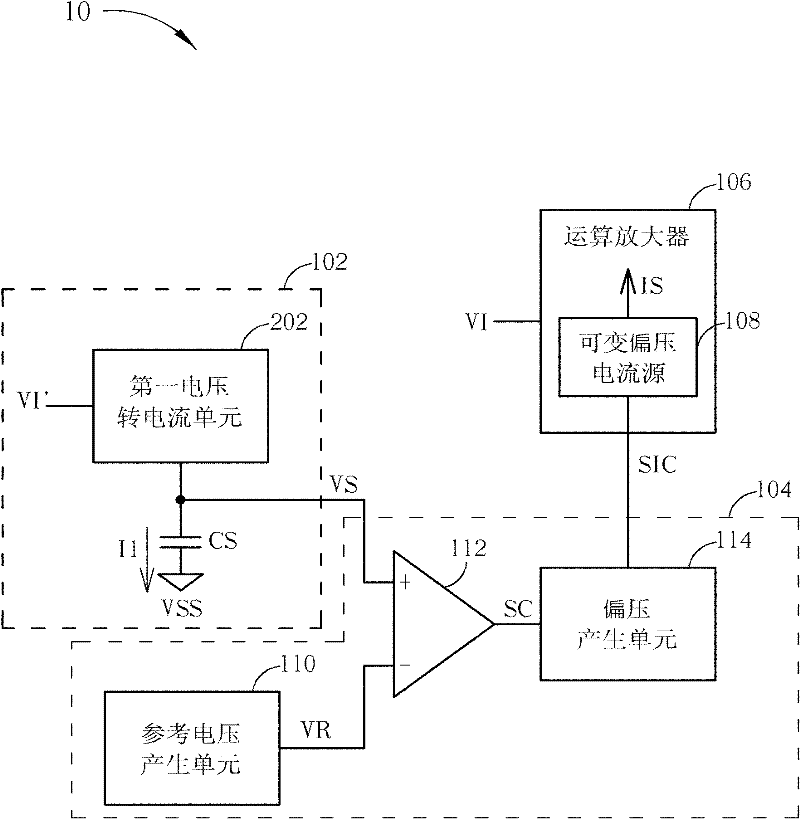

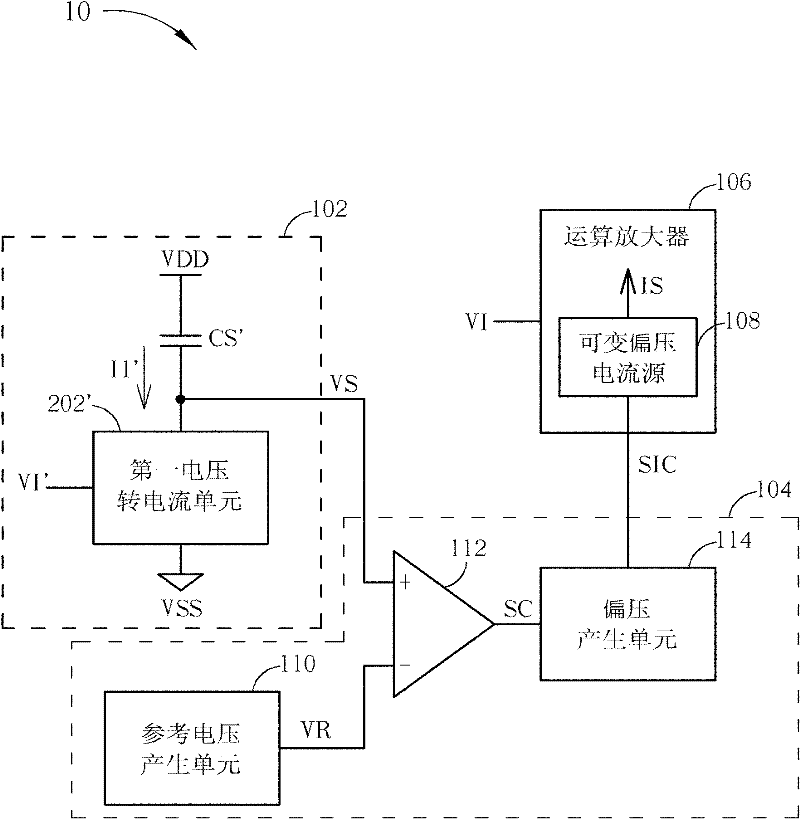

Adjustable amplification circuit

InactiveCN102545799AIncrease slew rateSolve the lack of driving forcePower amplifiersAmplifier modifications to raise efficiencyCurrent sourceAudio power amplifier

The invention discloses an adjustable amplification circuit, which comprises an operational amplifier, a simulation unit and a bias control unit, wherein the operational amplifier comprises a variable bias current source which is used for supplying a variable bias current to the operational amplifier; the simulation unit is used for simulating the operation characteristic of the operational amplifier and converting a simulation input voltage into a simulation output voltage; and the bias control unit is used for generating a bias control signal to the variable bias current source according to the simulation output voltage to adjust the size of the variable bias current.

Owner:NOVATEK MICROELECTRONICS CORP

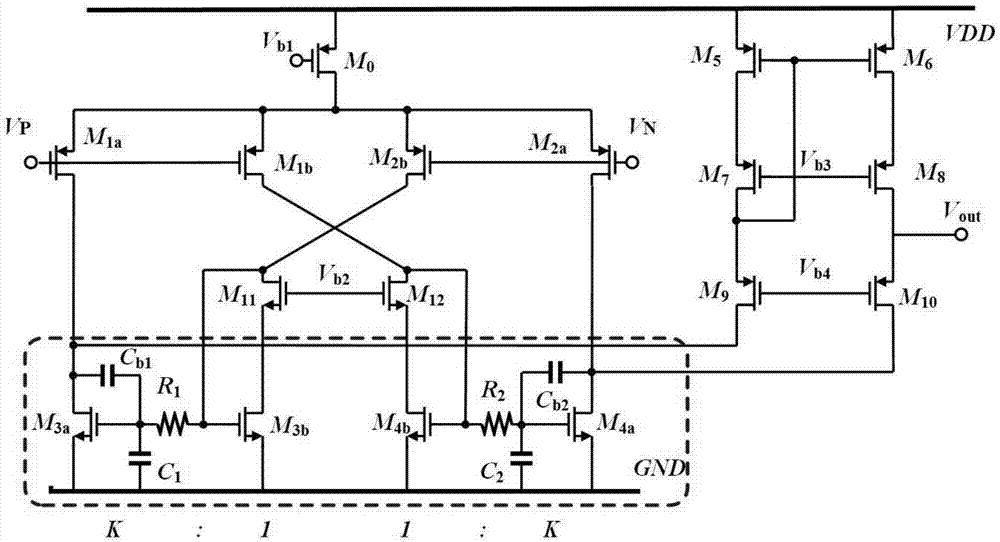

Slew rate enhanced operational amplifier suitable for restraining electromagnetic interference

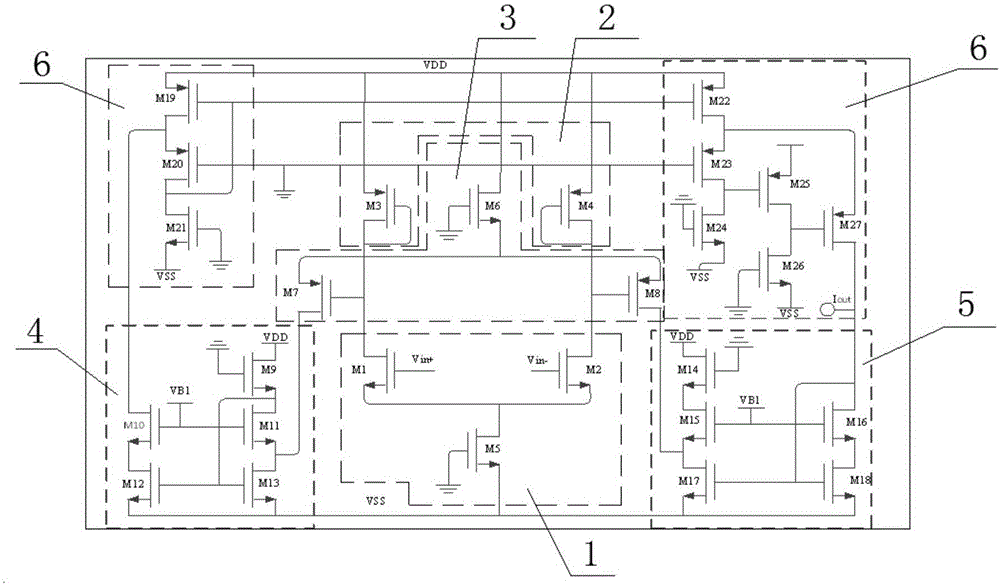

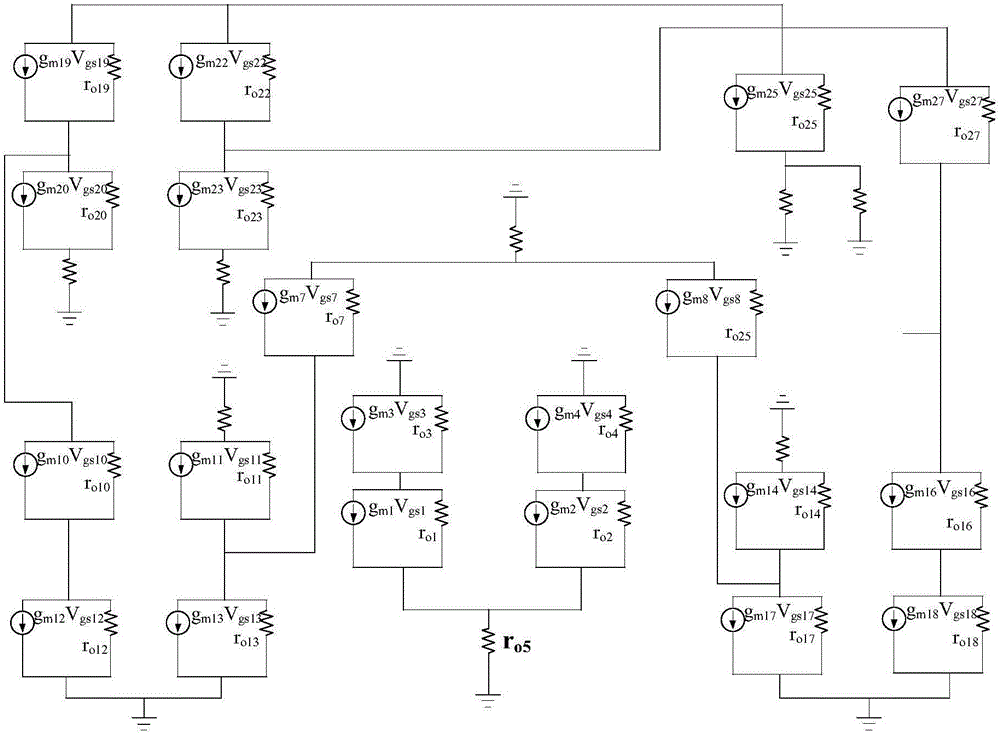

InactiveCN105450181AIncrease slew rateImprove inhibitionAmplifier modifications to reduce noise influenceDifferential amplifiersOxide semiconductorElectromagnetic interference

The invention discloses a slew rate enhanced operational amplifier suitable for restraining electromagnetic interference. The operational amplifier consists of seventeen MOS (Metal Oxide Semiconductor) transistors, namely, first to eleventh PMOS (P-channel Metal Oxide Semiconductor) transistors M0, M1a, M1b, M2a, M2b, M5, M6, M7, M8, M9 and M10 and first to sixth NMOS (N-channel Metal Oxide Semiconductor) transistors M3a, M3b, M4a, M4b, M11 and M12, wherein differential-mode signals Vin+ and Vin- are input through gate electrode input ends Vp of the second to third PMOS transistors M1a and M1b, and gate electrode input ends Vn of the fourth to fifth PMOS transistors M2a and M2b respectively; spurious signals are filtered through amplification of a Recycling folded cascode amplification stage and an electromagnetic interference restraining stage; meanwhile, a slew rate is increased; and a signal is output through a high-gain output end Vout. Through adoption of the operational amplifier in a low-voltage and low-power-consumption mixed signal circuit, an electromagnetic interference restraining ability specific to signals can be enhanced while the slew rate is increased.

Owner:TIANJIN UNIV

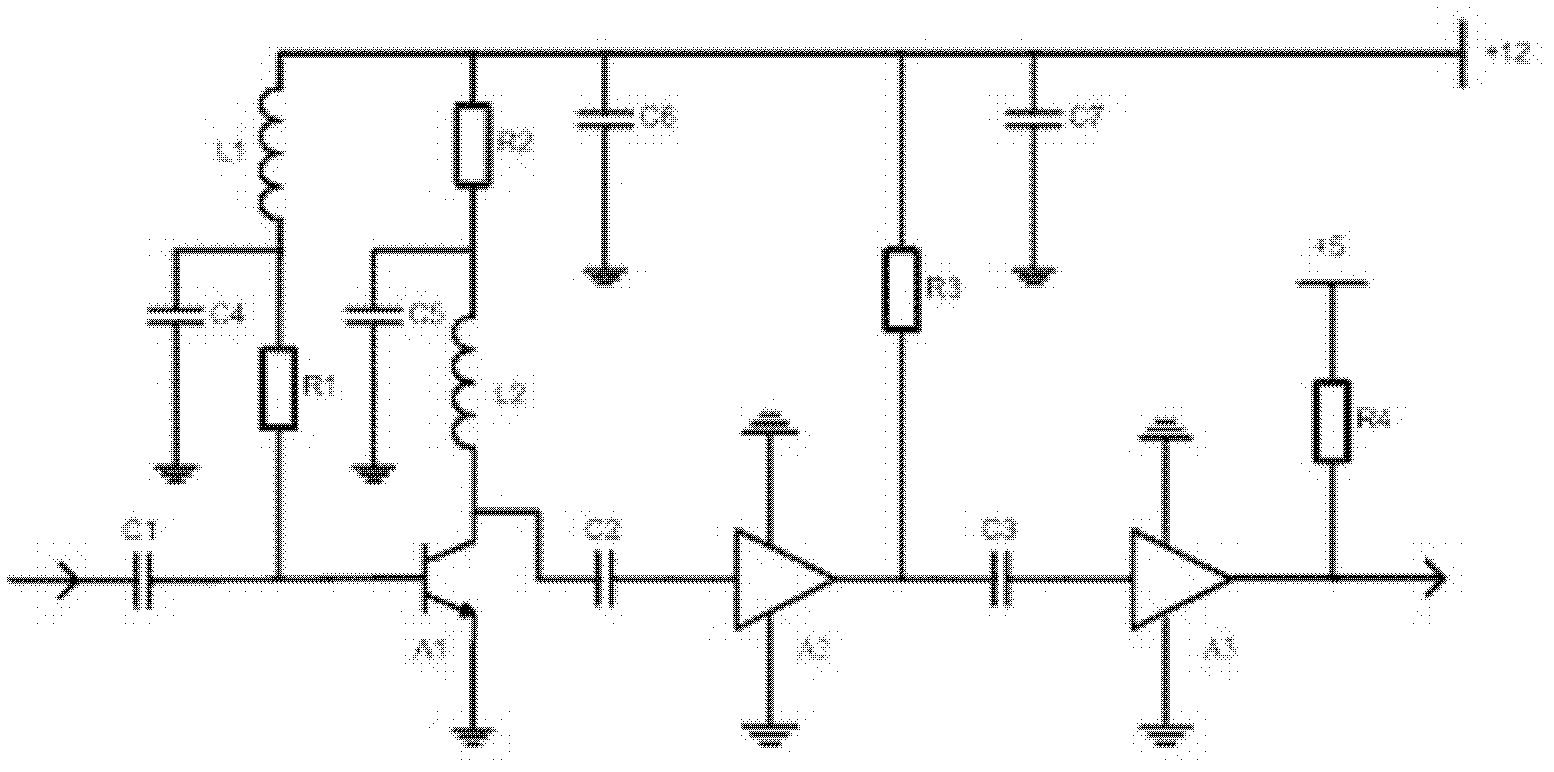

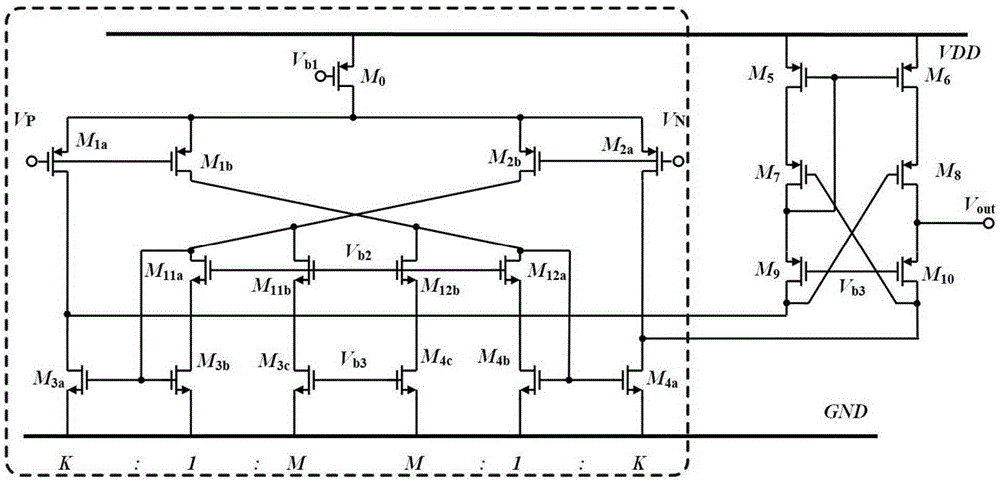

Low-power high-slew-rate operational amplifier suitable for ultra-wide band microwave detection

InactiveCN105262448AHigh bandwidthIncrease slew rateDifferential amplifiersPositive-feedback-circuit arrangementsAudio power amplifierBroadband

The invention relates to a large-scale integrated circuit, and discloses a low-power high-slew-rate operational amplifier suitable for ultra-wide band microwave detection, for realizing a high slew rate through simultaneously improving the PSRR and the CMRR of an amplifier. For this end, the technical scheme employed by the invention is as follows: the low-power high-slew-rate operational amplifier suitable for ultra-wide band microwave detection is composed of a Recycling folded cascade amplifying stage, a slew rate enhanced stage and a PSRR enhanced output stage. Differential mode signals Vin- and Vin+ are input by the Recycling folded cascade amplifying stage, and after being subjected to the slew rate enhancement effect of a cascade current mirror, finally reach to an output end Vout through the PSRR enhanced output stag. The low-power high-slew-rate operational amplifier is mainly applied to the design and manufacture of the large-scale integrated circuit.

Owner:TIANJIN UNIV

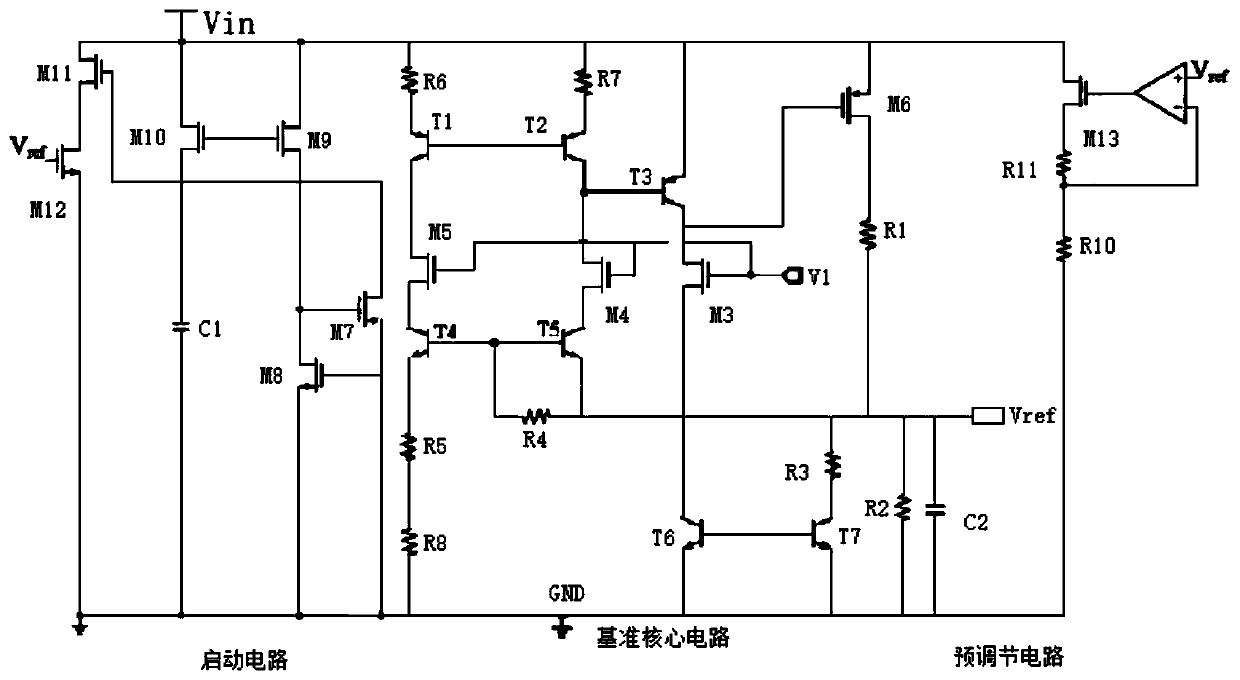

Power supply with wide input voltage

InactiveCN110928350AHigh currentIncrease slew rateElectric variable regulationCapacitanceHemt circuits

The invention discloses a power supply with wide input voltage. The power supply comprises a reference source circuit. The circuit is composed of a starting circuit, a reference core circuit and a pre-adjusting circuit. The reference core circuit comprises a cascade circuit, a parallel effect transistor circuit, a voltage division circuit and a negative feedback circuit. The negative feedback circuit comprises a field effect transistor M6, a resistor R1, a resistor R2, a resistor R3, a filter capacitor C2, a triode T6, a triode T7 and a triode T3. The pre-voltage-stabilizing circuit of a negative feedback structure enables the input voltage range to be wider and enables the input voltage range to bear larger input voltage fluctuation, and the reference source circuit with the pre-adjustingcircuit not only can provide a stable reference electric foot, but also has power supply noise suppression performance higher than that of a traditional reference. The stability and transient response speed of the low dropout linear voltage stabilizing circuit are improved, and the low dropout linear voltage stabilizing circuit can stably work within a wide temperature range without large capacitance.

Owner:STATE GRID SHANDONG ELECTRIC POWER +1

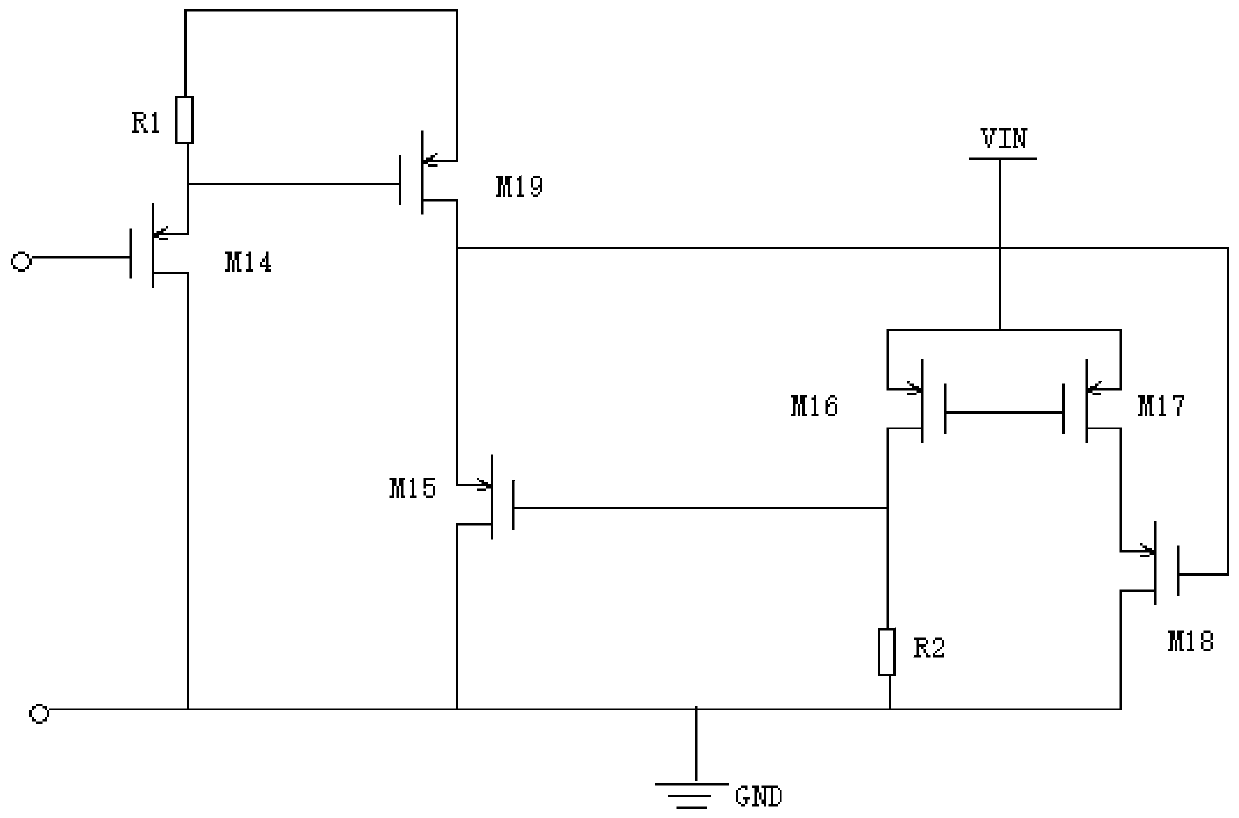

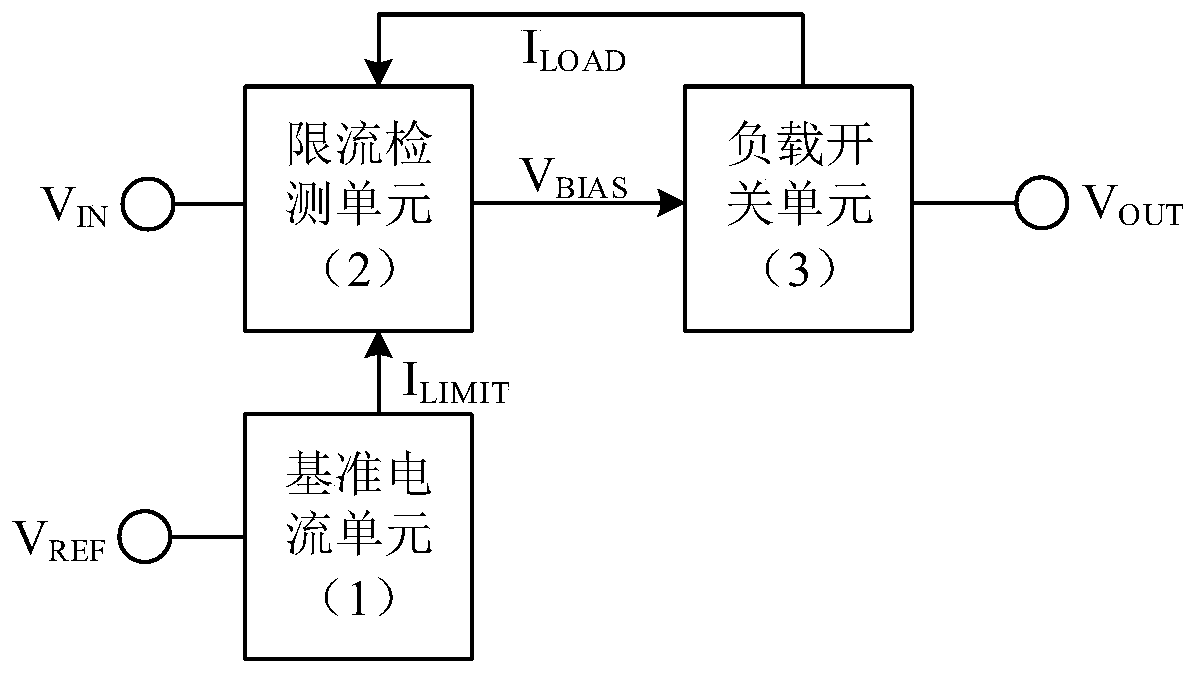

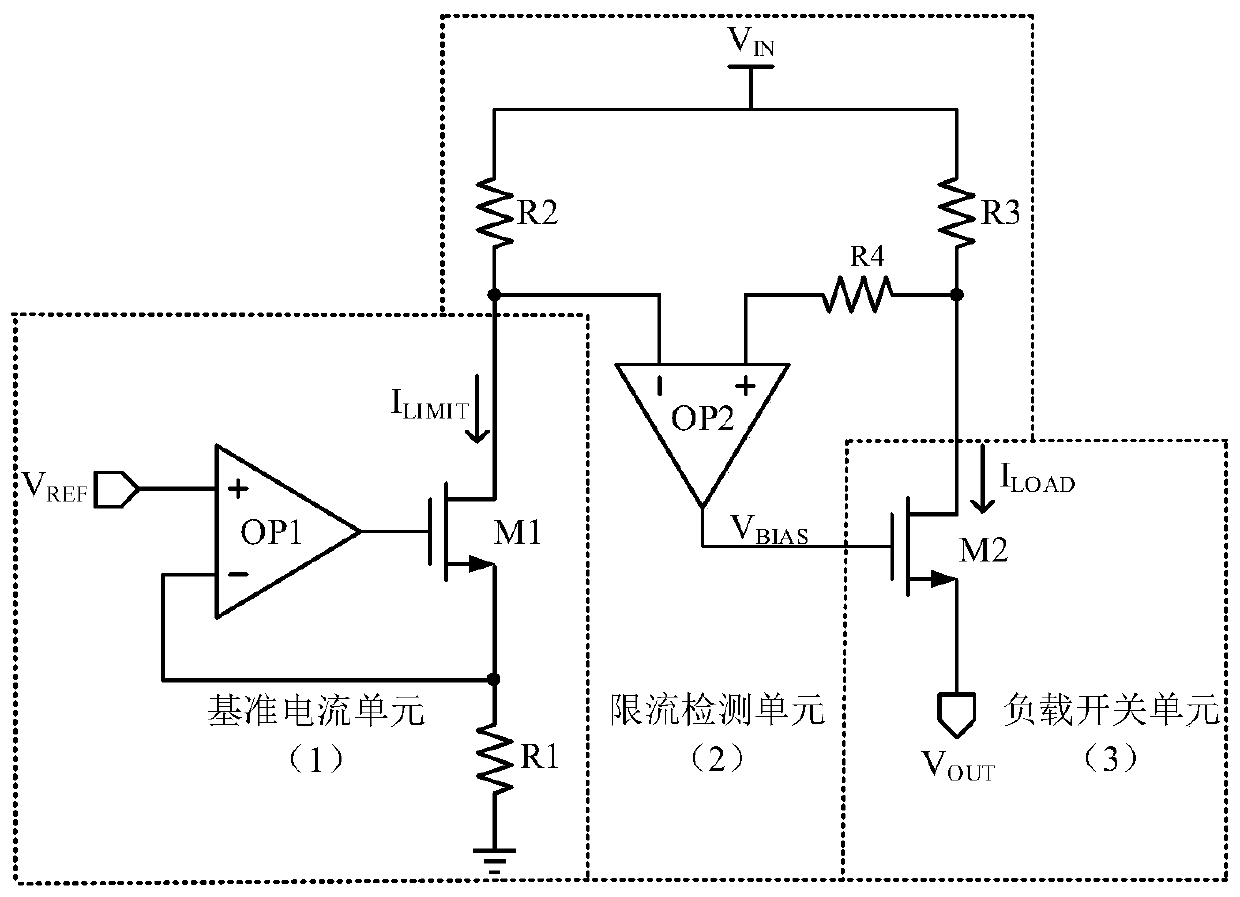

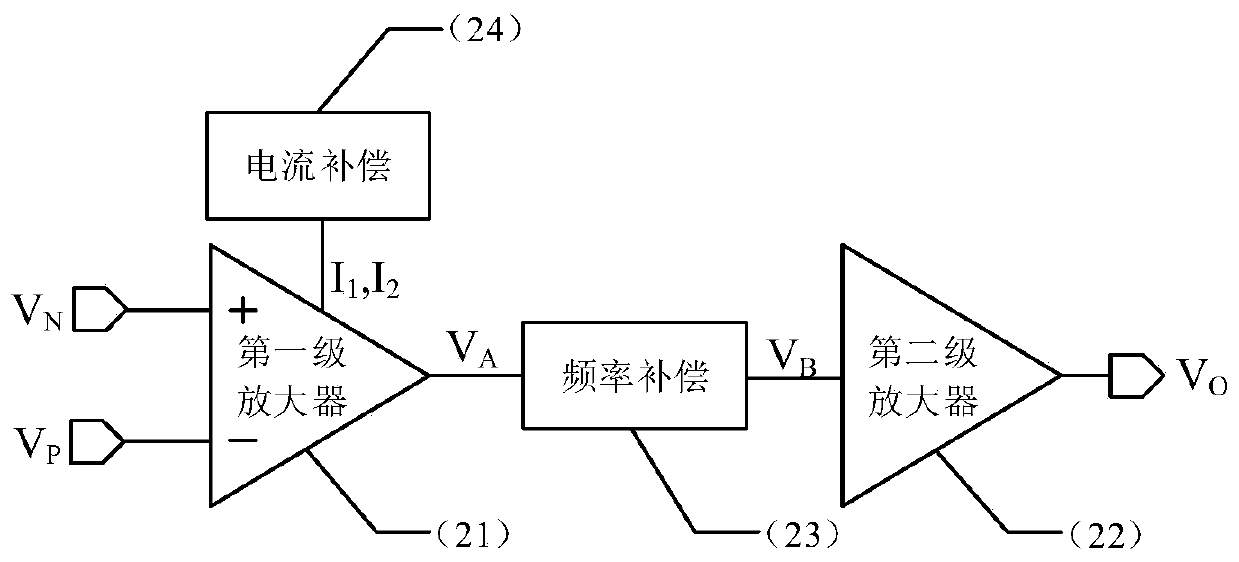

High-precision current-limiting load switch circuit

ActiveCN111478687AImproved Current Limit AccuracyQuick responseElectronic switchingSupply managementReference current

The invention discloses a high-precision current-limiting load switch circuit, a current-limiting load switch is connected between a power supply and a load, and the current-limiting load switch circuit mainly solves the problems of low precision and the low response speed of the existing current-limiting load switch circuit. The current-limiting load switch circuit comprises a reference current unit (1), a current-limiting detection unit (2) and a load switch unit (3), the reference current unit is used for generating a stable reference current signal and setting a limiting current; the current-limiting detection unit is used for detecting load current and outputting bias voltage to drive an NMOS load switch. When the load switch unit works in a deep linear region, the conduction impedance is small, and the power supply utilization efficiency is higher. Besides, the operational amplifier for the current-limiting detection unit provided by the invention has the lower offset voltage andthe higher slew rate, so that the current-limiting load switch circuit has the characteristics of high precision and the high response speed, and can be used in an intelligent and integrated power supply management system.

Owner:XIDIAN UNIV

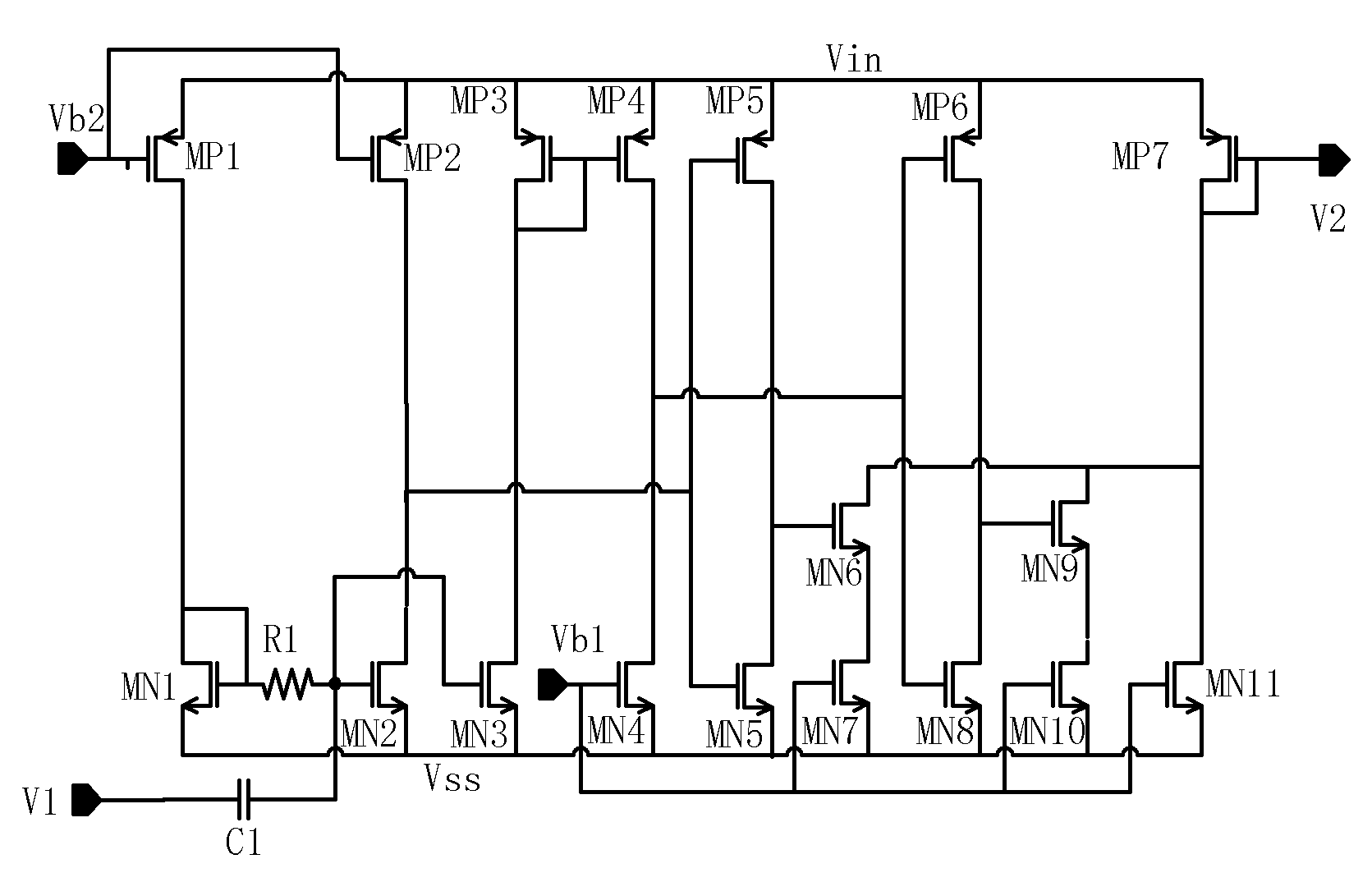

Dynamic current doubling circuit and linear voltage regulator integrated with the circuit

InactiveCN102609025BImprove performanceIncrease slew rateElectric variable regulationCapacitanceHemt circuits

The invention discloses a dynamic current doubling circuit and a linear voltage regulator integrated with the circuit. The dynamic current doubling circuit can dynamically regulate the magnitude of the output bias voltage according to the condition of an external output load. The low dropout linear voltage regulator integrated with the dynamic current doubling circuit can couple a leaping voltage to the dynamic current doubling circuit by a capacitor within a very short time when the output voltage leaps, a tail current source current of the differential pairs of a transconductance operational amplifier is increased instantaneously by controlling the magnitude of the bias voltage, the gate voltage of a regulating tube can be regulated rapidly, the problem of low slew rate caused by the slow change of the gate voltage of the regulating tube is solved, and the transconductance of the differential pair tube is increased by the increase of the tail current source current of the differential pairs, thereby increasing bandwidth of LDO (low dropout regulator), and the tail current source current only increases instantaneously without excessive power consumption.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

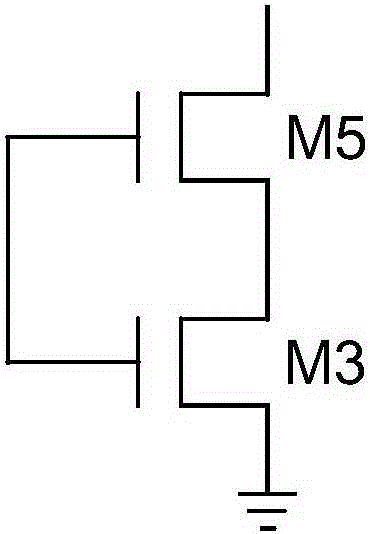

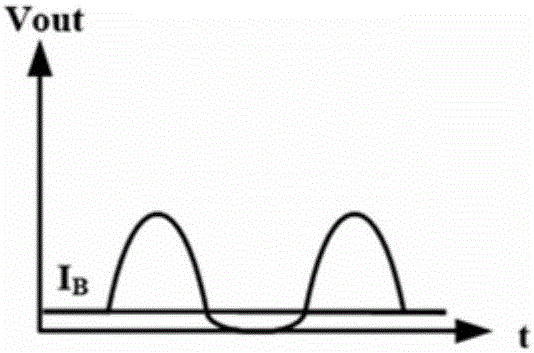

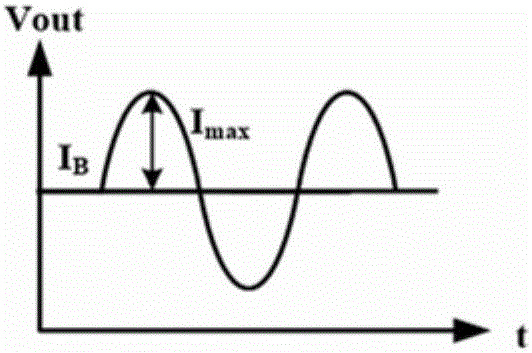

Slew rate enhancement type operational amplifier

ActiveCN106301264AIncrease slew rateIncrease static power consumptionDifferential amplifiersDc-amplifiers with dc-coupled stagesCapacitanceCharge and discharge

The invention provides a slew rate enhancement type operational amplifier, which at least comprises a biasing circuit, a first-stage circuit, a second-stage circuit and a drive current regulating circuit, wherein the first-stage circuit is connected to the biasing circuit; the second-stage circuit is respectively connected to the biasing circuit and the first-stage circuit; and the drive current regulating circuit is respectively connected to the biasing circuit, the first-stage circuit and the second-stage circuit and is used for regulating the drive current of the slew rate enhancement type operational amplifier when the slew rate enhancement type operational amplifier drives a load in order to make the drive current of the slew rate enhancement type operational amplifier greater than the bias current to enhance the slew rate of the slew rate enhancement type operational amplifier. In comparison with the class-A operational amplifier in the existing technology, the magnitude of the drive current of the slew rate enhancement type operational amplifier is not decided by the bias current of an output stage, and the drive current can be much larger than the bias current, so that quick charge and discharge under the large capacitance load can be realized without improving the bias current of the output stage, and thus the slew rate is greatly improved.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

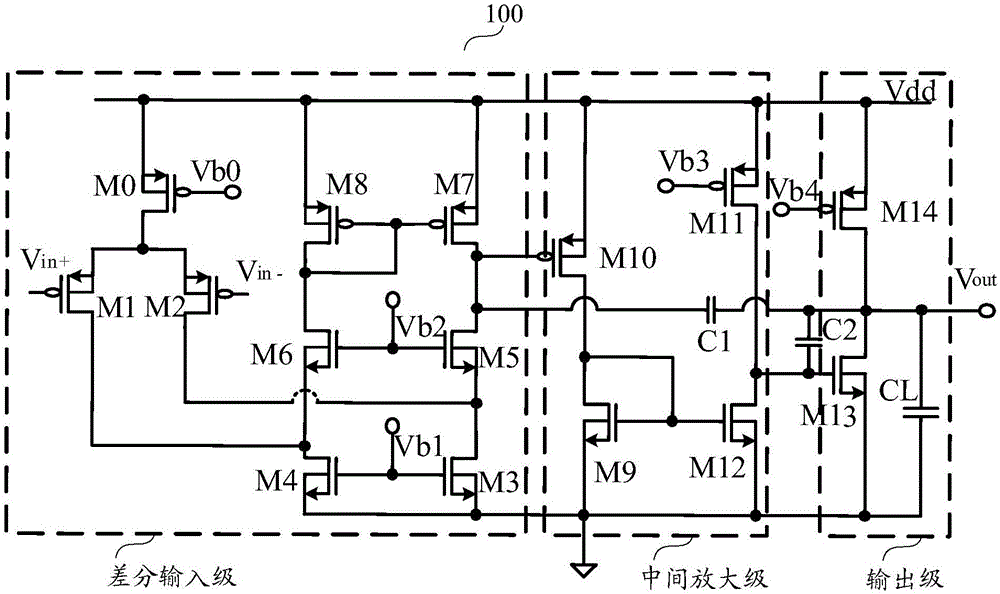

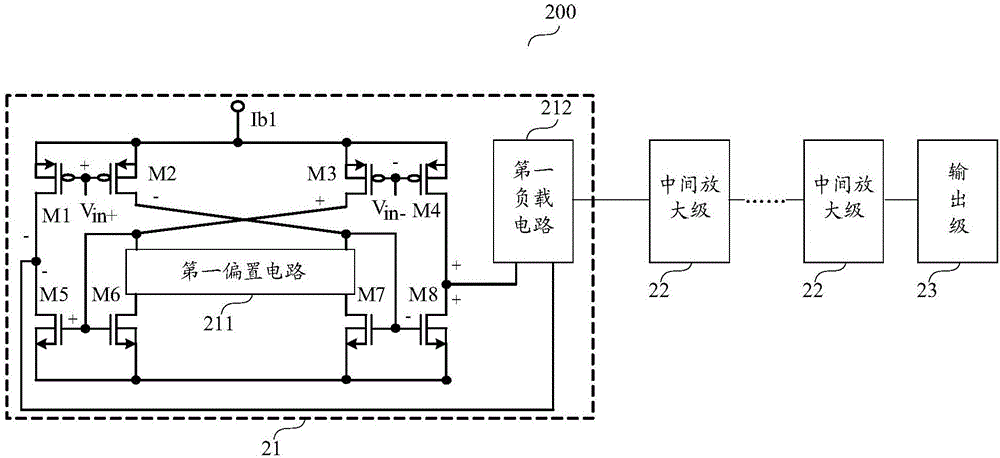

Multistage amplifier

ActiveCN106788295AHigh gainImprove transconductanceDifferential amplifiersDc-amplifiers with dc-coupled stagesLoad circuitPower flow

The invention discloses a multistage amplifier which comprises a differential input stage, at least one intermediate amplification stage and an output stage. The differential input stage, the intermediate amplification stages and the output stage are sequentially in cascade connection with one another; the differential input stage comprises a first MOS (metal oxide semiconductor) transistor, a second MOS transistors, a third MOS transistor, a fourth MOS transistor, a first current mirror circuit, a second current mirror circuit, a first bias circuit and a first load circuit, source electrodes and grid electrodes of the first MOS transistor and the second MOS transistor are coupled with one another, and first voltages can be received by the grid electrodes of the first MOS transistor and the second MOS transistor; source electrodes and grid electrodes of the third MOS transistor and the fourth MOS transistor are coupled with one another, second voltages can be received by the grid electrodes of the third MOS transistor and the fourth MOS transistor, the source electrodes of the third MOS transistor and the second MOS transistor are coupled with each other, and first bias currents can be received by the source electrodes of the third MOS transistor and the second MOS transistor; a common grid electrode of the first current mirror circuit is coupled with a drain electrode of the third MOS transistor, and a first drain electrode of the first current mirror circuit is coupled with a drain electrode of the first MOS transistor; a common grid electrode of the second current mirror circuit is coupled with a drain electrode of the second MOS transistor, and a first drain electrode of the second current mirror circuit is coupled with a drain electrode of the fourth MOS transistor; the first bias circuit is suitable for providing bias circuits for the first current mirror circuit and the second current mirror circuit; the first load circuit is suitable for providing load for the differential input stage. According to the scheme, the multistage amplifier has the advantages of high gain and wide unity gain bandwidth.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

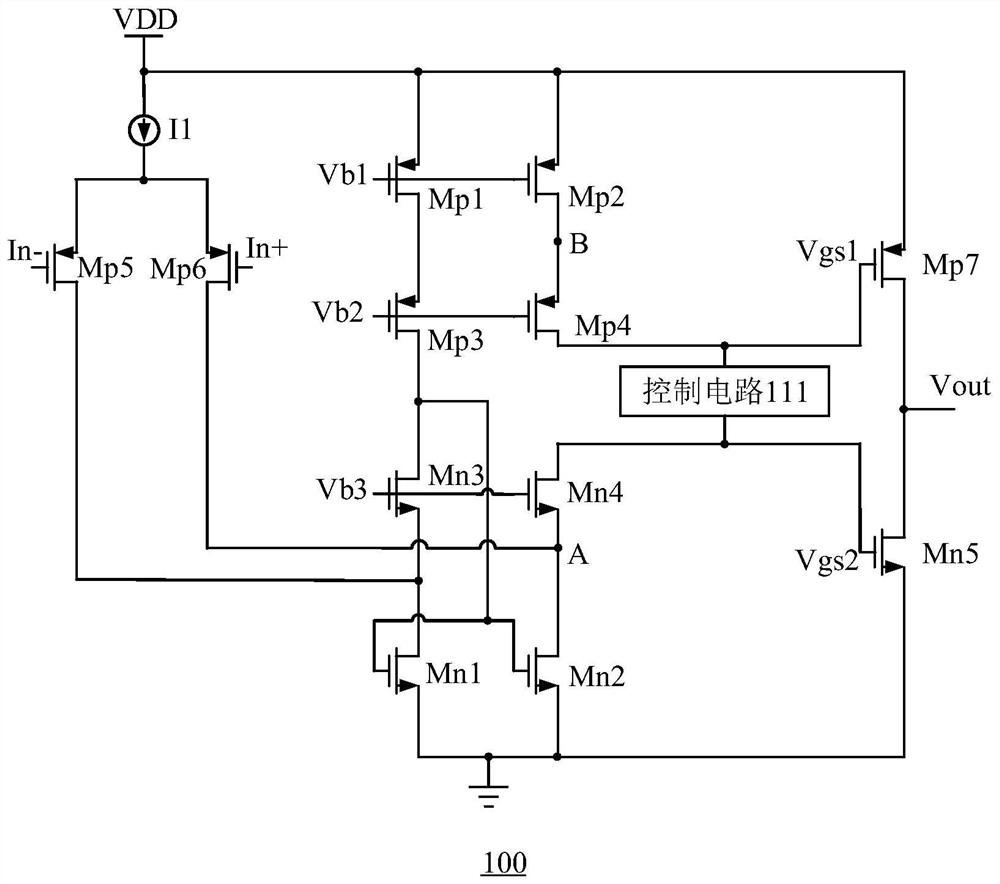

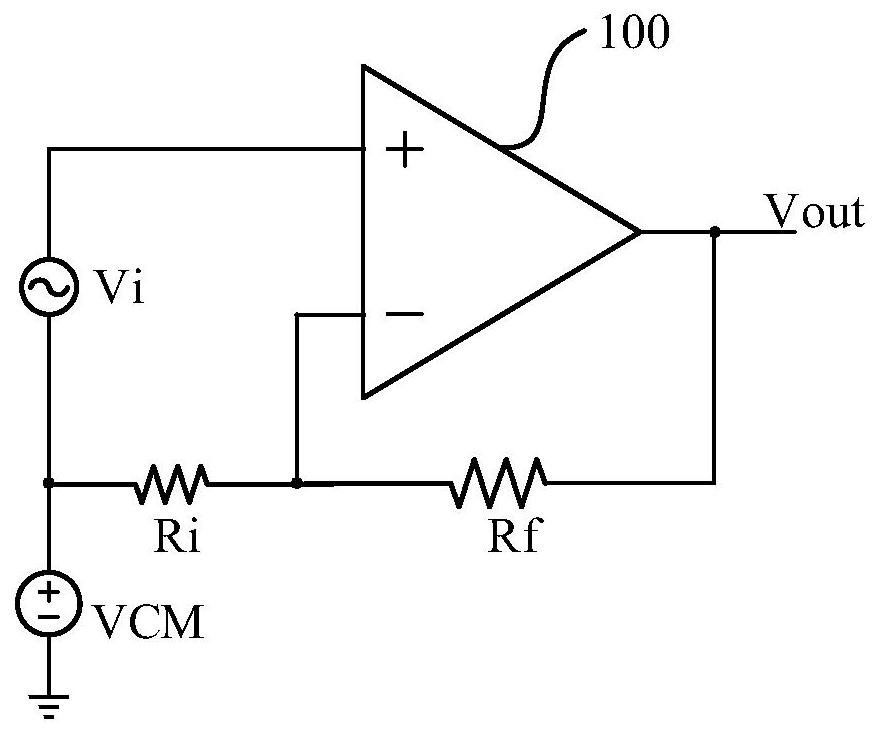

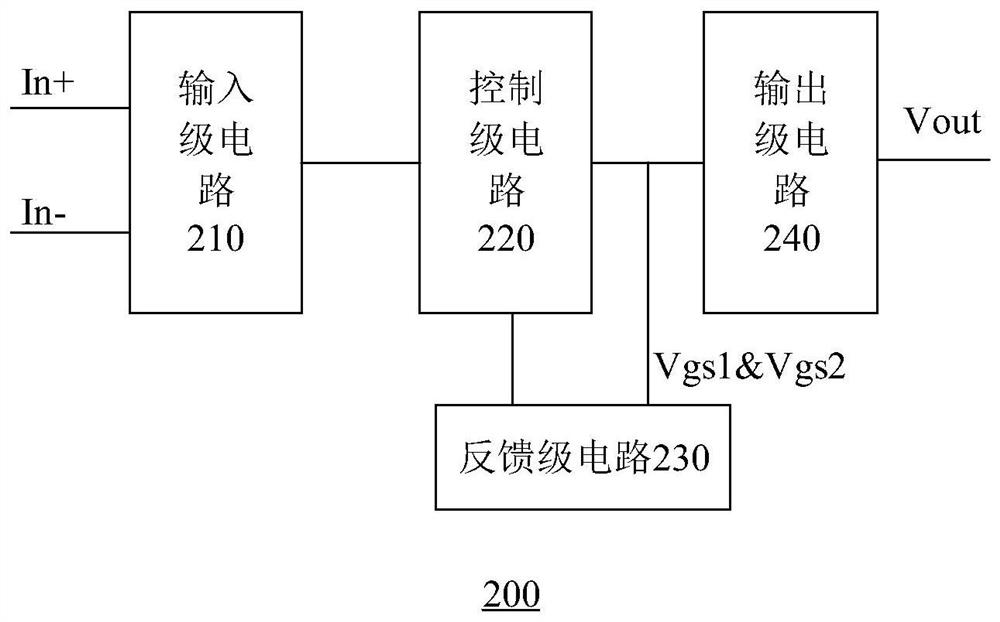

Operational amplifier

PendingCN114070213AImprove overloadIncrease slew rateAmplifier modifications to reduce noise influenceDifferential amplifiersHemt circuitsVoltage regulation

The invention relates to a semiconductor integrated circuit, and provides an operational amplifier. The operational amplifier can receive and amplify a positive differential input voltage and a negative differential input voltage through an input stage circuit and output a first positive differential output voltage and a first negative differential output voltage; the operational amplifier respectively output a first driving voltage and a second driving voltage by using a control stage circuit according to the first positive differential output voltage and the first negative differential output voltage; based on the fact that an output stage circuit is coupled to the control stage circuit, the operational amplifier generates an output voltage according to the first driving voltage and the second driving voltage. and a first control voltage or a second control voltage are correspondingly generated by using a feedback stage circuit according to the first driving voltage or the second driving voltage, so the operational amplifier provided by the invention can adjust the state of the control stage circuit by using the control stage circuit according to the first control voltage or the second control voltage so as to stabilize the offset voltage of the operational amplifier. Therefore, the offset voltage can be stabilized while high gain is ensured.

Owner:SG MICRO