Patents

Literature

115results about How to "Improve conversion speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

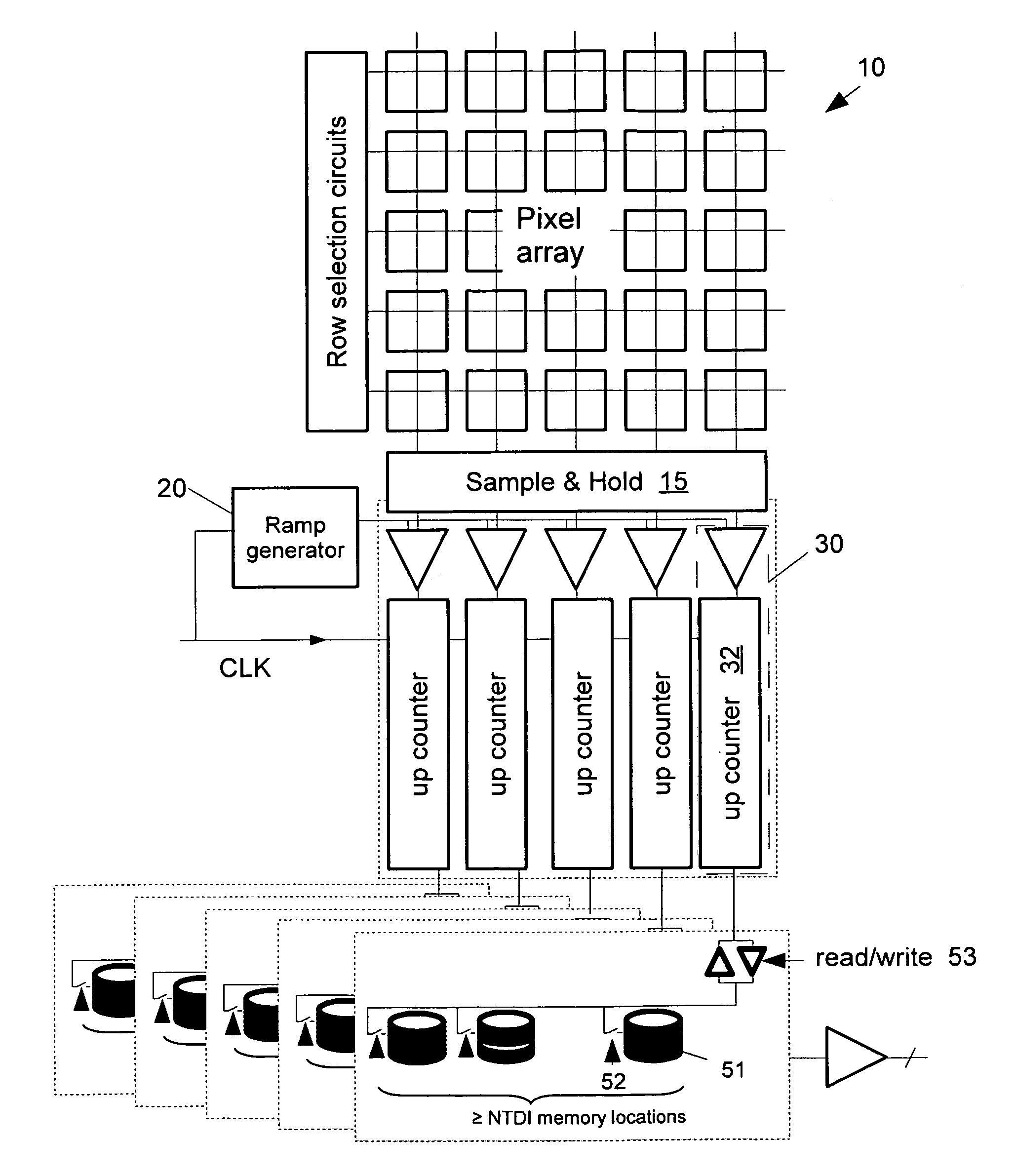

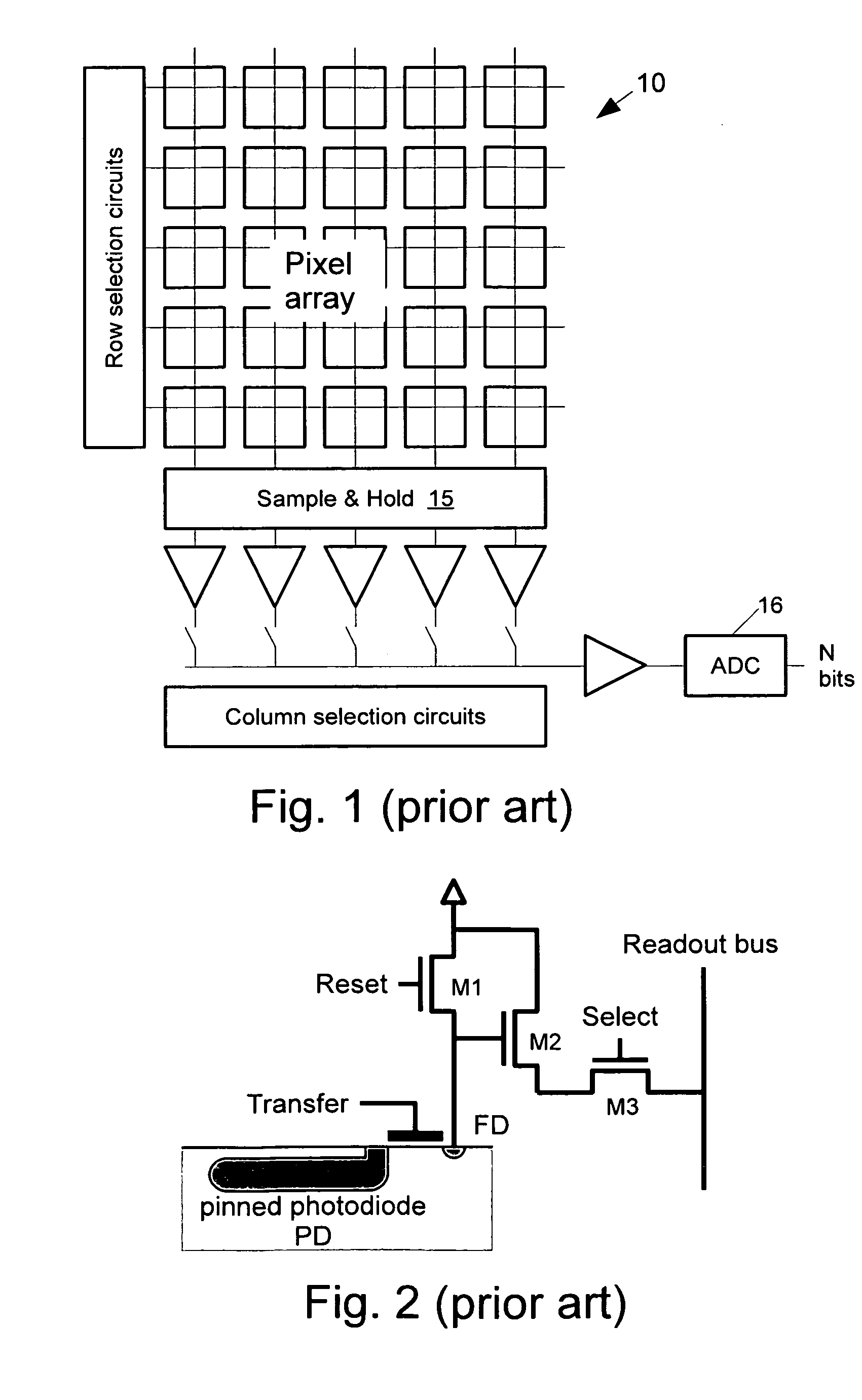

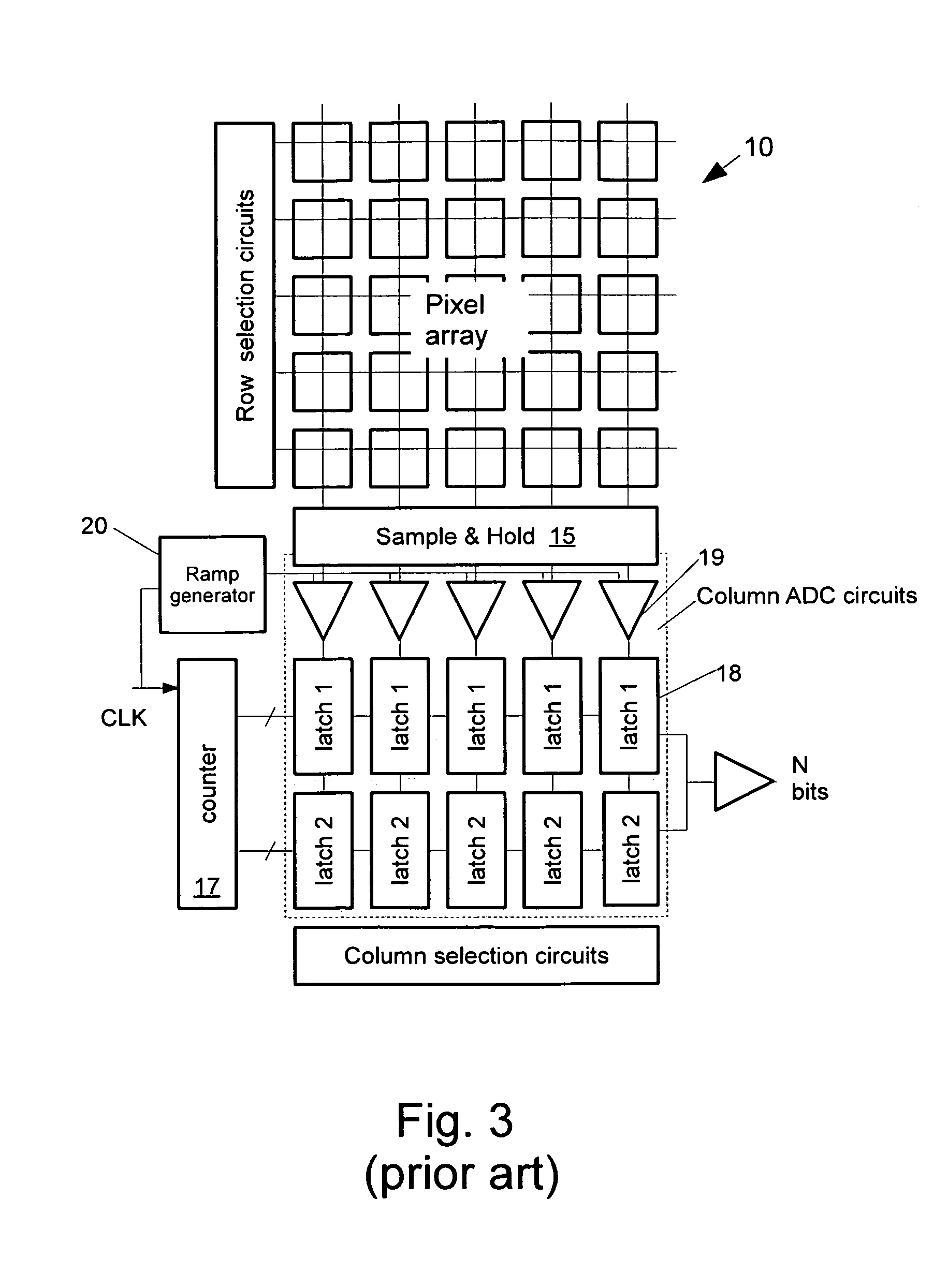

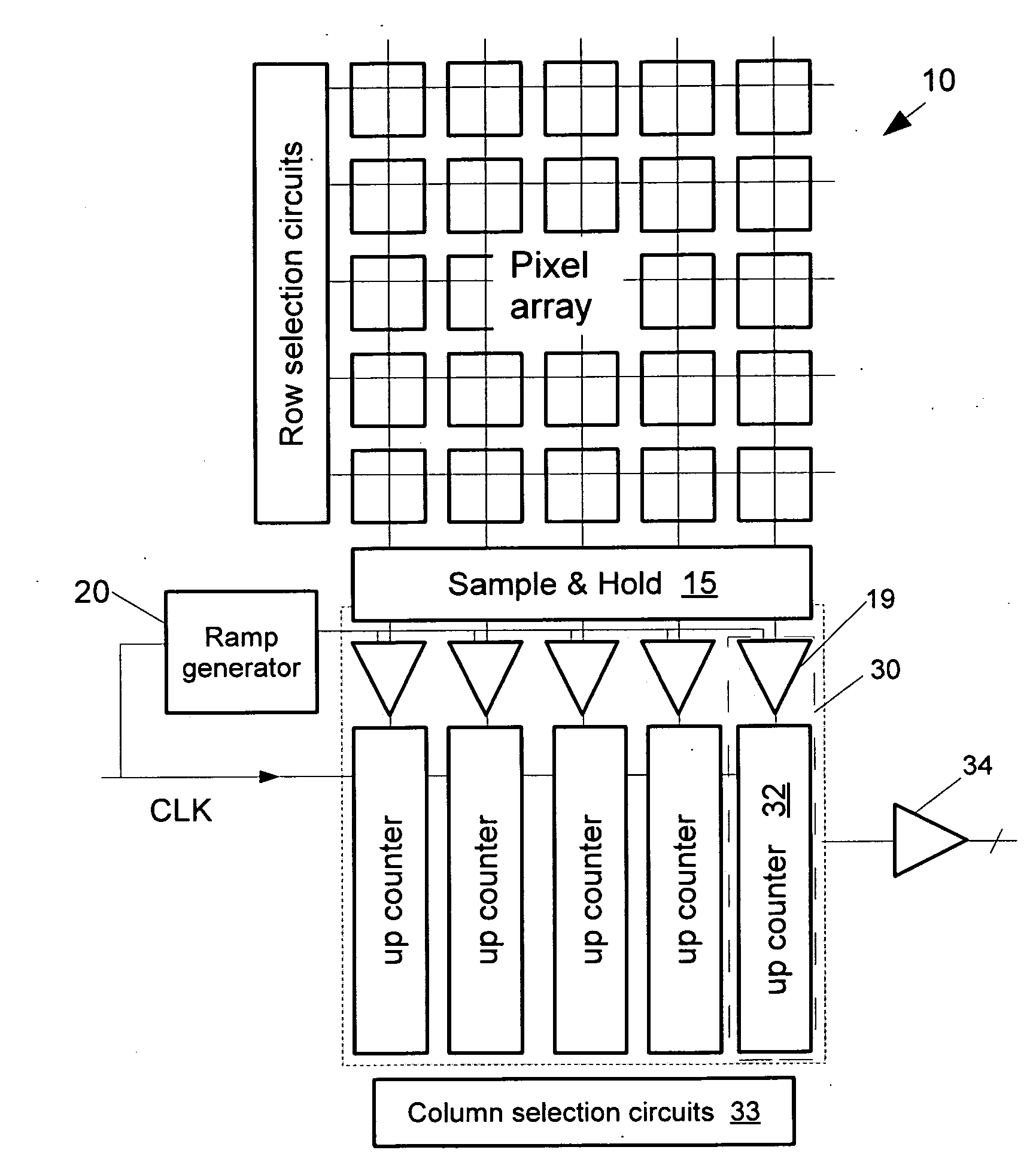

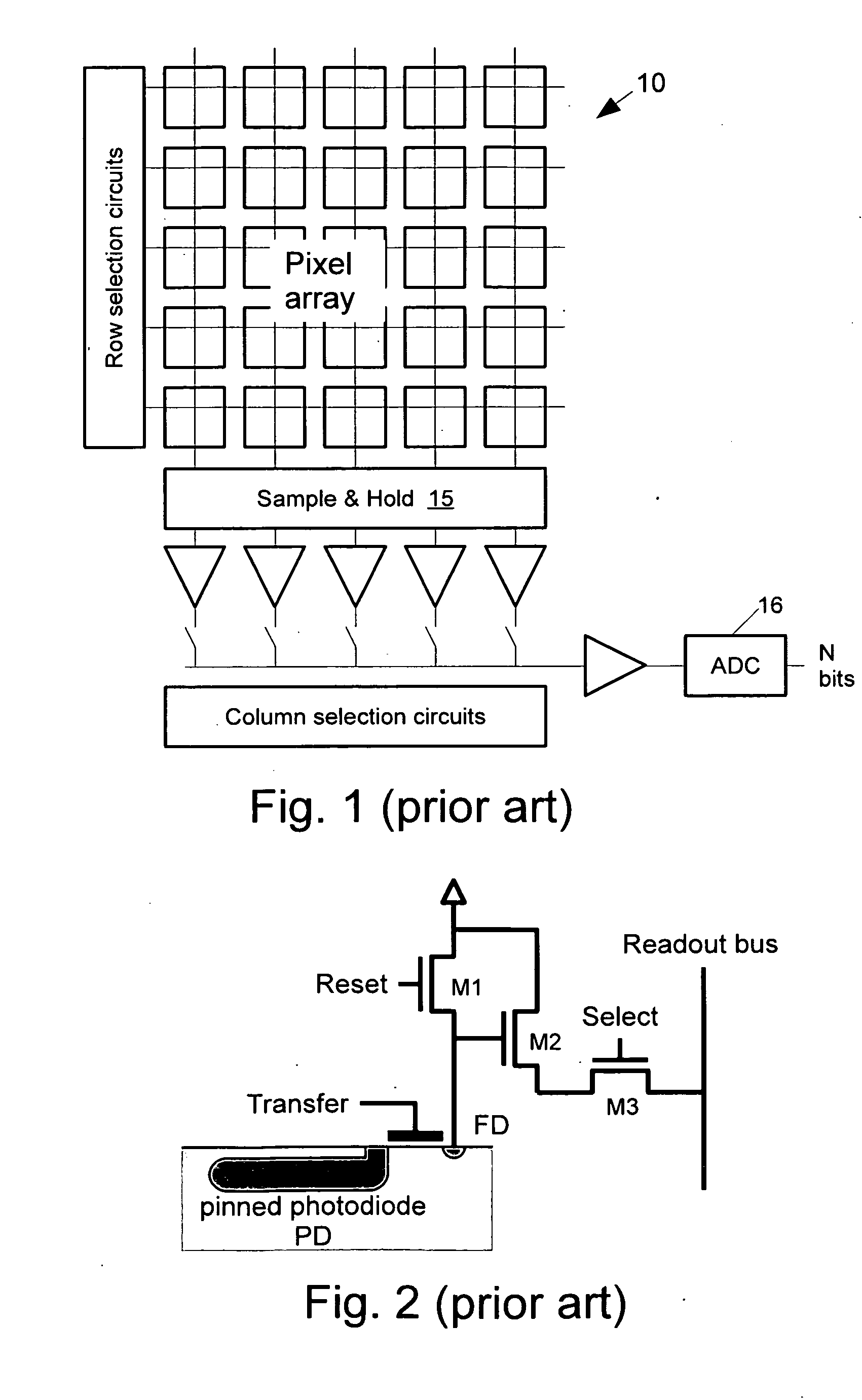

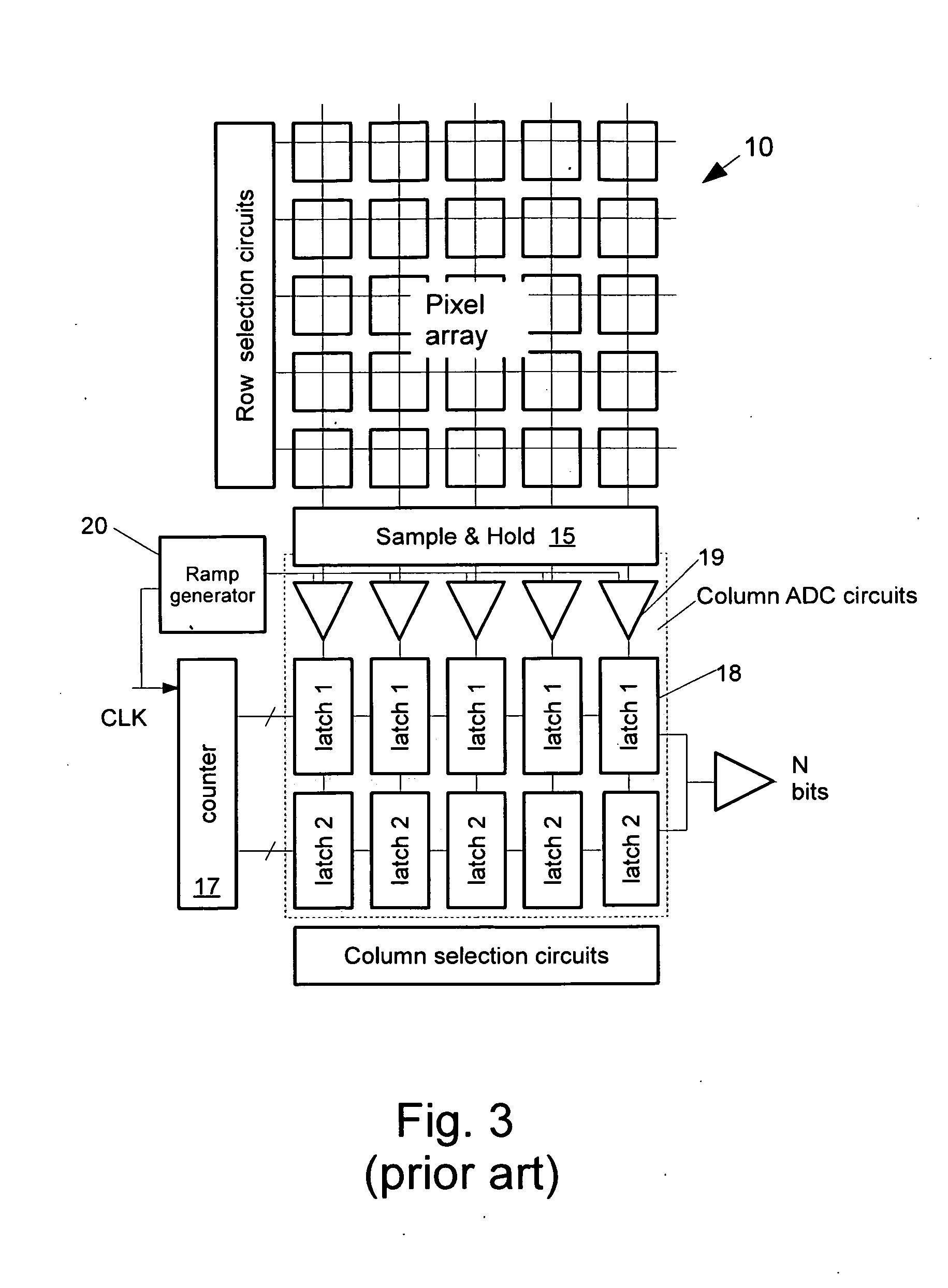

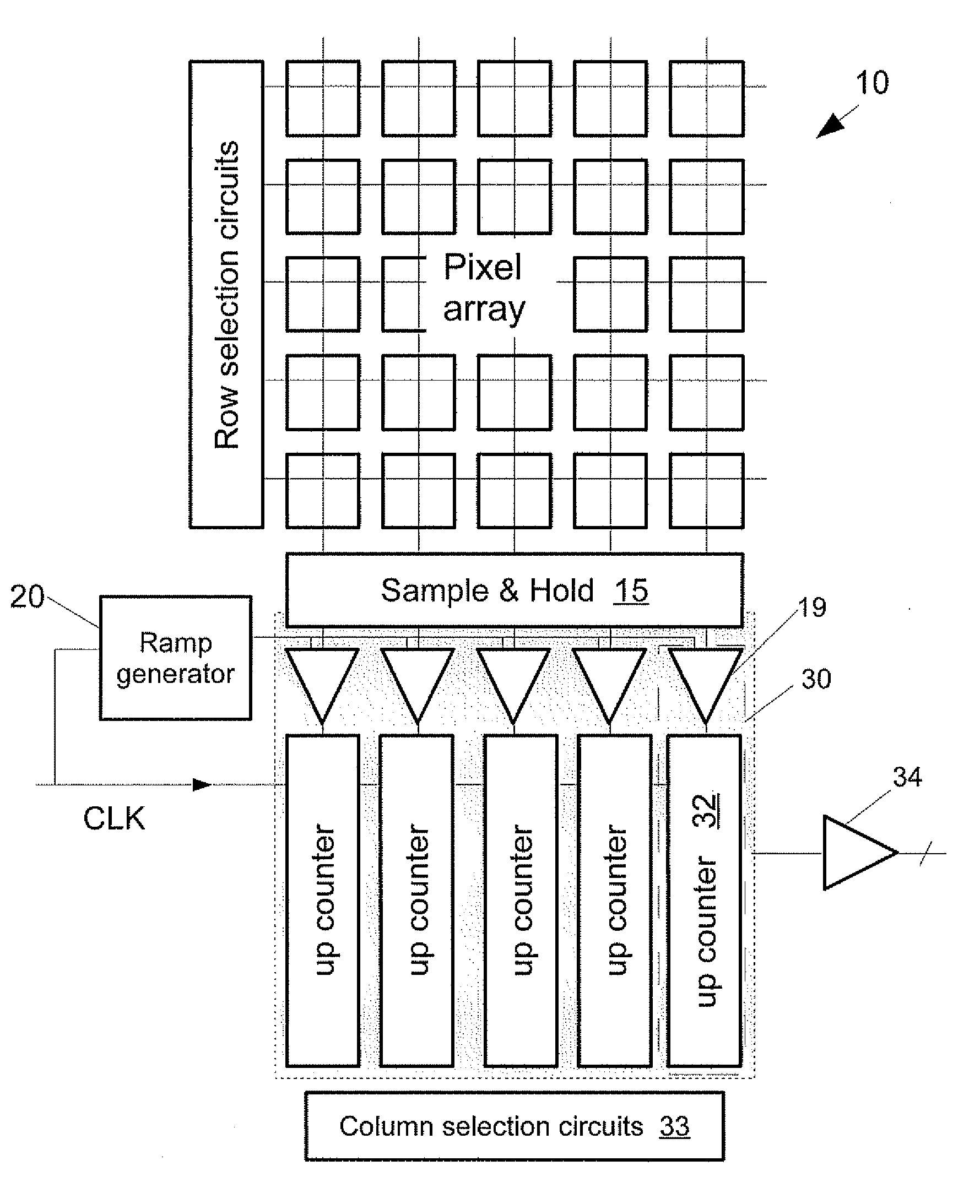

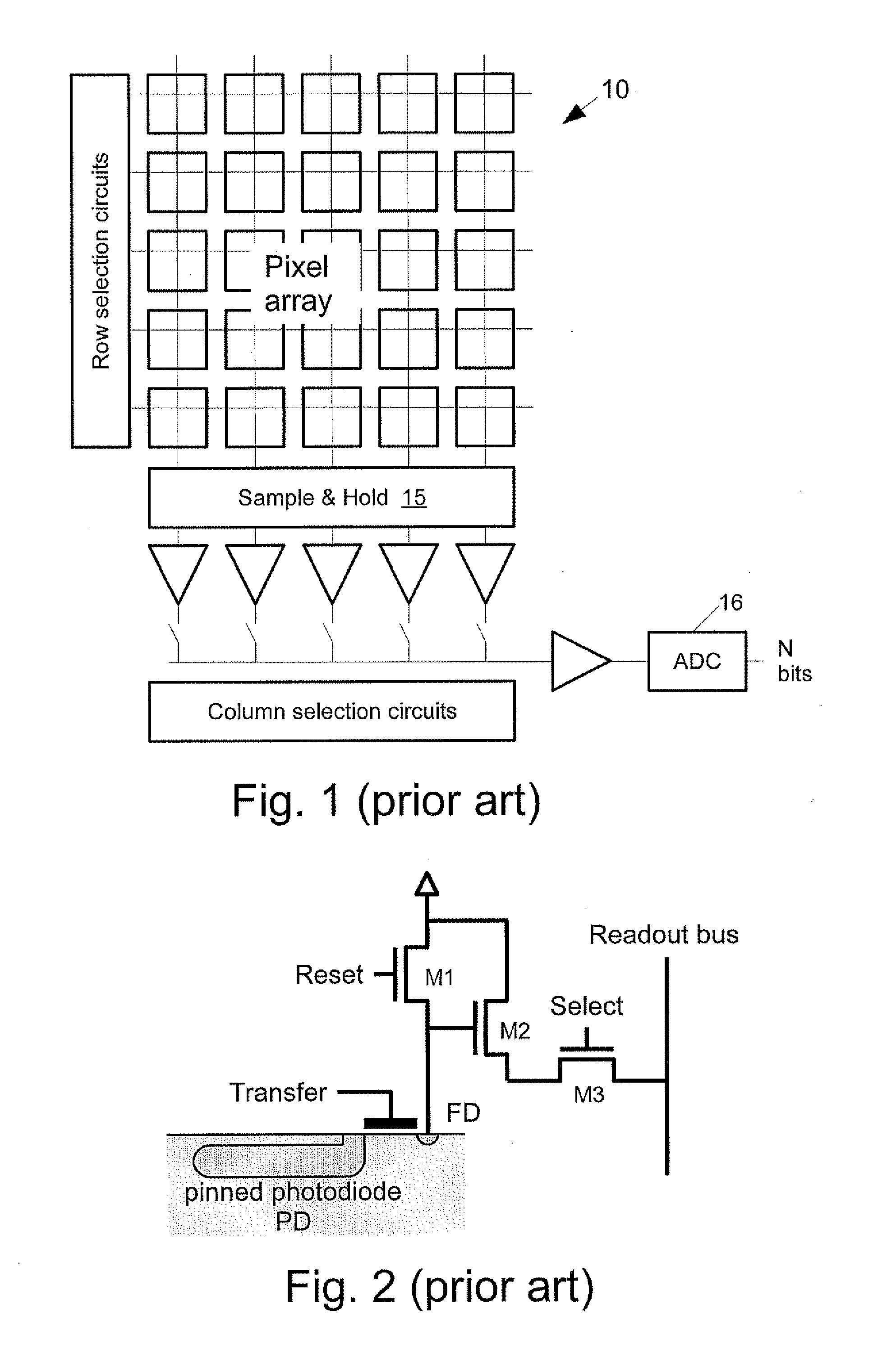

Analog-to-digital conversion in pixel arrays

ActiveUS7880662B2Improve accuracyAvoid the needAnalogue/digital conversionTelevision system detailsExposure periodAnalog signal

An analog-to-digital converter (ADC) generates an output digital value equivalent to the difference between two analog signal values. The ADC 30 receives a first analog signal level, a second analog signal level and a ramp signal. A counter 32 is operable to count in a single direction. A control stage is arranged to enable the counter 32 based on a comparison 19 of the ramp signal with the first analog signal and the second analog signal. A digital value accumulated by the counter during a period when it is enabled forms the output. The ADC can perform the conversion during a single cycle of the ramp signal. The counter 32 can be loaded with a starting digital value representing an exposure level accumulated during a previous exposure period. Techniques are described for reducing the conversion time.

Owner:CMOSIS

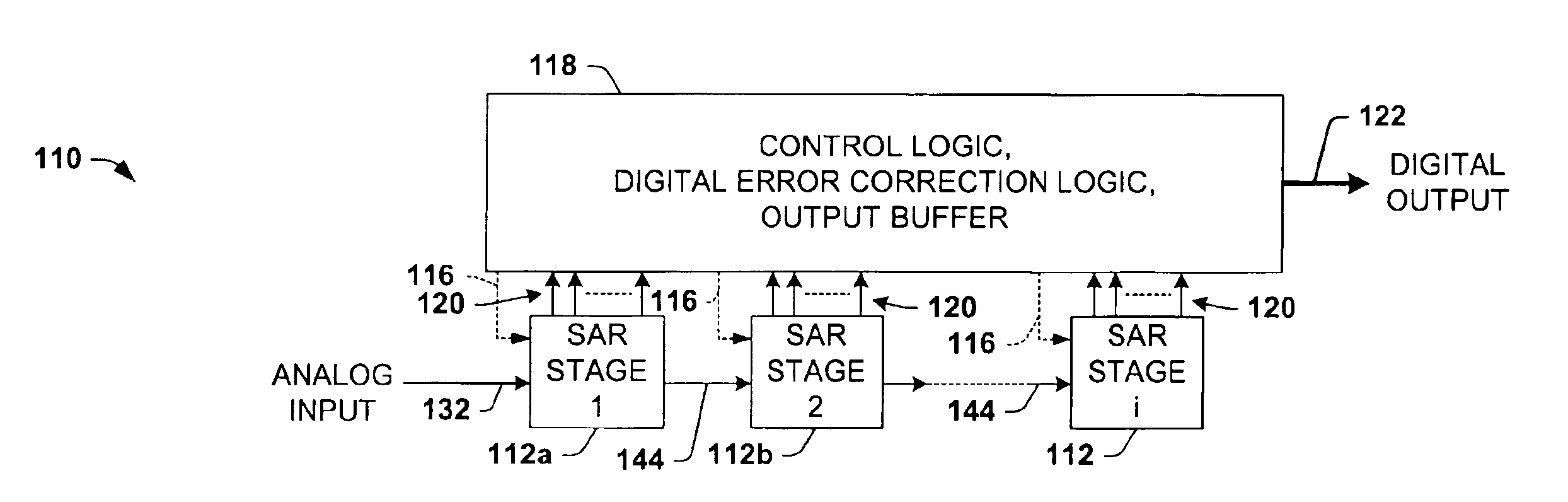

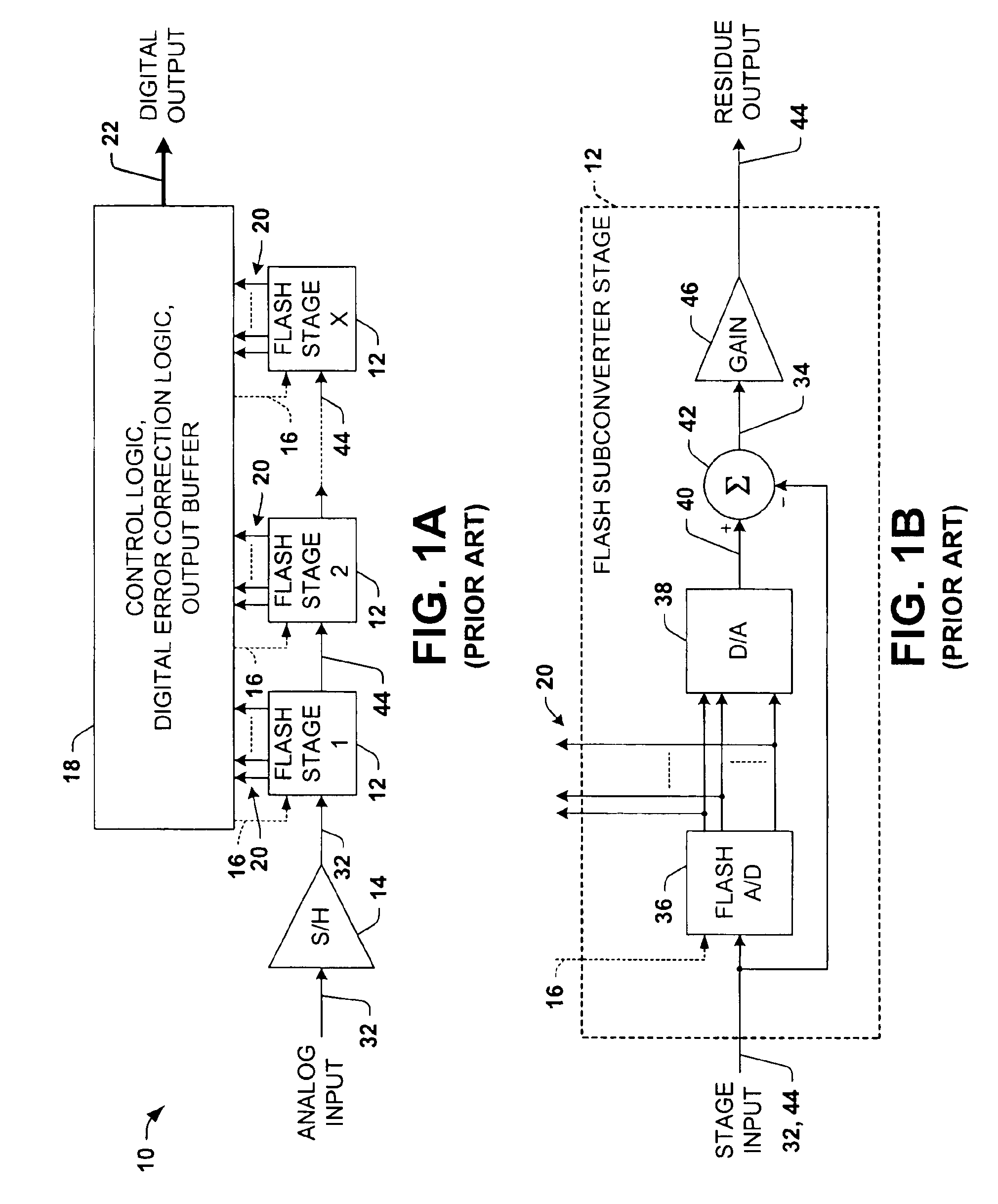

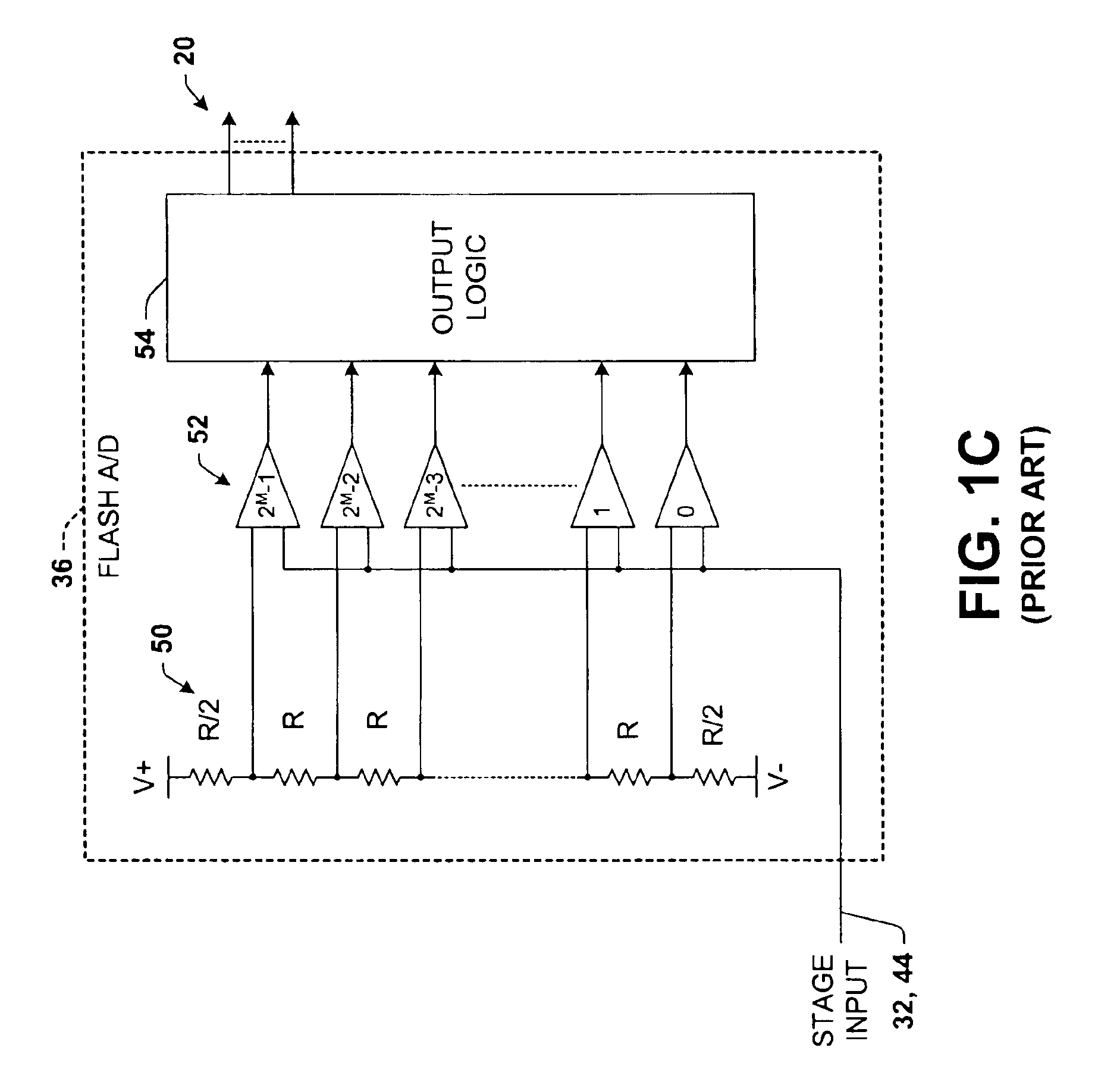

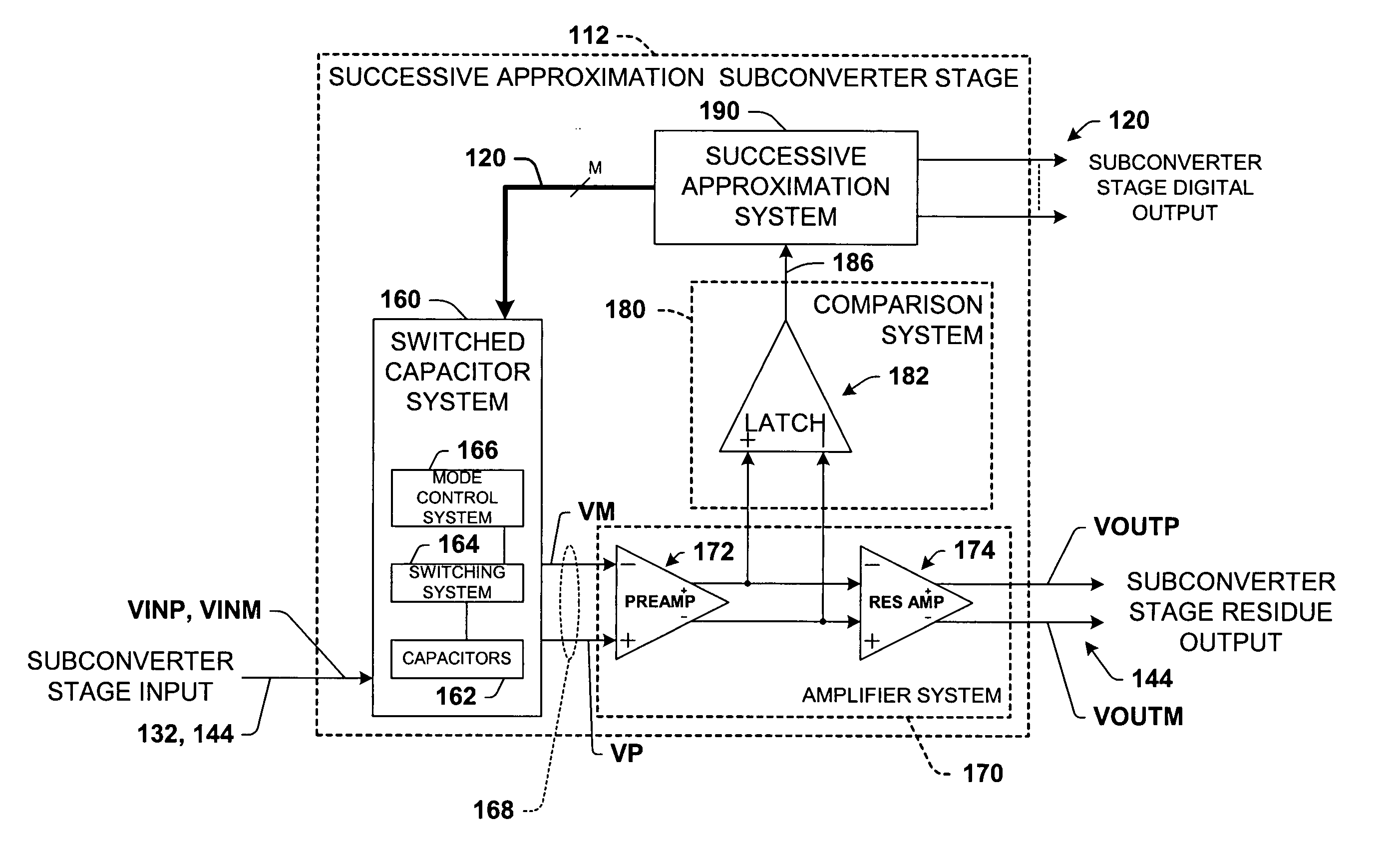

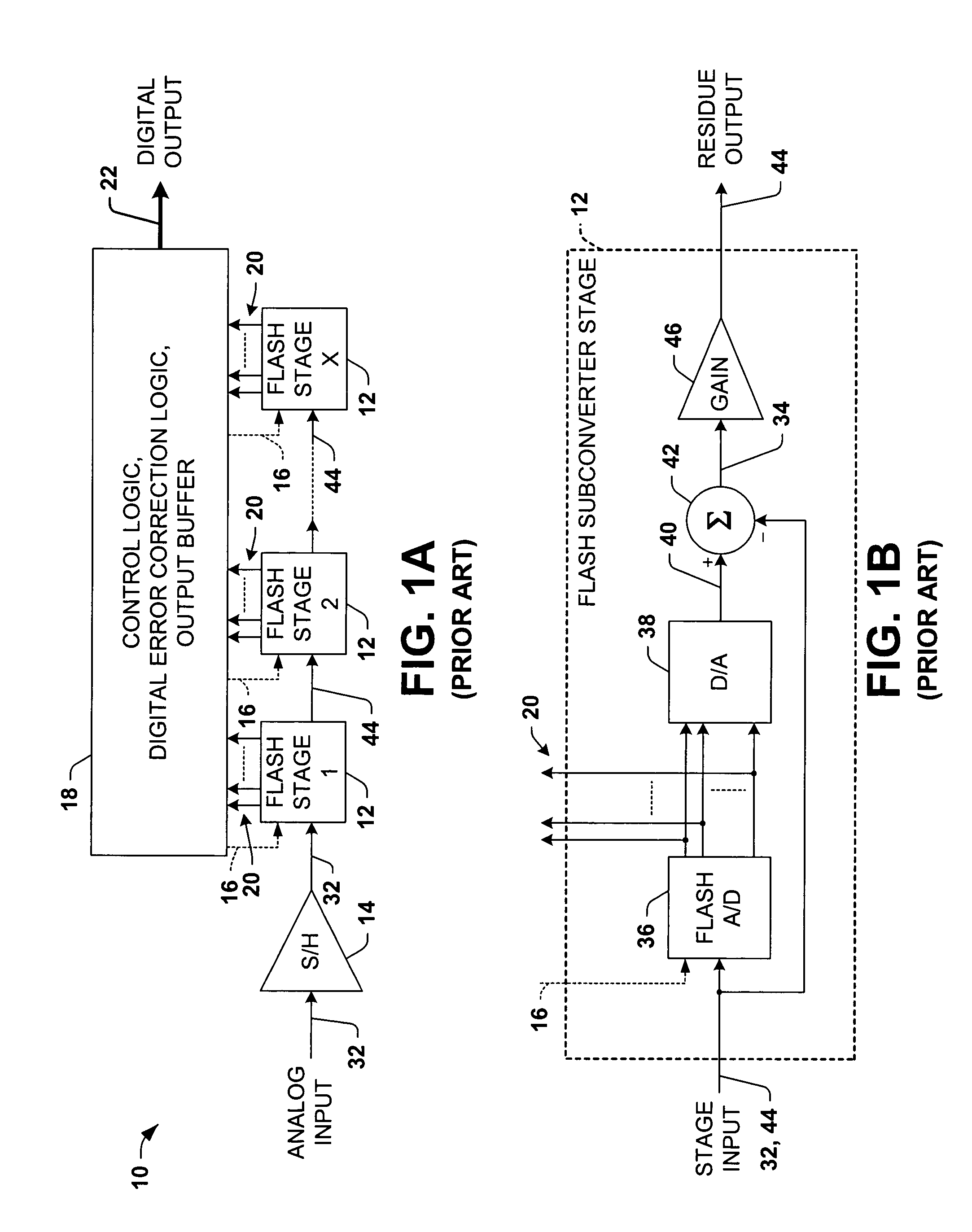

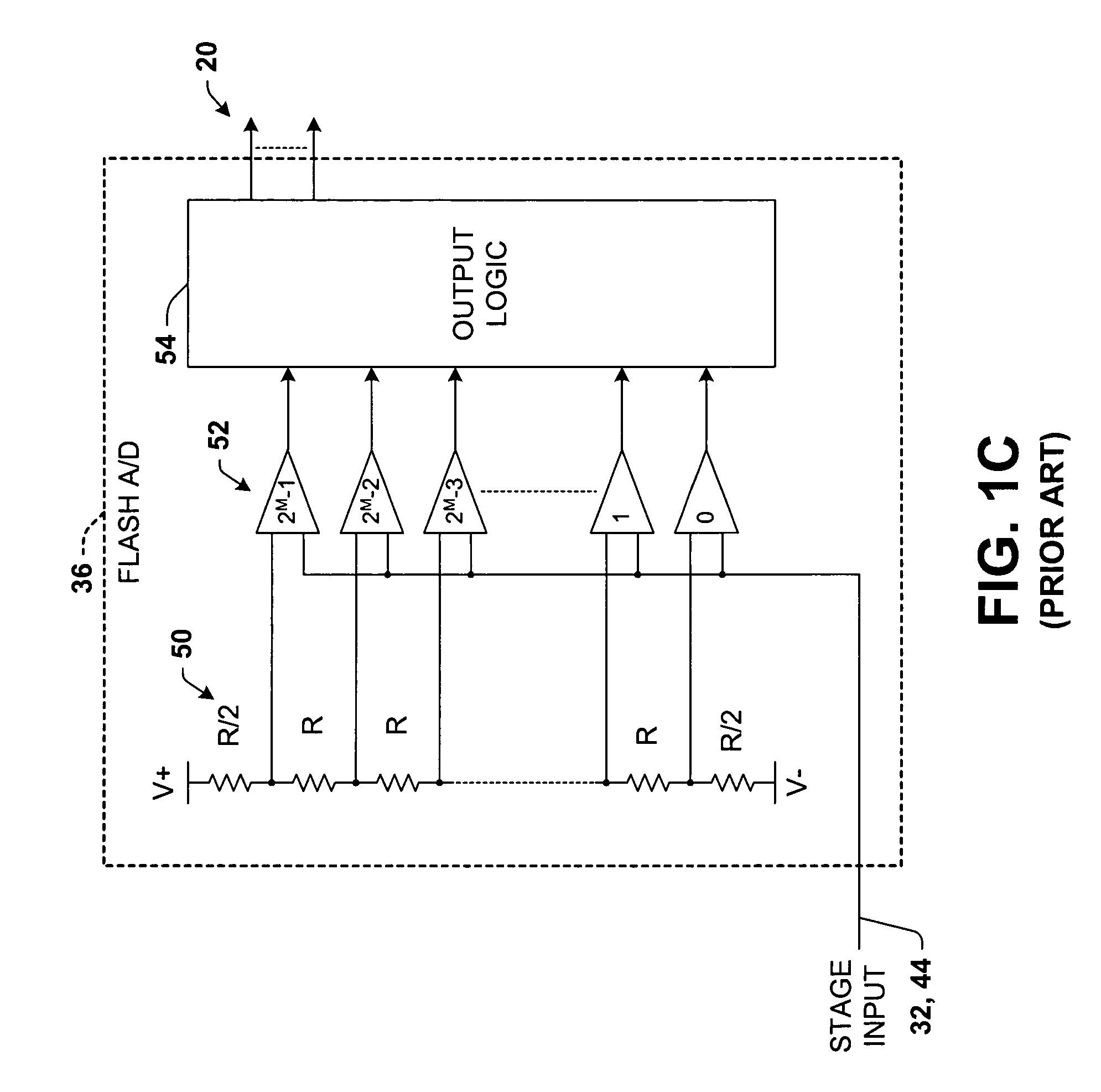

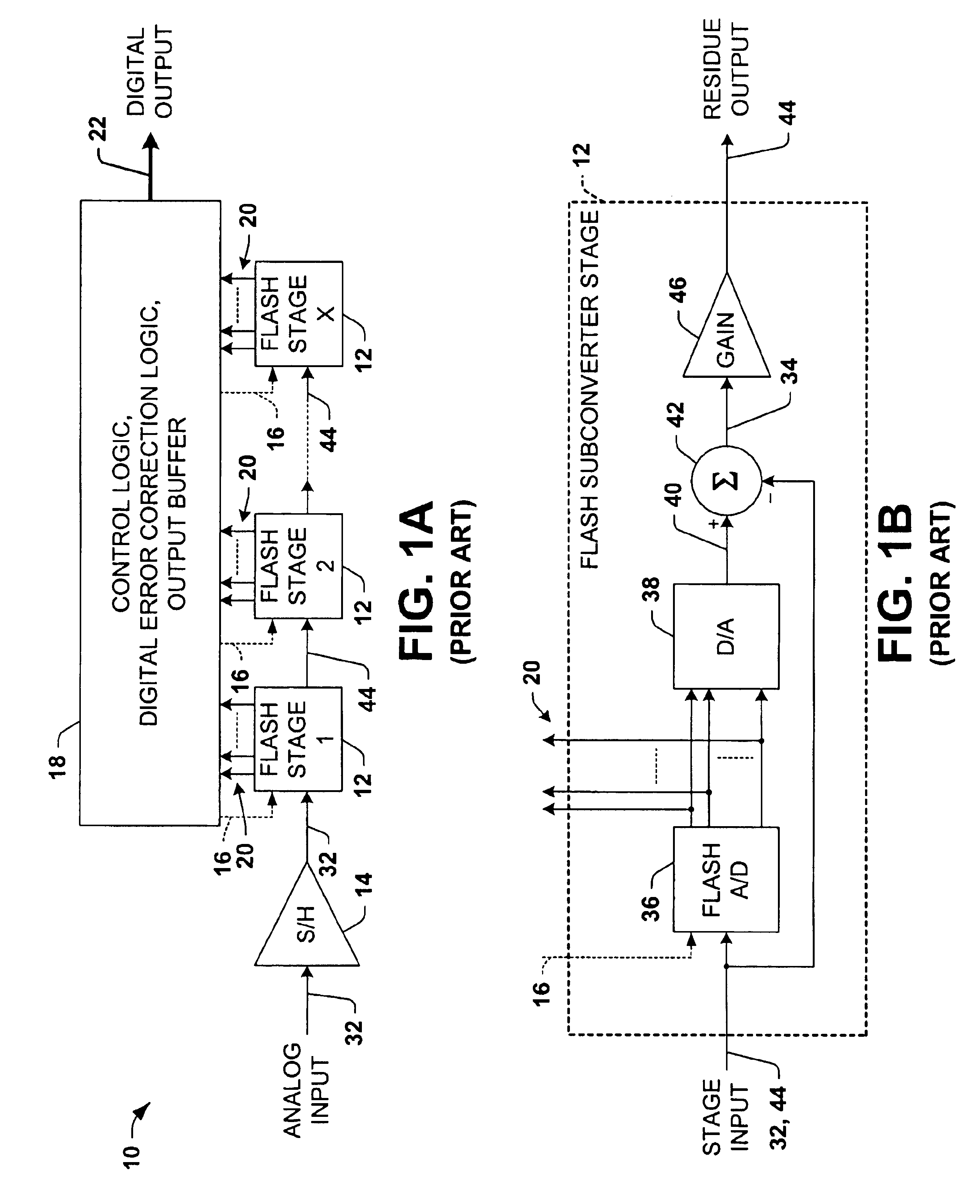

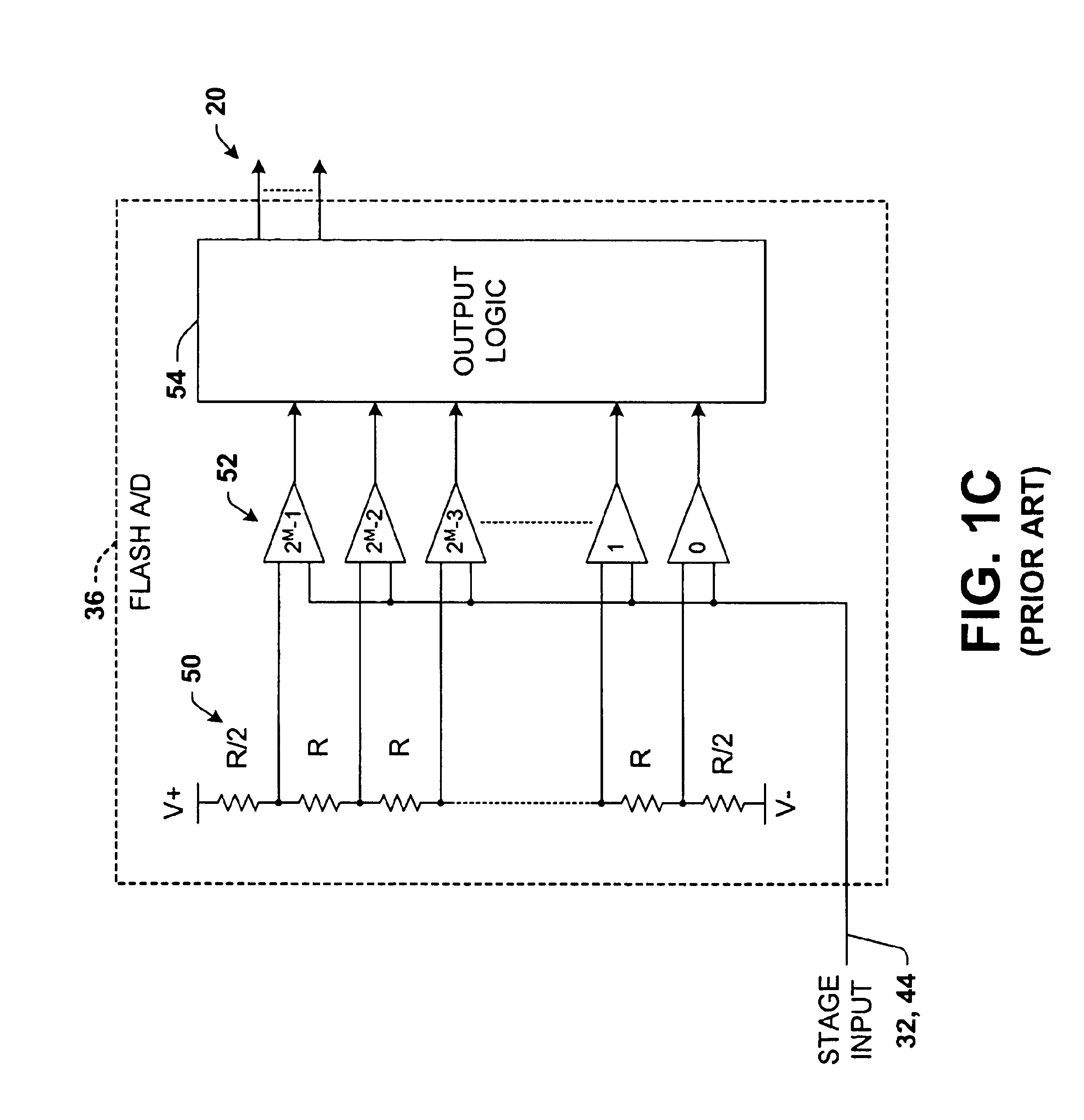

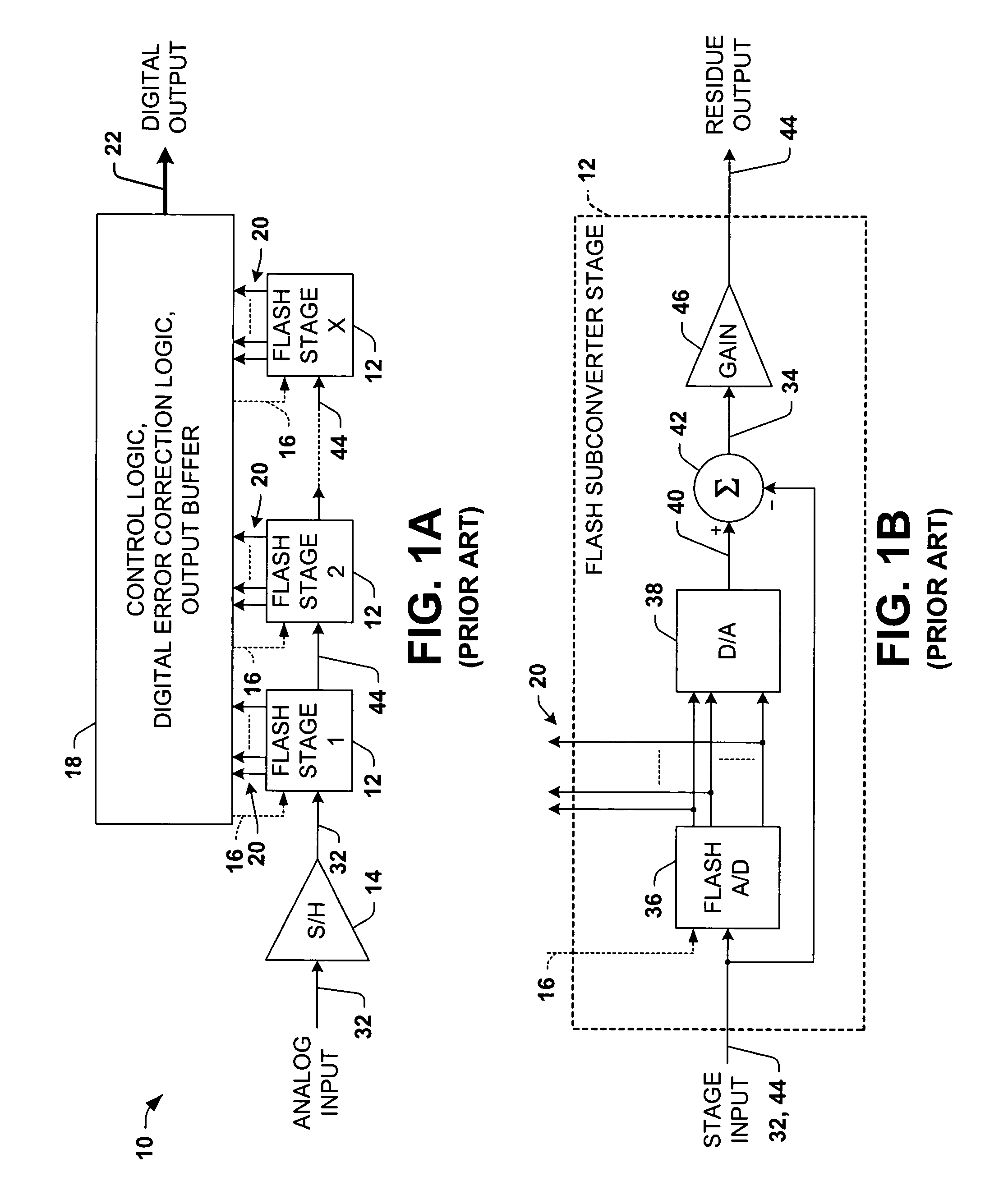

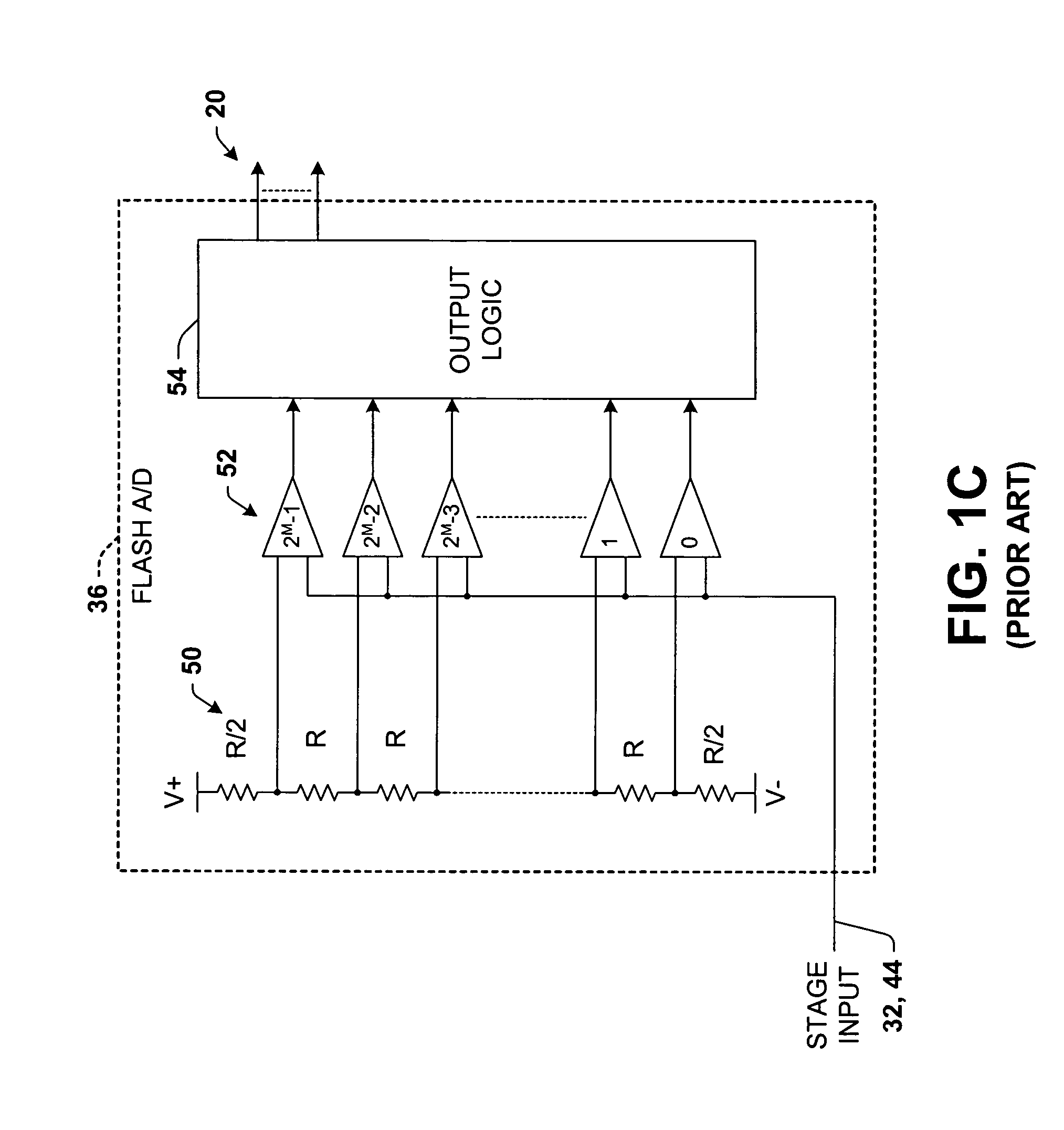

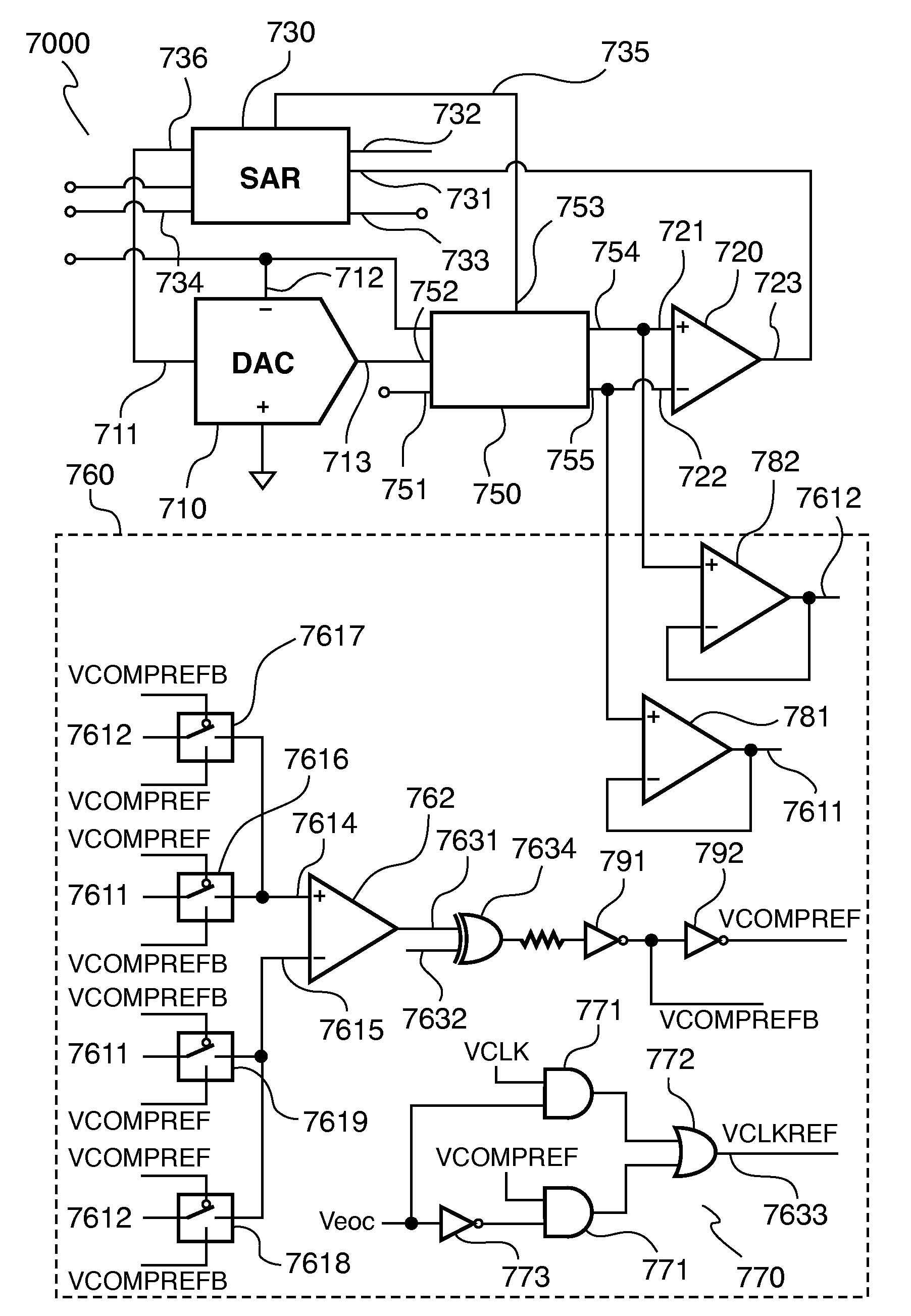

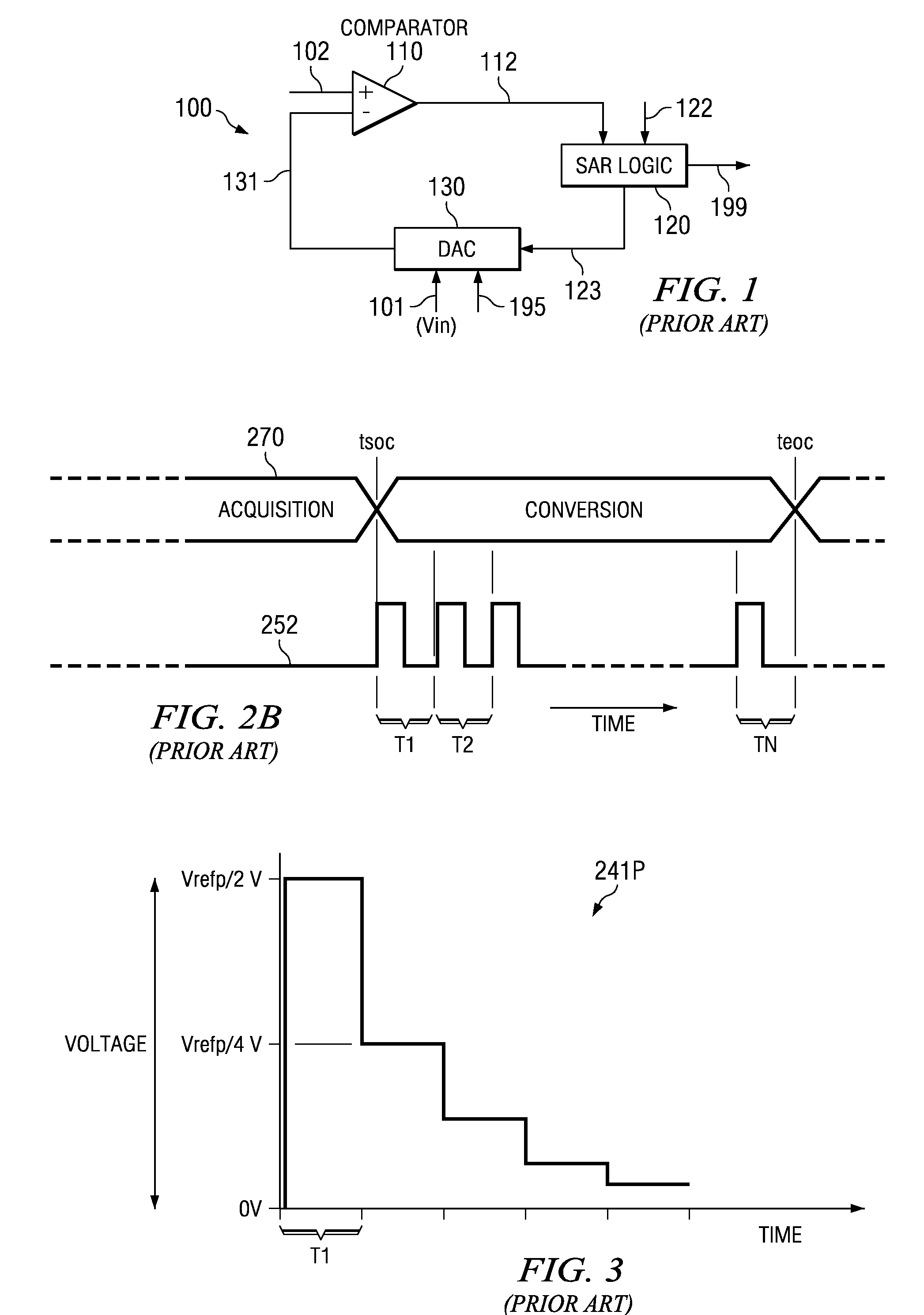

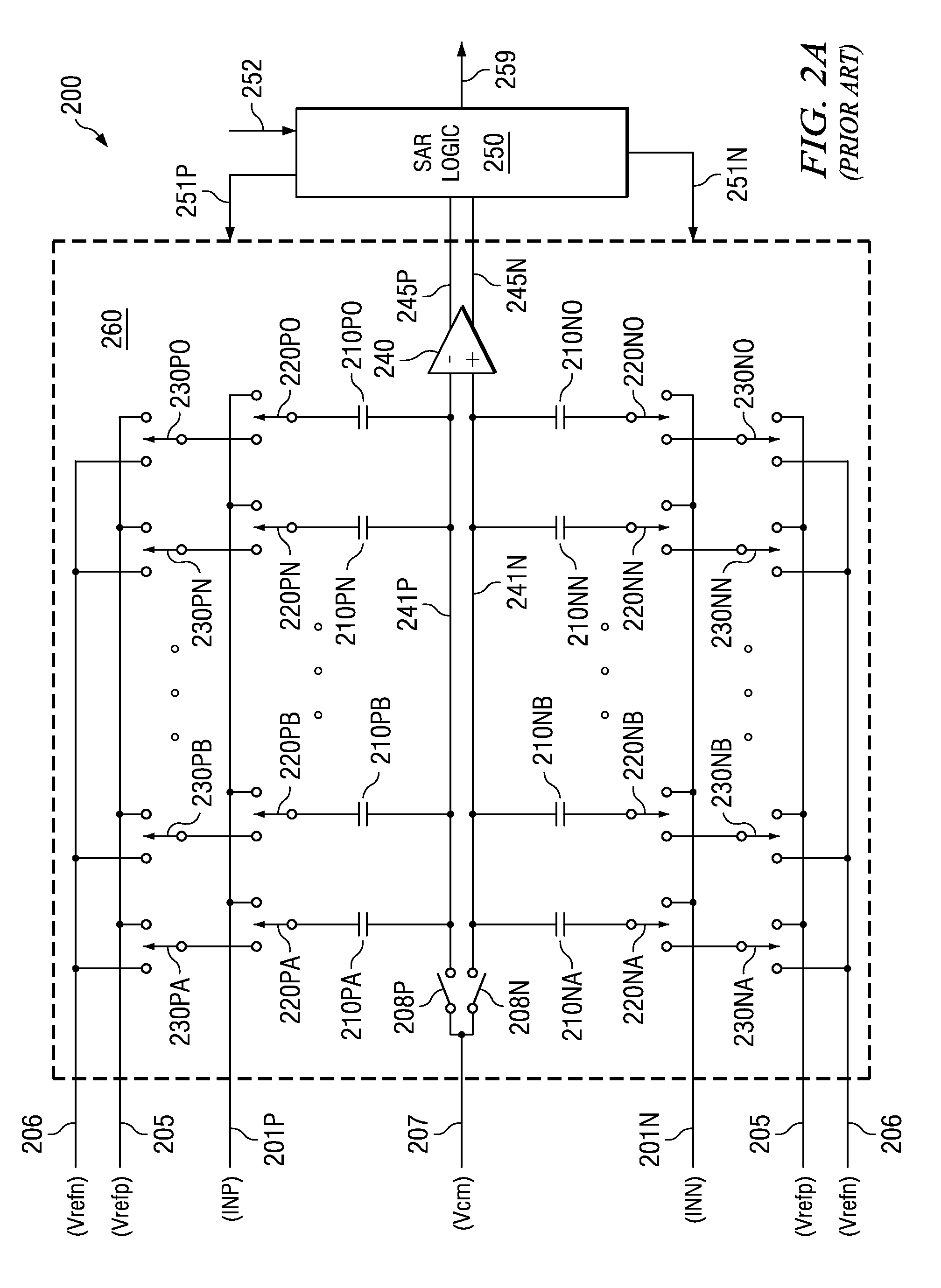

Differential pipelined analog to digital converter with successive approximation register subconverter stages using thermometer coding

InactiveUS6914550B2Improve conversion speedReduce power consumptionElectric signal transmission systemsAnalogue-digital convertersEngineeringAnalog-to-digital converter

Pipelined analog to digital conversion systems are provided having cascaded multi-bit successive approximation register subconverter stages using thermometer coding. Capacitor arrays are provided in the subconverter stages, where switching logic selectively couples the capacitors to operate in sample, conversion, and residue amplification modes for generating multi-bit subconverter digital outputs and analog subconverter residue outputs, wherein the capacitors are switched according to a thermometer code to reduce differential converter non-linearity.

Owner:TEXAS INSTR INC

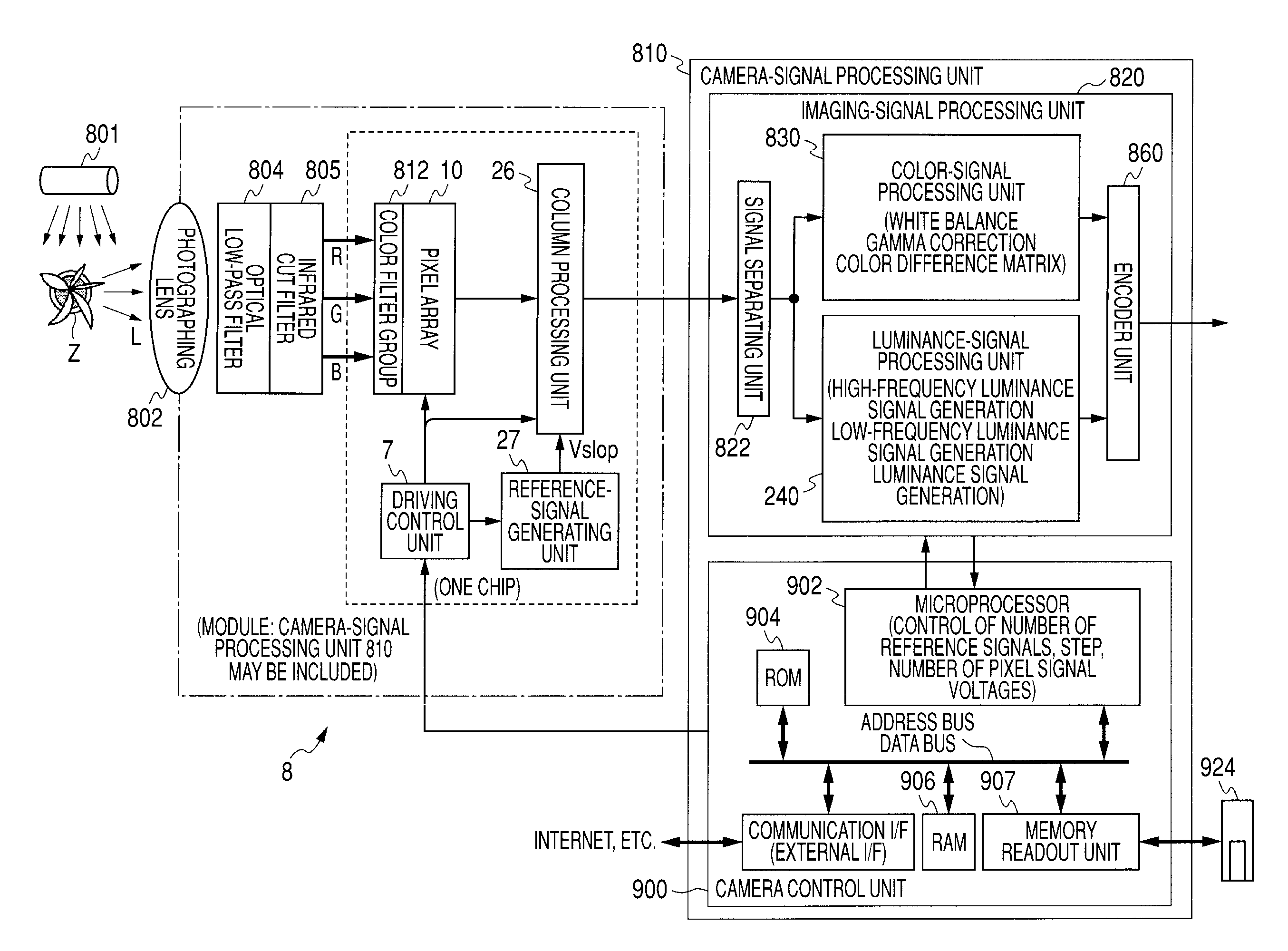

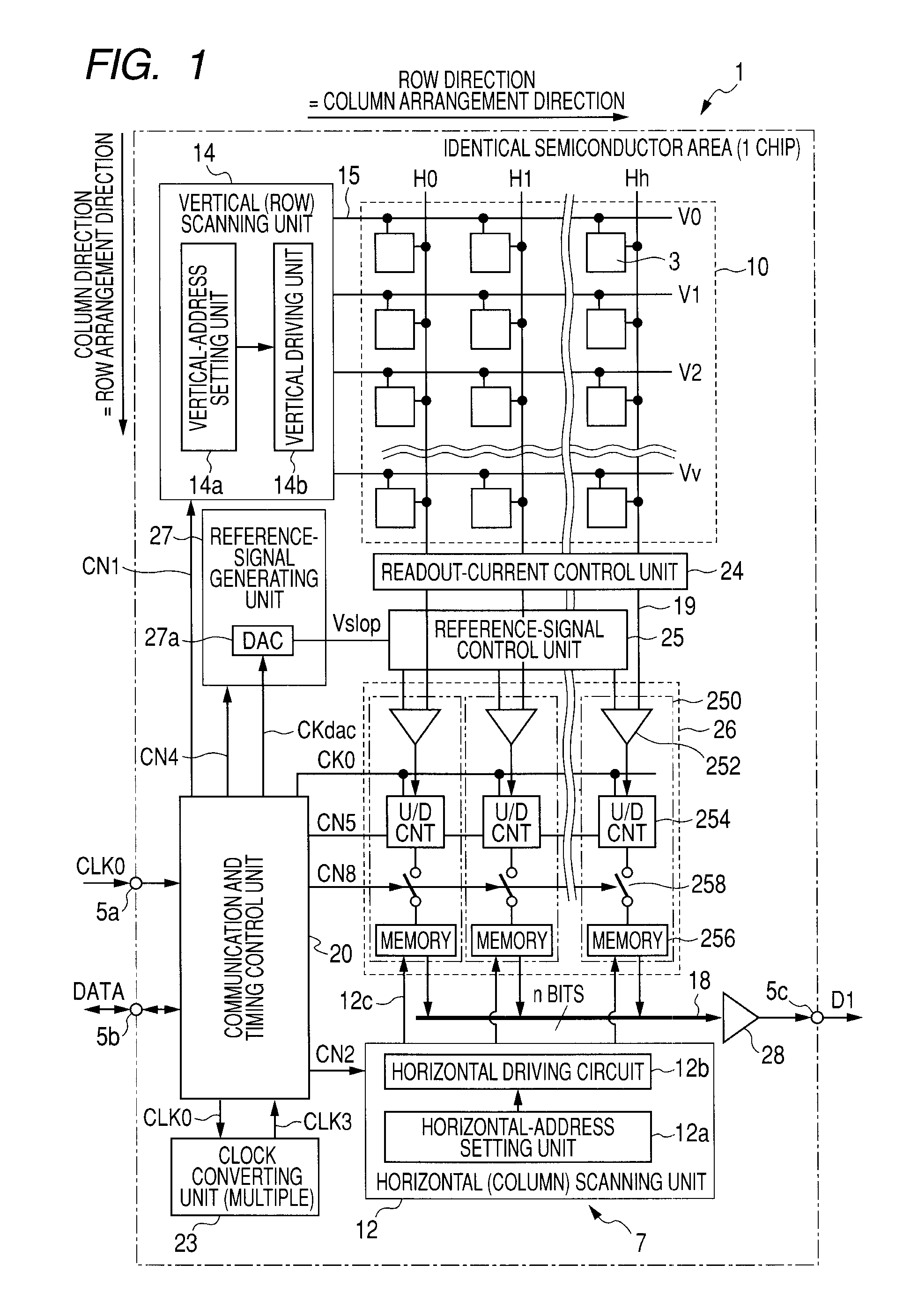

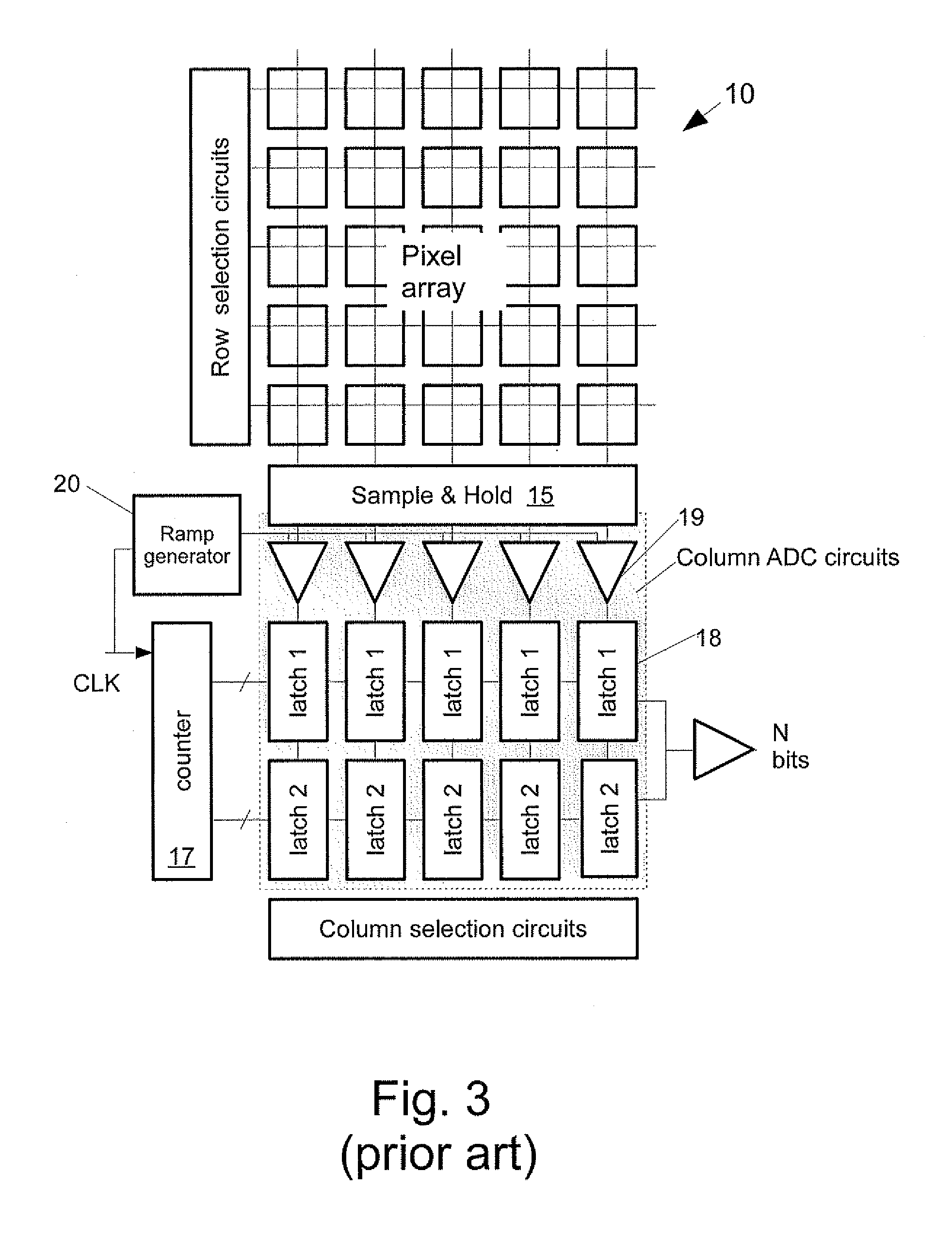

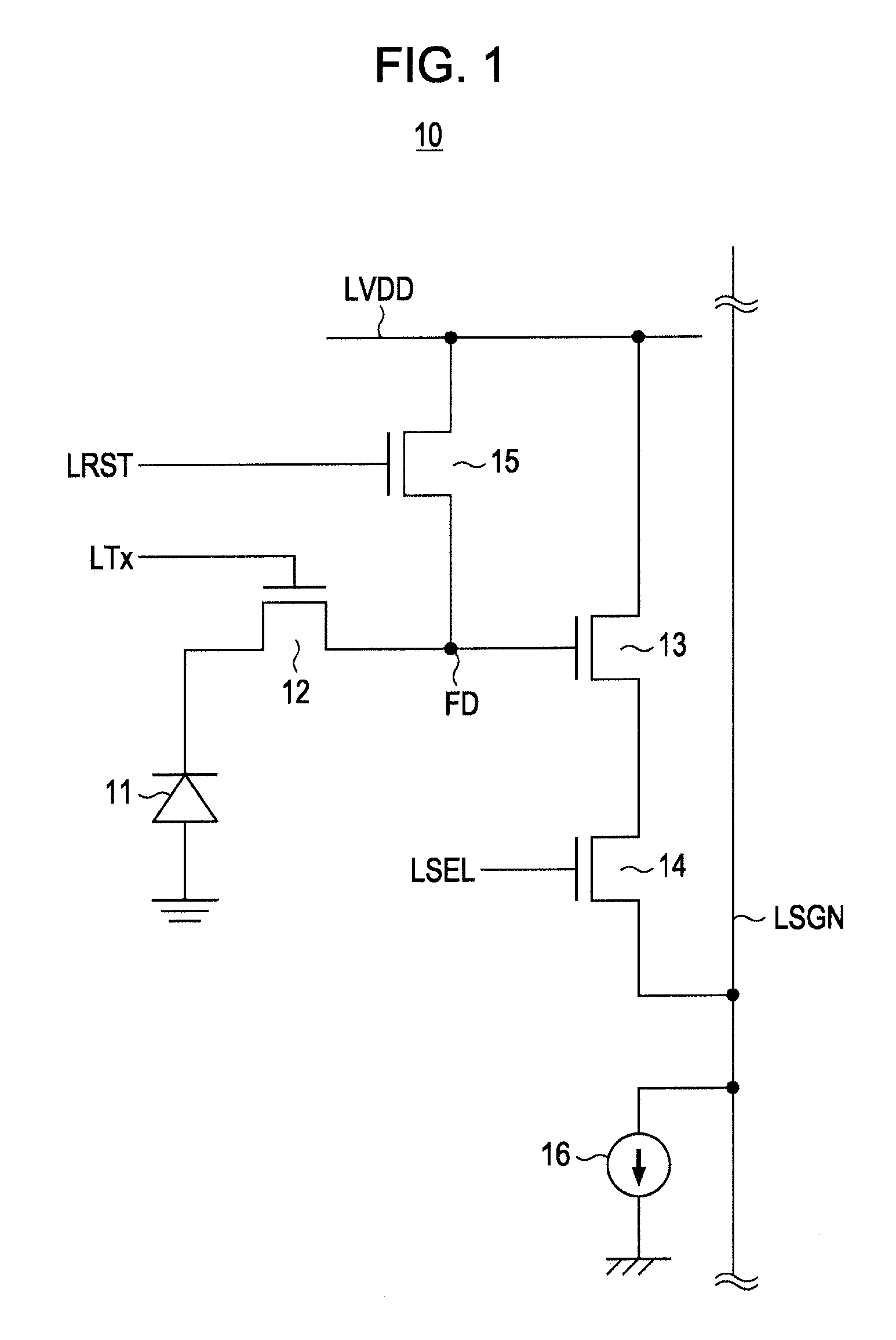

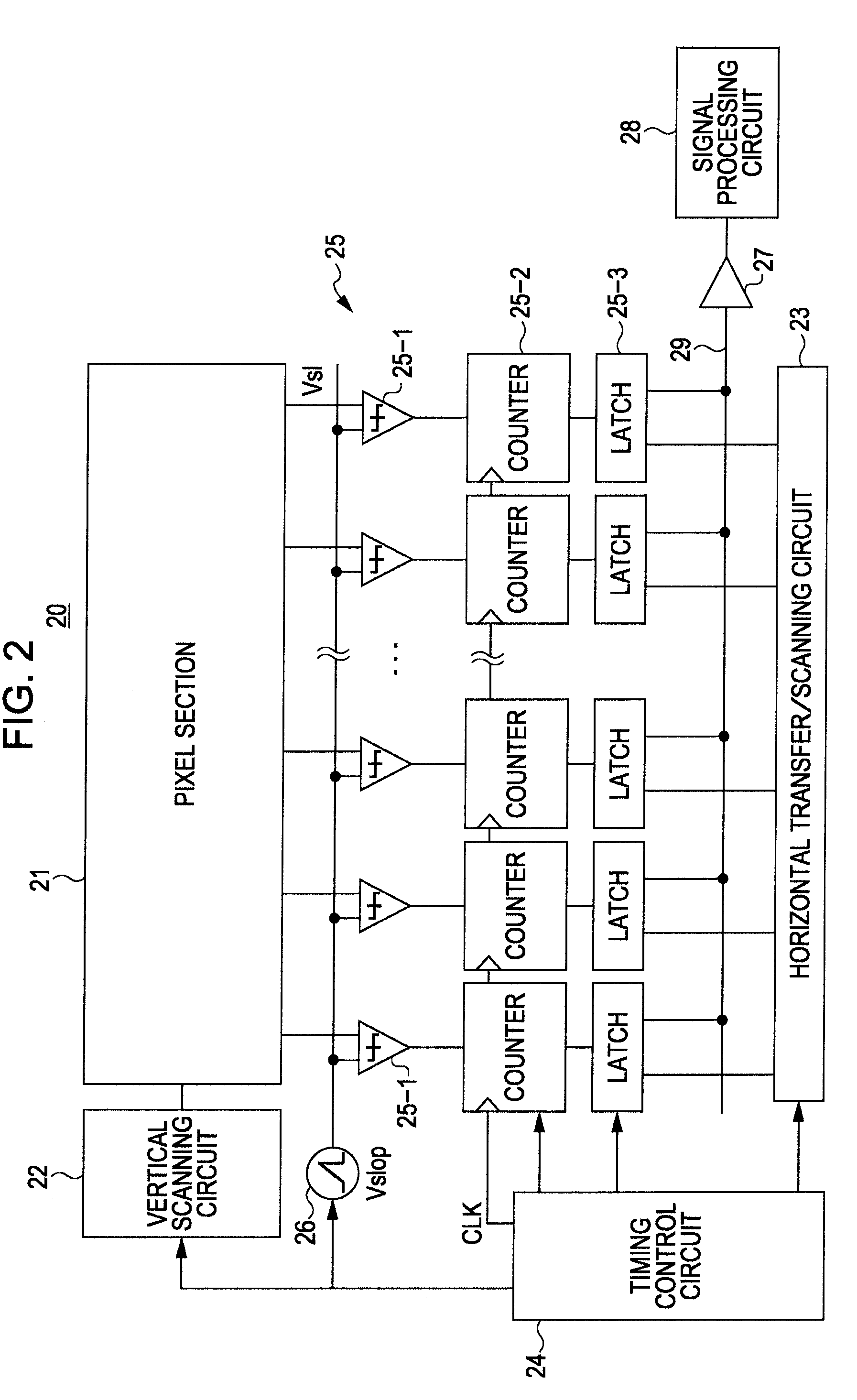

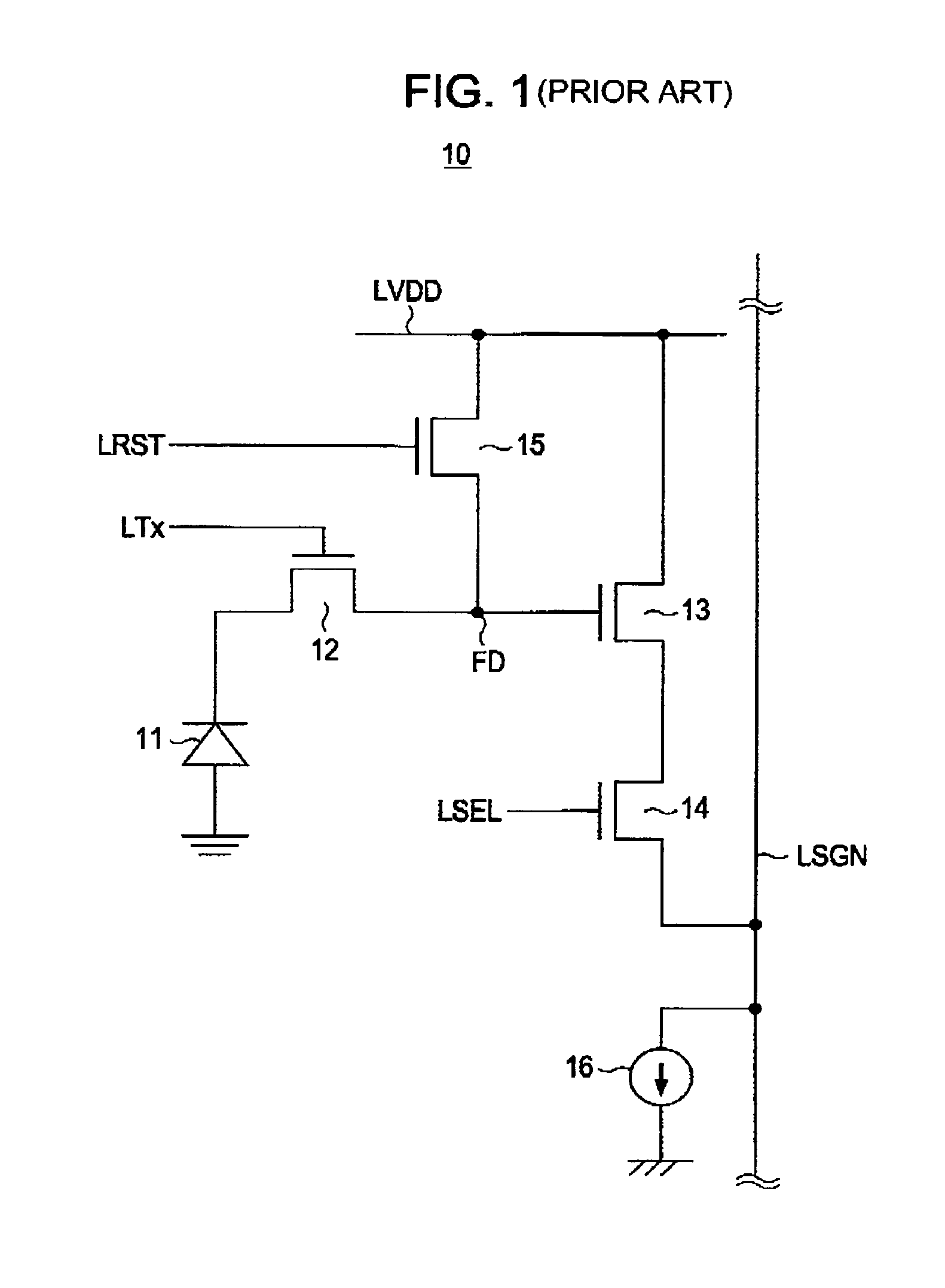

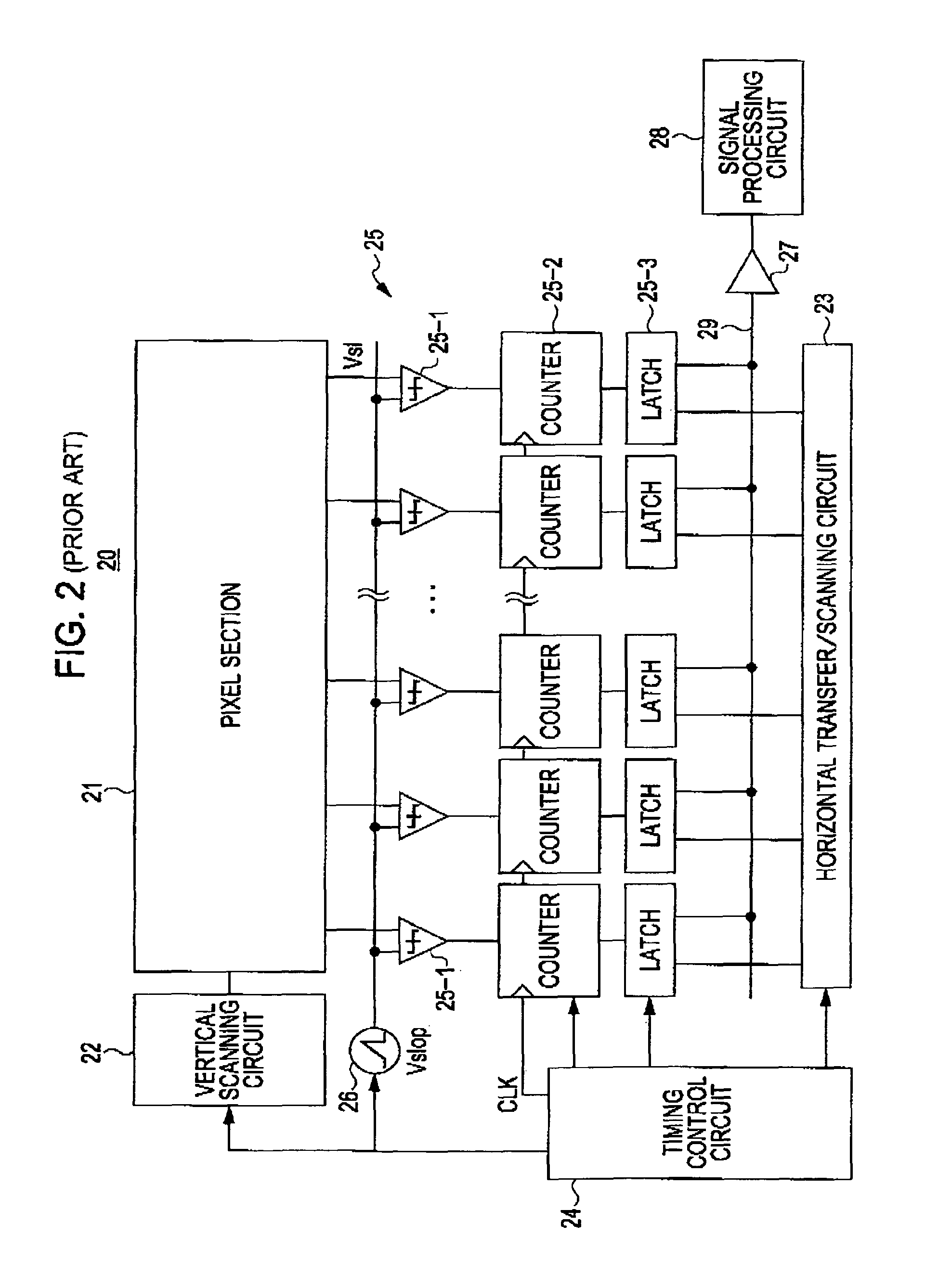

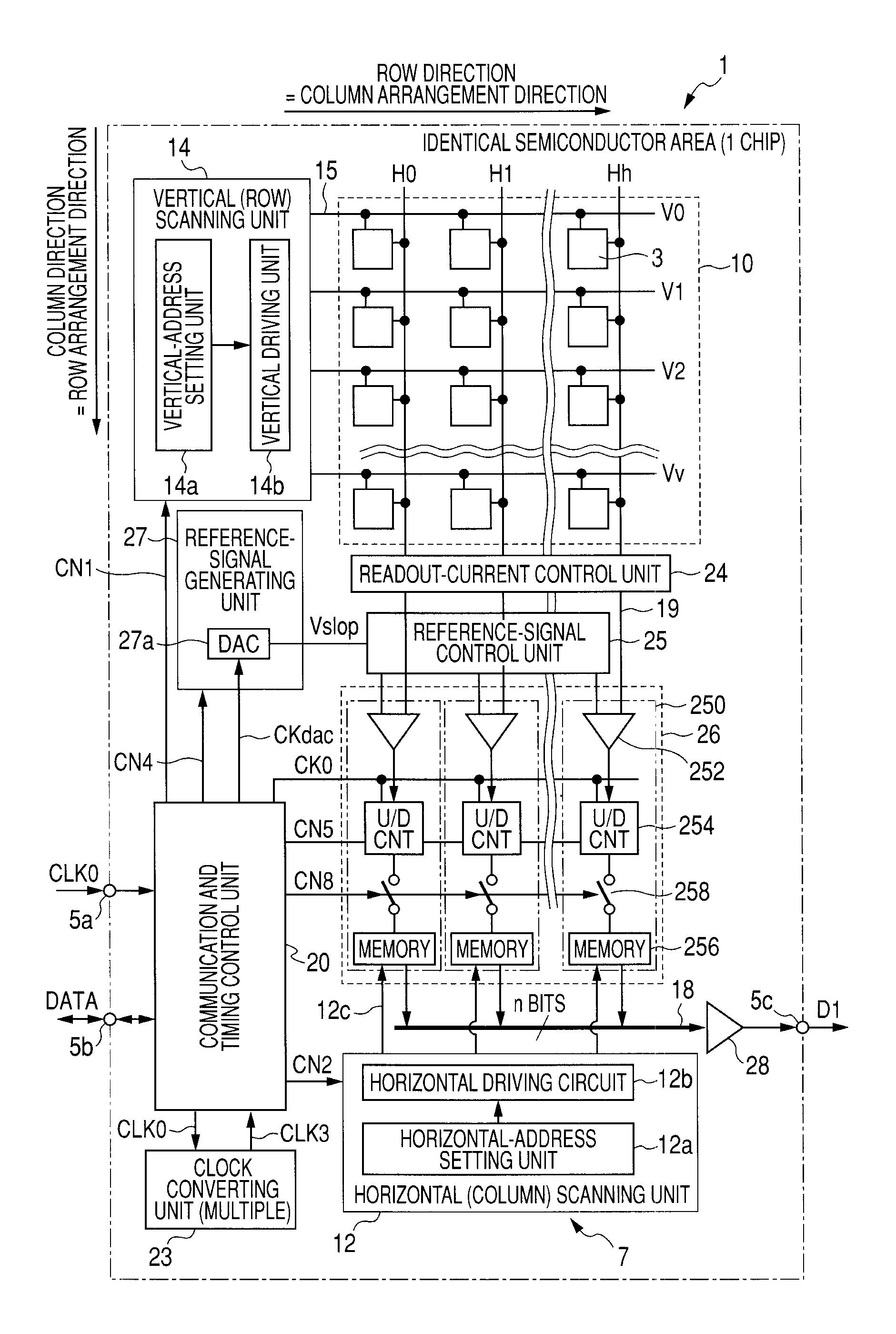

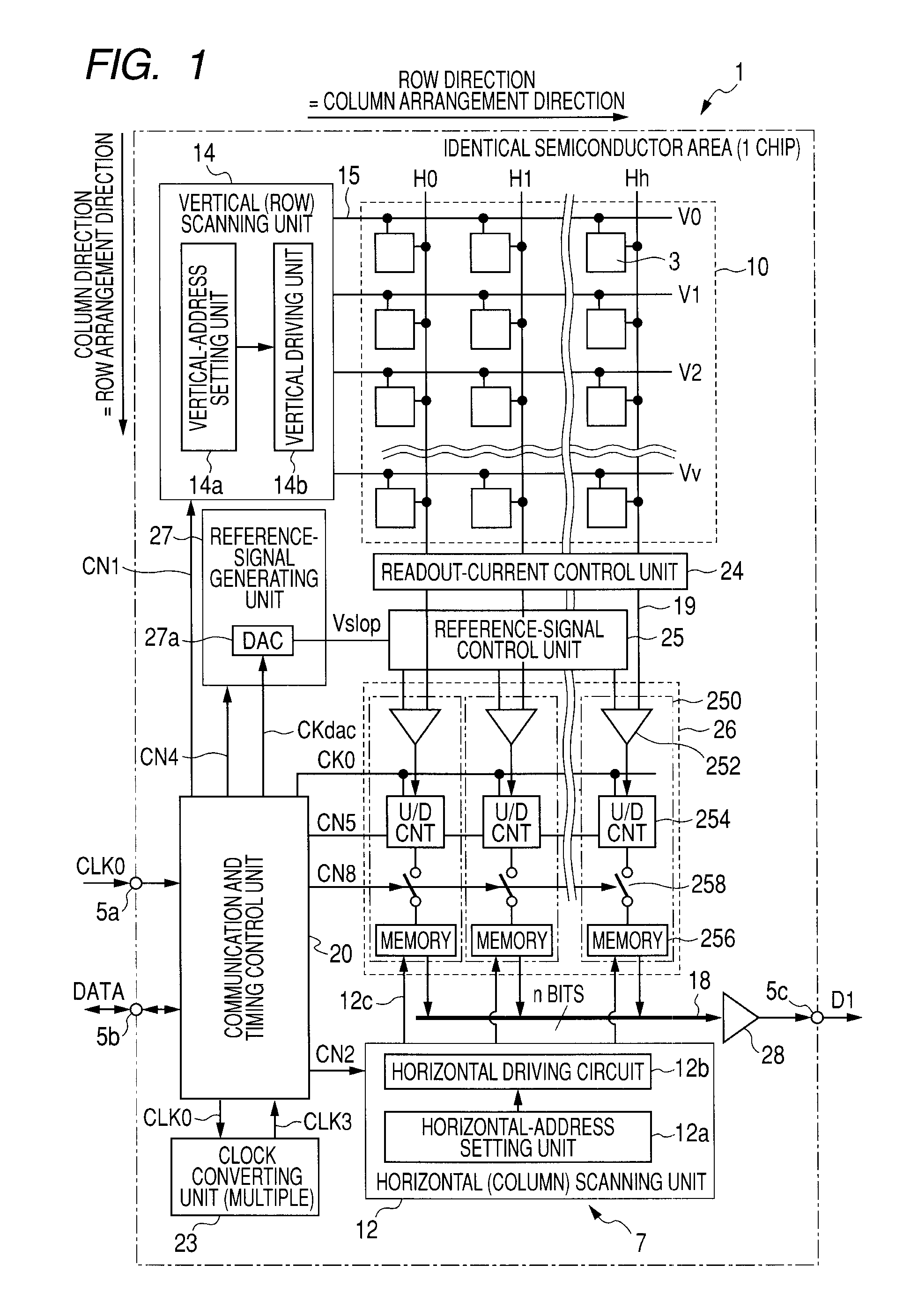

Solid-state imaging device and imaging apparatus

InactiveUS20080192127A1Reduce comparison processing timeIncrease speedAnalogue/digital conversionTelevision system detailsDigital dataComputer science

A solid-state imaging device includes a reference-signal generating unit that generates plural kinds of reference signals for converting an analog pixel signal into digital data, a reference-signal selecting unit that selects any one of the plural kinds of reference signals, a comparing unit that compares the pixel signal and the selected reference signal, and a count unit that performs count processing in parallel with comparison processing in the comparing unit and stores a count value at a point when the comparison processing is completed. The count unit decides digital data of the pixel signal in a 1 LSB step by storing a count value at a point when the comparison processing is completed for any one of the plural kinds of reference signals and correcting the stored count value on the basis of results of the comparison processing for respective remaining reference signals of the plural kinds of reference signals.

Owner:SONY CORP

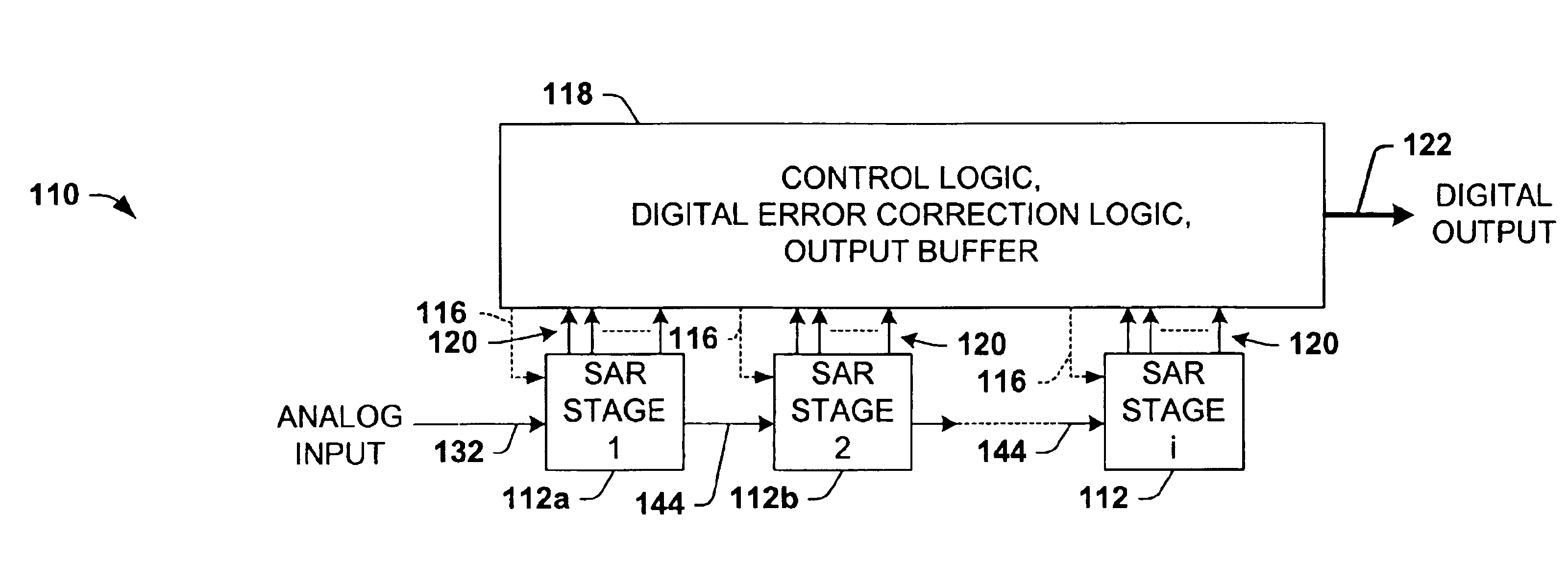

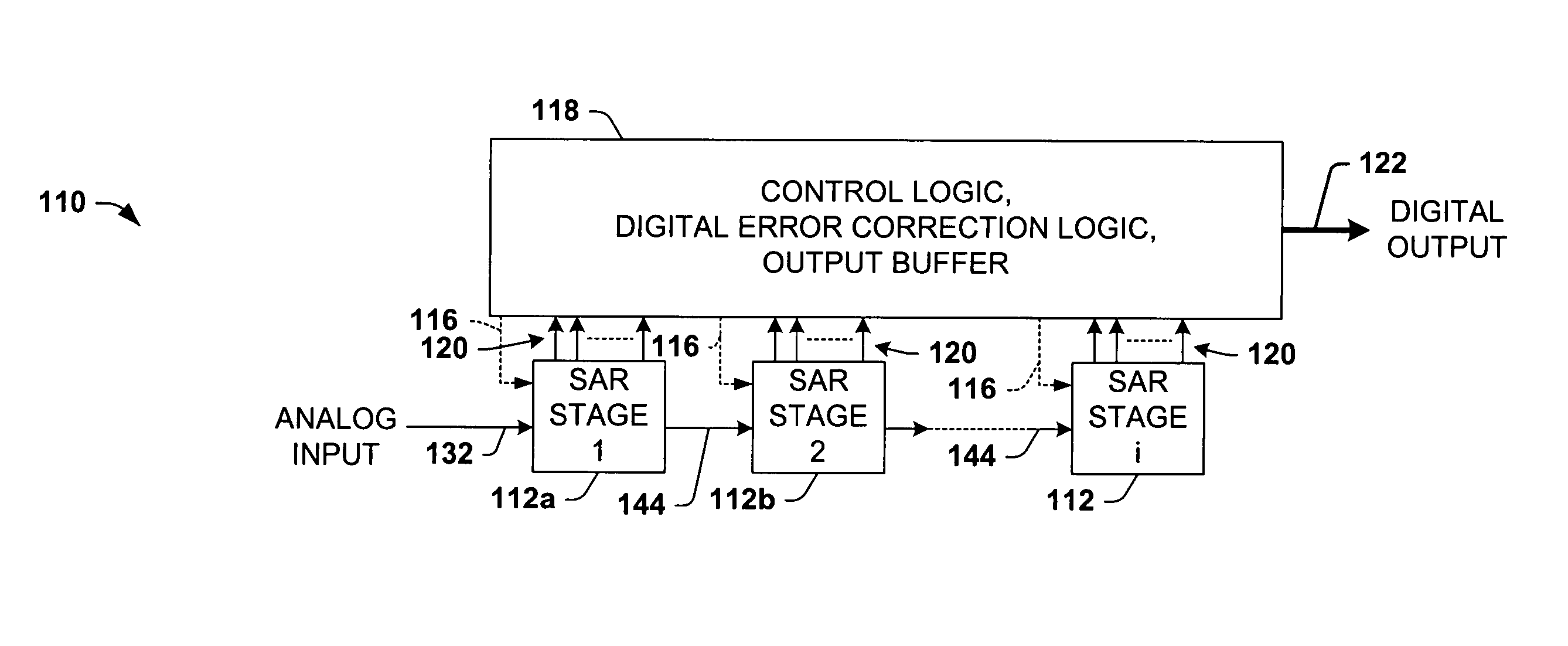

Differential pipelined analog to digital converter with successive approximation register subconverter stages

InactiveUS20050078026A1Improve conversion speedReduce power consumptionElectric signal transmission systemsAnalogue-digital convertersA d converterEngineering

Pipelined analog to digital conversion systems are provided having cascaded multi-bit successive approximation register subconverter stages. Capacitor arrays are provided in the subconverter stages, where switching logic selectively couples the capacitors to operate in sample, conversion, and residue amplification modes for generating multi-bit subconverter digital outputs and analog subconverter residue outputs. In one implementation, the capacitors are switched according to a thermometer code to reduce differential converter non-linearity, and the first subconverter stage gain is reduced to improve the conversion system bandwidth.

Owner:TEXAS INSTR INC

Analog-to-digital conversion in pixel arrays

ActiveUS20090256735A1Improve accuracyAvoid the needAnalogue/digital conversionTelevision system detailsExposure periodAnalog signal

An analog-to-digital converter (ADC) generates an output digital value equivalent to the difference between two analog signal values. The ADC 30 receives a first analog signal level, a second analog signal level and a ramp signal. A counter 32 is operable to count in a single direction. A control stage is arranged to enable the counter 32 based on a comparison 19 of the ramp signal with the first analog signal and the second analog signal. A digital value accumulated by the counter during a period when it is enabled forms the output. The ADC can perform the conversion during a single cycle of the ramp signal. The counter 32 can be loaded with a starting digital value representing an exposure level accumulated during a previous exposure period. Techniques are described for reducing the conversion time.

Owner:CMOSIS

Analog-to-digital conversion in pixel arrays

ActiveUS20110205100A1Improve accuracyAvoid the needTelevision system detailsElectric signal transmission systemsSoftware engineeringA d converter

An analog-to-digital converter (ADC) generates an output digital value equivalent to the difference between two analog signal values. The ADC 30 receives a first analog signal level, a second analog signal level and a ramp signal. A counter 32 is operable to count in a single direction. A control stage is arranged to enable the counter 32 based on a comparison 19 of the ramp signal with the first analog signal and the second analog signal. A digital value accumulated by the counter during a period when it is enabled forms the output. The ADC can perform the conversion during a single cycle of the ramp signal. The counter 32 can be loaded with a starting digital value representing an exposure level accumulated during a previous exposure period. Techniques are described for reducing the conversion time.

Owner:CMOSIS

Differential pipelined analog to digital converter with successive approximation register subconverter stages

ActiveUS6879277B1Improve system bandwidthReduce rangeElectric signal transmission systemsAnalogue-digital convertersAnalog to digital conversionAnalog-to-digital converter

Pipelined analog to digital conversion systems are provided having cascaded multi-bit successive approximation register subconverter stages. Capacitor arrays are provided in the subconverter stages, where switching logic selectively couples the capacitors to operate in sample, conversion, and residue amplification modes for generating multi-bit subconverter digital outputs and analog subconverter residue outputs. In one implementation, the capacitors are switched according to a thermometer code to reduce differential converter non-linearity, and the first subconverter stage gain is reduced to improve the conversion system bandwidth.

Owner:TEXAS INSTR INC

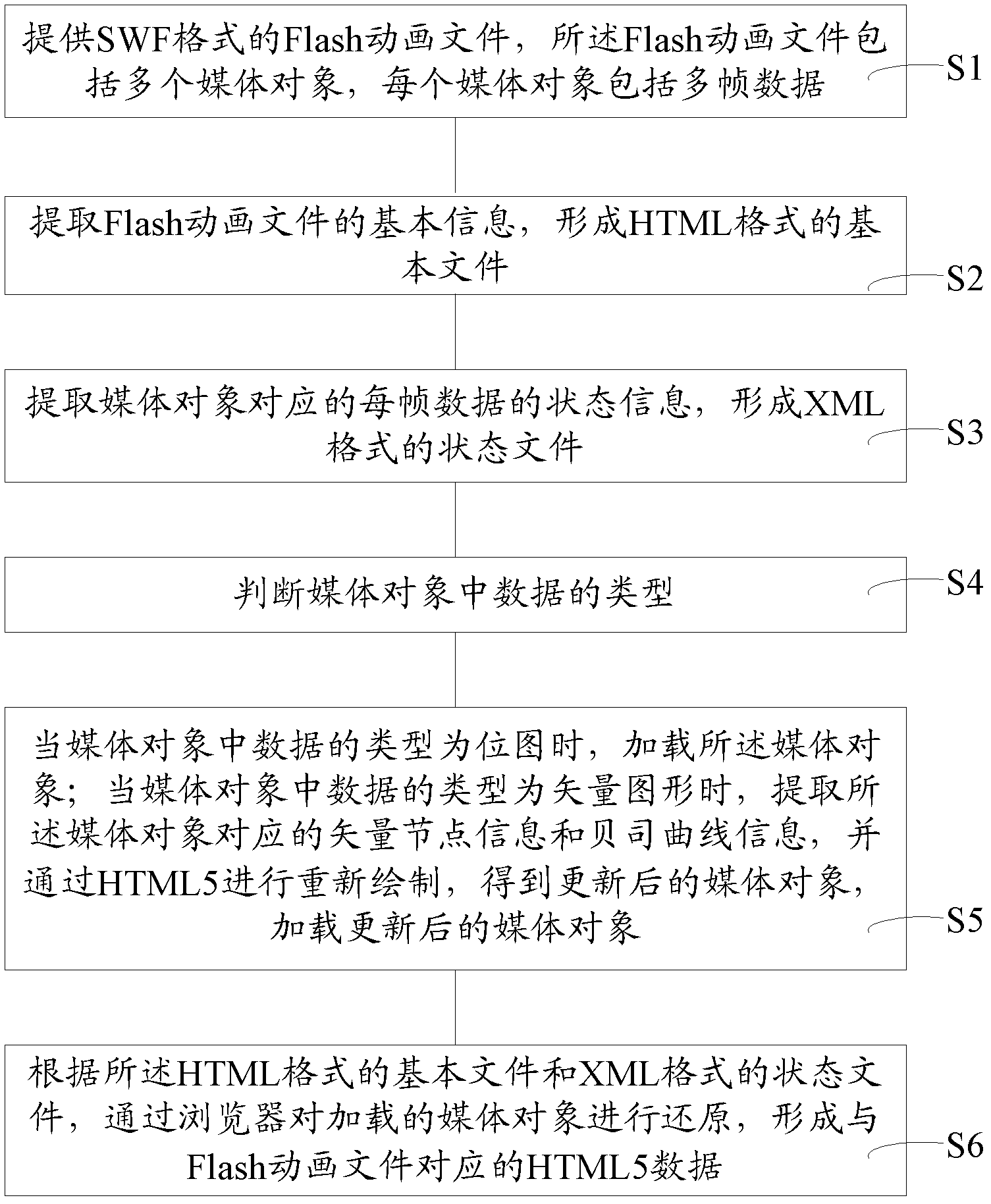

Method for converting flash animation data into hypertext markup language (HTML) 5 data

ActiveCN103176986AImprove conversion speedExpand the scope of applicationSpecial data processing applicationsData conversionHTML5

Disclosed is a method for converting flash animation data into hypertext markup language (HTML) 5 data. The method comprises the steps of providing a flash animation file in a small web format (SWF); extracting essential information of the flash animation file to form an elementary file in an HTML format; extracting state information of each frame of data corresponding to a media object to form a state file in an extensive makeup language (XML) format; judging the type of the data in the media object; loading the media object when the type of the data in the media object is a bitmap; extracting vector node information and Bezier curve information corresponding to the media object when the type of the data in the media object is a vector graph, repainting through a HTML5 to obtain an updated media object, and loading the updated media object; and according to the elementary file in the HTML format and the state file in the XML format, restoring the loaded media object through a browser and forming the HTML5 data corresponding to the flash animation file. By means of the method for converting the flash animation data into the HTML5 data, not only can off-line conversion be achieved, conversion speed is high, but also any version of adobe flash can be compatible, and a source file is needless.

Owner:SHANGHAI PATEO ELECTRONIC EQUIPMENT MANUFACTURING CO LTD

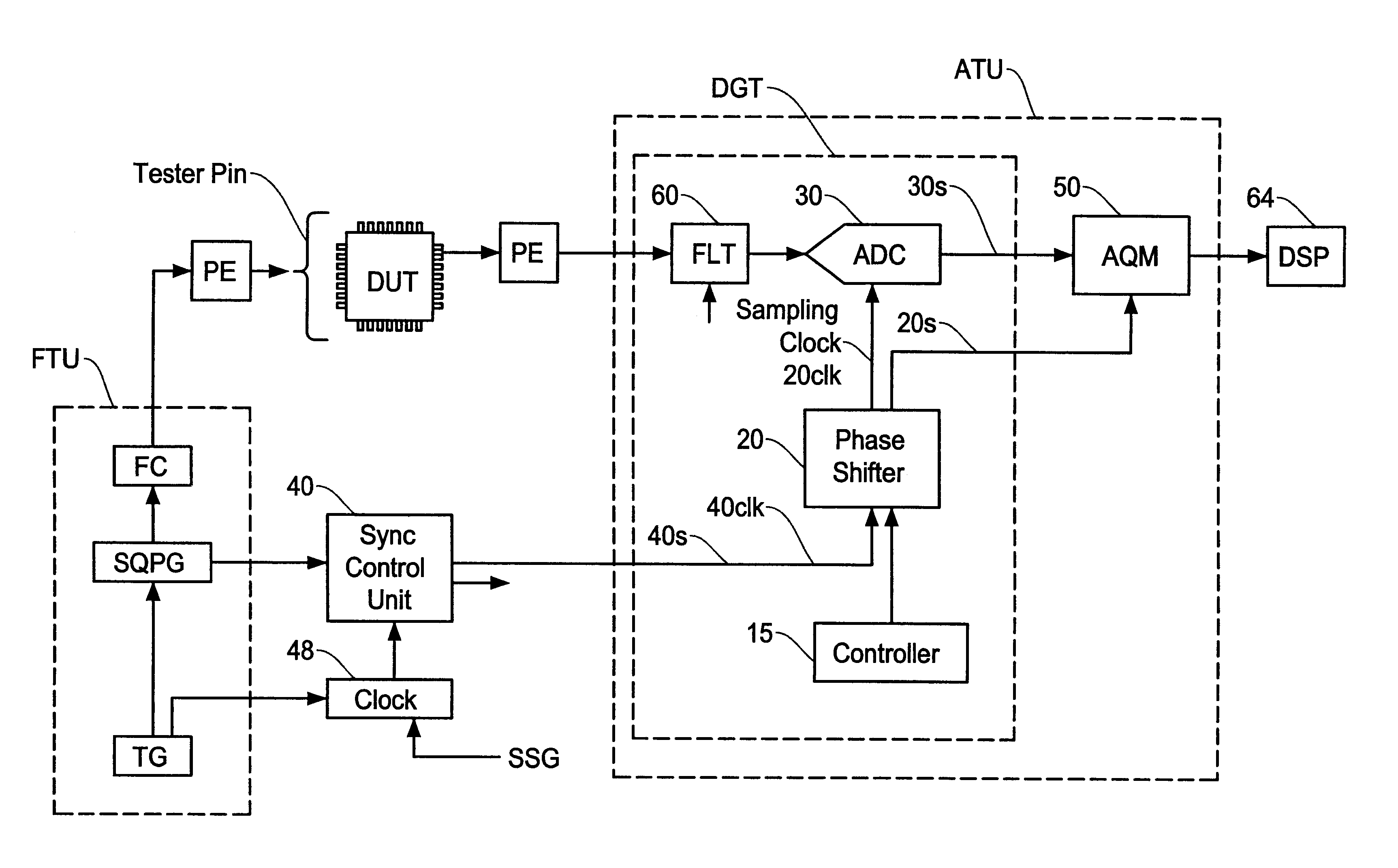

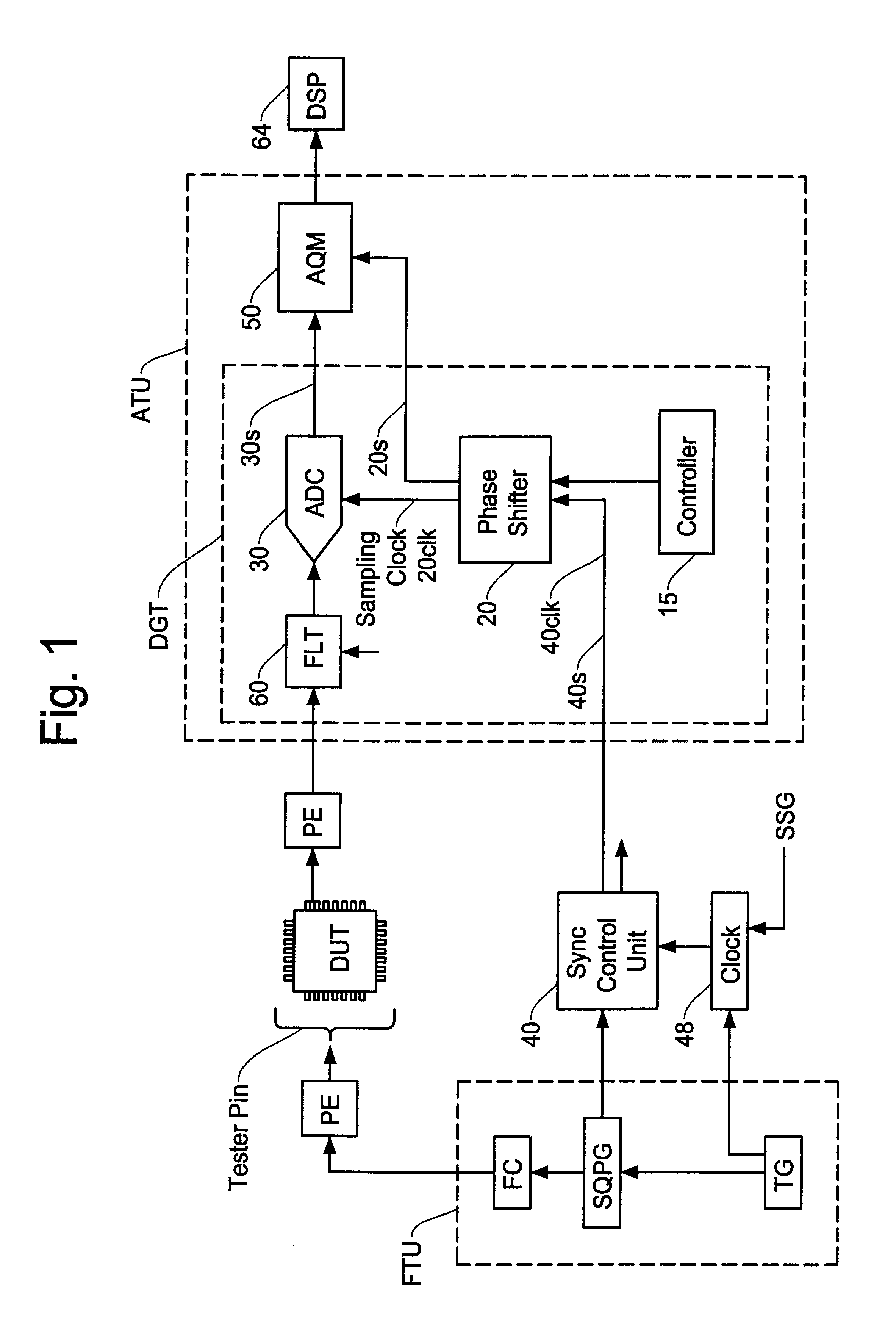

Semiconductor test system

ActiveUS7173443B1Low costSmall circuit sizeProduction of permanent recordsIndividual semiconductor device testingMixed signal testingEngineering

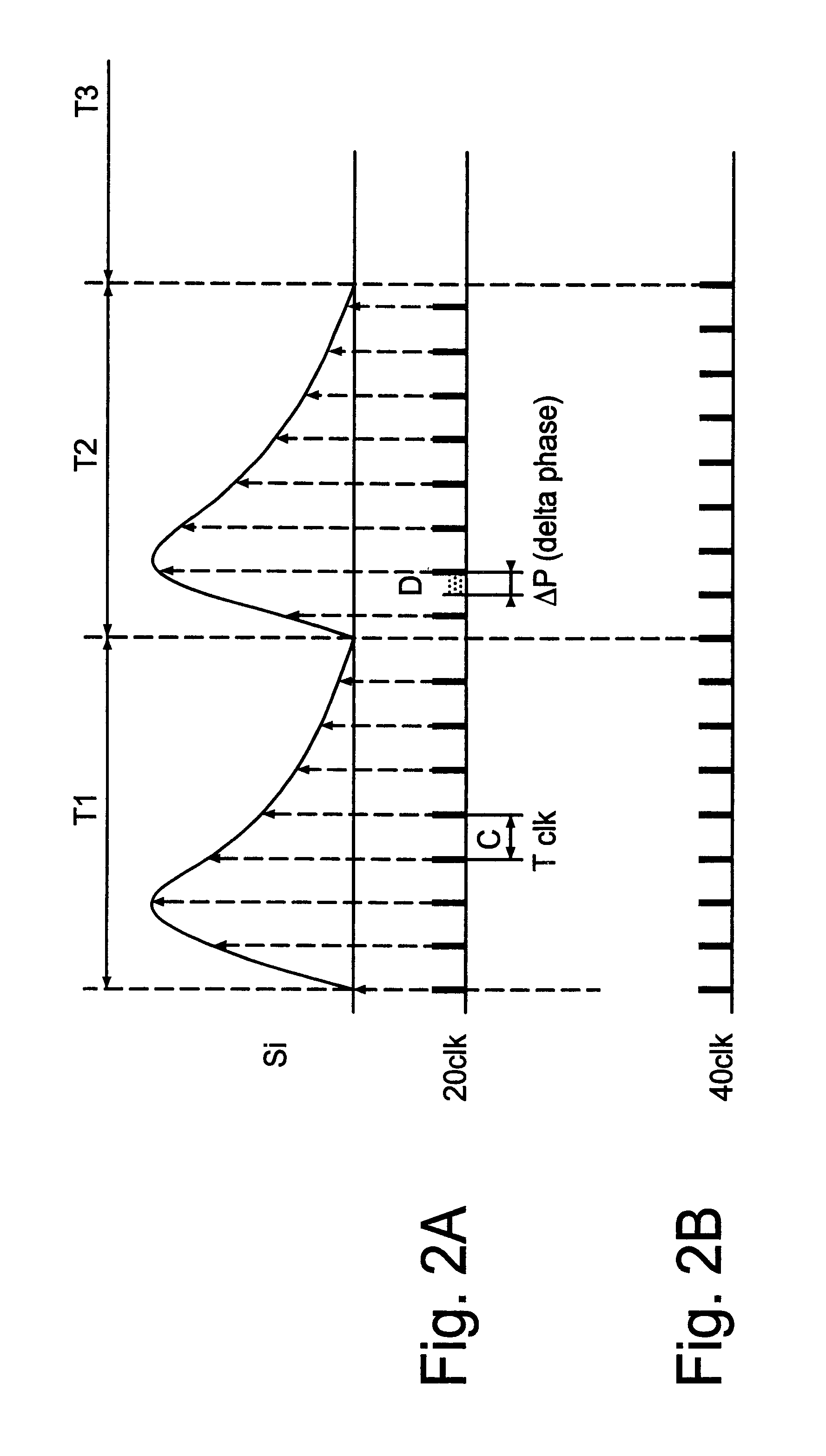

A mixed signal test system for testing a semiconductor device having both an analog function and a digital function achieves improved resolution and low cost. The test system is formed of a functional test unit for testing a digital function of a device under test (DUT), an analog test unit (ATU) for testing an analog function of the DUT, and a synchronous control unit for synchronizing operations between the functional test unit and the analog test unit. The analog test unit includes a digitizer for converting an analog output of the DUT into a digital signal, and an acquisition memory for storing the digital signal from the digitizer in specified addresses. The wave form of the analog output is repeated by a plurality of cycles and a sampling clock for the digitizer is phase shifted by a predetermined amount for each cycle.

Owner:ADVANTEST CORP

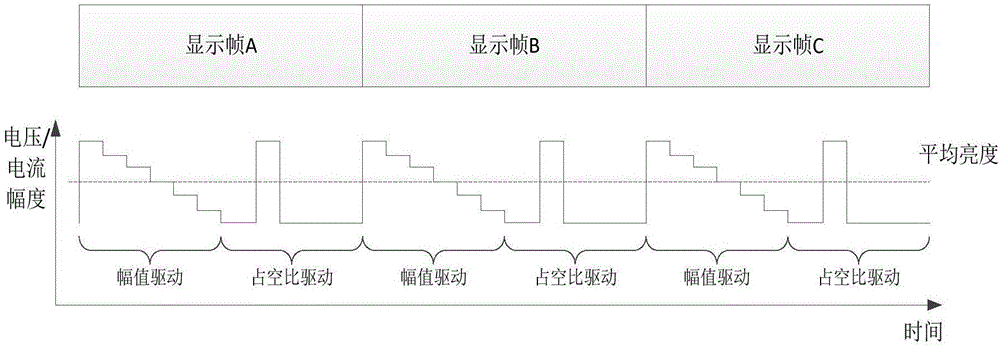

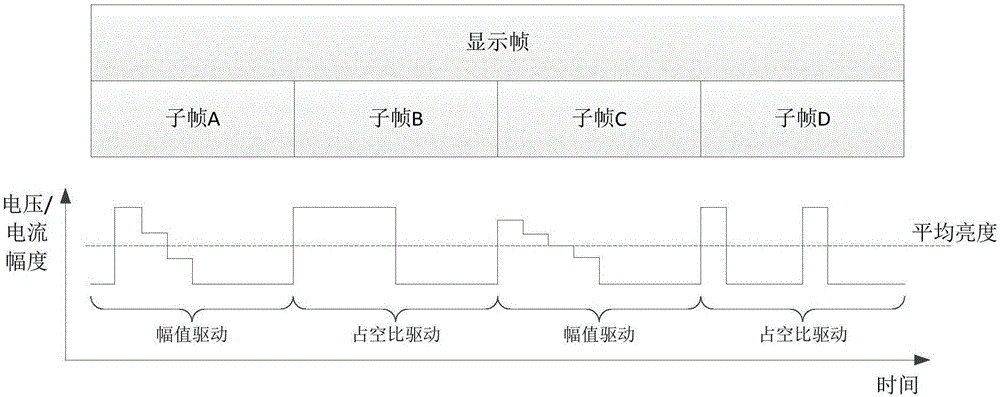

Silicon-based display adopting digital-analog hybrid drive

ActiveCN106652963AReduced precision requirementsImprove conversion accuracyStatic indicating devicesVoltage amplitudeDigital analog converter

The invention discloses a silicon-based display adopting digital-analog hybrid drive. Pixels are driven to emit light through the method of combining the simulation amplitude modulation drive strategy and a digital pulse width modulation drive strategy, wherein the luminance of the pixels is determined by output current or voltage amplitude of the pixels in the subframe and the duty ratio of time of the output current or voltage of the pixels in the subframe, the frame of image is divided into a plurality of different digital subframes and simulation subframes, the digital drive strategy is adopted for the digital subframes, the time proportionable drive mode or luminance proportionable drive mode is adopted, the simulation drive strategy is adopted for the simulation subframes, many digital-analog converters with few digits are adopted, input data is converted into amplitude quantity of voltage or current, so that the pixels emit light, and the simulation subframes and the digital subframes are combined to generate the final display frame. The requirements of the simulation amplitude modulation drive strategy for the digital-analog converter and the requirements of the pixel circuit for the precision of analog quantity are reduced, and the conversion speed of the digital-analog converter and the contrast of the pixel luminance are improved.

Owner:南京昀光科技有限公司

Apparatus and method for displaying sectional planes of target object utilizing 3-dimensional ultrasound data

InactiveUS20050187474A1Improve scan conversion speedImprove conversion speedUltrasonic/sonic/infrasonic diagnosticsGeometric image transformationComputer graphics (images)Display device

An apparatus for displaying sectional planes of a target object utilizing 3 dimensional (3D) ultrasound data. The apparatus is capable of scanning the target object in real time by improving a scan conversion speed and virtually scans the target object by storing previously acquired 3D data. The apparatus, which displays a target object by using 3D ultrasound data, includes 1) a scan conversion unit for performing scan conversion to convert Cartesian coordinates for display on a screen of a display device to conical coordinates of 3D data, and 2) a rendering unit for rendering multiple sectional plane images, based on the 3D scan conversion, parallel with a reference sectional plane.

Owner:MEDINCELL

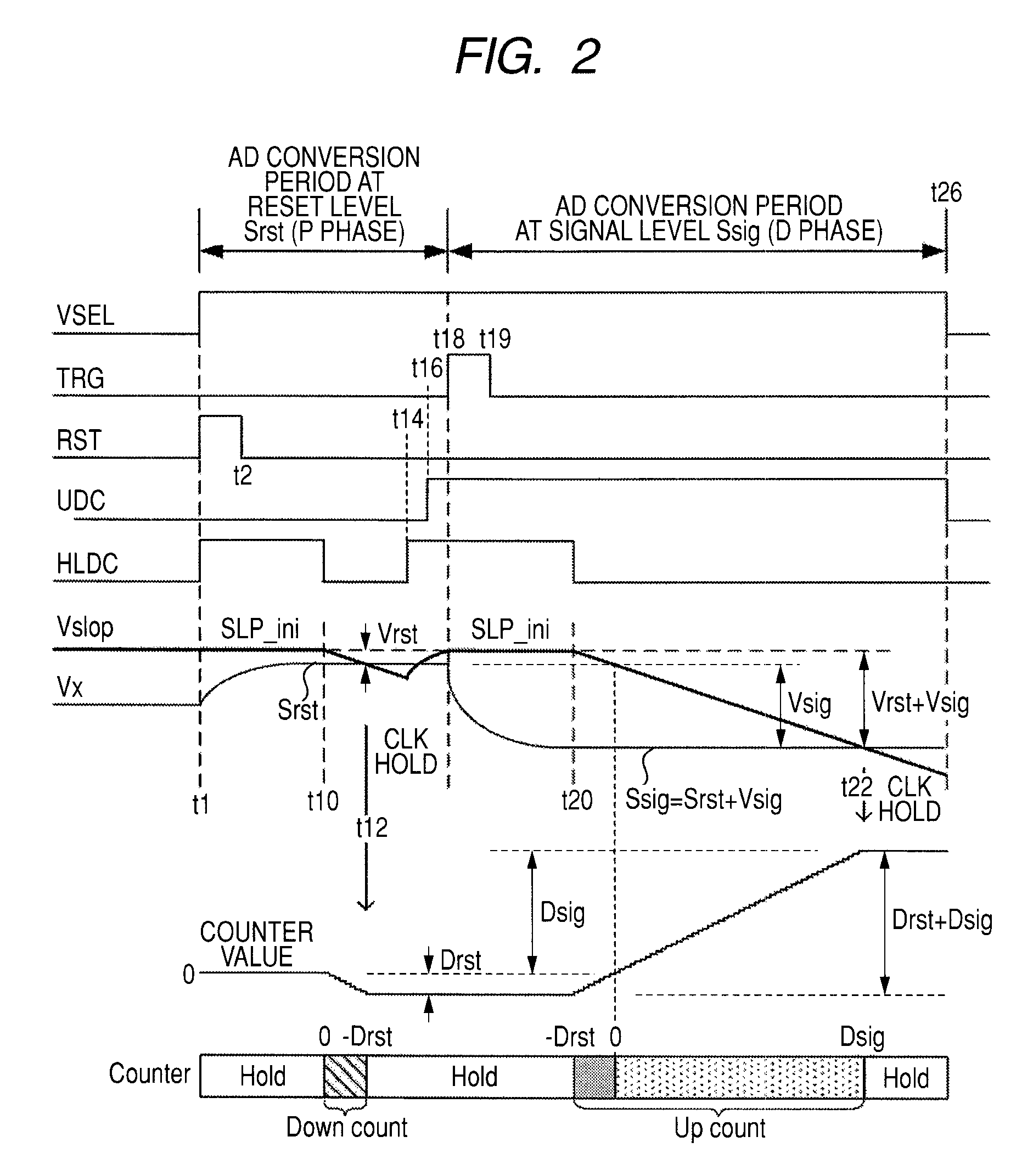

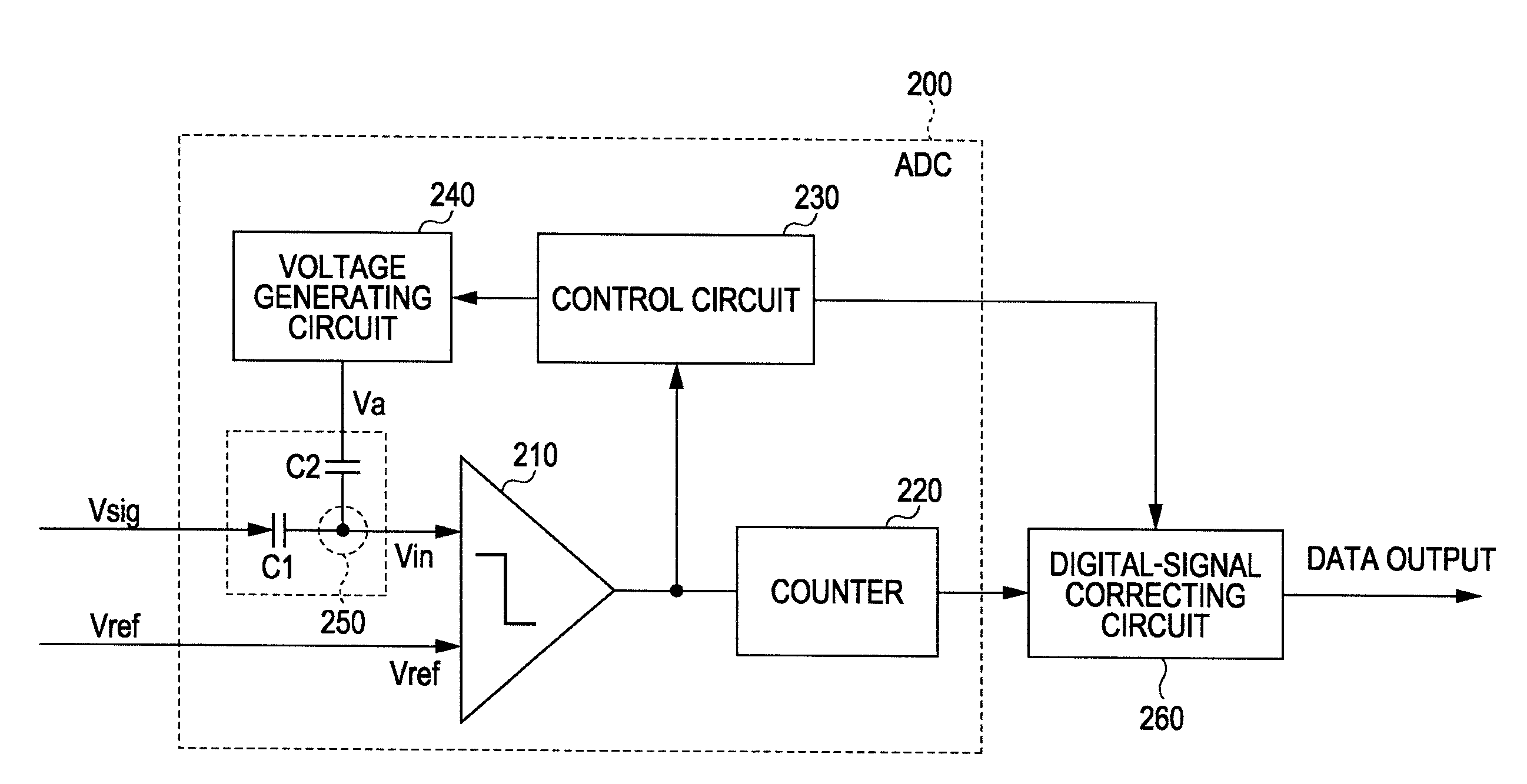

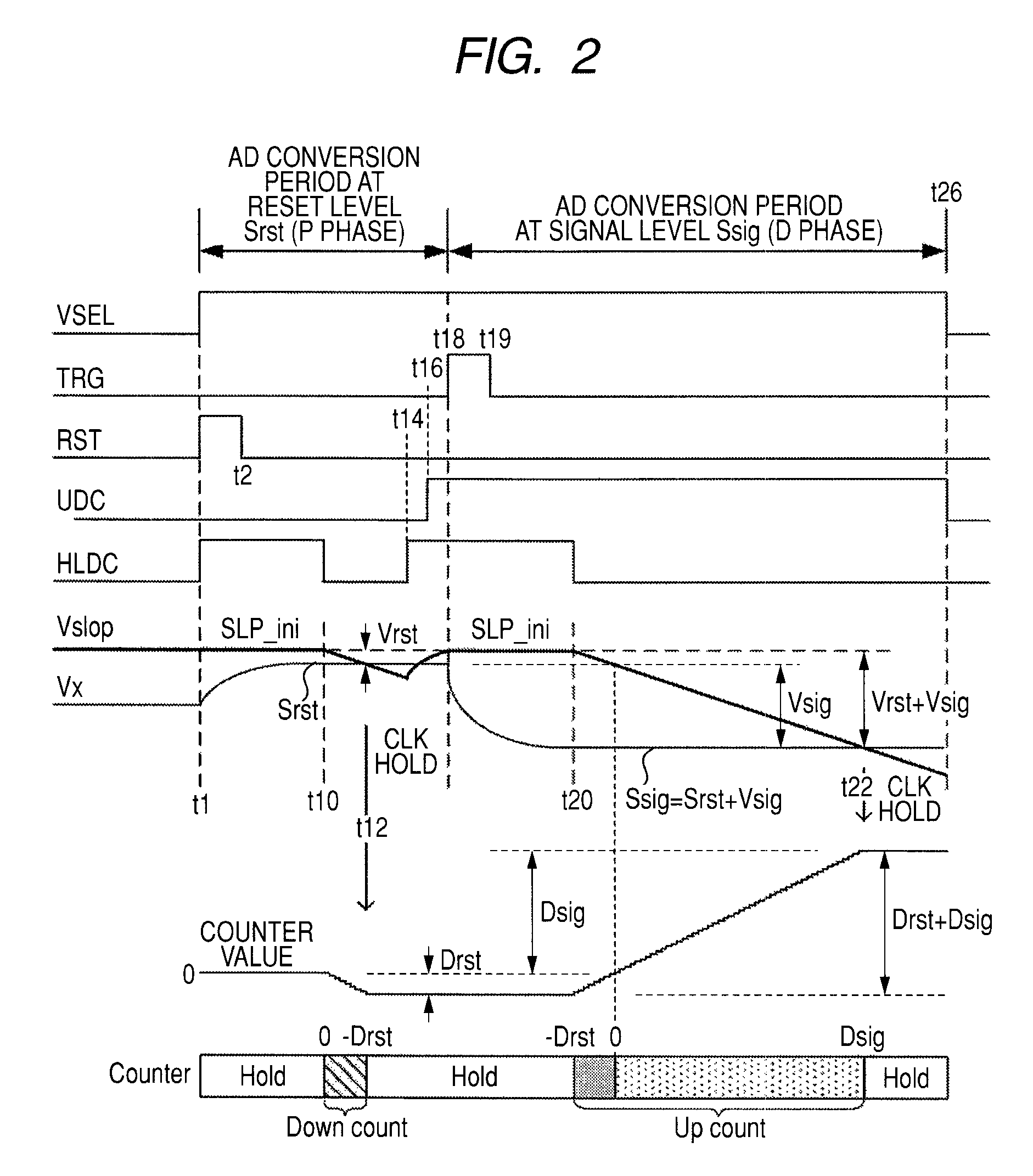

Analog-to-digital converter, analog-to-digital converting method, solid-state image pickup device, and camera system

ActiveUS20090237535A1Improve dynamic rangeImprove accuracyTelevision system detailsElectric signal transmission systemsEngineeringControl circuit

An analog-to-digital converter that converts an analog input signal into a digital signal includes a comparator configured to compare a reference signal with an input signal and, if the input signal matches the reference signal, inverts an output; a counter configured to count a comparison time of the comparator; a control circuit configured to monitor the output of the comparator; a voltage generating circuit configured to generate, if a monitoring result obtained by the control circuit indicates that the output of the comparator is at a predetermined level, a direct current voltage in accordance with the monitoring result; and an analog adder configured to add the voltage generated by the voltage generating circuit to the input signal and supply a sum signal to an input terminal of the comparator.

Owner:SONY CORP

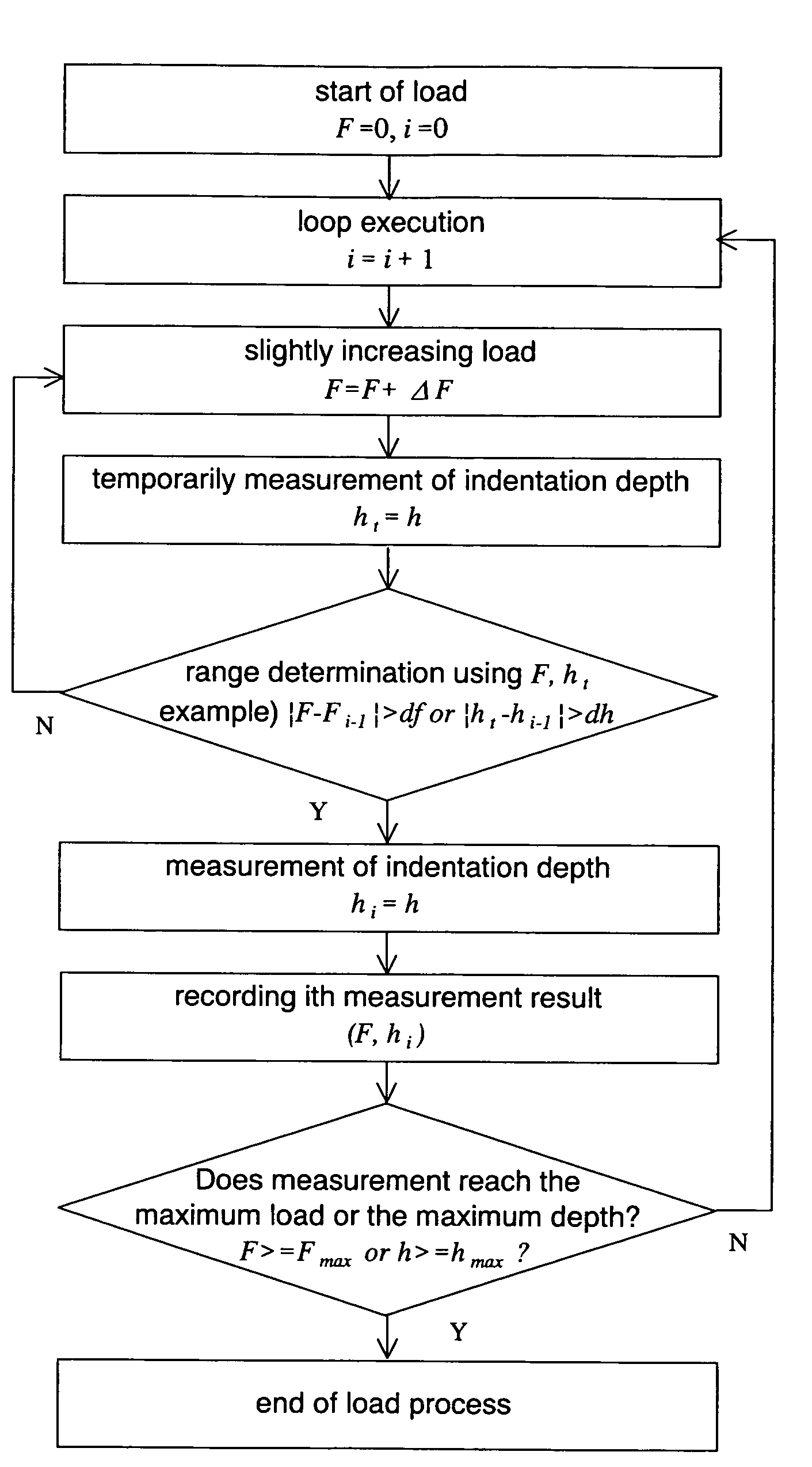

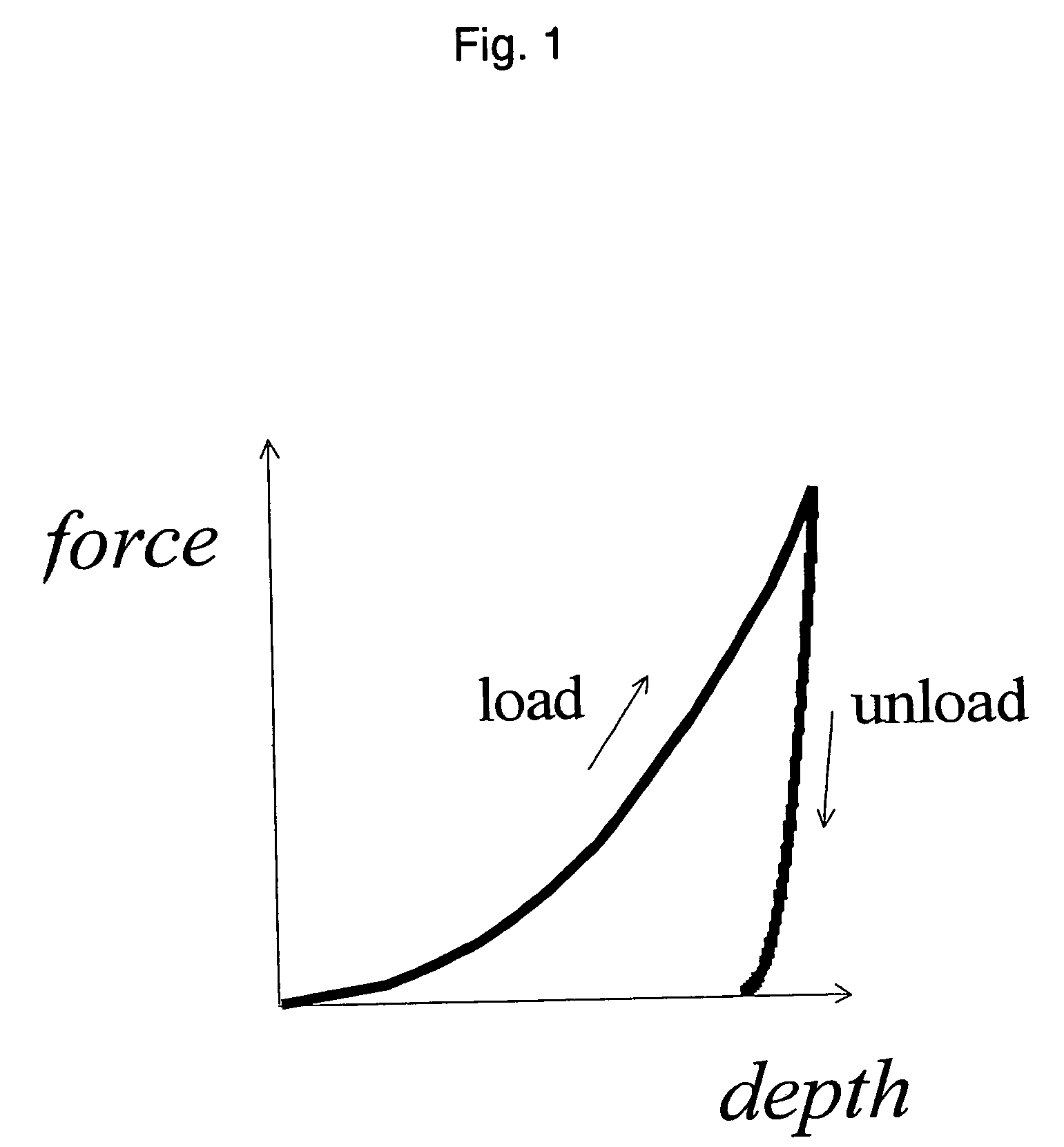

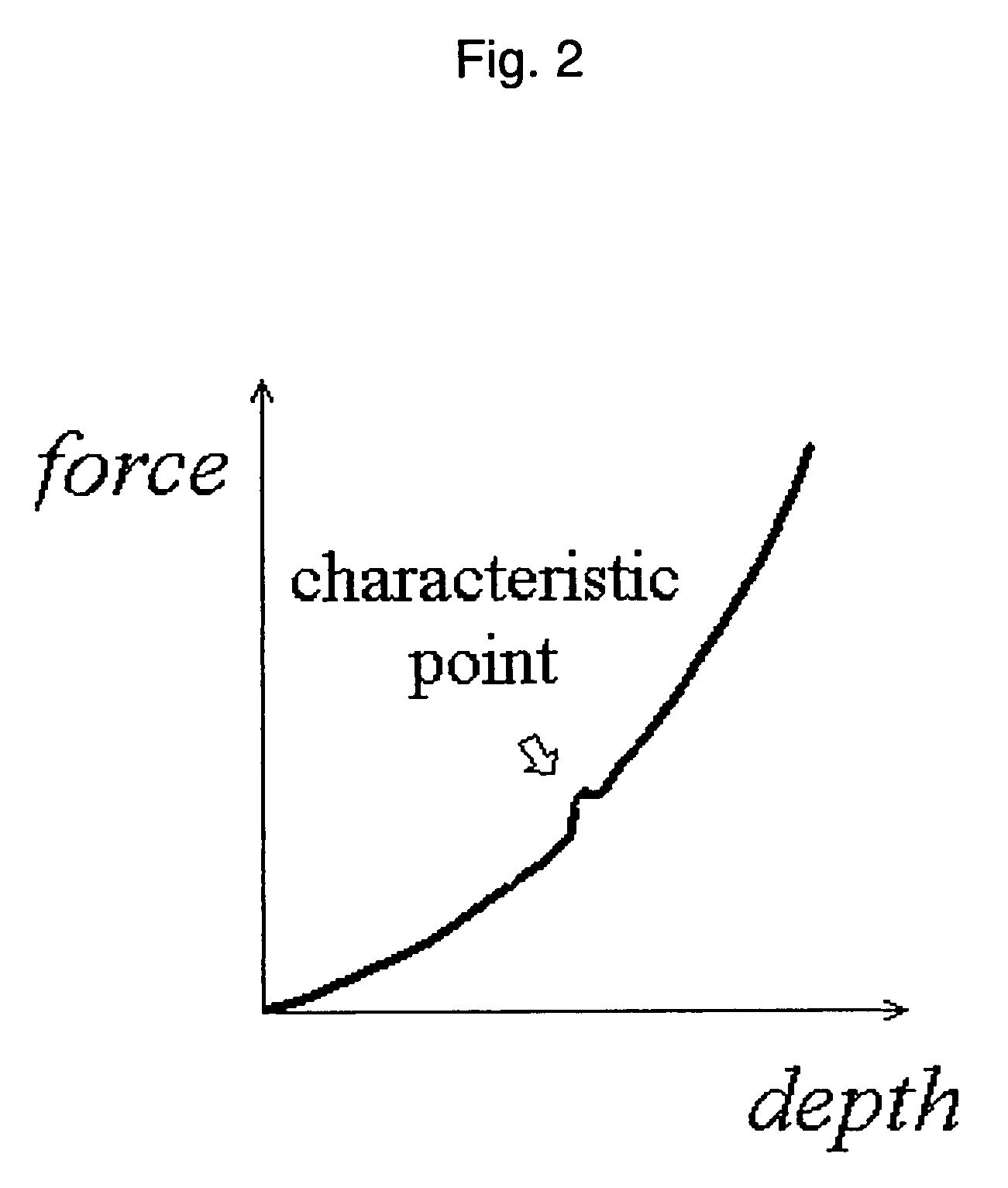

Production method of indentation curve and hardness test method

InactiveUS7565831B2Convenient and accurateFast measurement speedInvestigating material hardnessHardnessEnvironmental geology

Owner:NAT INST FOR MATERIALS SCI

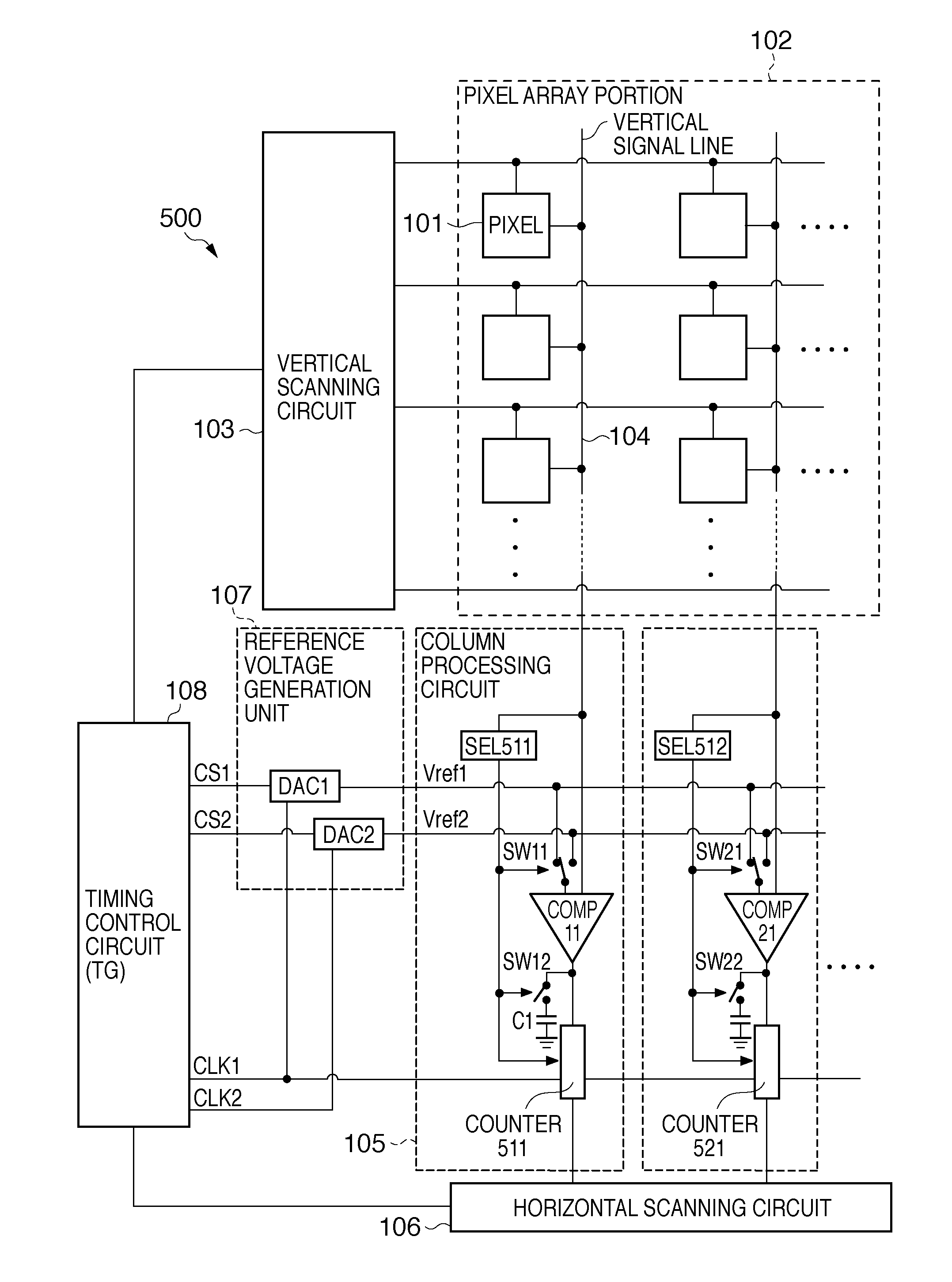

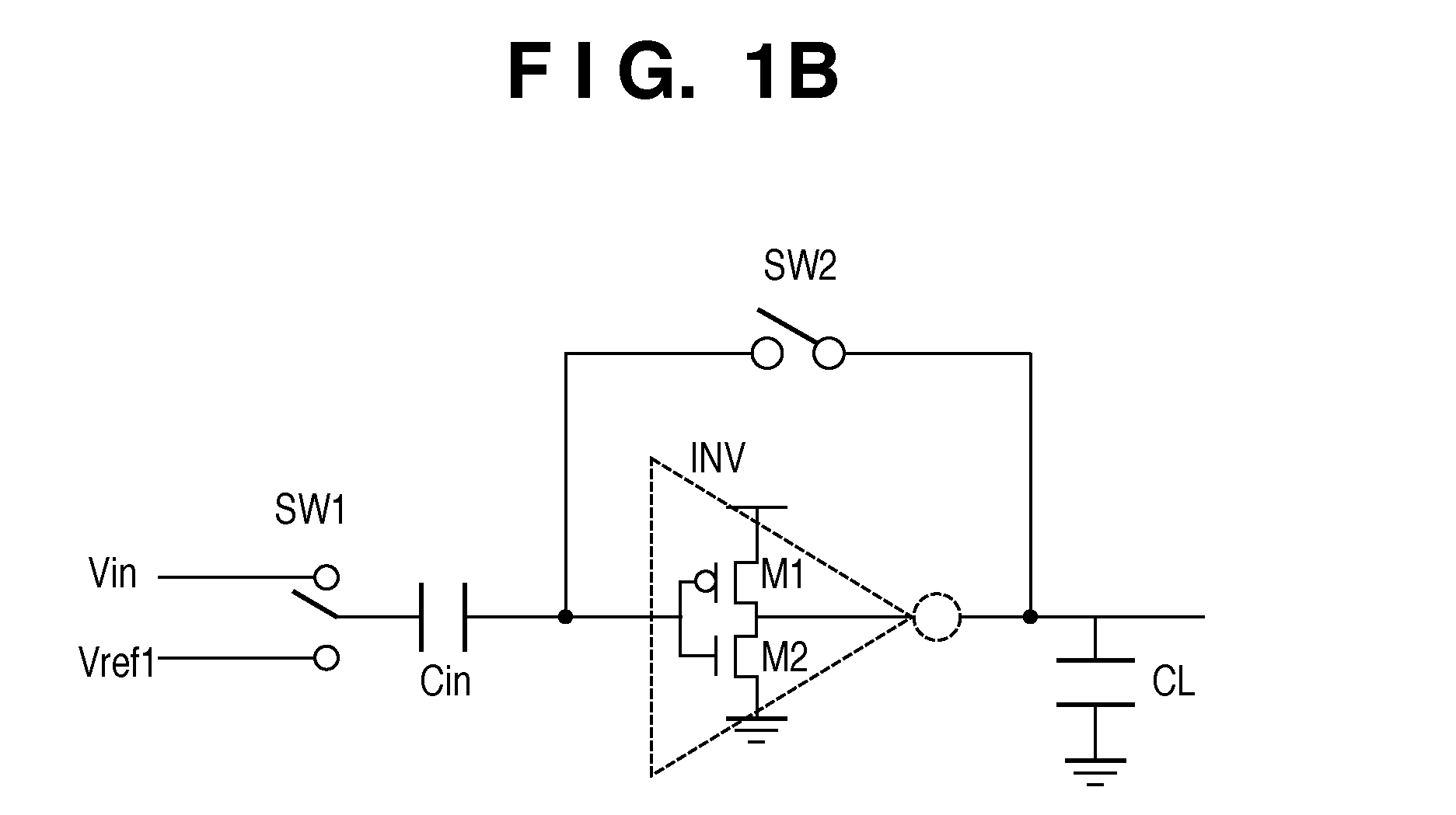

Solid-state image sensing element and image sensing system including comparison units with switchable frequency band characteristics

ActiveUS8922668B2Reduce noiseImprove conversion speedTelevision system detailsElectric signal transmission systemsEngineeringImage sensing

In a solid-state image sensing element which includes a pixel array portion in which a plurality of pixels each including a photoelectric converter are arranged two-dimensionally, and readout circuits which read out analog pixel signals from the pixel array portion by column, and in which each of the readout circuits includes an A / D conversion circuit which converts the analog pixel signal from the pixel array portion into a digital pixel signal, and the A / D conversion circuit performs A / D conversion by comparing, by a comparison unit, a signal level of the analog pixel signal from the pixel array portion with a temporally changing reference level, a frequency band characteristic of the comparison unit is switched in accordance with the signal level of the analog pixel signal from the pixel array portion.

Owner:CANON KK

Analog-to-digital converter, analog-to-digital converting method, solid-state image pickup device, and camera system

ActiveUS8269872B2Increase speedImprove dynamic rangeTelevision system detailsElectric signal transmission systemsAnalog-to-digital converterControl circuit

An analog-to-digital converter that converts an analog input signal into a digital signal includes a comparator configured to compare a reference signal with an input signal and, if the input signal matches the reference signal, inverts an output; a counter configured to count a comparison time of the comparator; a control circuit configured to monitor the output of the comparator; a voltage generating circuit configured to generate, if a monitoring result obtained by the control circuit indicates that the output of the comparator is at a predetermined level, a direct current voltage in accordance with the monitoring result; and an analog adder configured to add the voltage generated by the voltage generating circuit to the input signal and supply a sum signal to an input terminal of the comparator.

Owner:SONY CORP

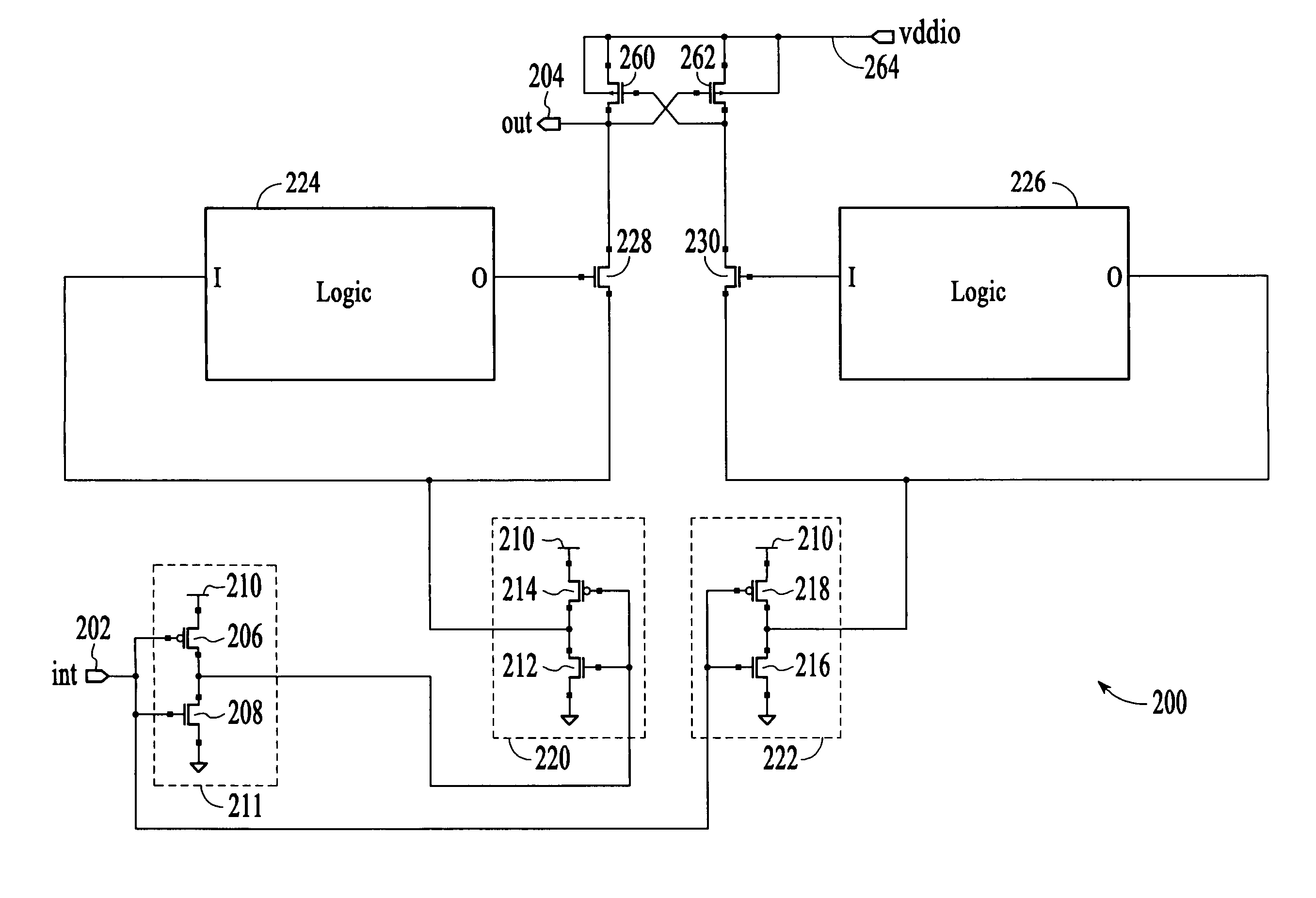

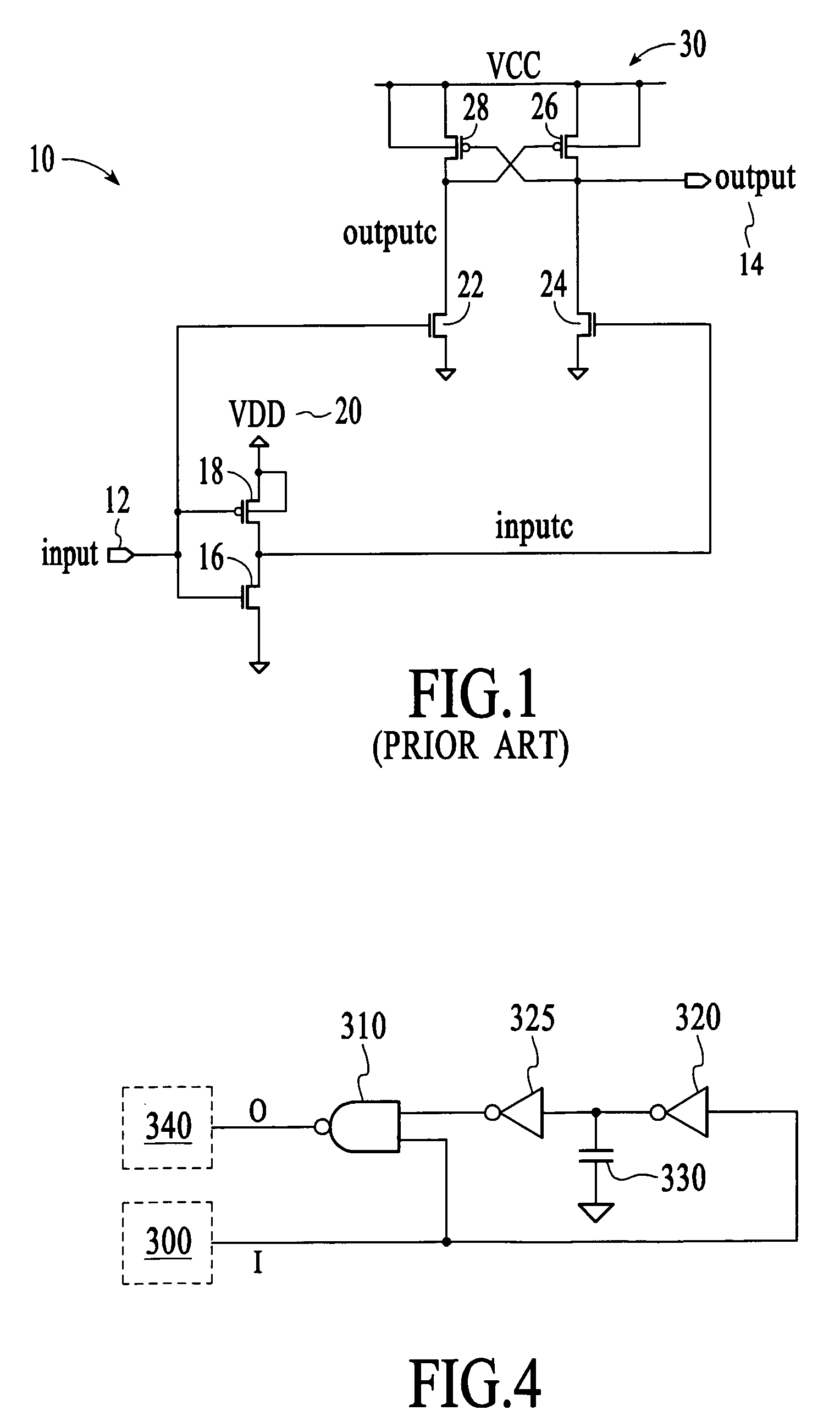

Voltage-level shifter

ActiveUS7245152B2Improve conversion speedLower resistancePulse automatic controlElectric pulse generatorHigh voltage transistorsHigh pressure

In a voltage-level shifter, an input line is configured to convey an input voltage to be shifted. A pair of transistors is coupled to and is configured to receive the input voltage from the input line. There is a first side and a second side, with each side comprising the following: a low-voltage transistor that is coupled to the pair of transistors, a medium-voltage transistor that is coupled to the low-voltage transistor, a high-voltage transistor that is coupled to the medium-voltage transistor, and an output line, which is coupled to the first and second sides, for providing an output voltage that is higher than the input voltage.

Owner:ATMEL CORP

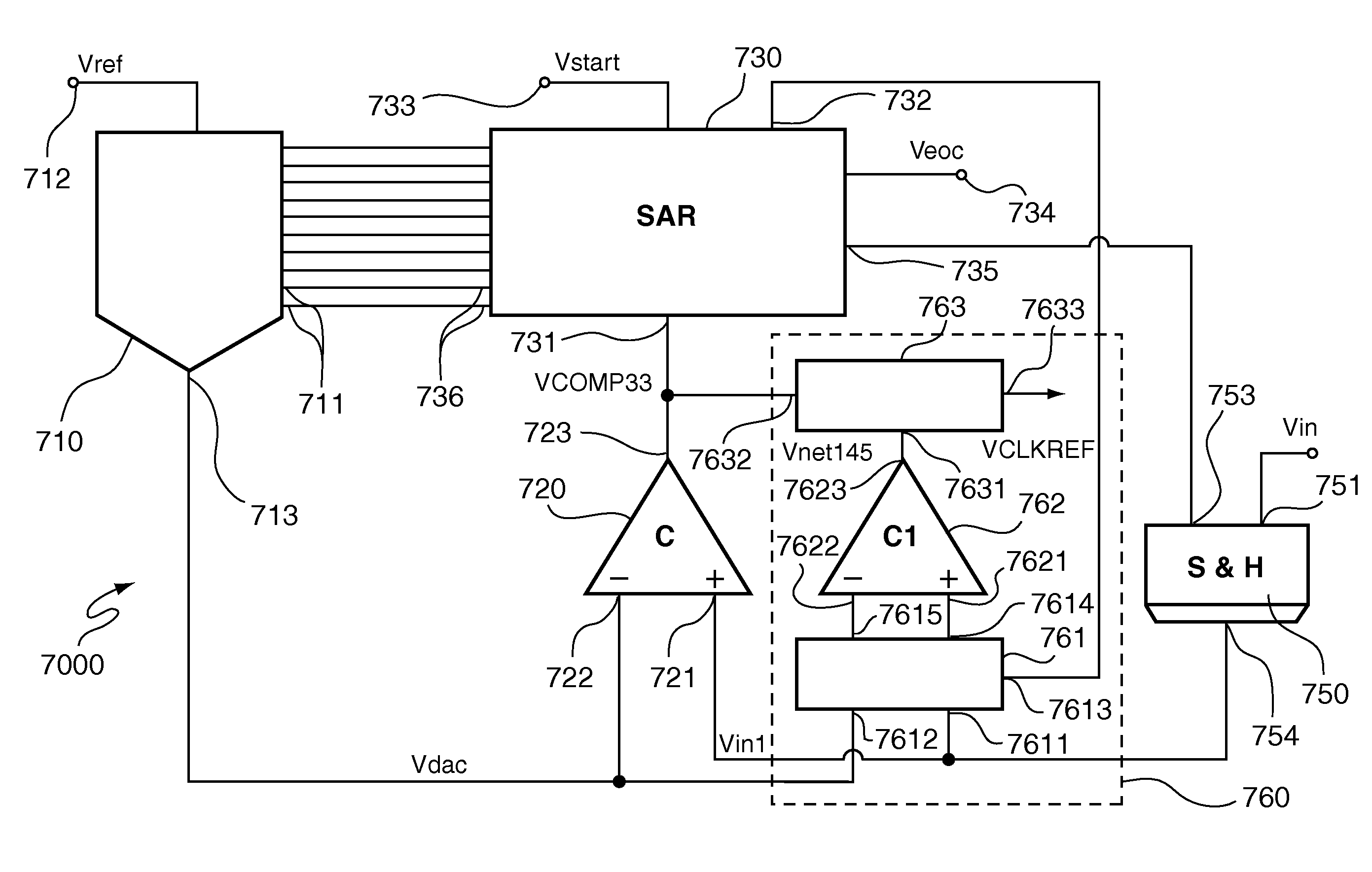

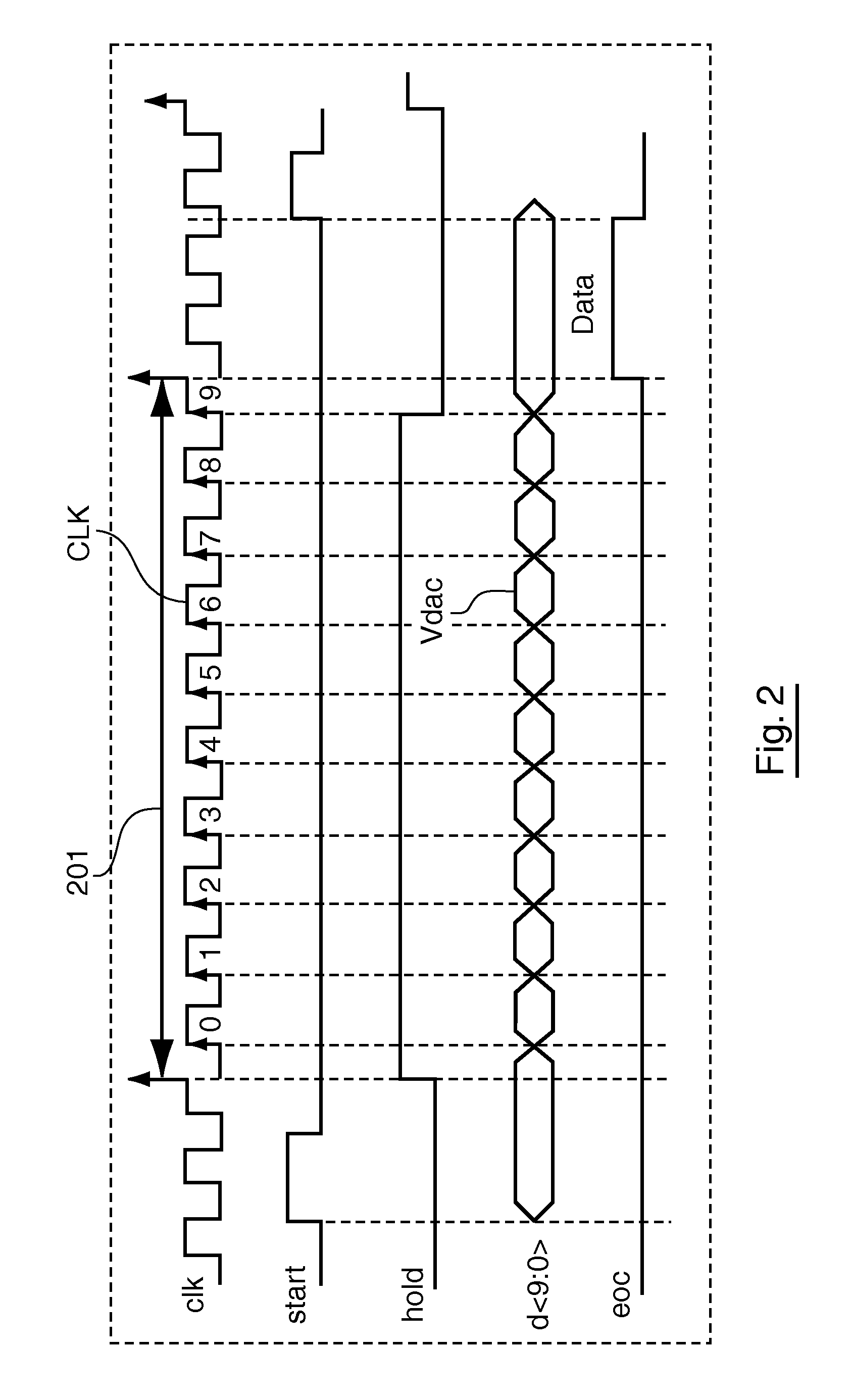

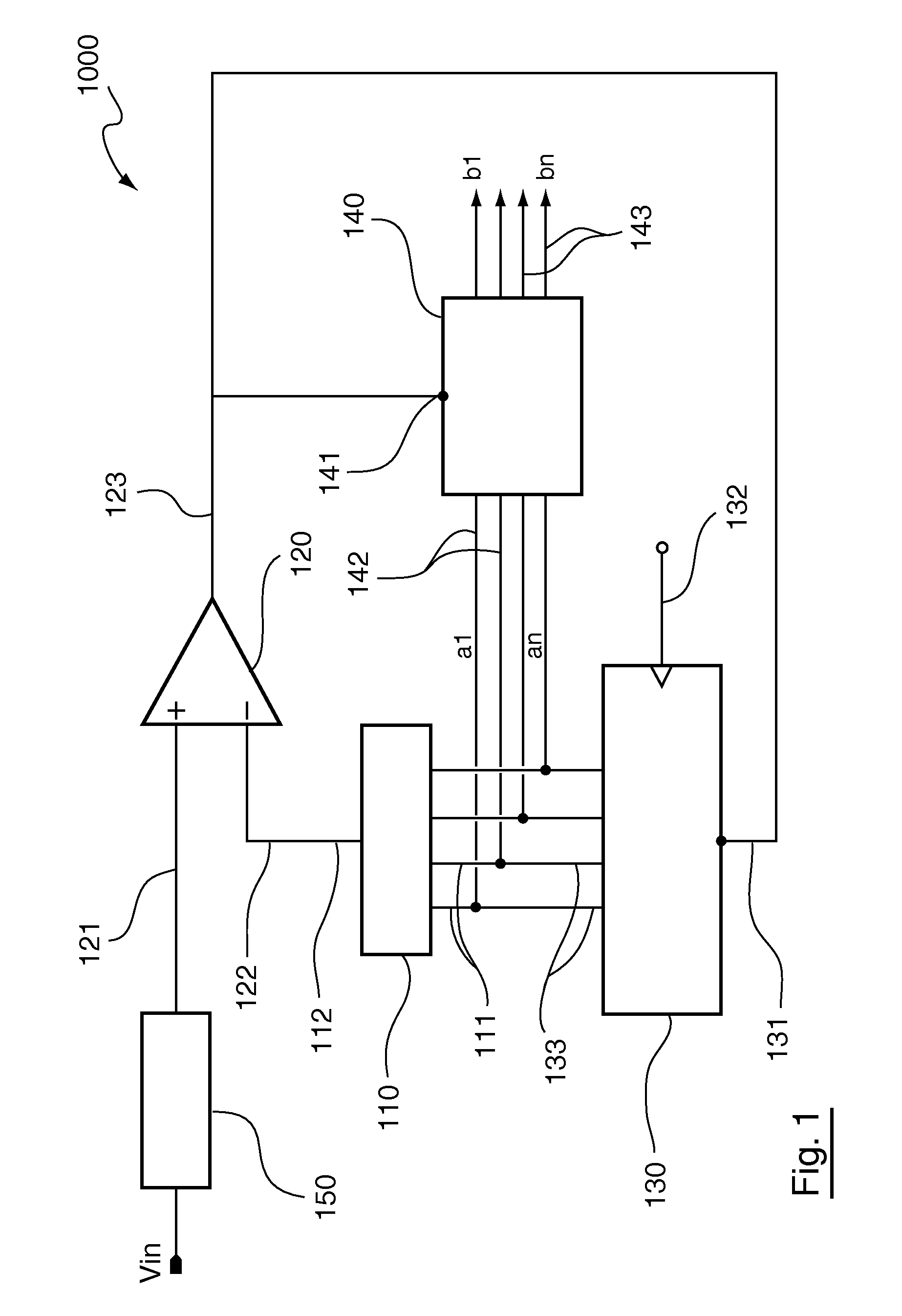

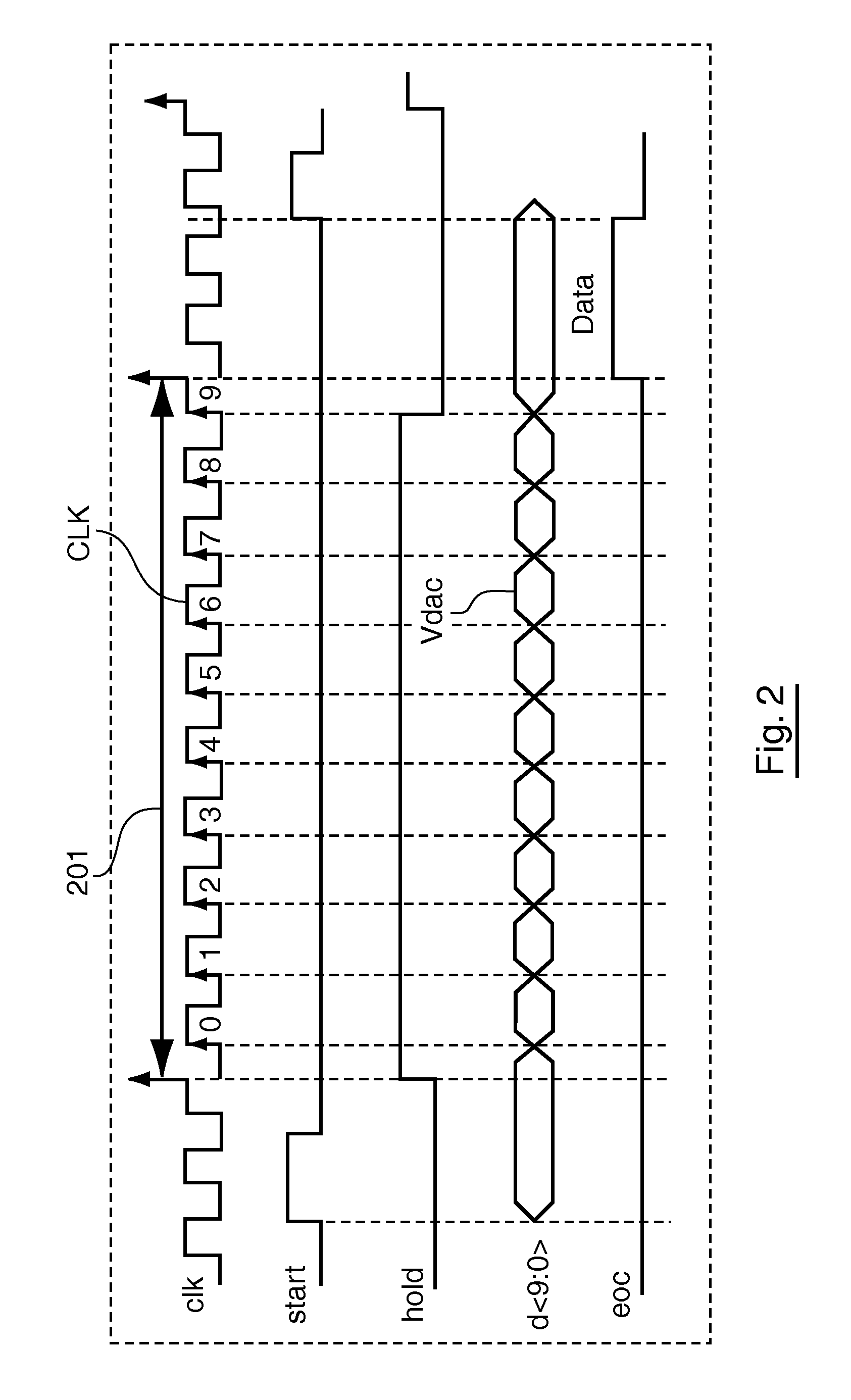

Successive approximation analog/digital converter and associated integrated component and conversion method

ActiveUS7576678B2Improve conversion speedReduce lost timeElectric signal transmission systemsAnalogue-digital convertersDigital down converterDigital converter

A successive approximation analog / digital converter is provided, which includes a successive approximation register supplying a digital / analog converter, first means of comparing an input signal of the analog / digital converter to an output signal of the digital / analog converter delivering a first comparison signal, said successive approximation analog / digital converter being synchronised by a clock signal coming from a conversion clock. A method such as this includes dynamic adaptation of the conversion clock period based on at least one parameter.

Owner:ATMEL CORP

Differential pipelined analog to digital converter with successive approximation register subconverter stages using thermometer coding

ActiveUS20050078025A1Facilitates improved system bandwidthIncreased gain factorElectric signal transmission systemsAnalogue-digital convertersA d converterAnalog to digital conversion

Pipelined analog to digital conversion systems are provided having cascaded multi-bit successive approximation register subconverter stages using thermometer coding. Capacitor arrays are provided in the subconverter stages, where switching logic selectively couples the capacitors to operate in sample, conversion, and residue amplification modes for generating multi-bit subconverter digital outputs and analog subconverter residue outputs, wherein the capacitors are switched according to a thermometer code to reduce differential converter non-linearity.

Owner:TEXAS INSTR INC

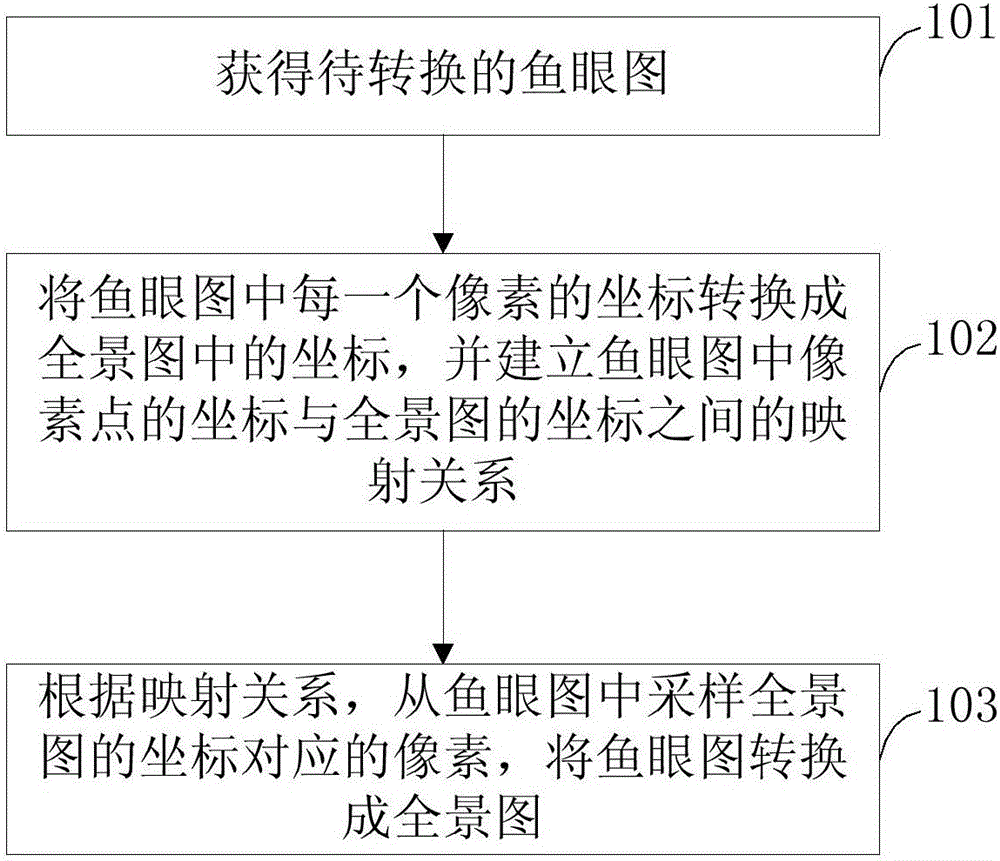

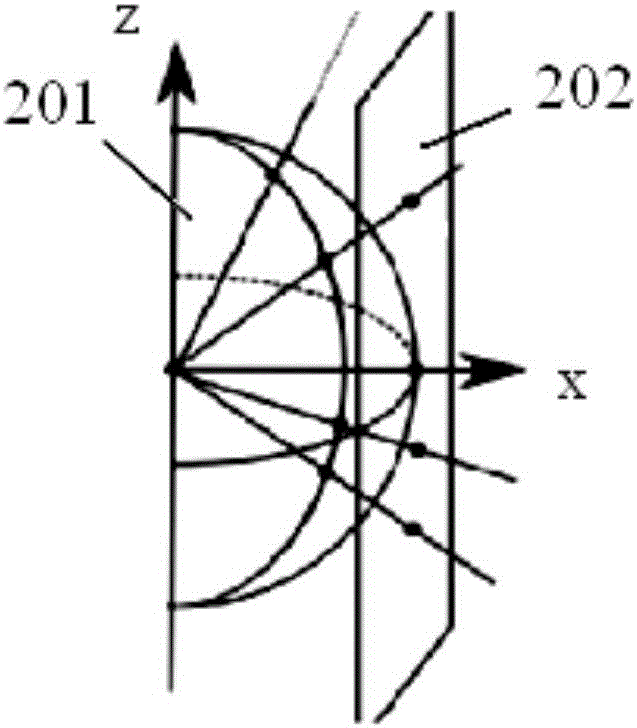

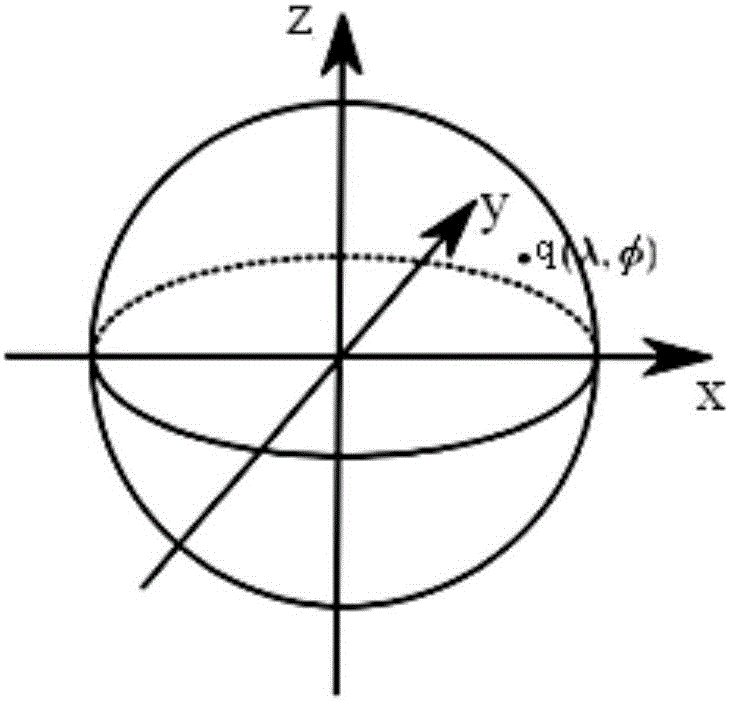

Fisheye image conversion method and device

ActiveCN106651808AAchieve real-time conversionGuaranteed accuracyImage enhancementComputer graphics (images)Image conversion

The embodiment of the invention provides a fisheye image conversion method and device. The method comprises: obtaining a fisheye image to be converted; converting the coordinates of each pixel in the fisheye image to the coordinates in a panorama, and establishing a mapping relation between the coordinates of each pixel in the fisheye image and the coordinates in the panorama; and according to the mapping relation, sampling the pixels corresponding to the coordinates in the panorama from the fisheye image, and converting the fisheye image to the panorama. The fisheye image conversion method and device do not need the steps of correcting the fisheye image to a planar graph without distortion and then converting the planar graph without distortion to the panorama to reduce the steps and links in the process, improve the conversion efficiency so as to realize the real-time conversion of the fisheye image obtained in real time.

Owner:BEIJING IQIYI TECH CO LTD

Successive appromixation analog/digital converter and associated integrated component and conversion method

ActiveUS20080100490A1Minimum widthReducing clock signal periodElectric signal transmission systemsAnalogue-digital convertersDigital down converterEngineering

A successive approximation analog / digital converter is provided, which includes a successive approximation register supplying a digital / analog converter, first means of comparing an input signal of the analog / digital converter to an output signal of the digital / analog converter delivering a first comparison signal, said successive approximation analog / digital converter being synchronised by a clock signal coming from a conversion clock. A method such as this includes dynamic adaptation of the conversion clock period based on at least one parameter.

Owner:ATMEL CORP

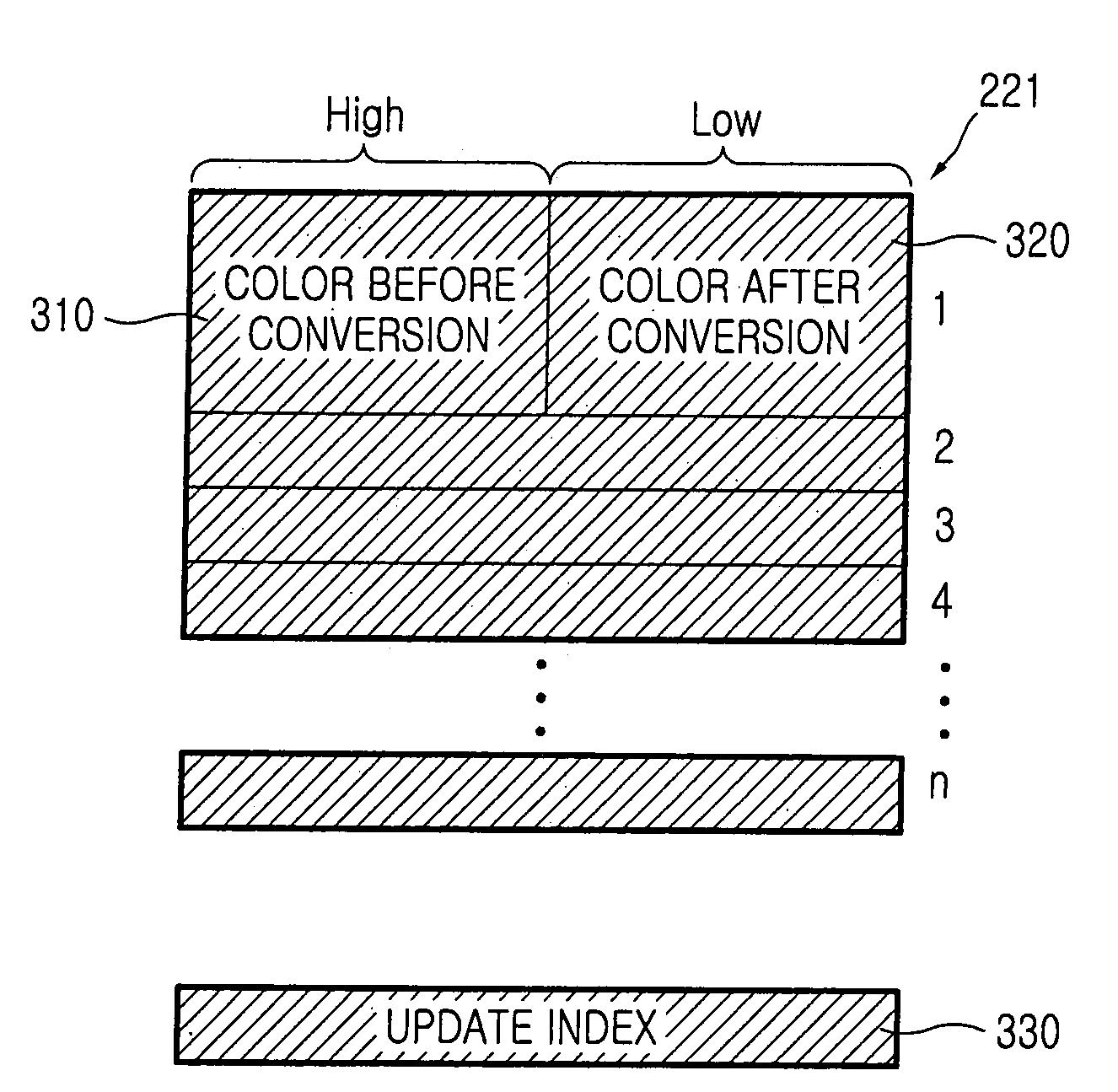

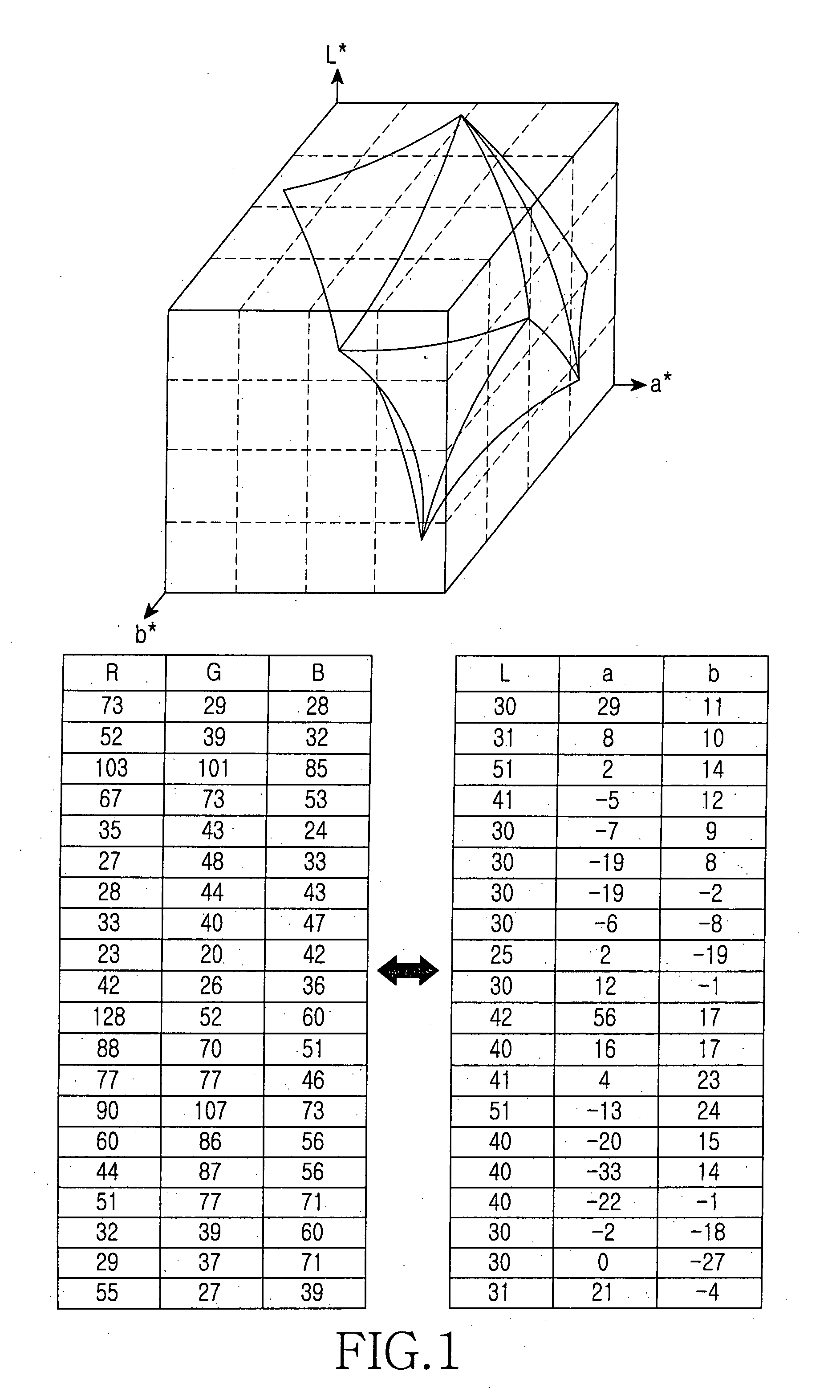

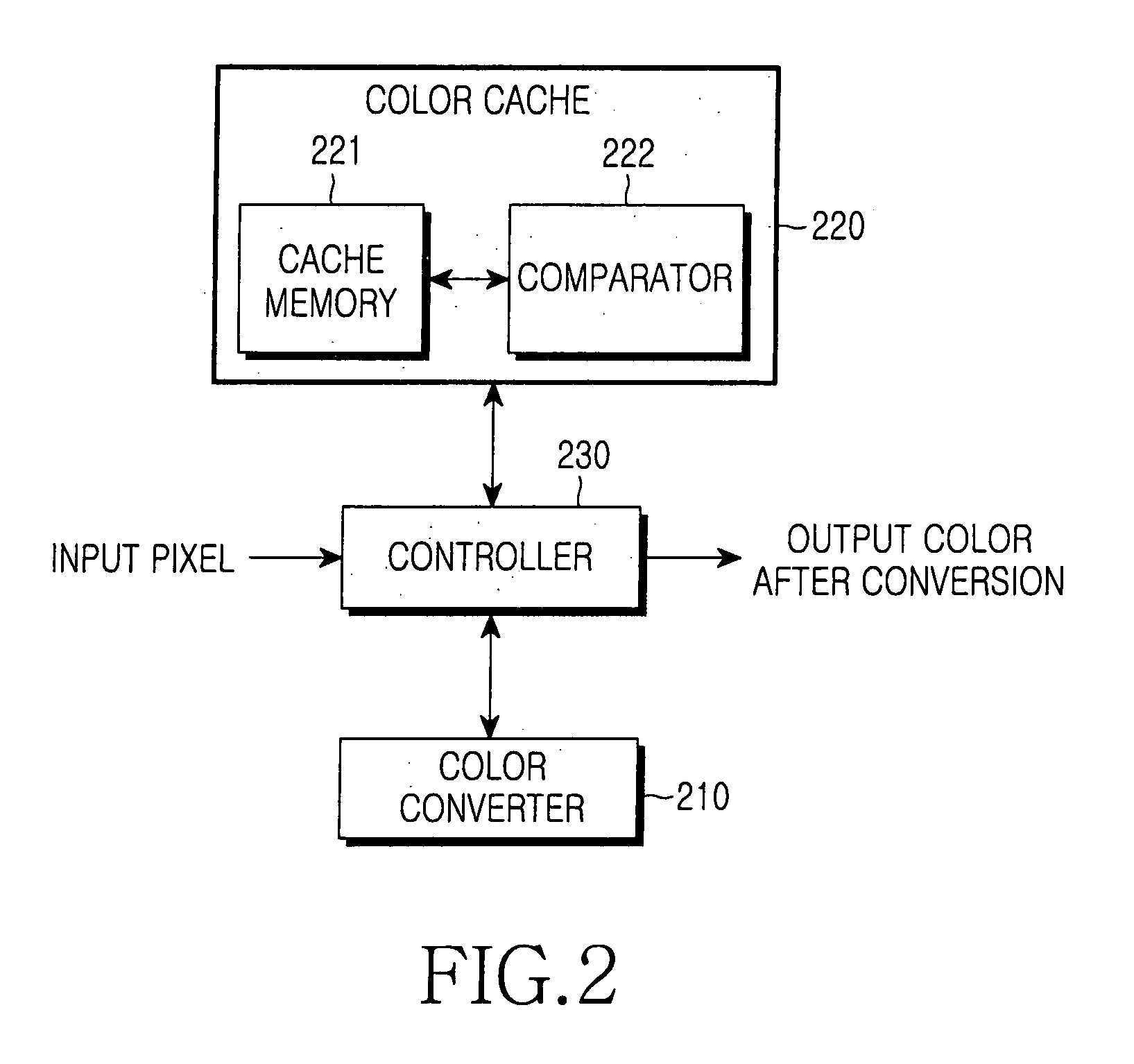

Apparatus and method for performing color conversion using color cache in image processing system

InactiveUS20080025602A1Increase color conversion speedReduce power consumptionColor signal processing circuitsCharacter and pattern recognitionImaging processingComputer graphics (images)

Owner:SAMSUNG ELECTRONICS CO LTD

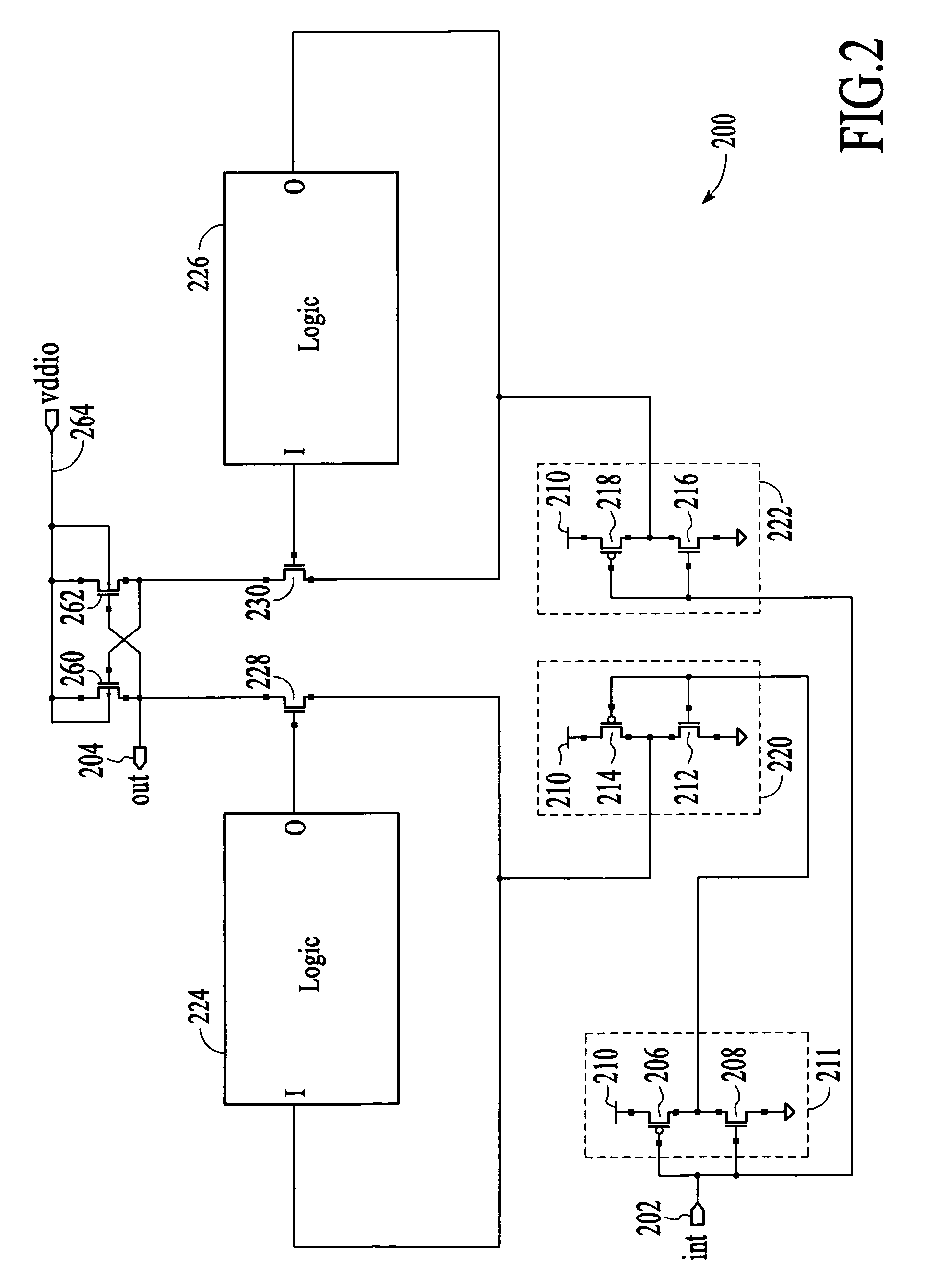

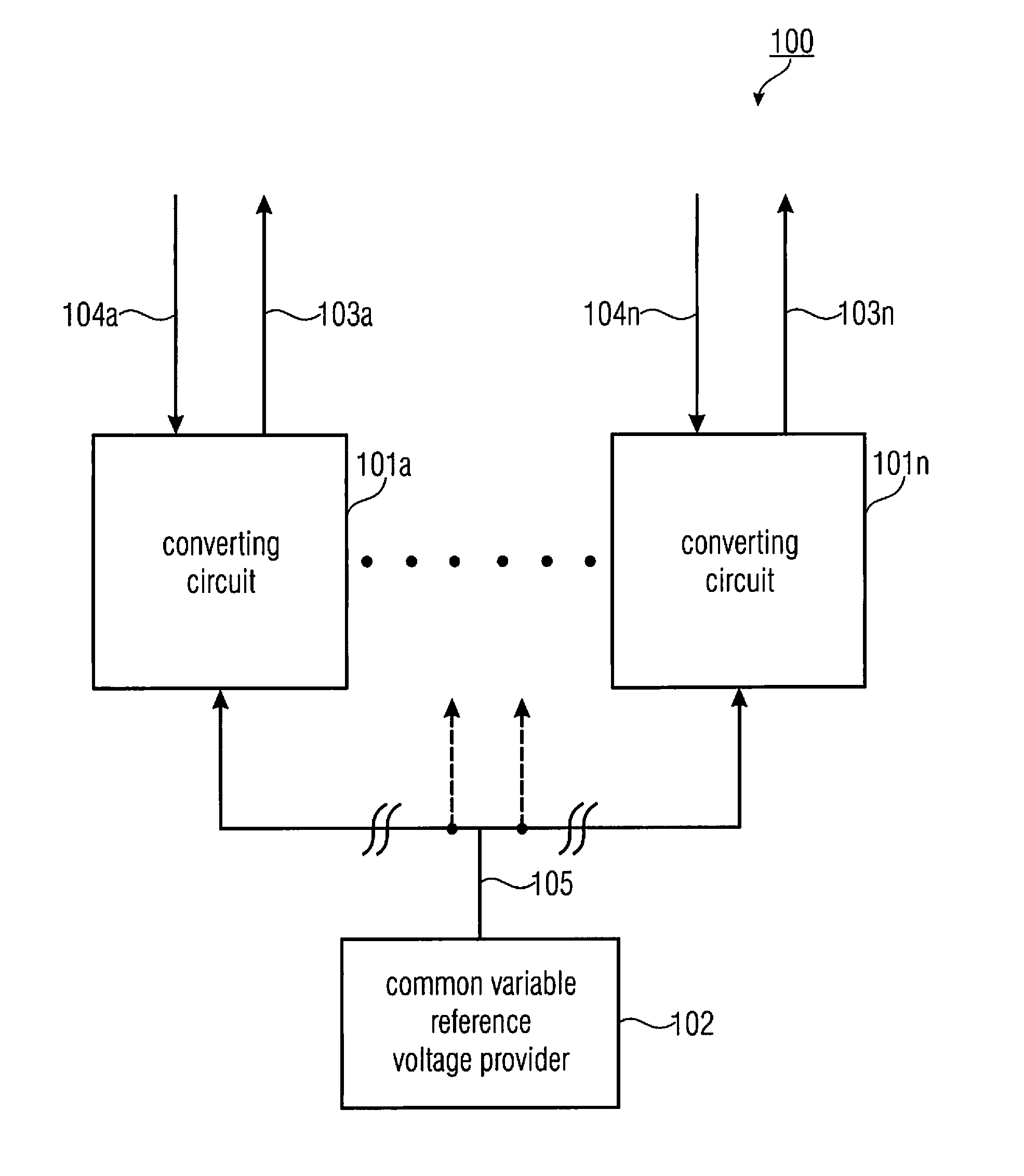

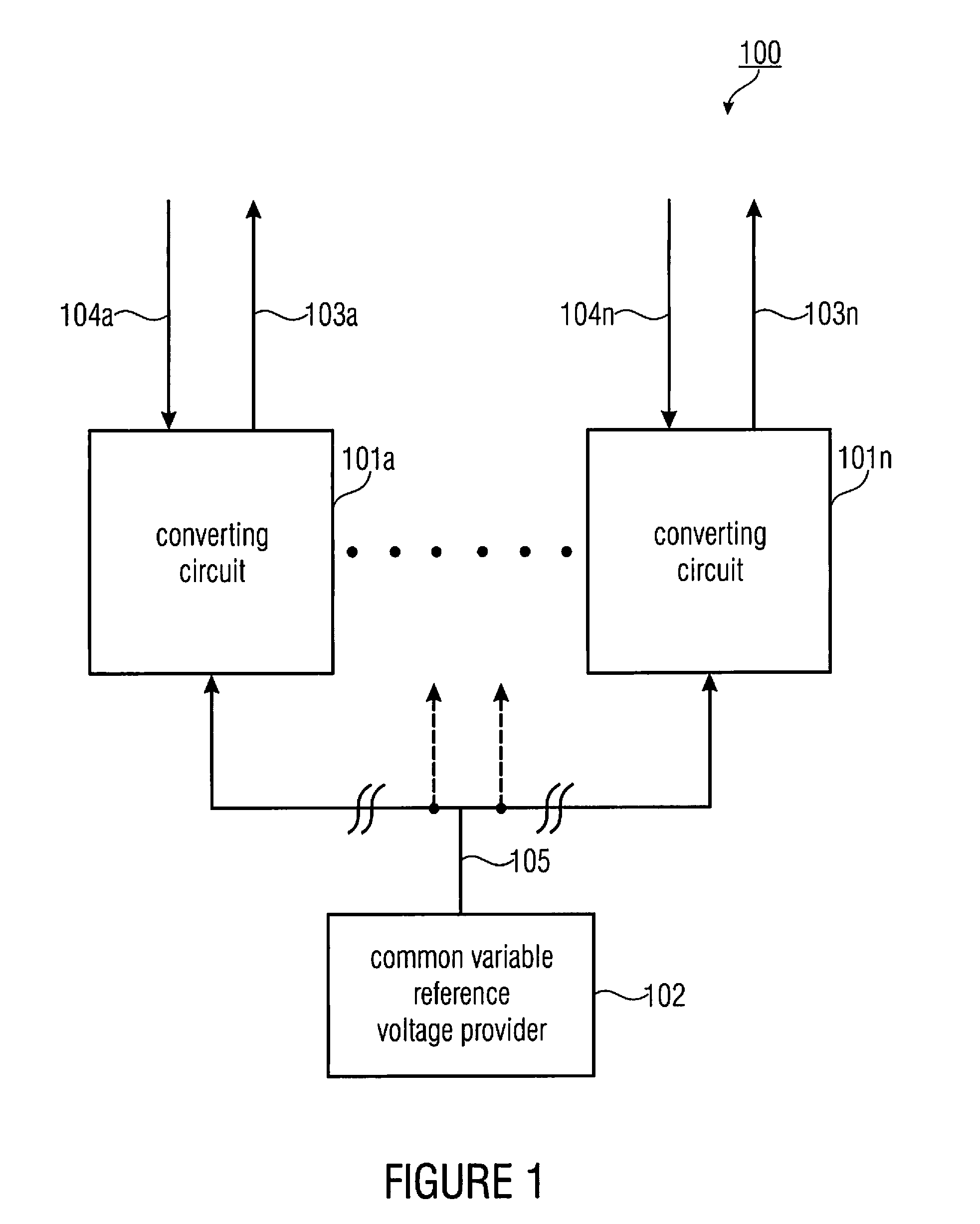

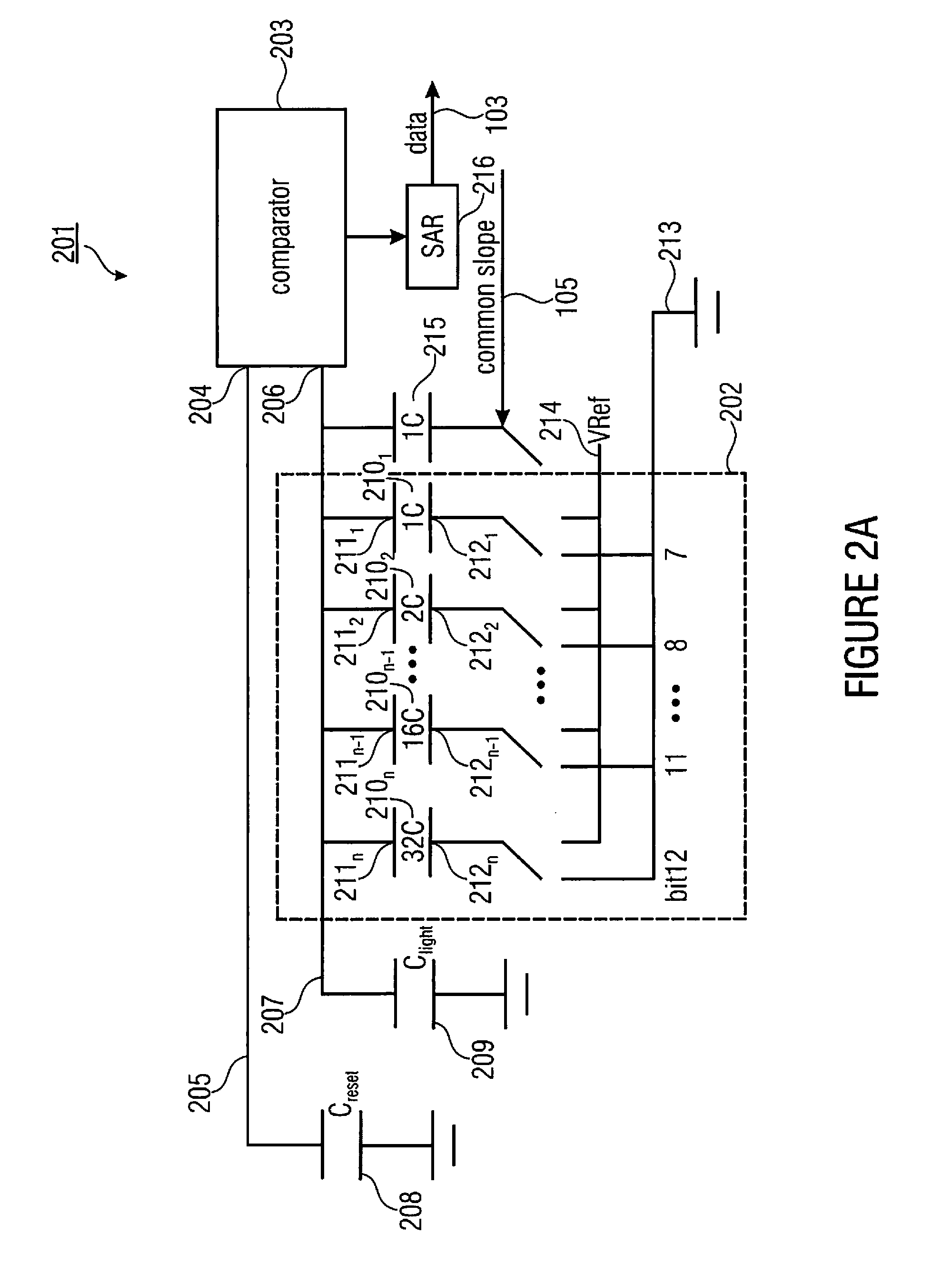

Hybrid analog-to-digital converter, an image sensor and a method for providing a plurality of digital signals

InactiveUS8492697B2Optimized areaImprove powerElectric signal transmission systemsSolid-state devicesDigital Signal 3Digital down converter

A hybrid analog-to-digital converter includes a plurality of converting circuits. Each converting circuit is configured to provide a digital signal based on an analog input signal by performing a successive approximation conversion to obtain, as a result of the successive approximation conversion, a first number of bits of the digital signal, and by subsequently performing a slope conversion based on a common variable reference voltage to obtain a second number of bits of the digital signal, the second number of bits corresponding to a residual between the analog input signal and the result of the successive approximation conversion. The hybrid analog-to-digital converter further includes a common variable reference voltage provider configured to provide to each converting circuit of the plurality of converting circuits the common variable reference voltage.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

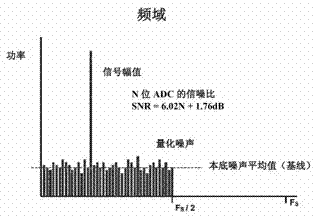

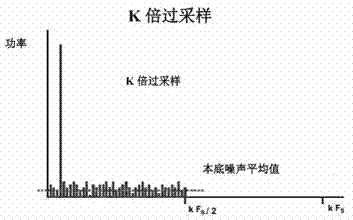

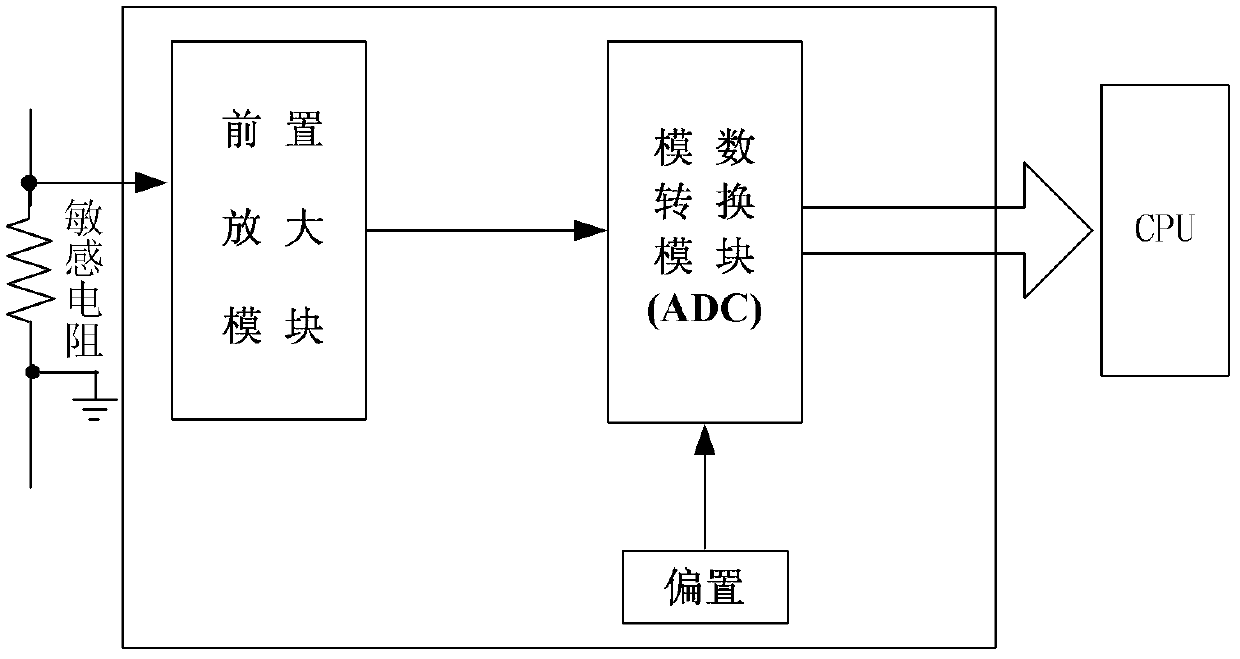

Quick high-precision method for sampling analog quantity in alternating current speed regulating system of mine hoist

InactiveCN102332918AReduce RMS noiseAccurate extractionAnalogue-digital convertersPulse streamElectric machine

The invention discloses a quick high-precision method for sampling the analog quantity in an alternating current speed regulating system of a mine hoist, belonging to a quick high-precision sampling method for a motor. The sampling method comprises a quick high-precision sampling circuit, wherein the circuit is provided with a module with a sigma-delta modulating function, an FPGA (Field Programmable Gate Array) for filtering and a DSP (Digital Signal Processor) for controlling, wherein the output of the module with the sigma-delta modulating function is a pulse stream Mdate and a high-frequency sampling clock input signal Mclk; the pulse stream Mdate and the high-frequency sampling clock input signal Mclk are used as inputs of a filter in the FPGA; and the FPGA communicates with the DSP through an external interface XINTF (eXternal INTerFace). The invention has the advantages that the quick high-precision method is simple, reliable and easy to realize; and high analog-to-digital conversion precision and conversion speed can be obtained by using a proper module with the sigma-delta modulating function. The quick high-precision method is applied to a motor for controlling the extraction of a voltage fundamental wave so as to quickly and accurately extract the fundamental wave of the voltage; and the extracted fundamental wave of the voltage can be directly applied to control or protection of the motor.

Owner:CHINA UNIV OF MINING & TECH +1

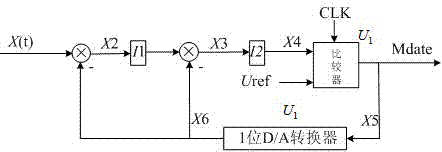

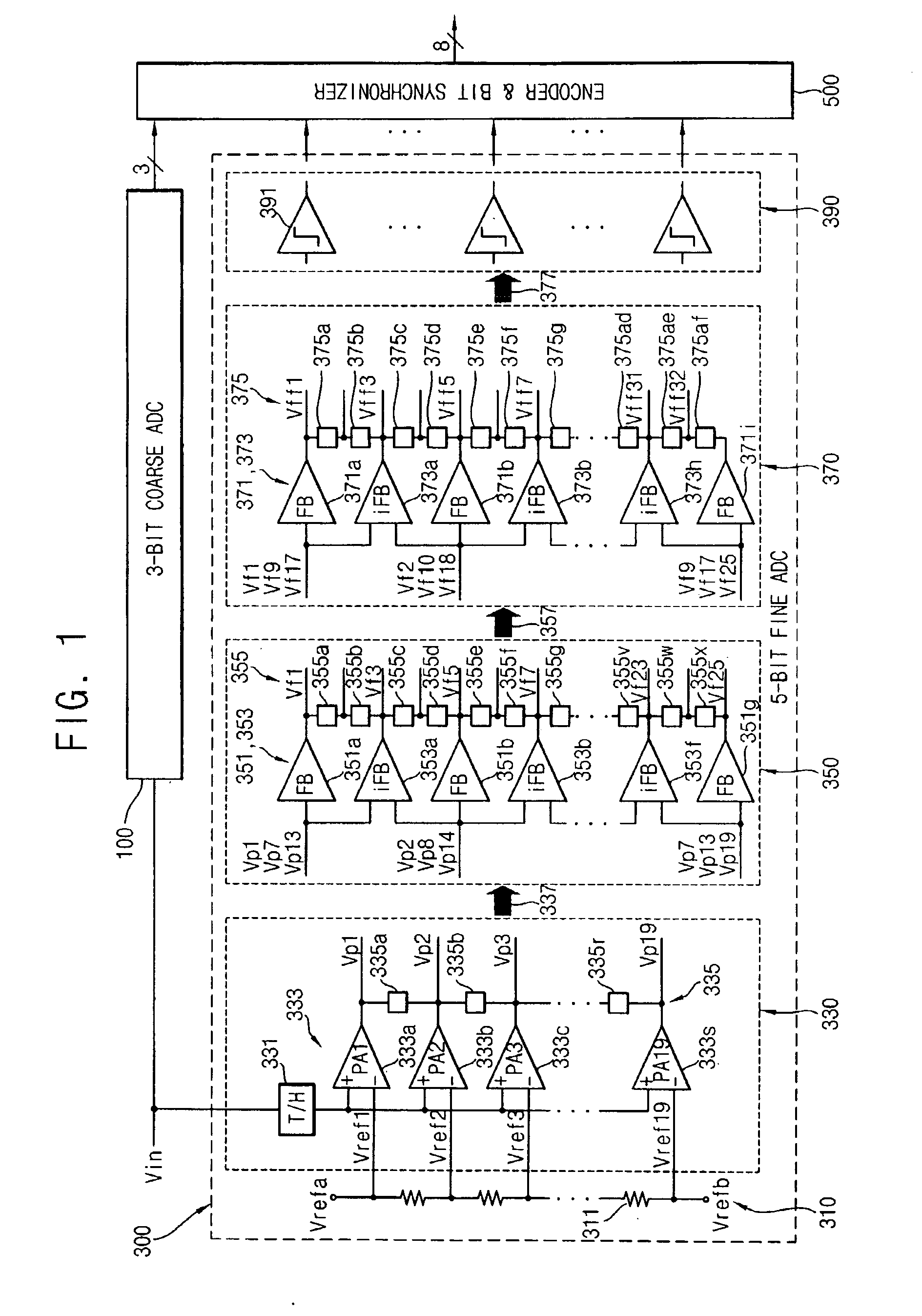

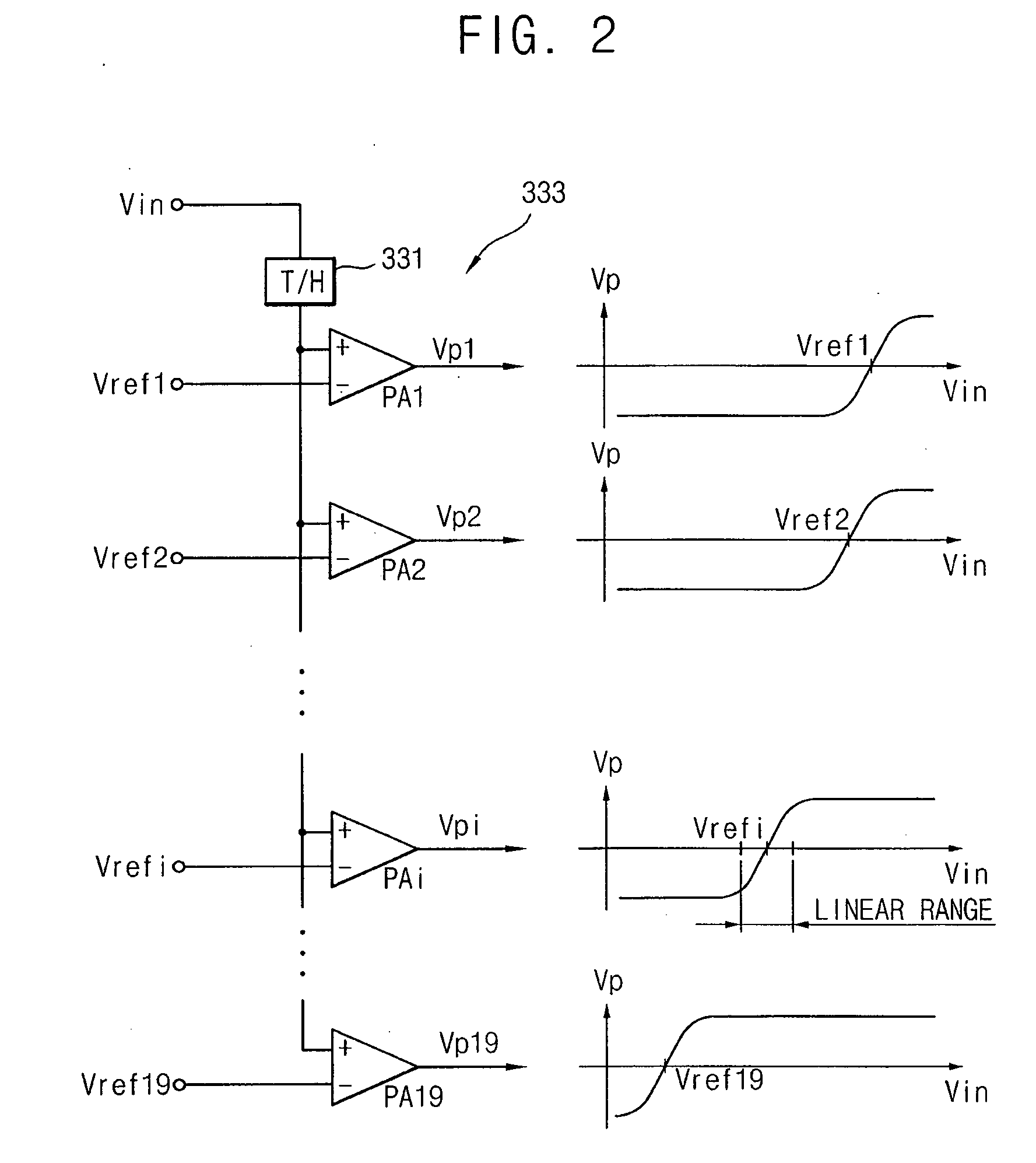

Folding and interpolating analog-to-digital converter and method of converting analog signal to digital signal

ActiveUS20070115162A1Improve resolutionImprove conversion speedElectric signal transmission systemsAnalogue-digital convertersAudio power amplifierImage resolution

A folding and interpolating analog-to-digital converter (ADC) includes a preamp unit, a first folding stage, a second folding stage, a comparison unit and an encoder. The preamp unit receives an analog input signal and reference voltages to generate reference signals. The first folding stage generates a first group of folding signals based on the reference signals. The second folding stage generates a second group of folding signals based the first group. The comparison unit generates a digital code based on the folding signals in the second group. The encoder encodes the digital code. Therefore, the ADC can increase a resolution and a conversion speed, but reduce interpolating errors.

Owner:SAMSUNG ELECTRONICS CO LTD

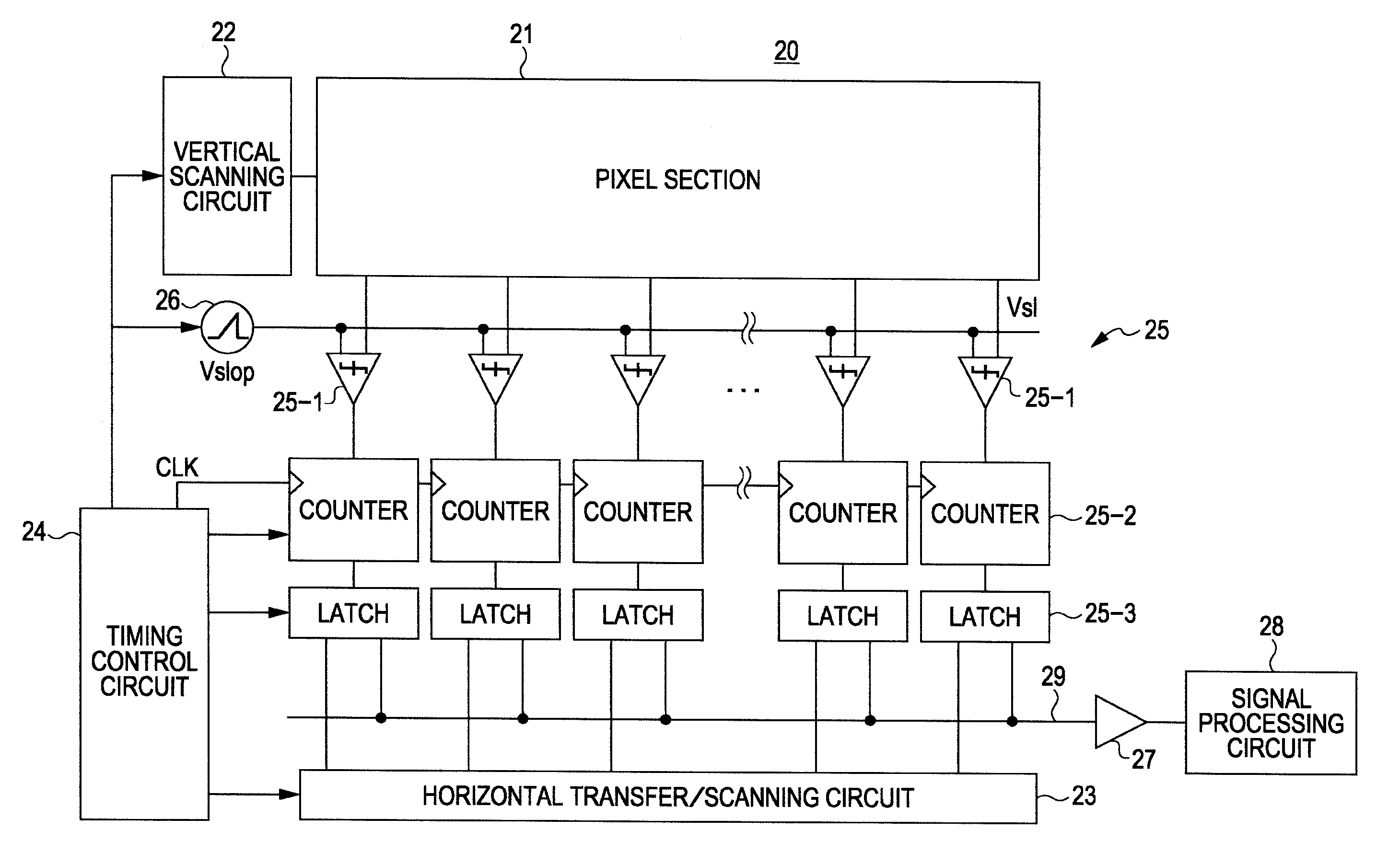

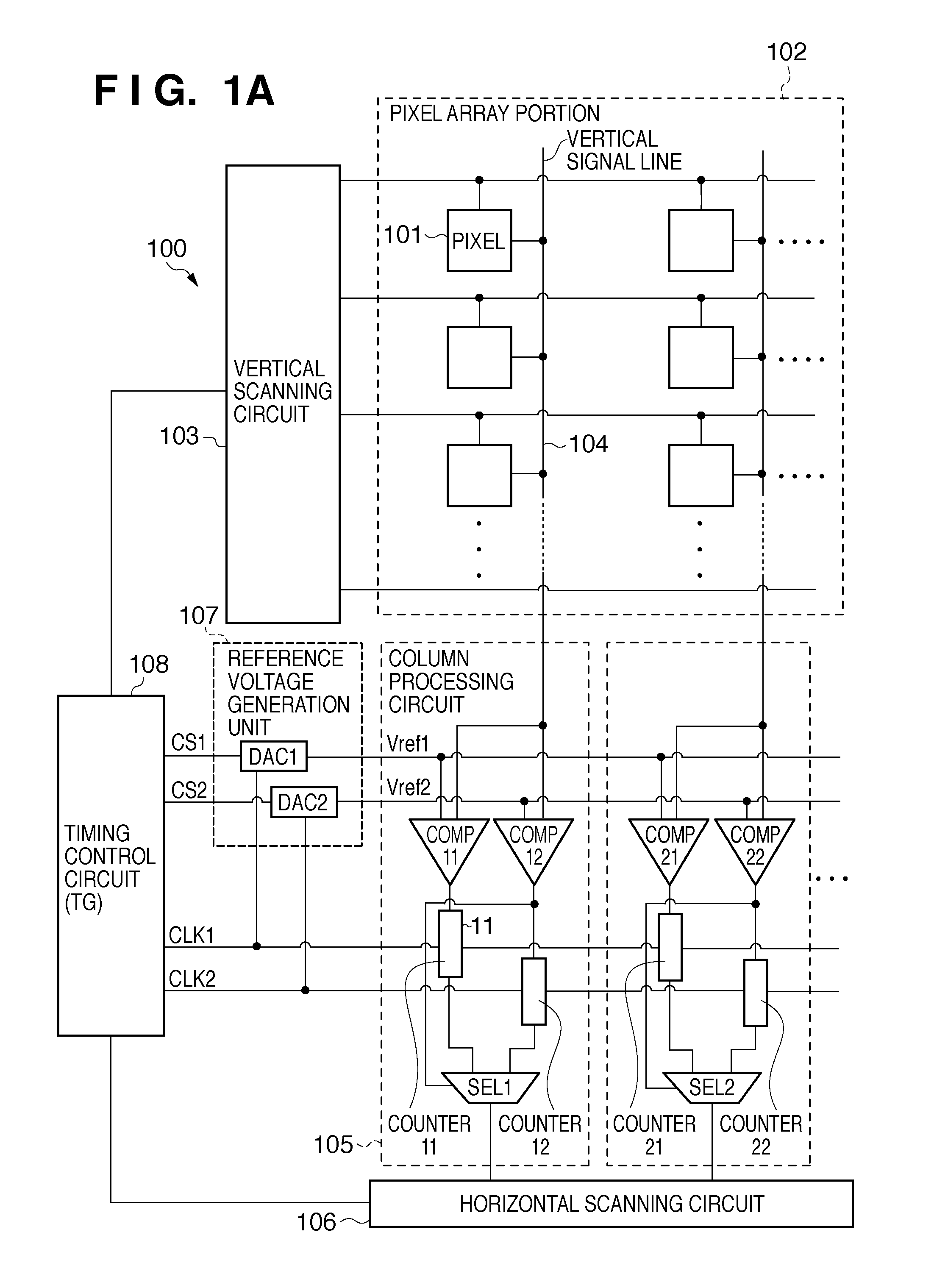

Solid-state imaging device and apparatus with an increased speed of analog to digital conversion

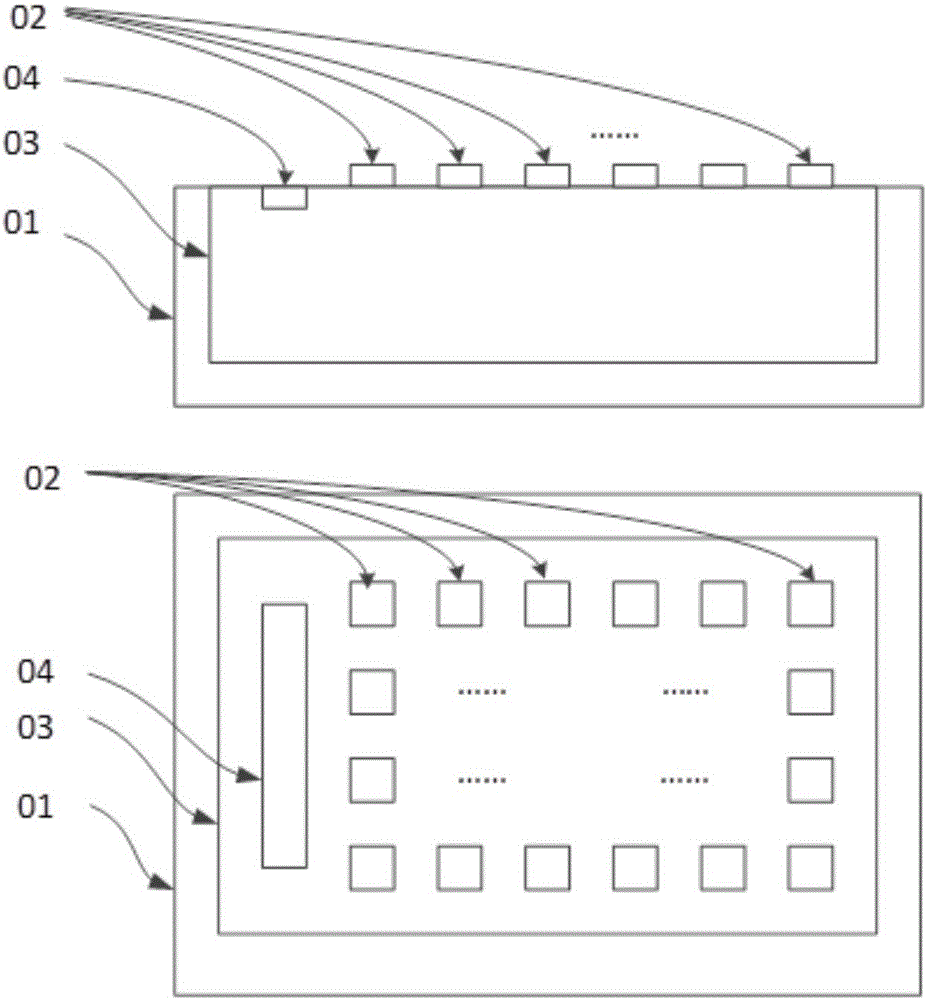

InactiveUS8063960B2Improve processing speedIncrease in speed of AD conversionAnalogue/digital conversionTelevision system detailsDigital dataComputer science

A solid-state imaging device includes a reference-signal generating unit that generates plural kinds of reference signals for converting an analog pixel signal into digital data, a reference-signal selecting unit that selects any one of the plural kinds of reference signals, a comparing unit that compares the pixel signal and the selected reference signal, and a count unit that performs count processing in parallel with comparison processing in the comparing unit and stores a count value at a point when the comparison processing is completed. The count unit decides digital data of the pixel signal in a 1 LSB step by storing a count value at a point when the comparison processing is completed for any one of the plural kinds of reference signals and correcting the stored count value on the basis of results of the comparison processing for respective remaining reference signals of the plural kinds of reference signals.

Owner:SONY CORP

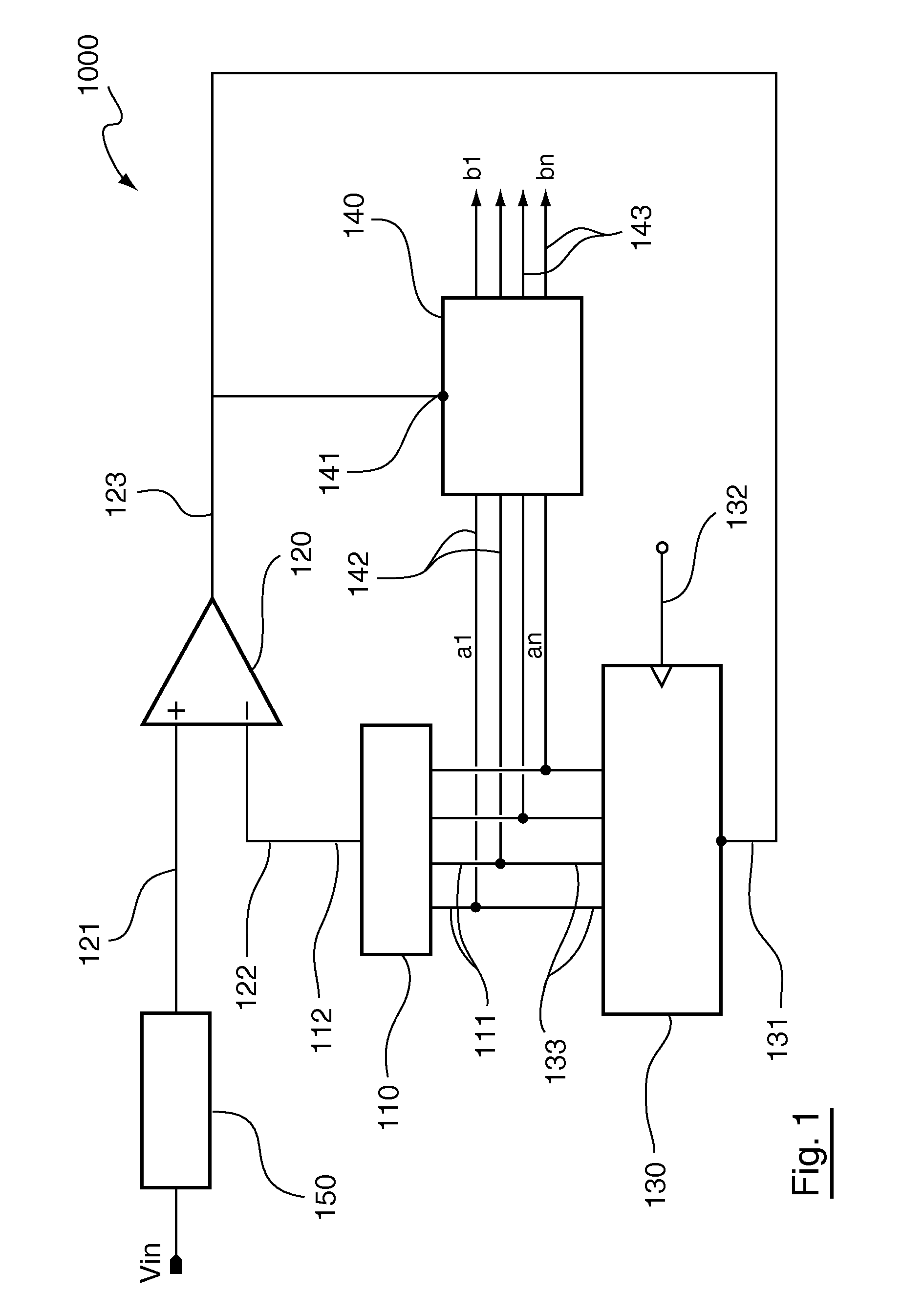

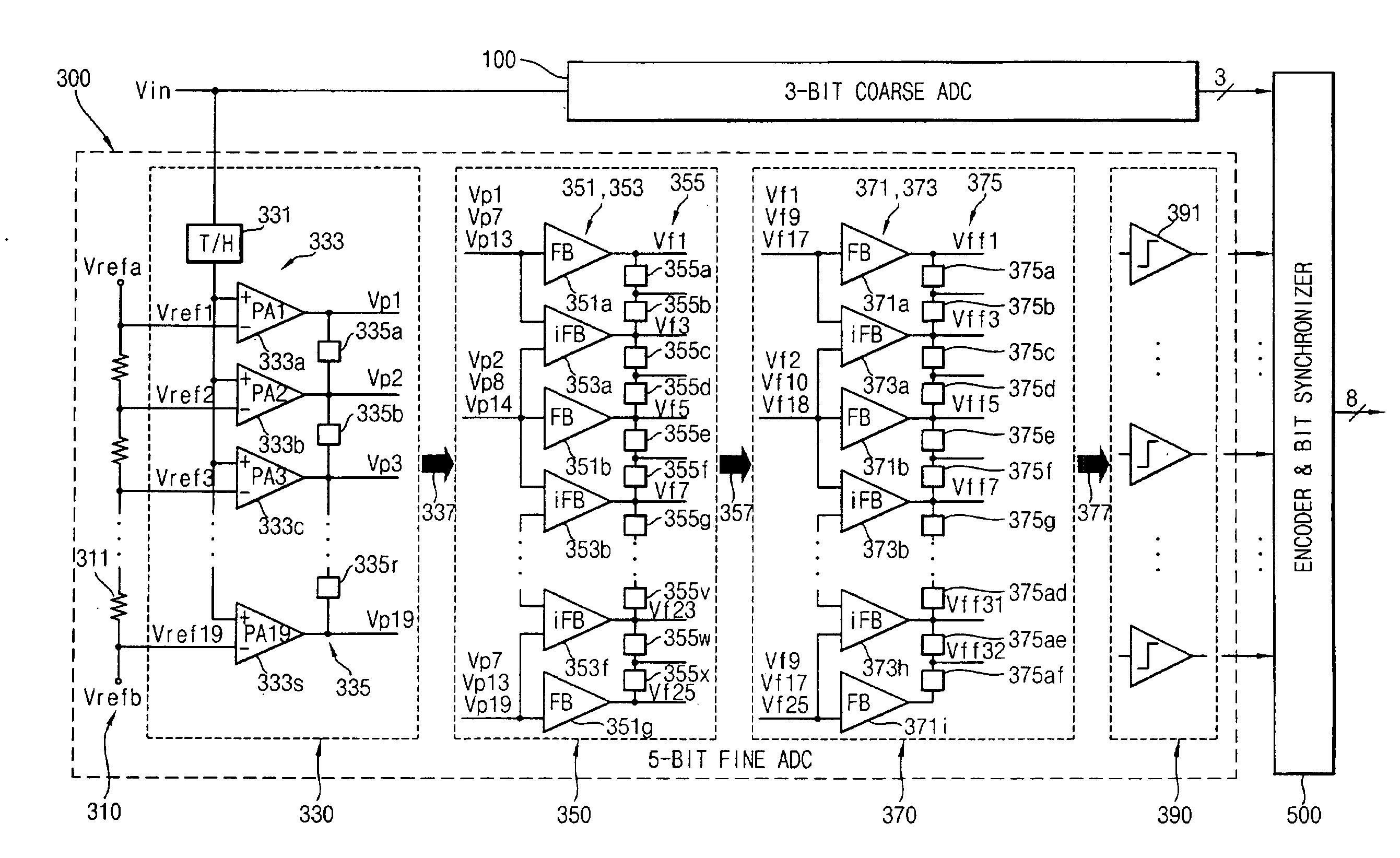

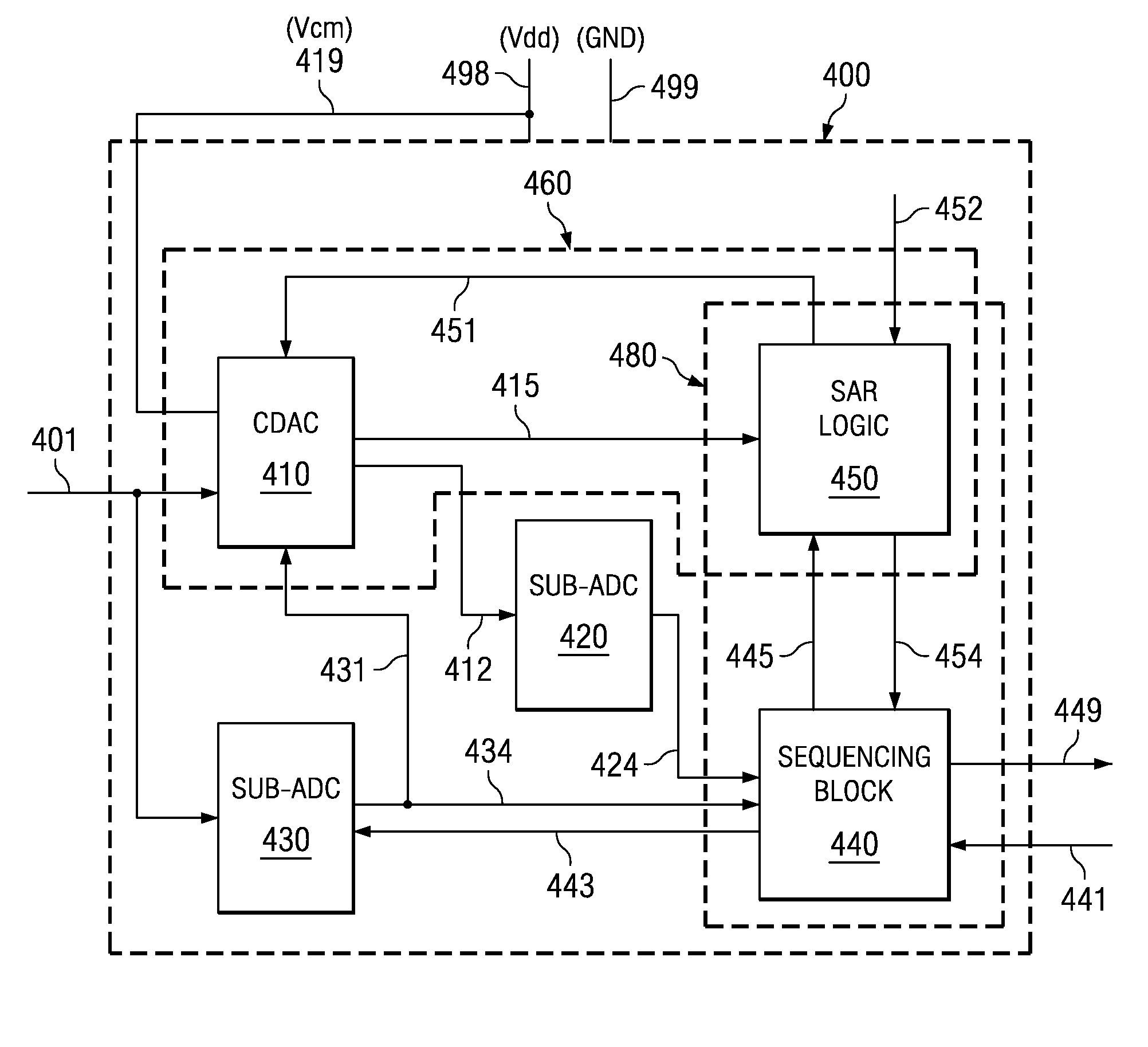

High speed high resolution ADC using successive approximation technique

ActiveUS7796077B2Improve conversion speedIncrease speedElectric signal transmission systemsAnalogue-digital convertersAudio power amplifierEngineering

An analog to digital converter (ADC) containing a sub-ADC to resolve at least some of the bits using successive approximation principle (SAP), while providing various improvements. According to one aspect, another sub-ADC is used to resolve some of the bits in parallel. According to another aspect, the sub-ADC using SAP is implemented using a charge redistribution principle, while another sub-ADC does not rely on charge conservation. According to yet another aspect of the present invention, a same component operates as a comparator when the sub-ADC using SAP resolves the corresponding bits, and operates as an amplifier when the sub-ADC generates a residue signal.

Owner:TEXAS INSTR INC

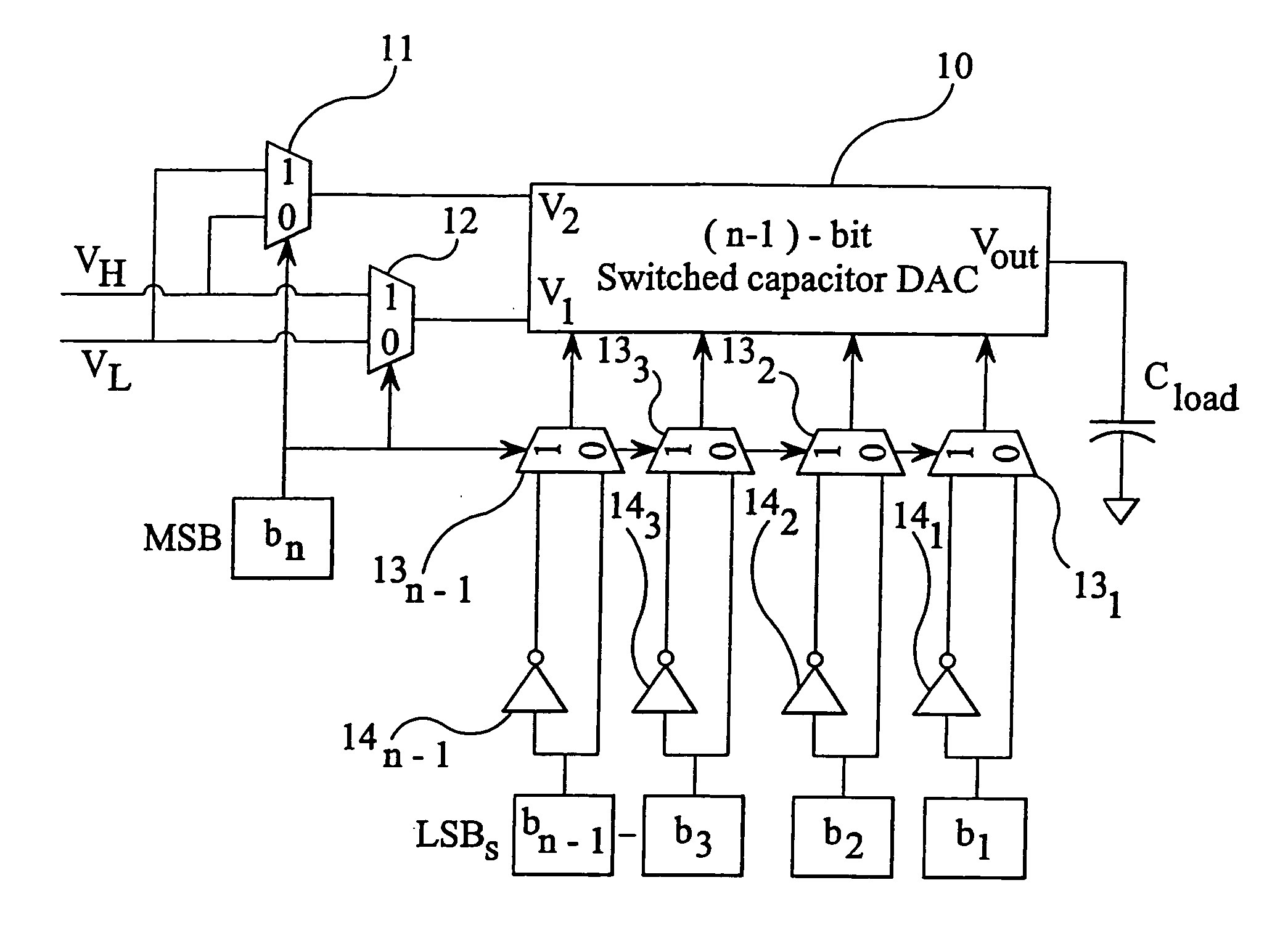

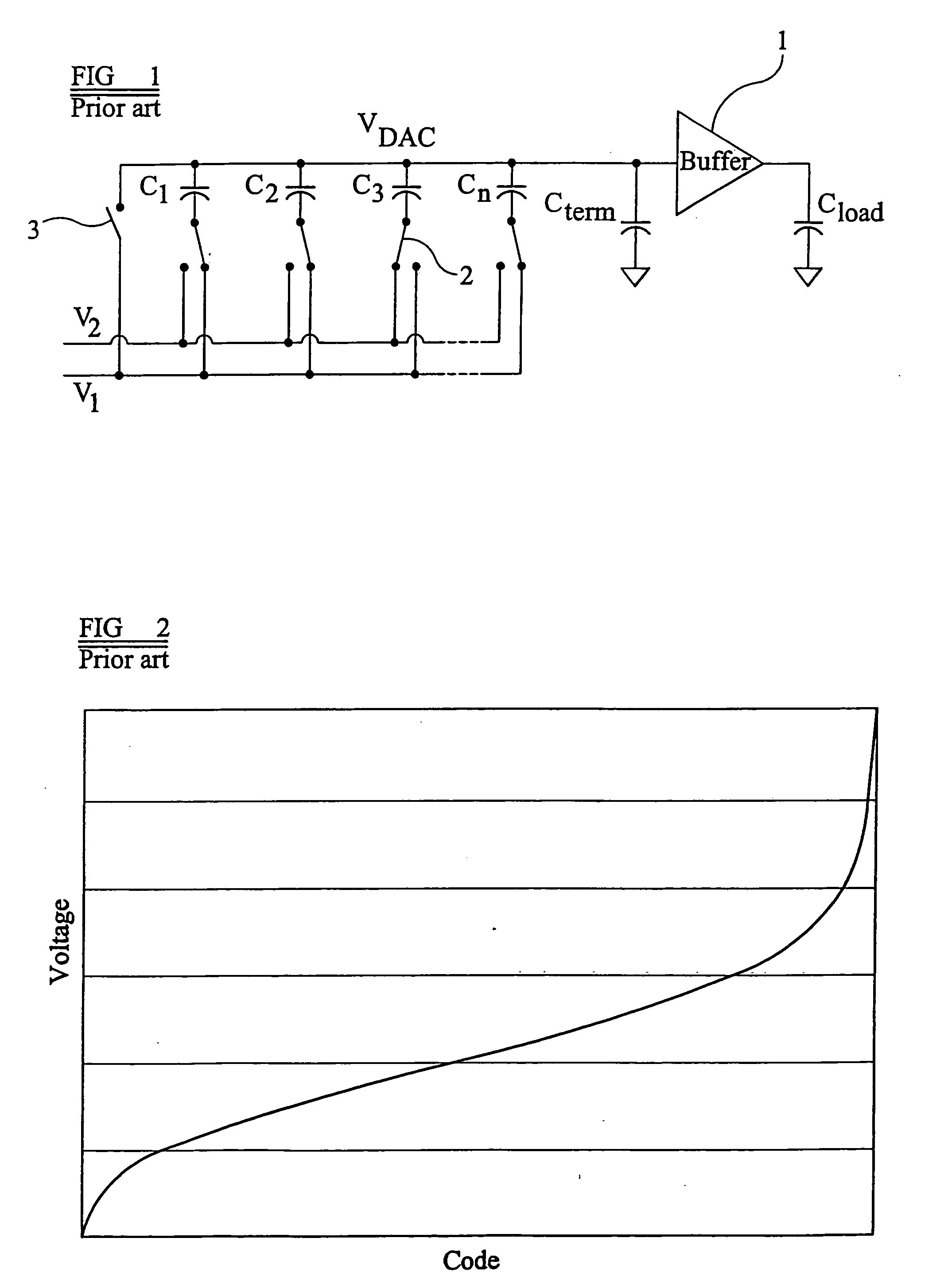

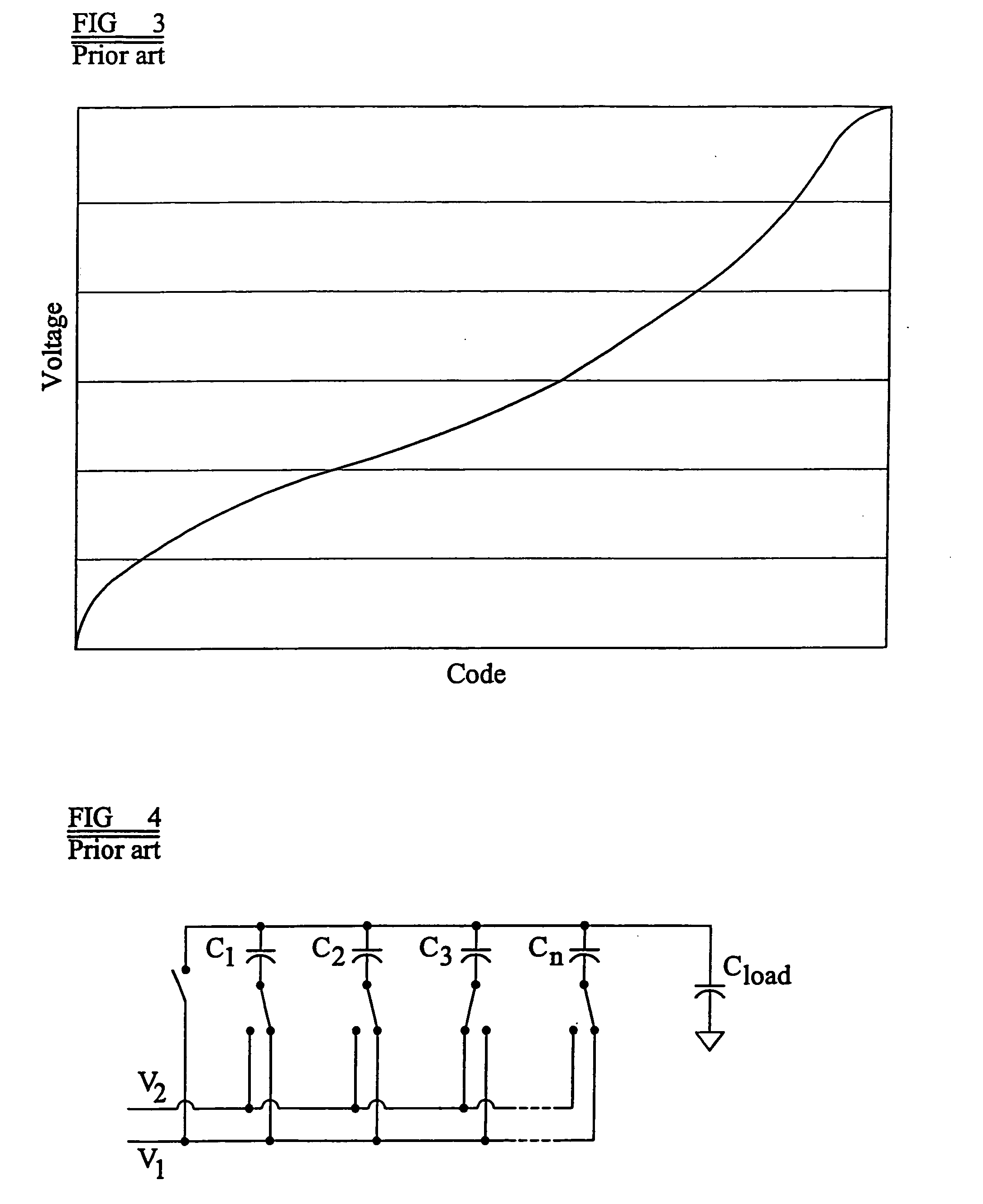

Digital/analog converter, display driver and display

InactiveUS20050171991A1Simplified generationReduce power consumptionElectric signal transmission systemsStatic indicating devicesLeast significant bitVoltage reference

An n-bit digital / analog converter is provided for converting an n-bit digital word to a corresponding voltage. The converter comprises an (n-1) bit bufferless switched capacitor digital / analog converter (10) having an output (Vout) for direct connection to a capacitive load (CLOAD). The (n-1) bit converter (10) also has first and second reference voltage inputs (V1, V2) and an (n-1) bit digital input. An (n-1) bit selective inverter (131, . . . , 13n-1, 141, . . . , 14n-1) supplies the (n-1) least significant bits to the digital input and inverts them if the most significant bit has a certain value. A switching arrangement (11, 12) connects the first and second reference voltage inputs (V1, V2) to receive first and second or second and first reference voltages depending on the value of the most significant bit.

Owner:SHARP KK

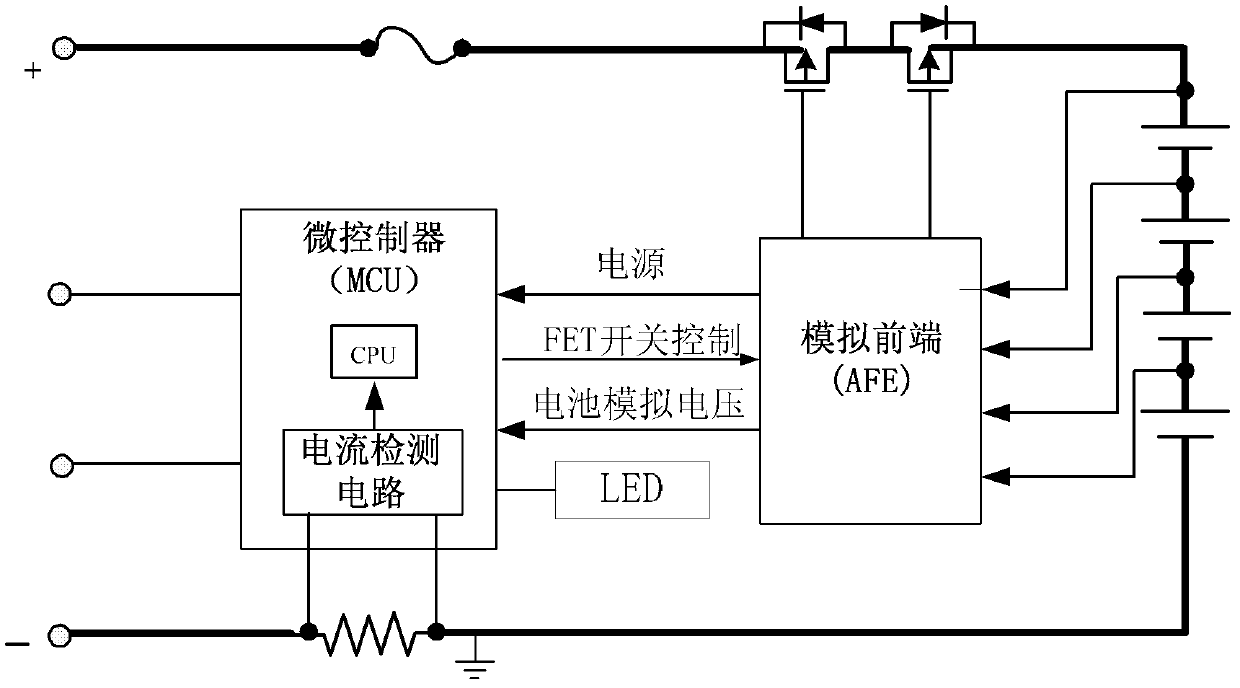

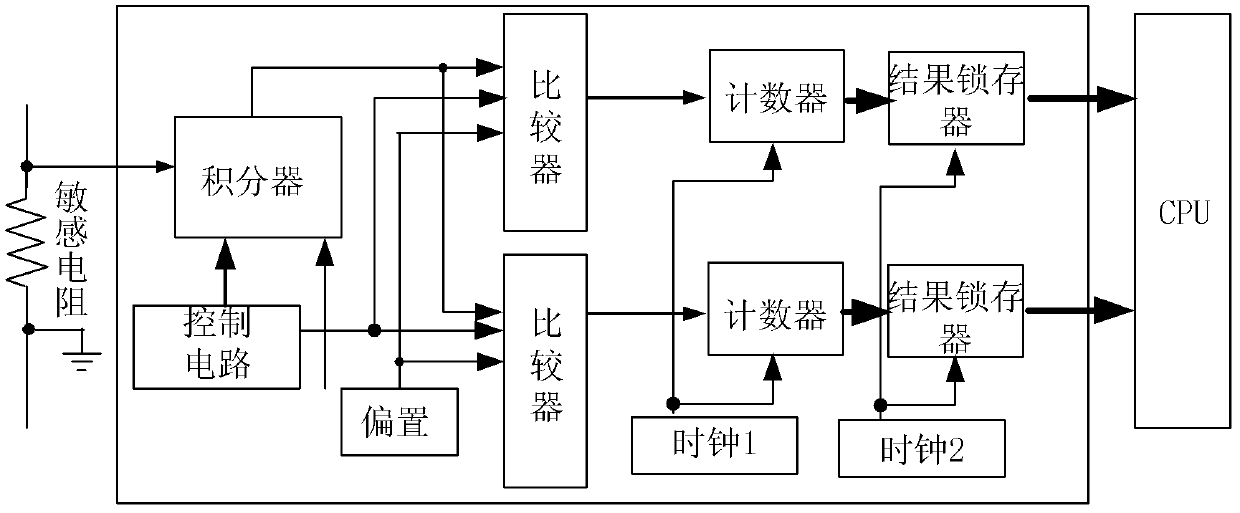

Voltage controlled delay chain-based time domain successive approximation digital intelligent battery current detection circuit and realizing method thereof

InactiveCN102636690AReduce the difficulty of implementationImprove conversion accuracyCurrent/voltage measurementLow speedElectrical battery

The invention discloses a voltage controlled delay chain-based time domain successive approximation digital intelligent battery current detection circuit and a realizing method thereof, belonging to a current detection circuit. In order to solve the problems of low speed and large process difficulty of the traditional intelligent battery detection circuit, the voltage controlled delay chain-based time domain successive approximation digital intelligent battery current detection circuit comprises a sensitive resistor, a level shift circuit, a charge and discharge mark decision circuit, a reference and biasing circuit, a voltage controlled delay chain, an adjustable voltage controlled delay chain, a delay regulation circuit, a time comparer, a time domain successive approximation control logic circuit, a result latch, a clock and a CPU (central processing unit). The realizing method comprises the following steps that: a level signal of the level shift circuit outputs to the voltage controlled delay chain to ensure that an output signal T1 delays one time relevant to the voltage; the delay regulation circuit, the adjustable voltage controlled delay chain, the time comparer and the time domain successive approximation control logic circuit form a feedback circuit, the output of a signal T2 of the adjustable voltage controlled delay chain is regulated until the T2 and the T1 are kept consistent; and the time domain successive approximation control logic circuit latches the output of a digital signal down. The realizing method is used in the intelligent battery current detection circuit.

Owner:HARBIN INST OF TECH

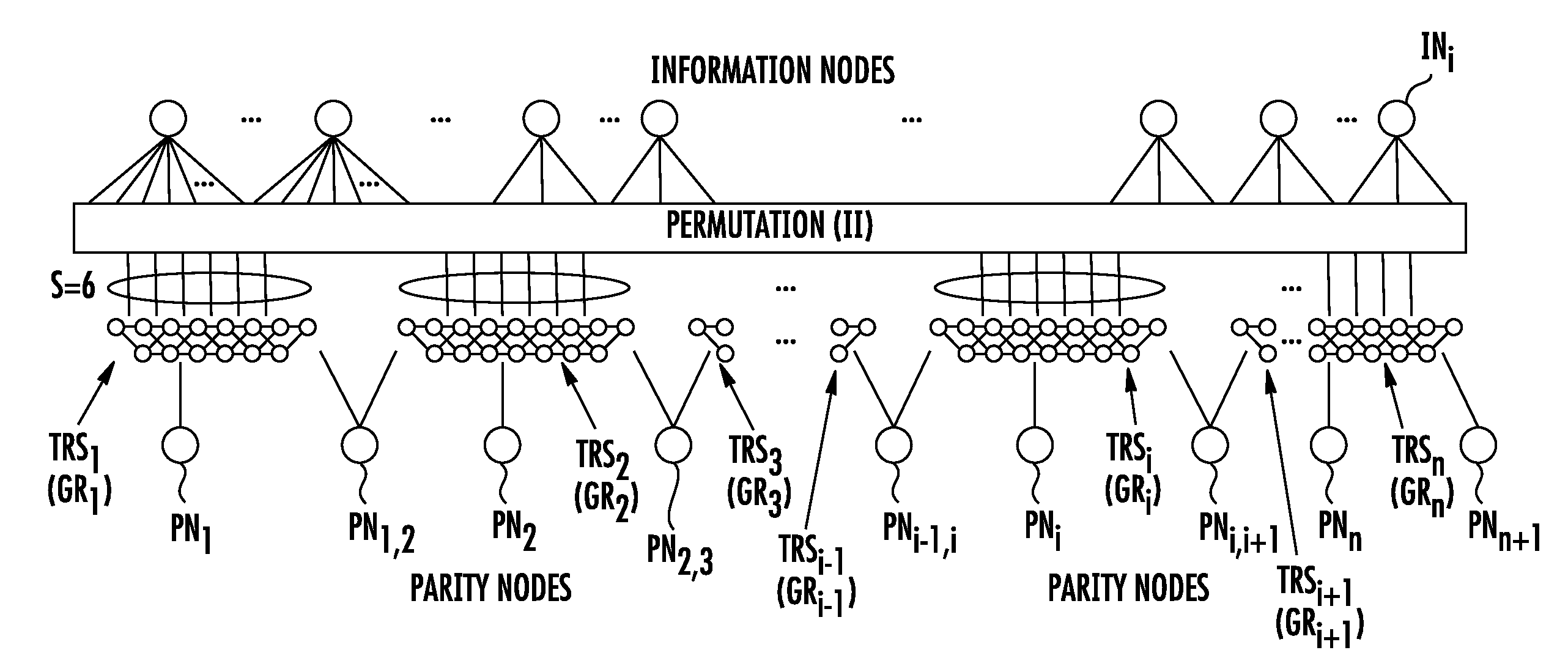

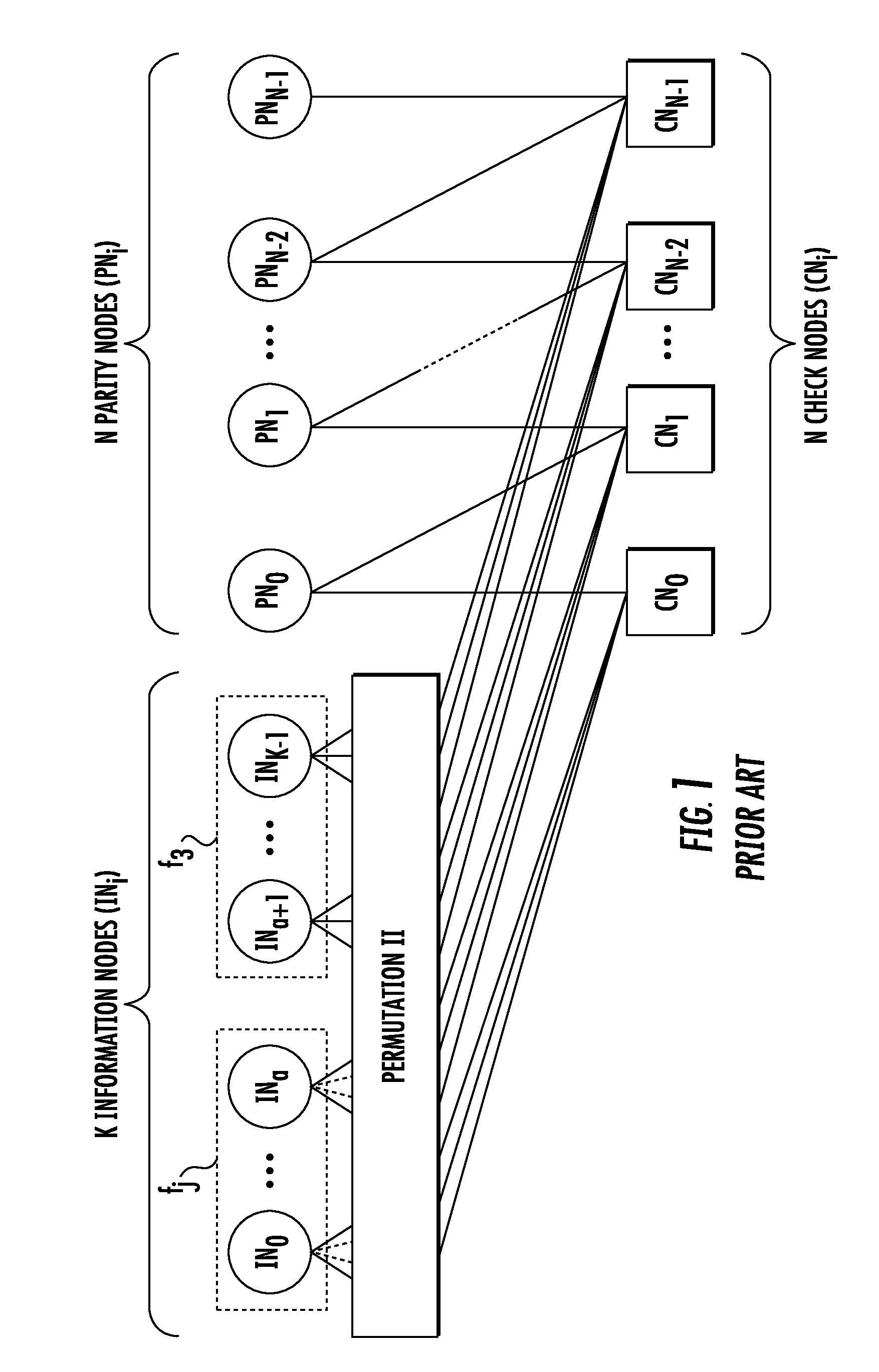

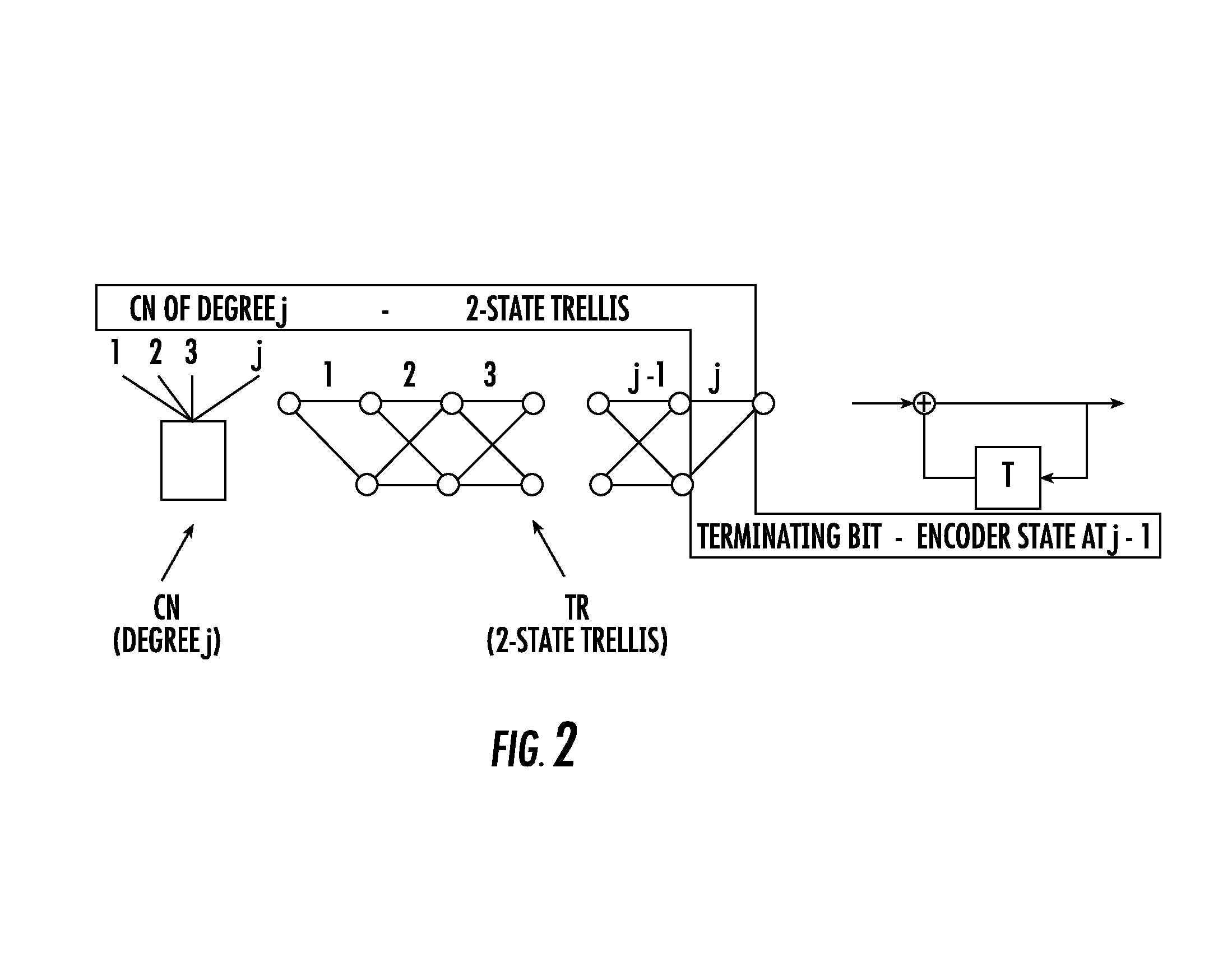

Method and device for decoding LDPC encoded codewords with a fast convergence speed

ActiveUS8196005B2Fast convergenceImprove conversion speedData representation error detection/correctionCode conversionTheoretical computer science

Owner:STMICROELECTRONICS INT NV

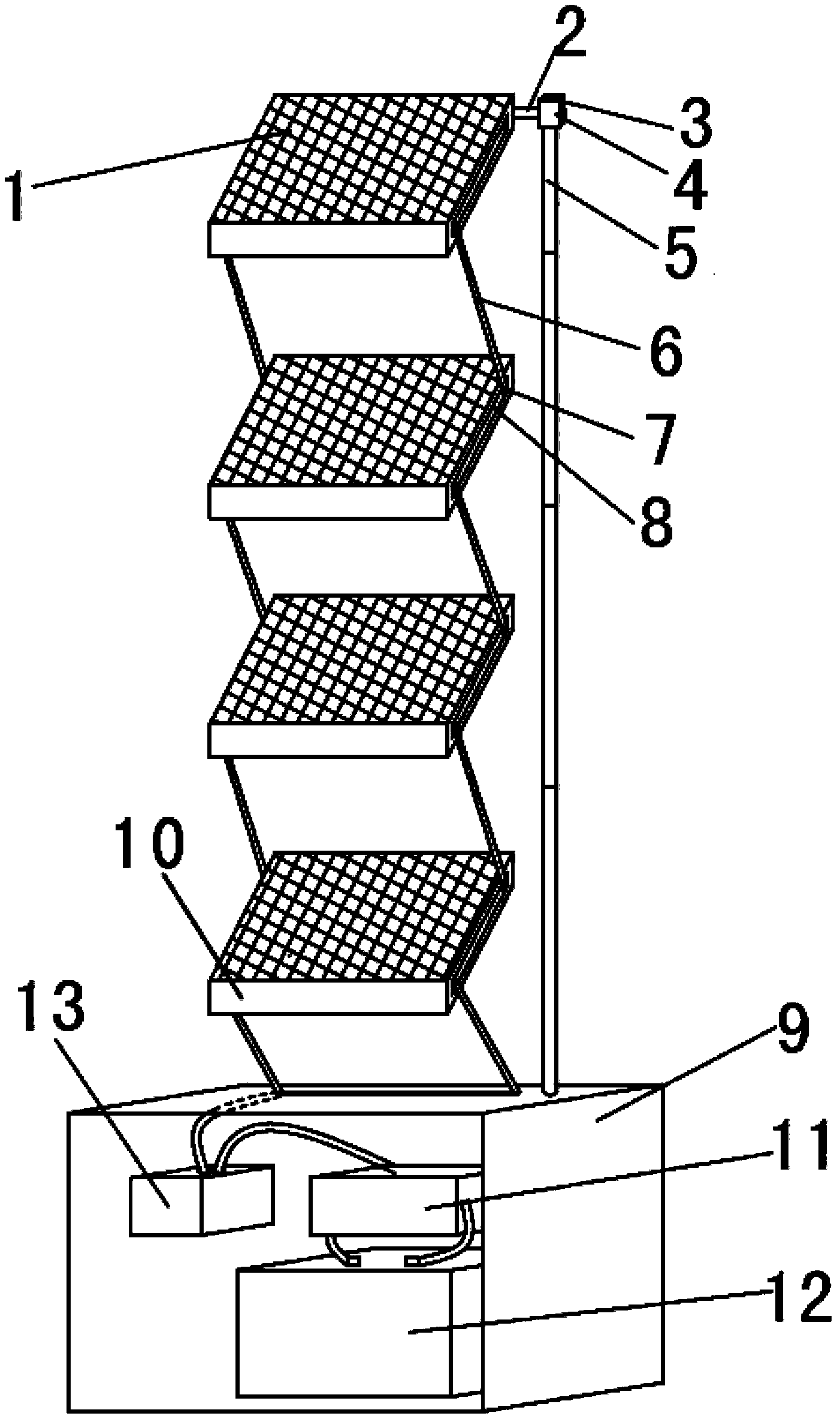

Foldable optical energy charger

InactiveCN103580078AImprove conversion efficiencyImprove conversion speedBatteries circuit arrangementsPhotovoltaicsEngineeringOptical energy

The invention discloses a foldable optical energy charger which comprises solar energy panels, a control box and a supporting rod, fixed folding rods are arranged on the two sides of each solar energy panel, rotating shafts are arranged at the two ends of each fixed folding rod, and the adjacent solar energy panels can be connected in an end-to-end mode through movable folding rods arranged on the rotating shafts. The first-level solar energy panel is arranged on the control box, and a controller, a DC-AC inverter and a storage battery are arranged in the control box and electrically connected in sequence. The foldable optical energy charger is used for solving the problems that an existing solar energy charger is low in conversion rate, and portability and conversion rate can not be taken into account, and is simple in structure, convenient to carry, high in conversion rate and conversion speed, capable of collecting optical energy faster and suitable for popularization and implementation.

Owner:XIAN FORT NEW ENERGY TECH