Patents

Literature

671 results about "Decision circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

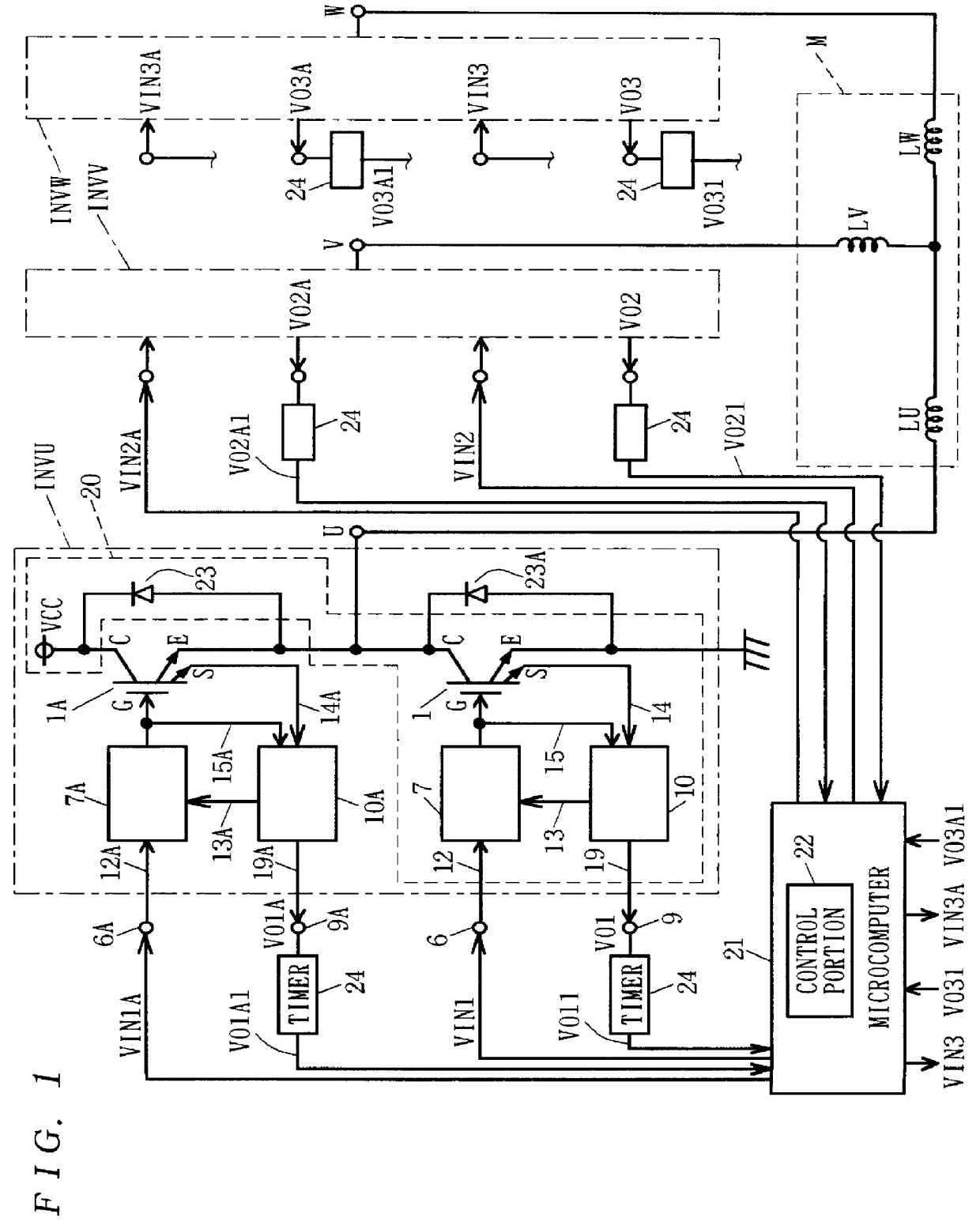

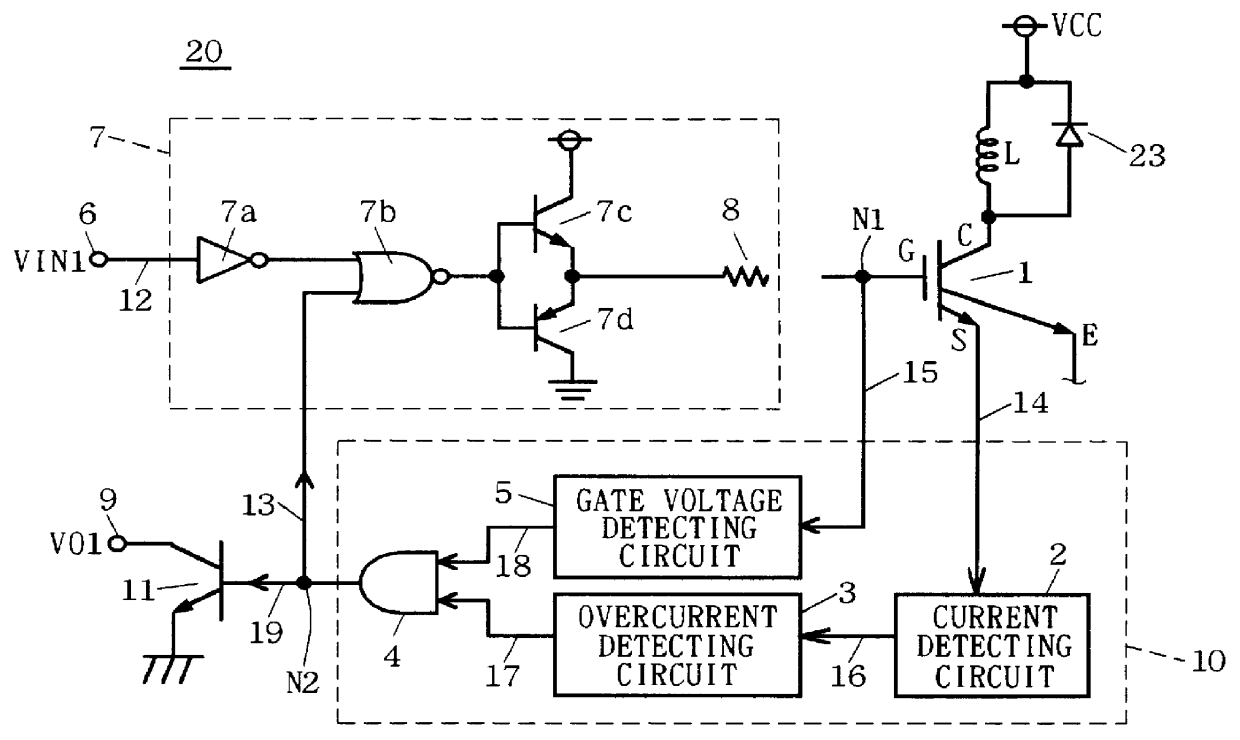

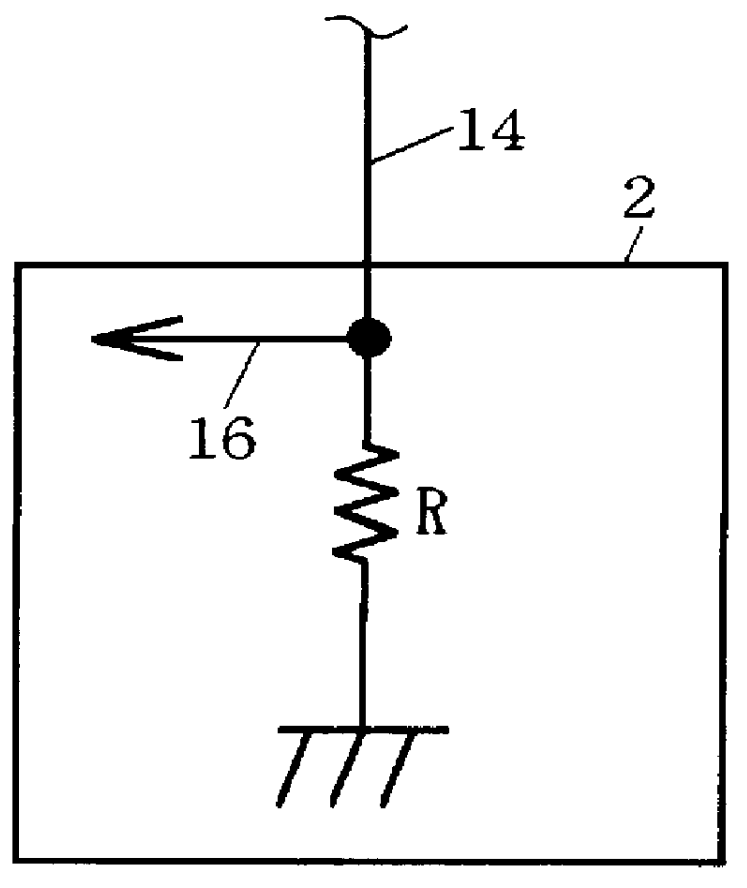

Semiconductor circuit and power transistor protection circuit

A decision circuit (10) monitors a main current flowing in an IGBT (1), and when operation of the IGBT (1) enters an overcurrent state and the control voltage applied to the control terminal (G) of the IGBT (1) is equal to or larger than the threshold voltage, it determines that the IGBT (1) is in the overcurrent state and places the IGBT (1) in an OFF state, and also outputs the result of the determination as an output signal to an external microcomputer from an error output terminal (9). Receiving this output signal, the microcomputer immediately fixes driving signals for the IGBT (1) and another IGBTs at an OFF signal level to disconnect these IGBTs, thus preventing the main current of the IGBT (1) from increasing to a still larger overcurrent to protect the IGBT (1). Generation of a turn-off surge voltage is suppressed in the overcurrent state by detecting the overcurrent state of the power transistor by earlier timing.

Owner:MITSUBISHI ELECTRIC CORP

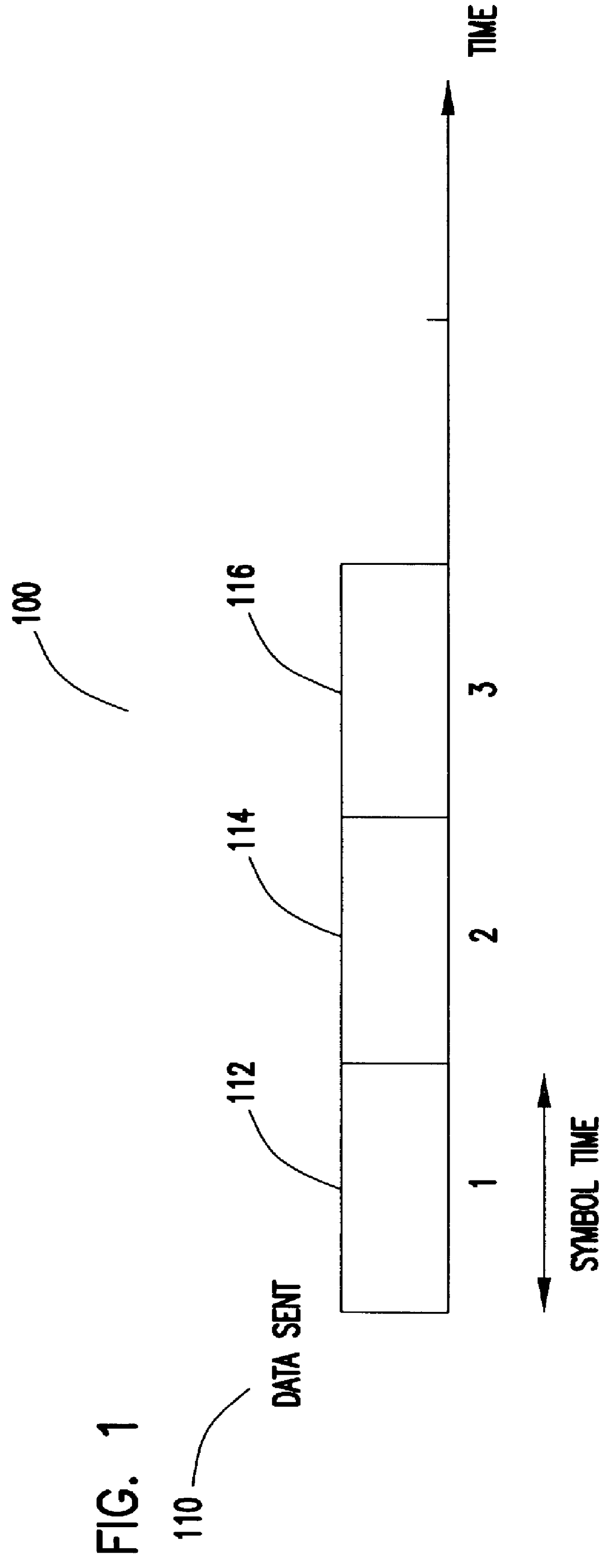

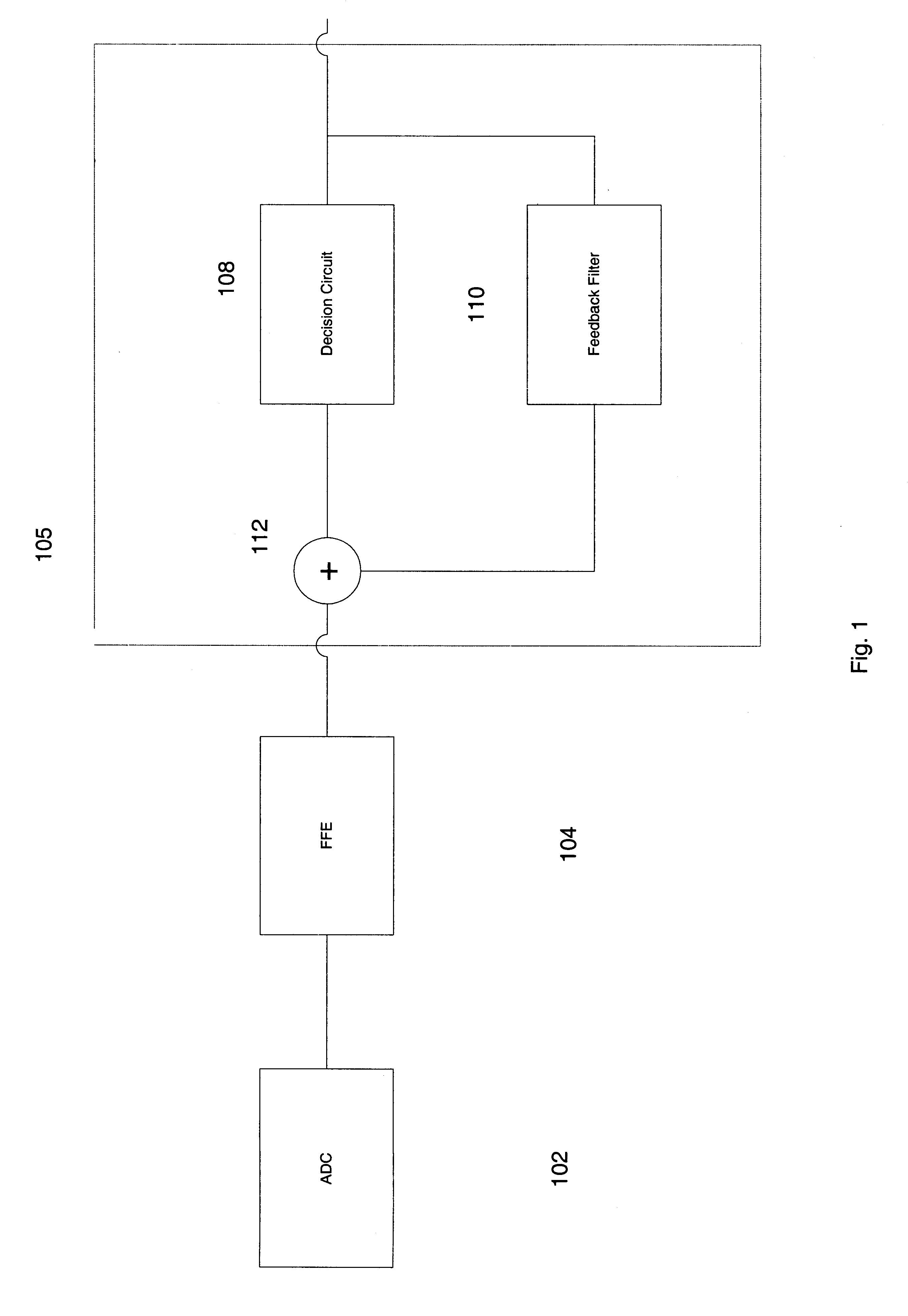

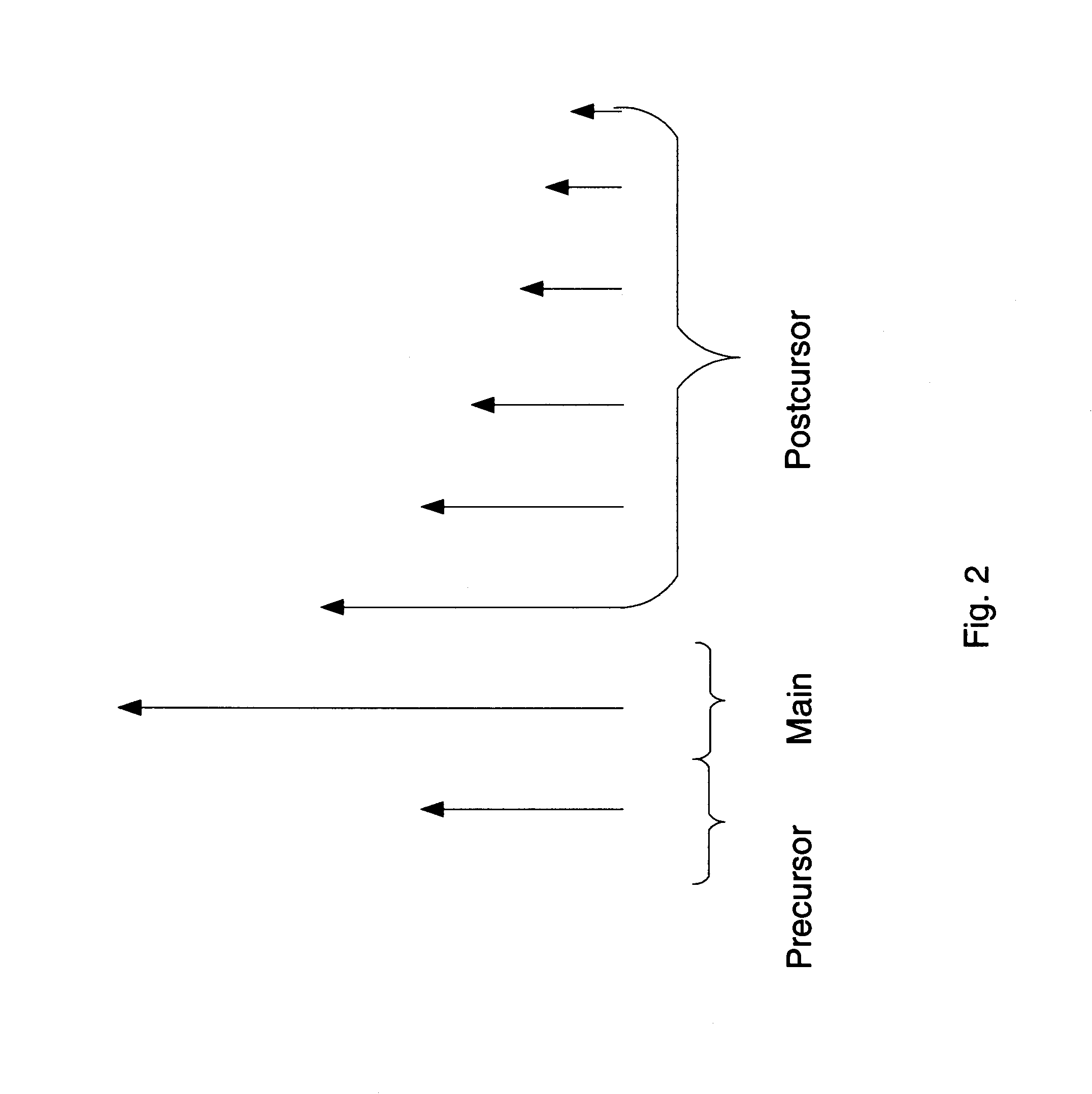

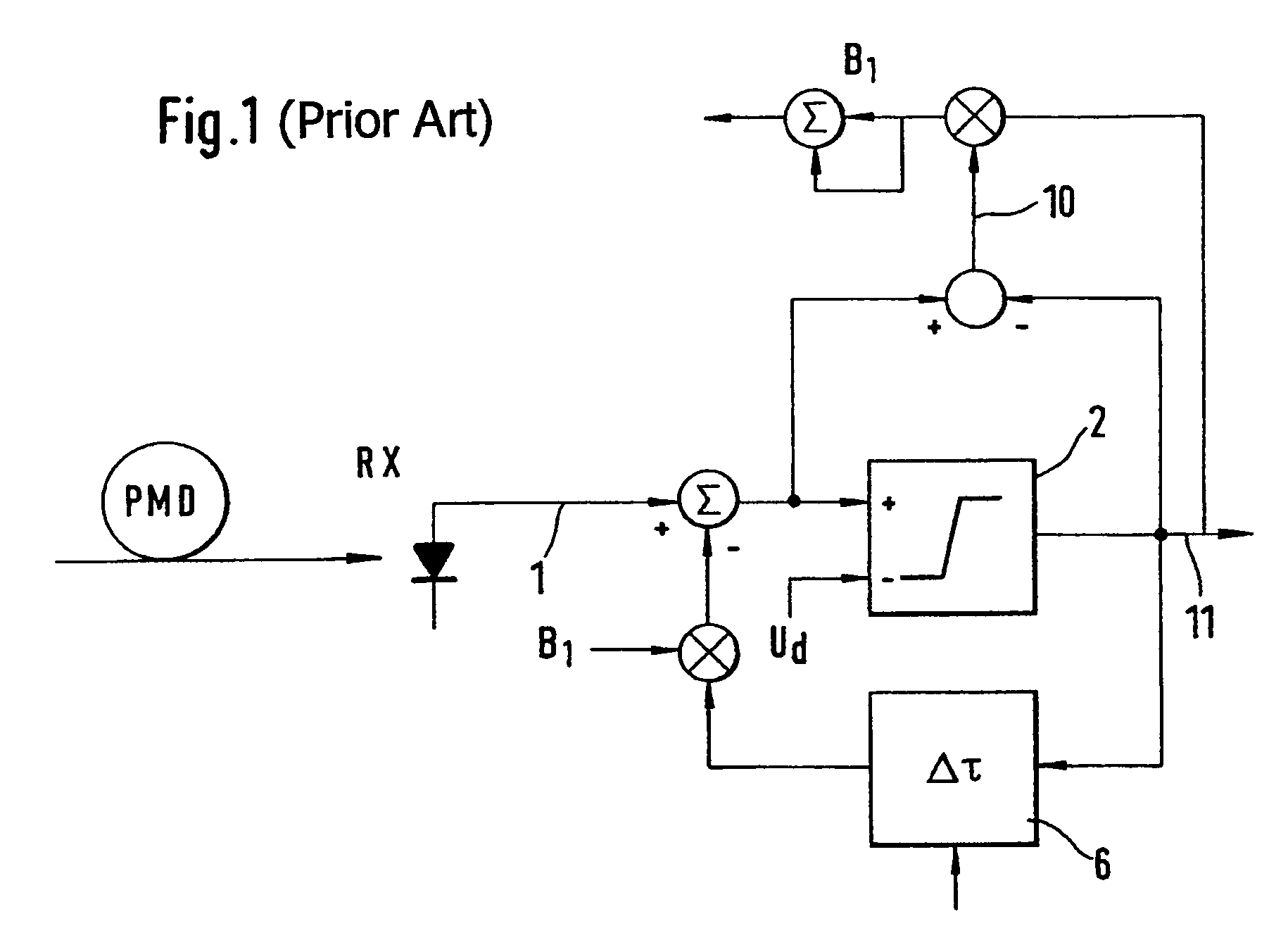

Adaptive equalizers and methods for carrying out equalization with a precoded transmitter

InactiveUS6167082AEliminateEliminate interferenceMultiple-port networksTransmission control/equlisationDecision circuitEqualization

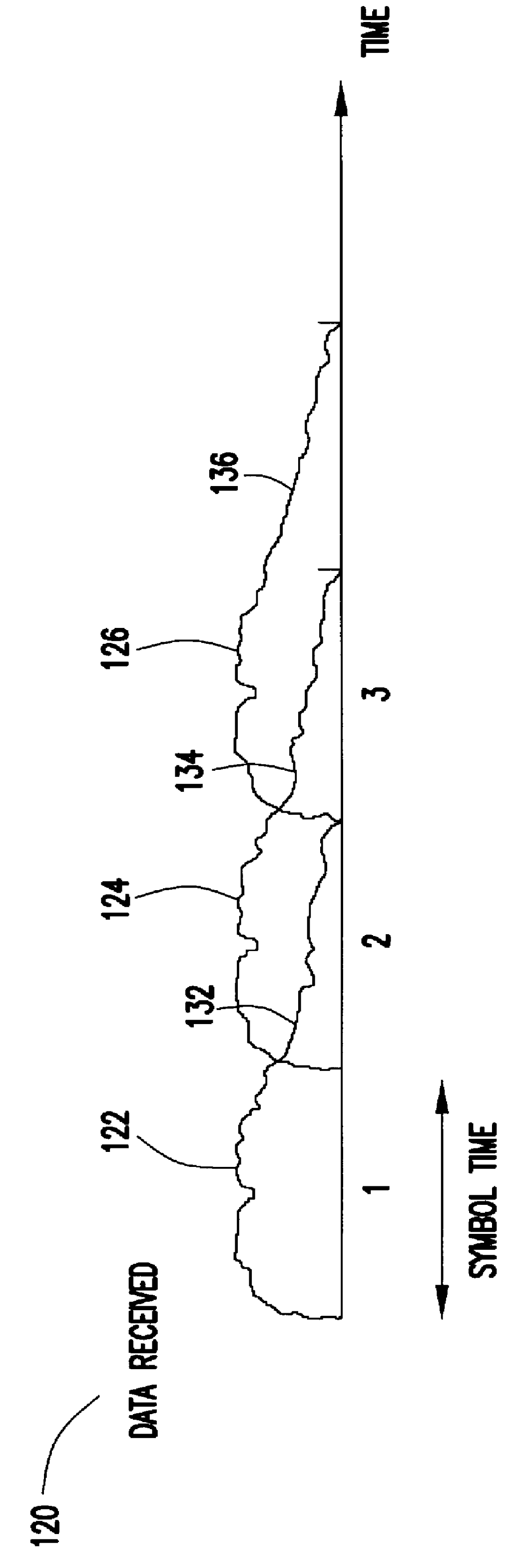

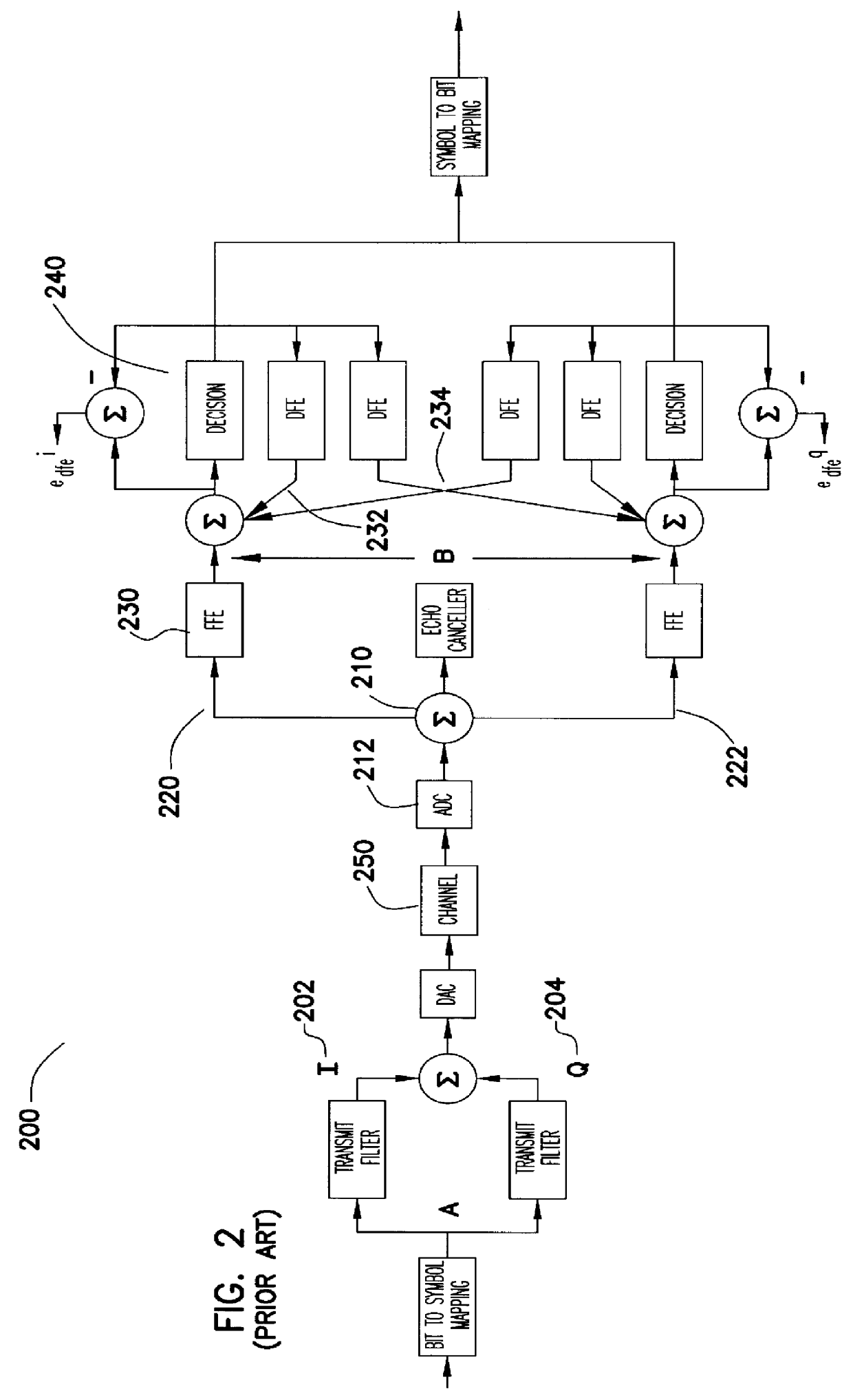

Adaptive equalization methods and adaptive equalizers used with precoded systems dominated by intersymbol interference (ISI) monitor the output of a DFE and compare it to a reference for updating a precoder in response to the comparison. To accomplish this, an adaptive equalizer includes a feed forward equalizer receiving a signal from a communication channel, the feed forward equalizer equalizing variations in pre-cursor intersymbol interference resulting from changes in characteristics of the channel and providing an output signal to an error correction decoder, a decision circuit, coupled to the feed forward equalizer, for generating error vectors in response to the output signal of the feed forward equalizer and a decision feedback equalizer, coupled to the decision circuit, the decision feedback equalizer monitoring the pre-cursor intersymbol interference of the channel, determining when the transmitter coefficients to the precoder warrant updating, and generating a signal indicating that an update to the transmitter coefficients to the precoder is warranted. The adaptive equalizer farther includes a comparison circuit, the comparison circuit receiving an output from the decision feedback equalizer and comparing the output from the decision feedback equalizer to a reference, the comparison circuit generating the signal indicating that an update to the transmitter coefficients to the precoder is warranted in response to the comparison.

Owner:LEVEL ONE COMM

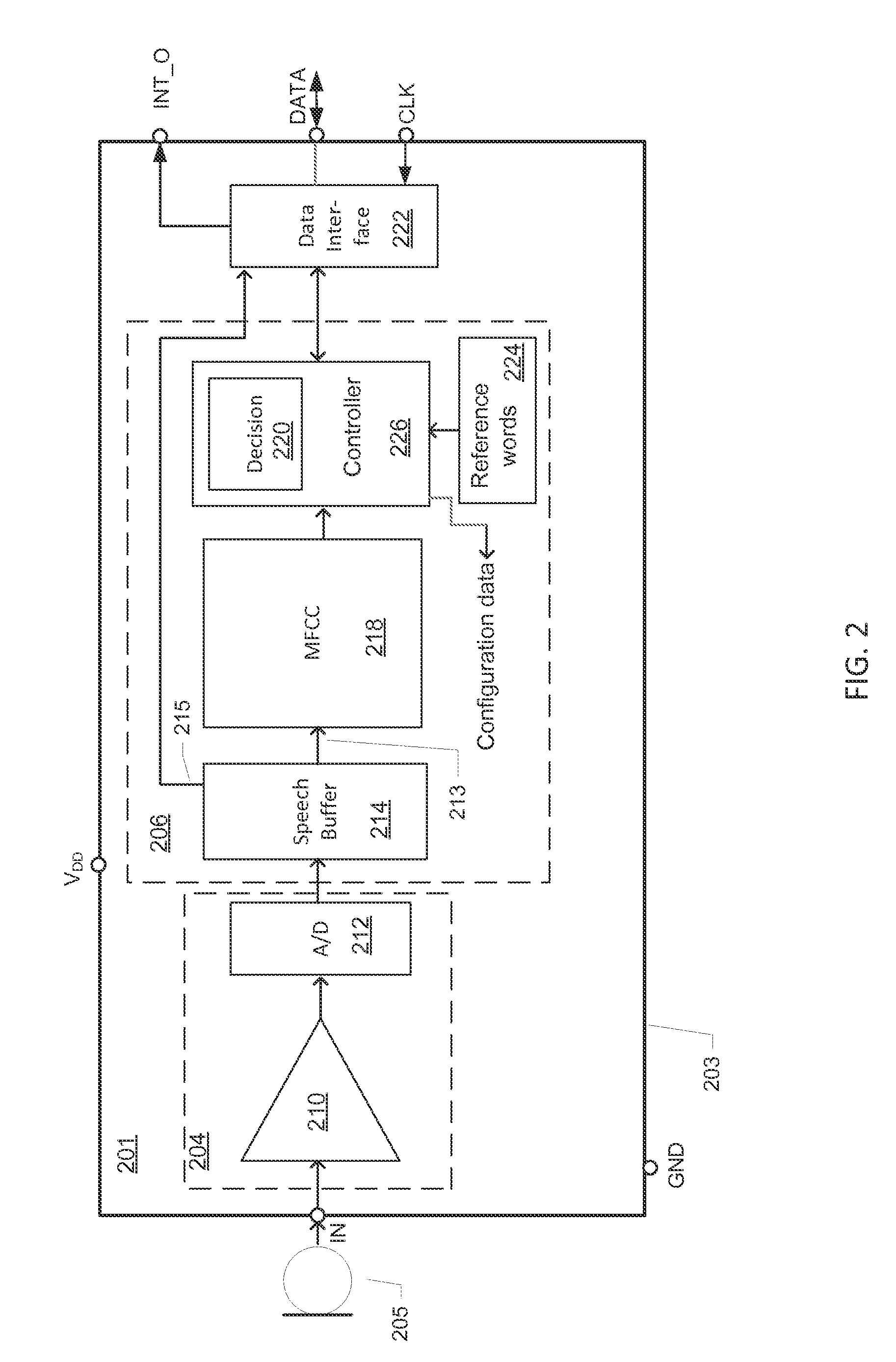

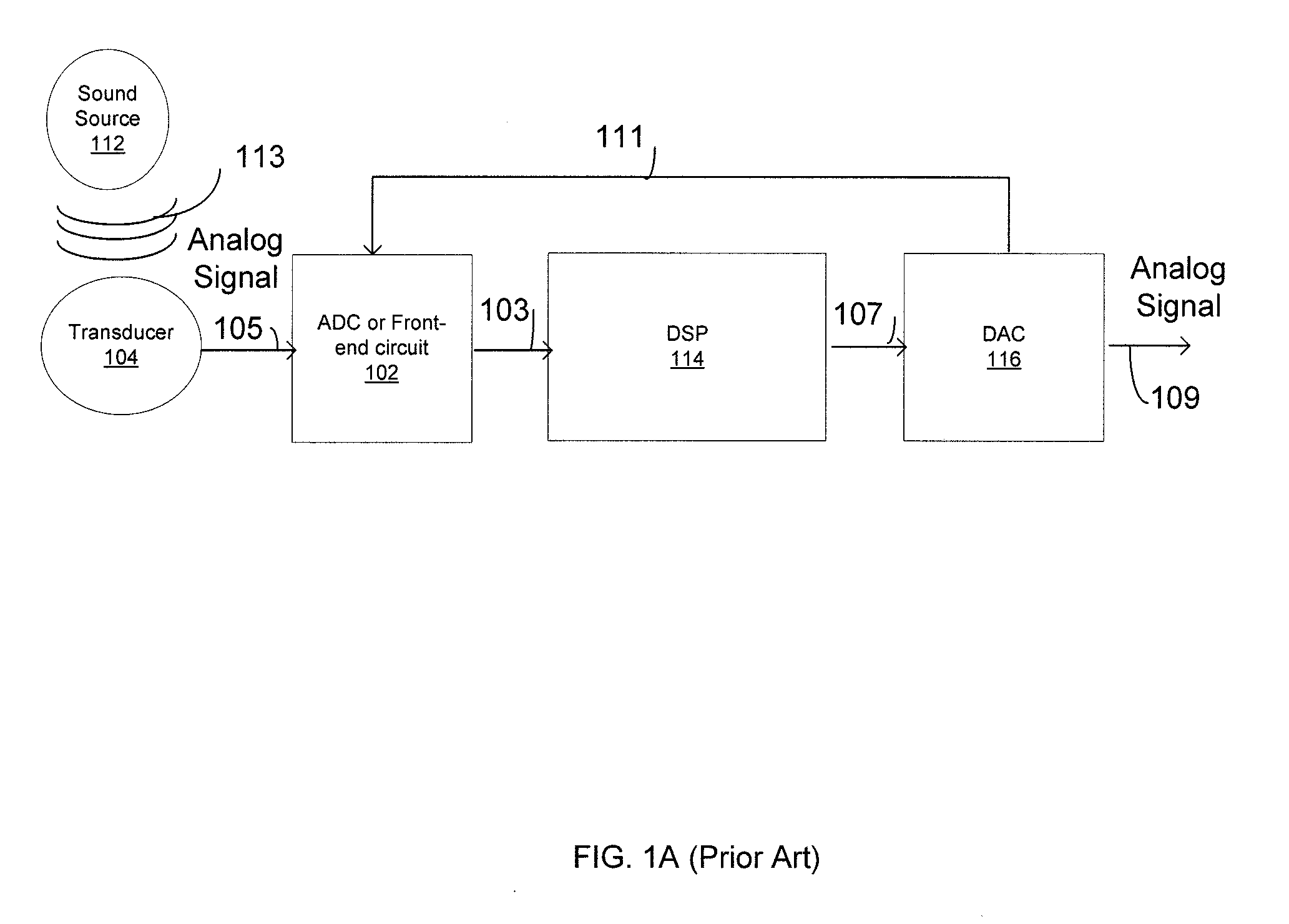

Microphone circuit assembly and system with speech recognition

ActiveUS20140257813A1Reduce consumptionReduce loadHearing aids signal processingSpeech recognitionAnalog-to-digital converterApplication processor

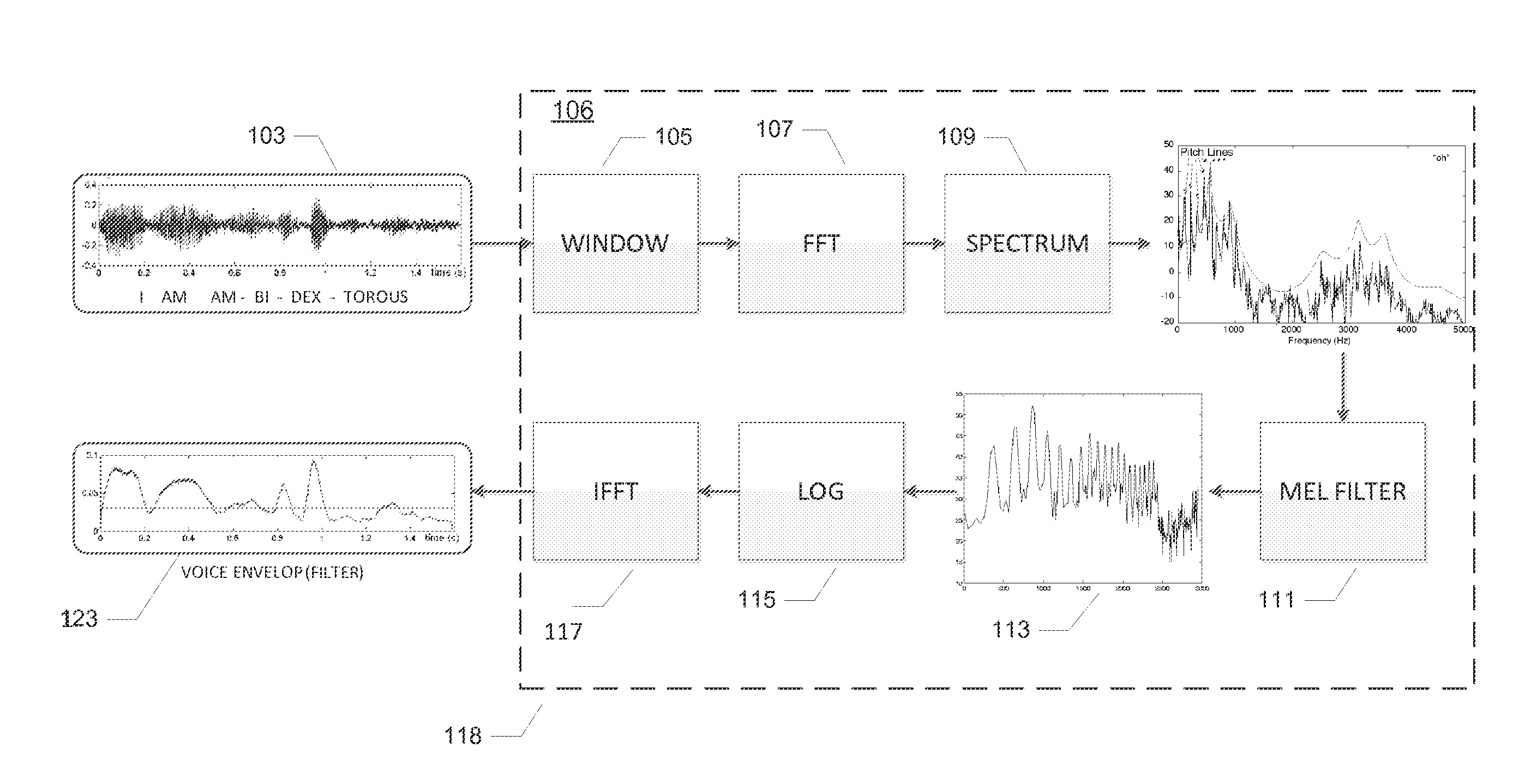

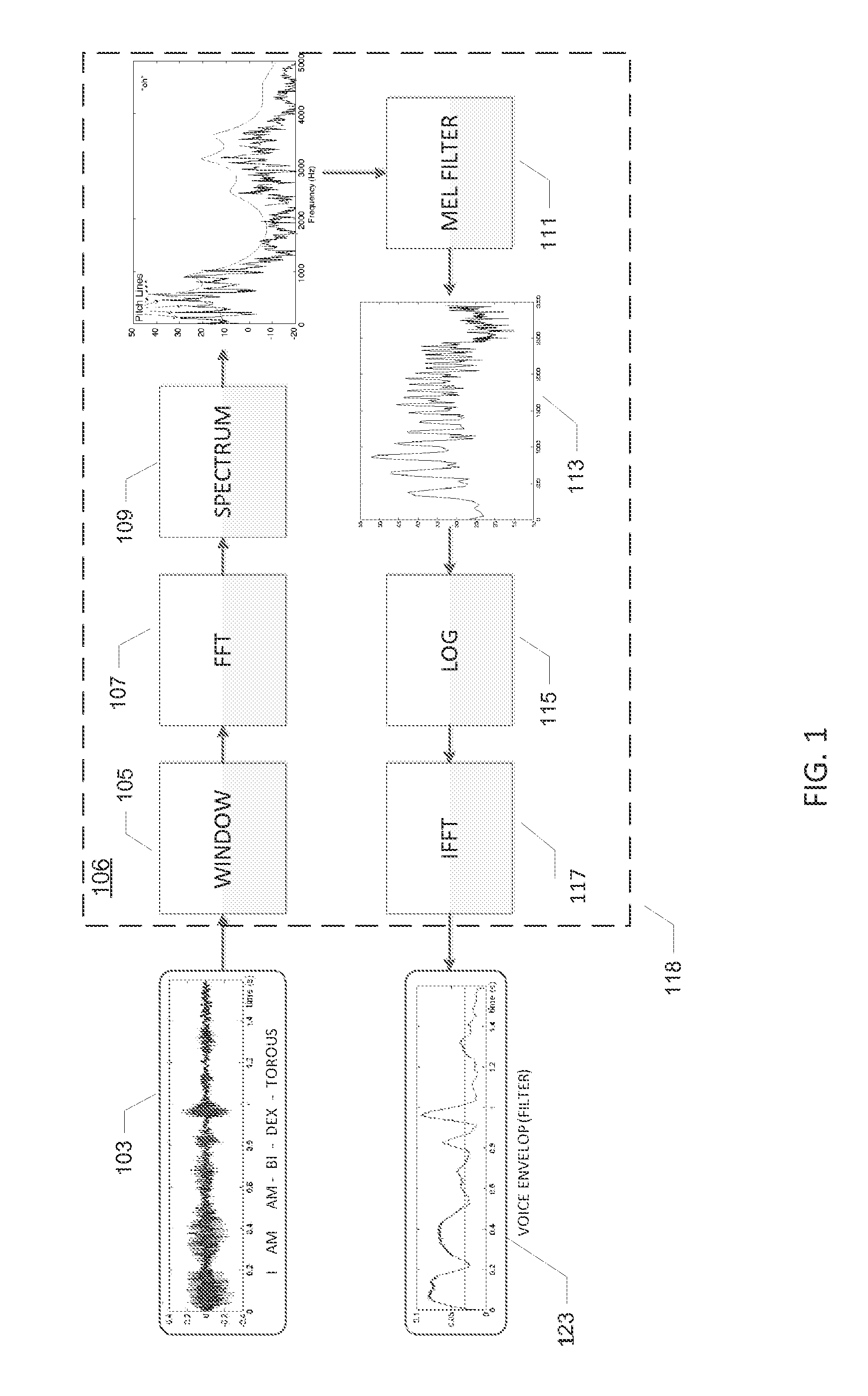

A microphone circuit assembly for an external application processor, such as a programmable Digital Signal Processor, may include a microphone preamplifier and analog-to-digital converter to generate microphone signal samples at a first predetermined sample rate. A speech feature extractor is configured for receipt and processing of predetermined blocks of the microphone signal samples to extract speech feature vectors representing speech features of the microphone signal samples. The microphone circuit assembly may include a speech vocabulary comprising a target word or target phrase of human speech encoded as a set of target feature vectors and a decision circuit is configured to compare the speech feature vectors generated by the speech feature extractor with the target feature vectors to detect the target speech word or phrase.

Owner:ANALOG DEVICES INT UNLTD

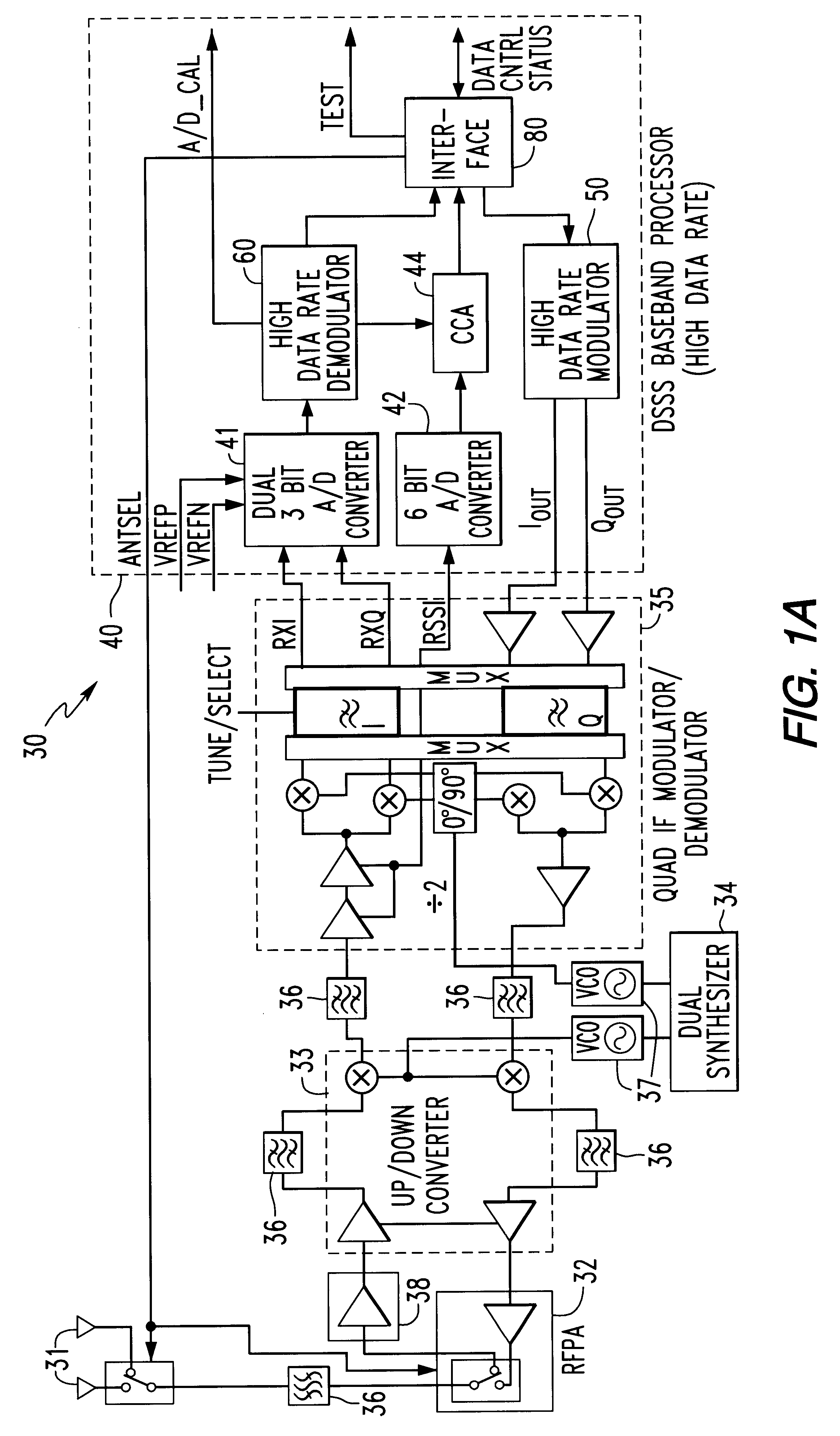

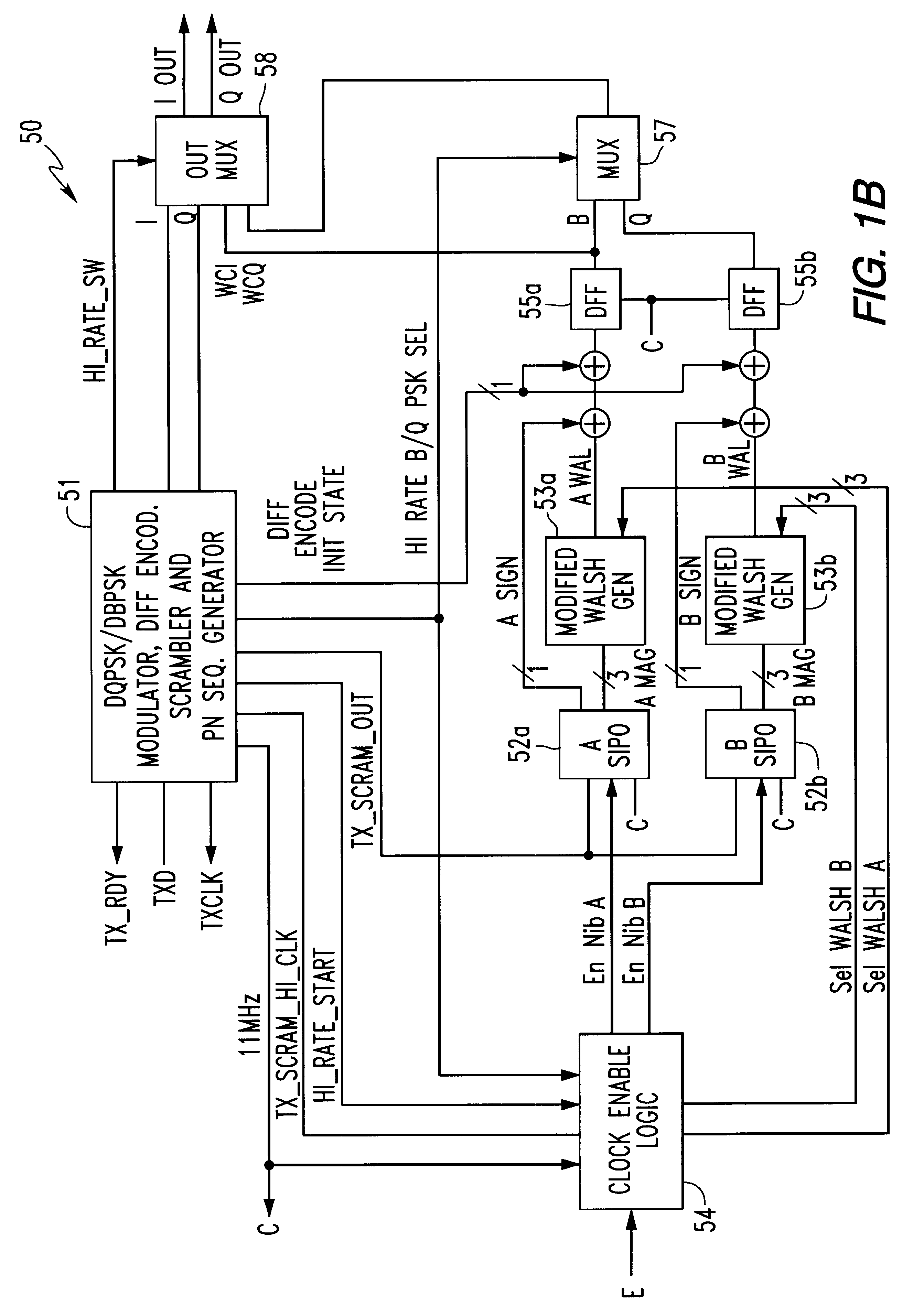

Wireless local area network spread spectrum transceiver with multipath mitigation

InactiveUS6678310B1Spatial transmit diversityNetwork traffic/resource managementFinite impulse responseHigh rate

Owner:HANGER SOLUTIONS LLC +1

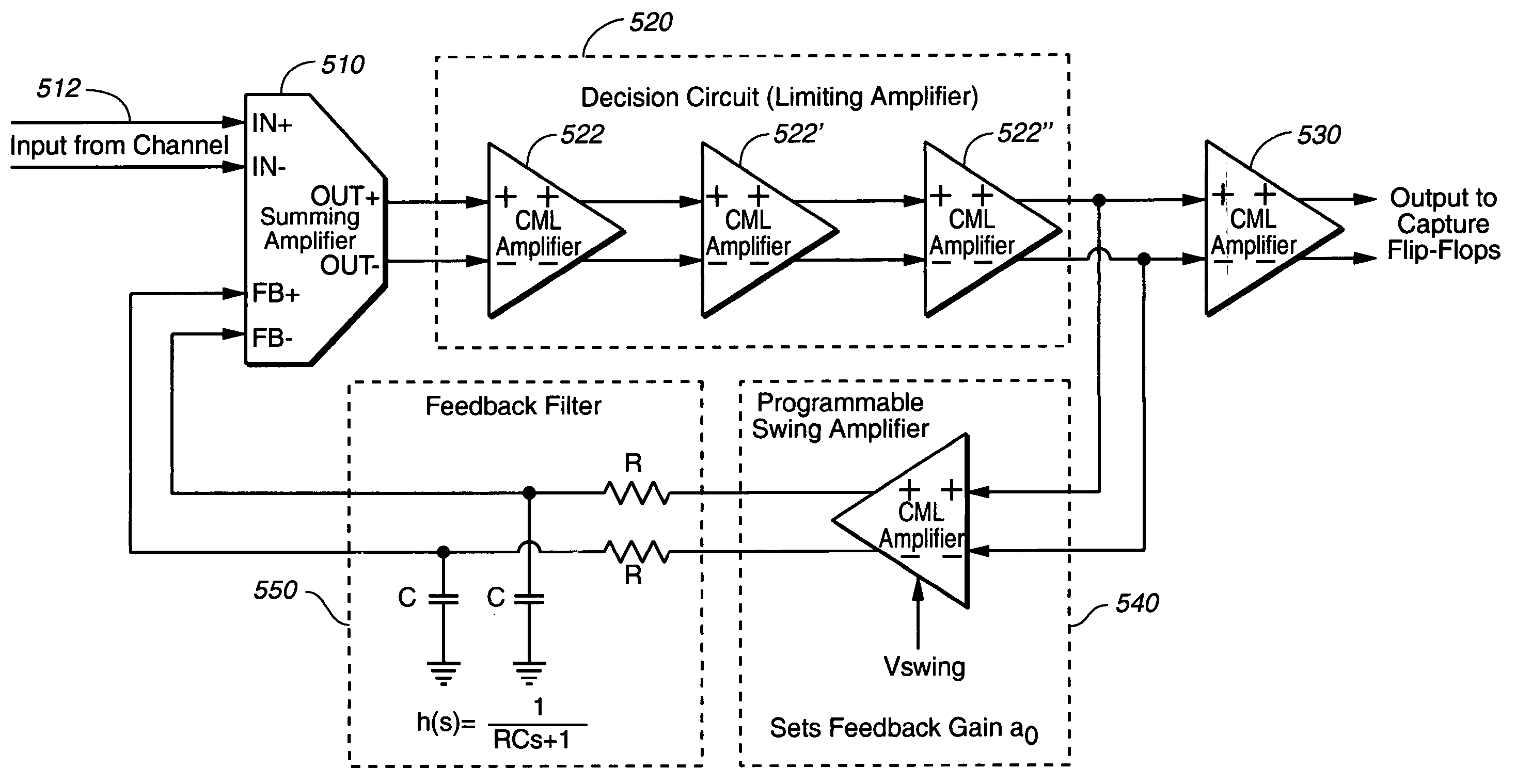

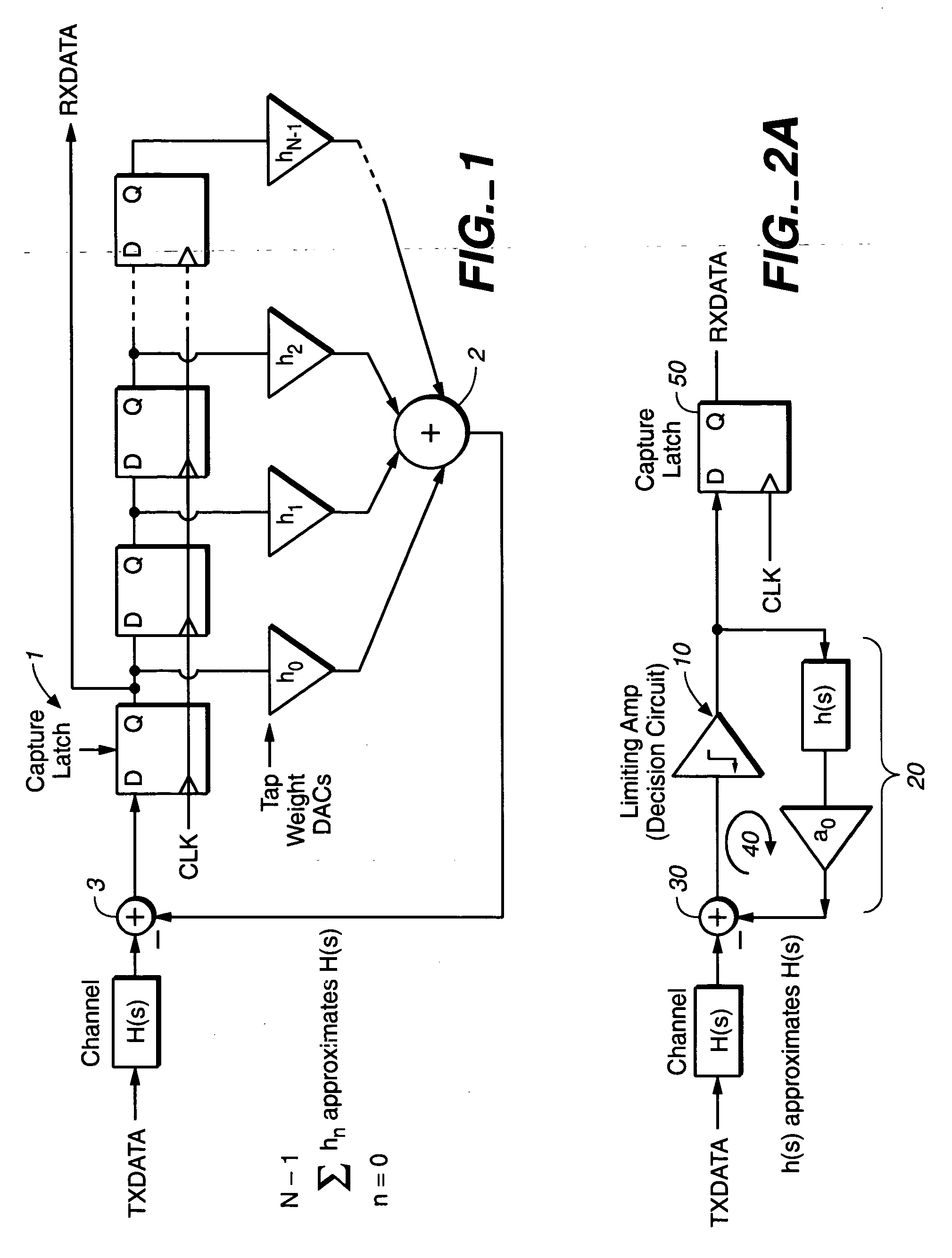

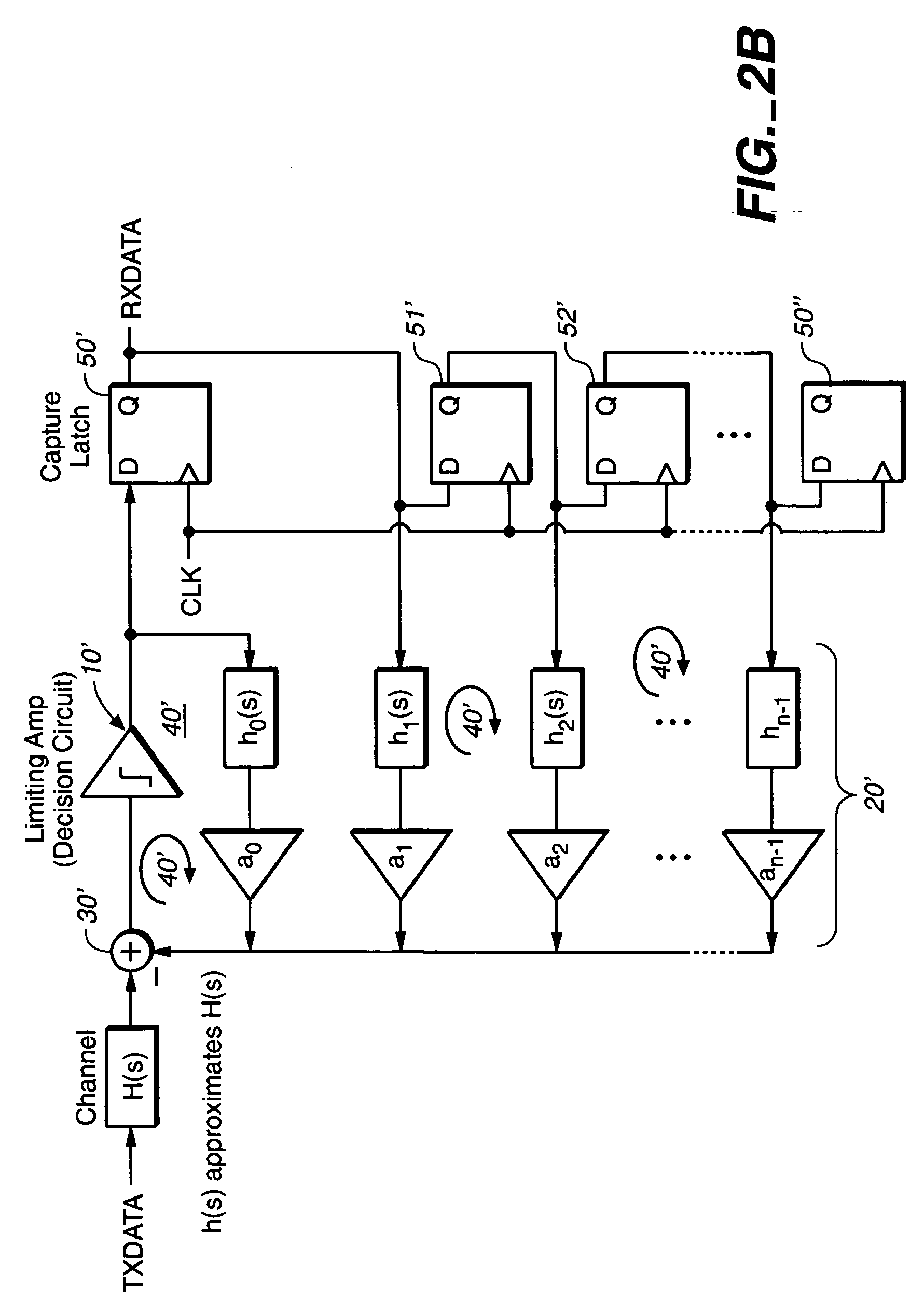

Continuous-time decision feedback equalizer

ActiveUS20060239341A1Low costSimple circuitMultiple-port networksDelay line applicationsNegative feedbackDecision circuit

A continuous-time domain Decision Feedback Equalizer (DFE) for use in a serial communication channel comprises in one embodiment a summer, a decision circuit, a capture flip-flop (FF) and an N-th order active filter. The DFE and its active filter operate in continuous time to give improved performance over a discrete-time DFE. In one embodiment involving a first-order active filter, the capture FF is outside the continuous-time negative feedback loop of the DFE and involves a differential signal amplifier. In another embodiment, the capture flip-flop is inside the DFE loop, and in a third embodiment the decision circuit comprises a comparator.

Owner:AVAGO TECH INT SALES PTE LTD

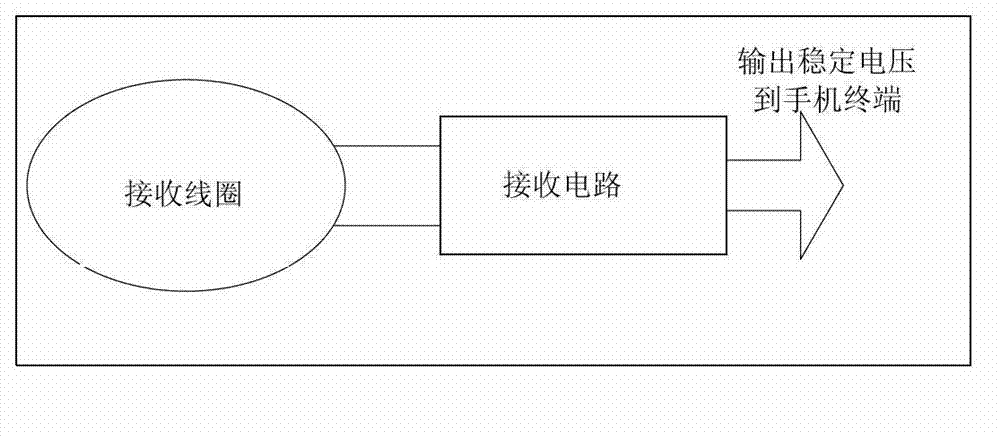

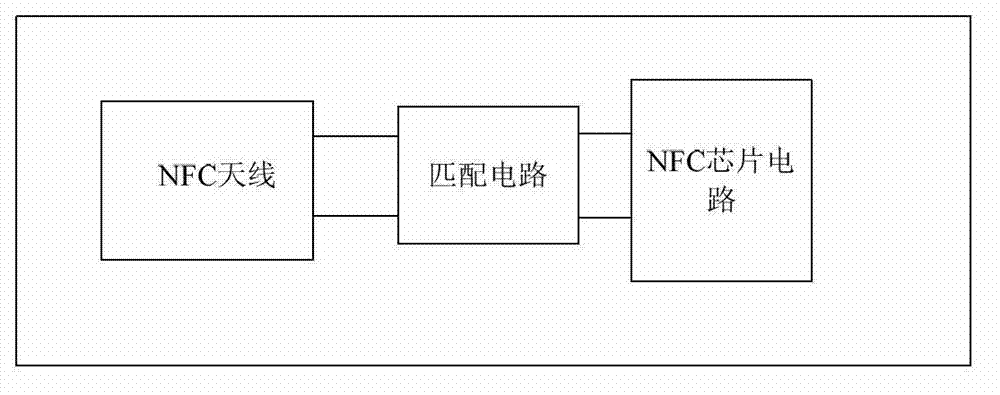

Method and apparatus for achieving compatibility of wireless charging and near field communication (NFC)

ActiveCN102780515AAchieving coexistence and compatibilitySolve the problem of sharing the same coilNear-field transmissionElectromagnetic wave systemDecision circuitComputer terminal

The invention discloses a method and an apparatus for achieving compatibility of wireless charging and near field communication (NFC), wherein the method comprises the steps of setting an antenna which is specially used for receiving a wireless charging signal and an NFC signal on a communication terminal; by a decision circuit module, judging whether the signal which is received currently by the antenna is a wireless charging signal or an NFC signal by the communication terminal; if the currently received signal is a wireless charging signal, transmitting the charging signal received by the antenna to a wireless receiving circuit module of the communication terminal by the decision circuit module, to receive wireless electric energy; if the currently received signal is an NFC signal, implementing communication of an NFC module of the communication terminal via the antenna by the decision circuit module. According to the invention, coexistence and compatibility of the wireless charging and the NFC are effectively achieved; meanwhile, the problem that a coil is shared by the wireless charging and the NFC is solved.

Owner:ZTE CORP

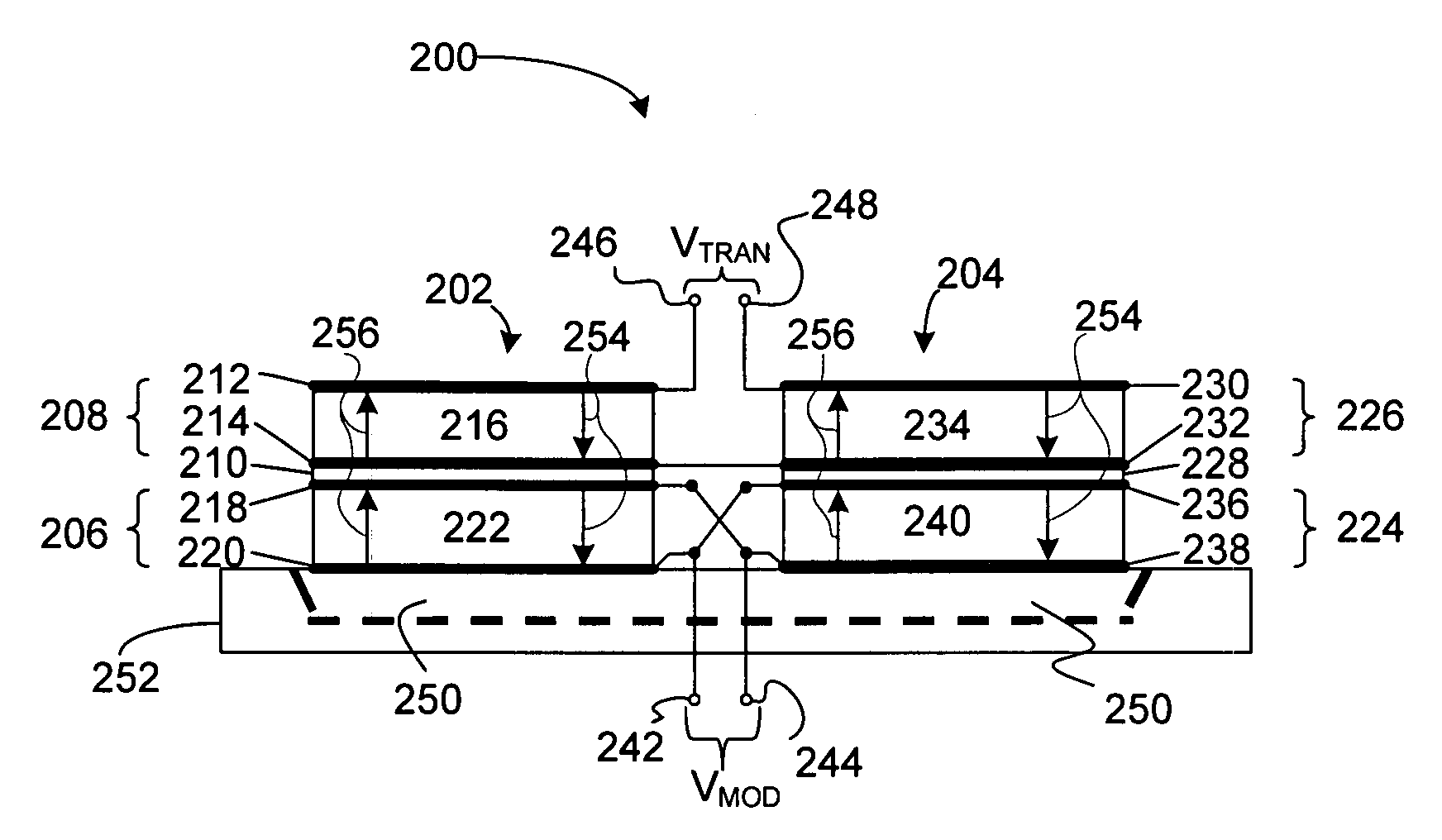

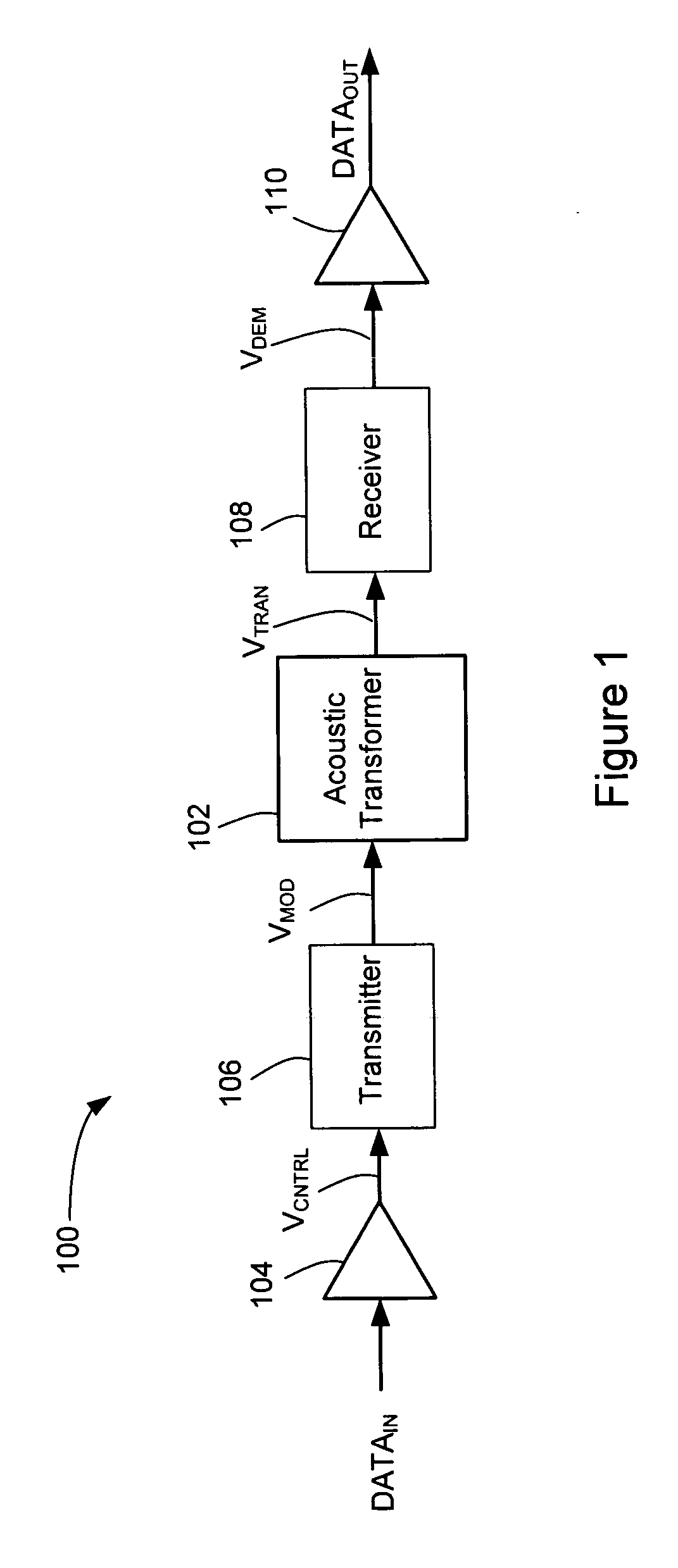

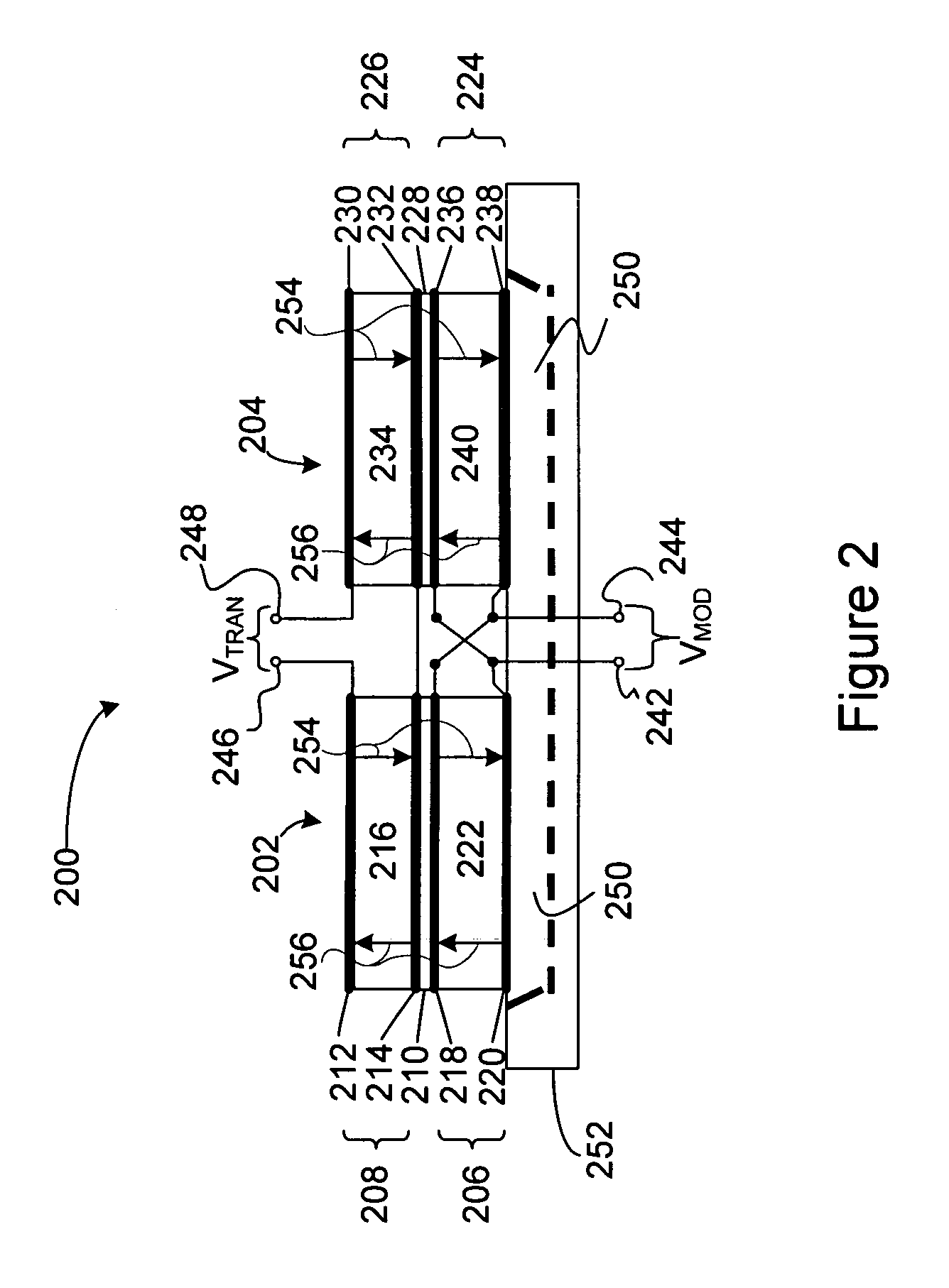

Dual path acoustic data coupling system and method

InactiveUS20070171002A1Non-electrical signal transmission systemsPiezoelectric/electrostriction/magnetostriction machinesDecision circuitEngineering

A data coupler includes first and second acoustic isolation transformers that develop first and second isolated output signals in response to first and second modulated input signals. A first and a second transmitter is coupled to the first and second acoustic isolation transformers to receive a first and a second data input signal and generate the first and second modulated input signal in response to the first and second data input signals. A first and a second receiver is coupled to the first and second acoustic isolation transformers to receive the first and a second isolated output signals and generate first and second demodulated signals responsive to the first and second isolated output signals. An output decision circuit is coupled to the first and second receivers to receive the first and second data output signals and generates a data output signal responsive to the first and second demodulated signals.

Owner:AVAGO TECH INT SALES PTE LTD

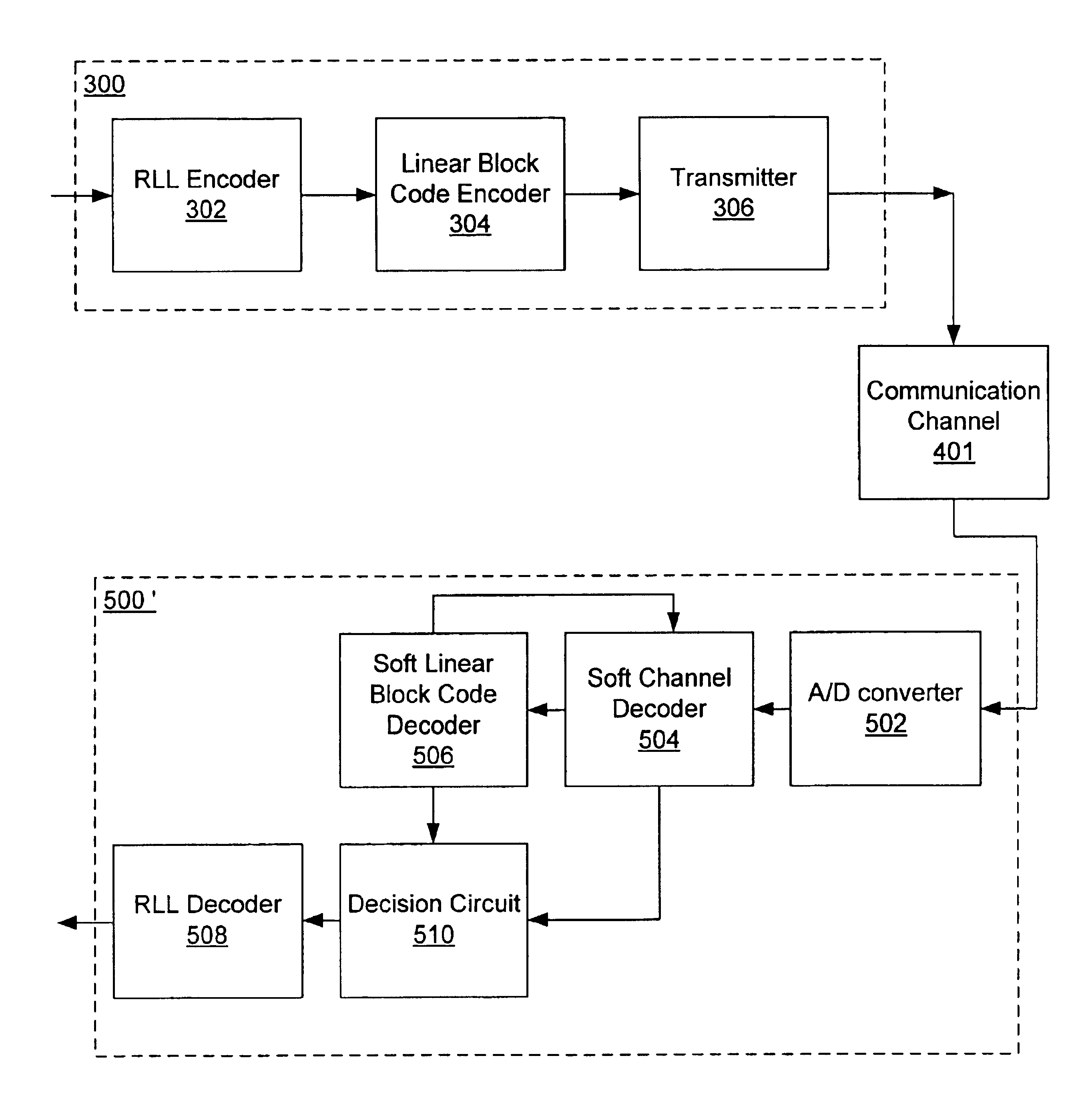

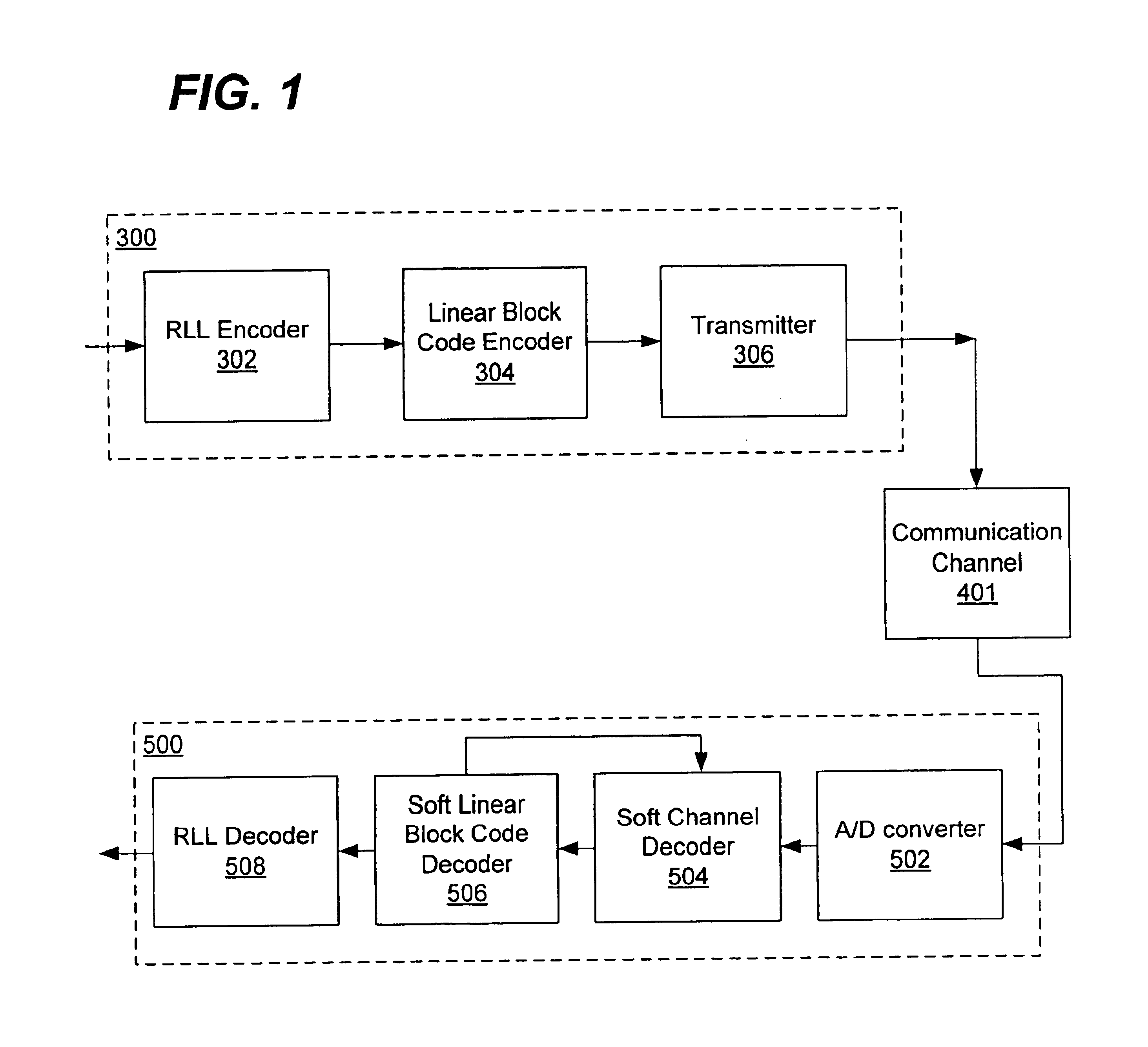

Multi-mode iterative detector

InactiveUS6888897B1Improve accuracyMiniaturizationModification of read/write signalsOther decoding techniquesDecision circuitBlock code

A transmitter is provided for transmitting data to a communication channel and a receiver receives the data from the communication channel. The transmitter comprises an encoder to encode data and a linear block encoder to encode data encoded by the encoder. The receiver comprises a soft channel decoder to decode the data, and a soft linear block code decoder to decode data decoded by the soft channel decoder. In the first iteration, the soft channel decoder decodes data received by the receiver. In succeeding iterations, the soft channel decoder decodes the data received by the receiver and utilizes information from the soft linear block decoder from an immediate preceding iteration. A decision circuit selects an output of the soft linear block decoder if an evaluated criterion is less than a threshold, or an output of the soft channel decoder if the evaluated criterion is greater than the threshold. A decoder decodes an output of the threshold check circuit.

Owner:MARVELL ASIA PTE LTD

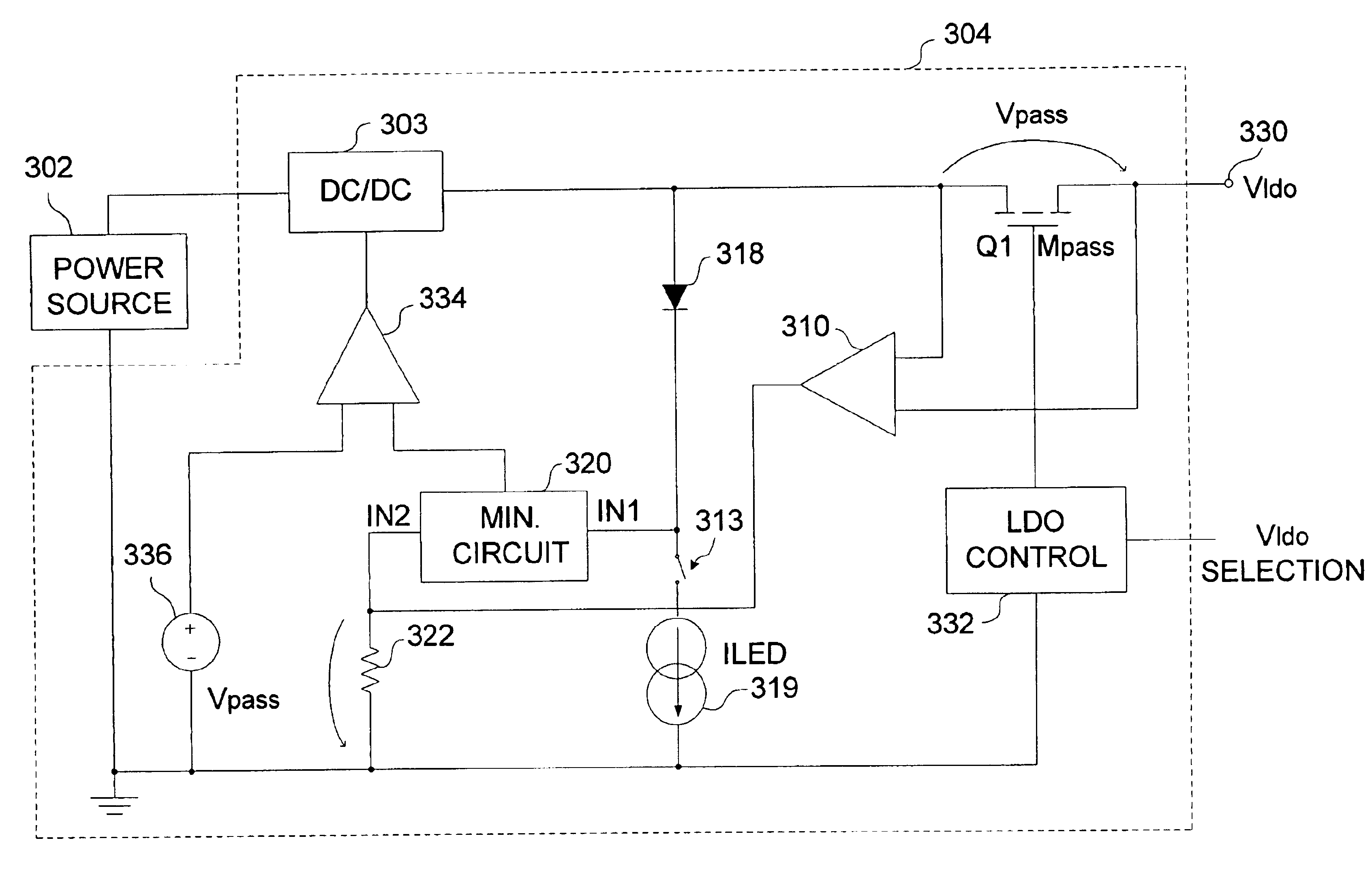

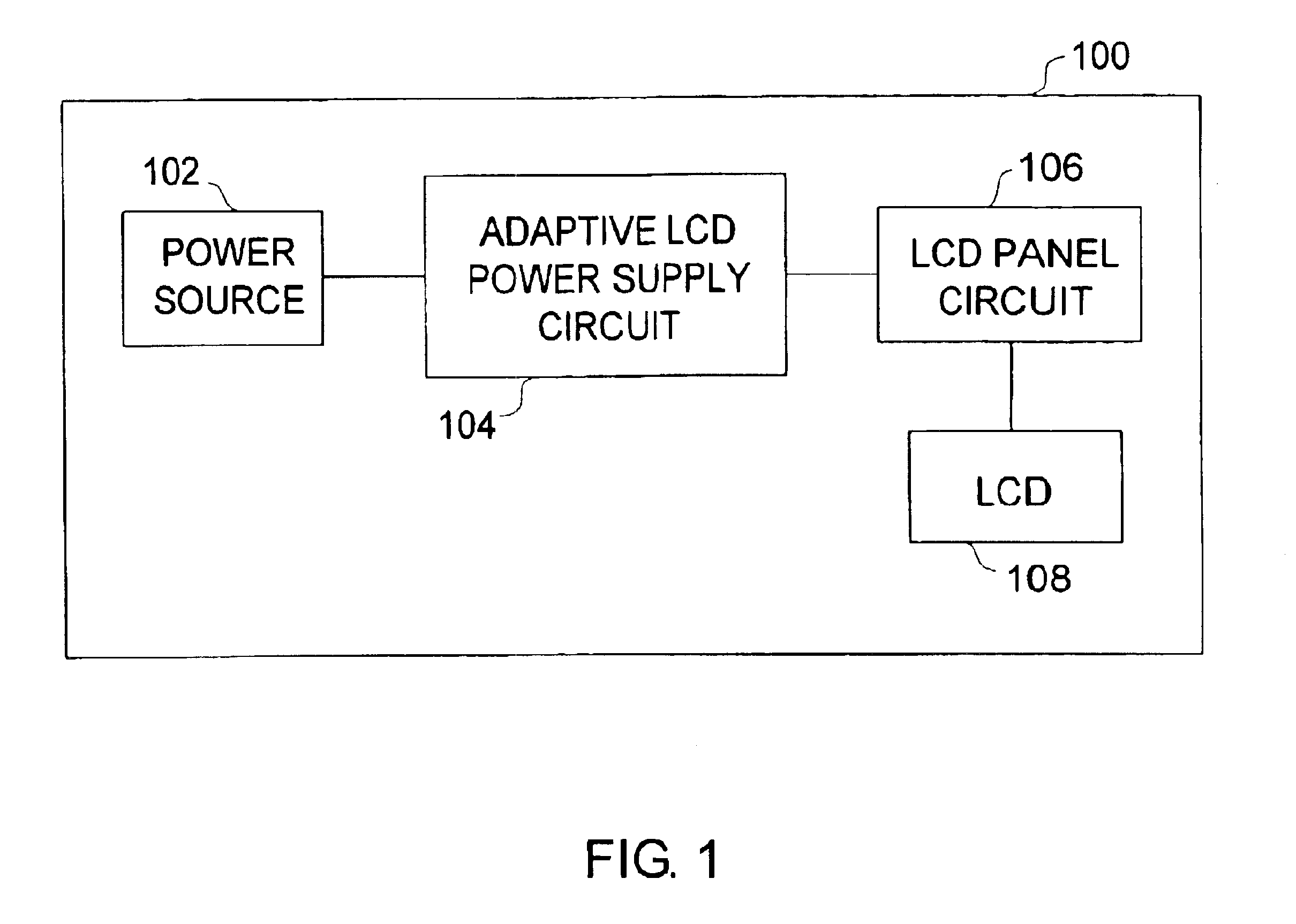

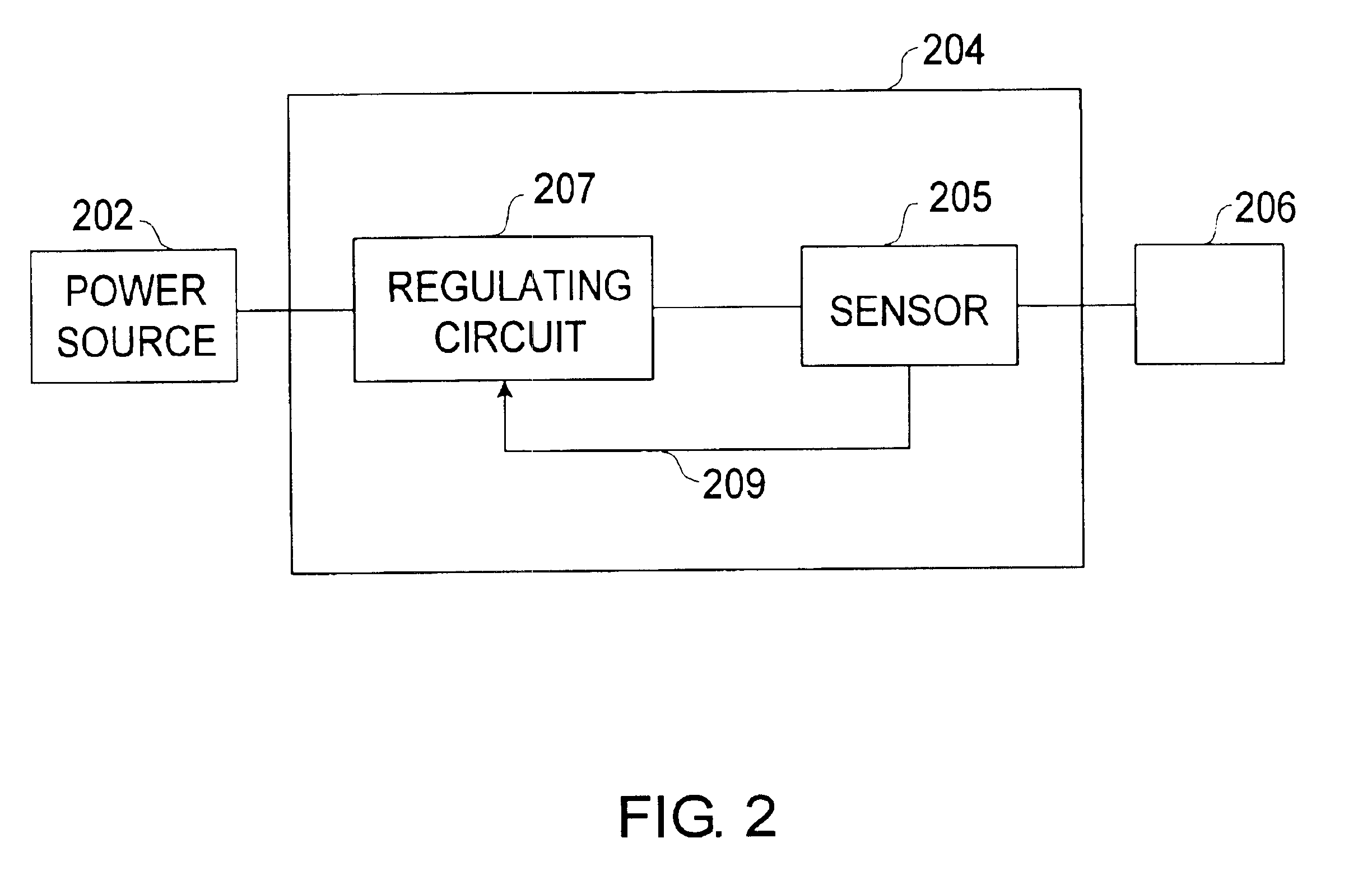

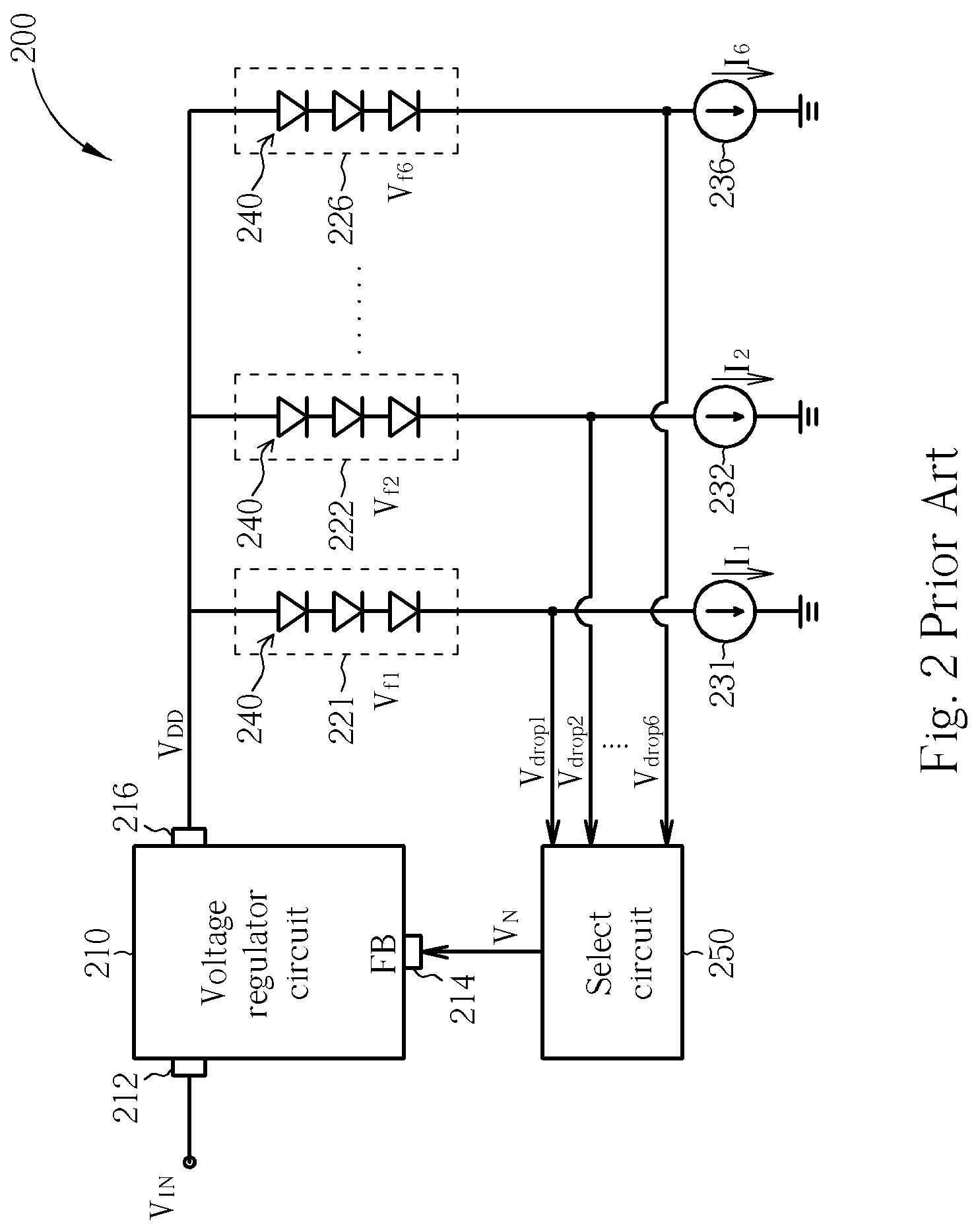

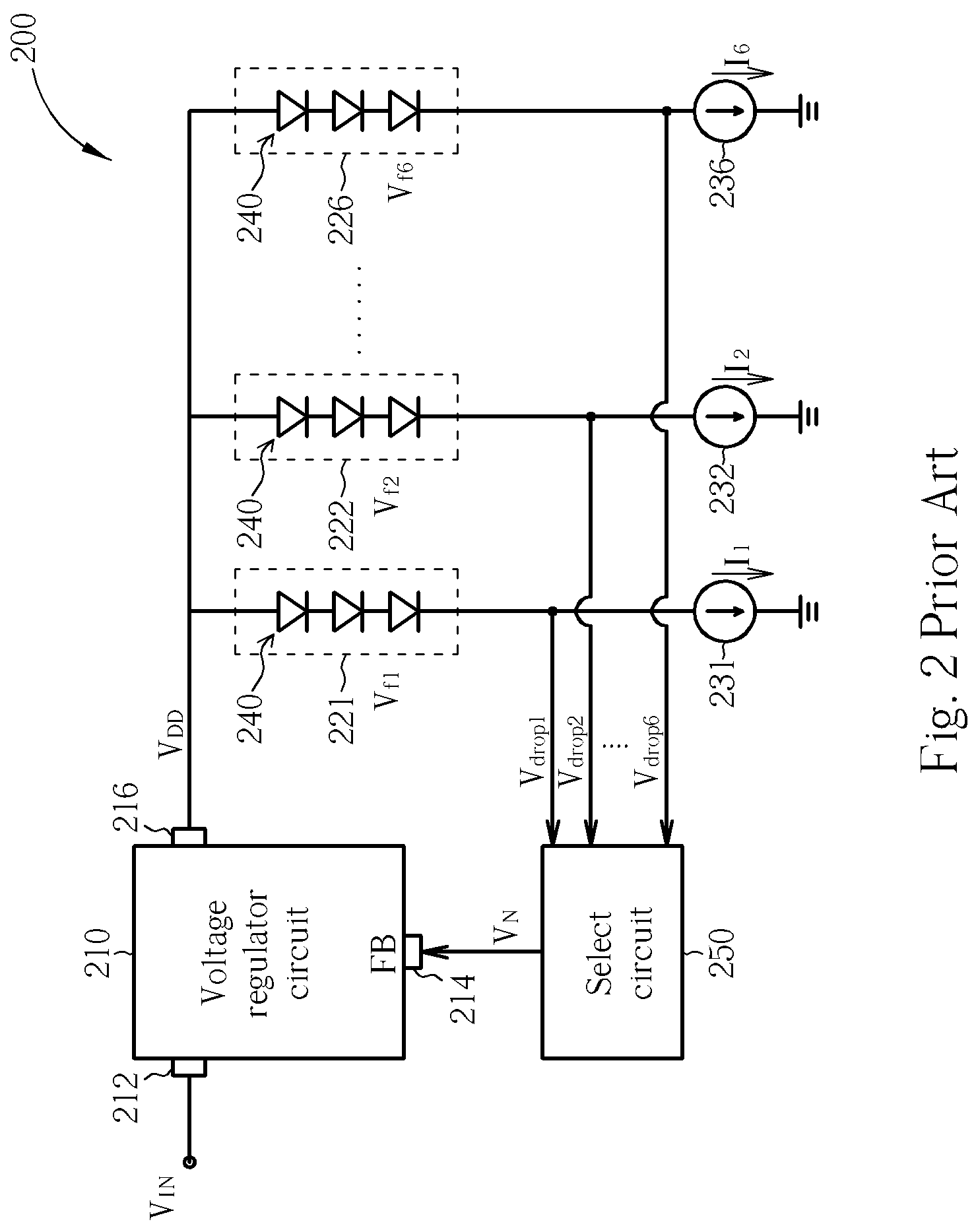

Adaptive LCD power supply circuit

InactiveUS6873322B2Electroluminescent light sourcesCathode-ray tube indicatorsDecision circuitControl signal

An adaptive LCD power supply circuit for adjusting at least one supply parameter in response to at least one load parameter of an associated load includes a feedback path configured to sense at least one load parameter and provide a control signal representative of at least one load parameter, and a regulating circuit configured to accept the control signal and regulate at least one supply parameter based on the control signal. The feedback path may include a first path to provide a first signal representative of a load condition of a first module, and a second path to provide a second signal representative of a load condition of a second load module, and a minimum decision circuit to output a third signal equal to the lesser of the first and second signals. An electronic device including an adaptive LCD power supply circuit is also provided.

Owner:O2 MICRO INT LTD

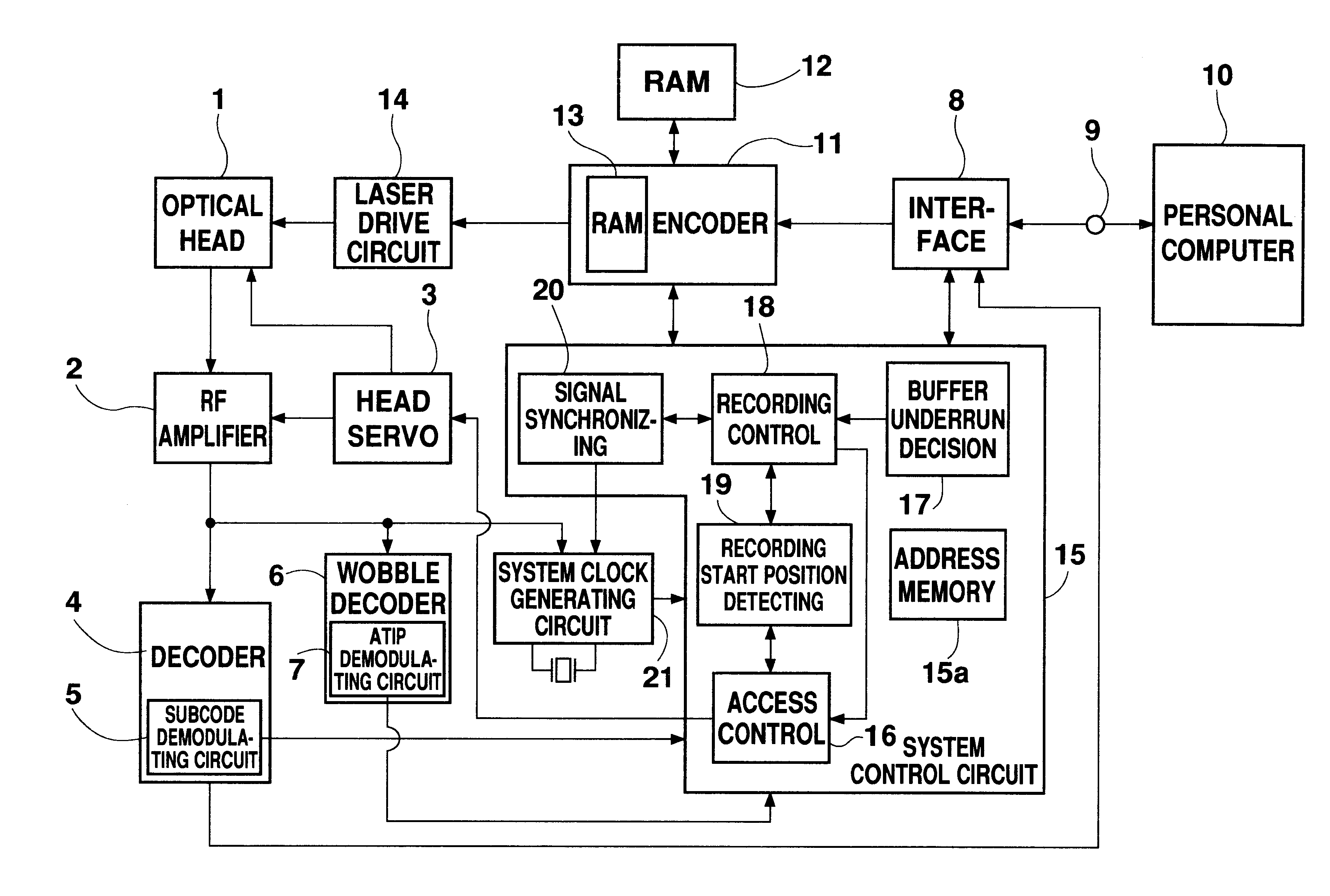

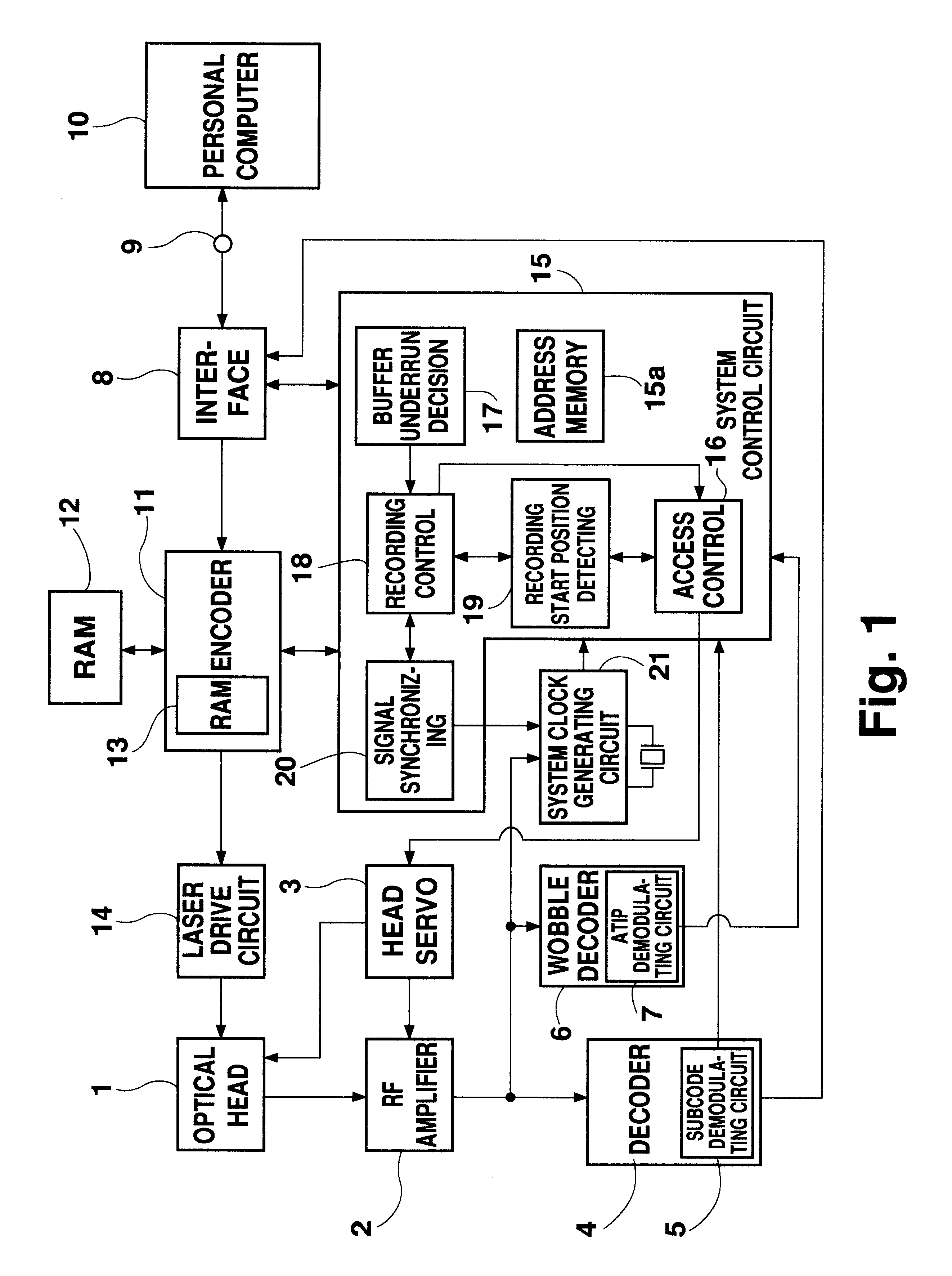

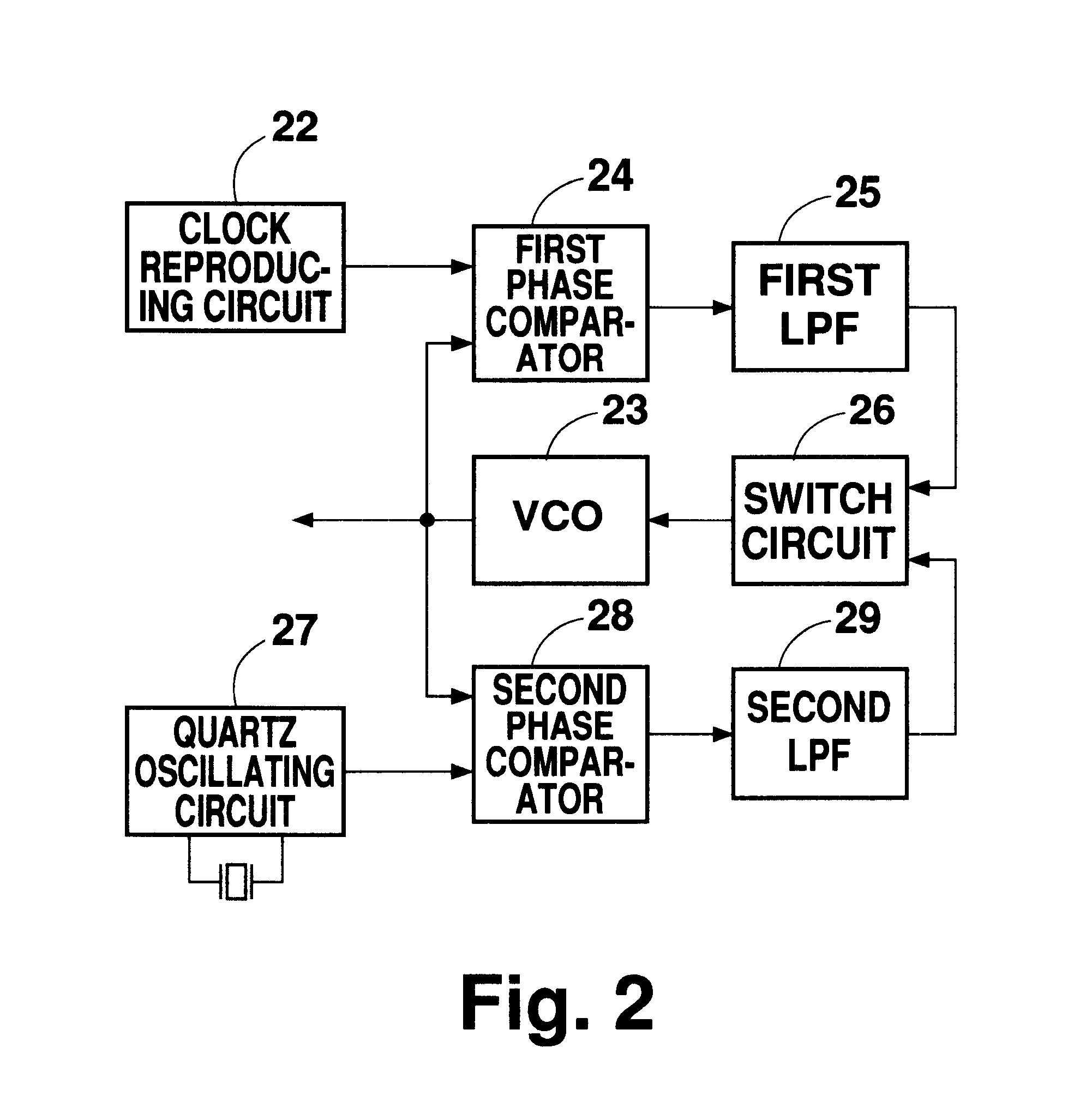

Disk recording system

When a buffer underrun decision circuit decides that a buffer underrun is about to occur, data recording on the disk is interrupted by a recording control circuit. On the other hand, when the buffer underrun decision circuit determines that a buffer underrun situation has been avoided, data recording is resumed by the recording control circuit. At this time, data recording is resumed from a position of the disk which is continuous to data recorded by the time the data recording was interrupted, thereby recording new data continuous to the last recorded data.

Owner:SANYO ELECTRIC CO LTD

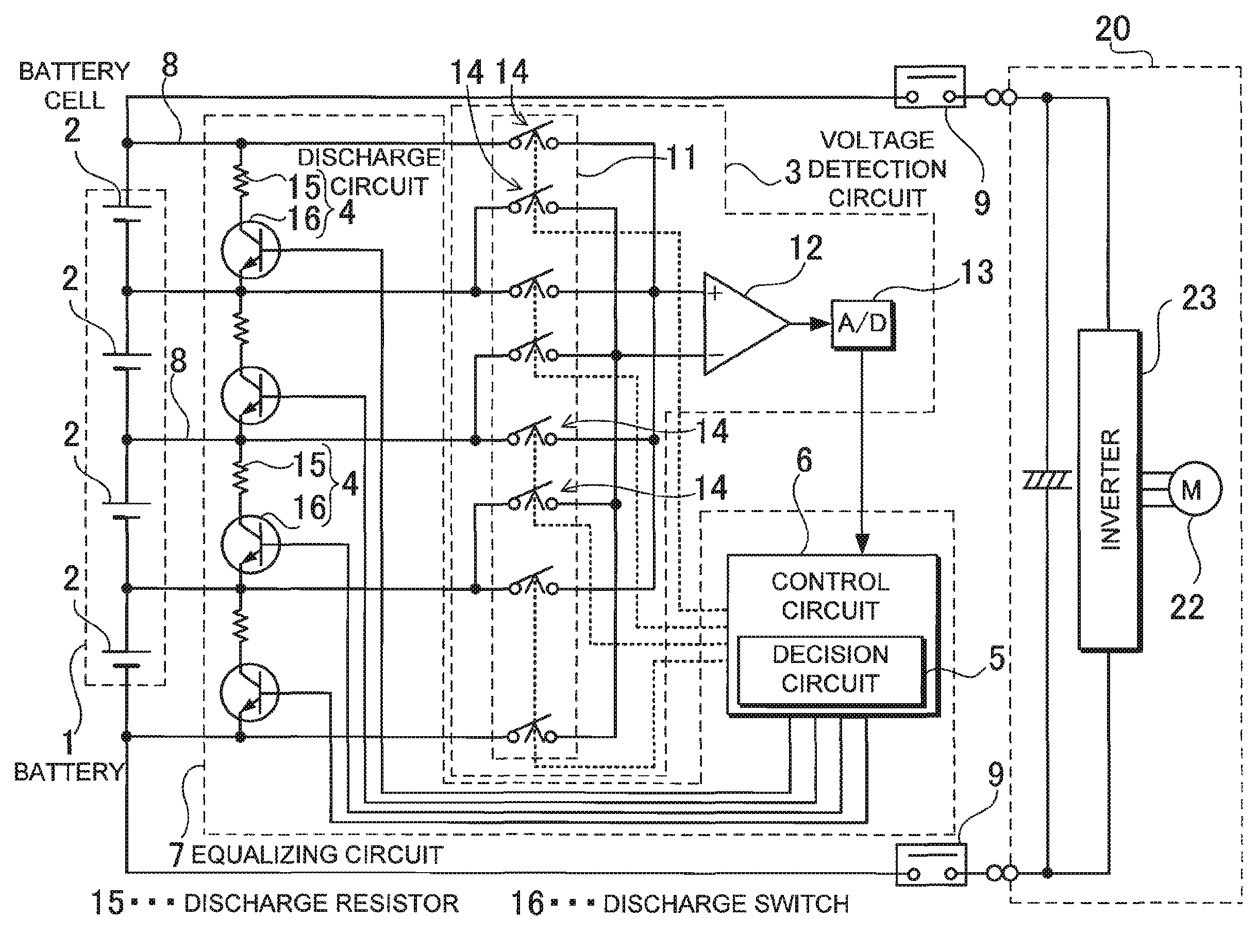

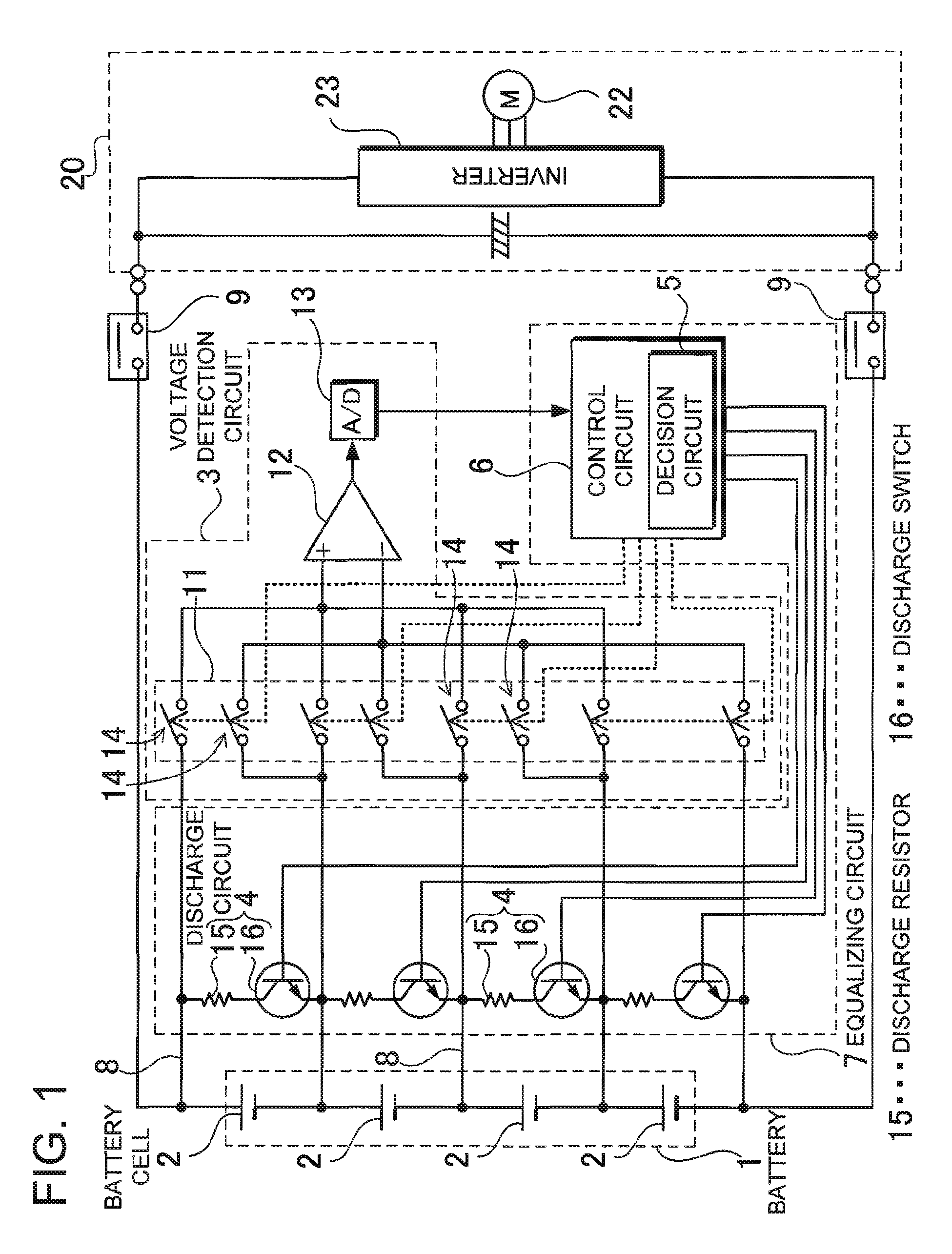

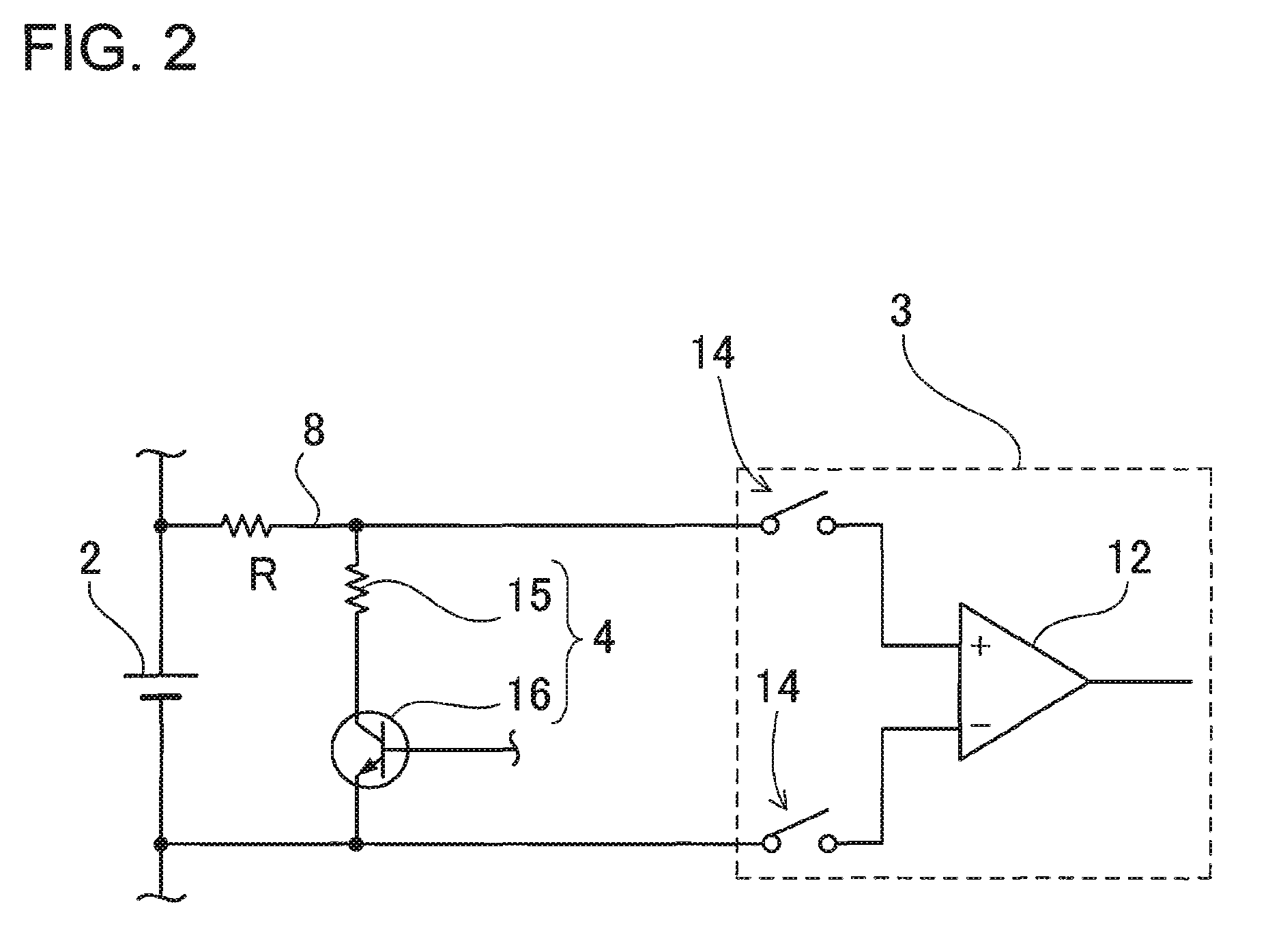

Battery system with practical voltage detection

InactiveUS20100134069A1Accurate measurementVoltage is accurateCharge equalisation circuitCircuit monitoring/indicationDecision circuitEngineering

The battery system has a battery 1 having a plurality of series-connected battery cells 2, a voltage detection circuit 3 that detects each battery cell voltage, discharge circuits 4 to discharge each battery cell, and a decision circuit 5 that judges the condition of the connection between a battery cell 2 and the voltage detection circuit 3 from the detected battery cell voltage measured by the voltage detection circuit. The voltage detection circuit 3 measures discharge voltage of a battery cell 2 with the discharge circuit 4 in the discharging state, and measures non-discharge voltage with the battery cell 2 in a non-discharging state. The decision circuit 5 compares the difference between the detected battery cell non-discharge voltage and discharge voltage with the normal voltage, or compares battery cell discharge voltage with the normal voltage to judge abnormal connection between the battery cell and the voltage detection circuit.

Owner:SANYO ELECTRIC CO LTD

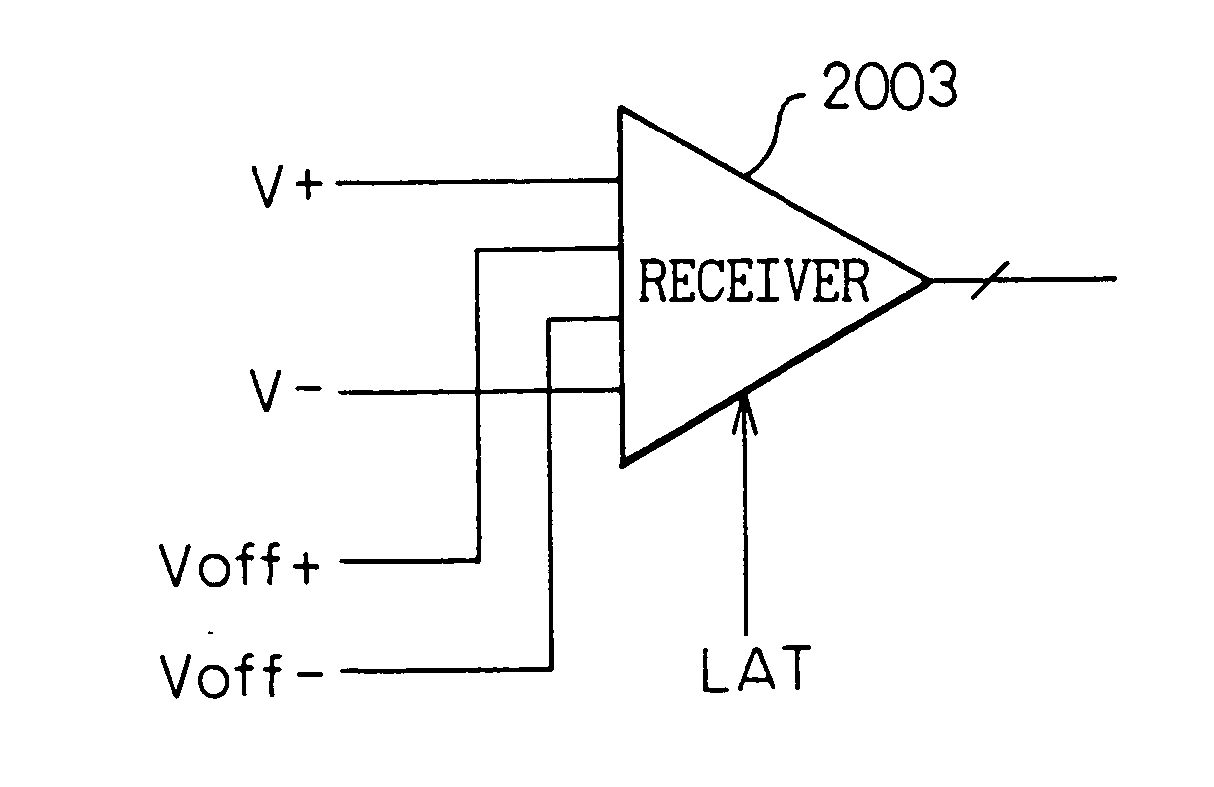

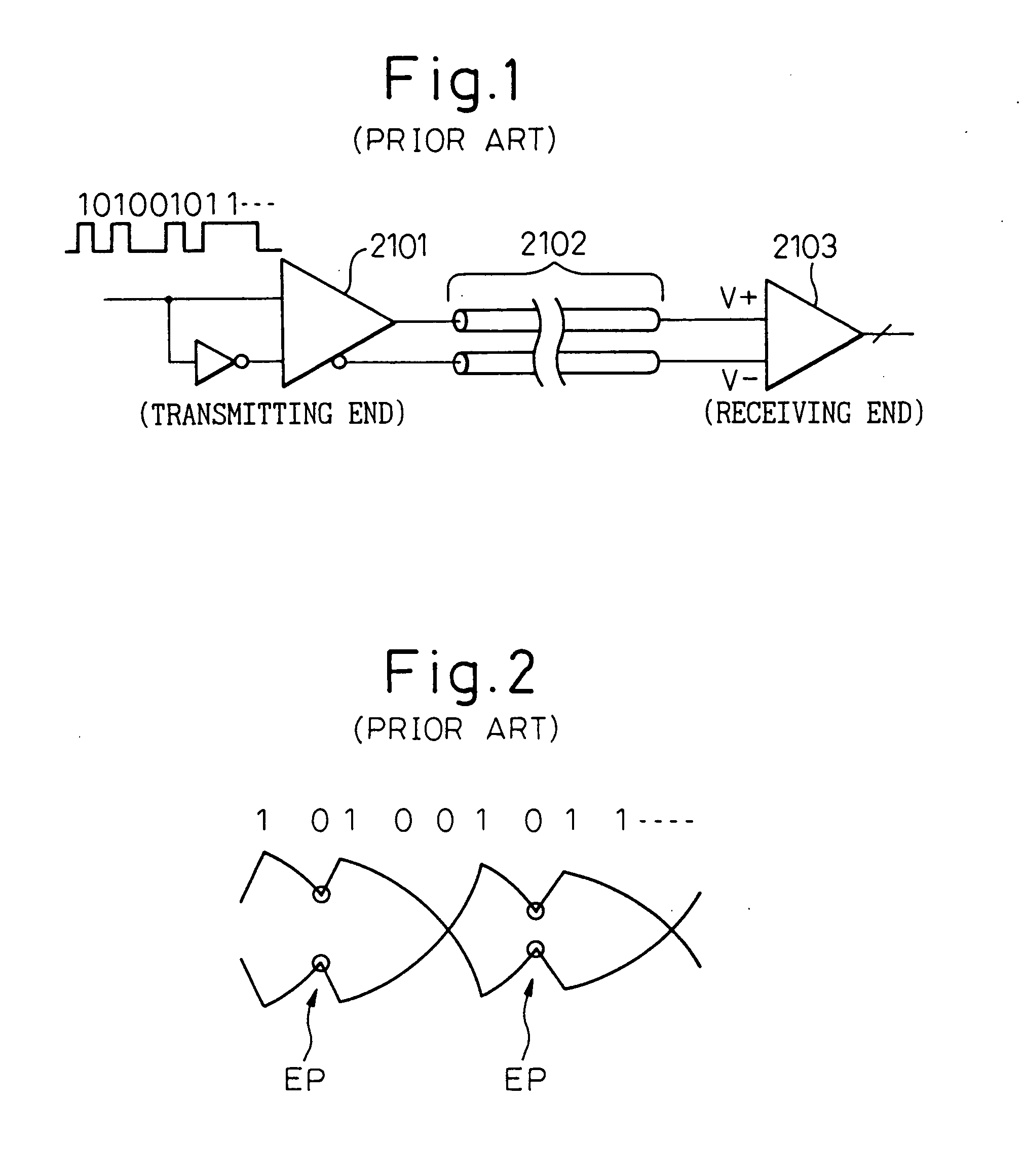

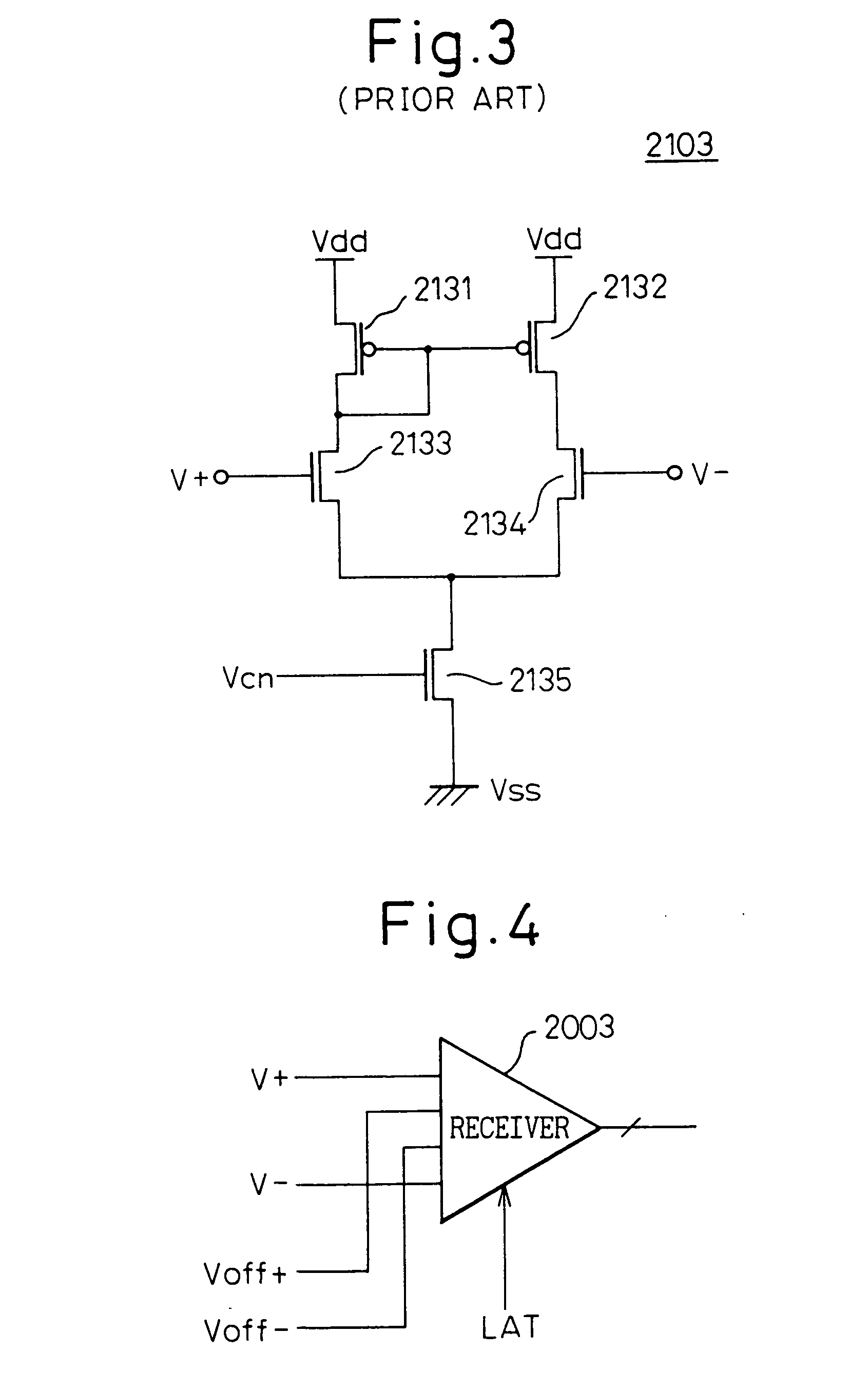

Receiver, transceiver circuit, signal transmission method, and signal transmission system

InactiveUS20050033902A1Optimize transmission/reception parametersImprove receiver sensitivityInstant pulse delivery arrangementsDc level restoring means or bias distort correctionDecision circuitTransceiver

A receiver has an offset application circuit for applying a known offset to an input signal, and a decision circuit for comparing the offset-applied input signal with a reference voltage. The level of the input signal is determined based on the known offset and on the result output from the decision circuit. With this configuration, a large common mode voltage can be eliminated in a circuit used for signal transmission.

Owner:FUJITSU LTD

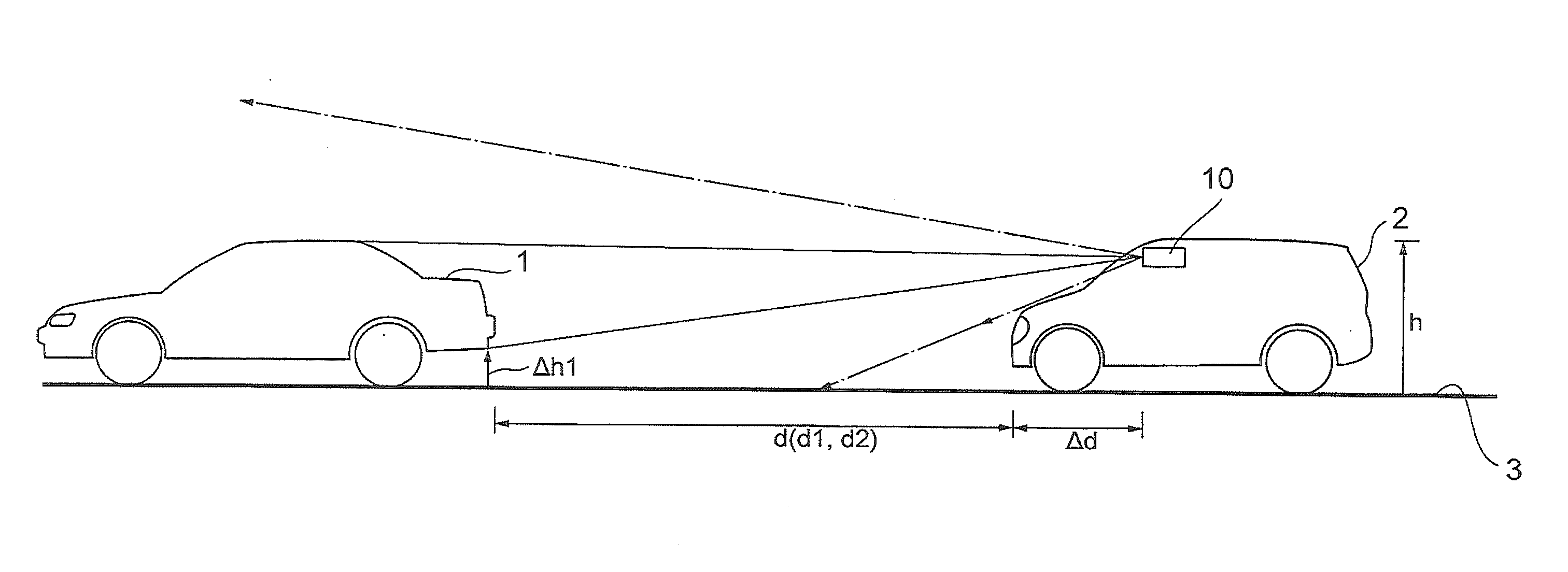

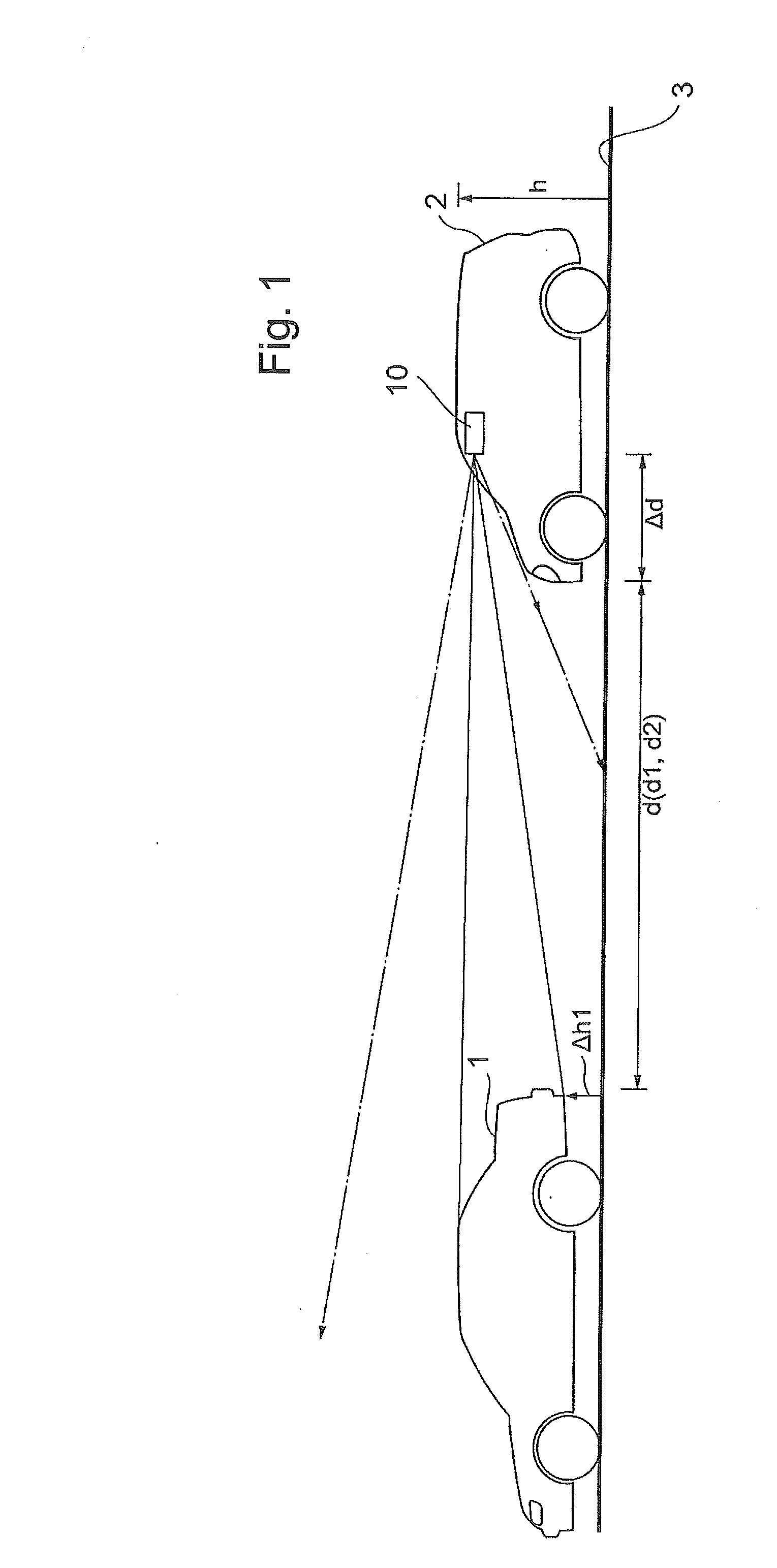

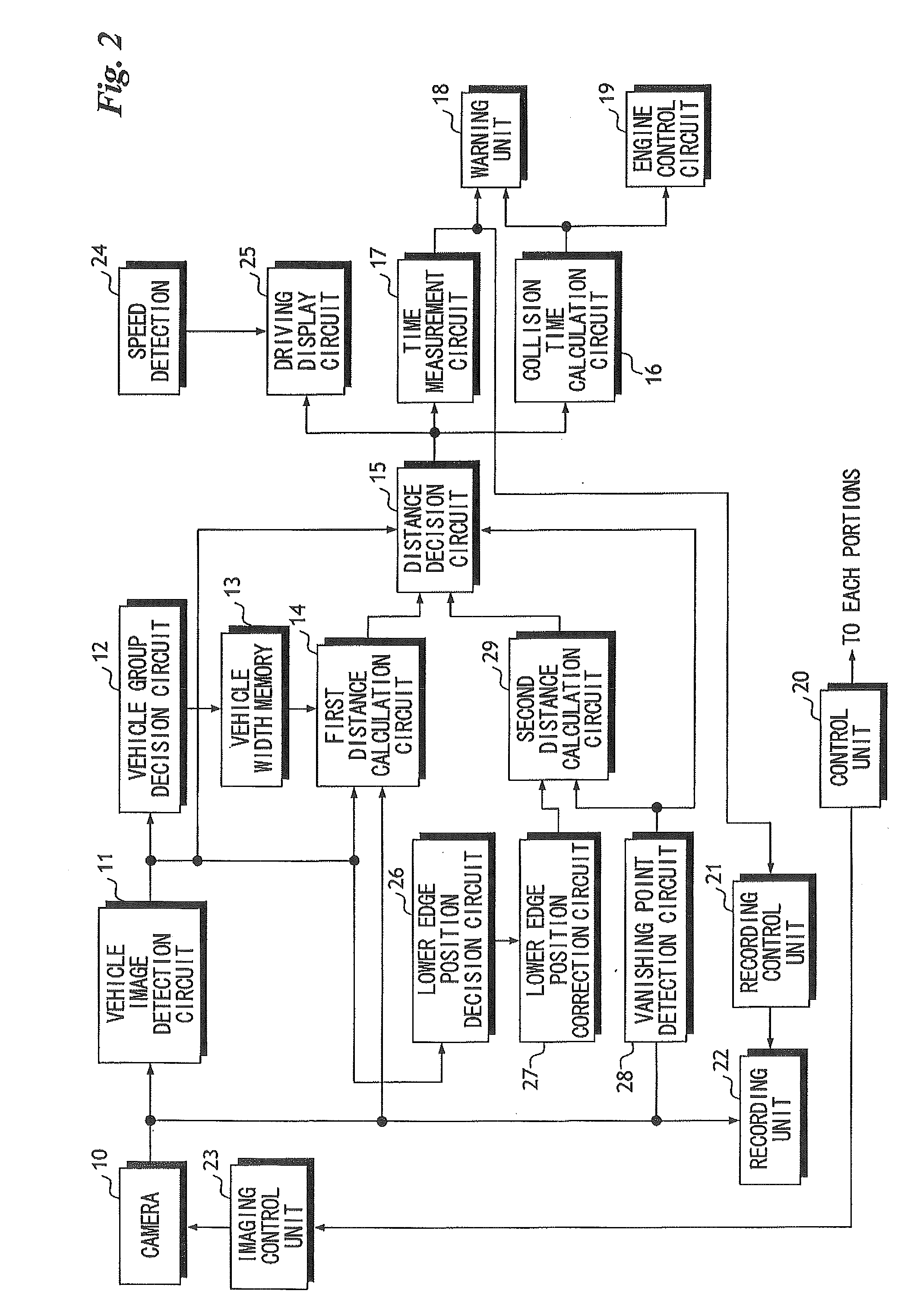

Vehicle-to-vehicle distance calculation apparatus and method

ActiveUS20140241579A1Accurate distanceImage enhancementImage analysisDecision circuitWeight coefficient

Owner:FUJIFILM CORP

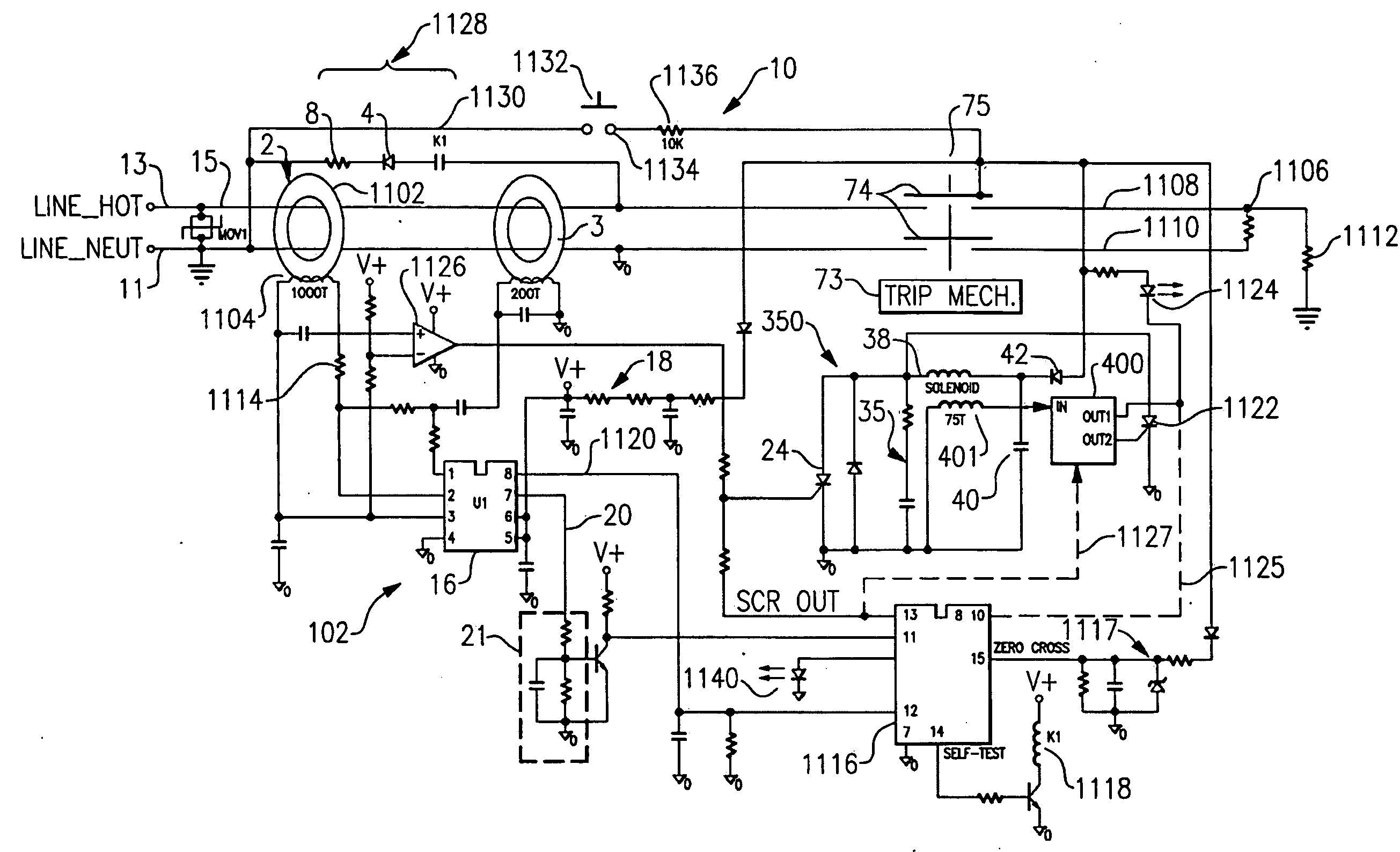

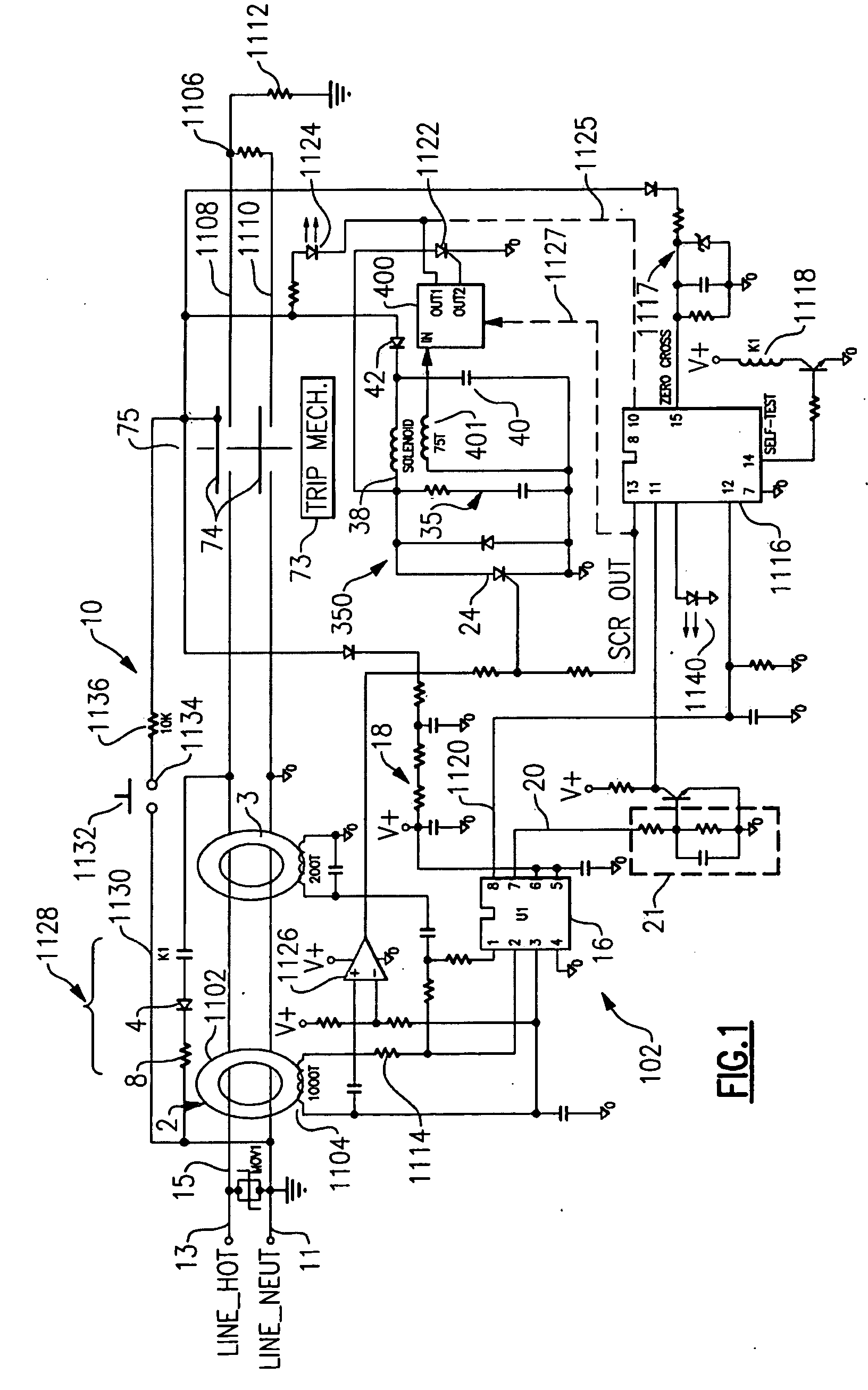

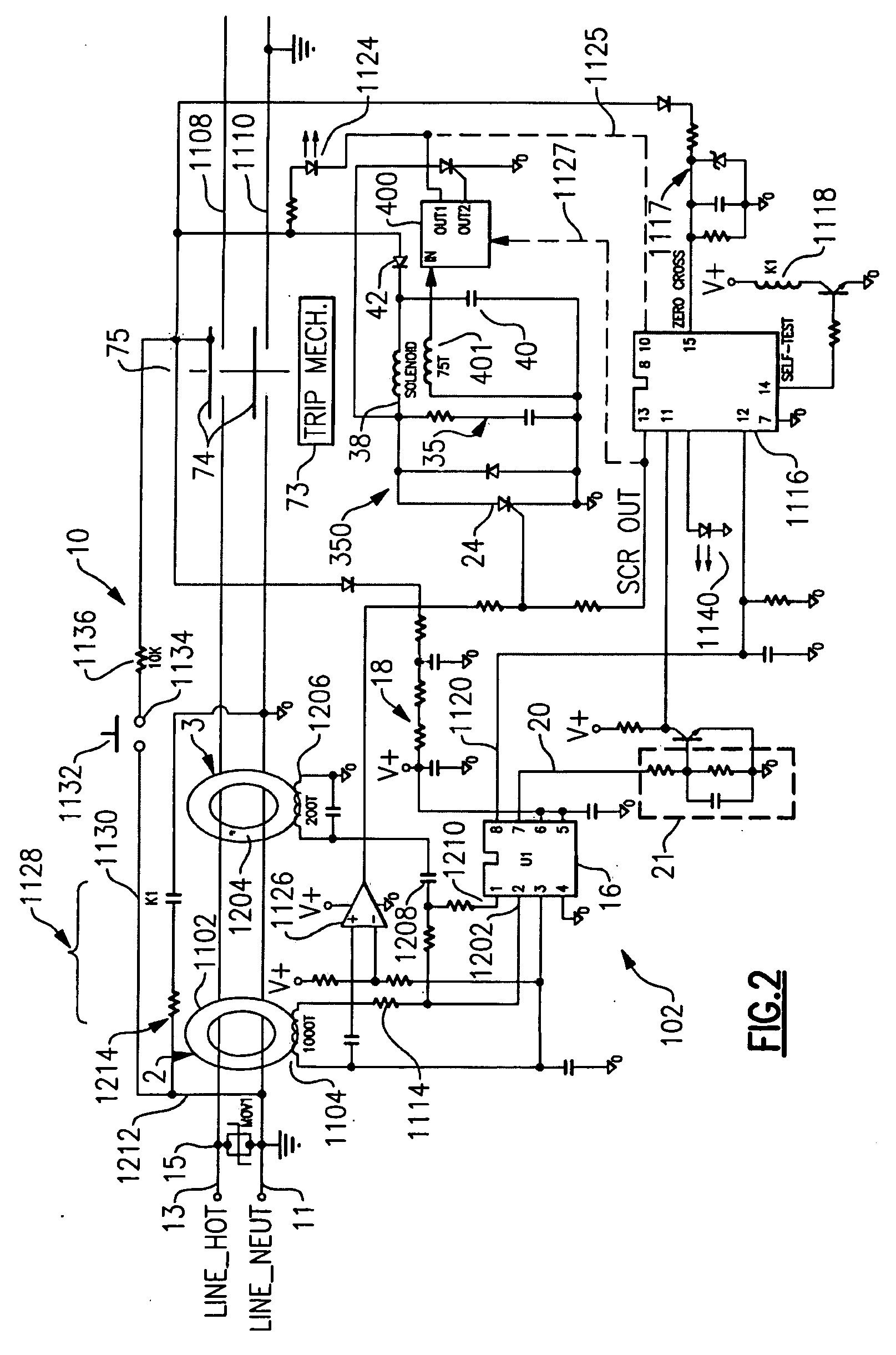

Protective Device with End-Of-Life Indication Before Power Denial

InactiveUS20090251148A1Protective switch detailsCircuit-breaking switches for excess currentsDecision circuitInterrupter

Owner:PASS SEYMOUR

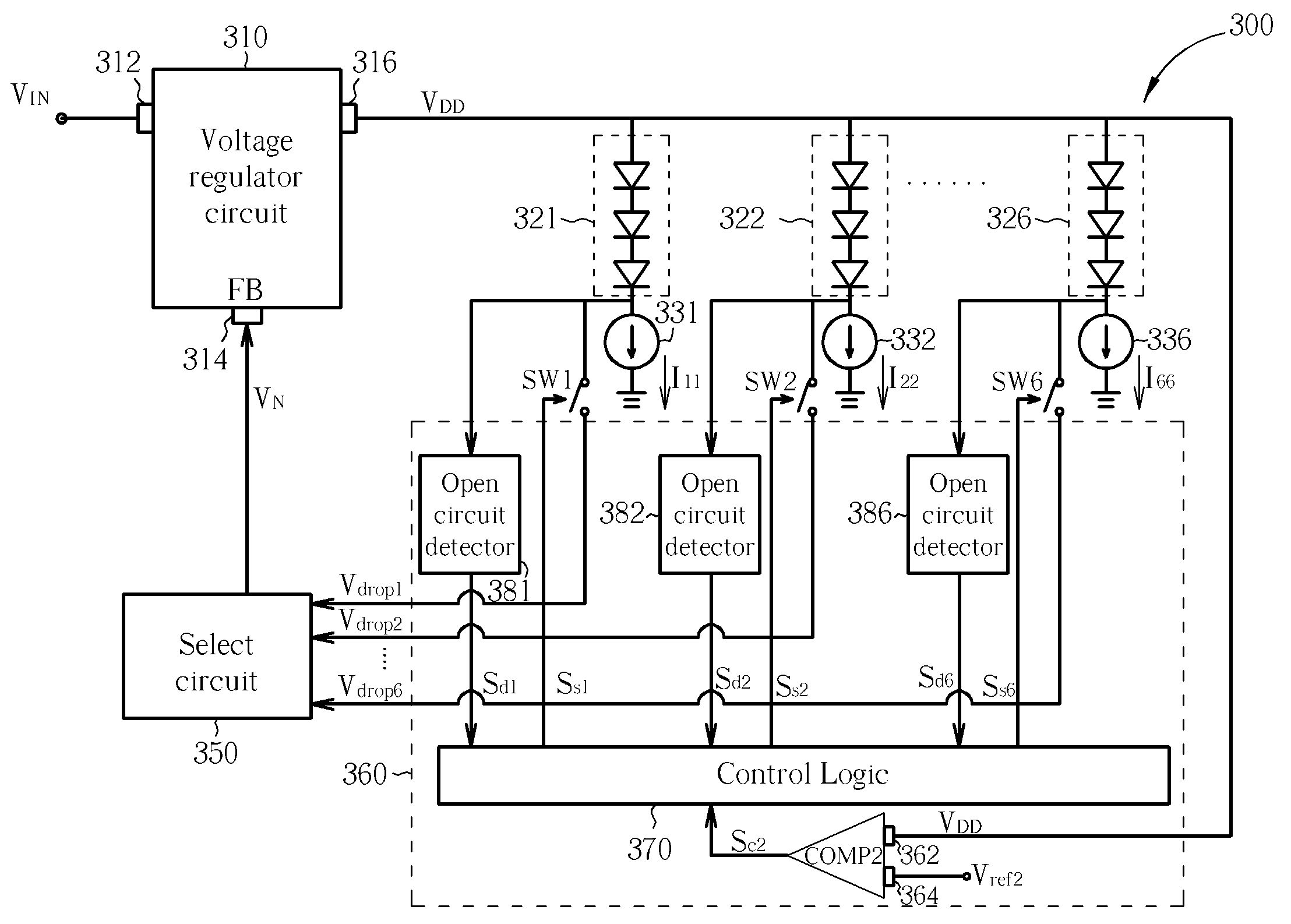

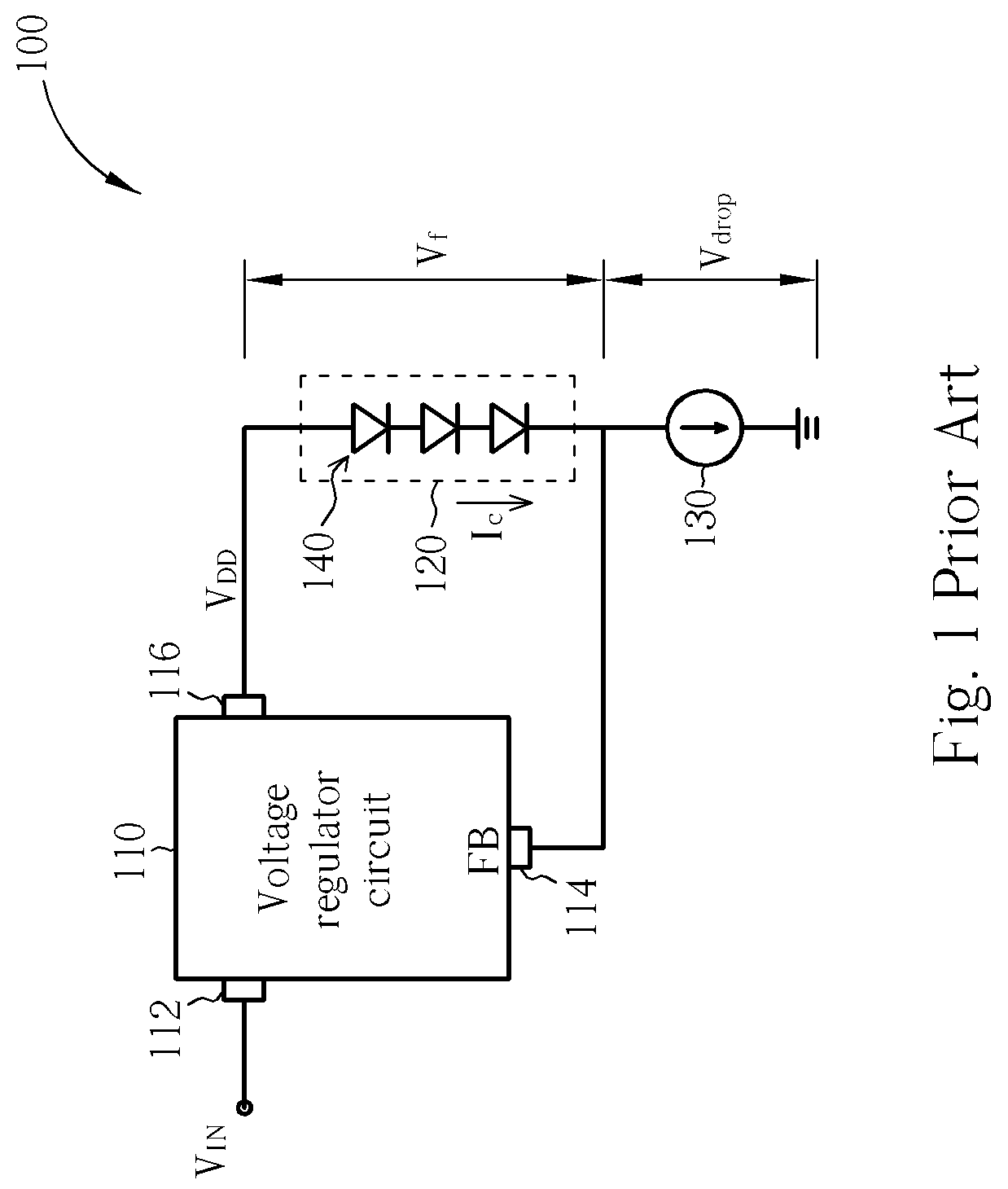

Driving circuit and related driving method for providing feedback control and open-circuit protection

ActiveUS20080144236A1Electroluminescent light sourcesSemiconductor lamp usageDecision circuitDriver circuit

A driving circuit includes a first light-emitting device, a first constant-current supplier, a voltage regulator circuit, an analysis and decision circuit, and a first switch. The first constant-current supplier provides a constant current to the first light-emitting device. The voltage regulator circuit provides a driving voltage to the first light-emitting device and adjusts driving voltage according to a feedback signal. The analysis and decision circuit is coupled to the voltage regulator circuit and the first light-emitting device. The analysis and decision circuit generates a first switch control signal. The first switch is coupled to the first light-emitting device, the analysis and decision circuit, and the voltage regulator circuit. The first switch is turned on and off according to the first switch control signal.

Owner:IML HONG KONG LTD

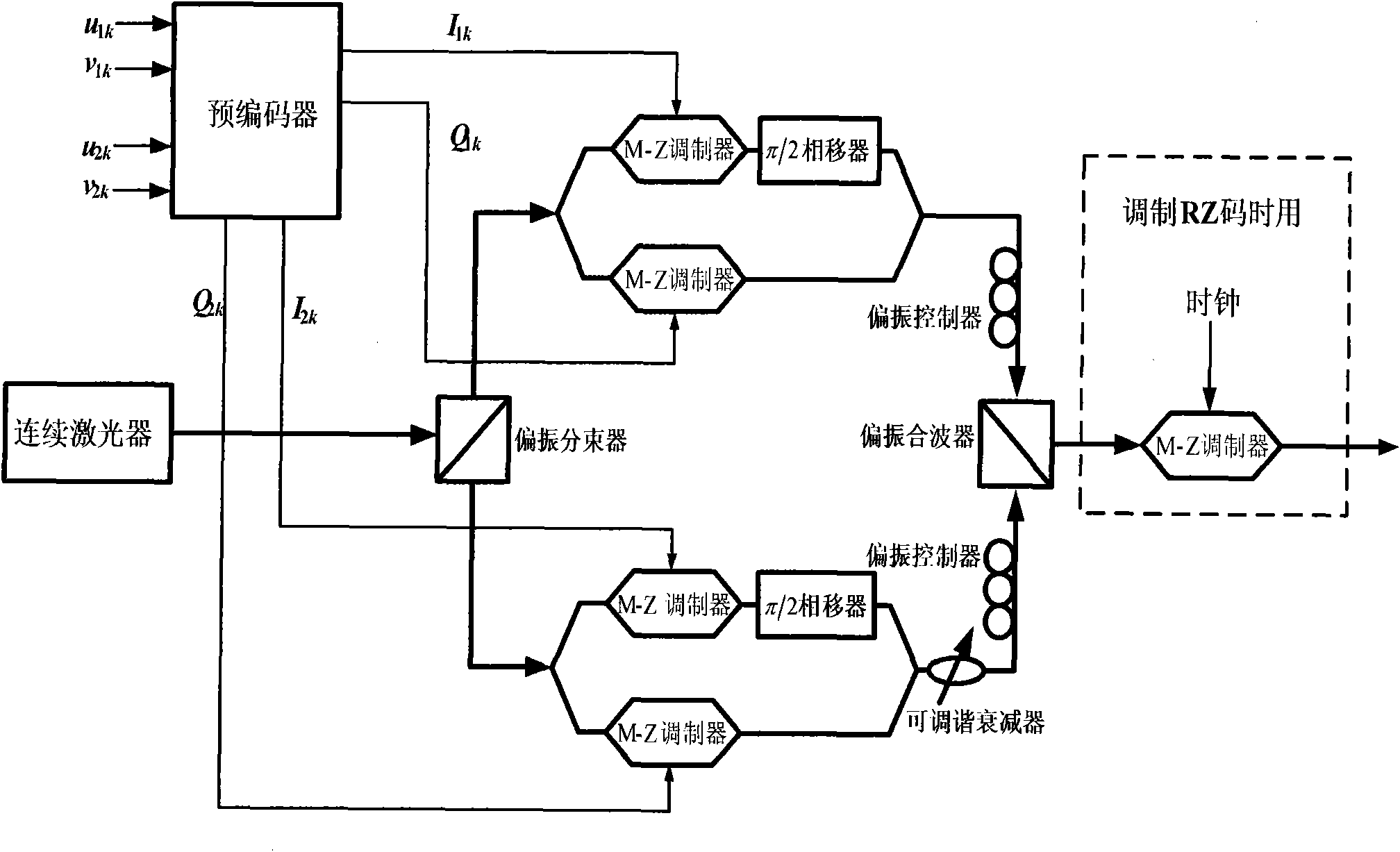

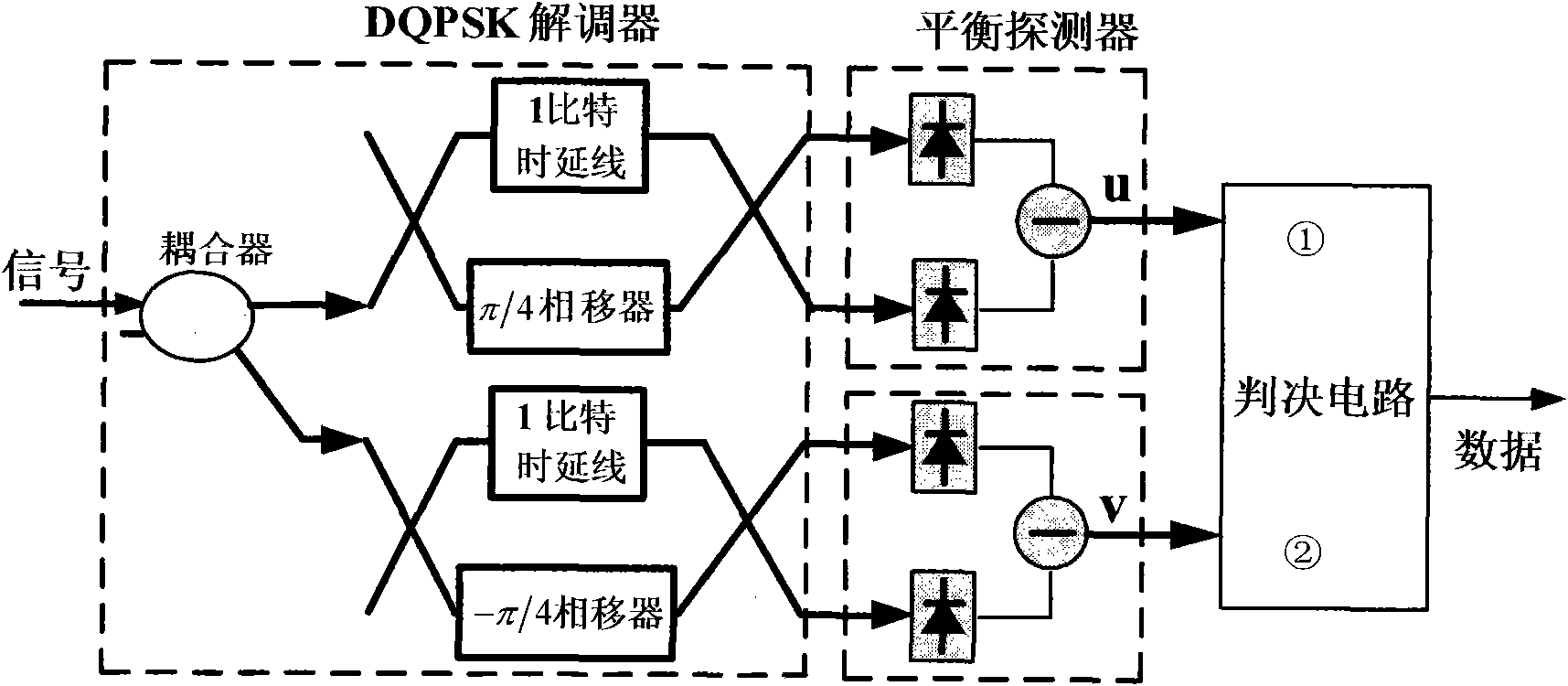

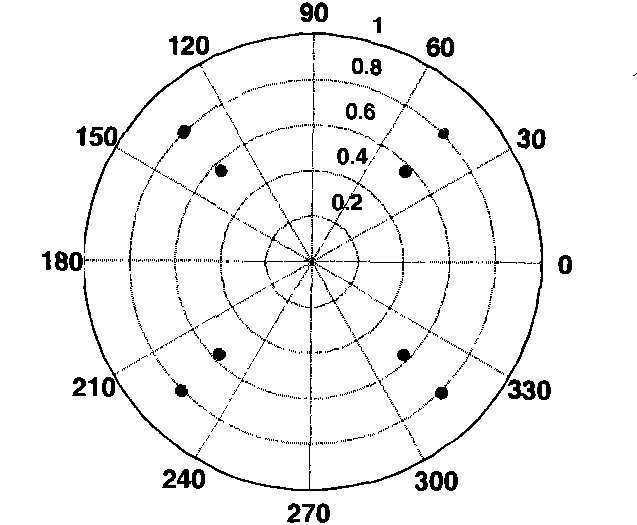

Method and system for transmitting and receiving by orthogonally dual-polarized differential quaternary phase shift keying

InactiveCN101895495AImprove stabilityReduce complexityPhase-modulated carrier systemsDecision circuitPolarization beam splitter

The invention relates to a method and a system for transmitting and receiving by orthogonally dual-polarized differential quaternary phase shift keying. The system comprises a transmitting device and a receiving device, wherein the transmitting device comprises a continuous laser; the continuous laser is connected with a polarization beam splitter which is connected with a DQPSK modulator; the DQPSK modulator is connected with a precoder of which the output end is connected with a tunable optical attenuator or a polarization controller; and the polarization controller is connected with a polarization beam combiner; and the receiving device comprises a DQPSK demodulator, and the DQPSK demodulator is connected with a balanced detector which is connected with a decision circuit. In the method, four paths of electrical signals can be multiplexed, and only one demodulator and two balanced detectors are used at a receiving end to demodulate two orthogonally polarized DQPSK signals at the same time; therefore, compared with D8PSK and x-QAM systems, the system has the advantages of greatly reducing the complexity and remarkably enhancing the stability of components.

Owner:BEIJING UNIV OF POSTS & TELECOMM

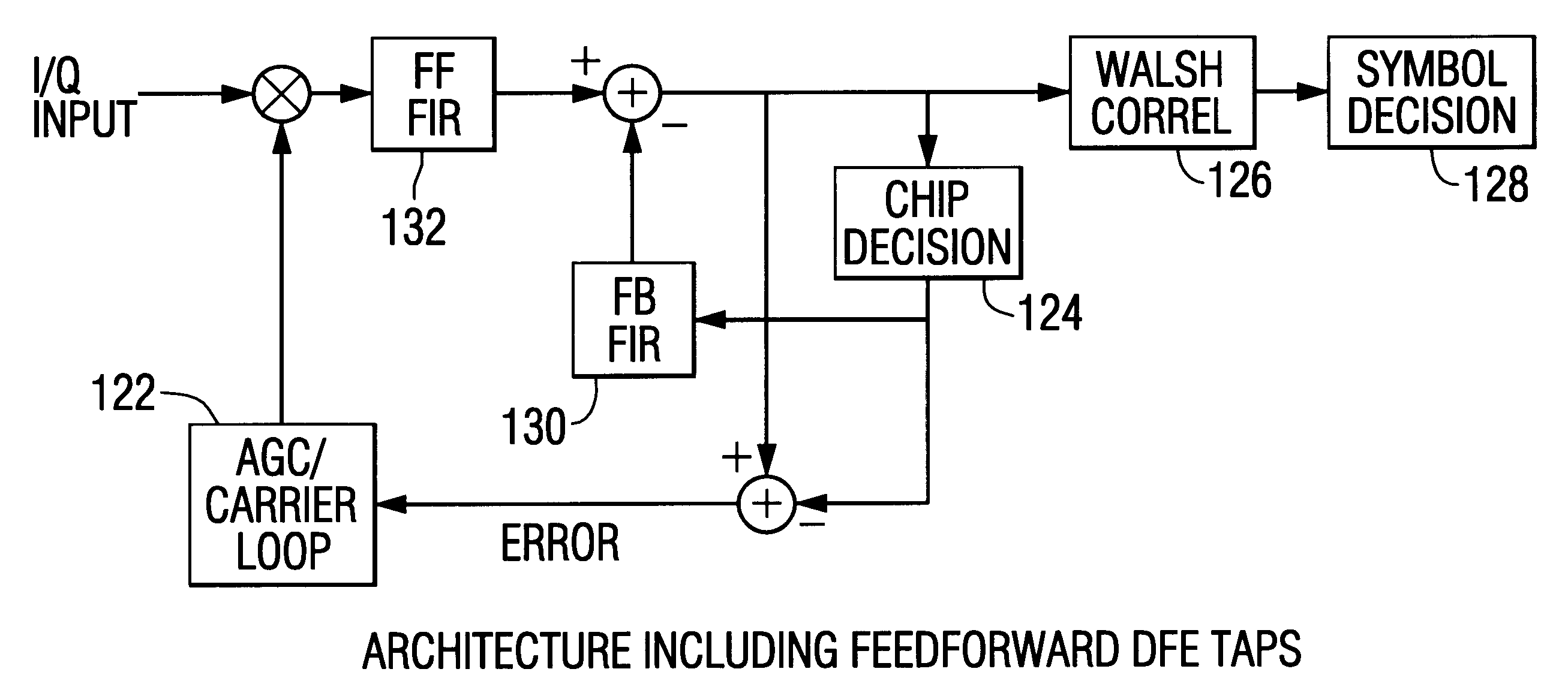

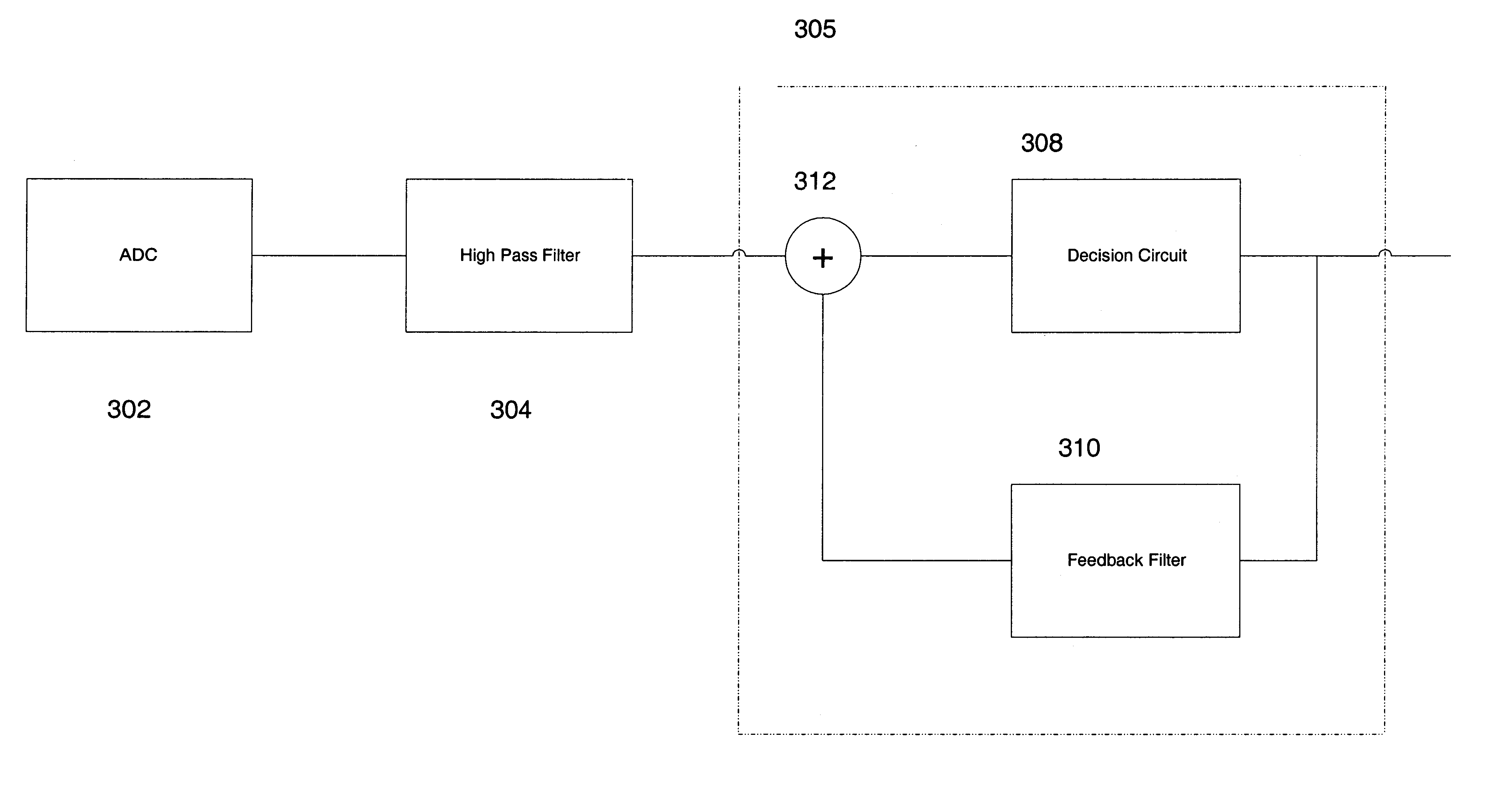

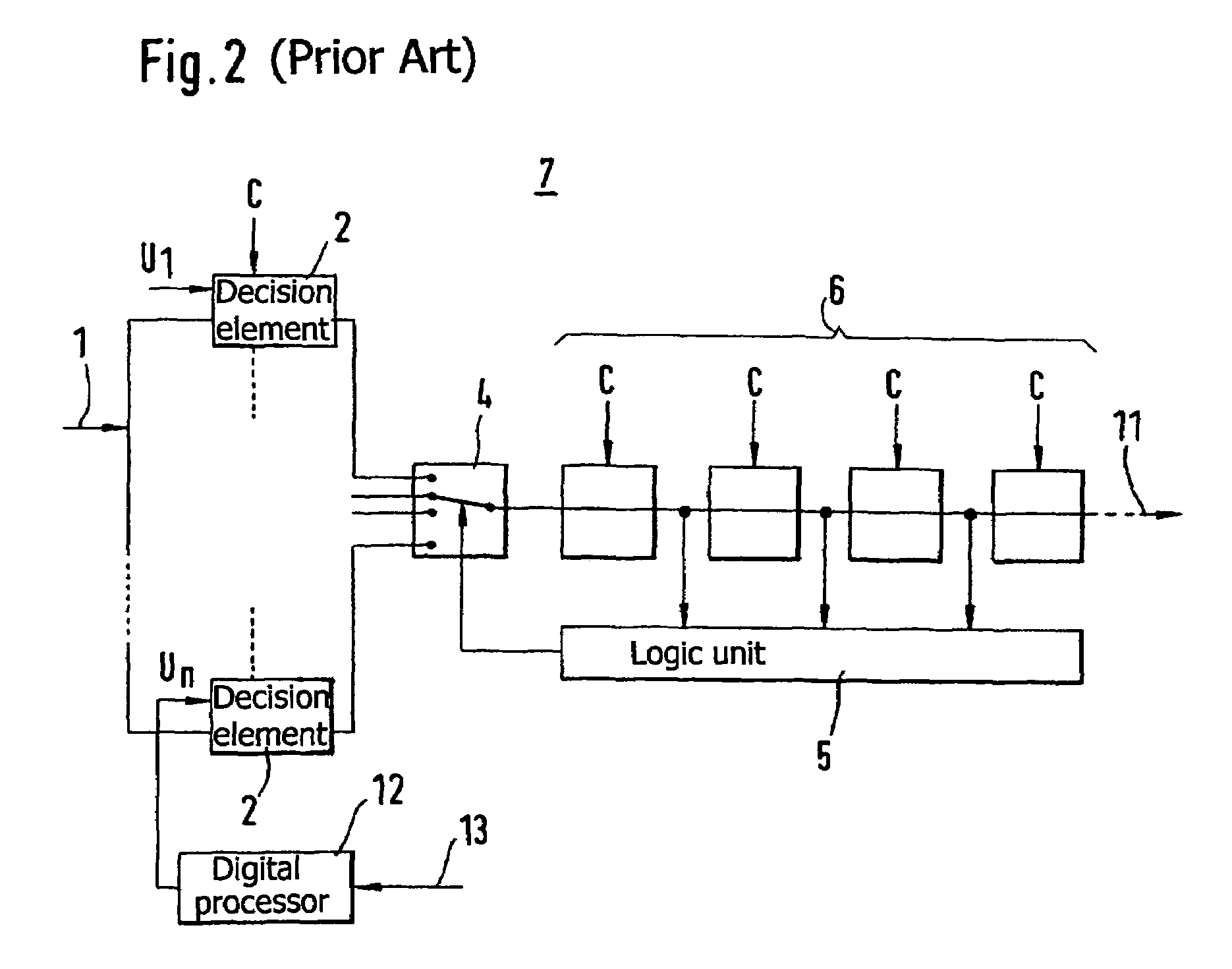

Feedforward equalizer for DFE based detector

InactiveUS6870881B1Low cutoff frequencySpeed up the descentMultiple-port networksDelay line applicationsDecision circuitAnalog signal

A feedforward equalizer for DFE based detector is provided comprising a digital to analog converter to convert an analog signal to a digital signal. A feedforward equalizer comprises a high-pass filter and is responsive to the input circuit. The high-pass filter has a low cutoff frequency, has a relatively flat response and has high attenuation at low frequencies. A decision feedback equalizer comprises a decision circuit responsive to the feedforward equalizer, and a feedback filter is responsive to the decision circuit. The decision circuit is also responsive to the feedback filter.

Owner:MARVELL INT LTD

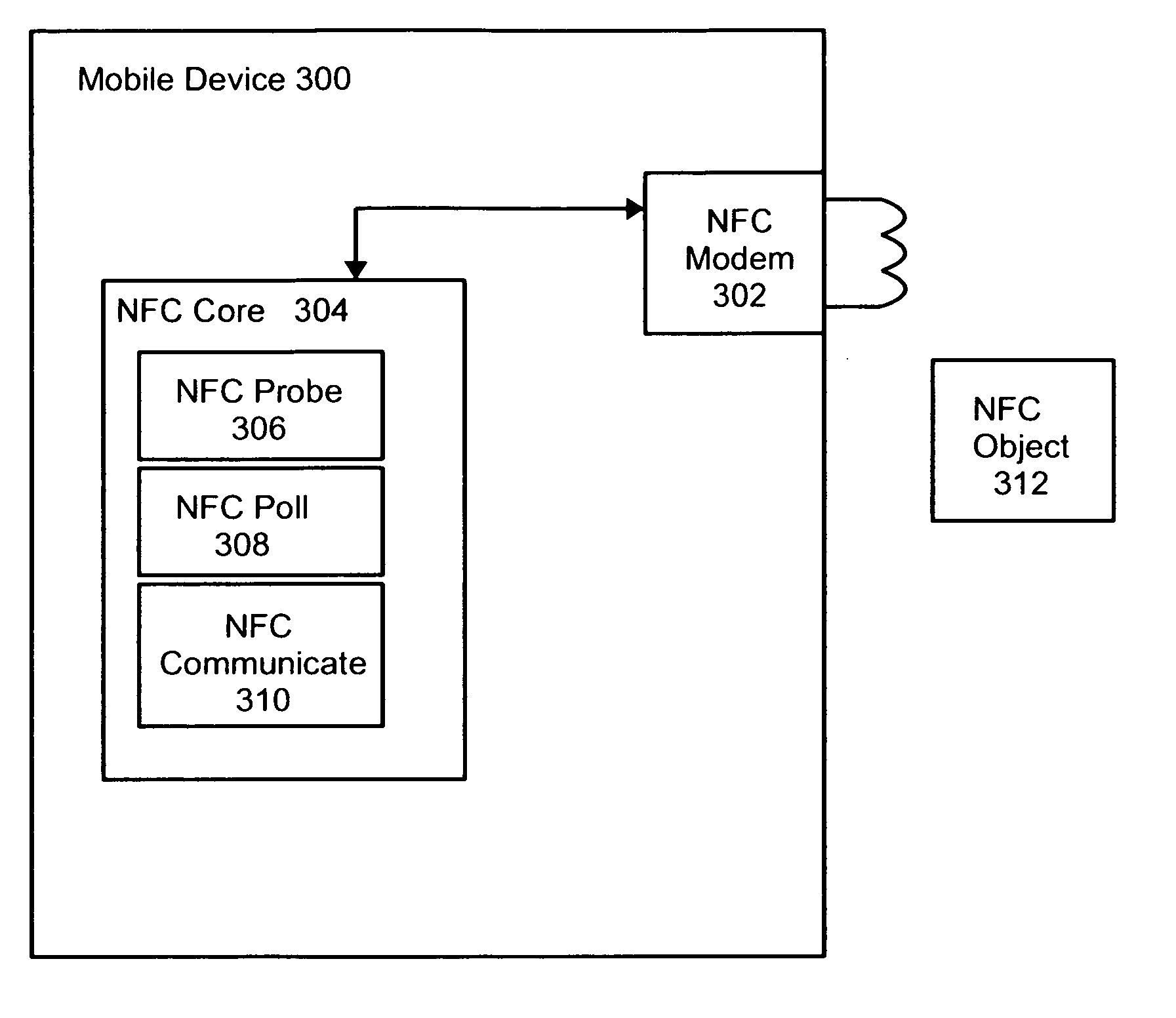

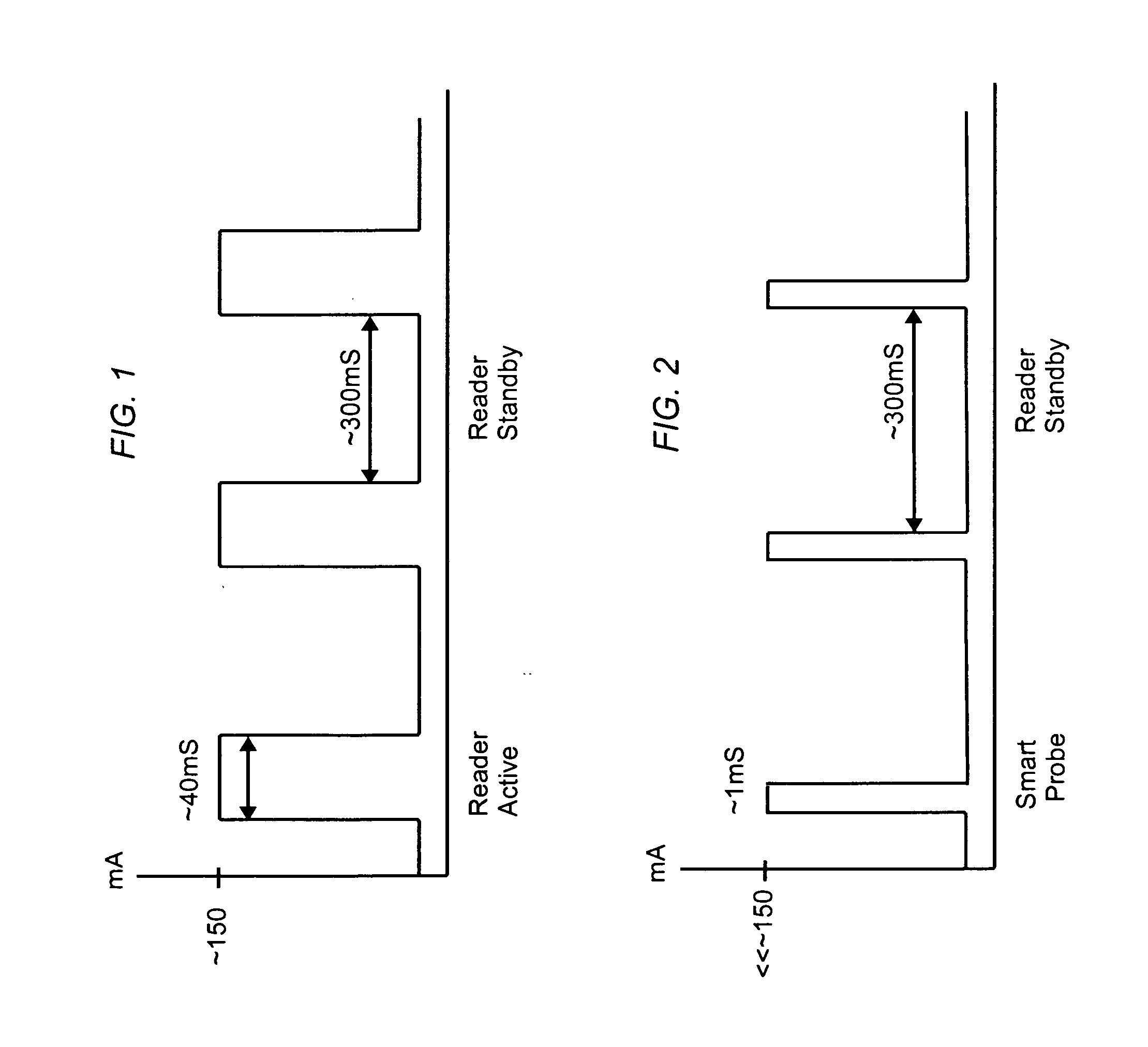

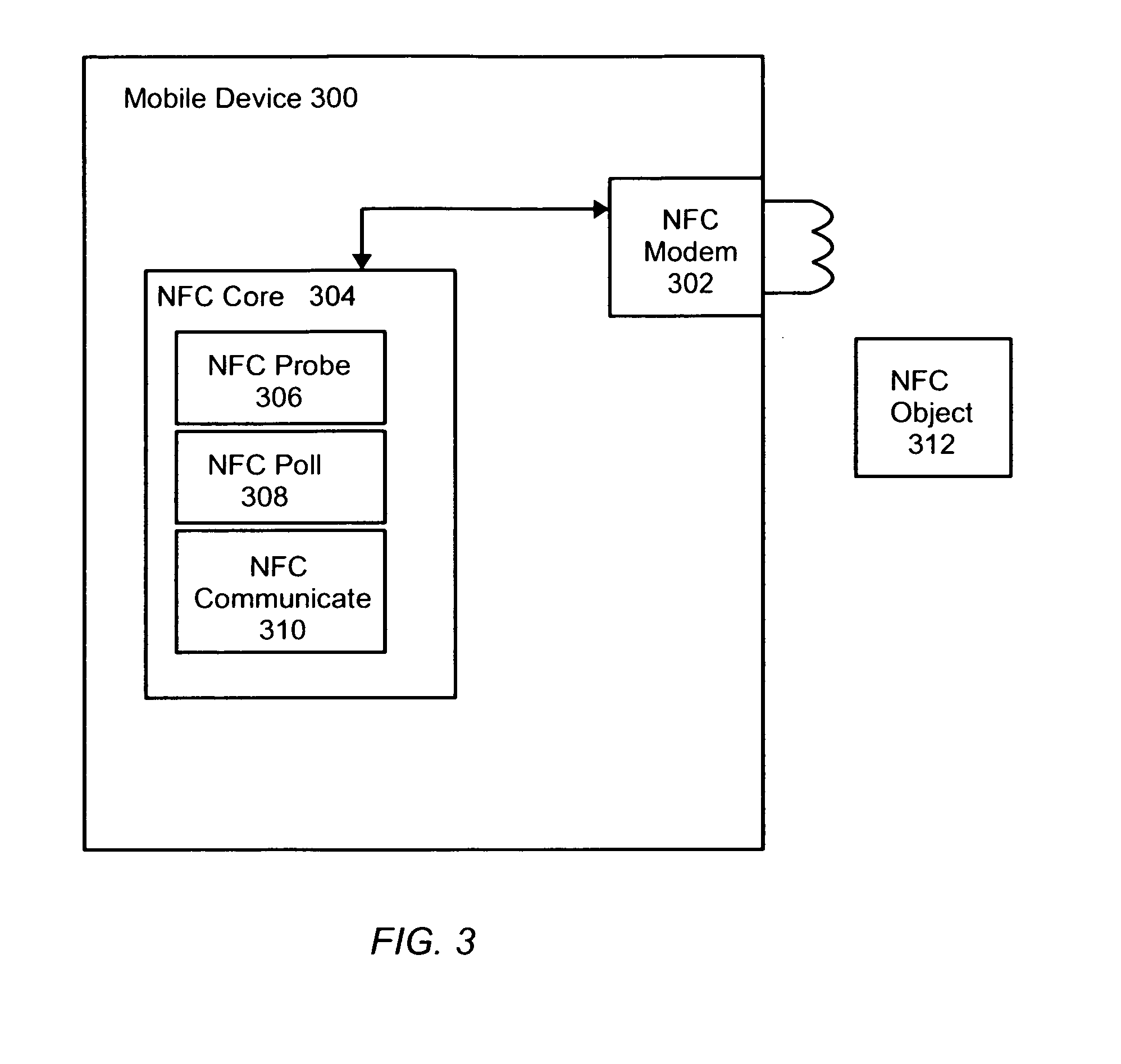

System and method of near field communication tag presence detection for smart polling

A system for detecting the presence of a near filed communication object includes a radiator configured to radiate a magnetic field from a near field communication reader device; a detector configured to detect a loading effect on the magnetic field caused by the near filed communication object; and a decision circuit configured to determine that the near field communication object is present based on the detected loading effect. Only once the presence of a nearby NFC object is detected will higher power-consuming communications take place. Accordingly a power-sensitive background polling feature can be implement within the NFC architecture.

Owner:TEXAS INSTR INC

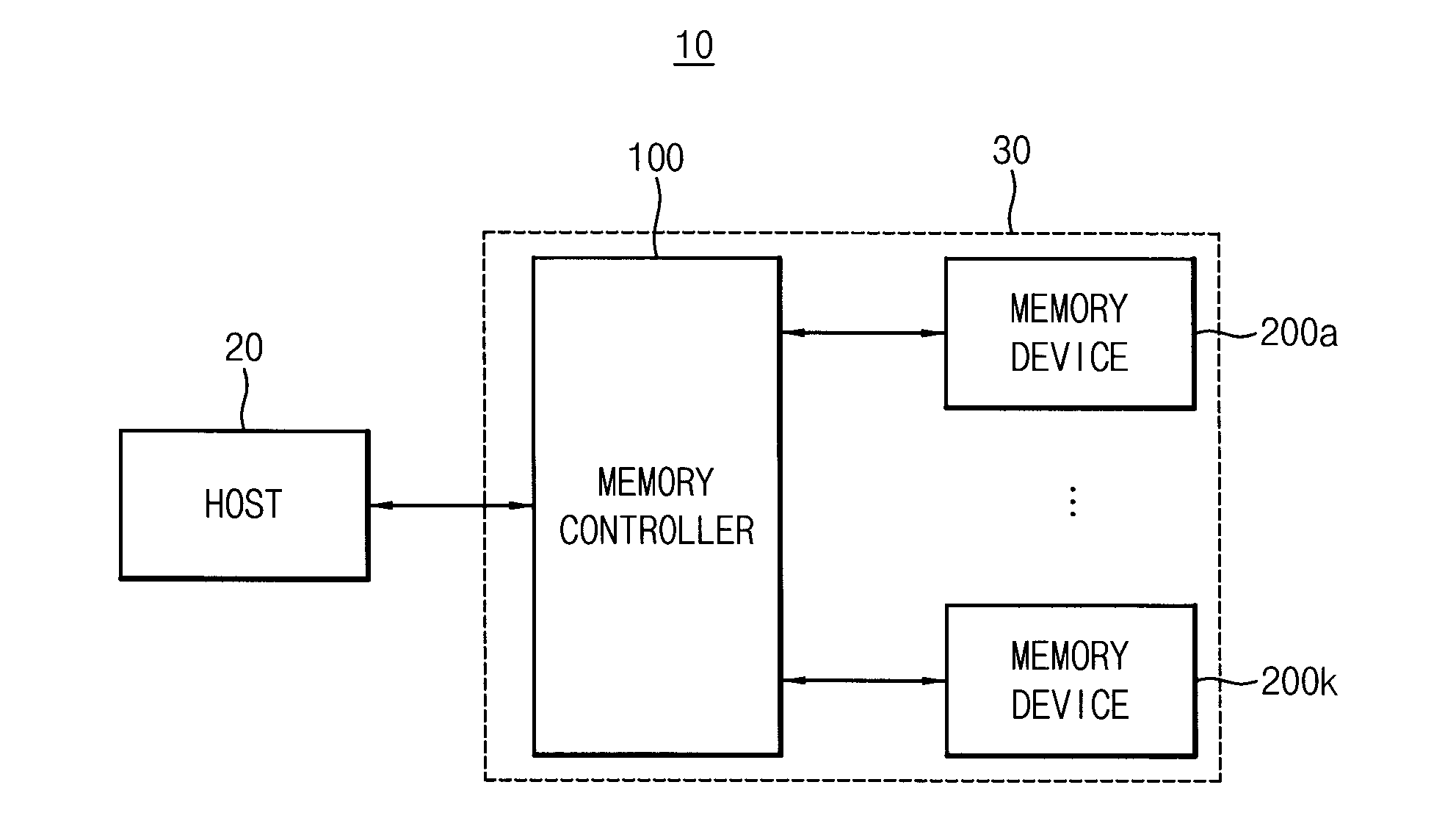

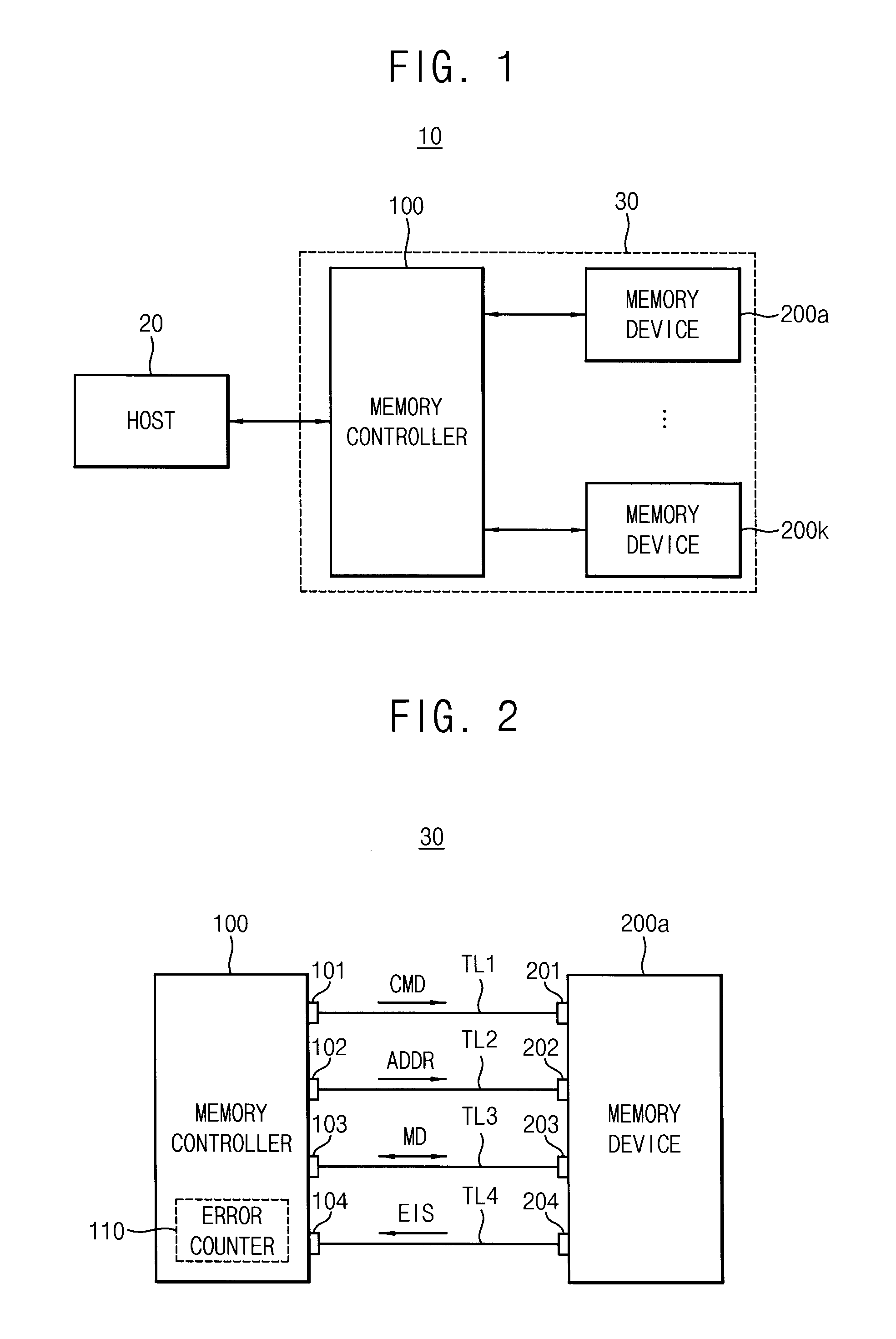

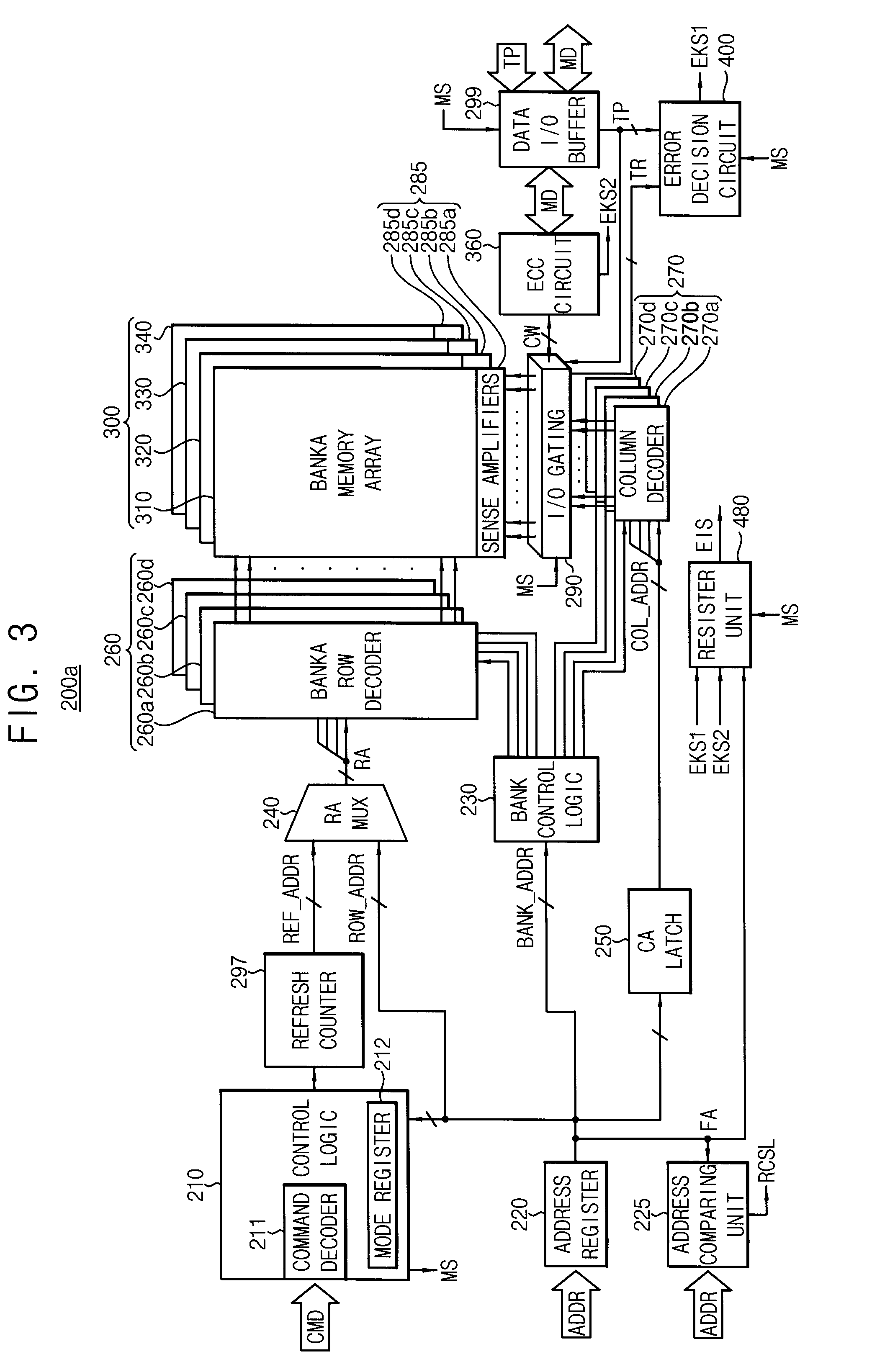

Semiconductor memory devices and memory systems including the same

A semiconductor memory device includes a memory cell array, an input / output (I / O) gating circuit, an error decision circuit and an error check and correction (ECC) circuit. The I / O gating circuit reads test pattern data to provide test result data in a test mode and reads a codeword in a normal mode. The error decision circuit determines the correctability of errors in the test result data by a first unit, based on the test pattern data and the test result data and provides a first error kind signal indicating a first determination result, in the test mode. The ECC circuit decodes the codeword including main data and parity data generated based on the main, determines correctability of errors in the codeword by a second unit and provides a second error kind signal indicating a second determination result, in the normal mode. The main data includes a plurality of unit data.

Owner:SAMSUNG ELECTRONICS CO LTD

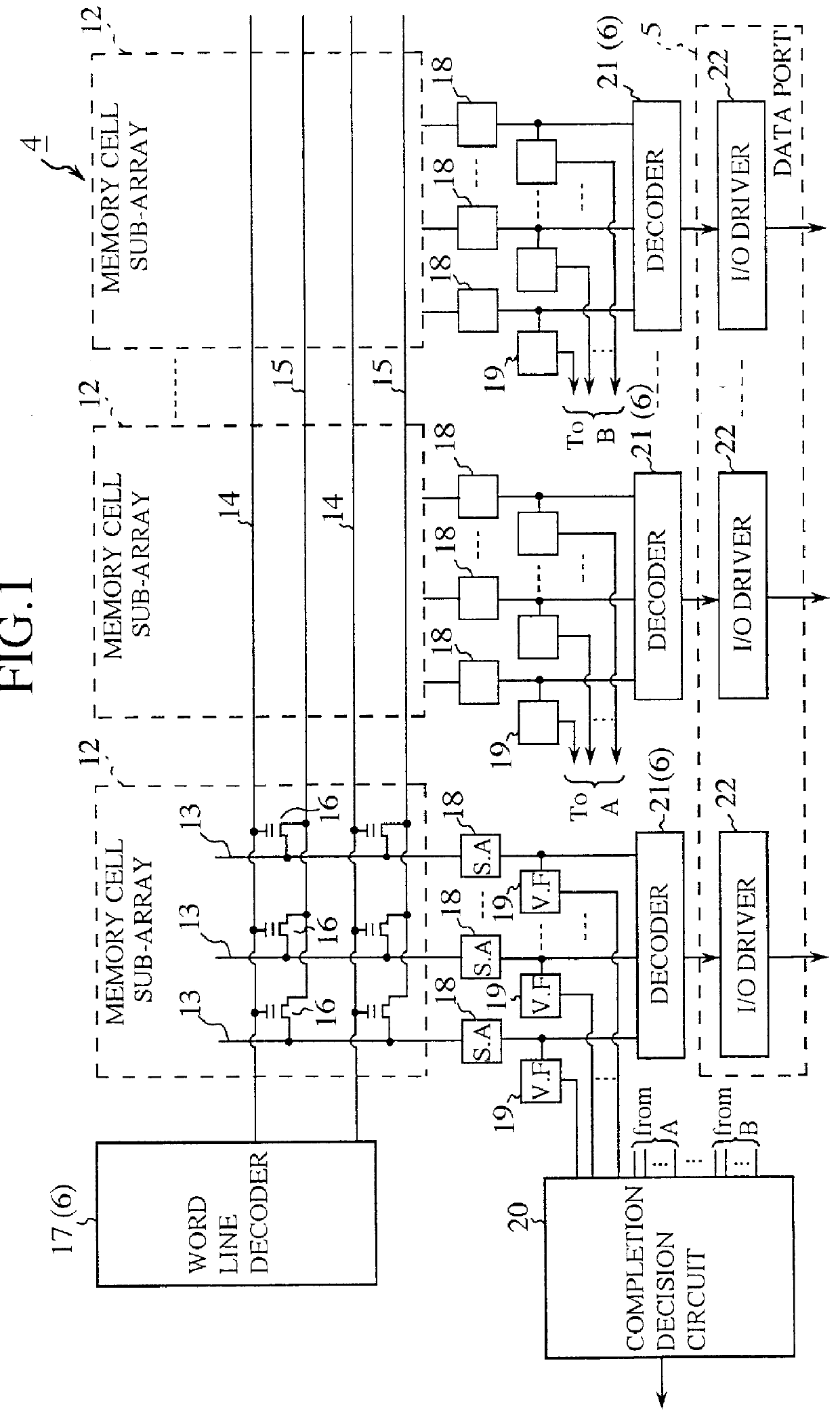

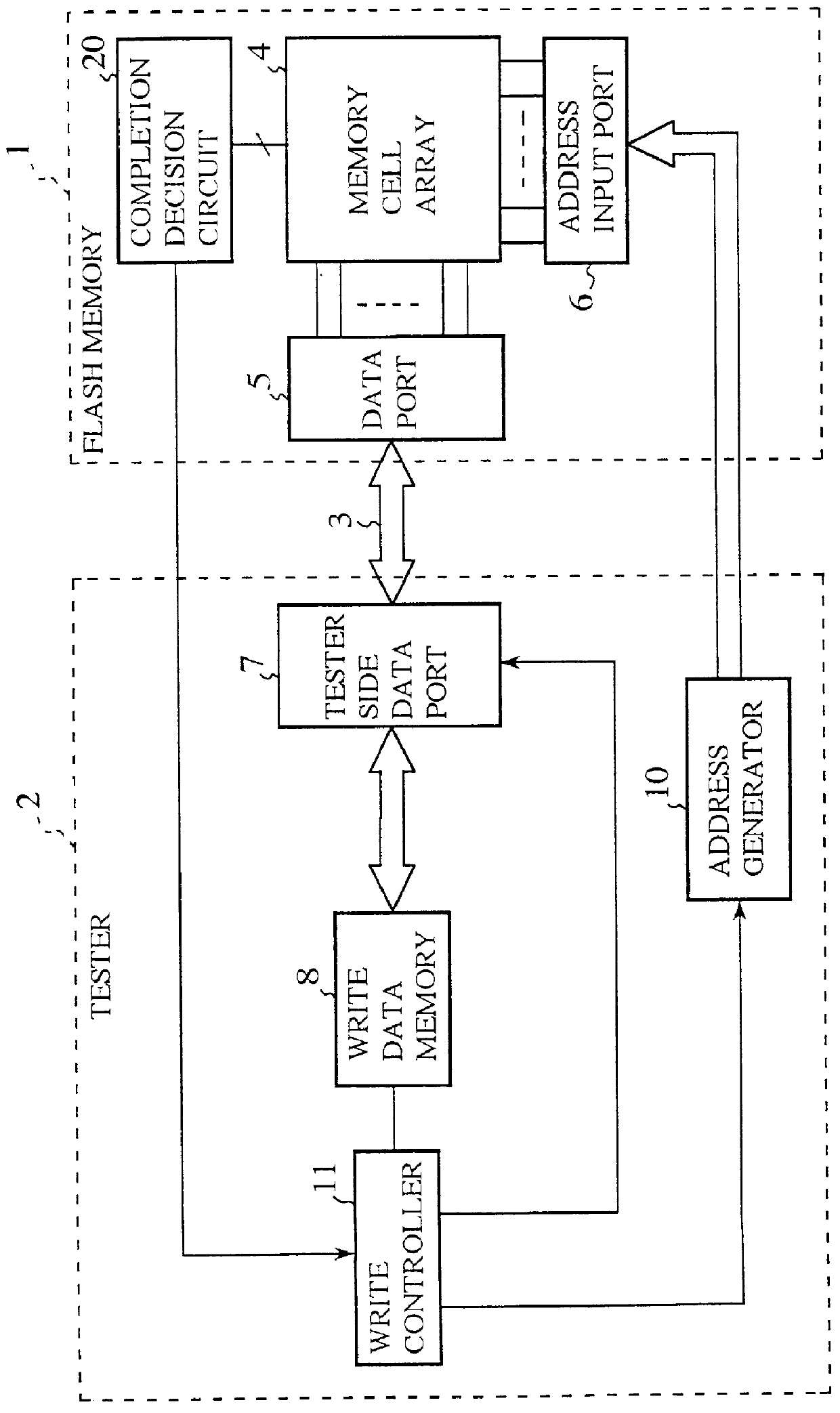

Nonvolatile memory with reduced write time/write verify time and semiconductor device thereof

An involatile memory which carries out, in a flash memory itself, verify check of the flash memory for respective bit lines, and produces an overall verify check result from a completion decision circuit to a tester. This makes it possible to solve a problem of a conventional flash memory in that the time taken by the verify check depends on the bus width of an external data bus, because it carries out the verify check by reading data from the flash memory through the external bus. Thus, the time taken by the verify check can be reduced.

Owner:RENESAS ELECTRONICS CORP

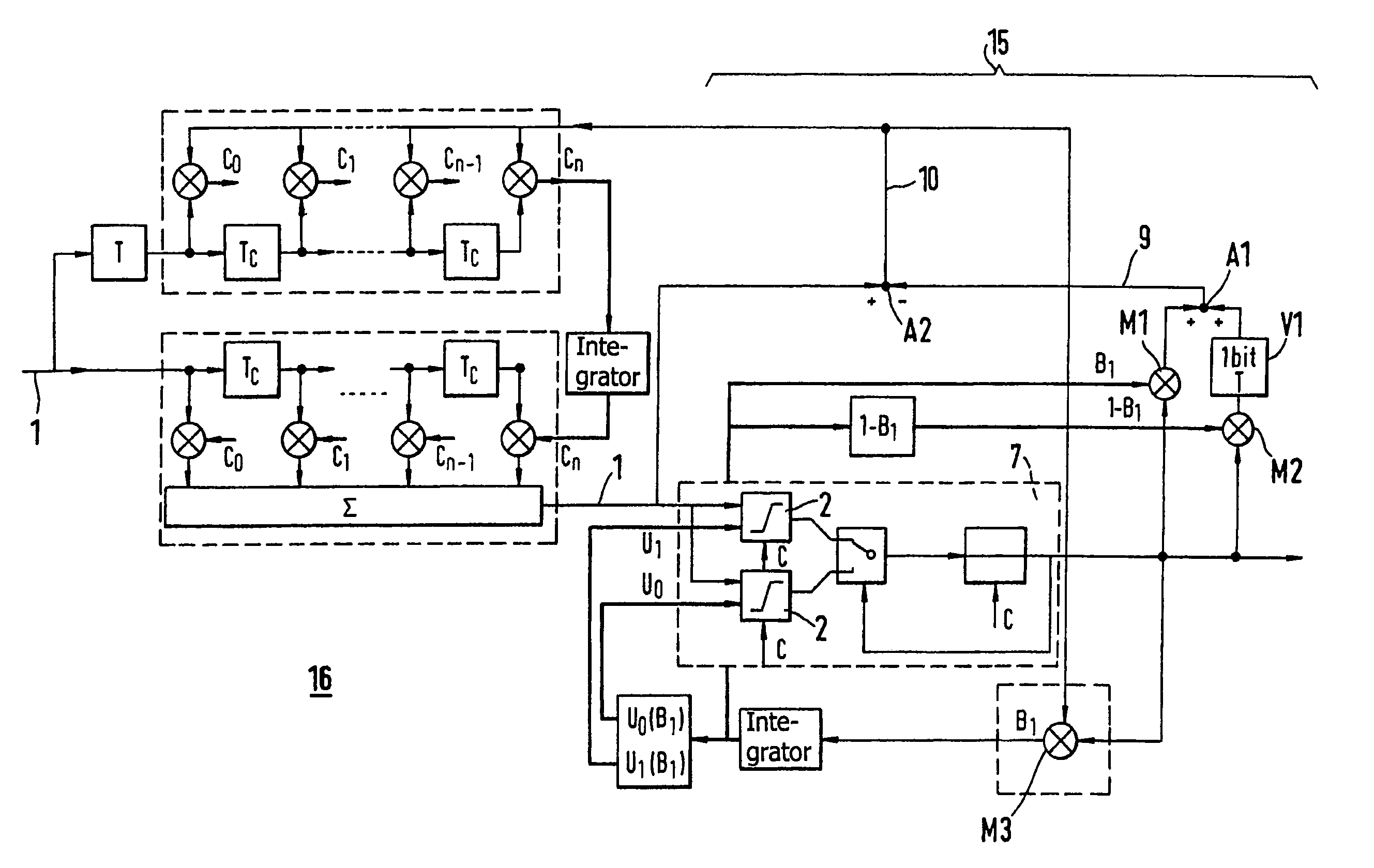

Process for recovering digital optical signals and a feedback decision circuit

InactiveUS6987804B2Simple and rapid adaptationImprove assessmentMultiple-port networksTransmission control/equlisationDecision circuitEngineering

A process is proposed for recovering disturbed digital signals, wherein the electrical signals pass through a feedback equalizer and an analogue control of the setting parameters of the equalizers is performed. A pseudo-error monitor, which facilitates a high-speed adjustment of decision element thresholds, is also provided.

Owner:ALCATEL LUCENT SAS

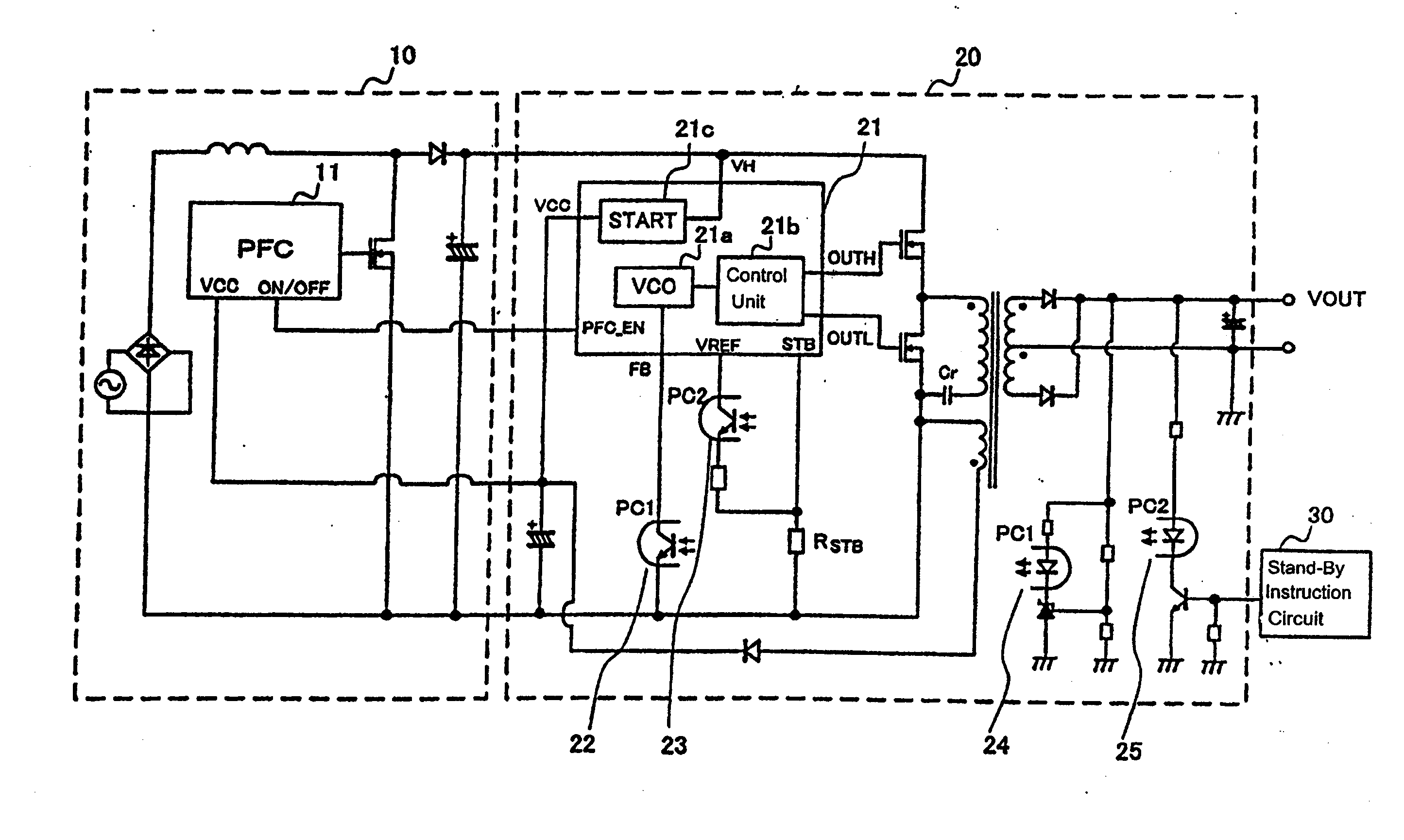

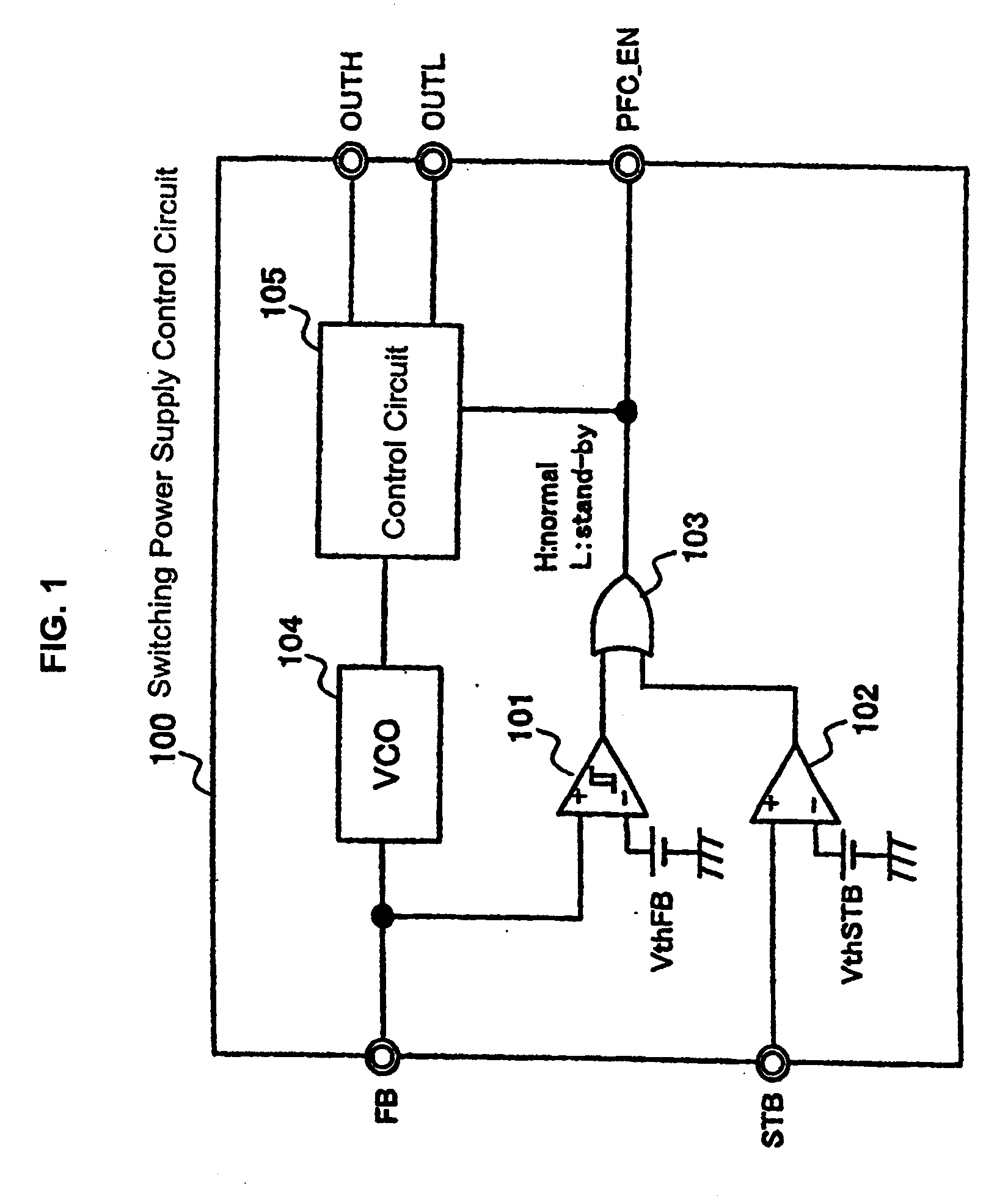

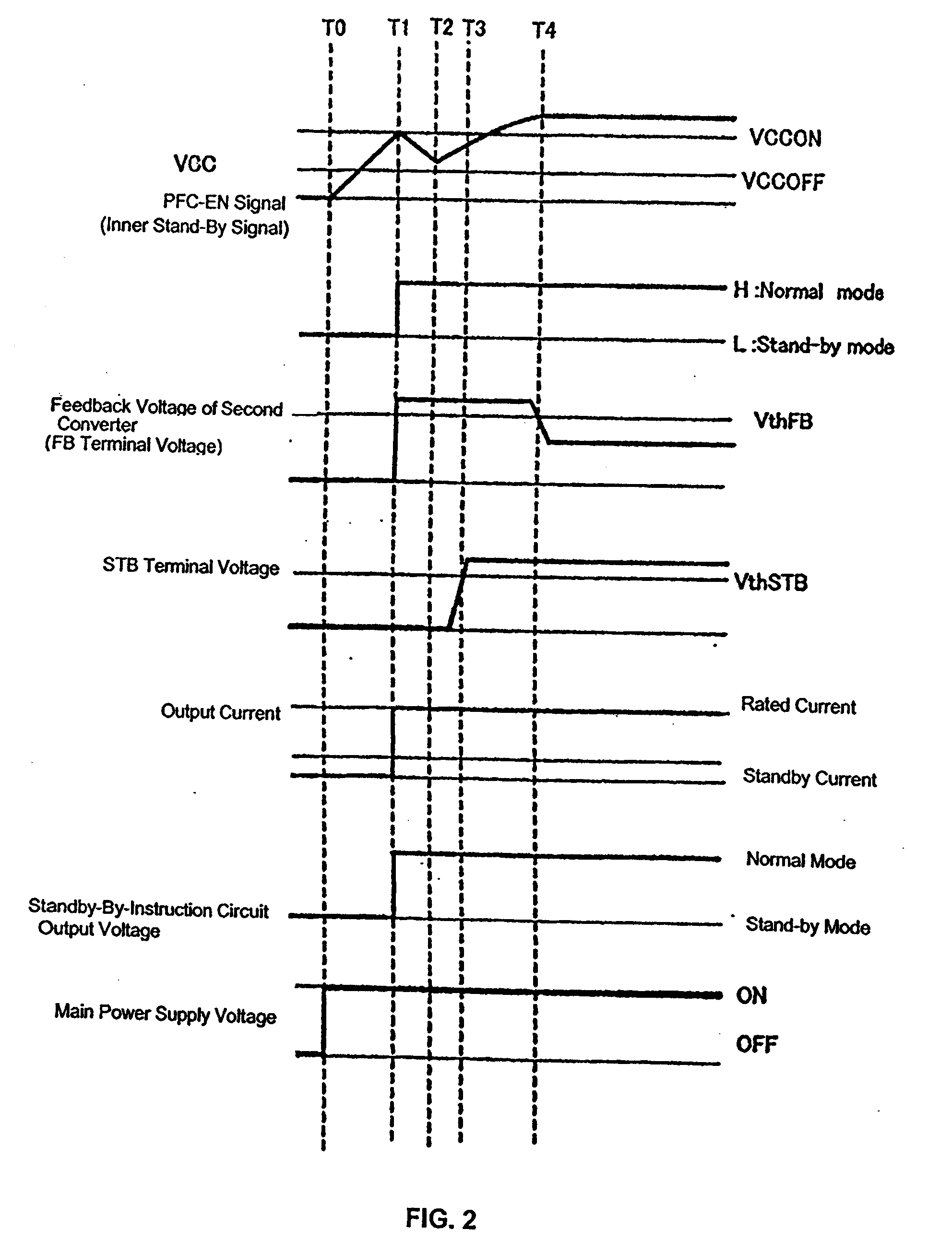

Switching power supply control circuit

ActiveUS20100135050A1Avoid disadvantagesEfficient power electronics conversionAc-dc conversionDecision circuitEngineering

A comparator detects whether a feedback signal of an output voltage detecting circuit for a switching power supply circuit reaches a control voltage. A comparator detects an operating state of the switching power supply circuit, which is instructed by a switching instruction signal, by comparing the instruction signal with a reference voltage. The comparators are connected to a decision circuit which outputs to a control circuit a signal instructing a normal state until the feedback signal reaches the control voltage, and thereafter a signal instructing a normal state or a stand-by state that is instructed by the switching instruction signal. Thus, the control circuit makes the switching power supply circuit operate in a normal state until the output voltage reaches the control voltage. After the output voltage reaches the control voltage, the switching power supply circuit operated in an operation state instructed by the switching instruction signal to enable stable startup.

Owner:FUJI ELECTRIC CO LTD

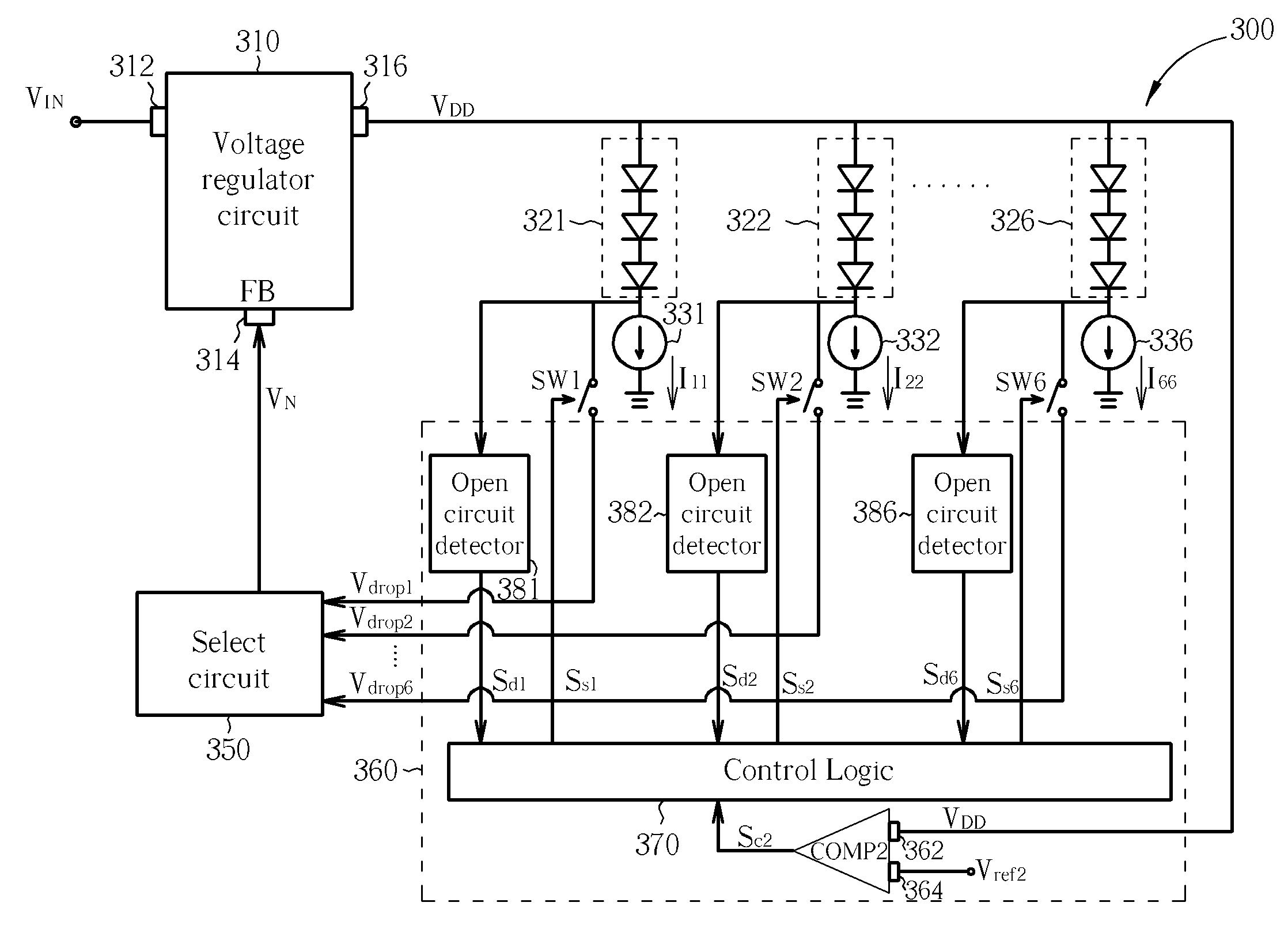

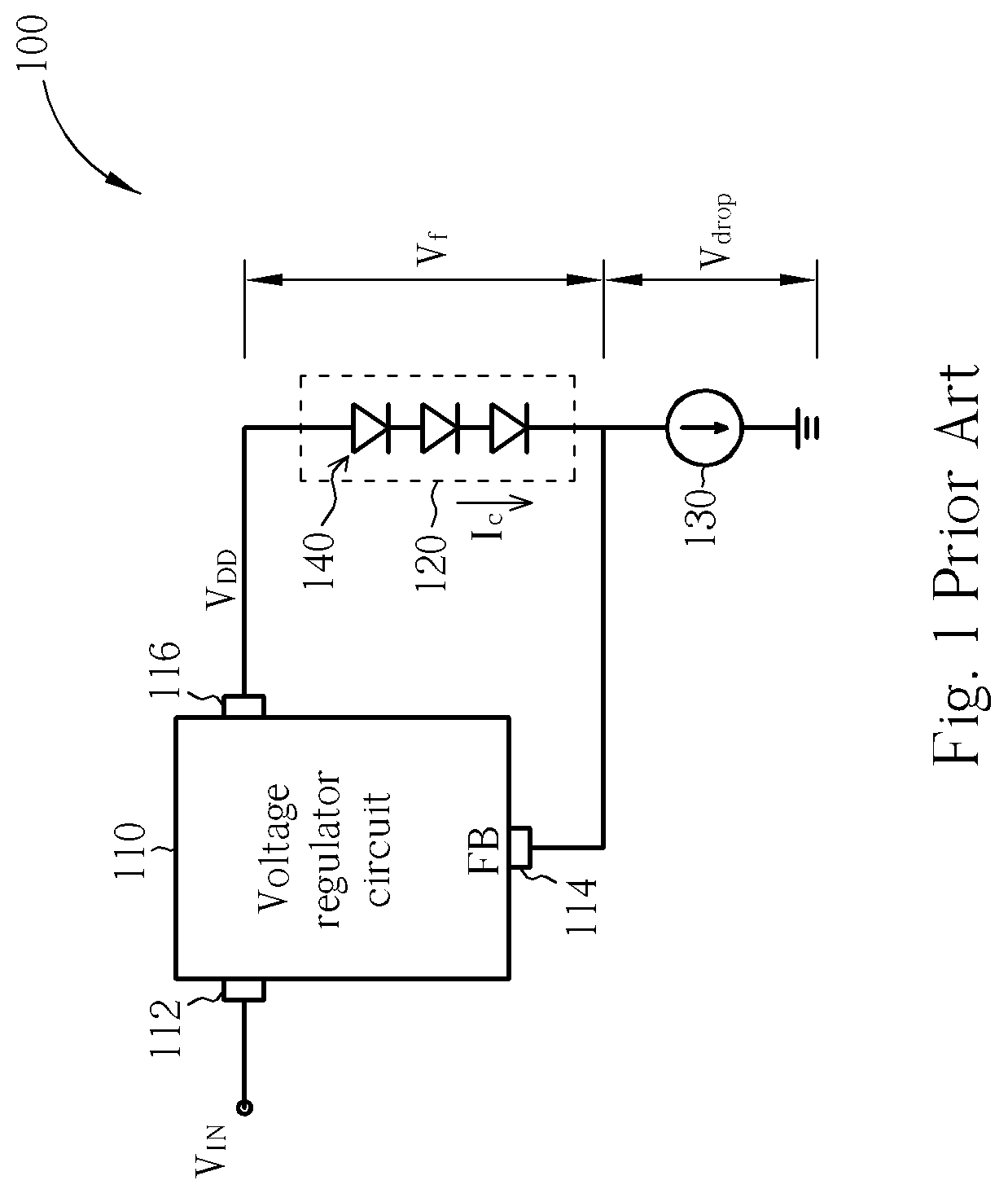

Driving circuit and related driving method for providing feedback control and open-circuit protection

ActiveUS7675246B2Electroluminescent light sourcesSemiconductor lamp usageDecision circuitDriver circuit

A driving circuit includes at least one light-emitting device, a voltage regulator circuit, an analysis and decision circuit, and a selecting circuit. The voltage regulator circuit is coupled to the light-emitting device for providing a driving voltage to drive the light-emitting device. The analysis and decision circuit is coupled to the light-emitting device for determining whether the light-emitting device is open-circuited to generate a decision result. The selecting circuit is coupled between the analysis and decision circuit and the voltage regulator circuit for selecting a maximum forward bias voltage corresponding to the light-emitting device to generate a feedback signal according to the decision result and for transmitting the feedback signal to the voltage regulator circuit. The voltage regulator circuit adjusts the driving voltage according to the feedback signal.

Owner:IML HONG KONG LTD

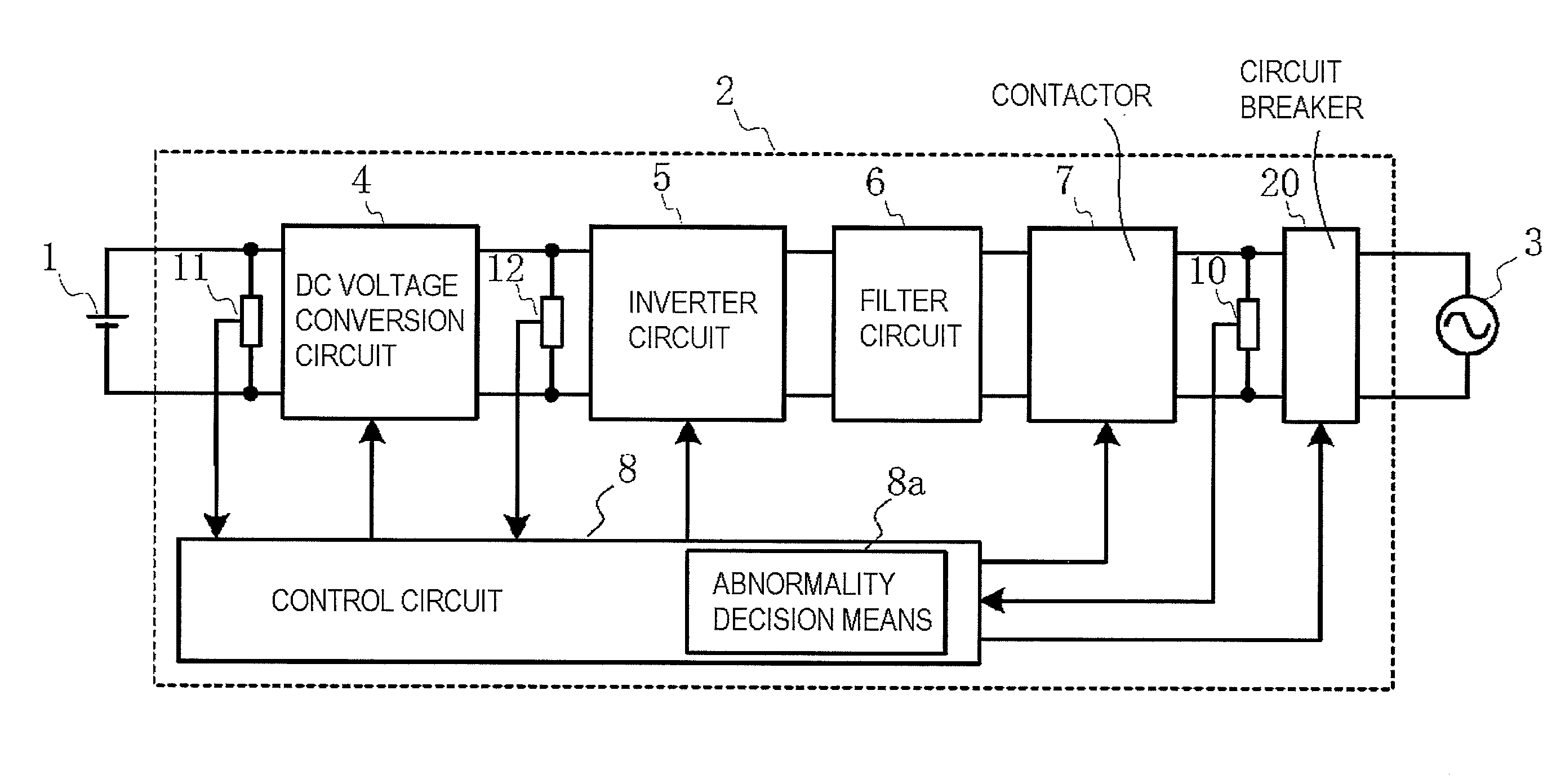

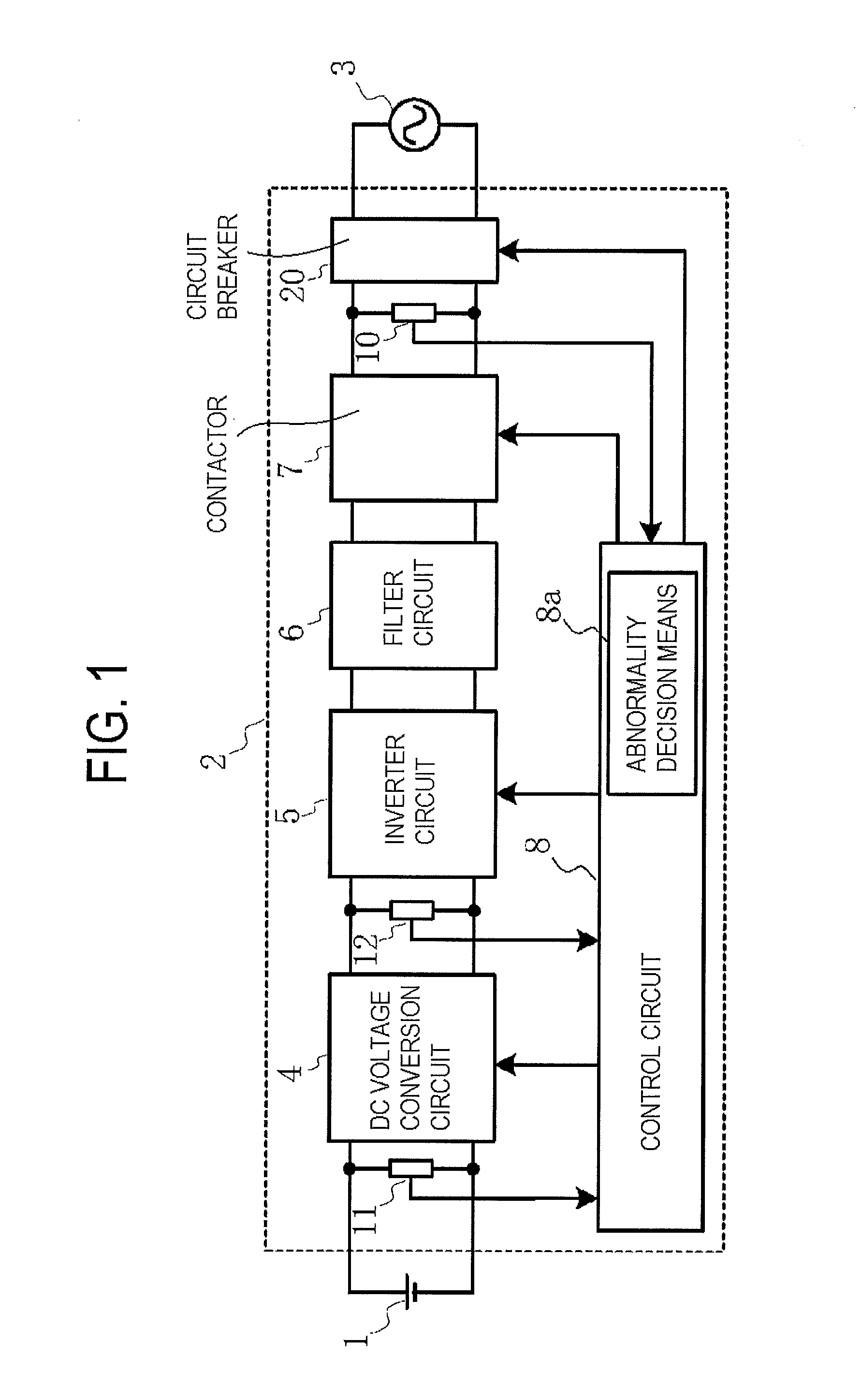

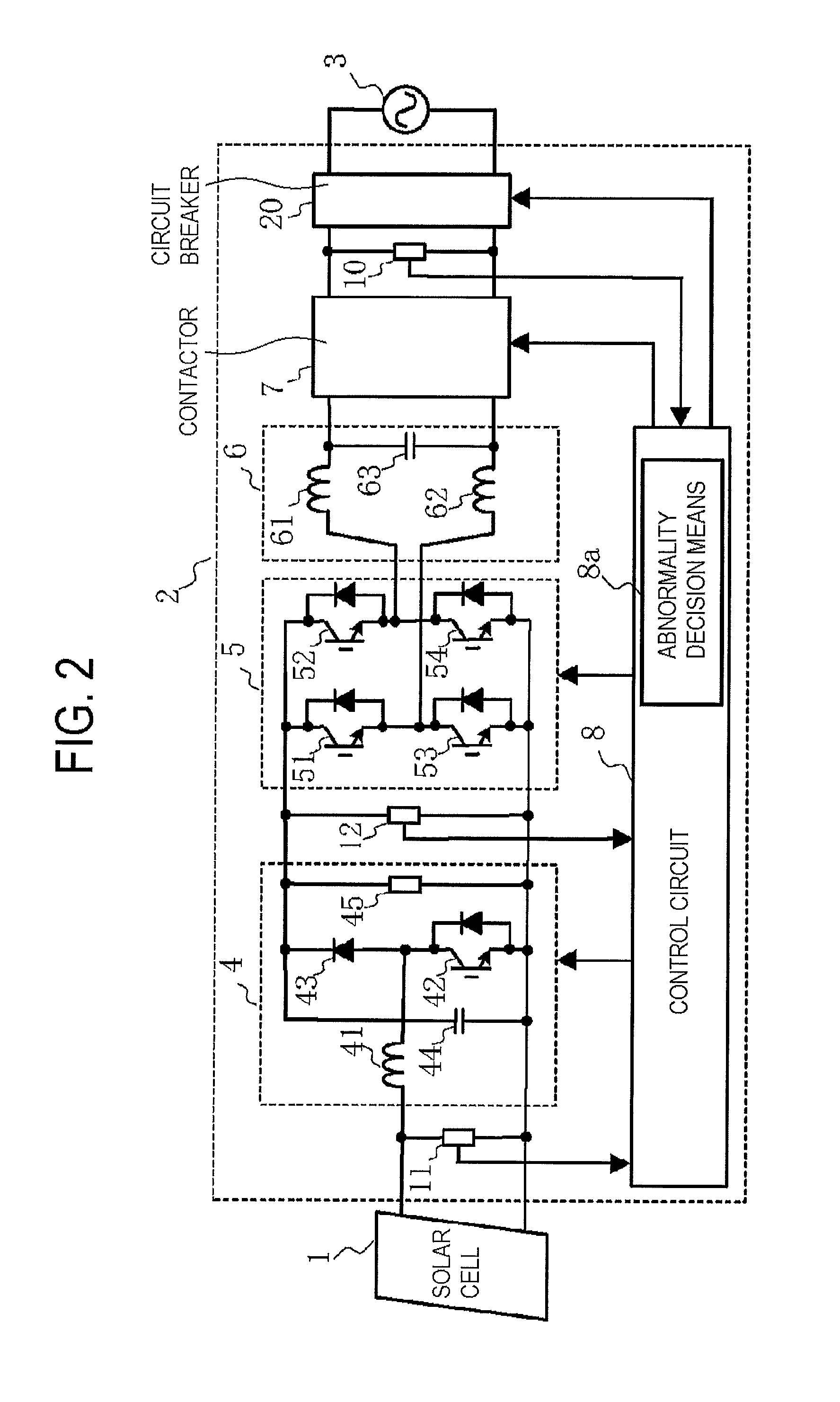

Grid-connected inverter

InactiveUS20110249475A1Improve reliabilitySafer disconnect from the systemEmergency protective circuit arrangementsPhotovoltaic energy generationDecision circuitGrid connected inverter

A grid-connected inverter includes first and second power conversion circuits, a contactor and a control circuit. The first conversion circuit converts a first DC voltage to a second DC voltage. The second conversion circuit converts the second DC voltage to an AC voltage. The contactor connects an output side of the second conversion circuit to a power system. The control circuit includes a decision circuit and controls start and stop operations of the conversion circuits, and opening and closing of the contactor. The decision circuit decides whether a condition of the contactor is abnormal by detecting, after the control circuit controls the contactor to be open, whether or not a value of the second DC voltage is less than a threshold value, and if the value of the second DC voltage is detected to be not less than the threshold value, decides that the condition of the contactor is abnormal.

Owner:FUJI ELECTRIC CO LTD

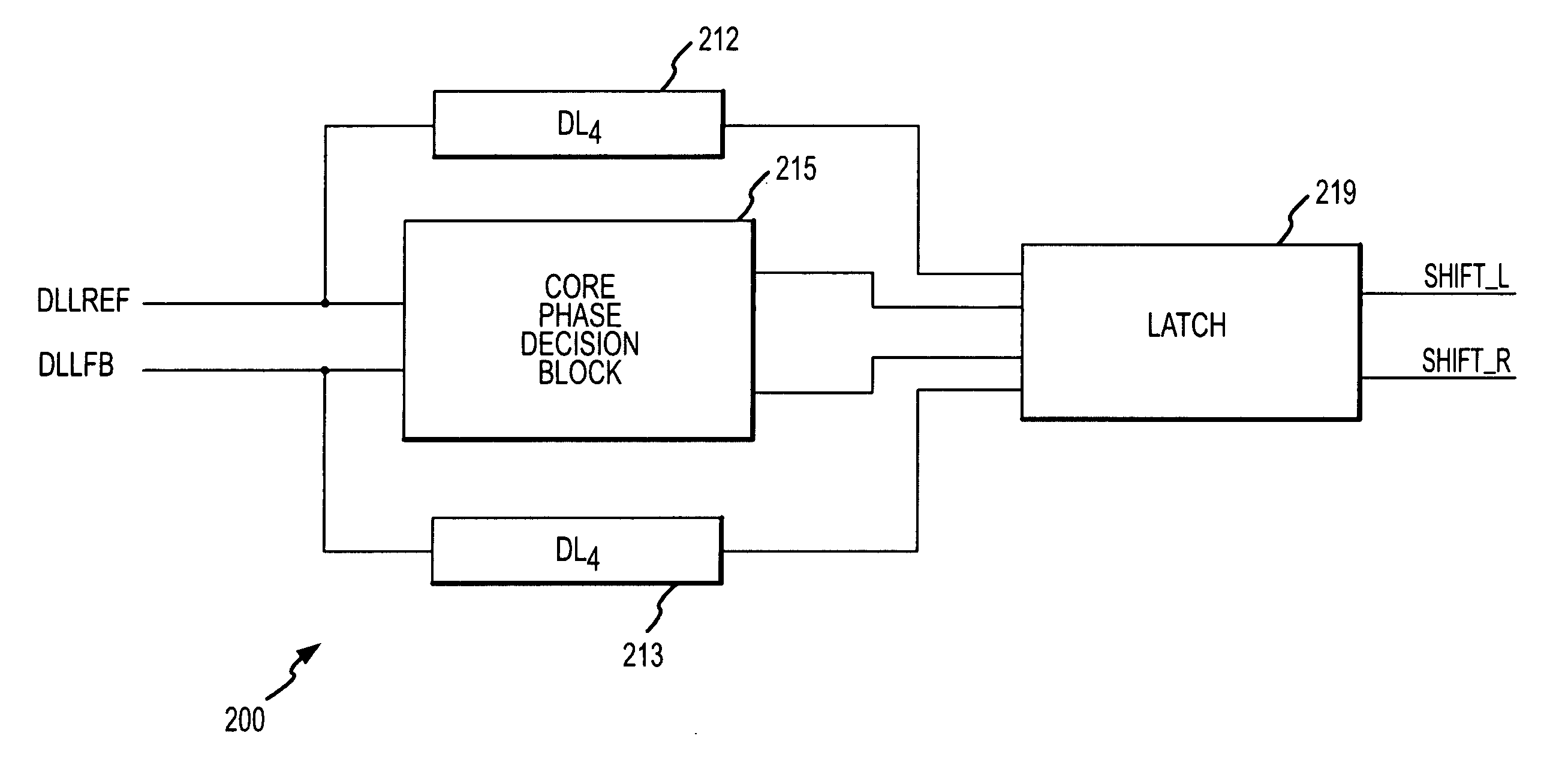

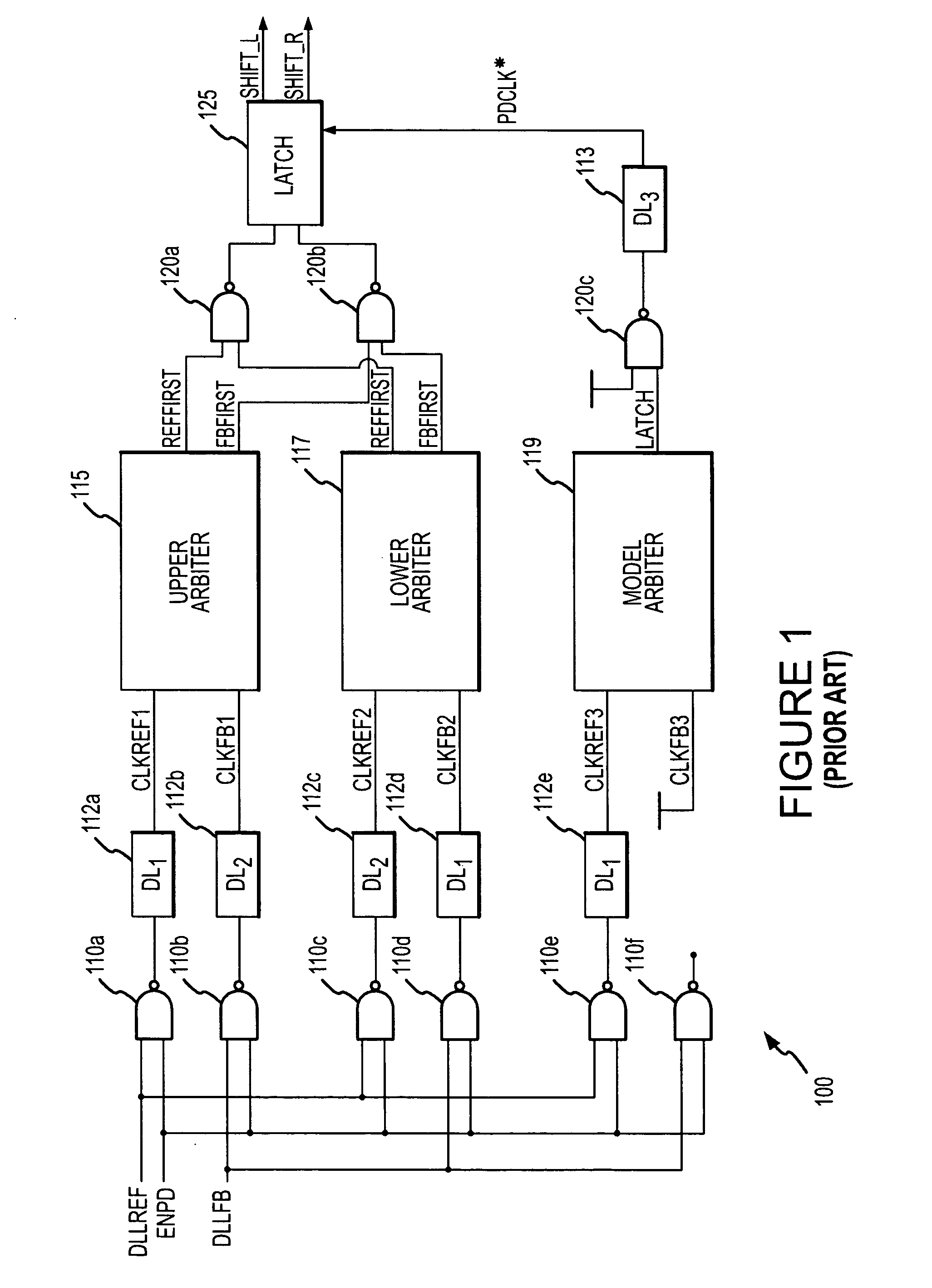

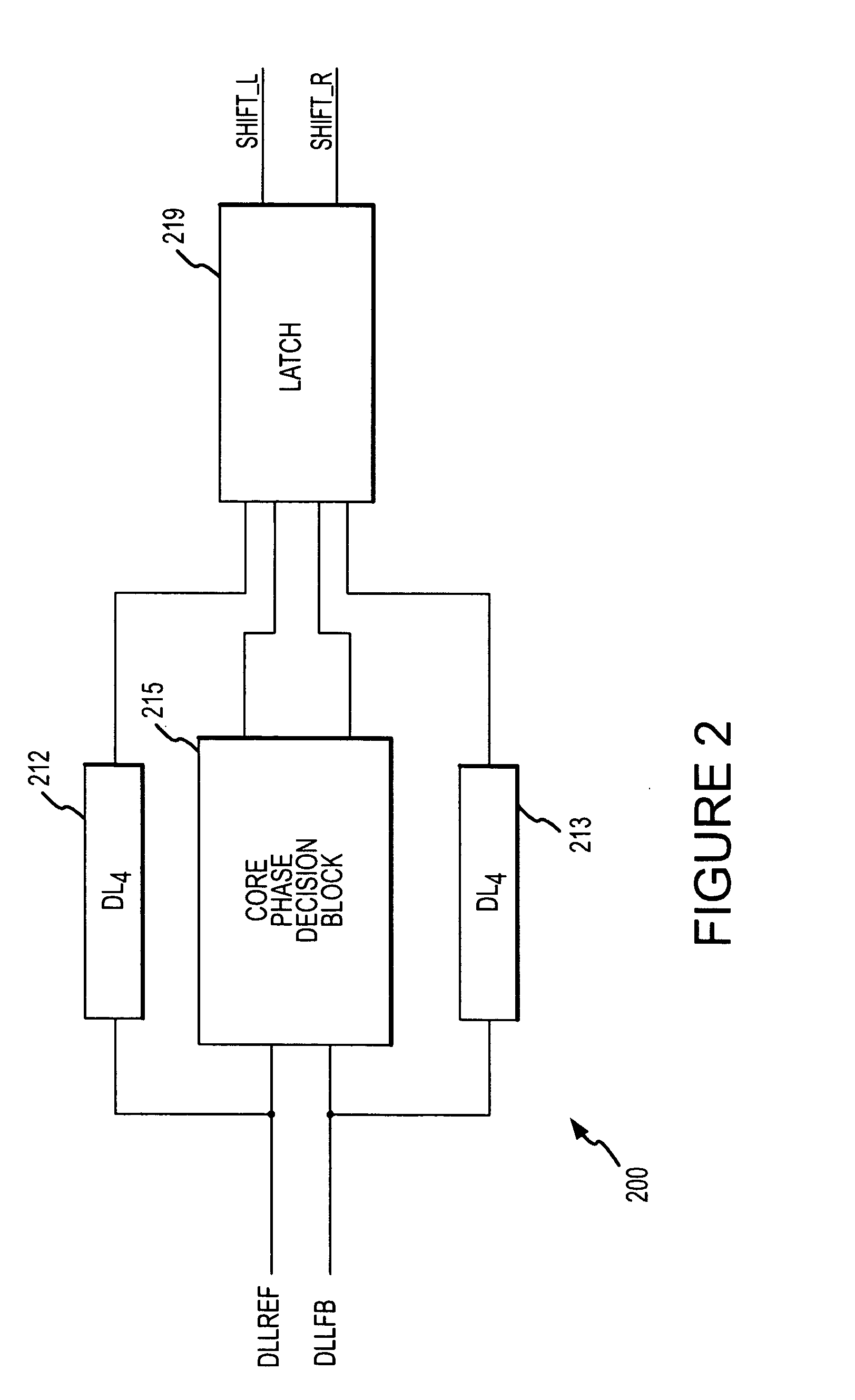

Fast response time, low power phase detector circuits, devices and systems incorporating the same, and associated methods

ActiveUS20080130396A1Reduce power consumptionRaise the possibilityMultiple input and output pulse circuitsPulse automatic controlDecision circuitPhase detector

A circuit for quickly accomplishing highly accurate phase detection using low power is described. The circuit includes a phase decision circuit that receives two clock signals and detects the phase relationship between the two signals by determining which signal was received first. In response, the phase decision circuit generates respective logic signals to reflect the phase relationship determination. The circuit also includes a latch circuit that receives the logic signals from the phase decision circuit and holds the phase relationship determination of the circuit a predetermined time after a predetermined transition of both clock signals have occurred. Methods and systems are also disclosed.

Owner:MICRON TECH INC

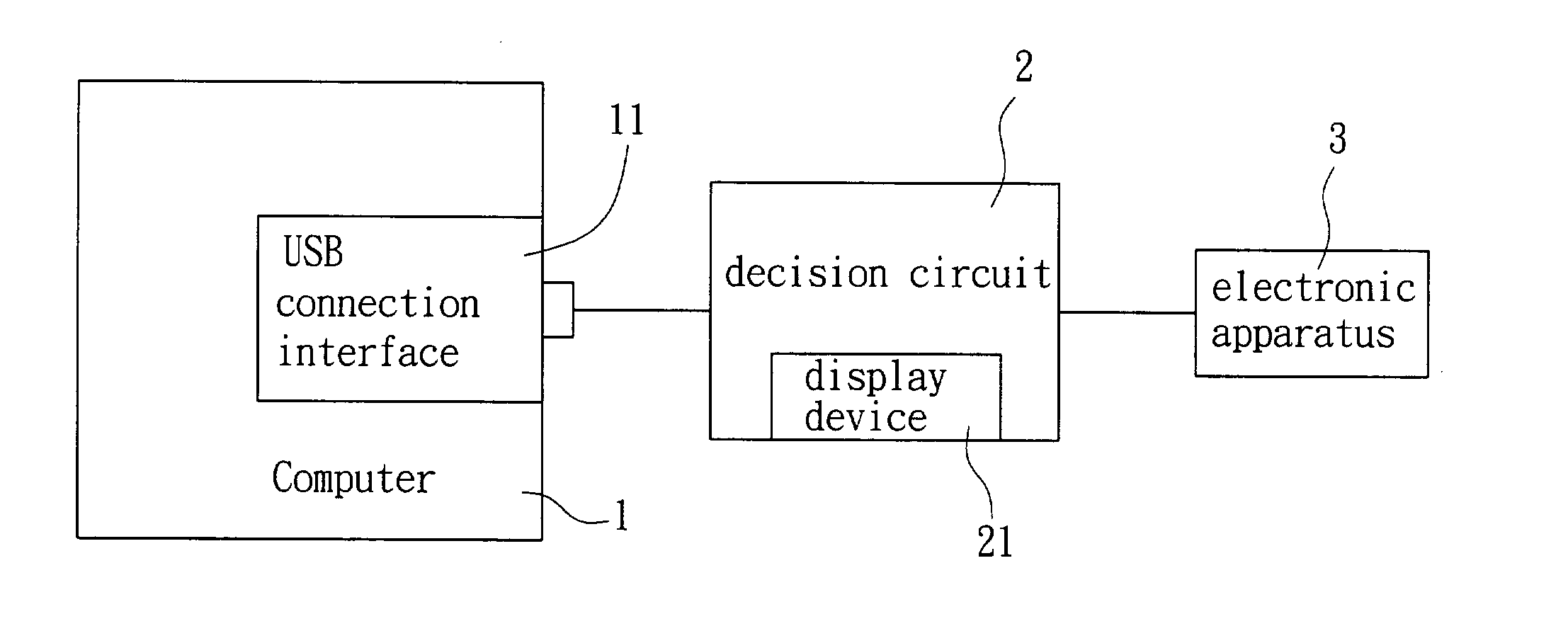

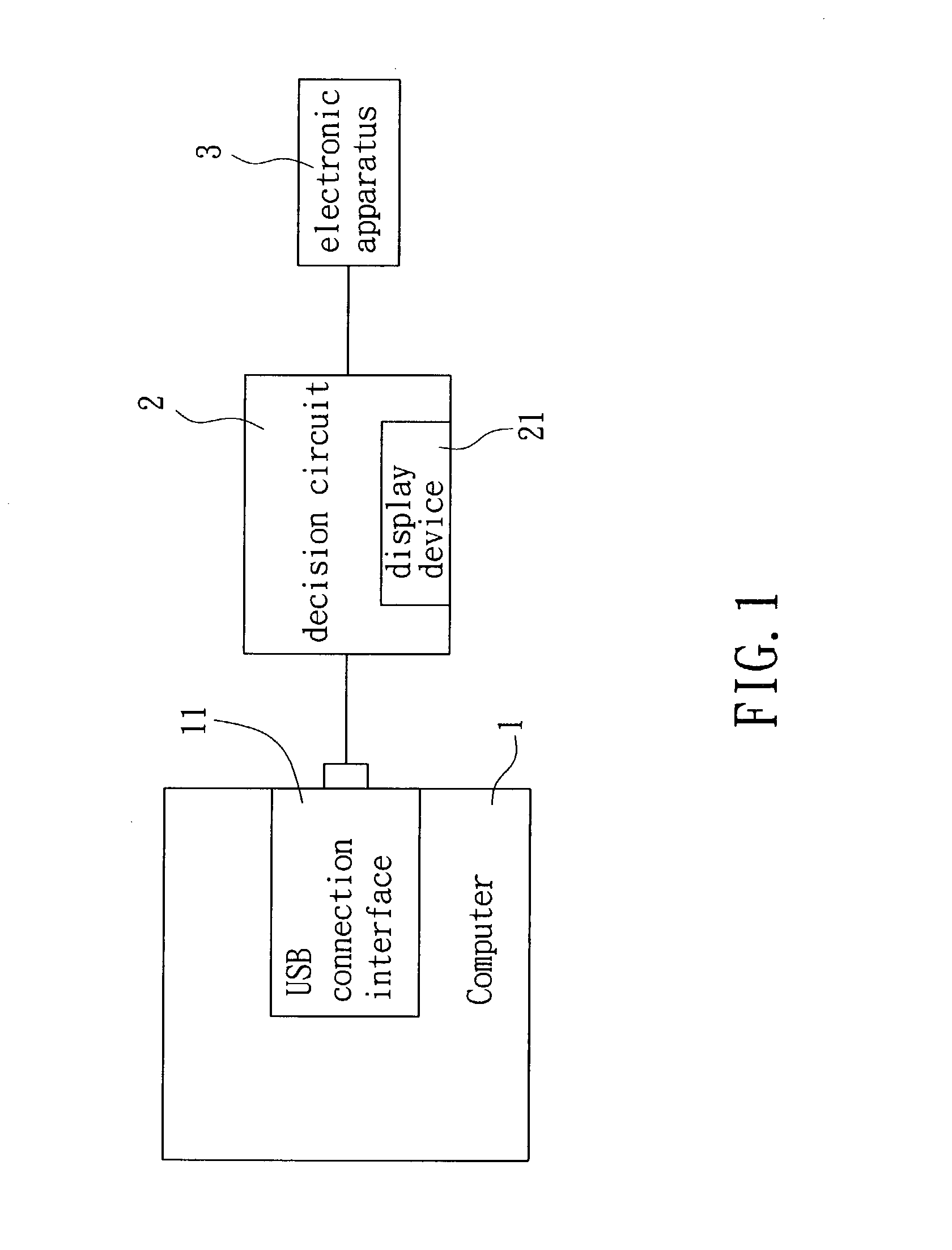

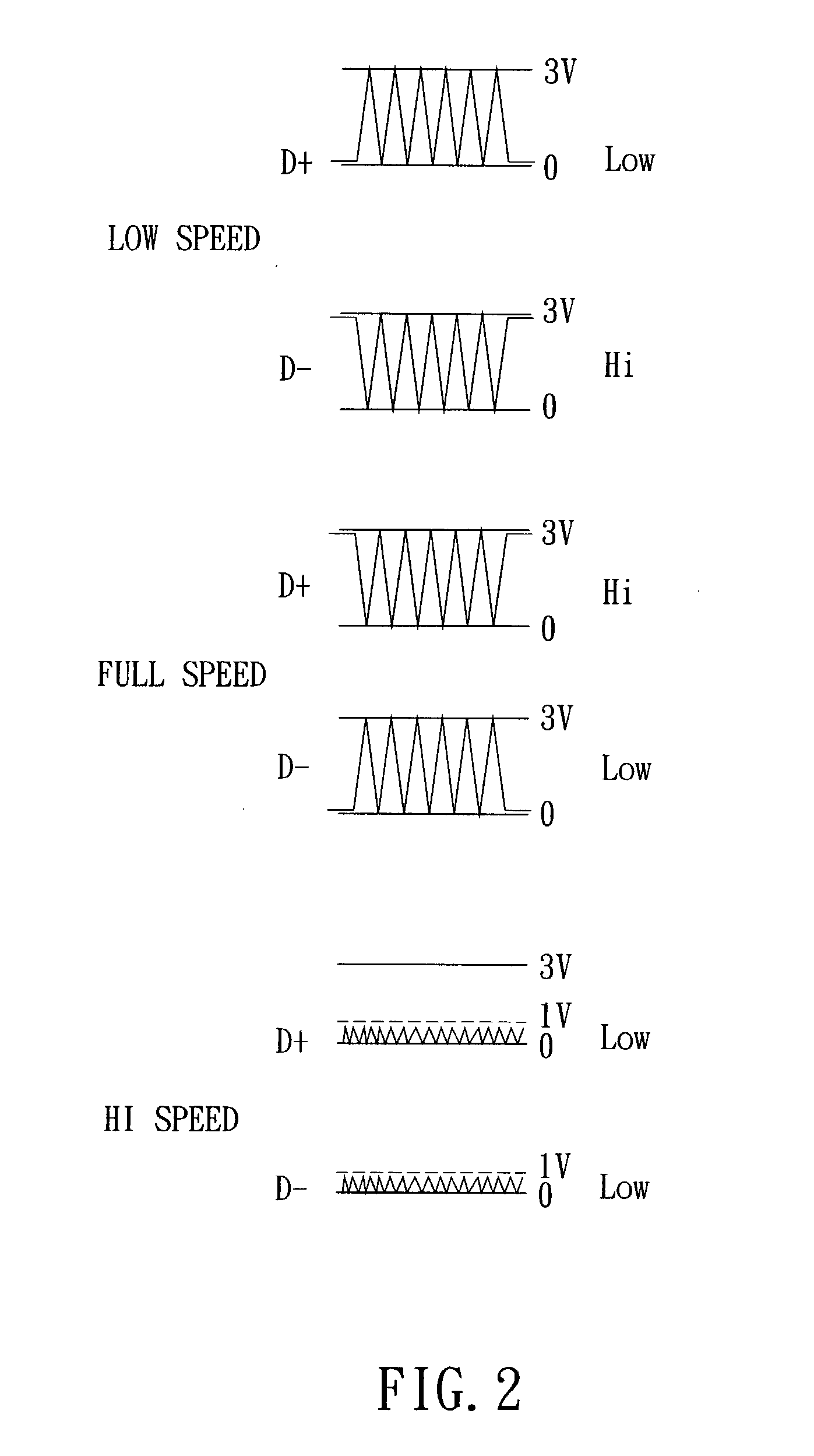

Apparatus for USB interface identification

The present invention is related to a device for USB interface identification, wherein a universal serial bus (USB) connection interface is installed on one side of computer exterior as a connection for external electronic apparatus, and more specifically, the present invention installs a decision circuit connecting to a display device between the USB connection interface and the electronic apparatus. Thus, messages illustrated on the display device are employed by user to determine whether the transmission speed between the computer and the electronic apparatus is in the low speed, full speed, or hi-speed.

Owner:ACTION STAR ENTERPRISE

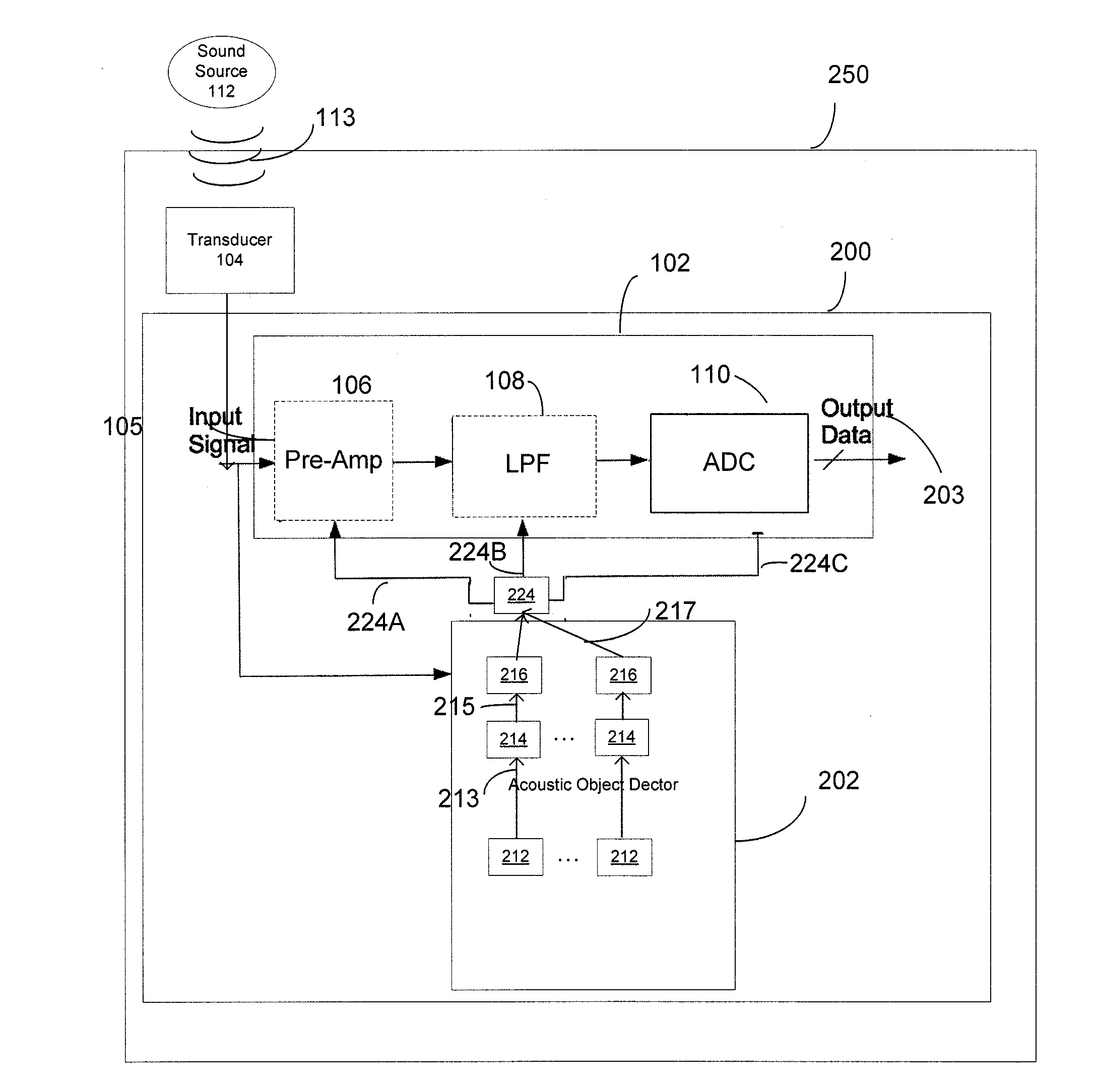

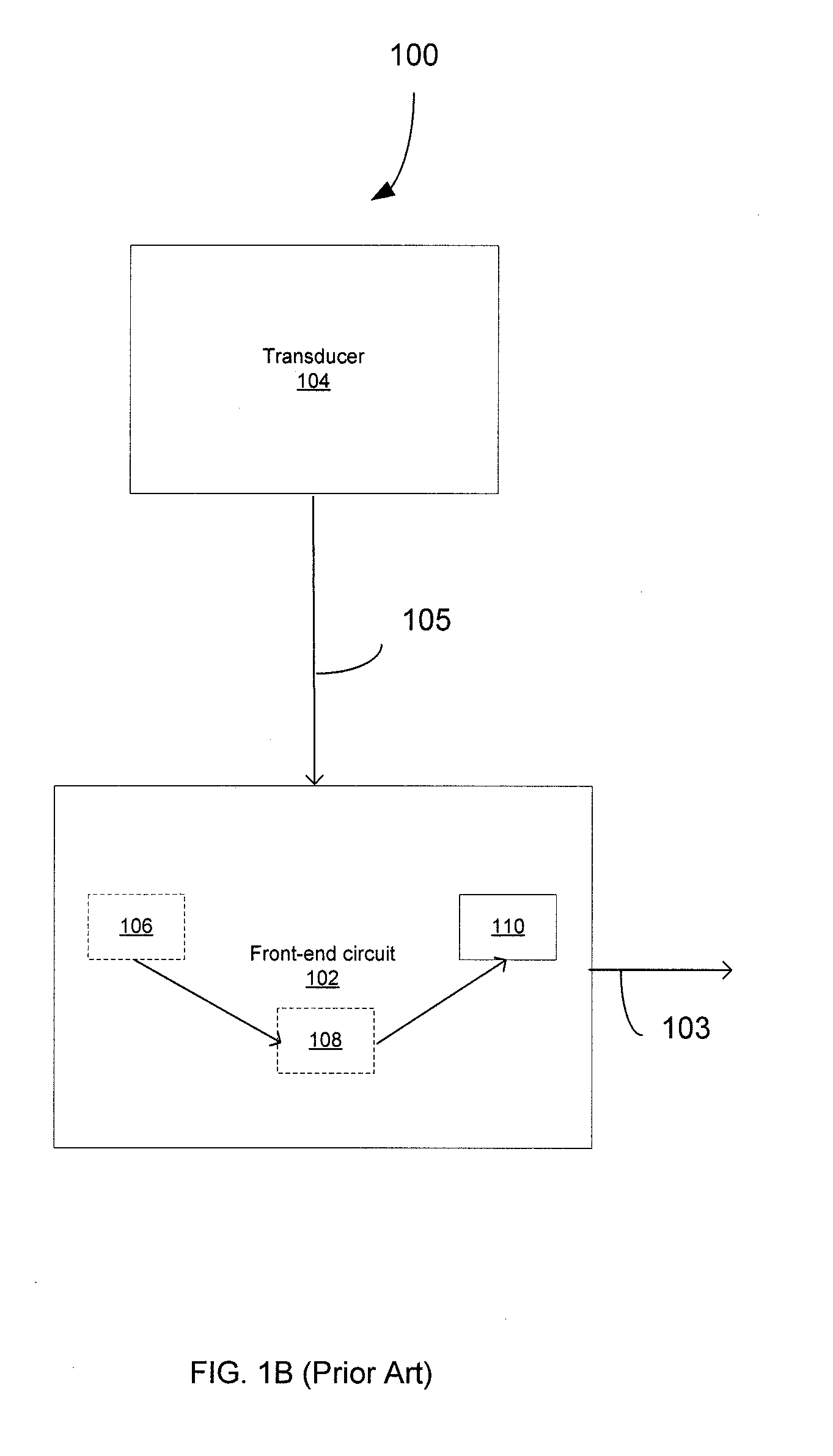

Acoustic Sensor With An Acoustic Object Detector For Reducing Power Consumption In Front-End Circuit

ActiveUS20130322215A1Improve power efficiencyReduce power consumptionSubsonic/sonic/ultrasonic wave measurementSpeech analysisBandpass filteringDecision circuit

An acoustic object detector for detecting presence of an acoustic signal is provided. The acoustic object detector includes a number of bandpass filters. Each bandpass filter is configured to convert an input signal into an analog signal within a frequency band. The acoustic object detector also includes a number of spike generating circuits each coupled to the respective bandpass filter. Each spike generating circuit is configured to generate a series of spike signals based upon an adaptive threshold for the analog signal. The acoustic object detection further includes a decision circuit configured to generate a digital signal at a time-frequency point from the series of spike signals.

Owner:TRUSTEES OF DARTMOUTH COLLEGE THE

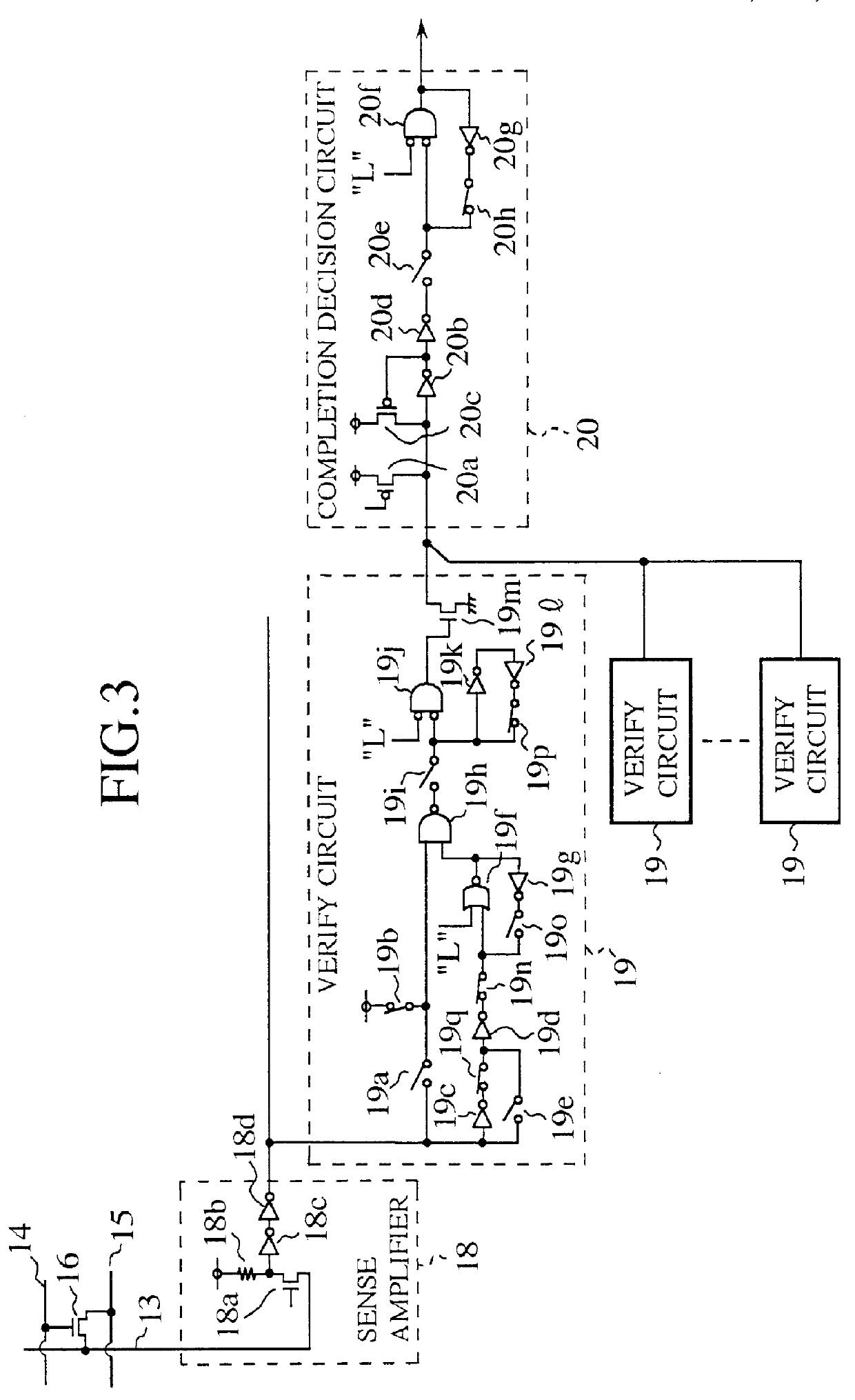

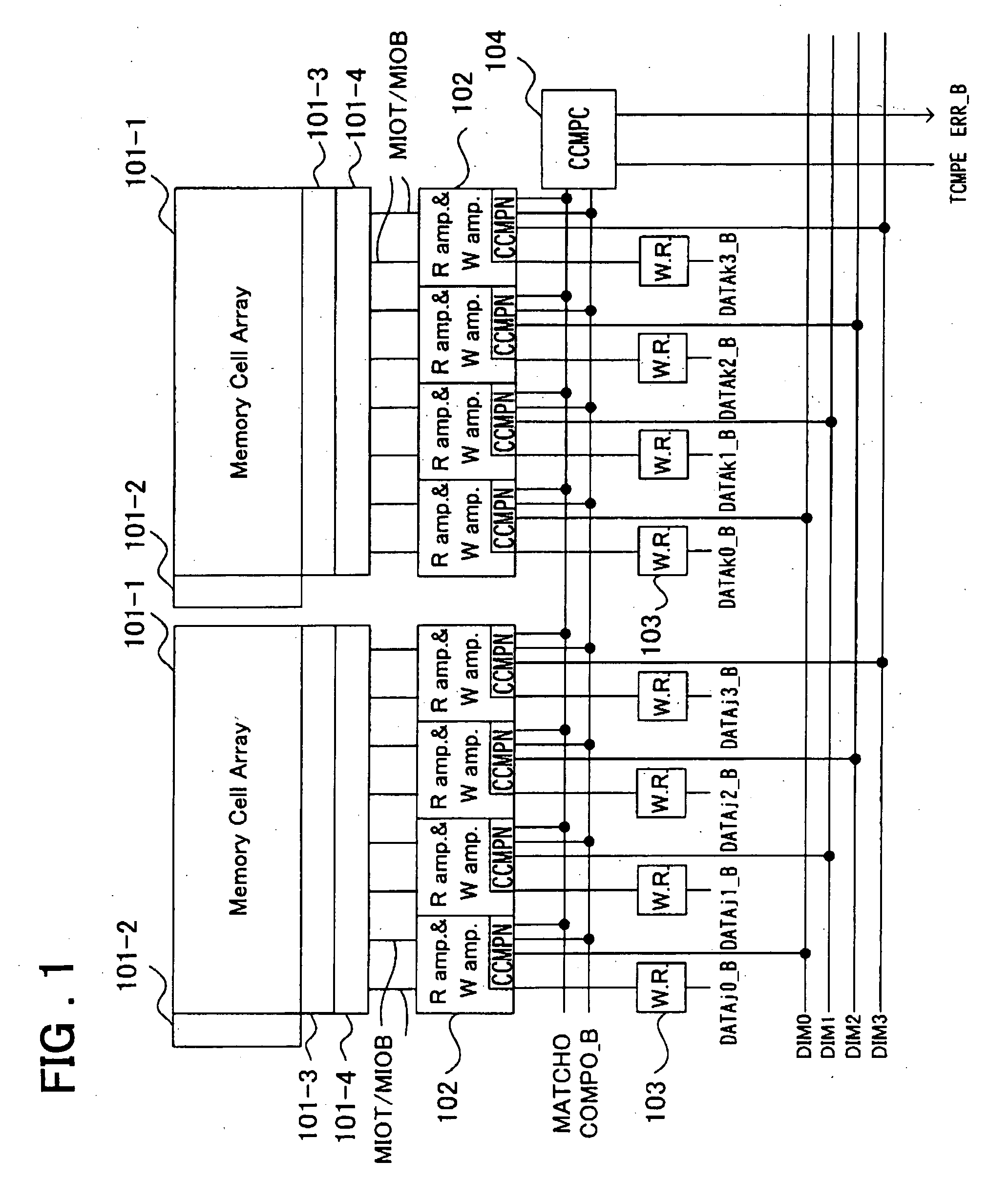

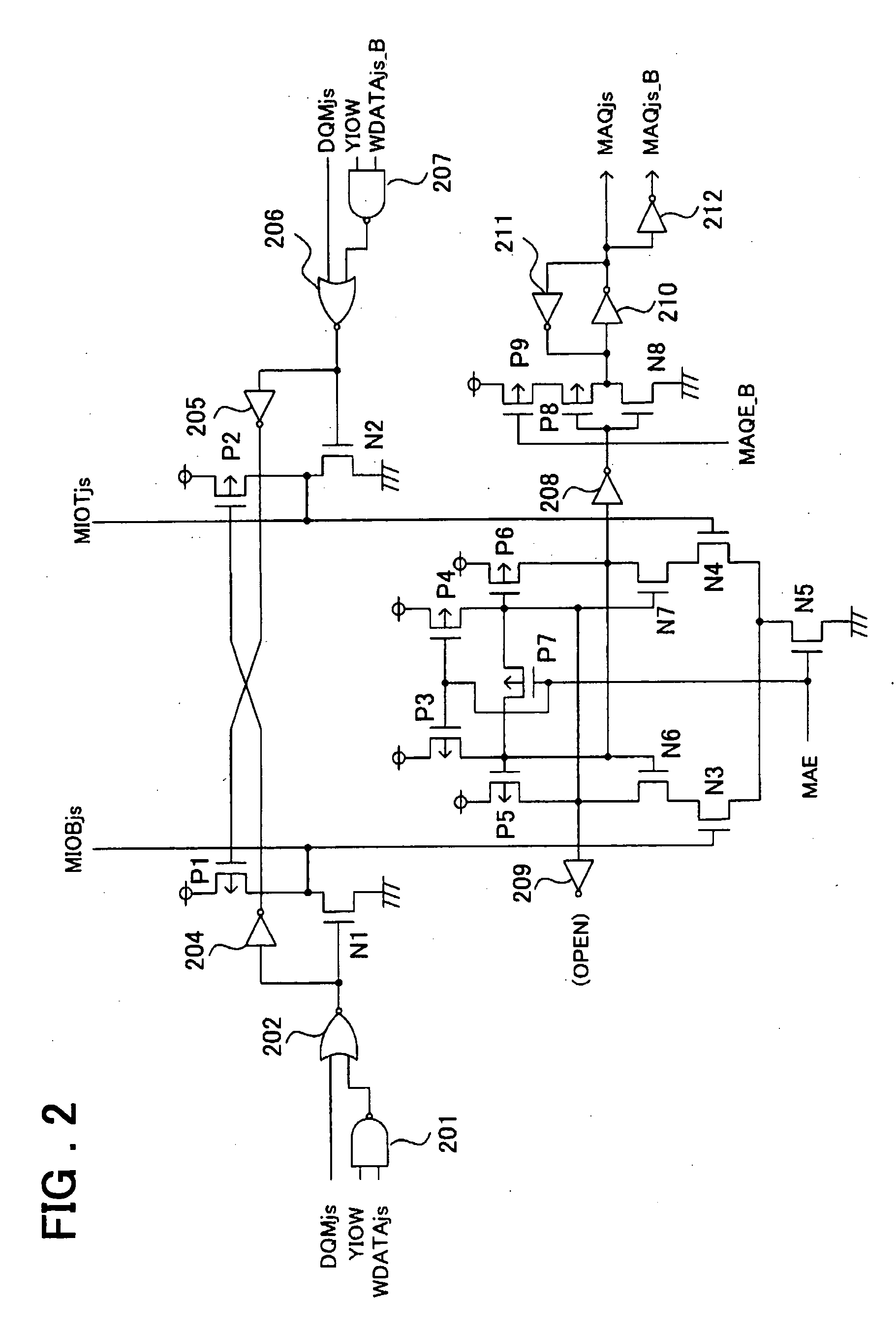

Semiconductor storage device

InactiveUS20040205429A1Improve testabilityFacilitate accommodationElectronic circuit testingDigital storageDecision circuitControl signal

A testing device for a semiconductor storage device which suppresses the increase in the circuit size, provides for facilitated accommodation to a test with frequent changes in the test pattern, and which improves testability of the semiconductor storage device. A plural number of holding circuits (103) are provided holding write data for memory cells of a memory cell array (101-1). The write data from the holding circuits (103) are written in the memory cells of the selected address. A plural number of comparators (CCMPN) are supplied with data read out from the memory cells and with data held by the holding circuits as expectation data to compare the readout data and the expectation data. The non-inverted value or the inverted value of the write data held by the holding circuits (103) is output as the write data to the memory cells and as expectation data to the comparators (CCMPN) depending on the value of the inversion control signal (DIM). A decision circuit (104) is provided which outputs an error flag based on a coincidence detection signal (MATCH0) coupled to the plural comparators.

Owner:LONGITUDE LICENSING LTD

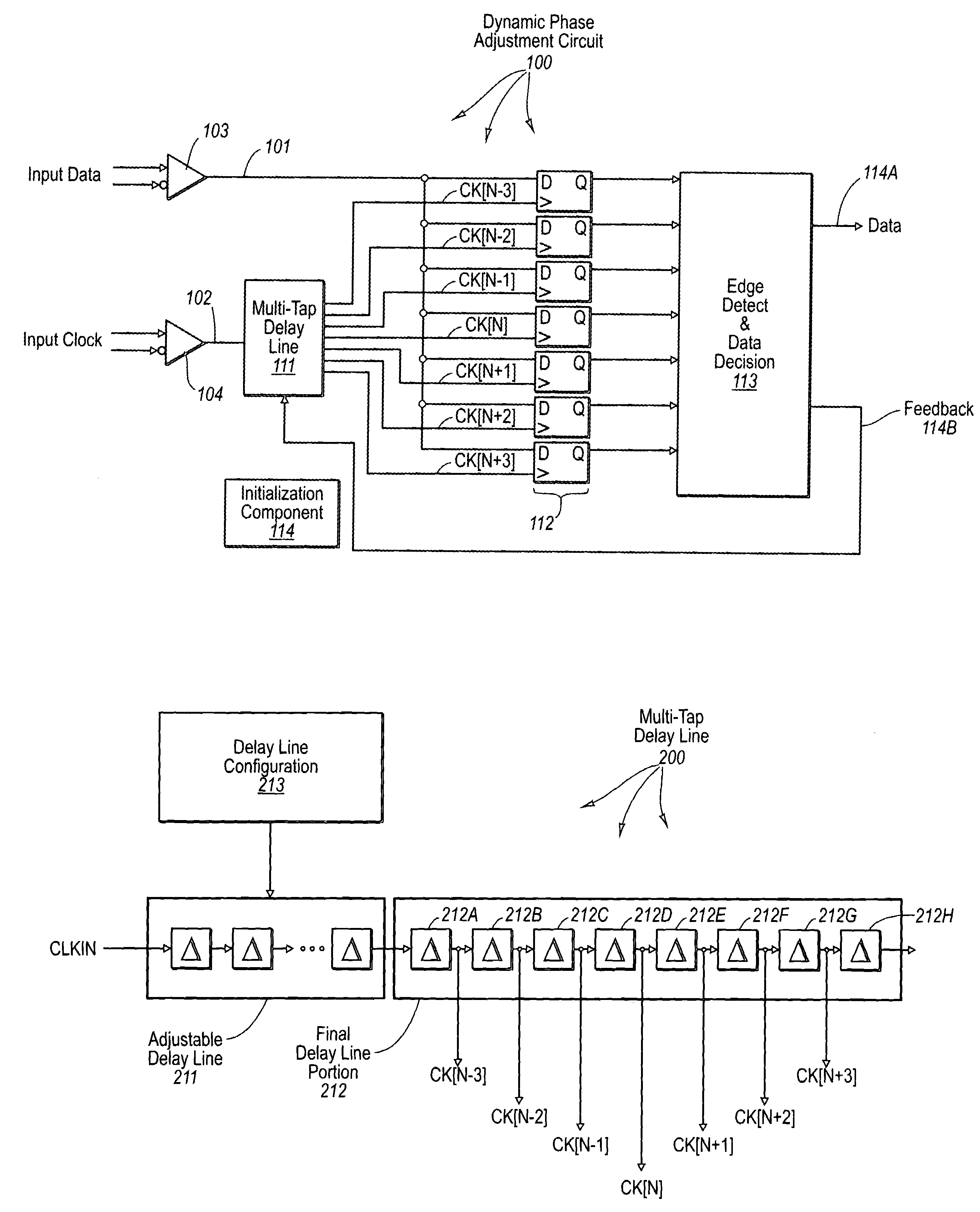

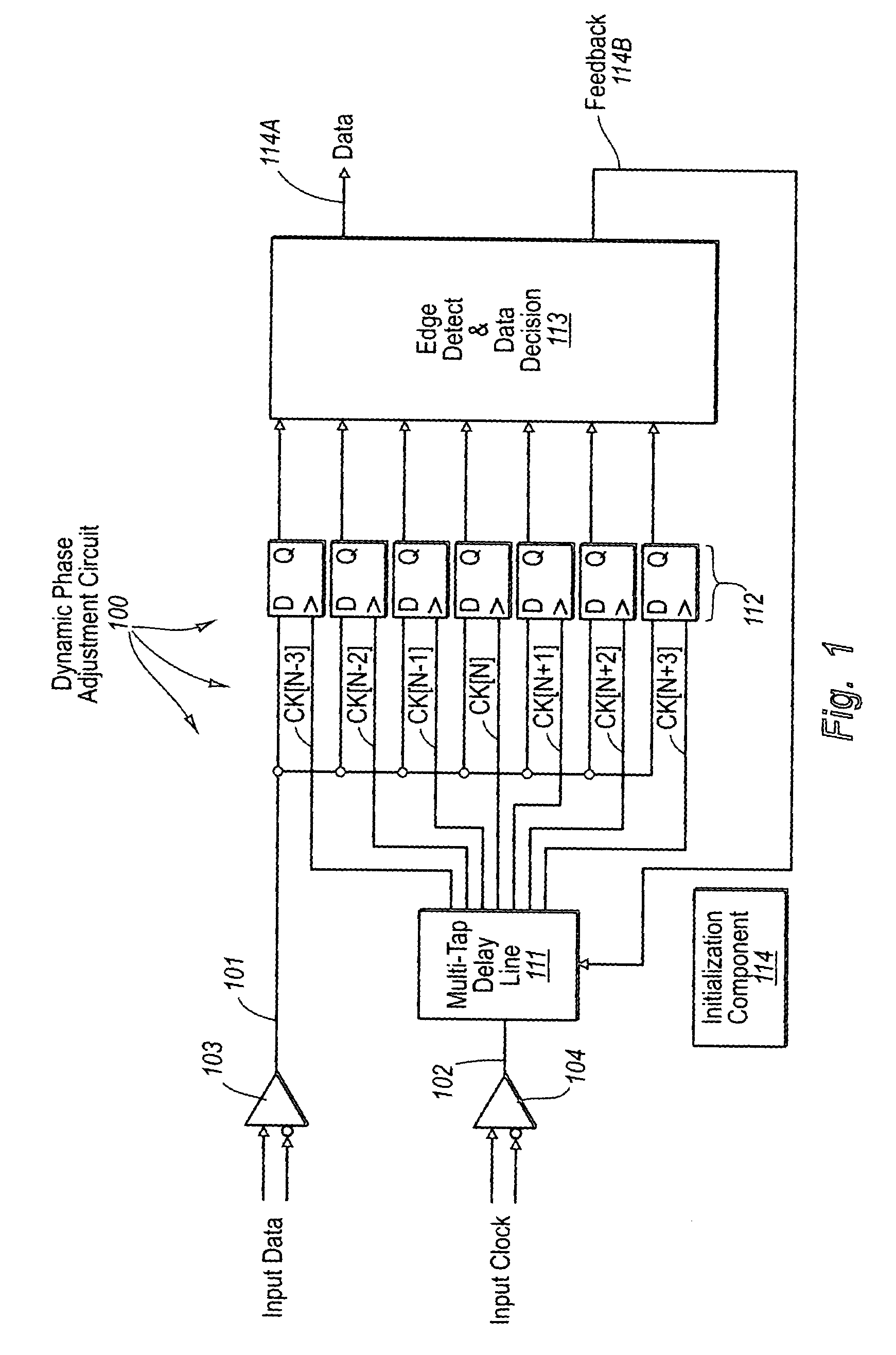

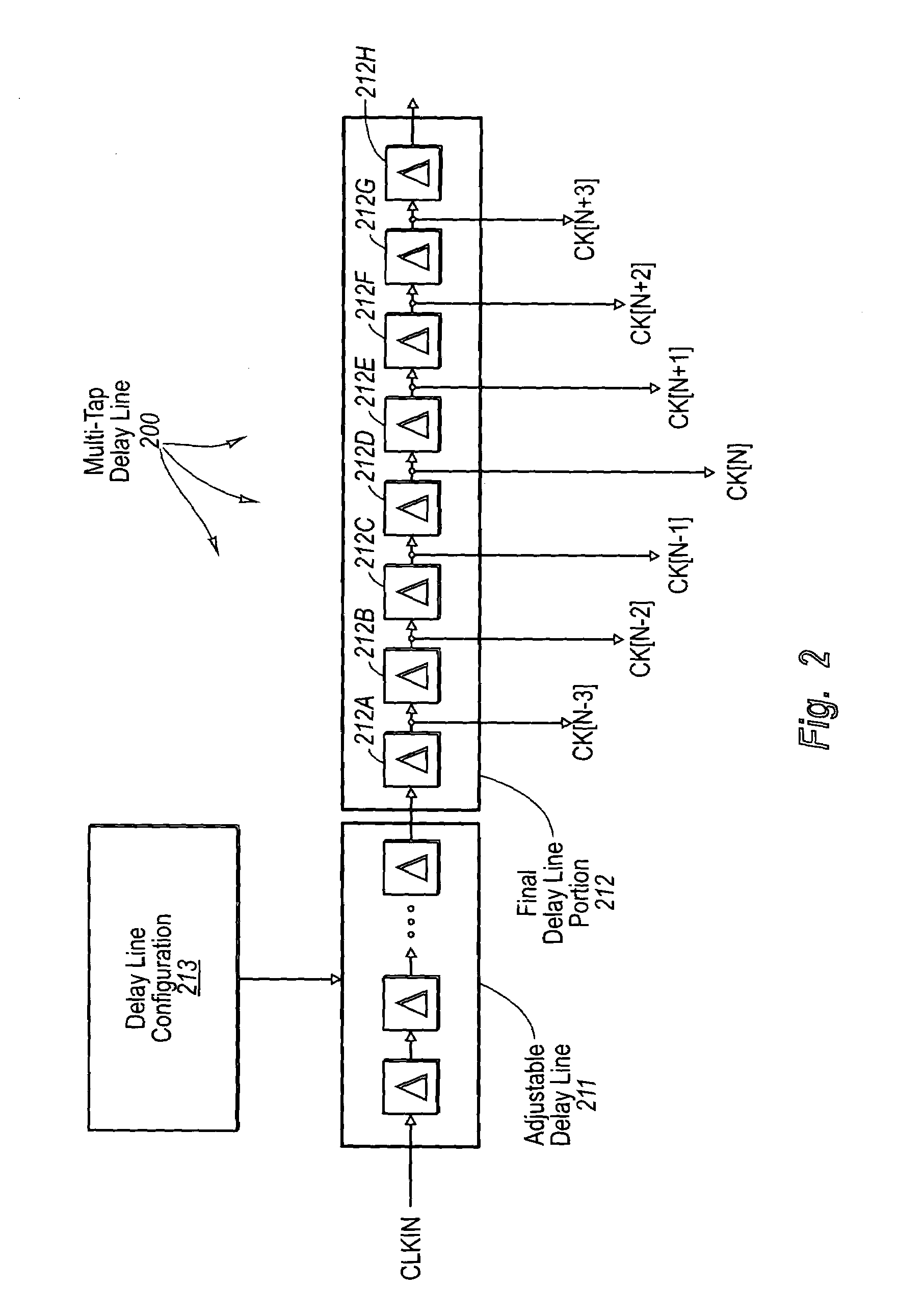

Dynamic phase alignment of a clock and data signal using an adjustable clock delay line

InactiveUS7034597B1High resolutionTo overcome the large delayPulse automatic controlSynchronising arrangementDecision circuitImage resolution

A dynamic phase adjustment circuit that includes a multi-tap delay line that receives a clock input signal. The multi-tap delay line includes an initial portion that is adjustable, and final portion after the adjustable portion. A number of registers receive the same data. However, the clock signal that causes the registers to sample is received from a corresponding delay element in the final portion of the multi-tap delay line. An edge detect and data decision circuit receives the sampled data values from each of the registers. Sampling resolution is improved over the PLL-based dynamic phase adjustment circuit since the clock signal is delayed using delay elements, which can be made with relatively small delays. Furthermore, the circuit does not contain excessive circuit elements thereby allowing the dynamic phase adjustment circuit to be contained in a small area.

Owner:SEMICON COMPONENTS IND LLC

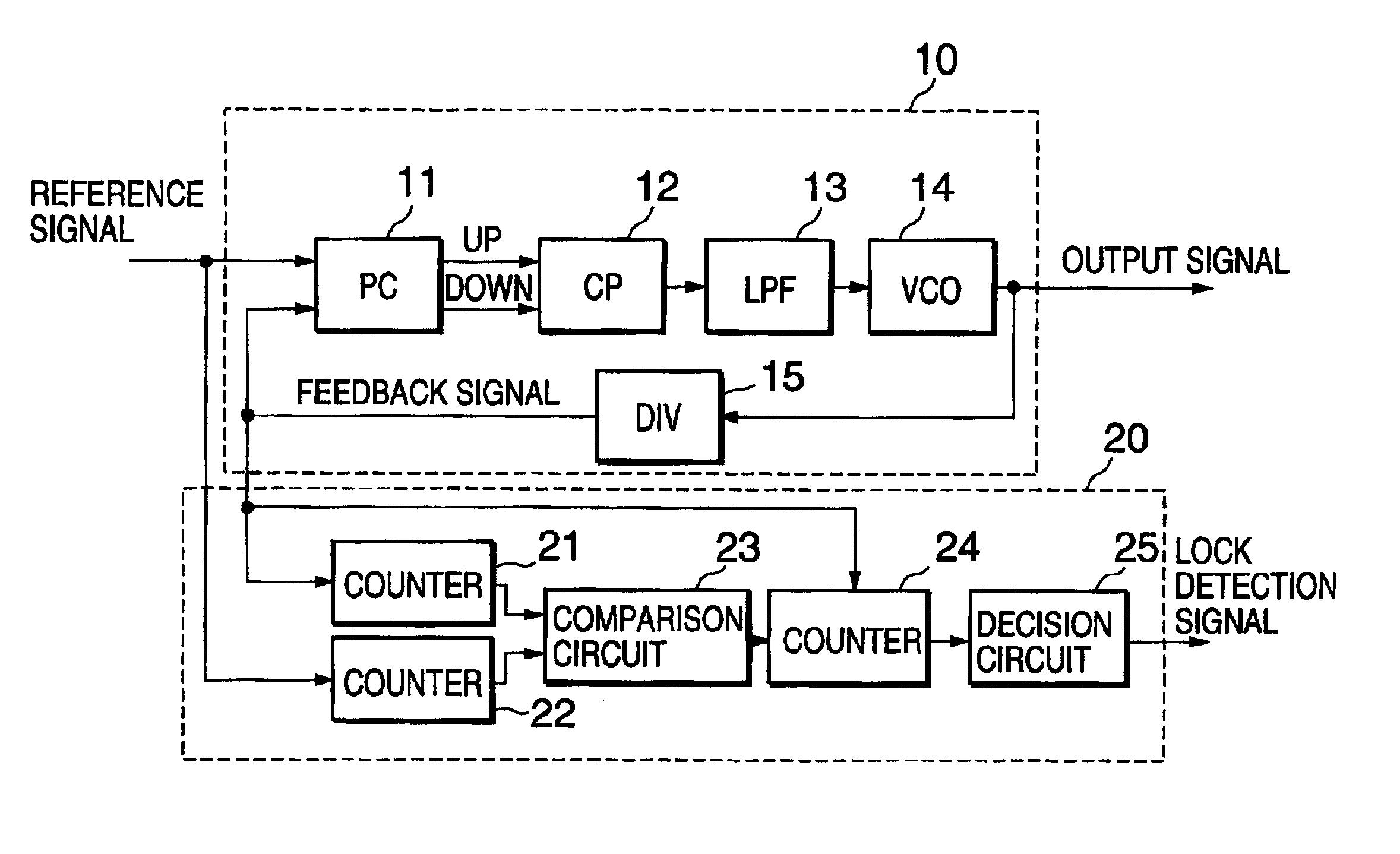

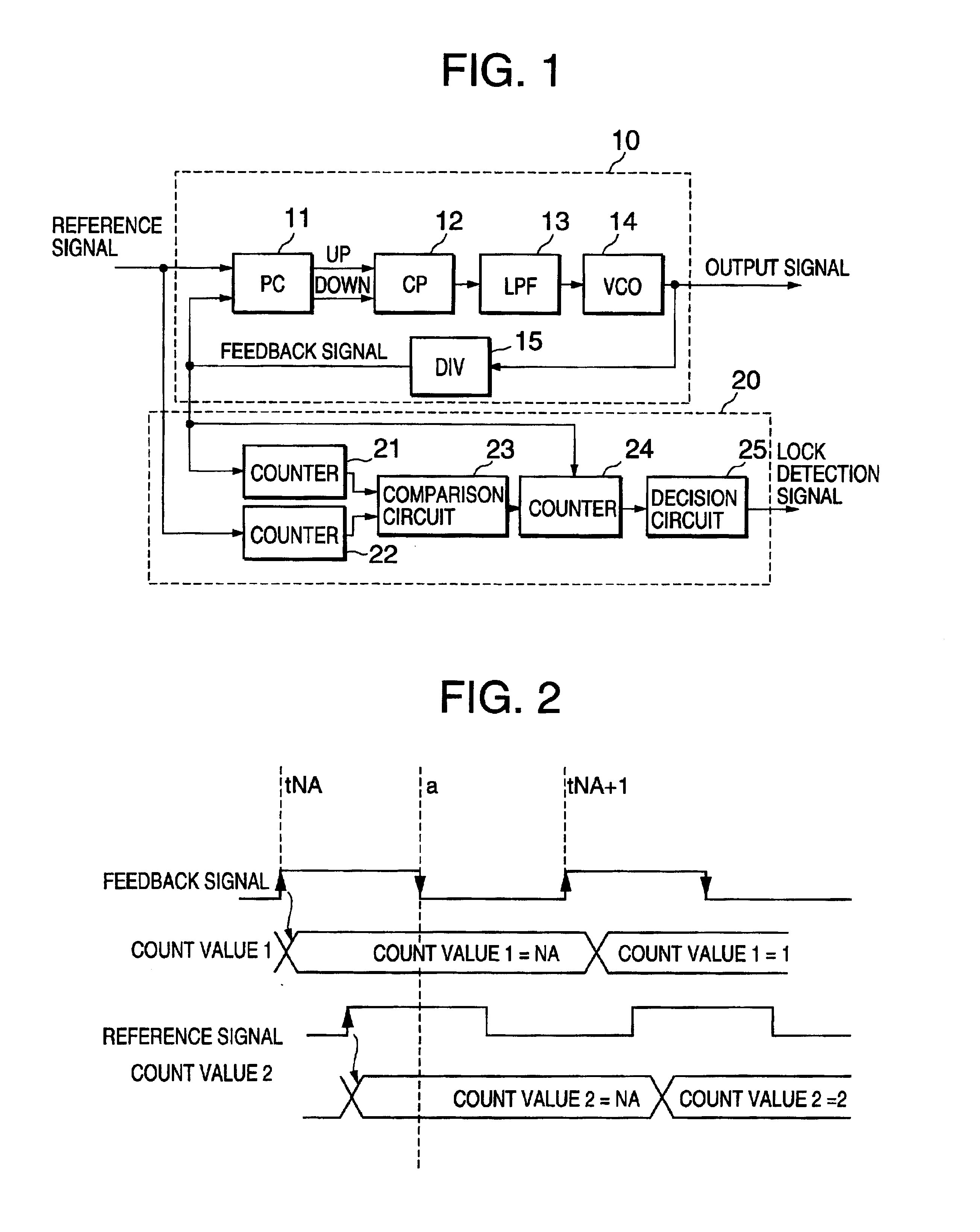

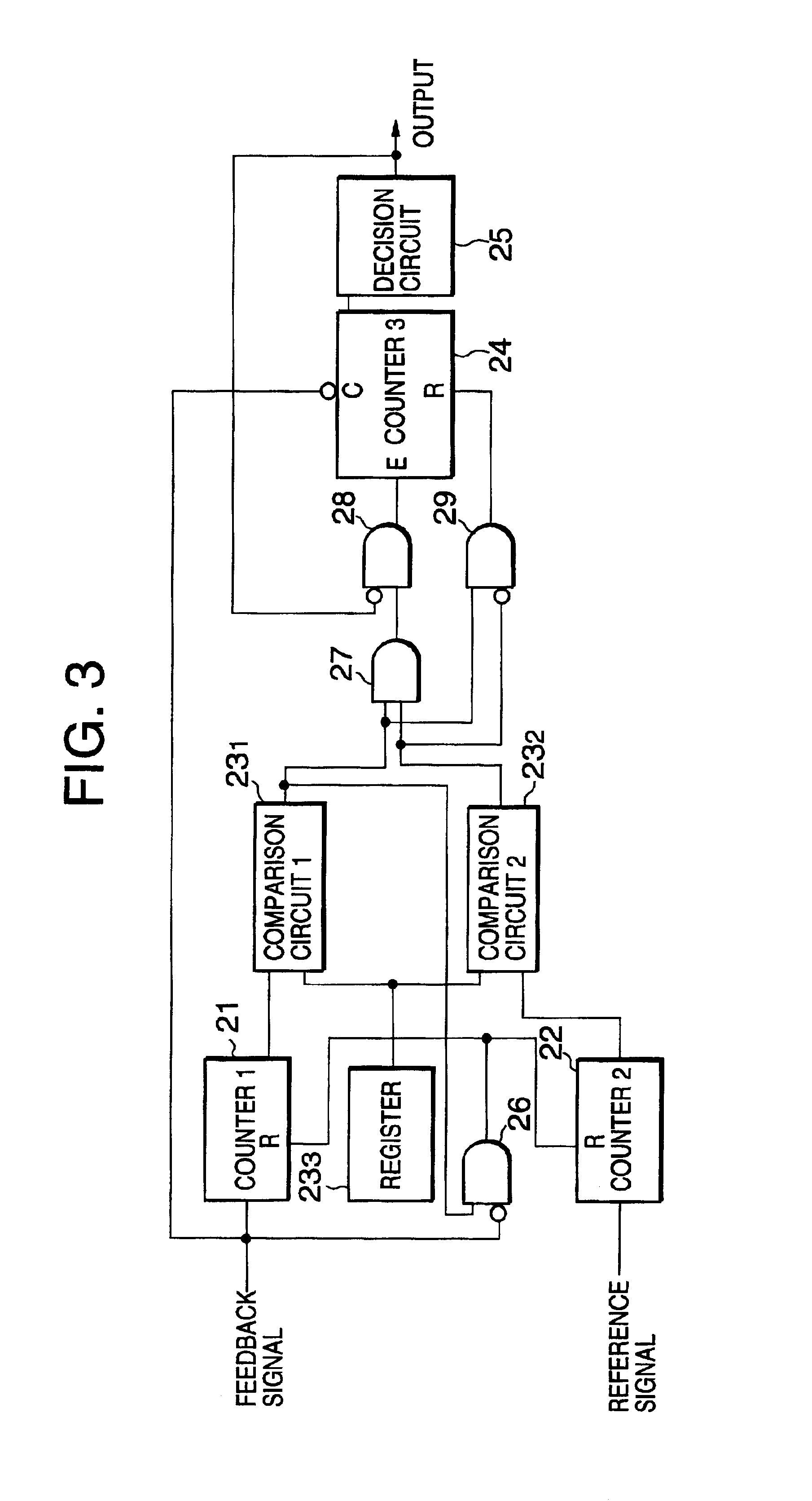

Lock detection circuit

Owner:RENESAS ELECTRONICS CORP