Patents

Literature

226results about How to "Improve testability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

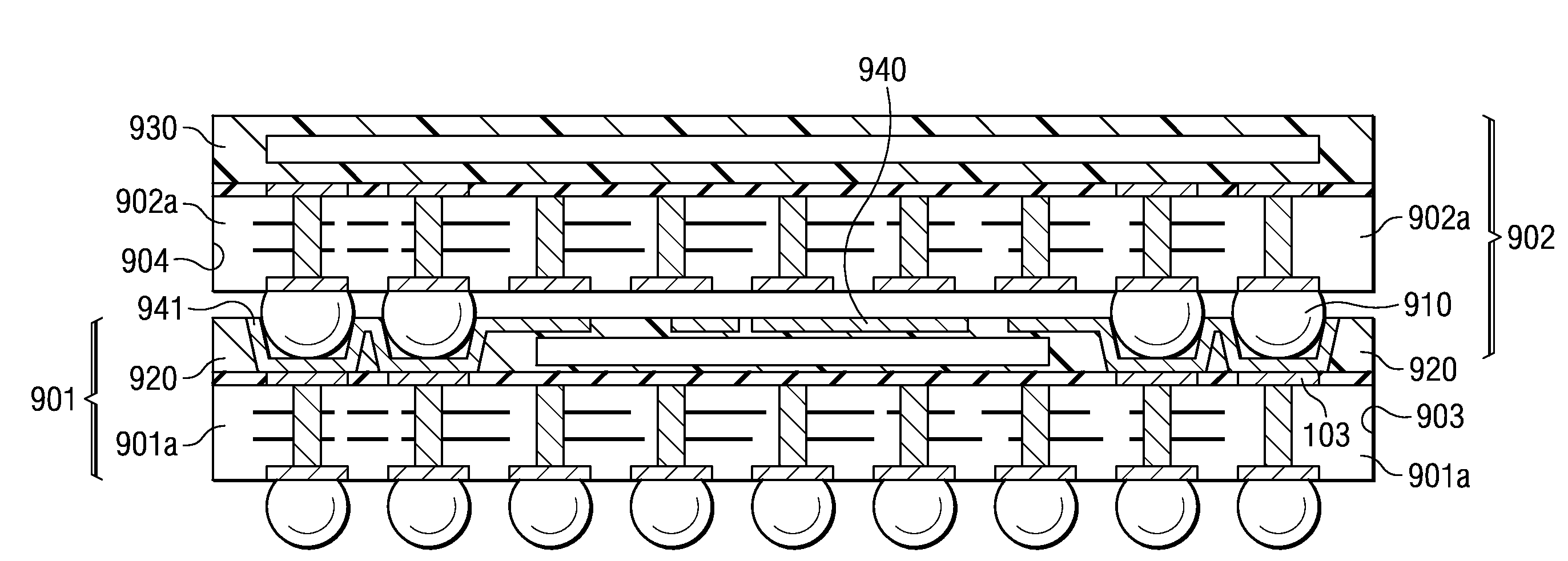

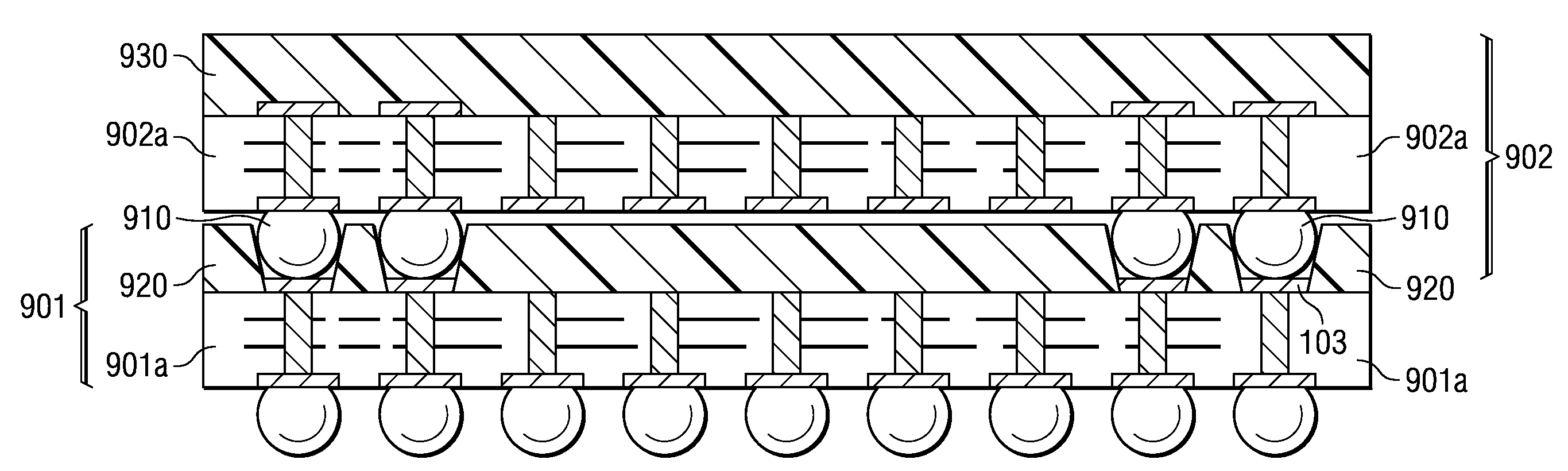

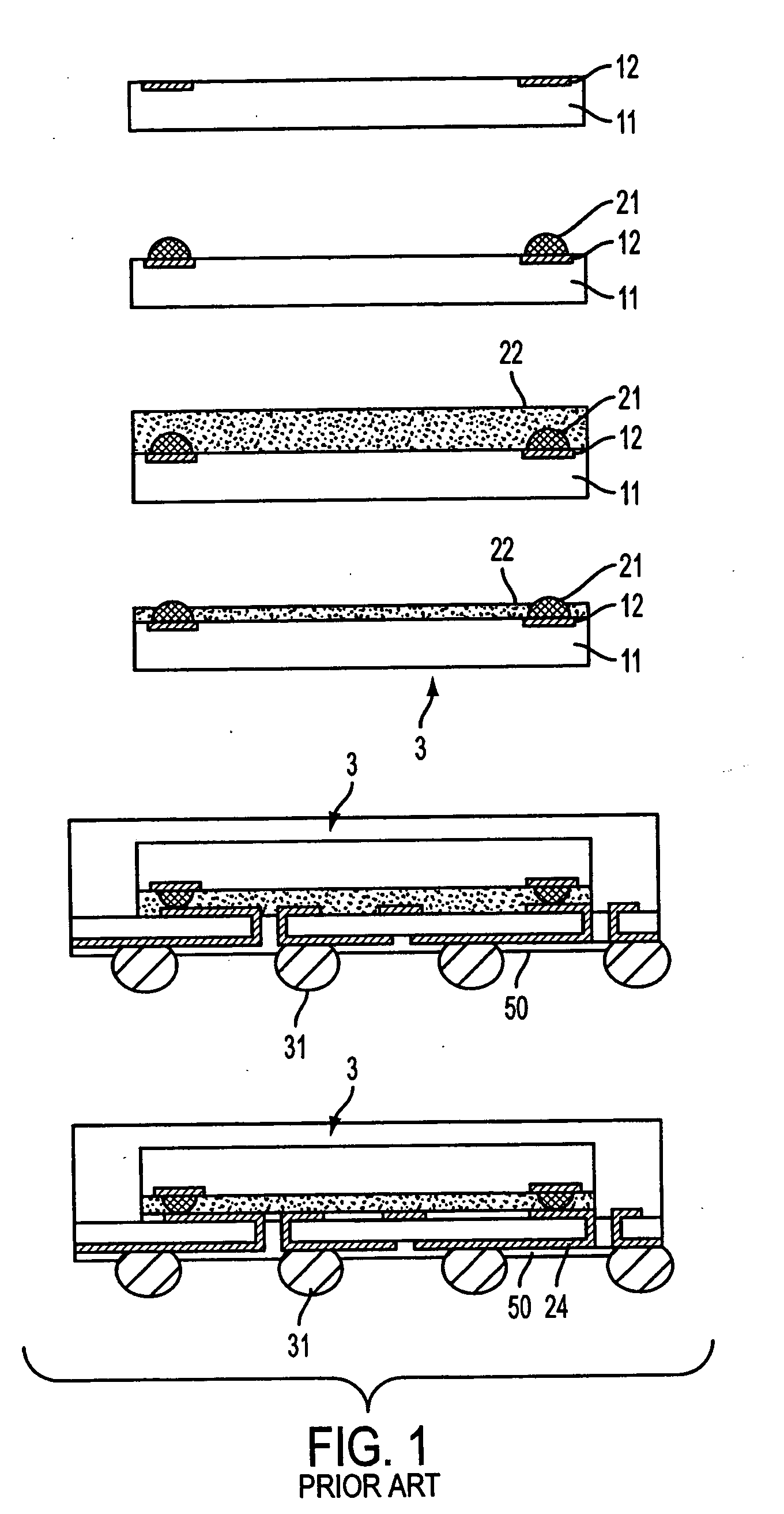

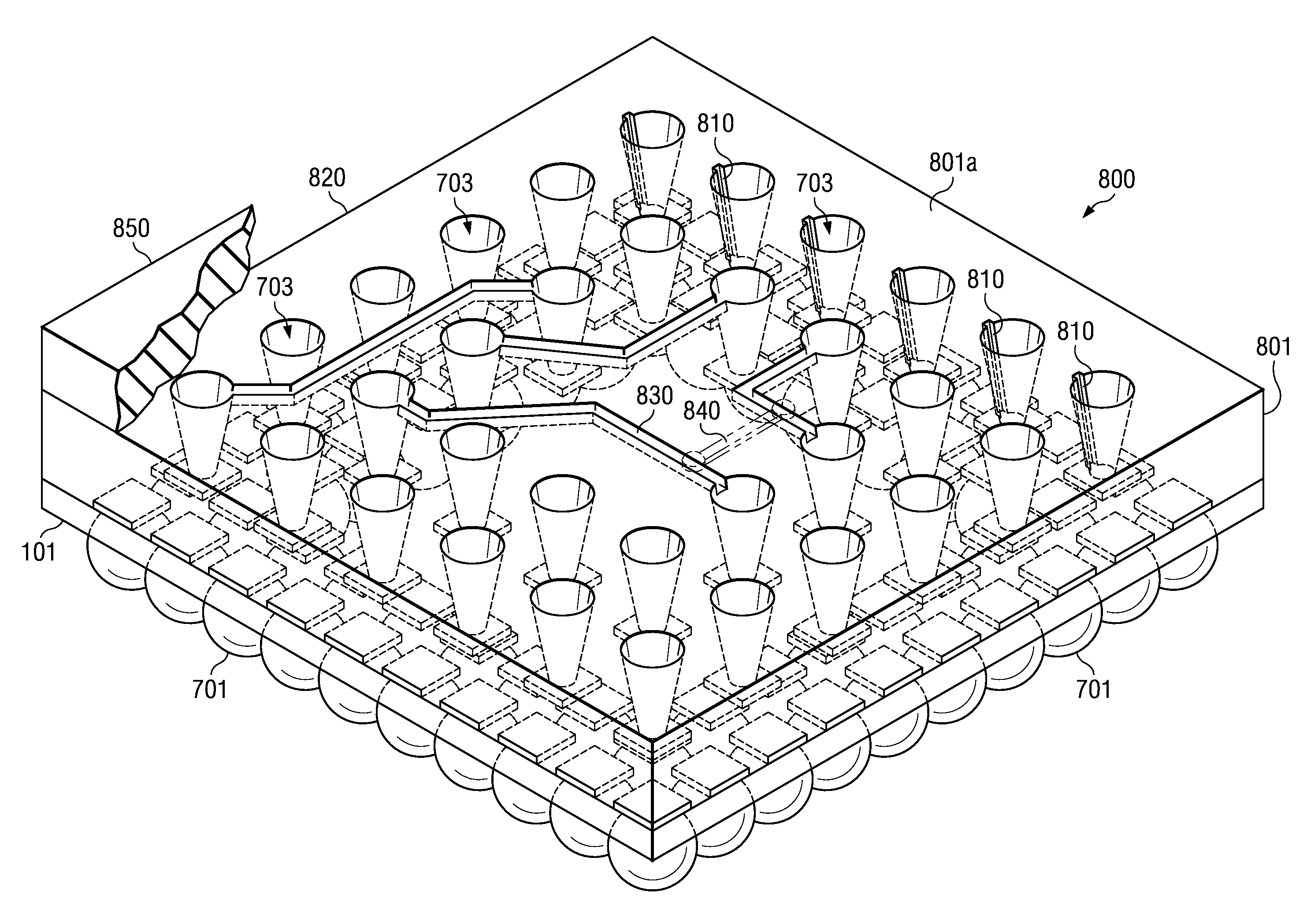

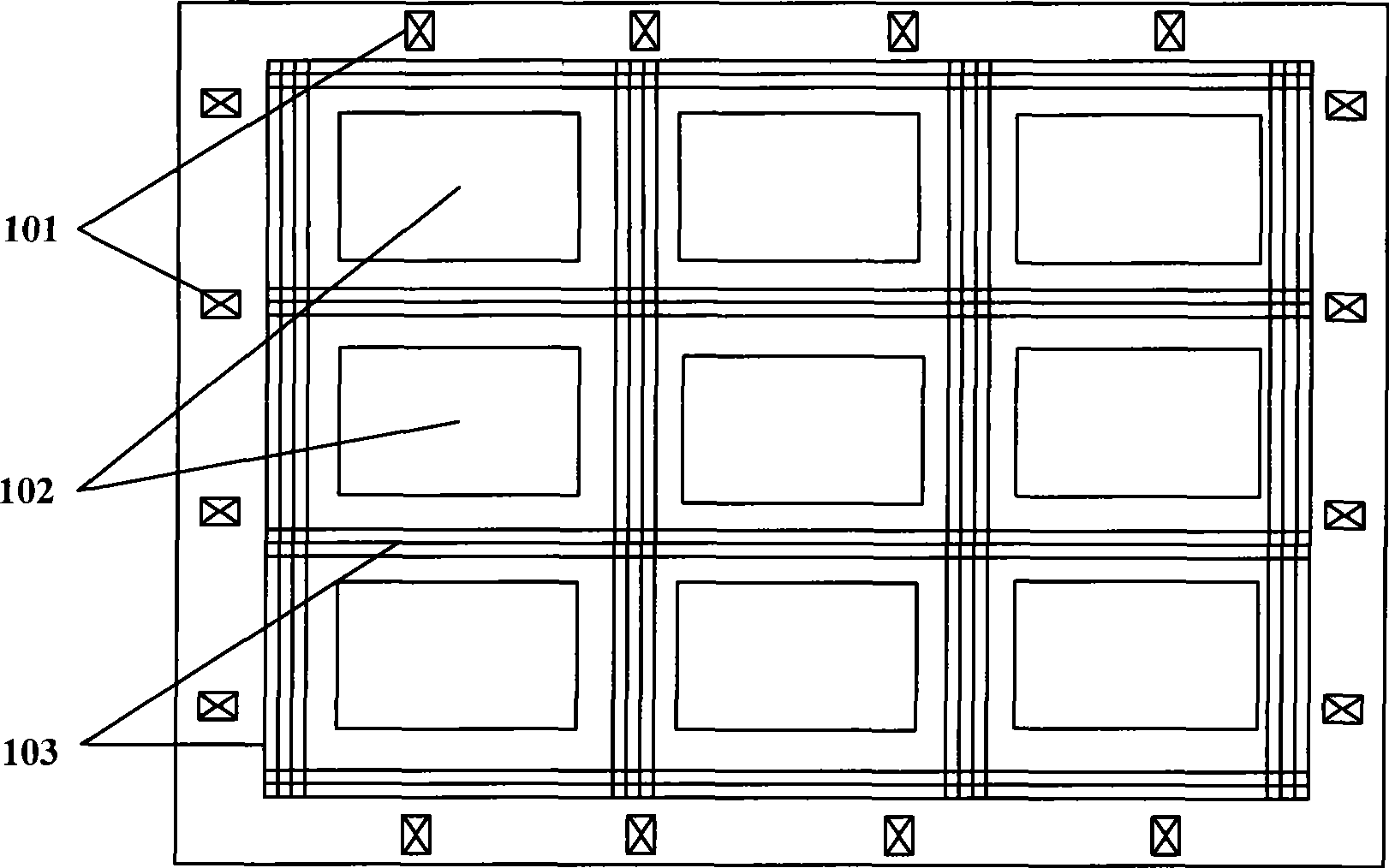

Array molded package-on-package having redistribution lines

ActiveUS20080315385A1Shorten the time to marketSimple methodSemiconductor/solid-state device detailsSolid-state devicesContact padCoupling

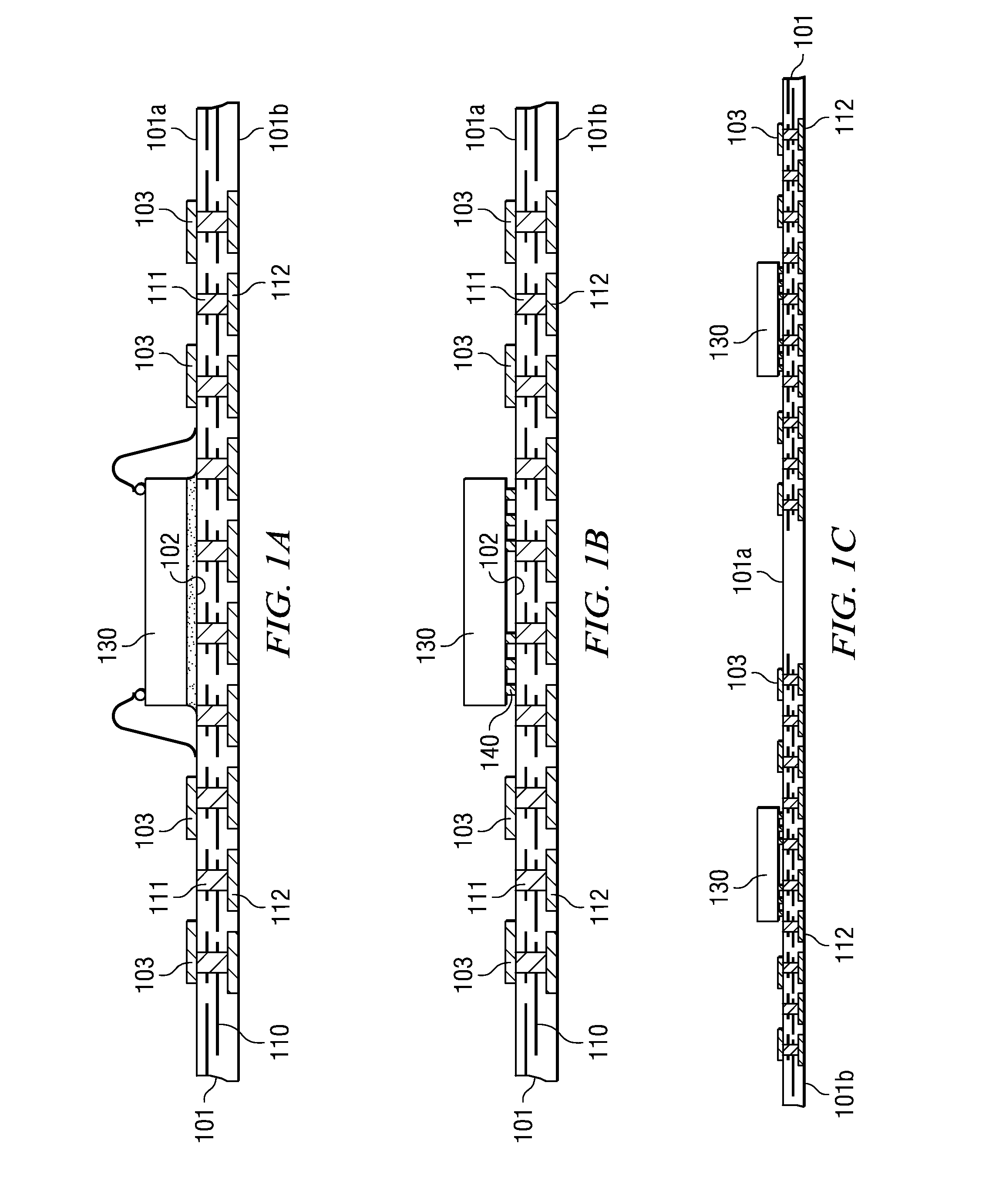

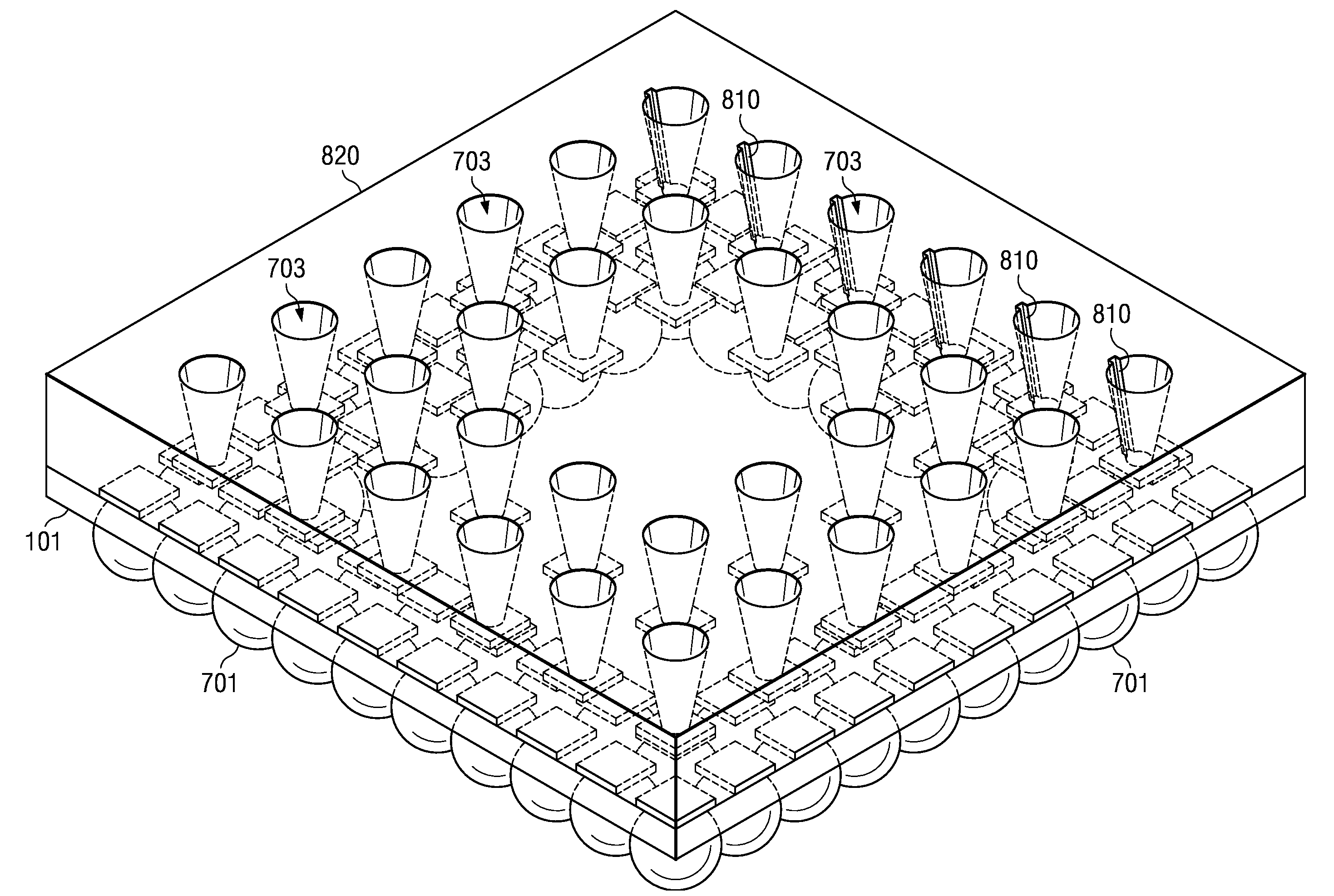

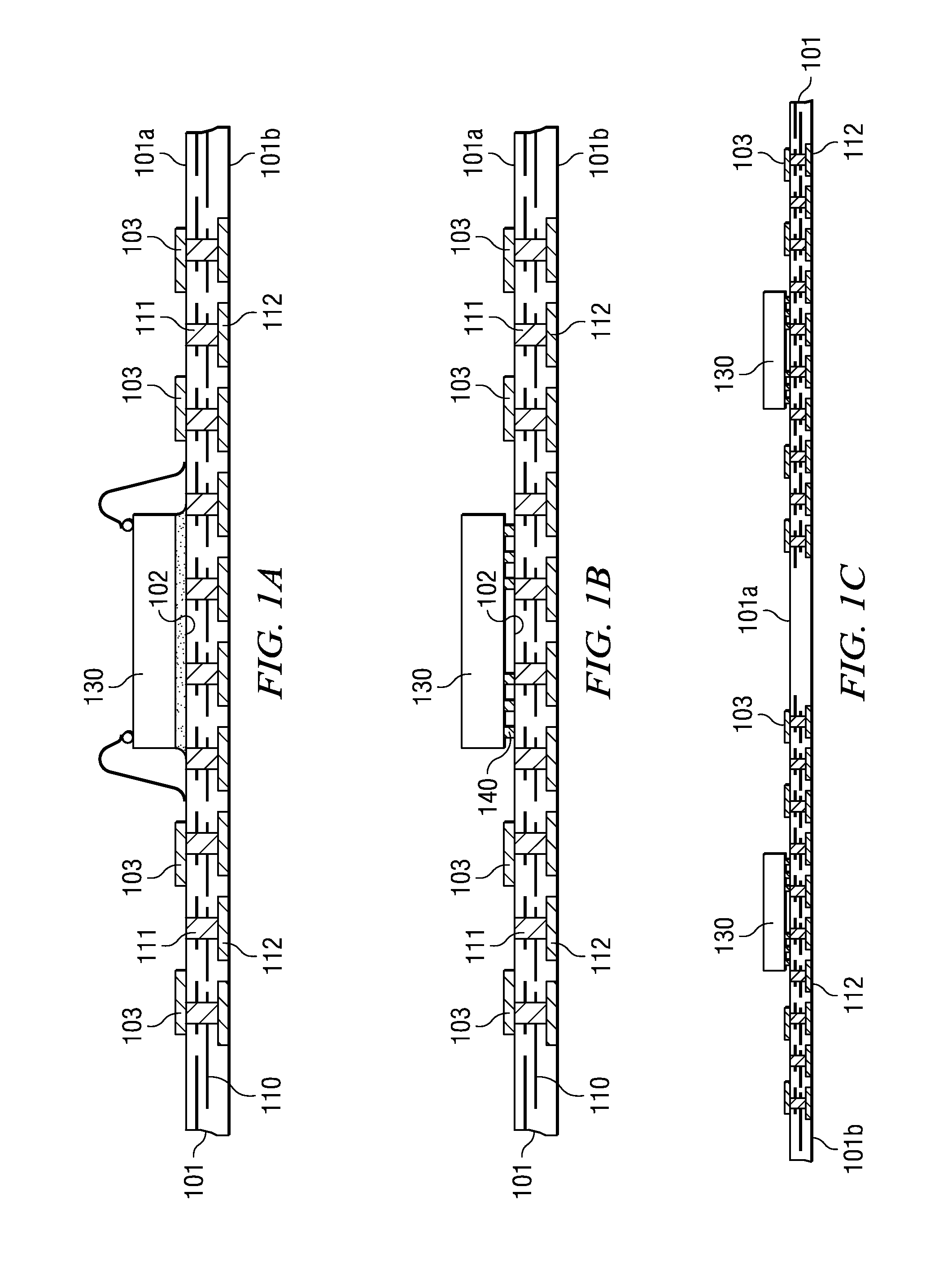

A semiconductor device with a sheet-like insulating substrate (101) integral with two or more patterned layers of conductive lines and vias, a chip attached to an assembly site, and contact pads (103) in pad locations has an encapsulated region on the top surface of the substrate, extending to the edge of the substrate, enclosing the chip, and having contact apertures (703) at the pad locations for external communication with the pad metal surfaces. The apertures may have not-smooth sidewall surfaces and may be filled with solder material (704) to contact the pads. Metal-filled surface grooves (710) in the encapsulated region, with smooth groove bottom and sidewalls, are selected to serve as customized routing interconnections, or redistribution lines, between selected apertures and thus to facilitate the coupling with another semiconductor device to form a package-on-package assembly.

Owner:TEXAS INSTR INC

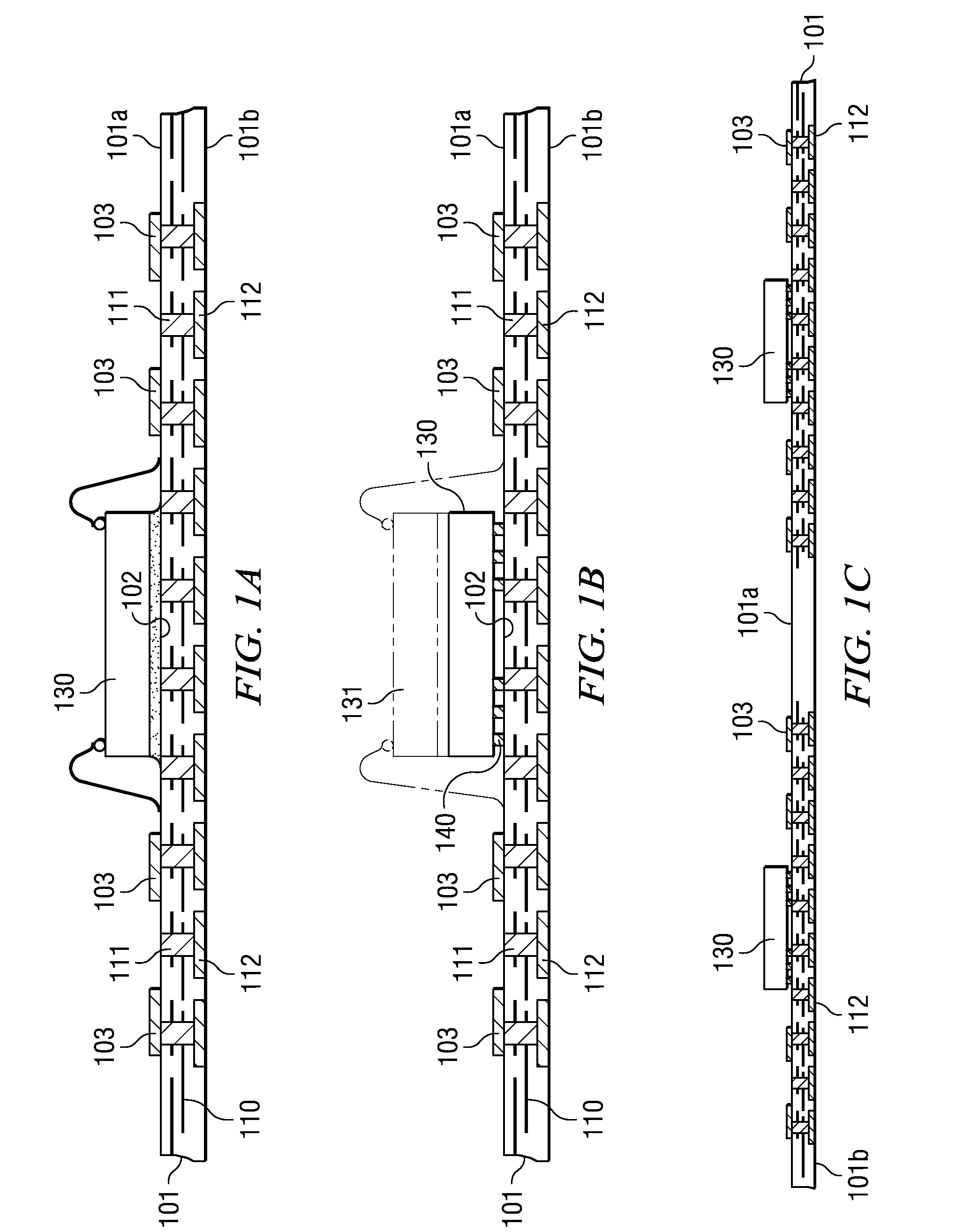

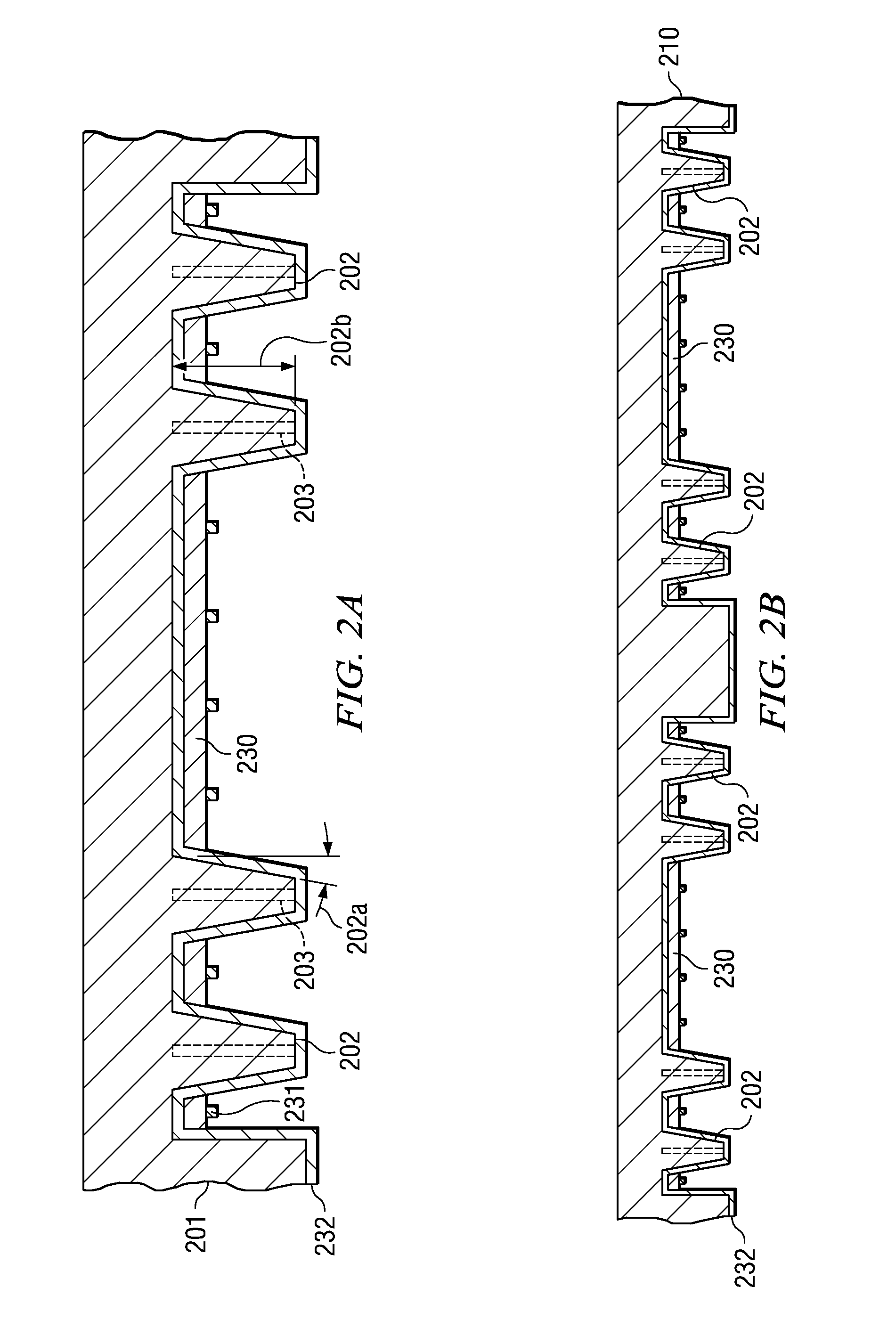

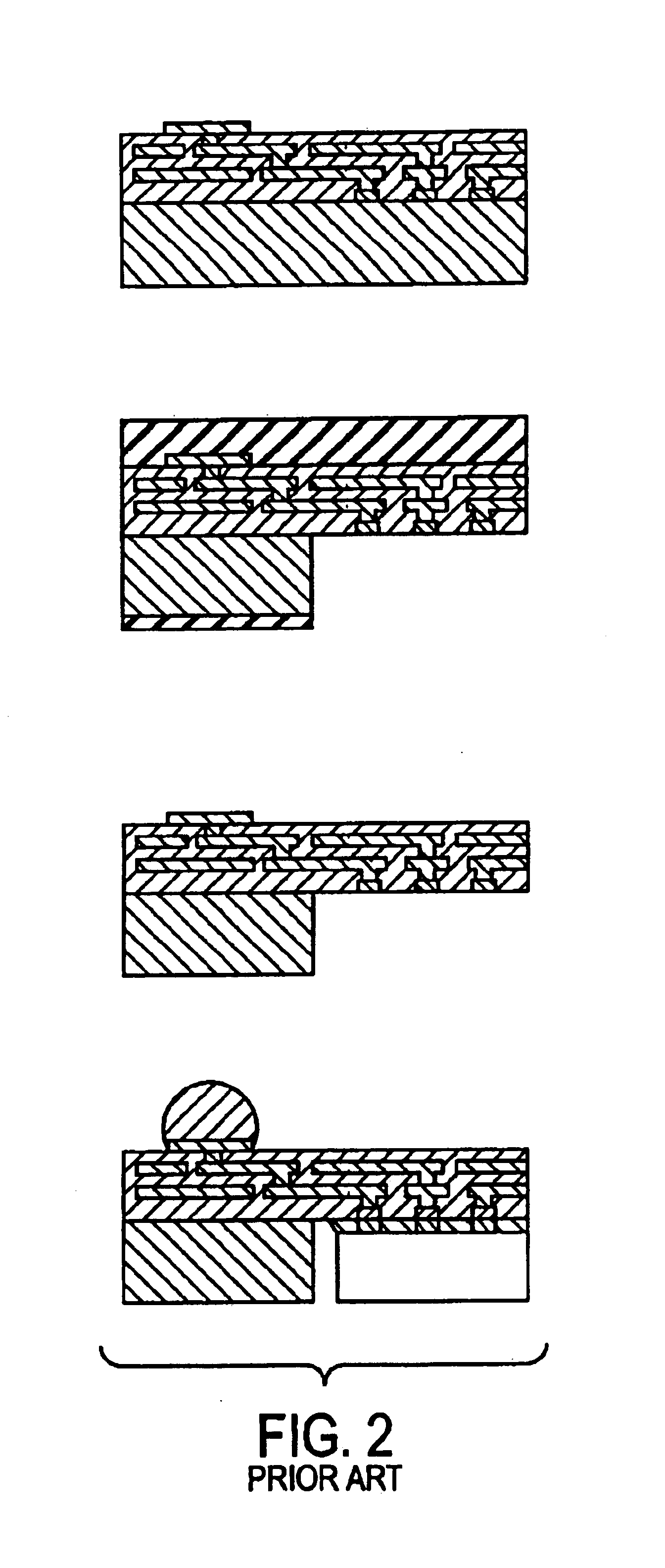

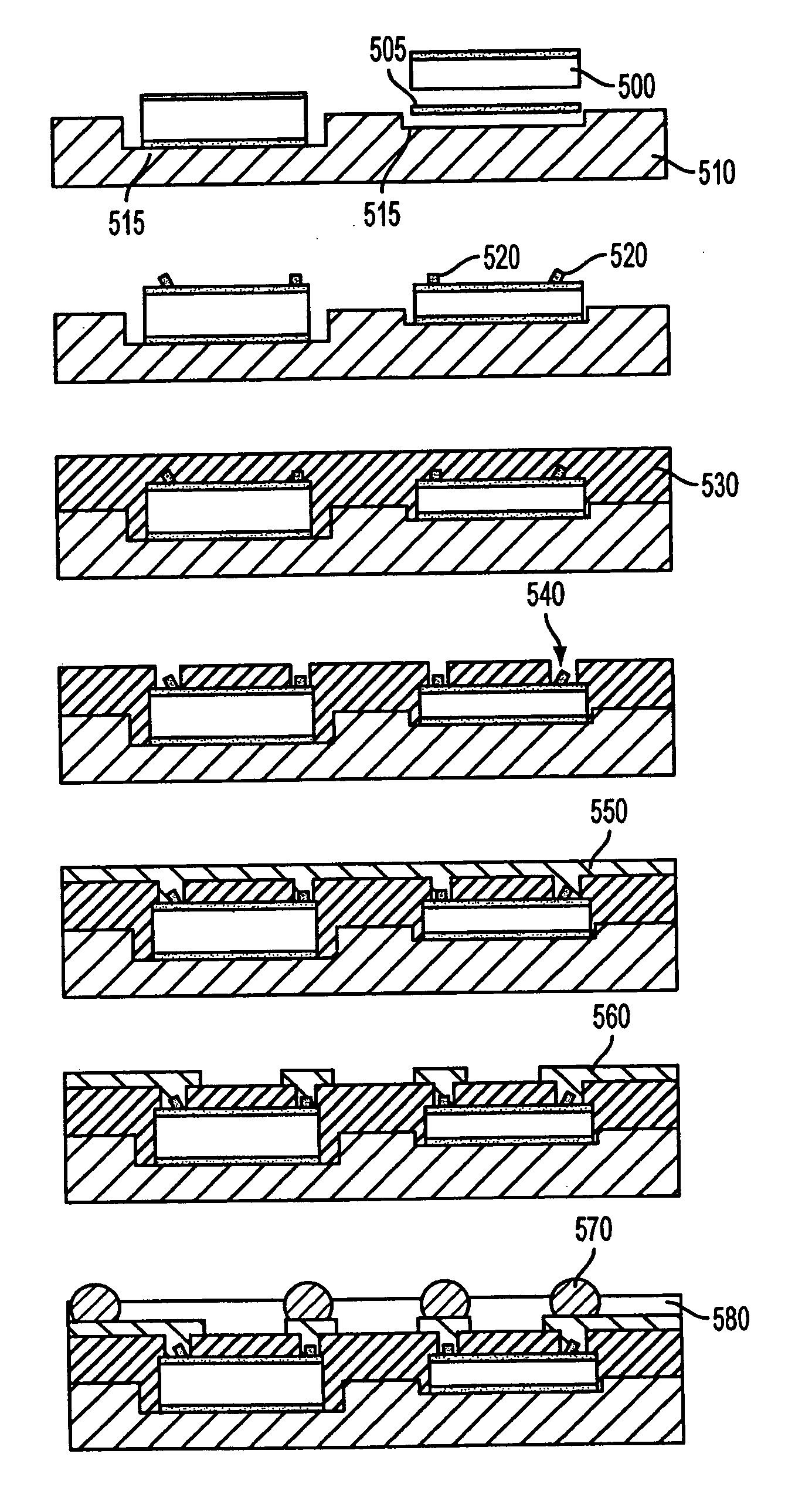

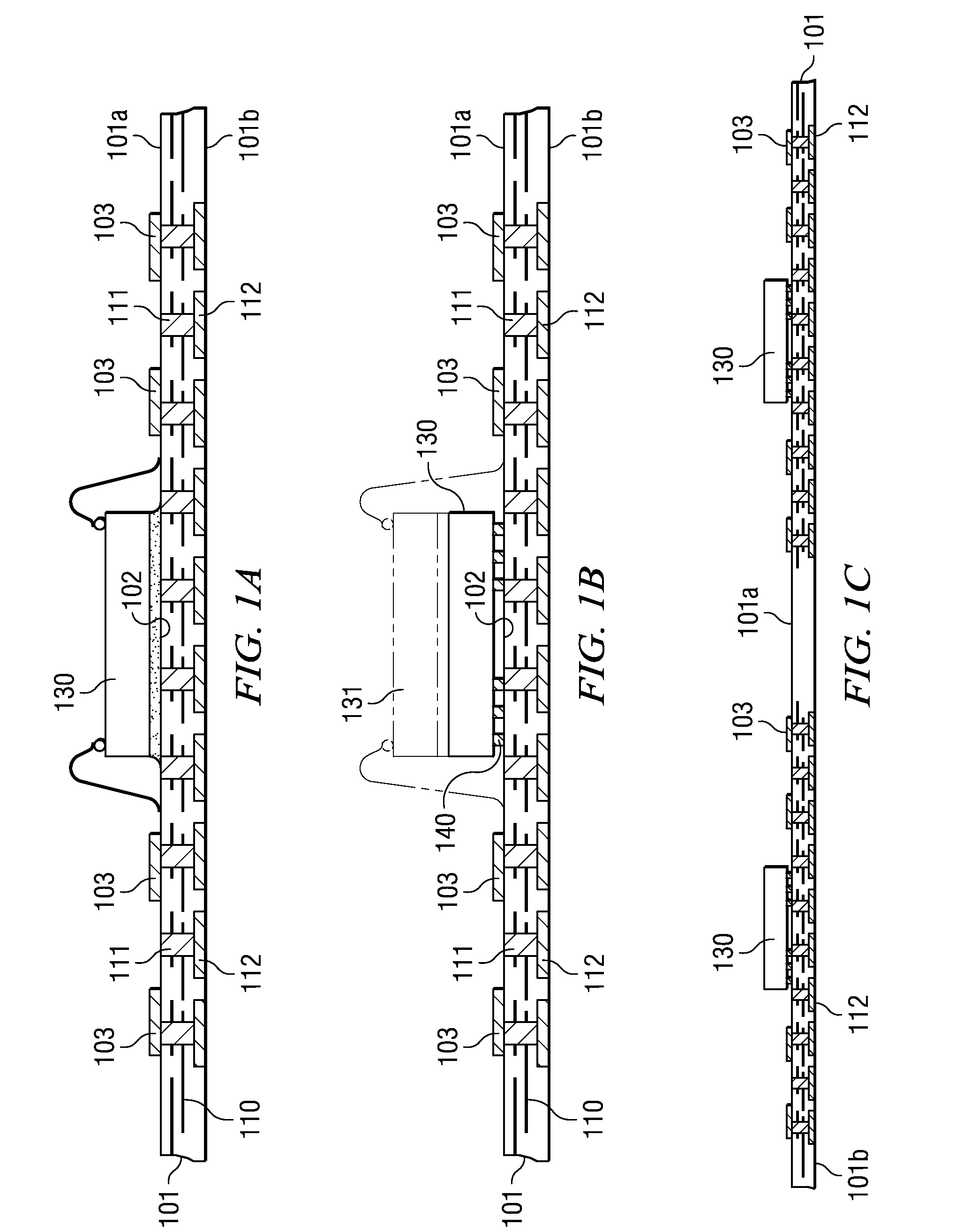

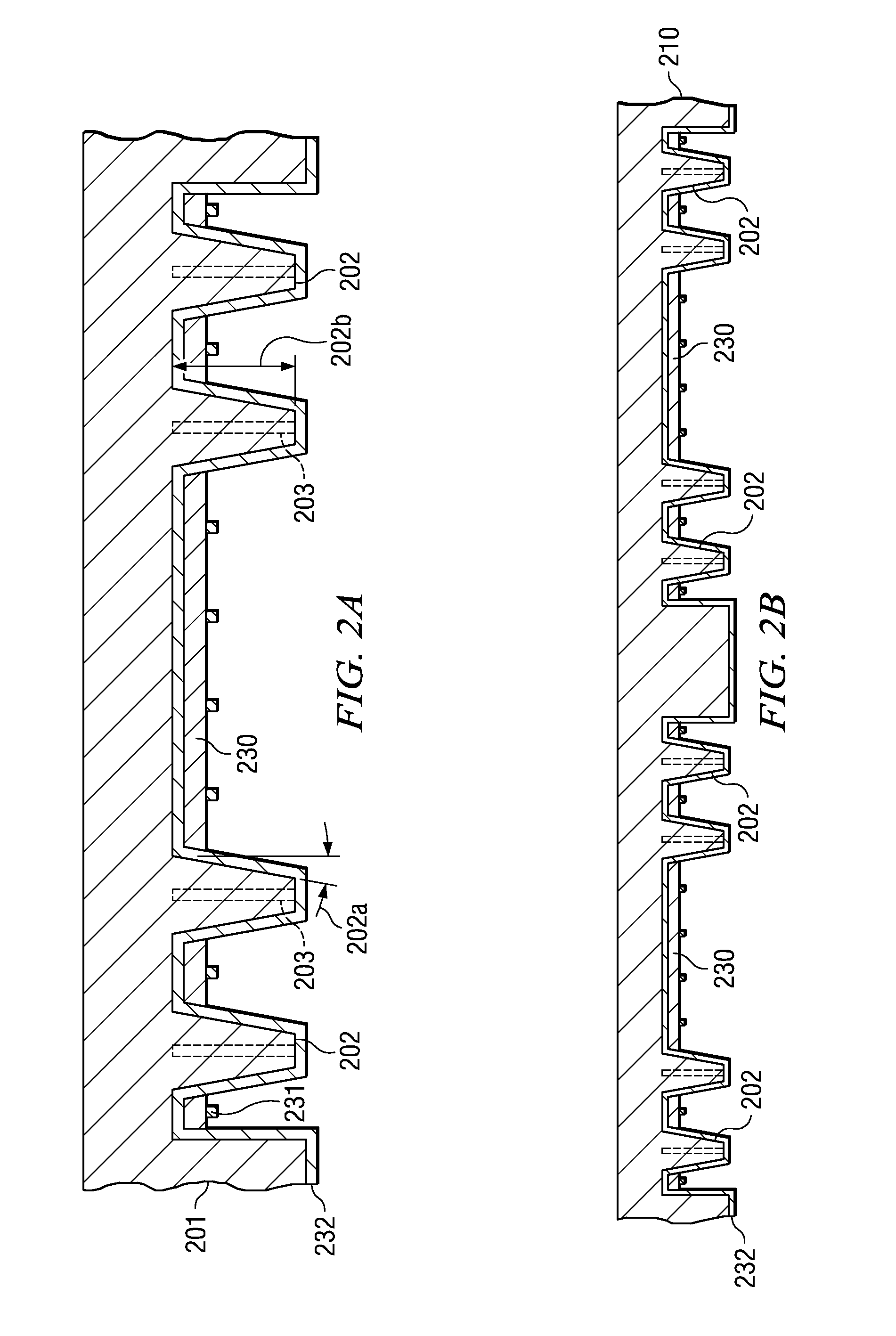

Method for Fabricating Array-Molded Package-On-Package

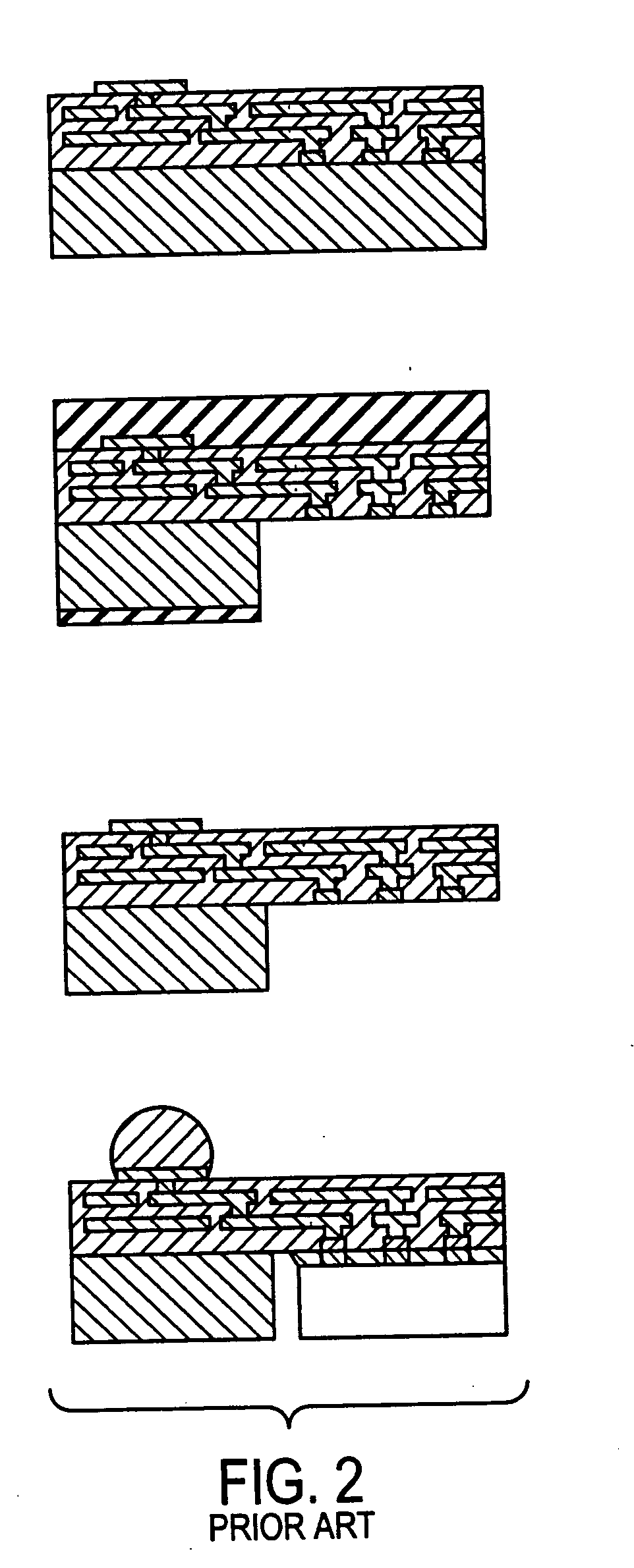

InactiveUS20080284045A1Low-cost and simplifyImprove testability and thus yieldLiquid surface applicatorsSemiconductor/solid-state device detailsContact padEngineering

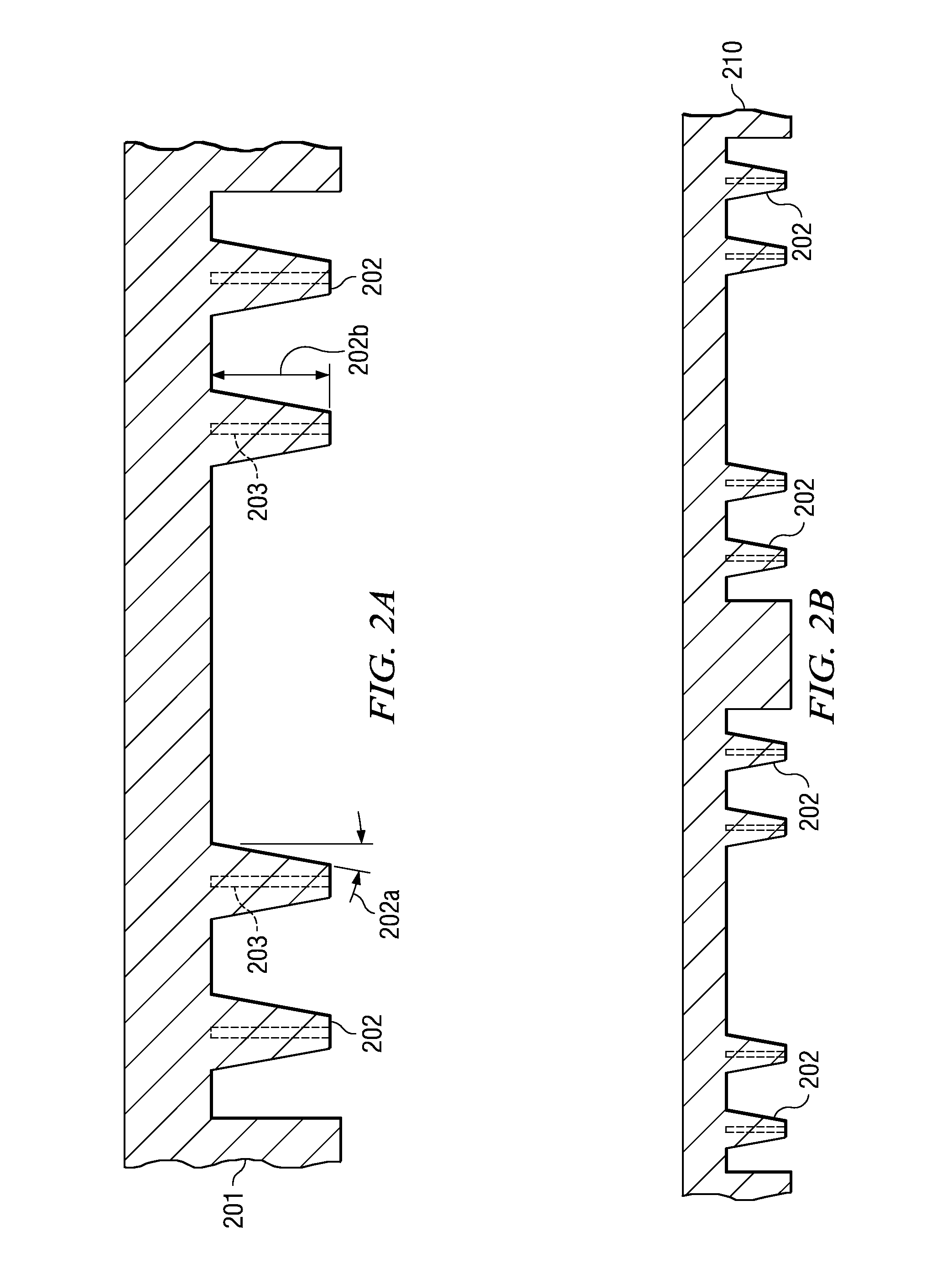

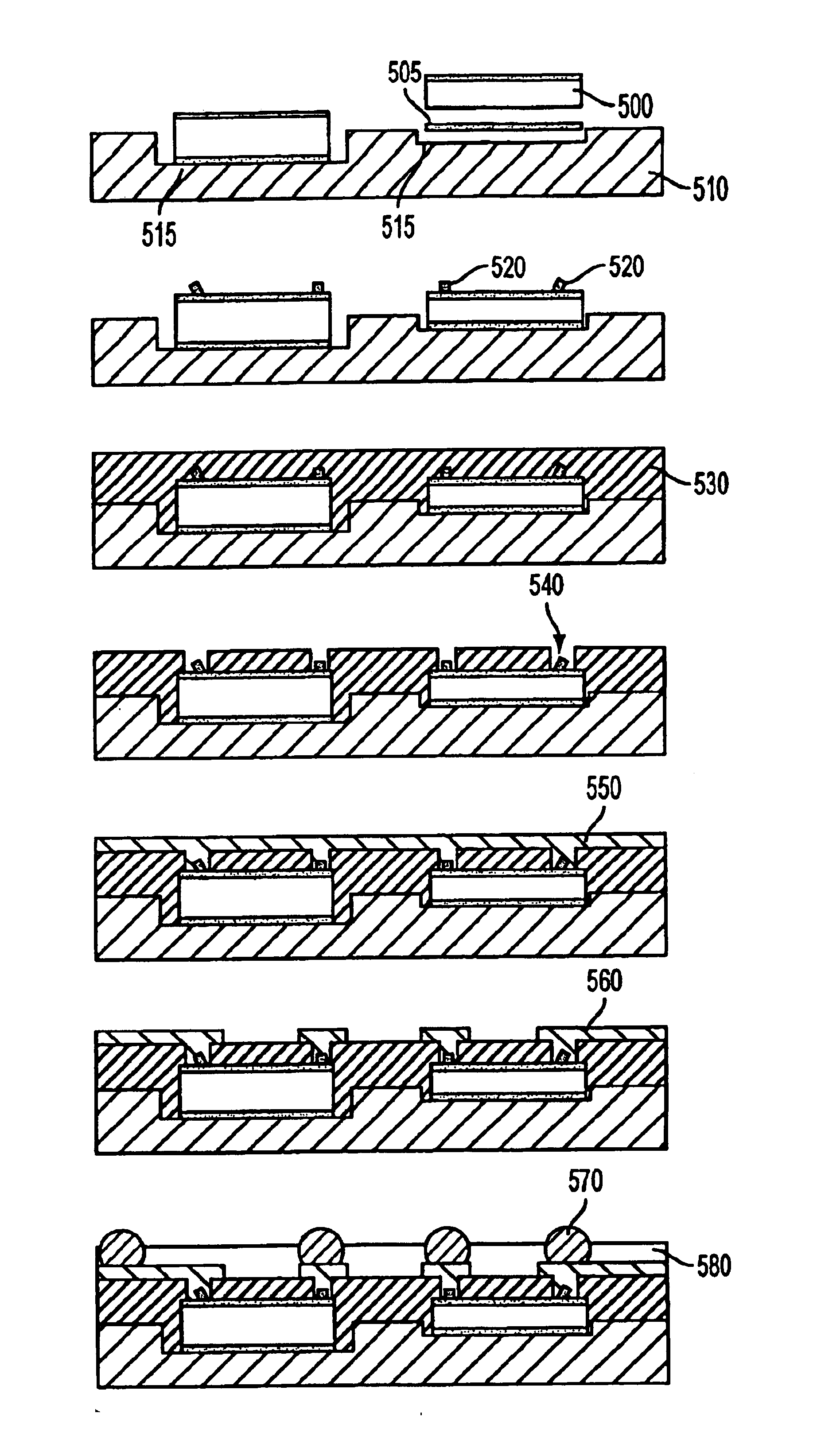

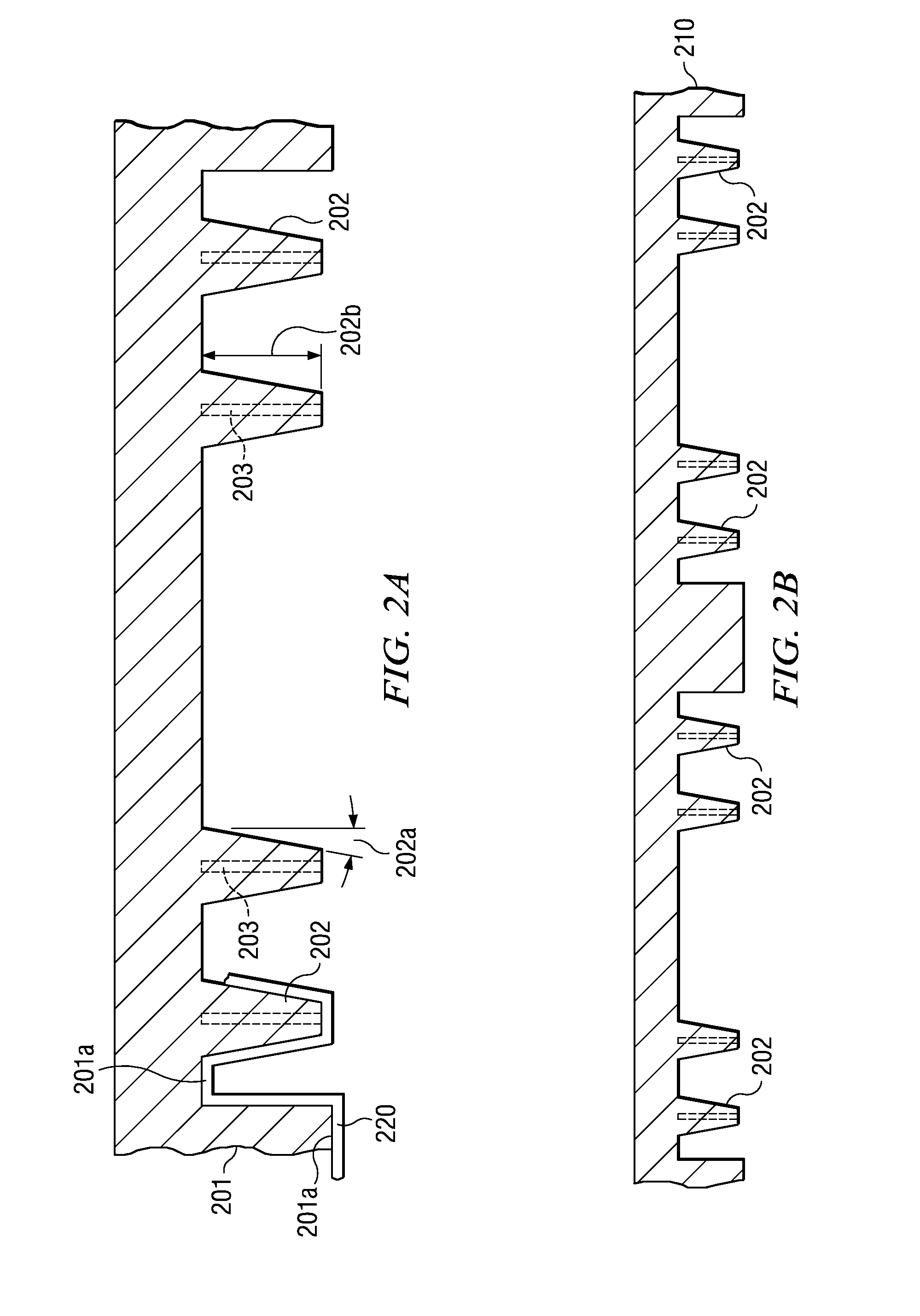

A method and apparatus for fabricating a semiconductor device are disclosed. The method attaches semiconductor chips (130) on a sheet-like insulating substrate (101) integral with two or more patterned layers of conductive lines and vias and with contact pads (103) in pad locations. A mold is provided, which has a top portion (210) with metal protrusions (202) at locations matching the pad locations. The protrusions are shaped as truncated cones of a height suitable to approach the pad metal surface in the closed mold cavity. The substrate and the chip are loaded onto the bottom mold portion (310); the mold is closed by clamping the top portion onto the bottom portion so that the protrusions are aligned with the contact pads, approaching the pad surface. After pressuring encapsulation compound into the cavity, the mold is opened; the encapsulated device has apertures to the pad locations. Any residual compound formed on the pads is removed by laser, plasma, or chemical to expose the metal surface.

Owner:TEXAS INSTR INC

Build-up structures with multi-angle vias for chip to chip interconnects and optical bussing

InactiveUS6919508B2Improve performanceIncrease speedTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesAnisotropic conductive filmCopper interconnect

A build-up structure for chip to chip interconnects and System-In-Package utilizing multi-angle vias for electrical and optical routing or bussing of electronic information and controlled CTE dielectrics including mesocomposites to achieve optimum electrical and optical performance of monolithic structures. Die, multiple die, Microelectromechanical Machines (MEMs) and / or other active or passive components such as transducers or capacitors can be accurately positioned on a substrate such as a copper heatsink and multi-angle stud bumps can be placed on the active sites of the components. A first dielectric layer is preferably placed on the components, thereby embedding the components in the structure. Through various processes of photolithography, laser machining, soft lithography or anisotropic conductive film bonding, escape routing and circuitry is formed on the first metal layer. Additional dielectric layers and metal circuitry are formed utilizing multi-angle vias to form escape routing from tight pitch bond pads on the die to other active and passive components. Multi-angle vias can carry electrical or optical information in the form of digital or analog electromagnetic current, or in the form of visible or non-visible optical bussing and interconnections.

Owner:CAPITALSOURCE FINANCE

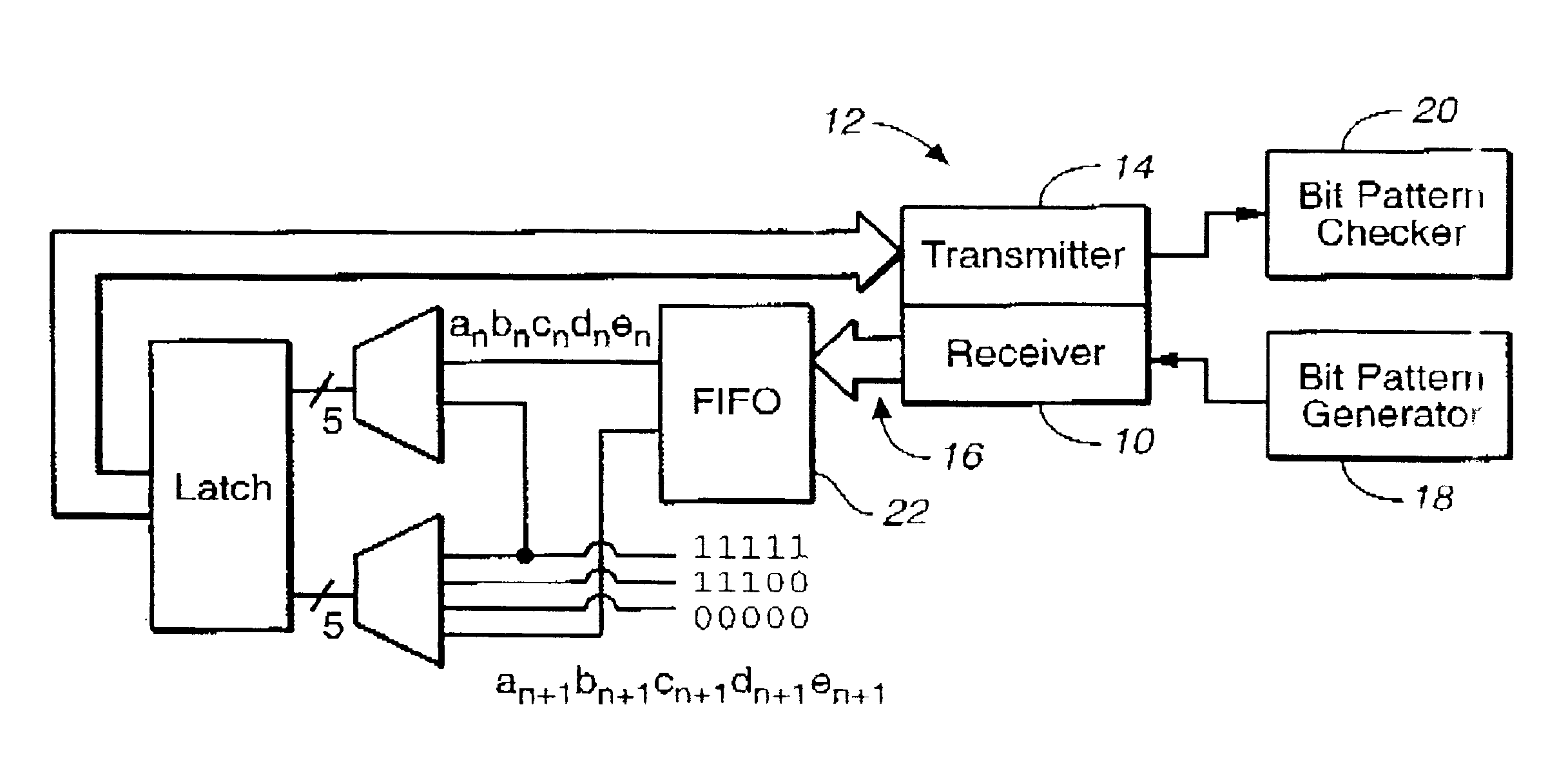

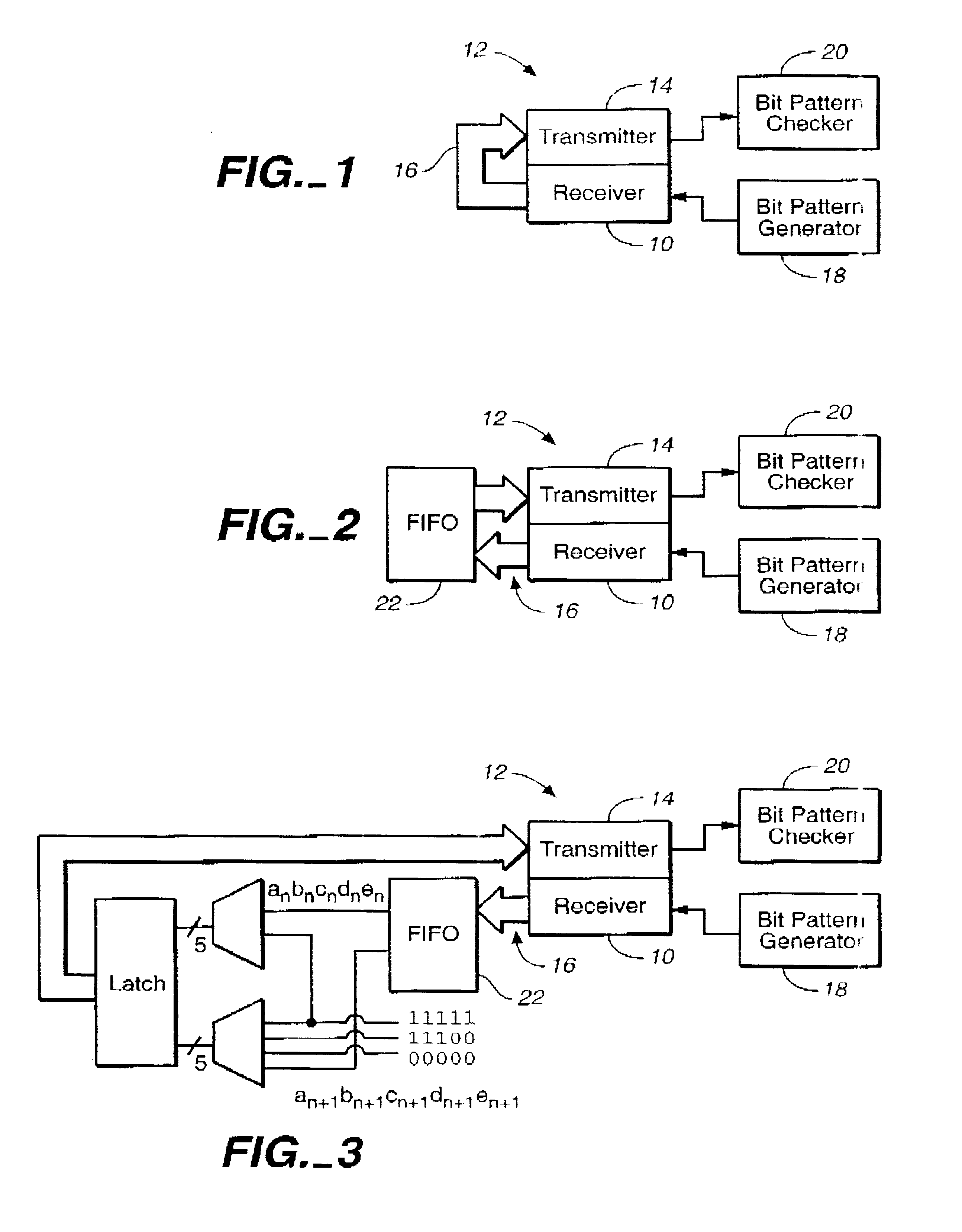

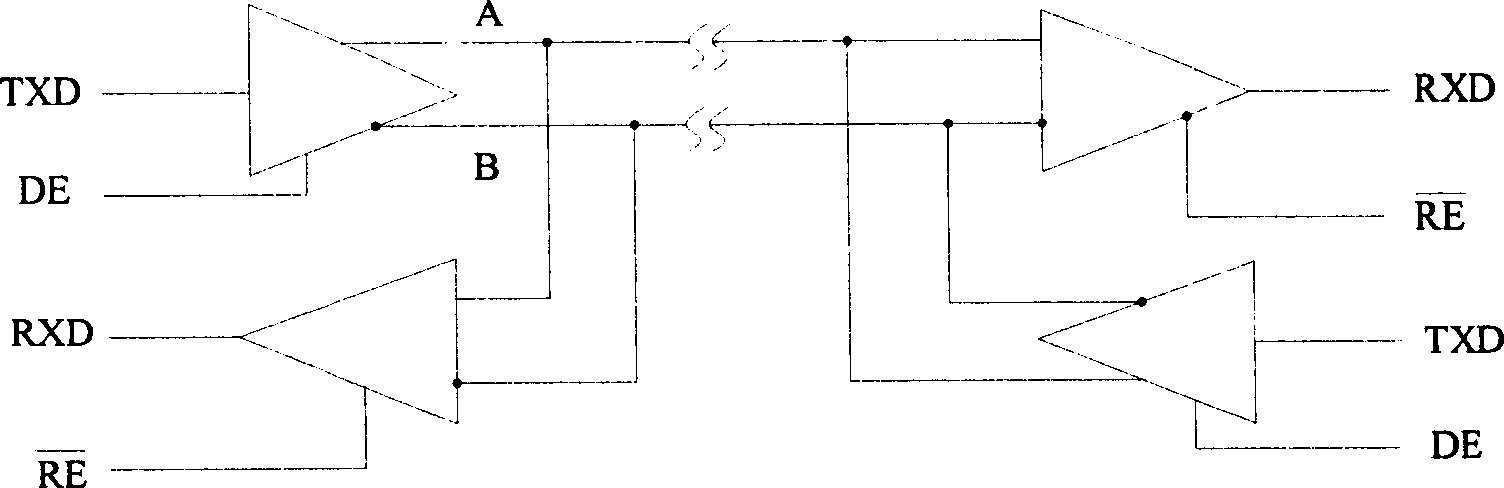

Method and Circuit for testing devices with serial data links

InactiveUS6385236B1Improve testabilityTransmitters monitoringReceivers monitoringData streamTransceiver

A circuit and method for testing a transceiver. The circuit includes a bit pattern generator connected to the transceiver such that the bit pattern generator can communicate a serial data stream to a receiver portion of the transceiver. The circuit also includes a bit pattern checker connected to the transceiver such that a transmitter portion of the transceiver can communicate a serial data stream to the bit pattern checker. The transceiver is configured such that the receiver portion of the transceiver is communicatingly looped back to the transmitter portion of the transceiver such that a data stream can be communicated from the receiver portion of the transceiver to the transmitter portion of the transceiver. Desirably, a loopback circuit in connected to the transceiver and includes fixed bit pattern means for communicating at least one fixed bit pattern to the transmitter portion of the transceiver. The loopback circuit is configured such that the FIFO component receives a set of bits from the receiver portion of the transceiver and at least one of the bits in the set is replaced by the fixed bit pattern before being communicated to the transmitter portion of the receiver.

Owner:AVAGO TECH INT SALES PTE LTD

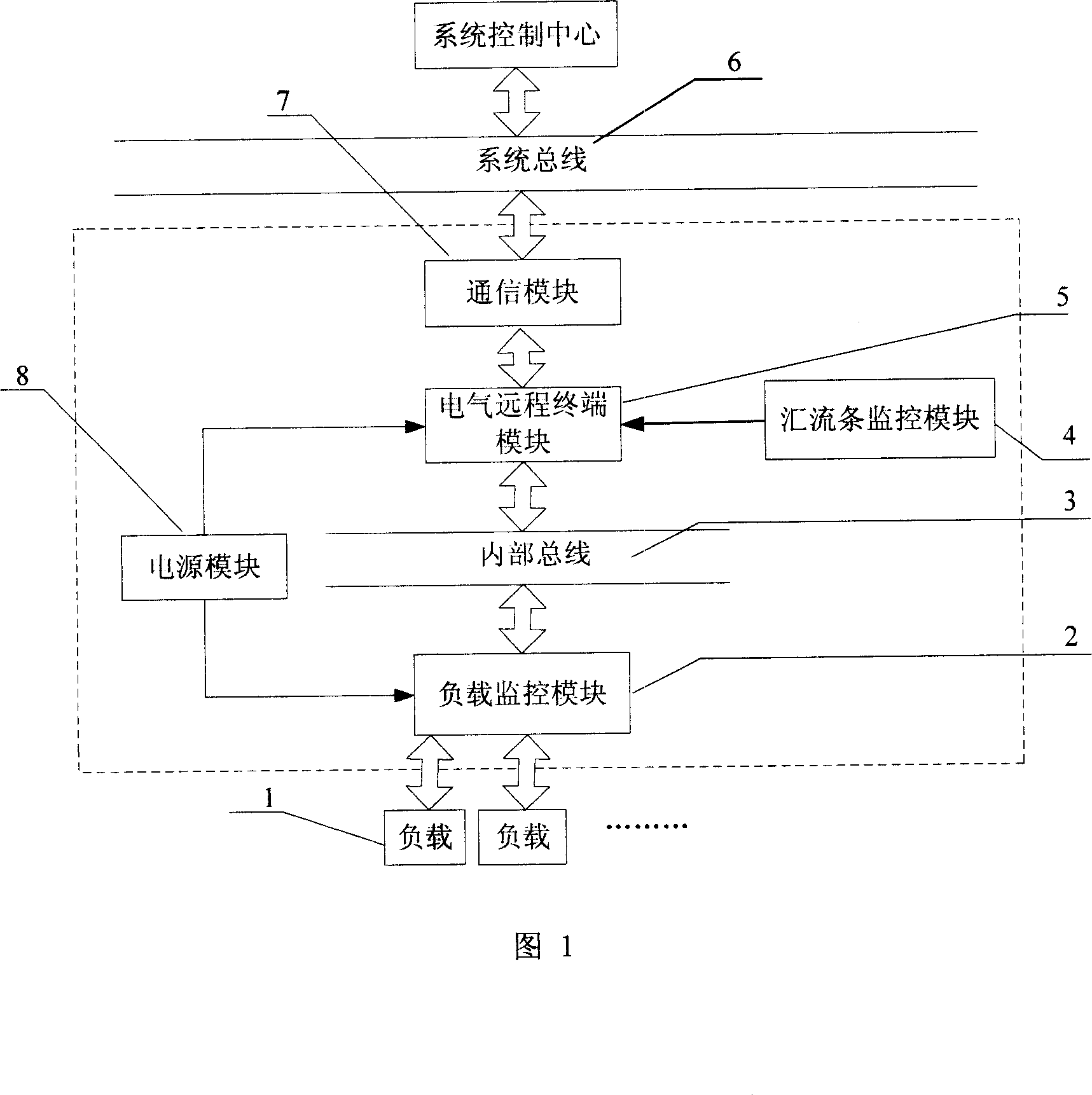

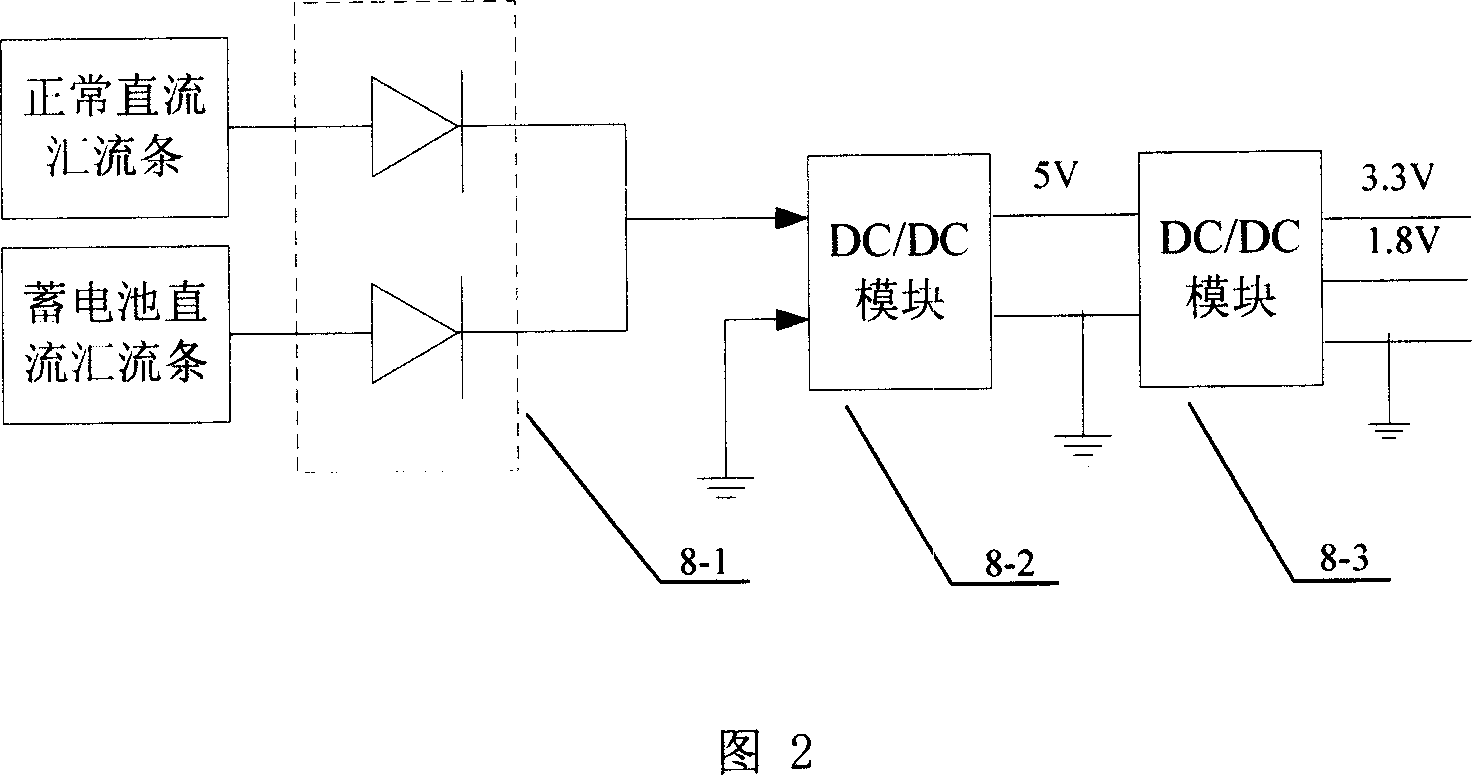

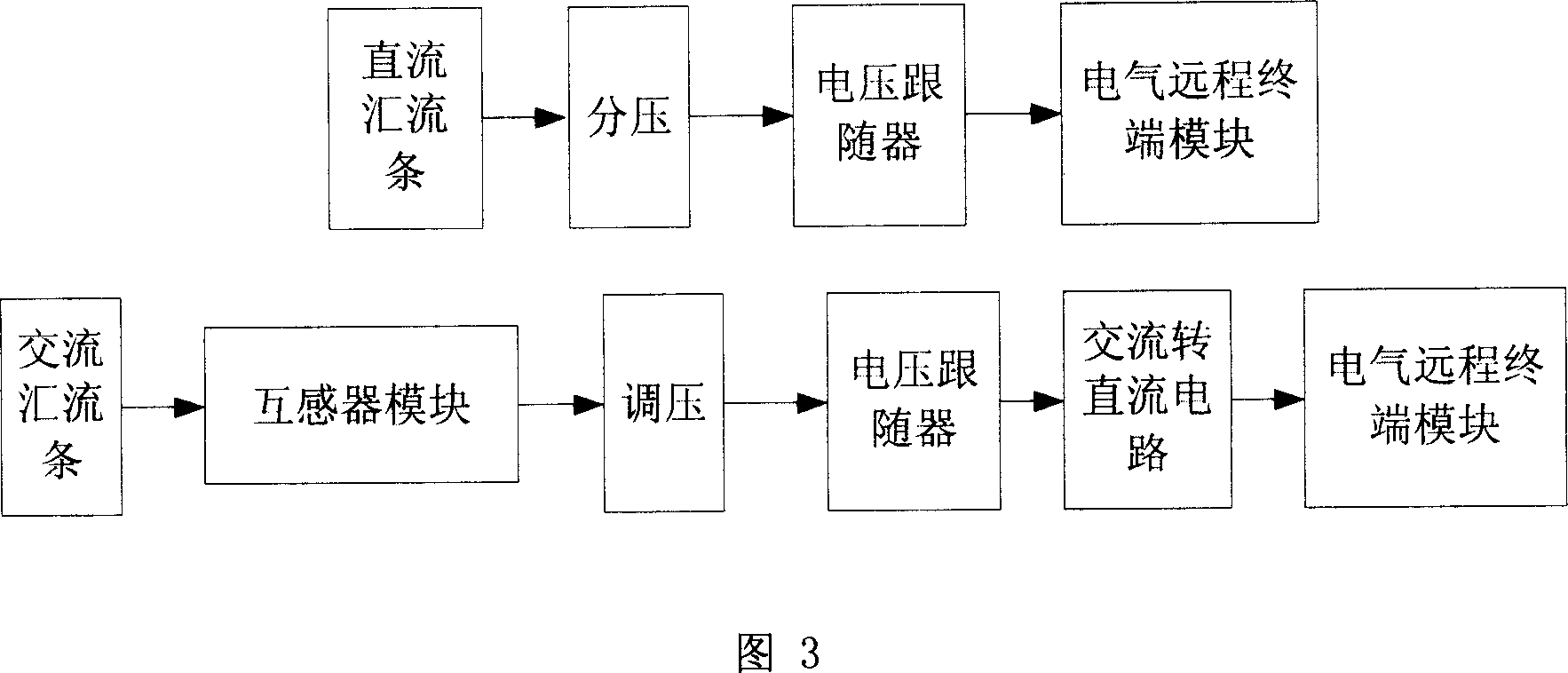

Intelligent power distribution administrative center

ActiveCN1921260AShorten the lengthReduce the burden onEnergy efficient ICTDc network circuit arrangementsPower controllerLow voltage

The invention relates to an intelligent distributing manager which comprises power module with low voltage, communication module, alternative-direct current detecting module, electric remote terminal and load detecting module. Wherein, the CPU of electric remote terminal is central processor, to collect and process parallel data, and analyze and send the load state to the system controller; the memory stores operation program, parameter and operation state. The manger via communication module and system bus is connected to the system control center, to receive instruction feedback; the load detecting module comprises several alternative-direct current solid power controllers, via internal bus to connect the electric remote terminal; the alternative-direct detecting module real time detects the voltage of each collecting bar of power. The invention is distributed secondary distributing manager, via system bus to connect the control center. The invention can power load, reduce cable length, reduce cost and improve reliability, with self-detection and protection.

Owner:G & A TECH

Build-up structures with multi-angle vias for chip to chip interconnects and optical bussing

InactiveUS20050269687A1Improve performanceIncrease speedTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesAnisotropic conductive filmEngineering

A build-up structure for chip to chip interconnects and System-In-Package utilizing multi-angle vias for electrical and optical routing or bussing of electronic information and controlled CTE dielectrics including mesocomposites to achieve optimum electrical and optical performance of monolithic structures. Die, multiple die, Microelectromechanical Machines (MEMs) and / or other active or passive components such as transducers or capacitors can be accurately positioned on a substrate such as a copper heatsink and multi-angle stud bumps can be placed on the active sites of the components. A first dielectric layer is preferably placed on the components, thereby embedding the components in the structure. Through various processes of photolithography, laser machining, soft lithography or anisotropic conductive film bonding, escape routing and circuitry is formed on the first metal layer. Additional dielectric layers and metal circuitry are formed utilizing multi-angle vias to form escape routing from tight pitch bond pads on the die to other active and passive components. Multi-angle vias can carry electrical or optical information in the form of digital or analog electromagnetic current, or in the form of visible or non-visible optical bussing and interconnections.

Owner:CAPITALSOURCE FINANCE

Array molded package-on-package having redistribution lines

ActiveUS7944034B2Shorten the time to marketSimple methodLiquid surface applicatorsSemiconductor/solid-state device detailsContact padCoupling

A semiconductor device with a sheet-like insulating substrate (101) integral with two or more patterned layers of conductive lines and vias, a chip attached to an assembly site, and contact pads (103) in pad locations has an encapsulated region on the top surface of the substrate, extending to the edge of the substrate, enclosing the chip, and having contact apertures (703) at the pad locations for external communication with the pad metal surfaces. The apertures may have not-smooth sidewall surfaces and may be filled with solder material (704) to contact the pads. Metal-filled surface grooves (710) in the encapsulated region, with smooth groove bottom and sidewalls, are selected to serve as customized routing interconnections, or redistribution lines, between selected apertures and thus to facilitate the coupling with another semiconductor device to form a package-on-package assembly.

Owner:TEXAS INSTR INC

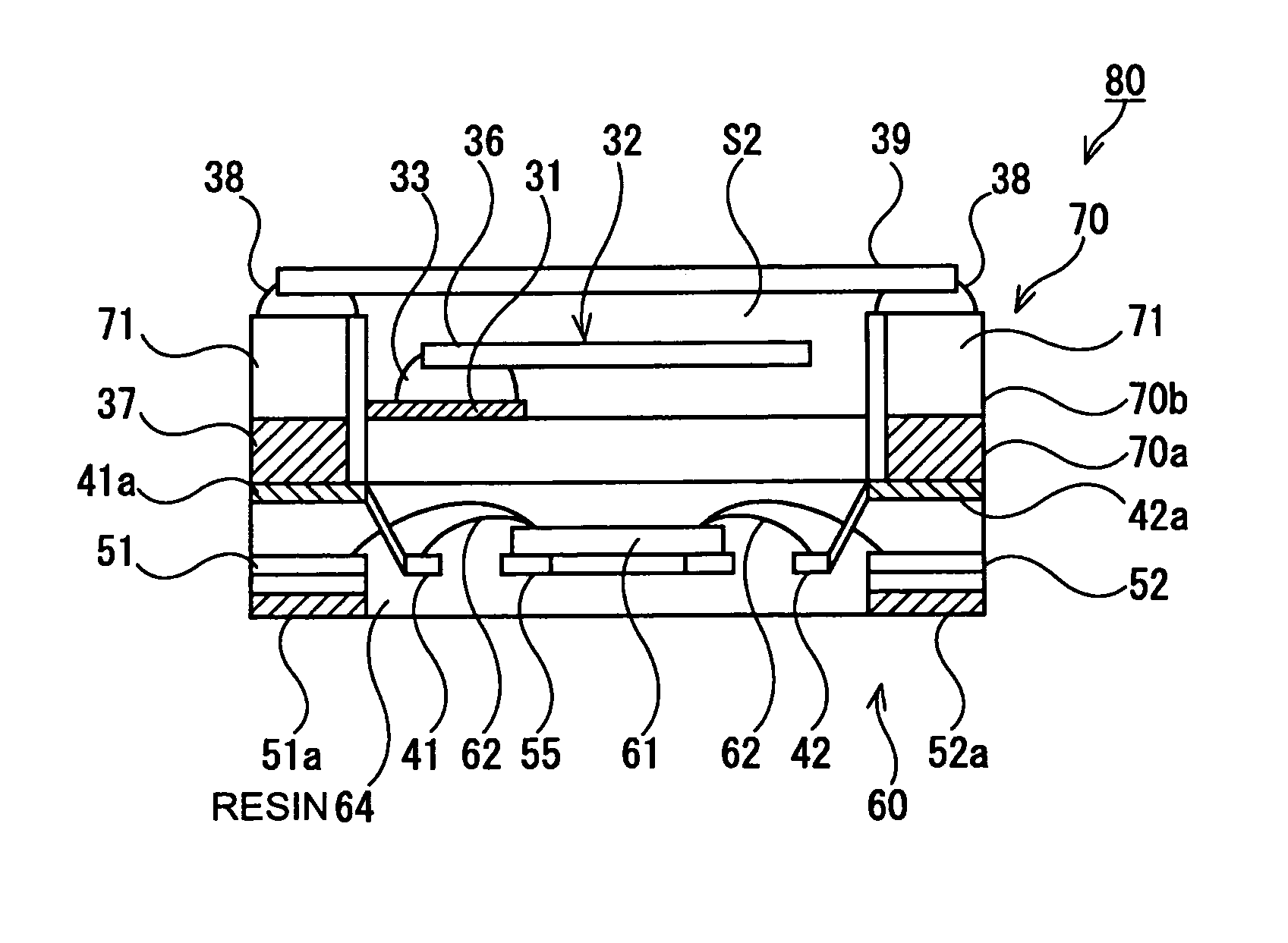

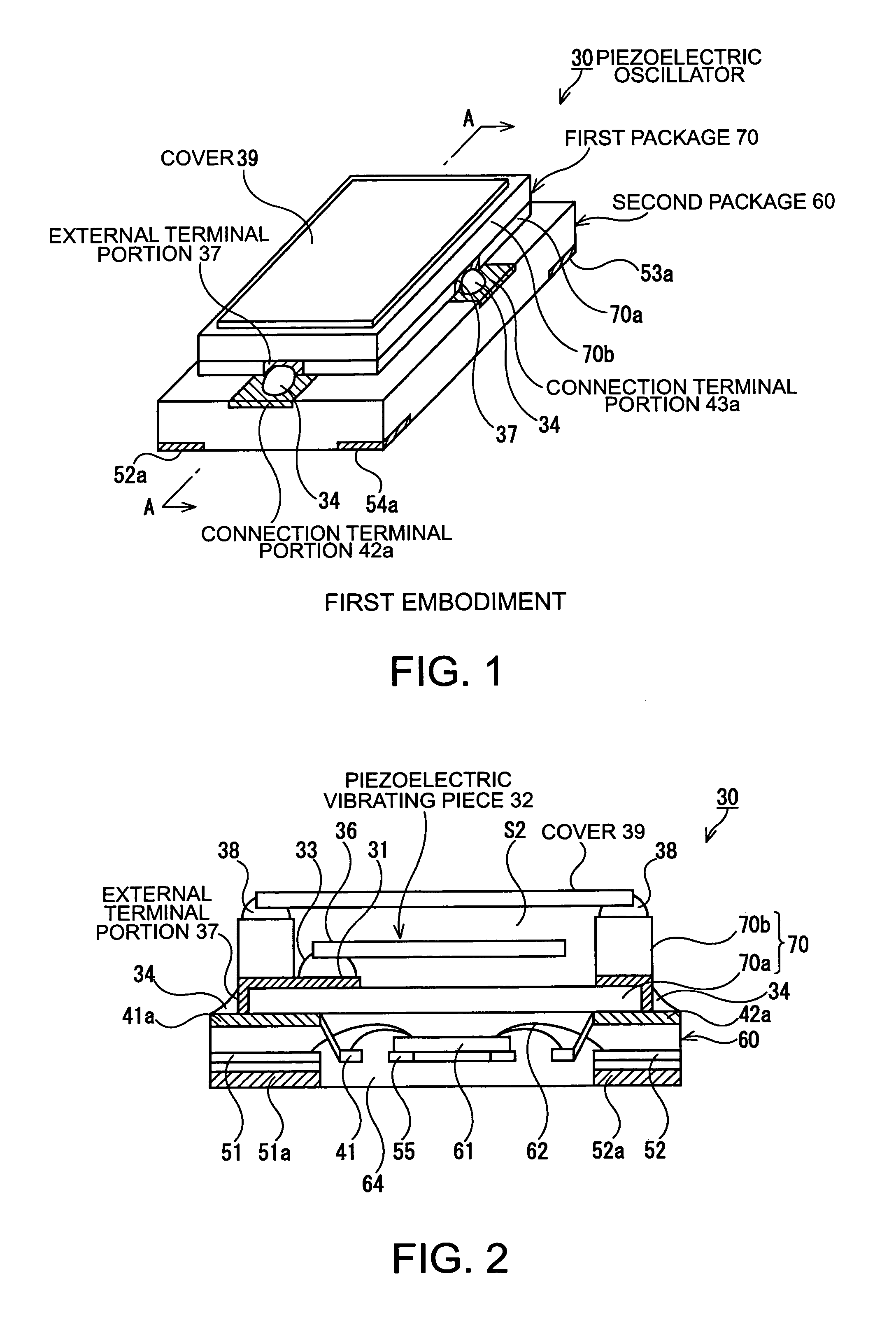

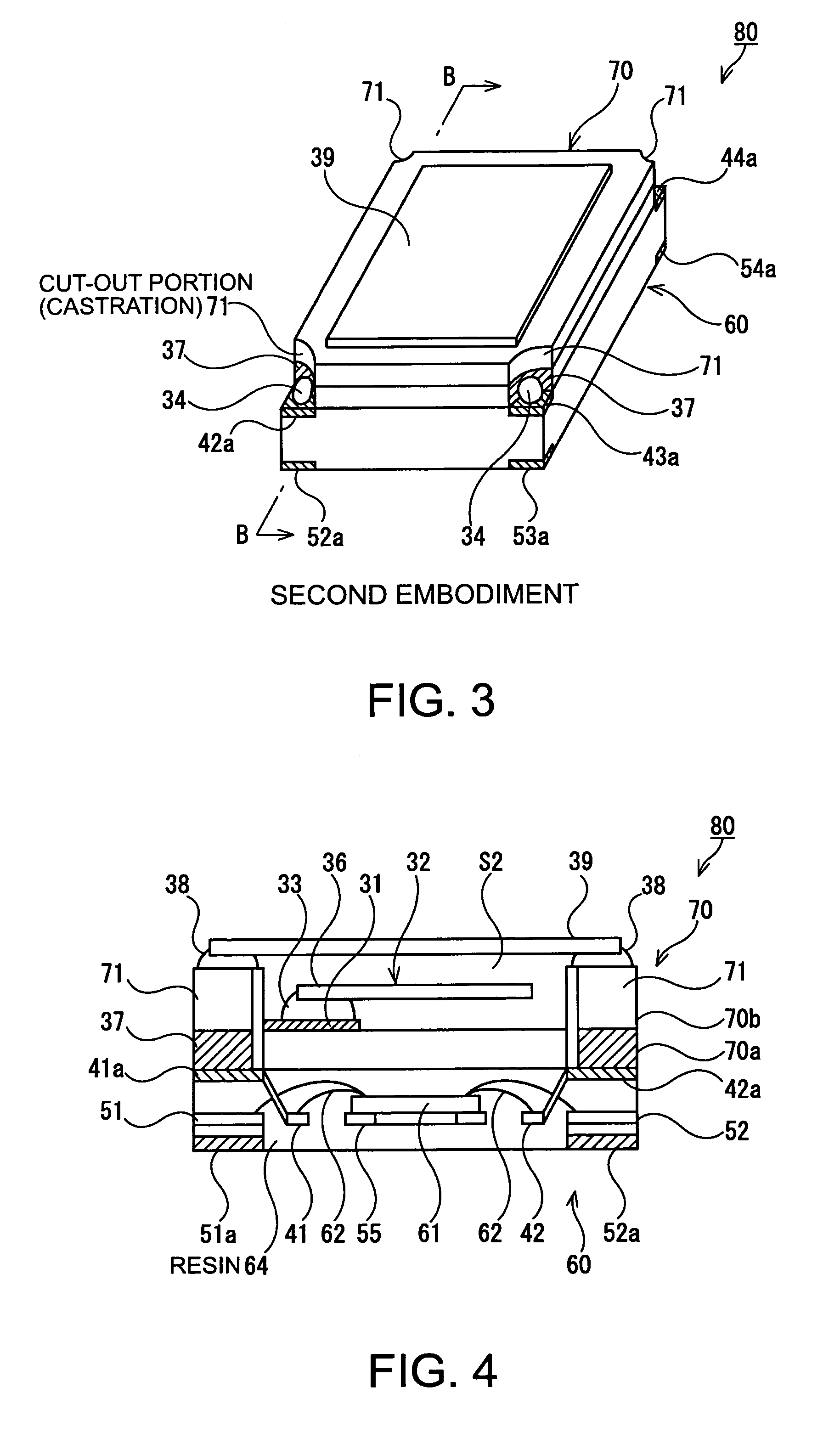

Piezoelectric oscillator, portable phone employing piezoelectric oscillator, and electronic apparatus employing piezoelectric oscillator

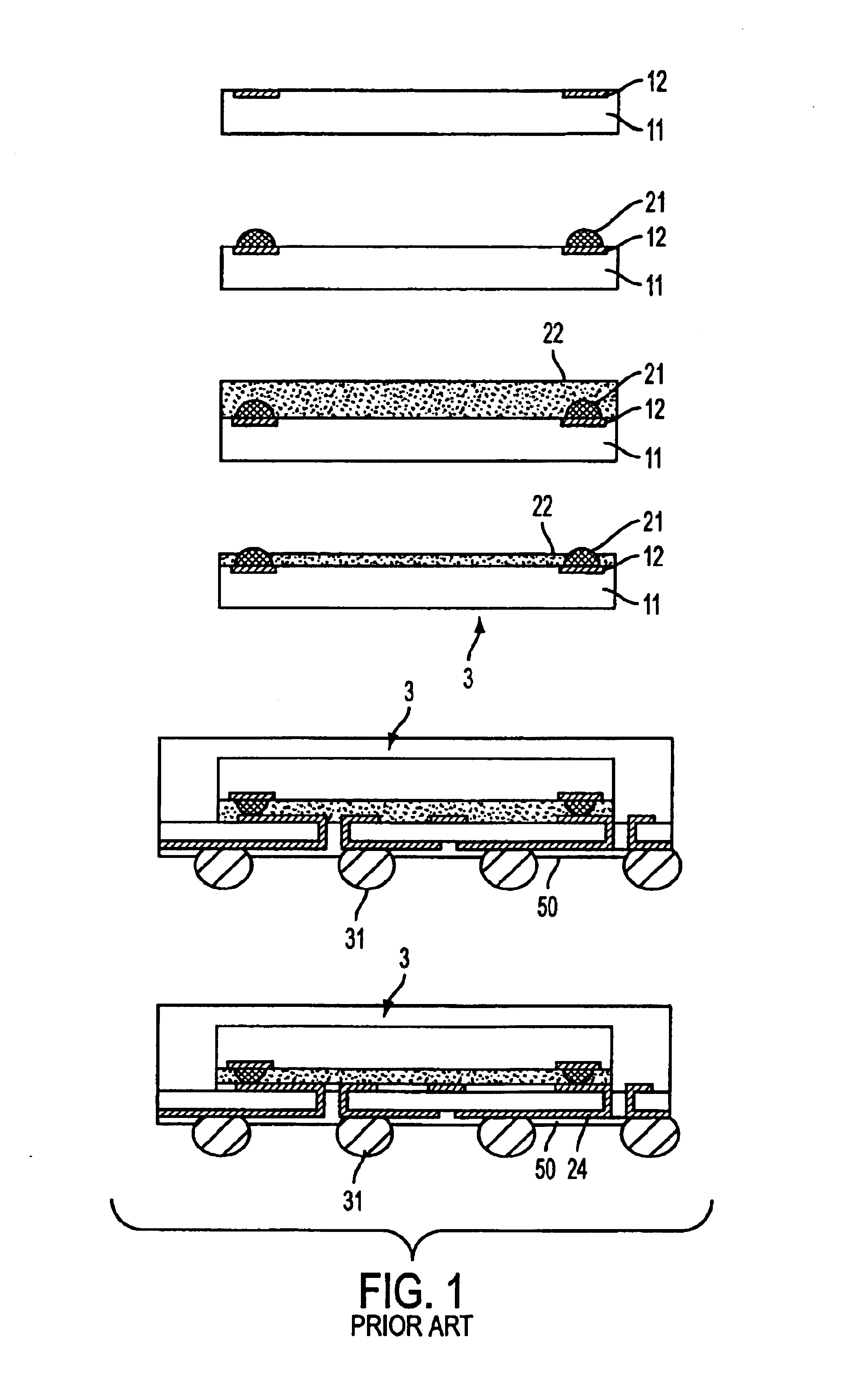

InactiveUS6998926B2Improve testabilityEasy to observeImpedence networksPiezoelectric/electrostriction/magnetostriction machinesSemiconductor packageConductive materials

To provide a piezoelectric oscillator in which, even after a first package and a second package are bonded to each other, the connection state can be easily observed externally, so that testability can be enhanced, and connection failure can be easily found out to perform a repair. A piezoelectric oscillator includes a first package housing a piezoelectric resonator element therein and having external terminal portions connected to excitation electrodes of the piezoelectric resonator element, and a second package housing an oscillating circuit element, the first package being superposed on and fixed to the second package. Herein, in the second package, the oscillating circuit element, which is connected to a lead frame, is molded out of resin, and connection terminal portions and mounting terminals formed of the lead frame are exposed at the second package. Furthermore, the external terminal portions of the first package are exposed at the side surfaces of the first package, and the external terminal portions and the connection terminal portions of the second package are electrically connected to each other by a conductive material.

Owner:SEIKO EPSON CORP

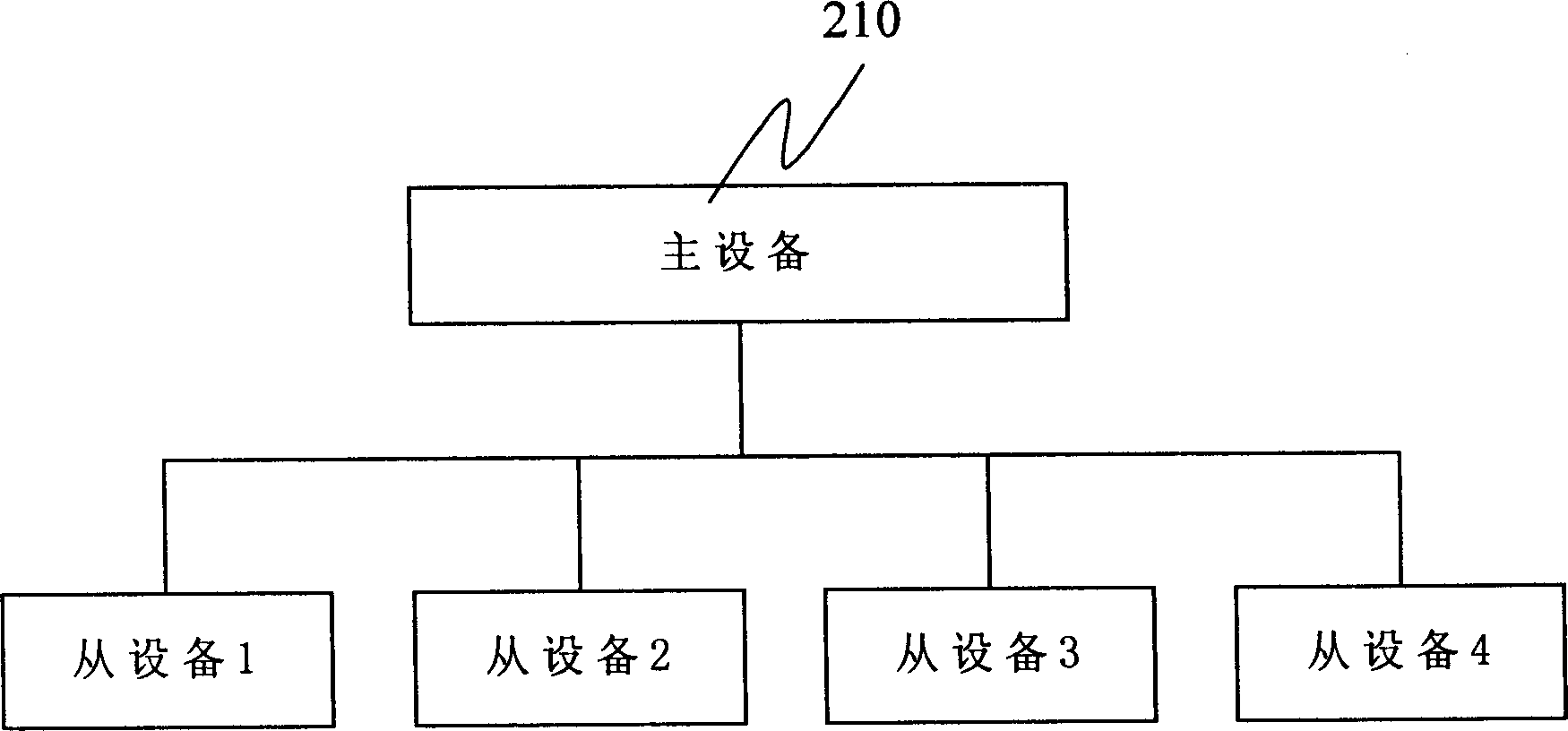

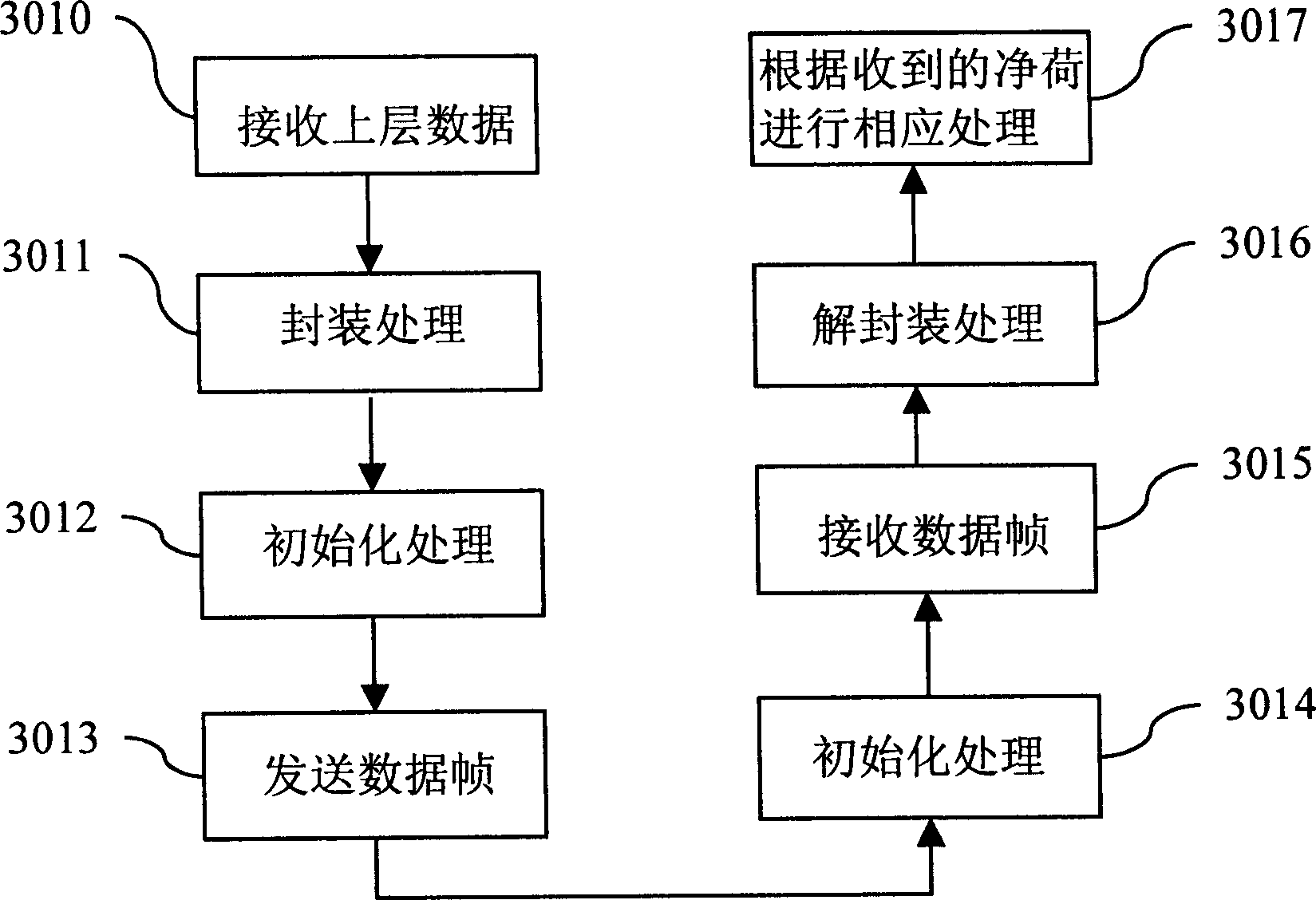

RS-485 multipoint communication method

InactiveCN1527561AImprove reliabilityImprove testabilityError detection onlyData switching networksByteCyclic redundancy check

The RS-485 multipoint communication method includes balanced sending and differential receiving for the communication between one master machine and several slave machines. In the sending end, upper layer data is first received, protocol head is added before the data byte and CRC check is added behind the data byte, before initializing treatment and sending the data frame. In the receiving end, after the data frame is received, the frame decomposing treatment including frame head distinction, dingle board address comparison, frame length checking, data byte determination and CRC is performed before the corresponding treatment of received pure load. The present invention raises communication efficiency, facilitates RS-485 debugging, locates error correctly and increases the measurement performance while ensuring the reliability of multipoint communication.

Owner:ZTE CORP

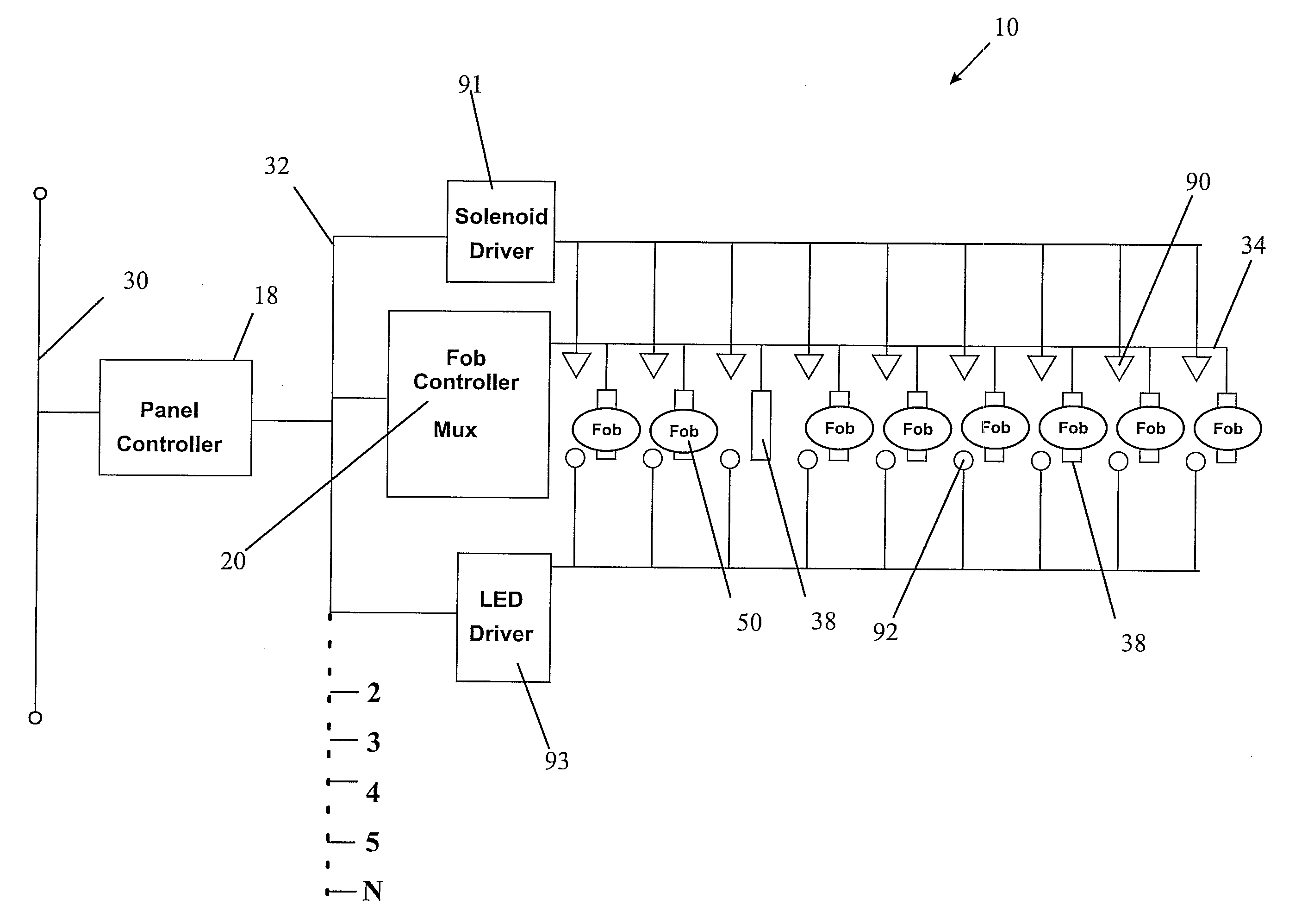

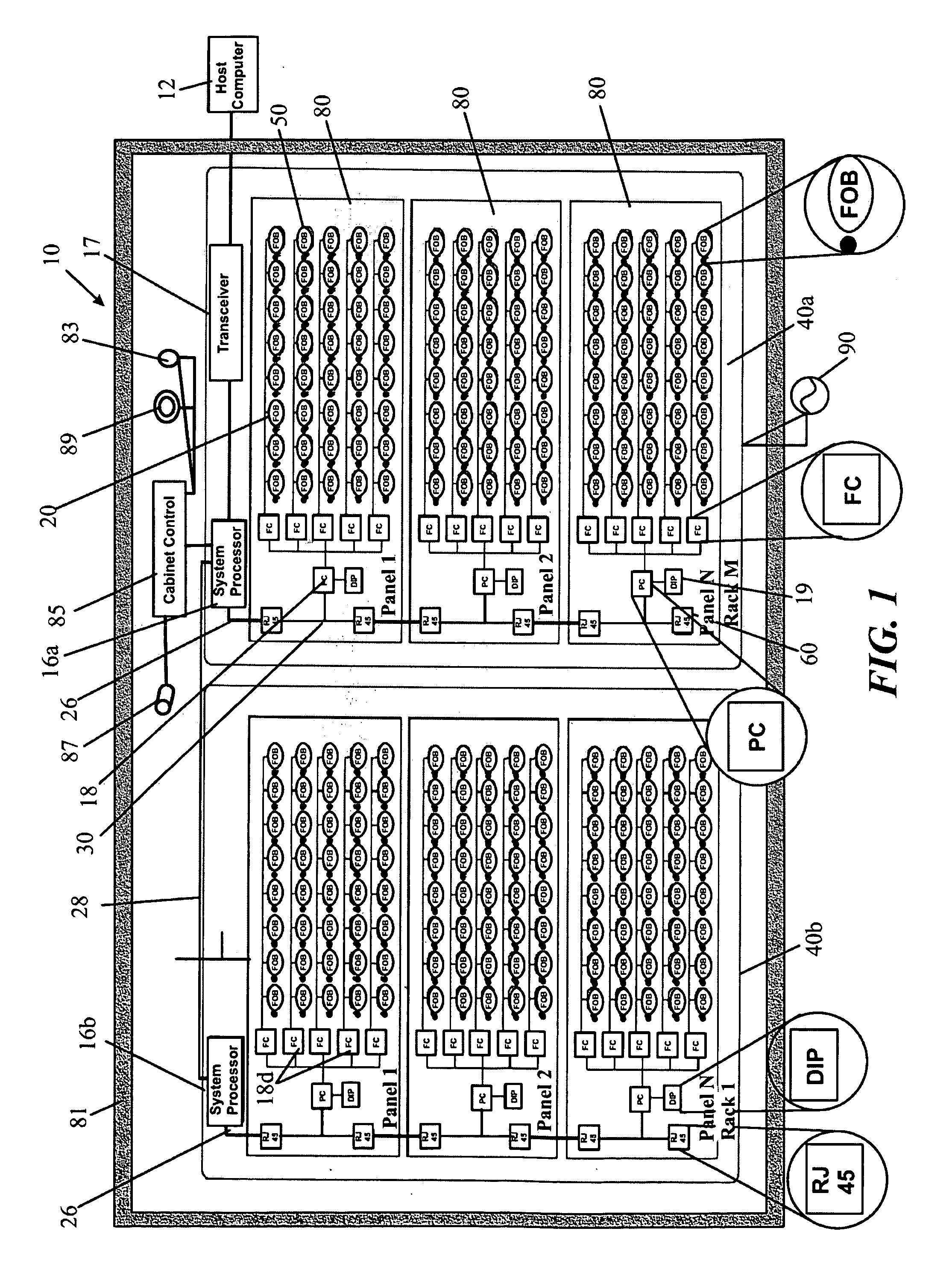

Key management system

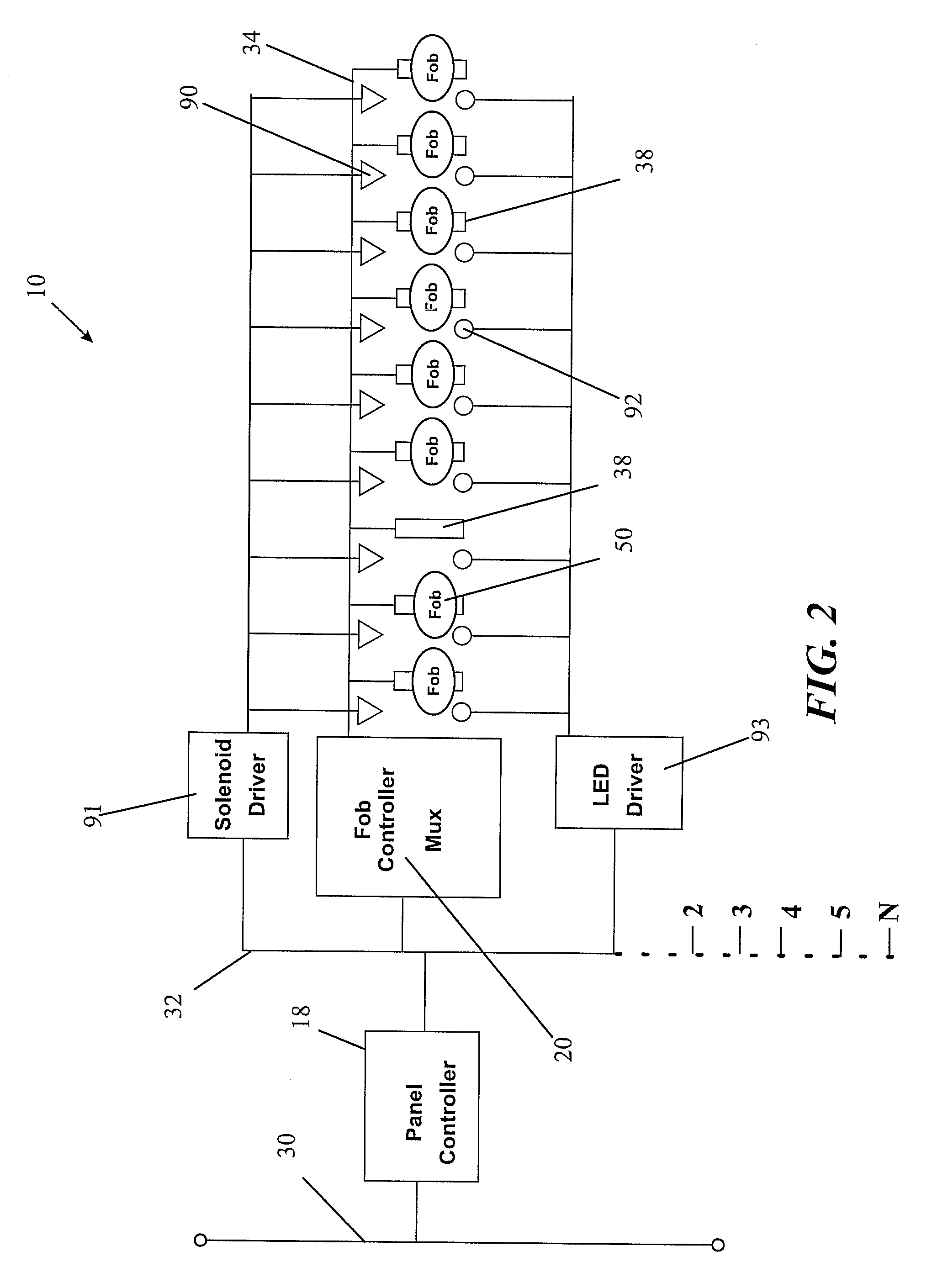

InactiveUS20080186130A1Reduce dependenceOpportunity for cost efficiencyElectric signal transmission systemsMultiple keys/algorithms usageManagement systemMuxponder

An asset management system includes a distributed network of hierarchical controllers to manage the dispensation of assets, such as keys and the like, where the an asset is attached to an electronic fob, and the fobs are removably connected to a connection port. The hierarchical controllers are a plurality of system microprocessors and multiplexers that control a plurality of panel controllers, which in turn control a plurality of fob controllers, which in turn are physically and electronically interfaced with a plurality of fobs. The asset management system specifically manages a unique physical location of each fob on a panel. The system microprocessors are in communication with a host computer, which in turn can be in communication with other computers and other asset management systems. The system microprocessor can also control subsequent system microprocessors through a master-slave control hierarchical system.

Owner:TREVINO ARTHUR A +1

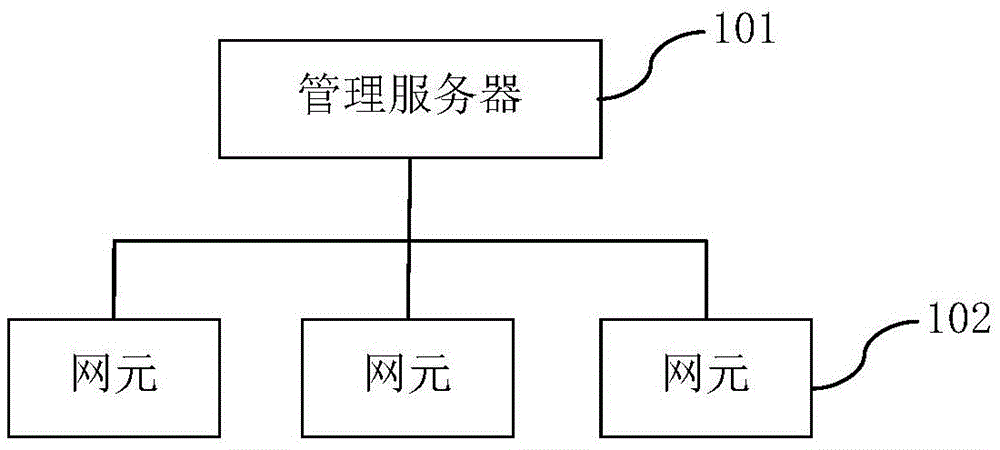

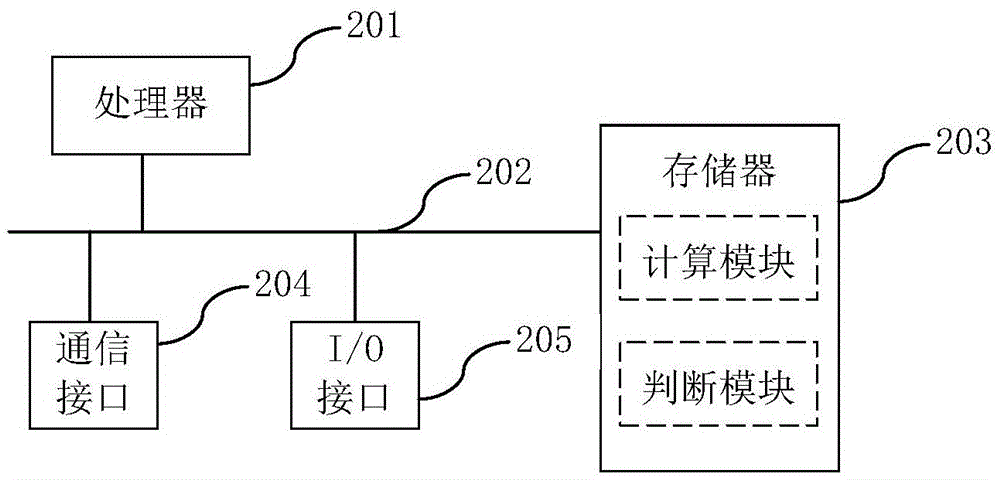

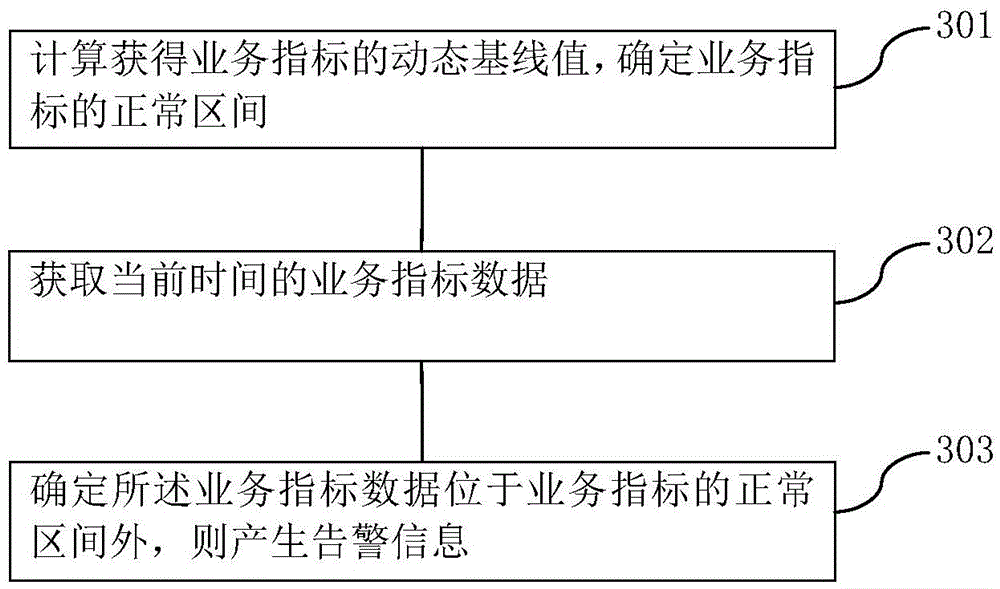

Service abnormity detection method and server

InactiveCN105610647AImprove testabilityImprove maintainabilityData switching networksMaintainabilityData mining

The invention provides a service abnormity detection method and a management server. The method comprises following steps that: the management server calculates to obtain dynamic baseline values of service indexes and determines the normal interval of the service indexes; then the service index data of present time are obtained; if it is determined that the service index data are located out of the normal interval of the service indexes, warning information is generated. According to the method and the server of the invention, the normal interval of the service indexes is determined through the calculated dynamic baseline values, especially using an average value and a variance; whether the service index data are abnormal is determined; and the measurability and the maintainability of the service system are improved.

Owner:HUAWEI TECH CO LTD

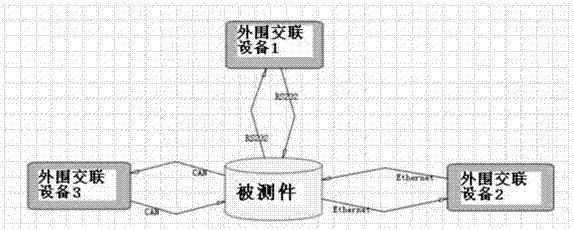

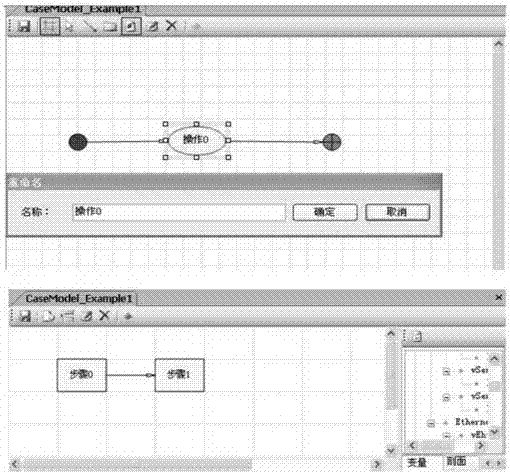

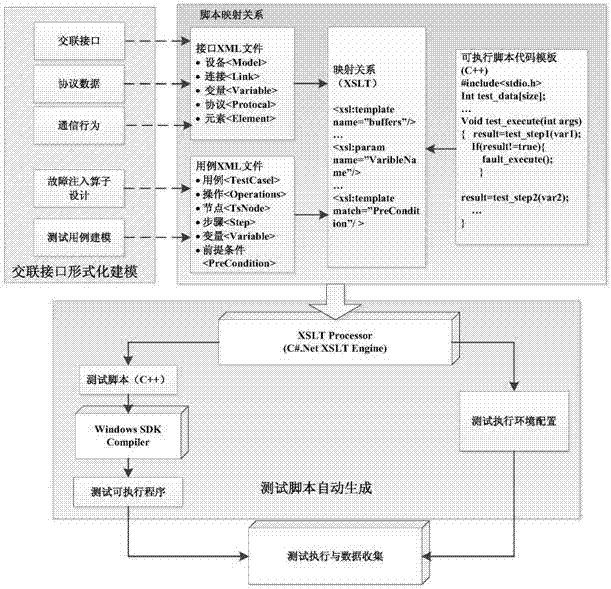

Interface-oriented automatic test method for software fault injection

InactiveCN107368408ALower requirementImprove versatilitySoftware testing/debuggingTest scriptData modeling

The invention provides an interface-oriented automatic test method for software fault injection, and aims at realizing the automatic test of interface fault injection. The method comprises the following steps of: firstly carrying out cross-linkage interface modeling, communication behavior modeling and protocol data modeling; designing a fault injection operator and carrying out test case modeling; automatically generating an XML-format test case on the basis of the model; and finally automatically generating the test case into a test script of C++ language on the basis of XSLT, calling windows SDK to automatically generate a test program and automatically executing the test program, realizing result collection through a Windows pipeline technology, and evaluating the test result so as to complete the fault injection test of the whole cross-linkage interface. According to the method, universality and usability realized by an interface fault injection test tool are effectively improved, the interface test efficiency is improved and the test cost is reduced.

Owner:中国船舶工业综合技术经济研究院

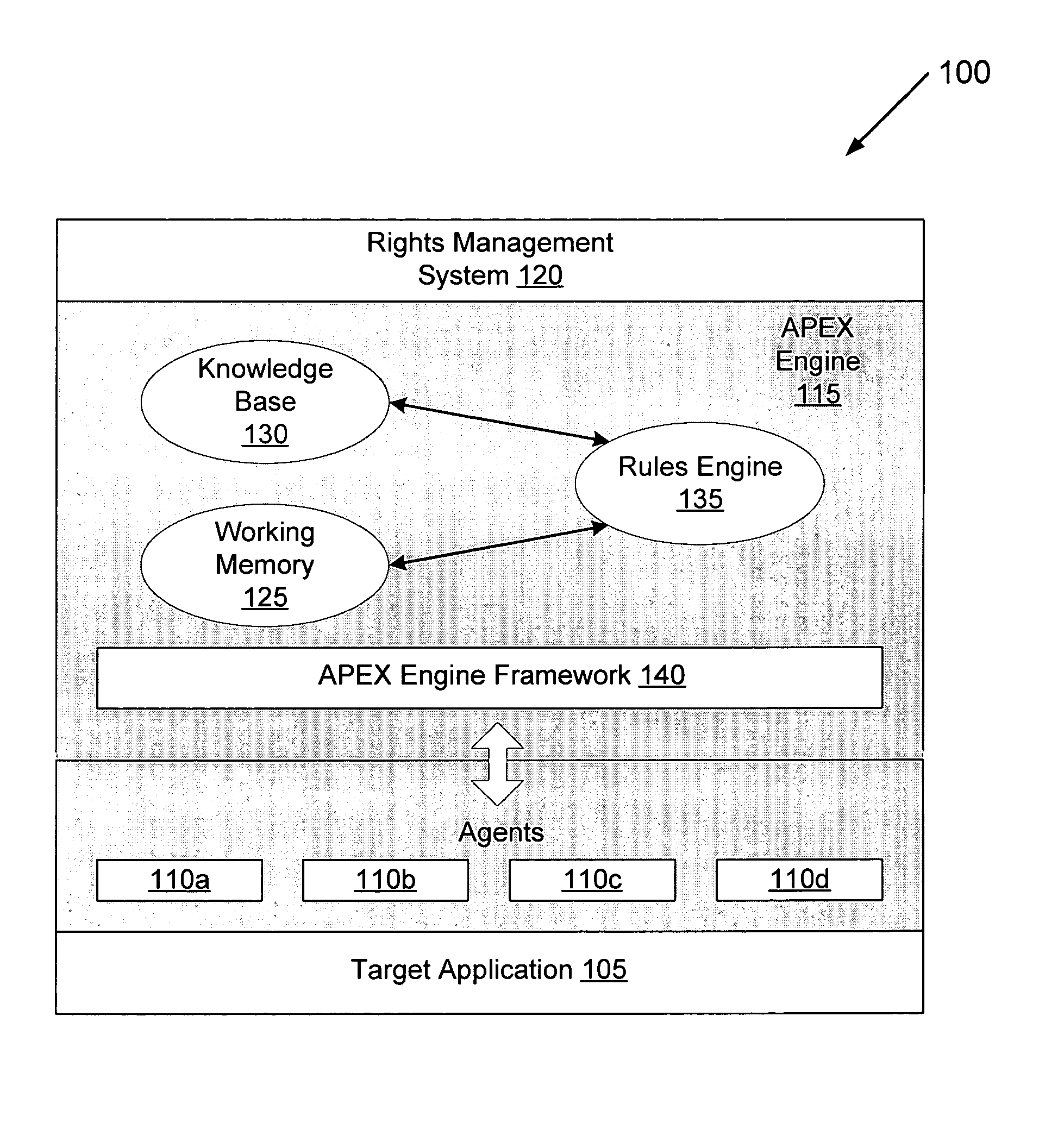

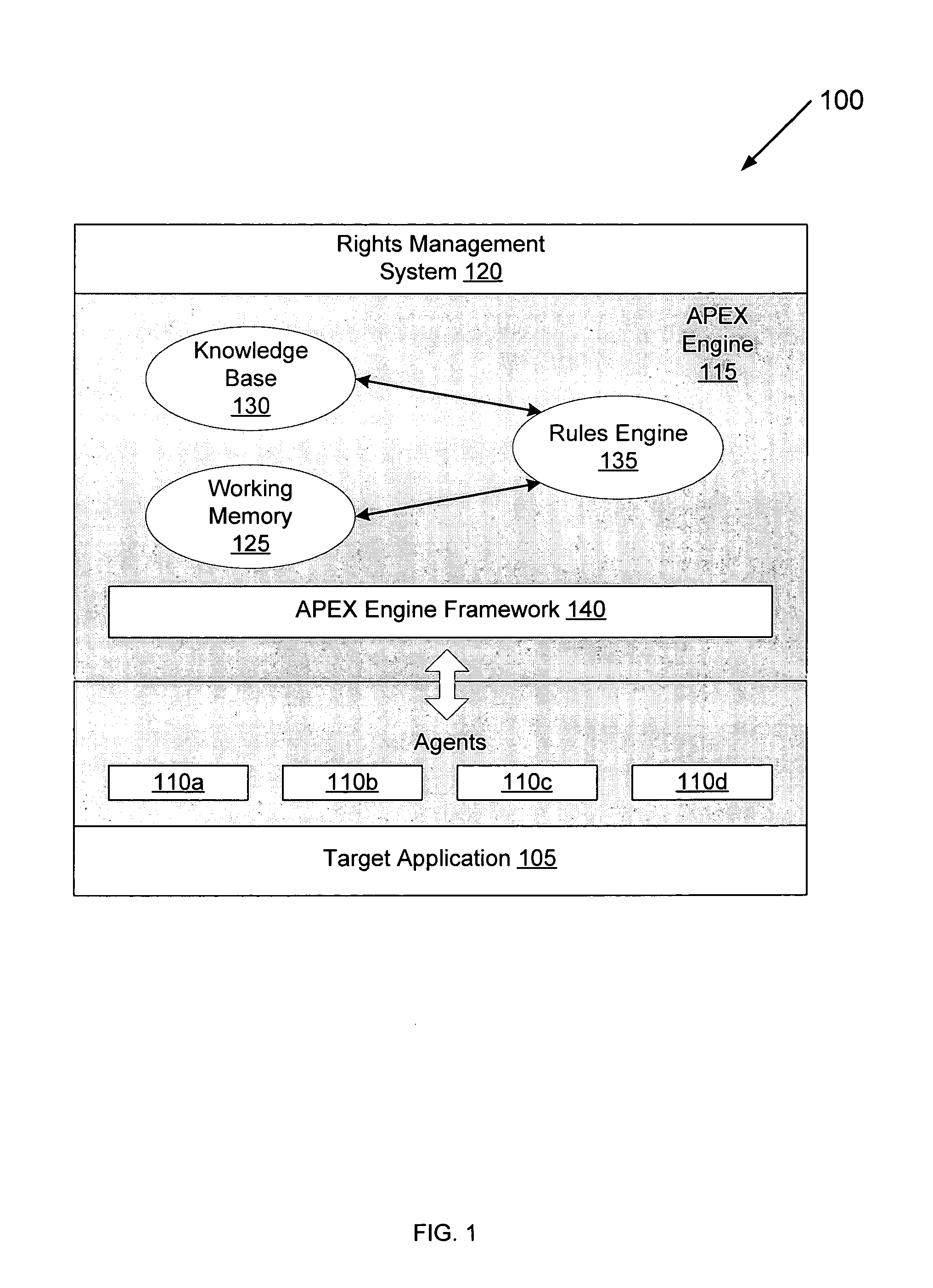

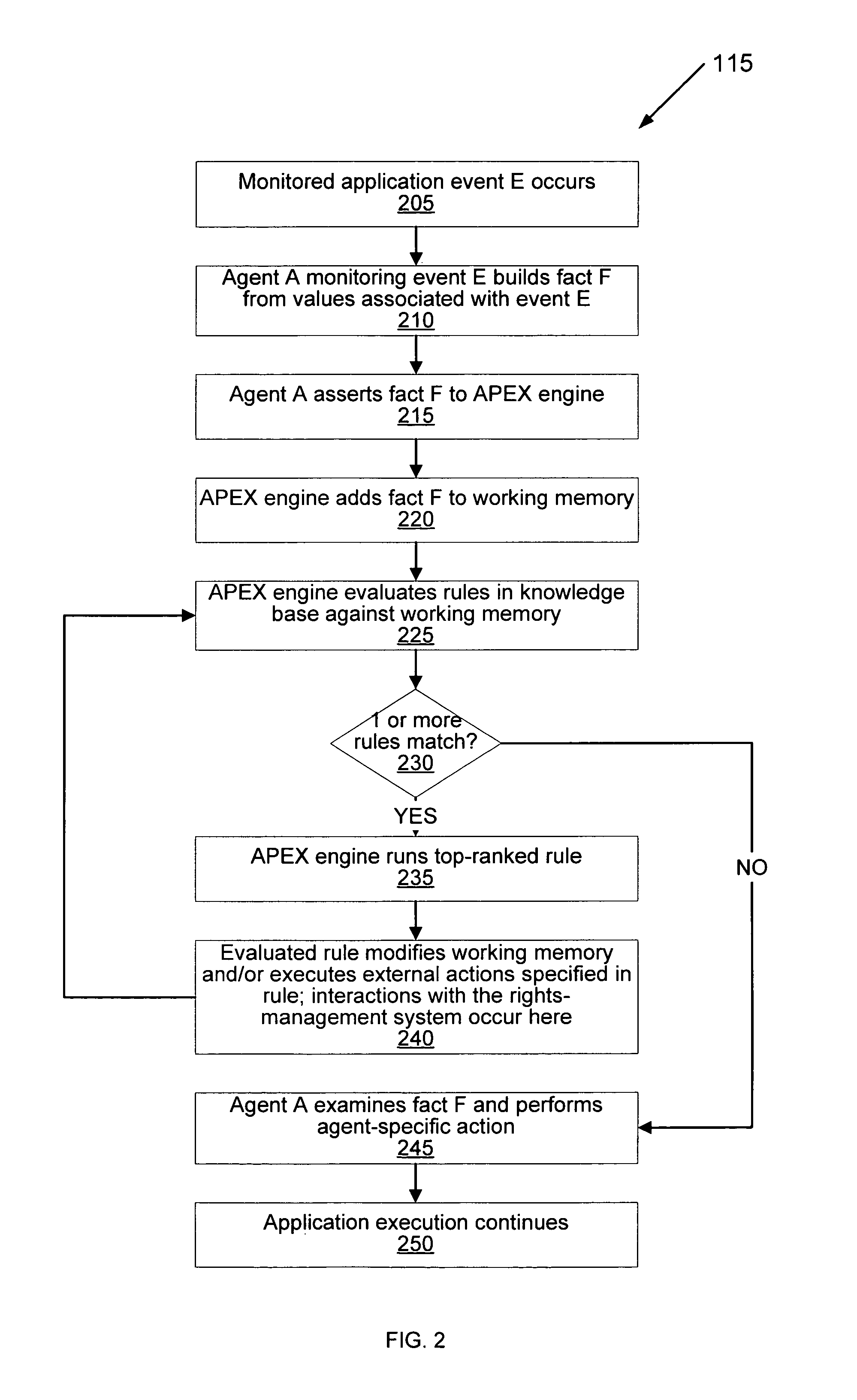

Method and system for using a rules engine for enforcing access and usage policies in rights-aware applications

InactiveUS7984513B1Improves robustness and testabilitySimplify the development processMemory loss protectionDigital data processing detailsApplication computersSoftware engineering

Computer system and method enforces control policies including access and usage policies. A rules-based engine member or assembly is coupled between a rights-management (or similar) system and one or more target applications. The rules-based engine member centralizes data security determinations for the target applications. One or more agents are responsive to the rules-based engine member and target applications, and handle low-level details in interactions between the rules-based engine member and target applications. A generic engine framework serves as a normalizing factor and enables scalability.

Owner:LIQUID MACHINES

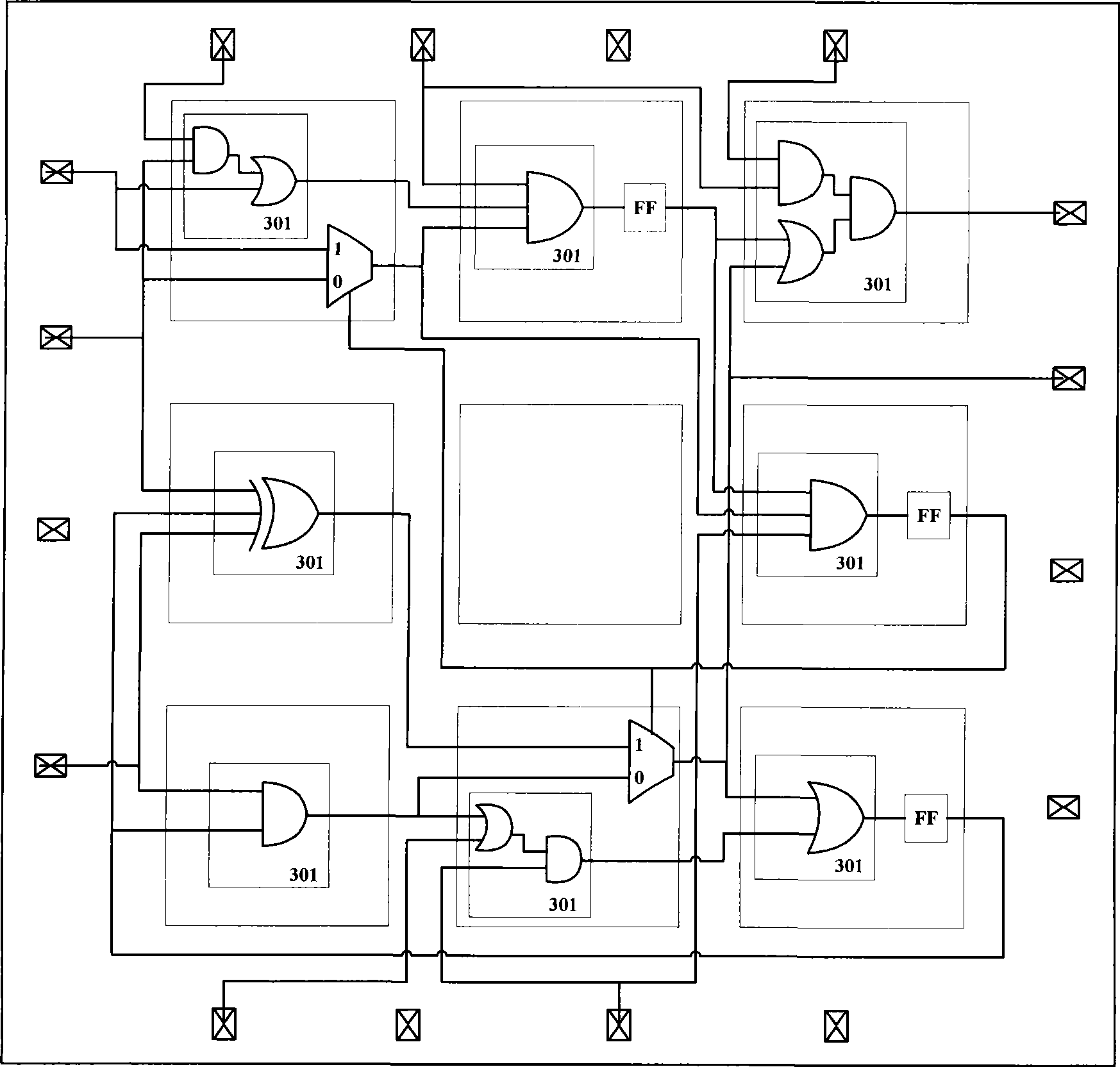

Method and system for testing on site programmable gate array

InactiveCN101413990AImprove ObservabilityImprove controllabilityElectrical testingGate arrayExclusive or

The invention relates to a testing method for a field programmable gate array (FPGA). The method comprises the following steps: obtaining an initial design netlist and an initial design configuration of the FPGA; replacing a look-up table function of the initial design netlist and the initial design configuration with an exclusive or function of a logic function to obtain an initial testing netlist and an initial testing configuration; selecting an observation node of the initial testing netlist based on a preset rule of a testability analysis method, and obtaining a testing netlist and a corresponding testing vector; configuring an output terminal of an output and input unit from the observation node to the initial testing configuration to obtain a testing configuration; connecting the testing configuration to an configuration device according to an excitation signal of the configuration device to obtain an output logic value of the testing vector; and analyzing the output logic value and a response value of the testing vector to obtain the testing result. The method can effectively detect permanent faults of interconnection lines used in the application design of FPGA chips.

Owner:无锡引速得科技有限公司

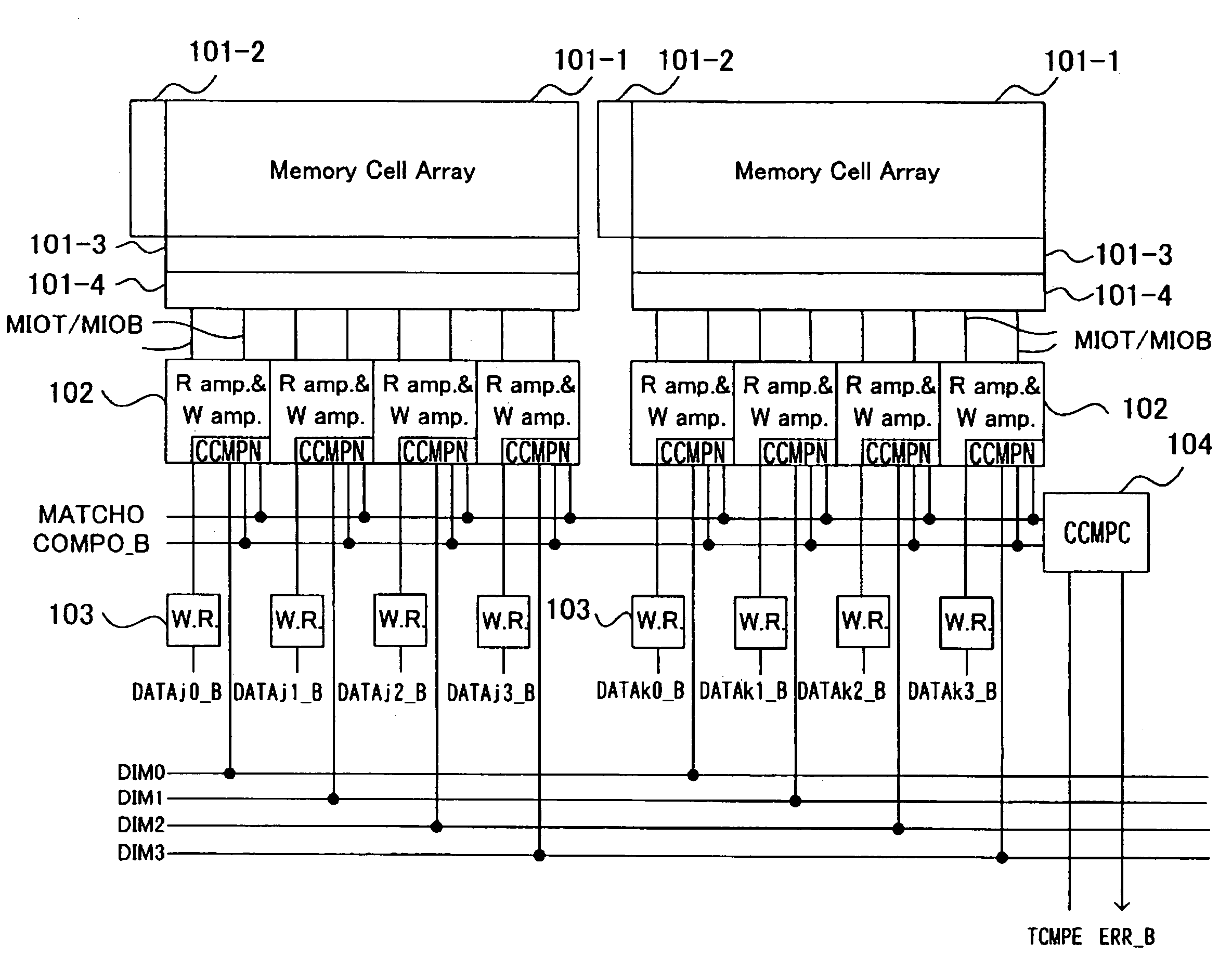

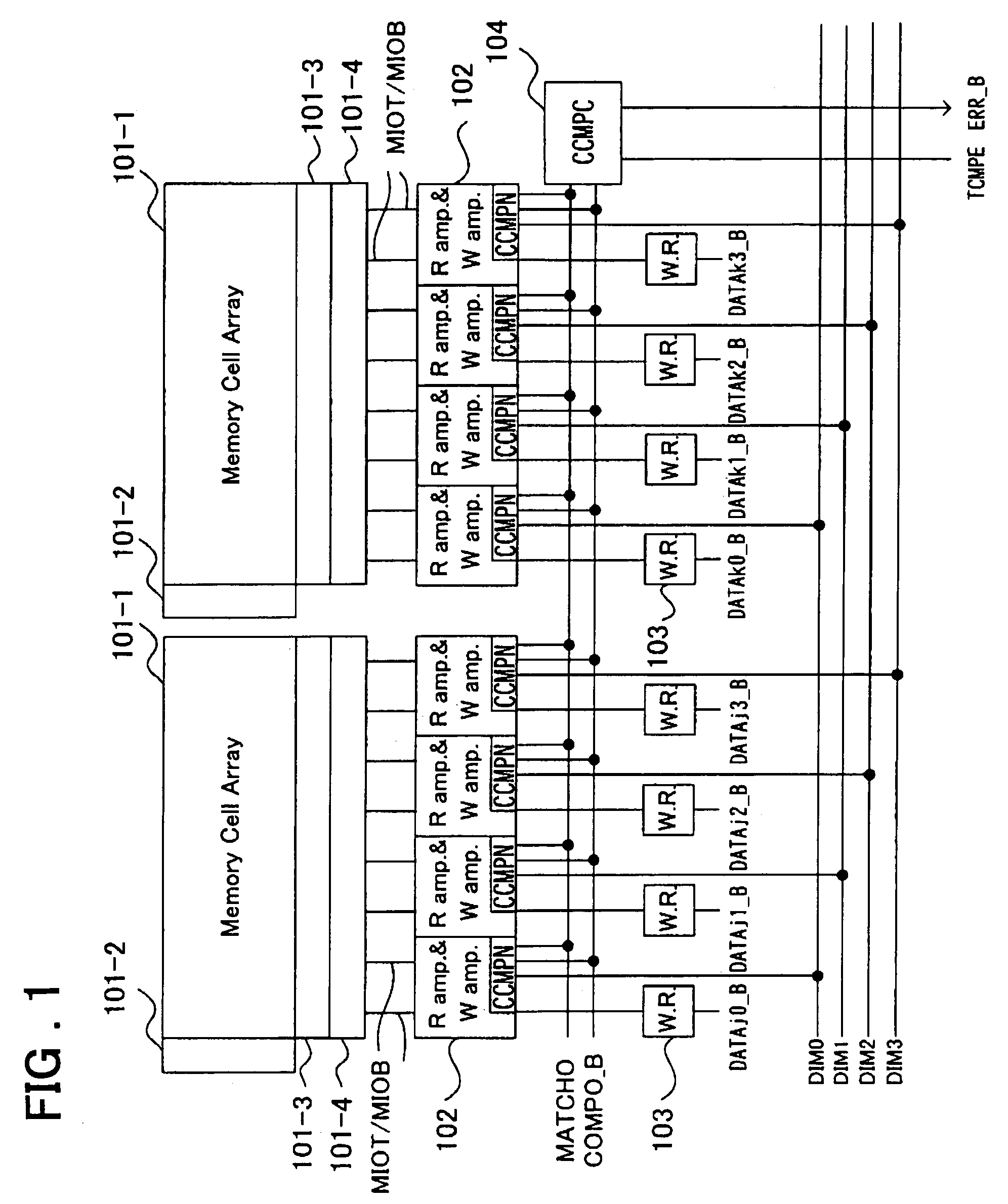

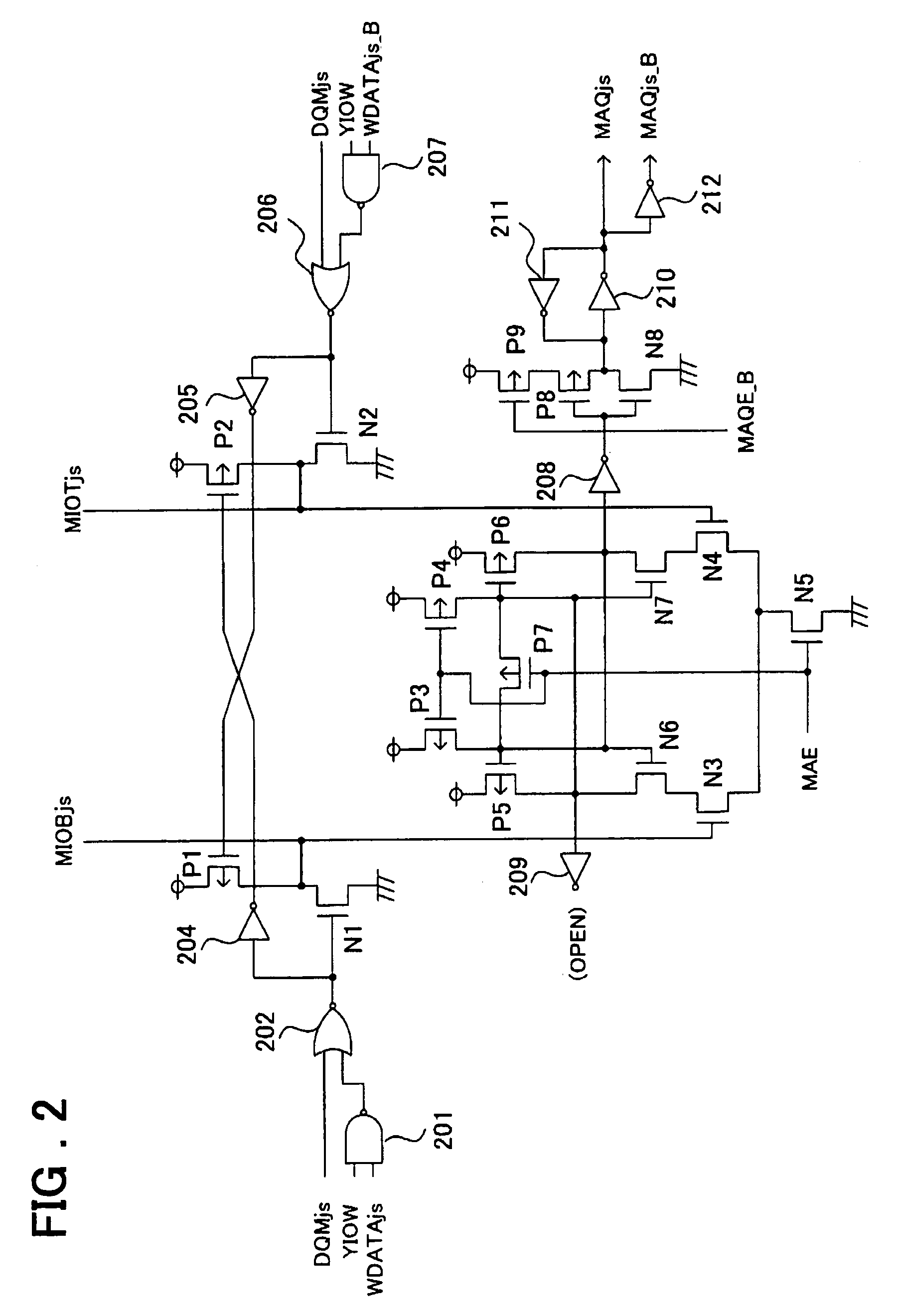

Semiconductor storage device

InactiveUS7240253B2Avoid simple structuresImprove testabilityElectronic circuit testingDigital storageCircuit sizingControl signal

A testing device for a semiconductor storage device suppresses the increase in the circuit size, provides for facilitated accommodation to a test with frequent changes in the test pattern, and improves testability of the semiconductor storage device. A plurality of holding circuits are provided holding write data for memory cells of a memory cell array. (Original) The write data from the holding circuits are written in the memory cells of the selected address. A plurality of comparators are supplied with data read out from the memory cells and with data held by the holding circuits as expectation data to compare the readout data and the expectation data. The non-inverted or inverted value of the write data held by the holding circuits is output as the write data to the memory cells and as expectation data to the comparators depending on the value of the inversion control signal.

Owner:LONGITUDE LICENSING LTD

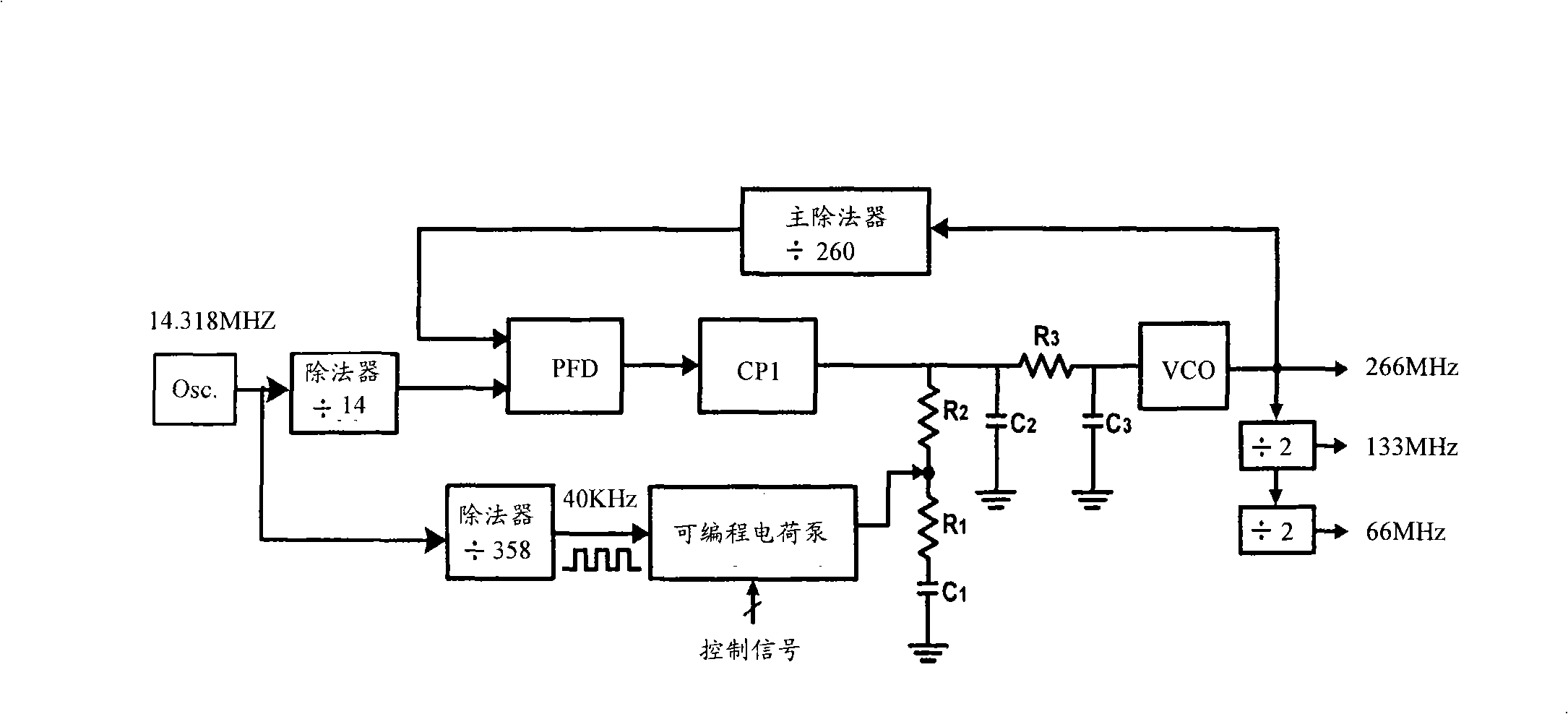

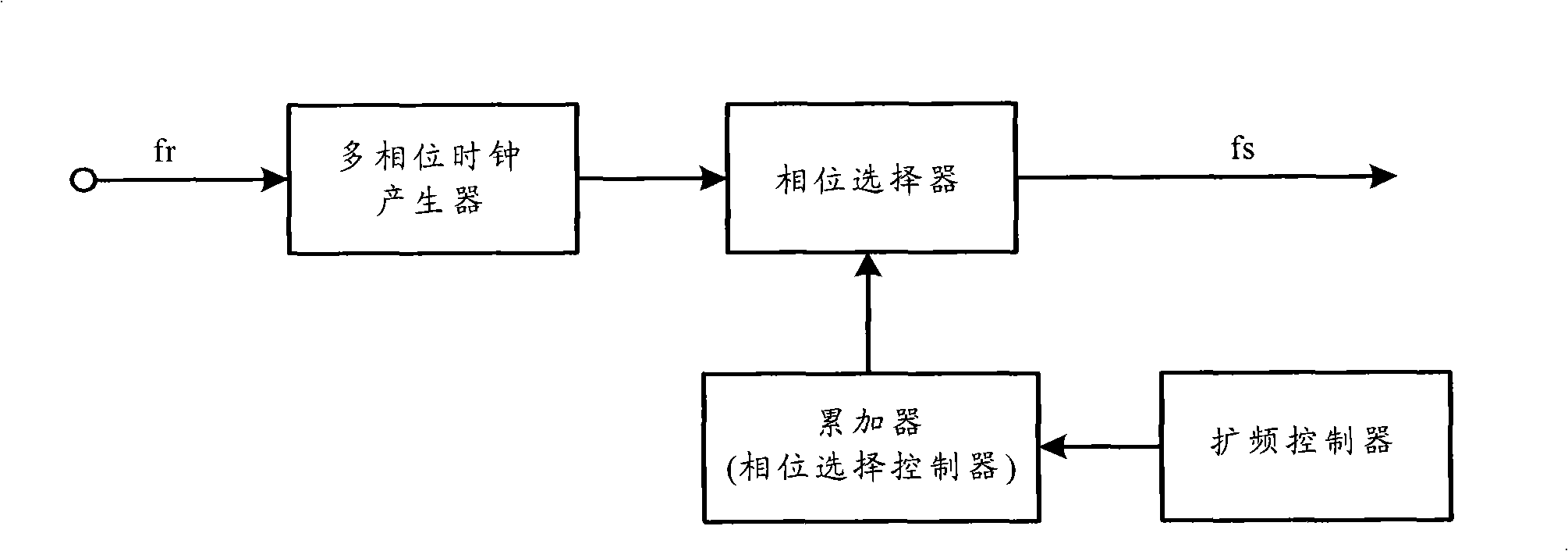

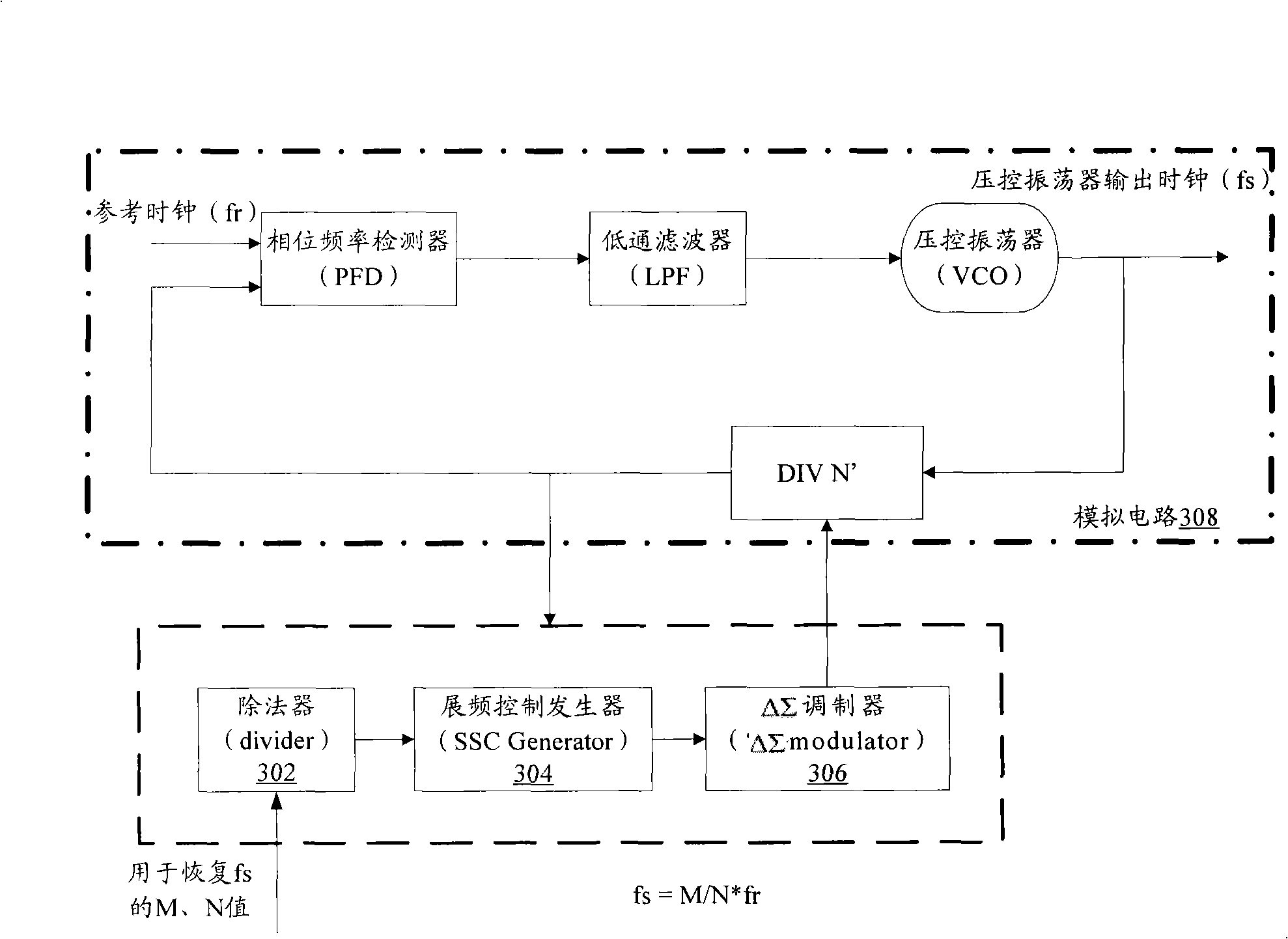

Apparatus and method for frequency expansion of reference clock signal

ActiveCN101404569AReduce design difficultyHigh precisionPulse automatic controlSynchronising arrangementExternal referenceFloating point

The invention provides a device for spreading spectrum of a reference clock signal and a method thereof, wherein, the device comprises a divider which is used for receiving an M value and an N value, generating a first floating point decimal according to the M value and the N value, and sending the first floating point decimal to a spread spectrum control generator; the spread spectrum control generator which is used for receiving the first floating point decimal from the divider and the reference clock signal from an analog circuit, generating a second floating point decimal for spreading the spectrum according to the first floating point decimal, the reference clock signal and modulation frequency, and sending the second floating point decimal to a delta sigma modulator; the delta sigma modulator which is used for generating a first integer distribution according to the second floating point decimal and sending the first integer distribution to the analog circuit; and the analog circuit which is used for sending the external reference clock signal to the spread spectrum control generator, generating a first frequency division clock signal according to the first integer distribution, and comparing and adjusting phases of the first frequency division clock signal, and spreading the spectrum of the reference clock signal.

Owner:ANALOGIX CHINA SEMICON

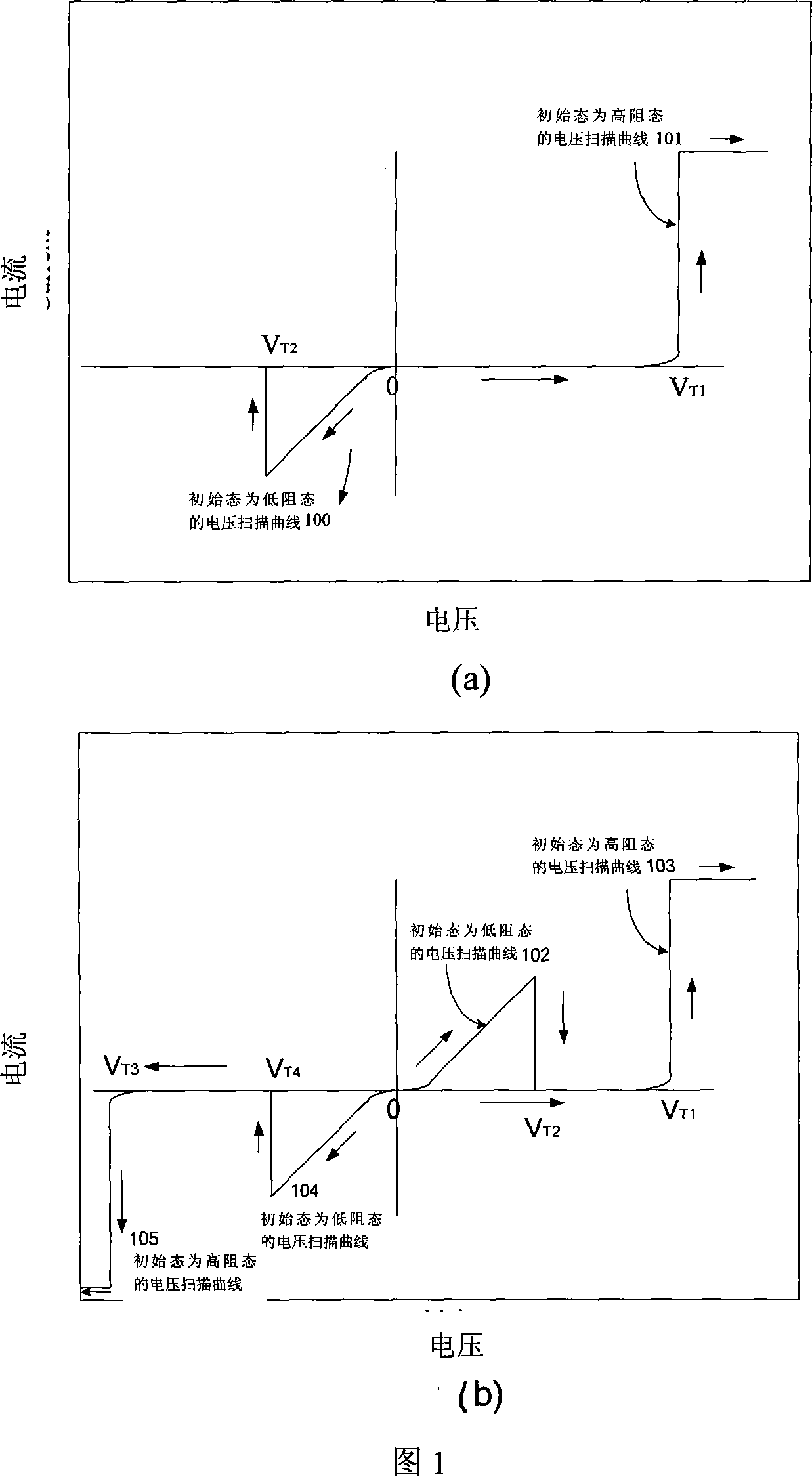

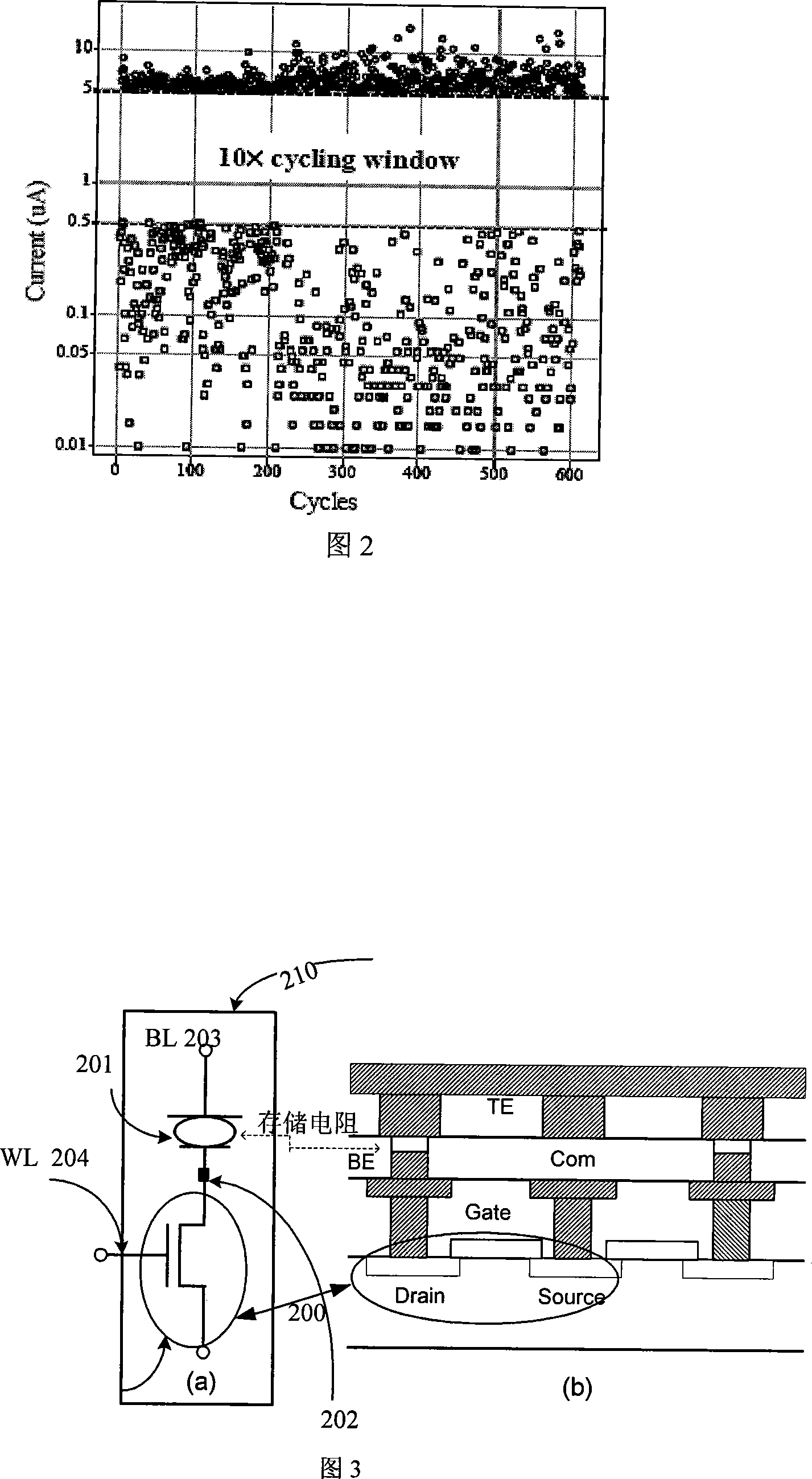

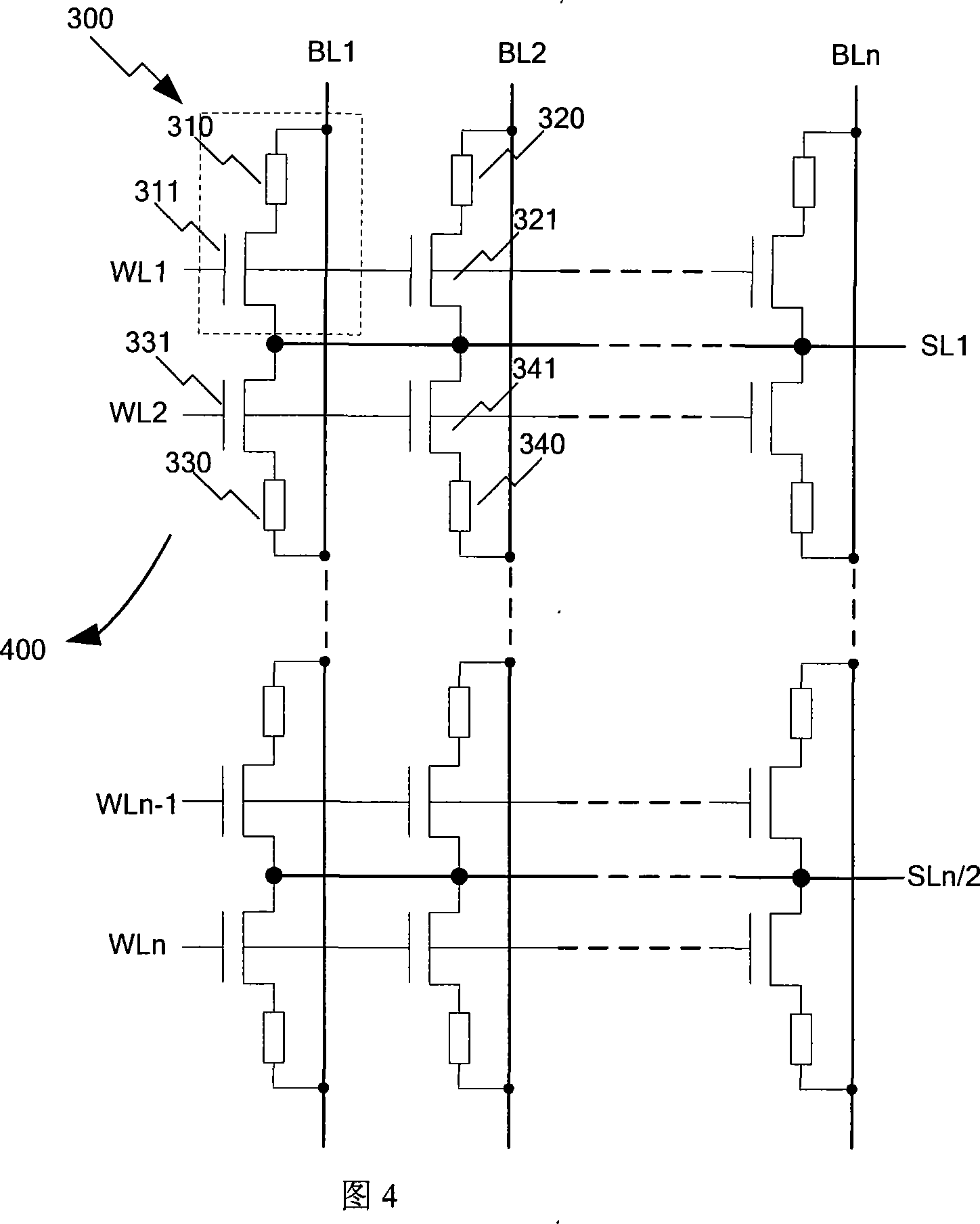

Once programming memory and its operation method using resistor memory media

InactiveCN101123120AReduce power consumptionReduce areaRead-only memoriesElectrical polarityComputer science

The invention belongs to the technical field of integrated circuit, and essentially relates to a one-time programming memory and a storing method. A metal oxide with two or more elements and the capability of repeated programming is used in the memory as storing media. Different voltages with different polarities are applied on both ends of the storing media for programming and erasing operations. The storing media of the invention has the capability of repeated programming, so the memory of the invention can be intelligently erased and tested for repeated programming. The yield rate and reliability of the memory of the invention are both increased, and the memory has low power consumption, high yield rate and high capacity matrix blocks.

Owner:FUDAN UNIV

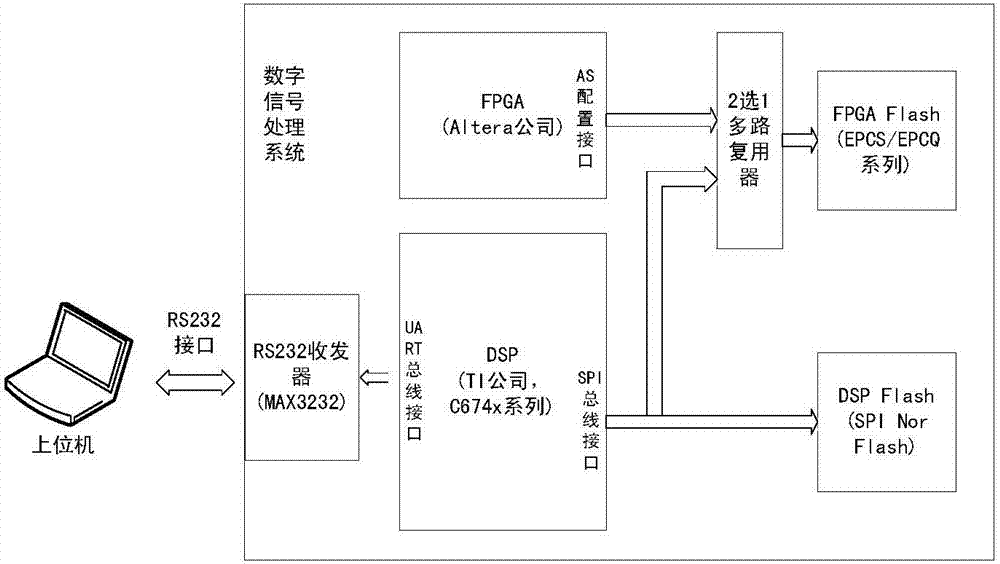

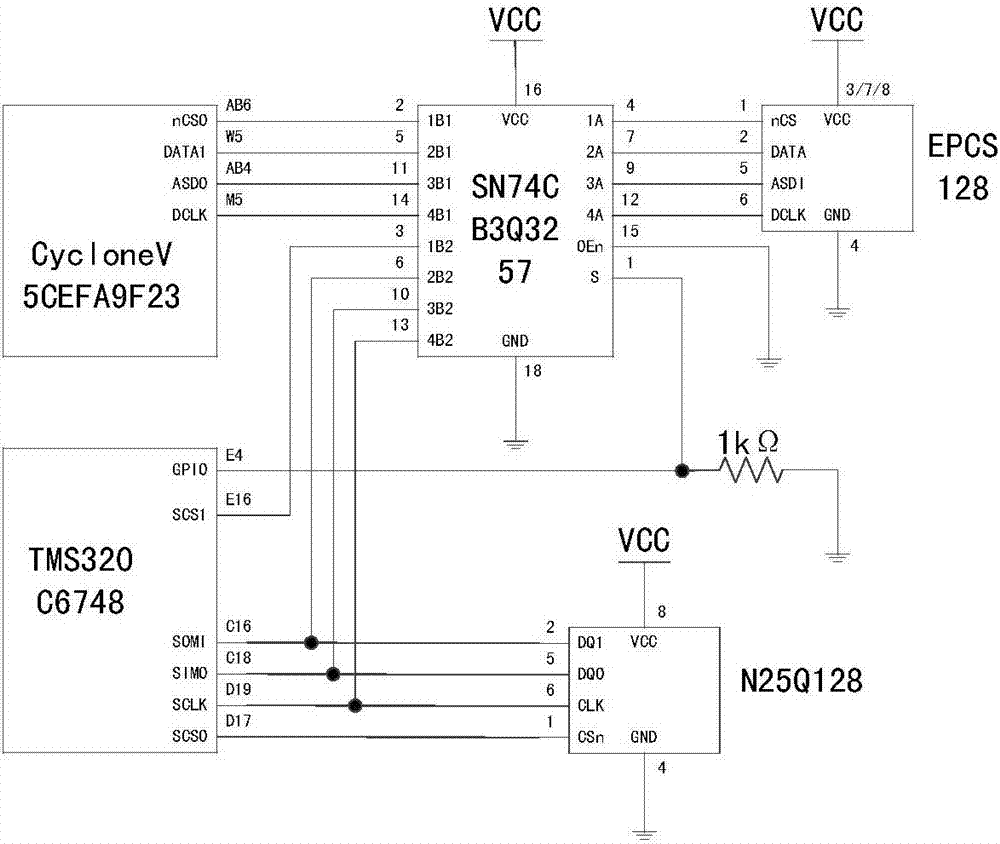

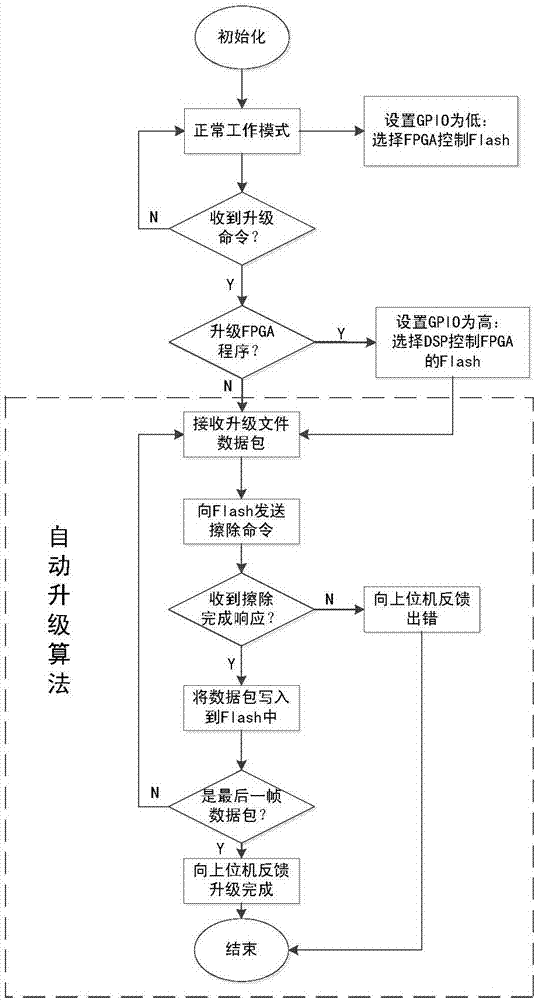

DSP (digital signal processor) and FPGA (field programmable gate array) system on-line updating method

ActiveCN106909425AReduce Design ComplexitySimple interfaceSoftware engineeringProgram loading/initiatingFpga field programmable gate arrayMultiplexer

The invention discloses a DSP (digital signal processor) and FPGA (field programmable gate array) system on-line updating method, which is used for solving the problem of program online updating of a DSP and FPGA digital signal processing system. The method has the technical scheme that through a universal serial bus interface, the interconnection between a host computer and a DSP is completed; a DSP and FPGA program file to be updated is transmitted to the DSP; a Flash memory of the DSP or the FPGA is controlled to be updated by a DSP automatic updating algorithm; one group of SPI interface bus of the DSP is used for completing the hardware connection and erasing and writing of two Flashes; the bus address coding is completed through a multiplexer; the bus conflict is avoided. The program updating of the two chips of DSP and FPGA is simultaneously completed under the condition without dismounting the equipment; the interface is simple; the software and hardware design complexity is low; a simple and effective method is provided for the online updating of the digital signal processing system.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

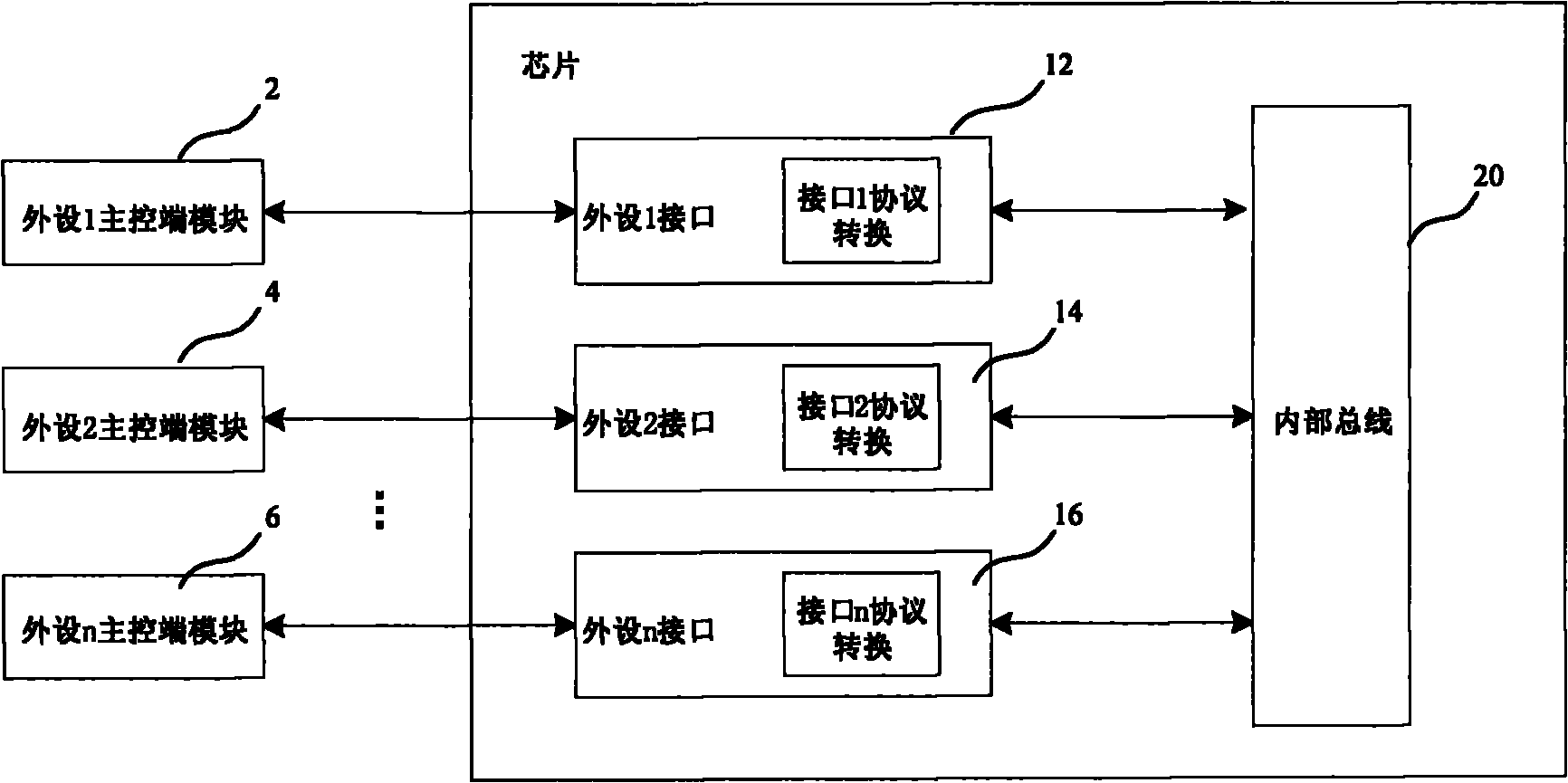

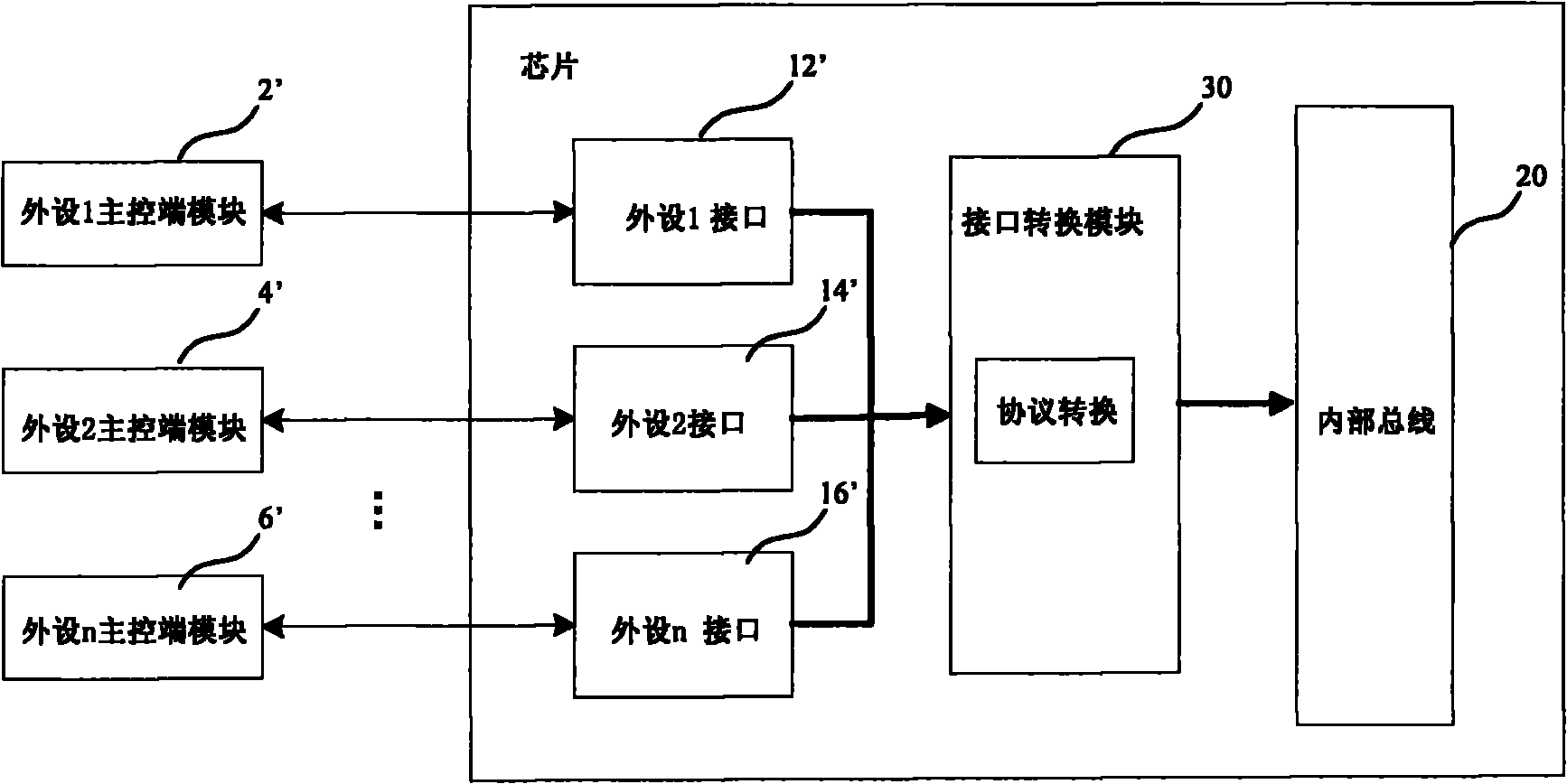

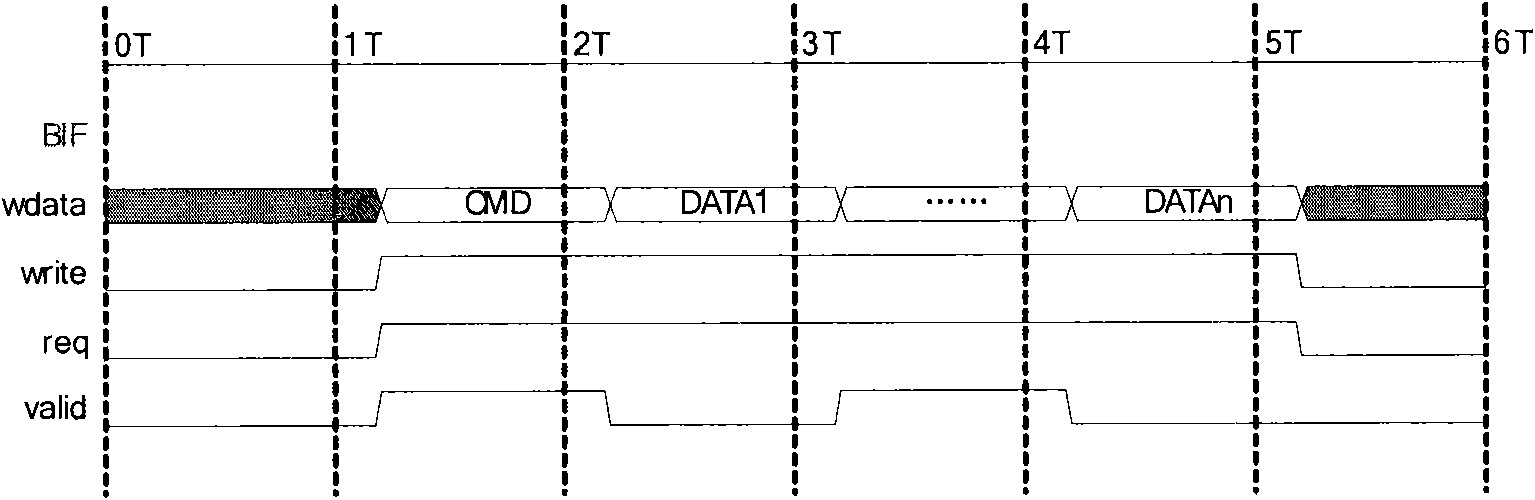

Data interaction system with a plurality of external interfaces and method

InactiveCN101770442ASimplify validationImprove reusabilityElectric digital data processingInteraction systemsInteractive design

The invention provides a data interaction system with a plurality of external interfaces, which comprises a plurality of external main control end modules, a plurality of external interface modules and interface conversion modules, wherein the external main control end modules correspond to the external interface module, command words and data are predefined according to an interaction protocol with an internal bus and are transmitted through the external interface modules, the external interface modules are respectively used for transmitting the corresponding command words and the data to the interface conversion modules, and the interface conversion modules analyze and convert the command words and the data according to the data interaction protocol for executing the data interaction with the internal bus. The invention can improve the consistency and the importance of the interactive design of the external interfaces and the internal data.

Owner:ISVUE TECH

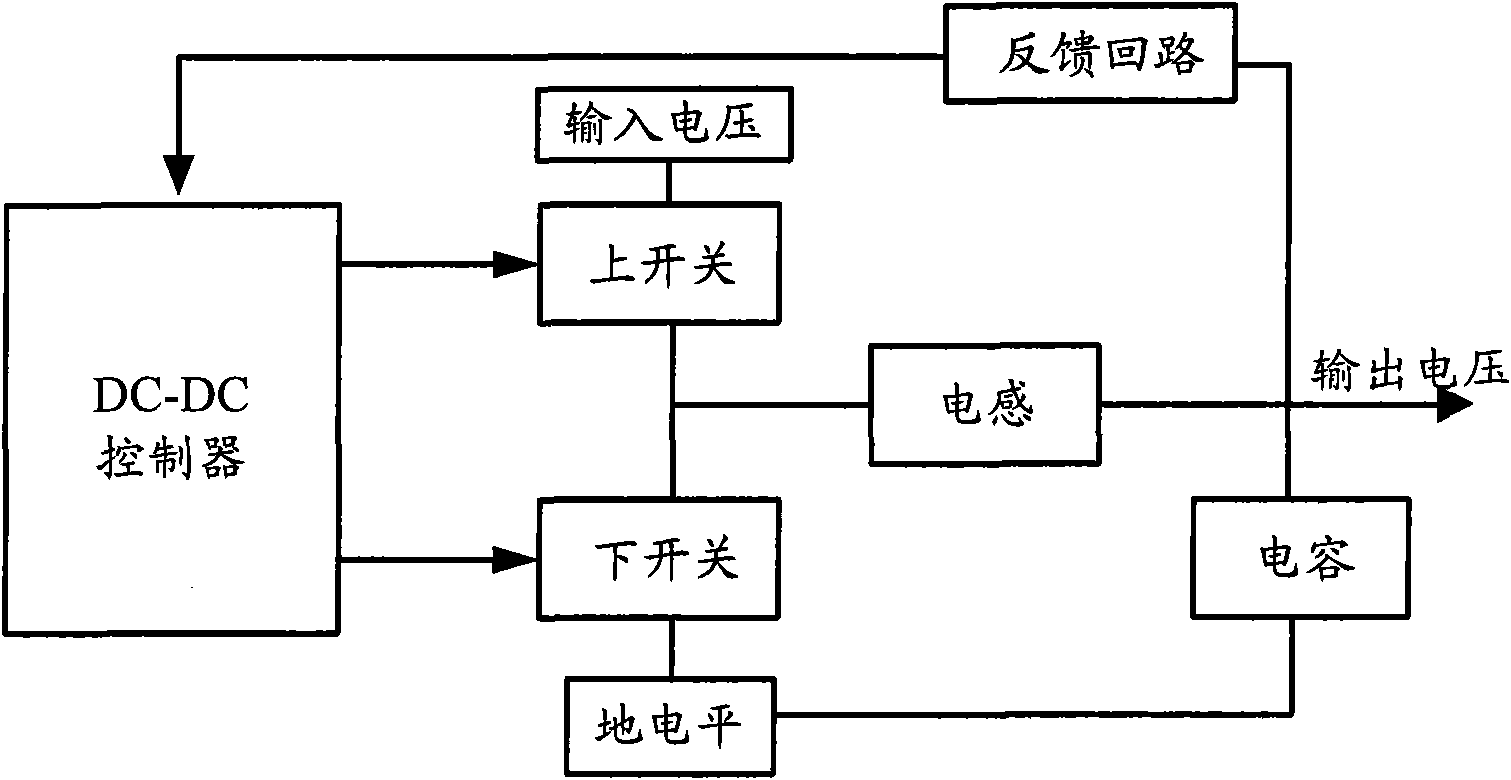

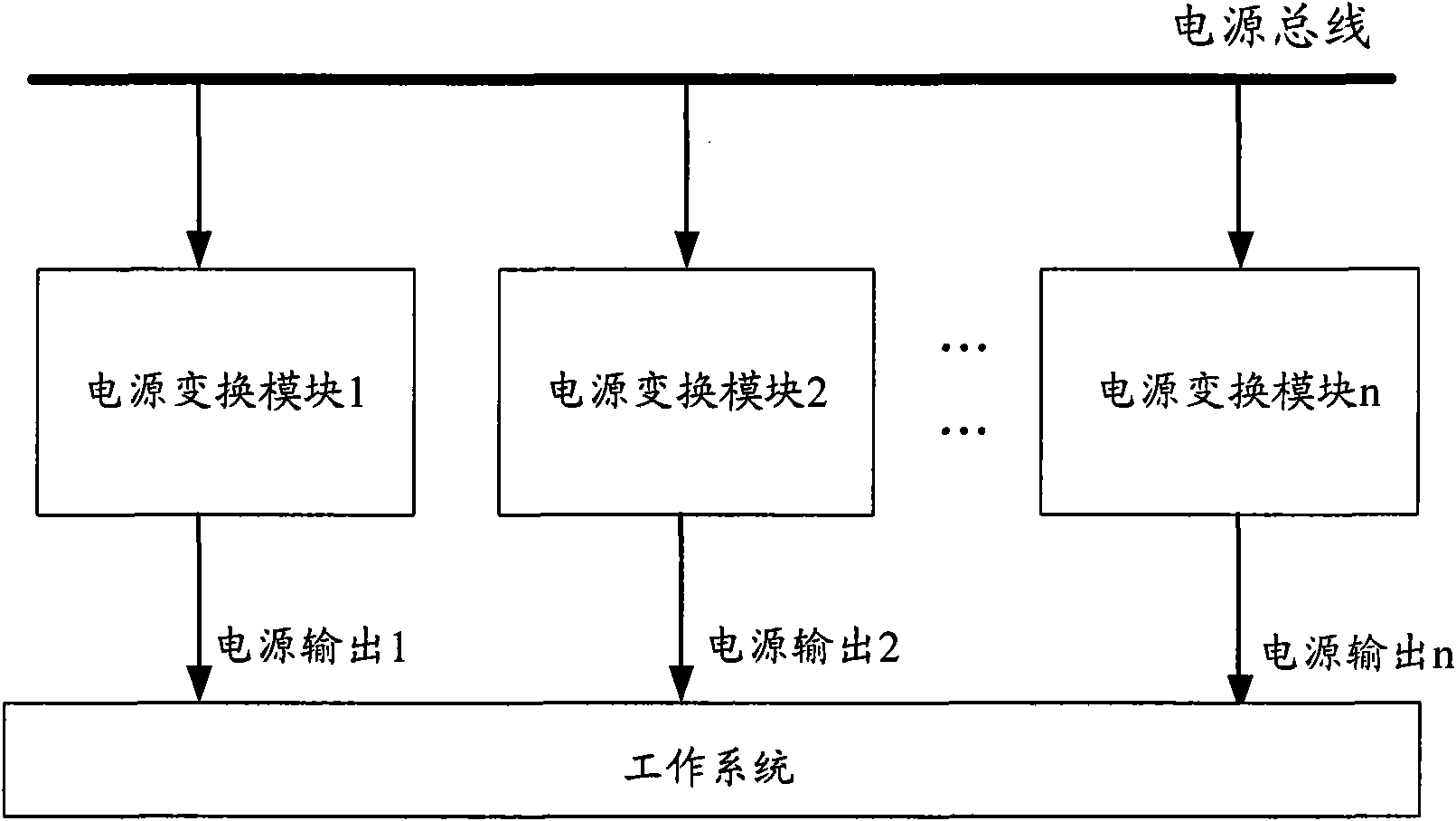

DC-DC power supply device, voltage regulation method and network equipment

ActiveCN101795071AImprove testabilityImprove stabilityApparatus with intermediate ac conversionElectrical resistance and conductanceVoltage regulation

The invention relates to the technical field of electronics and discloses a DC-DC power supply device, a voltage regulation method and network equipment in order to improve the testability of circuits. In the invention, at least one regulation module and a control module are arranged in the DC-DC power supply device, wherein the control module controls the conduction states of upper and lower switch tubes in a resistor array in the regulation module so as to regulate the offset of an output voltage to control the size of the output voltage. Thus, the synchronous regulation of one or more DC-DC switch power supply modules can be realized without manual box opening and power-interrupting operation and the precision regulation of the output voltages of the DC-DCs switch power supply modules is realized without a large amount of circuit hardware regulation and change, so that the testability of the circuit and operation smoothness of the whole circuit test process are improved effectivelyand the product test and examination work is very convenient. The invention also discloses the power supply method and the network equipment.

Owner:RUIJIE NETWORKS CO LTD

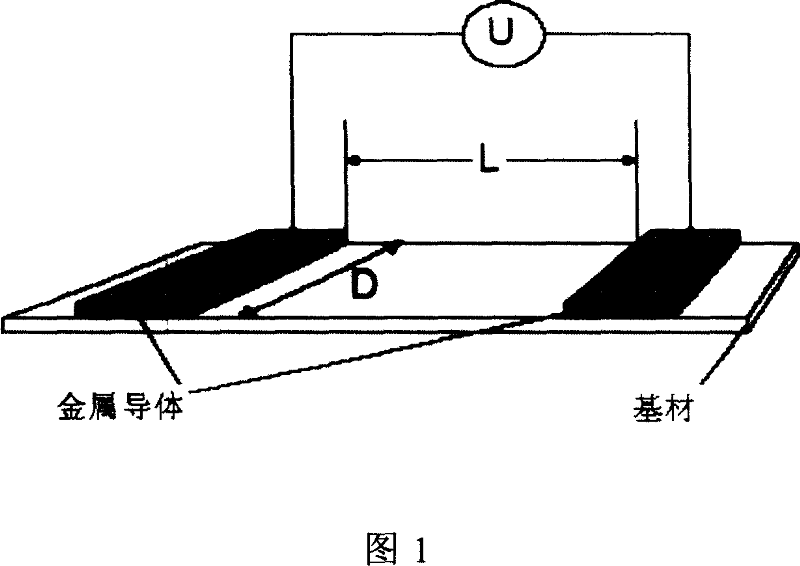

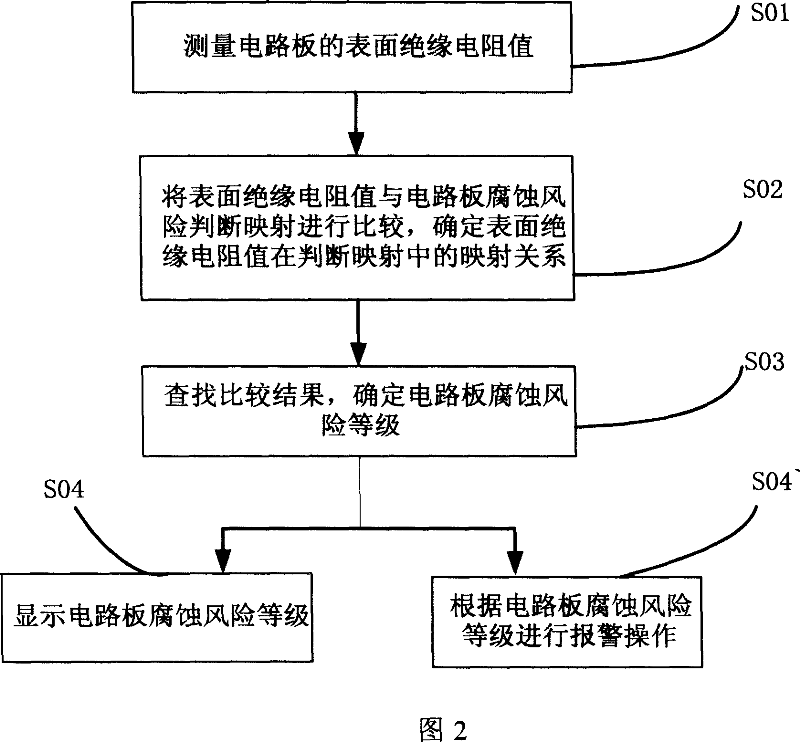

Method and system for estimating circuit board corrosion risk

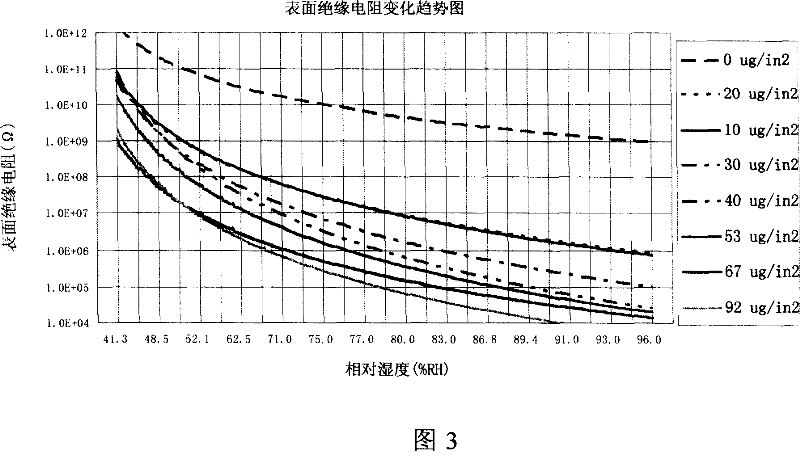

InactiveCN101038263AEasy accessInsulation resistance value dropsWeather/light/corrosion resistancePrinted circuit aspectsRisk levelElectrical resistance and conductance

The present invention relates to the testing technology field of electronic equipments, especially to a method and system used for assessing circuit boards corrosion risks. According to the method, the surface insulation resistance values of circuit boards are measured and are compared with the corrosion risks discrimination mapping of the circuit boards to get the corrosion risk levels of circuit boards. The present invention also provides a system used for quickly on-site assessing the circuit boards corrosion risks, which comprises a circuit board, a testing module and a discrimination module, wherein the testing module is used for measuring the surface insulation resistance value of the circuit board and sending the measured value to the discrimination module, the discrimination module is used for comparing the surface insulation resistance value measured with the corrosion risks discrimination mapping to get the corrosion risk level of the circuit board. By using surface insulation resistance values easily got on-site to indicate the circuit boards corrosion risks, the present invention is capable of quickly on-site assessing the corrosion risk of a circuit of a board, and then exhibits excellent effect about adopting some protection measures of the circuit board in time.

Owner:HUAWEI TECH CO LTD

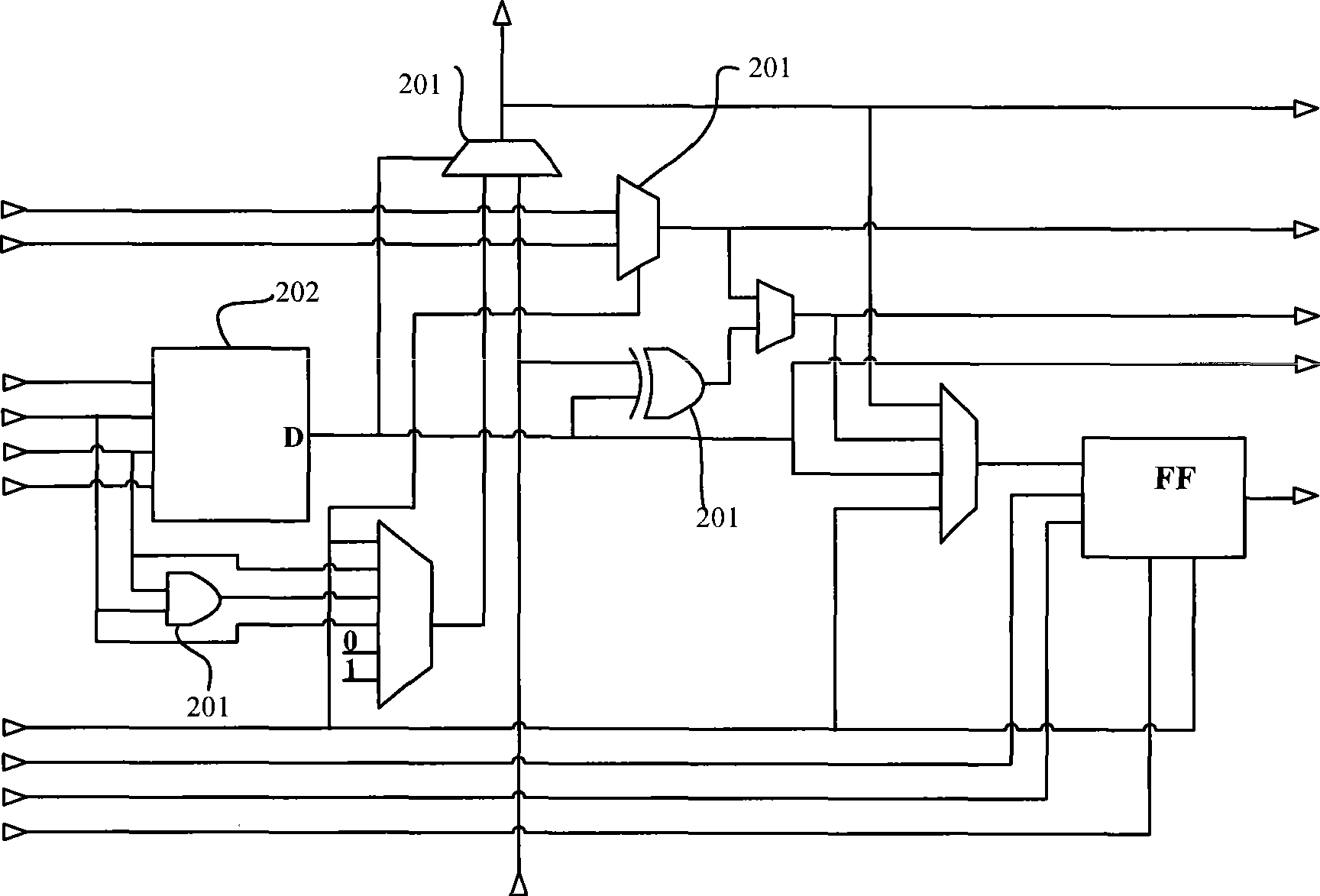

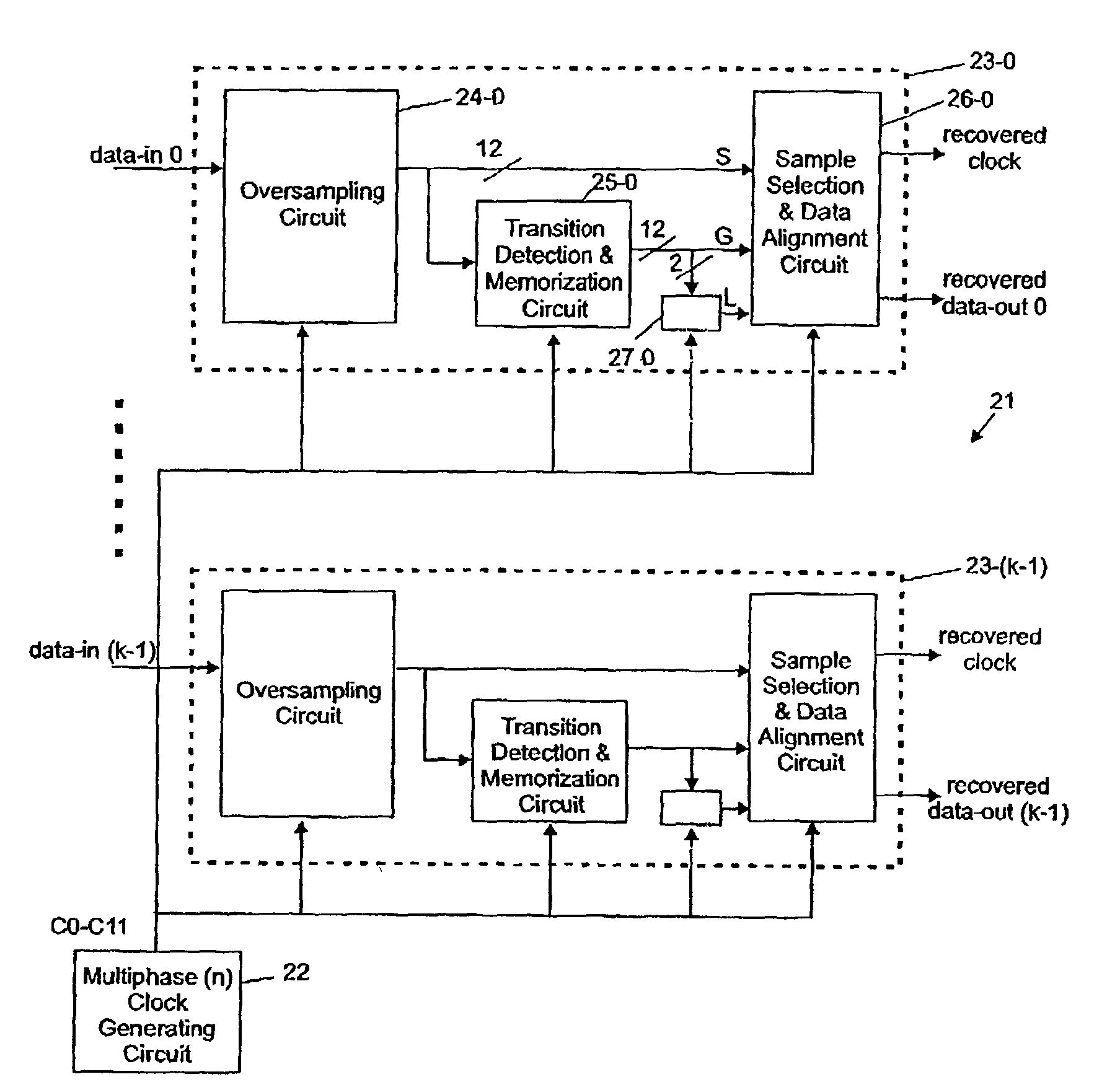

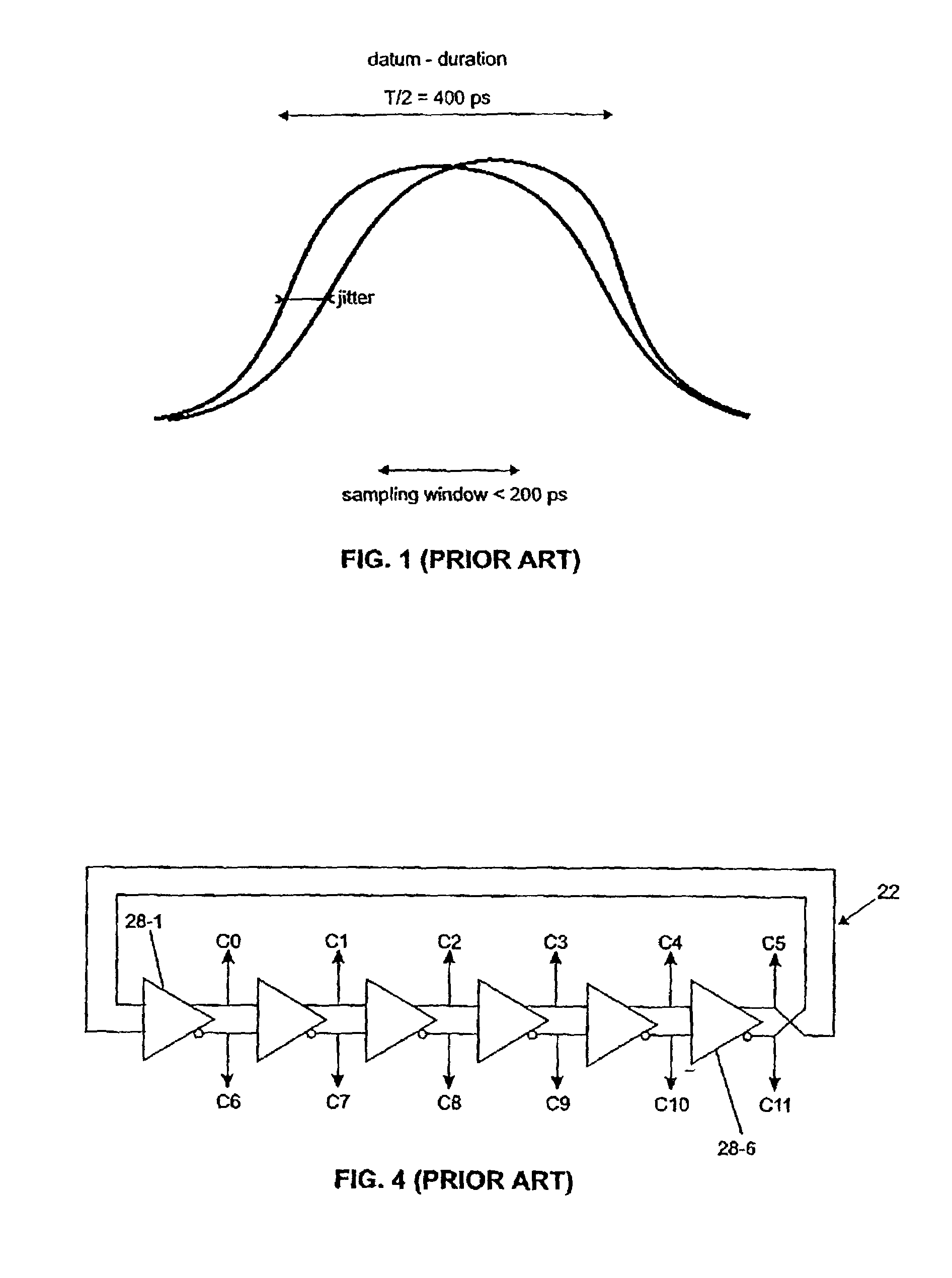

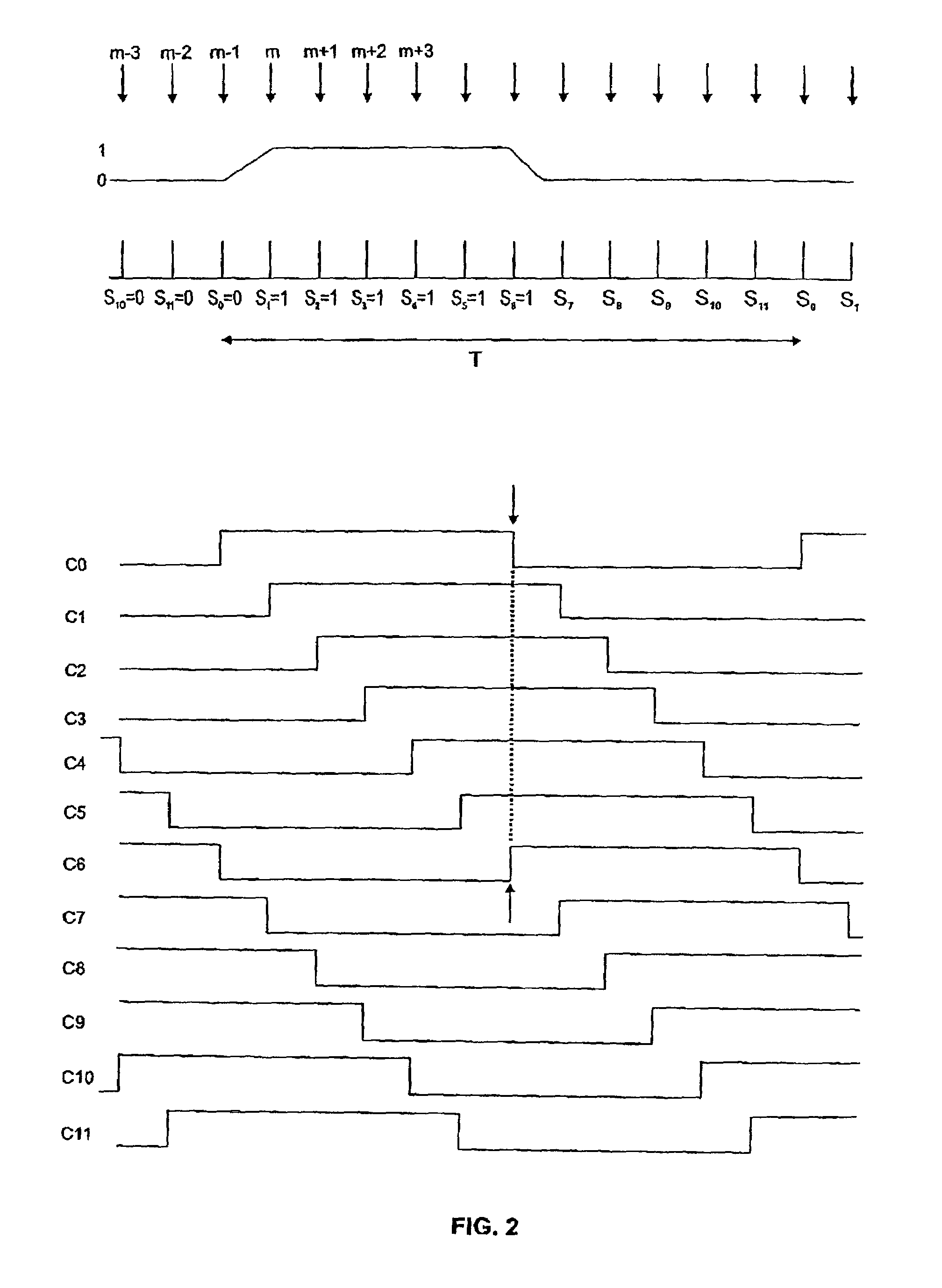

Sample selection and data alignment circuit

InactiveUS7136443B2Consumes minimal surface areaImprove testabilityModulated-carrier systemsError detection/correctionComputer scienceSample selection

There is disclosed a sample selection and data alignment circuit that is able to recover (retime) a data on a predefined phase of a multiphase clock signal. A plurality of over sampled signals (G0, . . . , Gn−1) is obtained by over sampling an incoming serial binary data (bits) stream with the n phases (G0, . . . , Gn−1) of a multiphase clock signal. A reliable over sampled signal is selected according to a selected signal (G0, . . . , Gn−1) generated by an edge detector which designates which over sampled signal is the best for subsequent processing.

Owner:IBM CORP

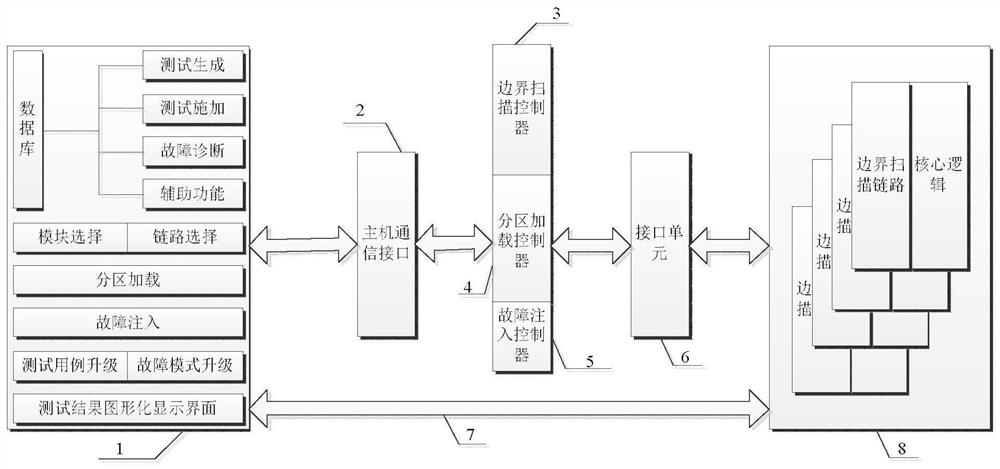

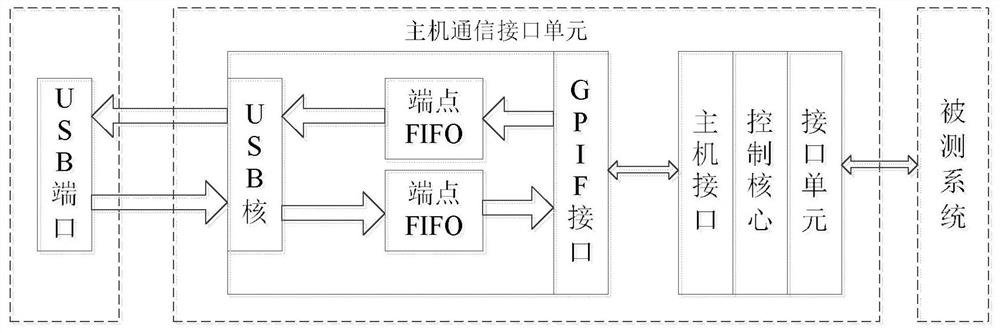

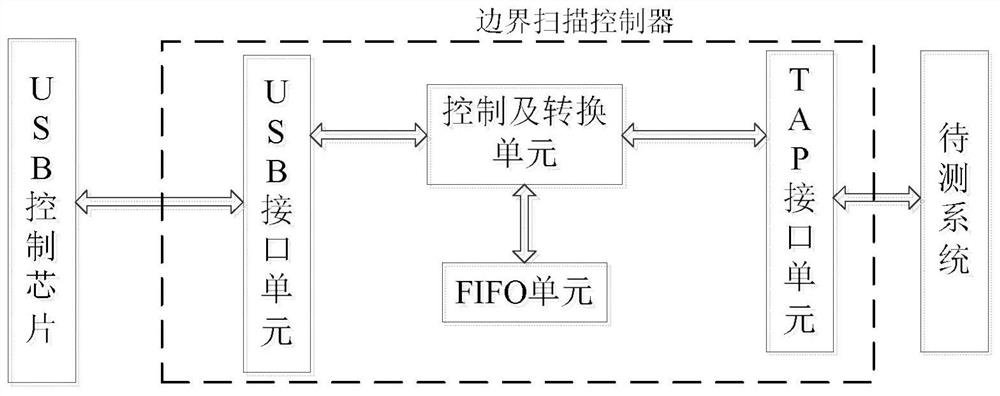

Test system for intelligently diagnosing faults of high-integration digital signal processing system

InactiveCN111624477AOvercoming Individual Measurement FlawsShorten test timeElectrical testingDigital signal processingTestware

The invention discloses a test system for intelligently diagnosing faults of a high-integration digital signal processing system, and aims to solve the problem of low fault diagnosis capability of anexisting boundary scanning test system. According to the technical scheme, an intelligent test platform management unit operates control software, collects data of multichannel signals, generates a test sequence, allocates physical addresses to all modules, lists all the modules connected to a system backboard on a software interface, processes the multichannel data and diagnoses faults; the control software calls boundary scanning test software to generate a test vector for the tested module, applies the test vector to the chip core logic input end to form a circuit fault criterion, and sendsthe circuit fault criterion to the boundary scanning controller; the test vectors of different regions are loaded to a tested module to generate a fault injection vector, and the fault injection vector is transmitted to a fault injection controller; and the fault injection vector is loaded to the tested module to complete the fault diagnosis of the multichannel signal processing subrack platformmodule-level digital chip.

Owner:10TH RES INST OF CETC

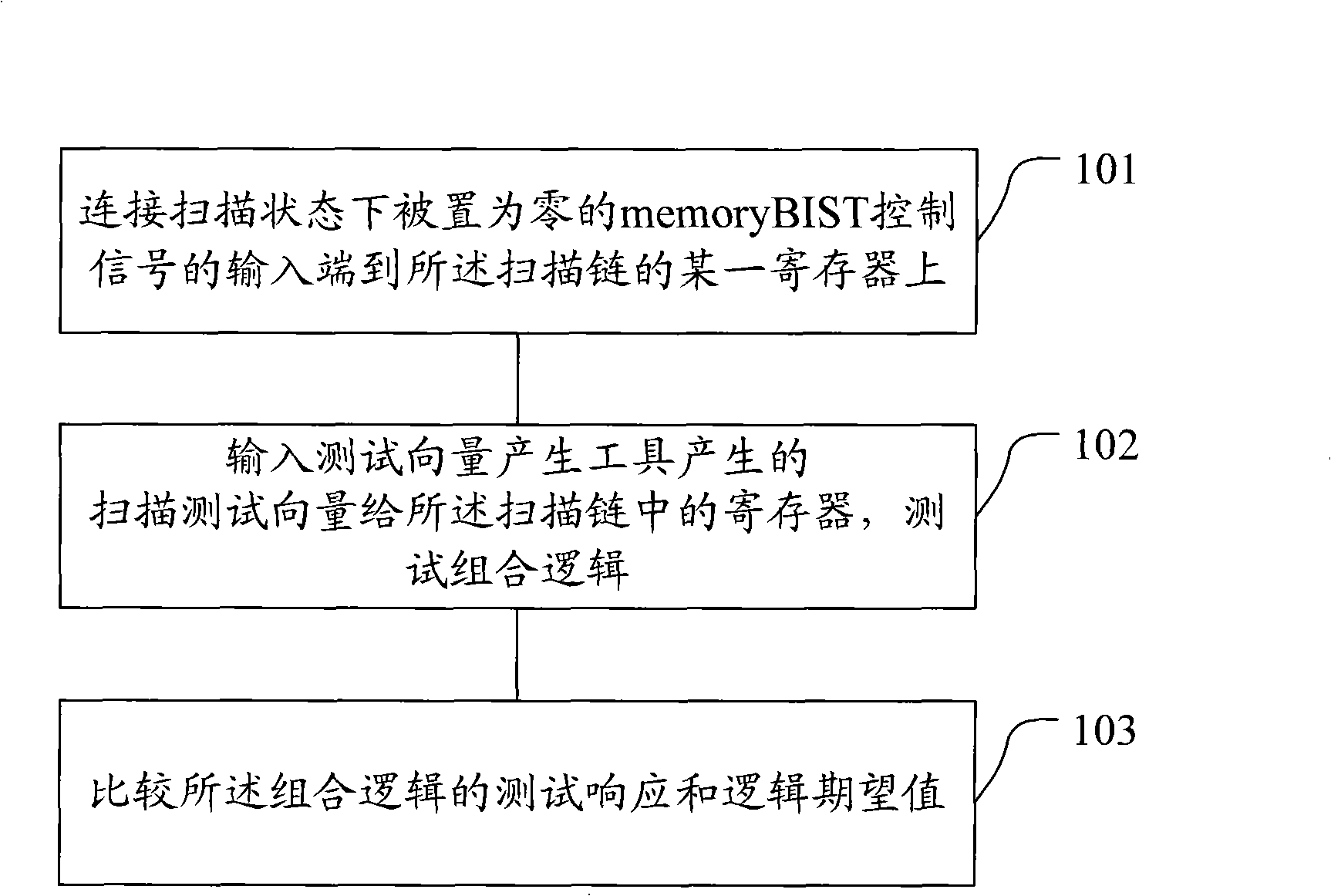

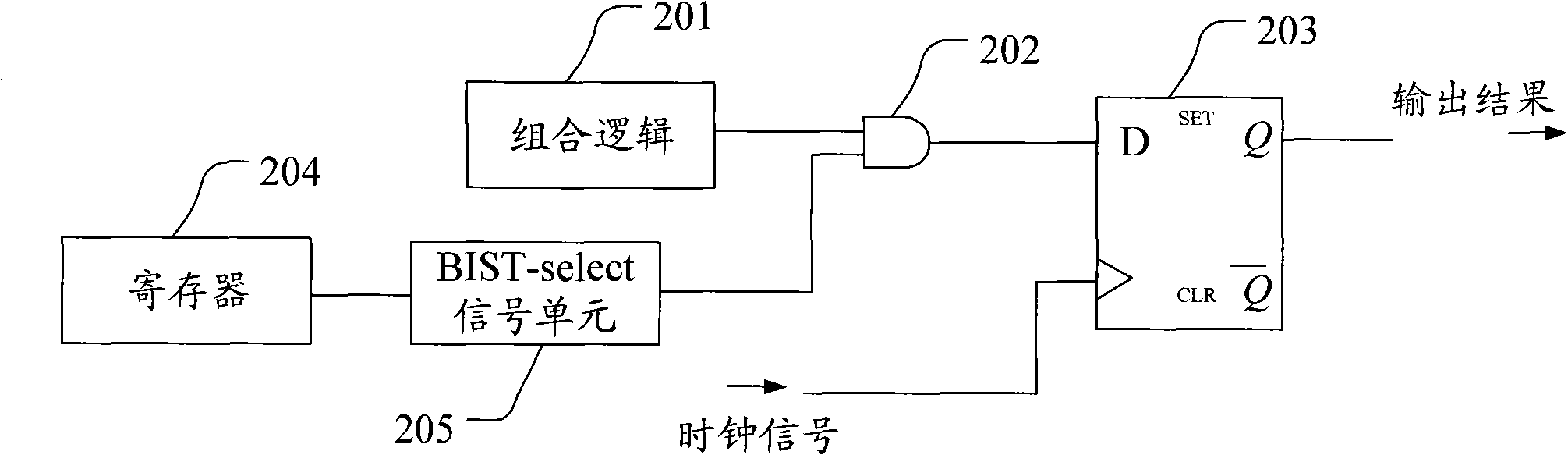

Method for increasing test coverage of scan chain and device thereof

ActiveCN101515479AImprove test coverageImprove testabilityStatic storageControl signalProcessor register

The invention provides a method for increasing the test coverage of a scan chain and a device thereof; wherein, the method for increasing the test coverage of the scan chain comprises: an input end of built-in self testing control signals of a memory being set to be zero in a scanning mode is connected into one register in the scan chain; scan test vector generated by a test vector generation tool is input into the scan chain comprising the register to test combinational logic; the test response and logic expected value of the combinational logic are compared. The method for increasing the test coverage of the scan chain provided by the invention causes that the built-in self testing control signals of the memory can be controlled when the scan chain tests, and realizes the testability of the built-in self testing logic of the memory in the scan mode, thus increasing the logic test coverage of the scan chain test and further increasing the whole test coverage of a chip.

Owner:BEIJING VIMICRO ARTIFICIAL INTELLIGENCE CHIP TECH CO LTD

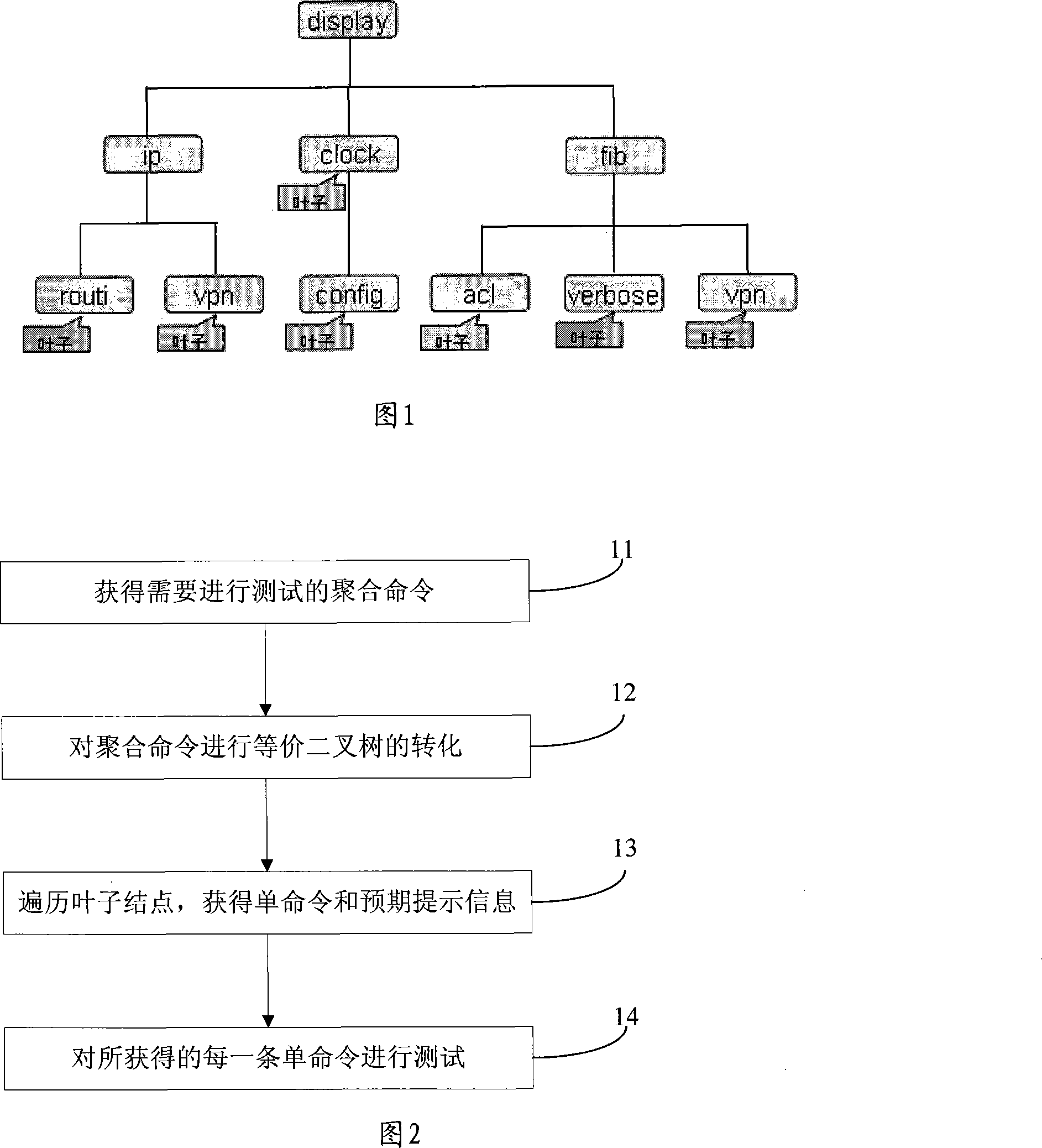

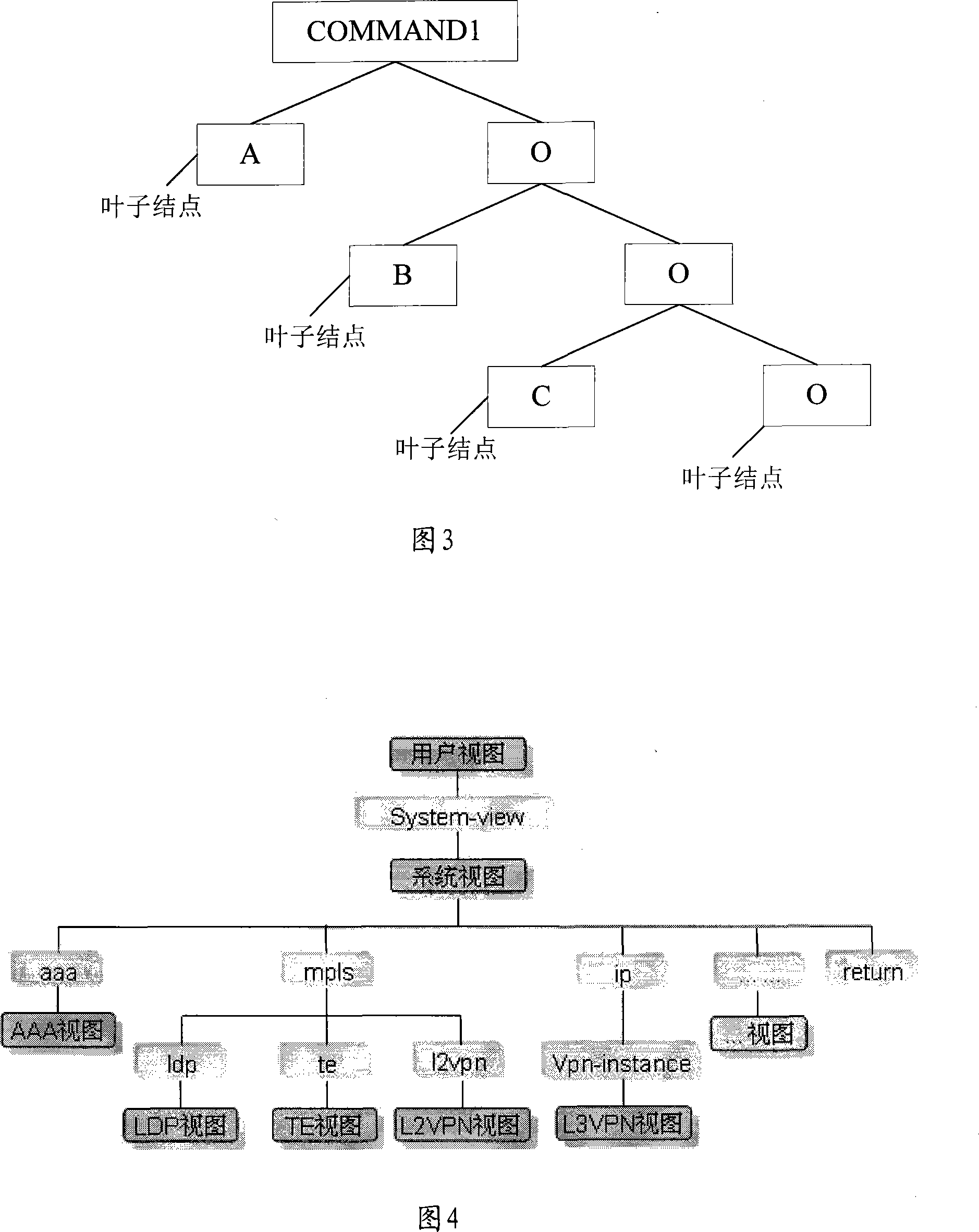

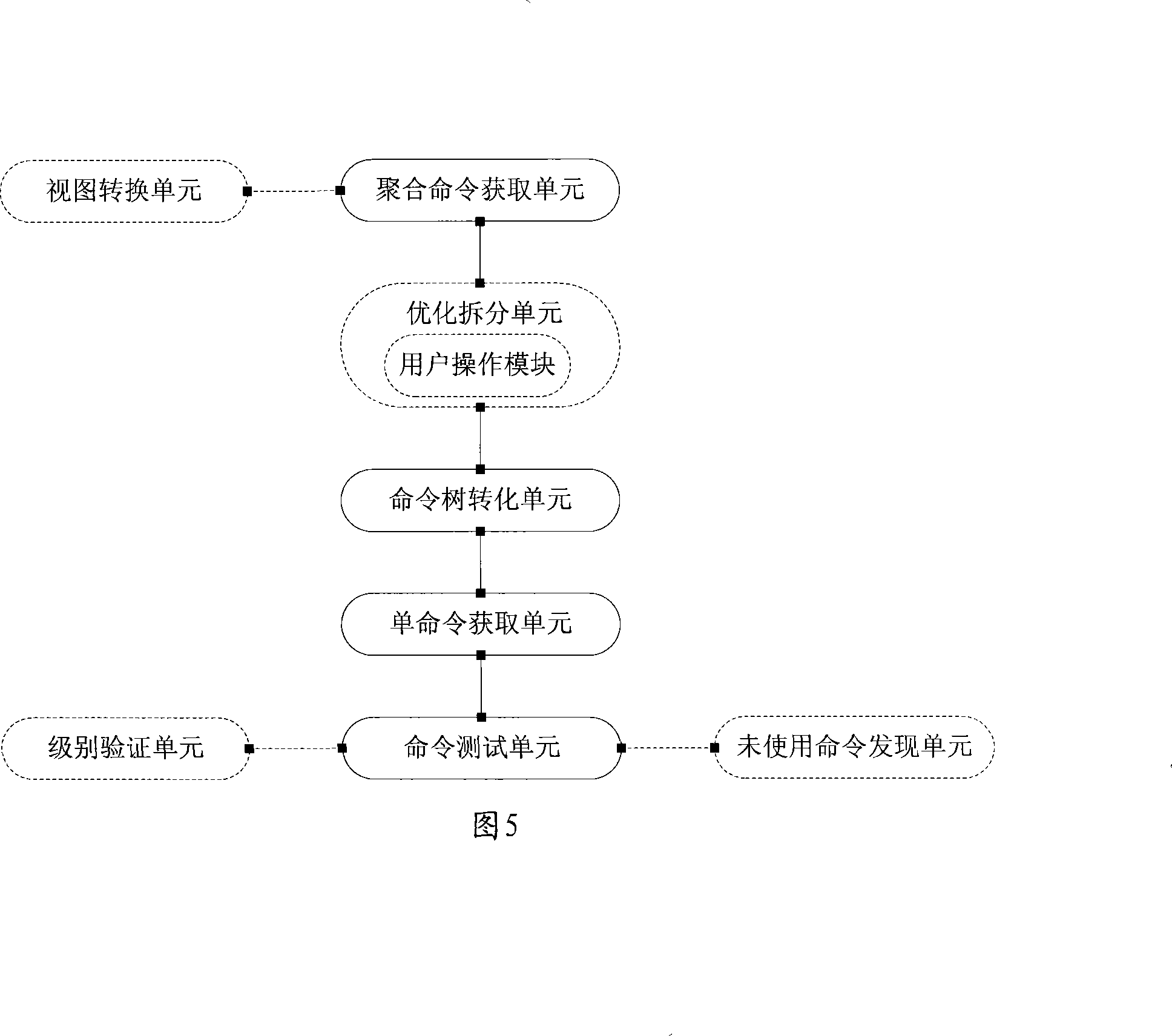

Test approach and device for command line interface

InactiveCN101197734ASimple structureReduce wasteData switching networksCommand-line interfaceTest efficiency

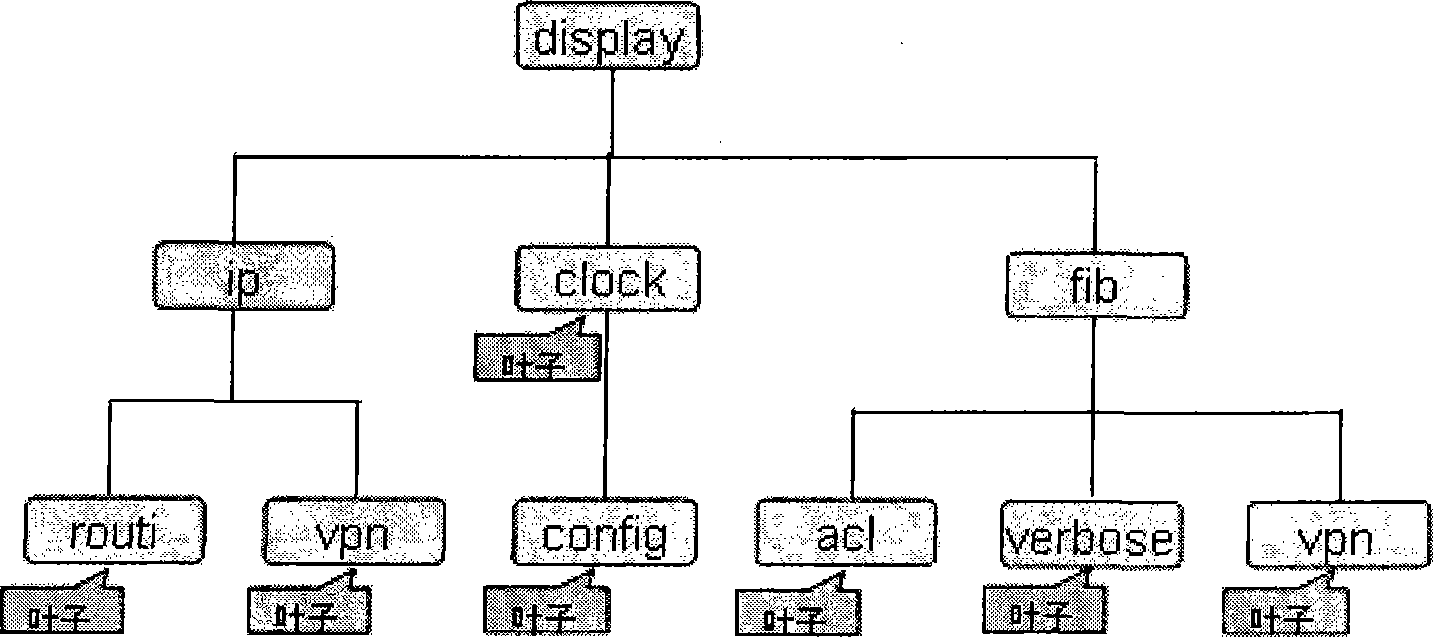

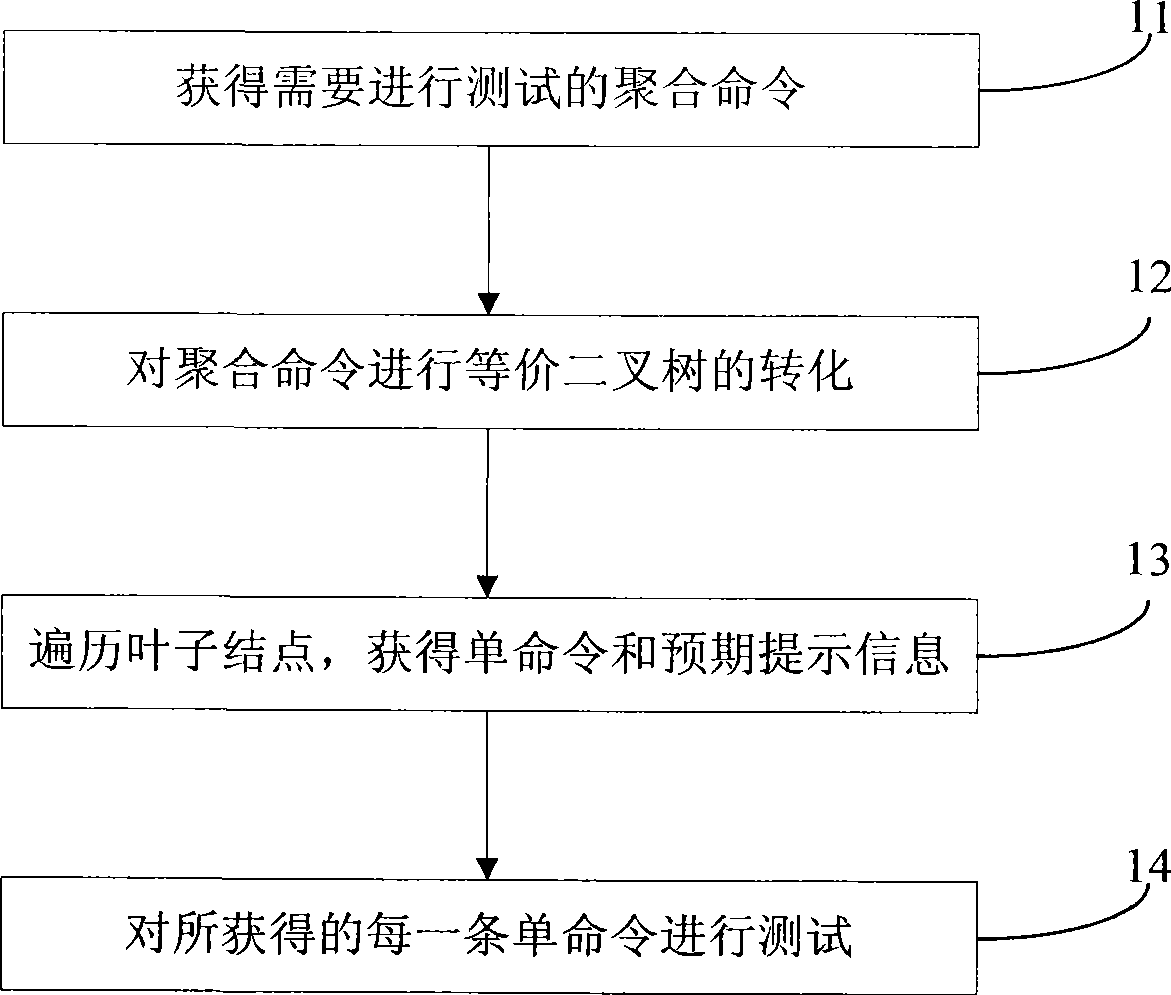

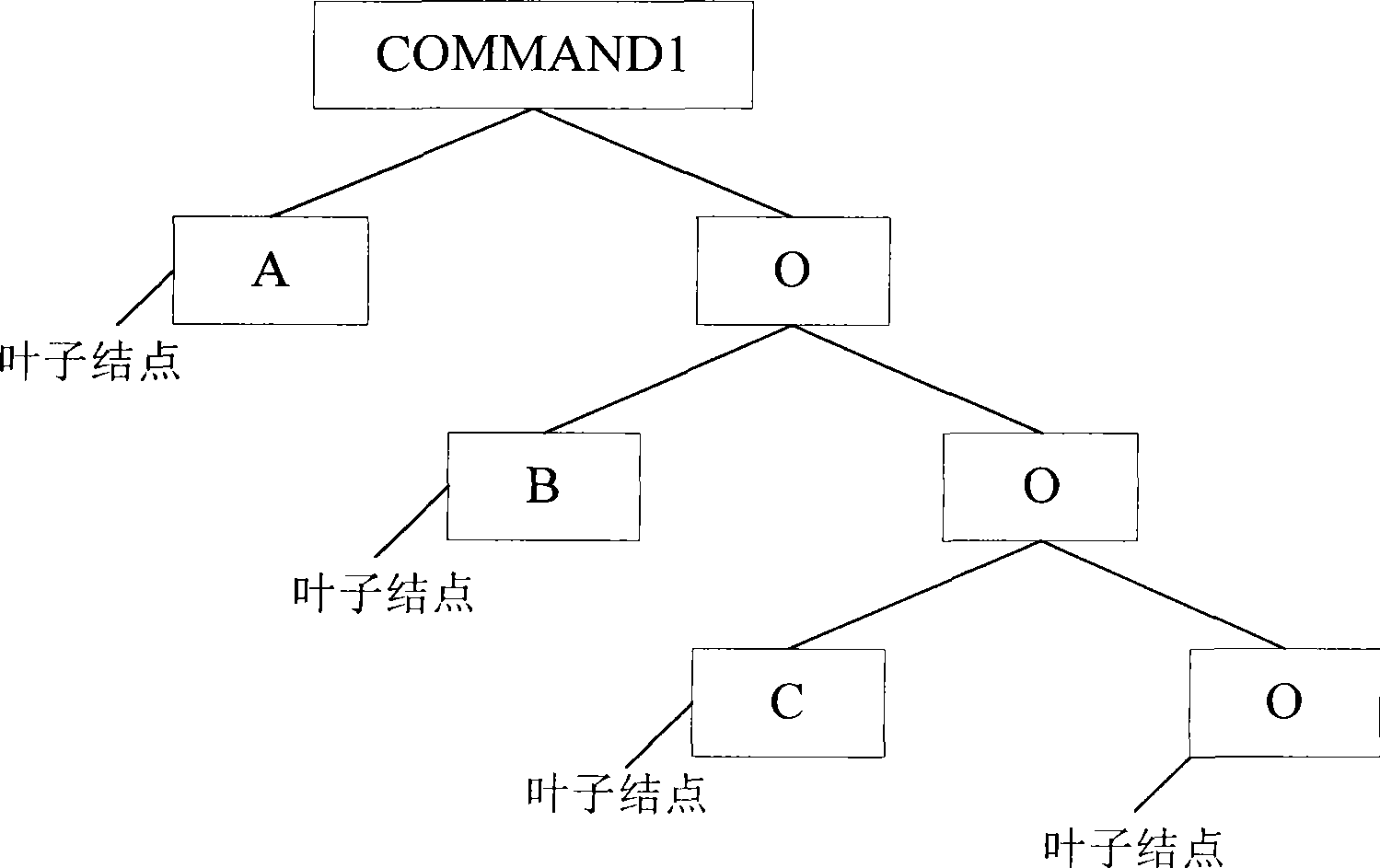

The invention provides a test method for command line interface and a device thereof; the method includes the following procedures: firstly, an aggregation command which needs to be tested is acquired; secondly, from the beginning of the root node of the aggregation command, the aggregation command is made the equivalence binary tree conversion; thirdly, the leaf node of the equivalence binary tree undergoes traverse, the route between the leaf node and the root node is accessed, each single command and the expectation prompting message corresponding to the single command are acquired; fourthly, each single command is tested. By the equivalence binary tree conversion, the structure of the command tree is simplified; moreover, the constructed command tree is easy to test, thereby enhancing the testability, reducing the waste of computing resource of equipment and greatly improving the test efficiency.

Owner:HUAWEI TECH CO LTD

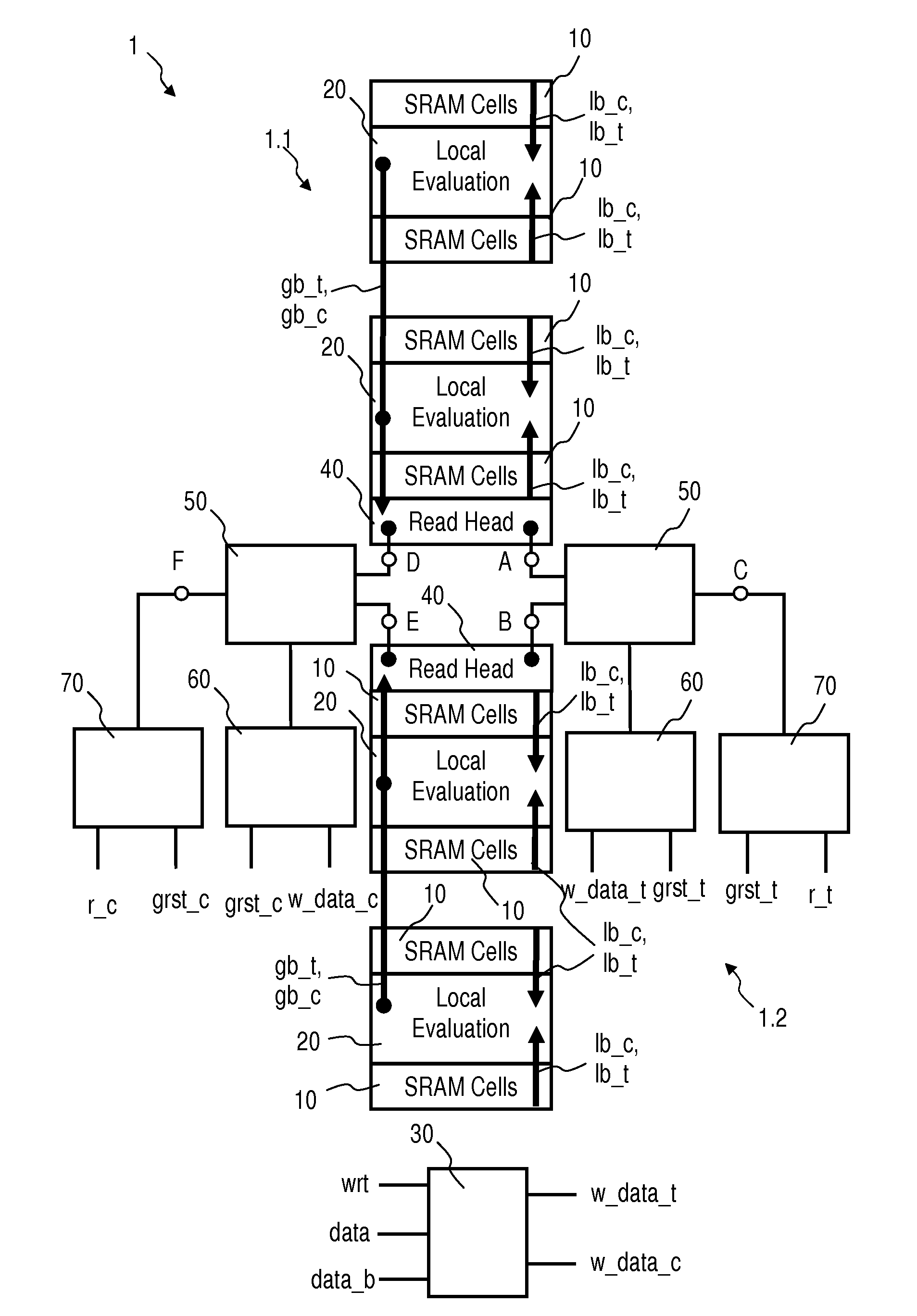

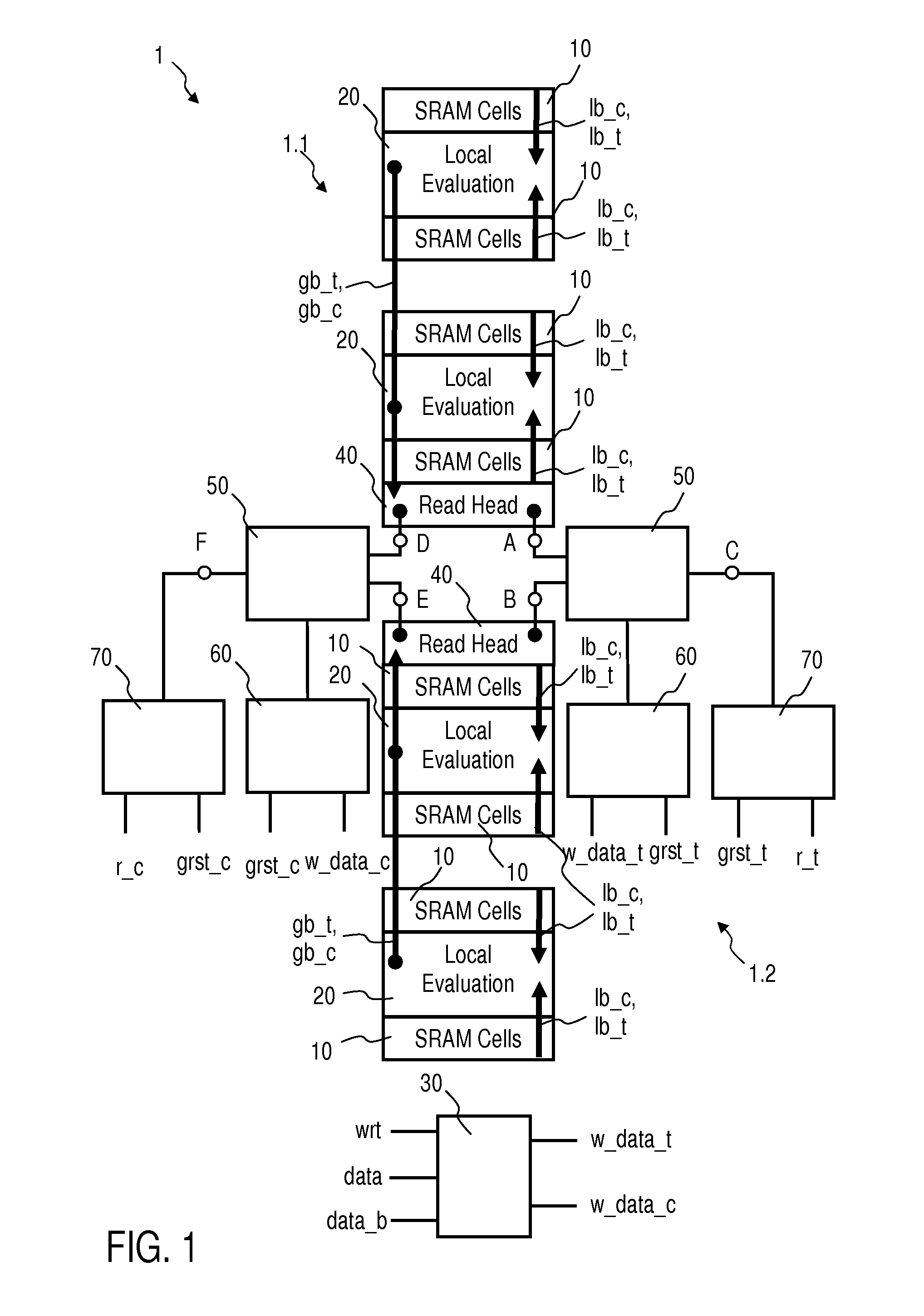

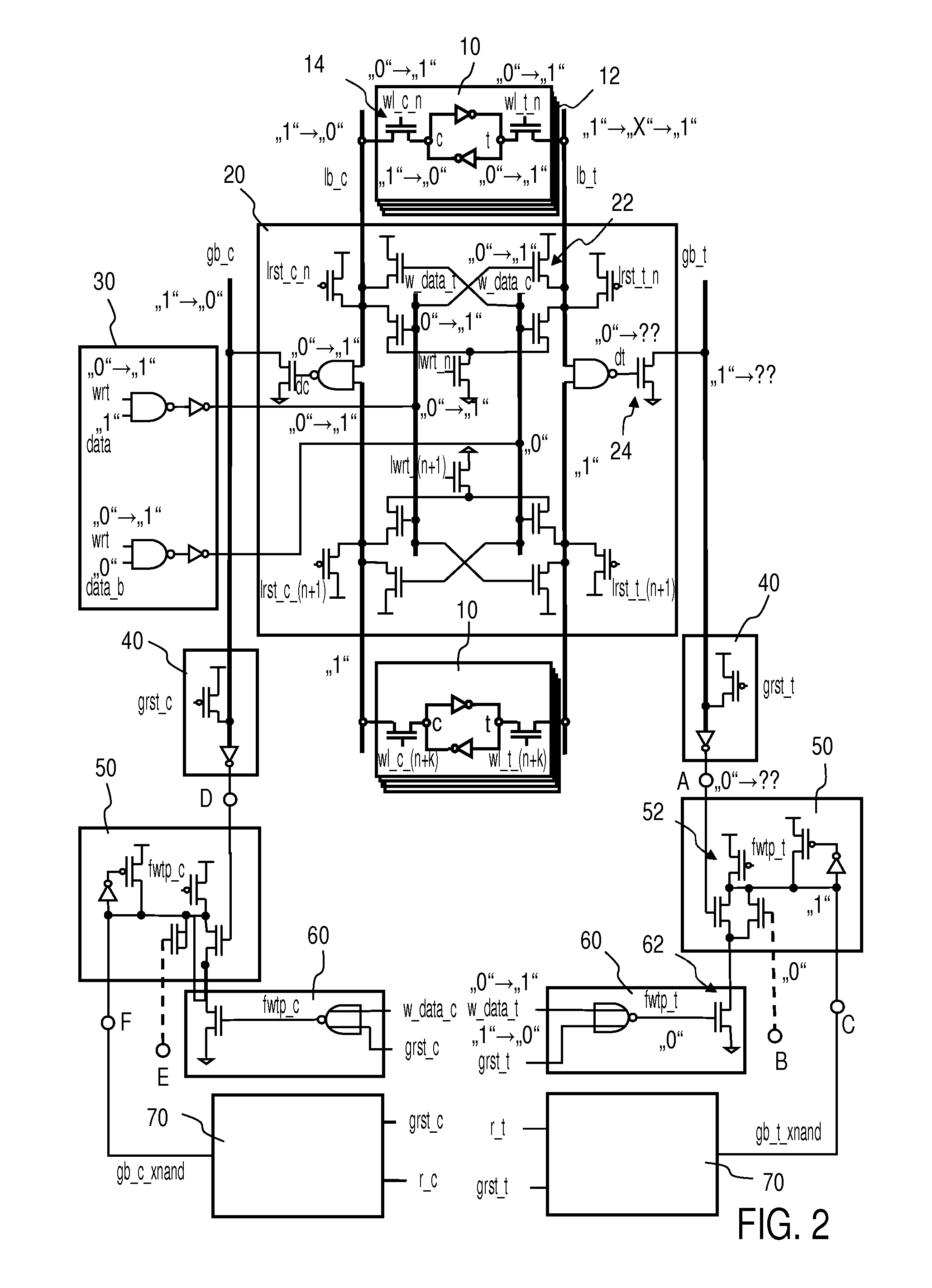

Method and Circuit Arrangement for Performing a Write Through Operation, and SRAM Array With Write Through Capability

An improved method for performing a write through operation during a write operation of a SRAM cell (10) of a SRAM array (1) is disclosed. The method comprises suppressing a false write through data propagation at an output node (C, F) of the SRAM array (1) in case of a failure causing transition at a first node (t) or a second node (c) of the SRAM cell (10) by using information about the input data (data, data_b) to be written in the SRAM cell (10) and read data propagation paths to retain the output node (C, F) after a global bit line (gb_t, gb_c) at a precharge level independently from a logical level of the global bit line (gb_t, gb_c), if a corresponding node (c, t) of the SRAM cell (10) is performing the failure causing transition based on input data (data, data_b) to be written in the SRAM cell (10).

Owner:IBM CORP

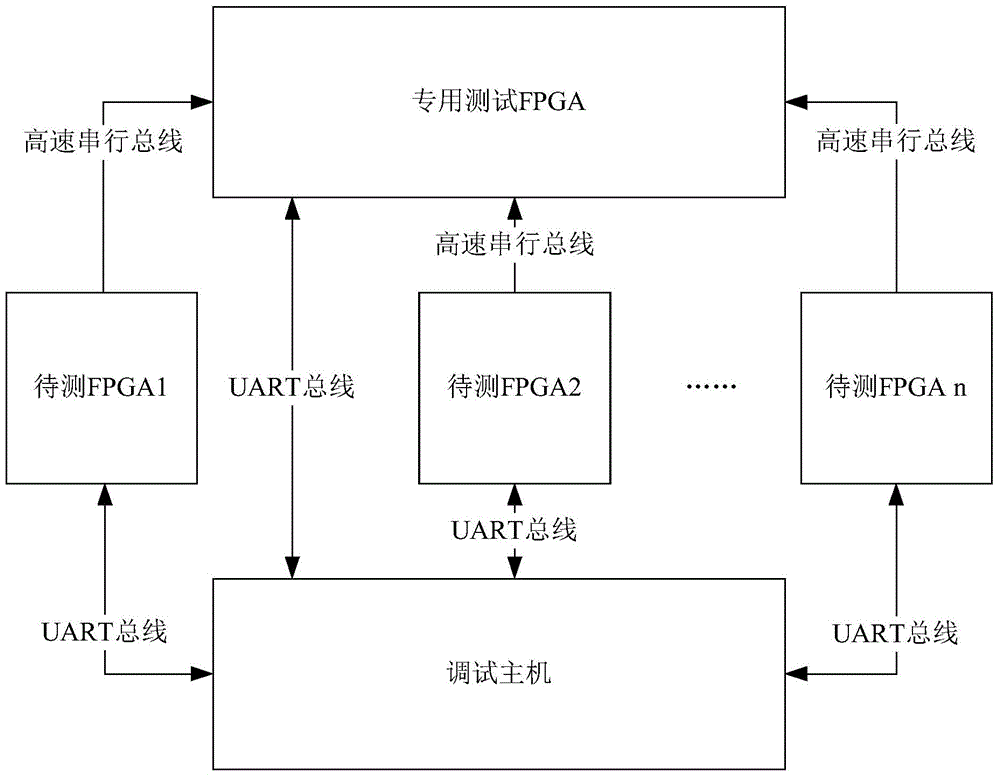

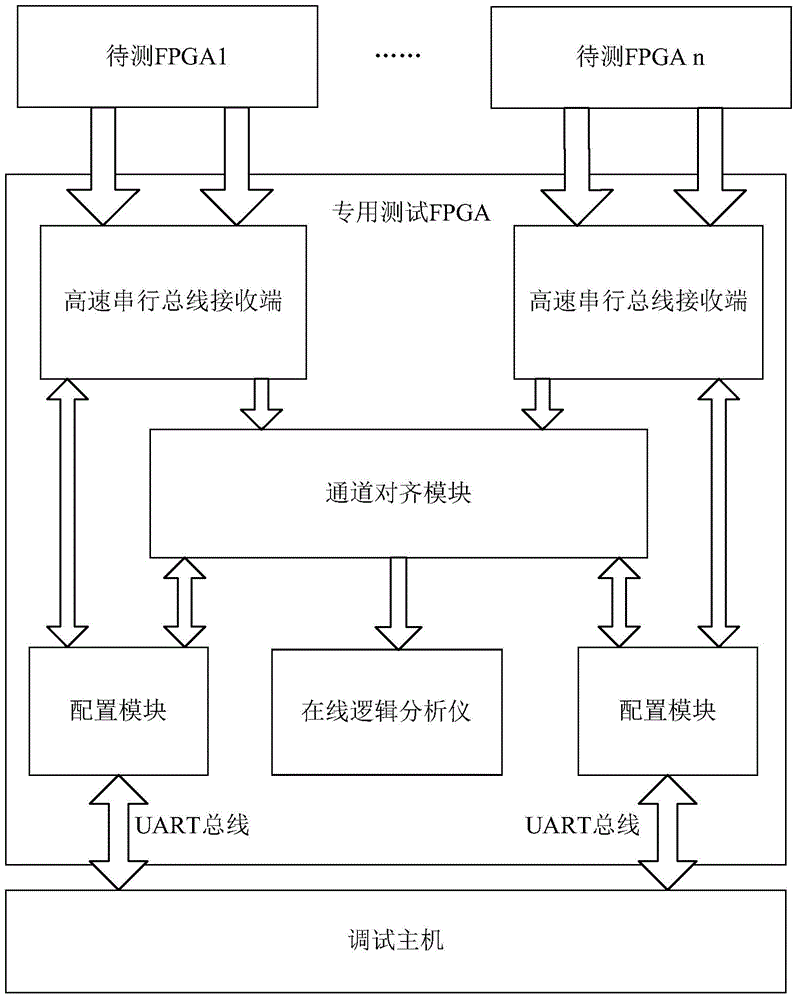

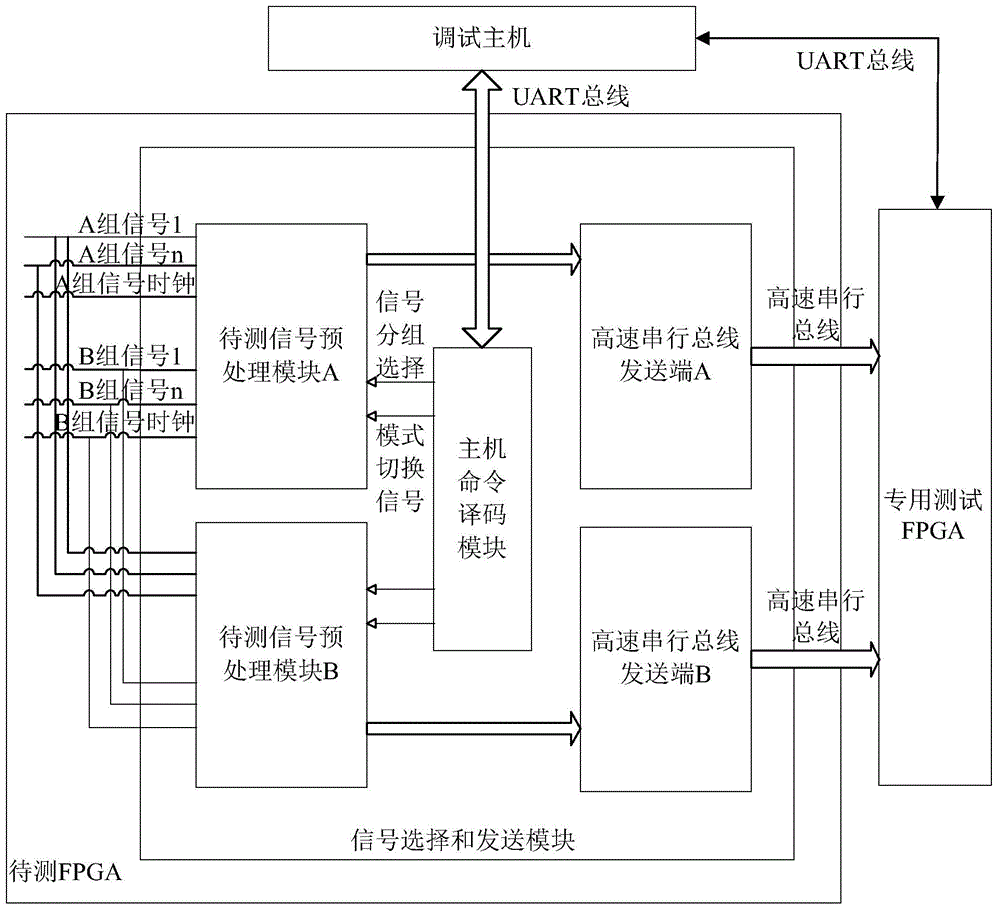

System and method for debugging multiple field-programmable gate arrays

The invention provides a system and a method for debugging multiple field-programmable gate arrays (FPGAs). The method comprises the following steps: selecting and grouping to-be-tested signals according to a clock domain by virtue of a signal selection and transmission module for instantiating each to-be-tested FPGA, and configuring a high-speed serial transceiver bus port of signal transmission; performing logic synthesis and location wiring on the design logic of the to-be-tested FPGAs and the signal selection and transmission module together; finding displacement information aligned with all channels according to the longest time delay in high-speed serial bus channels of all the to-be-tested FPGAs by using a special tested FPGA in a channel alignment operating mode selected by a debugging host; and selecting a to-be-tested signal group of the to-be-tested FPGA by the debugging host, and configuring the channel time delay value by using frequency information of the to-be-tested signal group. According to the system and the method disclosed by the invention, the cross-FPGA chip signal is observed and captured by using a special tested FPGA, and the fault tracing and positioning efficiency of a debugging system is improved.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND

Method for Fabricating Array-Molded Package-on-Package

InactiveUS20110165731A1Shorten the time to marketLow-cost and simplifiedSemiconductor/solid-state device detailsSolid-state devicesContact padSemiconductor chip

An improved semiconductor device package is manufactured by attaching semiconductor chips (130) on an insulating substrate (101) having contact pads (103). A mold is provided, which has a top portion (210) with metal protrusions (202) at locations matching the pad locations. The protrusions are shaped as truncated cones. The substrate and the chips are loaded onto the bottom mold portion (310); the mold is closed by clamping the top portion onto the bottom portion so that the protrusions approach the contact pads. Encapsulation compound is introduced into the cavity and the protrusions create apertures through the encapsulation compound towards the pad locations.

Owner:TEXAS INSTR INC

Test method and device for command line interface

InactiveCN101471826ASimple structureReduce wasteSoftware testing/debuggingData switching networksCommand-line interfaceComputer hardware

The invention provides a method and a device for testing a command line interface (CLI). The method comprises the following steps: acquiring a cluster command to be tested; conducting equivalent binary tree conversion to the cluster command from the root node of the cluster command; traversing the leaf node of the equivalent binary tree; accessing the path from the leaf node to the root node to acquire each single command and the corresponding expected prompting message; and testing the acquired single commands. The method simplifies the construction of the command tree through equivalent binary tree conversion and establishes a command tree which can be easily tested, thereby improving the testability, reducing the waste of computing resources of equipment and remarkably improving the testing efficiency.

Owner:HUAWEI TECH CO LTD

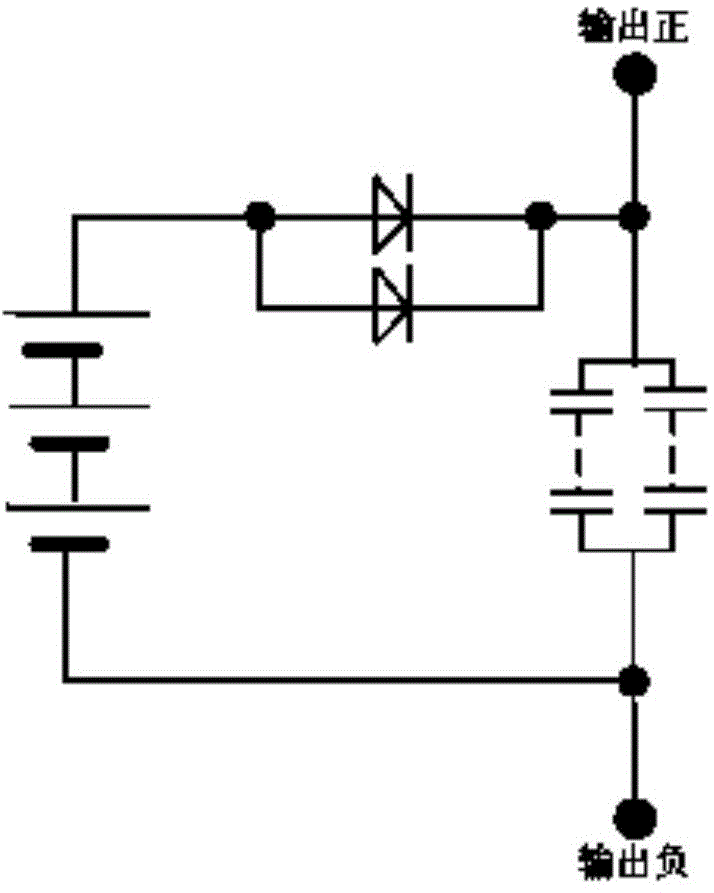

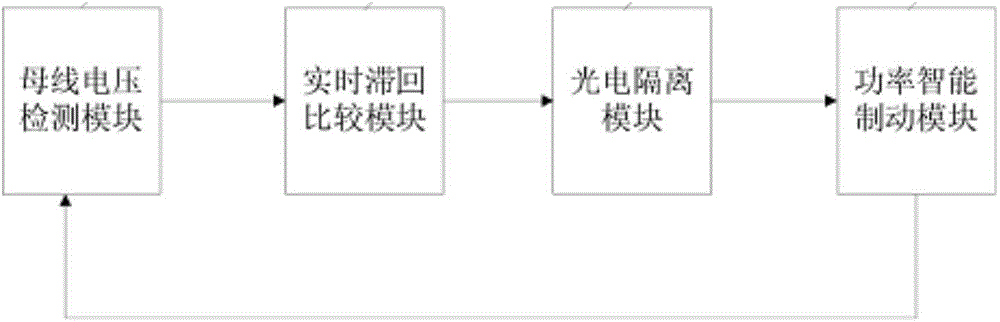

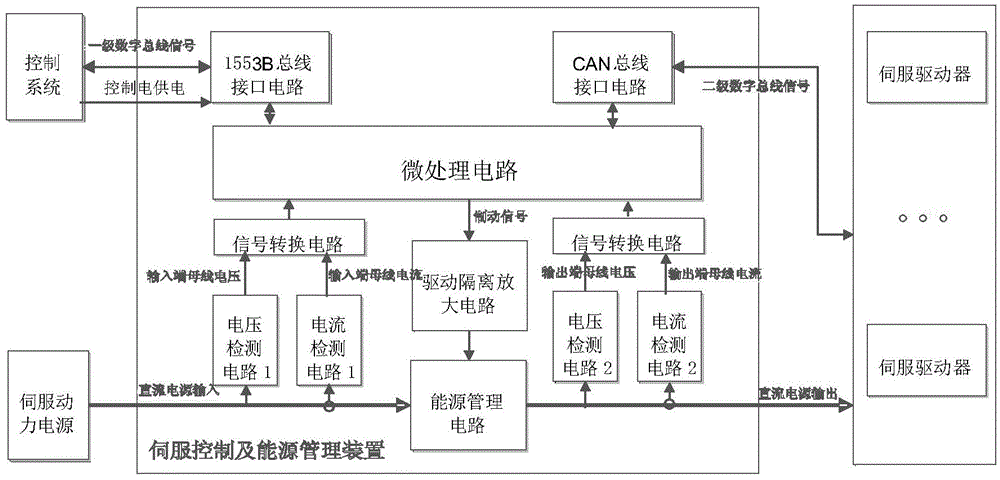

Electromechanical servo comprehensive control and energy source management device

ActiveCN104678830AAchieve volumeAchieved weightProgramme controlComputer controlElectric machineryMotor control

The invention provides an electromechanical servo comprehensive control and energy source management device, which is used for servo motor control and energy source management, and comprises a microprocessing circuit, detecting circuits, a signal conversion circuit, an isolation driving amplifying circuit and an energy source management circuit, wherein the detecting circuits comprise a first voltage detecting circuit, a first current detecting circuit, a second voltage detecting circuit and a second current detecting circuit. The electromechanical servo comprehensive control and energy source management device provided by the invention has the advantages that the comprehensive management of absorption and release of energy sources can be realized, in addition, the system composition is simplified, the system weight is reduced, and meanwhile, the self test of an electromechanical servo system can be realized.

Owner:BEIJING RES INST OF PRECISE MECHATRONICS CONTROLS +1