Patents

Literature

454 results about "Edge detector" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

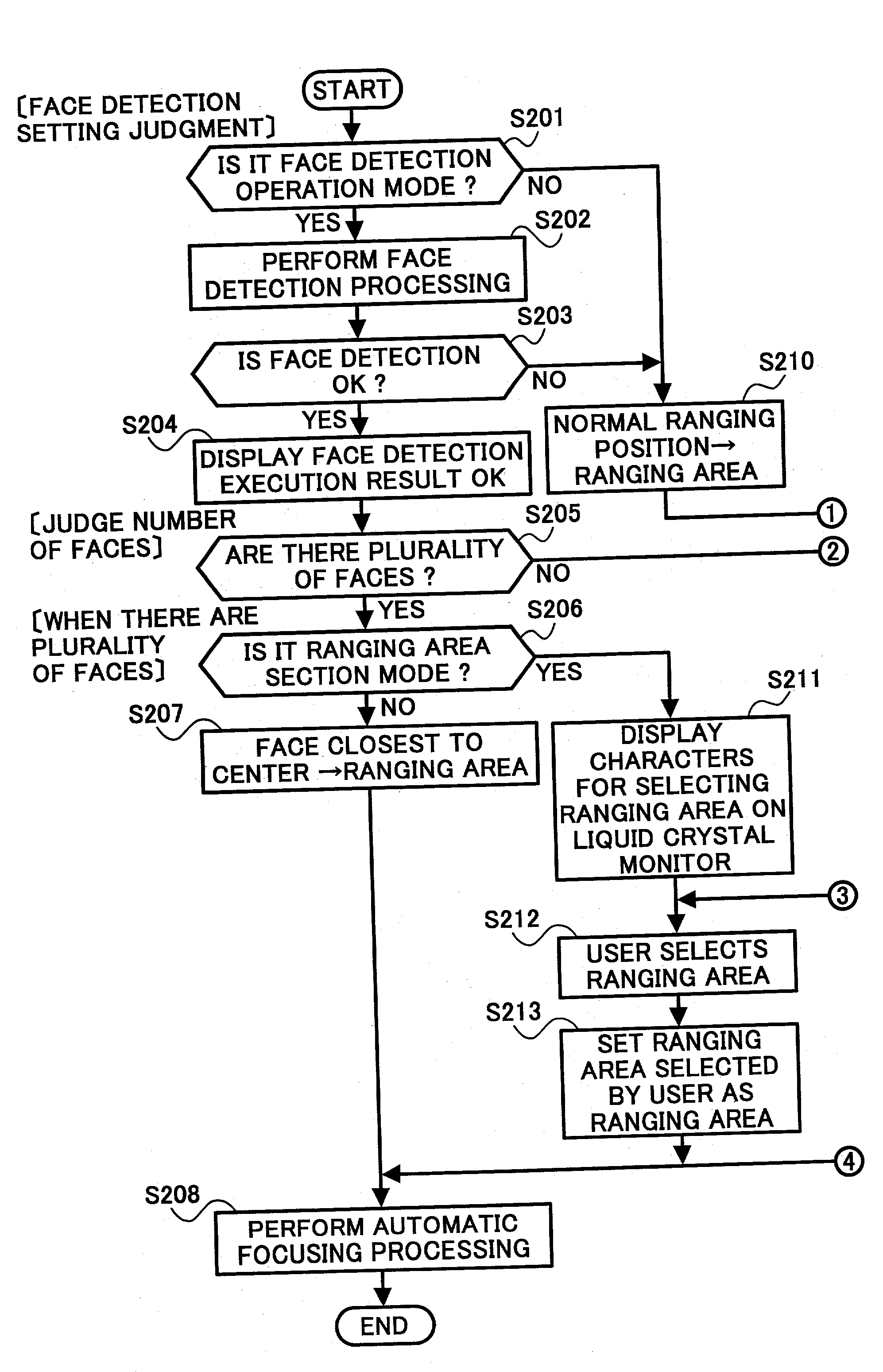

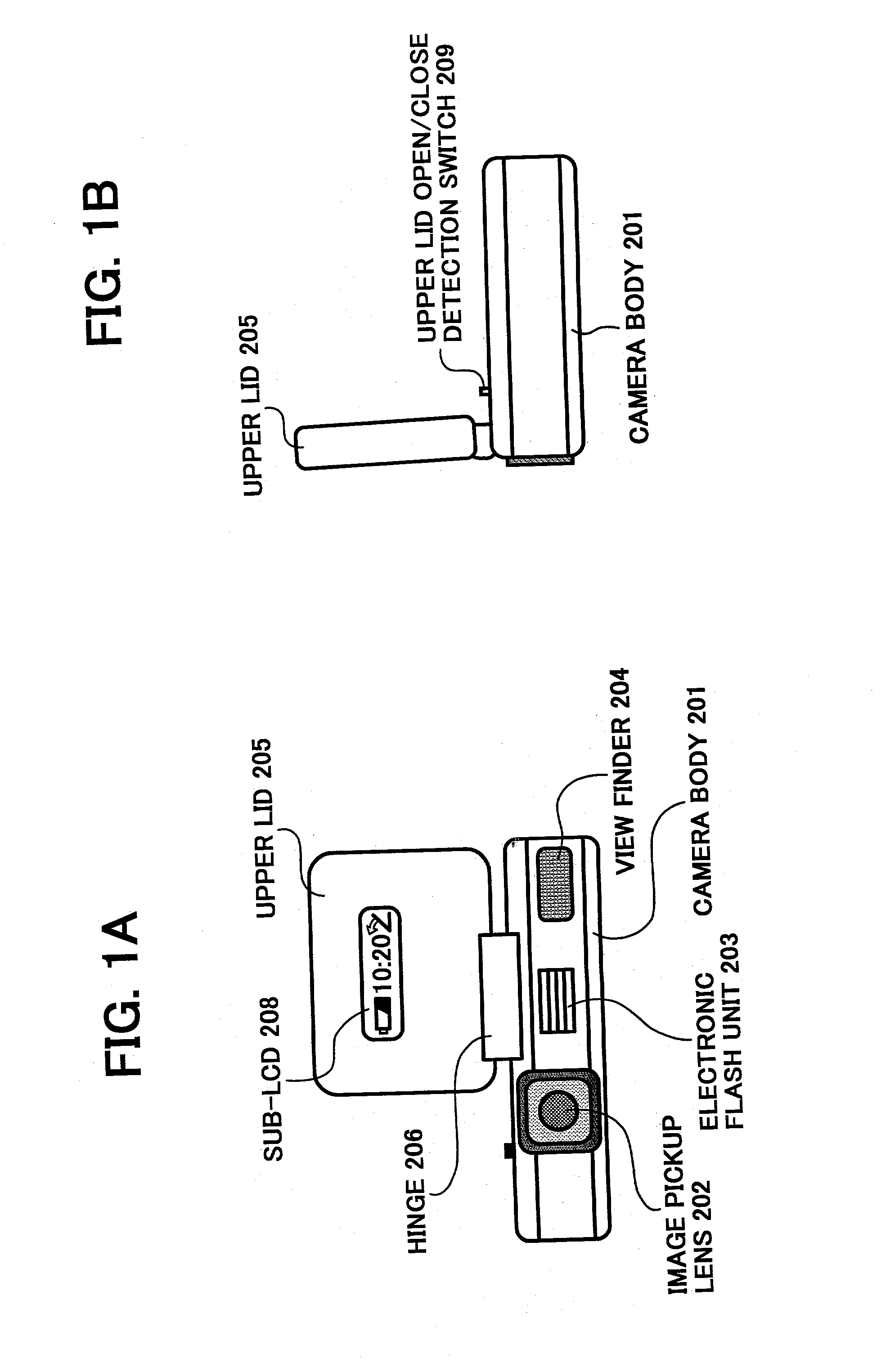

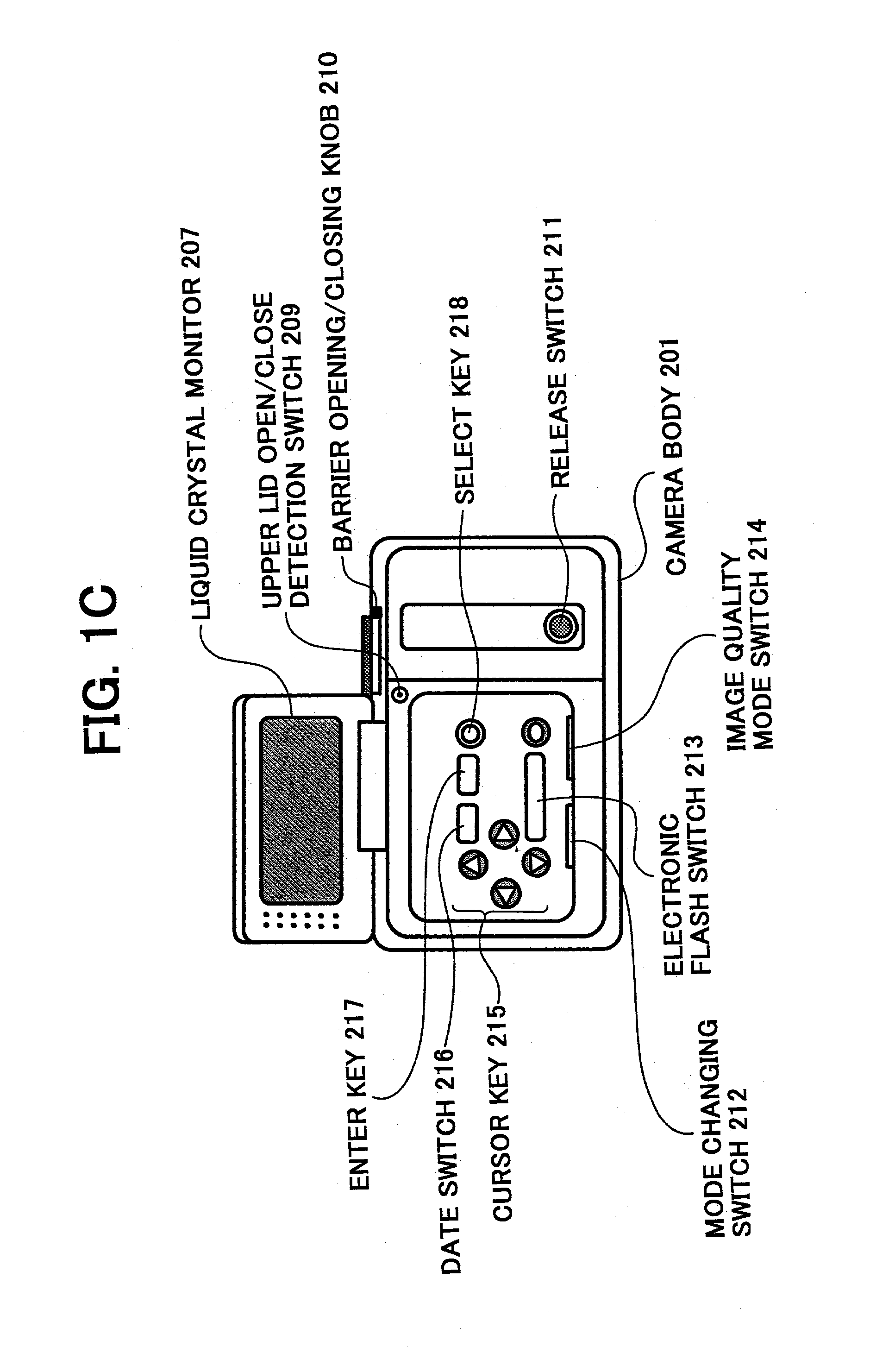

Image pickup device, automatic focusing method, automatic exposure method, electronic flash control method and computer program

InactiveUS20030071908A1Accurate exposurePhotograph can be preventedTelevision system detailsColor signal processing circuitsComputer graphics (images)Computer vision

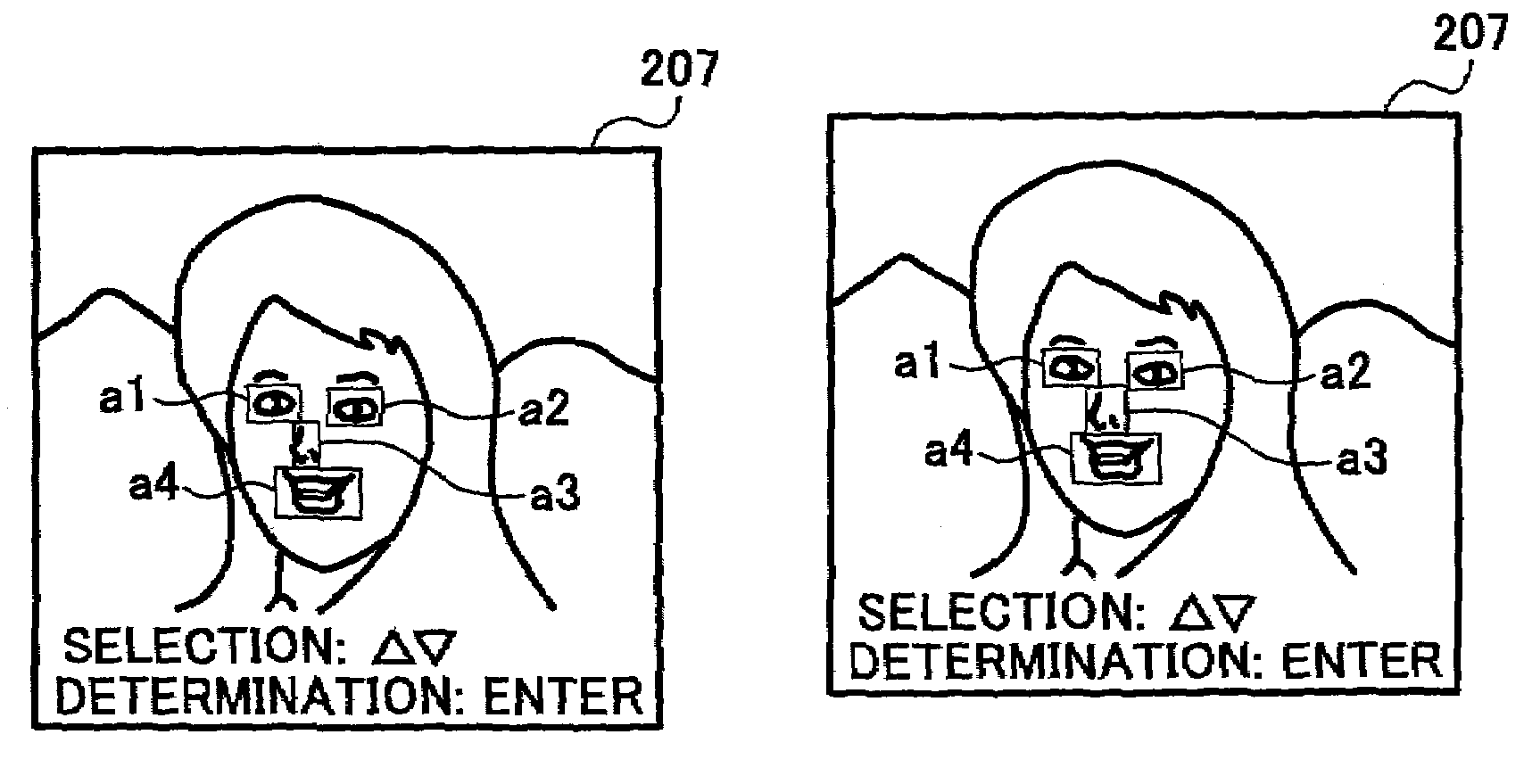

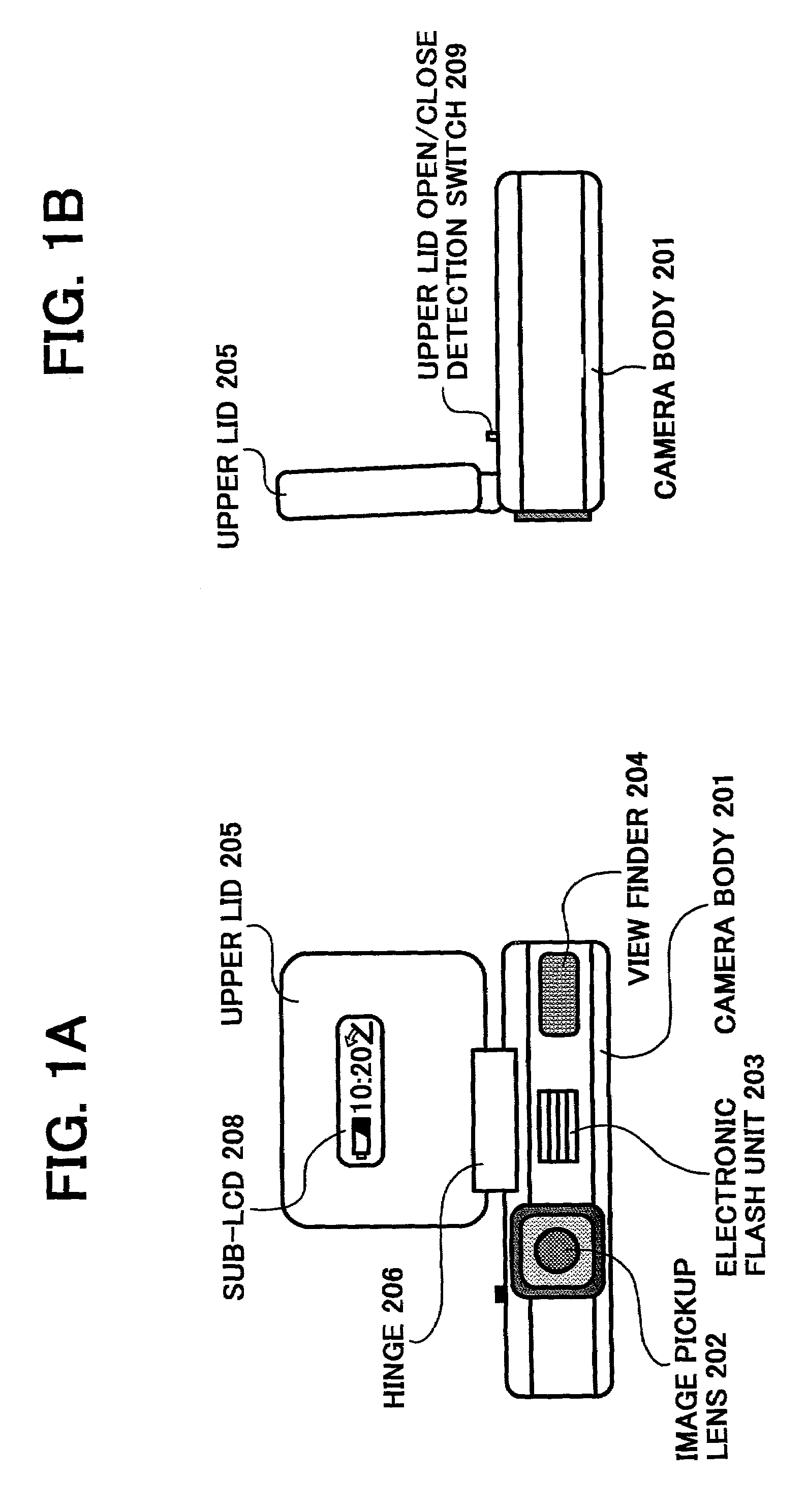

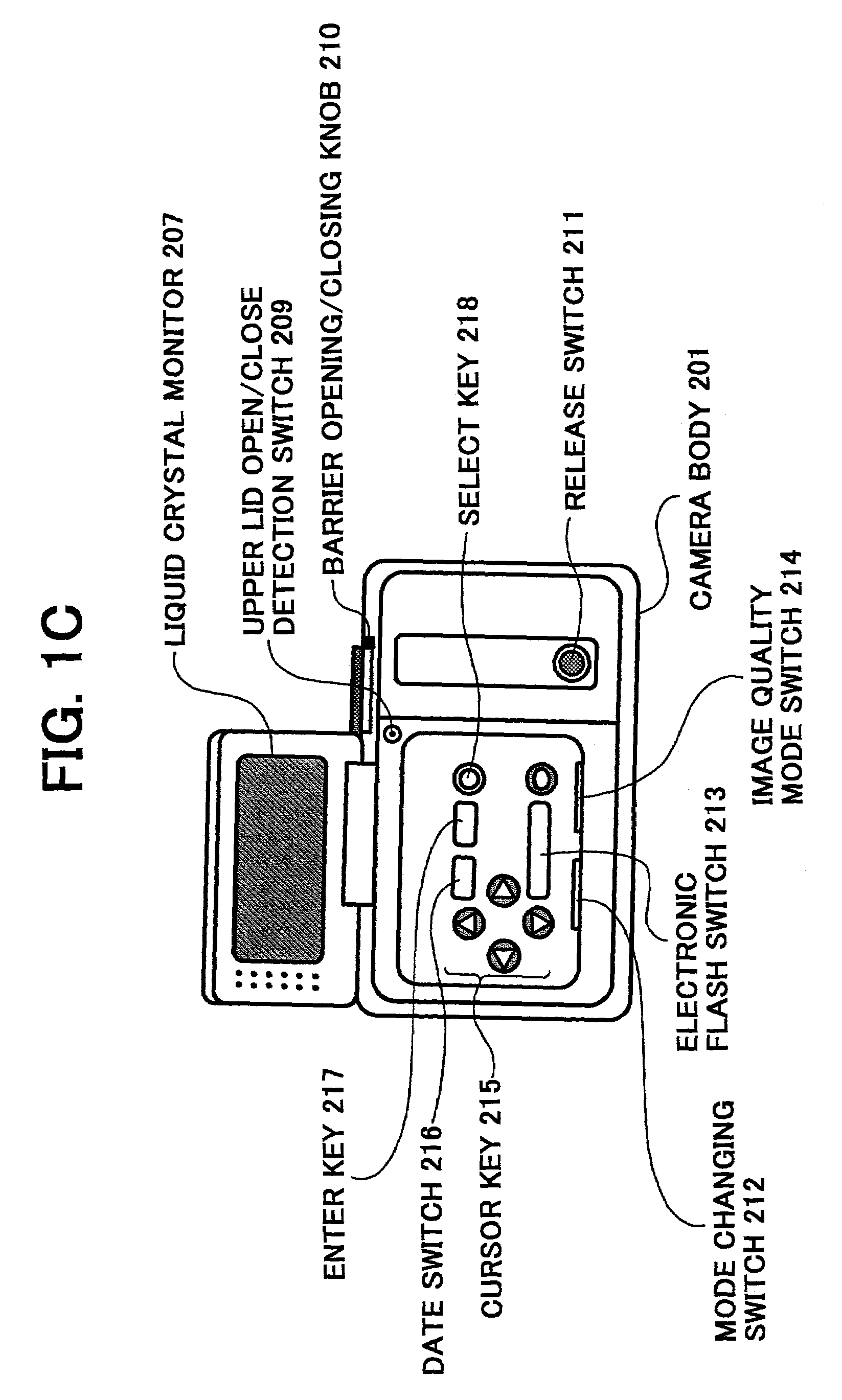

There are provided an image memory which stores one image of a subject, an image fetch section which takes in an image from the image memory to another memory or register in a predetermined unit, a control section which takes charge of the overall control, a face characteristic storage section which stores a plurality of characteristics of a face, a recognition and judgment section which recognizes a face from the data from the image fetch section and the data from the face characteristic storage section and judges each portion, an edge detector which detects an edge detection value from the result data thereof, and an output section which outputs the final judgment result to the outside.

Owner:RICOH KK

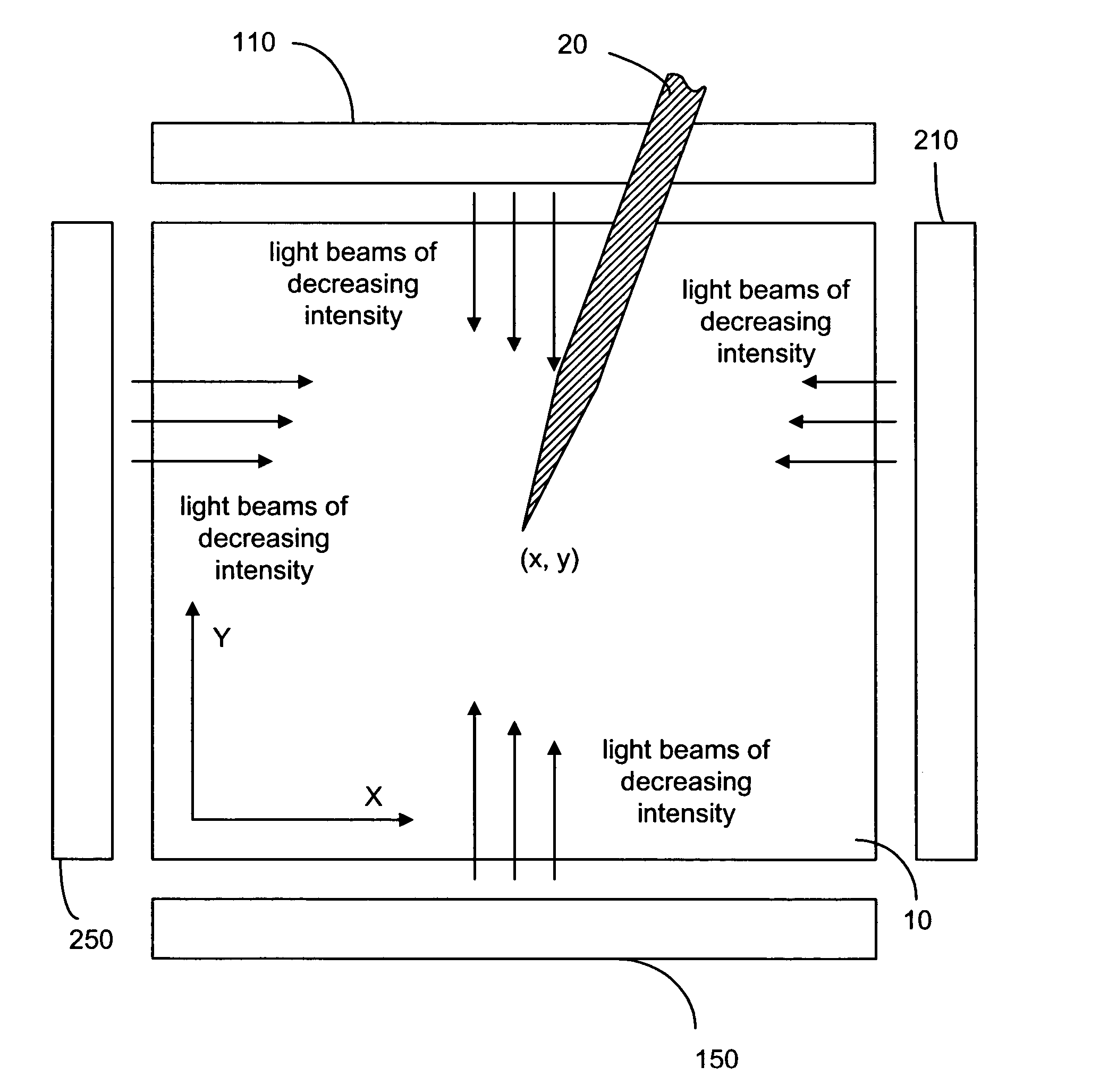

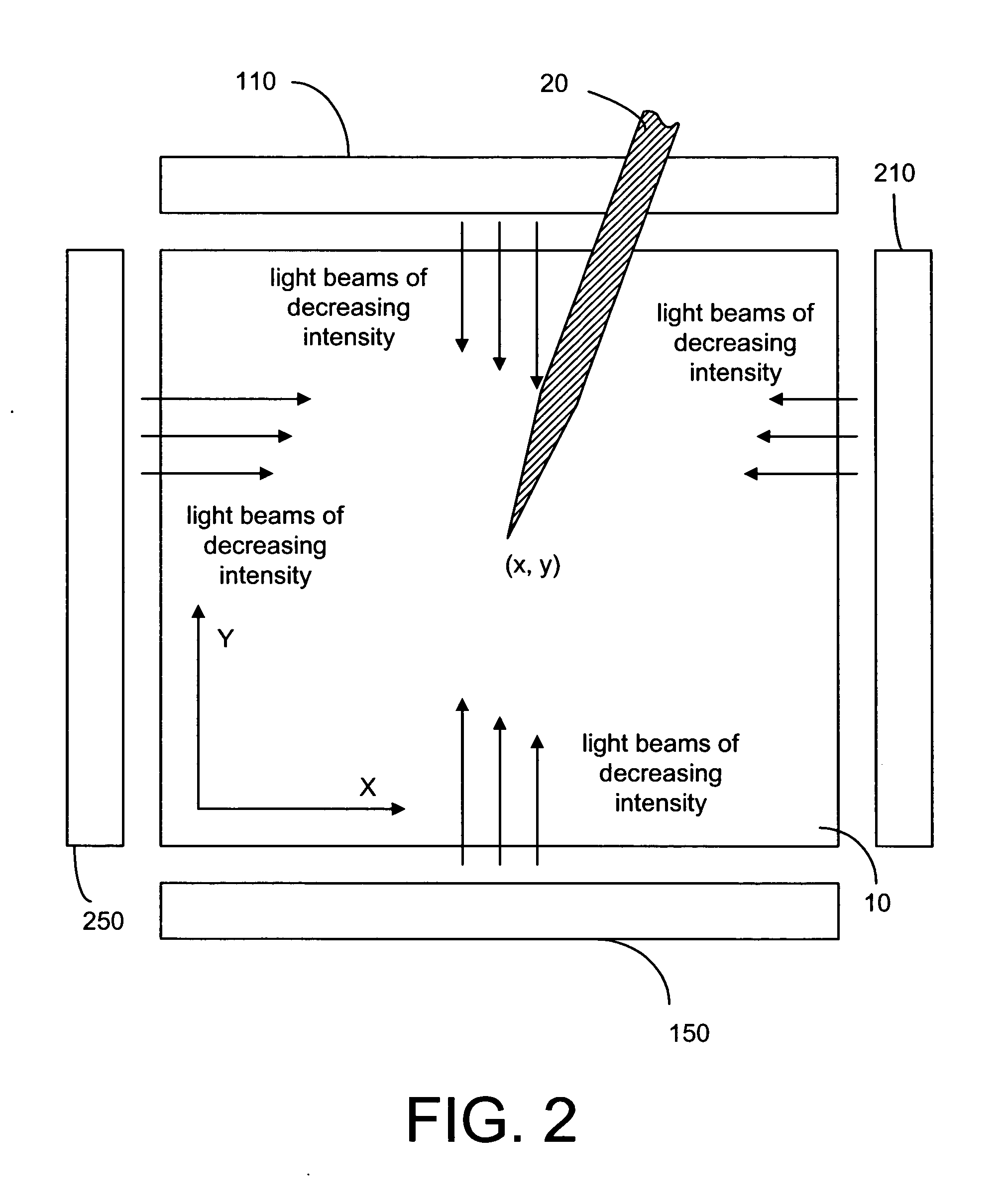

Method and device for detecting touch pad input

InactiveUS20050128190A1Cathode-ray tube indicatorsInput/output processes for data processingLight beamPartial reflection

A method and system for determining the location of an object touching a touch pad. A light source is used to provide a light beam and a plurality of reflecting surfaces are disposed along an edge of the touch pad to partially reflect the light beam in order to provide a light sheet over the touch pad, such that the reflected intensity varies monotonously along the edge. A detector structure is disposed on the opposite edge to measure the light intensity of the light sheet, part of which is blocked when the object touches the touch pad. The reduction in the measured light intensity is used to calculate the location of the touching object in one direction. A second light sheet and a corresponding detector structure can be used to determine the location of the touching object in a different direction.

Owner:NOKIA CORP

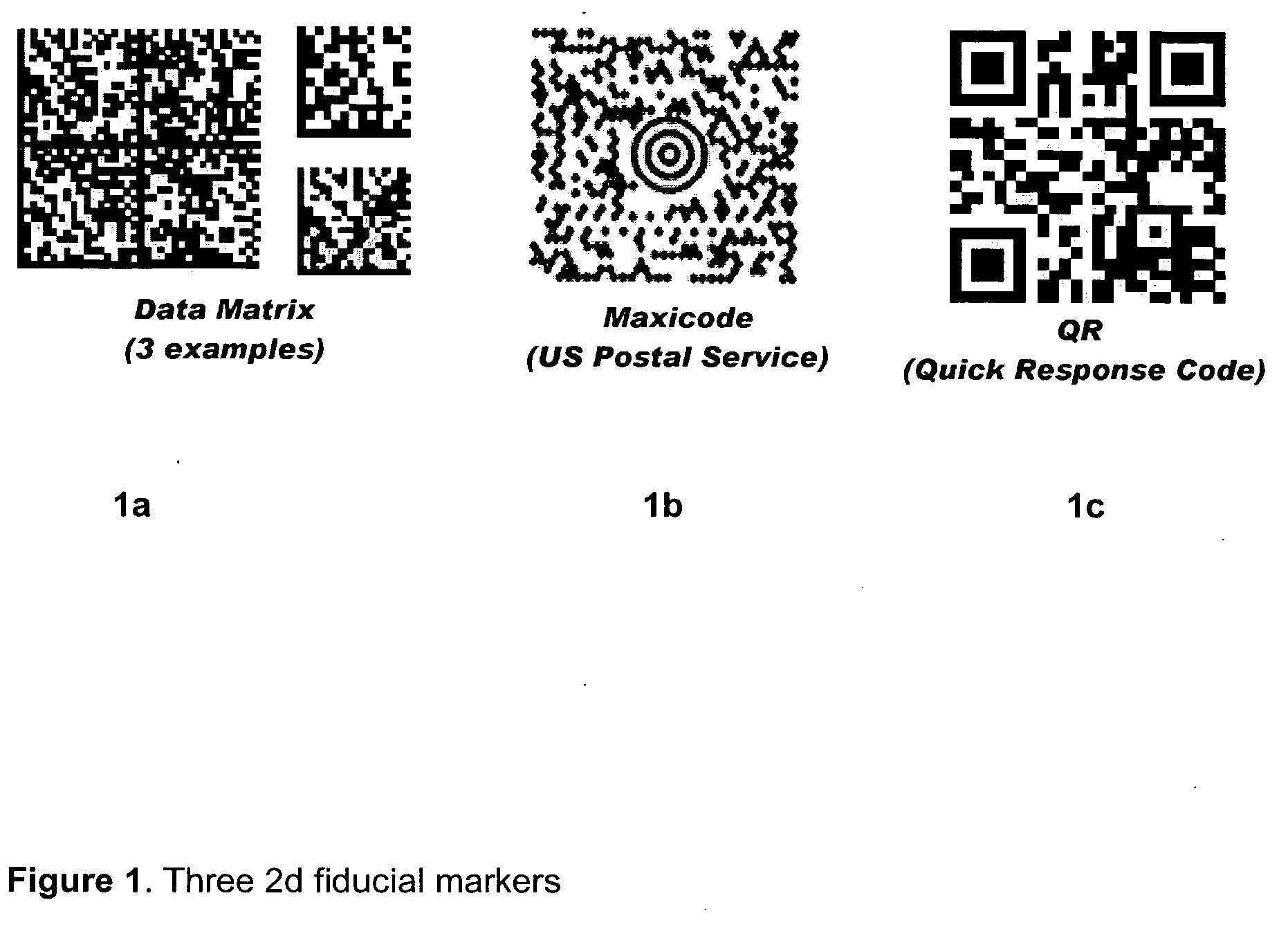

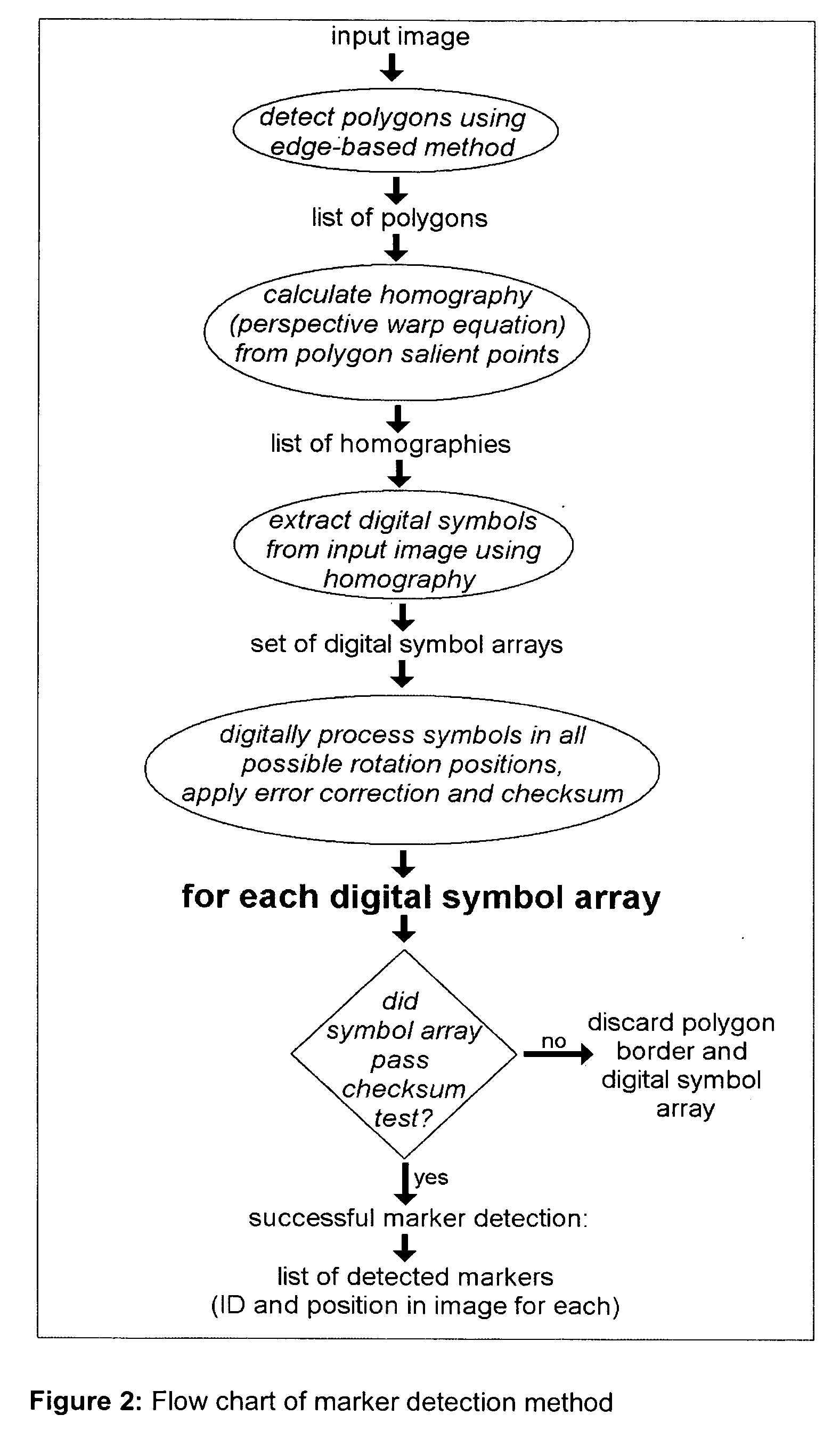

Marker and method for detecting said marker

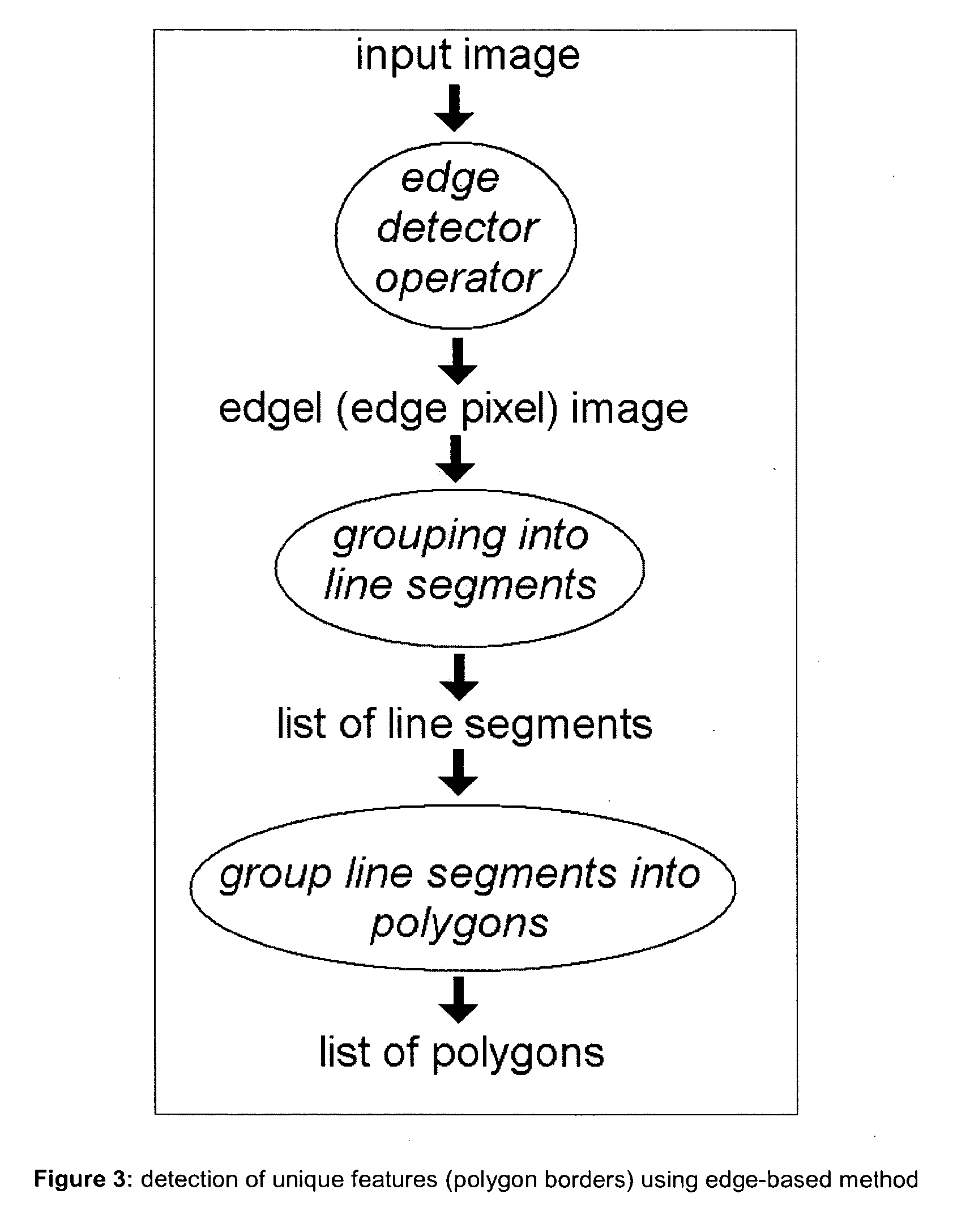

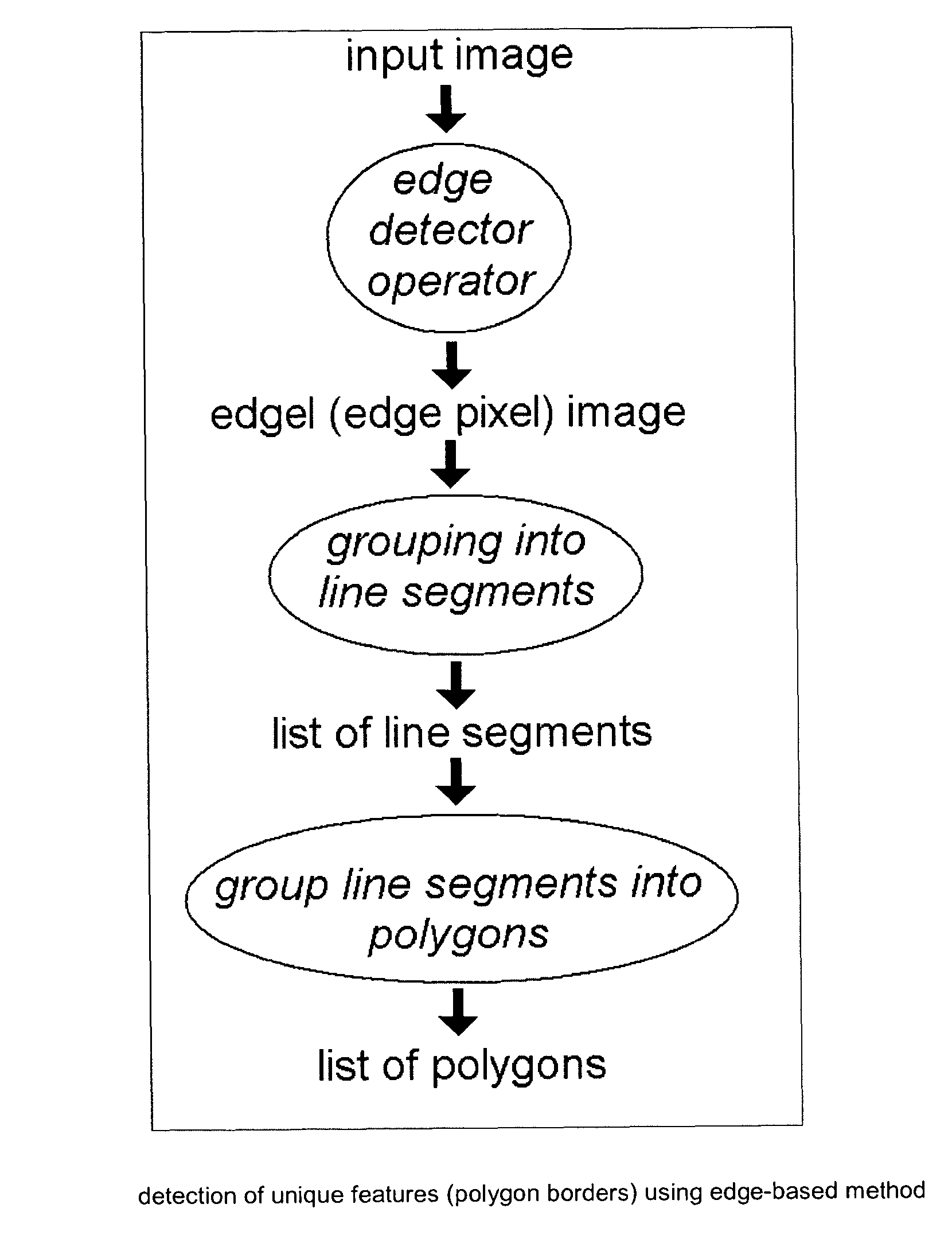

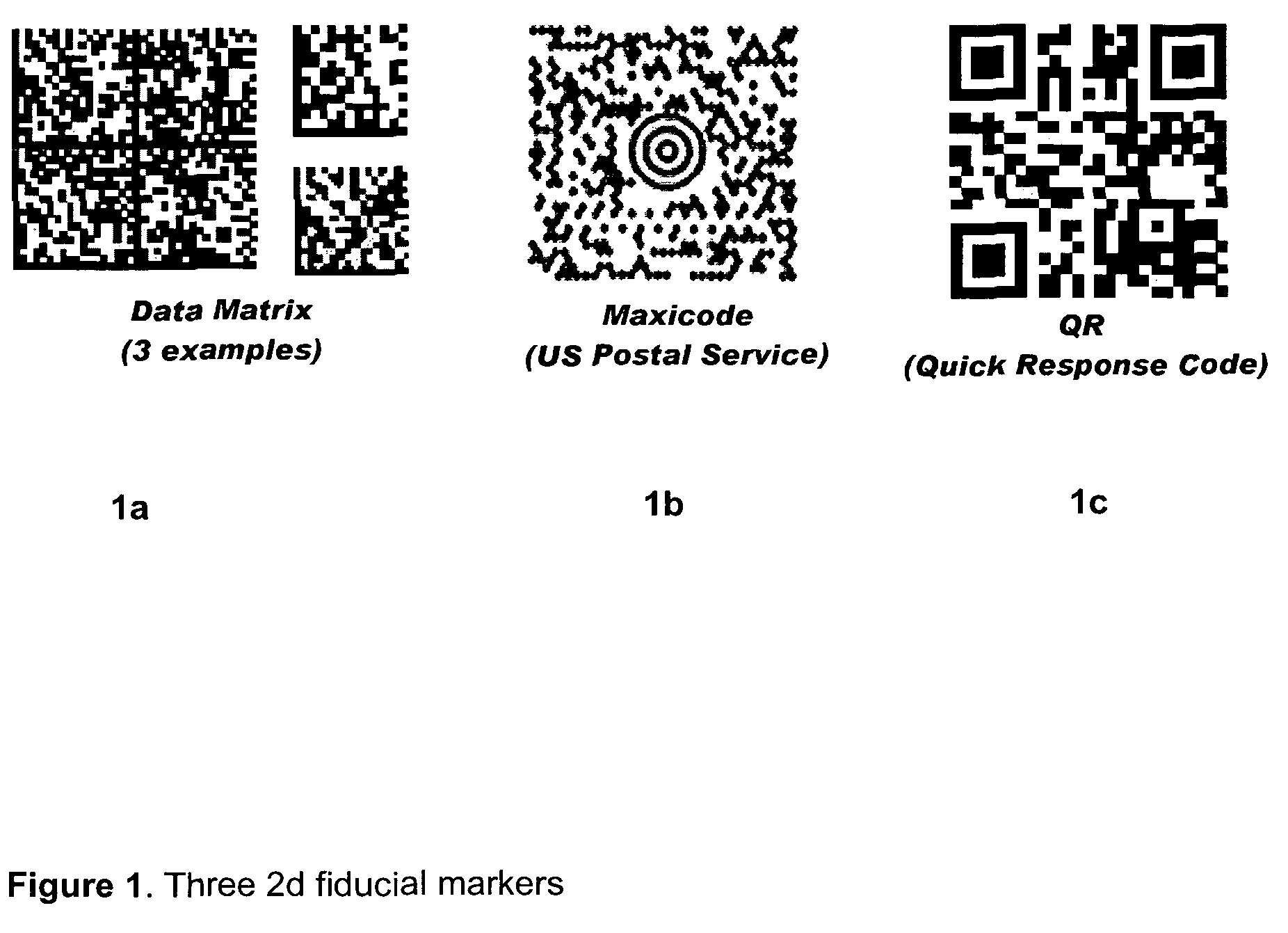

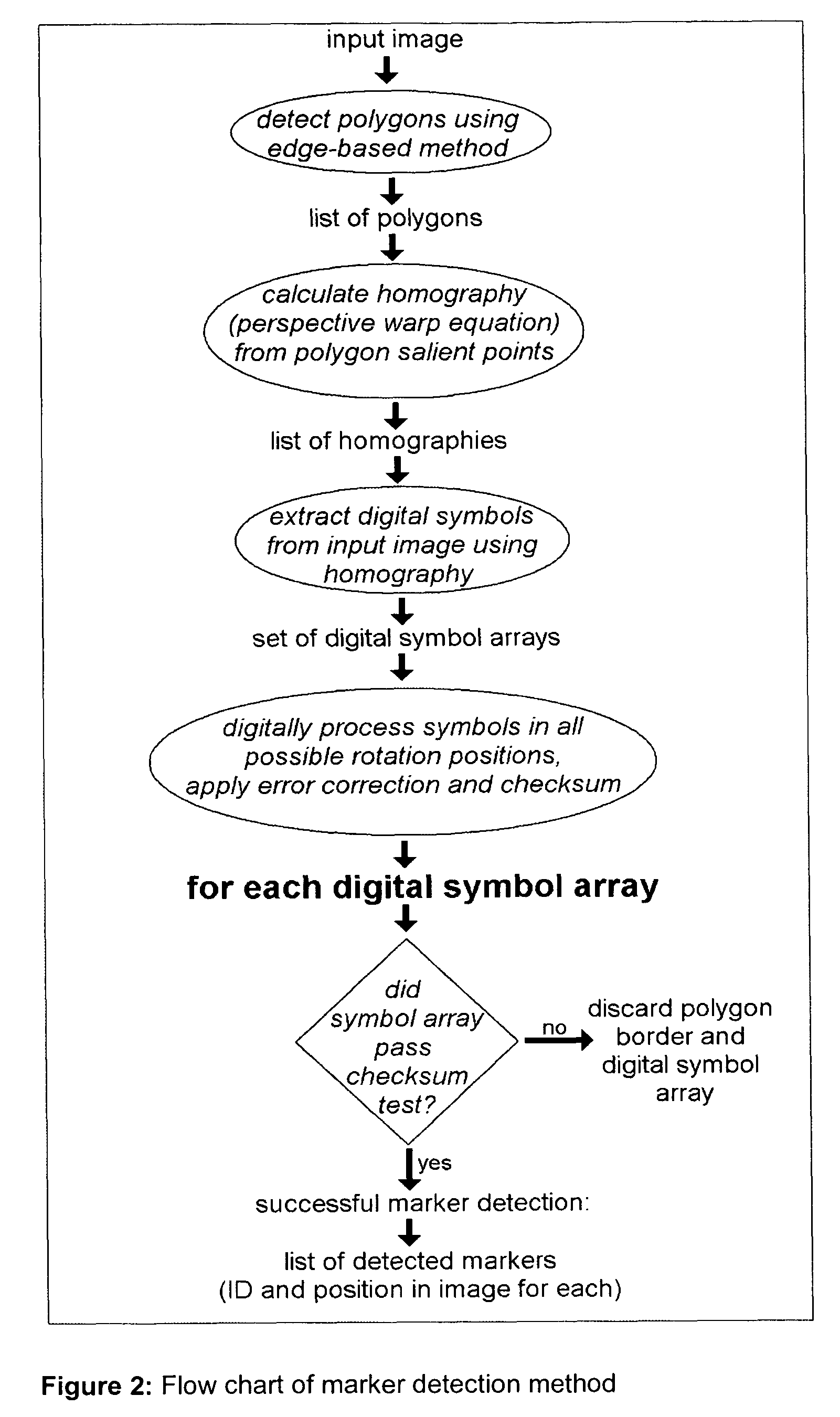

This invention discloses marker detectable by visual means comprising; a polygonal border having of at least four non collinear salient points. The marker has on it a pattern in binary digital code. The binary code data contains information data, checksum and error correction. The binary code data is on two levels; a first level of binary code readable at a first given distance, a second level of binary code readable at a second given distance, where the second given distance is less than the first given distance and the second level binary code is smaller in size than the first level binary code. The second level of binary code does not interfere with the reading of the first level binary code. It also discloses a method for detecting a marker comprising the steps of detecting an image, using an edge detector to detect an edge in said image, grouping more than one edge into a polygon having salient points, calculating homography from polygon salient points, generating a list of homographies, extracting binary data from input image having homographies, identifying and verifying binary data.

Owner:MILLENNIUM THREE TECH

Level 3 features for fingerprint matching

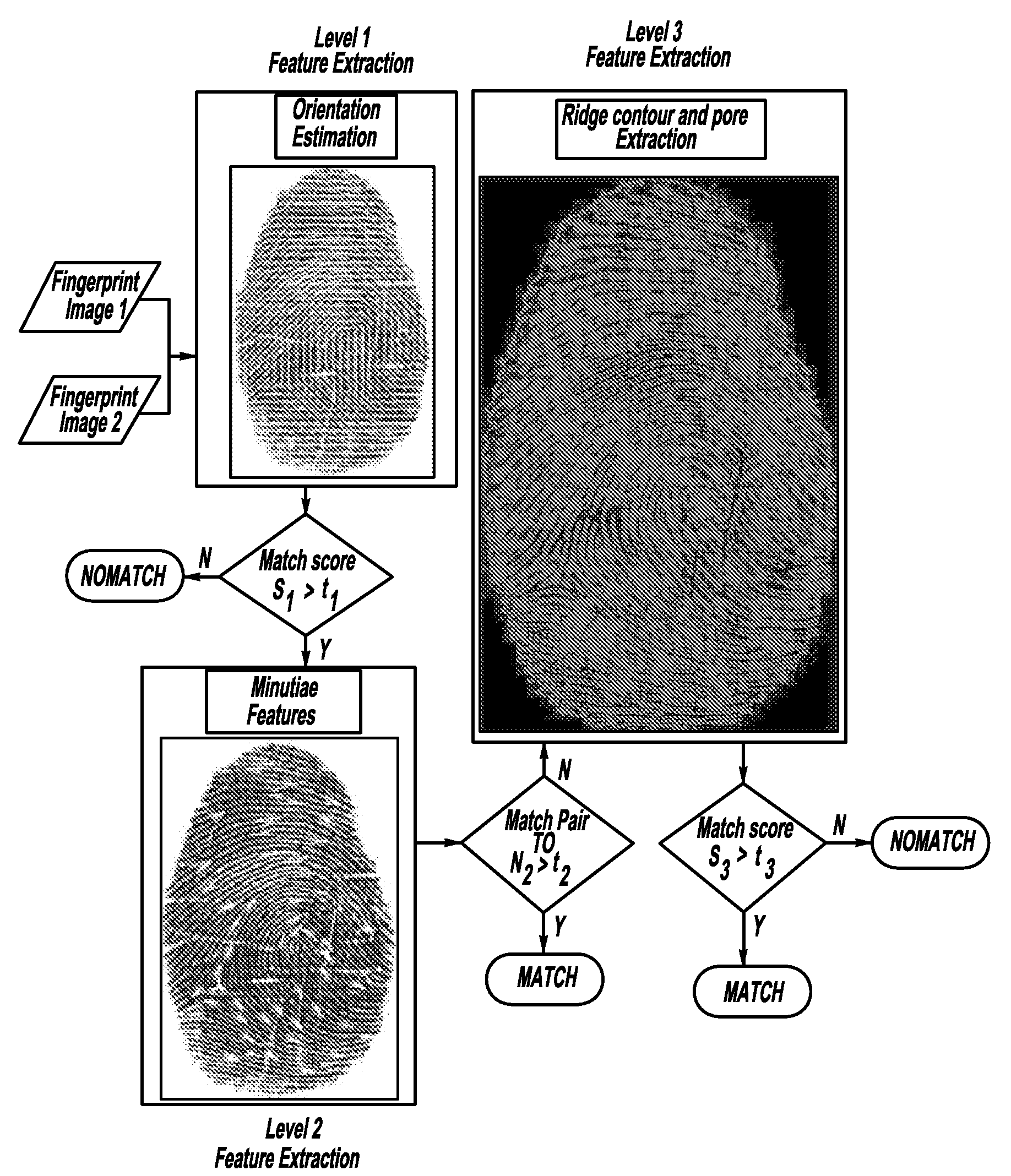

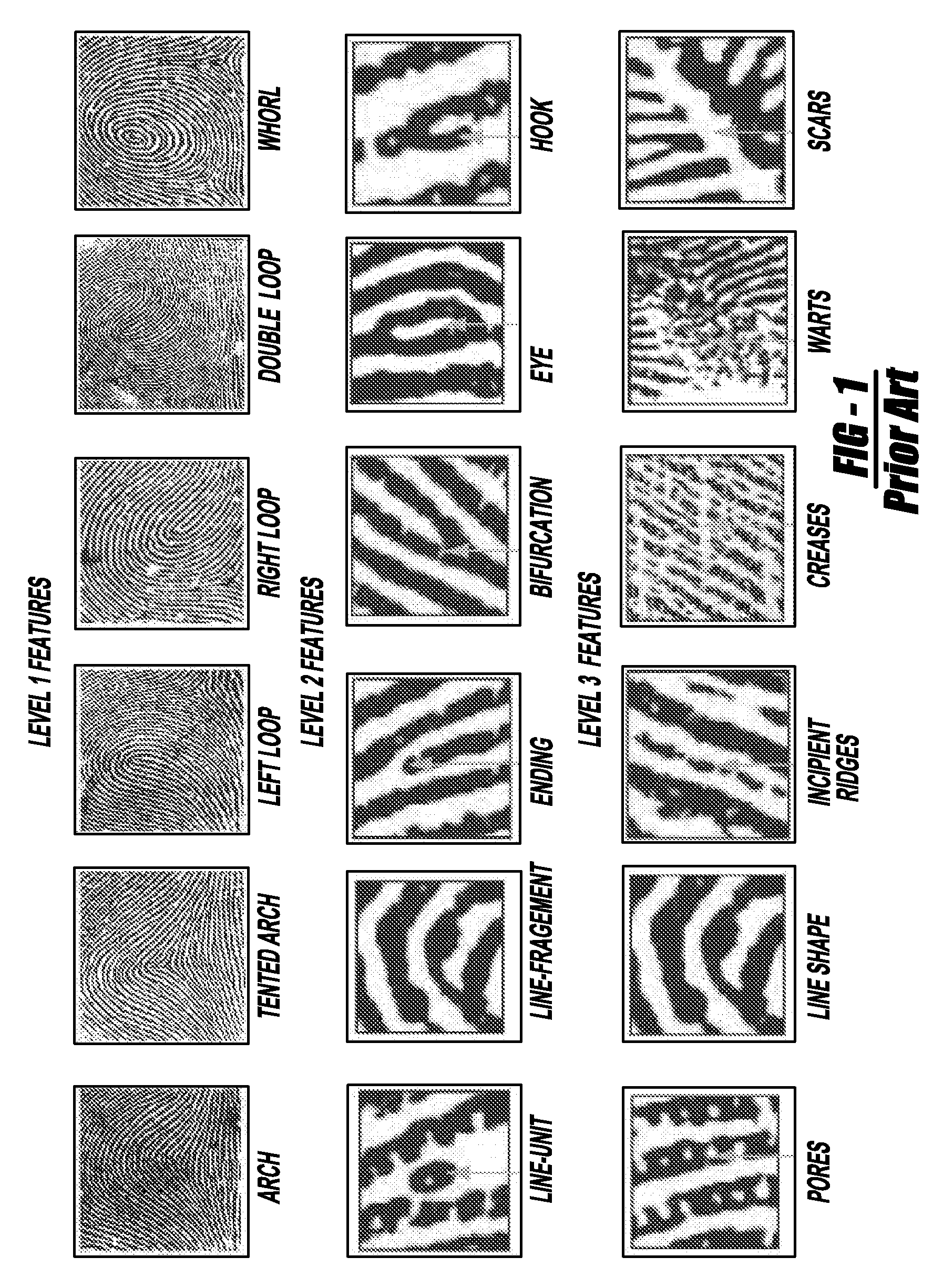

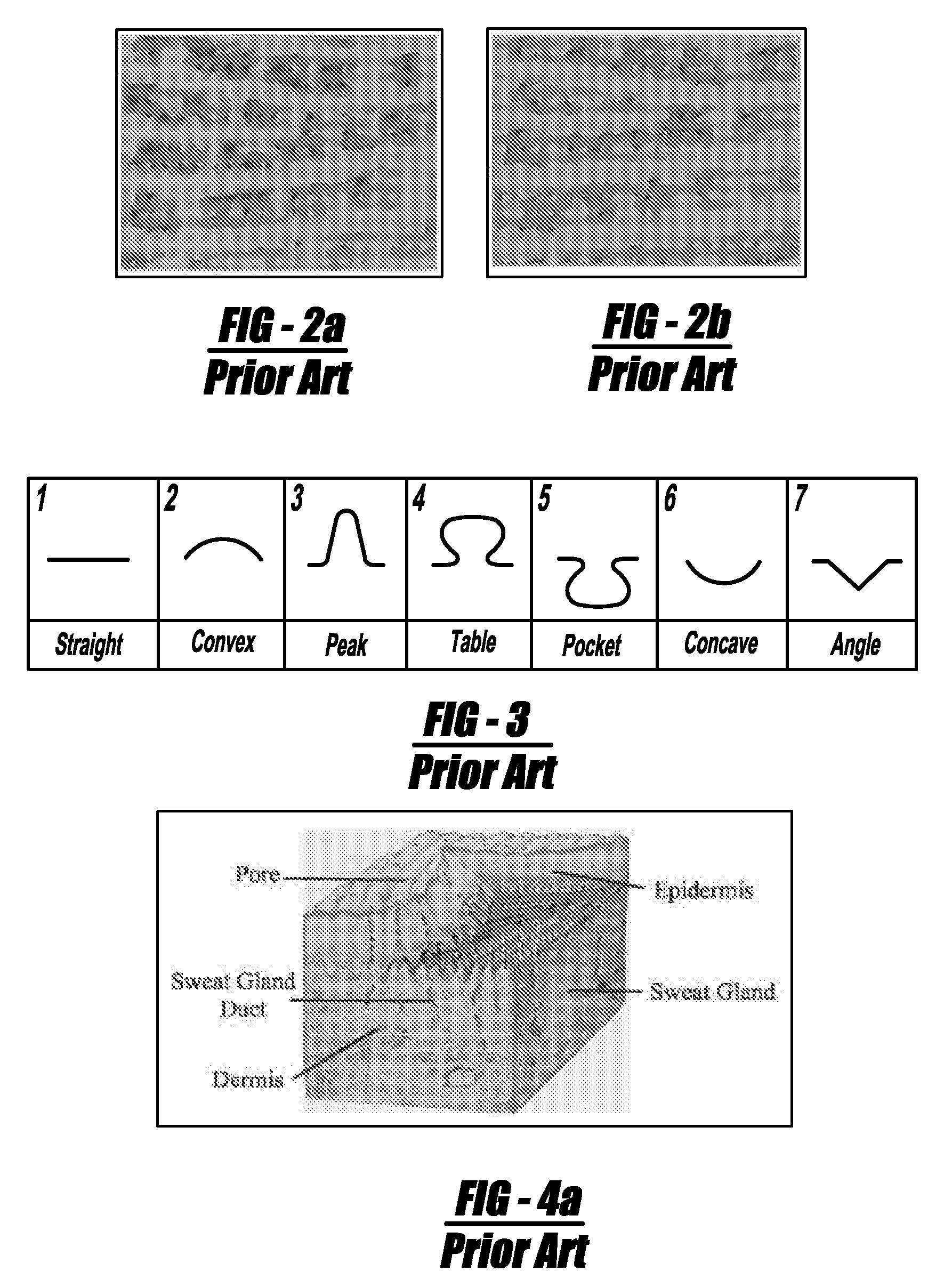

Fingerprint recognition and matching systems and methods are described that utilize features at all three fingerprint friction ridge detail levels, i.e., Level 1, Level 2 and Level 3, extracted from 1000 ppi fingerprint scans. Level 3 features, including but not limited to pore and ridge contour characteristics, were automatically extracted using various filters (e.g., Gabor filters, edge detector filters, and / or the like) and transforms (e.g., wavelet transforms) and were locally matched using various algorithms (e.g., the iterative closest point (ICP) algorithm). Because Level 3 features carry significant discriminatory and complementary information, there was a relative reduction of 20% in the equal error rate (EER) of the matching system when Level 3 features were employed in combination with Level 1 and Level 2 features, which were also automatically extracted. This significant performance gain was consistently observed across various quality fingerprint images.

Owner:BOARD OF TRUSTEES OPERATING MICHIGAN STATE UNIV

Image pickup device, automatic focusing method, automatic exposure method, electronic flash control method and computer program

InactiveUS7298412B2Accurate exposurePhotograph can be preventedTelevision system detailsColor television detailsComputer graphics (images)Image storage

There are provided an image memory which stores one image of a subject, an image fetch section which takes in an image from the image memory to another memory or register in a predetermined unit, a control section which takes charge of the overall control, a face characteristic storage section which stores a plurality of characteristics of a face, a recognition and judgment section which recognizes a face from the data from the image fetch section and the data from the face characteristic storage section and judges each portion, an edge detector which detects an edge detection value from the result data thereof, and an output section which outputs the final judgment result to the outside.

Owner:RICOH KK

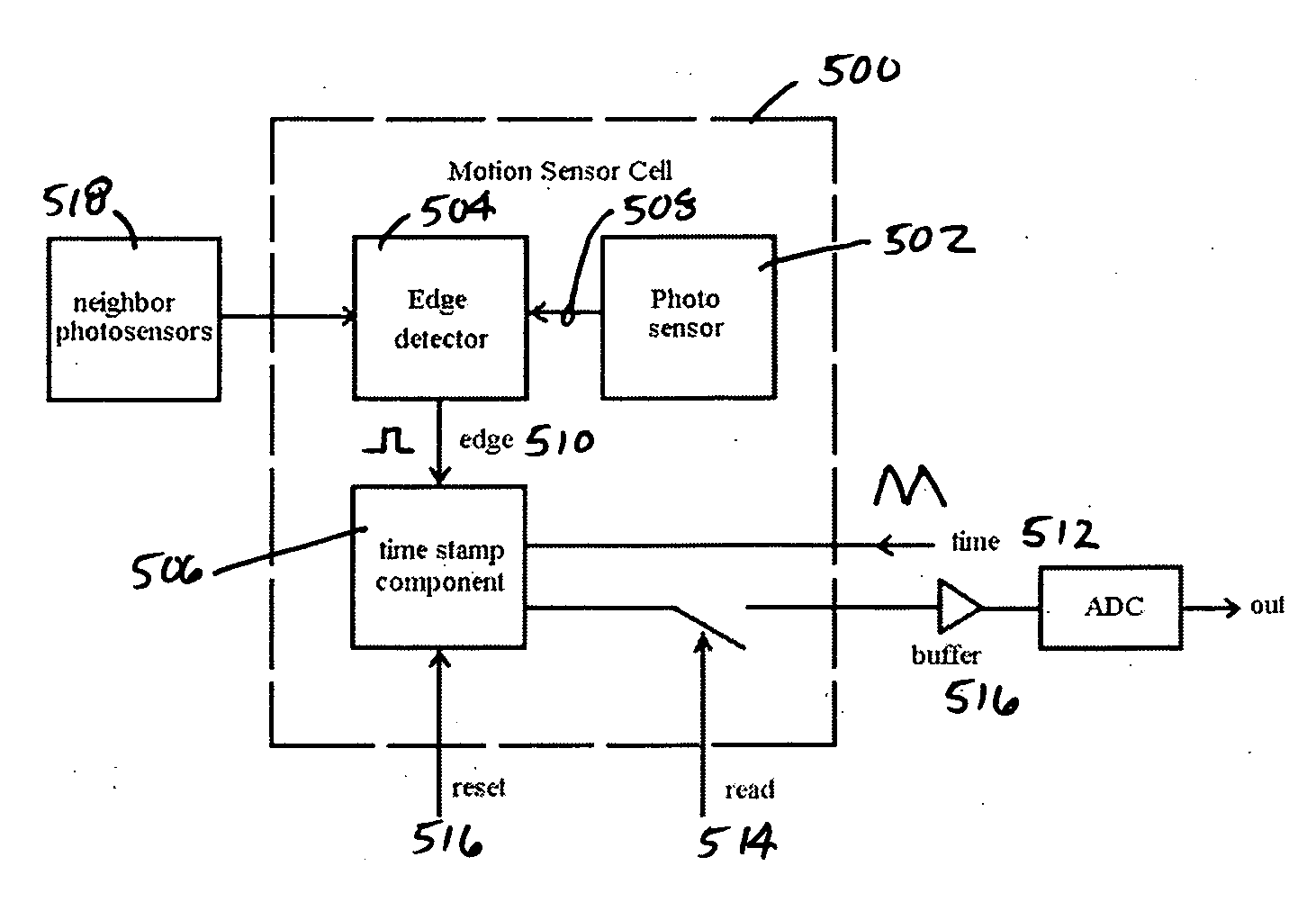

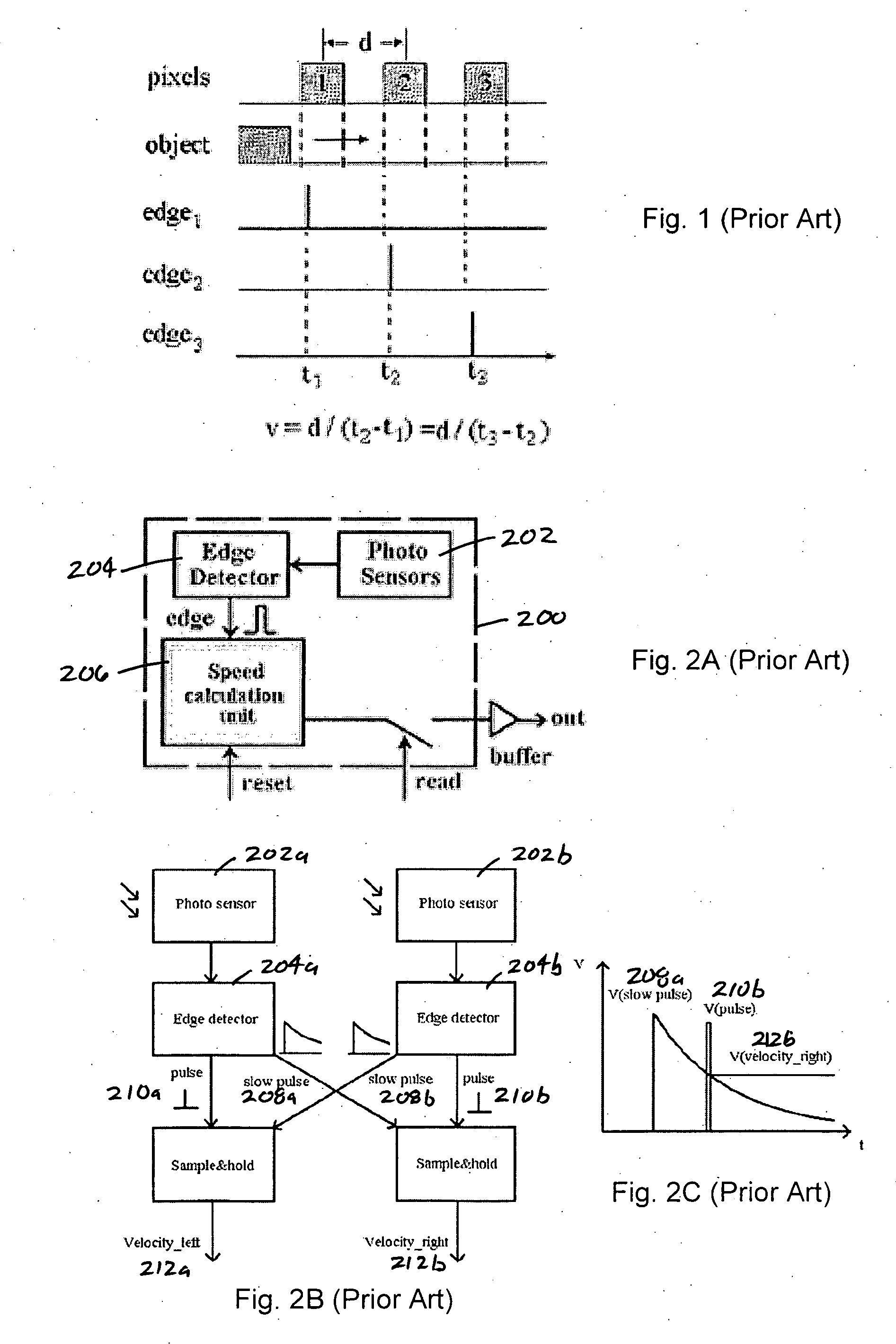

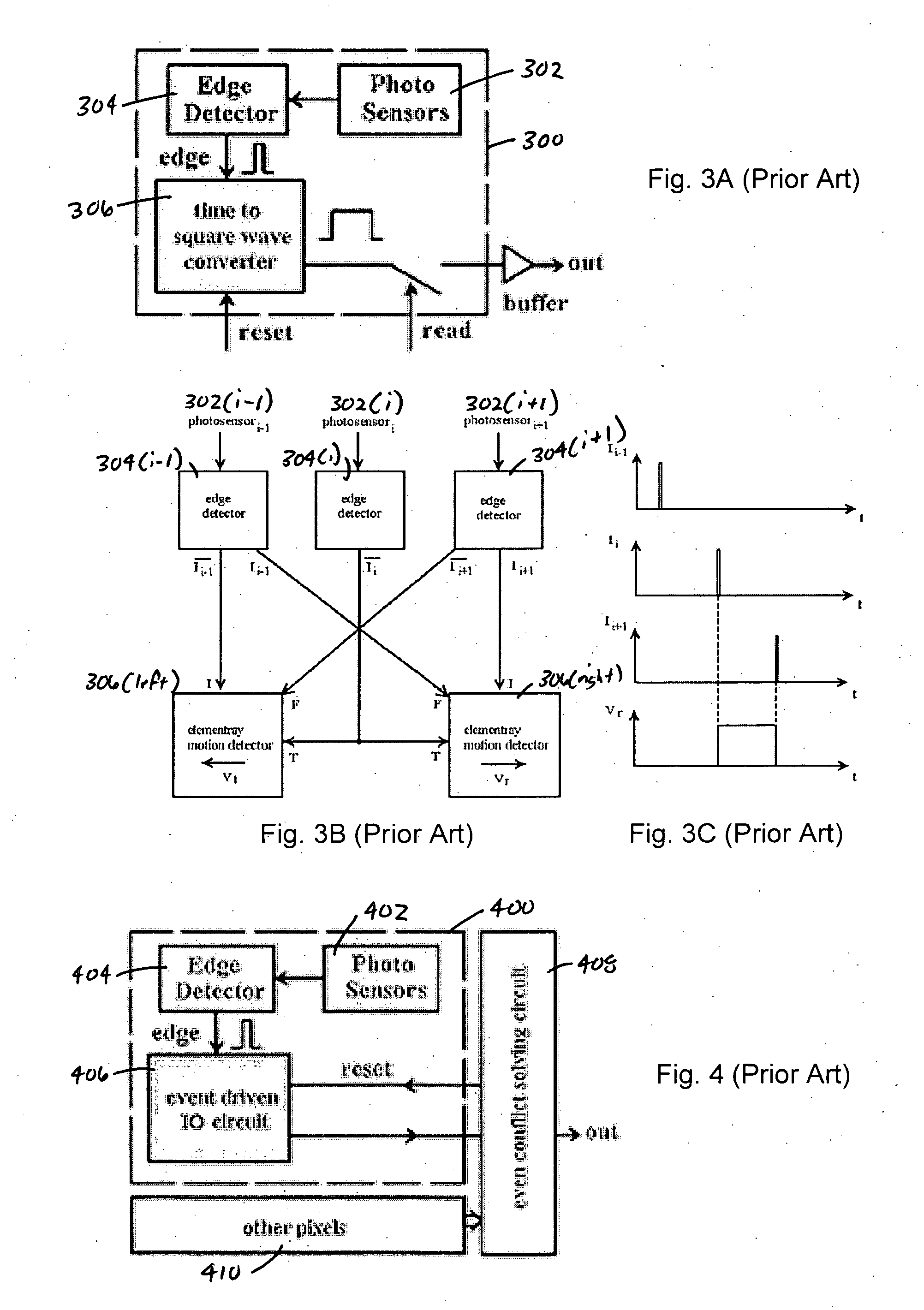

Method, system and apparatus for a time stamped visual motion sensor

InactiveUS20060197664A1Improve accuracyHigh detectionImage analysisMicrobiological testing/measurementData transmissionComputer science

The present invention provides a method, system and apparatus for a time stamped visual motion sensor that provides a compact pixel size, higher speed motion detection and accuracy in velocity computation, high resolution, low power integration and reduces the data transfer and computation load of the following digital processor. The present invention provides a visual motion sensor cell that includes a photosensor, an edge detector connected to the photosensor and a time stamp component connected to the edge detector. The edge detector receives inputs from the photosensor and generates a pulse when a moving edge is detected. The time stamp component tracks a time signal and samples a time voltage when the moving edge is detected. The sampled time voltage can be stored until the sampled time voltage is read. In addition, the edge detector can be connected to one or more neighboring photosensors to improve sensitivity and robustness.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

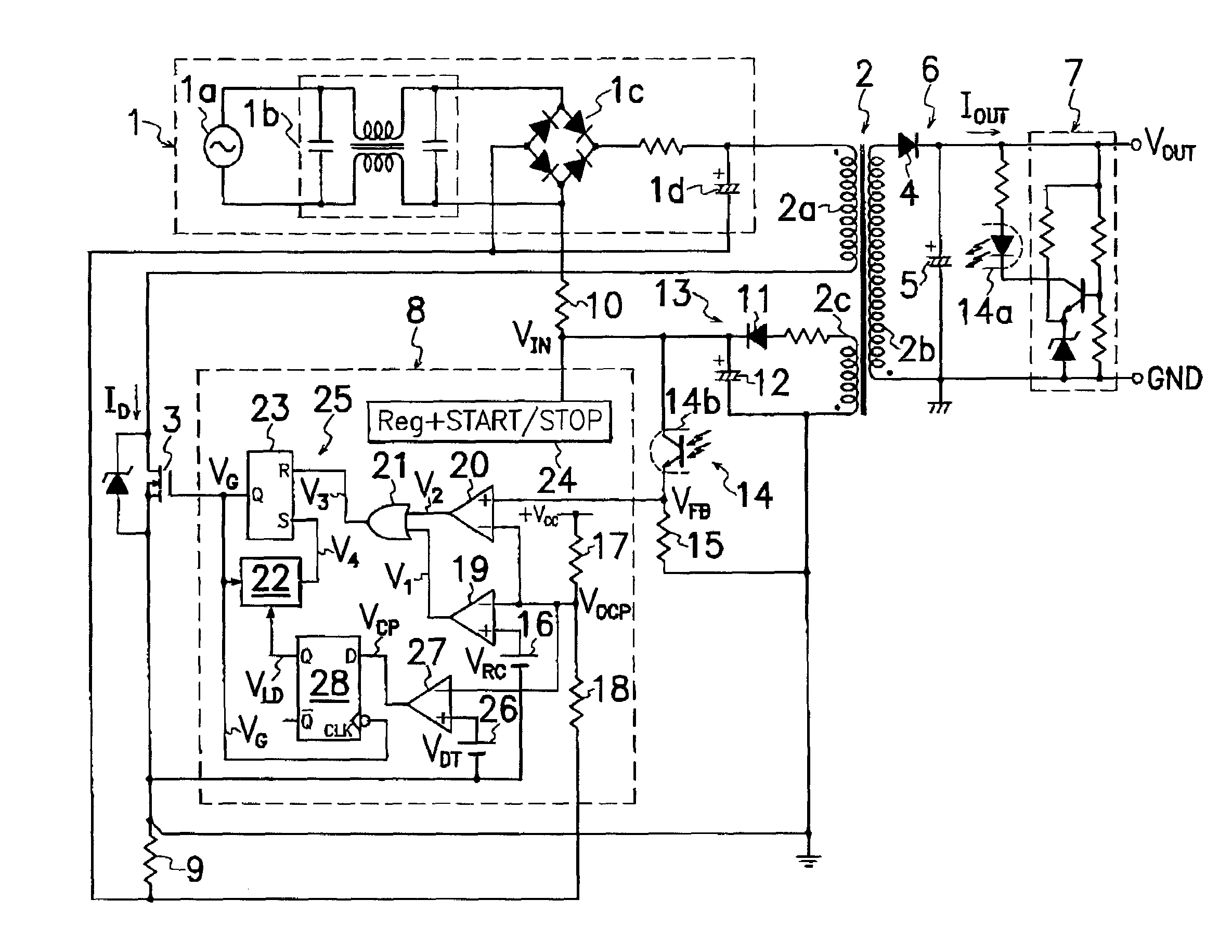

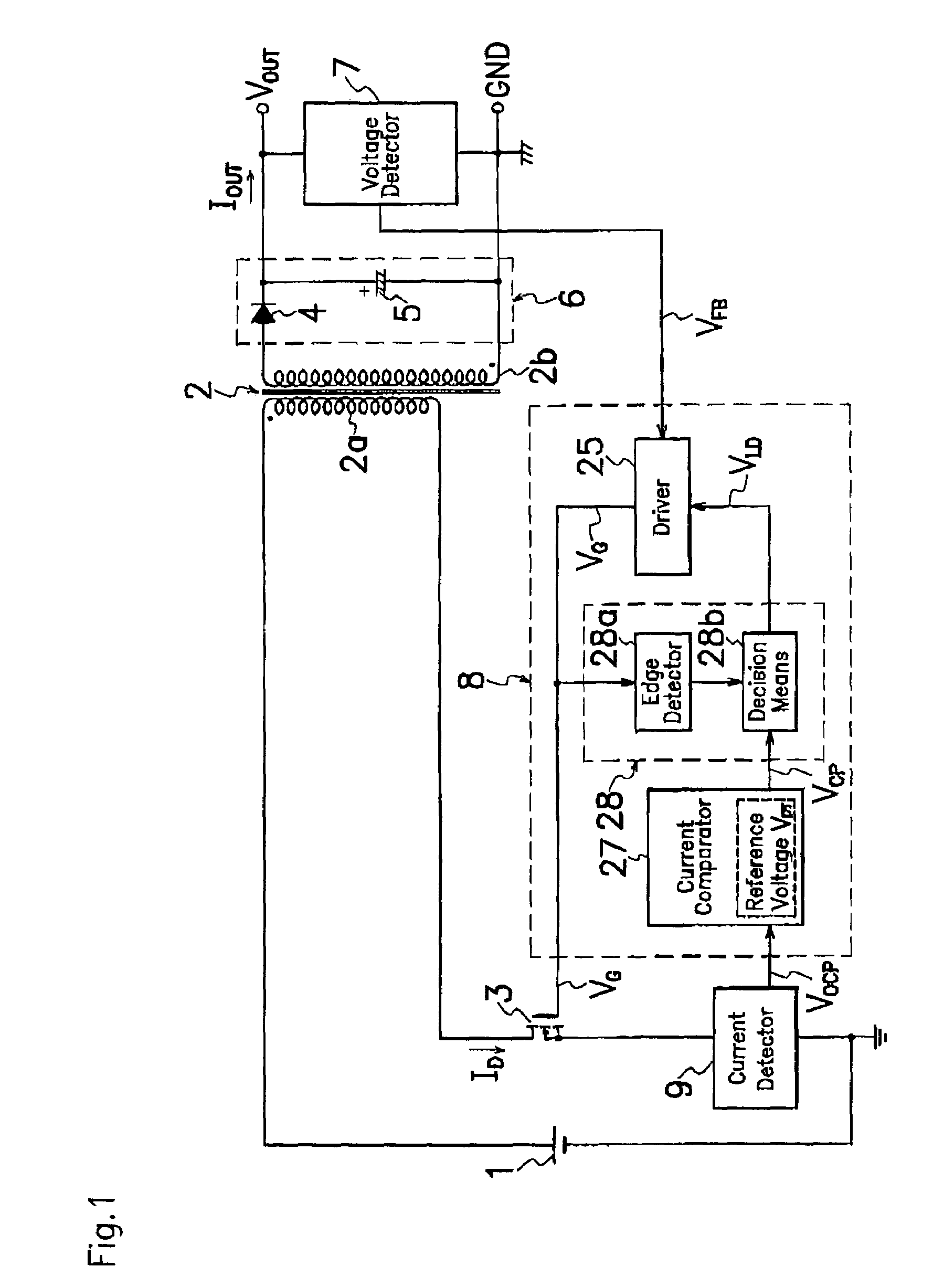

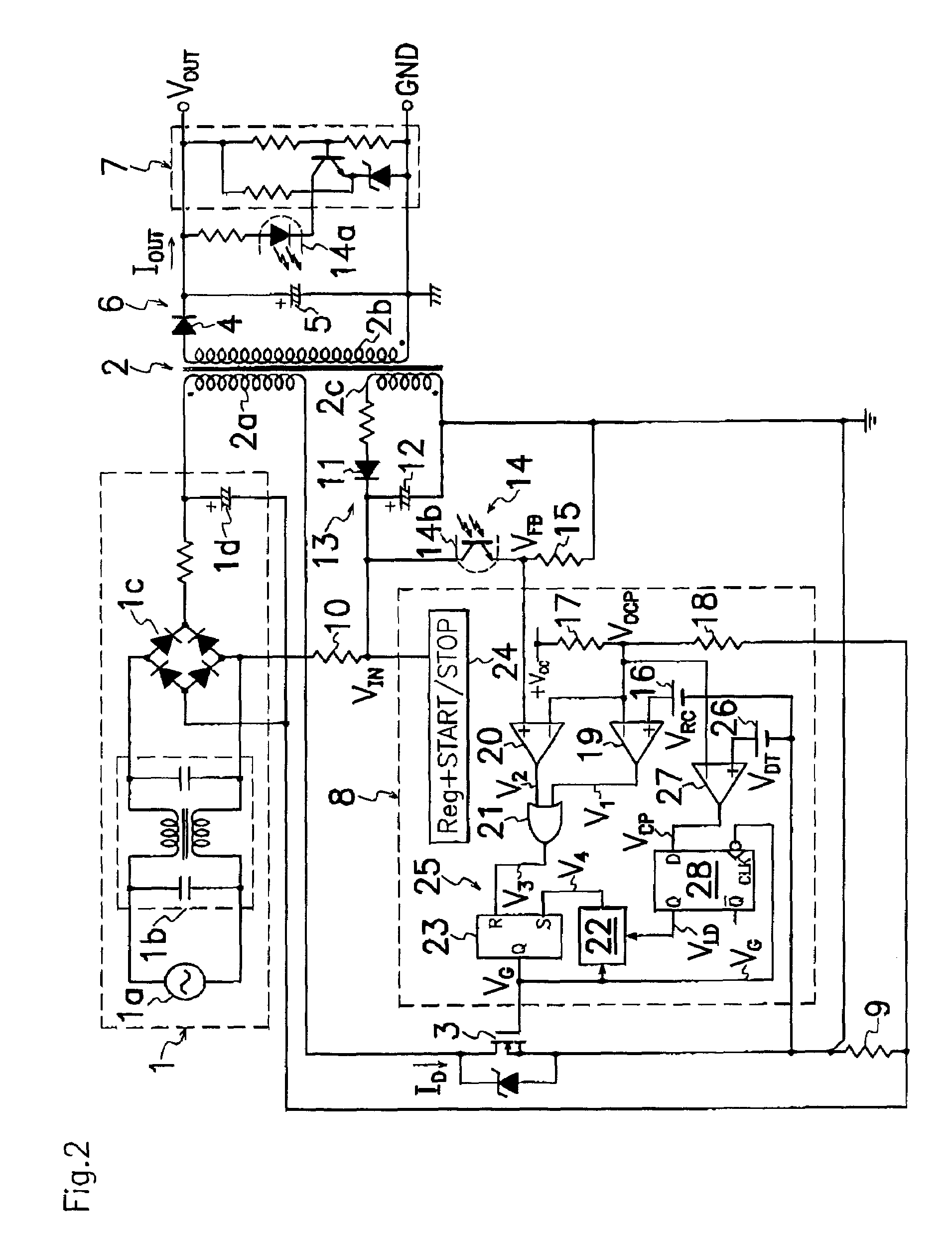

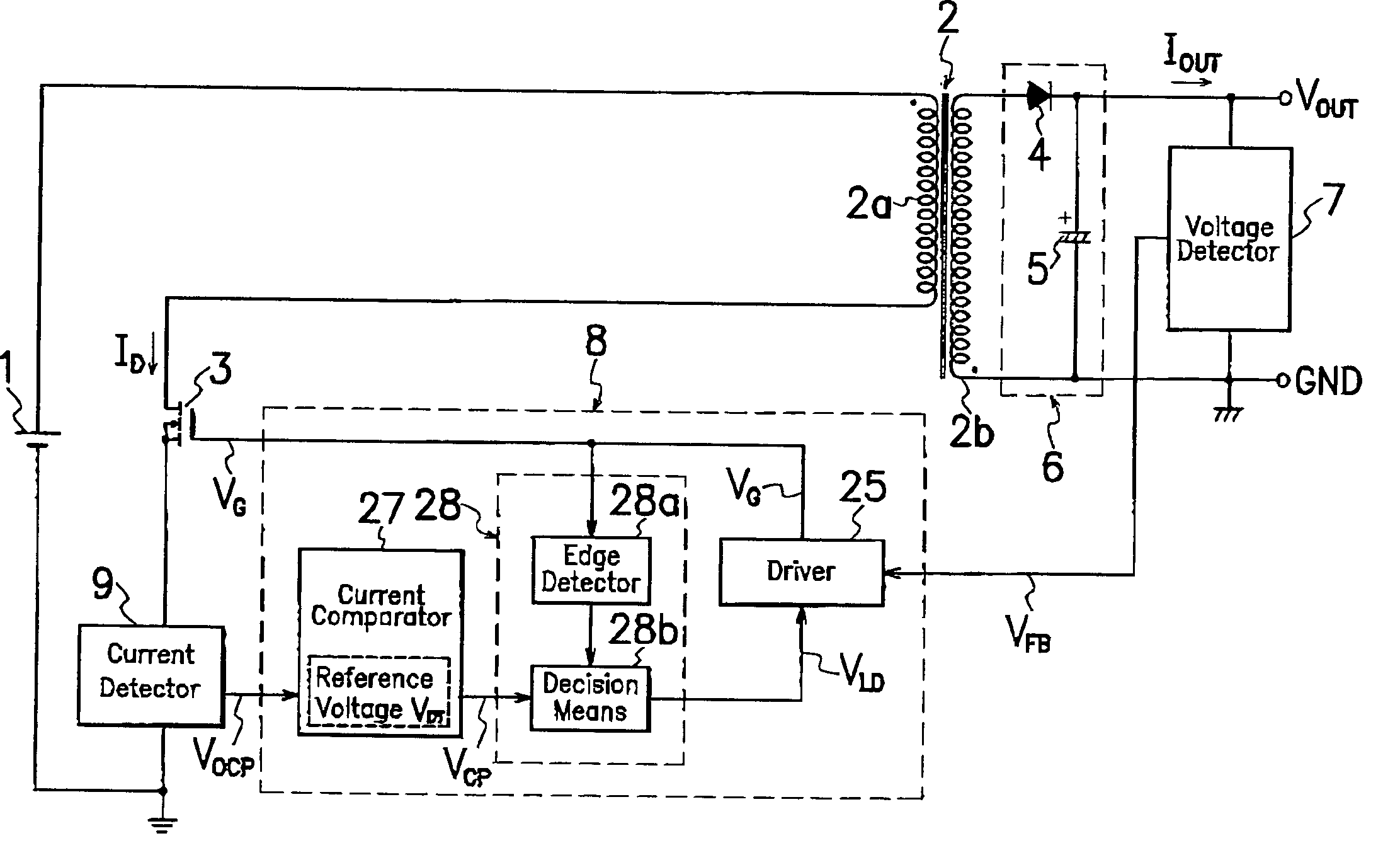

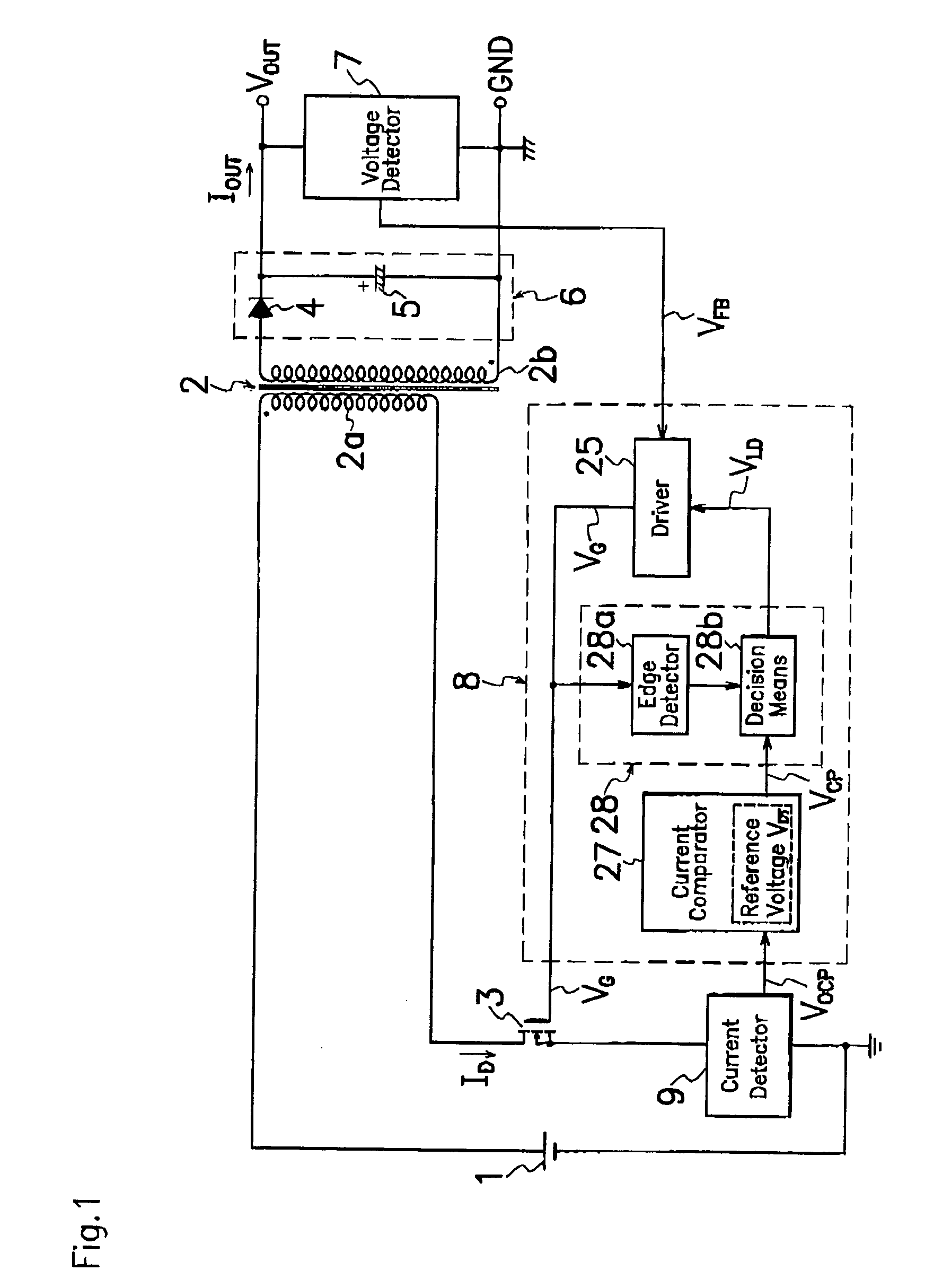

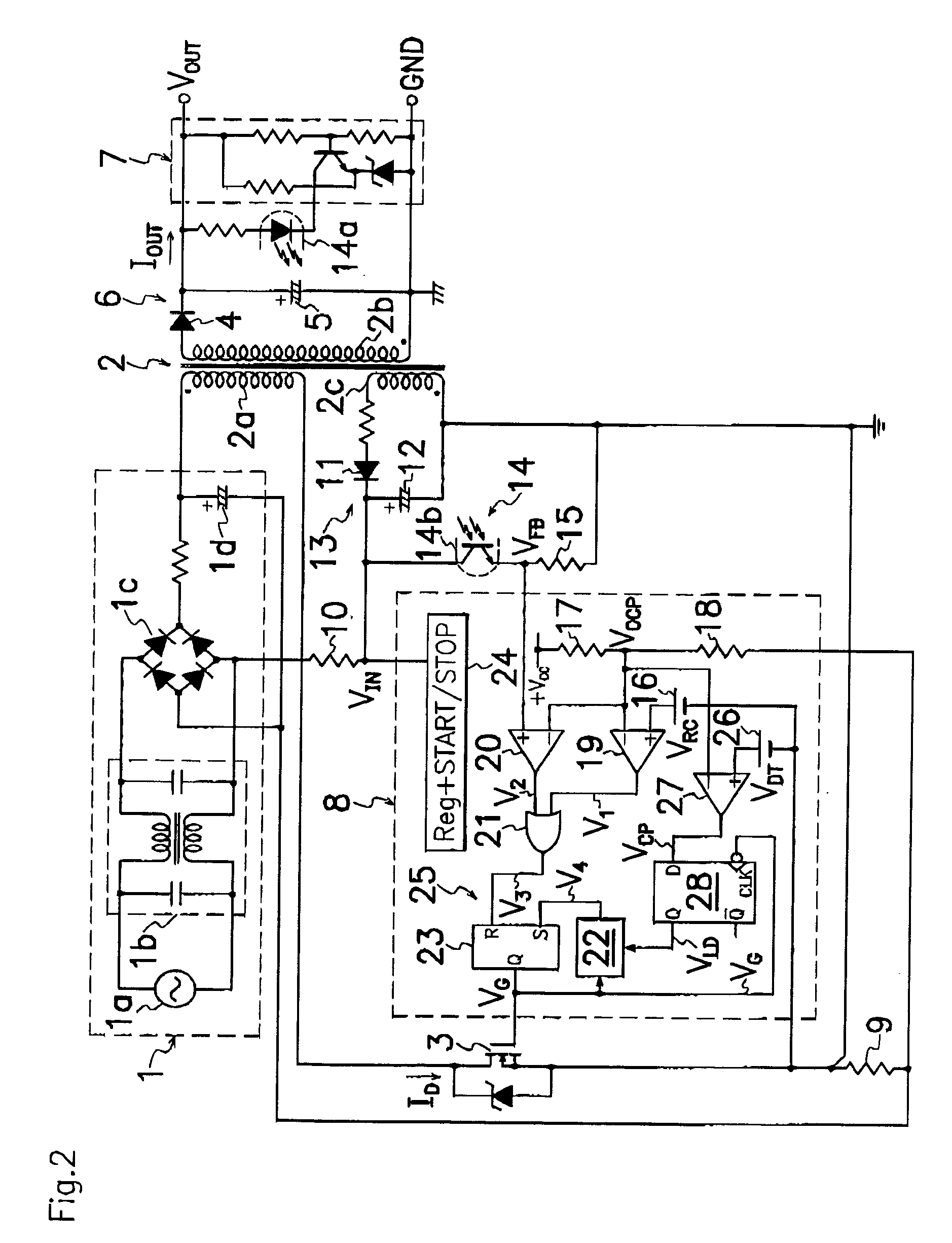

Switching power source device

InactiveUS7035119B2Reduce the oscillation frequencyImprove conversion efficiencyConversion with intermediate conversion to dcApparatus with intermediate ac conversionEngineeringVoltage reference

A switching power source comprises a current comparator 27 for comparing a voltage level of signals acquired by a current detector 9 with a reference voltage level VDT to produce detection signals VCP of first or second level L or H; an edge detector 28a for sensing an edge of drive signal VG supplied to a gate terminal of MOS-FET 3 during the period of transition from turning on to off of MOS-FET 3; and a decision means 28b for receiving a current detection signal VCP from current comparator 27 to produce an output signal VLD when edge detector 28a catches an edge of drive signal VG; wherein decision means 28b produces different output signals VLD of respectively first and second voltage levels L and H under the light and heavy load conditions to precisely and certainly detect on the primary side of transformer 2 the load condition on the secondary side of transformer 2 for improvement in conversion efficiency.

Owner:SANKEN ELECTRIC CO LTD

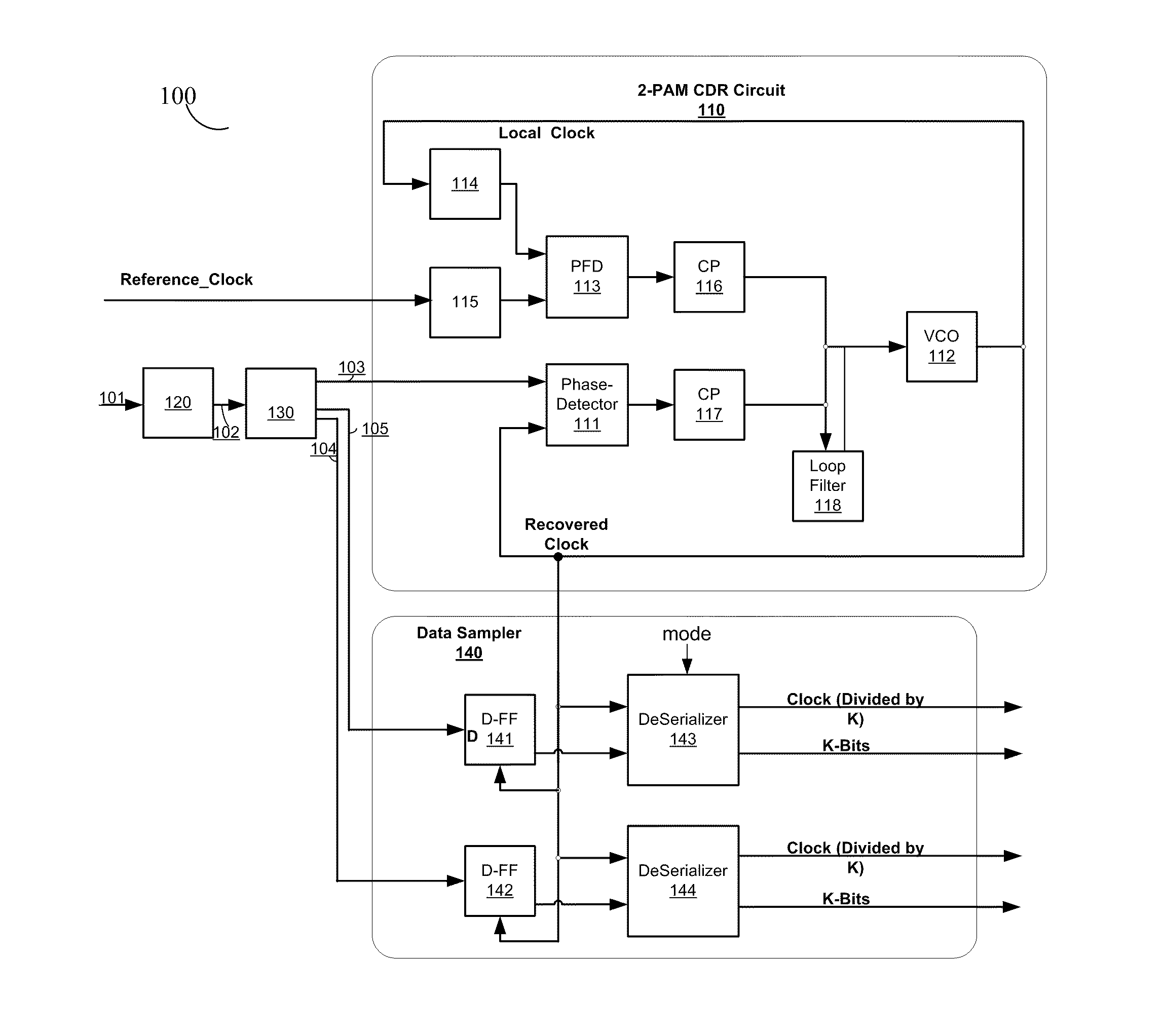

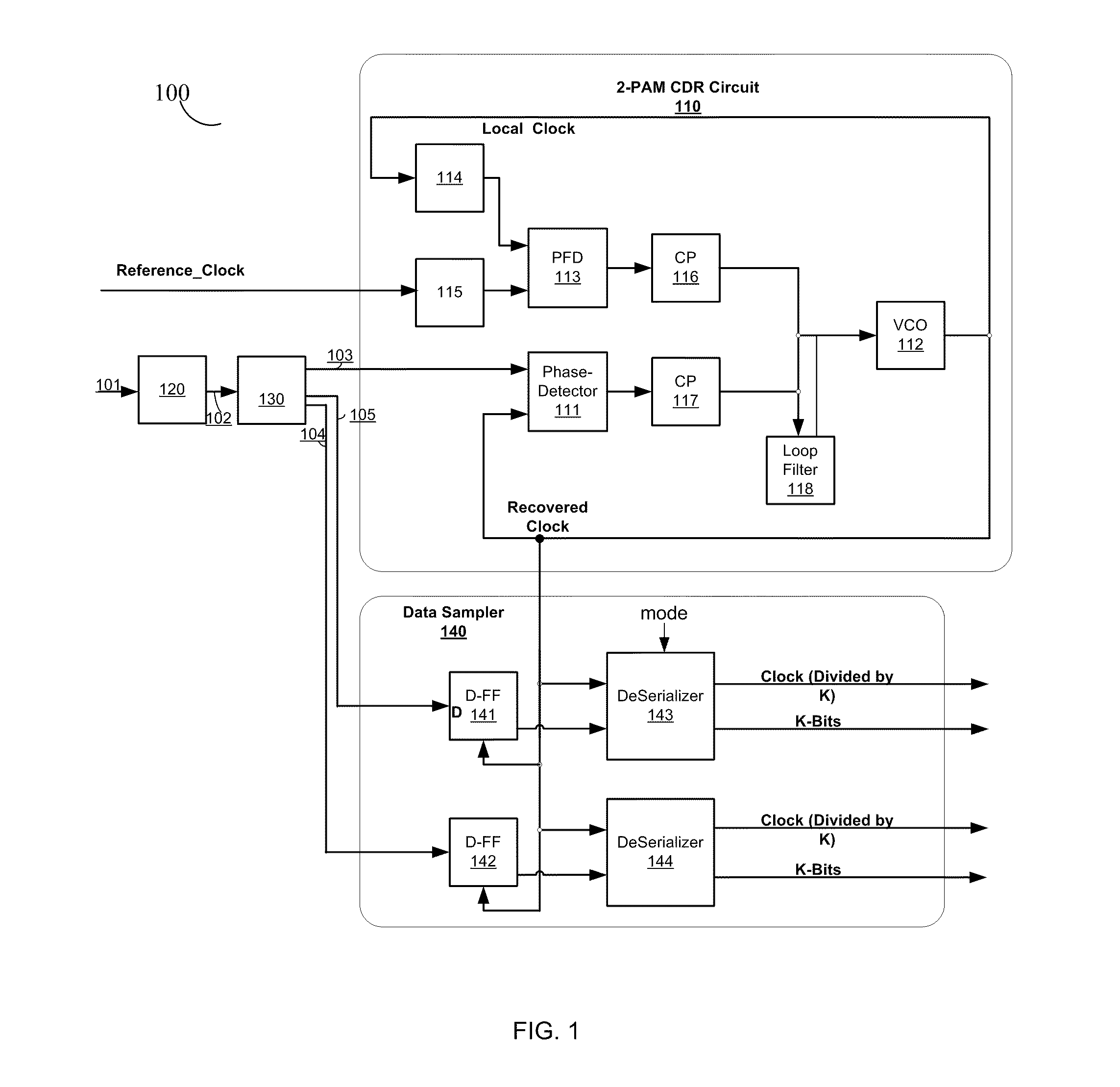

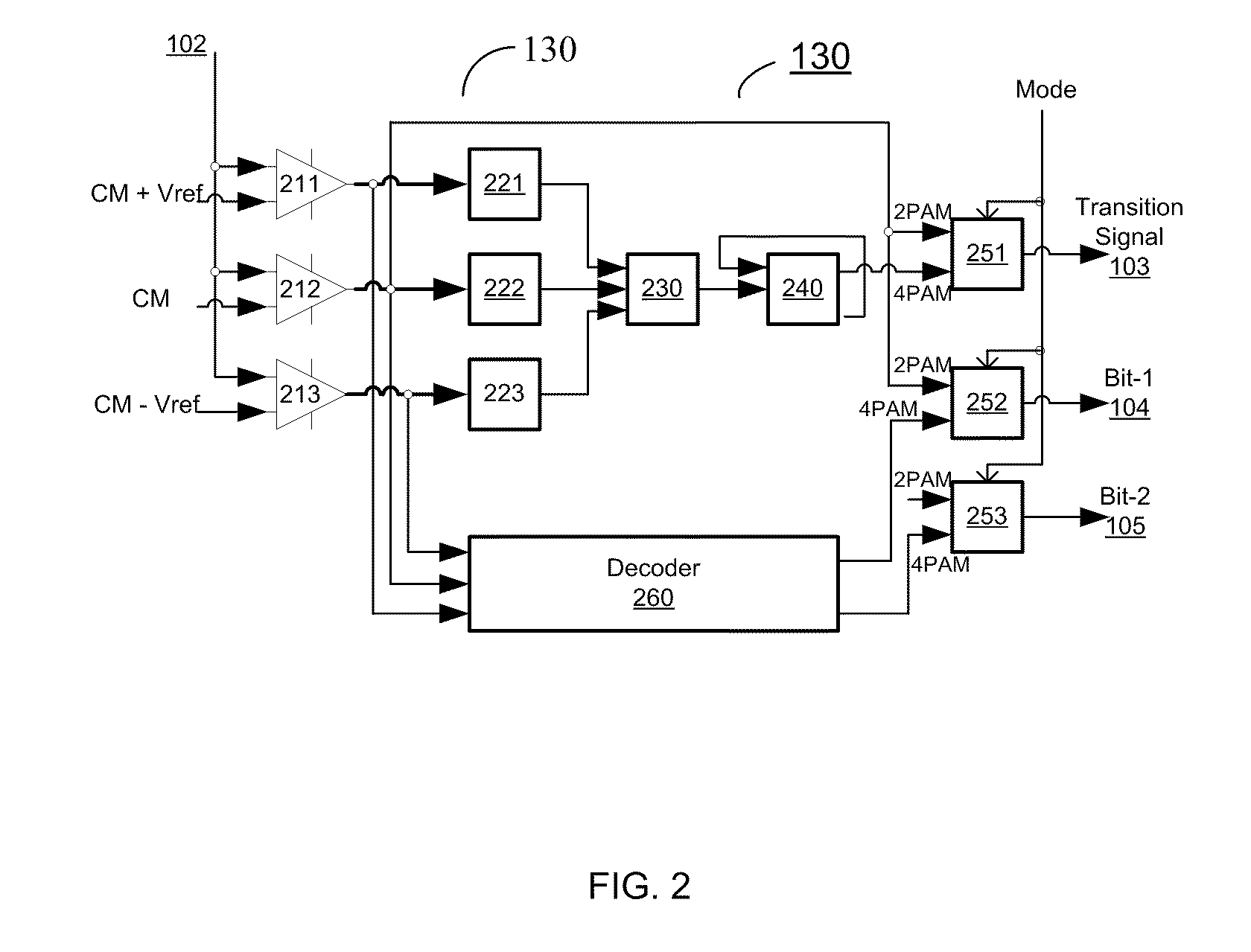

Apparatus and method thereof for clock and data recovery of n-PAM encoded signals using a conventional 2-PAM CDR circuit

An interface circuit for enabling clock and data recovery (CDR) of N-level pulse amplitude modulation (N-PAM) modulated data streams using a 2-PAM CDR circuit. The circuit comprises a number of N−1 comparators for comparing an input data stream to N−1 configurable thresholds, the input data stream is N-PAM modulated and the N−1 configurable thresholds are N−1 different voltage levels; a number of N−1 of edge detectors respectively connected to the N−1 comparators for detecting transitions from one logic value to another logic value, N is a discrete number greater than two; and a determination unit for determining if the detected transitions is any one of a major transition and a minor transition and asserting a transition signal if only a major transition or a minor transition has occurred, the transition signal is fed into a 2-PAM CDR circuit and utilized for recovering a clock signal of the input data stream.

Owner:CADENCE DESIGN SYST INC

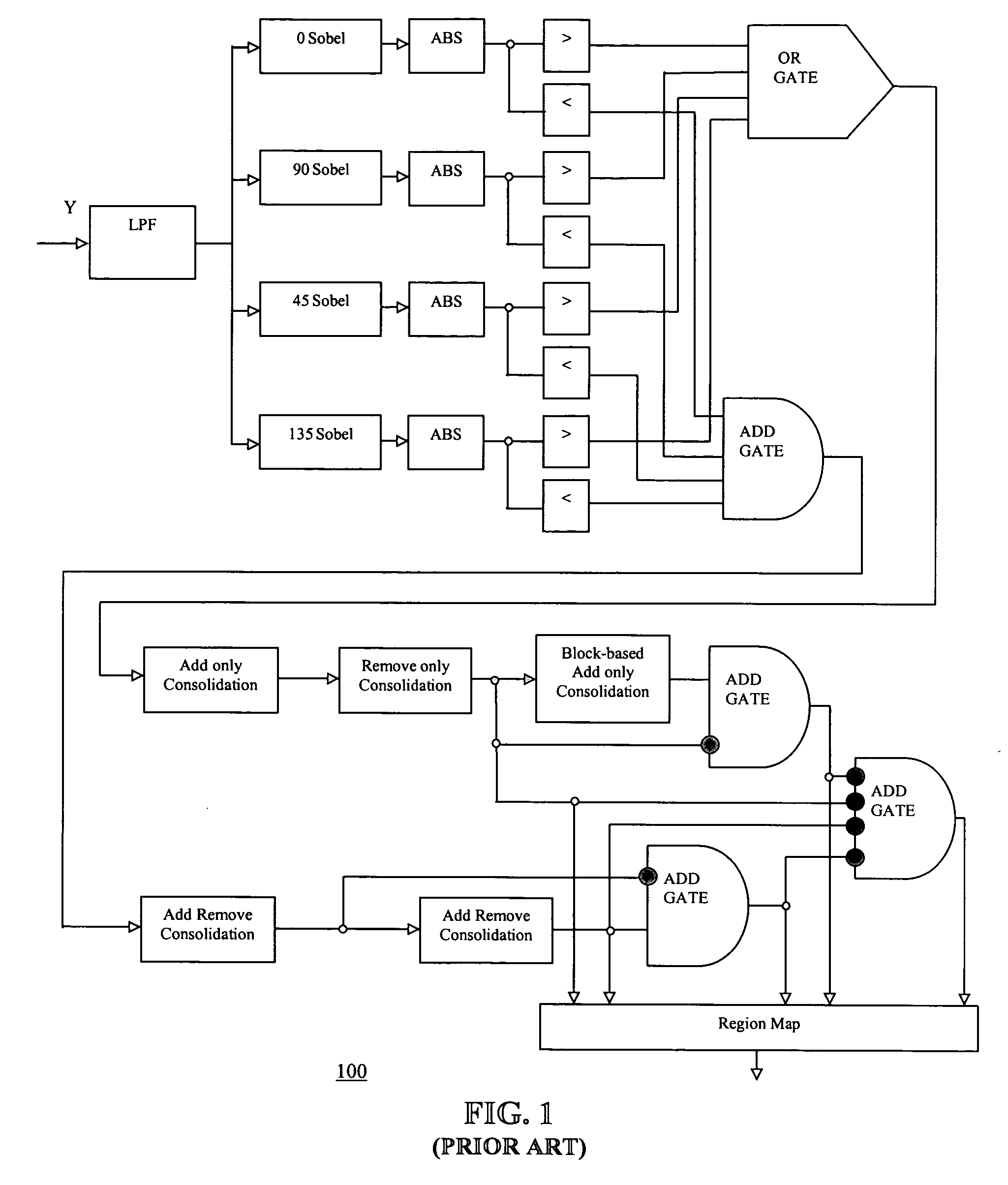

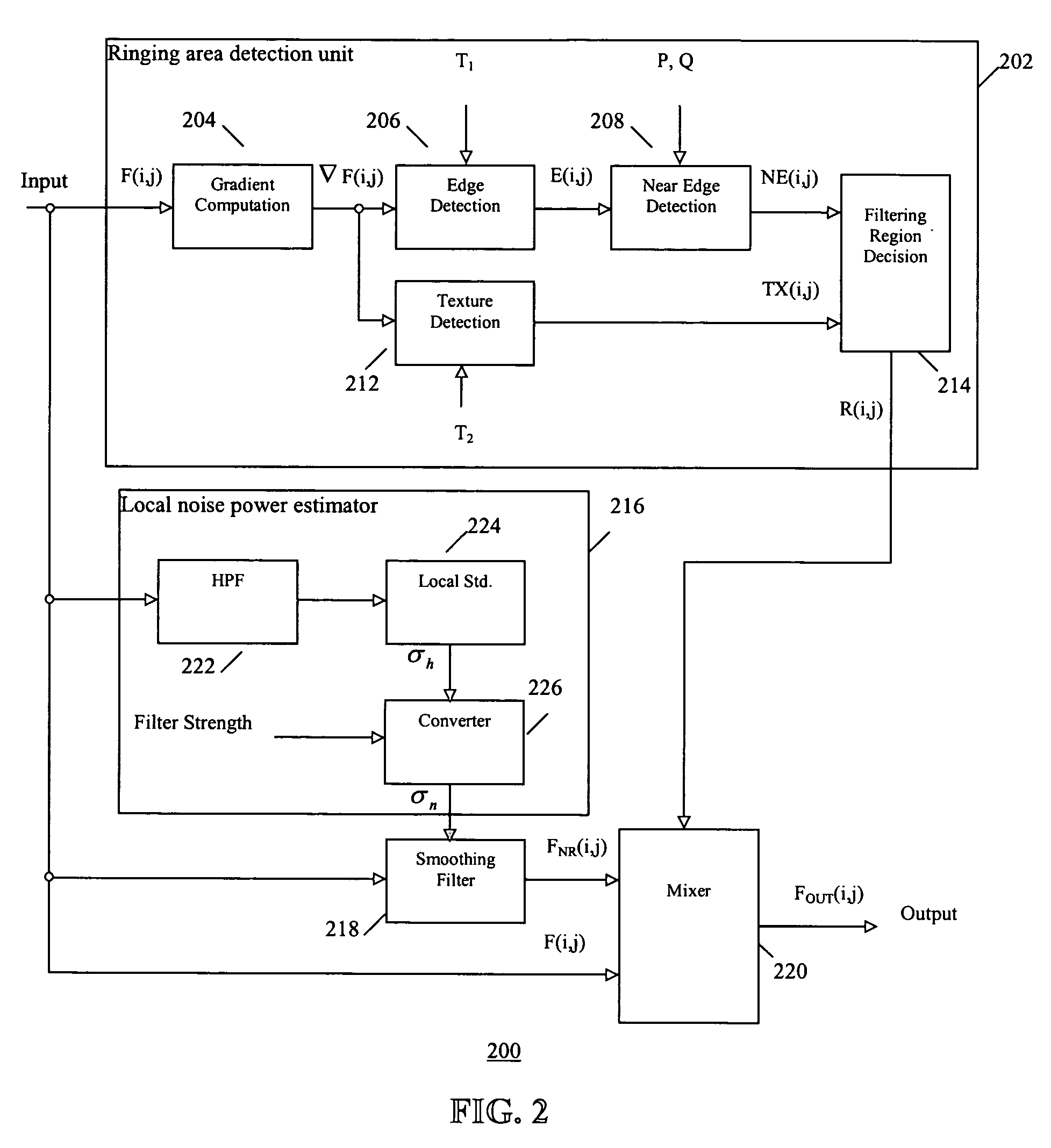

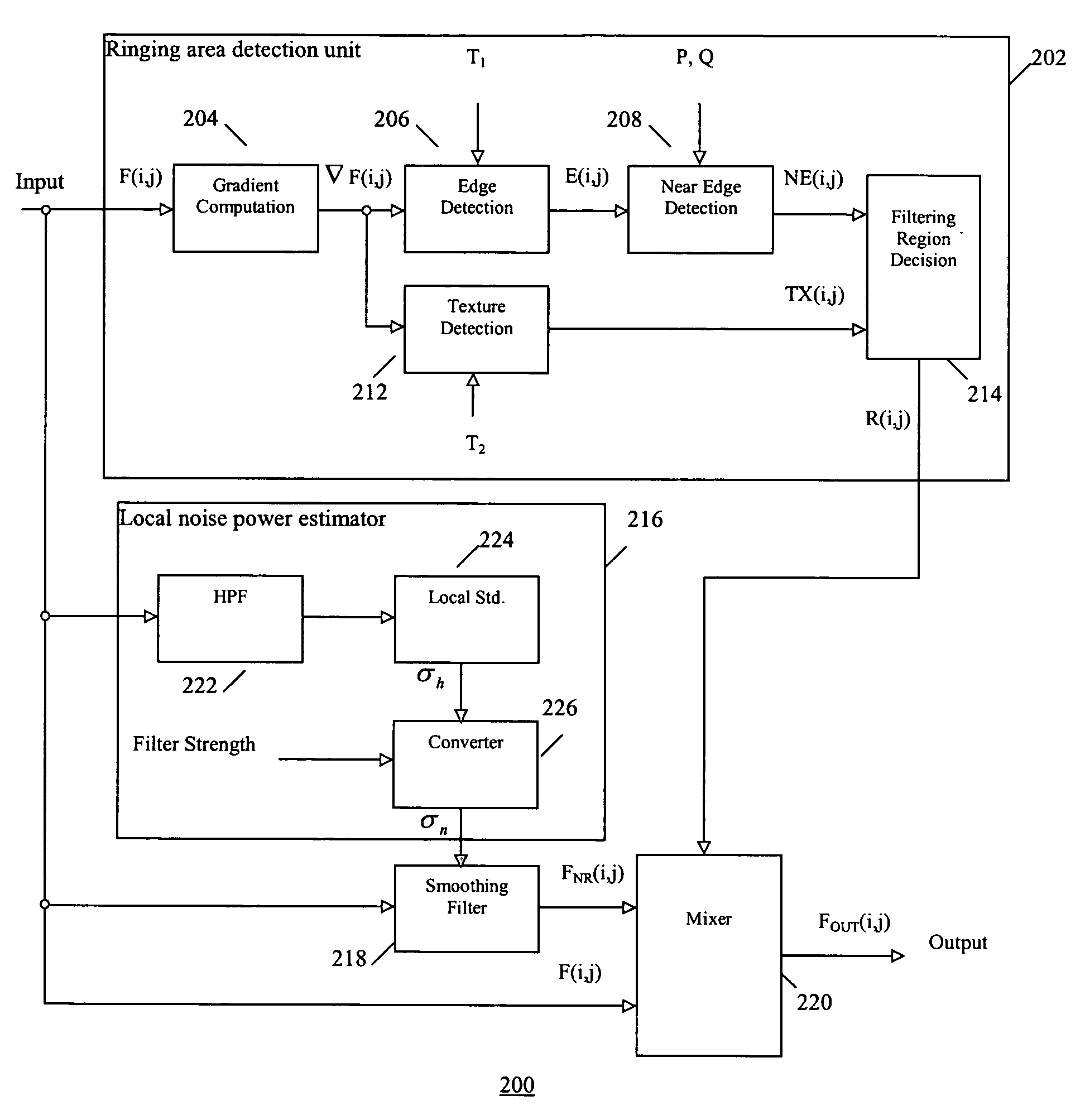

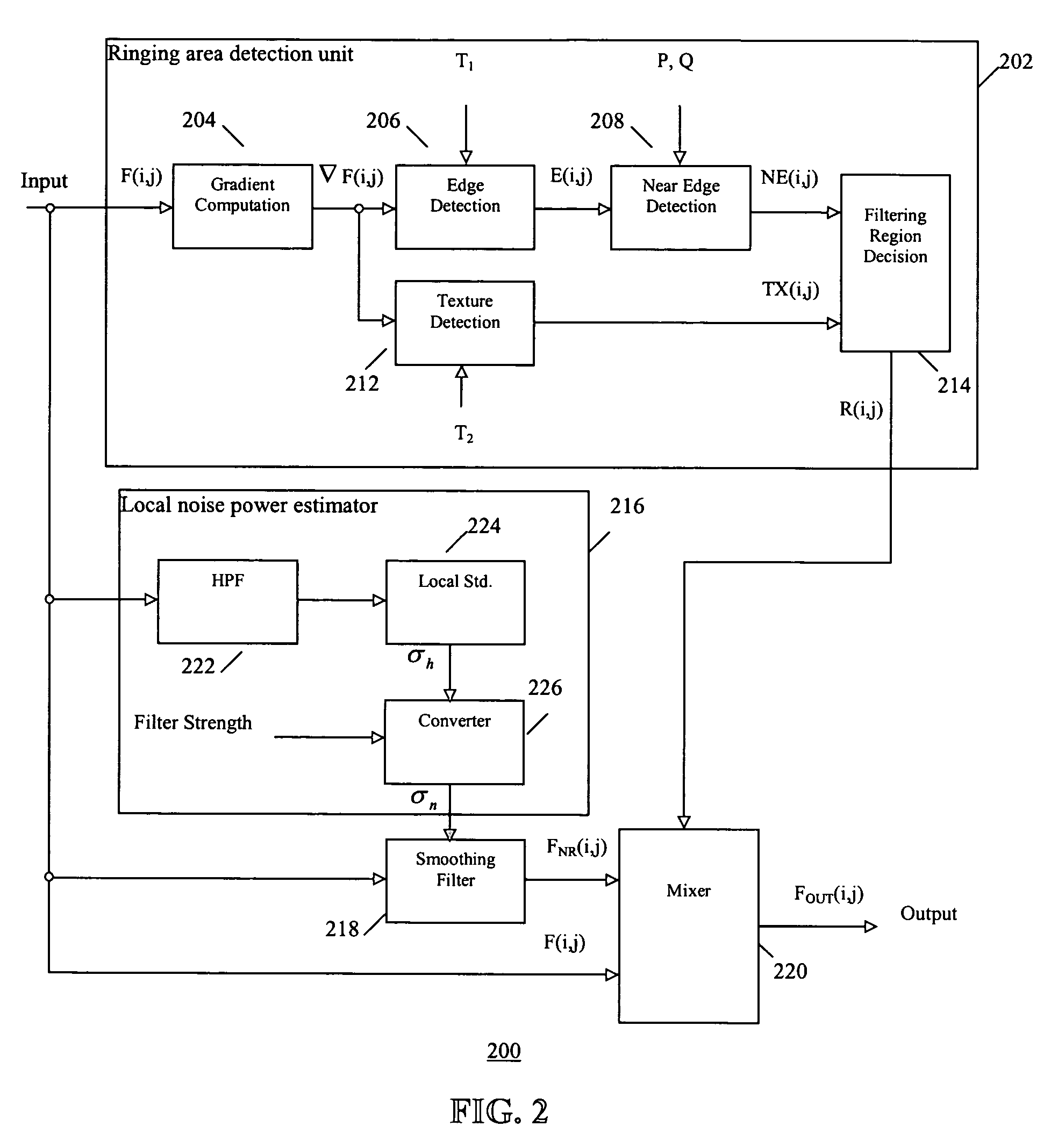

Method and apparatus for reducing mosquito noise in decoded video sequence

InactiveUS20060245506A1Reducing mosquito noiseSimple ringing (mosquito noise)Television system detailsPicture reproducers using cathode ray tubesVideo sequenceArea detector

A ringing area detector classifies the input image into two regions: a mosquito noise region (i.e. filtering region) and a non-mosquito noise region (i.e. non-filtering region), and uses this classification information to adaptively remove the mosquito noise in a mosquito noise reduction system. The mosquito noise reduction system includes a ringing area detector, a local noise power estimator, a smoothing filter, and a mixer. The ringing area detector includes an edge detector, a near edge detector, a texture detector, and a filtering region decision block. The ringing detection block detects the ringing area where the smoothing filter is to be applied. The local noise power estimator controls the filter strength of the smoothing filter. The smoothing filter smoothes the input image. The mixer mixes the smoothed image and the original image properly based on the region information from the ringing area detection block.

Owner:SAMSUNG ELECTRONICS CO LTD

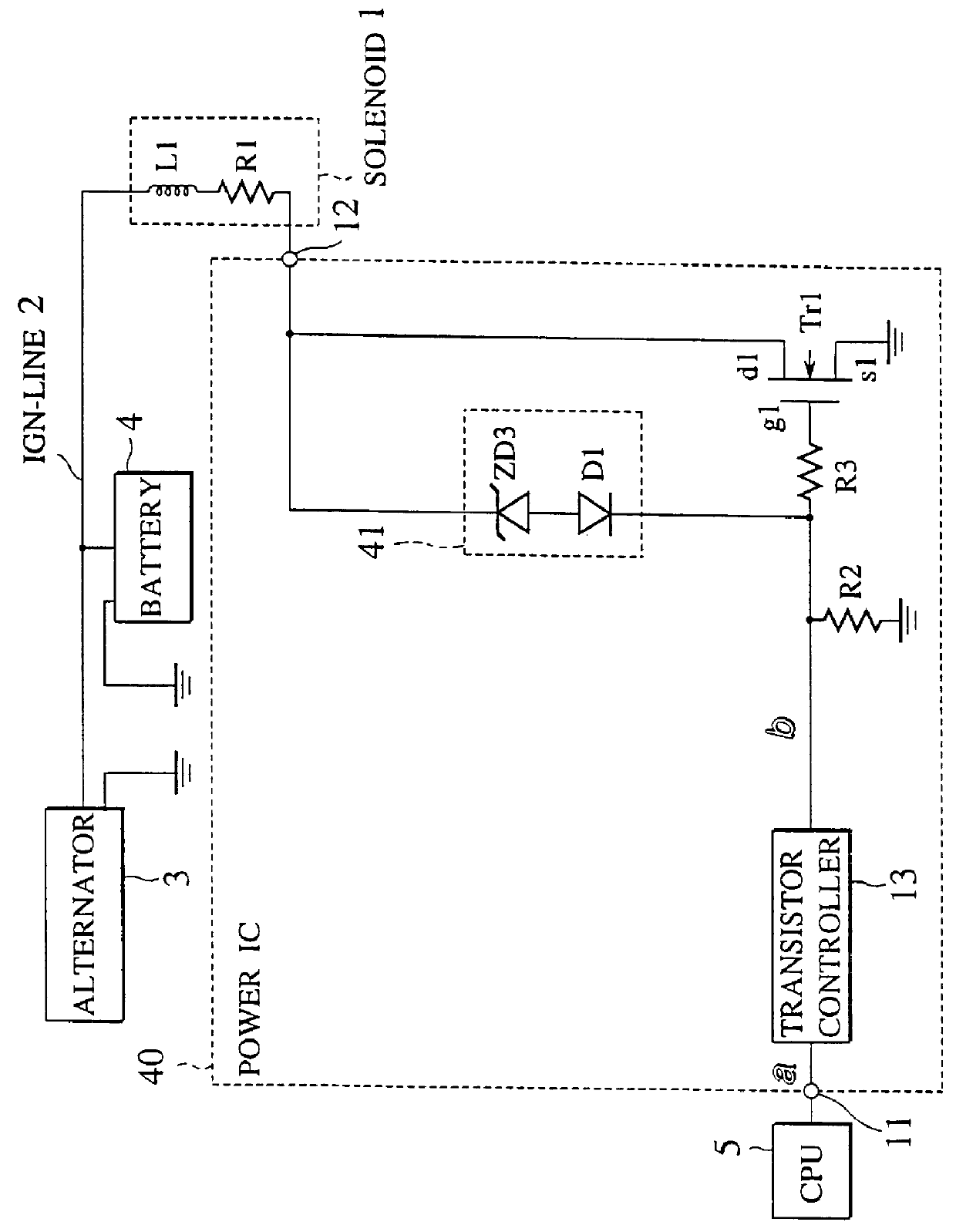

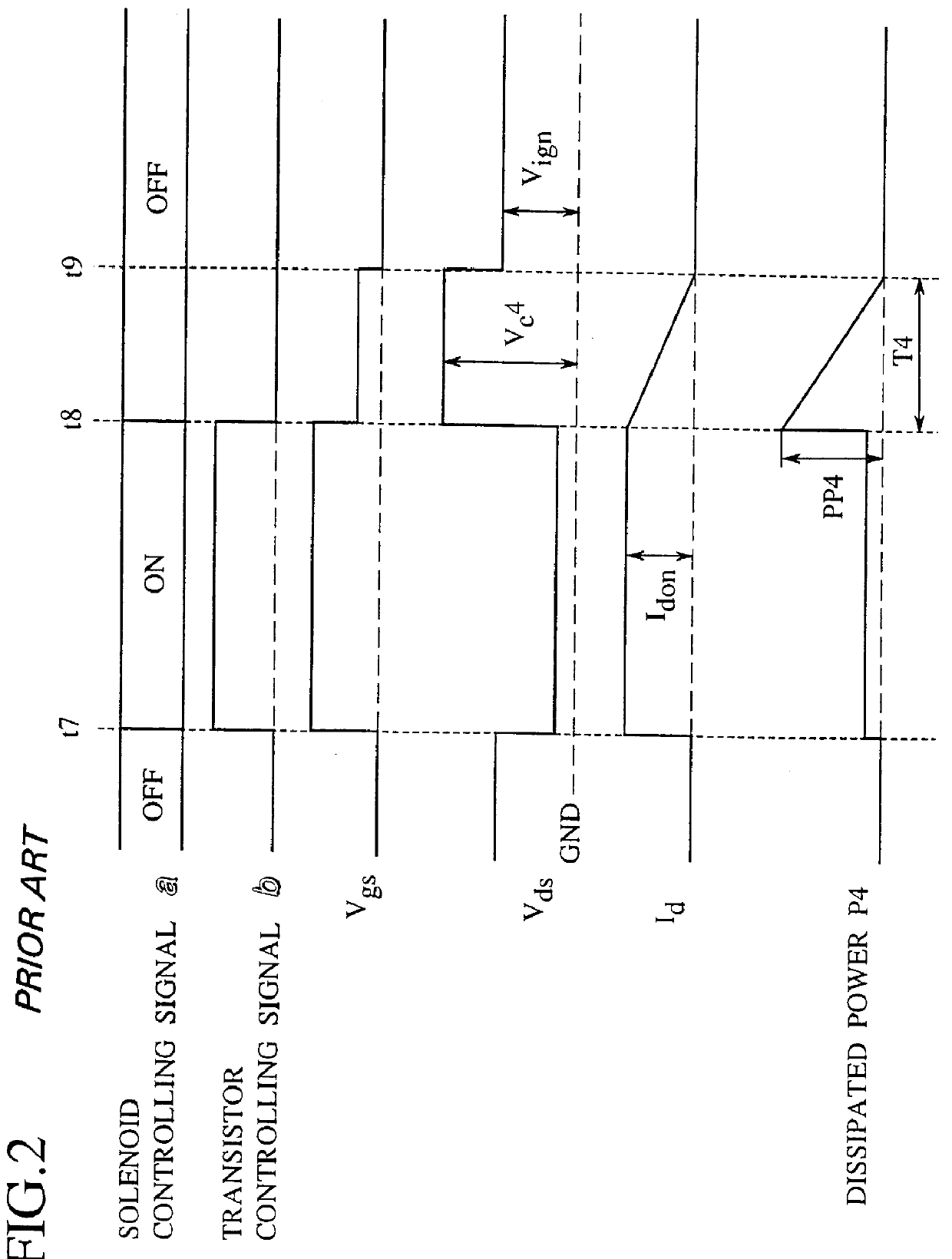

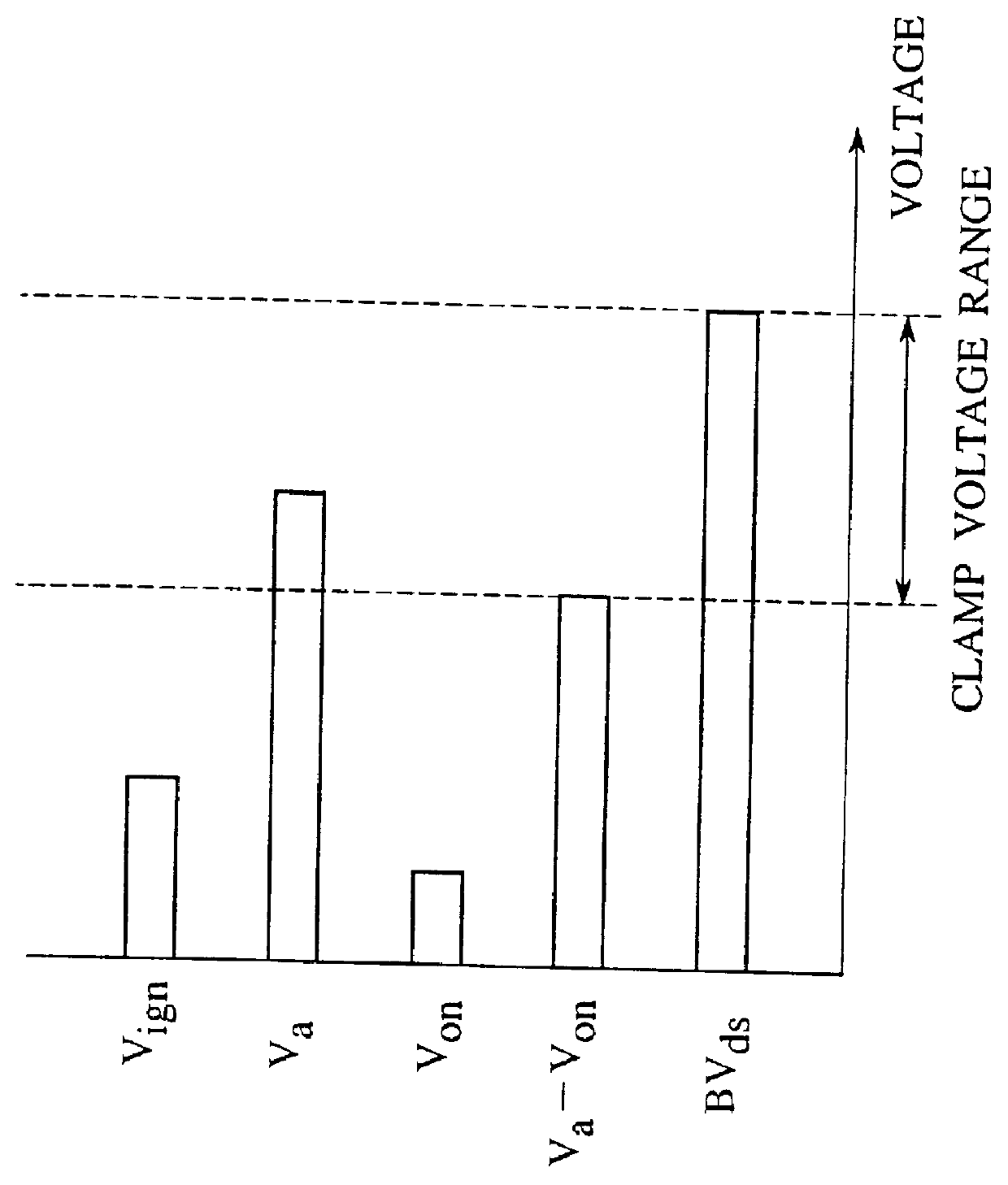

Integrated circuit having surge protection circuit

A trailing edge of a control signal of a transistor controller for controlling an output transistor is detected by an edge detector of a clamp controlling circuit. A surge voltage from a back electromotive voltage induced in an inductance L1 is absorbed from the output transistor, only for a given period immediately after the solenoid is turned off, by turning a switching transistor into an on-state by a timer to force a clamping circuit into conduction. At a normal operation, since the clamping circuit is cut off from an output terminal, the clamping voltage can be set in a manner to reduce to a normal voltage in an IGN-line. Therefore, a peak power value of a power loss caused by the surge voltage at the output transistor can be reduced, whereby generation of heat at the output transistor can be reduced. Therefore, the chip size of the power IC can be reduced.

Owner:NISSAN MOTOR CO LTD

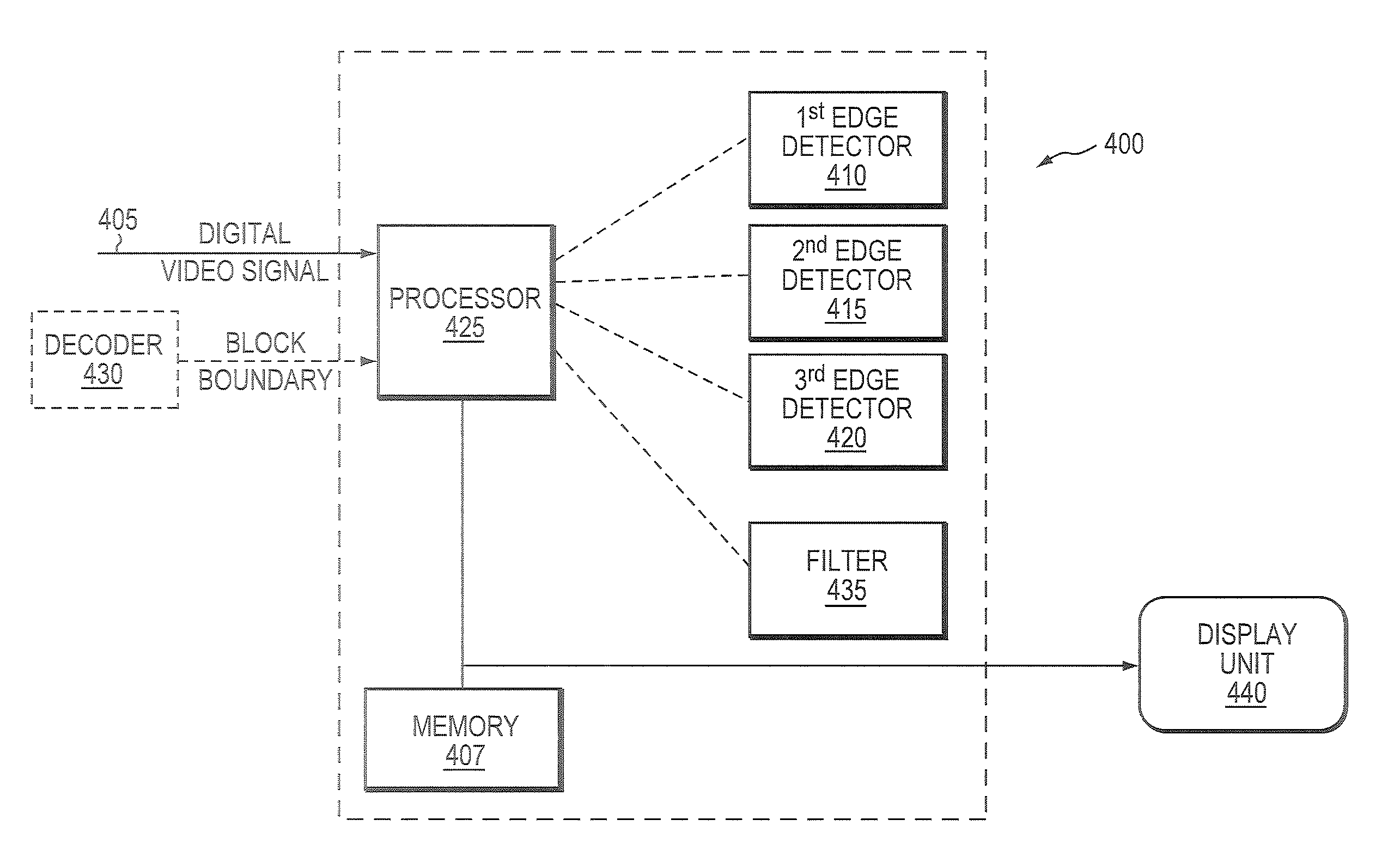

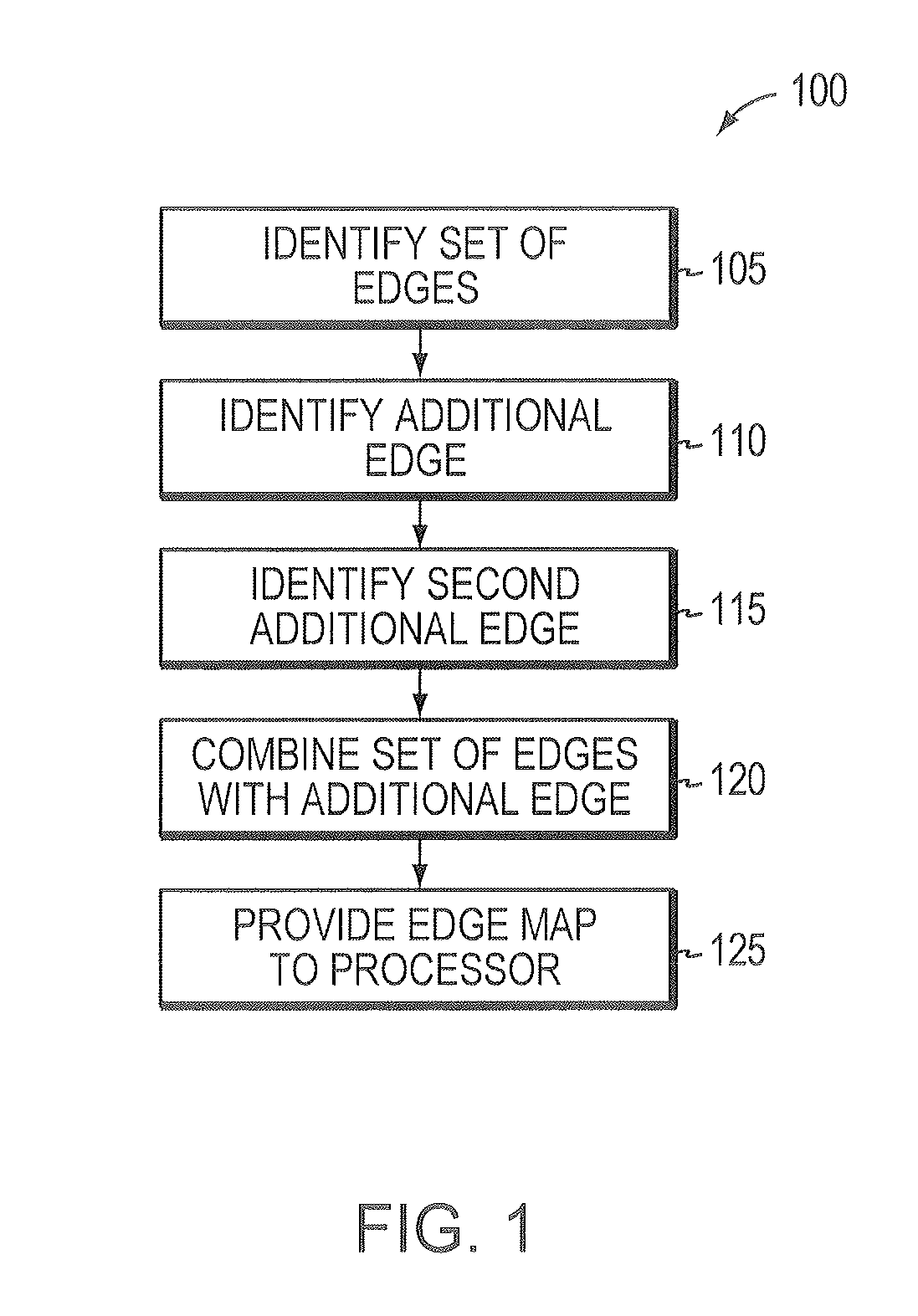

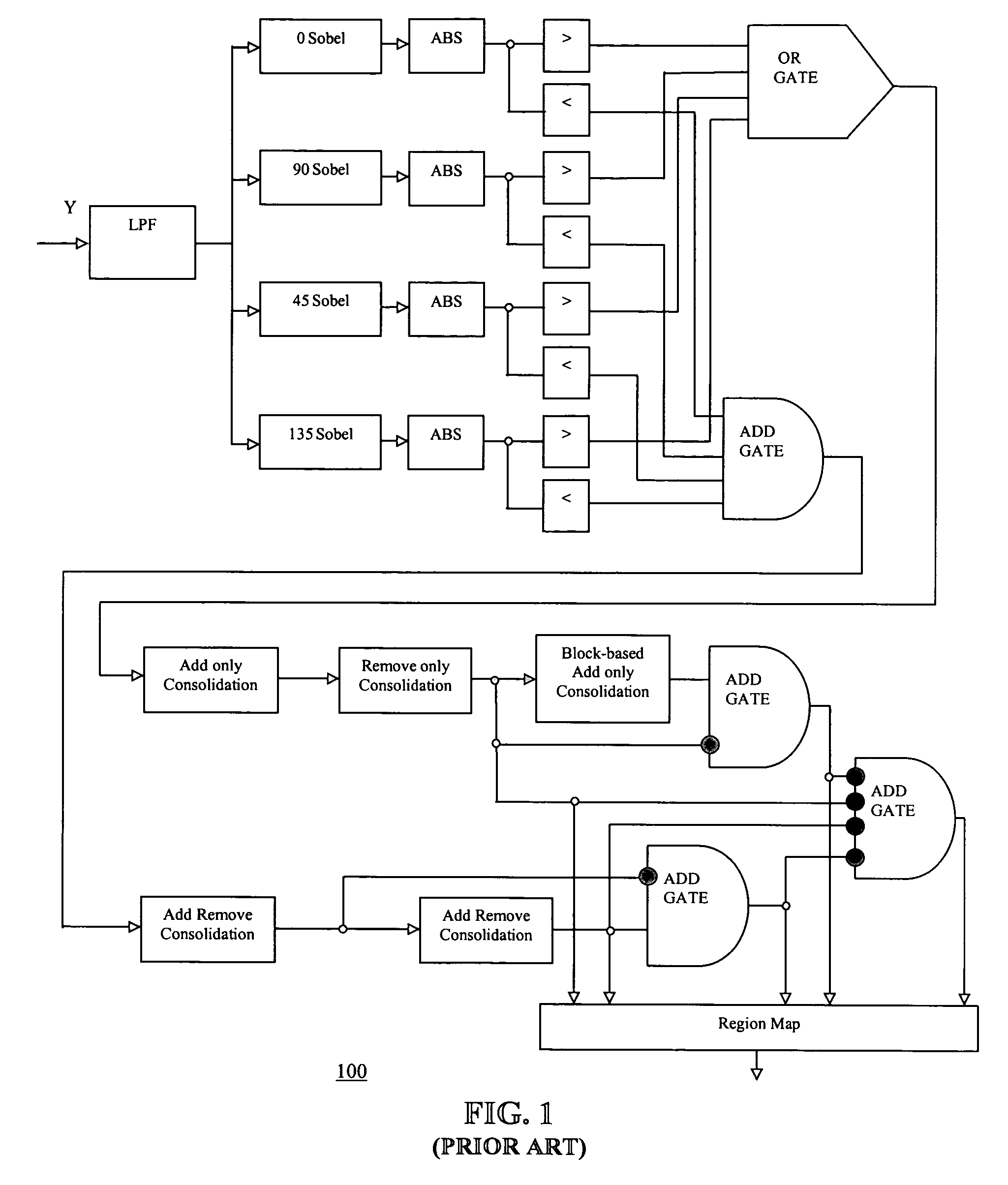

System and method for detecting edges in a video signal

A system and method for processing a digital video signal corresponding to an image are provided. A plurality of independent edge detecting processes or edge detector modules detect a set of edges and at least one additional edge that is not included in the set of edges. An edge map includes data regarding all edges identified by any edge detecting process or module, and a visually perceptible artifact of the image is altered based at least in part on an evaluation of the edge map. The system and method detects and filters block artifacts and ringing or other noise from digital images, resulting in reduced image distortion.

Owner:CSR TECH INC

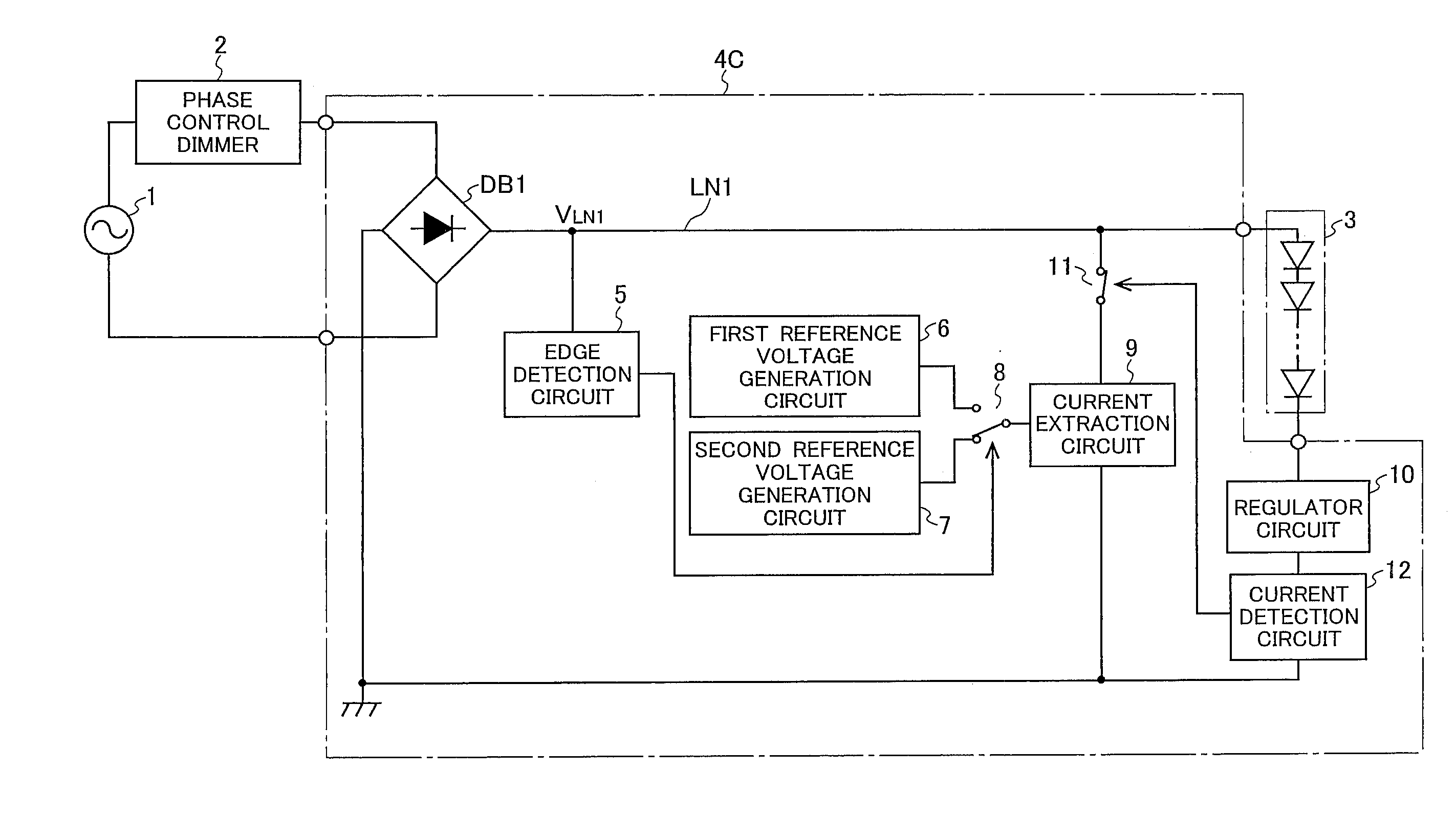

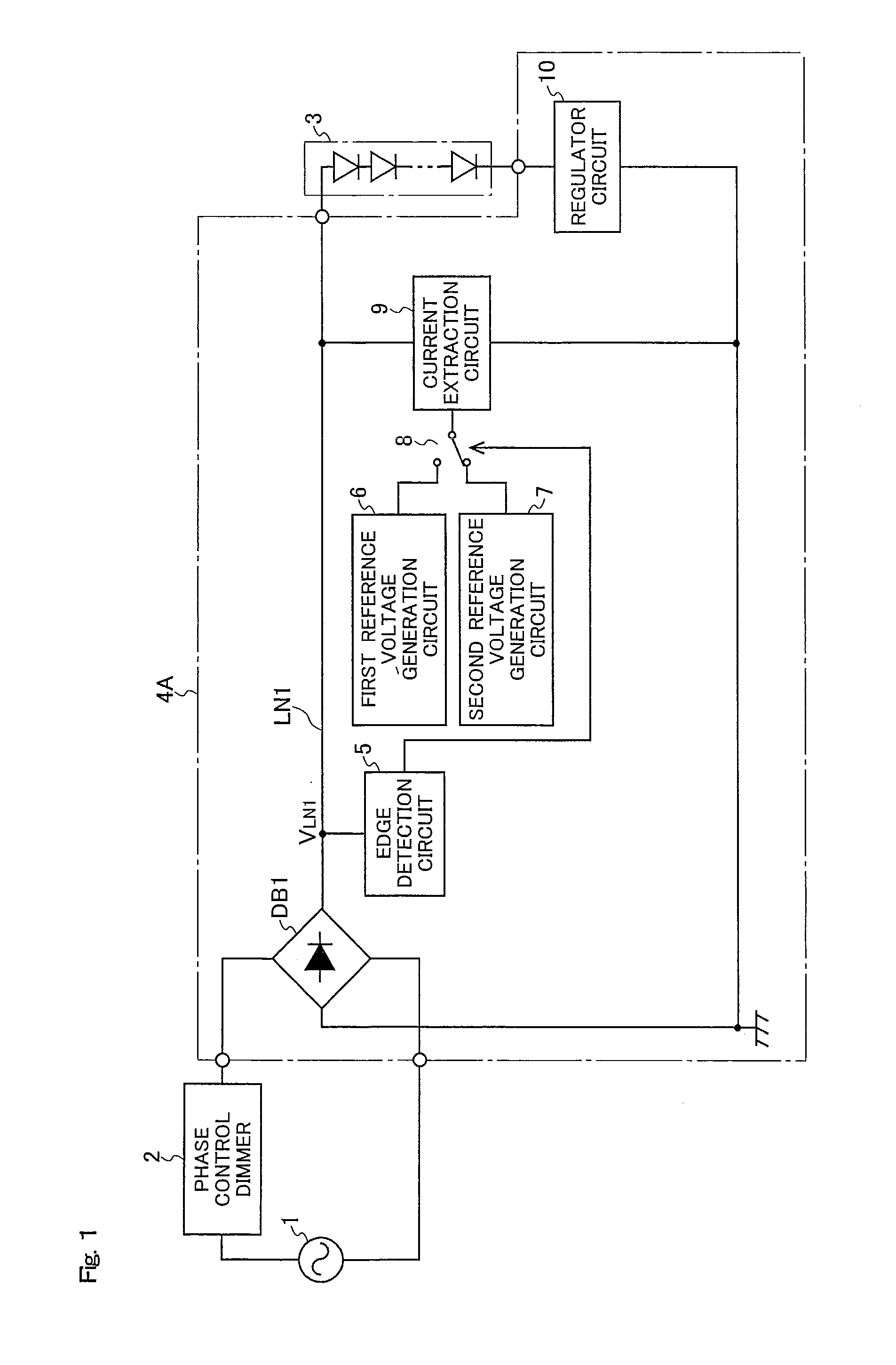

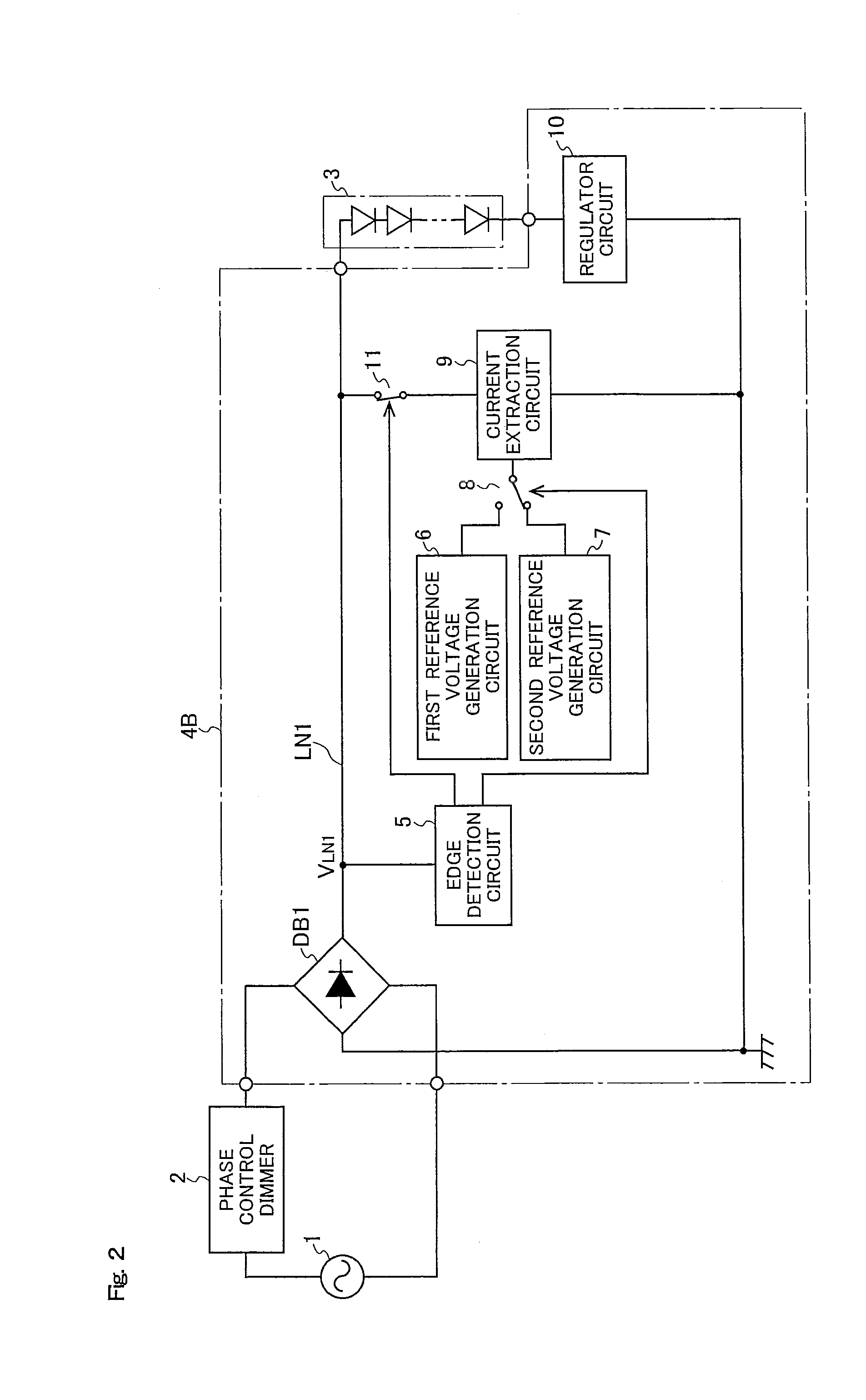

LED drive circuit, LED illumination fixture, LED illumination device, and LED illumination system

InactiveUS20110234115A1Reduce flickerReducing LED flickerElectrical apparatusElectroluminescent light sourcesDriving currentPower flow

Owner:SHARP KK

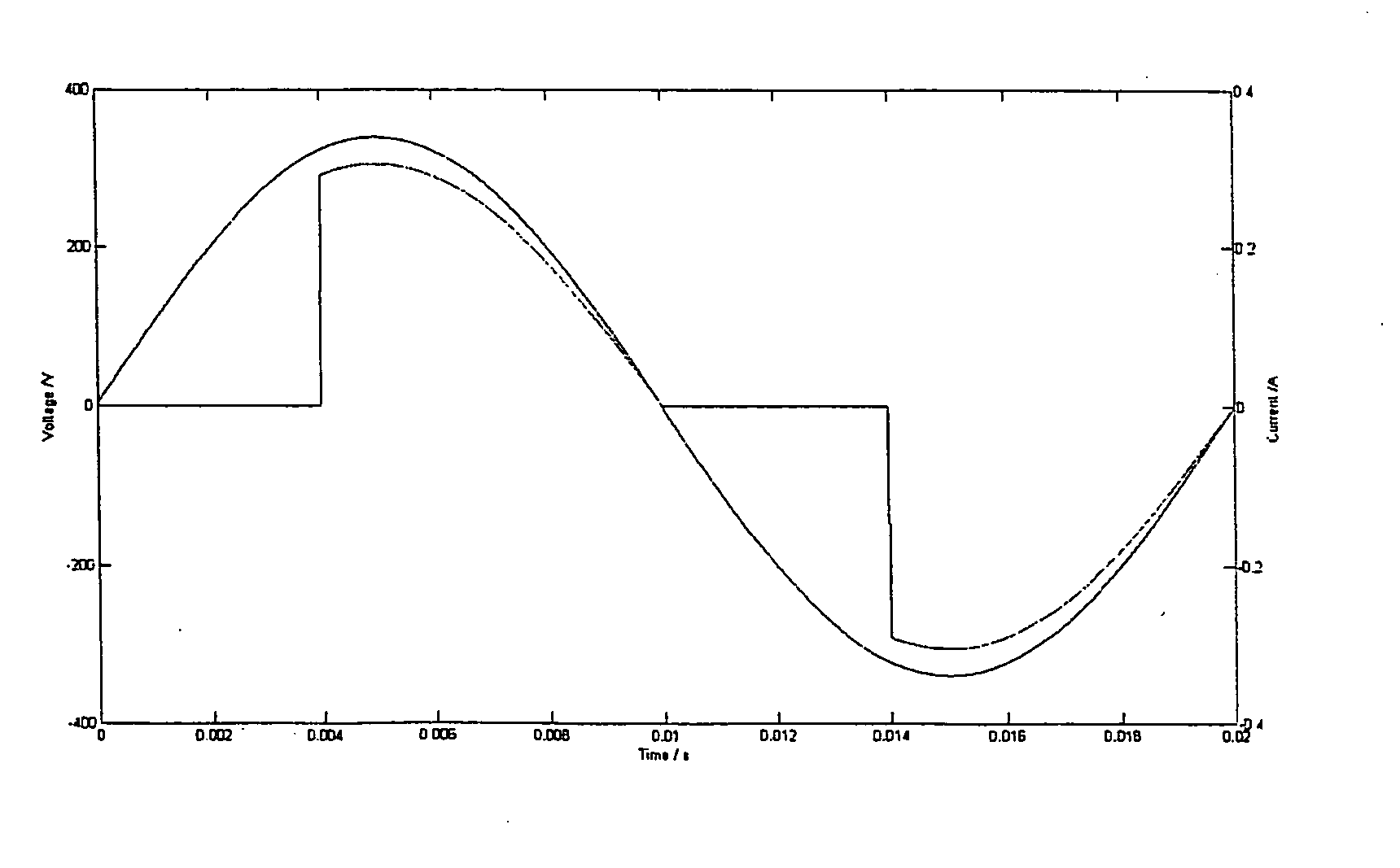

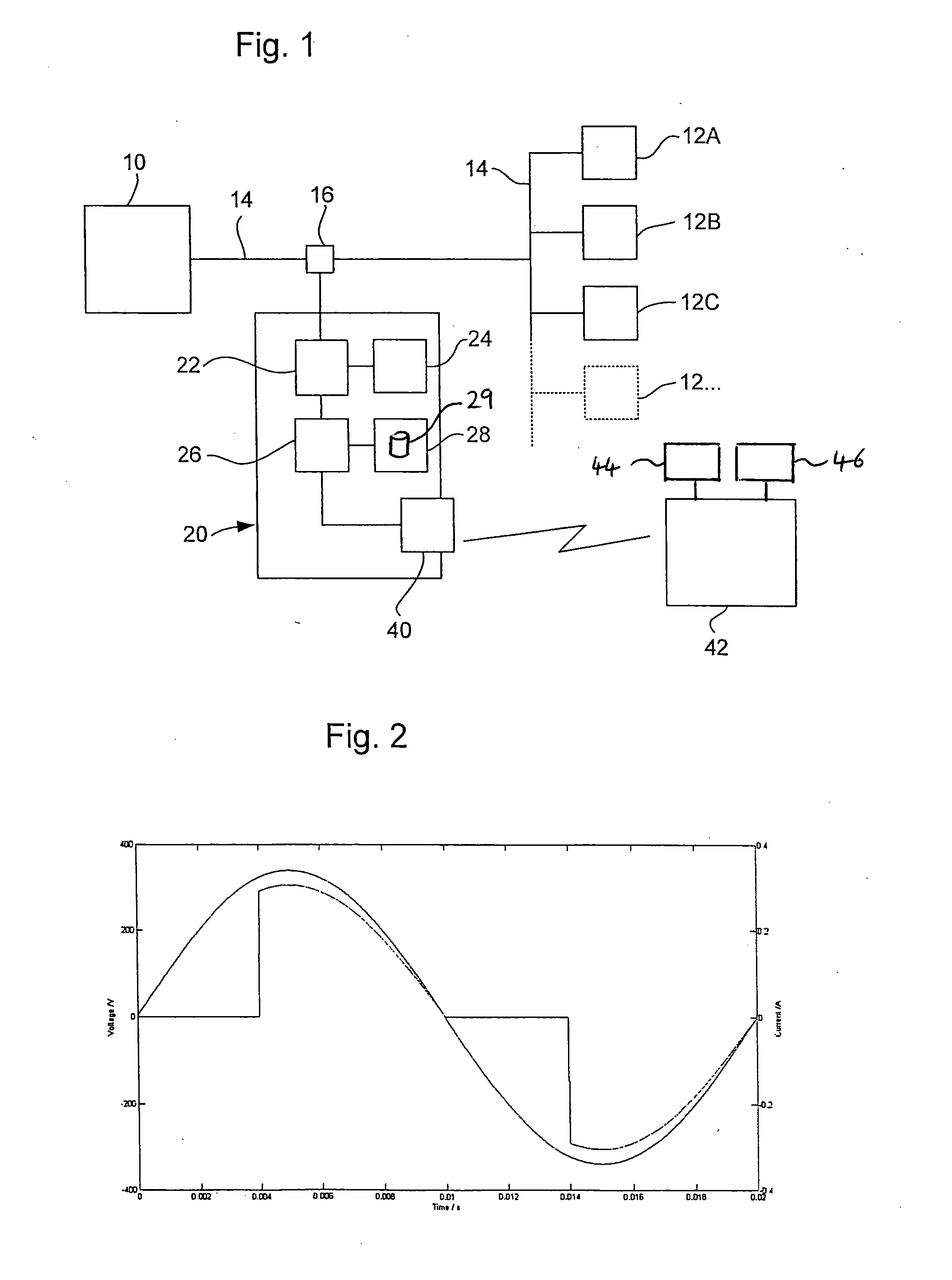

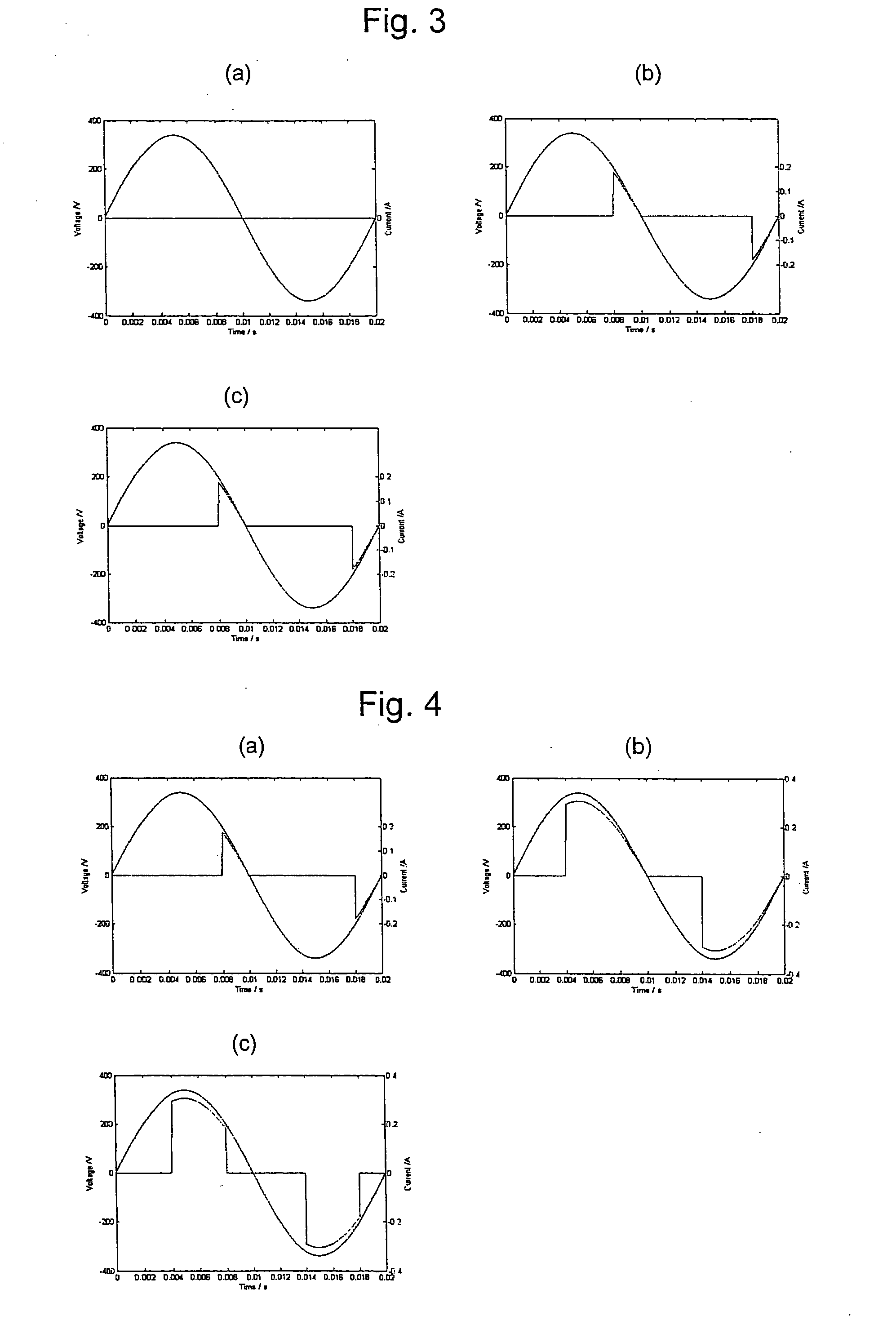

Utility metering

InactiveUS20110153246A1Present inventionAccurate methodTariff metering apparatusResistance/reactance/impedenceElectricityElectrical resistance and conductance

An apparatus has an input section arranged to receive values representative of the total instantaneous supply of electrical current as a function of time from an alternating voltage supply. Current waveforms comprising sets of values representative of the cyclic waveform of the electric current supply are obtained. A delta waveform generator calculates the difference between a current waveform and an earlier current waveform. An edge detector is arranged to detect an edge or edges in the delta waveform. An analysis section is arranged to identify at least one appliance load based at least on information on the edge or edges detected by the edge detector, and to determine the electrical energy consumed by said appliance load. Another apparatus has an input section arranged to receive values representative of the current supplied to an installation, such as a house. A store contains appliance data characteristic of the use of electricity by each of a plurality of appliances. A processor is arranged to analyse the received values to detect when an appliance is switched on and determine the fractional change in resistance of a heating appliance from the when it is switched on until it reaches its operating temperature. This information is used to identify what the particular appliance is, and to determine the electrical energy consumption by that appliance. A utility meter for metering the use of at least one utility supplied to a plurality of appliances is also disclosed. An input section is arranged to receive values representative of the use of a first utility. A store contains appliance data characteristic of the use of utilities by each of a plurality of appliances. A processor is arranged to analyse the received values and to determine information on the use of a second utility by each appliance, based on the received values and appliance data.

Owner:ISIS INNOVATION LTD

Switching power source device

InactiveUS20050259448A1Reduce the oscillation frequencyImprove conversion efficiencyConversion with intermediate conversion to dcApparatus with intermediate ac conversionVoltage referenceSecondary side

A switching power source comprises a current comparator 27 for comparing a voltage level of signals acquired by a current detector 9 with a reference voltage level VDT to produce detection signals VCP of first or second level L or H; an edge detector 28a for sensing an edge of drive singal VG supplied to a gate terminal of MOS-FET 3 during the period of transition from turning on to off of MOS-FET 3; and a decision means 28b for receiving a current detection signal VCP from current comparator 27 to produce an output signal VLD when edge detector 28a catches an edge of drive signal VG; wherein decision means 28b produces different output signals VLD of respectively first and second voltage levels L and H under the light and heavy load conditions to precisely and certainly detect on the primary side of transformer 2 the load condition on the secondary side of transformer 2 for improvement in conversion efficiency.

Owner:SANKEN ELECTRIC CO LTD

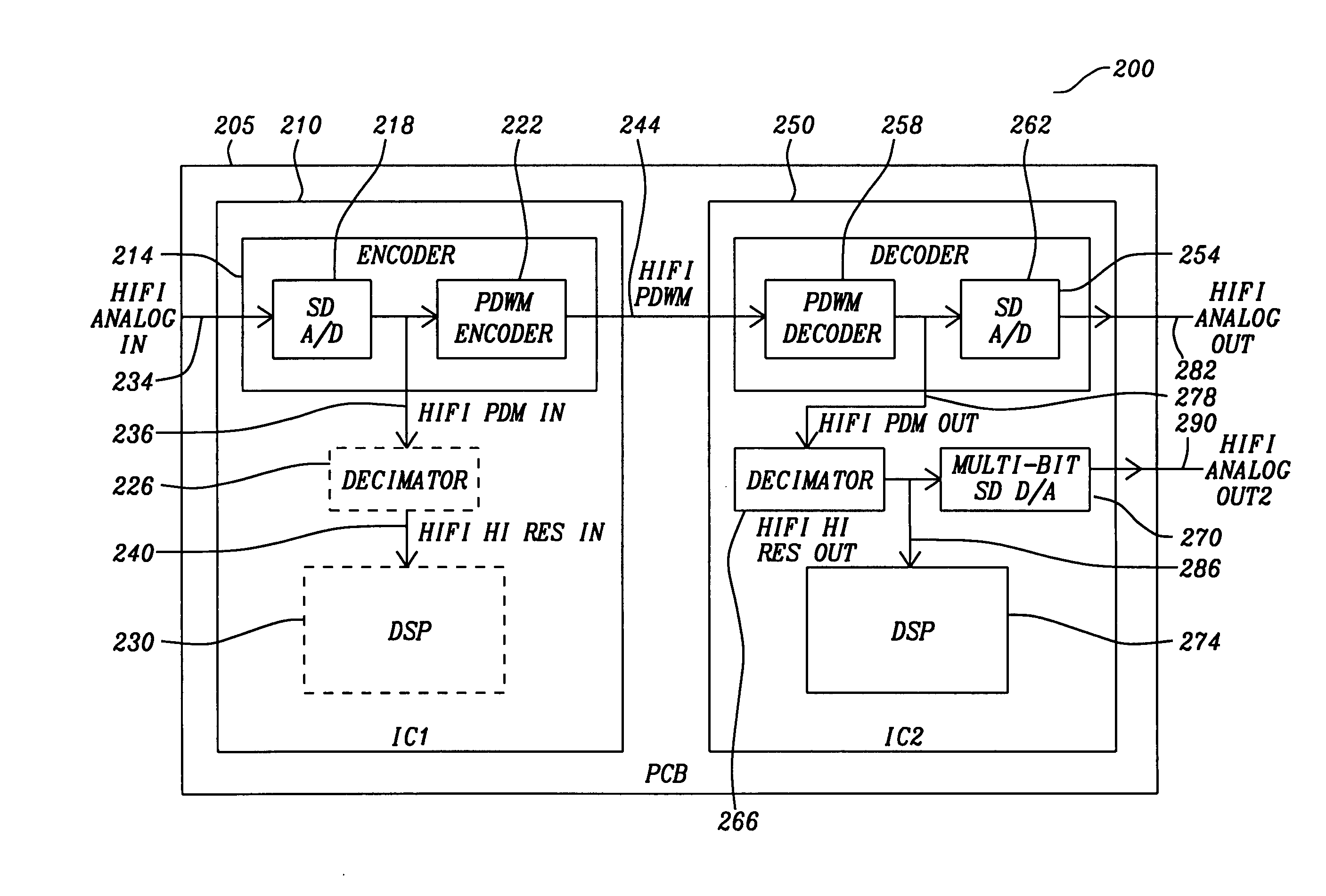

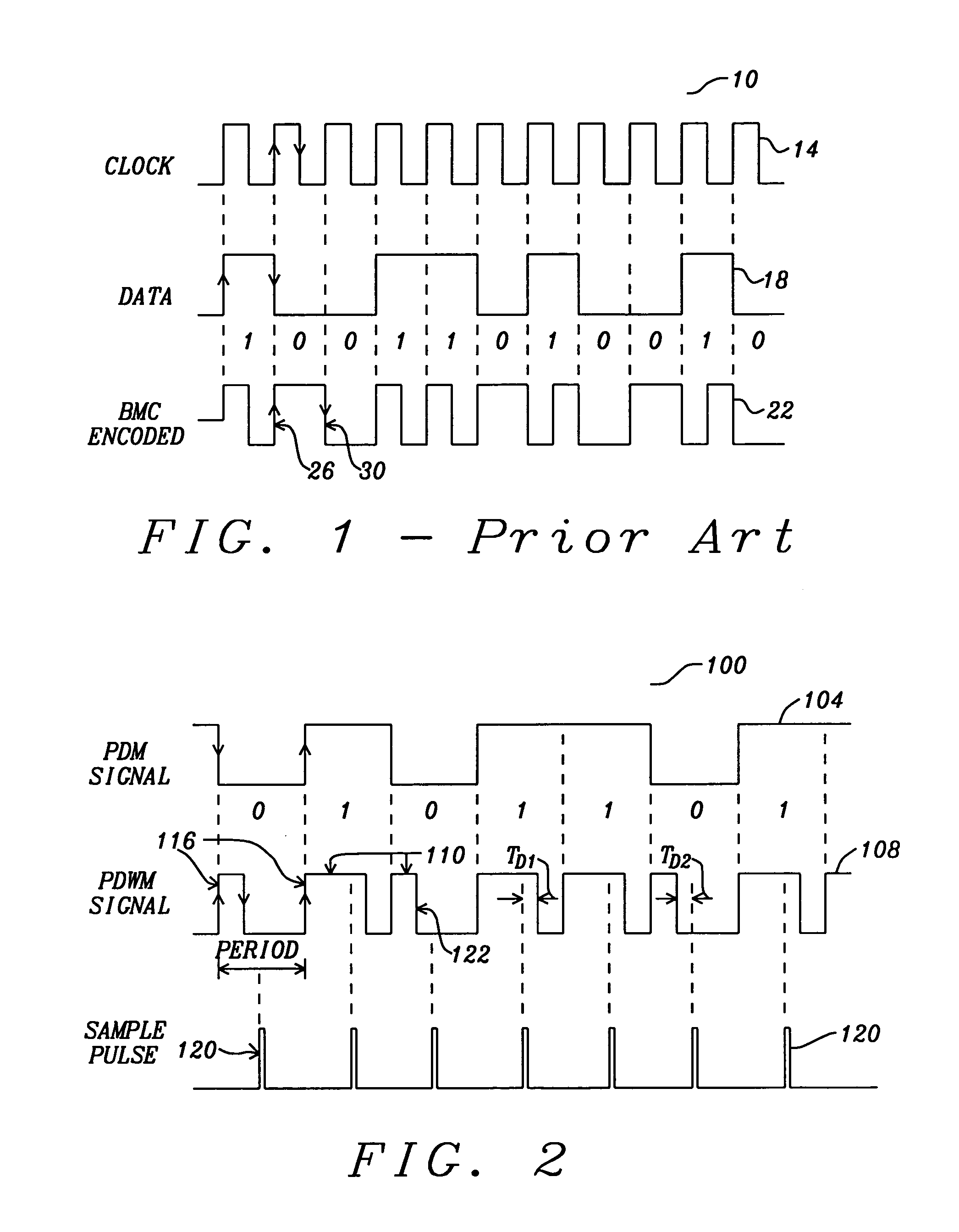

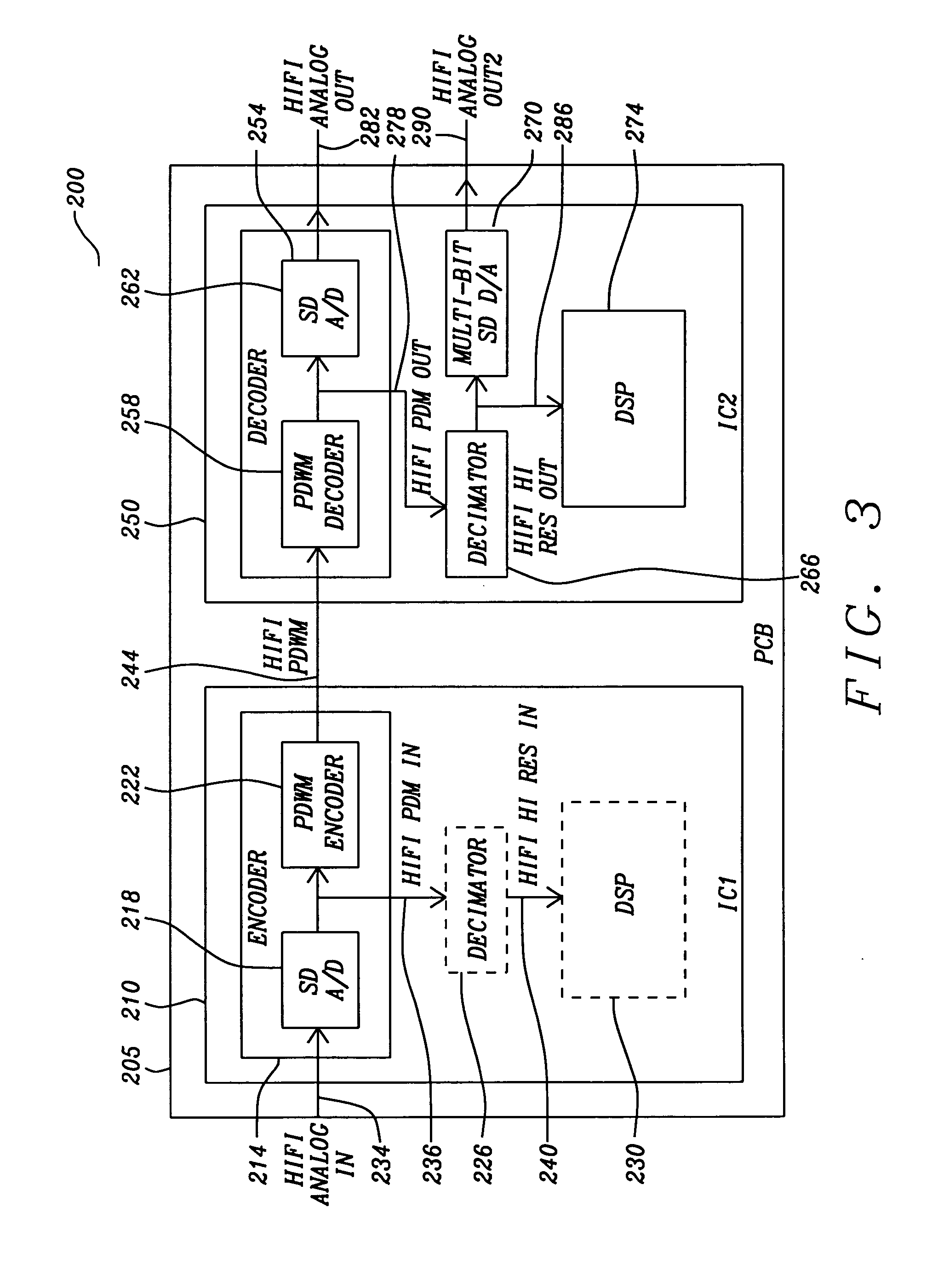

Device and method for the transmission and reception of high fidelity audio using a single wire

An audio device (200) includes a first and second ICs (210) and (250) and a substrate (205). The first IC includes a sigma-delta, A / D converter (218) operable to convert an analog signal (234) into a pulse density modulated signal (236). A pulse density width modulator encoder (222) is operable to encode the PDM signal into a PDWM signal (244). The PDWM has short and long pulse widths defining first and second bit levels. The leading edges of each pulse bounds each pulse period. The second IC (250) includes a means (254) to receive the PDWM signal, an edge detector (304) operable to detect the leading pulse edges of the PDWM signal, a time-averaging circuit (308) operable to calculate each pulse period from the leading pulse edges and to generate a sample pulse (120) at near the midpoint of each pulse period, and a latch (312) operable to sample and hold the PDWM signal at the sample pulse to decode a PDM signal (278). The substrate is operable to support the first and second ICs and to conduct the PDWM signal between the first and second ICs.

Owner:DIALOG SEMICONDUCTOR

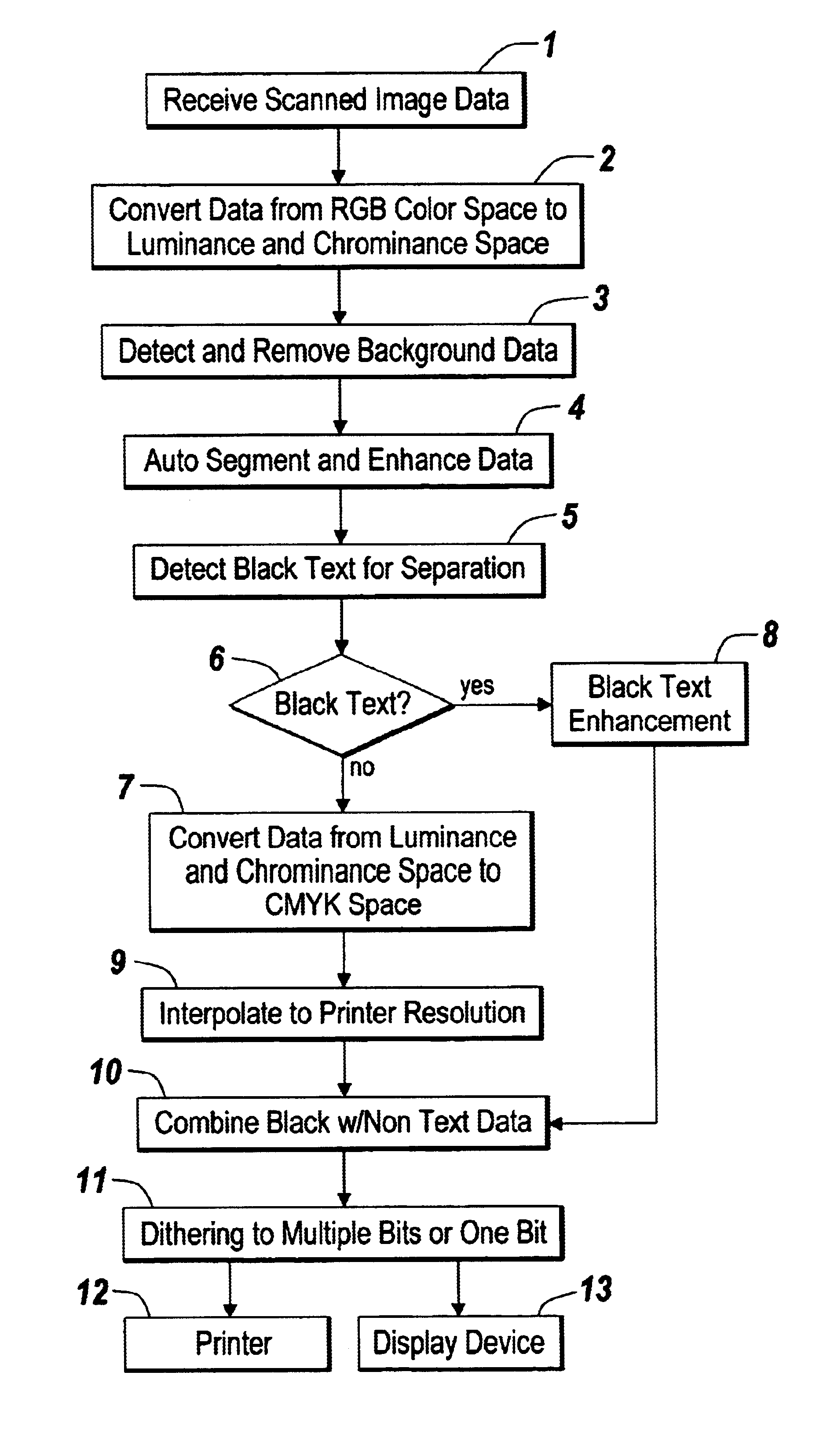

System and method for color copy image processing

InactiveUS6839151B1Reduce computing costLess errorDigitally marking record carriersDigital computer detailsPattern recognitionImaging processing

A system and method of processing an image including black text data and non-black text data are described. The system and method use a parametric analysis for discrimination of halftones, texts, and photographs. The parametric analysis provides results that track measurable image metrics without the inherent risk of errant decision making during classification. The creation of symbolic representations is intrinsically a classification process that is subject to error. It represents a fundamental departure from fuzzy logic image segmentation. In the parametric analysis, no pattern matching, no auto-correlation, no screening parameter calculation, and no conventional edge detector (such as a high pass filter) are used.

Owner:CSR IMAGING US

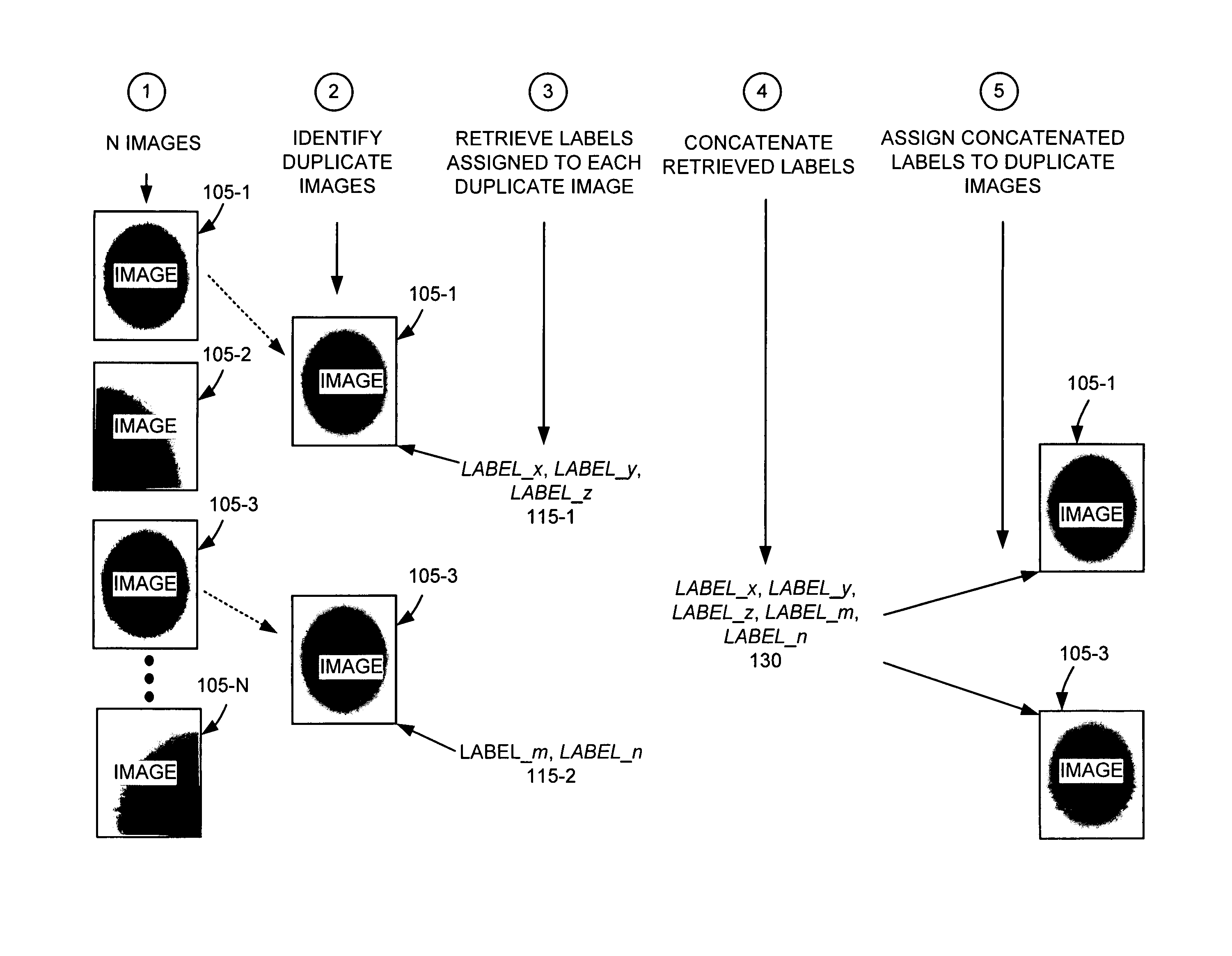

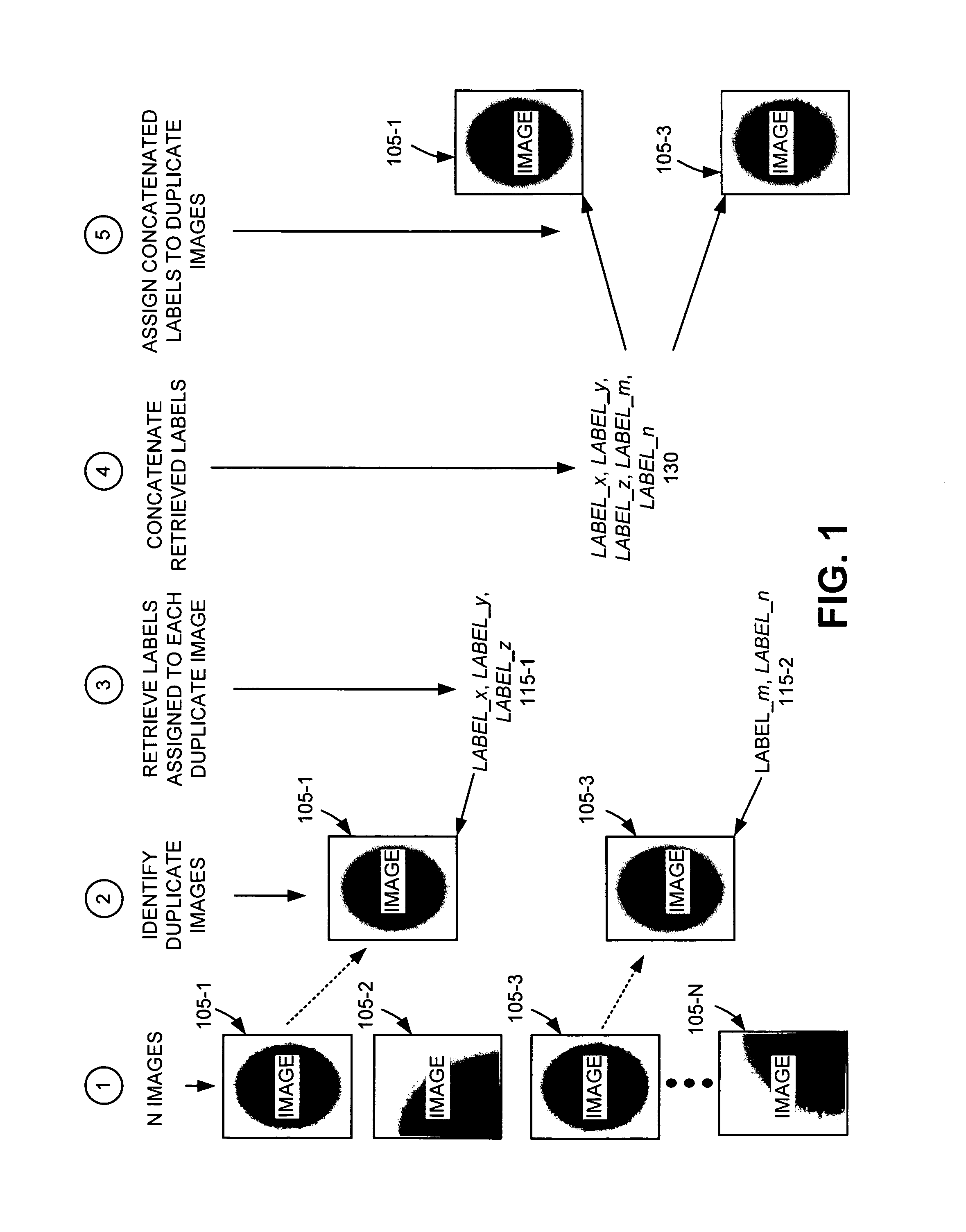

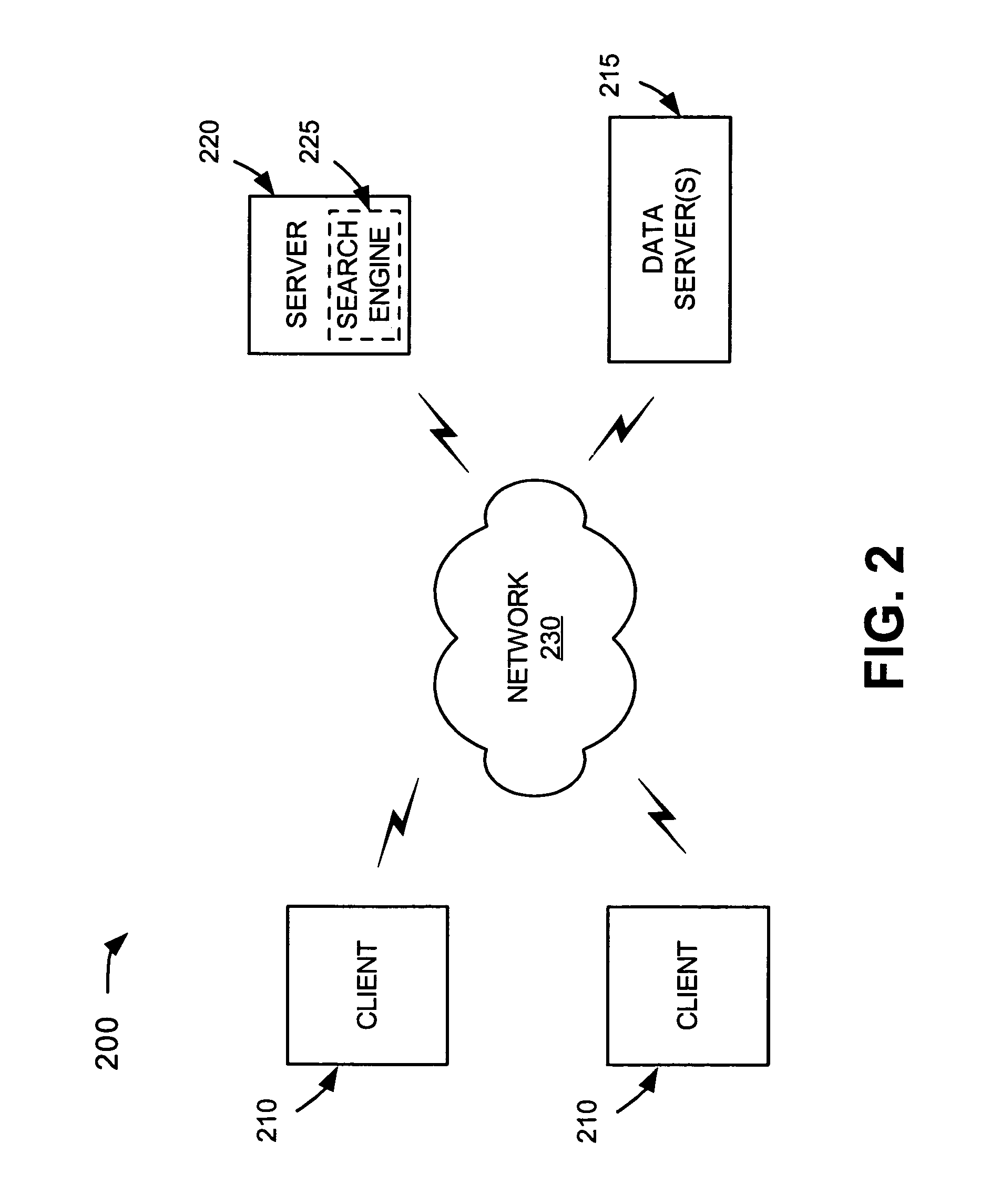

Systems and methods for using image duplicates to assign labels to images

ActiveUS7460735B1Data processing applicationsCharacter and pattern recognitionSystem usageComputer science

A system analyzes multiple images to identify similar images using histograms, image intensities, edge detectors, or wavelets. The system retrieves labels assigned to the identified similar images and selectively concatenates the extracted labels. The system assigns the concatenated labels to each of the identified similar images and uses the concatenated labels when performing a keyword search of the plurality of images.

Owner:GOOGLE LLC

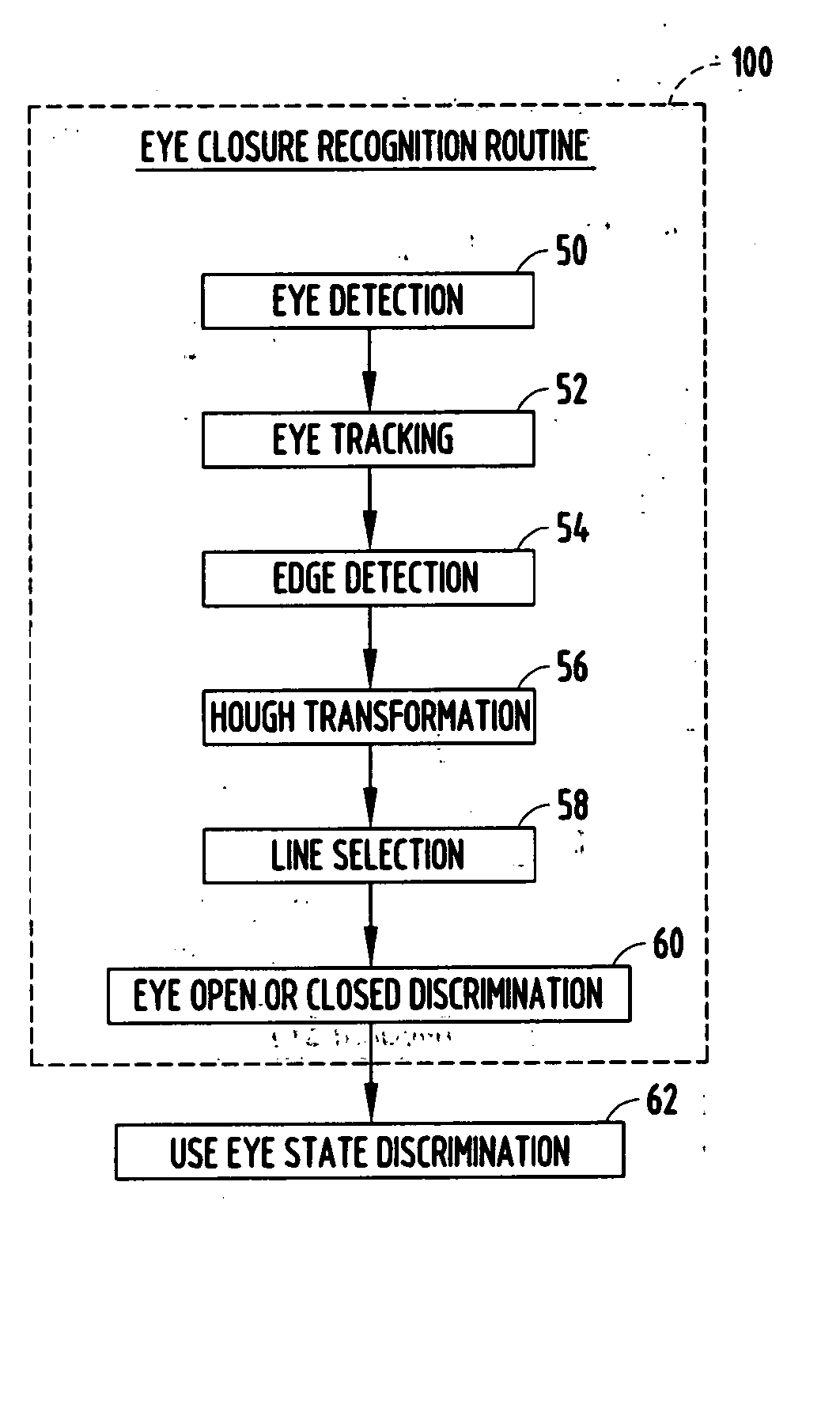

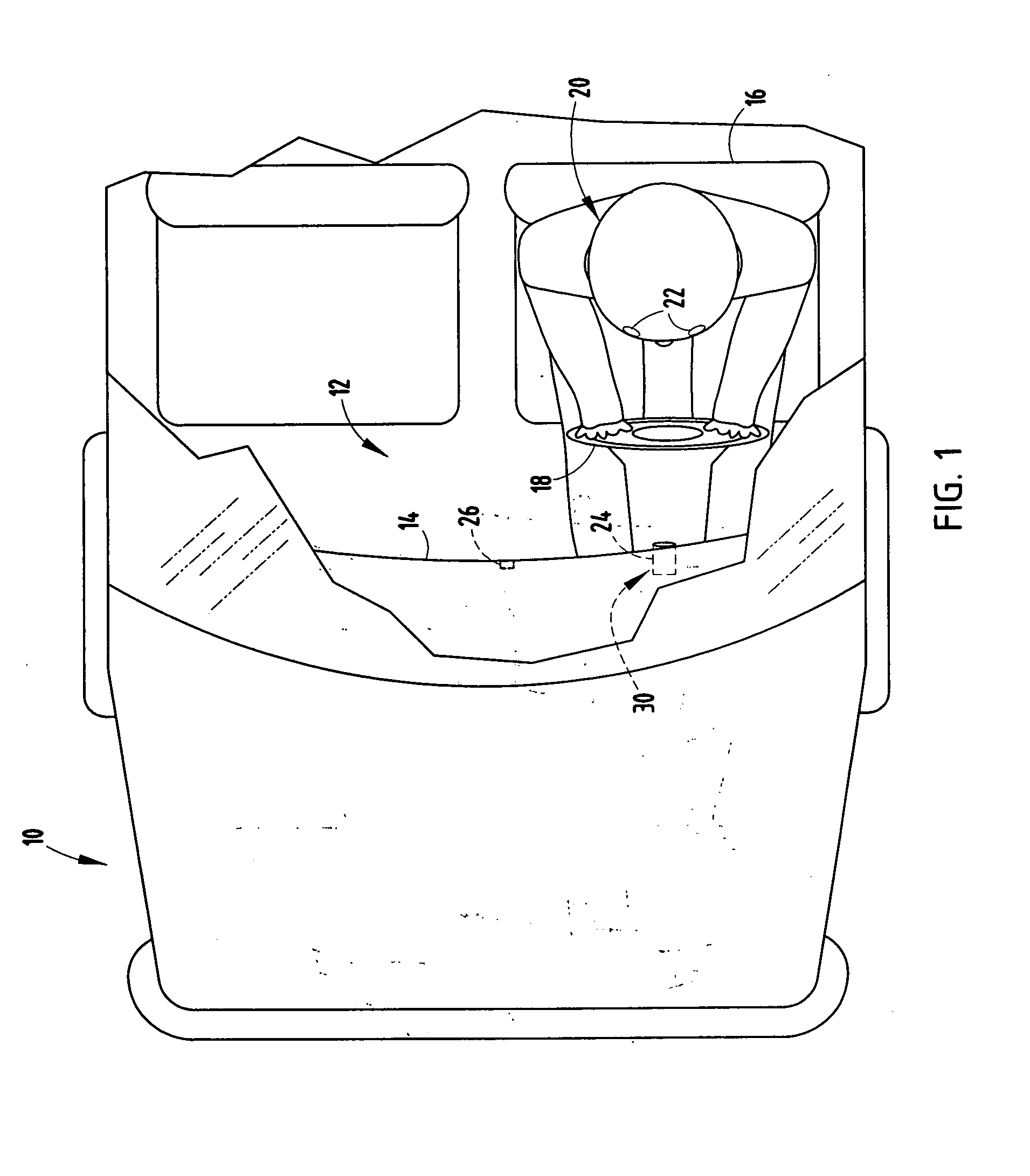

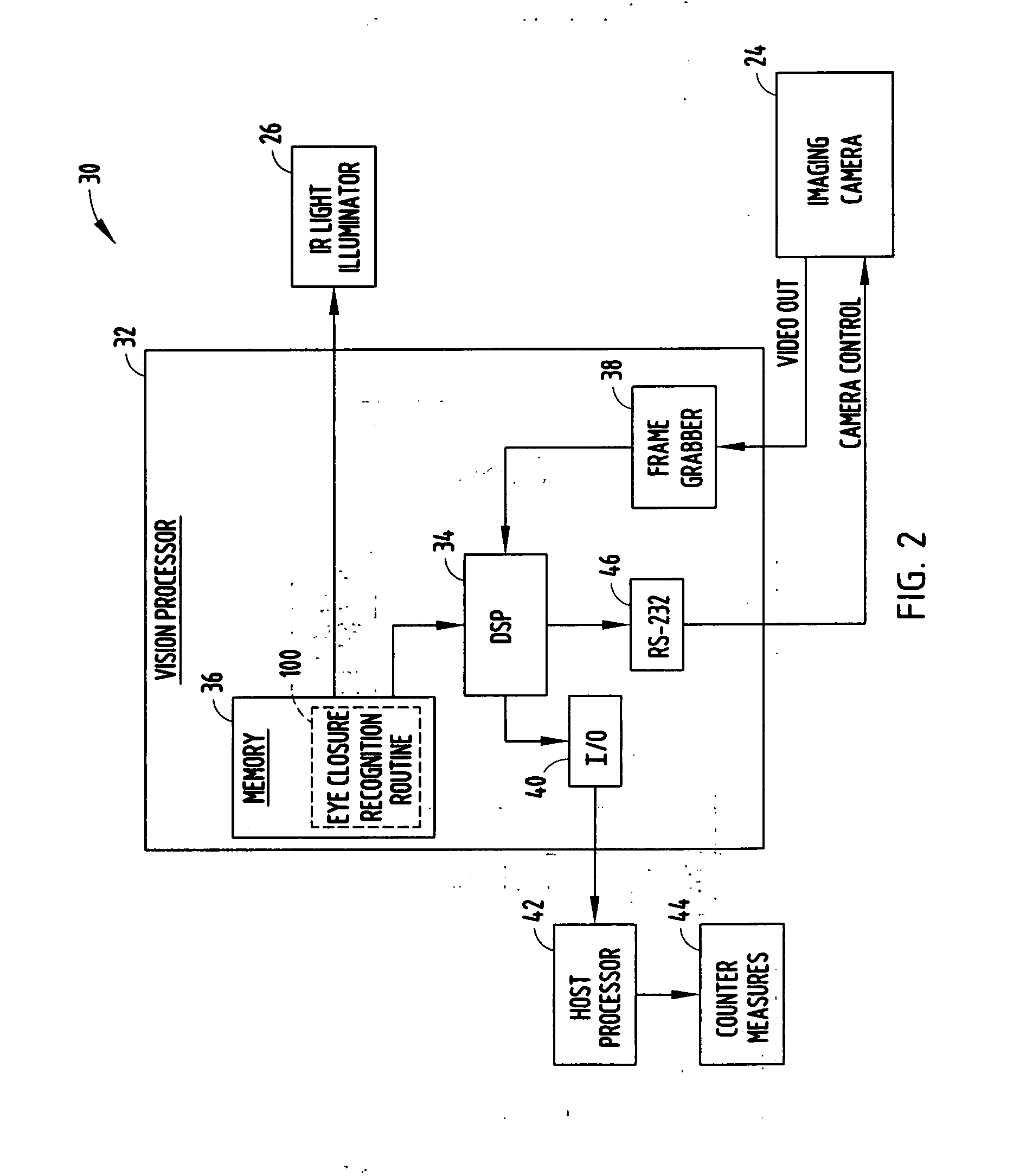

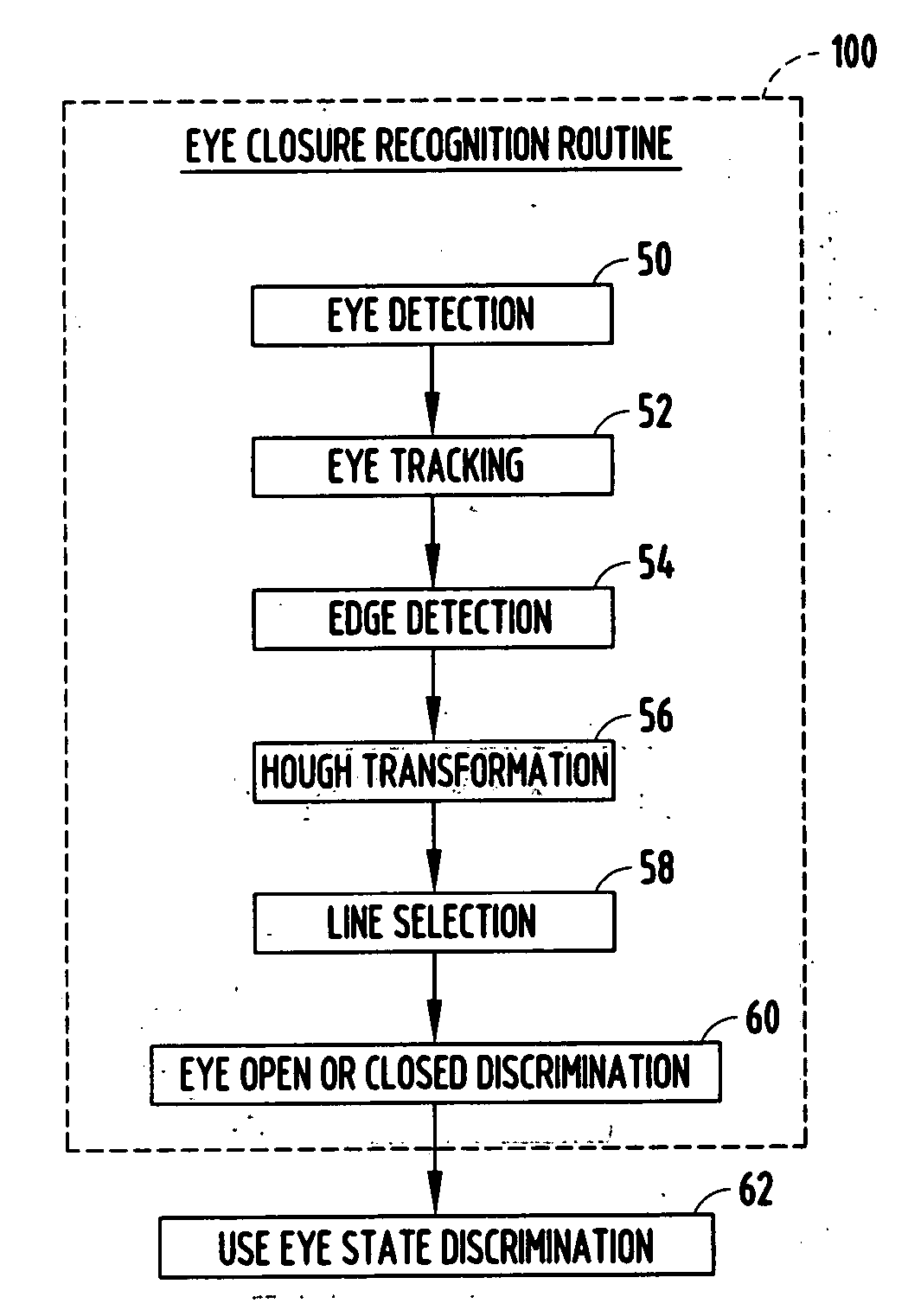

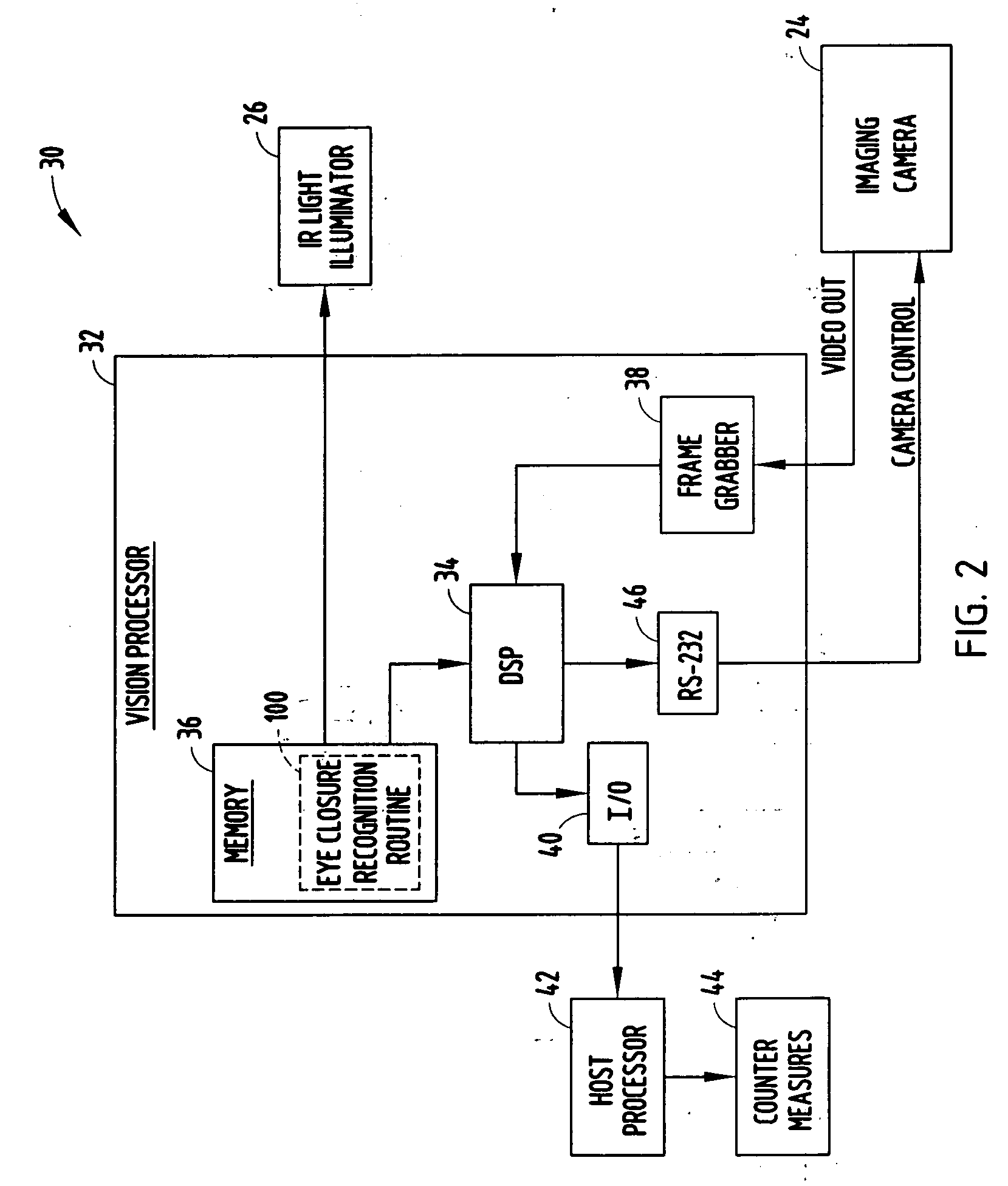

System and method for determining eye closure state

ActiveUS20060204042A1Affordable costEfficiently determinedAcquiring/recognising eyesColor television detailsDriver/operatorEye closure

A system and method are provided for monitoring an eye to determine eye closure. The system includes a video imaging camera oriented to generate images of an eye. The system also includes a video processor for processing the images generated with the video imaging camera. The processor includes an edge detector for detecting edges of the eye in the image and a line selector for generating substantially horizontal first and second lines representative of the detected edges. The processor determines the state of eye closure, such as eye open or eye closed, based on distance between the first and second lines. The system may be employed on a vehicle to determine the eye closure of a driver of the vehicle.

Owner:SAMSUNG ELECTRONICS CO LTD

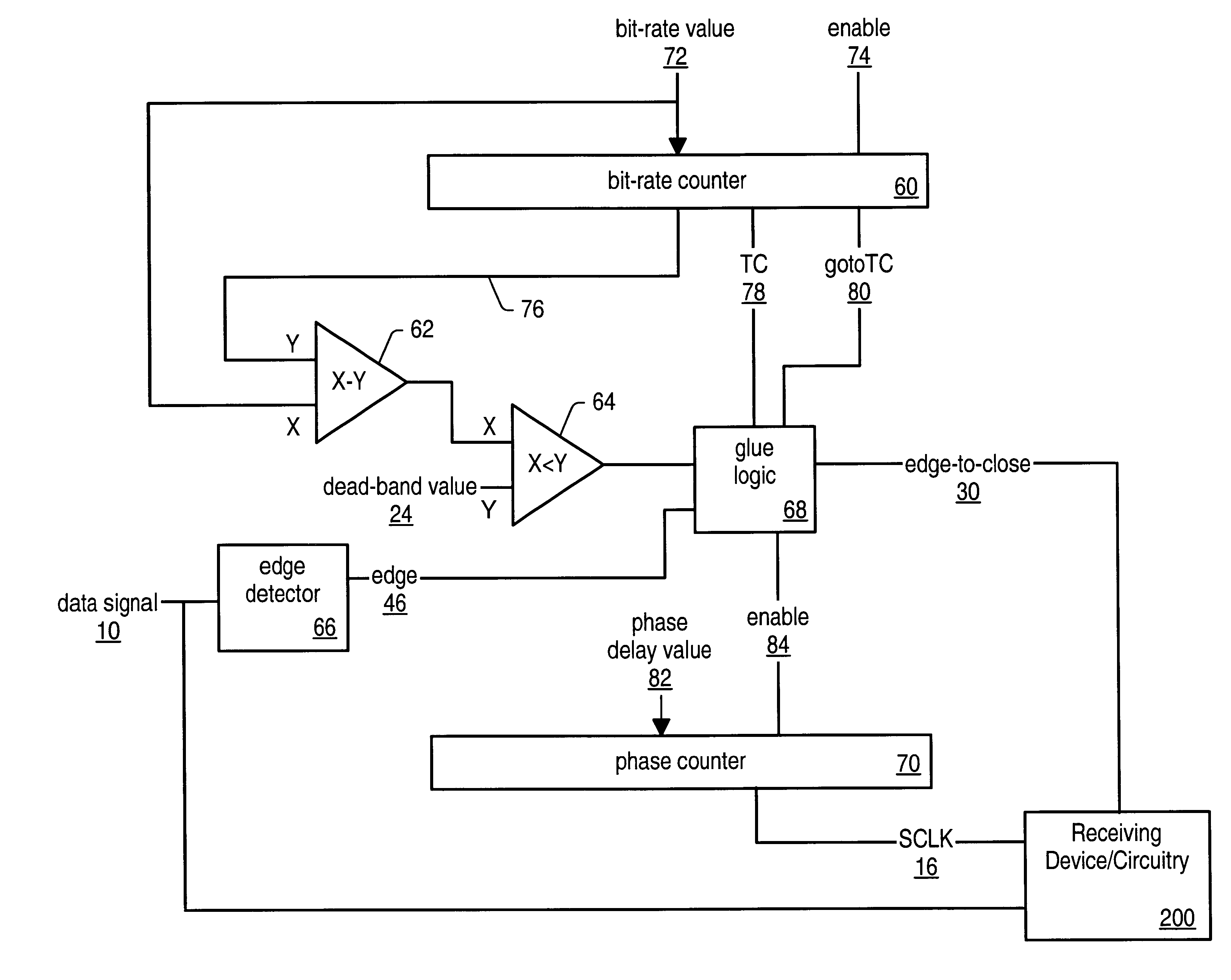

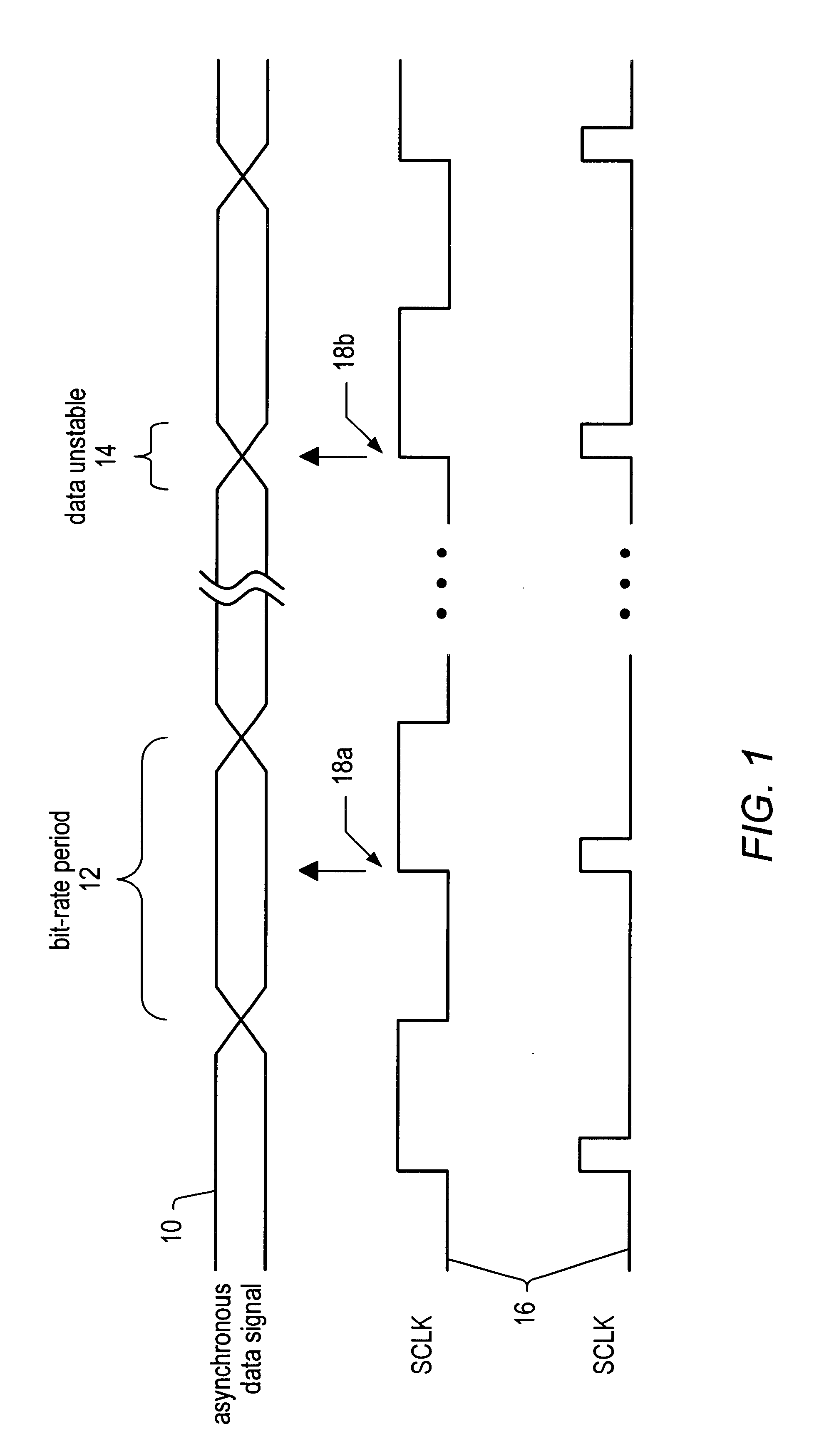

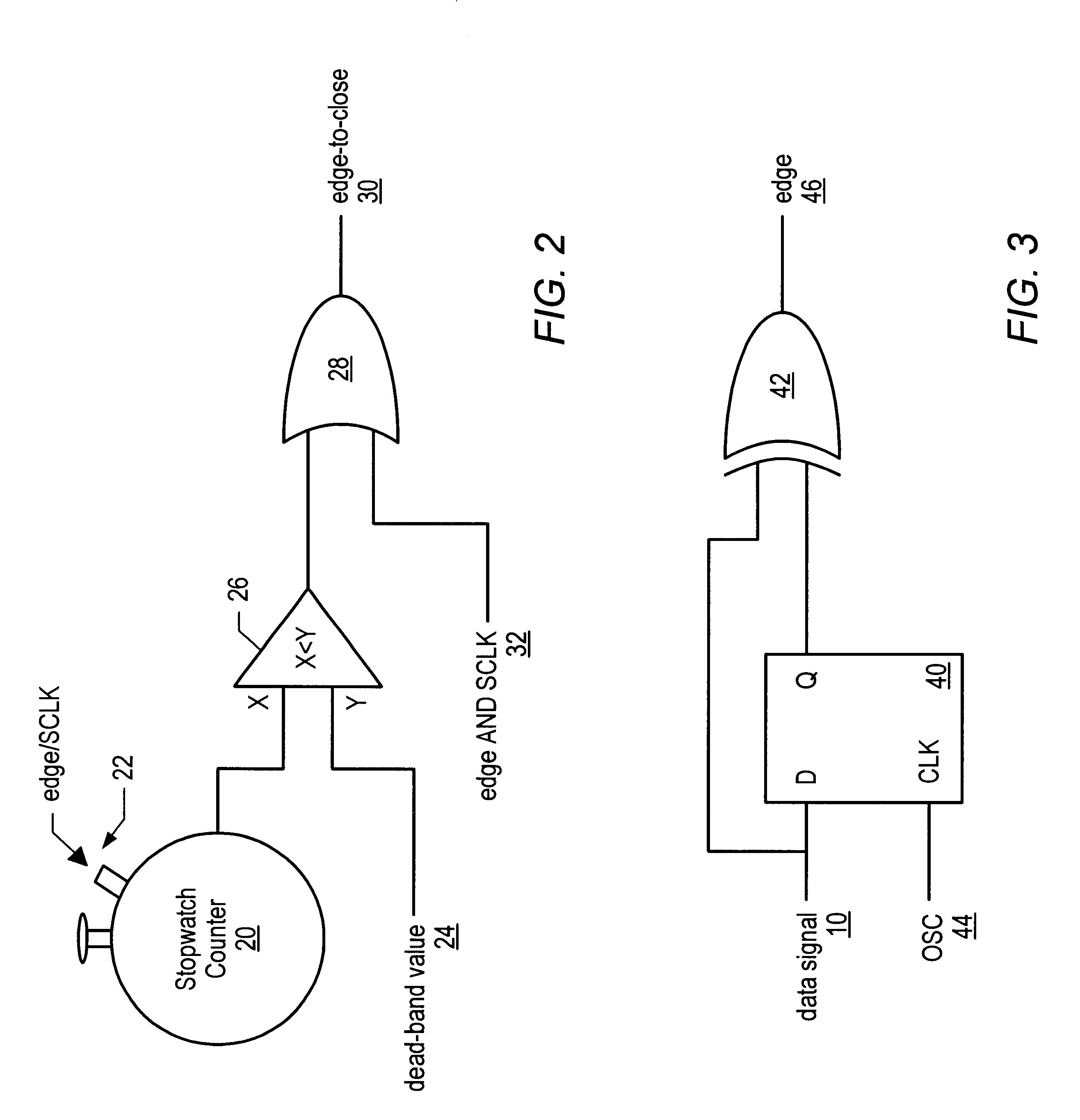

Clock synchronization for asynchronous data transmission

An apparatus for receiving an asynchronous data signal may include a clock generator that generates a clock signal having a frequency approximately equal to the bit rate of the asynchronous data signal. An edge detector may detect transitions of the asynchronous data signal. A dead-band detector may detect when a transition of the clock signal used to sample the data signal occurs within a predetermined amount of time of a transition of the asynchronous data signal so that data sampled on that transition of the clock signal may be invalid. The phase of the clock signal may be adjusted if the transition of the clock signal occurs within this predetermined amount of time. The clock generator may include two programmable counters, one which may be programmed with a bit-rate value so that it generates a signal approximately matching the bit rate of the asynchronous data signal, and the other programmed with a phase-delay value so that it generates a sample clock signal at a phase delay from the signal generated by the first counter. The phase of the sample clock may be adjusted by restarting the counters in response to a transition on the asynchronous data signal. Data may be supplied to a serial-to-parallel converter including a first shift register configured to shift a data word in serially and output the data word in parallel and a second shift register configured to track when the data word had been completely shifted into the first shift register.

Owner:NATIONAL INSTRUMENTS

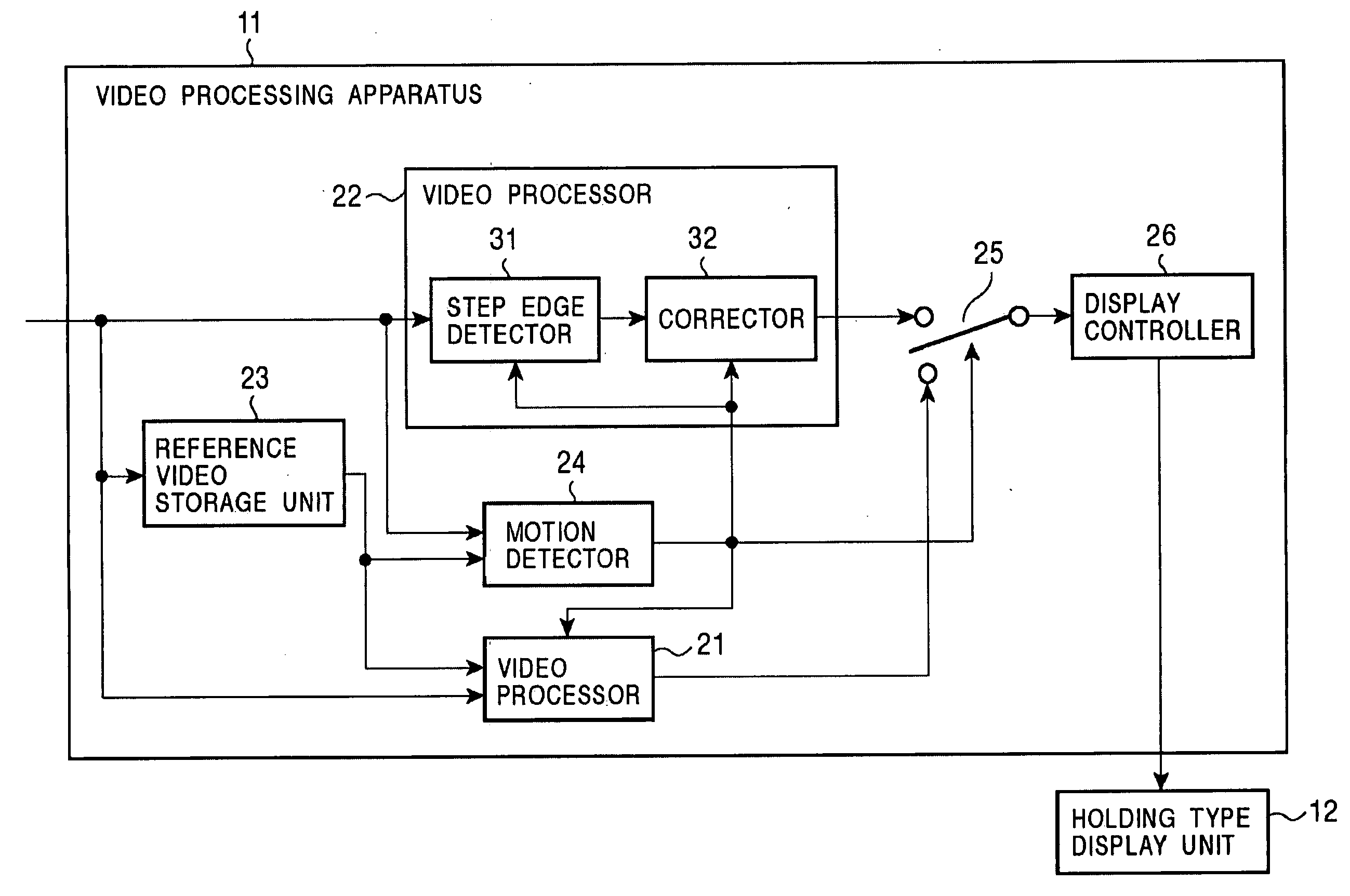

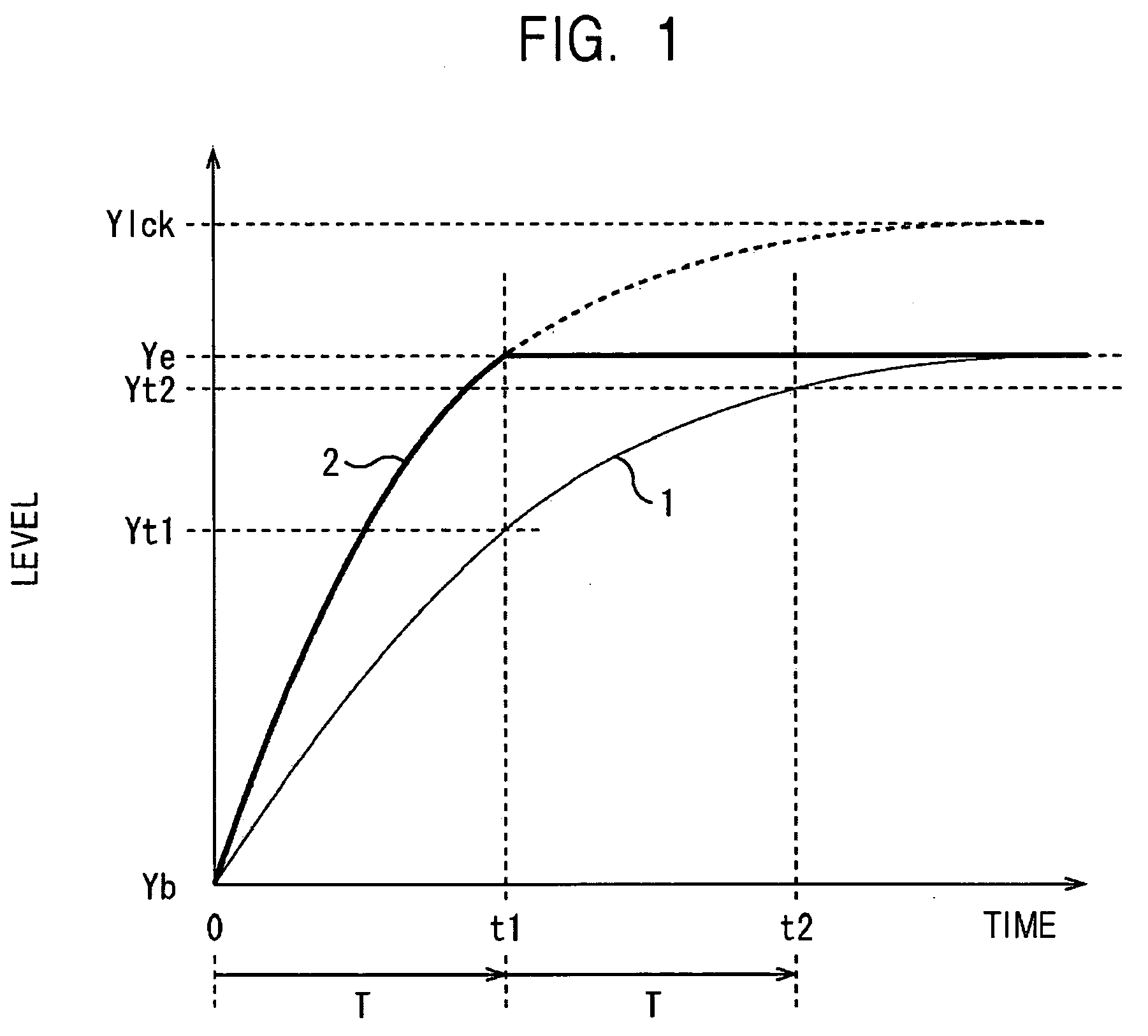

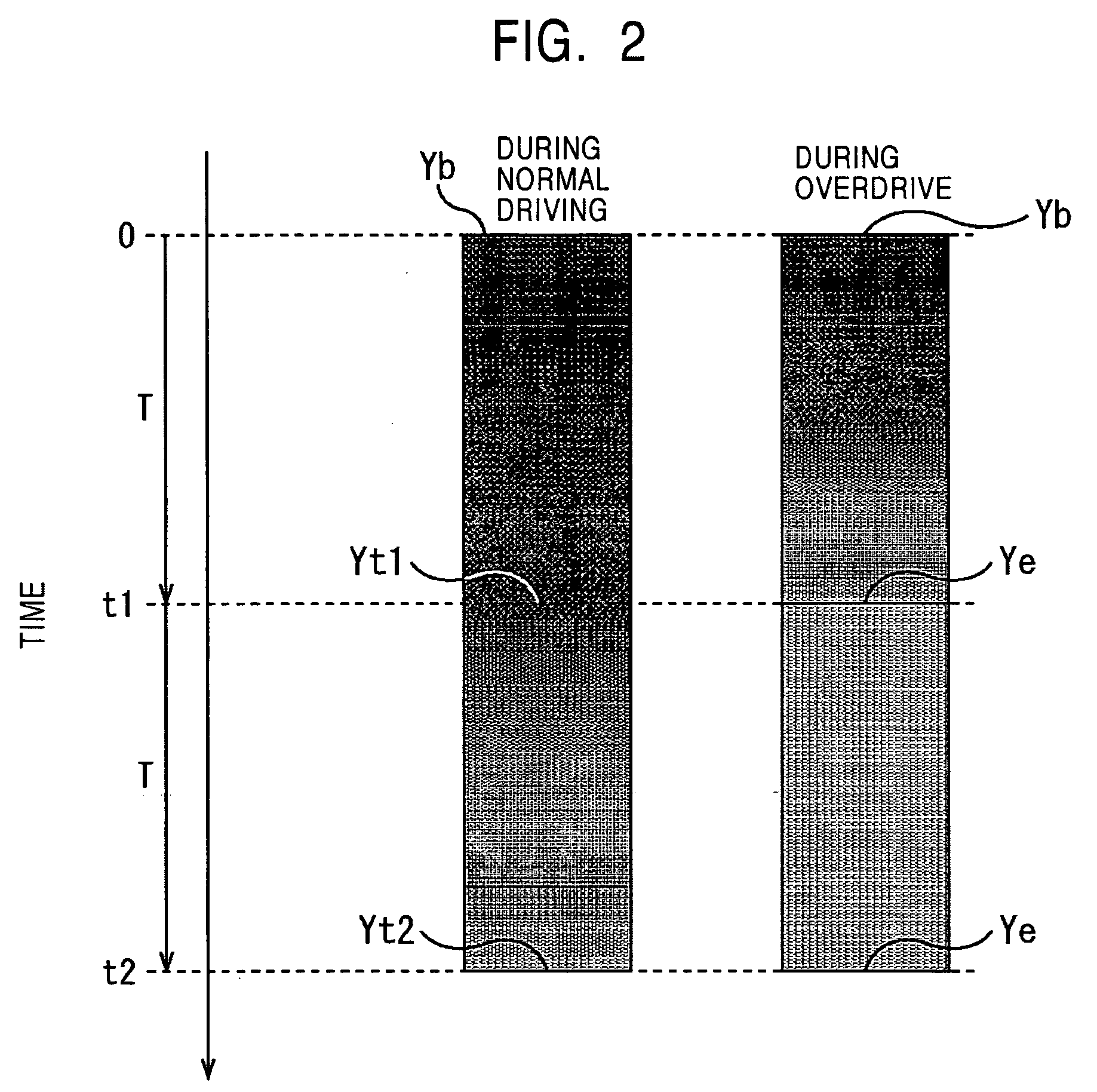

Video processing apparatus, video processing method, and computer program

A holding type display such as a liquid-crystal display for controlling motion blur is disclosed. A step edge detector detects an edge portion of a moving step edge in video data in an input frame or an input field. A corrector corrects a pixel value of a pixel at the edge portion of the step edge detected by the step edge detector, based on a spatial amount of motion of the corresponding pixel supplied by a motion detector.

Owner:SONY CORP

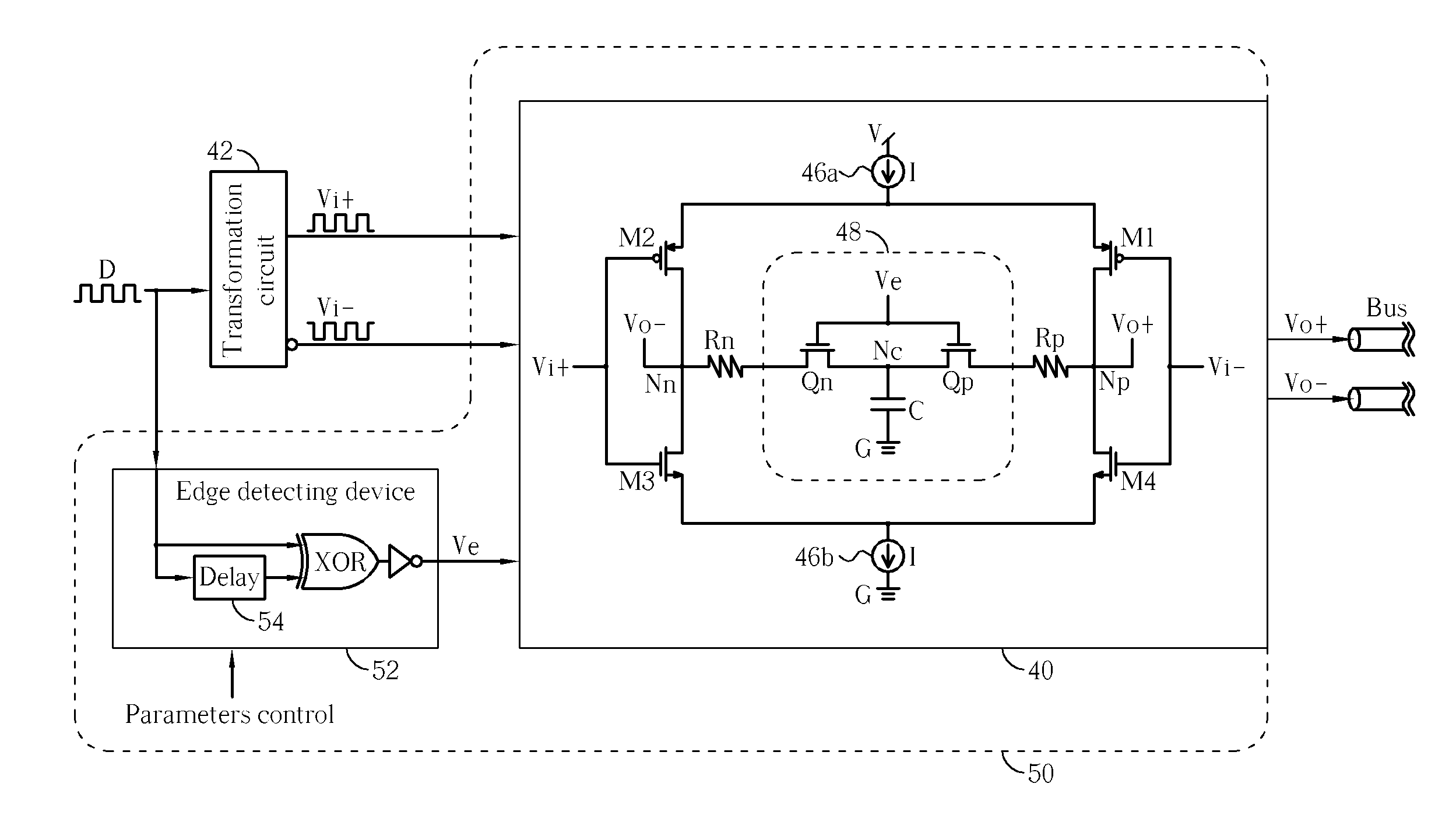

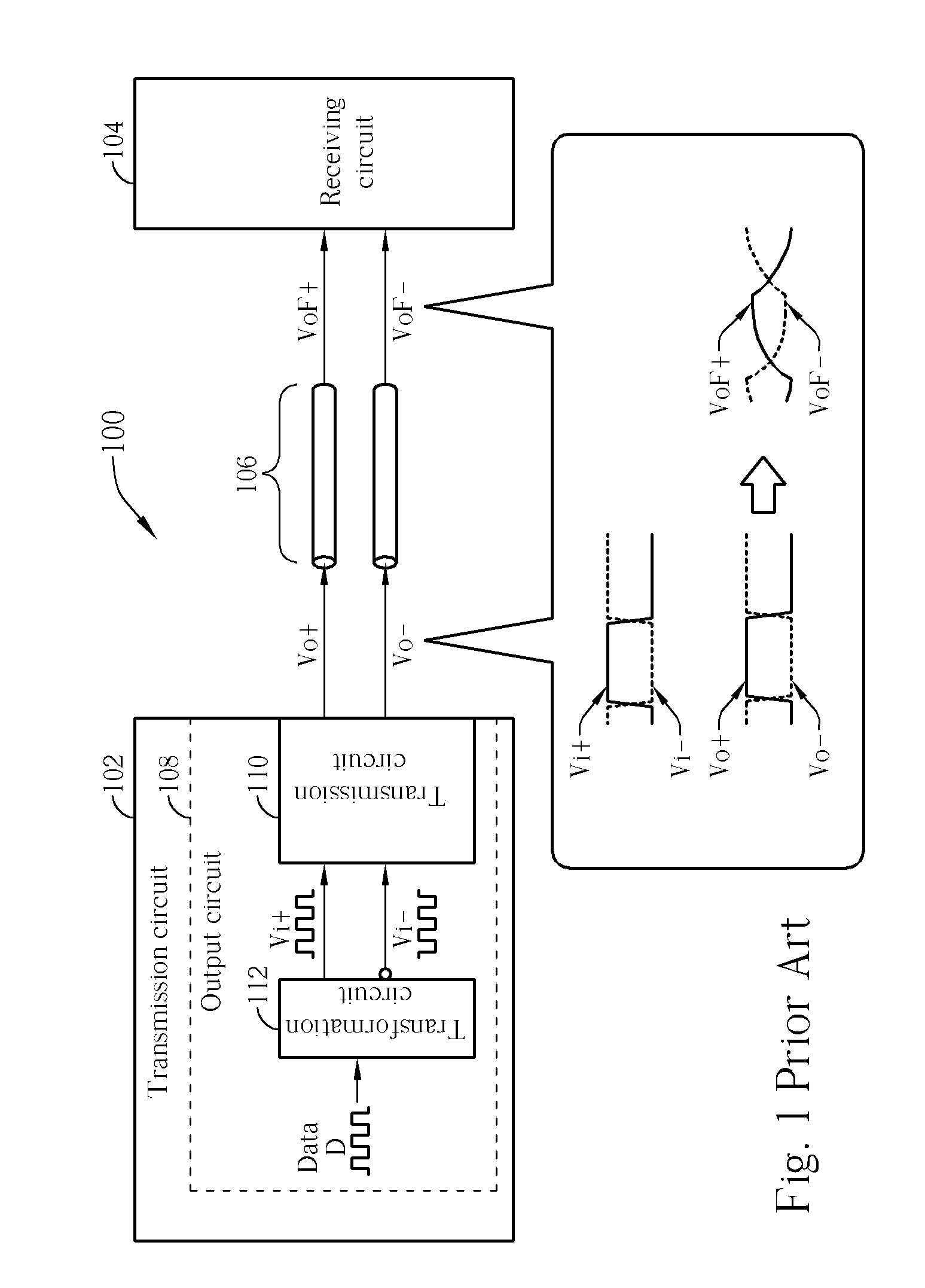

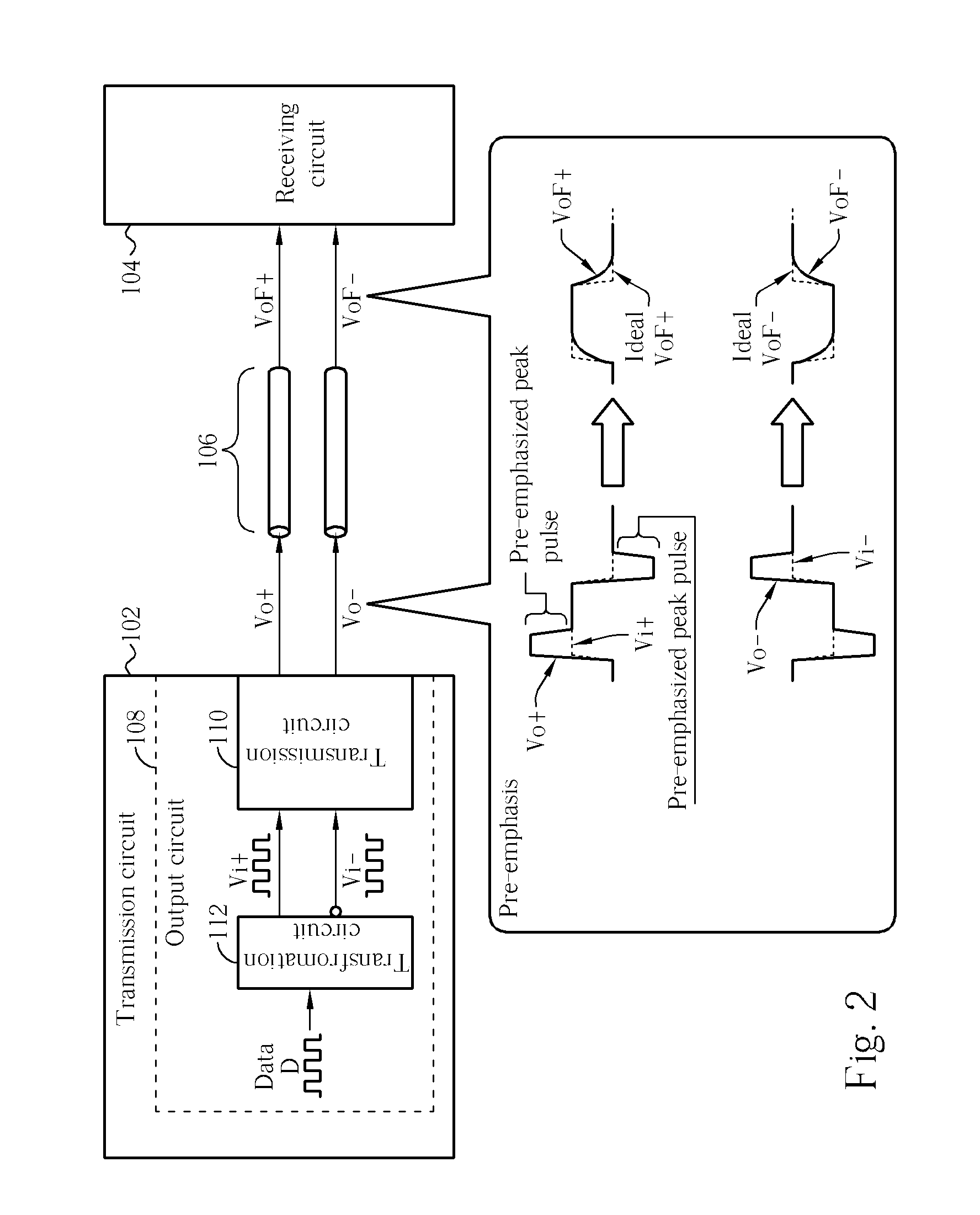

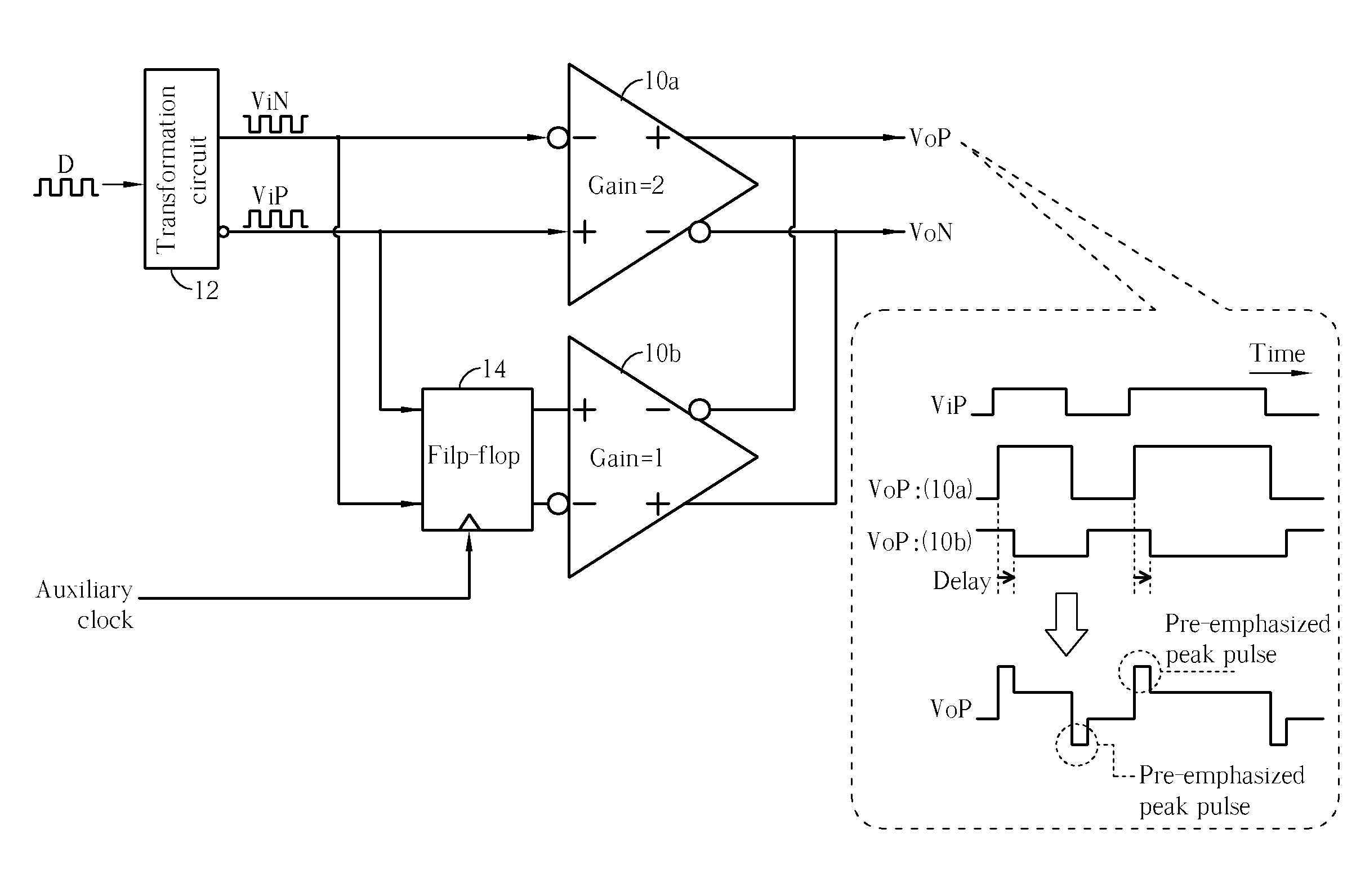

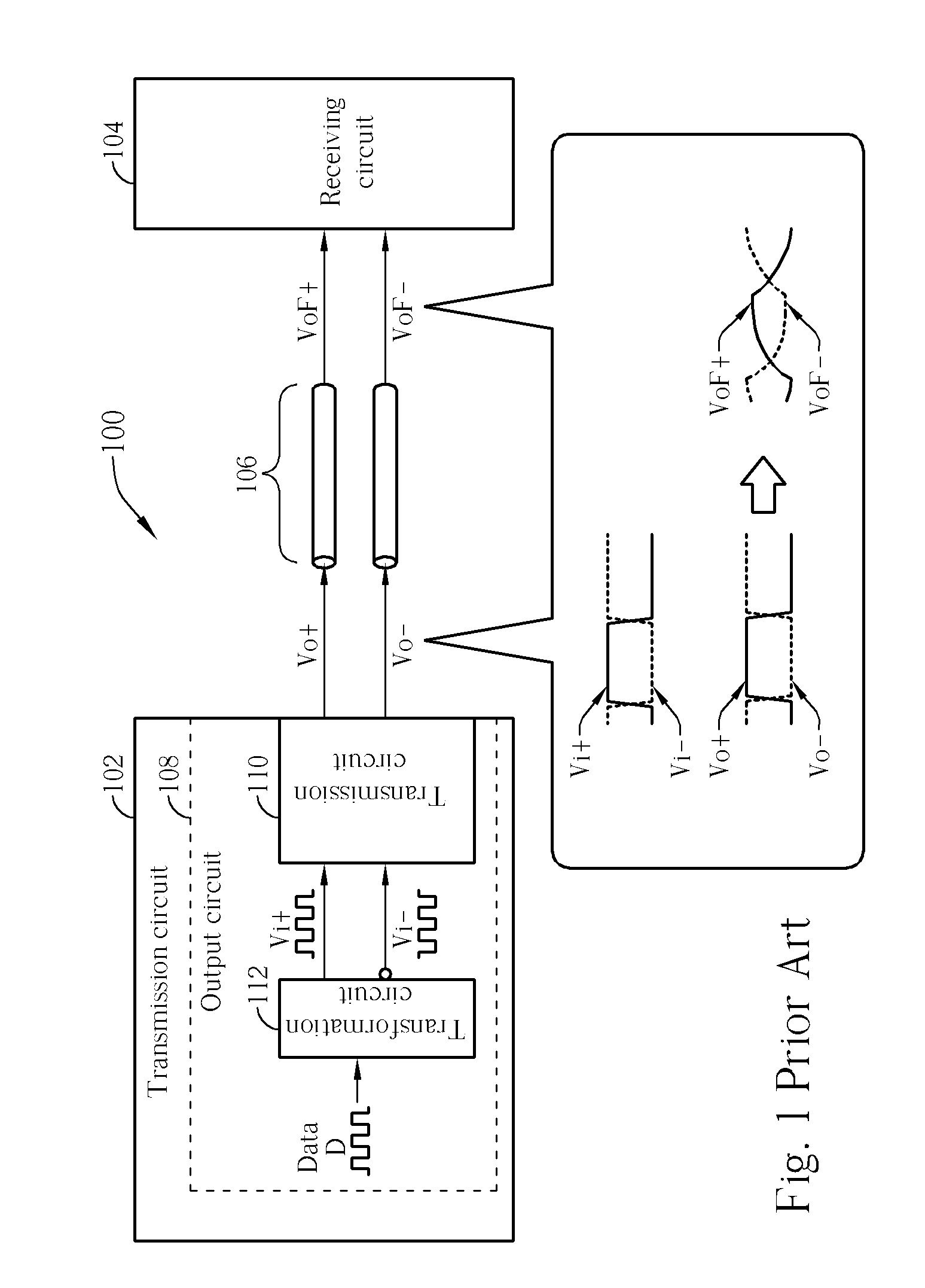

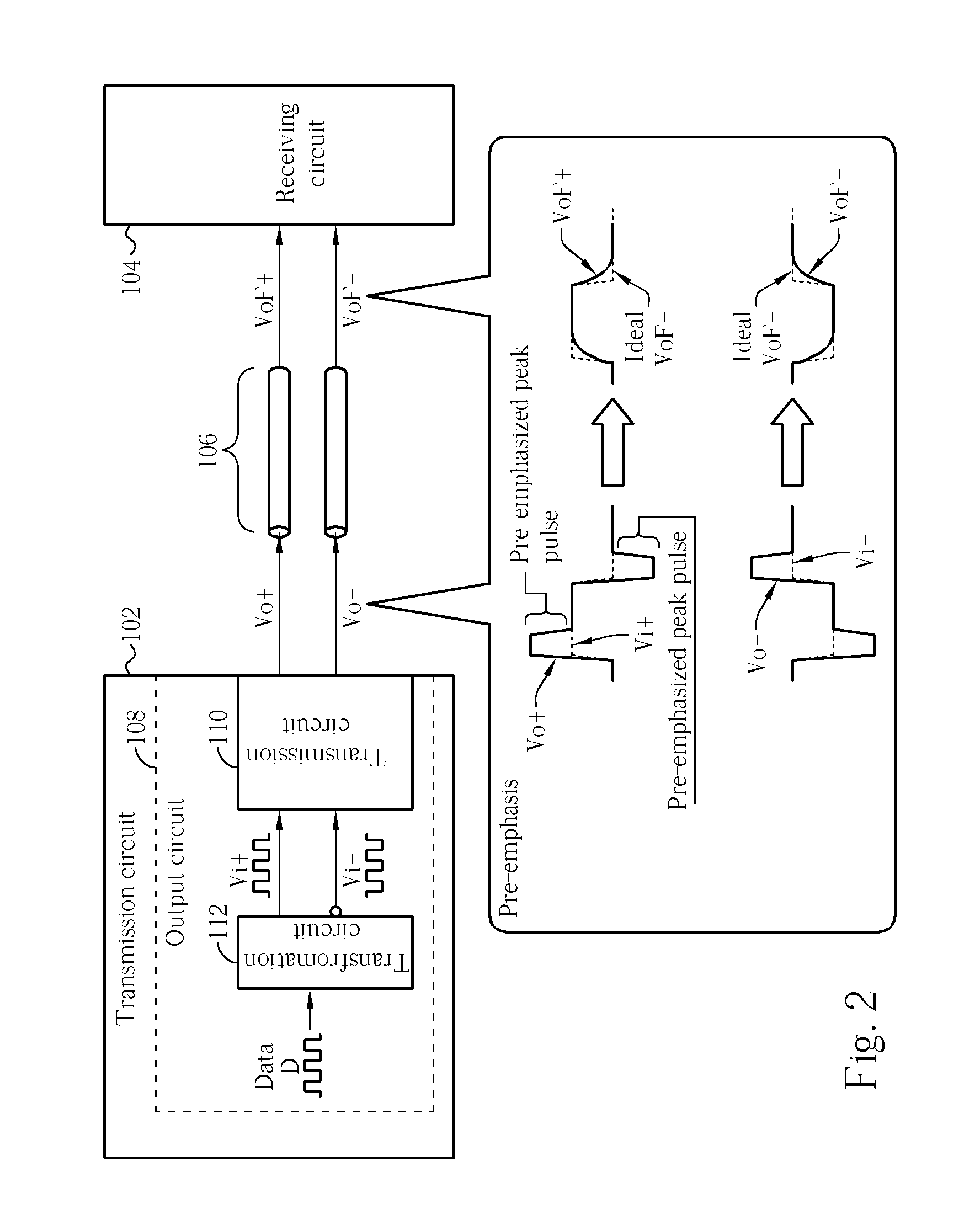

Transmitter and transmission circuit

Transmitter and transmission circuit. For realizing a differential transmitter, a switch circuit is connected between two load transistors of two complementary MOS pairs. The switch circuit can have two inductors. When the two complementary MOS pairs are conducting current to drive signal transition at output nodes, the inductors open to make the load transistors stop draining current. Also, the switch circuit can have switch transistor controlled by an edge detector for detecting raising and falling edges of the input signals, such that the switch circuit can make the load transistors stop draining current accordingly. In this way, raising and falling edges of the output signals are emphasized to improve signal propagation.

Owner:VIA TECH INC

Method and apparatus for reducing mosquito noise in decoded video sequence

InactiveUS7657098B2Simple ringing (mosquito noise)Reduce noiseTelevision system detailsPicture reproducers using cathode ray tubesVideo sequenceArea detector

A ringing area detector classifies the input image into two regions: a mosquito noise region (i.e. filtering region) and a non-mosquito noise region (i.e. non-filtering region), and uses this classification information to adaptively remove the mosquito noise in a mosquito noise reduction system. The mosquito noise reduction system includes a ringing area detector, a local noise power estimator, a smoothing filter, and a mixer. The ringing area detector includes an edge detector, a near edge detector, a texture detector, and a filtering region decision block. The ringing detection block detects the ringing area where the smoothing filter is to be applied. The local noise power estimator controls the filter strength of the smoothing filter. The smoothing filter smoothes the input image. The mixer mixes the smoothed image and the original image properly based on the region information from the ringing area detection block.

Owner:SAMSUNG ELECTRONICS CO LTD

System and method of detecting eye closure based on edge lines

ActiveUS20060204041A1Affordable costEfficiently determinedCharacter and pattern recognitionColor television detailsDriver/operatorEye closure

A system and method are provided for monitoring an eye to determine eye closure. The system includes a video imaging camera oriented to generate images of an eye, and a video processor for processing the images. The processor includes an edge detector for detecting edges of the eye in the image, and a line selector for generating a plurality of lines at multiple angles representative of the detected edges. The processor determines the state of eye closure, such as eye open or eye closed, based on the number of lines at selected angles. The system may be employed on a vehicle to determine the eye closure of a driver of the vehicle.

Owner:SAMSUNG ELECTRONICS CO LTD

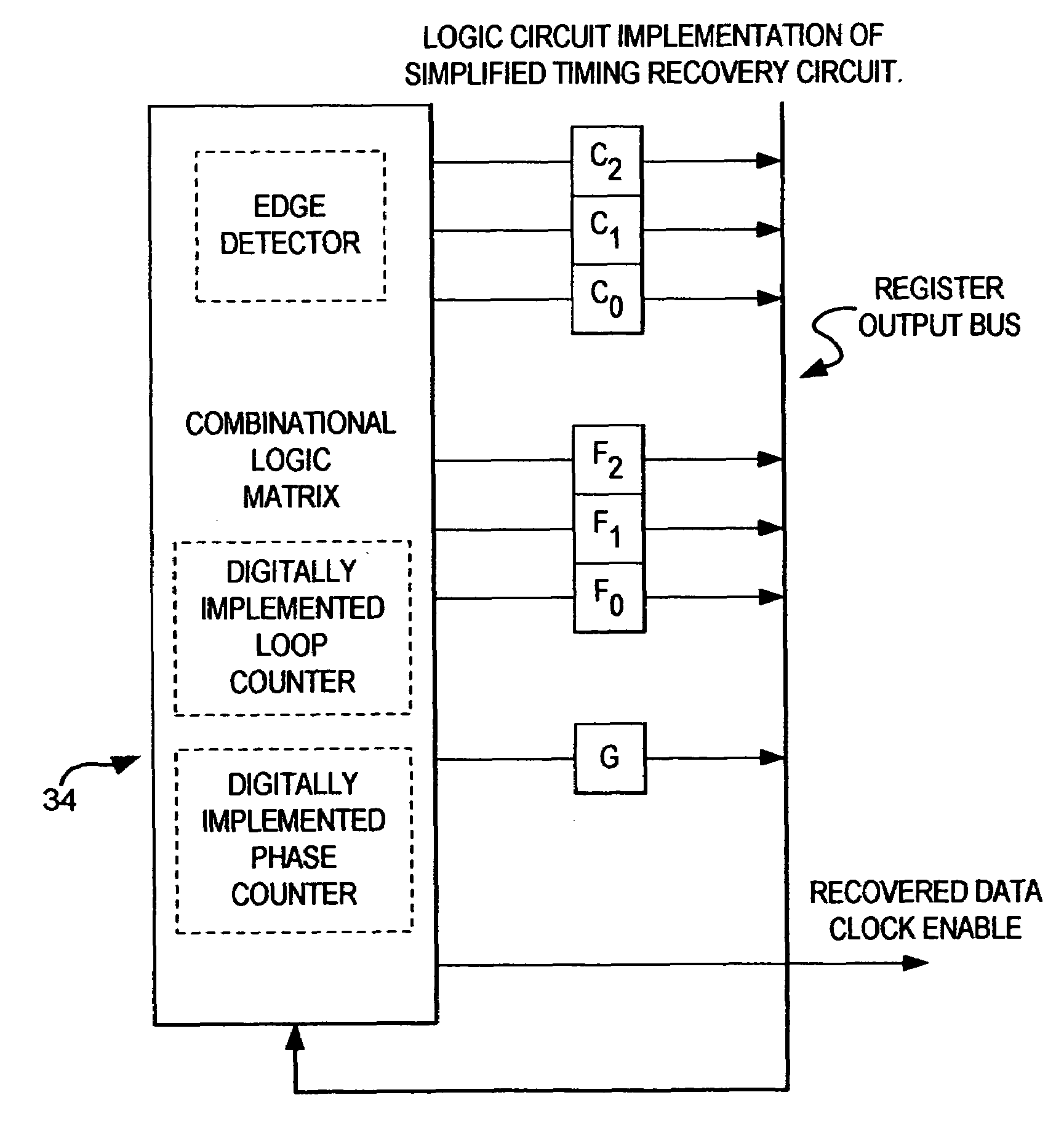

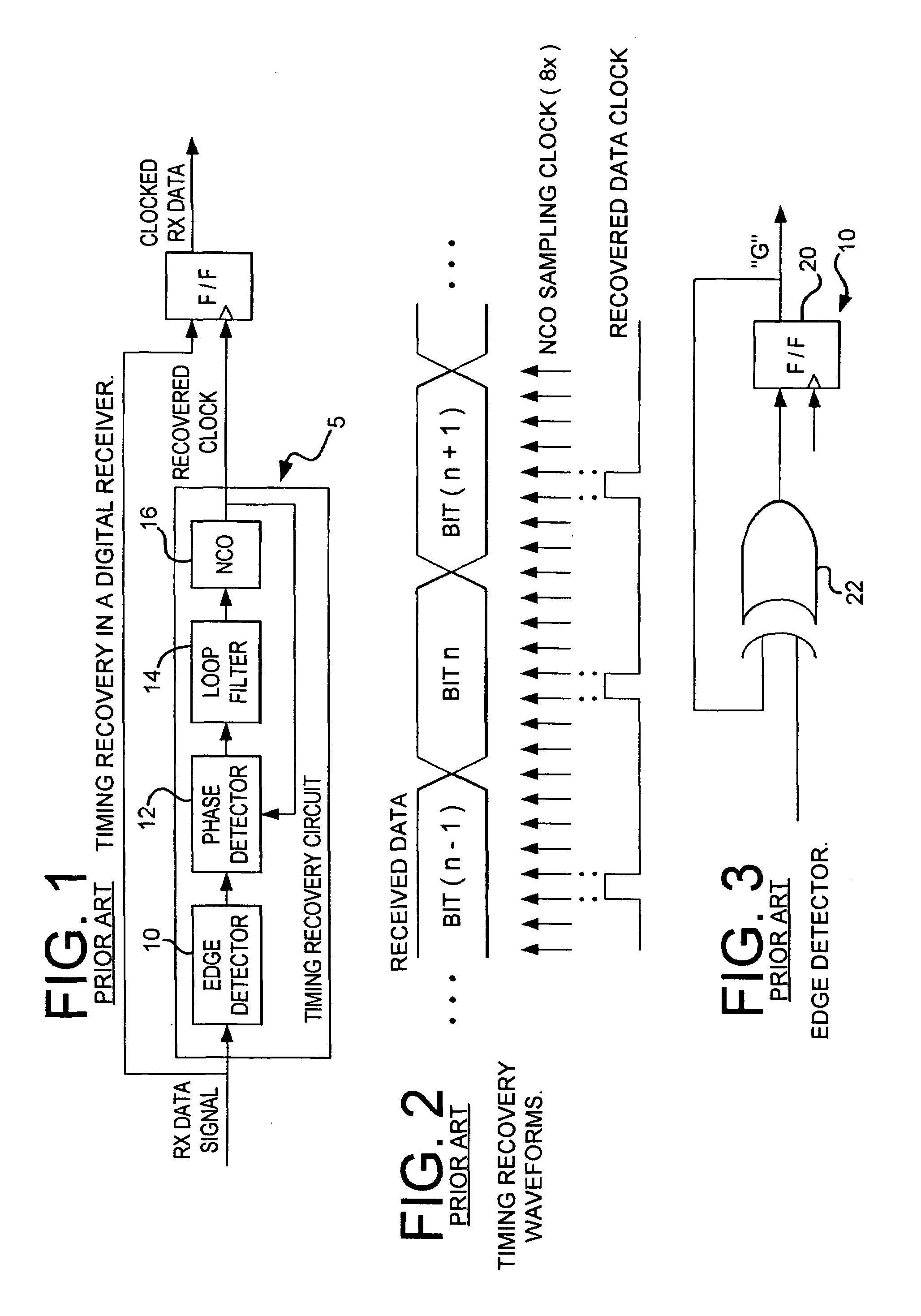

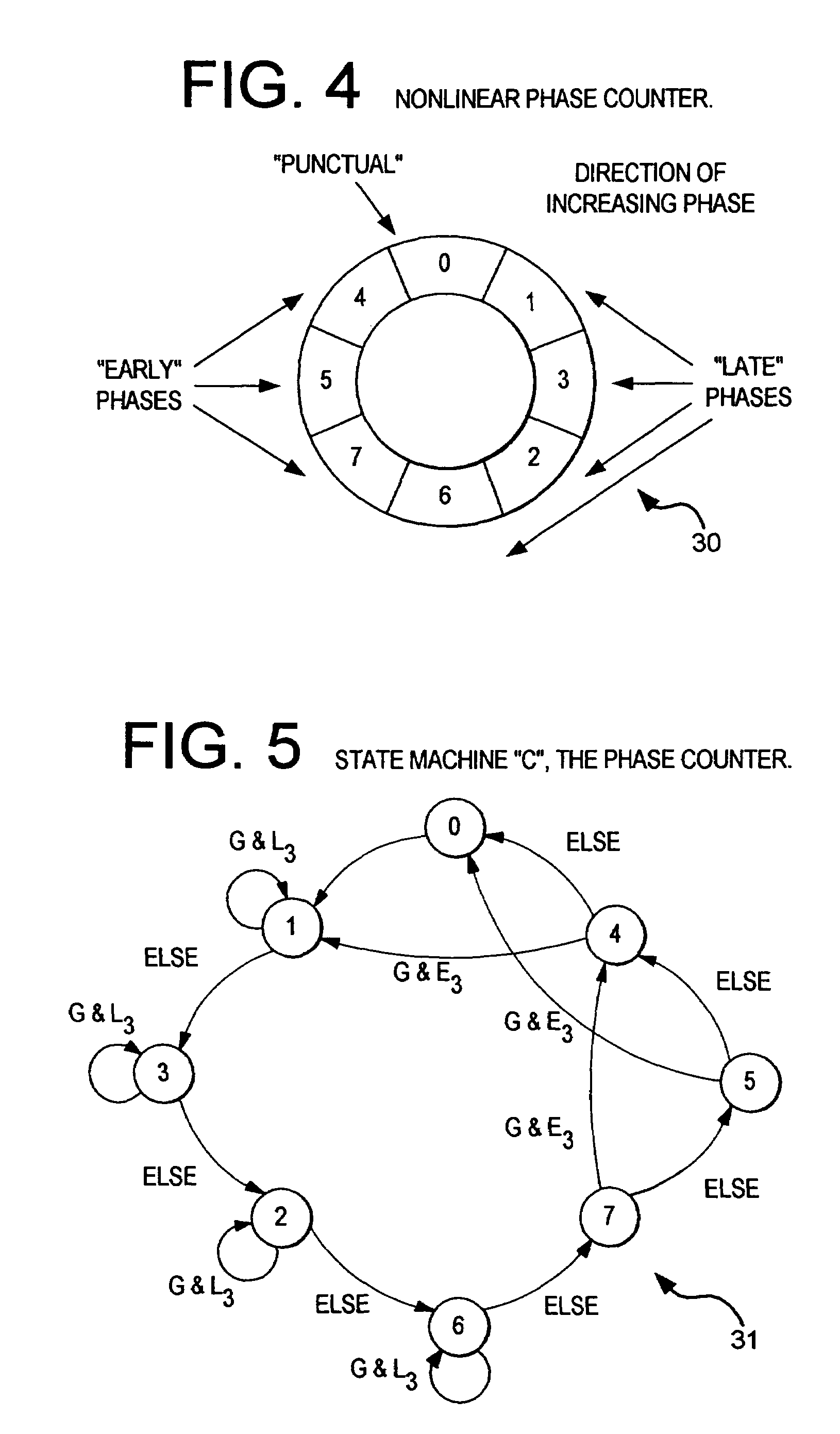

Compact digital timing recovery circuits, devices, systems and processes

InactiveUS6937683B1The process is compact and efficientMinimal requirementPulse automatic controlAngle demodulation by phase difference detectionProcessor registerComputer science

A digitally implemented timing recovery circuit for recovering a clock signal from an input bit stream. The recovery circuit comprising an edge detector for detecting a transition from “0” to “1” or “1” to “0” in the input bit stream, a phase counter having a plurality of registers indicative of the phase counter transition state, and a loop counter having a plurality of registers indicative of the loop counter transition state. When the phase counter reaches a particular transition state, a recovered clock pulse is enabled. The phase counter is preferably non-linear to optimize the circuit.

Owner:CIRRONET

Marker and method for detecting said marker

This invention discloses marker detectable by visual means comprising; a polygonal border having of at least four non collinear salient points. The marker has on it a pattern in binary digital code. The binary code data contains information data, checksum and error correction. The binary code data is on two levels; a first level of binary code readable at a first given distance, a second level of binary code readable at a second given distance, where the second given distance is less than the first given distance and the second level binary code is smaller in size than the first level binary code. The second level of binary code does not interfere with the reading of the first level binary code. It also discloses a method for detecting a marker comprising the steps of detecting an image, using an edge detector to detect an edge in said image, grouping more than one edge into a polygon having salient points, calculating homography from polygon salient points, generating a list of homographies, extracting binary data from input image having homographies, identifying and verifying binary data.

Owner:MILLENNIUM THREE TECH

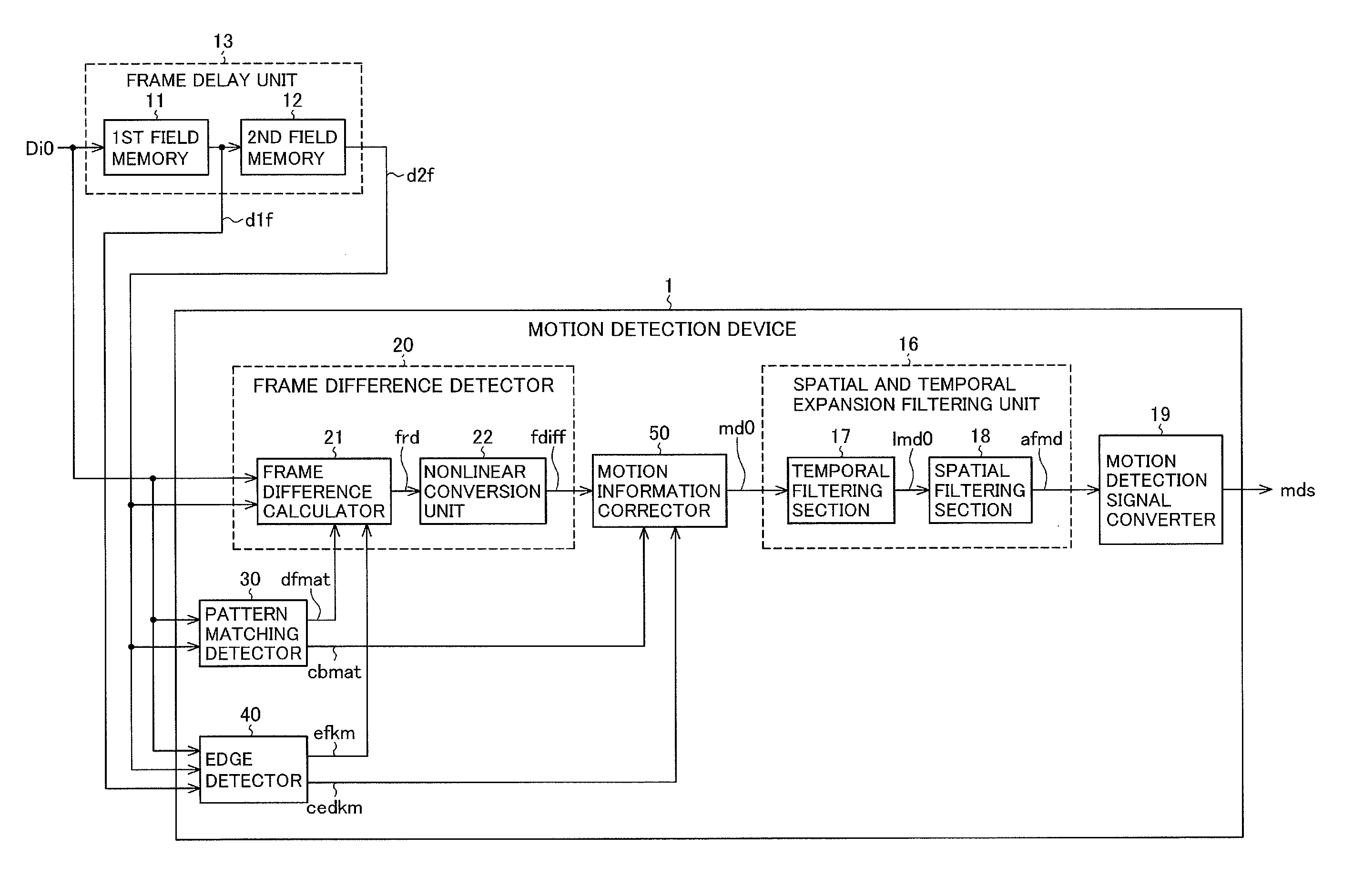

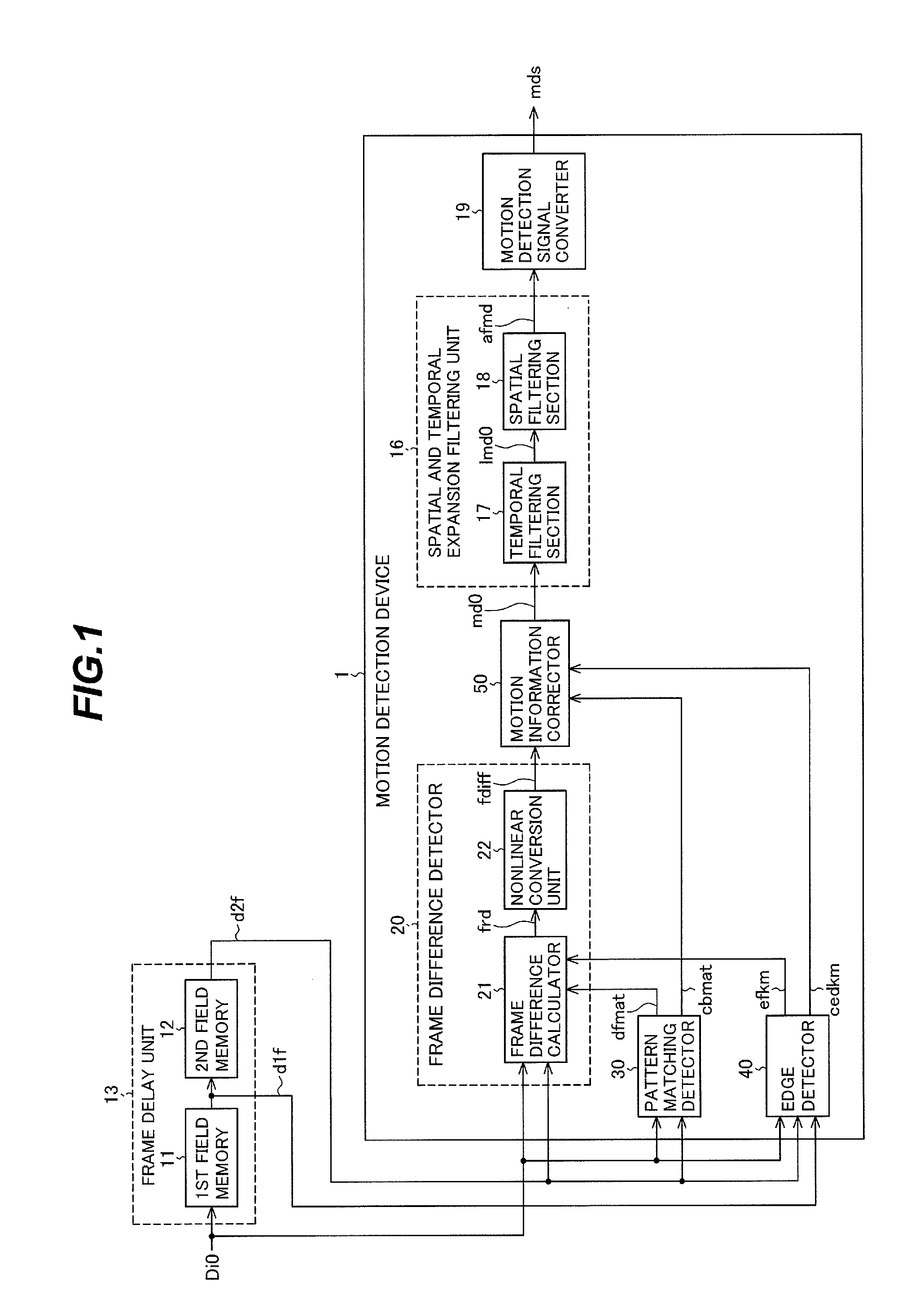

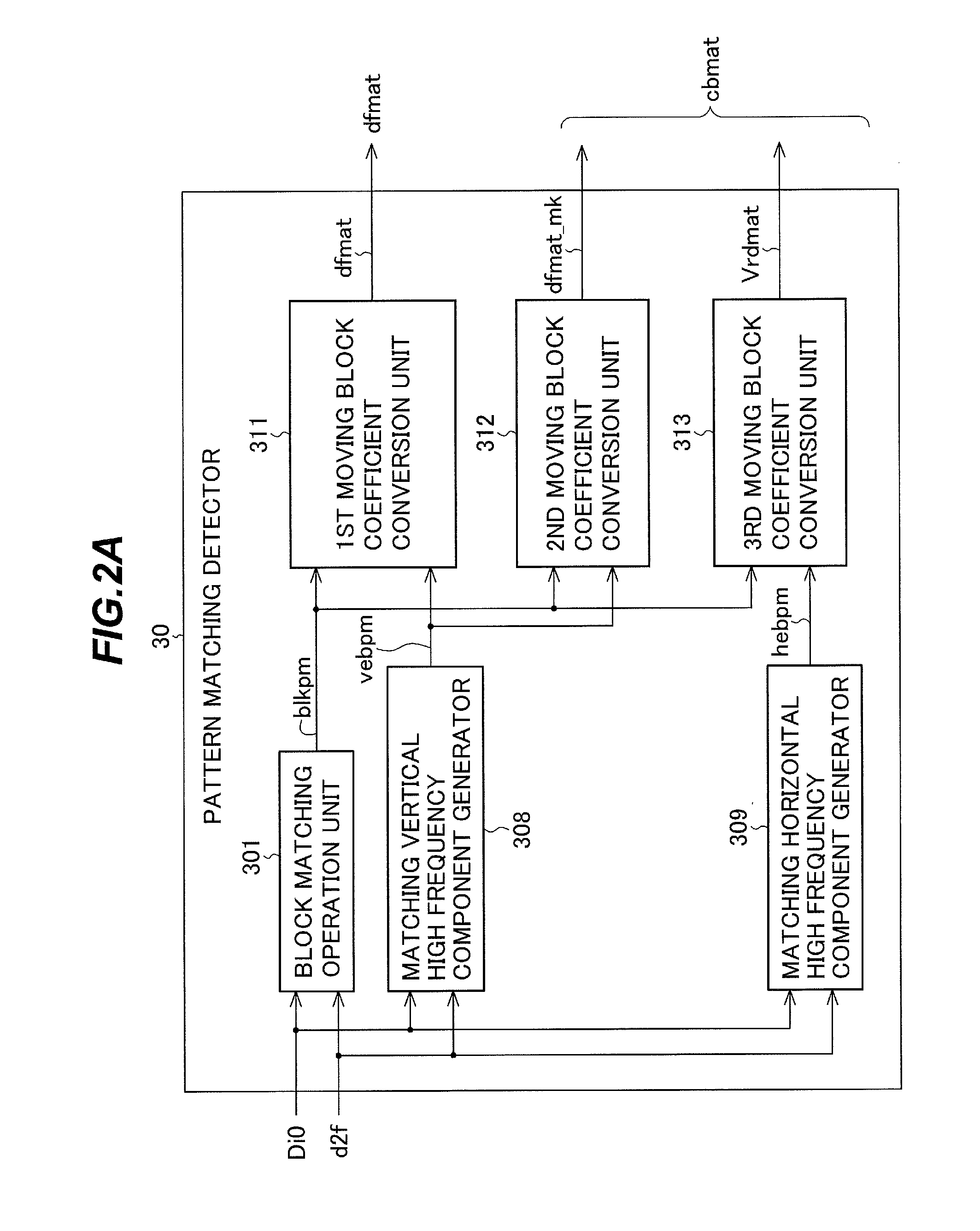

Motion detection device and method, video signal processing device and method and video display device

ActiveUS20120207218A1Improve accuracyQuality improvementColor television with pulse code modulationColor television with bandwidth reductionFrame differencePattern matching

In a motion detection device that detects motion from two frames of a video signal, a pattern matching detector determines pattern similarity between pixel blocks centered on a pixel of interest in the two frames to detect pattern motion. An edge detector detects edge presence and direction in a vicinity of the pixel of interest. A frame difference detector generates a smoothed frame difference signal for the pixel of interest. The smoothing is carried out within appropriate extents selected according to the detected pattern motion and edge direction. A motion information corrector generates motion information for the pixel of interest from the frame difference signal. Appropriate selection of the smoothing extent reduces motion detection mistakes. The motion information is useful in motion adaptive video signal processing.

Owner:MITSUBISHI ELECTRIC CORP

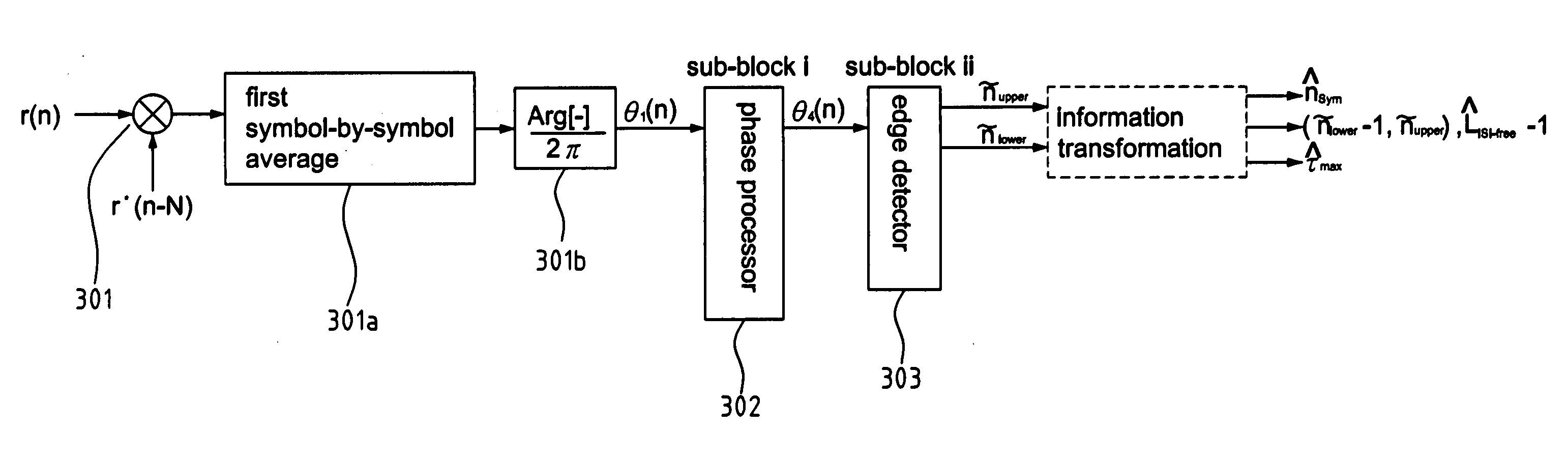

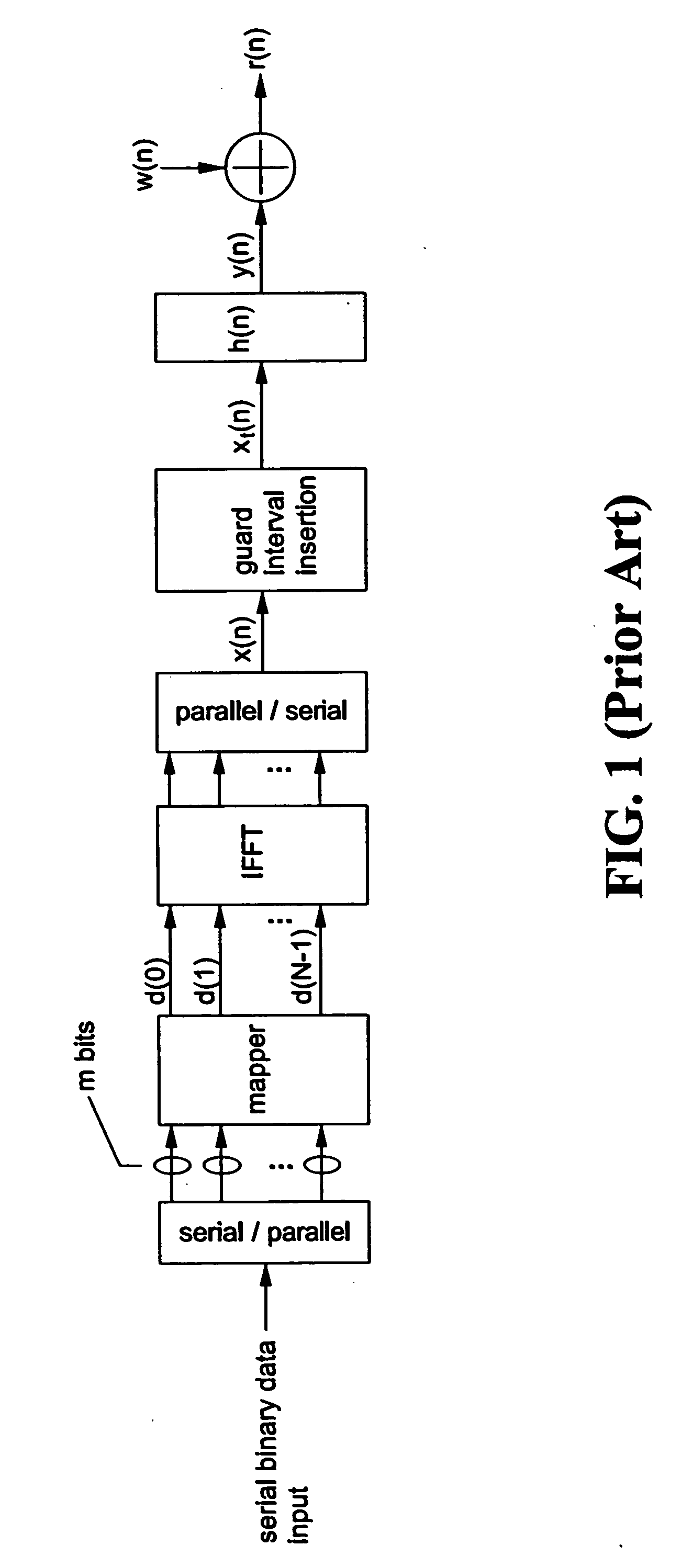

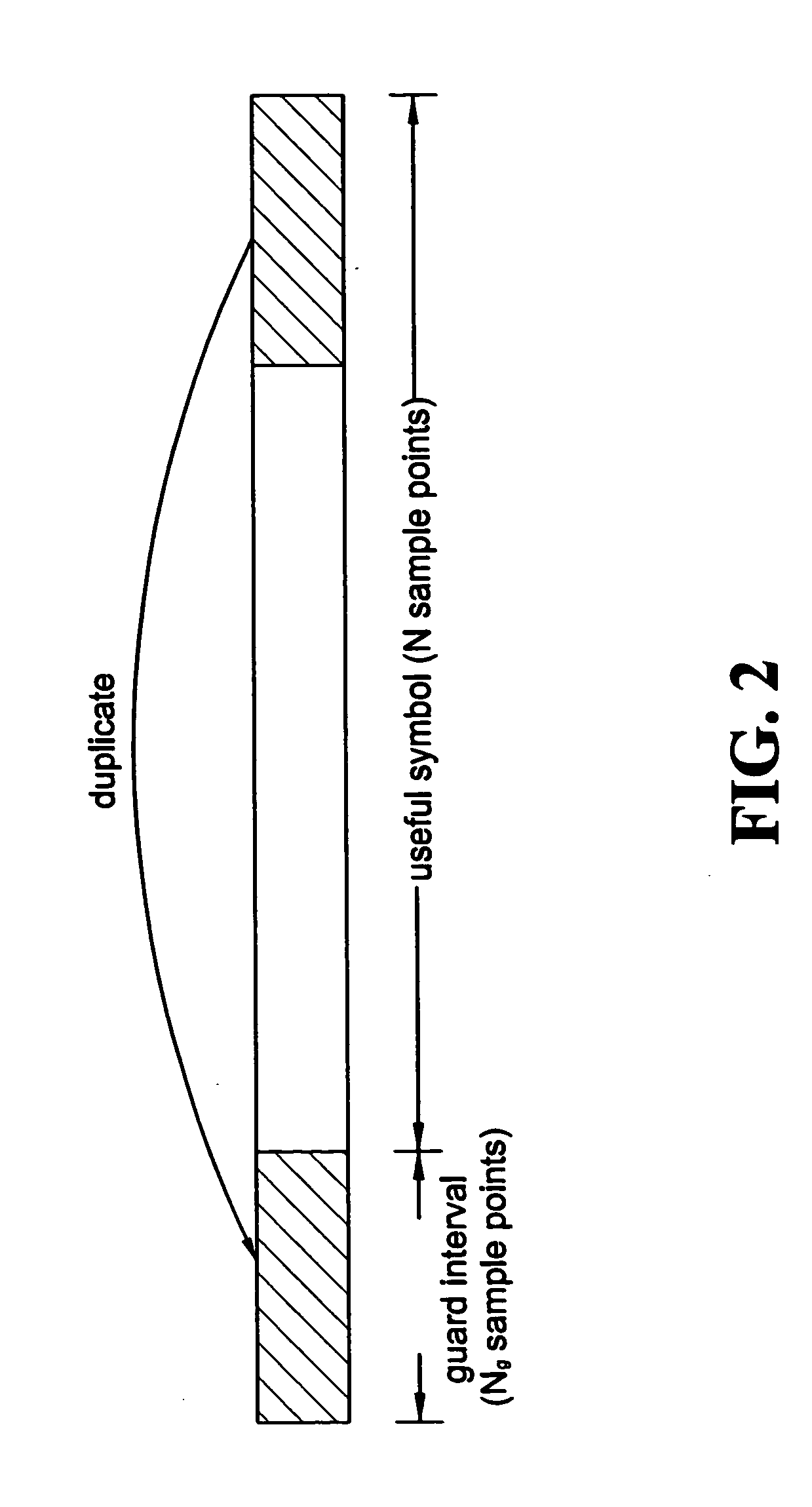

Method and apparatus for synchronization of the OFDM systems

ActiveUS20050105659A1Overcome disadvantagesReduce the impact of noiseError preventionBroadcast transmission systemsDelay spreadGuard interval

A method and apparatus for the signal synchronization of an OFDM system are proposed including a delay conjugate multiplication module, a phase processor and an edge detector. It provides estimates for the boundaries of ISI-free region by utilizing the characteristics of the guard interval and combining the techniques of the delay conjugate multiplication module, phase differential operation, symbol-by-symbol average operation, and edge detection. This method provides an improved performance in a multi-path fading channel with large delay spread, and can be utilized in a broadcasting system, such as the DAB and DVB-T systems. This invention is easy to determine a fixed optimal threshold that can directly separate the ISI region in any mobile environment, thereby most symbol information with ISI-free version can be obtained.

Owner:IND TECH RES INST

Transmitter and Transmission Circuit

Transmitter and transmission circuit. For realizing a differential transmitter, a switch circuit is connected between two load transistors of two complementary MOS pairs. The switch circuit can have two inductors. When the two complementary MOS pairs are conducting current to drive signal transition at output nodes, the inductors open to make the load transistors stop draining current. Also, the switch circuit can have switch transistor controlled by an edge detector for detecting raising and falling edges of the input signals, such that the switch circuit can make the load transistors stop draining current accordingly. In this way, raising and falling edges of the output signals are emphasized to improve signal propagation.

Owner:VIA TECH INC

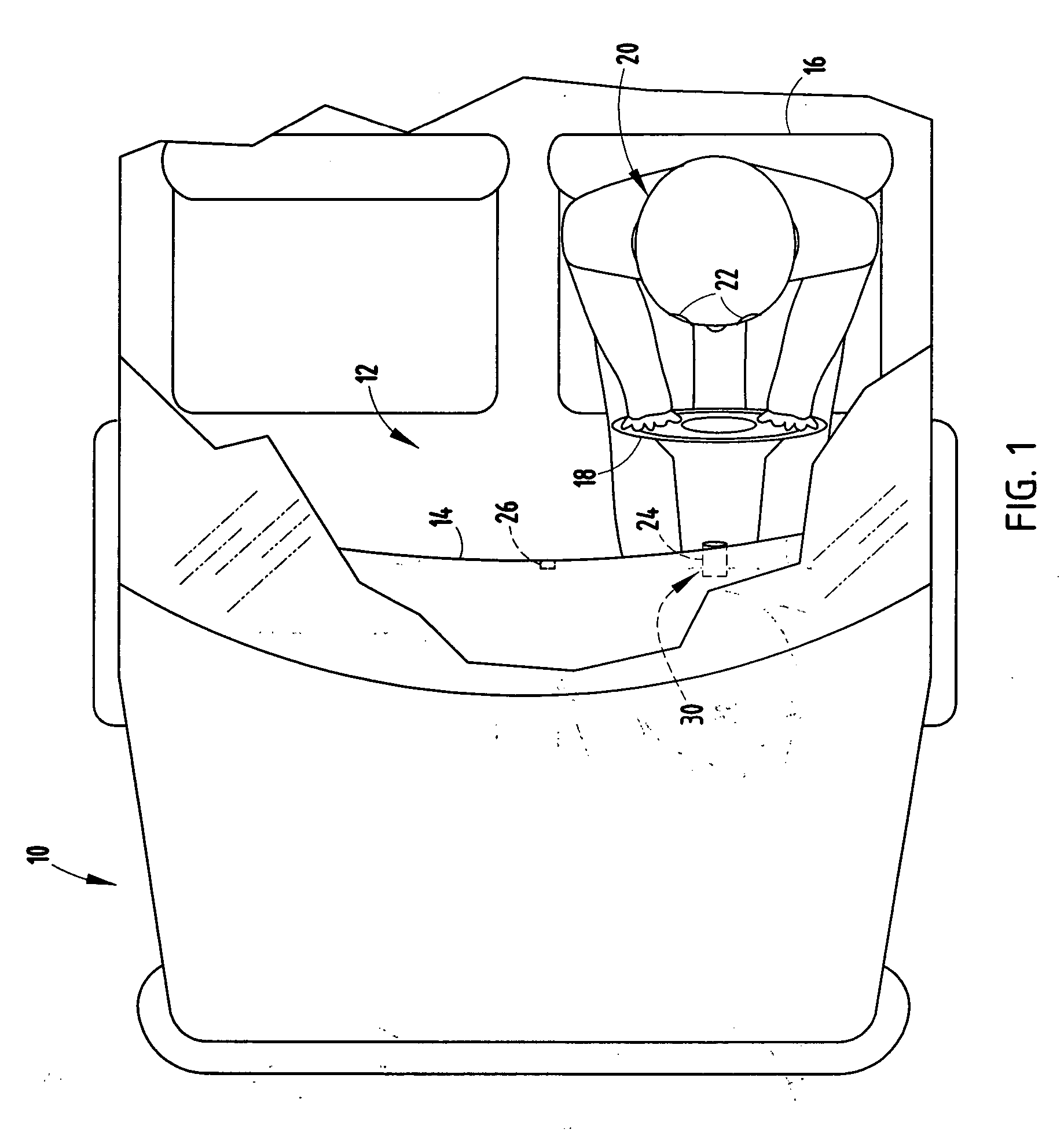

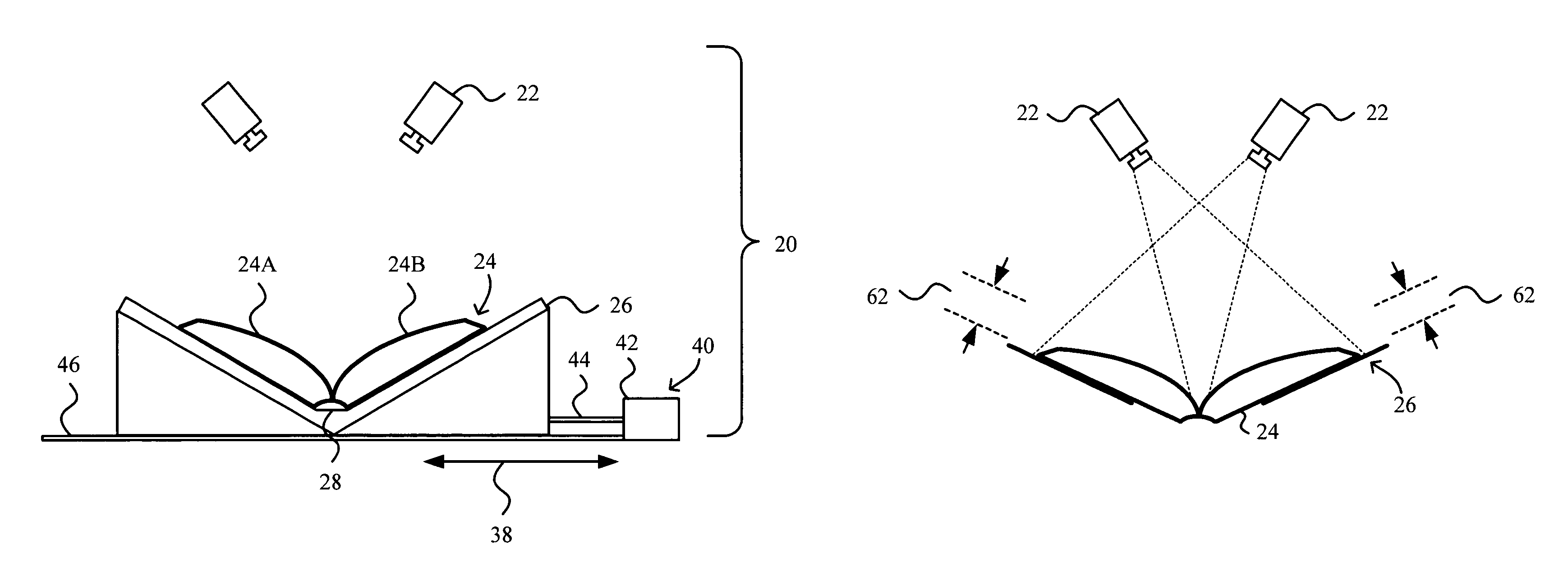

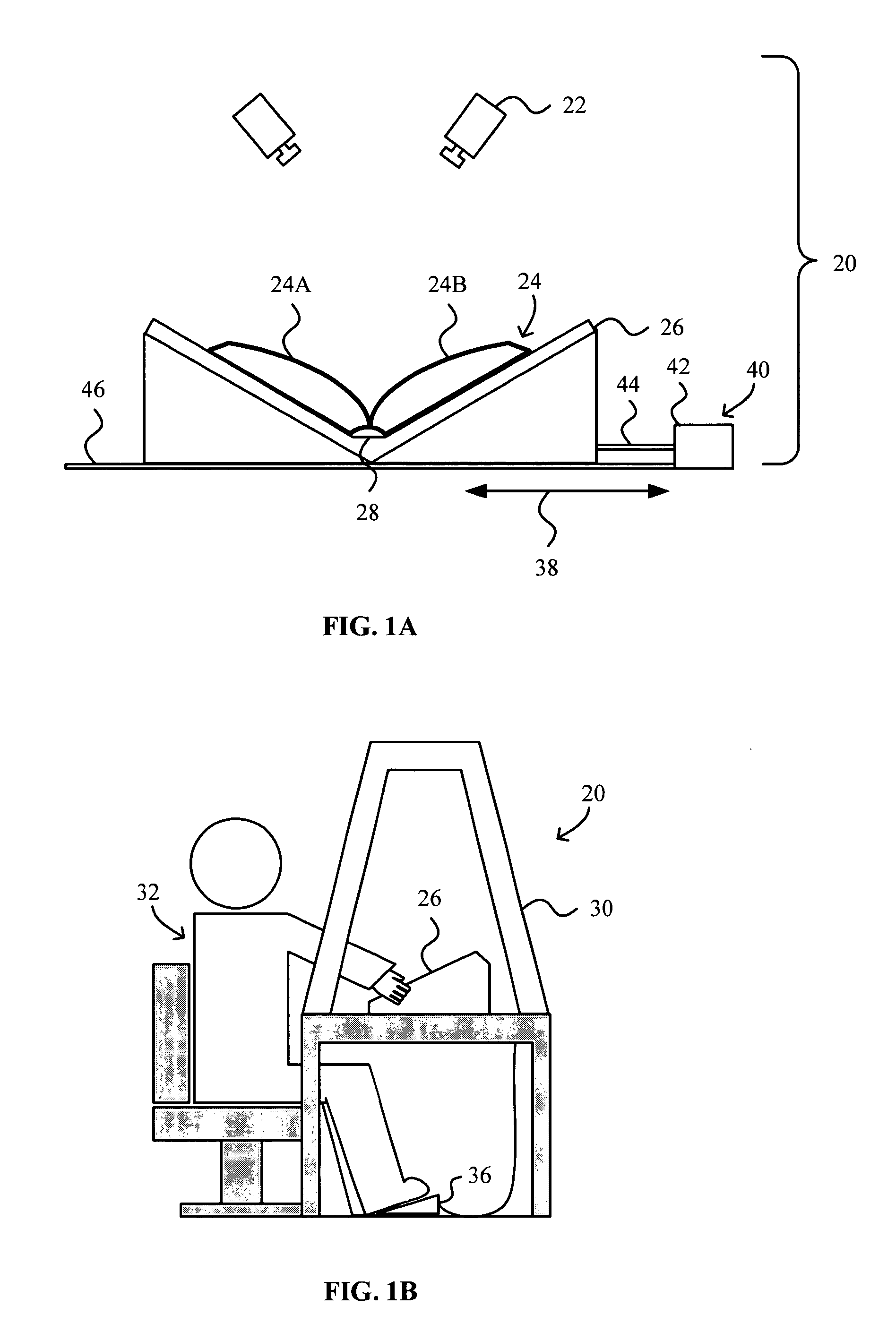

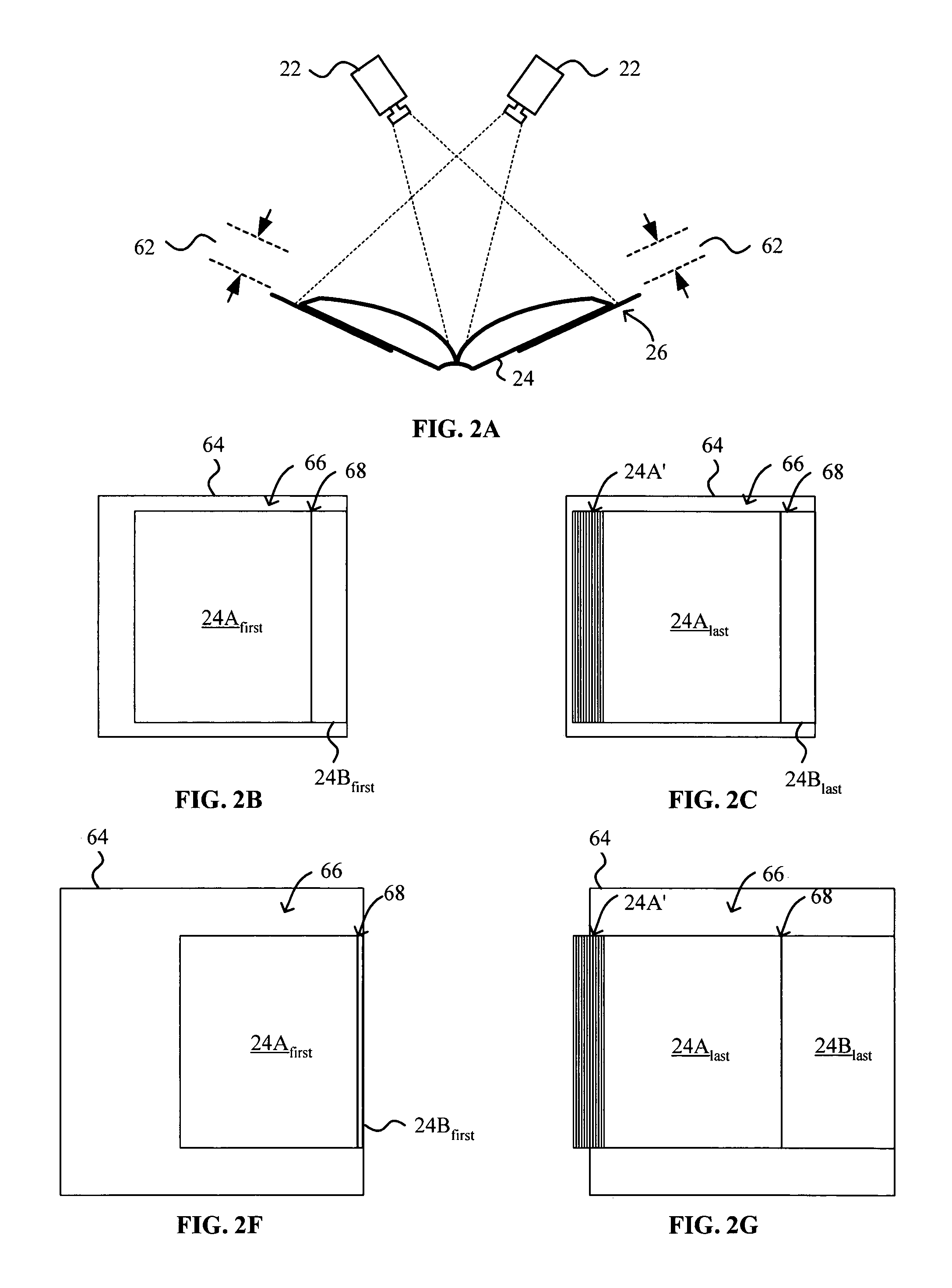

Movable document cradle for facilitating imaging of bound documents

Systems and methods for moving a document cradle to facilitate imaging of a bound document are disclosed. The system may include a cradle supporting a document, such as a book, a cradle positioner for selectively positioning the cradle relative to a camera, and a controller for controlling the positioner to automatically position the cradle based on the location of the page being imaged relative to the camera. The cradle may be positioned such that a gutter of the book or a surface plane of each page being imaged remains in approximately the same position relative to the camera. The cradle positioner may include a servo motor controlling a shaft to position the cradle supported and guided by a bearing. A sensor (e.g., 3D camera, range finder, laser, and / or edge detector) may be provided to facilitate the controller in controlling the cradle positioner based on the location of the page being imaged relative to the camera. The controller may control the positioner based on, for example, current page count tracked by the controller, total number of pages, thickness of the book, width of the gutter of the cradle, and / or weight of the book exerted on one or both sides of the cradle.

Owner:GOOGLE TECH +1

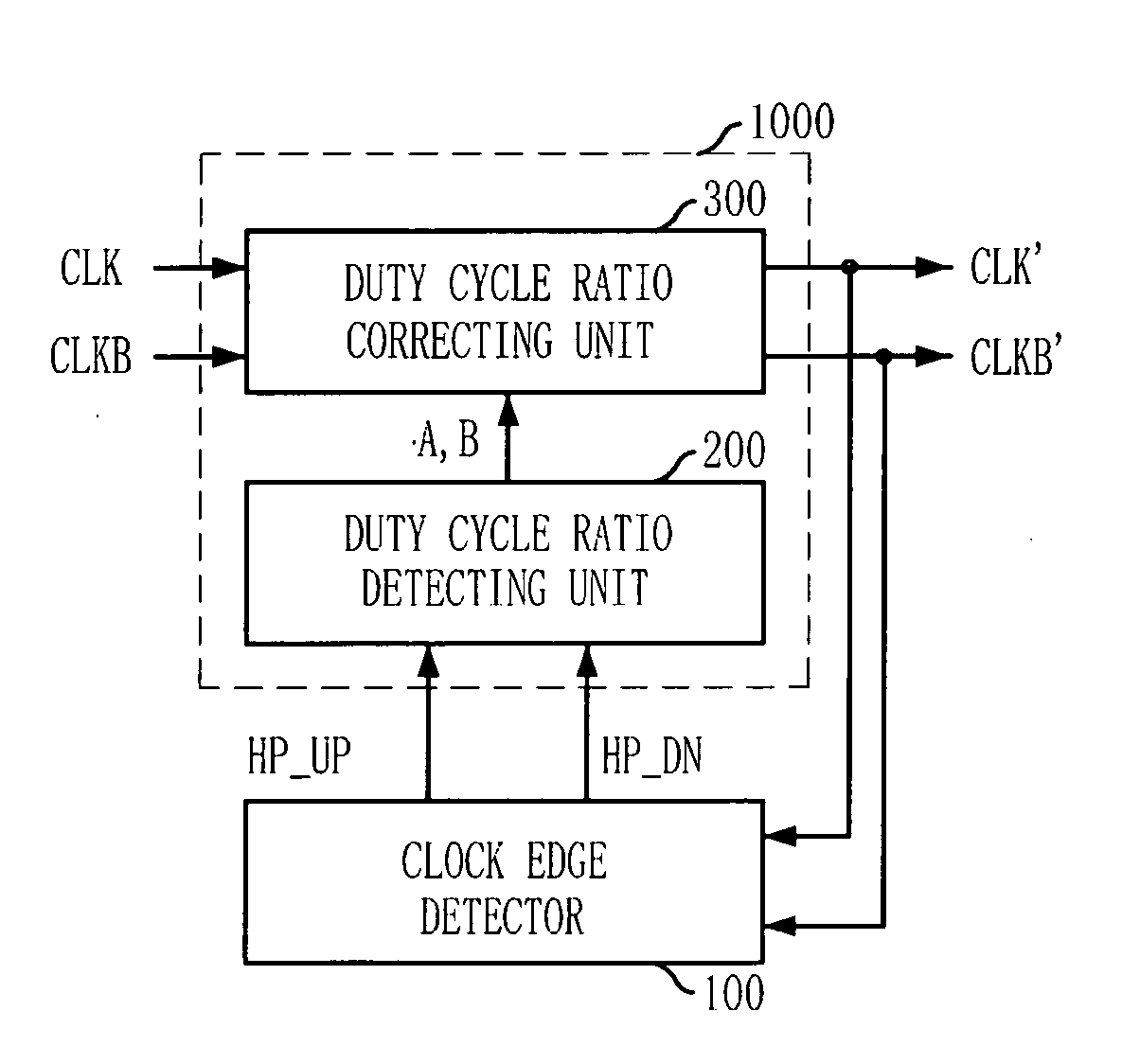

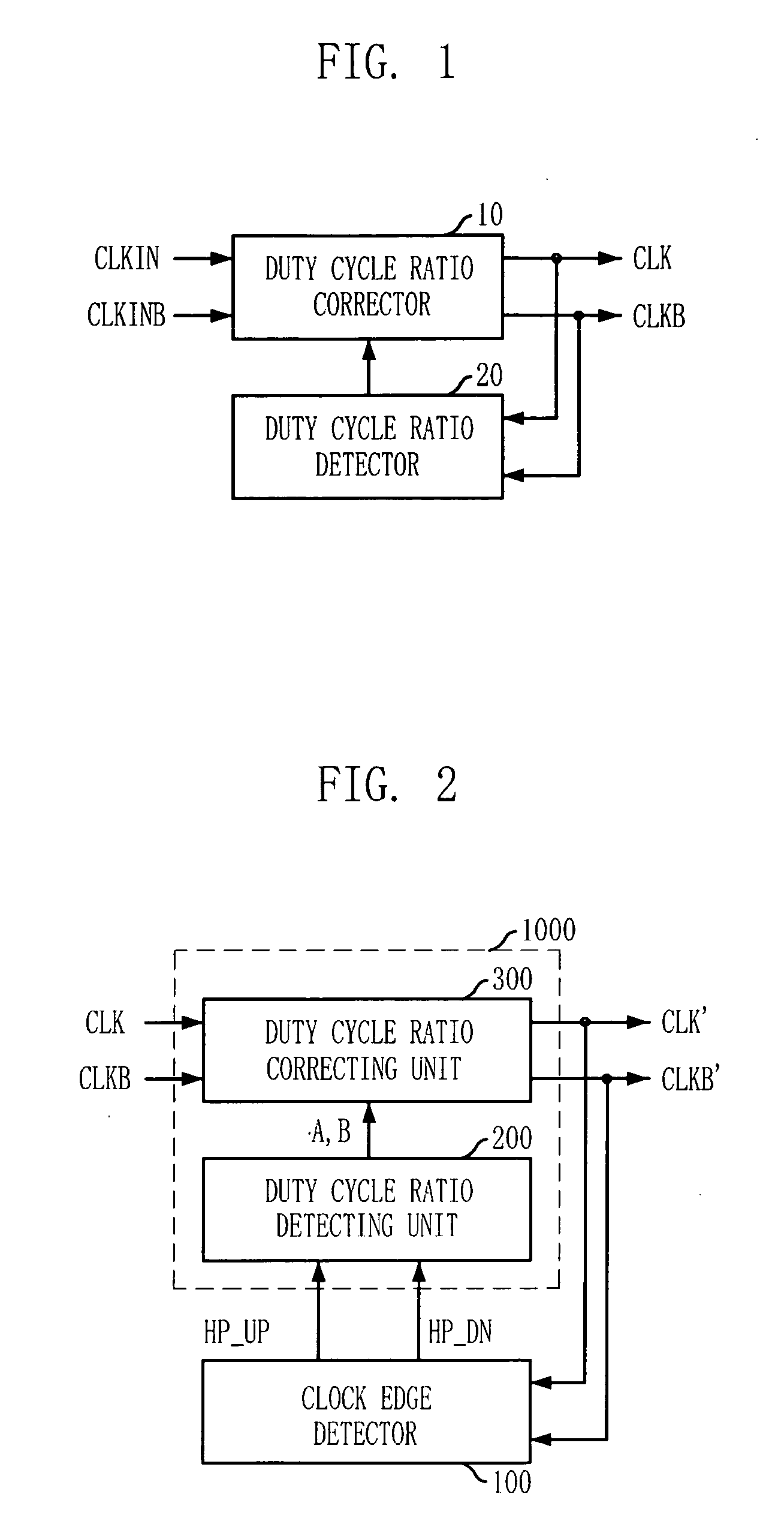

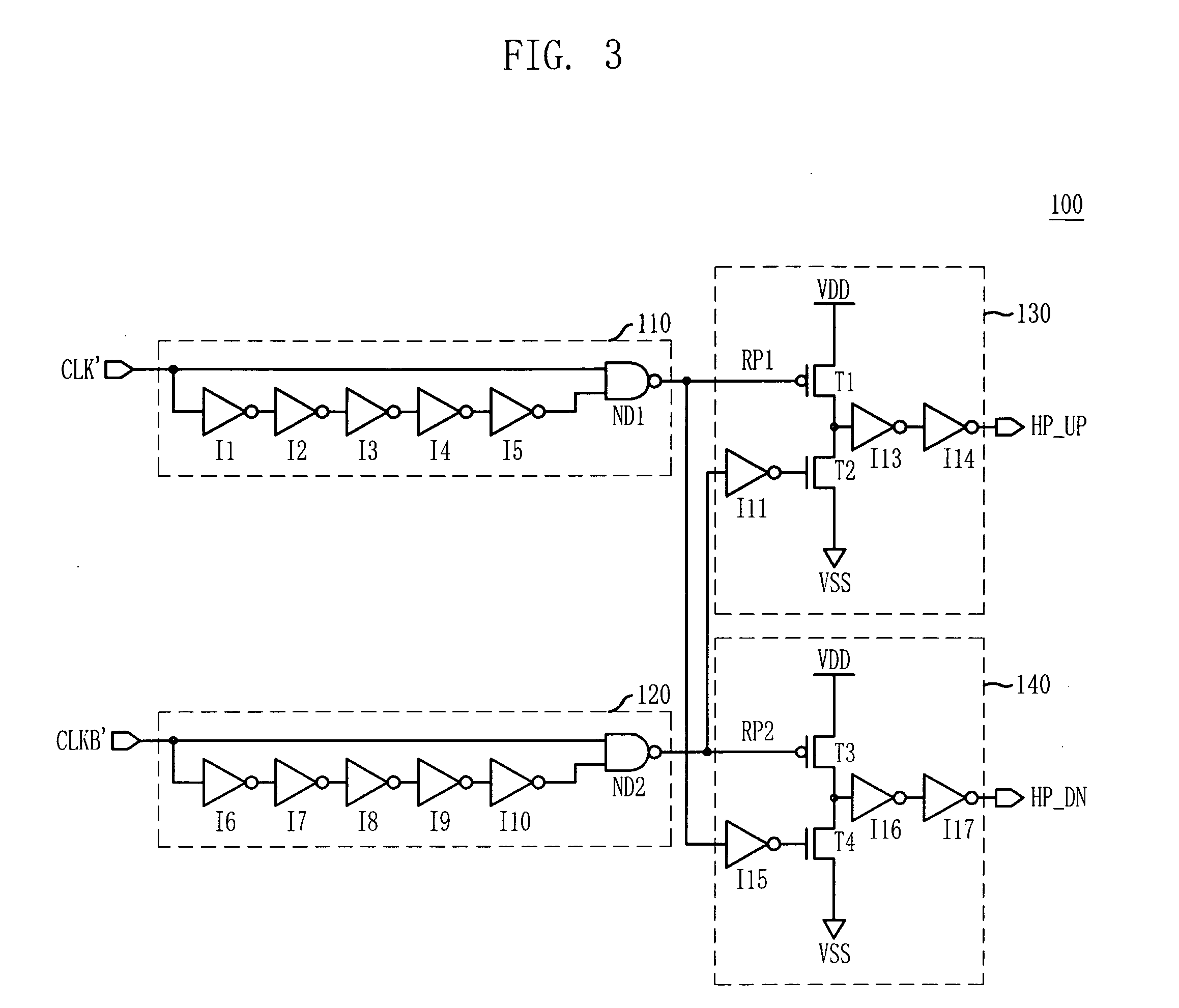

Semiconductor memory device and method for driving the same

A semiconductor memory device has a duty cycle correction circuit capable of outputting a duty cycle corrected clock and its inverted clock having substantially exactly 180° phase difference therebetween. The semiconductor memory device includes a duty cycle corrector configured to receive a first clock and a second clock to generate a first output clock and a second output clock whose duty cycle ratios are corrected in response to correction signals, and a clock edge detector configured to generate the correction signals corresponding to an interval between a reference transition timing of the first output clock and a reference transition timing of the second output clock.

Owner:SK HYNIX INC