Patents

Literature

1367 results about "Salient point" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

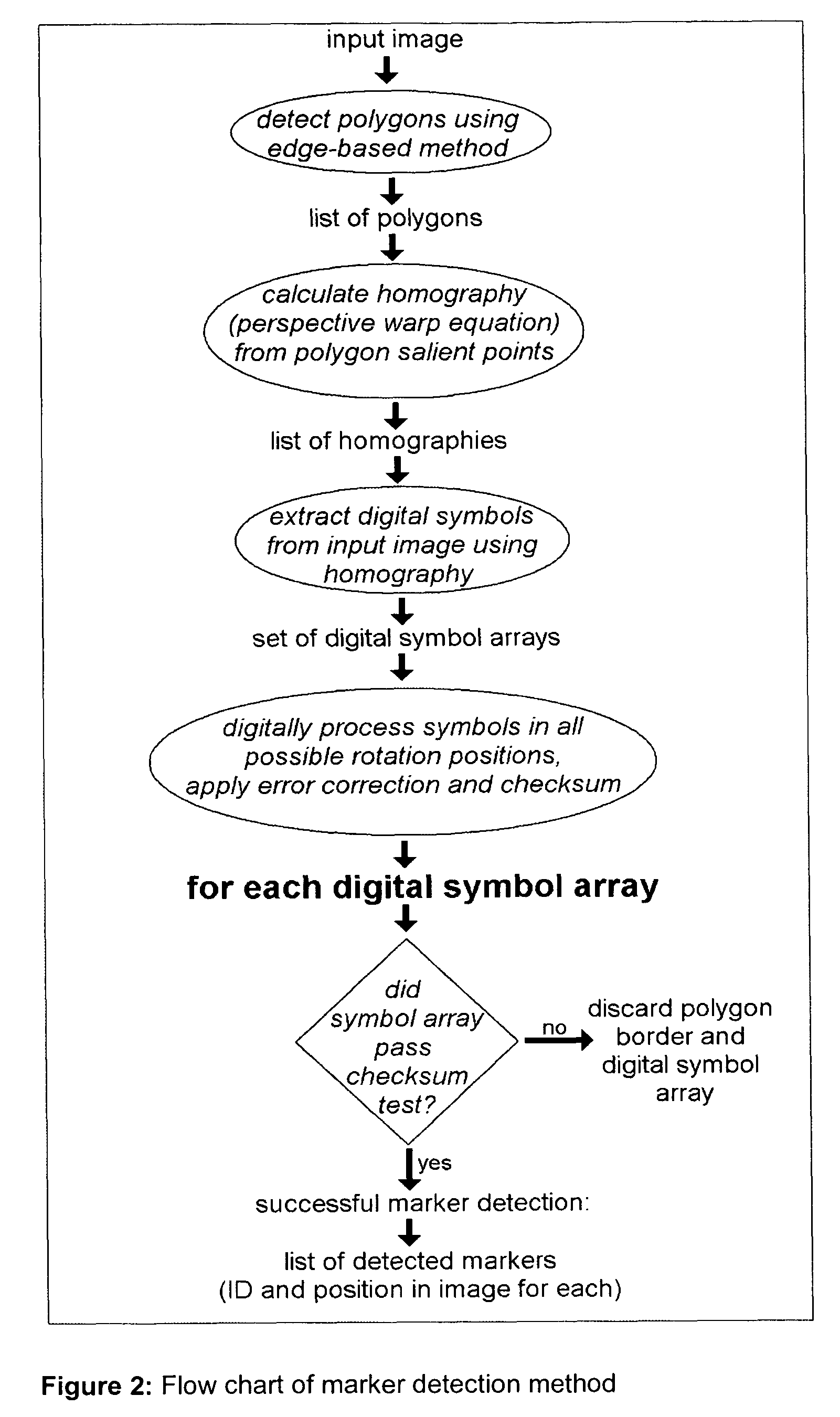

Marker and method for detecting said marker

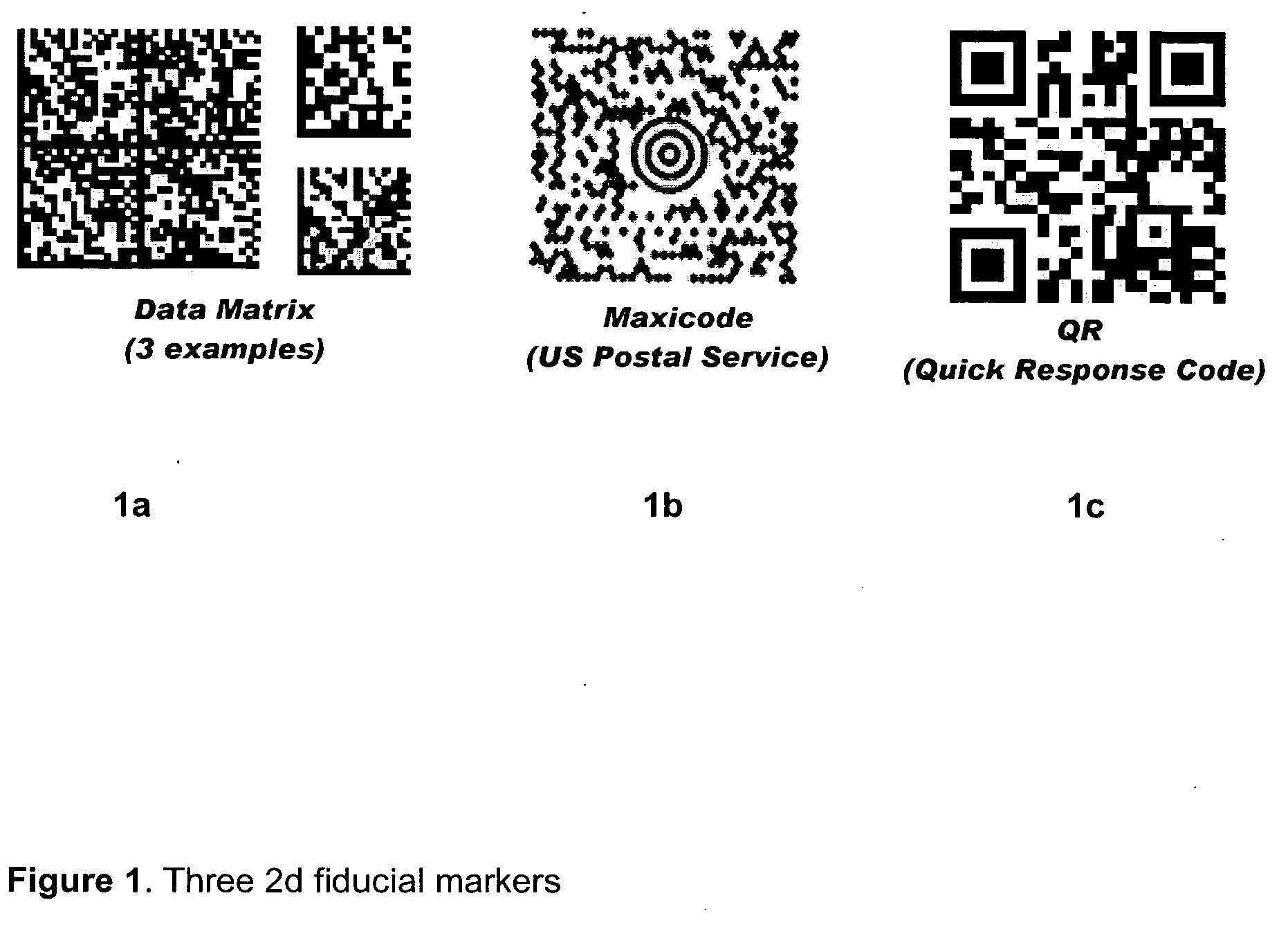

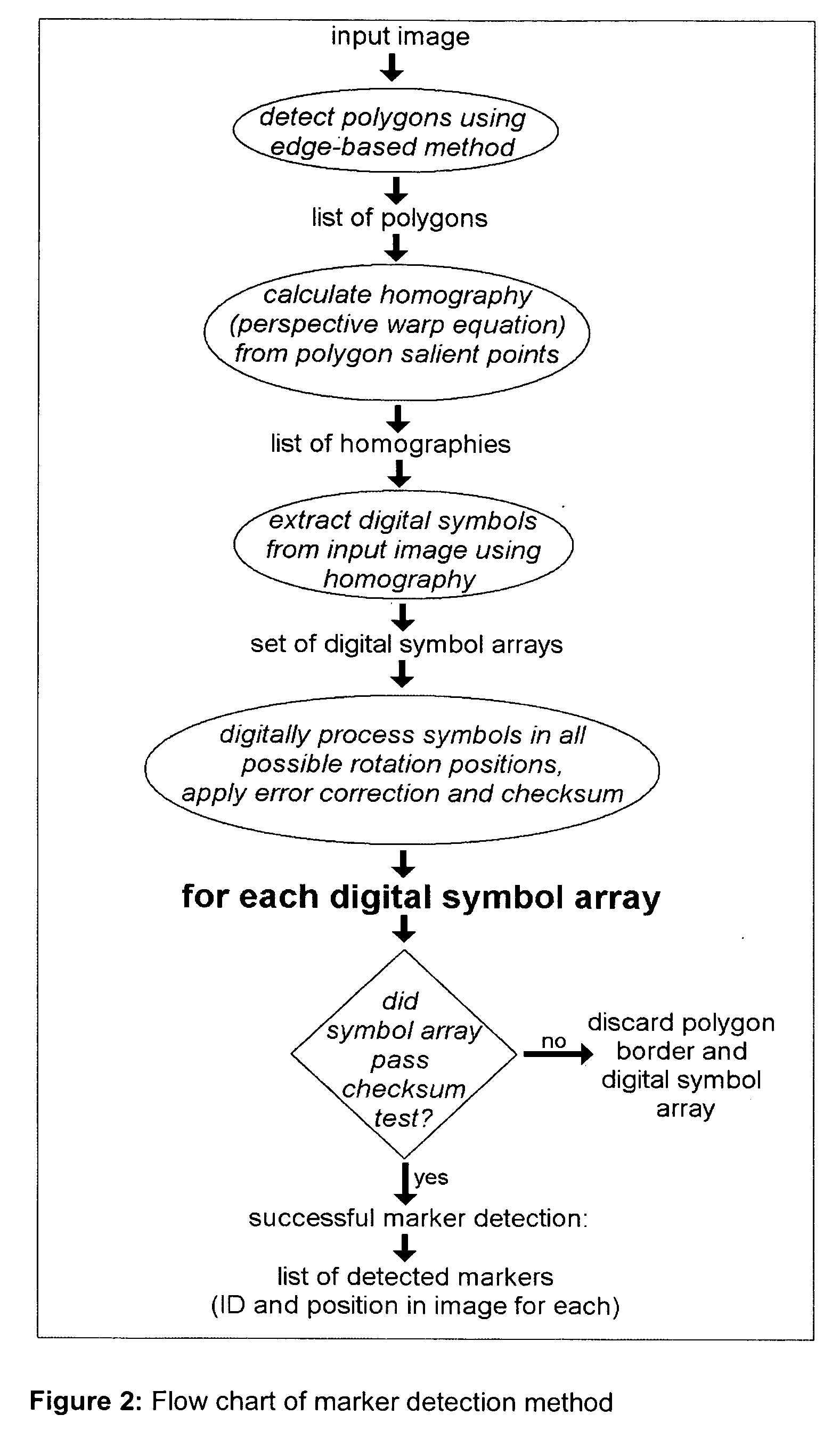

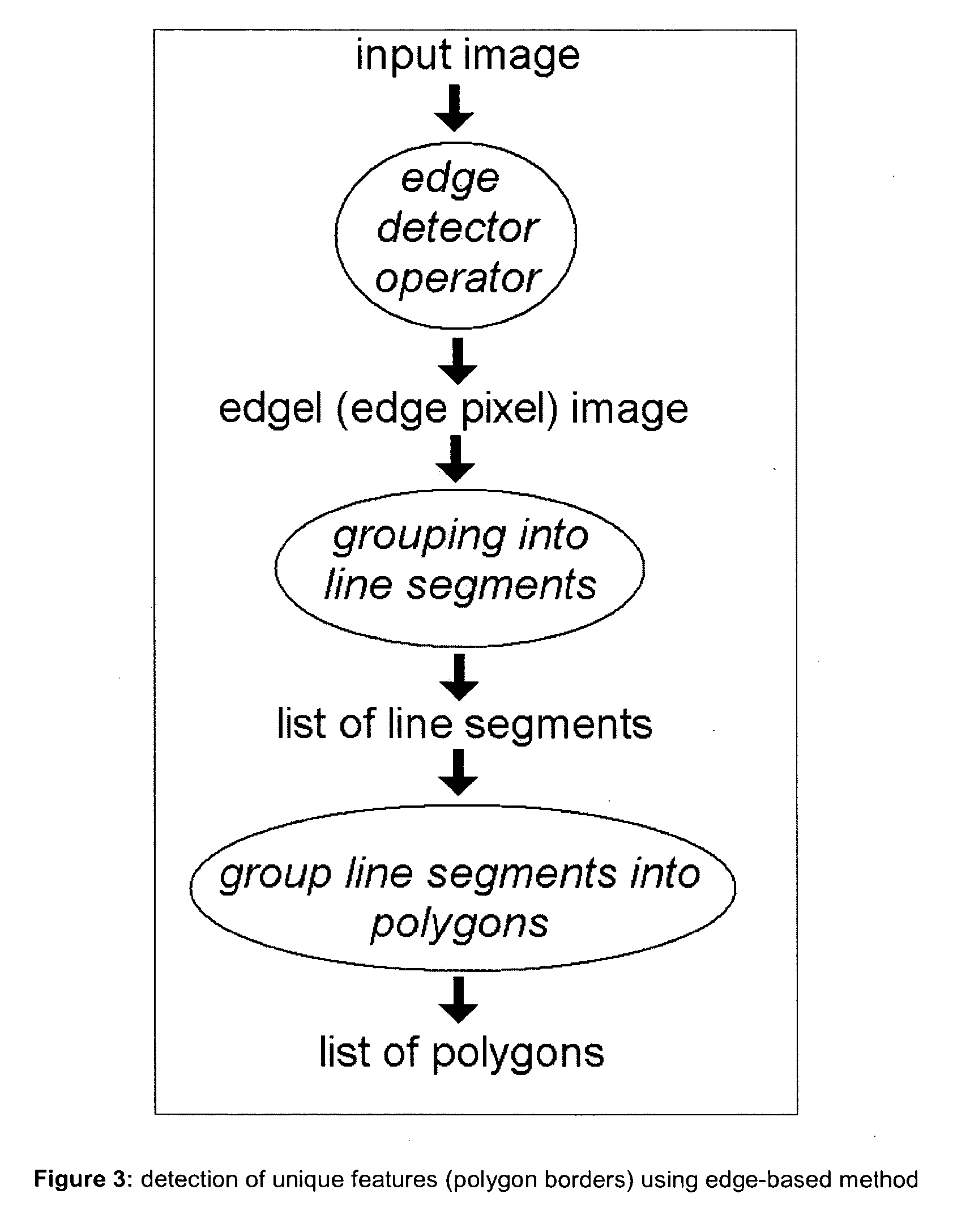

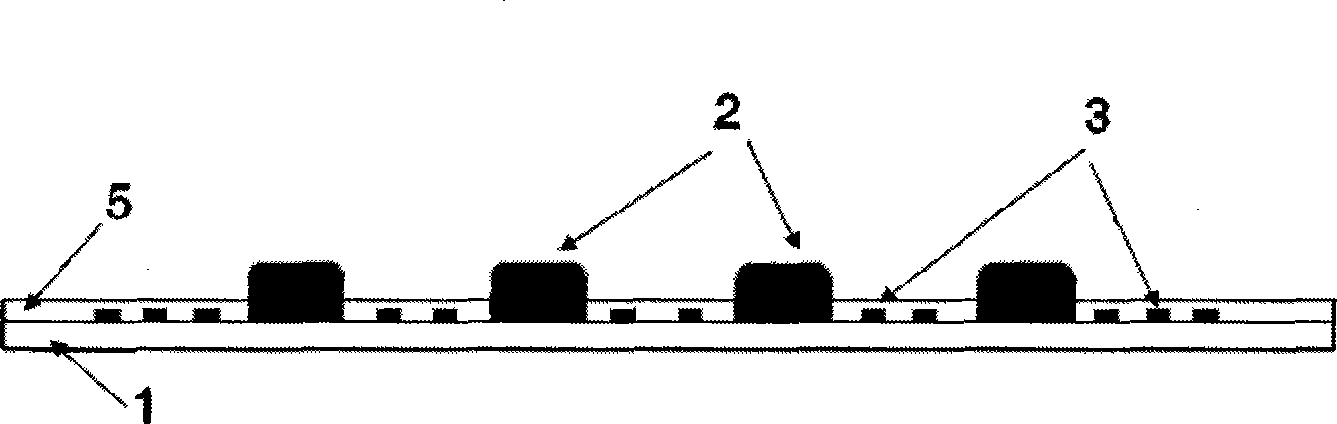

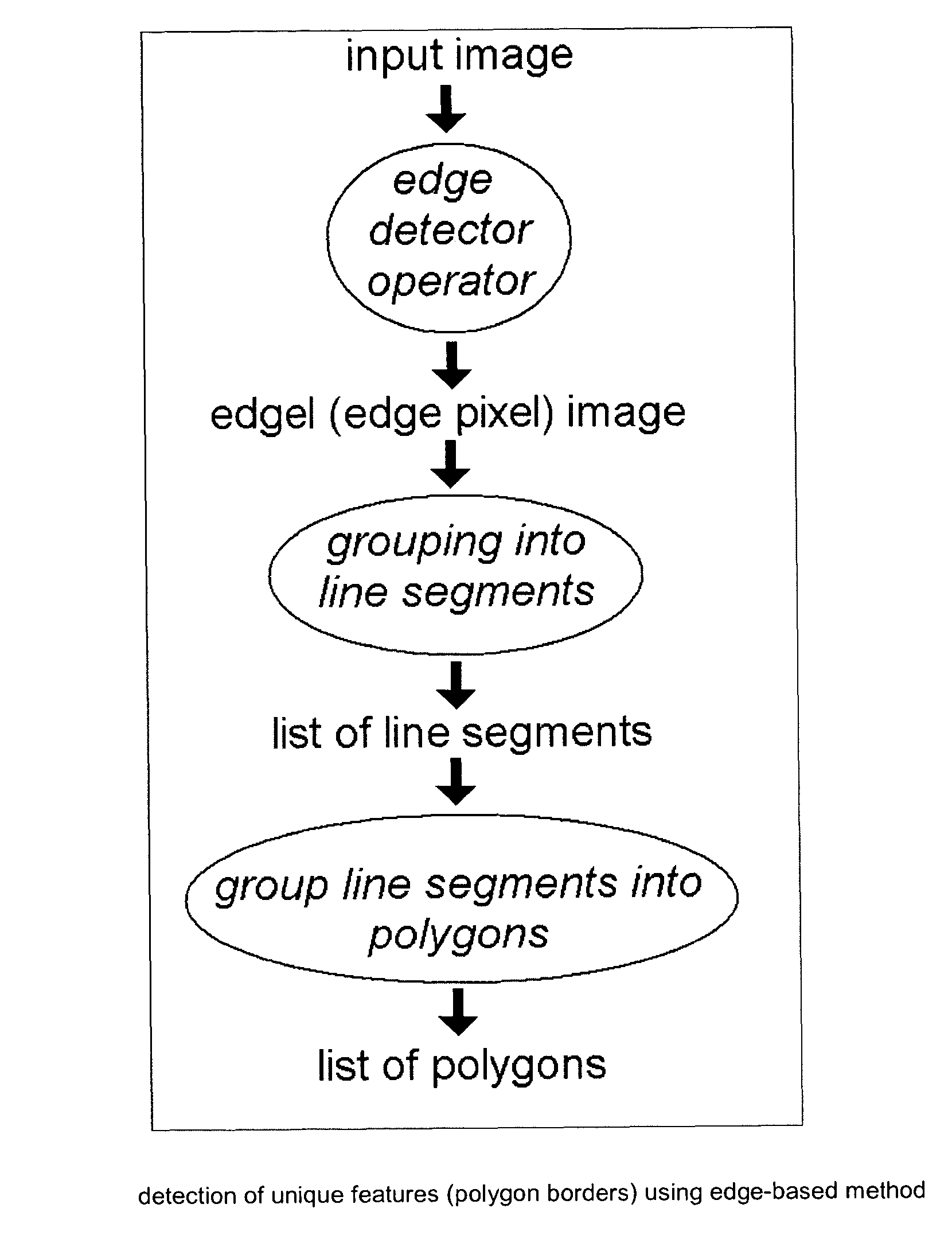

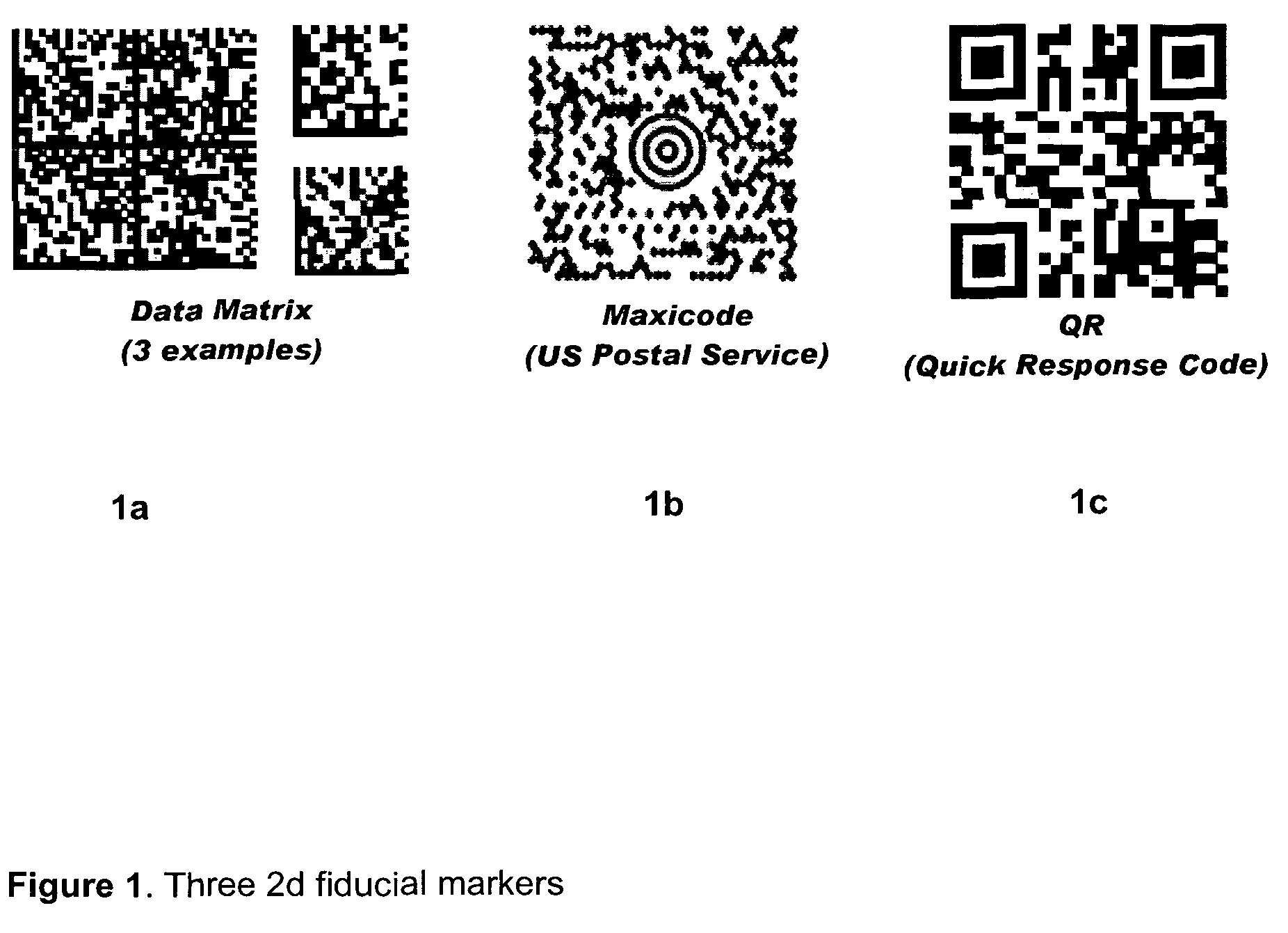

This invention discloses marker detectable by visual means comprising; a polygonal border having of at least four non collinear salient points. The marker has on it a pattern in binary digital code. The binary code data contains information data, checksum and error correction. The binary code data is on two levels; a first level of binary code readable at a first given distance, a second level of binary code readable at a second given distance, where the second given distance is less than the first given distance and the second level binary code is smaller in size than the first level binary code. The second level of binary code does not interfere with the reading of the first level binary code. It also discloses a method for detecting a marker comprising the steps of detecting an image, using an edge detector to detect an edge in said image, grouping more than one edge into a polygon having salient points, calculating homography from polygon salient points, generating a list of homographies, extracting binary data from input image having homographies, identifying and verifying binary data.

Owner:MILLENNIUM THREE TECH

Salient Point-Based Arrangements

ActiveUS20120275642A1Increase operating spaceSimple processImage enhancementImage analysisTablet computerComputer graphics (images)

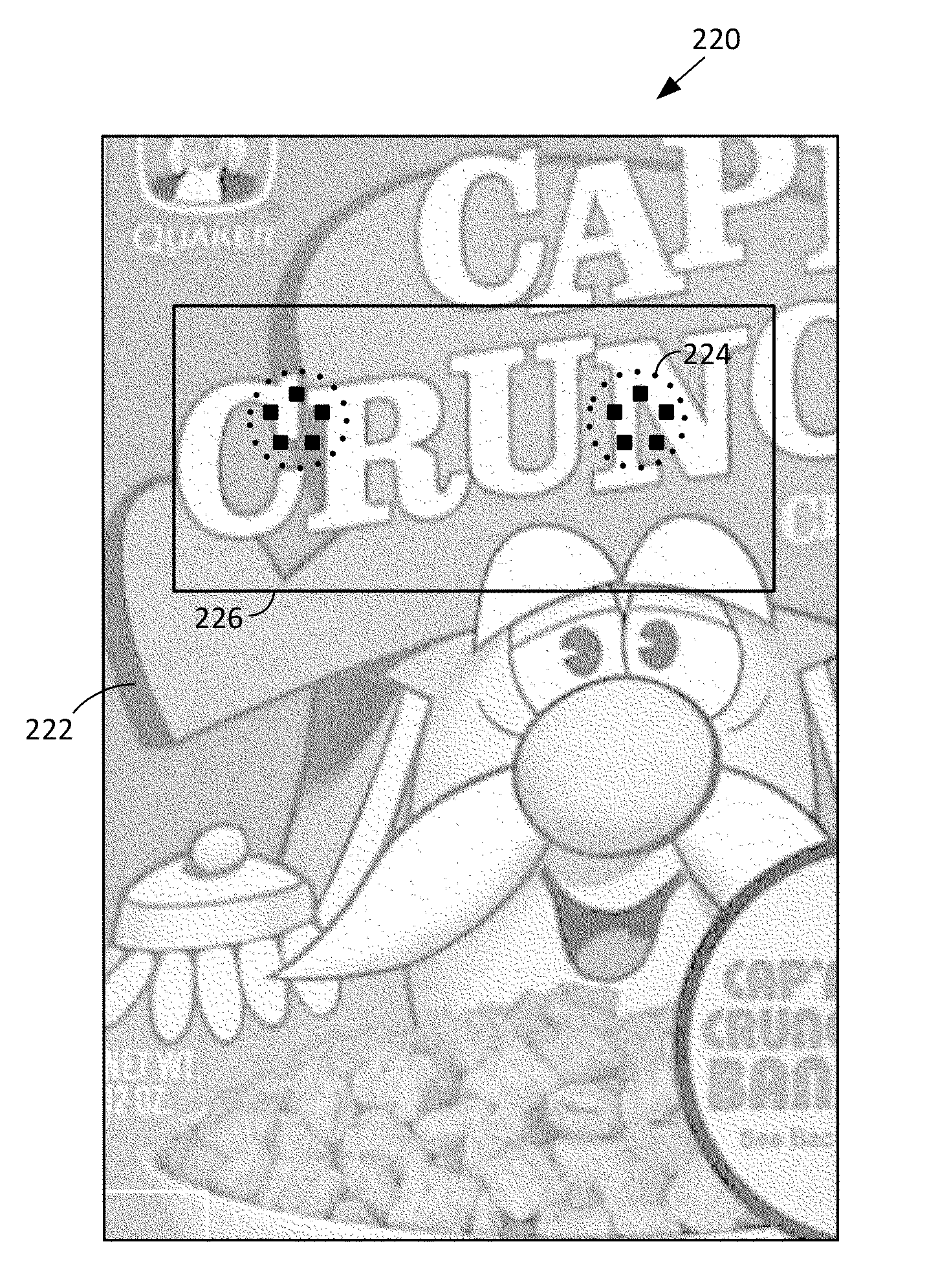

A variety of methods and systems involving sensor-equipped portable devices, such as smartphones and tablet computers, are described. One particular embodiment decodes a digital watermark from imagery captured by the device and, by reference to watermark payload data, obtains salient point data corresponding to an object depicted in the imagery. Other embodiments obtain salient point data for an object through use of other technologies (e.g., NFC chips). The salient point data enables the device to interact with the object in a spatially-dependent manner. Many other features and arrangements are also detailed.

Owner:DIGIMARC CORP

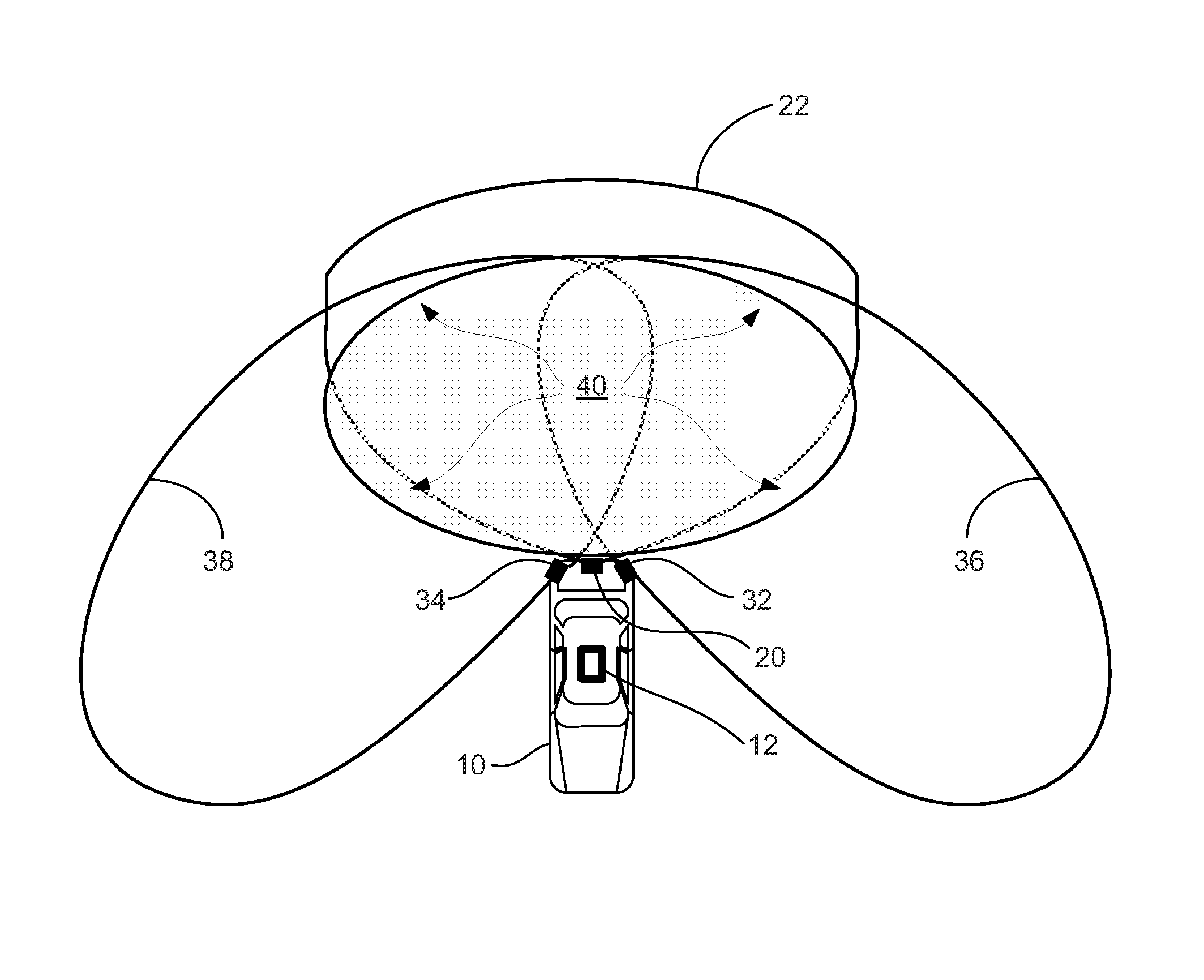

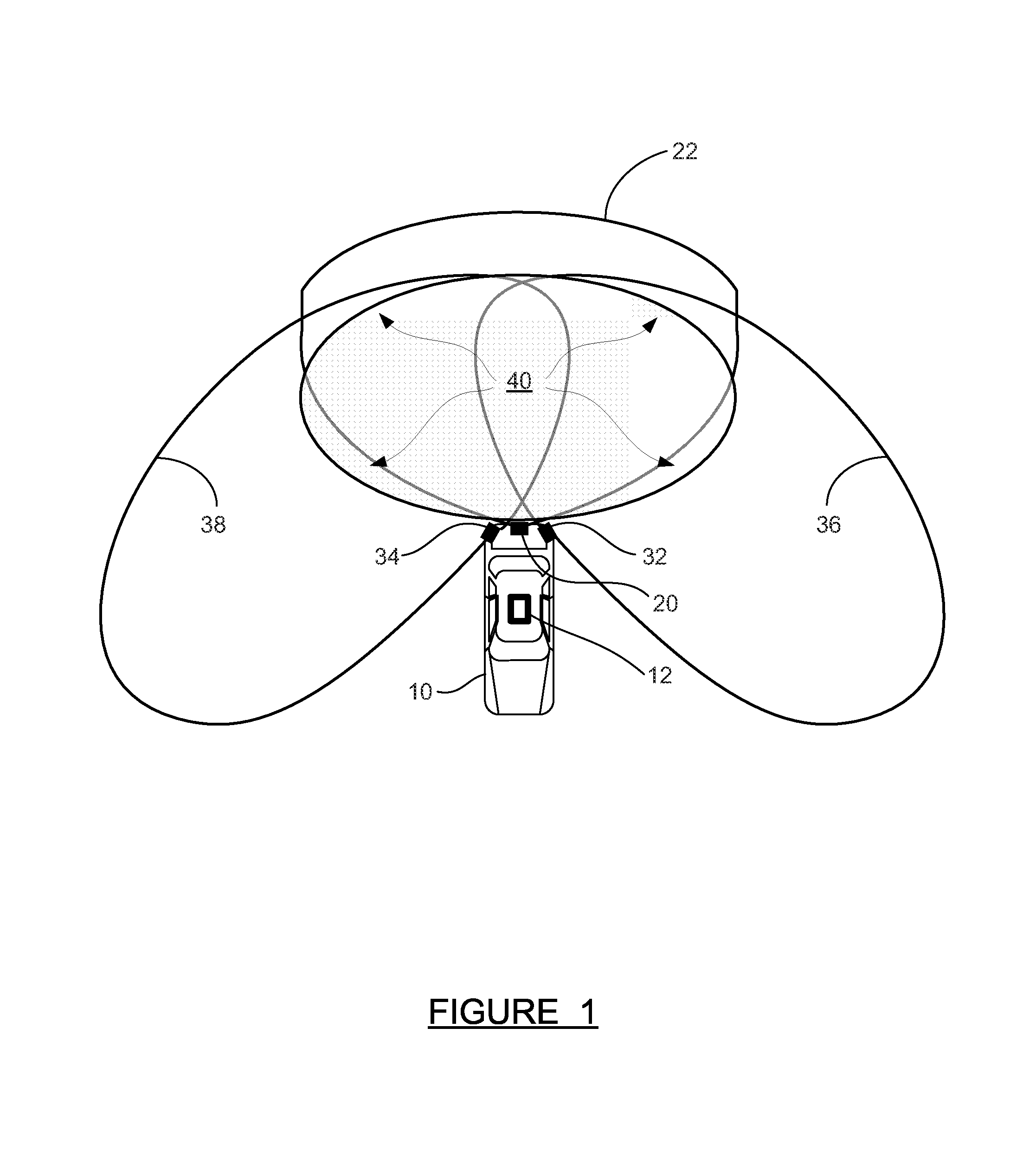

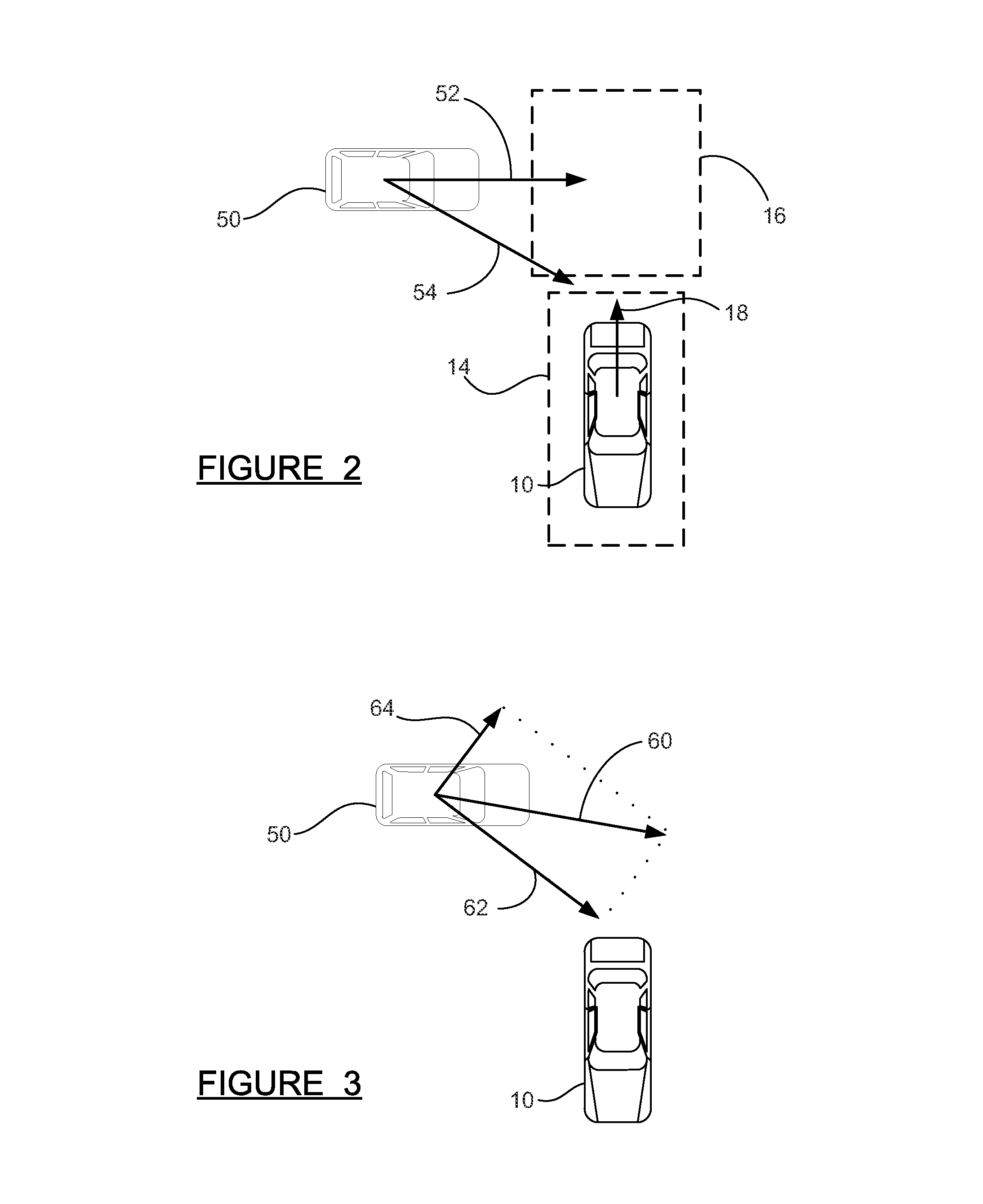

Fusion method for cross traffic application using radars and camera

ActiveUS20160291149A1Accurate estimateAutomatic initiationsSignalling/lighting devicesAutomatic brakingRadar

A method and system are disclosed for tracking objects which are crossing behind a host vehicle. Target data from a vision system and two radar sensors are provided to an object detection fusion system. Salient points on the target object are identified and tracked using the vision system data. The salient vision points are associated with corresponding radar points, where the radar points provide Doppler radial velocity data. A fusion calculation is performed on the salient vision points and the radar points, yielding an accurate estimate of the velocity of the target object, including its lateral component which is difficult to obtain using radar points only or traditional vision system methods. The position and velocity of the target object are used to trigger warnings or automatic braking in a Rear Cross Traffic Avoidance (RCTA) system.

Owner:GM GLOBAL TECH OPERATIONS LLC

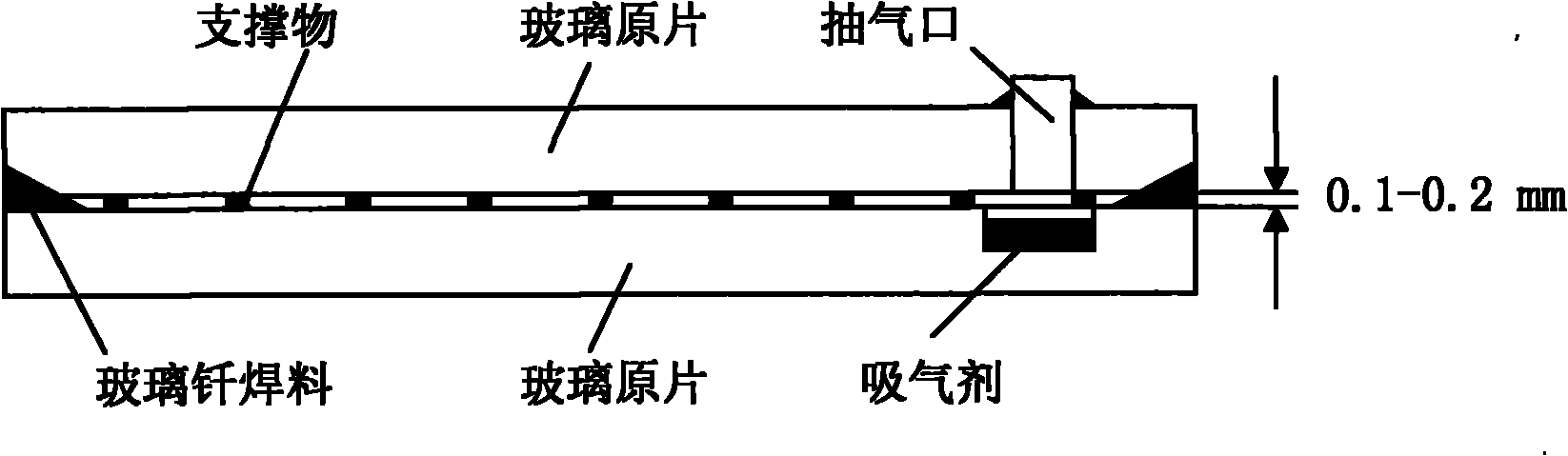

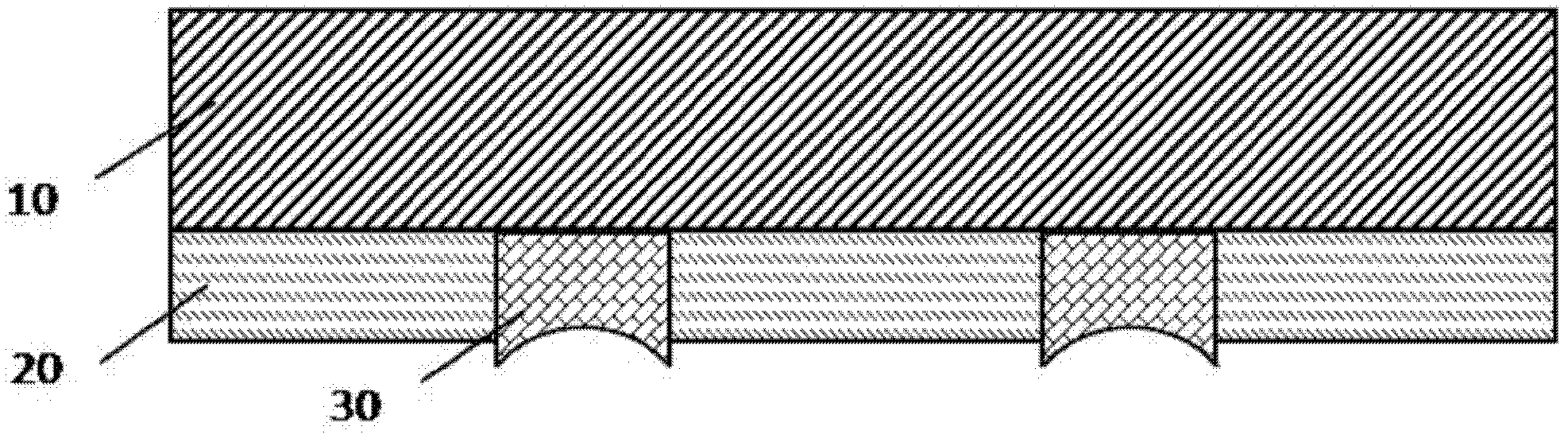

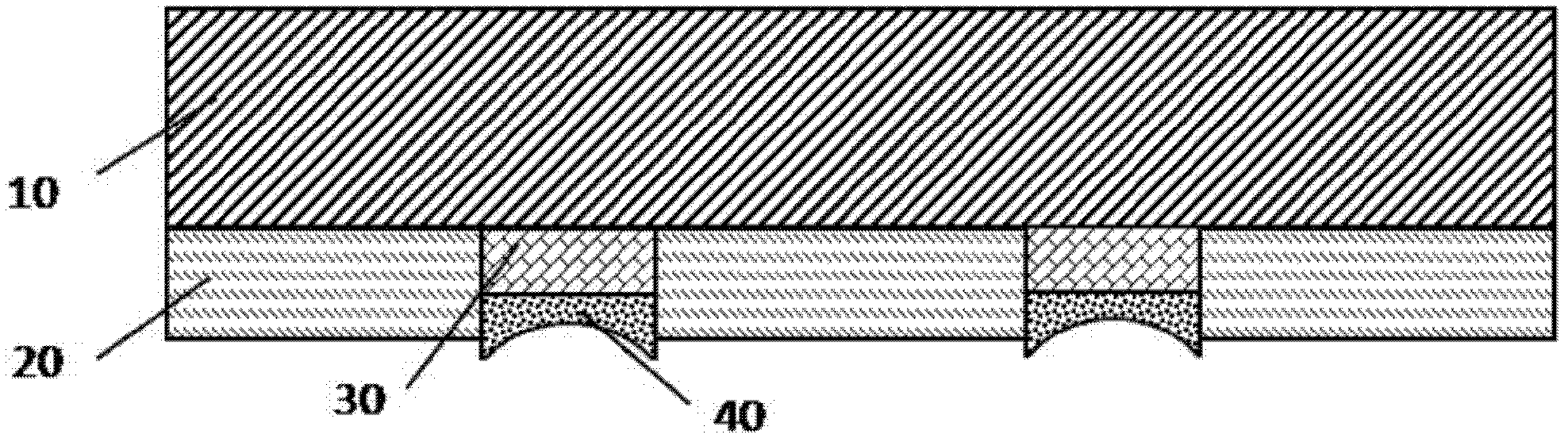

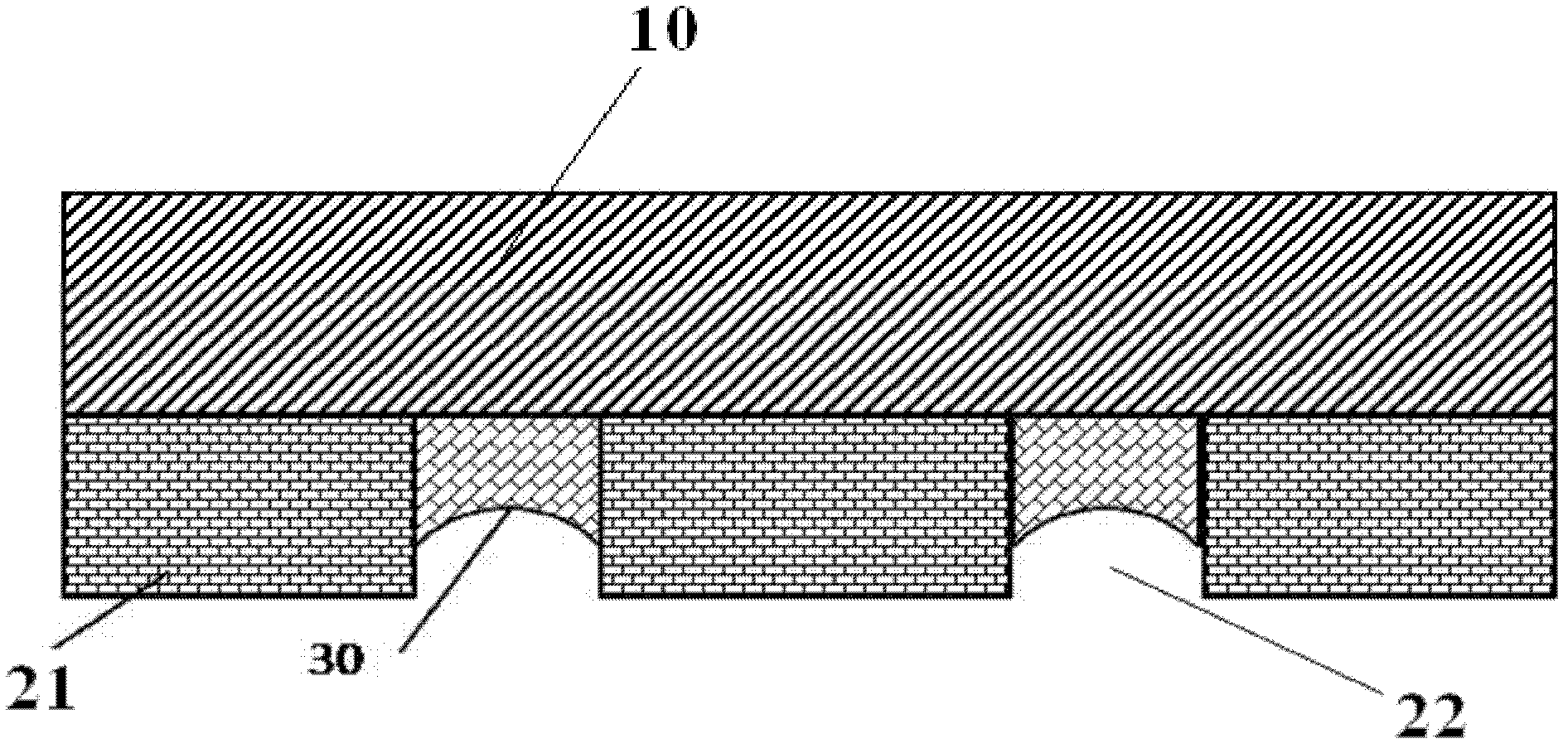

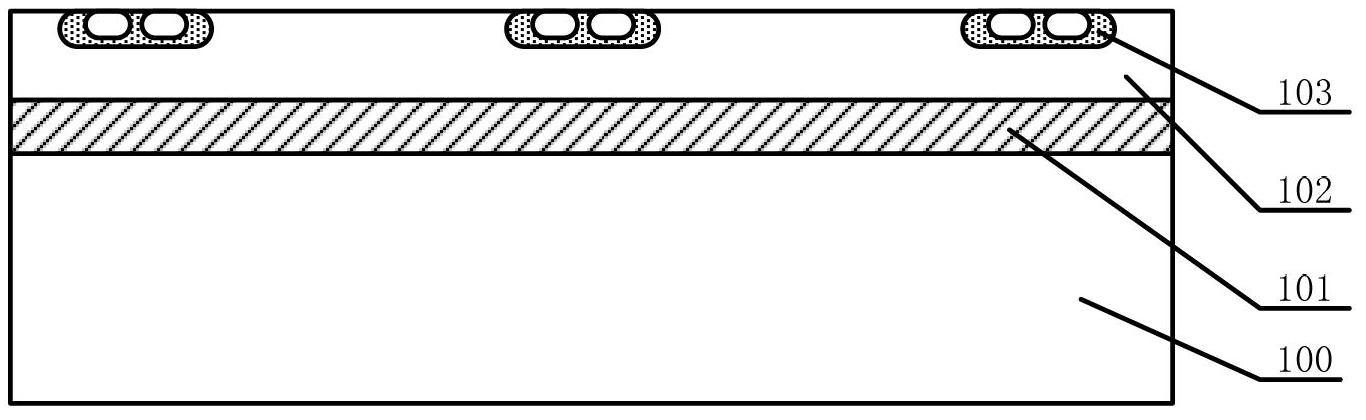

Low-cost toughened vacuum glass and manufacture method thereof

InactiveCN102050585ALow investment costReduce manufacturing costClimate change adaptationWindows/door improvementTransmittanceToughened glass

The invention provides vacuum glass and a manufacture method thereof, characterized in that micro-salient-point supporting objects melted together with an original glass sheet are used to substitute for a traditional stainless steel supporting object distributing process, a low-temperature metal braze-welding technology without causing the anneal of the original toughened glass sheet is used for sealing edges, and a traditional vacuum-layer vacuumizing process and an edge-sealing process are simplified and integrated into an integrated vacuumizing and edge-sealing process. Compared with traditional vacuum glass and the manufacture method thereof, the vacuum glass and the manufacture method thereof, which are provided by the invention, have simple process, high yield, low equipment investment and production cost, better heat and sound insulation, better appearance and light transmittance, high safety reaching the use standard of high-rise buildings, and the like.

Owner:刘伟杰

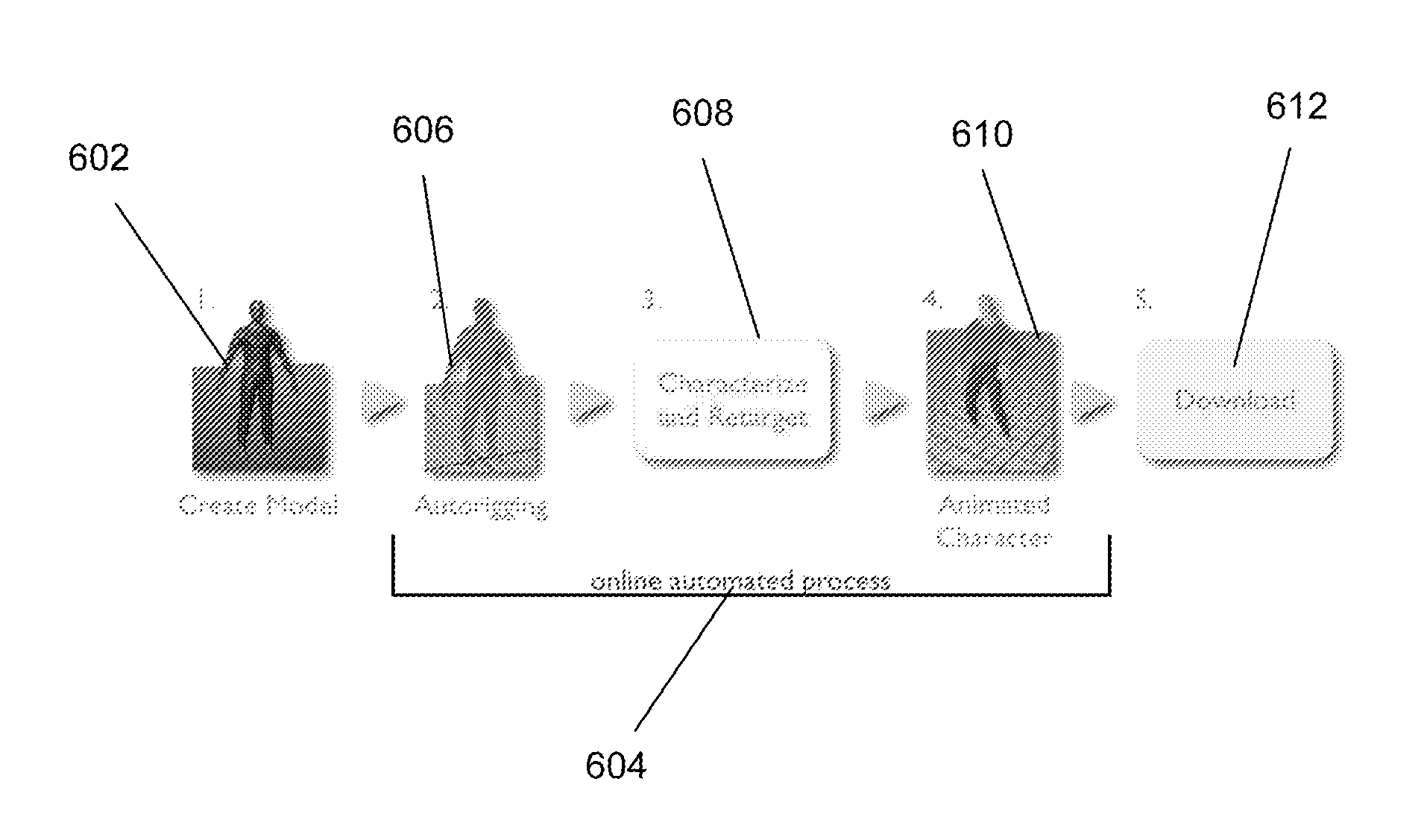

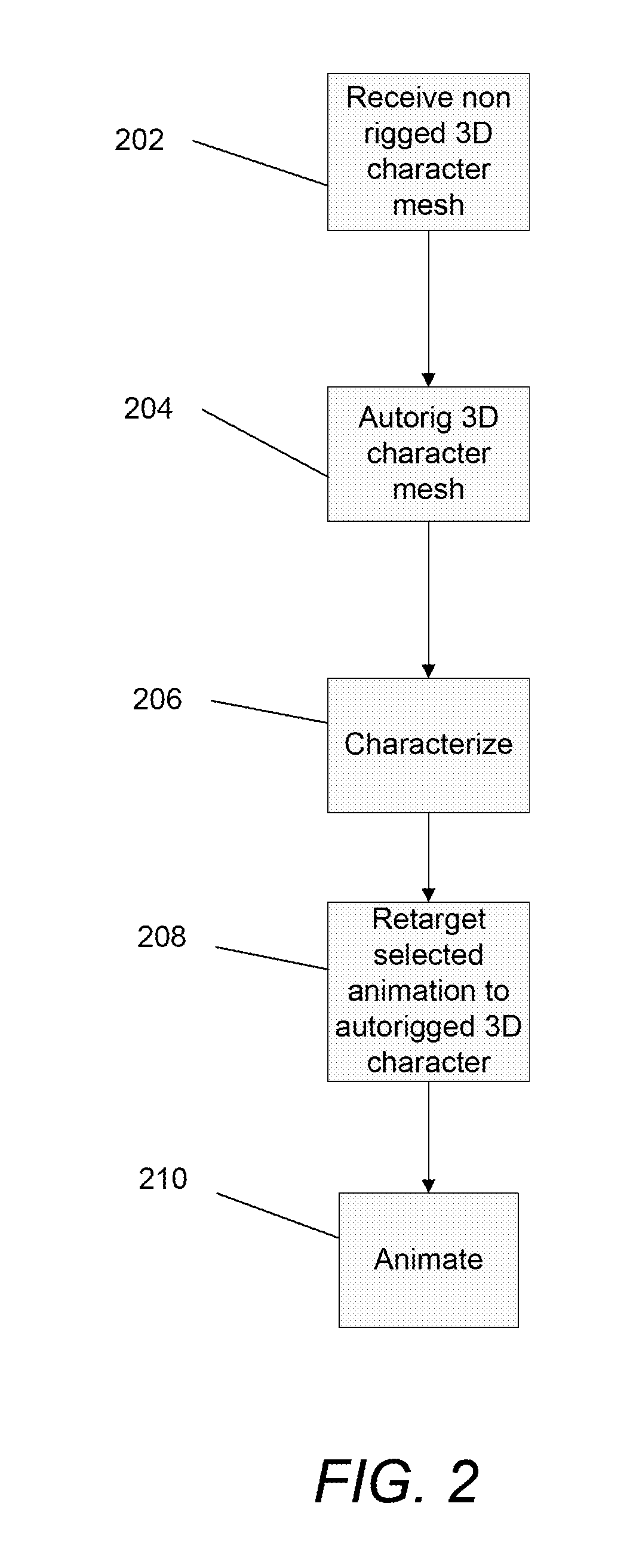

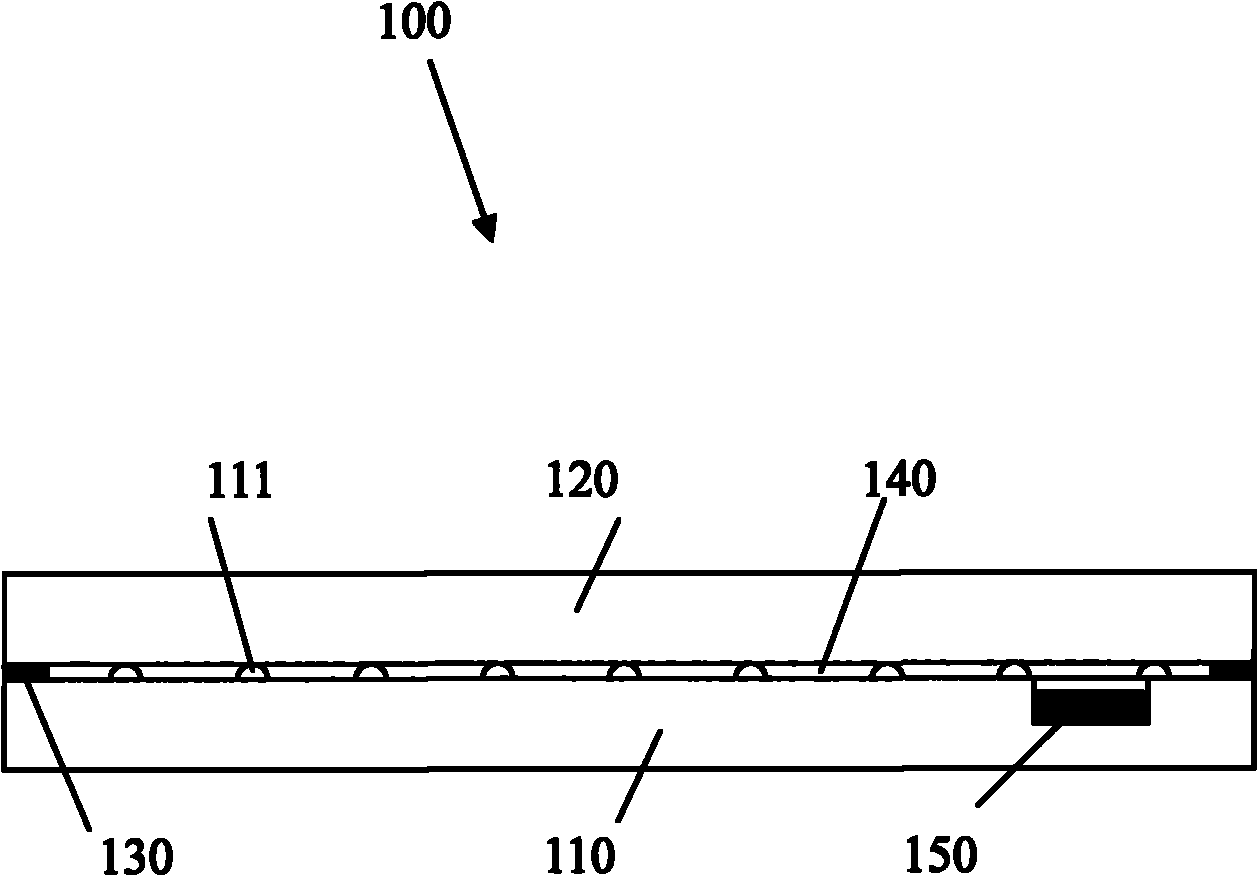

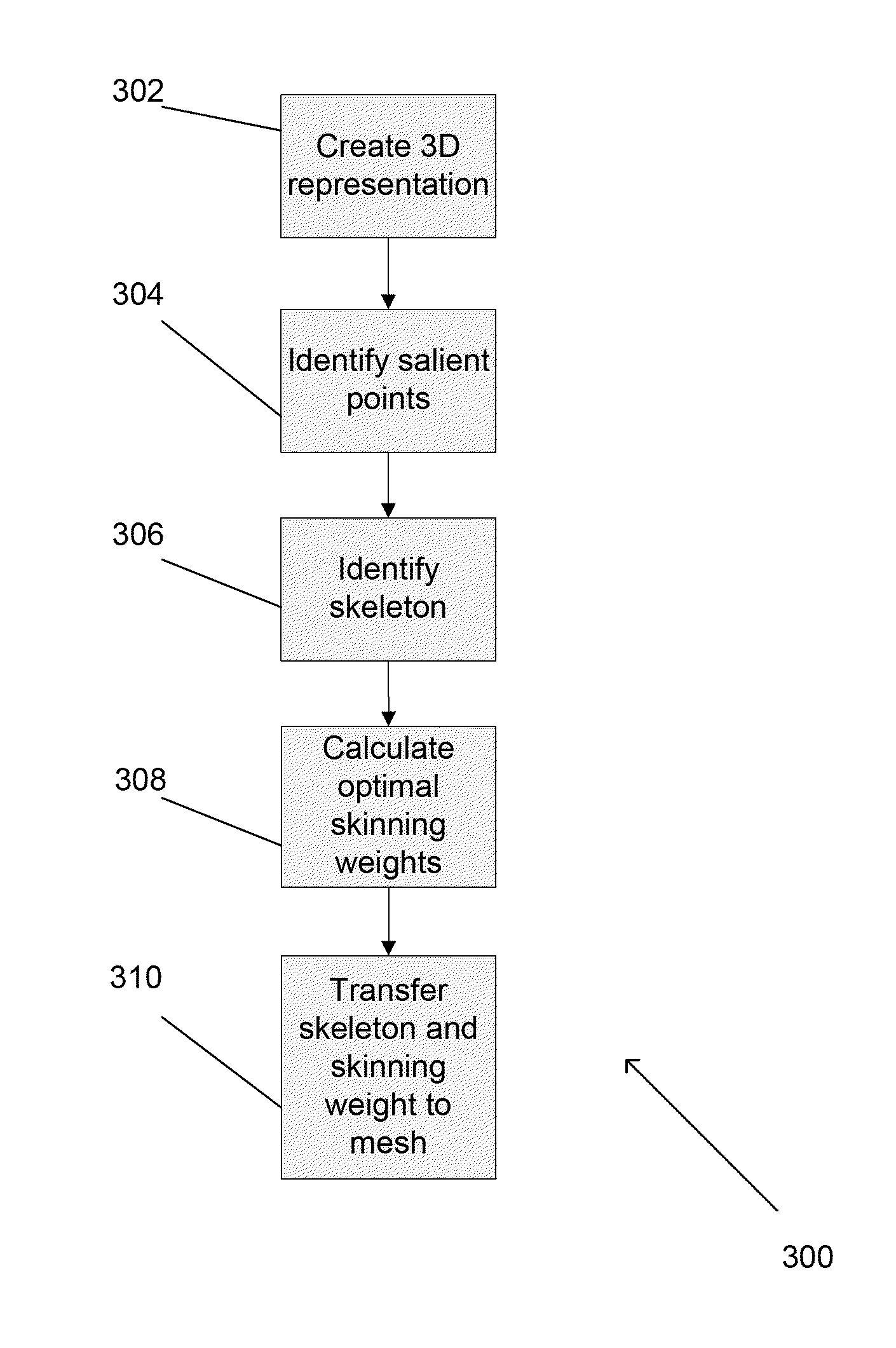

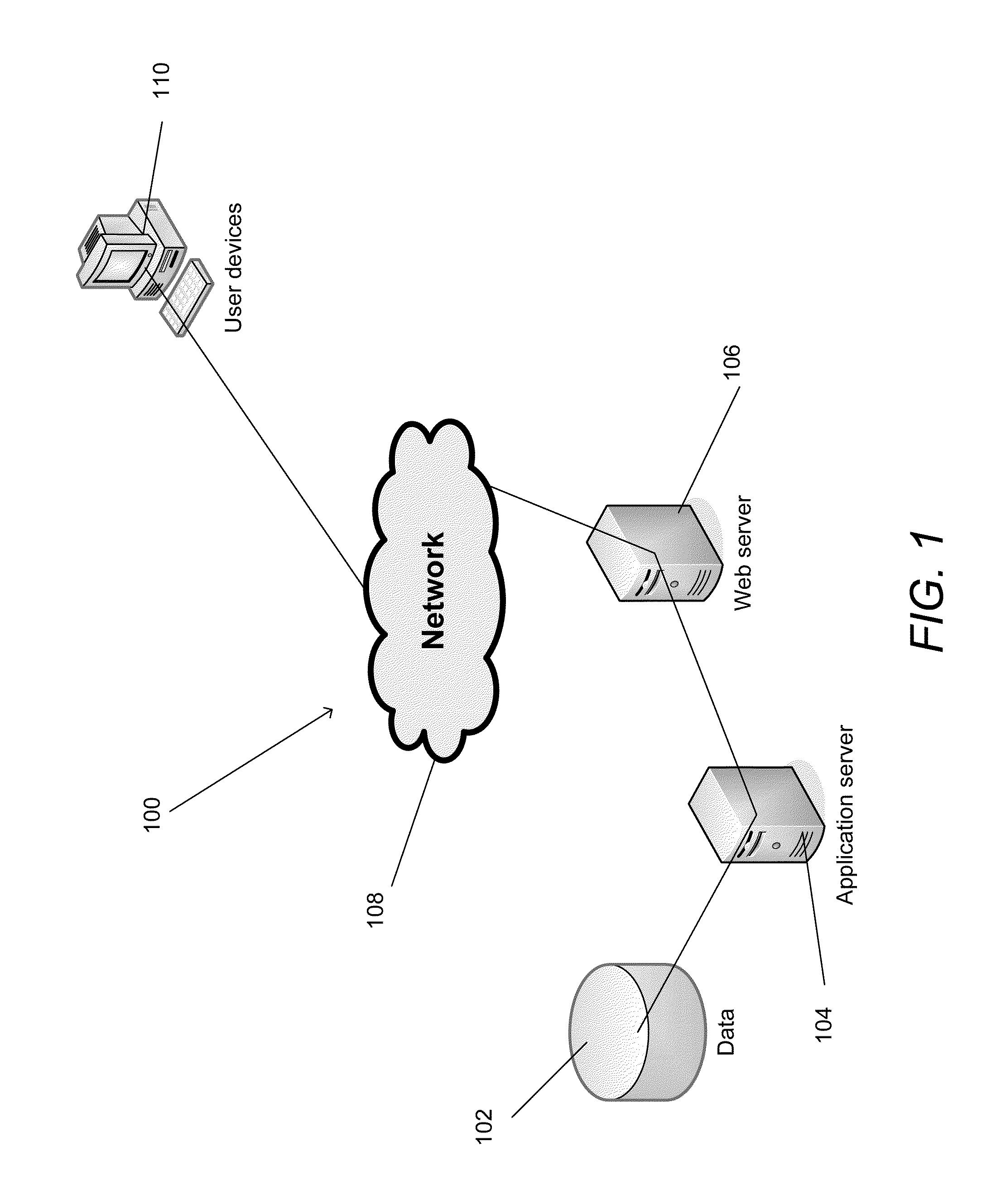

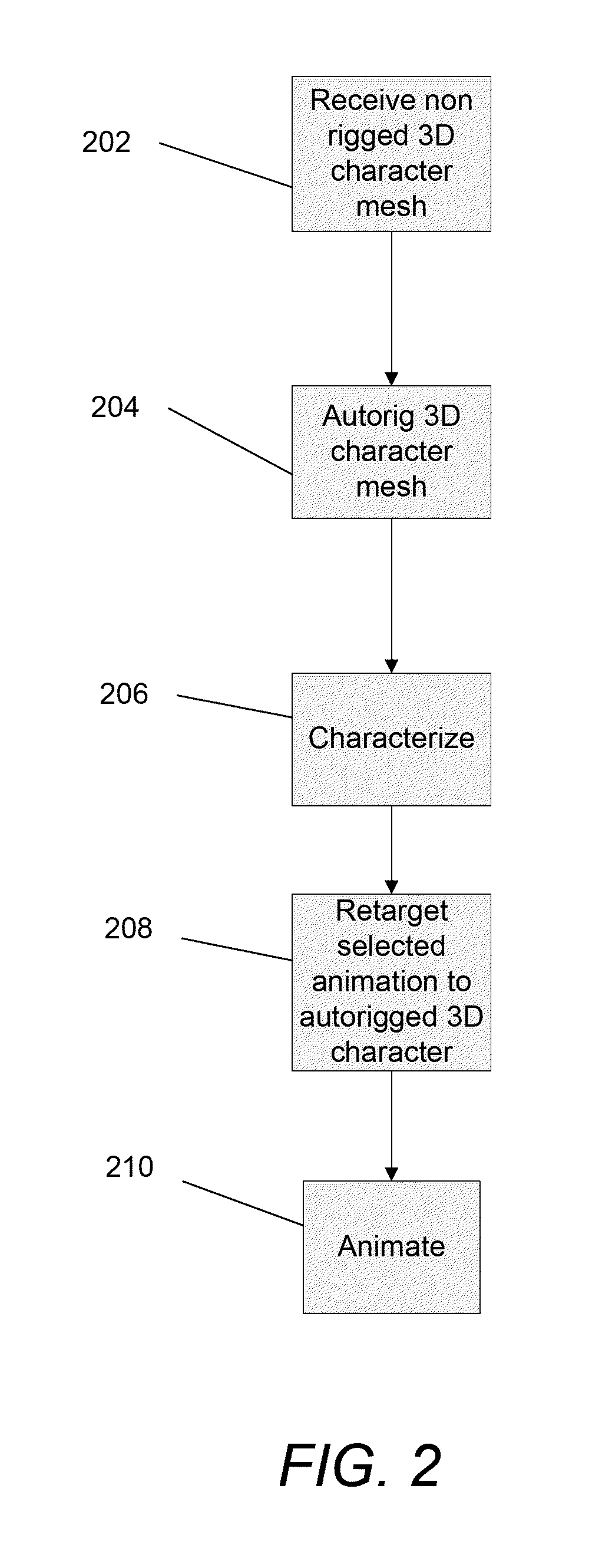

Automatic generation of 3D character animation from 3D meshes

Owner:ADOBE SYST INC

Enhanced pose determination for display device

ActiveUS20190188474A1Optimize locationInput/output for user-computer interactionCharacter and pattern recognitionDisplay deviceComputer vision

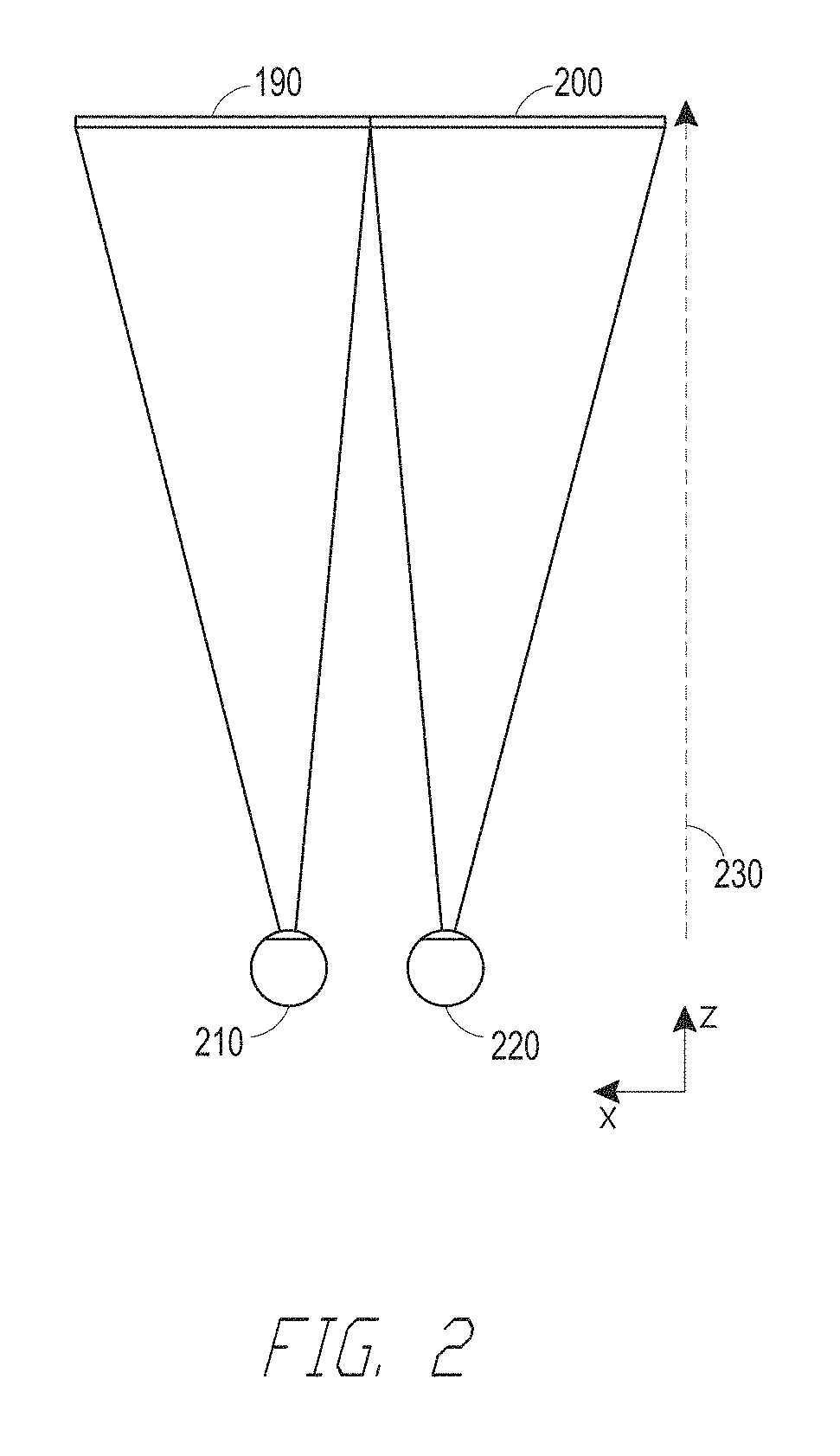

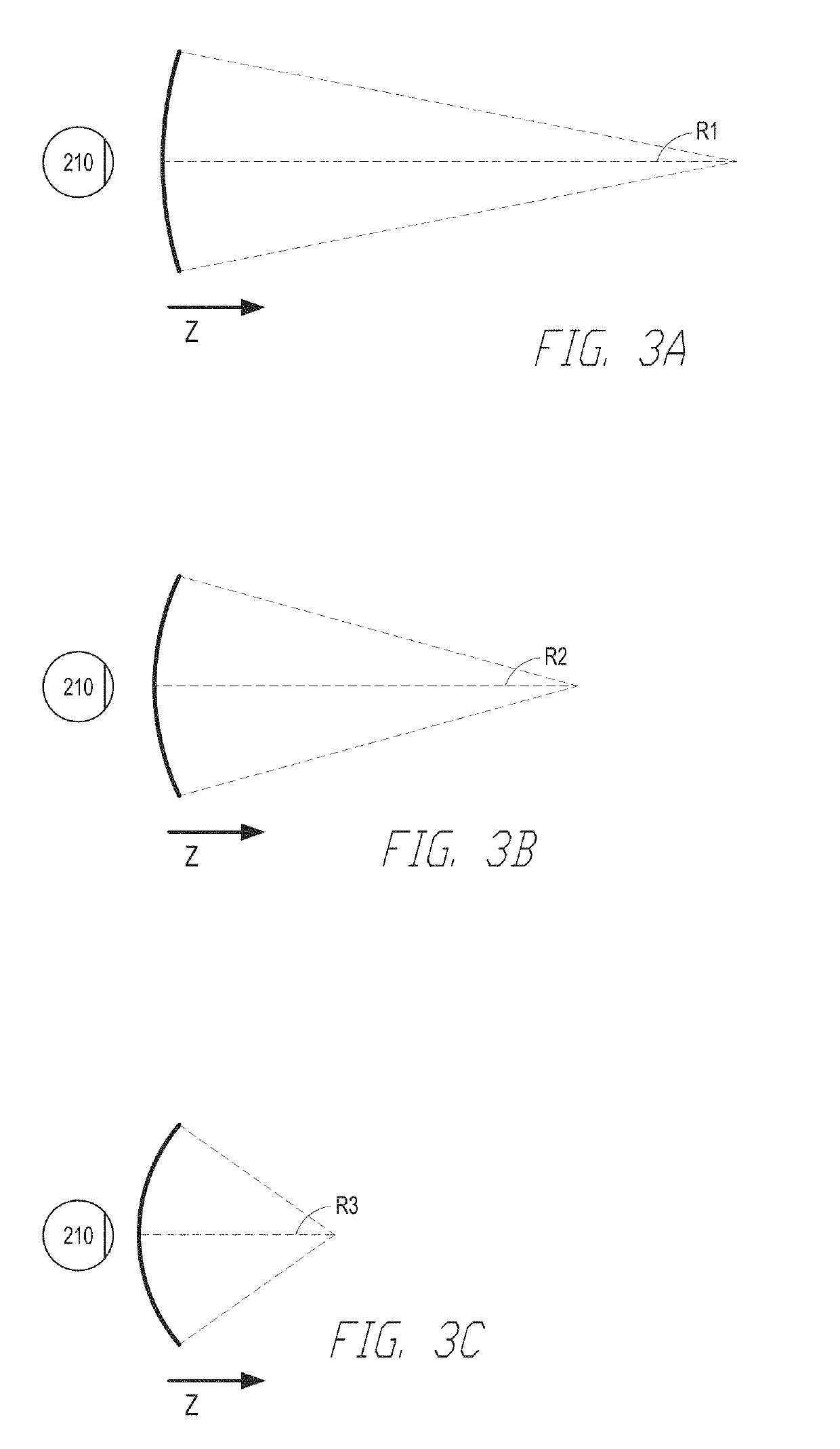

To determine the head pose of a user, a head-mounted display system having an imaging device can obtain a current image of a real-world environment, with points corresponding to salient points which will be used to determine the head pose. The salient points are patch-based and include: a first salient point being projected onto the current image from a previous image, and with a second salient point included in the current image being extracted from the current image. Each salient point is subsequently matched with real-world points based on descriptor-based map information indicating locations of salient points in the real-world environment. The orientation of the imaging devices is determined based on the matching and based on the relative positions of the salient points in the view captured in the current image. The orientation may be used to extrapolate the head pose of the wearer of the head-mounted display system.

Owner:MAGIC LEAP

Salient point-based arrangements

Owner:DIGIMARC CORP

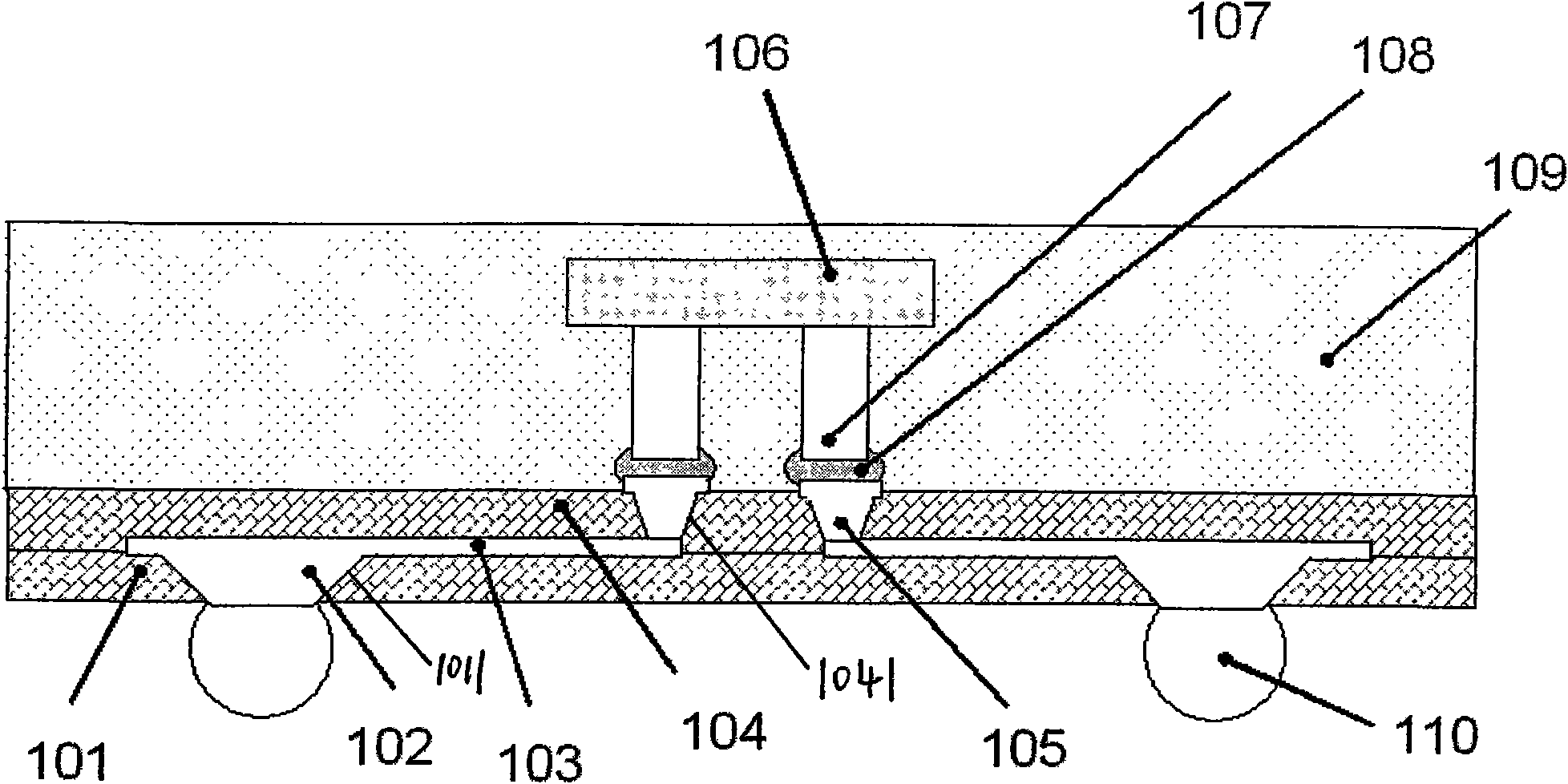

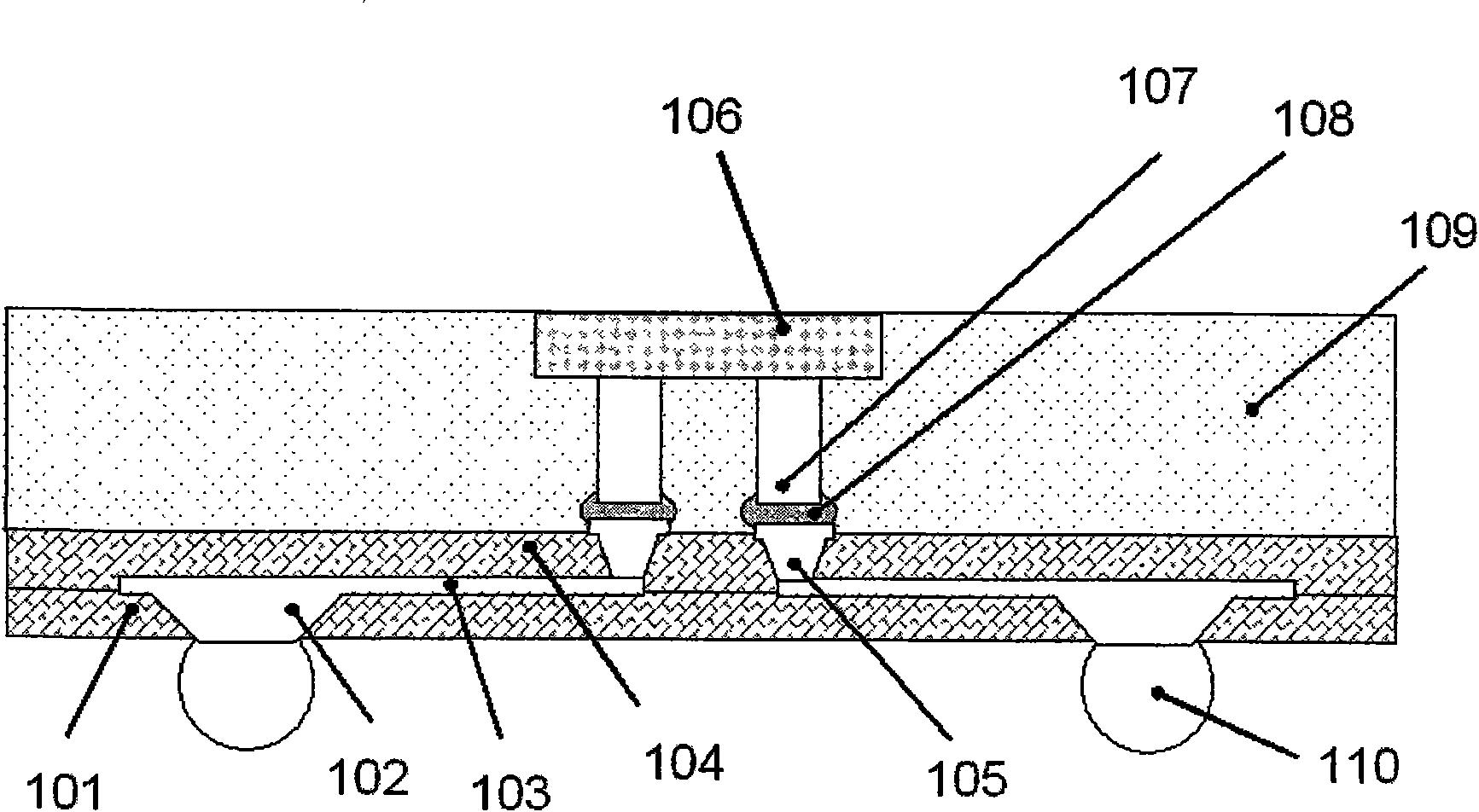

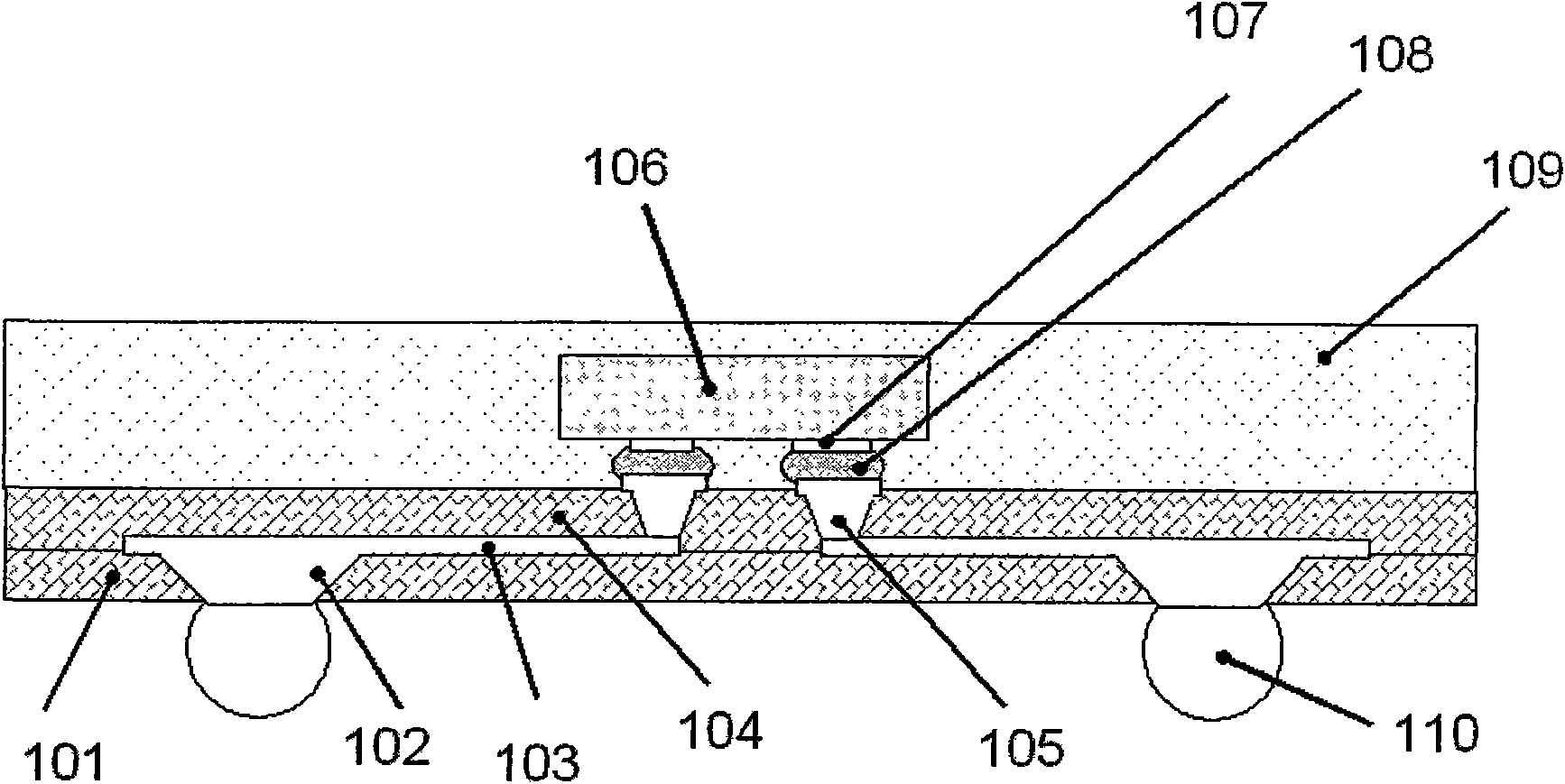

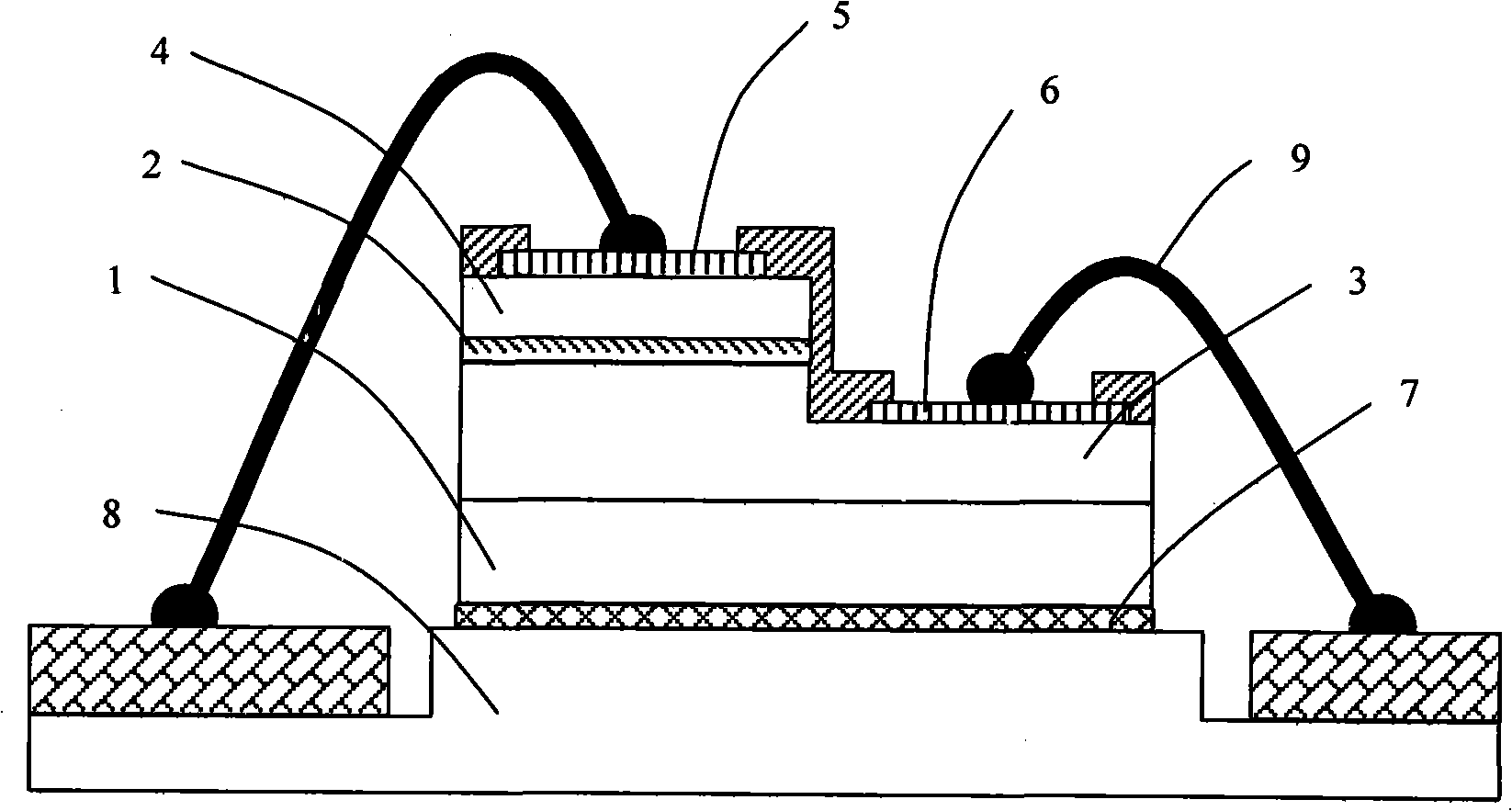

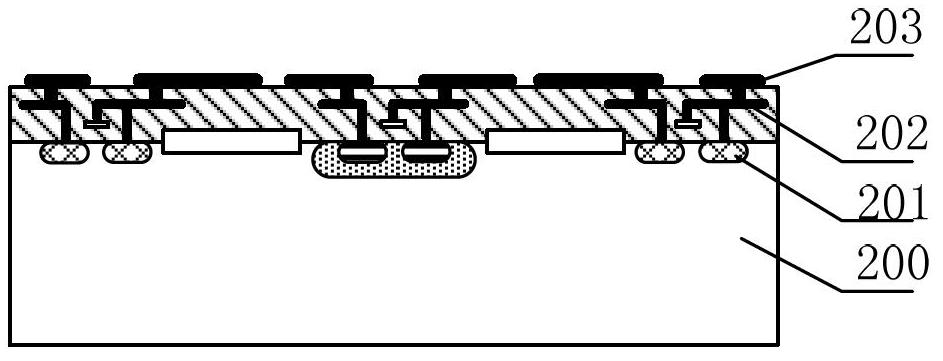

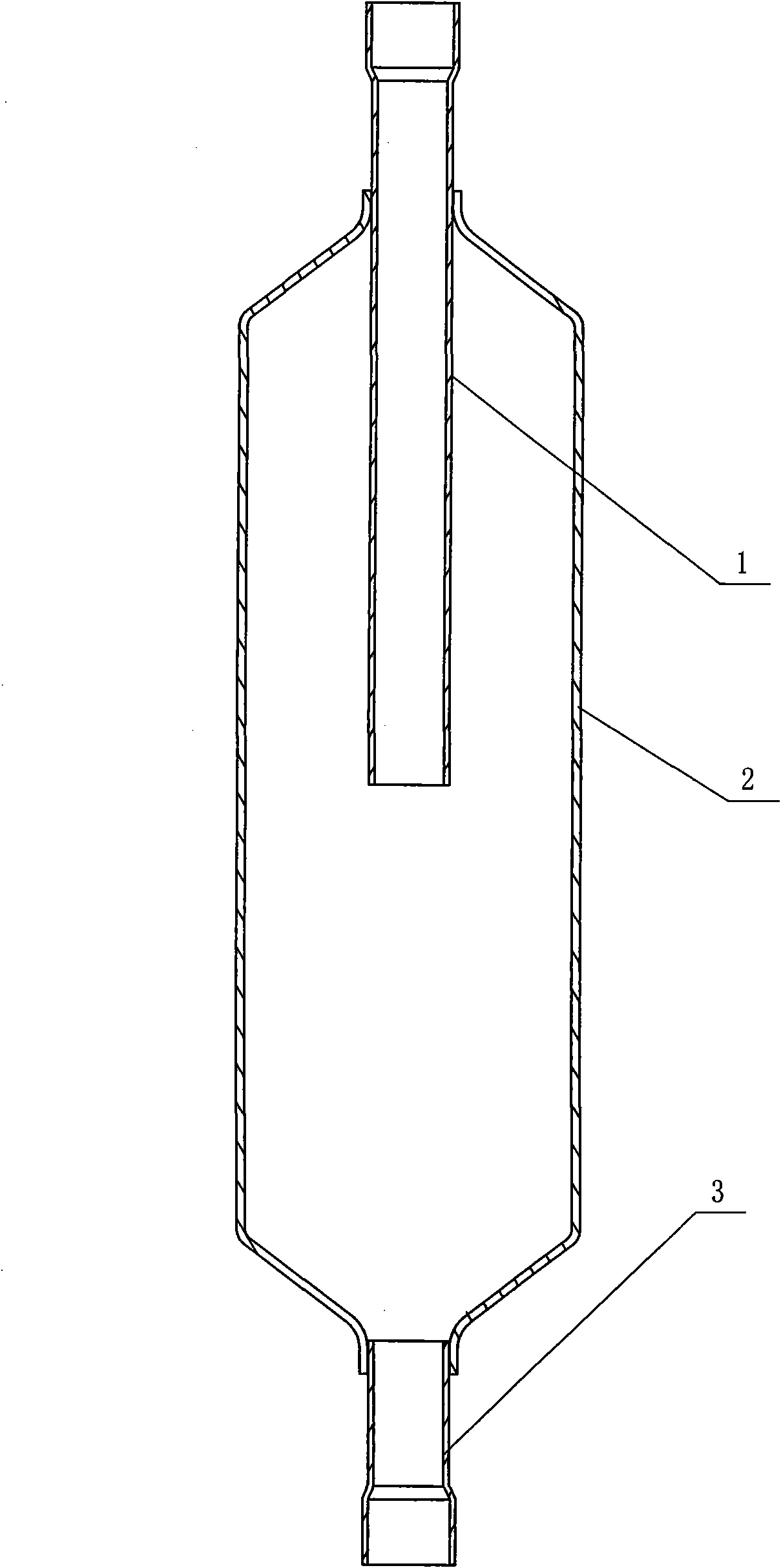

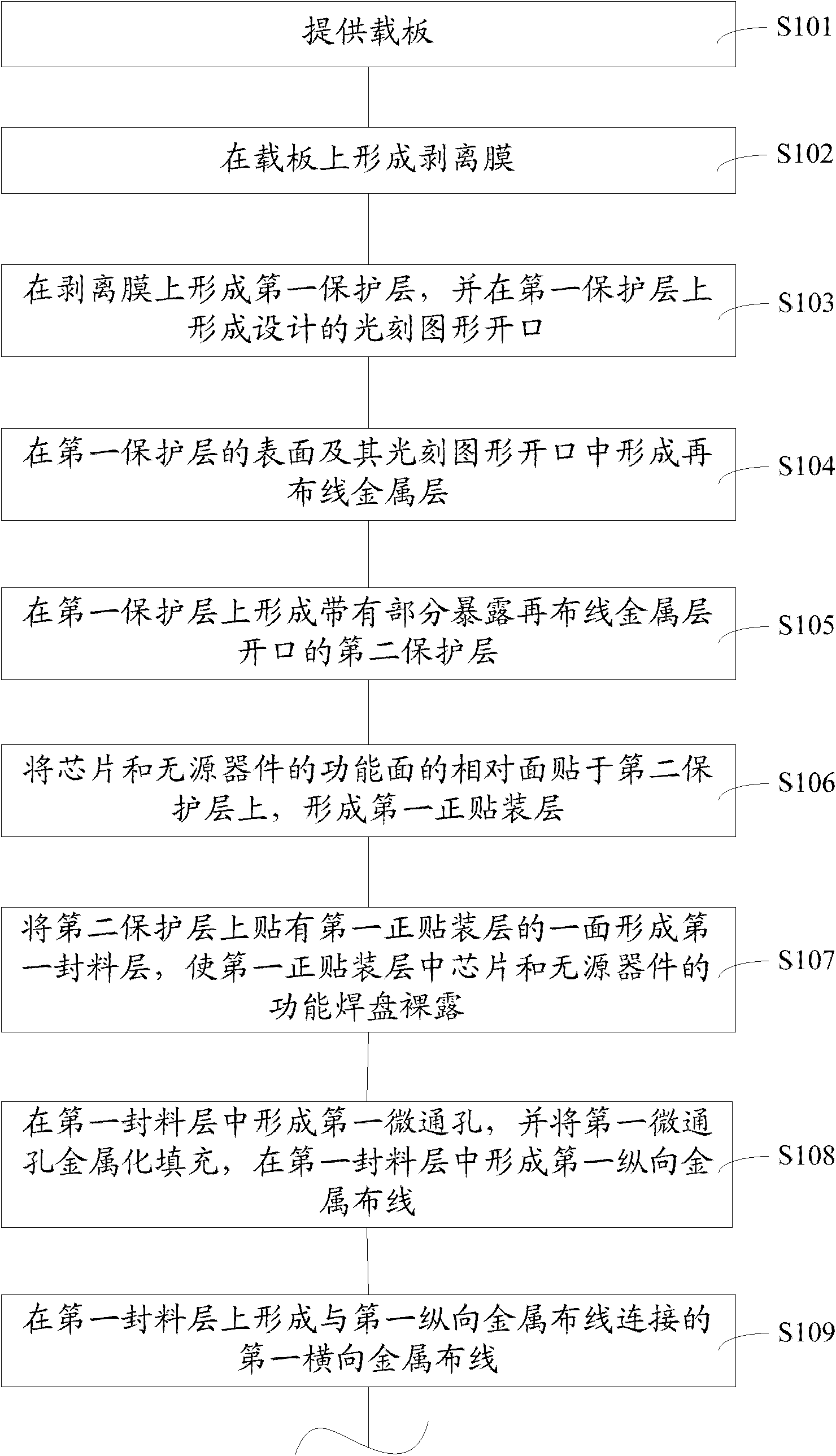

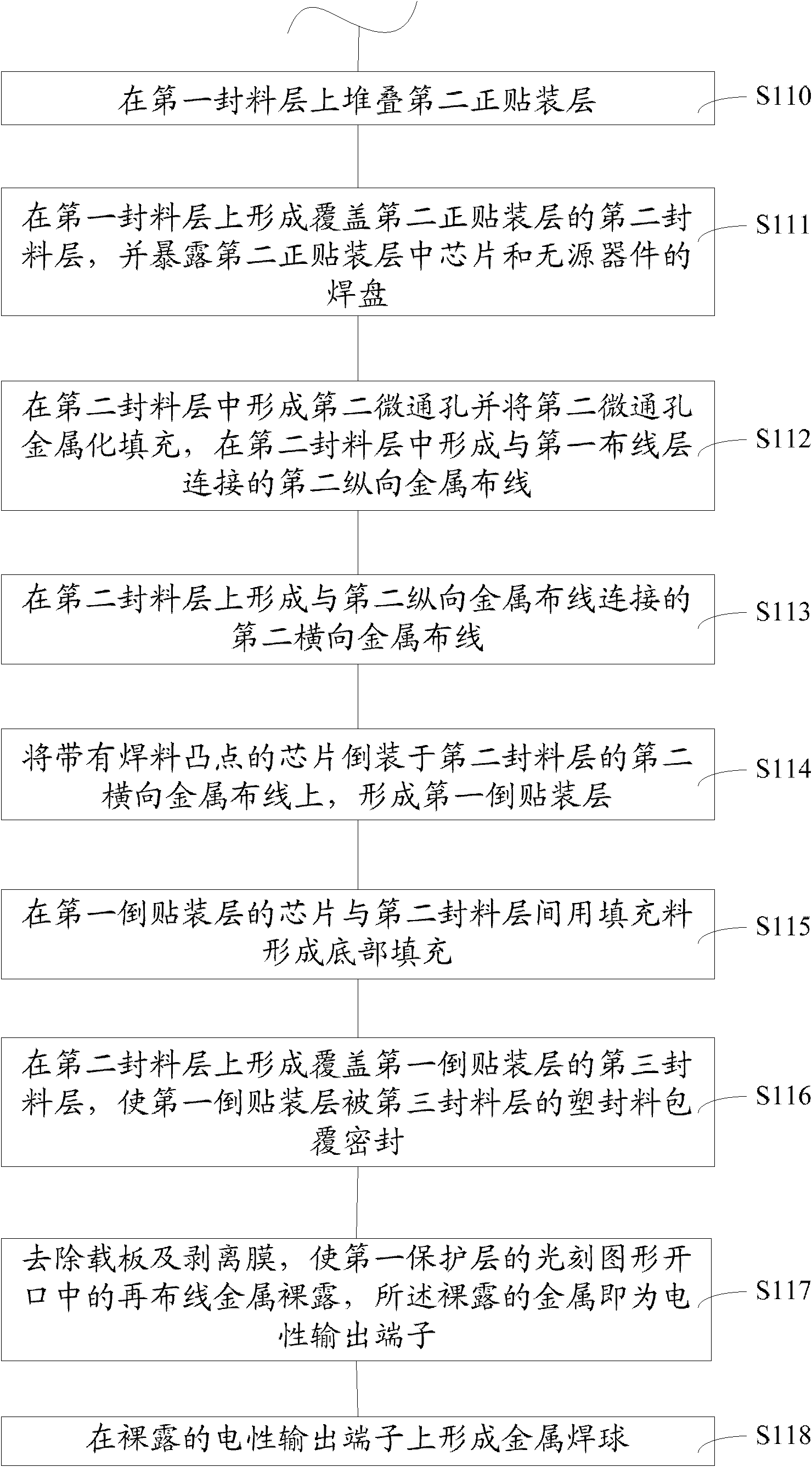

Wafer level fan-out chip packaging method

ActiveCN101604638AAchieve connectionAvoid displacementSolid-state devicesSemiconductor/solid-state device manufacturingPlastic packagingMetal electrodes

The invention relates to a wafer level fan-out chip packaging method, comprising the following technological processes: a stripping foil and a film dielectric layer I are sequentially covered on the surface of the wafer of a carrier, a photoetching pattern opening I is formed on the film dielectric layer I; a metal electrode and a re-wiring metal routing wire which are connected with a base plate end are arranged on the photoetching pattern opening and the surface thereof, a film dielectric layer II is covered on the surface of the metal electrode, the surface of the re-wiring metal routing wire, and the surface of the film dielectric layer I which are connected with the base plate end, and a photoetching pattern opening II is formed on the film dielectric layer II; a metal electrode connected with a chip end is arranged on the photoetching pattern opening II, after a chip is arranged on the metal electrode connected with the chip end in an inverting way, the injection molding of packaging material and solidification are carried out, so as to form a packaging body with plastic-packaging material; the wafer of the carrier and the stripping foil are separated from the packaging body with plastic-packaging material, so as to form a plastic-packaging wafer; a welding sphere back returns to form a welding ball salient point; cutting is carried out by uniwafers for forming the final structure of the fan-out chip. The method has low cost and a carrying function, and can well solve the problem that the chip is shifted in the technological process.

Owner:JIANGYIN CHANGDIAN ADVANCED PACKAGING CO LTD

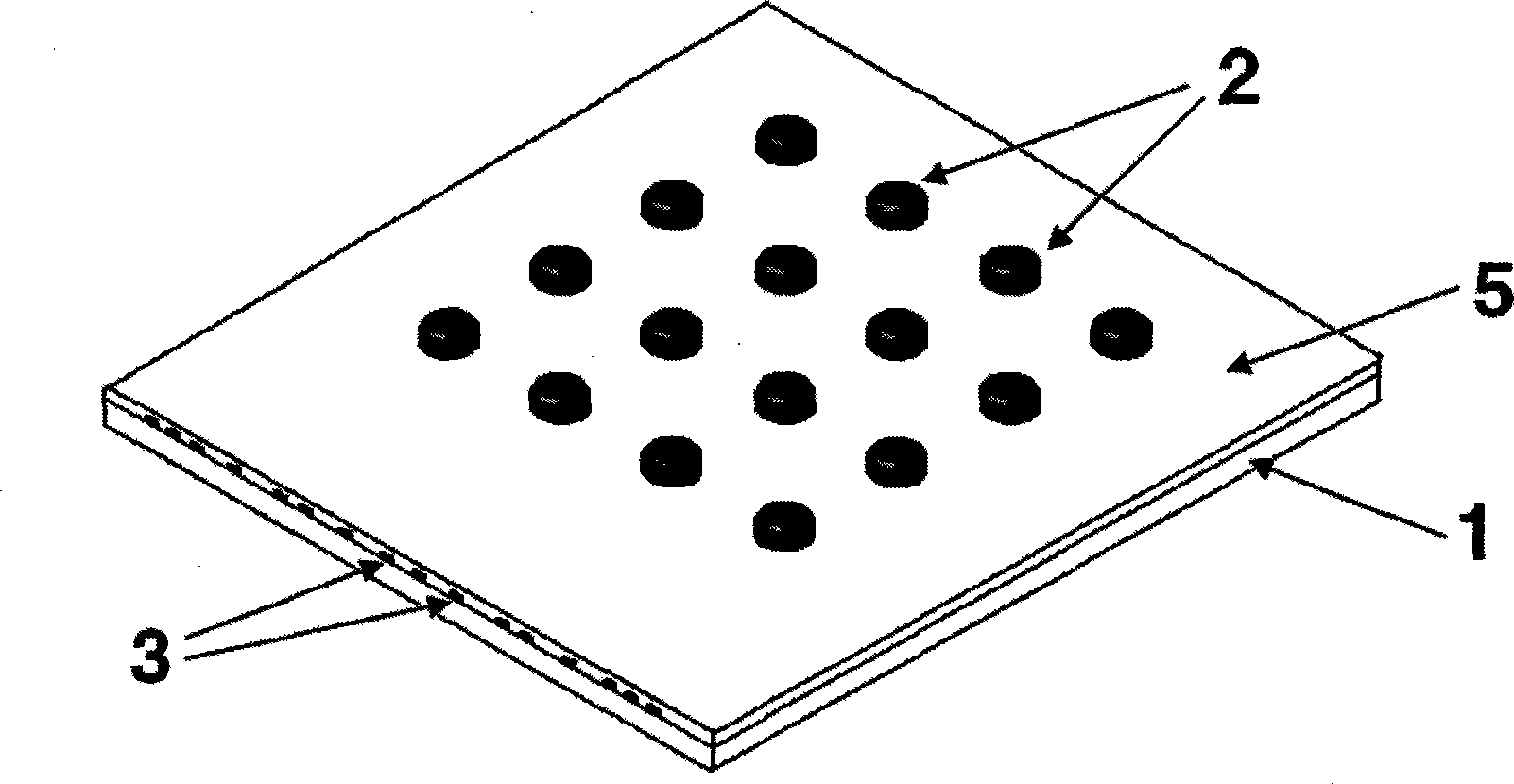

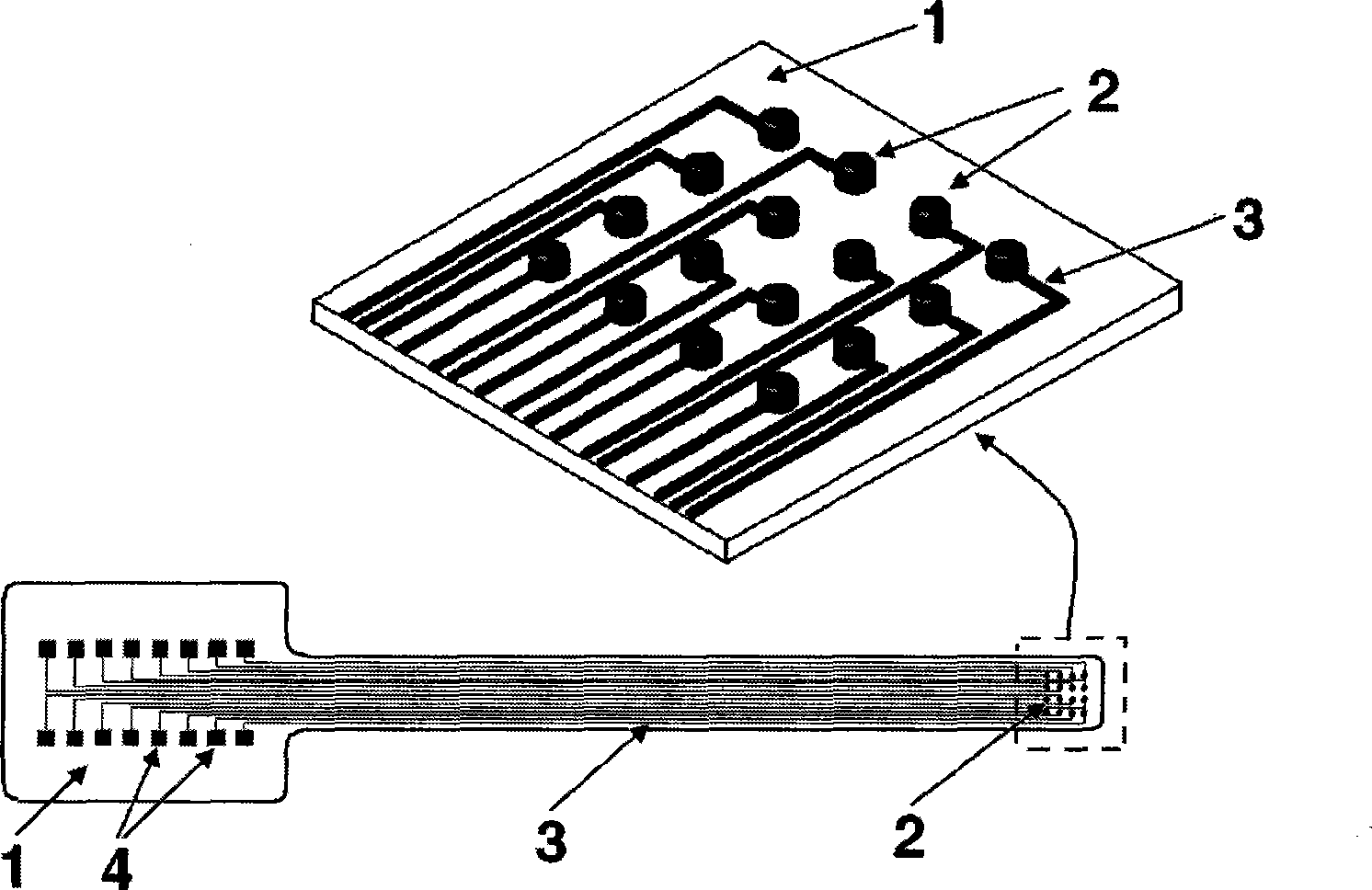

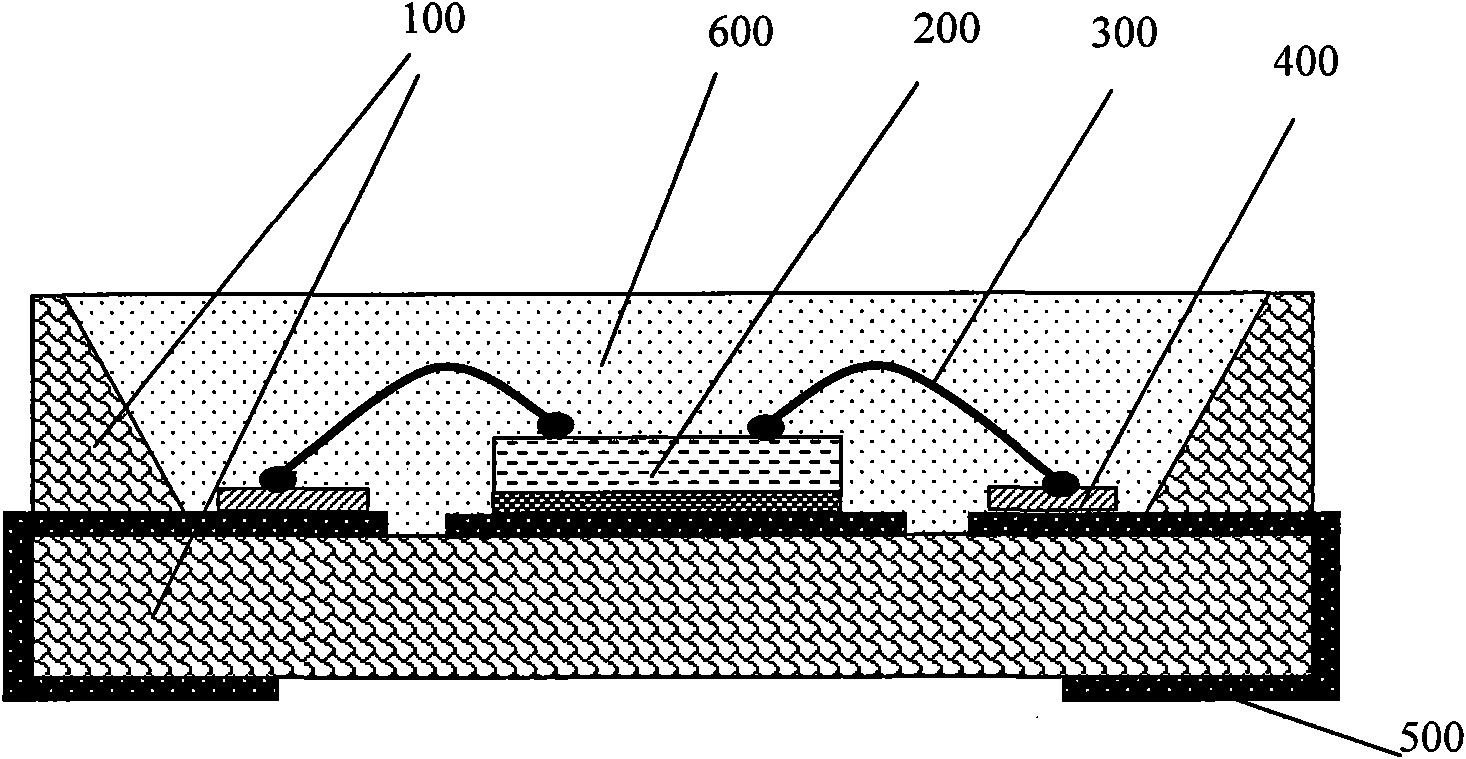

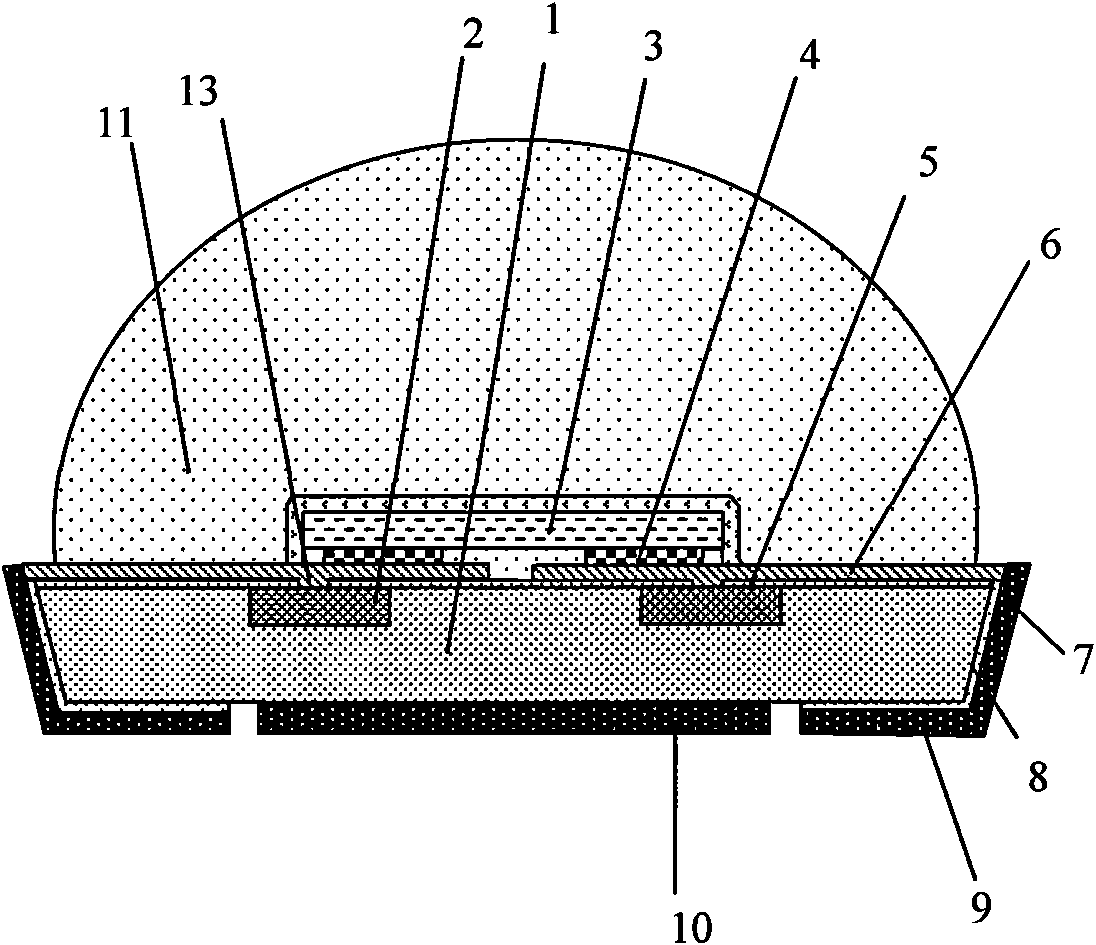

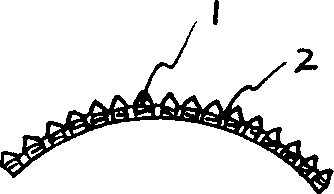

Flexible retina salient point micro-electrode chip and production method thereof

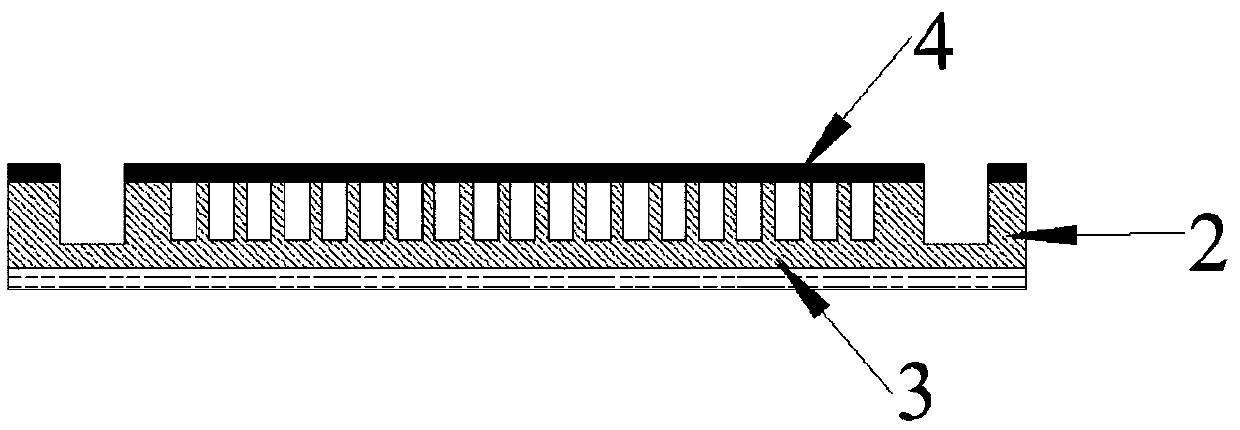

InactiveCN101380257AAchieve preparationReduce heat damageEye treatmentBiocompatibility TestingMicroelectromechanical systems

The invention discloses a flexible retina emboss micro-electrode chip in the technical field of a micro-electronic-mechanical-system and a manufacture method thereof. In the method, parylene C is used as a flexible substrate and an insulating material for preparing a micro-electrode array which is formed by the arrangement of a plurality of micro-electrode sensing elements; simultaneously, an electrode lead and a lead welding point are manufactured to form the flexible retina emboss micro-electrode chip which is planted into the retina part of a human eye, can realize the safe and effective contact with the neuron of the retina, effectively reduce the stimulation to a pulse current, reduce the inserting damage to a biological tissue caused by the planting of the micro-electrode and can improve the effect of electric simulating and neural signal recording, thereby better recovering the visual function. In the invention, the parylene C is used as the substrate of a flexible electrode; the excellent electric insulating performance and mechanical performance thereof can improve the biocompatibility of the micro-electrode chip to a larger extent and have good stability for a long period. In the invention, an MEMS technique is adopted, thus realizing the integration of a functional unit and the flexible substrate of the micro-electrode.

Owner:SHANGHAI JIAO TONG UNIV

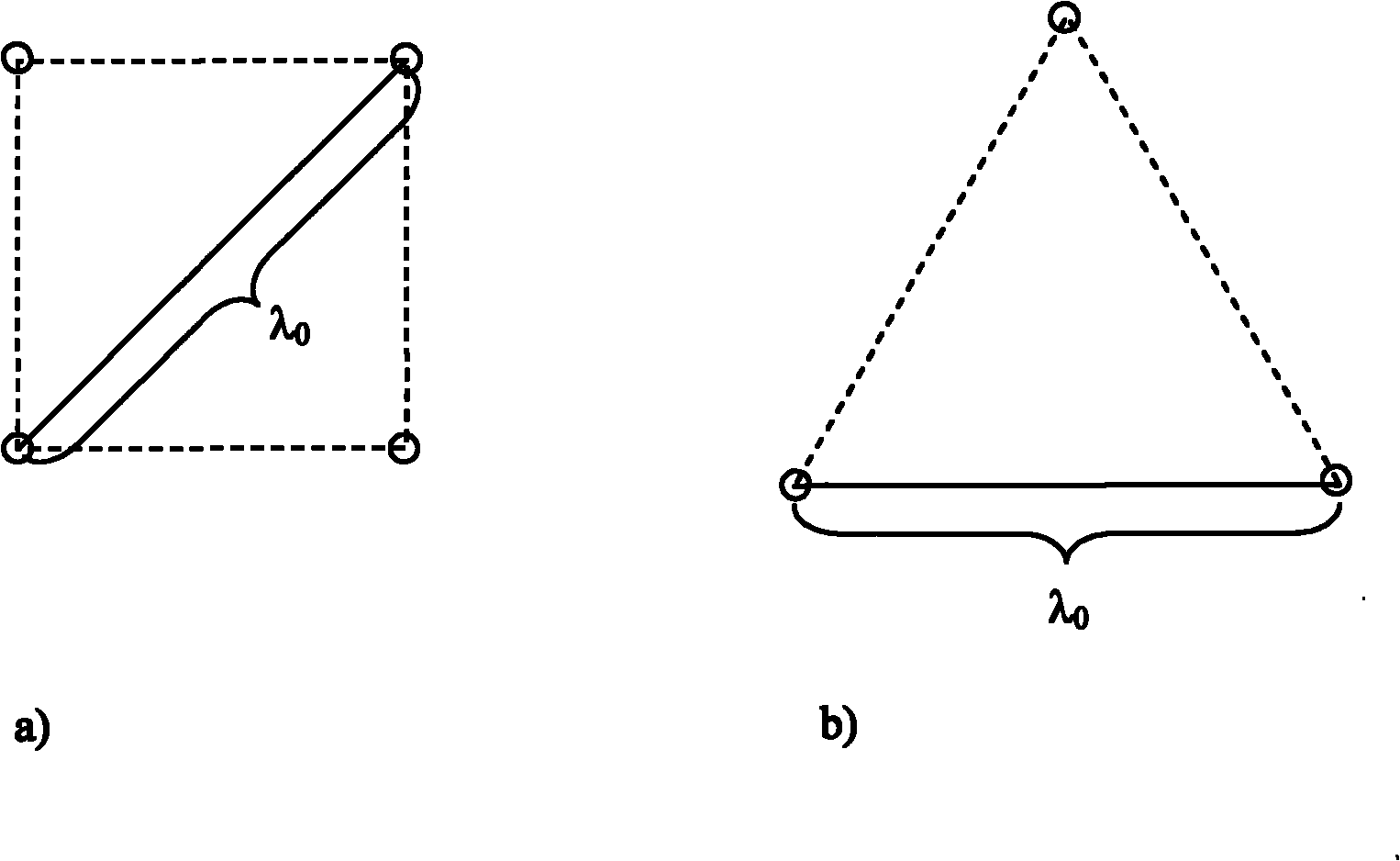

Marker and method for detecting said marker

This invention discloses marker detectable by visual means comprising; a polygonal border having of at least four non collinear salient points. The marker has on it a pattern in binary digital code. The binary code data contains information data, checksum and error correction. The binary code data is on two levels; a first level of binary code readable at a first given distance, a second level of binary code readable at a second given distance, where the second given distance is less than the first given distance and the second level binary code is smaller in size than the first level binary code. The second level of binary code does not interfere with the reading of the first level binary code. It also discloses a method for detecting a marker comprising the steps of detecting an image, using an edge detector to detect an edge in said image, grouping more than one edge into a polygon having salient points, calculating homography from polygon salient points, generating a list of homographies, extracting binary data from input image having homographies, identifying and verifying binary data.

Owner:MILLENNIUM THREE TECH

Mixed bonding structure for three-dimension integration and bonding method for mixed bonding structure

ActiveCN102593087AAvoid circuit breakingAvoid reliabilitySemiconductor/solid-state device detailsSolid-state devicesOptoelectronicsInterconnection

The invention relates to a mixed bonding structure for three-dimension integration and a bonding method for the mixed bonding structure. The mixed bonding structure for the three-dimension integration comprises a first substrate. The first substrate is provided with bonding interconnection metal electrically connected with the first substrate; the other end part of the bonding interconnection metal, which is correspondingly connected with the first substrate, is sunk to form a cavity; a first dielectric adhesion layer covers at the periphery of the bonding interconnection metal on the first substrate; the bonding interconnection metal is encircled by the first dielectric adhesion layer; and the first dielectric adhesion layer is lower than the edge of the bonding interconnection metal. According to the mixed bonding structure for the three-dimension integration, the first dielectric adhesion layer is lower than the edge of the top part of a salient point, and when bonding is performed under the pressure action, the edge of the top part of the salient point is bonded with a pad of a second substrate, and thereby, the dielectric adhesion layer can be stopped entering the surface of the bonding interconnection metal, which is bonded with the pad, and the open circuit problem and the reliability problem can be avoided. The mixed bonding structure for the three-dimension integration is compact in structure and is convenient in process operation.

Owner:NAT CENT FOR ADVANCED PACKAGING

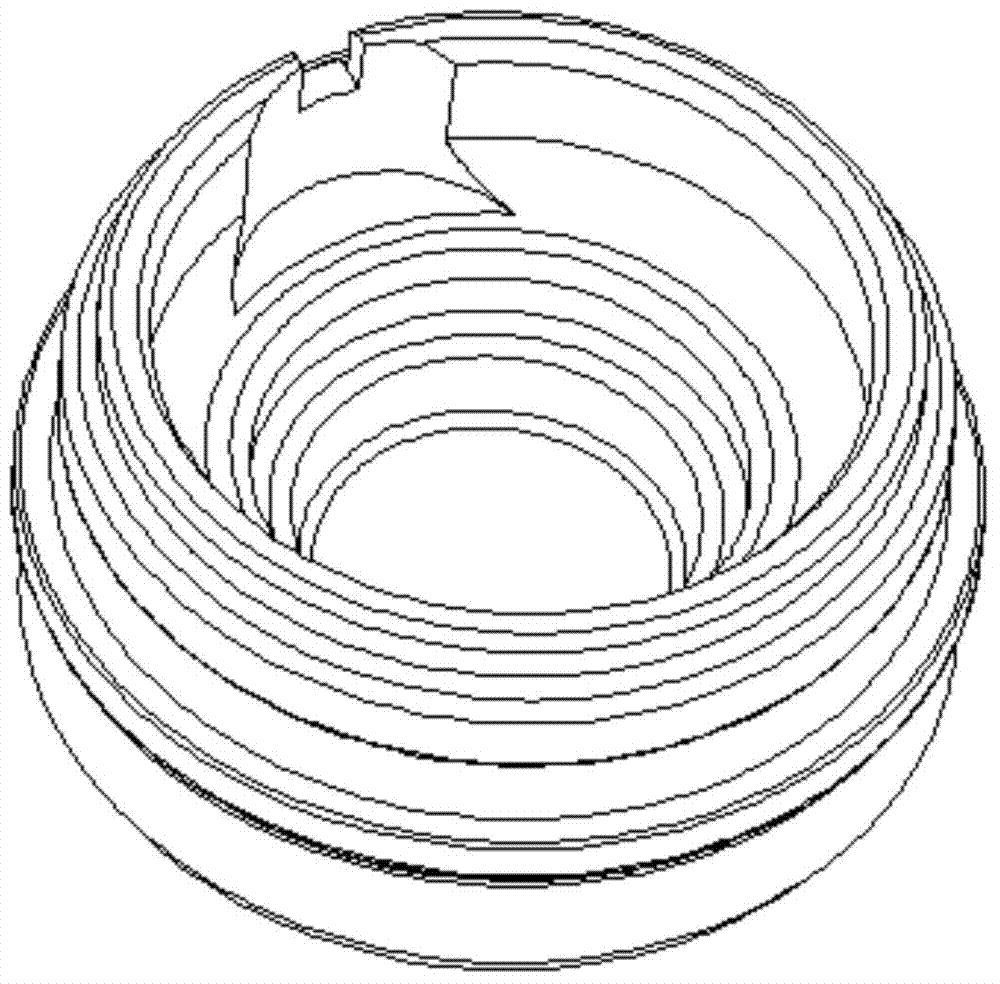

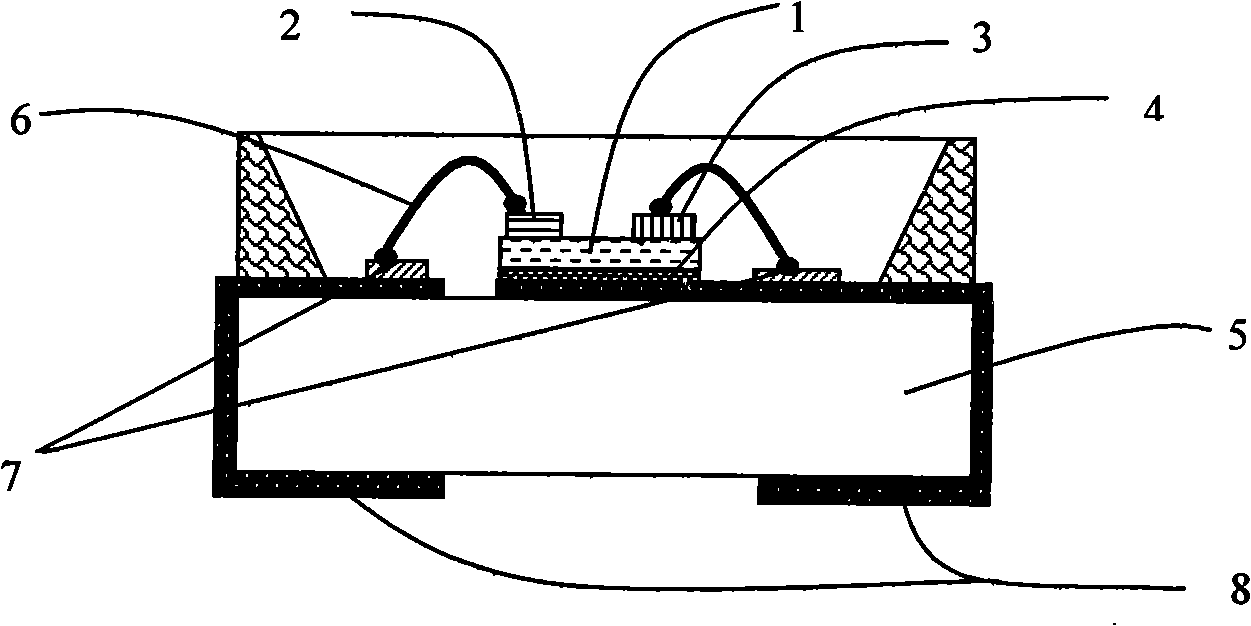

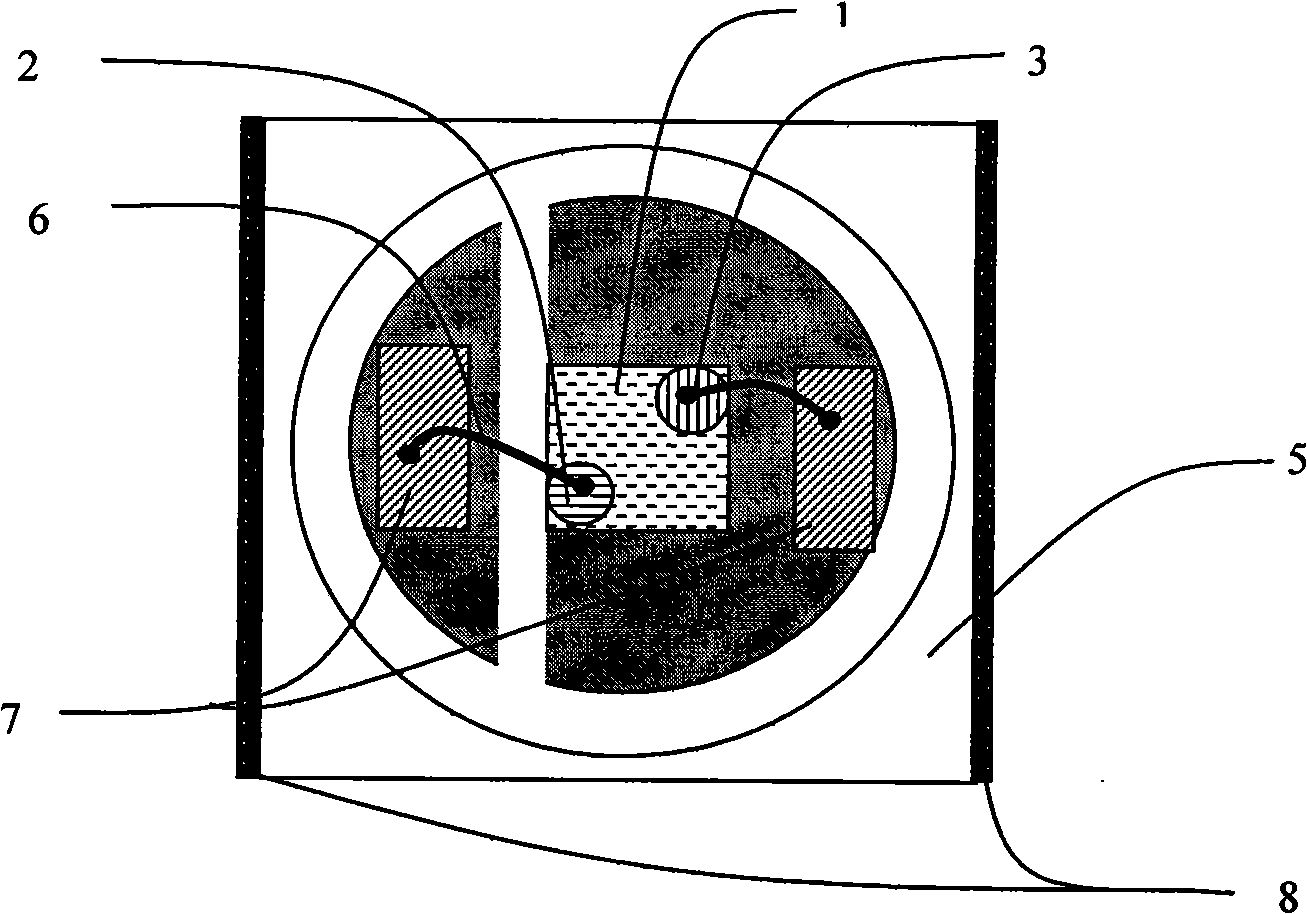

Salient point LED and manufacturing method thereof

ActiveCN101350381ASolve the problem of centralized heat dissipationRelaxed machining accuracy requirementsSemiconductor/solid-state device detailsSolid-state devicesMiniaturizationDie bonding

The invention relates to a protruding point luminescent diode, wherein a protruding point lower metal is plated on an electrode of a protruding point luminescent diode chip, metallic protruding points are grown on the upper portion of the protruding point lower metal, a passivation layer is grown on the surface of the upper portion of the luminescent diode chip excepting the surface of an electrode, a welding pad is made on a packing support, the metallic protruding points of the protruding point luminescent diode are inversely welded on the welding pad of the packing support. The method for preparing the diode comprises the following steps: making the passivation layer, sputtering a metal sacrificial layer, making a photoresist mask, forming the metallic protruding points, removing the photoresist mask, removing the metal sacrificial layer, reducing, cutting into separated chips and inversely welding on an SMD support, and then forming an inversely welded LED die set. The method enables the chip of the luminescent diode to be without the gold wire bonding and the die bond technique, directly switches a circuit and assembles the chip on a base plate or a metallic support, realizes the miniaturized package and the die set with multiple chips, and successfully solves the problem of the heat dissipation of the luminescent diode.

Owner:APT ELECTRONICS

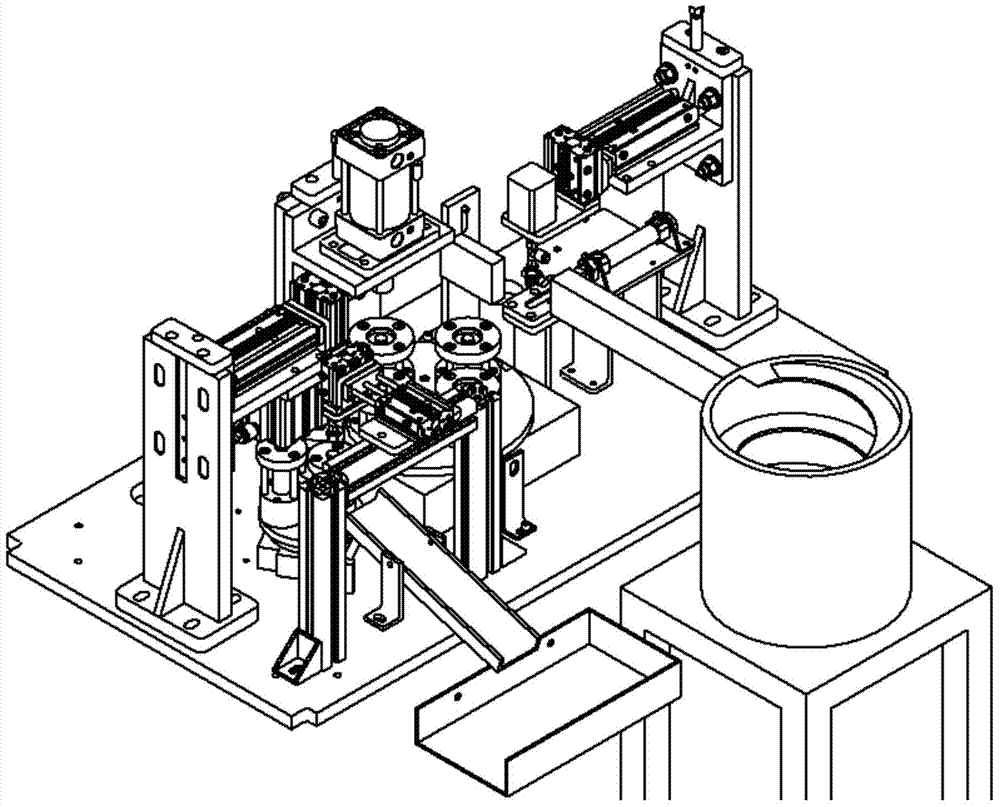

Full-automatic multi-station automobile ABS pile-up valve end cover stamping equipment

The invention relates to full-automatic multi-station automobile ABS pile-up valve end cover stamping equipment which comprises a feeding device, a feeding mechanical arm, a locating device, a salient point stamping die, a salient point stamping mechanism, a transfer mechanical arm, an extrusion rotary table, an unloading mechanical arm, a stamping rotary table, a receiving box, an extrusion die, a salient point extrusion mechanism and a push mechanism. Automatic machining is achieved, work efficiency is high, the quality of the products of an existing manual mode is prevented from being influenced, the number of workers is greatly reduced, production cost is lowered, pushing, feeding, stamping, transfer feeding and discharging and extrusion unloading are automatically completed between all processes, and the technological process is simplified.

Owner:LX PRECISION SHANGHAI CO LTD

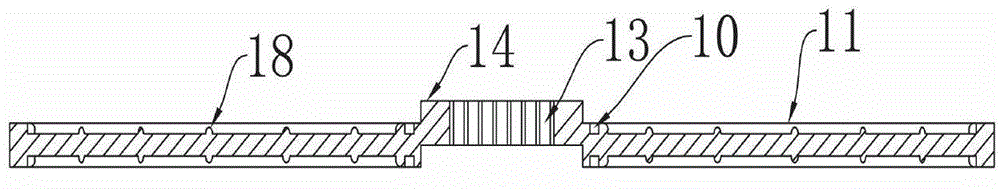

Supporting flow guide plate and separation filtering membrane column device

InactiveCN102908900ASmall pressure lossImprove production efficiencySemi-permeable membranesHigh concentrationEngineering

The invention discloses a supporting flow guide plate and a separation filtering membrane column device. The supporting flow guide plate is a disc with a central circular hole; a plurality of rings of flow blocking salient points are arranged on the disc; a radial rotational flow slit is also formed on the disc; one of two sides of the rotational flow slit of the disc upwarps to be extended into an upwarping part, and the other side is bent downwards to be extended into a lower bending part; and the upwarping part is parallel to the lower bending part. The separation filtering membrane column device comprises the supporting flow guide plate and a membrane; an inner pull rod for fixing the supporting flow guide plate and the membrane and upper and lower stacking plates are also installed in a bearing outer shell; a mounting hole is formed at the center of the membrane; a radial gap aligned with the rotational flow slit is also formed on the membrane; and an outer pull rod for supporting, tensioning and pressing upper and lower end cover flanges is installed outside the bearing outer shell. Compared with a traditional membrane component, the separation filtering membrane column device has the beneficial effects that the pressure loss is reduced by above 70 percent, and the product efficiency is improved. The separation filtering membrane column device is a special device with the advantages of antipollution and low energy consumption and is particularly suitable for an economical treatment process of a high-concentration fluid.

Owner:CHENGDU MEIFUTE MEMBRANE TECHNOLOGY CO LTD

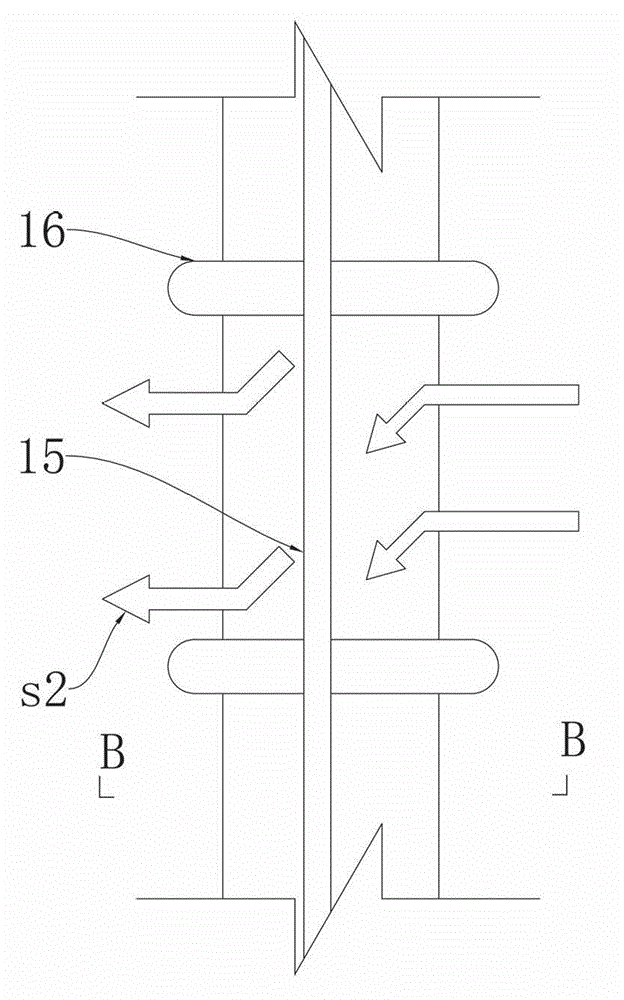

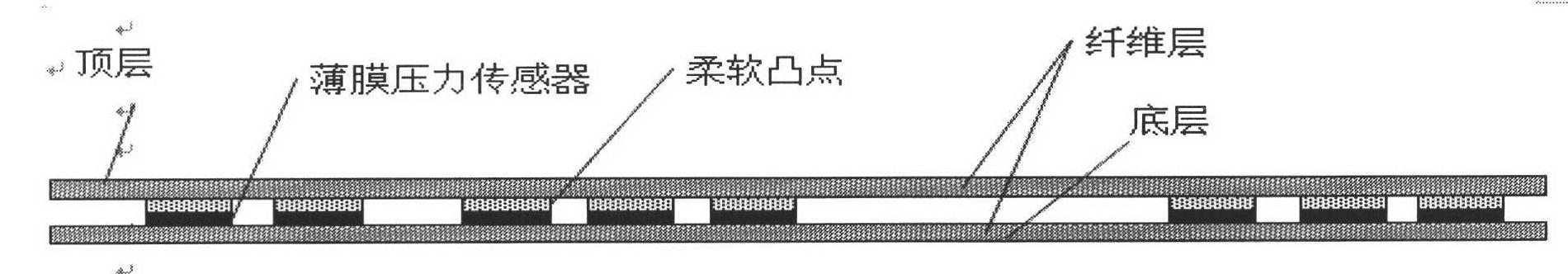

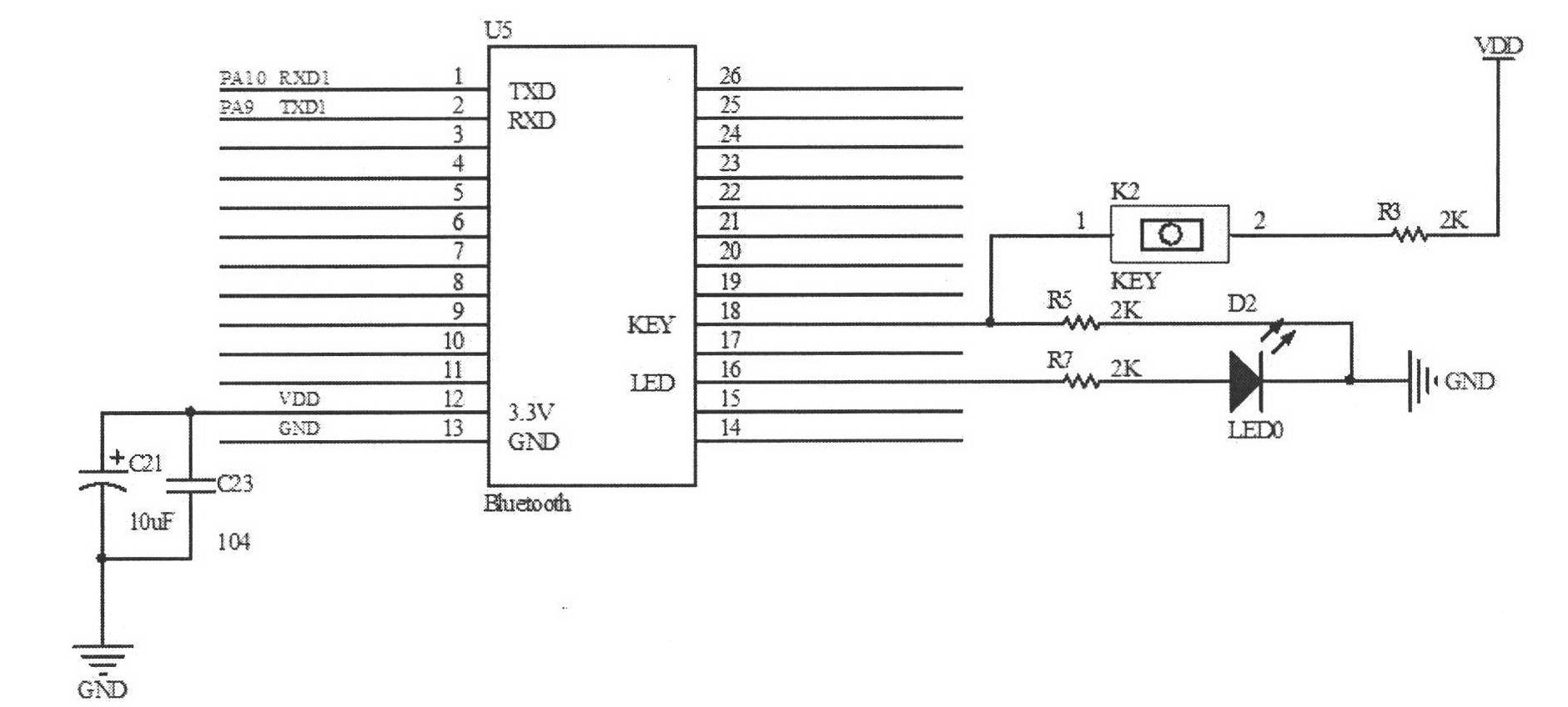

Method for measuring planta pressure for rehabilitation therapy

InactiveCN102090896AReduce in quantityIncrease sampling rateMuscle exercising devicesAcquired resistanceFiltration

The invention relates to a method for measuring planta pressure for rehabilitation therapy. The method is characterized in that thin film piezoresistive type pressure sensors are adopted to be placed on planta pressure points in left and right sock linings, each sock lining is of a three layer structure, and the top layer and the bottom layer are fiber layers; the thin film piezoresistive type pressure sensors are tightly adhered to and fixed on the bottom layers closely, are fixedly connected with the fibers at the top layers through soft salient points, and transmits the acquired resistance signals corresponding to the pressure to two signal processing transmitters which are corresponding to the pressure sensors of the left and right sock linings, the resistance signals are subjected to resistance-voltage conversion and wave filtration and then are output to two corresponding micro processors so as to be subjected to AD (analog-to-digital) conversion respectively; data acquired from two feet are merged into a data packet and is transmitted to a receiver; the receiver transmits the data of the left and right feet to a PC (personal computer) through a USB (universal serial bus); and the PC reads the data through the triggering of a timing device, and unpacks the data packet, and signal processing and three dimensional display are carried out through software.

Owner:SOUTHEAST UNIV

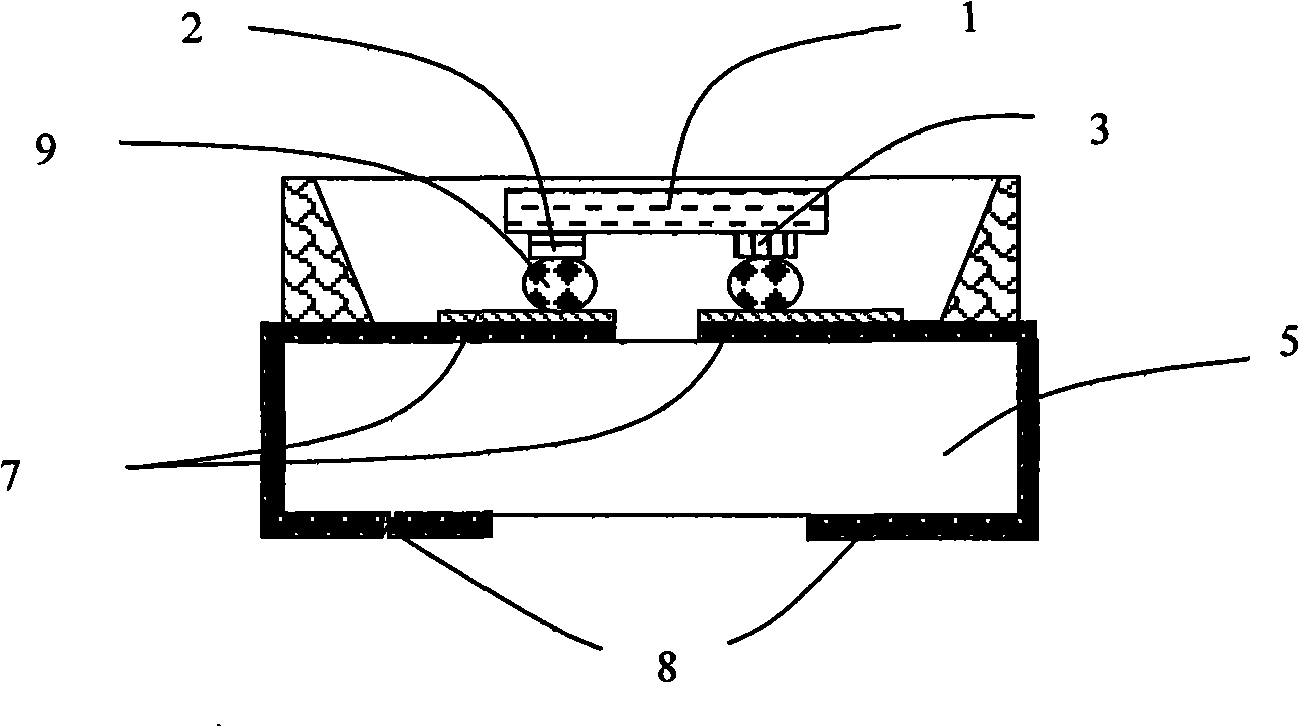

LED surface mounting structure for silicon substrate integrated with functional circuits and packaging method thereof

InactiveCN101958389AImprove cooling effectReduce volumeSolid-state devicesSemiconductor devicesHeat conductingSurface mounting

The invention relates to an LED surface mounting structure for a silicon substrate integrated with functional circuits, which comprises the silicon substrate and an LED chip. The upper surface of the silicon substrate has a planar groove-free structure; an oxidation layer cover the upper surface of the silicon substrate; a metal electrode layer is arranged on the upper surface of the oxidation layer; the upper surface of the metal electrode layer is provided with metal salient points; the LED chip is inversely arranged on the silicon substrate; the lower surface of the silicon substrate is provided with two conductive metal pads which are electrically connected with the metal electrode layer on the upper surface of the silicon substrate through metal leads arranged on the side wall of the silicon substrate; a heat conducting metal pad is arranged on the lower surface of the silicon substrate corresponding to the underside of the LED chip; and the upper surface of the silicon substrate is integrated with peripheral functional circuits required by the LED. The structure has the advantages of good radiating effect and small volume, LED driving and protecting functional circuits are directly integrated in the silicon substrate, wafer-scale industrial packaging is realized and the packaging and lamp cost is reduced.

Owner:APT ELECTRONICS

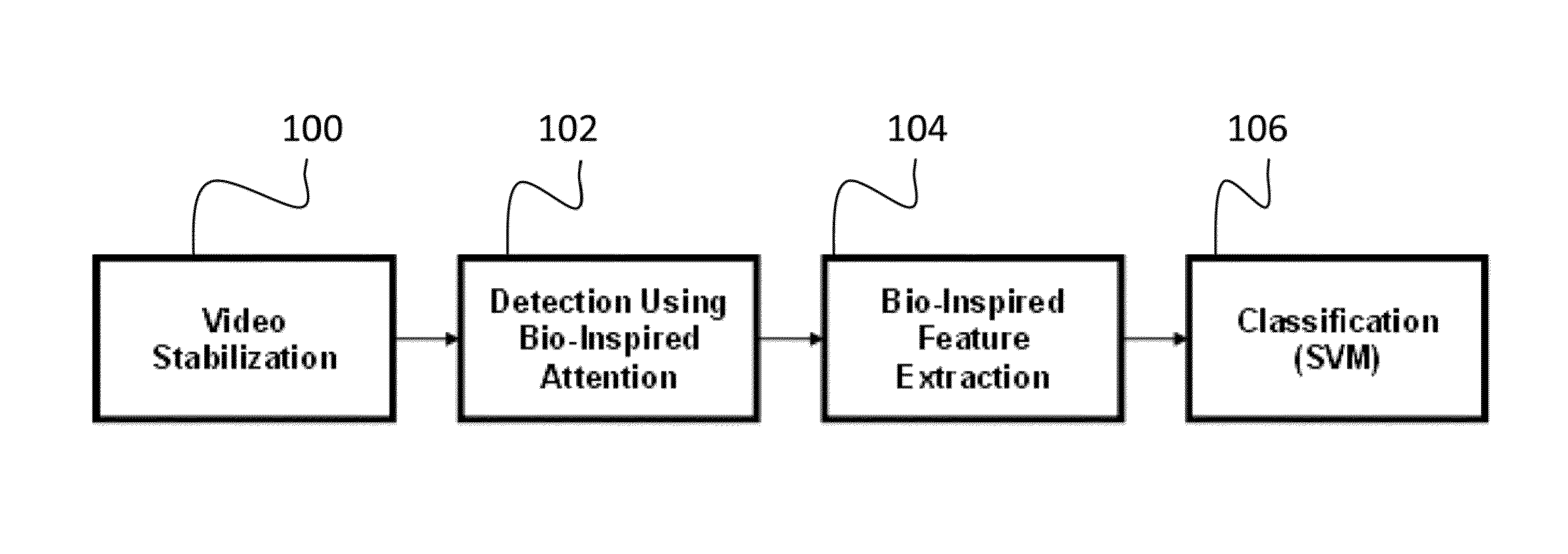

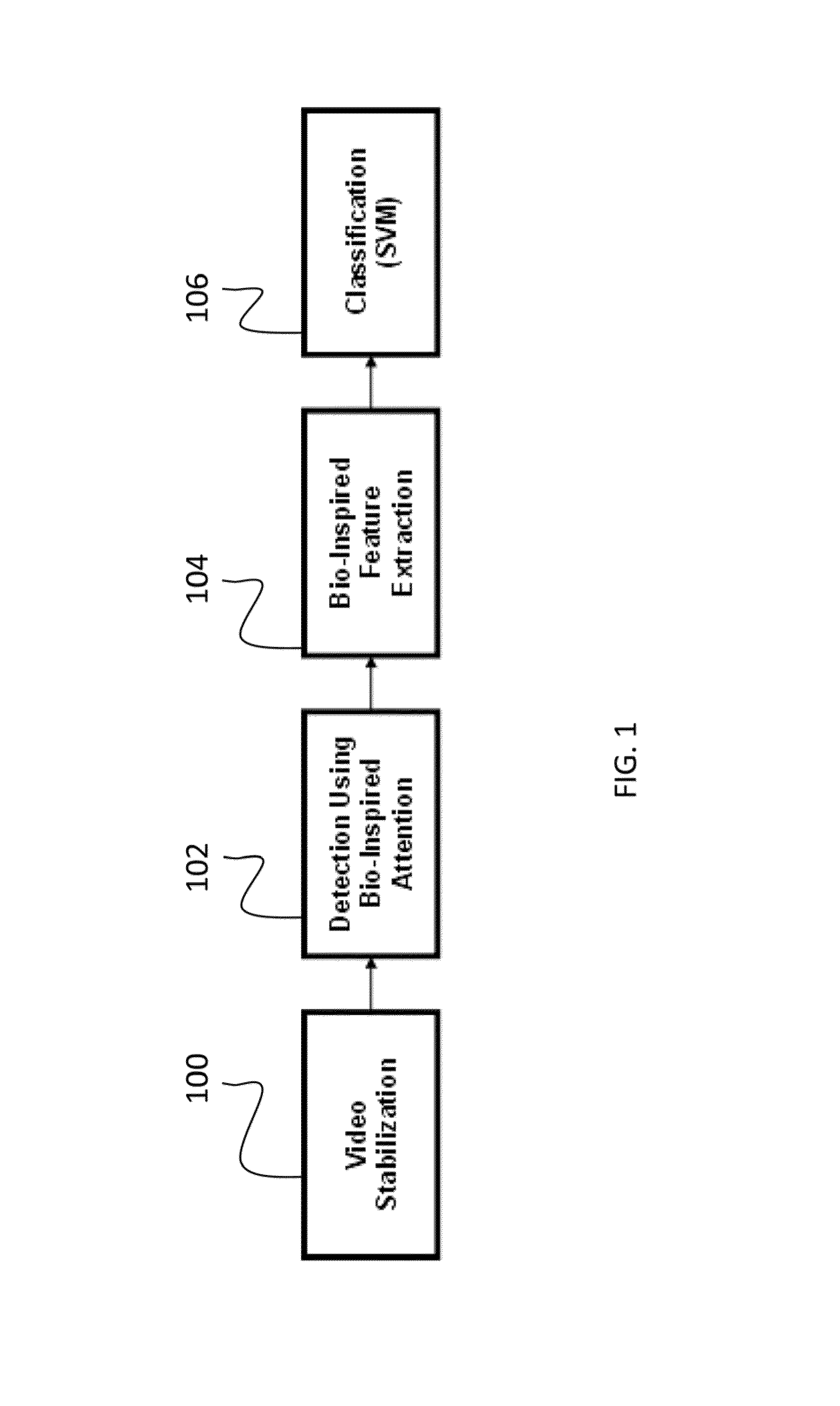

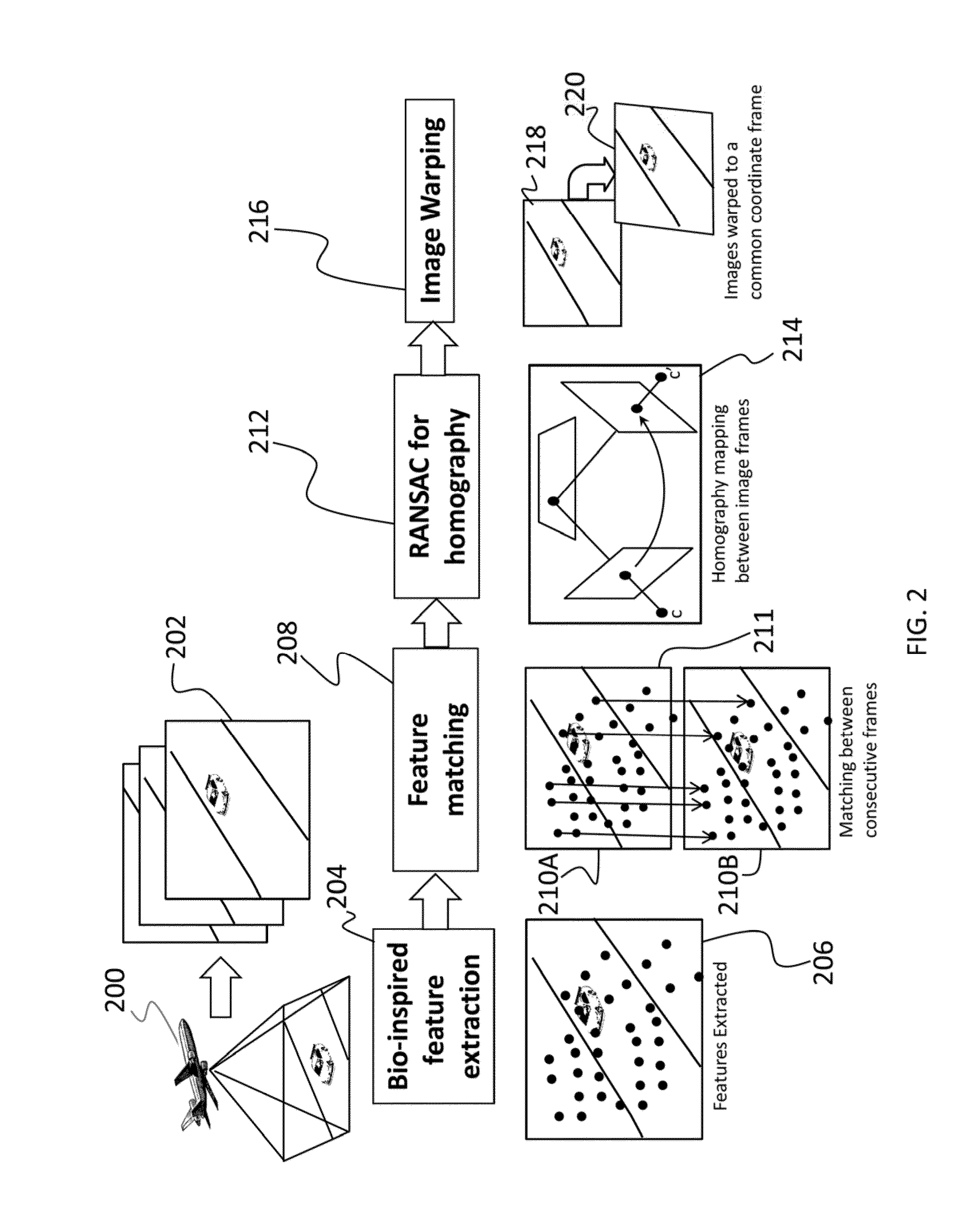

System for object detection and recognition in videos using stabilization

ActiveUS8885887B1Reduce and eliminate apparent image motionImage enhancementImage analysisFeature vectorObject Class

Described is a system for stabilizing, detecting, and recognizing objects in video captured from a mobile platform. The system first receives a video (with a plurality of image frames) captured from a mobile platform. The video is stabilized by registering the image frames to a global coordinate system to generate stabilized image frames. A bio-inspired attention algorithm is applied to the stabilized image frames to produce a set of locations in the stabilized image frames that are salient points representative of an object of interest. An image chip is generated that surrounds each salient point. High-dimensional feature vectors are extracted from the image chip. The feature vectors are then classified as an object class. Thus, through classifying the feature vectors, an object of interest can be identified in the video as captured from the mobile platform.

Owner:HRL LAB

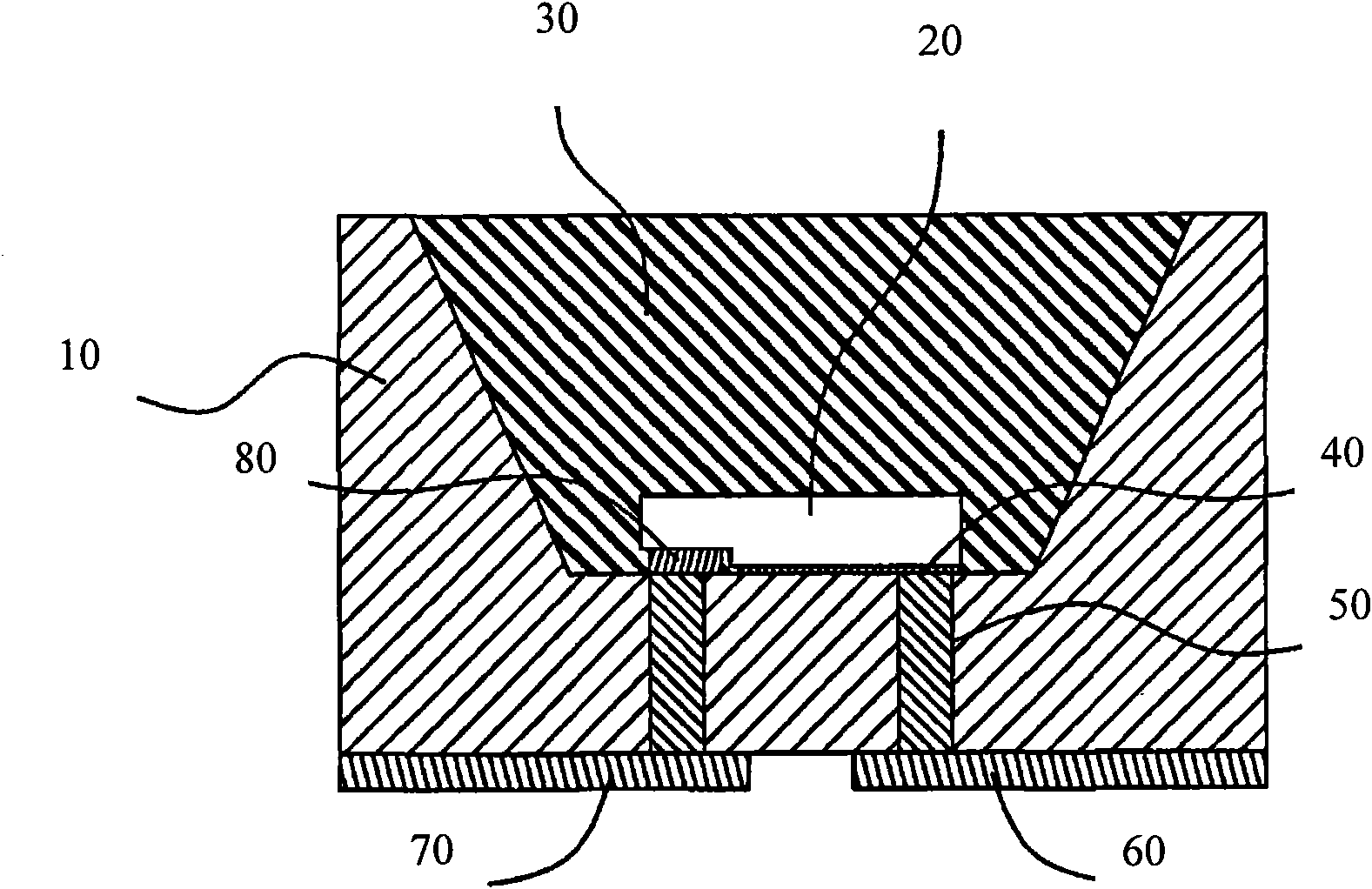

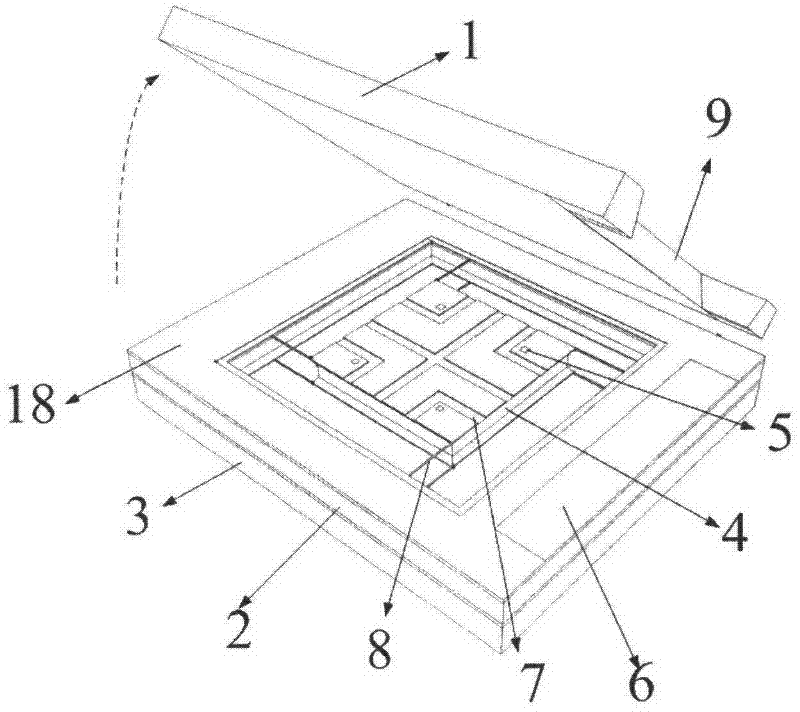

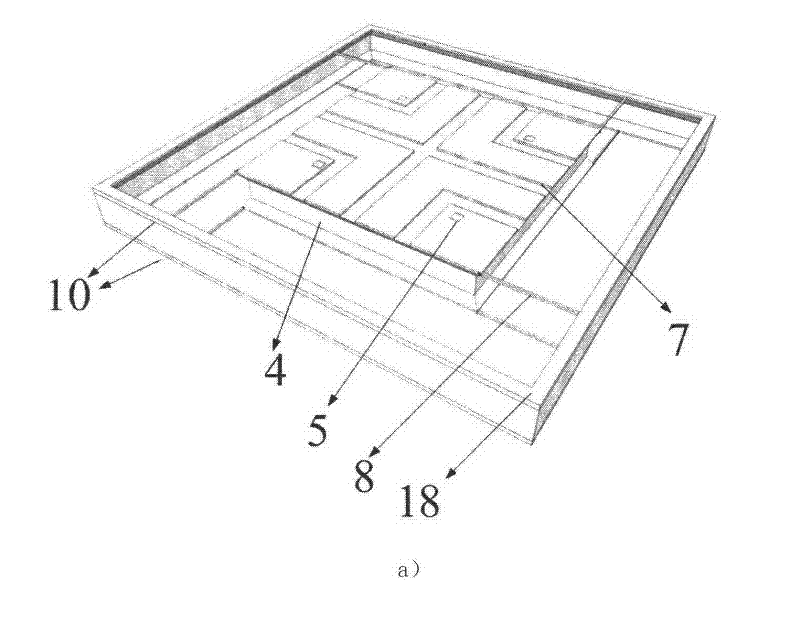

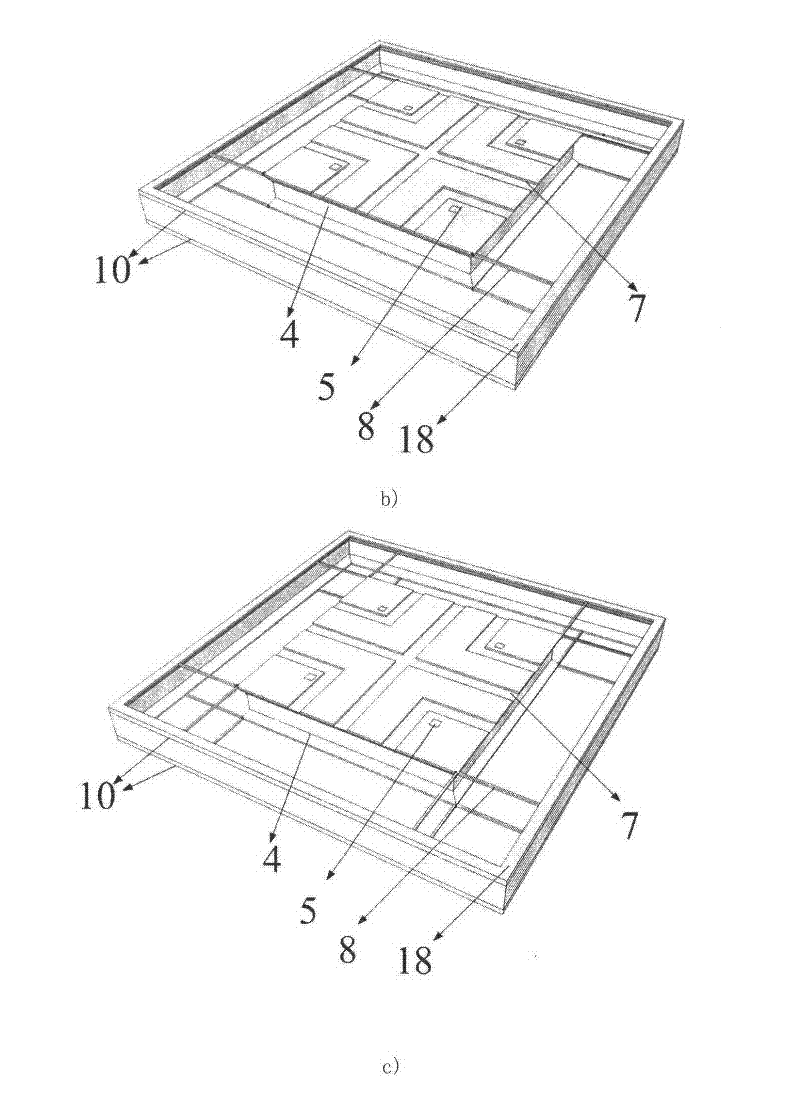

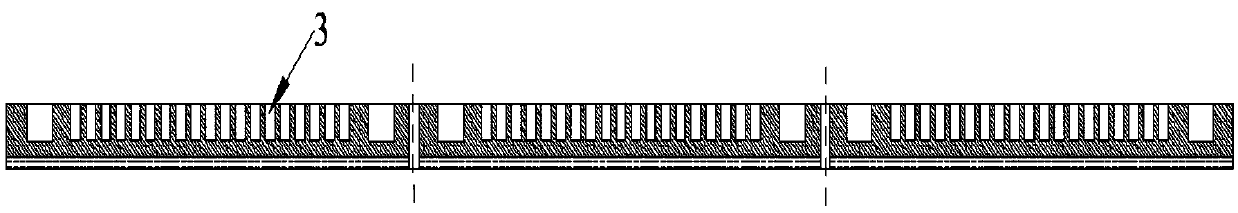

Capacitive type micro-acceleration sensor with double-sided symmetrical elastic beam structure and manufacturing method

ActiveCN102495234AImprove performanceHigh sensitivityDecorative surface effectsAcceleration measurementEtchingBlock structure

The invention relates to a capacitive type micro-acceleration sensor with a double-sided symmetrical elastic beam structure and a manufacturing method. The capacitive type micro-acceleration sensor is characterized in that: (1) an SOI silicon wafer of a double-device layer is a substrate with an elastic beam-mass block structure; (2) a fixed upper electrode and a fixed lower electrode are respectively located on the upper and lower sides of the mass block; (3) the elastic beam is a straight beam of which one end is connected with the mass block, and the other end is connected with a support frame; (4) overload protection salient points are formed on the upper and lower surfaces of the mass block; (5) damping regulation grooves are formed on the upper and lower surfaces of the mass block; and (6) an electrode leading through hole of the mass block is located above the support frame. By adopting the wet etching self-stop technology, the elastic beam-mass block structure which is the most important in the acceleration sensor is processed and formed once in the wet etching; and the bonding of three layers of silicon wafers is realized by a silicon-silicon direct bonding method, and the electrode leading through hole of the mass block is formed on the fixed upper electrode through infrared aligned photoetching. According to the invention, the cross-axis sensitivity is reduced while the device sensitivity is improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

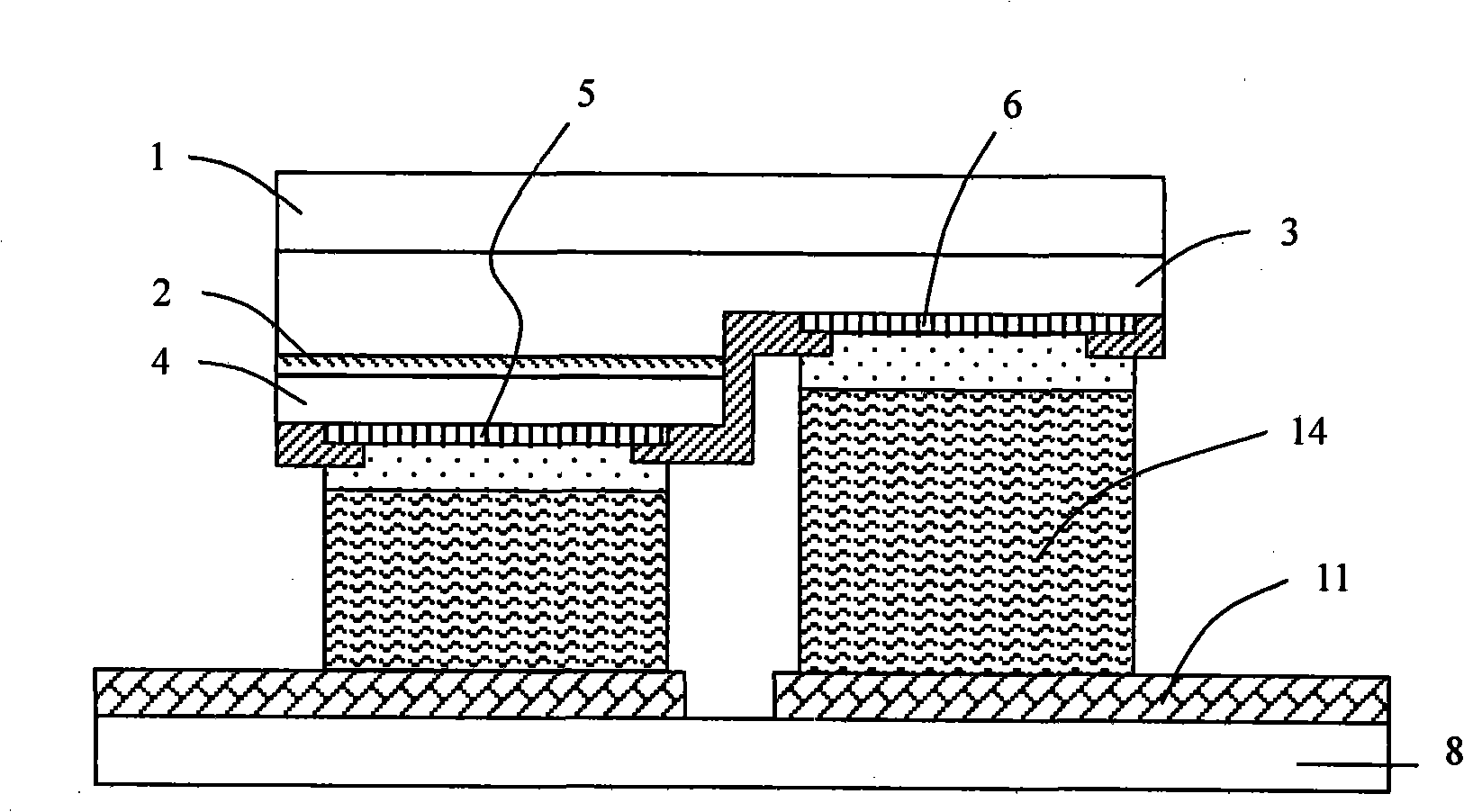

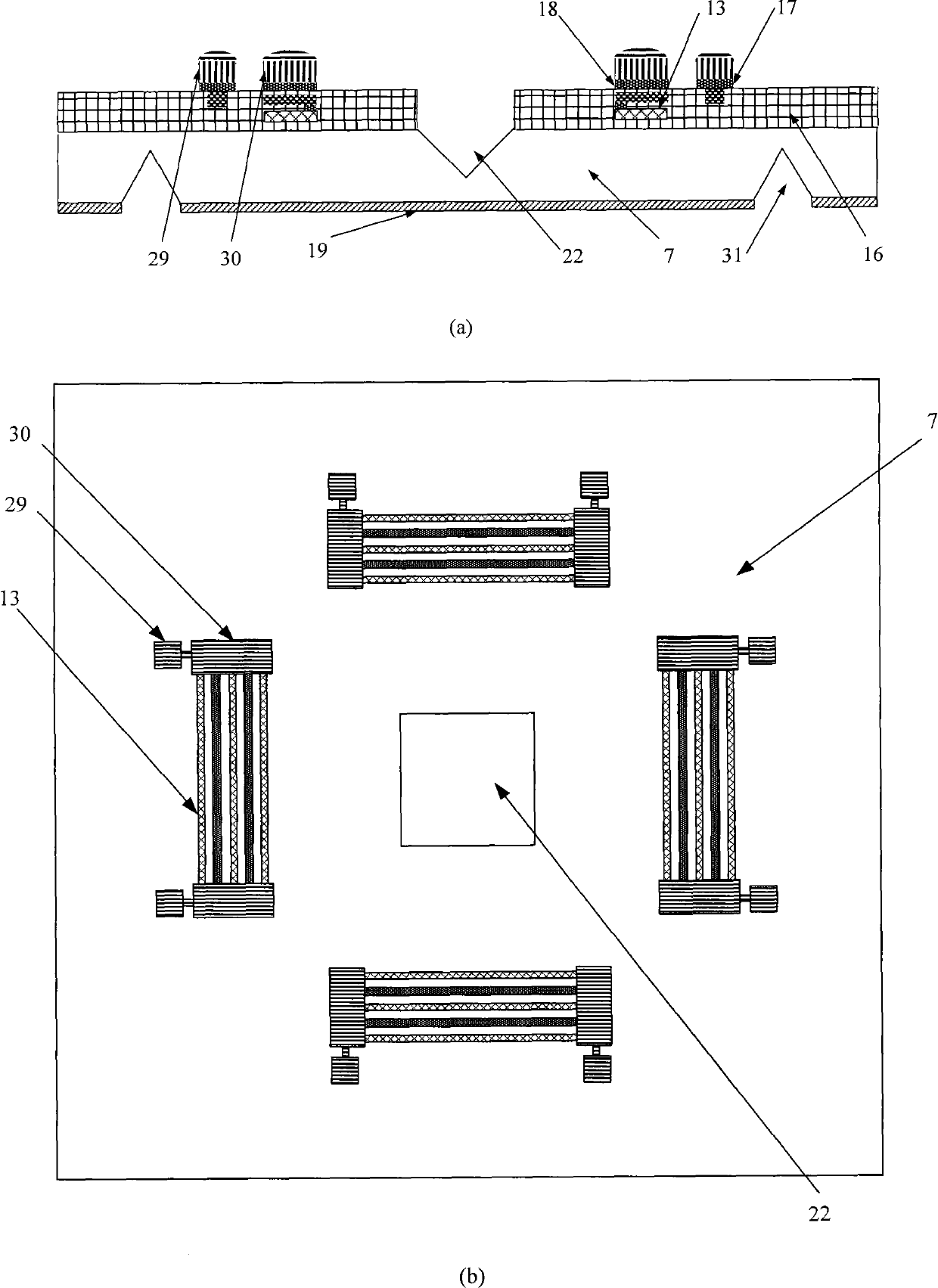

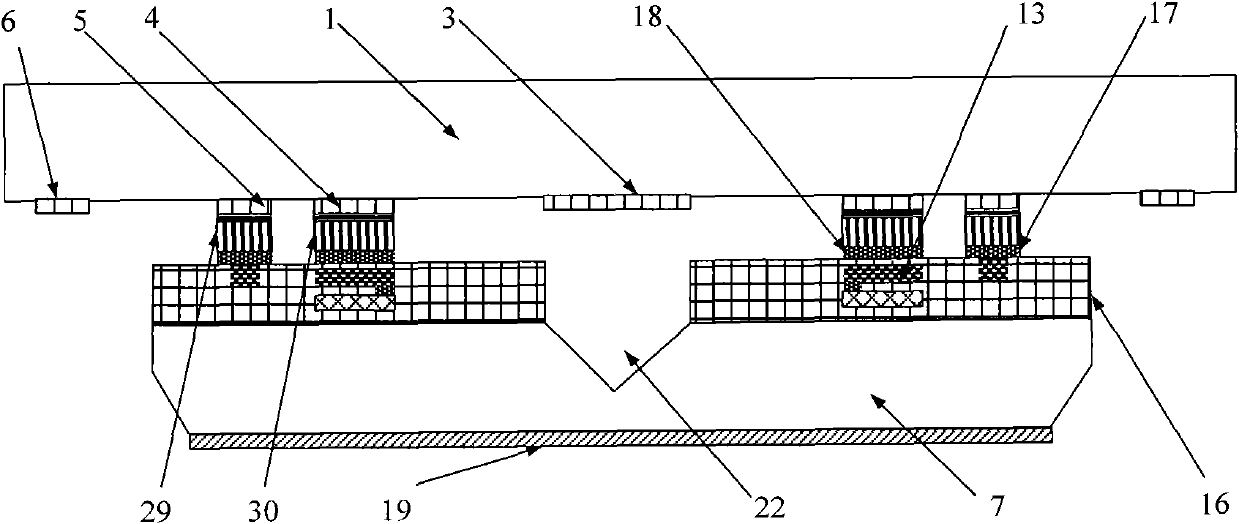

Three-dimensional active heat-dissipation packaging structure of embedded micro channel and manufacturing process thereof

ActiveCN109524373AEliminate interfacial thermal resistanceRealize multi-dimensionalSemiconductor/solid-state device detailsSolid-state devicesHigh densityEngineering

The invention, which belongs to the technical field of integrated circuit packaging, relates to a three-dimensional active heat-dissipation packaging structure of an embedded micro channel and a manufacturing process thereof. The three-dimensional active heat-dissipation packaging structure comprises a three-dimensional packaging structure. A micro channel chip structure unit is arranged at the top layer of the three-dimensional packaging structure and includes an IC chip having an embedded micro flow structure and a micro channel cover plate. A two-dimensional heterogeneous integrated structural unit is arranged at the bottom layer of the three-dimensional packaging structure and includes a TSV adapter board connected with a bottom filling layer through array salient points and an IC chip; the micro channel chip structure unit and the two-dimensional heterogeneous integrated structural unit are connected with the bottom filling layer through the array salient points; and then packaging with an embedded micro channel substrate and a housing is carried out to form a three-dimensional active heat-dissipation packaging structure. Therefore, the inter-layer thermal resistance of the three-dimensional packaging system is reduced substantially; the heat dissipation capability of the circuit is improved effectively; and the high-density and high-performance three-dimensional system-level packaging is enhanced and the safety and reliability are high.

Owner:58TH RES INST OF CETC

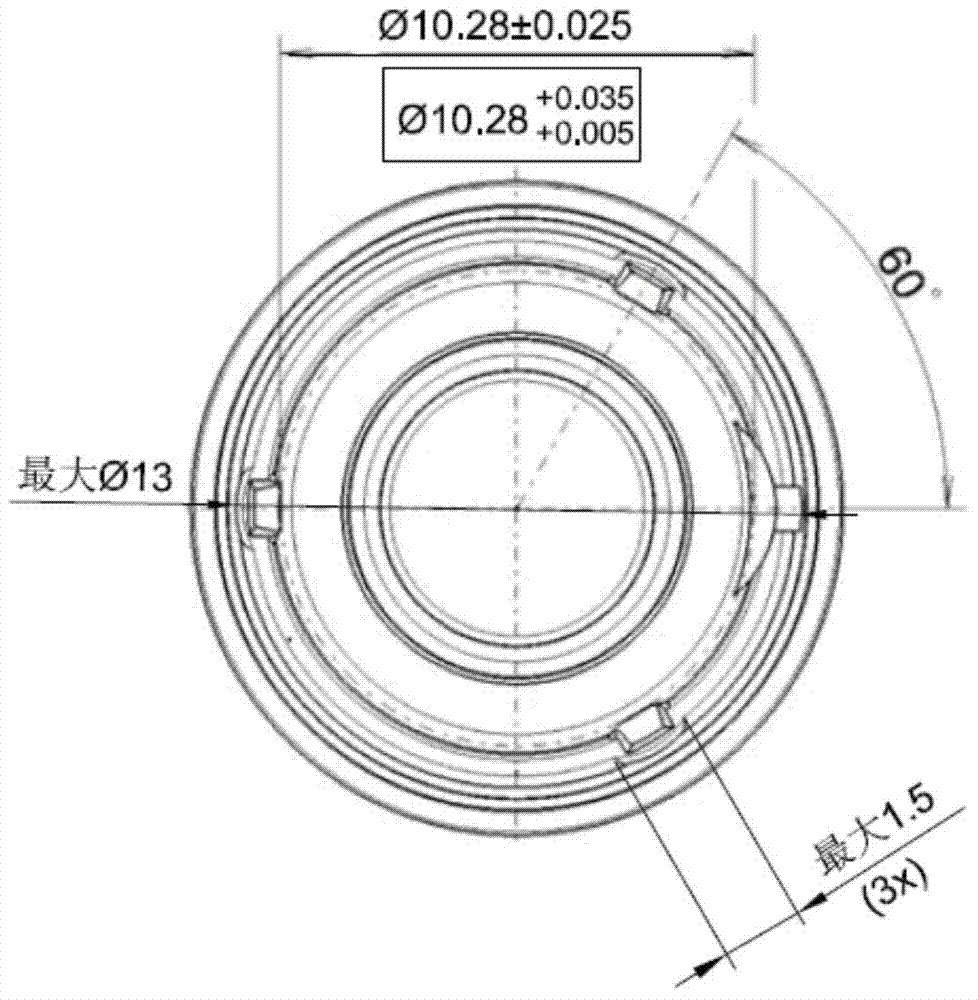

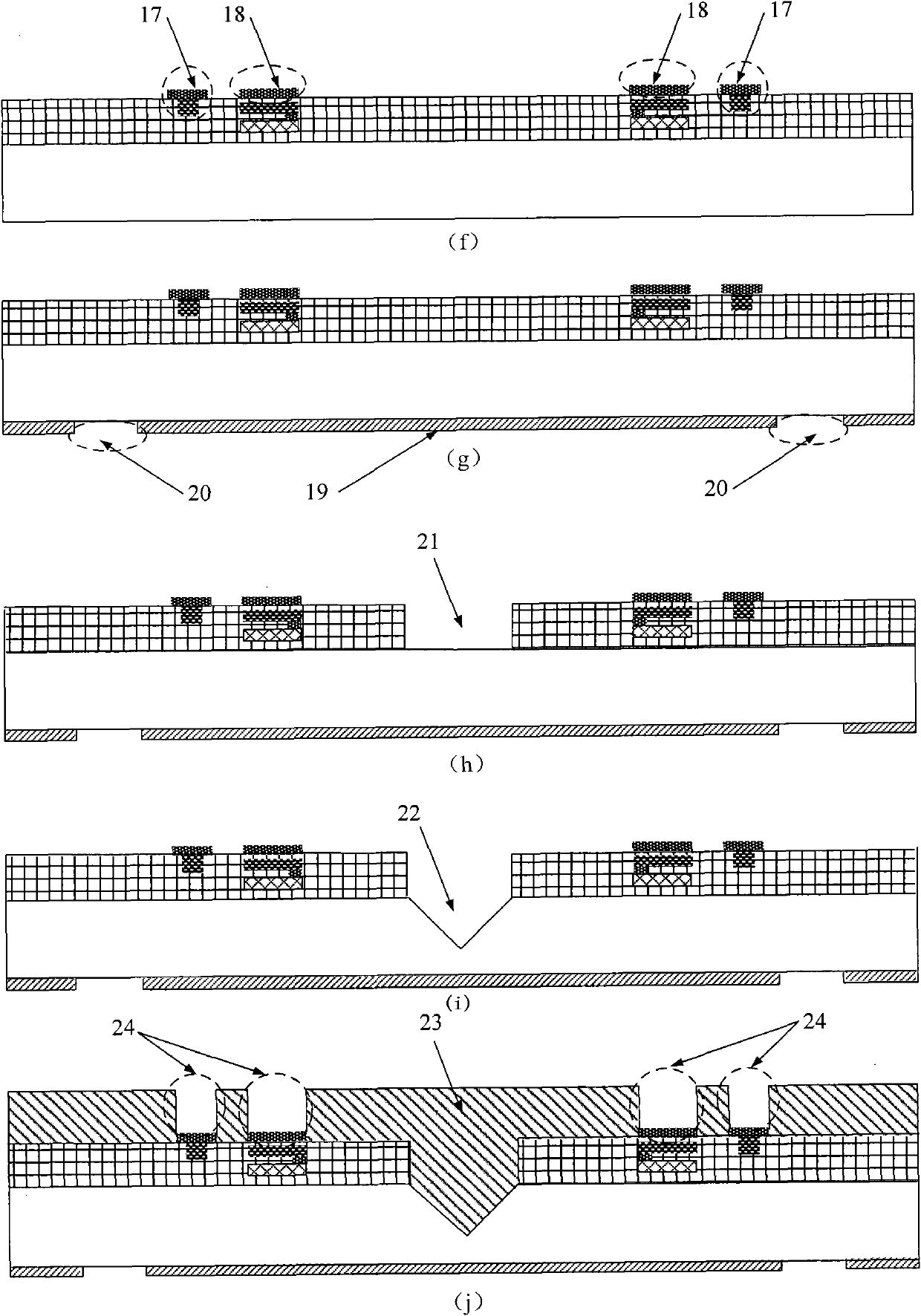

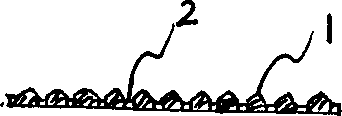

Method for preparing ball-shaped bump biological microelectrode array

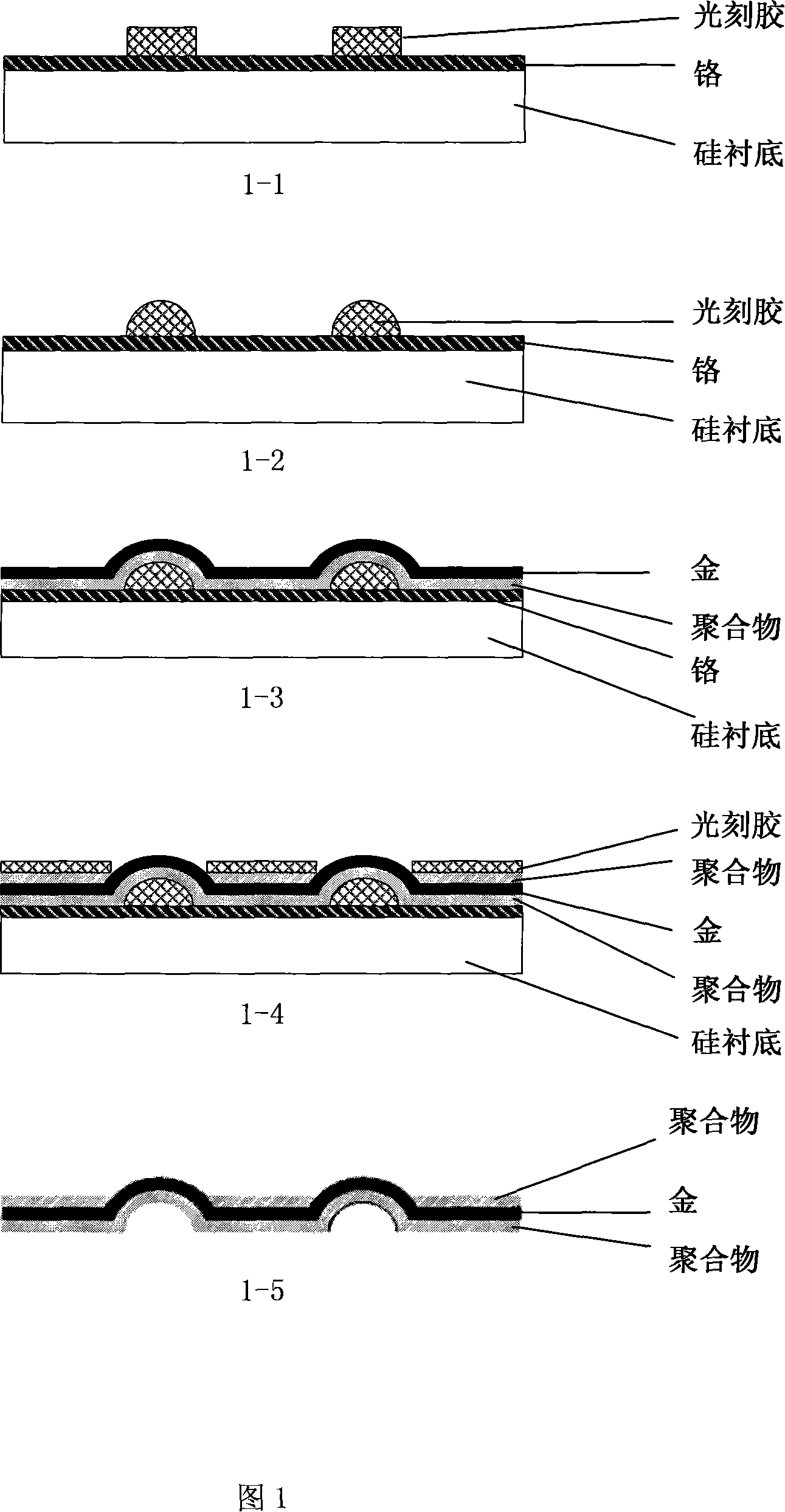

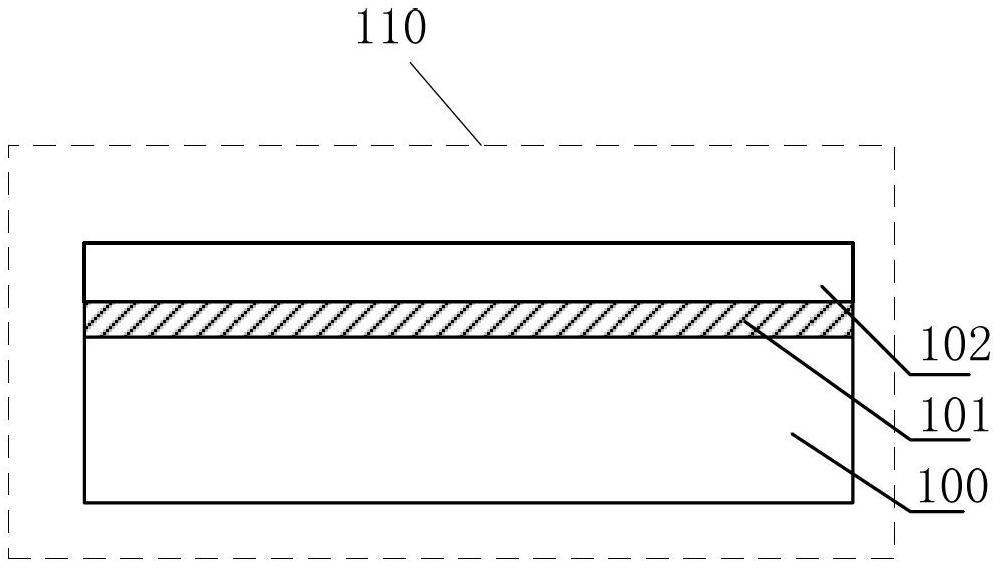

InactiveCN101149559ASimple processEasy to operateSemi-permeable membranesEye implantsLacquerRetinal Prosthesis

This invention discloses a sort of method that it uses the light-sensitive lacquer hot-melt method to prepare the roundness heave biologic micro-electrode array. It uses the light-sensitive lacquer technique to prepare the heave cylindrical light-sensitive lacquer, and it adopts the hot-melt circumfluence light-sensitive lacquer to form the roundness salient point. A bed of polymer which is covered in the underlay is used for the protecting material of the bottom of the device, and the presented in figures forms the metal electrode point and the lead, and then that it covers the polymer to be the protecting material of the top of the device. The presented in figures reveals the electrode point and the weld point, and it gets the needed roundness heave smooth micro-electrode array. The cost of the invention is low, also the technical process is simple, and it has the upper irritant effect. It is used for the preparation of the biologic micro-electrode array which has the nerve-cell stimulation of the retina prosthesis and so on.

Owner:SHANGHAI JIAO TONG UNIV

Three-dimensional integrated method of sensor array and signal processing circuits

InactiveCN102689874ARealize floatingSimplify the manufacturing processDecorative surface effectsChemical vapor deposition coatingSensor arraySignal processing circuits

The invention discloses a three-dimensional integrated method of a sensor array and signal processing circuits in the technical field of semiconductor three-dimensional integration. The three-dimensional integrated method comprises the following steps of: (1) manufacturing sensors on a top layer single crystal material of an insulating substrate device; (2) manufacturing the signal processing circuits and metal interconnection lines on the surface of a signal processing circuit substrate and manufacturing metal salient points on the metal interconnection lines; (3) carrying out a bonding process or a three-dimensional interconnection process; (4) carrying out metal thermocompression bonding on bonding metal salient points and the salient points; (5) removing a temporary bonding polymer layer and auxiliary wafers; and (6) manufacturing plane interconnection lines. By utilizing the three-dimensional integrated method, integration of the sensors and the signal processing circuits is realized, hovering of the sensors is realized, electric signal connection of the sensors and the signal processing circuits is realized by utilizing three-dimensional interconnection lines, the manufacture process is simple, the sensors can be suspended, and excellent consistency of the sensors and large-scale array structure can be obtained.

Owner:TSINGHUA UNIV

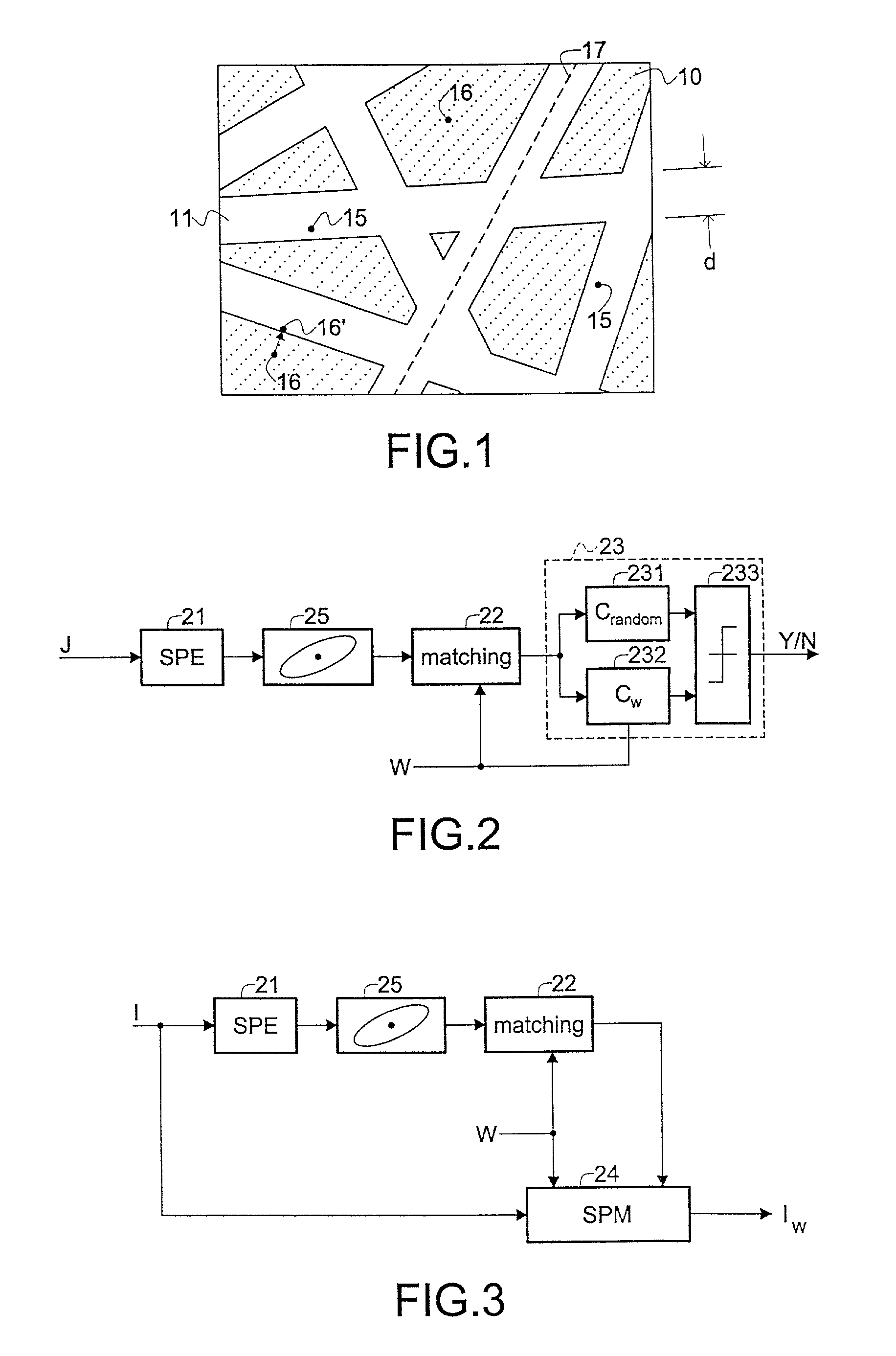

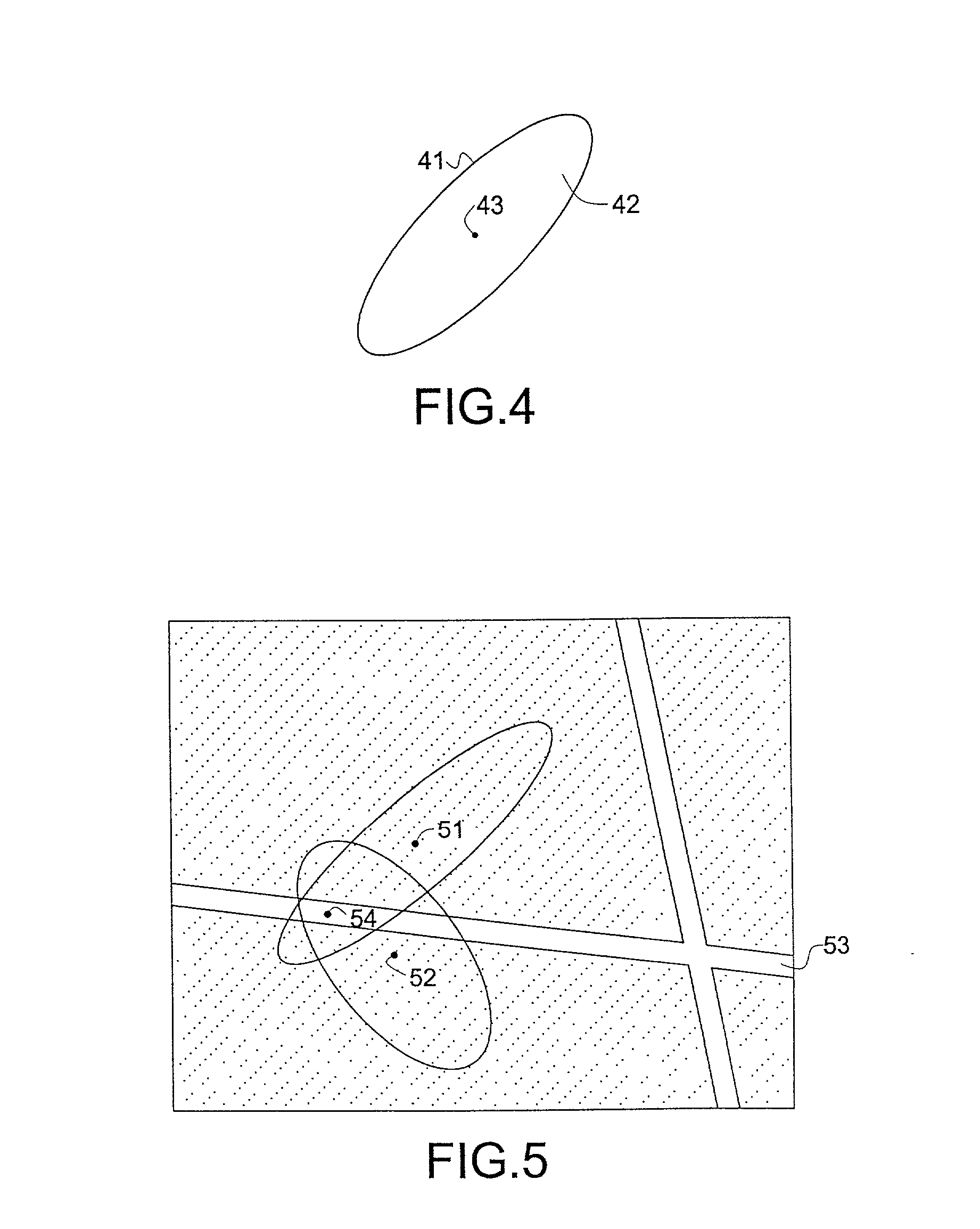

Embedding and detecting a watermark in an information signal

InactiveUS20010032315A1Easy to detectRobustness of watermark improvedTelevision system detailsUser identity/authority verificationAlgorithmSignal processing

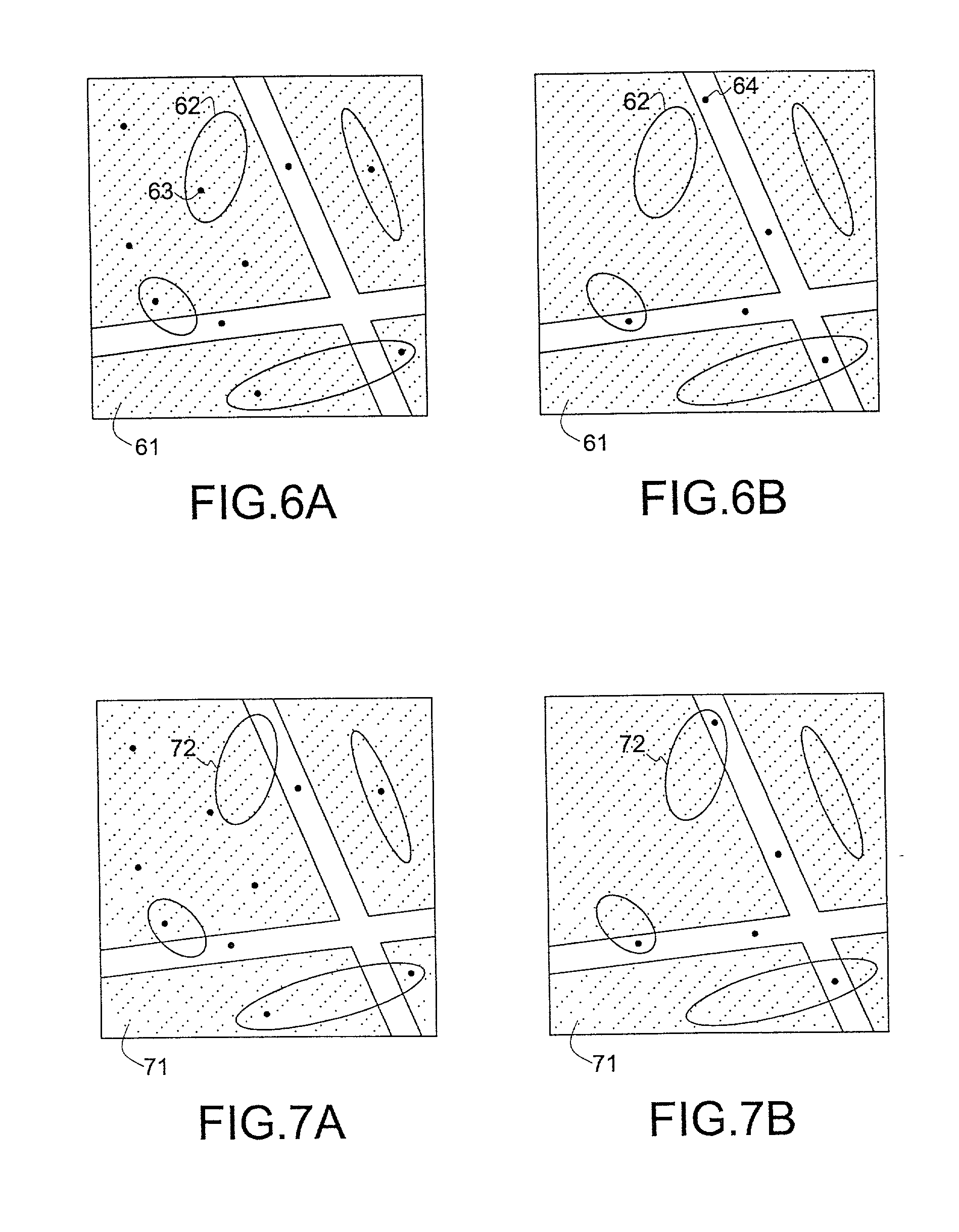

A known method of watermarking an information signal is based on extraction of salient points (21) of the signal (e.g. zero crossings in audio, edges of an image) and "warping" (24) said salient points towards a given watermark pattern (W). One step in the embedding and detection process is determining (22) whether or not salient points lie "on" or "off" the watermark. This is a hard decision. It is now proposed to extend salient points to salient "regions" (25). This turns the step of matching (22) into a soft decision, which is less vulnerable to signal processing. The robustness of the embedded watermark is thereby improved.

Owner:U S PHILIPS CORP

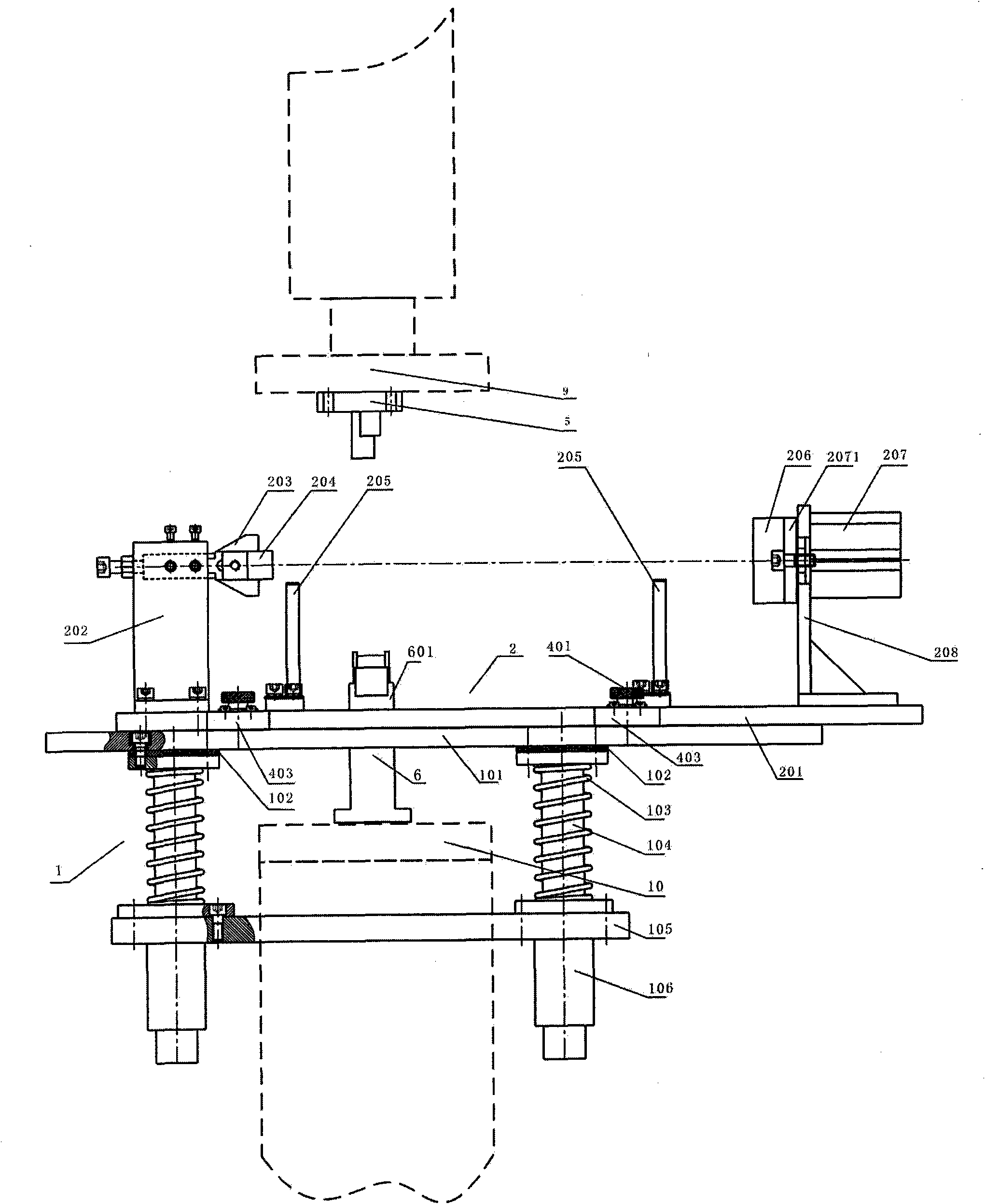

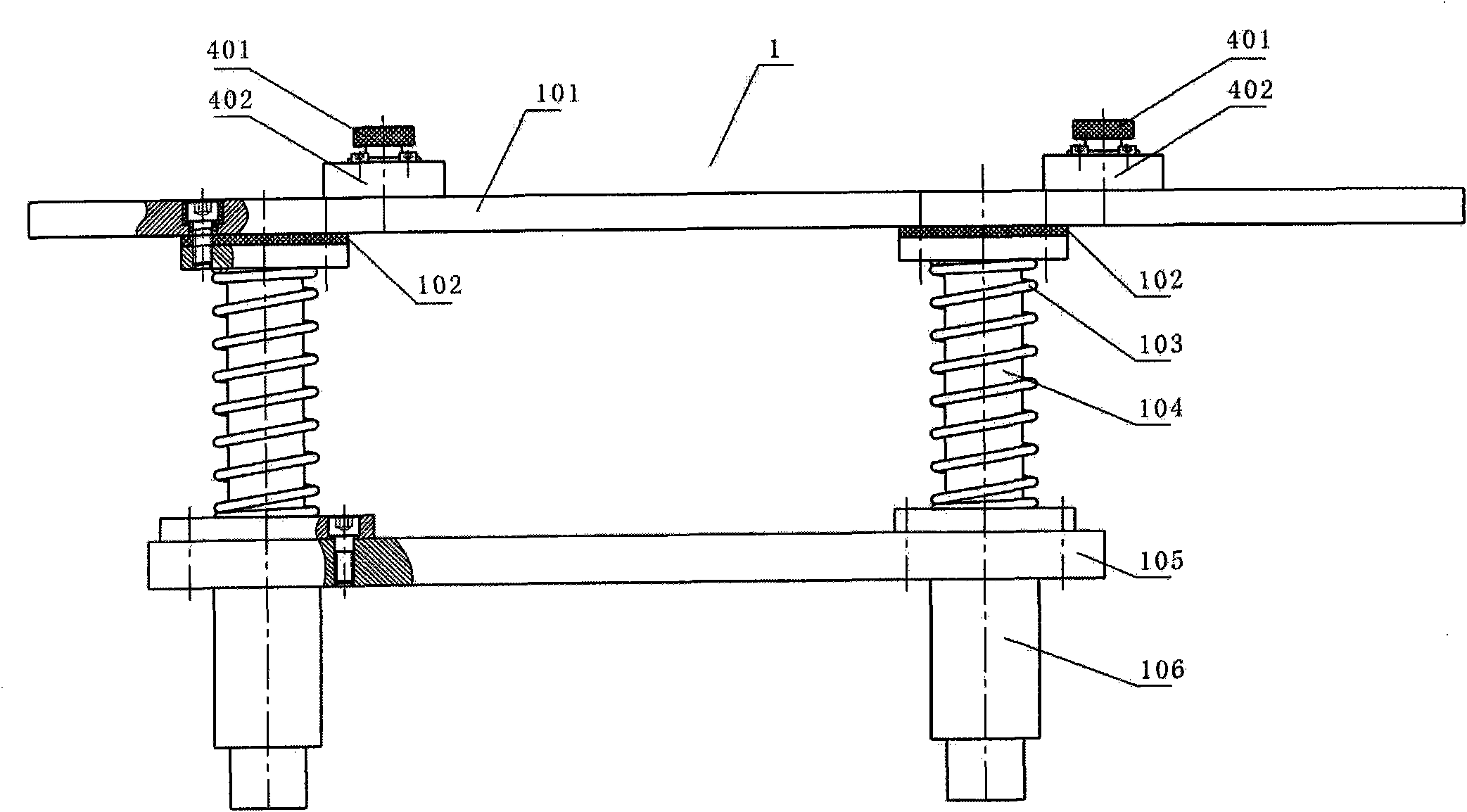

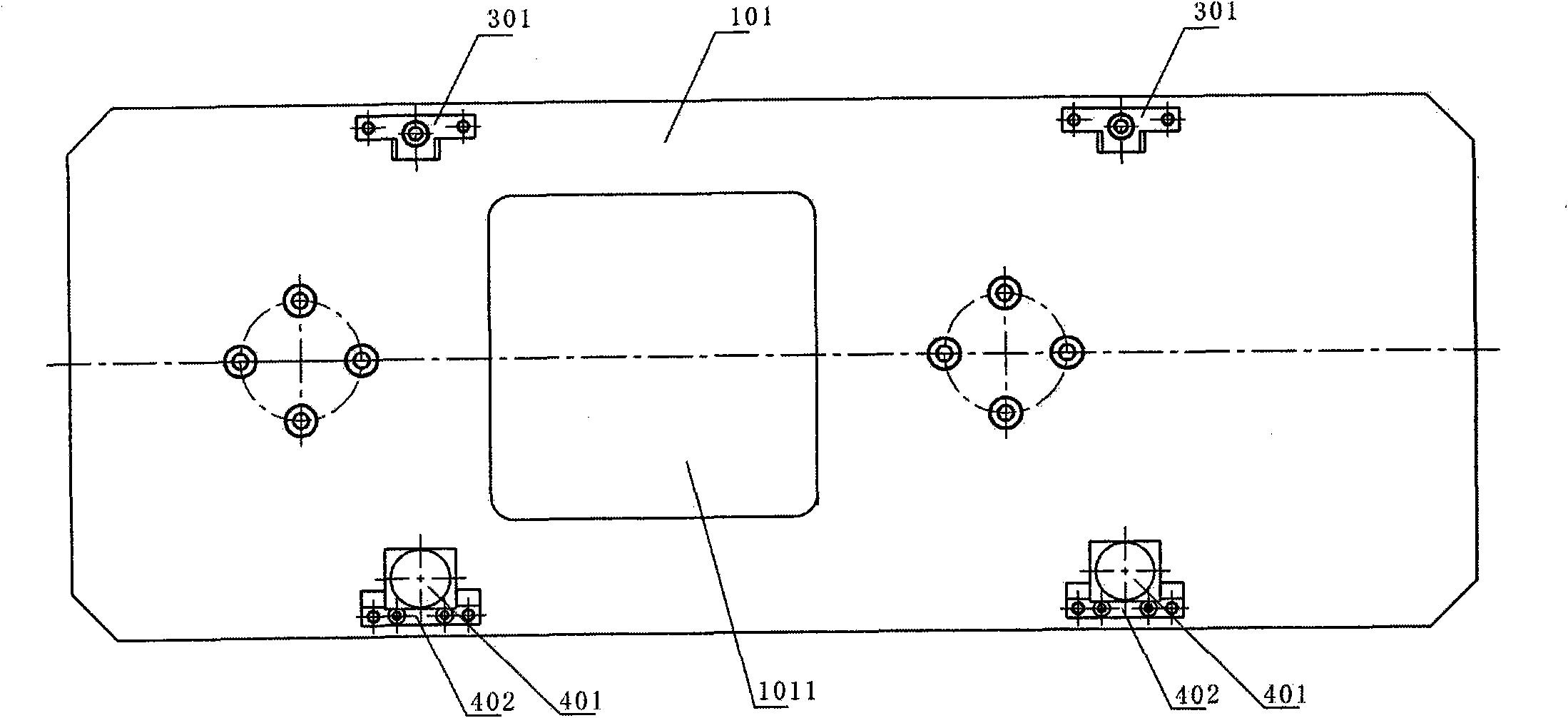

Automobile shock absorber support projection welding floating tool

The invention discloses an automobile shock absorber support frame projection welding floating tool, which relates to spot welding equipment and consists of a projection welding floating universal base, a replaceable automobile shock absorber support positioning frame, a replaceable positioning frame positioning mechanism, a wedge-shaped pressing mechanism, an upper electrode seat and a lower electrode seat, wherein the replaceable automobile shock absorber support positioning frame is arranged on the projection welding floating universal base through the replaceable positioning frame positioning mechanism and the wedge-shaped pressing mechanism, the projection welding floating universal base is arranged on a casing of a projection welder, the upper electrode seat is arranged under an upper electrode plate of the projection welder, and a lower electrode is arranged on a lower electrode plate of the projection welder. A spring is used for buffering in welding contact moment, thus the tool is stable and reliable, the salient point plastic deformation can not be caused, the salient point size is prevented from being changed by the upper electrode cylinder impact, and the welding strength stability is good.

Owner:浙江鼎信航天科技有限公司

Method for manufacturing LED directly mounted on a support upside-down

InactiveCN101350321AImprove reliabilityImprove light extraction efficiencySolid-state devicesSemiconductor/solid-state device manufacturingHeat resistanceMiniaturization

The invention relates to a process for preparing a luminescent diode which is directly and inversely installed in a support, in a support, a single chip or a plurality of chips are directly and inversely installed on the support through metallic salient points. The method saves the steps of fixing a wafer by a chip and bonding by a gold wire, thereby the manufacturing cost is reduced, and the manufacturing efficiency is improved, the heat resistance is reduced, and the heat dissipating problem of a power type chip is solved, the light trapping problem of a bonding pad and a lead wire during the packing of a small size LED is solved, and the luminous efficiency of the LED is greatly improved, the more miniaturization of the packing size of the LED is realized, and the increased requirements of the market to the miniaturization packing are satisfied.

Owner:APT ELECTRONICS

Integrated anemograph based on ceramics wafer level package and preparation method thereof

ActiveCN101819214ALow costReduce packaging costsTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesElectricityCMOS

The invention discloses a preparation method of CMOS (Complementary Metal-Oxide-Semiconductor) anemograph based on ceramics wafer level package, which comprises following steps: 1, preparing a ceramics chip comprising the step of manufacturing a heating element and a pad used for electric connection, hot link and electric induction on the lower surface of the ceramics chip by a sputtering and etching technology; 2, preparing a silicon chip comprising the steps of preparing a heat sense thermometric element by a standard CMOS technology, preparing an insulation cavity and a shredding slot which is arranged at the back of the silicon chip by an MEMS (Micro-Electromechanical System) anisotropy wet etching technology and then preparing copper salient points and solder on the surface of the silicon chip; 3, realizing the mutually-connected package, electric connection and hot link between the silicon chip and the ceramics chip; 4, scribing; and 5, shredding. The invention has the advantages that the preparation method is compatible with the standard CMOS technology in the whole prepare process of the anemograph, the aftertreatment technology is simple and the wafer level package of the anemograph is realized by adopting a flip-chip bonding packaging technology, thereby having the advantages of high process consistency, good compatibility, simple aftertreatment technology and low cost.

Owner:SOUTHEAST UNIV

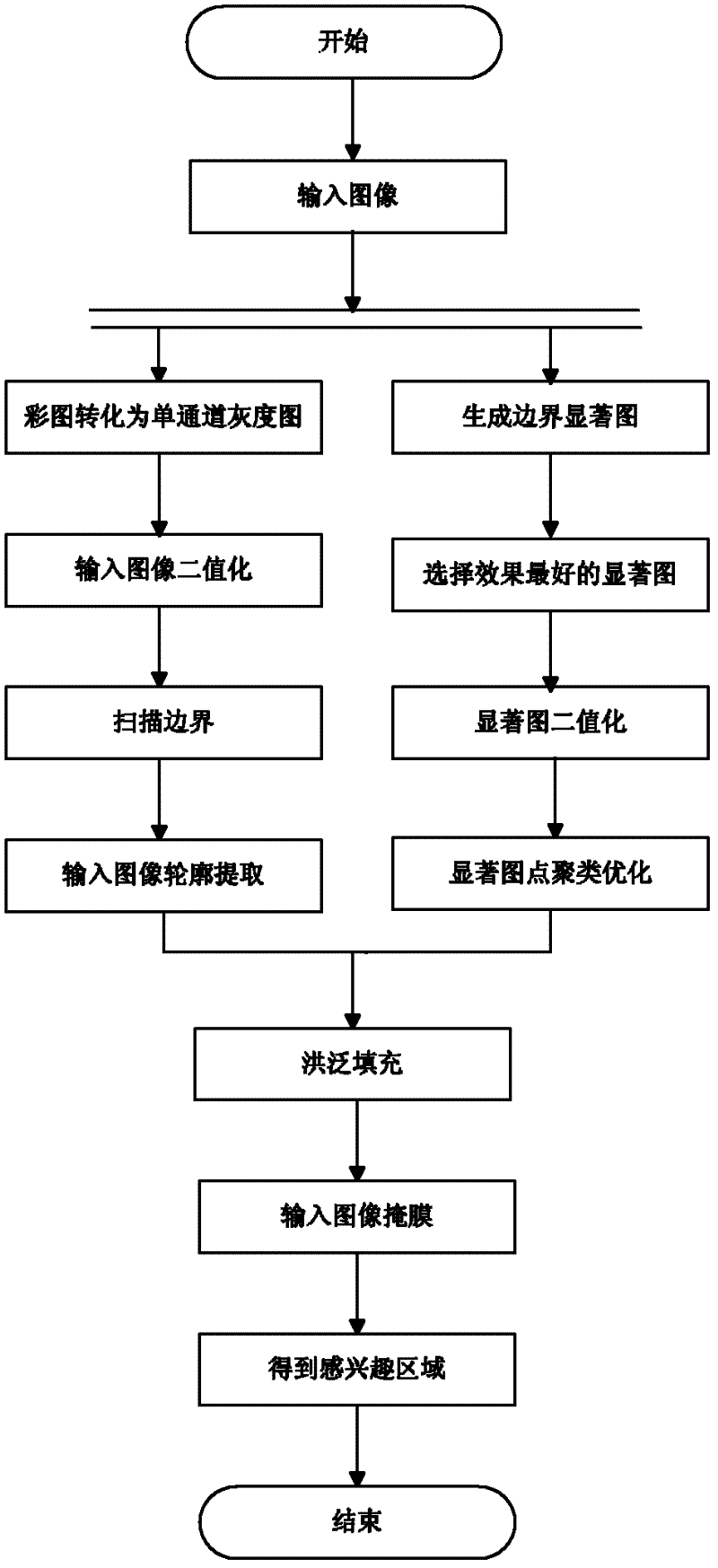

Region of interest extraction method of pixel level

InactiveCN102496023AImprove extraction efficiencyImprove extraction qualityImage analysisCharacter and pattern recognitionImaging processingSaliency map

The invention discloses a region of interest extraction method of a pixel level. The method is used to reduce a data scale and improve image processing efficiency. The method comprises the following steps: using visual attention models to obtain a saliency map and carrying out saliency map binarization; after a salient point is obtained, clustering, and optimizing a problem generated during the clustering; simultaneously, carrying out original image binarization and extracting a binary image outline of the original image through scanning the binary image; taking the optimized clustering point as a seed point to perform filling; performing mask with the original image and then extracting the region of interest of the image. In the invention, the saliency map is taken as a base; the pixel point which is the salient point in the saliency map is taken as a target. An operation speed of extracting the region of interest in the image can form a linear relation with a number of the salient point. A leakage point rate of the region of interest at least decreased to a half of the original leakage point rate and a classification error rate does not increase obviously.

Owner:CENT SOUTH UNIV

Water pricking non-woven fabric perforating mould and non-woven fabric production method

The present invention relates to a hydro-entangled non-woven fabric production method by using the components of perforation die, prepunching machine and hydropunching drum, etc. belonging to the field of non-woven fabric production equipment and its production method. On the die plate of said perforating die there are several projected salient points, several dehydrating small holes are distributed between said several projected salient points on the die plate. Said invention can make the cotton layer pass through the prepunching hydropunching machine and perforation channel formed from drum perforation die and hydropunching jet head and undergo the processes of prewetting, entanglement and hydropunching so as to obtain the invented product.

Owner:HANGZHOU NBOND NONWOVENS

Stainless steel muffler and manufacturing process thereof

The invention discloses a stainless steel muffler and a manufacturing process thereof, and belongs to the technical field of manufacturing refrigeration system components. The current muffler used by a refrigeration system is high in cost or easily pollutes the environment and is corroded by rusting. The stainless steel muffler consists of a stainless steel hush pipe and a copper air inlet pipe and a copper air outlet pipe welded at two ends of the hush pipe, and the manufacturing method for the stainless steel muffler comprises the following steps of: 1, preparing the hush pipe by using a stainless steel pipe; 2, preparing the air inlet pipe and the air outlet pipe by using copper pipes, and beating the side walls at welding positions of the copper pipes to form salient points which protrude from inside to outside; 3, assembling, namely inserting the air inlet pipe and the air outlet pipe into welding ports at two ends of the hush pipe respectively, fixing the air inlet pipe and the air outlet pipe, and filling a solid bronze solder into welding seams; 4, welding, namely passing the assembled muffler to be welded through a welding furnace, and controlling the temperature of the welding furnace to be between 900 and 1,065 DEG C and the passing speed to be between 0.25 to 0.7 meter / minute; and 5, performing leak checking. By the stainless steel muffler, an anti-rust spraying treatment is not needed, and the rusting of the muffler is avoided.

Owner:浙江三集不锈钢有限公司

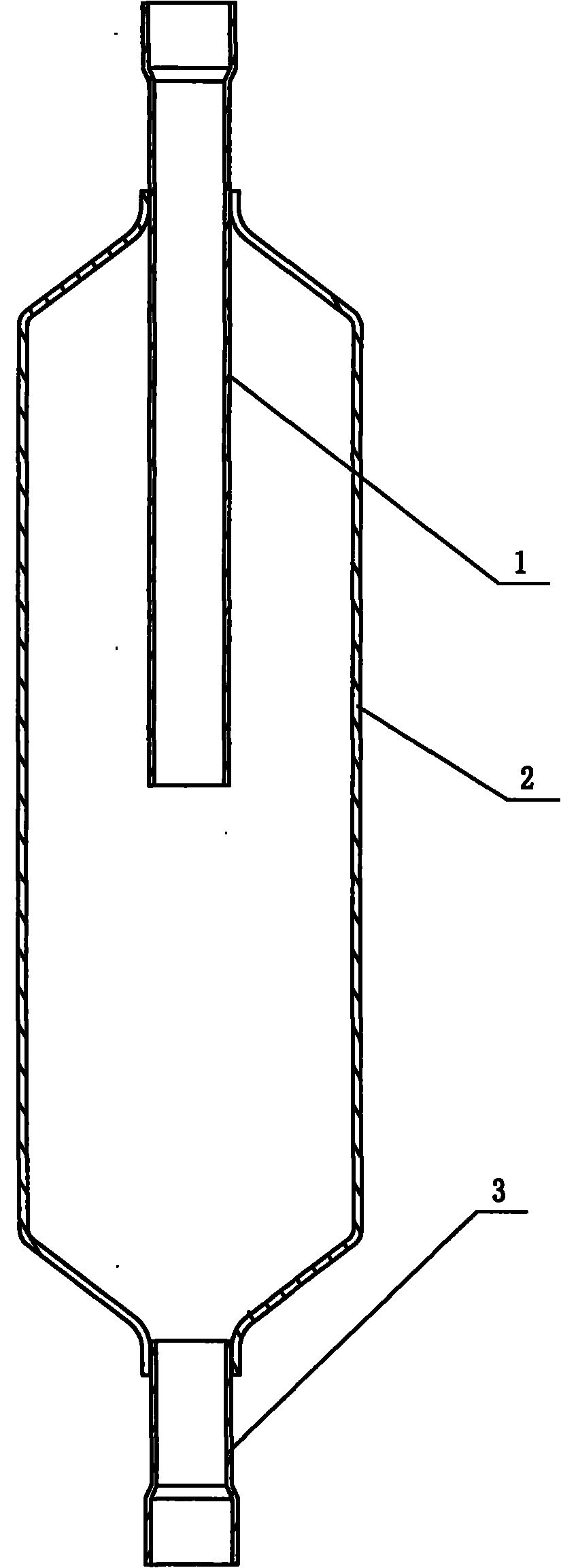

Fan-out high-density packaging method

ActiveCN102157393ALess distracting factorsComply with the trend of light, thin and shortSolid-state devicesSemiconductor/solid-state device manufacturingInterference factorEngineering

The invention relates to a fan-out high-density packaging method, which comprises the following steps of: providing a carrier plate; forming a stripping membrane on the carrier plate; forming protective layers on the stripping membrane; forming a rewiring metal layer in the protective layers; forming wiring packaging layers which are conductive with the rewiring metal layer on the protective layers; forming inversion packaging layers on the wiring packaging layers, wherein the packaging layers are connected electrically and mutually by wiring layers and welding flux salient points; removing the carrier plate and the stripping membrane, so that rewiring metal in a first protective layer is exposed; and forming a metal welded ball on the exposed rewiring metal. Compared with the prior art, the fan-out high-density packaging method has the advantages that: a final packaging product with an integral systemic function instead of a single chip function can be formed, and the resistance and inductance in a system and interference factors among chips are reduced. In addition, a complex multi-layer interconnection structure can be formed, so that the wafer system-level packaging of a higher integration level is realized.

Owner:NANTONG FUJITSU MICROELECTRONICS