Patents

Literature

709 results about "Direct bonding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Direct bonding, or fusion bonding, describes a wafer bonding process without any additional intermediate layers. The bonding process is based on chemical bonds between two surfaces of any material possible meeting numerous requirements. These requirements are specified for the wafer surface as sufficiently clean, flat and smooth. Otherwise unbonded areas so called voids, i.e. interface bubbles, can occur.

Method for Producing Direct Bonded Wafer and Direct Bonded Wafer

ActiveUS20080102603A1Reduce porosityReduce the generation of voidsSemiconductor/solid-state device manufacturingHydrogenWafering

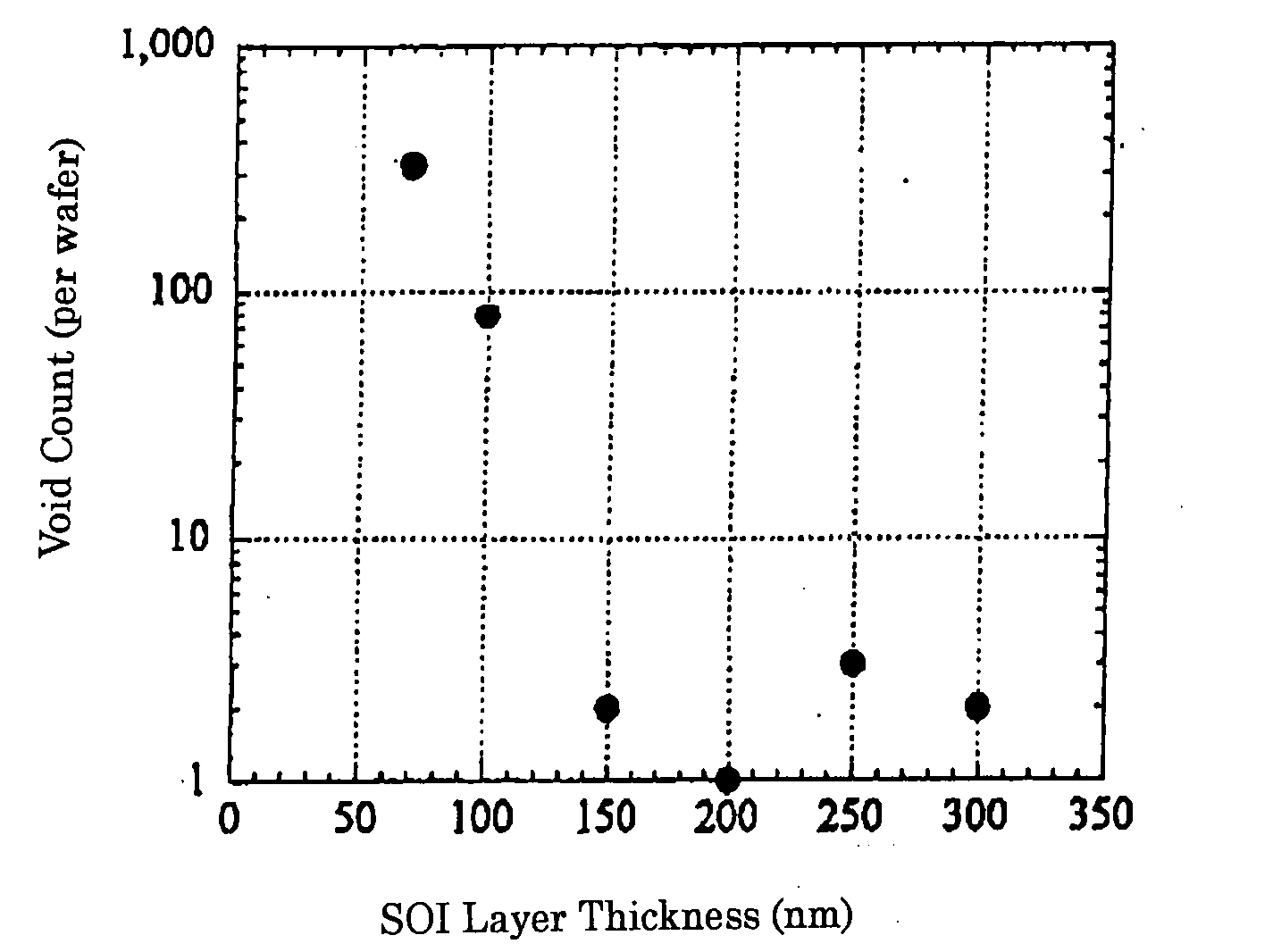

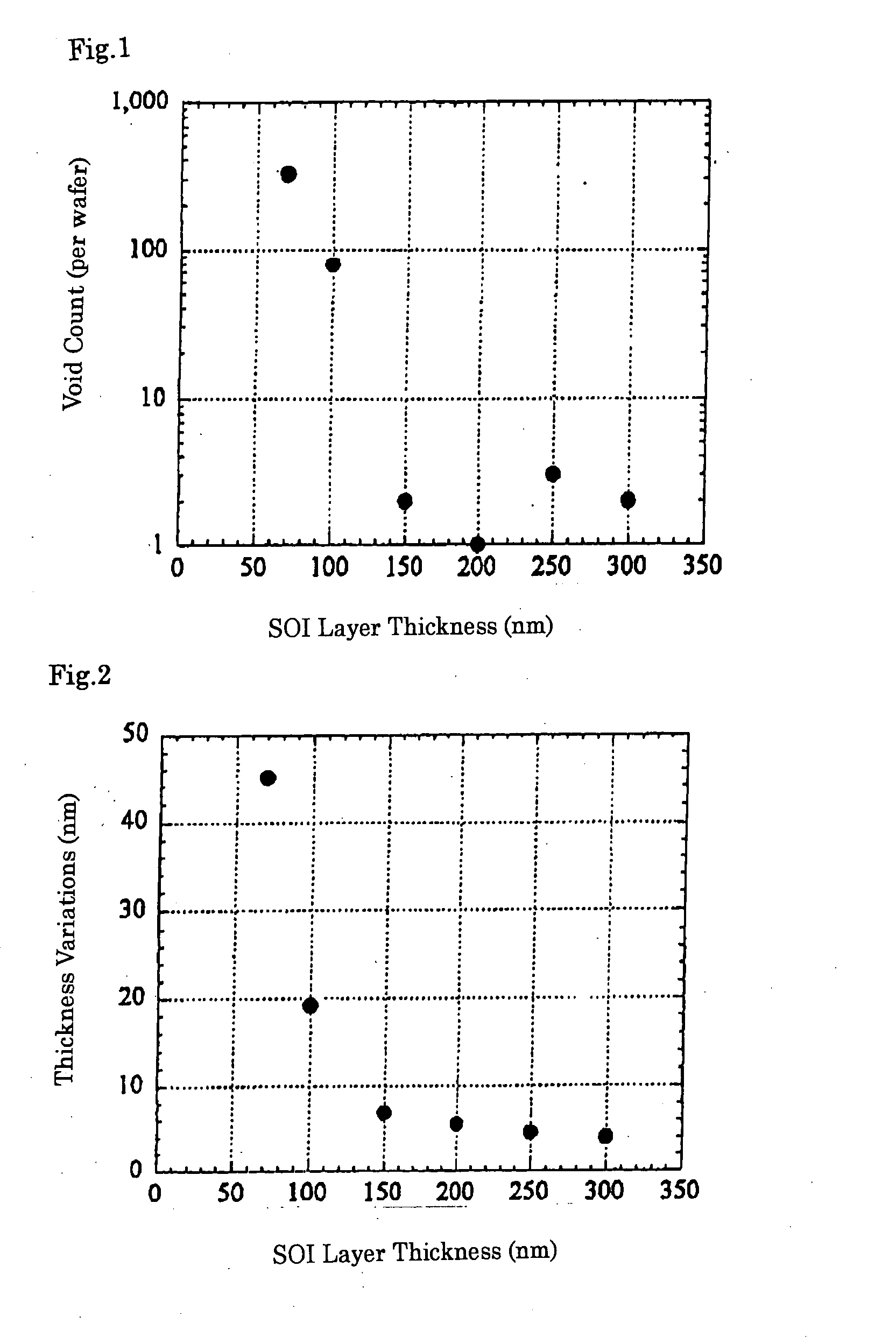

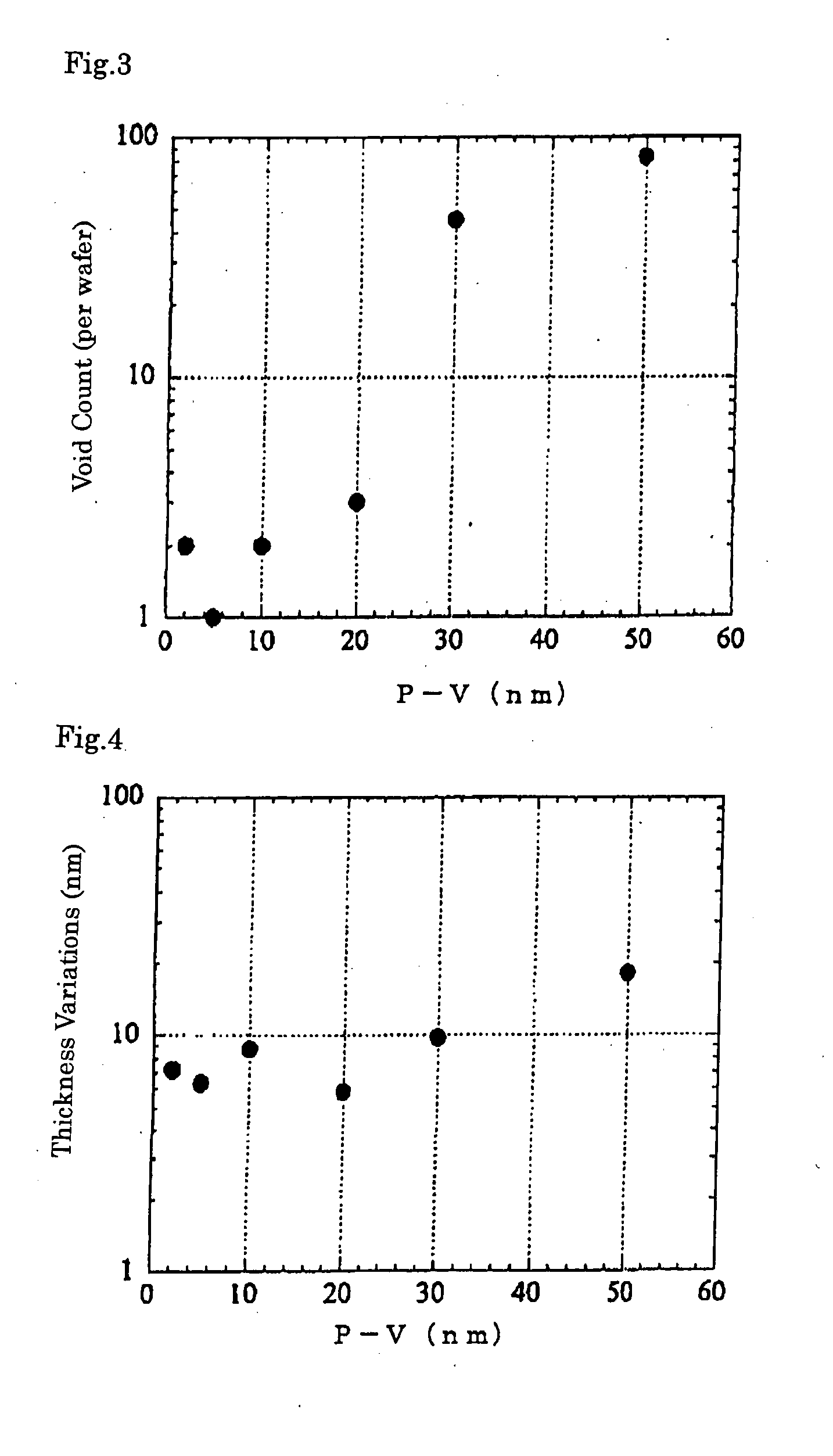

A method for producing a direct bonded wafer comprising: forming a thermal oxide film or a CVD oxide film on a surface of at least one of a bond wafer and a base wafer, and bonding the wafer to the other wafer via the oxide film; subsequently thinning the bond wafer to prepare a bonded wafer; and thereafter conducting a process of annealing the bonded wafer under an atmosphere including any one of an inert gas, hydrogen and a mixed gas of an inert gas and hydrogen so that the oxide film between the bond wafer and the base wafer is removed to bond the bond wafer directly to the base wafer. Thereby, there is provided a method for producing a direct bonded wafer in which generation of voids is reduced, and a direct bonded wafer with a low void count.

Owner:SHIN-ETSU HANDOTAI CO LTD

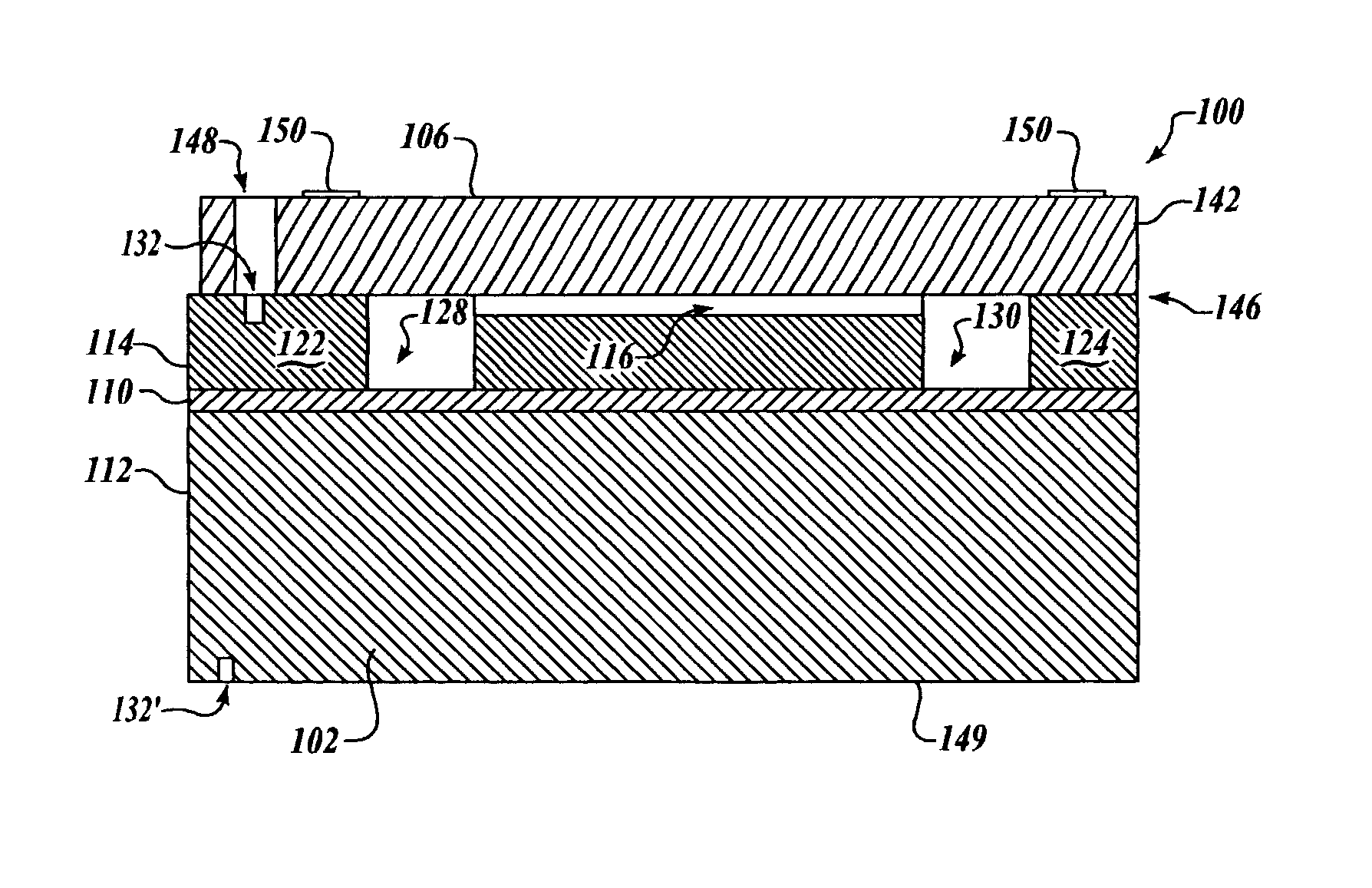

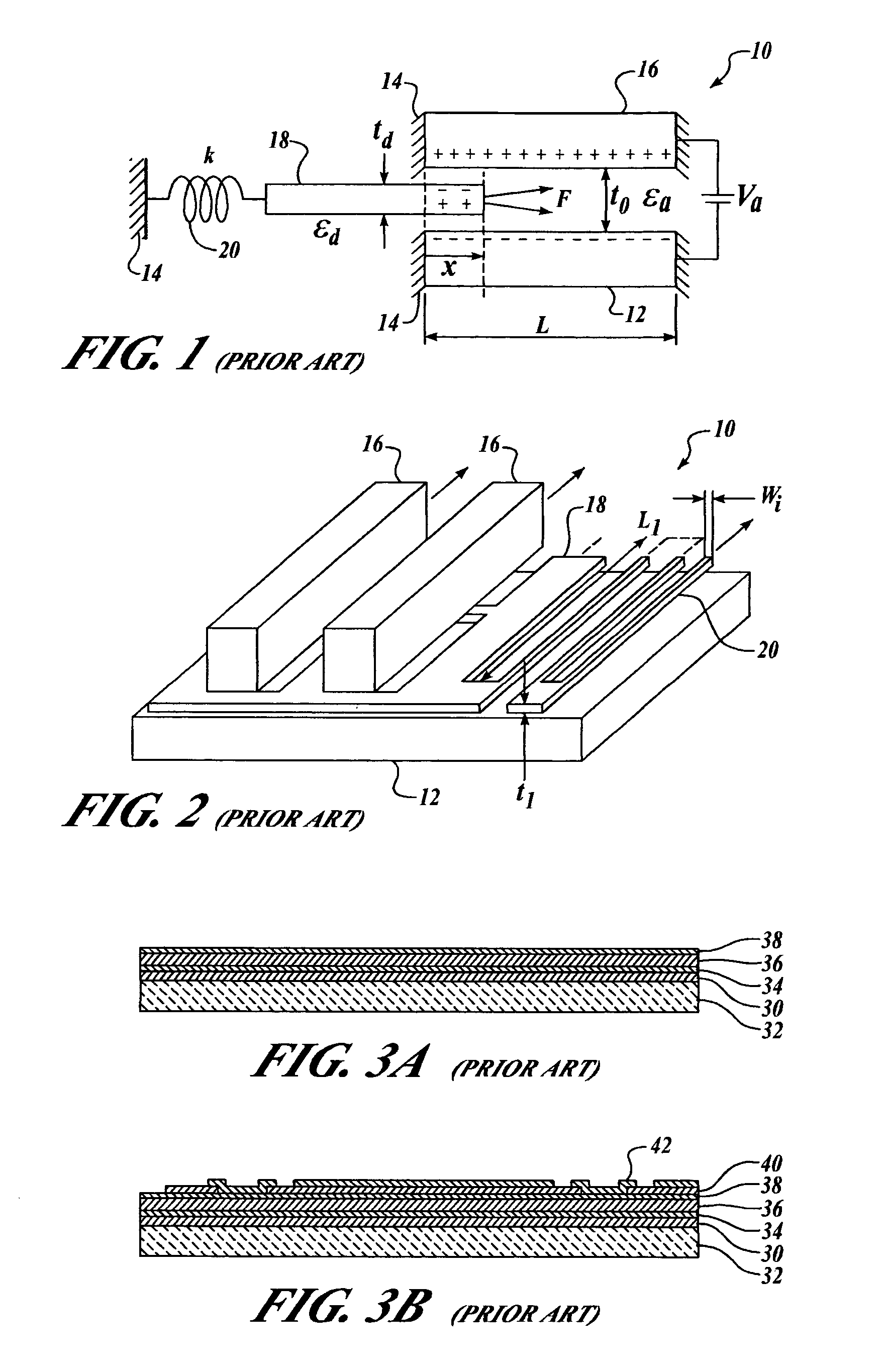

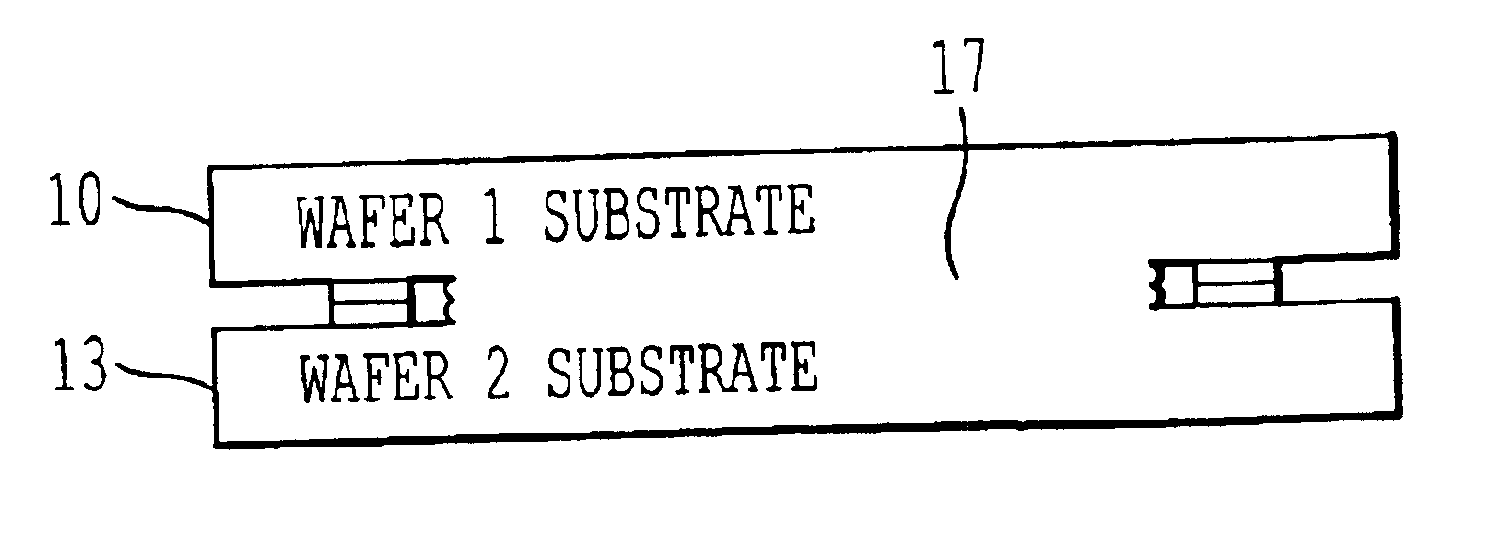

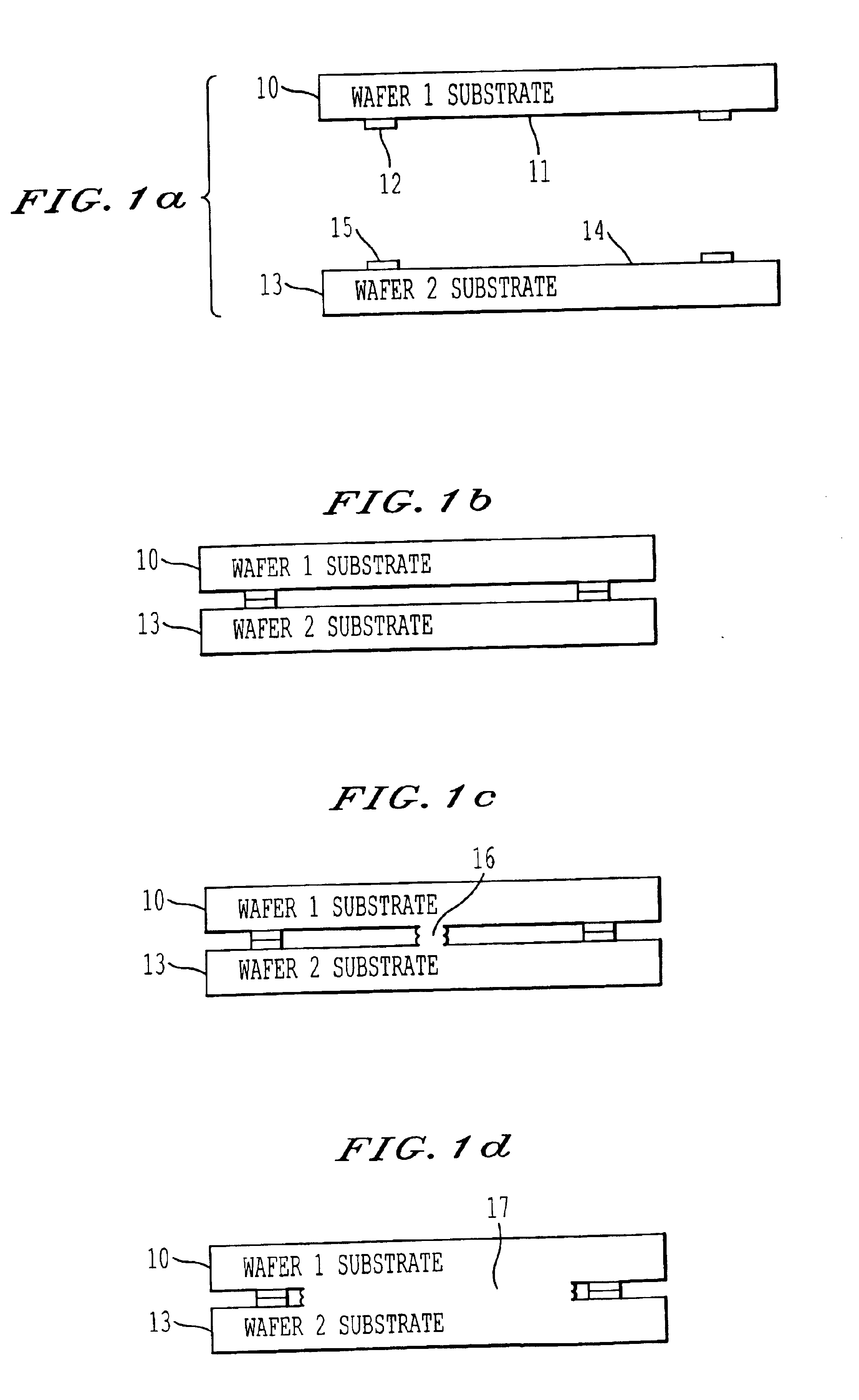

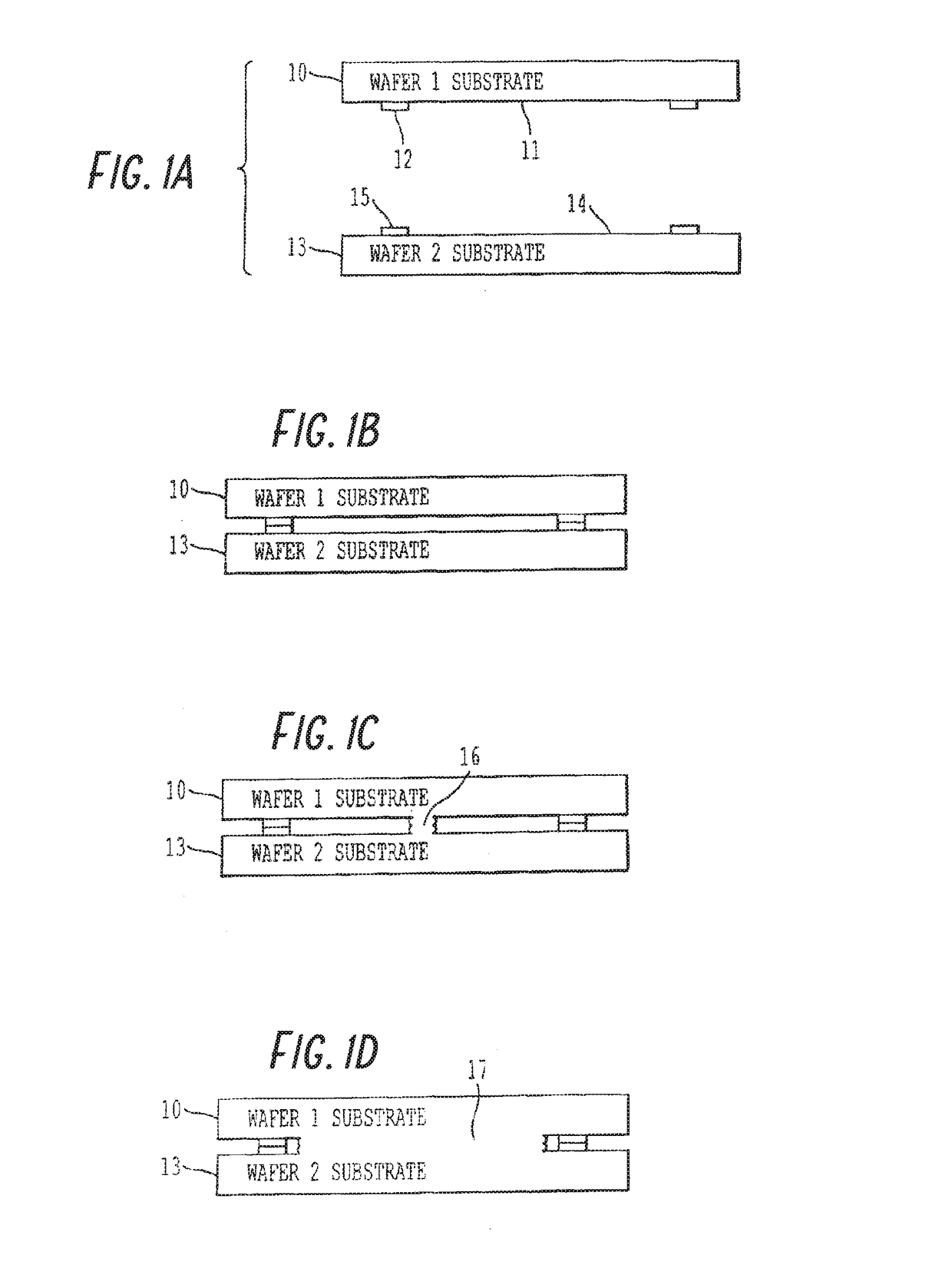

Method of manufacturing vibrating micromechanical structures

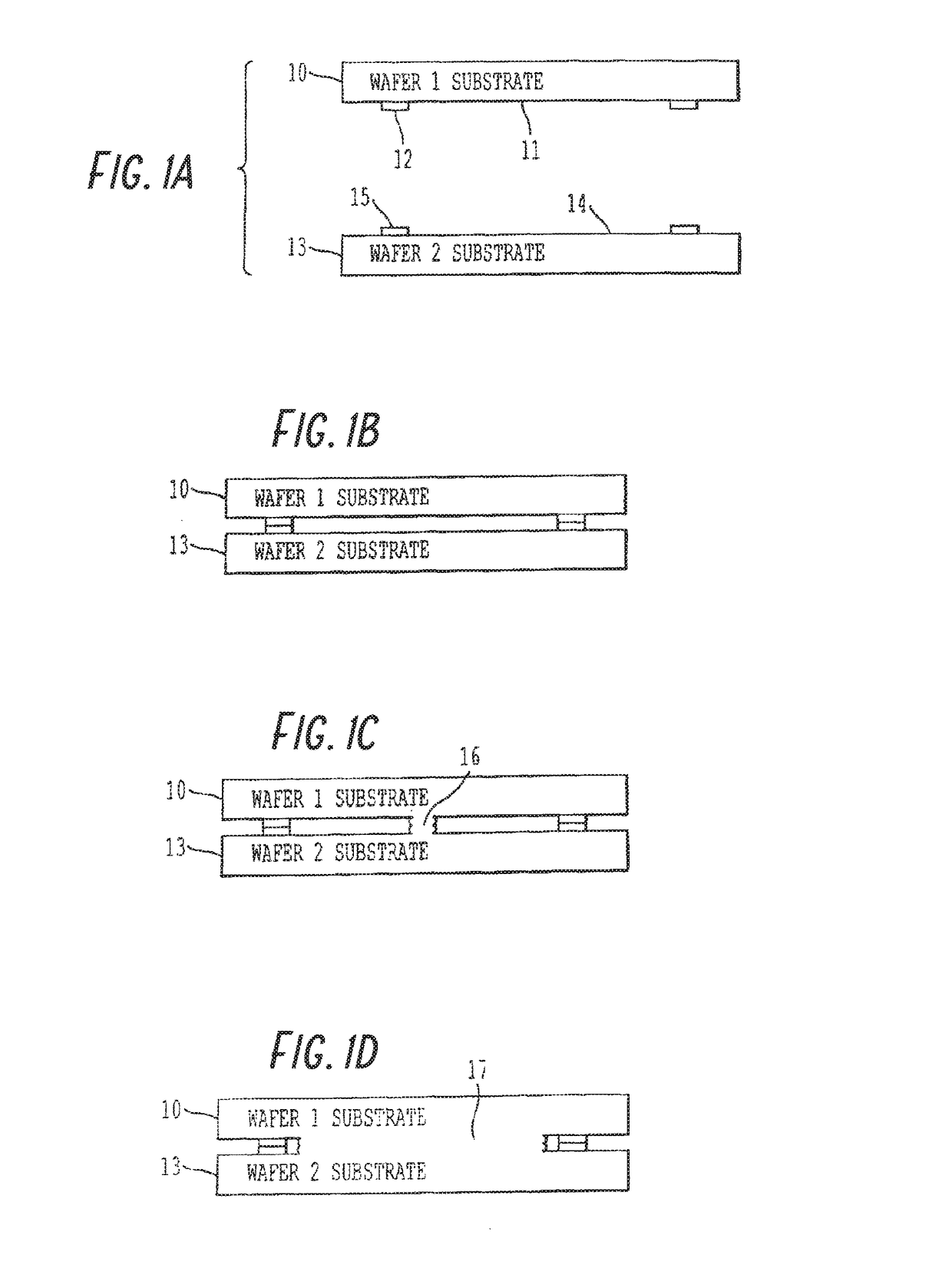

A method for fabrication of single crystal silicon micromechanical resonators using a two-wafer process, including either a Silicon-on-insulator (SOI) or insulating base and resonator wafers, wherein resonator anchors, a capacitive air gap, isolation trenches, and alignment marks are micromachined in an active layer of the base wafer; the active layer of the resonator wafer is bonded directly to the active layer of the base wafer; the handle and dielectric layers of the resonator wafer are removed; viewing windows are opened in the active layer of the resonator wafer; masking the single crystal silicon semiconductor material active layer of the resonator wafer with photoresist material; a single crystal silicon resonator is machined in the active layer of the resonator wafer using silicon dry etch micromachining technology; and the photoresist material is subsequently dry stripped.

Owner:HONEYWELL INT INC

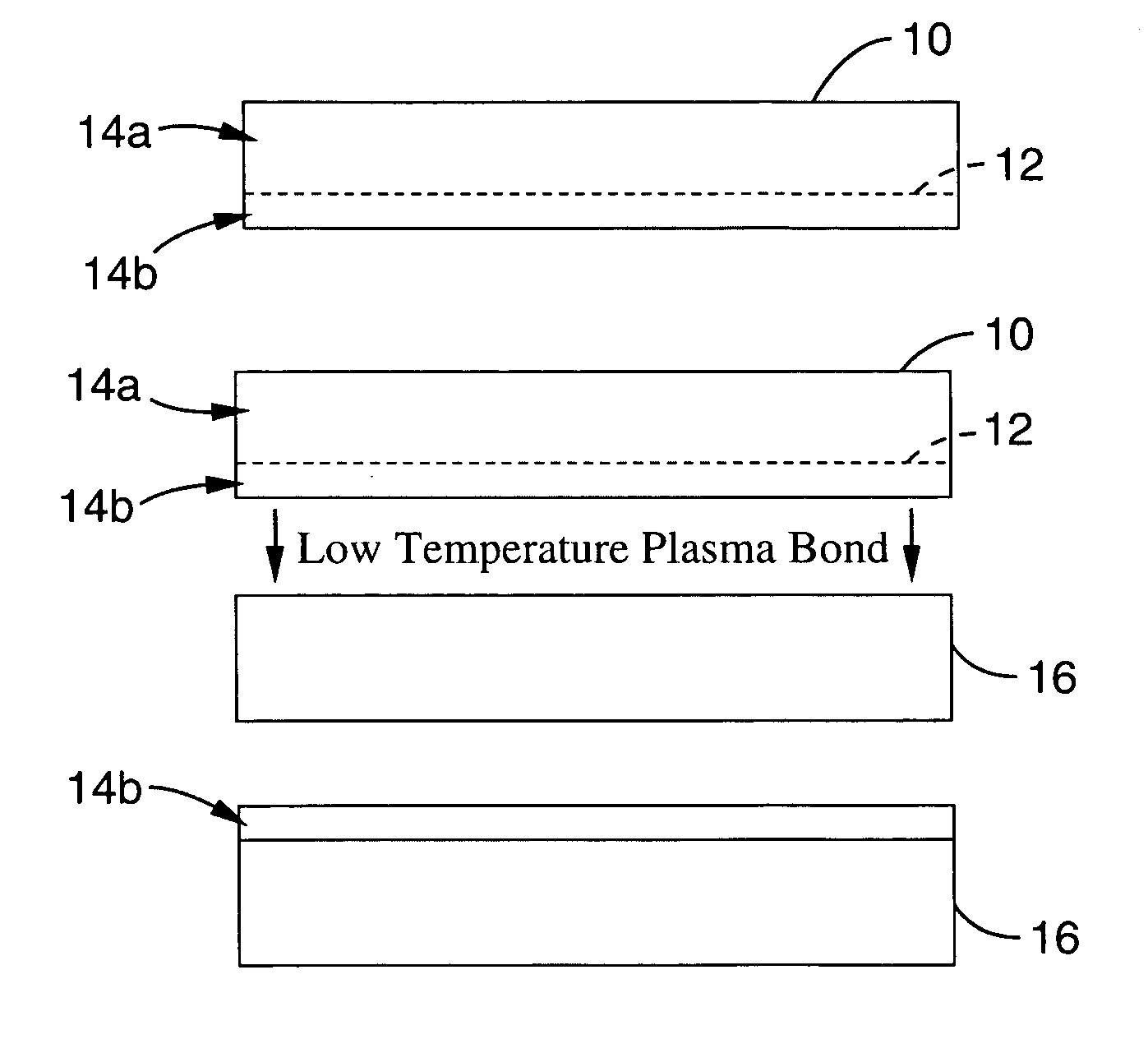

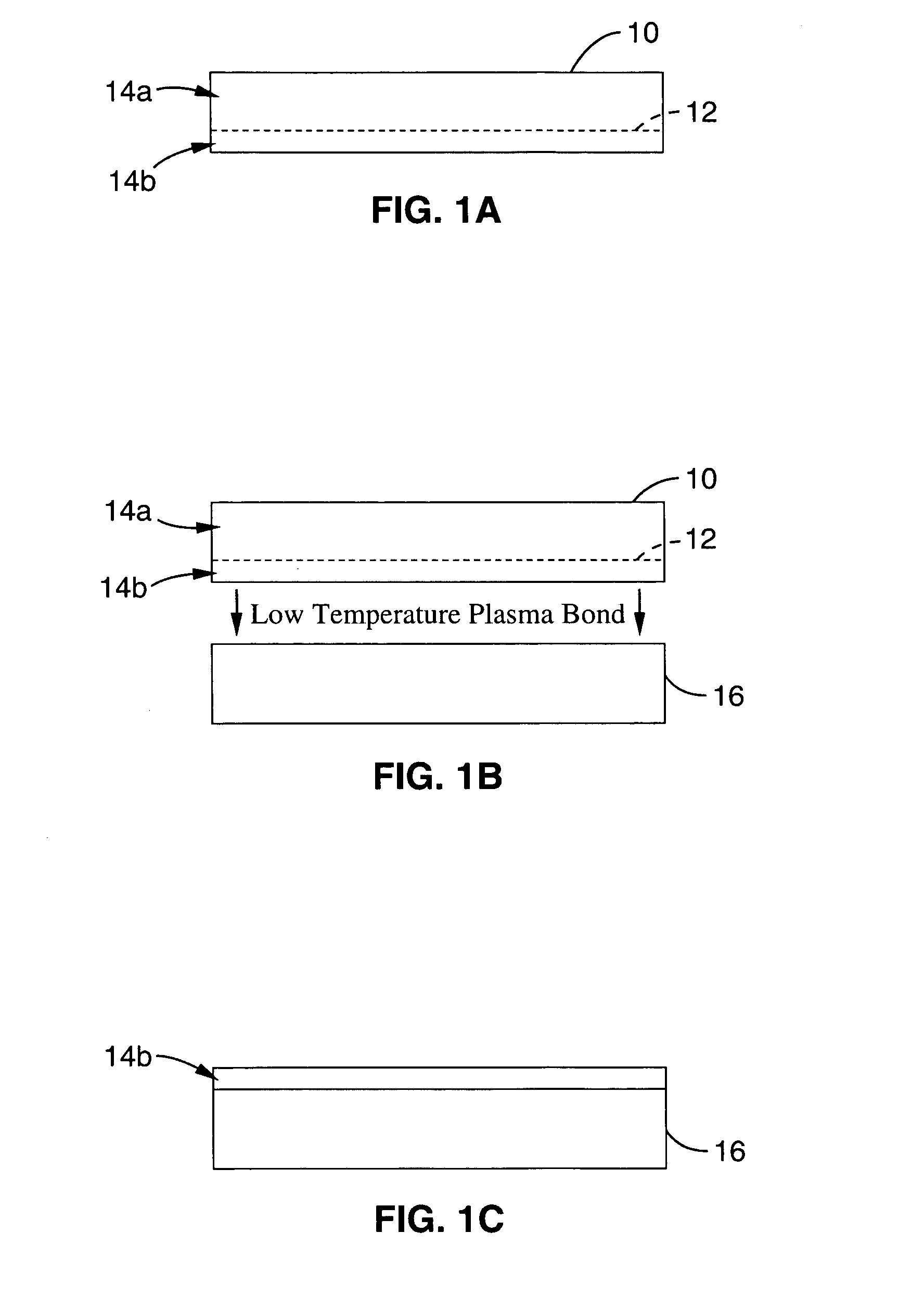

Smooth thin film layers produced by low temperature hydrogen ion cut

A method for producing wafer splitting from ion implantation into silicon after low temperature direct bonding with surface roughness that is ˜1 nm (RMS). This result is an order of magnitude smoother than the previous work (˜10 nm RMS). The key improvement in this work is the use of a low temperature bond resulting in a strong bond before the material is cut. The smooth as-split surfaces produced using a low temperature bond are very important for creation of very thin (<50 nm) silicon-on-insulator (SOI), three-dimensional bonded structures and nanostructures that are split after processing.

Owner:EPIR TECH INC

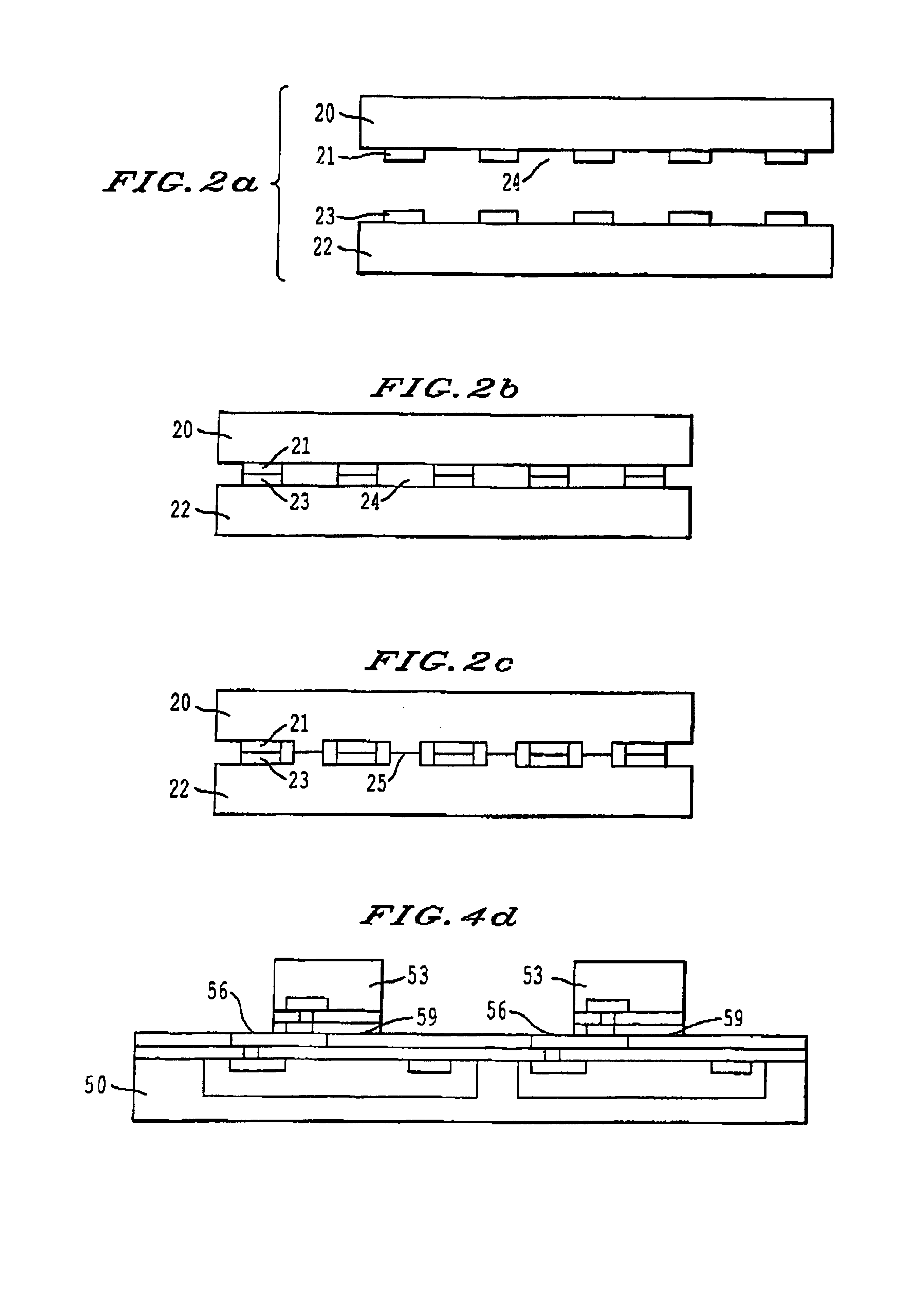

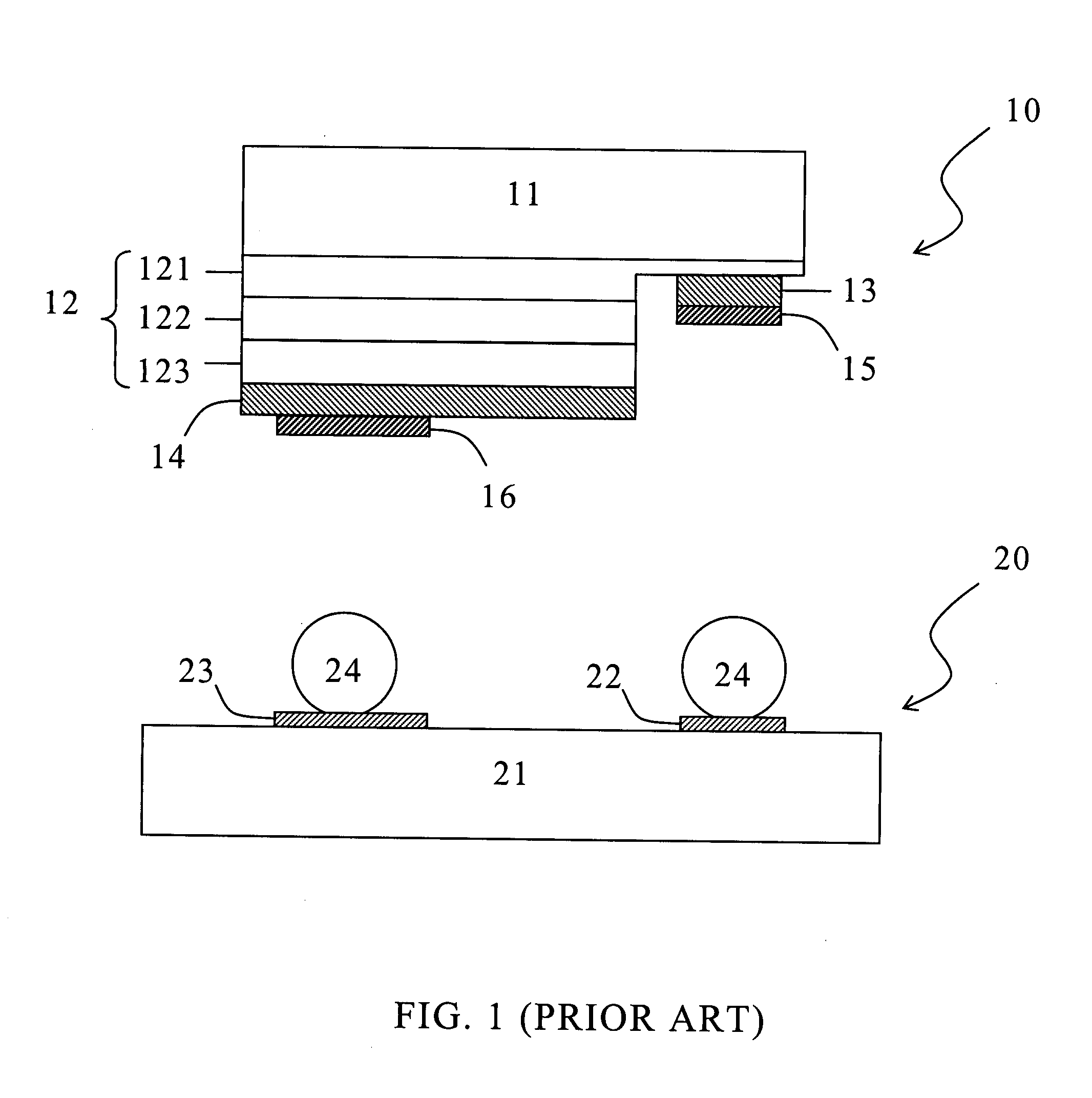

Method for room temperature metal direct bonding

InactiveUS6962835B2Solid-state devicesSemiconductor/solid-state device manufacturingBond interfaceRoom temperature

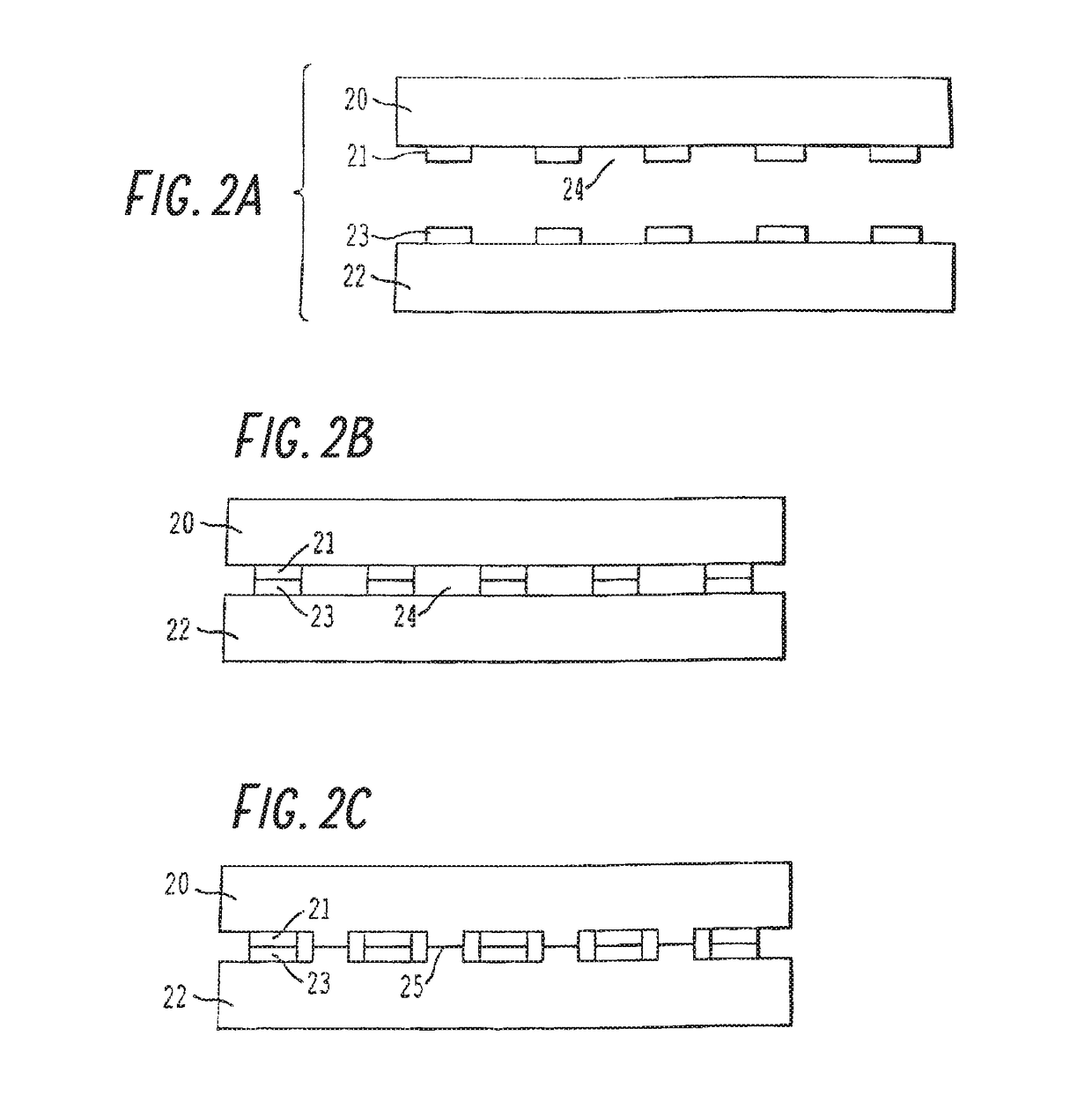

A bonded device structure including a first substrate having a first set of metallic bonding pads, preferably connected to a device or circuit, and having a first non-metallic region adjacent to the metallic bonding pads on the first substrate, a second substrate having a second set of metallic bonding pads aligned with the first set of metallic bonding pads, preferably connected to a device or circuit, and having a second non-metallic region adjacent to the metallic bonding pads on the second substrate, and a contact-bonded interface between the first and second set of metallic bonding pads formed by contact bonding of the first non-metallic region to the second non-metallic region. At least one of the first and second substrates may be elastically deformed.

Owner:INVENSAS BONDING TECH INC

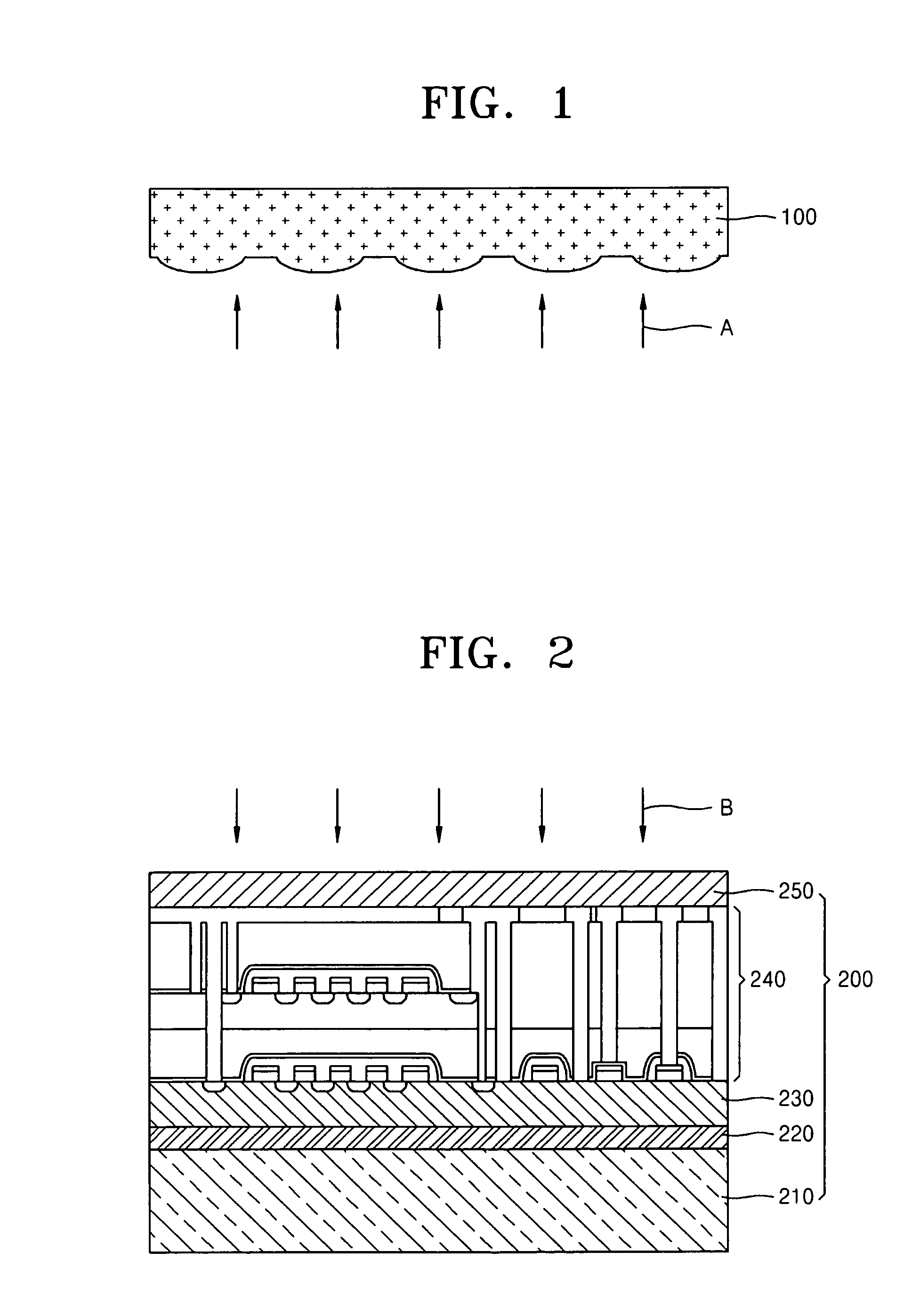

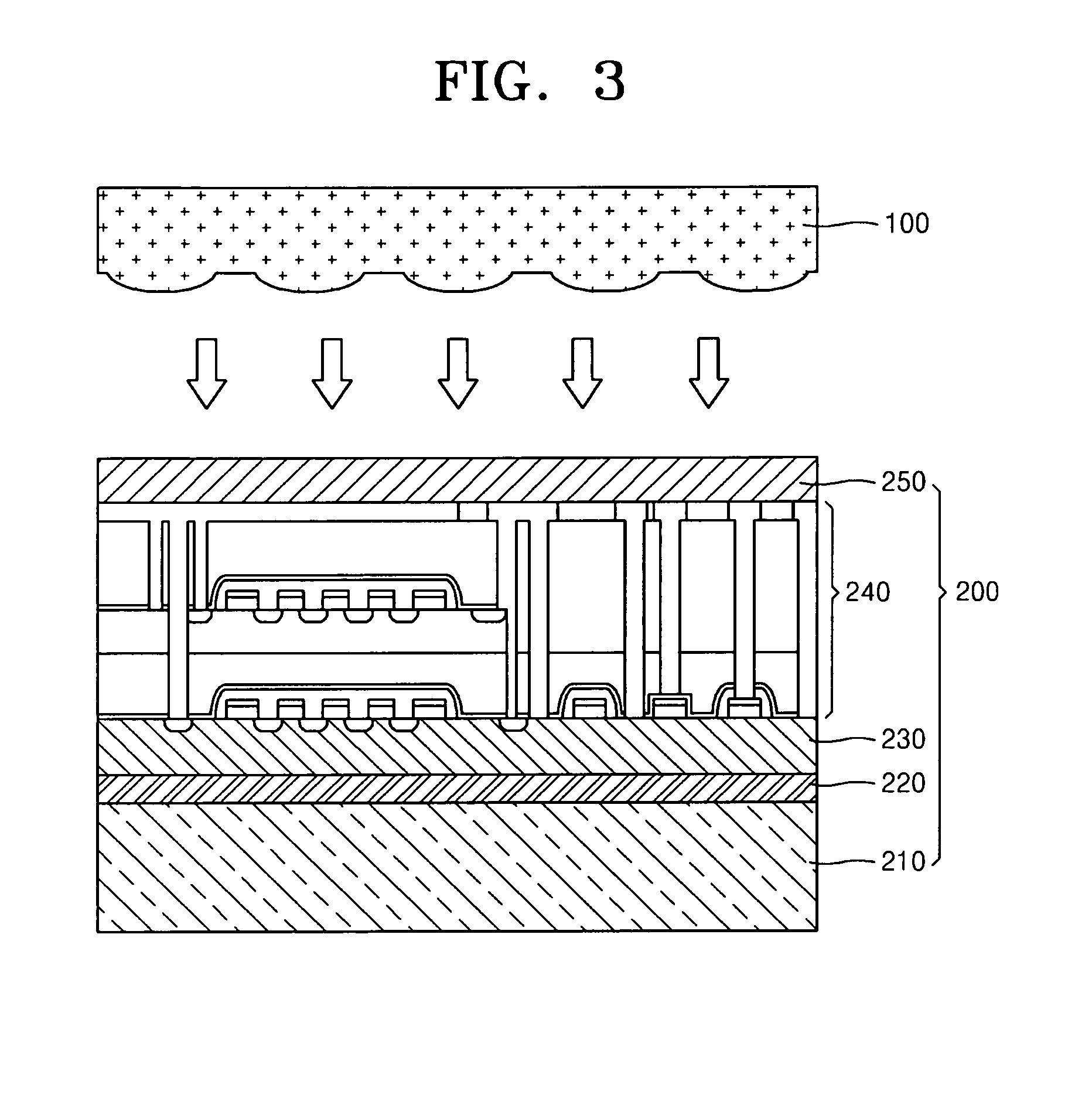

Wafer temporary bonding method using silicon direct bonding

A wafer temporary bonding method using silicon direct bonding (SDB) may include preparing a carrier wafer and a device wafer, adjusting roughness of a surface of the carrier wafer, and combining the carrier wafer and the device wafer using the SDB. Because the method uses SDB, instead of an adhesive layer, for a temporary bonding process, a module or process to generate and remove an adhesive is unnecessary. Also, a defect in a subsequent process, for example, a back-grinding process, due to irregularity of the adhesive may be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

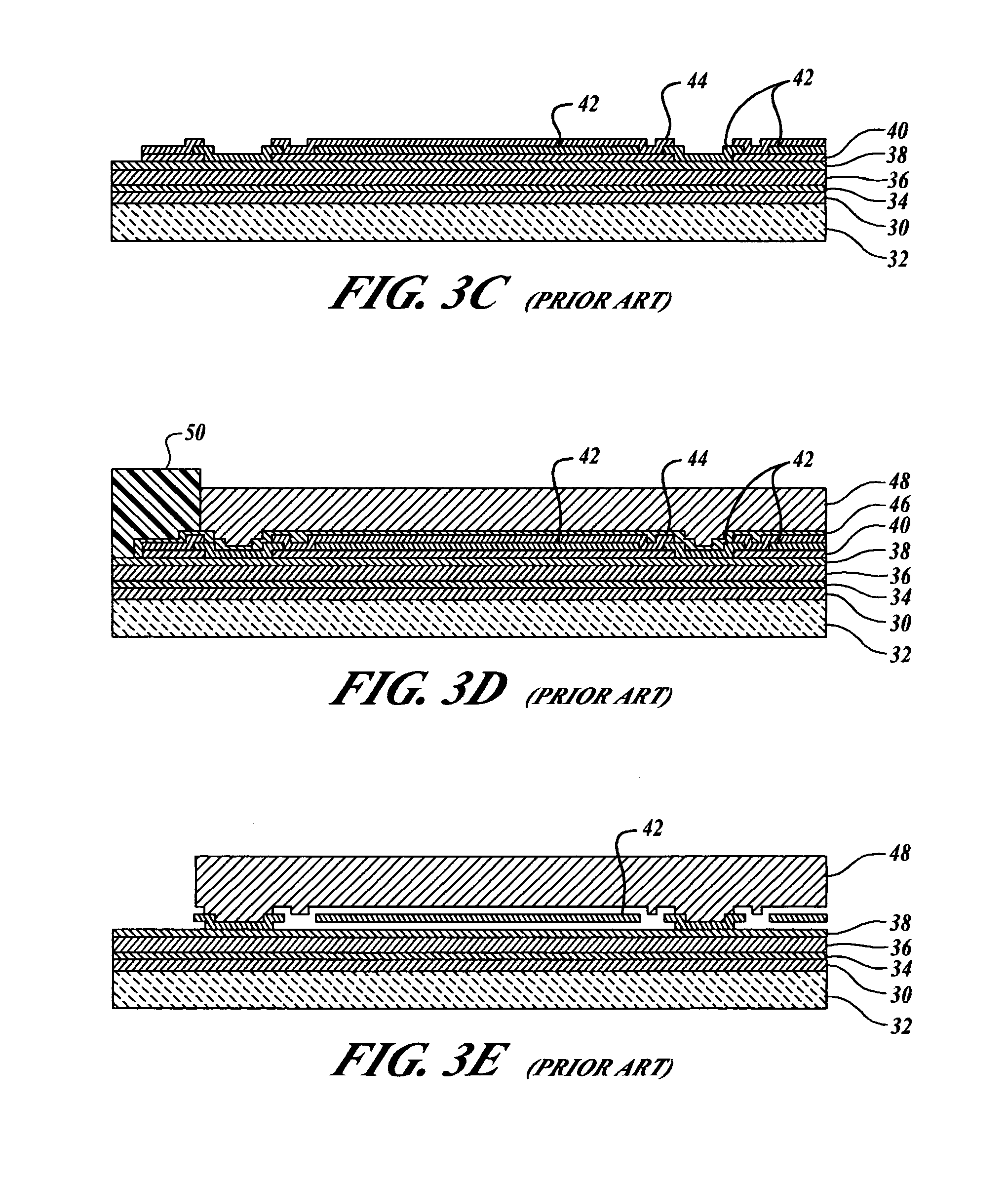

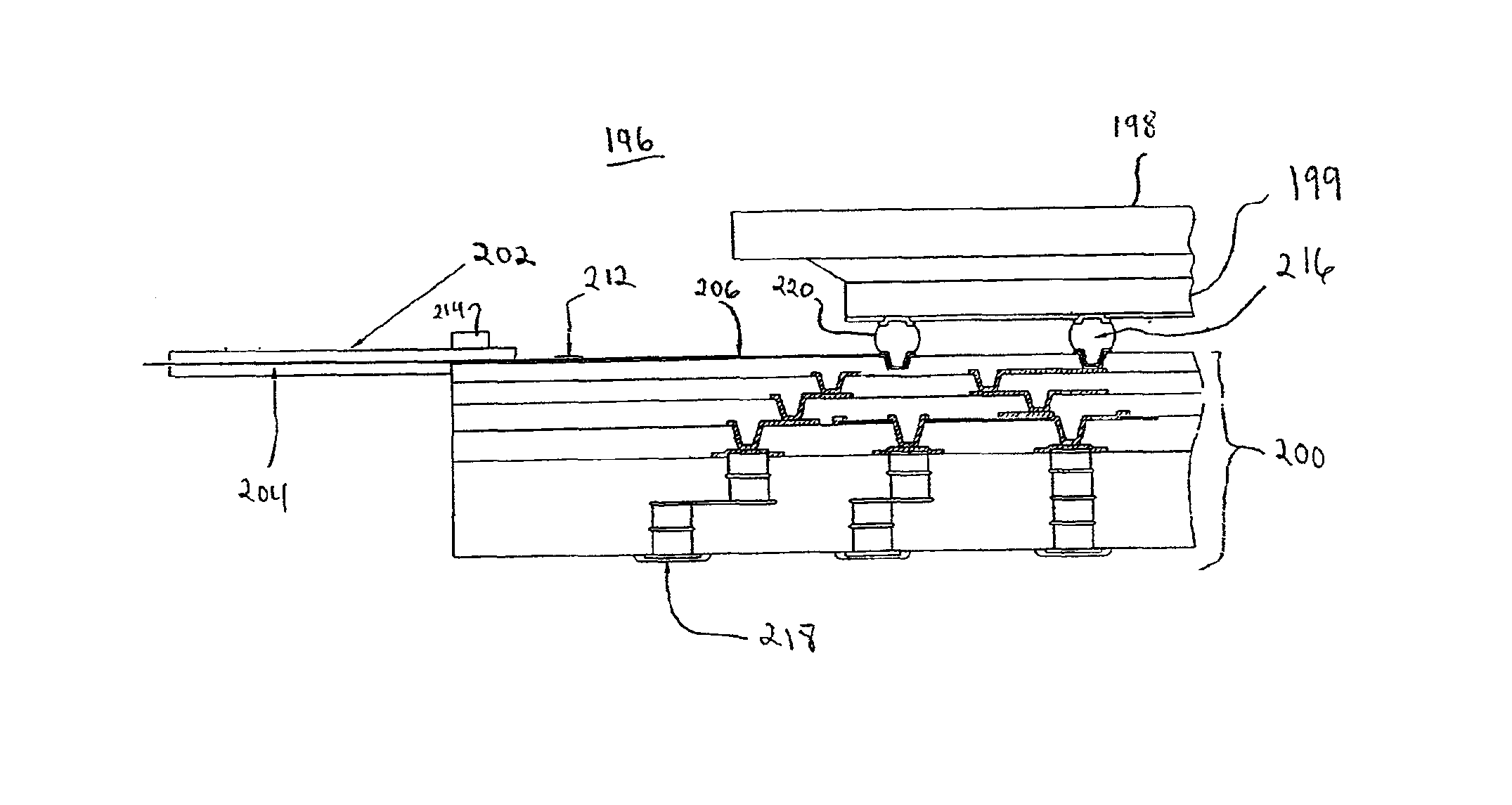

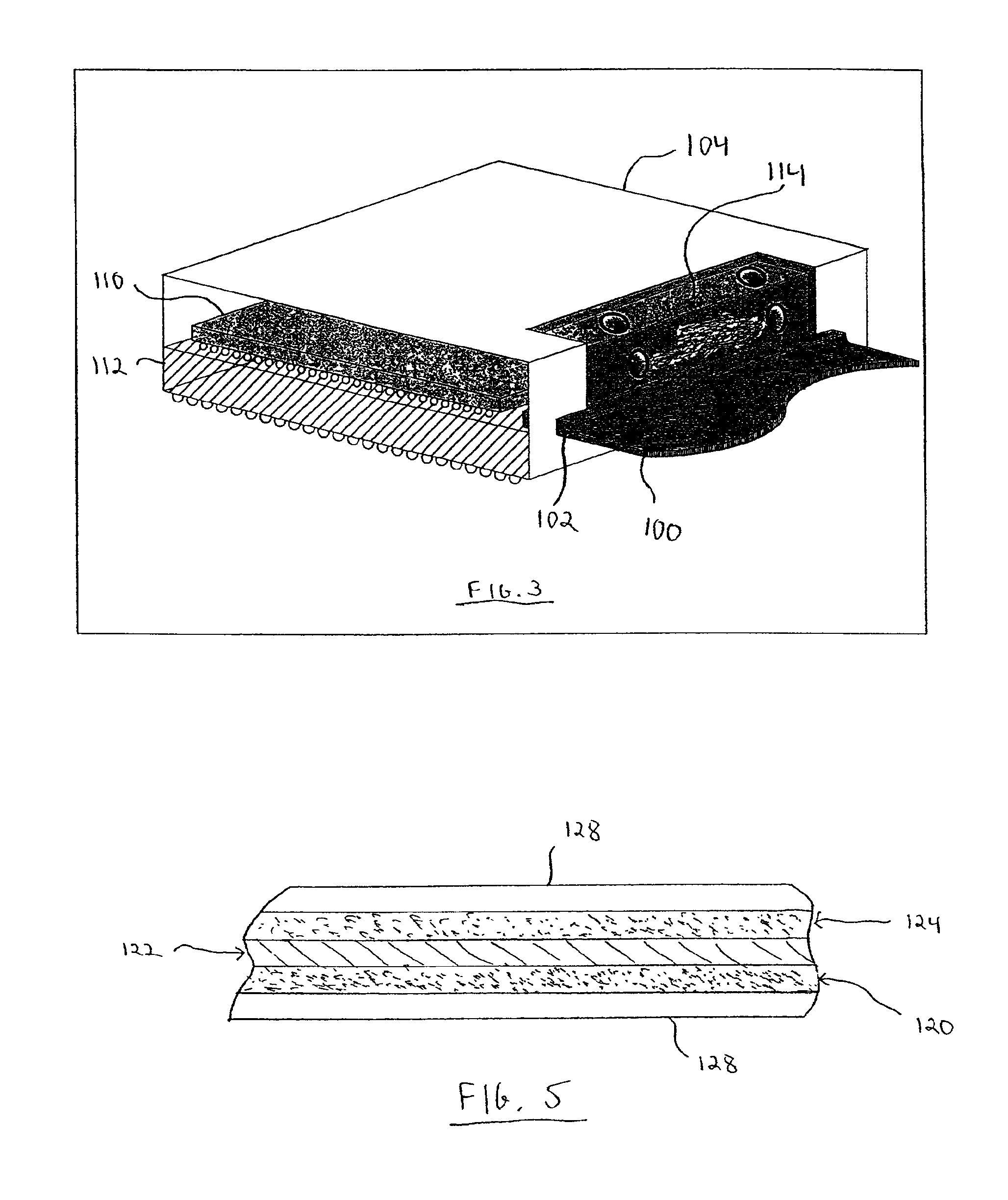

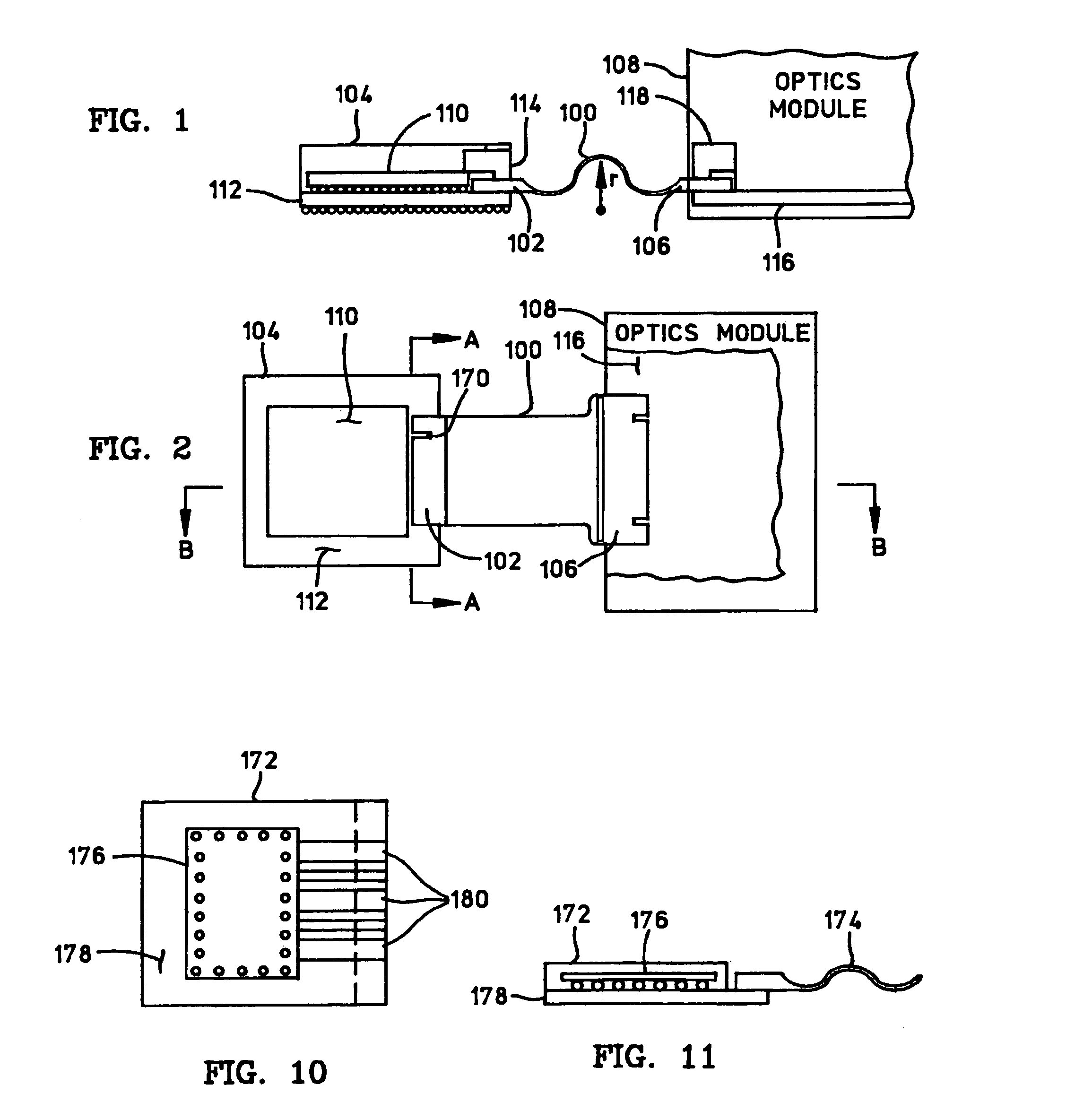

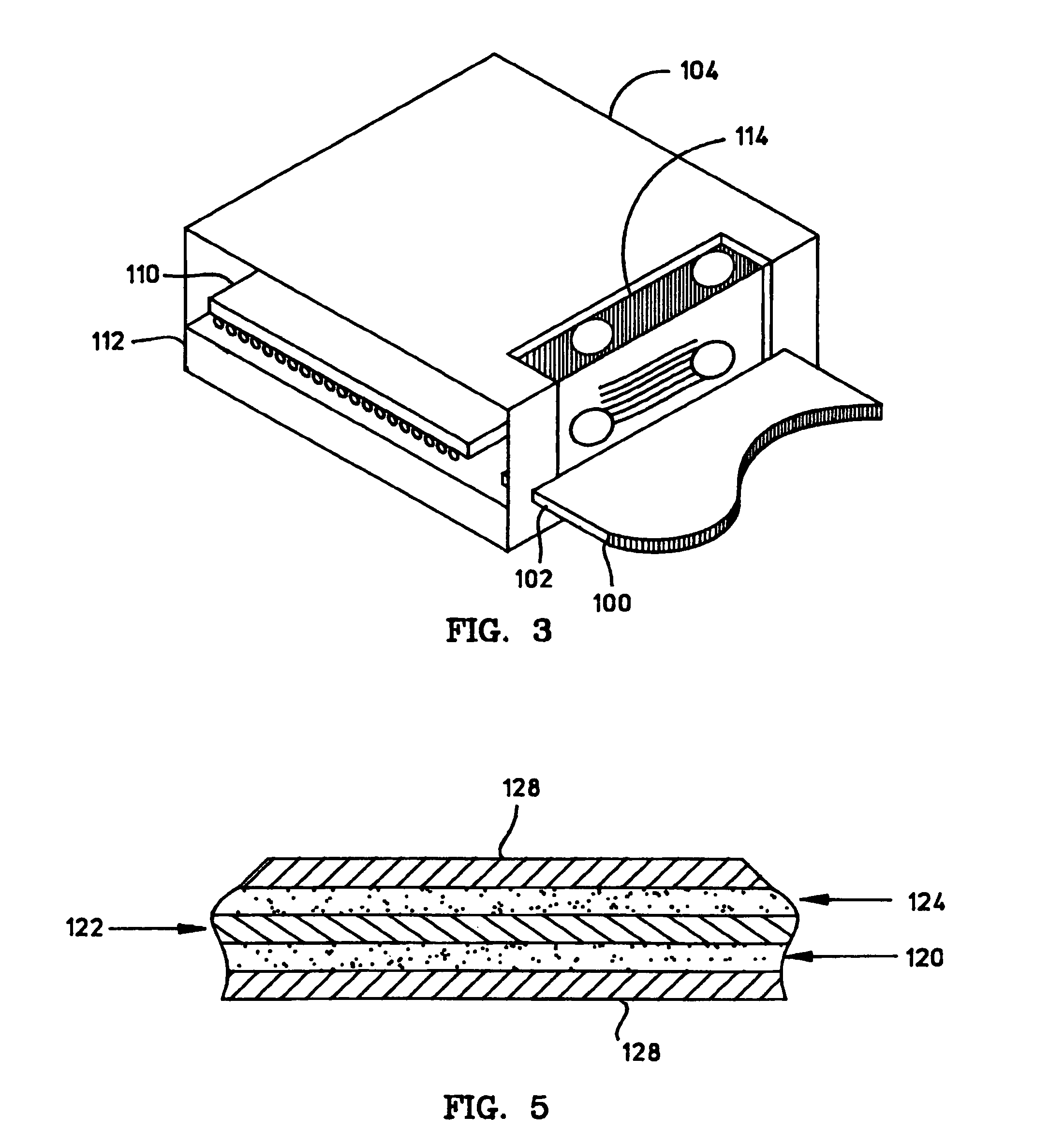

High frequency signal transmission from the surface of a circuit substrate to a flexible interconnect cable

InactiveUS6867668B1Facilitates high speed signal transmissionLow costPrinted circuit assemblingCross-talk/noise/interference reductionElectricityCoplanar waveguide

A high speed flexible interconnect cable includes a number of conductive layers and a number of dielectric layers. Conductive signal traces, located on the conductive layers, combine with the dielectric layers to form one or more high speed electrical transmission line structures. The transmission line structure may be realized as a grounded coplanar waveguide structure, a microstrip structure, a stripline structure, or the like. The cable can be coupled to destination components using a variety of connection techniques, e.g., direct bonding to a circuit substrate, direct soldering to a flip chip, mechanical attachment to a component, or integration with a circuit substrate. The cable can also be terminated with any number of known or standardized connector packages, e.g., SMA, GPPO, or V connectors.

Owner:QUALCOMM INC

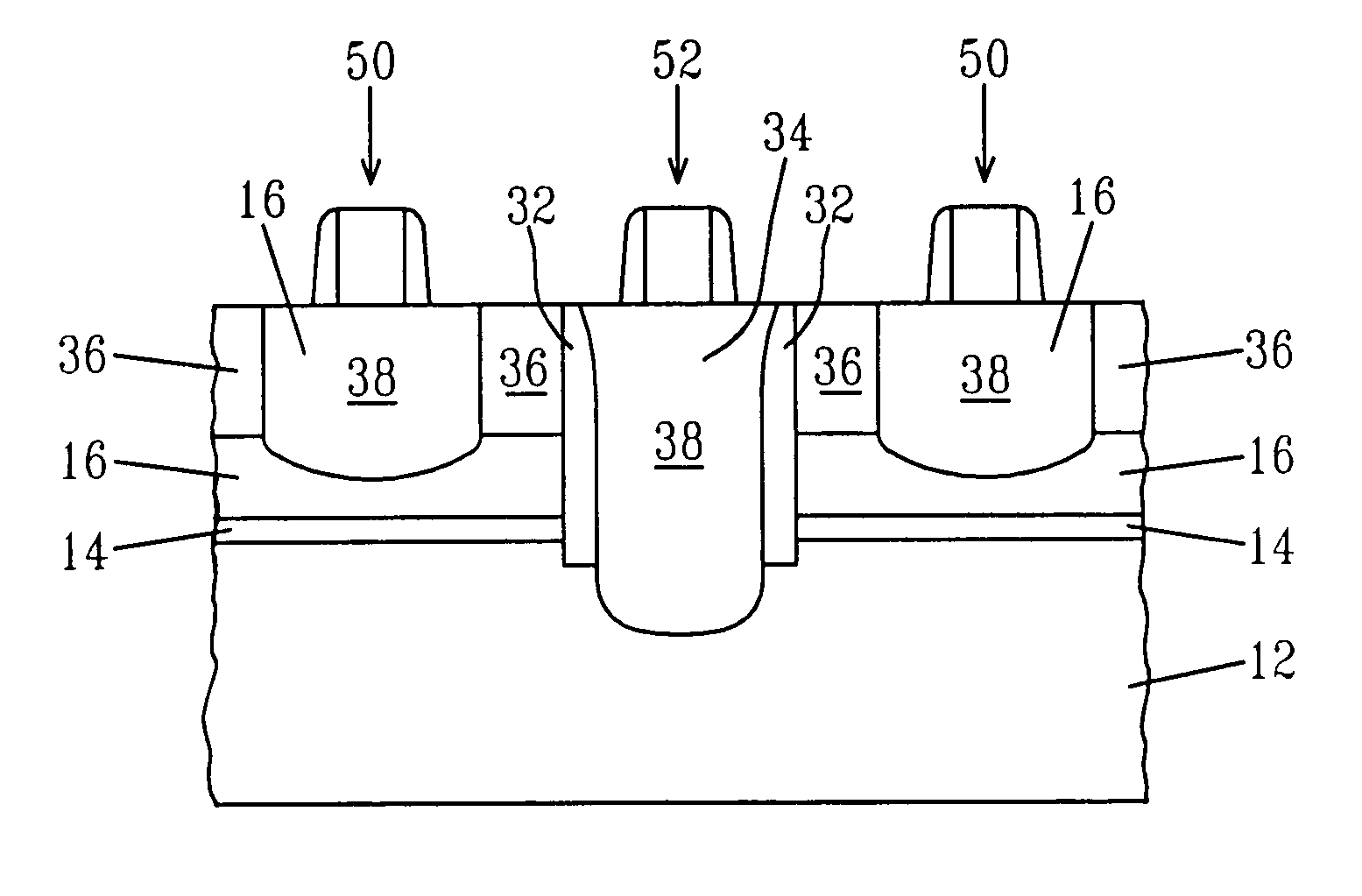

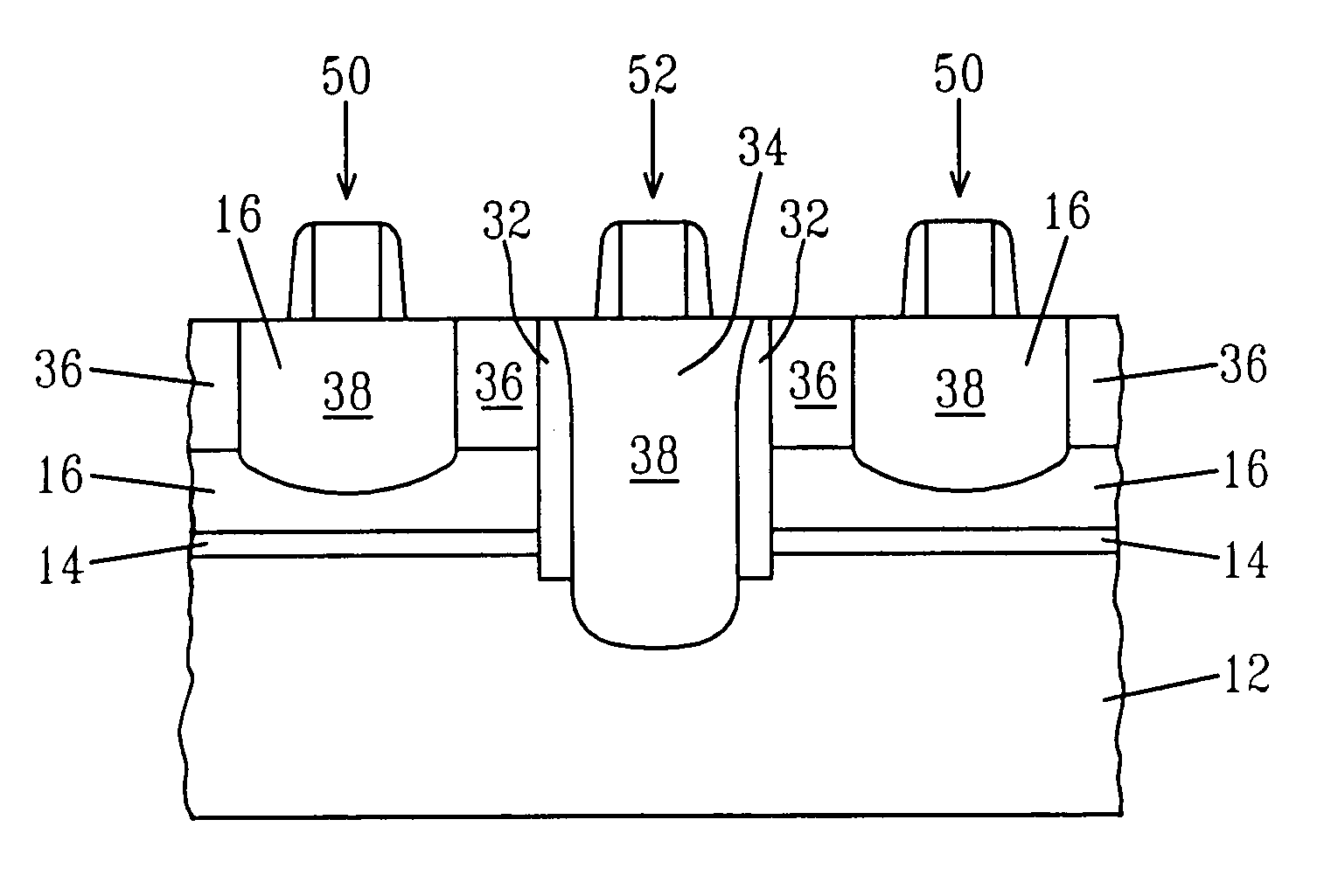

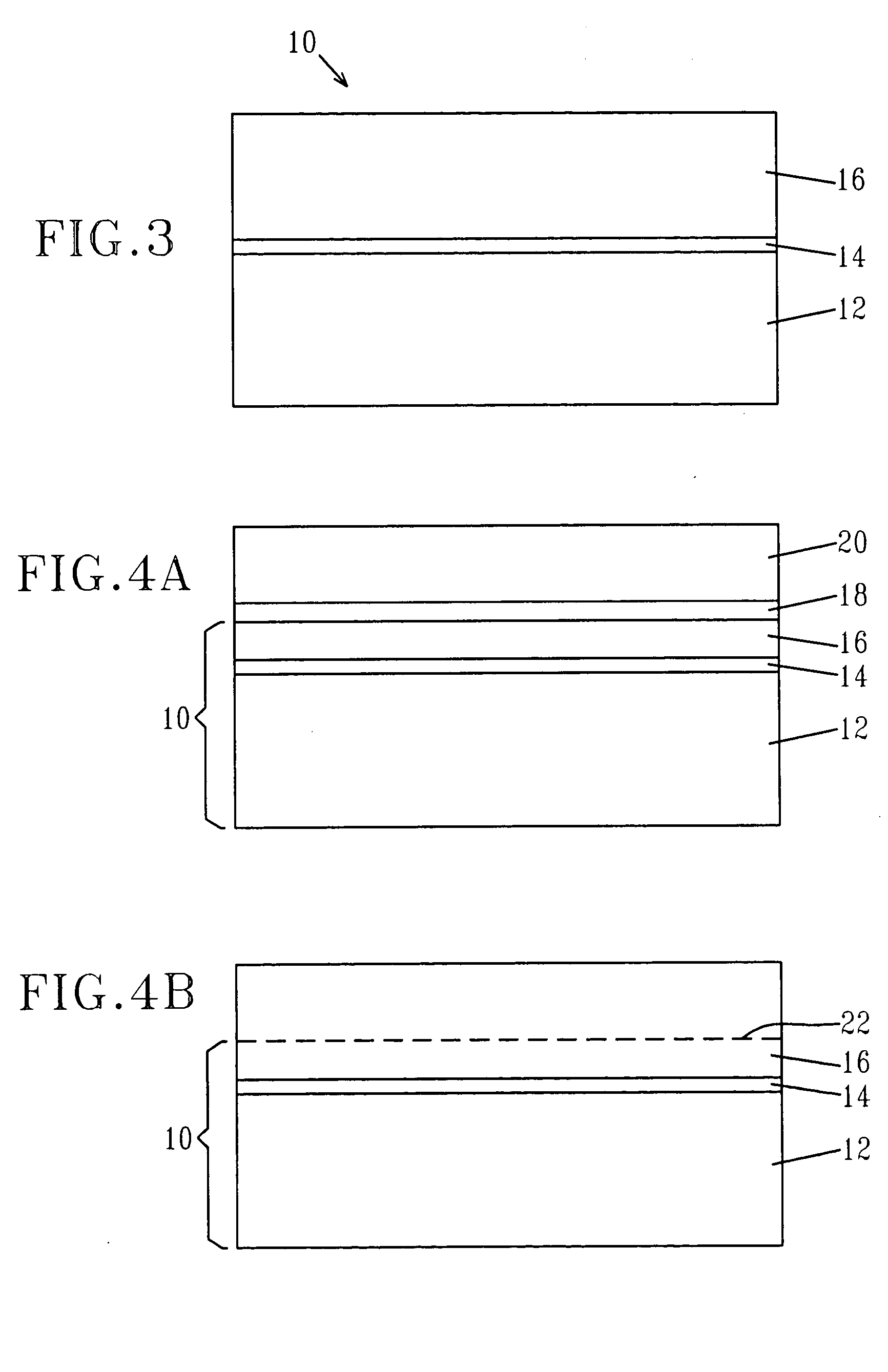

CMOS on hybrid substrate with different crystal orientations using silicon-to-silicon direct wafer bonding

InactiveUS7023055B2Improve performanceImprove device performanceTransistorSolid-state devicesCMOSSemiconductor structure

A method in which semiconductor-to-semiconductor direct wafer bonding is employed to provide a hybrid substrate having semiconductor layers of different crystallographic orientations that are separated by a conductive interface is provided. Also provided are the hybrid substrate produced by the method as well as using the direct bonding method to provide an integrated semiconductor structure in which various CMOS devices are built upon a surface orientation that enhances device performance.

Owner:GLOBALFOUNDRIES INC

CMOS on hybrid substrate with different crystal orientations using silicon-to-silicon direct wafer bonding

InactiveUS20050093104A1Improve performanceImprove device performanceTransistorSolid-state devicesCMOSSemiconductor structure

A method in which semiconductor-to-semiconductor direct wafer bonding is employed to provide a hybrid substrate having semiconductor layers of different crystallographic orientations that are separated by a conductive interface is provided. Also provided are the hybrid substrate produced by the method as well as using the direct bonding method to provide an integrated semiconductor structure in which various CMOS devices are built upon a surface orientation that enhances device performance.

Owner:GLOBALFOUNDRIES INC

Flexible differential interconnect cable with isolated high frequency electrical transmission line

InactiveUS7145411B1Easy to optimizeLow costCross-talk/noise/interference reductionPrinted circuit aspectsElectricityCoplanar waveguide

A high speed flexible interconnect cable includes a number of conductive layers and a number of dielectric layers. Conductive signal traces, located on the conductive layers, combine with the dielectric layers to form one or more high speed electrical transmission line structures. The transmission line structure may be realized as a grounded coplanar waveguide structure, a microstrip structure, a stripline structure, or the like. The cable can be coupled to destination components using a variety of connection techniques, e.g., direct bonding to a circuit substrate, direct soldering to a flip chip, mechanical attachment to a component, or integration with a circuit substrate. The cable can also be terminated with any number of known or standardized connector packages, e.g., SMA, GPPO, or V connectors.

Owner:QUALCOMM INC

Method of forming stacked dies

ActiveUS8158456B2High aspect ratioReduce riskSolid-state devicesSemiconductor/solid-state device manufacturingWafer backgrindingSilicon

The formation of through silicon vias (TSVs) in an integrated circuit (IC) die or wafer is described in which the TSV is formed in the integration process prior to metallization processing. TSVs may be fabricated with increased aspect ratio, extending deeper in a wafer substrate. The method generally reduces the risk of overly-thinning a wafer substrate in a wafer back-side grinding process typically used to expose and make electrical contacts to the TSVs. By providing deeper TSVs and bonding pads, individual wafers and dies may be bonded directly between the TSVs and bonding pads on an additional wafer.

Owner:TAIWAN SEMICON MFG CO LTD

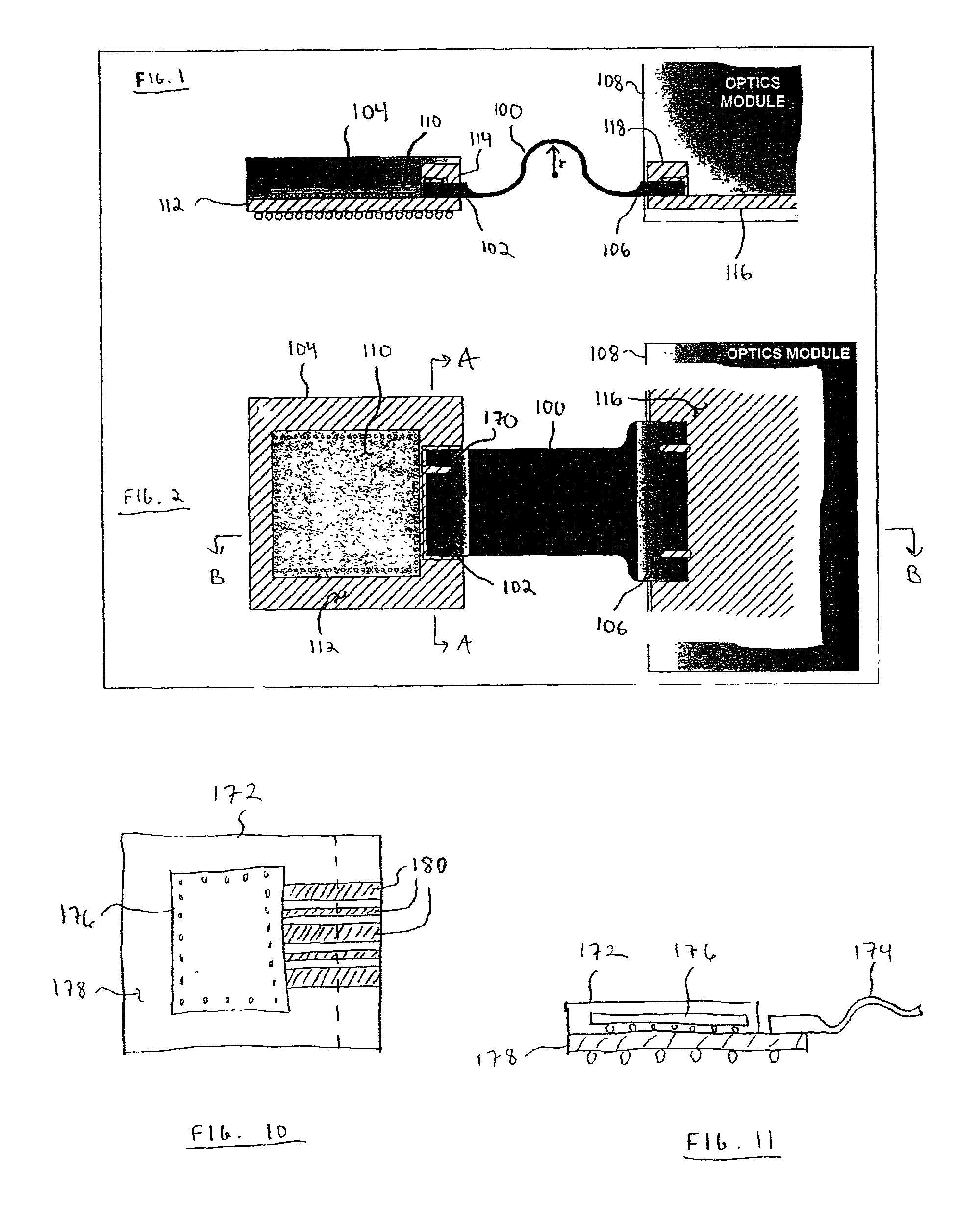

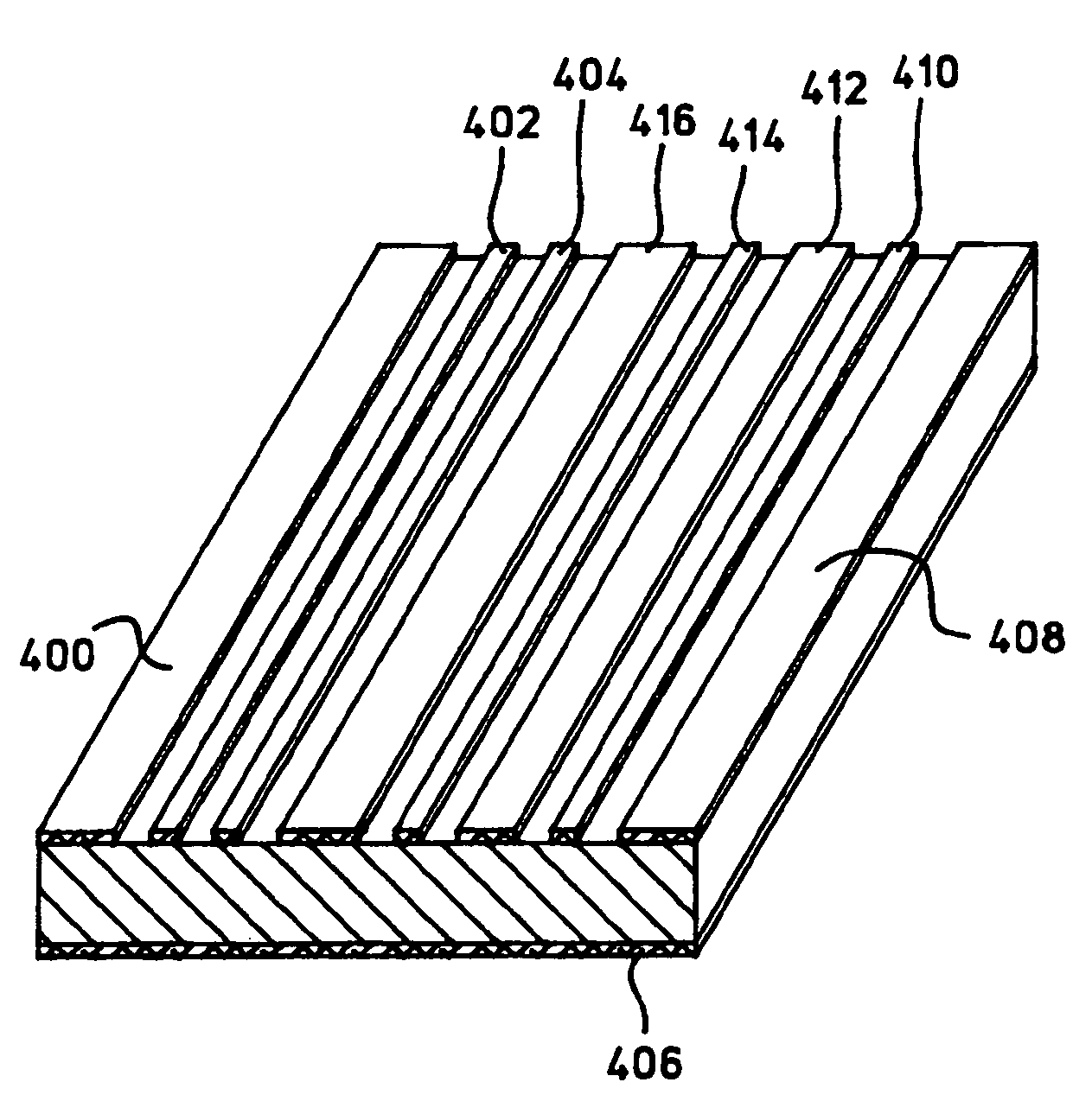

Hybrid organic-inorganic planar optical waveguide device

InactiveUS6511615B1Reduce stressStress induced polarization effects can be minimizedOptical articlesGlass shaping apparatusOptical radiationSilanes

A planar optical device is formed on a substrate. The device comprises an array of waveguide cores which guide optical radiation. A cladding layer is formed contiguously with the array of waveguide cores to confine the optical radiation to the array of waveguide cores. At least one of the array of waveguide cores and cladding layer is an inorganic-organic hybrid material that comprises an extended matrix containing silicon and oxygen atoms with at least a fraction of the silicon atoms being directly bonded to substituted or unsubstituted hydrocarbon moieties. This material can be designed with an index of refraction between 1.4 and 1.55 and can be deposited rapidly to thicknesses of up to 40 microns. In accordance with another embodiment of the invention, a method for forming a planar optical device obviates the need for a lithographic process. Illustratively, a method for forming an array of cores comprises the steps of: (1) preparing a waveguide core composition precursor material comprising at least one silane and a source of hydrocarbon moiety, (2) partially hydrolyzing and polymerizing the waveguide core precursor material to form a waveguide core composition, (3) using a mold, forming an array of waveguide cores comprising the waveguide core composition, and (4) completing hydrolysis and polymerization of the waveguide core composition under conditions effective to form an inorganic-organic hybrid material that comprises an extended matrix containing silicon and oxygen atoms with at least a fraction of the silicon atoms being directly bonded to substituted or unsubstituted hydrocarbon moieties. A cladding layer is then deposited over the array of waveguide cores. The use of the mold to pattern the array of waveguide cores obviates the need for a lithographic process.

Owner:CORNING INC

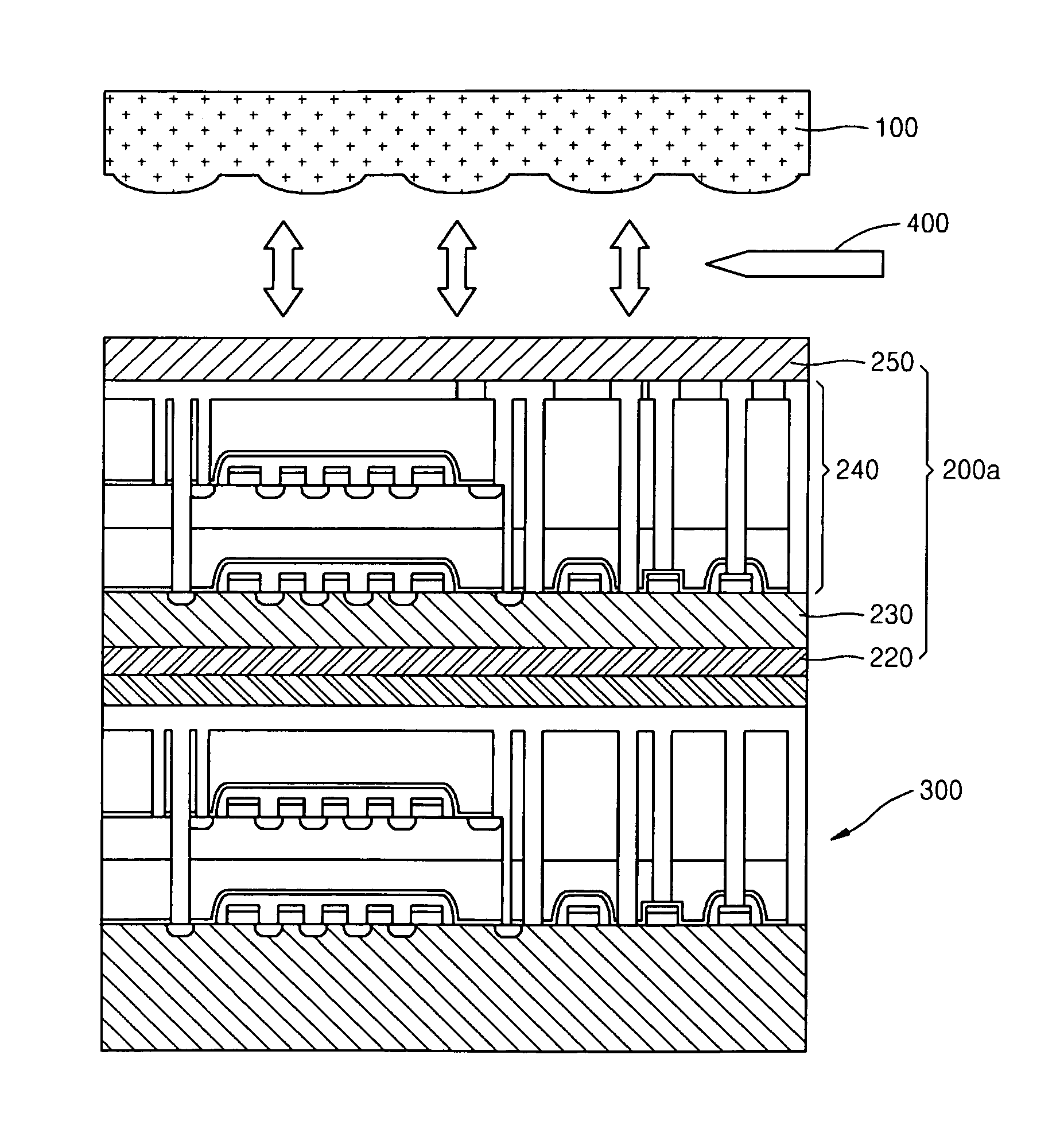

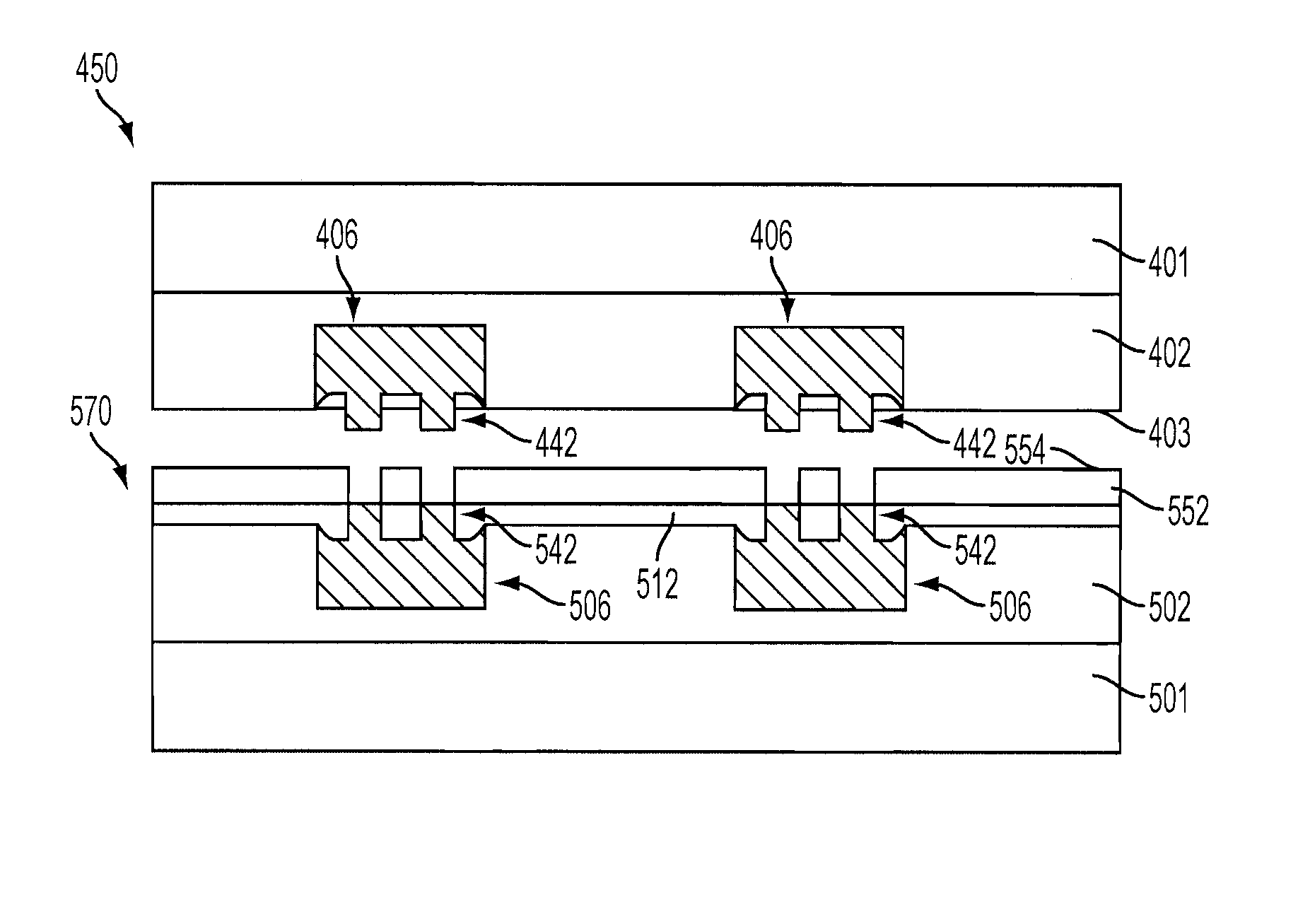

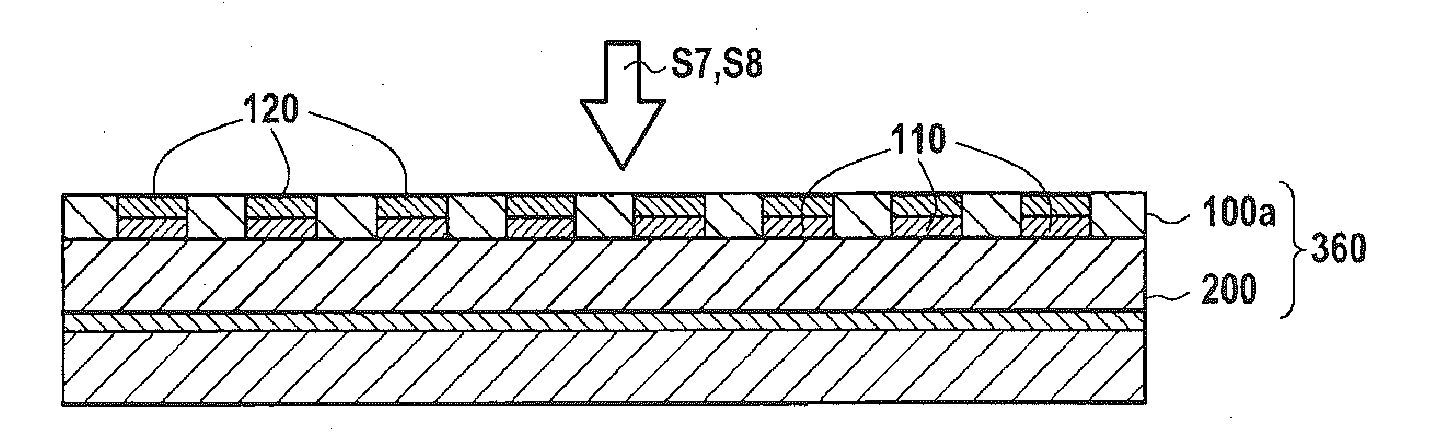

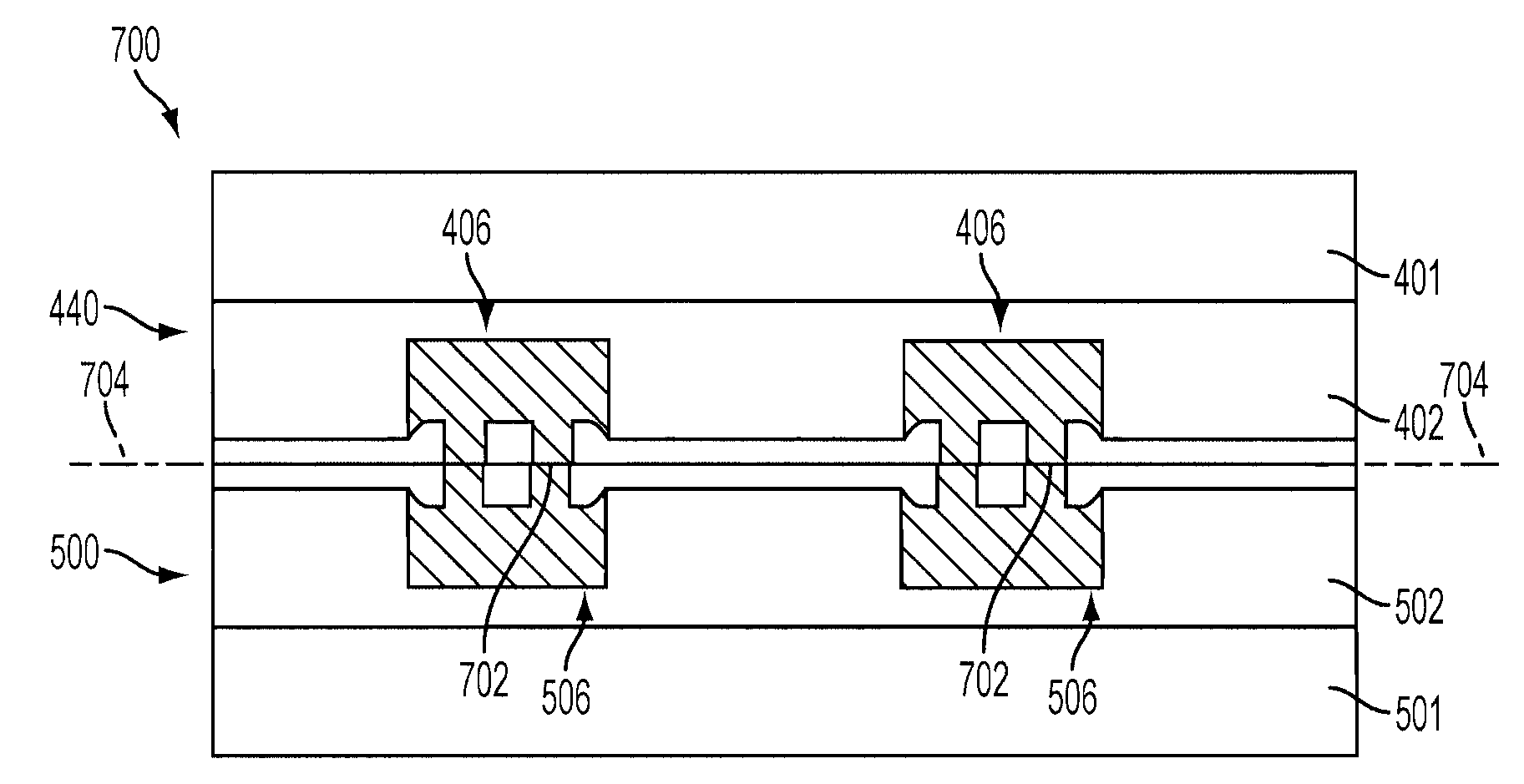

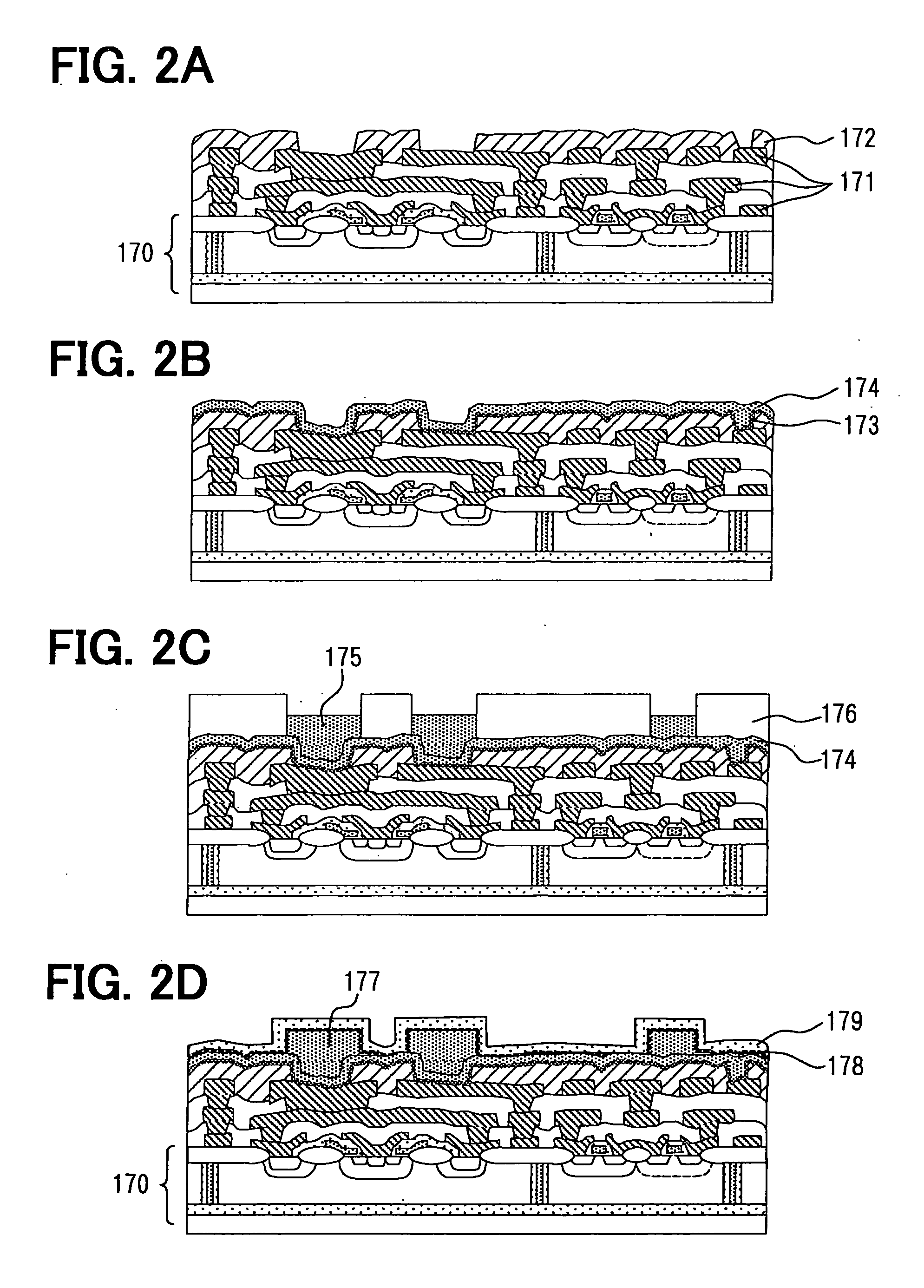

Methods for bonding semiconductor structures involving annealing processes, and bonded semiconductor structures and intermediate structures formed using such methods

InactiveUS8716105B2Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor structure

Owner:SONY SEMICON SOLUTIONS CORP

Light emitting device and the manufacture method thereof

ActiveUS20080054290A1Improve cooling efficiencySolid-state devicesSemiconductor/solid-state device manufacturingShortest distanceEngineering

This invention provides a light-emitting element and the manufacture method thereof. The light-emitting element is suitable for flip-chip bonding and comprises an electrode having a plurality of micro-bumps for direct bonding to a submount. Bonding within a relatively short distance between the light-emitting device and the submount can be formed so as to improve the heat dissipation efficiency of the light-emitting device.

Owner:EPISTAR CORP

Method of detachable direct bonding at low temperatures

ActiveUS20060264004A1Semiconductor/solid-state device manufacturingAmorphous siliconHydrogen content

A method for detachable bonding that forms an amorphous silicon layer, or a silicon oxide layer with a high hydrogen content, on an element such as a carrier substrate. A second element, such as a substrate, is bonded to the amorphous silicon layer or silicon oxide layer, and the second element may then have a portion removed. A third element, such as a host or carrier substrate, is bonded to the second element or to the remaining portion of the second element to form a bonded structure. The bonded structure is then heated to cause the first element to detach from the bonded structure.

Owner:INVENSAS BONDING TECH INC

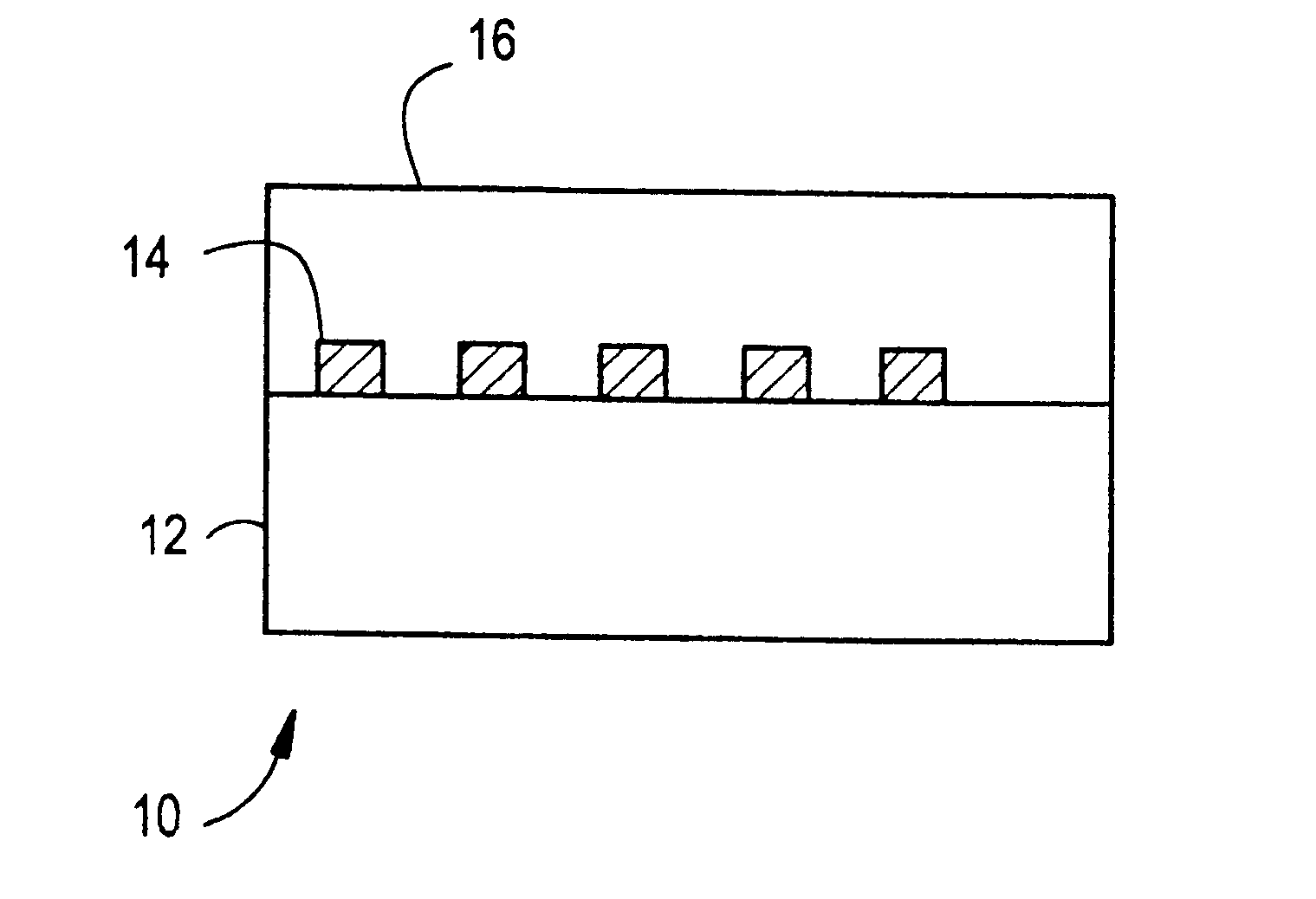

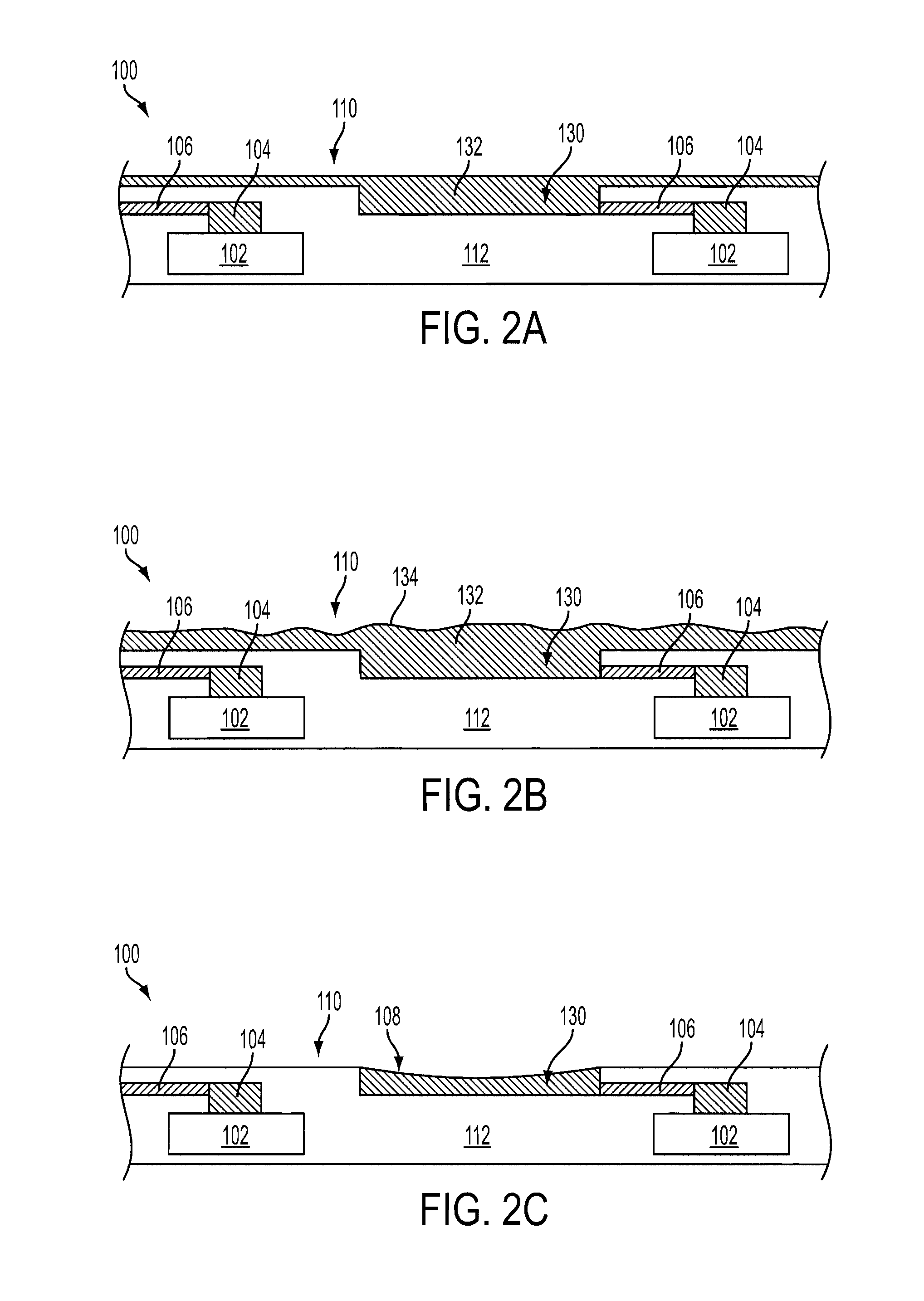

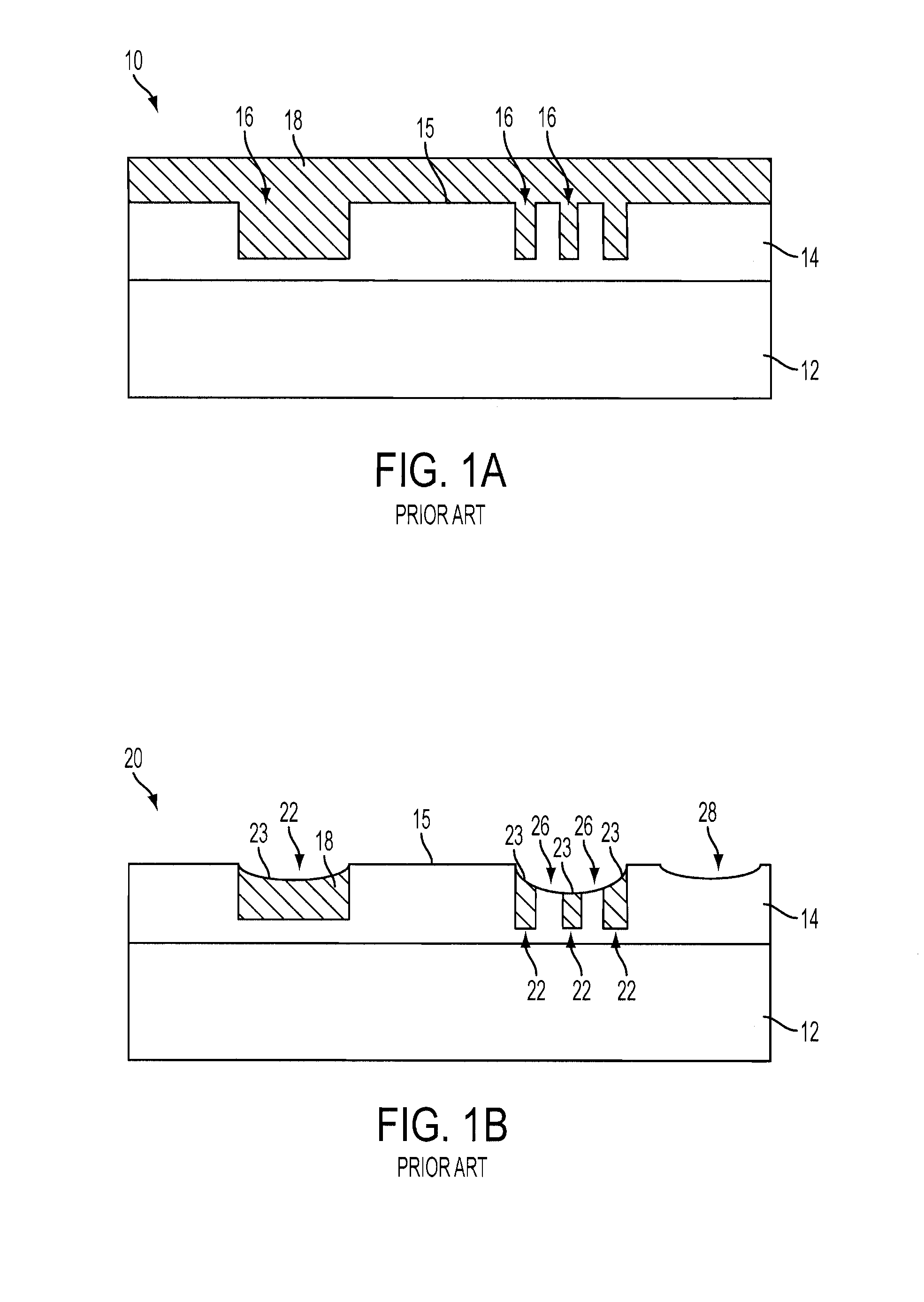

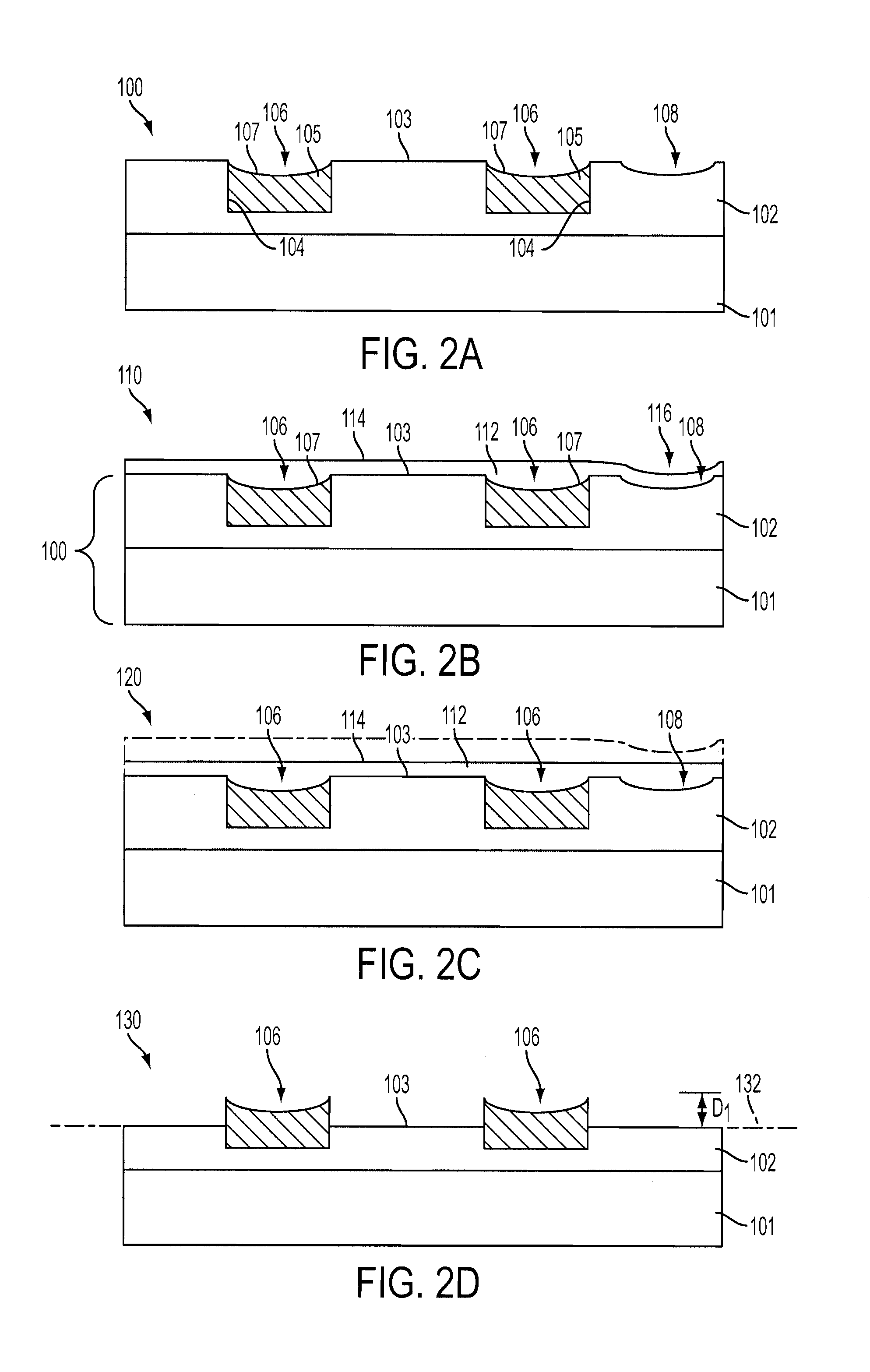

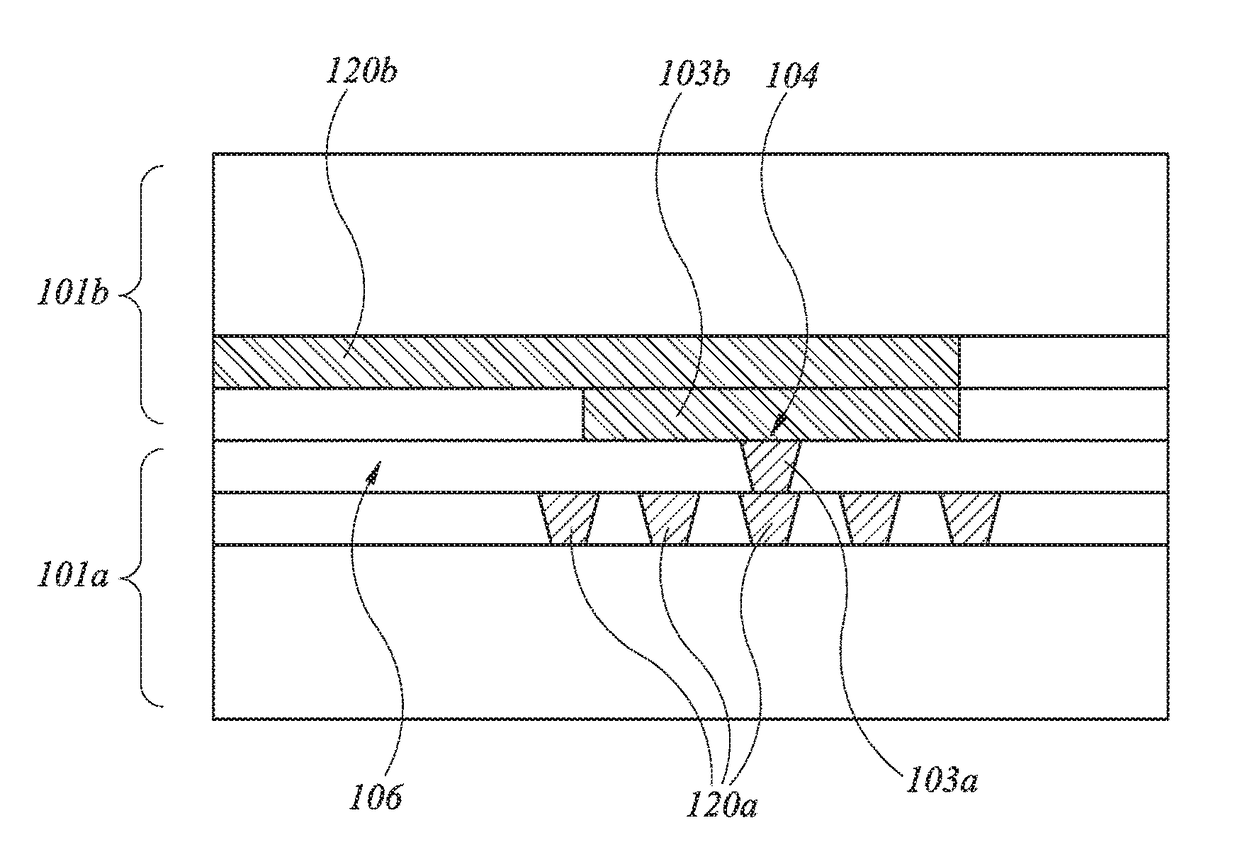

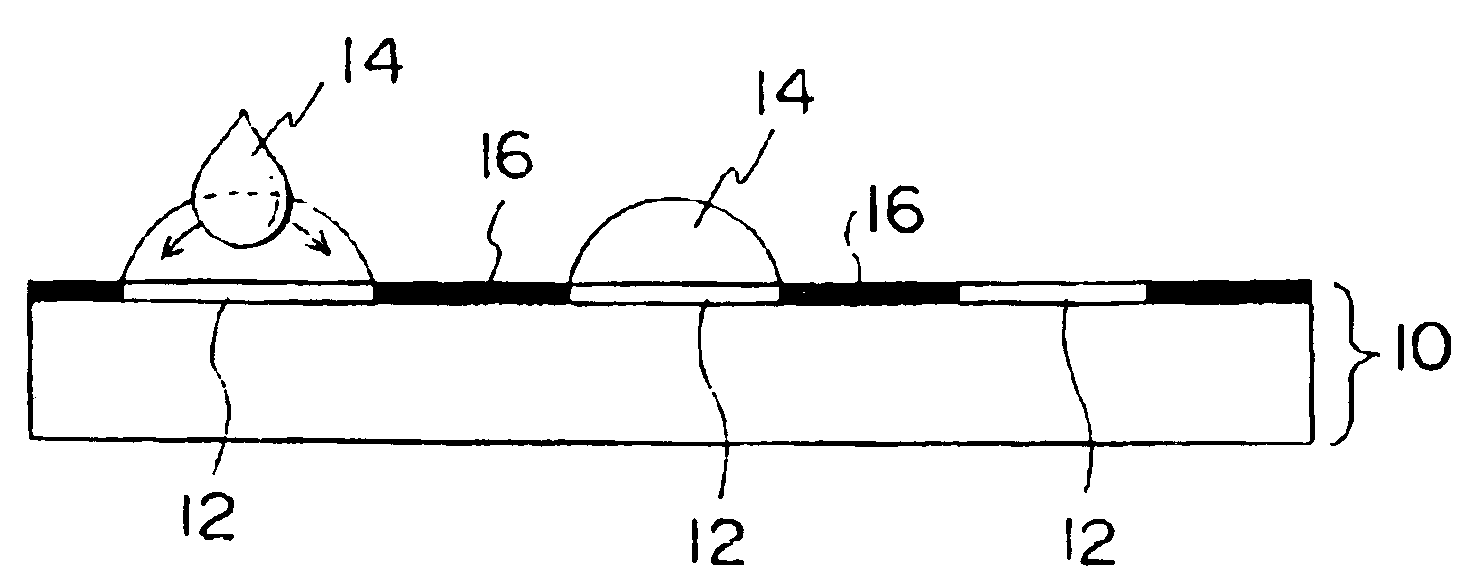

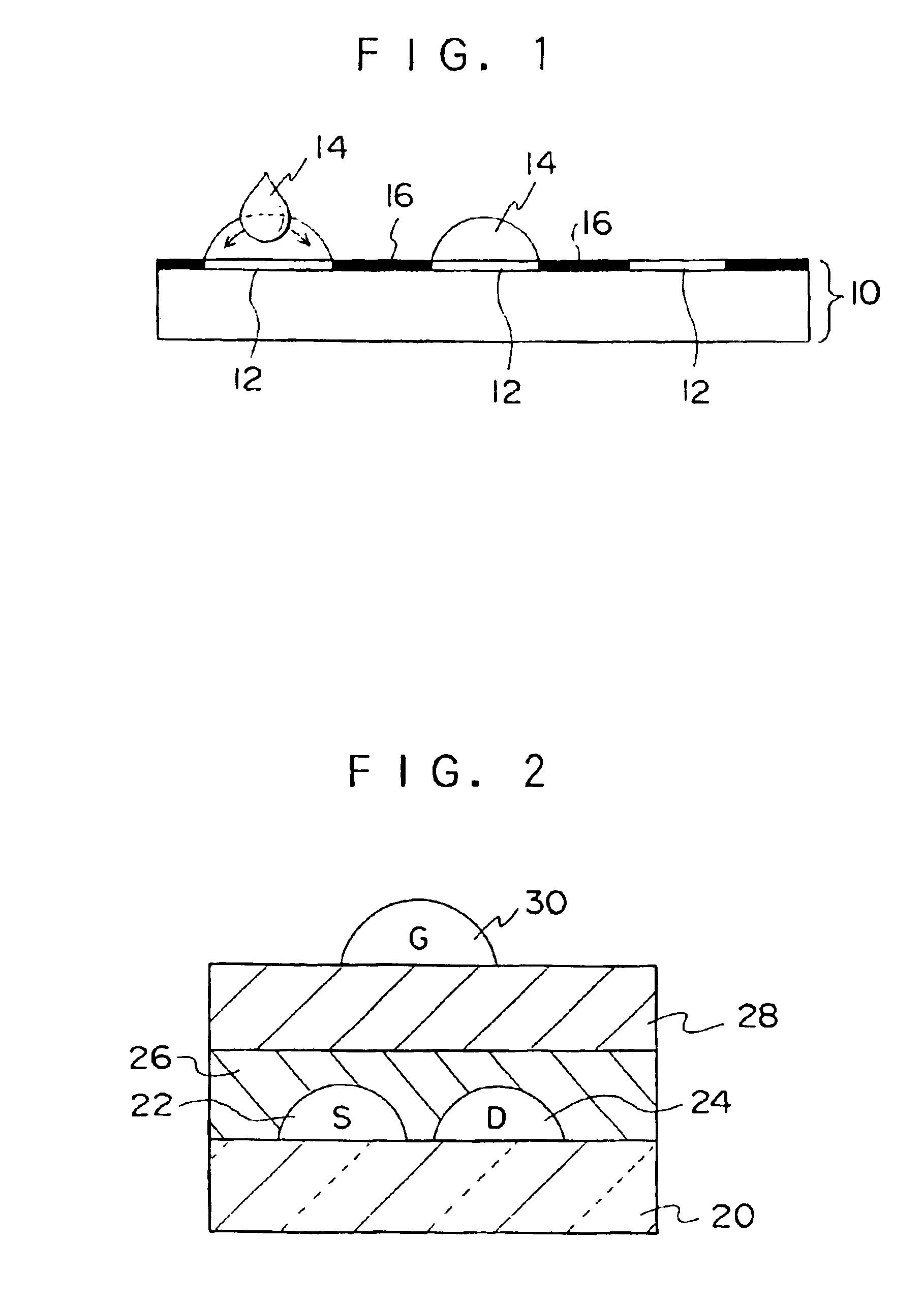

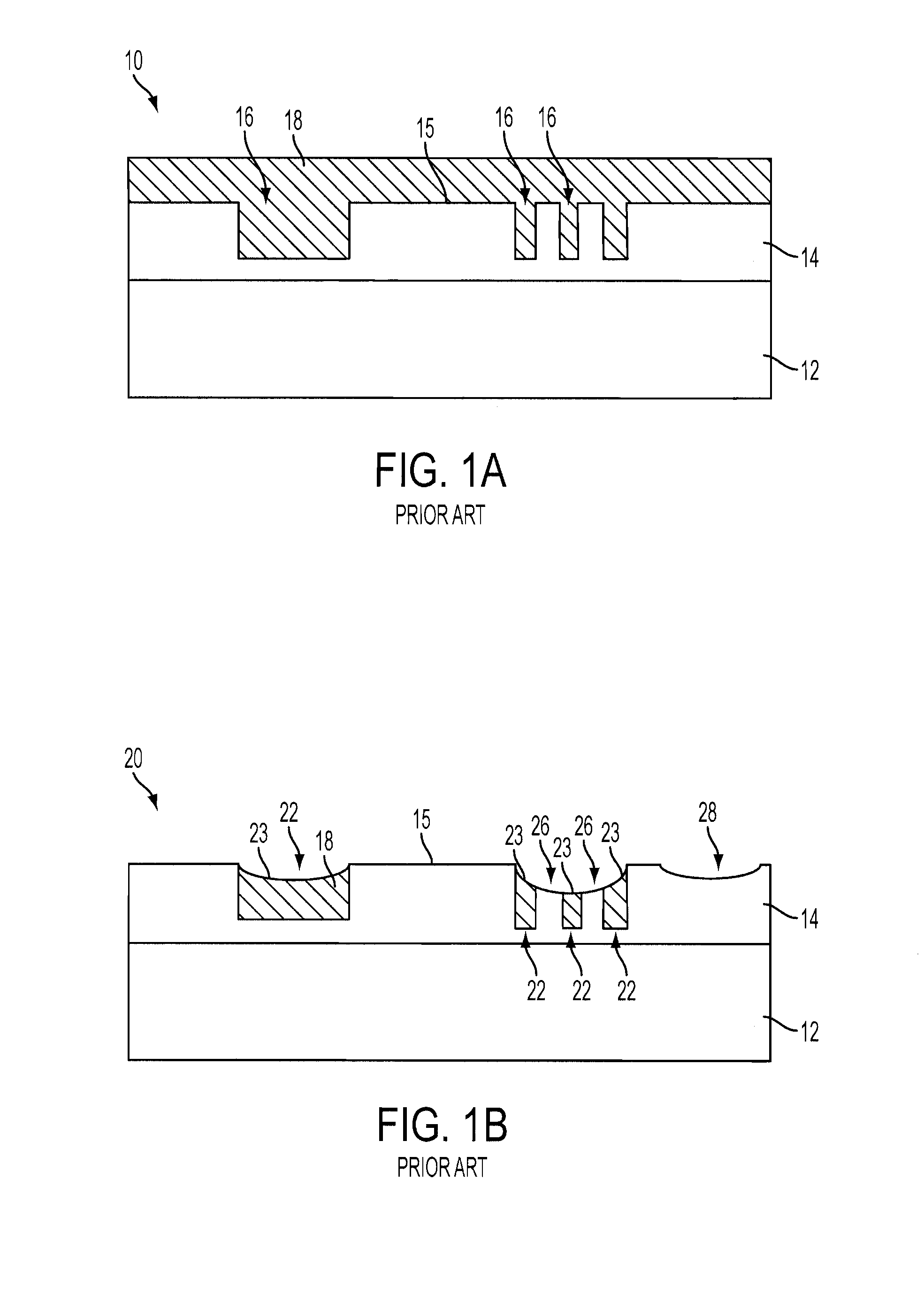

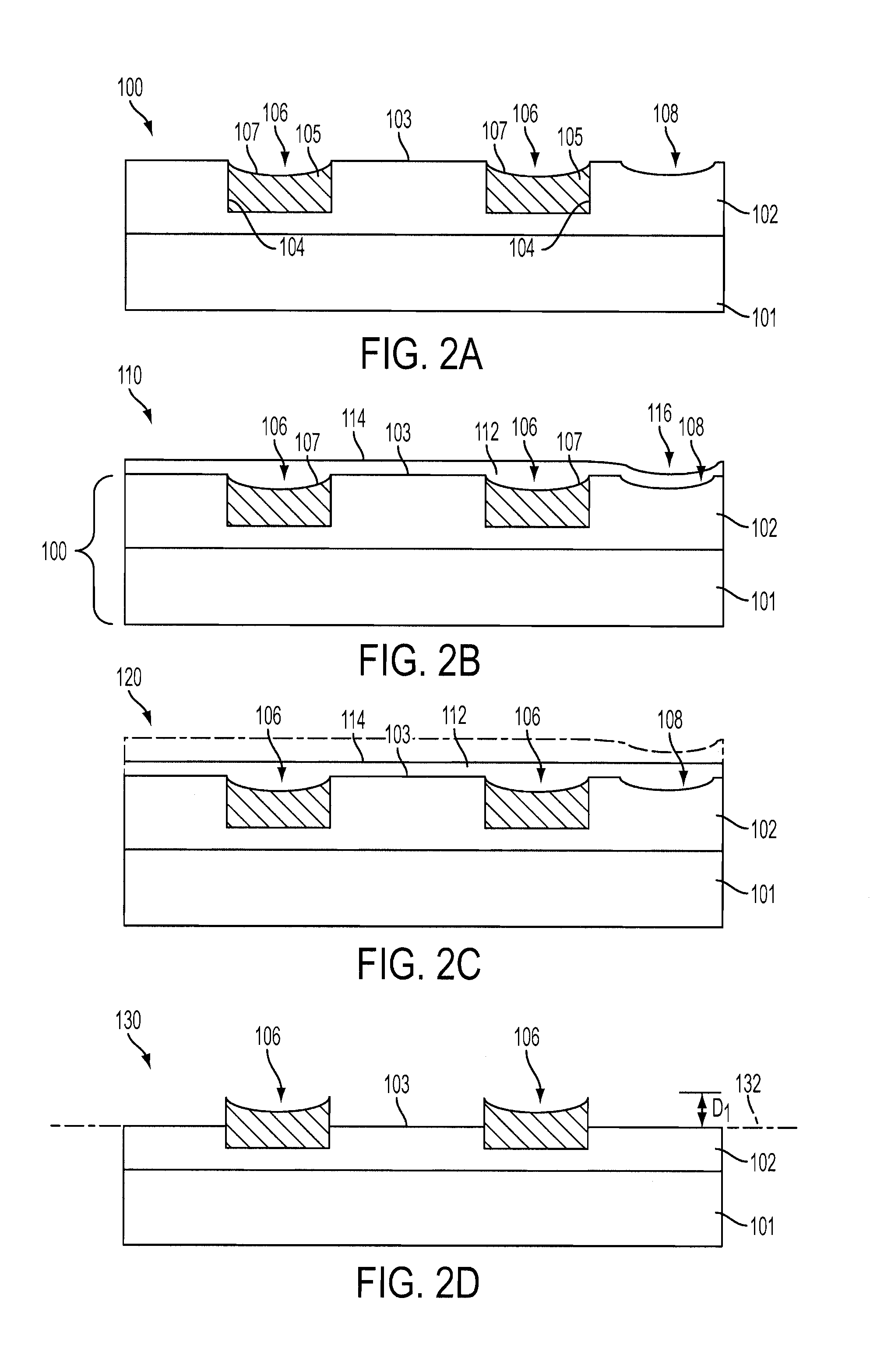

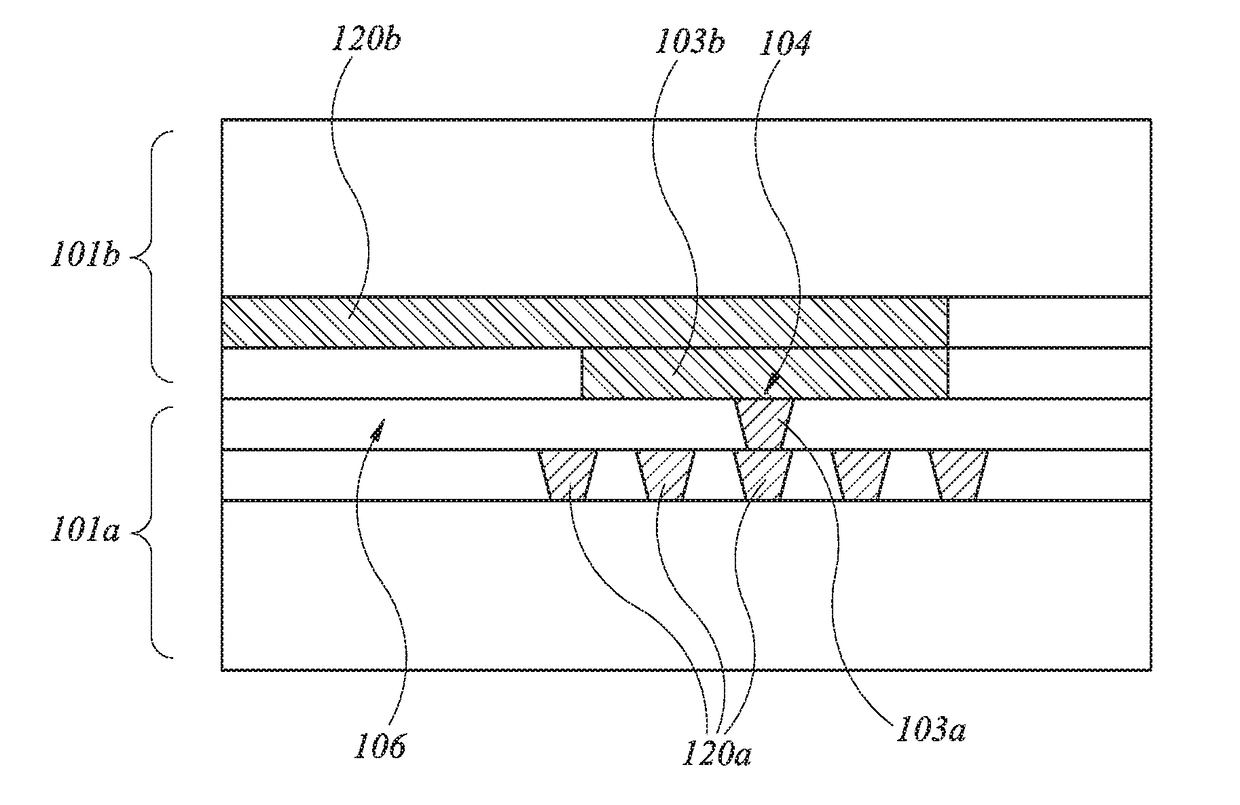

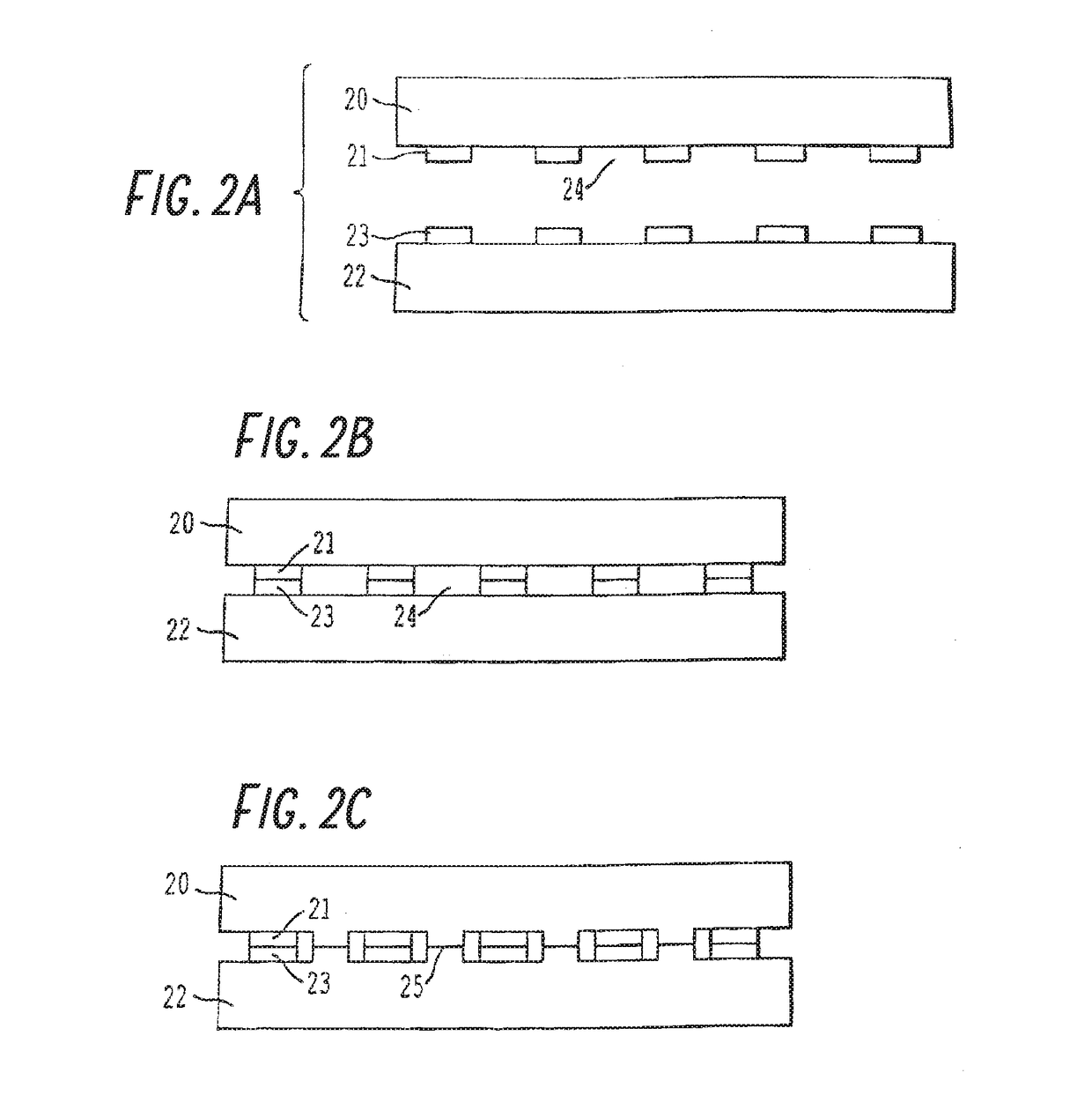

Bonding surfaces for direct bonding of semiconductor structures

InactiveUS8697493B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor structureBonding process

Methods of directly bonding a first semiconductor structure to a second semiconductor structure include directly bonding at least one device structure of a first semiconductor structure to at least one device structure of a second semiconductor structure in a conductive material-to-conductive material direct bonding process. In some embodiments, at least one device structure of the first semiconductor structure may be caused to project a distance beyond an adjacent dielectric material on the first semiconductor structure prior to the bonding process. In some embodiments, one or more of the device structures may include a plurality of integral protrusions that extend from a base structure. Bonded semiconductor structures are fabricated using such methods.

Owner:SONY SEMICON SOLUTIONS CORP

Increased contact alignment tolerance for direct bonding

ActiveUS9852988B2Easy temperatureSemiconductor/solid-state device detailsSolid-state devicesBond interfaceParasitic capacitance

Owner:INVENSAS BONDING TECH INC

Direct bonding method with reduction in overlay misalignment

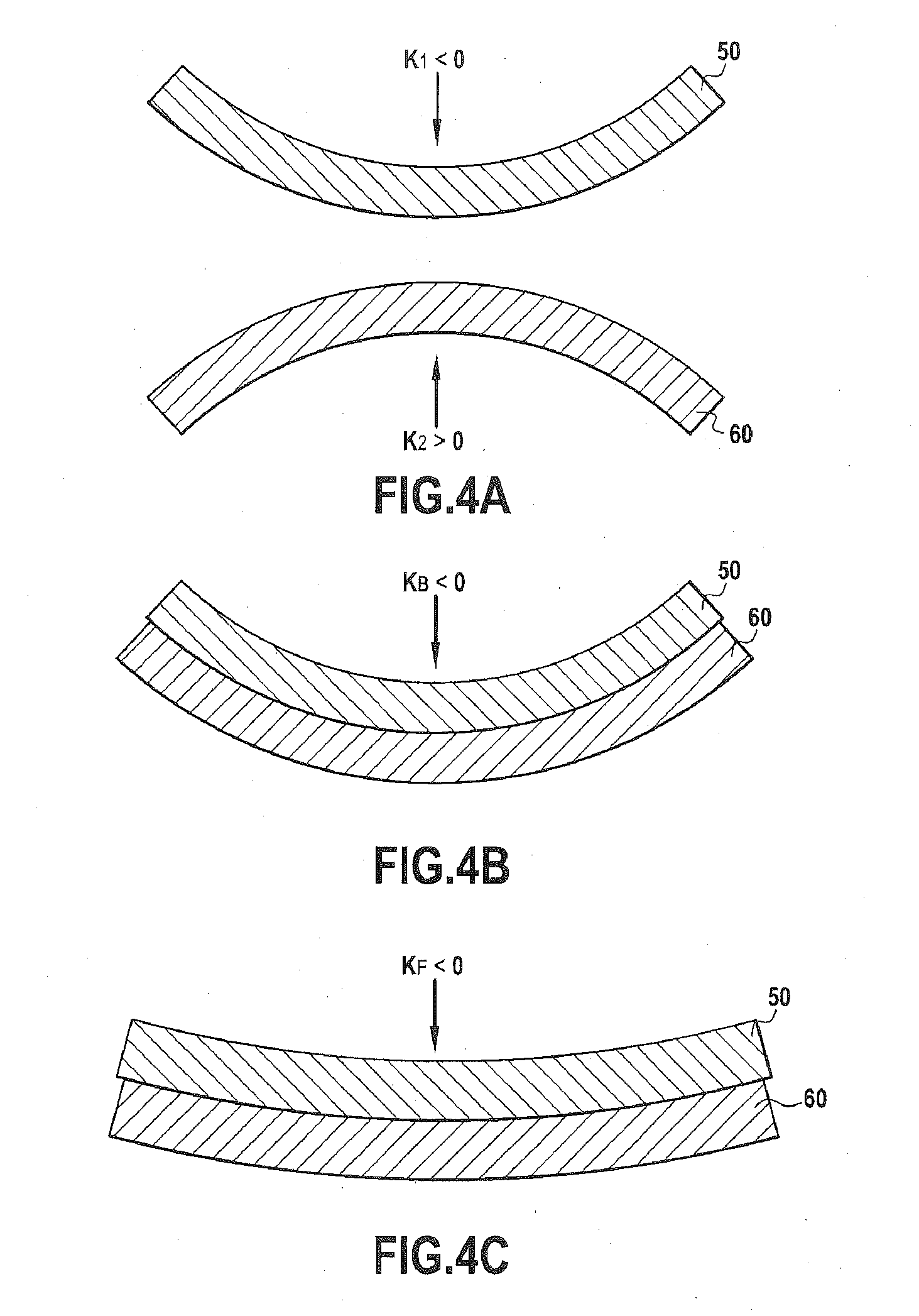

ActiveUS20120077329A1Reduce appearance problemsReduce and minimize overlay microcomponent misalignmentLamination ancillary operationsSemiconductor/solid-state device testing/measurementEngineeringParaboloid

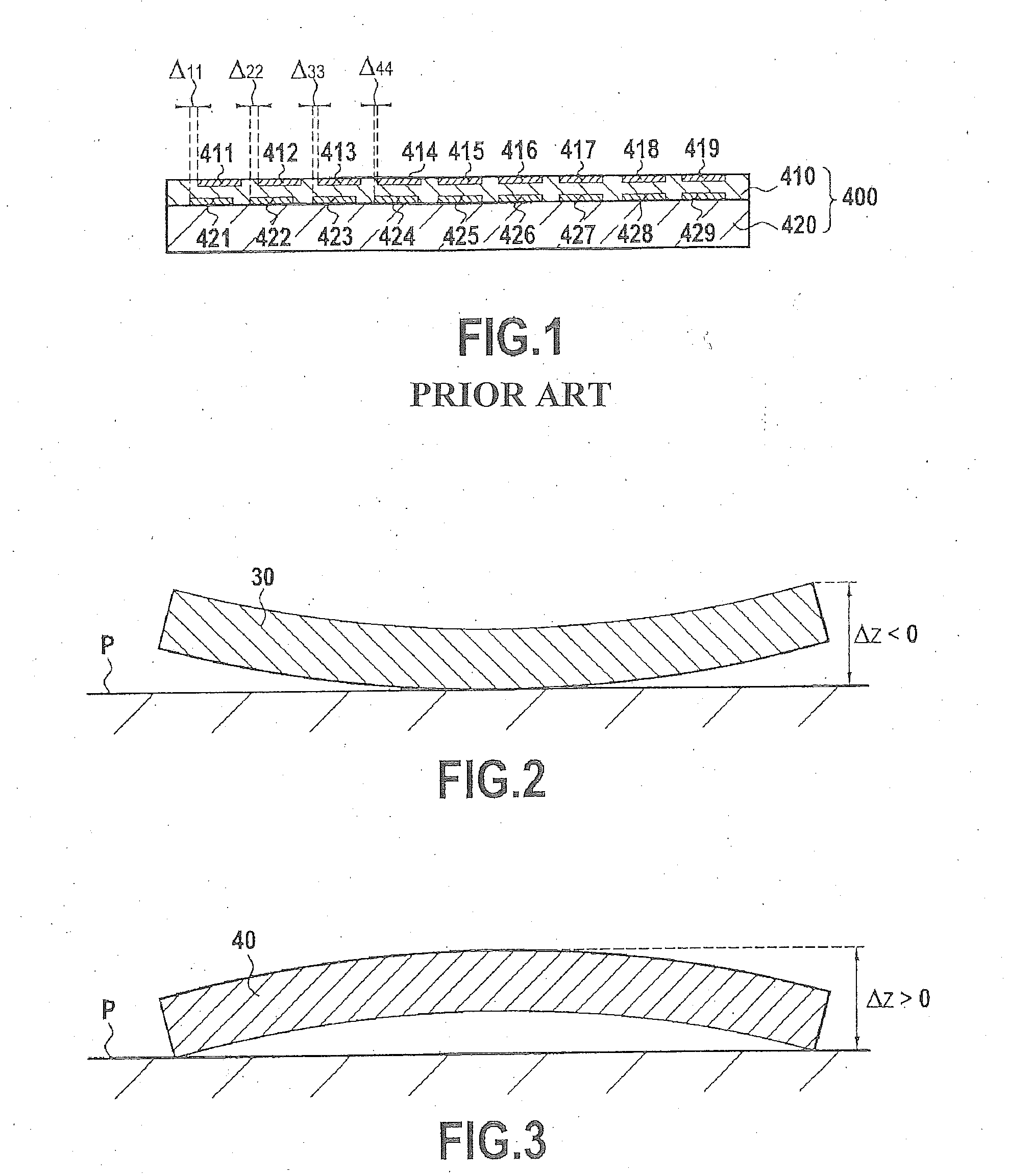

A method for the direct bonding of a first wafer having an intrinsic curvature before bonding to a second wafer having an intrinsic curvature before bonding, at least one of the two wafers comprising at least one series of microcomponents. The method includes of bringing the two wafers into contact with each other so as to initiate the propagation of a bonding wave therebetween while imposing a predefined bonding curvature in the form of a paraboloid of revolution on one of the two wafers depending at least upon the intrinsic curvature before bonding of the wafer that includes the microcomponents, with the other wafer being free to conform to the predefined bonding curvature.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

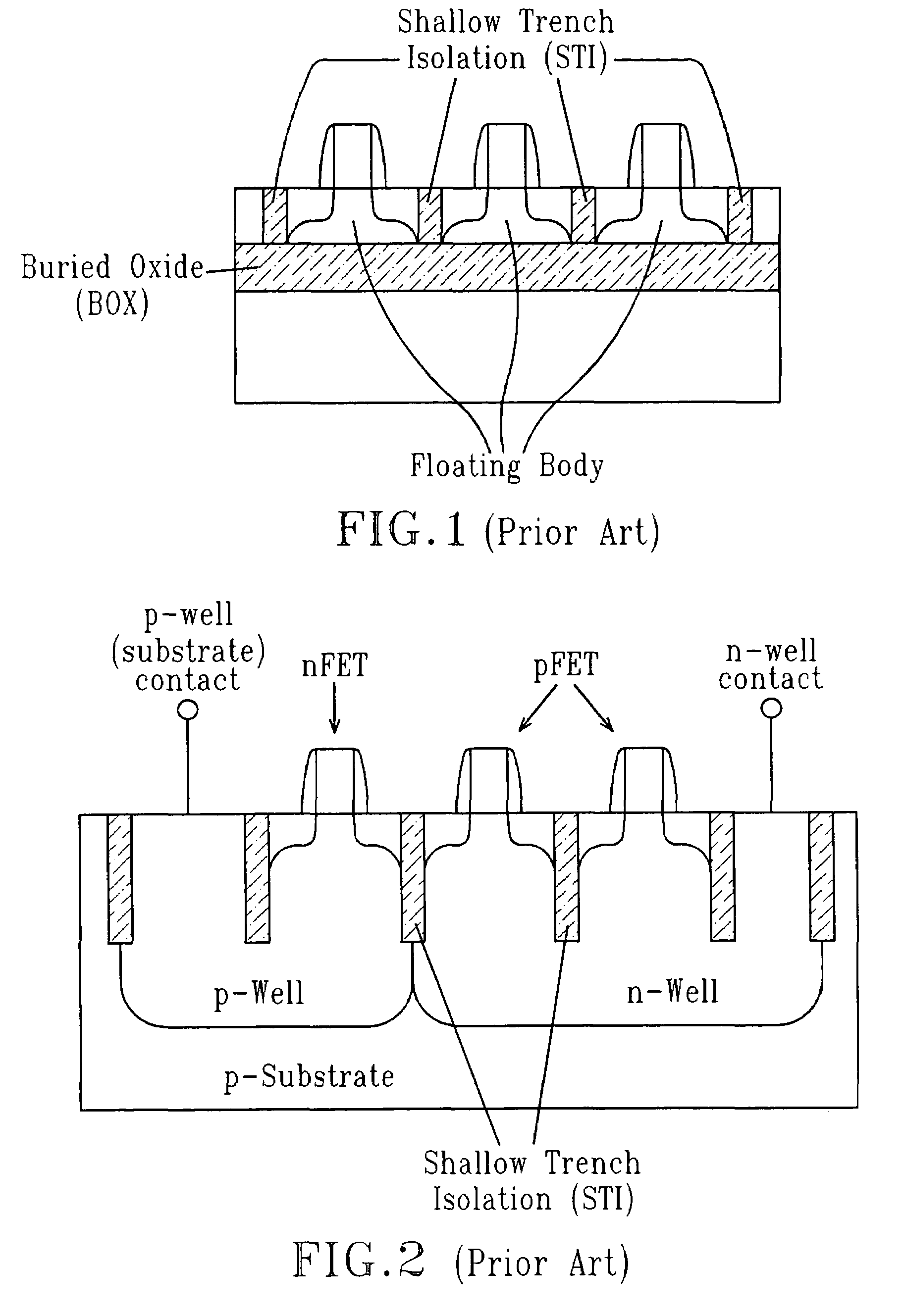

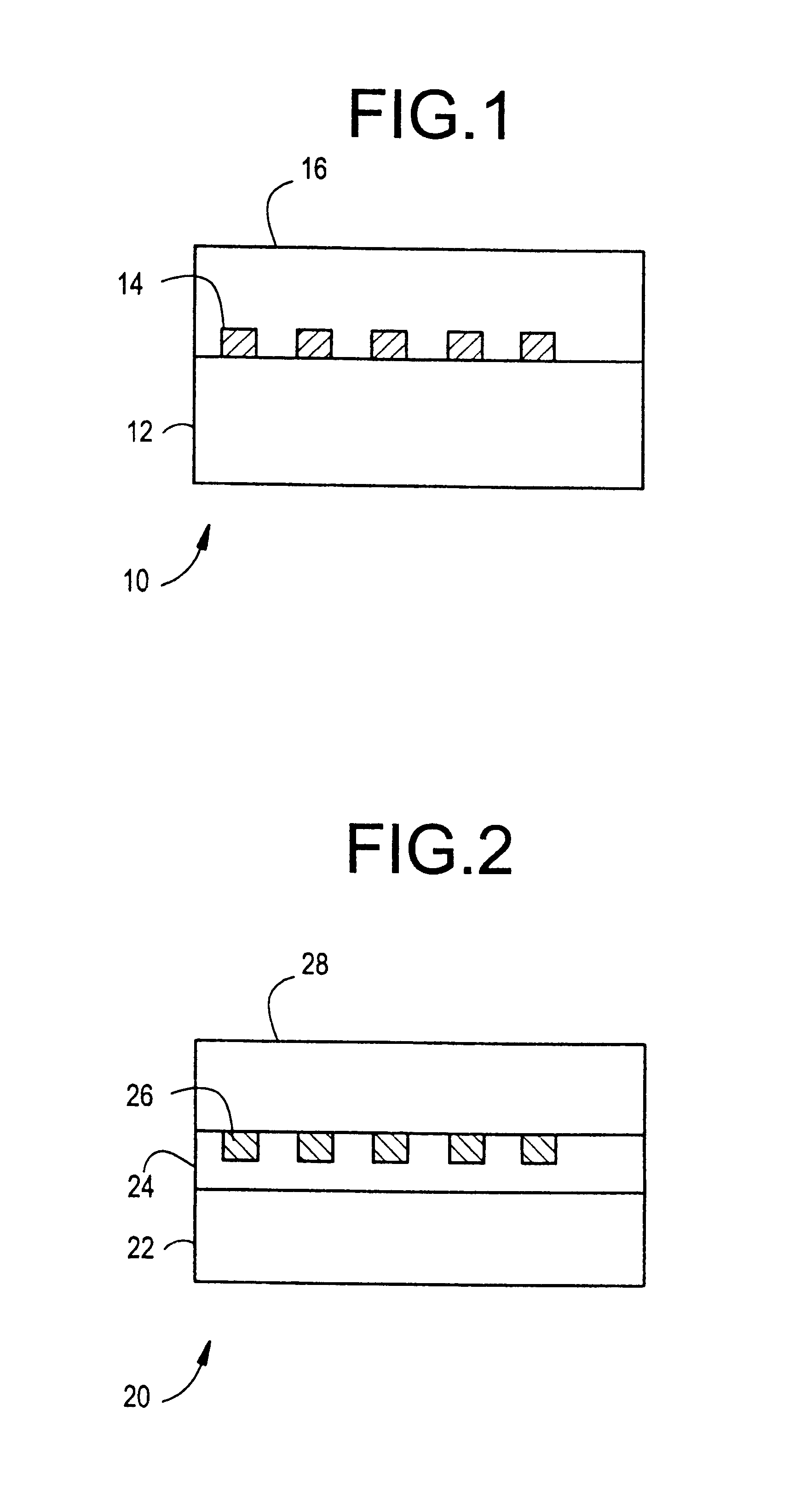

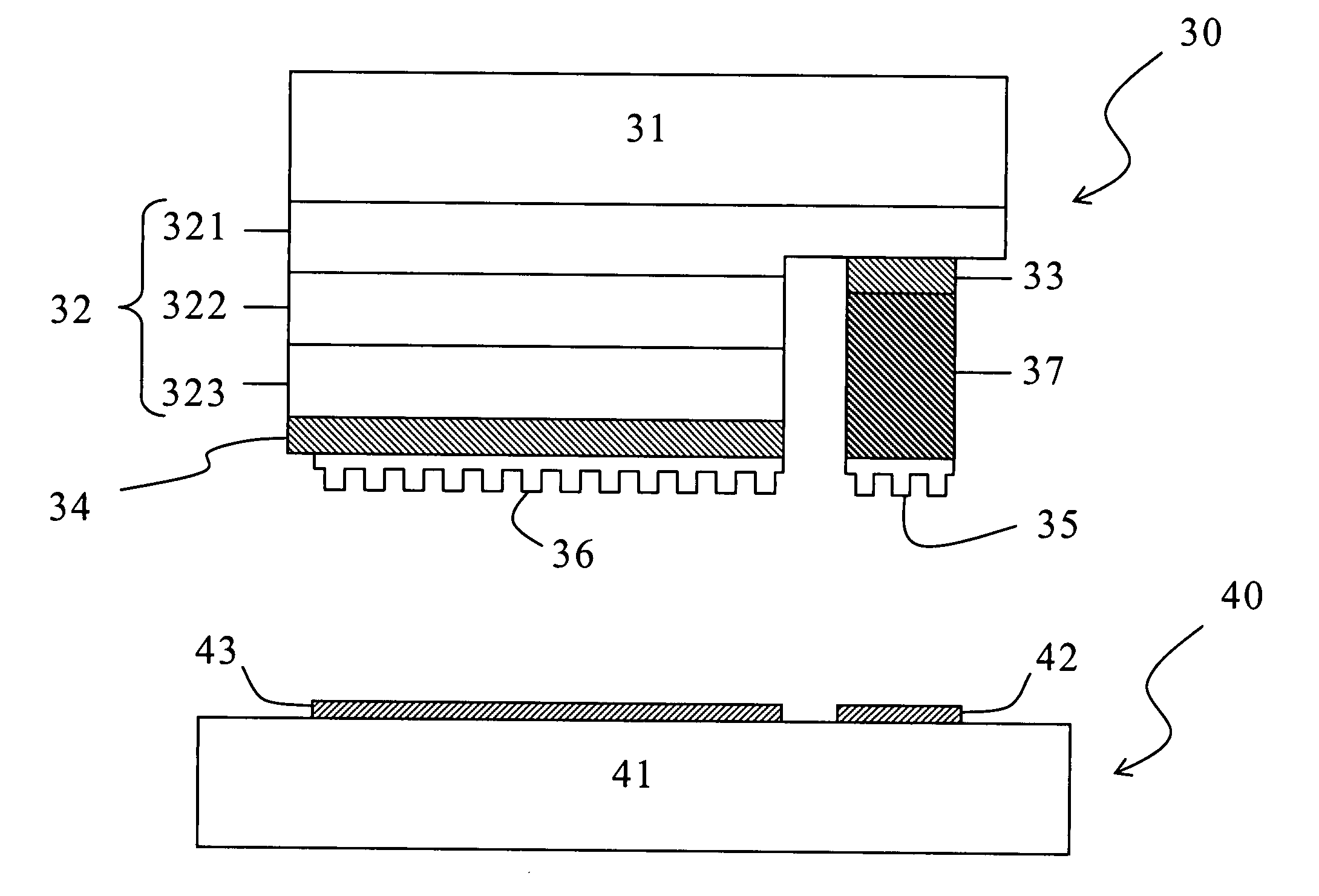

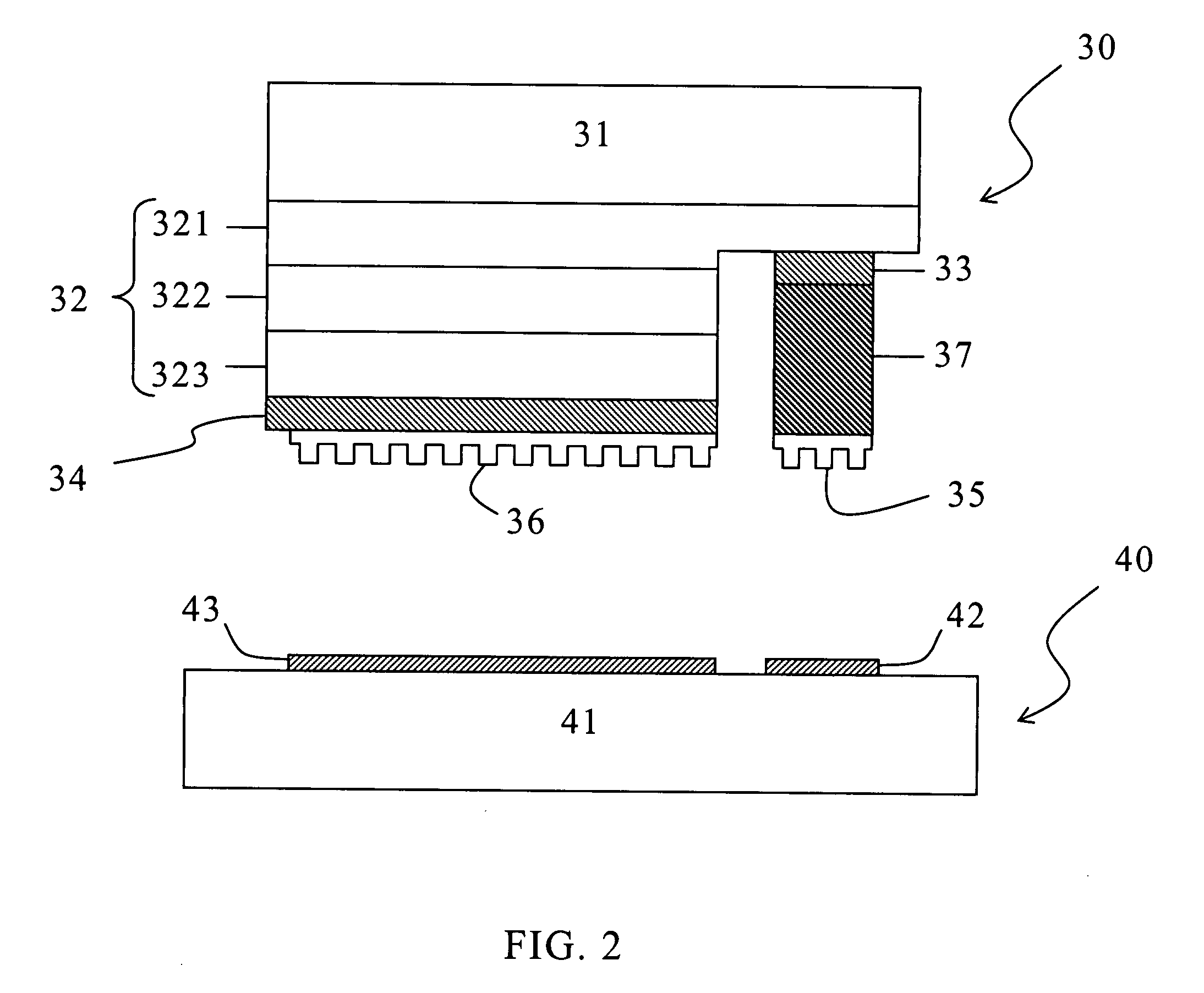

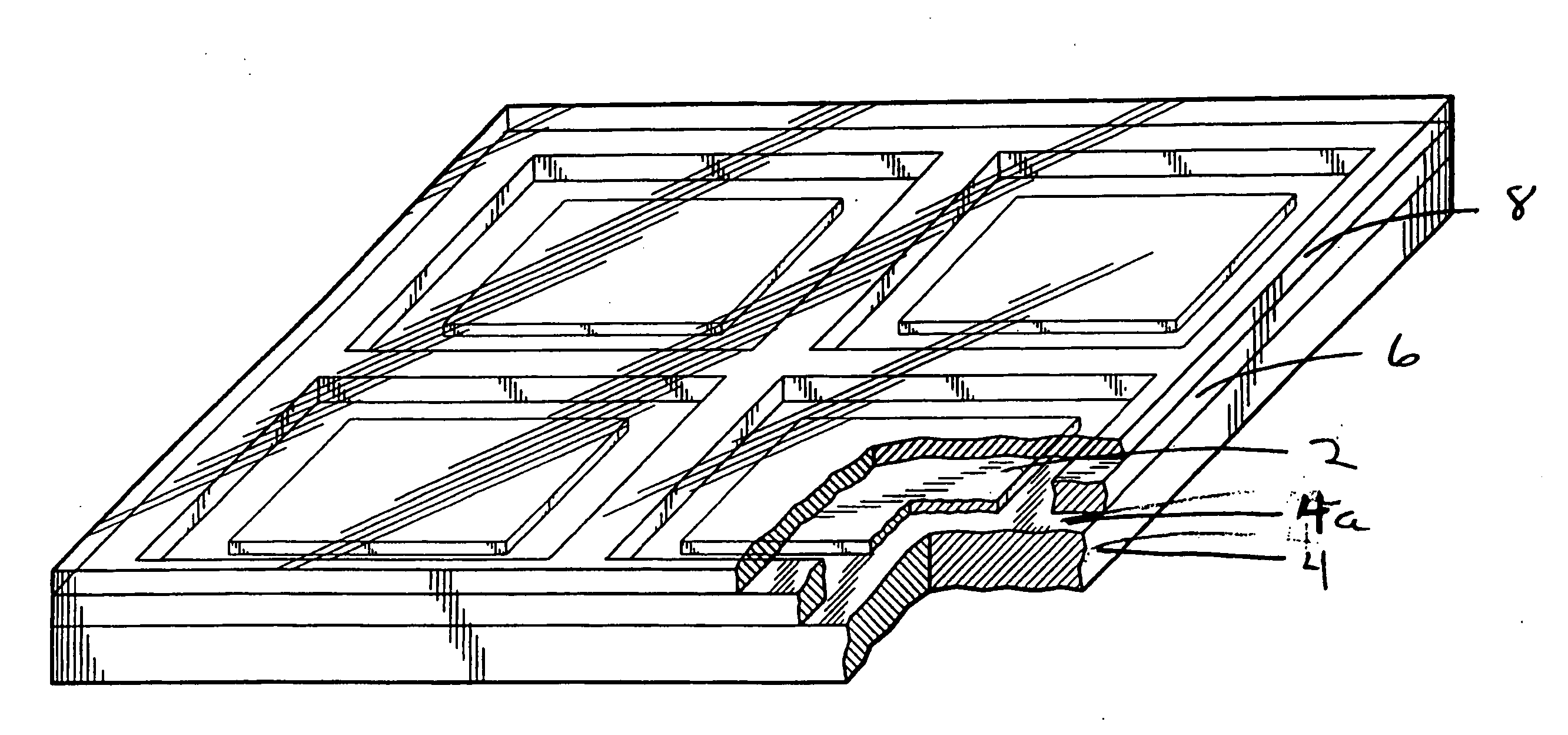

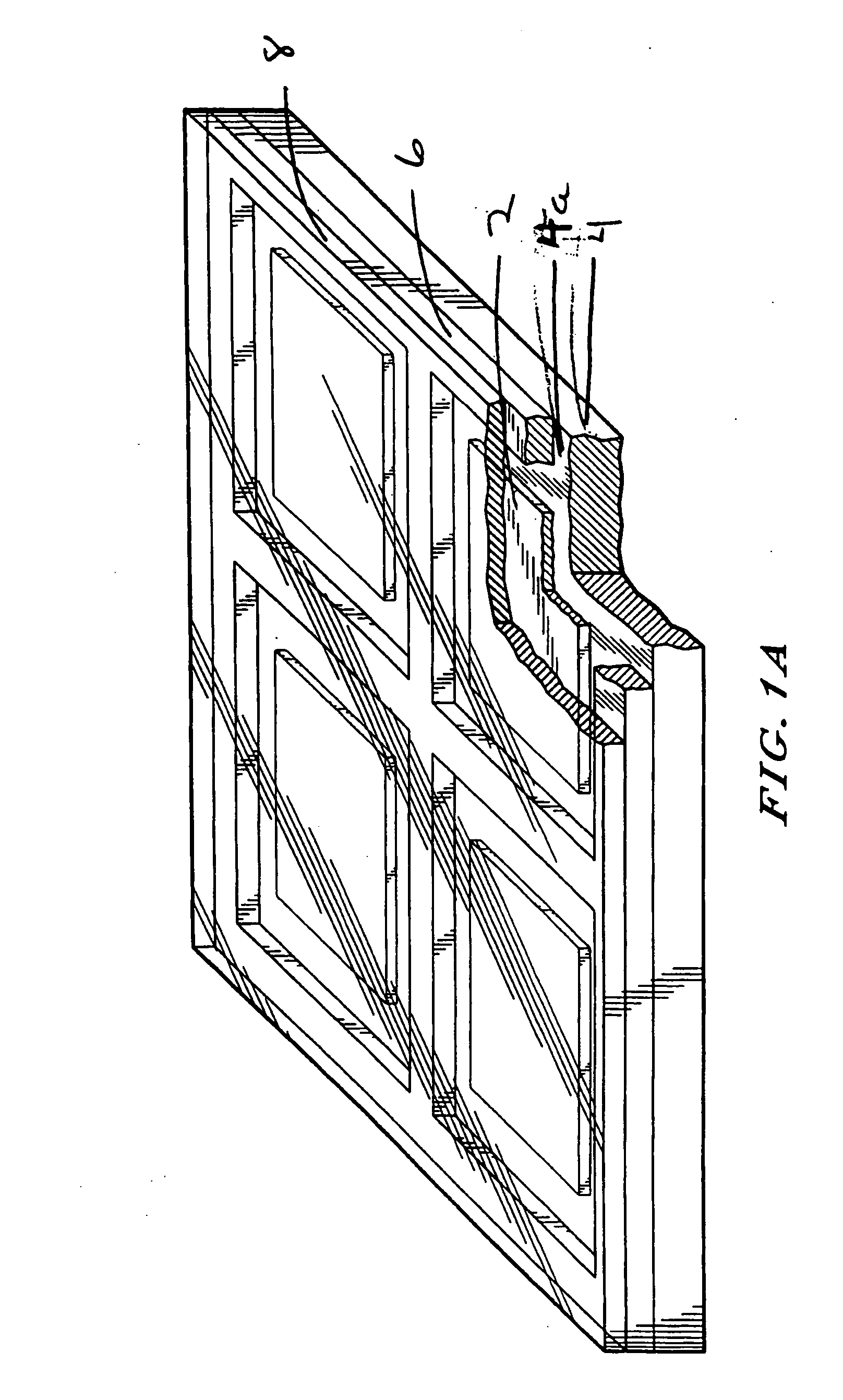

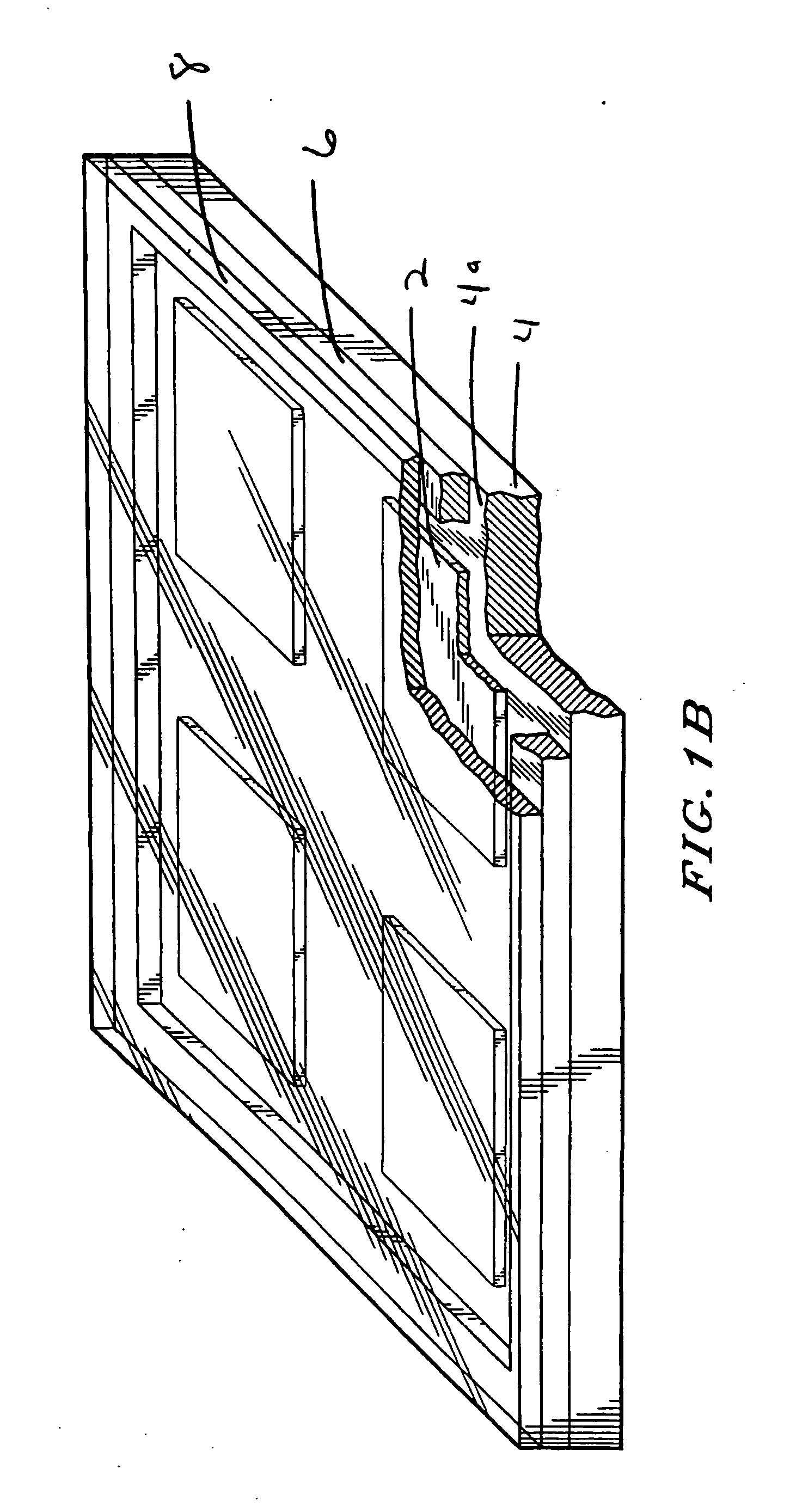

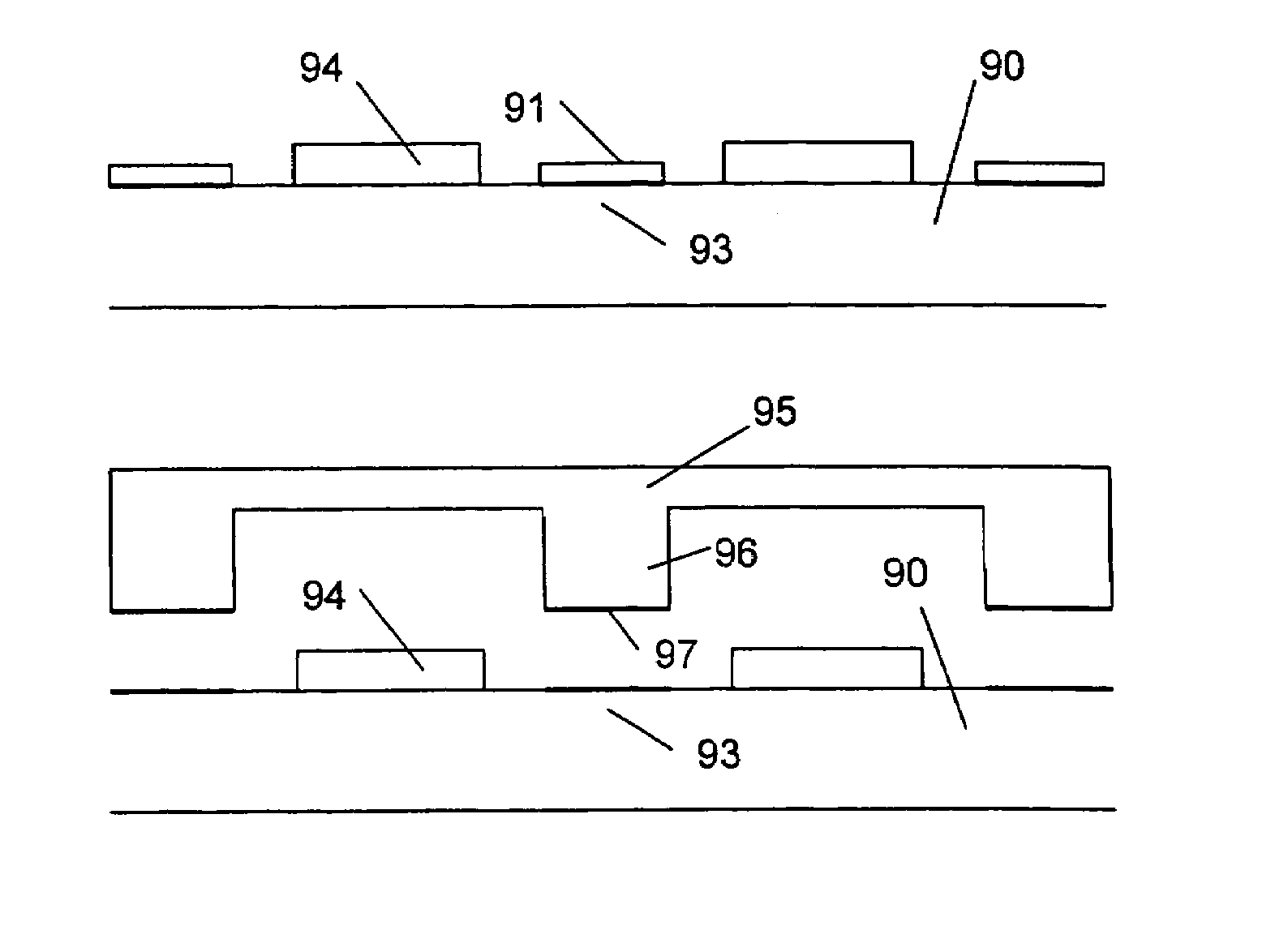

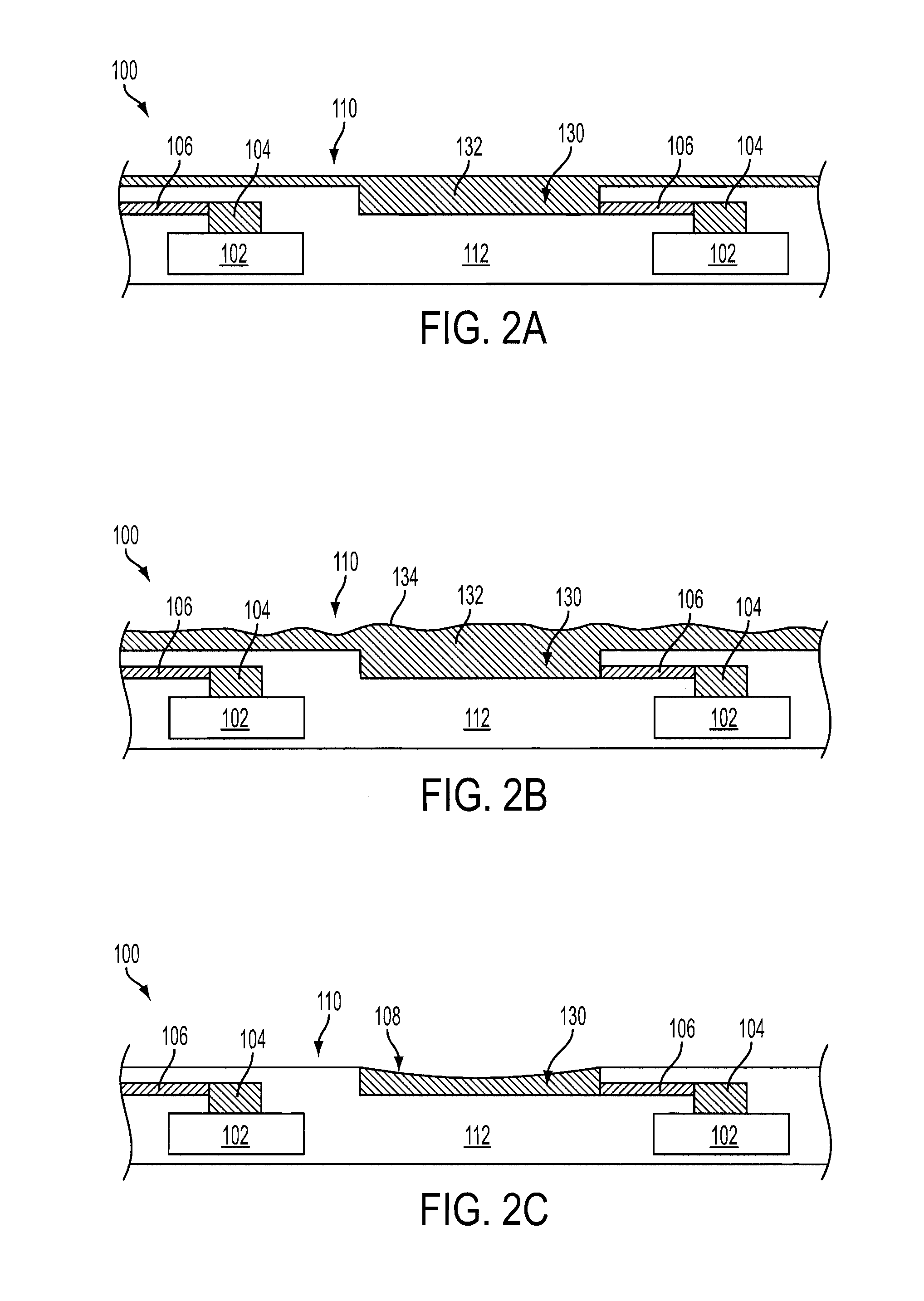

Wafer bonding hermetic encapsulation

InactiveUS20050009246A1Semiconductor/solid-state device detailsSolid-state devicesWafer bondingElectrical and Electronics engineering

A method for providing encapsulation of an electronic device which obtains an encapsulating member configured to enclose the electronic device, prepares a surface of the encapsulating member for non-adhesive direct bonding, prepares a surface of a device carrier including the electronic device for non-adhesive direct bonding, and bonds the prepared surface of the encapsulating member to the prepared surface of the device carrier to form an encapsulation of the electronic device. As such, an encapsulated electronic device results which includes the device carrier having a first bonding region encompassing the electronic device, includes the encapsulating member having at least one relief preventing contact between the electronic device and the encapsulating member and having a second bonding region bonded to the first bonding region of the device carrier, and includes a non-adhesive direct bond formed between the first and second bonding regions thereby to form an encapsulation of the electronic device. The encapsulated electronic device can be an electronic or optoelectronic device.

Owner:INVENSAS BONDING TECH INC

Wafer bonding hermetic encapsulation

InactiveUS7622324B2Semiconductor/solid-state device detailsSolid-state devicesWafer bondingDirect bonding

A method for providing encapsulation of an electronic device which obtains an encapsulating member configured to enclose the electronic device, prepares a surface of the encapsulating member for non-adhesive direct bonding, prepares a surface of a device carrier including the electronic device for non-adhesive direct bonding, and bonds the prepared surface of the encapsulating member to the prepared surface of the device carrier to form an encapsulation of the electronic device. As such, an encapsulated electronic device results which includes the device carrier having a first bonding region encompassing the electronic device, includes the encapsulating member having at least one relief preventing contact between the electronic device and the encapsulating member and having a second bonding region bonded to the first bonding region of the device carrier, and includes a non-adhesive direct bond formed between the first and second bonding regions thereby to form an encapsulation of the electronic device. The encapsulated electronic device can be an electronic or optoelectronic device.

Owner:INVENSAS BONDING TECH INC

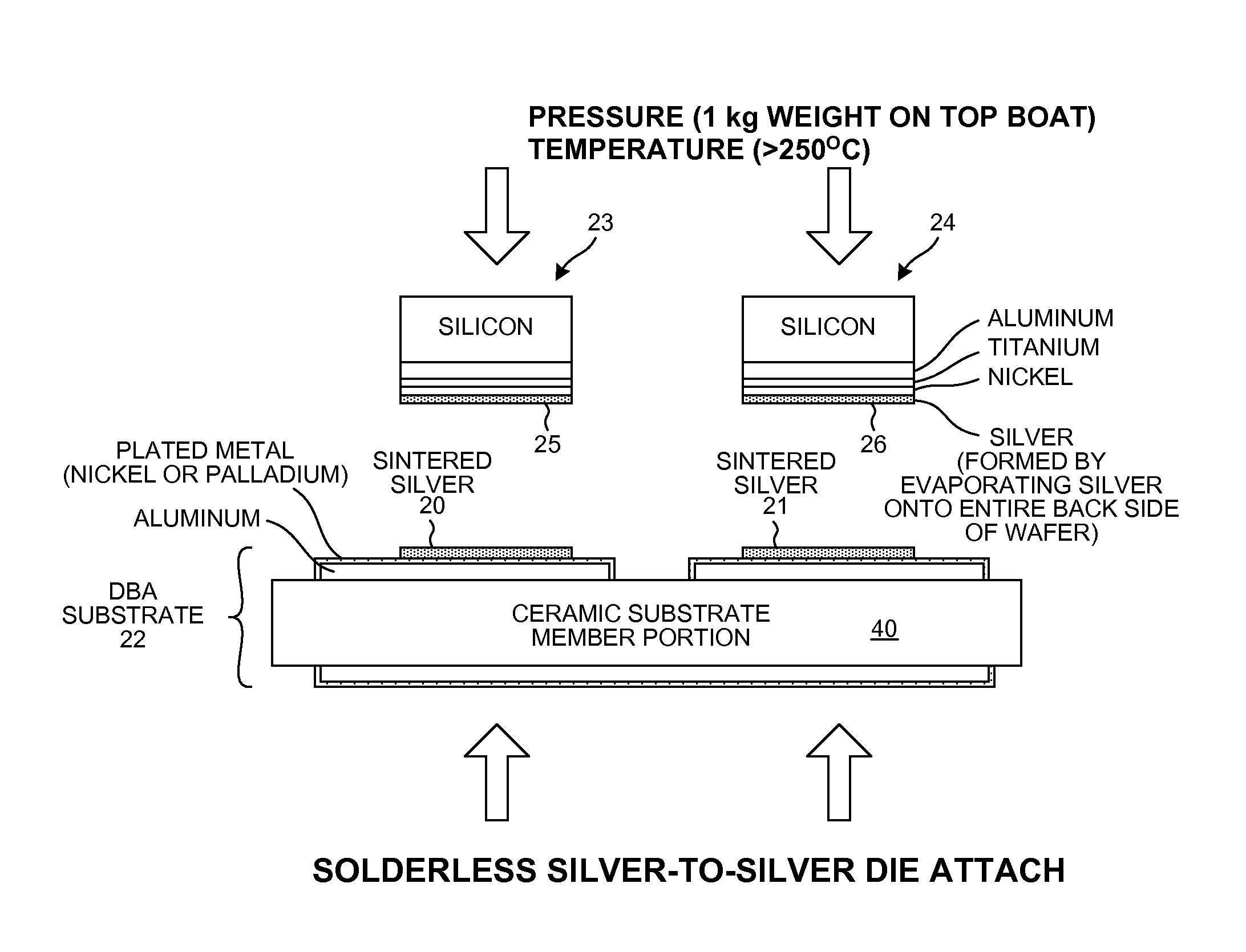

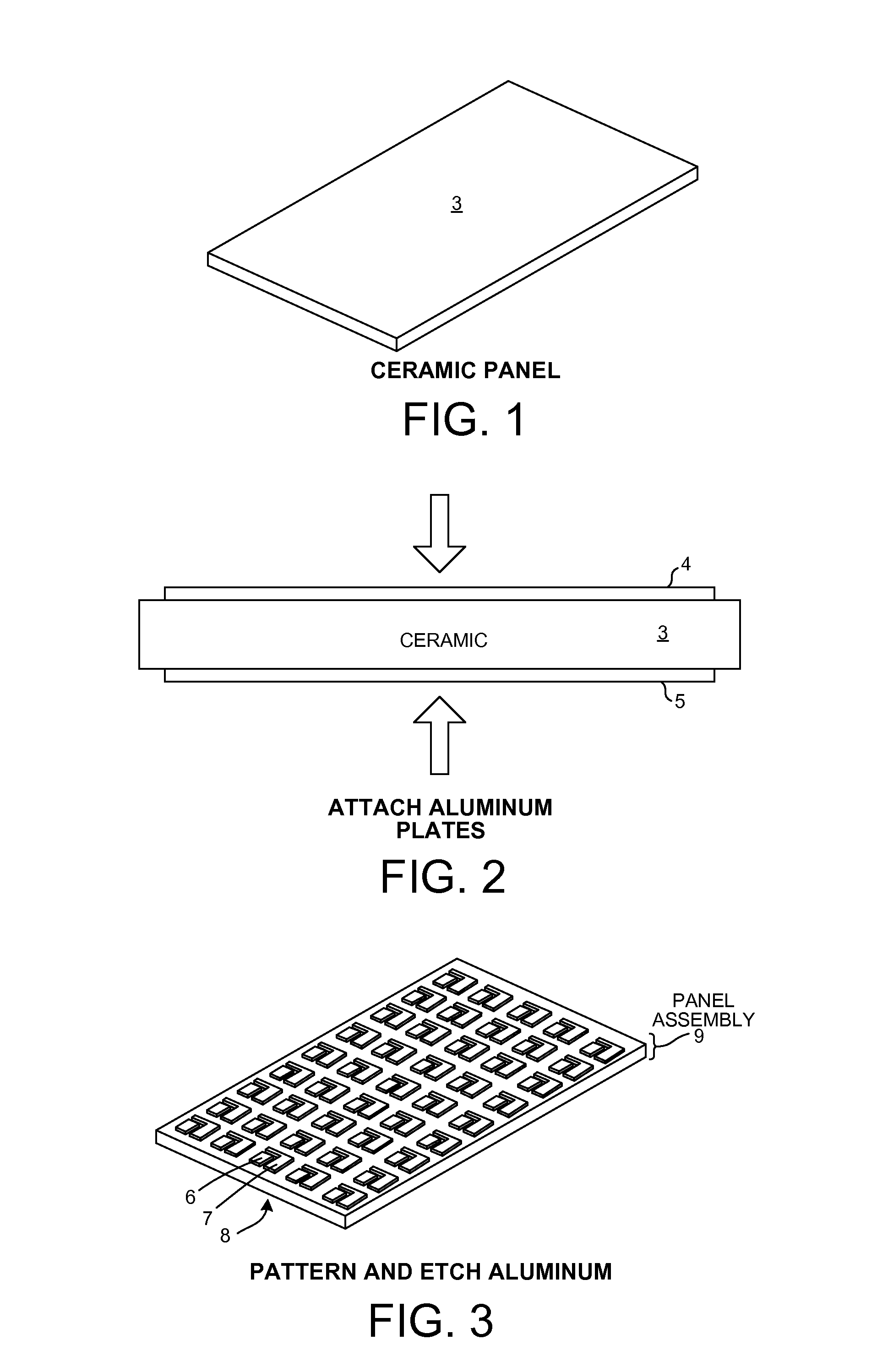

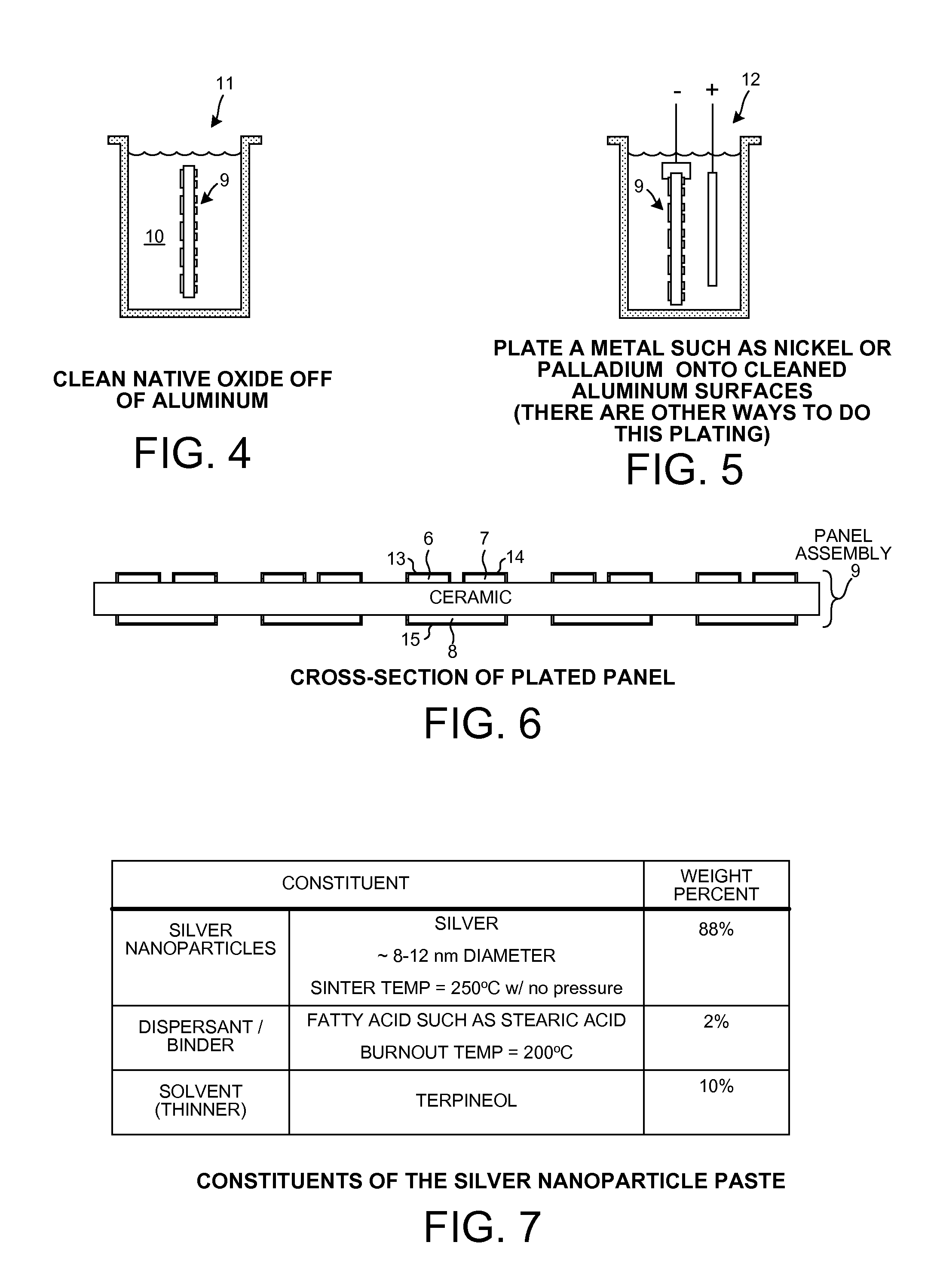

Solderless Die Attach to a Direct Bonded Aluminum Substrate

ActiveUS20130328204A1Cooking-vessel materialsSemiconductor/solid-state device detailsLead bondingLead frame

A DBA-based power device includes a DBA (Direct Bonded Aluminum) substrate. An amount of silver nanoparticle paste of a desired shape and size is deposited (for example by micro-jet deposition) onto a metal plate of the DBA. The paste is then sintered, thereby forming a sintered silver feature that is in electrical contact with an aluminum plate of the DBA. The DBA is bonded (for example, is ultrasonically welded) to a lead of a leadframe. Silver is deposited onto the wafer back side and the wafer is singulated into dice. In a solderless silver-to-silver die attach process, the silvered back side of a die is pressed down onto the sintered silver feature on the top side of the DBA. At an appropriate temperature and pressure, the silver of the die fuses to the sintered silver of the DBA. After wirebonding, encapsulation and lead trimming, the DBA-based power device is completed.

Owner:LITTELFUSE INC

Conductive pattern material and method for forming conductive pattern

InactiveUS6919158B2Wide applicationHigh sensitivityPhotoprinting processesSolid-state devicesConductive materialsSupport surface

There are provided a conductive pattern material and a pattern-forming method by which a fine pattern having a high resolution and no wire breakage is obtained. The conductive pattern material is such that on a support surface a pattern-forming layer is formed which allows the formation of a hydrophilic / hydrophobic region directly bonded to the support surface due to energy imparted. Energy is imparted to the pattern-forming material in an imagewise manner to form the conductive material layer.

Owner:FUJIFILM CORP

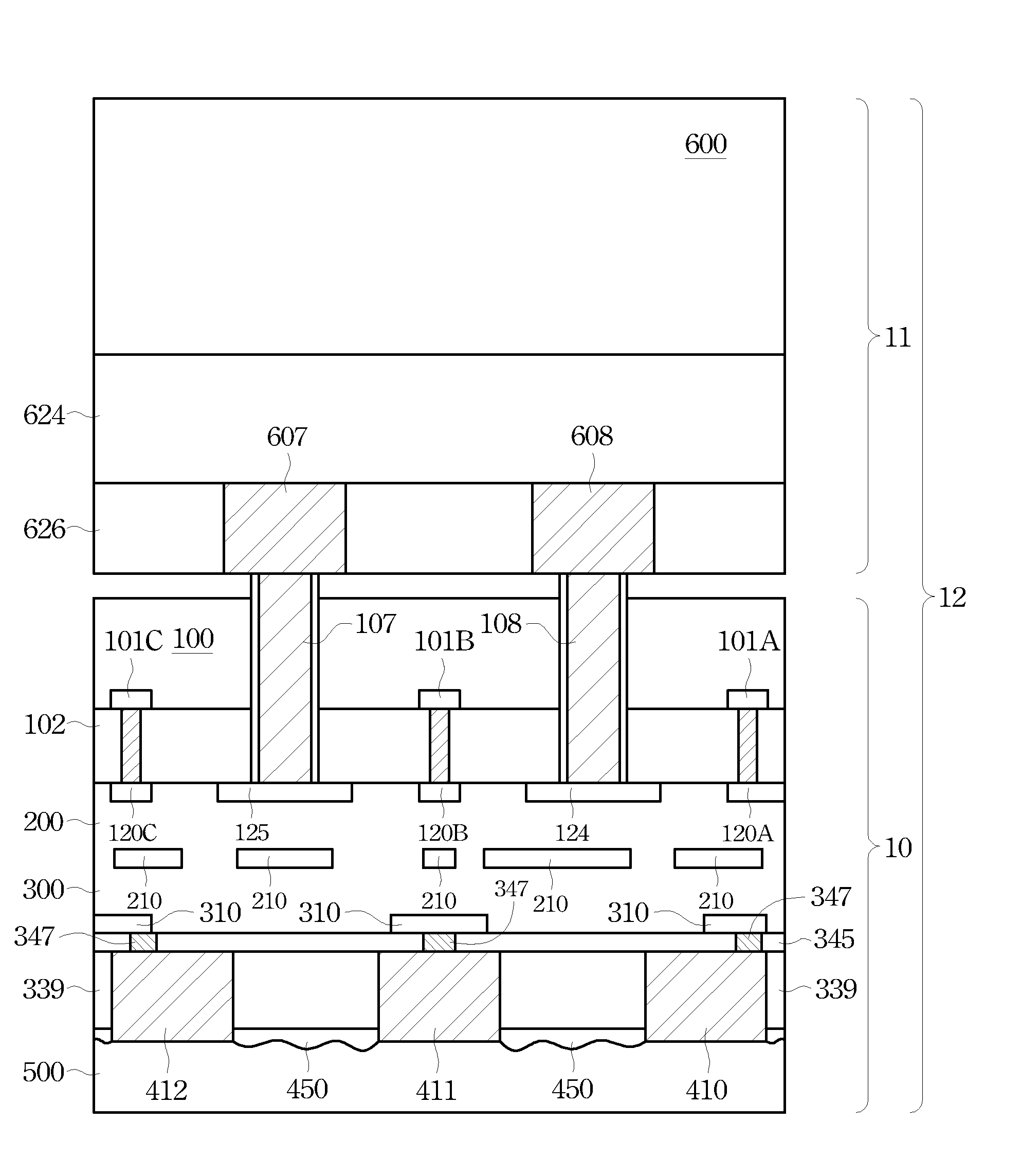

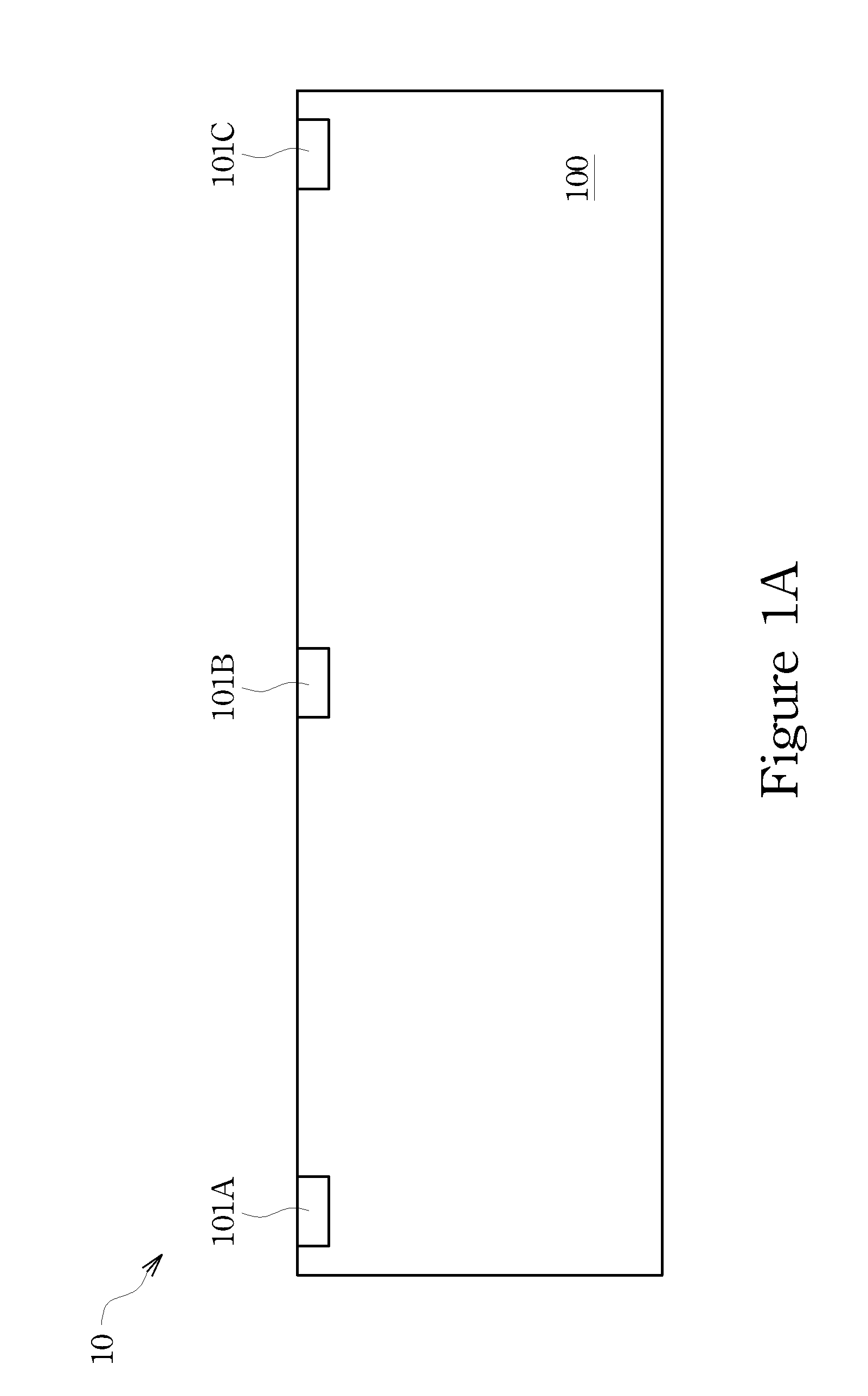

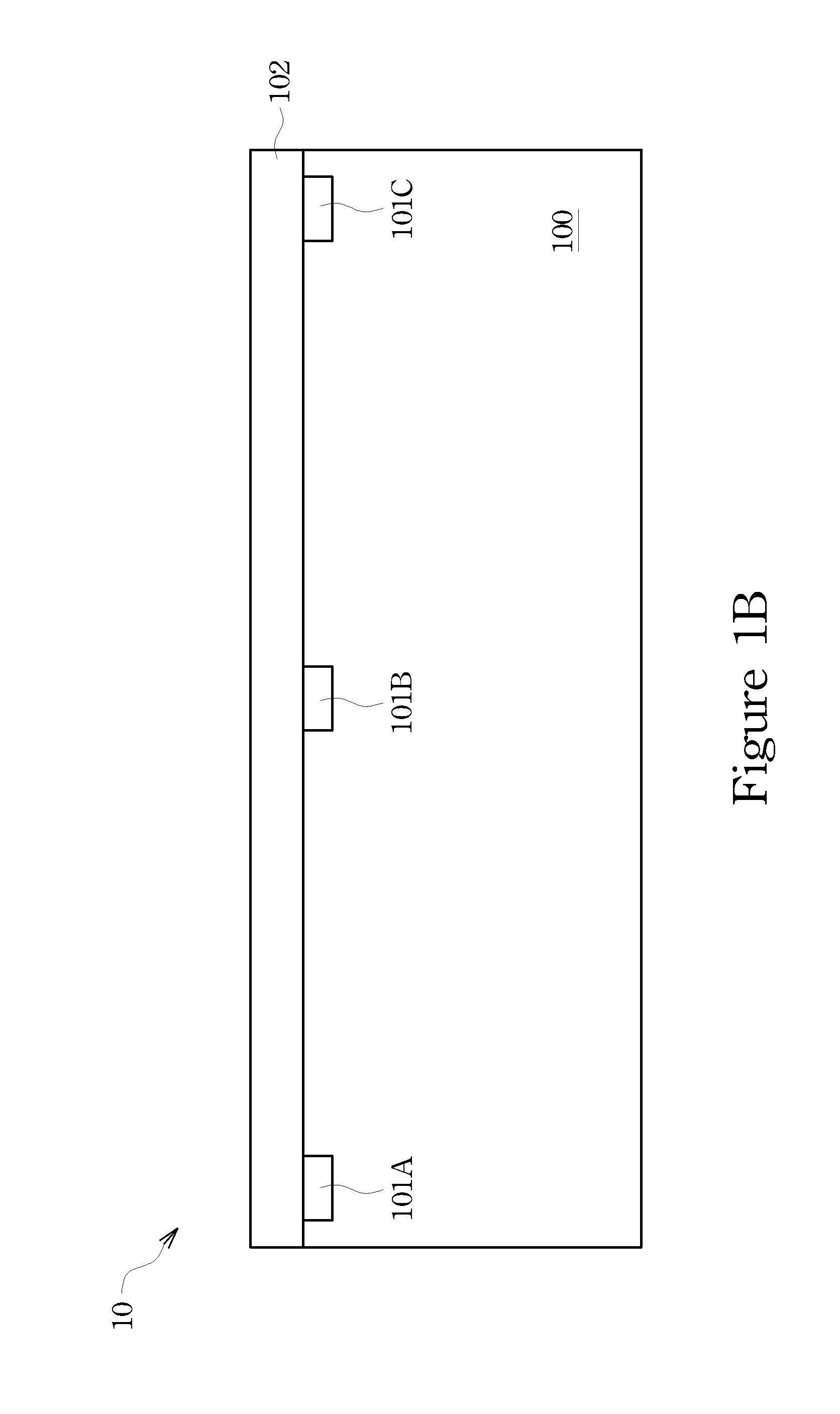

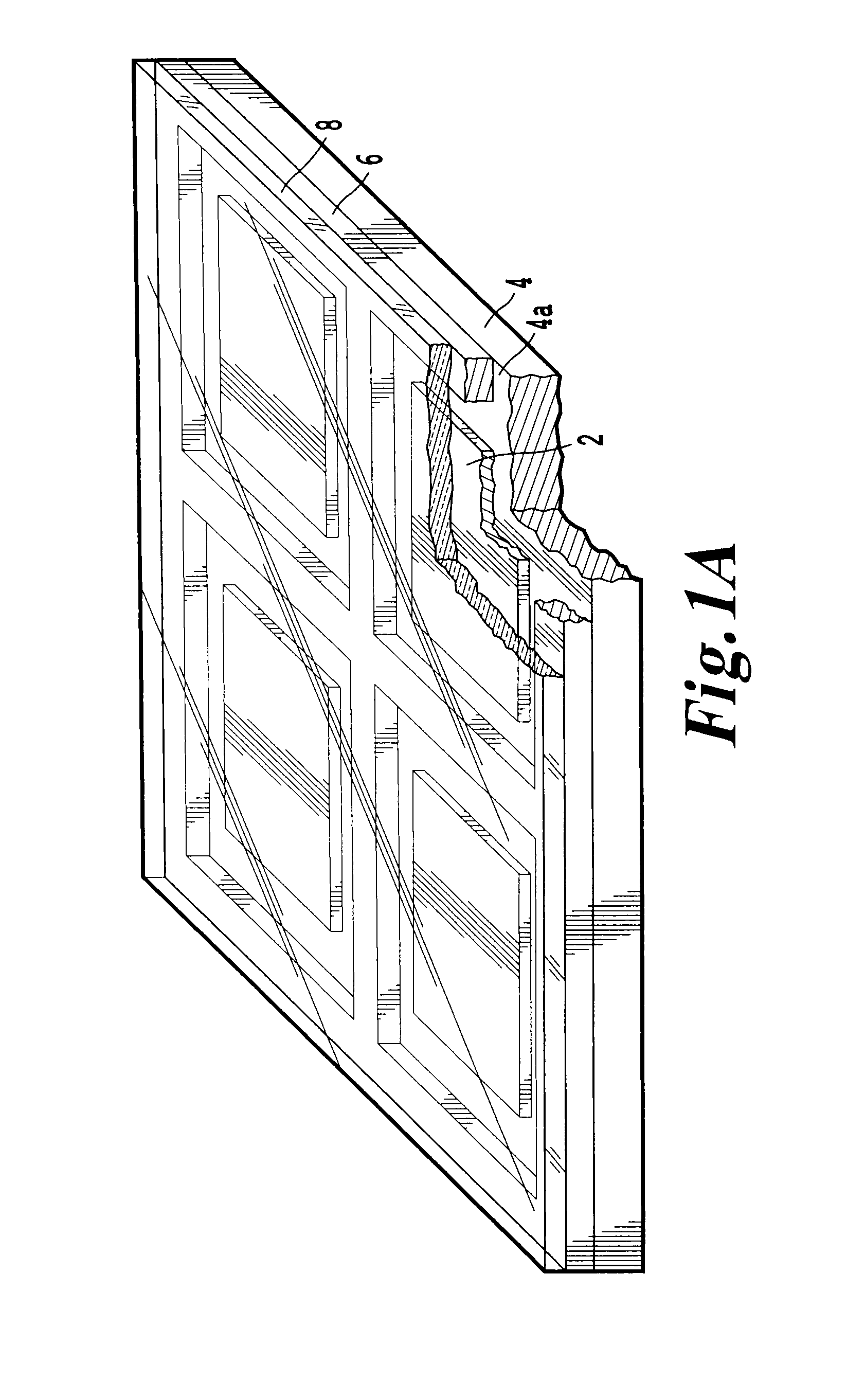

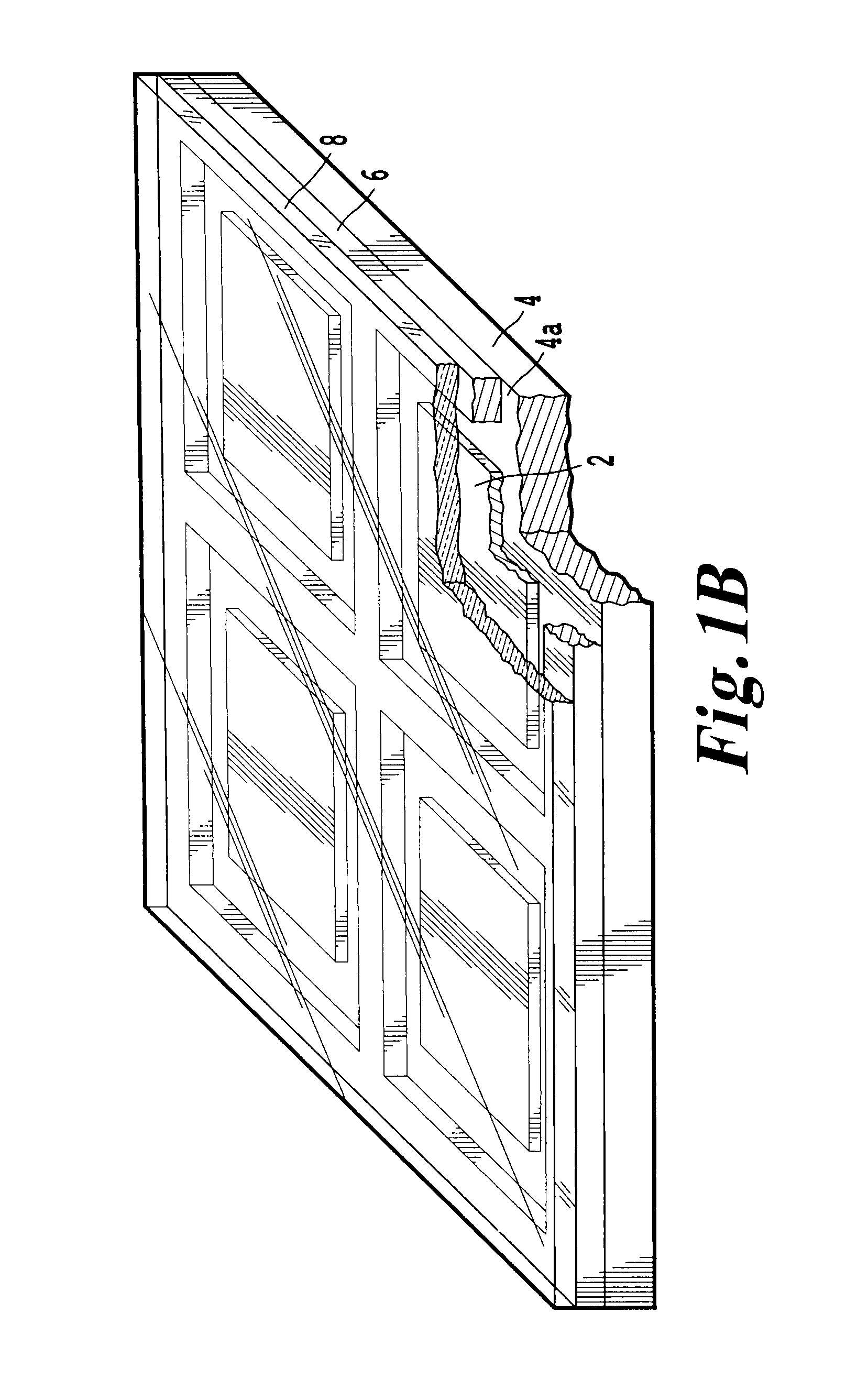

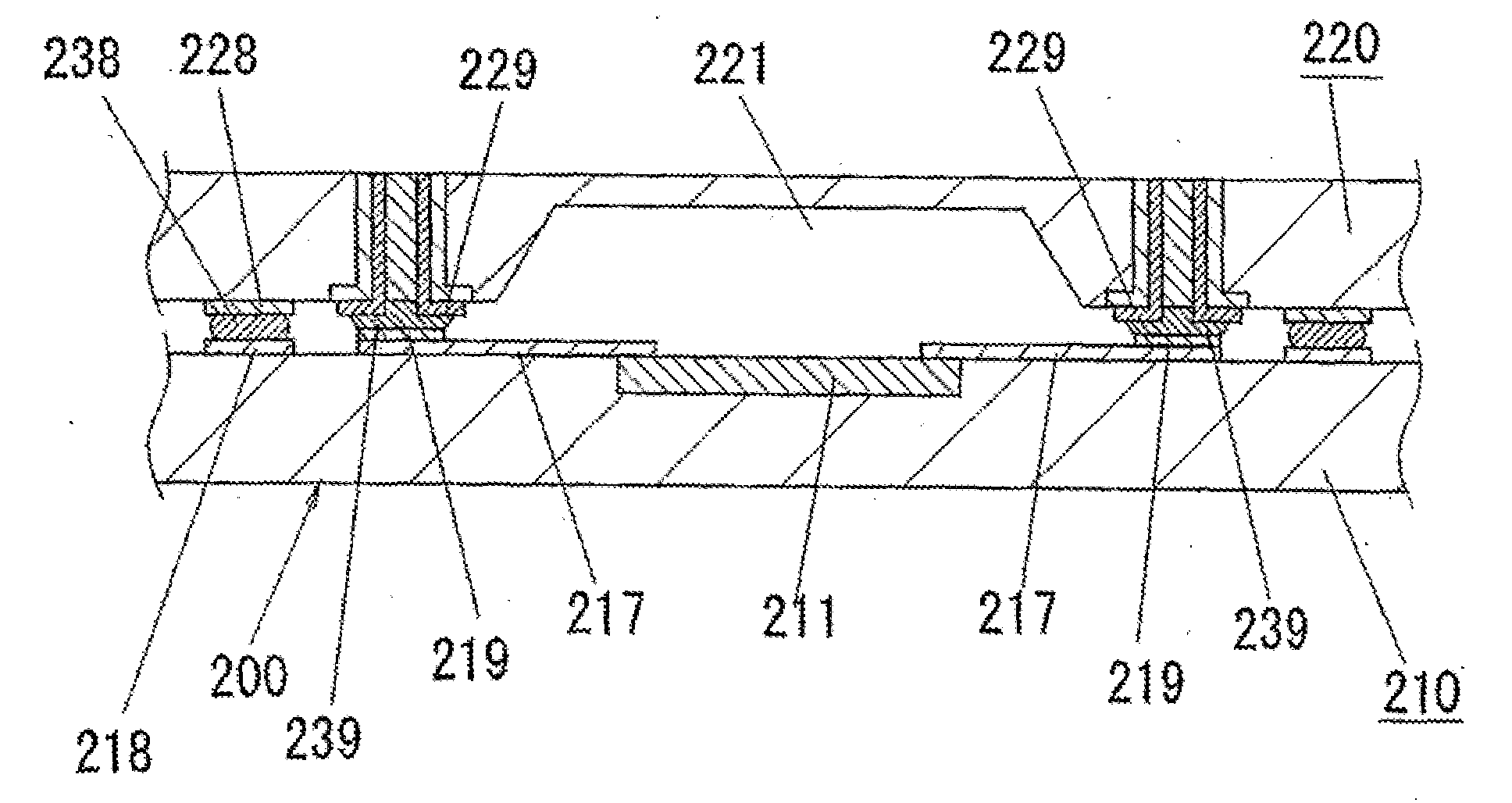

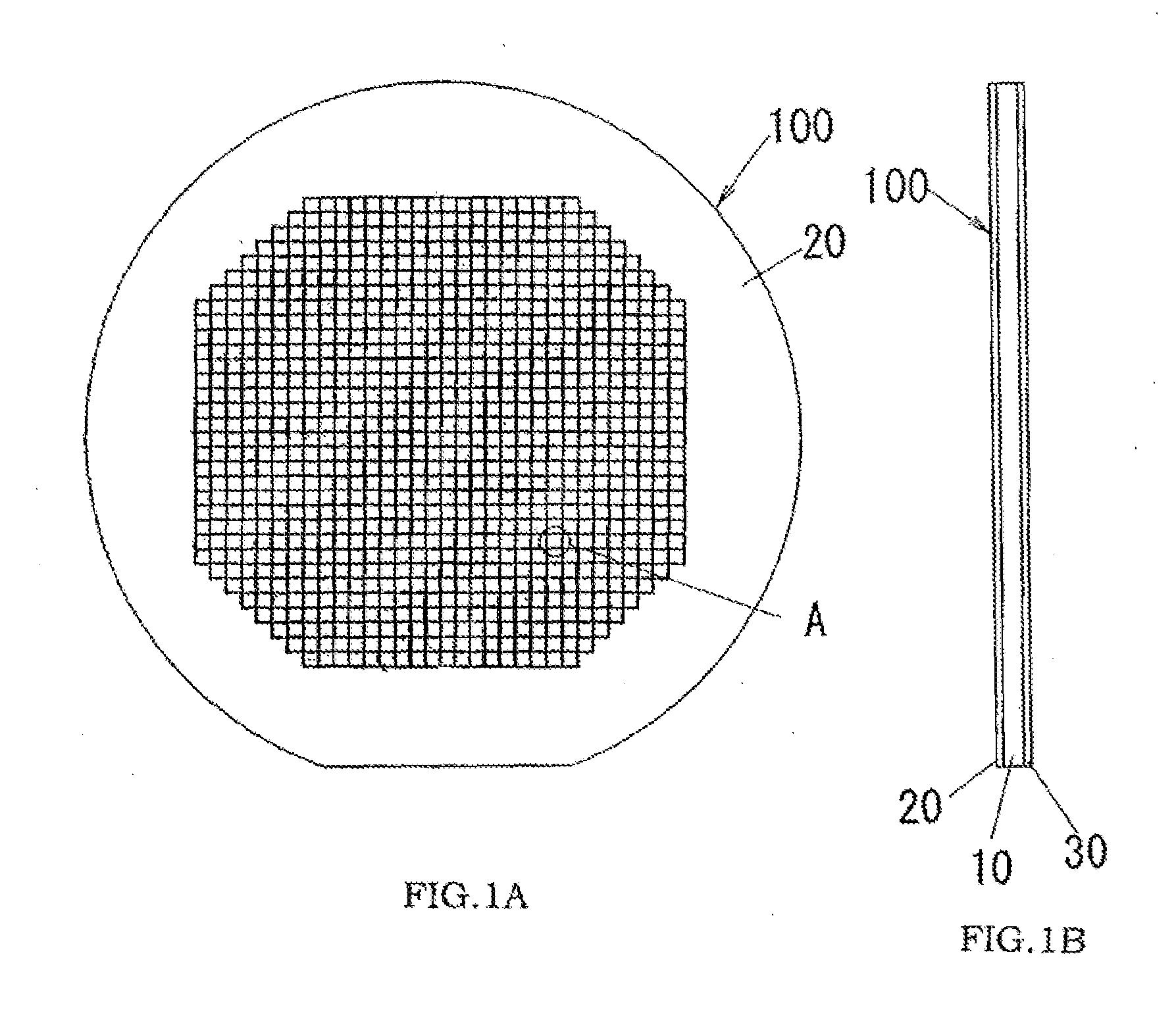

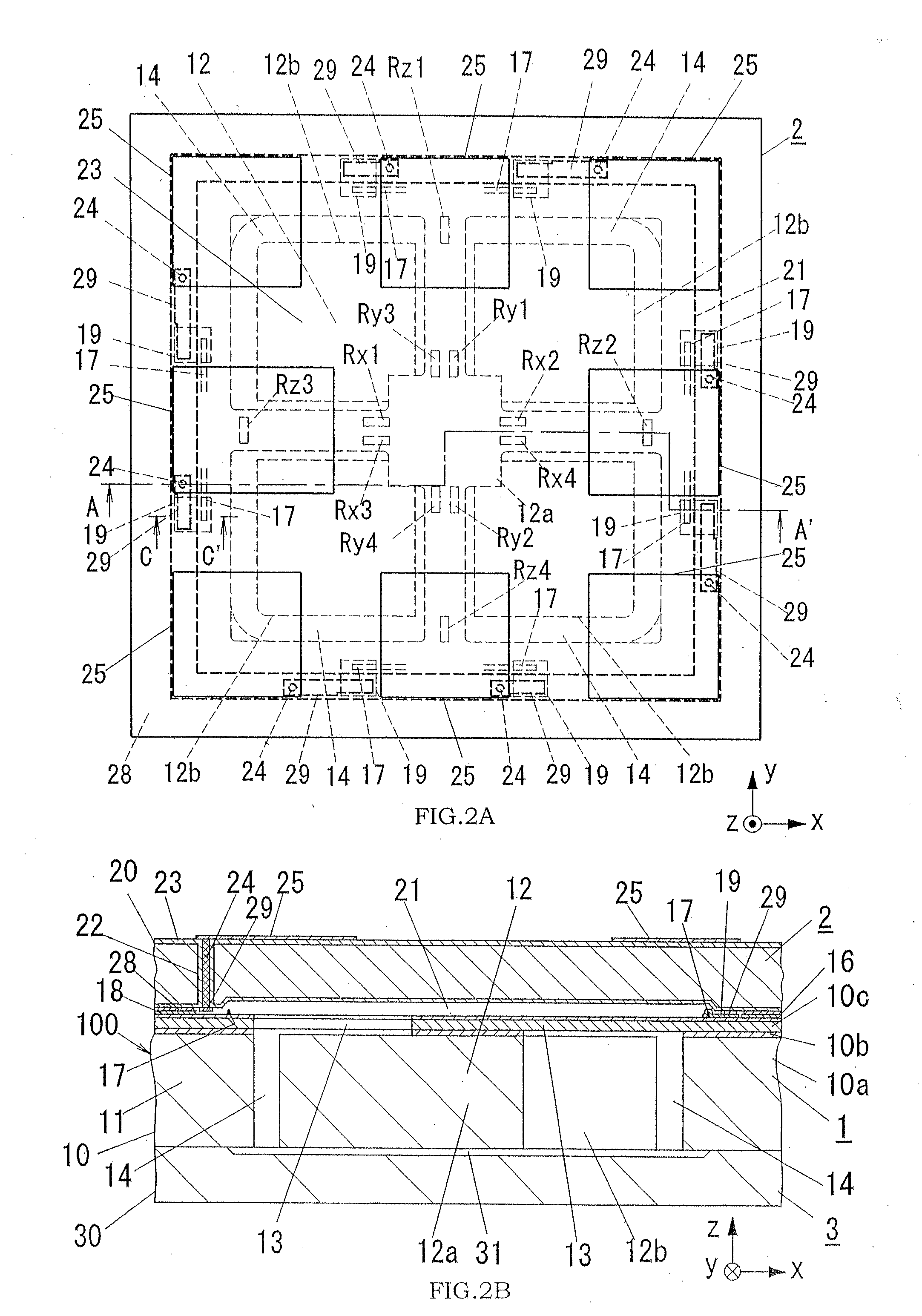

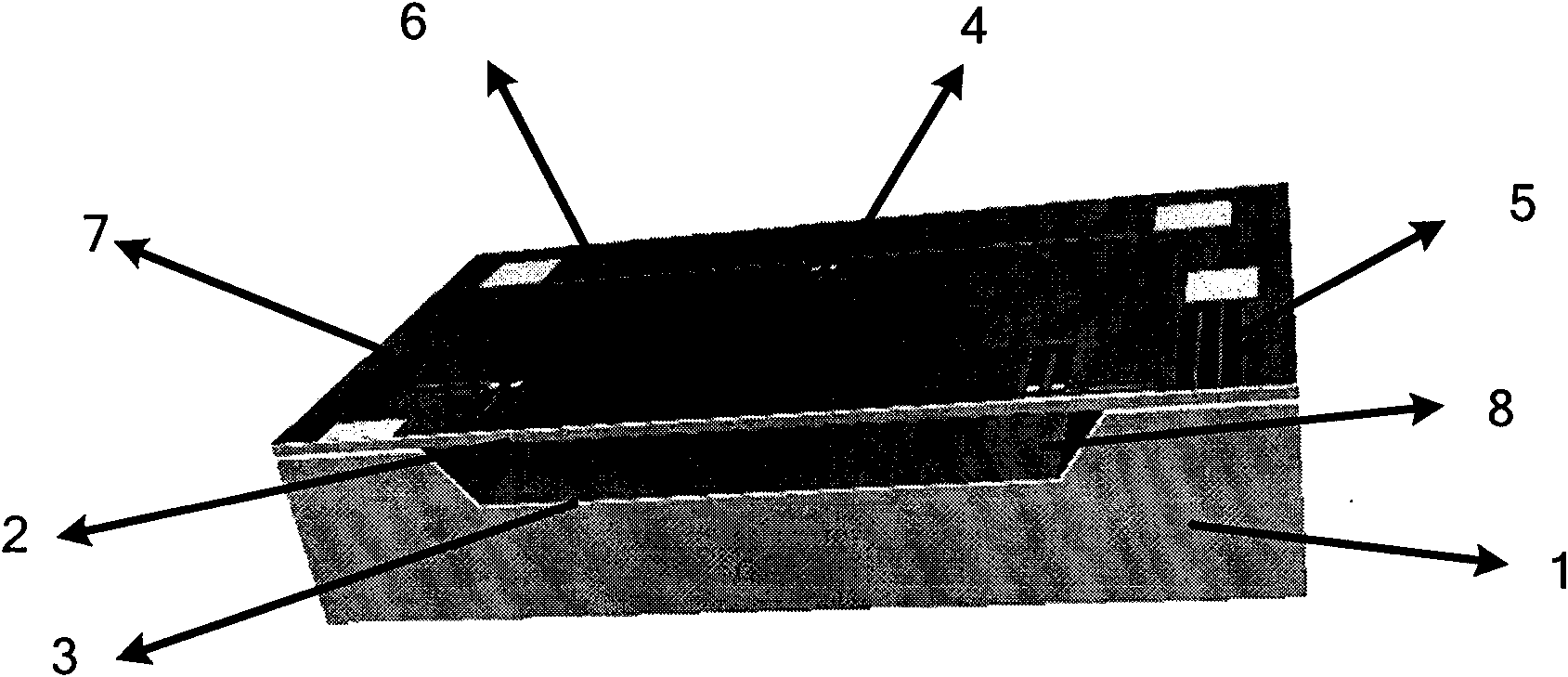

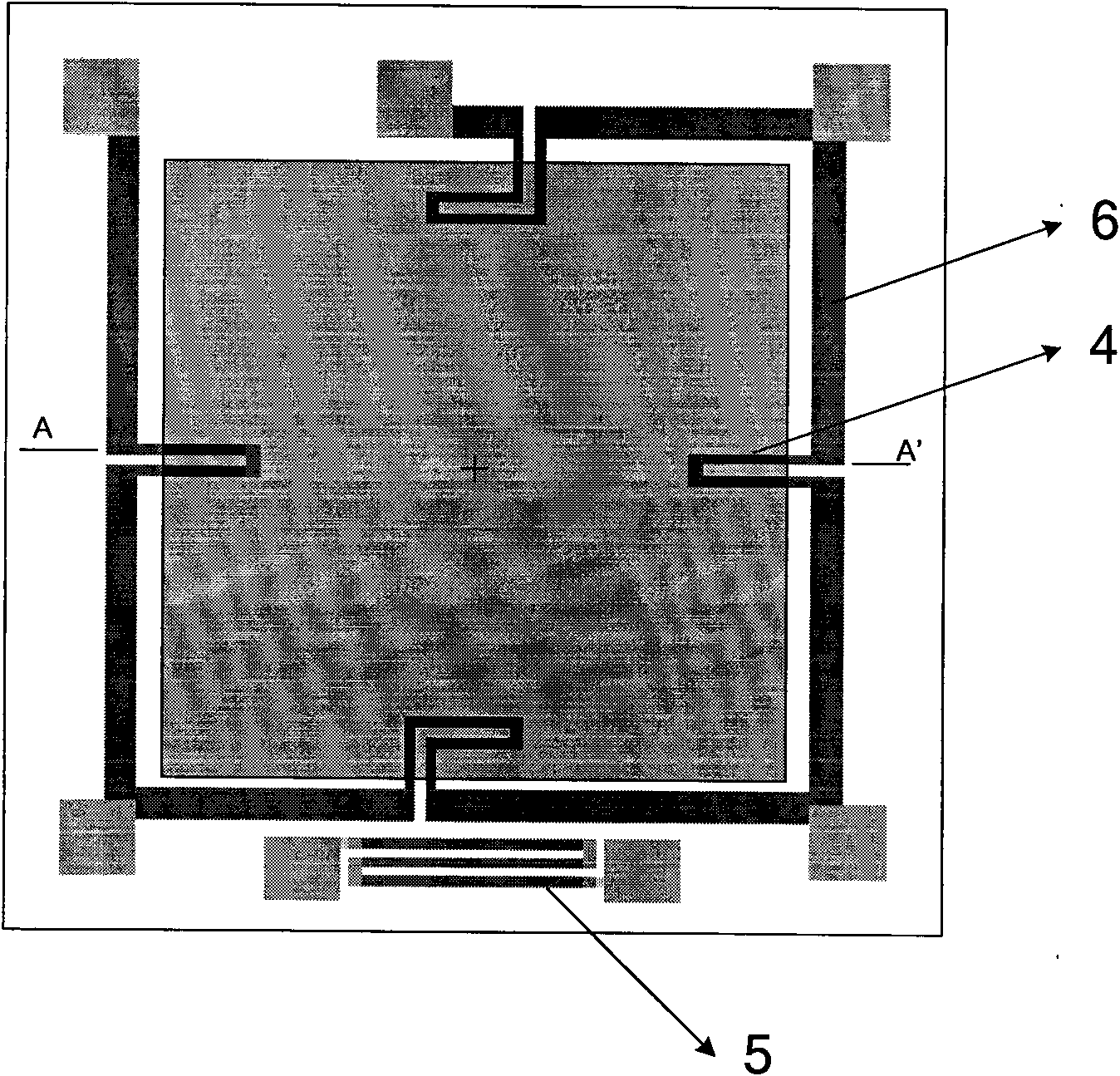

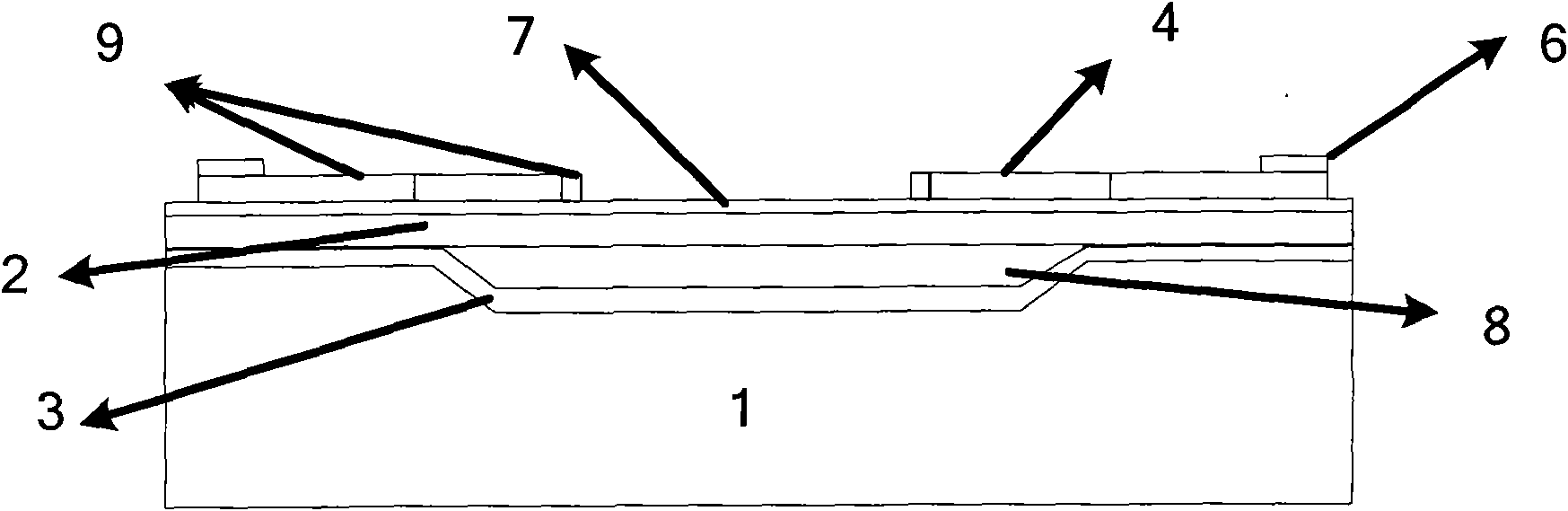

Wafer level package structure, and sensor device obtained from the same package structure

InactiveUS20090267165A1Little changeReducing atmosphereAcceleration measurement using interia forcesSemiconductor/solid-state device testing/measurementDiffusionGyroscope

A wafer level package structure with a plurality of compact sensors such as acceleration sensors and gyro sensors is provided. This package structure is composed of a semiconductor wafer with plural sensor units, and a pair of package wafers bonded to both surfaces of the semiconductor wafer. Each of the sensor units has a frame having an opening, a movable portion held in the opening to be movable relative to the frame, and a detecting portion for outputting an electric signal according to a positional displacement of the movable portion. Since the semiconductor wafer is bonded to each of the package wafers by a solid-phase direct bonding without diffusion between a surface-activated region formed on the frame and a surface-activated region formed on the package wafer, it is possible to prevent that variations in sensor characteristics occur due to residual stress at the bonding interface.

Owner:MATSUSHITA ELECTRIC WORKS LTD

Bonding surfaces for direct bonding of semiconductor structures

InactiveUS20130020704A1Simple introductionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureBonding process

Methods of directly bonding a first semiconductor structure to a second semiconductor structure include directly bonding at least one device structure of a first semiconductor structure to at least one device structure of a second semiconductor structure in a conductive material-to-conductive material direct bonding process. In some embodiments, at least one device structure of the first semiconductor structure may be caused to project a distance beyond an adjacent dielectric material on the first semiconductor structure prior to the bonding process. In some embodiments, one or more of the device structures may include a plurality of integral protrusions that extend from a base structure. Bonded semiconductor structures are fabricated using such methods.

Owner:SONY SEMICON SOLUTIONS CORP

Increased contact alignment tolerance for direct bonding

ActiveUS20170179029A1Easy temperatureSemiconductor/solid-state device detailsSolid-state devicesBond interfaceParasitic capacitance

A bonded device structure including a first substrate having a first set of conductive contact structures, preferably connected to a device or circuit, and having a first non-metallic region adjacent to the contact structures on the first substrate, a second substrate having a second set of conductive contact structures, preferably connected to a device or circuit, and having a second non-metallic region adjacent to the contact structures on the second substrate, and a contact-bonded interface between the first and second set of contact structures formed by contact bonding of the first non-metallic region to the second non-metallic region. The contact structures include elongated contact features, such as individual lines or lines connected in a grid, that are non-parallel on the two substrates, making contact at intersections. Alignment tolerances are thus improved while minimizing dishing and parasitic capacitance.

Owner:INVENSAS BONDING TECH INC

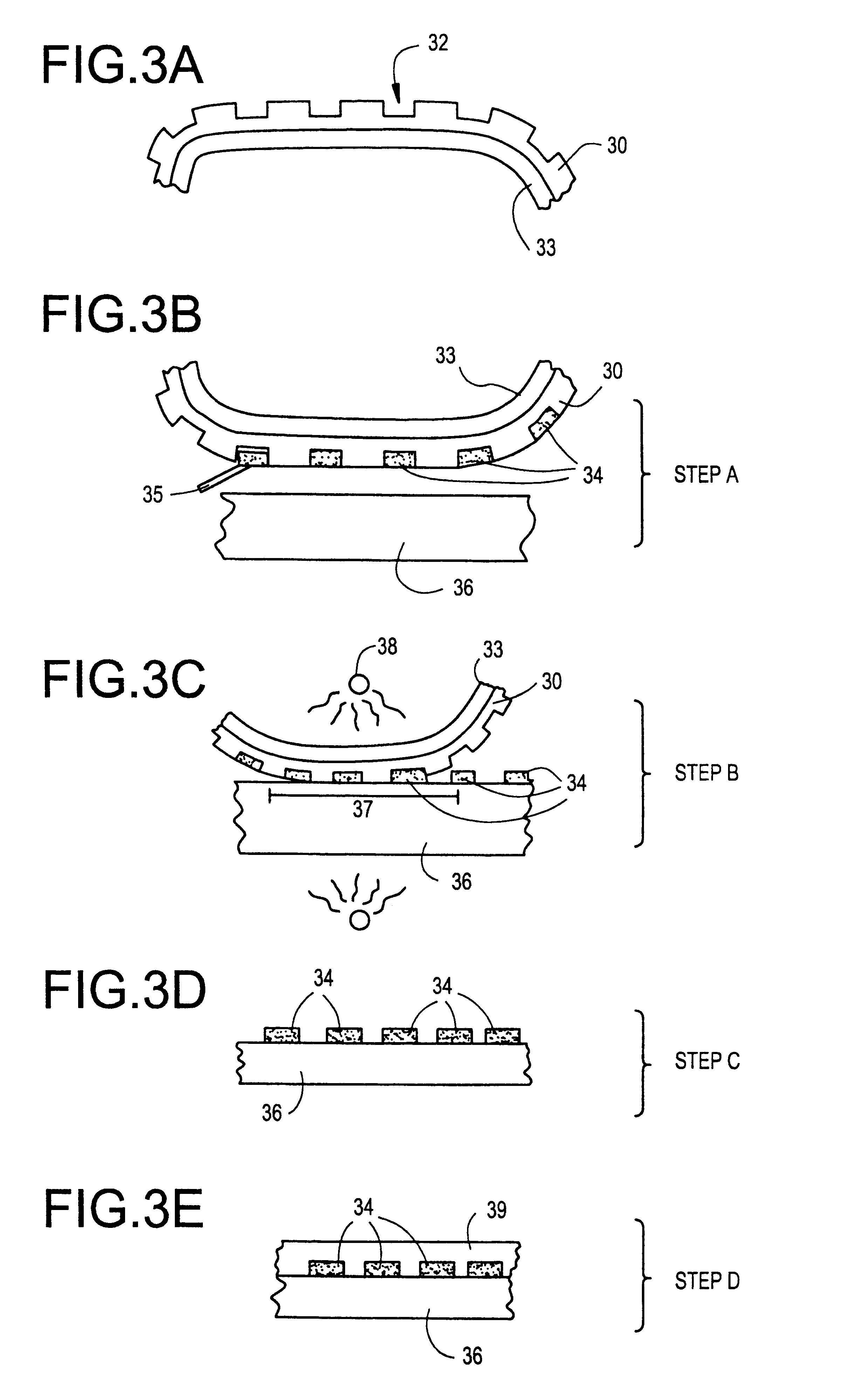

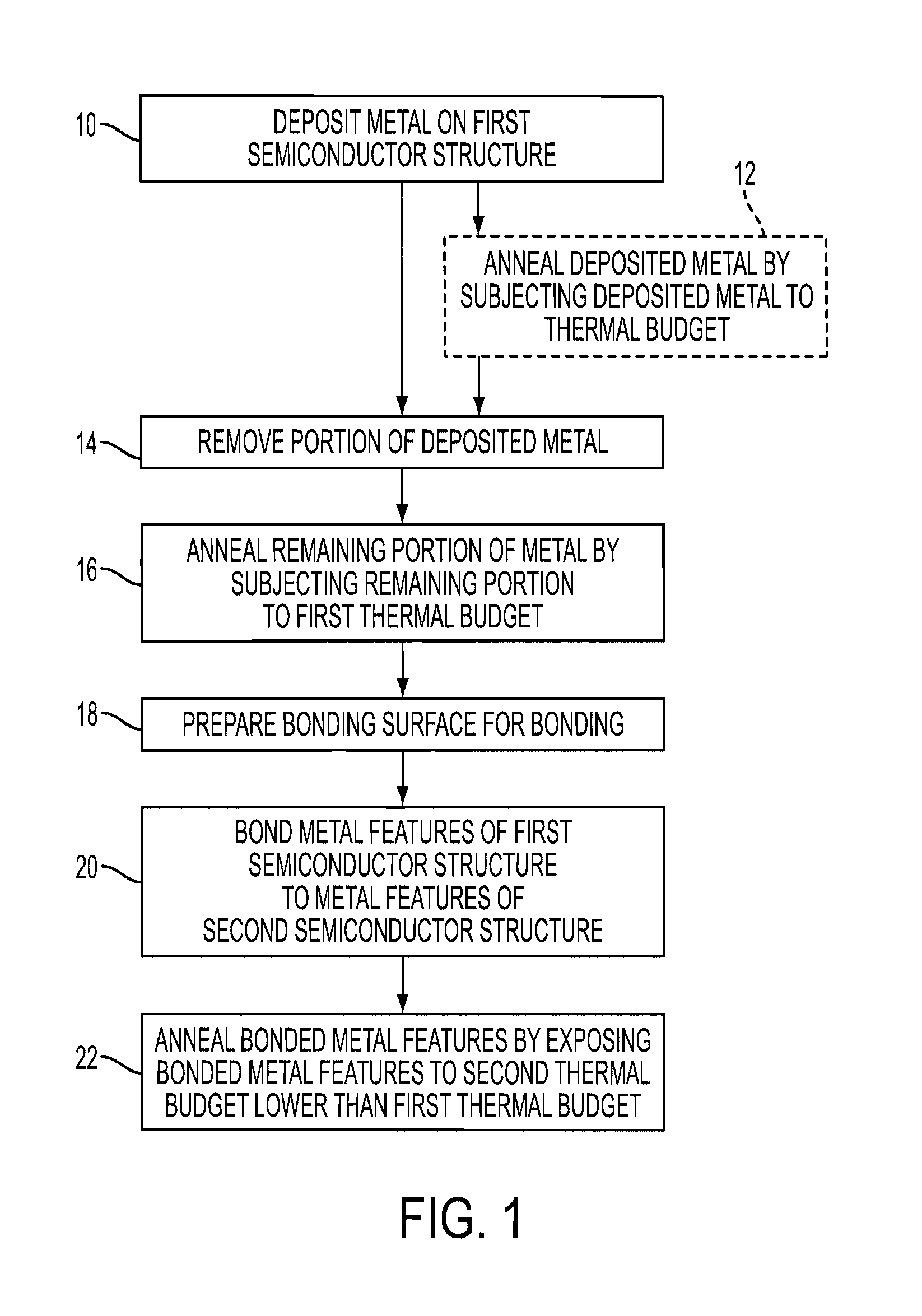

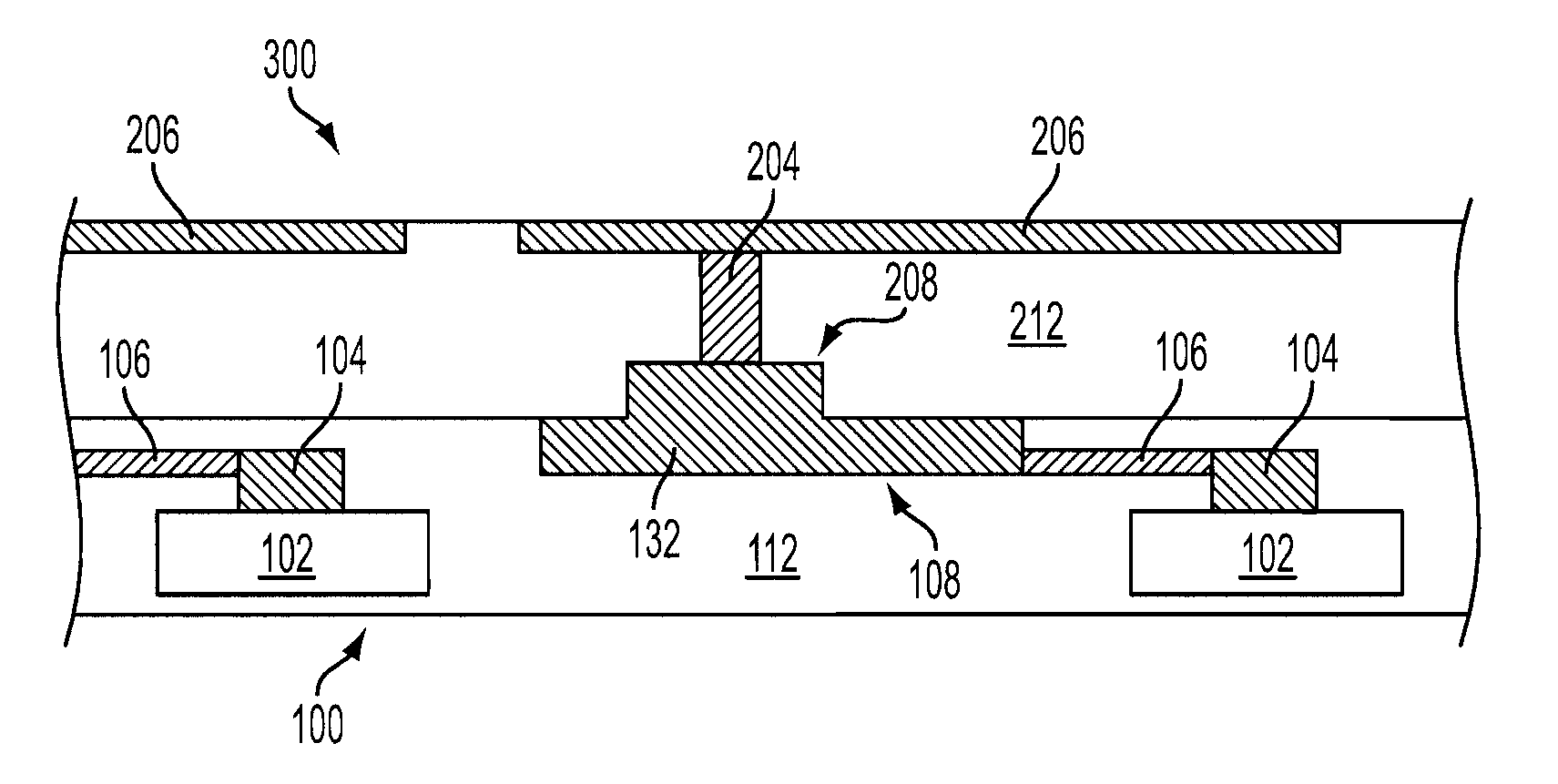

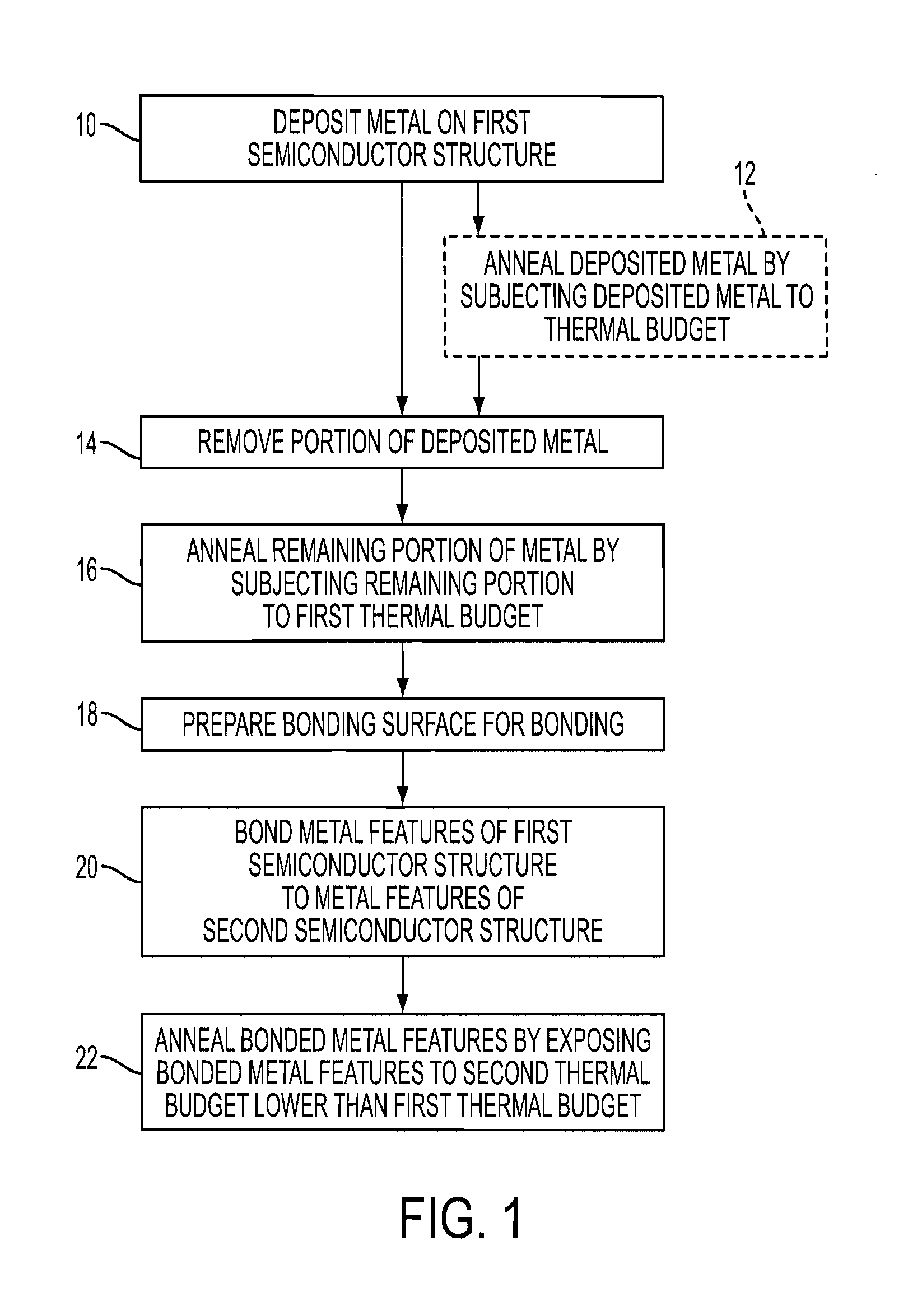

Methods for bonding semiconductor structures involving annealing processes, and bonded semiconductor structures and intermediate structures formed using such methods

InactiveUS20120252189A1Limit scopeSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor structure

Methods of bonding together semiconductor structures include annealing metal of a feature on a semiconductor structure prior to directly bonding the feature to a metal feature of another semiconductor structure to form a bonded metal structure, and annealing the bonded metal structure after the bonding process. The thermal budget of the first annealing process may be at least as high as a thermal budget of a later annealing process. Additional methods involve forming a void in a metal feature, and annealing the metal feature to expand the metal of the feature into the void. Bonded semiconductor structures and intermediate structures are formed using such methods.

Owner:SONY SEMICON SOLUTIONS CORP

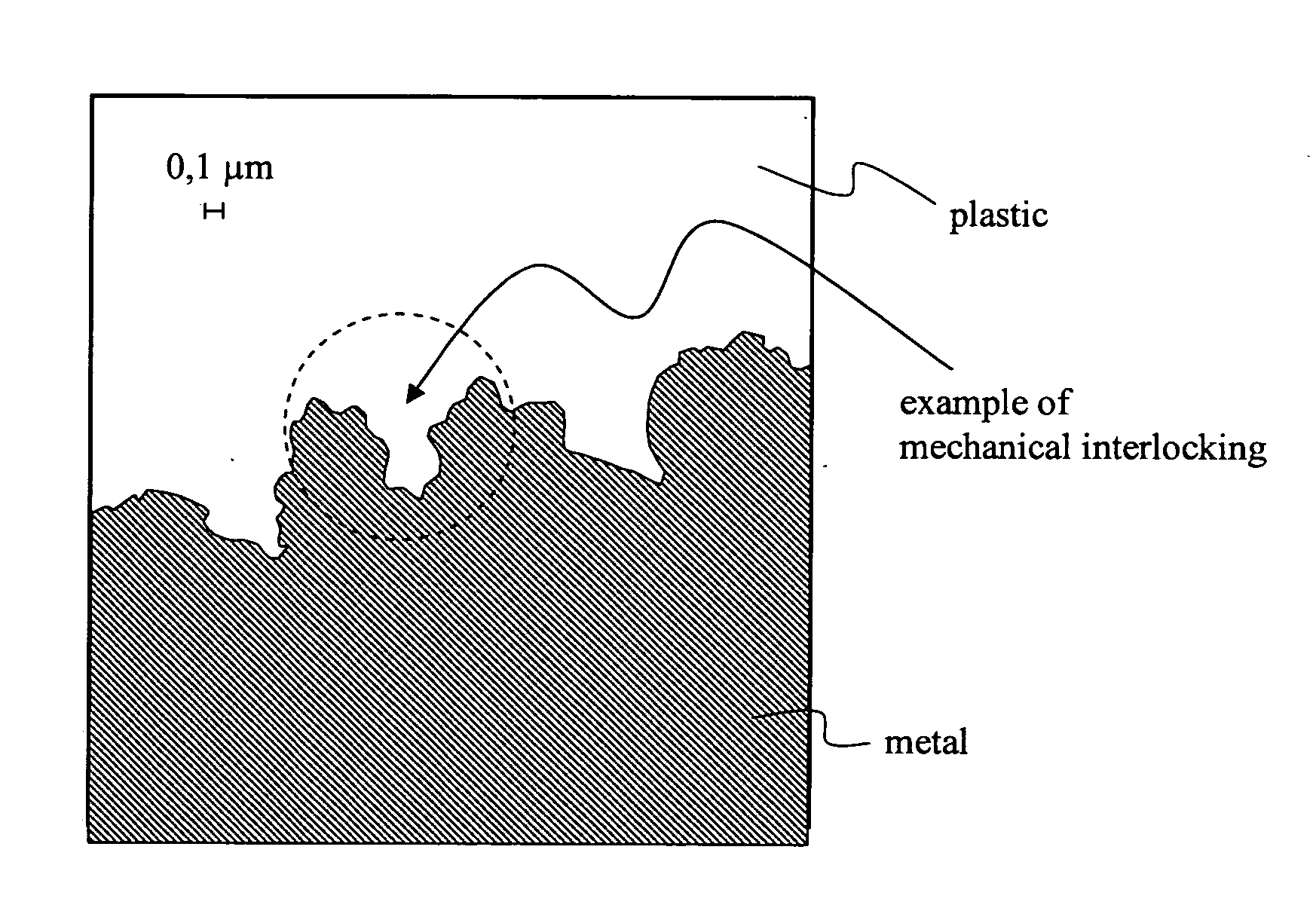

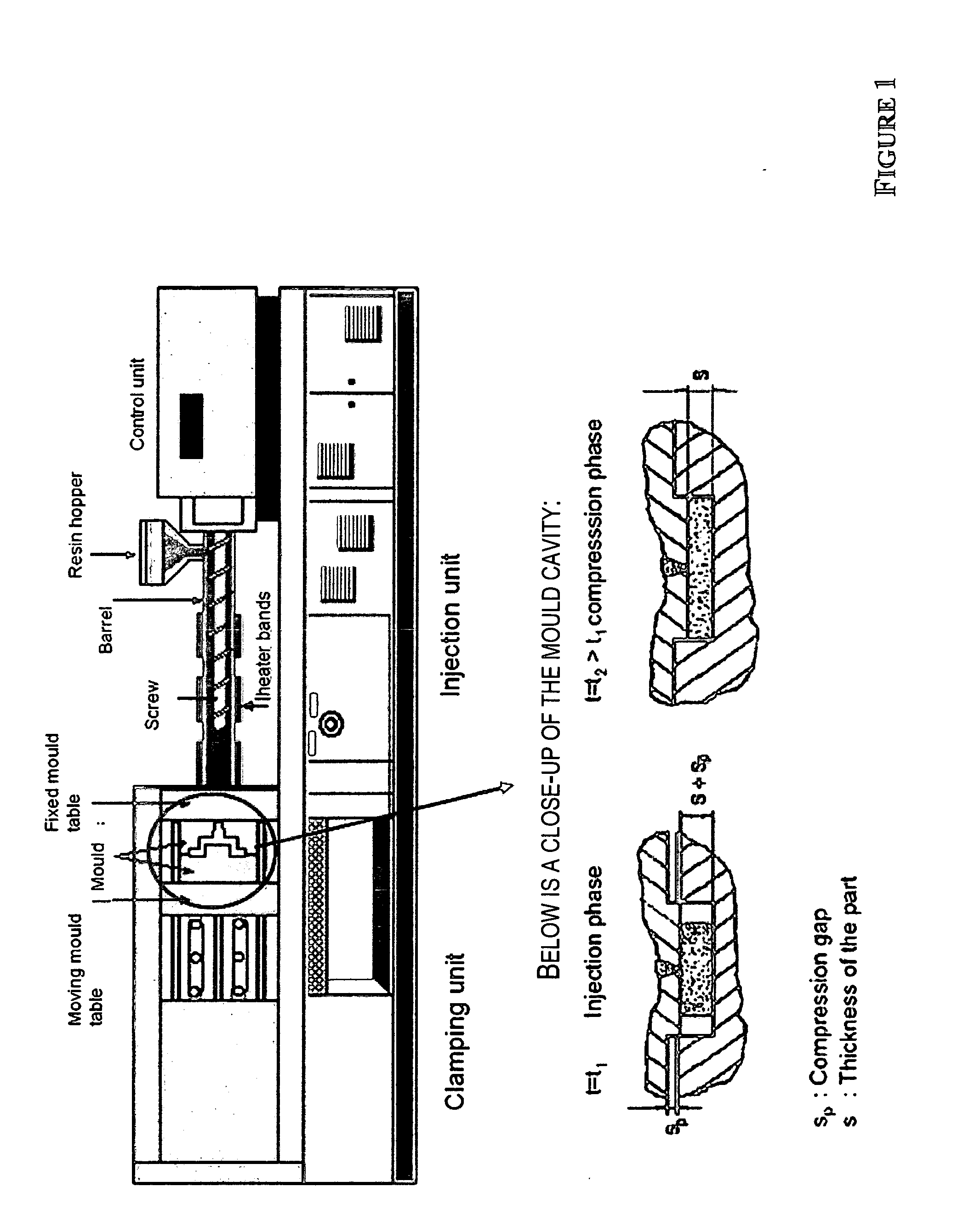

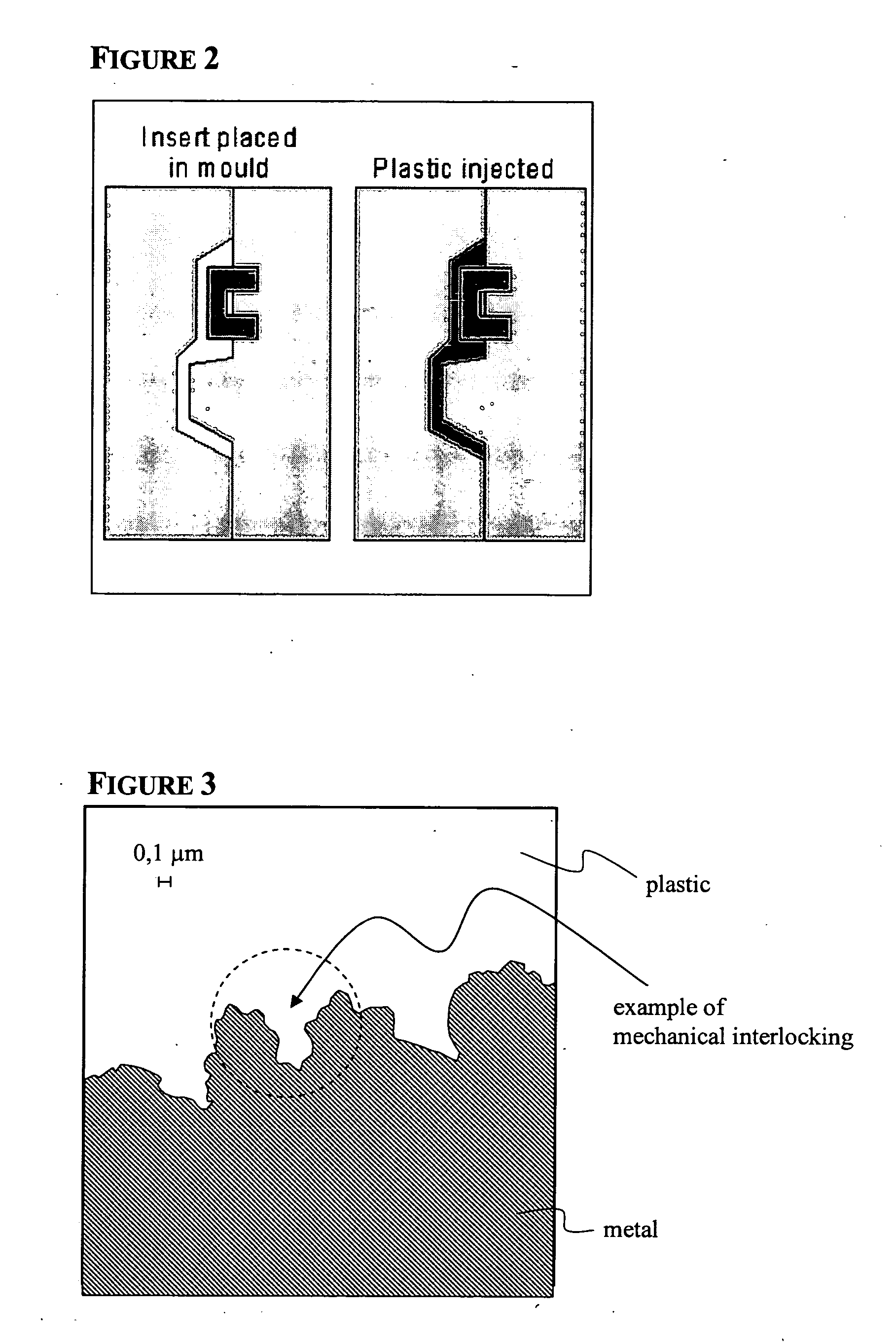

Plastic-acceptor hybrid components

InactiveUS20080070001A1High bonding strengthLess internal stressRecord information storageMagnetic recordingEngineeringInjection moulding

The present invention relates generally to plastic-acceptor hybrid components and, more particularly, to the direct bonding of over-moulded plastics to an acceptor insert, such as a metal, in an injection moulding tool. A method and apparatus are provided allowing the production of the present plastic-acceptor hybrid components in which the bonding of said components is obtained by anchoring the plastic component in micro-holes formed in the surface of an acceptor component.

Owner:NOKIA CORP

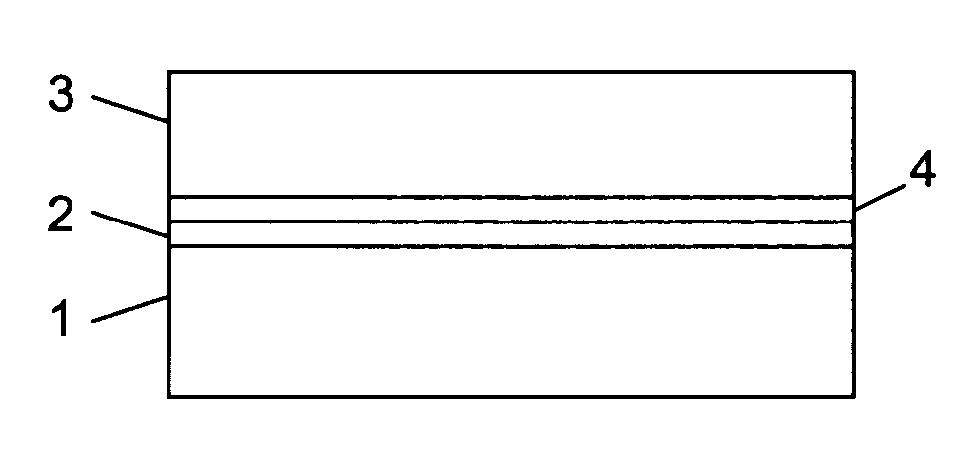

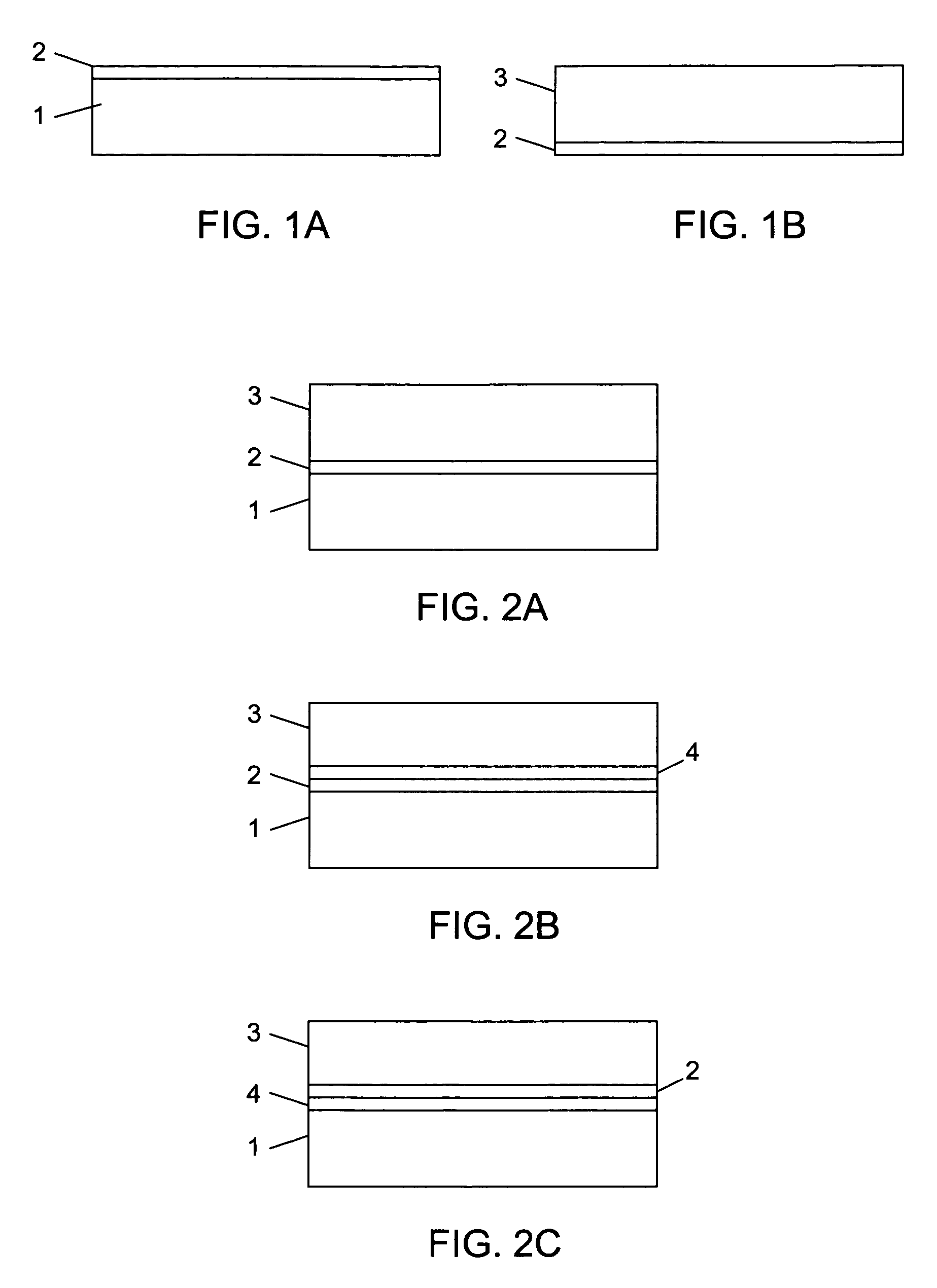

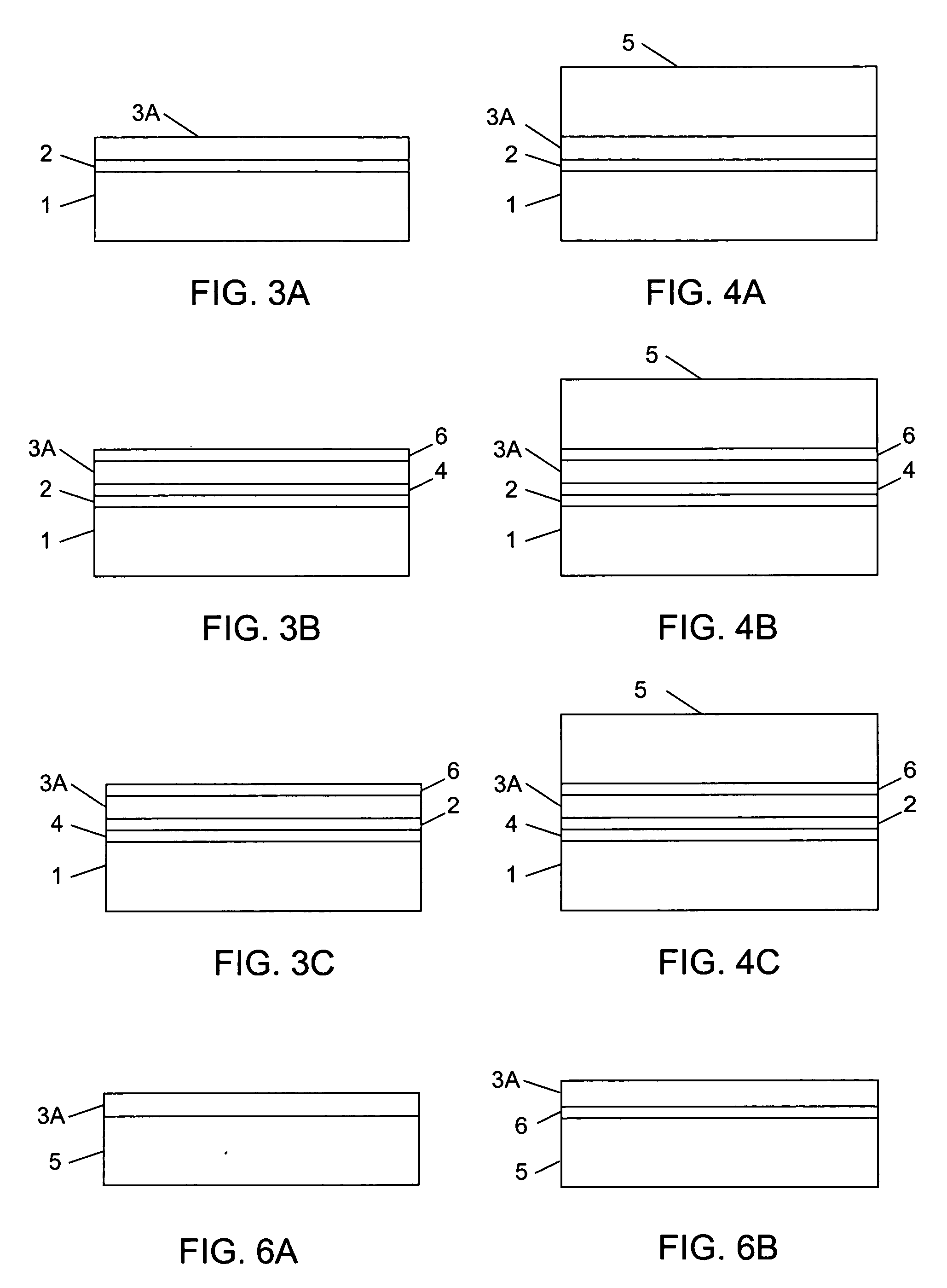

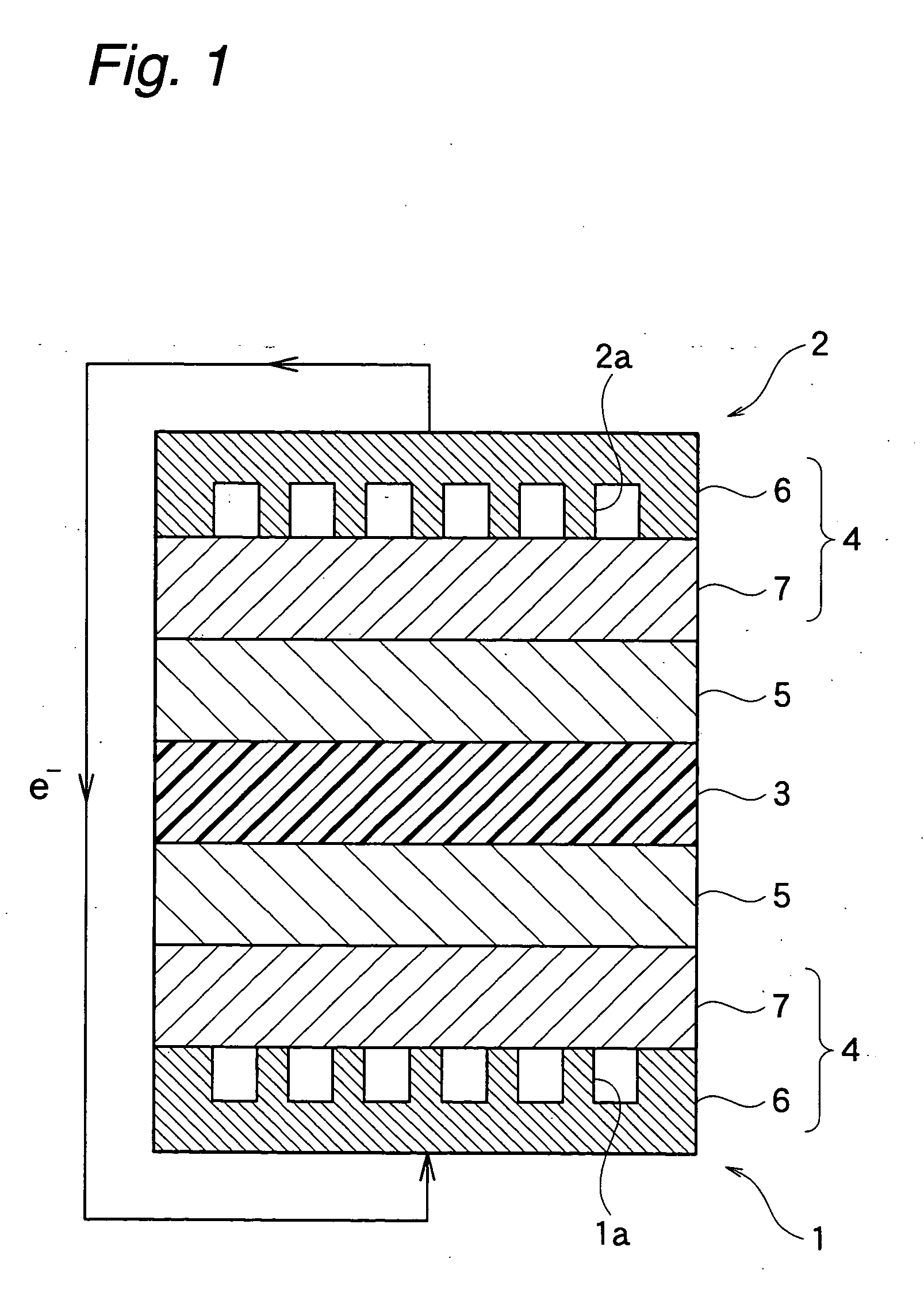

Pressure sensor based on Si-Si direct bonding and manufacturing method thereof

InactiveCN101551284APrecise size controlOvercome performance degradation flawsTelevision system detailsSemi-permeable membranesWorking temperatureBoron

The invention discloses a pressure sensor based on Si-Si direct bonding, comprising a silicon substrate (1) with a shallow groove (8); the silicon substrate (1) is provided with a single crystal silicon stress membrane (2); a silicon dioxide layer (3) is arranged between the silicon substrate (1) and the stress membrane (2); four P-type single crystal silicon piezoresistors (4) are arranged on the stress membrane (2); an insulating medium silicon dioxide layer (7) is arranged among the stress membrane (2) and the piezoresistors (4); and a Wheatstone bridge is formed among the piezoresistors (4) by utilizing concentrated boron doped silicon (9) and a golden lead (6). The pressure sensor adopts Si-Si direct bonding technology to form the stress membrane and the sealing cavity; the piezoresistors thereof adopt silicon dioxide as an insulating layer and the working temperature can be up to 300 DEG C; and the pressure sensor has firm structure and excellent performance and can meet the requirements on high-temperature pressure sensors in the fields of automobile, aerospace and the like. The invention also relates to a manufacturing method of the pressure sensor.

Owner:江苏英特神斯科技有限公司

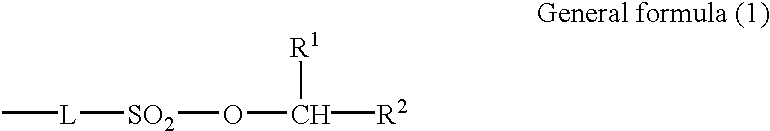

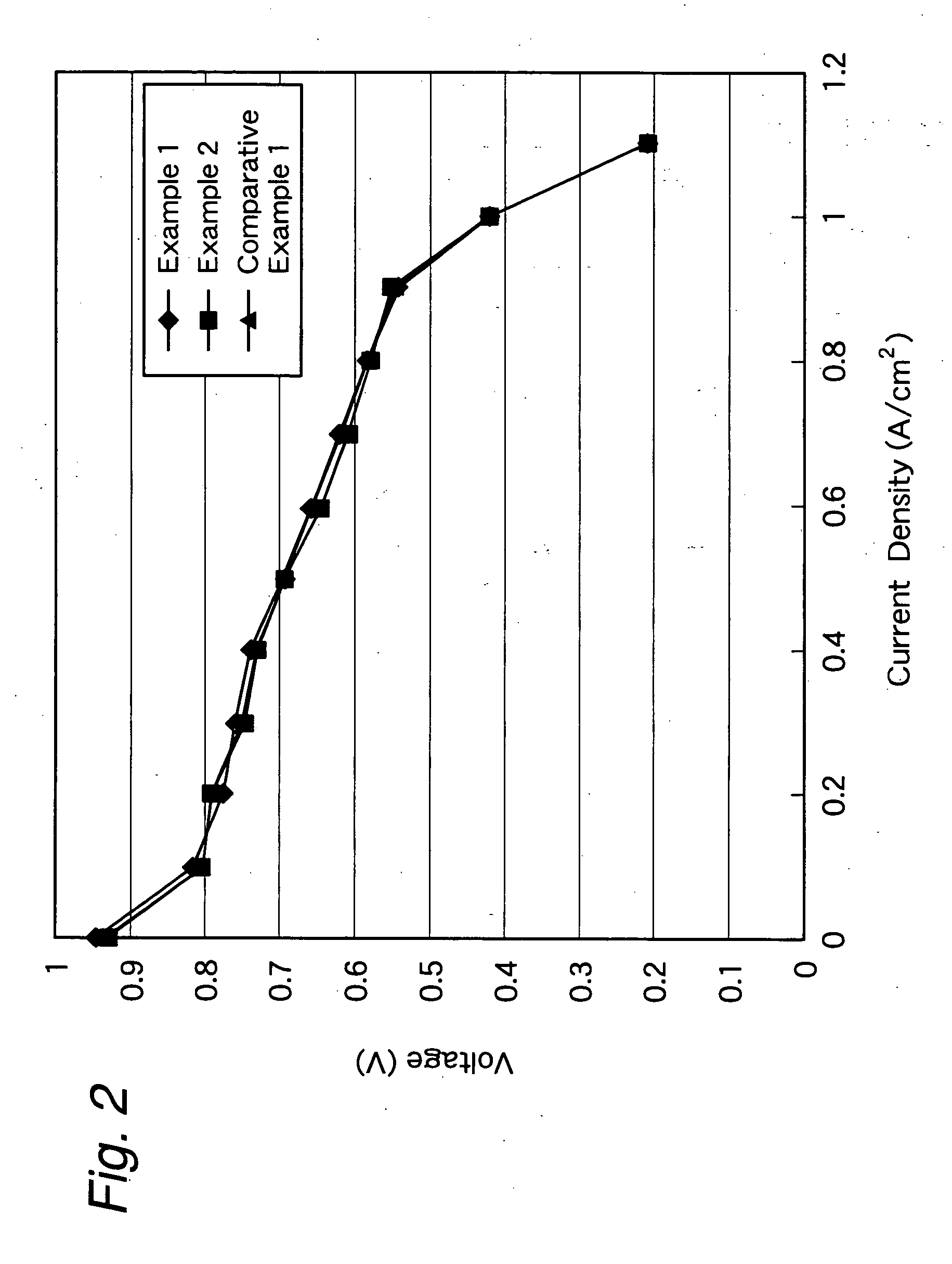

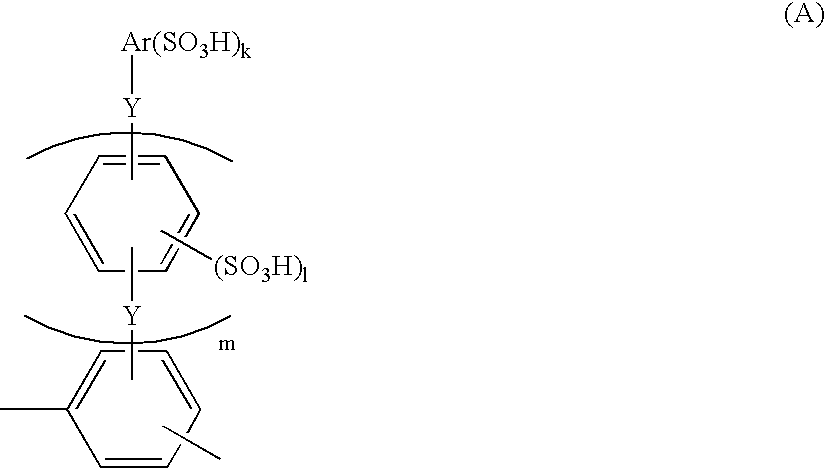

Membrane-electrode structure for solid polymer fuel cell

InactiveUS20050064260A1Improve power generation effectPromote recoverySolid electrolytesFuel cell auxillariesElectronPolymer

Disclosed is a membrane-electrode structure for a solid polymer fuel cell comprising a pair of electrode catalyst layers and a polyeletrolyte membrane sandwiched between the electrode catalyst layers, wherein the electrode catalyst layers contain polyarylene having a sulfonic acid group, said polyarylene comprising a recurring unit represented by the following formula (A) and a recurring unit represented by the following formula (B); wherein Y is a direct bonding or a group selected from a divalent electron withdrawing group and a divalent electron donating group, Ar is a mononuclear or polynuclear aromatic group, m is an integer of 0 to 10, k is an integer of 0 to 5, l is an integer of 0 to 4, and k+1≧1; wherein R1 to R8 are each a hydrogen atom, a fluorine atom, an alkyl group, a fluorine-substituted alkyl group, an aryl group or an allyl group, W is a divalent electron withdrawing group or a direct bonding, T is a direct bonding, a divalent electron withdrawing group, a divalent electron donating group or the like, and n is an integer of 2 or more. The membrane-electrode structure for a solid polymer fuel cell of the present invention exhibits excellent electricity generation performance.

Owner:JSR CORPORATIOON +1

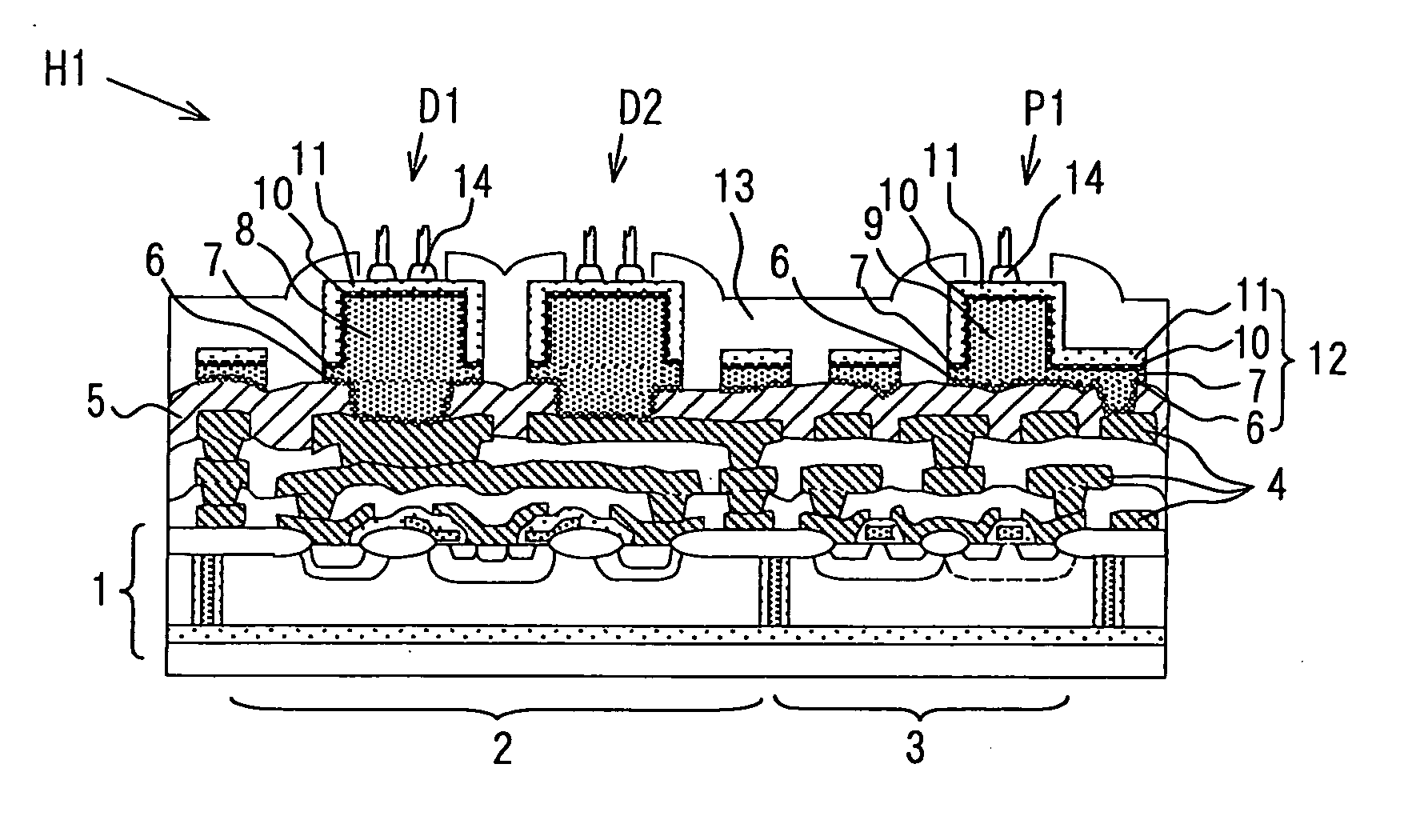

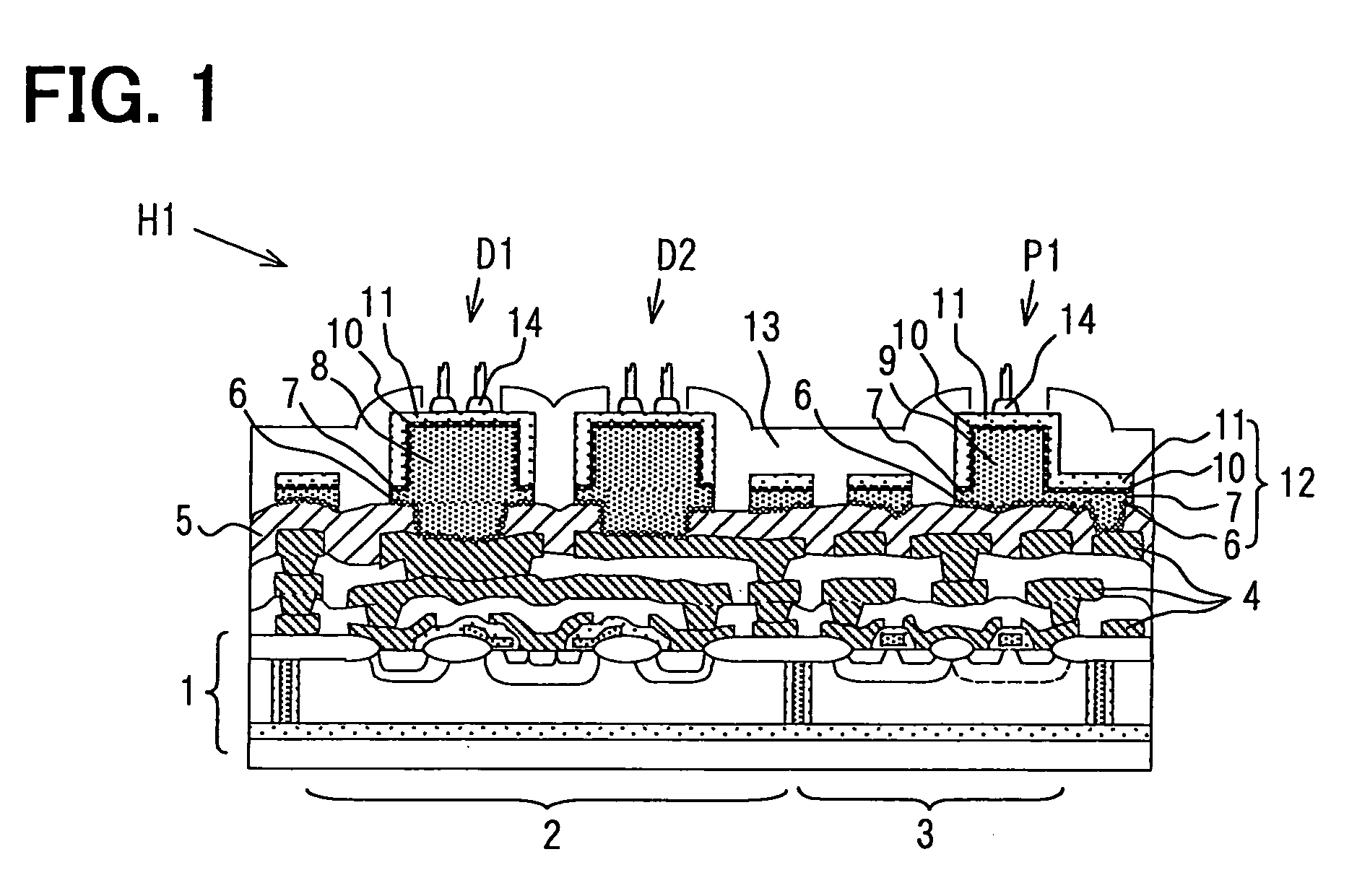

Power composite integrated semiconductor device and manufacturing method thereof

ActiveUS20050258484A1Lower on-resistanceFirmly connectedSemiconductor/solid-state device detailsSolid-state devicesLead bondingDevice material

A high-reliability power composite integrated semiconductor device uses thick copper electrodes as current collecting electrodes of a power device portion to resist wire resistance needed for reducing ON-resistance. Furthermore, wire bonding connection of the copper electrodes is secured, and also the time-lapse degradation under high temperature which causes diffusion of copper and corrosion of copper is suppressed. Still furthermore, direct bonding connection can be established to current collecting electrodes in the power device portion, and also established to a bonding pad formed on the control circuit portion in the control circuit portion. A pad area at the device peripheral portion which has been hitherto needed is reduced, so that the area of the device is saved, and the manufacturing cost is reduced.

Owner:DENSO CORP

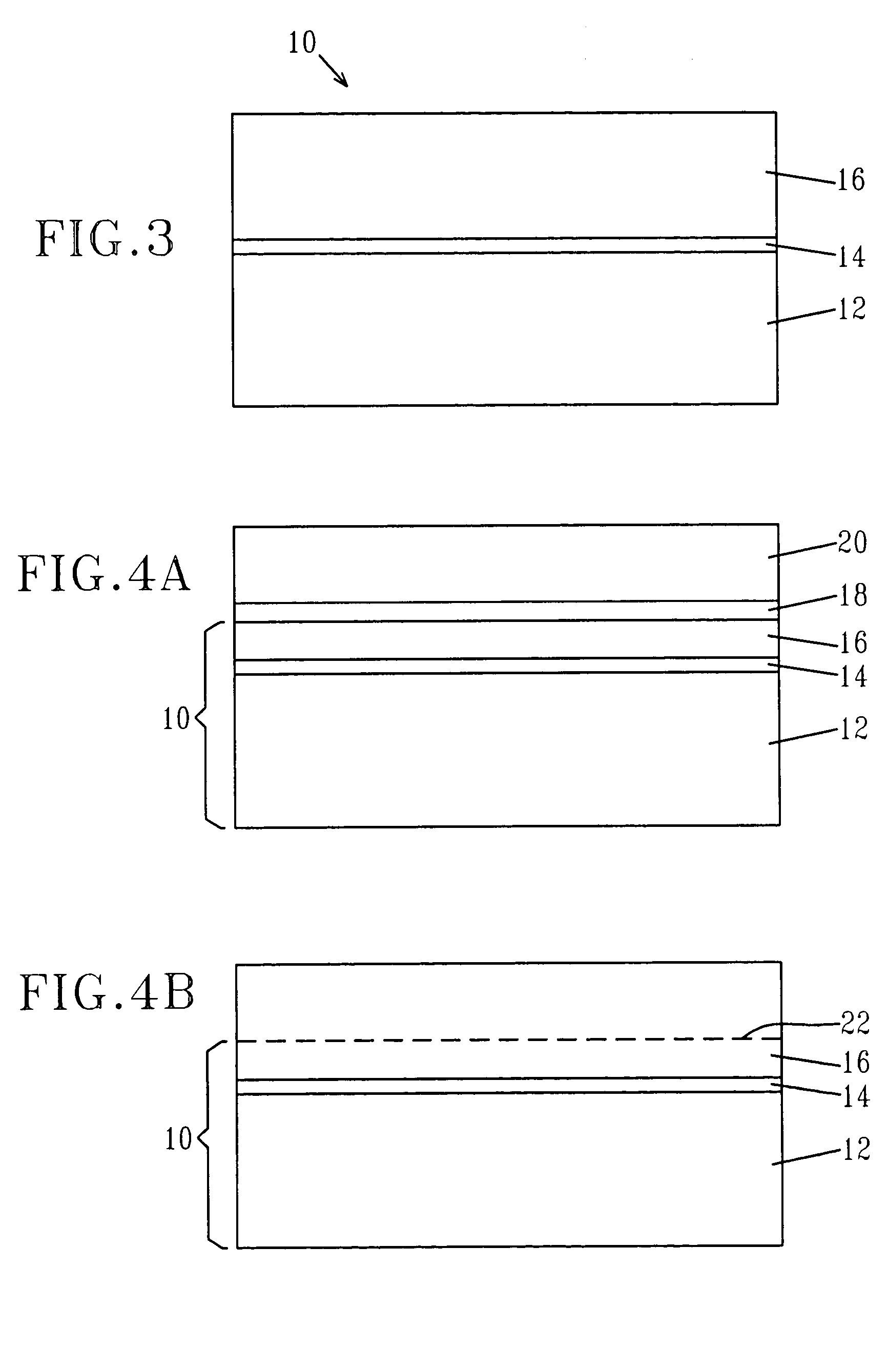

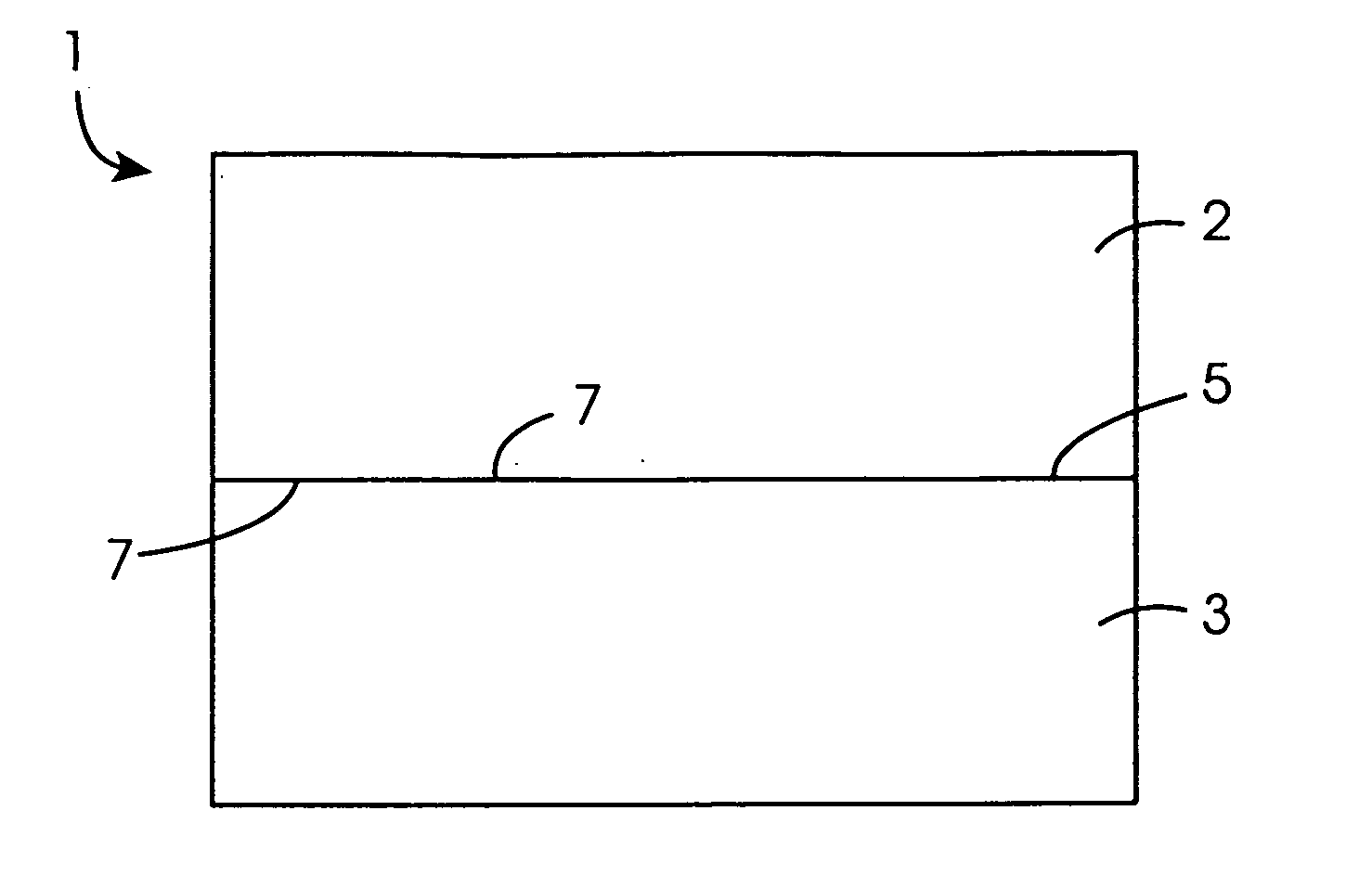

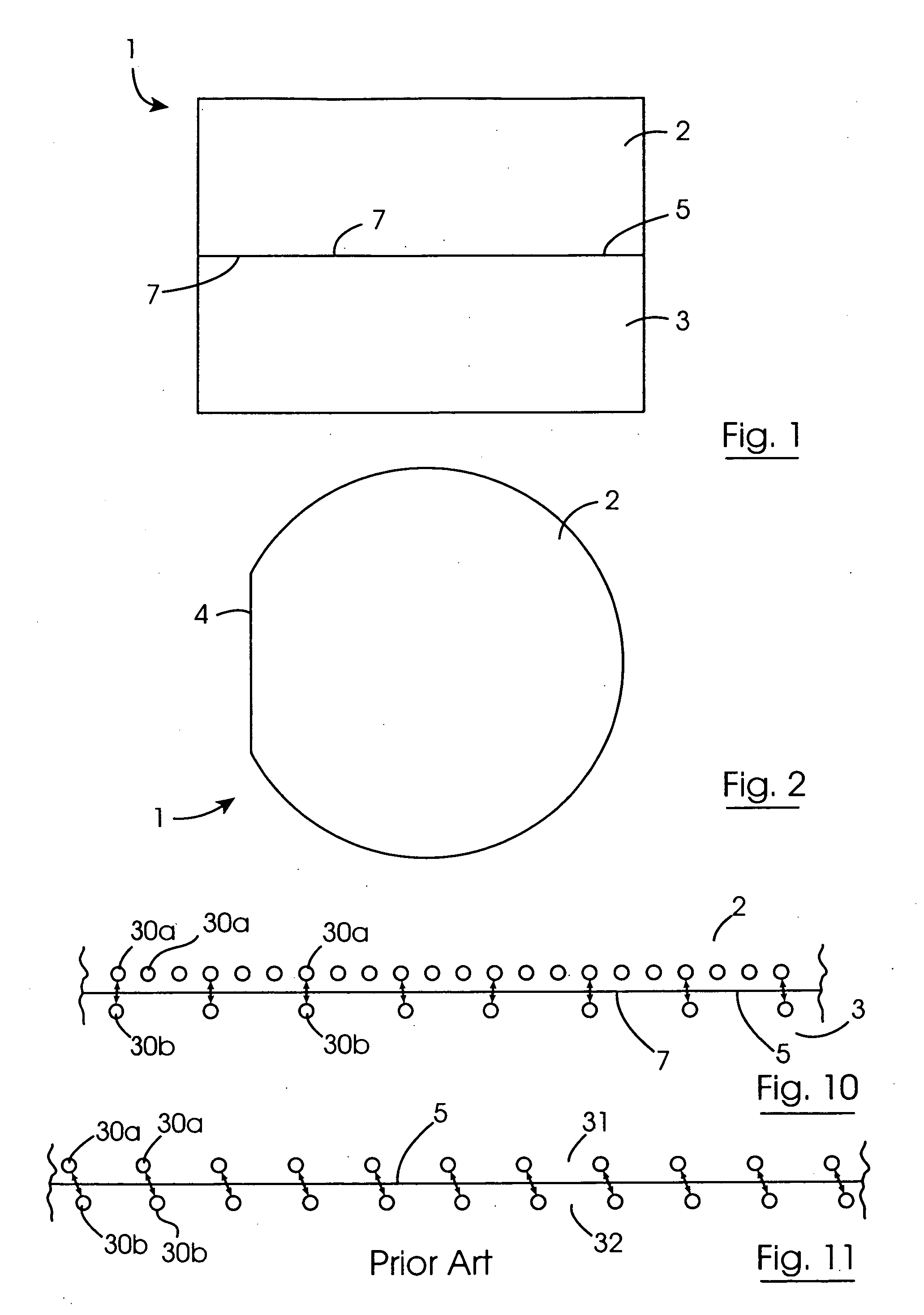

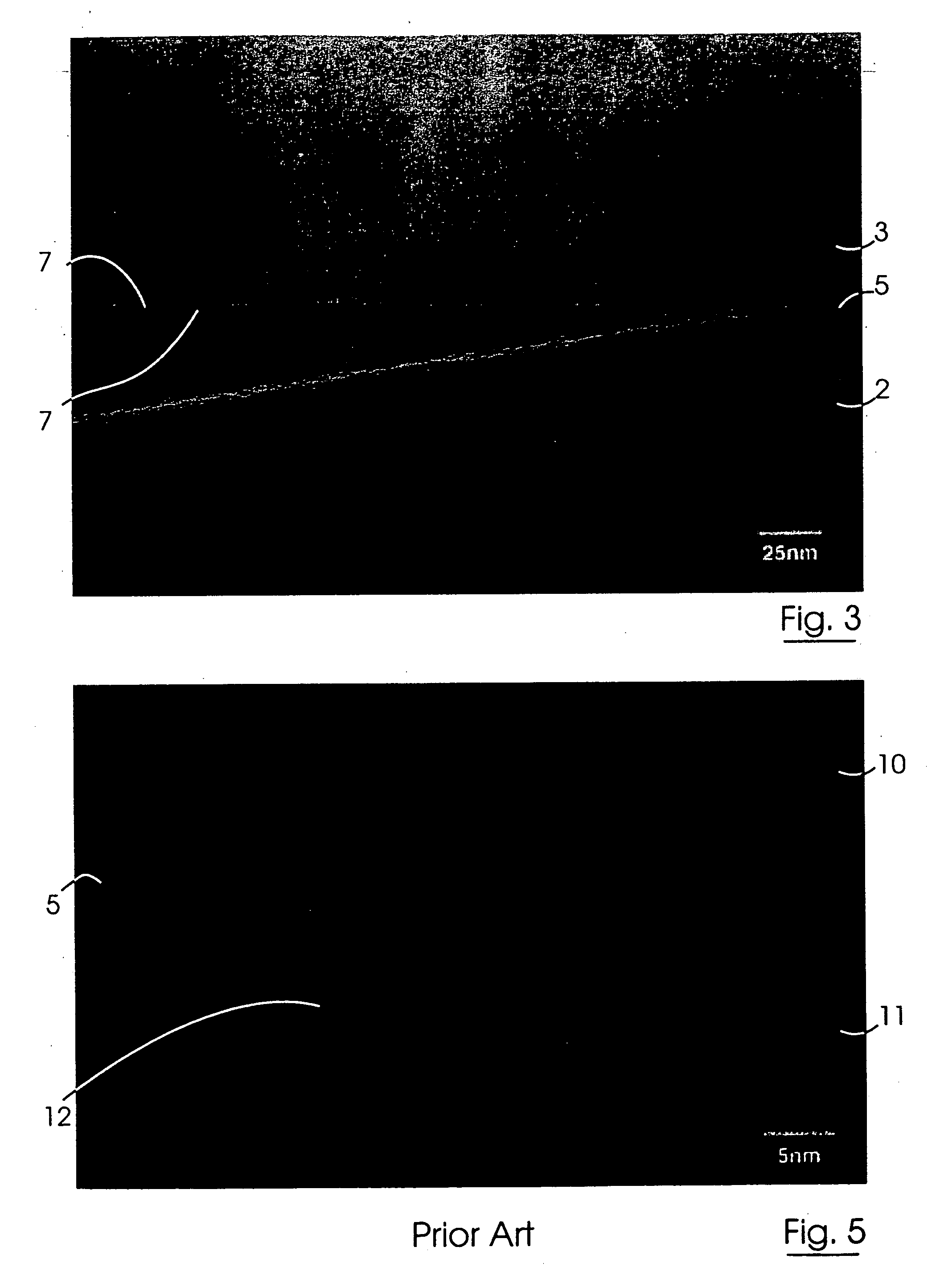

Method for direct bonding two silicon wafers for minimising interfacial oxide and stresses at the bond interface, and an SOI structure

InactiveUS20040087109A1Semiconductor/solid-state device manufacturingInterfacial oxideBond interface

A semiconductor substrate (1) comprises first and second silicon wafers (2,3) directly bonded together with interfacial oxide and interfacial stresses minimised along a bond interface (5), which is defined by bond faces (7) of the first and second wafers (2,3). Interfacial oxide is minimised by selecting the first and second wafers (2,3) to be of relatively low oxygen content, well below the limit of solid solubility of oxygen in the wafers. In order to minimise interfacial stresses, the first and second wafers are selected to have respective different crystal plane orientations. The bond faces (7) of the first and second wafers (2,3) are polished and cleaned, and are subsequently dried in a nitrogen atmosphere. Immediately upon being dried, the bond faces (7) of the first and second wafers (2,3) are abutted together and the wafers (2,3) are subjected to a preliminary anneal at a temperature of at least 400° C. for a time period of a few hours. As soon as possible after the preliminary anneal, and preferably, within forty-eight hours of the preliminary anneal, the first and second wafers (2,3) are fusion bonded at a bond anneal temperature of approximately 1,150° C. for a time period of approximately three hours. The preliminary anneal may be omitted if fusion bonding at the bond anneal temperature is carried out within approximately six hours of the wafers (2,3) being abutted together. An SOI structure (50) may subsequently be prepared from the semiconductor structure (1) which forms a substrate layer (52) supported on a handle layer (55) with a buried insulating layer (57) between the substrate layer (52) and the handle layer (55).

Owner:ANALOG DEVICES INC