Patents

Literature

120 results about "Interfacial oxide" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

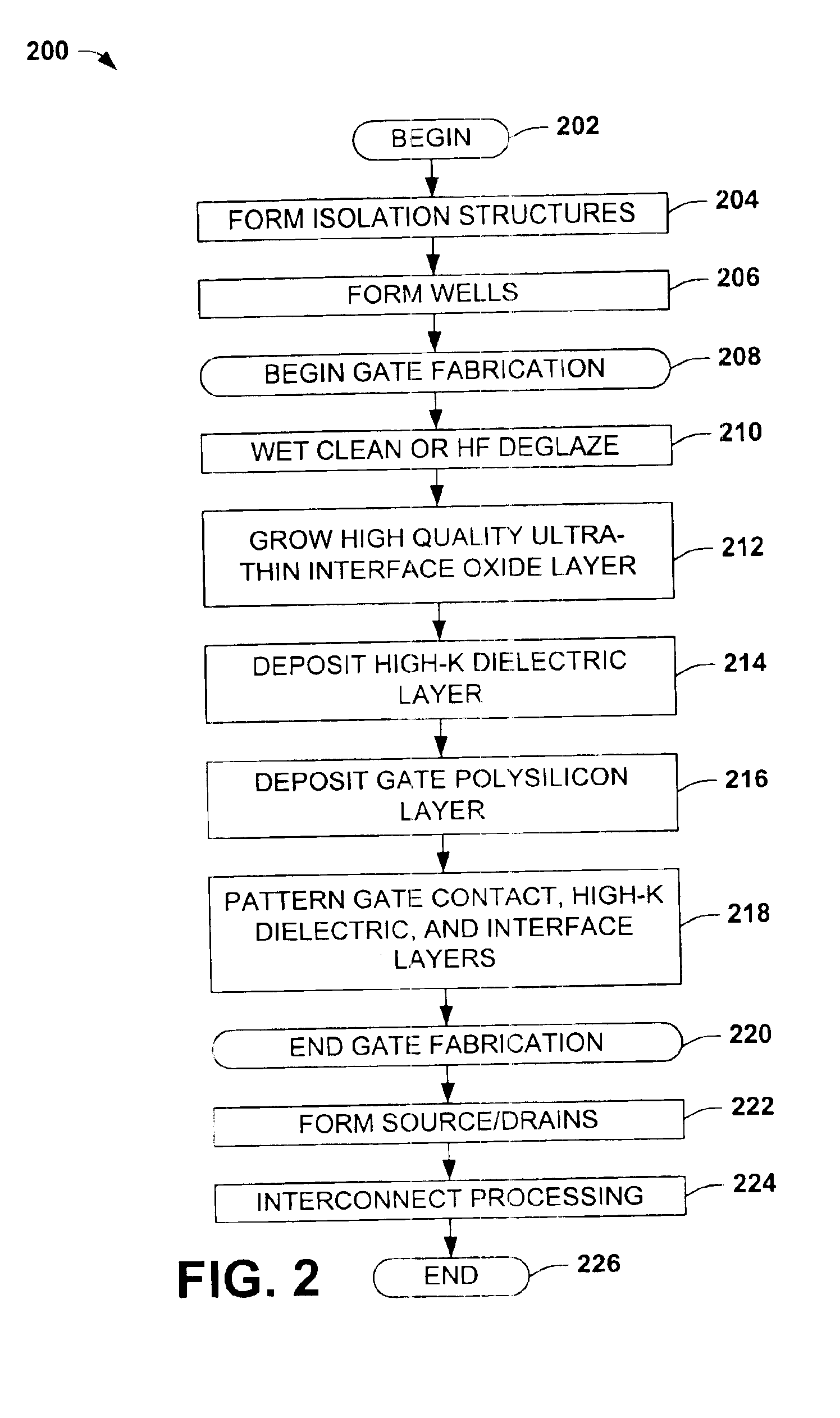

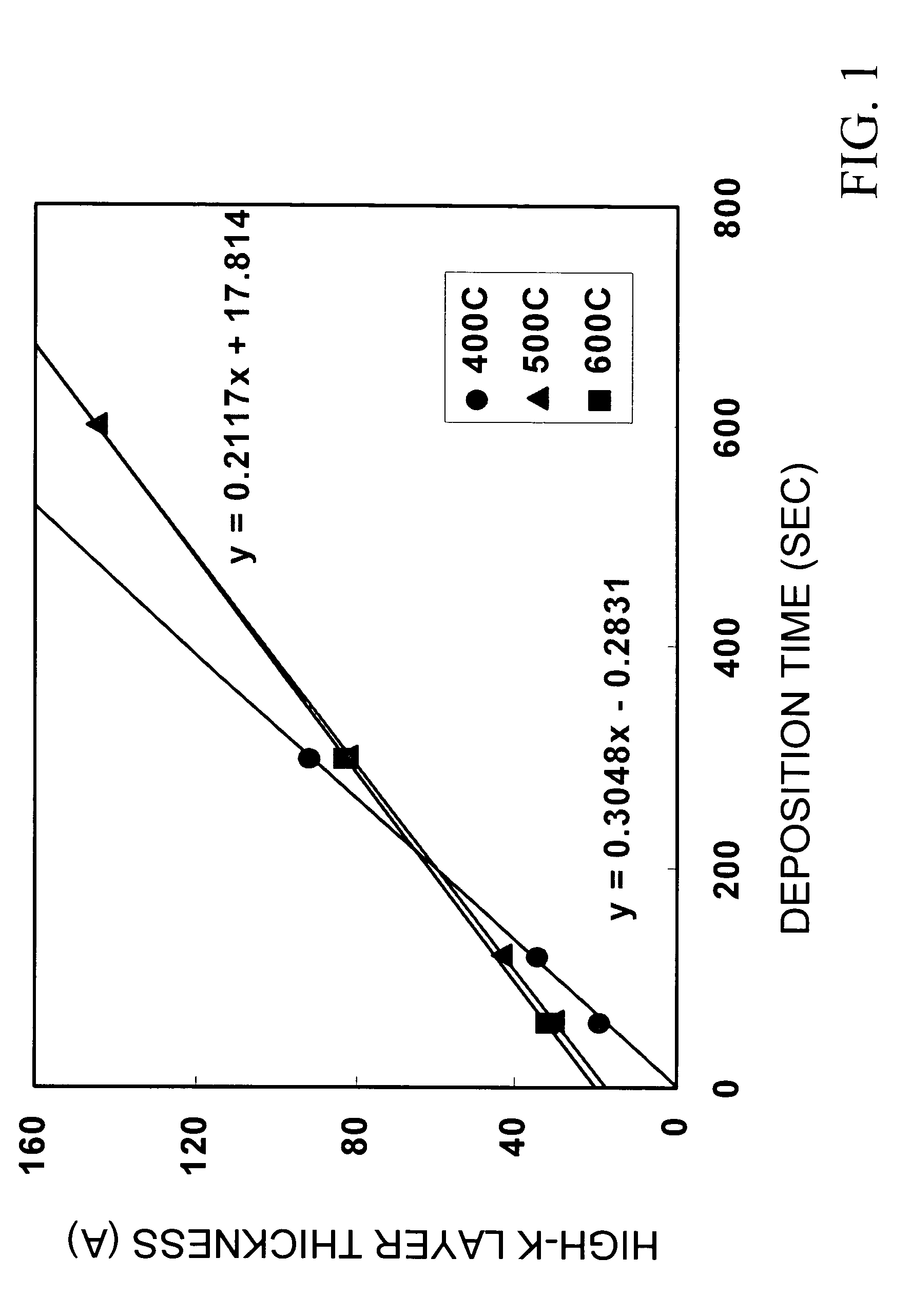

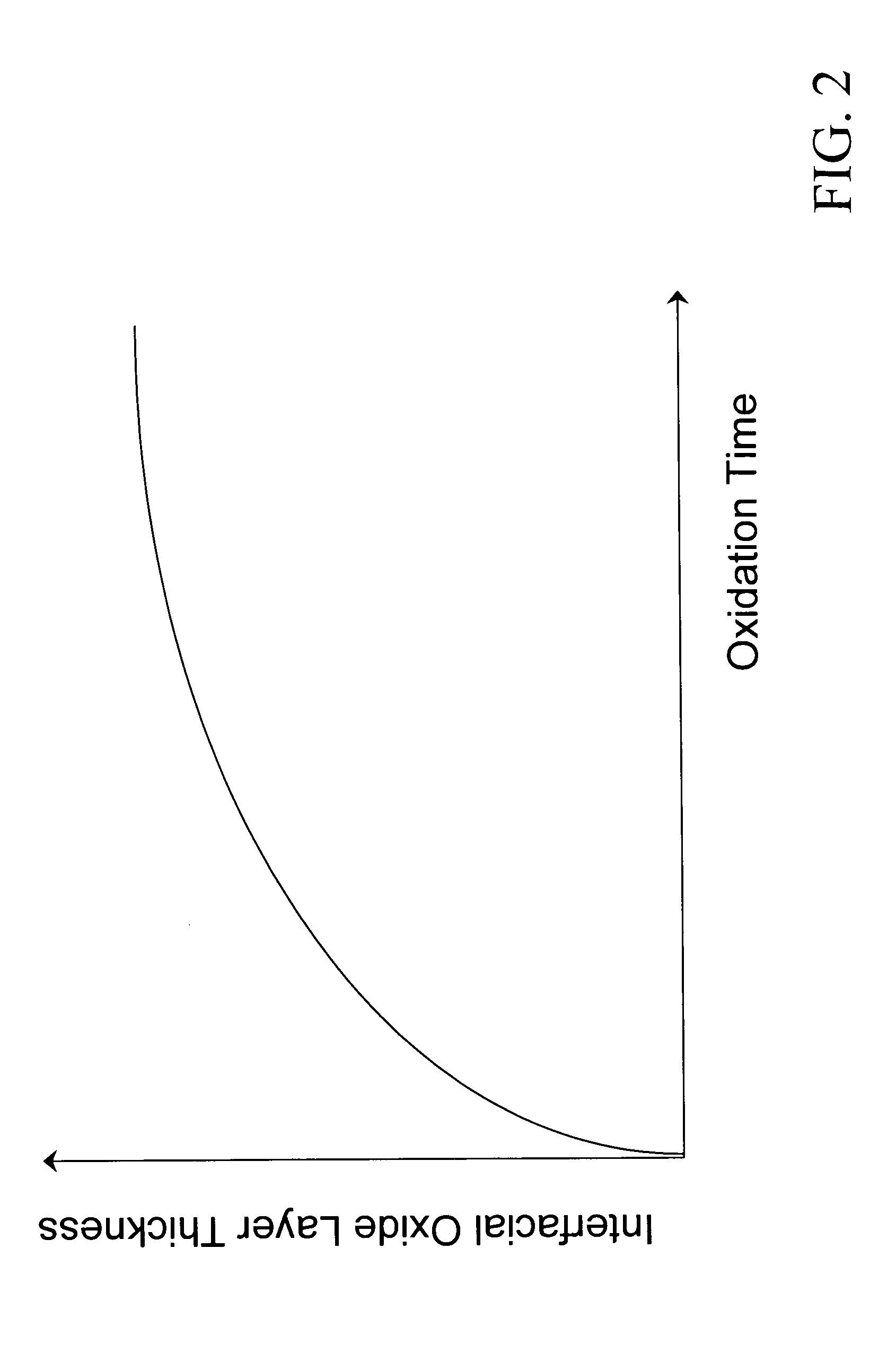

High temperature interface layer growth for high-k gate dielectric

InactiveUS6852645B2Semiconductor/solid-state device manufacturingCapacitorsInterfacial oxideCelsius Degree

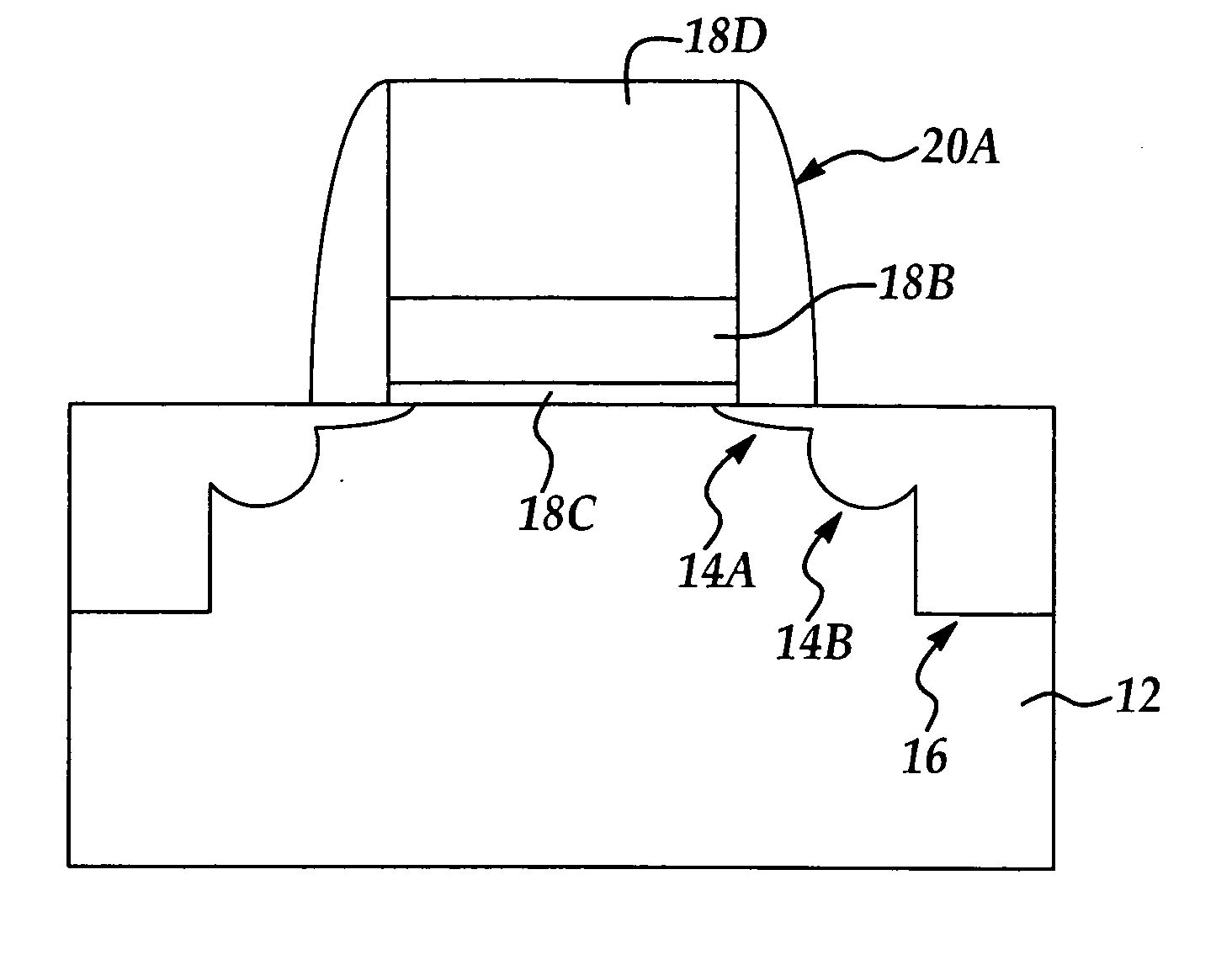

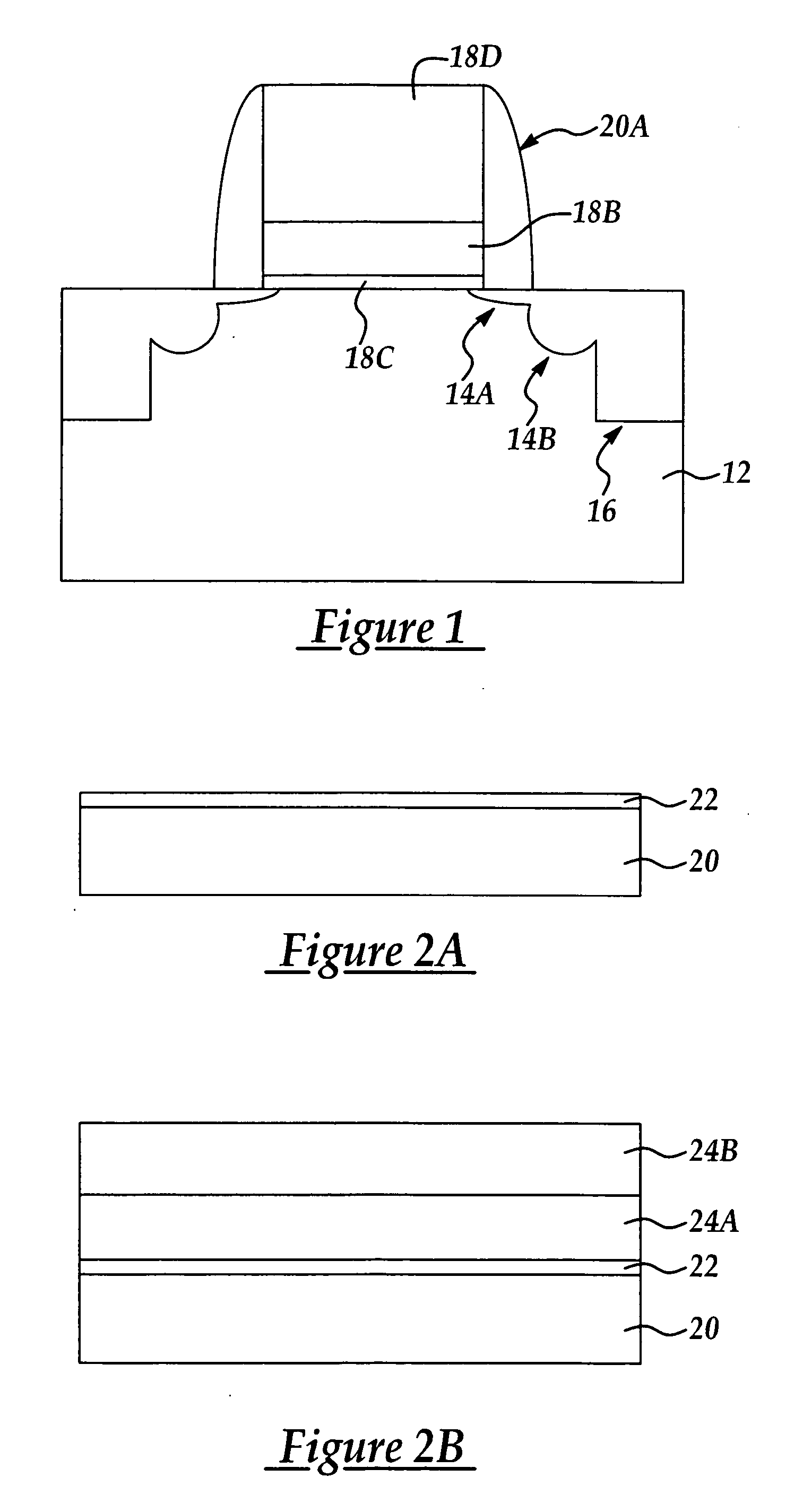

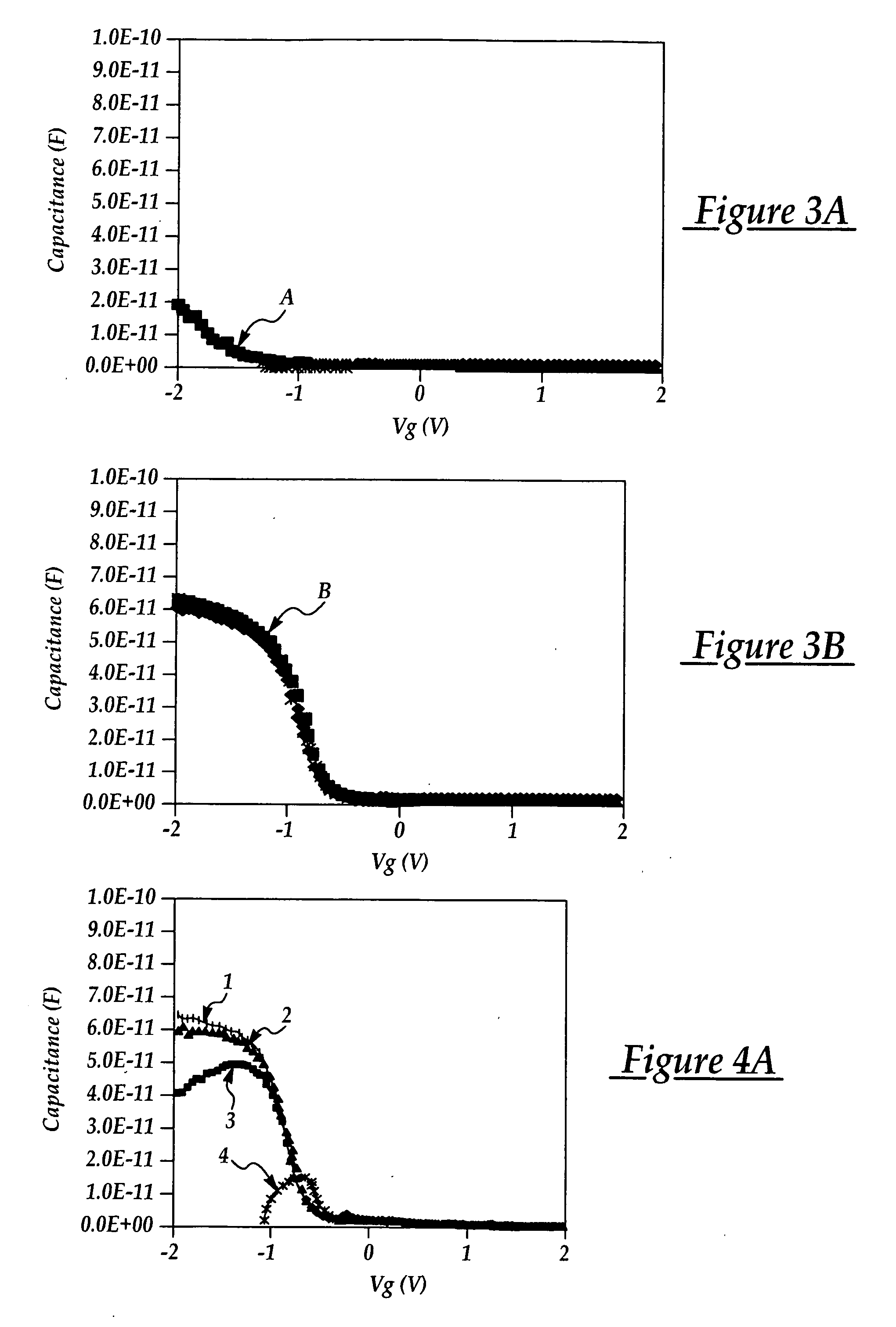

The present invention pertains to methods for forming high quality thin interface oxide layers suitable for use with high-k gate dielectrics in the manufacture of semiconductor devices. An ambient that contains oxygen and a reducing agent is utilized to grow the layers. The oxygen facilitates growth of the layers, while the reducing agent simultaneously counteracts that growth. The rate of growth of the layers can thus be controlled by regulating the partial pressure of the reducing agent, which is the fraction of the reducing agent in the gas phase times the total pressure. Controlling and slowing the growth rate of the layers facilitates production of the layers to thicknesses of about 10 Angstroms or less at temperatures of about 850 degrees Celsius or more. Growing the layers at high temperatures facilitates better bonding and production of higher quality layers, which in turn yields better performing and more reliable resulting products.

Owner:PACIFIC SEISMIC PRODS +1

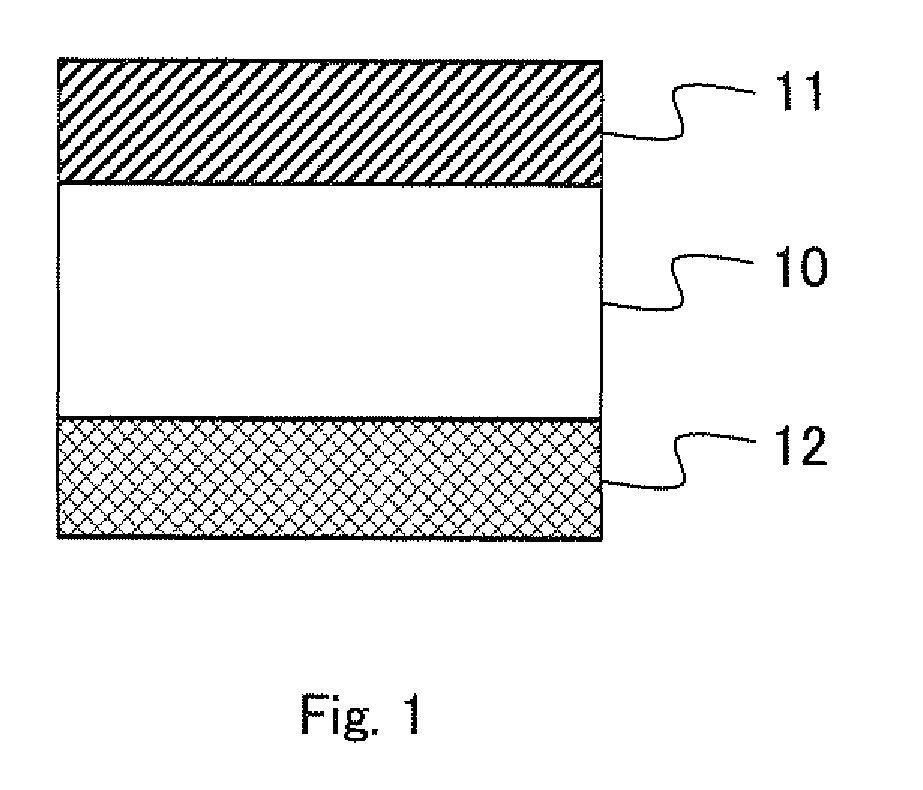

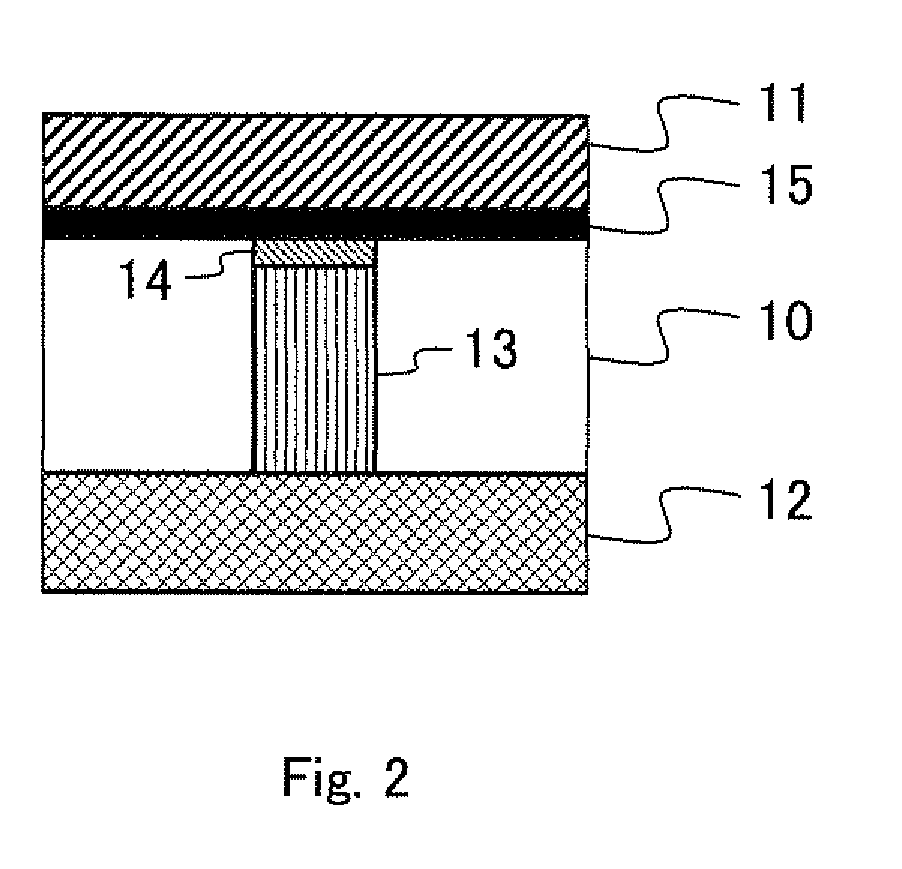

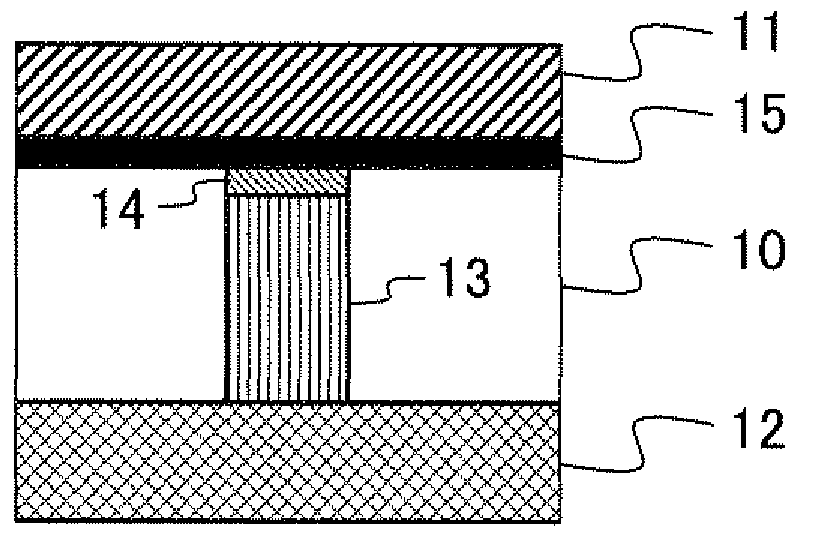

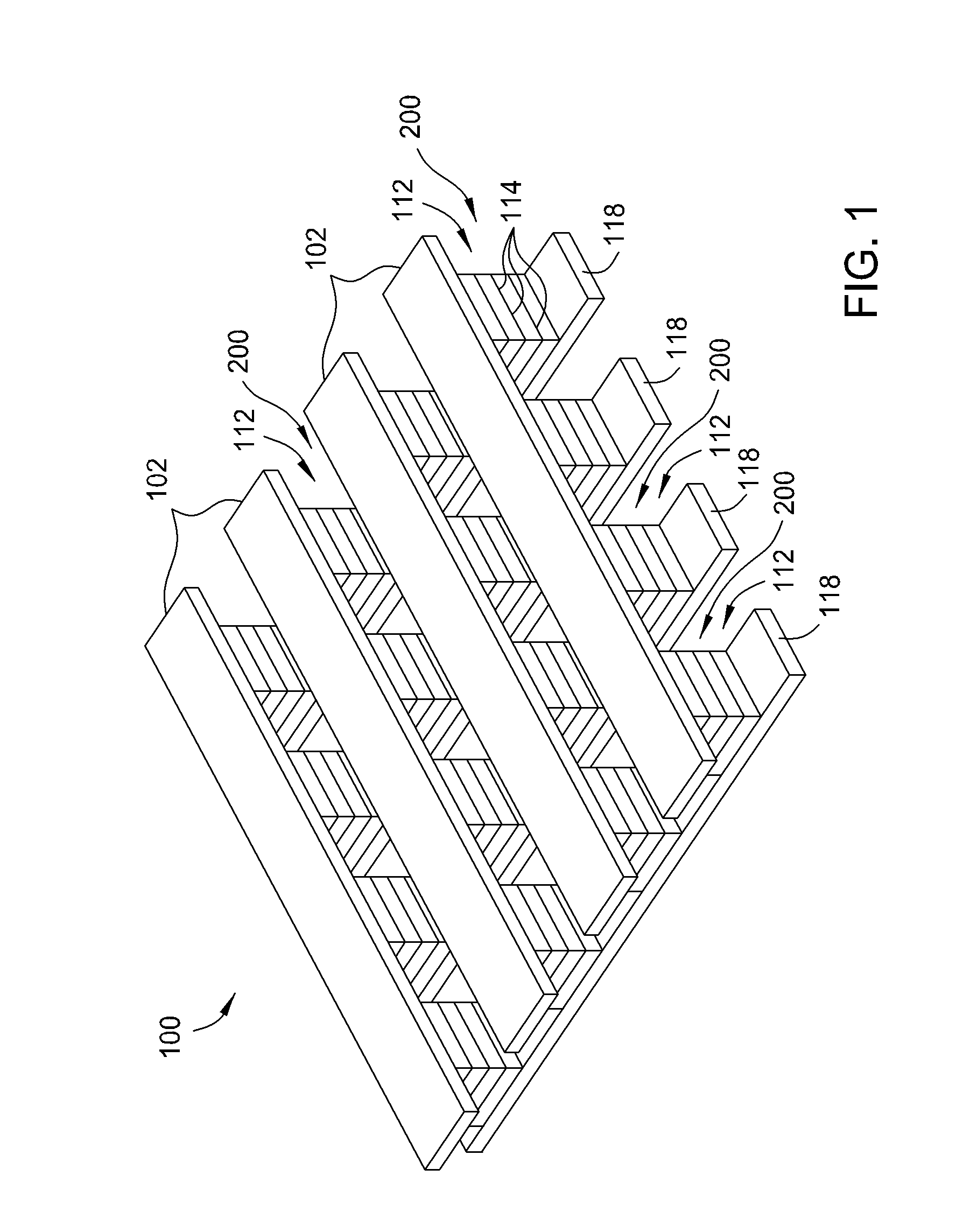

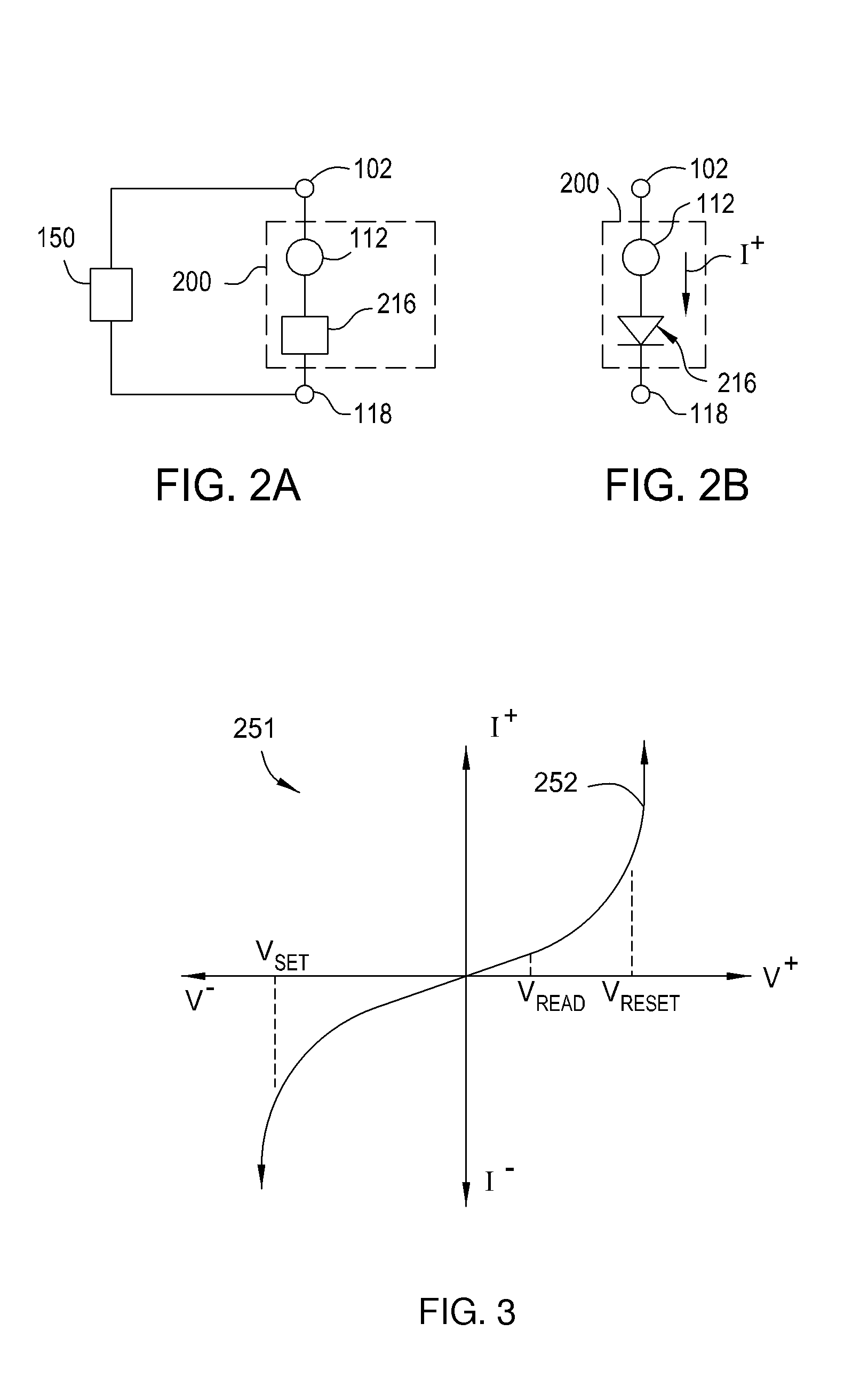

Variable resistive element, manufacturing method for same, and non-volatile semiconductor memory device

ActiveUS8054674B2Improve processingSimple compositionSolid-state devicesDigital storageInterfacial oxidePower flow

Provided is a variable resistive element which performs high speed and low power consumption operation. The variable resistive element comprises a metal oxide layer between first and second electrodes wherein electrical resistance between the first and second electrodes reversibly changes in accordance with application of electrical stress across the first and second electrodes. The metal oxide layer has a filament, which is a current path where the density of a current flowing between the first and second electrodes locally increases. A portion including at least the vicinity of an interface between the certain electrode, which is one or both of the first and second electrodes, and the filament, on an interface between the certain electrode and the metal oxide layer is provided with an interface oxide which is an oxide of at least one element included in the certain electrode and different from the oxide of the metal oxide layer.

Owner:SHARP KK +1

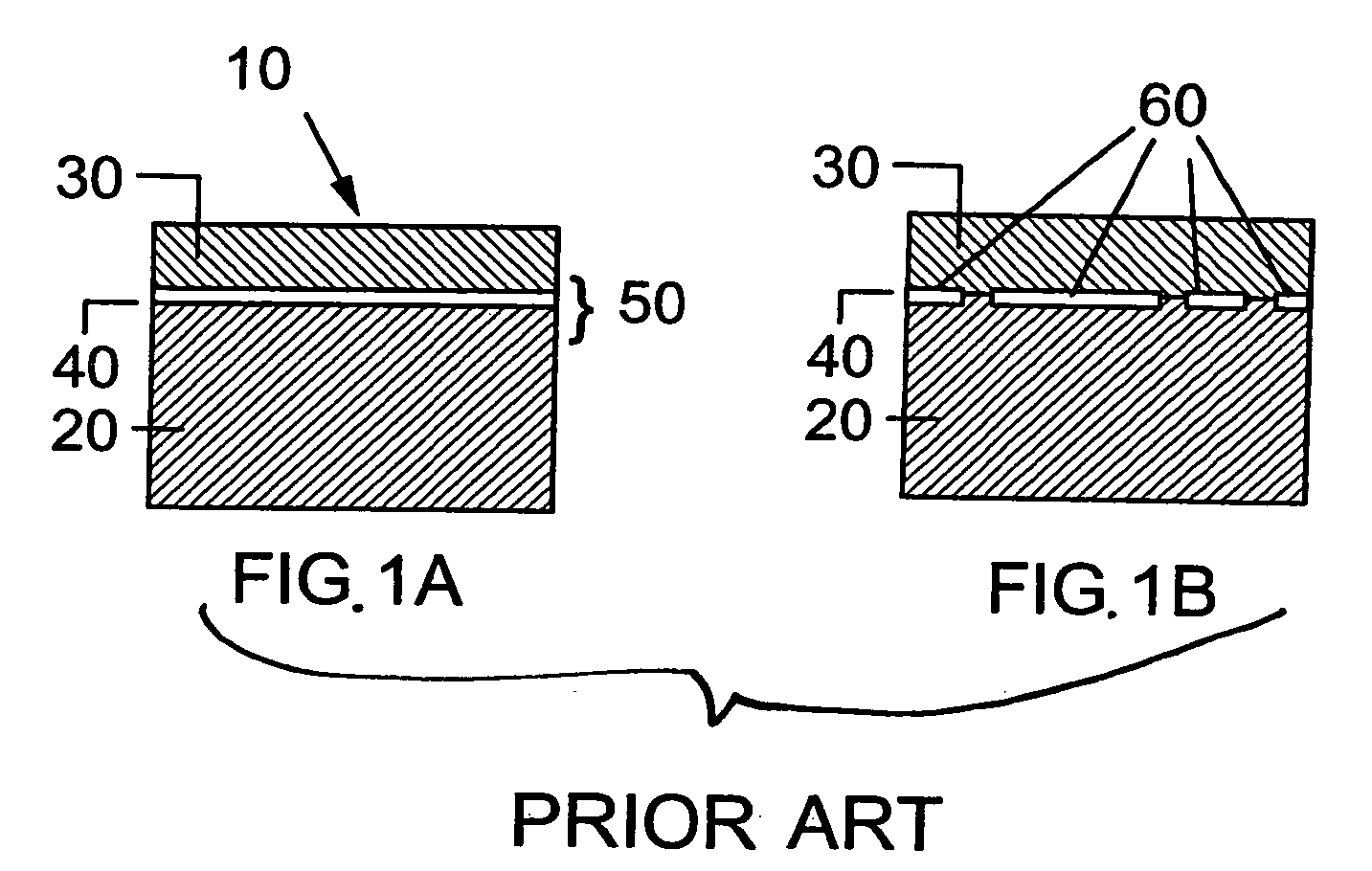

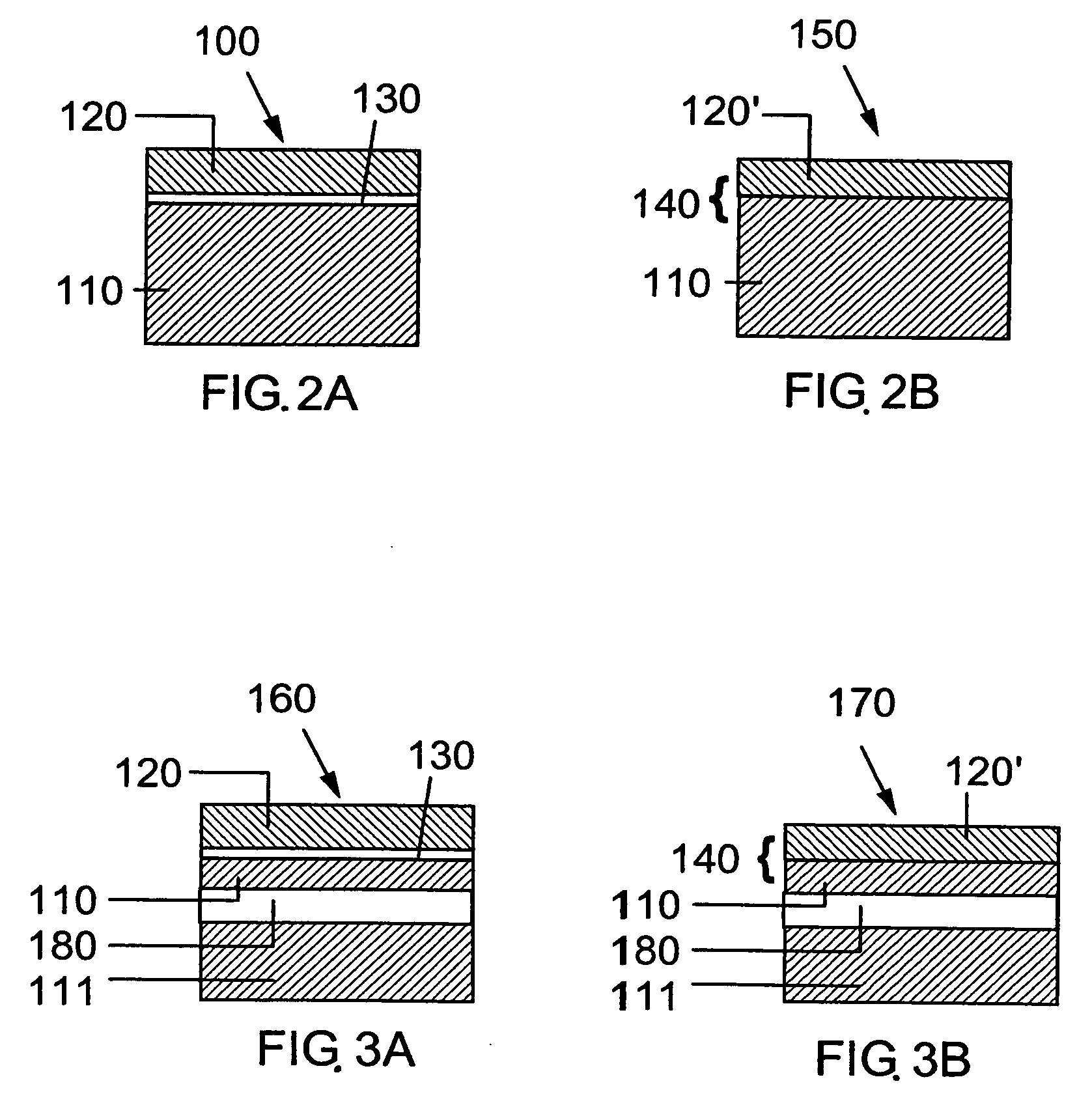

Quasi-hydrophobic Si-Si wafer bonding using hydrophilic Si surfaces and dissolution of interfacial bonding oxide

InactiveUS20060154442A1Thinning and removing materialSemiconductor/solid-state device manufacturingInterfacial oxideSemiconductor materials

The present invention provides a method for removing or reducing the thickness of ultrathin interfacial oxides remaining at Si—Si interfaces after silicon wafer bonding. In particular, the invention provides a method for removing ultrathin interfacial oxides remaining after hydrophilic Si—Si wafer bonding to create bonded Si—Si interfaces having properties comparable to those achieved with hydrophobic bonding. Interfacial oxide layers of order of about 2 to about 3 nm are dissolved away by high temperature annealing, for example, an anneal at 1300°-1330° C. for 1-5 hours. The inventive method is used to best advantage when the Si surfaces at the bonded interface have different surface orientations, for example, when a Si surface having a (100) orientation is bonded to a Si surface having a (110) orientation. In a more general aspect of the invention, the similar annealing processes may be used to remove undesired material disposed at a bonded interface of two silicon-containing semiconductor materials. The two silicon-containing semiconductor materials may be the same or different in surface crystal orientation, microstructure (single-crystal, polycrystalline, or amorphous), and composition.

Owner:GLOBALFOUNDRIES INC

Variable resistive element, manufacturing method for same, and non-volatile semiconductor memory device

ActiveUS20100172170A1Reduce power consumptionInconsistency in resistanceSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceInterfacial oxide

Provided is a variable resistive element which performs high speed and low power consumption operation. The variable resistive element comprises a metal oxide layer between first and second electrodes wherein electrical resistance between the first and second electrodes reversibly changes in accordance with application of electrical stress across the first and second electrodes. The metal oxide layer has a filament, which is a current path where the density of a current flowing between the first and second electrodes locally increases. A portion including at least the vicinity of an interface between the certain electrode, which is one or both of the first and second electrodes, and the filament, on an interface between the certain electrode and the metal oxide layer is provided with an interface oxide which is an oxide of at least one element included in the certain electrode and different from the oxide of the metal oxide layer.

Owner:SHARP KK +1

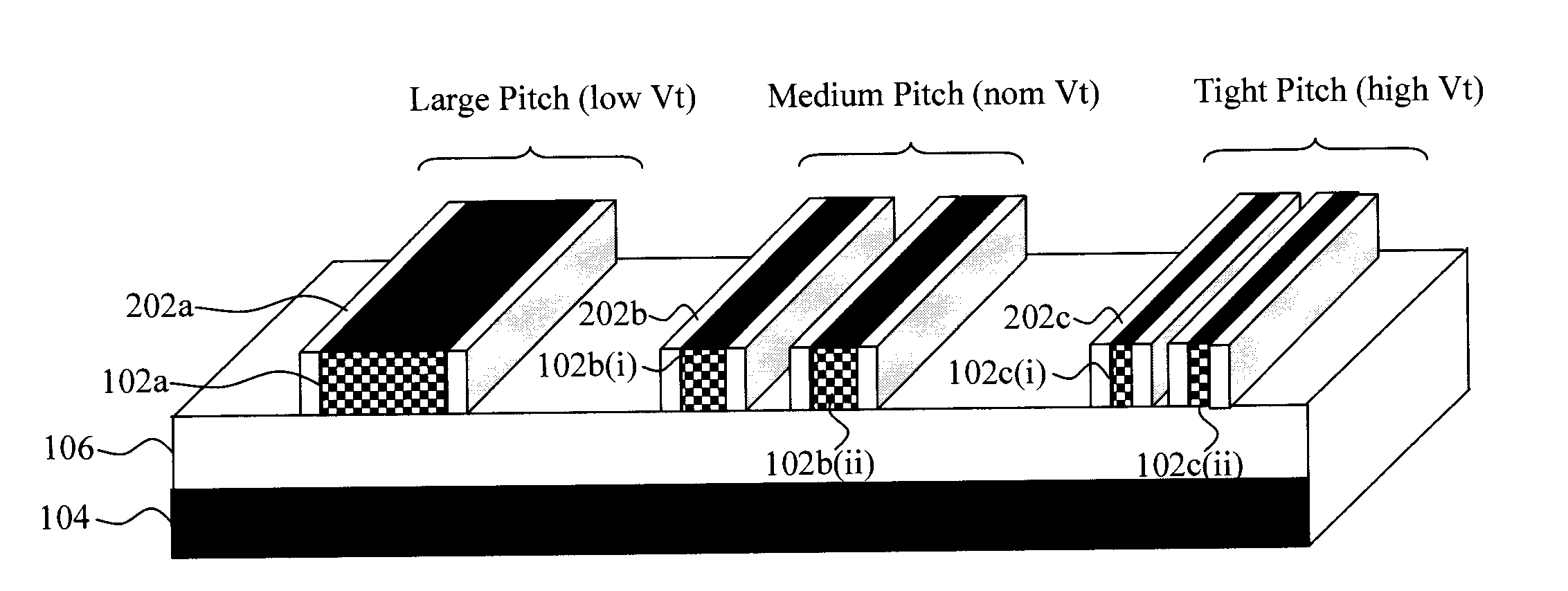

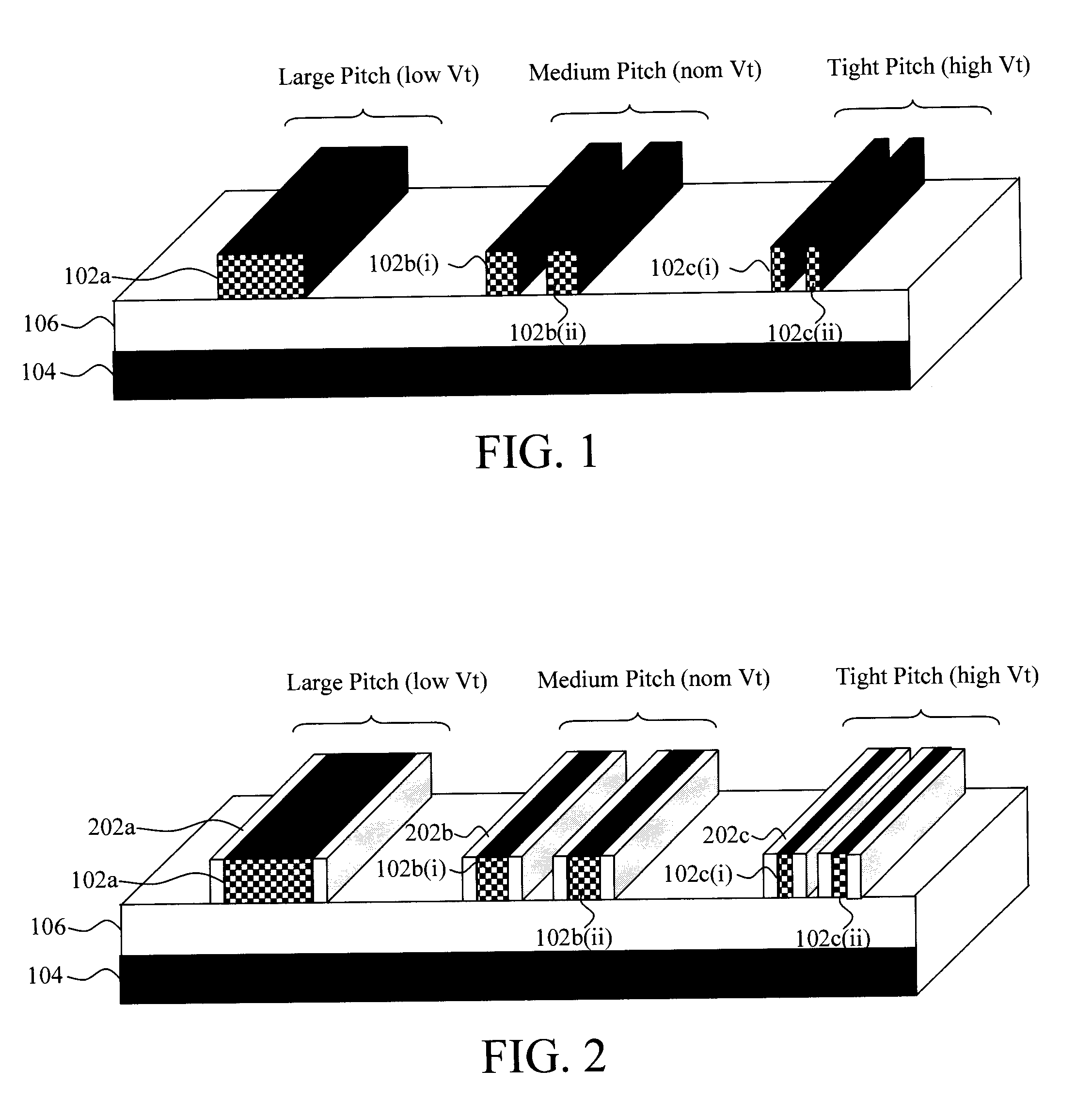

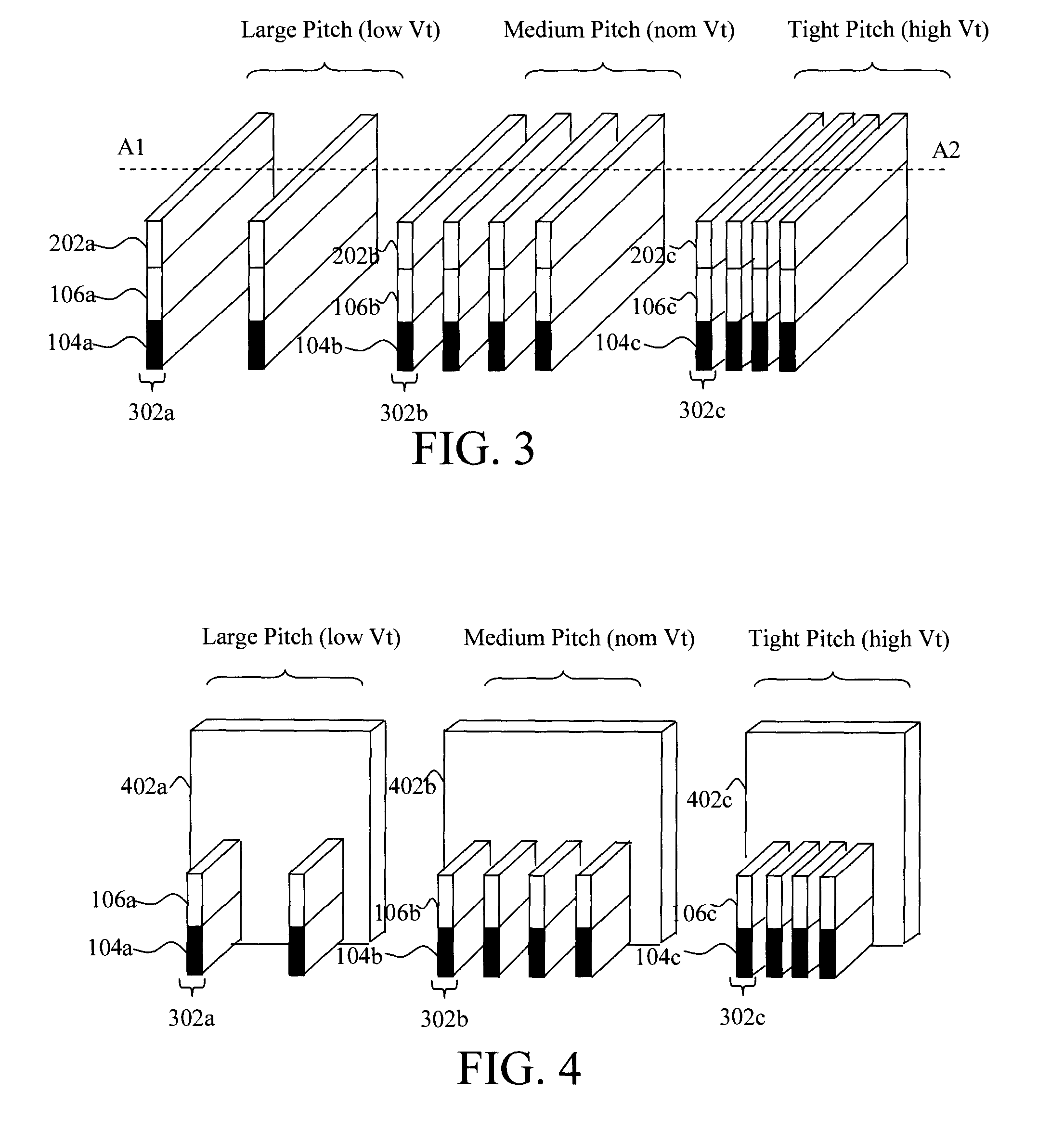

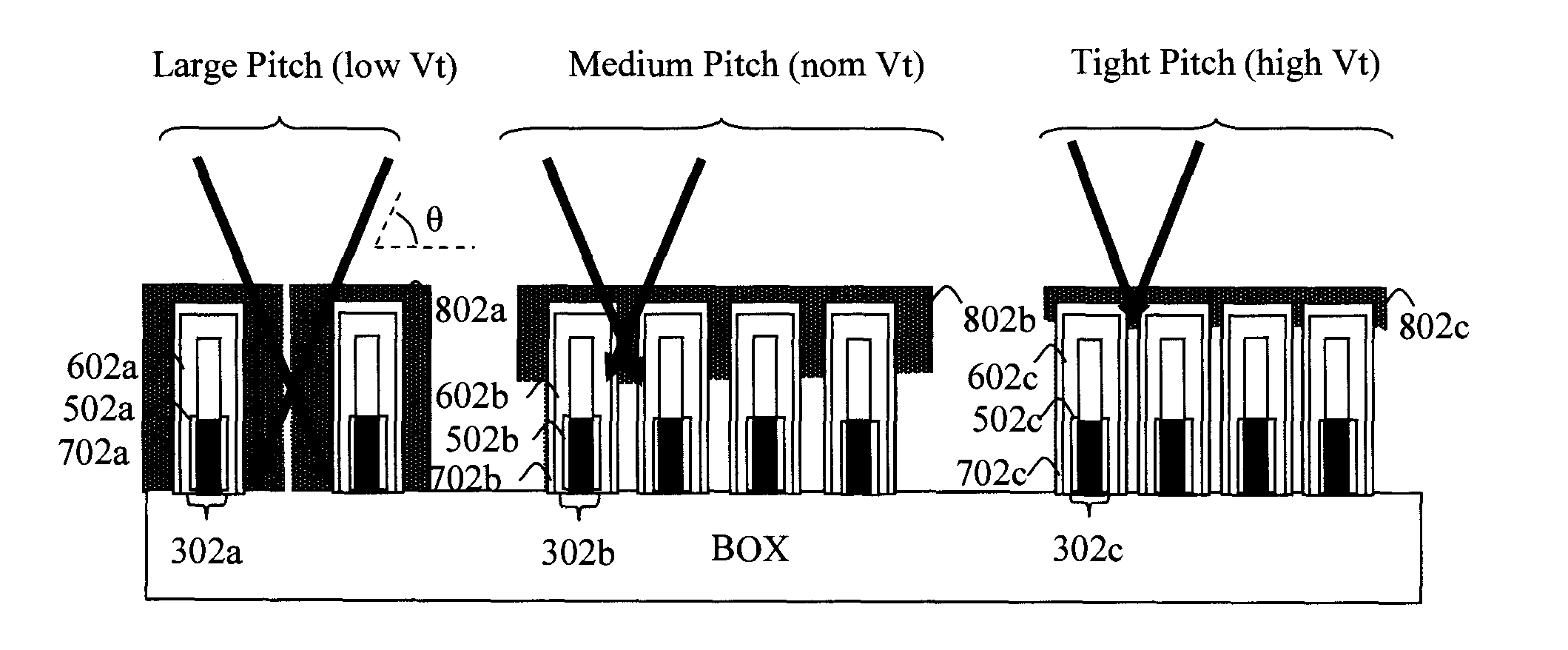

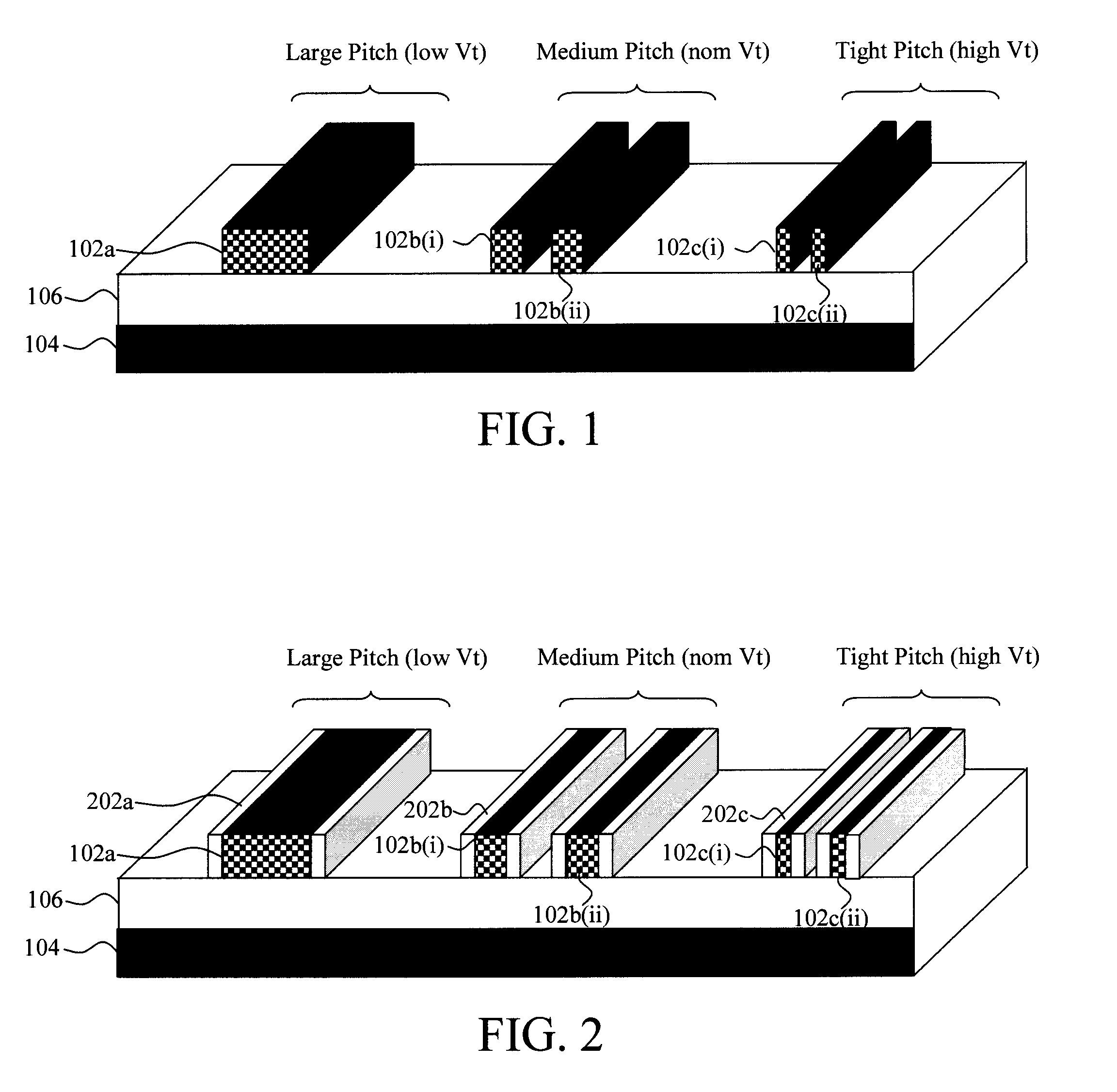

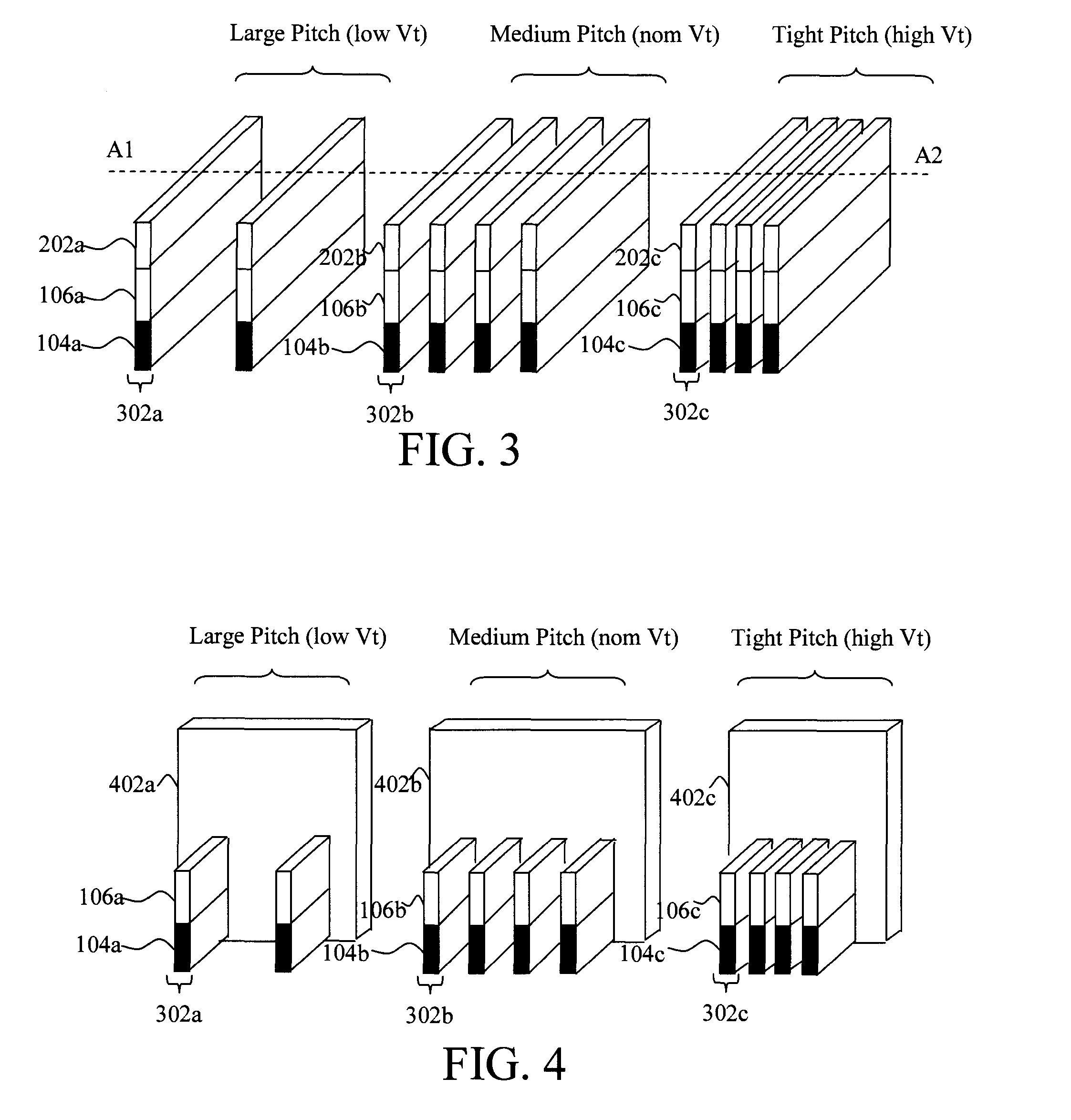

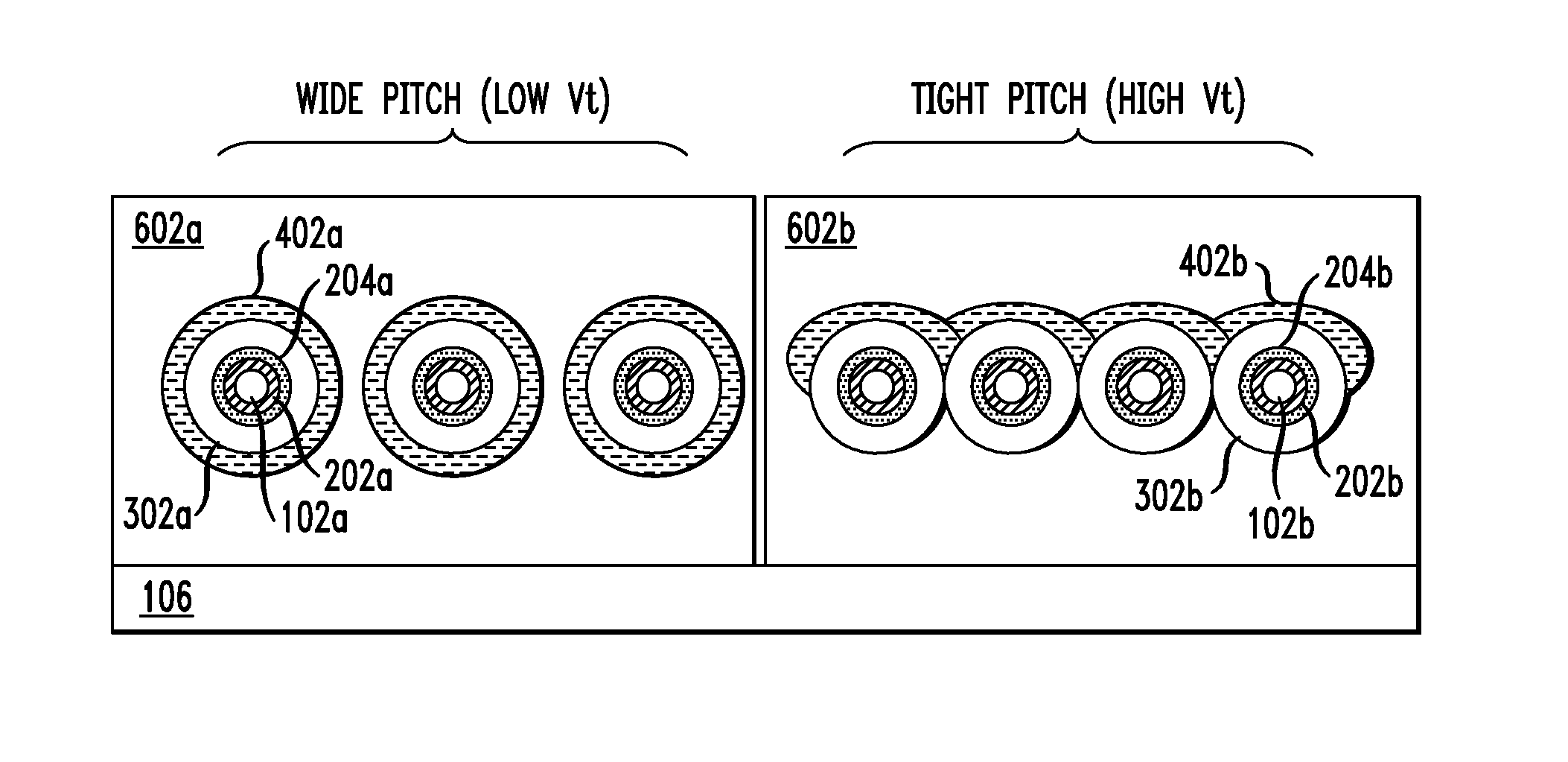

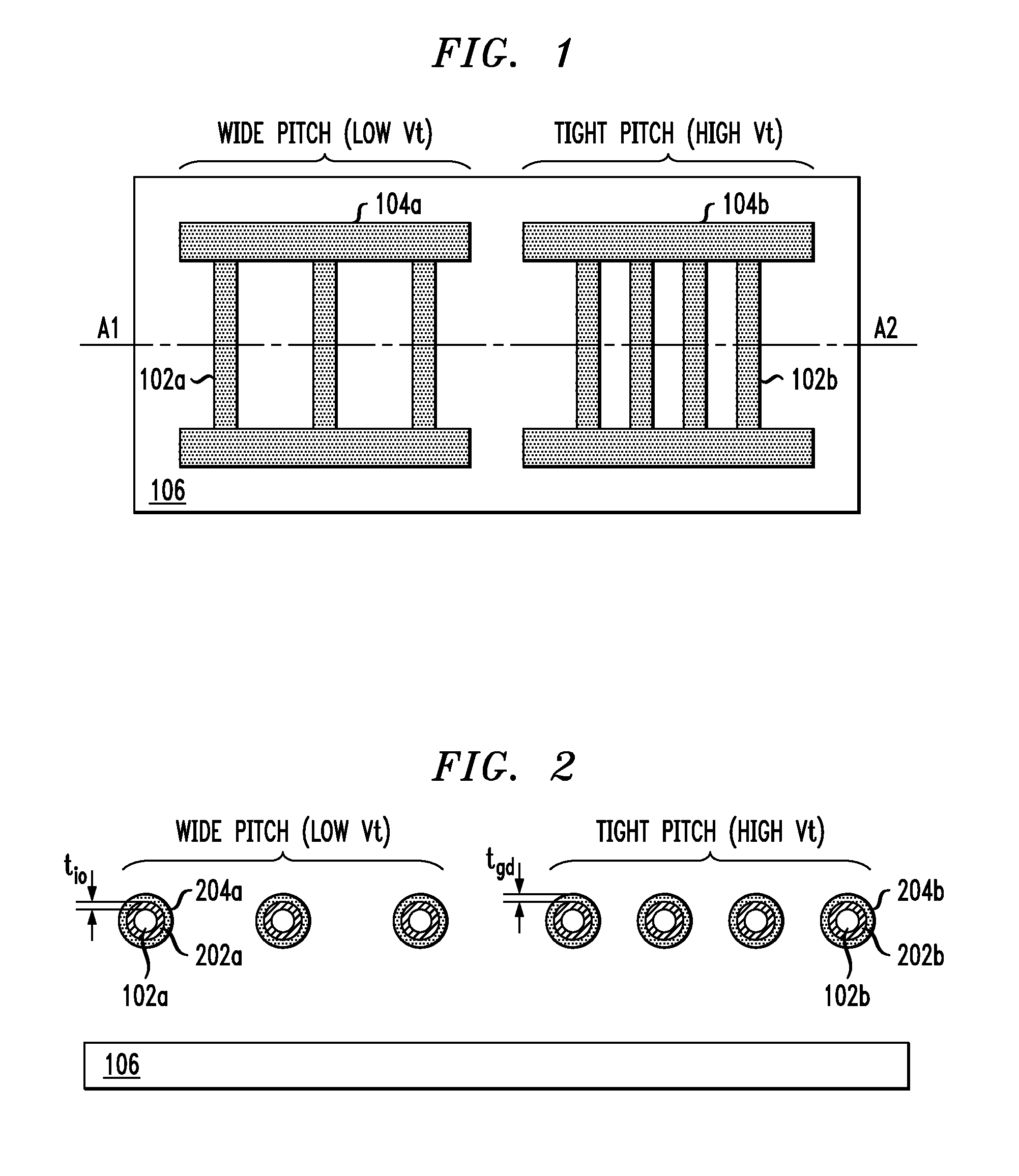

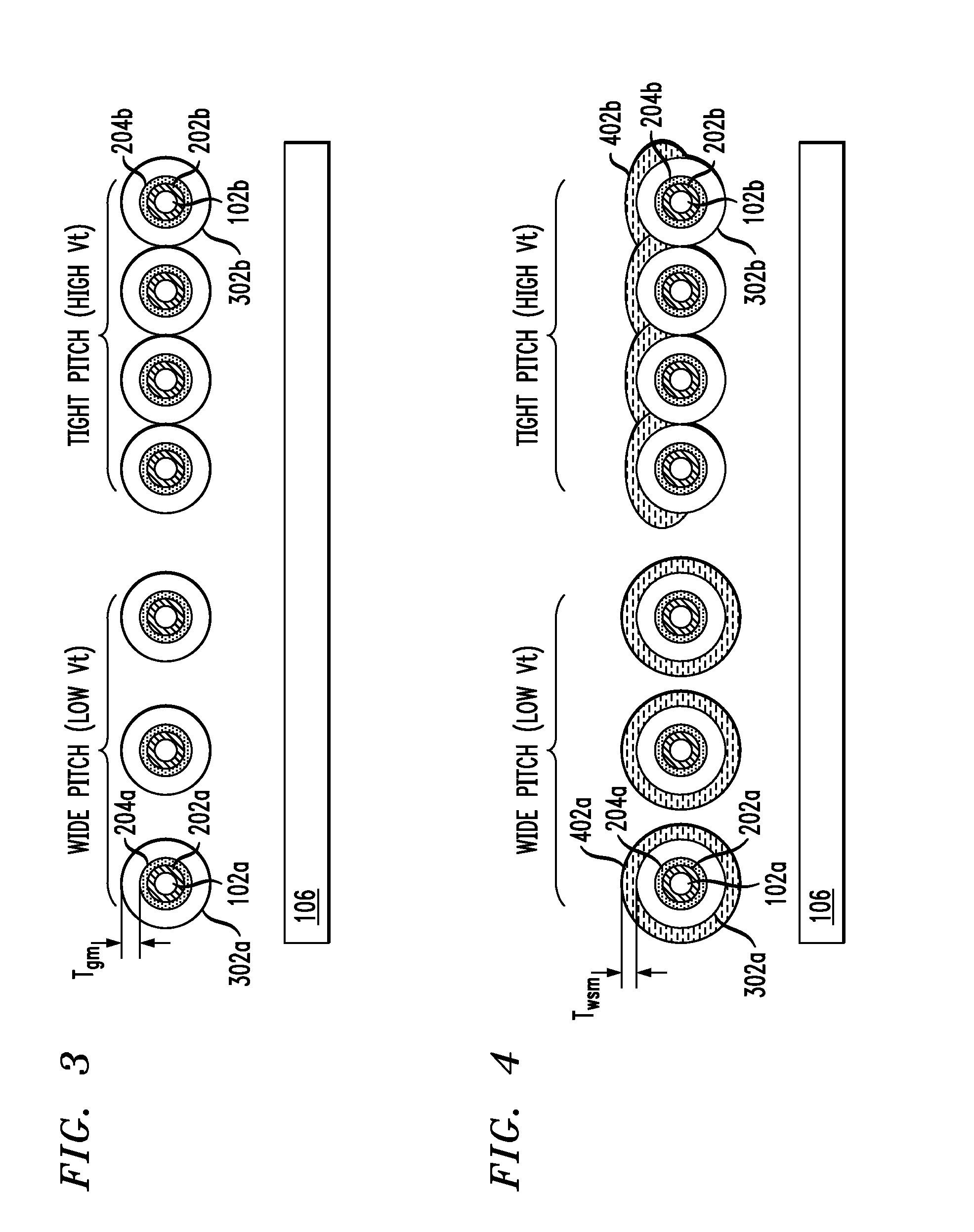

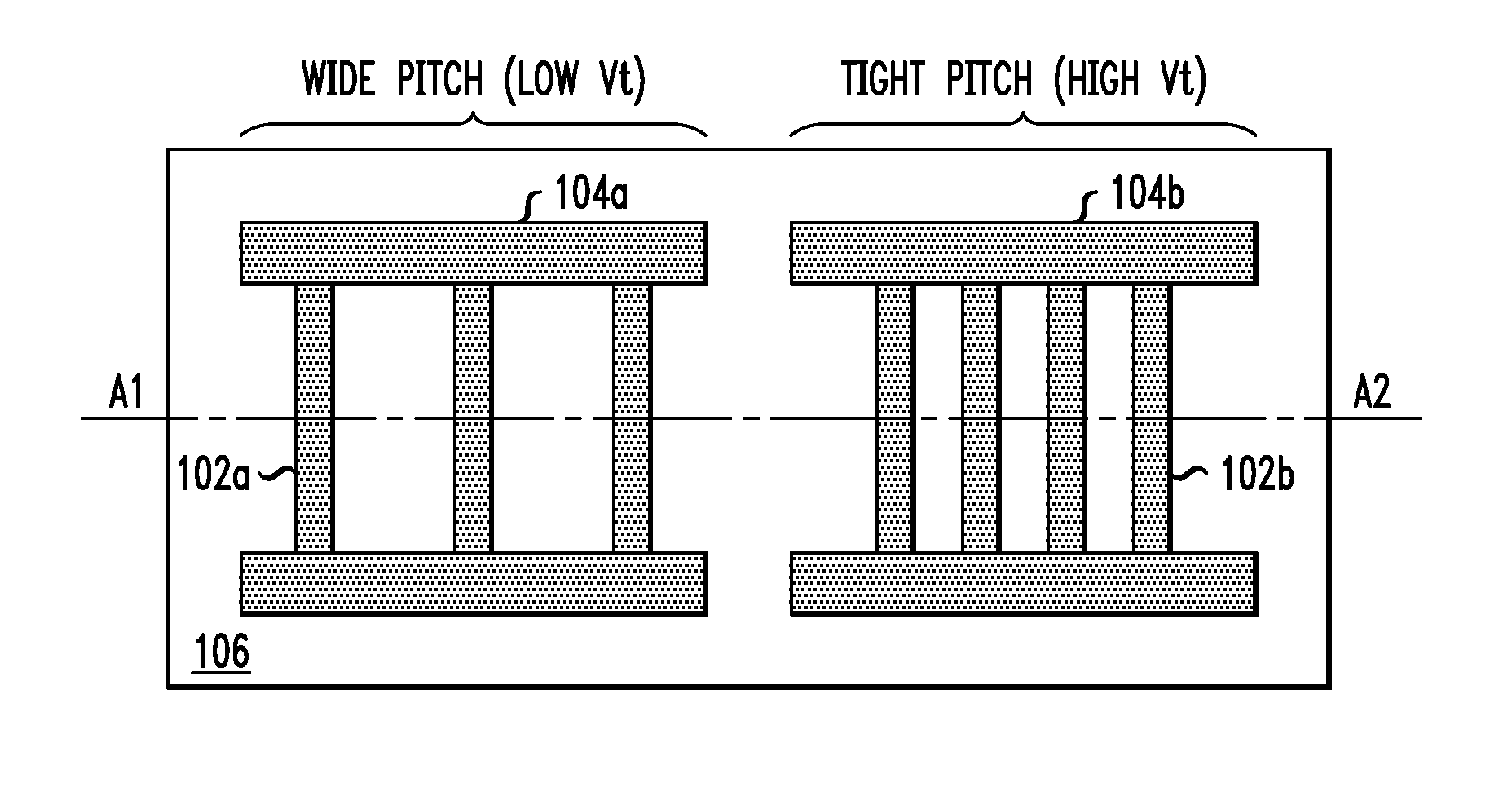

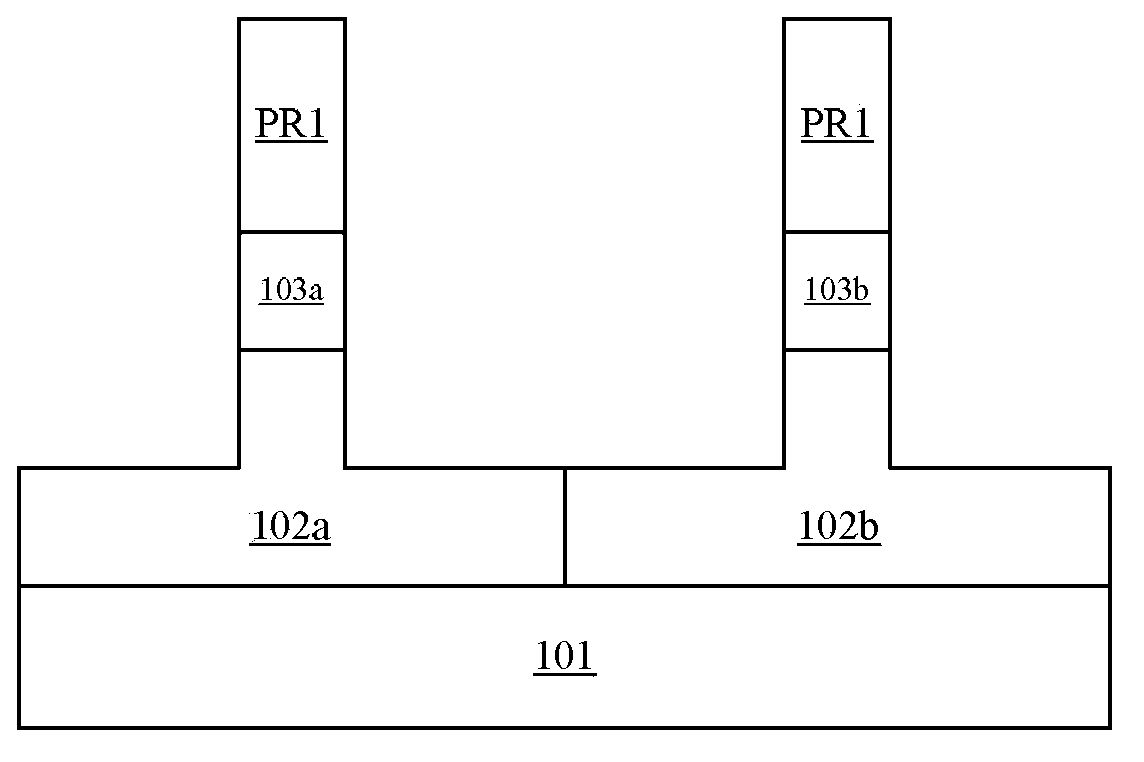

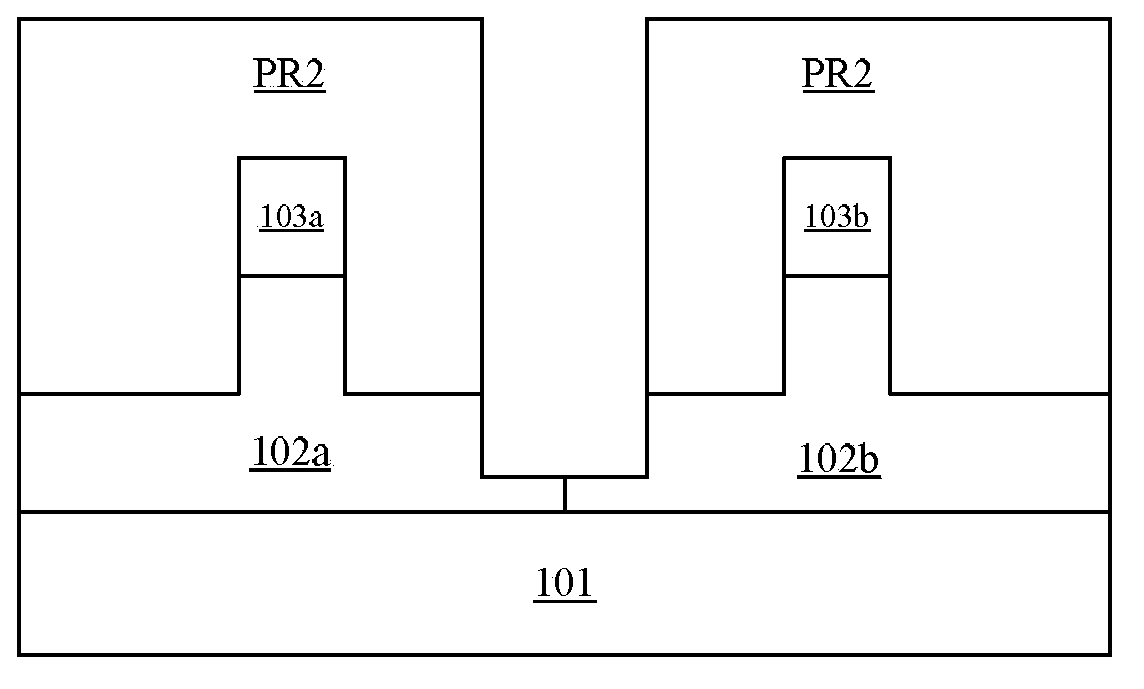

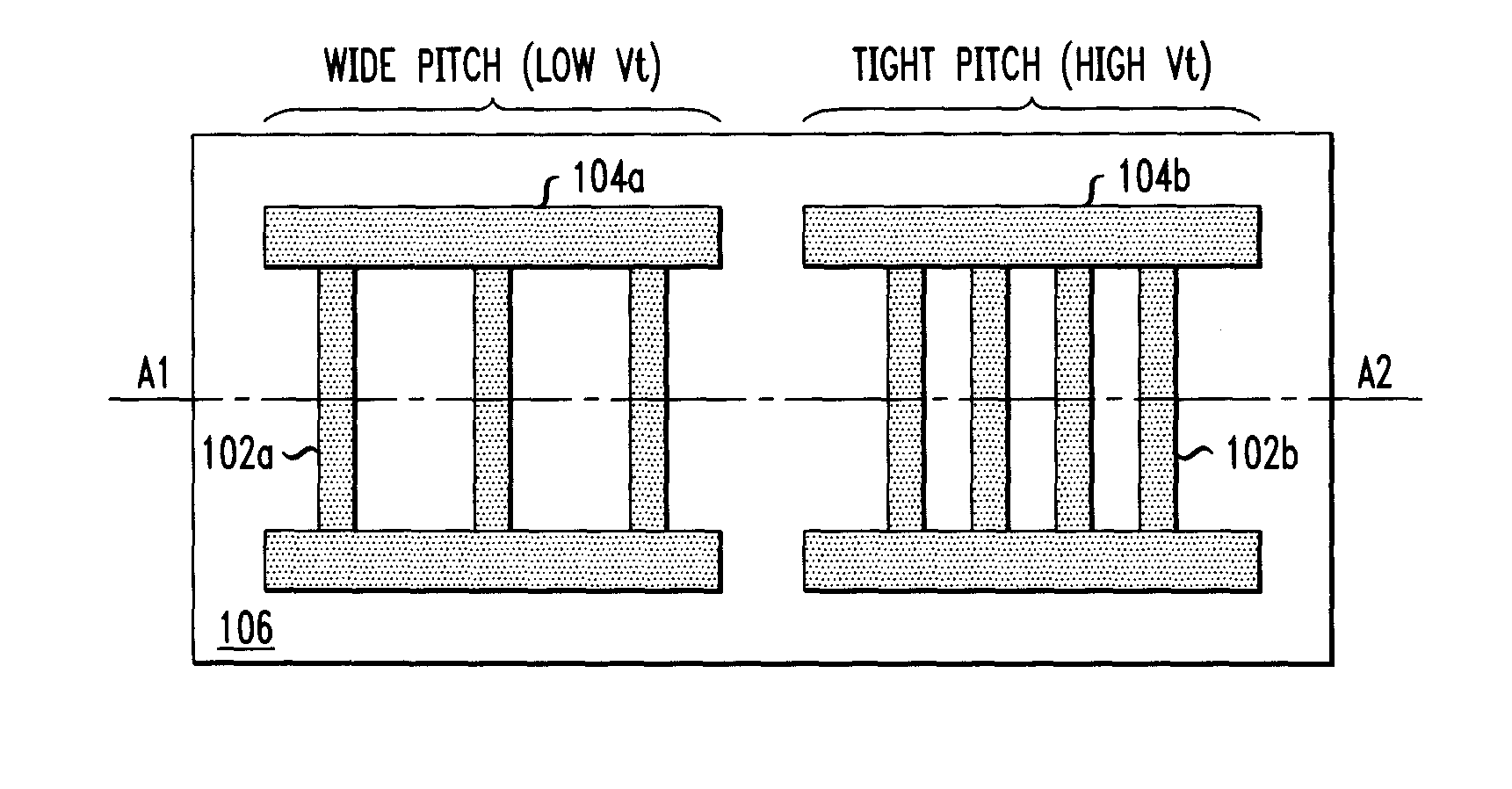

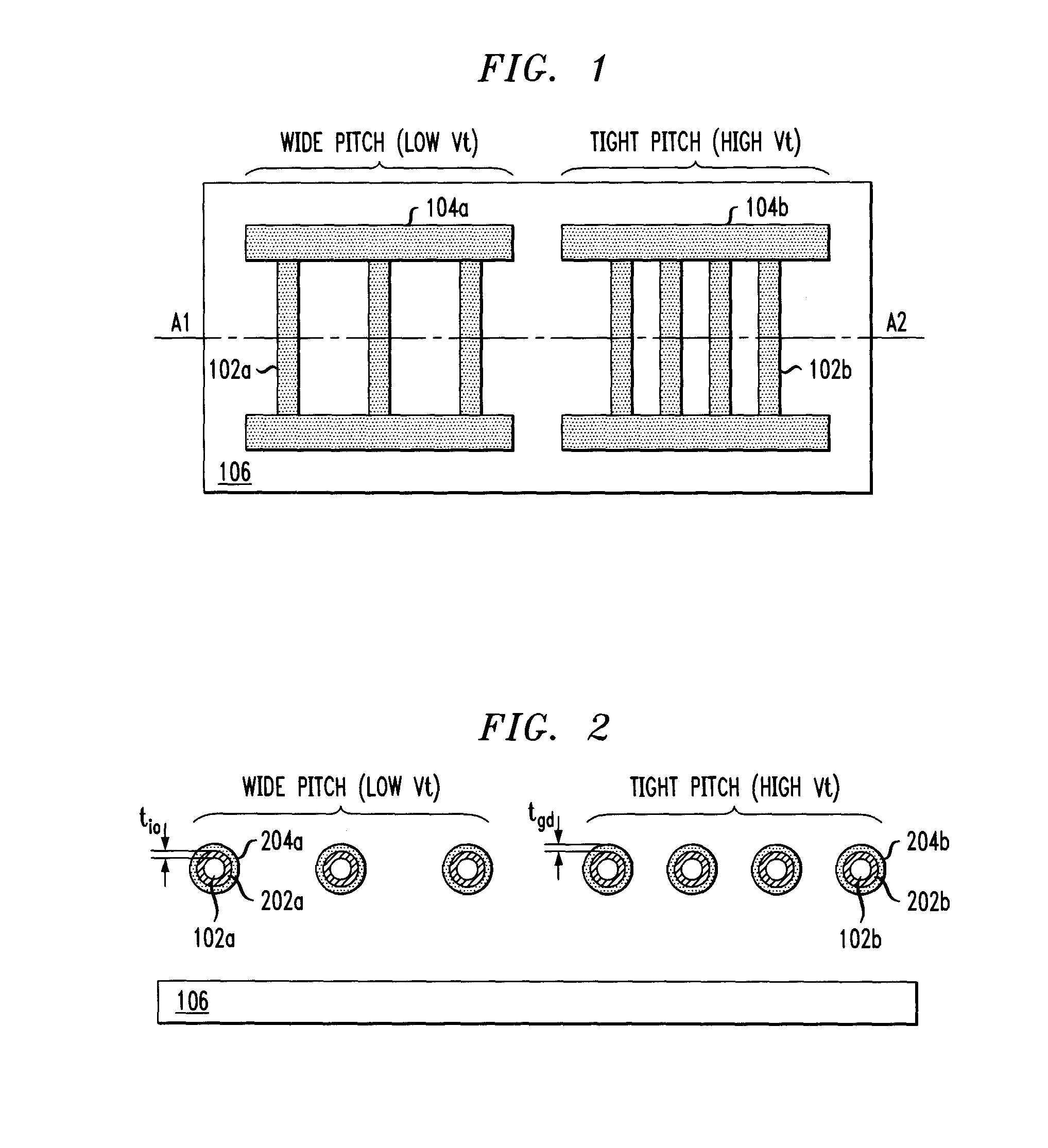

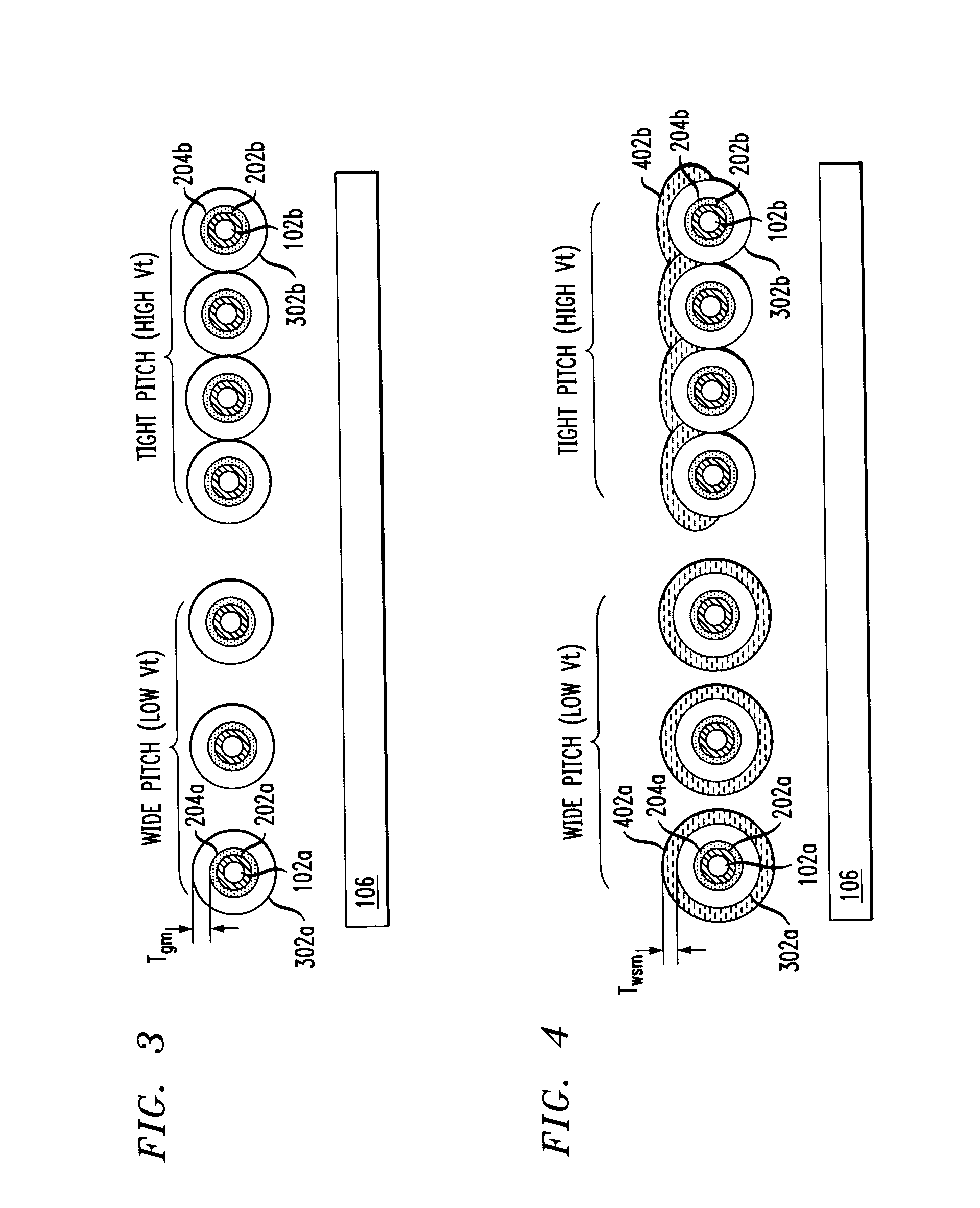

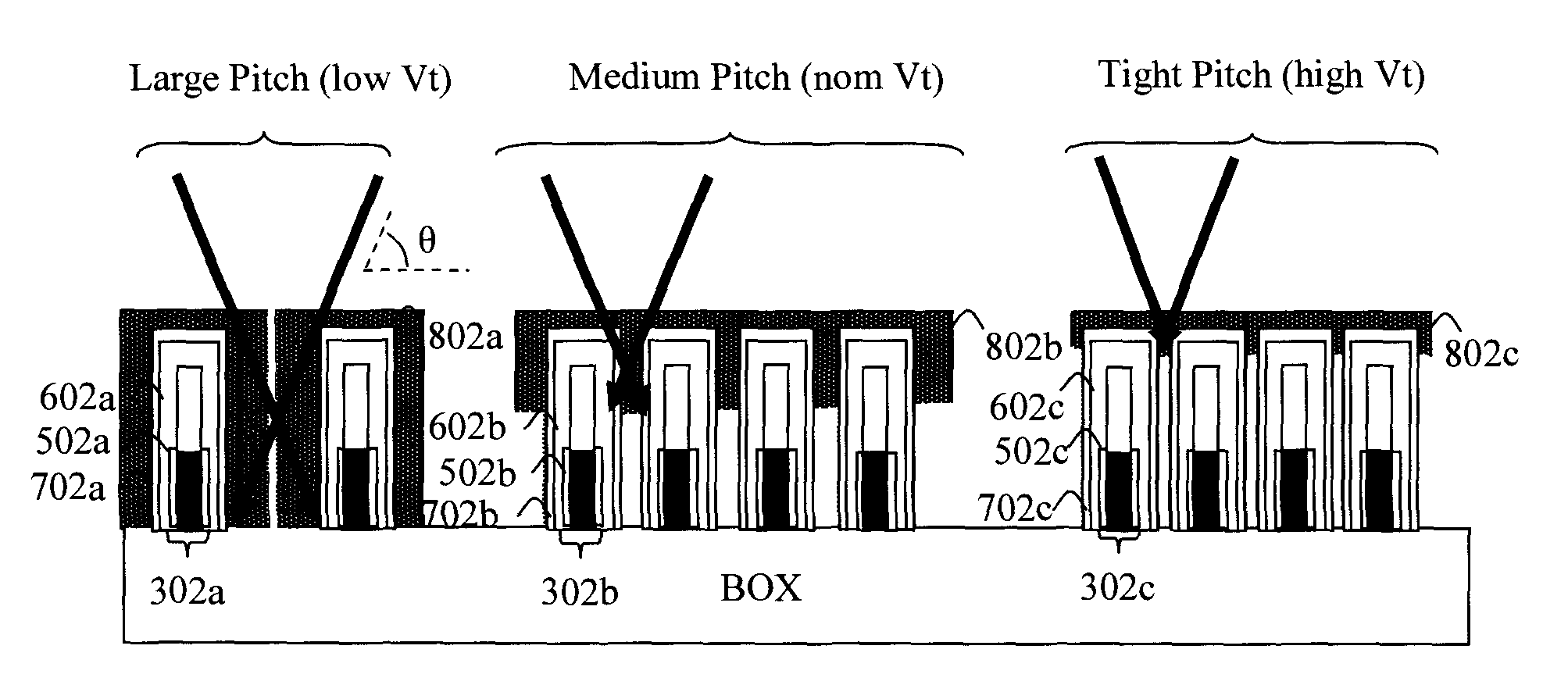

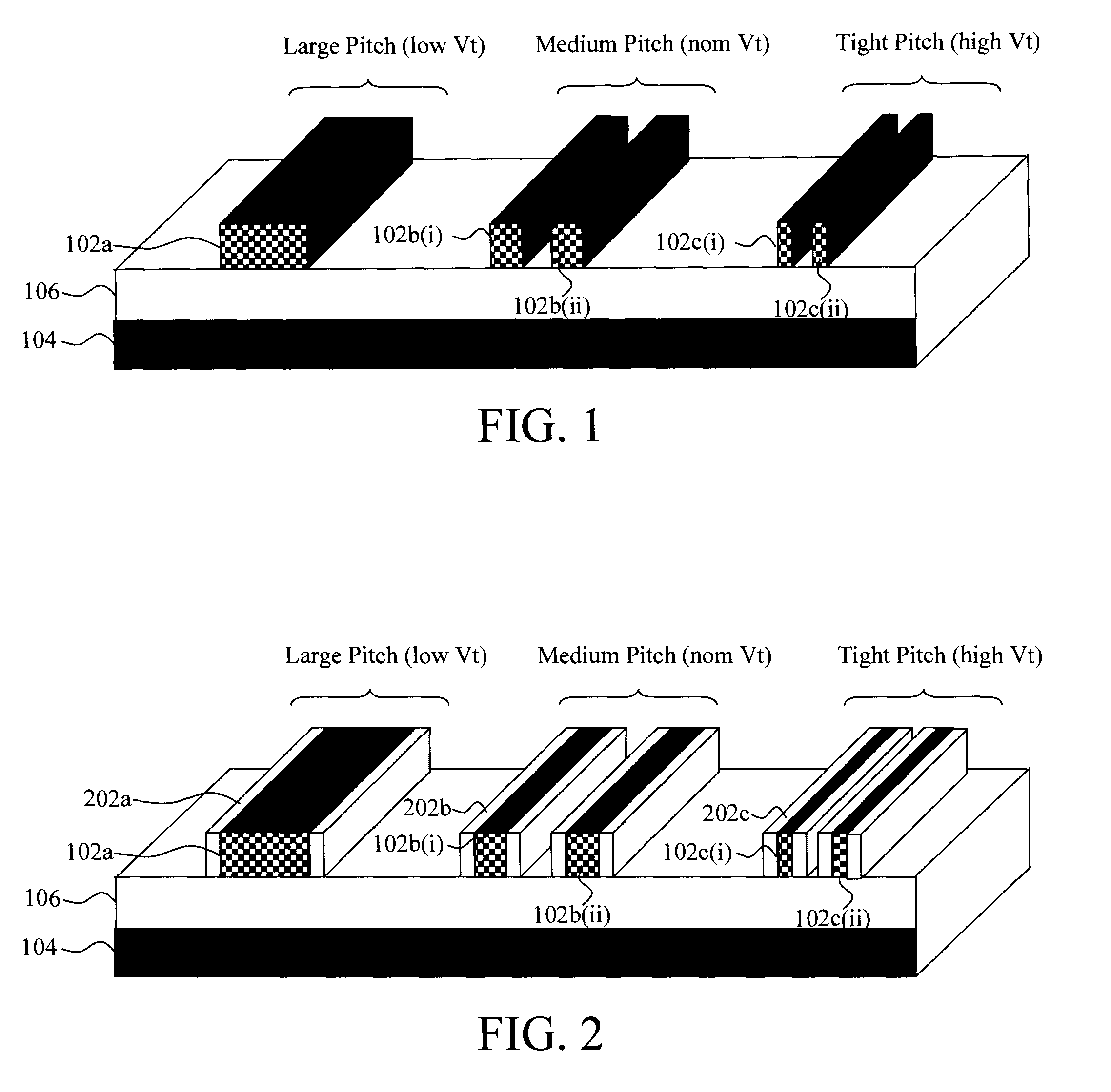

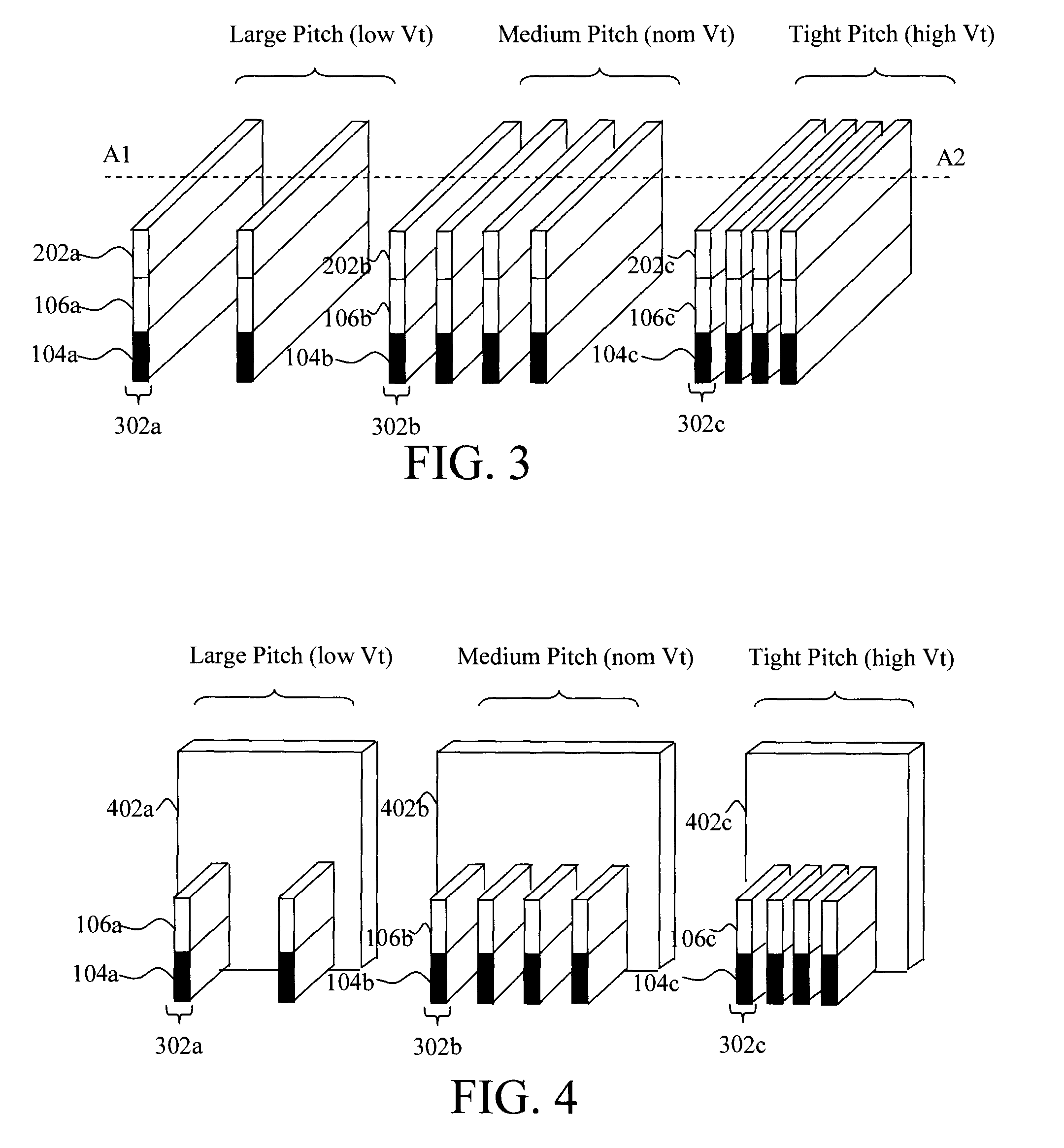

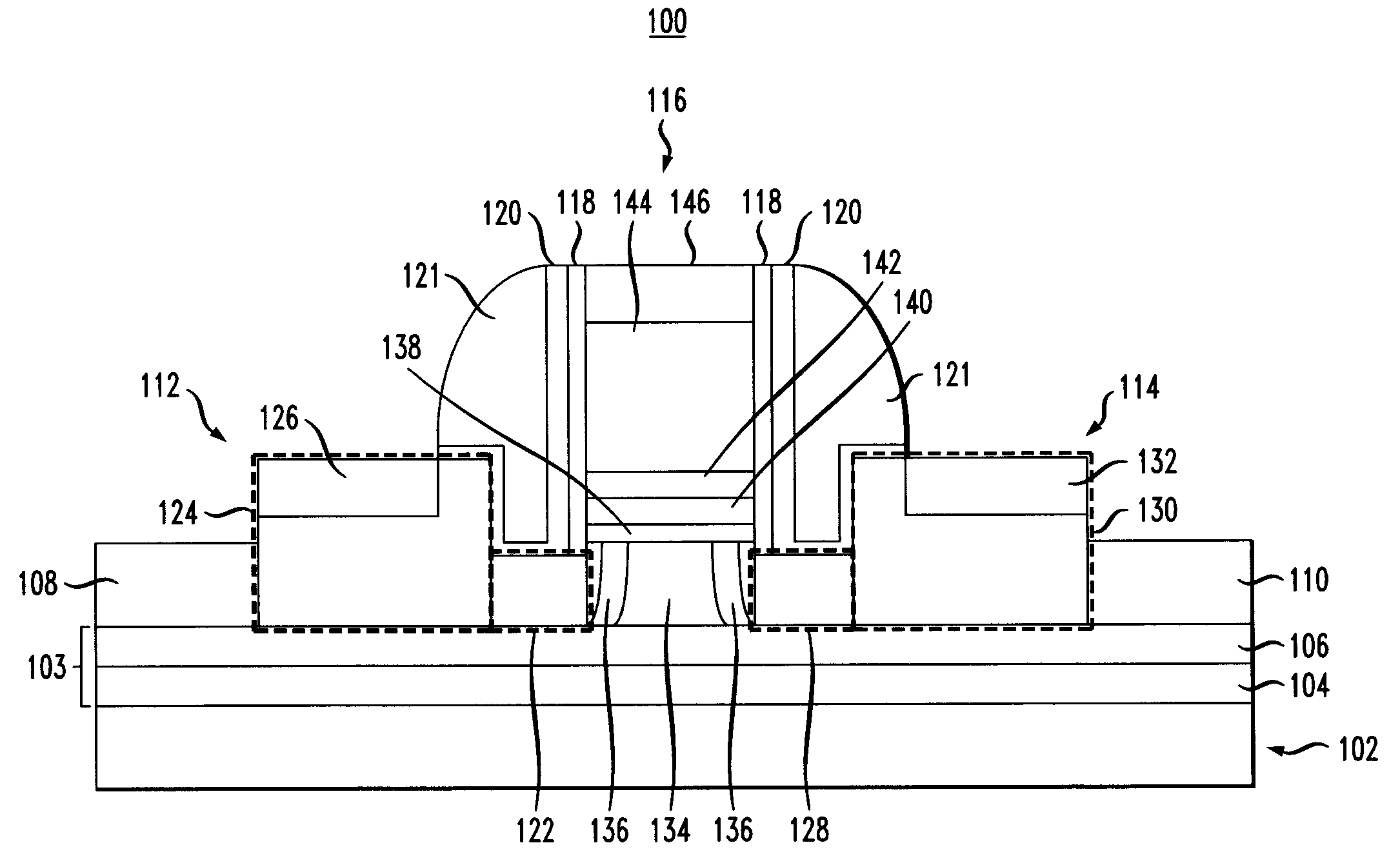

Techniques for metal gate workfunction engineering to enable multiple threshold voltage finfet devices

ActiveUS20140065802A1Solid-state devicesSemiconductor/solid-state device manufacturingInterfacial oxideWork function engineering

Techniques are provided for gate work function engineering in FIN FET devices using a work function setting material an amount of which is provided proportional to fin pitch. In one aspect, a method of fabricating a FIN FET device includes the following steps. A SOI wafer having a SOI layer over a BOX is provided. An oxide layer is formed over the SOI layer. A plurality of fins is patterned in the SOI layer and the oxide layer. An interfacial oxide is formed on the fins. A conformal gate dielectric layer, a conformal gate metal layer and a conformal work function setting material layer are deposited on the fins. A volume of the conformal gate metal layer and a volume of the conformal work function setting material layer deposited over the fins is proportional to a pitch of the fins. A FIN FET device is also provided.

Owner:GLOBALFOUNDRIES US INC

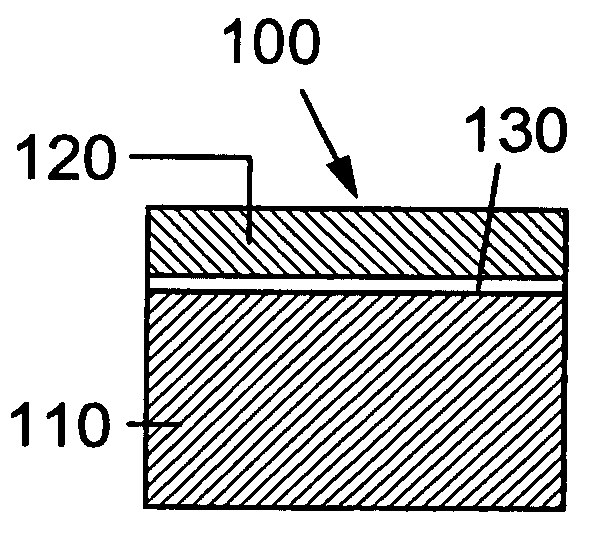

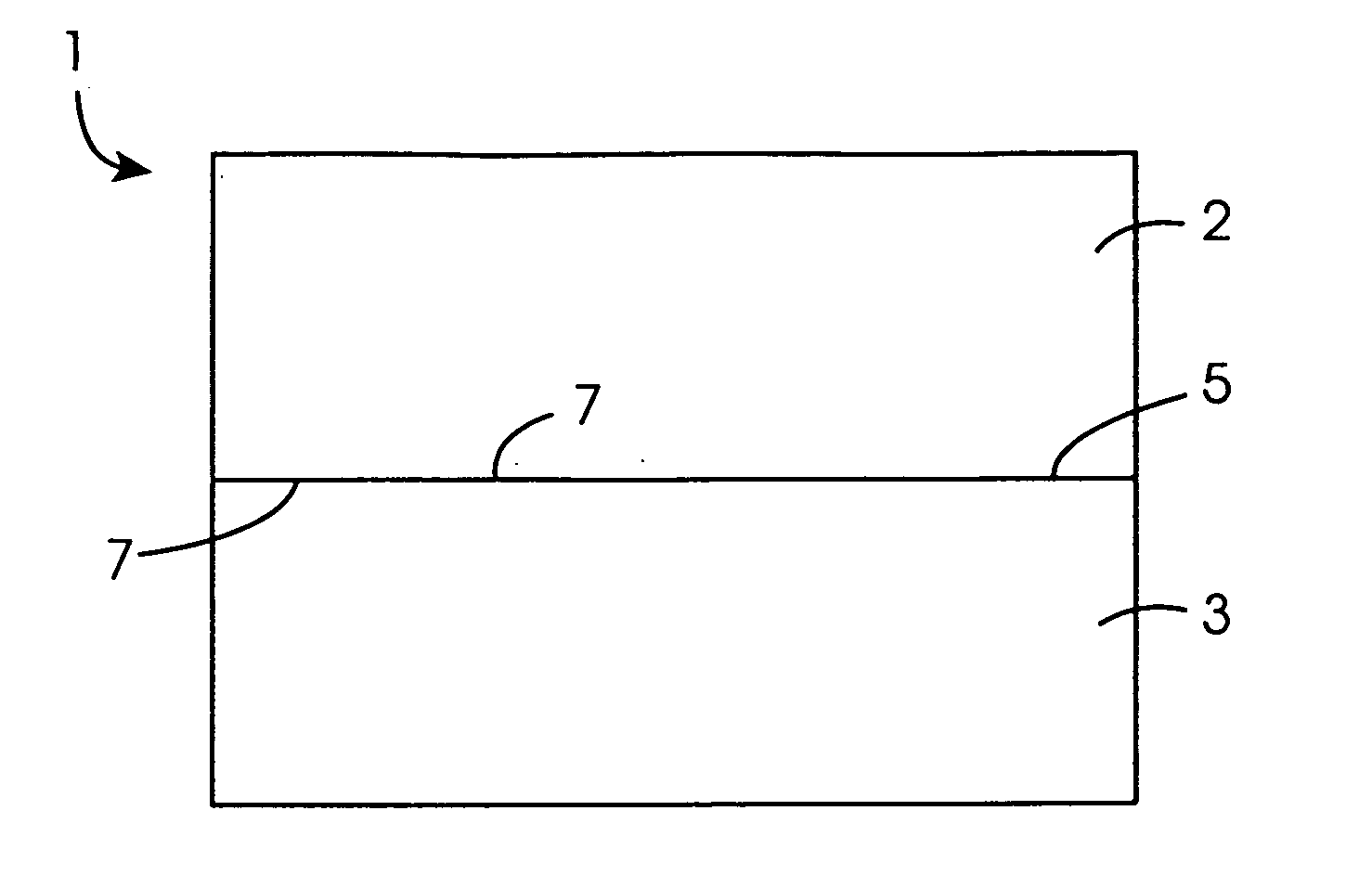

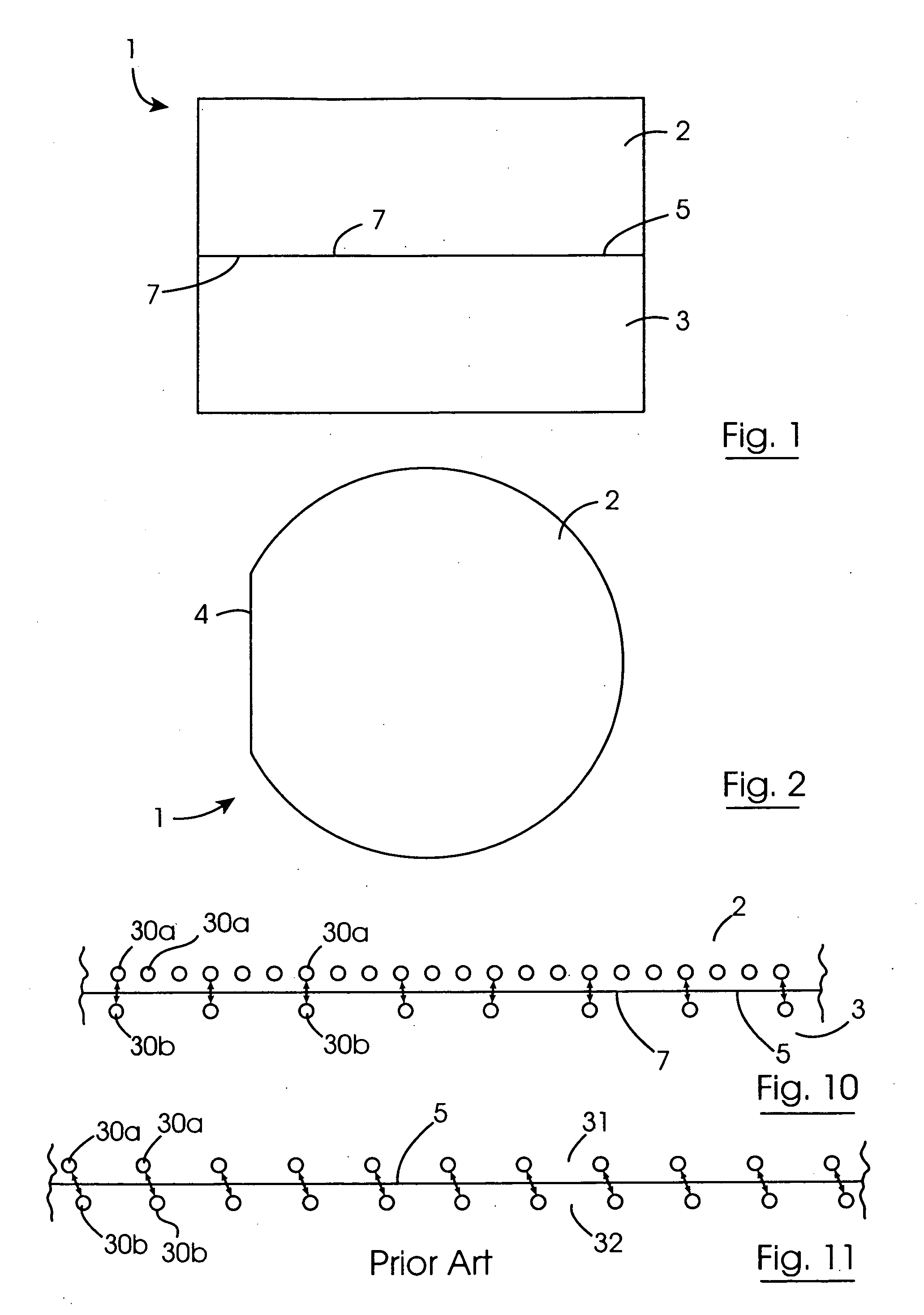

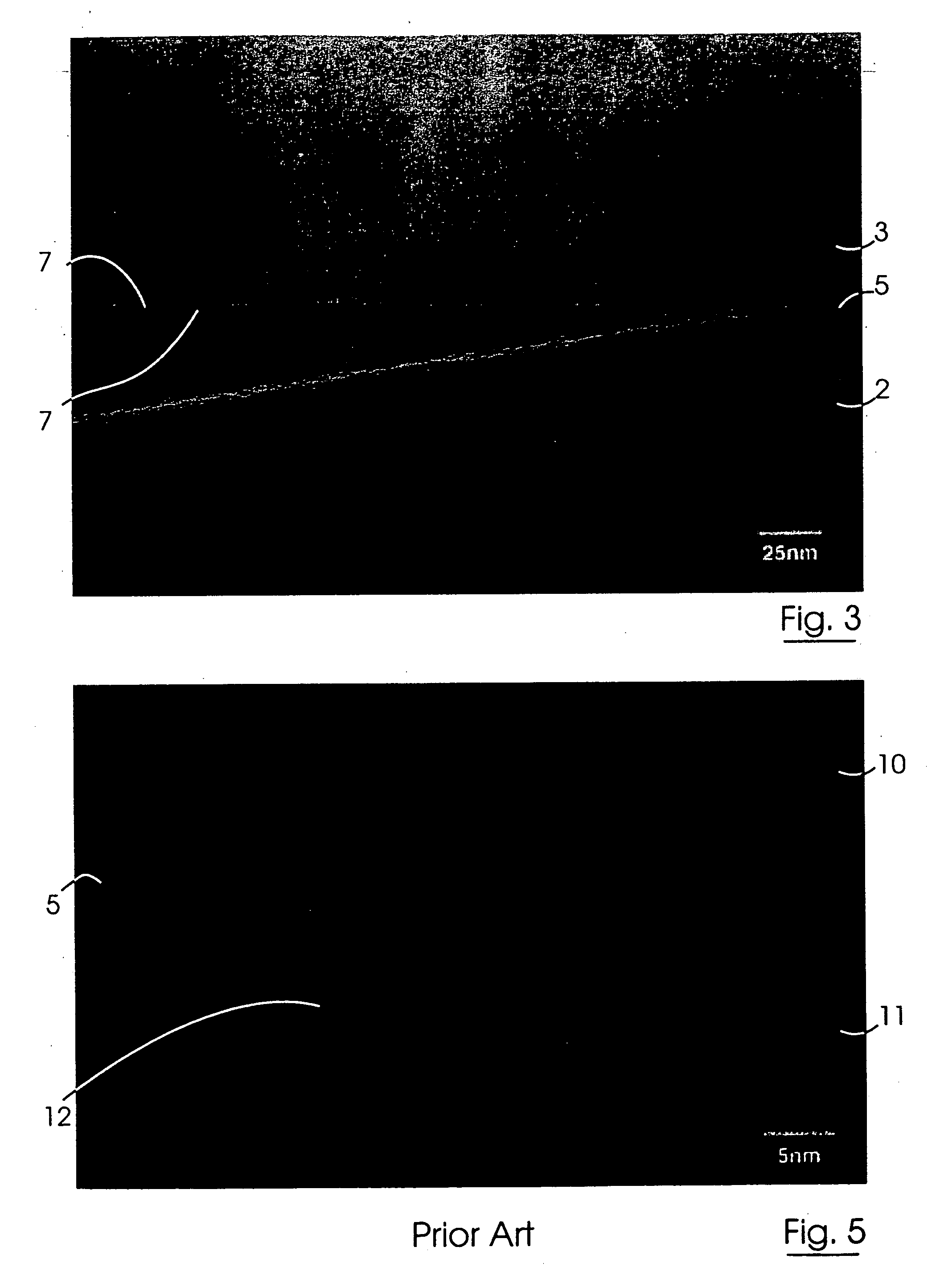

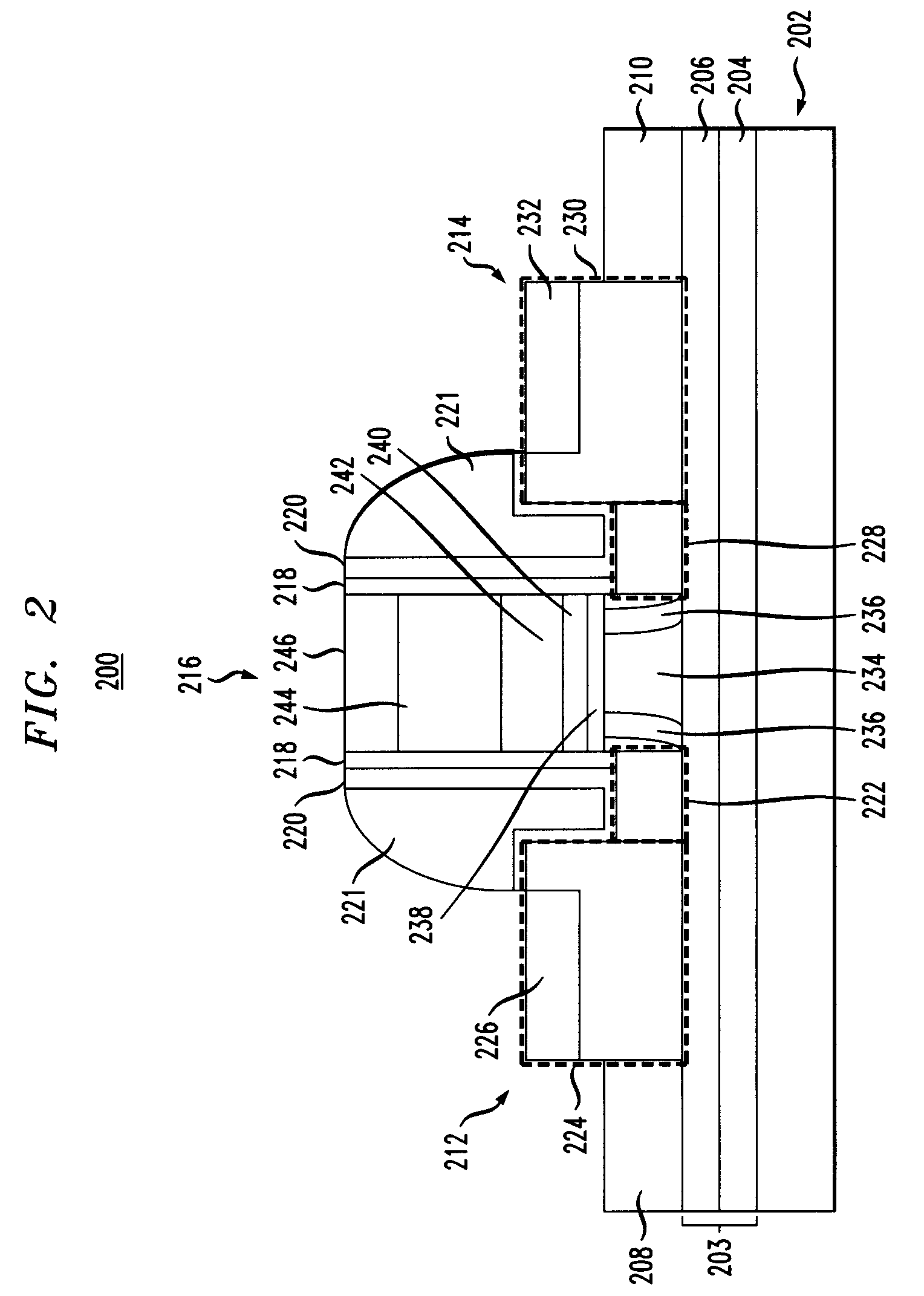

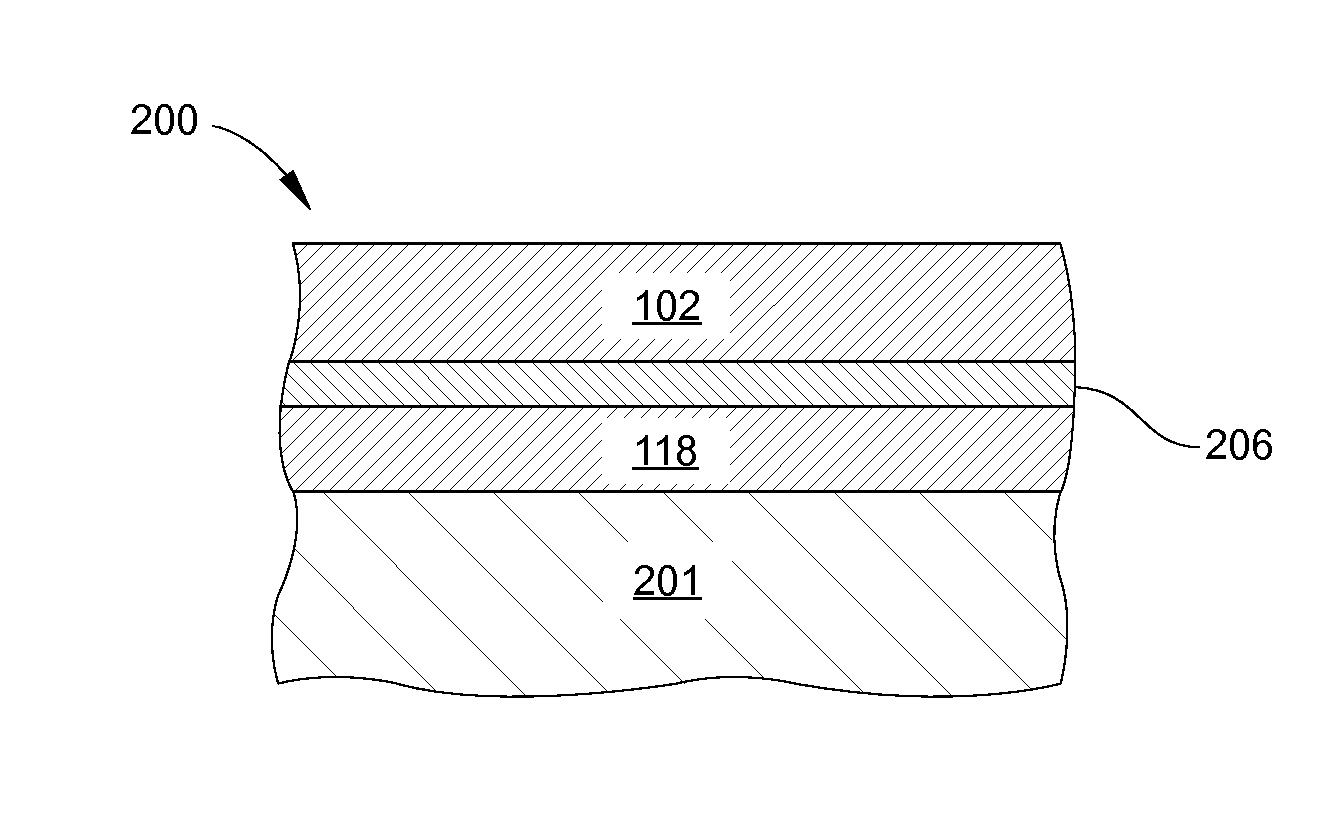

Method for direct bonding two silicon wafers for minimising interfacial oxide and stresses at the bond interface, and an SOI structure

InactiveUS20040087109A1Semiconductor/solid-state device manufacturingInterfacial oxideBond interface

A semiconductor substrate (1) comprises first and second silicon wafers (2,3) directly bonded together with interfacial oxide and interfacial stresses minimised along a bond interface (5), which is defined by bond faces (7) of the first and second wafers (2,3). Interfacial oxide is minimised by selecting the first and second wafers (2,3) to be of relatively low oxygen content, well below the limit of solid solubility of oxygen in the wafers. In order to minimise interfacial stresses, the first and second wafers are selected to have respective different crystal plane orientations. The bond faces (7) of the first and second wafers (2,3) are polished and cleaned, and are subsequently dried in a nitrogen atmosphere. Immediately upon being dried, the bond faces (7) of the first and second wafers (2,3) are abutted together and the wafers (2,3) are subjected to a preliminary anneal at a temperature of at least 400° C. for a time period of a few hours. As soon as possible after the preliminary anneal, and preferably, within forty-eight hours of the preliminary anneal, the first and second wafers (2,3) are fusion bonded at a bond anneal temperature of approximately 1,150° C. for a time period of approximately three hours. The preliminary anneal may be omitted if fusion bonding at the bond anneal temperature is carried out within approximately six hours of the wafers (2,3) being abutted together. An SOI structure (50) may subsequently be prepared from the semiconductor structure (1) which forms a substrate layer (52) supported on a handle layer (55) with a buried insulating layer (57) between the substrate layer (52) and the handle layer (55).

Owner:ANALOG DEVICES INC

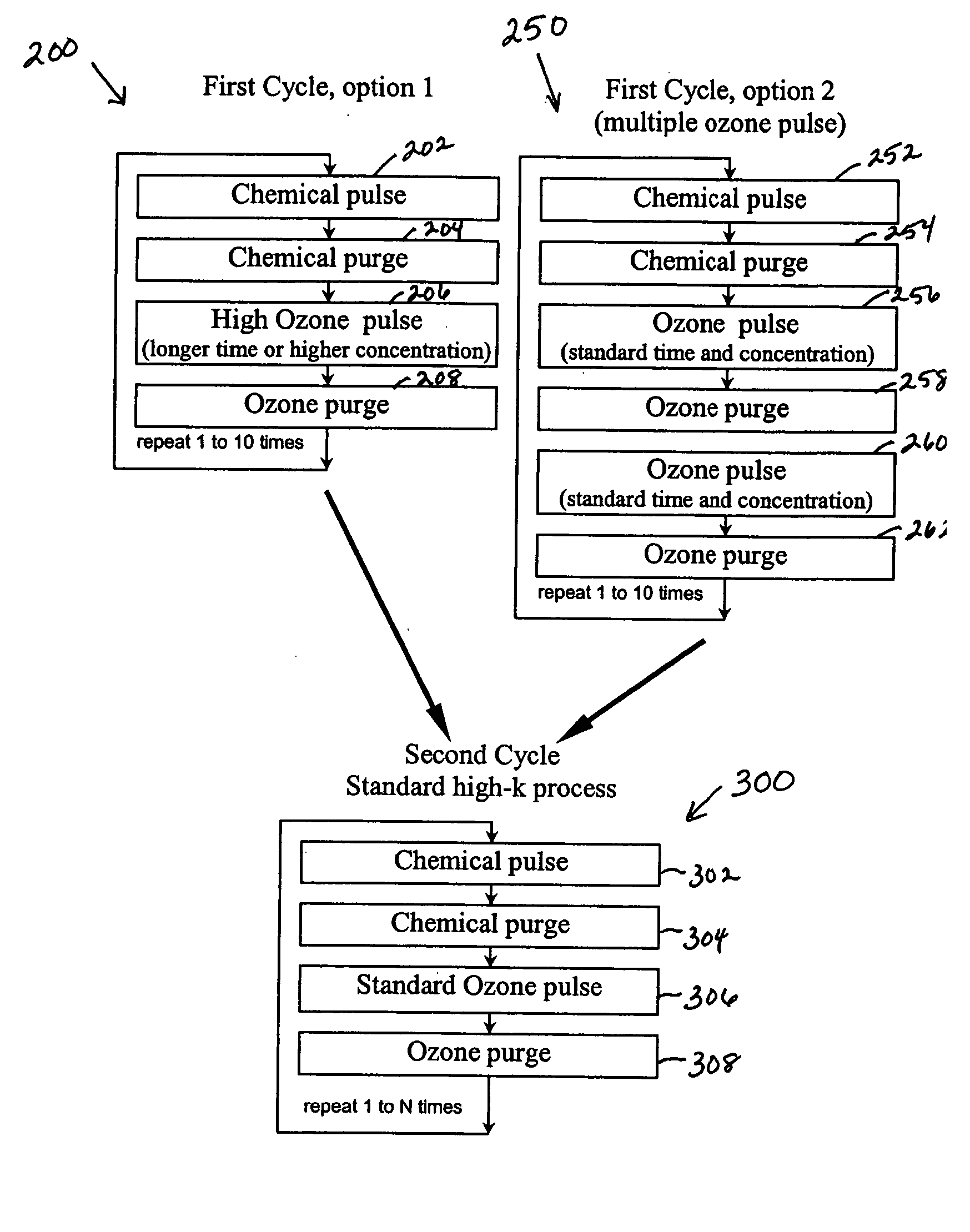

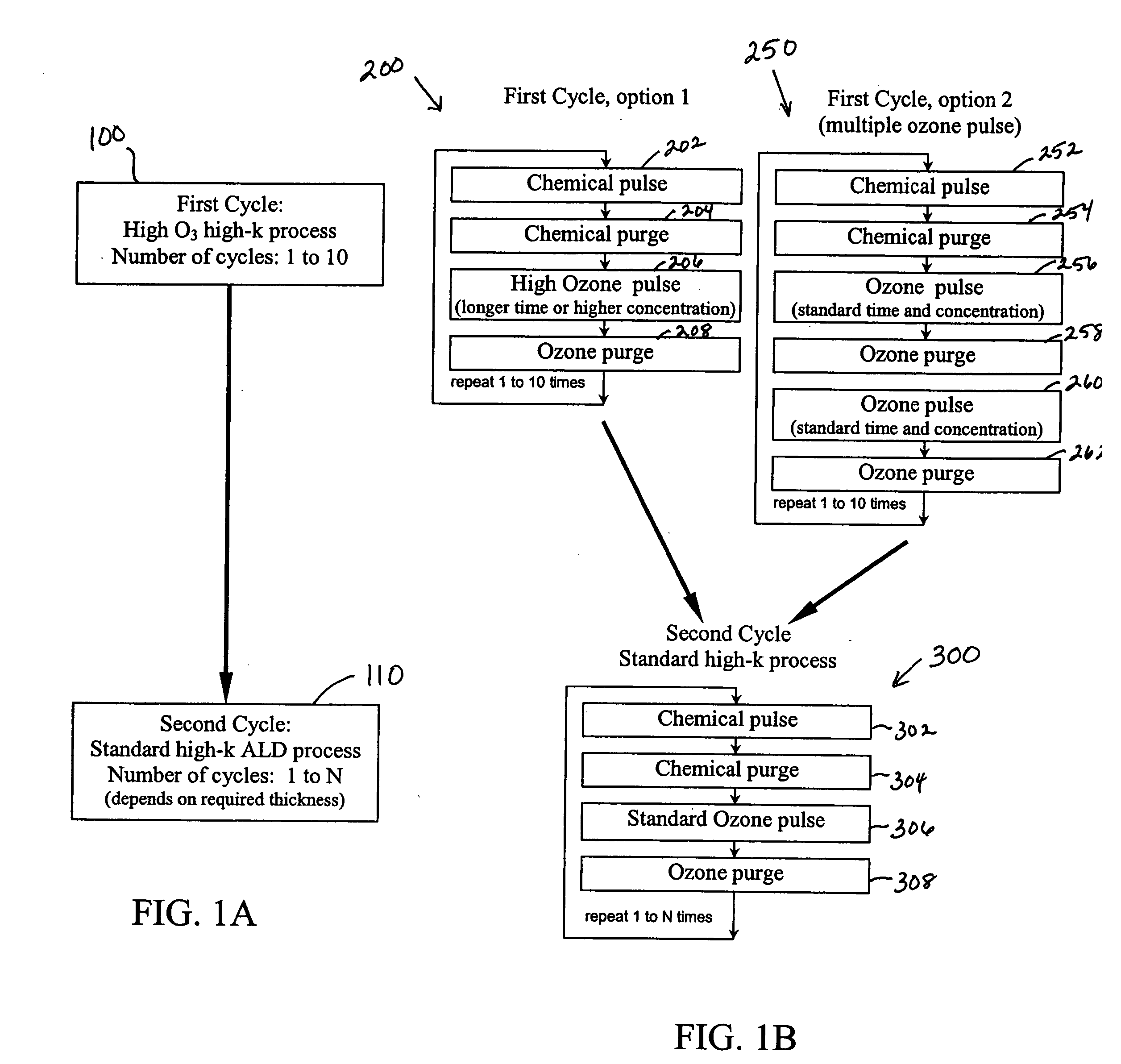

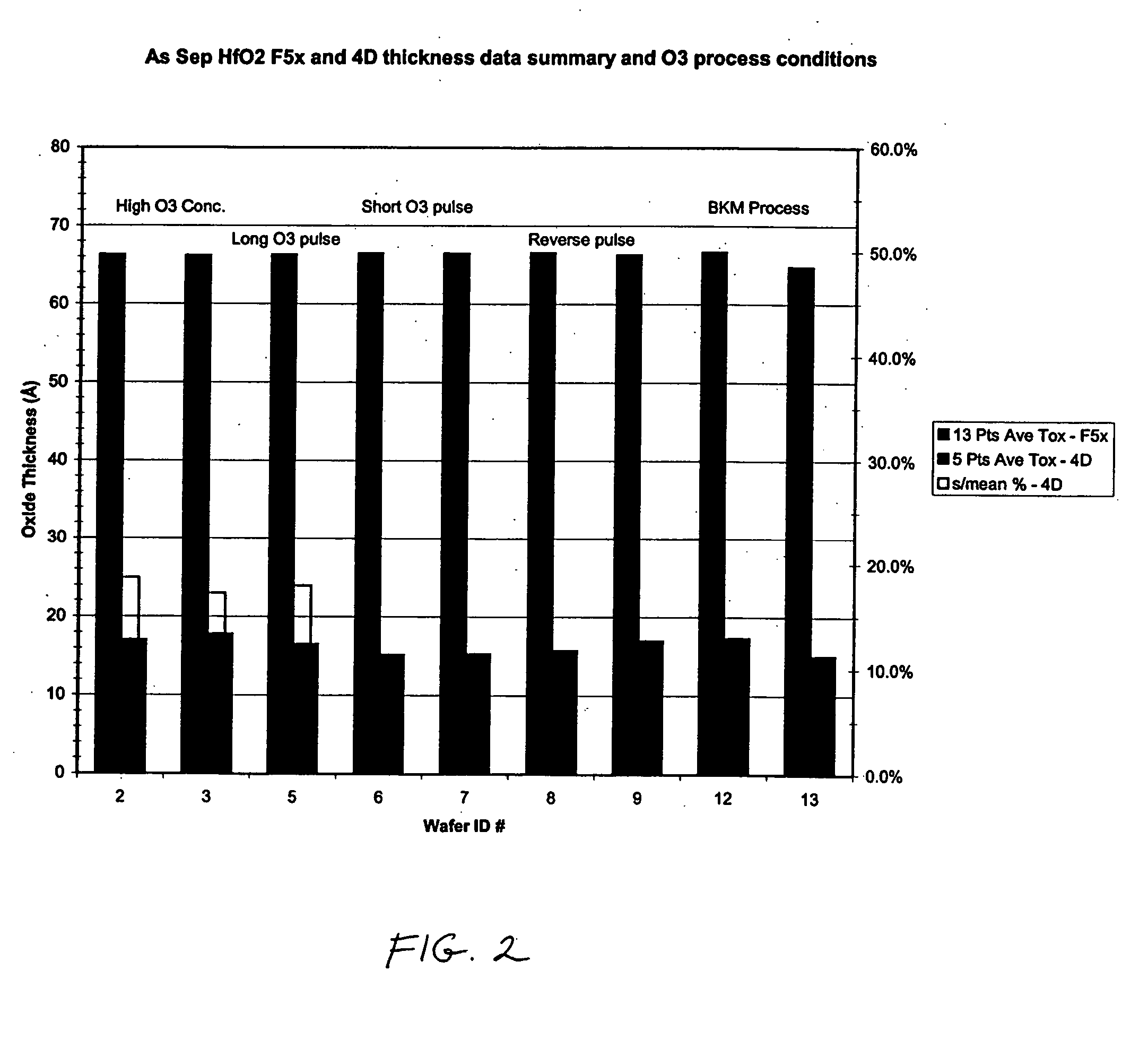

Growth of high-k dielectrics by atomic layer deposition

InactiveUS20050239297A1Minimal thicknessReduce ozone concentrationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricInterfacial oxide

In general, the present invention provides a method of depositing high-k dielectric films or layers, such as but not limited to high-k gate dielectric films. In one embodiment, atomic layer deposition (ALD) cycles are carried out where ozone is selectively conveyed to a chamber in separate cycles to form a metal oxide layer on the surface of a substrate where the metal oxide layer has an interfacial oxide layer of minimal thickness.

Owner:SENZAKI YOSHIHIDE +2

Techniques for metal gate workfunction engineering to enable multiple threshold voltage FINFET devices

Techniques are provided for gate work function engineering in FIN FET devices using a work function setting material an amount of which is provided proportional to fin pitch. In one aspect, a FIN FET device is provided. The FIN FET device includes a SOI wafer having an oxide layer and a SOI layer over a BOX, and a plurality of fins patterned in the oxide layer and the SOI layer; an interfacial oxide on the fins; and at least one gate stack on the interfacial oxide, the gate stack having (i) a conformal gate dielectric layer present, (ii) a conformal gate metal layer, and (iii) a conformal work function setting material layer. A volume of the conformal gate metal layer and a volume of the conformal work function setting material layer present in the gate stack is proportional to a pitch of the fins.

Owner:GLOBALFOUNDRIES US INC

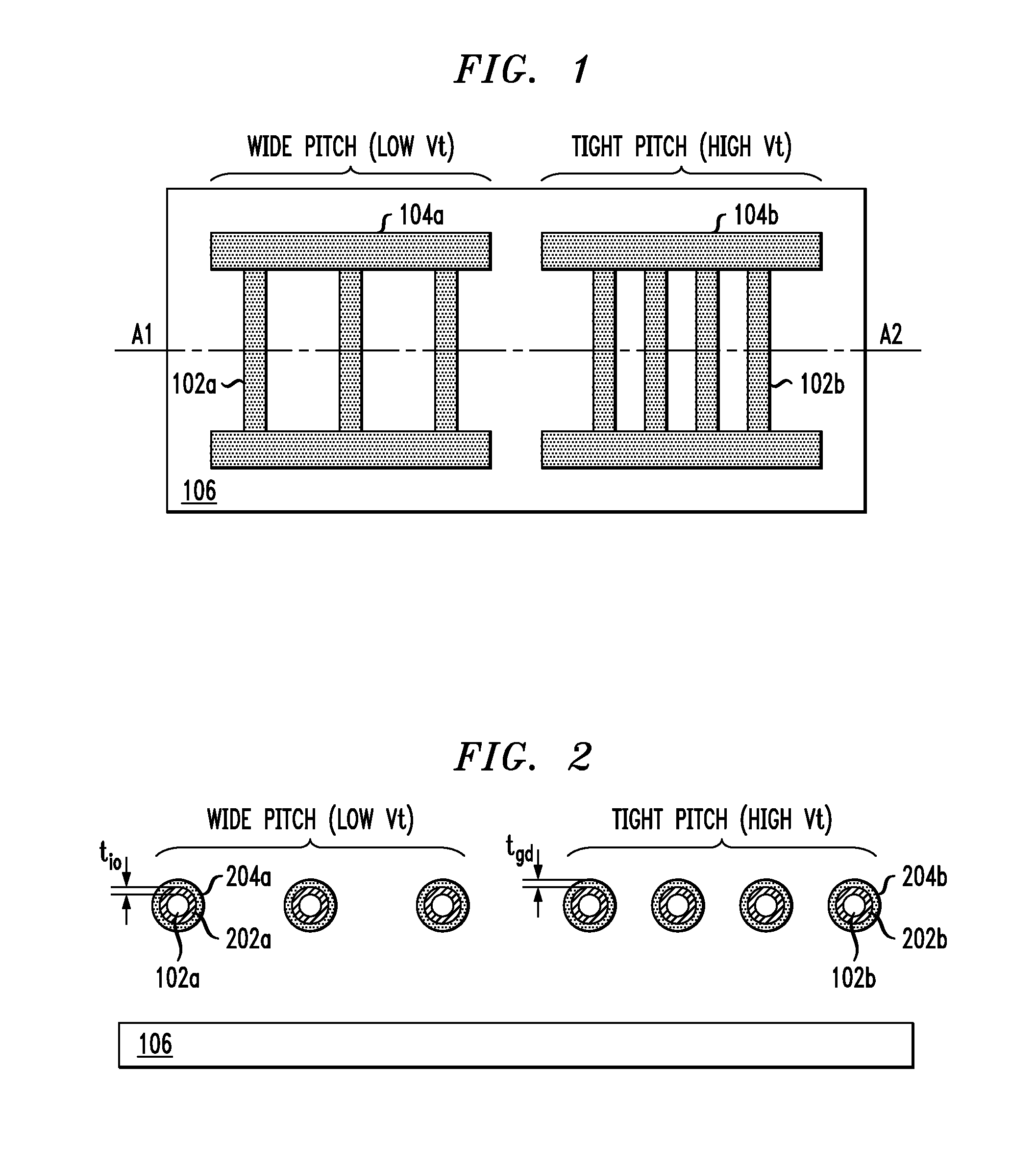

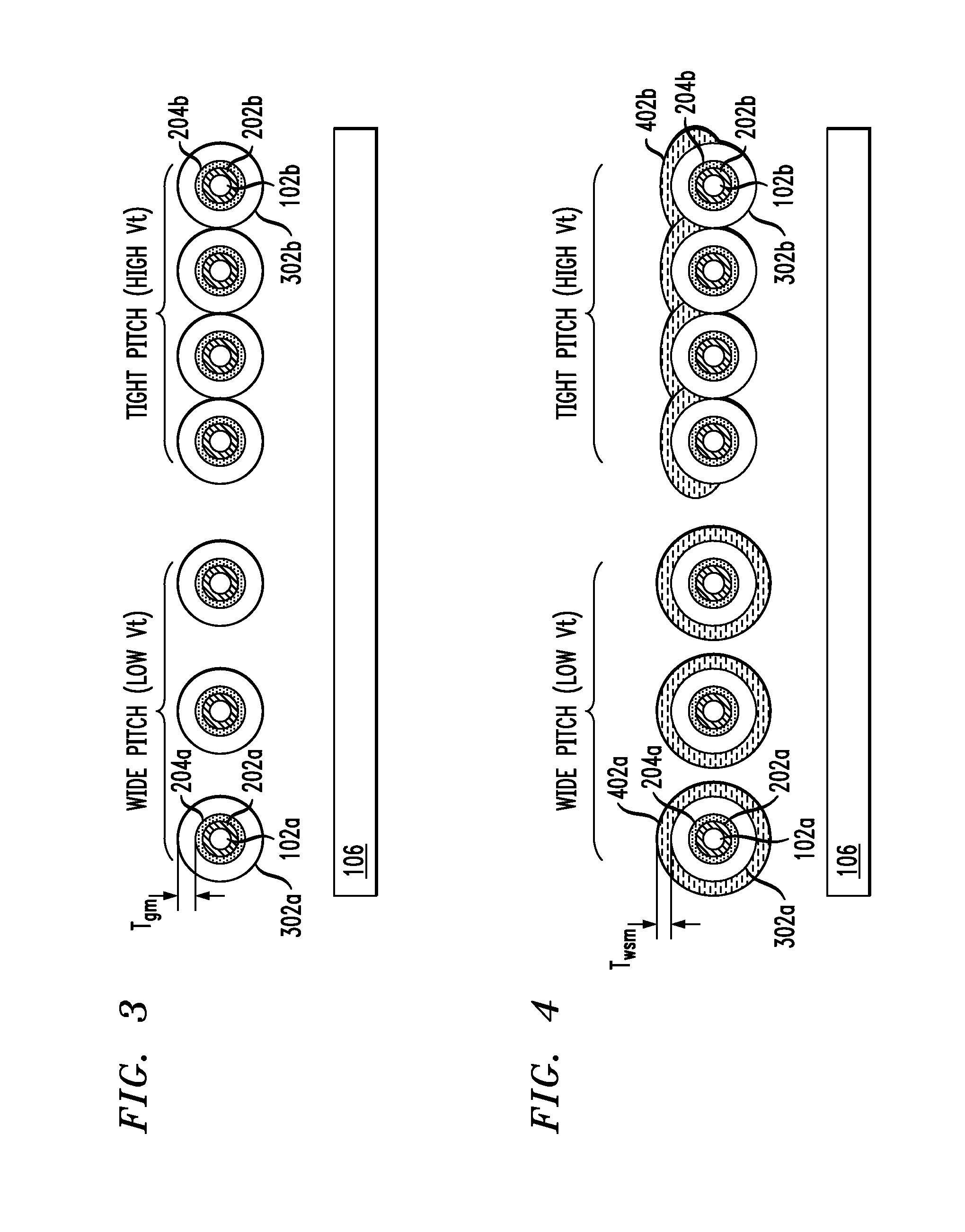

Techniques for Metal Gate Work Function Engineering to Enable Multiple Threshold Voltage Nanowire FET Devices

ActiveUS20140051213A1NanoinformaticsSemiconductor/solid-state device manufacturingInterfacial oxideWork function engineering

A method of fabricating a nanowire FET device includes the following steps. A SOI wafer is provided having a SOI layer over a BOX. Nanowires and pads are etched in the SOI layer. The nanowires are suspended over the BOX. An interfacial oxide is formed surrounding each of the nanowires. A conformal gate dielectric is deposited on the interfacial oxide. A conformal first gate material is deposited on the conformal gate dielectric. A work function setting material is deposited on the conformal first gate material. A second gate material is deposited on the work function setting material to form at least one gate stack over the nanowires. A volume of the conformal first gate material and / or a volume of the work function setting material in the gate stack are / is proportional to a pitch of the nanowires.

Owner:GLOBALFOUNDRIES US INC

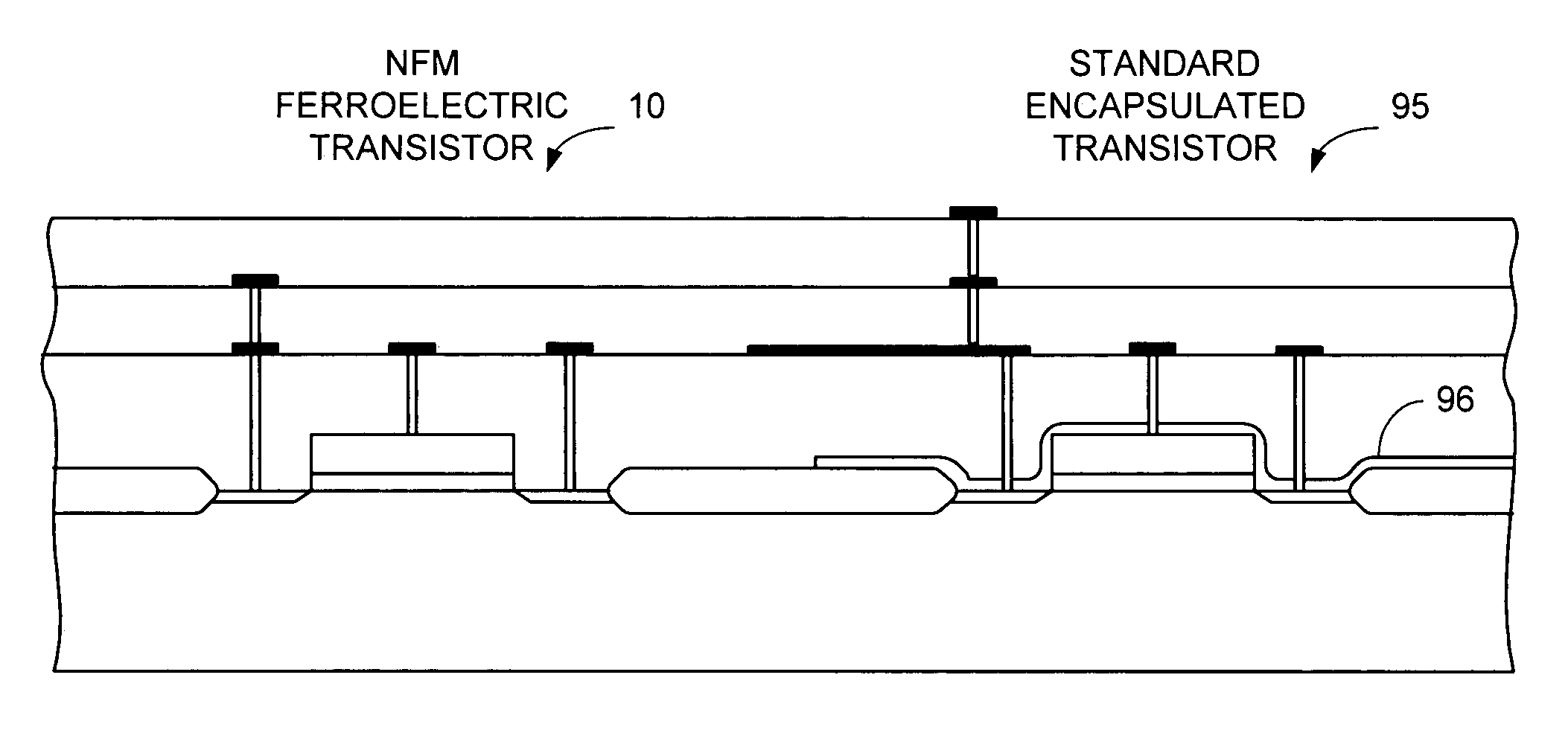

Single transistor rare earth manganite ferroelectric nonvolatile memory cell

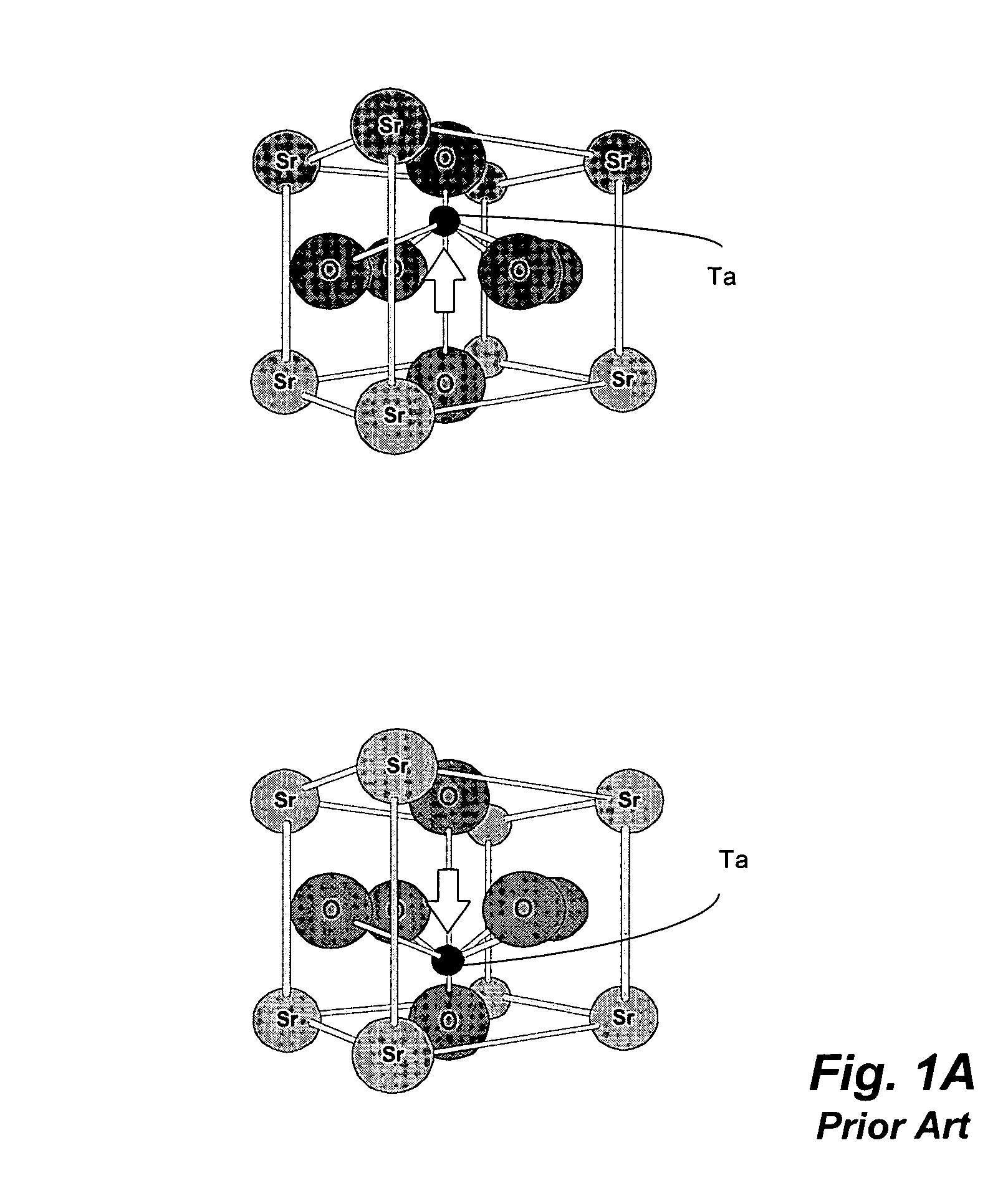

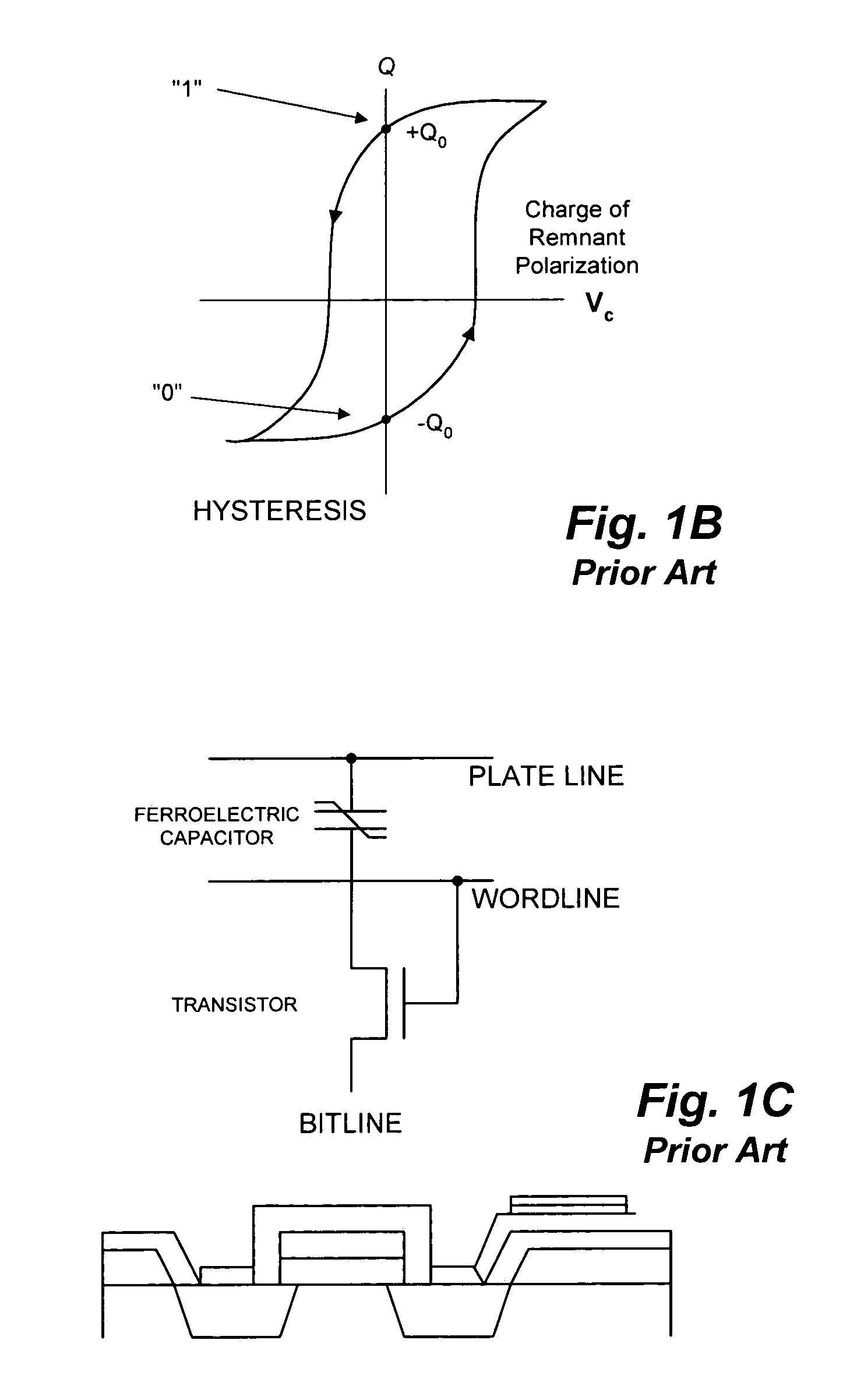

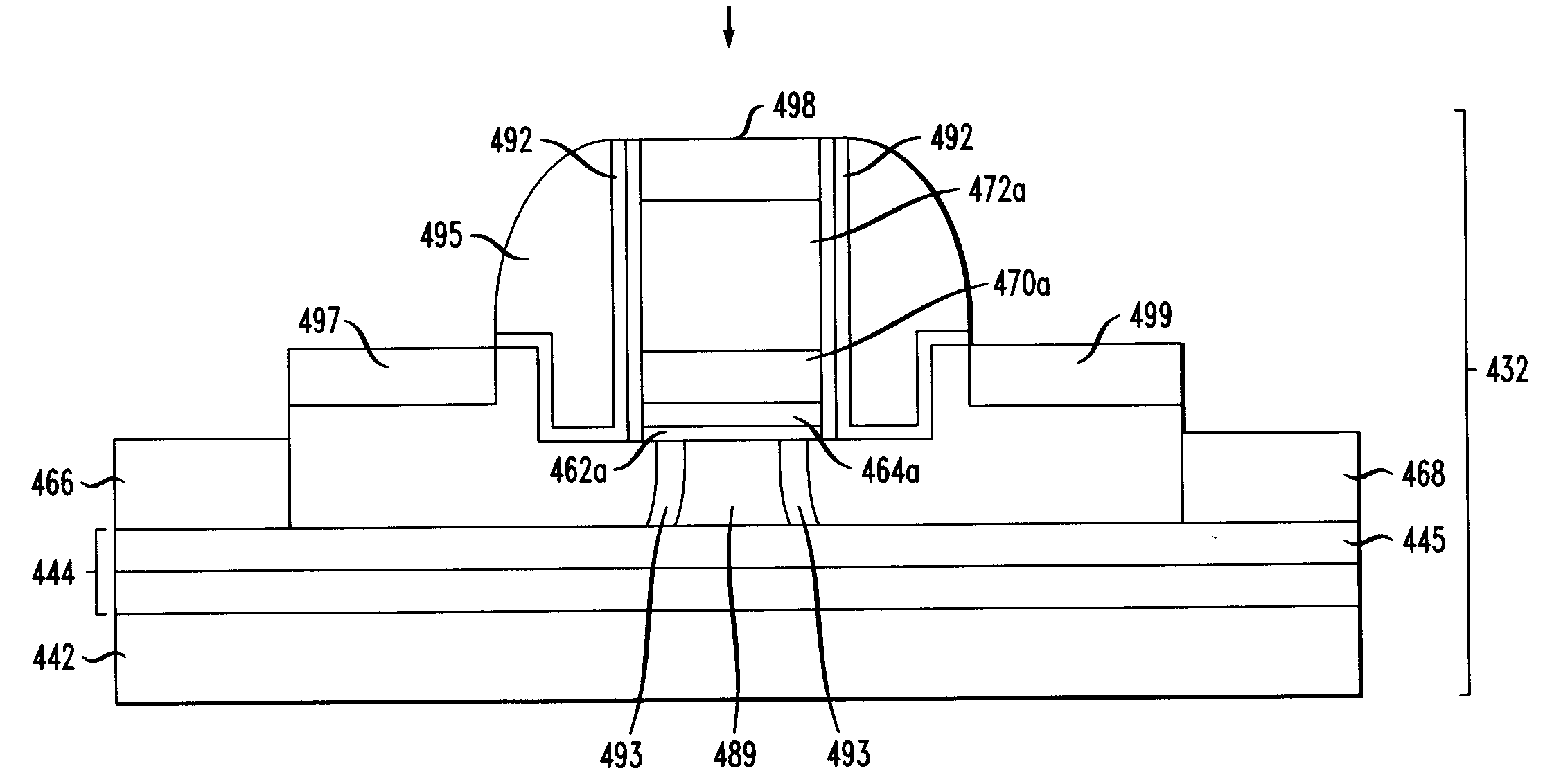

InactiveUS7030435B2Avoid problemsLow vapor pressureTransistorSolid-state devicesInterfacial oxideRare earth

A memory device is formed of the one transistor cell type. Such a device has a substrate, a ferroelectric layer which is a film of rare earth manganite, and an interfacial oxide layer being positioned between the substrate and the ferroelectric layer. The invention includes such a device and methods of making the same.

Owner:COVA TECH

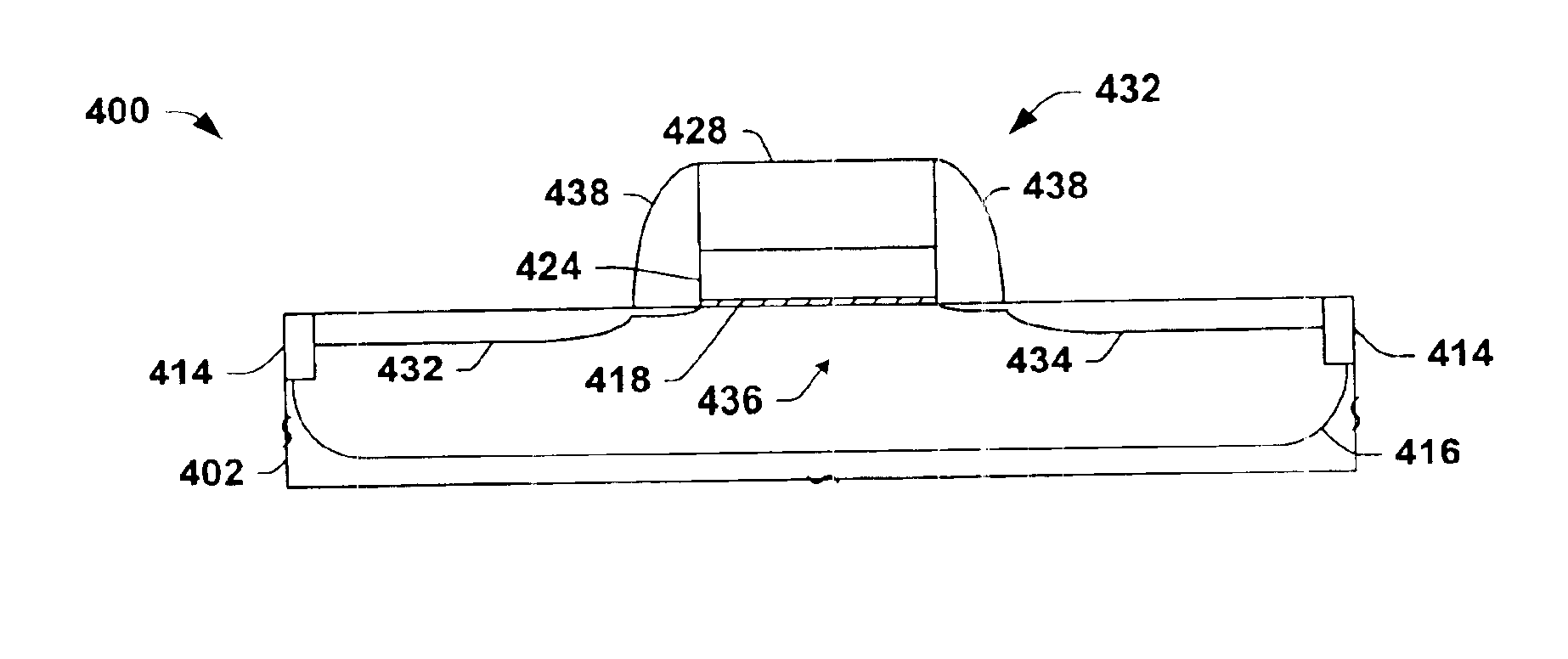

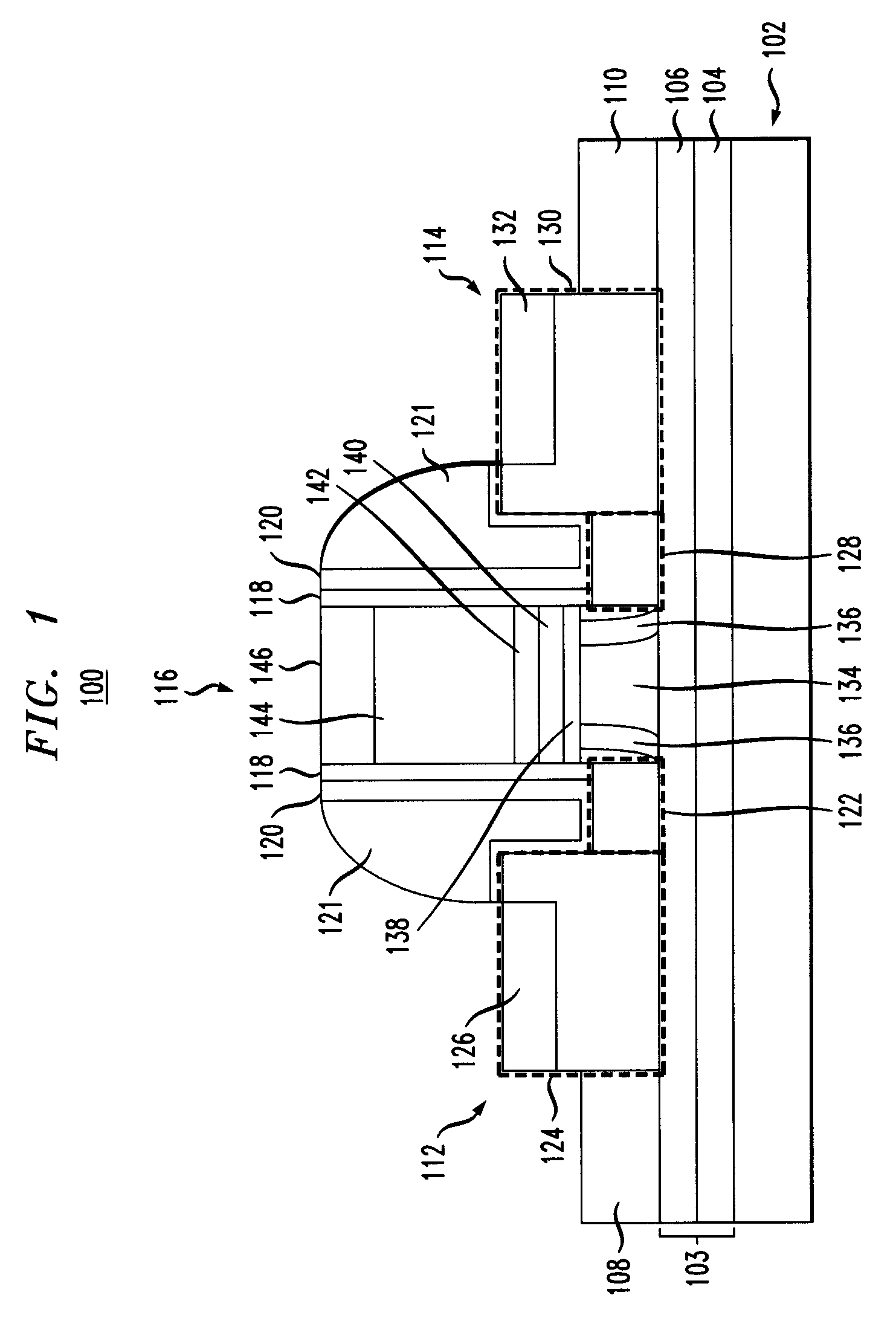

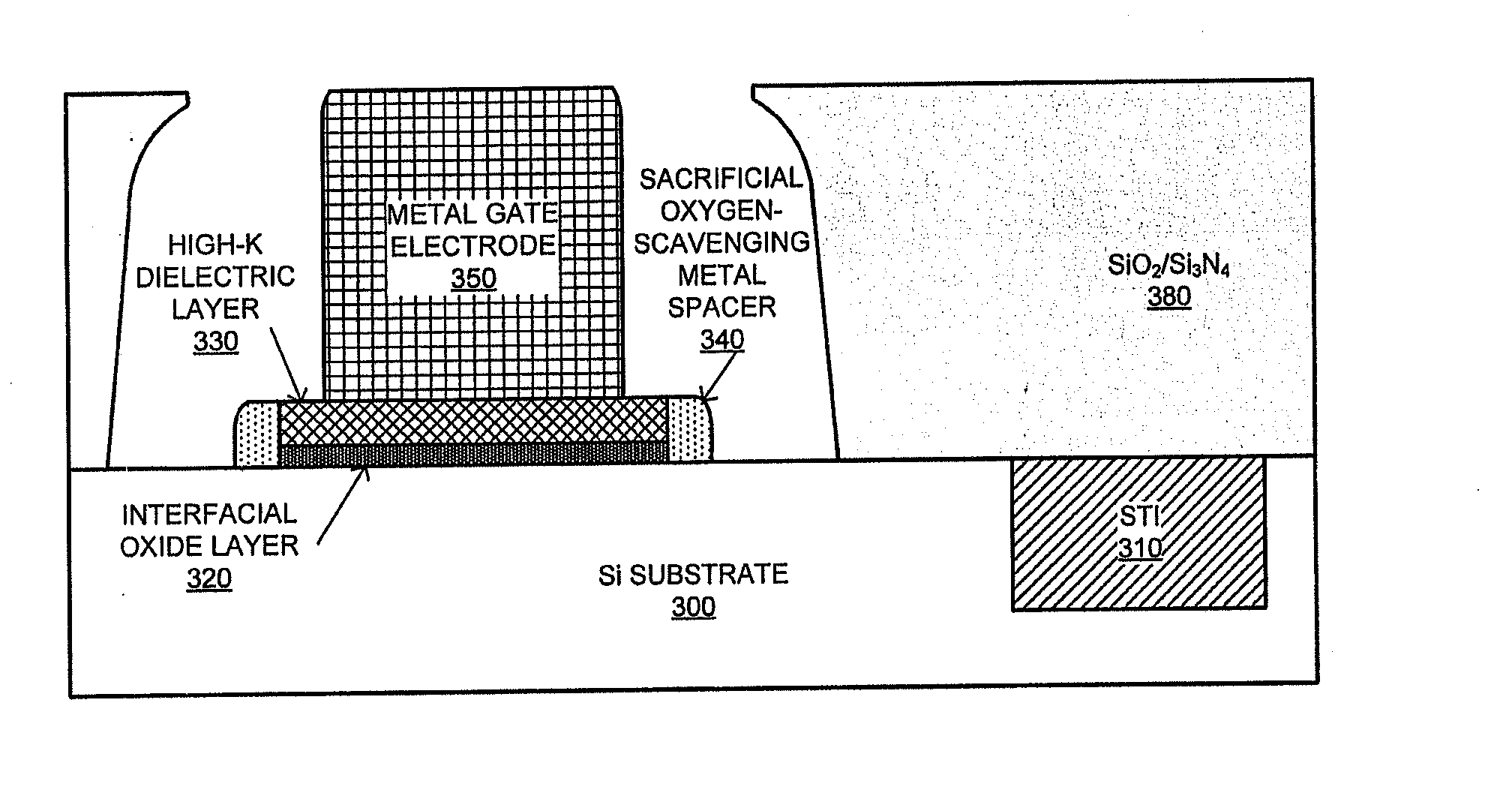

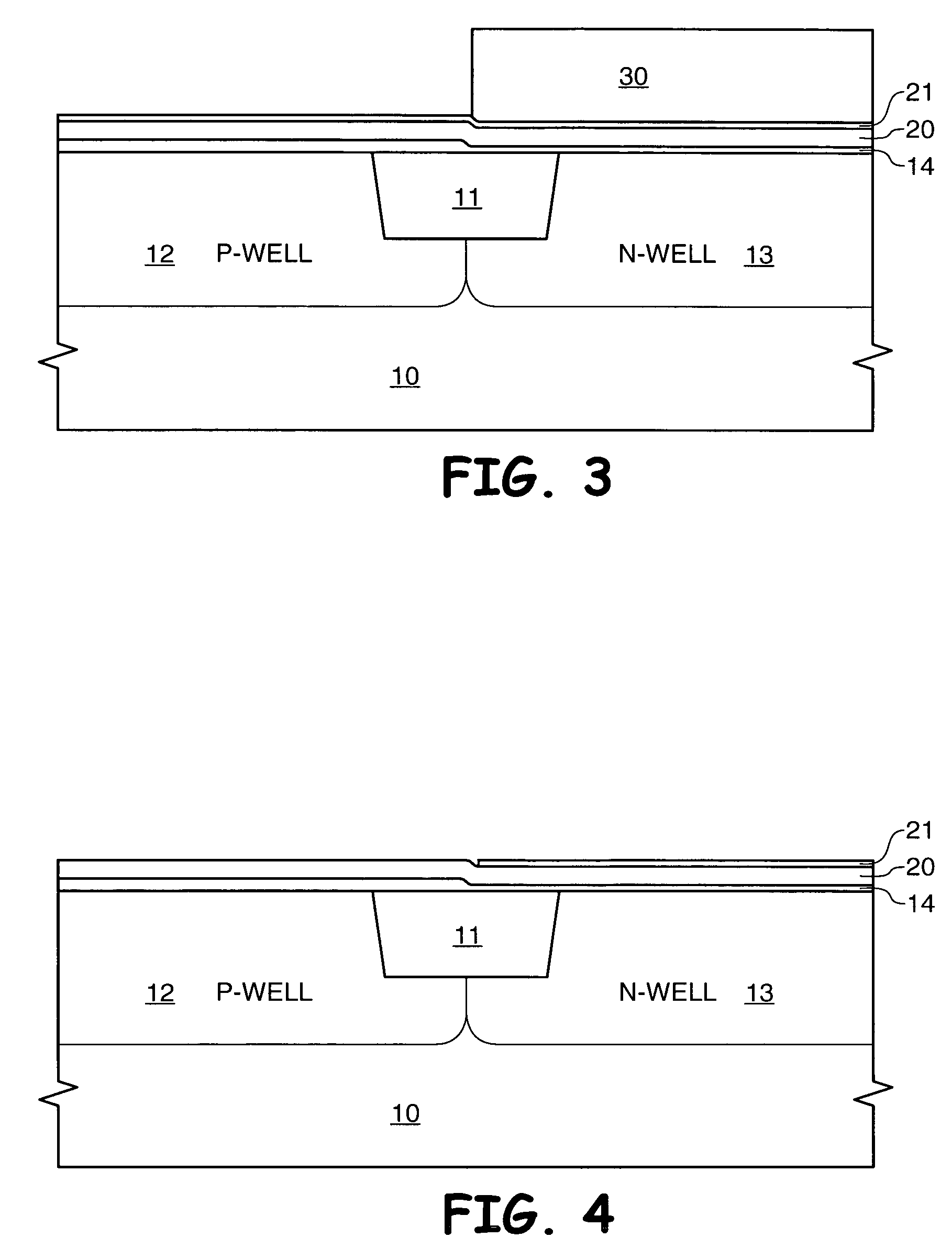

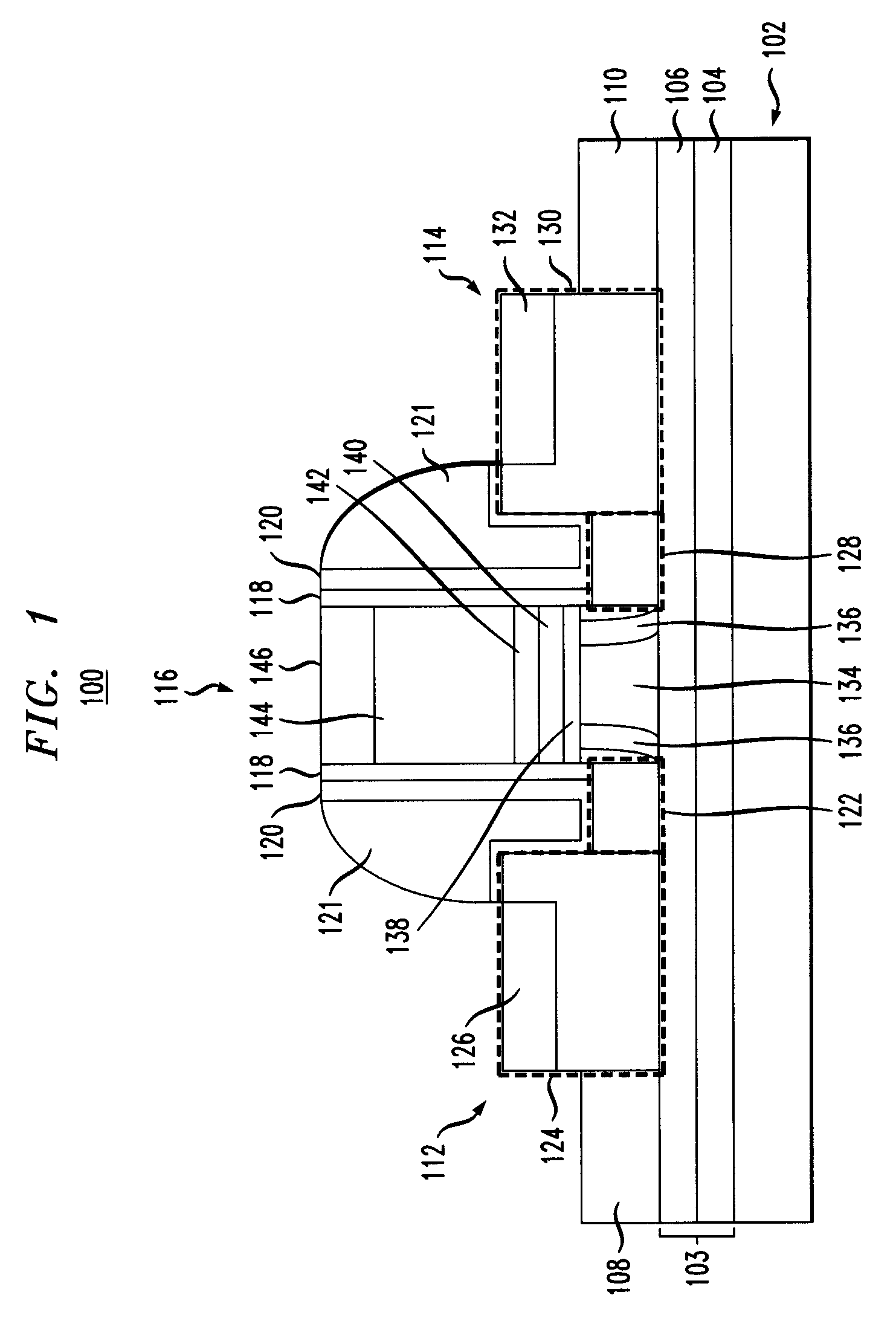

Metal-Gated MOSFET Devices Having Scaled Gate Stack Thickness

Metal-oxide semiconductor field effect transistor (MOSFET) devices having metal gate stacks and techniques for improving performance thereof are provided. In one aspect, a metal-oxide semiconductor device is provided comprising a substrate having a buried oxide layer at least a portion of which is configured to serve as a primary background oxygen getterer of the device; and a gate stack separated from the substrate by an interfacial oxide layer. The gate stack comprises a high-K layer over the interfacial oxide layer; and a metal gate layer over the high-K layer.

Owner:GLOBALFOUNDRIES INC

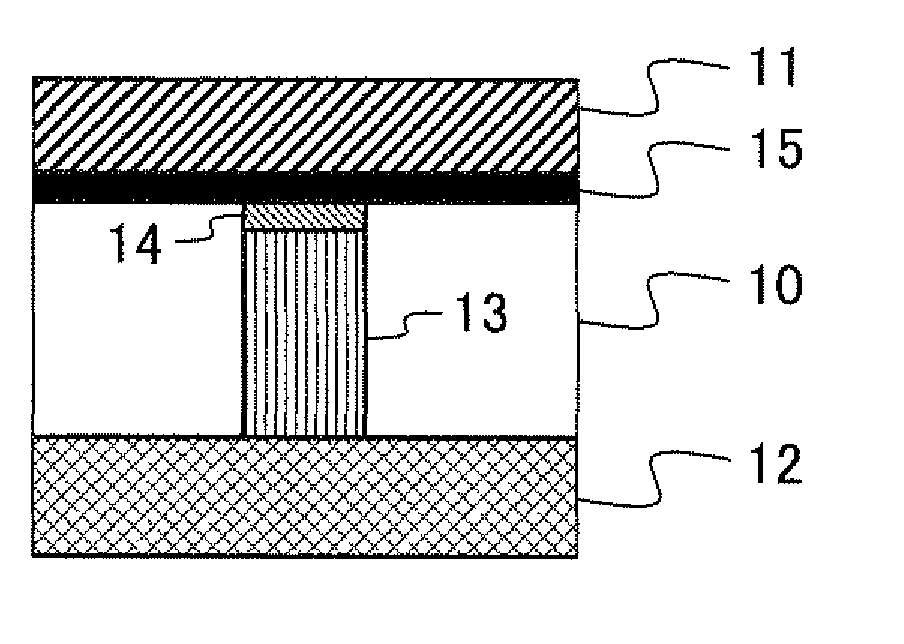

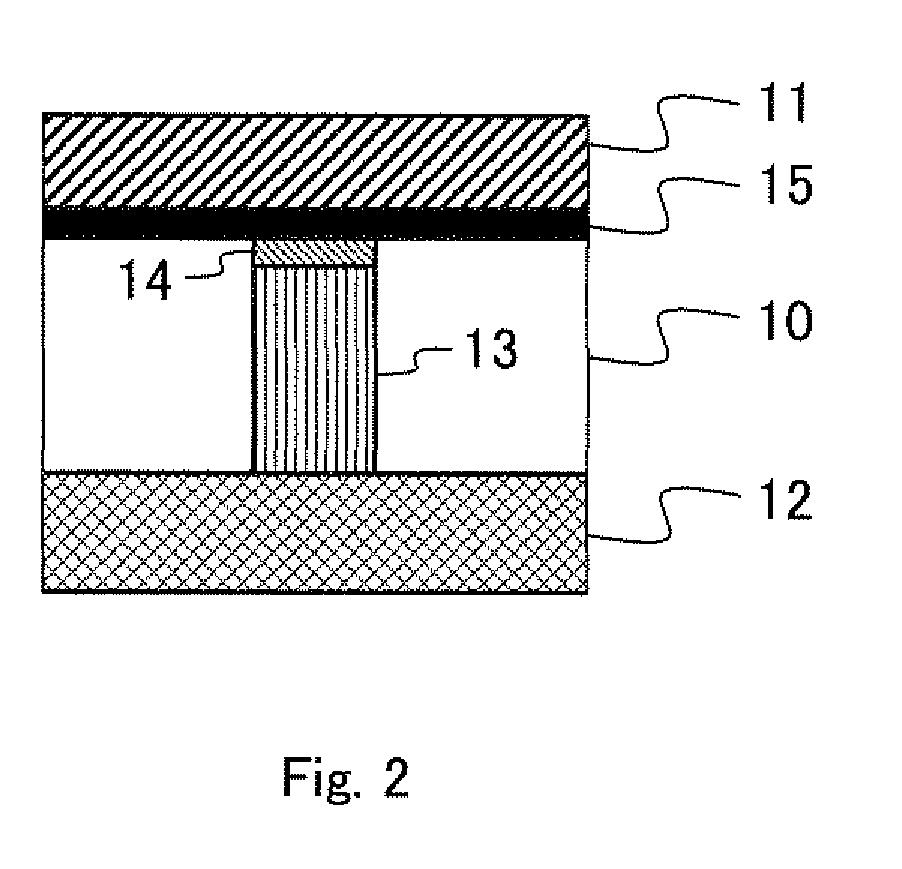

Manufacturing method of gate stack and semiconductor device

ActiveUS20110298053A1Work function instabilitySemiconductor/solid-state device manufacturingNanotechnologyInterfacial oxideGate stack

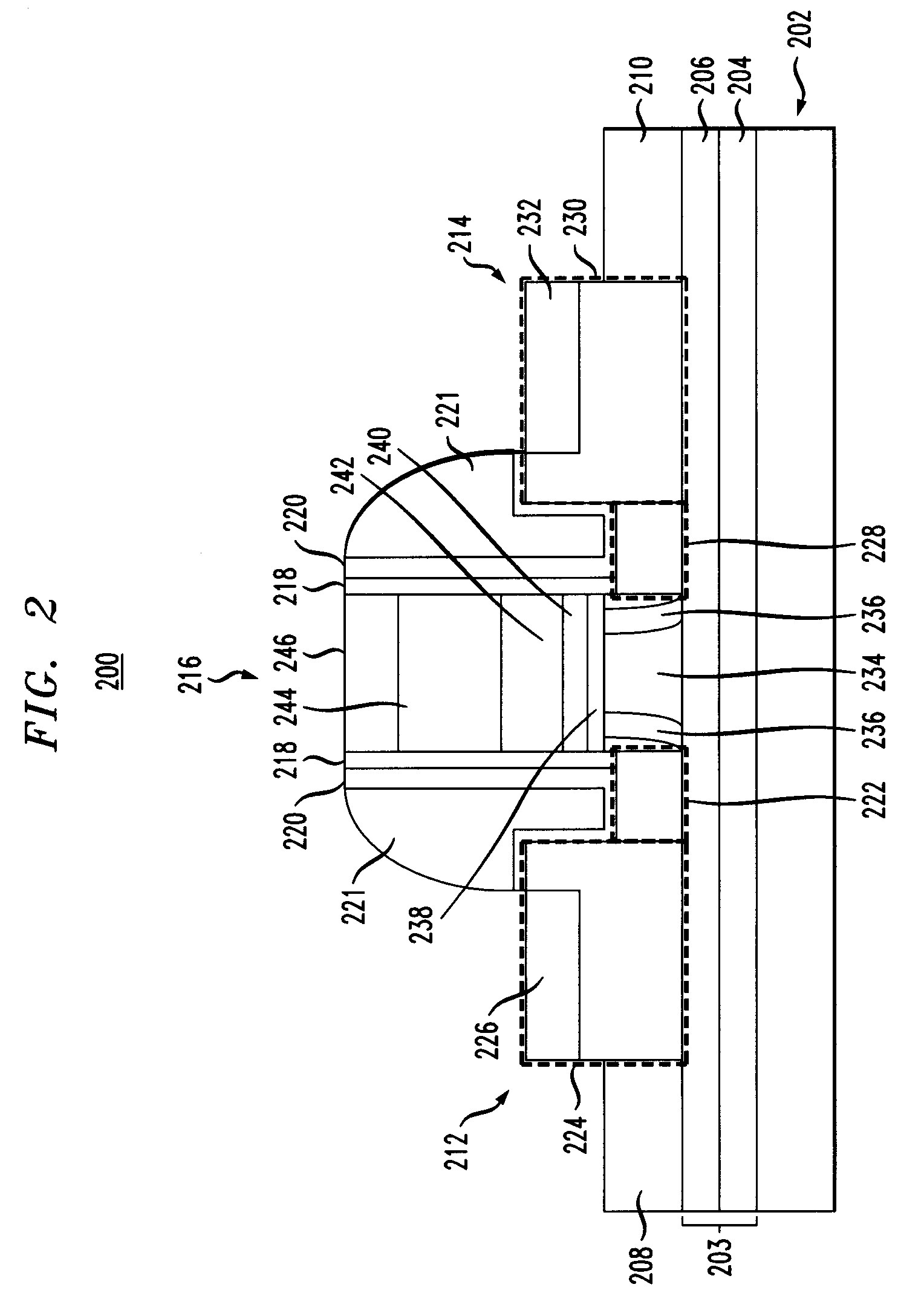

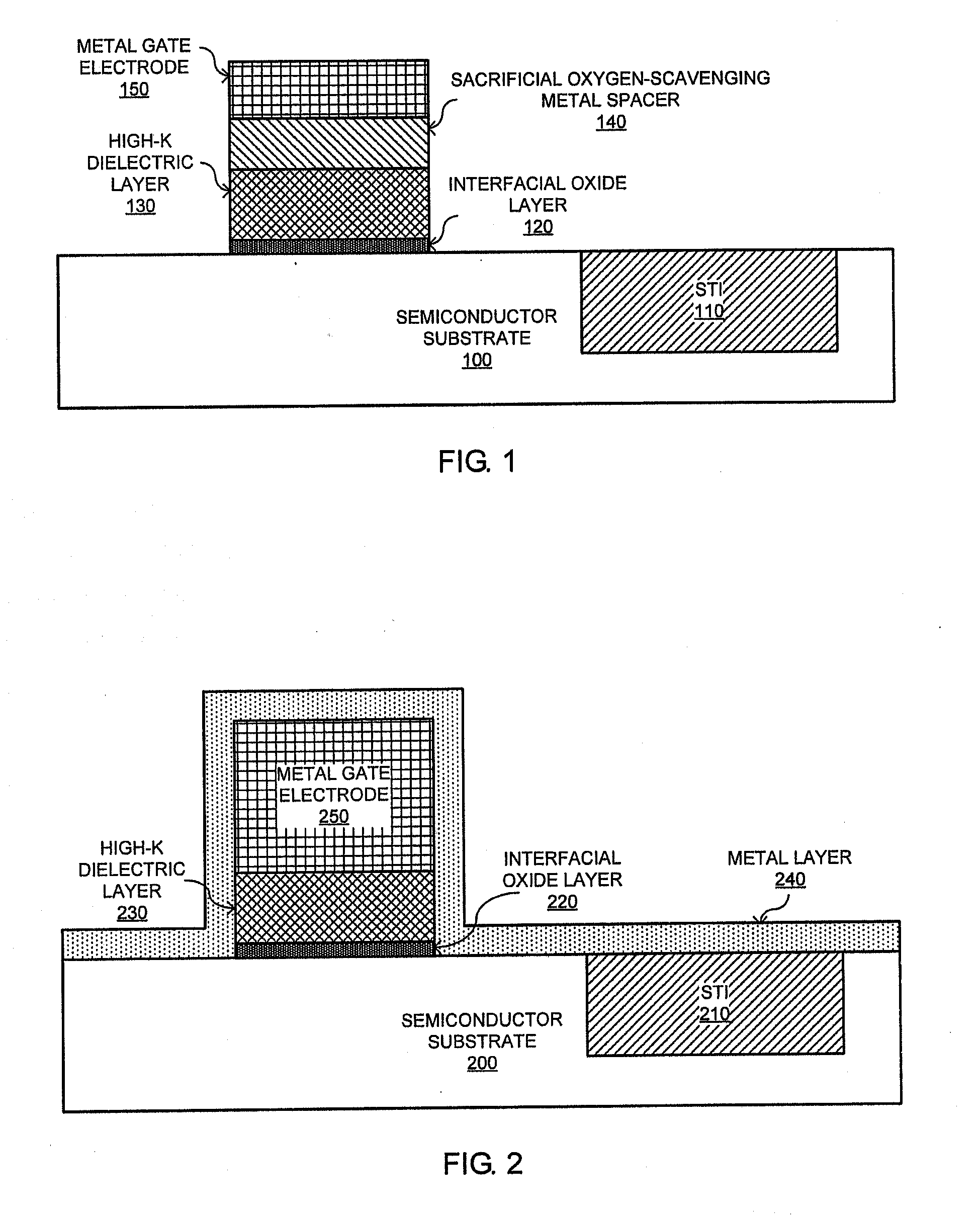

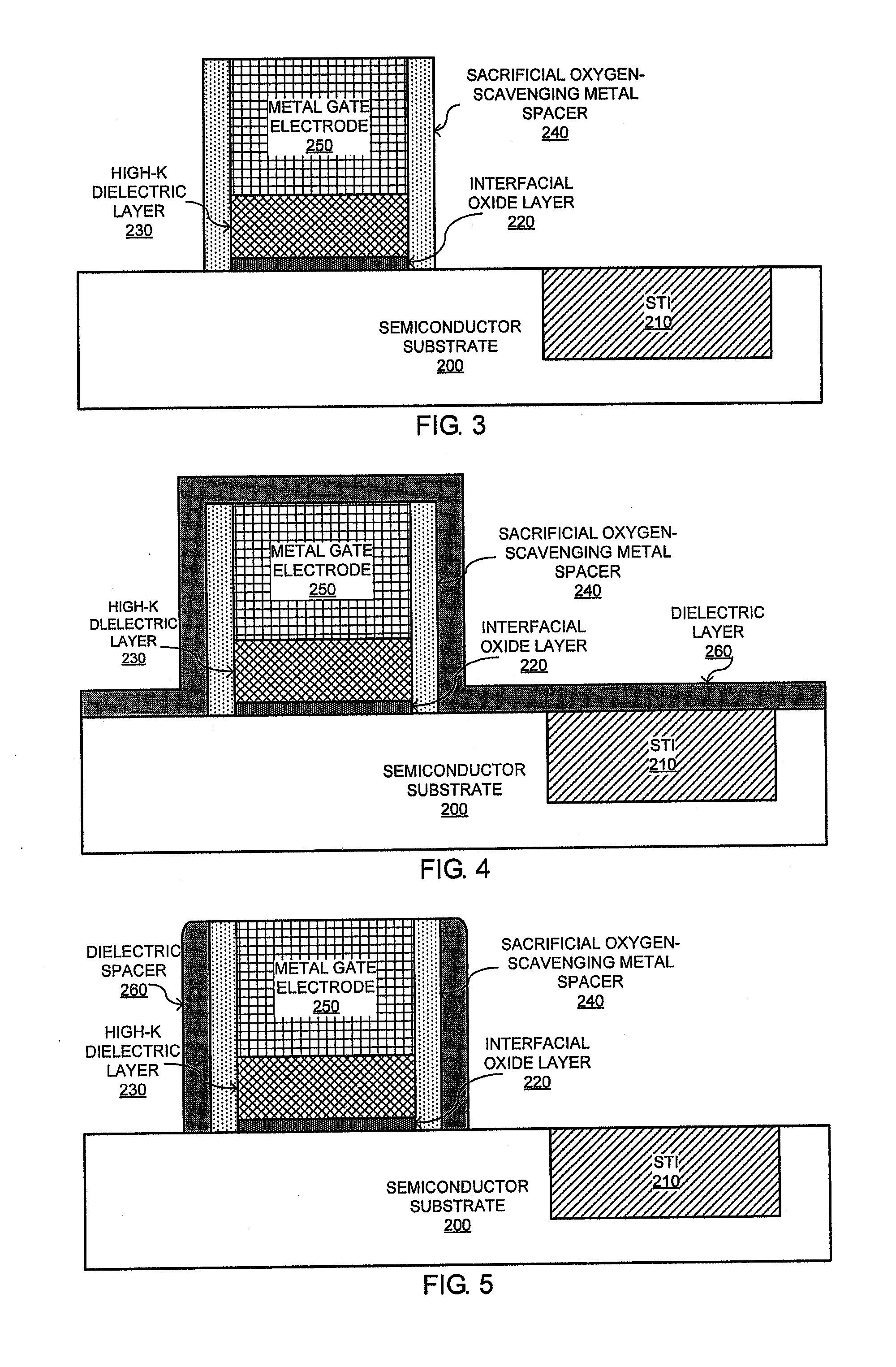

A manufacturing method of a gate stack with sacrificial oxygen-scavenging metal spacers includes: forming a gate stack structure consisting of an interfacial oxide layer, a high-K dielectric layer and a metal gate electrode, on a semiconductor substrate; conformally depositing a metal layer covering the semiconductor substrate and the gate stack structure; and selectively etching the metal layer to remove the portions of the metal layer covering the top surface of the gate stack structure and the semiconductor substrate, so as to only keep the sacrificial oxygen-scavenging metal spacers surrounding the gate stack structure in the outer periphery of the gate stack structure. A semiconductor device manufactured by this process.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for treating base oxide to improve high-K material deposition

InactiveUS20060094192A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingInterfacial oxideSilicon dioxide

A method for forming a high-K material layer in a semiconductor device fabrication process including providing a silicon semiconductor substrate or thermally growing interfacial oxide layer comprising silicon dioxide over the silicon substrate; treating with an aqueous base solution or nitridation and depositing a high-K material layer.

Owner:TAIWAN SEMICON MFG CO LTD

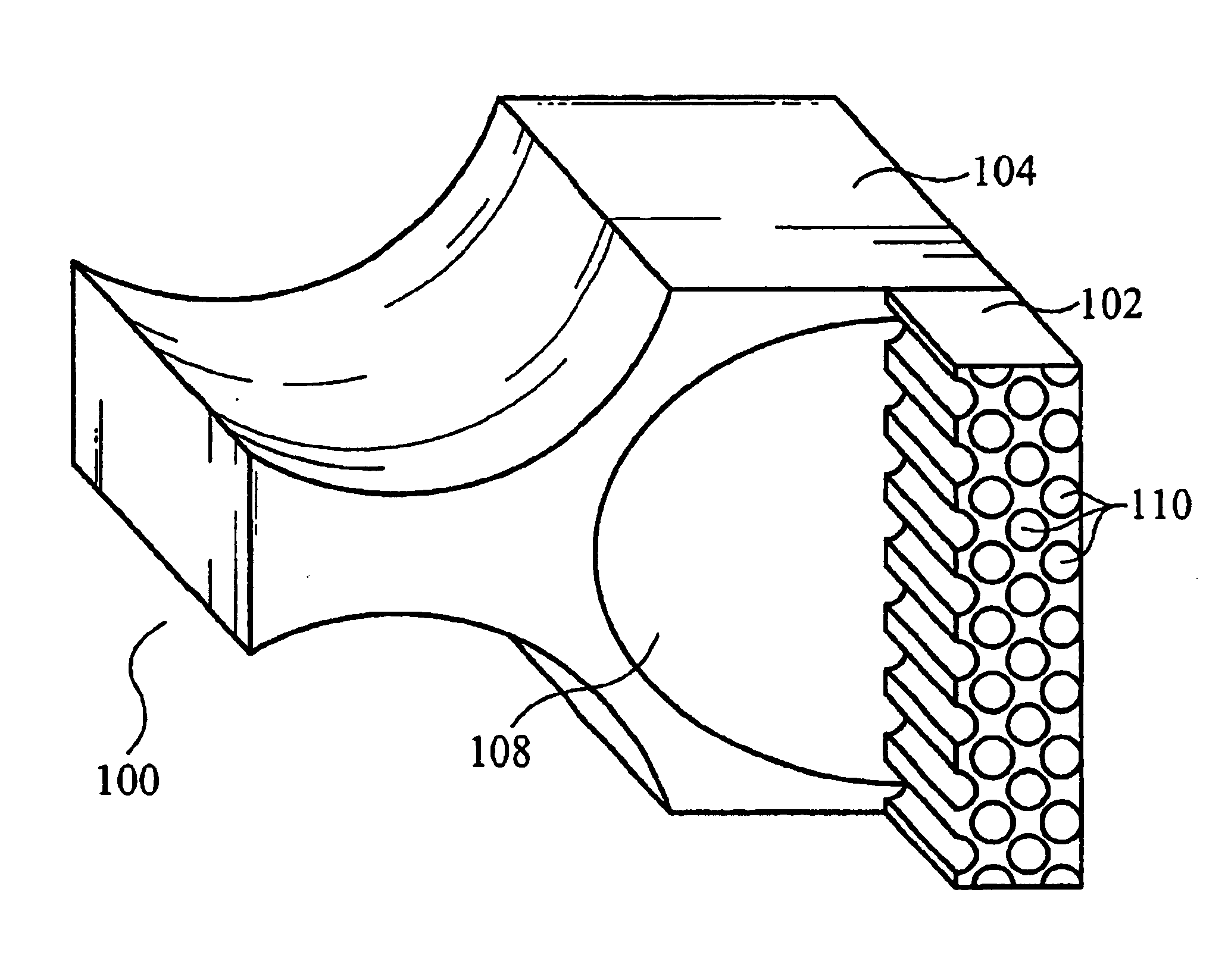

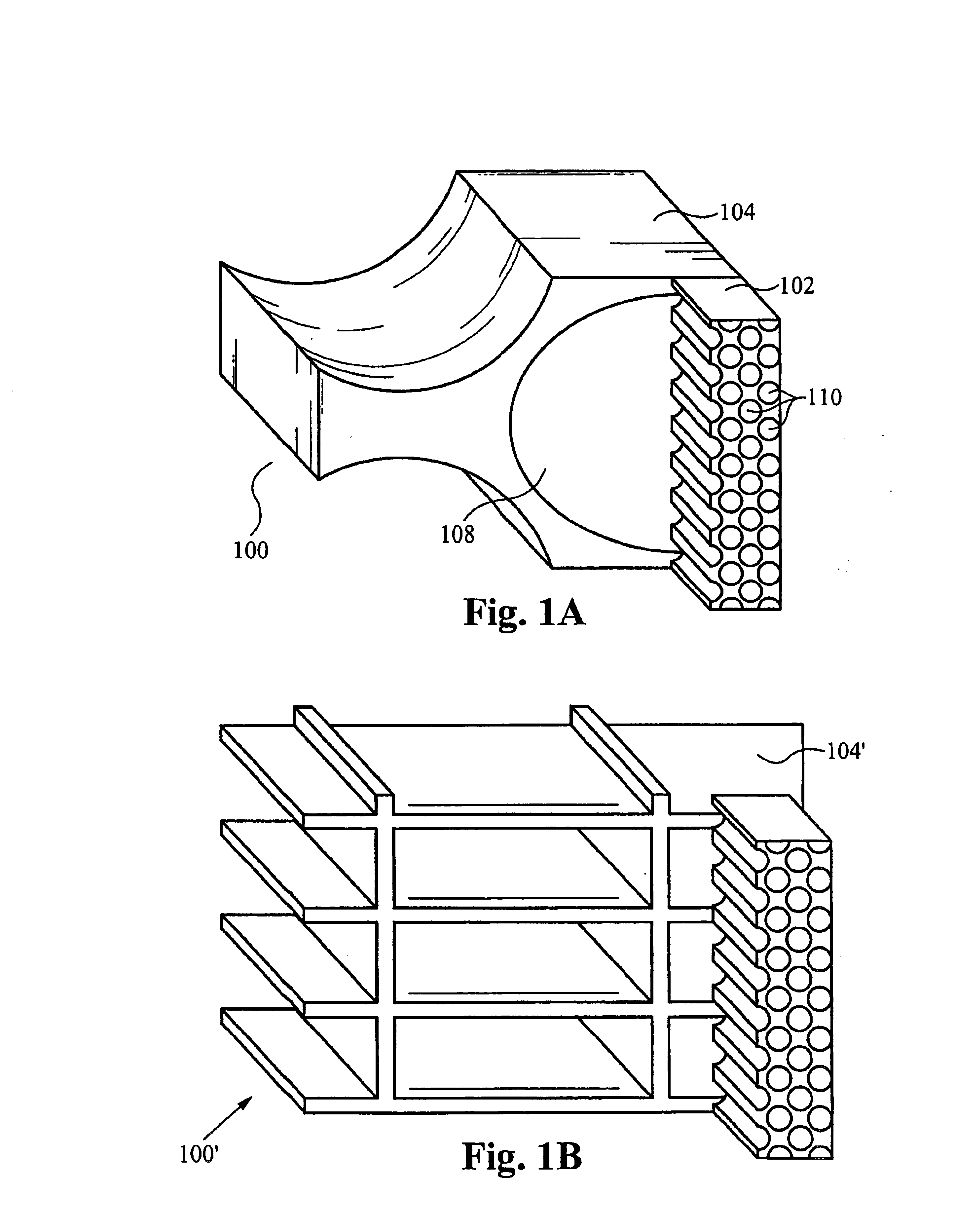

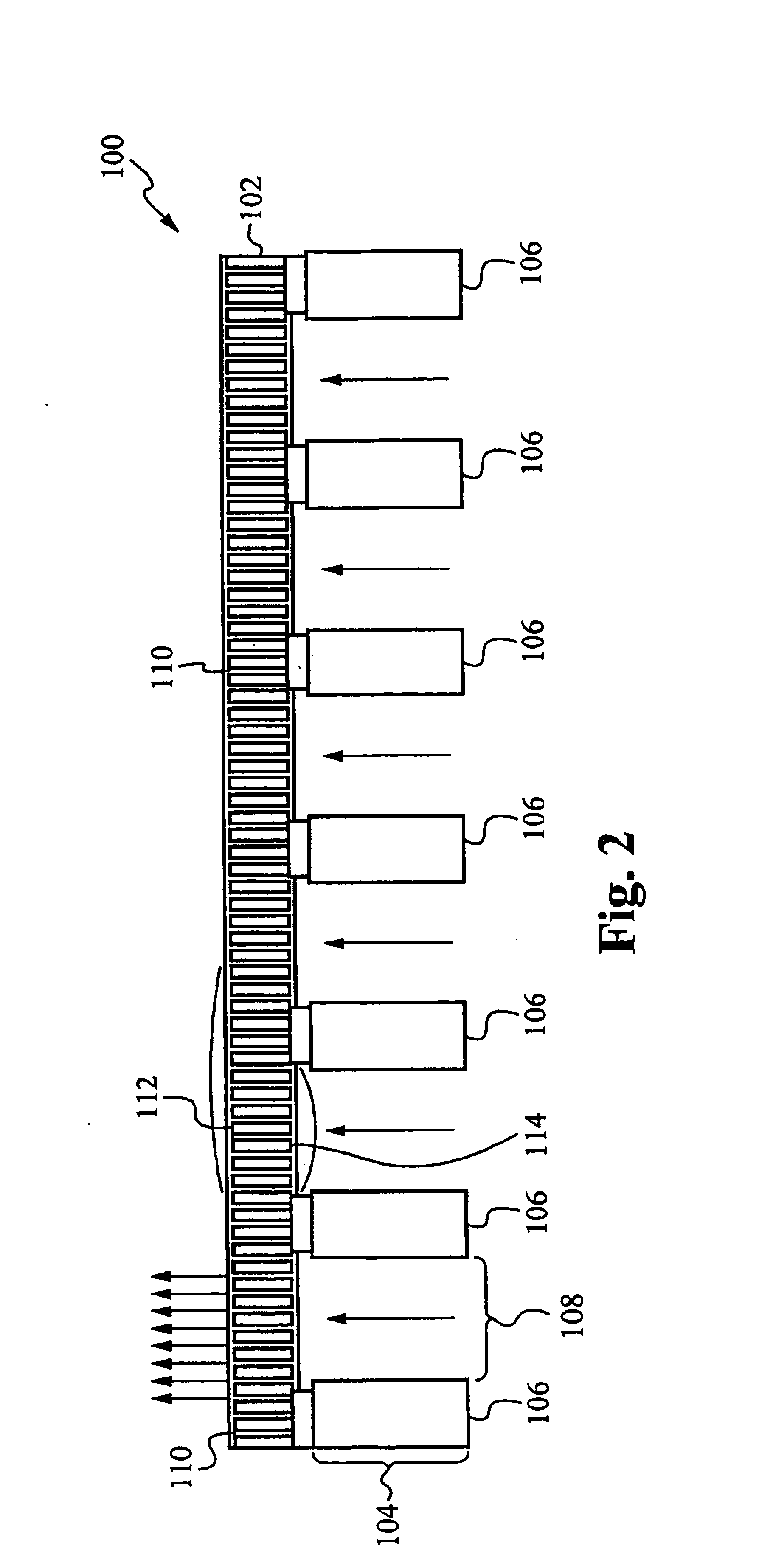

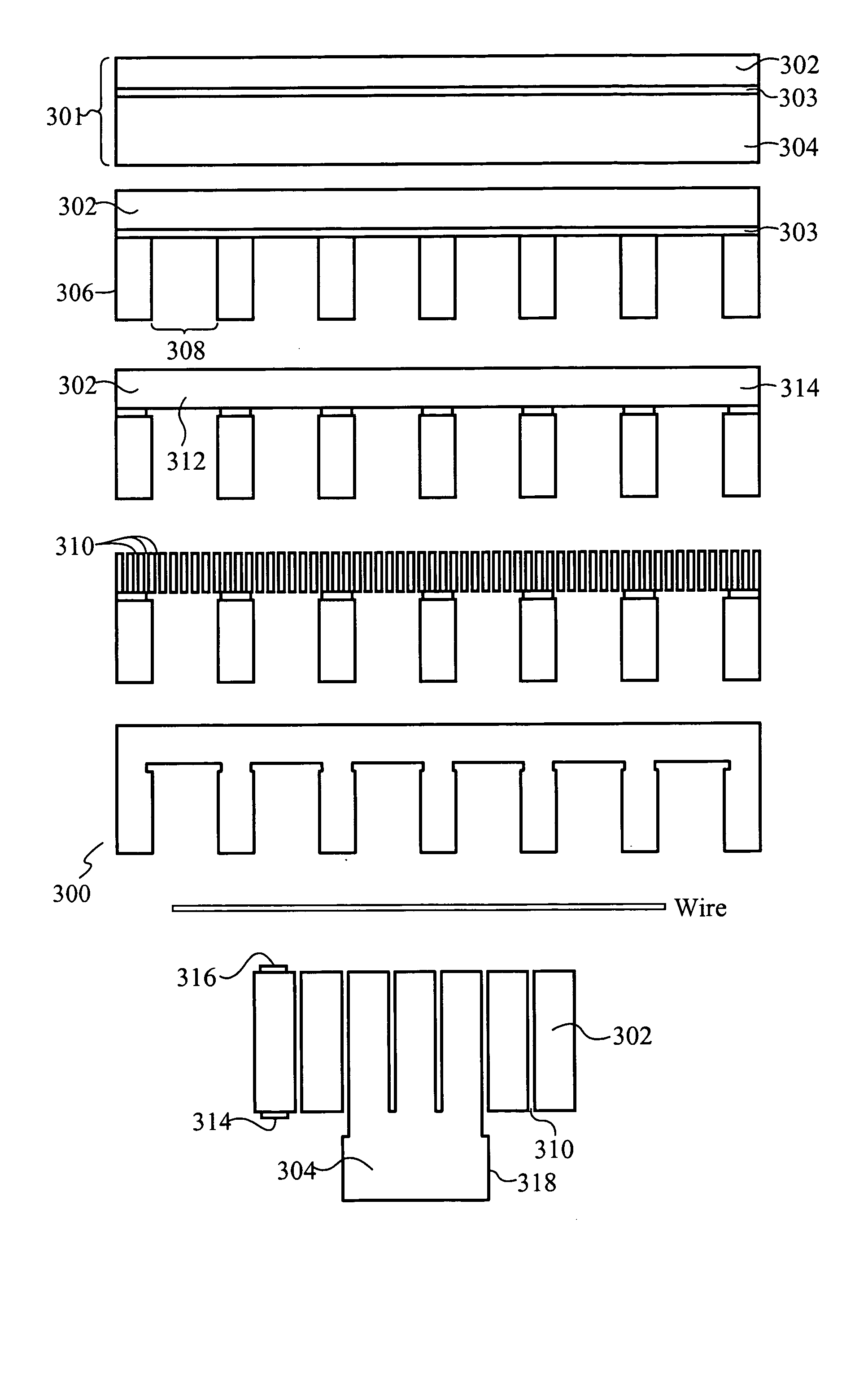

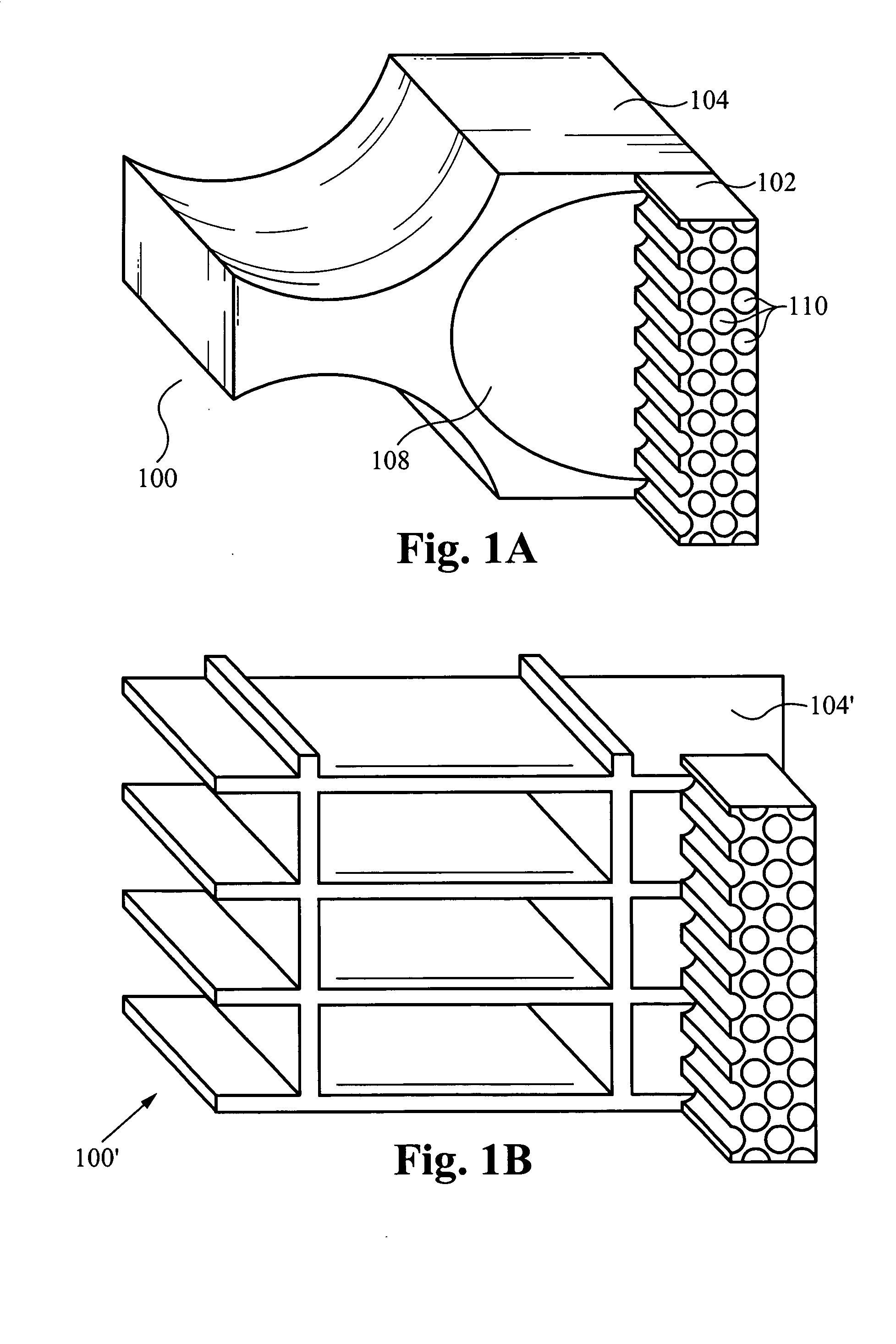

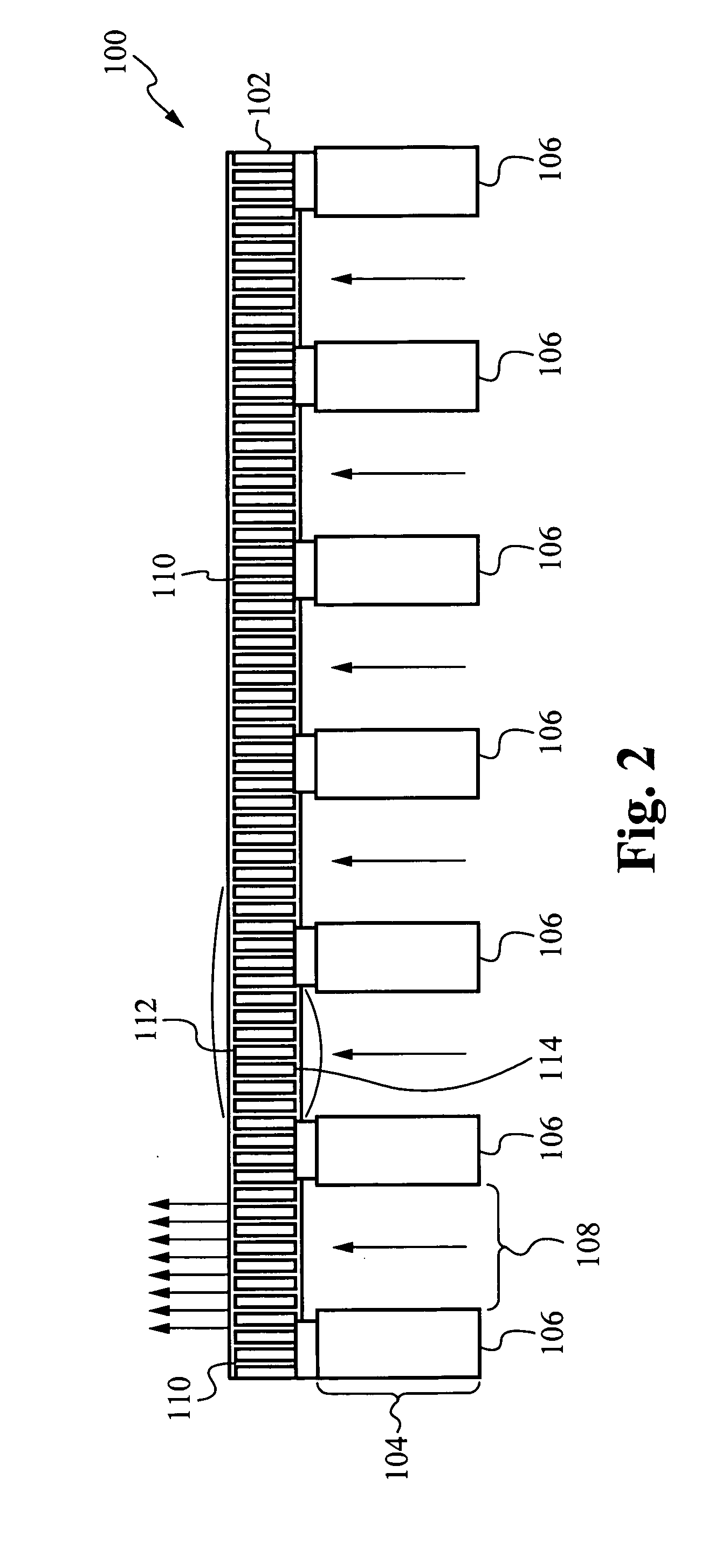

Micro-fabricated electrokinetic pump

An electrokinetic pump for pumping a liquid includes a pumping body having a plurality of narrow, short and straight pore apertures for channeling the liquid through the body. A pair of electrodes for applying a voltage differential are formed on opposing surfaces of the pumping body at opposite ends of the pore apertures. The pumping body is formed on a support structure to maintain a mechanical integrity of the pumping body. The pump can be fabricated using conventional semiconductor processing steps. The pores are preferably formed using plasma etching. The structure is oxidized to insulate the structure and also narrow the pores. A support structure is formed by etching a substrate and removing an interface oxide layer. Electrodes are formed to apply a voltage potential across the pumping body. Another method of fabricating an electrokinetic pump includes providing etch stop alignment marks so that the etch step self-terminates.

Owner:VERTIV CORP

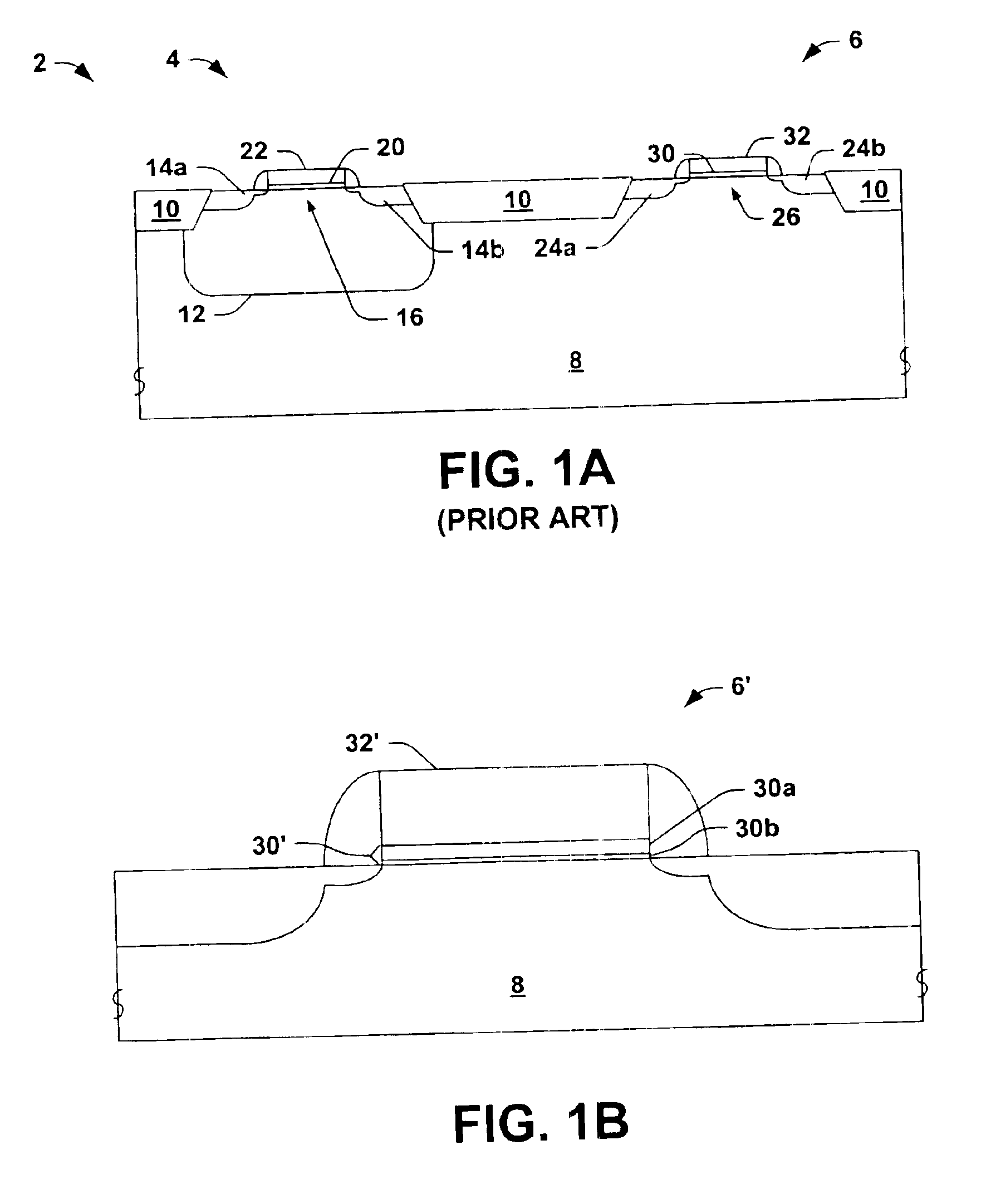

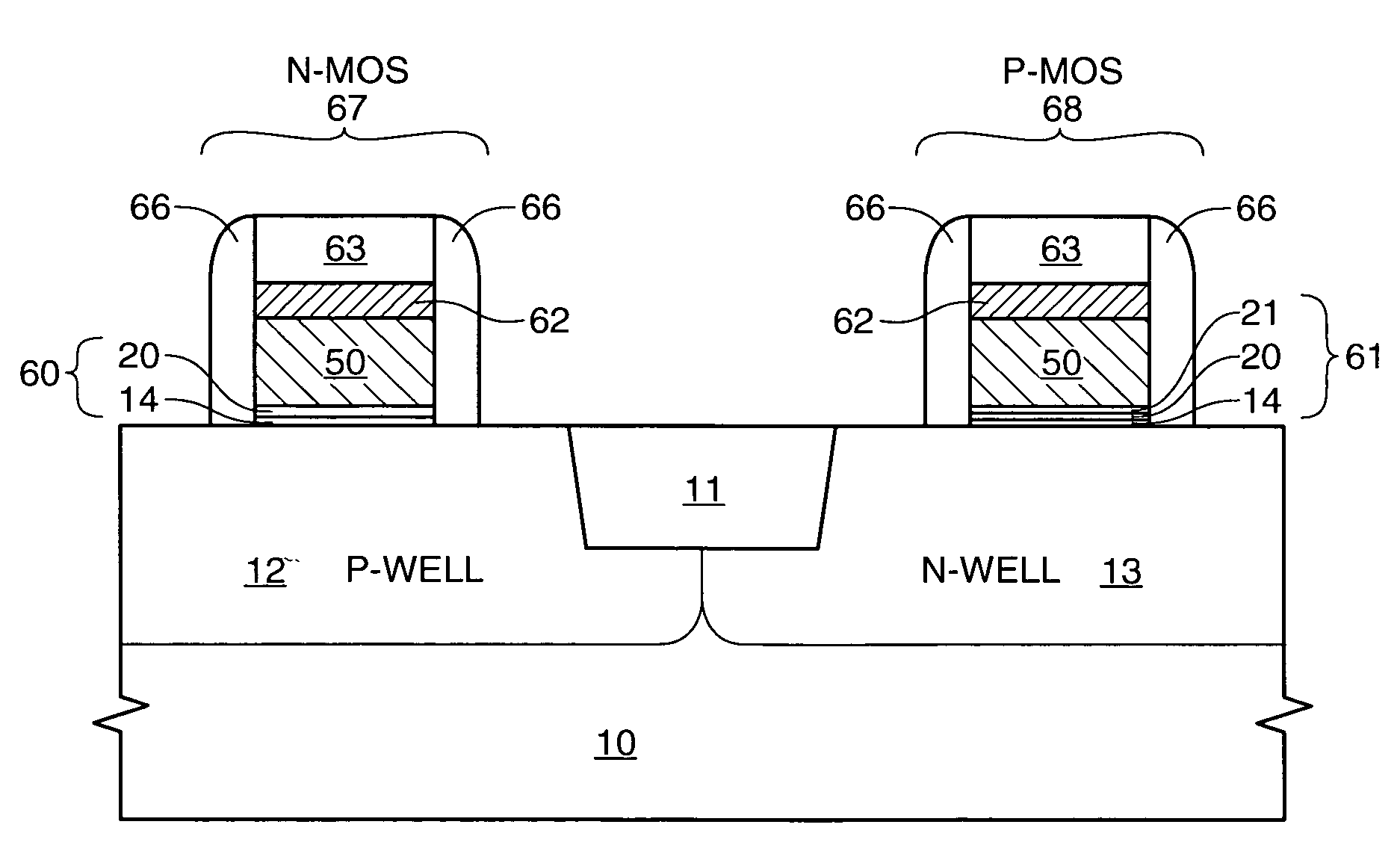

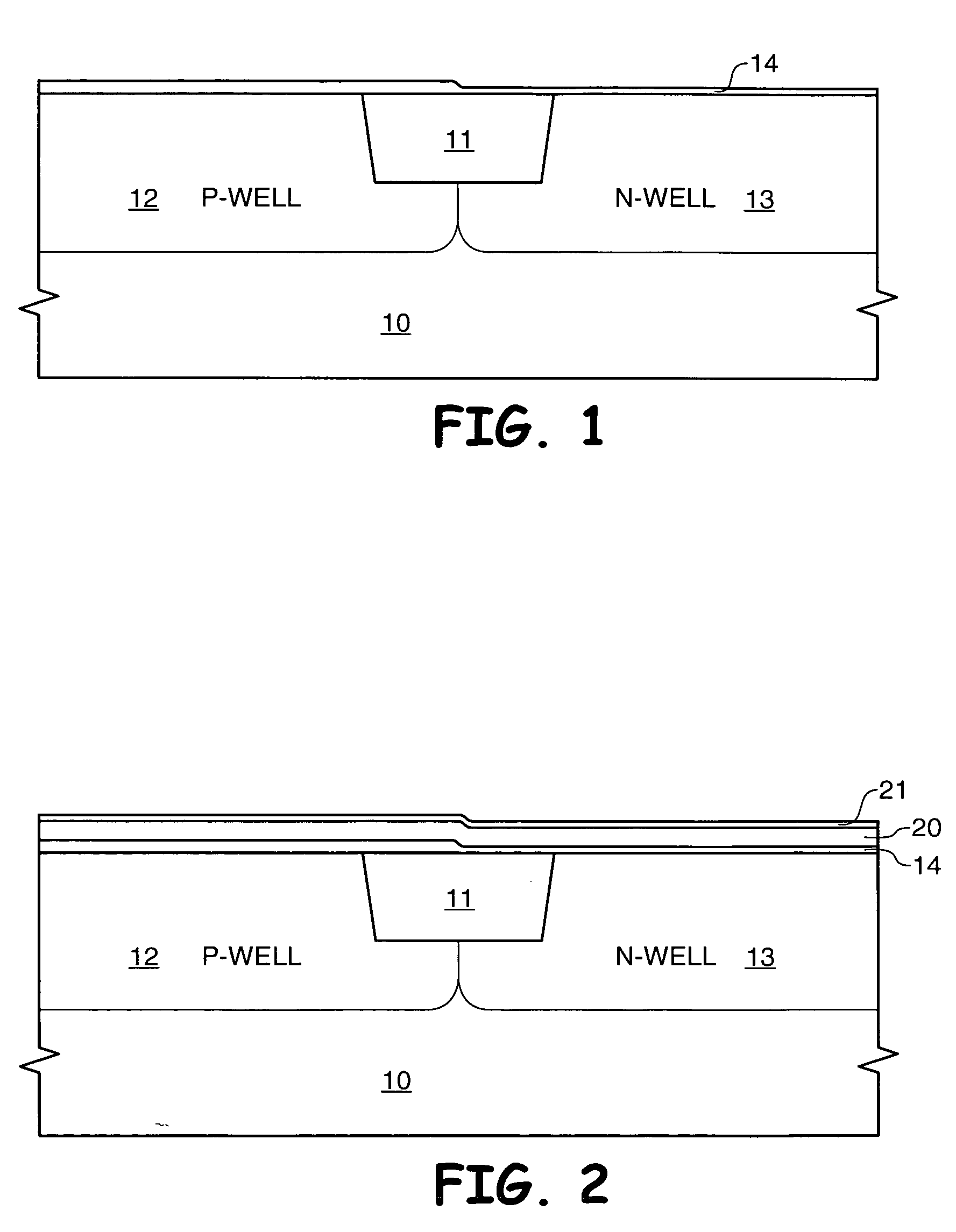

Methods of enabling polysilicon gate electrodes for high-k gate dieletrics

ActiveUS20060030096A1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricInterfacial oxide

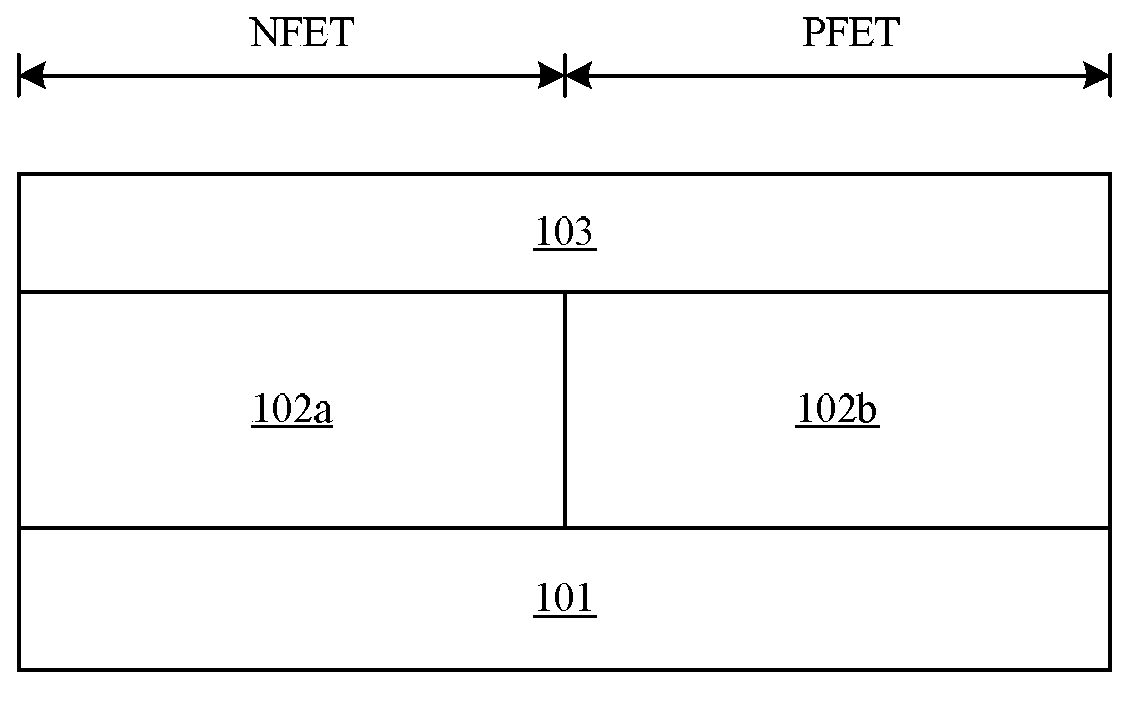

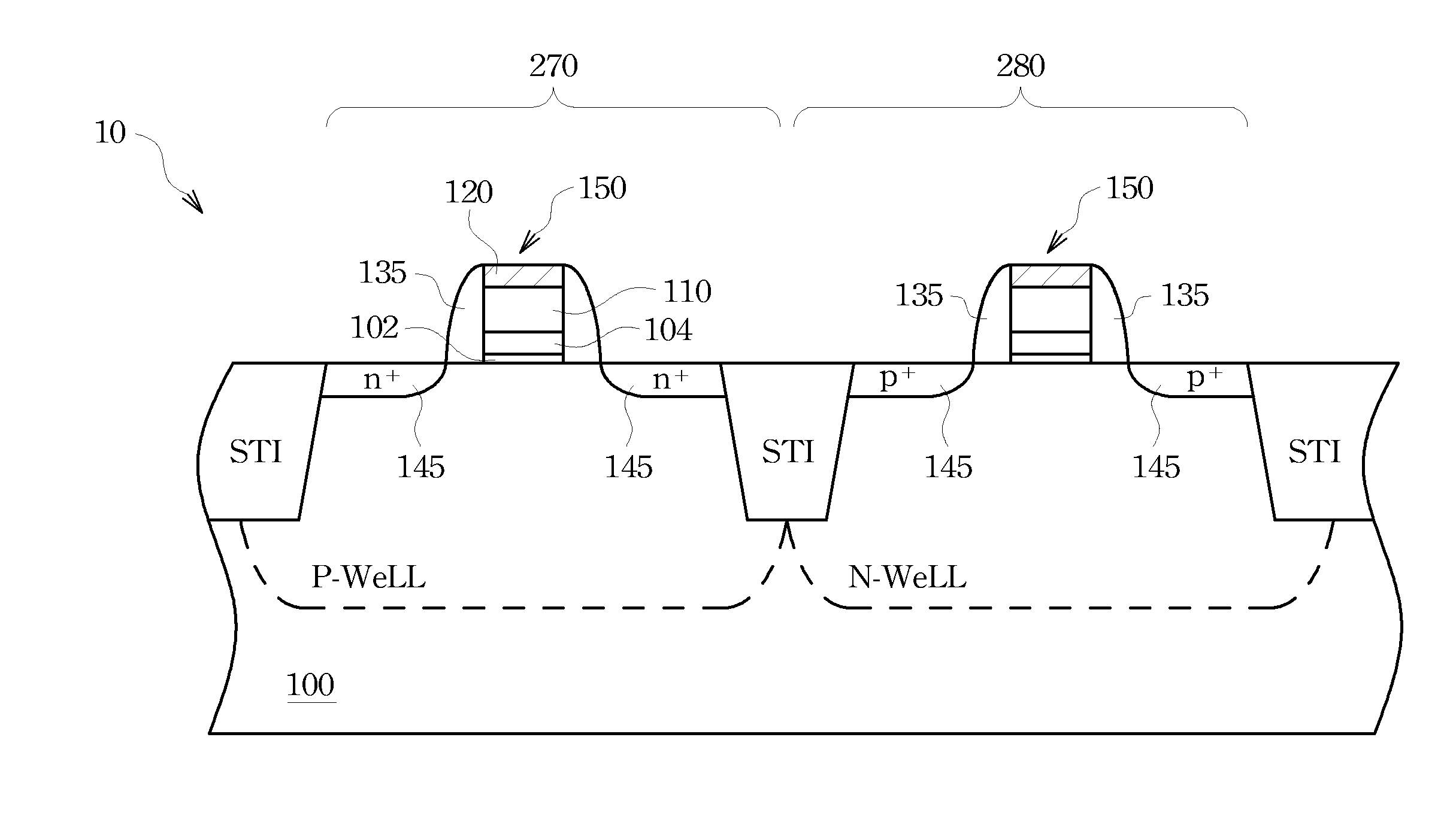

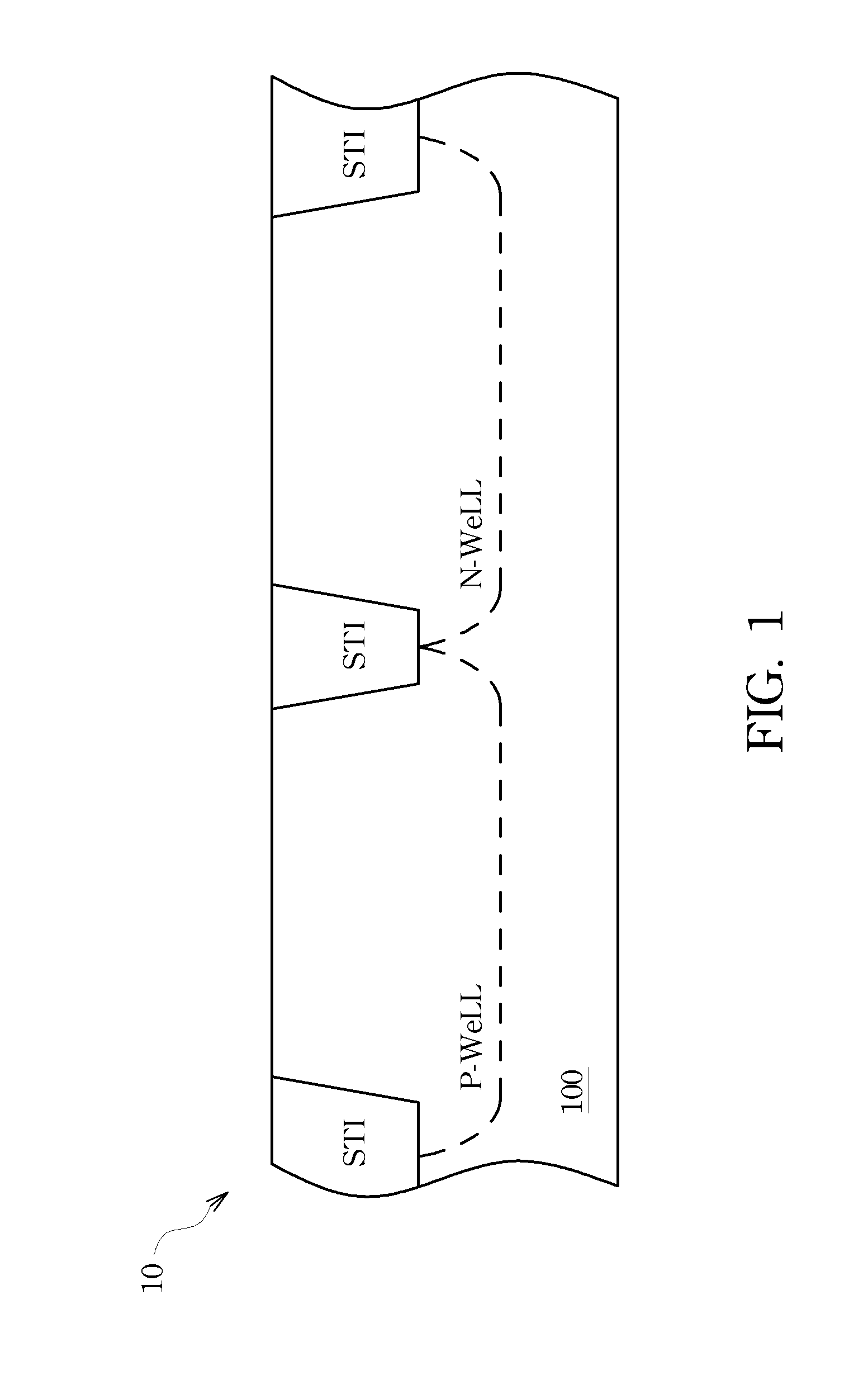

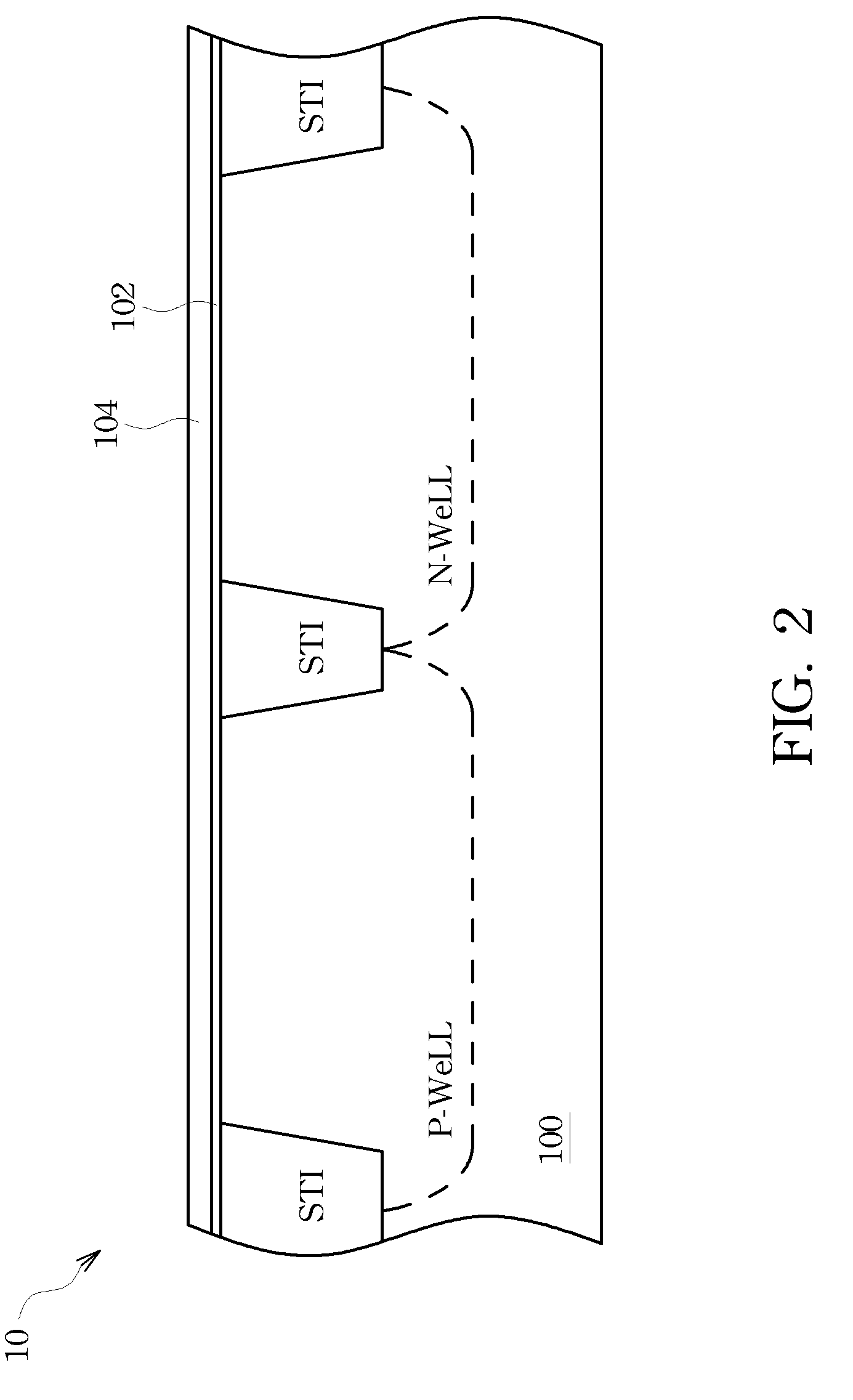

Complementary transistors and methods of forming the complementary transistors on a semiconductor assembly are described. The transistors are formed with an optional interfacial oxide, such as SiO2 or oxy-nitride, to overlay a semiconductor substrate which will be conductively doped for PMOS and NMOS regions. Then a dielectric possessing a high dielectric constant of least seven or greater (also referred to as a high-k dielectric) is deposited on the interfacial oxide. The high-k dielectric is covered with a thin monolayer of metal oxide (i.e., aluminum oxide, Al2O3) that is removed from the NMOS regions, but remains in the PMOS regions. The resulting NMOS transistor diffusion regions contain predominately metal to silicon bonds that create predominately Fermi level pinning near the valence band while the resulting PMOS transistor diffusion regions contain metal to silicon bonds that create predominately Fermi level pinning near the conduction band.

Owner:MICRON TECH INC

Techniques for metal gate work function engineering to enable multiple threshold voltage nanowire FET devices

ActiveUS8658518B1NanoinformaticsSemiconductor/solid-state device manufacturingInterfacial oxideWork function engineering

A method of fabricating a nanowire FET device includes the following steps. A SOI wafer is provided having a SOI layer over a BOX. Nanowires and pads are etched in the SOI layer. The nanowires are suspended over the BOX. An interfacial oxide is formed surrounding each of the nanowires. A conformal gate dielectric is deposited on the interfacial oxide. A conformal first gate material is deposited on the conformal gate dielectric. A work function setting material is deposited on the conformal first gate material. A second gate material is deposited on the work function setting material to form at least one gate stack over the nanowires. A volume of the conformal first gate material and / or a volume of the work function setting material in the gate stack are / is proportional to a pitch of the nanowires.

Owner:GLOBALFOUNDRIES US INC

Micro-fabricated electrokinetic pump

An electrokinetic pump for pumping a liquid includes a pumping body having a plurality of narrow, short and straight pore apertures for channeling the liquid through the body. A pair of electrodes for applying a voltage differential are formed on opposing surfaces of the pumping body at opposite ends of the pore apertures. The pumping body is formed on a support structure to maintain a mechanical integrity of the pumping body. The pump can be fabricated using conventional semiconductor processing steps. The pores are preferably formed using plasma etching. The structure is oxidized to insulate the structure and also narrow the pores. A support structure is formed by etching a substrate and removing an interface oxide layer. Electrodes are formed to apply a voltage potential across the pumping body. Another method of fabricating an electrokinetic pump includes providing etch stop alignment marks so that the etch step self-terminates.

Owner:VERTIV CORP

Semiconductor device and manufacturing method thereof

ActiveCN103855093AImprove distribution uniformityAdjust the effective work functionTransistorSolid-state devicesInterfacial reactionInterfacial oxide

The invention discloses a semiconductor device and a manufacturing method thereof. The manufacturing method of the semiconductor device includes the following steps that: semiconductor fins are formed on a semiconductor substrate; interfacial oxide layers are formed on the surfaces of the tops and side walls of the semiconductor fins; high K gate dielectrics are formed on the interfacial oxide layers; first metal gate layers are formed on the high K gate dielectrics; and doping agents are implanted into the first metal gate layers through conformal doping; and annealing is performed, so that the doping agents can be diffused and accumulated at upper interfaces between the high K gate dielectrics and the first metal gate layers and lower interfaces between the high K gate dielectrics and the interfacial oxide layers, and electric dipoles can be generated at the lower interfaces between the high K gate dielectrics and interfacial oxides through interfacial reaction.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

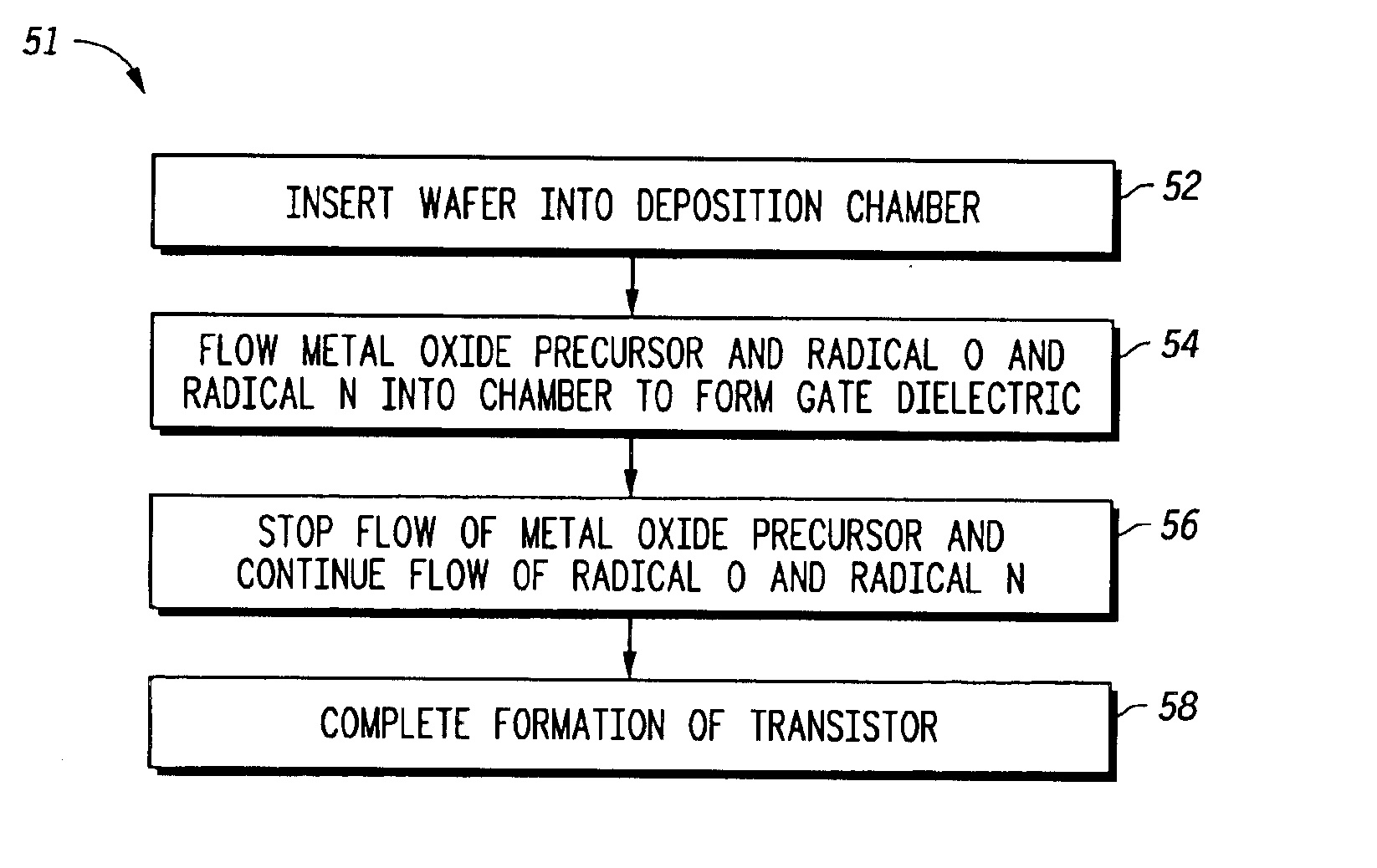

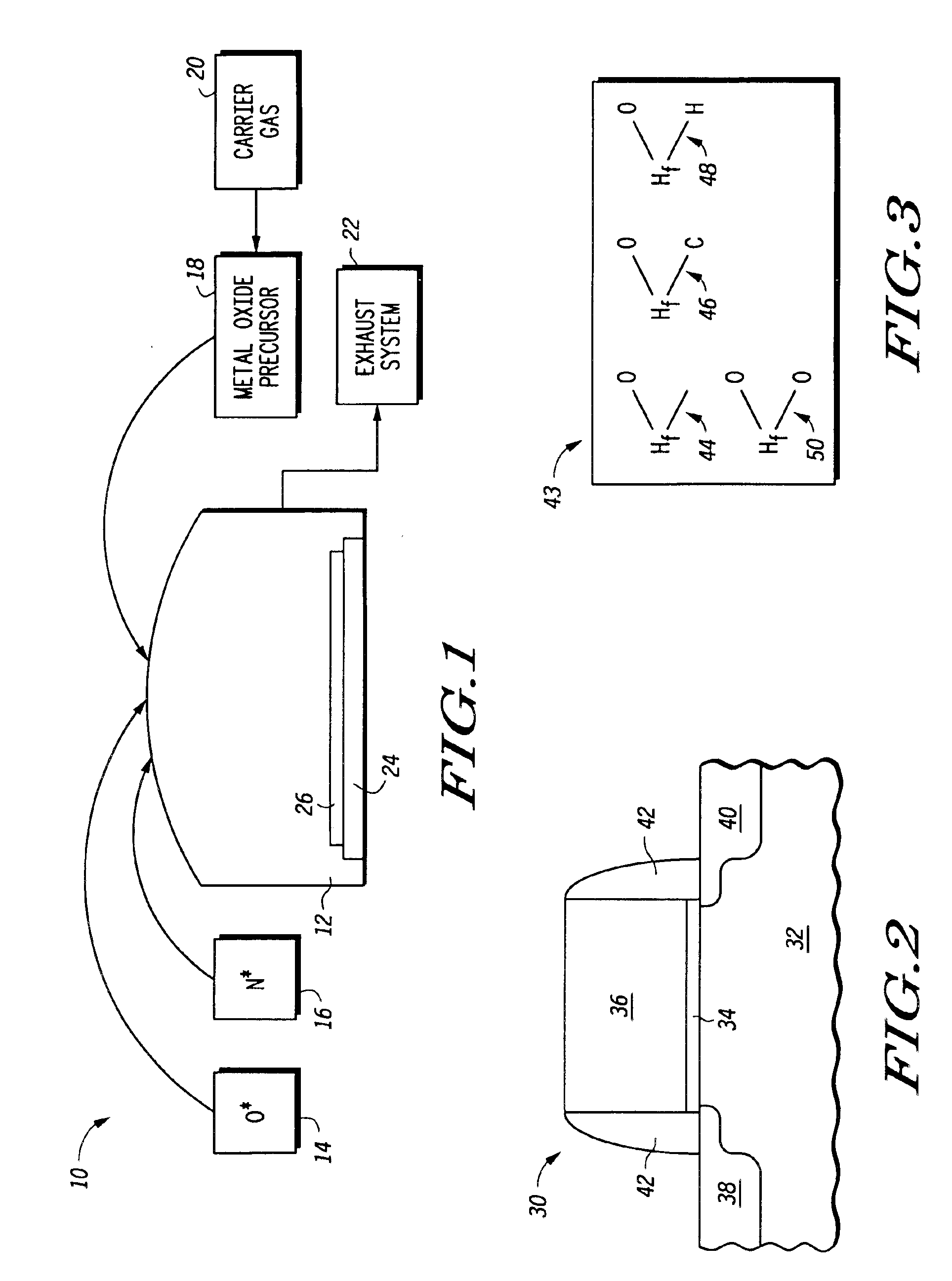

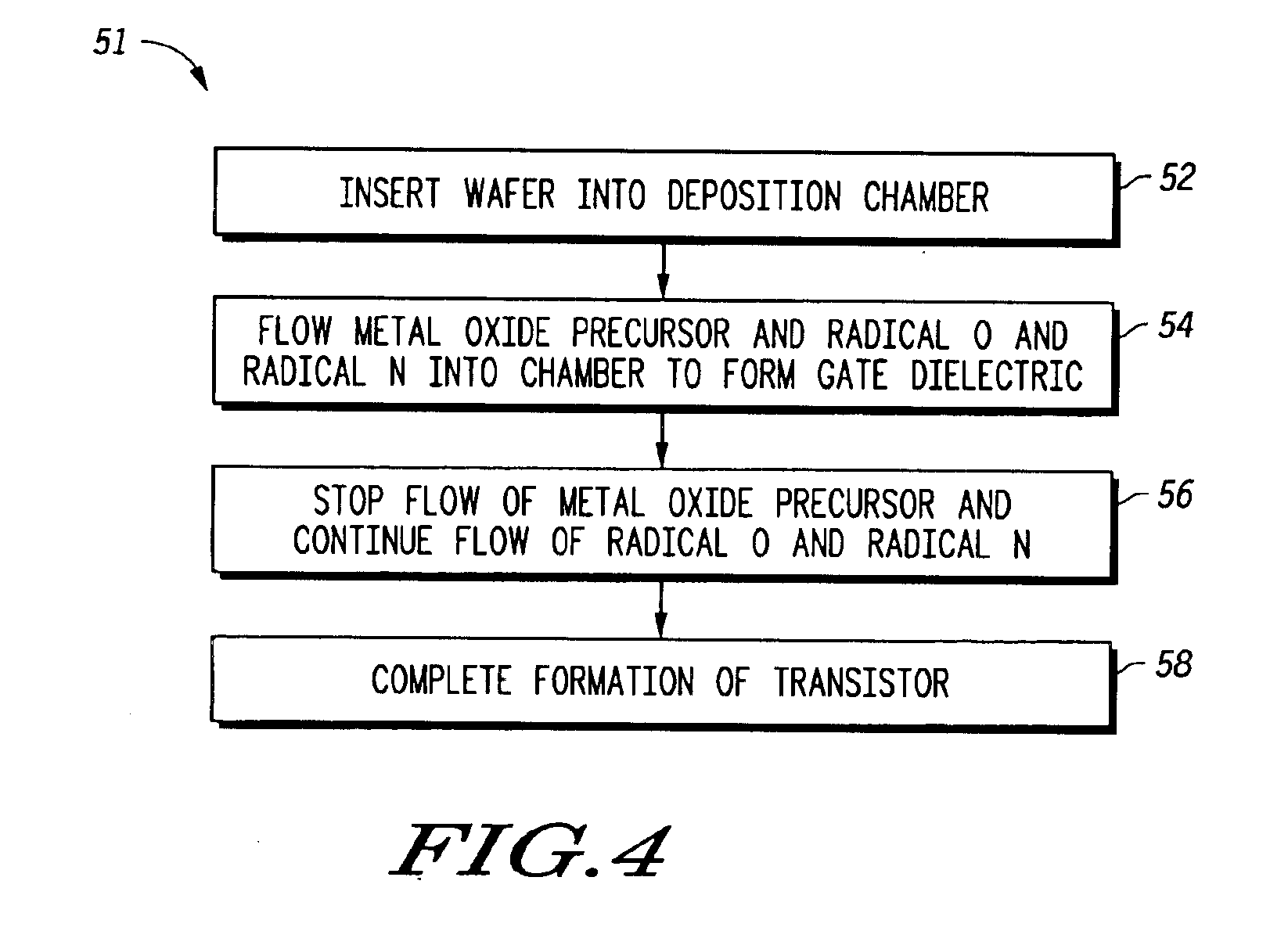

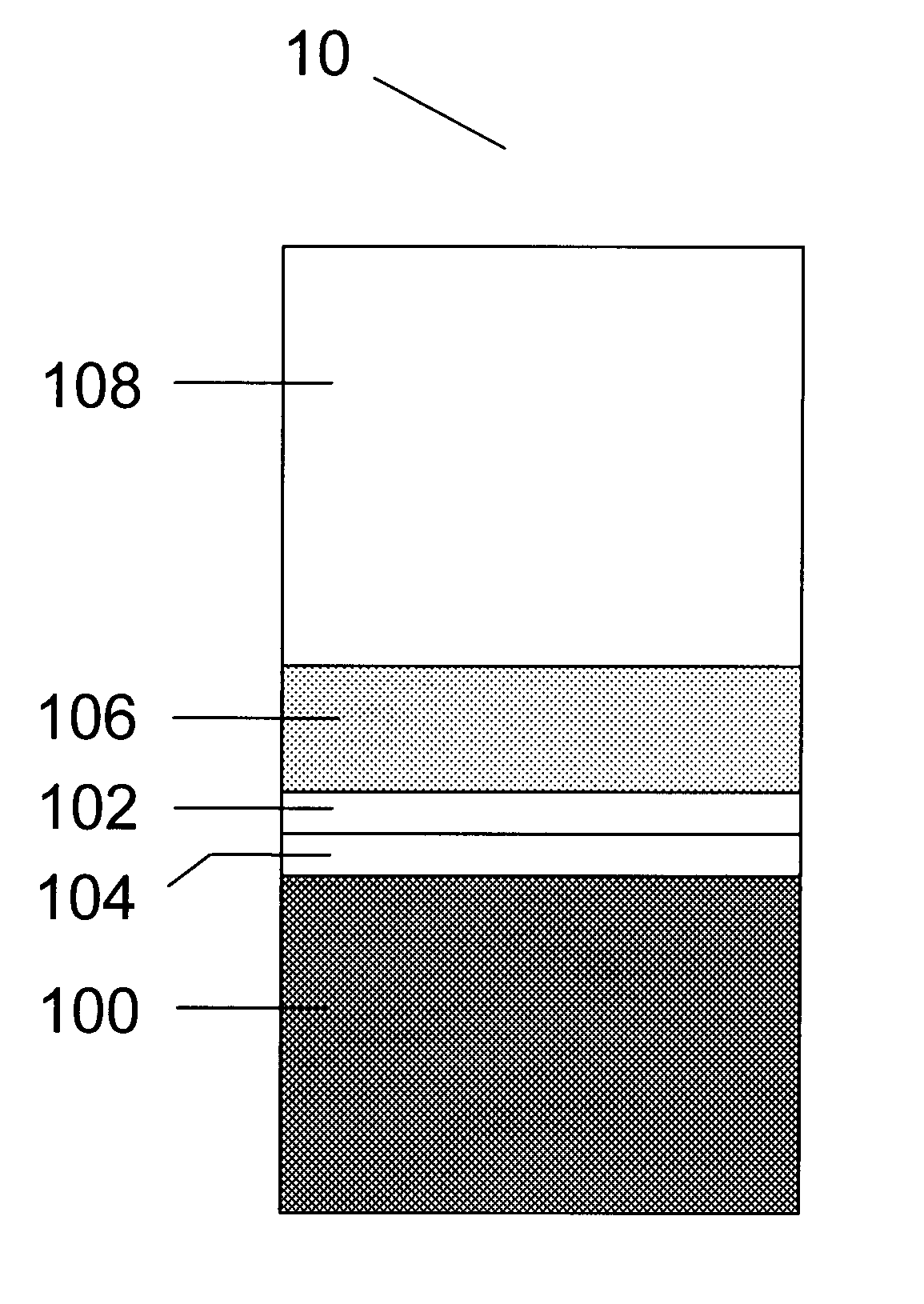

Radical oxidation and/or nitridation during metal oxide layer deposition process

InactiveUS6884685B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingInterfacial oxideRadical oxidation

Owner:NXP USA INC

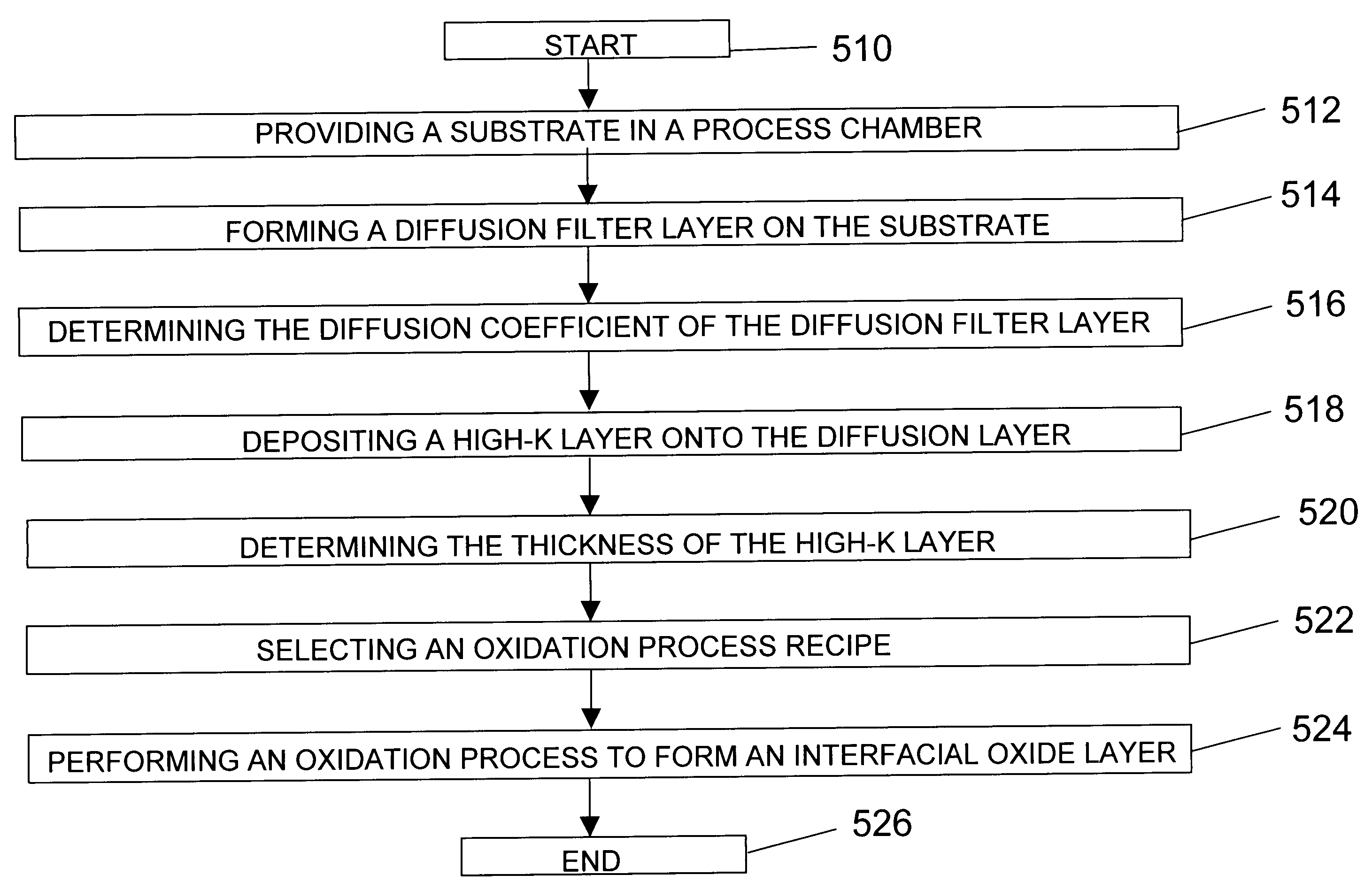

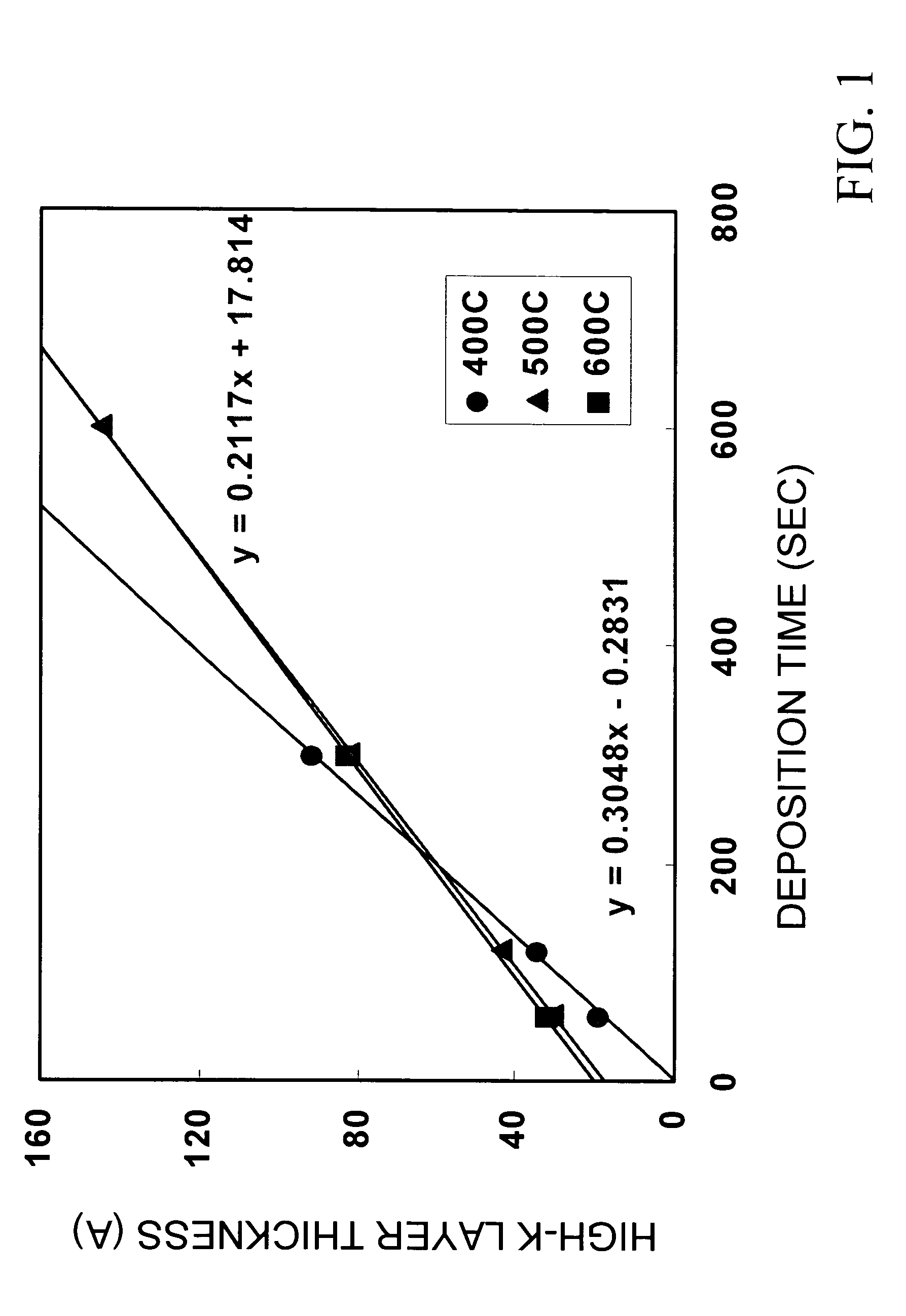

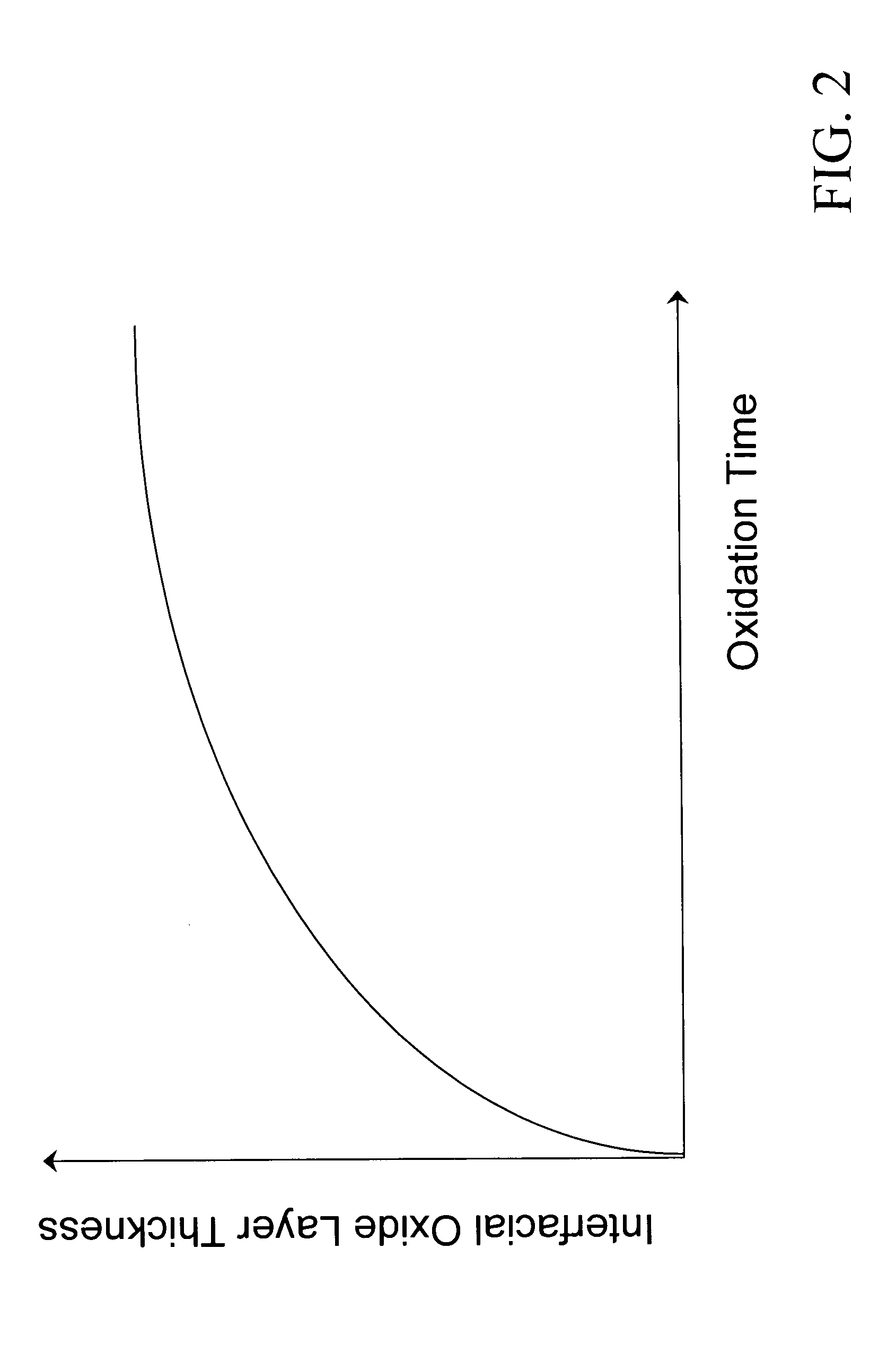

Interfacial oxidation process for high-k gate dielectric process integration

ActiveUS6974779B2Semiconductor/solid-state device manufacturingSemiconductor devicesInterfacial oxideGate dielectric

A method is provided for forming a microstructure with an interfacial oxide layer by using a diffusion filter layer to control the oxidation properties of a substrate associated with formation of a high-k layer into the microstructure. The diffusion filter layer controls the oxidation of the surface. The interfacial oxide layer can be formed during an oxidation process that is carried out following deposition of a high-k layer onto the diffusion filter layer, or during deposition of a high-k layer onto the diffusion filter layer.

Owner:IBM CORP +1

Interfacial oxidation process for high-k gate dielectric process integration

ActiveUS20050059259A1Semiconductor/solid-state device manufacturingSemiconductor devicesInterfacial oxideGate dielectric

A method is provided for forming a microstructure with an interfacial oxide layer by using a diffusion filter layer to control the oxidation properties of a substrate associated with formation of a high-k layer into the microstructure. The diffusion filter layer controls the oxidation of the surface. The interfacial oxide layer can be formed during an oxidation process that is carried out following deposition of a high-k layer onto the diffusion filter layer, or during deposition of a high-k layer onto the diffusion filter layer.

Owner:IBM CORP +1

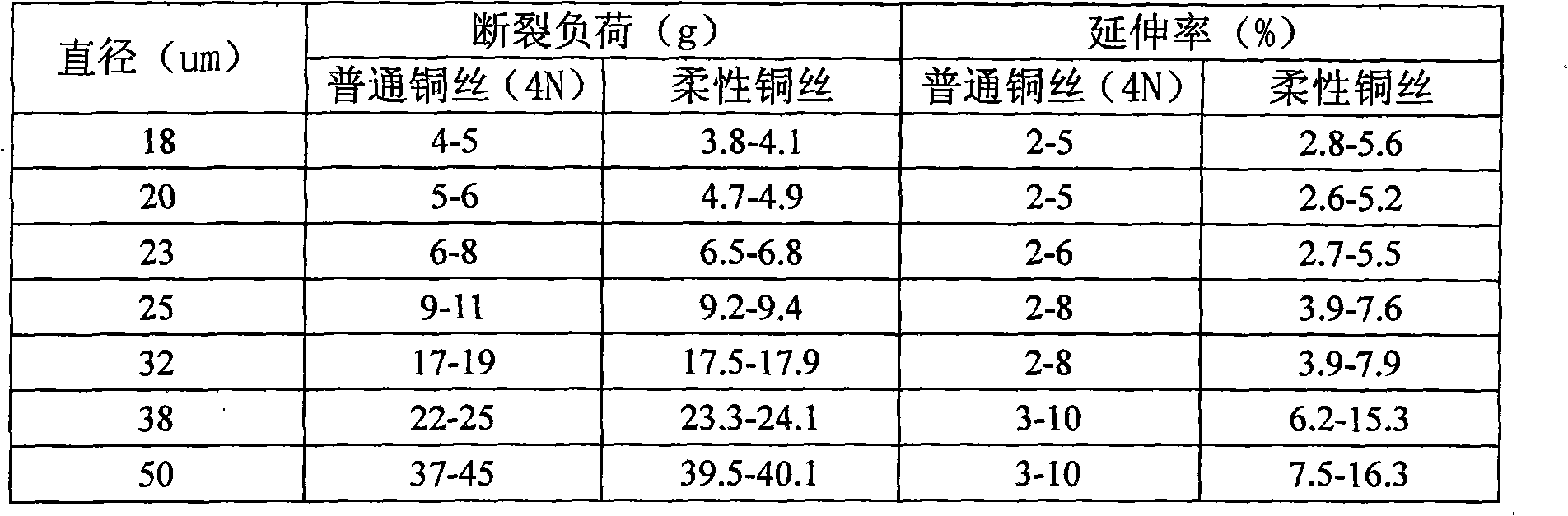

Flexible bonding copper wire and preparation method thereof

ActiveCN101626006AReduce hardnessReduce impactSemiconductor/solid-state device detailsSolid-state devicesBond energyInterfacial oxide

The invention relates to a flexible bonding copper wire and a preparation method thereof. The flexible bonding copper wire comprises the components: 0.001-0.005% of Ce, 0.003-0.005% of Pd, 0.005-0.009% of Pt and the rest of Cu. The invention adopts multielement doped alloy which is added with other components, so as to reduce the rigidity of copper, especially the balling rigidity, reduce the impact force and the damage for a chip, lower the bonding energy, prevent the generation of interfacial oxide and the crack, and ensure the combination performance to be stable, thus improving the combination performance, the electrical conductivity and the inoxidizability; by controlling the conditions of fusion casting, processing and hot treatment, the invention further optimizes the structure and guarantees the proper mechanical capacity, so as to meet different needs.

Owner:烟台一诺电子材料有限公司

Techniques for Metal Gate Work Function Engineering to Enable Multiple Threshold Voltage Nanowire FET Devices

A nanowire FET device includes a SOI wafer having a SOI layer over a BOX, and a plurality of nanowires and pads patterned in the SOI layer, wherein the nanowires are suspended over the BOX; an interfacial oxide surrounding each of the nanowires; and at least one gate stack surrounding each of the nanowires, the gate stack having (i) a conformal gate dielectric present on the interfacial oxide (ii) a conformal first gate material on the conformal gate dielectric (iii) a work function setting material on the conformal first gate material, and (iv) a second gate material on the work function setting material. A volume of the conformal first gate material and / or a volume of the work function setting material in the gate stack are / is proportional to a pitch of the nanowires.

Owner:GLOBALFOUNDRIES US INC

Techniques for metal gate workfunction engineering to enable multiple threshold voltage FINFET devices

Techniques are provided for gate work function engineering in FIN FET devices using a work function setting material an amount of which is provided proportional to fin pitch. In one aspect, a method of fabricating a FIN FET device includes the following steps. A SOI wafer having a SOI layer over a BOX is provided. An oxide layer is formed over the SOI layer. A plurality of fins is patterned in the SOI layer and the oxide layer. An interfacial oxide is formed on the fins. A conformal gate dielectric layer, a conformal gate metal layer and a conformal work function setting material layer are deposited on the fins. A volume of the conformal gate metal layer and a volume of the conformal work function setting material layer deposited over the fins is proportional to a pitch of the fins. A FIN FET device is also provided.

Owner:GLOBALFOUNDRIES U S INC

Metal-gated MOSFET devices having scaled gate stack thickness

InactiveUS7648868B2Solid-state devicesSemiconductor/solid-state device manufacturingInterfacial oxideMOSFET

Metal-oxide semiconductor field effect transistor (MOSFET) devices having metal gate stacks and techniques for improving performance thereof are provided. In one aspect, a metal-oxide semiconductor device is provided comprising a substrate having a buried oxide layer at least a portion of which is configured to serve as a primary background oxygen getterer of the device; and a gate stack separated from the substrate by an interfacial oxide layer. The gate stack comprises a high-K layer over the interfacial oxide layer; and a metal gate layer over the high-K layer.

Owner:GLOBALFOUNDRIES INC

Bonding filamentary silver and preparation method thereof

ActiveCN101626005AImprove conductivityRigidity (moderate strengthSemiconductor/solid-state device detailsSolid-state devicesInterfacial oxideAlloy

The invention relates to a bonding filamentary silver and a preparation method thereof. The bonding filamentary silver comprises the components of 0.30-0.80% of Cu, 0.20-0.50% of Ce, 0.05-0.09% of Pd and the rest of Ag. On the basis of high purity silver material, the invention adopts multielement doped alloy which is added with other components, so as to reduce the formation of metallic compound, prevent the generation of interfacial oxide and the crack, reduce the degradation of combination performance, and ensure the stability of the combination performance to be the same as that of filamentary gold, thus improving the combination performance, the electrical conductivity and the inoxidizability; by controlling the conditions of fusion casting, processing and hot treatment, the invention further optimizes the structure and guarantees the proper mechanical capacity, so as to meet different needs, be applied into advanced packaging such as an integrated circuit and the like in deed, and partly or completely replace the filamentary gold.

Owner:烟台一诺电子材料有限公司

MOSFETS Having Stacked Metal Gate Electrodes and Method

InactiveUS20090280632A1Prevent interfacial oxide layer regrowthLow oxygenSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETInterfacial oxide

MOSFETs having stacked metal gate electrodes and methods of making the same are provided. The MOSFET gate electrode includes a gate metal layer formed atop a high-k gate dielectric layer. The metal gate electrode is formed through a low oxygen content deposition process without charged-ion bombardment to the wafer substrate. Metal gate layer thus formed has low oxygen content and may prevent interfacial oxide layer regrowth. The process of forming the gate metal layer generally avoids plasma damage to the wafer substrate.

Owner:TAIWAN SEMICON MFG CO LTD

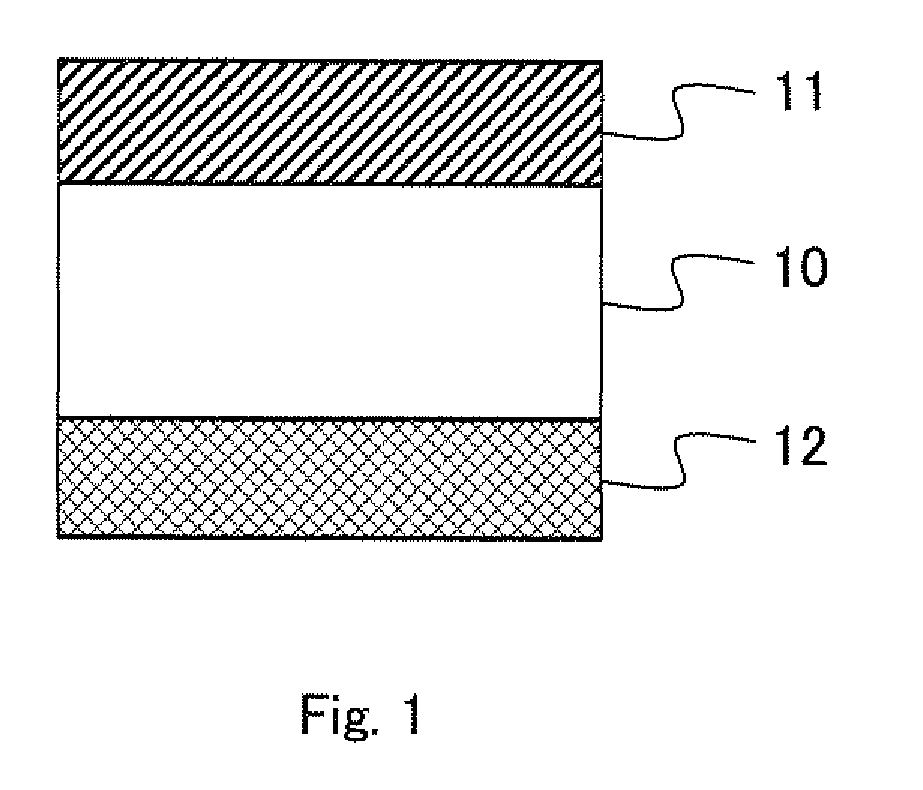

Interfacial oxide used as switching layer in a nonvolatile resistive memory element

InactiveUS20130228735A1Solid-state devicesSemiconductor/solid-state device manufacturingInterfacial oxideSurface oxidation

A nonvolatile resistive memory element includes a host oxide formed from an interfacial oxide layer. The interfacial oxide layer is formed on the surface of a deposited electrode layer via in situ or post-deposition surface oxidation treatments. The switching performance of a resistive memory device based on such an interfacial oxide layer is equivalent or superior to the performance of a conventional resistive memory element.

Owner:INTERMOLECULAR

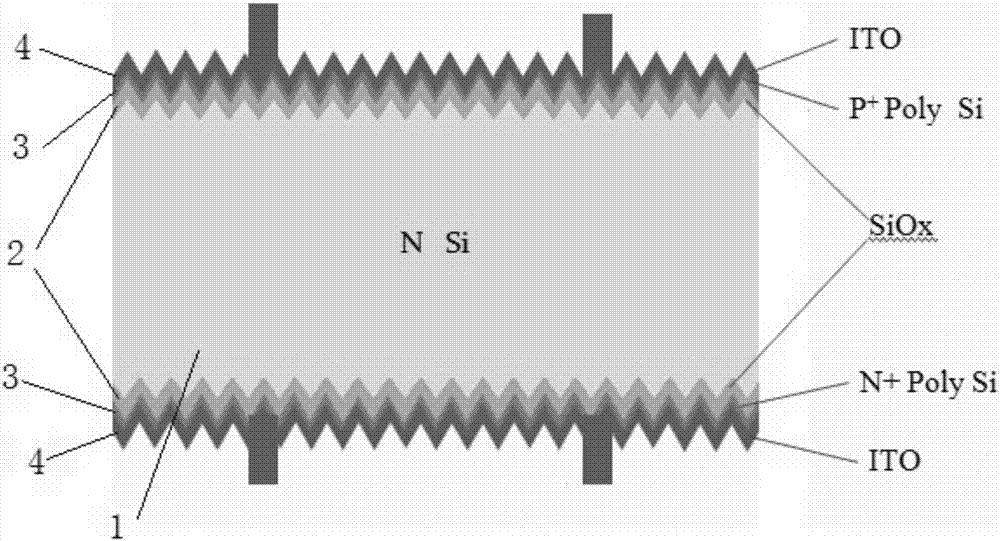

Double-sided POLO (POLy-Si on passivating interfacial Oxides) battery and preparation method thereof

InactiveCN107342332APassivated contactIncrease low light responseFinal product manufacturePhotovoltaic energy generationInterfacial oxideSilicon oxide

The invention relates to the technical field of solar cell preparation, and especially relates to a double-sided POLO (POLy-Si on passivating interfacial Oxides) battery and a preparation method thereof. Silicon oxide and a polysilicon layer are used to perform double-sided passivation, wherein the first function is that the surface defects of a silicon wafer surface are not only passivated and the response of weak light is increased, but also the contact between metals on the back and a semiconductor is passivated, and a contact negative charge value is reduced; and the second function is that there is no point contact due to complete passivation, a base region has no transverse transmission of minority carries or majority carries; and the third function is that the polycrystalline silicon is an indirect band gap, and the current loss is small.

Owner:EGING PHOTOVOLTAIC TECHNOLOGY CO LTD

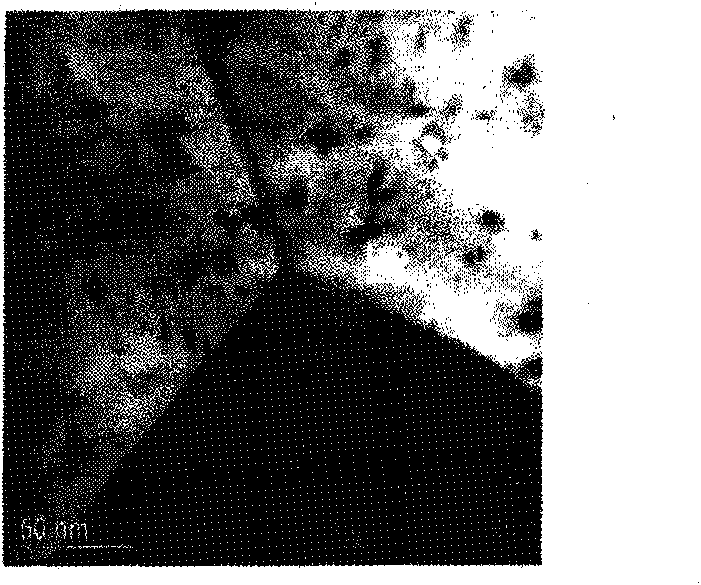

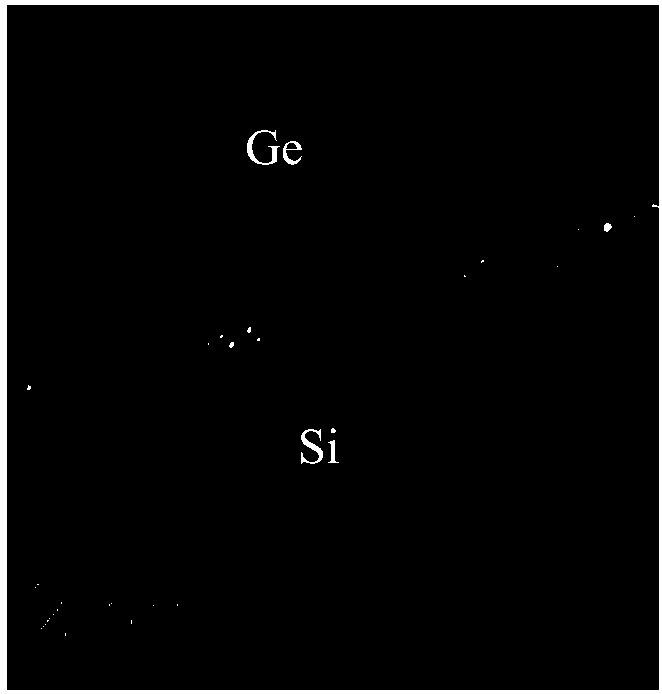

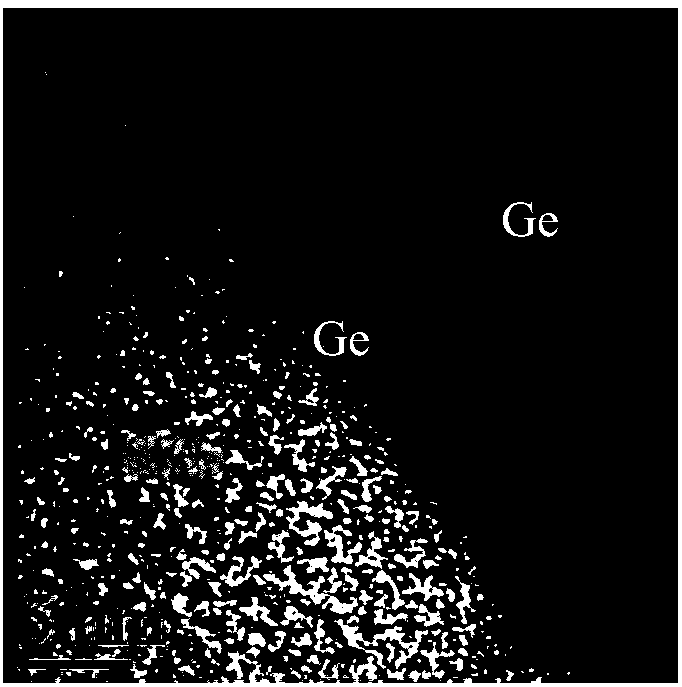

Low-temperature bonding method for semiconductor without oxide layer

InactiveCN108573878AAchieve bondingSolve the problem of introducing a hydrophilic oxide layerSemiconductor/solid-state device manufacturingInterfacial oxideBond interface

The invention relates to a low-temperature bonding method for a semiconductor without an oxide layer, which relates to a semiconductor bonding process. A transition layer technology is adopted, a thinGe layer is introduced at a Si, Ge and SiO2 semiconductor bonding interface, and the low-temperature crystallization characteristics and the crystallization atomic migration characteristics of the Gematerial are used to realize non-oxide layer Si wafer bonding, Ge / Si bonding and GOI bonding. The low-temperature crystallization characteristics of a magnetron sputtering Ge layer are used to realize a non-interfacial oxide layer semiconductor bonding interface, a semiconductor Ge transition layer grows on the surface of a wafer after being cleaned, the low-temperature crystallization characteristics of the Ge are used, crystallization of the Ge transition layer is realized through low-temperature annealing, migration of atoms at the bonding interface is thus driven, and the oxide layer is finally dissociated. According to the method in the invention, the problem of introducing a hydrophilic oxide layer at the interface during a direct hydrophilic bonding process can be solved, crystallization of the semiconductor bonding interface transition layer can also be realized under the low temperature of 300 to 400 DEG C, and atomic bond bonding is thus realized.

Owner:XIAMEN UNIV