Patents

Literature

2603 results about "Bonding process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

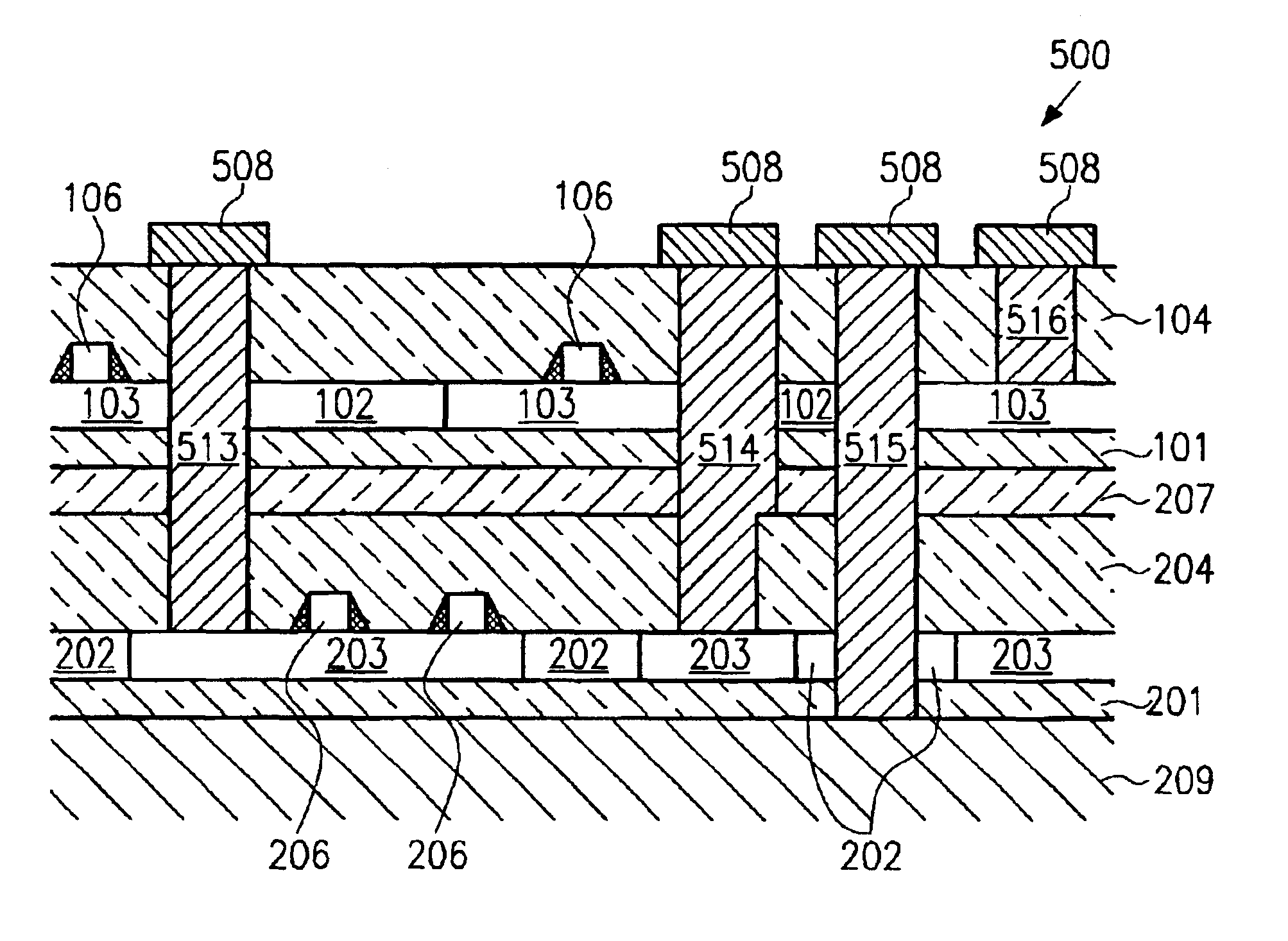

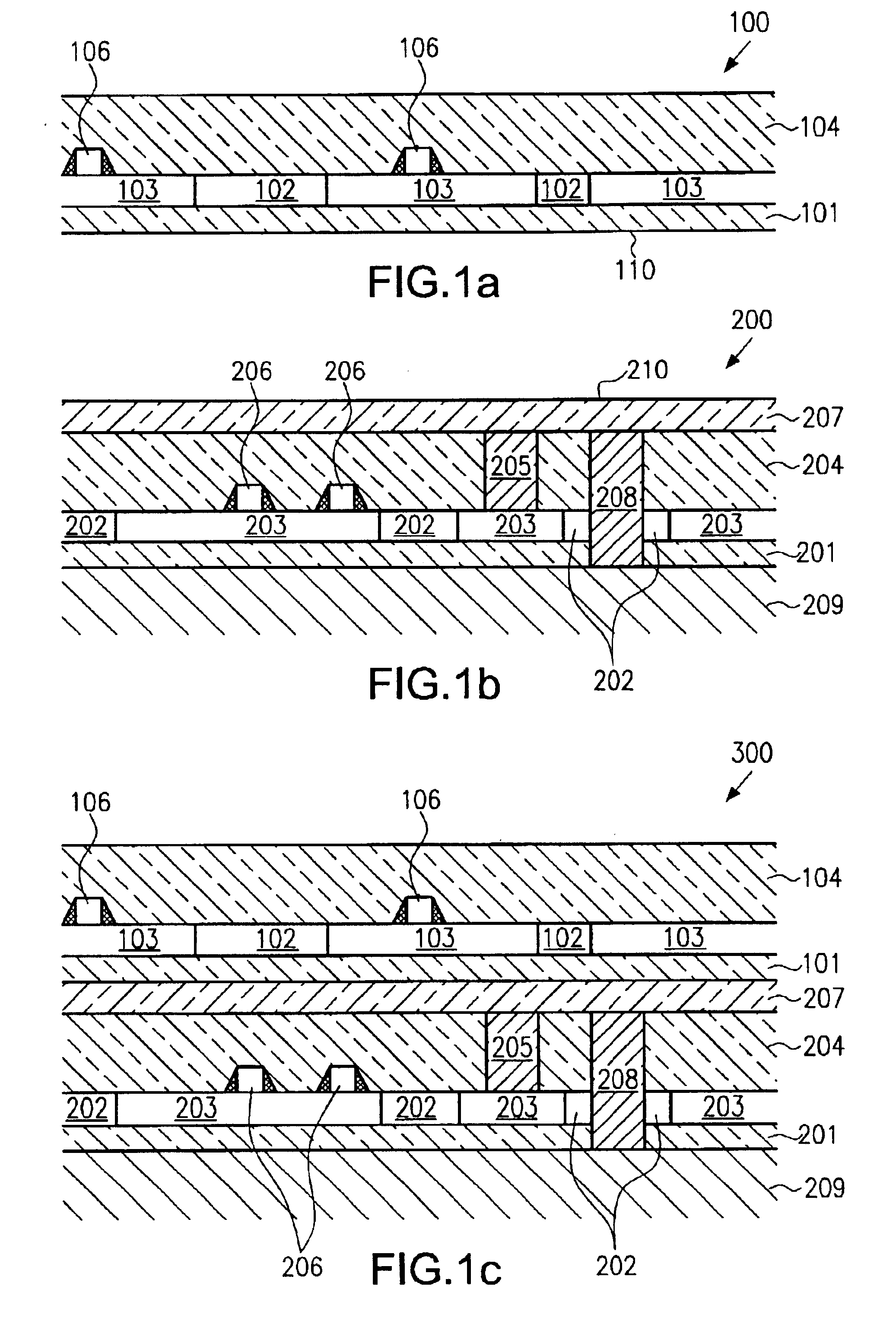

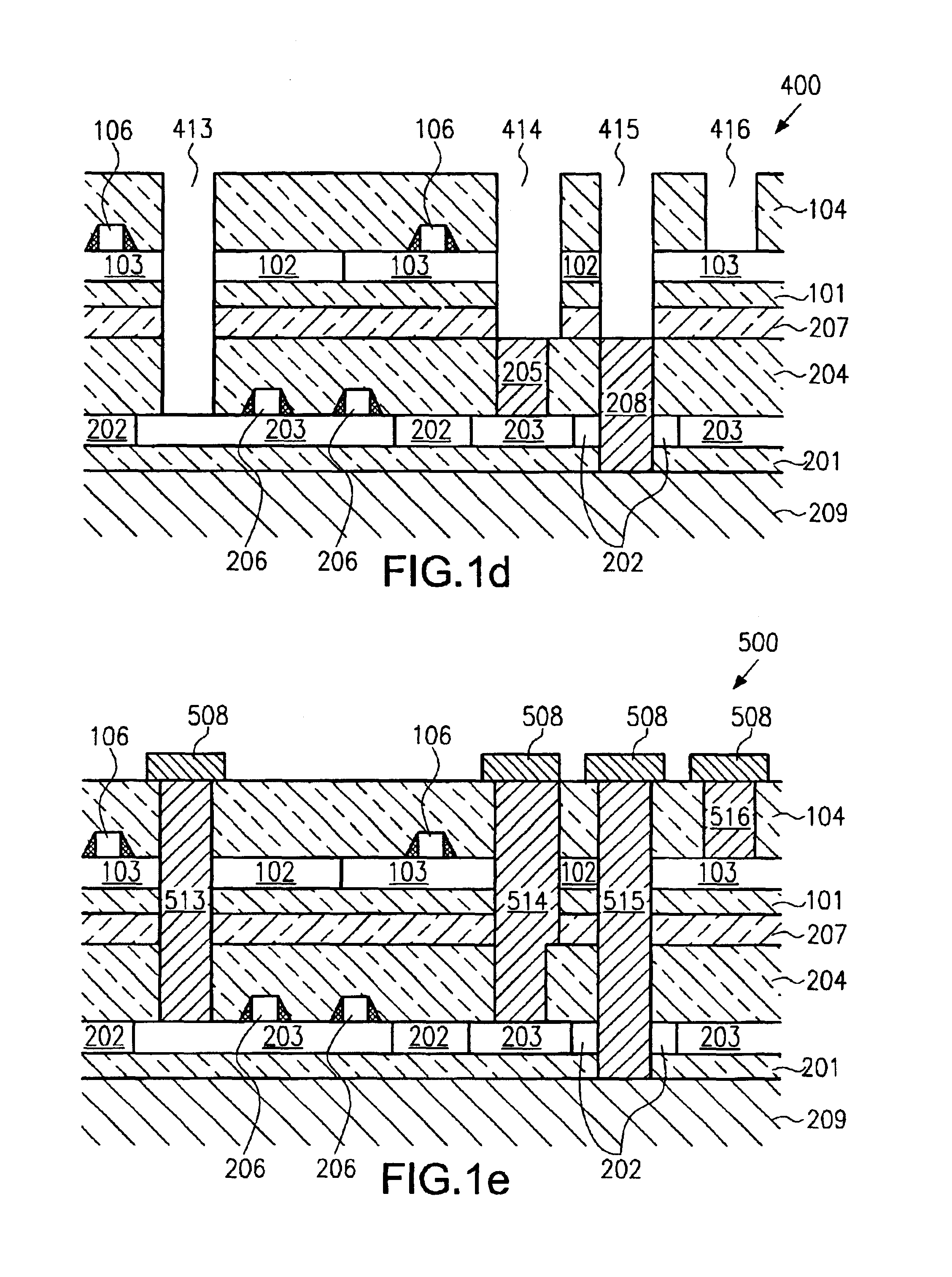

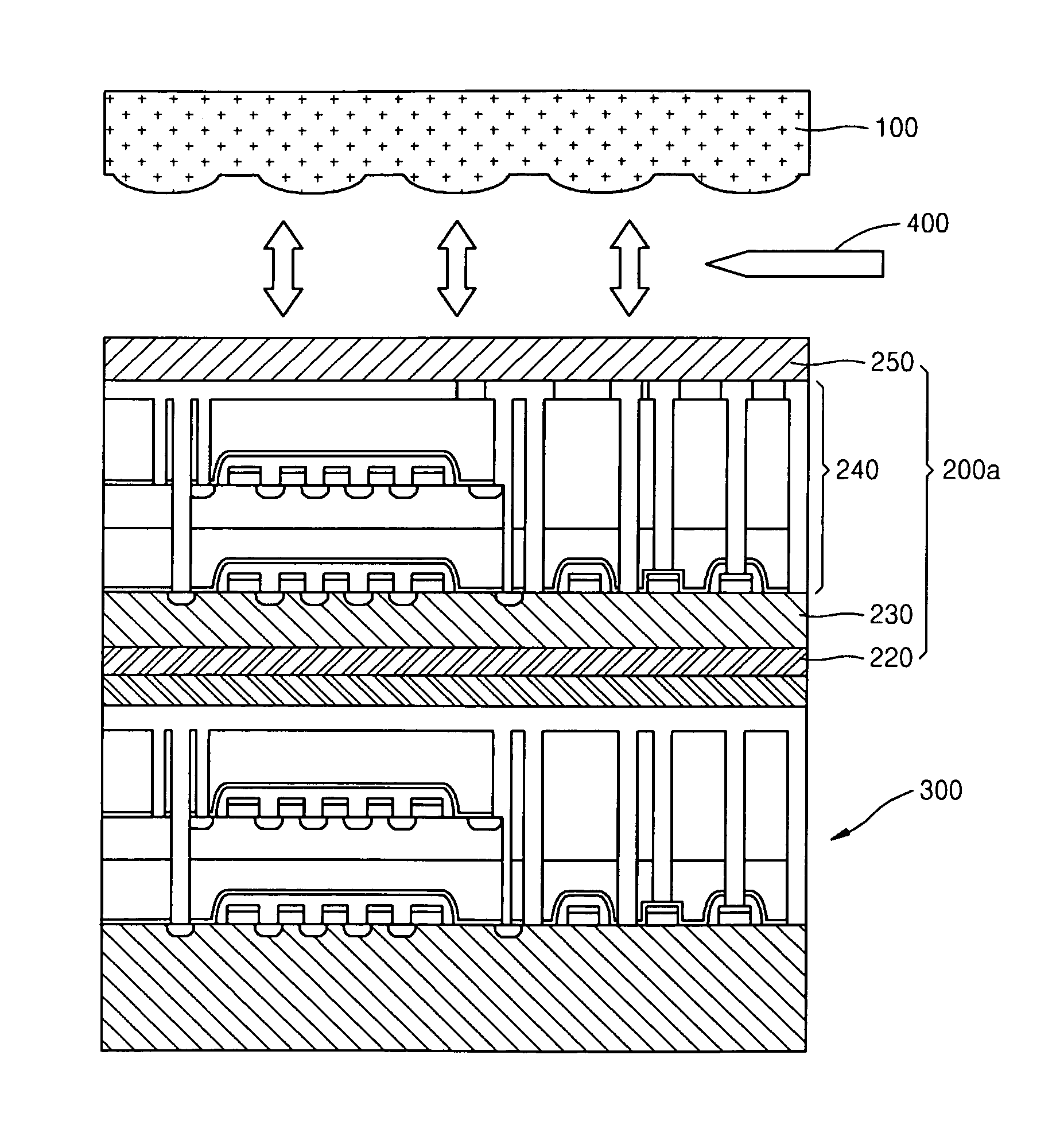

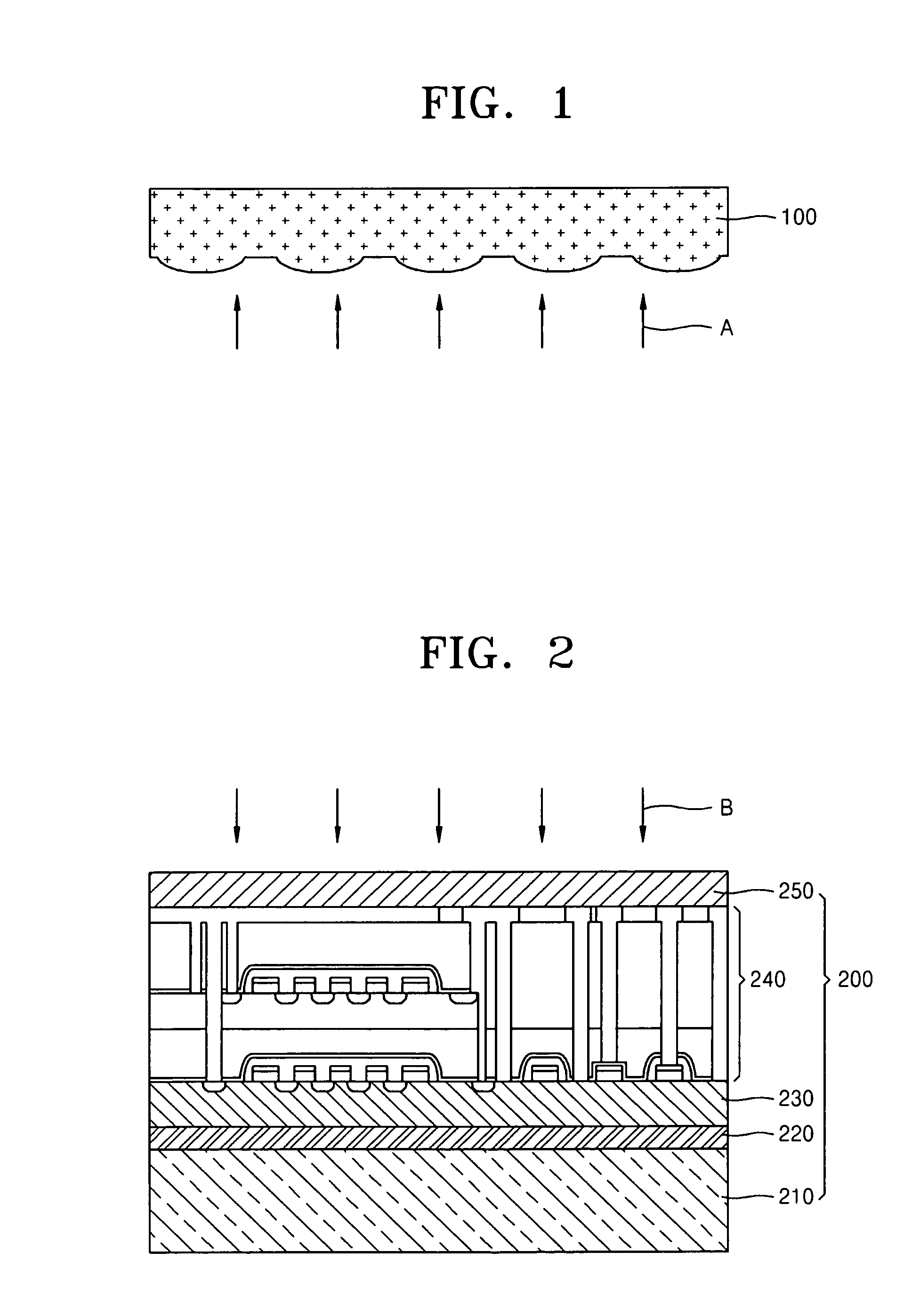

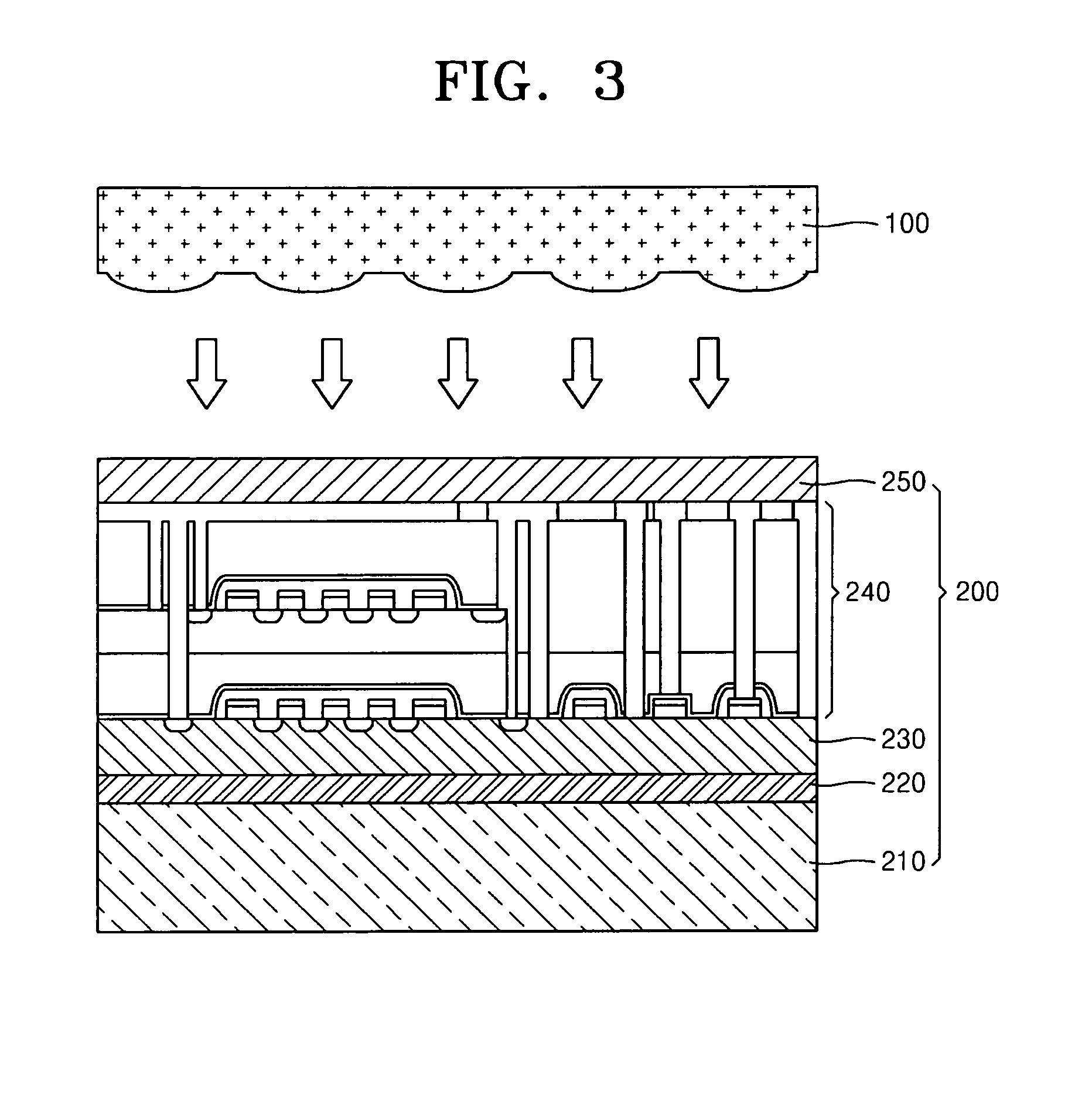

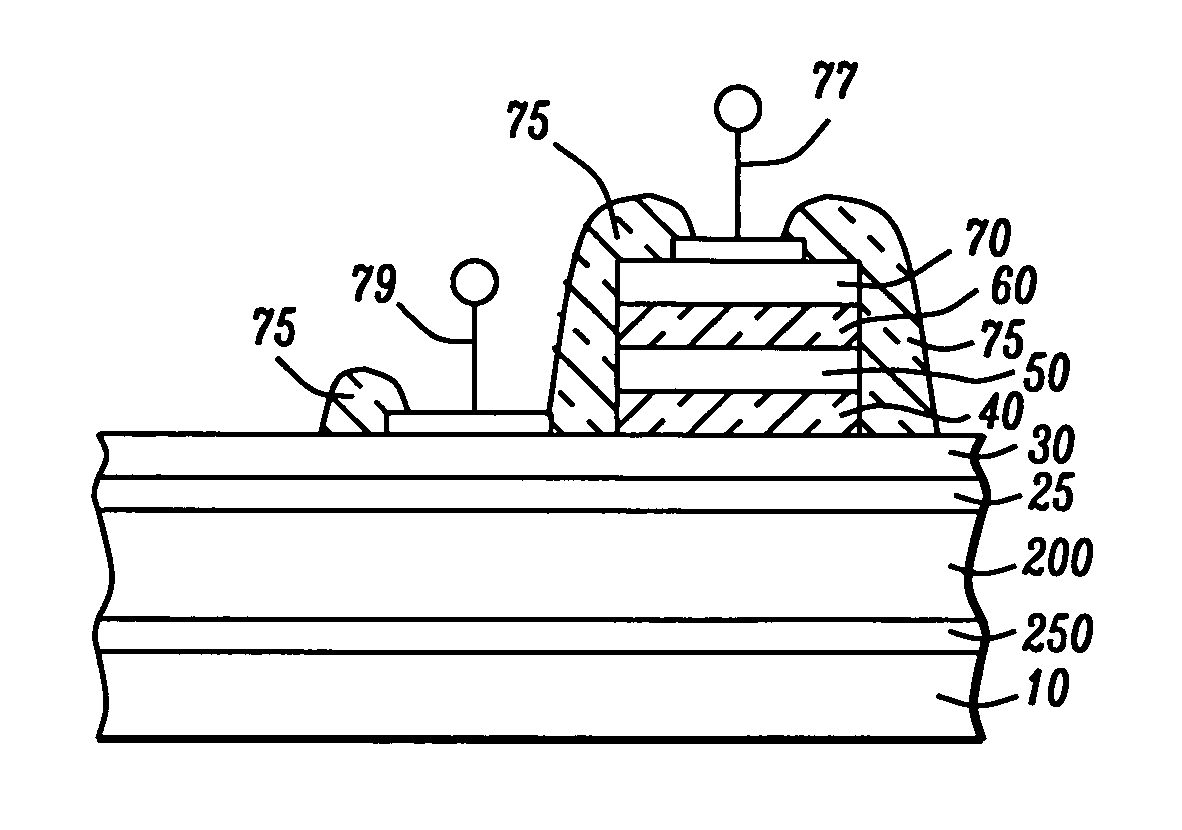

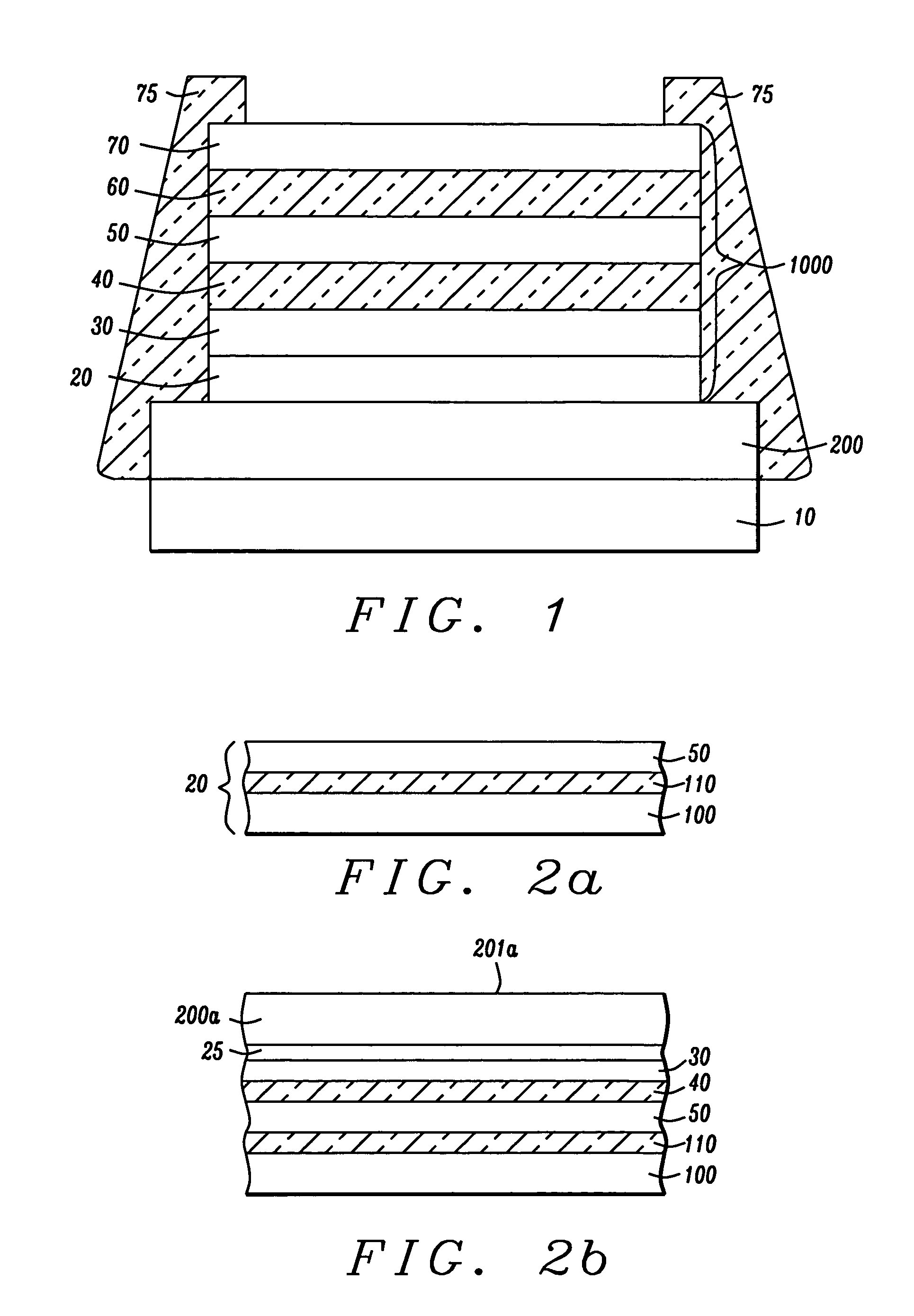

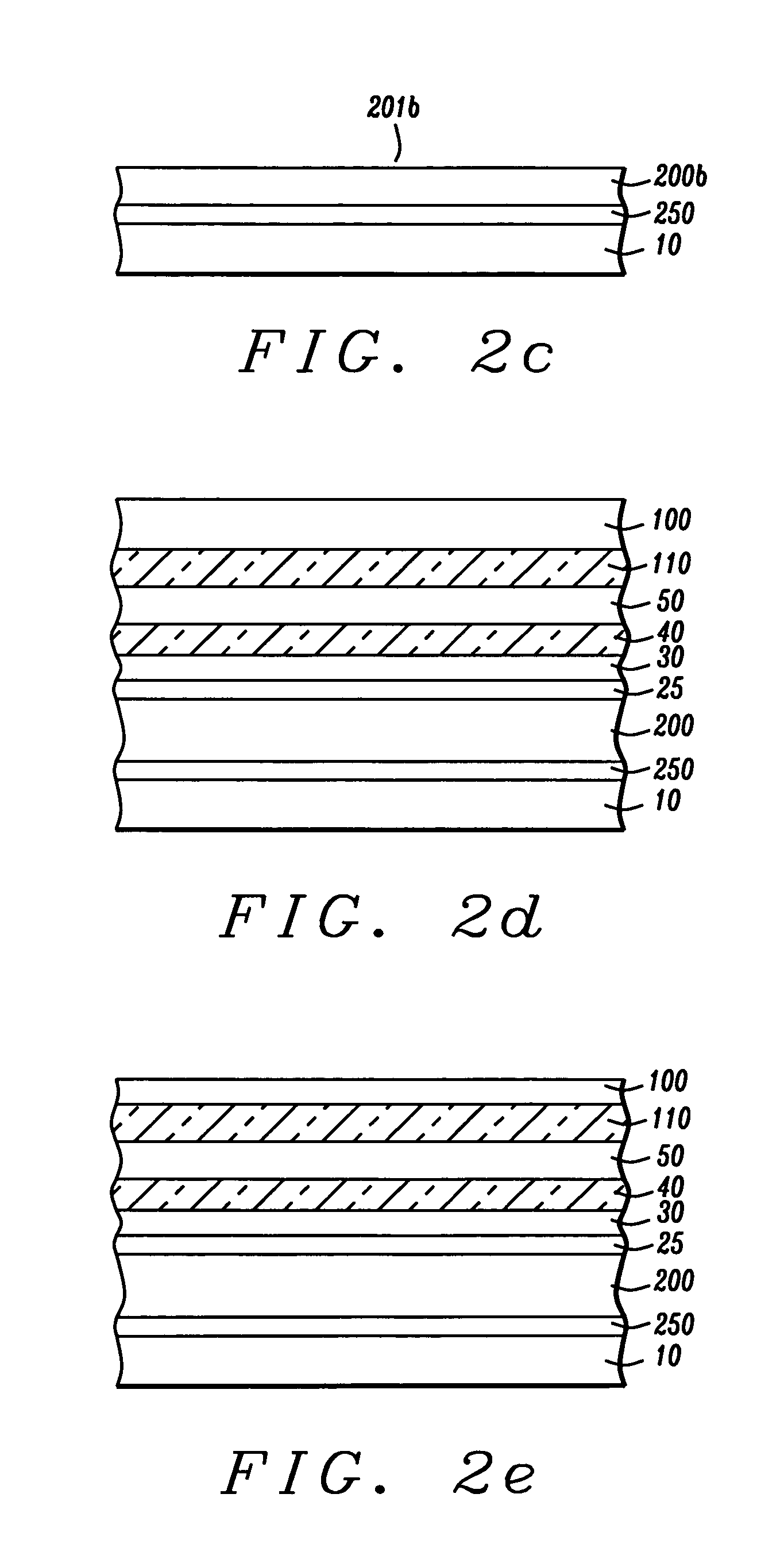

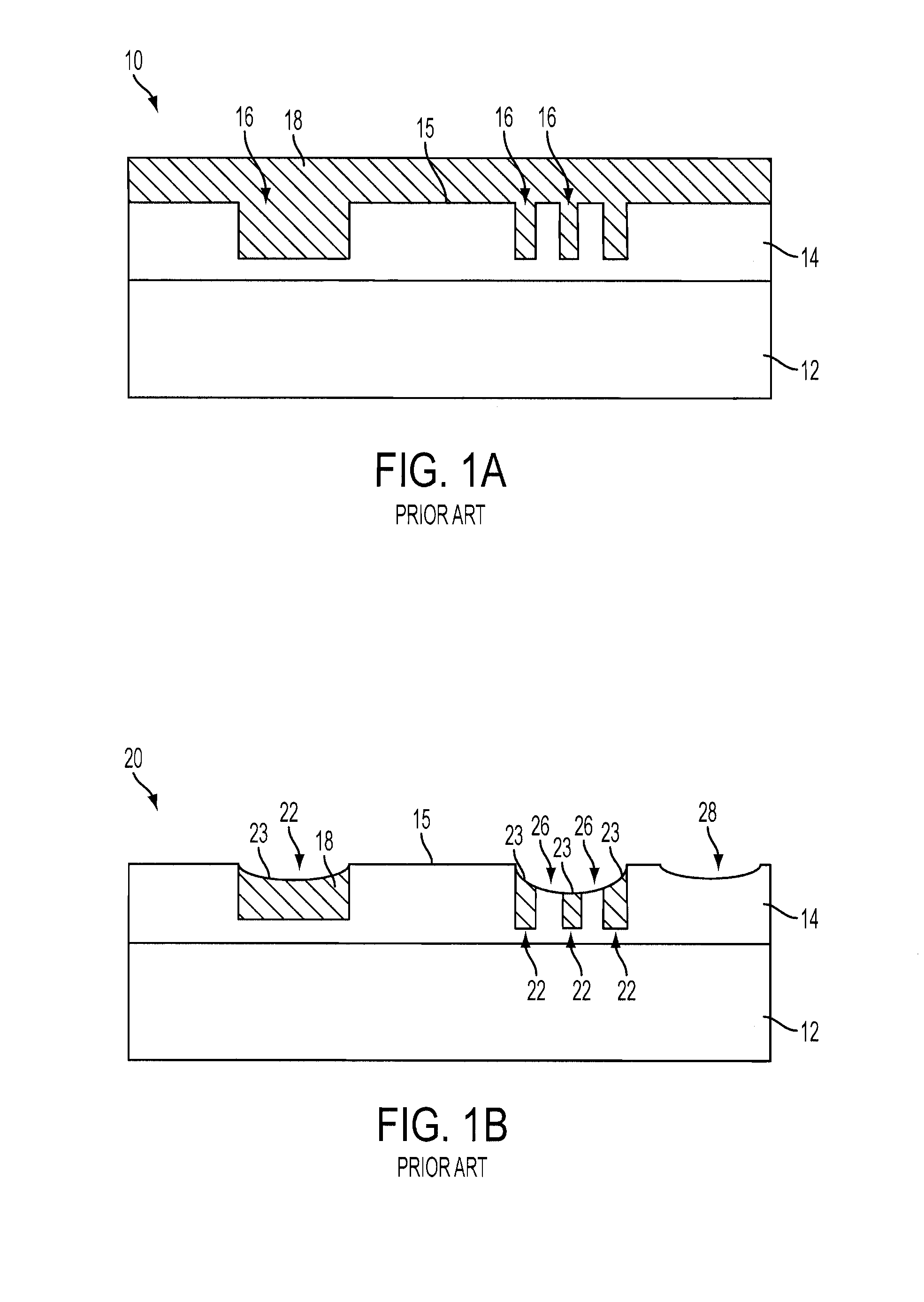

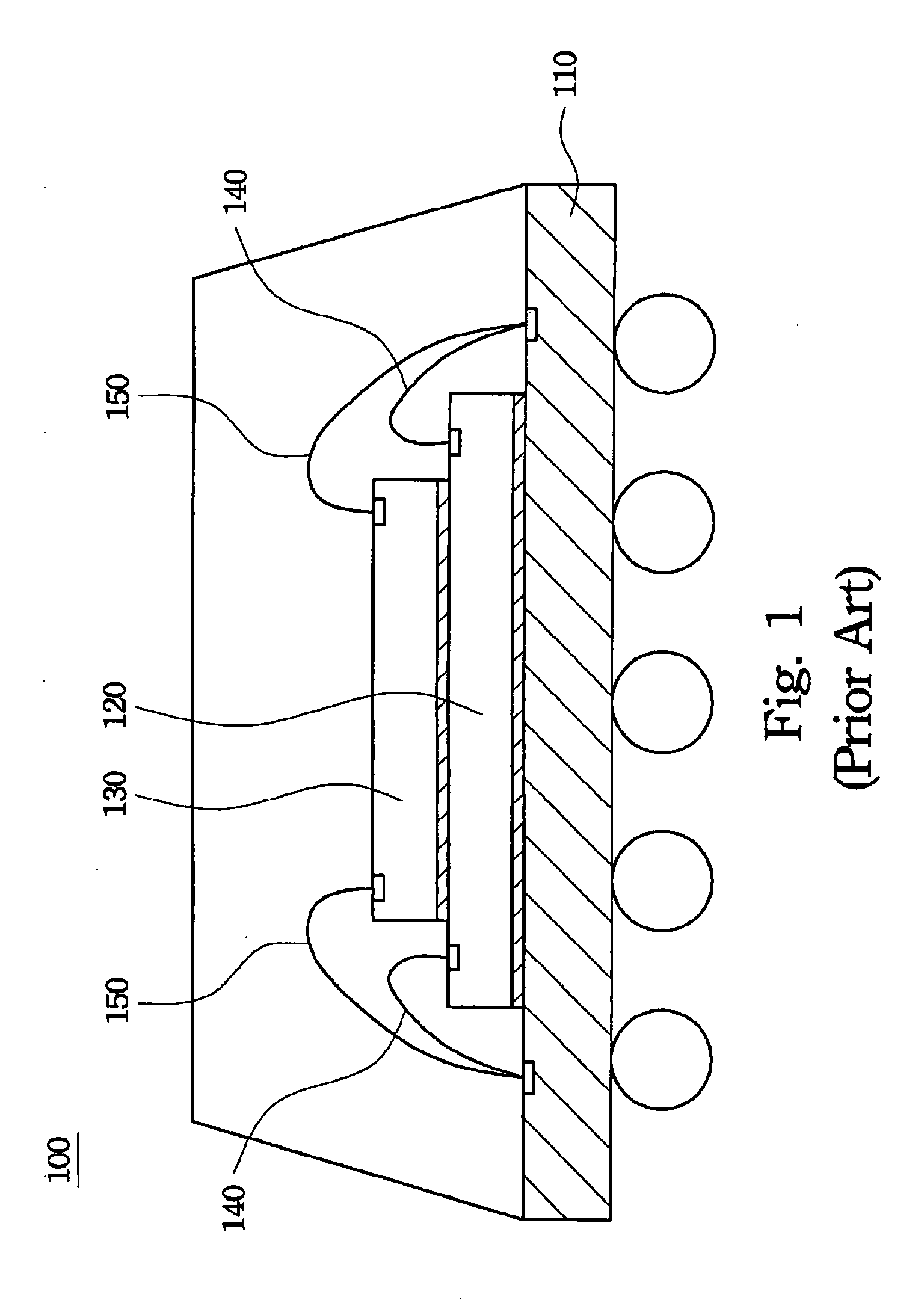

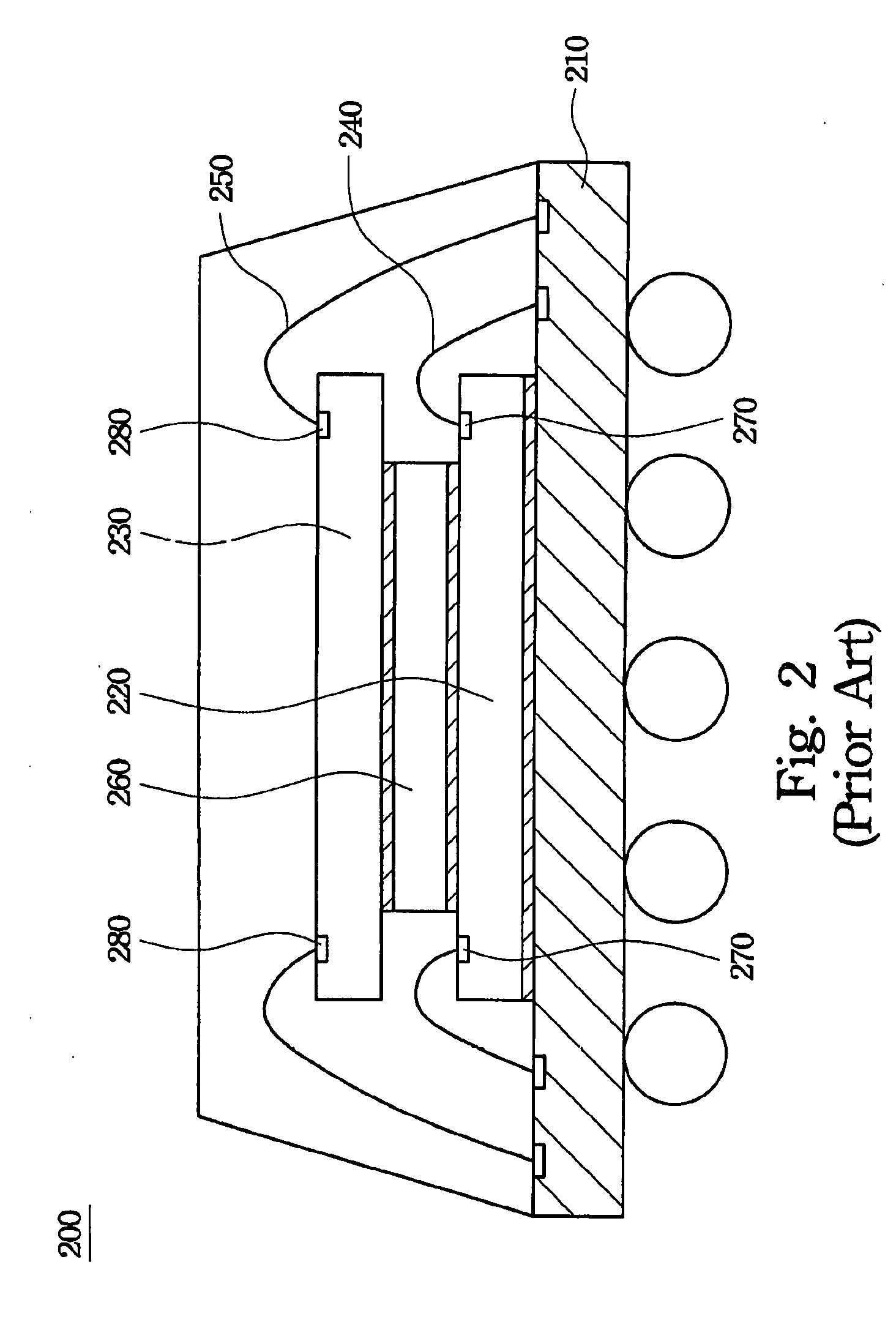

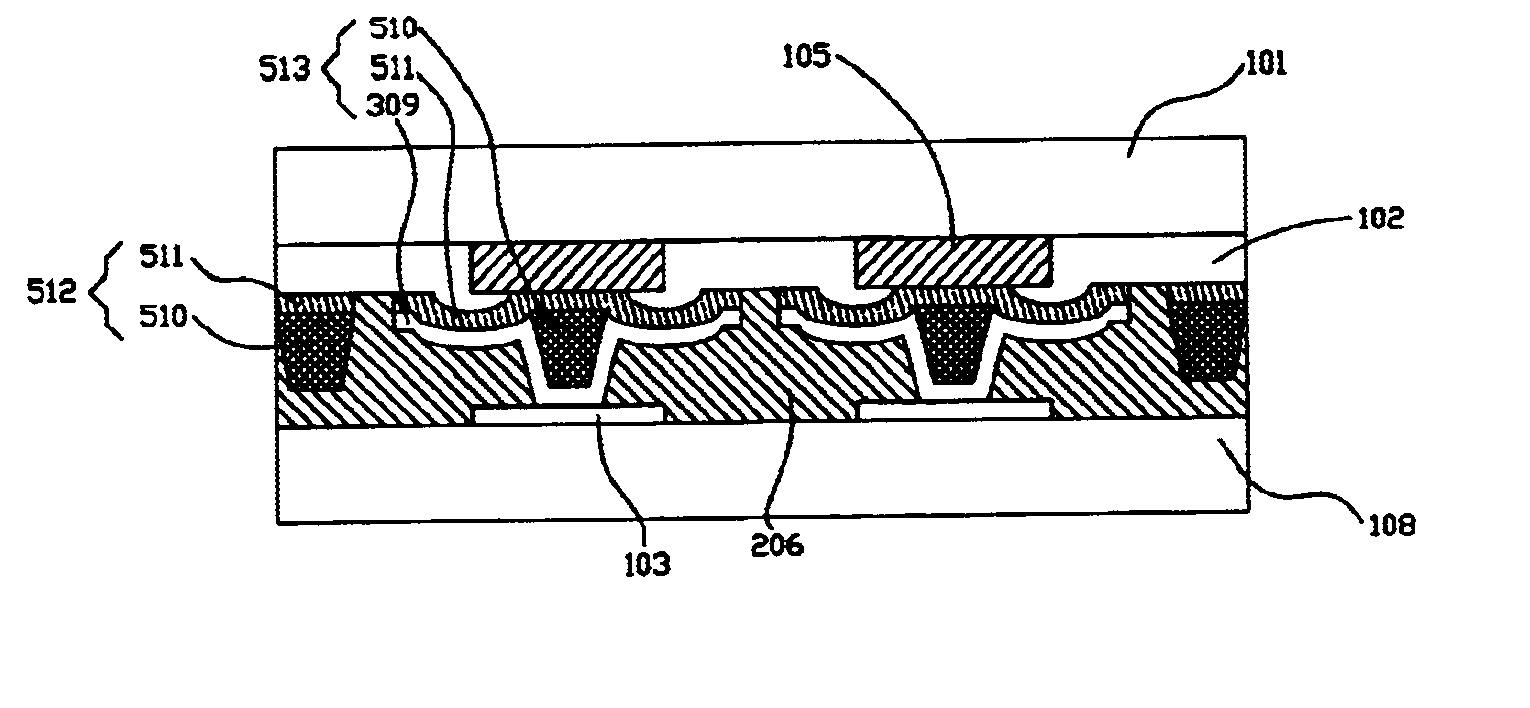

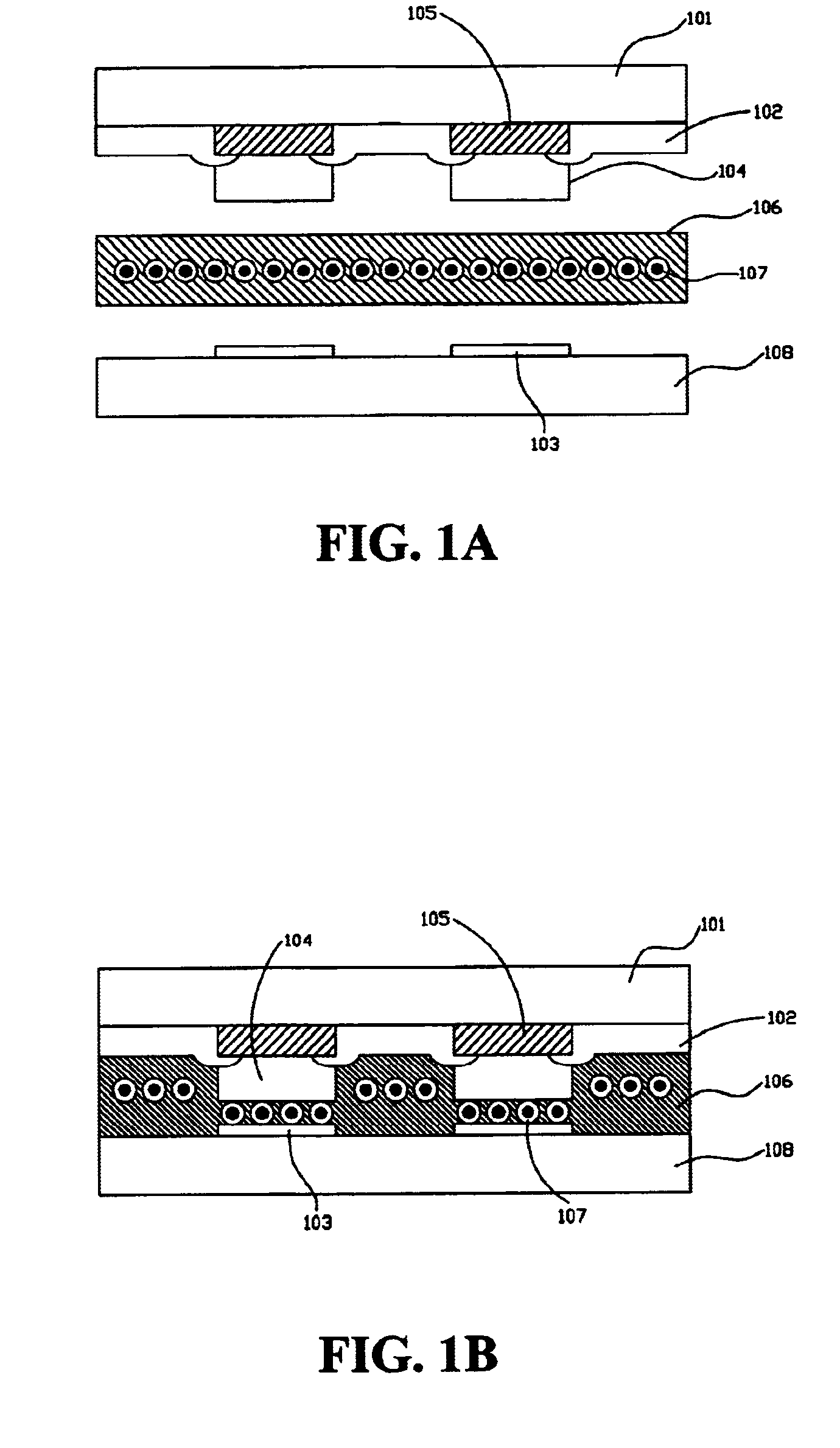

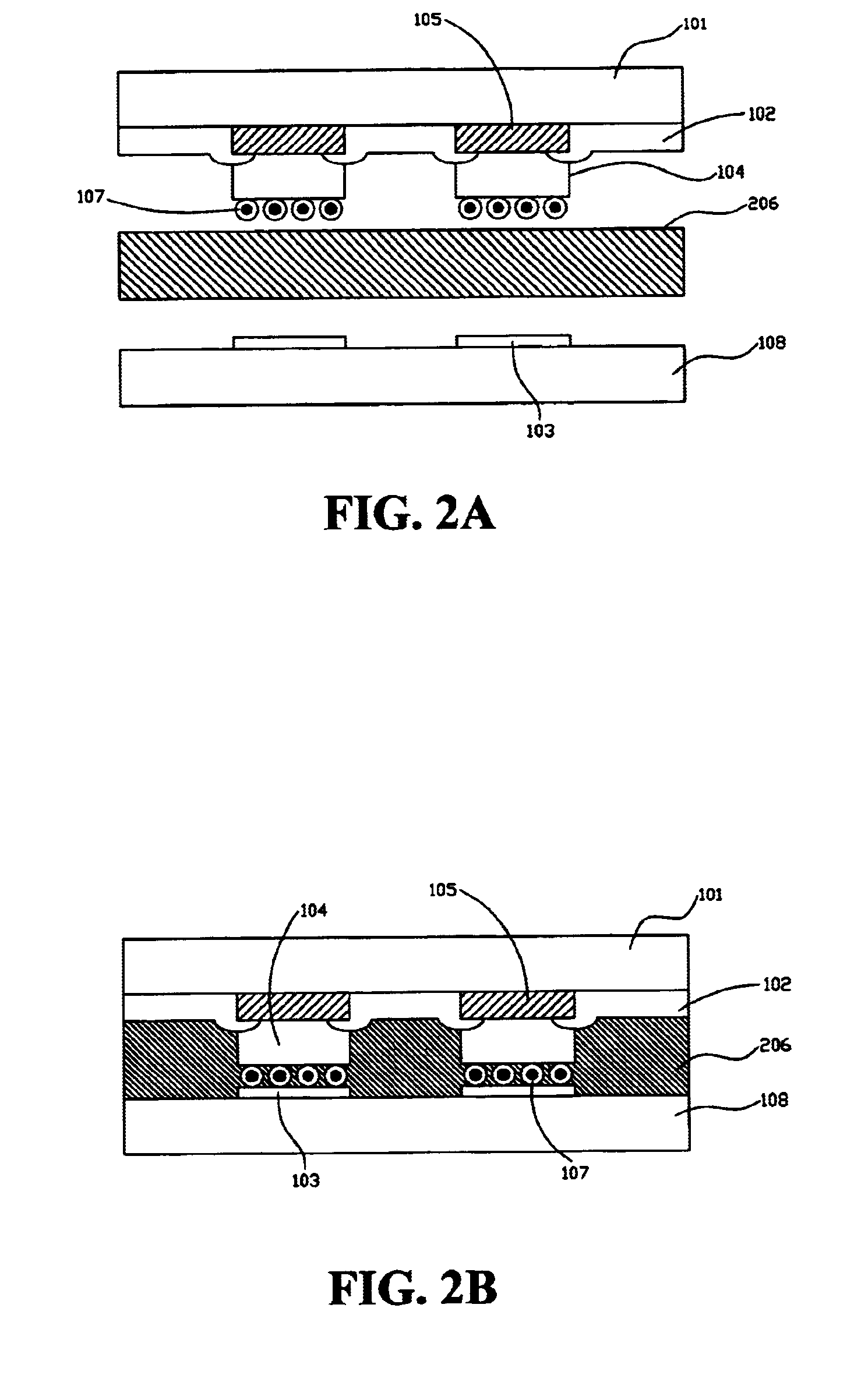

Three-dimensional integrated semiconductor devices

InactiveUS6943067B2Semiconductor/solid-state device detailsSolid-state devicesBonding processEngineering

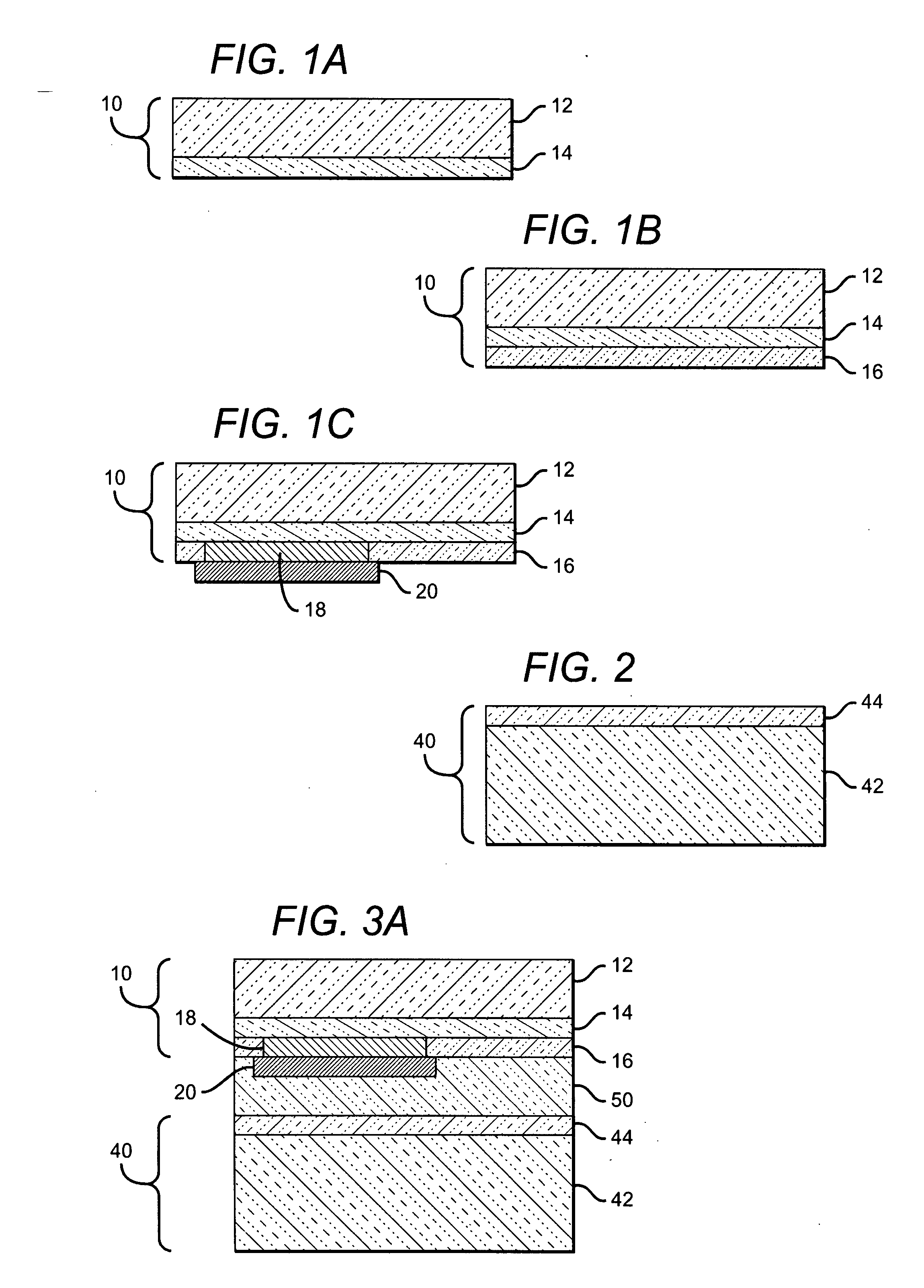

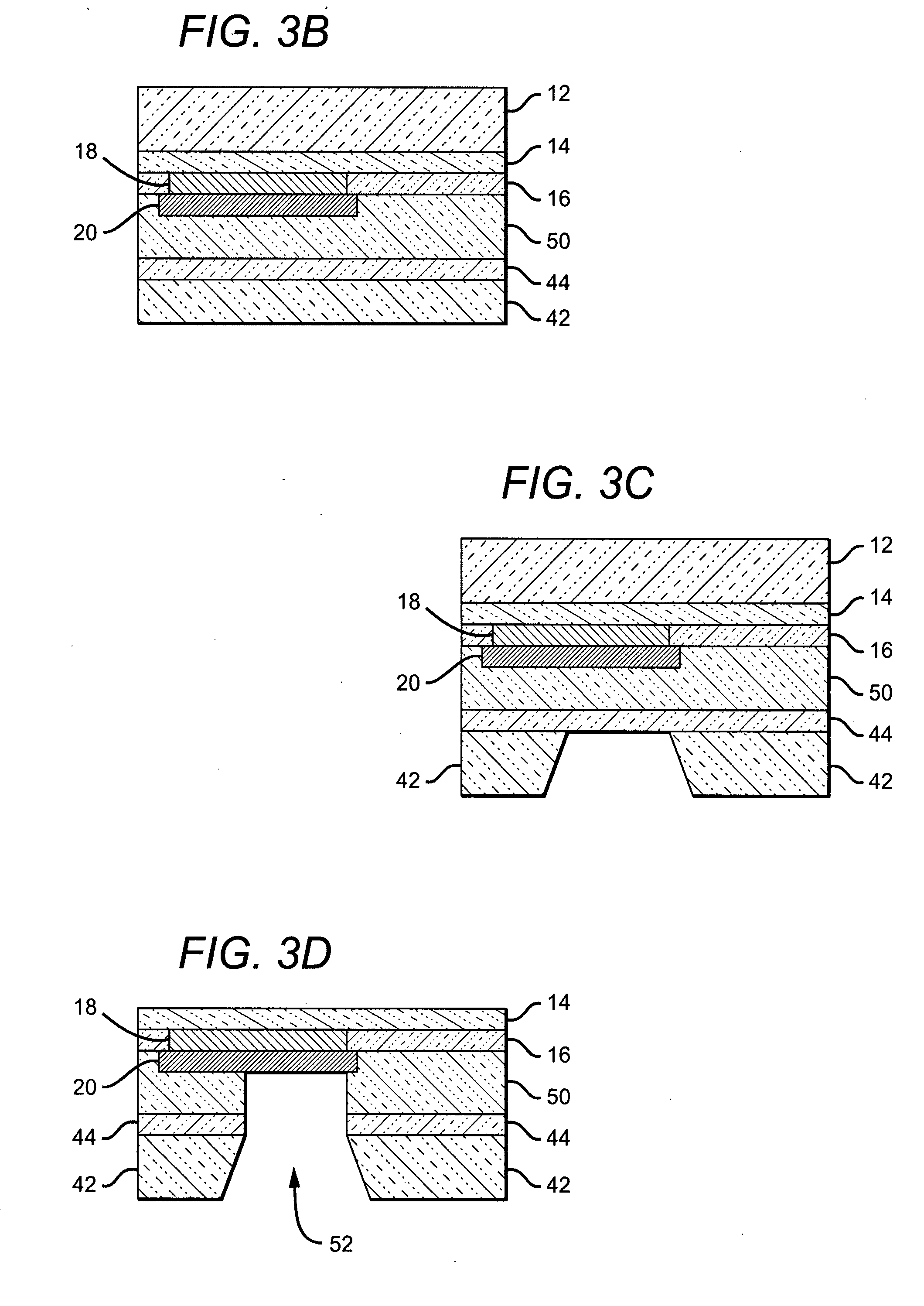

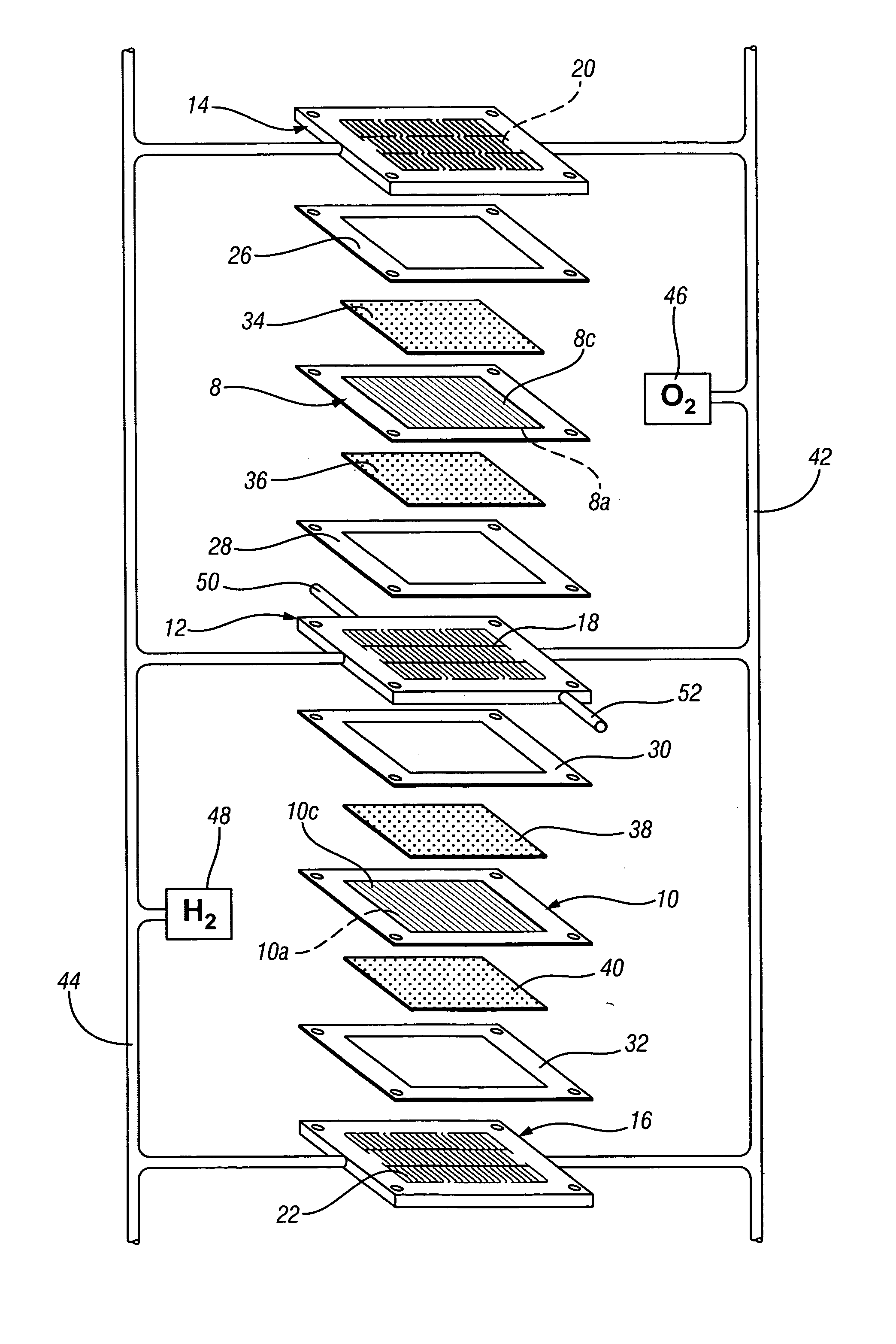

The present invention describes a process for three-dimensional integration of semiconductor devices and a resulting device. The process combines low temperature wafer bonding methods with backside / substrate contact processing methods, preferably with silicon on insulator devices. The present invention utilizes, in an inventive fashion, low temperature bonding processes used for bonded silicon on insulator (SOI) wafer technology. This low temperature bonding technology is adopted for stacking several silicon layers on top of each other and building active transistors and other circuit elements in each one. The back-side / substrate contact processing methods allow the interconnection of the bonded SOI layers.

Owner:ADVANCED MICRO DEVICES INC

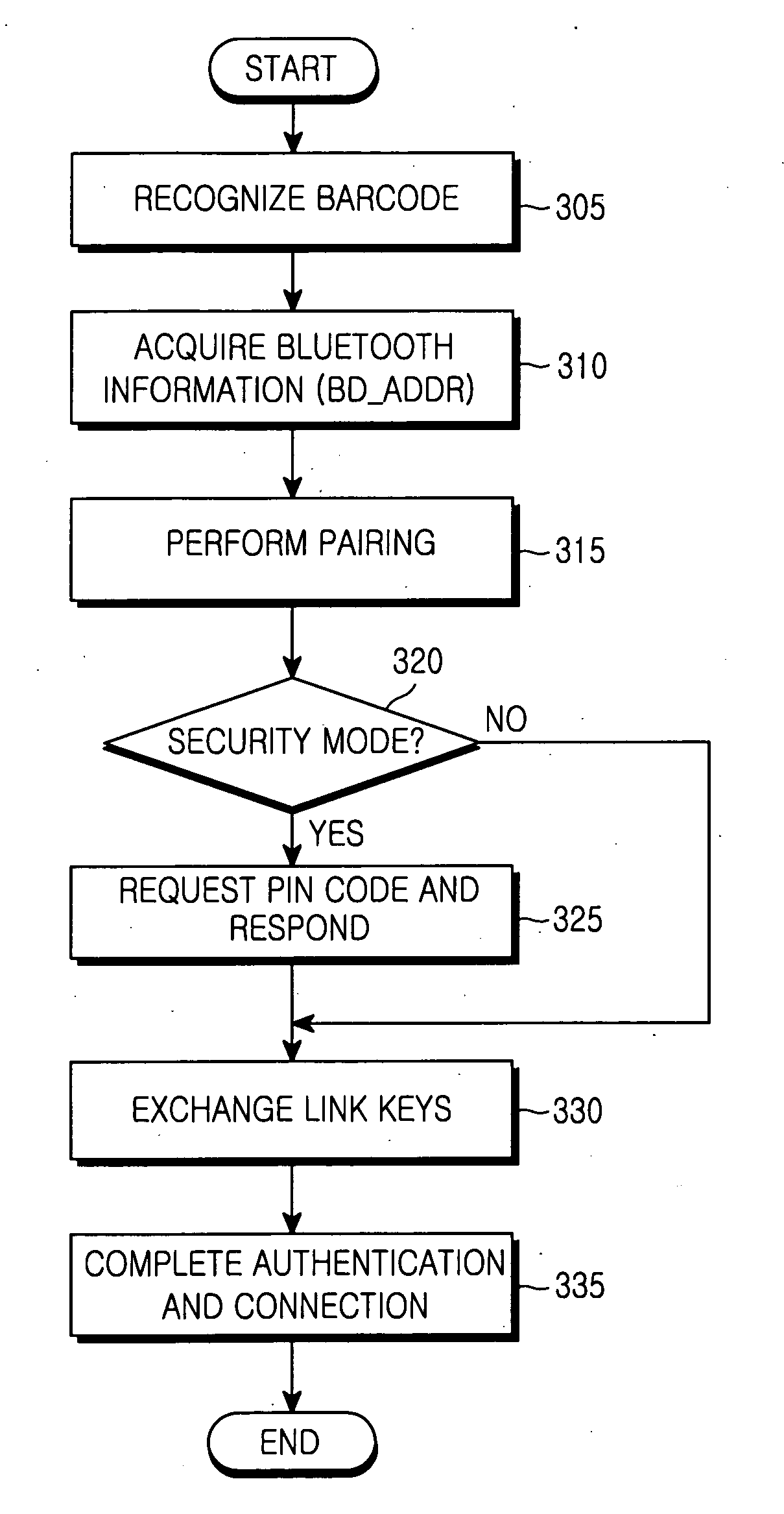

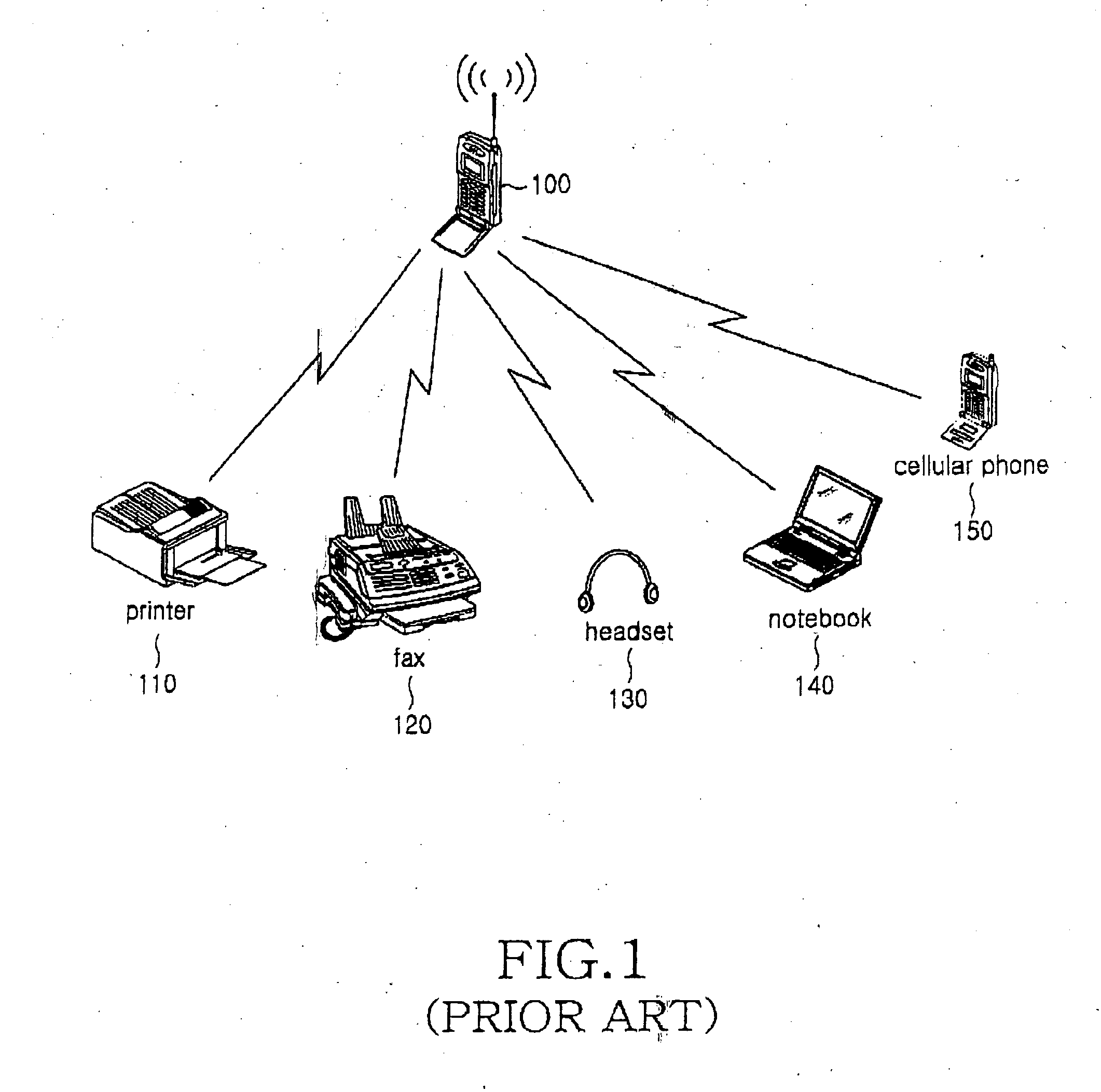

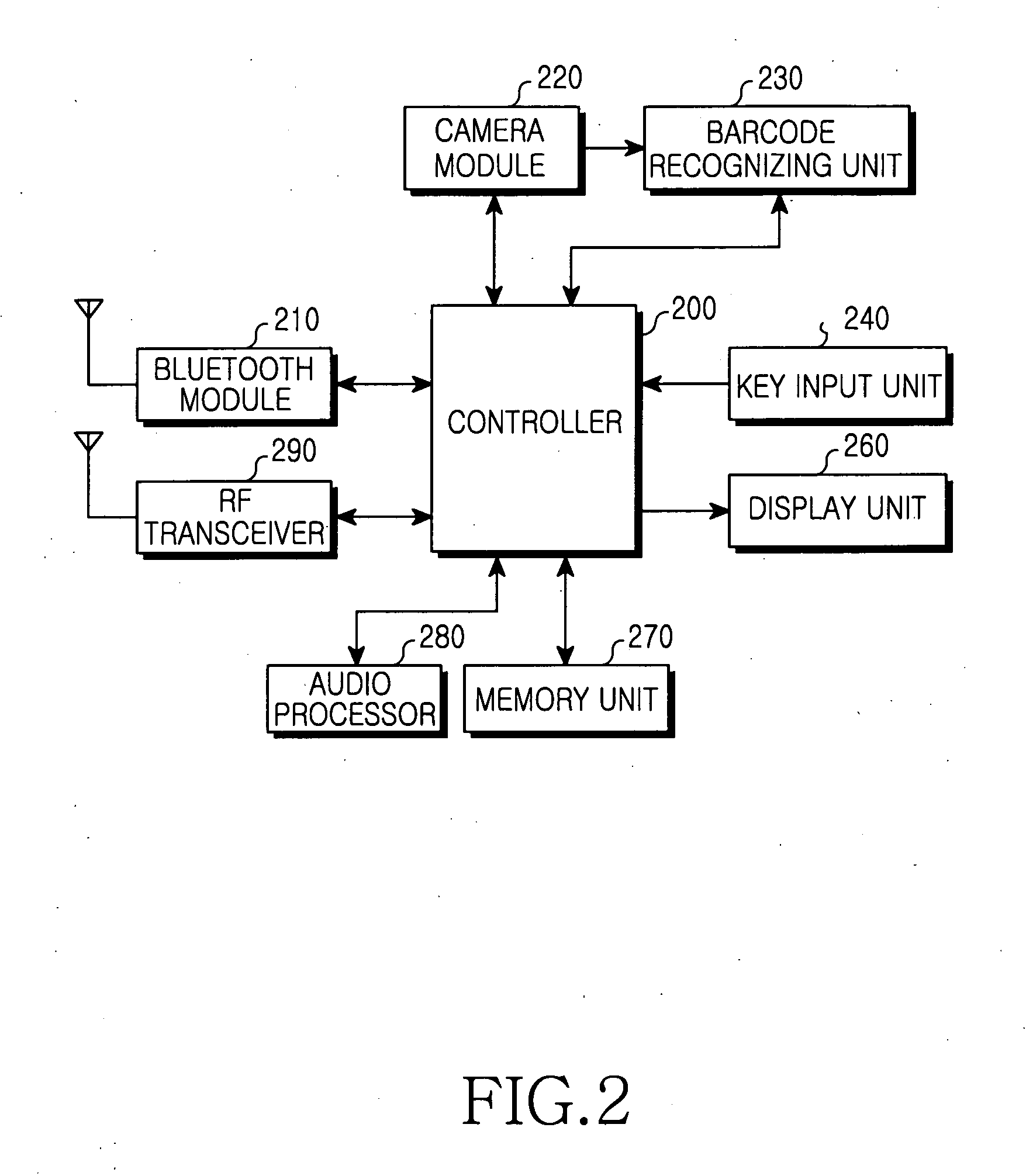

Method and apparatus for bonding process in bluetooth device

InactiveUS20060135064A1Simplify the pairing processEasy to understandNear-field transmissionNetwork topologiesBonding processBarcode

A method and apparatus for a bonding process in a user terminal having a Bluetooth module. The method includes recognizing a barcode of a Bluetooth device to be connected using a camera module, acquiring bonding information of the Bluetooth device from the barcode, performing pairing with the Bluetooth device using the acquired bonding information, and establishing a connection between the user terminal and the Bluetooth device after performing pairing. The bonding information may also be acquired using a secure cable in another embodiment.

Owner:SAMSUNG ELECTRONICS CO LTD

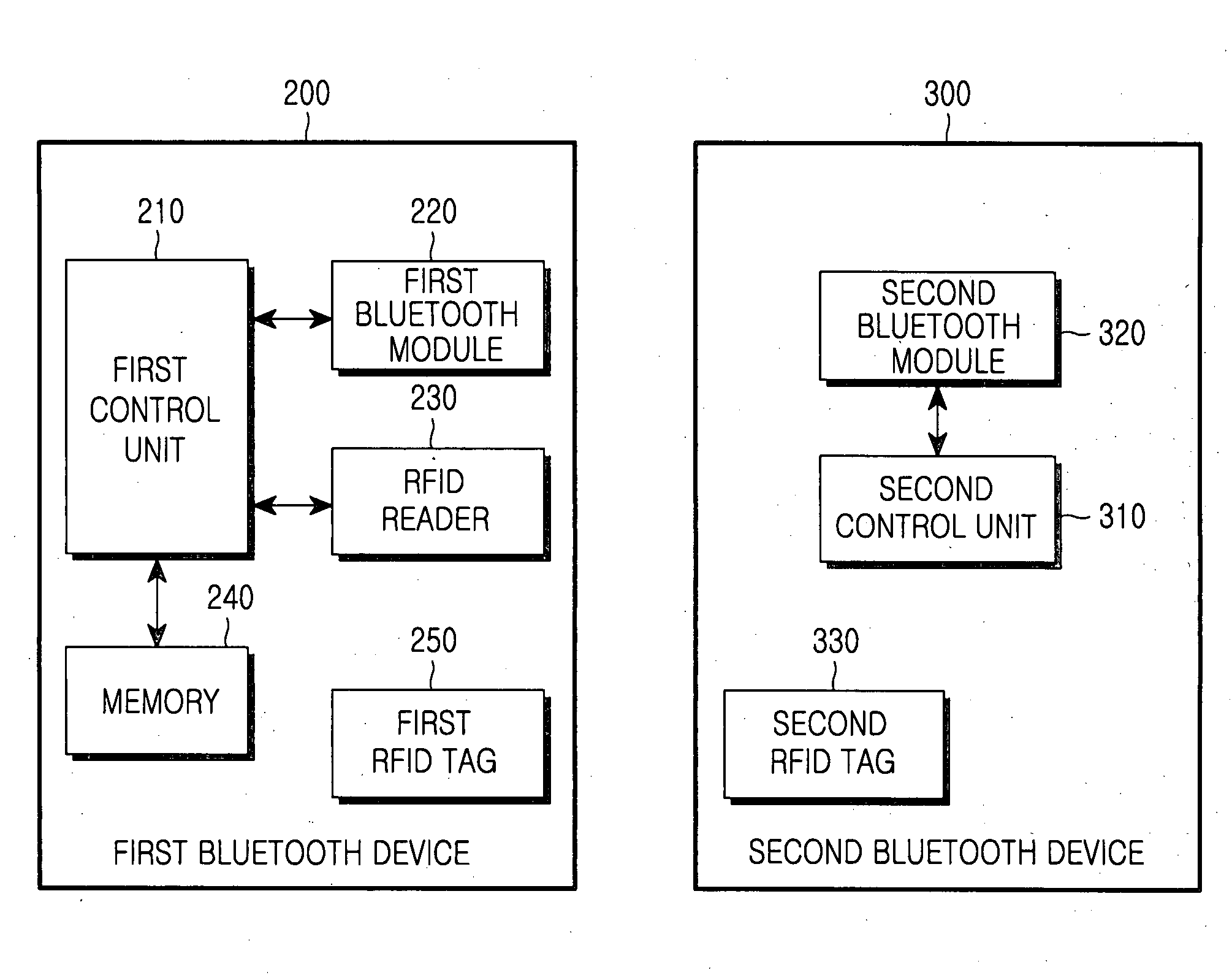

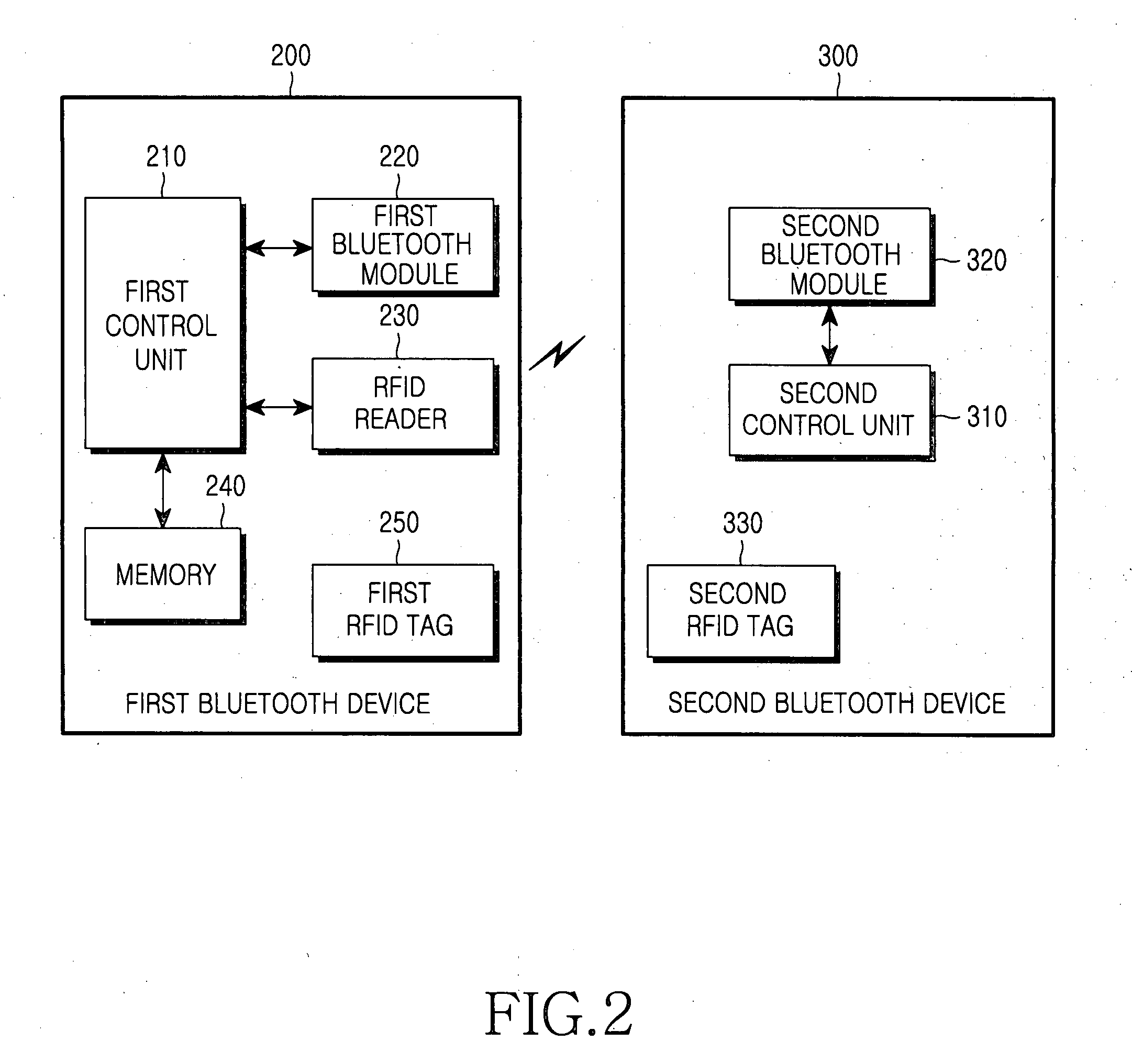

Bluetooth(R) system and Bluetooth(R) bonding process

ActiveUS20070202807A1Easy to implementNear-field in RFIDNear-field systems using receiversComputer hardwareBonding process

Disclosed are a method and a system for Bluetooth communication. In the Bluetooth system, a Bluetooth device includes: a Radio Frequency Identification (RFID) reader for reading out RFID information from the RFID Tag within an effective transmission and receiving range and outputting the RFID information; a control unit for activating the RFID reader when a request for Bluetooth connection using the RFID is inputted by a user in a Bluetooth communication mode, extracting the bonding information from the RFID information inputted from the RFID reader, and outputting the bonding information; and a Bluetooth module for receiving the bonding information outputted from the control unit, pairing the first Bluetooth device using the bonding information, and performing Bluetooth communication.

Owner:SAMSUNG ELECTRONICS CO LTD

Wafer temporary bonding method using silicon direct bonding

A wafer temporary bonding method using silicon direct bonding (SDB) may include preparing a carrier wafer and a device wafer, adjusting roughness of a surface of the carrier wafer, and combining the carrier wafer and the device wafer using the SDB. Because the method uses SDB, instead of an adhesive layer, for a temporary bonding process, a module or process to generate and remove an adhesive is unnecessary. Also, a defect in a subsequent process, for example, a back-grinding process, due to irregularity of the adhesive may be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

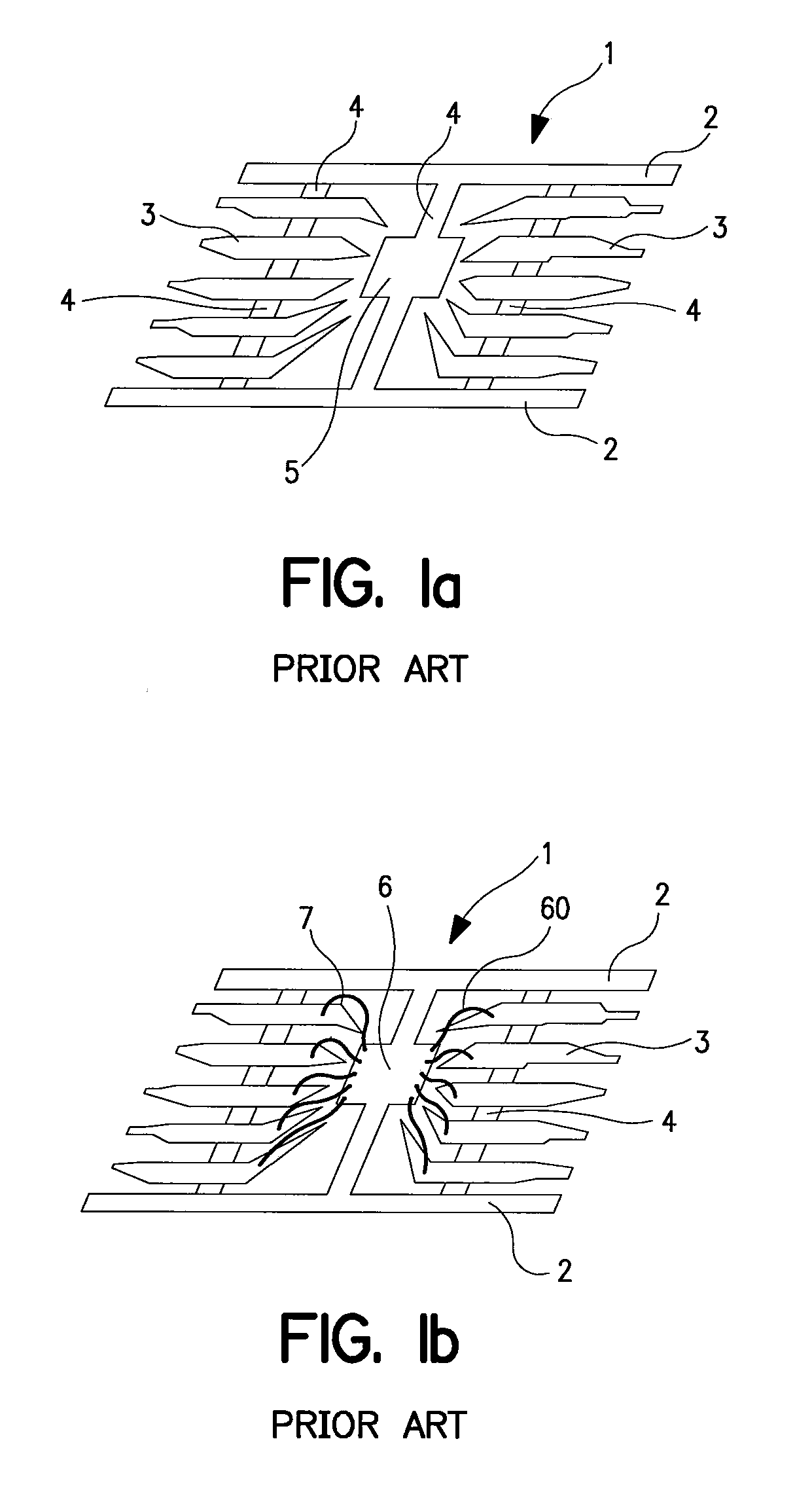

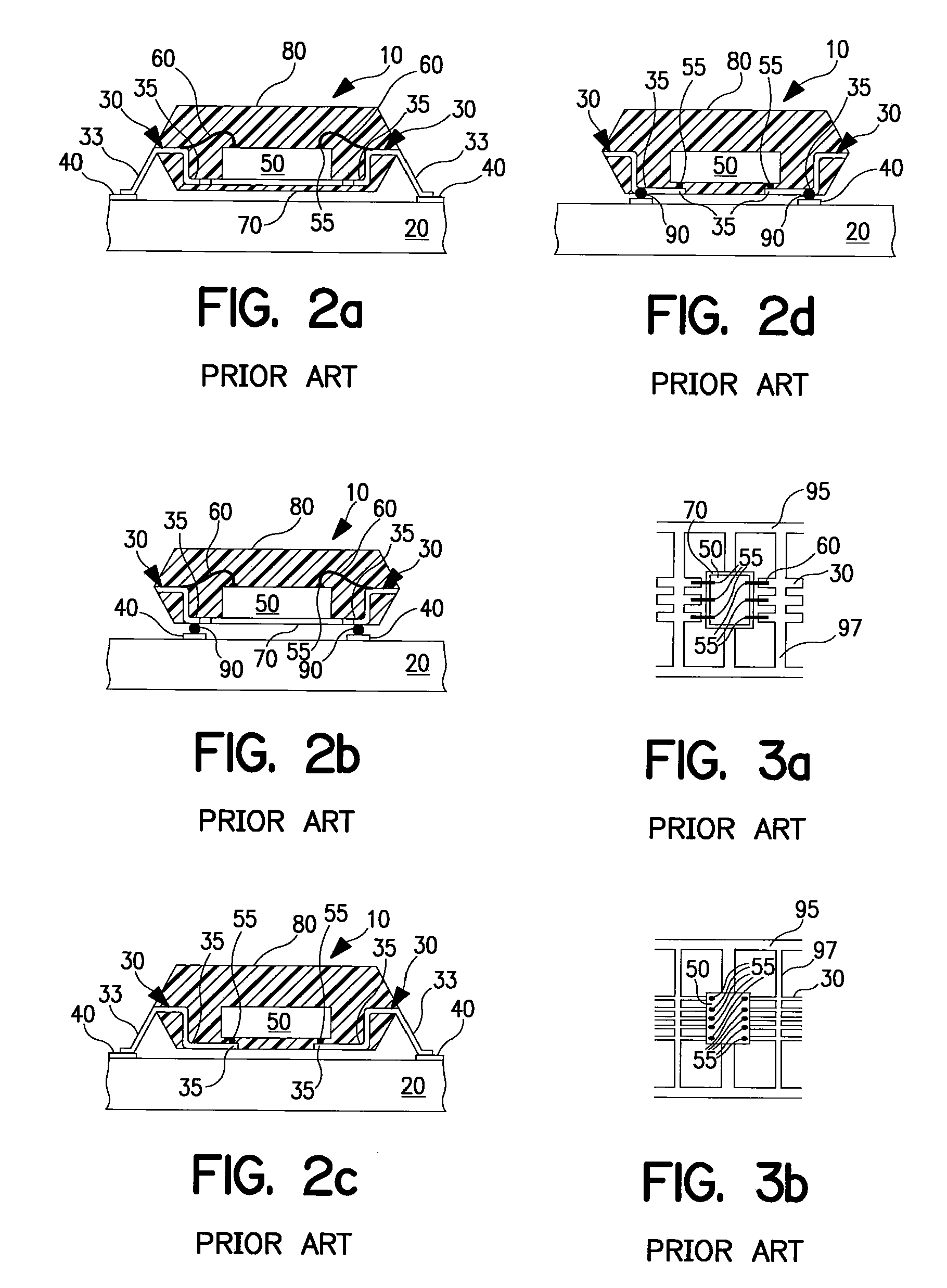

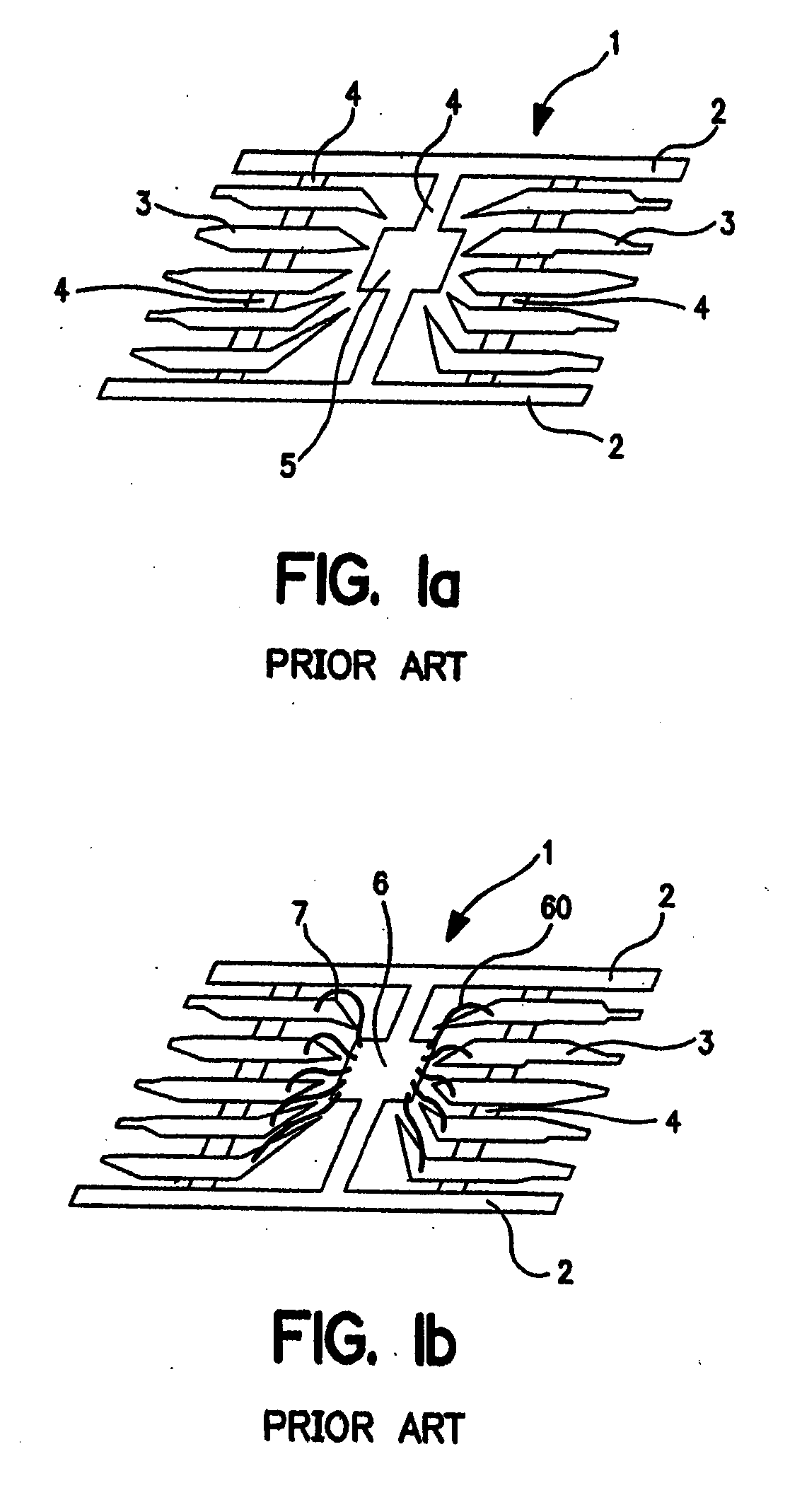

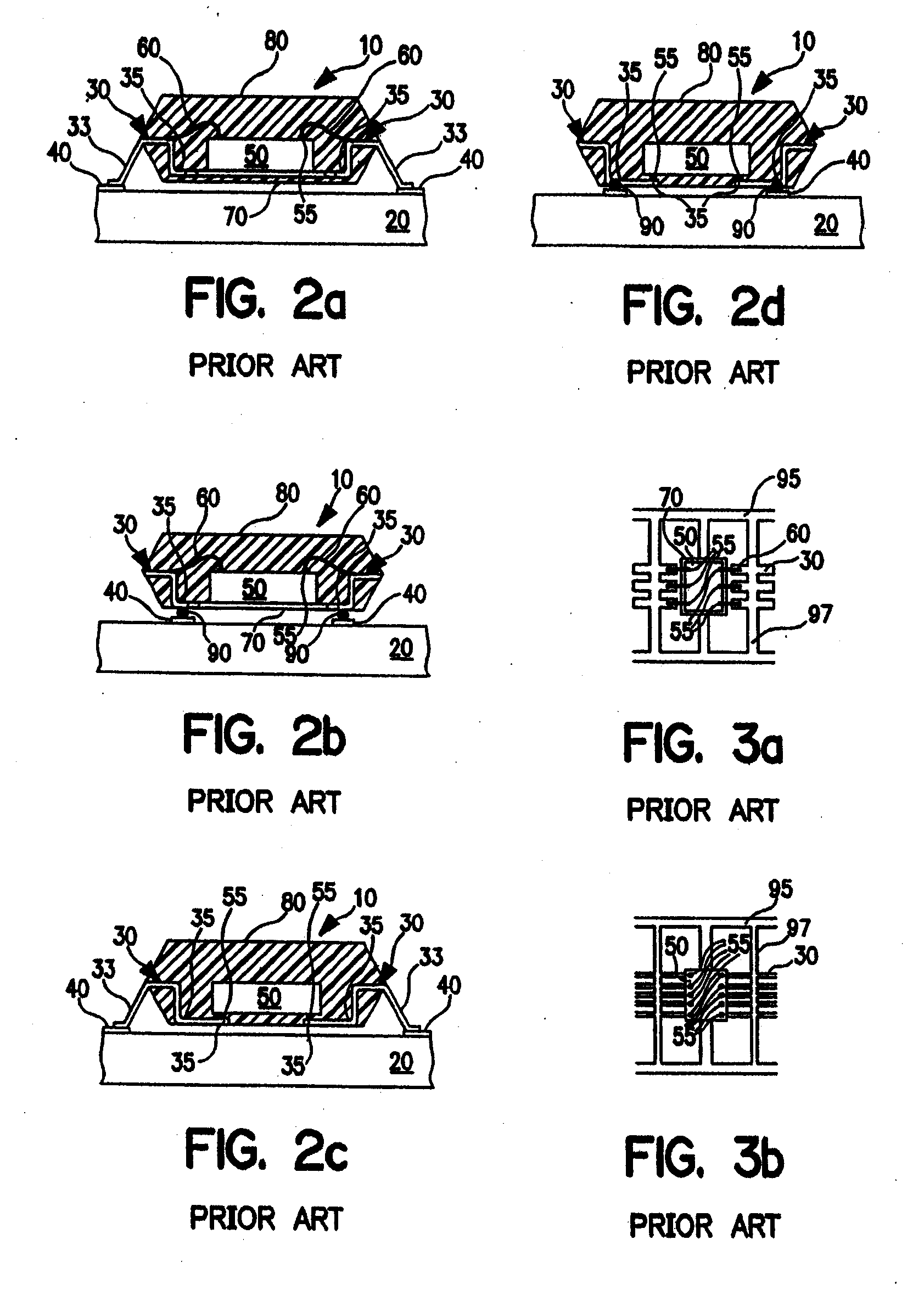

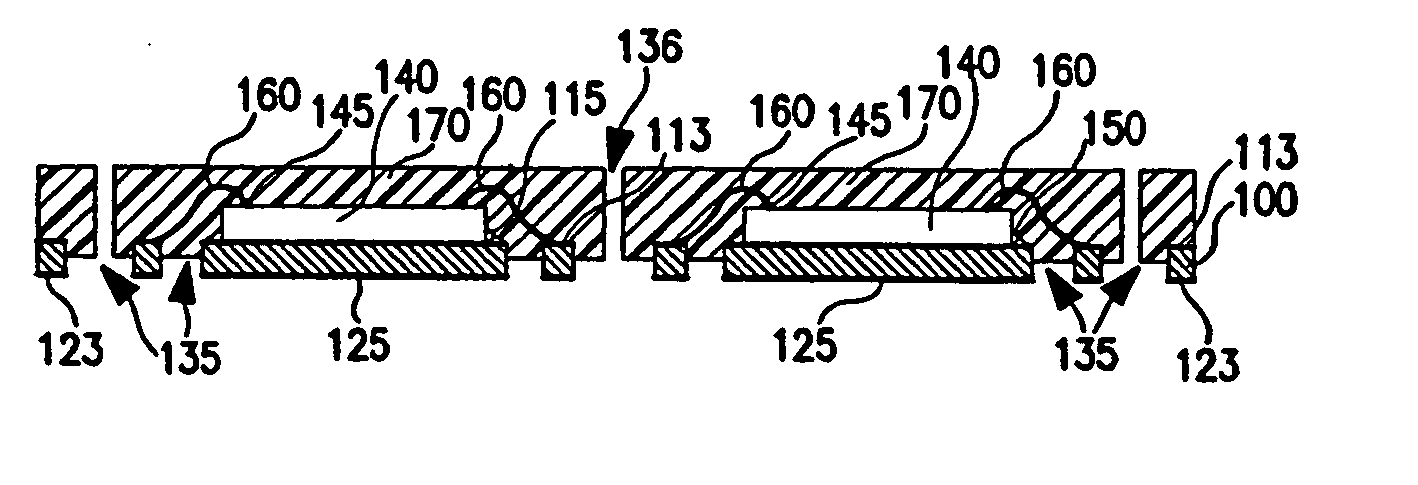

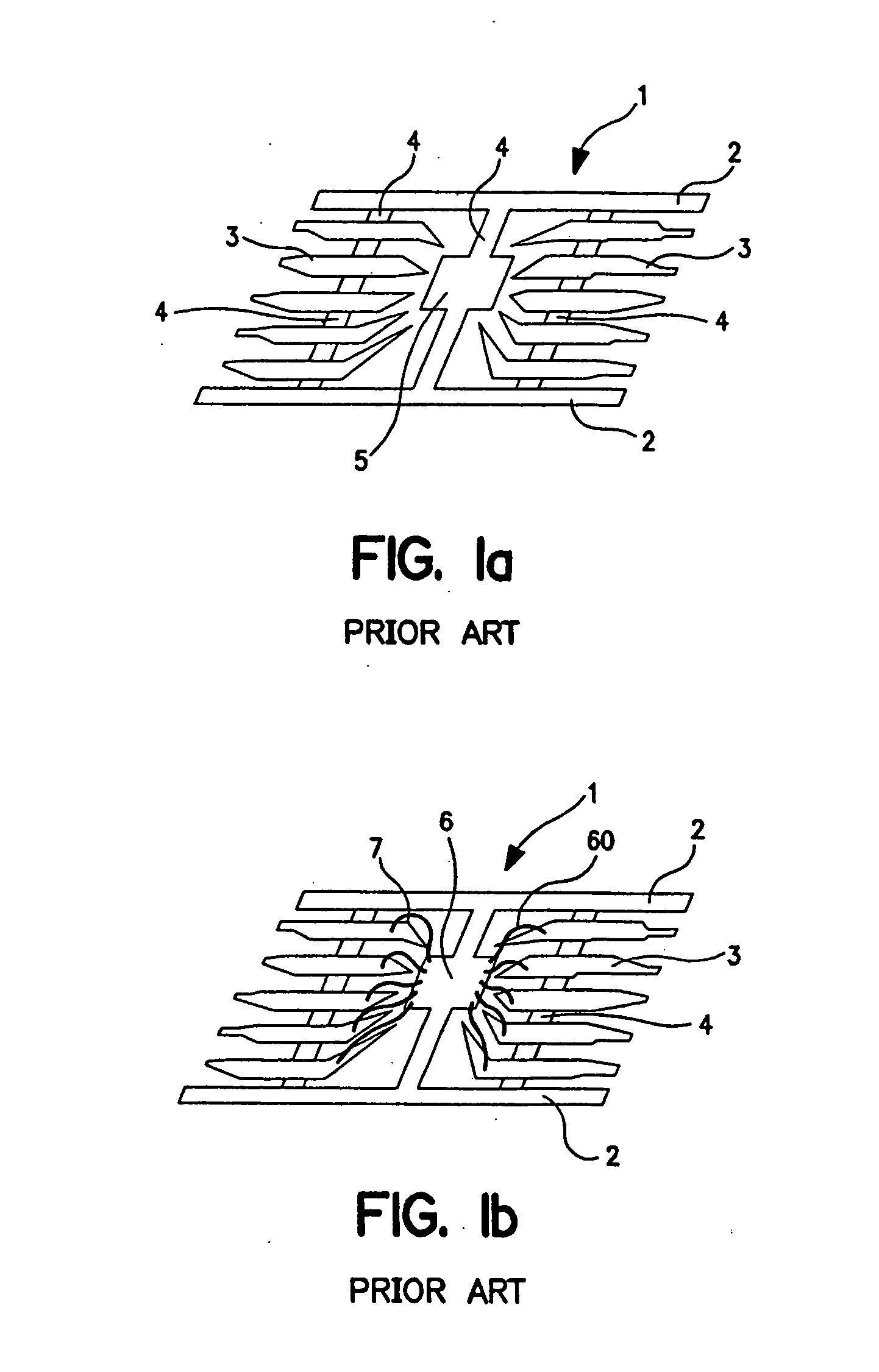

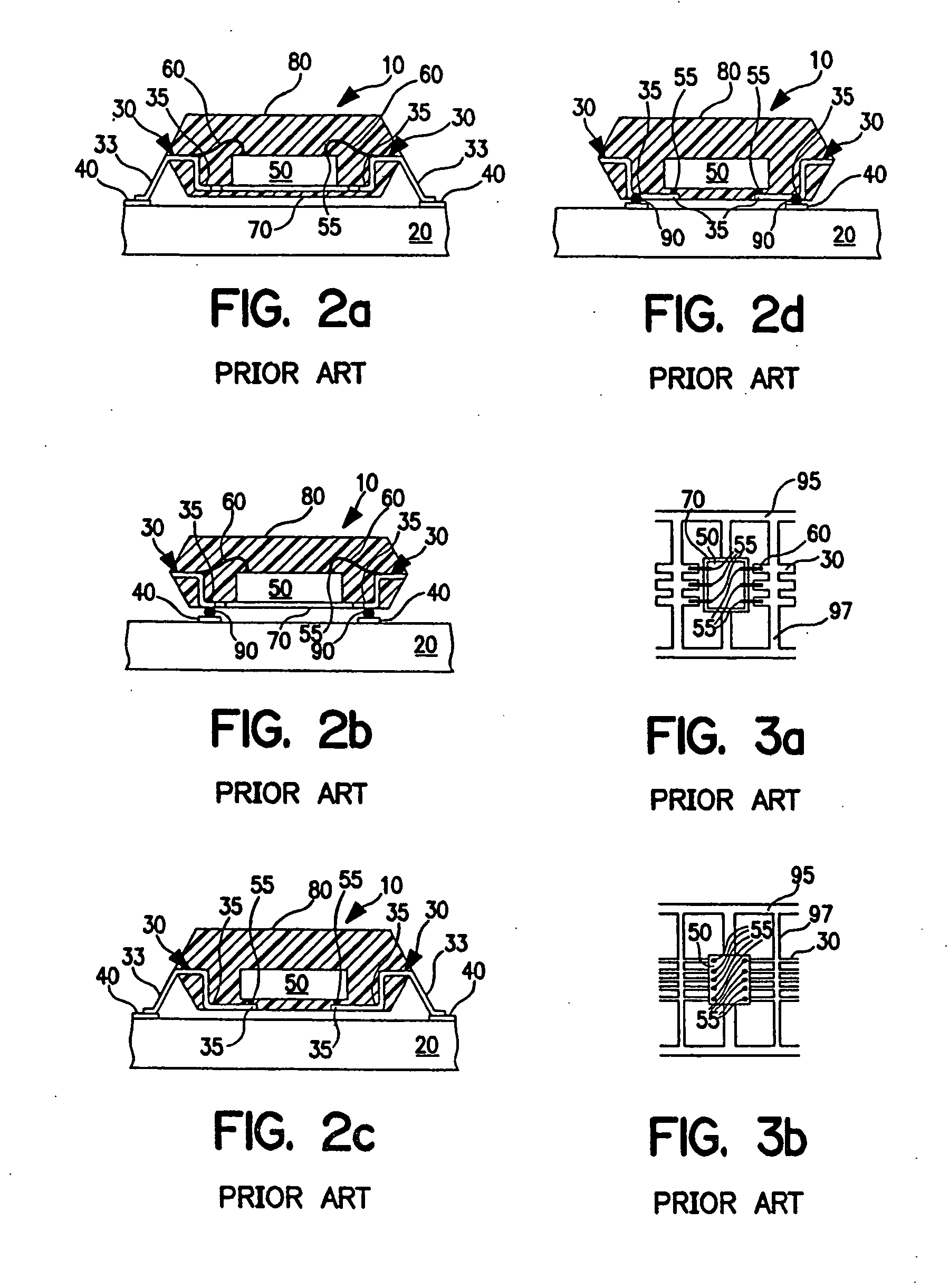

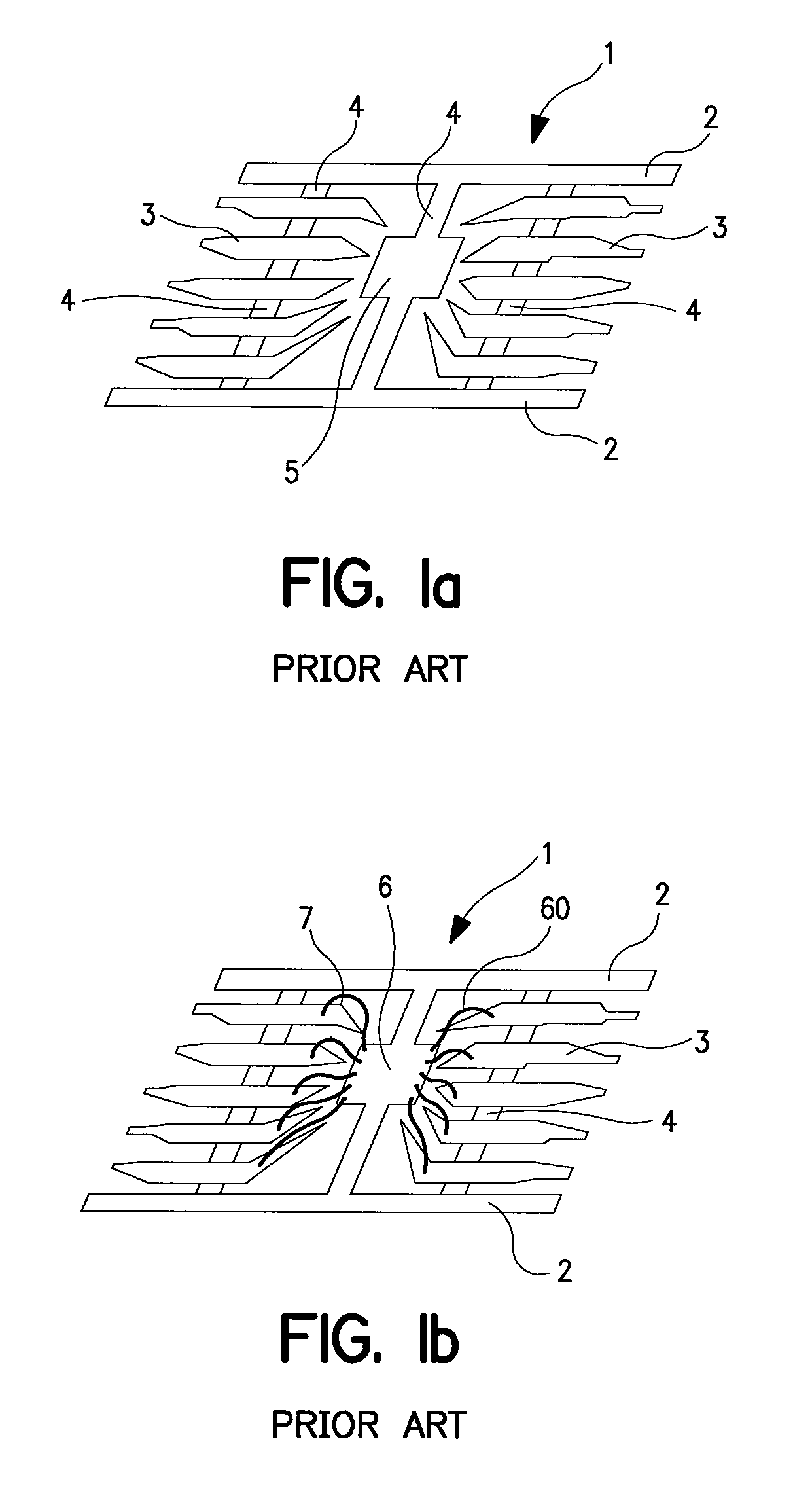

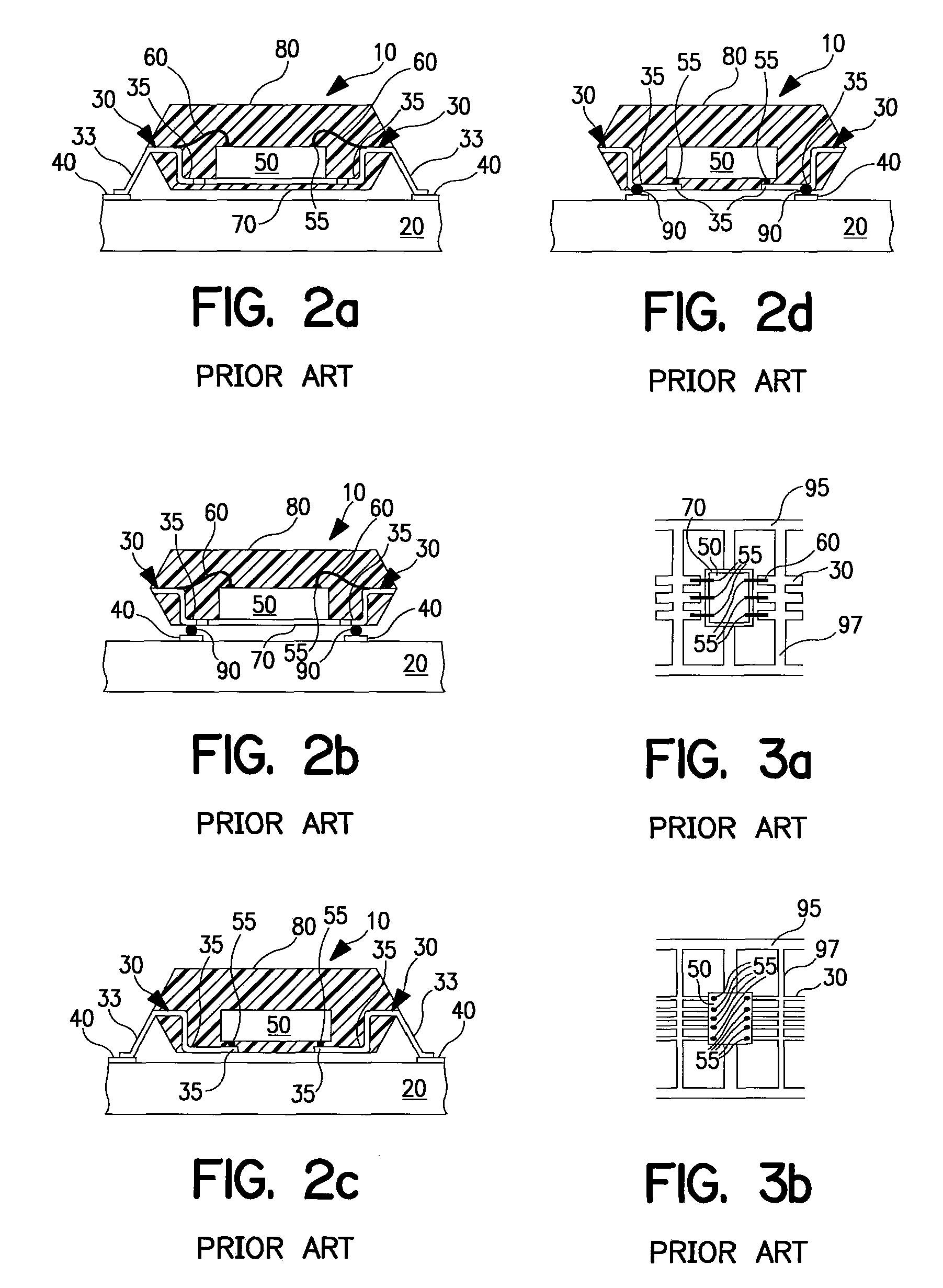

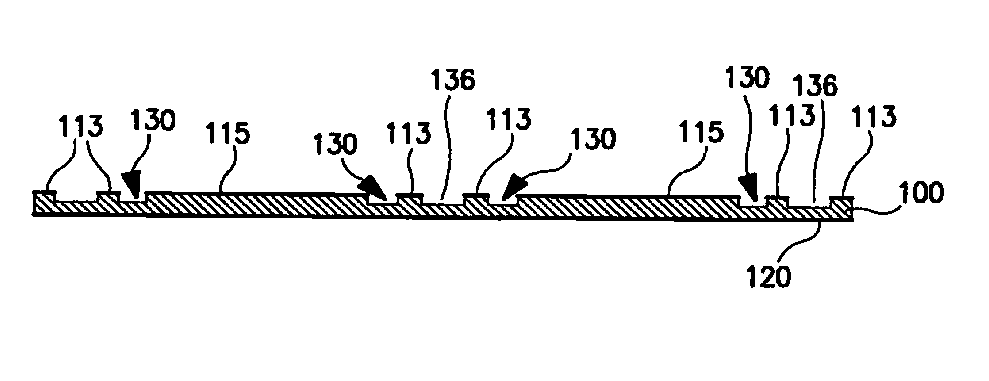

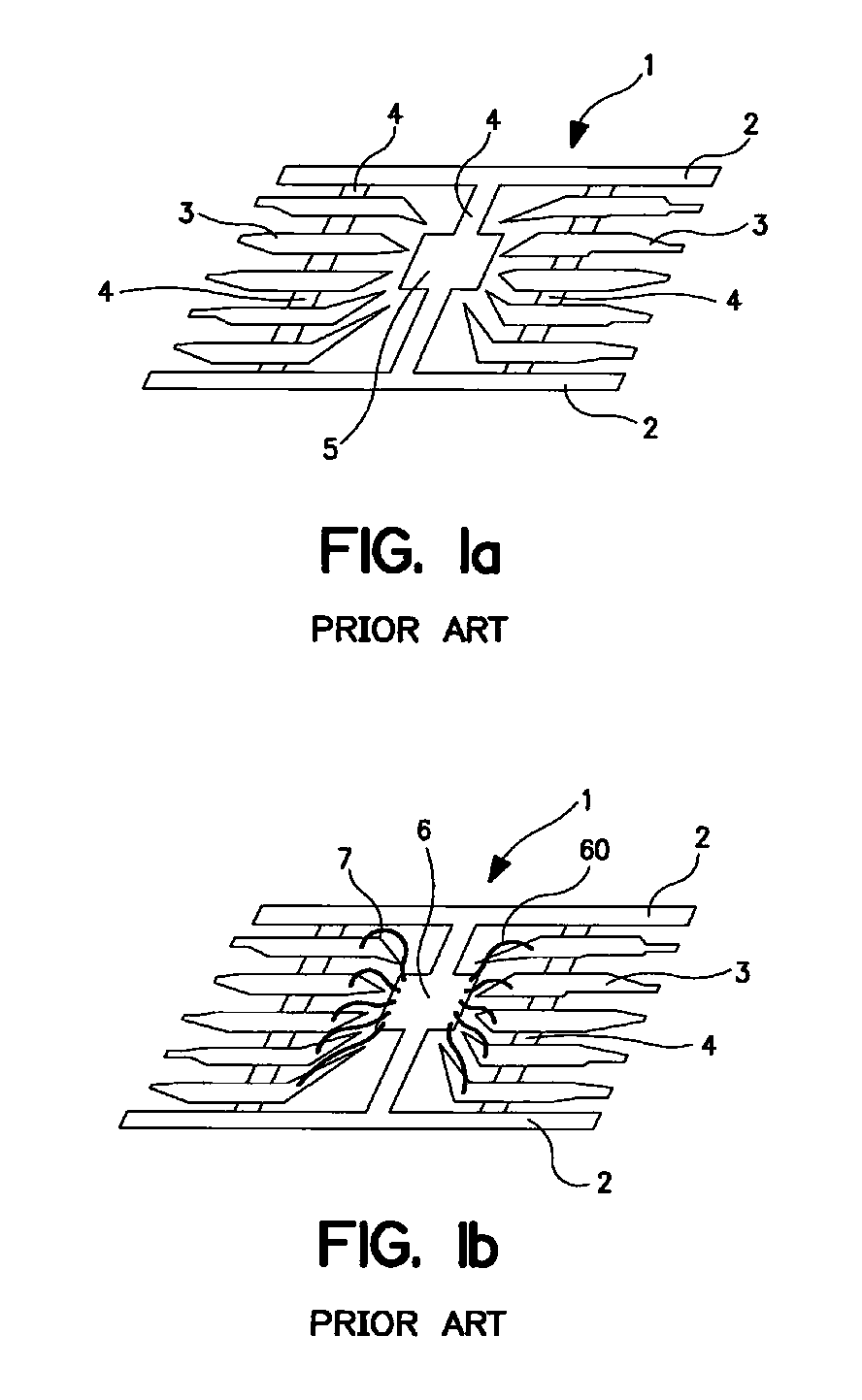

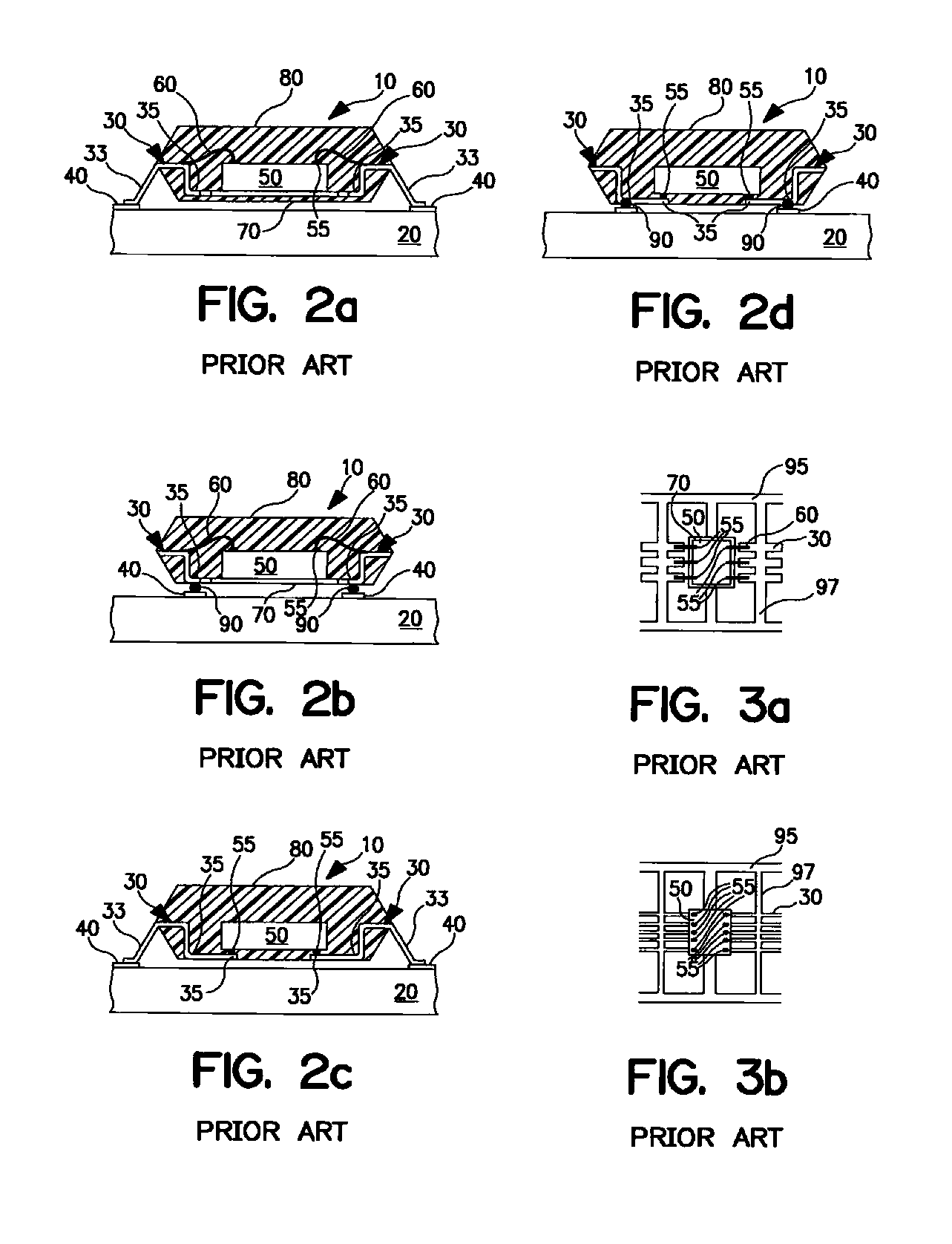

Partially patterned lead frames and methods of making and using the same in semiconductor packaging

InactiveUS20080258278A1Reduce thicknessImprove structural rigiditySemiconductor/solid-state device detailsSolid-state devicesLead bondingBonding process

A method of making a lead frame and a partially patterned lead frame package with near-chip scale packaging lead-count, wherein the method lends itself to better automation of the manufacturing line and improved quality and reliability of the packages produced therefrom. A major portion of the manufacturing process steps is performed with a partially patterned strip of metal formed into a web-like lead frame on one side so that the web-like lead frame is also rigid mechanically and robust thermally to perform without distortion or deformation during the chip-attach and wire bond processes, both at the chip level and the package level. The bottom side of the metal lead frame is patterned to isolate the chip-pad and the wire bond contacts only after the front side, including the chip and wires, is hermetically sealed with an encapsulant. The resultant package being electrically isolated enables strip testing and reliable singulation.

Owner:UNISEM M BERHAD

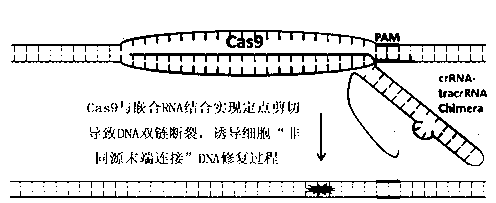

Specie limitation-free eucaryote gene targeting method having no bio-safety influence and helical-structure DNA sequence

ActiveCN103233028AUnable to cutImprove accuracyFermentationVector-based foreign material introductionDNA repairEucoenogenes

The invention discloses a specie limitation-free eucaryote gene targeting method having no bio-safety influence and a helical-structure DNA sequence, and belongs to the field of gene engineering. The specie limitation-free eucaryote gene targeting method comprises the following steps of 1, designing and constructing CRISPR / Cas9 and chimeric RNA, and 2, carrying out Cas9mRNA internal translation so that Cas9 nuclease and the chimeric RNA are bonded, carrying out fixed point clipping so that DNA double-chain cleavage is realized after the clipping, and introducing an exogenous DNA by induction of a natural DNA restoration process which is a non-homologous end bonding process of cells so that cell endogenous gene modification is realized. The specie limitation-free eucaryote gene targeting method has simple processes, realizes flexible site recognition and has low energy consumption.

Owner:NANJING SYNC BIOTECH

Partially Patterned Lead Frames and Methods of Making and Using the Same in Semiconductor Packaging

ActiveUS20070052076A1Increase surface areaImprove adhesionSemiconductor/solid-state device detailsSolid-state devicesManufacturing technologyLead bonding

A method of making a lead frame and a partially patterned lead frame package with near-chip scale packaging (CSP) lead-counts is disclosed, wherein the method lends itself to better automation of the manufacturing line as well as to improving the quality and reliability of the packages produced therefrom. This is accomplished by performing a major portion of the manufacturing process steps with a partially patterned strip of metal formed into a web-like lead frame on one side, in contrast with the conventional fully etched stencil-like lead frames, so that the web-like lead frame, which is solid and flat on the other side is also rigid mechanically and robust thermally to perform without distortion or deformation during the chip-attach and wire bond processes, both at the chip level and the package level. The bottom side of the metal lead frame is patterned to isolate the chip-pad and the wire bond contacts only after the front side, including the chip and wires, is hermetically sealed with an encapsulant. The resultant package being electrically isolated enables strip testing and reliable singulation without having to cut into any additional metal. The use of the instant partially patterned lead frame in making ELP, ELPF and ELGA-type CSPs is also disclosed.

Owner:UNISEM M BERHAD

Methods and devices for enhancing bonded substrate yields and regulating temperature

InactiveUS7351377B2Reduce thermal couplingReduce transportationSludge treatmentHeating or cooling apparatusBonding processEngineering

Owner:CAPLIPER LIFE SCI INC

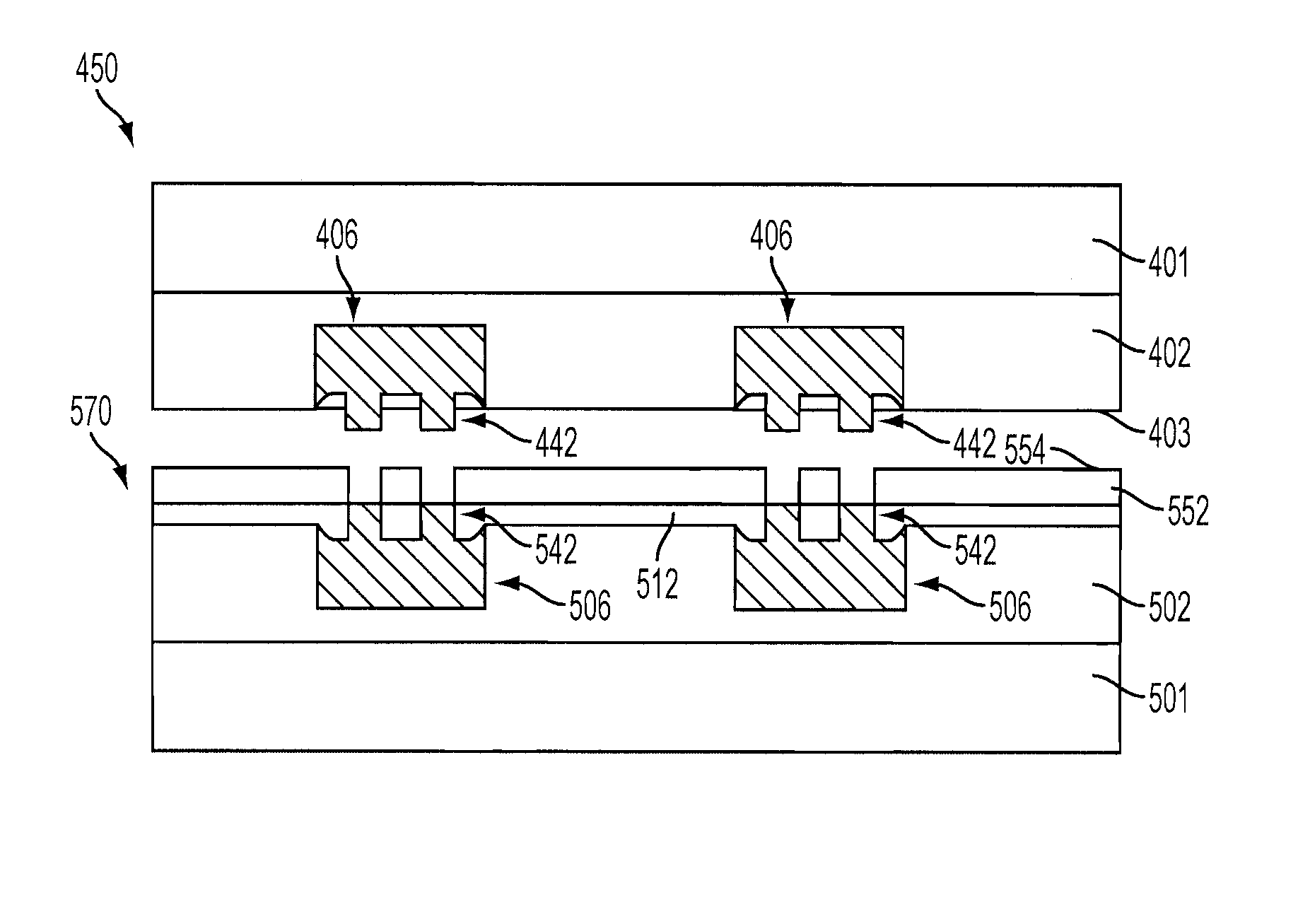

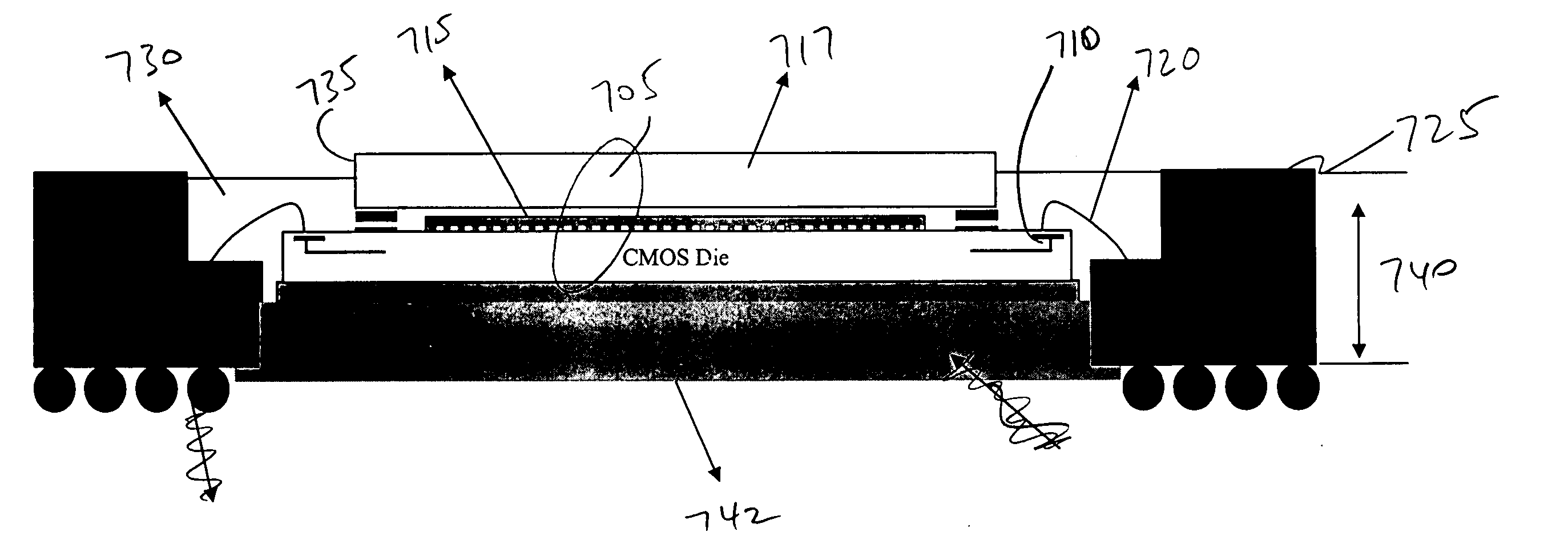

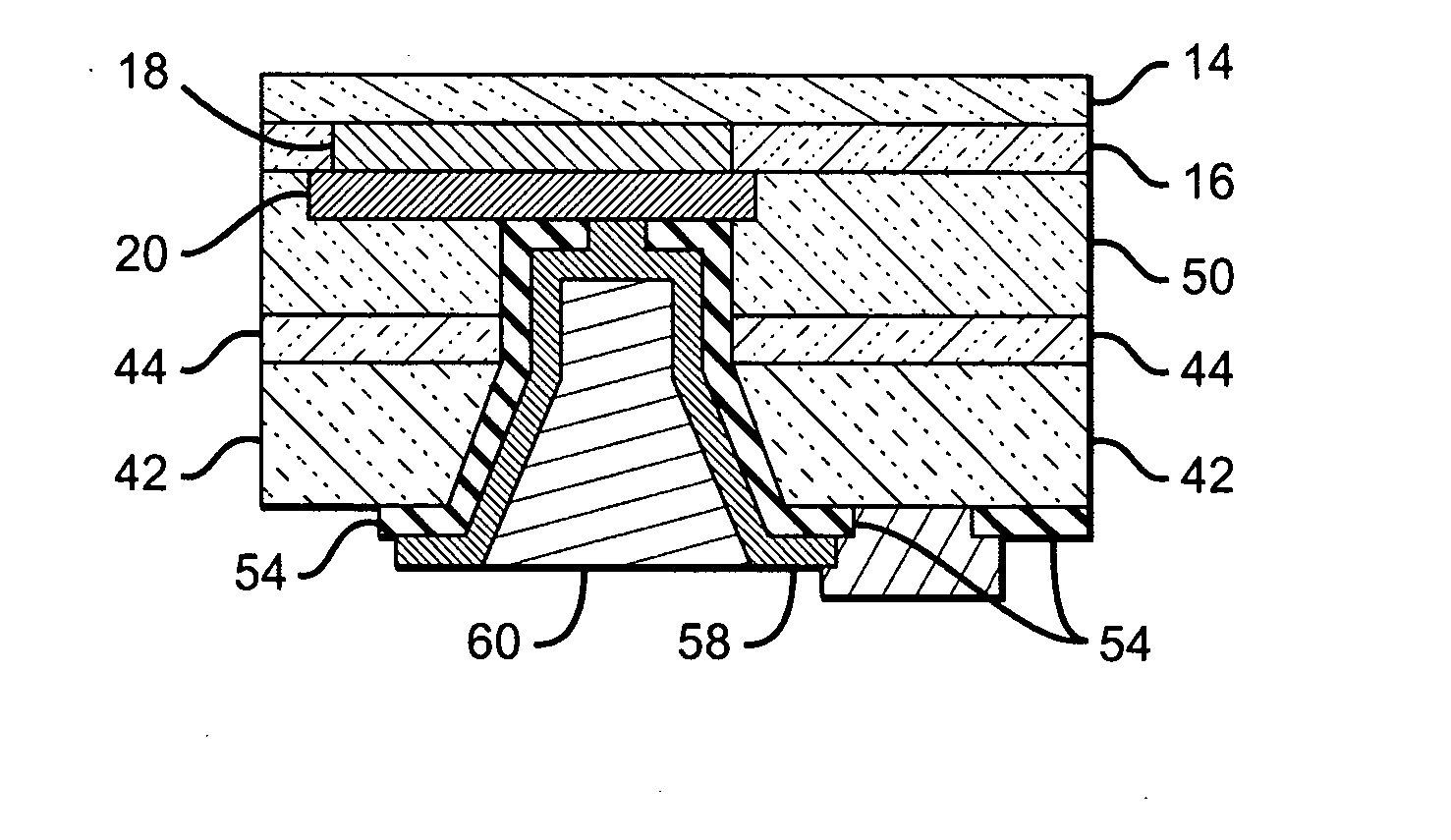

Method of making resonant tunneling diodes and CMOS backend-process-compatible three dimensional (3-D) integration

InactiveUS7002175B1Improve performanceEase of fabricationSemiconductor/solid-state device detailsNanoinformaticsLow noiseElectrical connection

A double barrier resonant tunneling diode (RTD) is formed and integrated with a level of CMOS / BJT / SiGe devices and circuits through processes such as metal-to-metal thermocompressional bonding, anodic bonding, eutectic bonding, plasma bonding, silicon-to-silicon bonding, silicon dioxide bonding, silicon nitride bonding and polymer bonding or plasma bonding. The electrical connections are made using conducting interconnects aligned during the bonding process. The resulting circuitry has a three-dimensional architecture. The tunneling barrier layers of the RTD are formed of high-K dielectric materials such as SiO2, Si3N4, Al2O3, Y2O3, Ta2O5, TiO2, HfO2, Pr2O3, ZrO2, or their alloys and laminates, having higher band-gaps than the material forming the quantum well, which includes Si, Ge or SiGe. The inherently fast operational speed of the RTD, combined with the 3-D integrated architecture that reduces interconnect delays, will produce ultra-fast circuits with low noise characteristics.

Owner:AGENCY FOR SCI TECH & RES

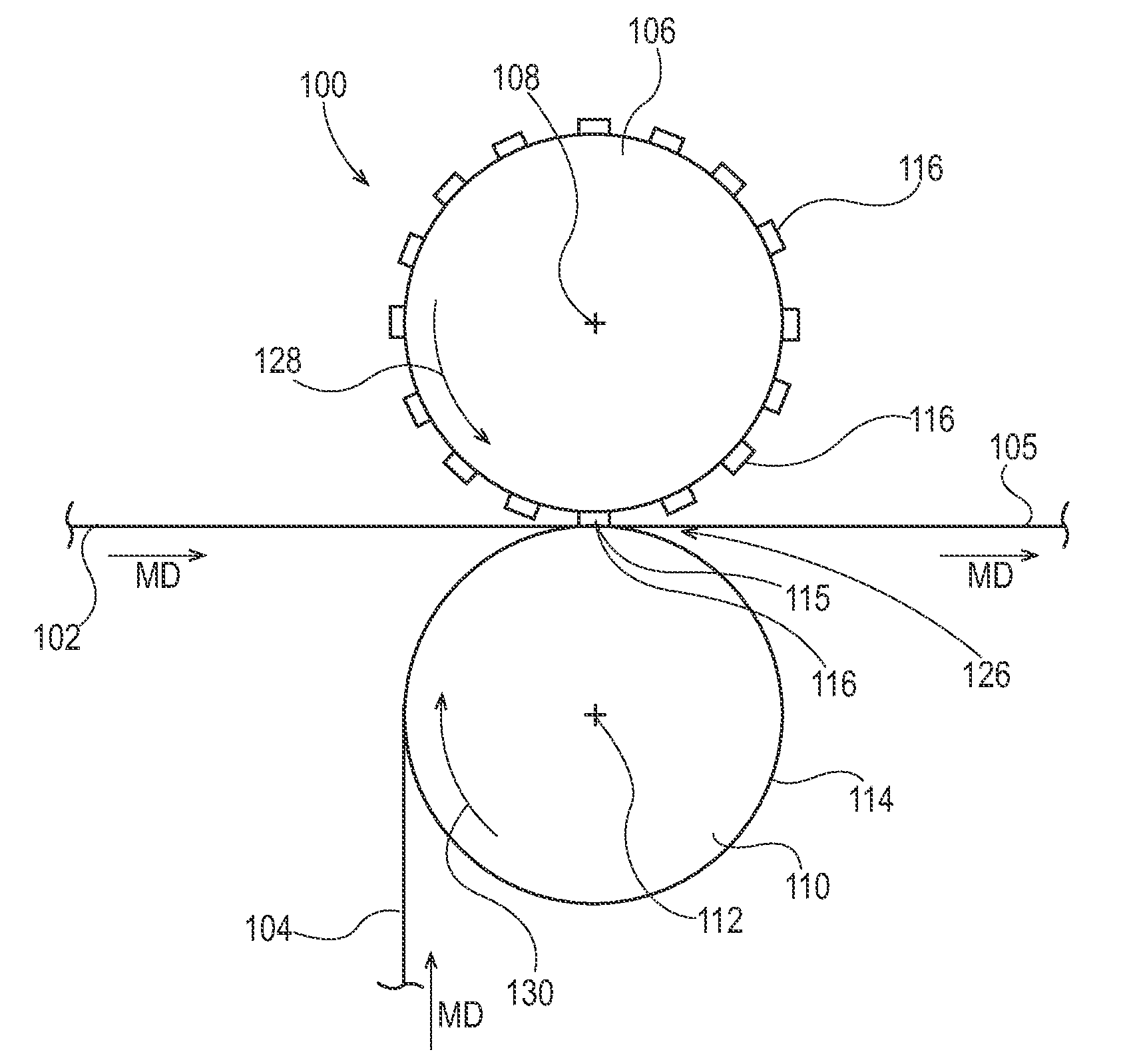

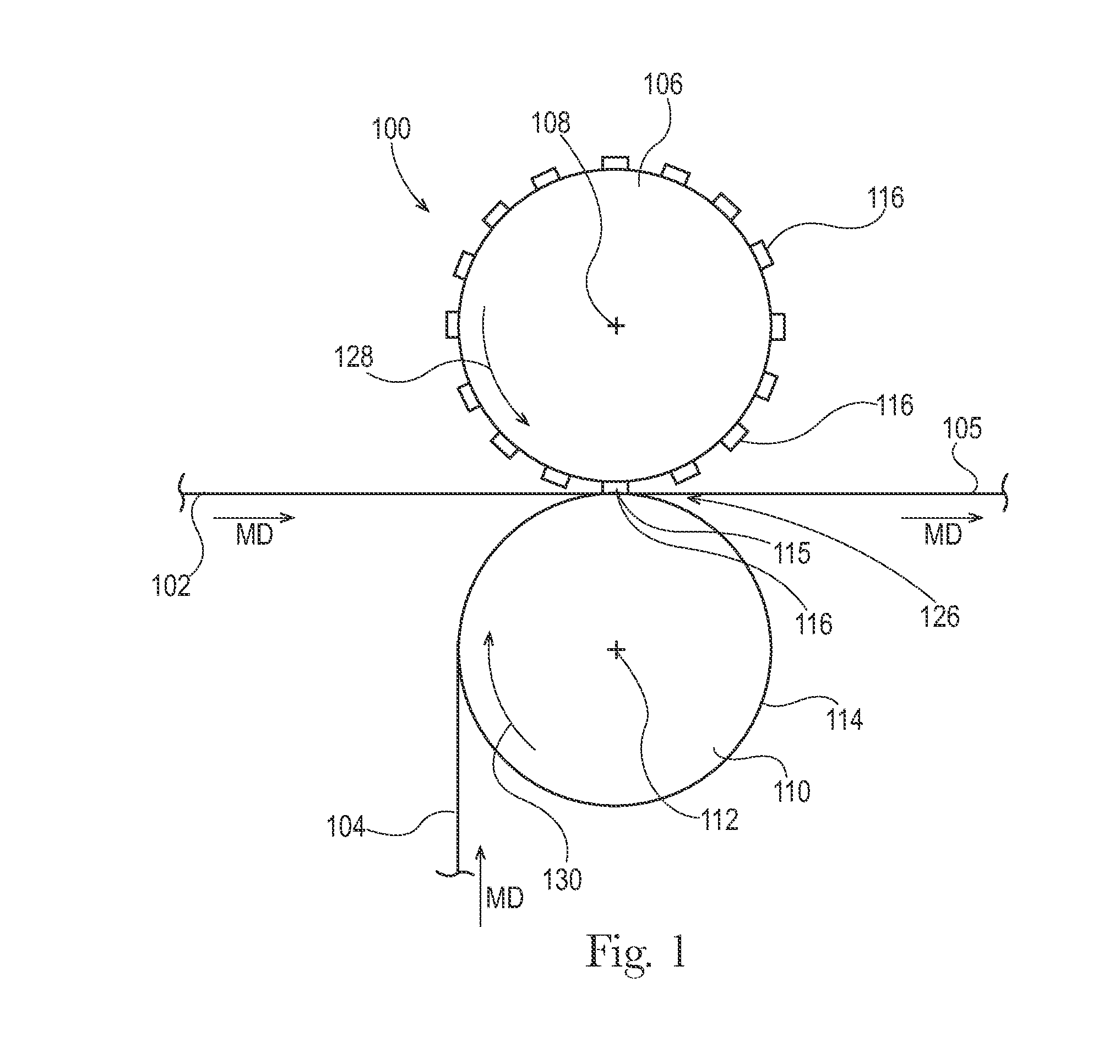

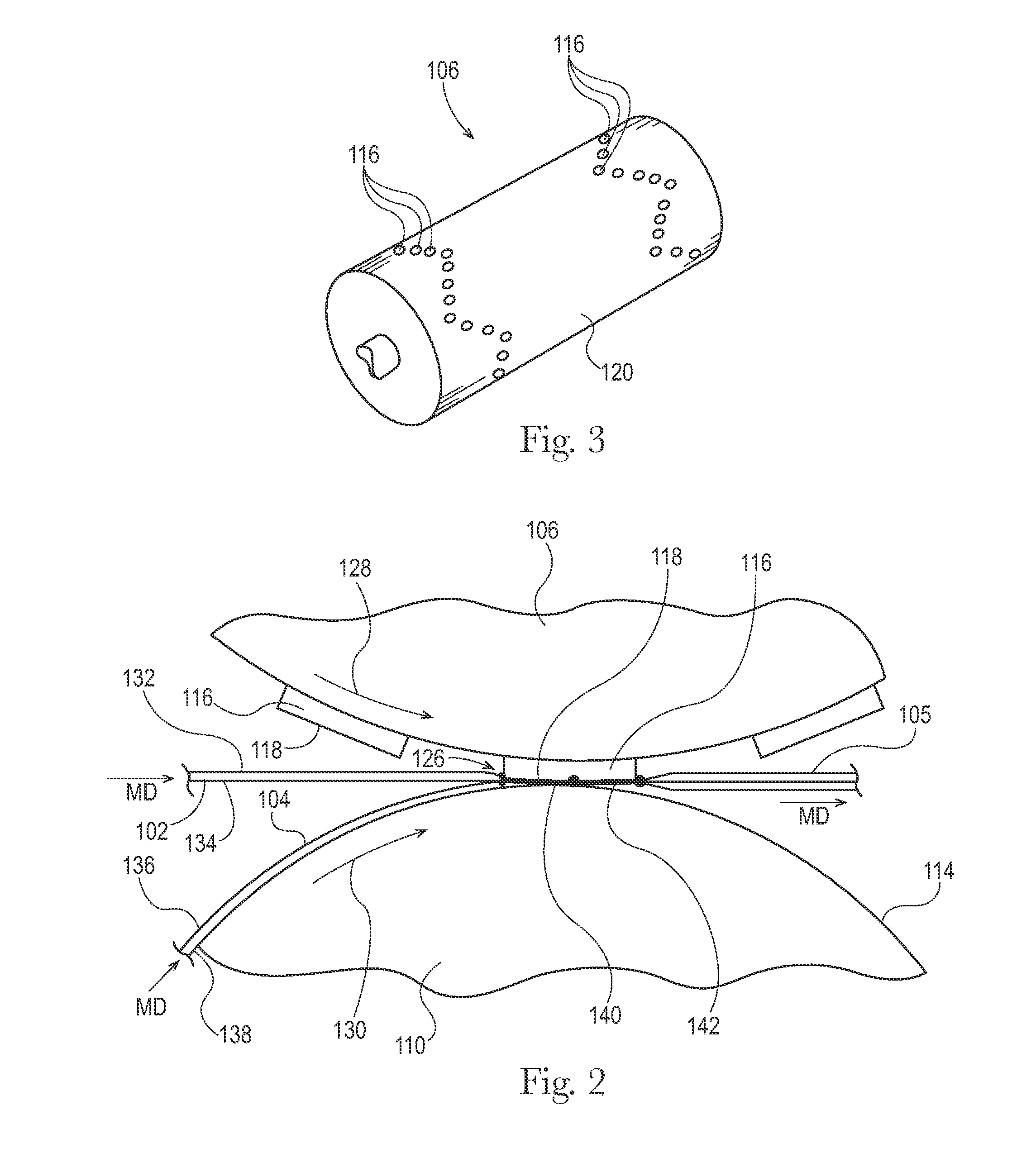

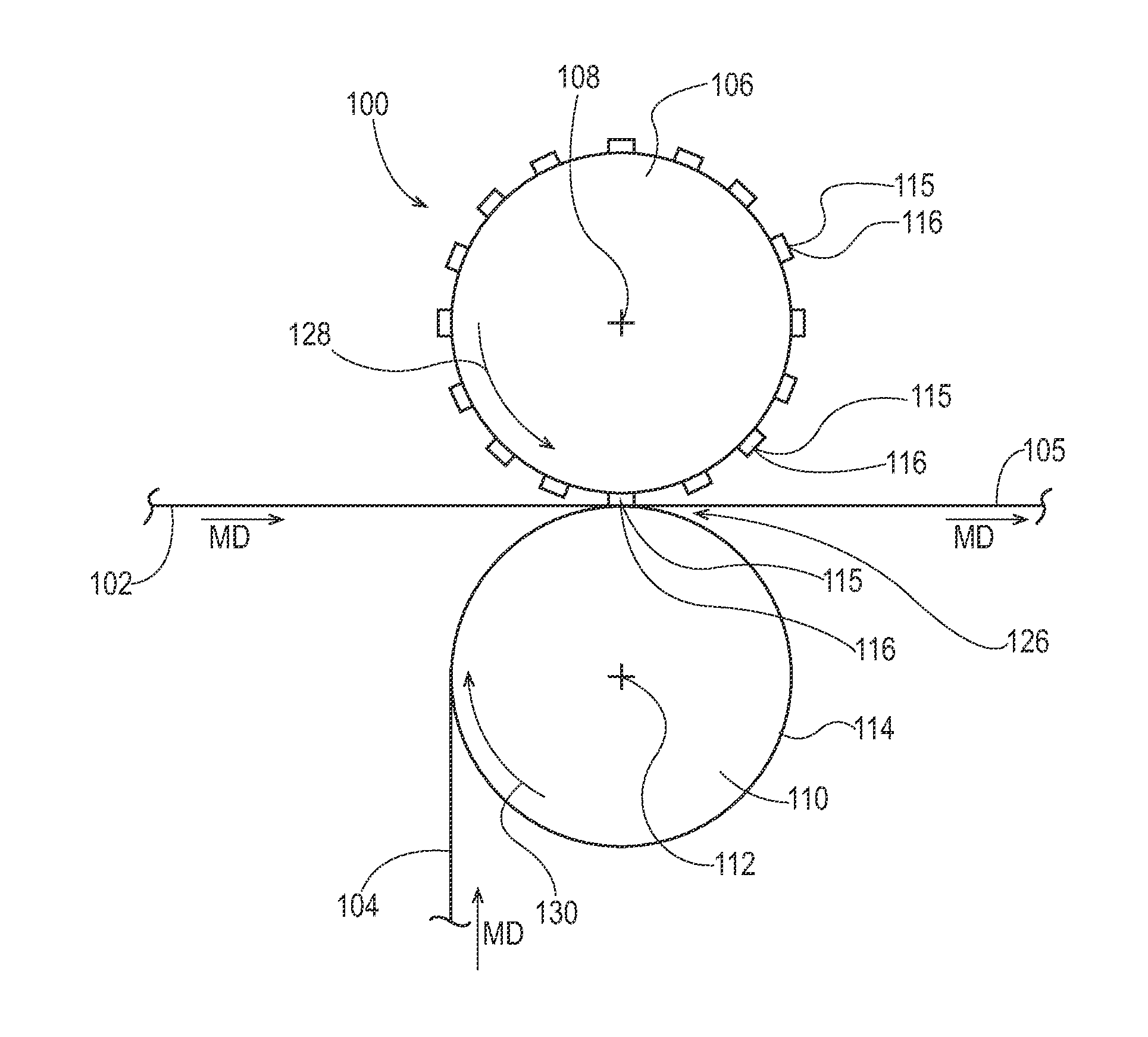

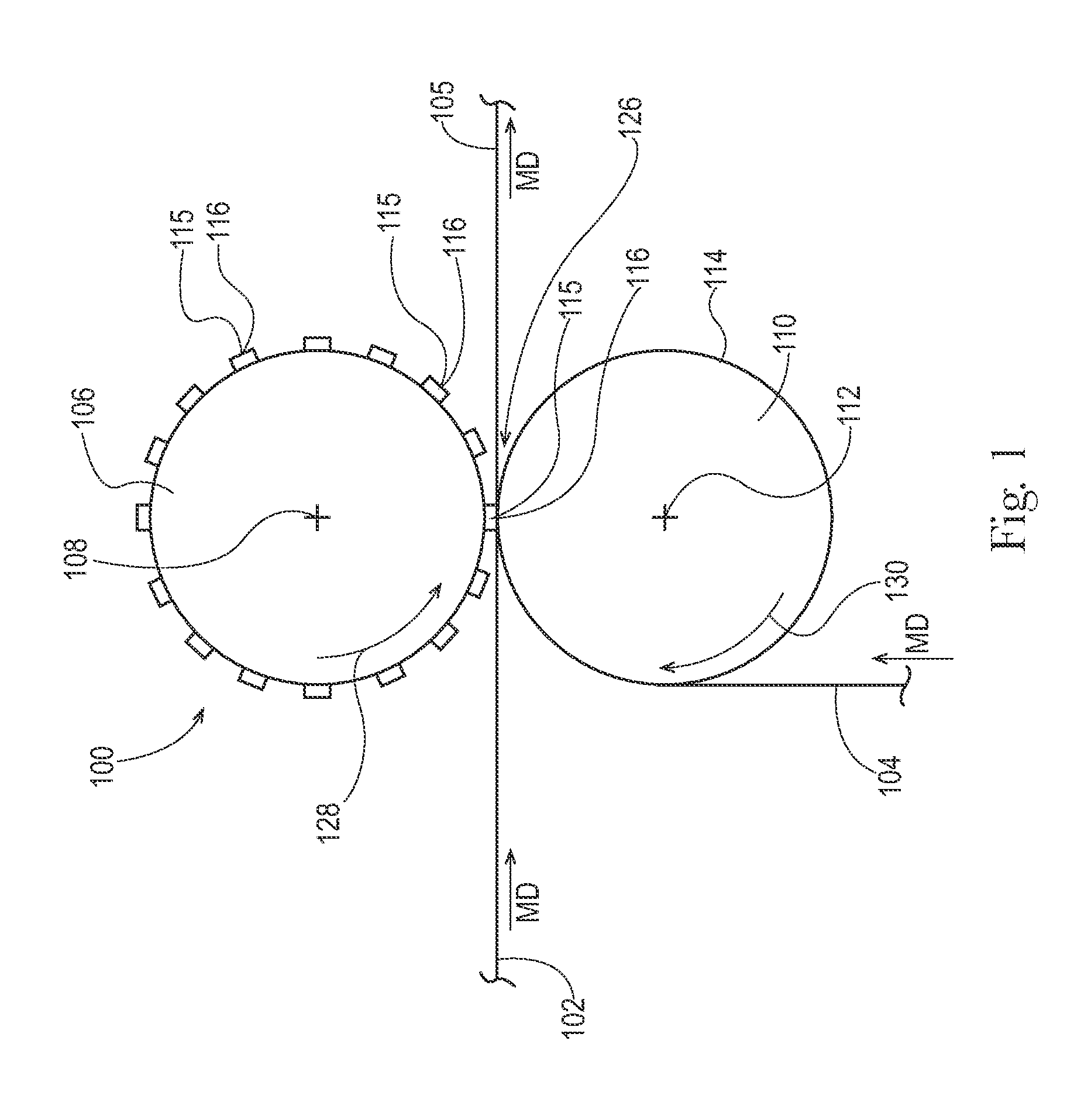

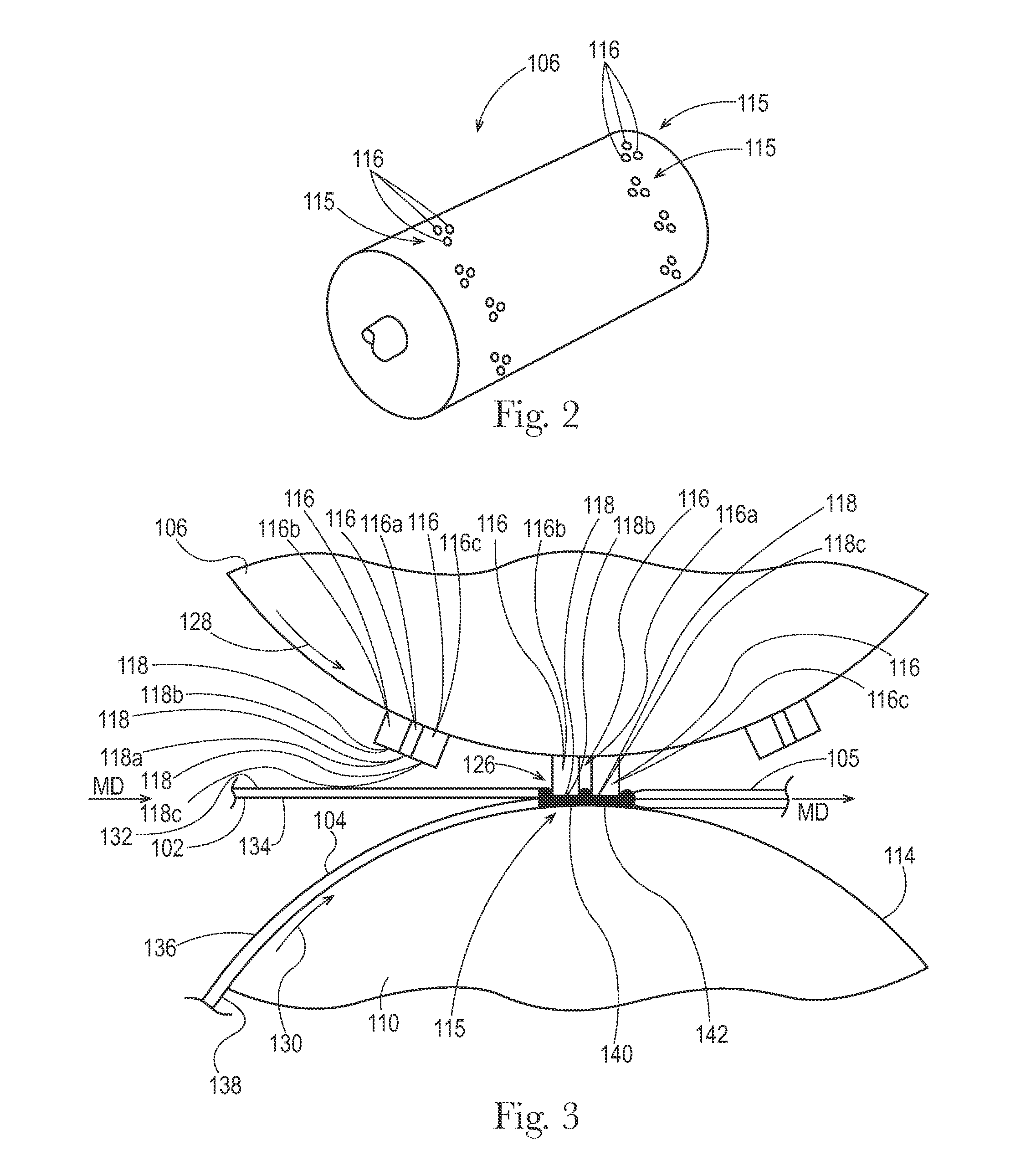

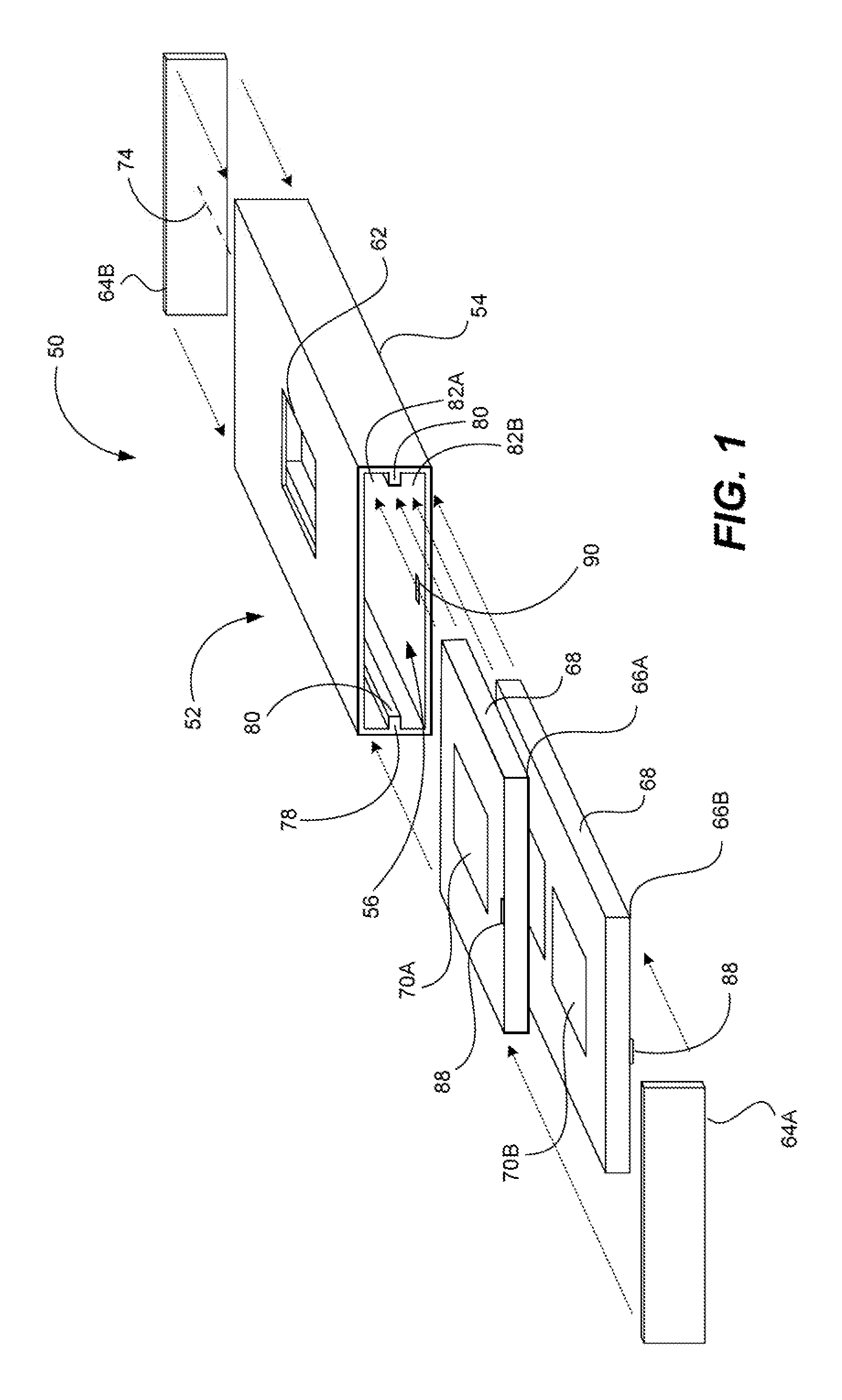

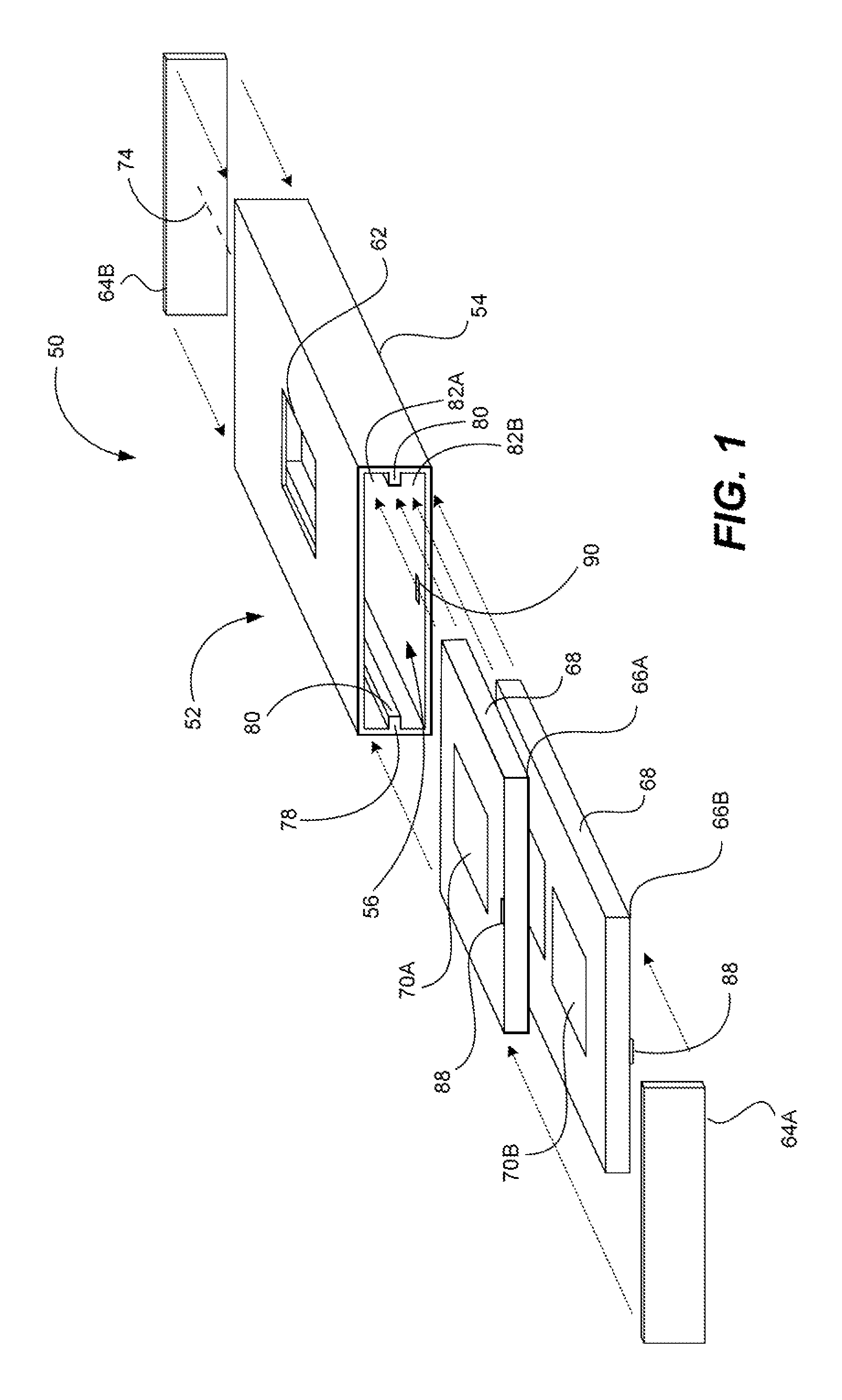

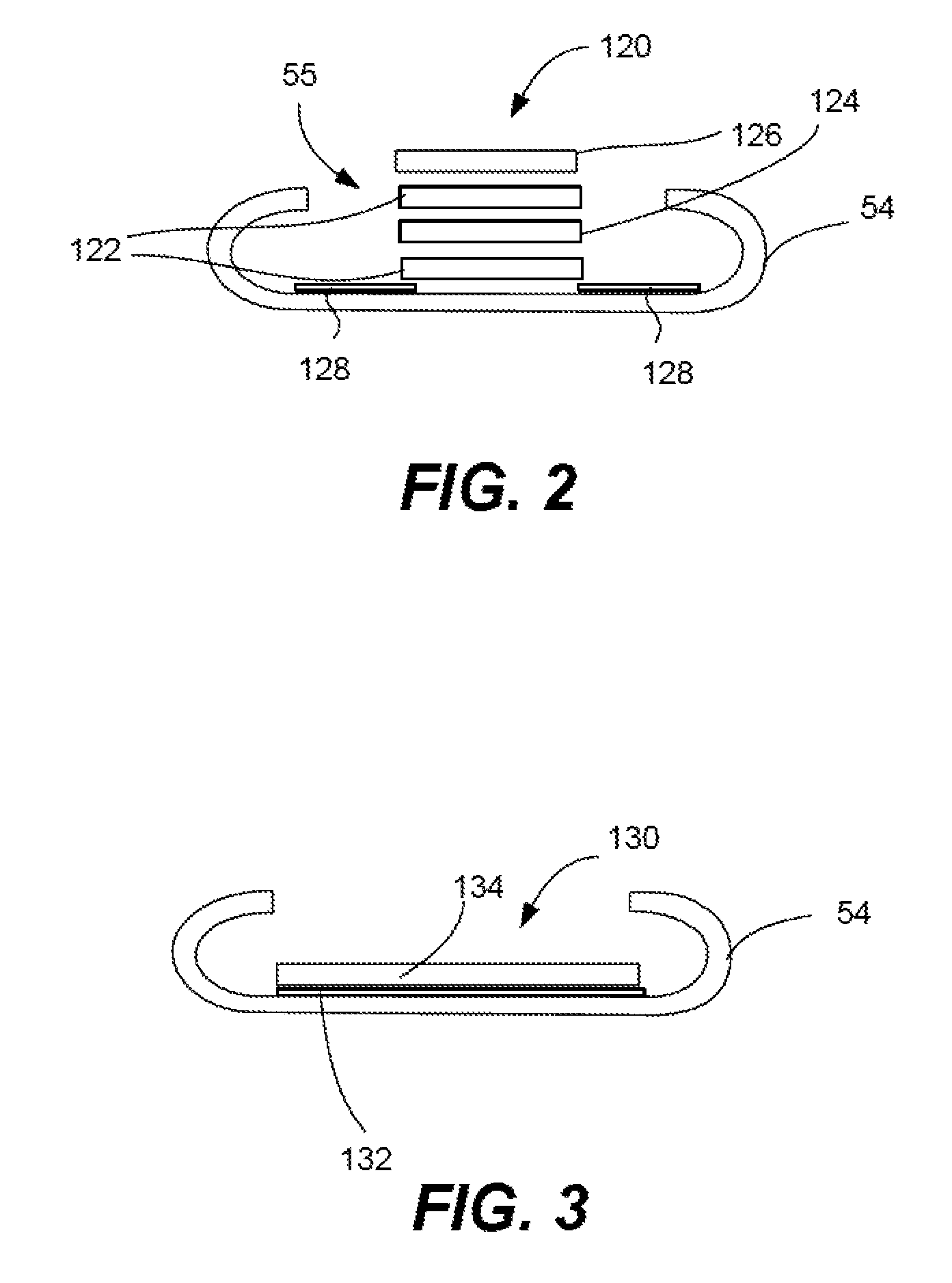

Bonding Apparatus and Method

The present disclosure relates to methods and apparatuses for mechanically bonding substrates together. The apparatuses may include a pattern roll including a pattern element protruding radially outward. The pattern element includes a pattern surface and includes one or more channels adjacent the pattern surface. The pattern roll may be positioned adjacent an anvil roll to define a nip between the pattern surface and the anvil roll, wherein the pattern roll is biased toward the anvil roll to define a nip pressure between pattern surface and the anvil roll. As substrates advance between the pattern roll and anvil roll, the substrates are compressed between the anvil roll and the pattern surface to form a discrete bond region between the first and second substrates. As such, during the bonding process, some yielded substrate material flows from under the pattern surface and into the channel to form a channel grommet region.

Owner:THE PROCTER & GAMBLE COMPANY

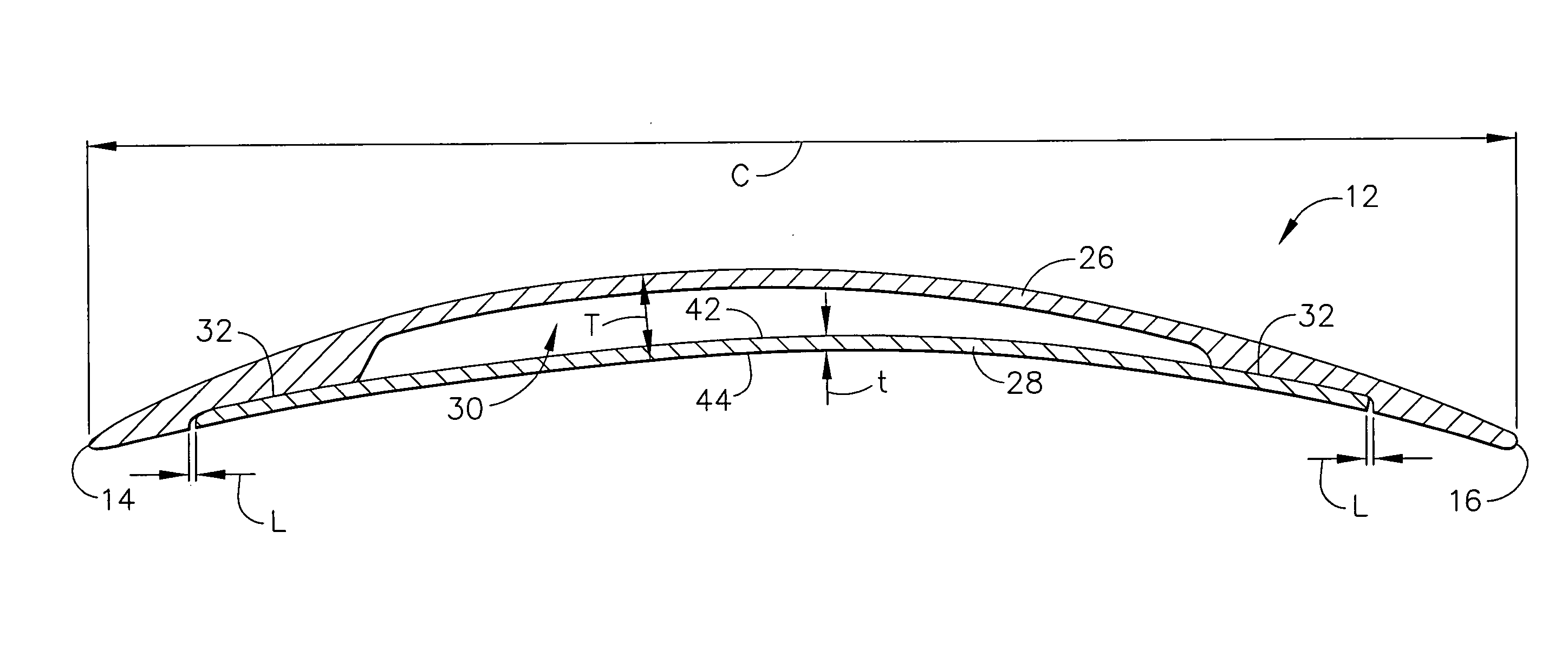

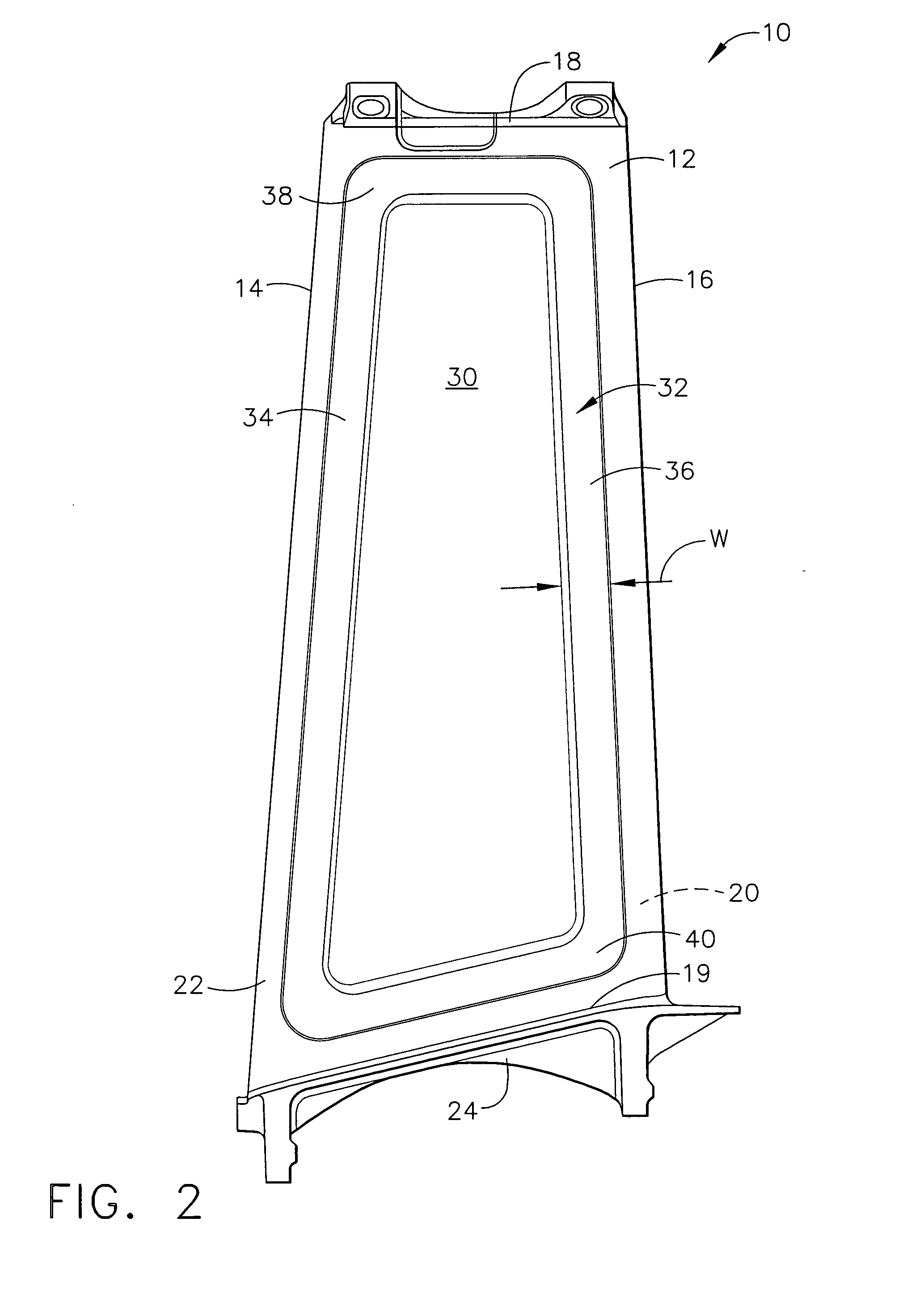

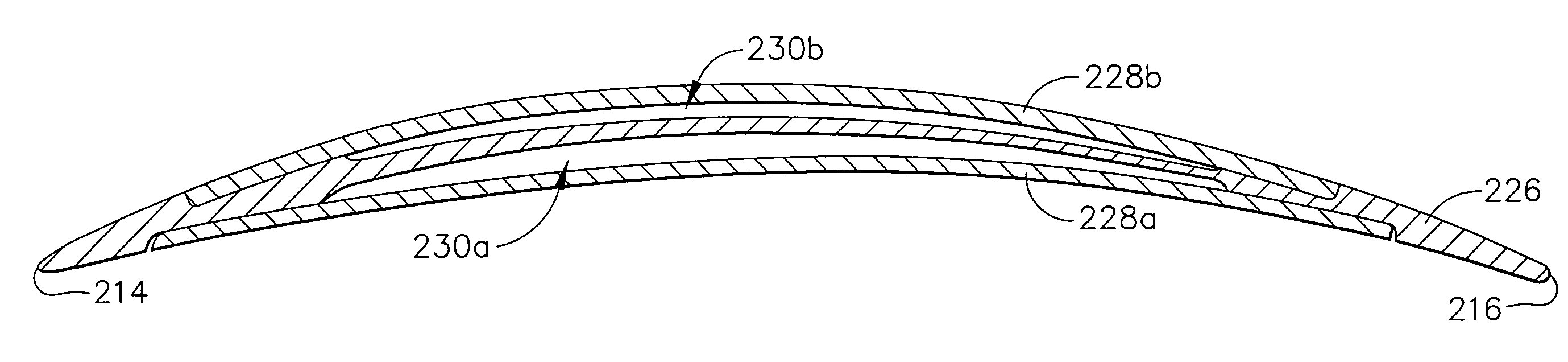

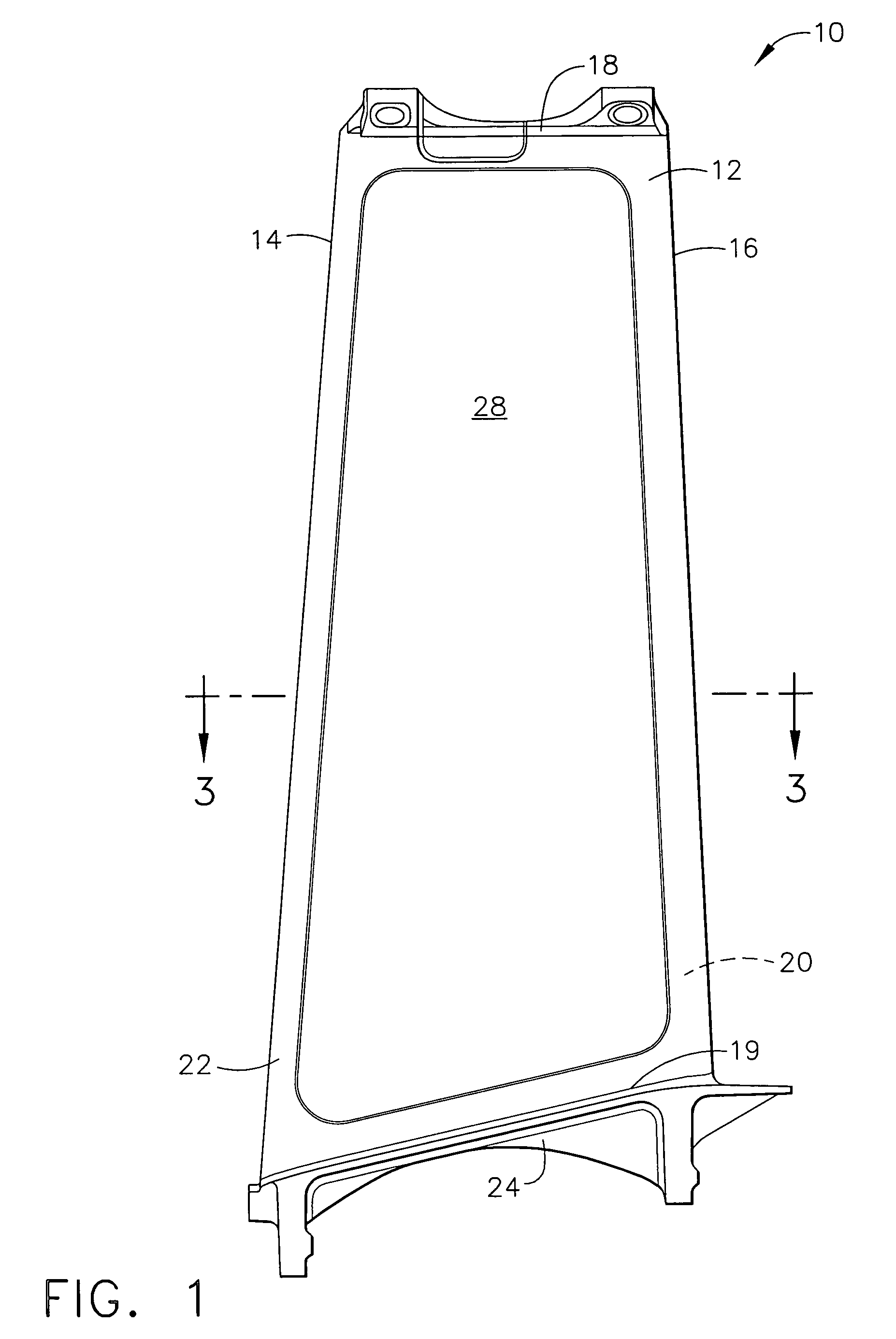

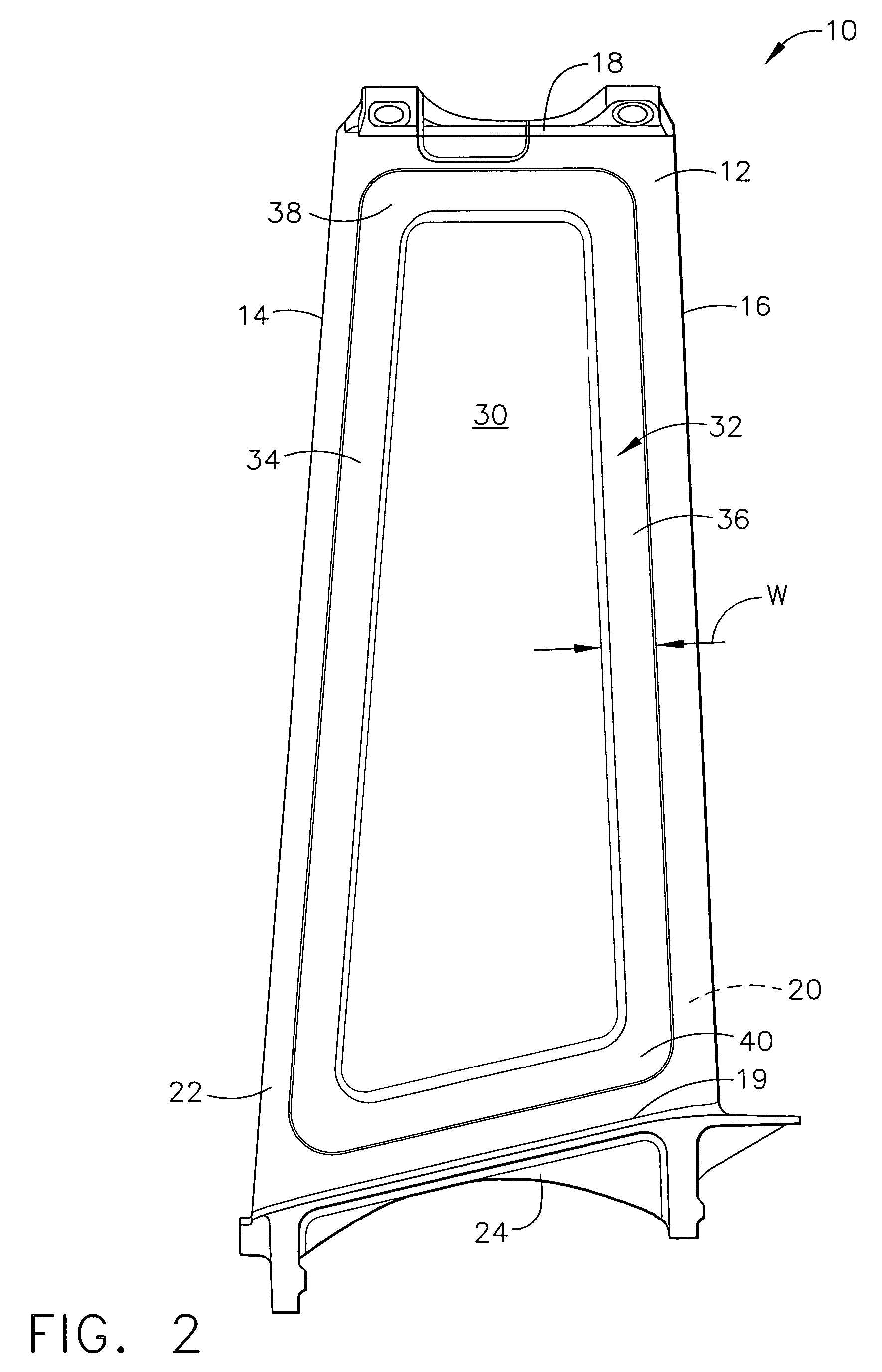

Friction stir welded hollow airfoils and method therefor

A hollow component for gas turbine engine, for example an outlet guide vane, is assembled from a body having at recessed pocket formed therein, and an aerodynamic cover bonded over the pocket. Both the cover and the body are constructed from materials which are not readily fusion weldable. The cover is attached to the body by a solid state bonding process, for example friction stir welding. The hollow component may also be built up from multiple individual components which are bonded to each other by a solid state bonding process such as friction stir welding.

Owner:GENERAL ELECTRIC CO

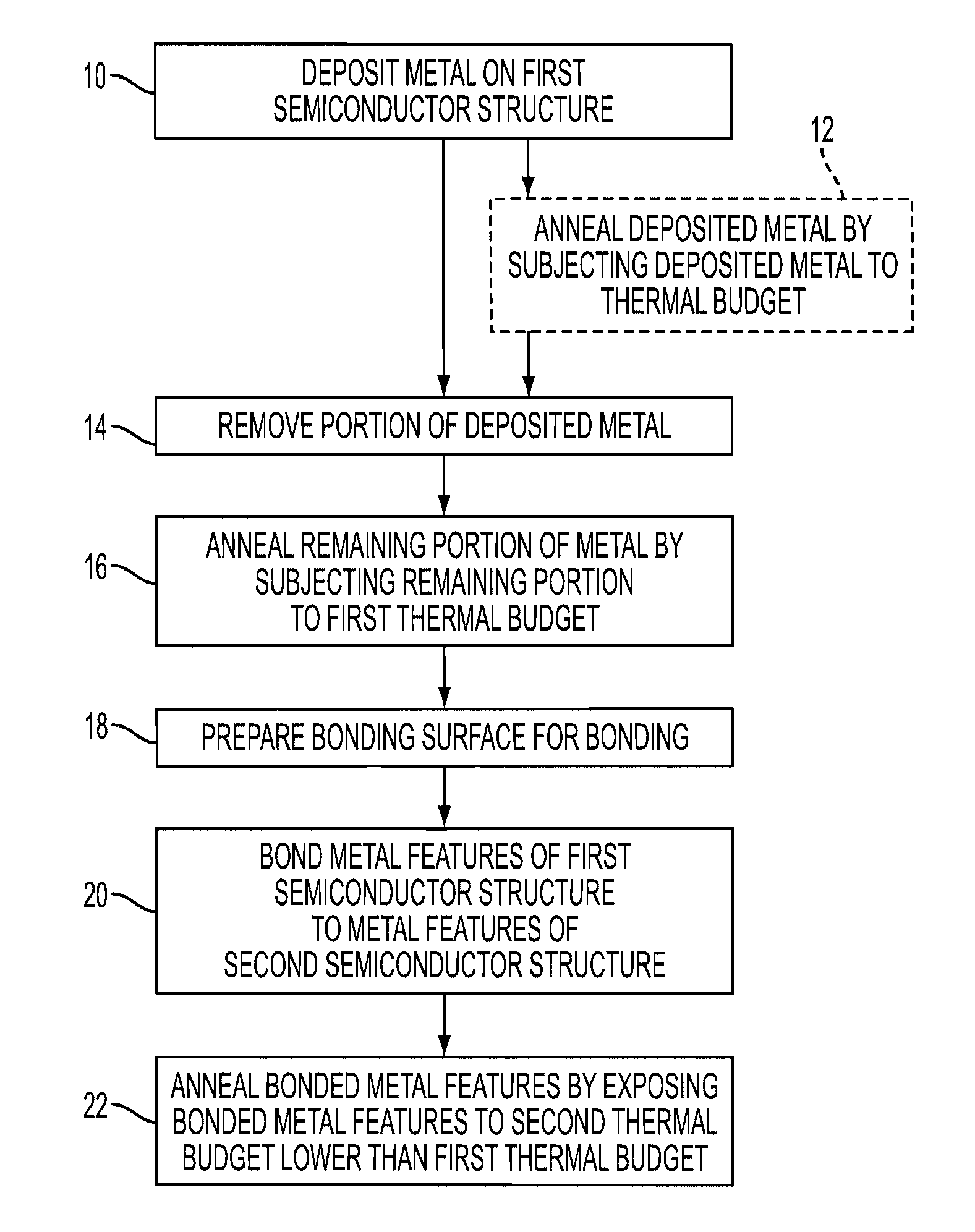

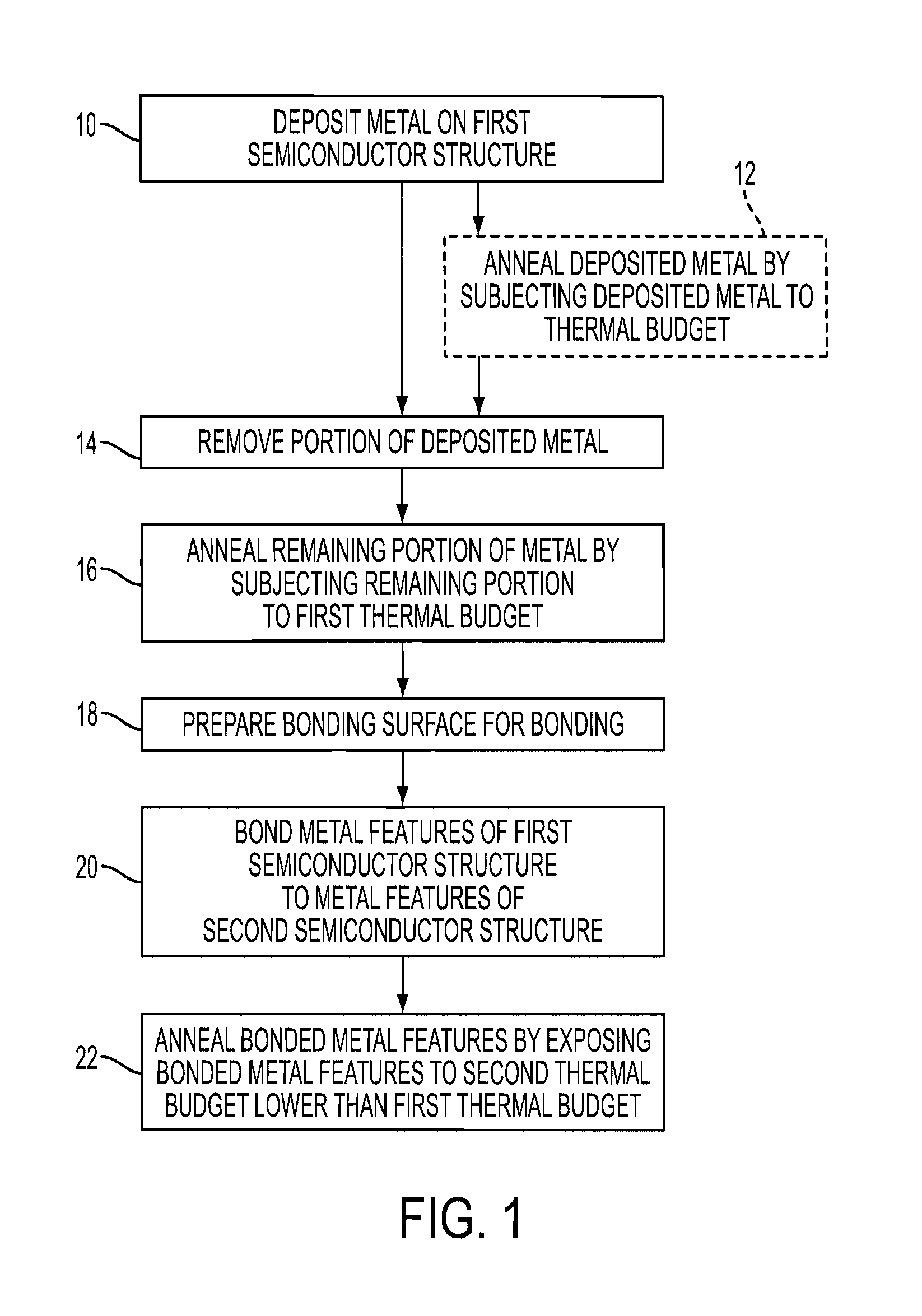

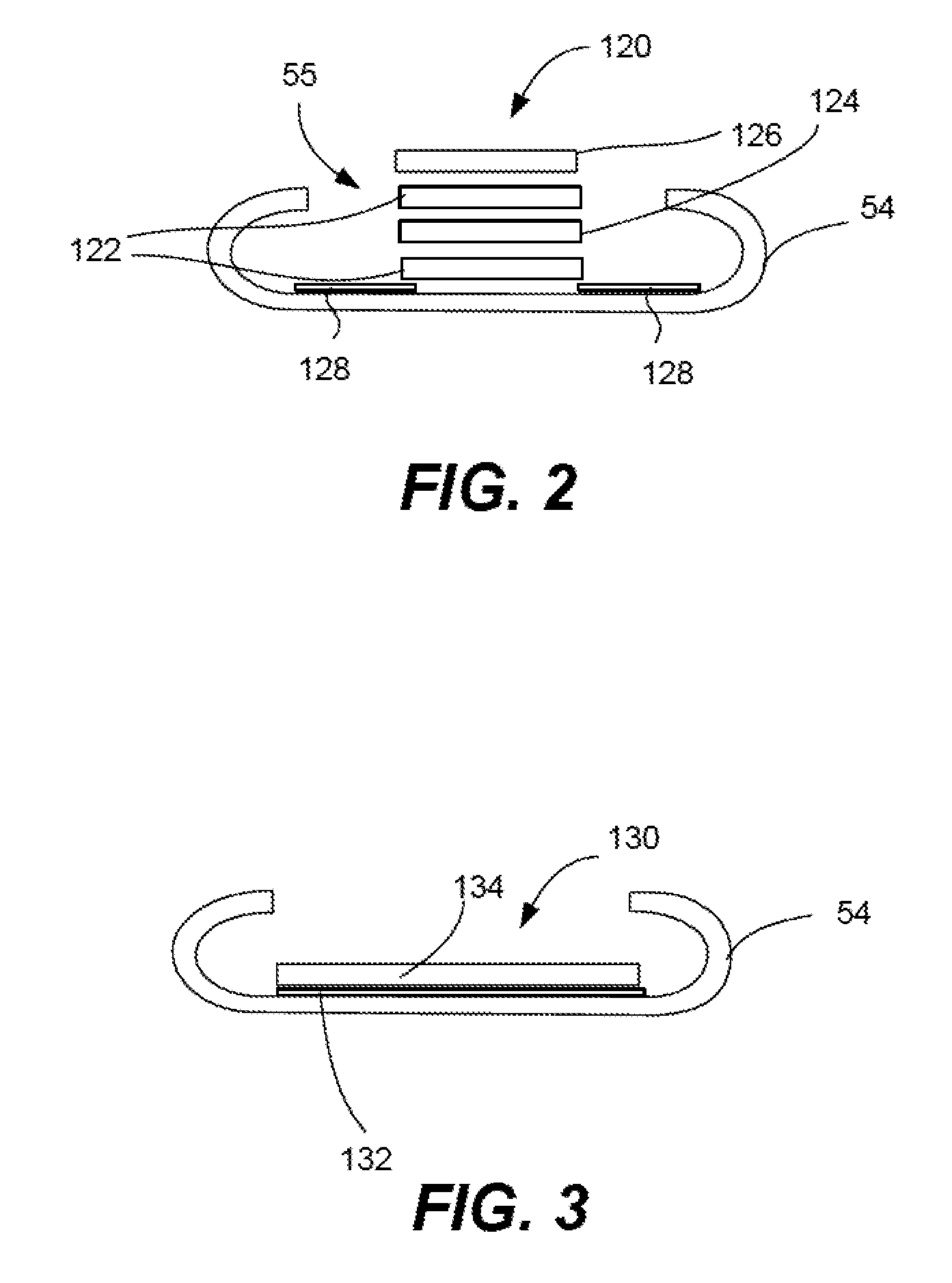

Methods for bonding semiconductor structures involving annealing processes, and bonded semiconductor structures and intermediate structures formed using such methods

InactiveUS8716105B2Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor structure

Owner:SONY SEMICON SOLUTIONS CORP

Bonding Apparatus and Method

The present disclosure relates to methods and apparatuses for mechanically bonding substrates together. The apparatuses may include a pattern roll having three or more pattern elements protruding radially outward, wherein each pattern element includes a pattern surface. The pattern surfaces are also separated from each other by gaps having minimum widths. The pattern roll may be adjacent an anvil roll to define a nip between the pattern surfaces and the anvil roll, wherein the pattern roll is biased toward the anvil roll to define a nip pressure between pattern surfaces and the anvil roll. As substrates advance between the pattern roll and anvil roll, the substrates are compressed between the anvil roll and the pattern surfaces to form a discrete bond region between the substrates. During the bonding process, some of yielded substrate material also flows from under the pattern surfaces and into the gaps to form gap grommet regions.

Owner:THE PROCTER & GAMBLE COMPANY

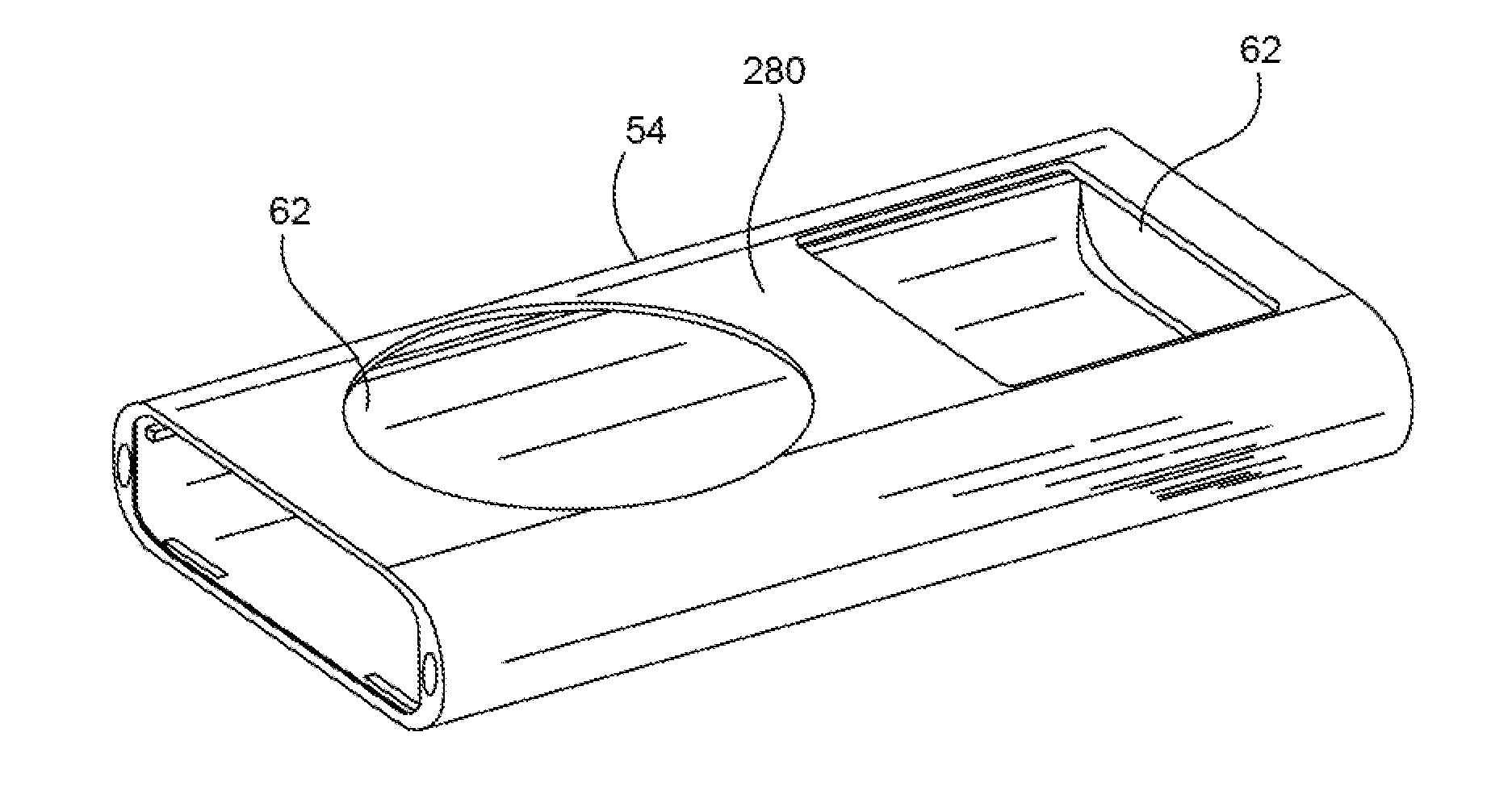

Glass enclosure

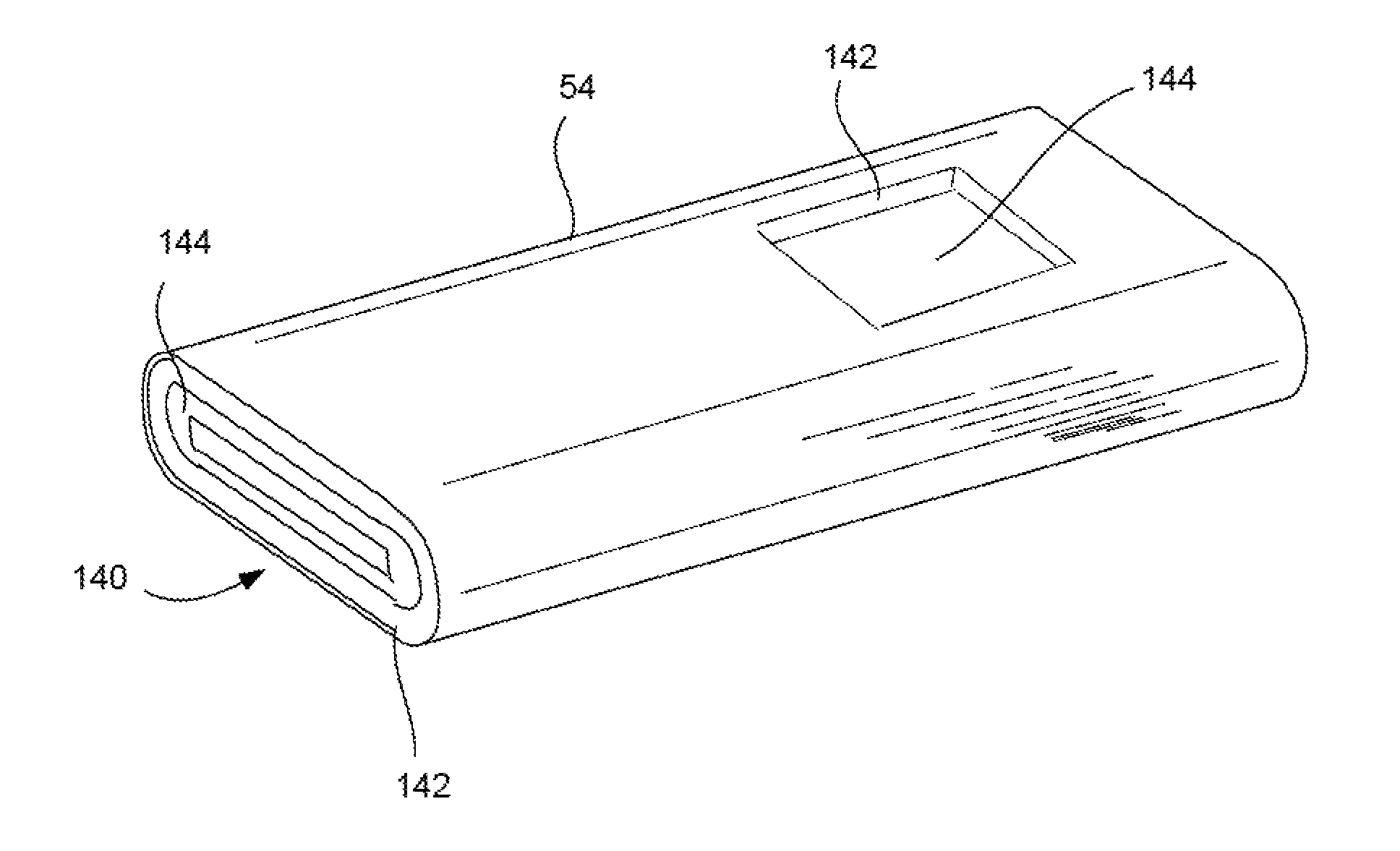

A handheld computing device that includes an enclosure having structural walls formed from a glass material that can be radio-transparent. The enclosure can be formed from a hollow glass tube or two glass members bonded together. A laser frit bonding process may be used to hermetically seal the two glass members together to create a water resistant electronic device.

Owner:APPLE INC

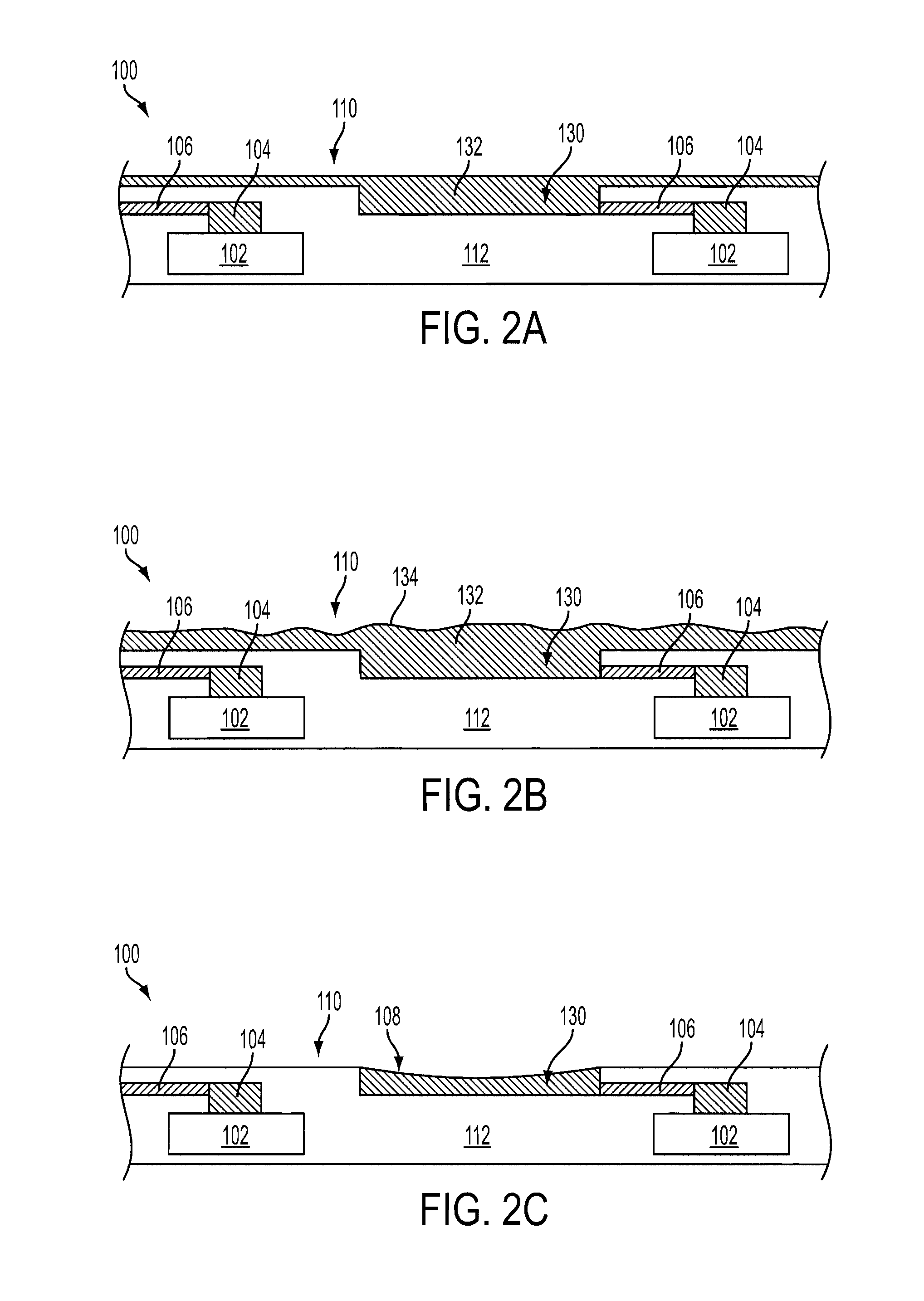

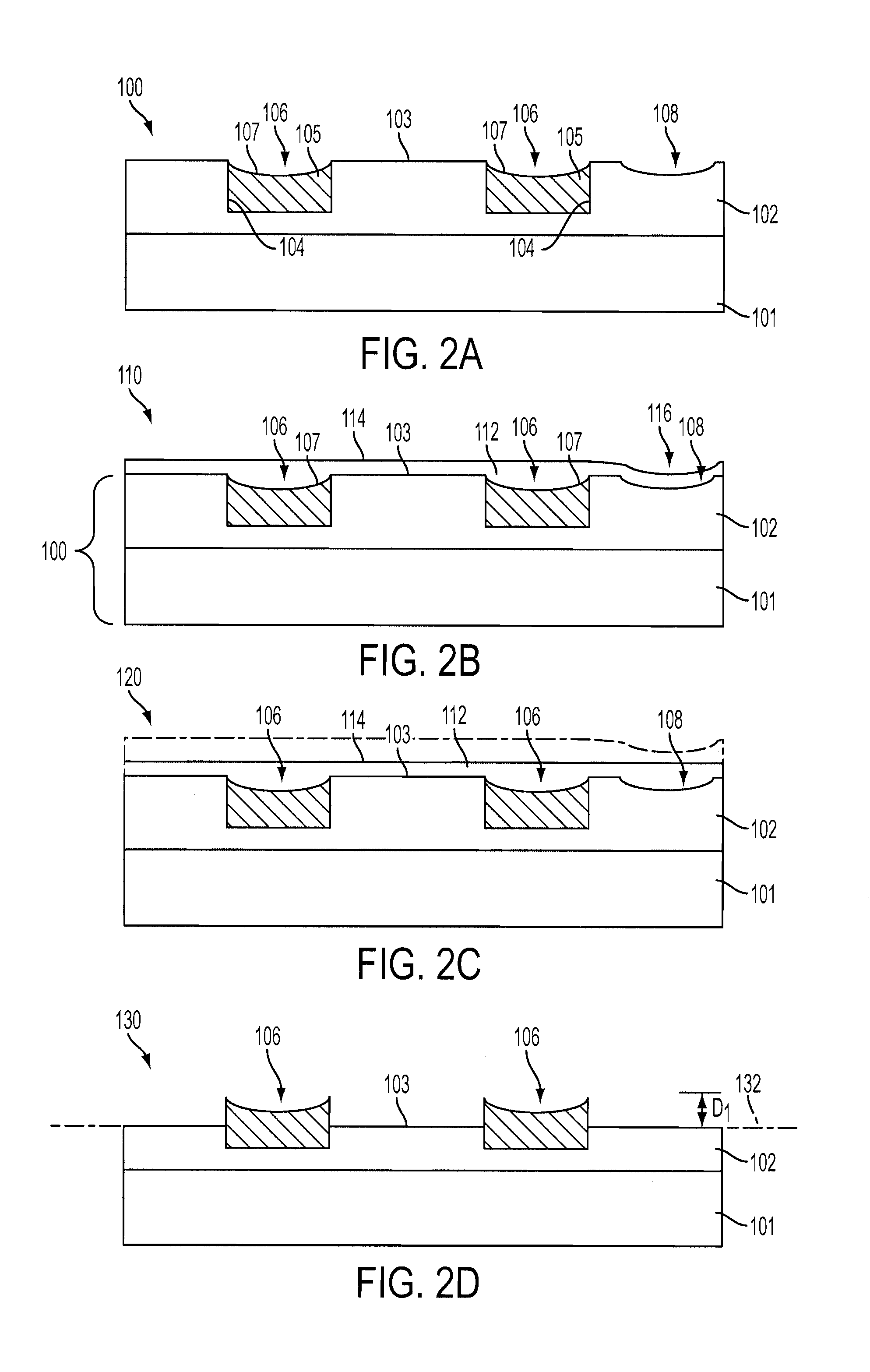

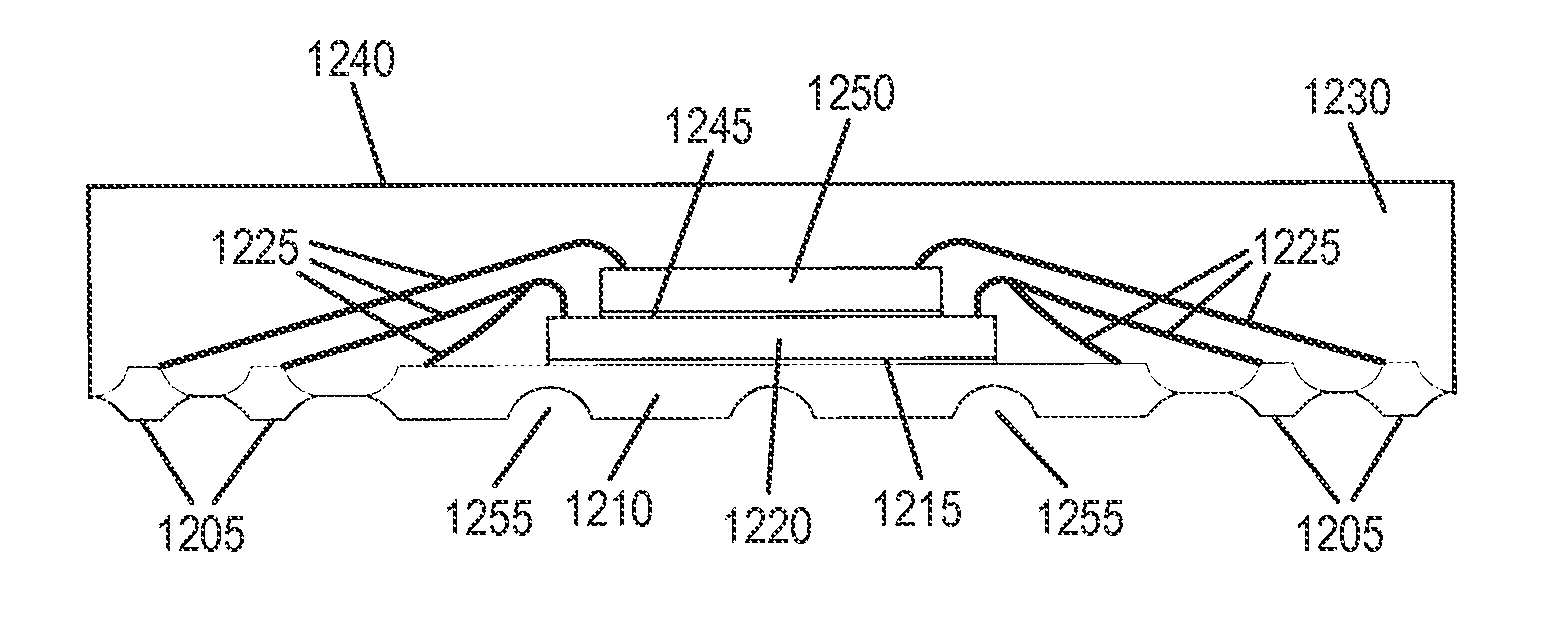

Bonding surfaces for direct bonding of semiconductor structures

InactiveUS8697493B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor structureBonding process

Methods of directly bonding a first semiconductor structure to a second semiconductor structure include directly bonding at least one device structure of a first semiconductor structure to at least one device structure of a second semiconductor structure in a conductive material-to-conductive material direct bonding process. In some embodiments, at least one device structure of the first semiconductor structure may be caused to project a distance beyond an adjacent dielectric material on the first semiconductor structure prior to the bonding process. In some embodiments, one or more of the device structures may include a plurality of integral protrusions that extend from a base structure. Bonded semiconductor structures are fabricated using such methods.

Owner:SONY SEMICON SOLUTIONS CORP

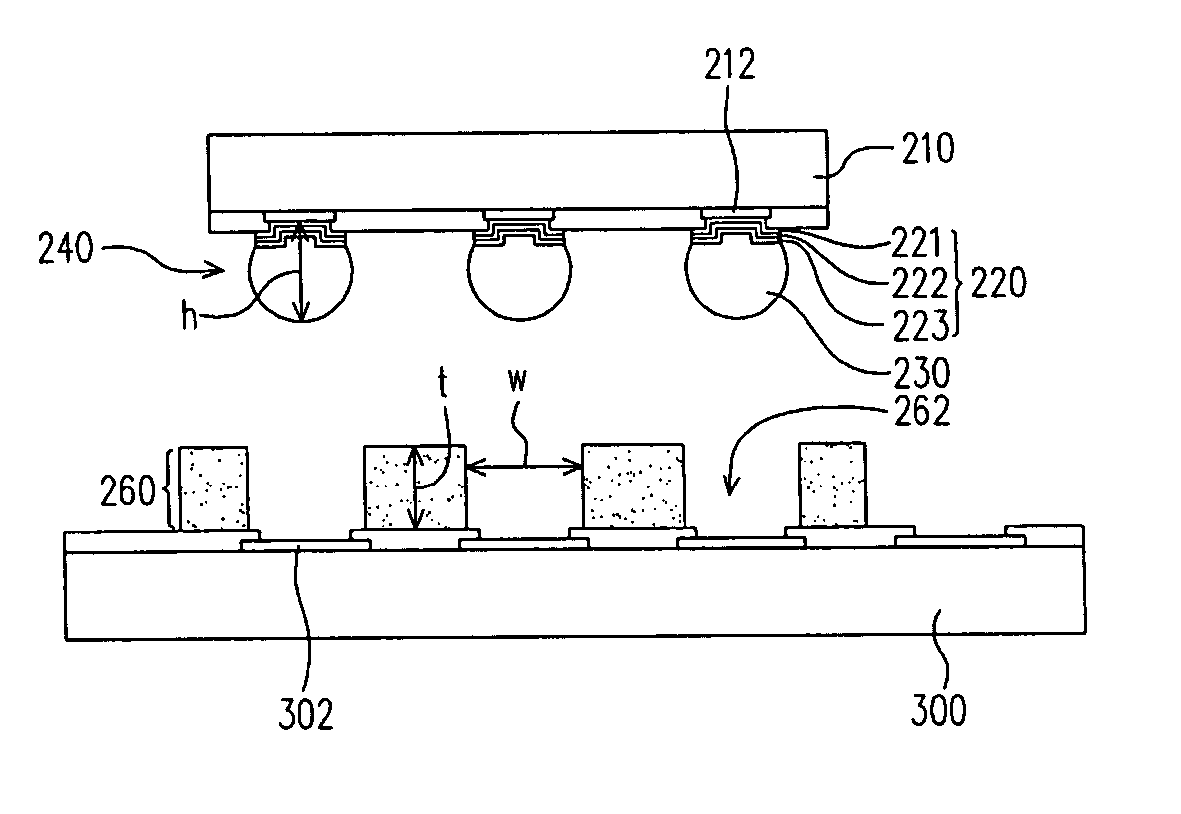

Chip bonding process

ActiveUS20050266670A1Avoid pollutionImprove productivitySemiconductor/solid-state device detailsSolid-state devicesInsulation layerBonding process

A bonding process includes the following process. A bump is formed on a first electric device. A patterned insulation layer is formed on a second electric device, wherein the patterned insulation layer has a thickness between 5 μm and 400 μm, and an opening is in the patterned insulation layer and exposes the second electric device. The bump is joined to the second electric device exposed by the opening in the patterned insulation layer.

Owner:QUALCOMM INC

Partially patterned lead frames and methods of making and using the same in semiconductor packaging

InactiveUS20050263864A1Improve structural rigidityProcess stabilityLine/current collector detailsSemiconductor/solid-state device detailsLead bondingBonding process

A method of making a lead frame and a partially patterned lead frame package with near-chip scale packaging (CSP) lead-counts is disclosed, wherein the method lends itself to better automation of the manufacturing line as well as to improving the quality and reliability of the packages produced therefrom. This is accomplished by performing a major portion of the manufacturing process steps with a partially patterned strip of metal formed into a web-like lead frame on one side, in contrast with the conventional fully etched stencil-like lead frames, so that the web-like lead frame, which is solid and flat on the other side is also rigid mechanically and robust thermally to perform without distortion or deformation during the chip-attach and wire bond processes. The bottom side of the metal lead frame is patterned to isolate the chip-pad and the wire bond contacts only after the front side, including the chip and wires, is hermetically sealed with an encapsulant. The resultant package being electrically isolated enables strip testing and reliable singulation without having to cut into any additional metal. The use of the instant partially patterned lead frame in making ELP, ELPF and ELGA-type CSPs is also disclosed.

Owner:UNISEM M BERHAD

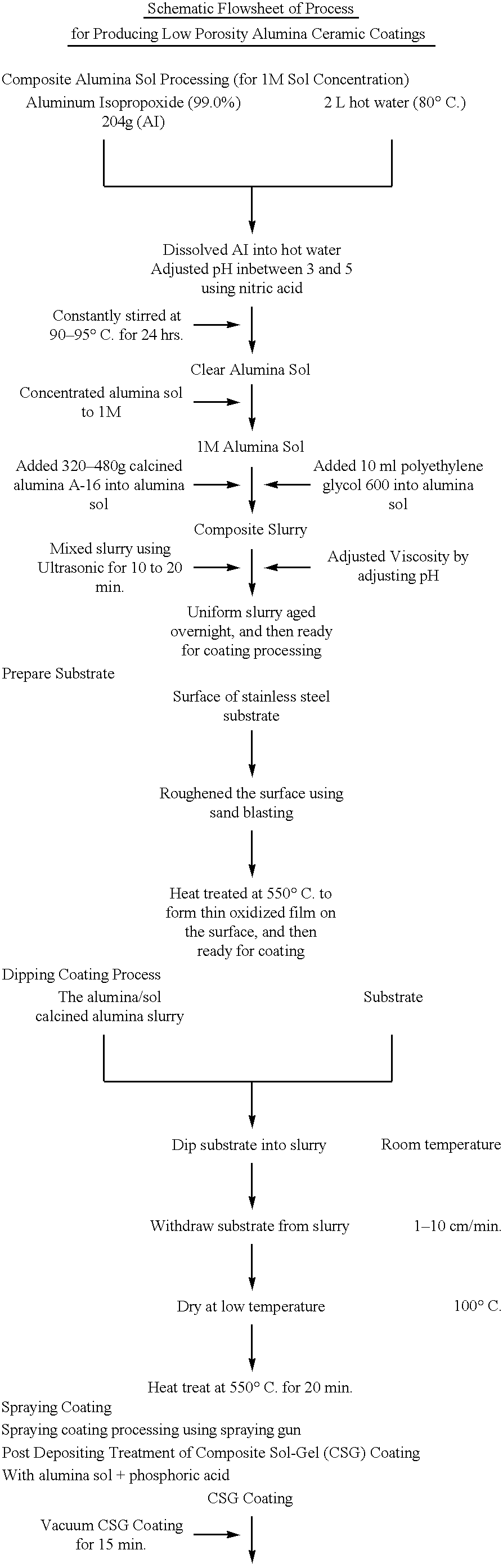

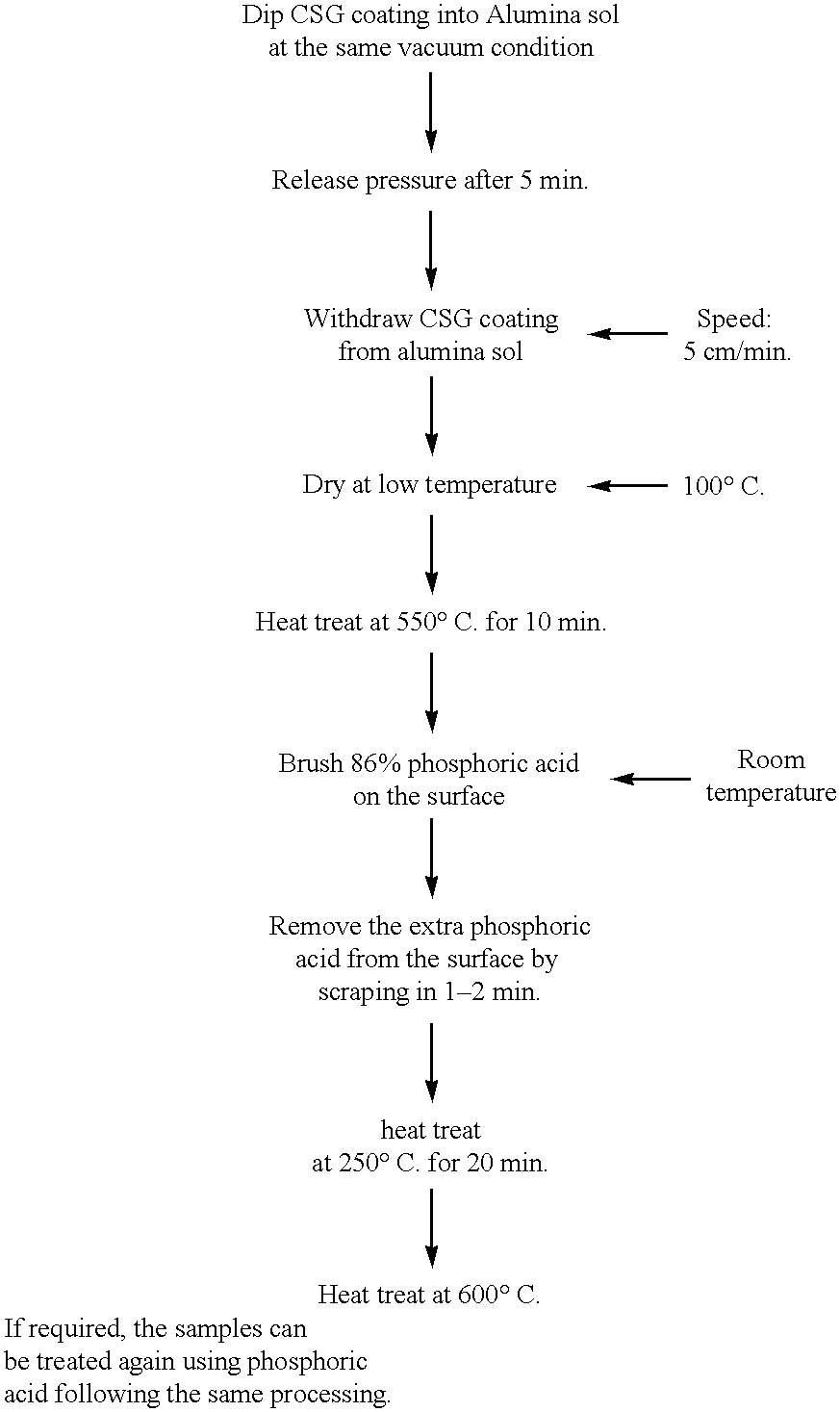

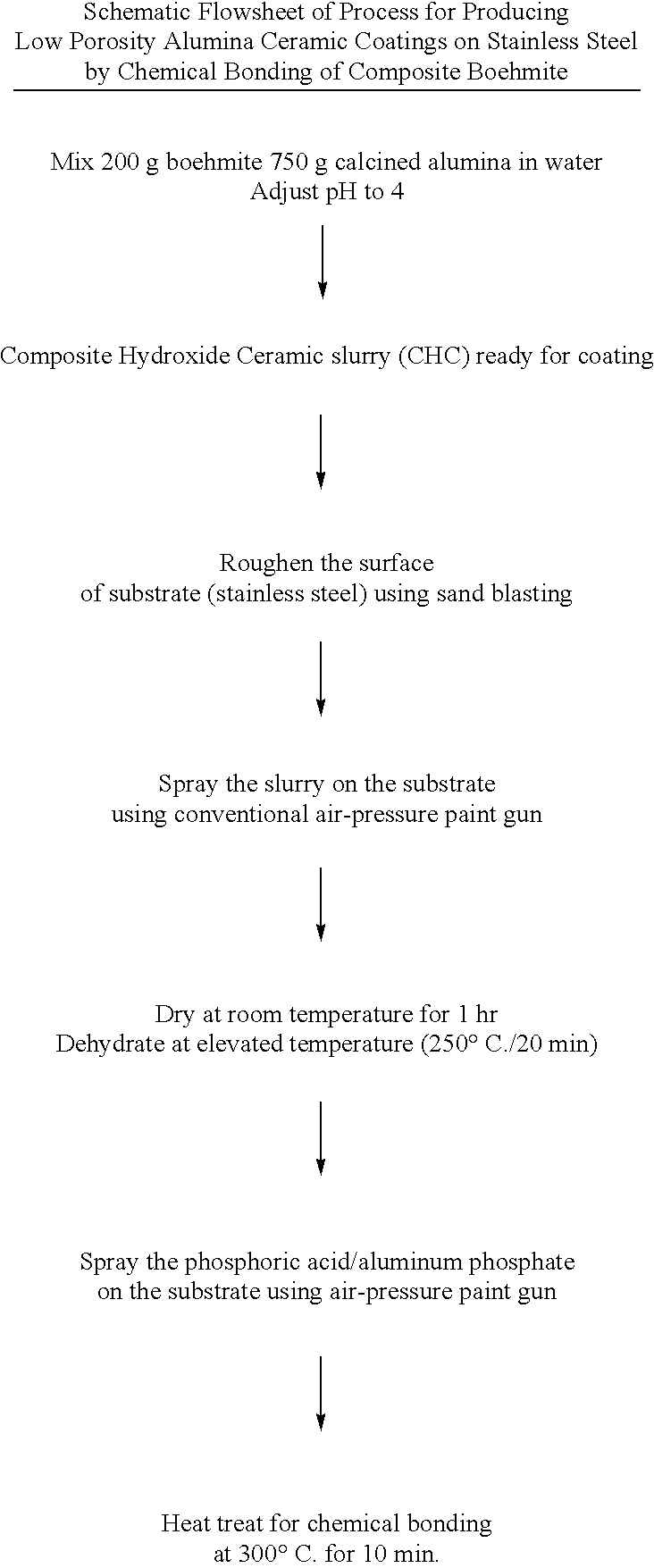

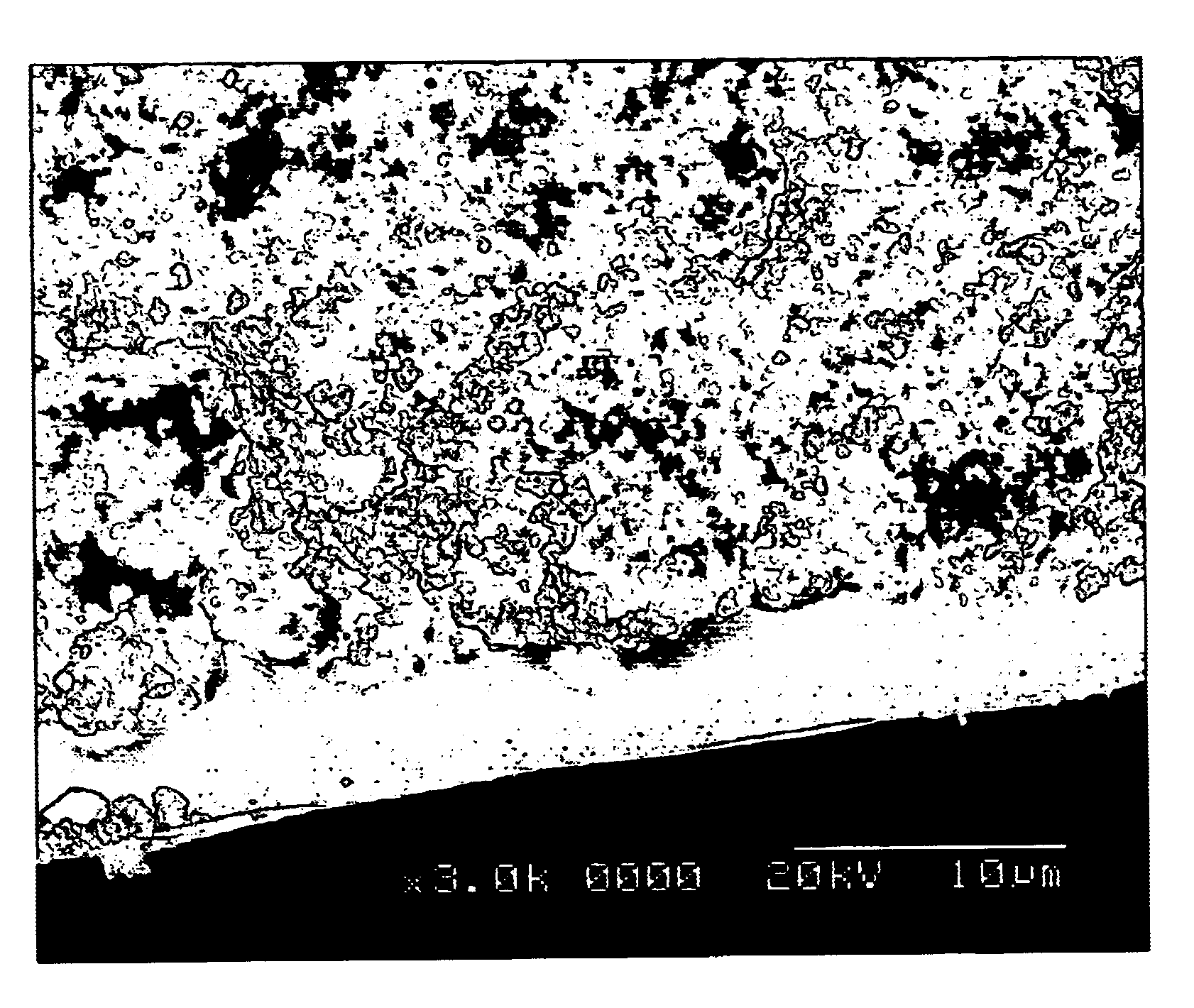

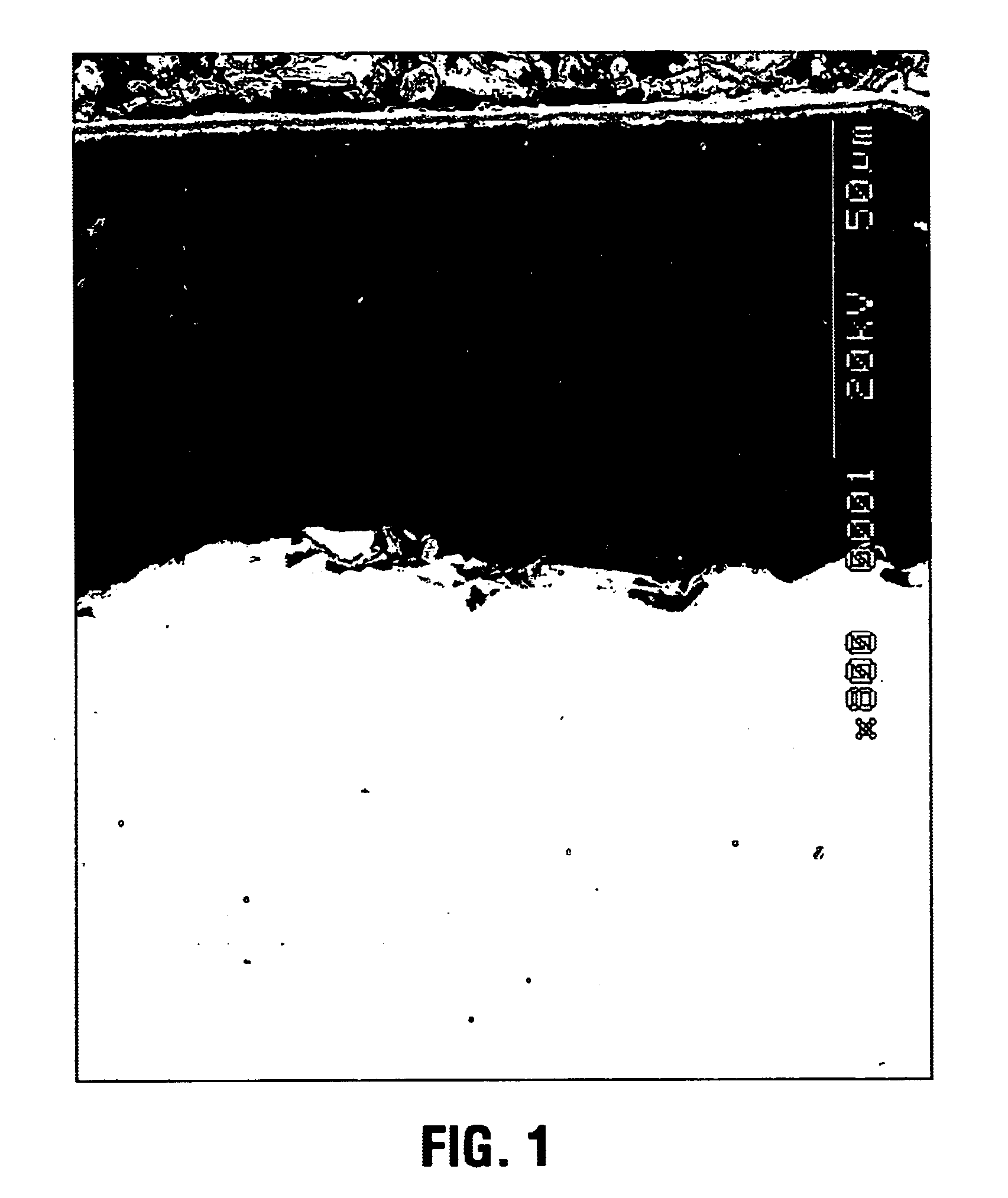

Process for making chemically bonded sol-gel ceramics

InactiveUS6284682B1Liquid/solution decomposition chemical coatingSuperimposed coating processPorosityCeramic coating

This invention relates to a novel method of decreasing porosity of ceramics produced by sol-gel processing. The process of preparing chemically bonded sol-gel ceramics comprises phosphating a sol-gel derived oxide or hydrated oxide and polymerizing the phosphated product with heat treatment. Such combined sol-gel / chemical bonding process can be used to fabricate dense, thick ceramics or ceramic coatings for a variety of applications, including high temperature corrosion protection, wear resistance, dielectric properties, non-sticky surfaces, bio-active ceramics, thermal barrier ceramics, non-wetted surfaces, and others.

Owner:THE UNIV OF BRITISH COLUMBIA

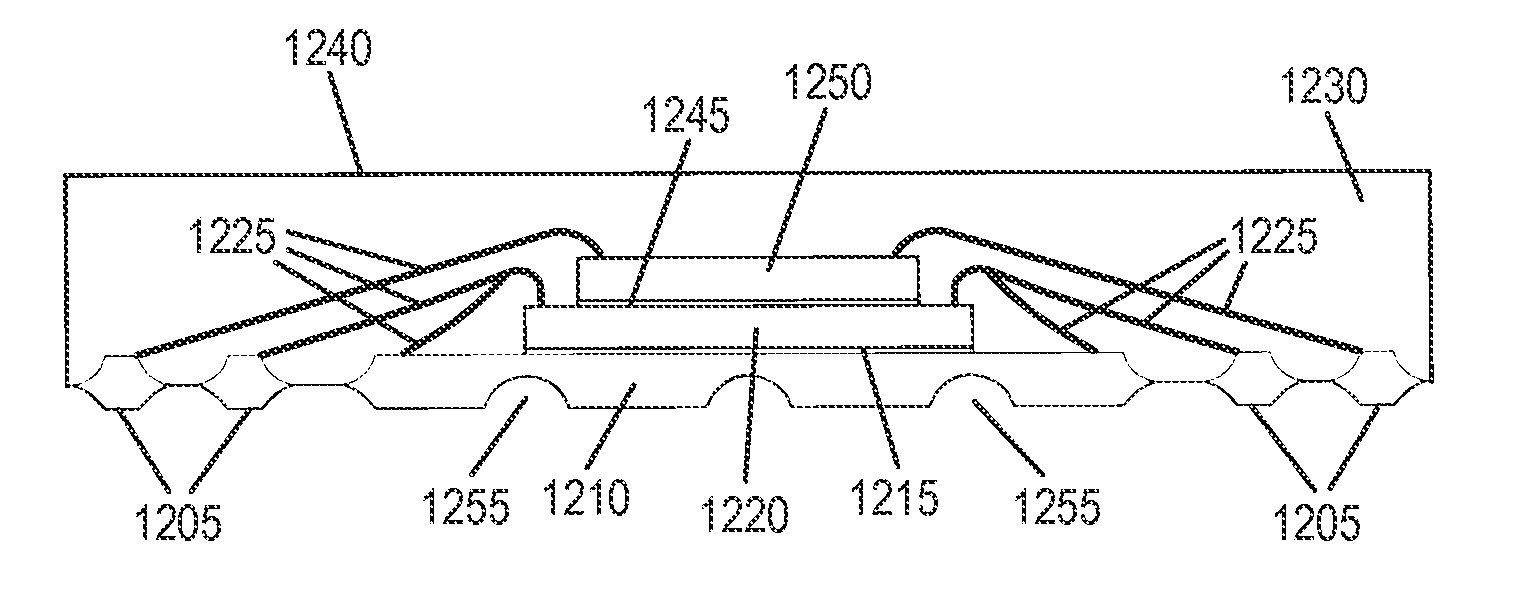

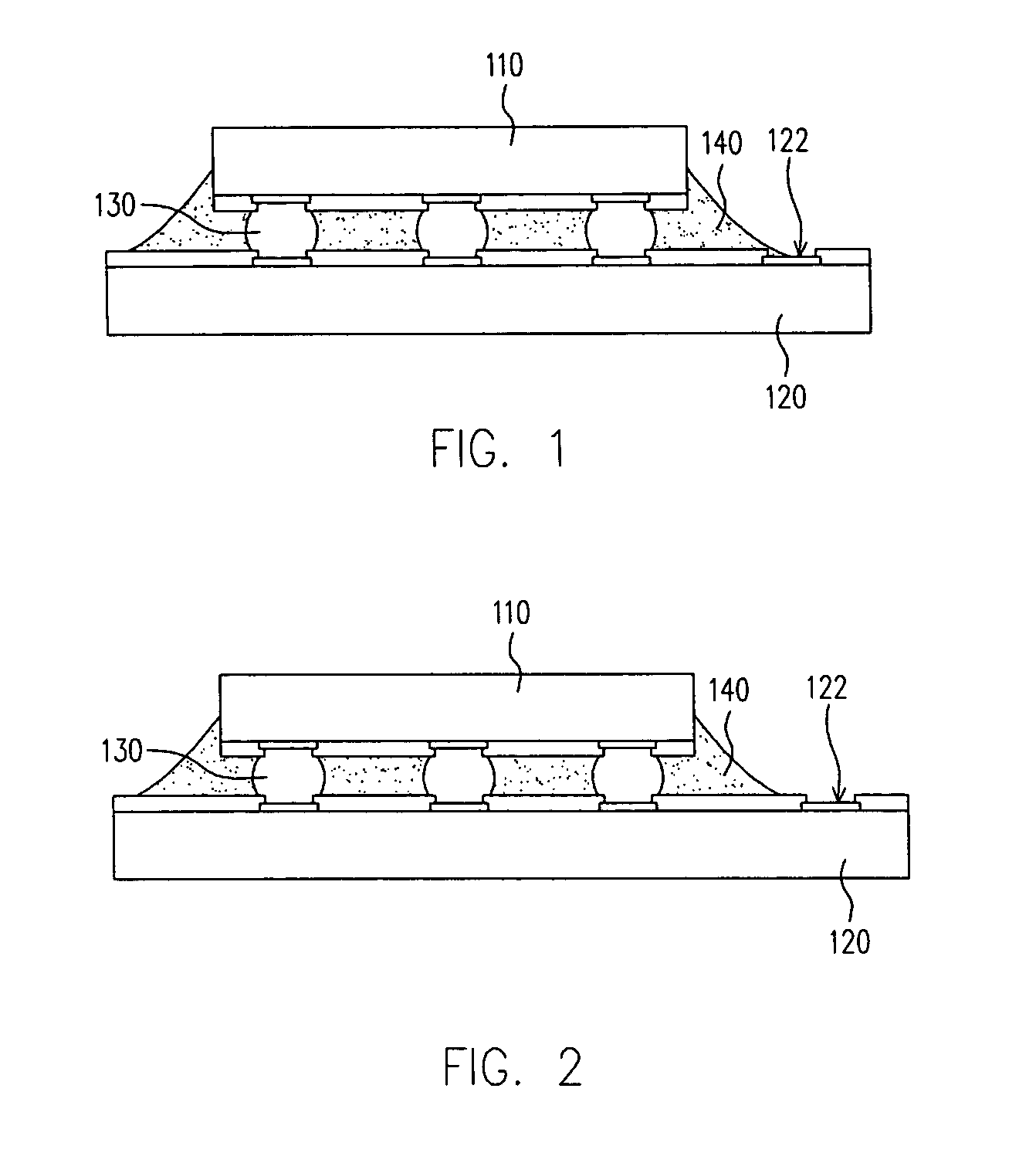

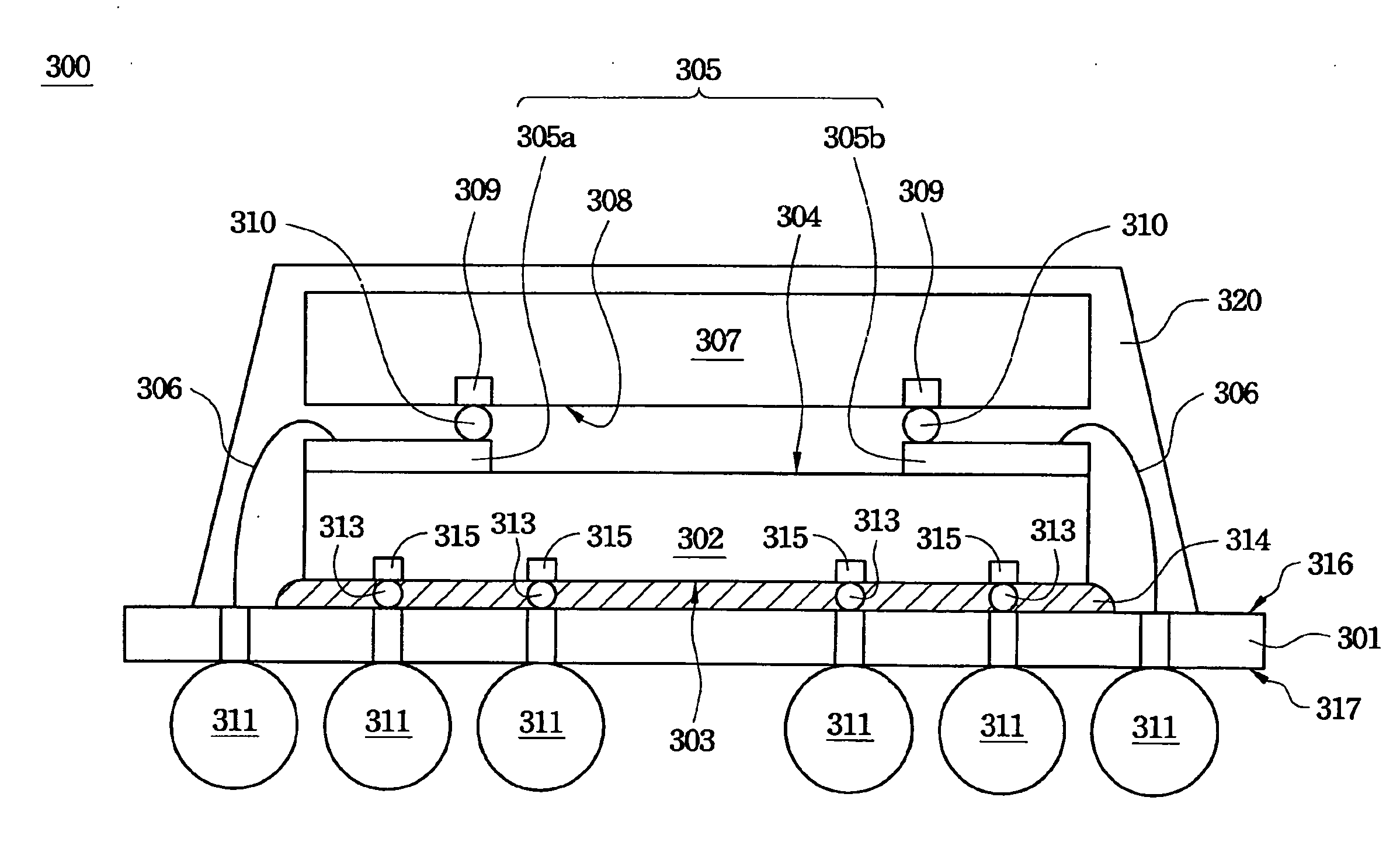

Chip-Stacked Package Structure

InactiveUS20080265397A1Extend length and radianSmall sizeSemiconductor/solid-state device detailsSolid-state devicesBonding processEngineering

A chip stacked package structure and applications are provided, wherein the chip stacked package structure comprises a substrate, a first chip, a patterned circuit layer and a second chip. The substrate has a first surface and an opposite second surface. The first chip with a first active area and an opposite first rear surface is electrically connected to first surface of substrate by a flip chip bonding process. The patterned circuit layer set on the dielectric layer is electrically connected to the substrate via a bonding wire. The second chip set on the patterned circuit layer has a second active area and a plurality of second pads formed on the second active area, wherein the second bonding pad is electrically connected to the patterned circuit layer.

Owner:CHIPMOS TECH INC +1

Glass enclosure

ActiveUS8824140B2Digital data processing detailsCasings with display/control unitsFritBonding process

Owner:APPLE INC

Partially patterned lead frames and methods of making and using the same in semiconductor packaging

InactiveUS7790500B2Improve structural rigiditySemiconductor/solid-state device detailsSolid-state devicesLead bondingBonding process

A method of making a lead frame and a partially patterned lead frame package with near-chip scale packaging lead-count, wherein the method lends itself to better automation of the manufacturing line and improved quality and reliability of the packages produced therefrom. A major portion of the manufacturing process steps is performed with a partially patterned strip of metal formed into a web-like lead frame on one side so that the web-like lead frame is also rigid mechanically and robust thermally to perform without distortion or deformation during the chip-attach and wire bond processes, both at the chip level and the package level. The bottom side of the metal lead frame is patterned to isolate the chip-pad and the wire bond contacts only after the front side, including the chip and wires, is hermetically sealed with an encapsulant. The resultant package being electrically isolated enables strip testing and reliable singulation.

Owner:UNISEM M BERHAD

Friction stir welded hollow airfoils and method therefor

A hollow component for gas turbine engine, for example an outlet guide vane, is assembled from a body having at recessed pocket formed therein, and an aerodynamic cover bonded over the pocket. Both the cover and the body are constructed from materials which are not readily fusion weldable. The cover is attached to the body by a solid state bonding process, for example friction stir welding. The hollow component may also be built up from multiple individual components which are bonded to each other by a solid state bonding process such as friction stir welding.

Owner:GENERAL ELECTRIC CO

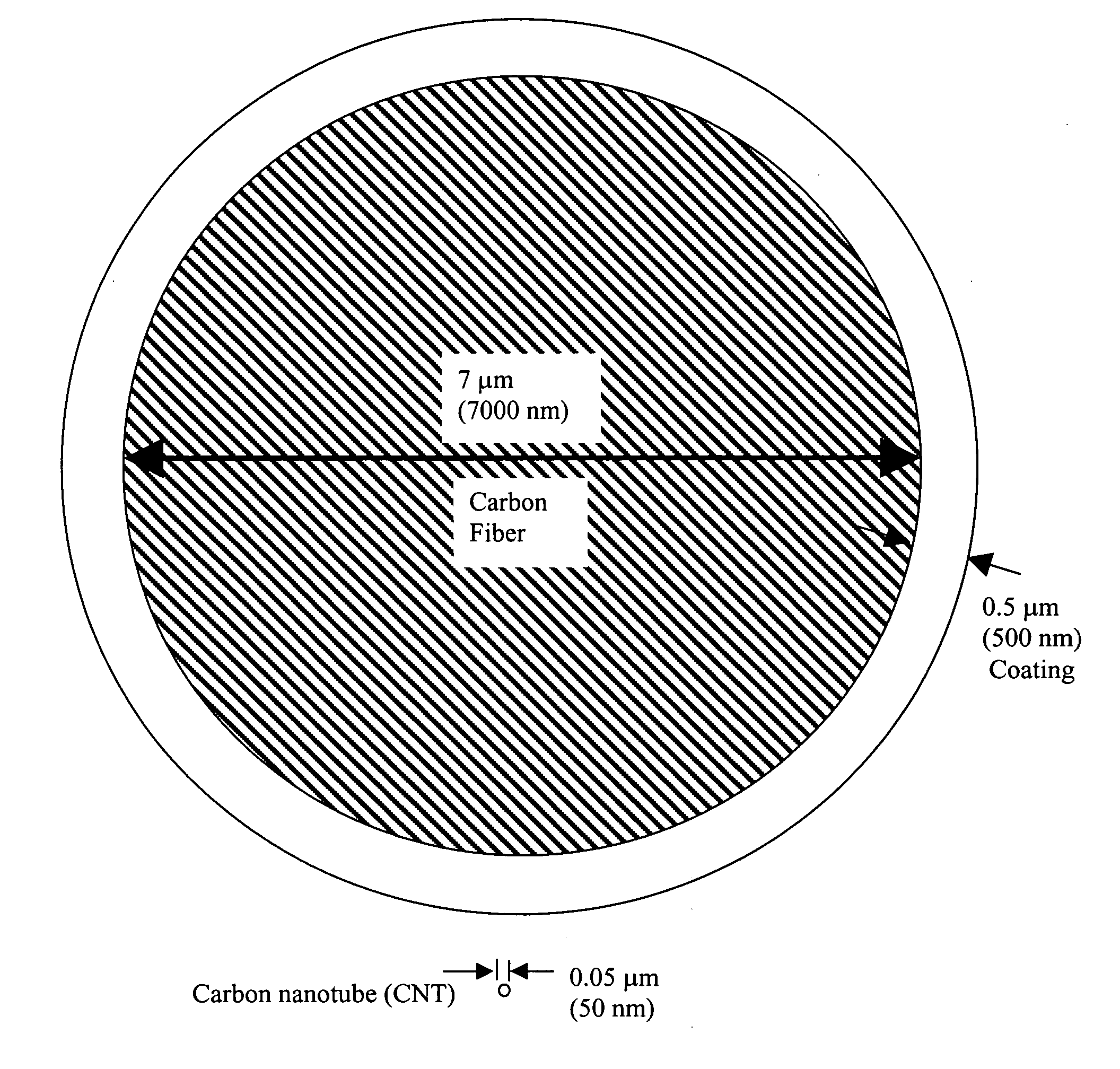

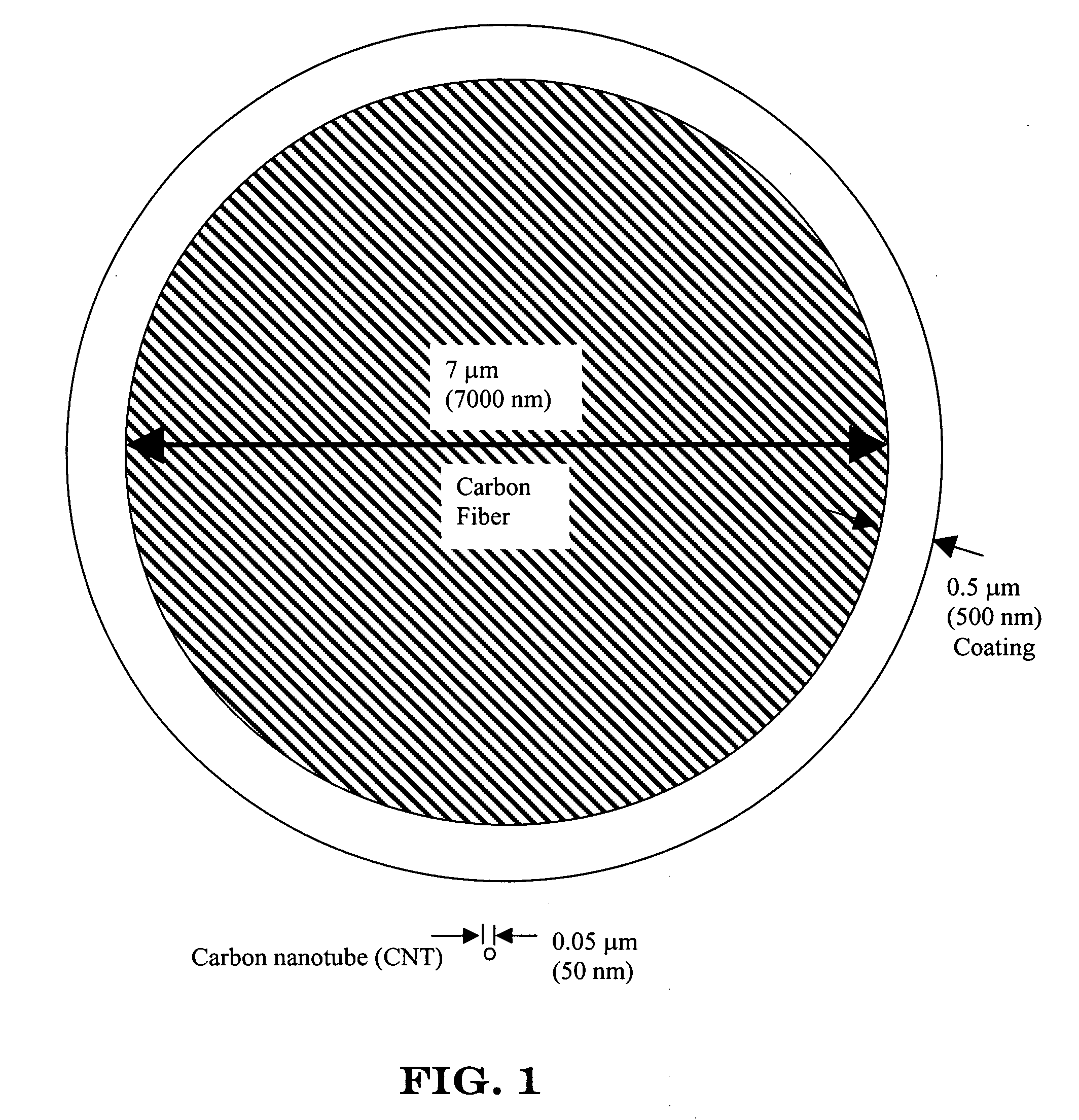

Nanotube-containing composite bodies, and methods for making same

A composite material featuring carbon nanotubes reinforcing a matrix featuring metal or silicon carbide, or both. Such composites can be produced using a molten silicon metal infiltration technique, for example, a siliconizing or a reaction-bonding process. Here, the carbon nanotubes are prevented from chemically reacting with the silicon infiltrant by an interfacial coating disposed between the carbon nanotubes and the infiltrant. Preferably, the coating is free carbon or a carbonaceous precursor material added during preform processing, or after. The reaction-bonding system is designed such that the molten infiltrant of silicon metal or silicon alloy reacts with at least some of the interfacial carbon layer to form in-situ silicon carbide, and that the formed SiC is sufficiently dense that it effectively seals off the underlying carbon nanotube from exposure to additional molten infiltrant. A reaction-bonded composite body containing even a small percentage of carbon nanotubes possessed a significant increase in electrical conductivity as compared to a reaction-bonded composite not containing such nanotubes, reflecting the high electrical conductivity of the nanotubes.

Owner:KARANDIKAR PRASHANT G

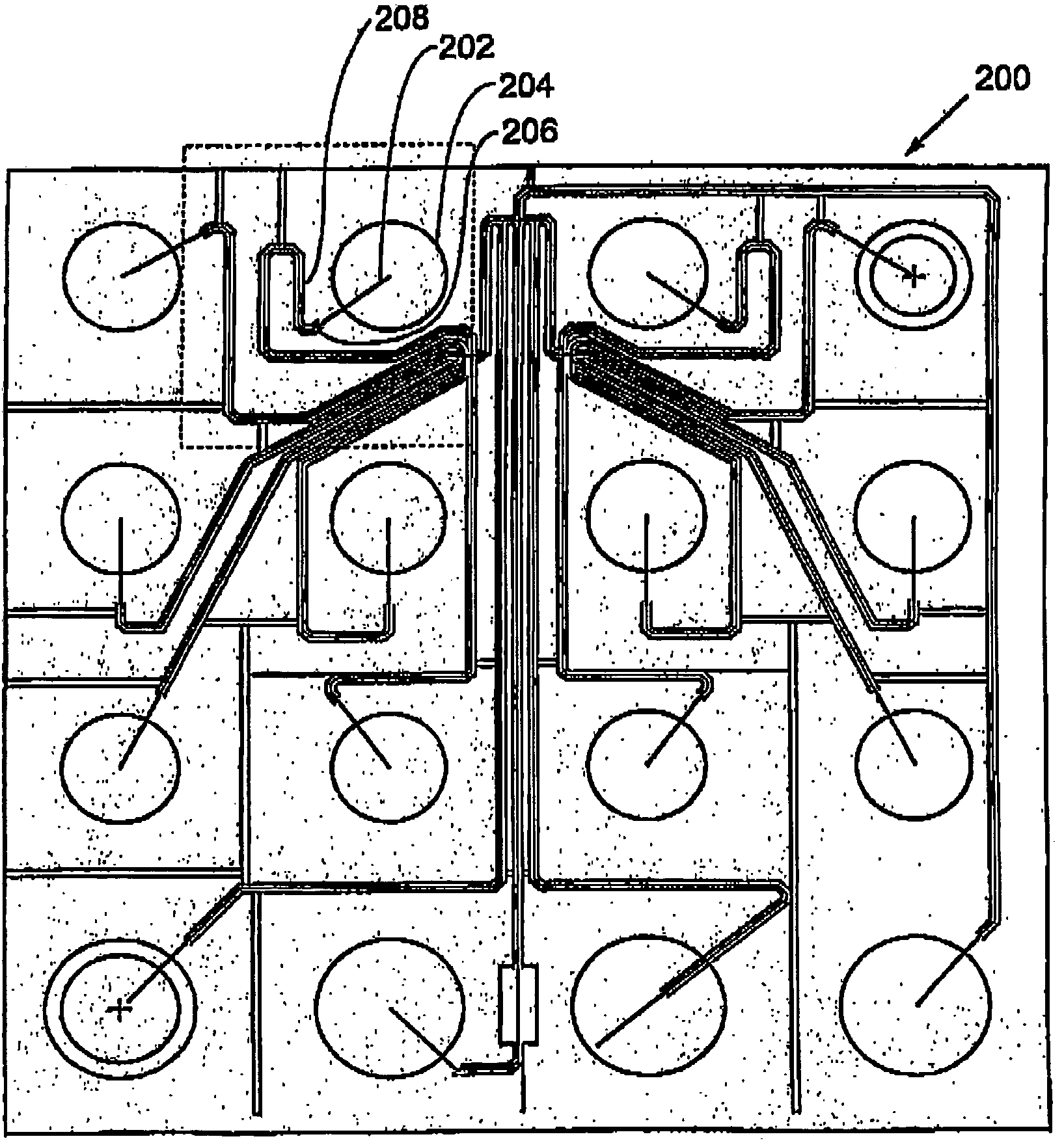

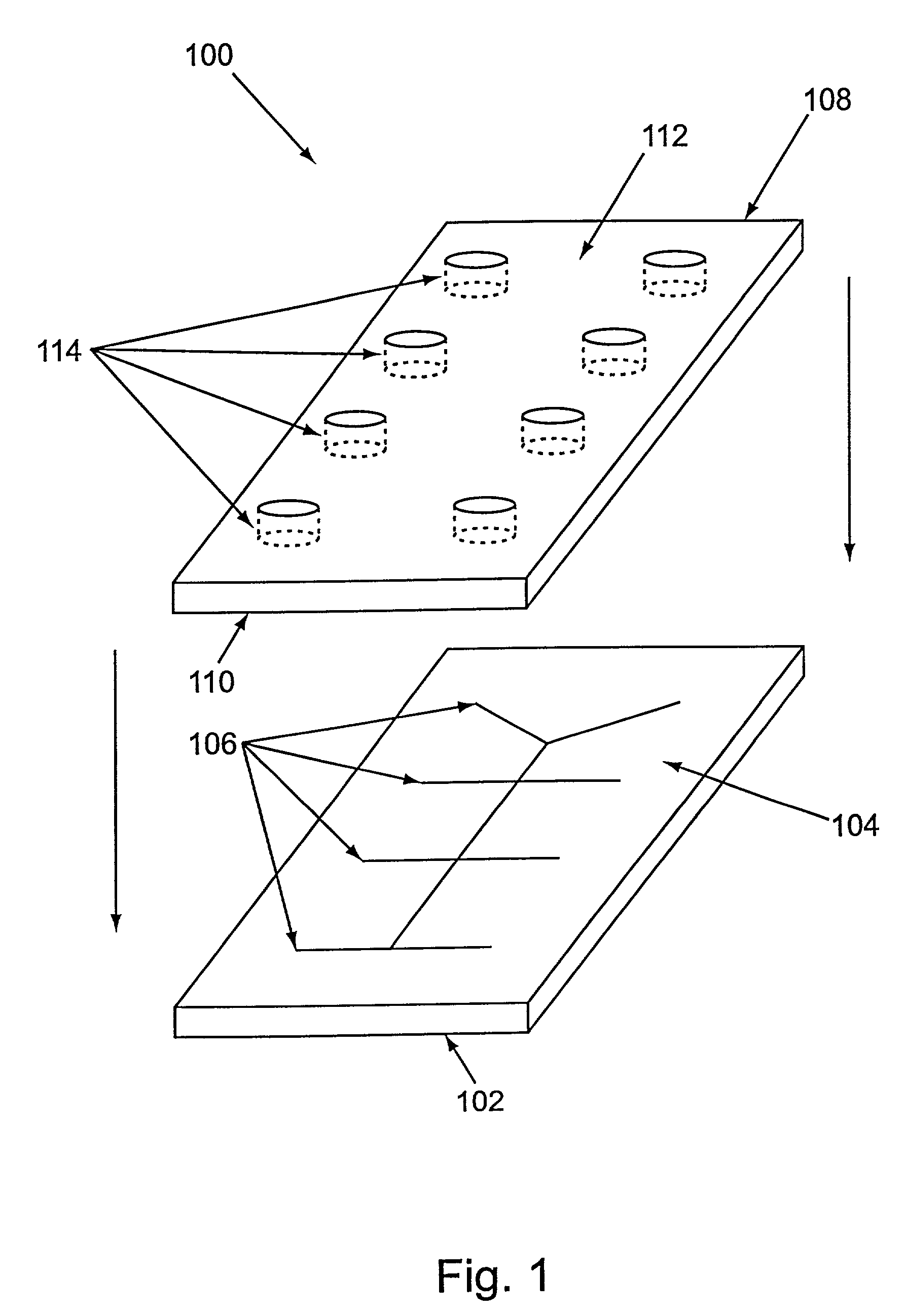

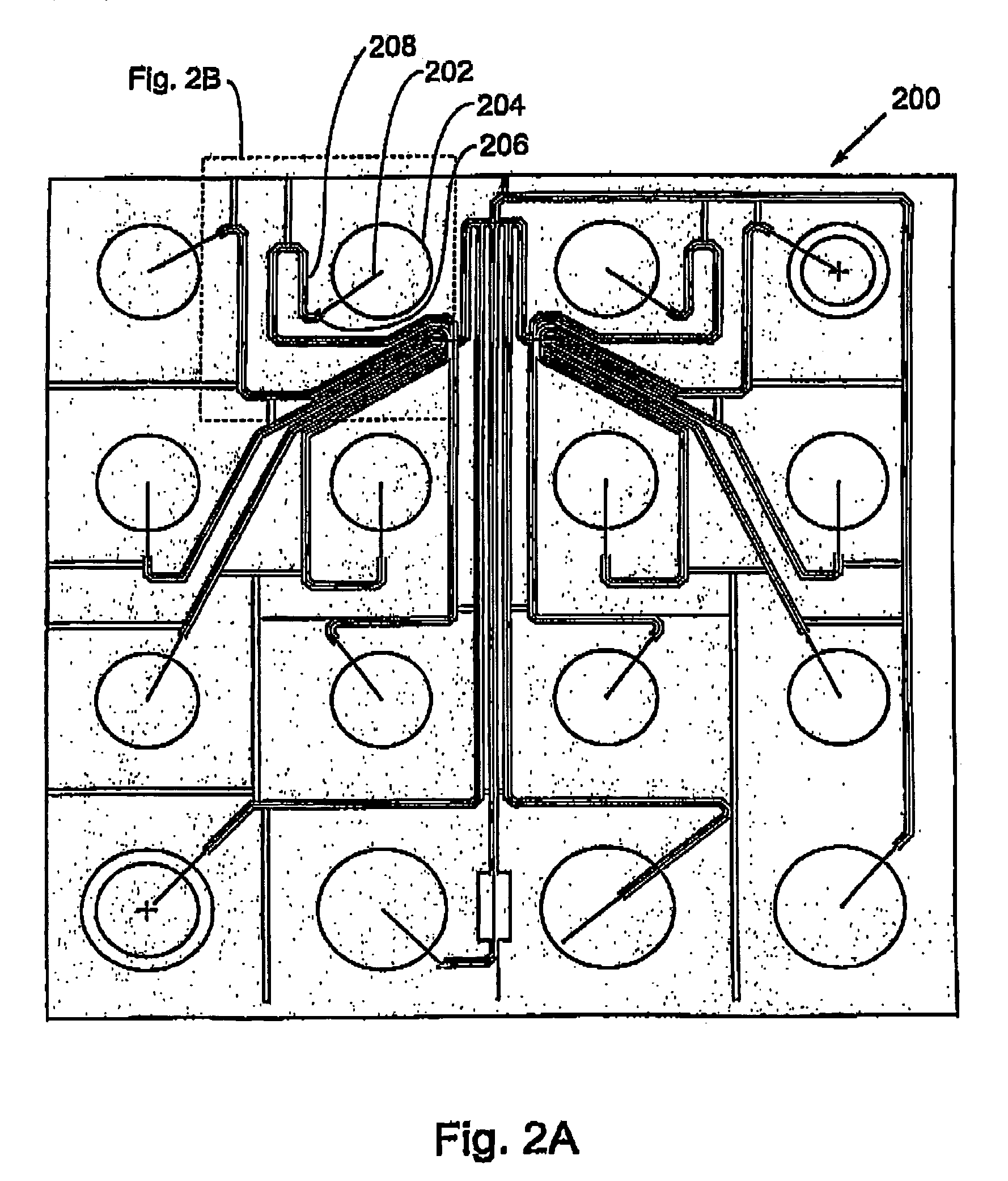

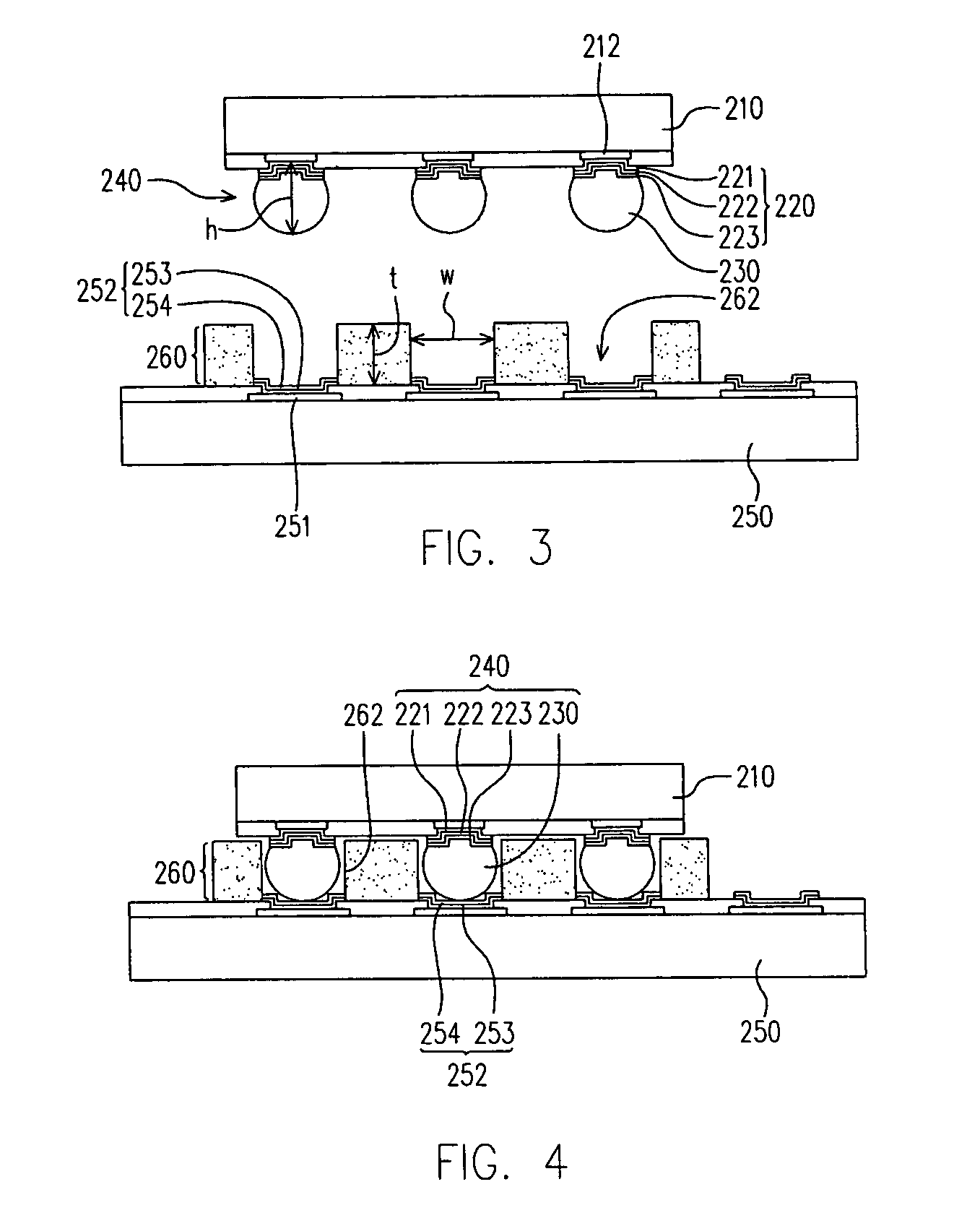

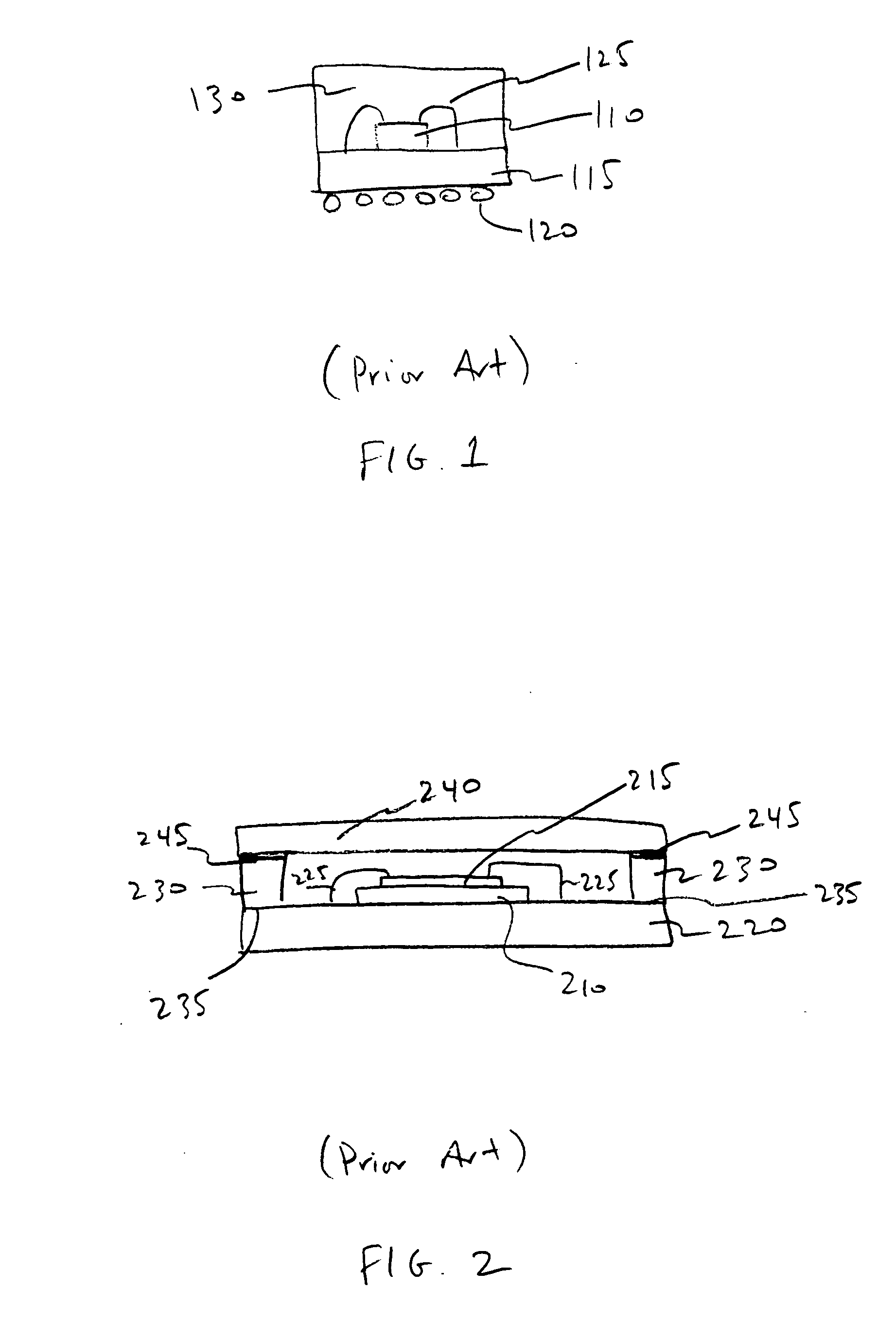

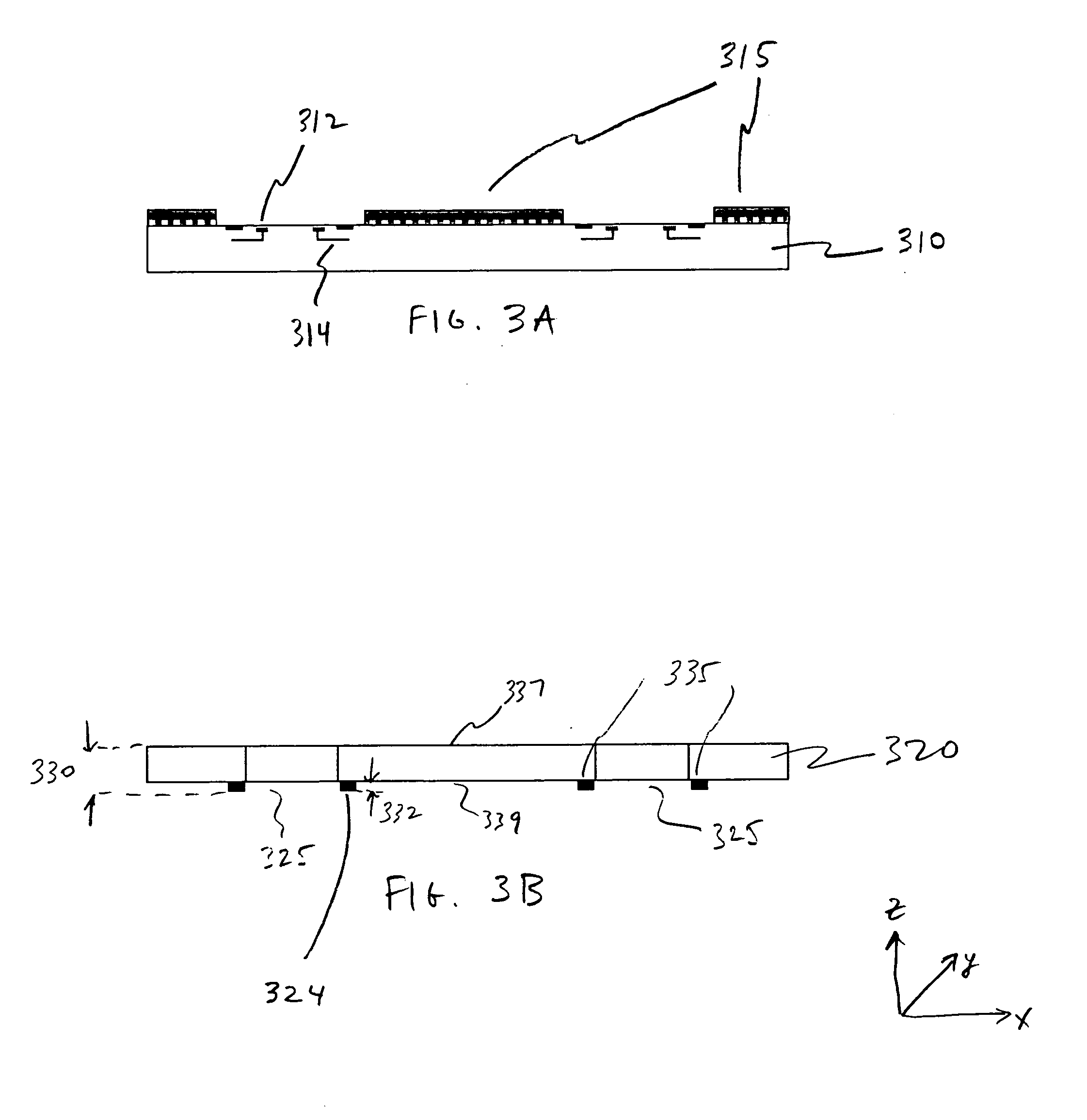

Method and system for hermetically sealing packages for optics

ActiveUS20050101059A1Covering/liningsSemiconductor/solid-state device detailsHermetic sealBonding process

A method for hermetically sealing devices. The method includes providing a substrate which includes a plurality of individual chips. Each of the chips includes a plurality of devices and each of the chips are arranged in a spatial manner as a first array. The method also provides a transparent member of a predetermined thickness which includes a plurality of recessed regions arranged in a spatial manner as a second array and a standoff region. The method also includes aligning the transparent member in a manner to couple each of the plurality of recessed regions to a respective one of said plurality of chips. The method further includes hermetically sealing each of the chips within one of the respective recessed regions by using at least a bonding process to isolate each of the chips within one of the recessed regions.

Owner:MIRADIA INC

Bonding structure with compliant bumps

InactiveUS6972490B2Reduce the modulus of elasticityReduce pressurePrinted circuit assemblingSemiconductor/solid-state device detailsBonding processEngineering

A bonding structure with compliant bumps includes a stopper structure and a protection layer. Compliant bumps include at least a polymer bump, a metal layer and a surface conductive layer. Both the stopper structure and protection layer are formed with polymer bumps and metal layer. Compliant bumps provide bonding pad and conductive channel. Stoppers are used to prevent compliant bumps from crushing for overpressure in bonding process. The protection layer provides functions of grounding and shielding. The stoppers can be outside or connected with the compliant bumps. The protection layer has thickness smaller than the stopper structure and compliant bumps. It can be separated or connected with stoppers.

Owner:IND TECH RES INST

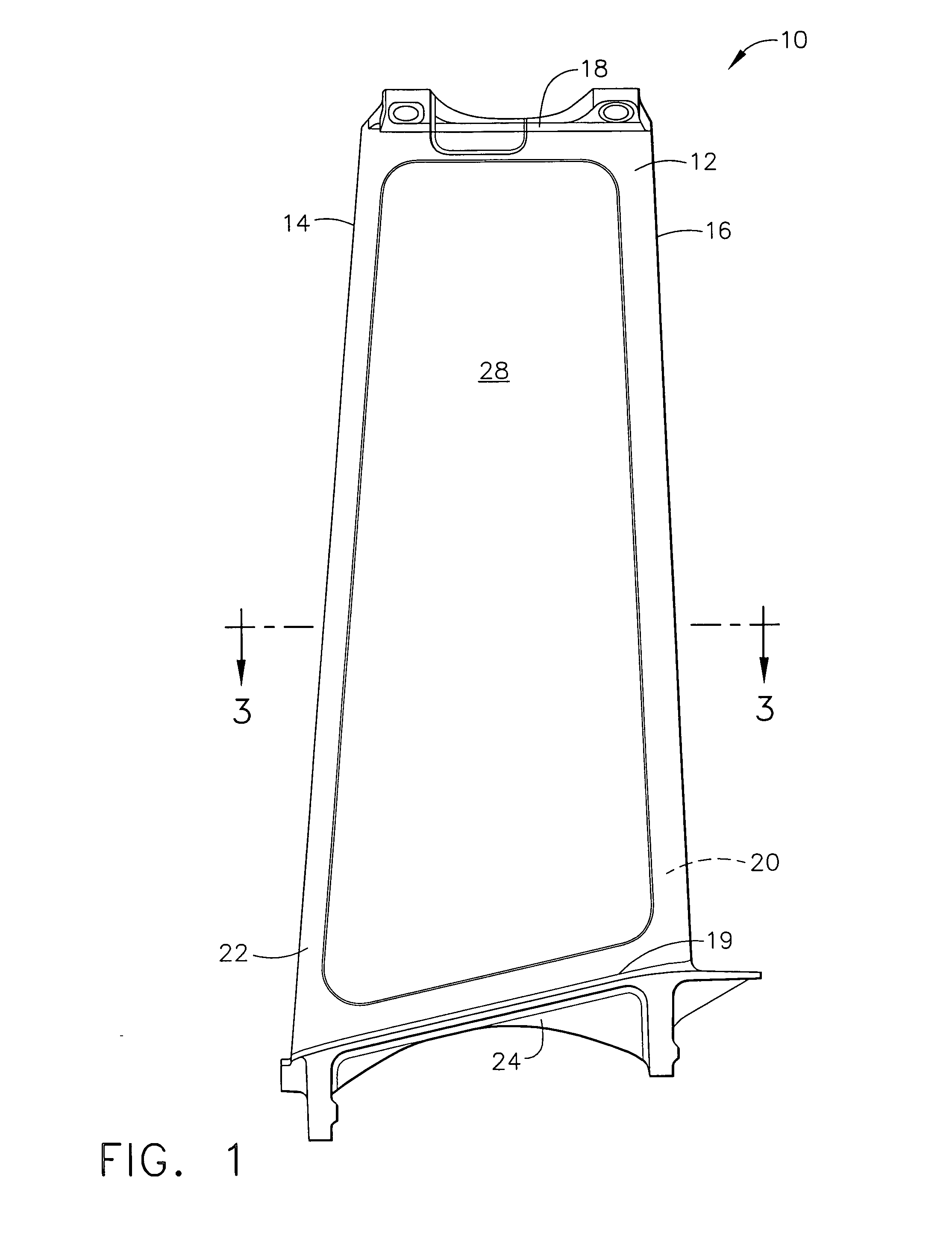

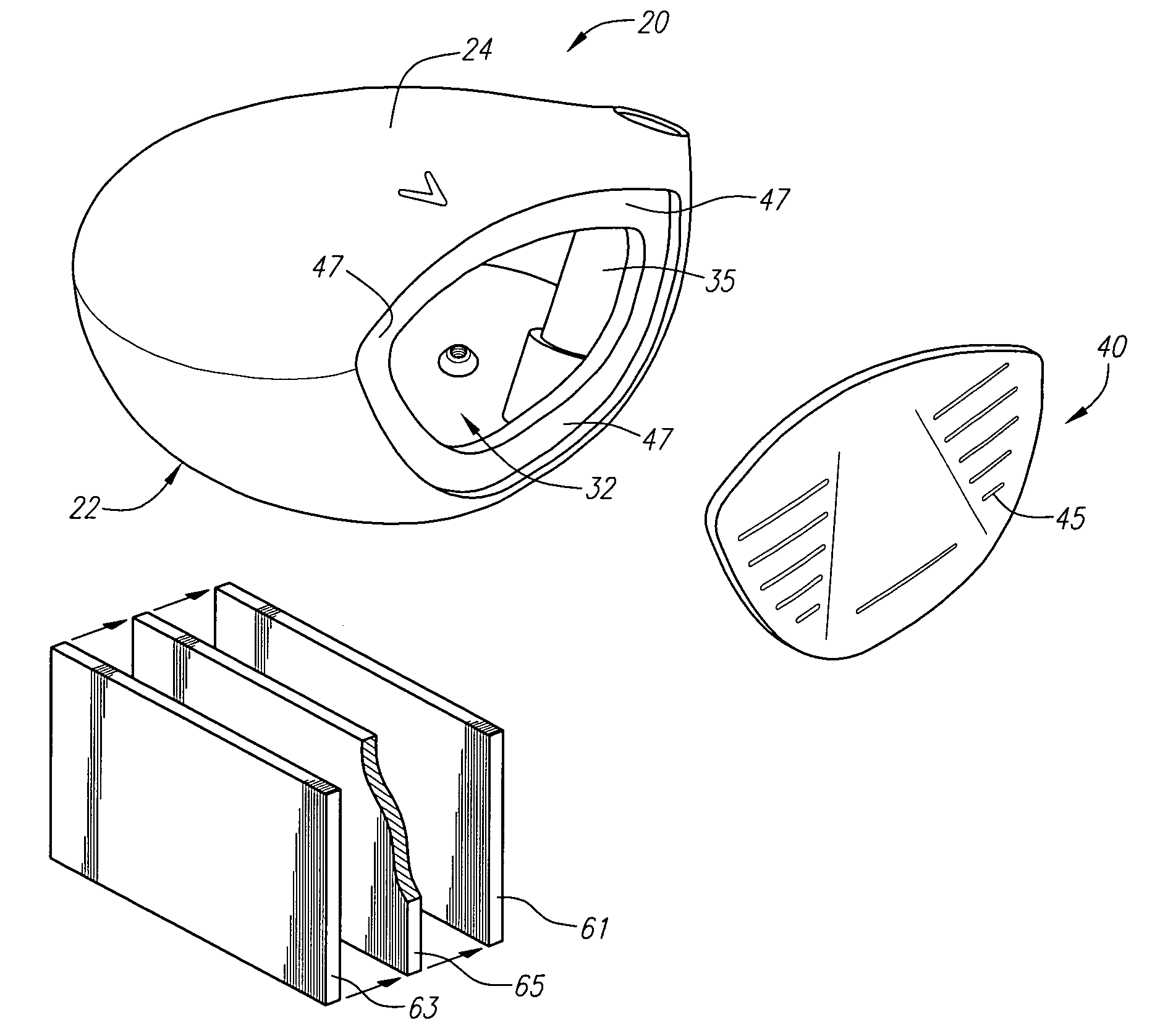

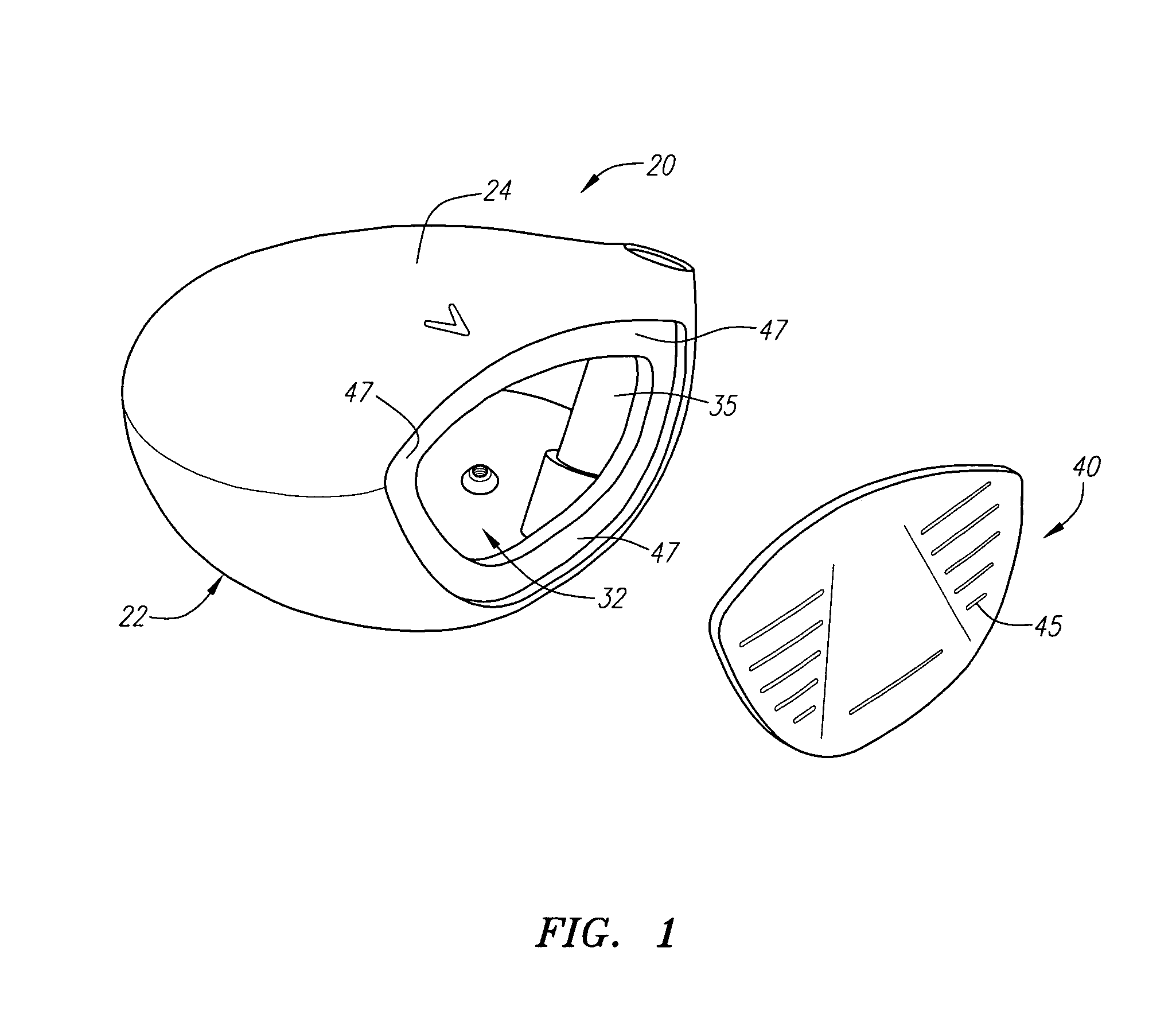

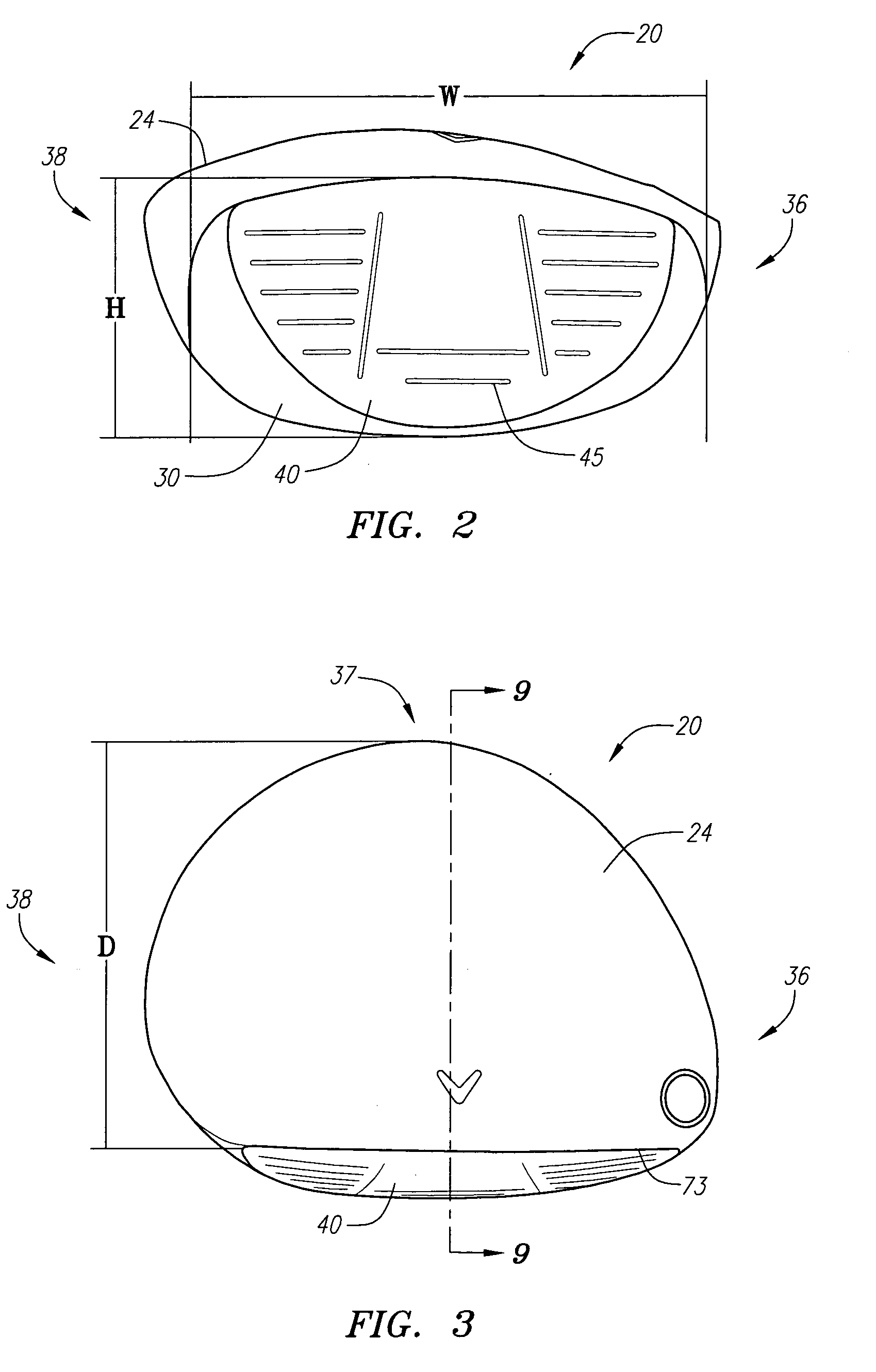

Golf club head with a face insert

InactiveUS6986715B2Improve performanceLaminate strength is lowGolf clubsRacket sportsBonding processEngineering

A golf club head (20) having a body (22) with a front wall (30) with an opening (32) and a striking plate insert (40) is disclosed herein. The striking plate insert (40) preferably includes an outer layer (61) and an inner layer (65) that are joined together by an explosion bonding process. The inner layer (65) is preferably composed of a material that has a lower yield strength than that of the outer layer (61). The explosion bonding process results in the striking plate insert having an increased yield strength relative to the yield strengths of the individual layers. The golf club head (20) preferably has a moment of inertia, Izz, about the Z axis through the center of gravity of the golf club head ranging from 2700 g-cm2 to 4000 g-cm2.

Owner:TOPGOLF CALLAWAY BRANDS CORP

Process for making chemically bonded composite hydroxide ceramics

InactiveUS6770325B2Reduce reactivityMinimizes shrinkageImpression capsPretreated surfacesPhosphateCeramic coating

This invention relates to novel process of preparing chemically bonded composite hydroxide ceramics by exposing a thermally treated hydroxide ceramic to phosphate reagent and subsequent heat treating the resulting system to initiate a rapid chemical bonding reaction. Such combined hydroxide / chemical bonding process can be used to fabricate ceramics or ceramic coatings for a variety of high and low temperature applications, including corrosion protection, wear resistance, dielectric properties, metal reinforced ceramics, ceramic membranes, non-sticky surfaces, bio-active ceramics, thermal barrier ceramics, non-wetted surfaces, and others.

Owner:THE UNIV OF BRITISH COLUMBIA

Partially Patterned Lead Frames and Methods of Making and Using the Same in Semiconductor Packaging

InactiveUS20110111562A1Improve structural rigiditySemiconductor/solid-state device detailsSolid-state devicesLead bondingBonding process

A method of making a lead frame and a partially patterned lead frame package with near-chip scale packaging lead-count, wherein the method lends itself to better automation of the manufacturing line and improved quality and reliability of the packages produced therefrom. A major portion of the manufacturing process steps is performed with a partially patterned strip of metal formed into a web-like lead frame on one side so that the web-like lead frame is also rigid mechanically and robust thermally to perform without distortion or deformation during the chip-attach and wire bond processes, both at the chip level and the package level. The bottom side of the metal lead frame is patterned to isolate the chip-pad and the wire bond contacts only after the front side, including the chip and wires, is hermetically sealed with an encapsulant. The resultant package being electrically isolated enables strip testing and reliable singulation.

Owner:UNISEM M BERHAD

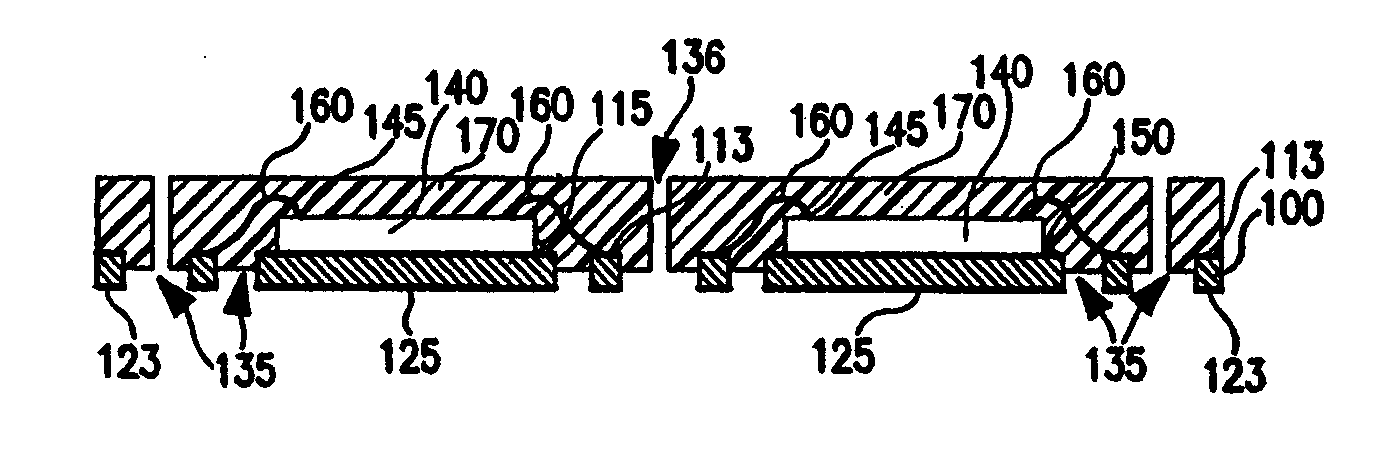

Dielectric wafer level bonding with conductive feed-throughs for electrical connection and thermal management

ActiveUS20070284602A1Increase the number ofMinimization requirementsSemiconductor/solid-state device detailsSolid-state devicesContact padDevice material

A method for fabricating semiconductor and electronic devices at the wafer level is described. In this method, dielectric material is used to wafer bond a device wafer to a submount wafer, after which vias can be structured into the submount wafer and dielectric bonding material to access contact pads on the bonded surface of the device wafer. The vias may subsequently be filled with electrically and thermally conducting material to provide electrical contacts to the device and improve the thermal properties of the finished device, respectively. The post-bonding process described provides a simple, cost-effective, non-alignment method for fabricating a variety of electronic and semiconductor devices, particularly light emitting diodes with electrical contacts at the bottom of the chip.

Owner:CREELED INC

Conductive adhesive bonding

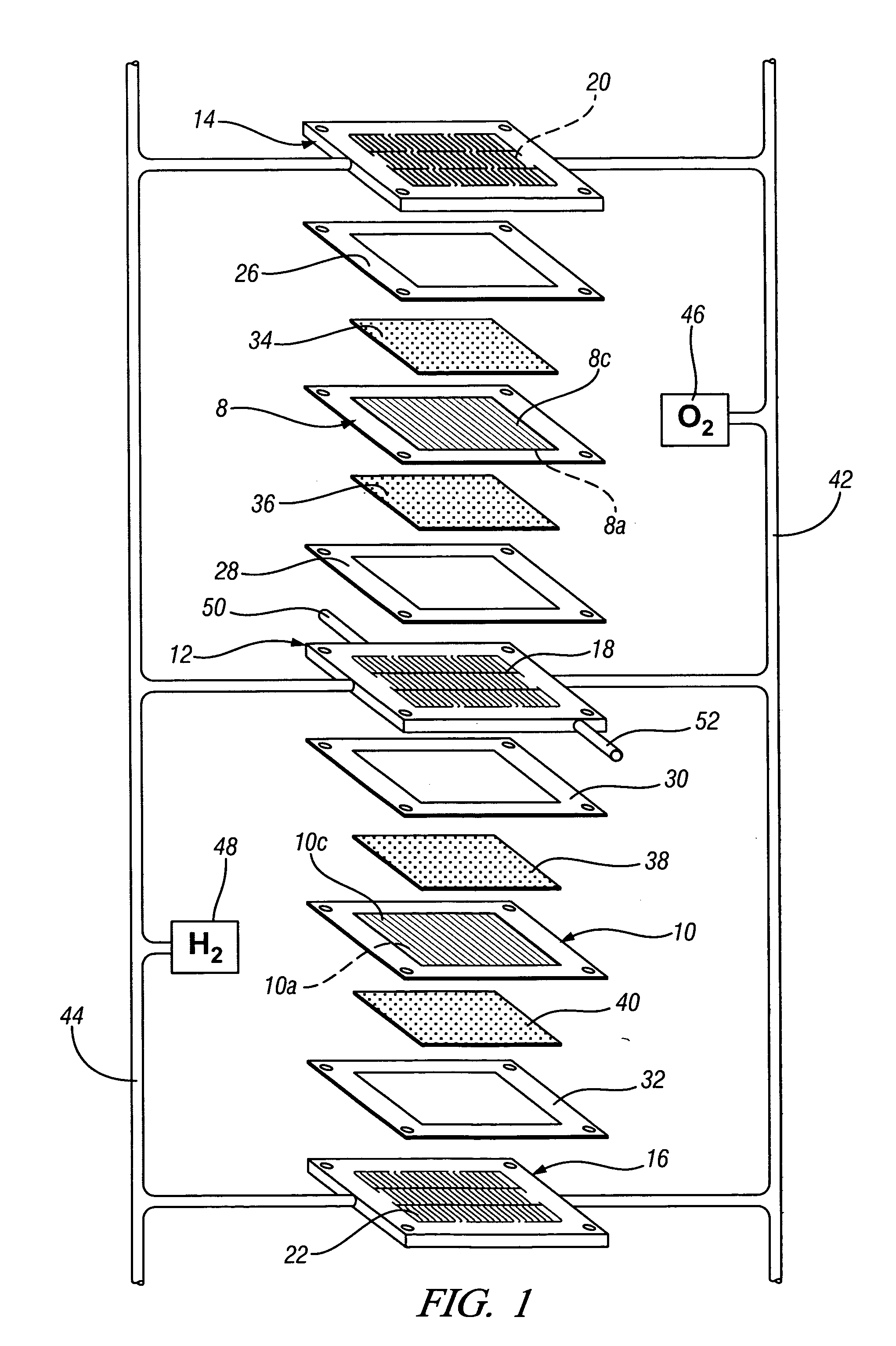

InactiveUS20060060296A1Reduce resistanceMechanical working/deformationLamination ancillary operationsSurface reactionFuel cells

Electrically conductive workpieces with facing surfaces are bonded with an adhesive that is filled with conductive metal particles that are reactive with the surfaces of the workpieces. In the bonding process the surfaces are coated with the adhesive, pressed together and an electric current passed between them to momentarily melt the conductive particles. The molten droplets agglomerate and wet the facing surfaces. When the molten clusters re-solidify, electrically conductive paths are formed between the workpieces. For example, the practice is useful for bonding ferrous-based or aluminum-based alloy sheets, strips or plates in making products such as bipolar plates for fuel cells.

Owner:GM GLOBAL TECH OPERATIONS LLC