Patents

Literature

249 results about "Eutectic bonding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Eutectic bonding, also referred to as eutectic soldering, describes a wafer bonding technique with an intermediate metal layer that can produce a eutectic system. Those eutectic metals are alloys that transform directly from solid to liquid state, or vice versa from liquid to solid state, at a specific composition and temperature without passing a two-phase equilibrium, i.e. liquid and solid state. The fact that the eutectic temperature can be much lower than the melting temperature of the two or more pure elements can be important in eutectic bonding.

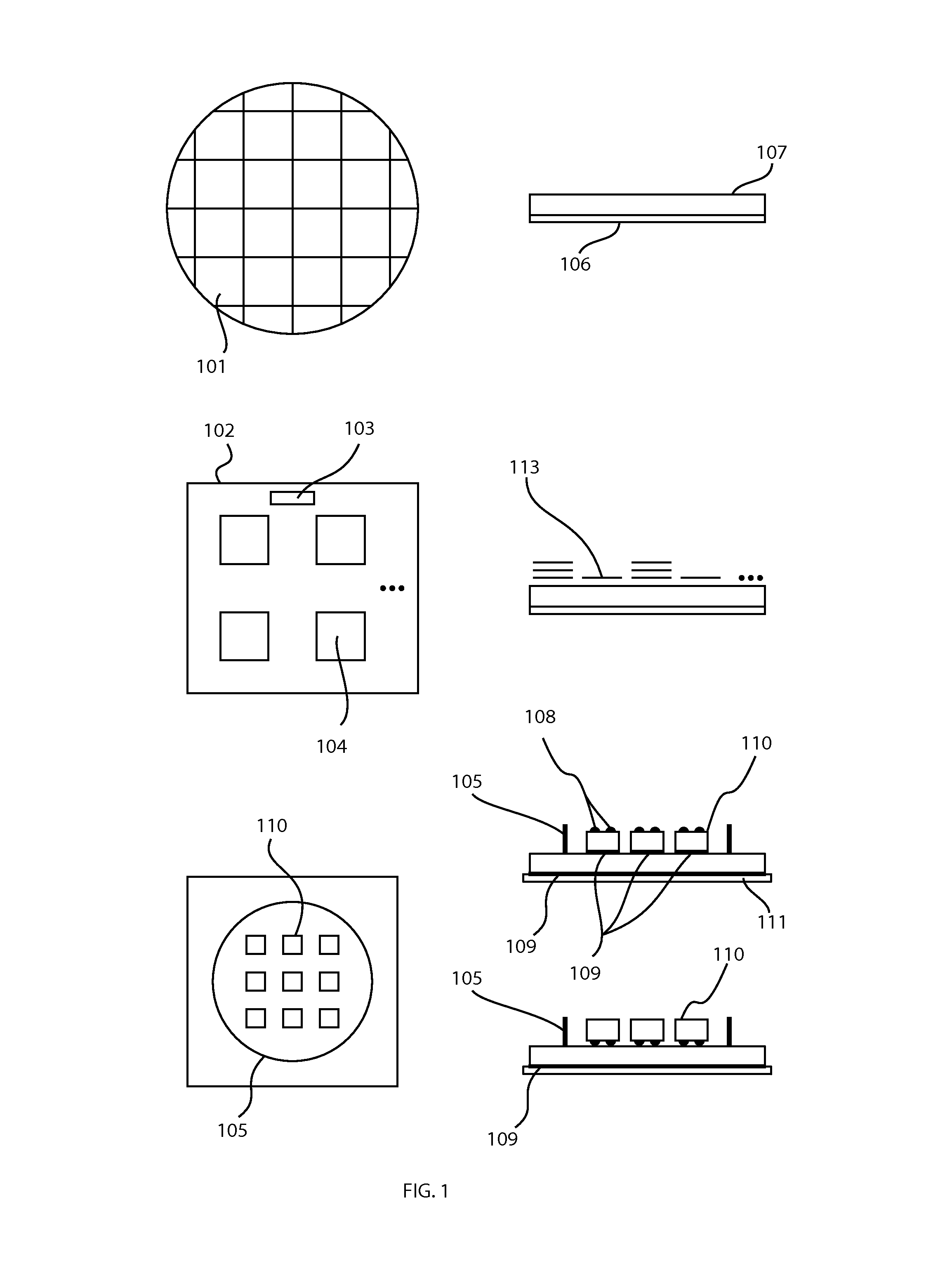

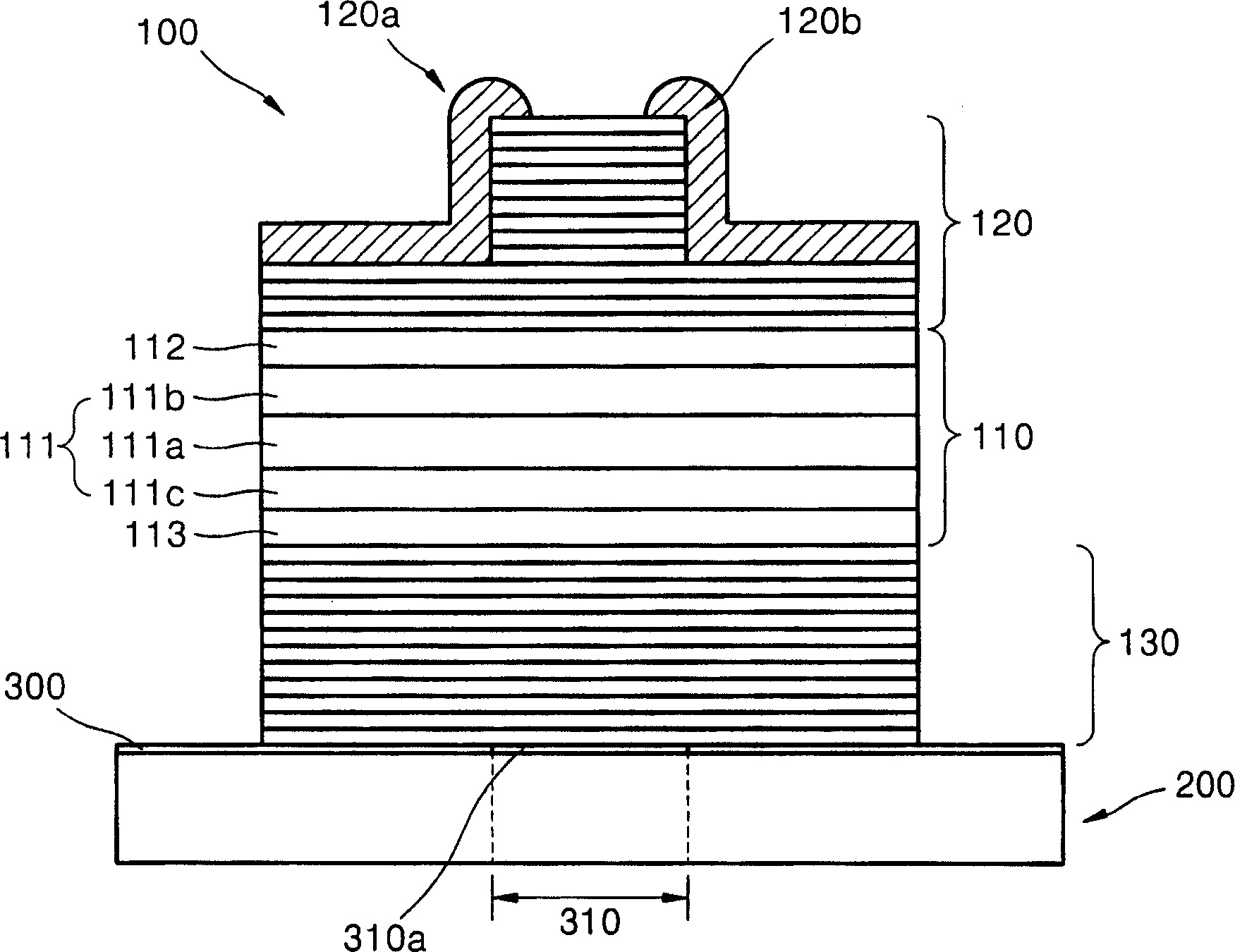

Integrated compact MEMS device with deep trench contacts

InactiveUS20130168740A1High aspect ratioIncrease contactSolid-state devicesSpeed/acceleration/shock instrument detailsCMOSSolder ball

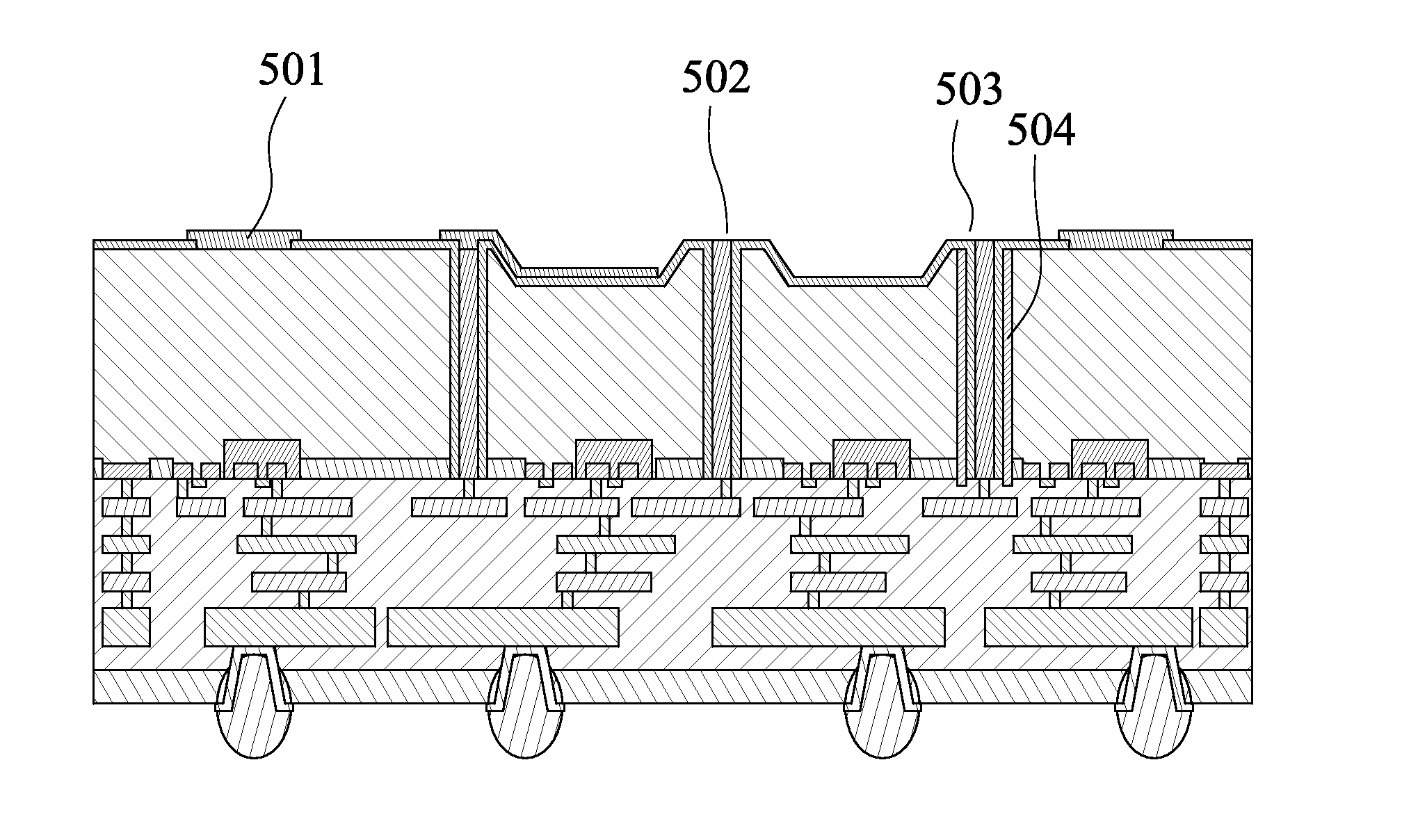

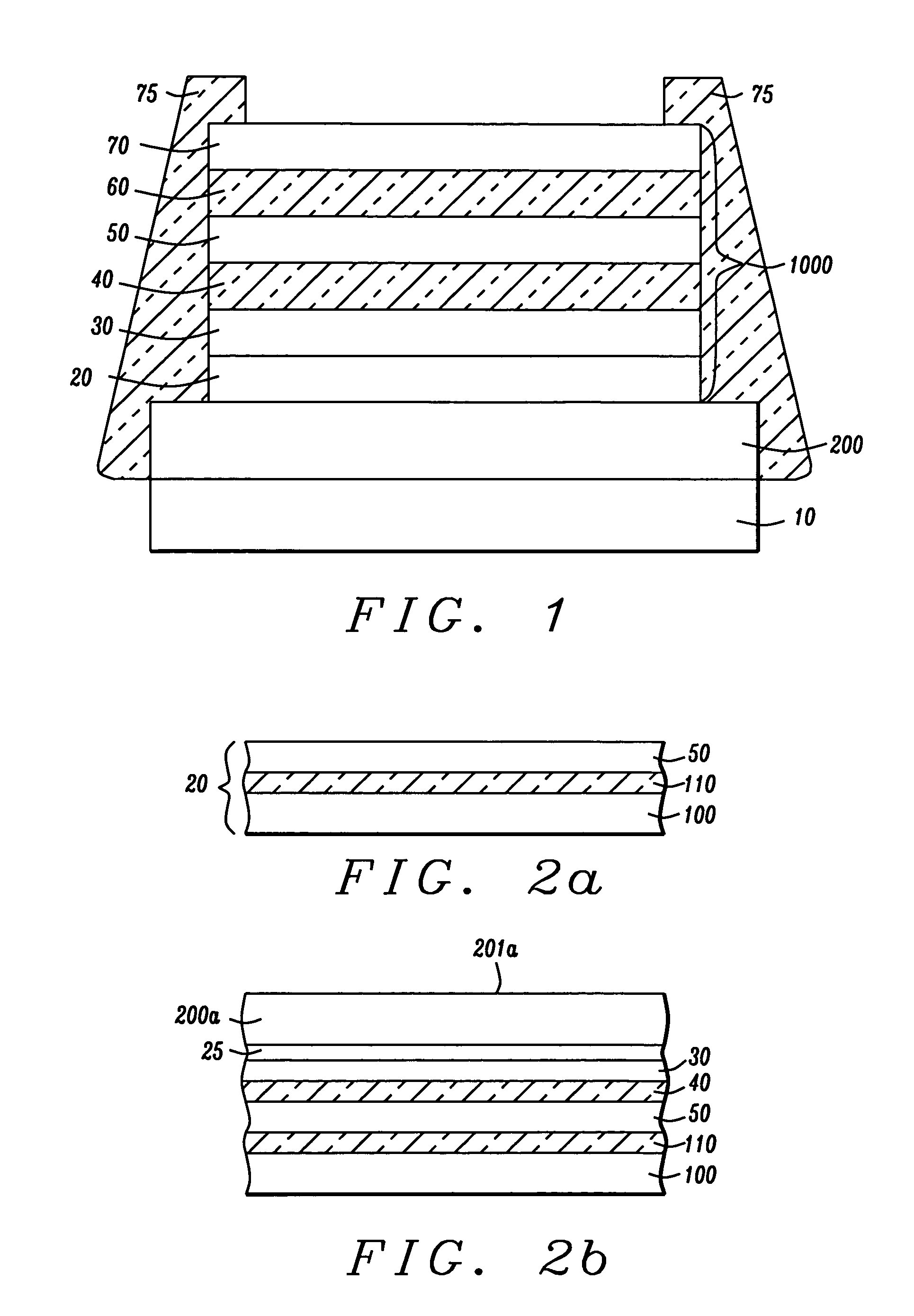

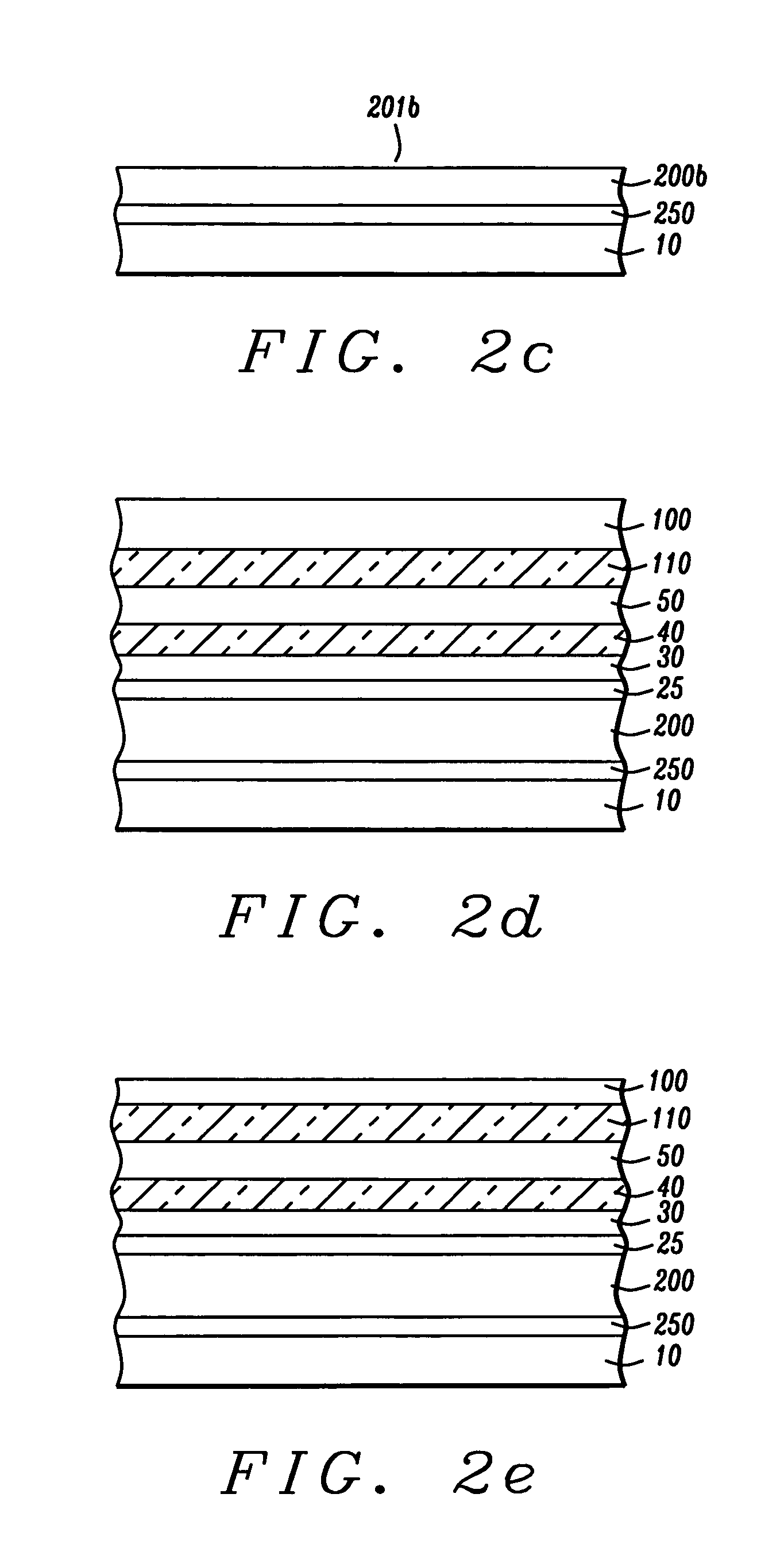

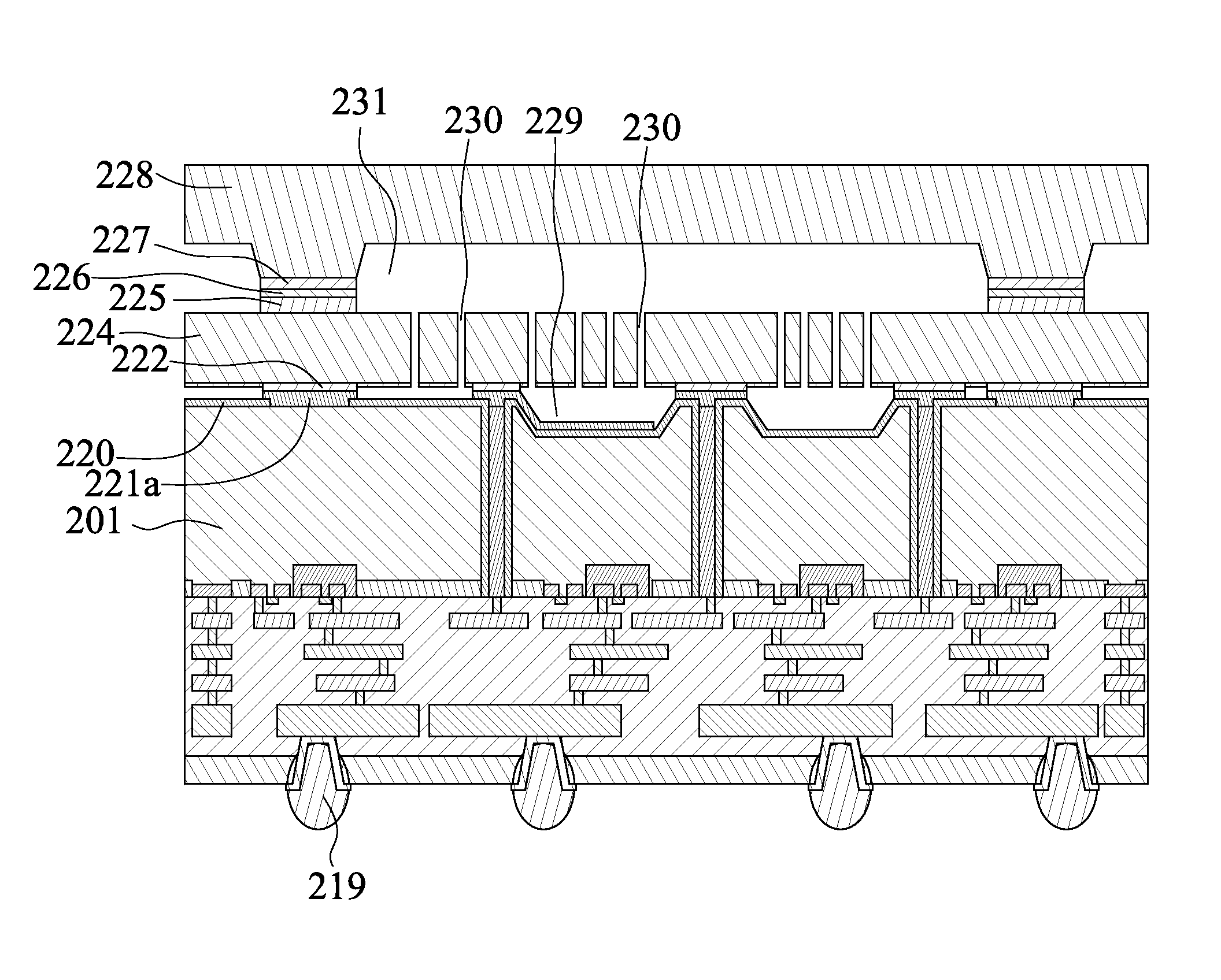

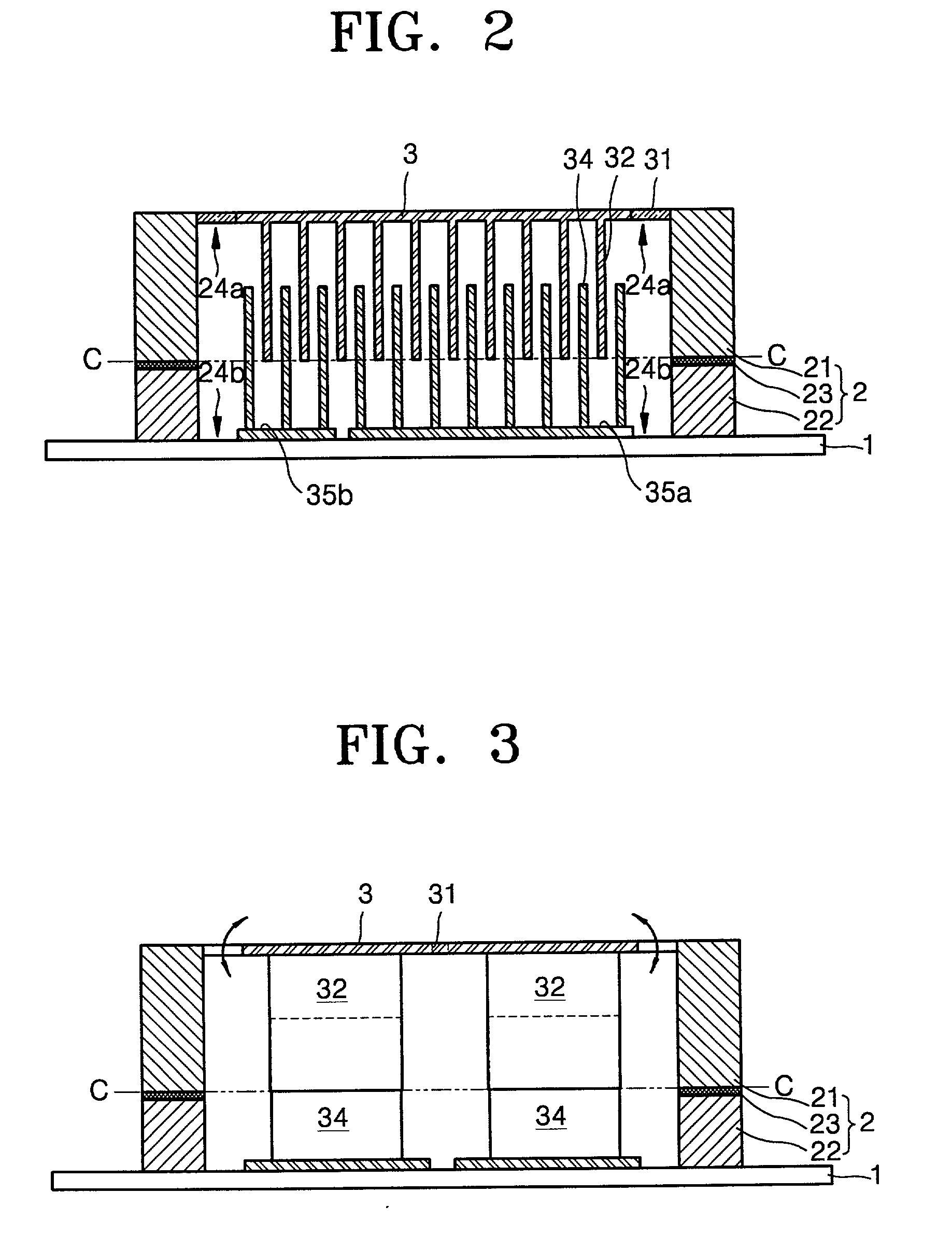

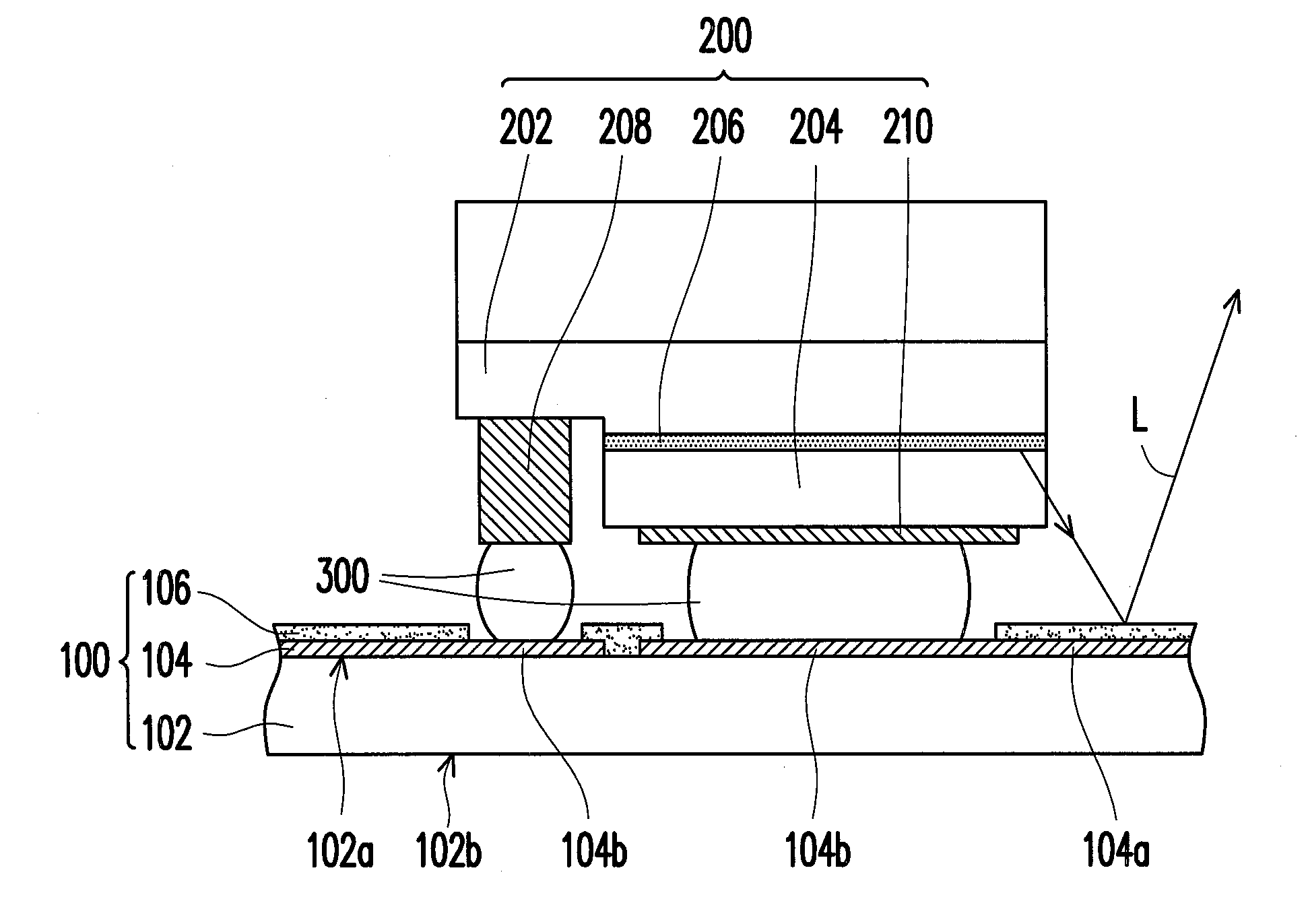

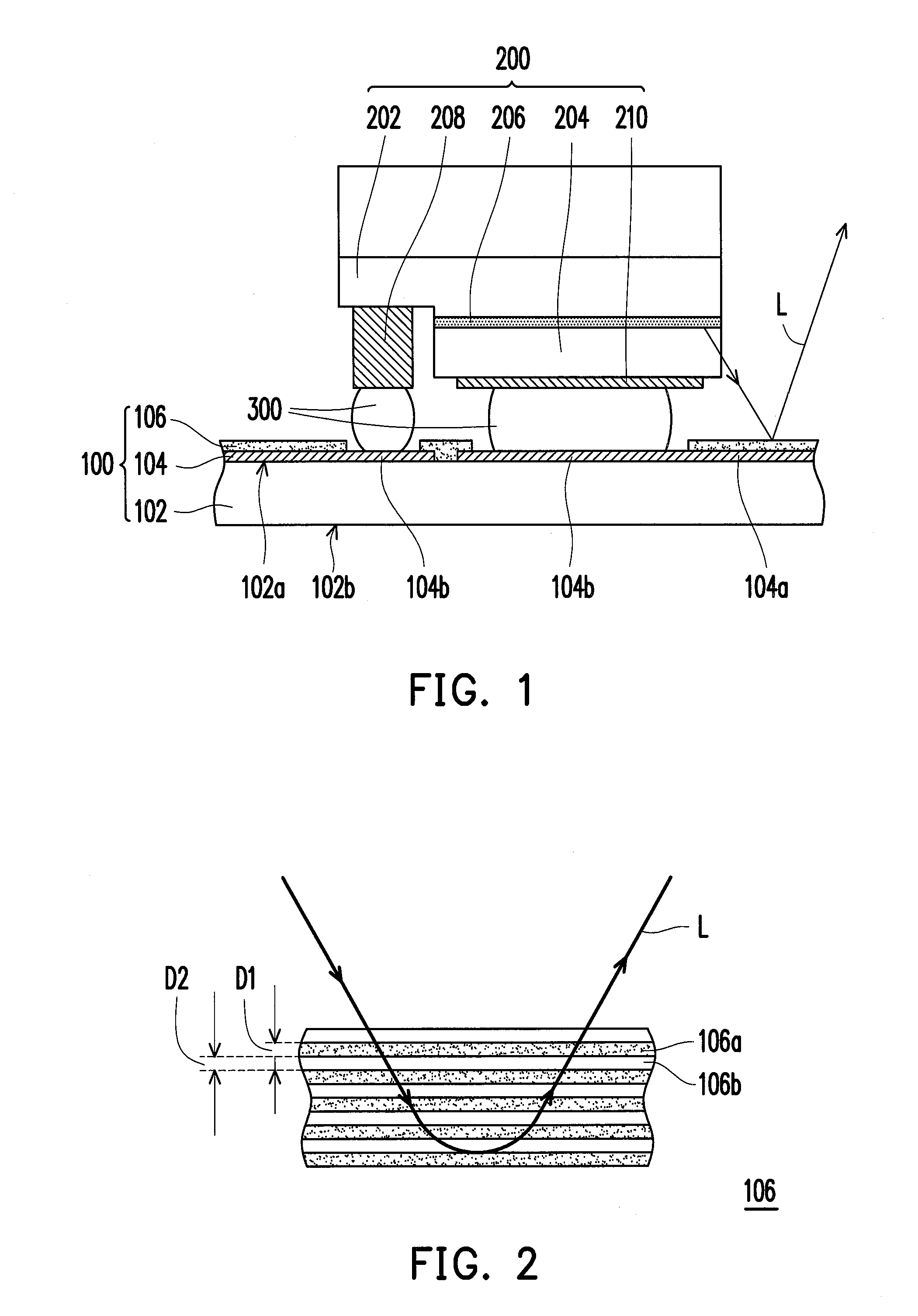

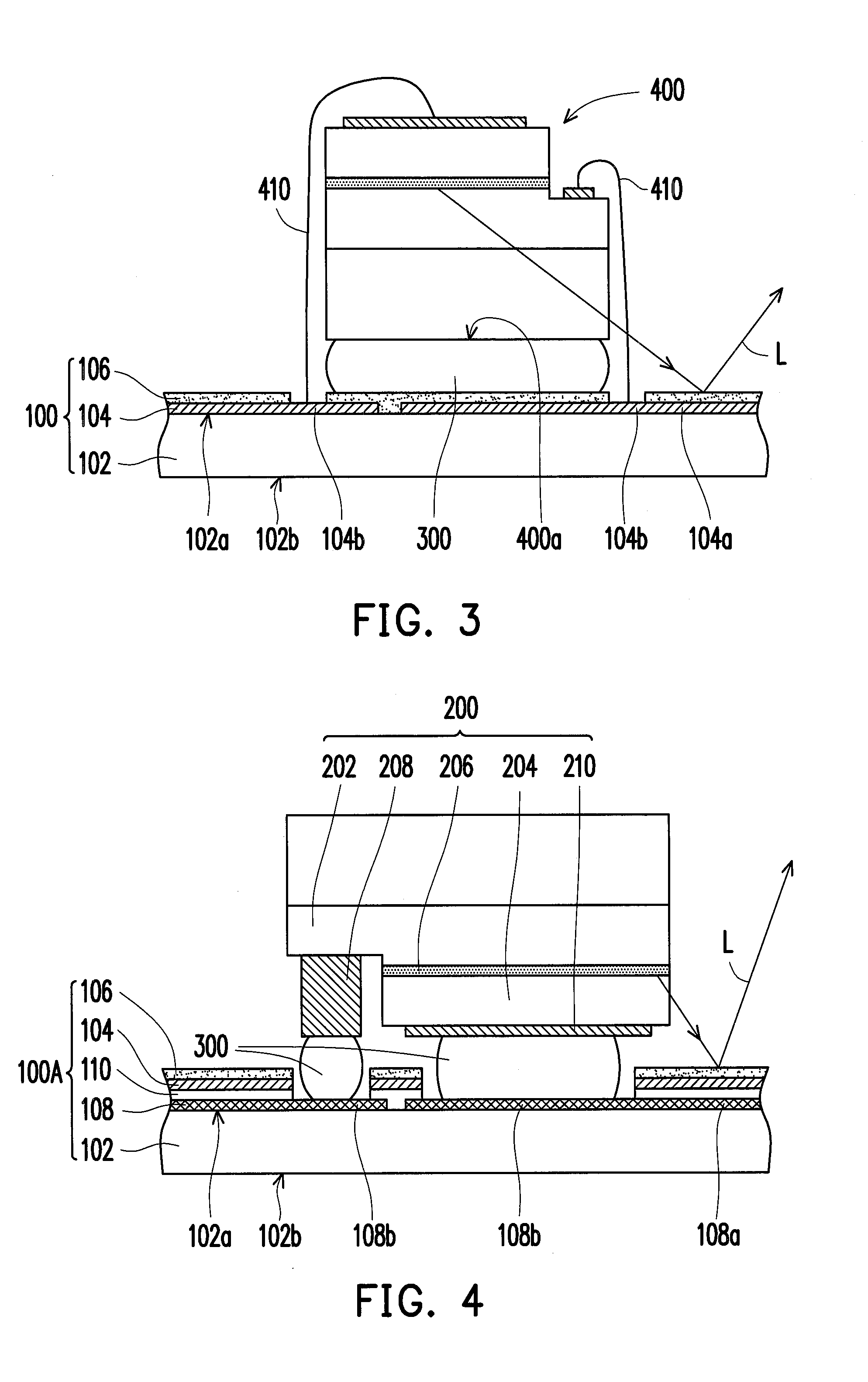

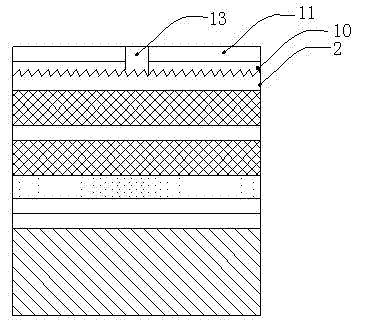

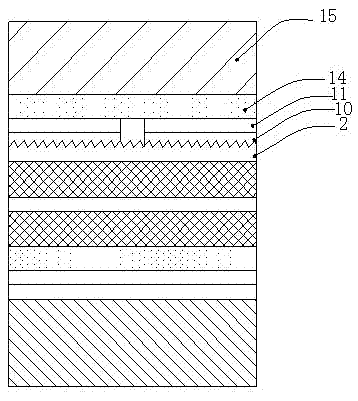

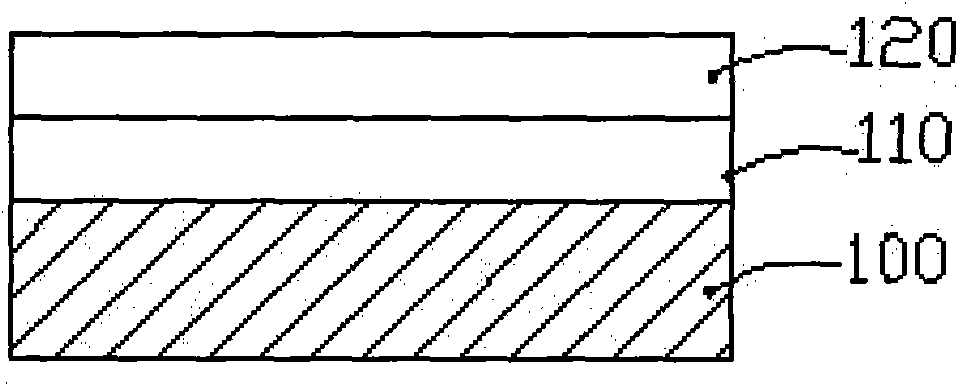

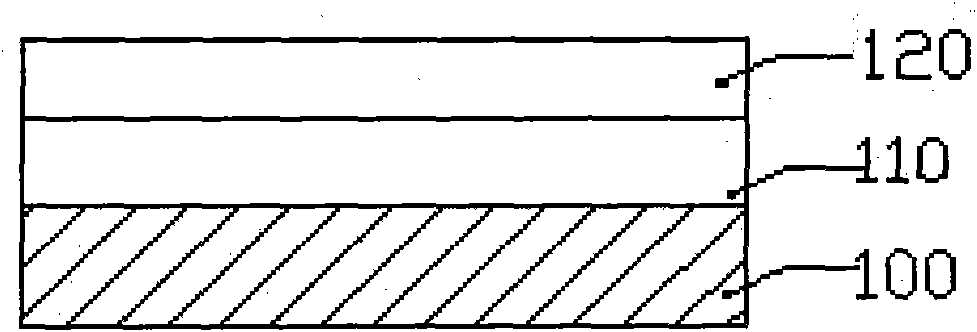

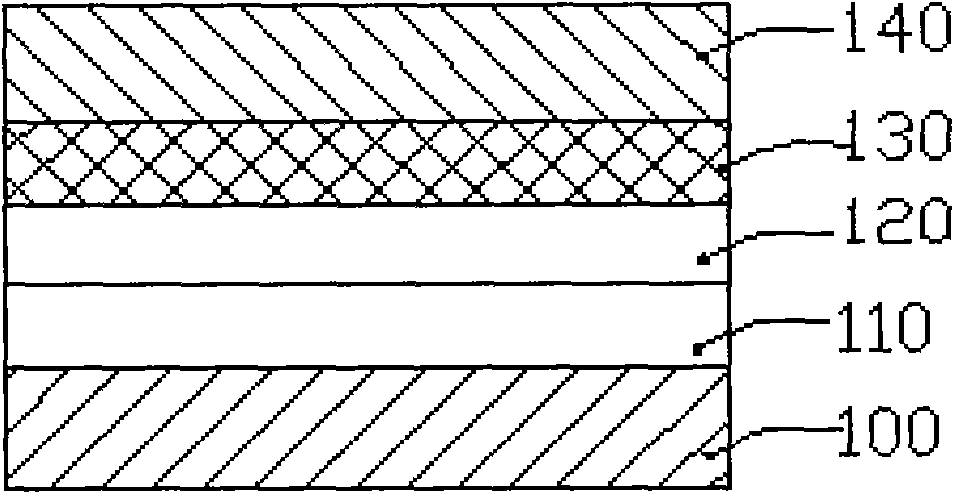

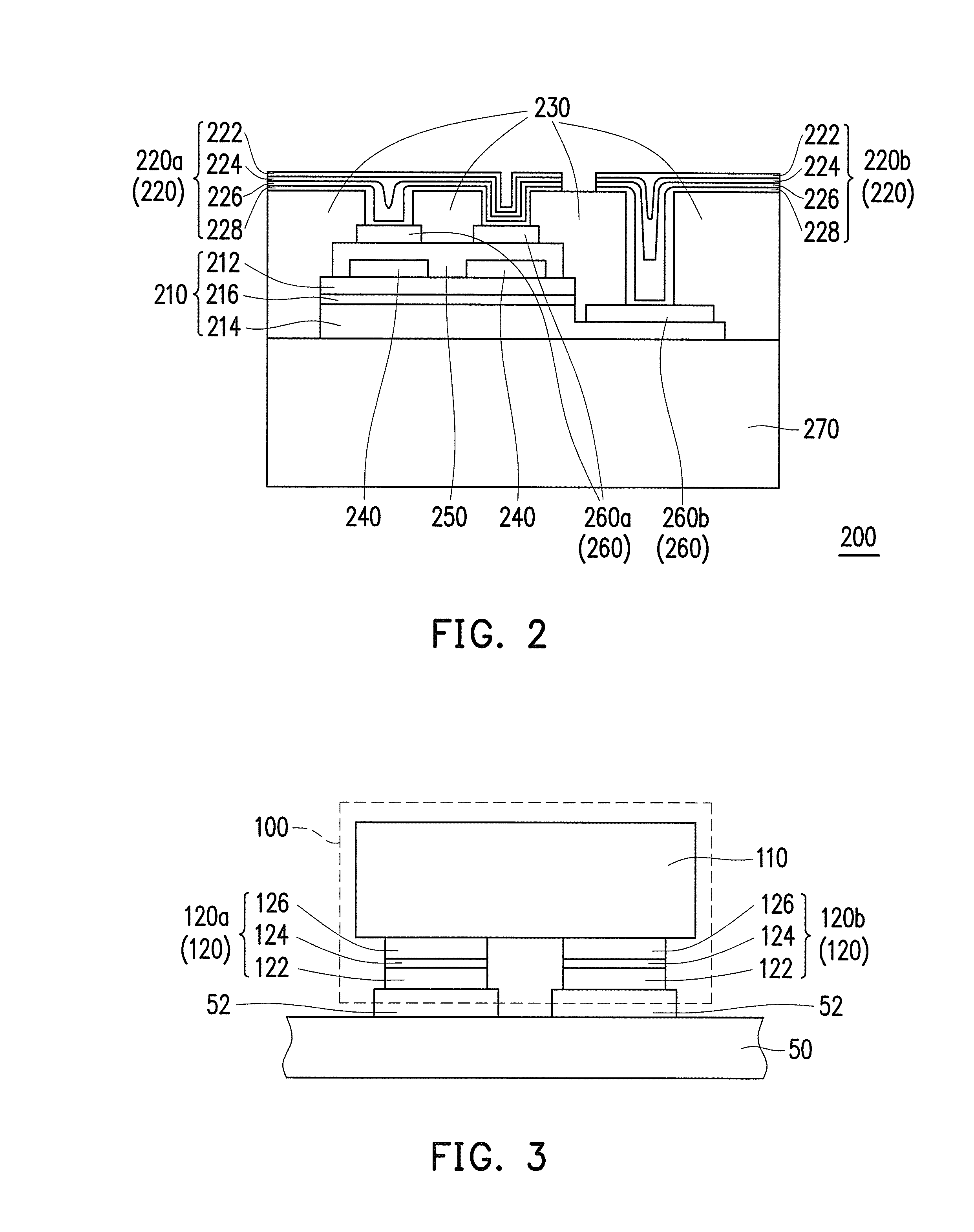

A compact MEMS motion sensor device is provided, including a CMOS substrate layer, with plural anchor posts having an isolation oxide layer surrounding a conductive layer. On one side of CMOS substrate layer, the device further includes a field oxide (FOX) layer, a first set and a second set of implant doped silicon areas, a first polysilicon layer, an oxide layer embedded with plural metal layers interleaved with via hole layers, a Nitride deposition layer, an under bump metal (UBM) layer and a plurality of solder spheres. On the other side of CMOS substrate layer, the present invention further includes a backside interconnect isolation oxide layer, a first MEMS bonding layer, a first metal compound layer, a second MEMS bonding layer, a MEMS layer, a first MEMS eutectic bonding layer, a second metal compound layer, a second MEMS eutectic bonding layer, and a MEMS cap layer.

Owner:WINDTOP TECH CORP

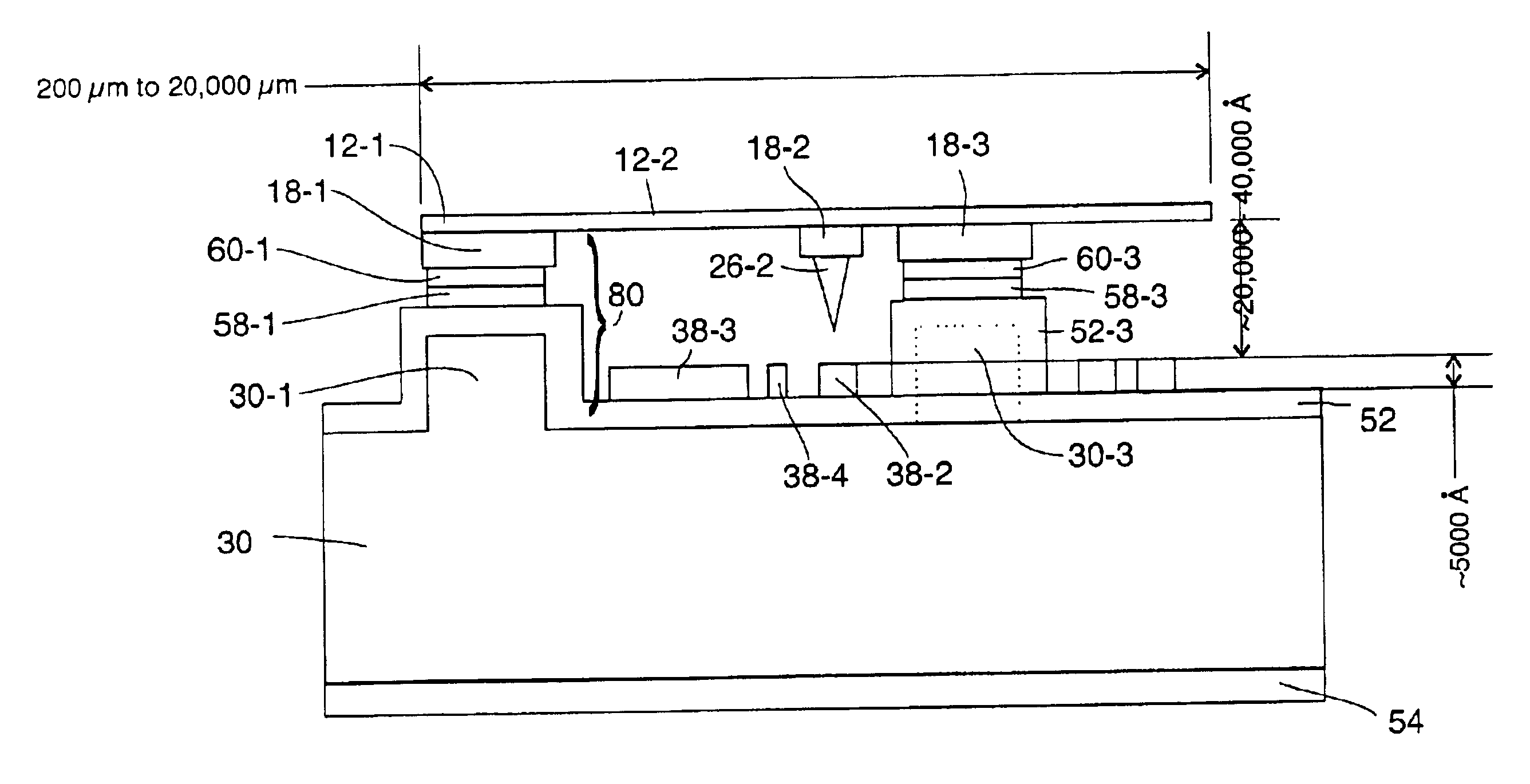

Method of making resonant tunneling diodes and CMOS backend-process-compatible three dimensional (3-D) integration

InactiveUS7002175B1Improve performanceEase of fabricationSemiconductor/solid-state device detailsNanoinformaticsLow noiseElectrical connection

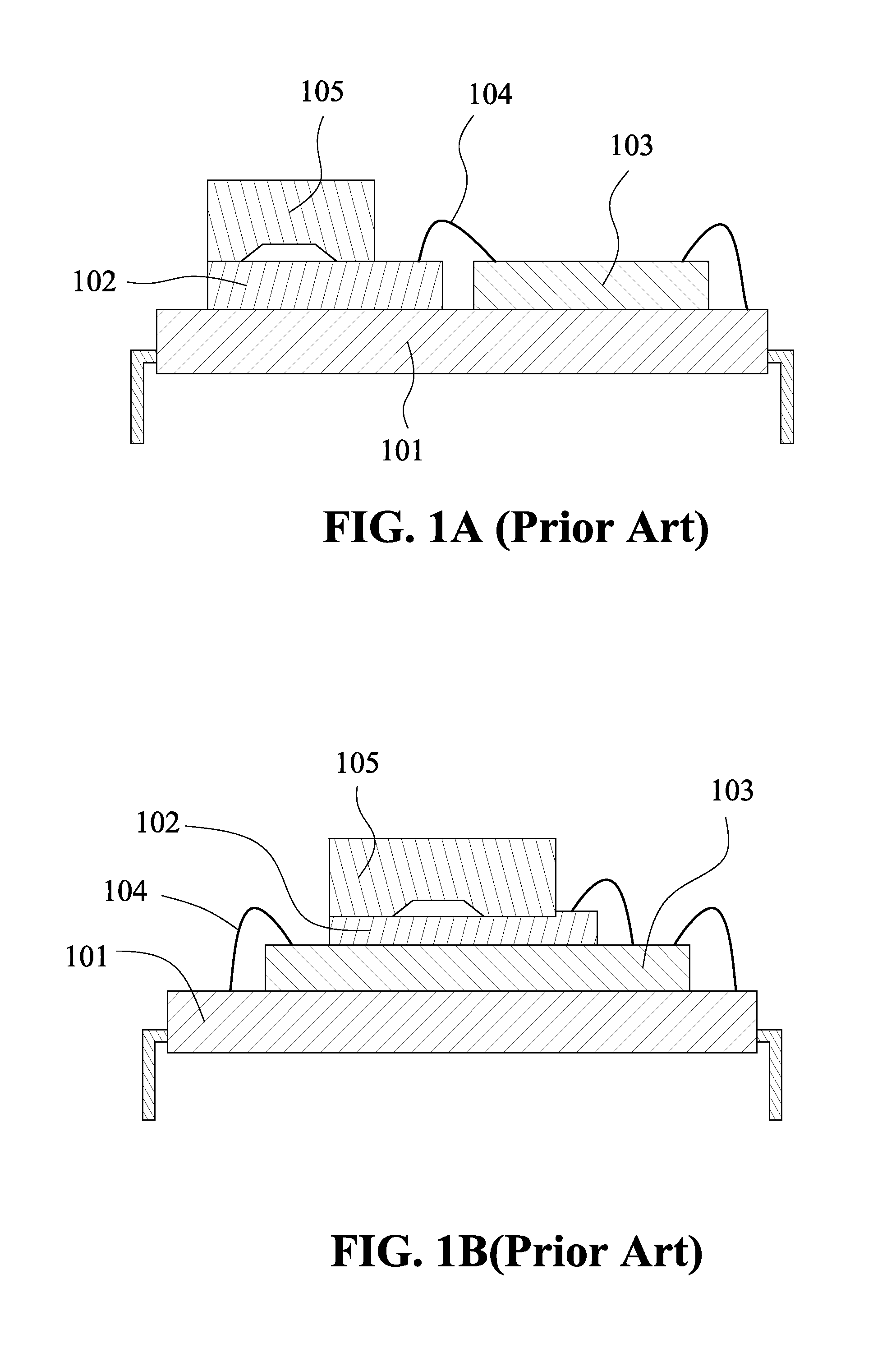

A double barrier resonant tunneling diode (RTD) is formed and integrated with a level of CMOS / BJT / SiGe devices and circuits through processes such as metal-to-metal thermocompressional bonding, anodic bonding, eutectic bonding, plasma bonding, silicon-to-silicon bonding, silicon dioxide bonding, silicon nitride bonding and polymer bonding or plasma bonding. The electrical connections are made using conducting interconnects aligned during the bonding process. The resulting circuitry has a three-dimensional architecture. The tunneling barrier layers of the RTD are formed of high-K dielectric materials such as SiO2, Si3N4, Al2O3, Y2O3, Ta2O5, TiO2, HfO2, Pr2O3, ZrO2, or their alloys and laminates, having higher band-gaps than the material forming the quantum well, which includes Si, Ge or SiGe. The inherently fast operational speed of the RTD, combined with the 3-D integrated architecture that reduces interconnect delays, will produce ultra-fast circuits with low noise characteristics.

Owner:AGENCY FOR SCI TECH & RES

Integrated compact MEMS device with deep trench contacts

InactiveUS8587077B2Increase contactAvoid interferenceSolid-state devicesSpeed/acceleration/shock instrument detailsCMOSSolder ball

A compact MEMS motion sensor device is provided, including a CMOS substrate layer, with plural anchor posts having an isolation oxide layer surrounding a conductive layer. On one side of the CMOS substrate layer, the device further includes a field oxide (FOX) layer, a first set and a second set of implant doped silicon areas, a first polysilicon layer, an oxide layer embedded with plural metal layers interleaved with via hole layers, a Nitride deposition layer, an under bump metal (UBM) layer and a plurality of solder spheres. On the other side of the CMOS substrate layer, it further includes a backside interconnect isolation oxide layer, a first MEMS bonding layer, a first metal compound layer, a second MEMS bonding layer, a MEMS layer, a first MEMS eutectic bonding layer, a second metal compound layer, a second MEMS eutectic bonding layer, and a MEMS cap layer.

Owner:WINDTOP TECH CORP

Substrate bonded MEMS sensor

InactiveUS20100072563A1Acceleration measurement using interia forcesTransducer detailsMems sensorsElectrical and Electronics engineering

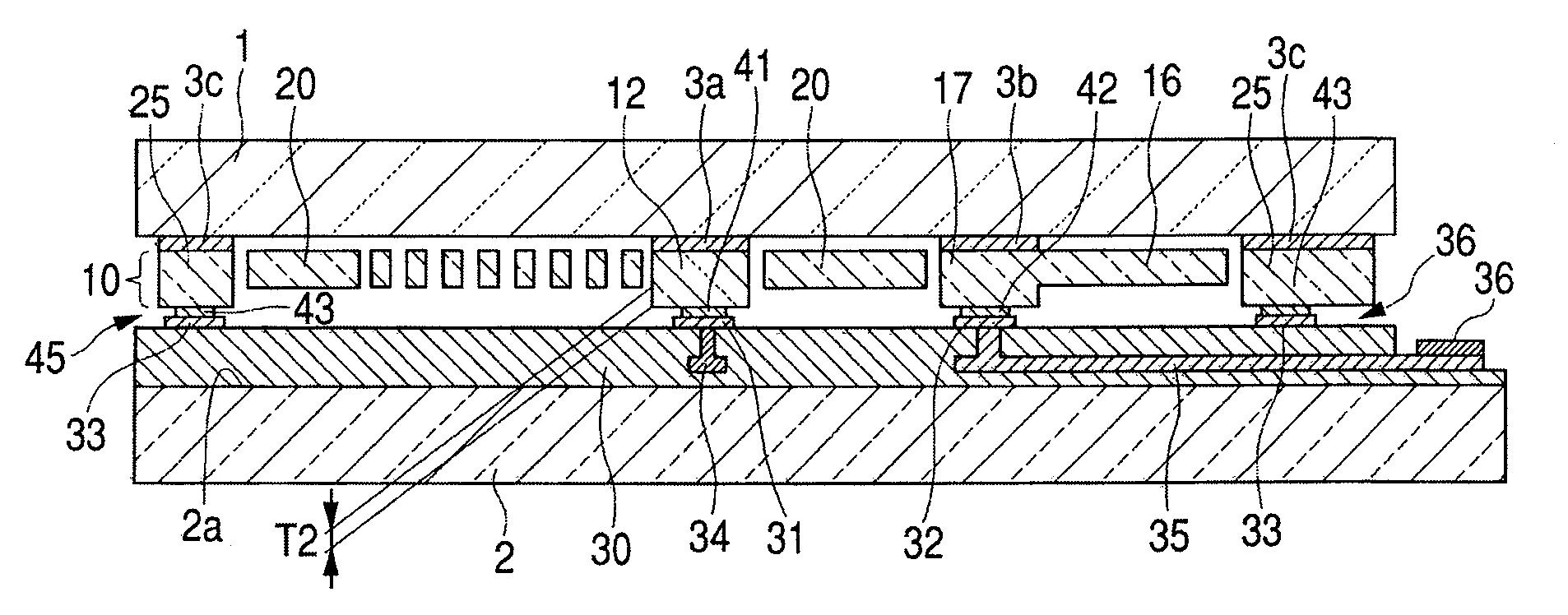

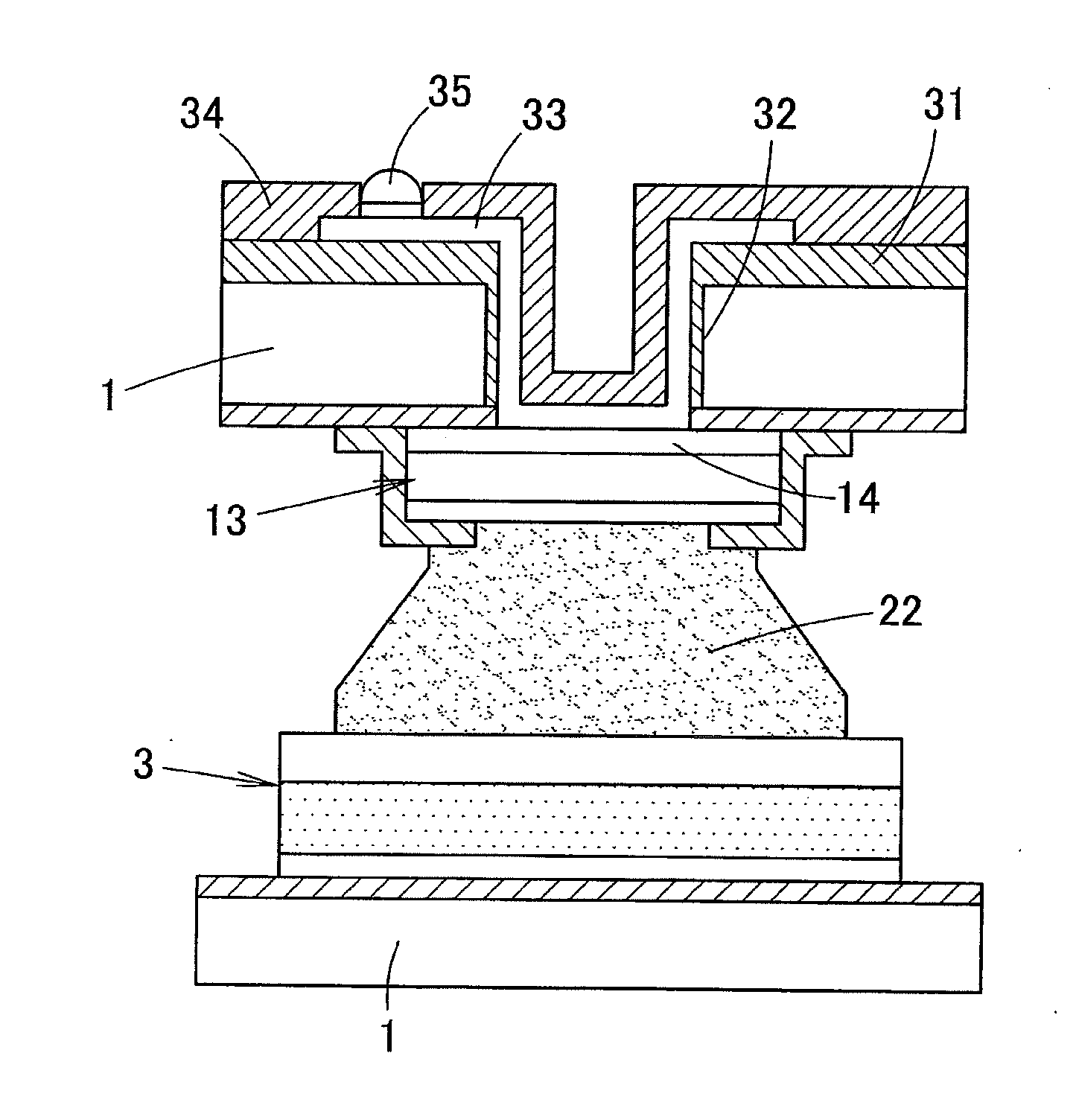

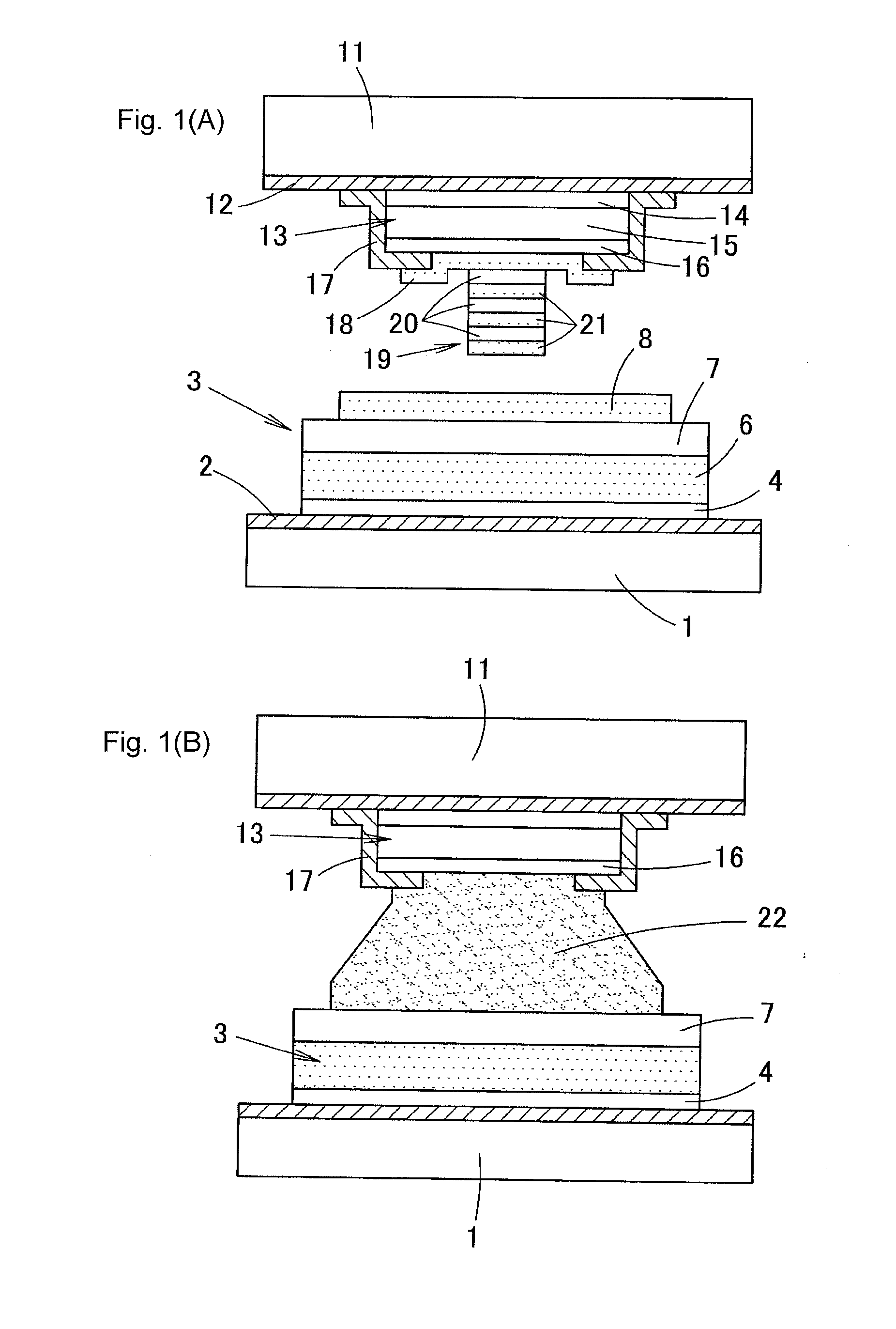

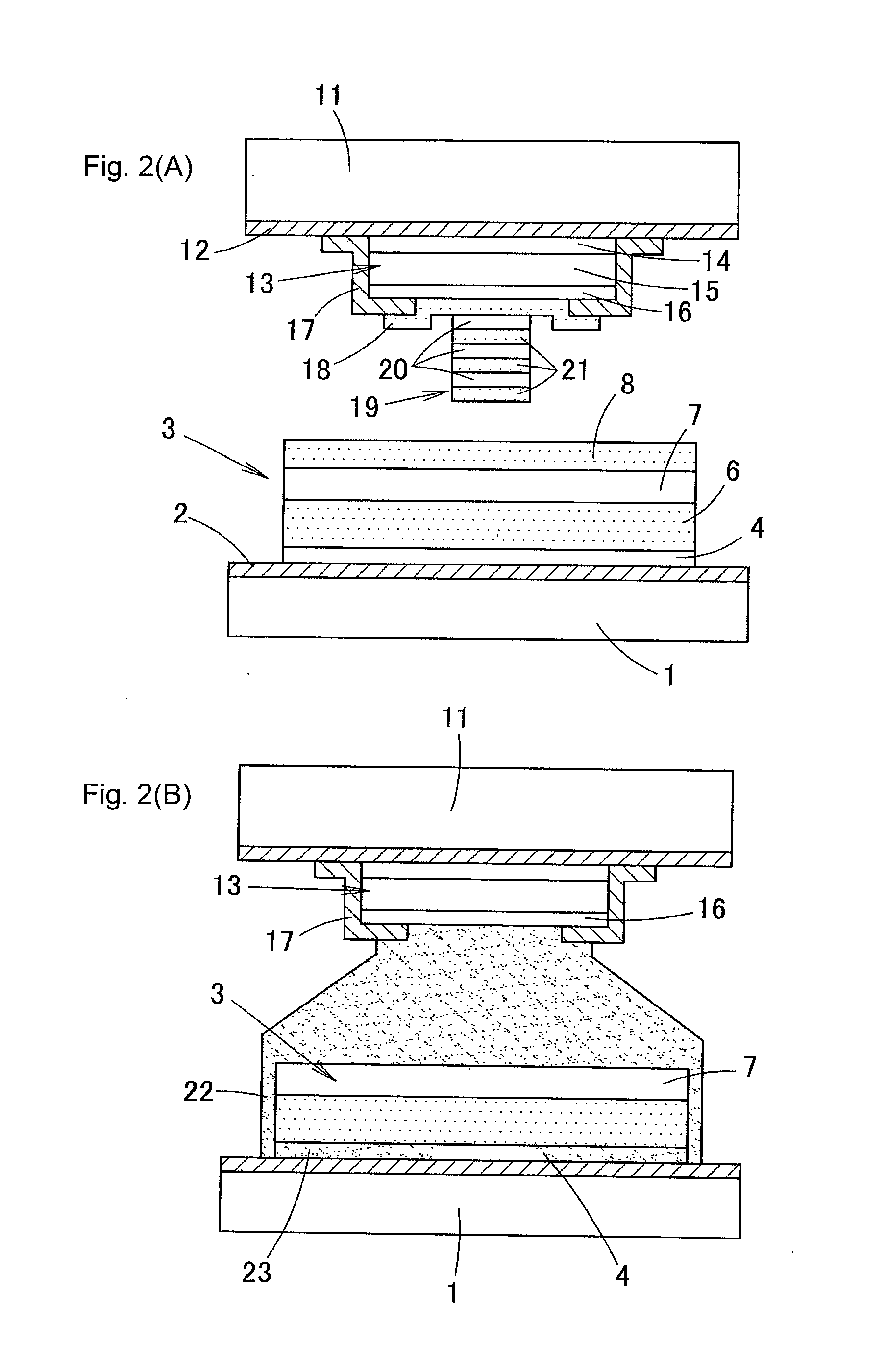

A MEMS sensor includes a first substrate; a second substrate; a movable electrode portion and a fixed electrode portion which are arranged between the first substrate and the second substrate, wherein: conductive supporting portions of the movable electrode portion and the fixed electrode portion are, respectively, fixedly secured to a surface of the first substrate via a first insulating layer; a second insulating layer, a lead layer buried into the second insulating layer, and connection electrode portions that are electrically connected to the lead layer to be individually connected to the conductive supporting portions are provided on a surface of the second substrate; a metallic connection layer is formed on the surface of one of the respective conductive supporting portions; one of the respective connection electrode portions and the metallic connection layer are bonded together by eutectic bonding or diffusion bonding; and, at least each of the connection electrode portions has a thickness of about 4 μm or smaller.

Owner:ALPS ALPINE CO LTD

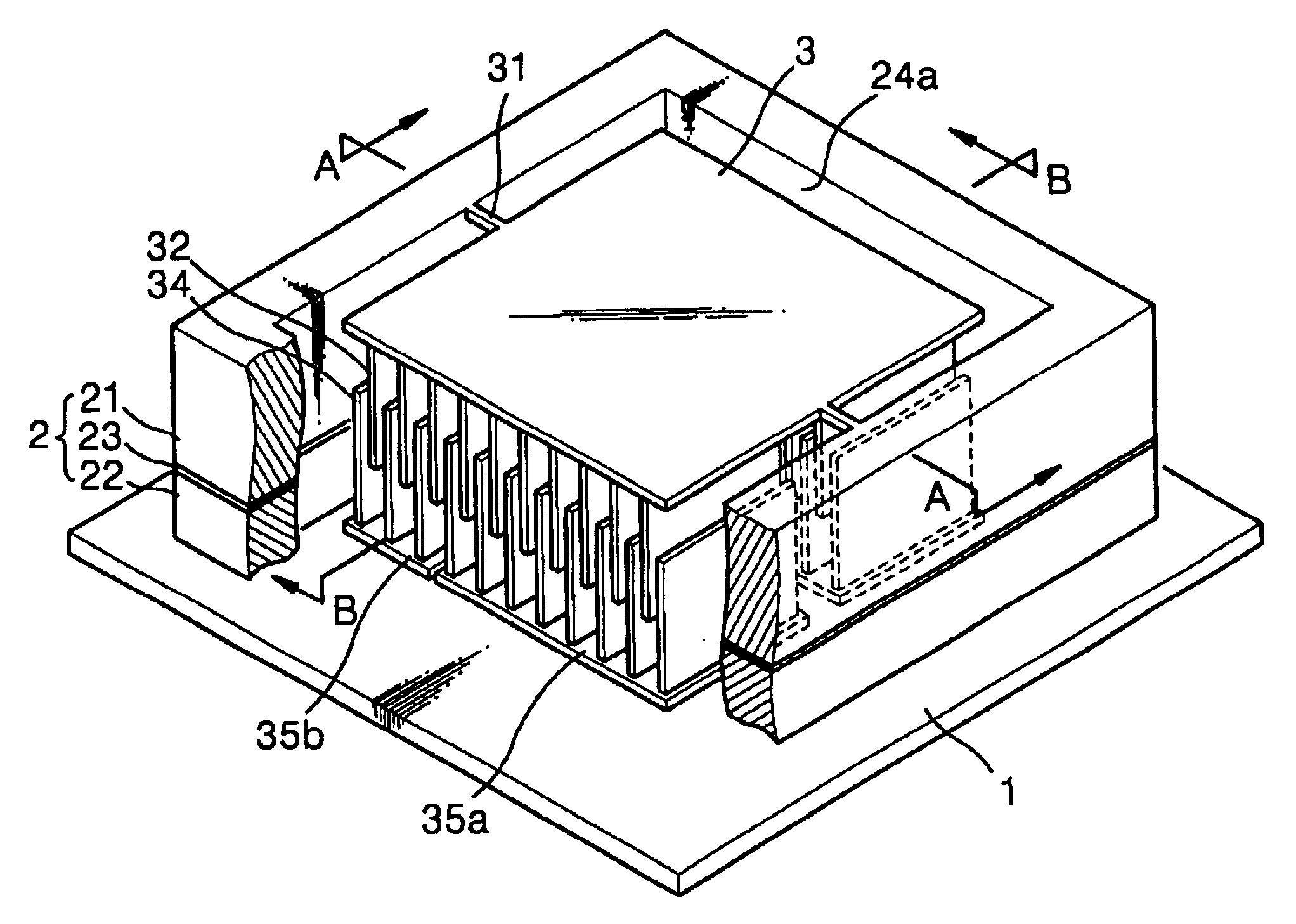

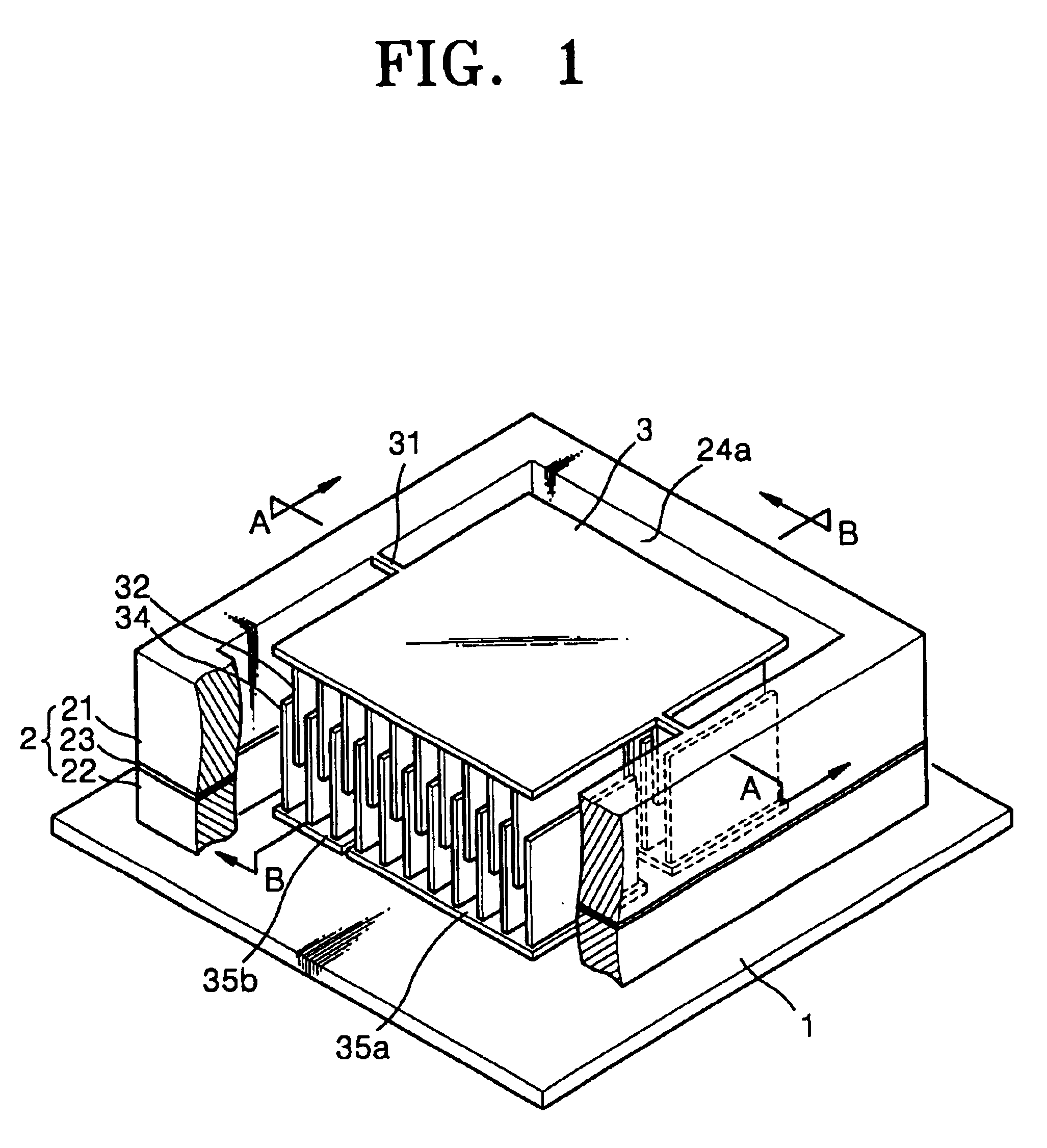

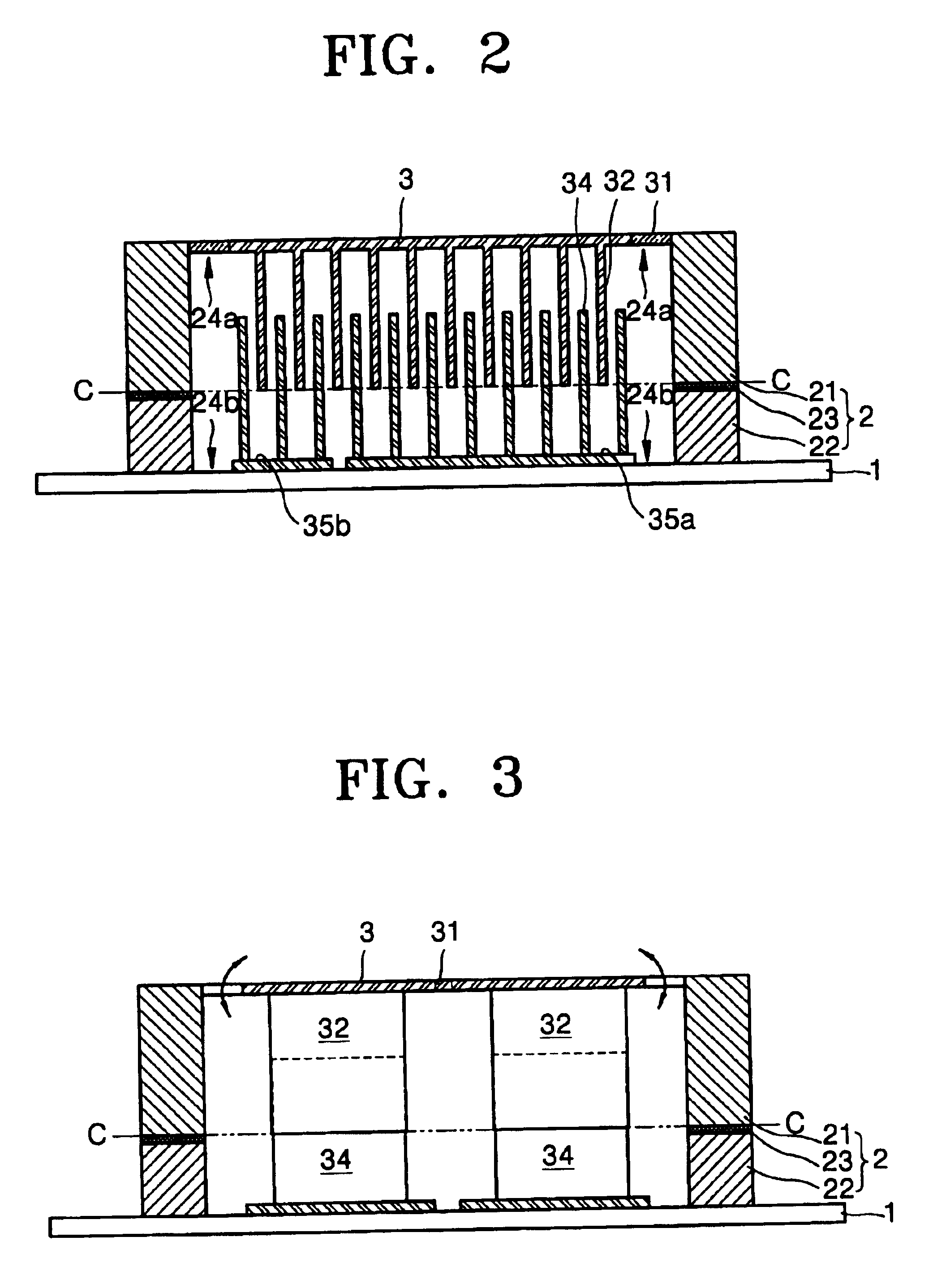

Micro-actuator and manufacturing method thereof

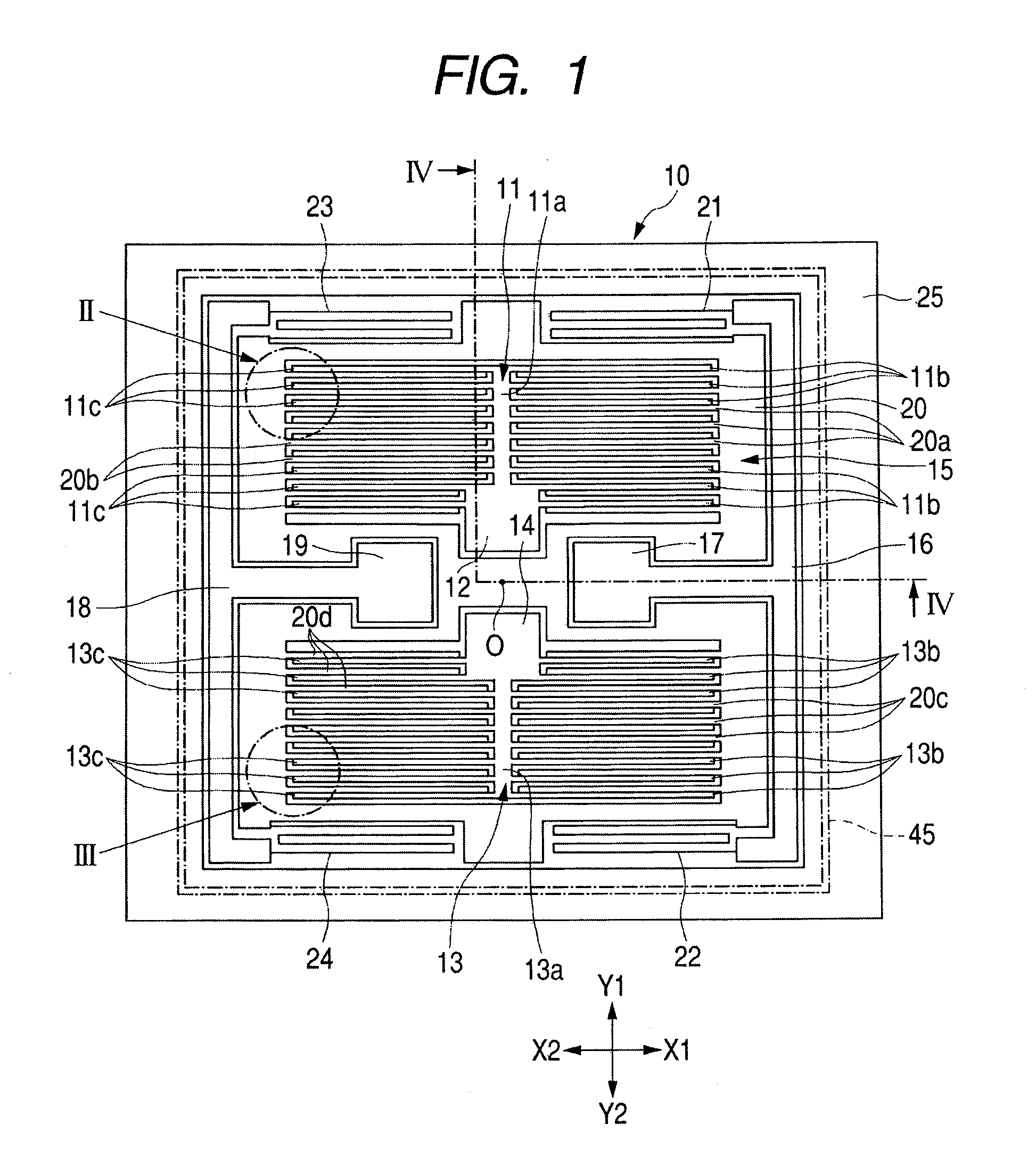

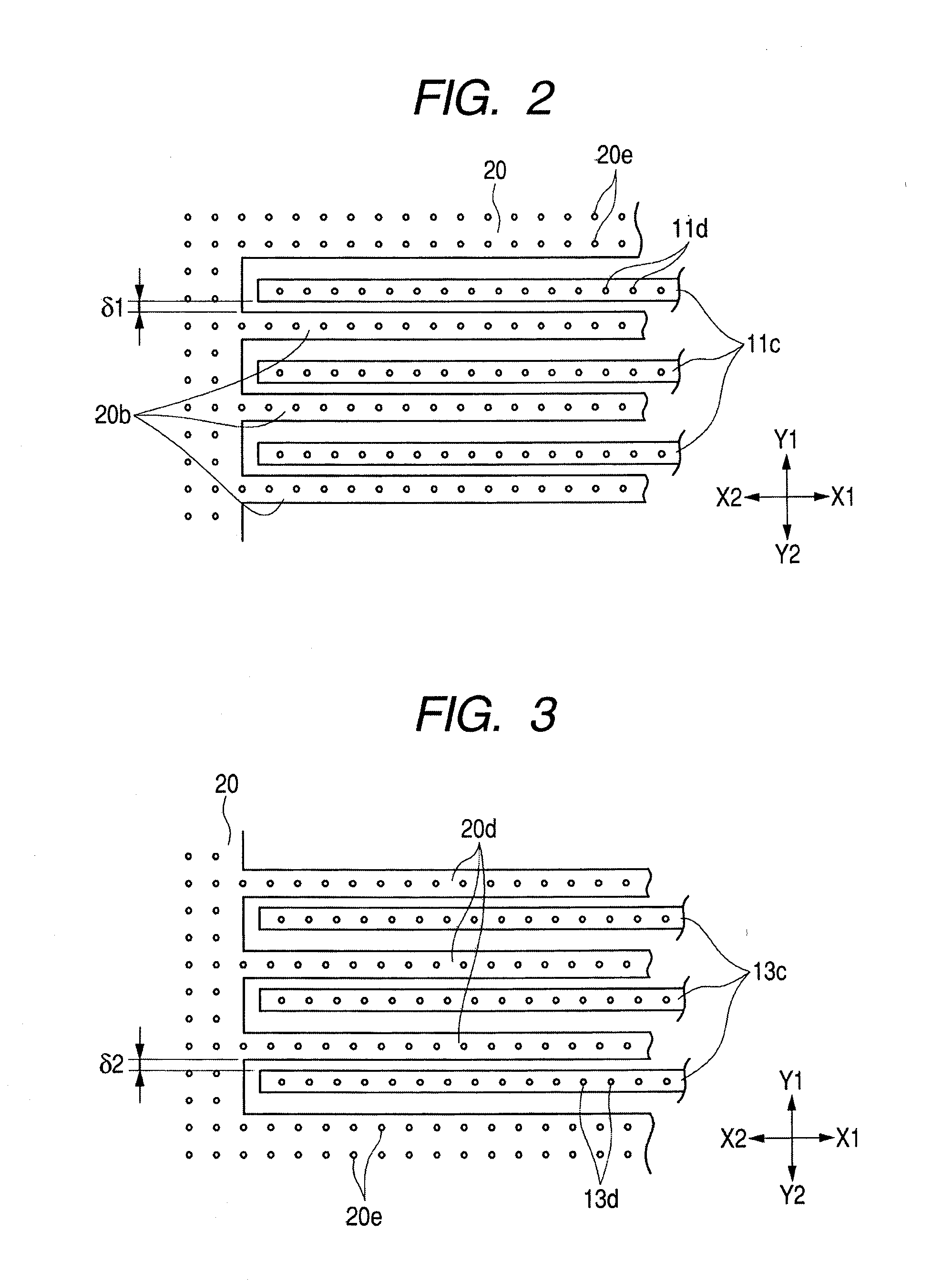

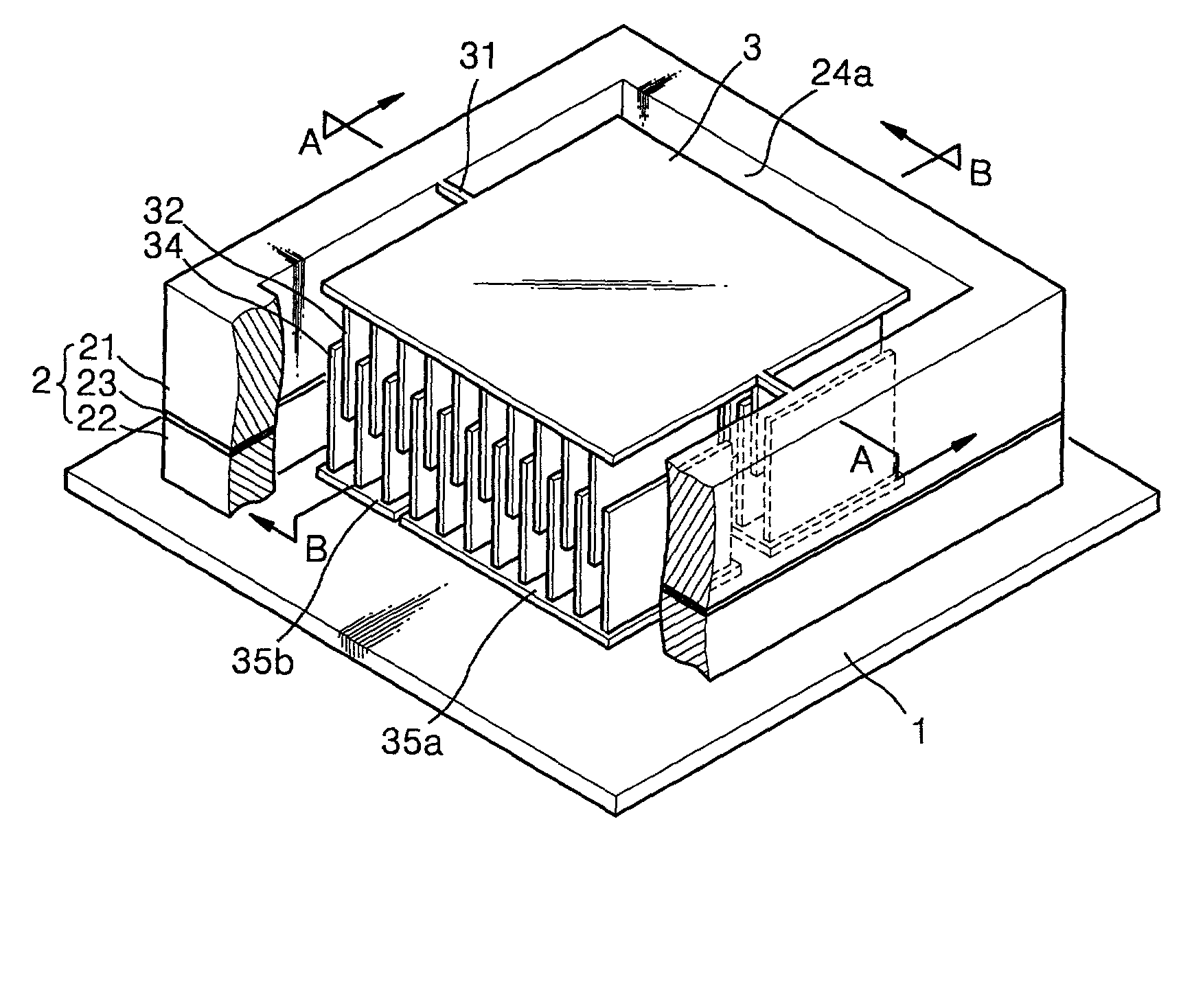

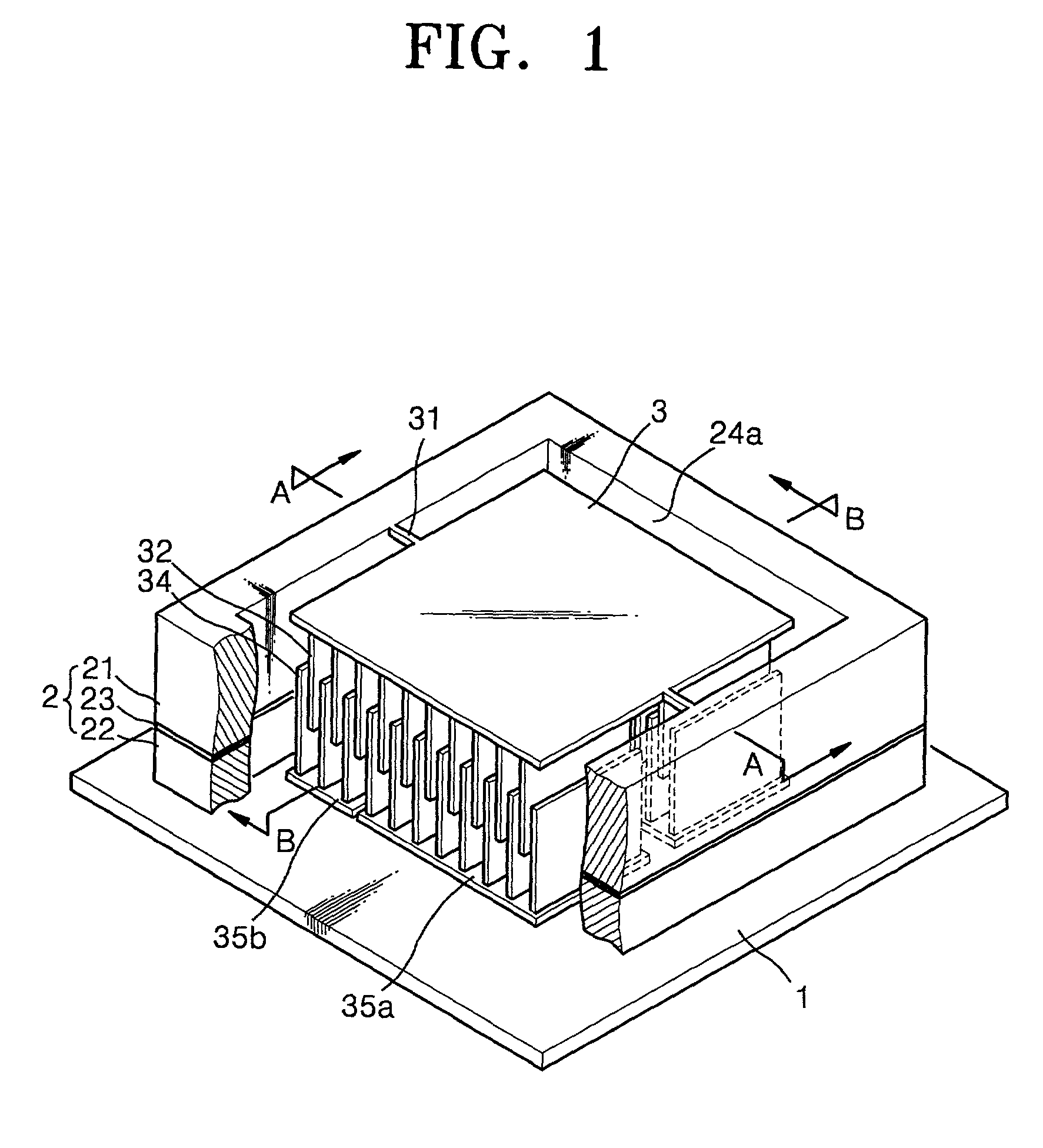

A micro-actuator having a stage capable of a see-saw motion and a method for its manufacture are disclosed. In the micro-actuator according to the present invention, a plurality of parallel driving comb-type electrodes are formed on the bottom of the stage, and a plurality of parallel fixed comb-type electrodes are formed on a base plate. At both sides of the stage is a torsion bar that enables the see-saw motion. The torsion bar is supported by a frame comprised of a first frame layer and a second frame layer. The torsion bar and the first frame layer form one body. The first and second frame layers are bonded by a metal eutectic bonding layer between metal layers.

Owner:SAMSUNG ELECTRONICS CO LTD

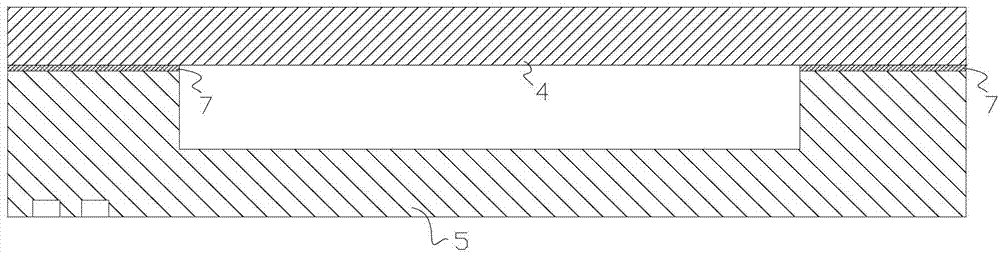

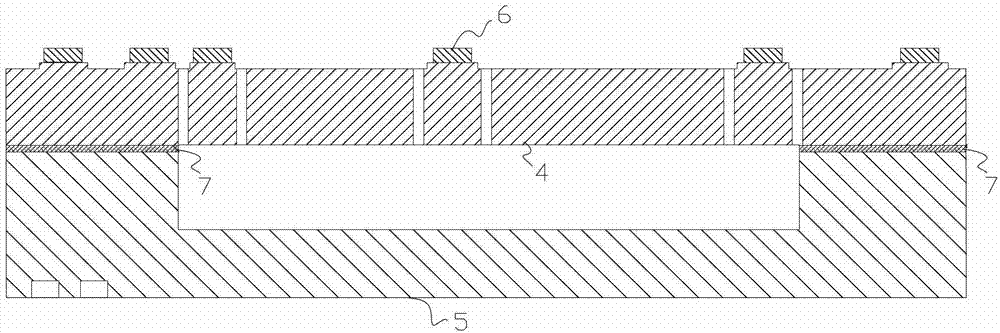

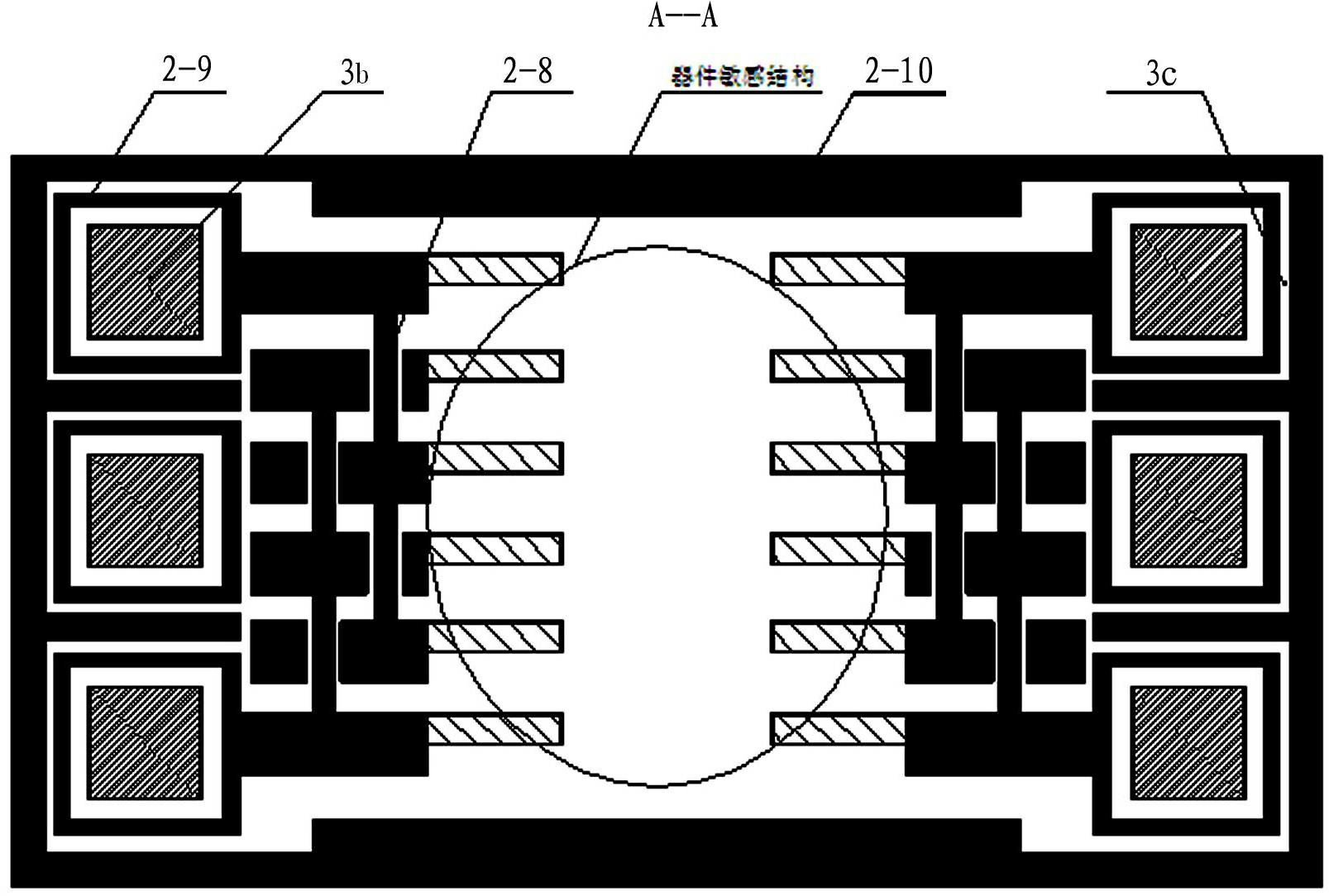

Inertial sensor production and wafer level package process based on MEMS (micro-electromechanical system)

InactiveCN103922267AEffective spaceImprove performanceDecorative surface effectsSolid-state devicesFoundryChip size

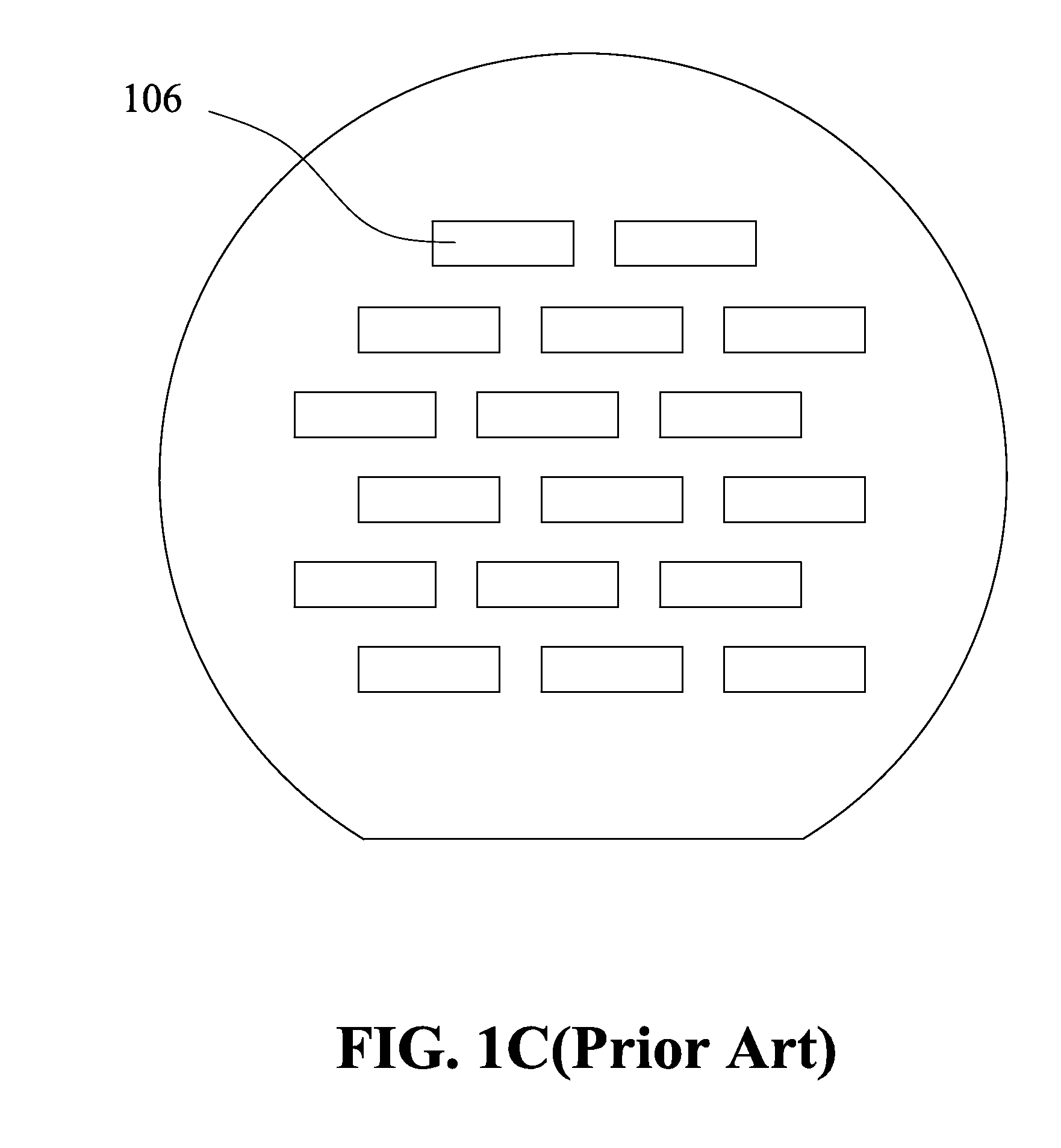

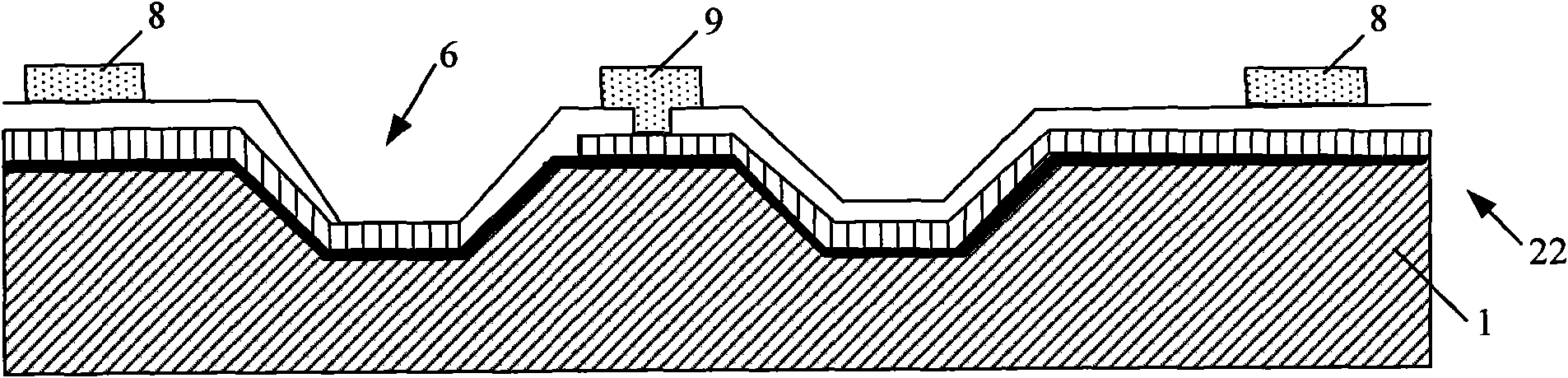

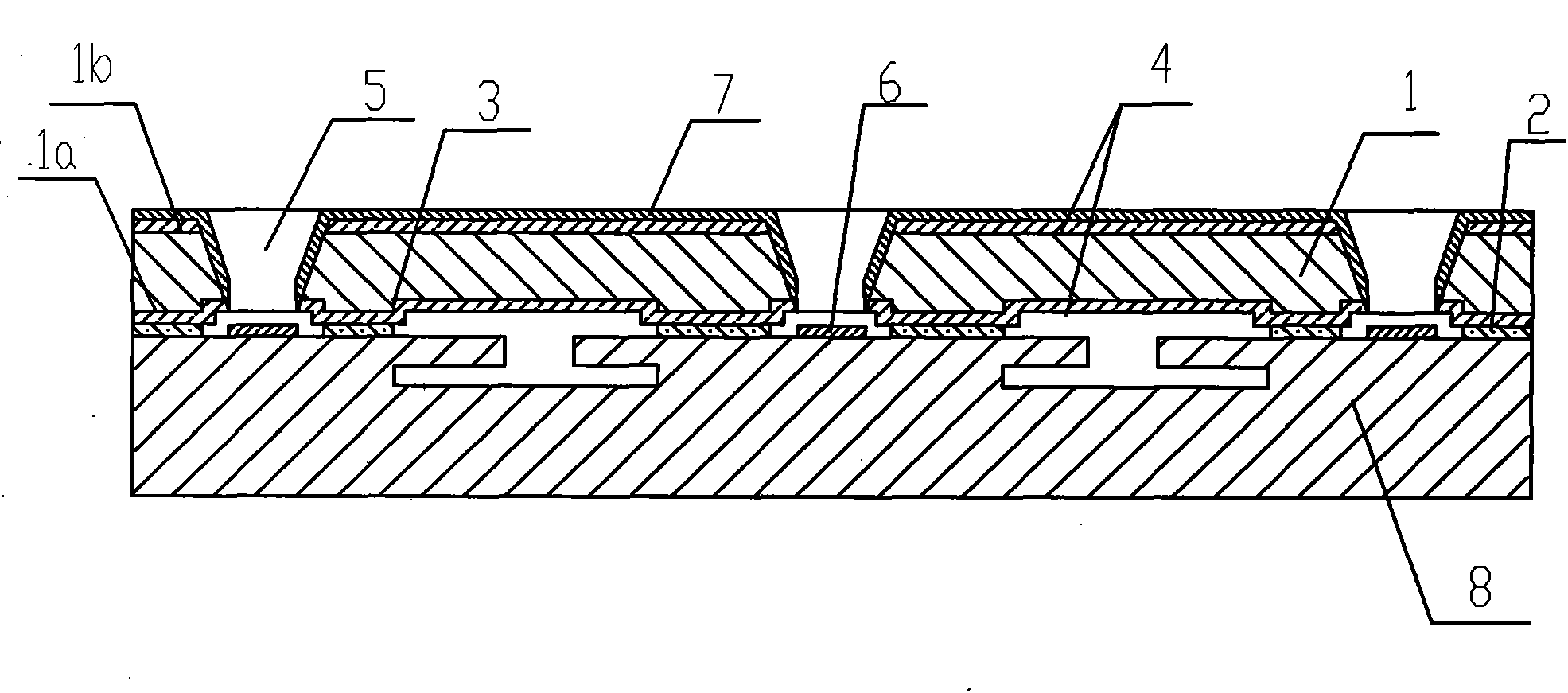

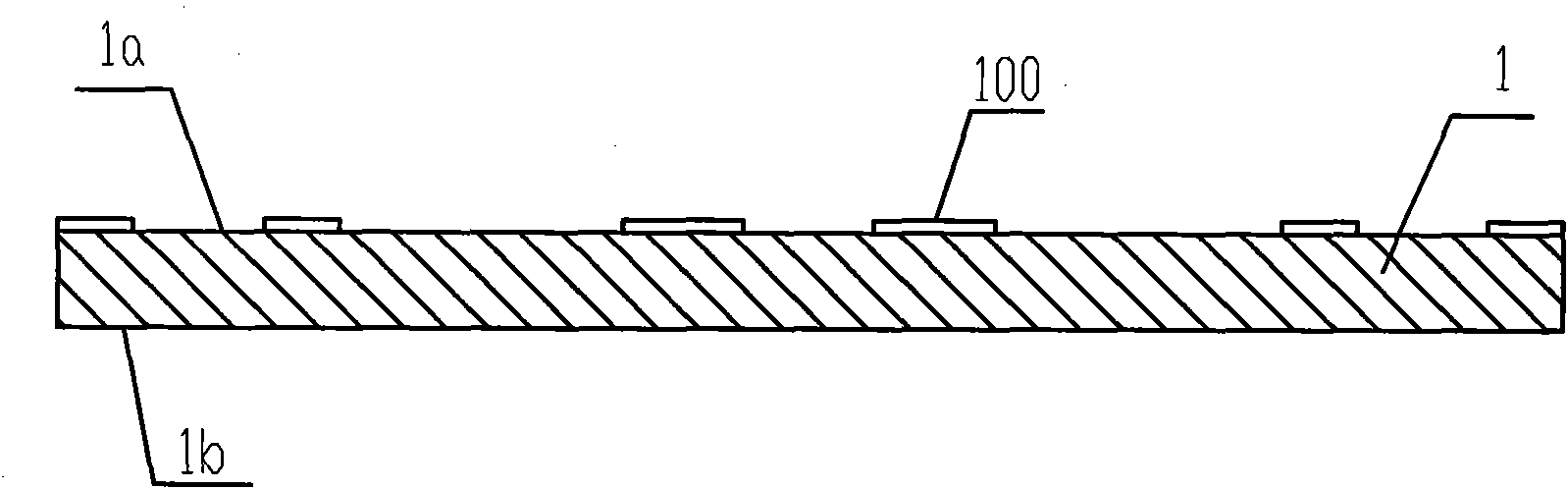

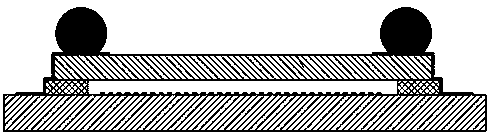

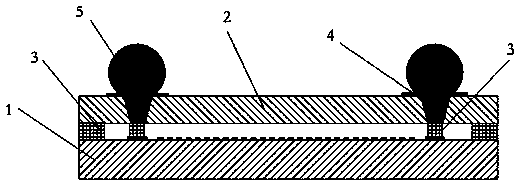

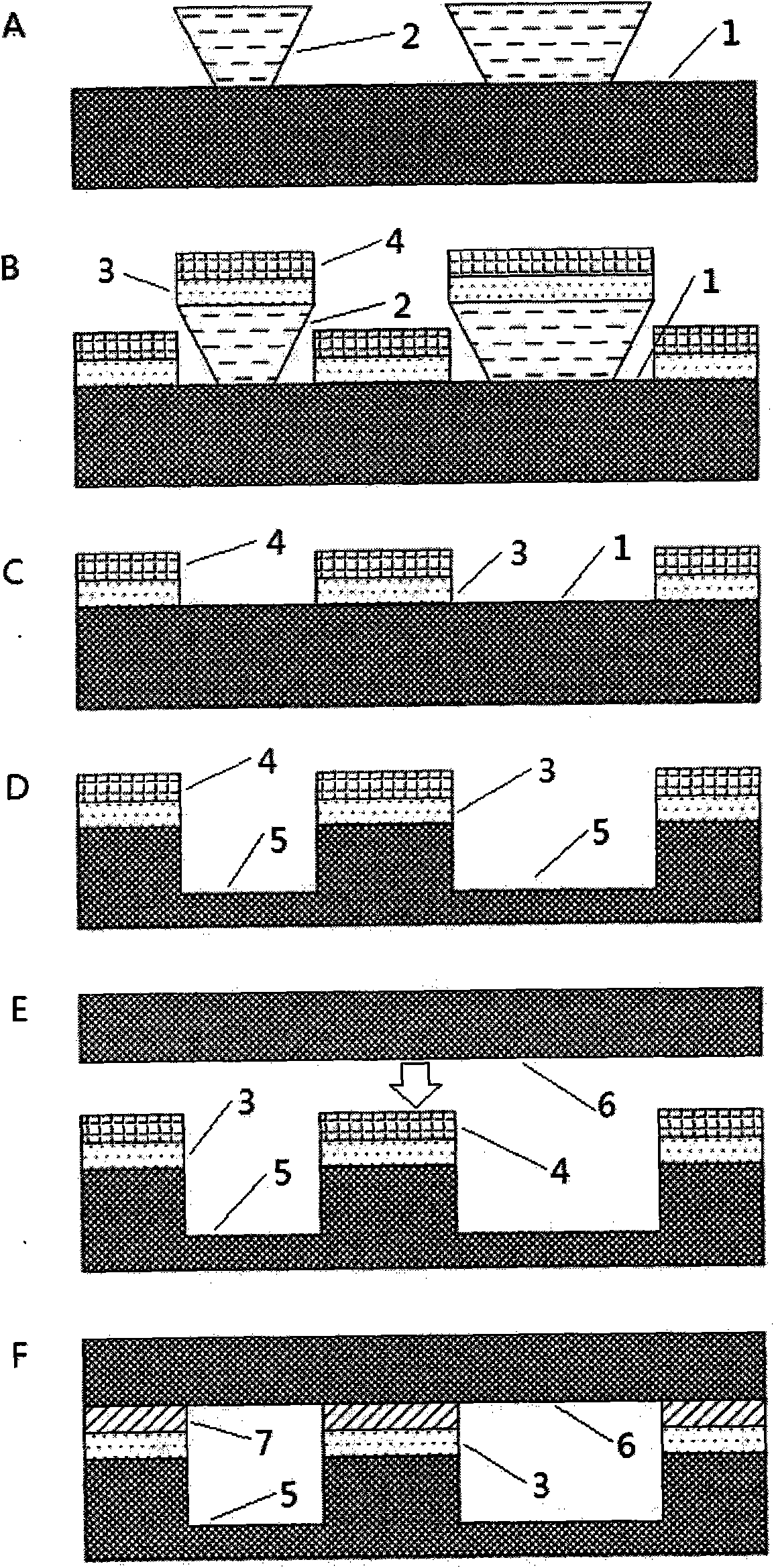

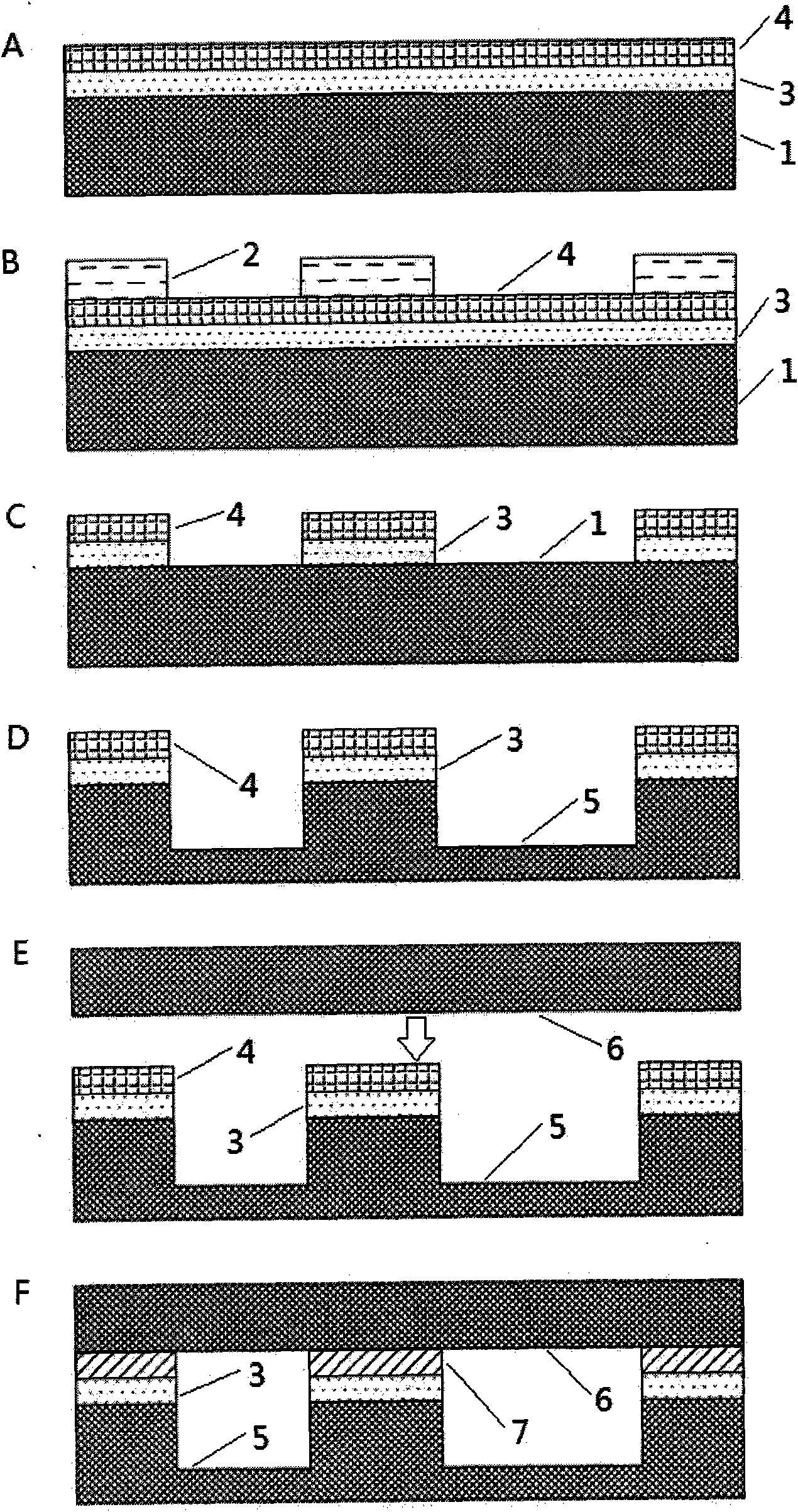

The invention discloses an inertial sensor production and wafer level package process based on an MEMS (micro-electromechanical system). The process includes the steps: 1) forming an E-SOI (engineering-silicon on insulator); 2) performing surface machining on an MEMS wafer; 3) producing an ASIC (application specific integrated circuit) wafer on a standard ASIC foundry; 4) performing metal eutectic bonding for the MEMS wafer and the ASIC wafer; 5) performing WLCSP (wafer level chip size packaging). The area of an ASIC chip is identical with that of an MEMS chip, the effective areas of the MEMS chip and the ASIC chip are sufficiently used, the most effective space is provided for the design of the MEMS chip and the ASIC chip, subsequent package procedures of the chips are omitted by the aid of the wafer level chip size packaging, Flip-Chip of a terminal circuit board is finished directly through a BGA (ball grid array), and the sizes of the chips and production cost are greatly reduced.

Owner:SENODIA TECH (SHANGHAI) CO LTD

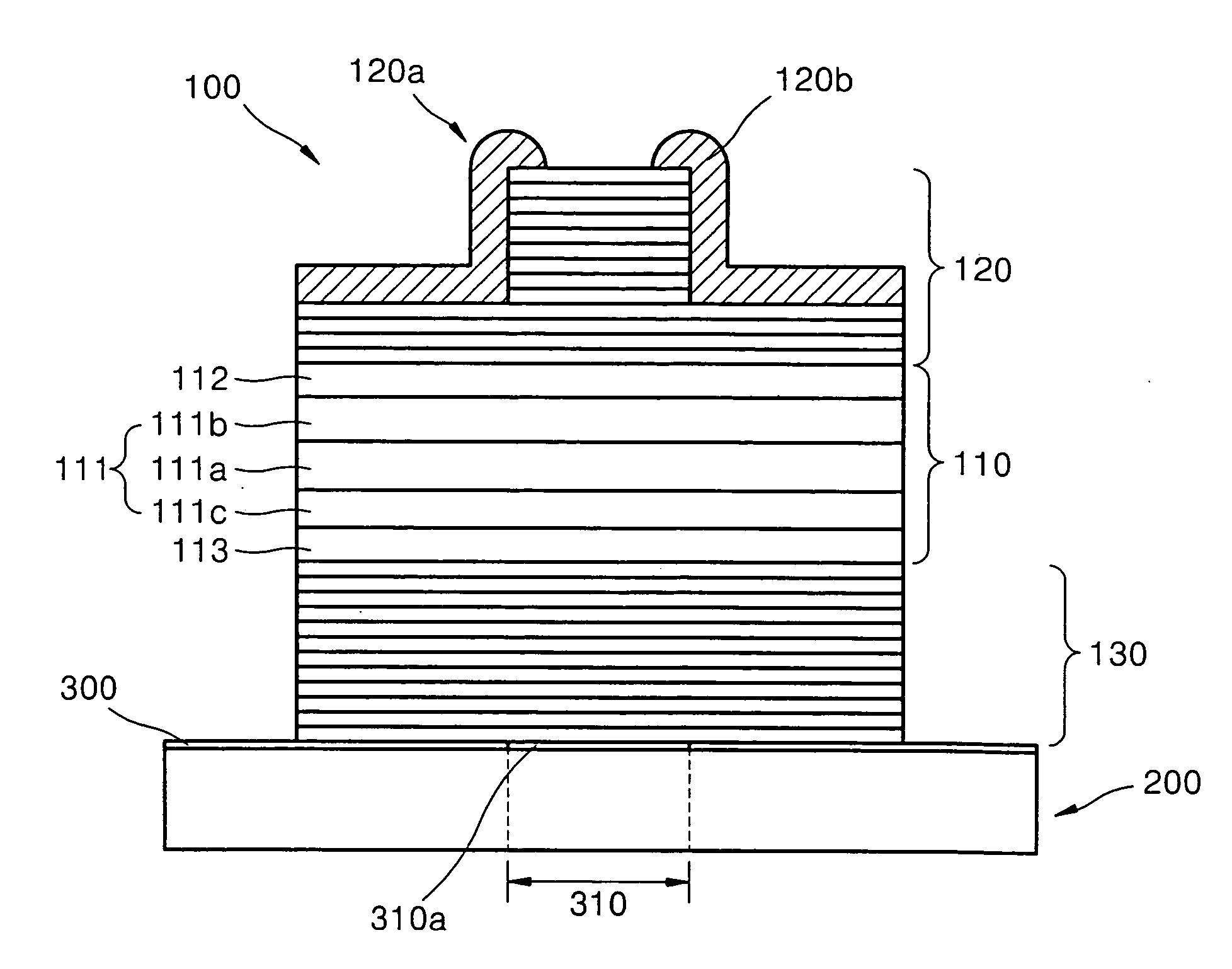

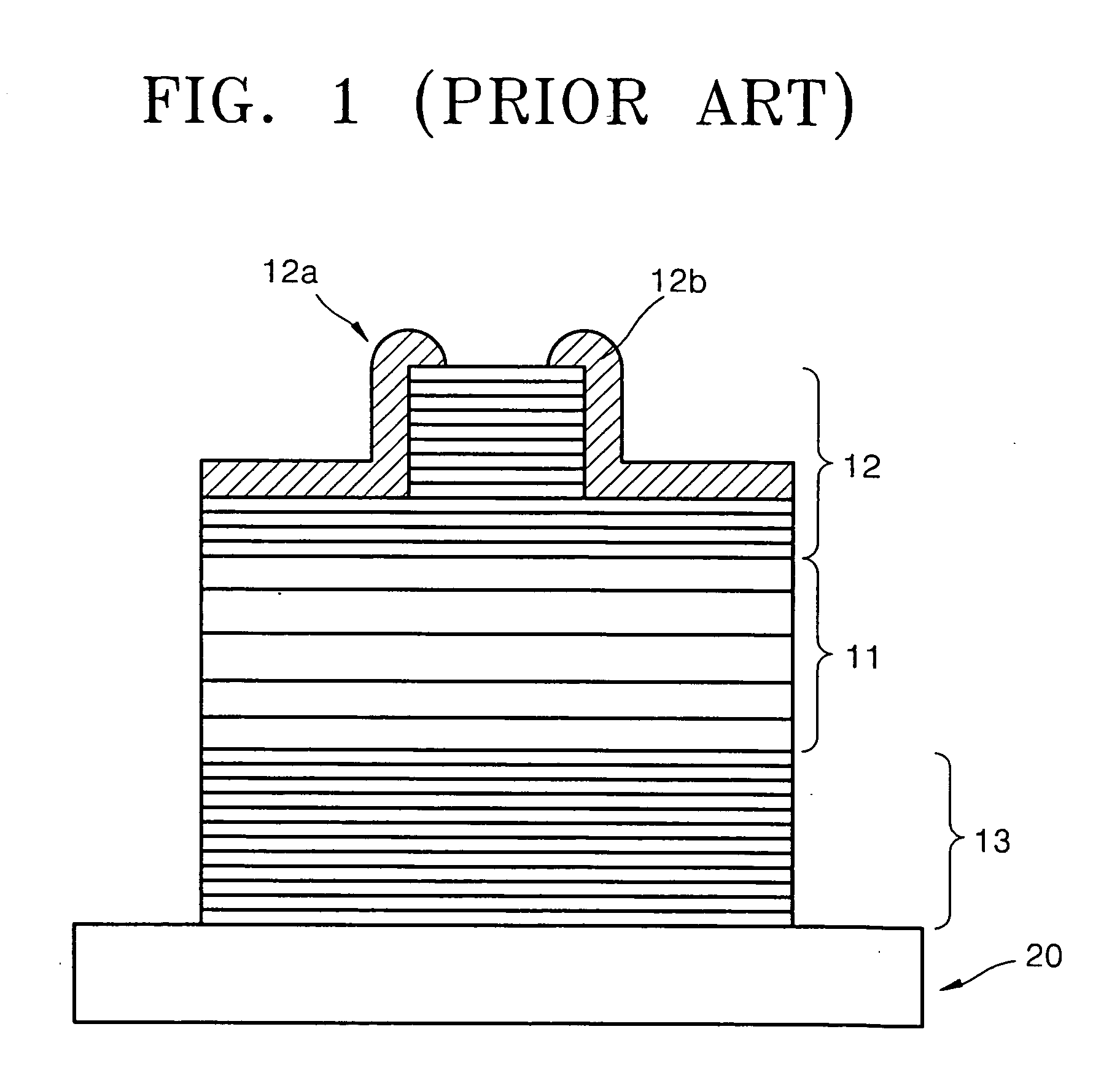

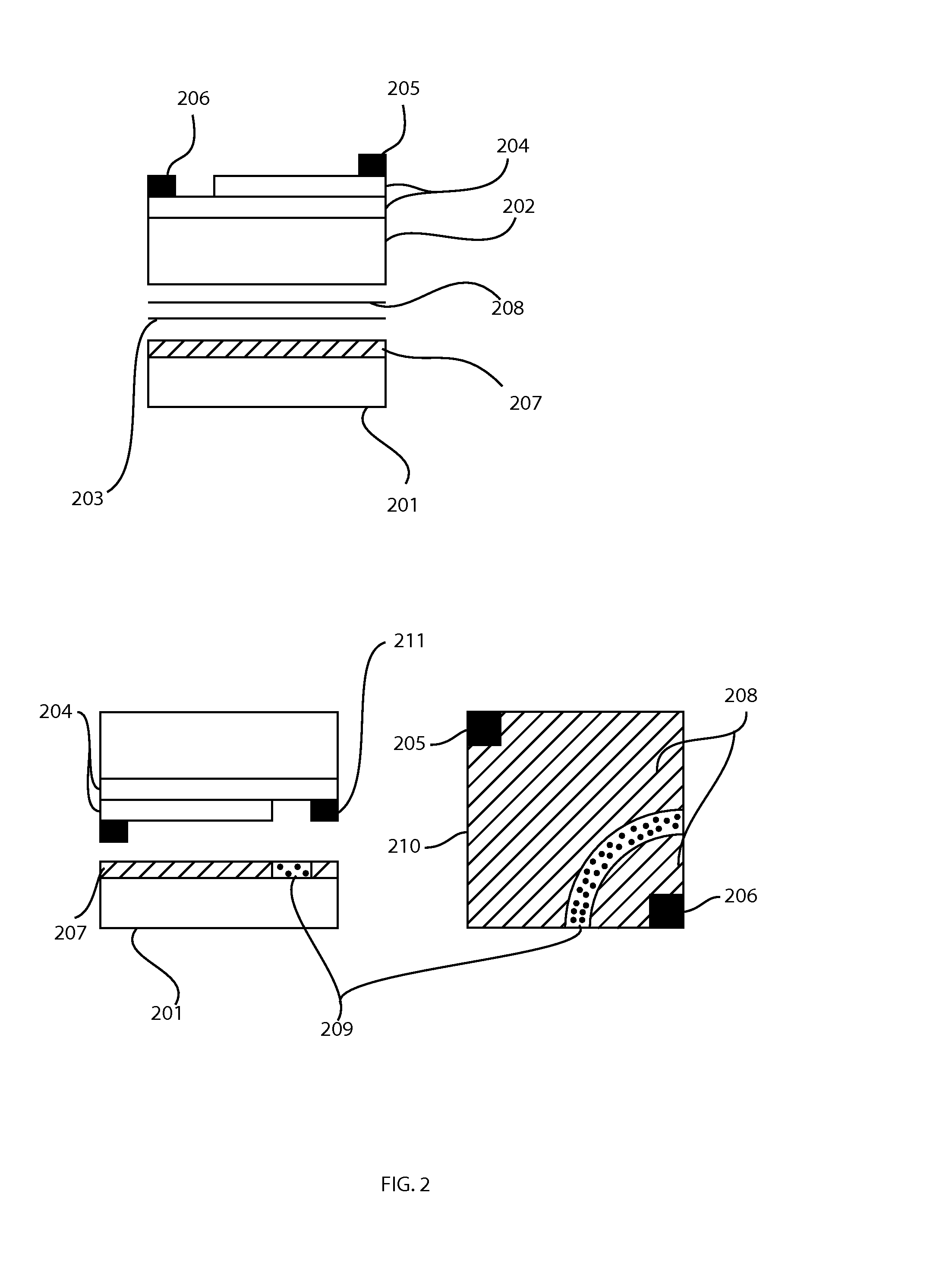

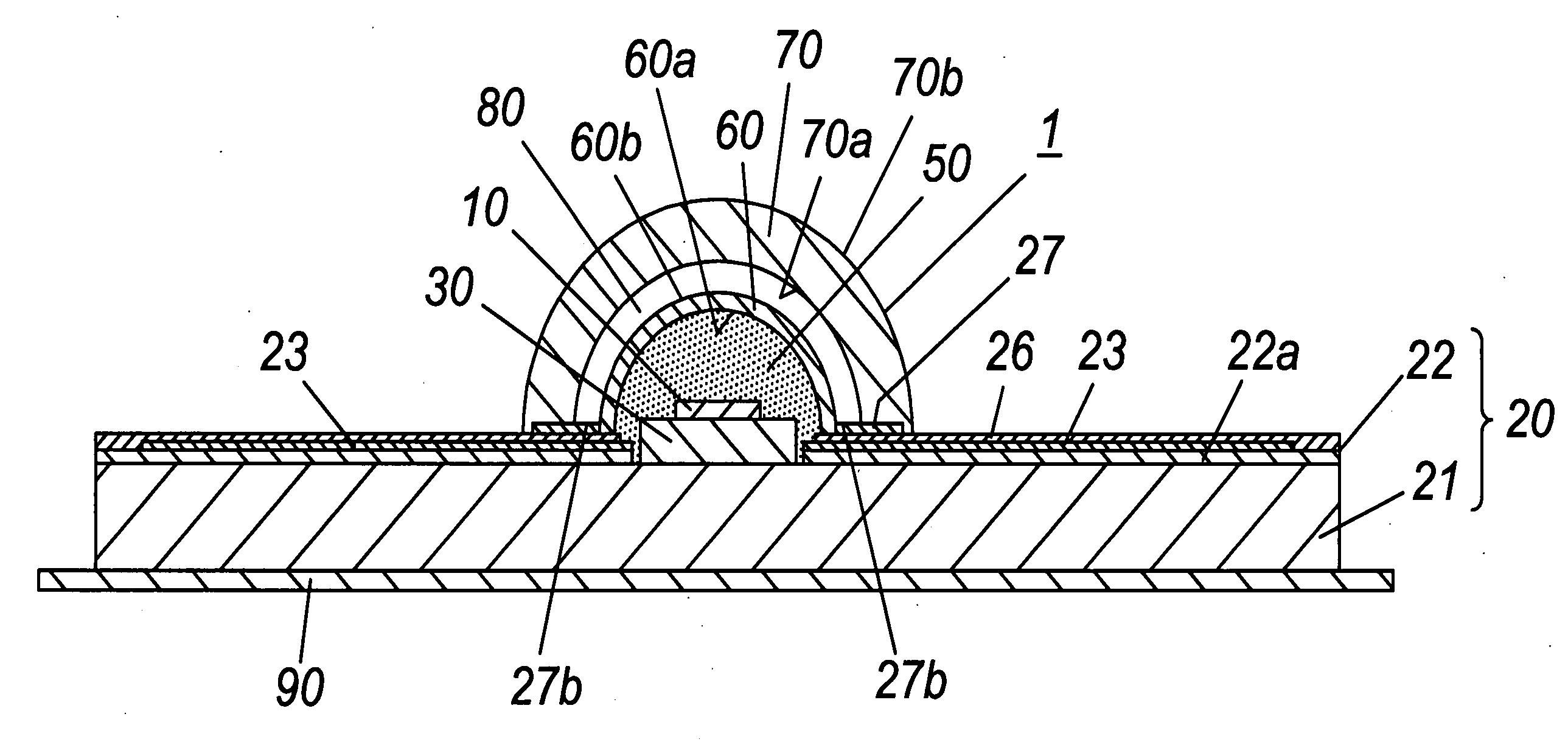

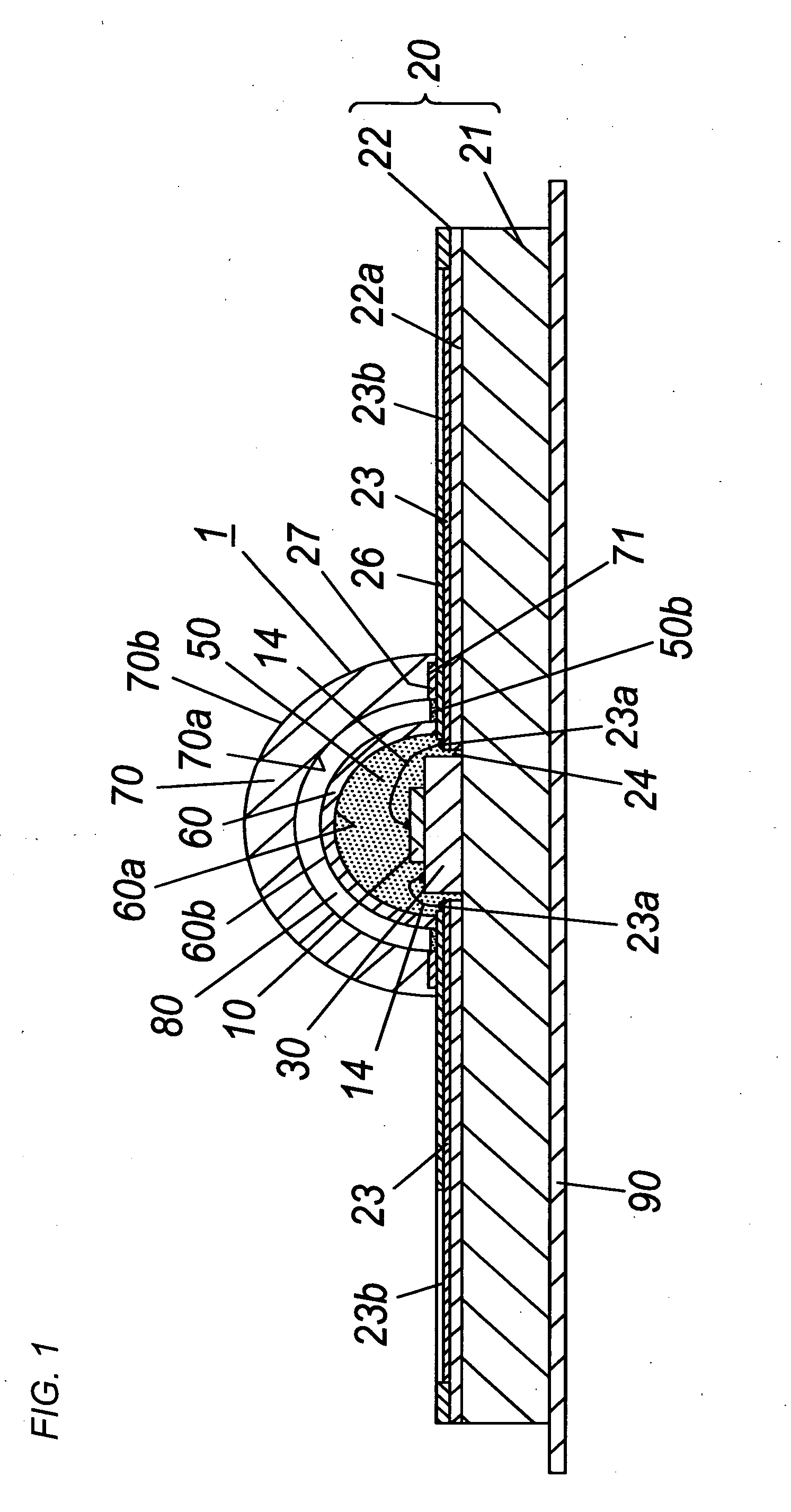

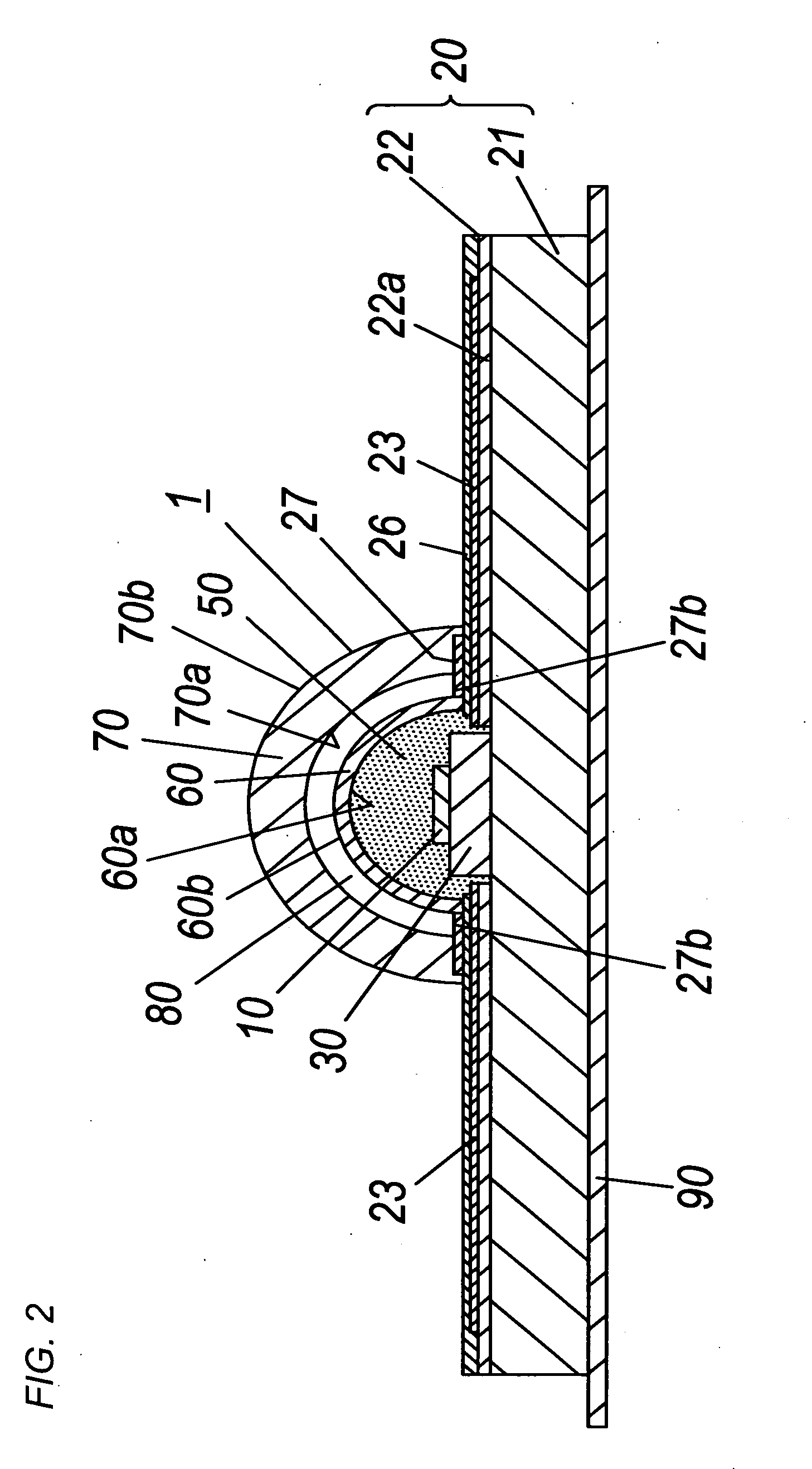

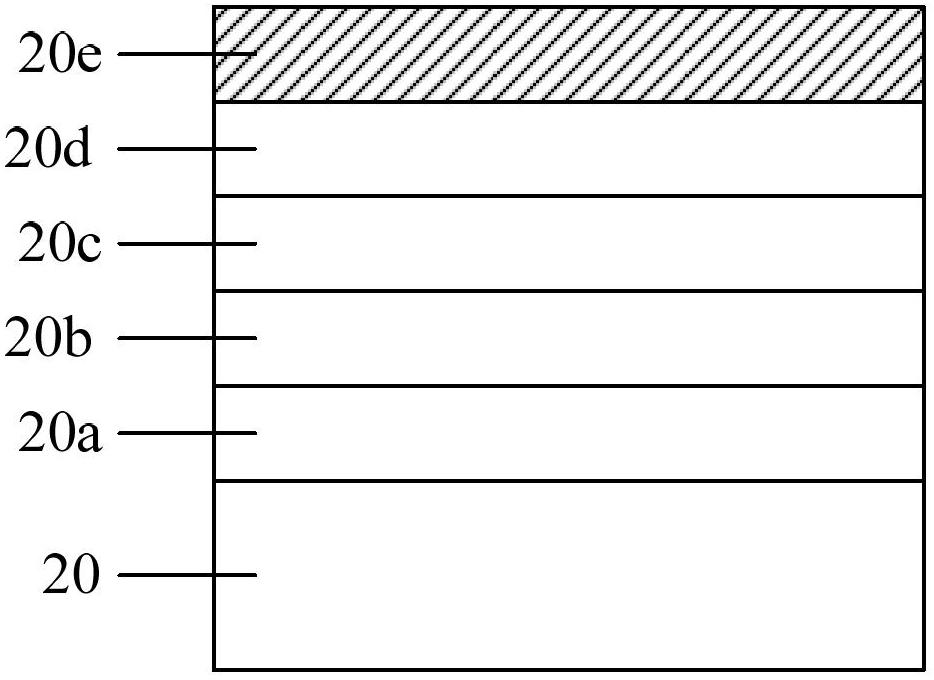

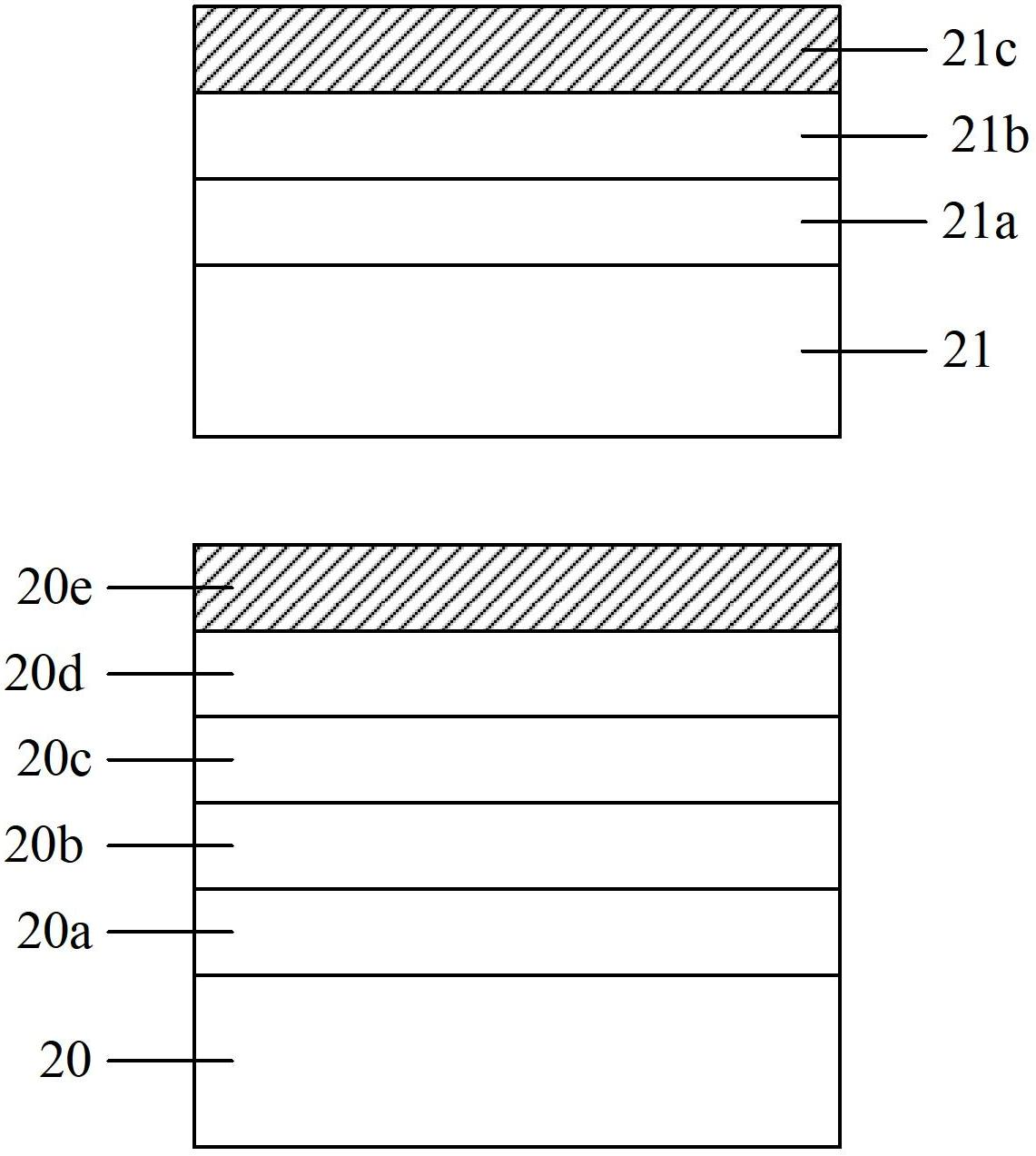

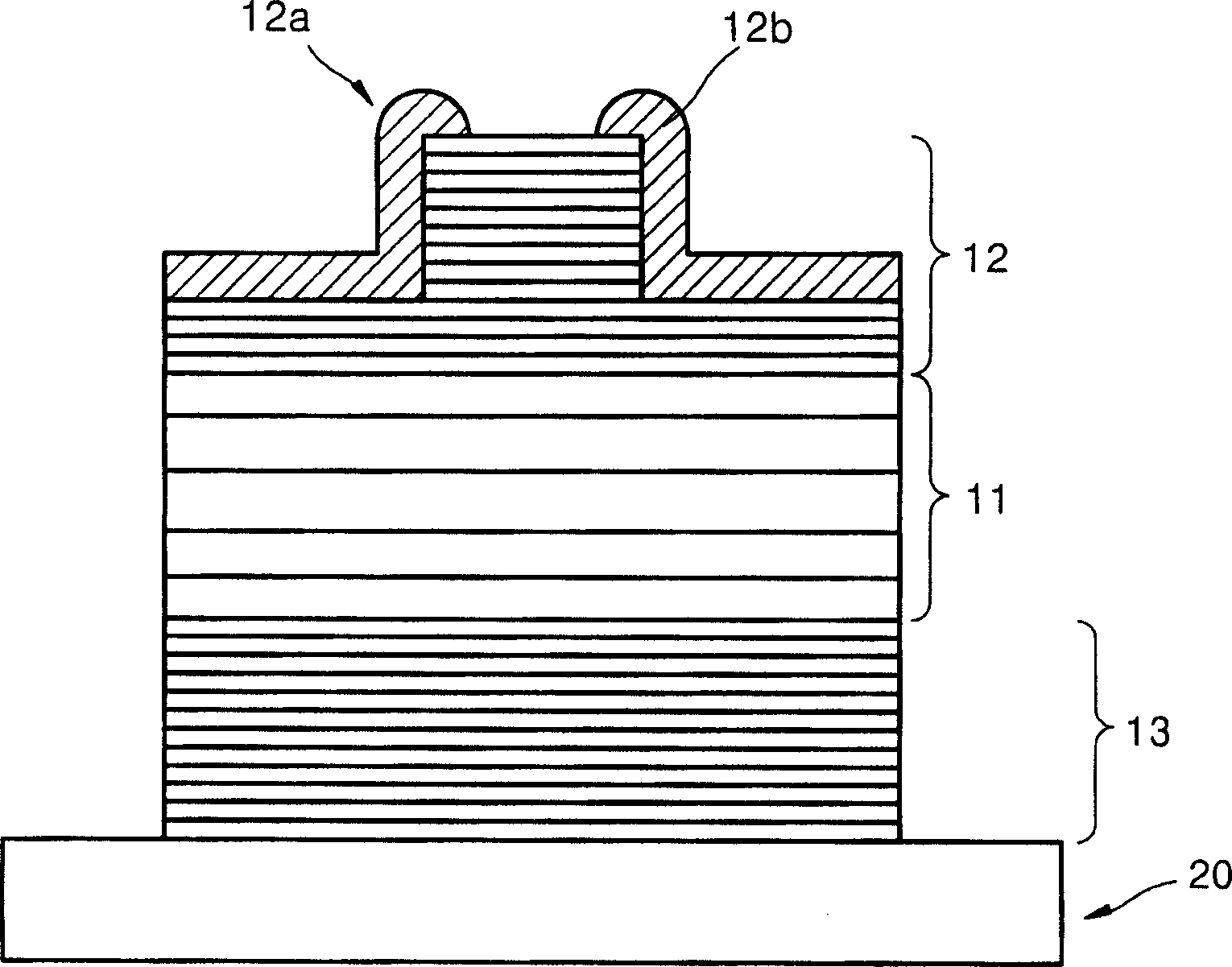

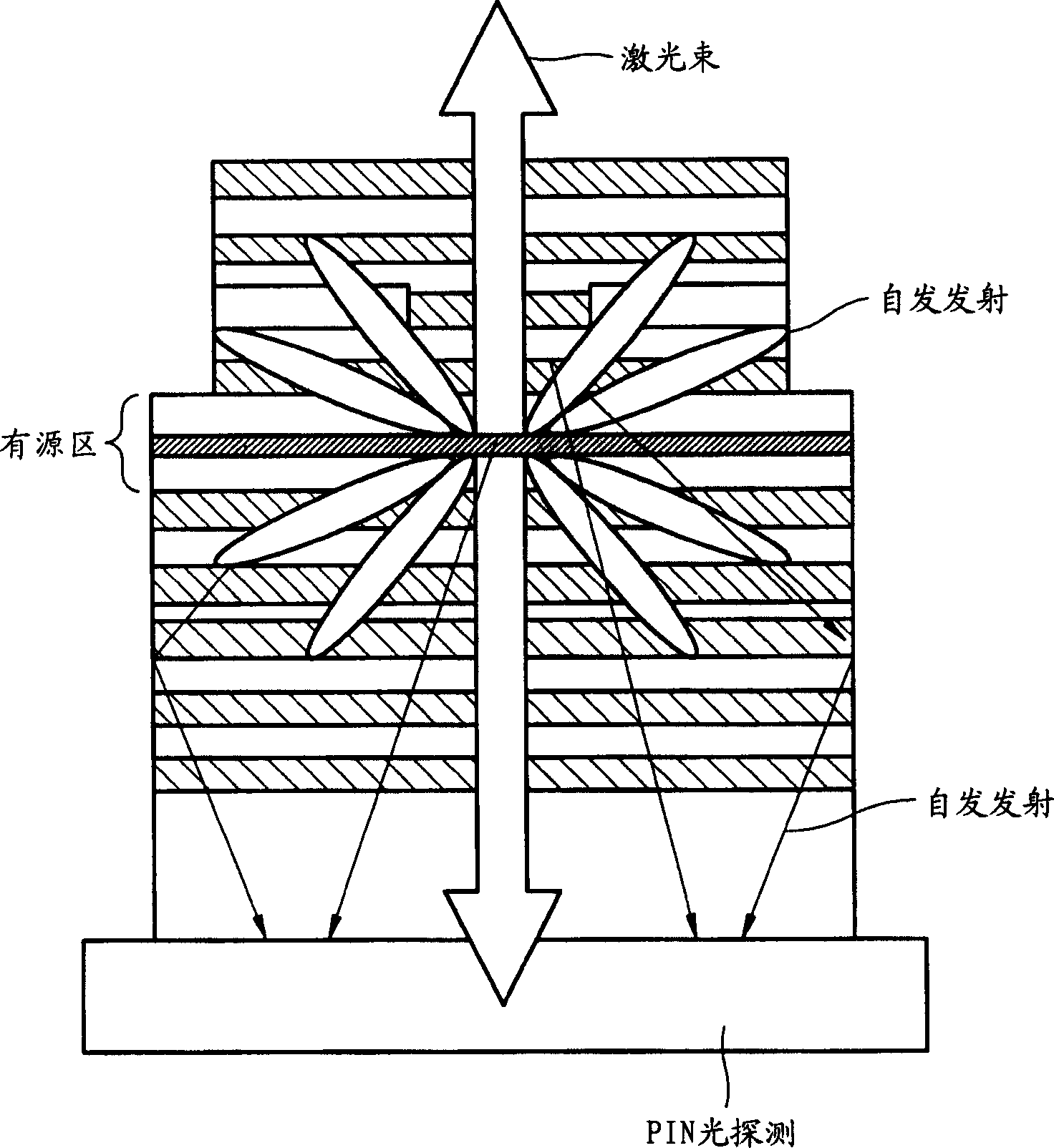

Long wavelength vertical cavity surface emitting laser with integrated photodetector

InactiveUS20050041715A1Accurate detectionReduce the amount requiredNanoinformaticsSemiconductor laser structural detailsVertical-cavity surface-emitting laserPhotovoltaic detectors

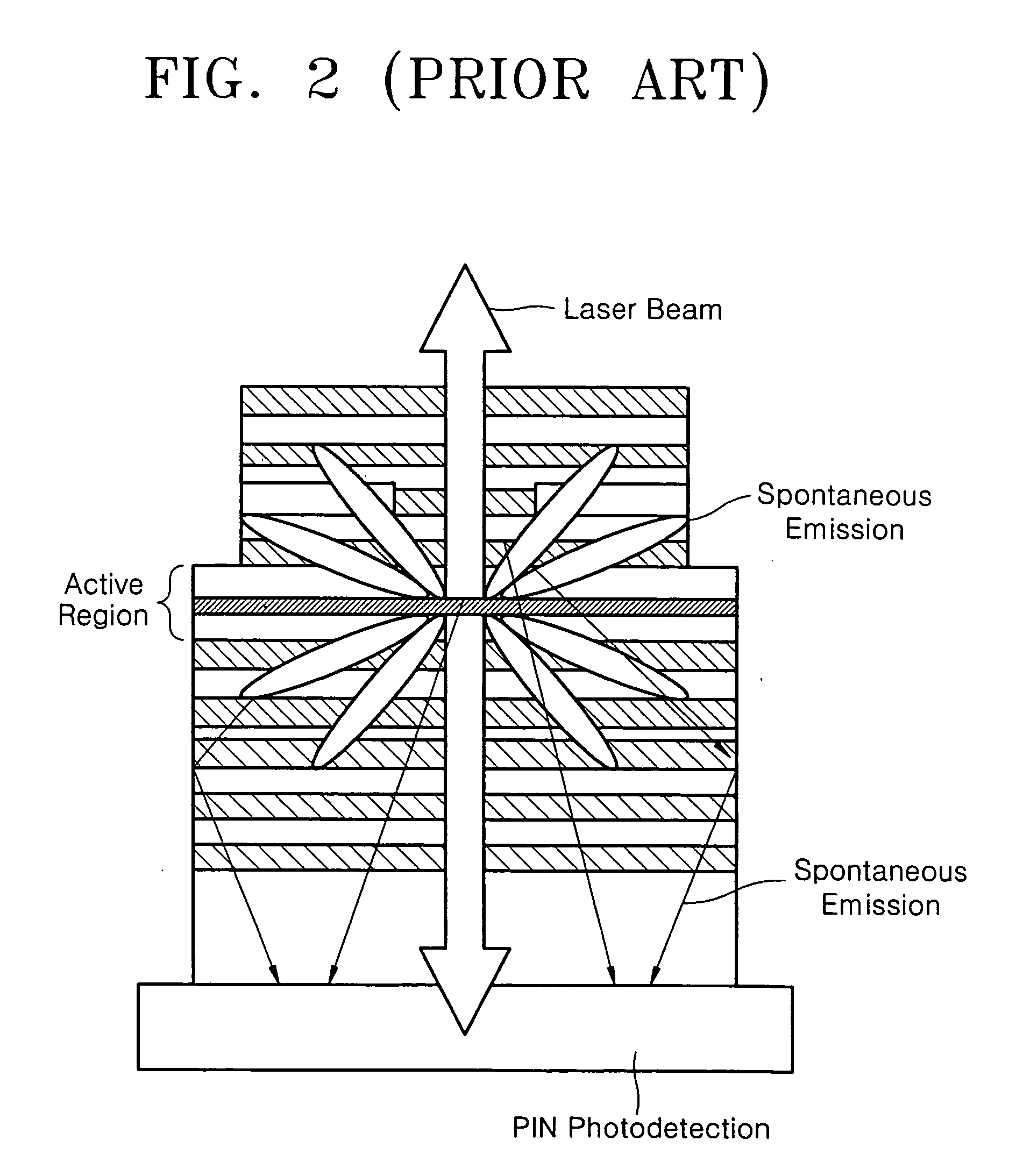

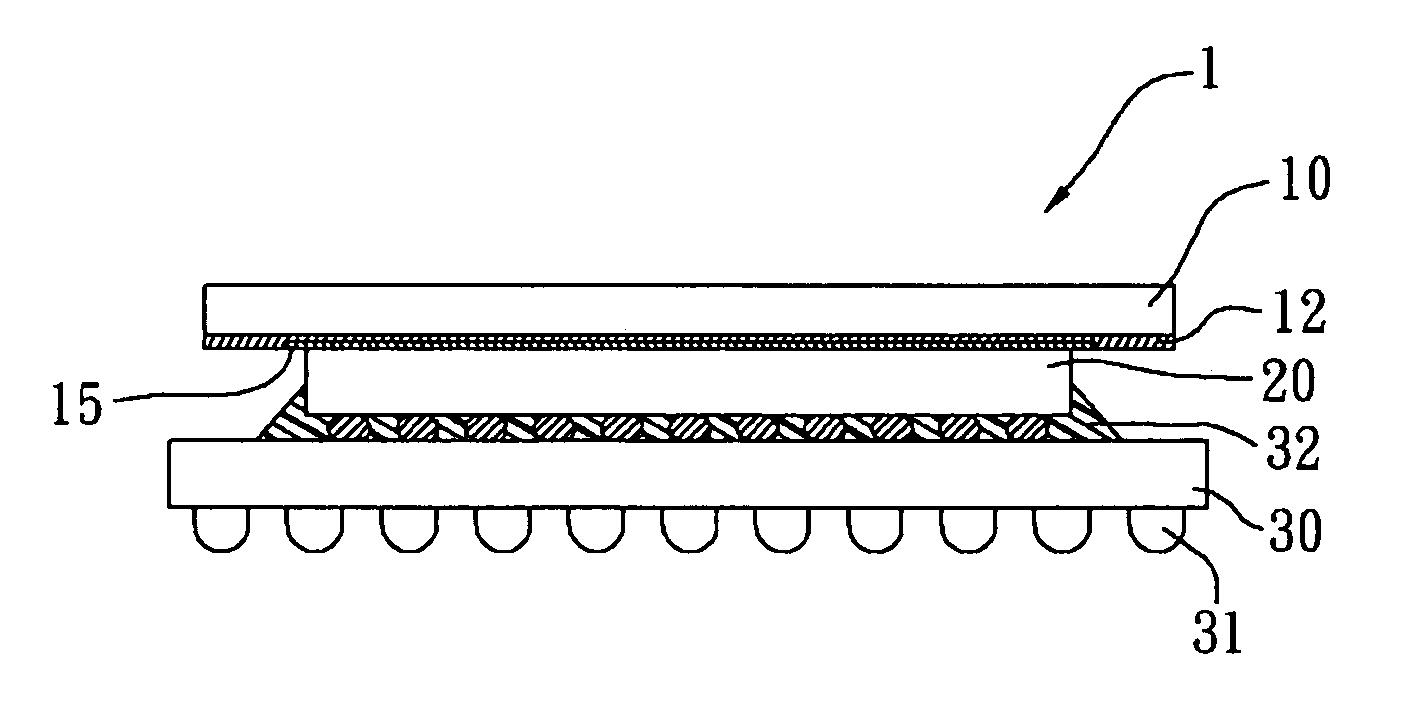

A vertical cavity surface emitting laser (VCSEL) integrated with a photodetector is provided. The photodetector is attached to a bottom surface of the VCSEL by a bonding layer, which includes a window of a predetermined diameter. The bonding layer is a eutectic bonding layer. An air gap exists within the window and mainly transmits a laser beam. Most of spontaneous emission light incident at an angle is blocked by an area of the bonding layer other than the window, and even some of the spontaneous emission light that heads toward the window cannot easily passes through the window due to a big difference between refractive indices of a semiconductor layer and the air. Thus, the eutectic bonding layer greatly reduces a voltage drop at an interface between the VCSEL and the photodetector, thereby contributing to mass production.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for flip chip package and structure thereof

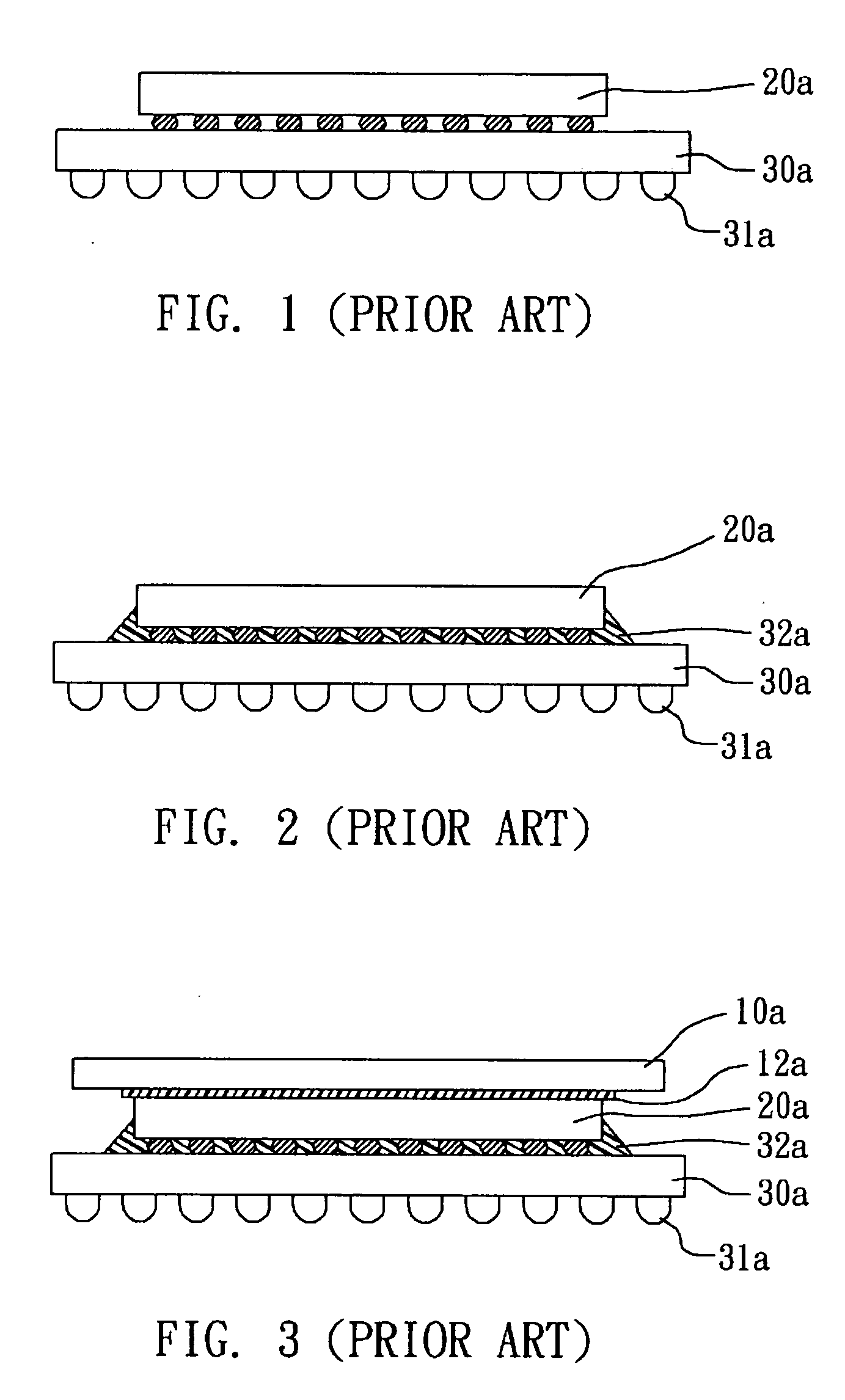

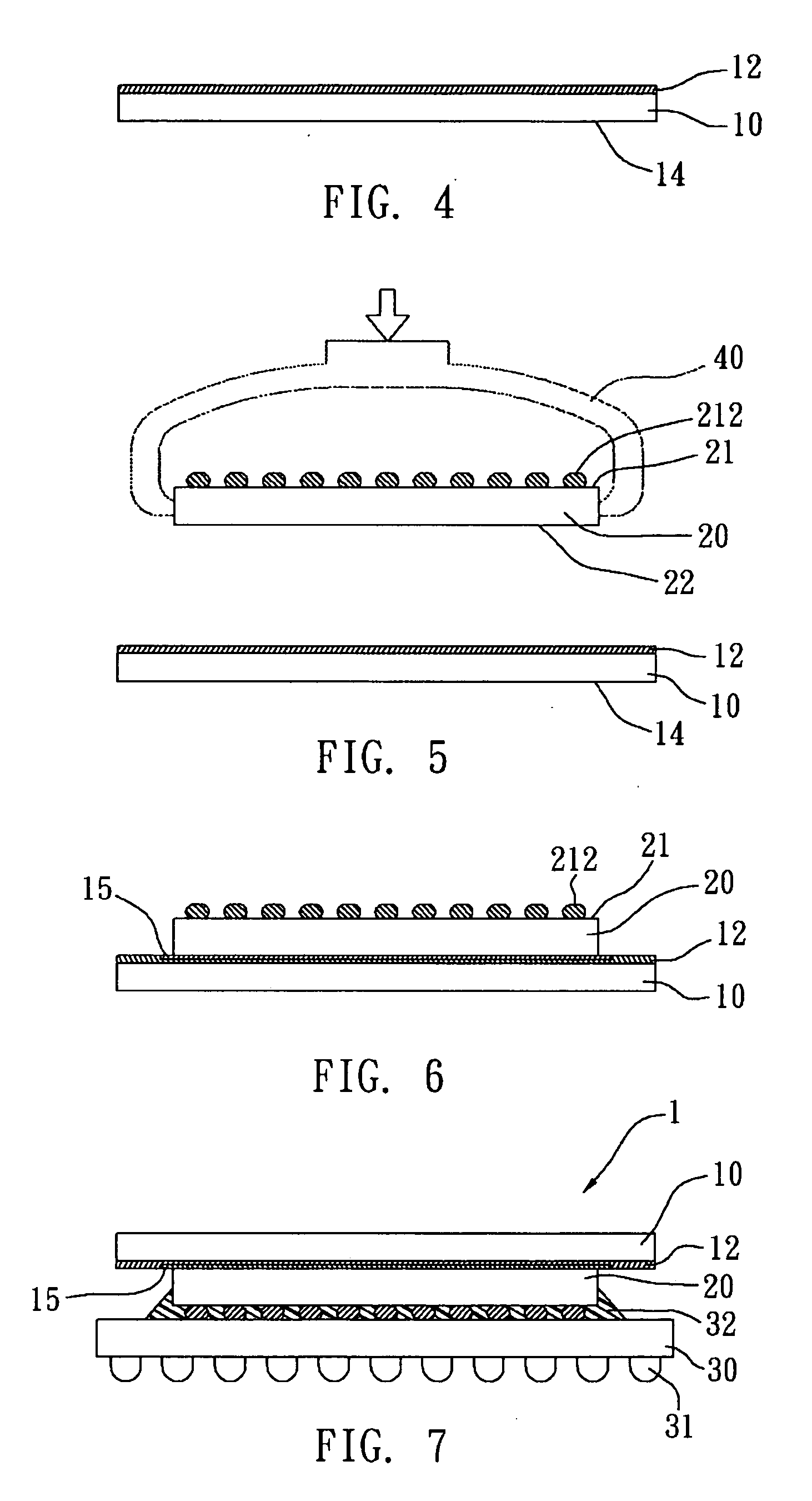

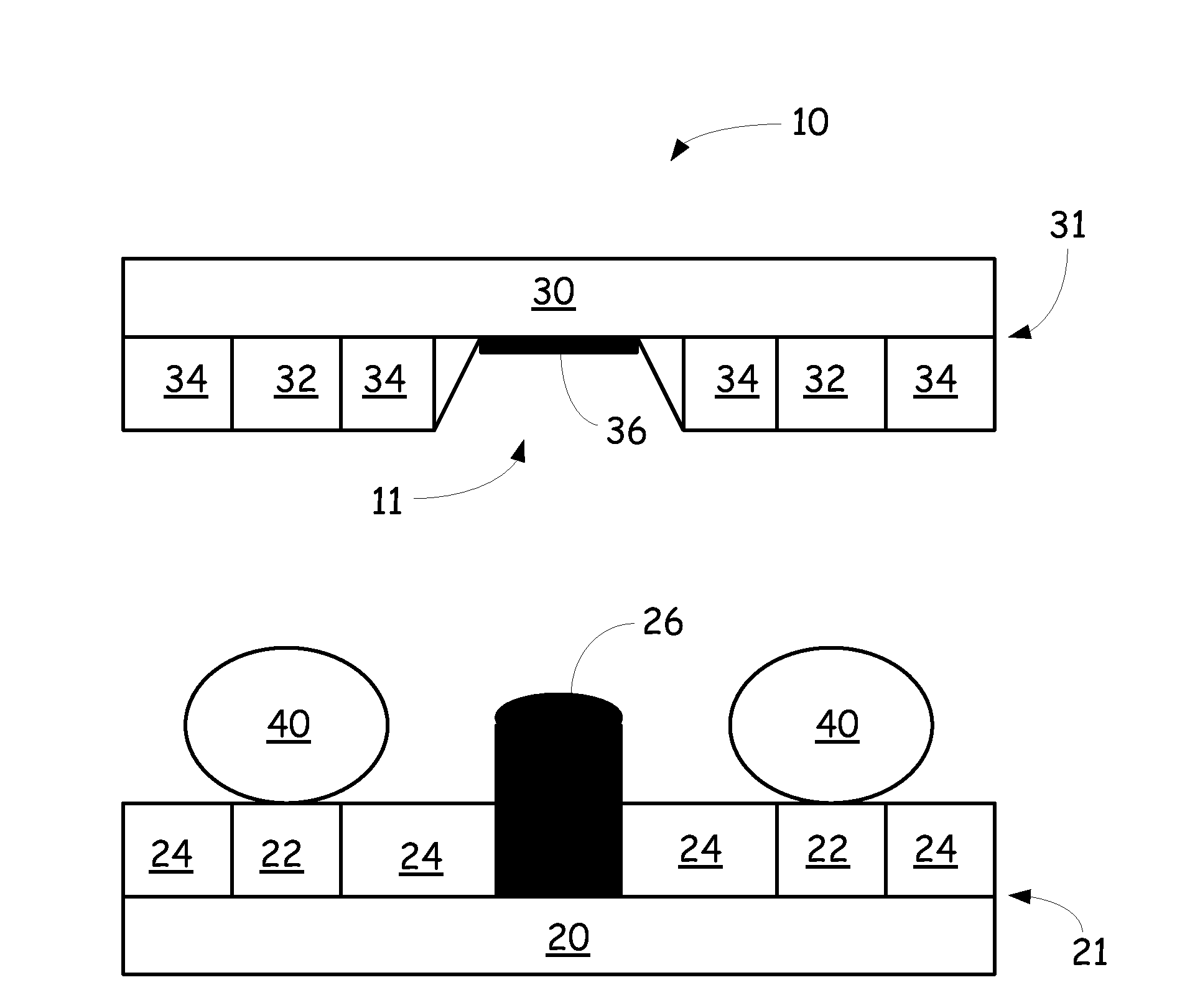

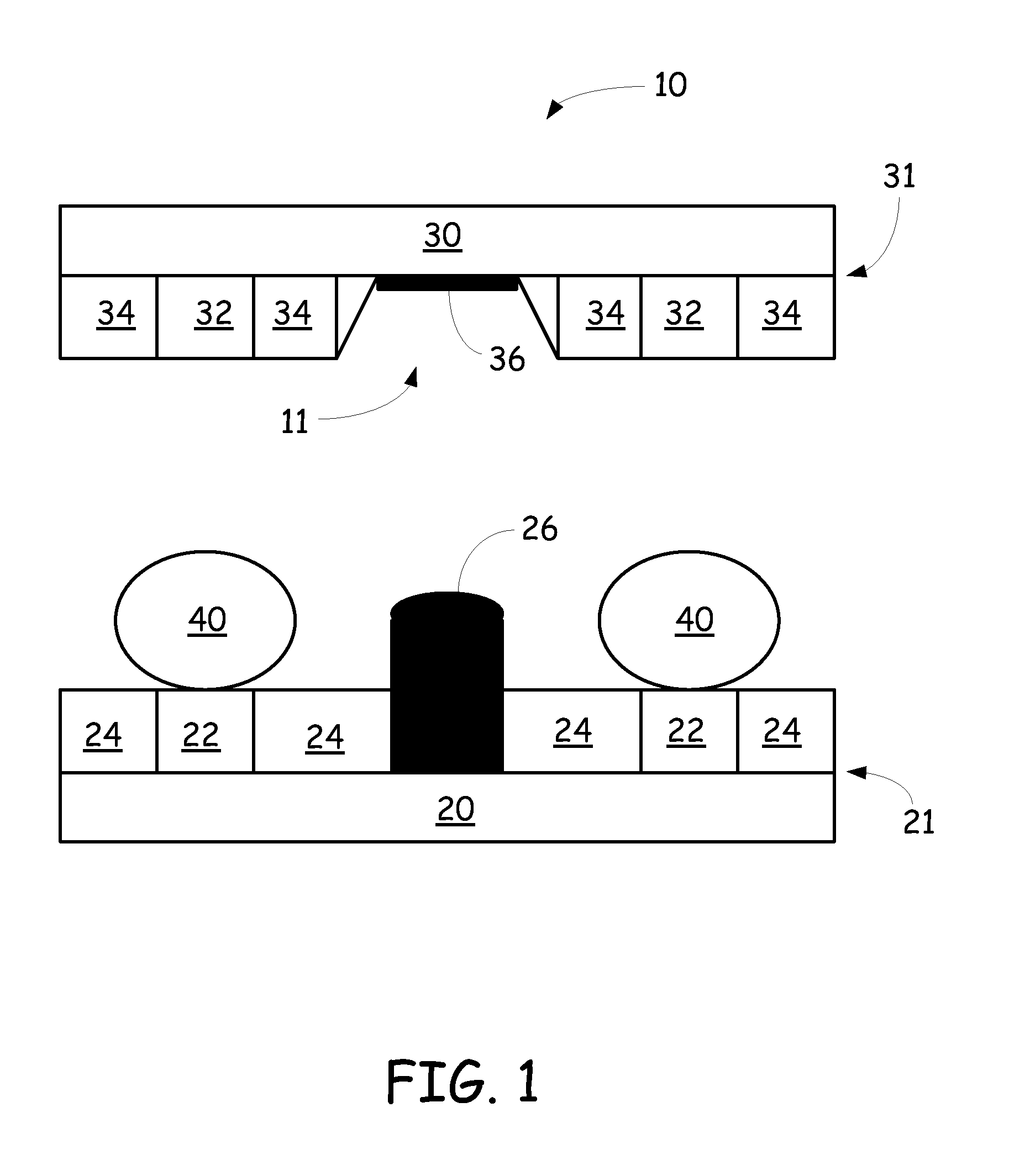

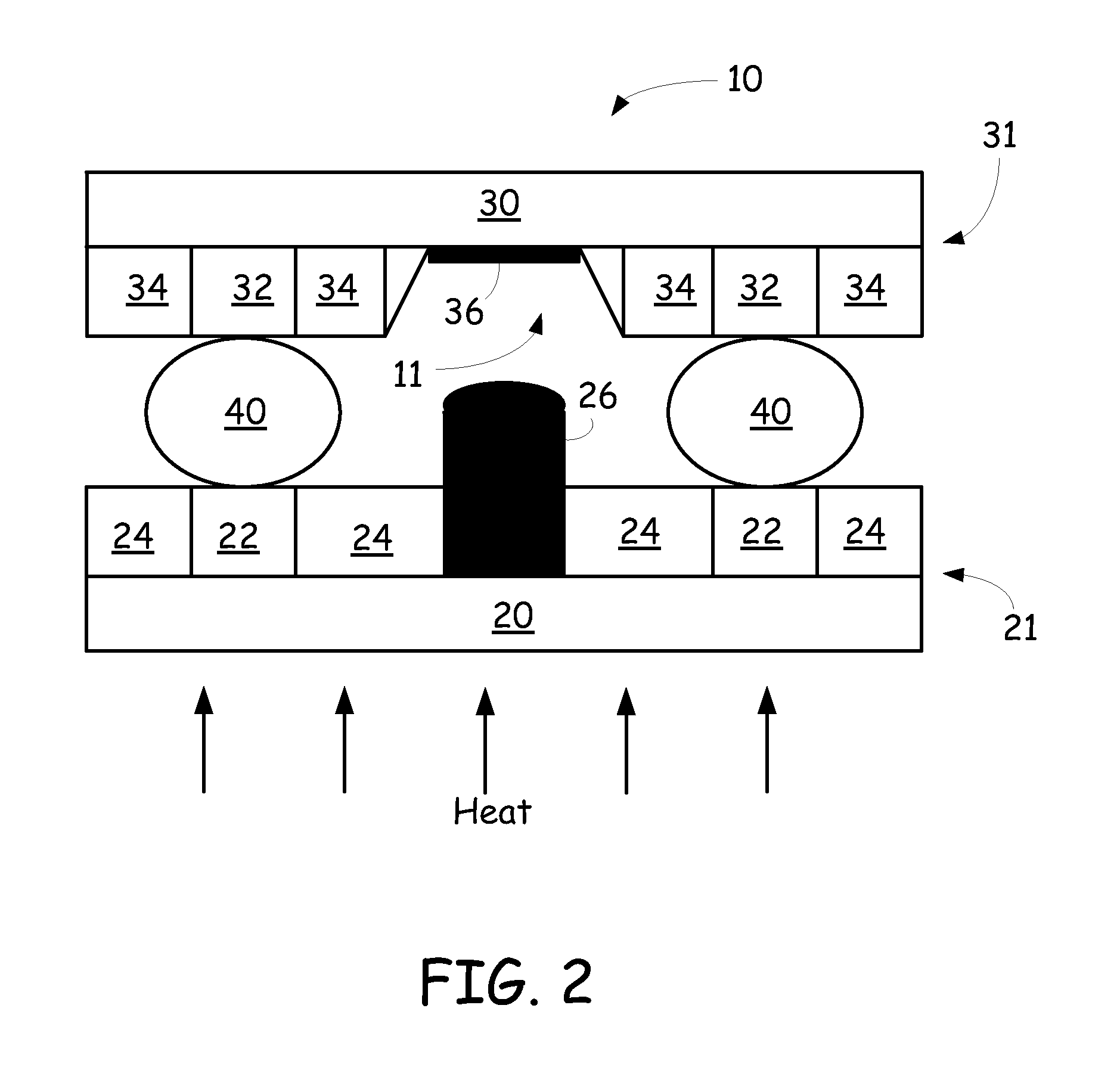

InactiveUS20060079021A1Improve cooling effectImprove thermal conductivitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringGold film

A method for flip chip package and structure thereof is disclosed. The present invention is using an eutectic bonding process to connect a chip and a heatsink for enhancing thermal dissipation capability from the chip to the heatsink and ensuring the chip working well. The method for flip chip package at least includes the steps of providing a heatsink having a surface plated with a gold film and a bare surface, providing a chip having a join surface and an active surface with a plurality of contacts, eutectic bonding the join surface of the chip to the gold film of the heatsink by gold-silicon diffusion for connecting the chip to the heatsink, connecting the active surface of the chip to a substrate by flip chip technology; and dispensing an underfill into the gap between the chip and the substrate.

Owner:VIA TECH INC

Plate

ActiveUS20130056776A1Easy to oxidizePrevent oxidationPrinted circuit aspectsSolid-state devicesReflective layerProtection layer

A plate including a substrate, a metal reflection layer and an oxidation protection layer is provided. The substrate has a first surface and a second surface opposite to the first surface. The metal reflection layer is disposed on the first surface of the substrate. The oxidation protection layer covers the metal reflection layer. The metal reflection layer is disposed between the oxidation protection layer and the first surface of the substrate. At least one light emitting diode chip is adapted to eutectic bonding on the plate.

Owner:GENESIS PHOTONICS

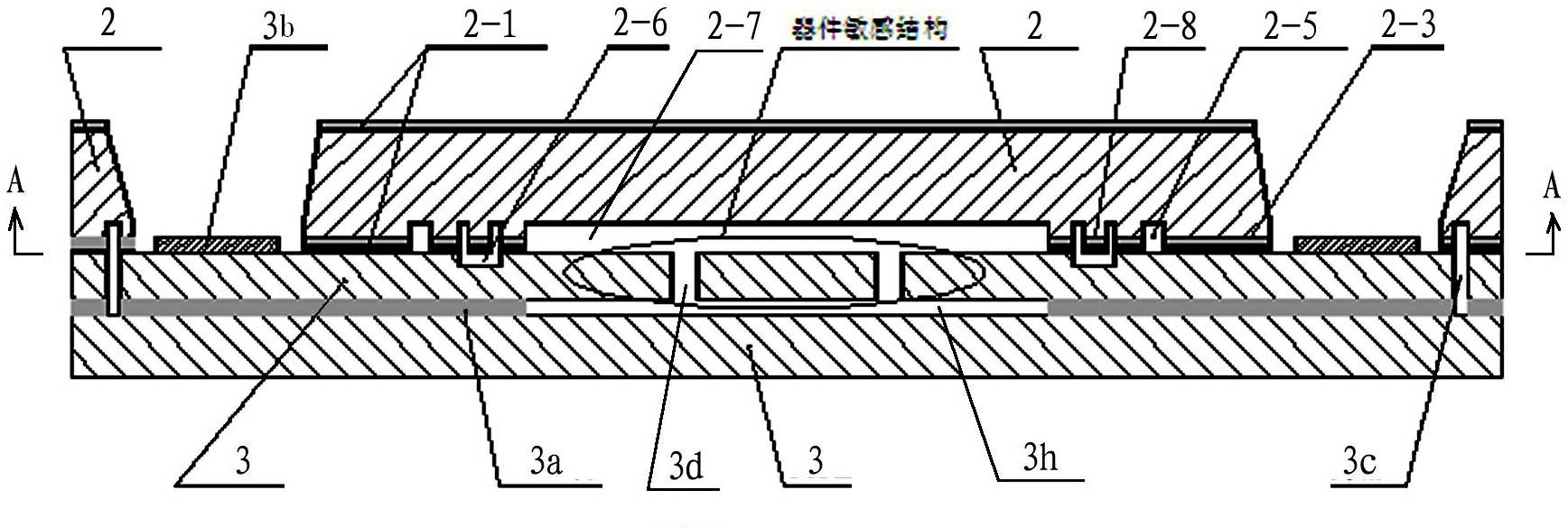

Method for interconnecting electrodes of MEMS (micro electro mechanical system) device based on SOI (silicon-on-insulator)

ActiveCN102367165ASuitable for productionSimple methodDecorative surface effectsChemical vapor deposition coatingElectricityEngineering

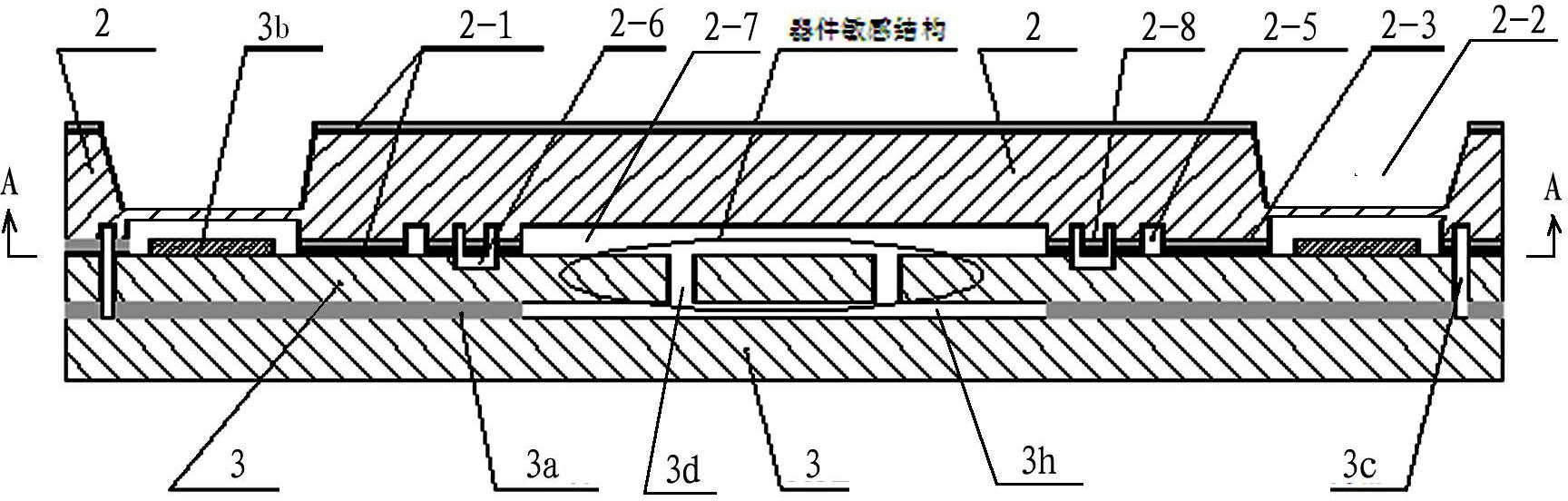

The invention relates to a method for interconnecting electrodes of an MEMS (micro electro mechanical system) device based on an SOI (silicon-on-insulator). In the method, a metal interconnection lead (2-8) and various electric isolation grooves (2-5, 2-6) are made on a silicon cover plate (2); and then, a structure layer (3) of the MEMS device is stuck with the silicon cover plate (2) through gold-silicon eutectic bonding, so that the electrodes of the MEMS device are interconnected together through the metal lead on the cover plate and led out to metal pressure welding points. The method provided by the invention overcomes the technical problems caused by the prior art adopting the techniques such as medium filling, flattening and the like, simplifies the techniques, is easy to operate, and is suitable for manufacturing various SOIMEMS devices.

Owner:EAST CHINA INST OF OPTOELECTRONICS INTEGRATEDDEVICE

Manufacturing method of biaxial MEMS (micro-electro-mechanical system) gyroscope

ActiveCN102134053AReduce areaReduce manufacturing costTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesGyroscopeBonding process

The invention discloses a manufacturing method of a biaxial MEMS (micro-electro-mechanical system) gyroscope. The method comprises the following seven steps of: providing a bottom wafer, and performing photoetching and anisotropic corrosion to form a bottom cavity; depositing a first layer of metal on the bottom wafer, and performing photoetching and etching processes on the first layer of metal to form a first layer of metal lower electrode and connection line; depositing a second layer of metal on the second layer of silicon oxide of the bottom wafer, and performing photoetching and etchingprocesses on the second layer of metal to form a second layer of metal seal ring and conductive block; providing a top wafer, and forming a top cavity on the top wafer through a dry method or wet method; providing an MEMS wafer, and bonding the MEMS wafer and the top wafer together through a melting and bonding process; reducing the thickness of the MEMS wafer in a first group of wafers to the thickness required in design through a chemically mechanical polishing process; and bonding a second group of wafers and the bottom wafer together through a eutectic bonding method. The biaxial gyroscope has the advantages of small area and low cost.

Owner:SENODIA TECH (SHANGHAI) CO LTD

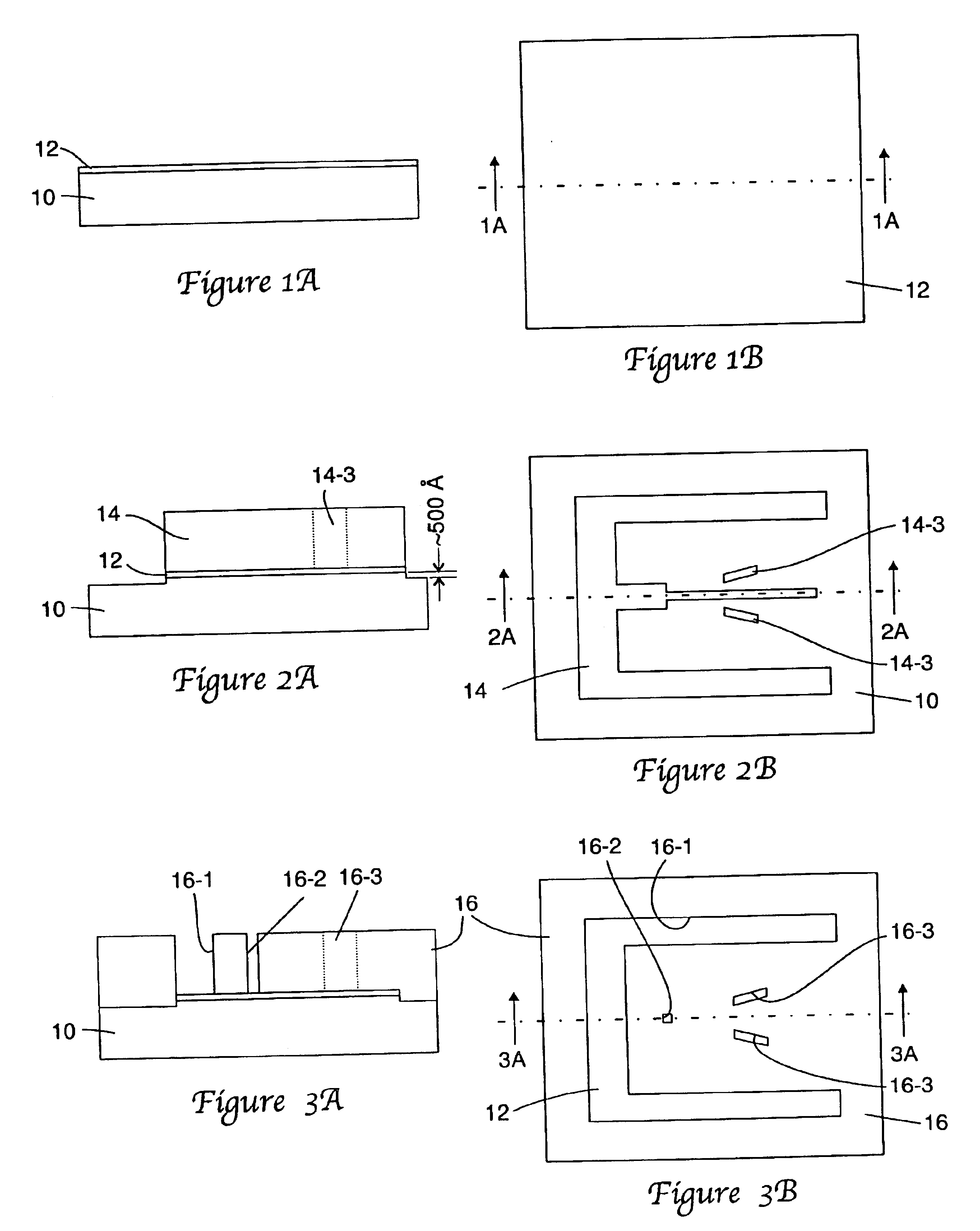

Self-aligned wafer bonding

ActiveUS20110008632A1Semiconductor/solid-state device detailsSolid-state devicesWafer dicingEngineering

A wafer article includes a substrate, two or more hydrophilic areas disposed on the substrate, hydrophobic areas surrounding the hydrophilic areas, and a eutectic bonding material disposed on the substrate. A wafer apparatus including two wafers having complimentary hydrophilic regions and eutectic bonding material is disclosed and a method of forming a bonded wafer articles is disclosed.

Owner:SEAGATE TECH LLC

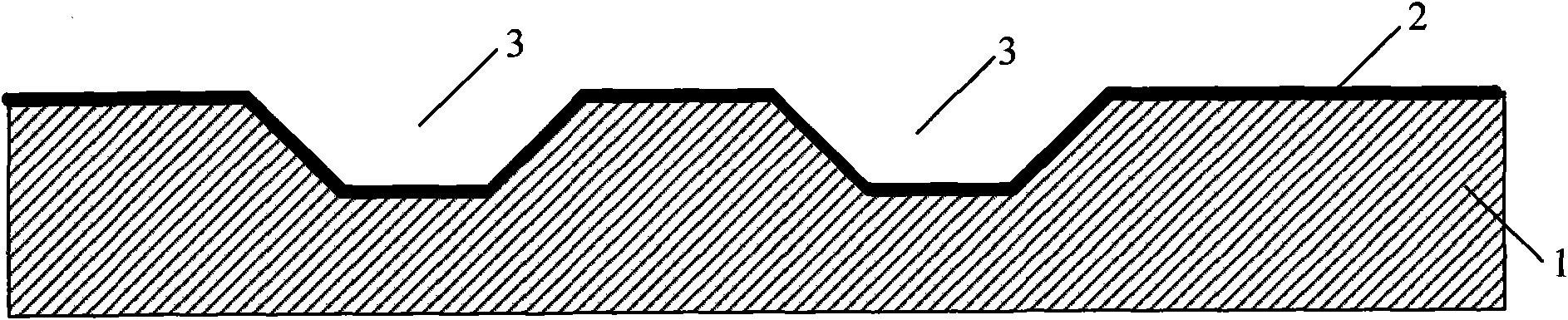

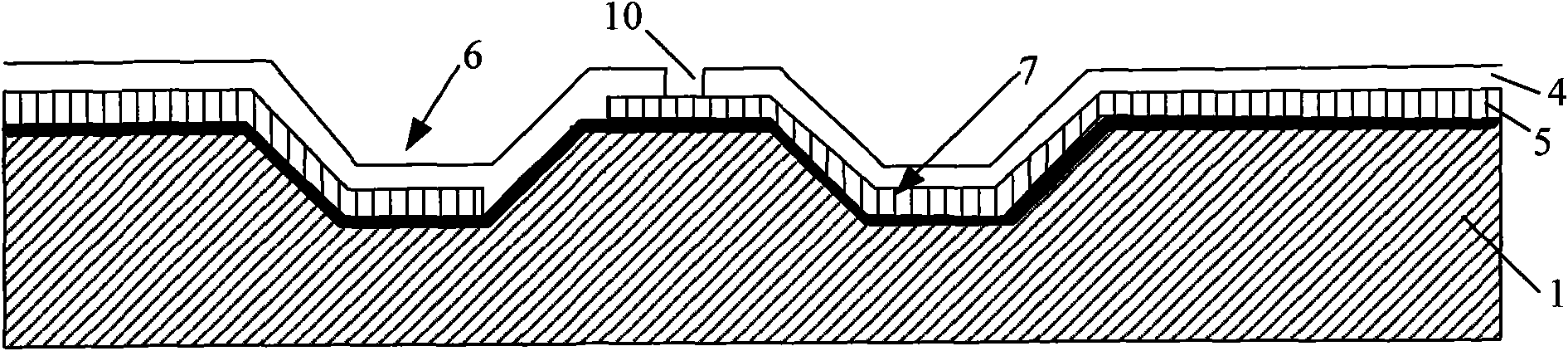

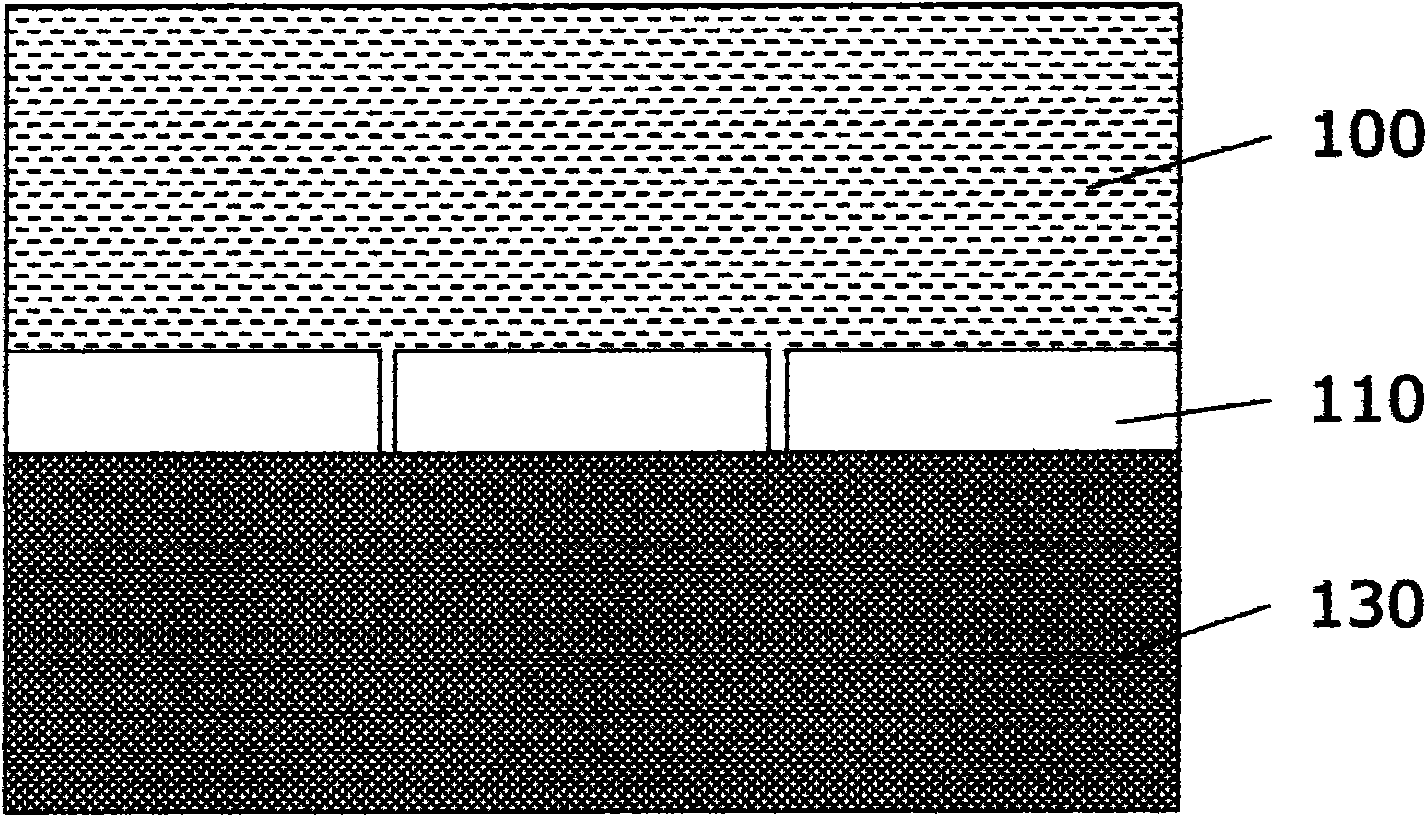

Wafer level vacuum packaging method of MEMS (Micro-electromechanical System) component

ActiveCN101780942AReduce pollutionImprove performanceDecorative surface effectsChemical vapor deposition coatingEngineeringMachining process

The invention discloses a wafer level vacuum packaging method of an MEMS (Micro-electromechanical System) component, which realizes the packaging of a packaging cover plate and the MEMS component by adopting an eutectic bonding technology. The method comprises the steps of: (1) carrying out double-side polishing on the packaging cover plate; (2) depositing insulating media on two sides of the packaging cover plate; (3) preparing a metal film which is used for metal-silicon bonding on the packaging cover plate; (4) preparing an electrode outlet through hole; and (5) carrying out bonding packaging on the packaging cover plate and the MEMS component. By preparing the metal film which is used for metal-silicon bonding on the packaging cover plate, the invention omits the process for preparing bonding metal layer during processing the MEMS component, reduces the pollution of metal to MEMS components in production process, improves the process compatibility and further improves the performance of the MEMS components.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

Integrated Heat Conductive Light Emitting Diode (LED) White Light Source Module

InactiveUS20120043886A1High performance/cost ratioEasy to mass producePrinted circuit aspectsSolid-state devicesDriver circuitSurface mounting

This invention discloses a new and advanced light emitting diodes (LEDs) light source module, and more specifically surface mounting LED dice and / or driver circuits on a slim linear Silicon wafer to provide superior heat dissipation capability through eutectic bonding onto a small Silicon base and the overall performance / cost ratio of the LED white light source module by an advanced integrated.

Owner:HARBOR LED LIGHTING

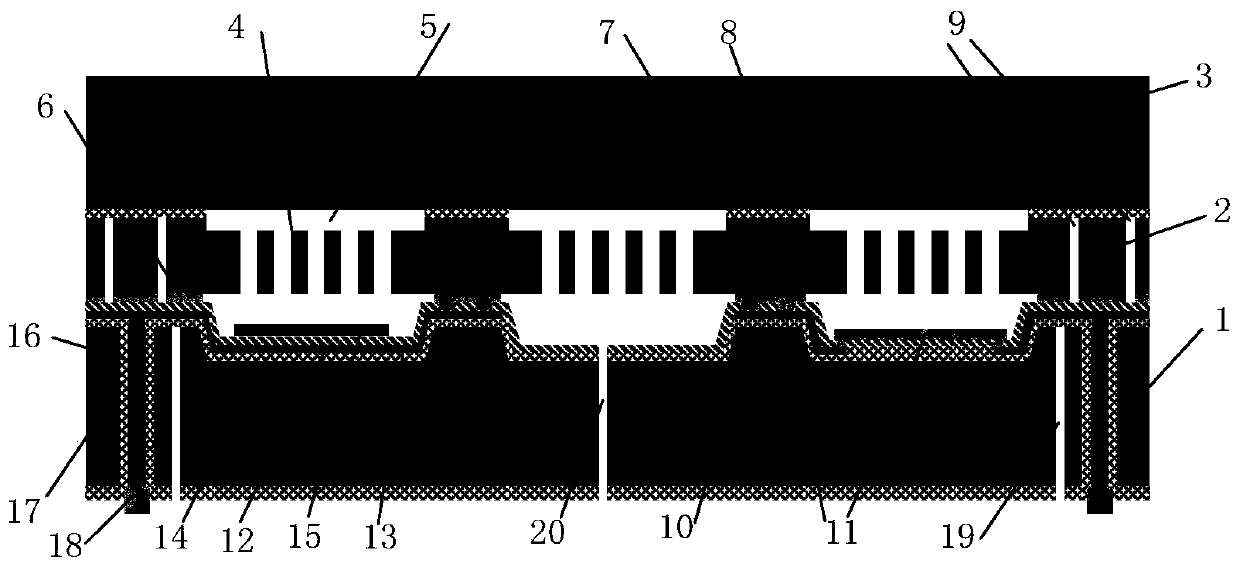

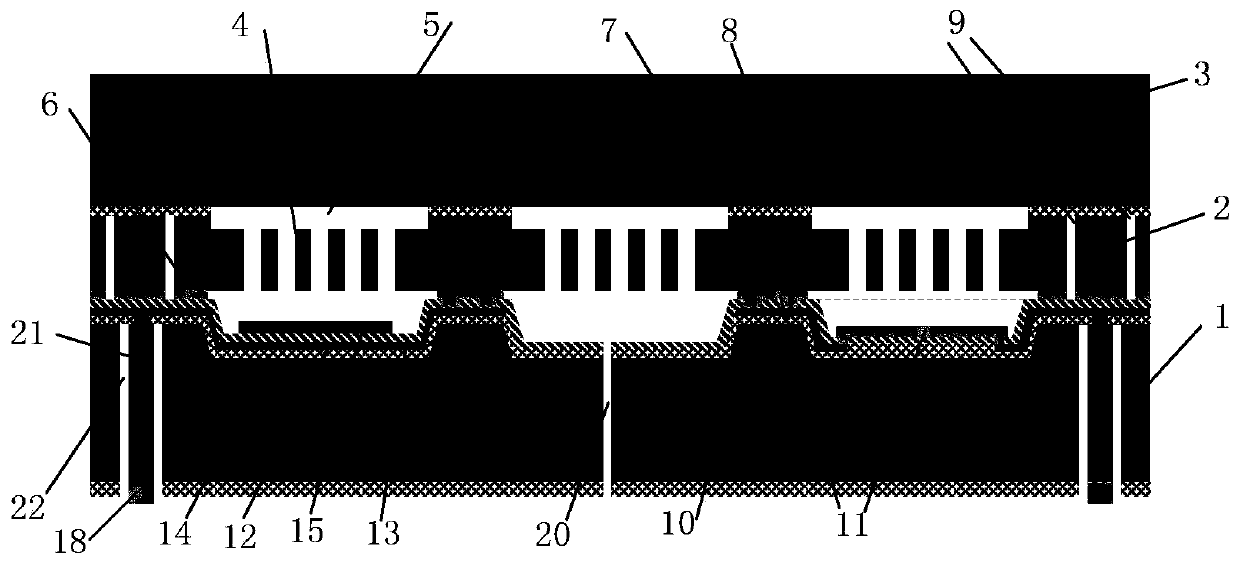

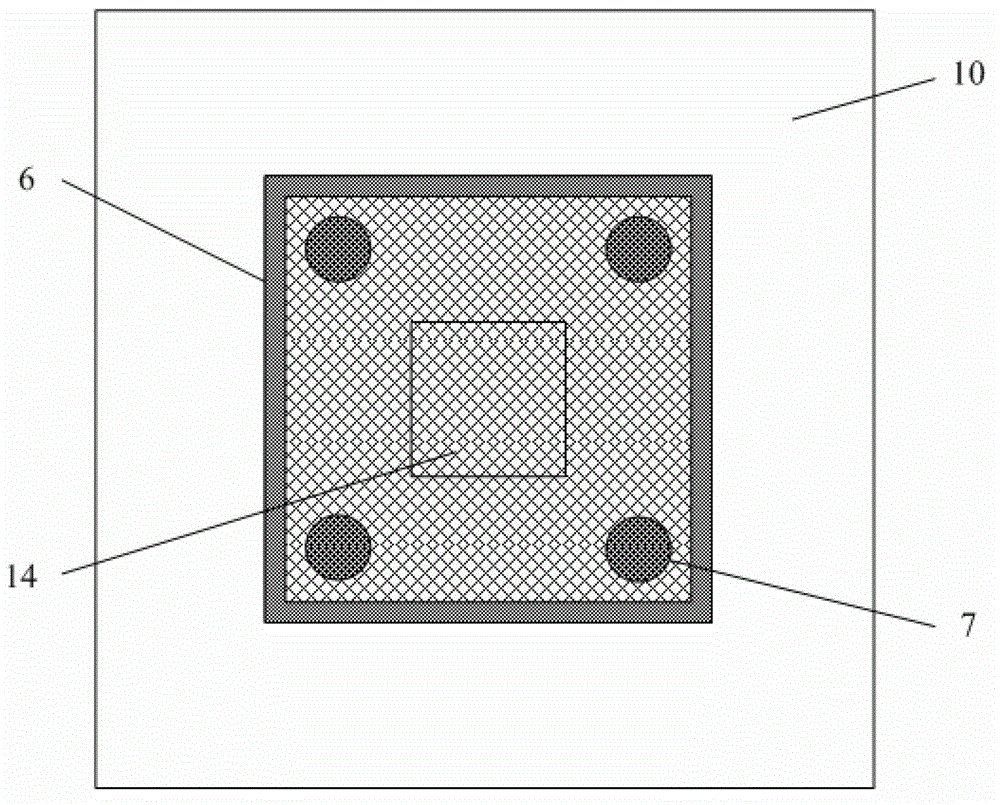

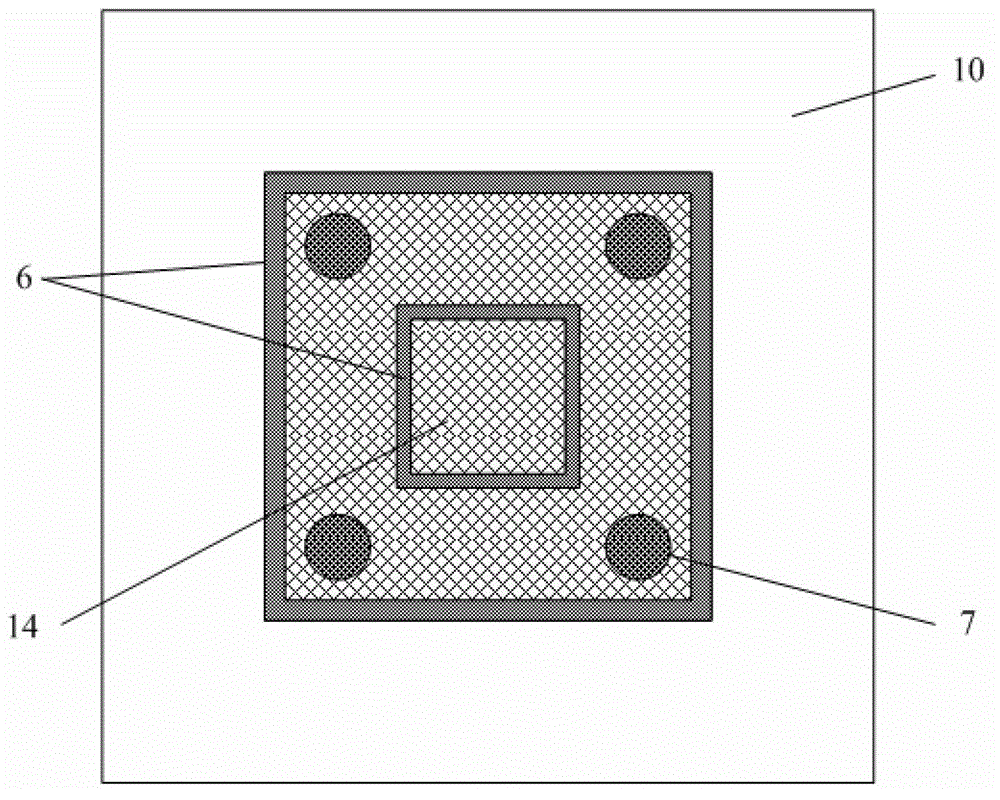

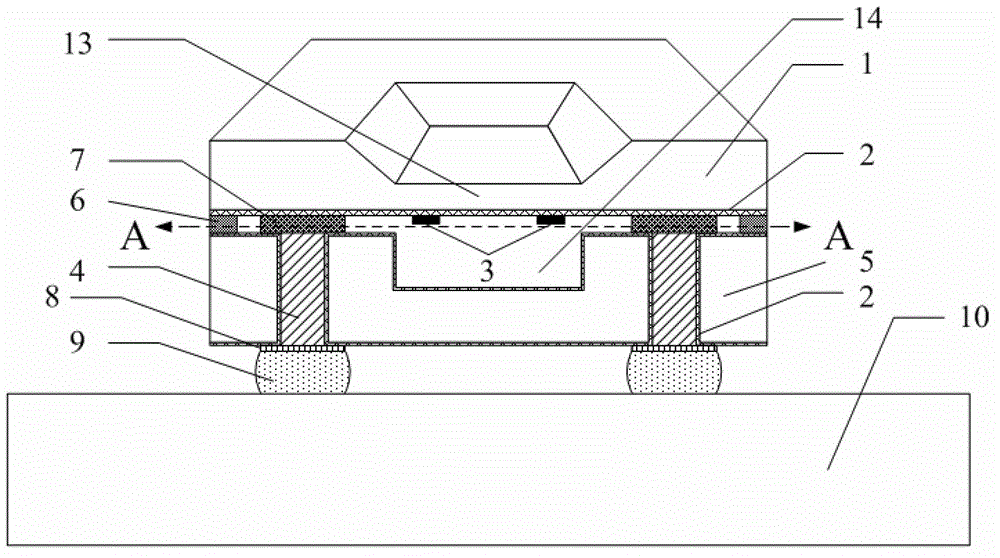

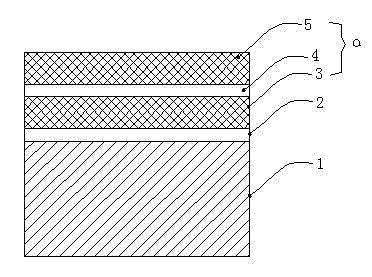

Wafer level packaging MEMS chip structure and processing method thereof

ActiveCN110467148APrevent air leakageGood package sealingDecorative surface effectsSolid-state devicesThermal dilatationSignal processing circuits

The invention relates to a wafer level packaging MEMS chip structure and a processing method thereof, and the structure forms a cavity structure for the movement of a comb tooth microstructure of a device layer through the sequential bonding of a cap layer, the device layer and a substrate layer. Electrical signals in the packaging cavity are led out from the side surface of the structure by crossing a substrate bonding sealing ring by a first-layer lead of a double-layer metal lead arranged on the substrate layer; after metal eutectic bonding wafer-level vacuum packaging is completed, deep silicon etching is carried out at a position corresponding to a metal electrode on the back surface of a substrate wafer to form a through hole, a conductive material is used for filling the through hole or forming a conductive silicon column, and electrode leading-out is carried out on the back surface. The structure can be integrated with a signal processing circuit in a flip-chip bonding mode. Compared with a mode of manufacturing a TSV through hole in a packaging cavity for electrical lead-out, the problem of packaging air tightness caused by filling a cavity with an insulating medium is avoided, and the problems of temperature stability and reliability caused by mismatching of thermal expansion coefficients of a filling material and a silicon material are also avoided.

Owner:BEIJING INST OF AEROSPACE CONTROL DEVICES

Pressure sensor encapsulation structure containing silicon through holes

InactiveCN102749167APackage structure is simpleReduce package sizeSolid-state devicesFluid pressure measurementMembrane technologyAir tightness

The invention provides a pressure sensor encapsulation structure containing silicon through holes, which uses a silicon base to substitute a traditional boron-phosphorosilicate glass base, and adopts a flip chip bonding technology and a bonding technology (such as CuSn bonding, AuSn eutectic bonding, Cu-Cu bonding and Au-Au bonding) to realize the airtight vacuum encapsulation of pressure sensors; a monocycle or bi-cycle bonding metal ring is adopted for encapsulation, and plays the role of reducing the bonding stress on the encapsulation of the pressure sensors with different piezoresistance strip distribution under the condition of ensuring the measurement sensitivity; and conductive columns are adopted for replacing metal wires to be used as signal lead wires, so the mutual connection reliability is increased. Compared with encapsulation structures of the silicon glass electrostatic bonding technology, the metal wire bonding technology, the metal isolating membrane technology and the airtight cavity silicone oil filling technology which are adopted traditionally, the pressure sensor encapsulation structure cancelled silicone oil filling and the metal isolating membrane, contributes to the improvement in the pressure sensor sensitivity, can also be used for dynamic pressure detection, and has the advantages of small size and high integration level.

Owner:PEKING UNIV

LED preparation method for improving light-emitting efficiency

The invention relates to a light-emitting diode (LED) preparation method for improving light-emitting efficiency and relates to a preparation process for a semiconductor luminescent device. The method aims to improve the light-emitting efficiency and the yield of products. In the technical scheme, the preparation method comprises the following steps of: allowing an epitaxy membrane to grow on a sapphire substrate, and performing vapor deposition and alloying on a transparent conducting layer to grow a SiO2 protective layer; coating mucilage glue on the SiO2 protective layer, and curing with a temporary support baseplate; stripping the sapphire substrate by laser; coarsening the N surface of the stripped epitaxy membrane; manufacturing a transparent bonding material layer capable of being cured on the N surface of the stripped epitaxy membrane, and curing the bonding material layer; preparing a reflective layer, and curing with the bonding material layer at high temperature; manufacturing an N electrode in a groove formed on a layer on the coarsened surface; evaporating a bonding metal layer, and performing eutectic bonding with a conducting and heat-conducting perpetual baseplate; and removing the temporary support baseplate and the SiO2 protective layer, and manufacturing a P electrode on the transparent conducting layer.

Owner:LATTICE POWER (JIANGXI) CORP

Airtight wafer level packaging structure and process of surface acoustic wave device

PendingCN107919862AIncreased shear strengthImprove air tightnessImpedence networksElectrical connectionHermetic packaging

The invention discloses an airtight wafer level packaging structure and process of a surface acoustic wave device. A circle of bonding layer metal is plated on the periphery of a working surface of afunctional chip, a circle of bonding layer metal is plated on a position corresponding to each piece of chip bonding layer metal on a sealing cover wafer, and the functional chip and the sealing coverwafer are correspondingly combined together through gold-gold bonding or eutectic bonding; an external circuit wiring circuit and an external electrode are arranged on one surface of the sealing cover wafer deviating from the working surface of the functional chip; an external welding ball is made on the external electrode; and a conduction hole is formed in the sealing cover wafer to electrically connect the working surface circuit of the functional chip with the external welding ball through the conduction hole and the external electrode in sequence. By adoption of the airtight wafer levelpackaging structure and process, high chip shear strength, good heat dissipation performance, and airtight package of the wafer level (WLP) surface acoustic wave device with controllable internal atmosphere are achieved, and the reliability is high.

Owner:CETC CHIPS TECH GRP CO LTD

Manufacturing method for GaN-based film chip

The invention provides a manufacturing method for a GaN-based film chip and relates to a manufacturing process of semiconductor light-emitting devices. According to the manufacturing method, the problem that an epitaxial film is broken when a sapphire substrate is stripped is solved. The manufacturing method comprises the following steps: sequentially growing an n-type GaN layer, an active layer and a p-type GaN layer on the sapphire substrate to form a semiconductor multilayer structure; carrying out thinning and polishing treatment on the sapphire substrate; coating a first adhesive on the semiconductor multilayer structure and a conducting reflective composite metal layer and curing the first adhesive with a first temporary substrate; carrying out laser stripping on the sapphire substrate, coating a second adhesive on the stripping surface and curing the second adhesive to a second temporary substrate; removing the first temporary substrate and the first adhesive; combining the semiconductor multilayer structure with a permanent support substrate by adopting an eutectic bonding way; and removing the second temporary substrate and the second adhesive. According to the manufacturing method disclosed by the invention, the damage to a GaN film can be reduced and the yield of a GaN-based film chip obtained by the process can be greatly increased.

Owner:晶能光電股份有限公司 +1

Preparation method of integral GaN-based film

ActiveCN101660206AReduce crackingIntegrity guaranteedPolycrystalline material growthSolid-state devicesOptoelectronicsGas release

The invention discloses a preparation method of an integral GaN-based film. a channel is preset in the unit spot edge area, on one hand, the break of a GaN extension wafer or a supporting substrate caused during transferring the substrate by eutectic bonding can be greatly reduced; on the other hand, after the substrate is transferred, the preset channel is naturally exposed by thinning a sapphiresubstrate, a gas release channel for laser stripping process is provided, and meanwhile, absolute separation of the sapphire substrate in an adjacent spot area and the extension film thereof is realized; and the stripping units are independent and are not influenced by the stress, so the damage problem of the edge of a unit GaN-based film can be solved, that is to say, the integrity of the GaN-based film subjected to laser stripping of the sapphire substrate can be ensured and the finished product rate of a GaN-based film device can be improved.

Owner:XIAMEN SANAN OPTOELECTRONICS TECH CO LTD

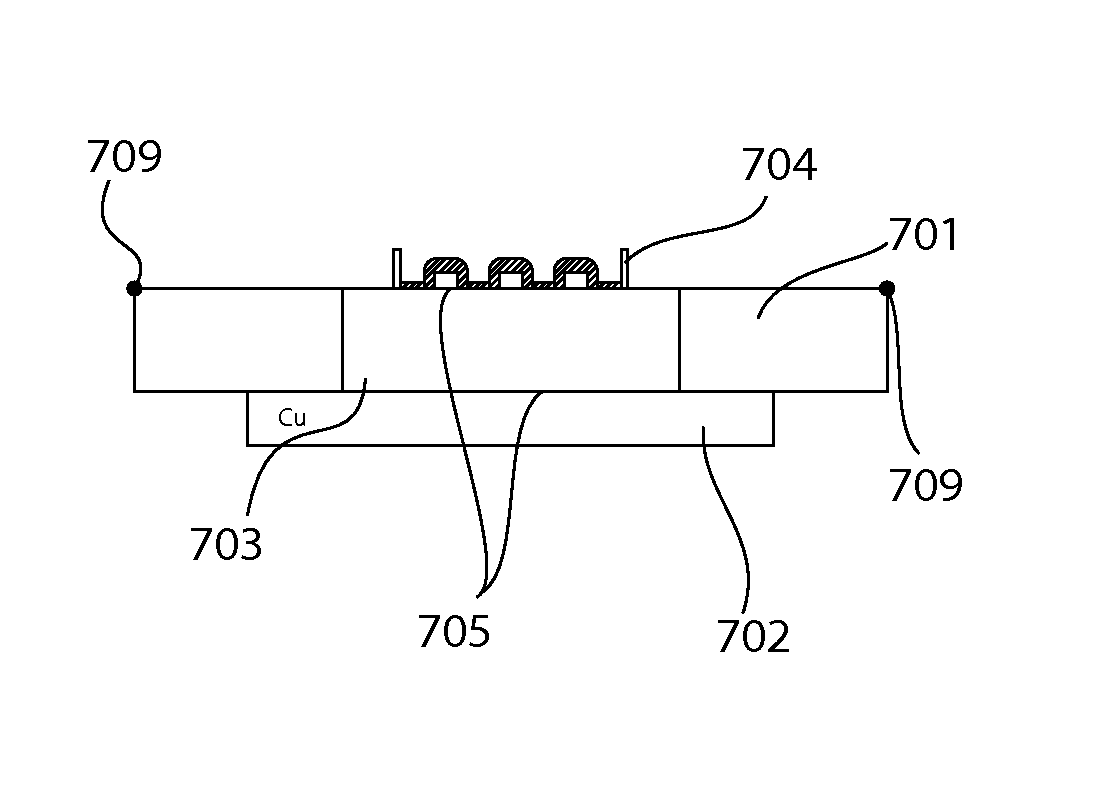

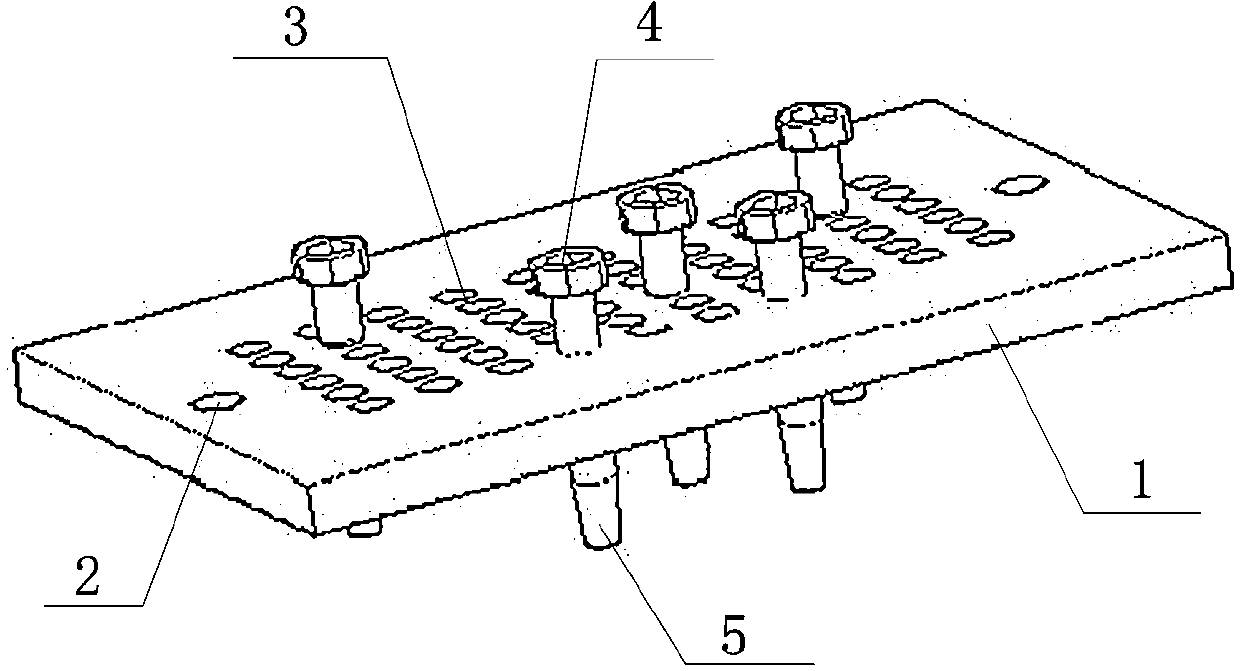

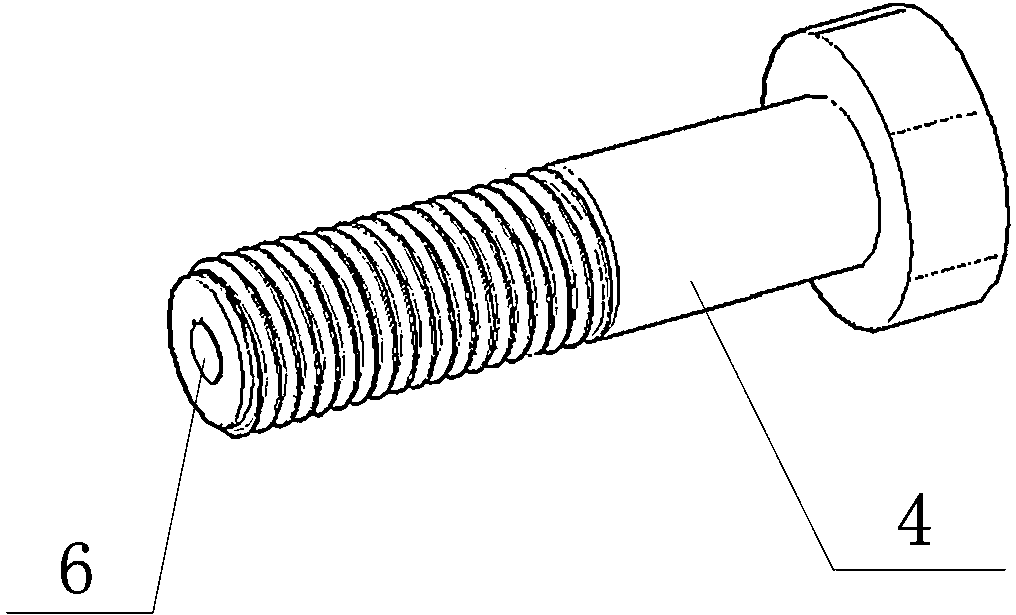

Multi-chip eutectic-bonding pressure dividing device

InactiveCN104174988AAvoid damageAvoid undervoltageSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringGraphite

The invention discloses a multi-chip eutectic-bonding pressure dividing device. The multi-chip eutectic-bonding pressure dividing device comprises a pressure plate (1), the pressure plate (1) is provided with positioning holes (2) matched with positioning columns (14) of a graphite clamp (13), a screw hole array (3) running through the pressure plate is arranged on the top side of the pressure plate, bolts (4) are arranged in the screw array (3) in a threaded match, and the bottoms of the bolts are provided with pressure heads (5) used for pressing chips; the bottoms of the bolts are provided with socket holes (6), the tops of the pressure heads (5) are provided with plugs (7) matched with the socket holes (6), and the pressure heads are socketed with the bolts; the pressure heads are made of flexible materials, and the bottoms of the pressure heads are conical, stand-shaped or specially-shaped; requirements of the chips different in thickness can be met by adjusting height of the bolts, the pressure heads matched with the chips in areas can be replaced according to positions and areas of the chips, reasonable division of pressure is realized, and damage to the chips can be avoided by the aid of the flexible pressure heads; according to the number and the positions of the chips, the number and the positions of the bolts and the pressure heads can be changed, different circuit welding pressures are obtained, and the multi-chip eutectic-bonding pressure dividing device is reusable, and waste is thereby avoided.

Owner:EAST CHINA INST OF OPTOELECTRONICS INTEGRATEDDEVICE

Method of mounting LED chip

InactiveUS20100210048A1Improve uniformityReduce bondingSolid-state devicesSemiconductor/solid-state device manufacturingDielectric substrateMaterials science

A method of mounting an LED chip, which is intended to suppress void-generation inside an eutectic bonding without use of flux. This method includes a step of eutectically bonding a first metal layer (e.g., AuSn layer) on a rear surface of the LED chip, with a metal ground layer on a dielectric substrate (mounting member). This method includes a step of providing a second metal layer having the same metal component as the first metal layer, to the top surface of the metal ground layer on a dielectric substrate; and subsequently connecting the LED chip and the dielectric substrate by way of eutectically bond while the dielectric substrate is heated at its bottom surface remote from the metal ground layer to melt the second metal layer by heat source (heater or the like).

Owner:PANASONIC CORP

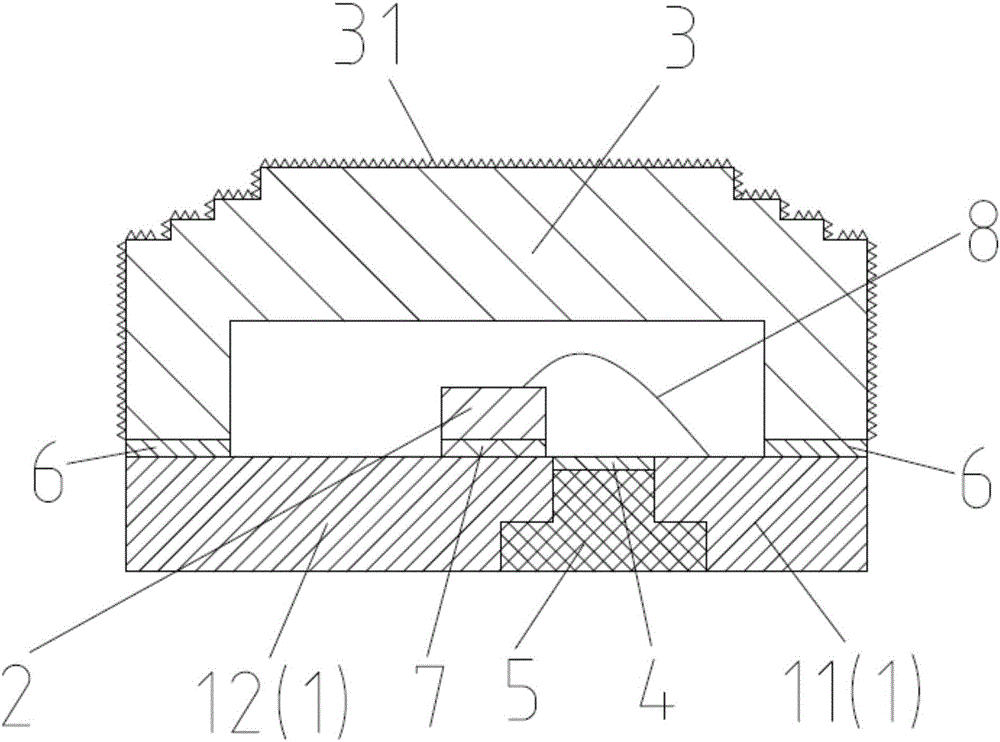

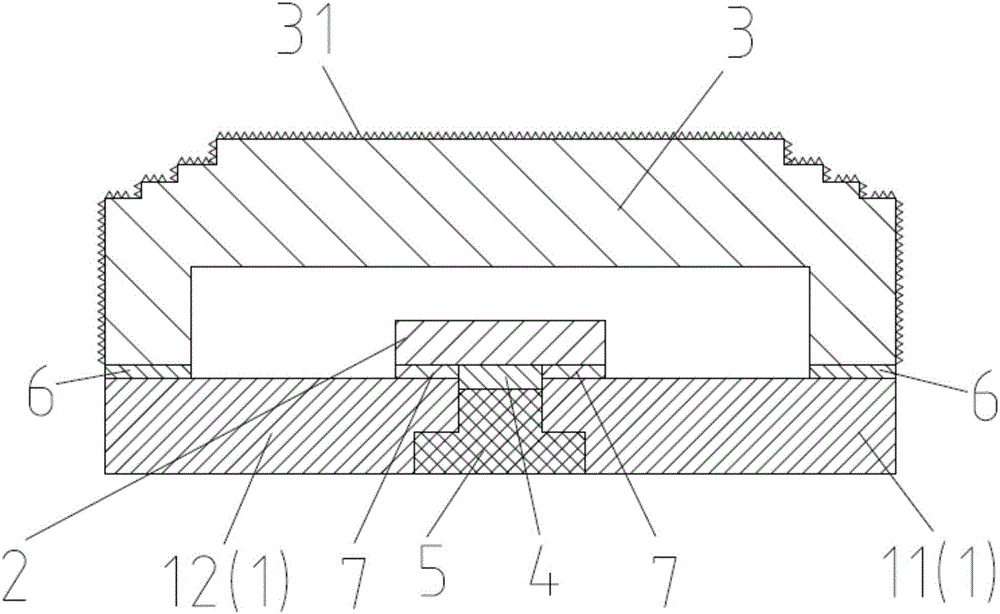

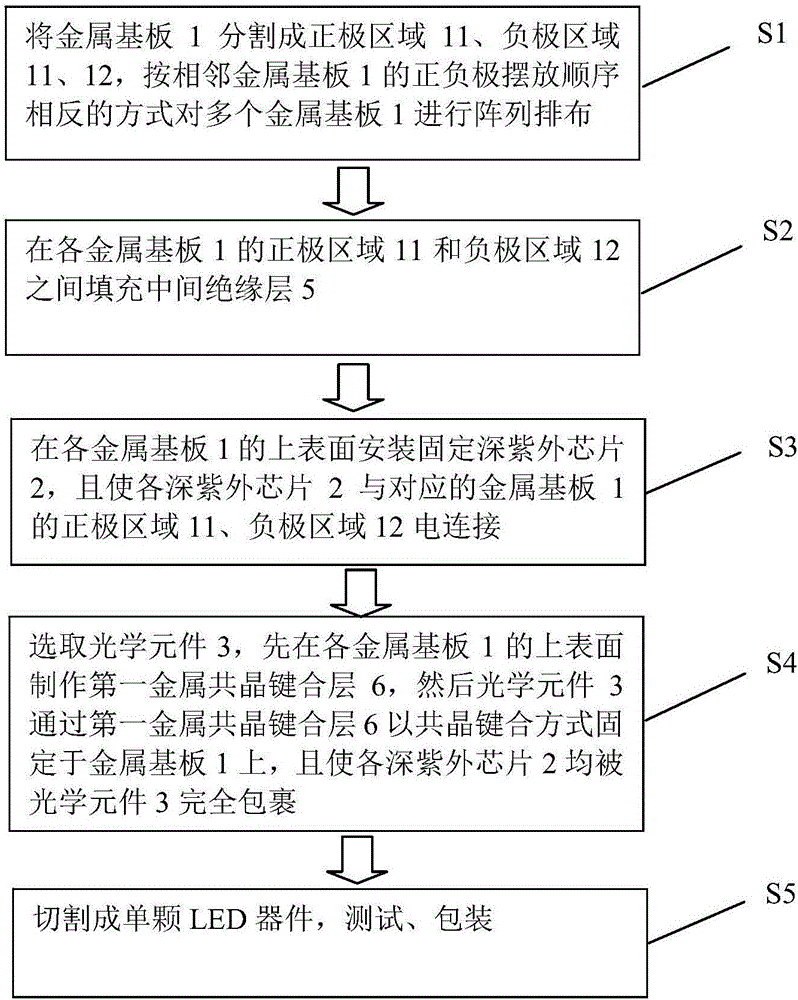

Deep ultraviolet LED packaging device and preparation method thereof

ActiveCN106784243AImprove luminous performanceImprove reliabilitySolid-state devicesSemiconductor devicesProduction lineUltraviolet

The invention discloses a deep ultraviolet LED packaging device. The device comprises a metal substrate, a deep ultraviolet chip, an optical element, an intermediate insulating layer and a first metal eutectic bonding layer, wherein a positive electrode region and a negative electrode region of the metal substrate are separated by the intermediate insulating layer; the deep ultraviolet chip is fixed on the metal substrate and electrically connected with the positive electrode region and the negative electrode region of the metal substrate; the optical element is fixed on the metal substrate through the first metal eutectic bonding layer and completely wraps the deep ultraviolet chip; the device further comprises an SiO2 insulating layer which covers the inner surface of the intermediate insulating layer. The invention further discloses a preparation method of the deep ultraviolet LED packaging device. The deep ultraviolet LED packaging device has the advantages of high luminous power, good heat dissipation, significantly improved product reliability and significantly prolonged service life, the packaging structure is simple, and reduction of the preparation cost is facilitated; the preparation method of the deep ultraviolet LED packaging device is simple and easy in process, suitable for production line work and high in preparation efficiency.

Owner:APT ELECTRONICS

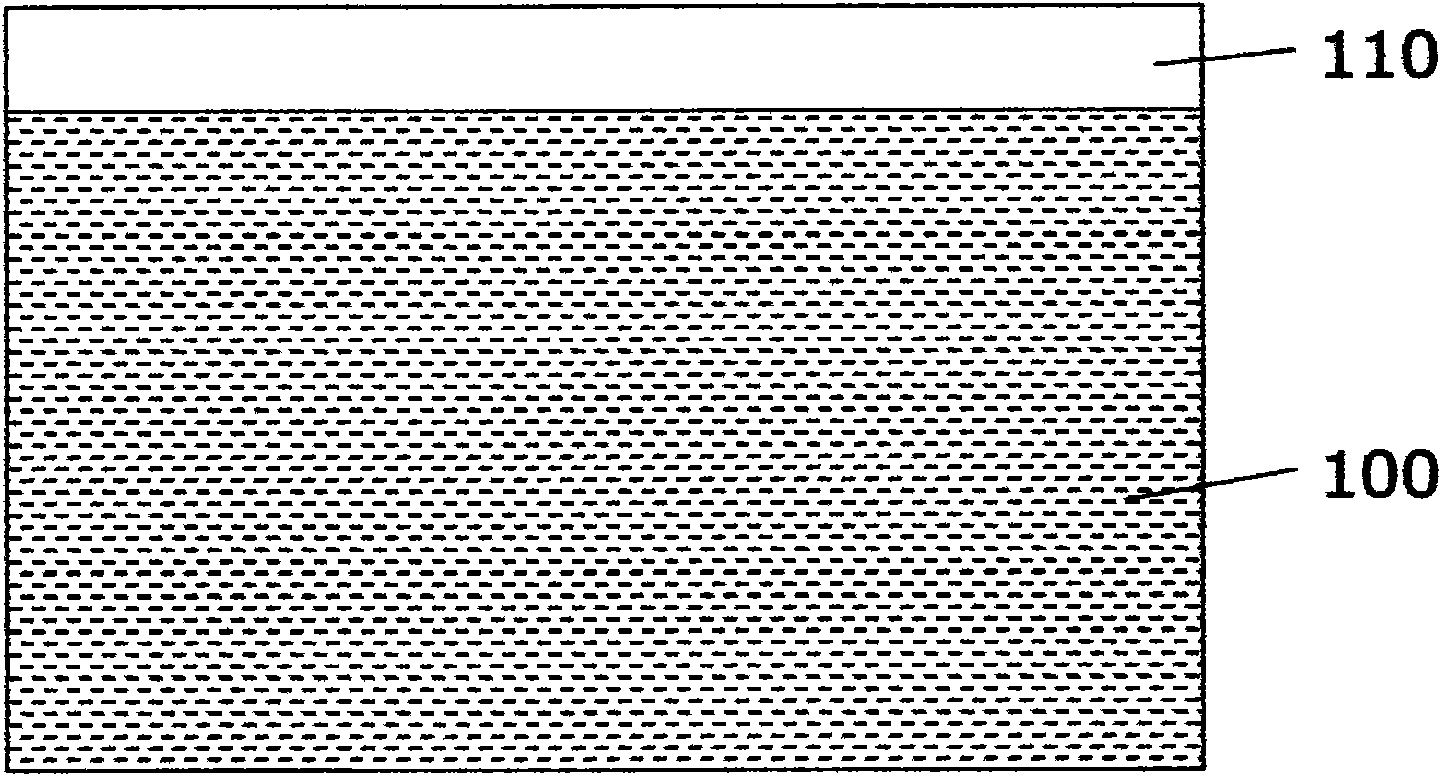

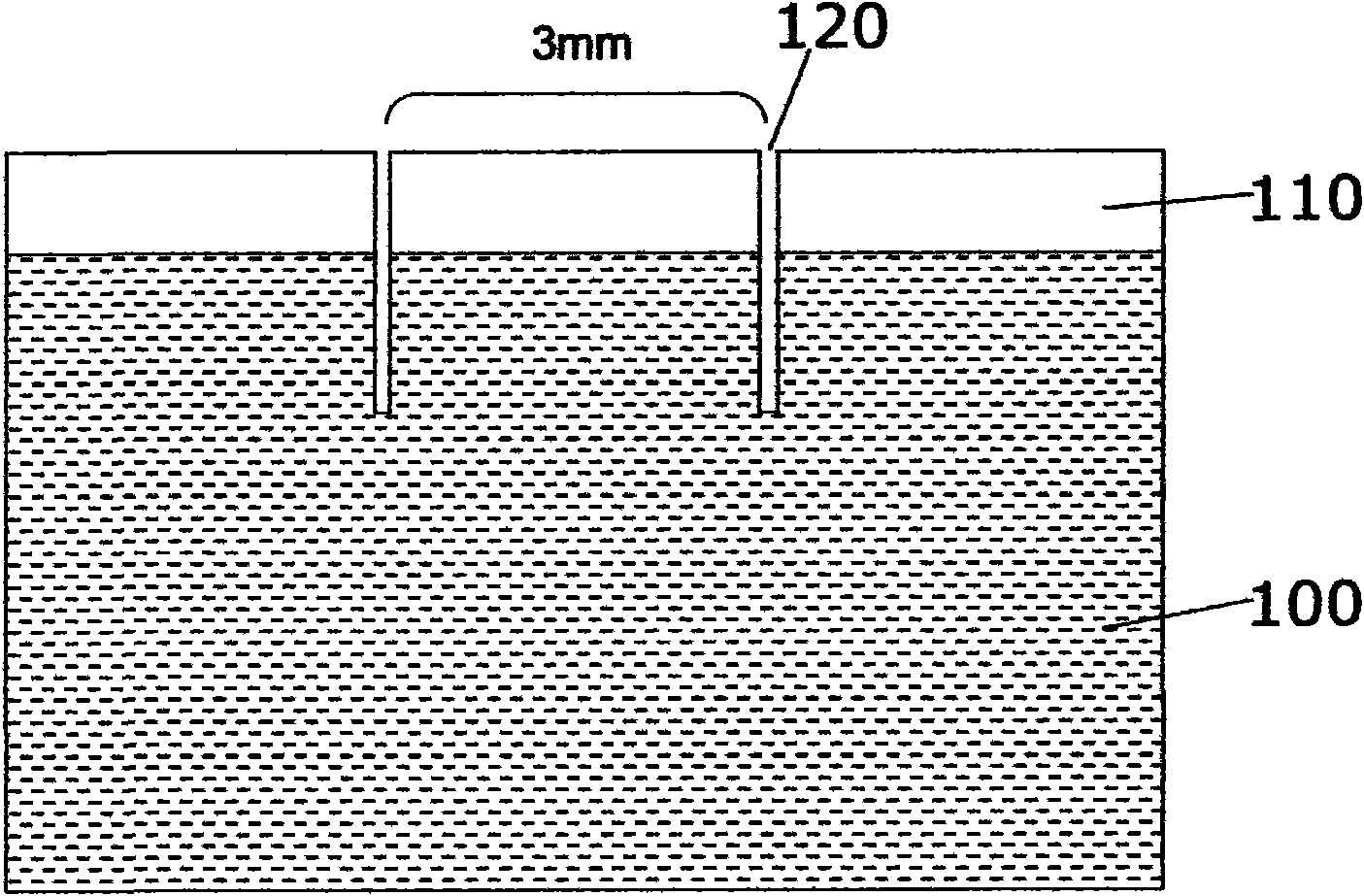

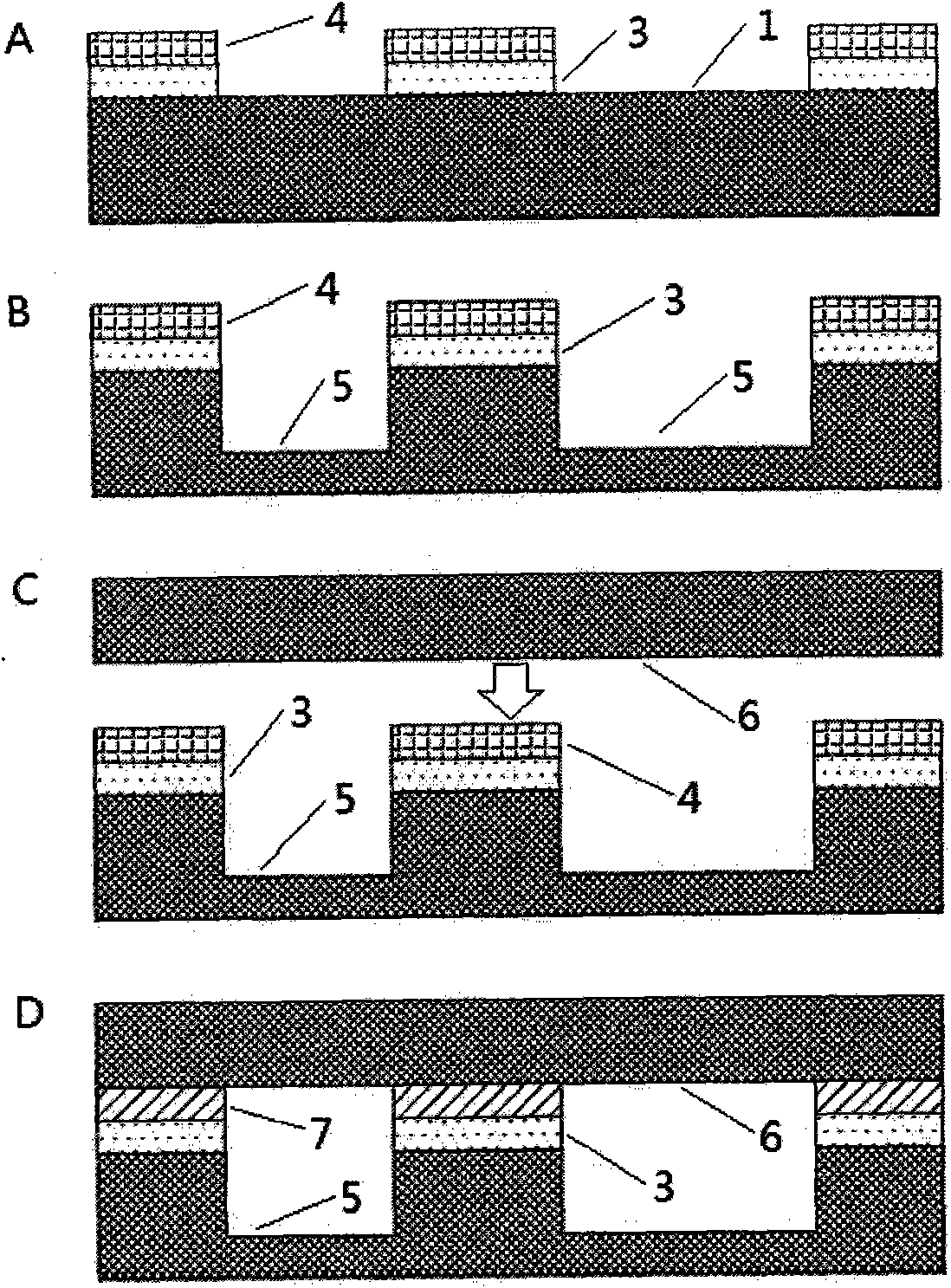

Bulk silicon etching and gold silicon bonding combined process method

ActiveCN101913553AThe process steps are simpleImprove efficiencyDecorative surface effectsChemical vapor deposition coatingGold filmSilicon etching

The invention discloses a bulk silicon etching and gold silicon bonding combined process method, which comprises the following steps of: firstly, forming a gold mask pattern on a first silicon wafer; secondly, dryly etching or wetly corroding the first silicon wafer by using a gold mask to form a bulk silicon microstructure; and finally, positioning a second silicon wafer on the first silicon wafer with a pattern structure to perform the gold silicon bonding. In the process method, a gold film layer is ingenuously used as a masking layer for forming the silicon microstructure in the etching process and also used as a bonding layer in a subsequent eutectic bonding process. In the traditional process, the etching of silicon and the bonding of the silicon wafer are two independent steps; while in the process method of the invention, the etching and the bonding are organically combined together, so that a process flow is simplified and production efficiency is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Light emitting diode

InactiveUS20160240758A1Relieve pressureAvoid crackingSolid-state devicesSemiconductor devicesThermal expansionLight-emitting diode

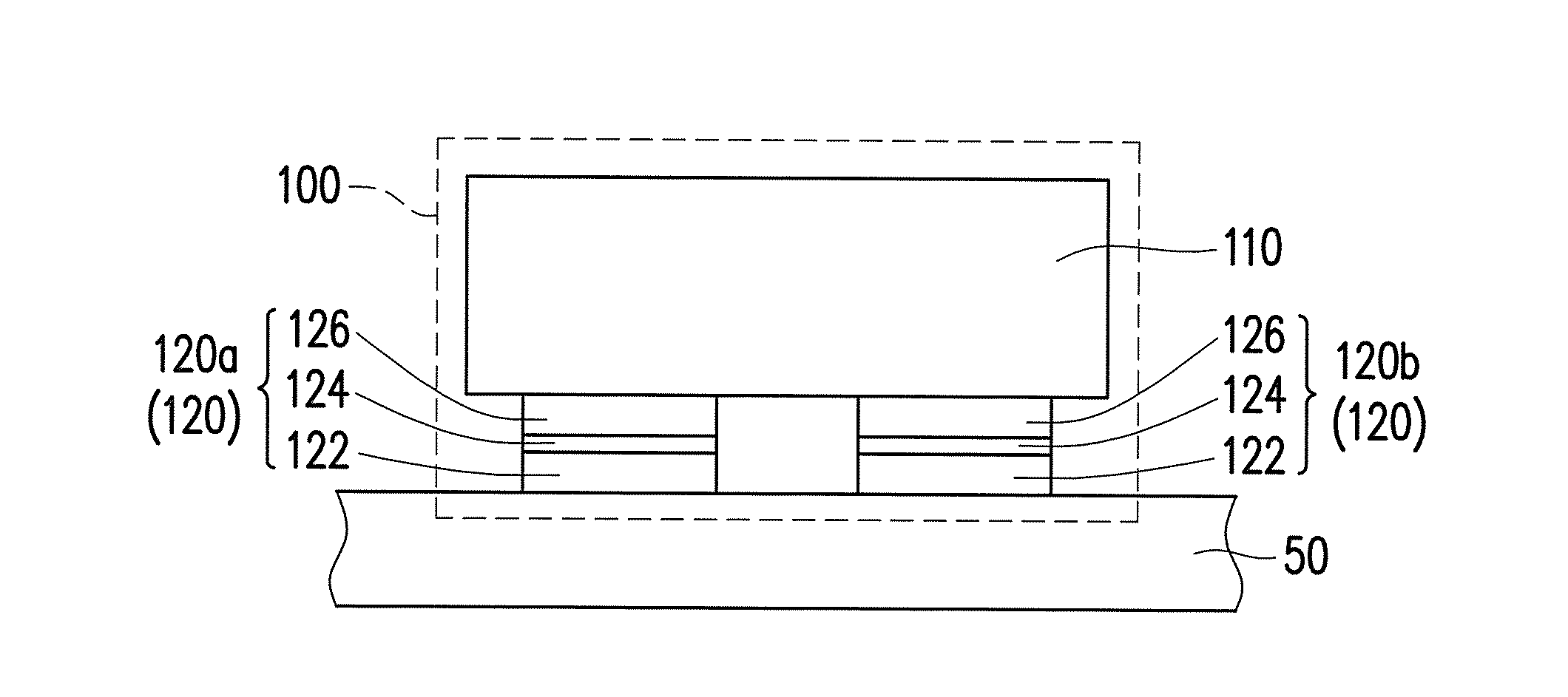

Provided is a light emitting diode (LED) mounted on a carrier substrate and including a semiconductor epitaxial structure and at least one electrode pad structure. The semiconductor epitaxial structure is electrically connected to the carrier substrate. The electrode pad structure includes a eutectic layer, a blocking layer and an extension layer. The eutectic layer is adapted for eutectic bonding to the carrier substrate. The blocking layer is between the eutectic layer and the semiconductor epitaxial structure. The blocking layer blocks the diffusion of the material of the eutectic layer in the eutectic bonding process. The extension layer is between the eutectic layer and the semiconductor epitaxial structure. The extension layer reduces the stress on the LED produced by thermal expansion and contraction of the substrate during the eutectic bonding process, so as to prevent the electrode pad structure from cracking, and maintain the quality of the LED.

Owner:GENESIS PHOTONICS

Method for bonding wafers and structure of bonding part

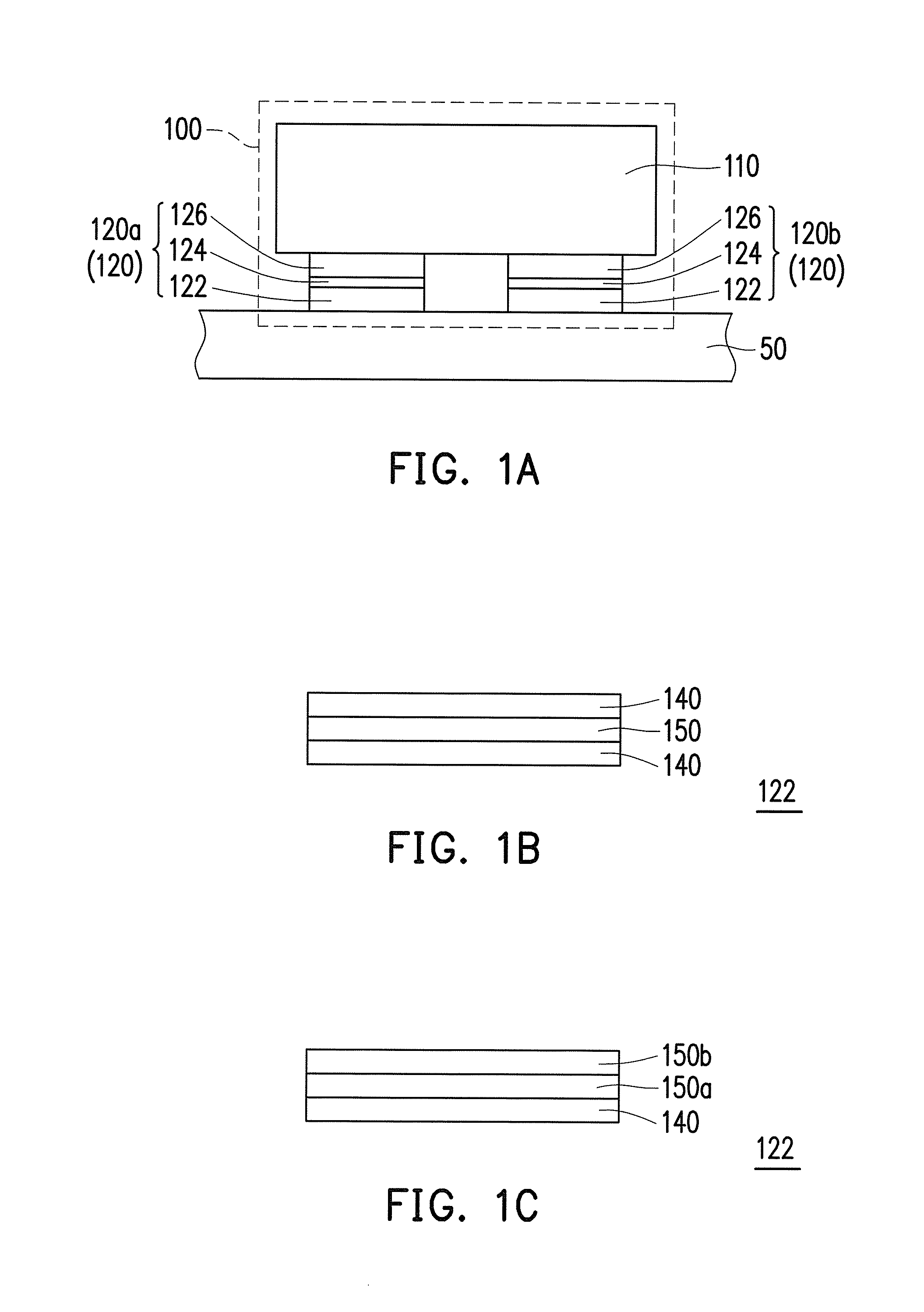

ActiveUS20140339710A1Preventing bonding partAvoid partialSemiconductor/solid-state device detailsSolid-state devicesEutectic bondingEngineering

A method for bonding wafers includes forming a first bonding part on a surface of a first wafer by stacking a diffusion preventing layer formed of a material having low wettability with AuSn above the first wafer and forming a bonding layer on a surface of the diffusion preventing layer such that the bonding layer stays back of an edge of the diffusion preventing layer, forming a second bonding part on a surface of a second wafer, and bonding the first bonding part and the second bonding part by eutectic bonding with an AuSn solder under a condition that the first wafer and the second wafer are opposed to each other.

Owner:ORMON CORP

Micro-actuator with interdigitated combs perpendicular to a base

A micro-actuator having a stage capable of a see-saw motion and a method for its manufacture are disclosed. In the micro-actuator according to the present invention, a plurality of parallel driving comb-type electrodes are formed on the bottom of the stage, and a plurality of parallel fixed comb-type electrodes are formed on a base plate. At both sides of the stage is a torsion bar that enables the see-saw motion. The torsion bar is supported by a frame comprised of a first frame layer and a second frame layer. The torsion bar and the first frame layer form one body. The first and second frame layers are bonded by a metal eutectic bonding layer between metal layers.

Owner:SAMSUNG ELECTRONICS CO LTD

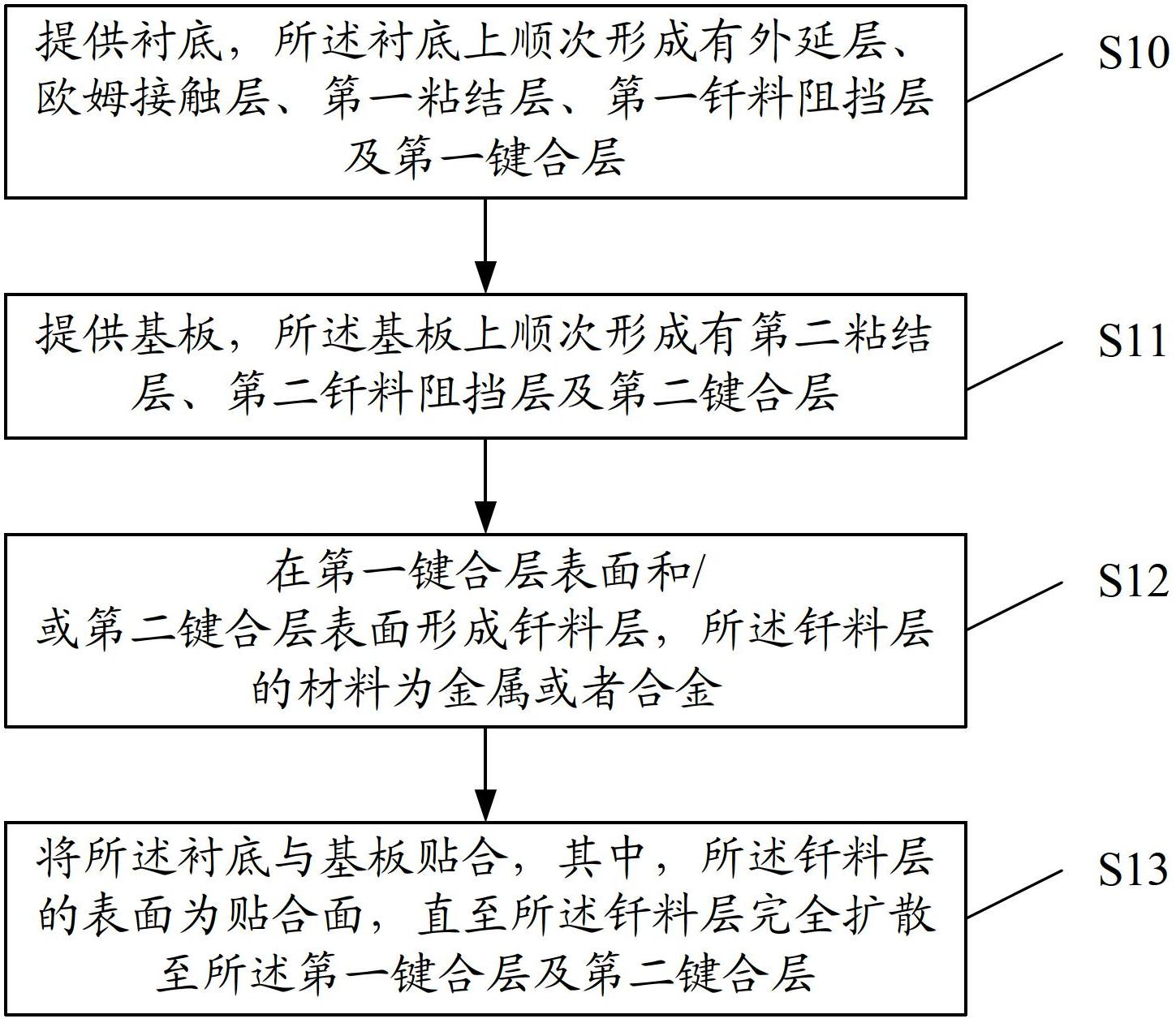

Bonding method for light-emitting diode (LED) chip and LED chip

ActiveCN102694089AReduce manufacturing costAvoid or reduce useWelding/cutting media/materialsSoldering mediaOhmic contactOptoelectronics

The invention provides a bonding method for a light-emitting diode (LED) chip and the LED chip. The bonding method for the LED chip comprises the following steps of: providing a substrate, wherein an epitaxial layer, an ohmic contact layer, a first adhesive layer, a first brazing filler metal barrier layer and a first bonding layer are sequentially formed on the substrate; providing a base plate, wherein a second adhesive layer, a second brazing filler metal barrier layer and a second bonding layer are sequentially formed on the base plate; forming a brazing filler metal layer on the surface of the first bonding layer and / or the surface of the second bonding layer, wherein the brazing filler metal layer is made of metal or an alloy; and attaching the substrate to the base plate by taking the surface of the brazing filler metal layer as an attachment surface until the brazing filler metal layer is completely diffused to the first and second bonding layers. Au-Au solid-phase diffusion bonding or Au-Sn eutectic bonding is avoided, so that the use of noble metal is avoided or reduced, and the manufacture cost of the LED chip is lowered.

Owner:HANGZHOU SILAN AZURE

Long wavelength vertical cavity surface emitting laser with integrated photodetector

Owner:SAMSUNG ELECTRONICS CO LTD

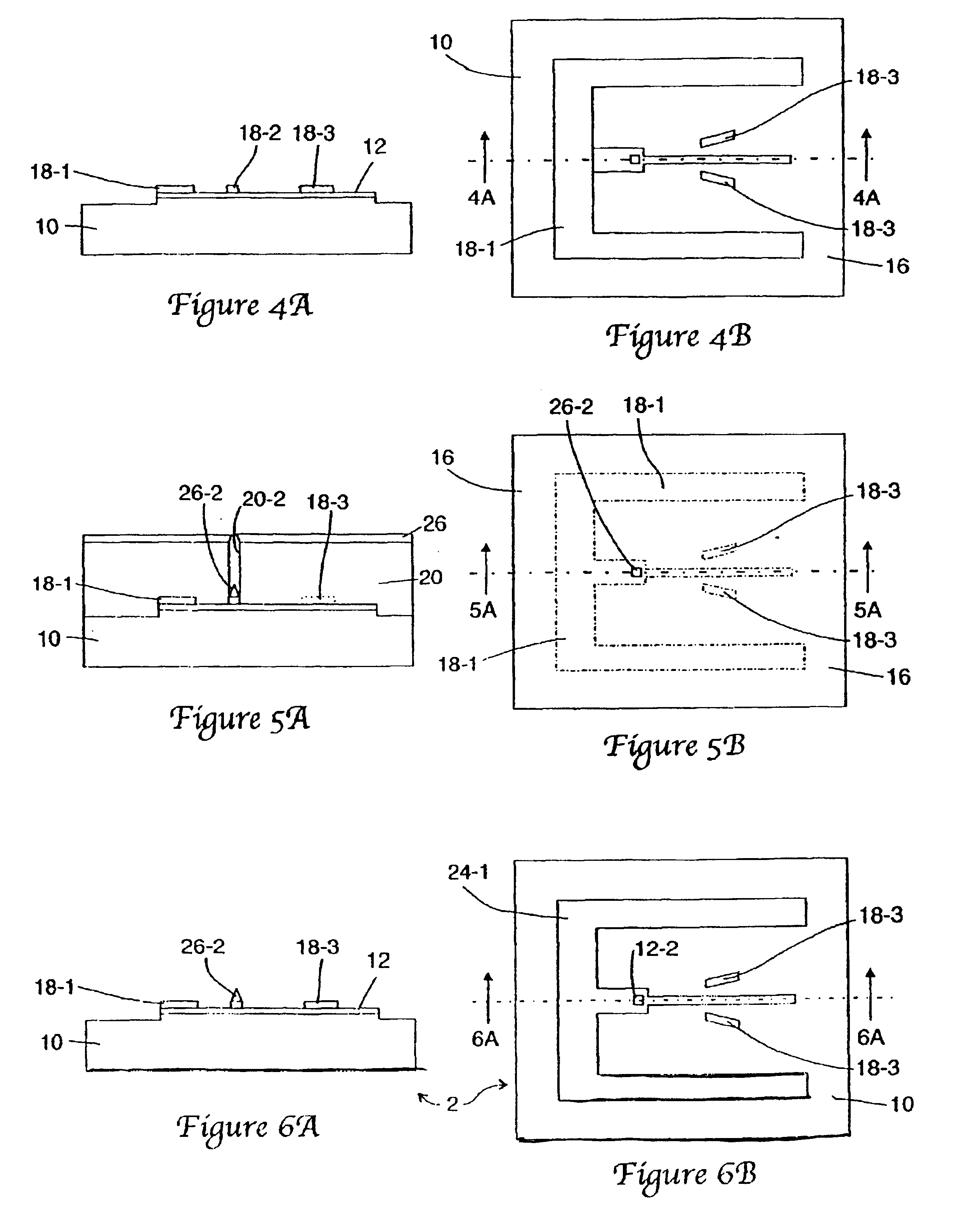

Microelectromechanical tunneling gyroscope and an assembly for making a microelectromechanical tunneling gyroscope therefrom

InactiveUS6841838B2Low costReduce total powerAcceleration measurement using interia forcesTransducer detailsCantilevered beamGyroscope

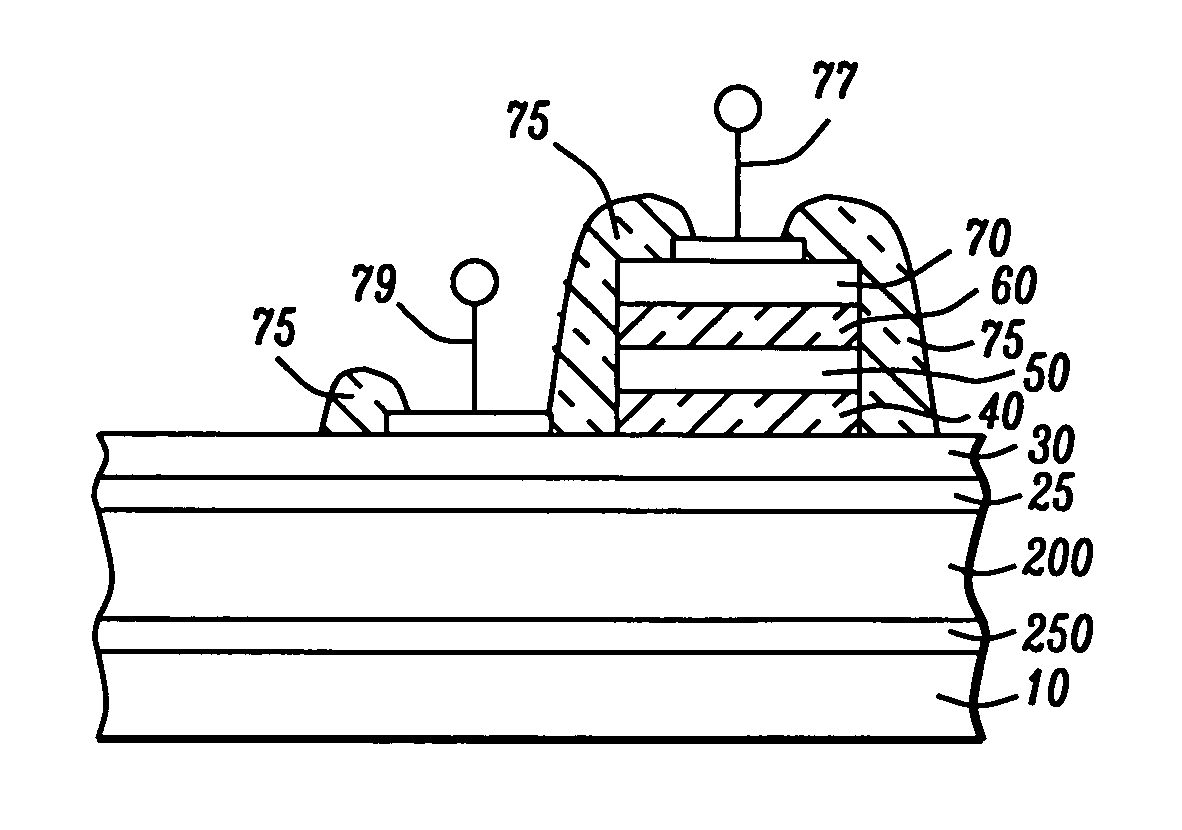

A method of making a micro electromechanical gyroscope. A cantilevered beam structure, first portions of side drive electrodes and a mating structure are defined on a first substrate or wafer; and at least one contact structure, second portions of the side drive electrodes and a mating structure are defined on a second substrate or wafer, the mating structure on the second substrate or wafer being of a complementary shape to the mating structure on the first substrate or wafer and the first and second portions of the side drive electrodes being of a complementary shape to each other. A bonding layer, preferably a eutectic bonding layer, is provided on at least one of the mating structures and one or the first and second portions of the side drive electrodes. The mating structure of the first substrate is moved into a confronting relationship with the mating structure of the second substrate or wafer. Pressure is applied between the two substrates so as to cause a bond to occur between the two mating structures at the bonding or eutectic layer and also between the first and second portions of the side drive electrodes to cause a bond to occur therebetween. Then the first substrate or wafer is removed to free the cantilevered beam structure for movement relative to the second substrate or wafer. The bonds are preferably eutectic bonds.

Owner:HRL LAB