Wafer level packaging MEMS chip structure and processing method thereof

A wafer-level packaging and chip structure technology, used in microstructure technology, microstructure devices, manufacturing microstructure devices, etc., can solve the problems of poor sealing and large drift of characteristic parameters, achieve good packaging sealing and reduce wiring difficulty. , the effect of avoiding air leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

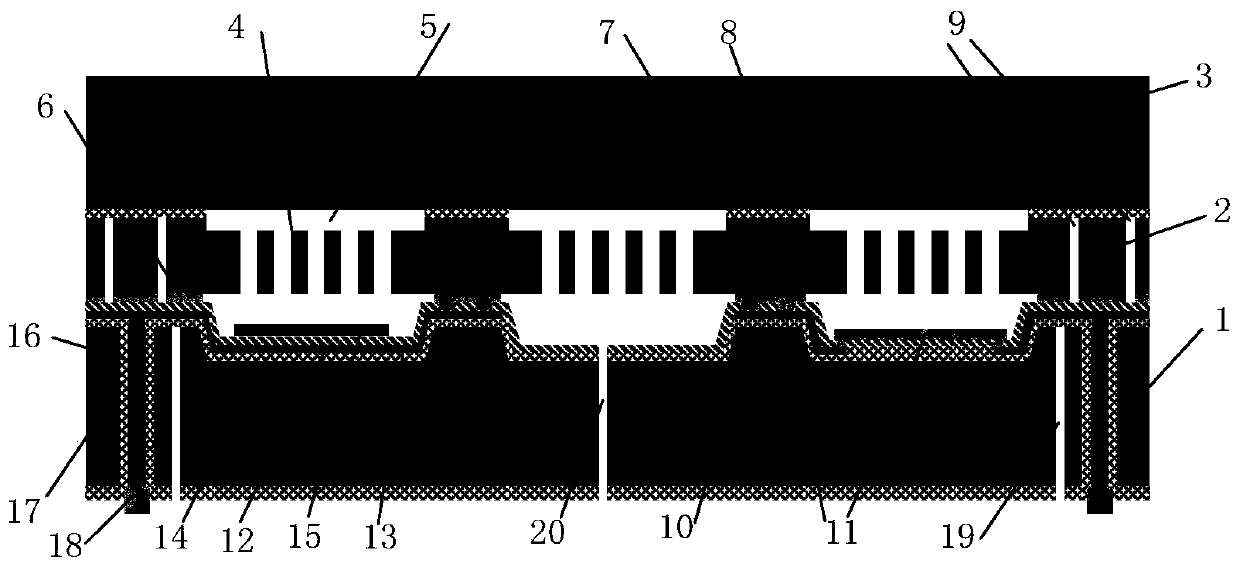

Embodiment 1

[0083] The cavity depth of the substrate sheet of the present invention is 2 μm-20 μm, the thickness of the first silicon oxide layer 14 is 1 μm-3 μm; the first metal electrode layer 15 is made of tungsten, aluminum, titanium, copper, gold, nickel, chromium, tantalum, cobalt One or more compositions, the thickness is 100nm-300nm; the thickness of the second silicon oxide layer 16 is 300nm-600nm, and the second metal layer 11 is also used as a bonding medium layer including an adhesion barrier layer and a metal eutectic solder layer , the adhesion barrier layer adopts one or several combinations of Cr, Ti, Ni, W, and the metal eutectic solder layer adopts one of AuSi, AuSn, AlGe, CuSn; the thickness of the adhesion barrier layer is 10nm-50nm; the metal eutectic solder layer The thickness of the crystal solder layer is 0.5 μm-2 μm; in the cavity on the substrate layer, there is also a getter layer 18; the getter is Ti, Zr, V or a combination of several kinds. The thickness of th...

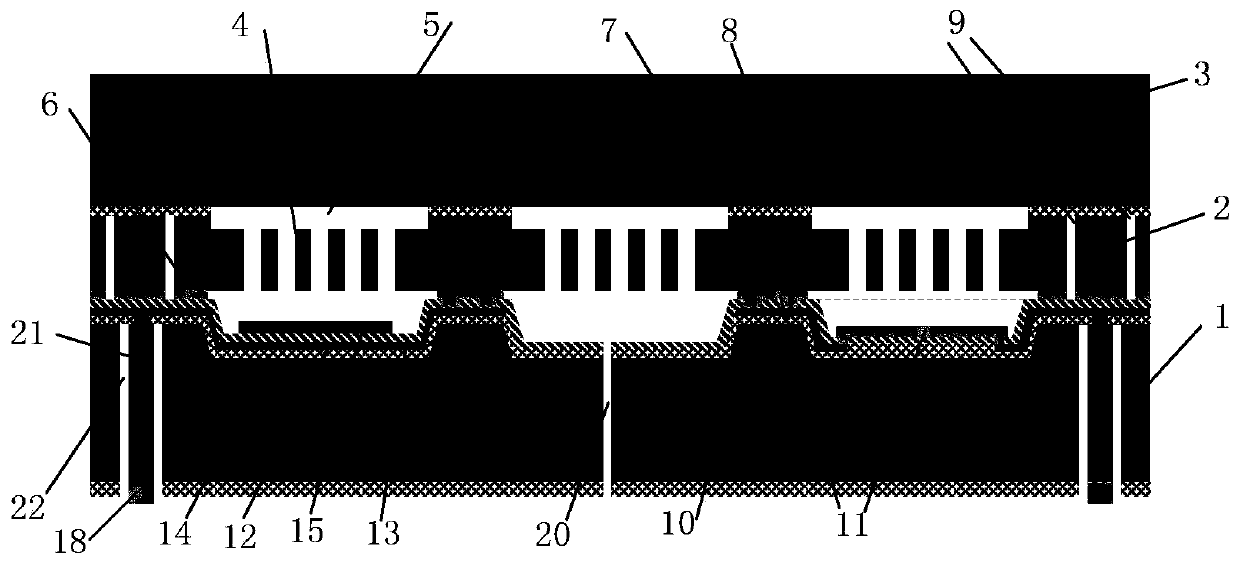

Embodiment 2

[0088] The first process is the processing of the device layer and the capping layer. The processing flow is shown in Figure 2. The detailed processing process is described as follows in conjunction with Figure 2:

[0089] 1) Silicon oxidation of the device layer, such as Figure 2a ;

[0090] 2) Etch silicon oxide by photolithography, and form a silicon oxide pattern consistent with the pattern of the anchor region on the bonding surface, such as Figure 2b ;

[0091] 3) The silicon wafer of the device layer is subjected to photolithography and dry etching to form an anchor region pattern, such as Figure 2c shown;

[0092] 4) The device layer silicon wafer and the cap layer silicon wafer are directly bonded to silicon-silicon oxide, such as Figure 2d shown;

[0093] 5) Thinning the device layer silicon wafer, such as Figure 2e shown;

[0094]6) The device layer is subjected to photolithography and dry etching to realize the etching of the microstructure on the devic...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More