Patents

Literature

122 results about "Bare surface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Mold and method of producing the same

InactiveUS6156243AEasy to produceHighly precise transfer molding surfaceDecorative surface effectsOptical articlesShell moldingTransfer molding

(1) Alignment mark transfer portion(s) is / are formed on the transfer molding surface of a mold that is used for press-molding a optical element fixing member and having alignment marks; (2) alignment mark(s) is / are formed on the mold material by dry-etching, and the mold material is worked using the alignment mark(s) as a reference to form the transfer molding surface constituted by a plurality of transfer patterns, in order to obtain a mold for press-molding; and (3) the transfer patterns are formed by dry-etching, or a transfer molding bare surface for transfer patterns is formed by dry-etching and a mold release film is formed thereon to reflect the shape of the transfer molding base surface, in order to obtain a mold for press-molding.

Owner:HOYA CORP

Method of planting lawn in saline-alkali soil

InactiveCN101828477AEffective coverageReduce water evaporationHorticultureSoil-working methodsAlkali soilEcological environment

The invention discloses a method for planting lawn in saline-alkali soil and relates to the fields of the saline-alkali soil control and planting technology. The method comprises the steps of: 1, soil arrangement; 2, establishment of a drainage canal; 3, straw application; 4, sand covering on a surface; 5, selection of grass seeds; 6, planting technology; 7, fertilizer application according to formulas; and 8, cultivation management. In the method, the bare surface of the saline-alkali soil can be covered effectively in short time, the water evaporation of the ground is reduced, and the saltness of the surface soil is reduced; the saline-alkali soil can be utilized comprehensively in a large area, and the vegetation structure of the saline-alkali soil can be adjusted; and the vegetation cover area of the saline-alkali soil is enlarged, and the ecological environment is protected and improved.

Owner:WUHAN BOTANICAL GARDEN CHINESE ACAD OF SCI

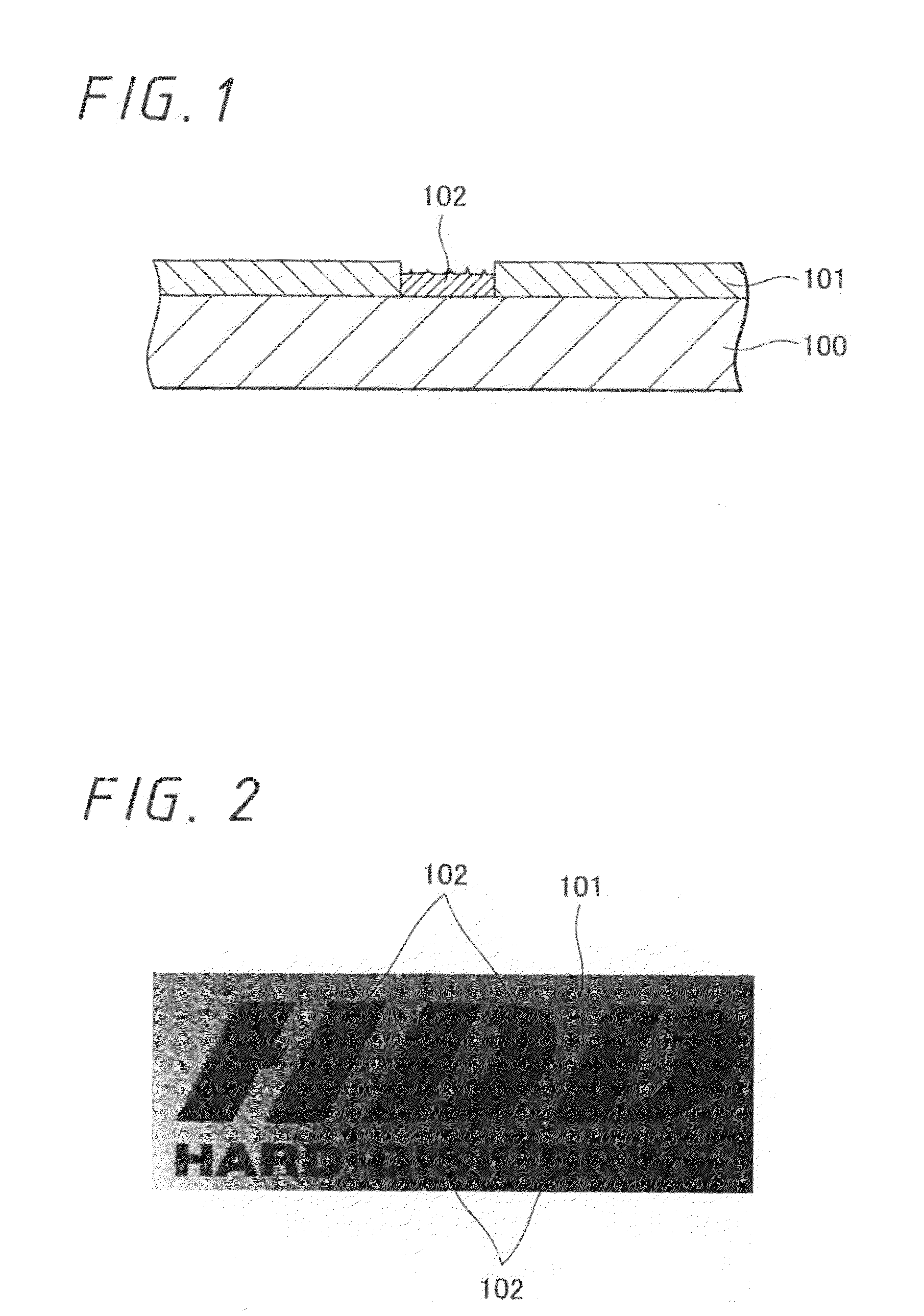

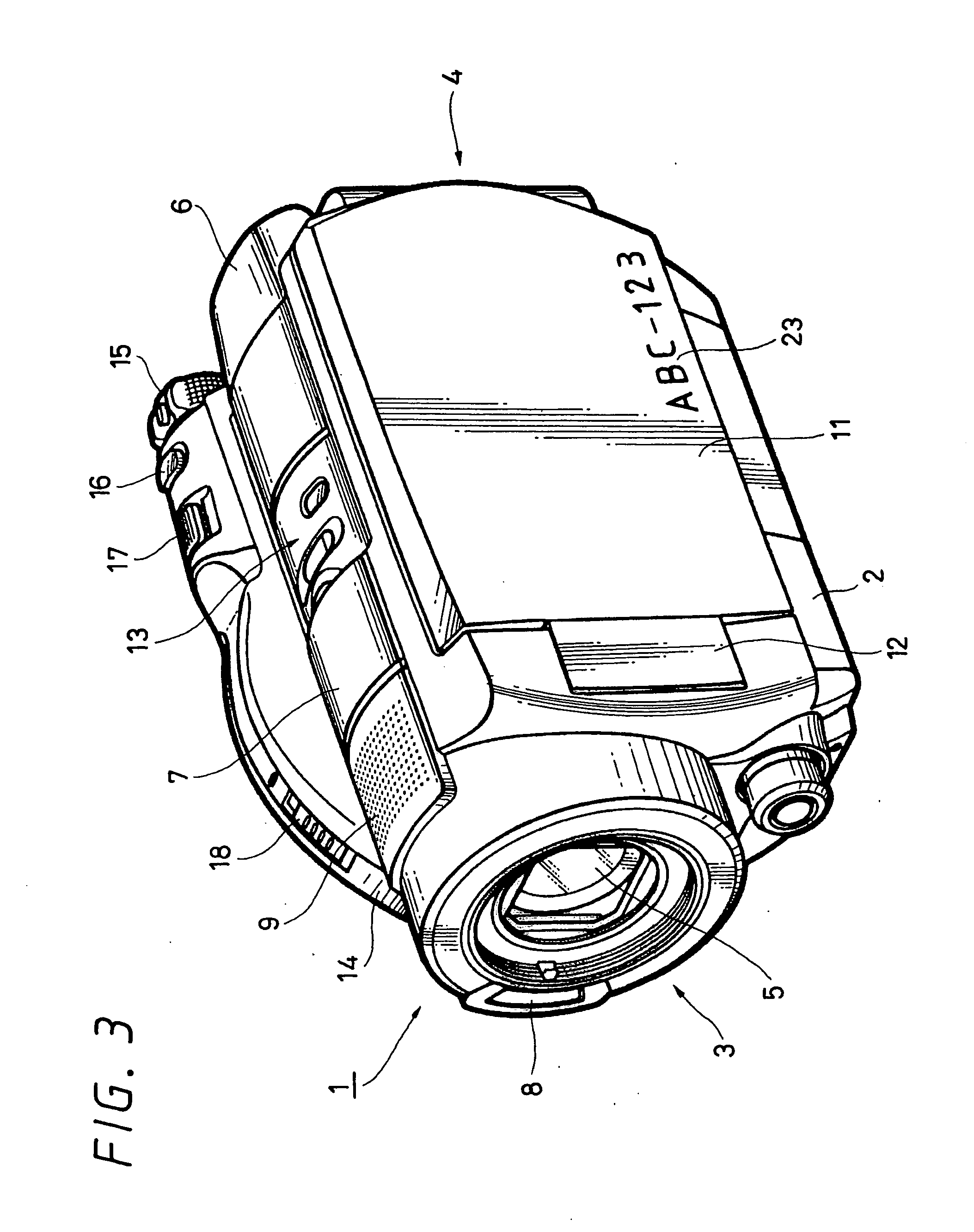

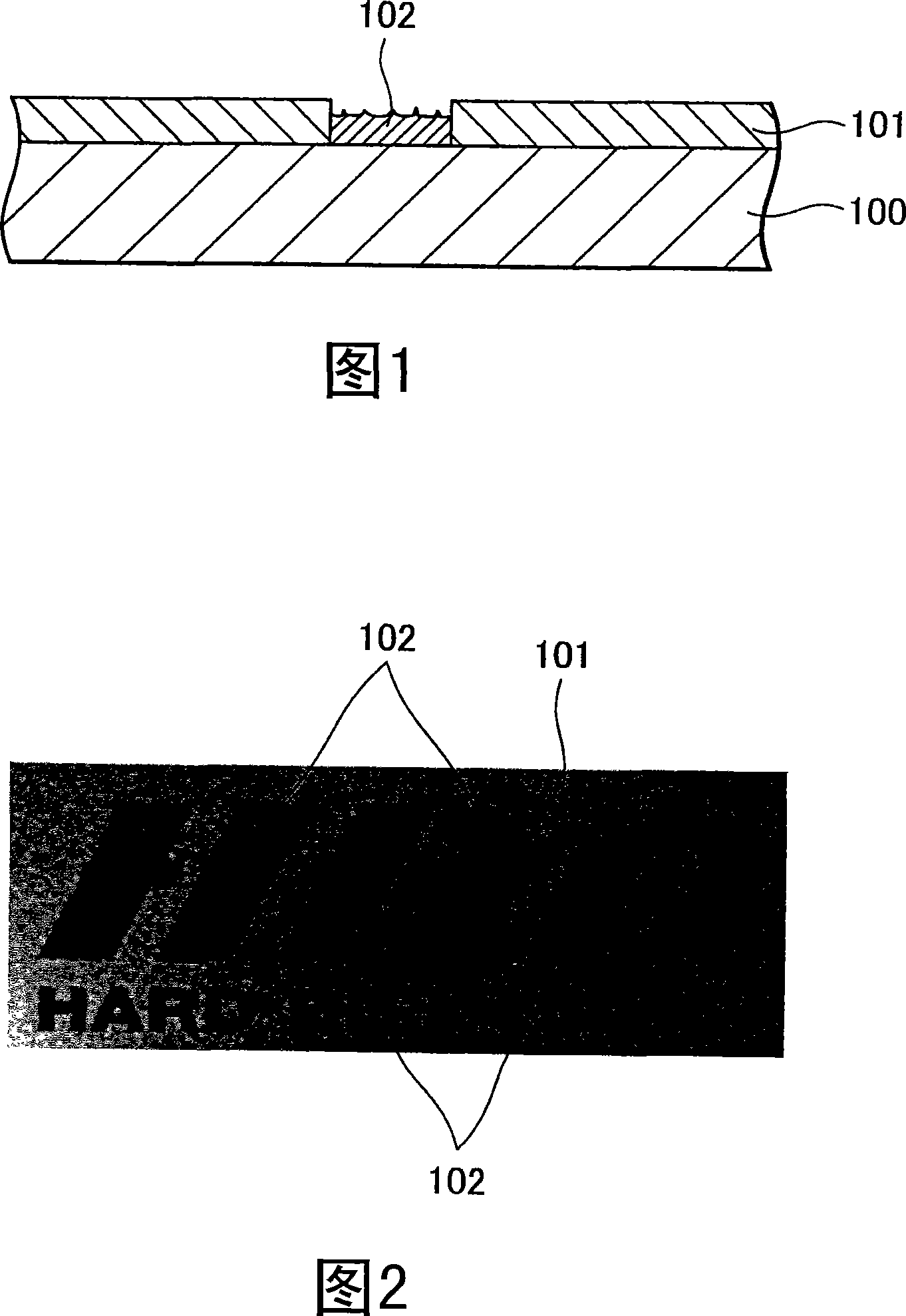

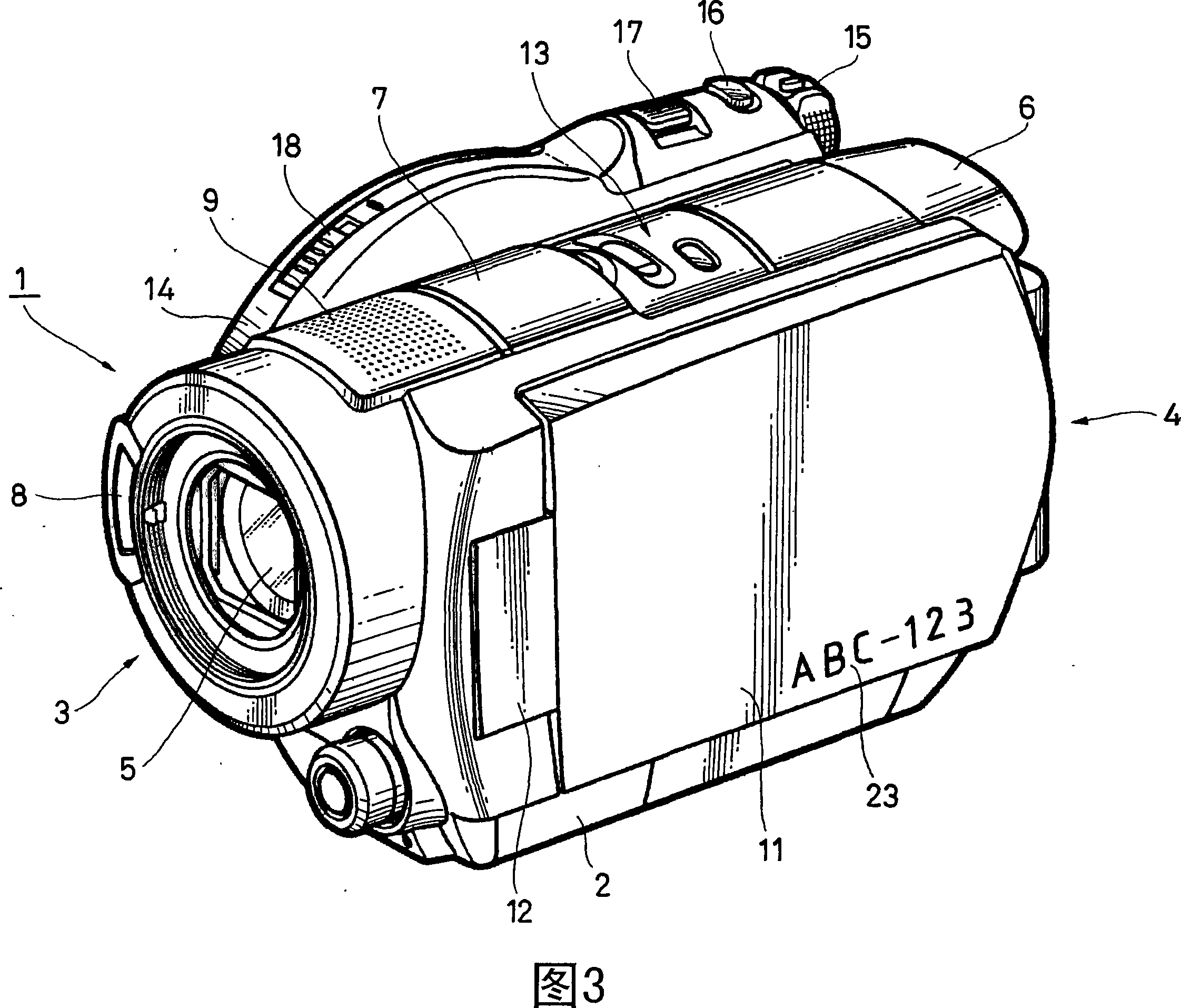

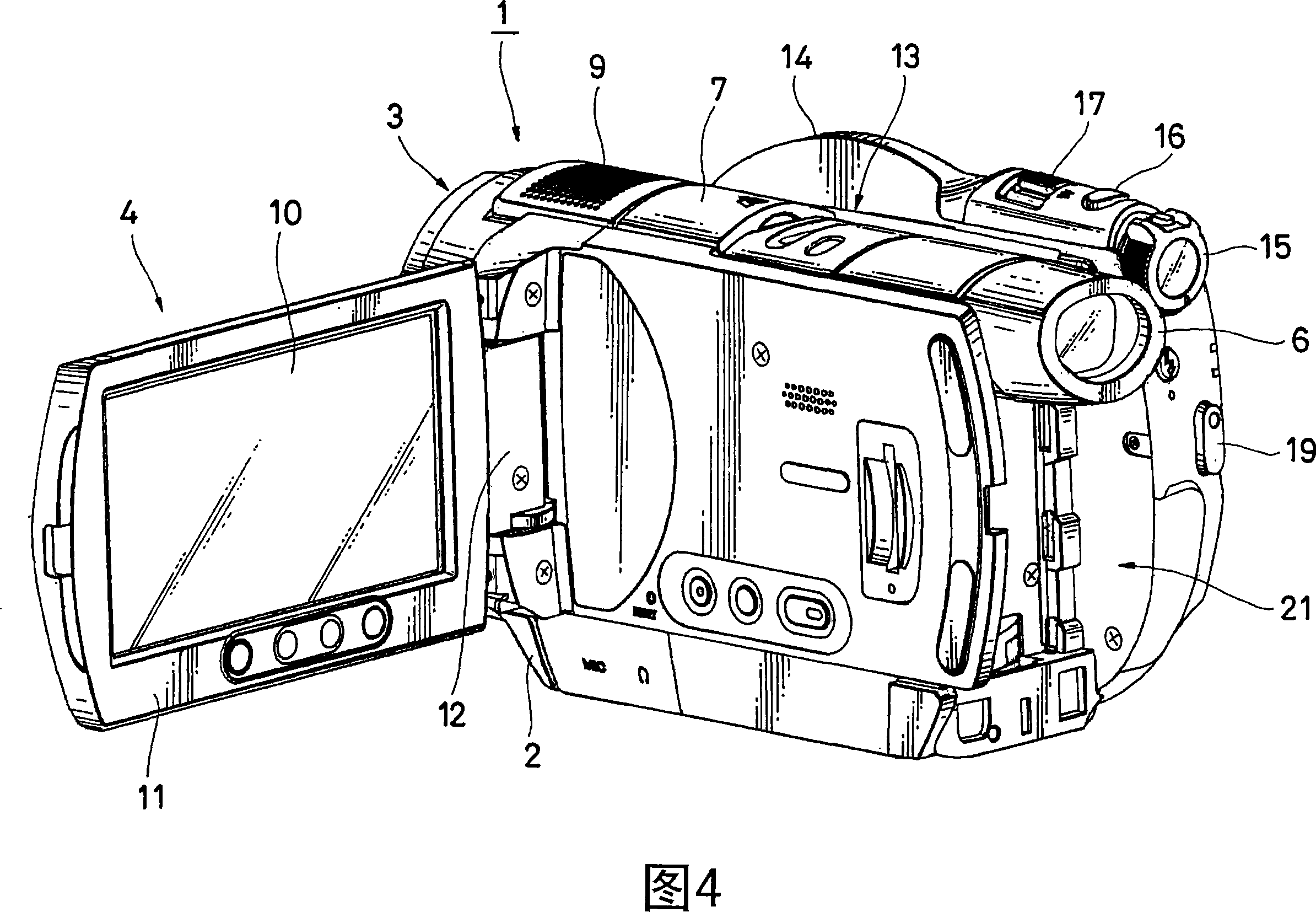

Coated-product with marking, process for manufacturing the same, and enclosure for electronic apparatus

Disclosed is a coated-product with marking. The coated-product is obtained by the steps of forming a coating layer having brightness higher than the brightness of a bare surface of a molding on the surface of the molding made of resin colored with dye, and removing a predetermined portion of the coating layer by laser marking and exposing the bare surface of the coated-product to form a marking portion.

Owner:SONY CORP

Coated-product with marking, process for manufacturing the same, and enclosure for electronic apparatus

Disclosed is a coated-product with marking. The coated-product is obtained by the steps of forming a coating layer having brightness higher than the brightness of a bare surface of a molding on the surface of the molding made of resin colored with dye, and removing a predetermined portion of the coating layer by laser marking and exposing the bare surface of the coated-product to form a marking portion.

Owner:SONY CORP

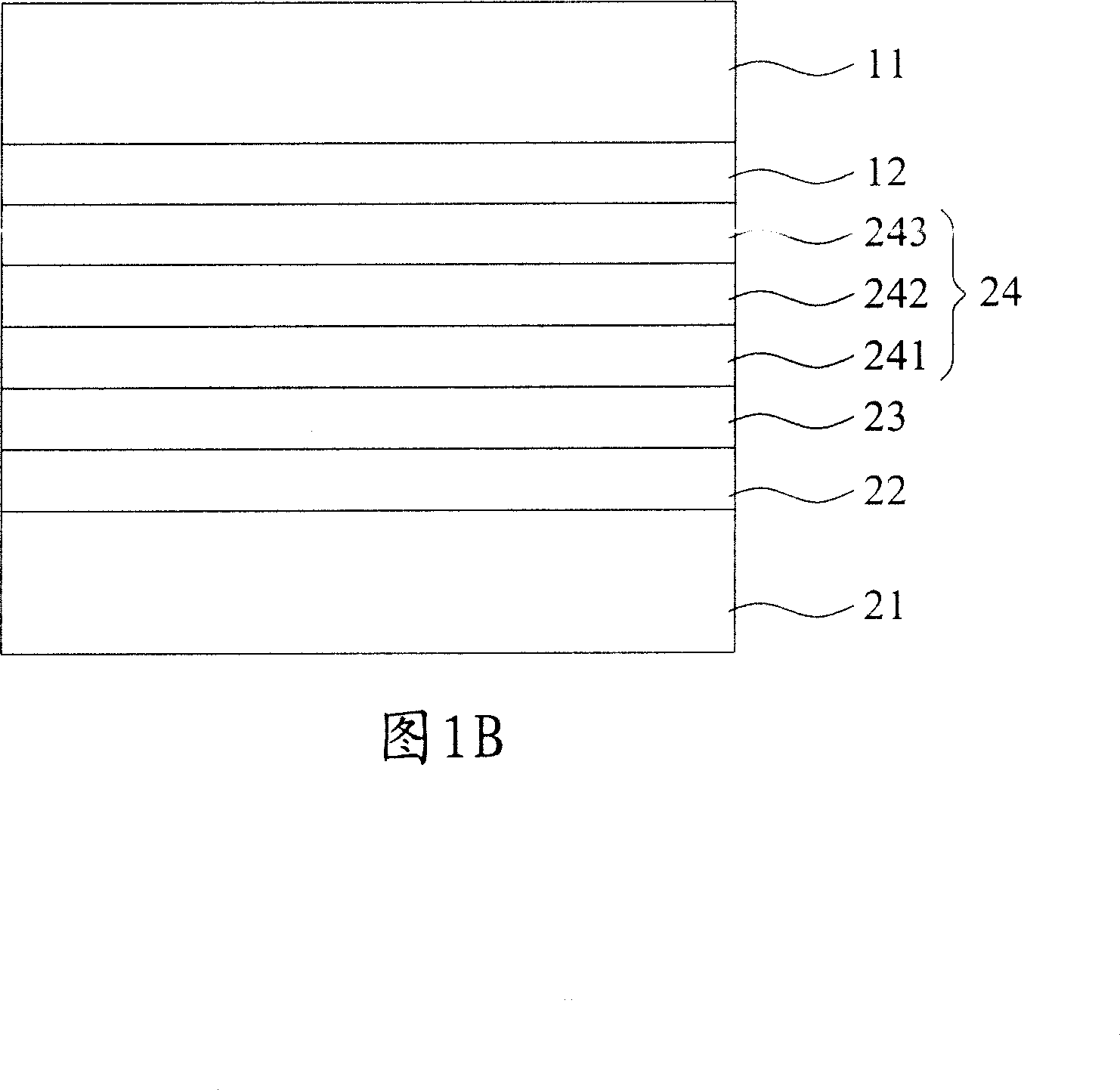

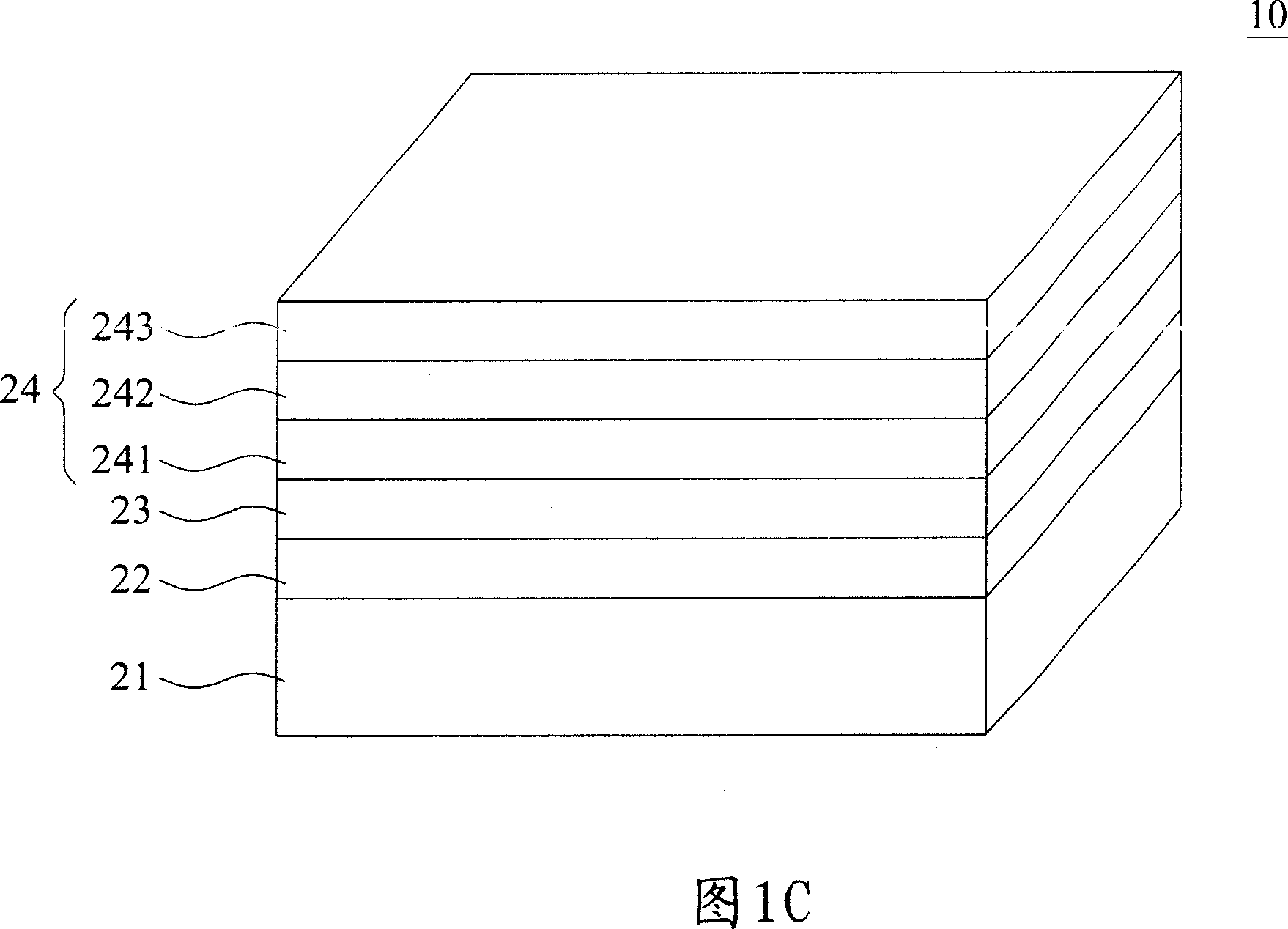

LED structure

InactiveCN101145570AConvenient series/parallel circuit connectionSimplify the linkSolid-state devicesSemiconductor devicesHigh pressureBare surface

The invention relates to a light-emitting diode structure which comprises a first substrate, an adhesive layer formed on the first substrate, a first ohmic connection layer formed on the adhesive layer, an epitaxial layer formed on the first ohmic connection layer, a first insulating layer covered on the exposed surfaces of the first ohmic connection layer and the epitaxial layer, a first current-conducting plate and a second current-conducting plate both formed inside the first insulating layer and electrically connected with the one end of the first ohmic connection layer and the epitaxial layer. With the arrangement of a first groove and a second groove, the complicated series / parallel circuit connection of the light-emitting diode structure can be performed conveniently, and thus the light-emitting diode structure, in a monomer form, is adapted to various operations in high pressure environment.

Owner:HELIO OPTOELECTRONICS

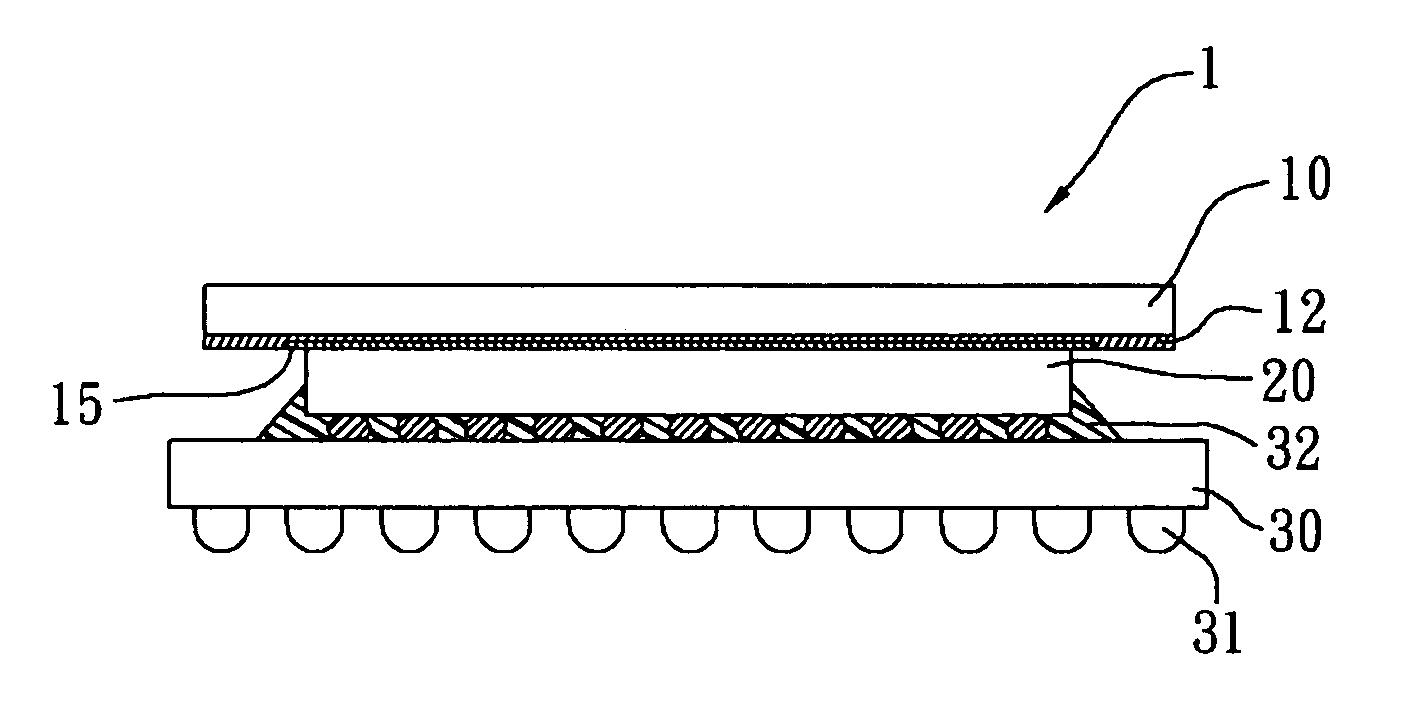

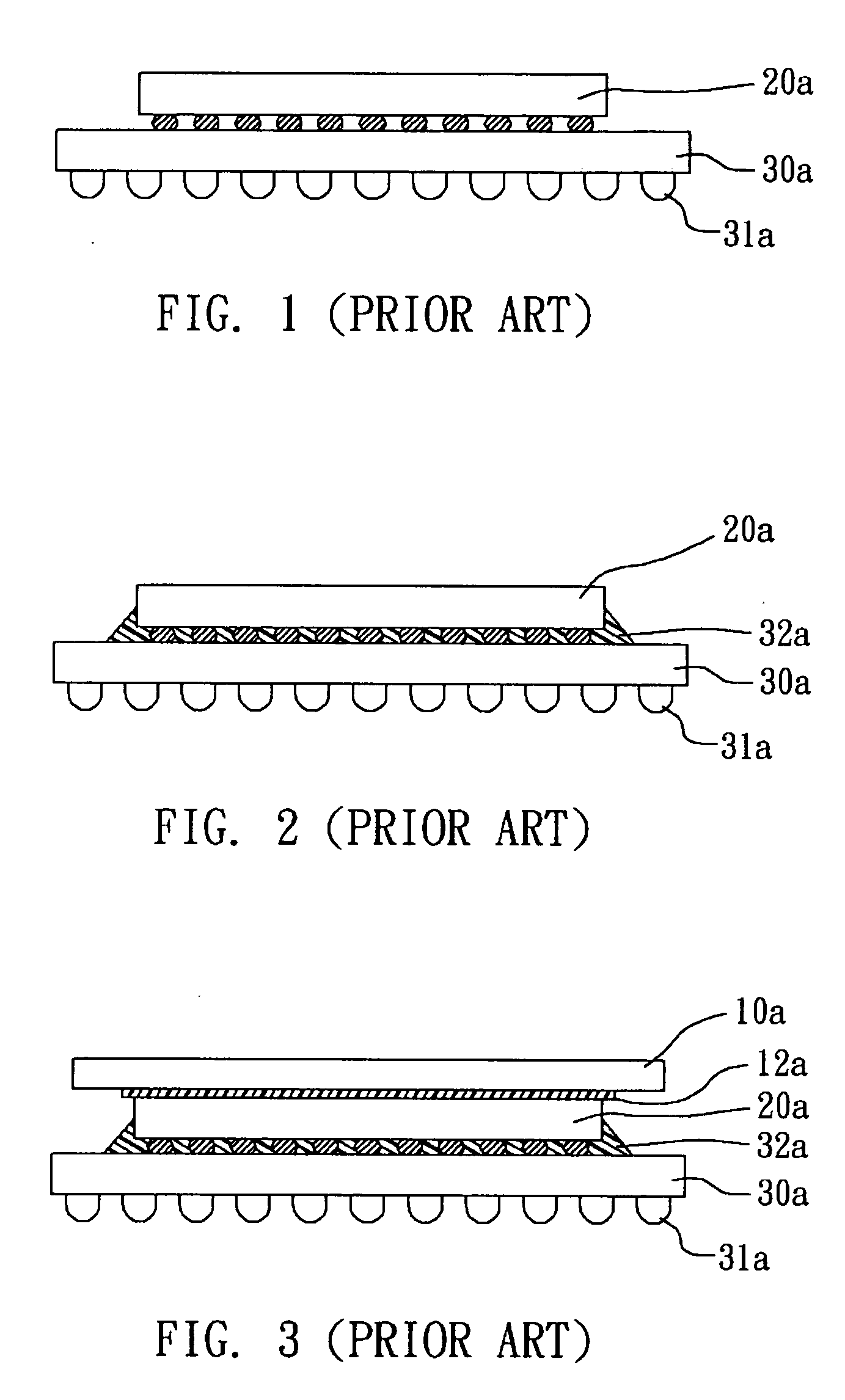

Method for flip chip package and structure thereof

InactiveUS20060079021A1Improve cooling effectImprove thermal conductivitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringGold film

A method for flip chip package and structure thereof is disclosed. The present invention is using an eutectic bonding process to connect a chip and a heatsink for enhancing thermal dissipation capability from the chip to the heatsink and ensuring the chip working well. The method for flip chip package at least includes the steps of providing a heatsink having a surface plated with a gold film and a bare surface, providing a chip having a join surface and an active surface with a plurality of contacts, eutectic bonding the join surface of the chip to the gold film of the heatsink by gold-silicon diffusion for connecting the chip to the heatsink, connecting the active surface of the chip to a substrate by flip chip technology; and dispensing an underfill into the gap between the chip and the substrate.

Owner:VIA TECH INC

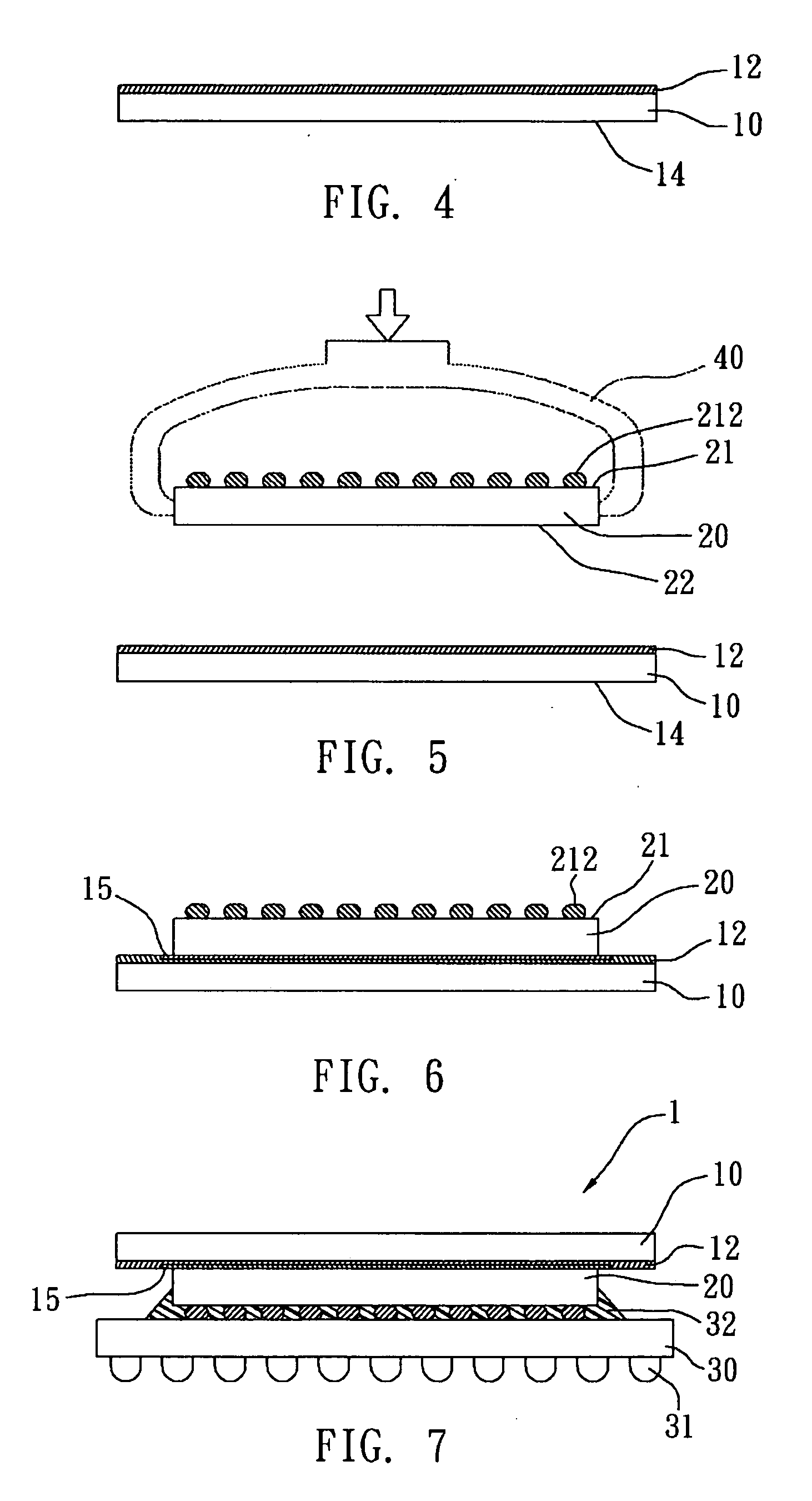

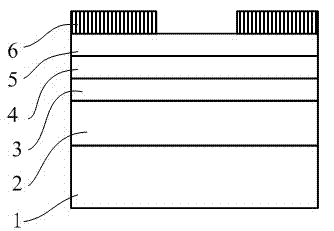

Longitudinally-conductive GaN (gallium nitride) normally-closed MISFET (metal integrated semiconductor field effect transistor) device and manufacturing method thereof

ActiveCN102332469AImprove mobilityRaise the gate threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationField-effect transistor

The invention discloses a longitudinally-conductive GaN (gallium nitride) normally-closed MISFET (metal integrated semiconductor field effect transistor) device and a manufacturing method thereof. The device successively comprises a substrate (1), an n-type GaN layer (2), an electronic barrier layer (3), a non-doped GaN layer (4) and a heterostructure potential barrier layer (5) from bottom to top, wherein a groove is etched in the n-type GaN layer from the surface of the heterostructure potential barrier layer; a p-type GaN layer is formed on the groove by secondary growth so as to realize a grid conducting channel (7); two ends of the heterostructure potential barrier layer form source electrodes (9); an insulating layer (8) is covered on the grid conducting channel and the exposed surface of the heterostructure potential barrier layer; a grid electrode (11) is covered at a channel position on the insulating layer; and drain electrodes (10) are covered on the underside of the substrate. In the invention, a two-dimensional electron gas heterostructure with high concentration is taken as an access area, thus effectively reducing the on resistance; and the thin p-type GaN layer is formed in the etching groove by secondary growth, thus being easy to improve the threshold voltage and channel mobility of the longitudinally-conductive normally-closed MISFET.

Owner:SHANGHAI XINYUANJI SEMICON TECH

Agricultural planting facility with external nutrient source

InactiveCN102232349AEasy to controlAchieve plantingClimate change adaptationSaving energy measuresTemperature controlNew energy

The invention aims to provide an industrial planting facility realized by using an external nutrient source. The industrial planting facility is a facility which can realize agricultural plantation in large-scale, intelligent, modular, newly energetic and industrial modes, and energy sources and nutrient of the facility are directly derived from an external supply system. The direct control of the temperature in the planting process is realized by arranging a temperature control device inside a planting box body, so that the accurate, dynamic, partitioned, intelligent and energy-saving control of plant temperature is realized; planted species are planted on an internal planting dish of a heat preservation box body, and a nonopaque or bare surface is arranged on the top surface, so that the photosynthesis of plants is realized; and the electric energy, heat energy and nutrition are directly conveyed into the heat preservation box body to realize the intellectualization of the planting process, so that the industrial and low-cost large-scale plantation of plants with external nutrient sources is realized.

Owner:BEIJING WISWORD HI TECH

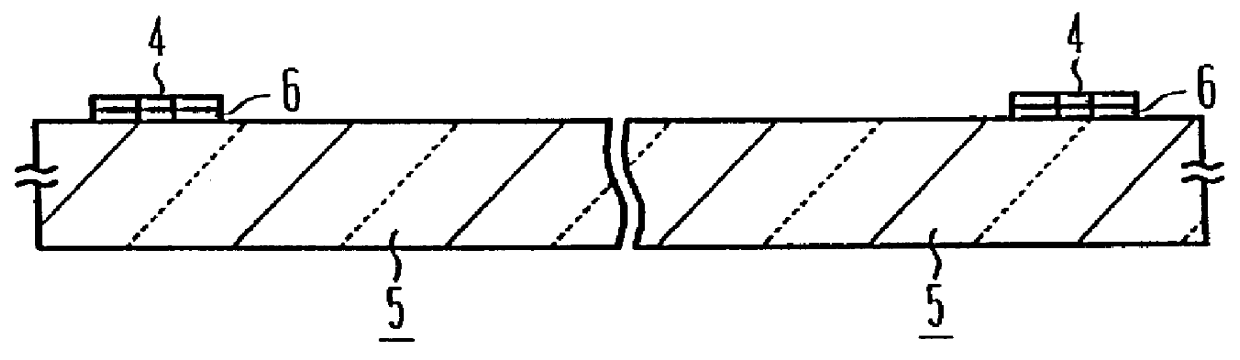

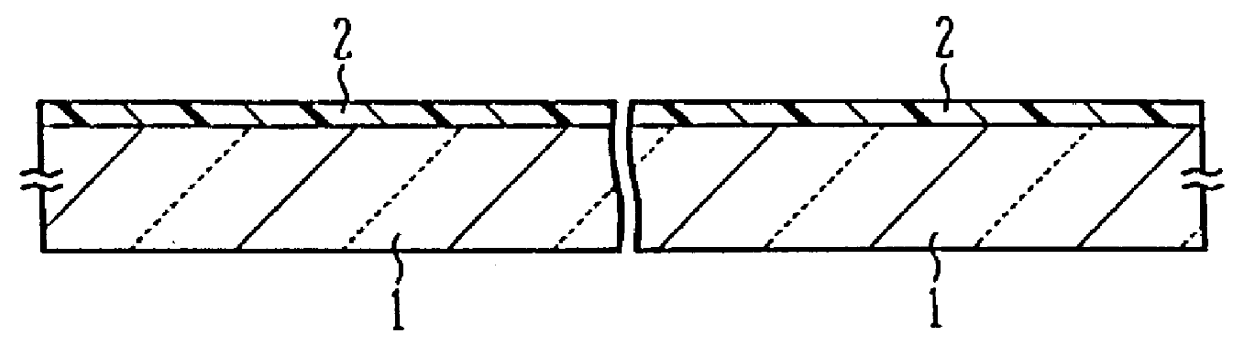

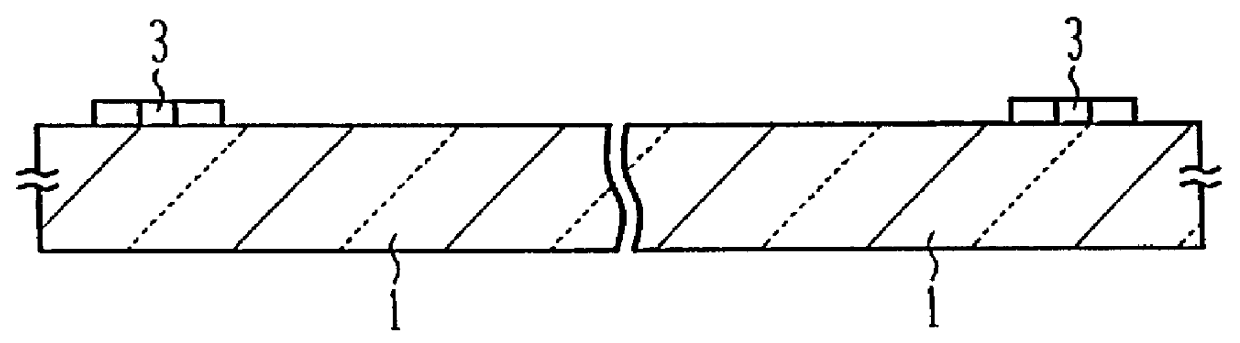

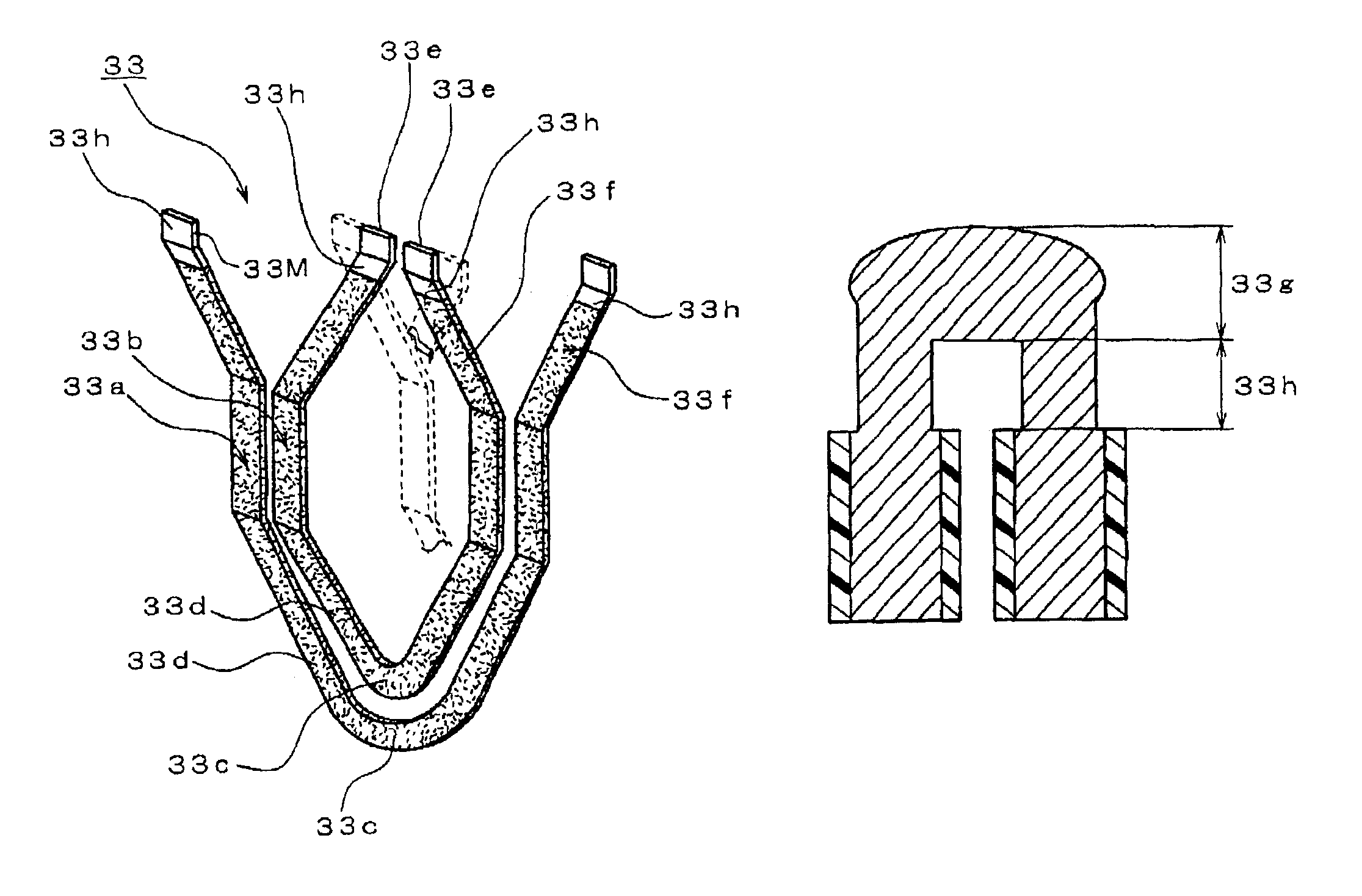

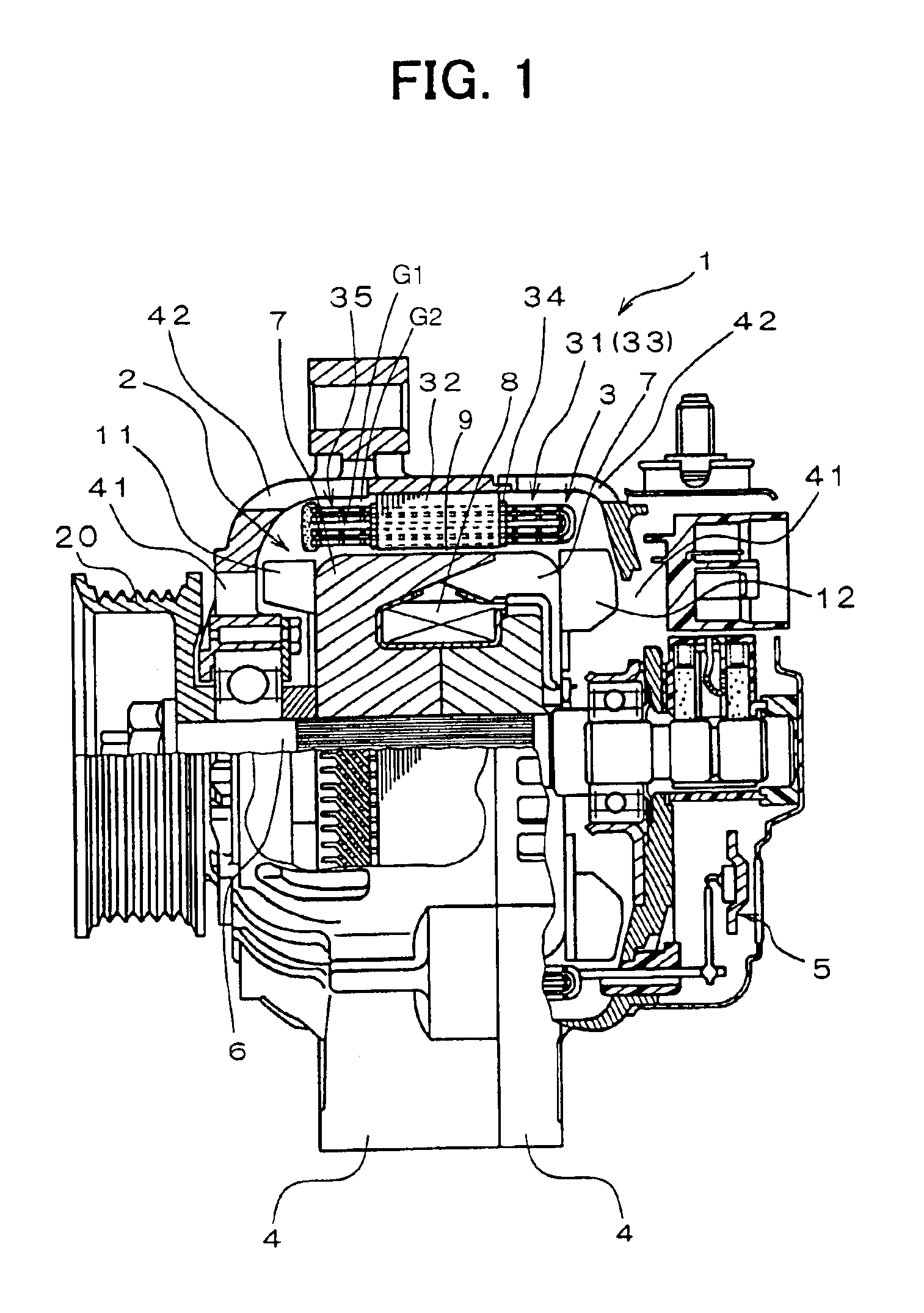

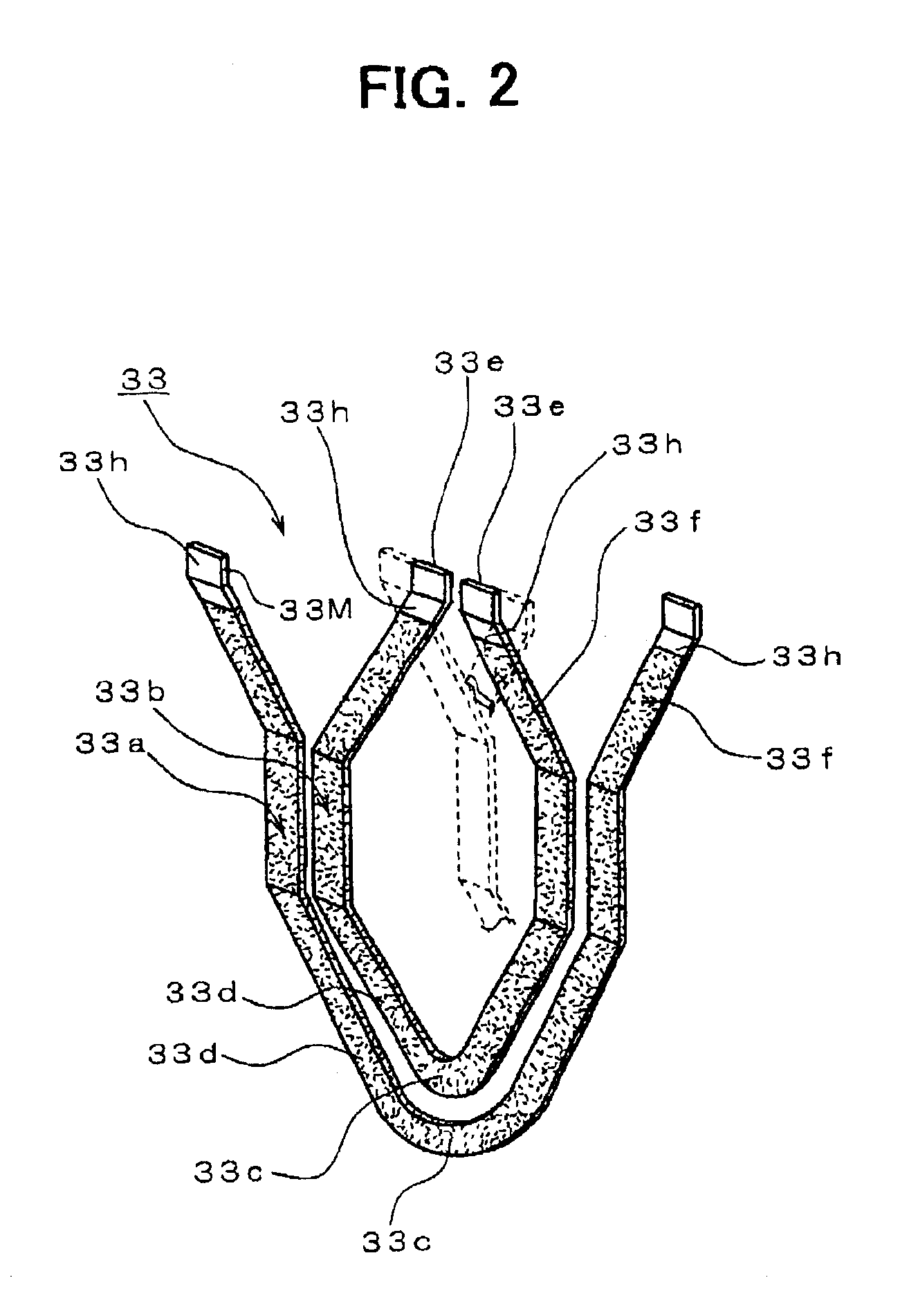

Stator arrangement of rotary electric machine

InactiveUS6894415B2Avoid stayingEasy to stickSynchronous generatorsWindings insulation shape/form/constructionElectrical conductorElectric machine

A vehicle rotary electric machine includes a rotor, a stator having a stator core and a stator winding mounted in the stator core and a pair of frames for supporting the rotor and the stator. The stator winding has a plurality of conductor segments coated with insulation film. Each of the conductor segments has segment ends that are circumferentially aligned and form two or more rings. The segment ends that contact each other are welded and form joints of winding that have a bare surface. Therefore, electrolyte or foreign particles are prevented from staying at otherwise deteriorated insulation film.

Owner:DENSO CORP

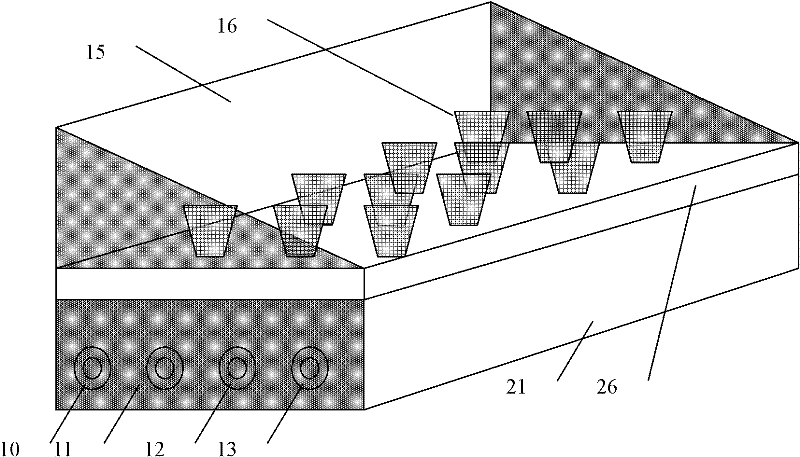

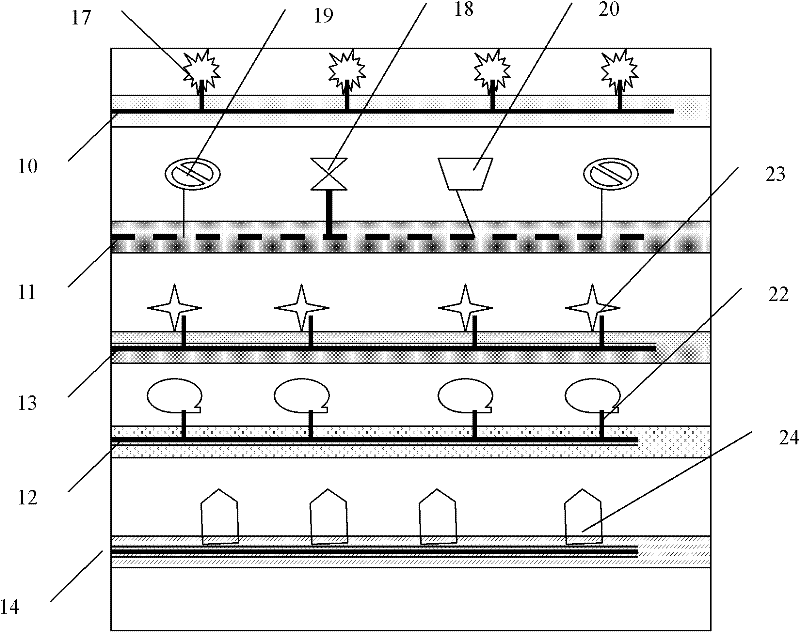

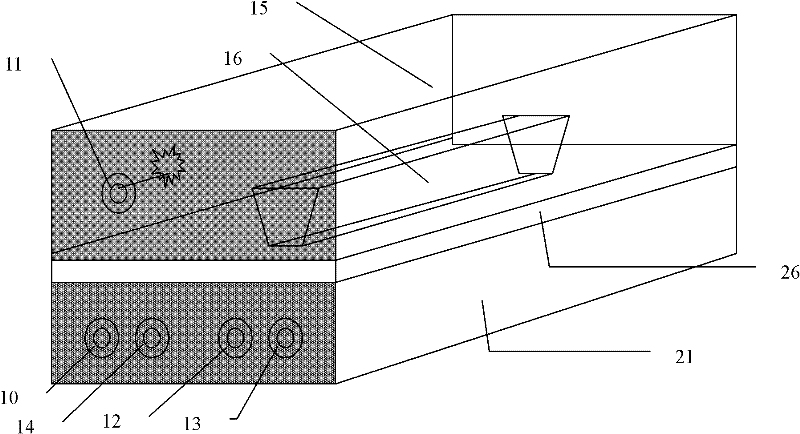

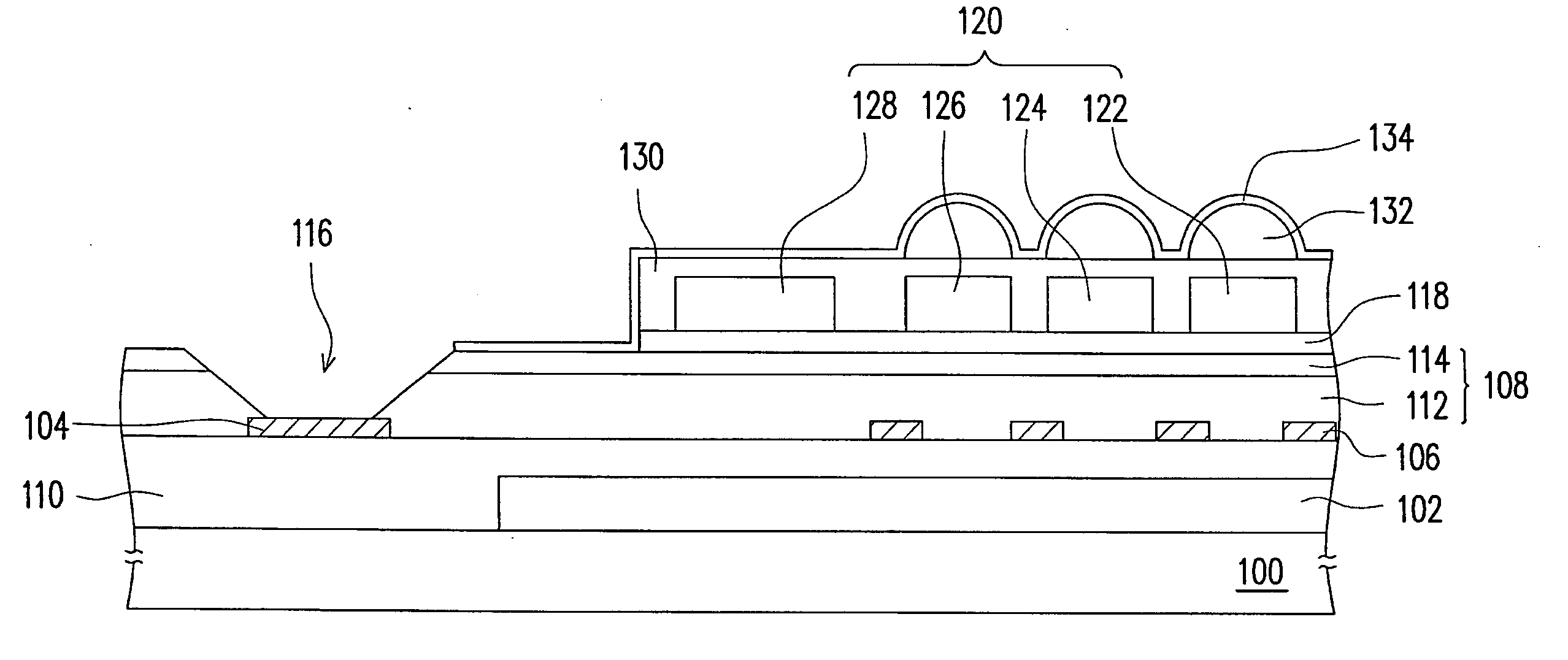

Image sensor and fabricating method thereof

ActiveUS20090321862A1Efficient removalAvoid damageSolid-state devicesSemiconductor/solid-state device manufacturingSensor arrayOptoelectronics

A method for fabricating an image sensor, which includes the following steps, is provided. A semiconductor substrate including a sensor array, a pad and a passivation layer is provided, and the passivation layer covers the sensor array and the pad. An opening, which comprises tapered sidewalls not perpendicular to a bared surface of the pad, is formed in the semiconductor substrate to expose the pad. An under layer is formed on the semiconductor substrate, and covers the pad and the passivation layer. A color filter array is formed on the under layer and over the corresponding sensor array. A planar layer is formed on the color filter array. A portion of the under layer is removed to expose the pad. A plurality of U-lenses is formed on the planar layer.

Owner:UNITED MICROELECTRONICS CORP

Method for controlling weeds in tea plantation

InactiveCN102124888AImprove ecologyGrowth inhibitionPlant protective coveringsBare surfaceTea plantation

The invention provides a method for controlling weeds in a tea plantation. In the method, bare surface soil between tea rows and on the altar in tea plantations is covered by straw or weed preventing cloth after weeding in spring and summer or after plowing and fertilizing in winter. The weed preventing cloth is made of cloth-like material which is woven by adhering non-woven fabrics to propene polymer (PP) filaments. Weeds in tea plantations are prevented and controlled by a physical method, the growth of weeds can be suppressed obviously, chemical herbicide is reduced or even avoided, and artificial and mechanical weeding cost is reduced. Adverse influence of weeds on the growth of tea trees is reduced, soil fertility in tea plantations is improved, water and soil are maintained, and ecology in tea plantations is improved. The method is easy to operate and can be easily accepted by tea growers and has an excellent popularization and application prospect.

Owner:INST OF SOIL & FERTILIZER FUJIAN ACADEMY OF AGRI SCI

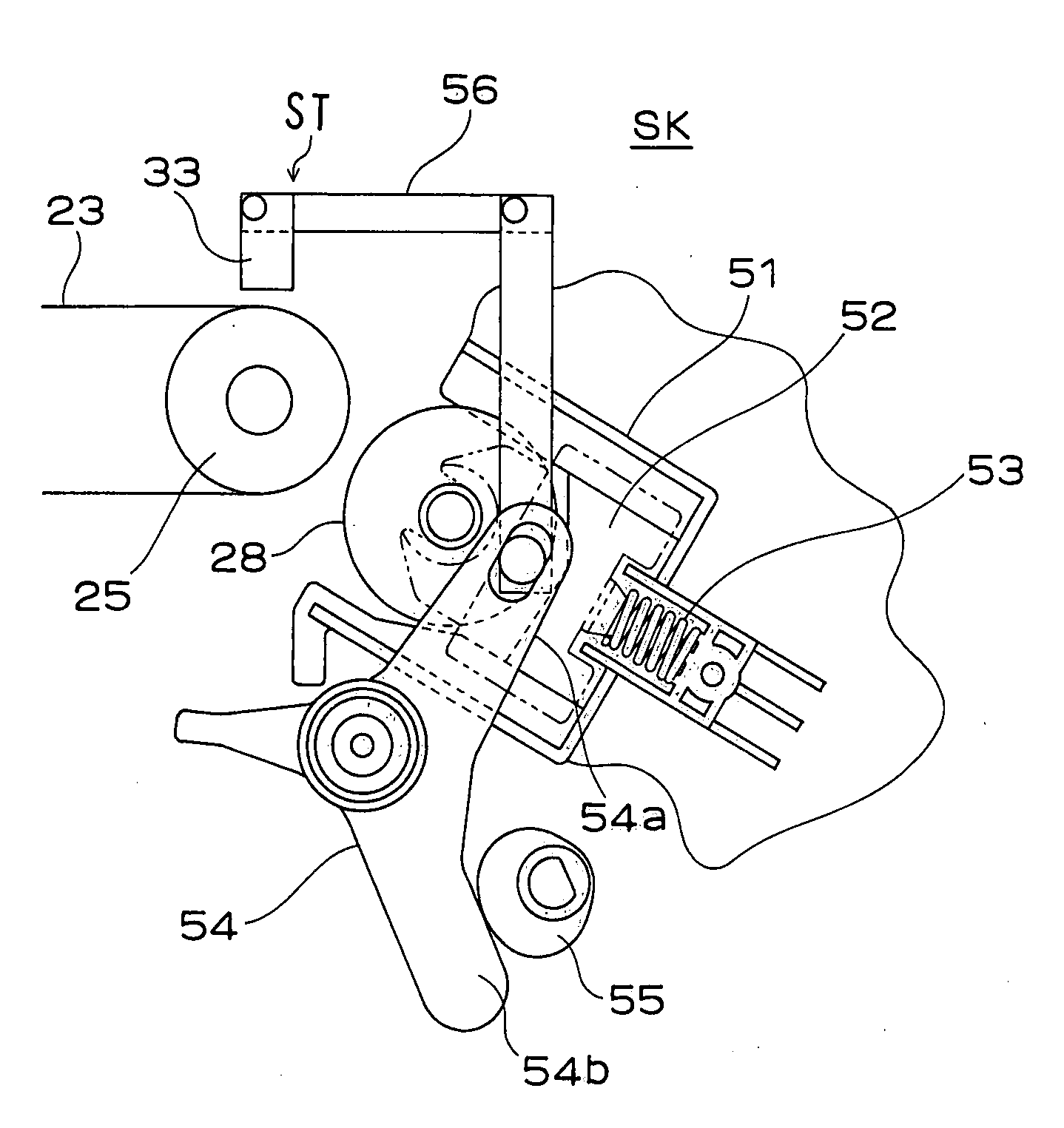

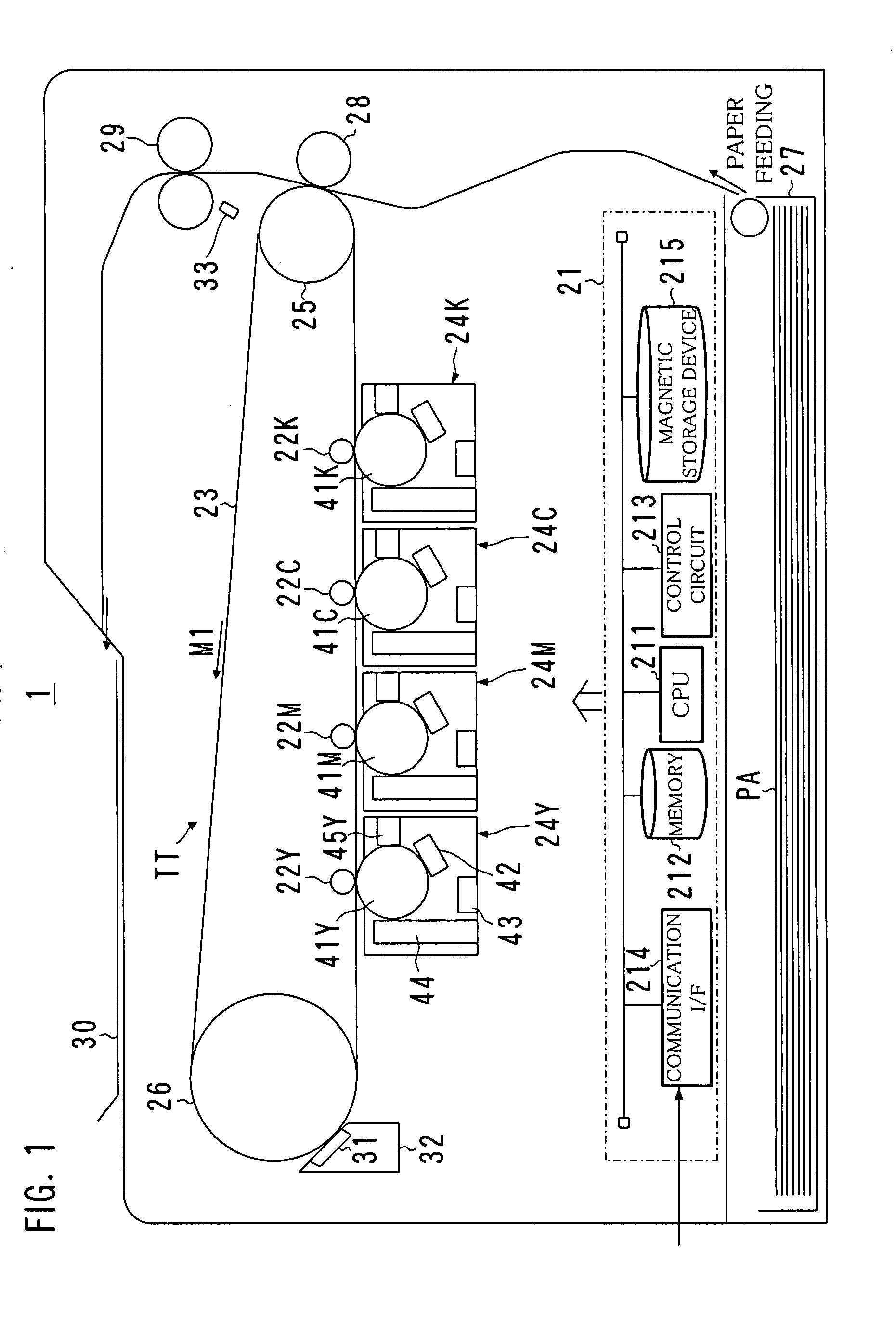

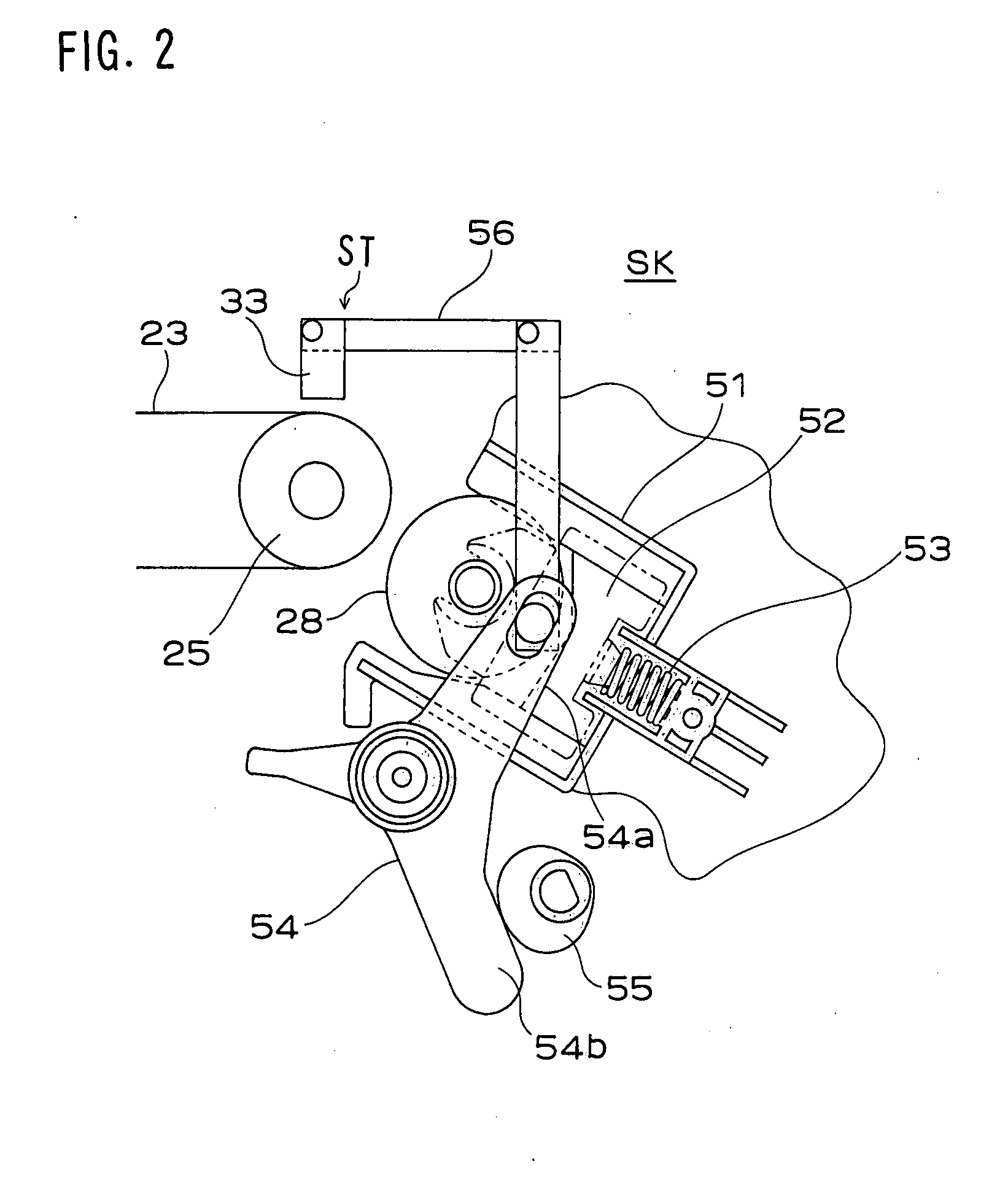

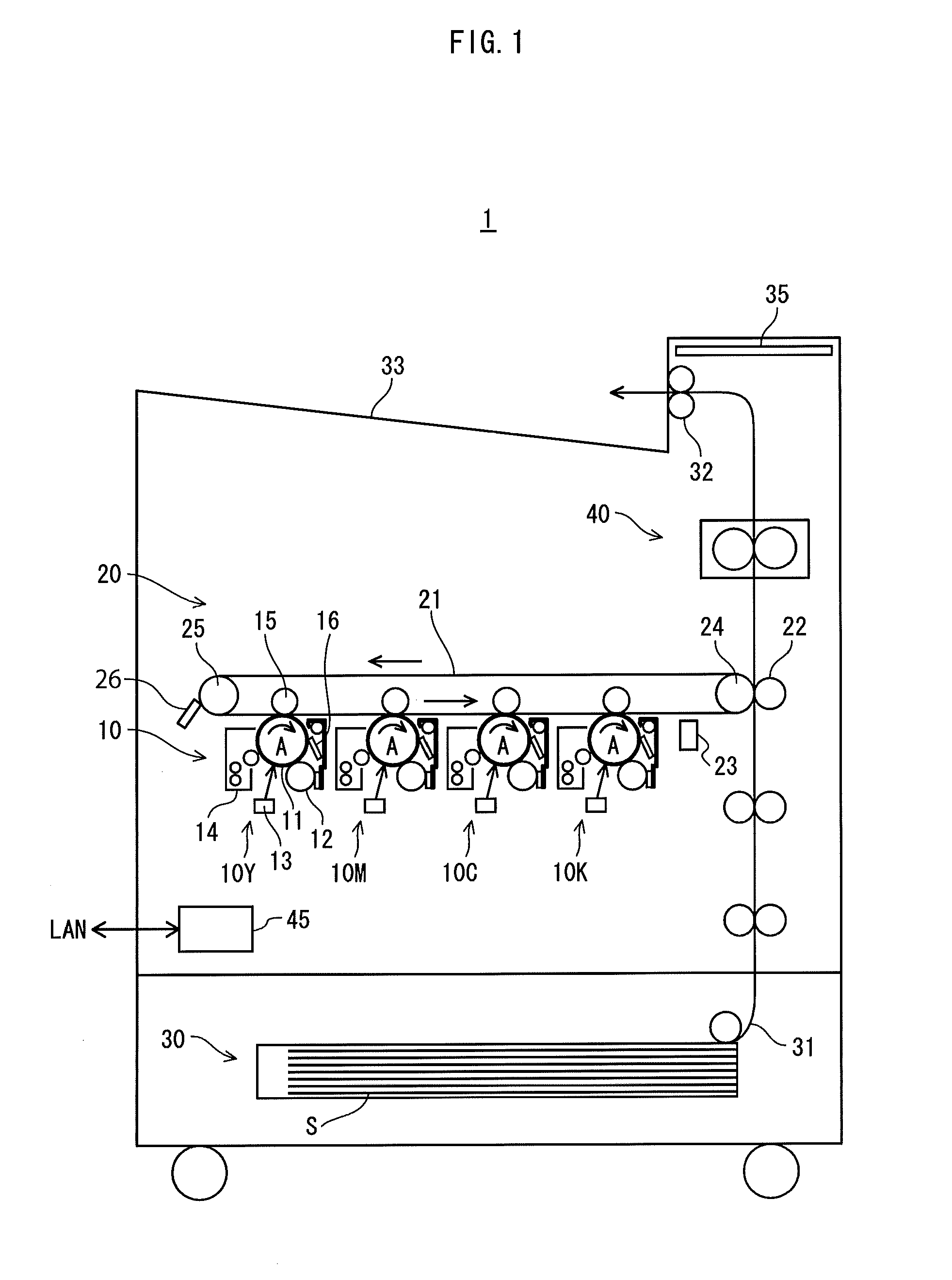

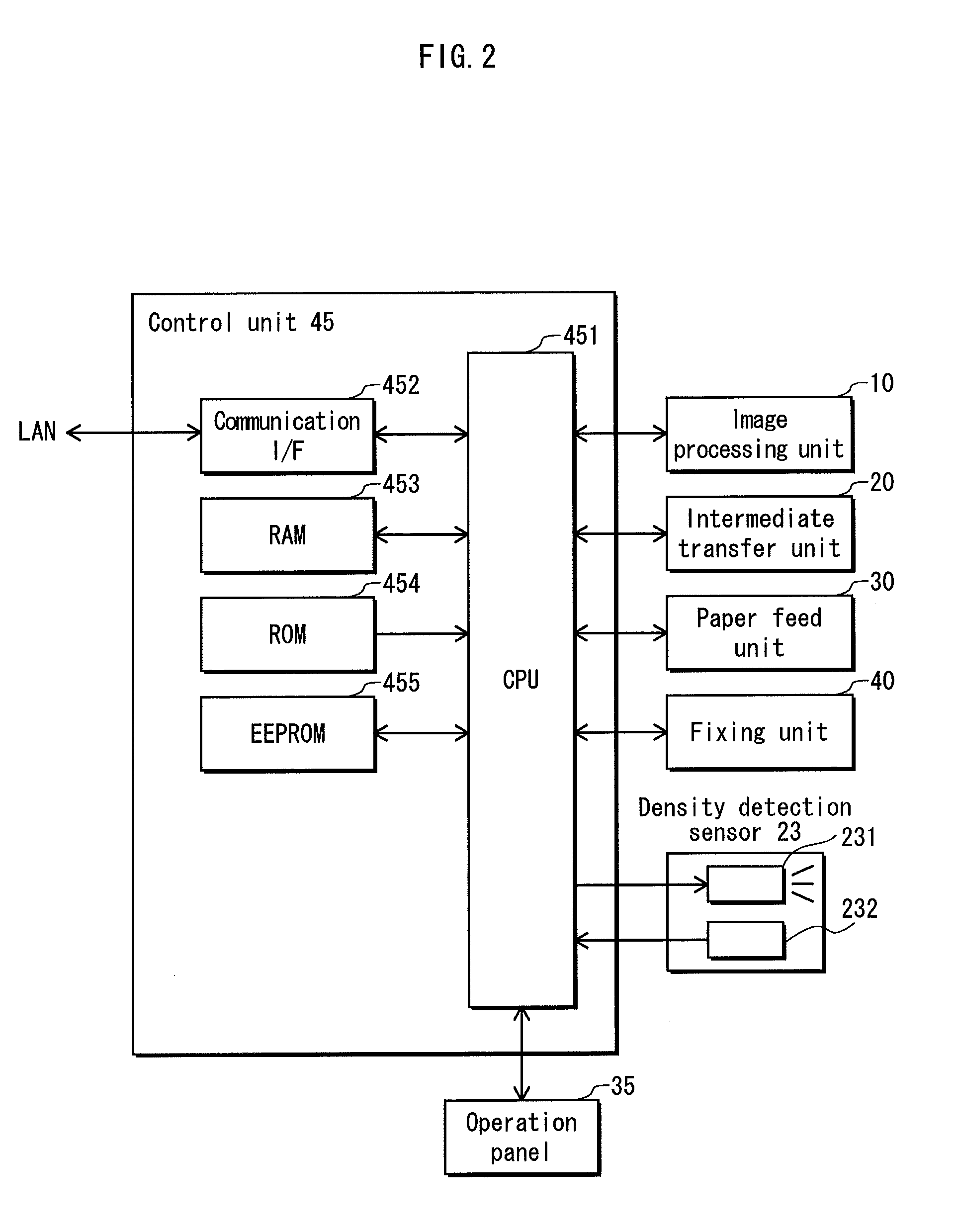

Image forming apparatus and method for detecting separated state of transfer unit

An image forming apparatus has a structure in which a toner image formed in an electrophotographic process is transferred from an intermediate transfer belt to a member to be transferred. The apparatus includes a secondary transfer roller that becomes a pressure contact state with respect to the intermediate transfer belt to make it perform a transfer process and can move between the pressure contact state and a separated state, and a press and separation driving device for driving the secondary transfer roller to become the pressure contact state and the separated state. The pressure contact state or the separated state of the secondary transfer roller is detected in accordance with a variation of an output of an IDC sensor for detecting a state of a bare surface of the intermediate transfer belt.

Owner:KONICA MINOLTA INC

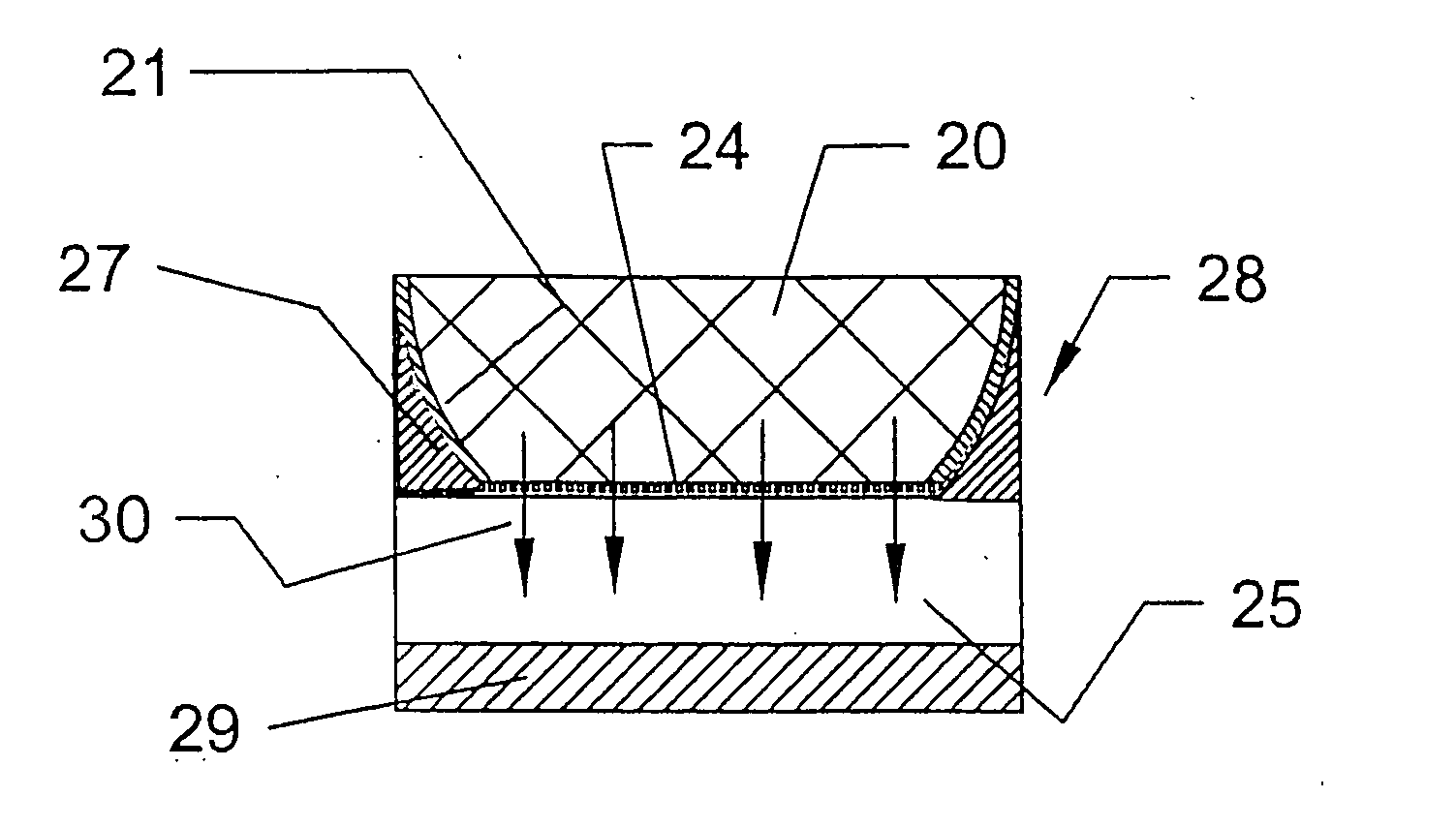

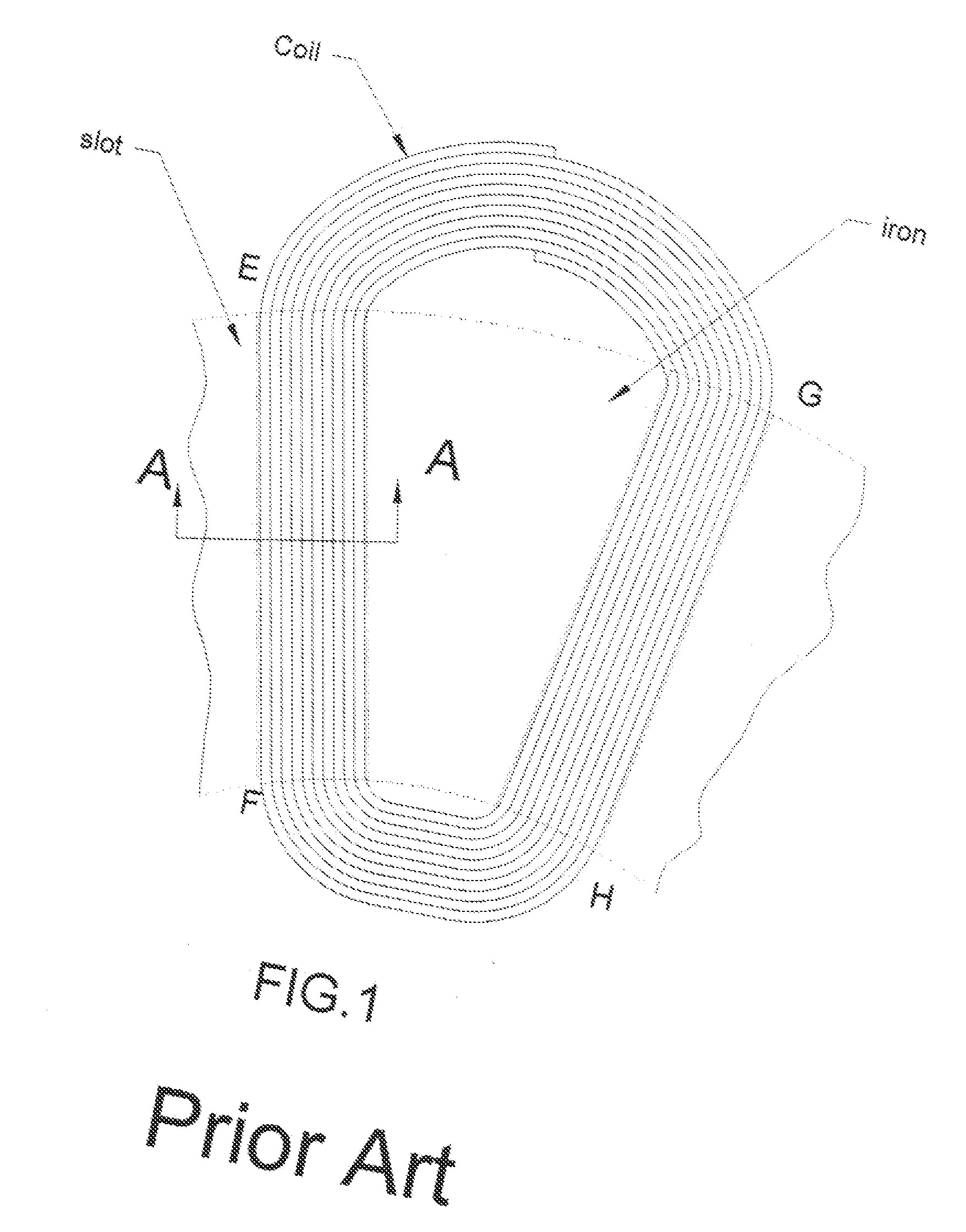

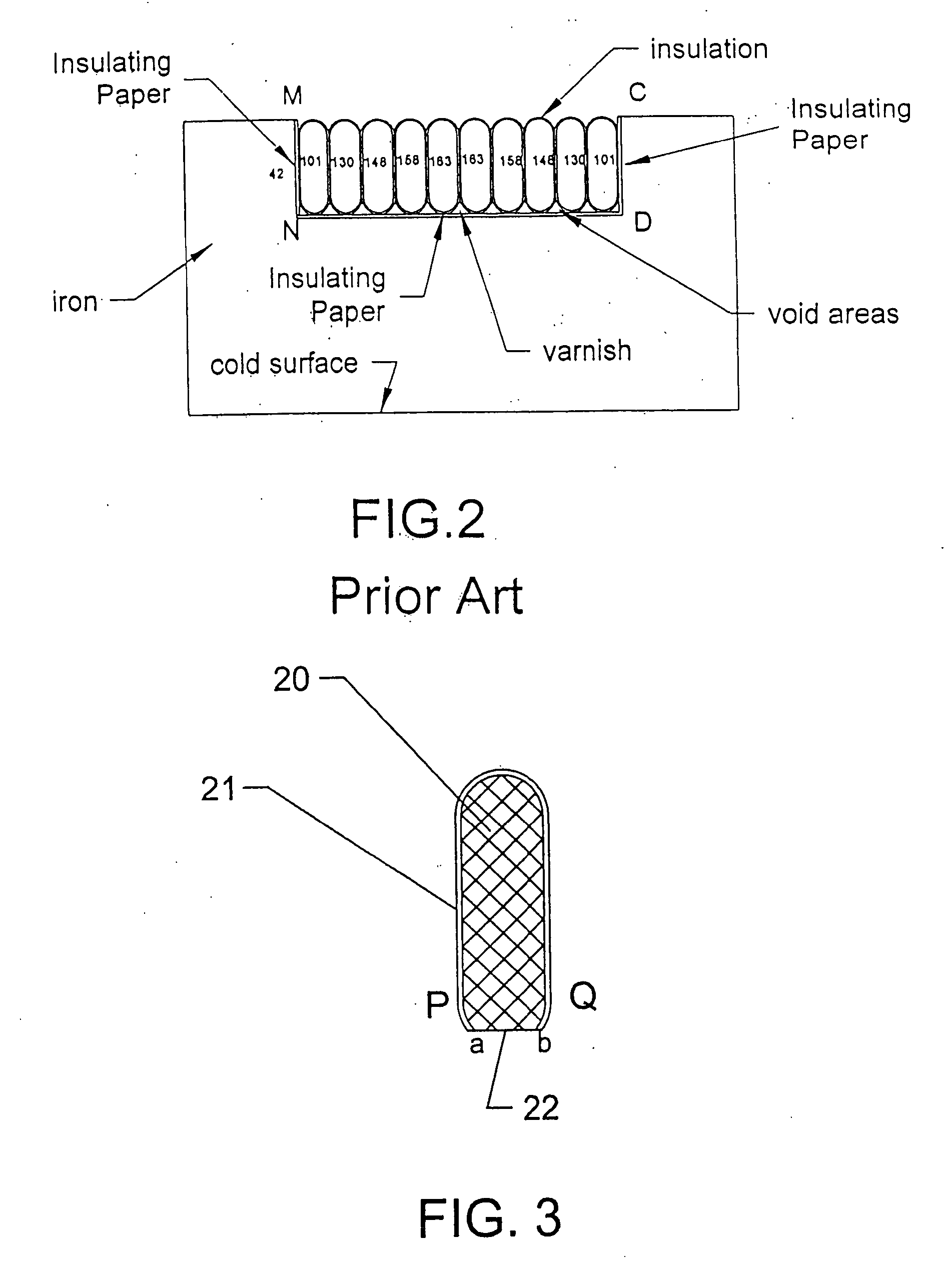

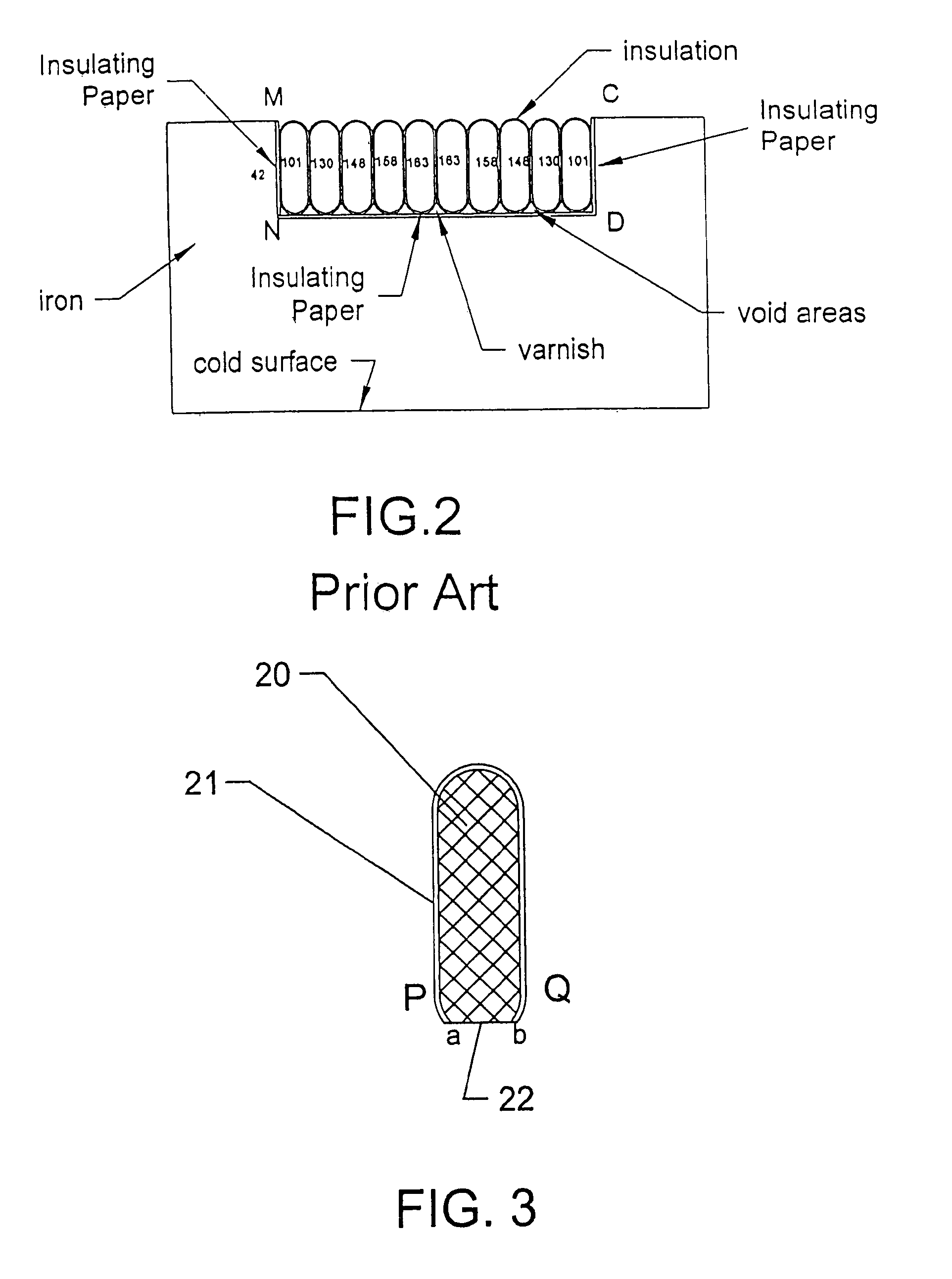

Cooling of stator windings

InactiveUS20070228846A1Reduce the temperatureImprove thermal conductivityWindings insulation shape/form/constructionMagnetic circuit rotating partsCopper conductorEpoxy

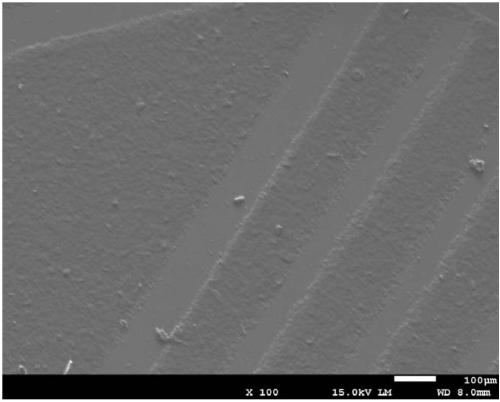

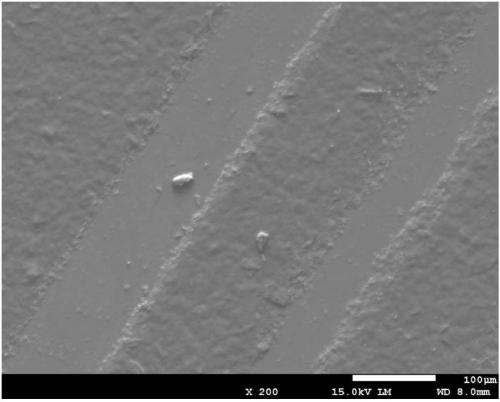

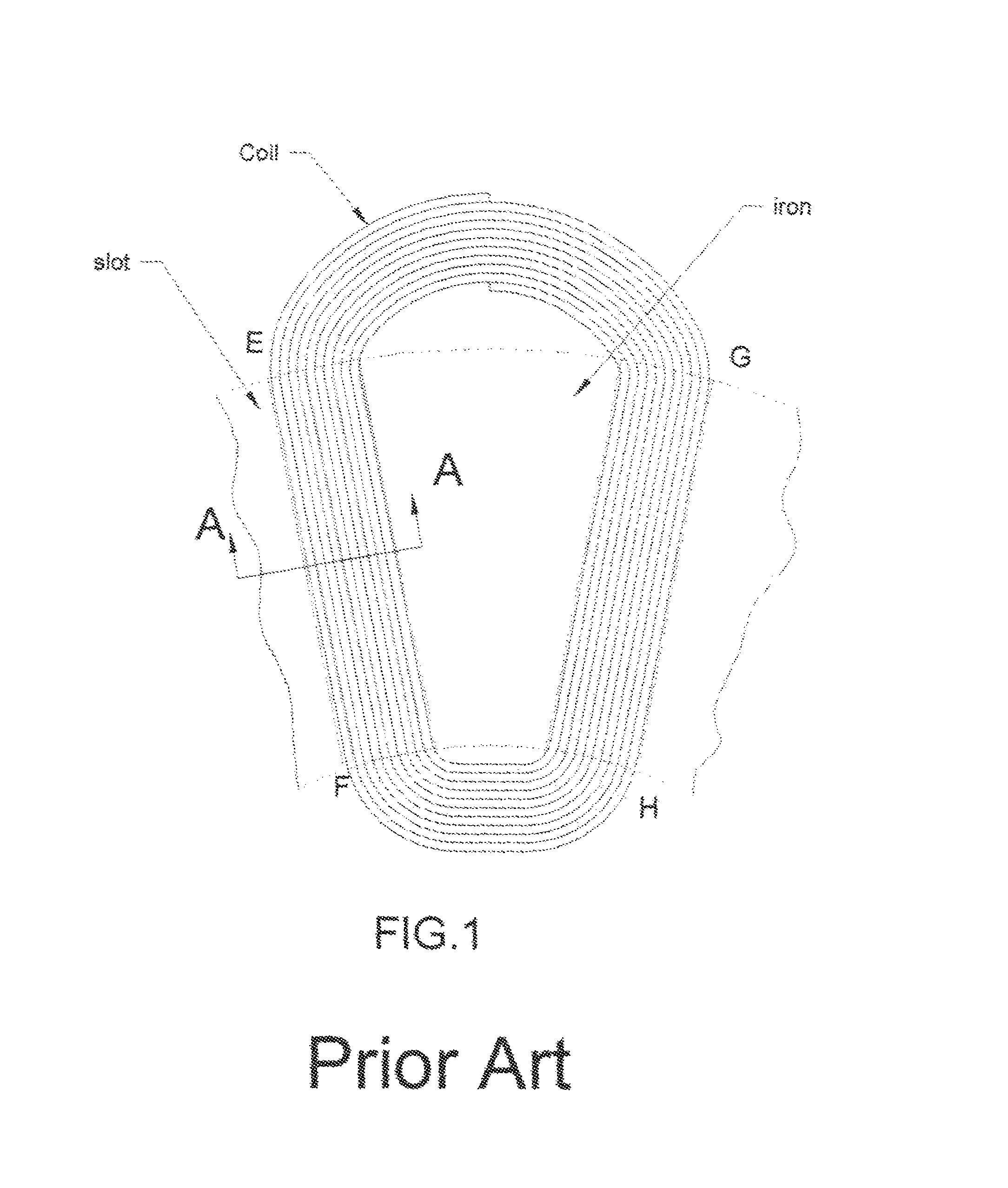

An arrangement for cooling an electric motor's stator winding coil is described. One area of a conductor insulation is removed to expose the copper conductor. The conductor is wound into a coil with bared, exposed conductor areas facing inward. The vertical edges of a slot or recess in an iron stator are lined with electrically insulating paper. A thermally conductive electrically insulating, ceramic substrate is bonded to the floor or base of the slot. The coil is inserted within the slot over the ceramic substrate with the exposed conductor facing and contacting the ceramic substrate. The coil is bonded to the ceramic substrate by thermally conductive and electrically insulative epoxy that fills the voids between the two. Heat flows from the conductor, through the bared copper surface, into the ceramic and the iron core stator with little resistance. A ceramic strip can be used alone or with copper traces bonded to the ceramic or conductor bared surface. Using a thermally conductive epoxy bond reduces resistance due to epoxy smear and reduces thermal resistance of the heat transfer path.

Owner:PRECISION MAGNETIC BEARING SYST

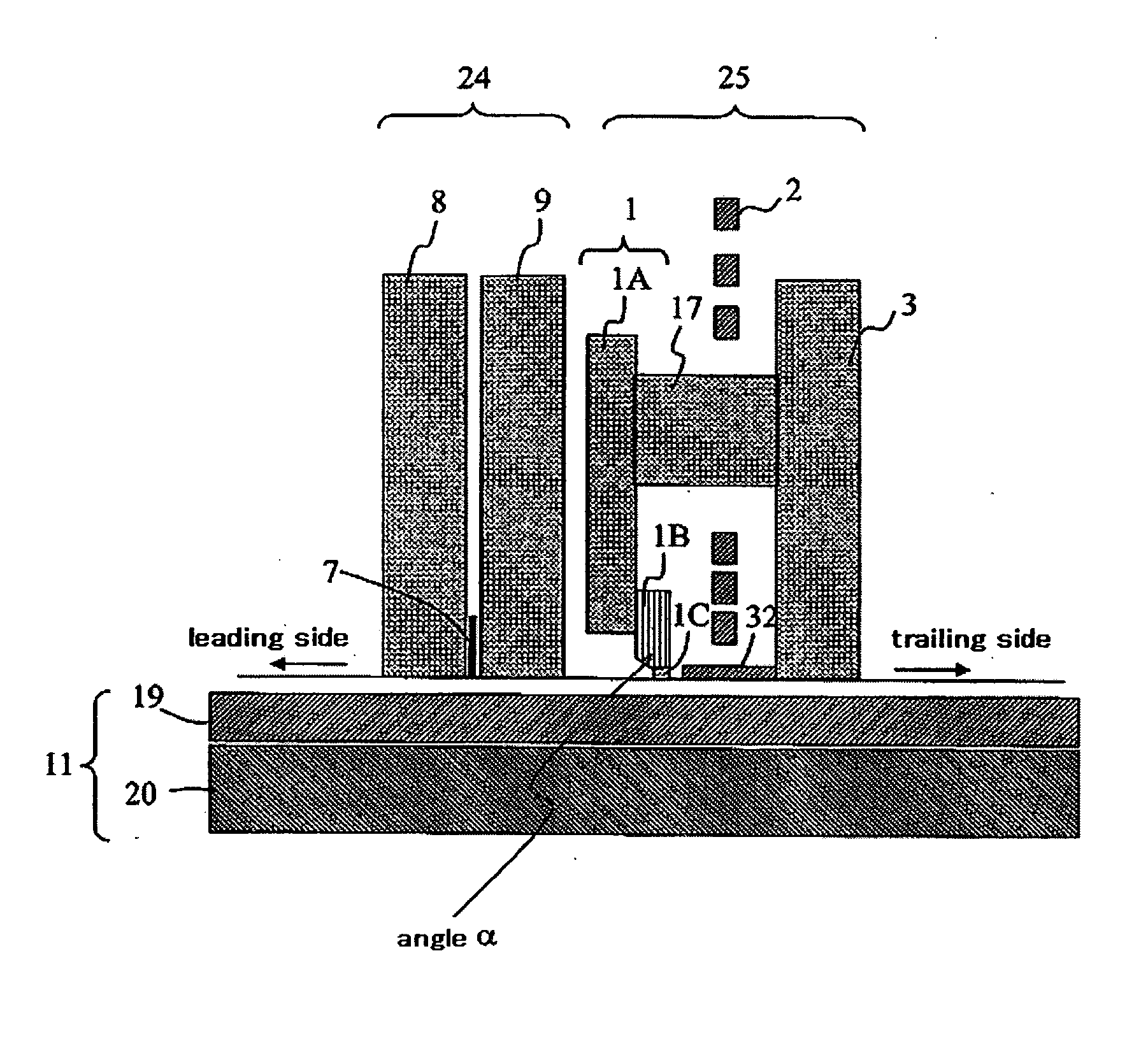

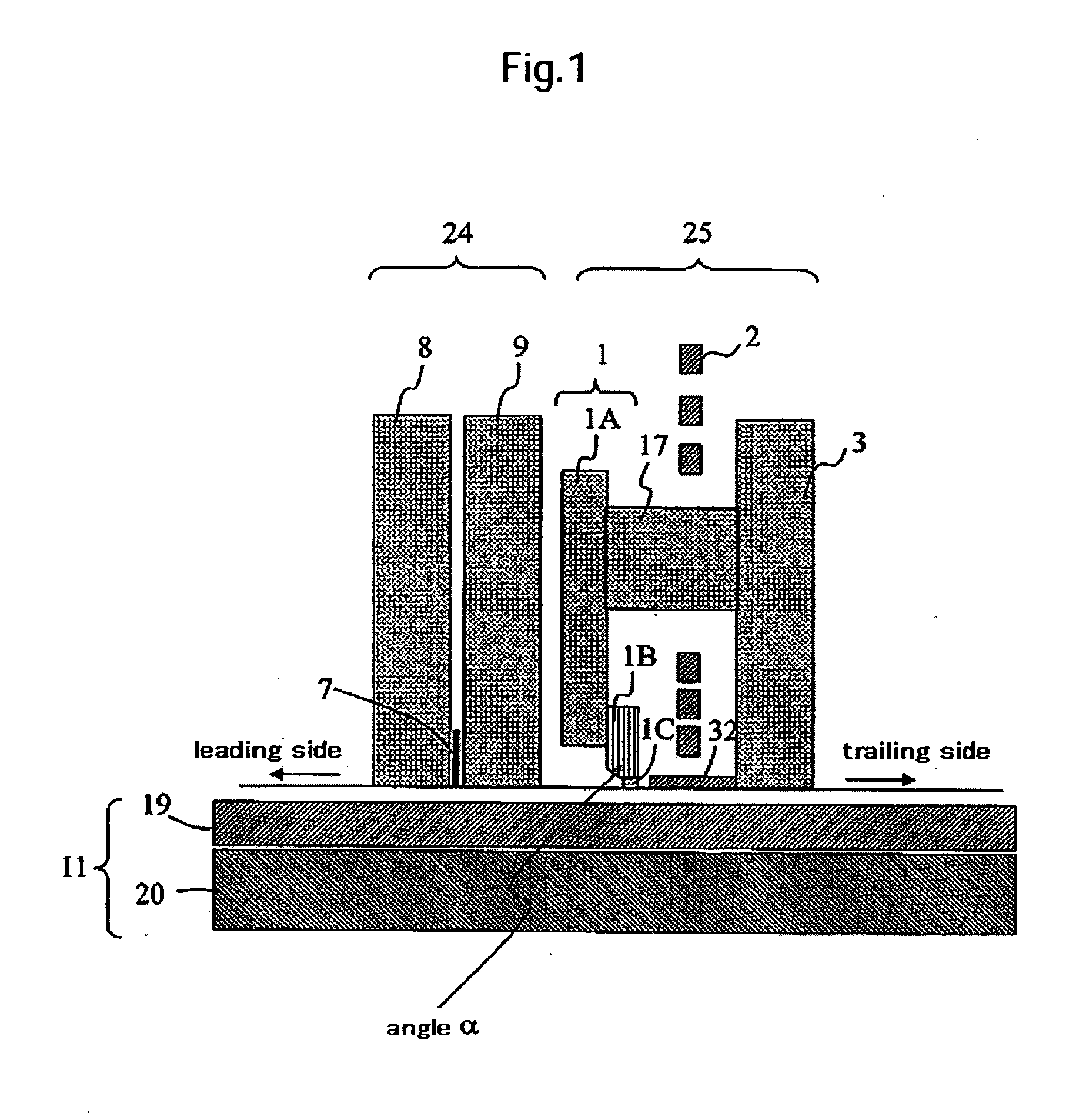

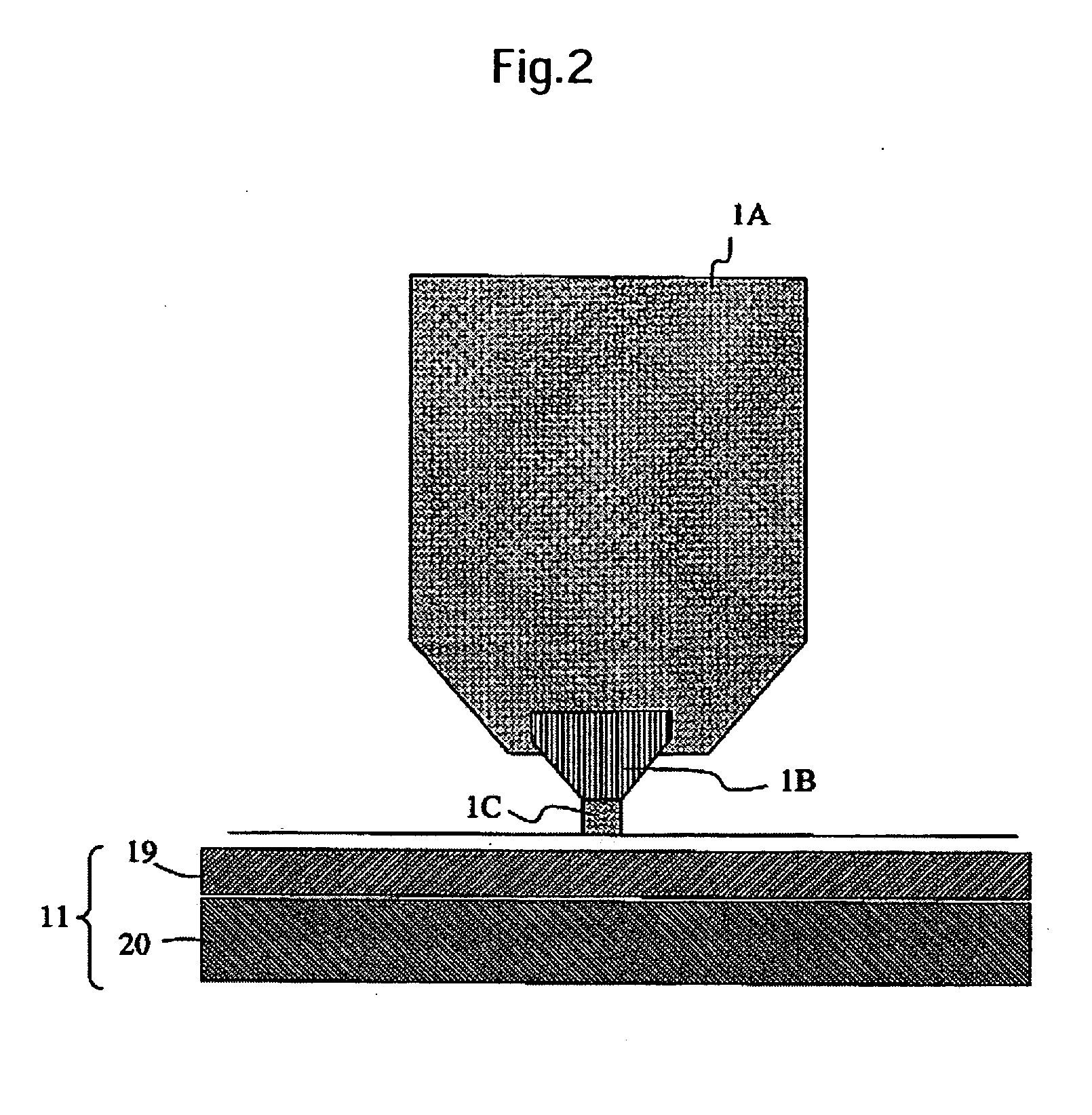

Magnetic head for perpendicular recording and fabrication process

InactiveUS20060198050A1Improve the immunityHigh strengthElectrical transducersRecord information storageSkew angleEngineering

Embodiments of the invention provide an easy-to-fabricate magnetic head which can generate a high magnetic field without eliminating adjacent tracks even if a skew angle is created. In one embodiment, a structure which comprises a pole tip of main pole exposed on the air bearing surface, a part which is recessed from the air baring surface and having a tapered face at leading side against the air bearing surface, and a magnetic material connected thereto is adopted for the main pole.

Owner:WESTERN DIGITAL TECH INC

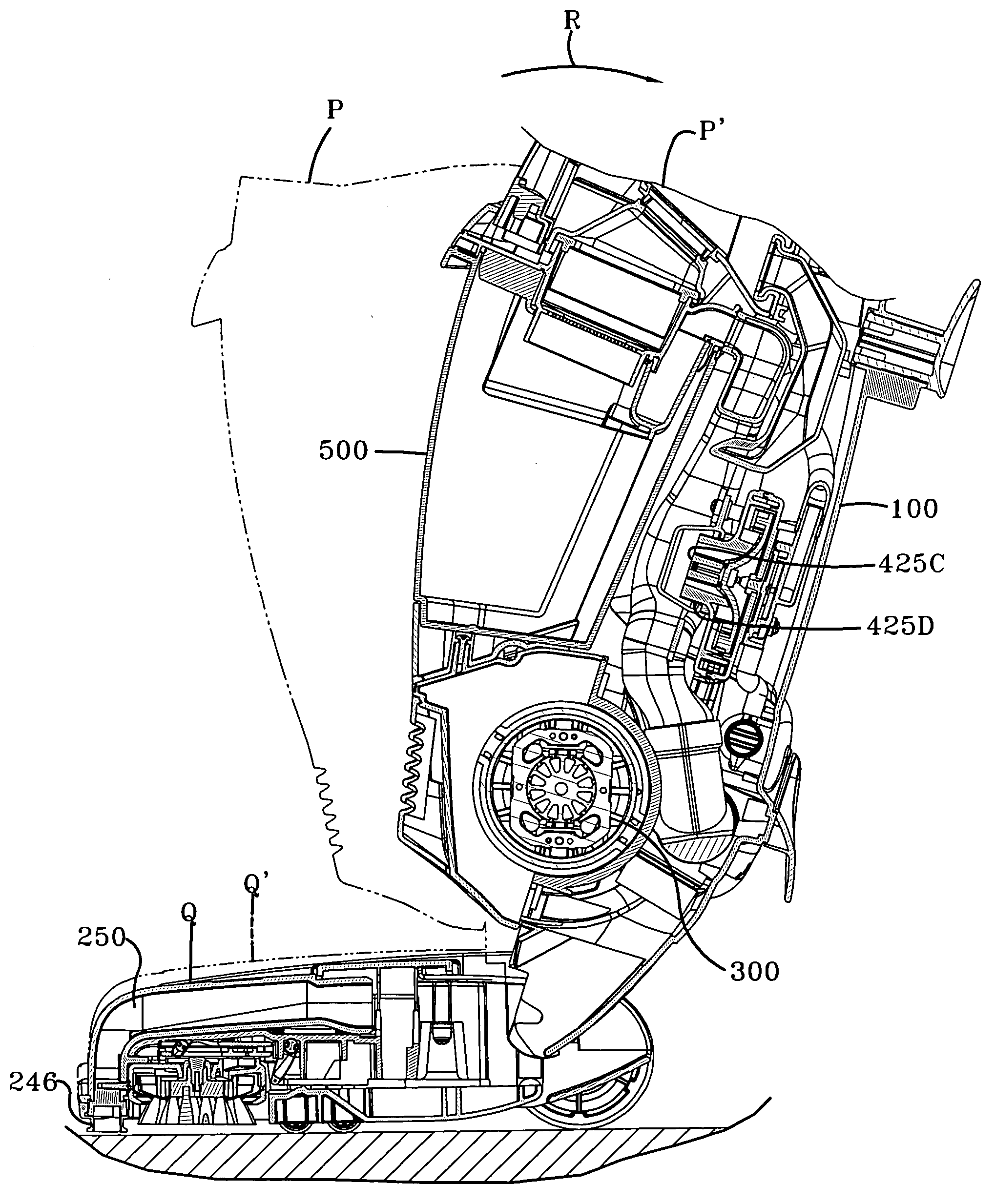

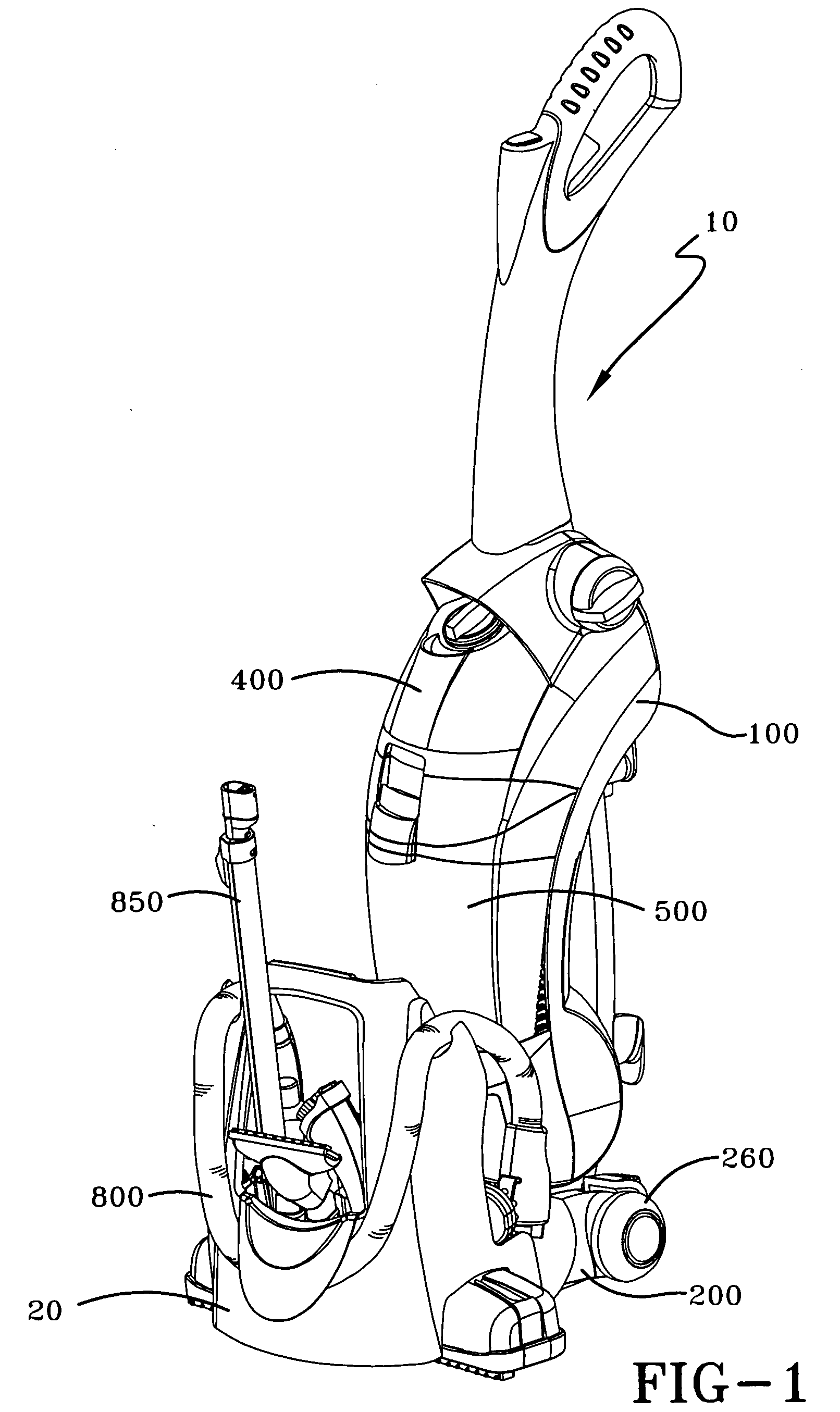

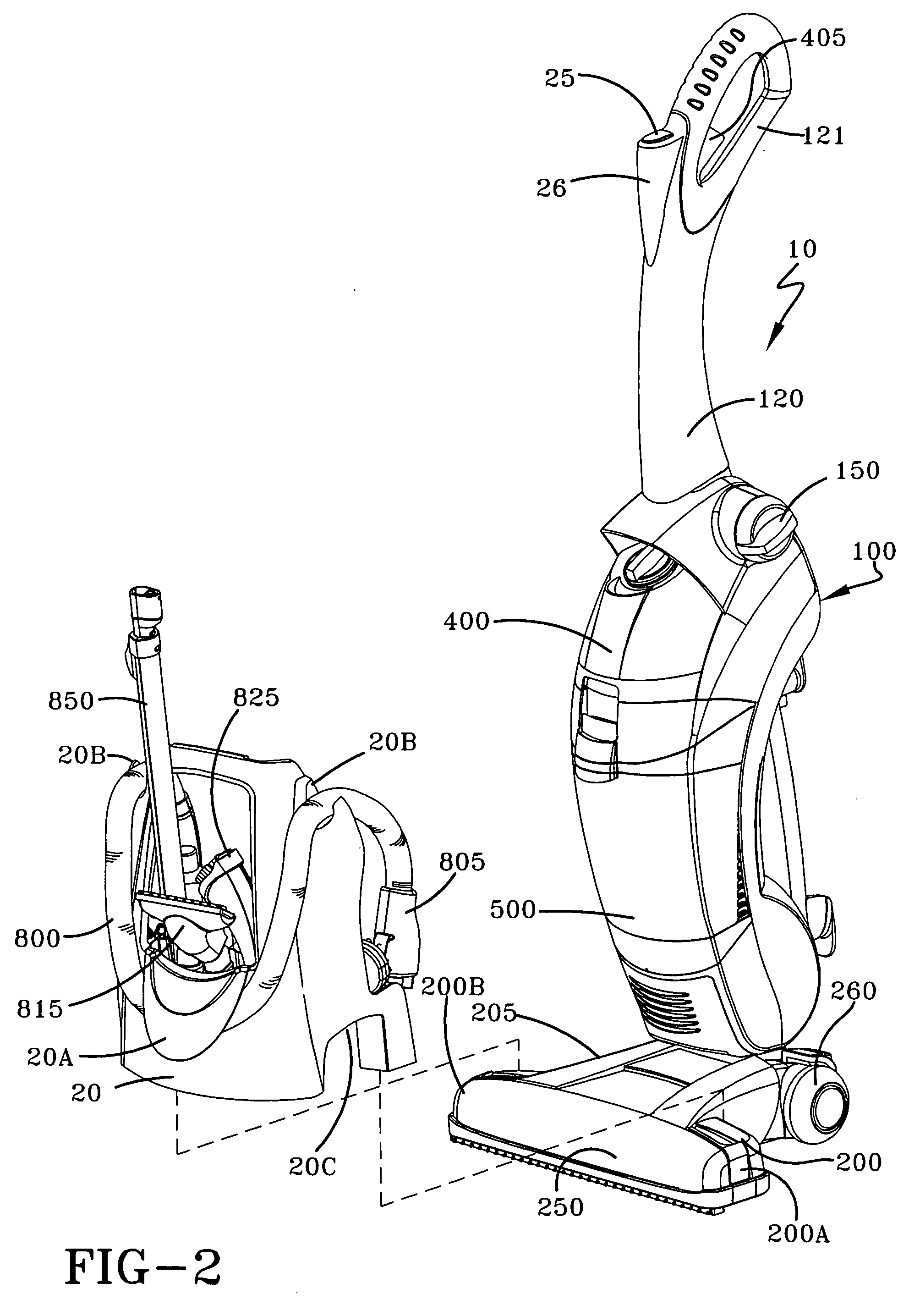

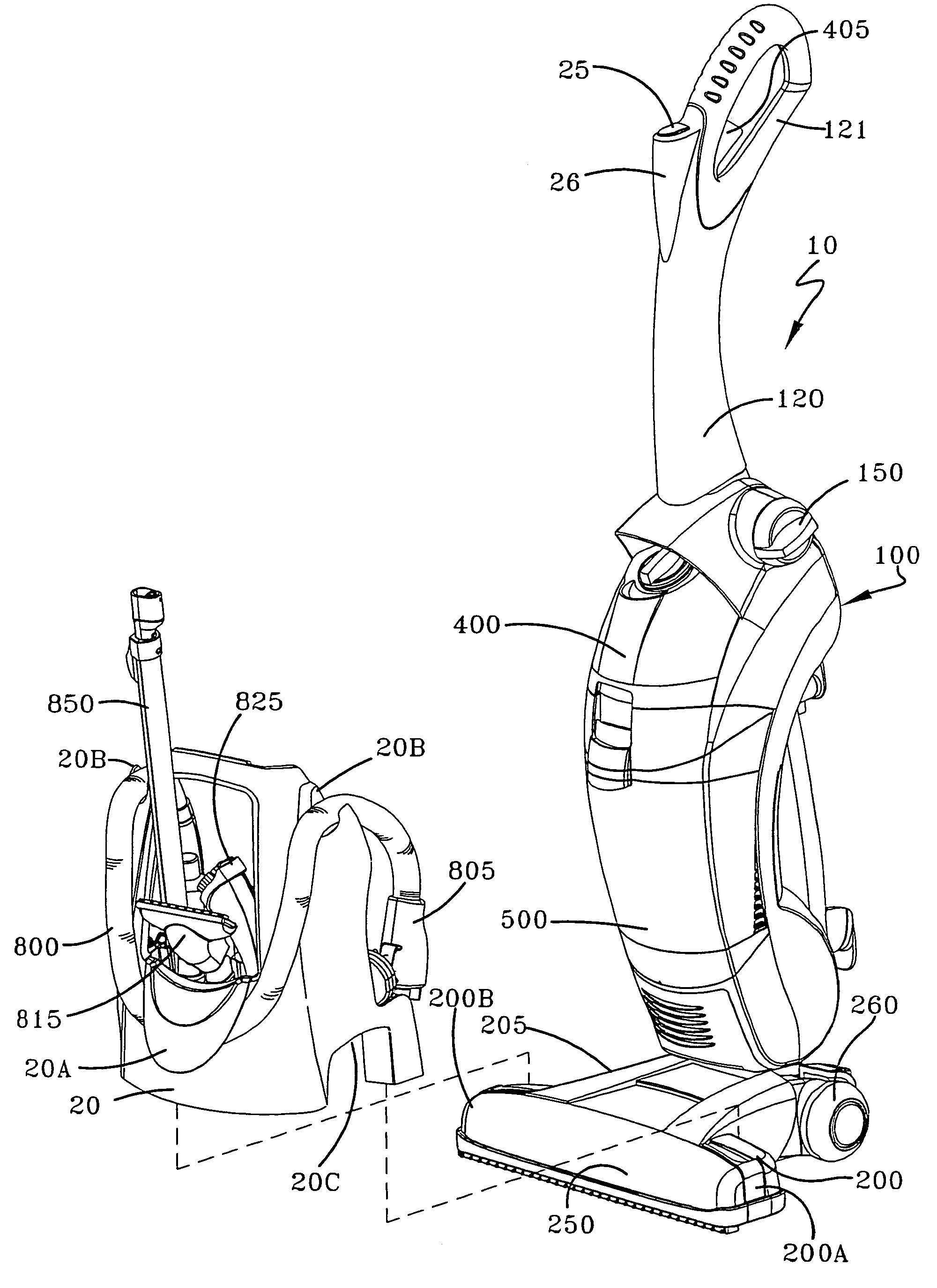

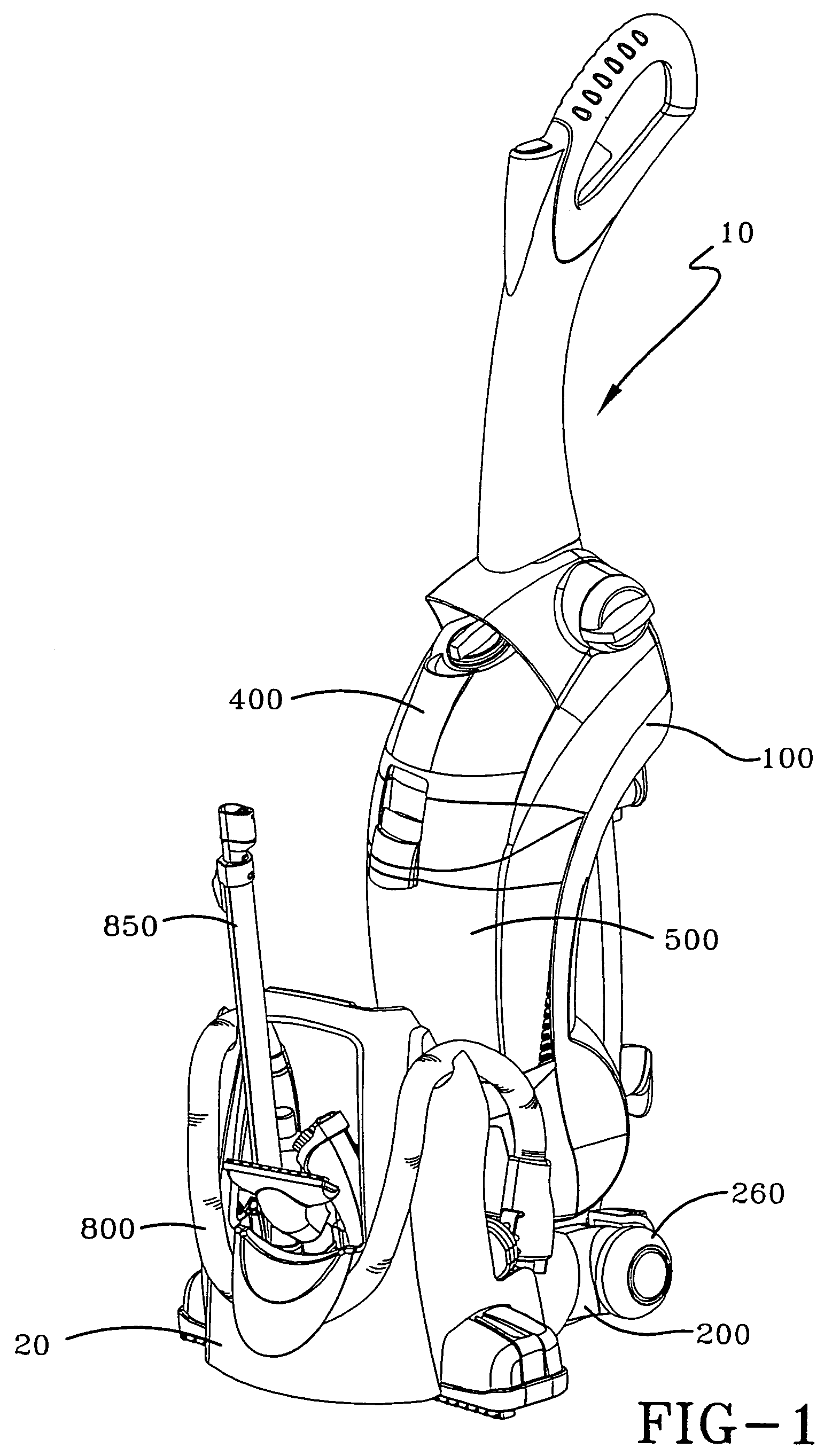

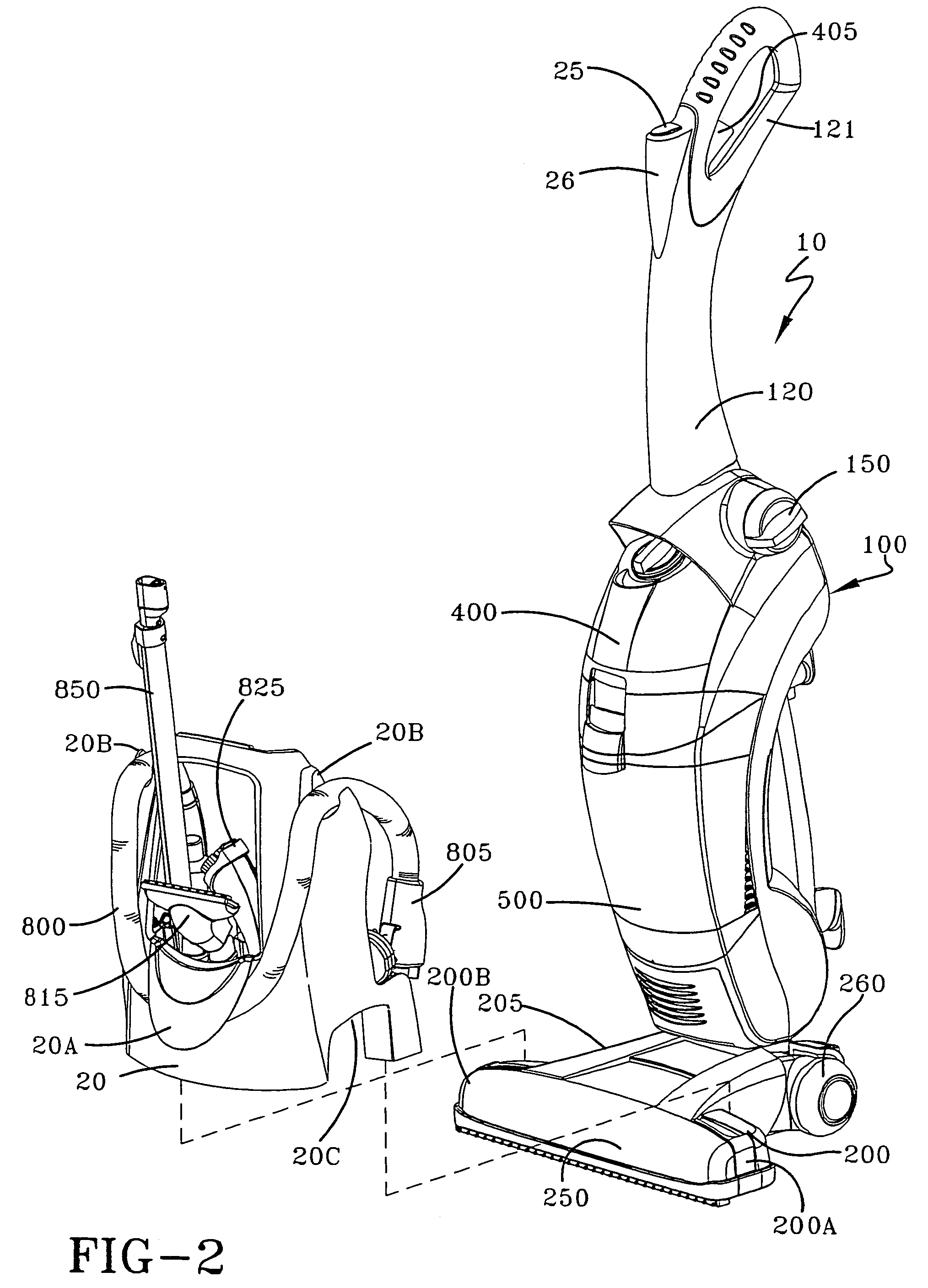

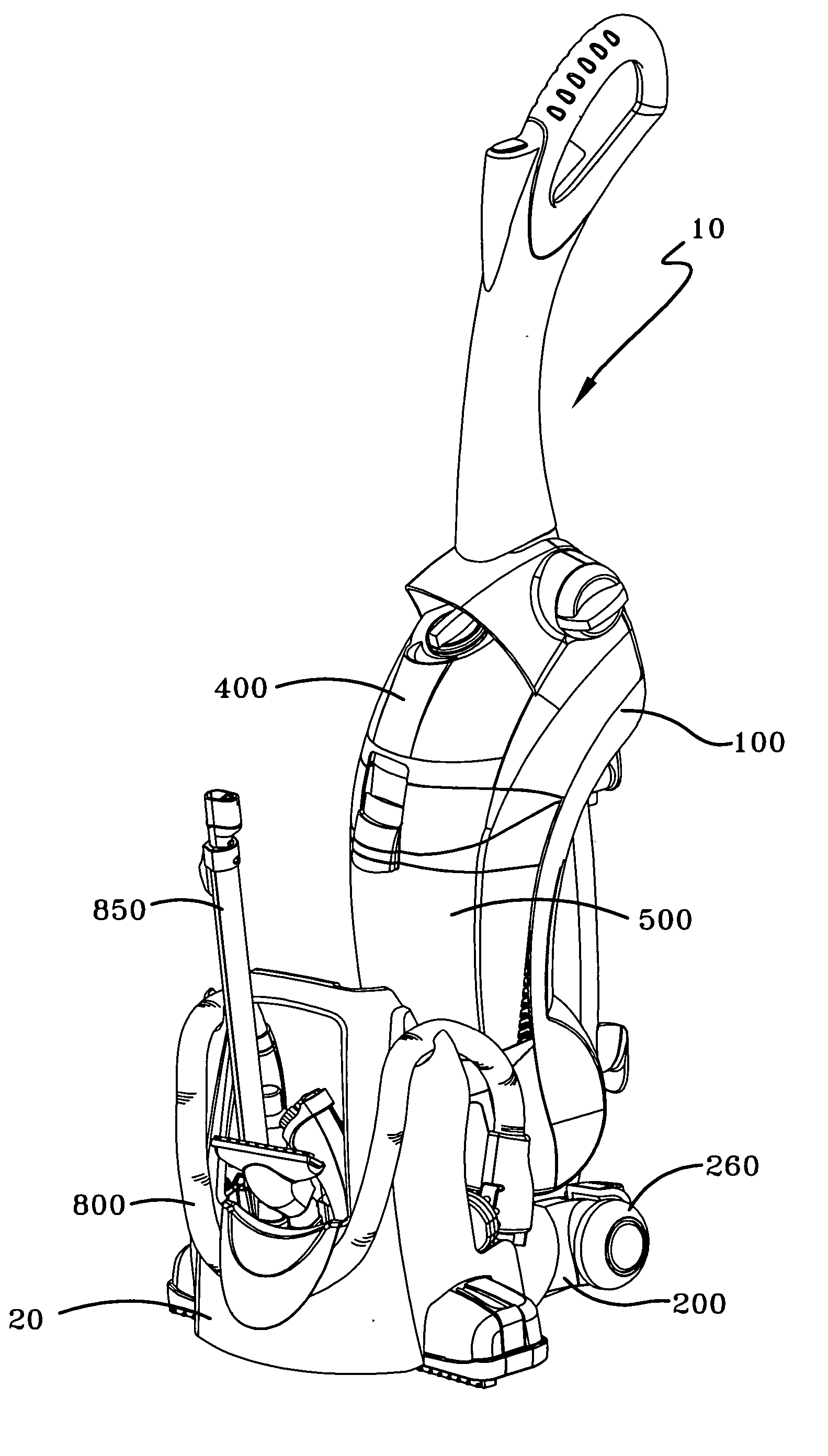

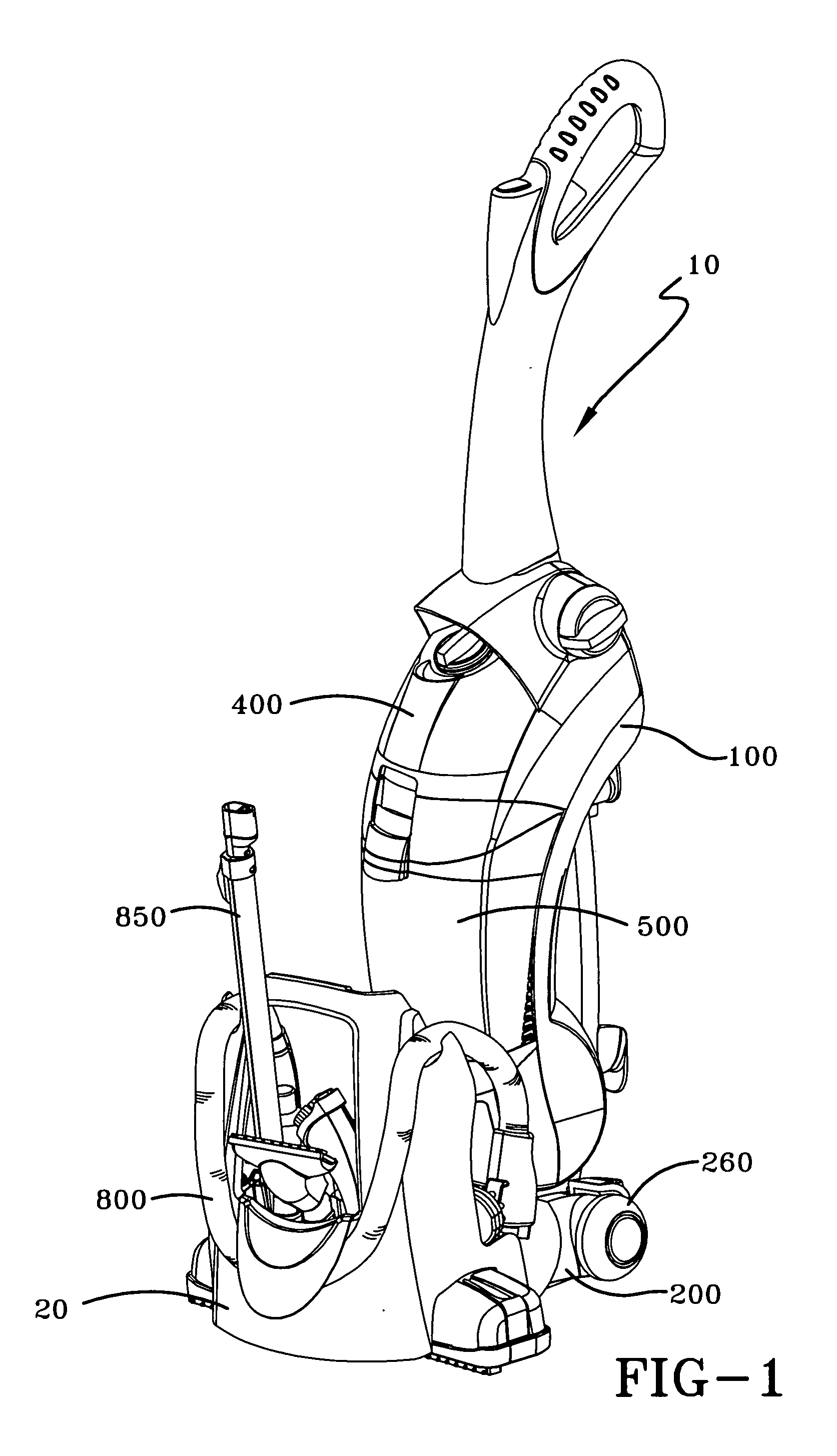

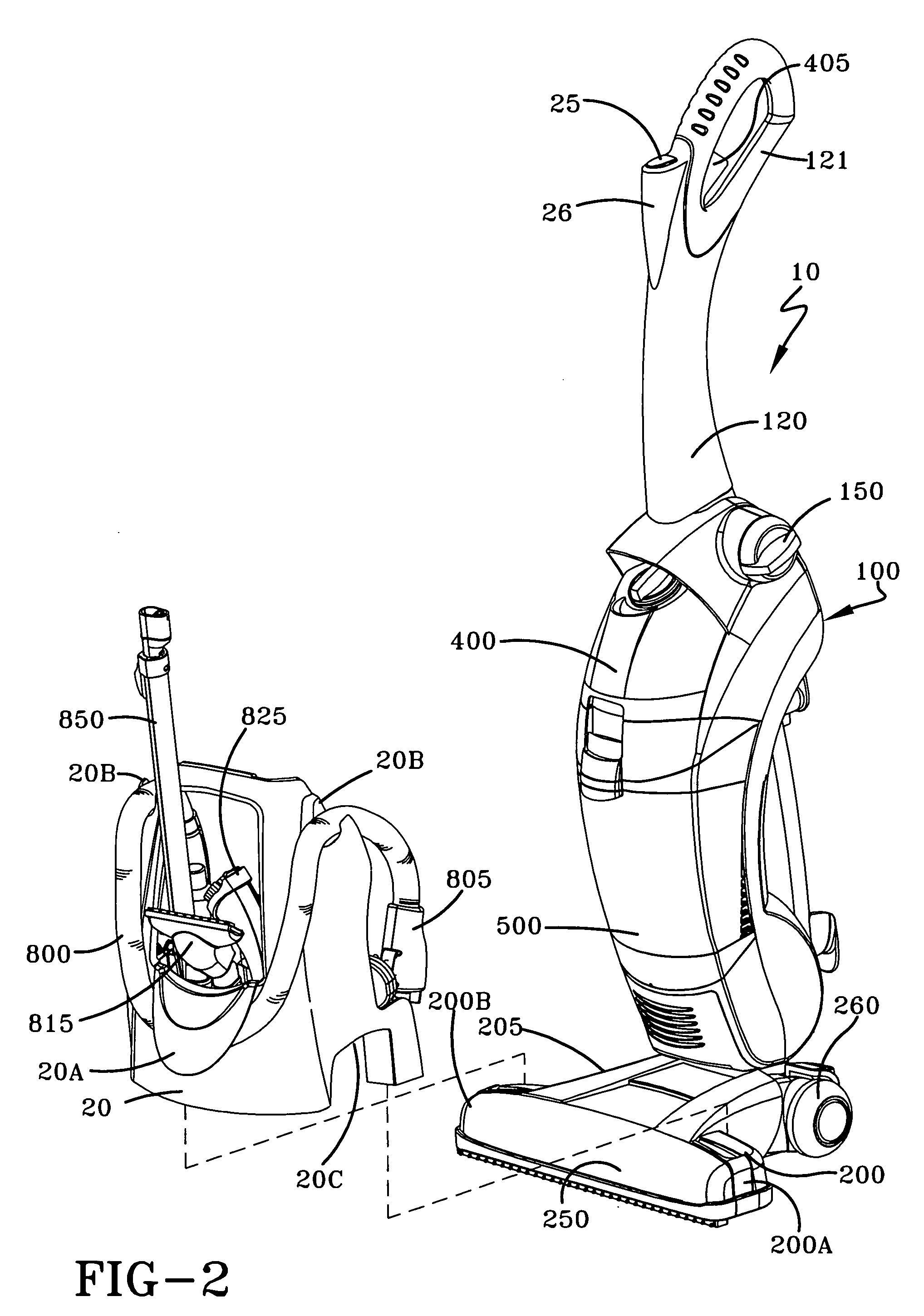

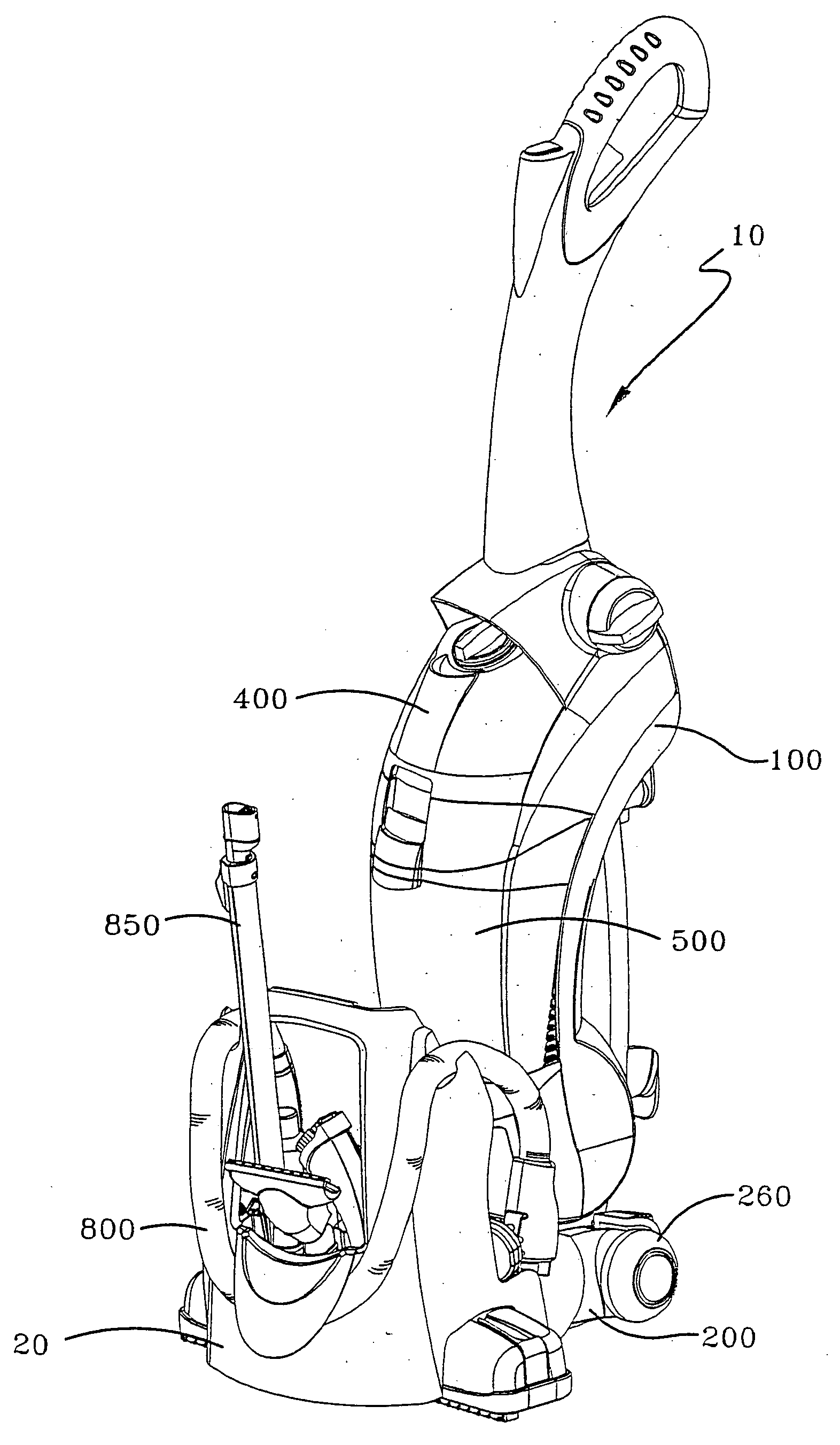

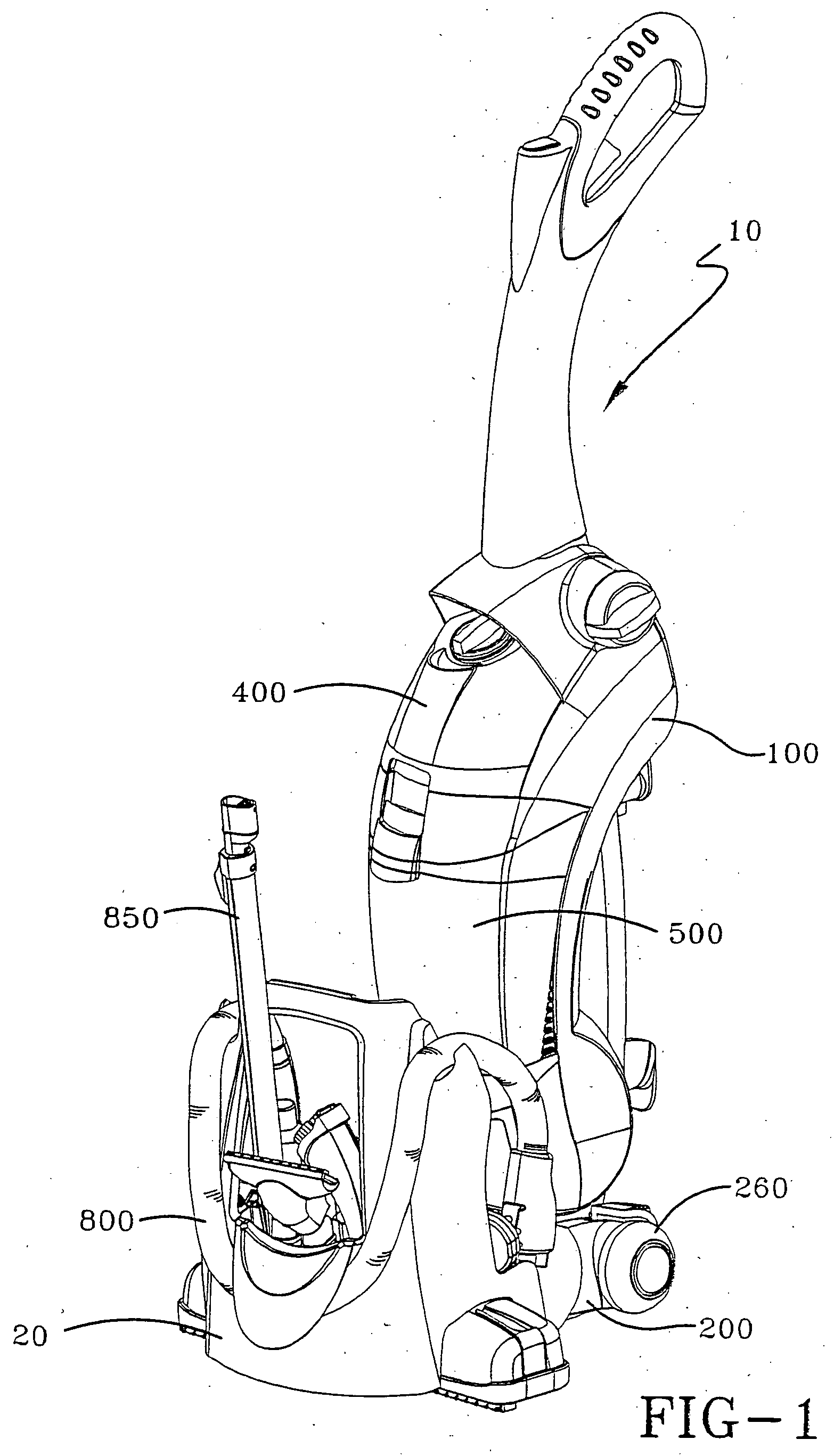

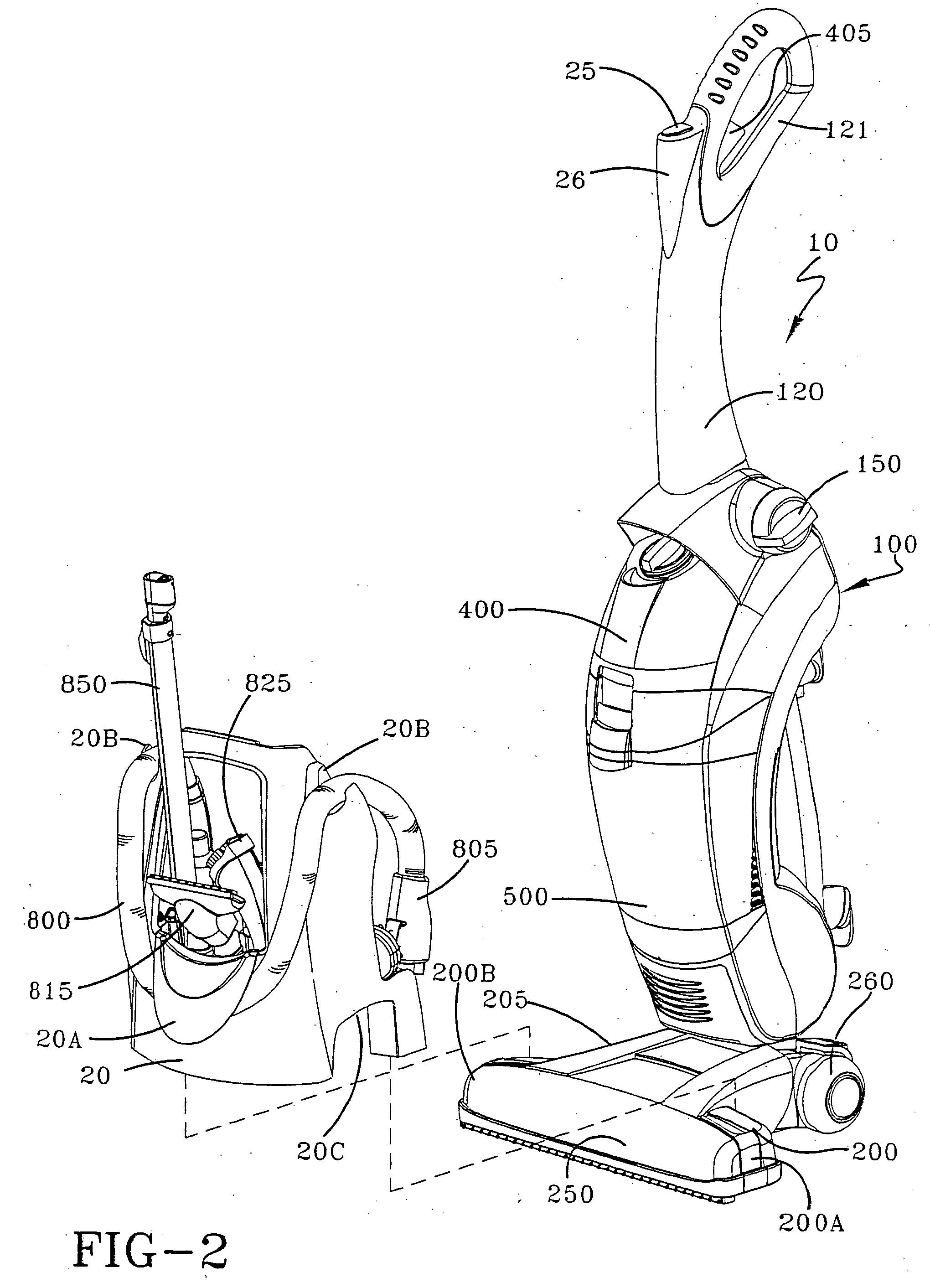

Floor care appliance with a plurali

A floor care appliance is provided for cleaning bare surfaces such as tile, marble, linoleum and wood. The floor care appliance is comprised of a base portion having a suction nozzle and a brush block having a plurality of vertical axis rotary agitators for cleaning bare floors. The rotary agitators are driven by an independent motor for agitating the floor surface. With the addition of an accessory hose and tools, the cleaning utility can be expanded to areas wherein the suction nozzle cannot normally reach such as behind the toilet, shower walls, and the grout between tile. While used in the capacity for cleaning bare floors, the floor care appliance can be moved between three modes by a rotating a member located on the upper housing. The first mode is dry mode, the second mode is wet scrub mode and the third mode is wet pickup mode. The accessory tools are stored in an accessory caddy that is placed freestanding over the suction nozzle and in front of the housing.

Owner:TECHTRONIC FLOOR CARE TECH LTD

Floor care appliance with tool caddy

A floor care appliance is provided for cleaning bare surfaces such as tile, marble, linoleum and wood. The floor care appliance includes an accessory caddy for storing an accessory hose, telescoping wand, cleaning implements and cleaning supplies. The accessory caddy is placed over the suction nozzle in front of the cleaner housing for storage. A pair of arcuate cutouts on the caddy are provided for placement over the suction nozzle. A handle is provided for transporting the accessory caddy.

Owner:HEALTHY GAIN INVESTMENTS

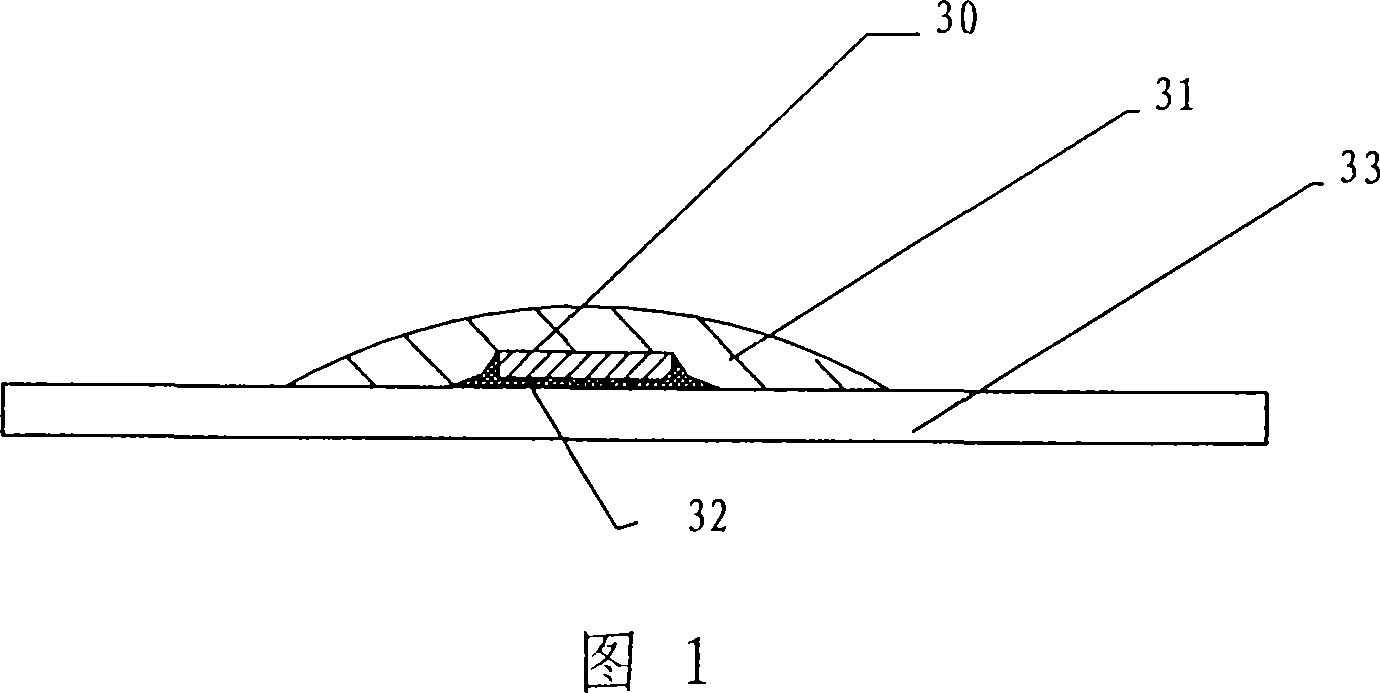

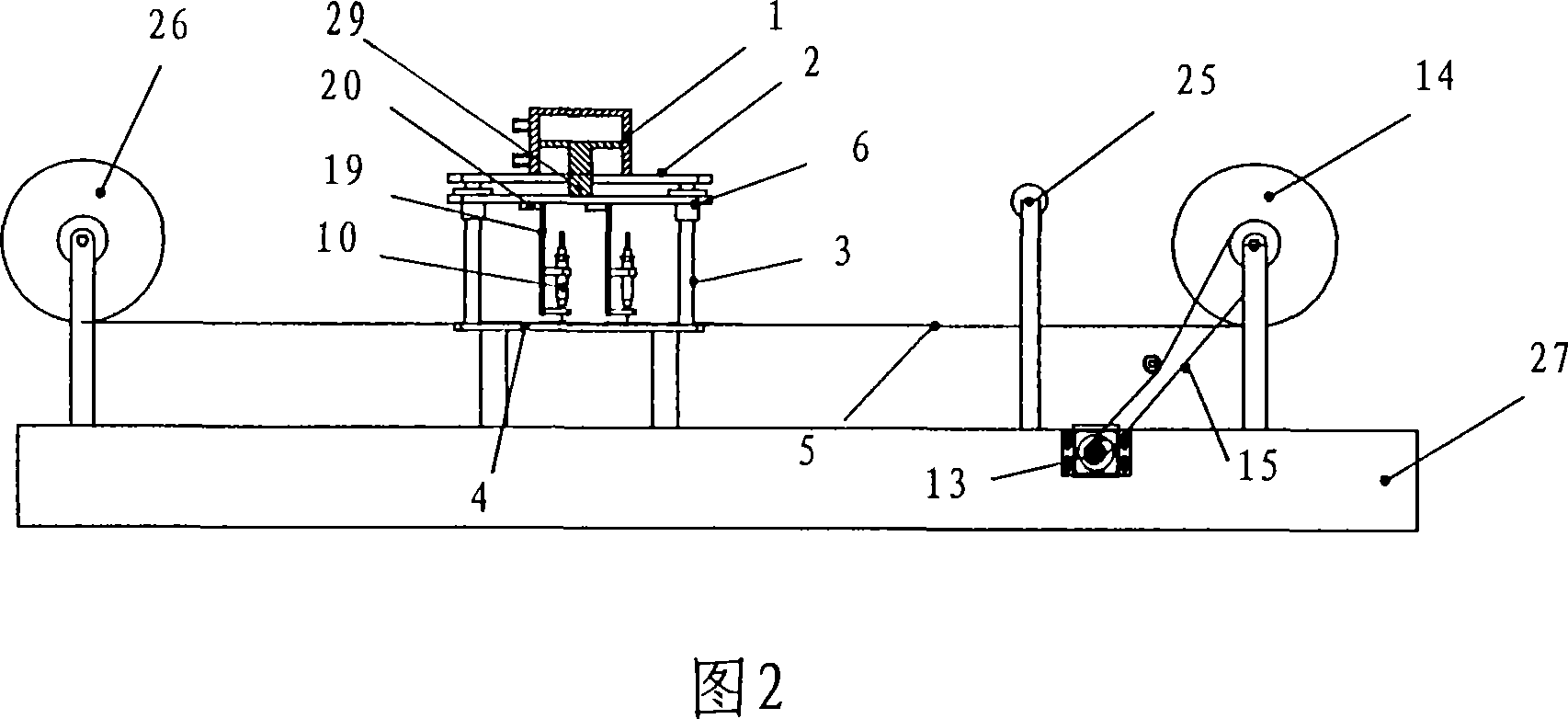

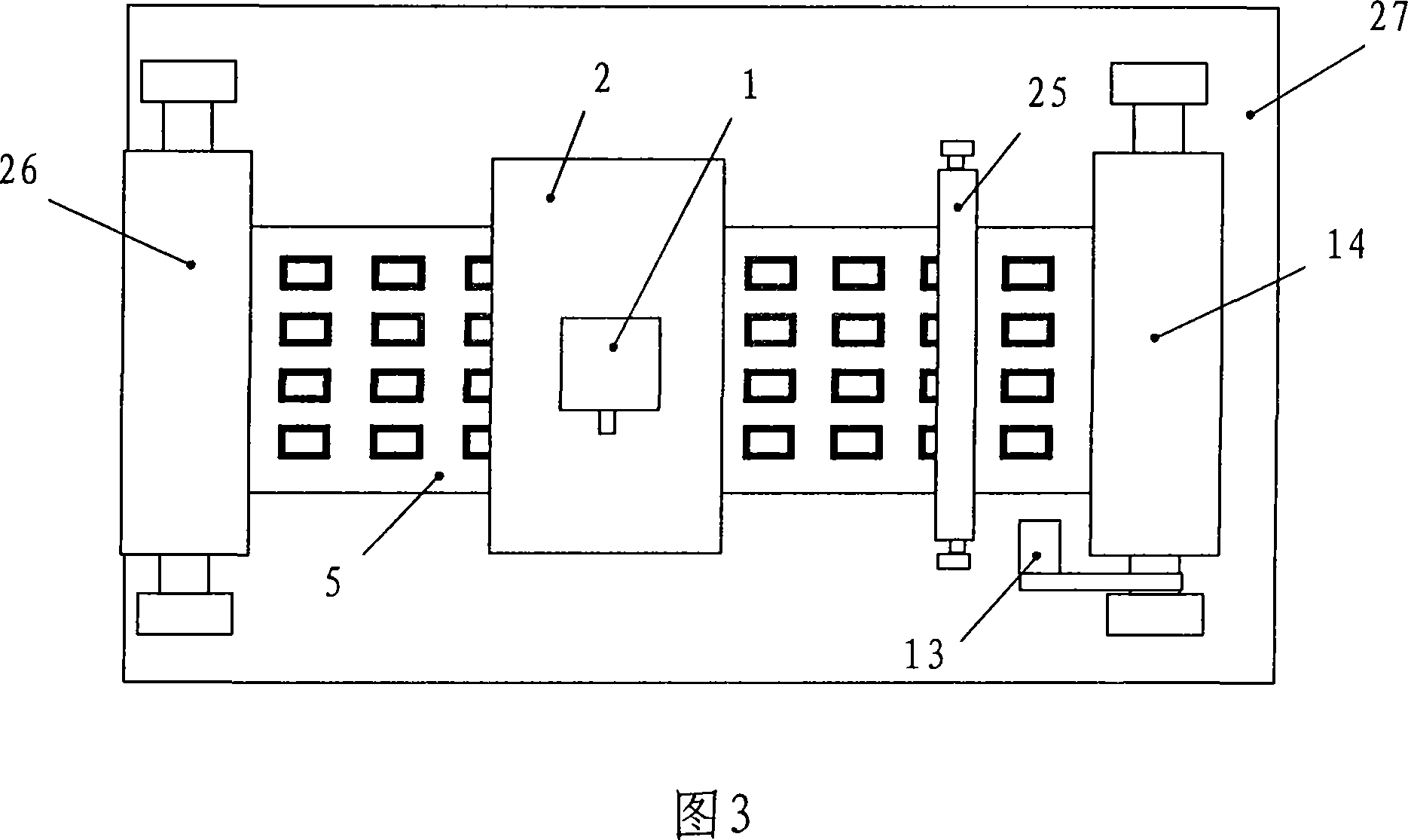

Intelligent label and its glueing method and device

InactiveCN101051358ANot easy to damageMoisture-proof, anti-corrosion and radiation-proofSolid-state devicesPretreated surfacesDrive motorBare surface

The present invention relates to an intelligent tag, its glue-coating method and device, belonging to a solid device. The intelligent tag includes silicon wafer and antenna which are connected into one body by means of conducting glue, in which on the bare surface of said silicon wafer is coated a protective glue. Its glue-coating method adopts a glue-dropping method, and its glue-coating device includes the following several portions: drive motor, three screw rods or three cylinders, sensor, special-purpose controller, high-speed drawing system, automatic glue-dropping table and solidifying device, etc.

Owner:BEIJING GOLDEN SPRING TECH DEV

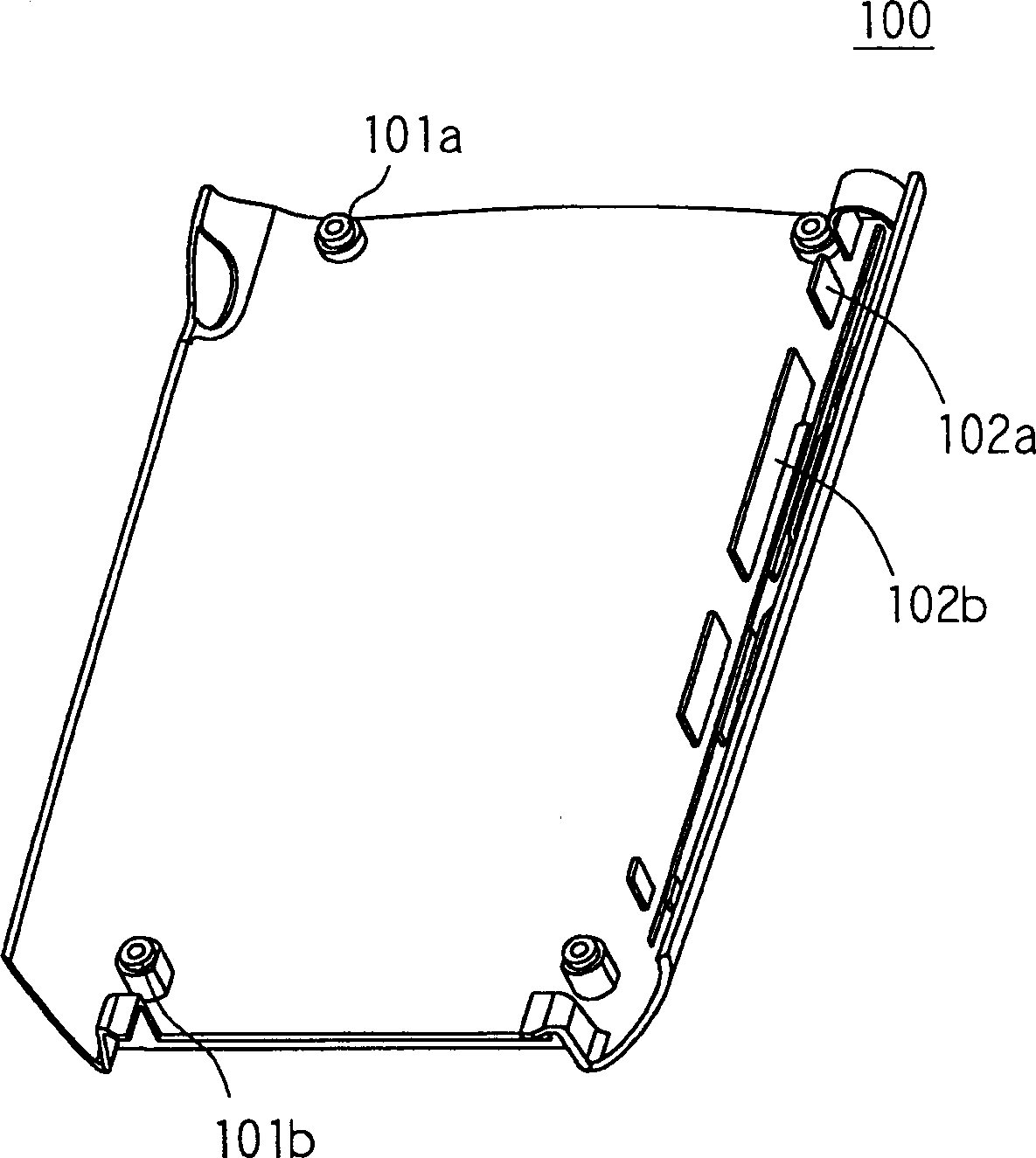

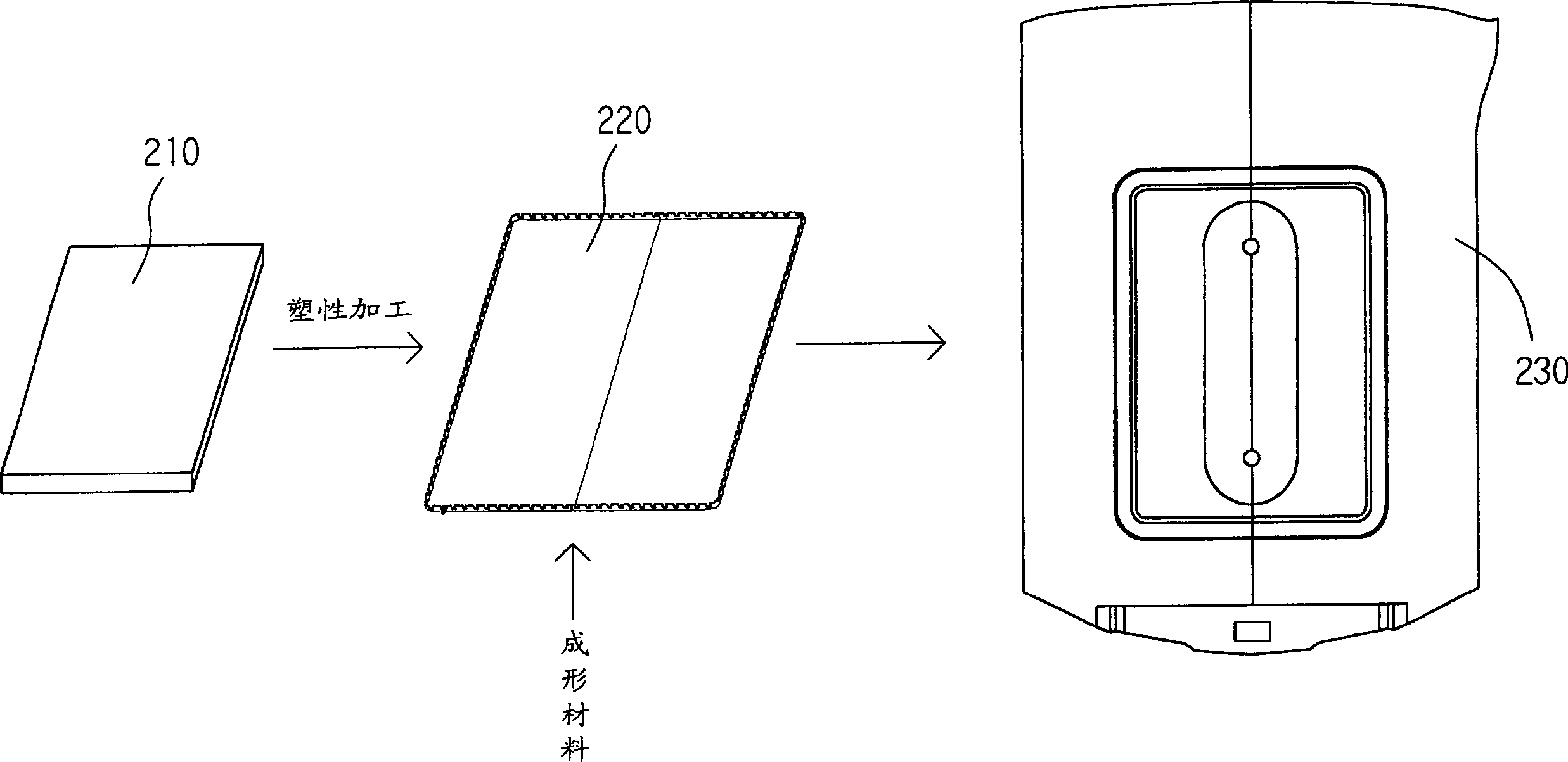

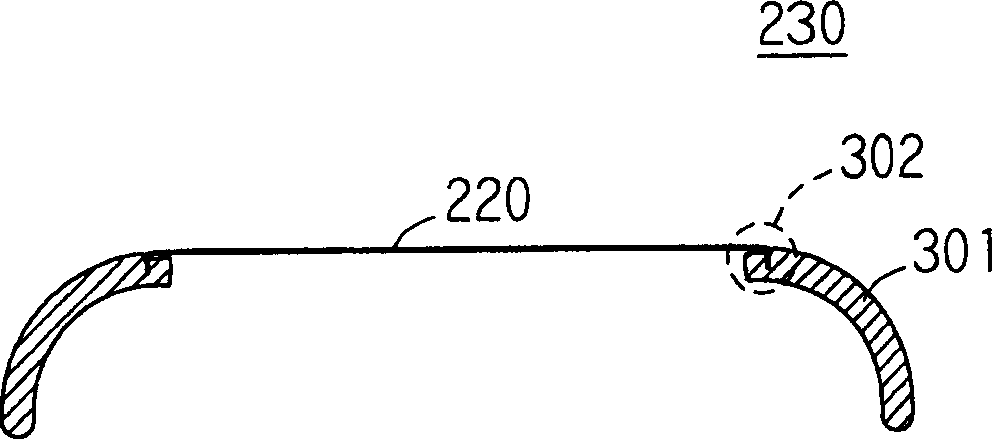

Portable electronic product outer shell and its making method

A shell of a portable electronic product and its method is able to have complicated combination structure with smaller thickness containing first to produce metal plates to thin metal shell plates then to process the metal plate with a formed material to semi-manufactured goods, finally to handle surface of the semi-manufactured goods to a shell characterizing in bare surface metal shells. Apart from smaller thickness, the built-in typing technology can satisfy the dvariable change on structure.

Owner:HONGDA INT

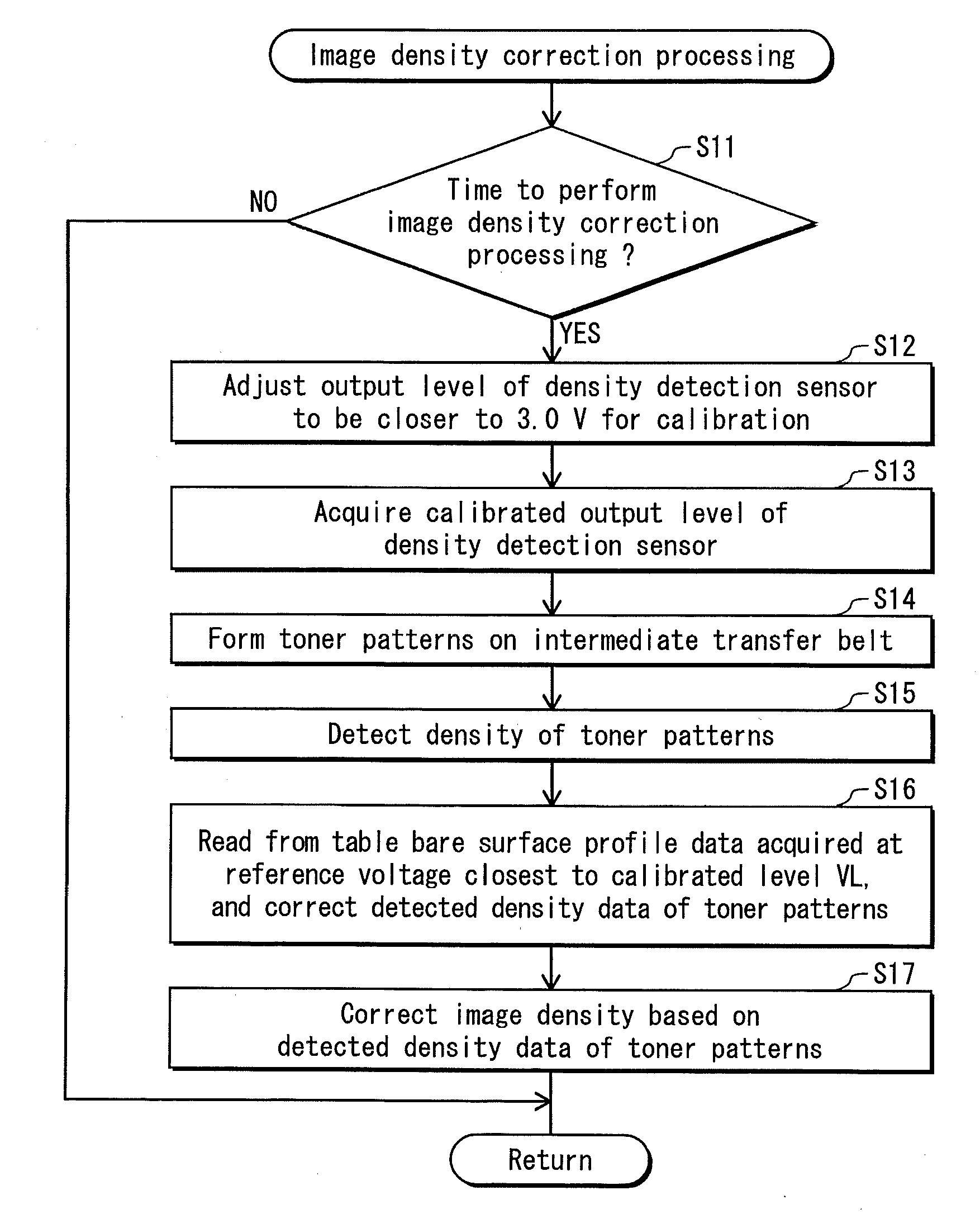

Image forming apparatus and image density correction method therefor

ActiveUS20110311245A1Electrographic process apparatusCorona dischargeImage formationData acquisition

An image forming apparatus includes: sensor detecting light intensity and output voltage based on the light intensity; data acquisition part setting reference voltages for the sensor to detect light intensity of bare surface of intermediate transfer member, acquiring, at set reference voltage, voltage output by the sensor on the bare surface as detection data; storage storing the detection data corresponding to the reference voltages; judgment part judging whether to perform image density correction processing; voltage calibration part adjusting output level at light intensity detection; density acquisition part forming toner pattern, and acquiring density data of the toner pattern by causing the sensor having adjusted output level to detect its light intensity; density data correction part reading one piece of detection data referring to output level, and correcting the density data based on the detection data; and image density correction part performing the processing based on the density data.

Owner:KONICA MINOLTA BUSINESS TECH INC

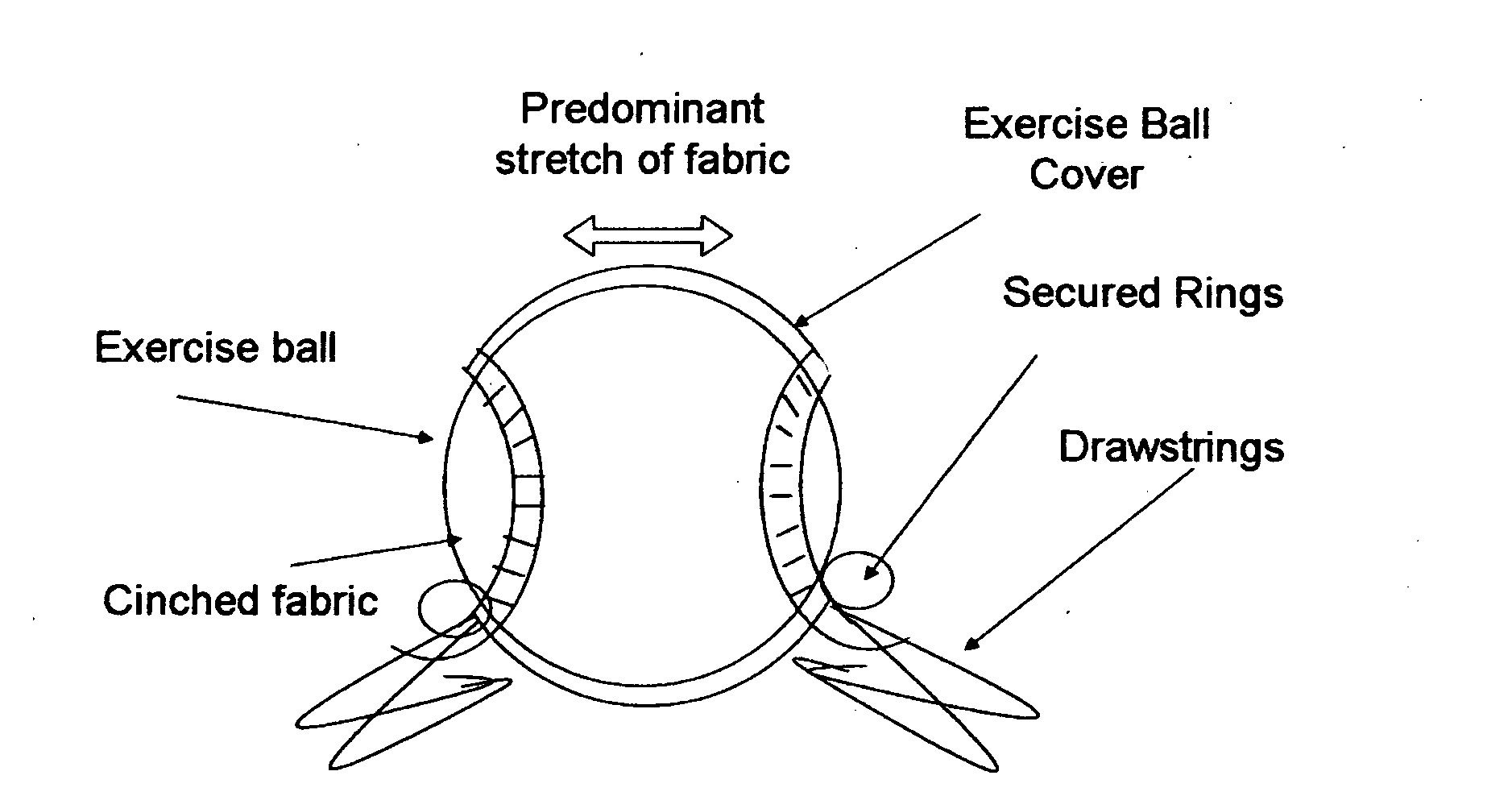

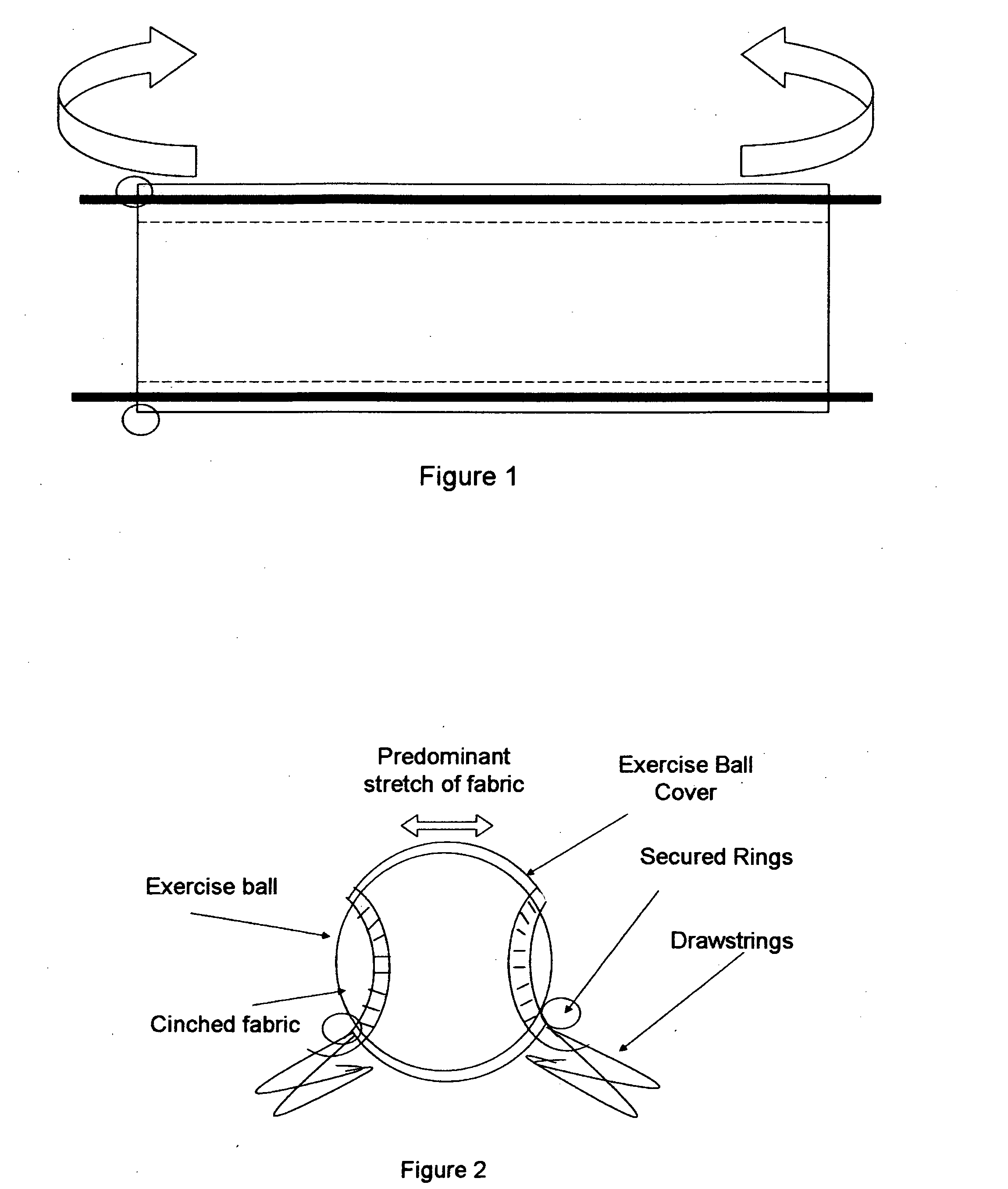

Personal exercise equipment cover

An exercise Swiss ball cover with the capability of performing integrated resistance exercises and temporarily store personal belongings. The cover is a fabric rectangle secured at its shortest sides, or a fabric tube, into which the exercise Swiss ball is inserted and covered at the centermost, widest circumference. There are two perimeters, each having a small ring or grommet to attach and detach exercise accessories and personal belongings. The cover is cinched at its two perimeters to secure the cover to the exercise Swiss ball. It provides a 360 degree forward and backward rotation capability and a variable lateral rotation of up to 180 degrees without interference from excess material or the bare surface of the exercise Swiss ball. Variable side coverage depends upon stretch and width of fabric used. The cover can be folded into a flat rectangle, making it suitable to neatly drape over a workout bench.

Owner:POWER REBECCA MICHELLE

Plasma excimer nanometer laser

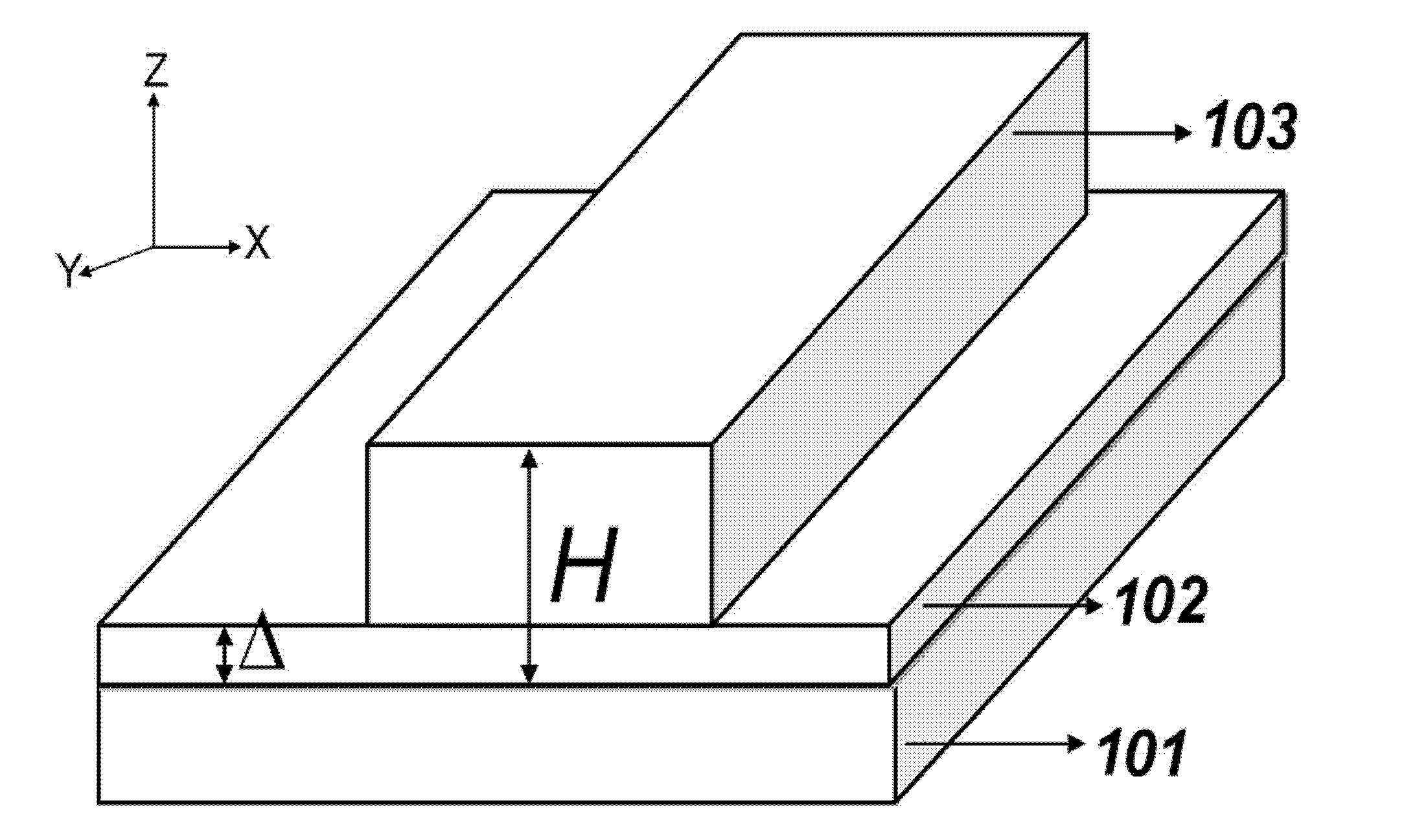

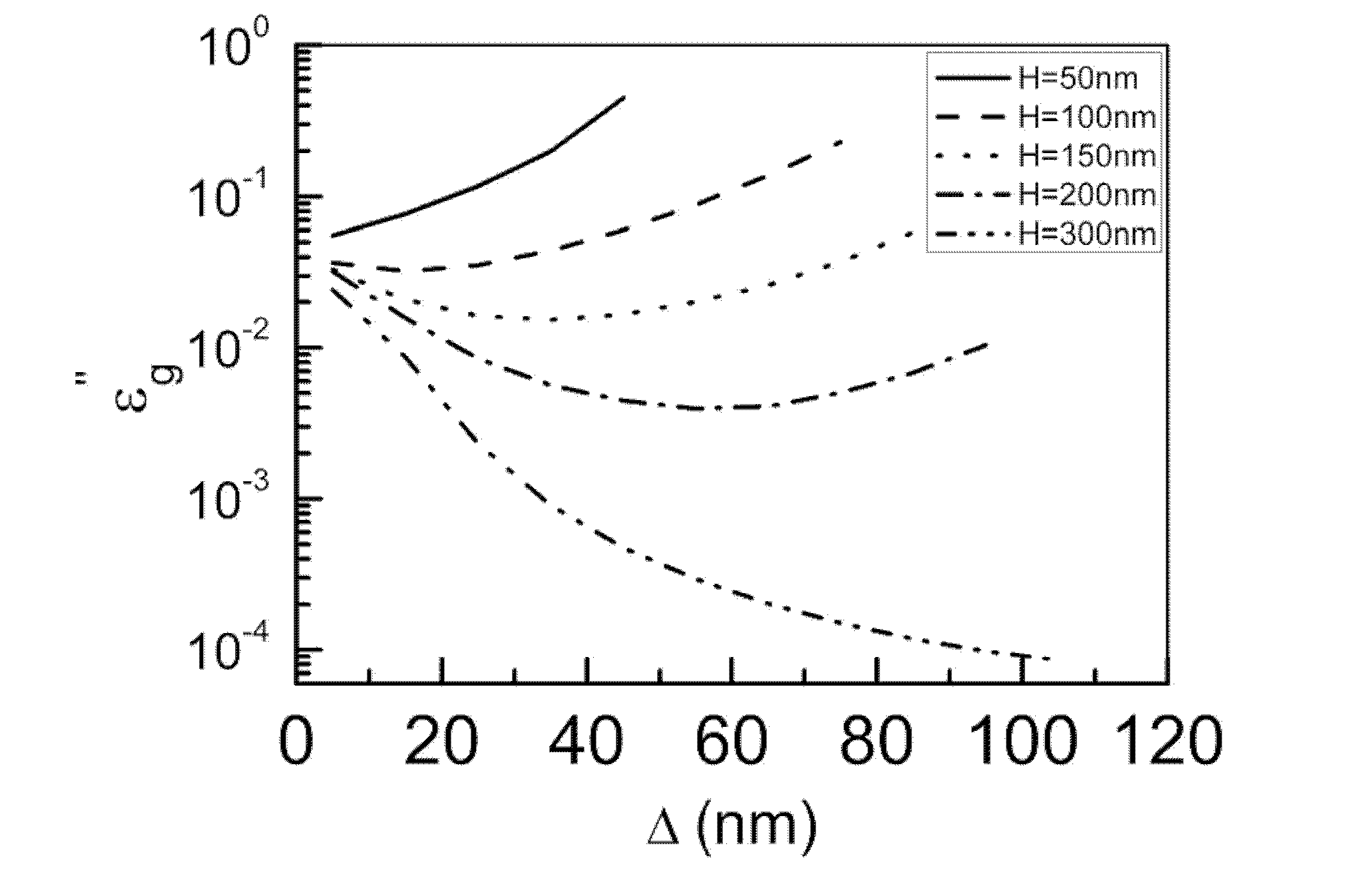

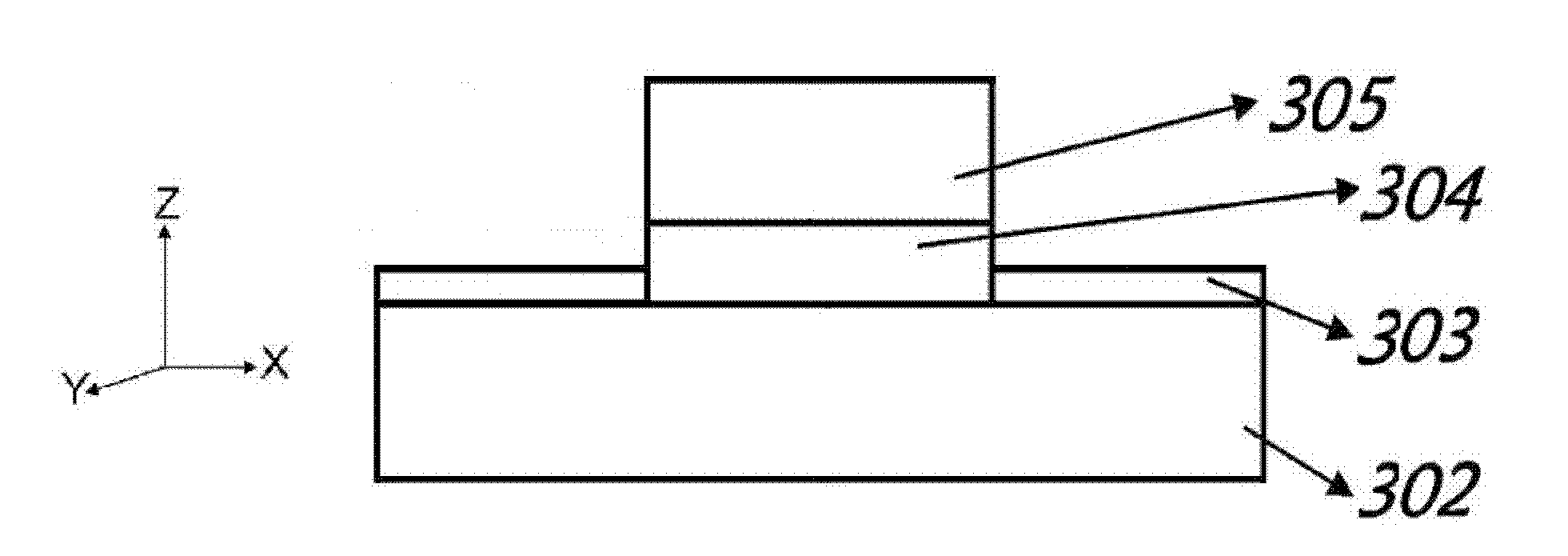

ActiveCN102664350AOscillation heat loss is smallLower the thresholdOptical wave guidanceLaser active region structureLaser technologyMicro nano

The invention relates to a micro-nano photonic device and the field of laser technology. The invention provides a plasma excimer nanometer laser, comprising a first medium layer, a first isolated layer and a gain medium cavity. The first isolated layer is placed on the bare surface of the first medium layer. The gain medium cavity is placed on the bare surface of the first isolated layer. The laser is characterized in that the specific value scope between the thickness of the first isolated layer and the vertical thickness of the gain medium cavity body is less than 0.5. The plasma excimer nanometer laser provided by the invention has an advantage of decreasing the threshold value of laser.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI +1

3D decorative glass and preparation method thereof

ActiveCN108947270ASmooth edgesHigh precisionSynthetic resin layered productsBare surfaceMaterials science

The invention relates to the field of 3D glass surface decoration, and discloses 3D decorative glass and a preparation method thereof. The 3D decorative glass comprises a 3D glass substrate, a partially hollow decorative ink layer, a metal mirror filling layer and a black shading ink layer, wherein the decorative ink layer is attached to one side surface of the 3D glass substrate, the metal mirrorfilling layer is attached to the other side surface of the 3D glass substrate and filled in the hollow region of the decorative ink layer, and bare surfaces of the decorative ink layer and metal mirror filling layer are covered with the black shading ink layer. A beautiful three-dimensional pattern can be exhibited by the 3D decorative glass, the precision of the exhibited three-dimensional pattern is high, and the boundary between the decorative ink layer and the metal mirror filling layer is clear and substantially has no jags.

Owner:BYD CO LTD

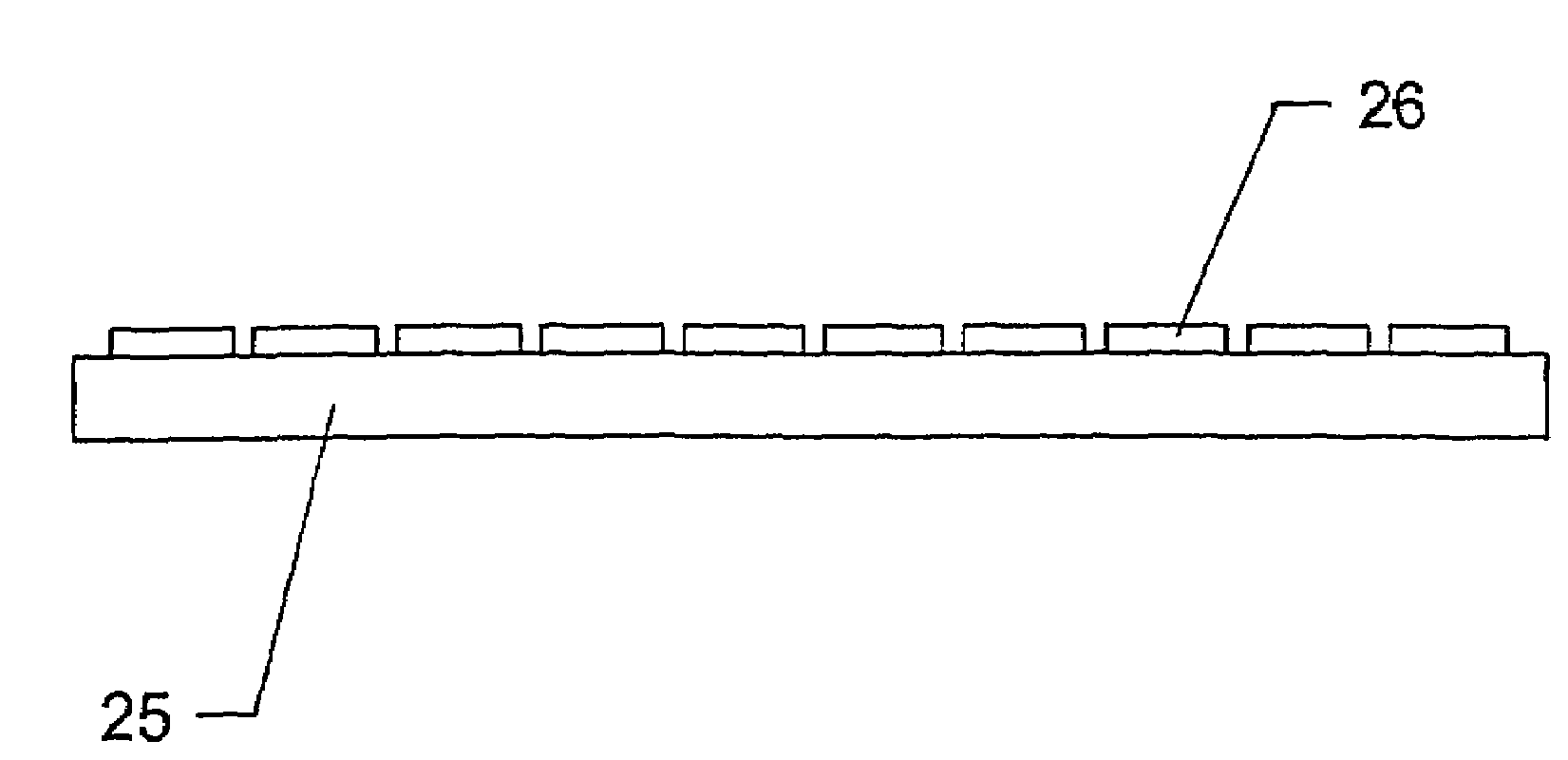

Cooling of stator windings

InactiveUS7498710B2Reduce the temperatureImprove thermal conductivityWindings insulation shape/form/constructionMagnetic circuit rotating partsCopper conductorEpoxy

An arrangement for cooling an electric motor's stator winding coil is described. One area of a conductor insulation is removed to expose the copper conductor. The conductor is wound into a coil with bared, exposed conductor areas facing inward. The vertical edges of a slot or recess in an iron stator are lined with electrically insulating paper. A thermally conductive electrically insulating, ceramic substrate is bonded to the floor or base of the slot. The coil is inserted within the slot over the ceramic substrate with the exposed conductor facing and contacting the ceramic substrate. The coil is bonded to the ceramic substrate by thermally conductive and electrically insulative epoxy that fills the voids between the two. Heat flows from the conductor, through the bared copper surface, into the ceramic and the iron core stator with little resistance. A ceramic strip can be used alone or with copper traces bonded to the ceramic or conductor bared surface. Using a thermally conductive epoxy bond reduces resistance due to epoxy smear and reduces thermal resistance of the heat transfer path.

Owner:PRECISION MAGNETIC BEARING SYST

Floor care appliance with a plurality of cleaning modes

A floor care appliance is provided for cleaning bare surfaces such as tile, marble, linoleum and wood. The floor care appliance includes a port for the connection of an accessory hose and wand for off the floor cleaning. A variety of cleaning implements can be attached to the wand for cleaning hard to reach bare surfaces such as tile and grout. The port includes a suction inlet, cleaning solution outlet, and an air turbine inlet for an air turbine pump which pressurizes the cleaning solution. A pivoting door seals the suction inlet, cleaning solution outlet, and air turbine inlet when the accessory hose and wand are not in use.

Owner:HEALTHY GAIN INVESTMENTS

Latch arrangement for a floor care appliance

A floor care appliance is provided for cleaning bare surfaces such as tile, marble, linoleum and wood. The floor care appliance includes an accessory hose, telescoping wand and accessory tools for cleaning bare surfaces. A latch having a latch cover is provided for connecting the telescoping wand to the handgrip portion of the accessory hose. The latch and latch cover arrangement could also be utilized for connecting the accessory tools such as a accessory suction nozzle and grout tool to the telescoping wand.

Owner:TECHTRONIC FLOOR CARE TECH LTD

Humic acid incrusting dust suppressant for barren greening and preparation method thereof

InactiveCN106634845ANo operational hazardReduce pollutionOther chemical processesCarboxymethyl celluloseBryophyte

The invention relates to a humic acid incrusting dust suppressant for barren greening and a preparation method thereof. The humic acid incrusting dust suppressant for barren greening comprises the following components in parts by weight: 4-8 parts of humic acid, 2-6 parts of galactomannan gum or sodium carboxymethyl cellulose (CMC) and 1000 parts of water. The humic acid incrusting dust suppressant also comprises a preservative which accounts for 0.4-0.8% of the total weight except water, and moss seeds which account for 0.5-2% of the total weight of the humic acid incrusting dust suppressant. The humic acid incrusting dust suppressant can be used in various barrens in need of greening and dust suppression, can obviously reduce the flying dust pollution on various bare surfaces after being sprayed, and utilizes bryophytes to green the barren. The bryophytes and humic acid supplement each other; the humic acid provides necessary organic nutrients for the bryophytes; and the bryophytes can effectively increase the water retention property of soil on the premise of greening the bare surface, thereby performing the function of reducing the flying dust pollution on the ground surface.

Owner:北京首创北科环境科技研究院有限公司

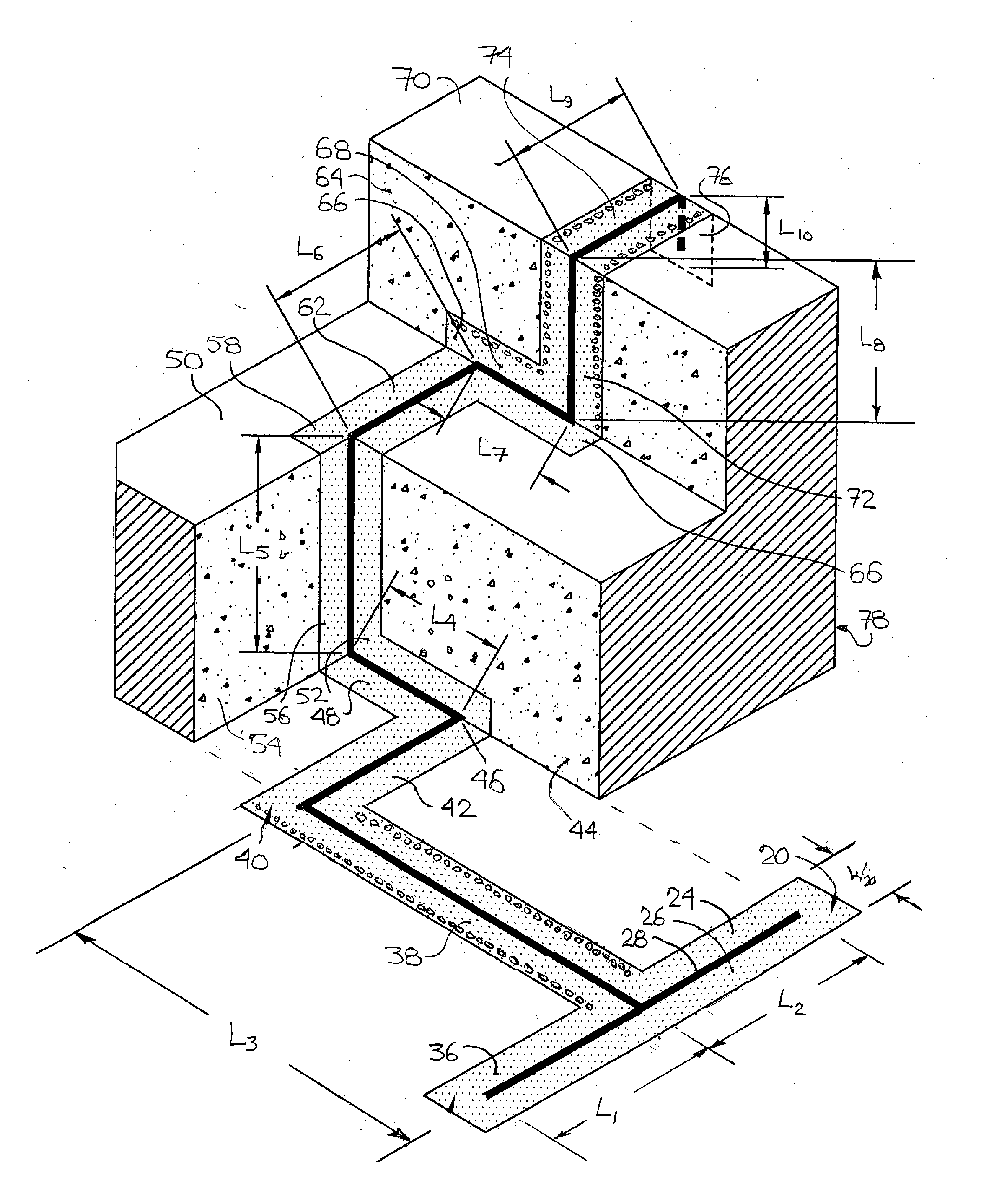

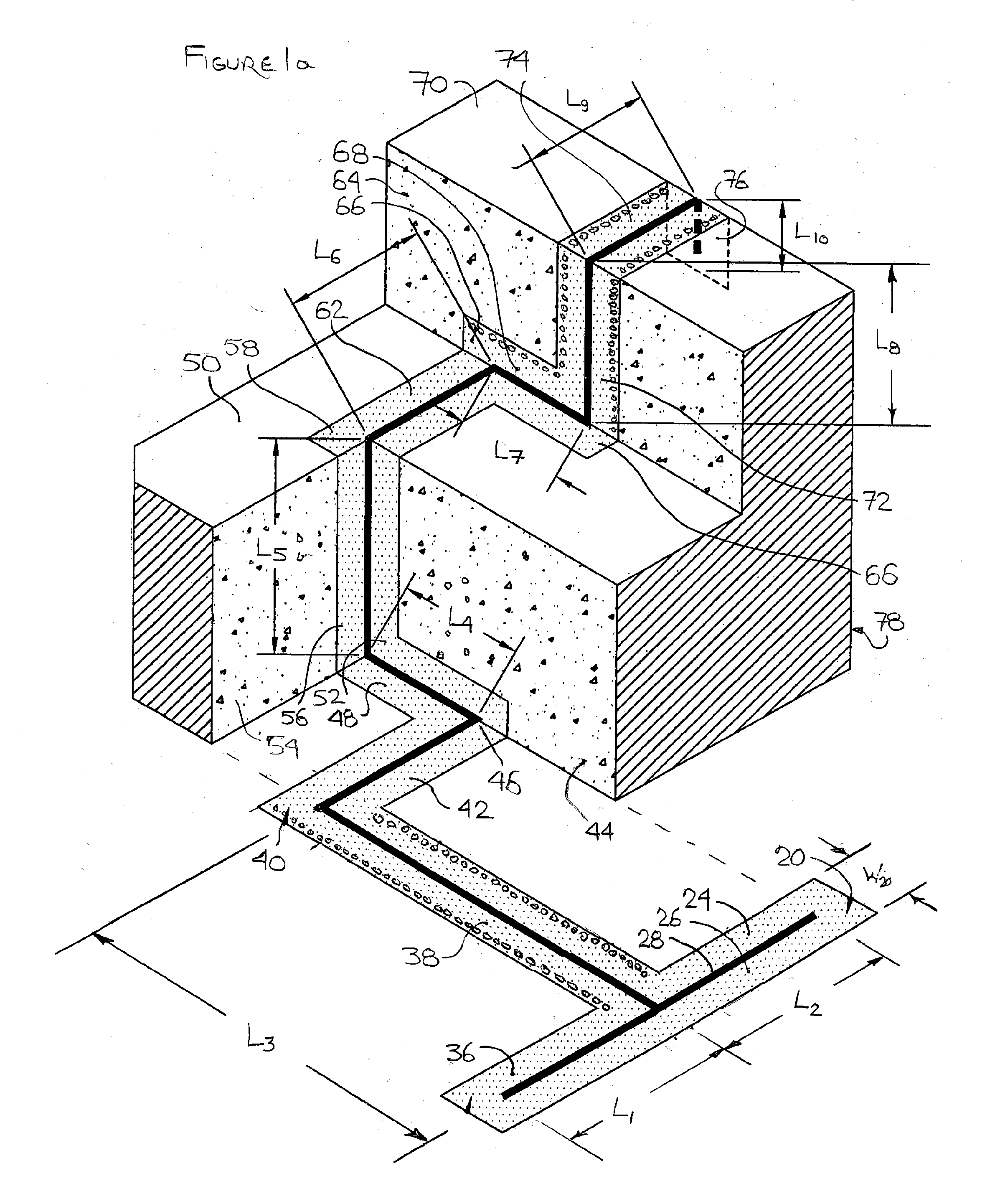

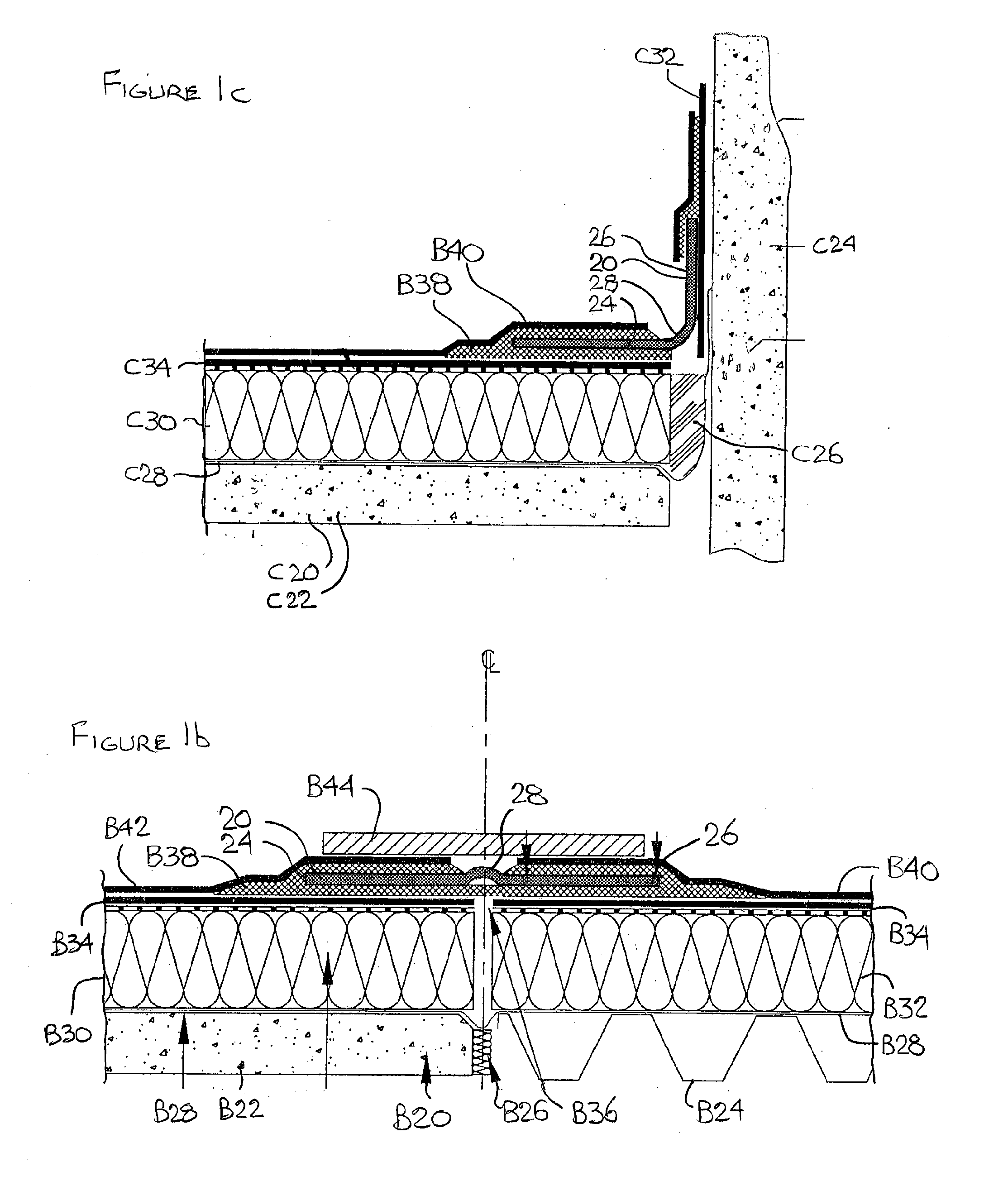

Expansion joint and method

An expansion joint has an elongated flat sheet of flexible and resilient polymeric material. The flat sheet has having a width and a length; upper and lower surfaces; and first and second edges. The sheet has selvage edges and a central gland. The selvage edges have a pair of parallel elongate first and second scrims. The scrims may be formed or embedded on each of the opposite surfaces along the length of the sheet. The rough strips on each surface bracket the elongated strip of bare surface of the gland. The sheet has an array of apertures located in one of the selvage edges. An additional array of apertures may be formed in the opposite selvage edge. The apertures pass through, but are not limited to passing through, the sheet and the strips.

Owner:ZIELONKA KRZYSZTOF

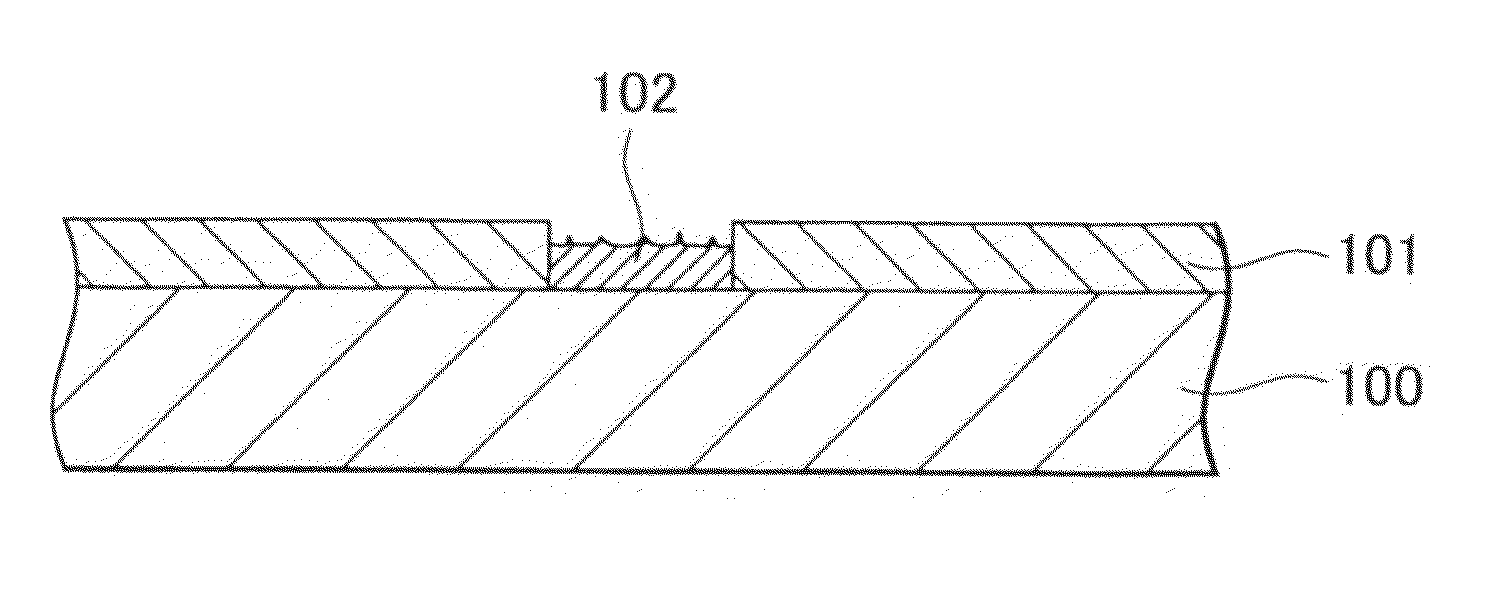

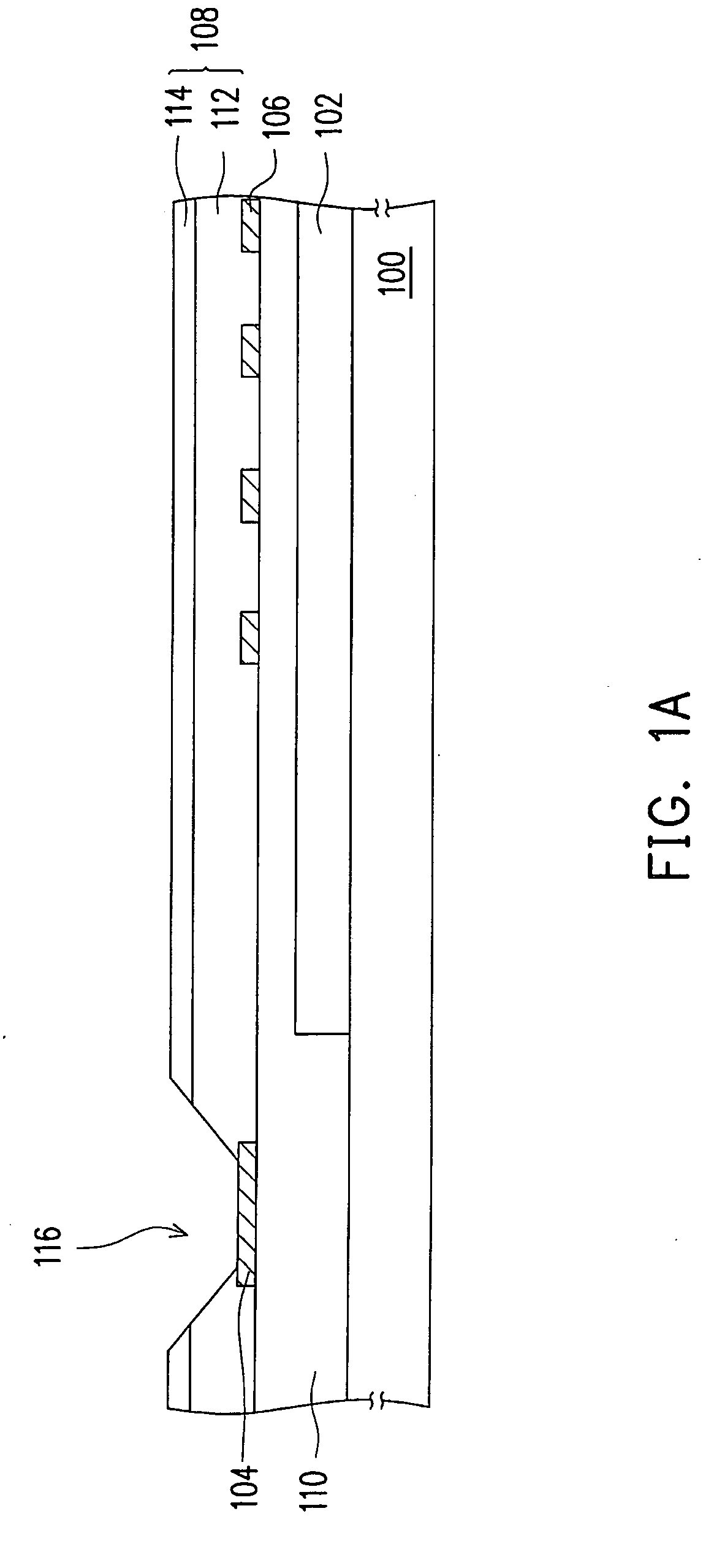

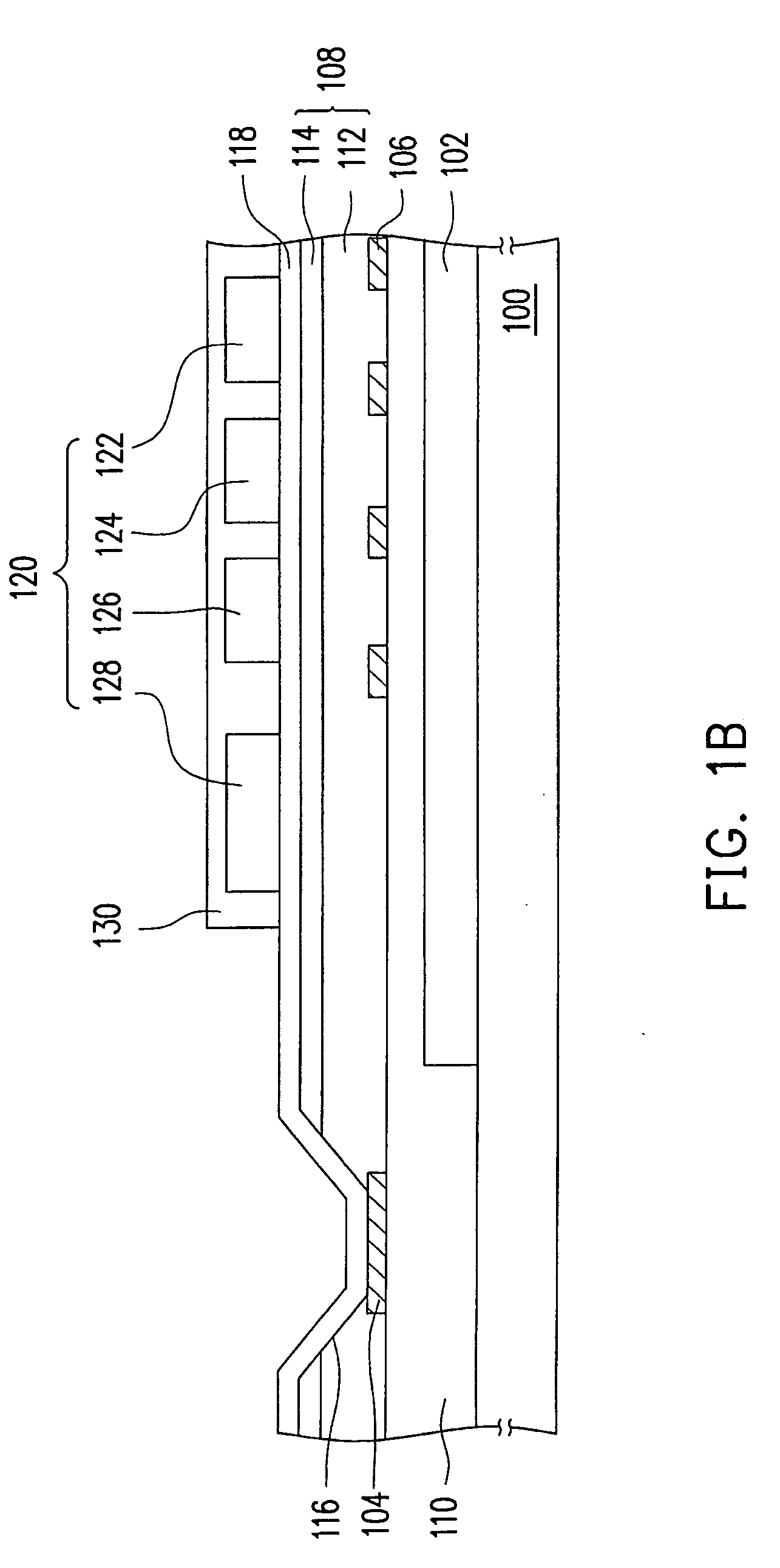

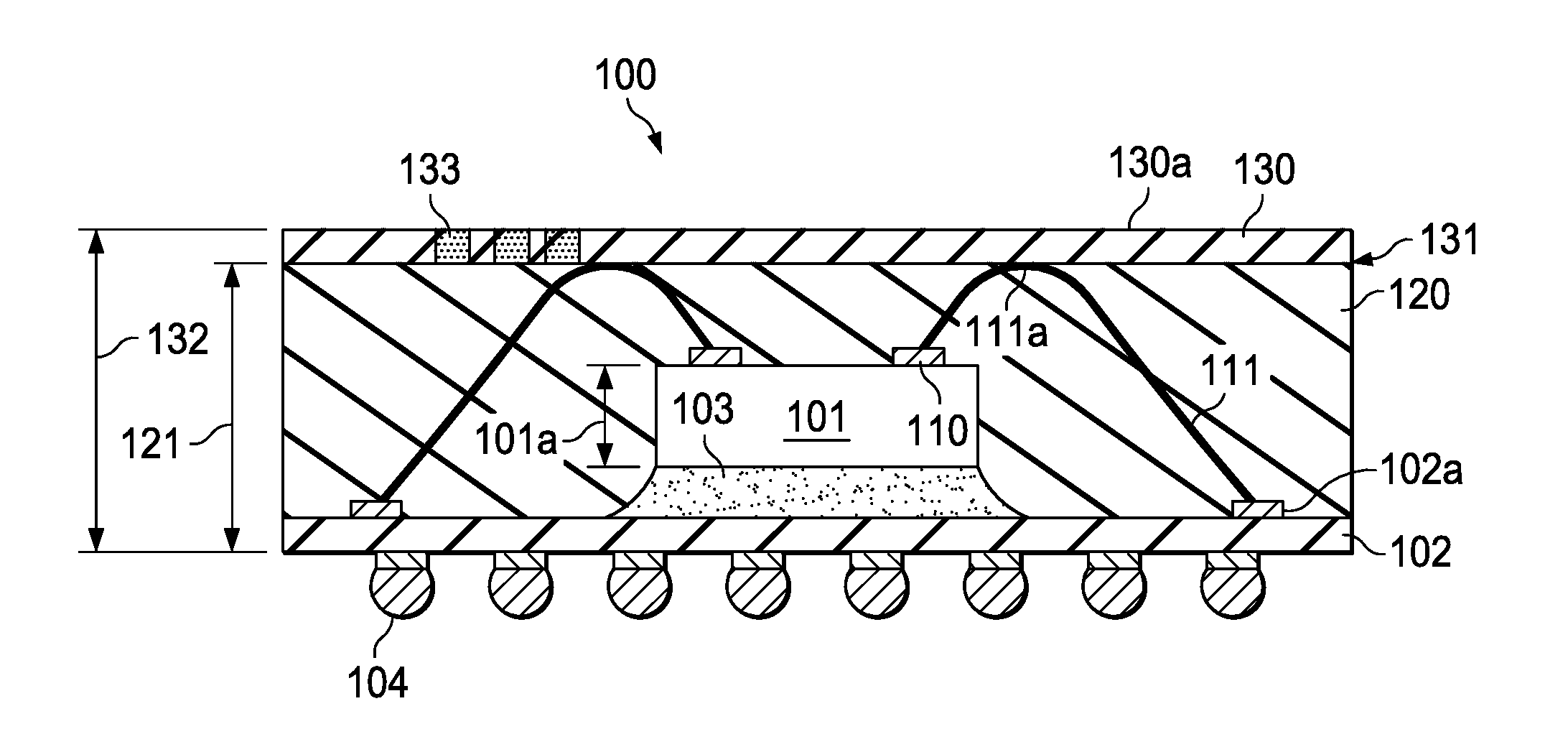

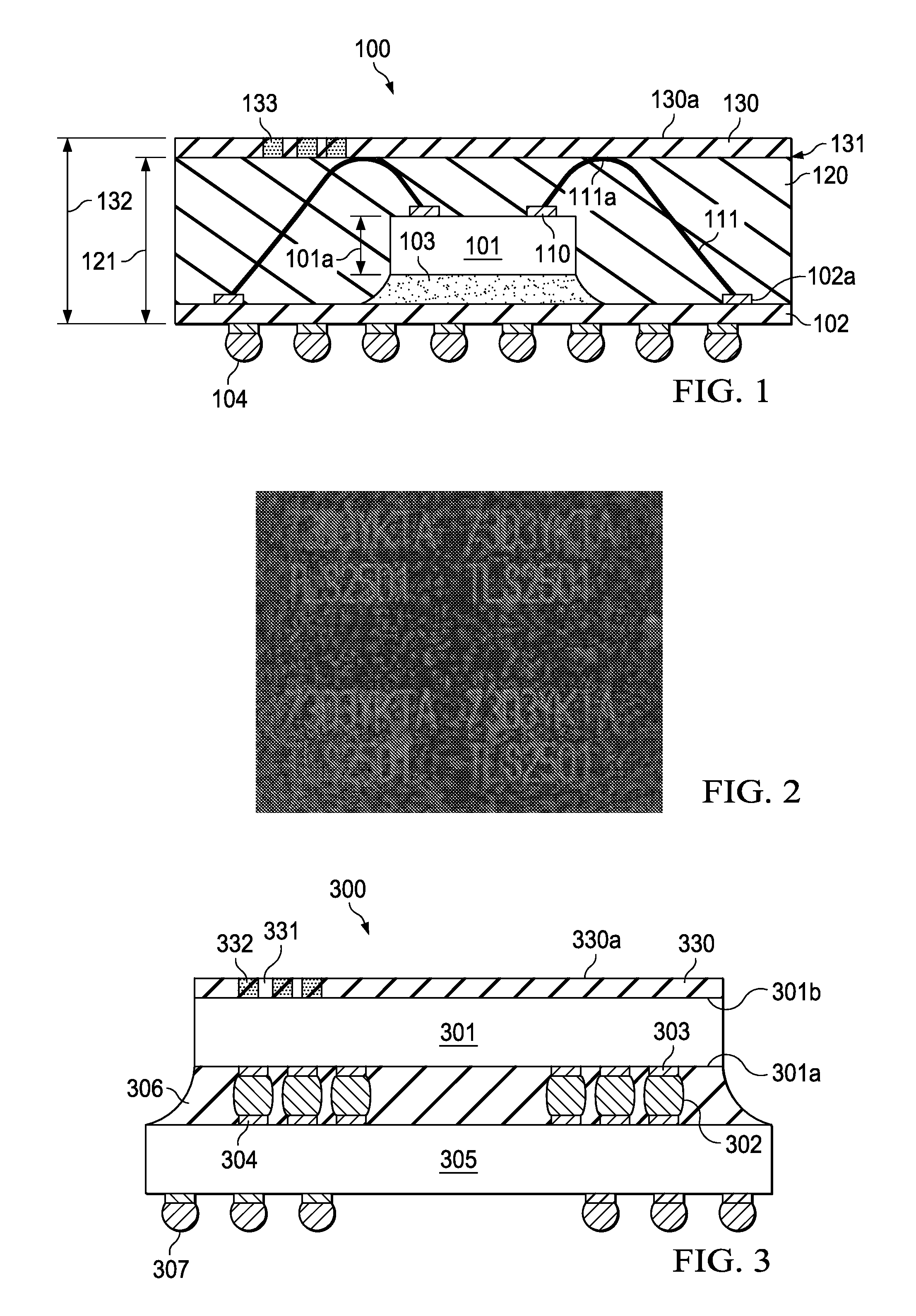

Semiconductor package having marking layer

ActiveUS20090091029A1Improve flatnessMaintaining thinnessSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

The symbolization of a semiconductor device (100) is incorporated in a thin sheet (130) attached to the top of the device, facing outwardly with its bare surface. The material of the sheet (about 1 to 10 μm thick) includes regions of a first optical reflectivity and a first color, and regions (133) of a second optical reflectivity and a second color, which differ from, and contrast with, the first reflectivity and color. Preferred choices for the sheet material include the compound o-cresol novolac epoxy and the compound bisphenol-A, more preferably with the chemical imidazole added to the film material. A preferred embodiment of the invention is a packaged device with a semiconductor chip a (101) connected to a substrate (102); the connection is achieved by bonding wires (111) forming an arch with a top 111a. The chip, the wire arches, and the substrate are embedded in an encapsulation material (120), which borders on the attached top sheet so that the arch tops touch the border (131).

Owner:TEXAS INSTR INC

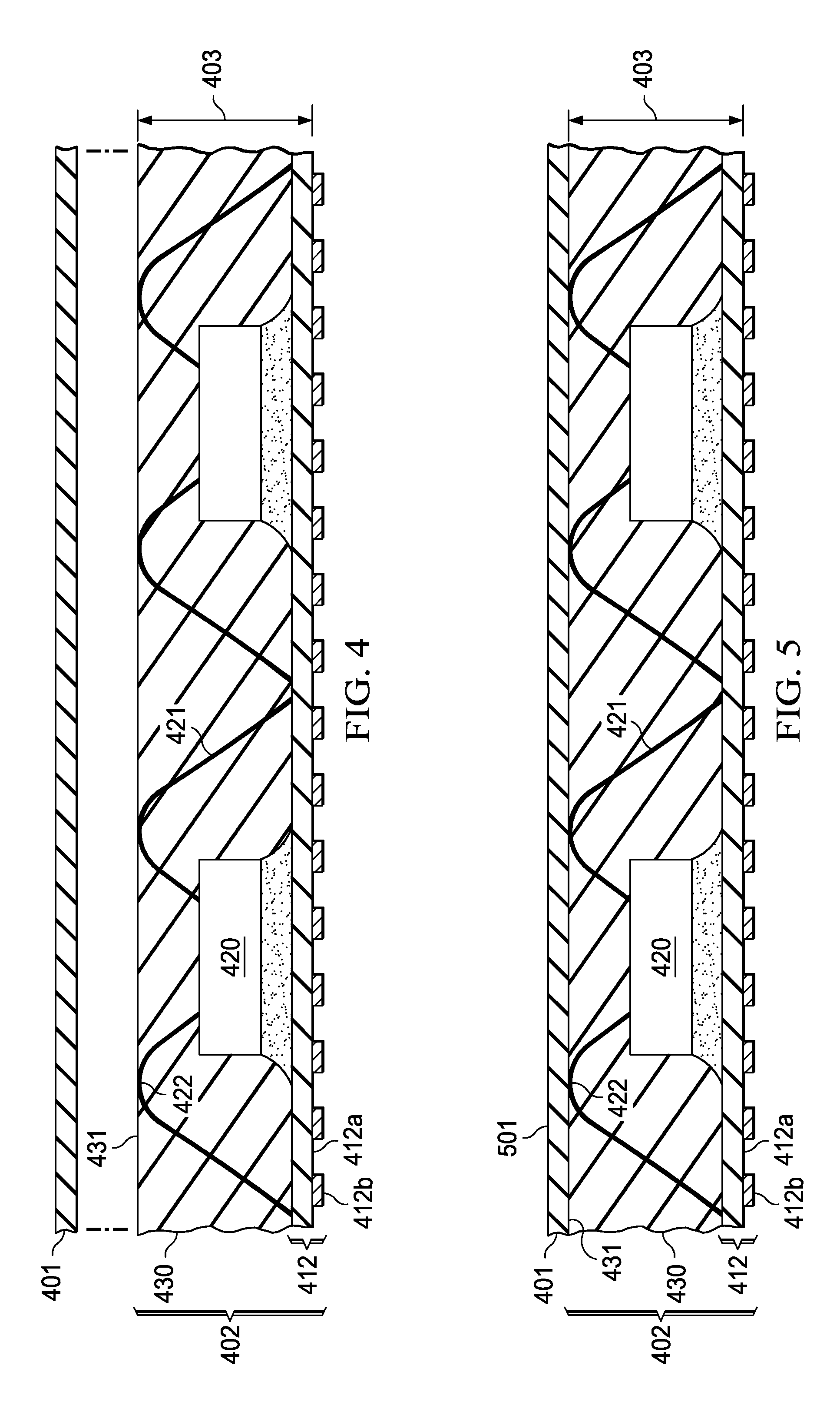

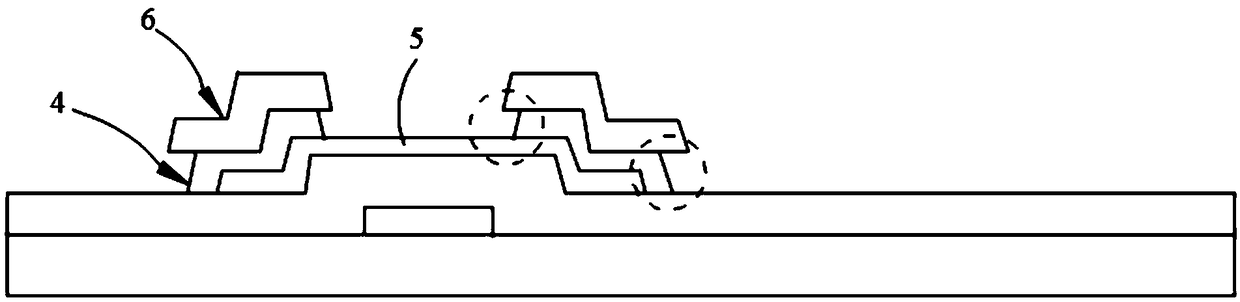

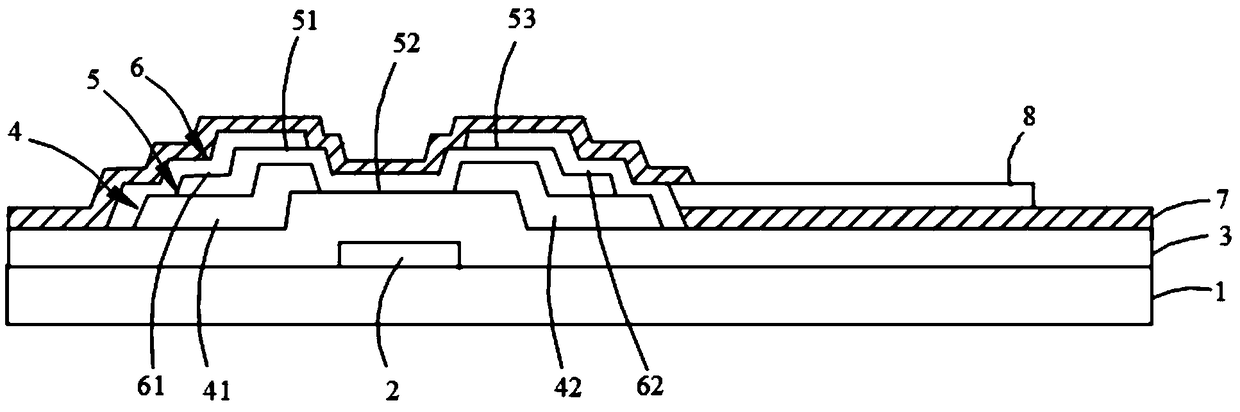

Thin film transistor and preparation method thereof, and array substrate

InactiveCN109037350AImprove electrical performanceImprove contact effectSolid-state devicesSemiconductor/solid-state device manufacturingComposition processEngineering

A thin film transistor and a preparation method thereof and an array substrate are provided, the thin film transistor includes a substrate, a gate, a gate insulating layer, a first metal layer, an active layer, a second metal layer, and a passivation layer, the gate is disposed on the substrate, the gate insulating layer covers the gate, the first metal layer includes a first electrode and a second electrode spaced apart on the gate insulating layer, the second metal layer includes a source and a drain spaced apart, one end of the active layer is sandwiched between the first electrode and thesource electrode, the other end of the active layer is sandwiched between the second electrode and the drain electrode, and the passivation layer covers the exposed surfaces of the source electrode, the drain electrode and the active layer. By sandwiching the active layer between the first metal layer and the second metal layer, the contact performance between the active layer and the second metallayer is improved. In the preparation method of the present invention, the first metal layer and the second metal layer are formed by two times ofa composition process, thereby avoiding the occurrence of a chamfer.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

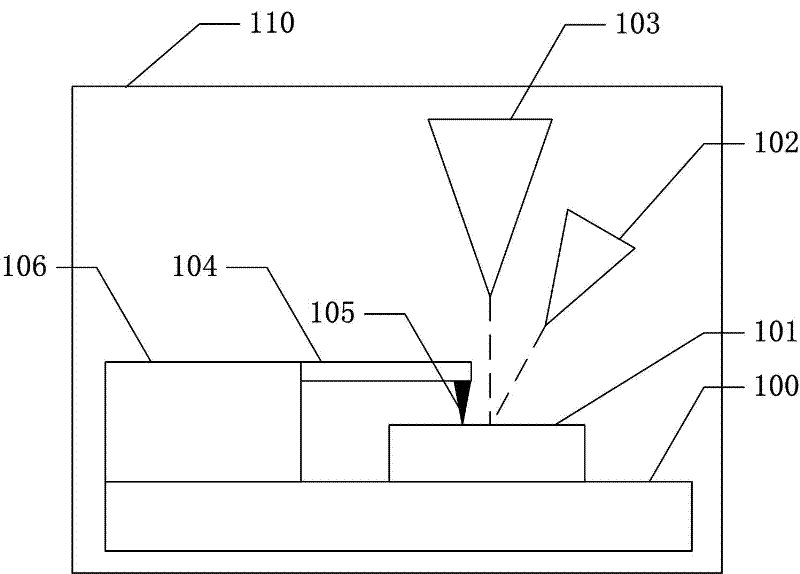

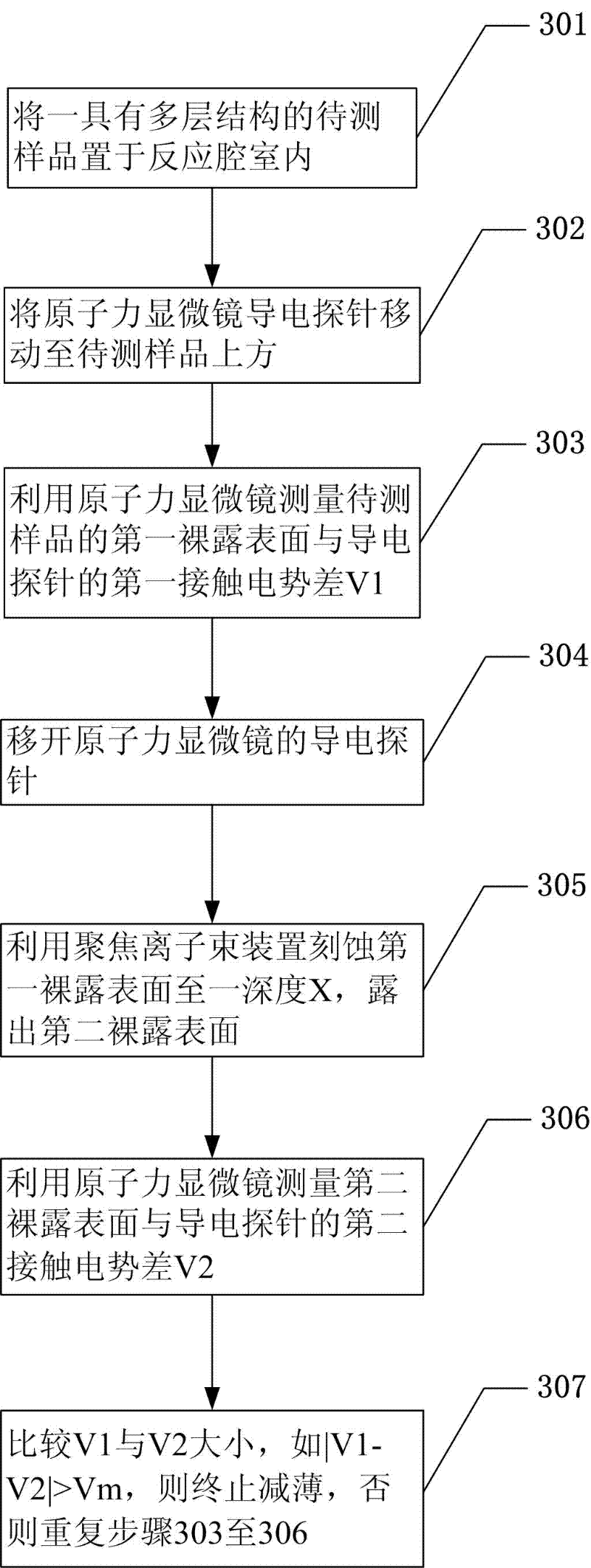

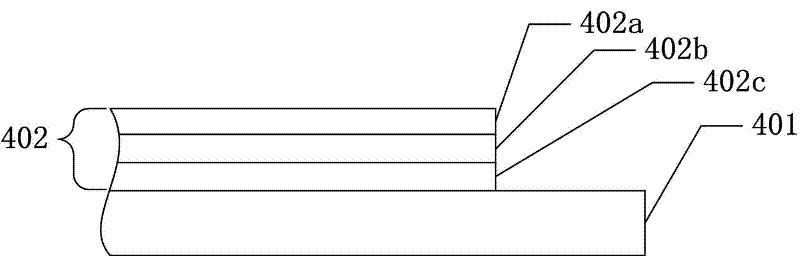

Device for thinning multi-layer material and method for thinning to-be-detected sample

InactiveCN102520212ASolving In-Situ Etch Control ProblemsScanning probe microscopyPotential differenceElectron microscope

The invention provides a device for thinning a multi-layer material and a method for thinning a to-be-detected sample, belonging to the field of testing of semiconductors. The device comprises a reaction chamber, an atomic force microscope, an electron microscope and a sample table. The sample table, the atomic force microscope and the electron microscope are positioned in the reaction chamber. The method for thinning the to-be-detected sample comprises the following steps of: putting a sample in the reaction chamber; measuring first contact potential difference V1 of a first bared surface of the to-be-detected sample; moving away a conducting probe of the atomic force microscope; etching the first bared surface at the depth X to expose a second surface; measuring first contact potential difference V2 of a second bared surface of the to-be-detected sample; and comparing the V1 with the V2 to judge whether to etch continuously. The device and the method disclosed by the invention are used for solving the problem of being incapable of precisely dissecting in the prior art. The device and the method are capable of precisely dissecting hetero-junction devices and have important meanings on preparation and property research of semiconductor devices.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI