Patents

Literature

2605 results about "On resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

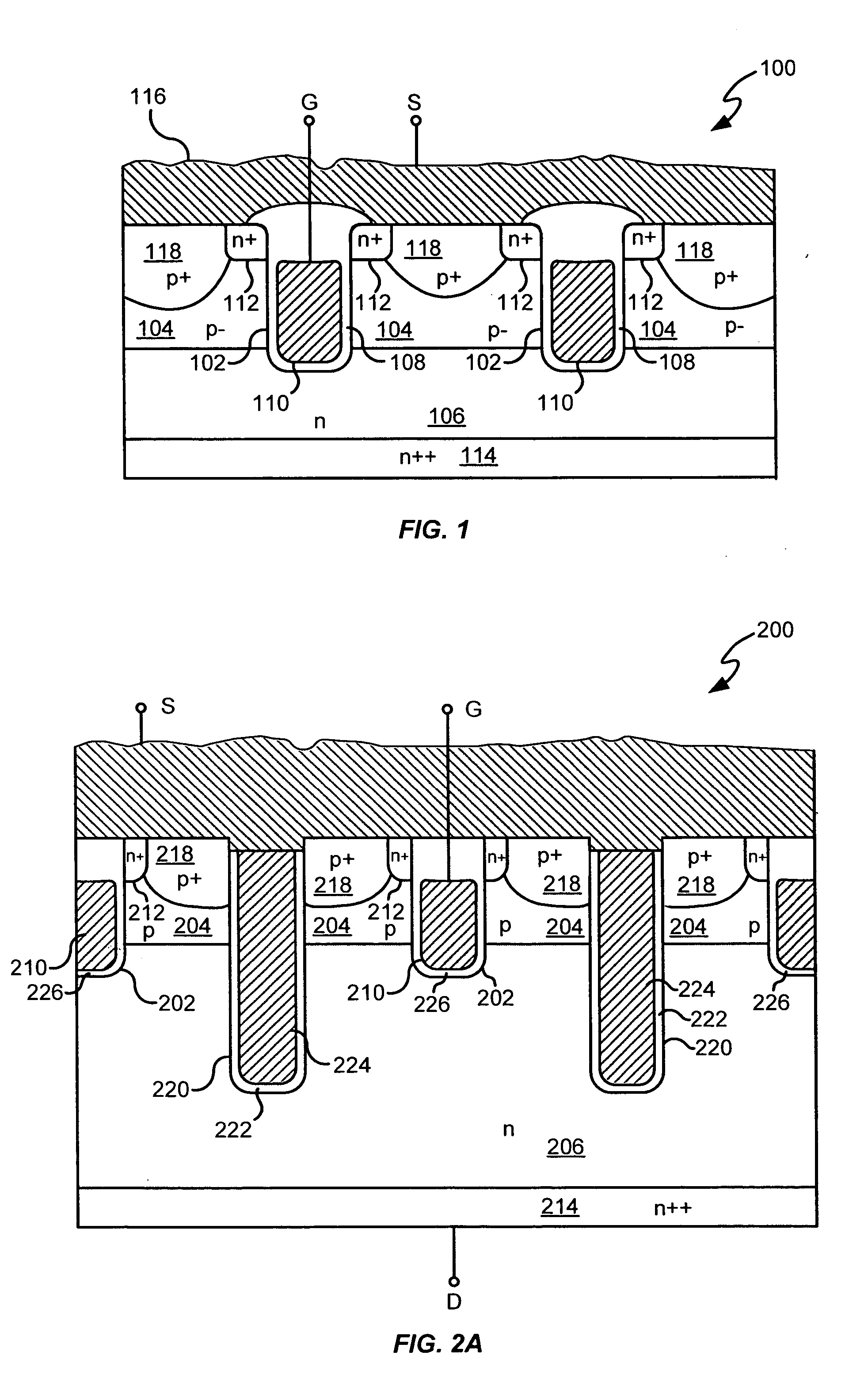

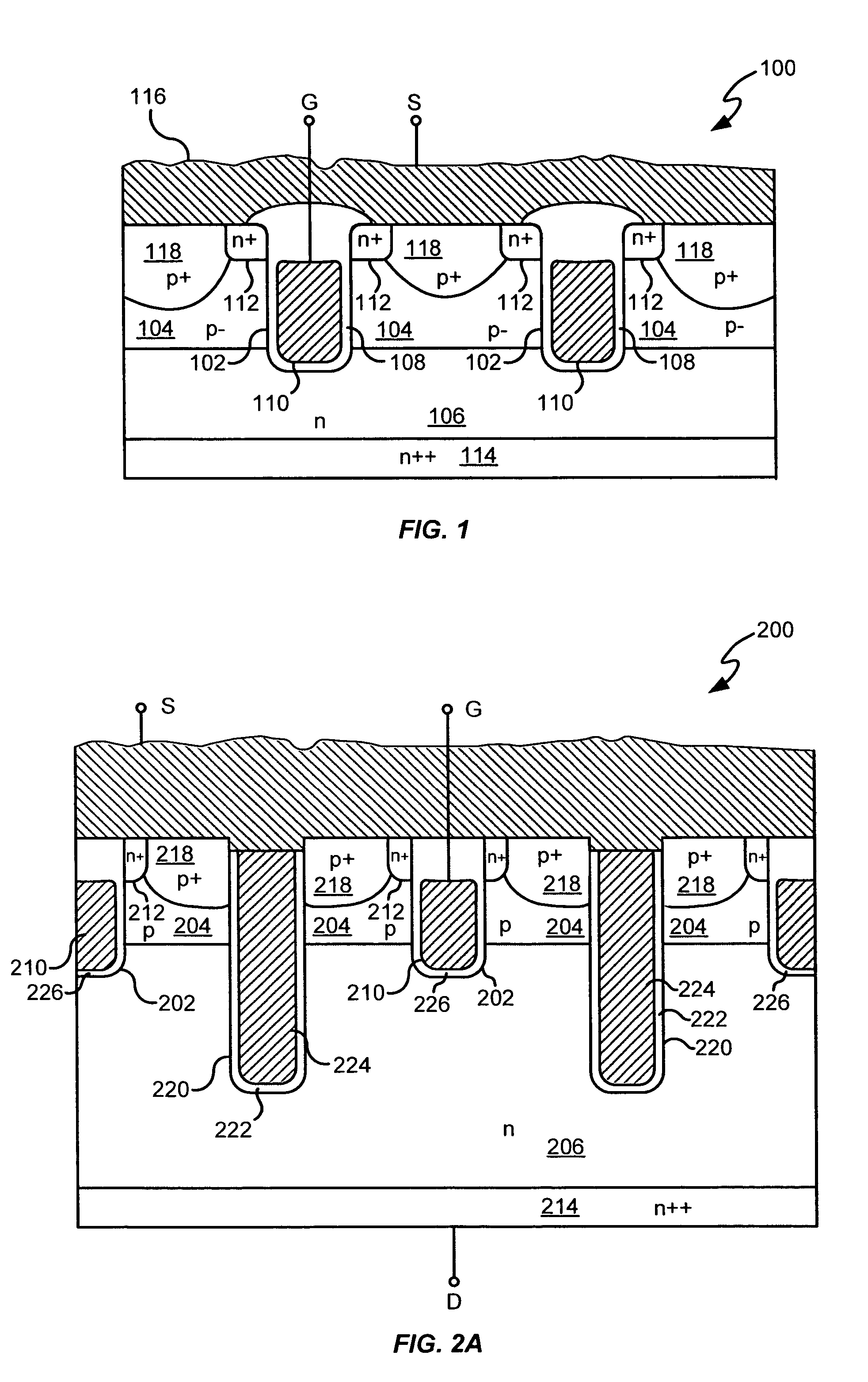

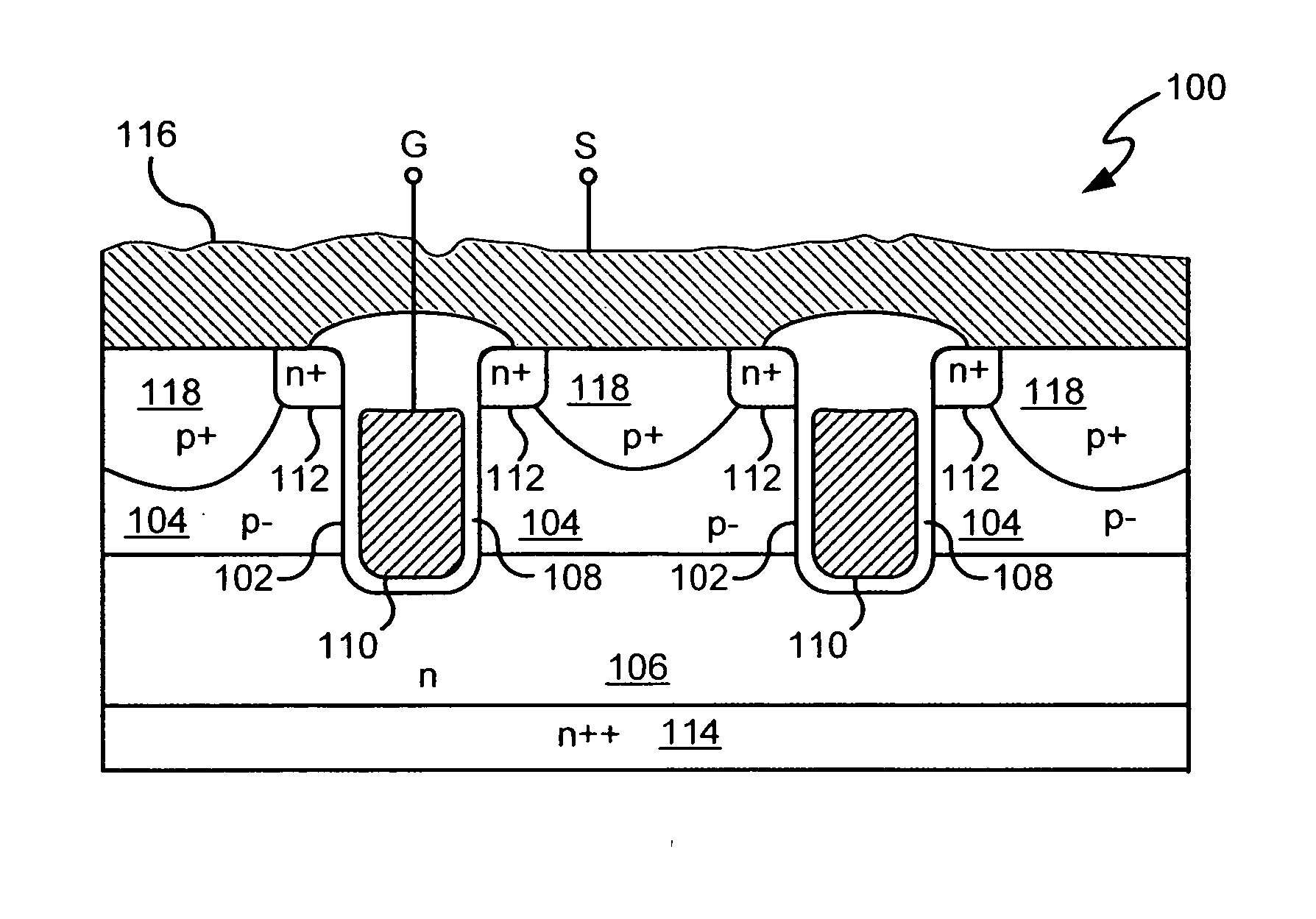

Power semiconductor devices and methods of manufacture

ActiveUS20050167742A1Improved voltage performanceFast switching speedEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh voltage

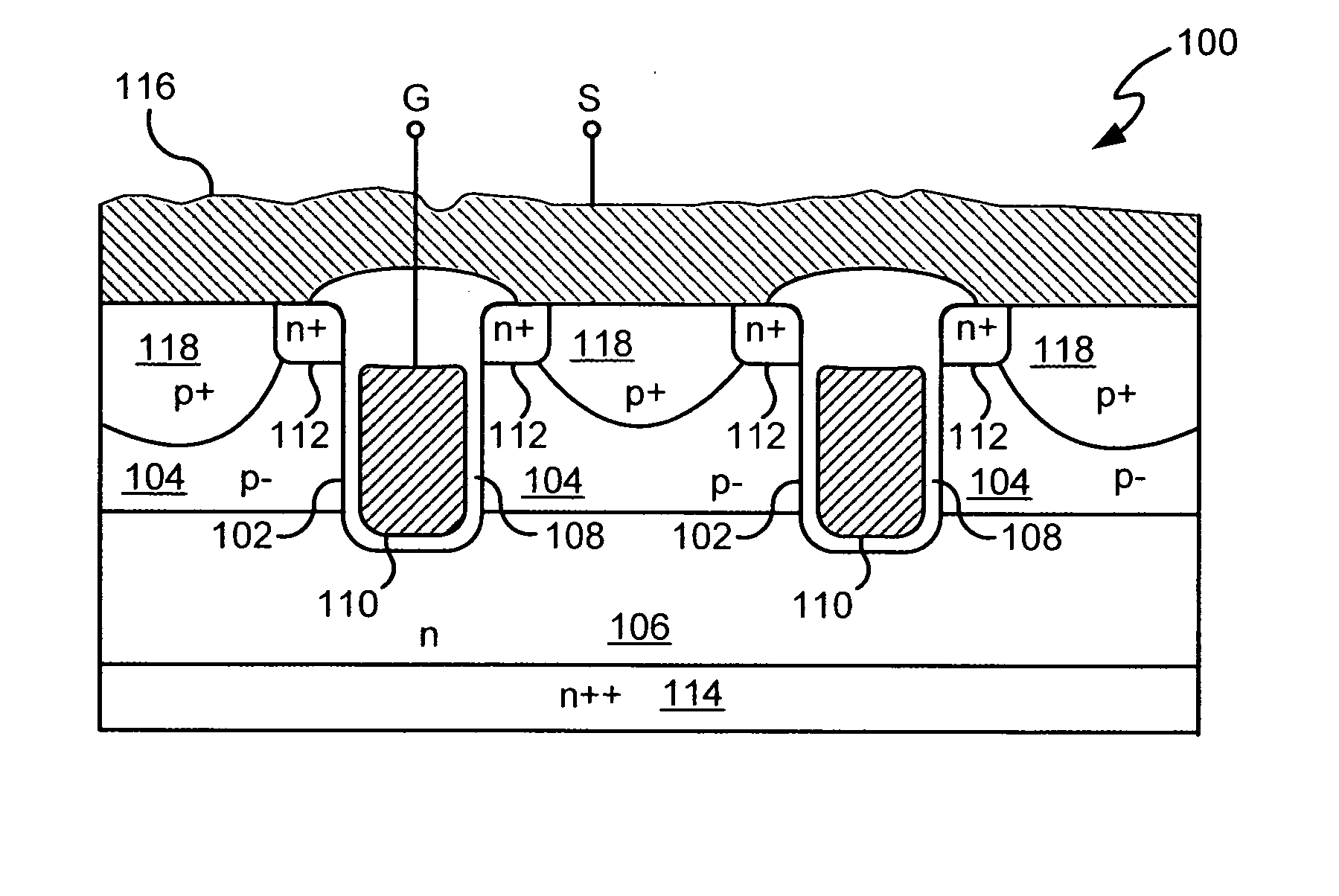

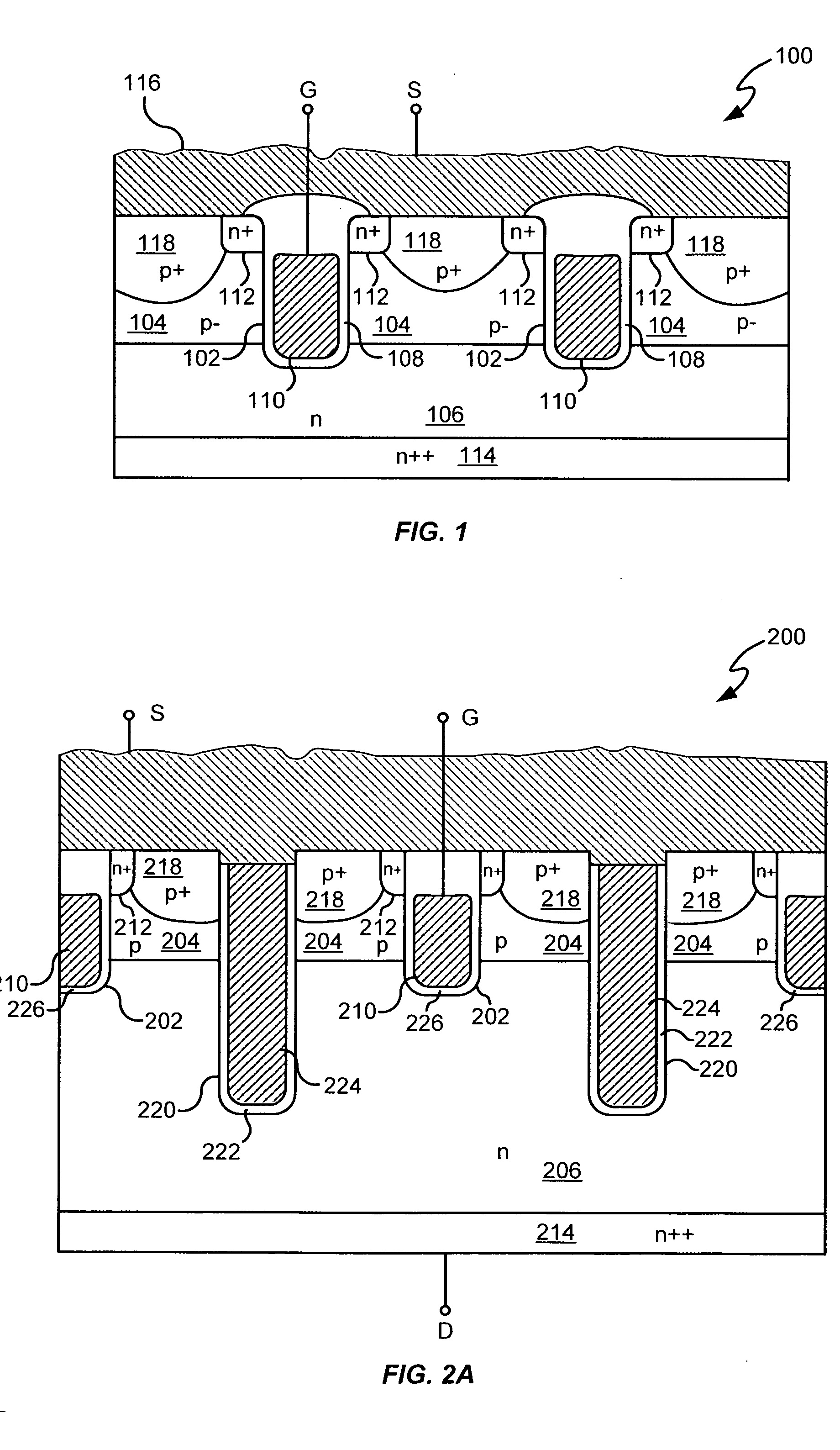

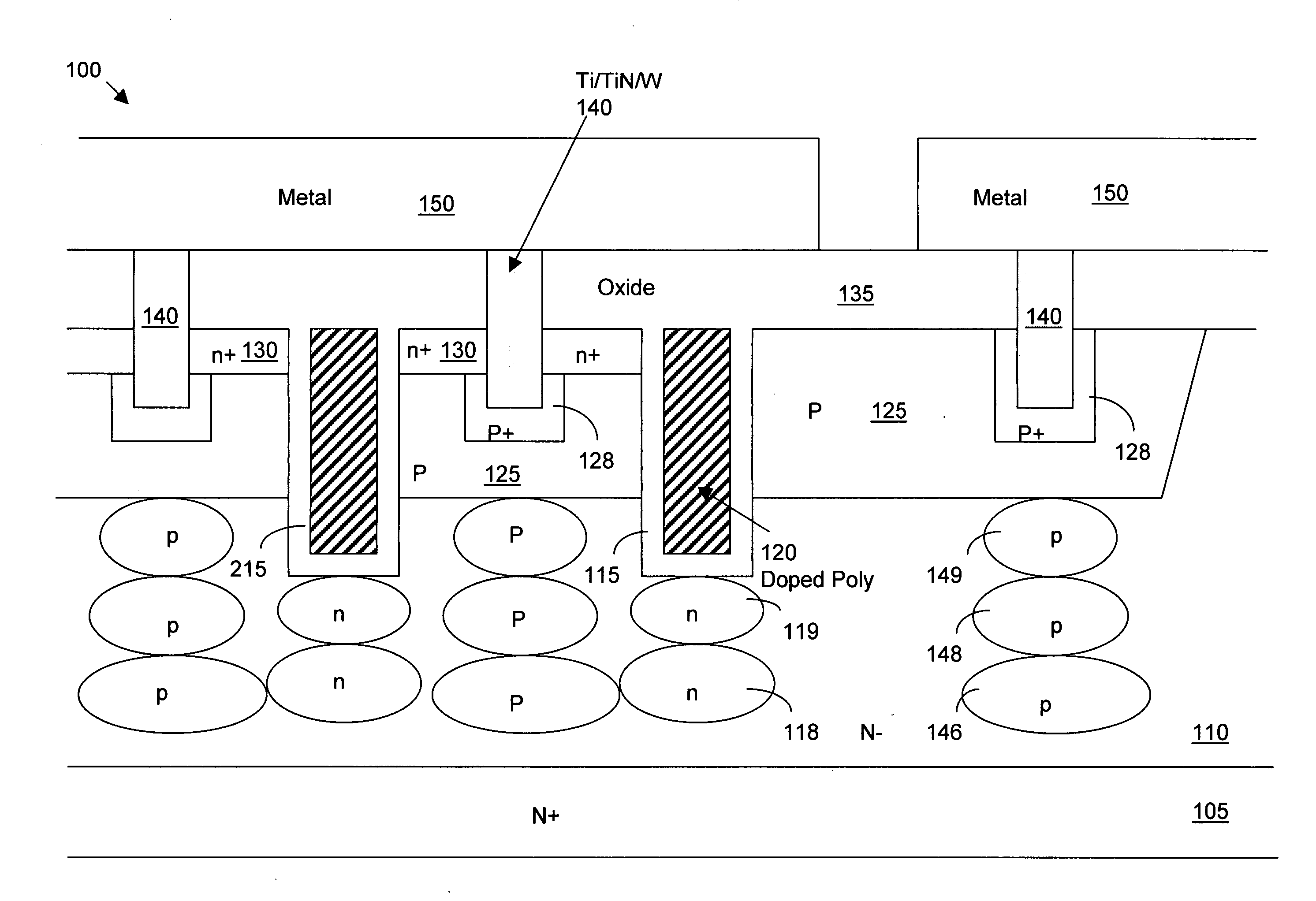

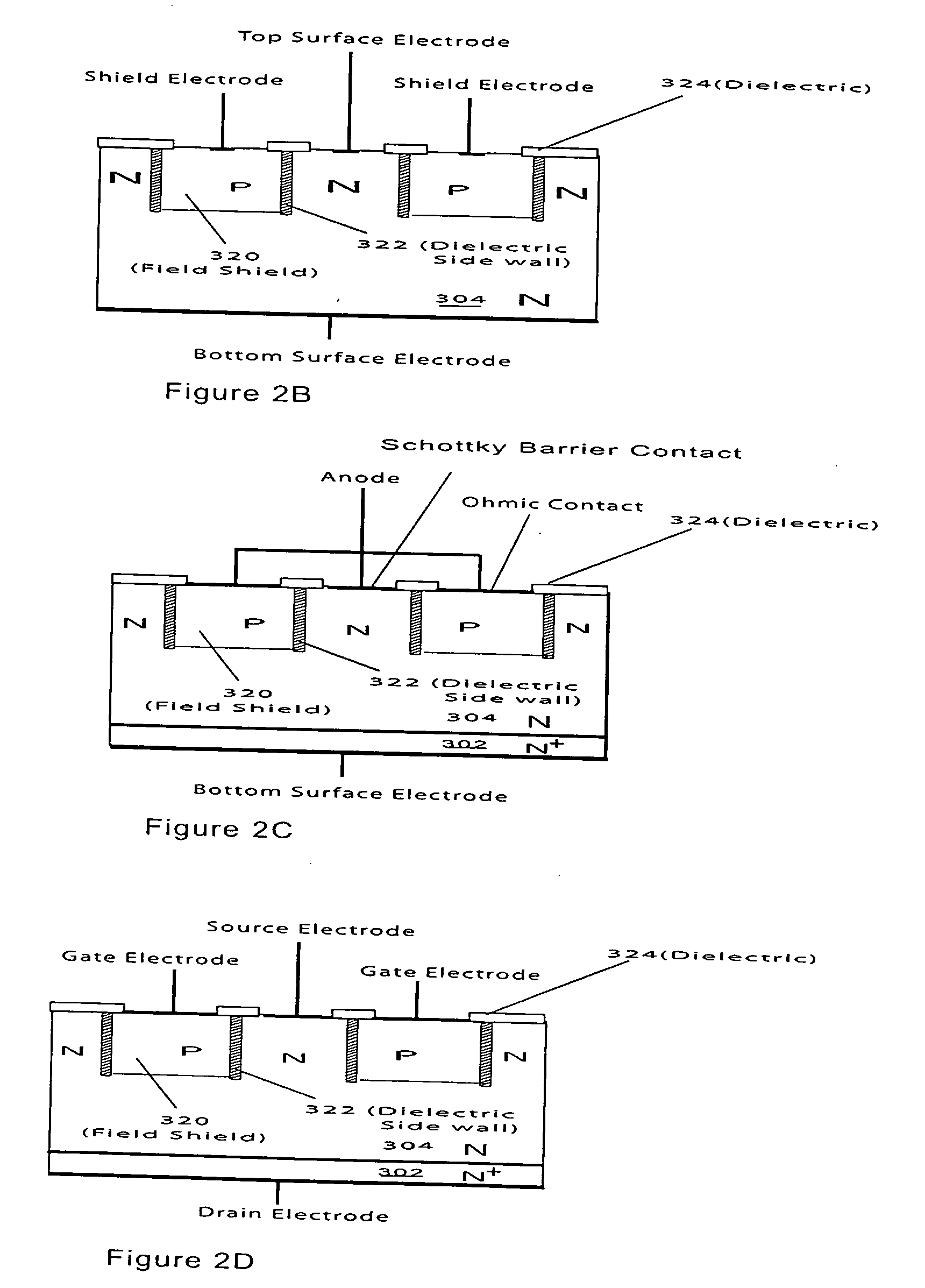

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

Power semiconductor devices and methods of manufacture

ActiveUS7345342B2Simple structureEasy to packEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

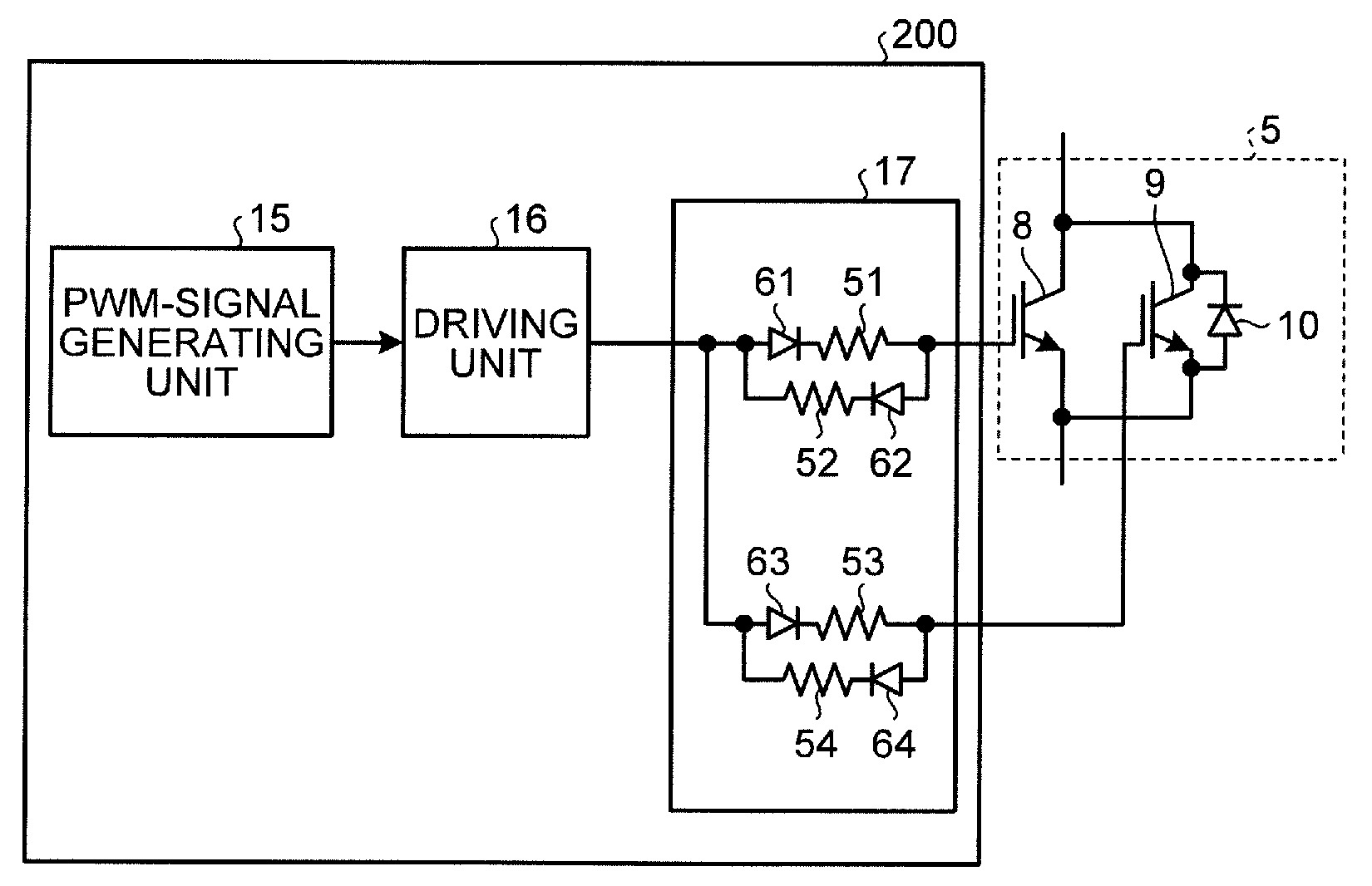

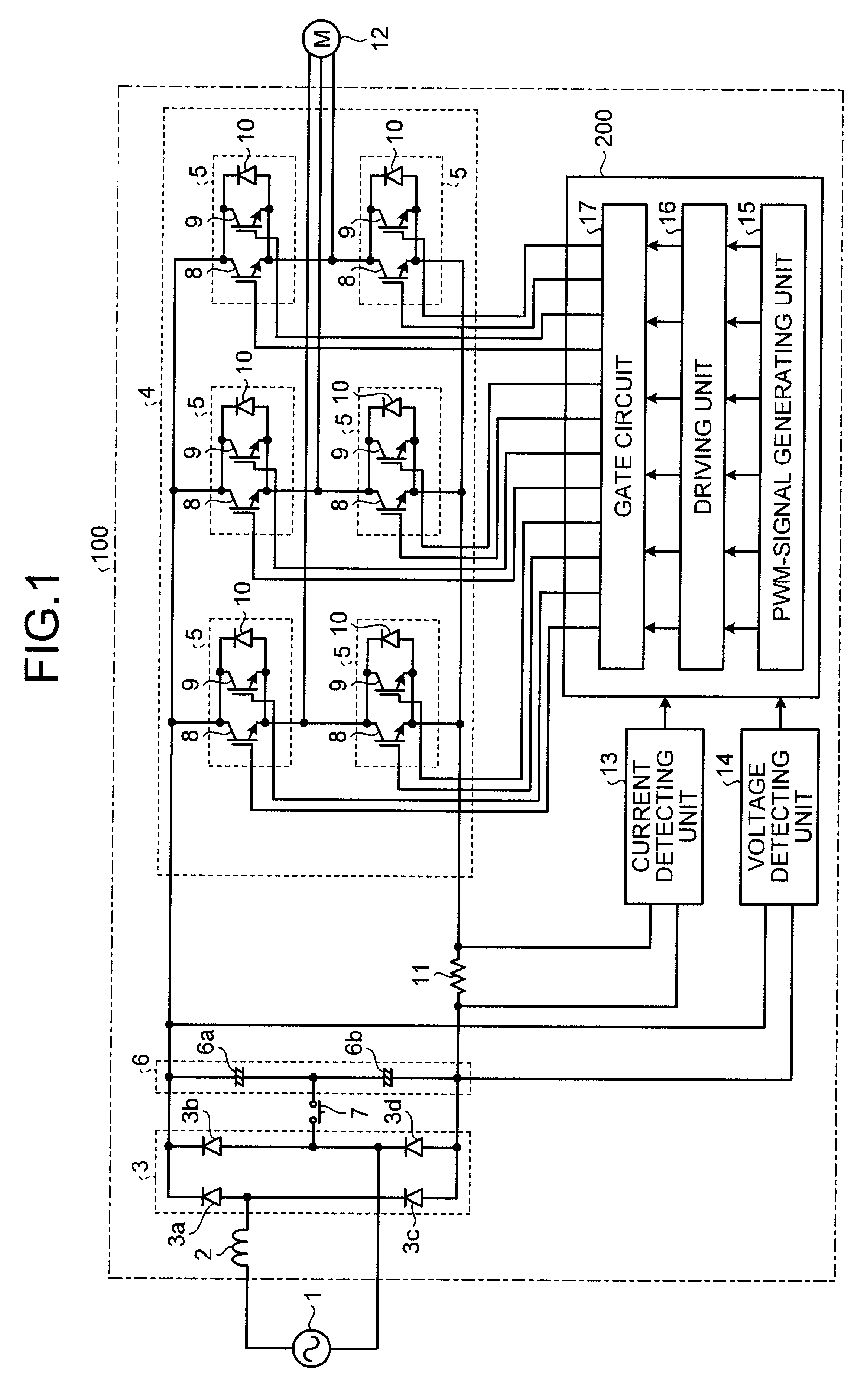

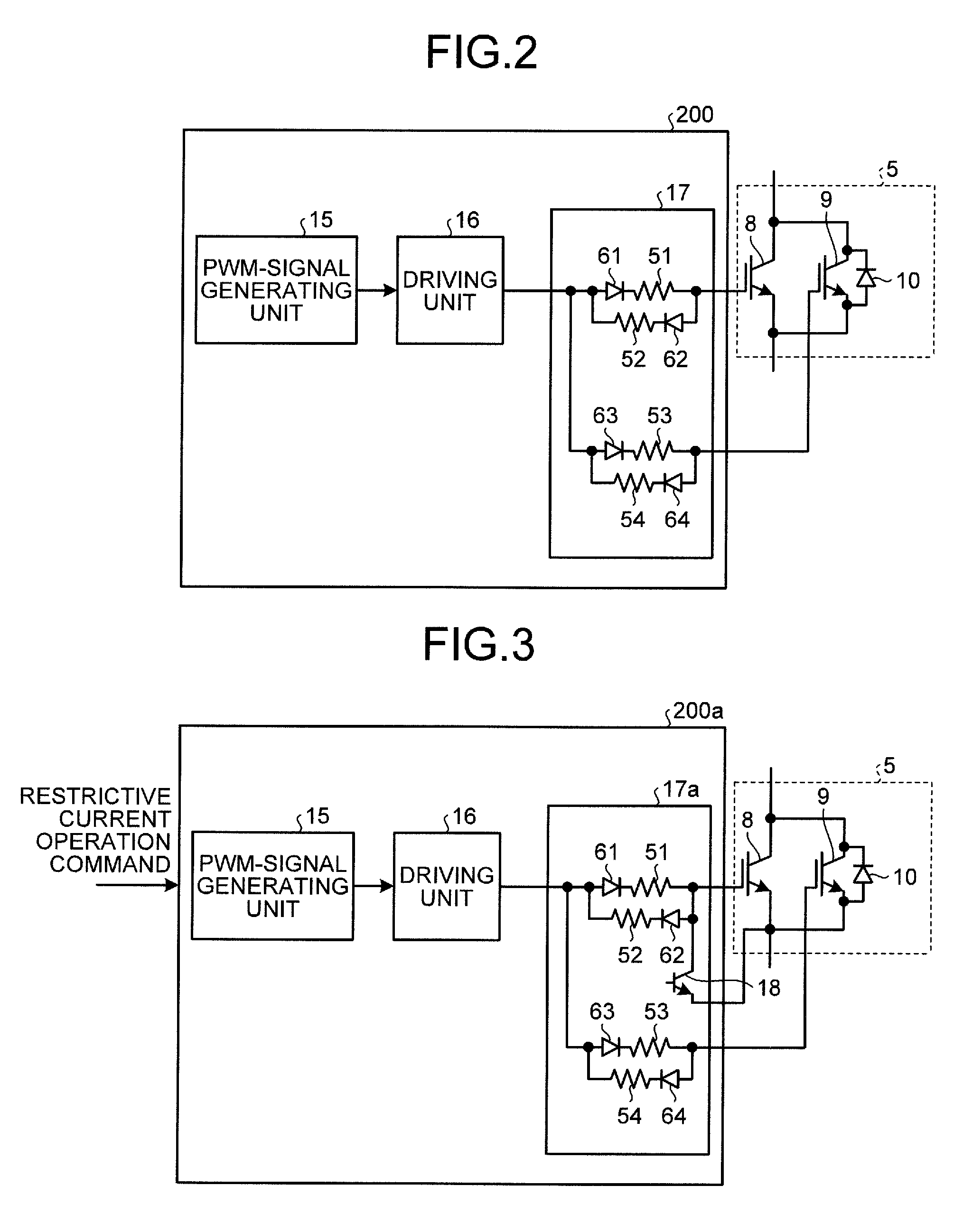

Inverter device and air conditioner including the same

Owner:MITSUBISHI ELECTRIC CORP

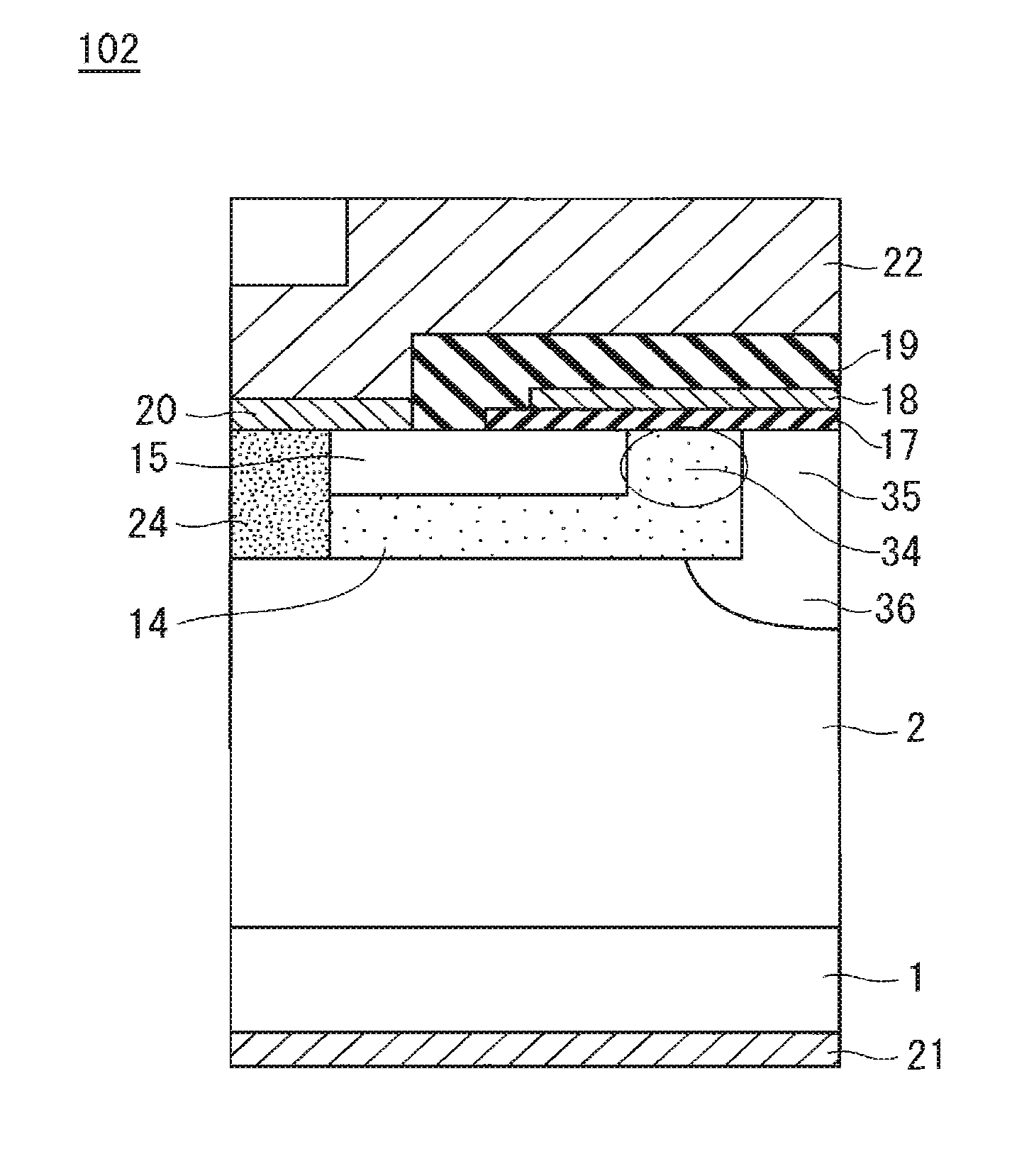

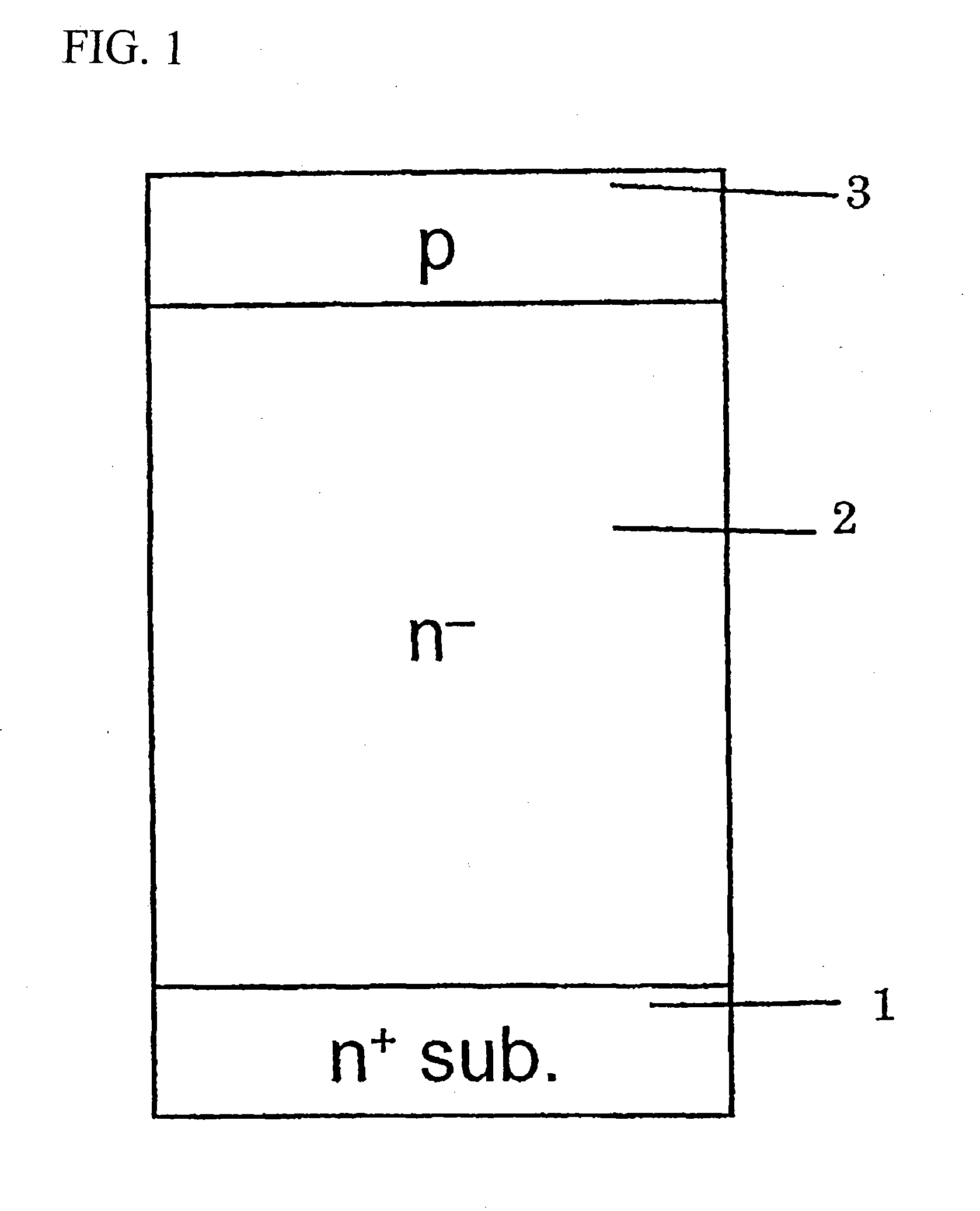

Silicon carbide semiconductor device and silicon carbide semiconductor device manufacturing method

ActiveUS20160336392A1Lower on-resistanceImprove breakdown voltageSemiconductor devicesDevice materialSemiconductor

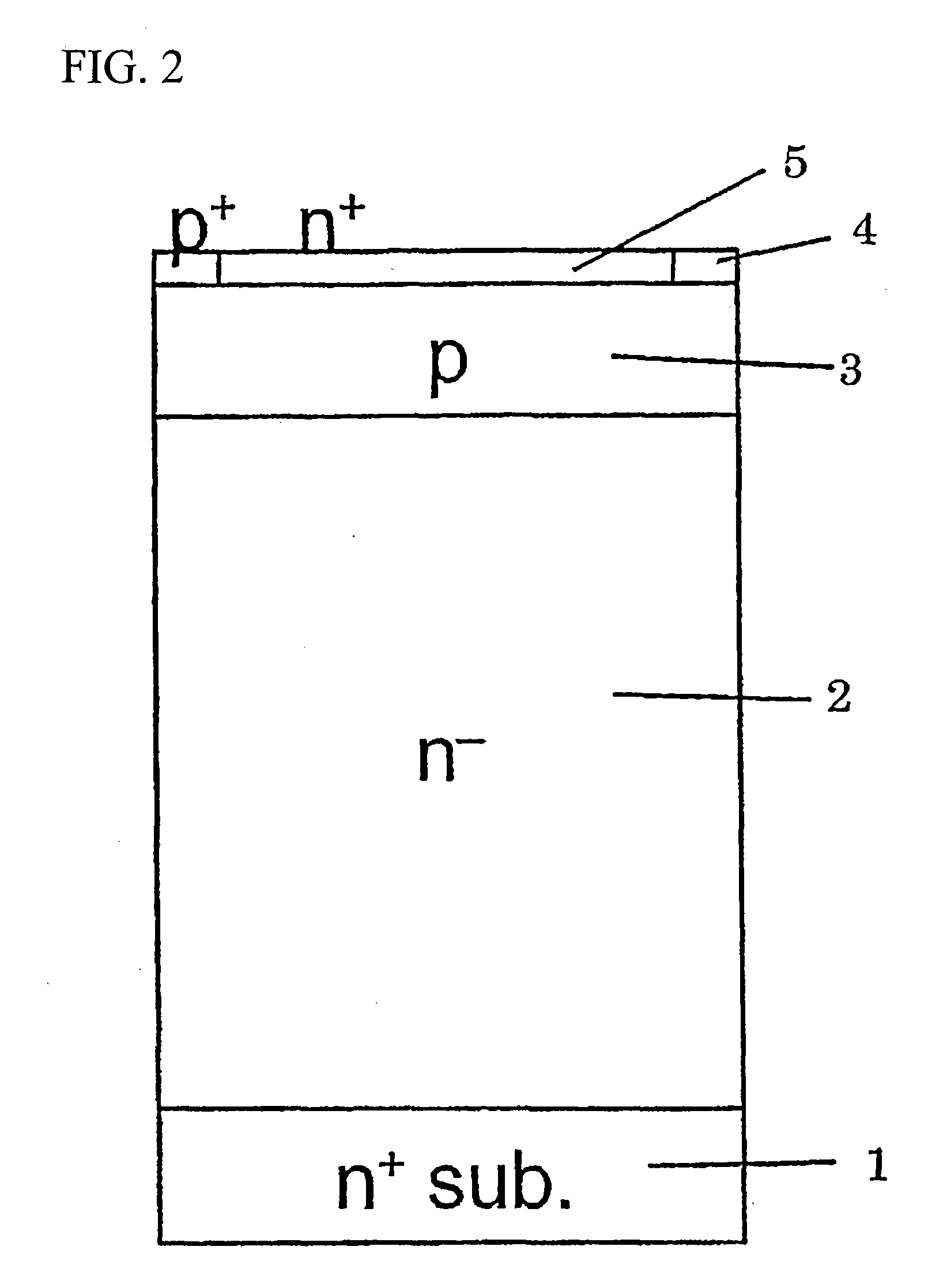

A silicon carbide semiconductor device capable of achieving a decrease in ON resistance and an increase in breakdown voltage and a method for manufacturing a silicon carbide semiconductor device. A silicon carbide semiconductor device includes a silicon carbide substrate and a drift layer. The drift layer includes a breakdown voltage holding layer extending from a point where a doping concentration has a predetermined value to a surface of the drift layer. The doping concentration in the breakdown voltage holding layer continuously decreases from the point where the doping concentration has the predetermined value to a modulation point located further toward the surface of the drift layer than a midpoint in a film thickness direction of the breakdown voltage holding layer. The doping concentration in the breakdown voltage holding layer continuously increases from the modulation point to the surface of the drift layer.

Owner:MITSUBISHI ELECTRIC CORP

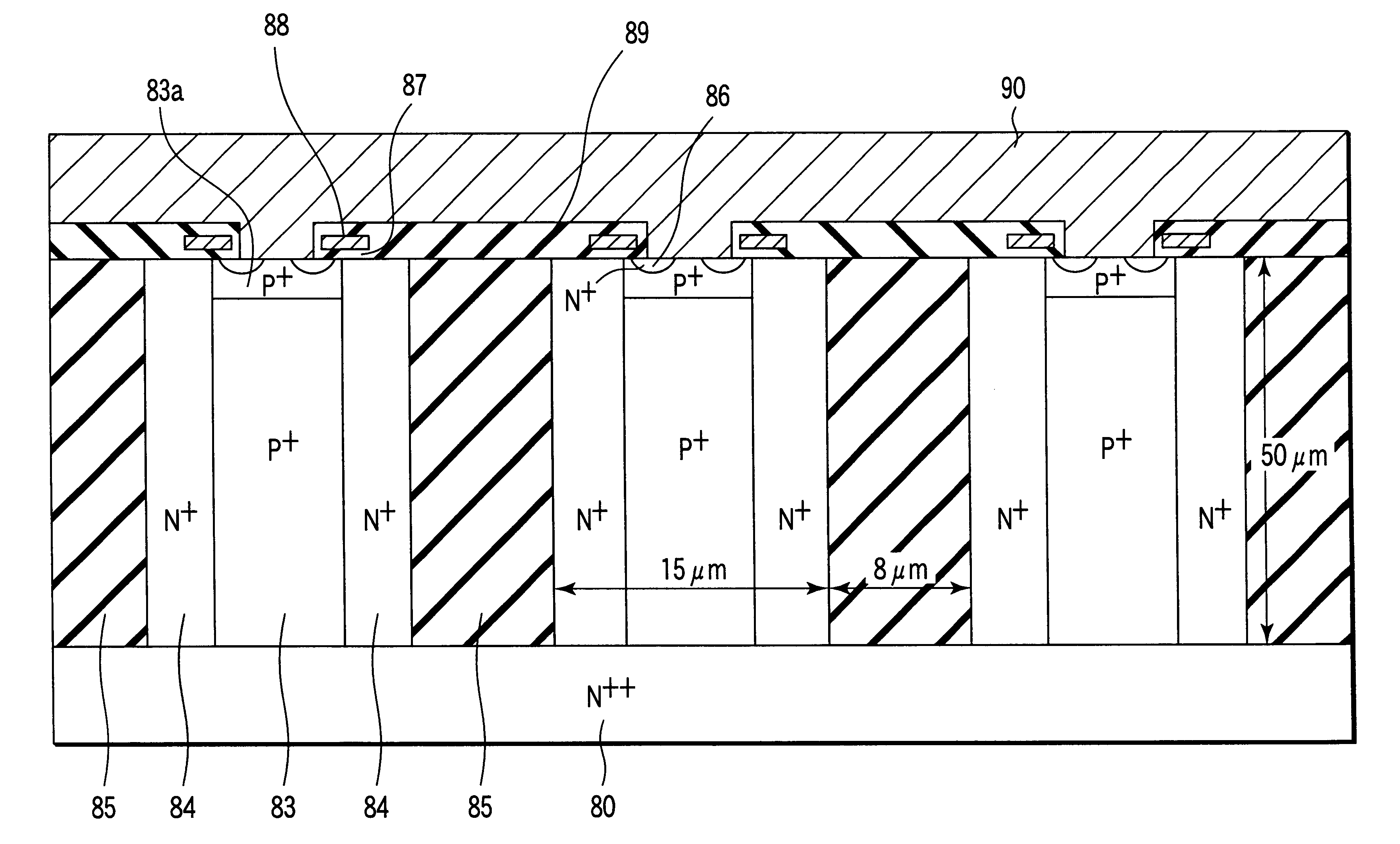

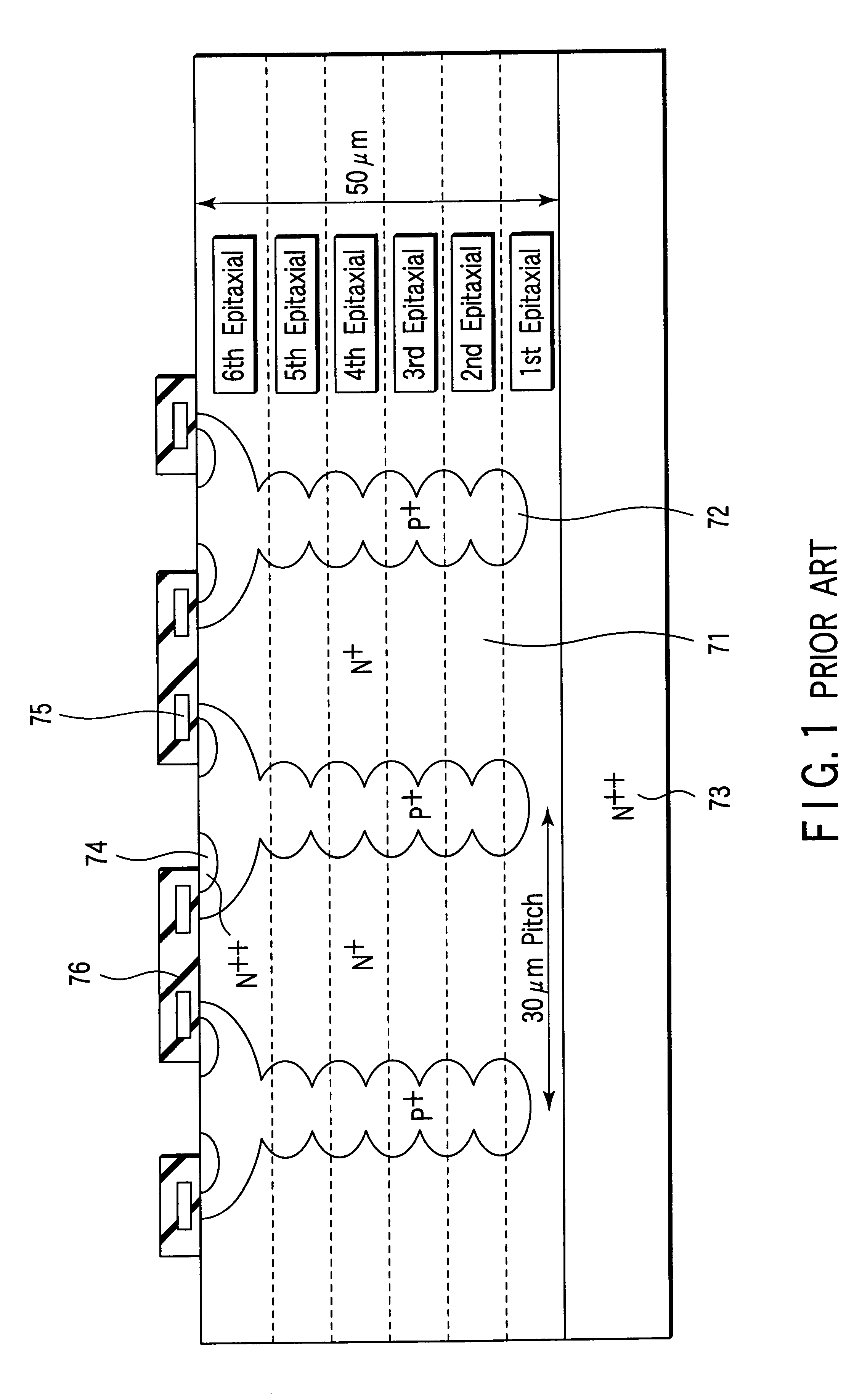

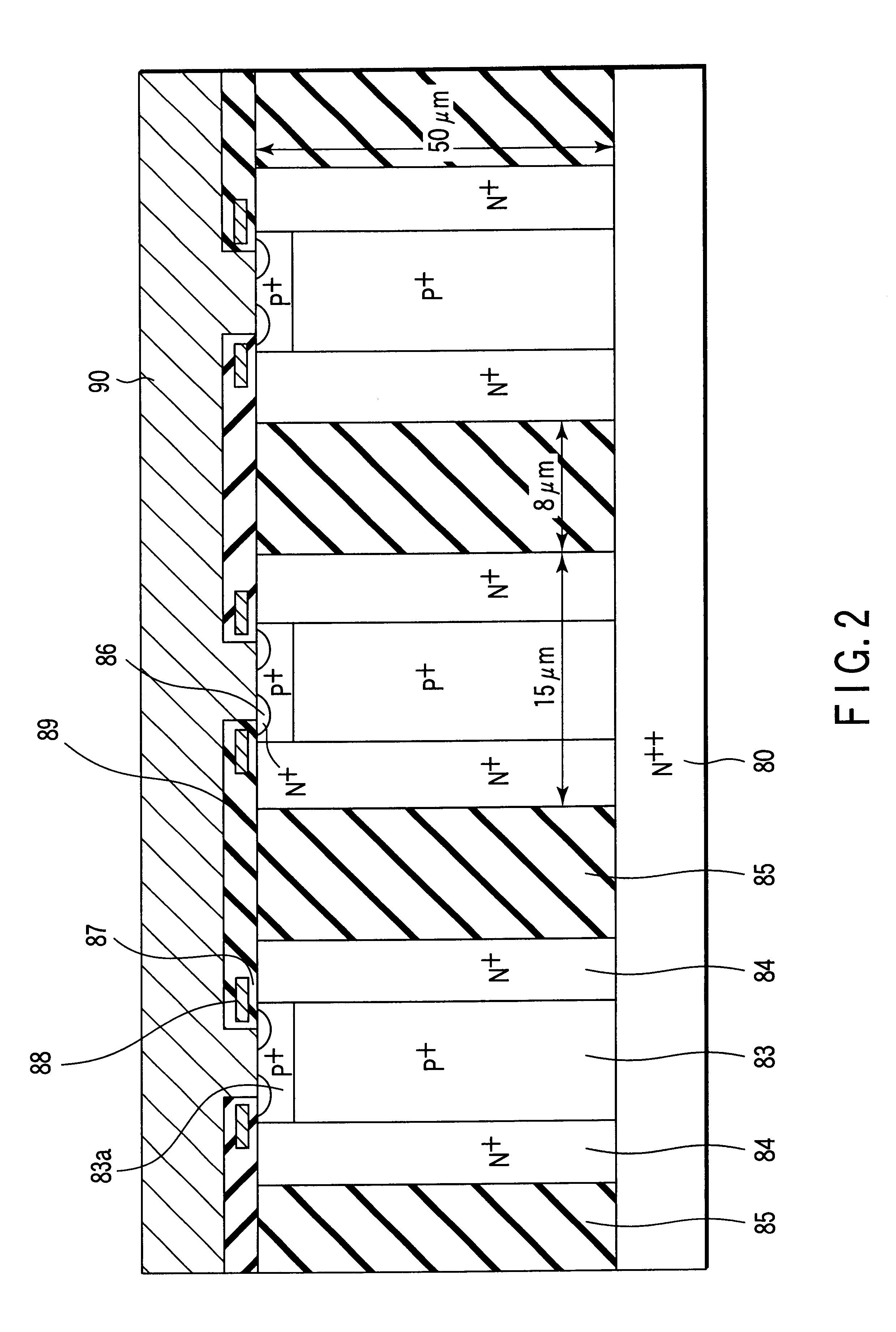

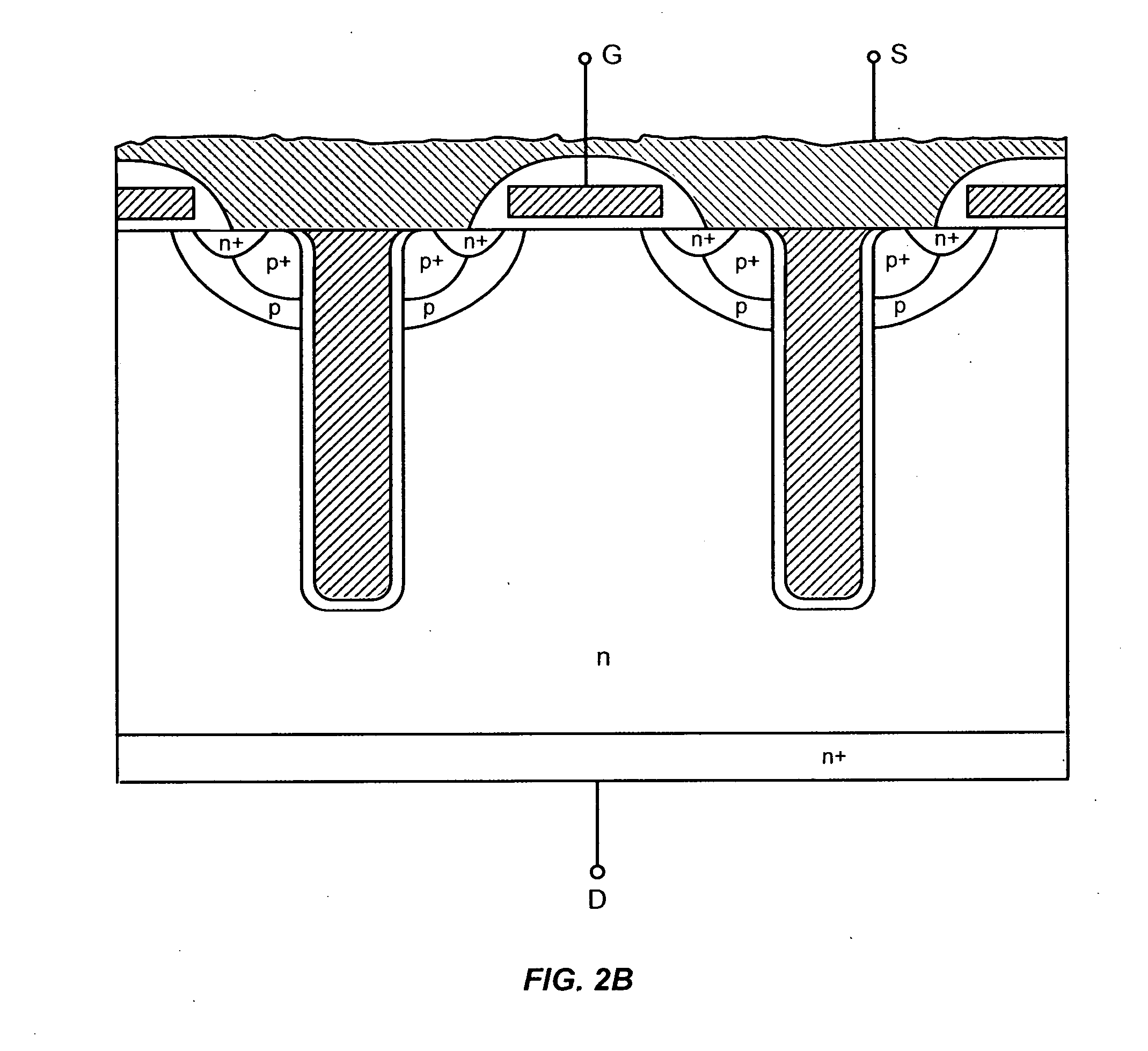

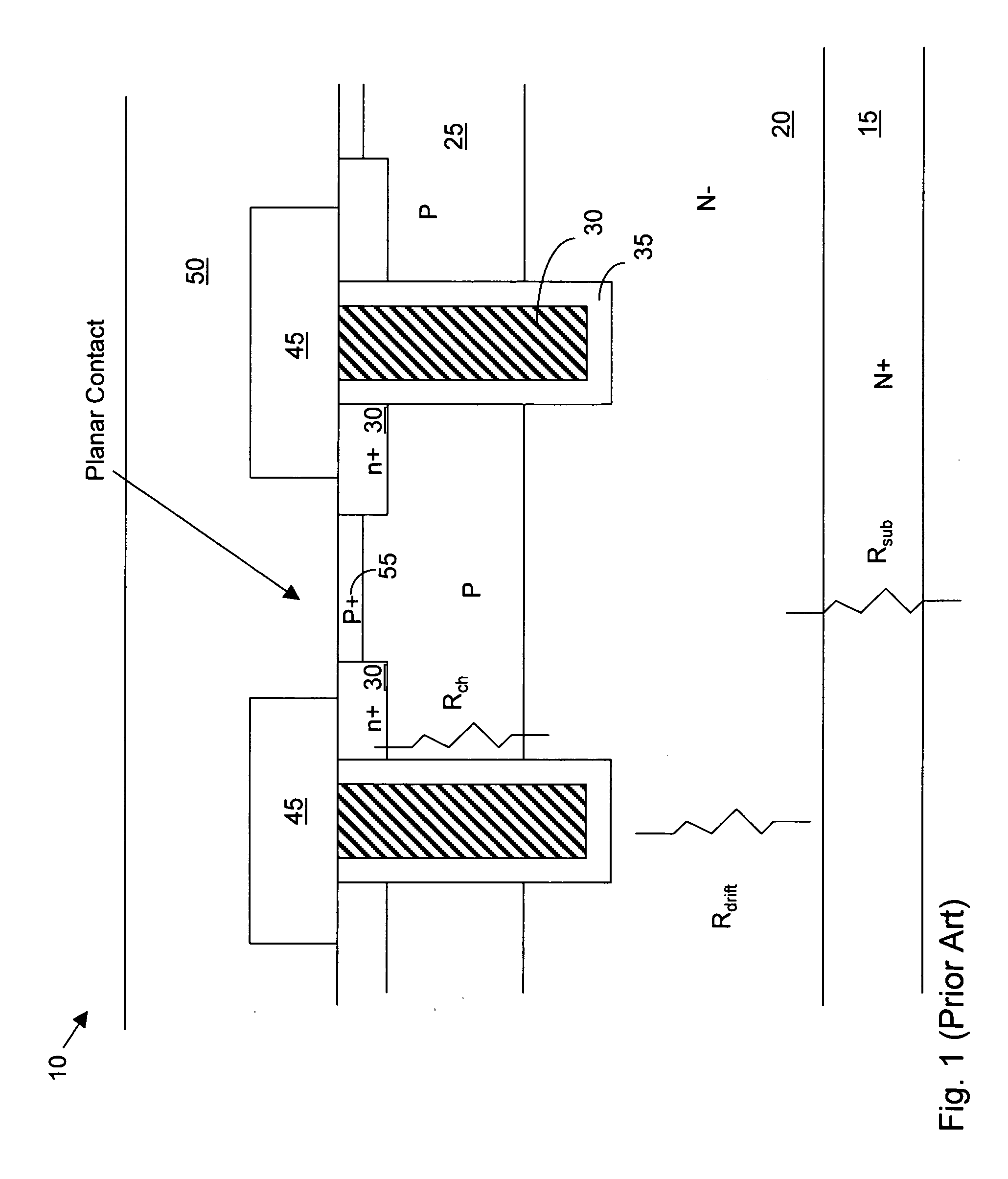

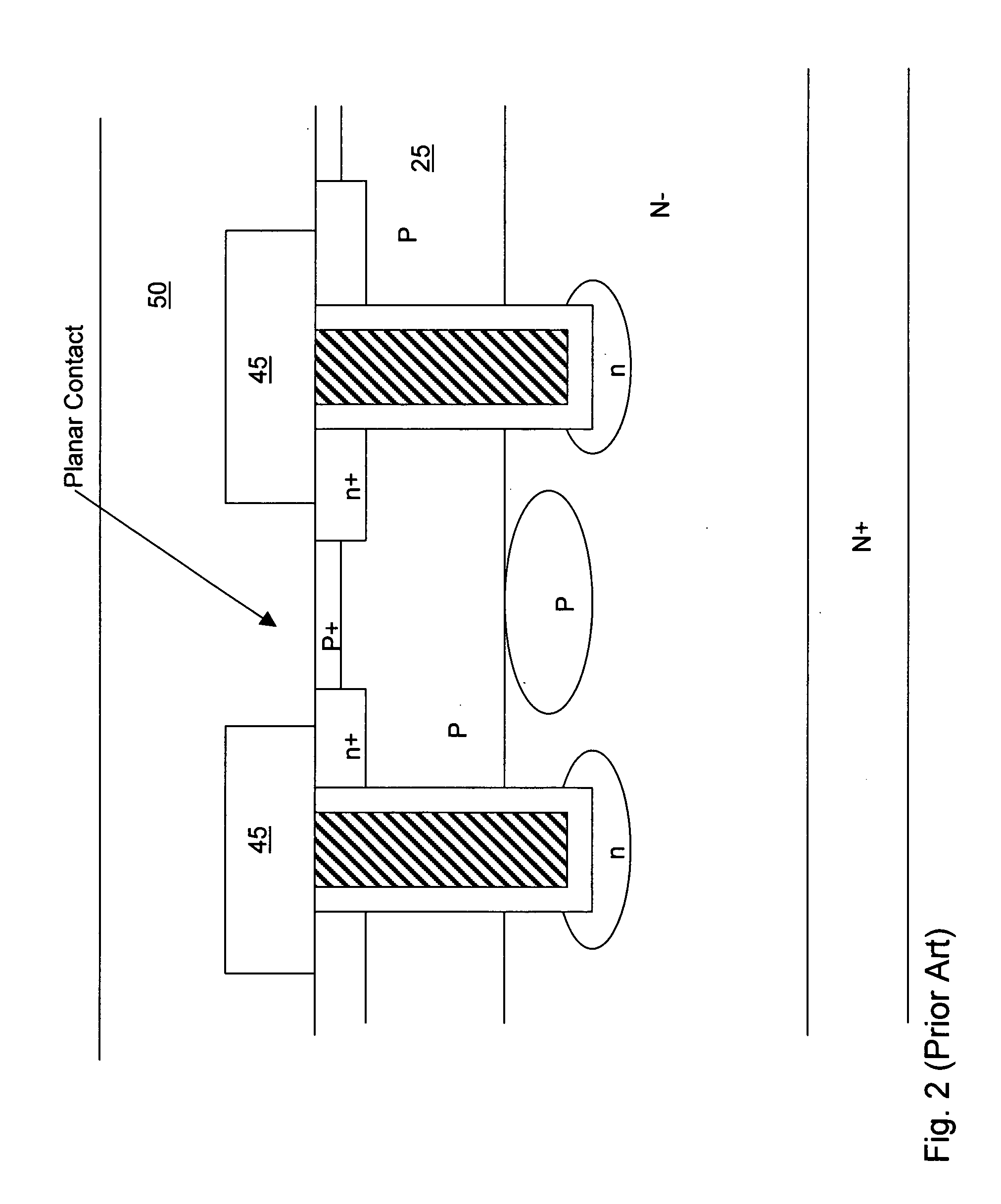

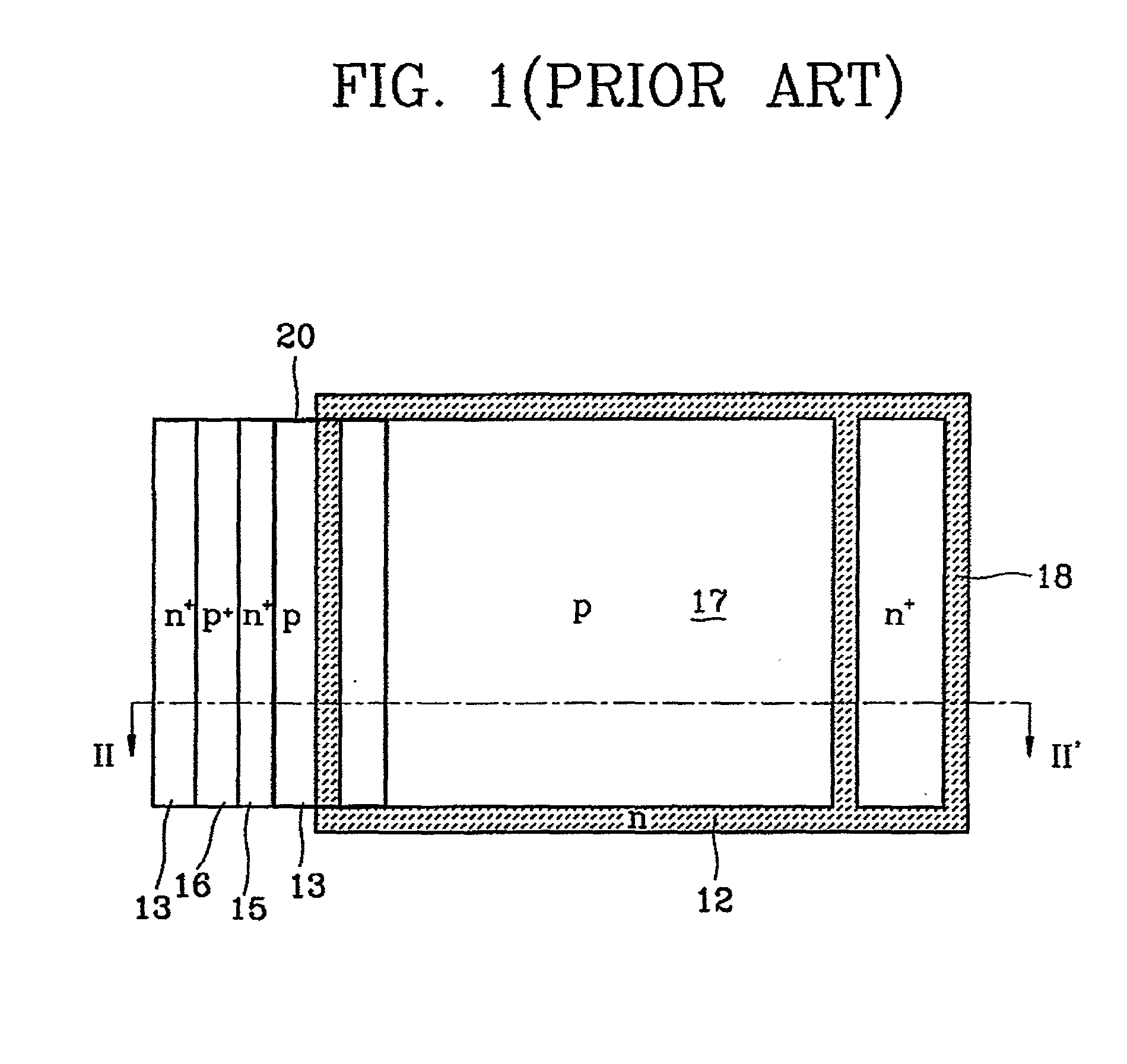

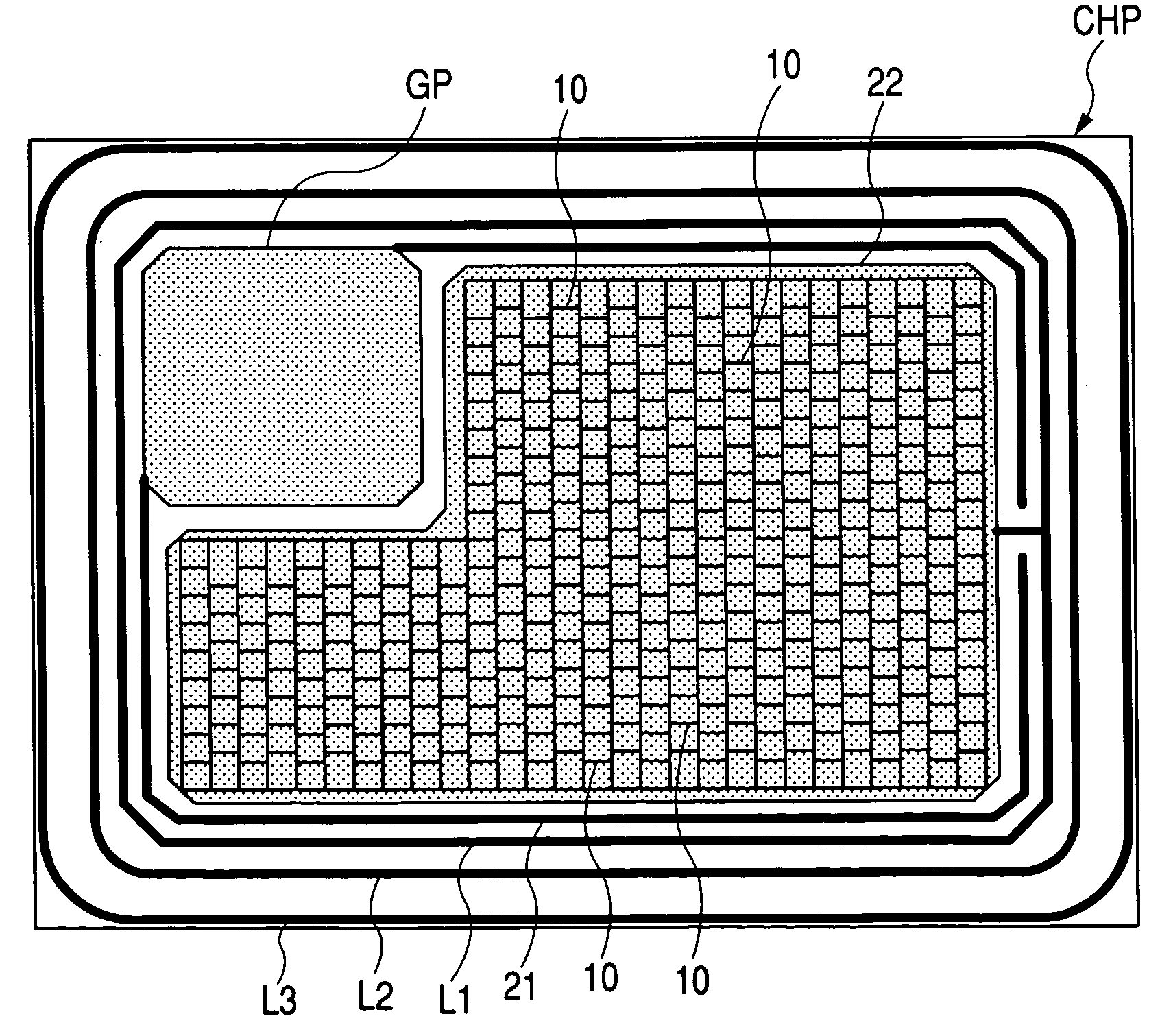

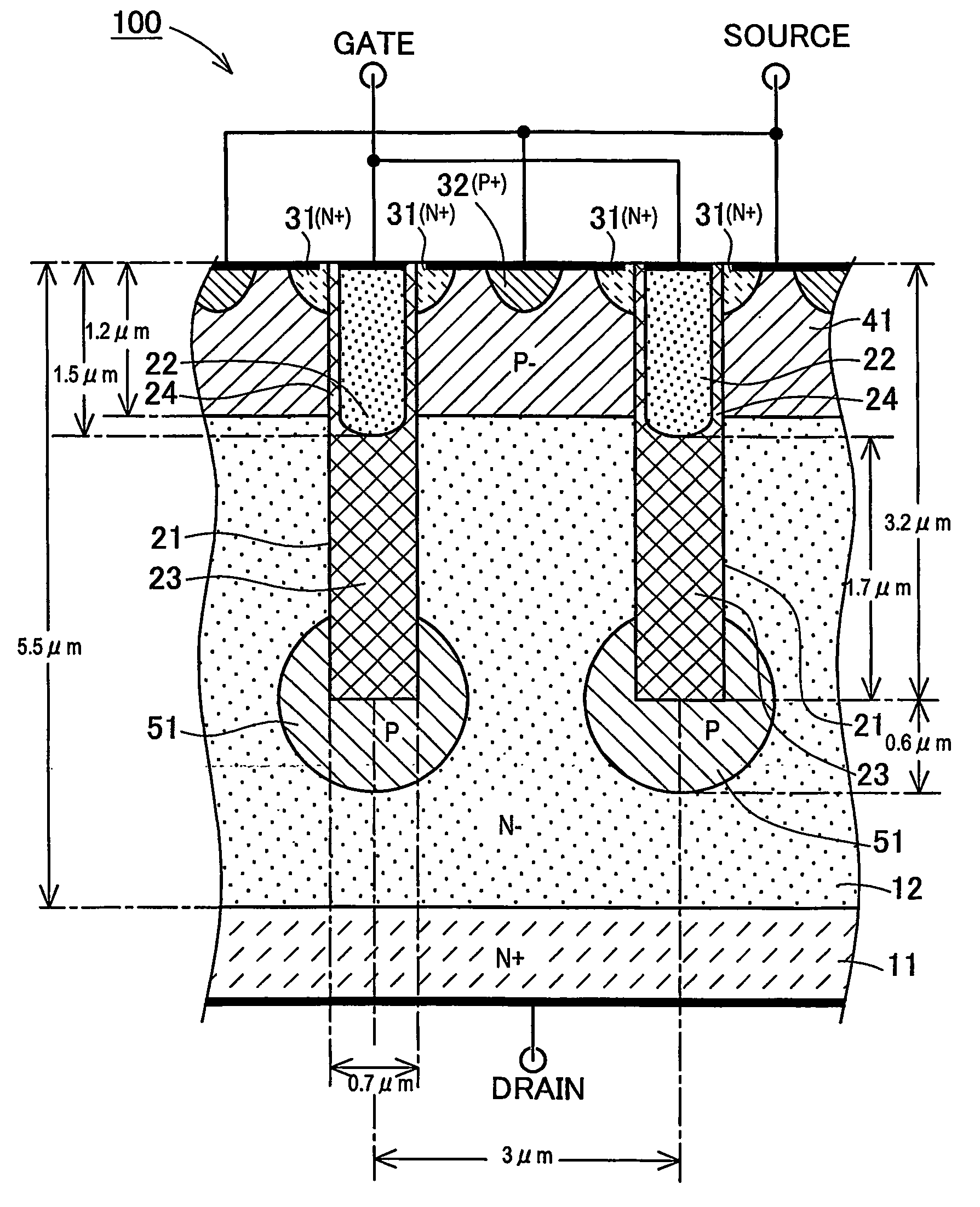

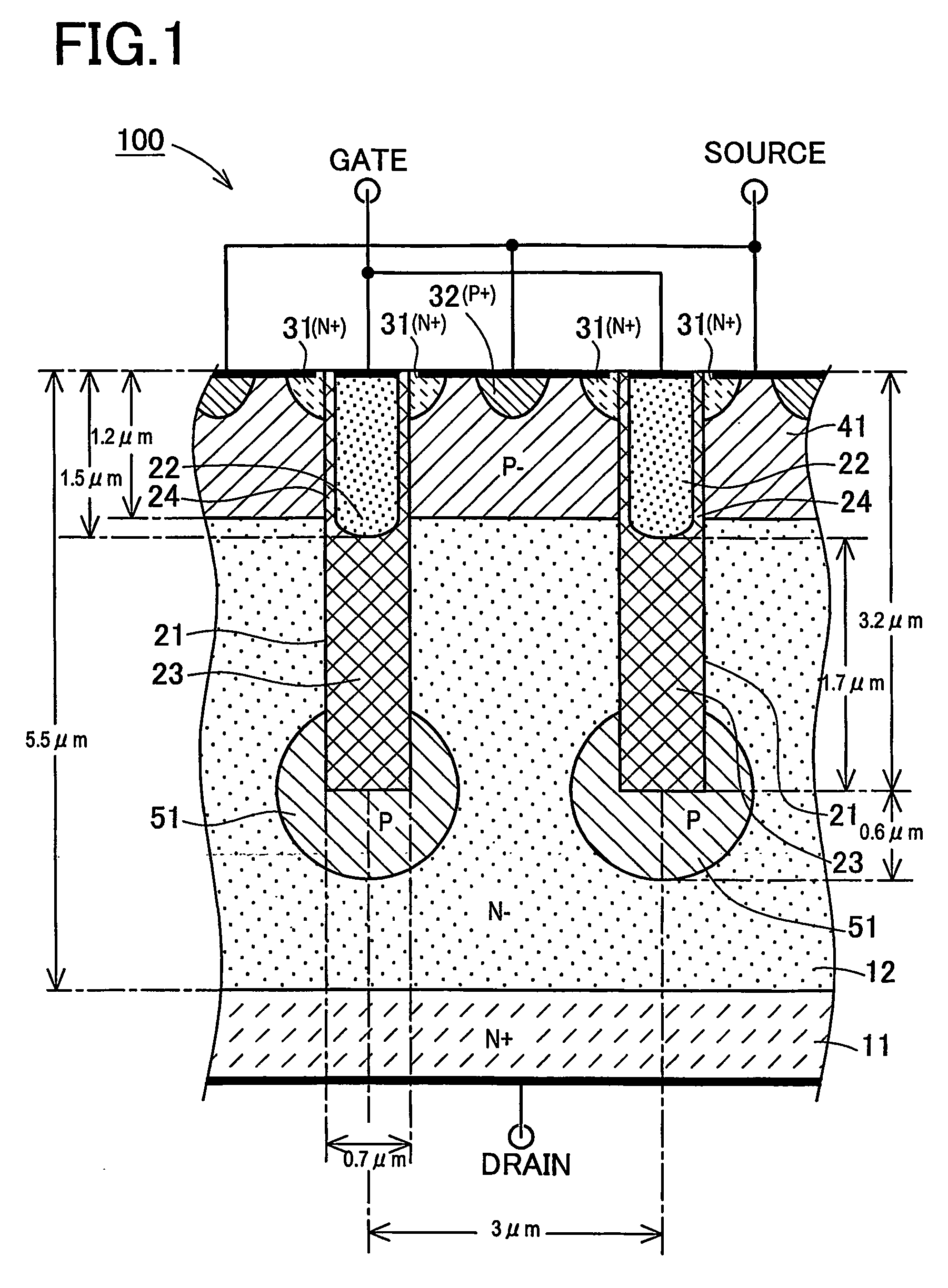

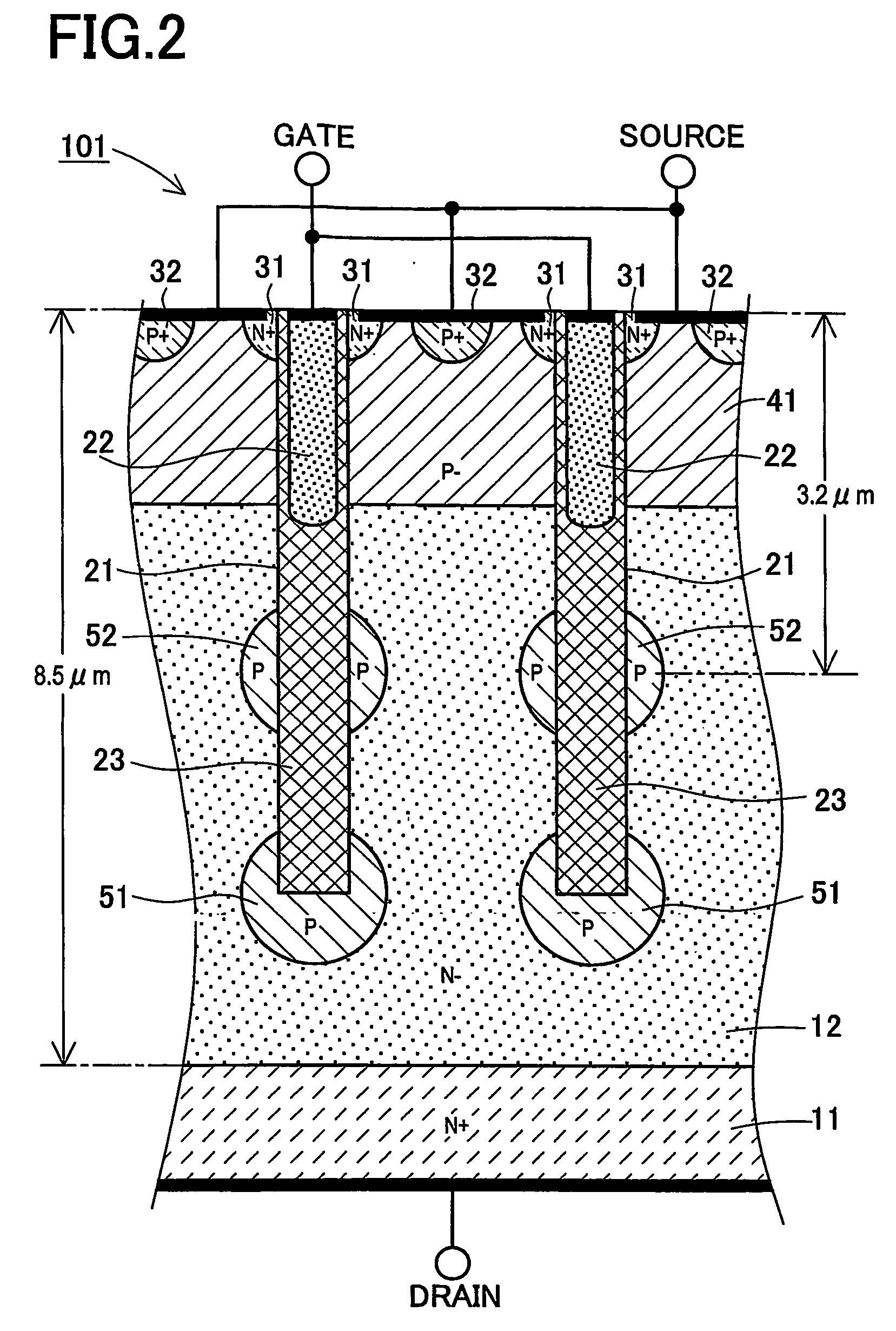

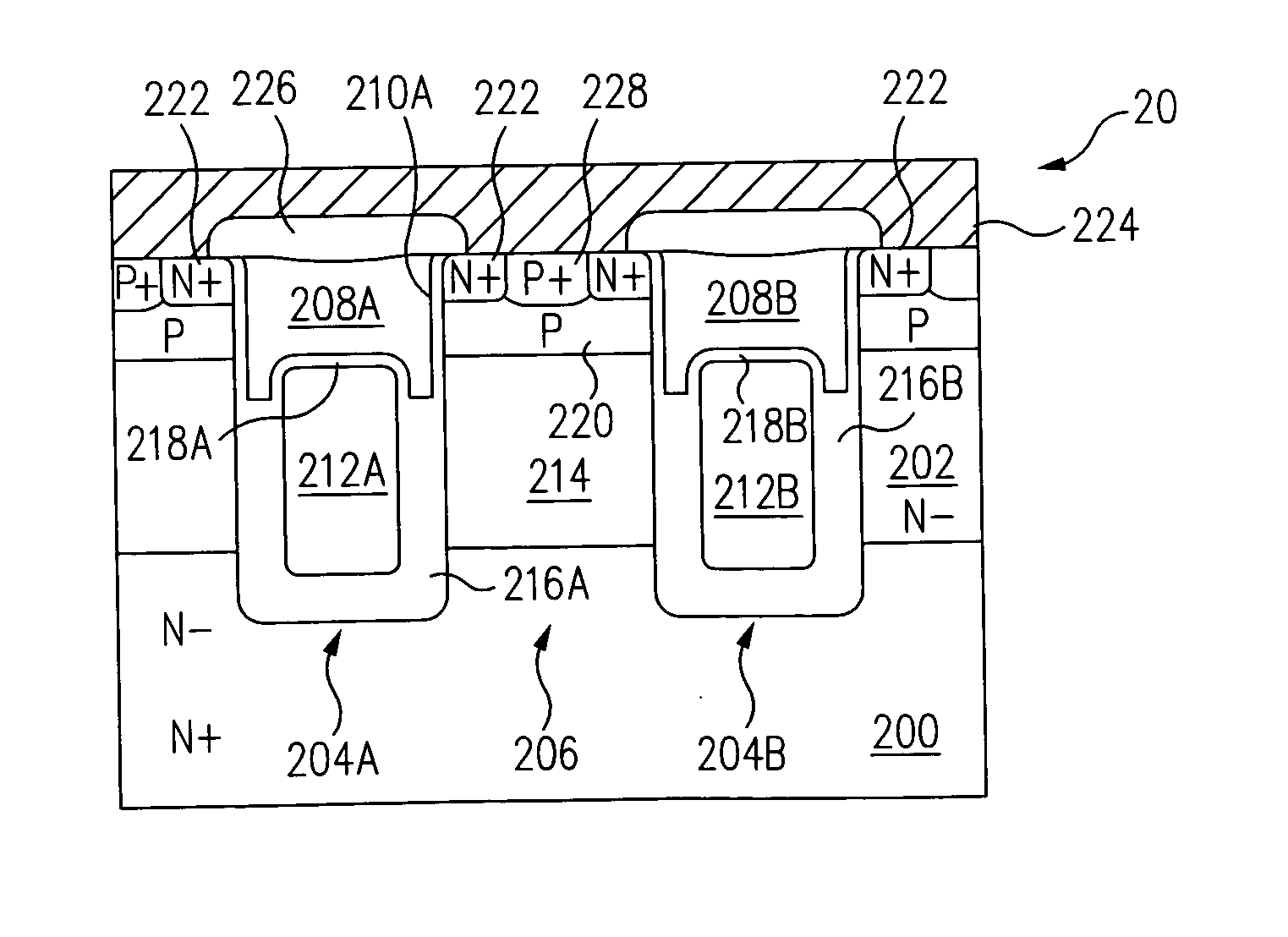

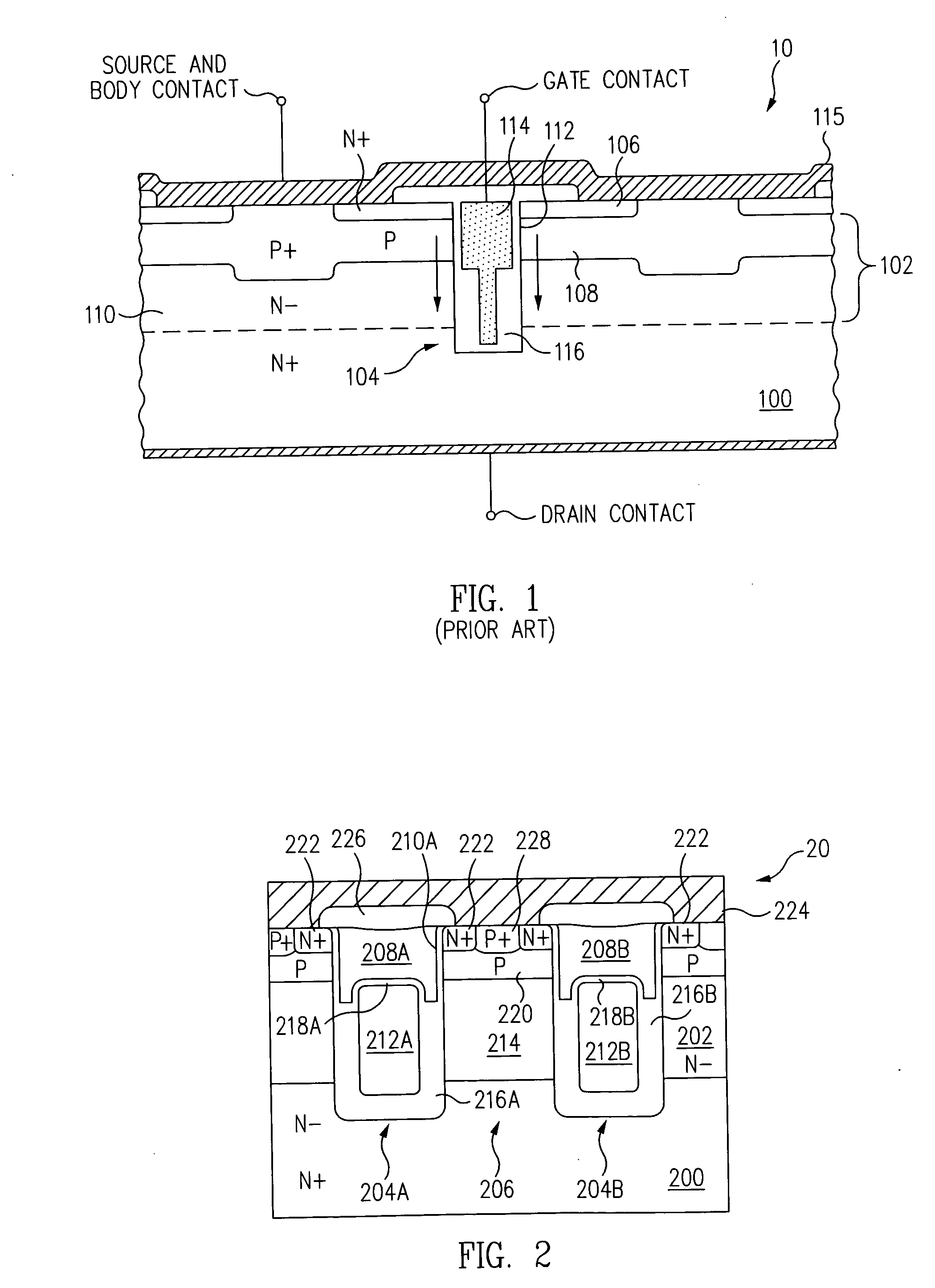

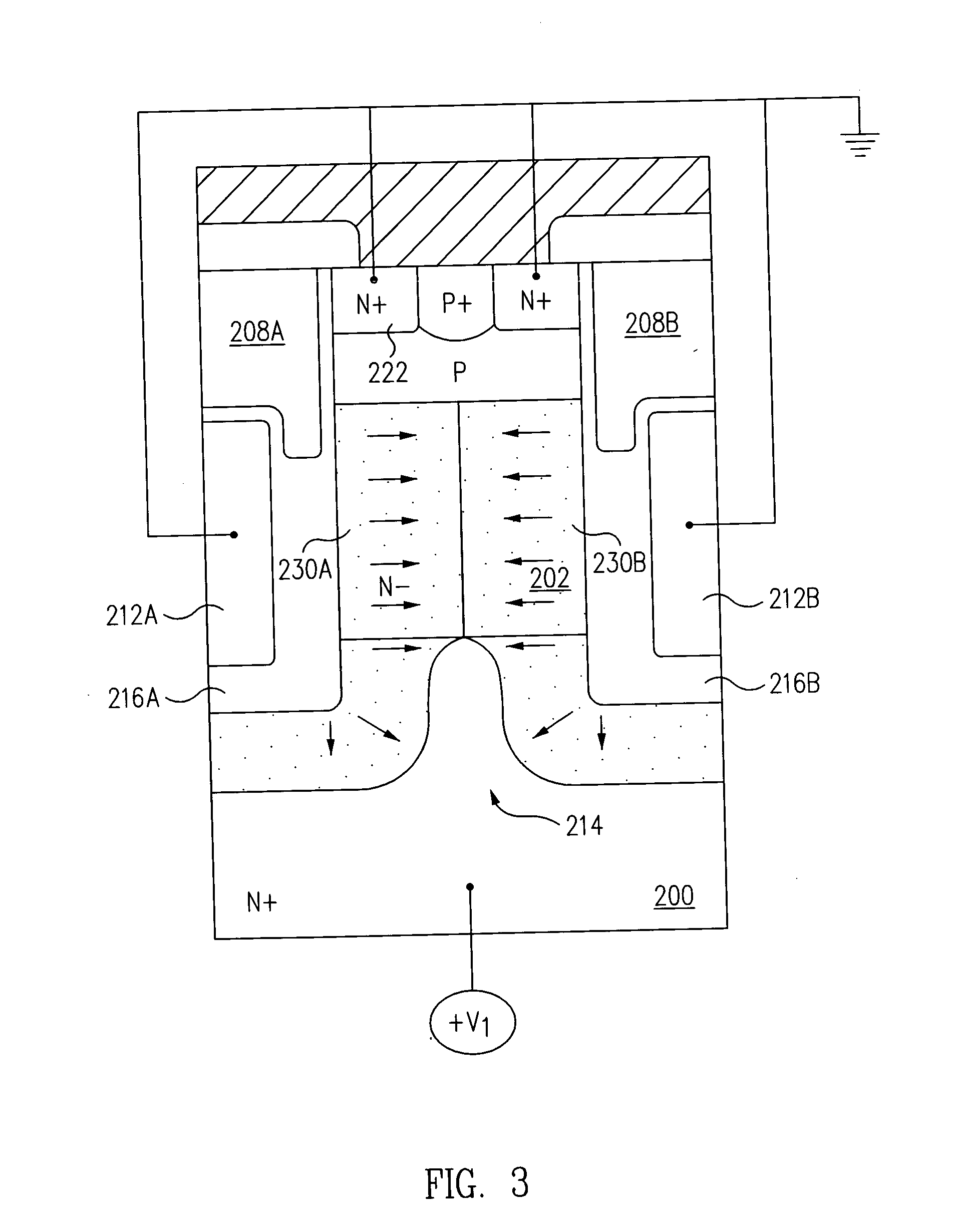

Power MOSFET having laterally three-layered structure formed among element isolation regions

A semiconductor apparatus has an NPN (or PNP) laterally three-layered pillar formed in a mesh form among a plurality of trench type element isolation regions, and having a source and gate on an upper surface of the three-layered pillar, and a drain on a lower surface thereof. A depth DT and minimum planar width WTmin of the element isolation region and a width WP of the three-layered pillar are configured to satisfy a relation of 3.75<=DT / WP<=60 or 5.5<=DT / WTmin<=14.3. The above configuration realizes a high breakdown voltage and low on-resistance are realized.

Owner:KK TOSHIBA

Power semiconductor devices and methods of manufacture

InactiveUS20060214221A1Improved voltage performanceFast switching speedTransistorEfficient power electronics conversionEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

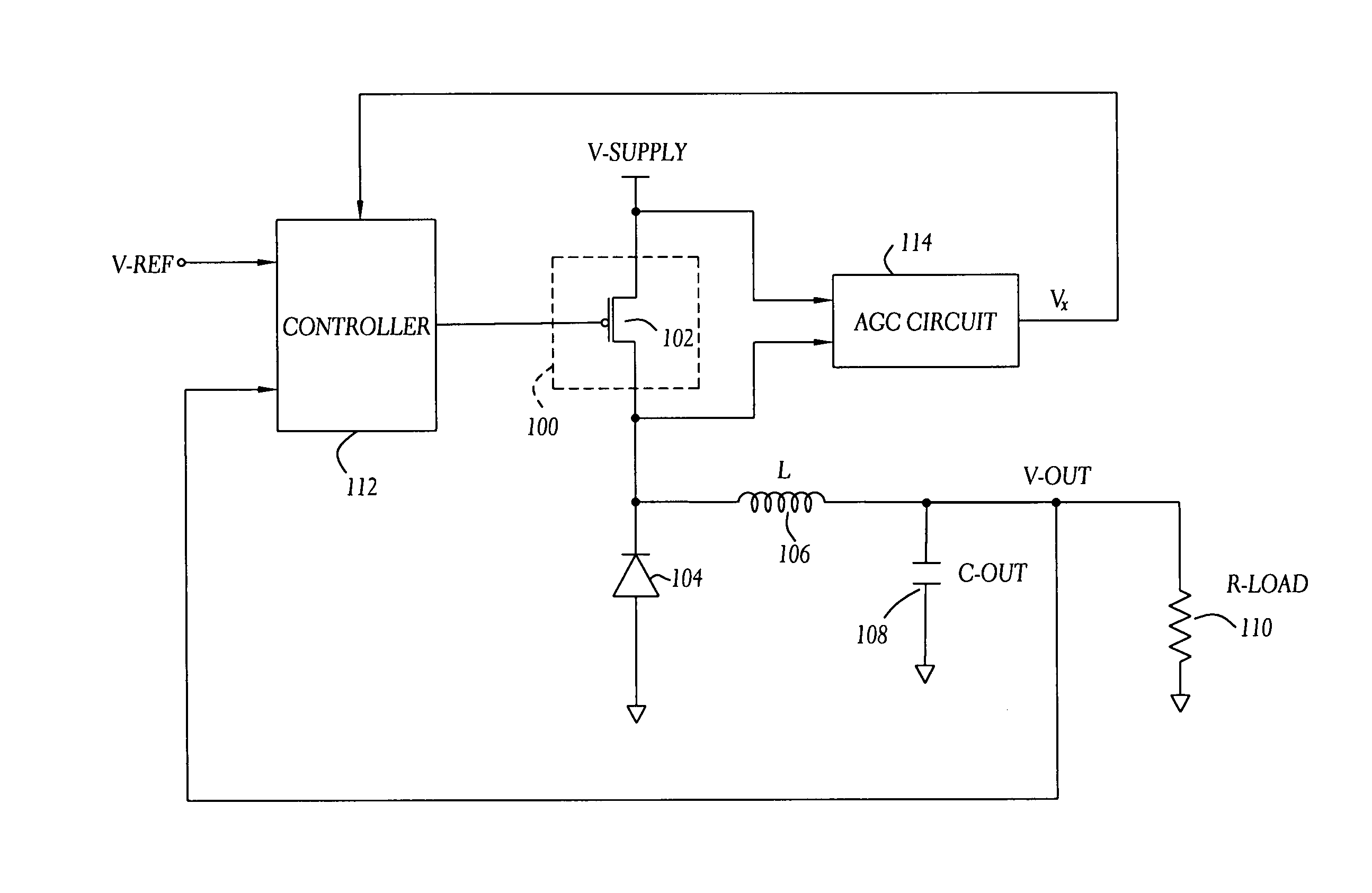

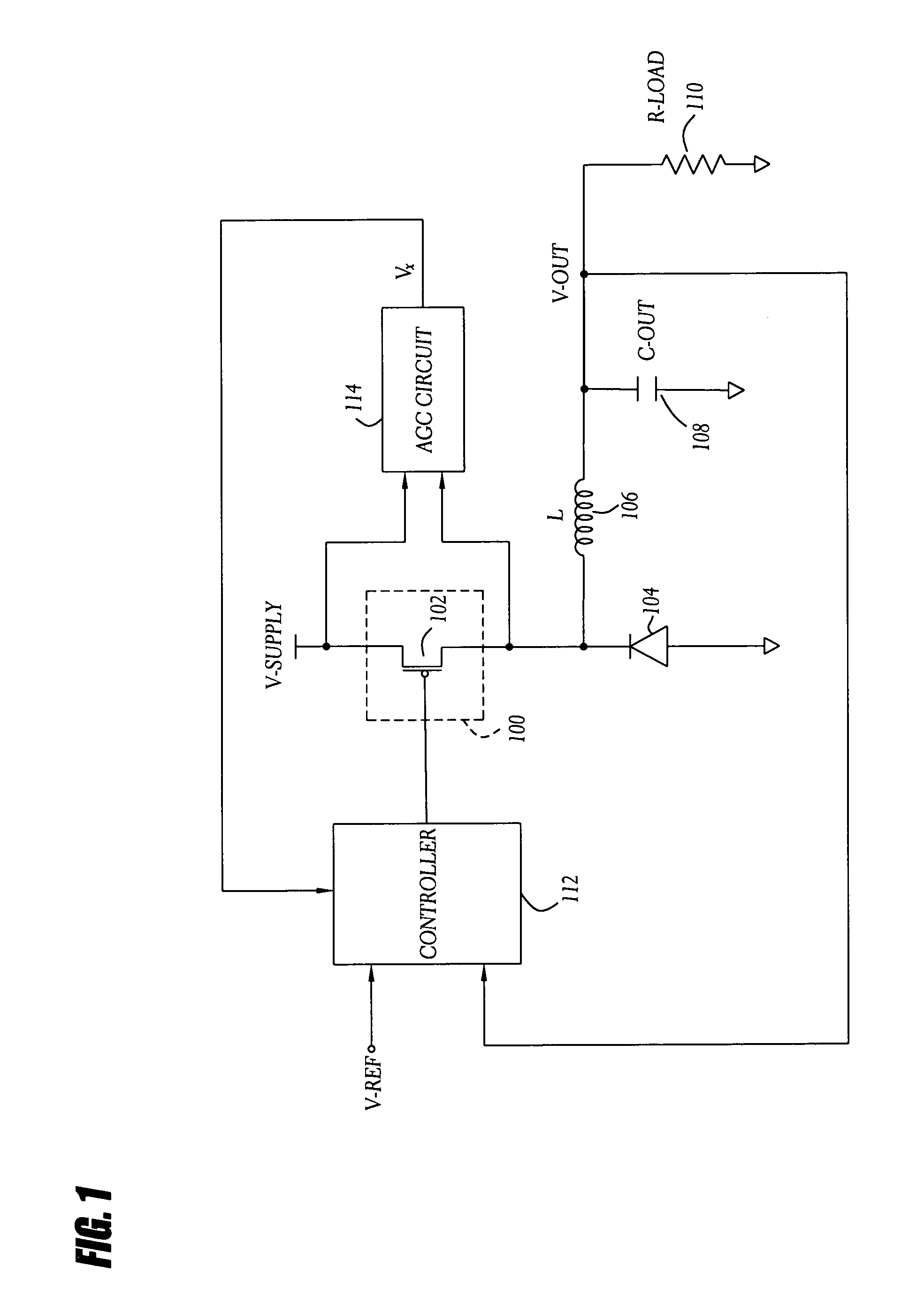

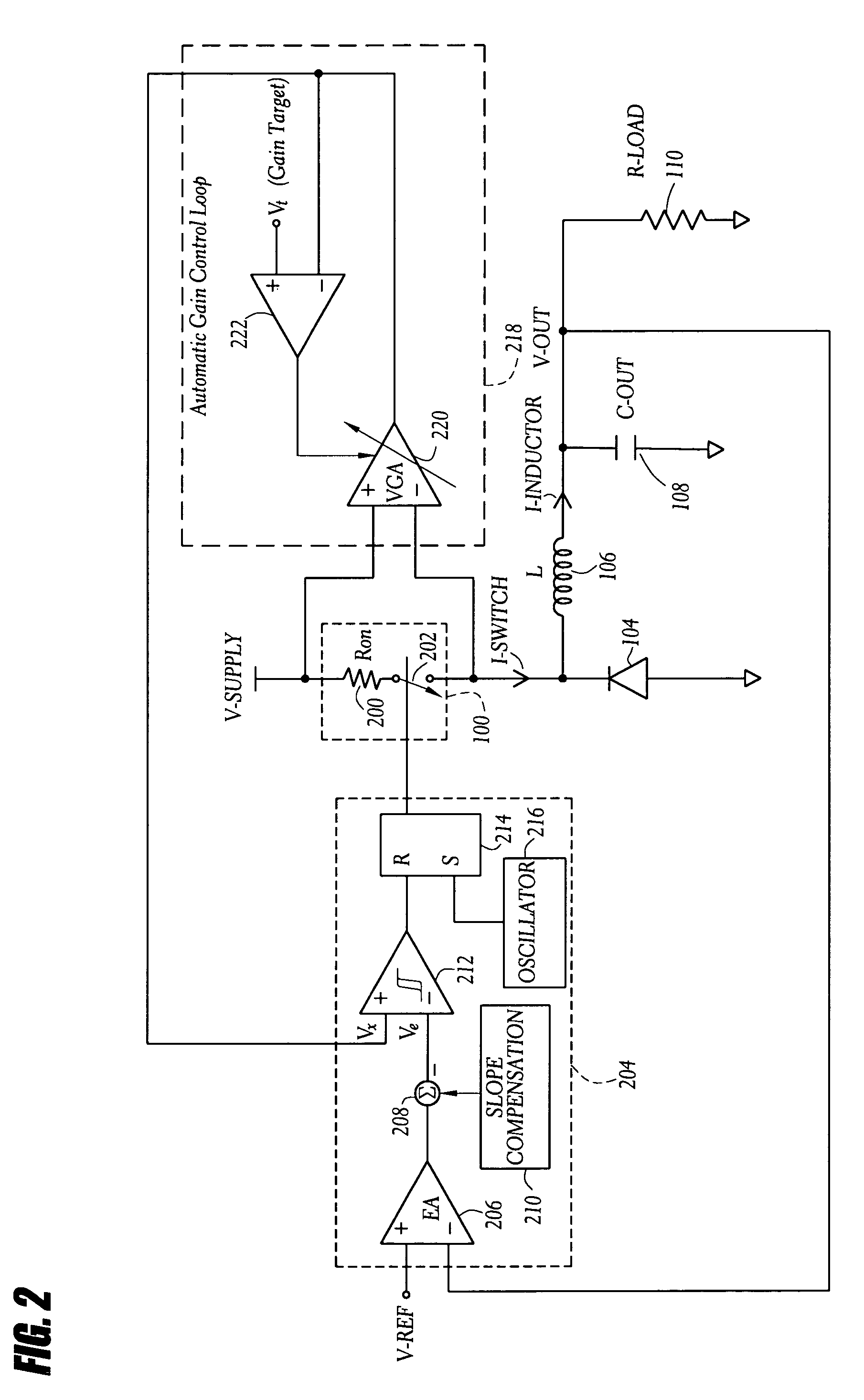

Automatic gain control technique for current monitoring in current-mode switching regulators

InactiveUS7919952B1Reduce component count and circuit board sizeFacilitates efficient and reliable monitoringDc-dc conversionElectric variable regulationEngineeringCurrent mode

A current-mode switching regulator uses adaptive current sensing to reliably monitor an inductor current in a cost-efficient and power-efficient manner. A semiconductor switch periodically turns on to conduct the inductor current. A voltage drop across the semiconductor switch is monitored when the semiconductor switch is on. A variable gain amplifier with an automatic gain control loop generates a feedback signal from the voltage drop of the semiconductor switch when conducting to provide an indication of the inductor current to a controller. The automatic gain control loop compensates for any variations in the on-resistance of the semiconductor switch.

Owner:MICROSEMI

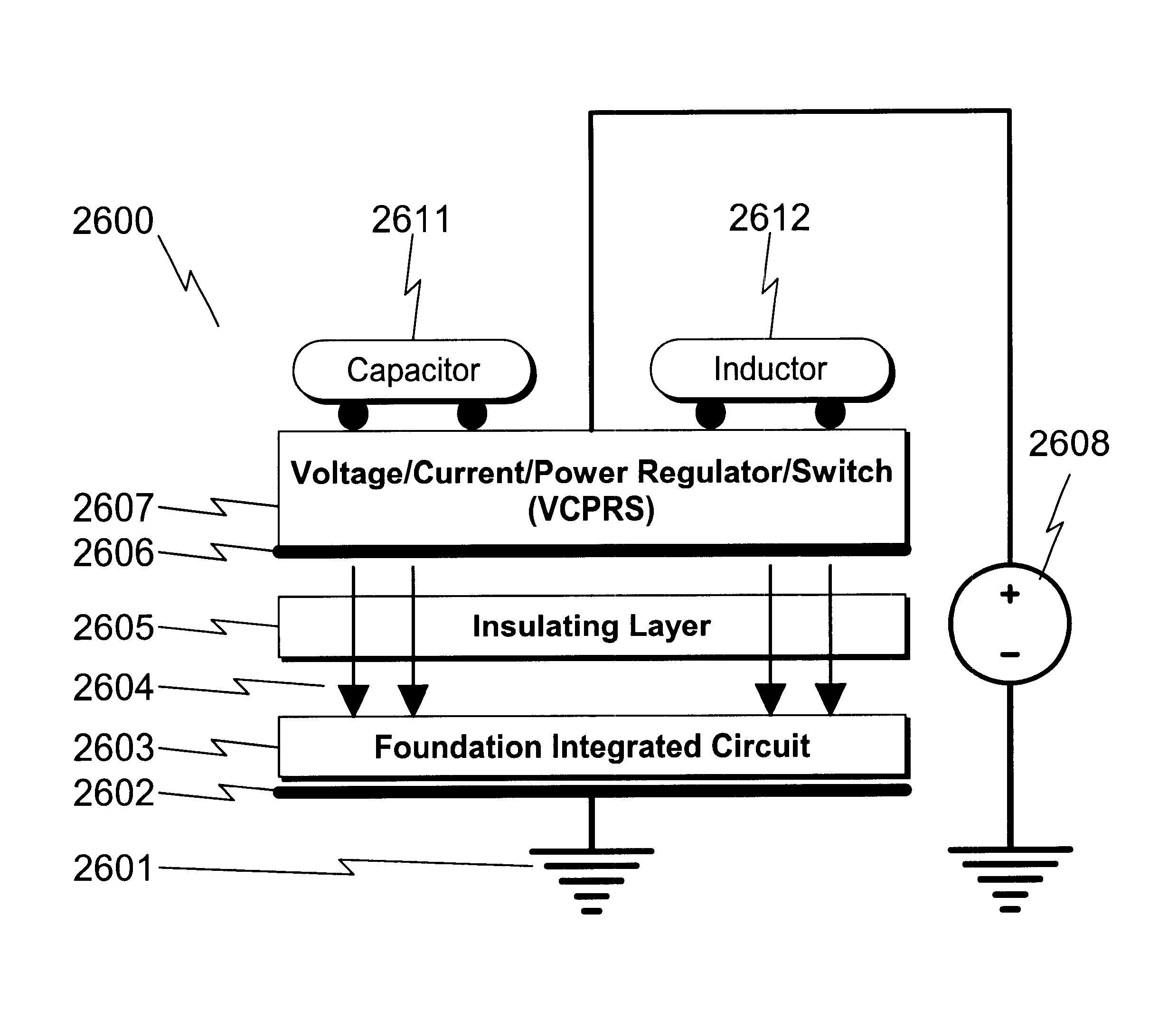

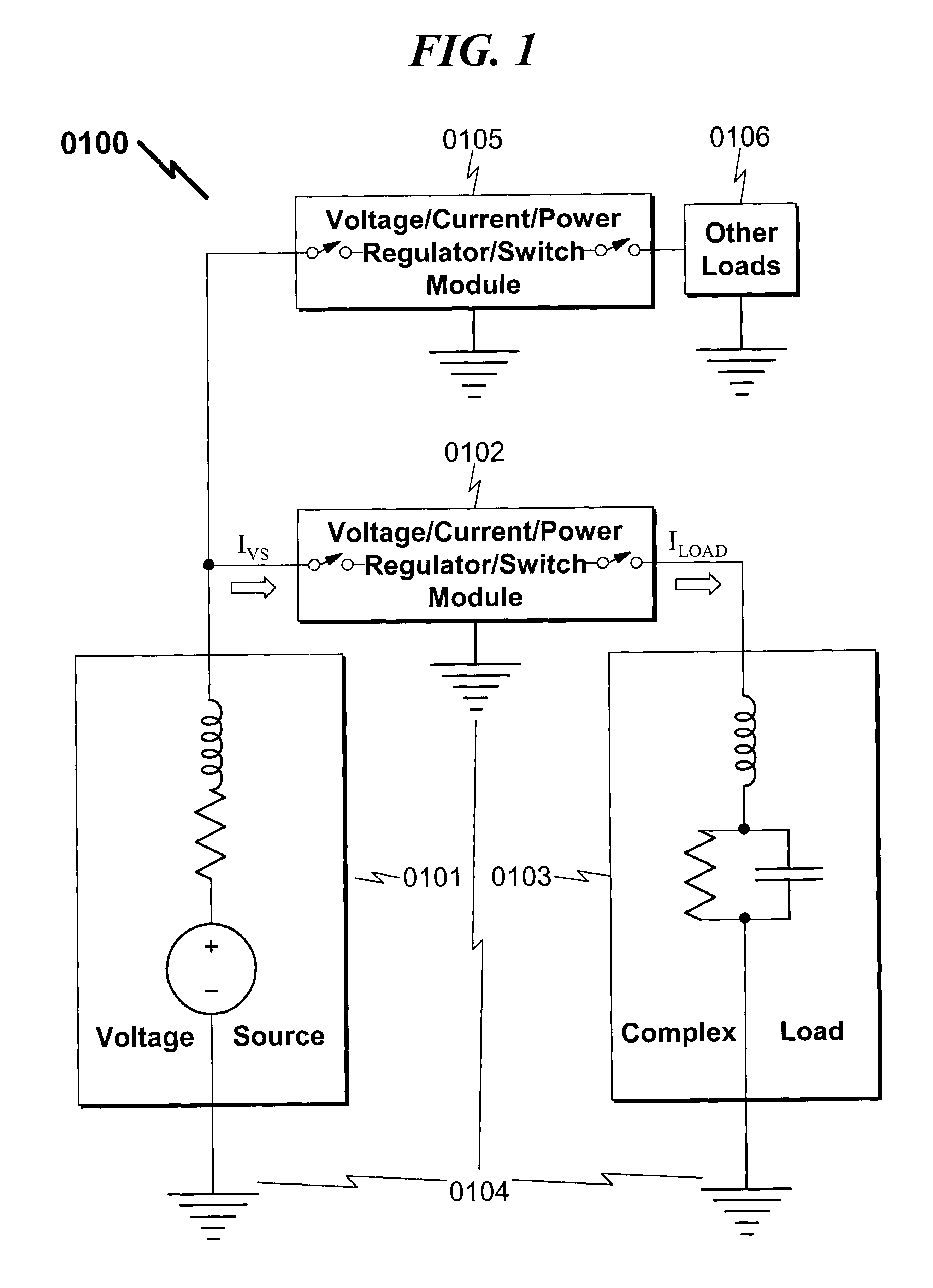

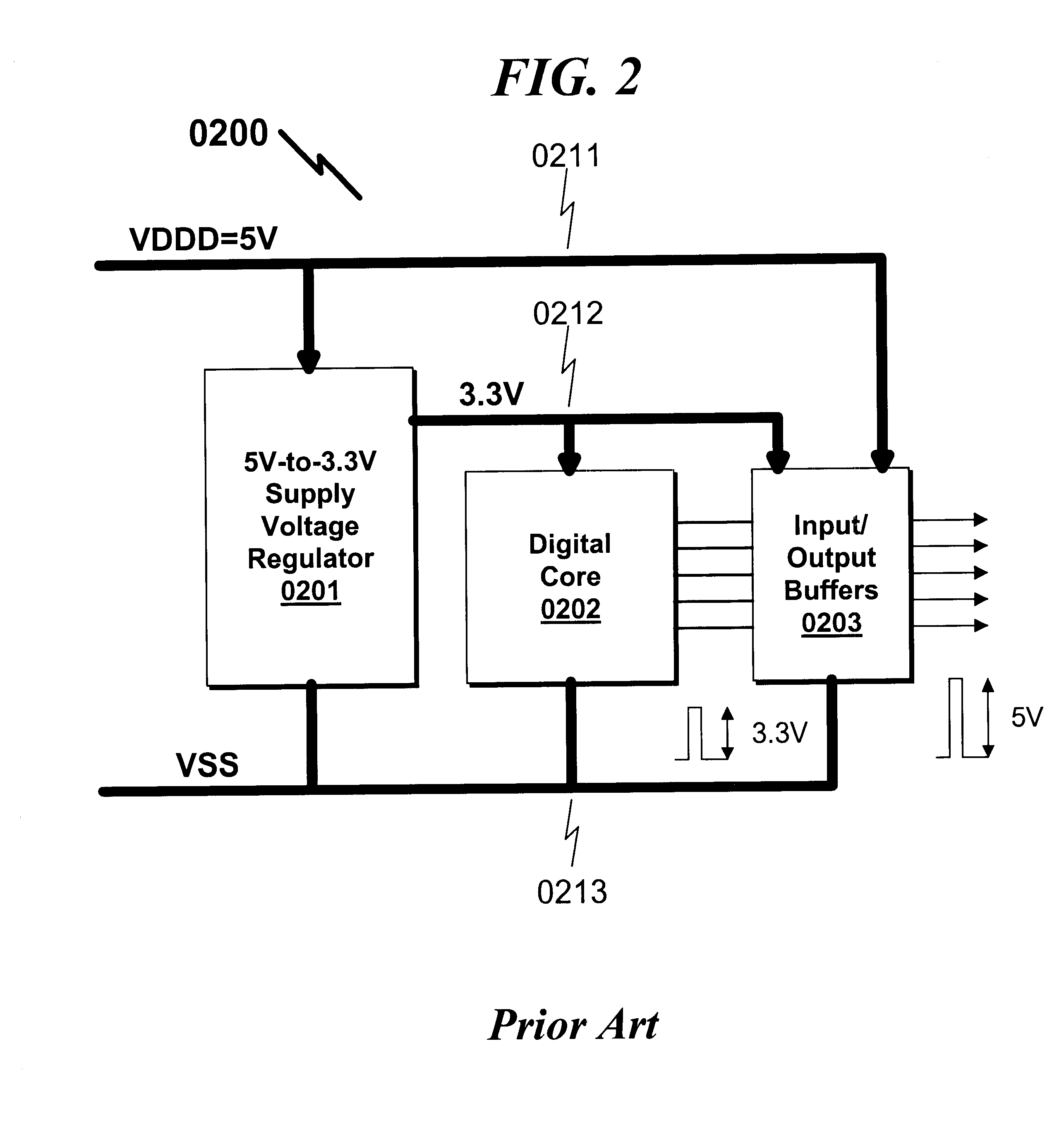

Integrated voltage/current/power regulator/switch system and method

InactiveUS6396137B1Minimal noiseGood PSRRSemiconductor/solid-state device detailsDc-dc conversionPower applicationPower capability

An integrated voltage / current / power regulator / switch (VCPRS) system and method are disclosed in which regulator / switch circuitry is vertically integrated on top of an existing integrated circuit. The present invention does not require additional integrated circuit chip area for the regulator pass device as is required in the prior art, and by virtue of its construction provides a significantly reduced on-resistance as compared to all prior art implementations. The present invention both stabilizes the power supply for large area integrated circuits and permits individual areas of the integrated circuit to have switched power capability, a highly desirable feature in low power and battery power applications. The present invention permits an increase in the power supply rejection ratio (PSRR) for digital, analog, and especially mixed-signal integrated circuit designs by permitting various circuit blocks to have localized power regulation that is obtained from a common power supply plane within the integrated circuit framework. Finally, the present invention appears to be the only economically practical method of addressing the power supply regulation requirements of modern and future integrated microprocessor designs.

Owner:KLUGHART KEVIN MARK

Power semiconductor devices and methods of manufacture

ActiveUS20060214222A1Improved voltage performanceFast switching speedTransistorEfficient power electronics conversionEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

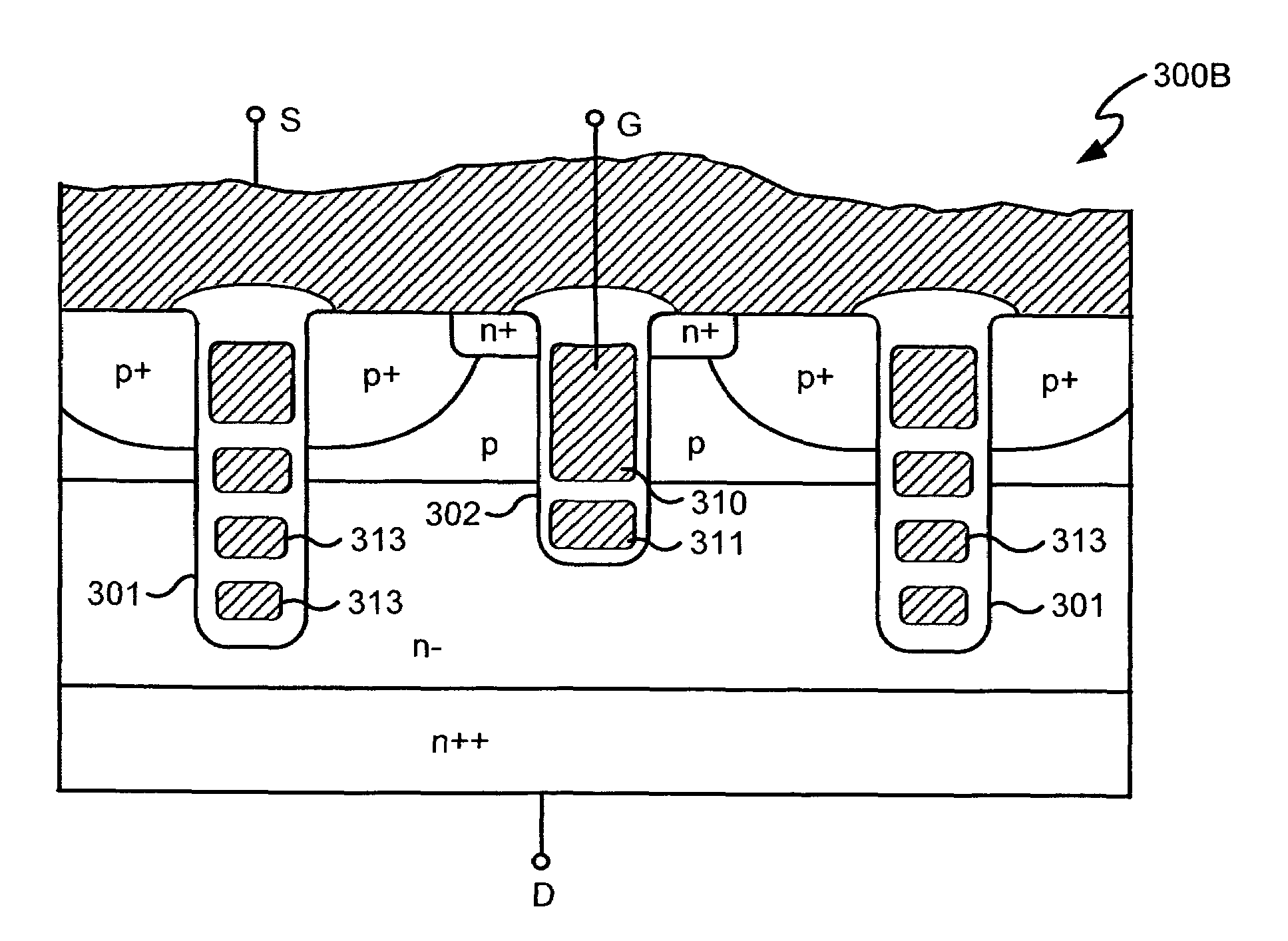

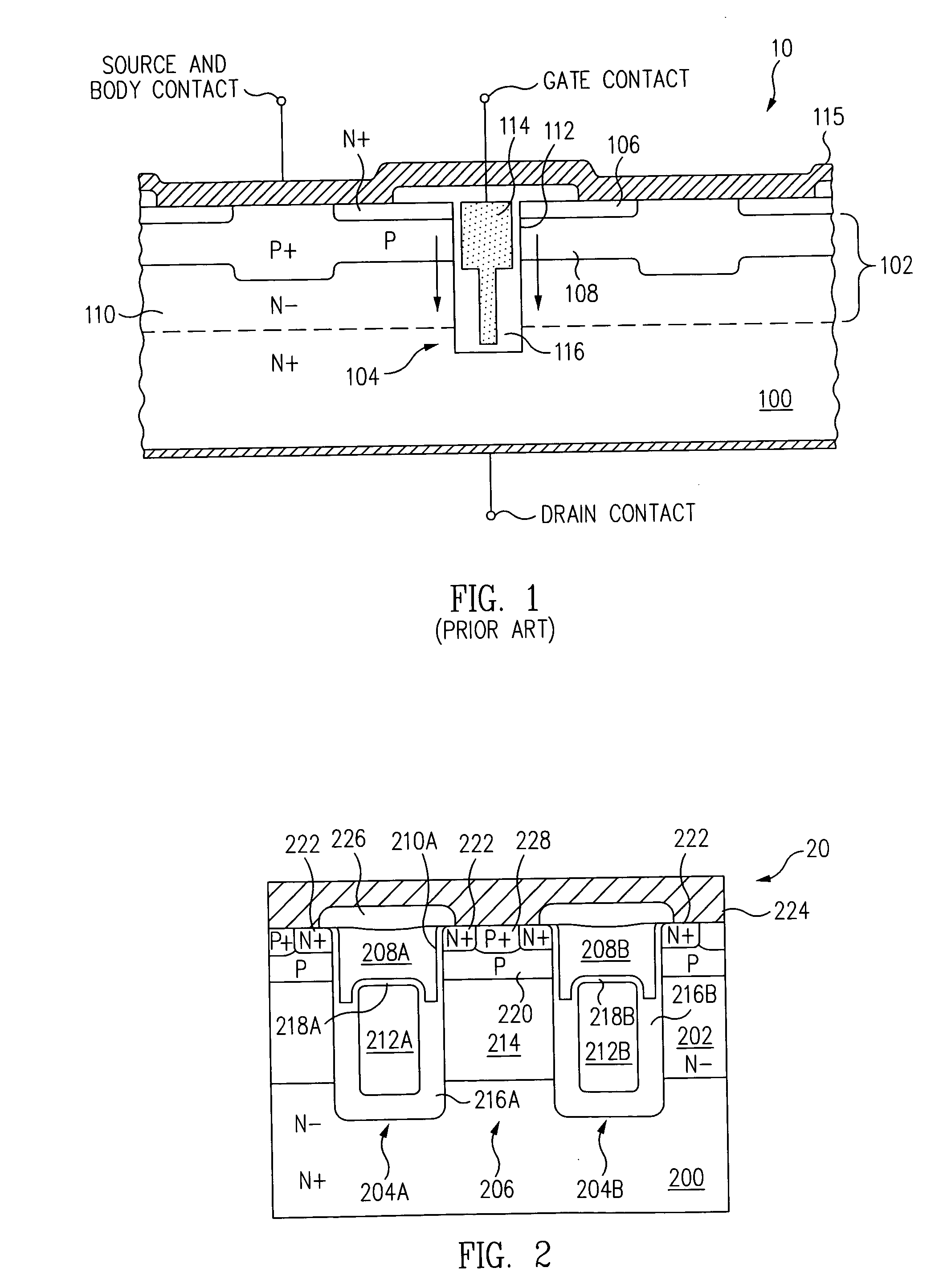

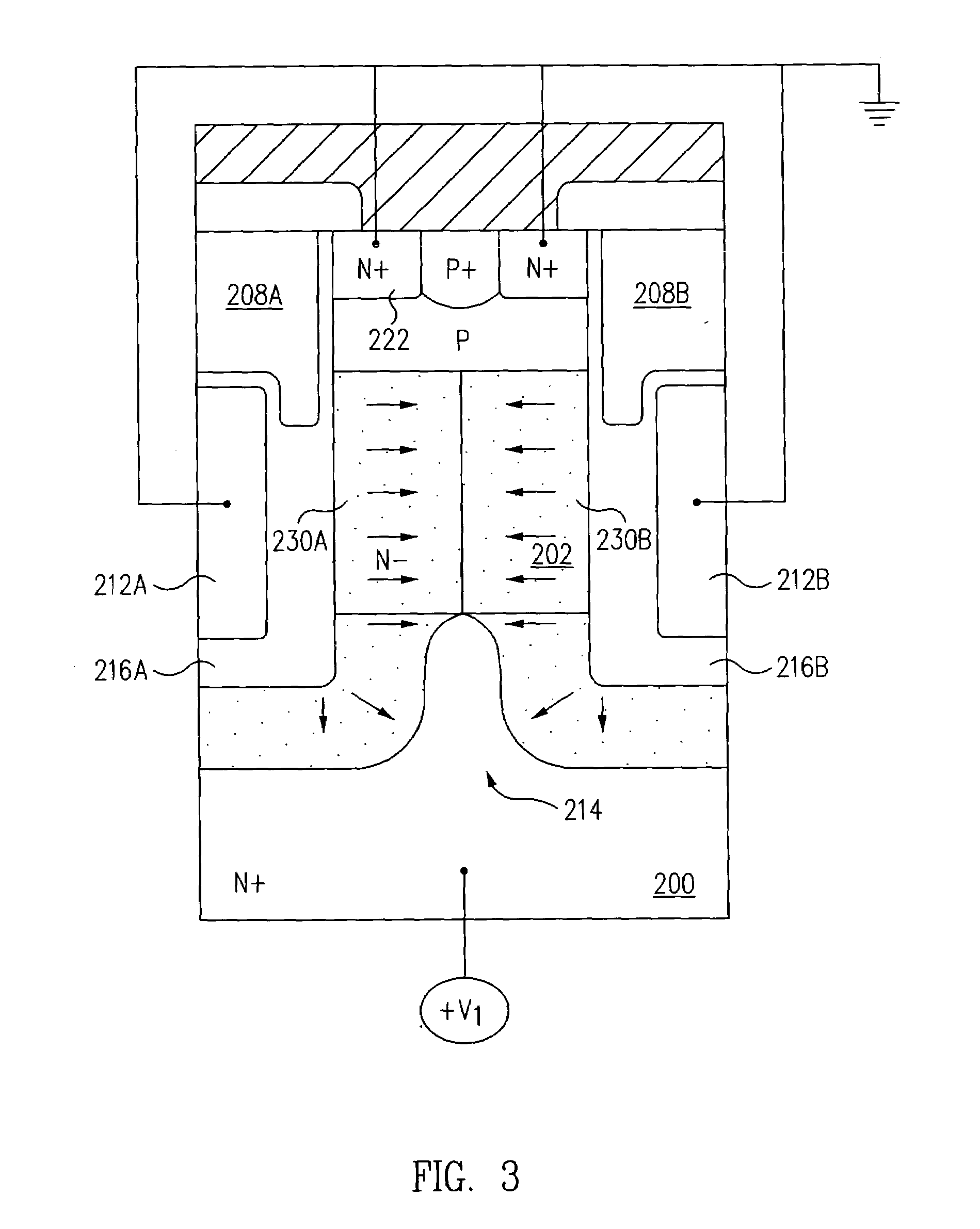

High density trench MOSFET with reduced on-resistance

InactiveUS20070114599A1Reduce resistanceImprove breakdown voltageSemiconductor devicesInsulation layerBody contact

Owner:M MOS SEMICON

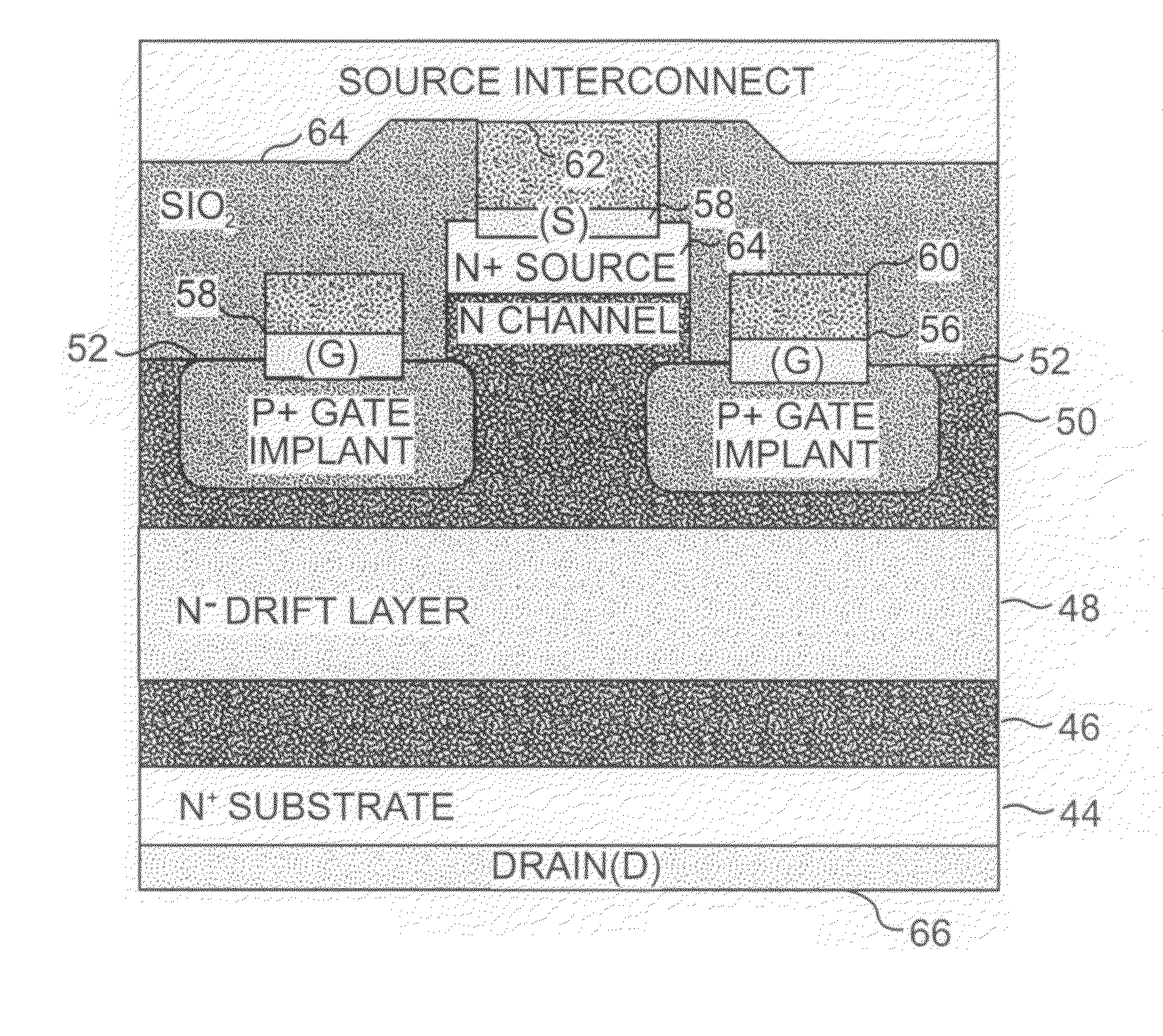

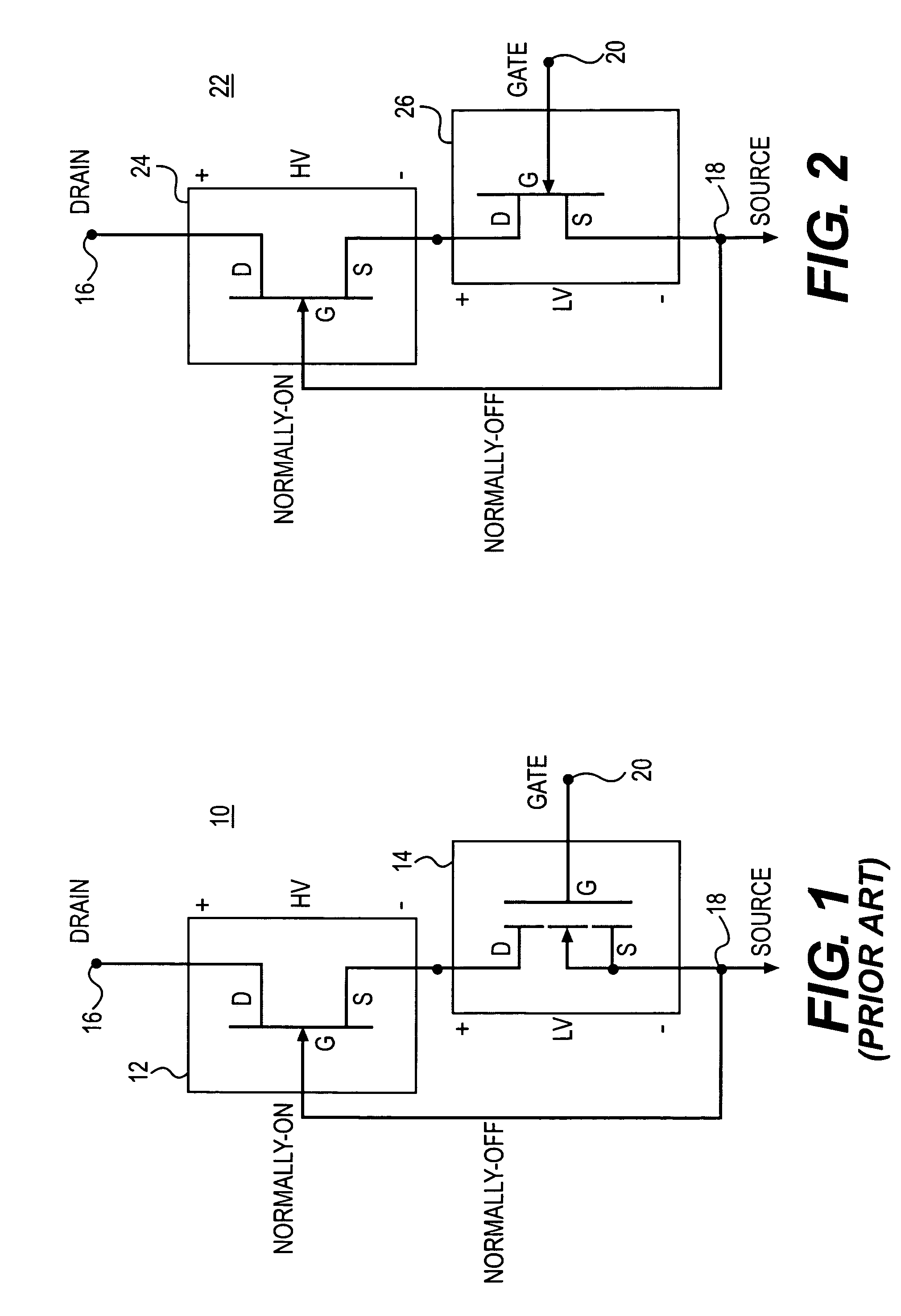

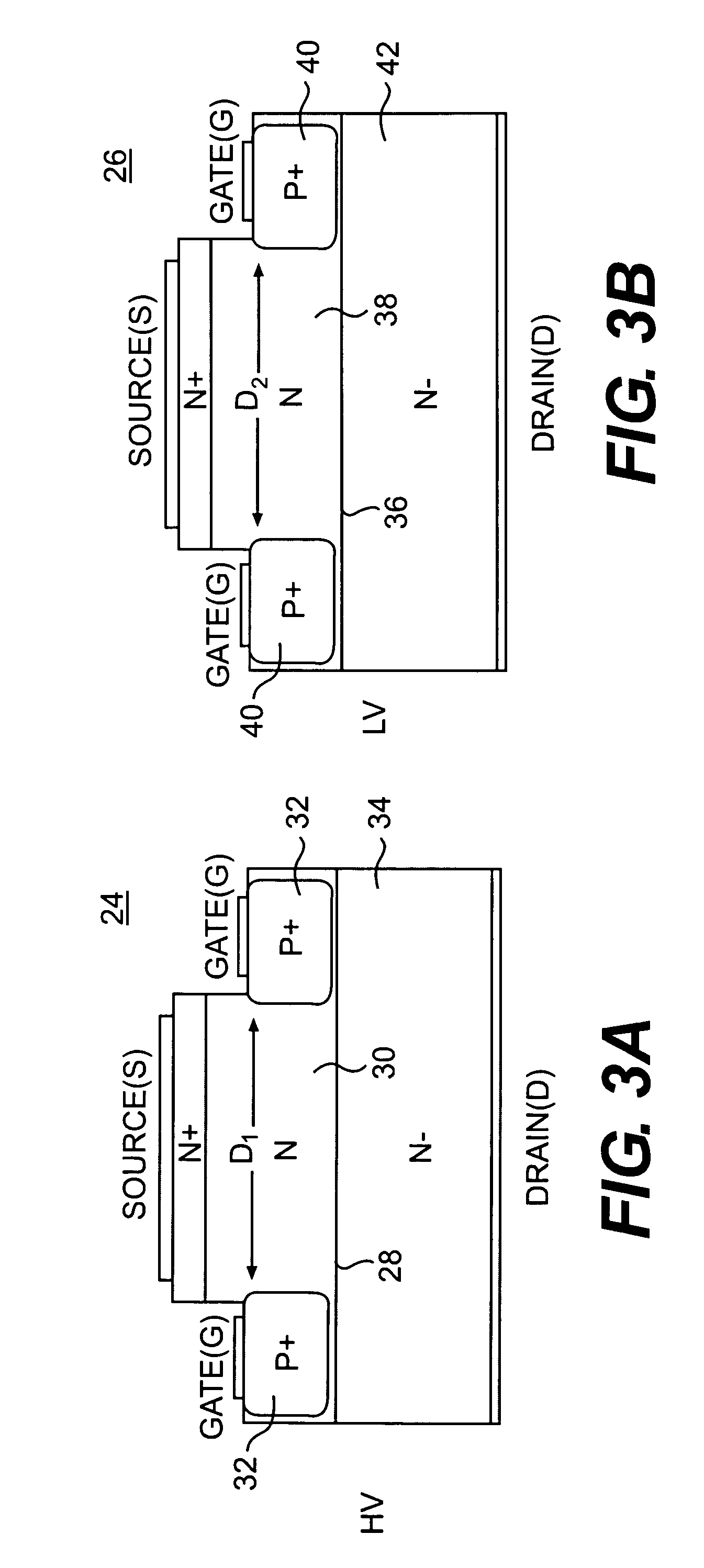

Cascode power switch topologies

ActiveUS7719055B1Increase temperatureHigh blocking voltageElectronic switchingSemiconductor devicesCascodeGallium nitride

A normally-off cascode power switch circuit is disclosed fabricated in wide bandgap semiconductor material such as silicon carbide or gallium nitride and which is capable of conducting current in the forward and reverse direction under the influence of a positive gate bias. The switch includes cascoded junction field effect transistors (JFETs) that enable increased gain, and hence blocking voltage, while minimizing specific on-resistance.

Owner:NORTHROP GRUMMAN SYST CORP

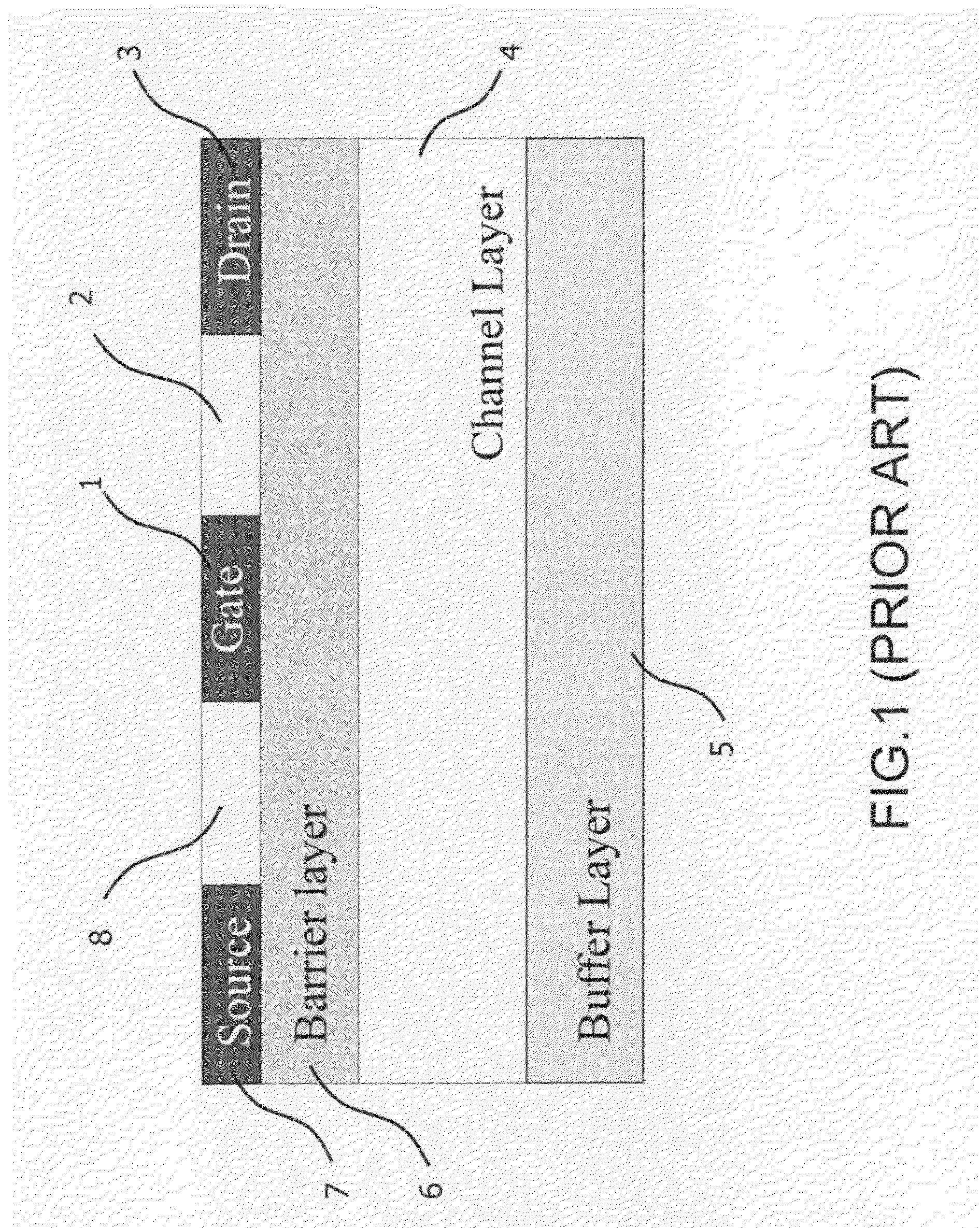

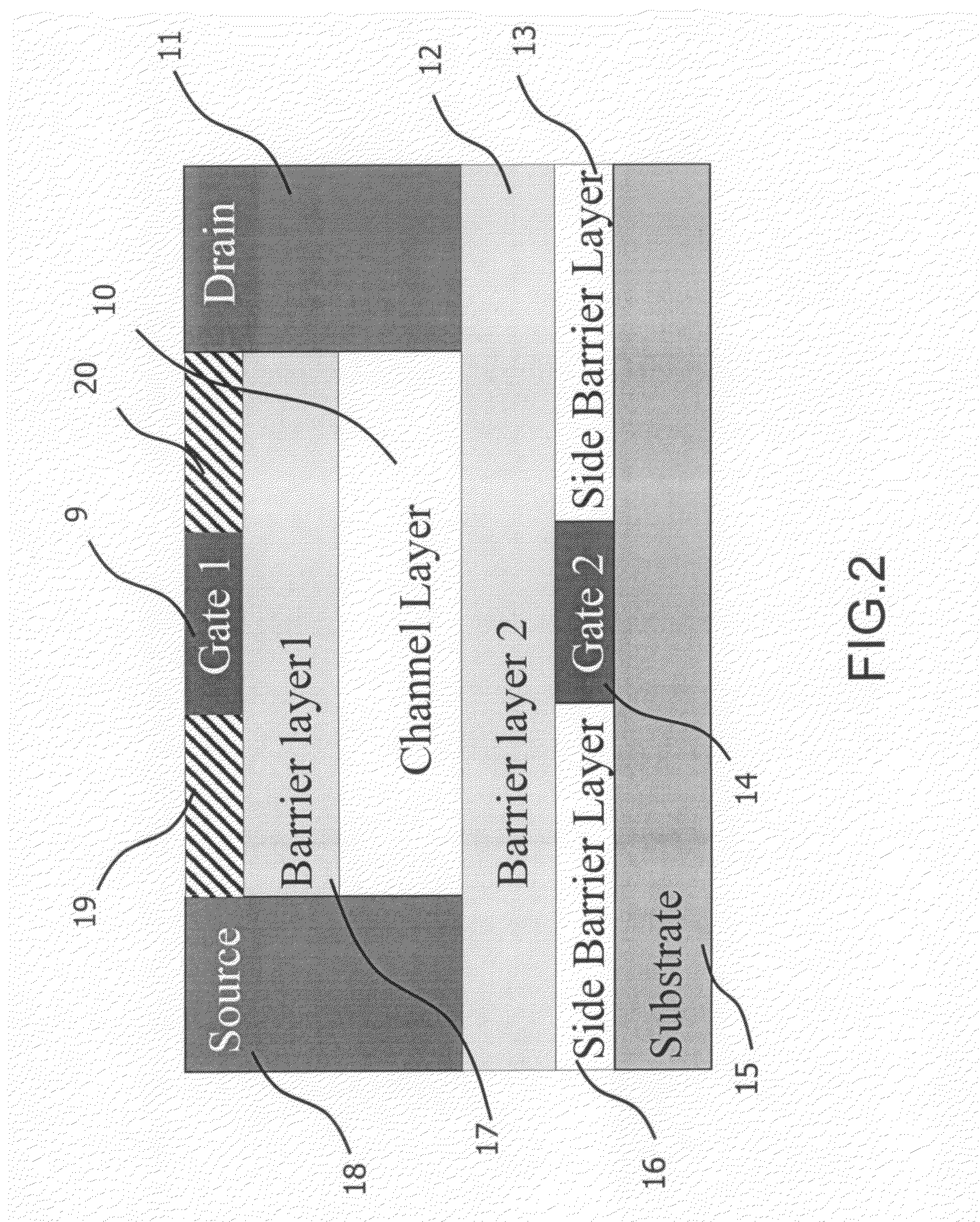

High performance multigate transistor

ActiveUS20120292665A1SpecificEasy to controlTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsSemiconductor structure

A novel semiconductor power transistor is presented. The semiconductor structure is simple and is based on a FET structure, where multiple channels and multiple gate regions are formed in order to achieve a lower specific on-resistance, and a higher control on the transport properties of the device. No dielectric layer is present between gate electrodes and device channels, decreasing the parasitic capacitance associated with the gate terminal. The fabrication of the device does not require Silicon On Insulator techniques and it is not limited to Silicon semiconductor materials. It can be fabricated as an enhancement or depletion device with much more control on the threshold voltage of the device, and with superior RF performance.

Owner:QUALCOMM INC

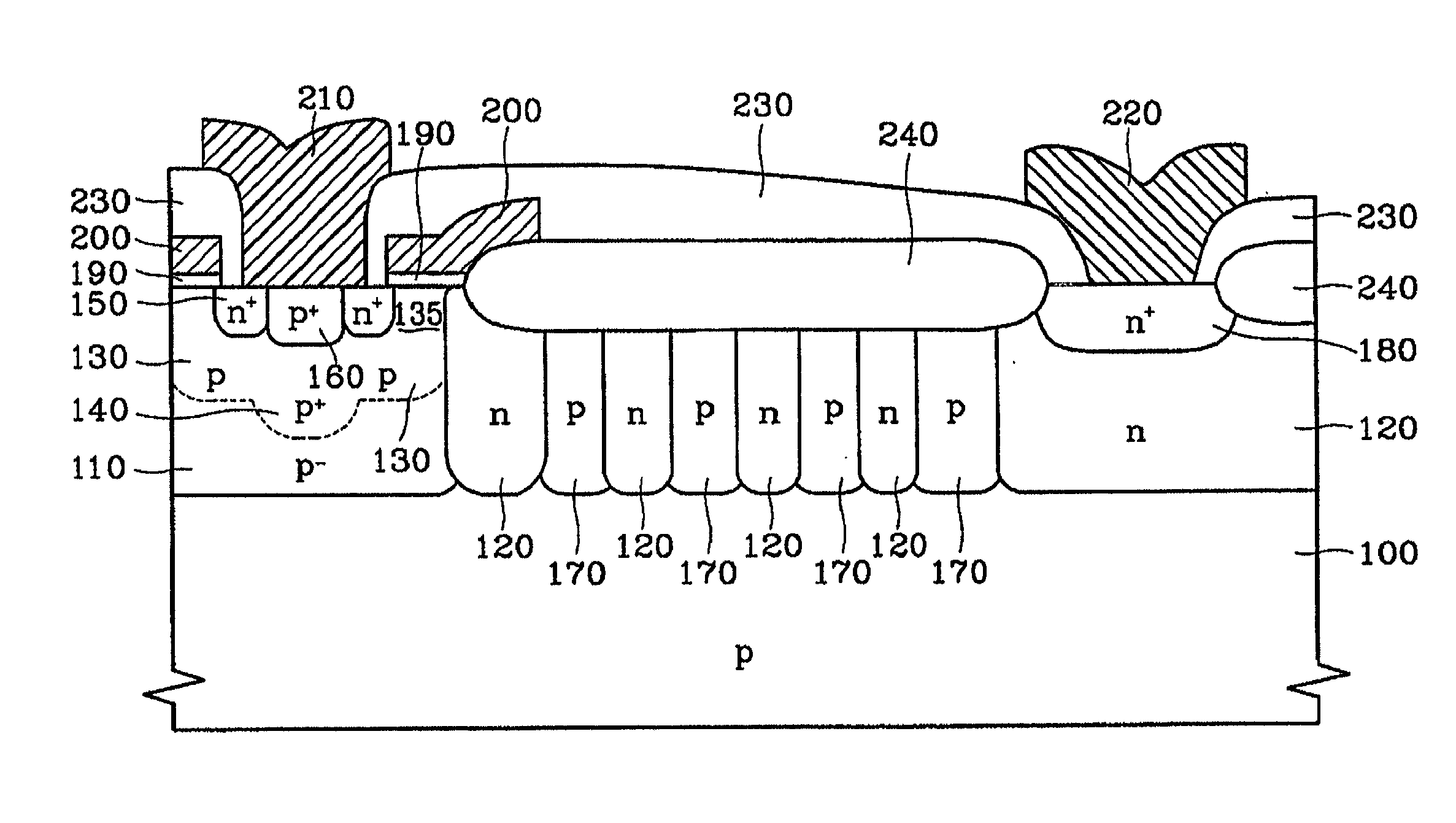

High voltage lateral DMOS transistor having low on-resistance and high breakdown voltage

InactiveUS20030193067A1Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringHigh pressure

A high voltage lateral Double diffused Metal Oxide Semiconductor (DMOS) transistor includes a plurality of well regions of a first conductivity type formed to be spaced out within a well region of a second conductivity type between a channel region of the first conductivity type and a drain region of the second conductivity type. Most current is carried through some portions of the well region of the second conductivity type in which the well regions of the first conductivity do not appear so that the current carrying performance of the device is improved. When a bias voltage is applied to the drain region, the well region of the second conductivity type is completely depleted at other portions where the well region of the second conductivity type and the well regions of the first conductivity type alternately appear so that the breakdown voltage of the device can be increased. In addition, since the well region of the second conductivity type can be easily depleted, not only the breakdown voltage can be increased, but also the impurity concentration of the well region of the second conductivity type can be increased. Accordingly, the on-resistance of the device can be decreased.

Owner:SEMICON COMPONENTS IND LLC

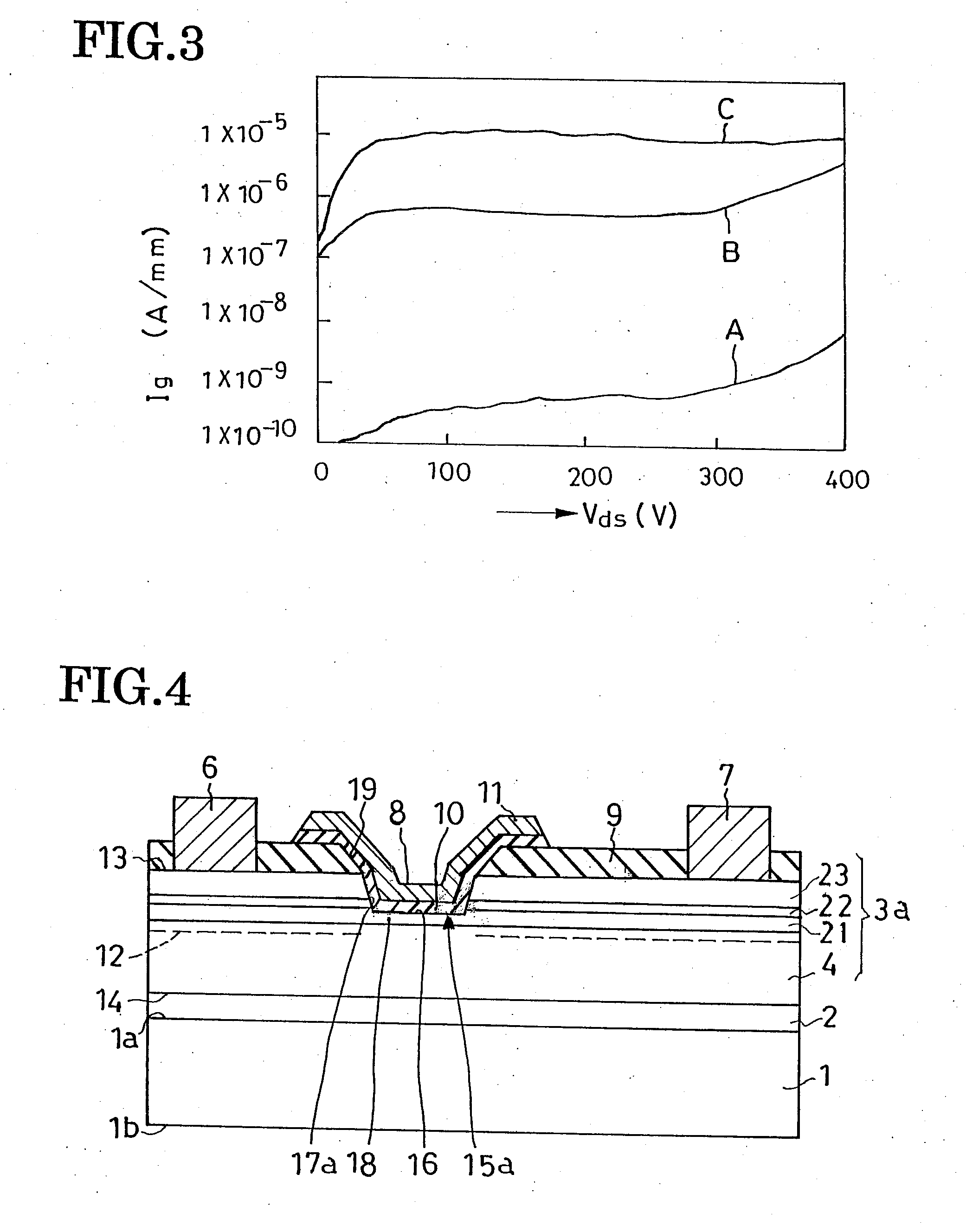

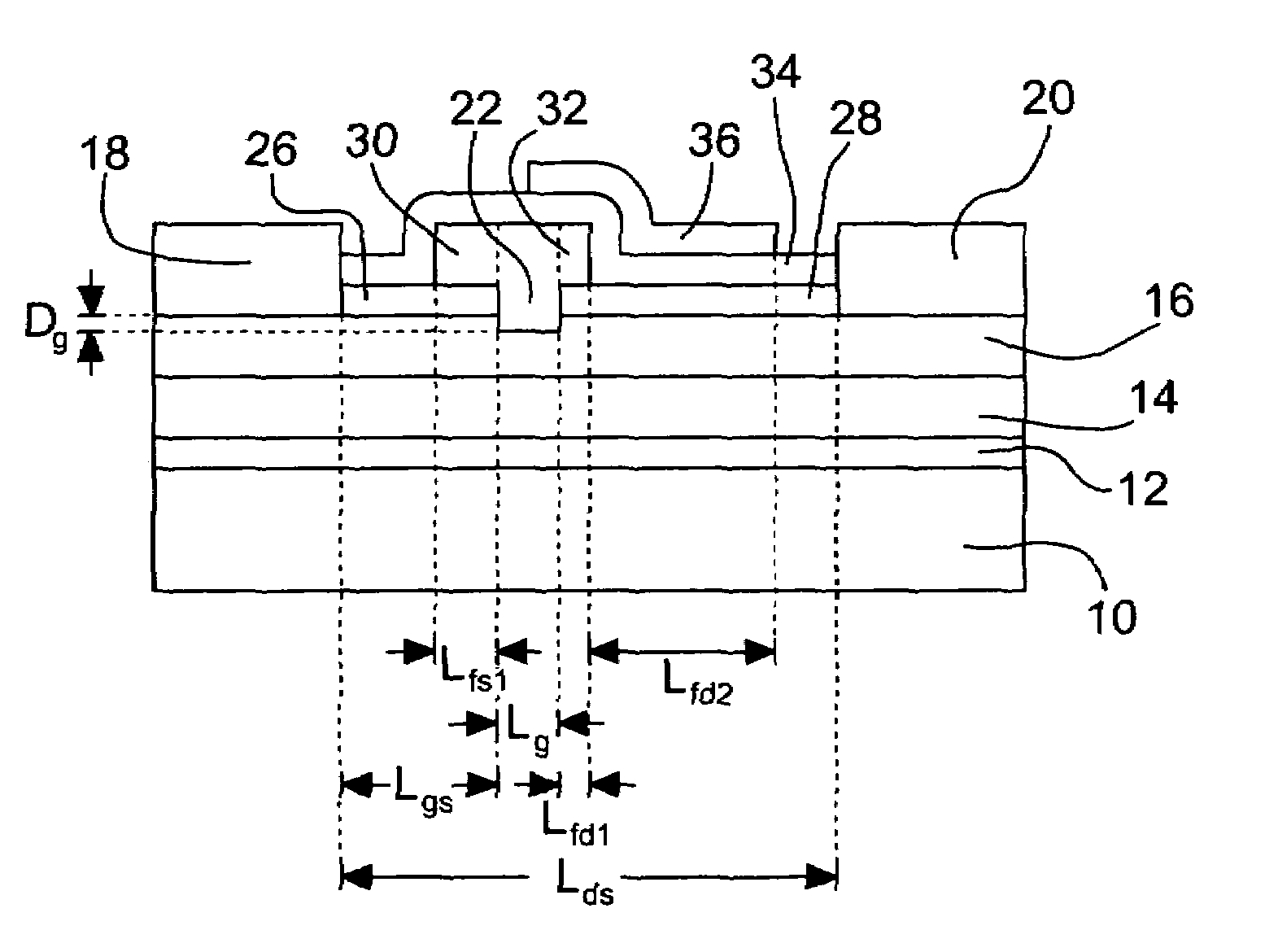

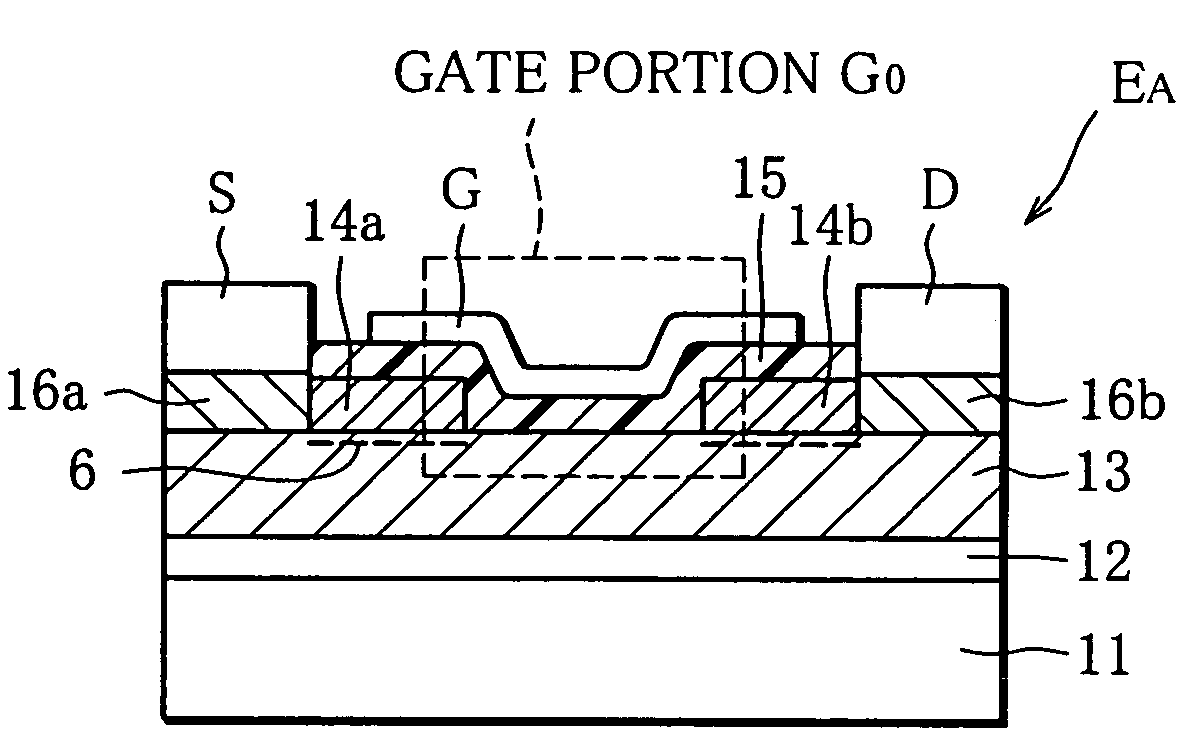

Field-Effect Semiconductor Device, and Method of Fabrication

ActiveUS20090057720A1Reduce leakage currentPreventing current collapseSemiconductor/solid-state device detailsSolid-state devicesHeterojunctionField effect

A HEMT-type field-effect semiconductor device has a main semiconductor region comprising two layers of dissimilar materials such that a two-dimensional electron gas layer is generated along the heterojunction between the two layers. A source and a drain electrode are placed in spaced positions on a major surface of the main semiconductor region. Between these electrodes, a gate electrode is received in a recess in the major surface of the main semiconductor region via a p-type metal oxide semiconductor film whereby a depletion zone is normally created in the electron gas layer, with a minimum of turn-on resistance and gate leak current.

Owner:SANKEN ELECTRIC CO LTD

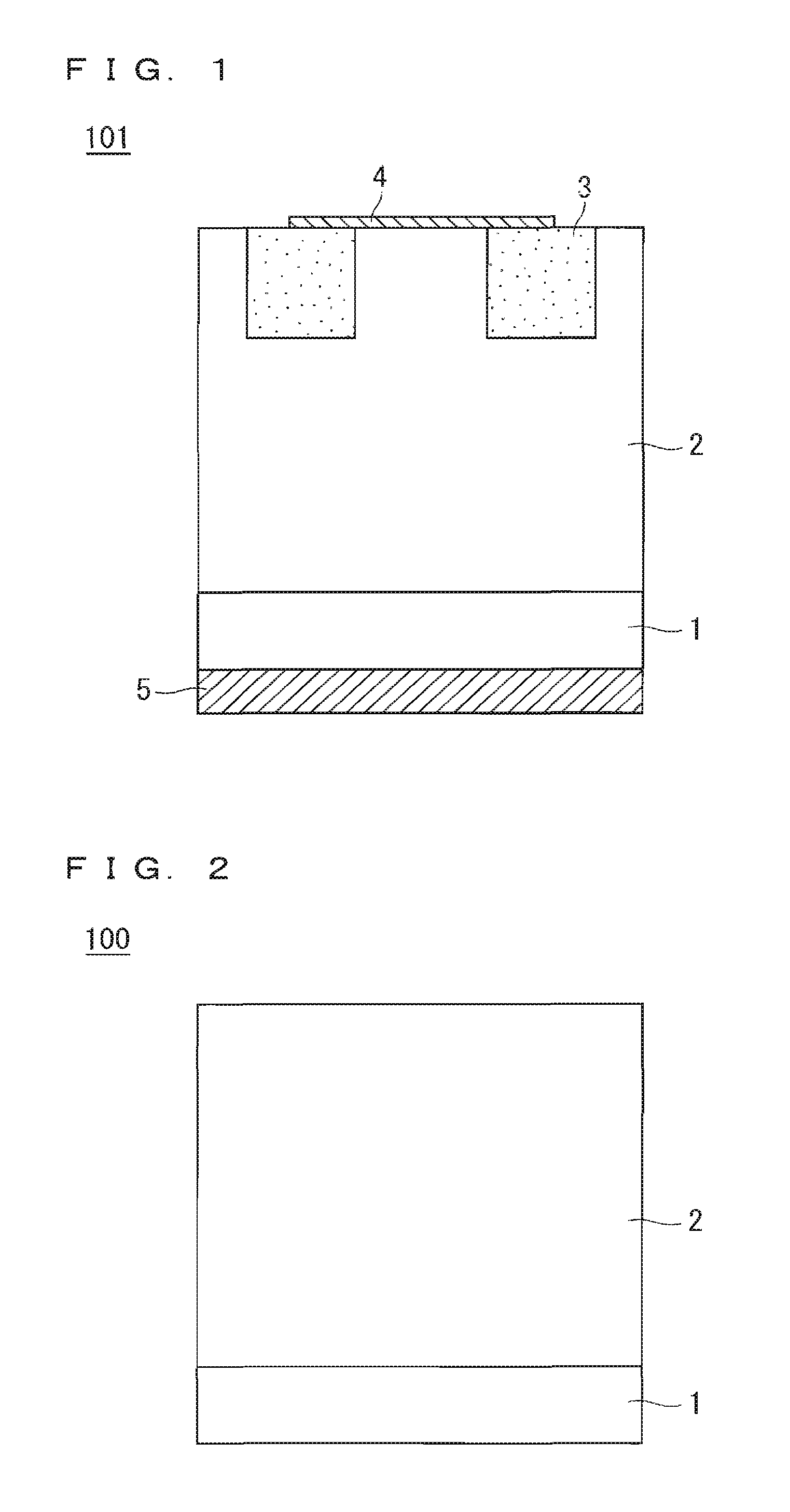

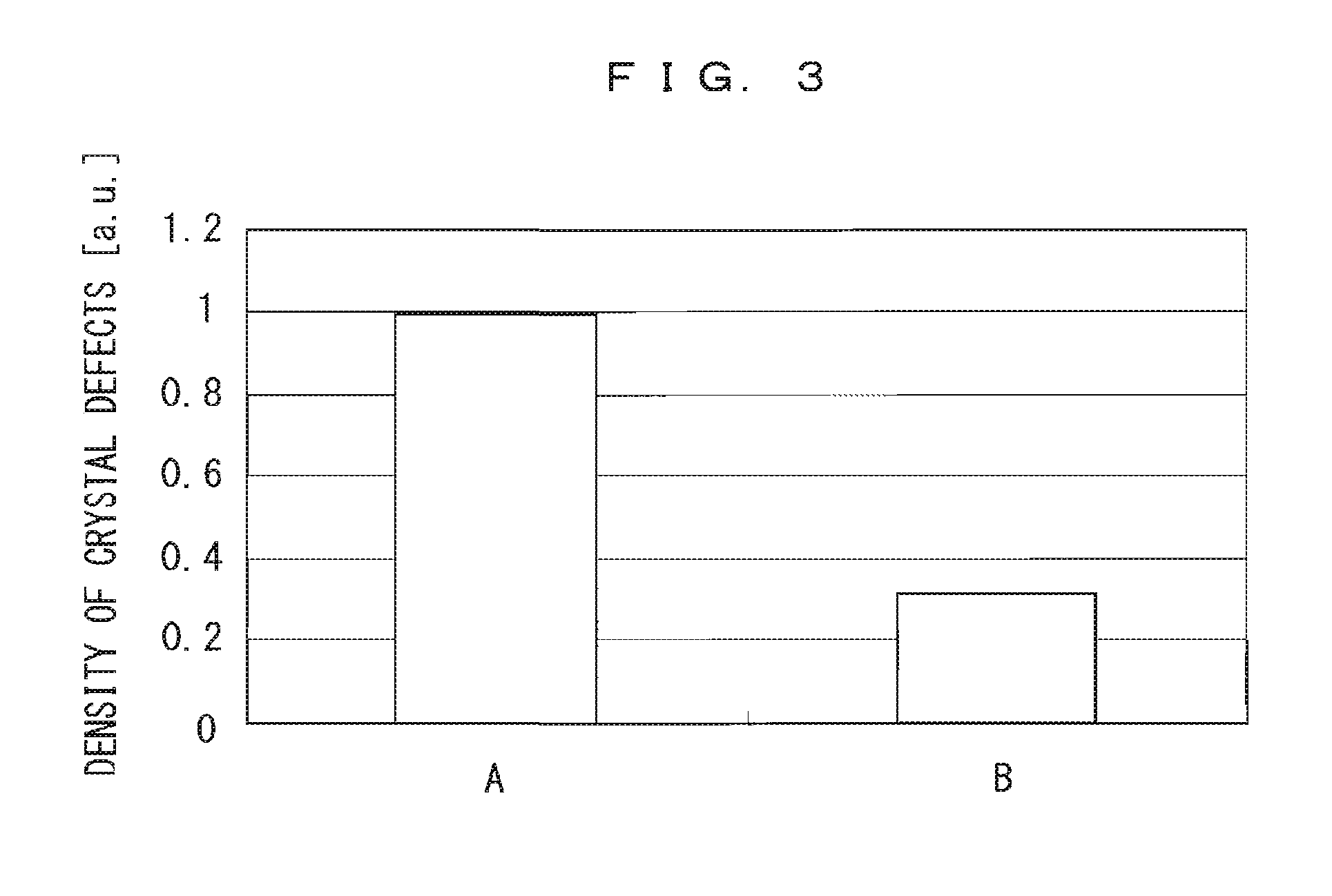

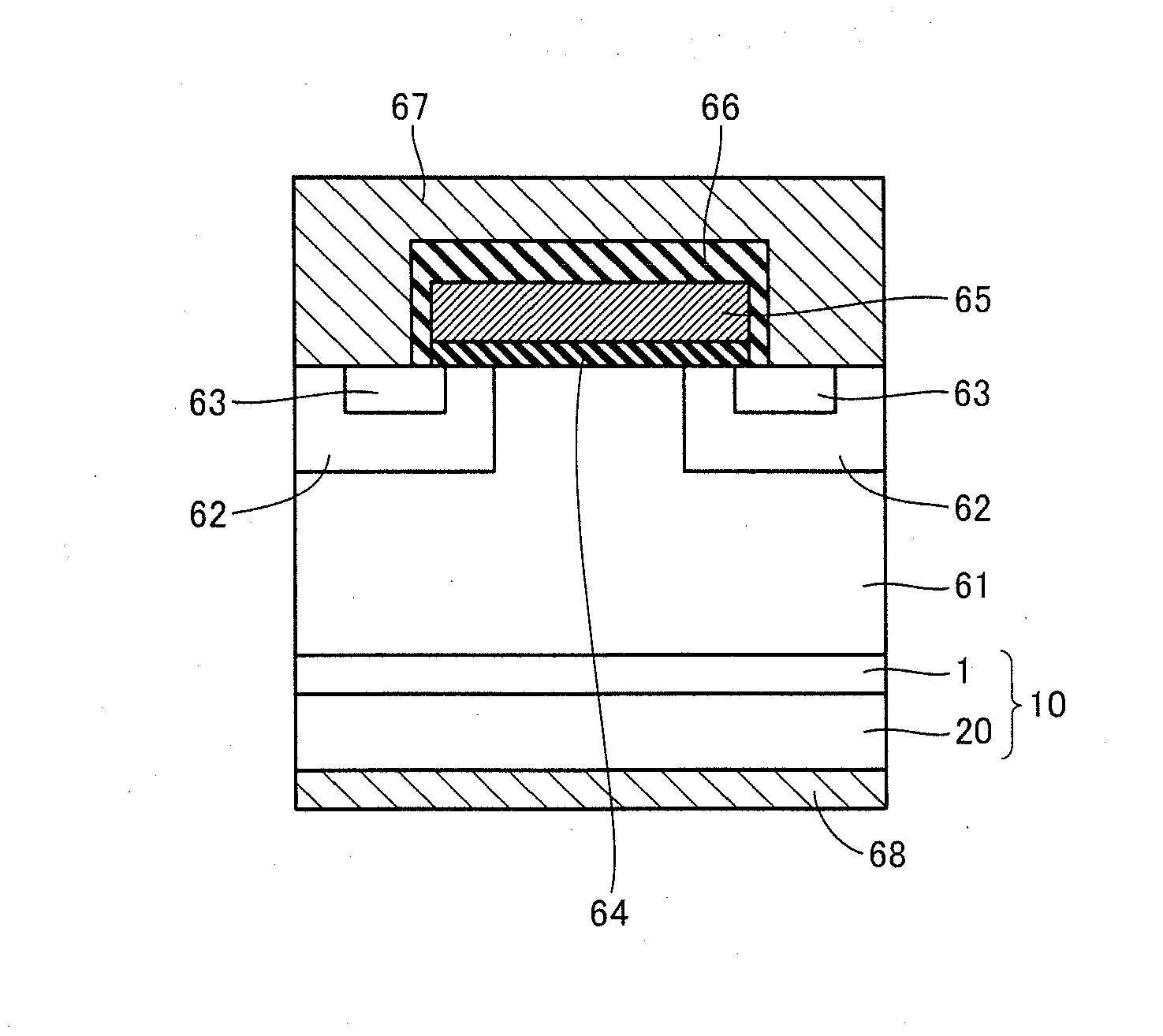

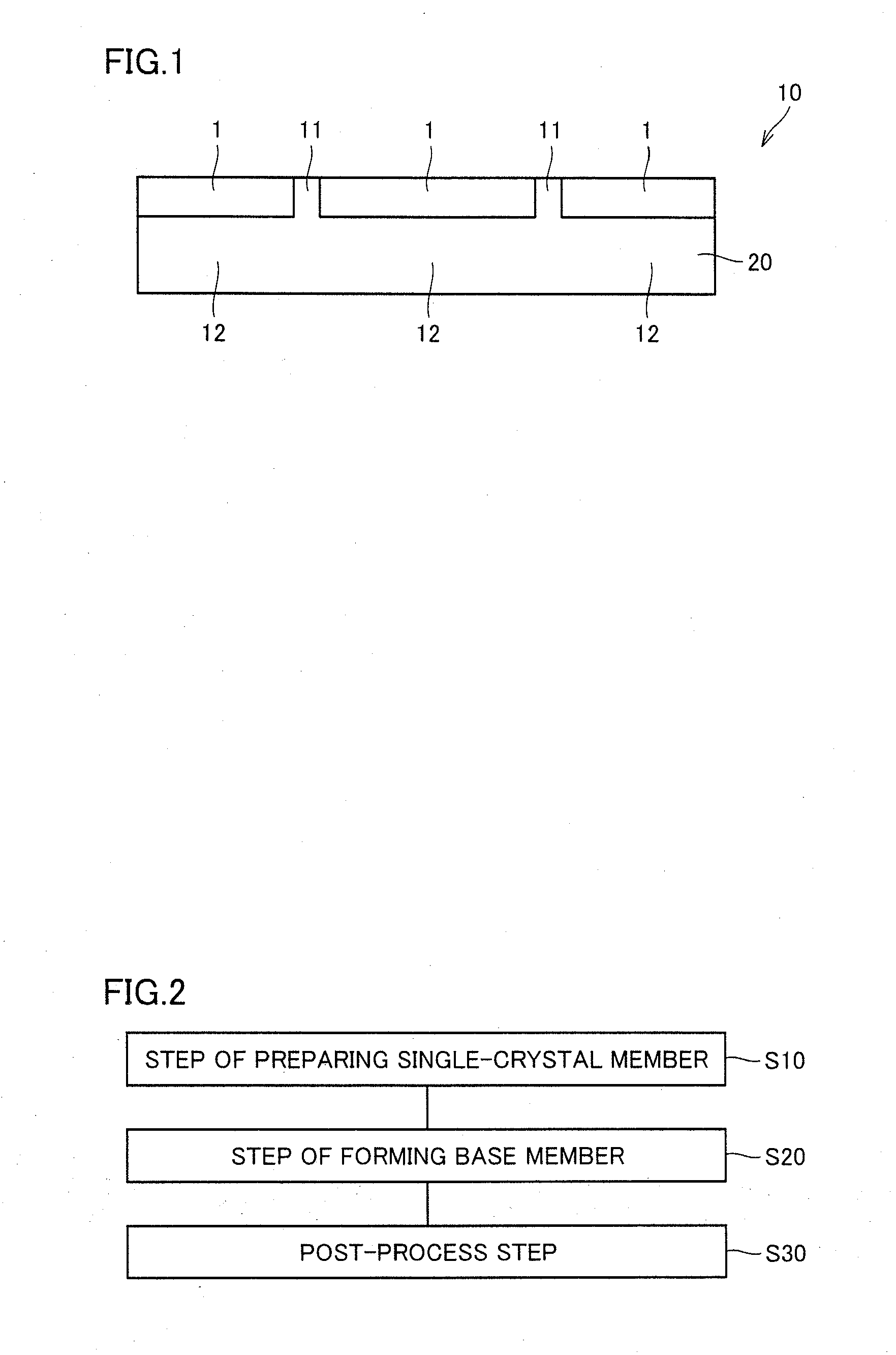

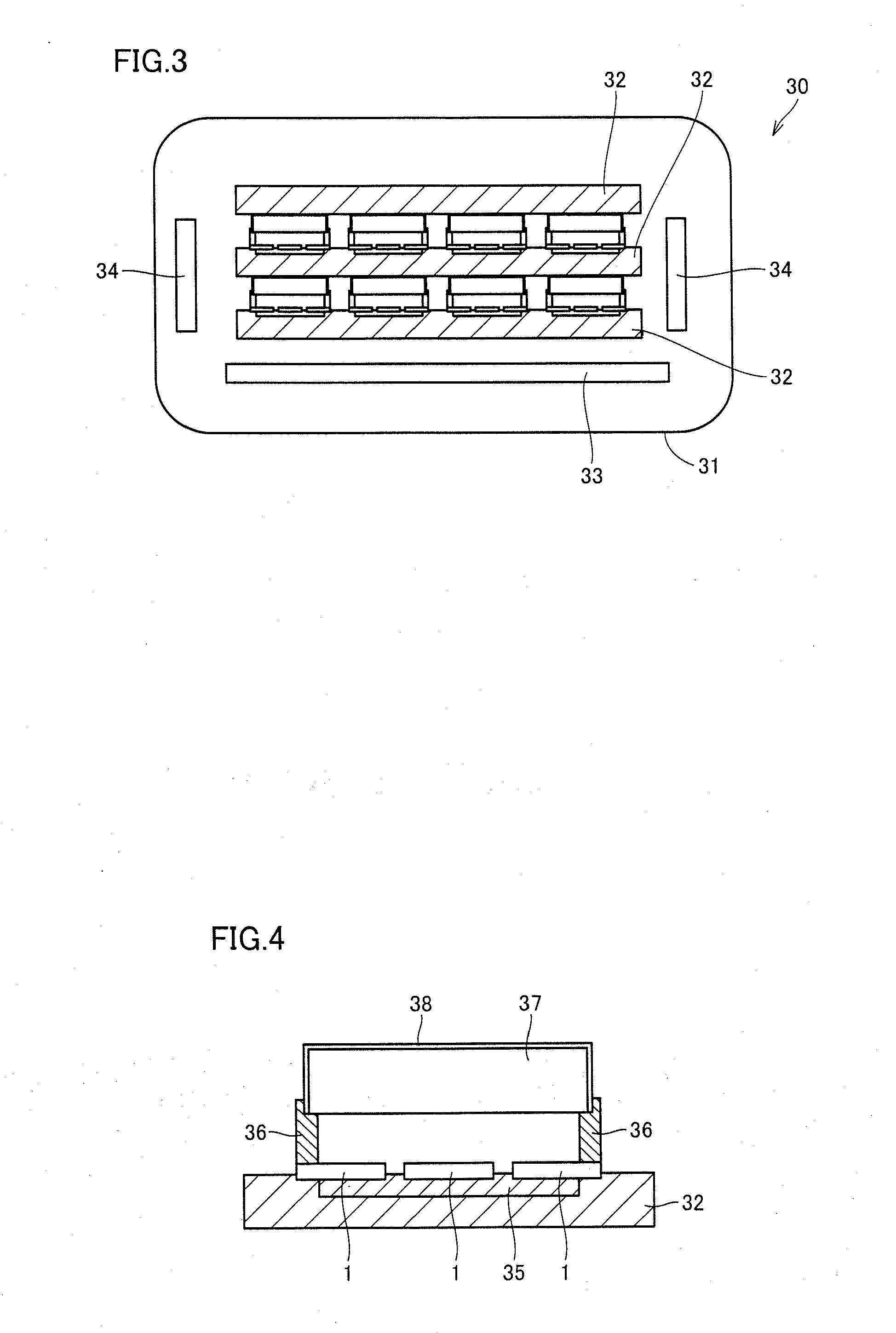

Silicon carbide substrate, epitaxial layer provided substrate, semiconductor device, and method for manufacturing silicon carbide substrate

InactiveUS20120119225A1Lower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSingle crystal substrateSingle crystal

The present invention provides a silicon carbide substrate, an epitaxial layer provided substrate, a semiconductor device, and a method for manufacturing the silicon carbide substrate, each of which achieves reduced on-resistance. The silicon carbide substrate is a silicon carbide substrate having a main surface, and includes: a SiC single-crystal substrate formed in at least a portion of the main surface; and a base member disposed to surround the SiC single-crystal substrate. The base member includes a boundary region and a base region. The boundary region is adjacent to the SiC single-crystal substrate in a direction along the main surface, and has a crystal grain boundary therein. The base region is adjacent to the SiC single-crystal substrate in a direction perpendicular to the main surface, and has an impurity concentration higher than that of the SiC single-crystal substrate.

Owner:SUMITOMO ELECTRIC IND LTD

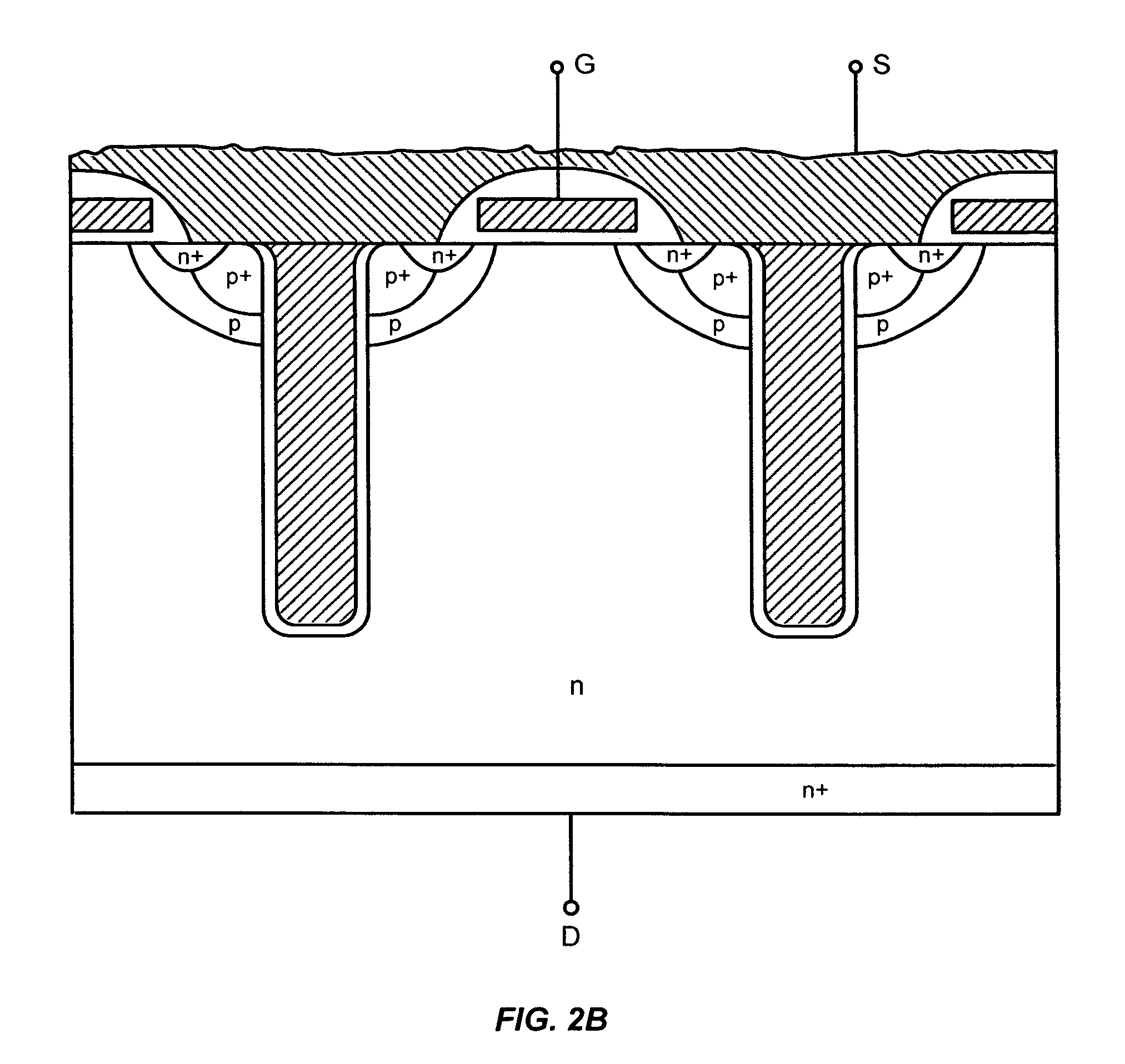

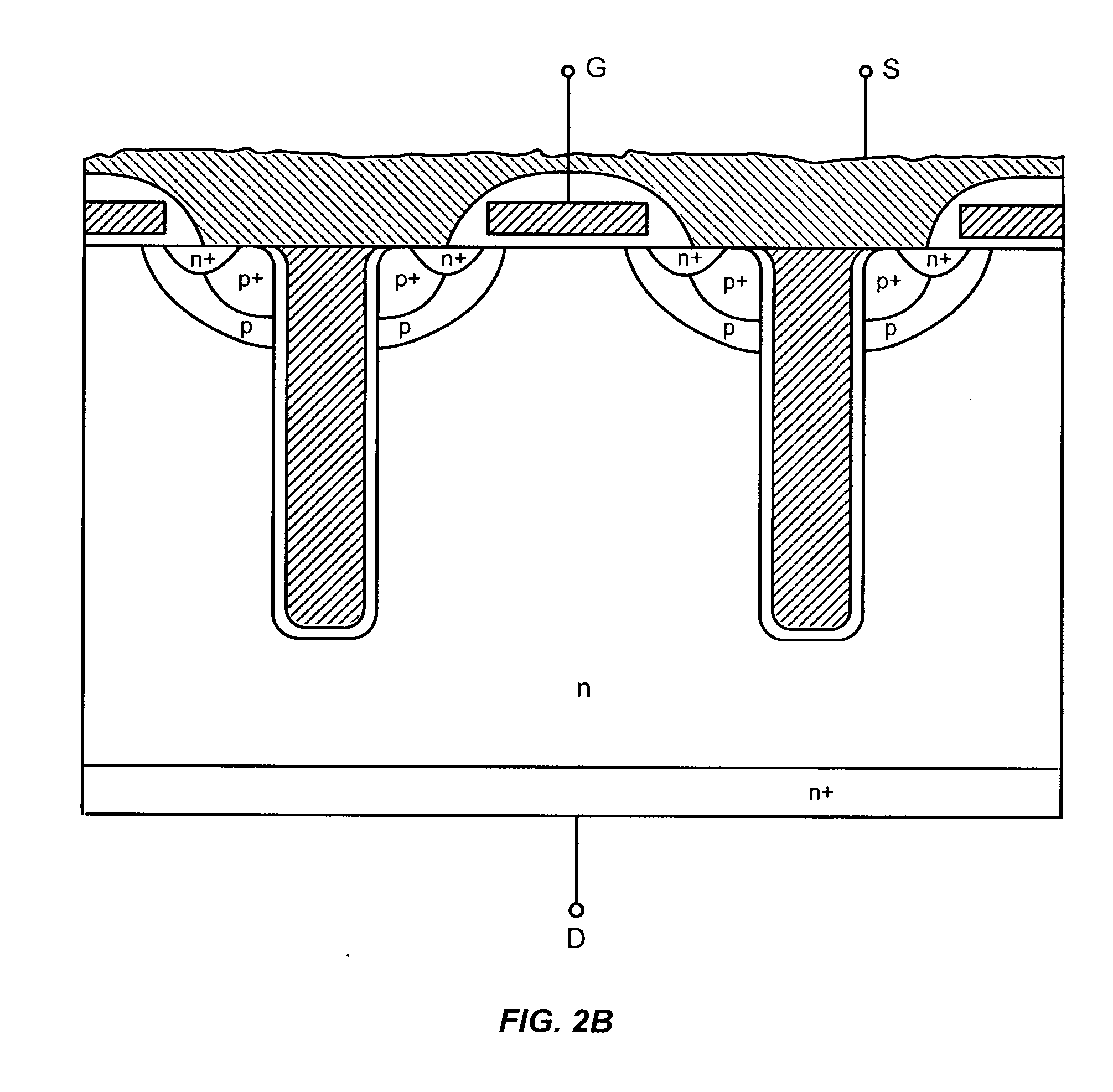

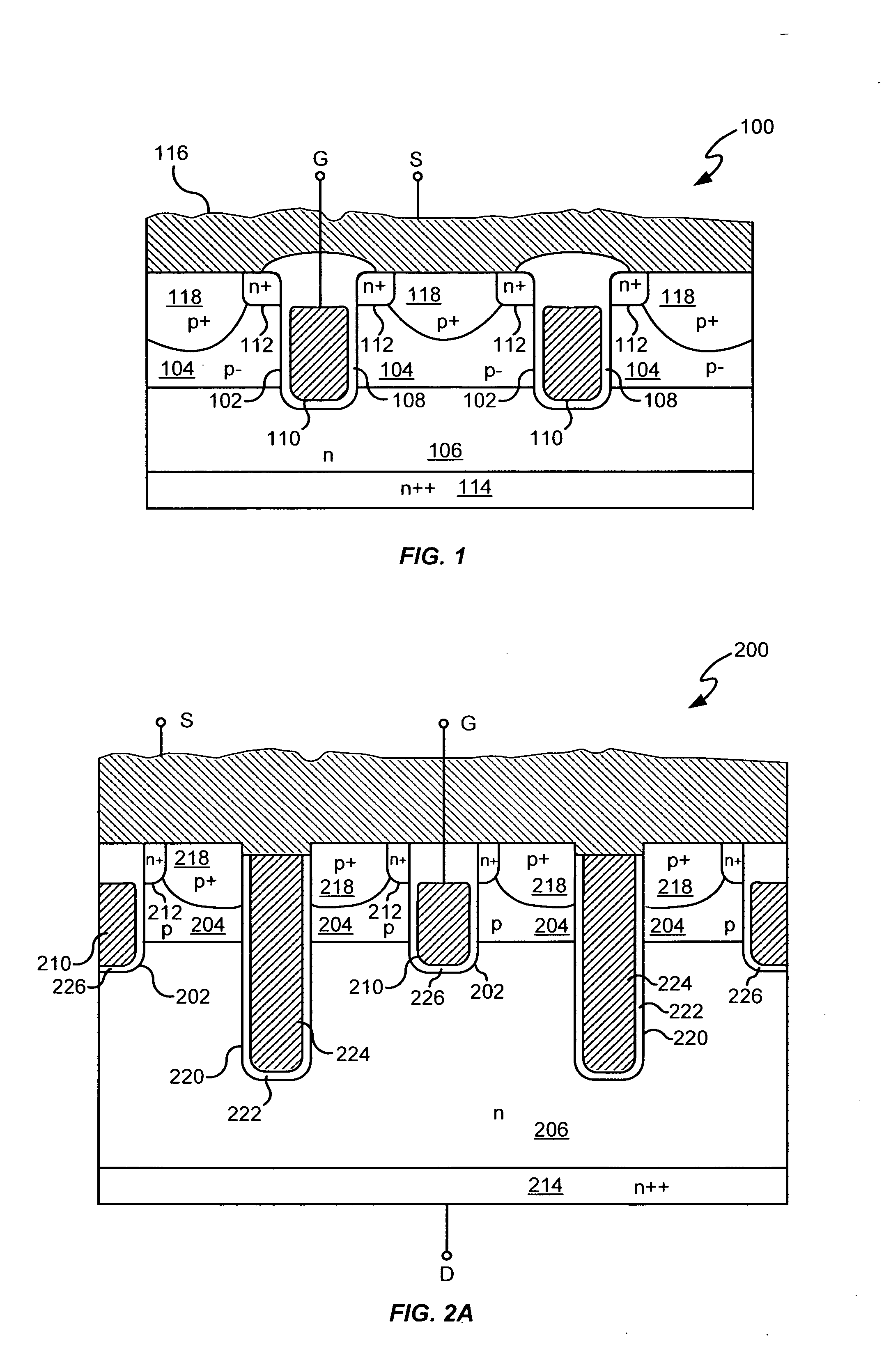

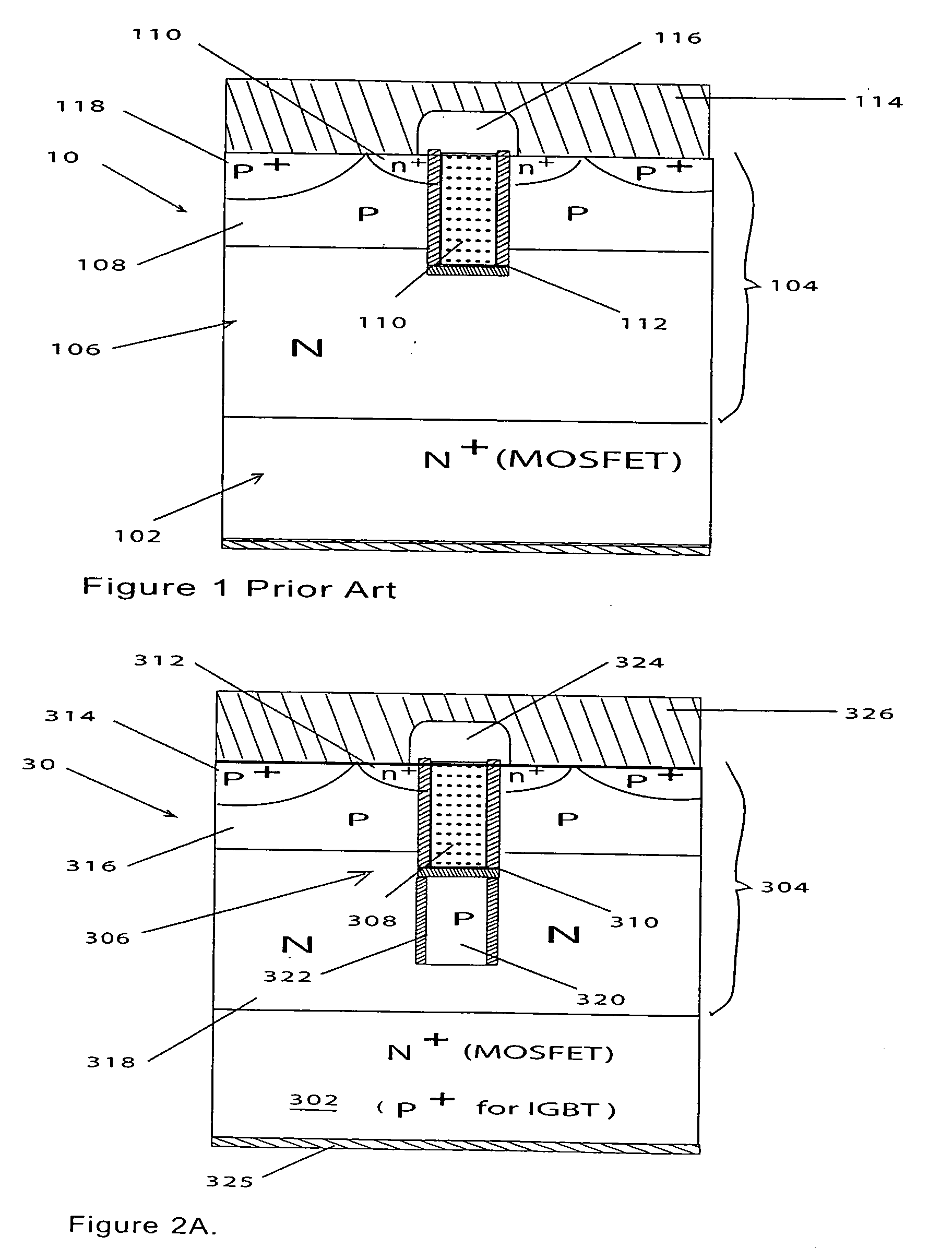

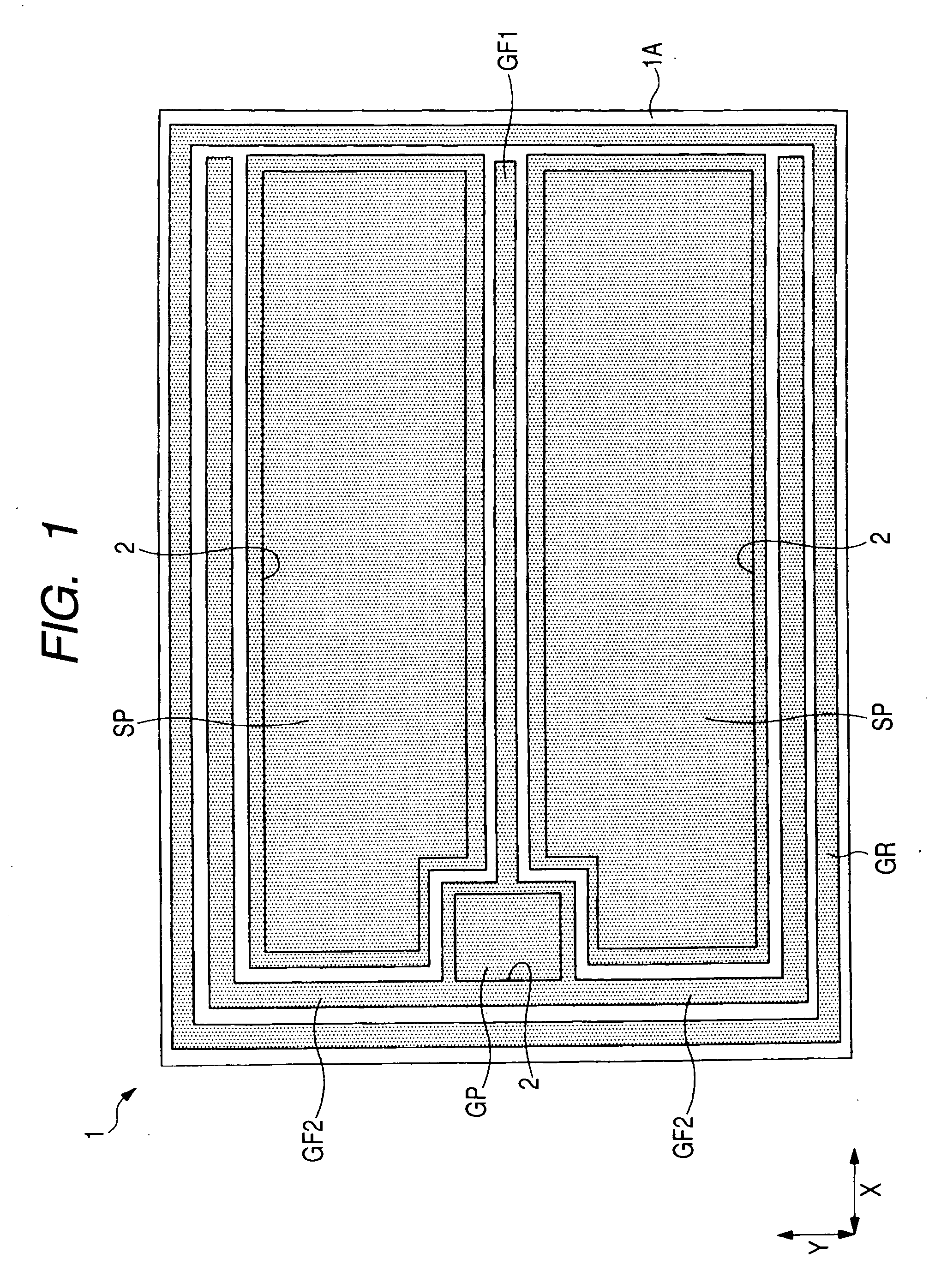

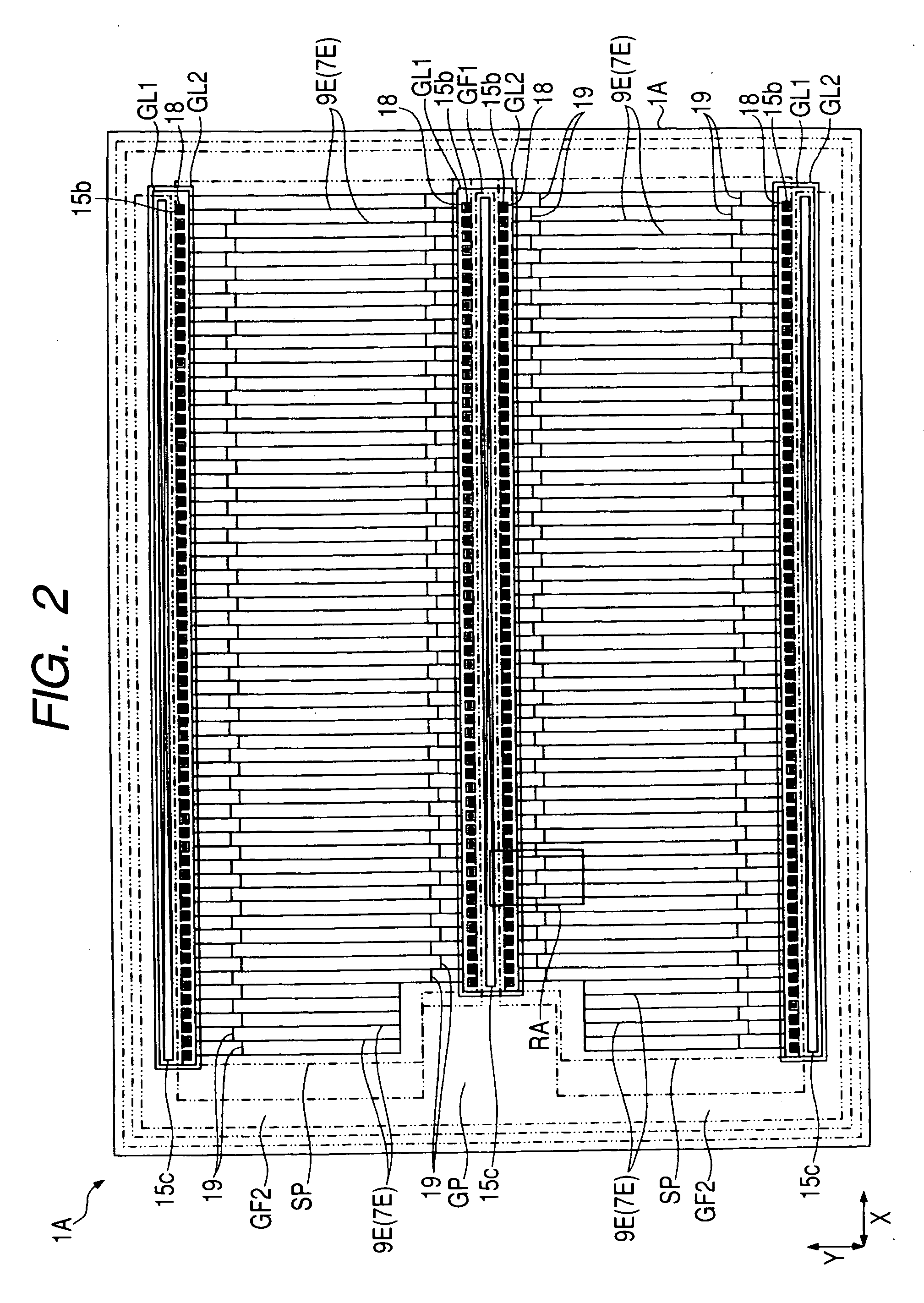

Super trench MOSFET including buried source electrode and method of fabricating the same

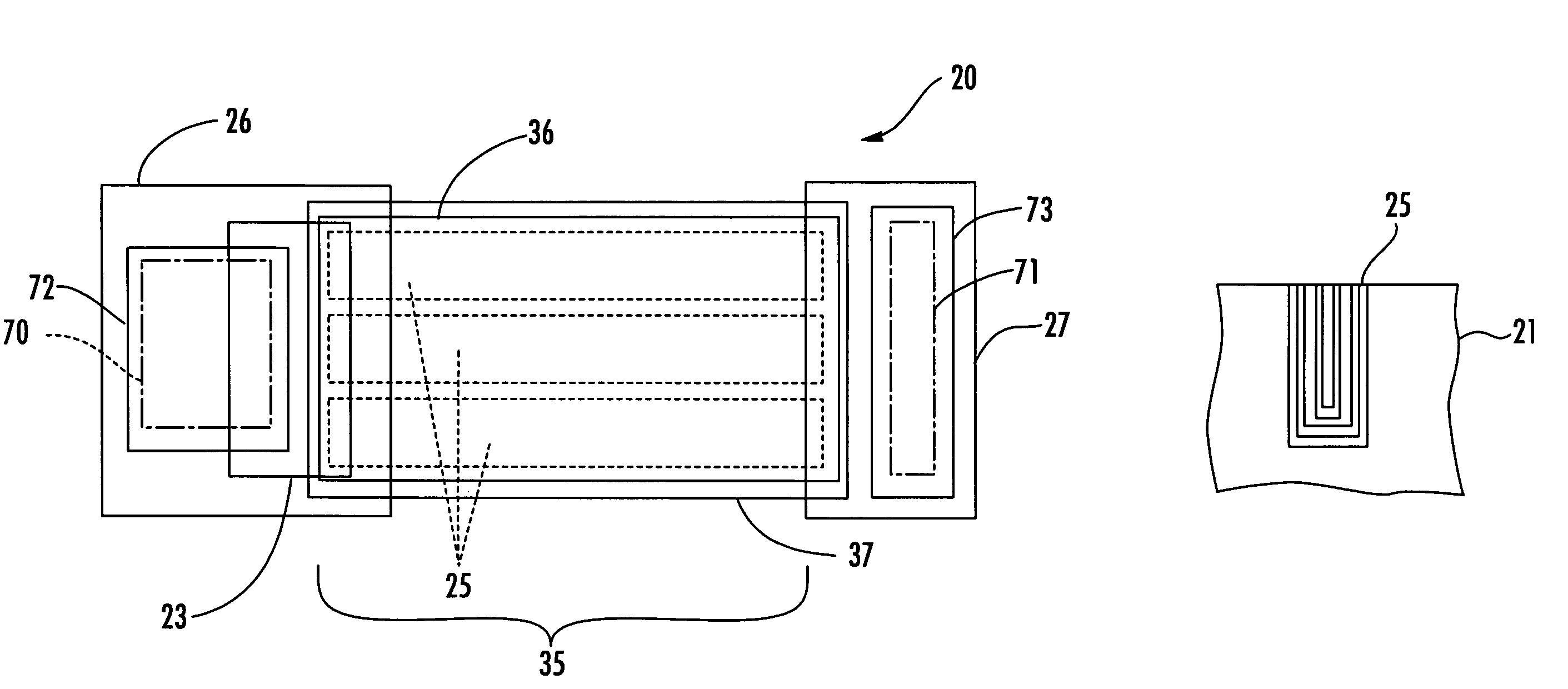

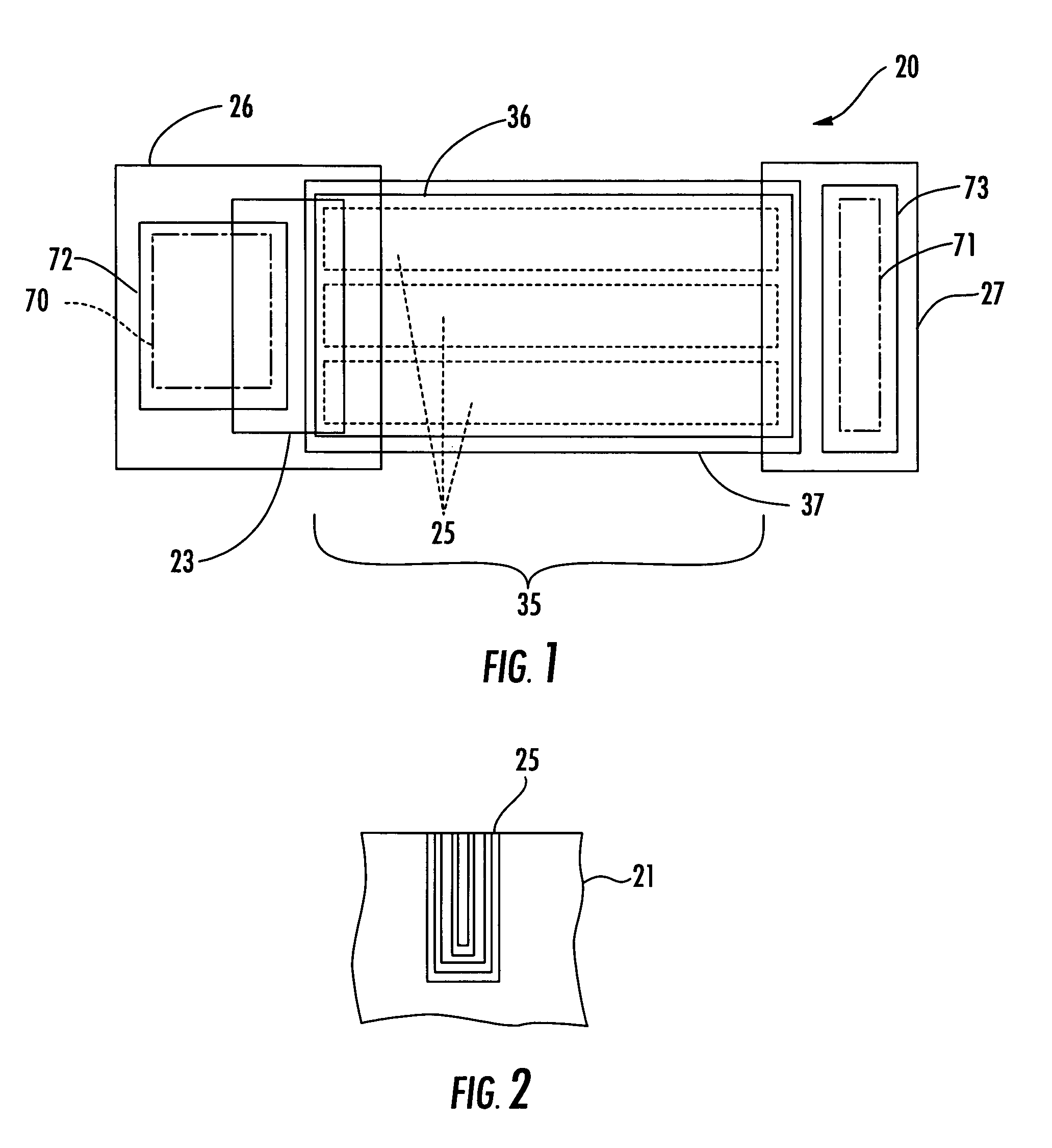

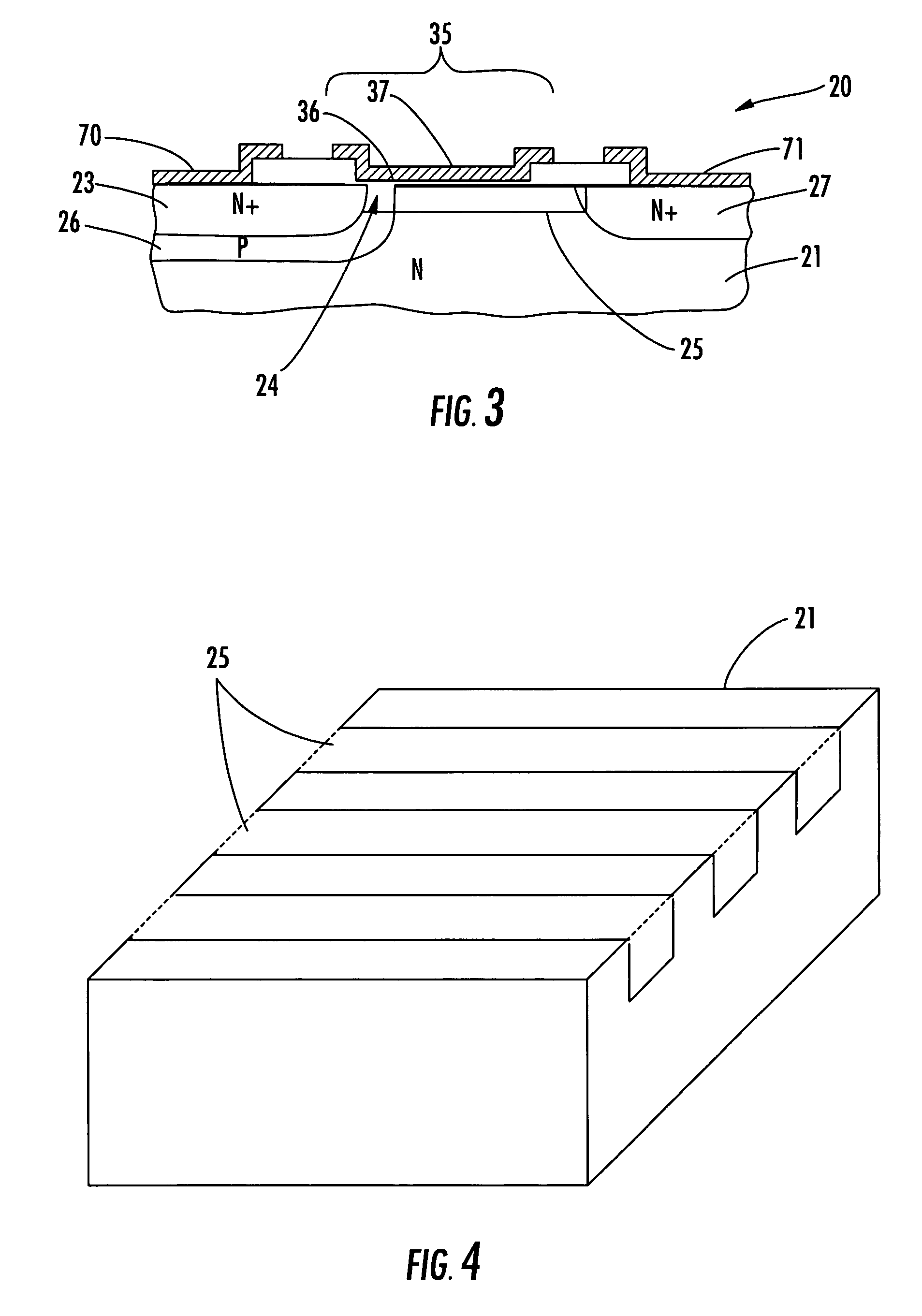

InactiveUS7183610B2Less resistivityIncrease concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceTrench mosfet

In a trench MOSFET, the lower portion of the trench contains a buried source electrode, which is insulated from the epitaxial layer and semiconductor substrate but in electrical contact with the source region. When the MOSFET is in an “off” condition, the bias of the buried source electrode causes the “drift” region of the mesa to become depleted, enhancing the ability of the MOSFET to block current. The doping concentration of the drift region can therefore be increased, reducing the on-resistance of the MOSFET. The buried source electrode also reduces the gate-to-drain capacitance of the MOSFET, improving the ability of the MOSFET to operate at high frequencies. The substrate may advantageously include a plurality of annular trenches separated by annular mesas and a gate metal layer that extends outward from a central region in a plurality of gate metal legs separated by source metal regions.

Owner:SILICONIX

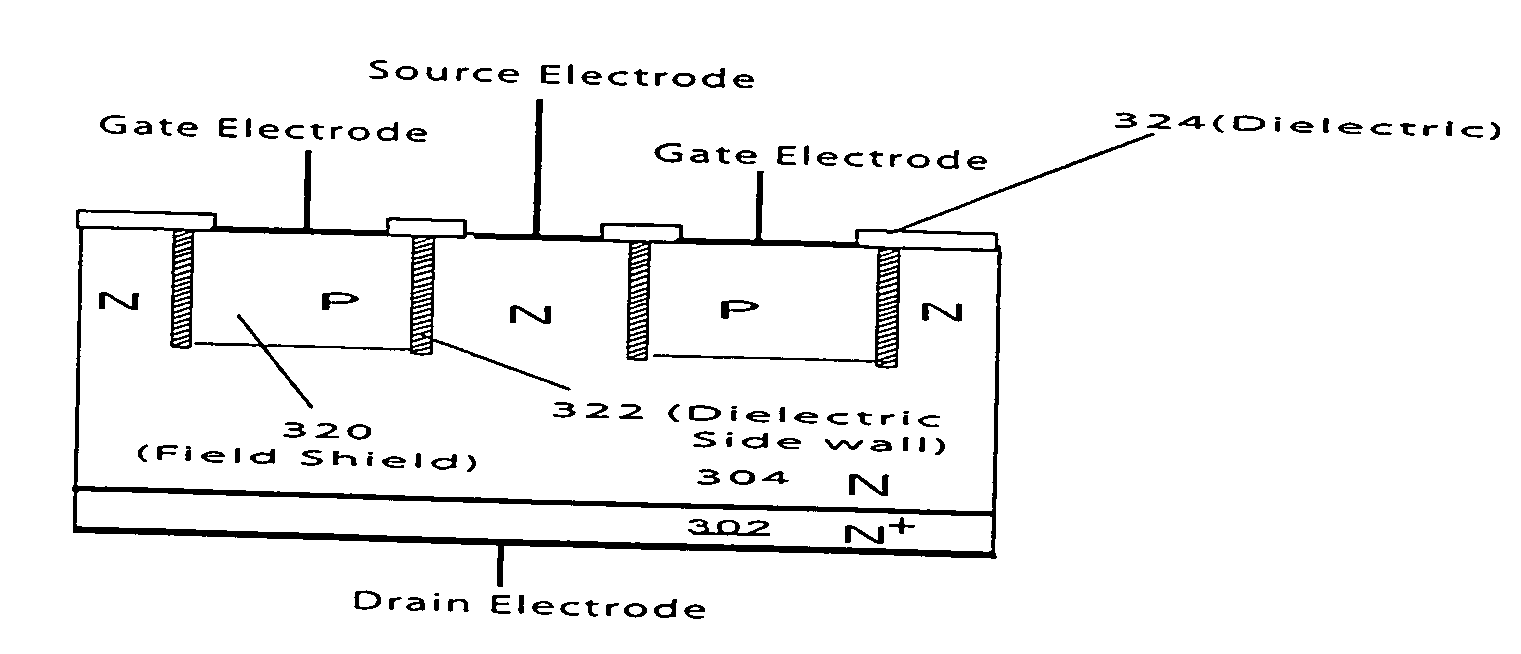

Semiconductor device containing dielectrically isolated pn junction for enhanced breakdown characteristics

InactiveUS20050167695A1Increased avalanche breakdown voltageLower on-resistanceThyristorSemiconductor/solid-state device manufacturingDevice materialPower MOSFET

A semiconductor device includes a field shield region that is doped opposite to the conductivity of the substrate and is bounded laterally by dielectric sidewall spacers and from below by a PN junction. For example, in a trench-gated MOSFET the field shield region may be located beneath the trench and may be electrically connected to the source region. When the MOSFET is reverse-biased, depletion regions extend from the dielectric sidewall spacers into the “drift” region, shielding the gate oxide from high electric fields and increasing the avalanche breakdown voltage of the device. This permits the drift region to be more heavily doped and reduces the on-resistance of the device. It also allows the use of a thin, 20 Å gate oxide for a power MOSFET that is to be switched with a 1V signal applied to its gate while being able to block over 30V applied across its drain and source electrodes, for example.

Owner:ALPHA & OMEGA SEMICON INC

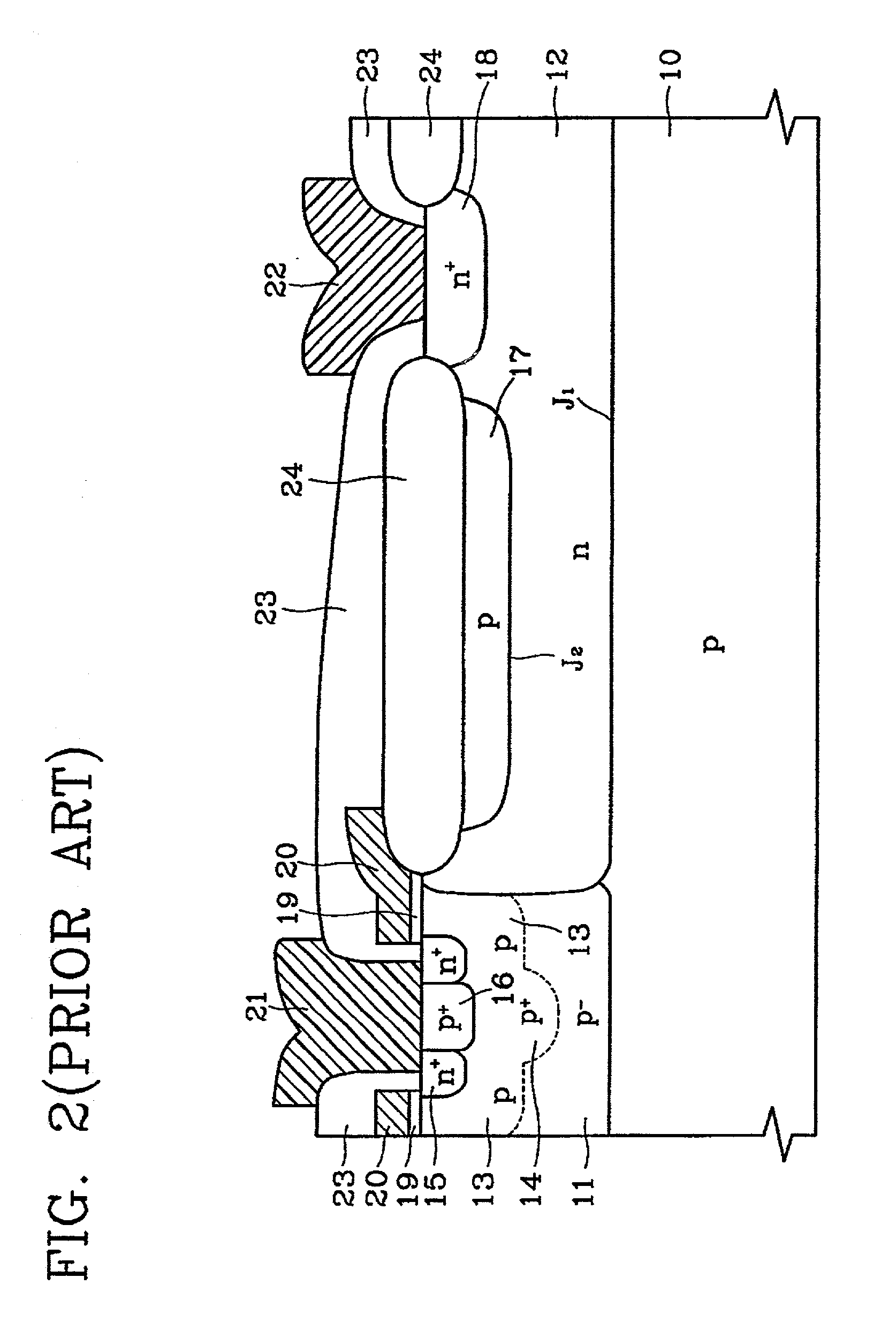

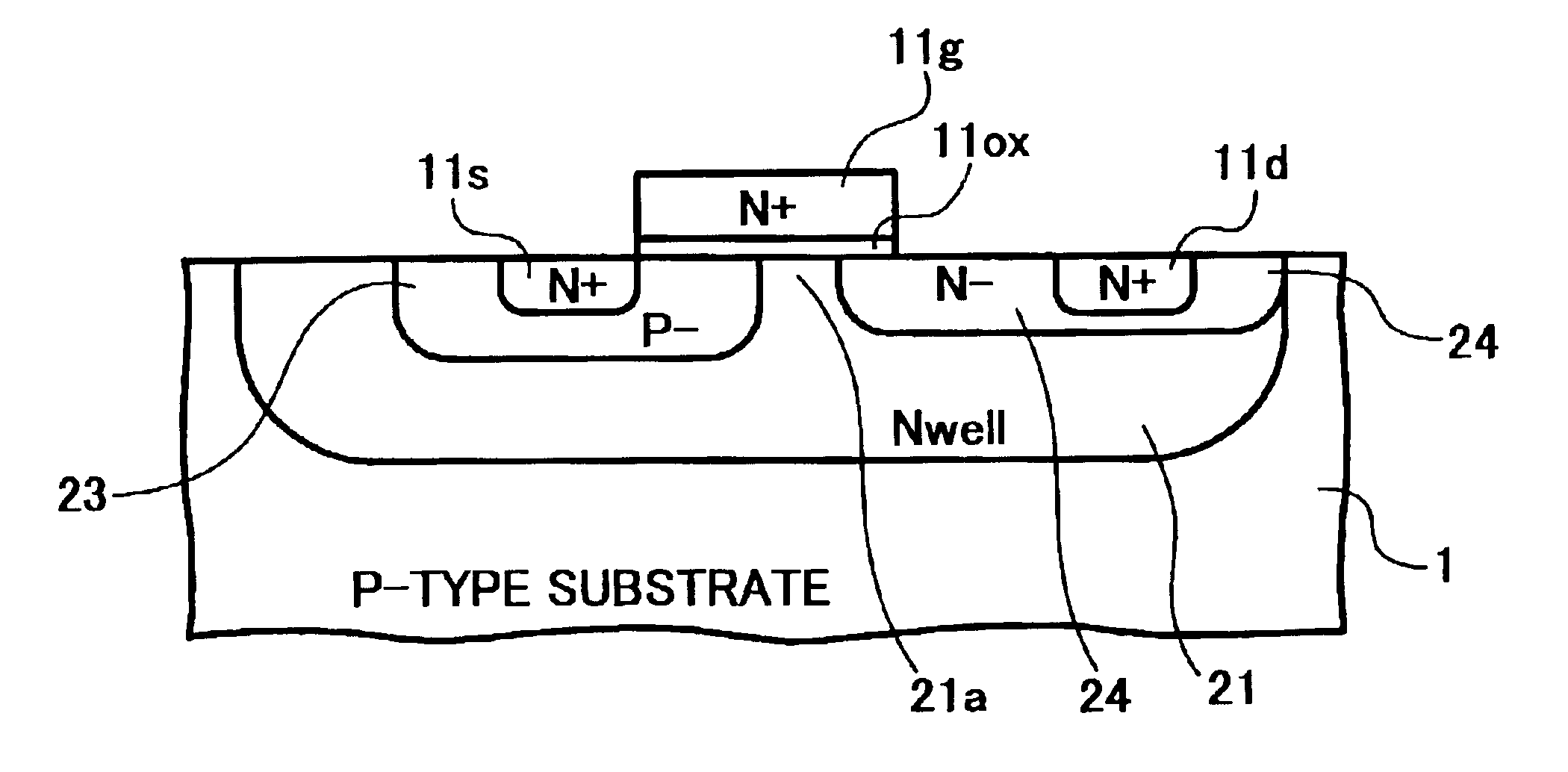

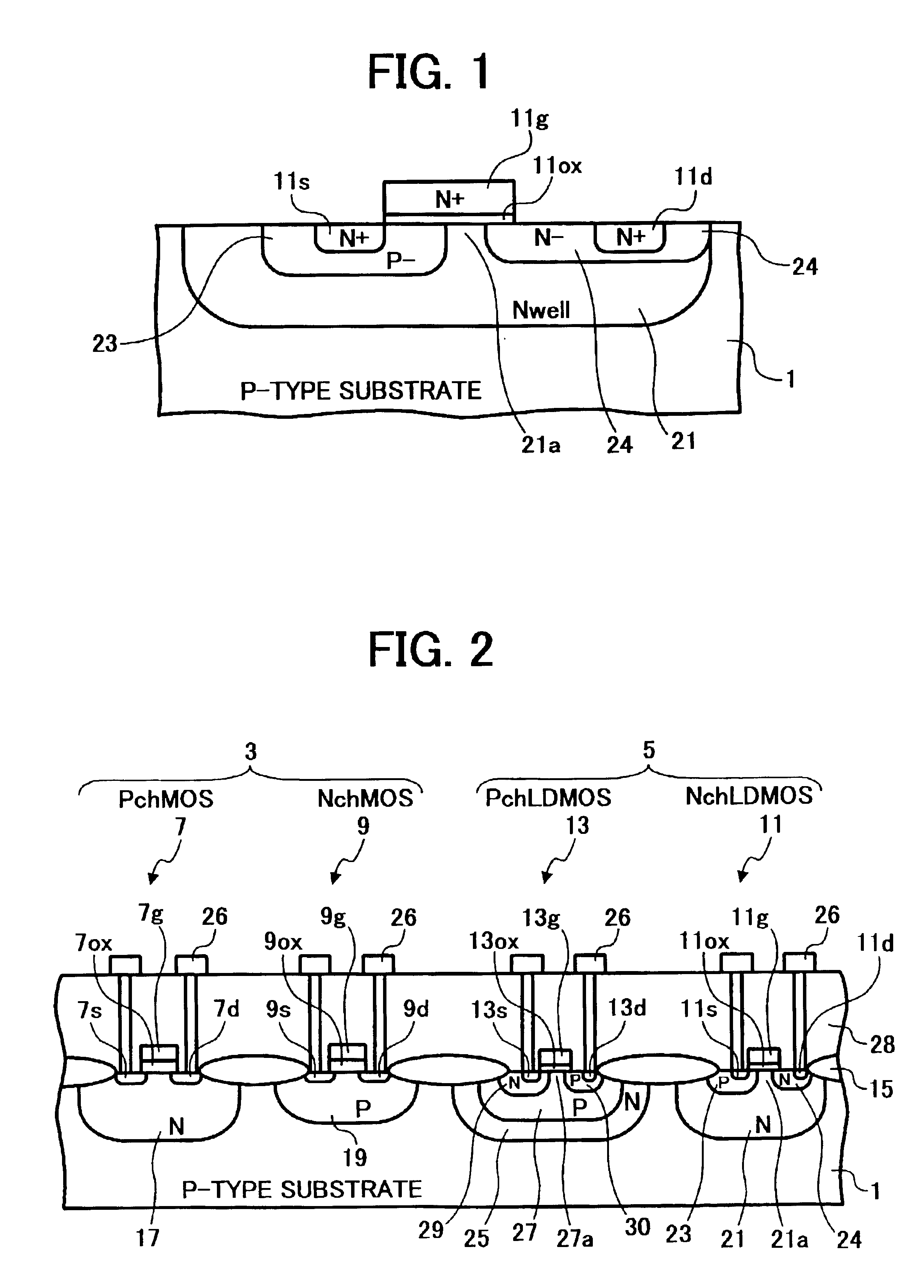

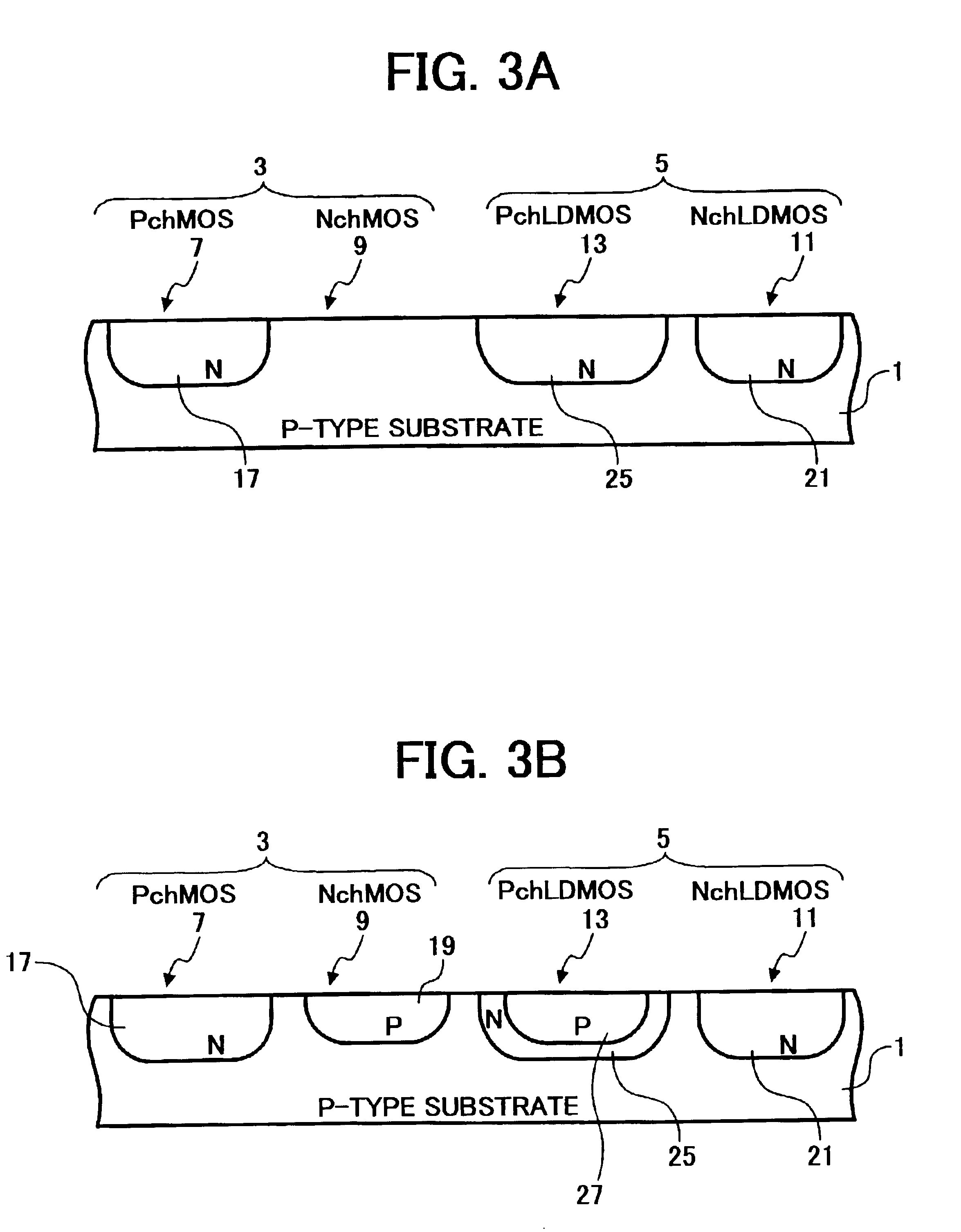

Semiconductor device and method for fabricating such device

InactiveUS6911694B2Stable operational characteristicAvoid layeringTransistorSolid-state devicesLDMOSGate dielectric

An LDMOS transistor and a bipolar transistor with LDMOS structures are disclosed for suitable use in high withstand voltage device applications, among others. The LDMOS transistor includes a drain well region 21 formed in P-type substrate 1, and also formed therein spatially separated one another are a channel well region 23 and a medium concentration drain region 24 having an impurity concentration larger than that of drain well region 21, which are simultaneously formed having a large diffusion depth through thermal processing. A source 11s is formed in channel well region 23, while a drain 11d is formed in drain region 24 having an impurity concentration larger than that of drain region 24. In addition, a gate electrode 11g is formed over the well region, overlying the partially overlapped portions with well region 23 and drain region 24 and being separated from drain 11d. Since the source 11s, well region 23, and drain region 24 are respectively self-aligned to the gate electrode 11g, resultant transistor characteristics are stabilized, and the decrease in the on resistance and improved drain threshold voltages can be achieved. Also disclosed herein are bipolar transistors with LDMOS structures, which are capable of obviating the breakdown of gate dielectric layers even at high applied voltage and achieving improved stability in transistor characteristics.

Owner:RICOH KK

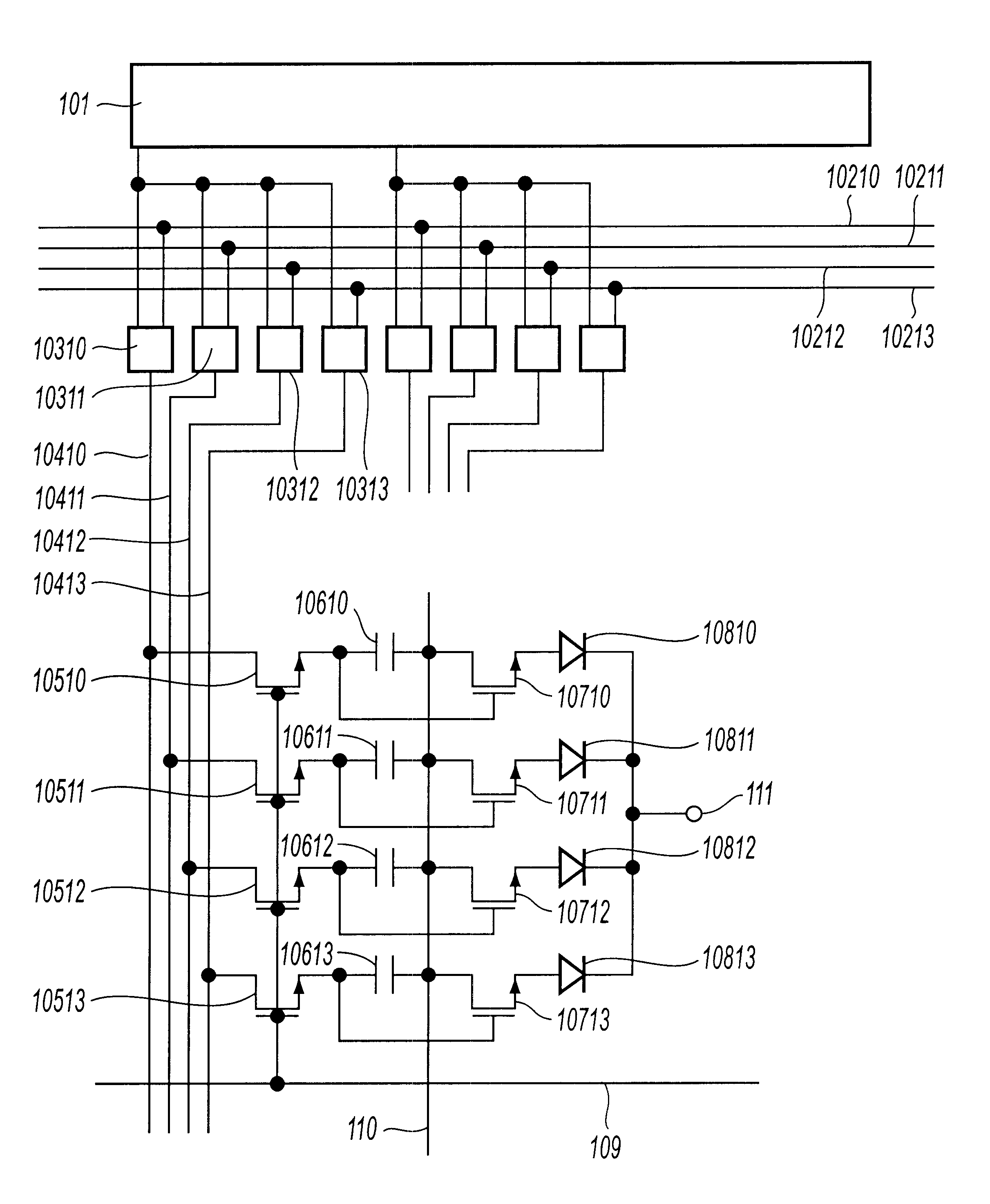

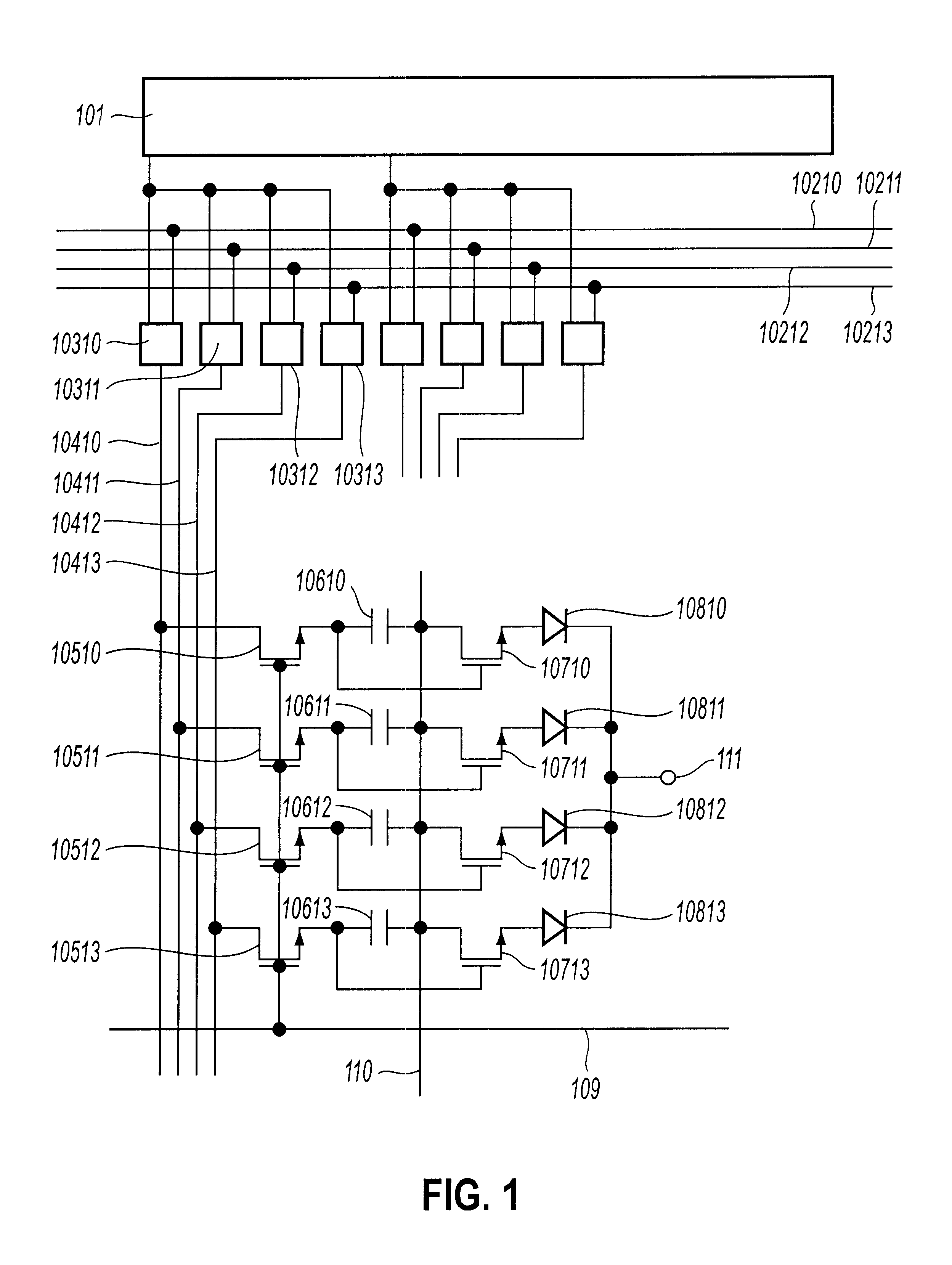

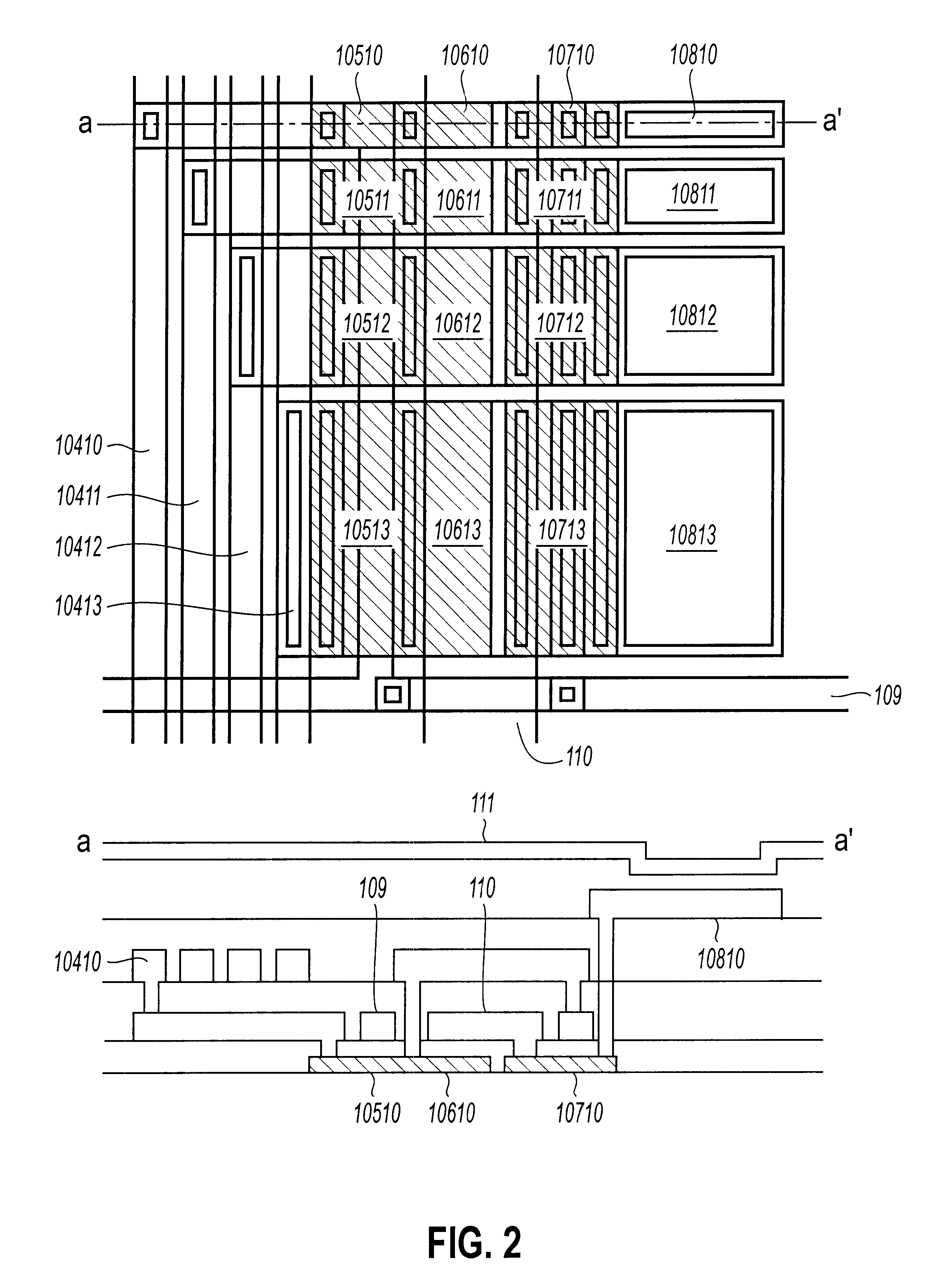

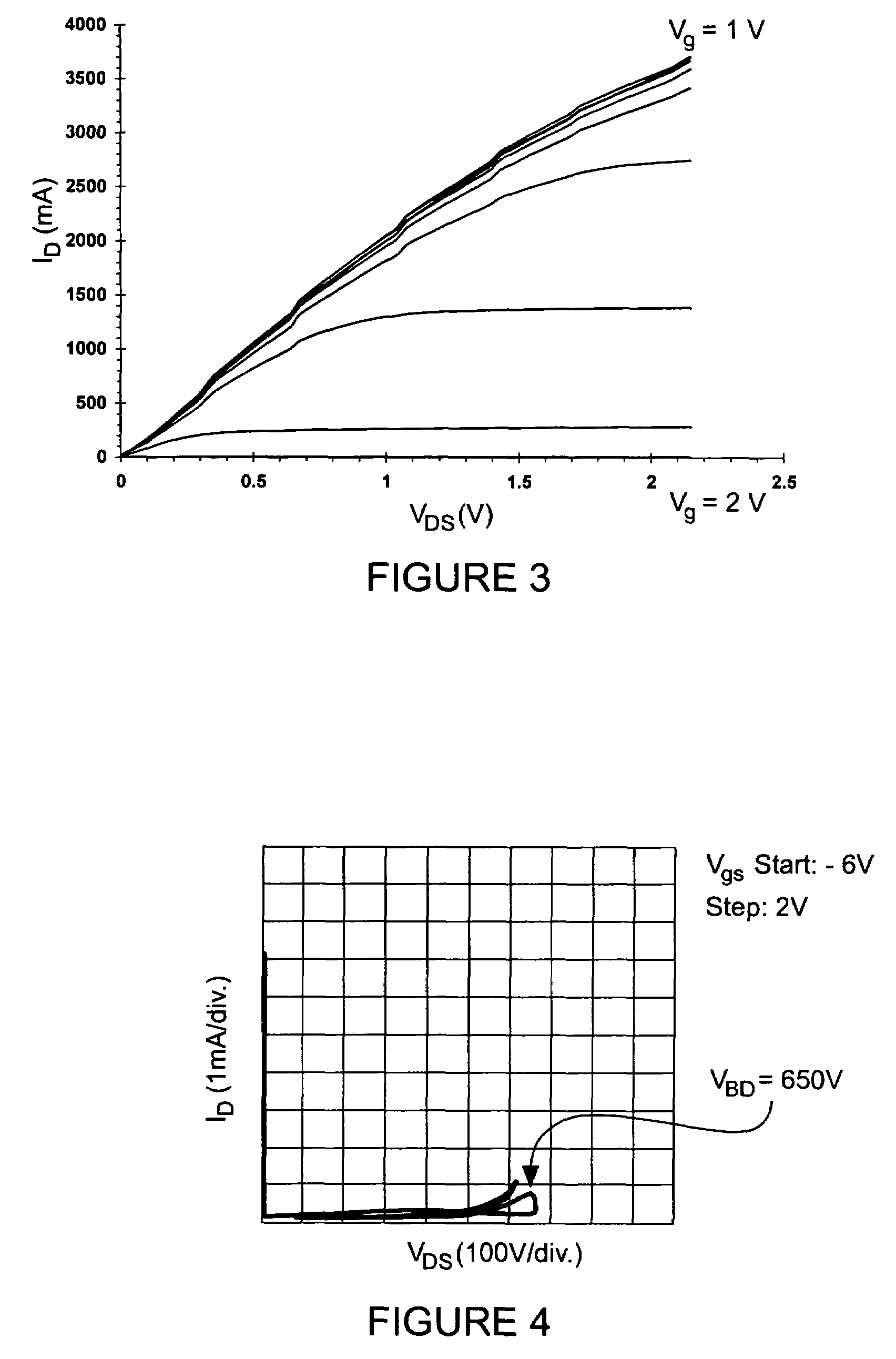

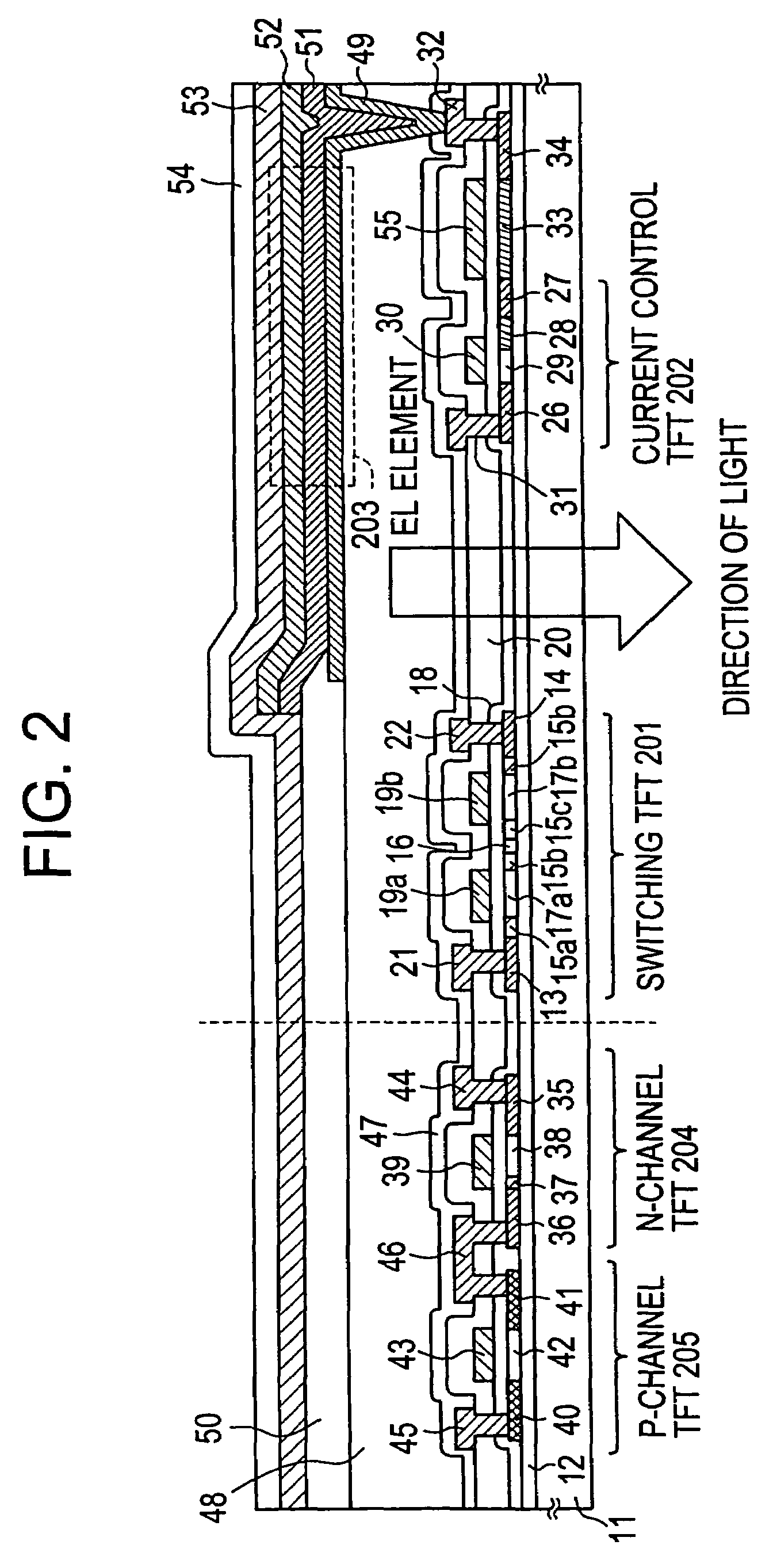

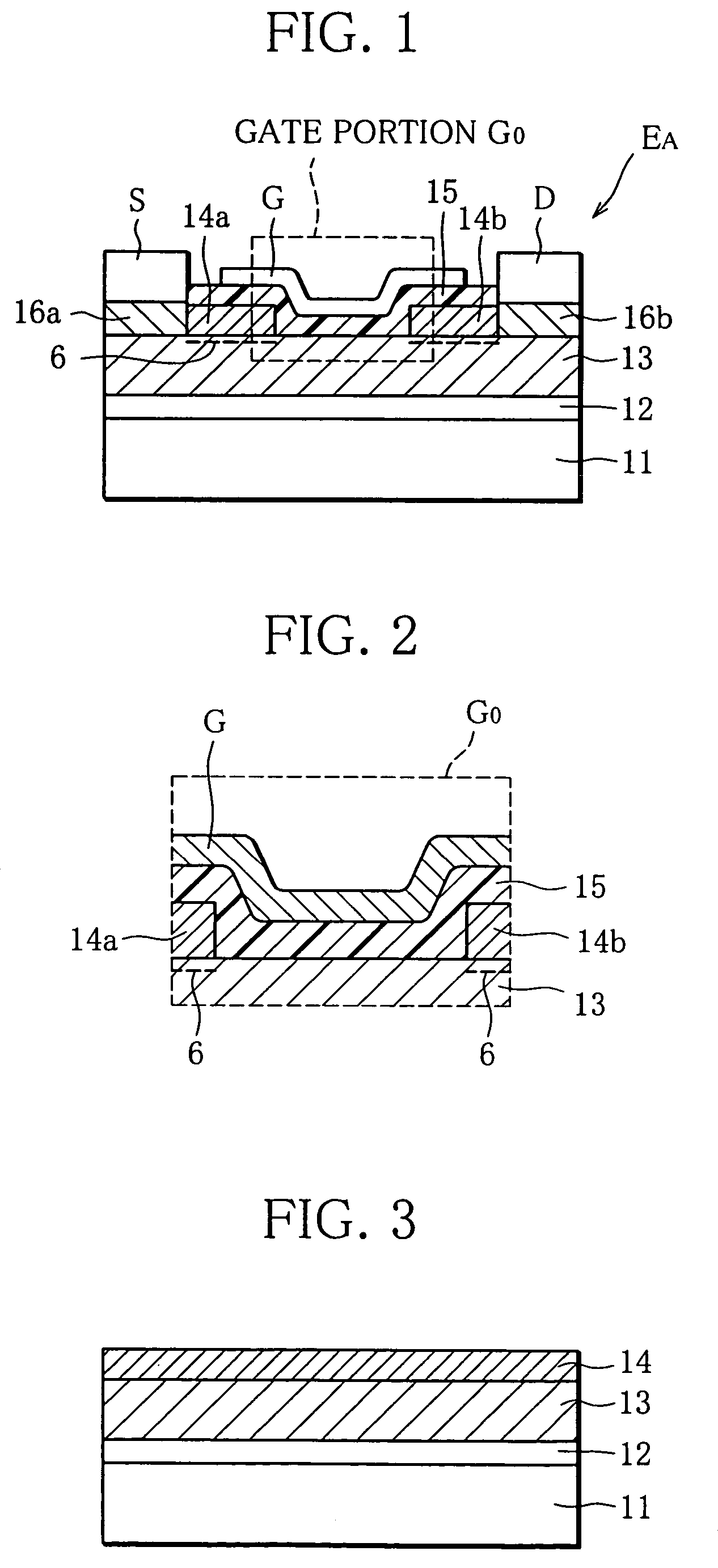

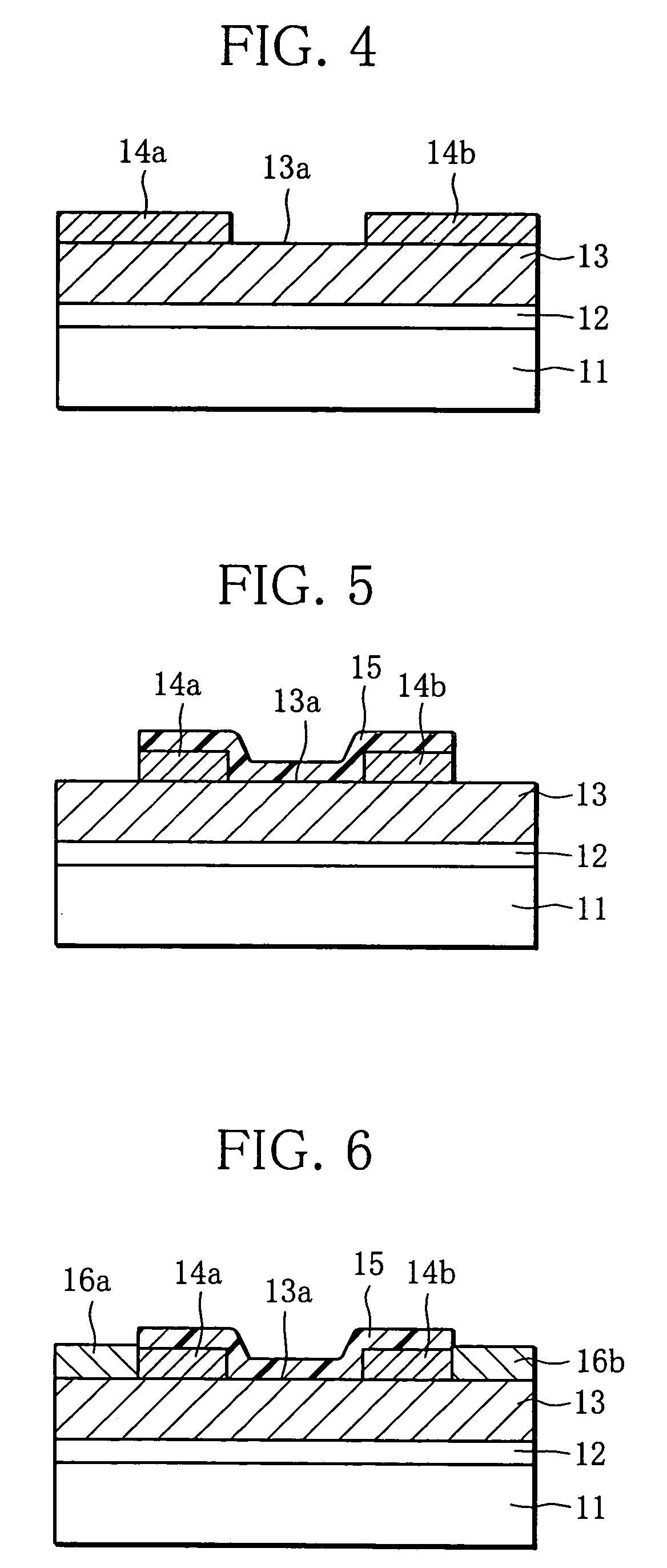

Display device

InactiveUS6518941B1Solid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceLuminous intensity

In a display device in accordance with the present invention, each pixel includes a plurality of luminescent elements having different luminous intensities to represent gray scales by controlling the turning ON / OFF of the luminescent elements. A digital signal is transmitted to each pixel to carry out control by thin film transistors connected in series with the luminescent elements. The luminous intensities of the luminescent elements are the geometric progressions of a common ratio of 2. The ON resistance of the thin film transistors is set to be lower than the ON resistance of the luminescent elements, while the OFF resistance of the thin film transistors is set to be higher than the OFF resistance of the luminescent elements. These features have reduced the nonuniformity in the luminous intensities of the luminescent elements caused by the nonuniformity in the conductance of the transistors, thus achieving improved image quality.

Owner:INTELLECTUAL KEYSTONE TECH LLC

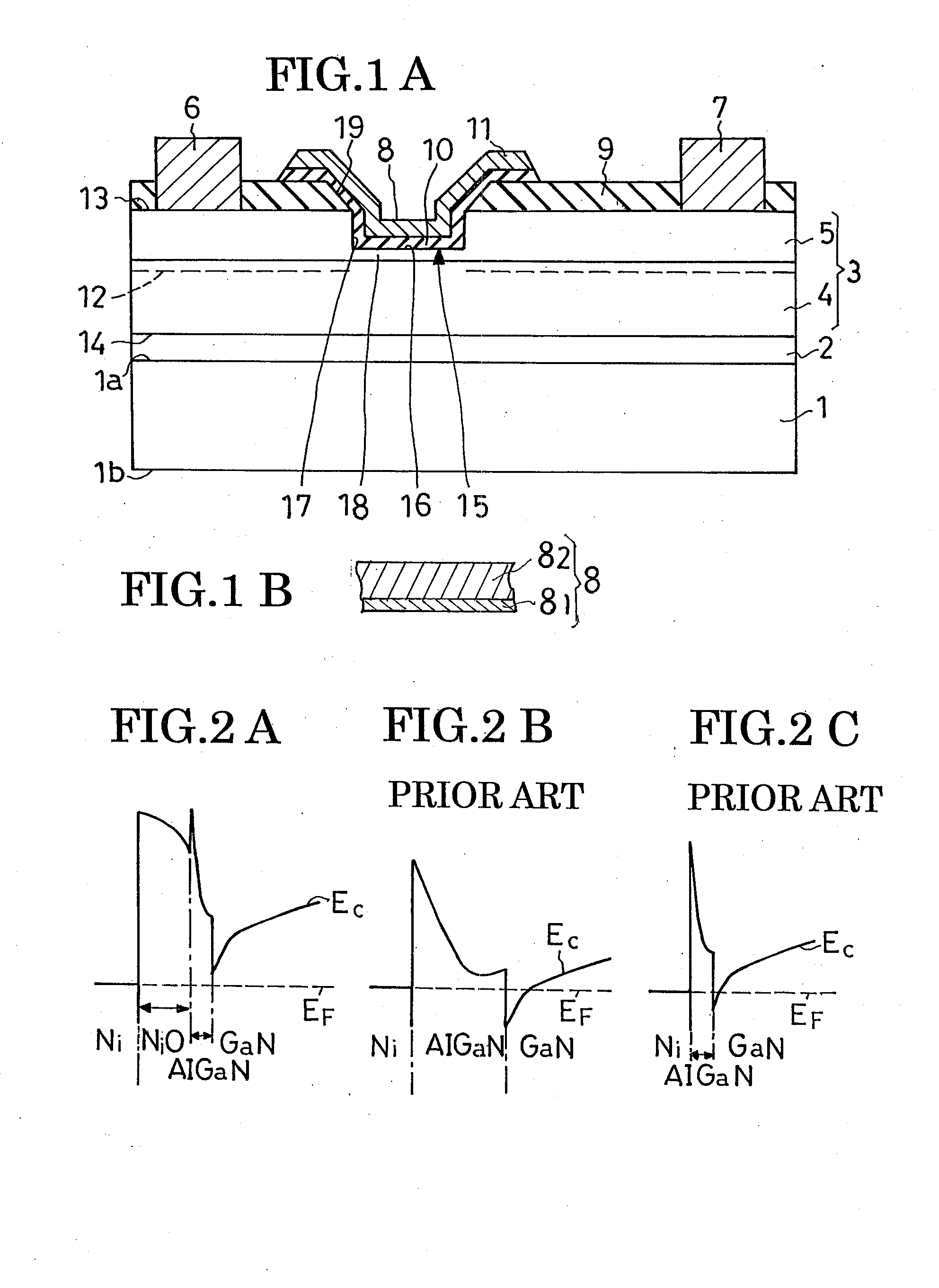

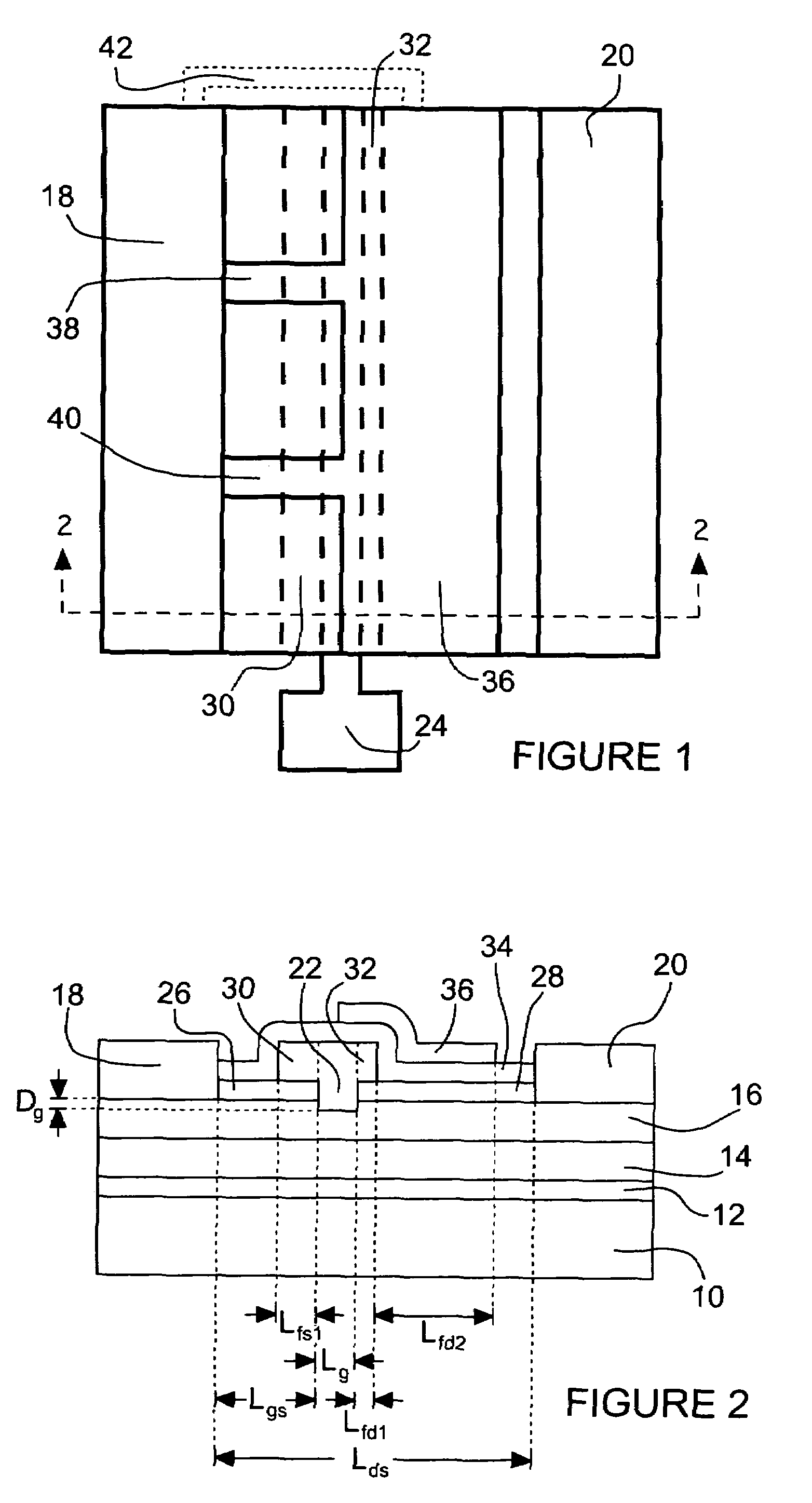

High voltage GaN transistors

A multiple field plate transistor includes an active region, with a source, a drain, and a gate. A first spacer layer is over the active region between the source and the gate and a second spacer layer over the active region between the drain and the gate. A first field plate on the first spacer layer is connected to the gate. A second field plate on the second spacer layer is connected to the gate. A third spacer layer is on the first spacer layer, the second spacer layer, the first field plate, the gate, and the second field plate, with a third field plate on the third spacer layer and connected to the source. The transistor exhibits a blocking voltage of at least 600 Volts while supporting a current of at least 2 Amps with an on resistance of no more than 5.0 mΩ-cm2, of at least 600 Volts while supporting a current of at least 3 Amps with an on resistance of no more than 5.3 mΩ-cm2, of at least 900 Volts while supporting a current of at least 2 Amps with an on resistance of no more than 6.6 mΩ-cm2, or a blocking voltage of at least 900 Volts while supporting a current of at least 3 Amps with an on resistance of no more than 7.0 mΩ-cm2.

Owner:CREE INC

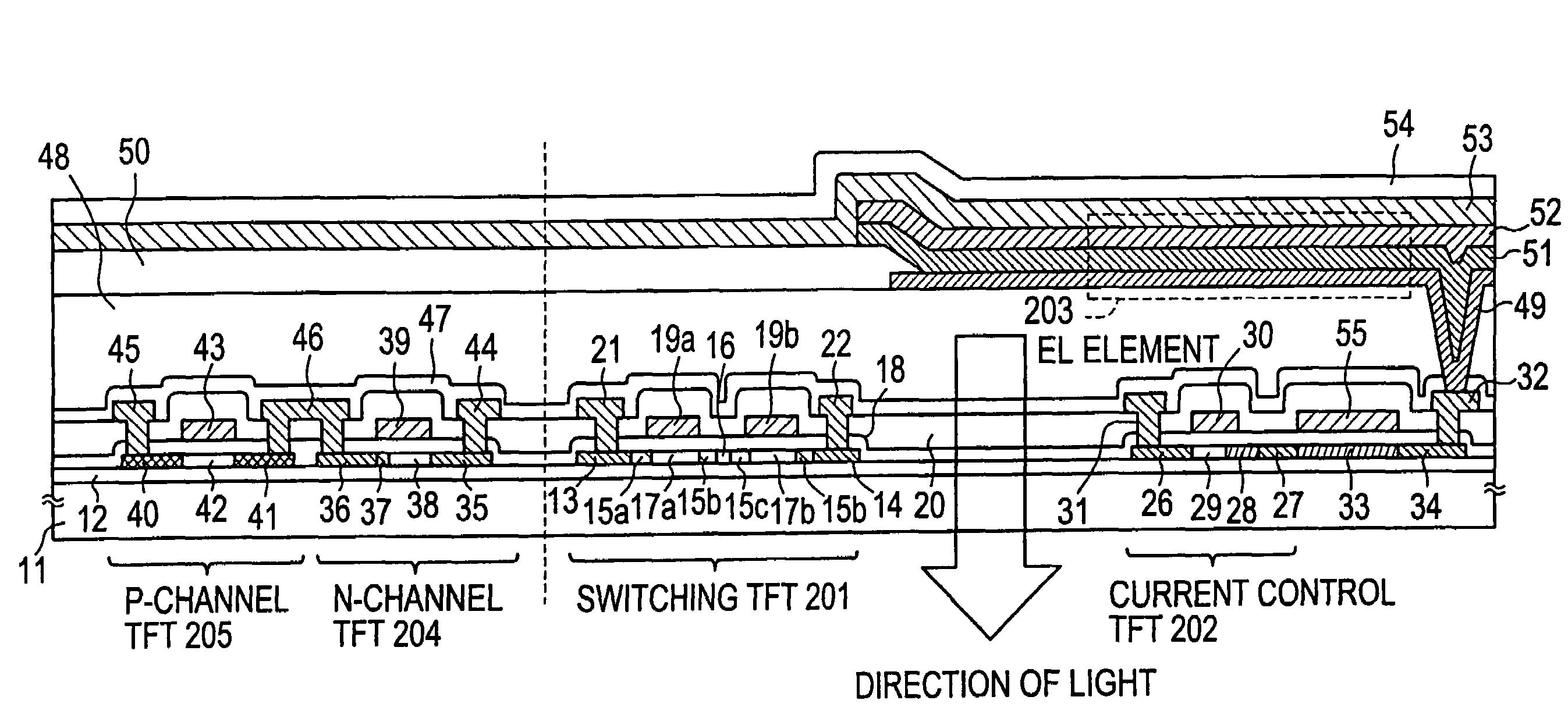

EL display device and electronic device

InactiveUS7358531B2Prevent defect in gradationImprove performanceStatic indicating devicesElectroluminescent light sourcesDisplay deviceEngineering

An EL display device capable of producing a vivid multi-gradation color display, and an electronic device having the EL display device. An electric current supplied to an EL element 110 is controlled by providing a resistor 109 between a current control TFT 108 and the EL element 110 formed in a pixel 104, the resistor 109 having a resistance higher than the on-resistance of the current control TFT 108. The gradation display is executed by a time-division drive system which controls the emission and non-emission of light of the EL element 110 by time, preventing the effect caused by a dispersion in the characteristics of the current control TFT 108.

Owner:SEMICON ENERGY LAB CO LTD

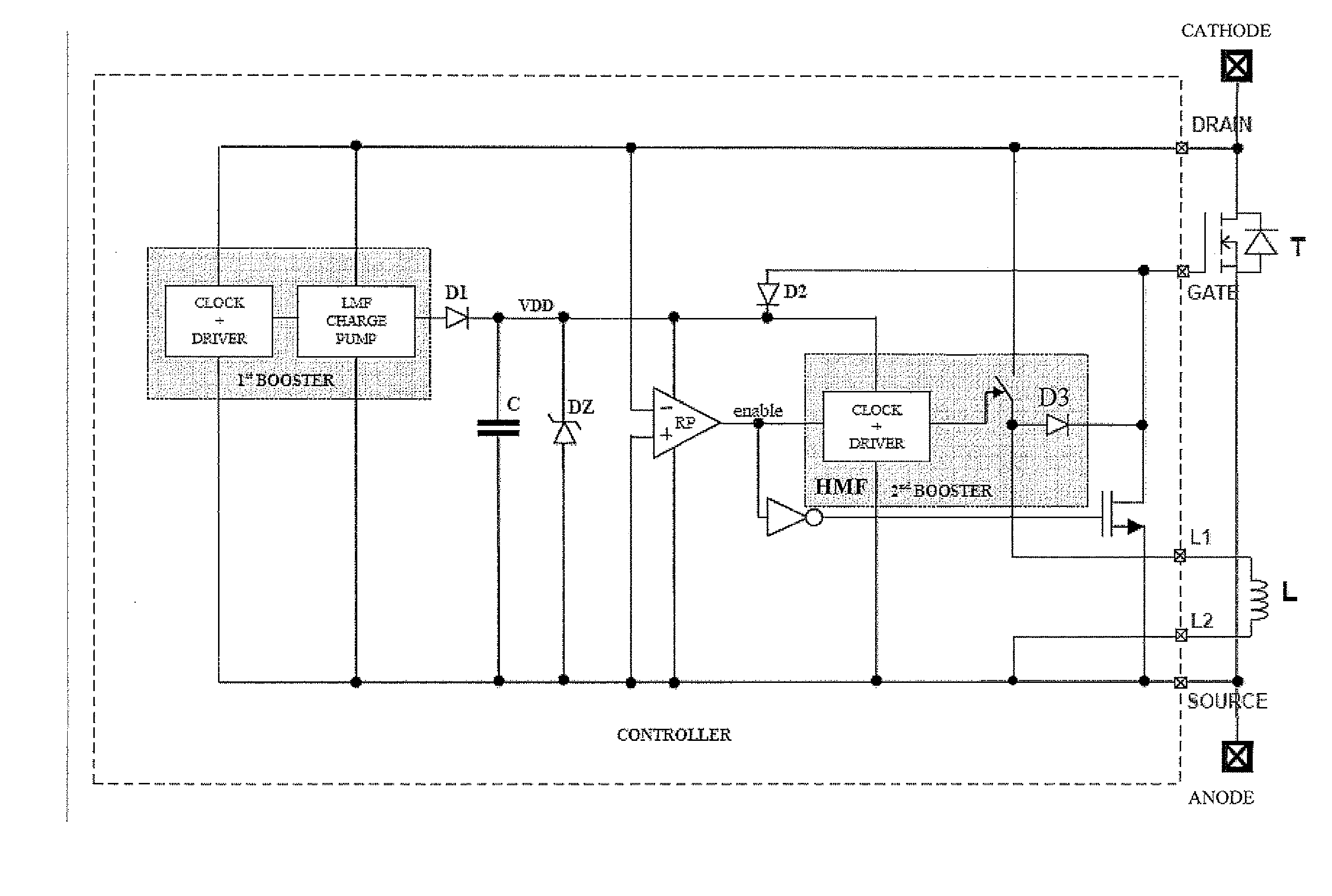

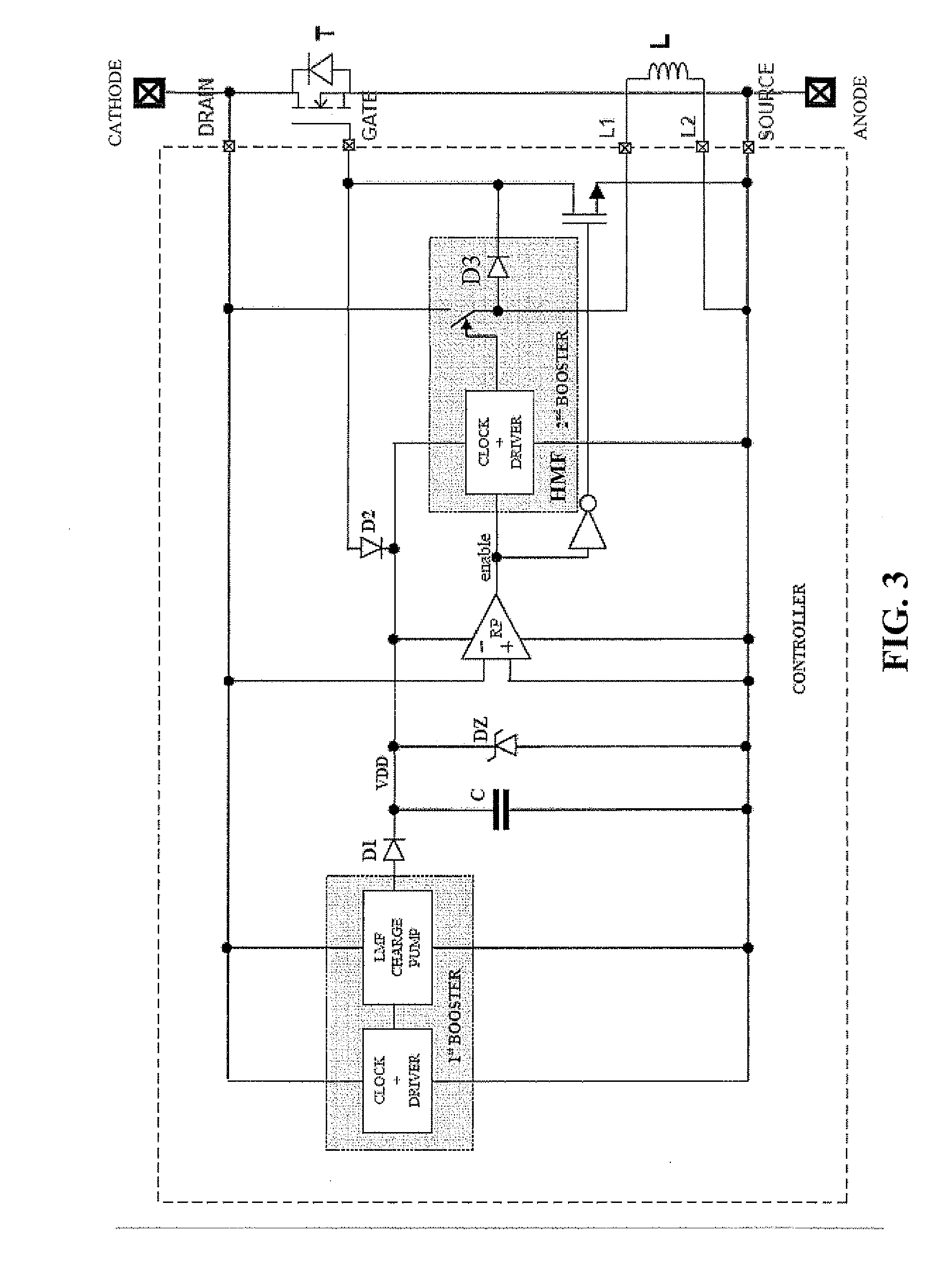

Low on-resistance mosfet implemented, by-pass diode or circuit breaker and related self-powering and control circuit

A MOSFET implemented self-powered current by-pass or circuit breaker device is based on the use of a high multiplication factor (HMF) inductive voltage booster, adapted to boost a voltage as low as few tens of mV up to several Volts, assisted by a start-up low multiplication factor (LMF) charge pump made with low threshold transistors for providing a supply voltage to a polarity inversion detecting comparator of the drain-to-source voltage difference of a power MOSFET connected in parallel to a DC source or string of series connected DC sources or battery, in series to other DC sources during normal operation of the parallel connected DC source or string of series connected DC sources or battery. The inductance for the high multiplication factor, inductive voltage booster for most of the considered power applications is on the order of a few pH and such a relatively send inductor may be included as a discrete component in a compact package or “system-in-package” of monolithically integrated circuits.

Owner:STMICROELECTRONICS SRL

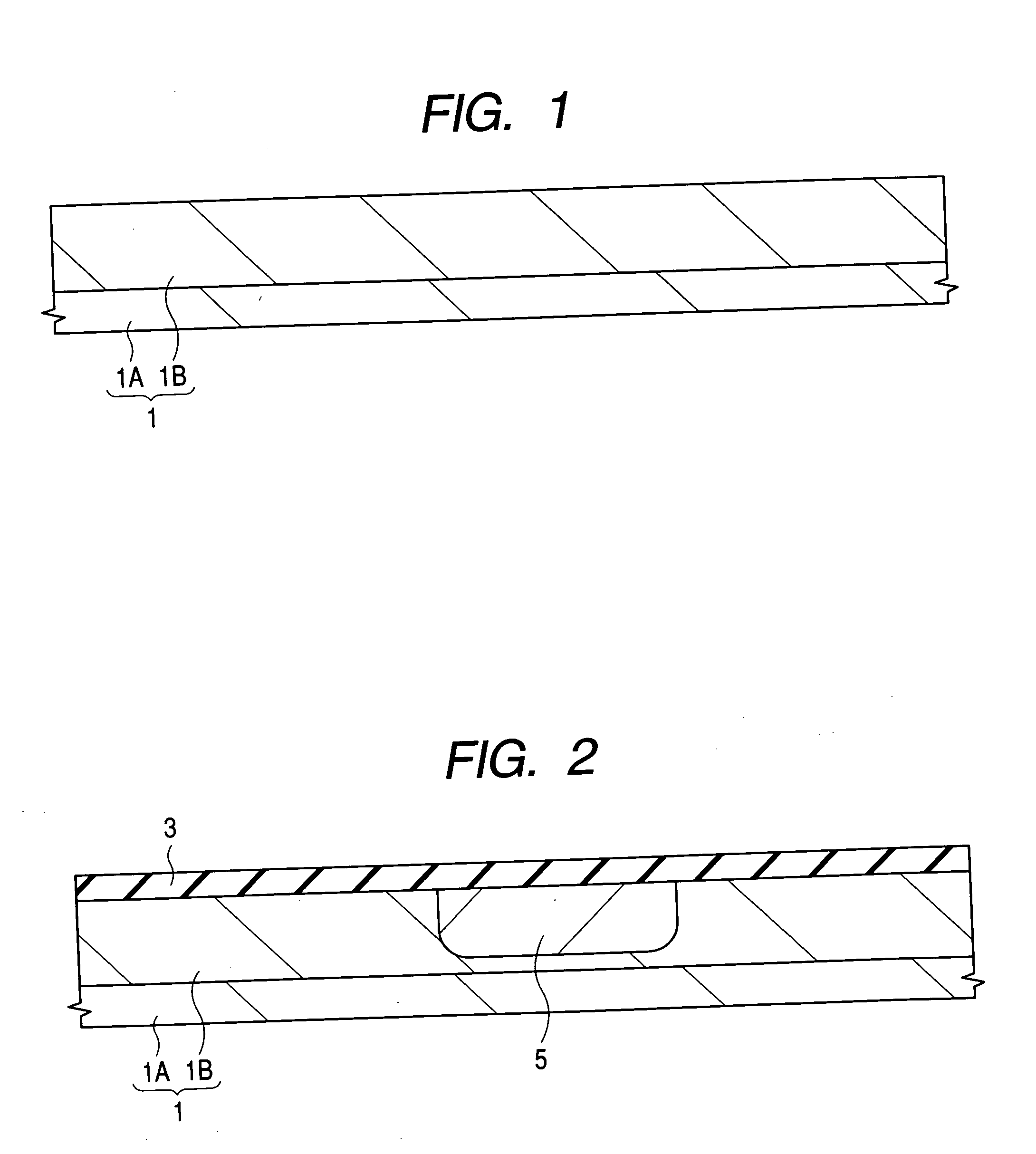

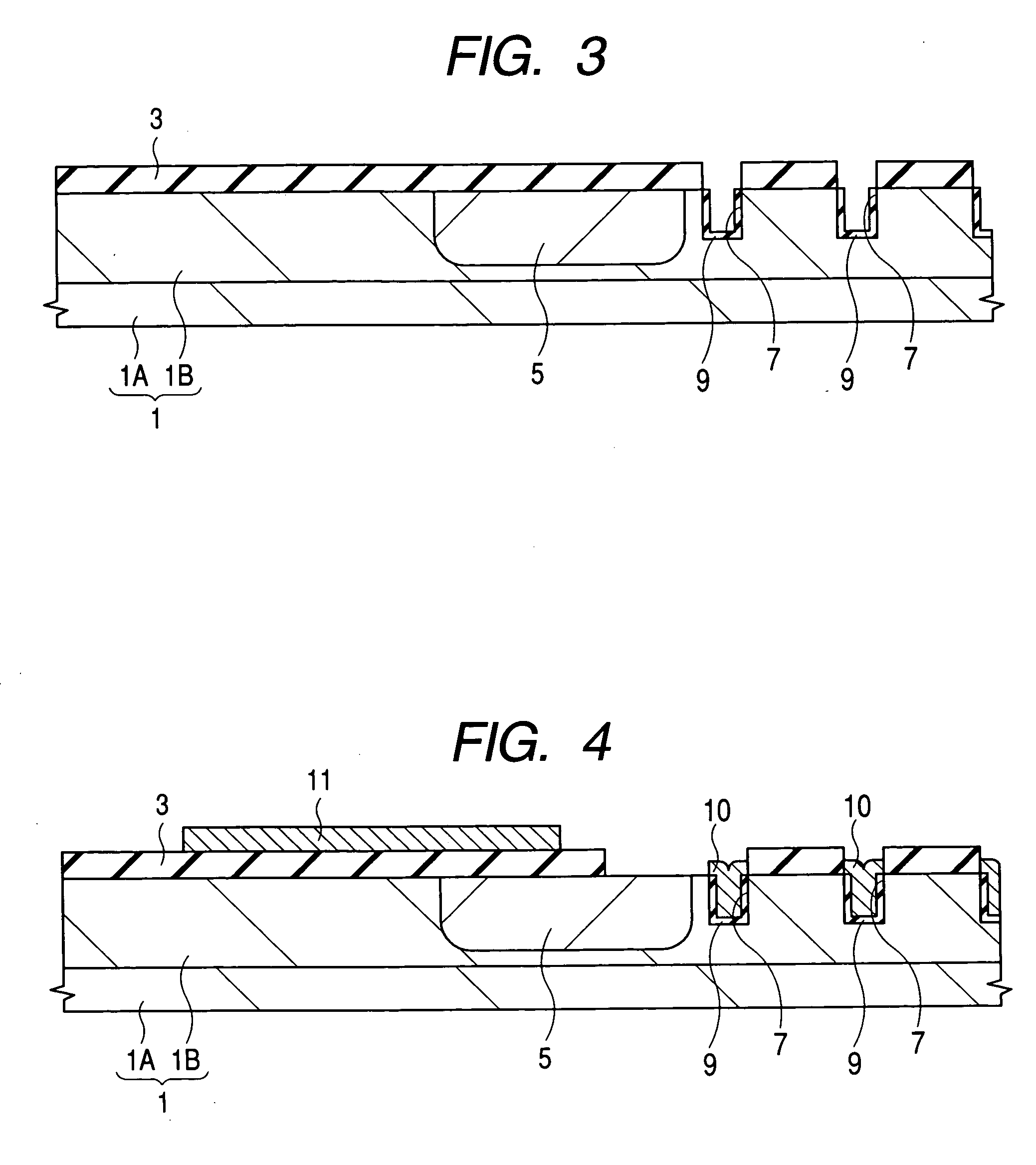

Semiconductor device and a method of manufacturing the same

InactiveUS20050029584A1Easy to integrateReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceFeedback capacitance

A technology is provided to reduce ON-resistance, and the prevention of punch through is achieved with respect to a trench gate type power MISFET. Input capacitance and a feedback capacitance are reduced by forming a groove in which a gate electrode is formed so as to have a depth as shallow as about 1 μm or less, a p−type semiconductor region is formed to a depth so as not to cover the bottom of the groove, and a p-type semiconductor region higher in impurity concentration than the p−type semiconductor region is formed under a n+type semiconductor region serving as a source region of the trench gate type power MISFET, causing the p-type semiconductor region to serve as a punch-through stopper layer of the trench gate type power MISFET.

Owner:RENESAS TECH CORP

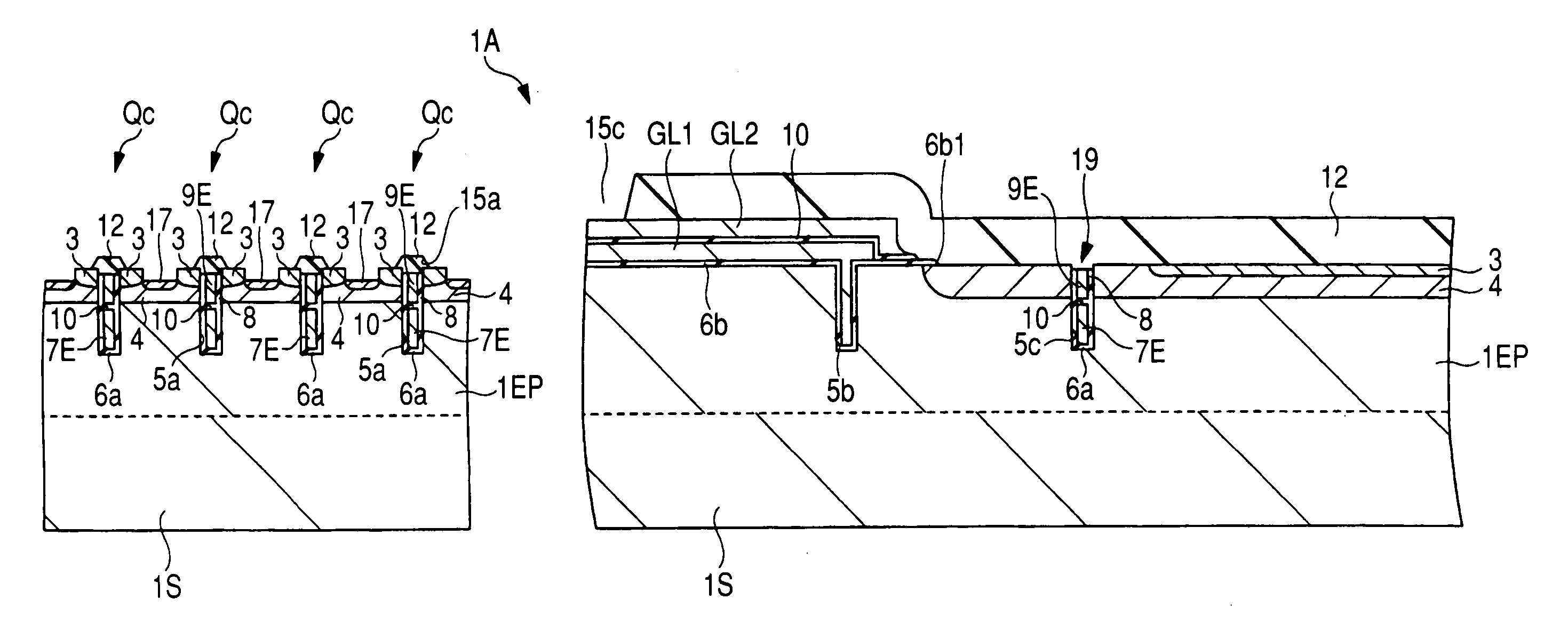

Semiconductor device and manufacturing method of the same

ActiveUS20060157779A1Lower on-resistanceSuppress and prevent operation of parasiticSolid-state devicesSemiconductor devicesElectrical resistance and conductanceDevice material

The on-resistance of a semiconductor device having a power transistor with a trench gate structure is reduced. A power MIS-FET with a trench gate structure is so formed that the relation expressed as 0≦b≦a holds, where a is the distance between an end of an interlayer insulating layer over the upper face of a semiconductor region for source and the end (position on the periphery of a trench) of the upper face of the semiconductor region for source farther from the gate electrode; and b is the length of the overlap between the interlayer insulating layer and the upper face of the semiconductor region for source. (b is the distance between the position of the end of the interlayer insulating layer over the upper face of the semiconductor region for source and position on the periphery of a trench). As a result, the area of contact between source pads and the semiconductor regions for source is increased, and further the distance between the source pads and a channel forming region can be shortened. Therefore, the on-resistance of the power MIS-FET with a trench gate structure can be reduced.

Owner:RENESAS ELECTRONICS CORP

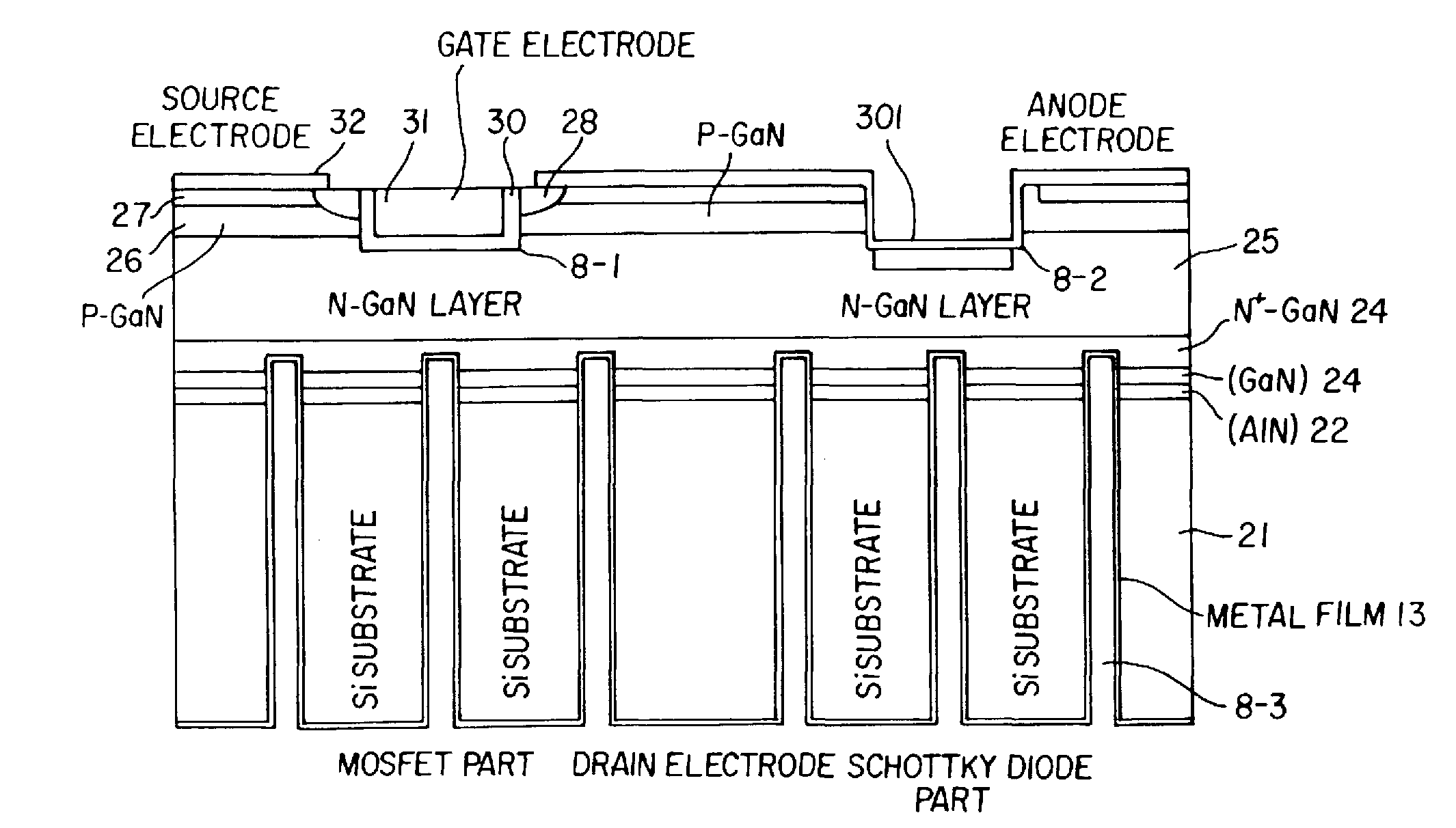

Wide band gap semiconductor device and method for producing the same

ActiveUS20090283776A1Lower on-resistanceShort reverse recovery timeSemiconductor/solid-state device manufacturingDiodeBroadbandWide band

A wide band gap semiconductor device is disclosed. A first trench in a gate electrode part and a second trench in a source electrode part (Schottky diode part) are disposed so that the first and second trenches are close to each other while and the second trench is deeper than the first trench. A metal electrode is formed in the second trench to form a Schottky junction on a surface of an n-type drift layer in the bottom of the second trench. Further, a p+-type region is provided in part of the built-in Schottky diode part being in contact with the surface of the n-type drift layer, preferably in the bottom of the second trench. The result is a wide band gap semiconductor device which is small in size and low in on-resistance and loss, and in which electric field concentration applied on a gate insulating film is relaxed to suppress lowering of withstand voltage to thereby increase avalanche breakdown tolerance at turning-off time.

Owner:FUJI ELECTRIC CO LTD

Semiconductor device including regions of band-engineered semiconductor superlattice to reduce device-on resistance

A semiconductor device may include a substrate and spaced apart source and drain regions defining a channel region therebetween in the substrate. The substrate may have a plurality of spaced apart superlattices in the channel and / or drain regions. Each superlattice may include a plurality of stacked groups of layers, with each group including a plurality of stacked base semiconductor monolayers defining a base semiconductor portion and at least one non-semiconductor monolayer thereon. The at least one non-semiconductor monolayer may be constrained within a crystal lattice of adjacent base semiconductor portions.

Owner:ATOMERA INC

Insulated gate type semiconductor device and manufacturing method thereof

ActiveUS20060289928A1Improve design flexibilityLow reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringBody region

The invention is intended to present an insulated gate type semiconductor device that can be manufactured easily and its manufacturing method while realizing both higher withstand voltage design and lower on-resistance design. The semiconductor device comprises N+ source region 31, N+ drain region 11, P− body region 41, and N− drift region 12. By excavating part of the upper side of the semiconductor device, a gate trench 21 is formed. The gate trench 21 floating region 51 is provided beneath the gate trench 21. A further trench 35 differing in depth from the gate trench 21 may be formed, a P floating region 54 being provided beneath the trench 25.

Owner:TOYOTA JIDOSHA KK +1

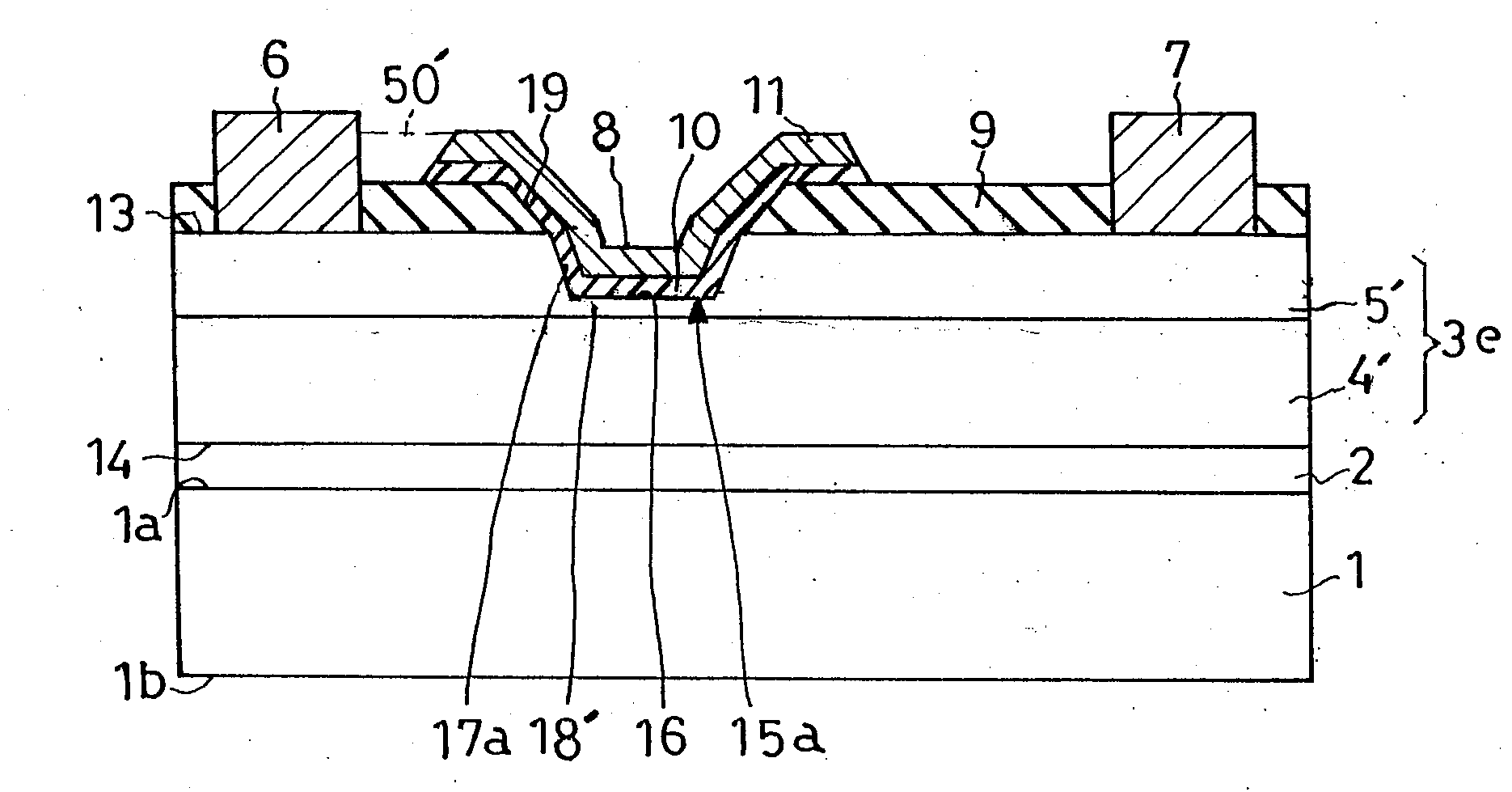

GaN-based field effect transistor of a normally-off type

InactiveUS7038253B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsEngineering

According to the present invention, there is provided a new GaN-based field effect transistor of a normally-off type, which has an extremely small ON resistance during operation and is capable of a large-current operation. The GaN-based field effect transistor according to the present invention comprises source and drain electrodes; a channel portion made of a first GaN-based semiconducting material that is an i-GaN-based semiconducting material or a p-GaN-based semiconducting material, the channel portion being so formed as to be electrically connected to the source and drain electrodes; first and second electron supply portions made of a second GaN-based semiconducting material having greater bandgap energy than the first GaN-based semiconducting material, the first and second electron supply portions being joined to the channel portion and located separately from each other; an insulating layer formed on the surface of the channel portion, which spreads between the first and second electron supply portions; and a gate electrode disposed on the insulating layer.

Owner:FURUKAWA ELECTRIC CO LTD

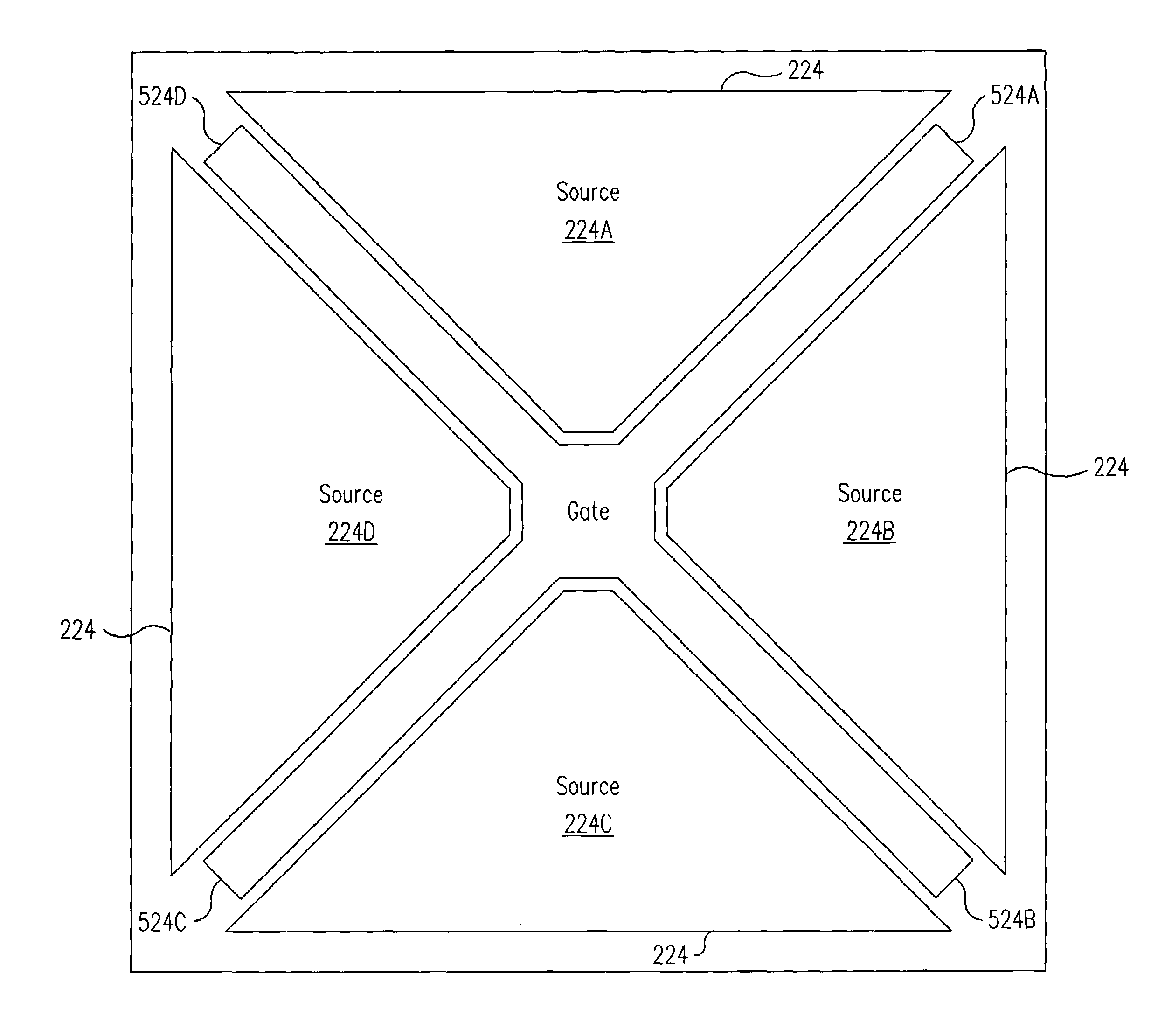

Super trench MOSFET including buried source electrode and method of fabricating the same

InactiveUS20050242392A1Less resistivityIncrease concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceTrench mosfet

In a trench MOSFET, the lower portion of the trench contains a buried source electrode, which is insulated from the epitaxial layer and semiconductor substrate but in electrical contact with the source region. When the MOSFET is in an “off” condition, the bias of the buried source electrode causes the “drift” region of the mesa to become depleted, enhancing the ability of the MOSFET to block current. The doping concentration of the drift region can therefore be increased, reducing the on-resistance of the MOSFET. The buried source electrode also reduces the gate-to-drain capacitance of the MOSFET, improving the ability of the MOSFET to operate at high frequencies. The substrate may advantageously include a plurality of annular trenches separated by annular mesas and a gate metal layer that extends outward from a central region in a plurality of gate metal legs separated by source metal regions.

Owner:SILICONIX

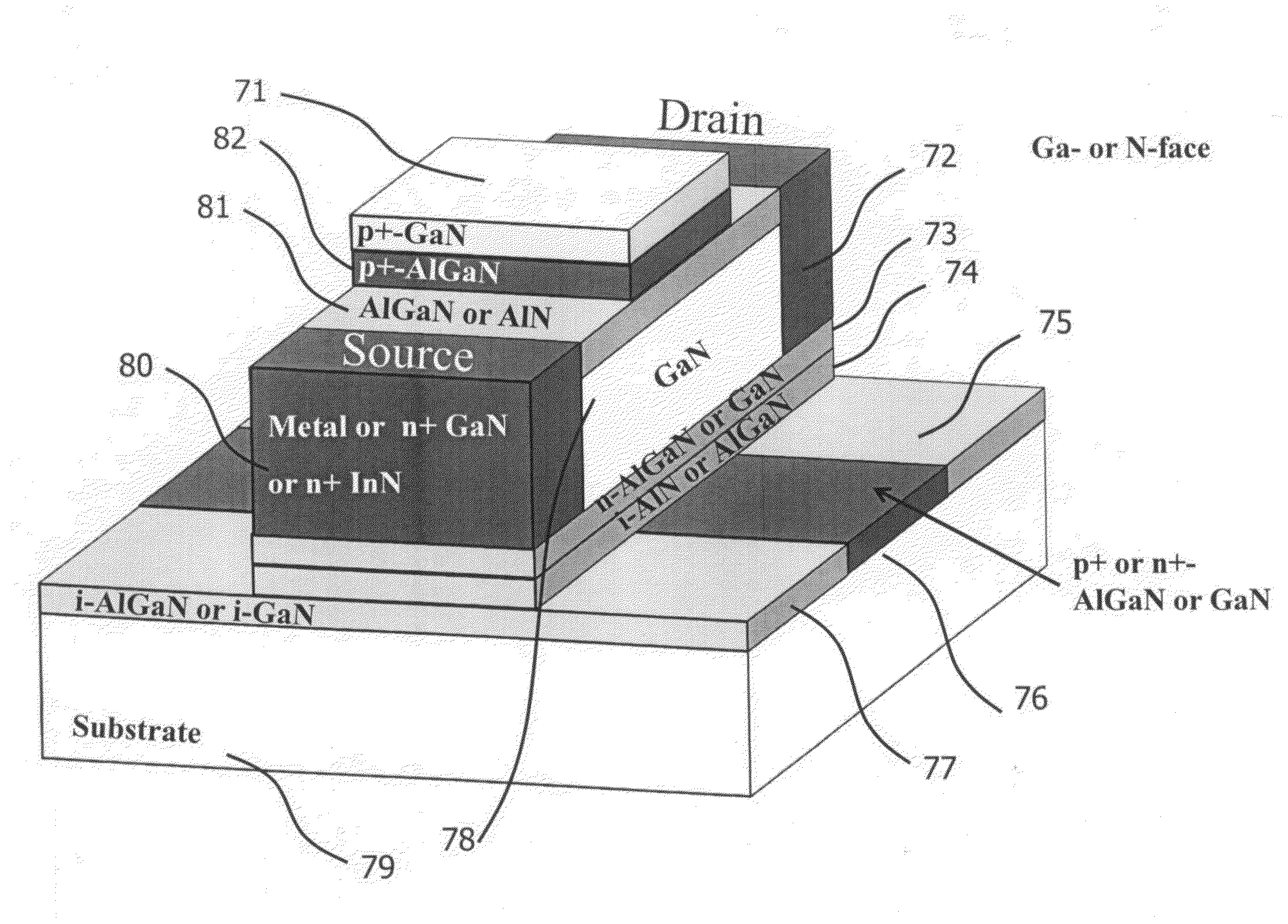

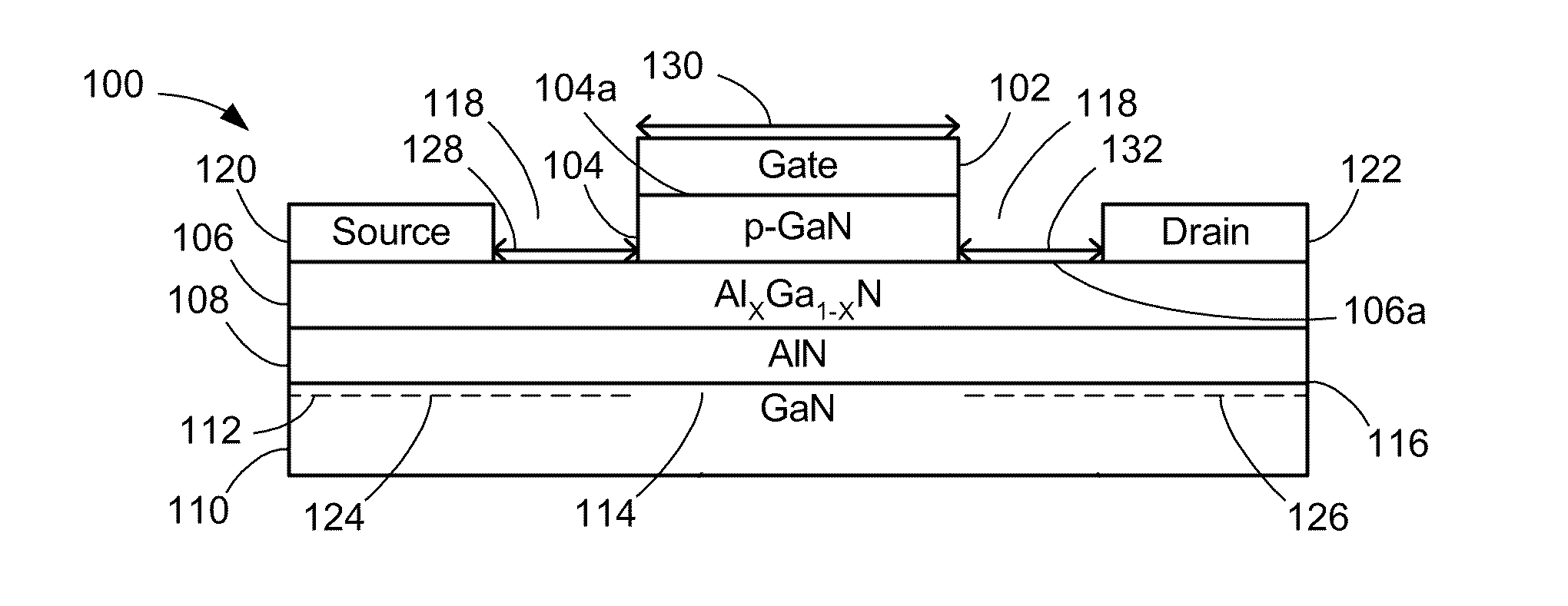

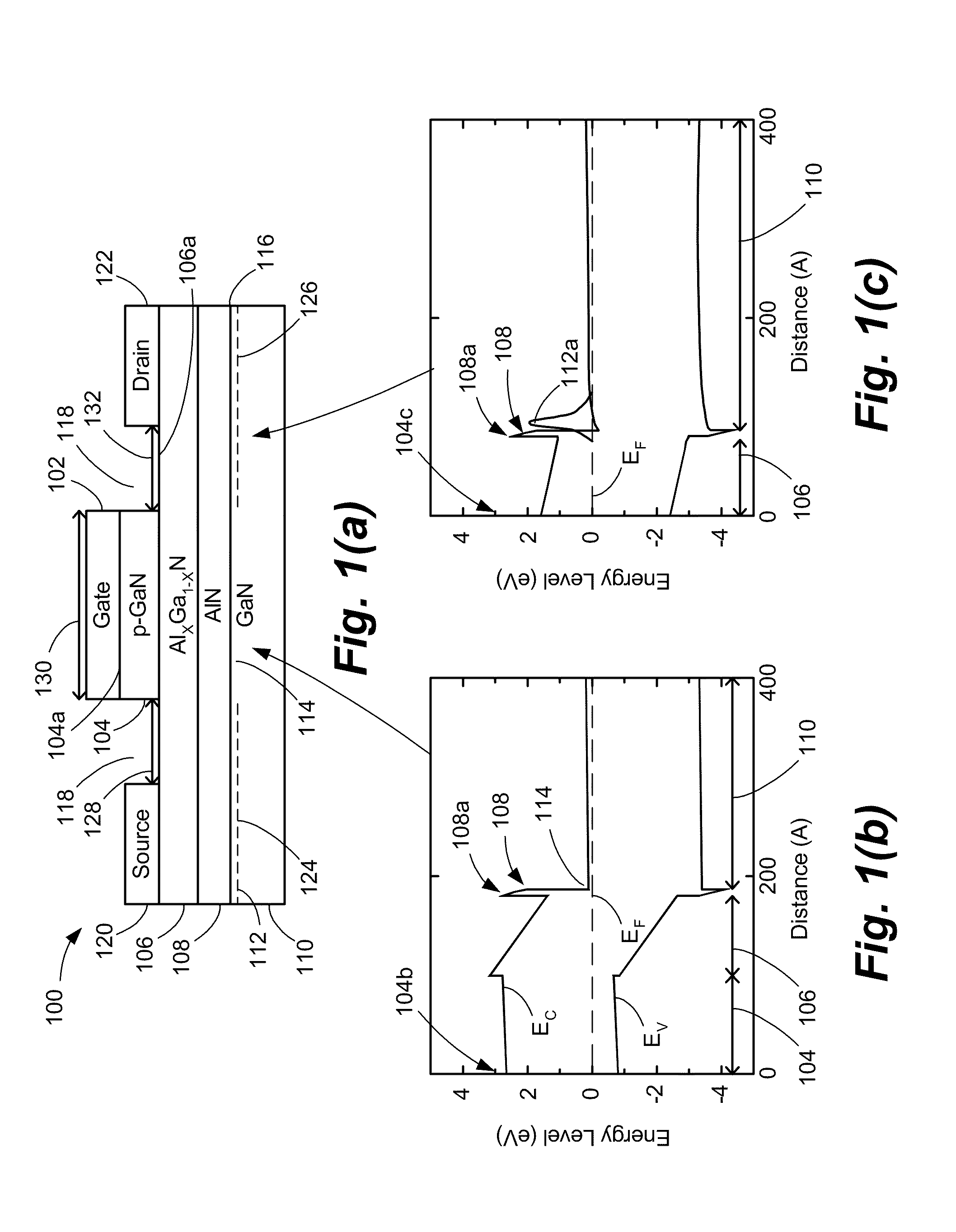

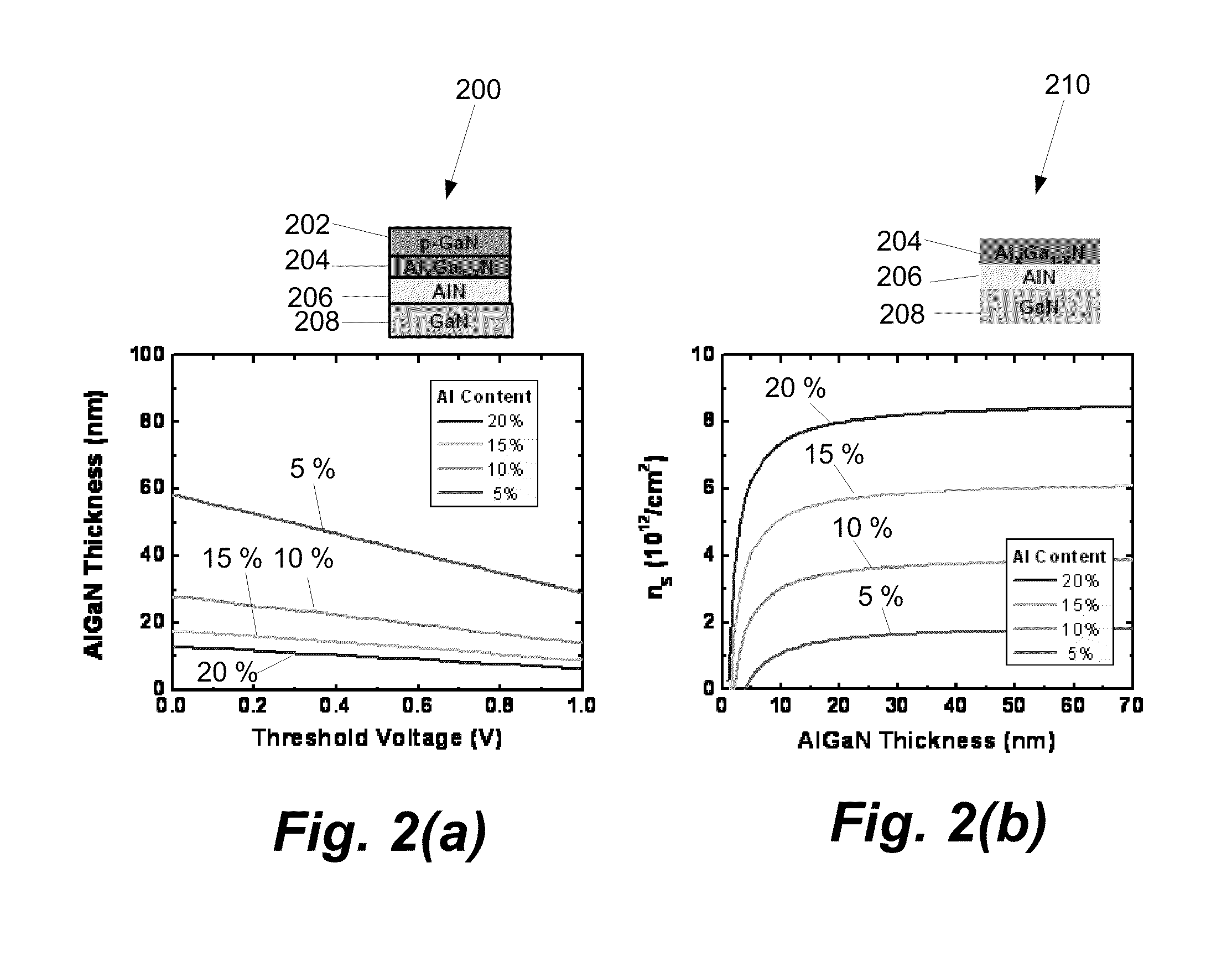

P-GaN/AlGaN/AlN/GaN enhancement-mode field effect transistor

ActiveUS7728356B2High electron mobilityLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectron populationField-effect transistor

Owner:RGT UNIV OF CALIFORNIA