Patents

Literature

92results about How to "High blocking voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

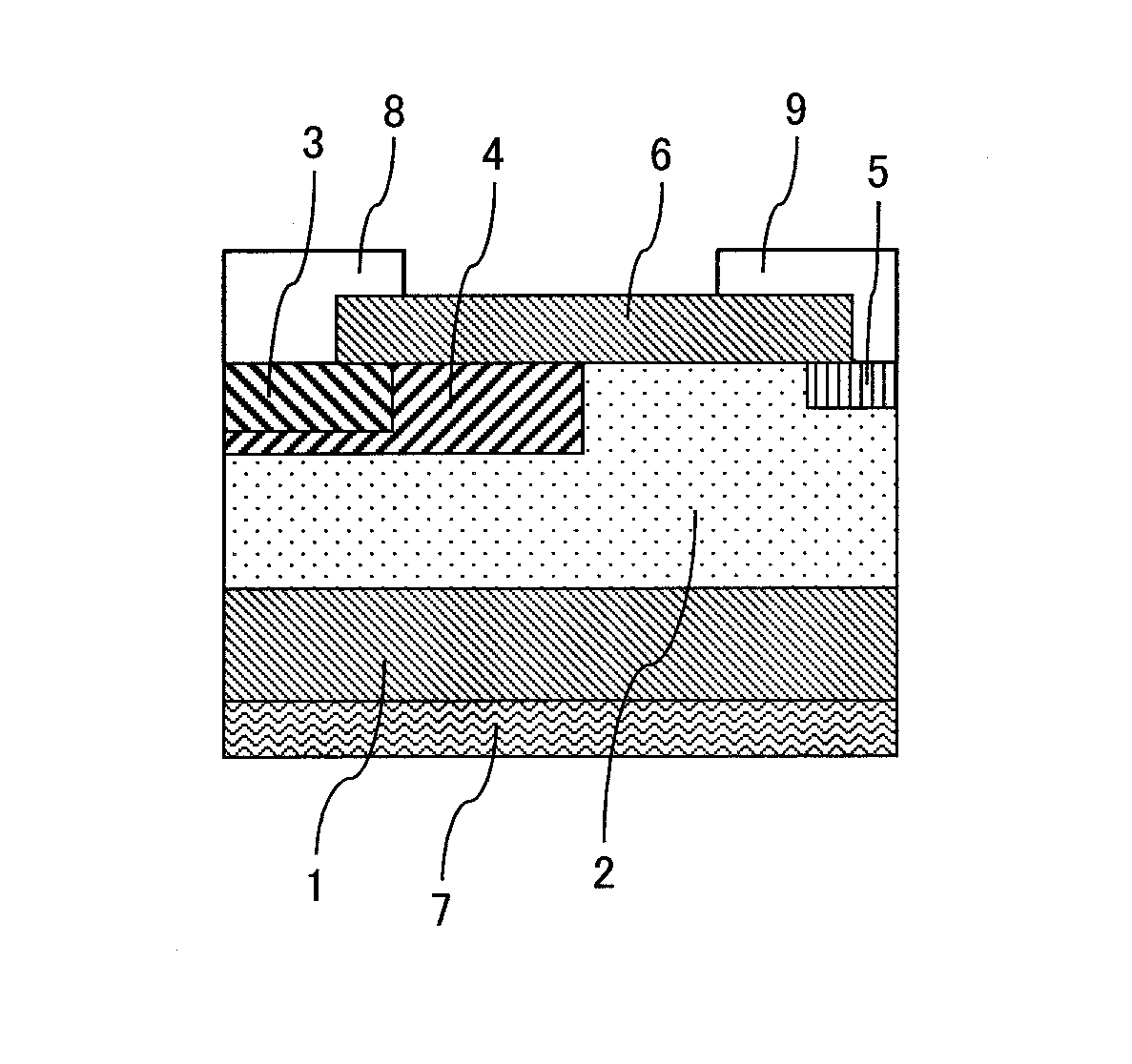

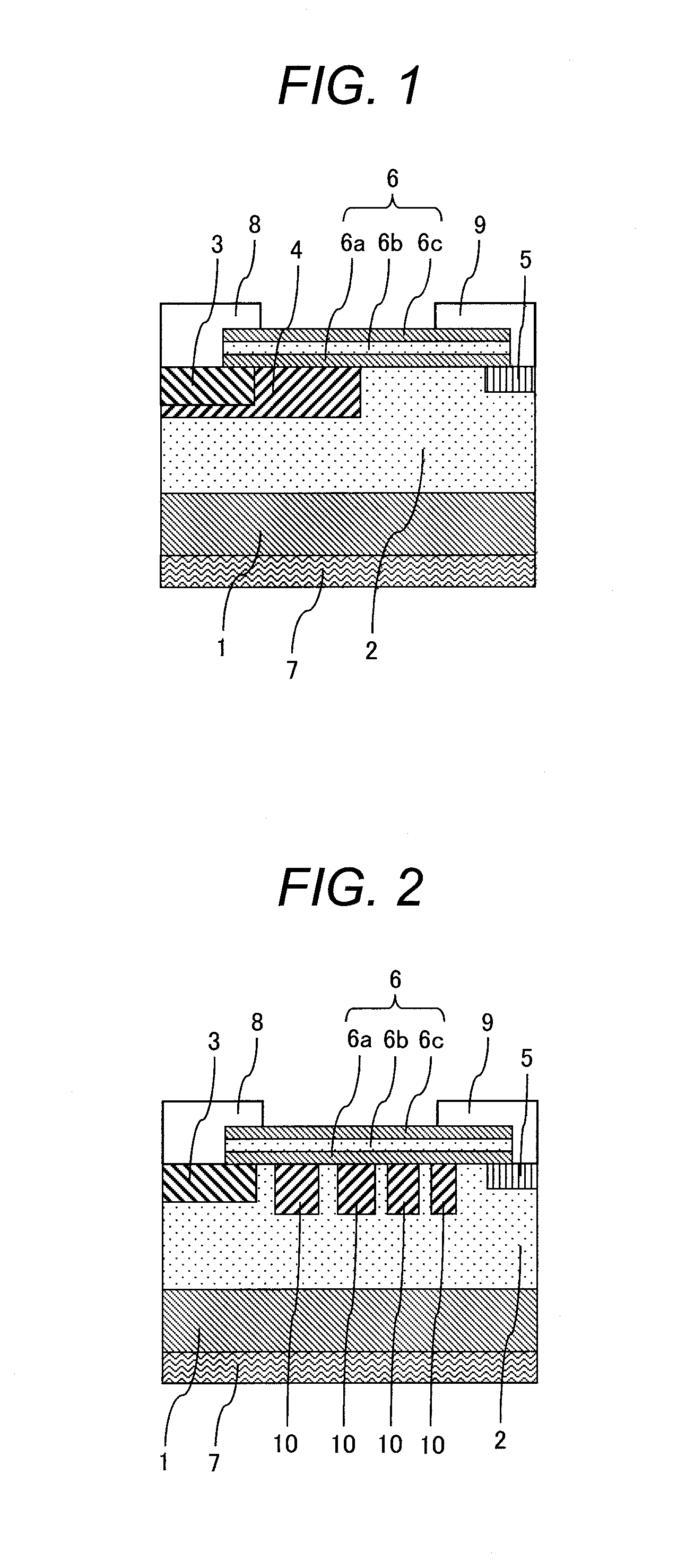

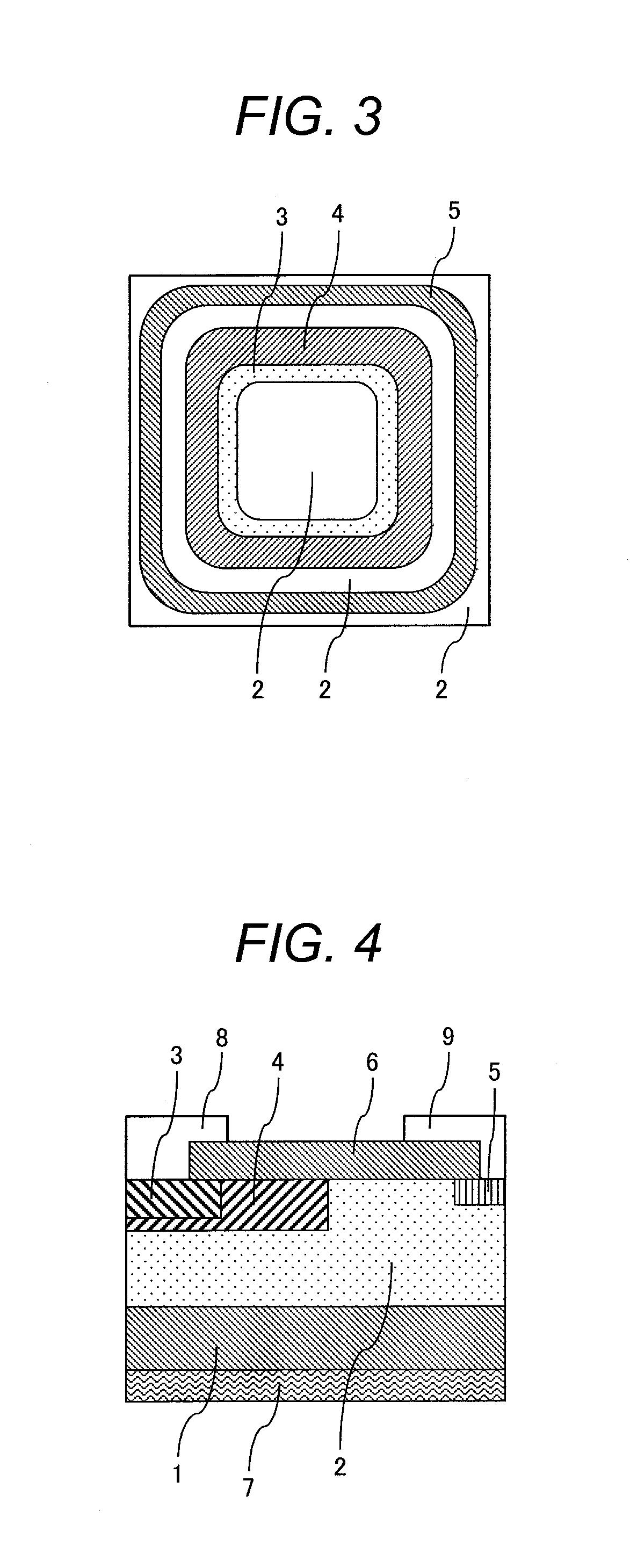

Power semiconductor device

ActiveUS20070215903A1High blocking voltageLow thermal resistanceSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceEngineering

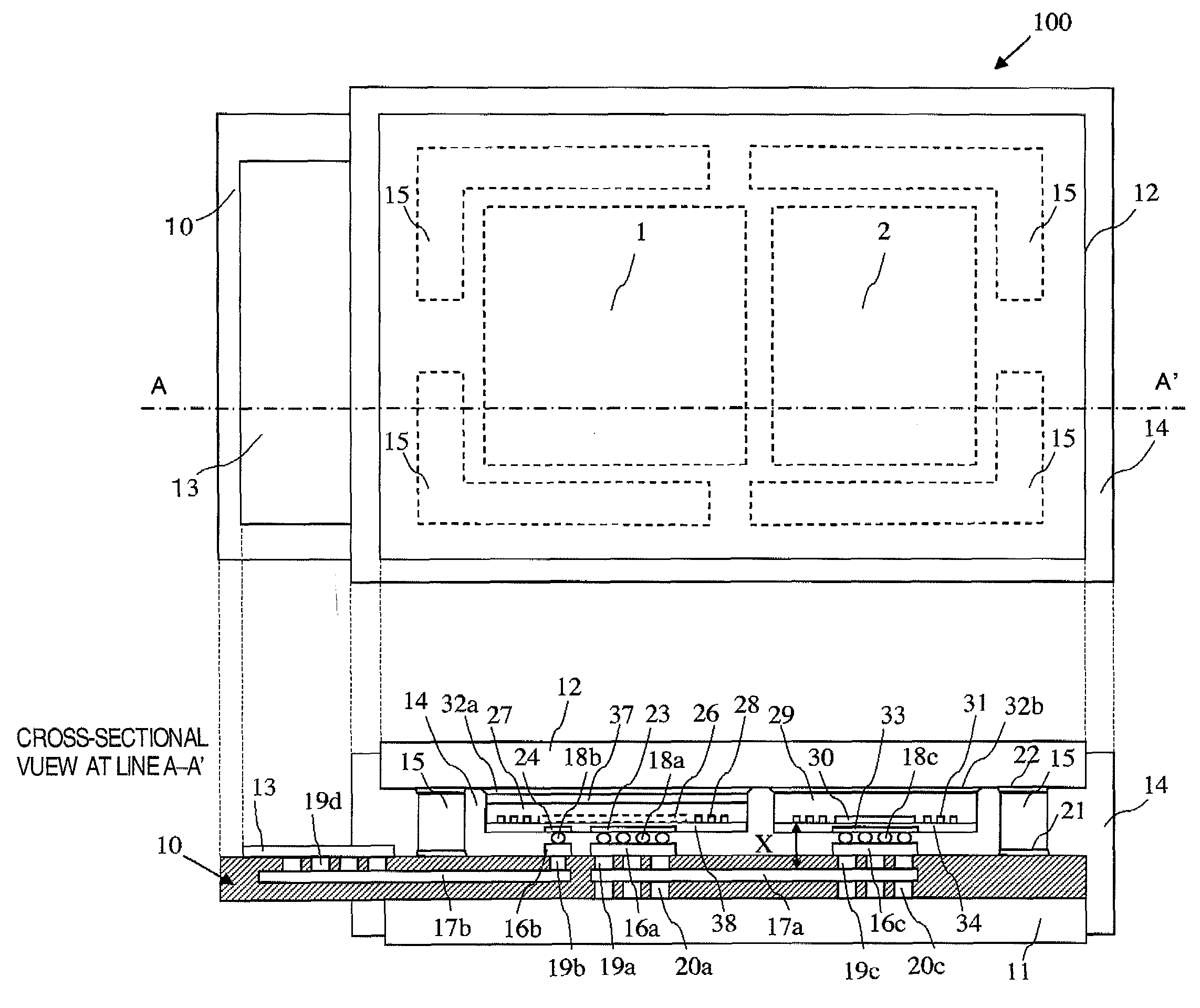

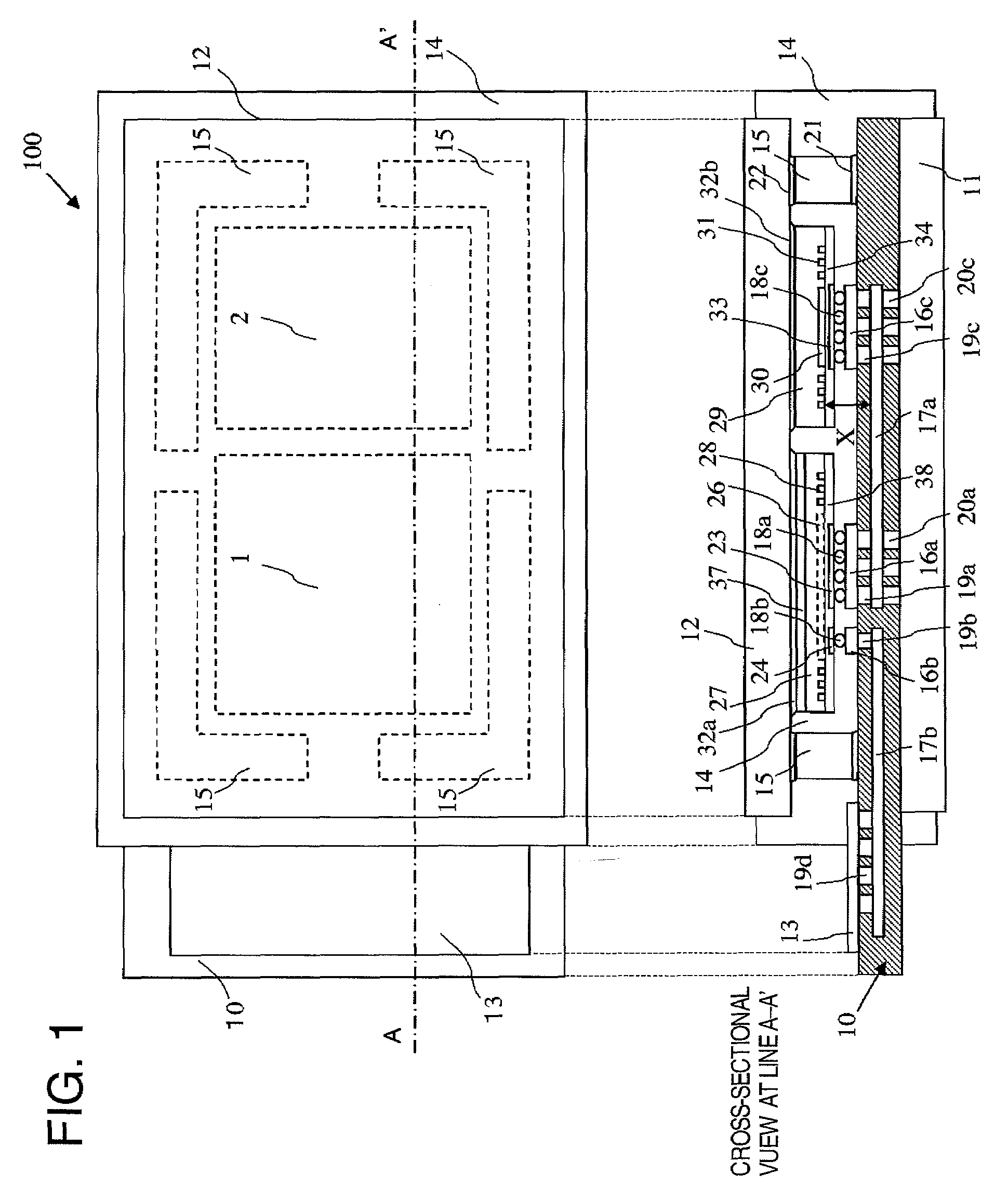

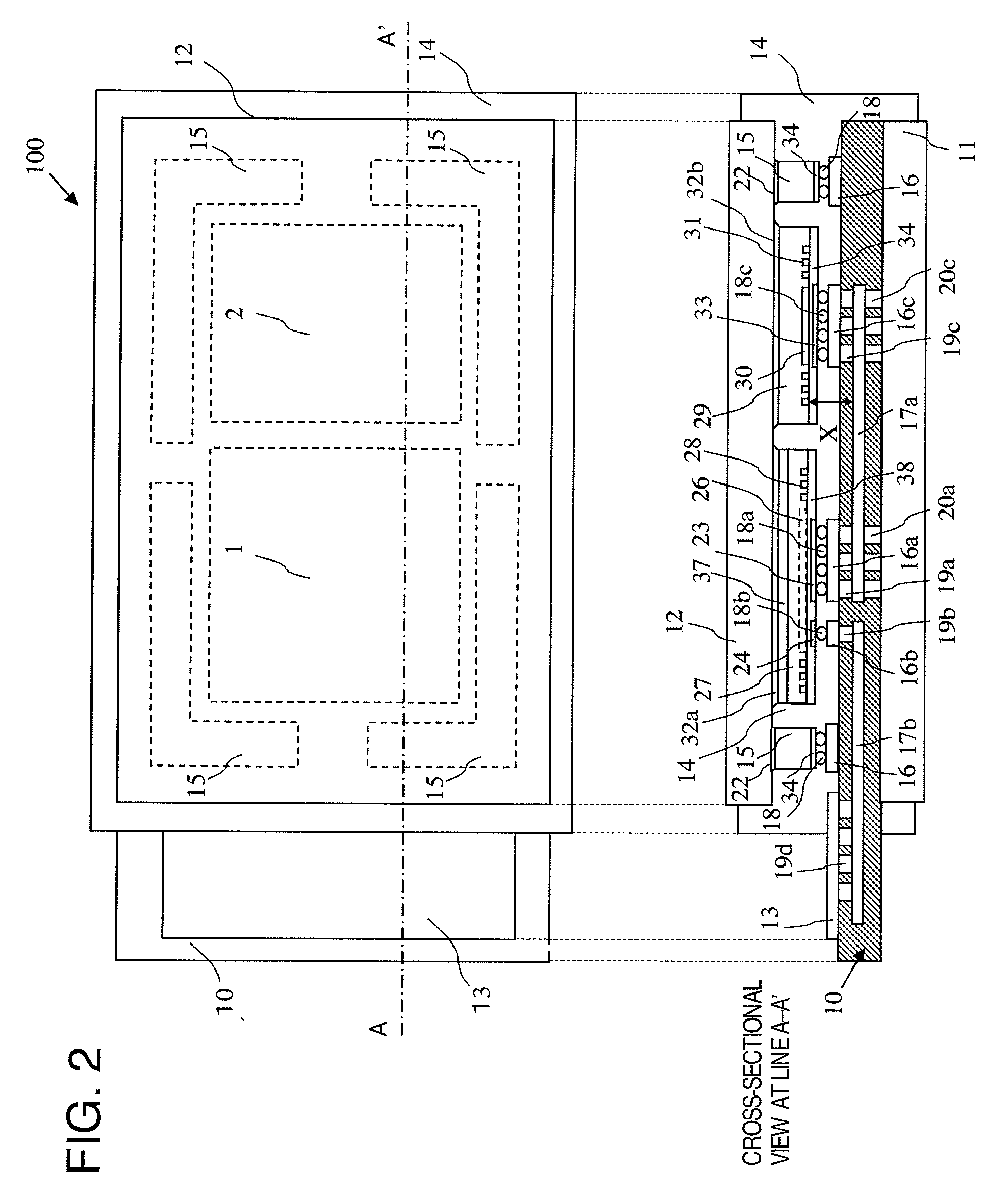

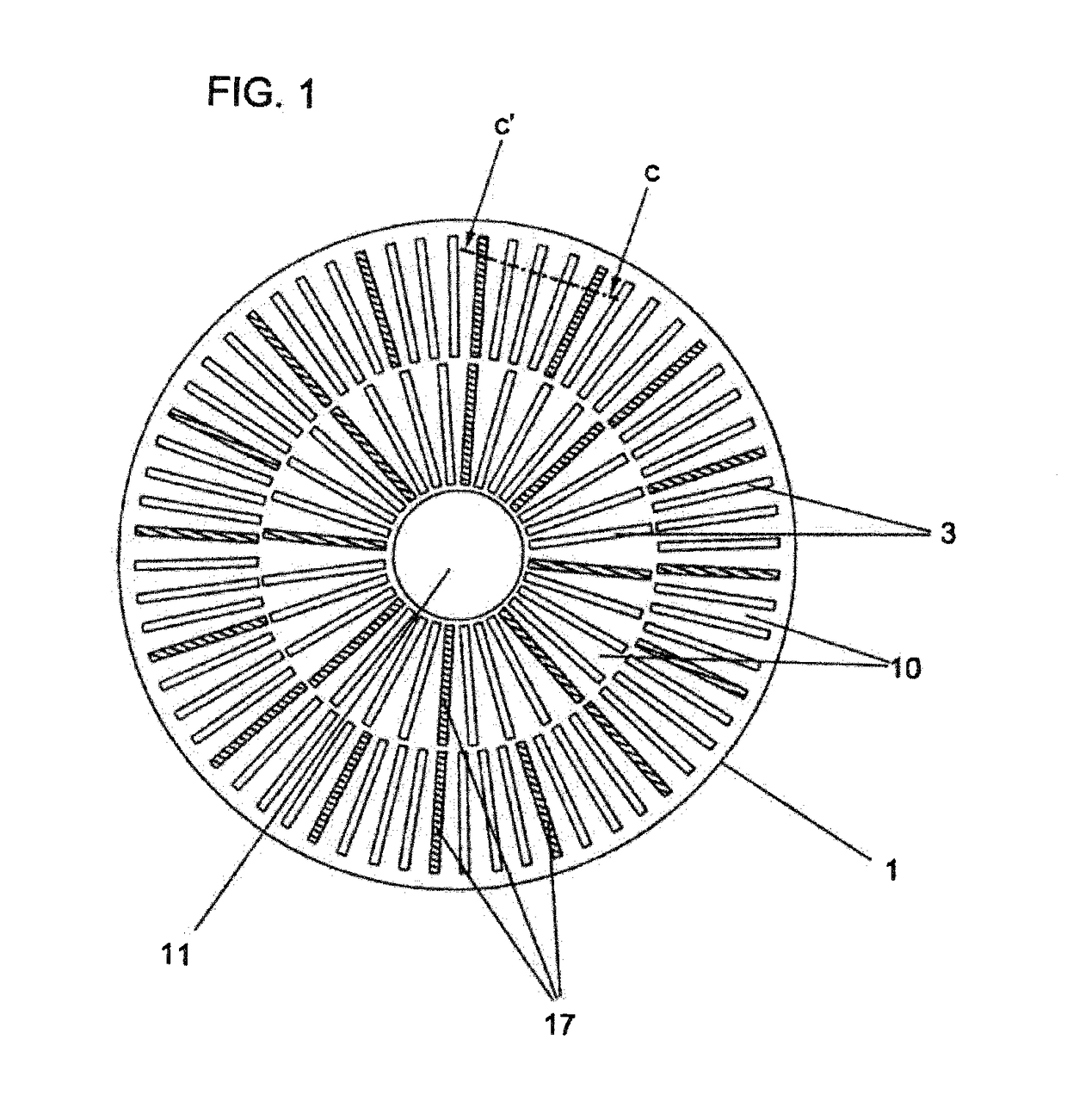

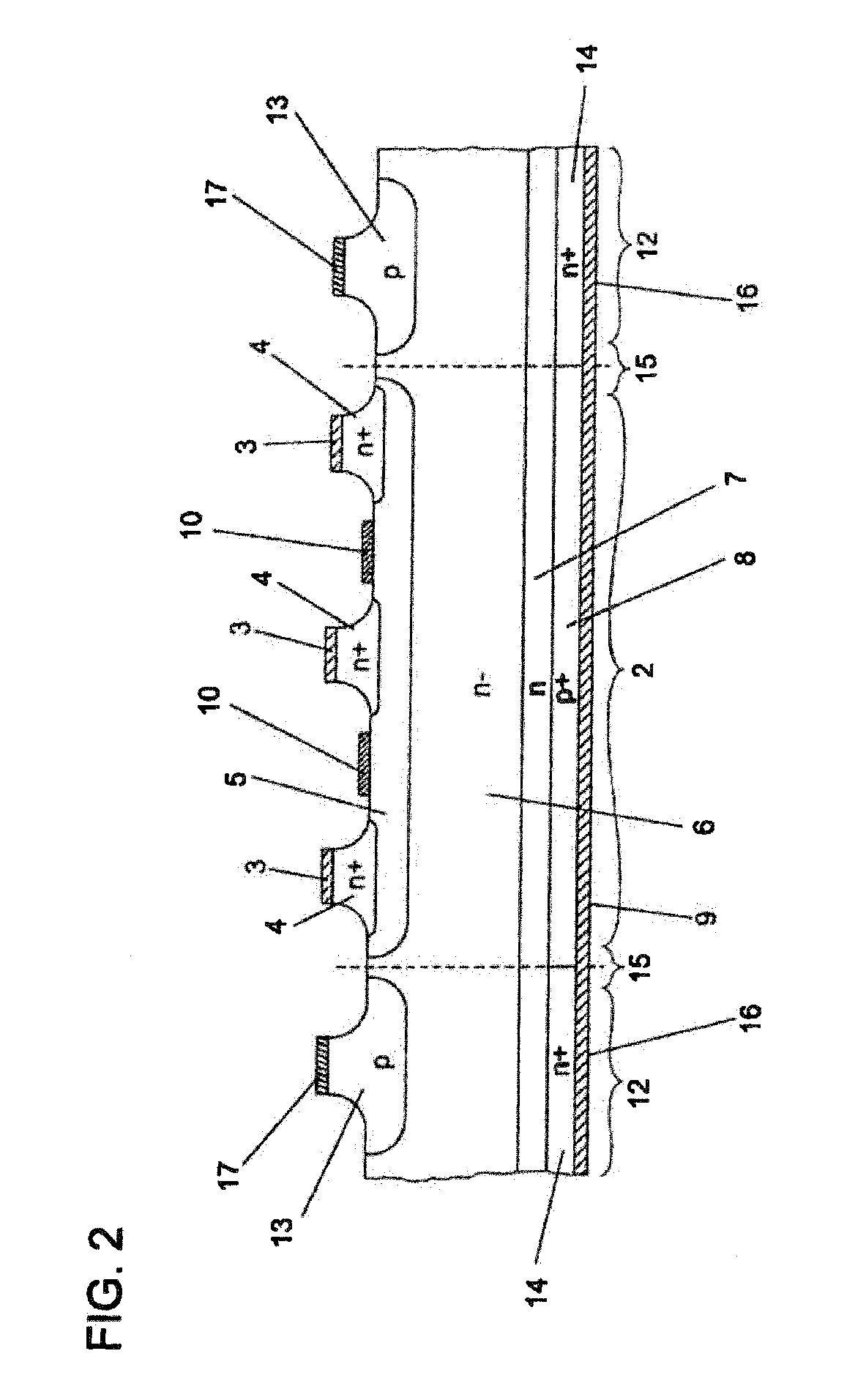

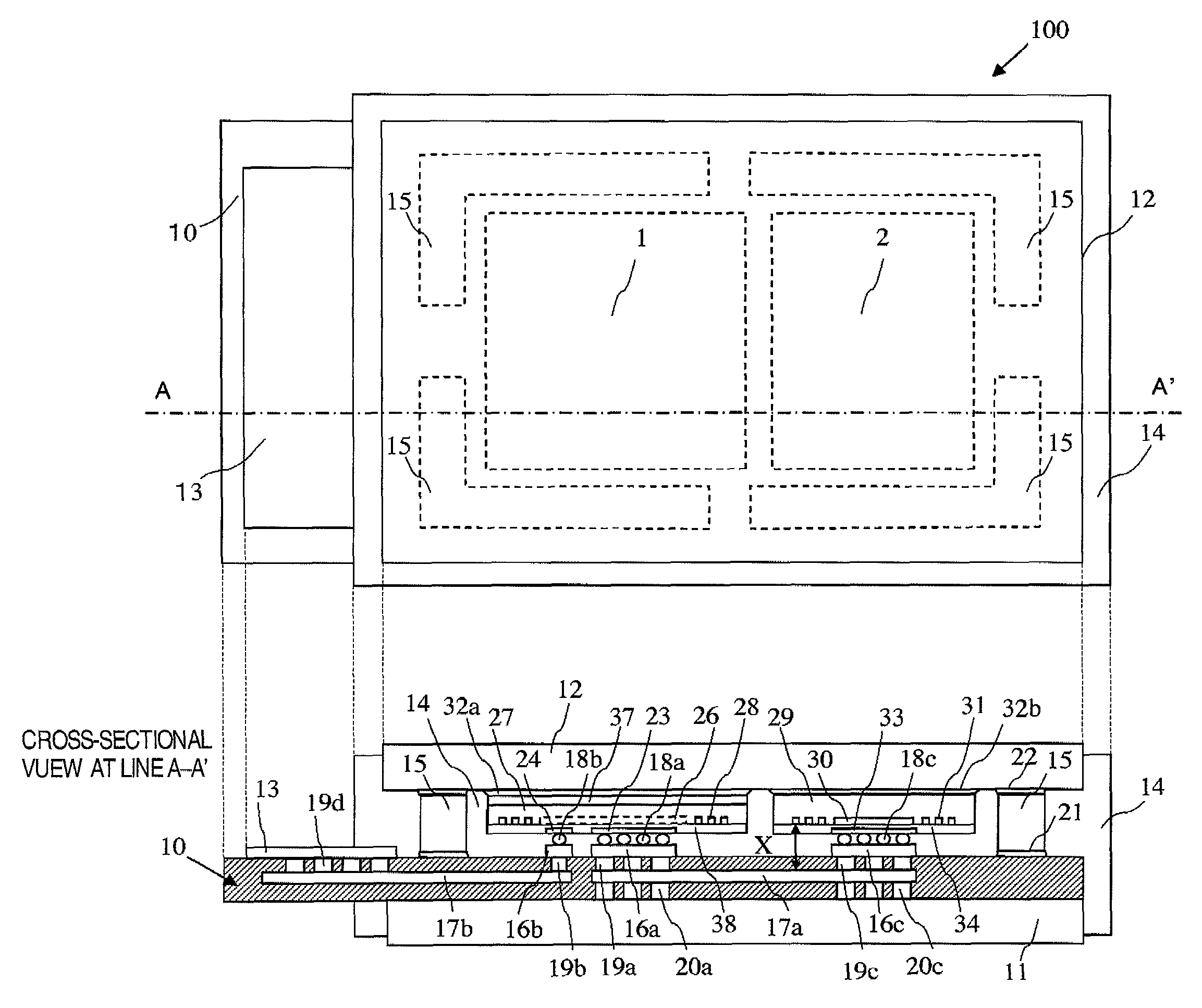

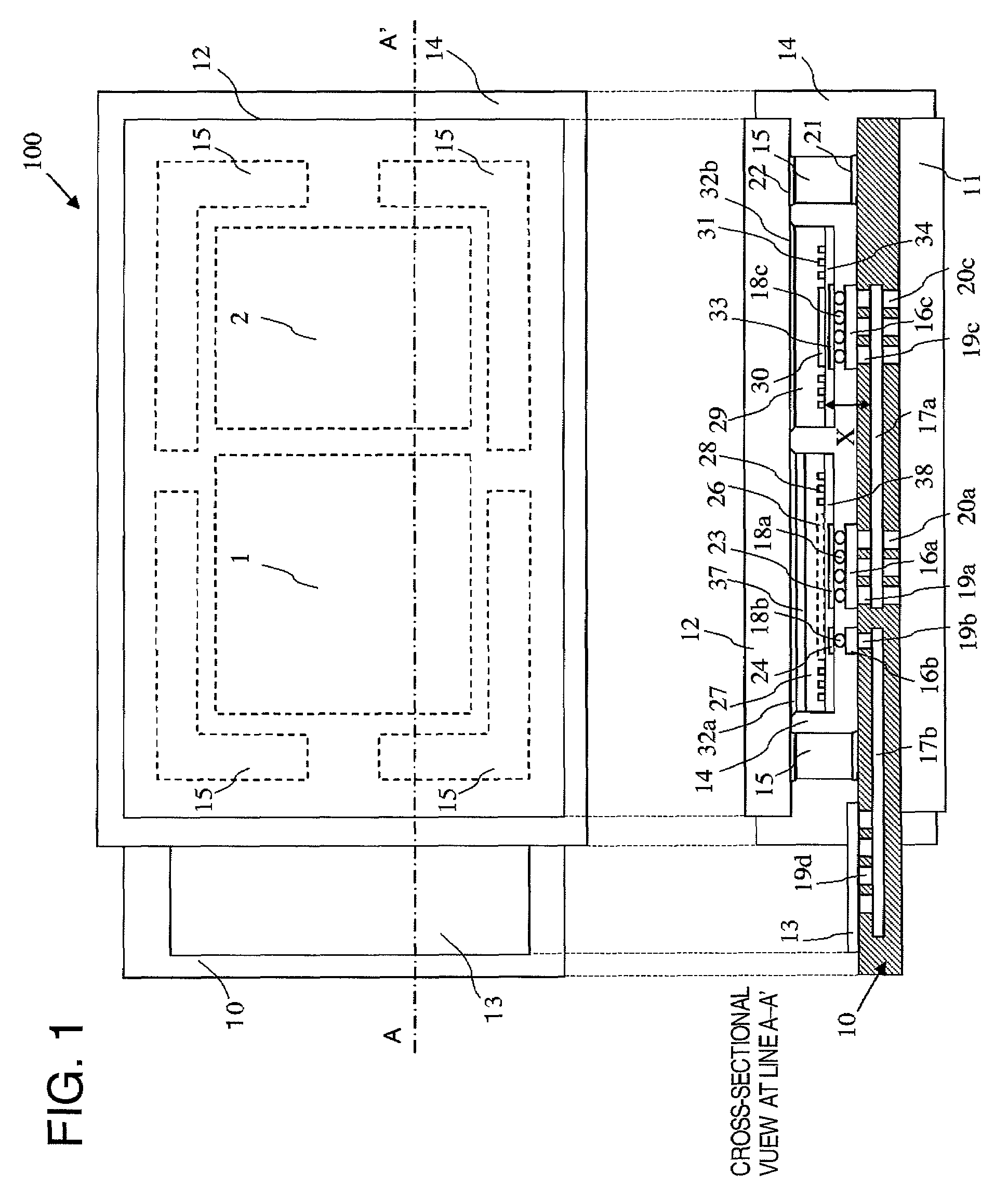

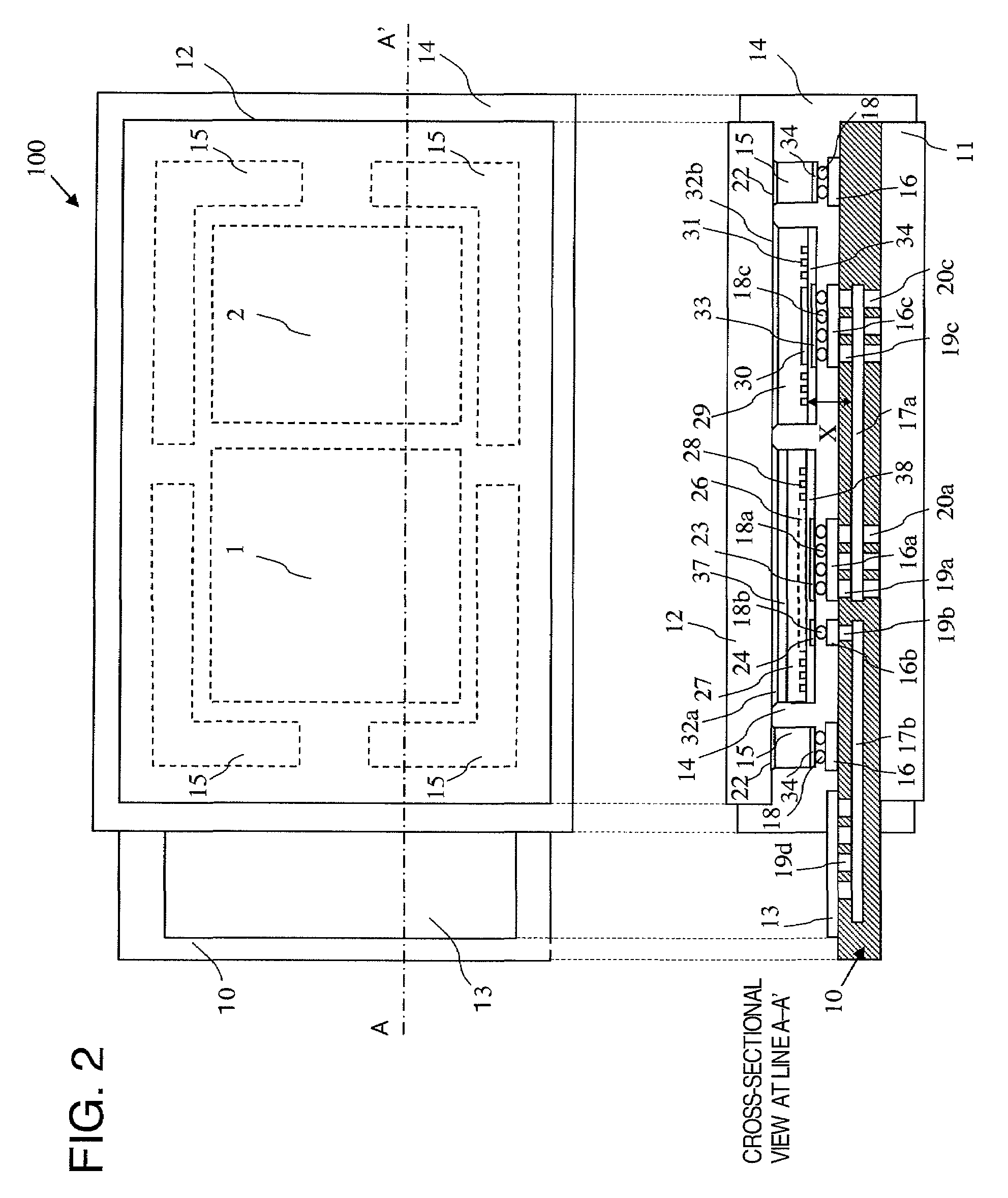

A power semiconductor device, having a first semiconductor region, and a second semiconductor region; mounted with a first electrode pad on a semiconductor substrate main surface at the inside surrounded by the third semiconductor region, mounted in the second semiconductor region, and a multilayer substrate having first and second wiring layers, to take out an electrode of the semiconductor chip; joining the first wiring layer part for the first electrode, mounted on the multilayer substrate, in a region opposing to the semiconductor substrate main surface at the inside surrounded by the third semiconductor region, and the first electrode pad, by a conductive material; joining the first wiring layer part for the first electrode, and the second wiring layer at a conductive part; and extending the second wiring layer to the outside of a region opposing the semiconductor substrate main surface at the inside surrounded by the third semiconductor region.

Owner:HITACHI LTD

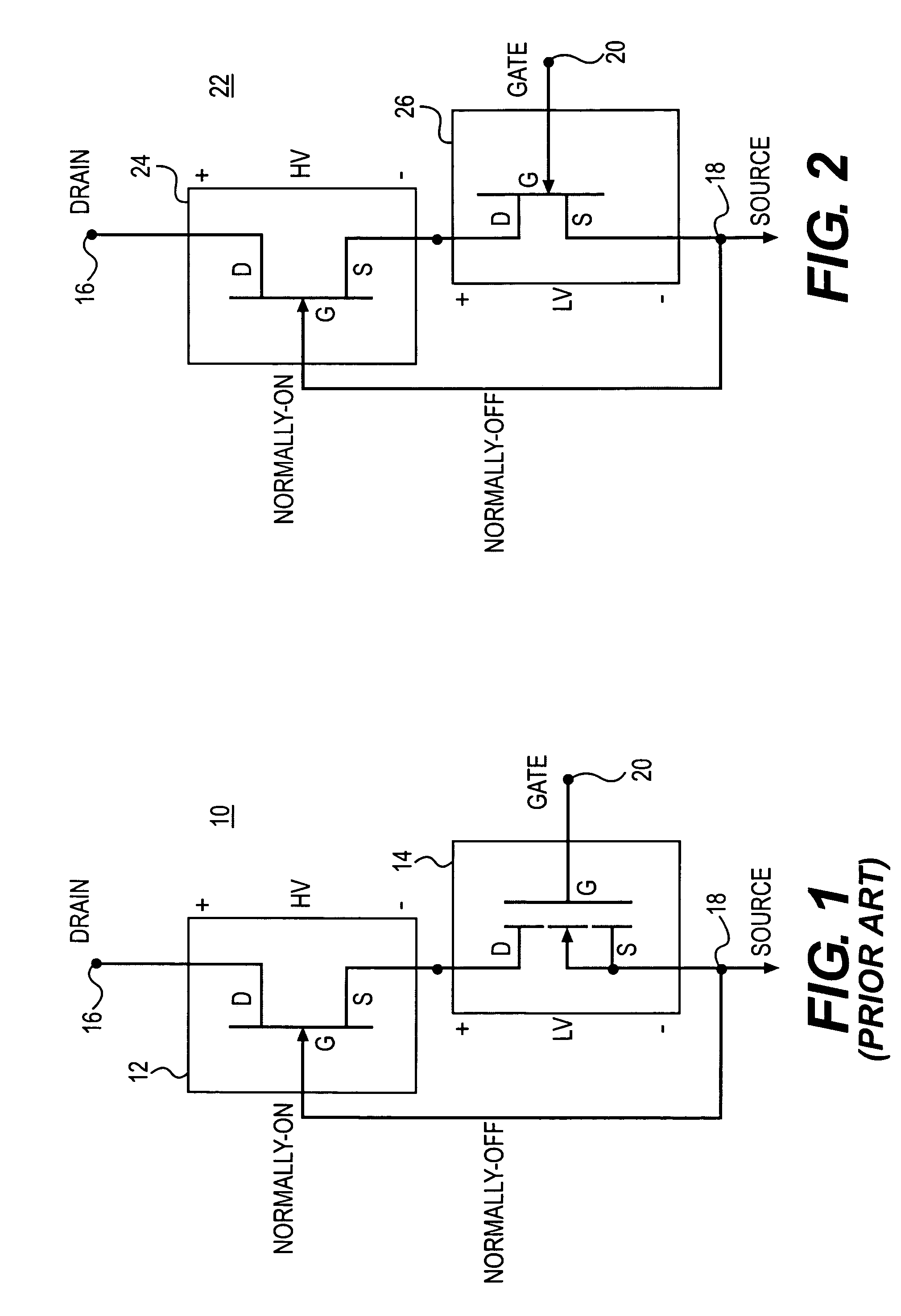

Cascode power switch topologies

ActiveUS7719055B1Increase temperatureHigh blocking voltageElectronic switchingSemiconductor devicesCascodeGallium nitride

A normally-off cascode power switch circuit is disclosed fabricated in wide bandgap semiconductor material such as silicon carbide or gallium nitride and which is capable of conducting current in the forward and reverse direction under the influence of a positive gate bias. The switch includes cascoded junction field effect transistors (JFETs) that enable increased gain, and hence blocking voltage, while minimizing specific on-resistance.

Owner:NORTHROP GRUMMAN SYST CORP

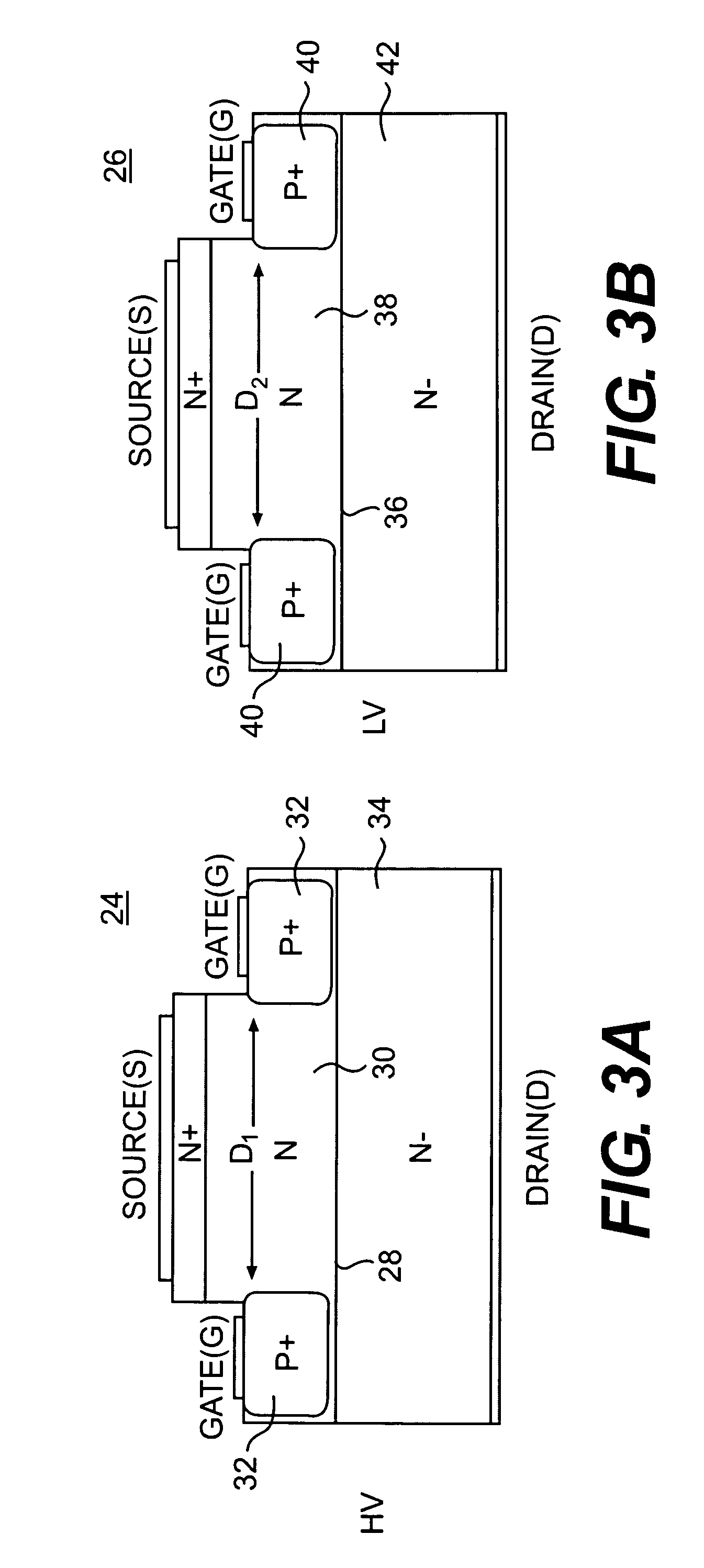

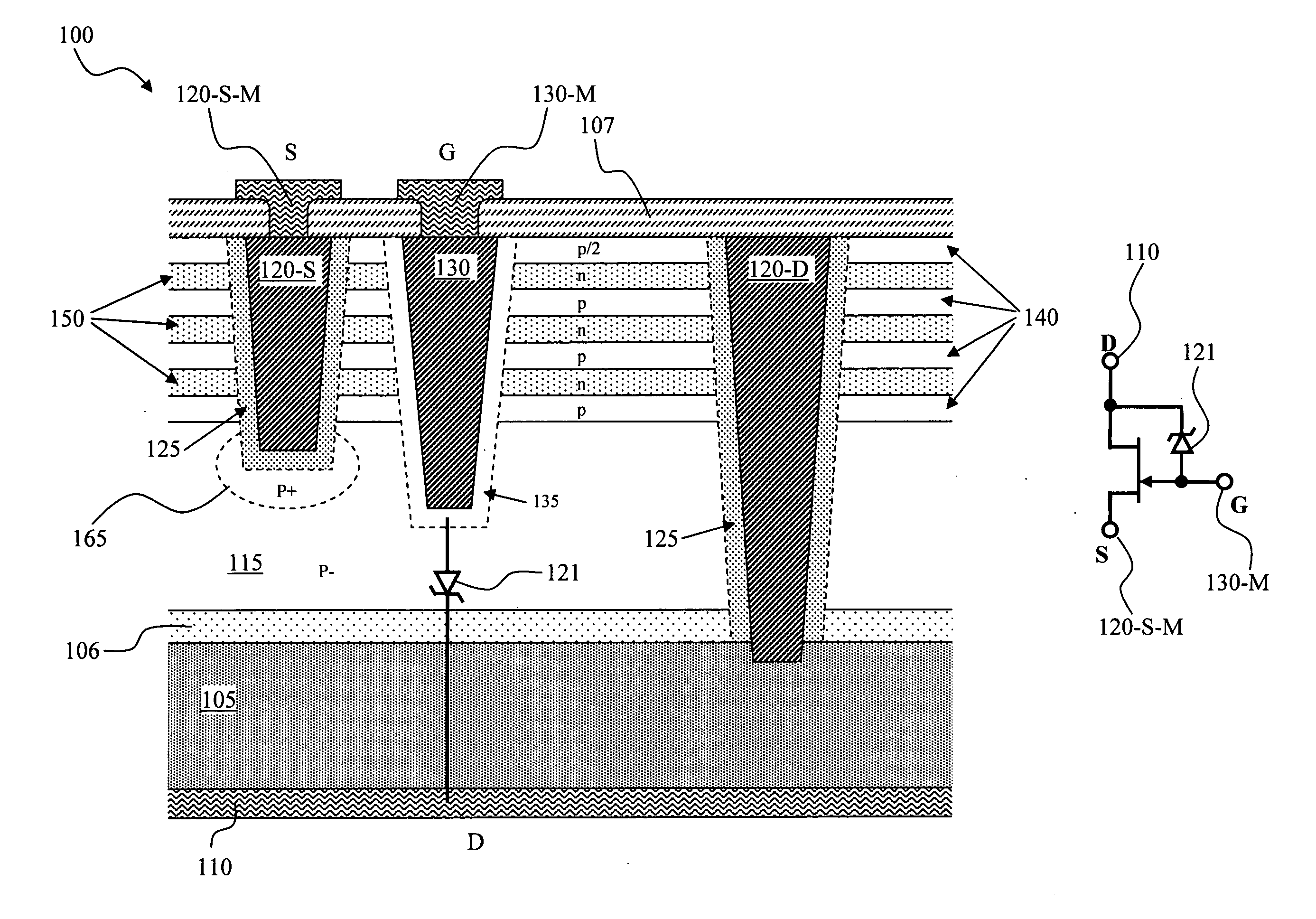

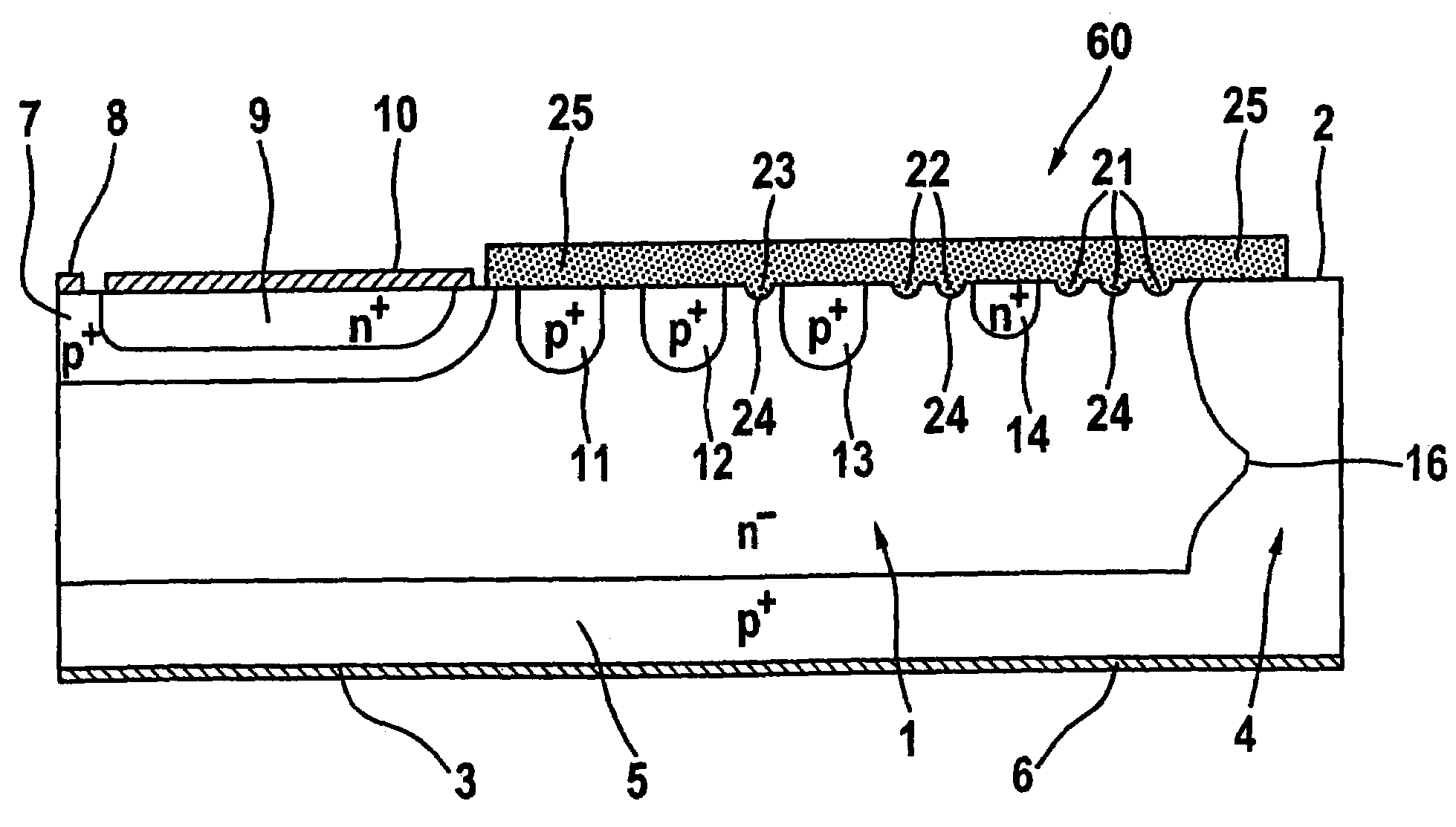

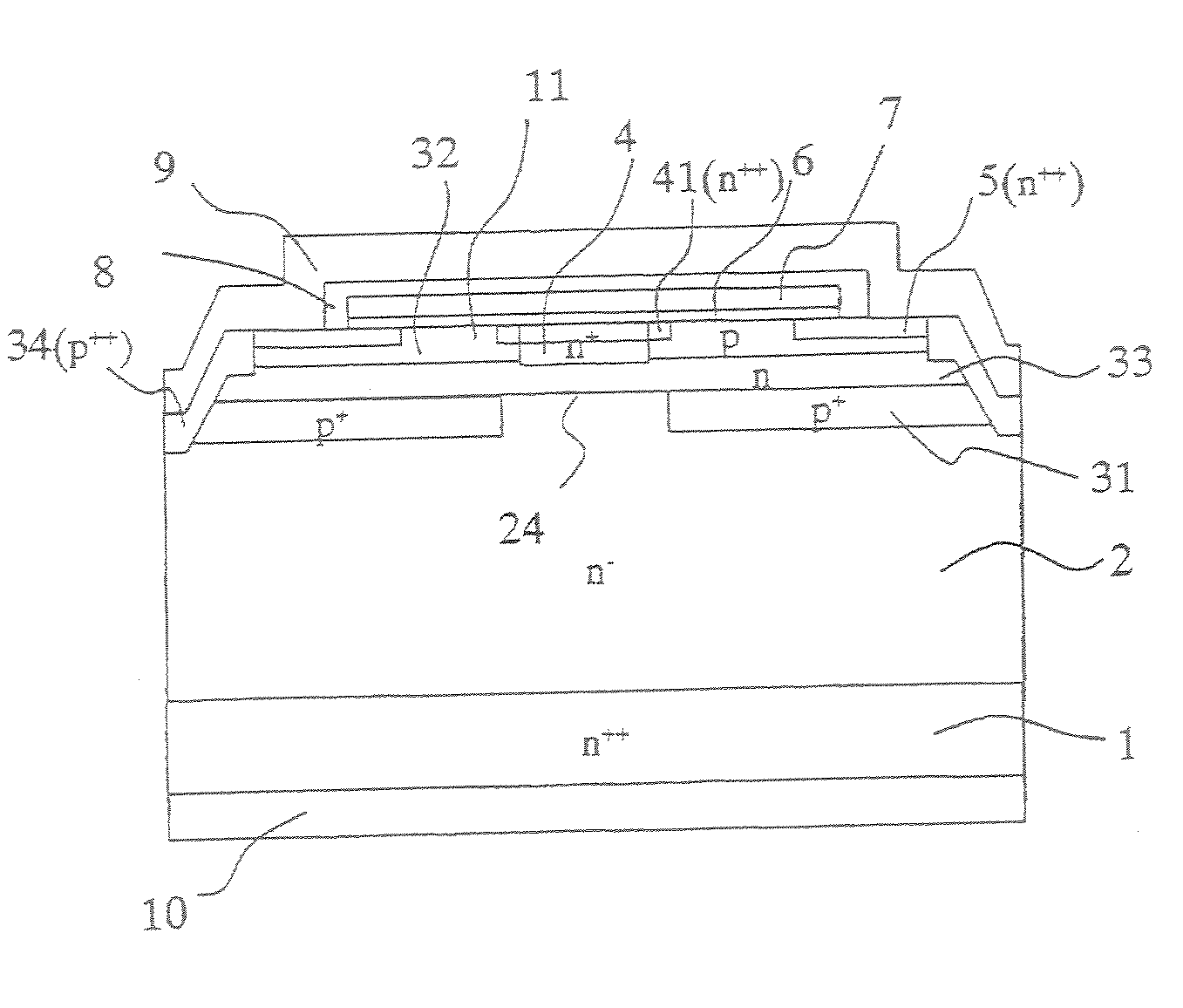

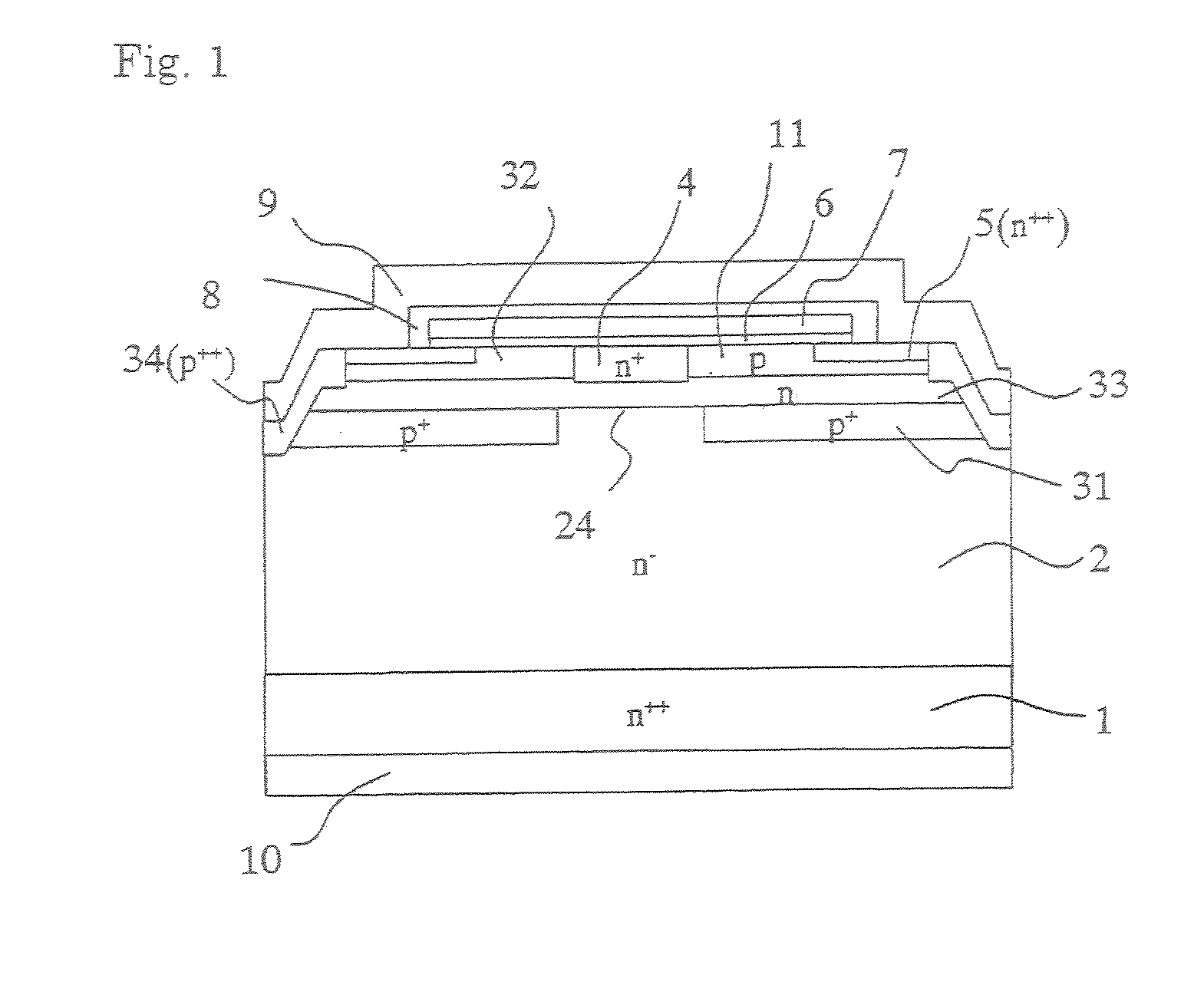

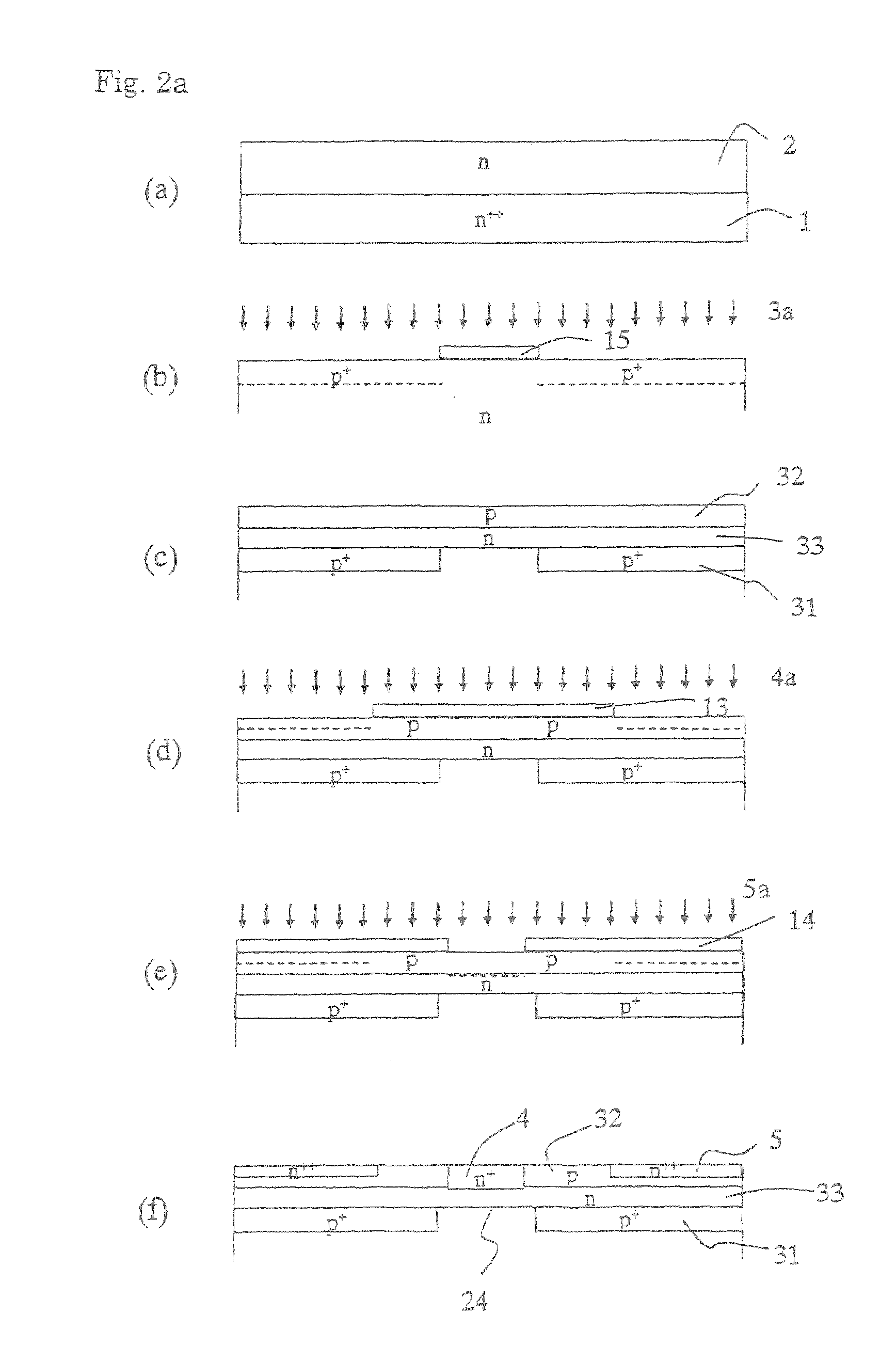

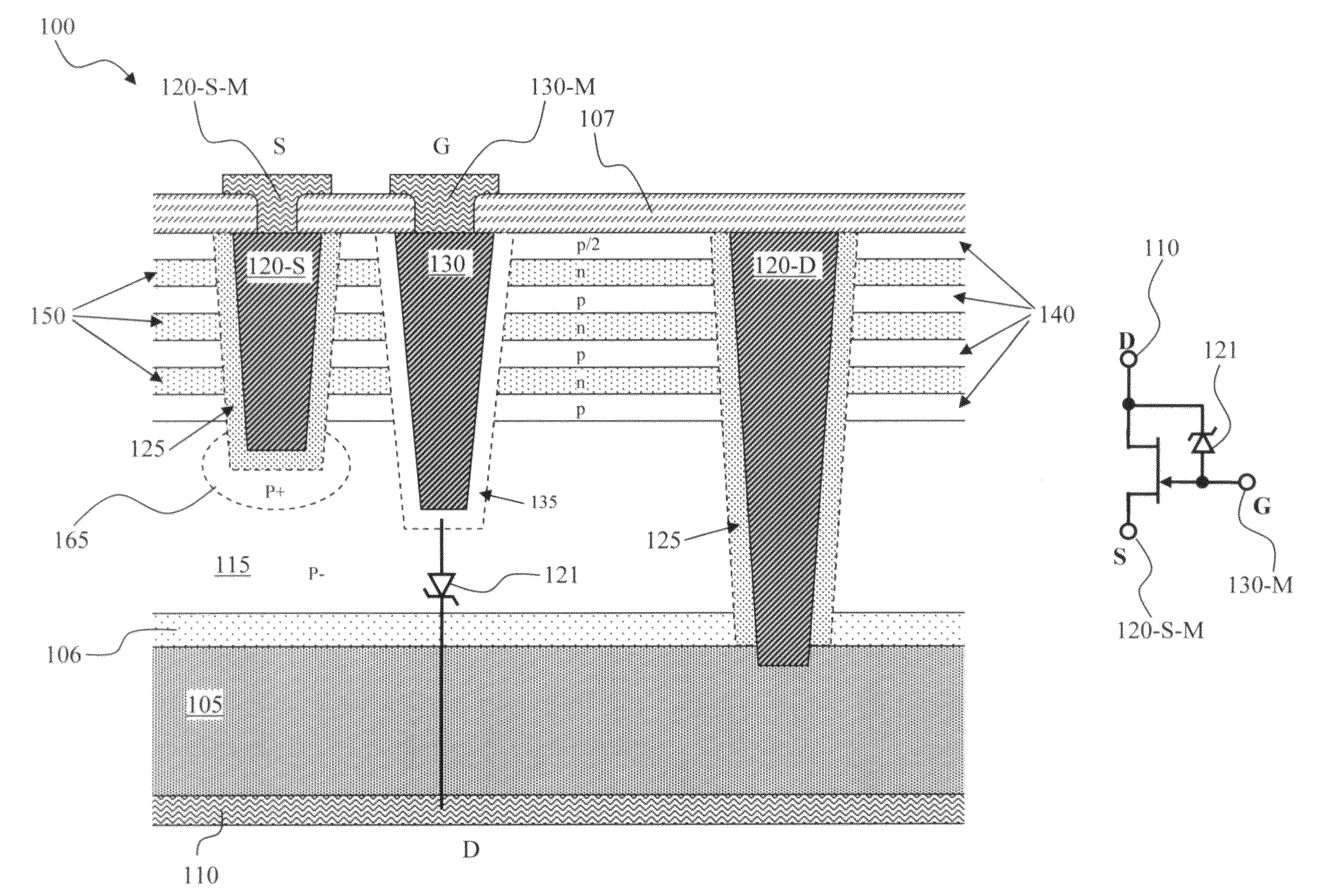

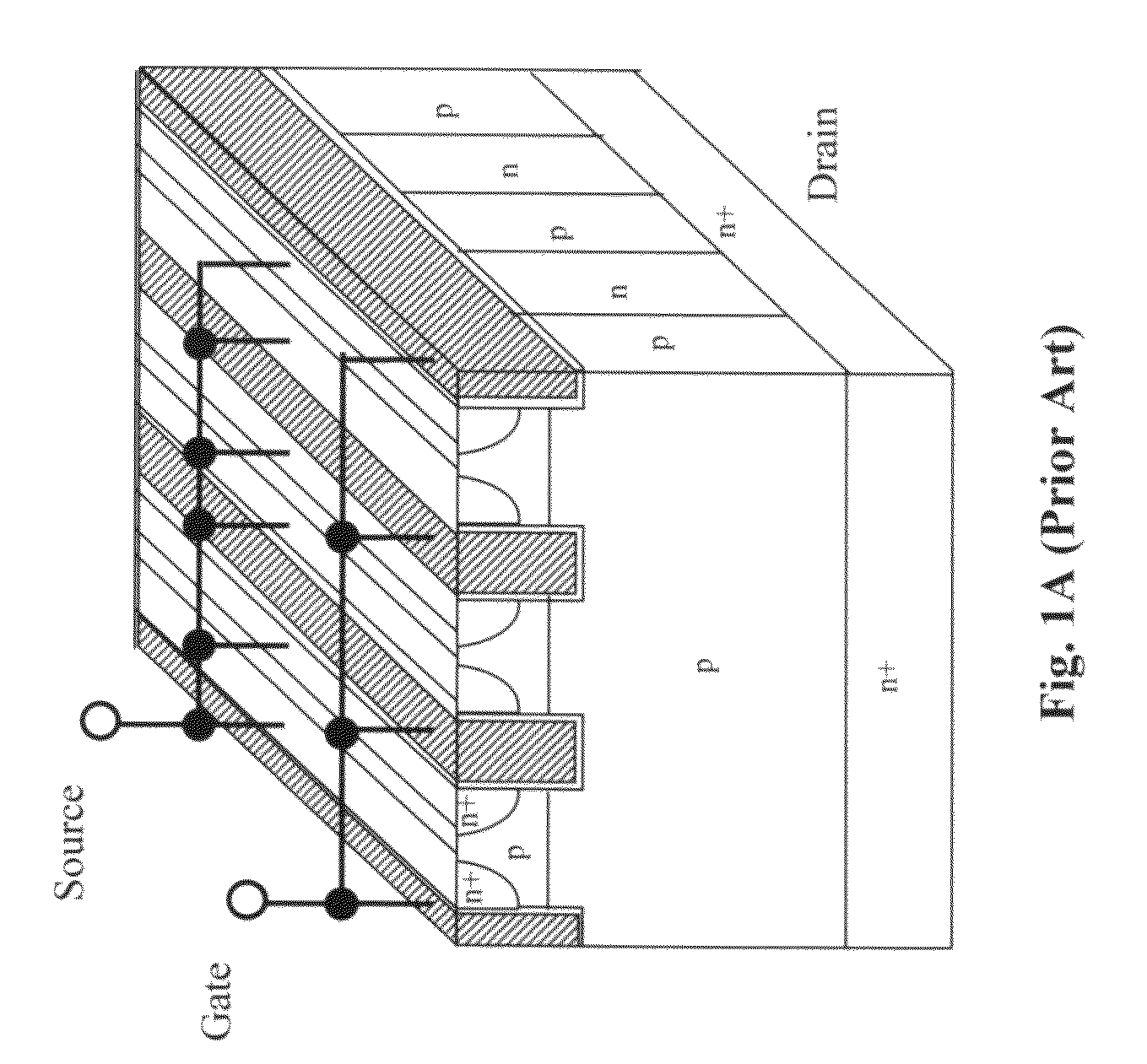

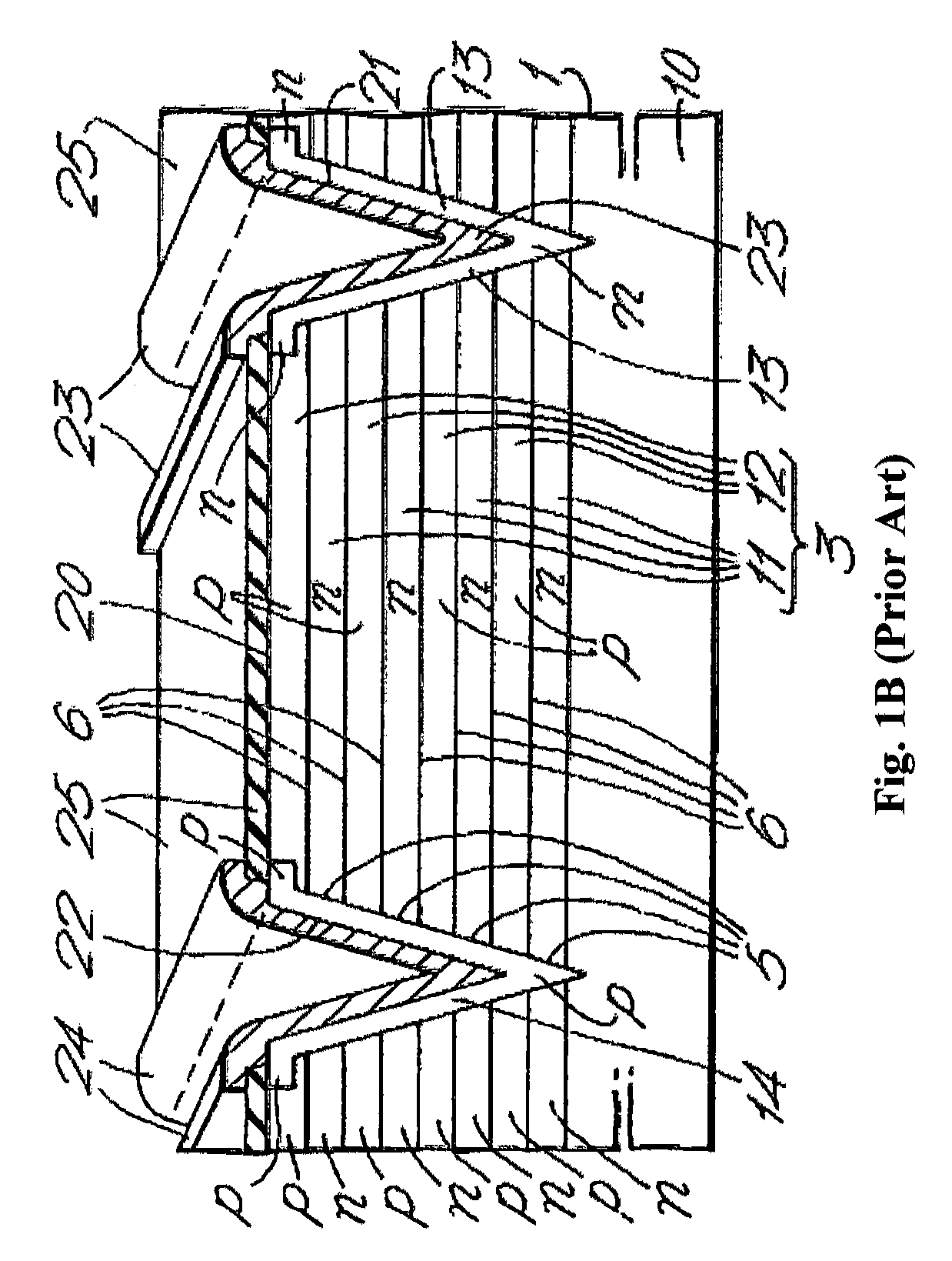

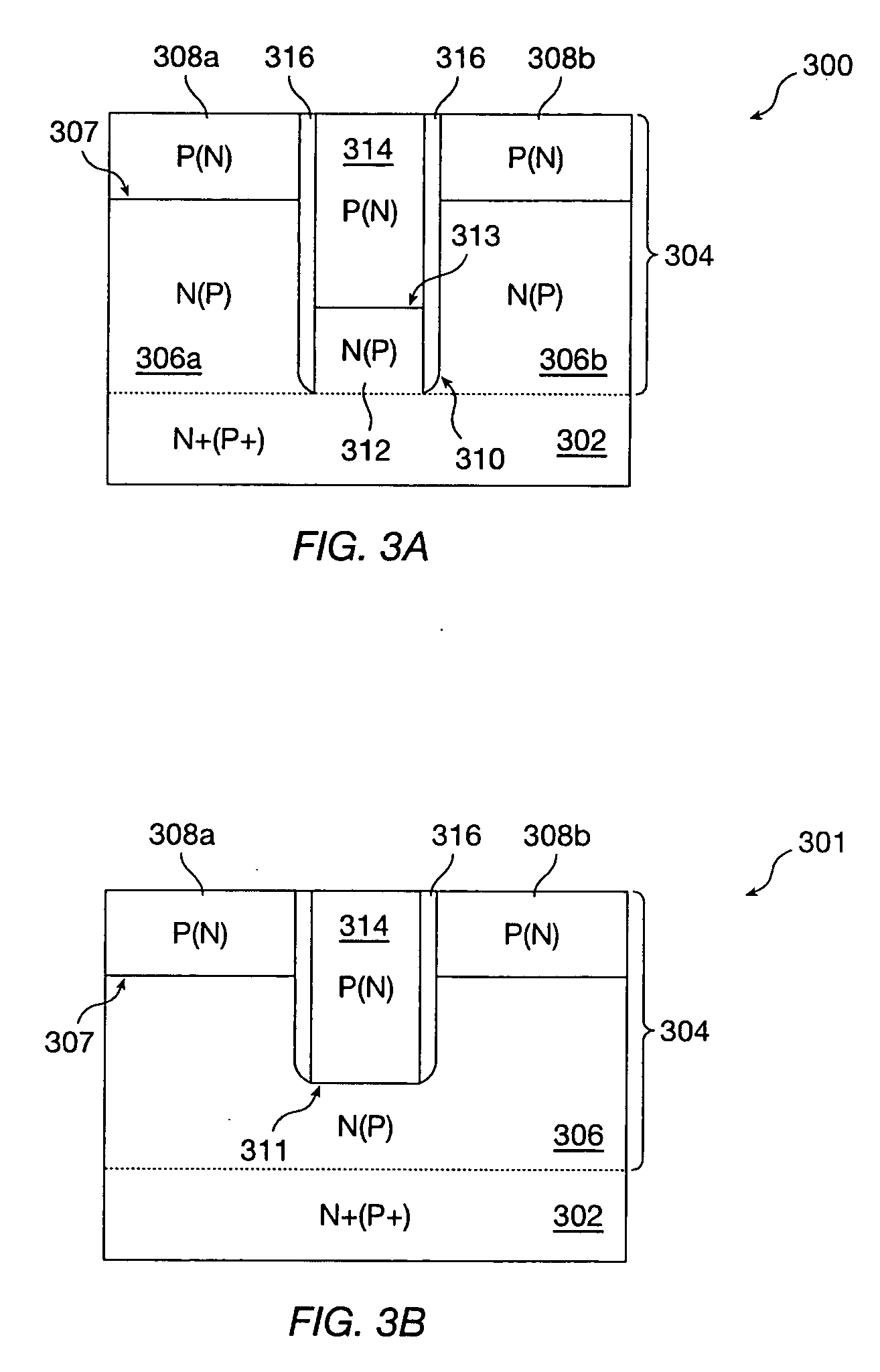

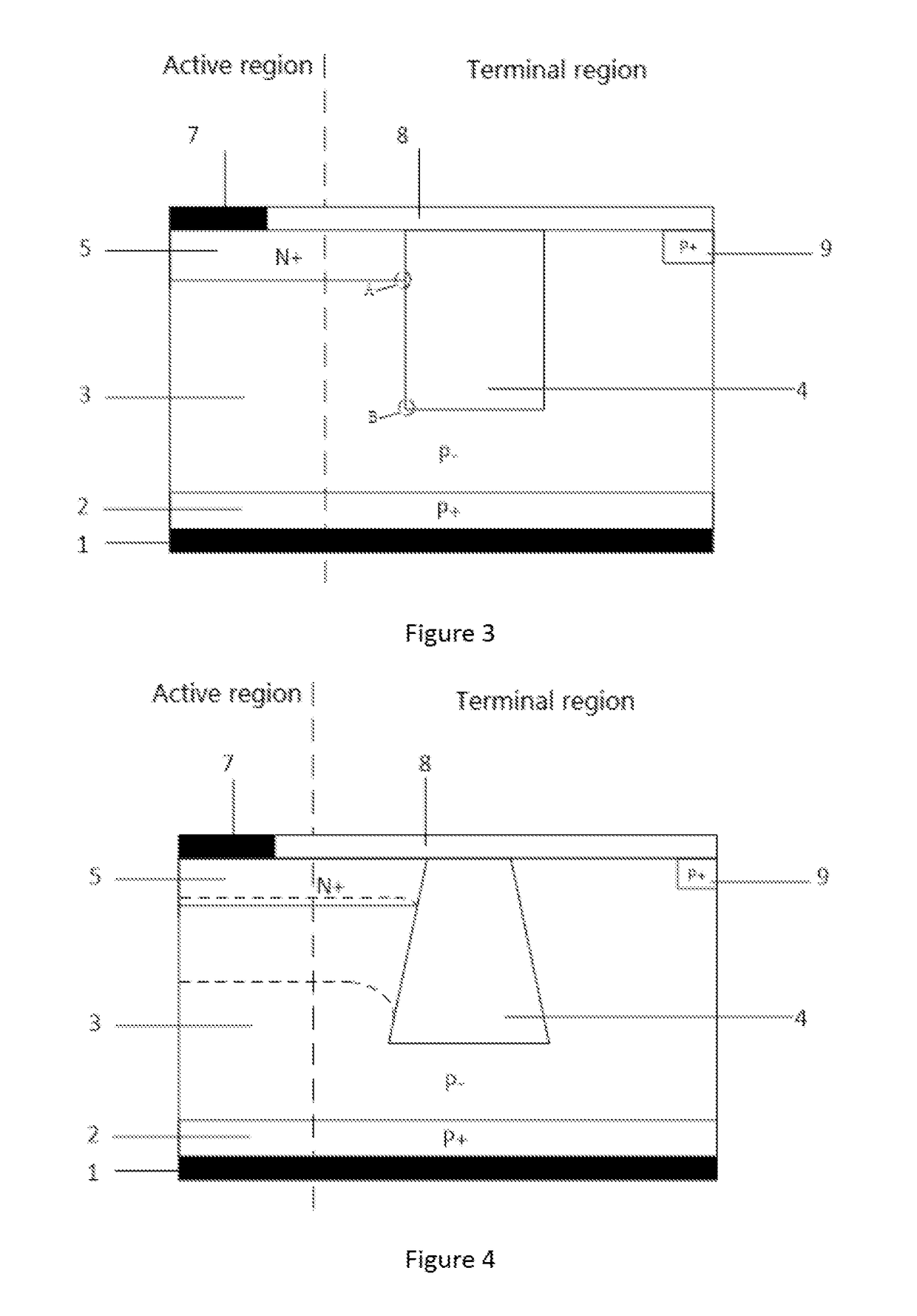

Lateral super junction device with high substrate-gate breakdown and built-in avalanche clamp diode

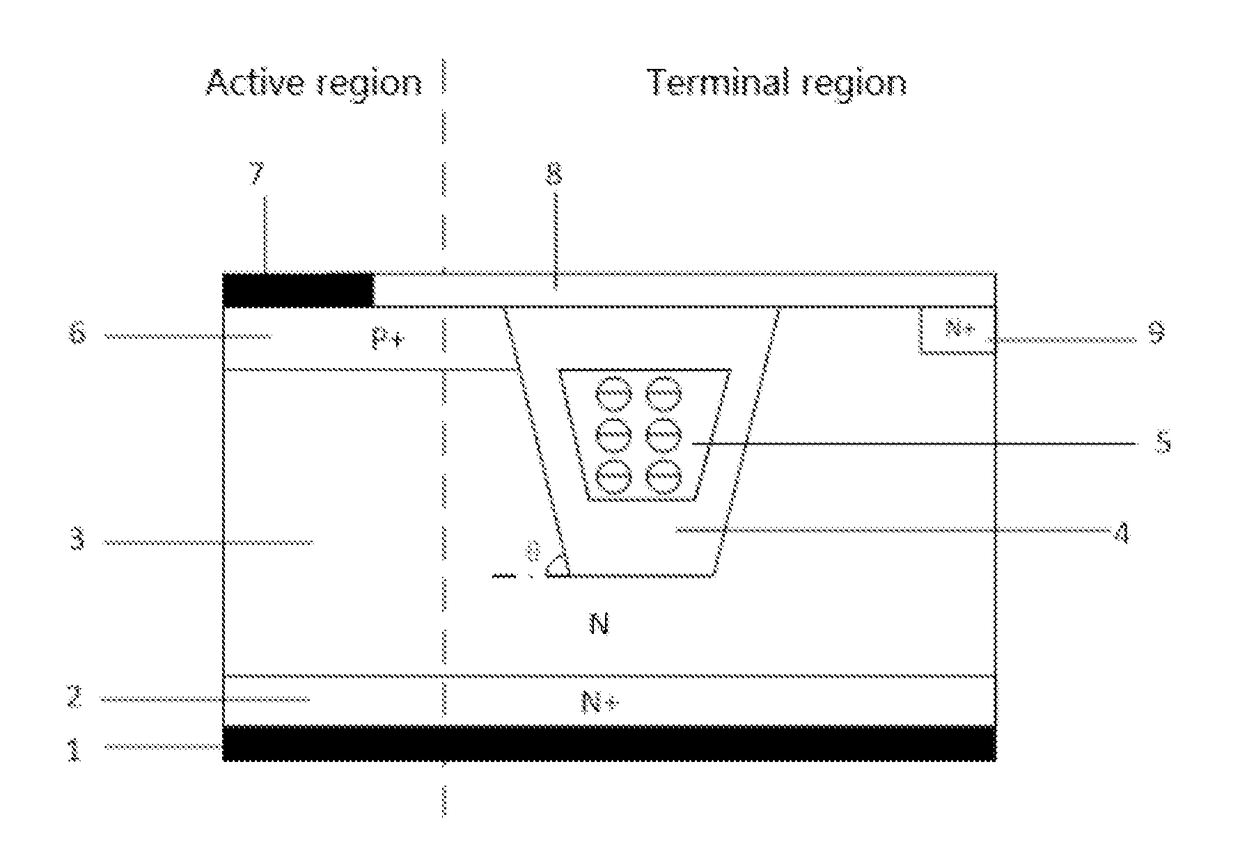

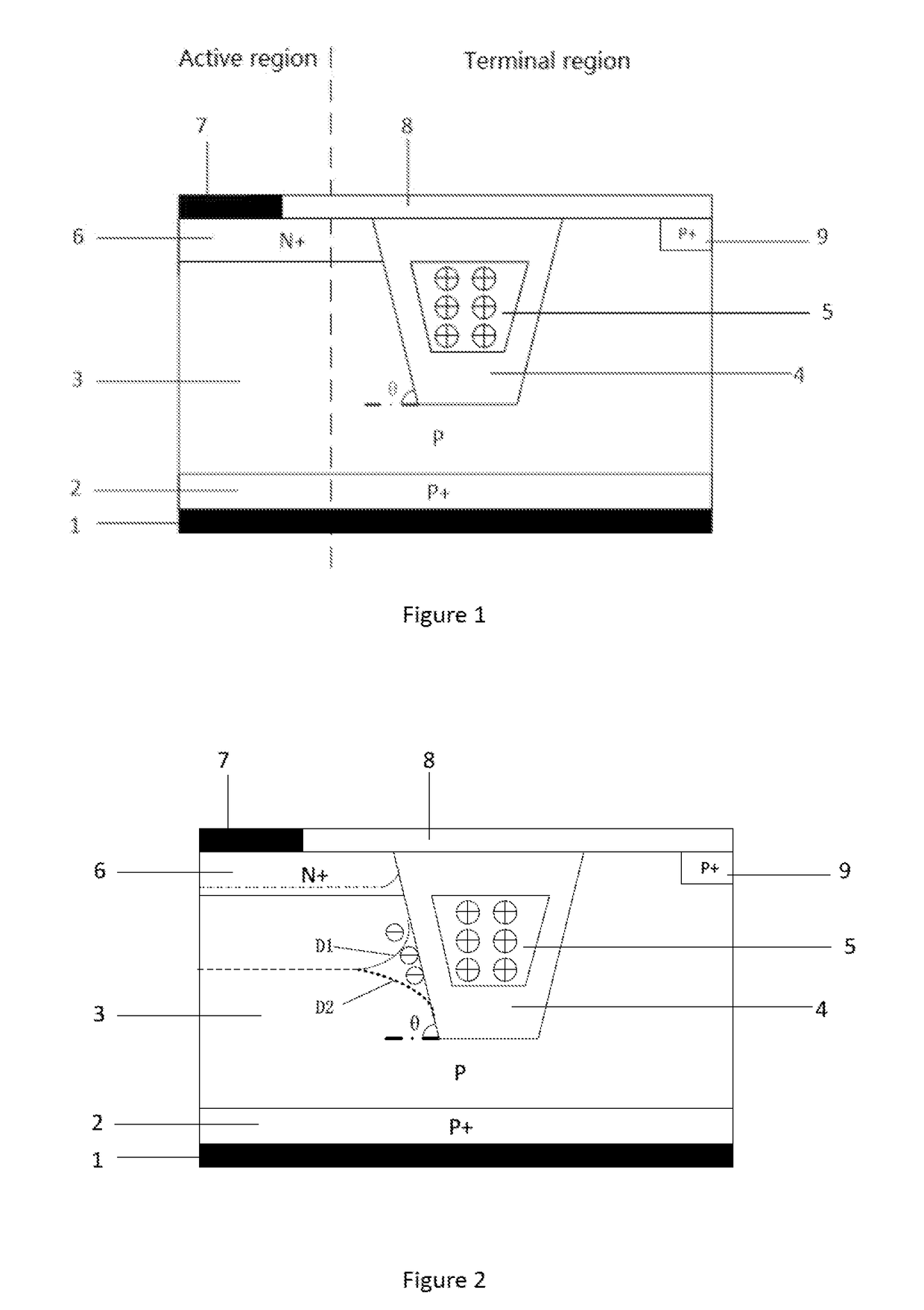

ActiveUS20110127586A1Improve current spreading effectHigh blocking voltageTransistorThyristorEngineeringSemiconductor

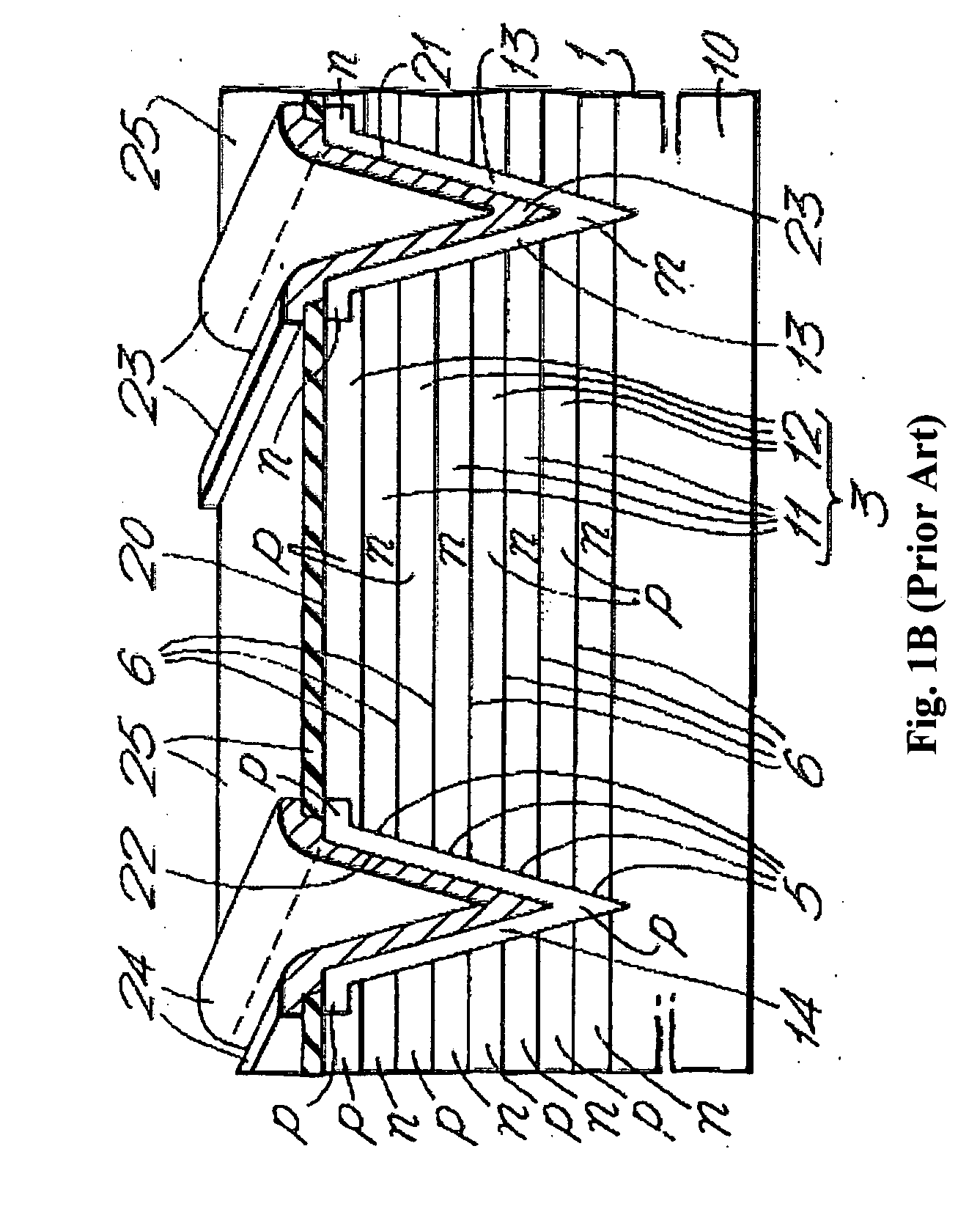

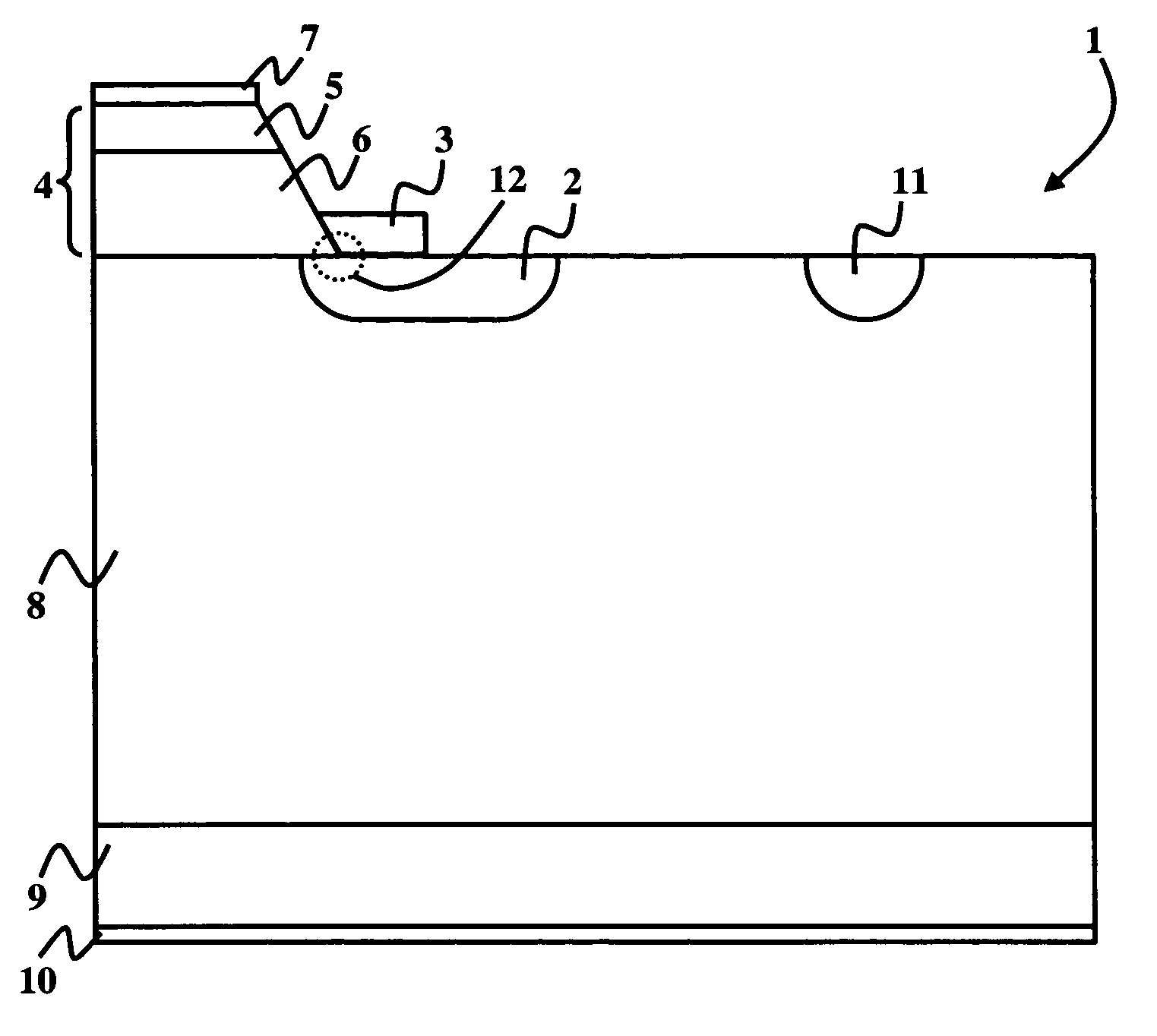

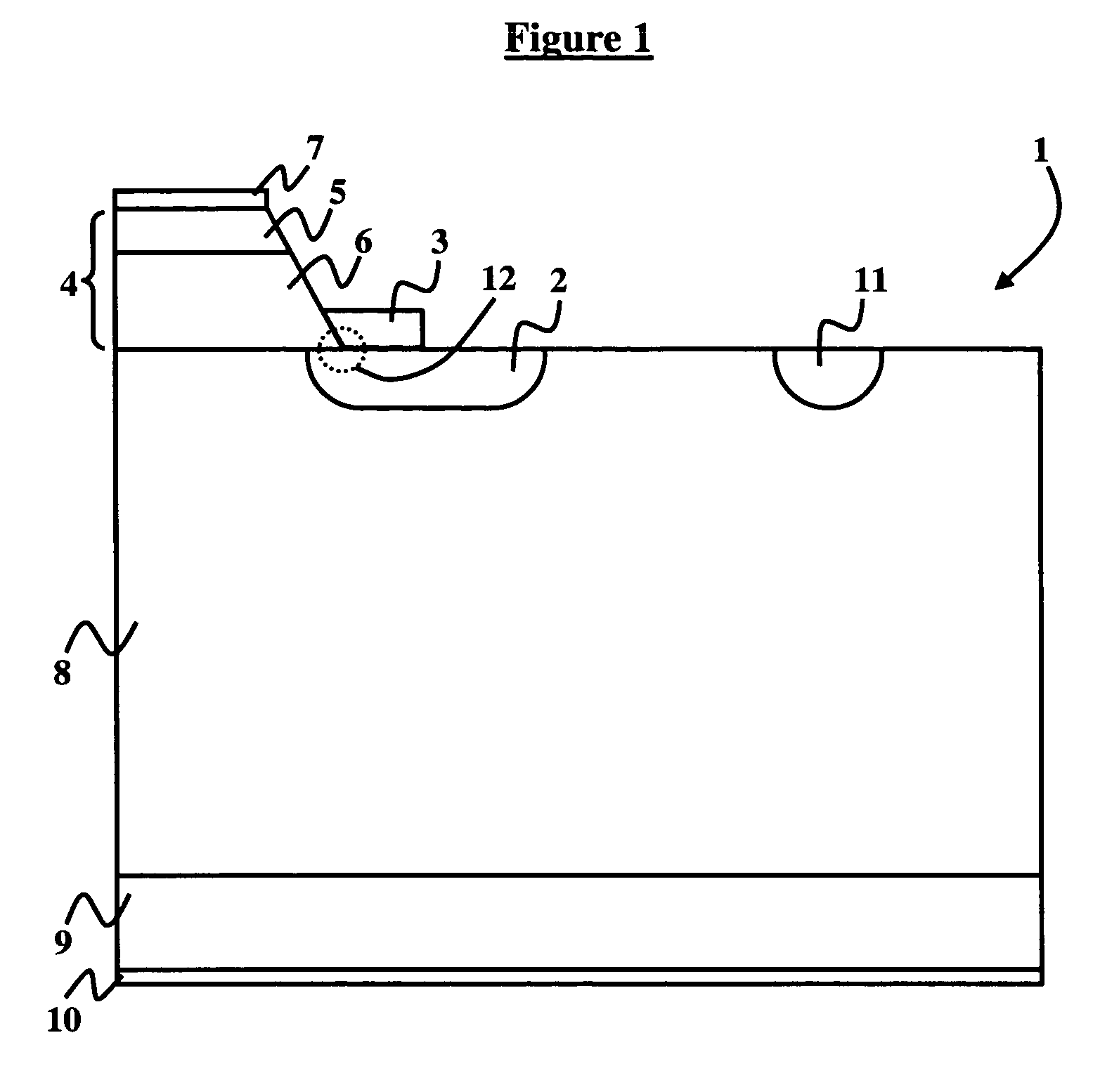

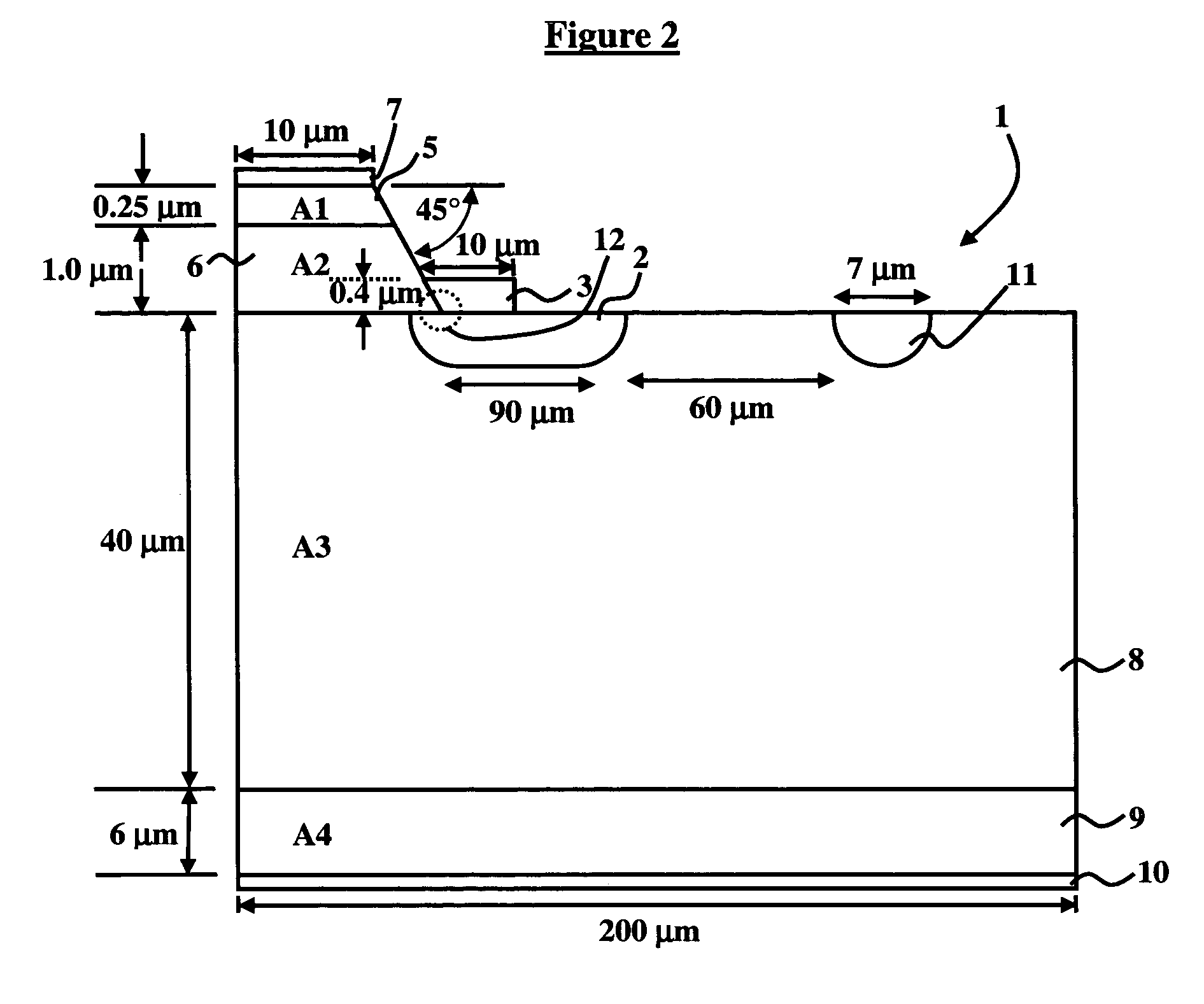

A lateral super junction JFET is formed from stacked alternating P type and N type semiconductor layers over a P-epi layer supported on an N+ substrate. An N+ drain column extends down through the super junction structure and the P-epi to connect to the N+ substrate to make the device a bottom drain device. N+ source column and P+ gate column extend through the super junction but stop at the P-epi layer. A gate-drain avalanche clamp diode is formed from the bottom the P+ gate column through the P-epi to the N+ drain substrate.

Owner:ALPHA & OMEGA SEMICON INC

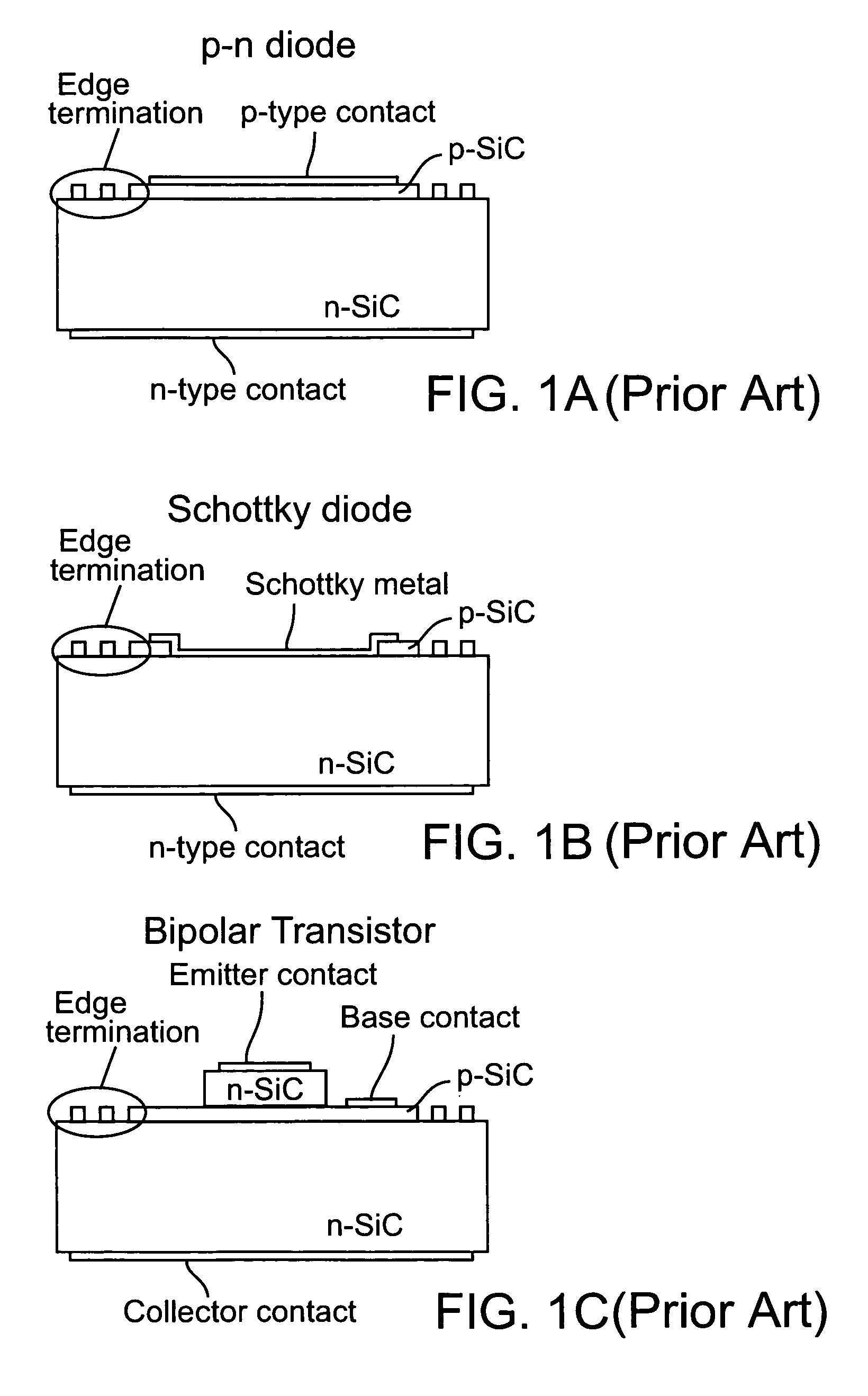

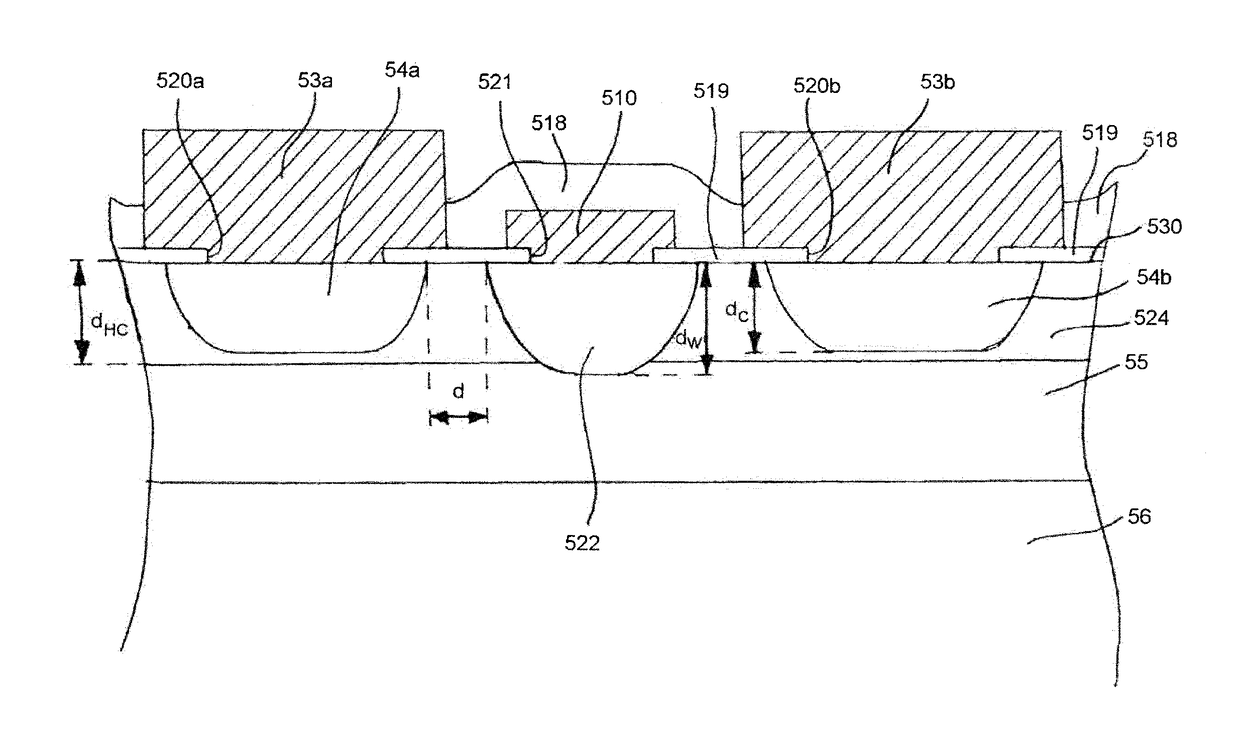

Interacting current spreader and junction extender to increase the voltage blocked in the off state of a high power semiconductor device

ActiveUS7304363B1Reduce concentrationLow densitySemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceField line

A technique of spreading current flowing in a semiconductor device comprising an electrode, a drift region adjacent to the electrode, a junction termination extension implant region in the drift region, and a current spreader adjacent to the junction termination extension implant region and the electrode. The current spreader is adapted to reduce current densities and electrostatic fields (preferably simultaneously) in an area connecting the electrode with the drift region. Moreover, the current spreader is adapted to spread current flowing from the electrode into the drift region. The semiconductor device further comprises an ohmic metal contact connected to the electrode and an implant pocket in the drift region, wherein the implant pocket is adapted for terminating electrostatic field lines in the semiconductor device. Preferably, the current spreader comprises an ohmic metal and the electrode comprises any of an anode and a cathode.

Owner:ARMY US SEC THE

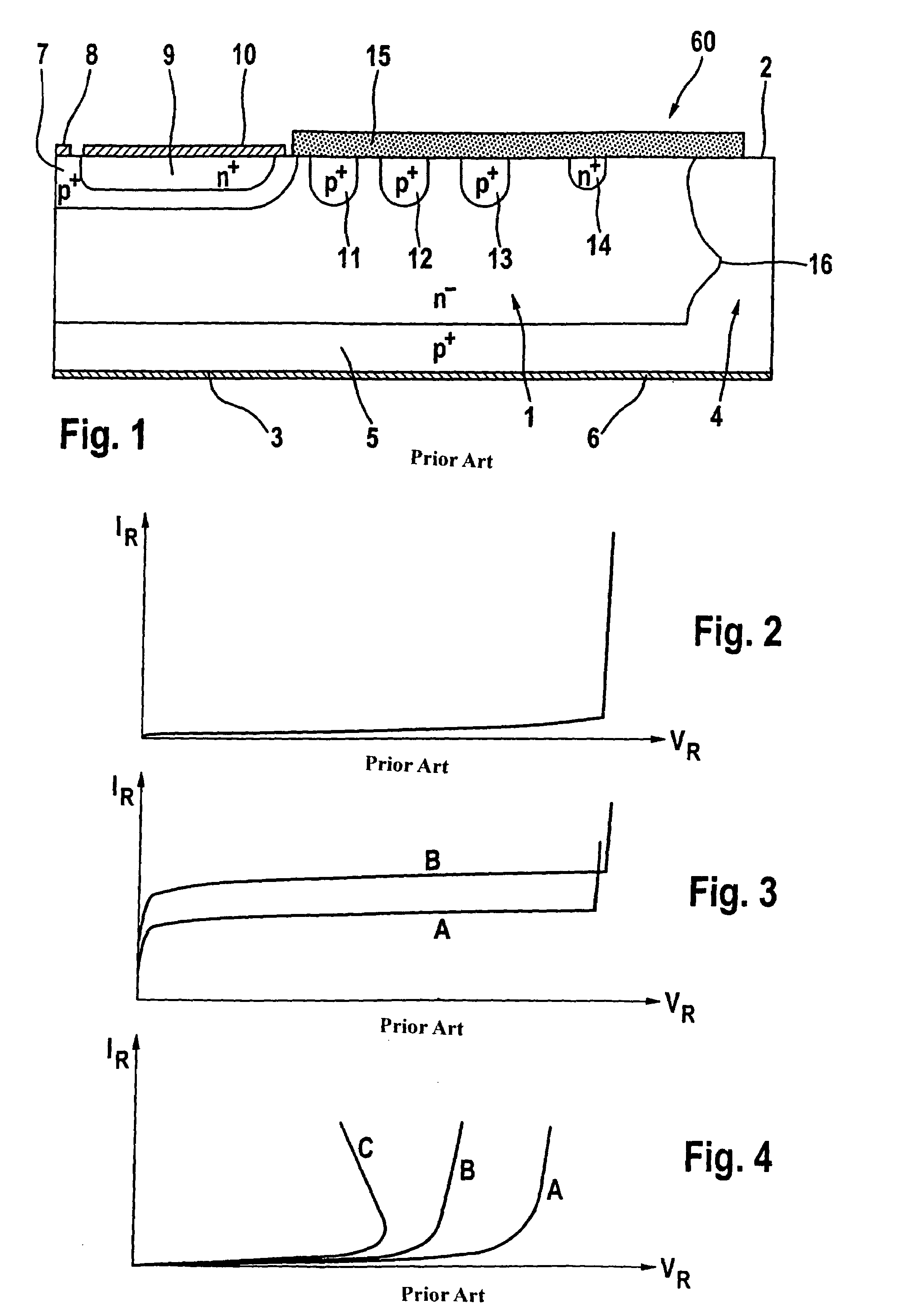

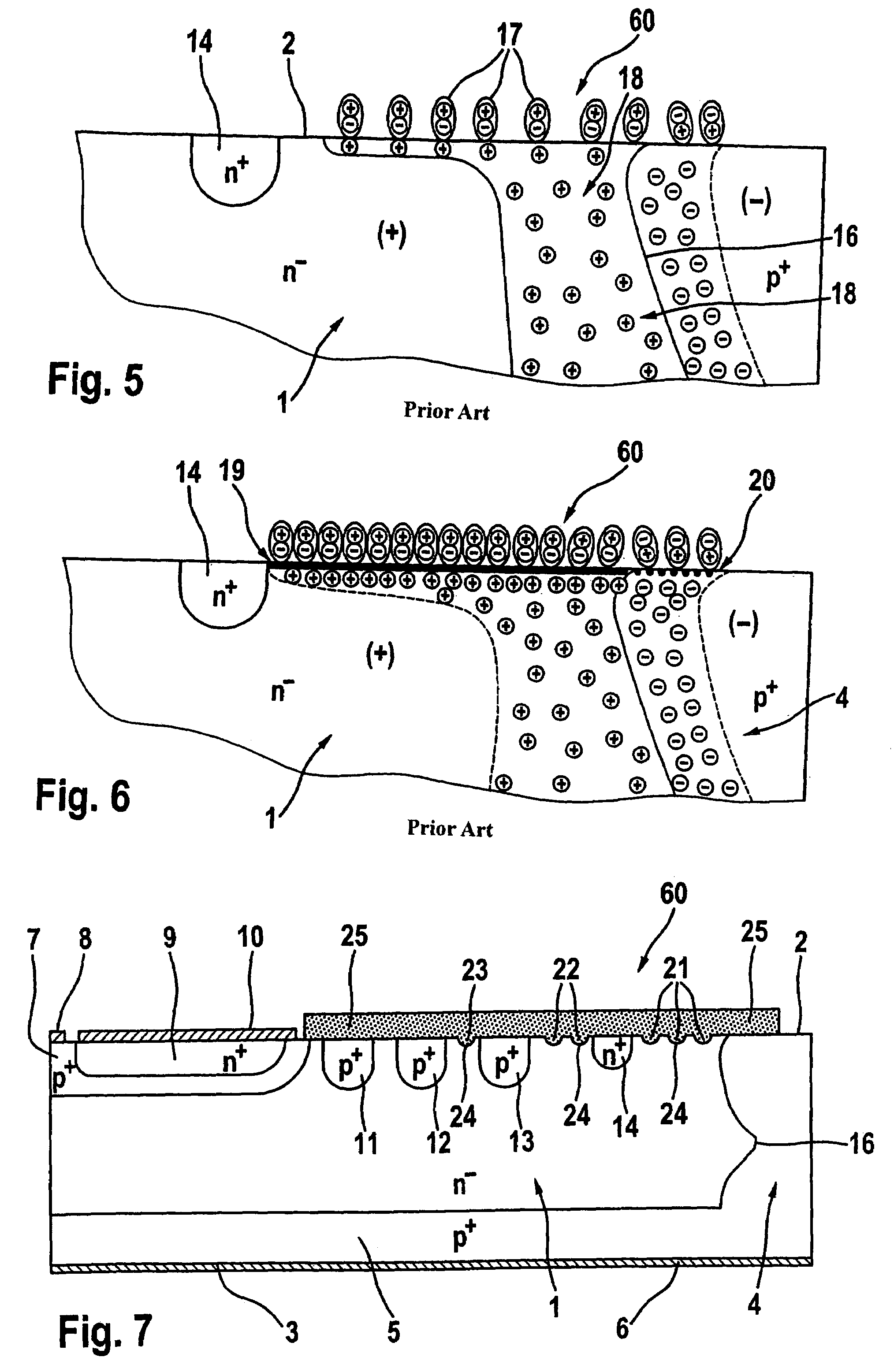

Power semiconductor component in the planar technique

InactiveUS7030426B2High surface resistanceEliminate the effects ofSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSurface structure

In a power semiconductor component produced in a planar technique, a near-surface structure having at least one depression is formed in a surface region of an edge termination adjacent a main surface of the semiconductor body. The structure lies inside a space charge region formed when a voltage is applied at a junction between semiconductor regions of opposite conduction type. Dielectric material may fill the depression and form a passivation layer on the surface region. The depression may be an annular trench having a width to depth ratio ≦1. Alternatively, the structure may be waffle-shaped with multiple depressions.

Owner:IXYS SEMICON

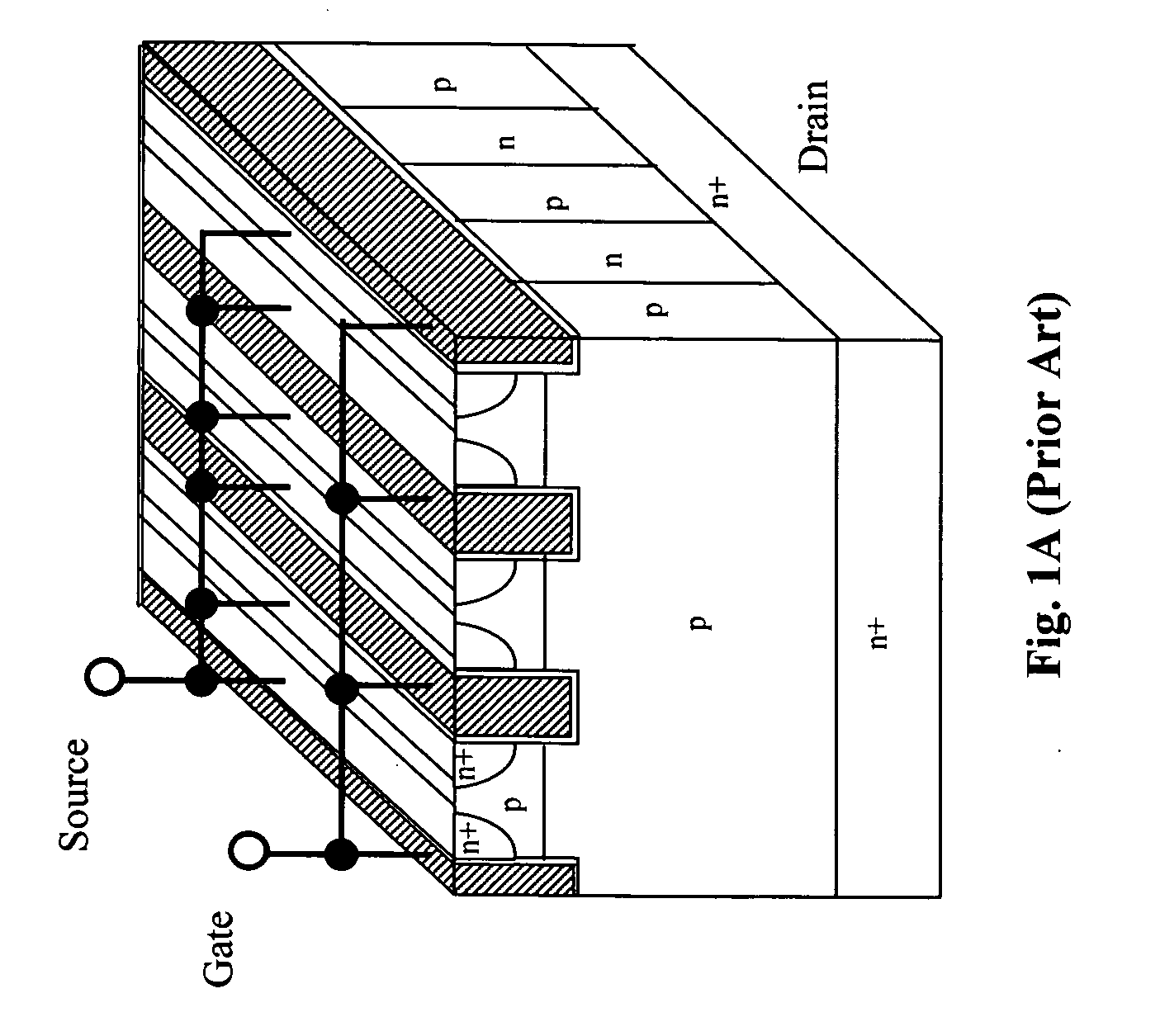

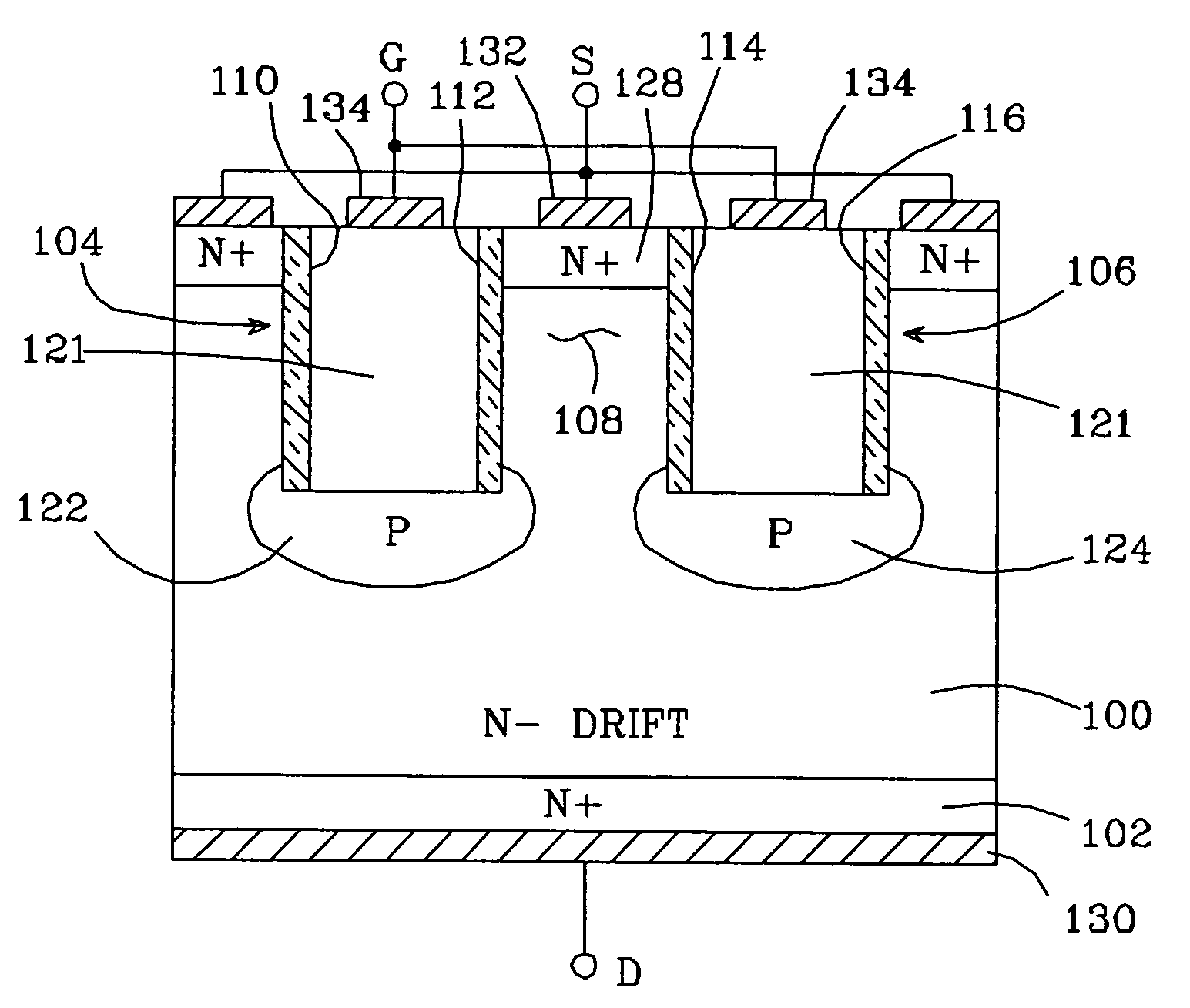

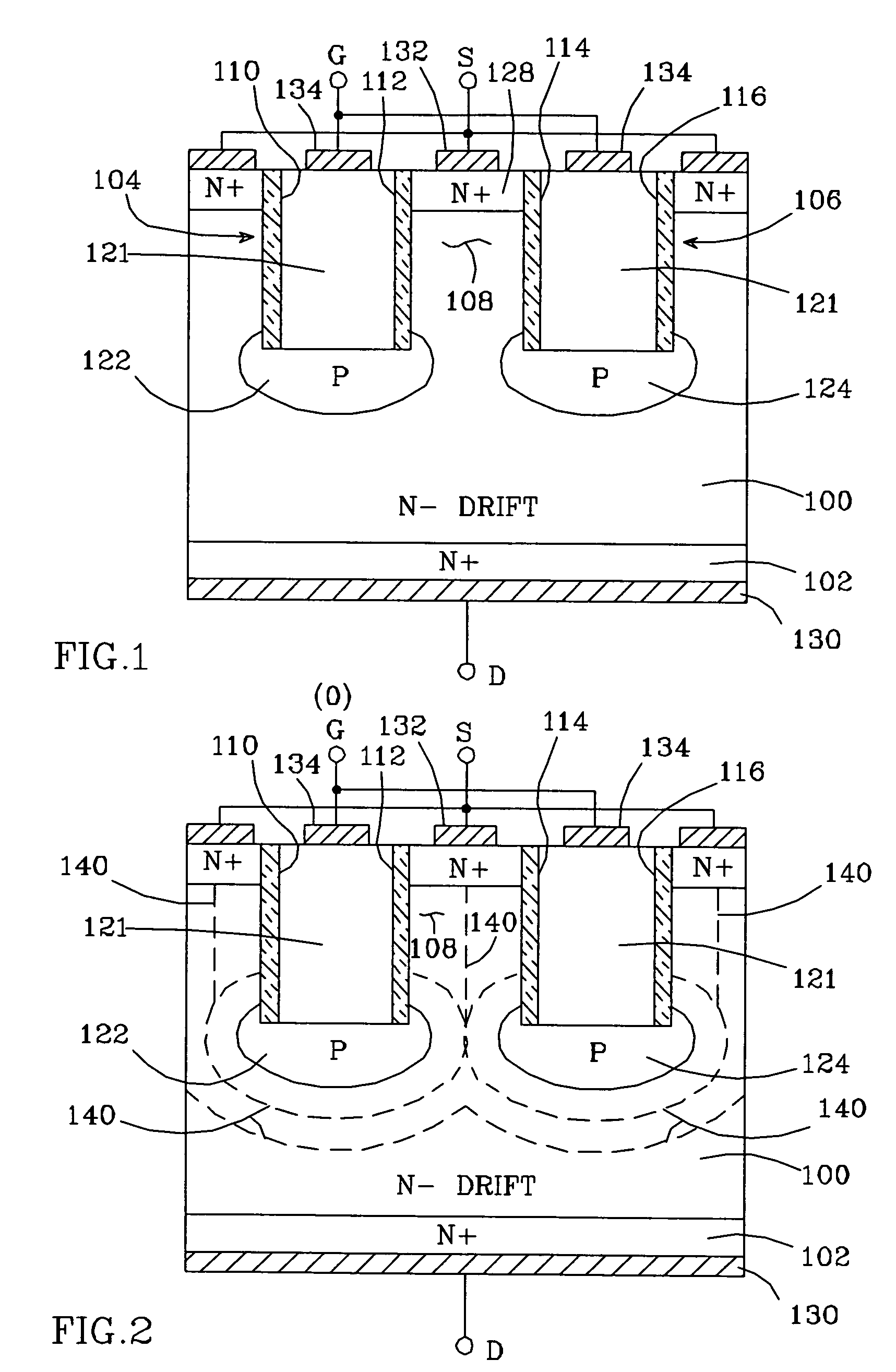

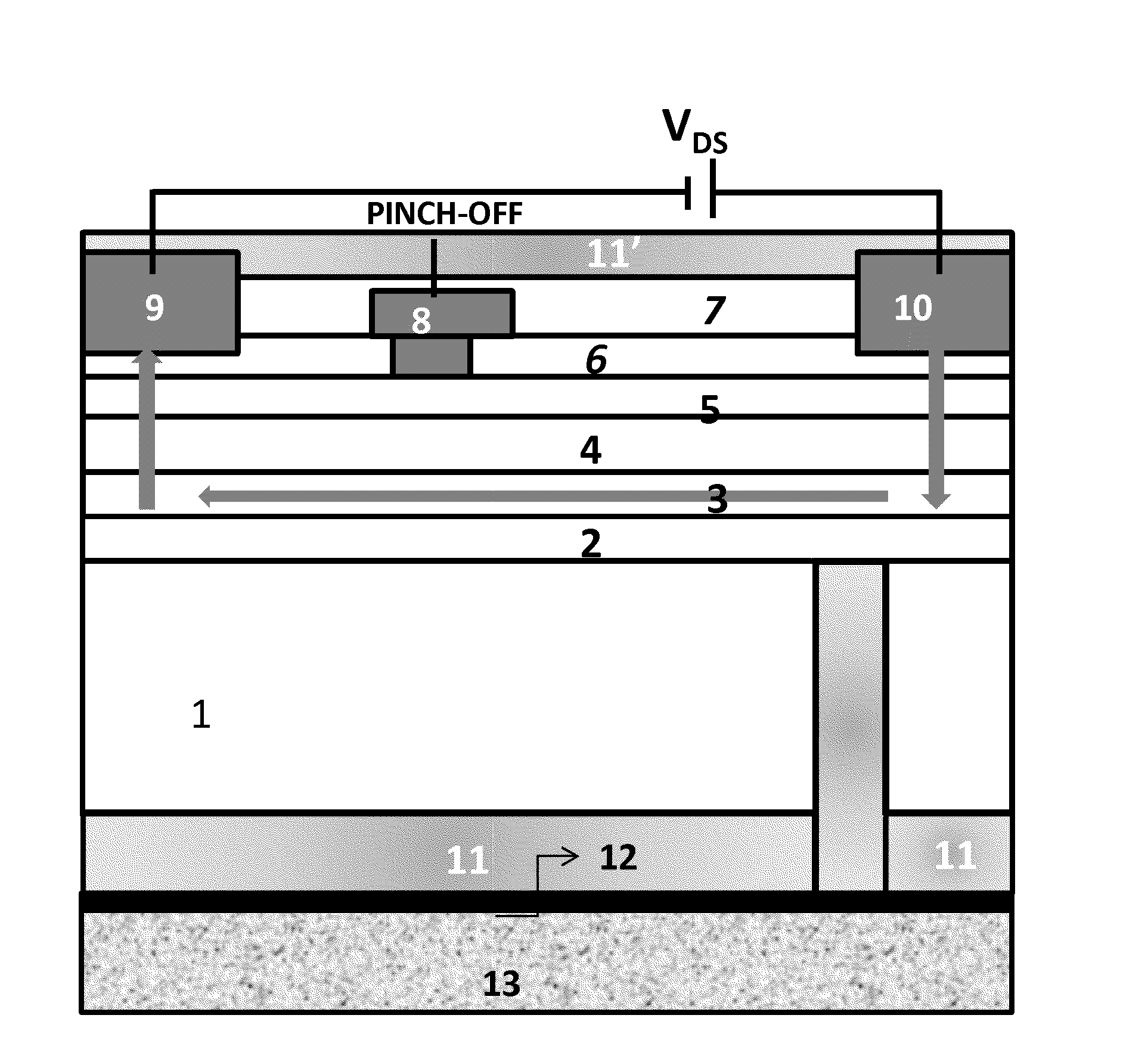

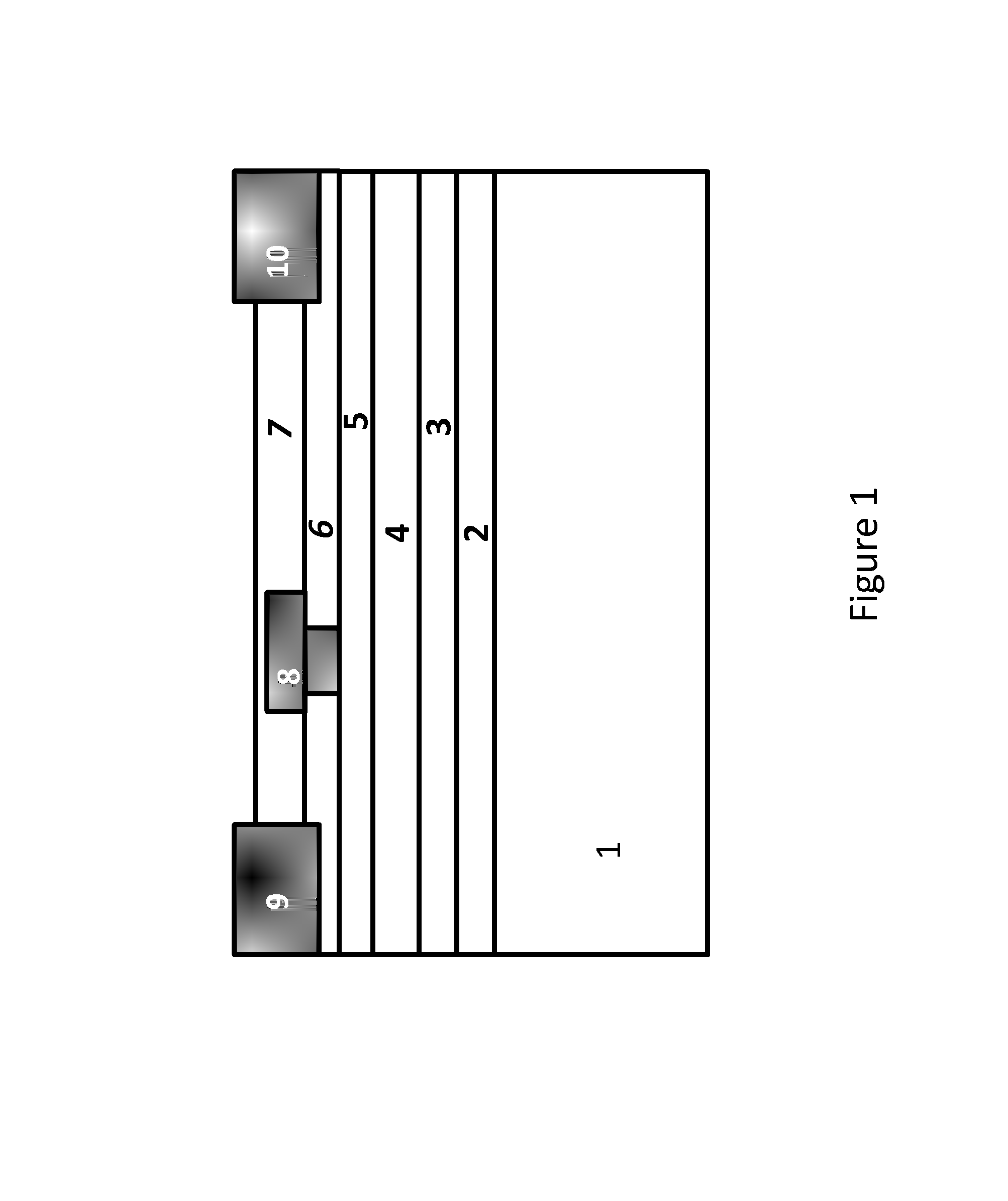

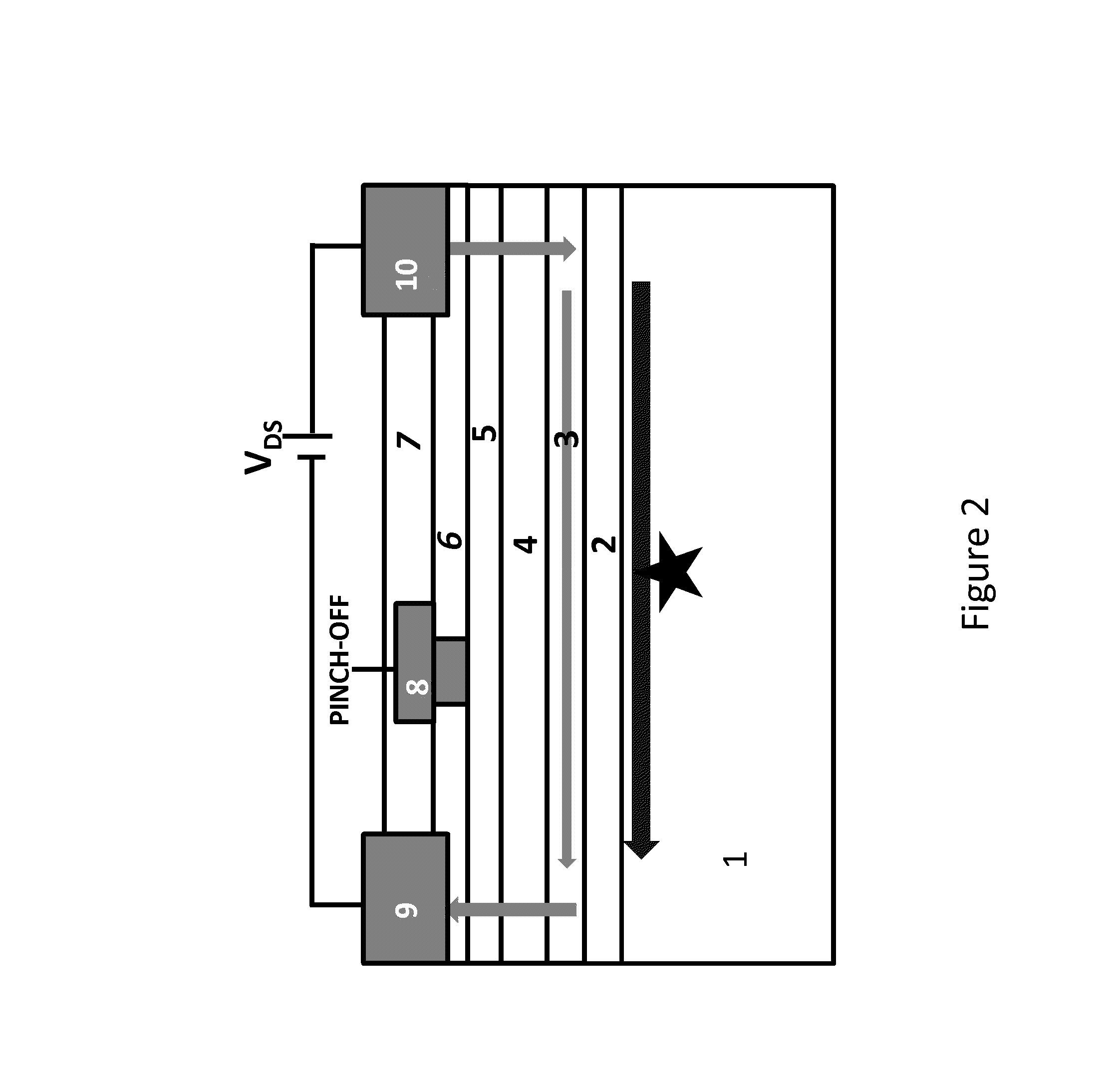

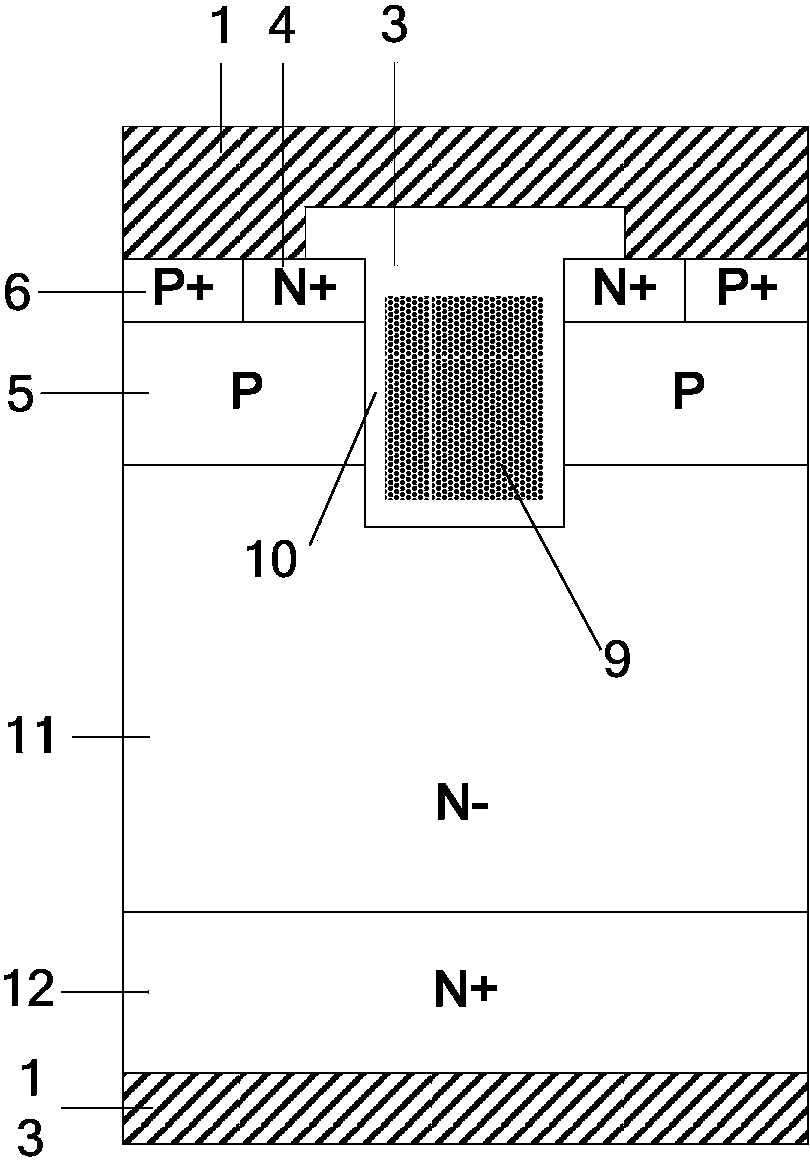

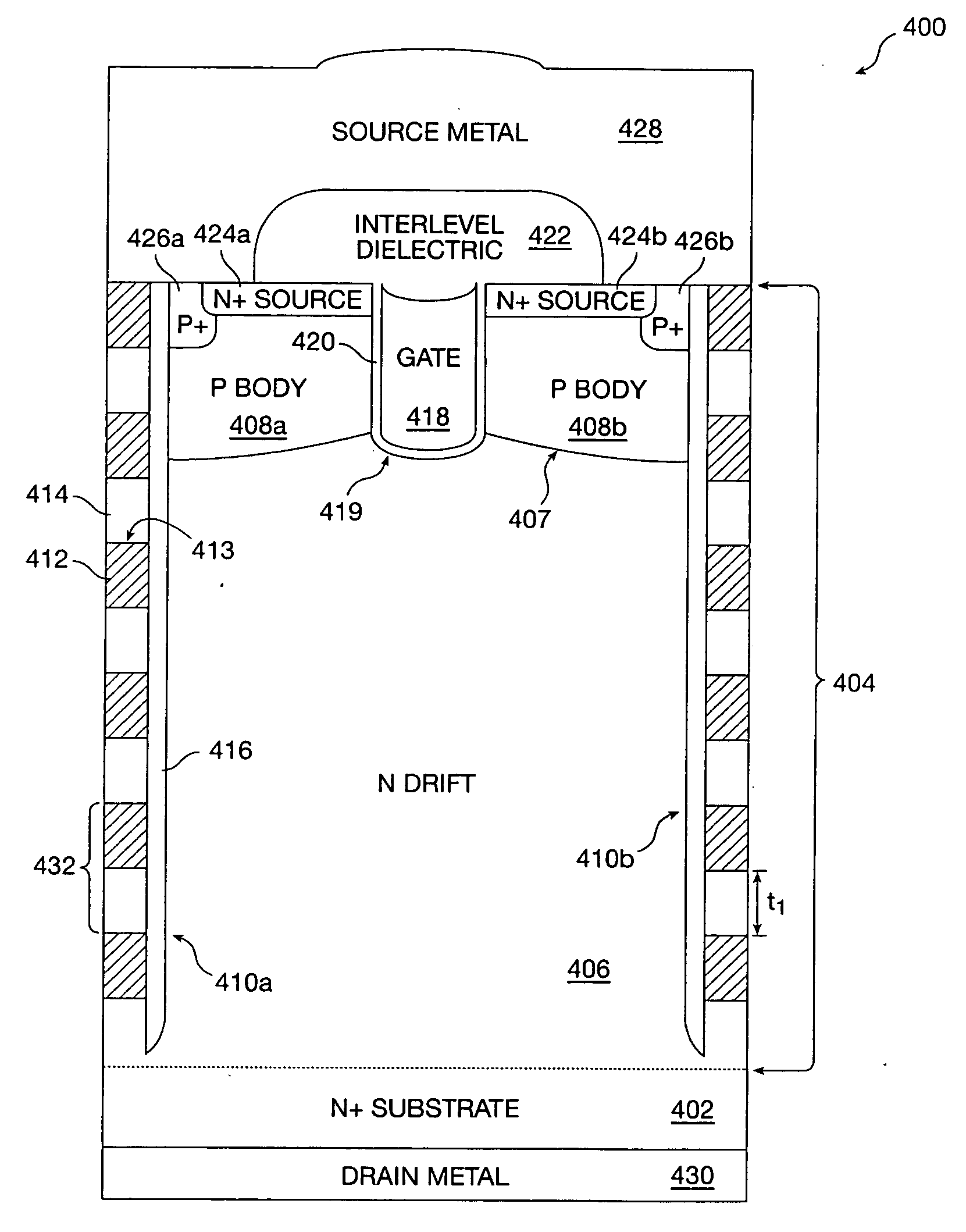

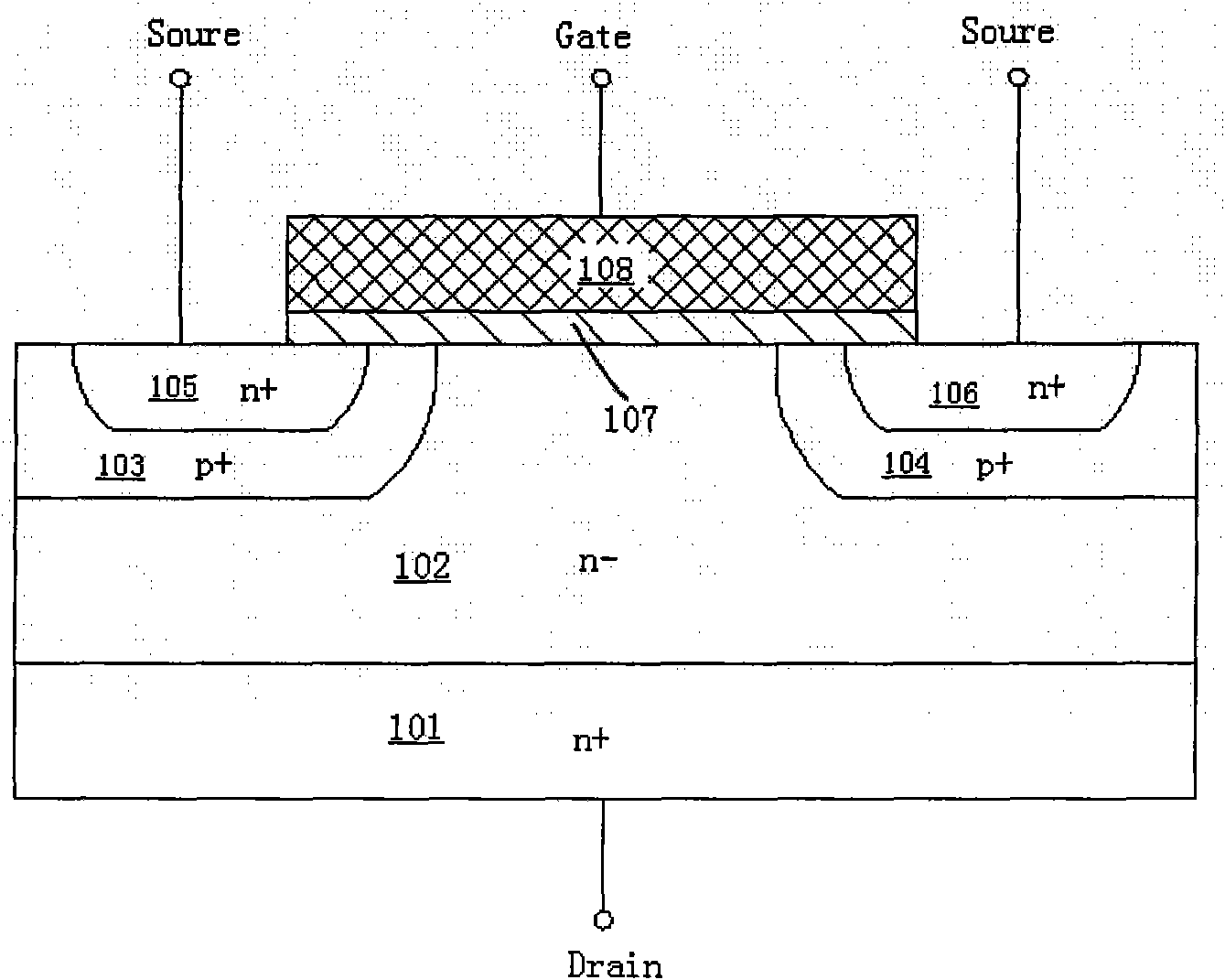

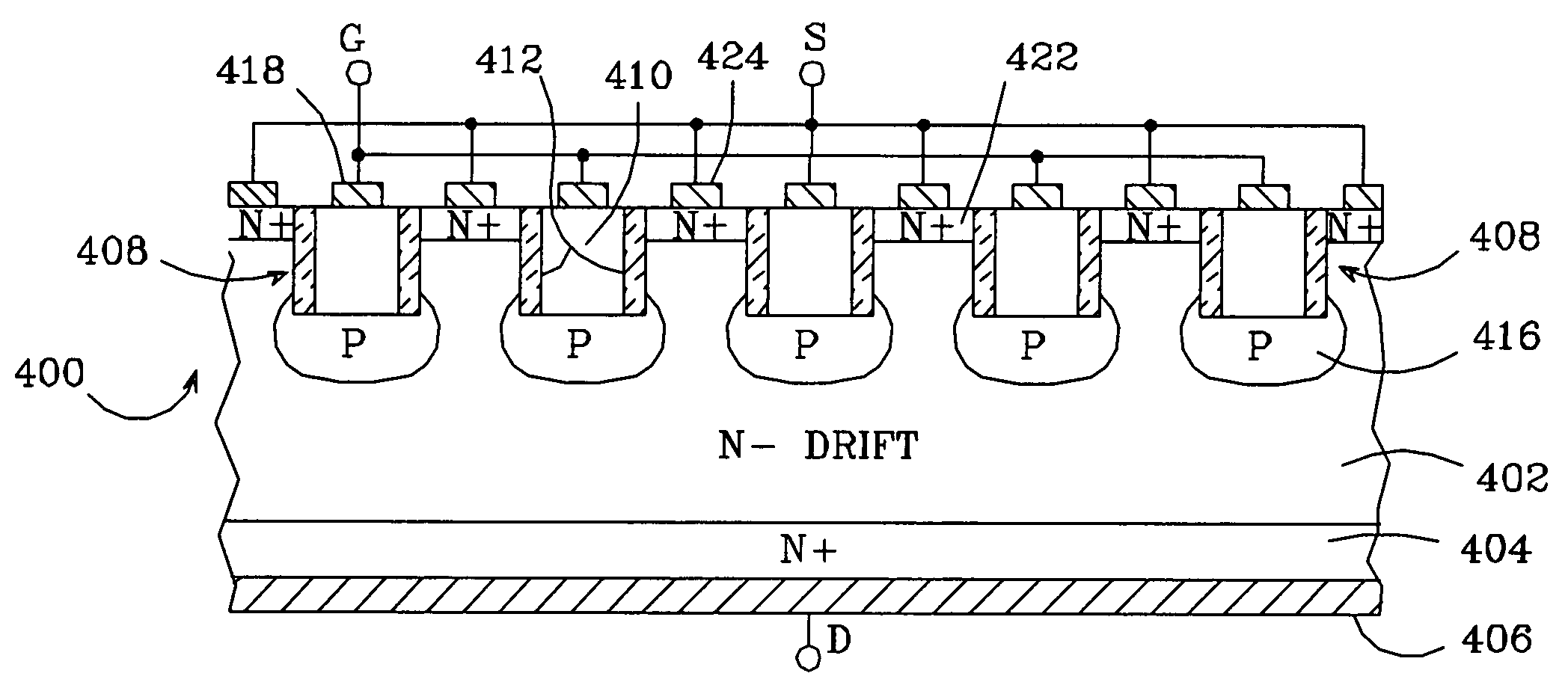

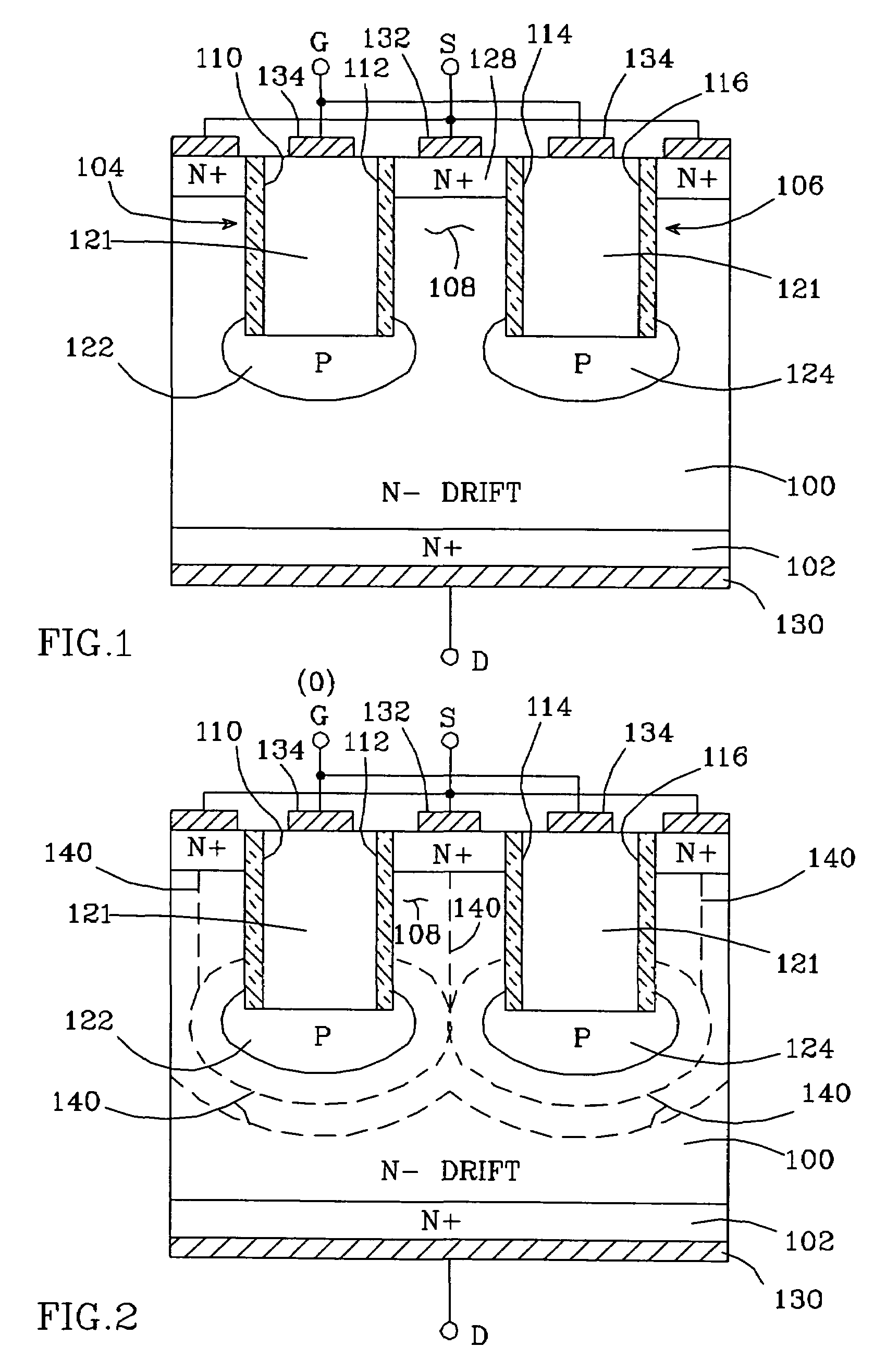

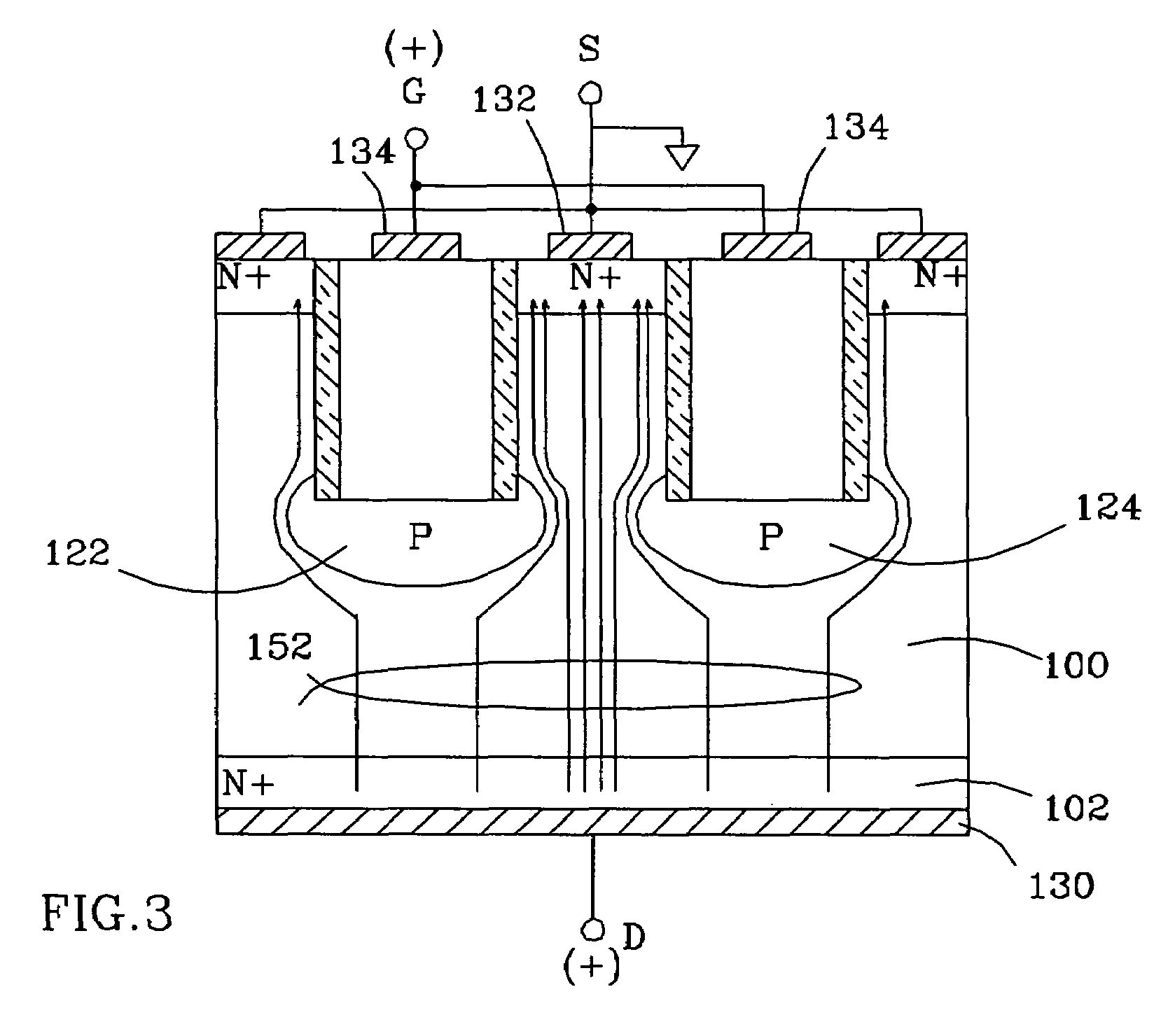

High voltage FET switch with conductivity modulation

ActiveUS20060071295A1Negligible switching lossLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesConductive materialsGate voltage

A high power FET switch comprises an N− drift layer, in which pairs of trenches are recessed to a predetermined depth; oxide side-walls extend to the trench bottoms, and each trench is filled with a conductive material. N+ and metal layers on opposite sides of the drift layer provide drain and source connections for the FET, and the conductive material in each trench is connected together to provide a gate connection. A shallow P region extends across the bottom and around the corners of each trench's side-walls into the drift layer. The application of a sufficient gate voltage causes holes to be injected from the shallow P regions into the N− drift layer, thereby modulating the drift layer's conductivity and lowering the device's on-resistance, and enabling current to flow between the drain and source connections.

Owner:CALLAHAN CELLULAR L L C

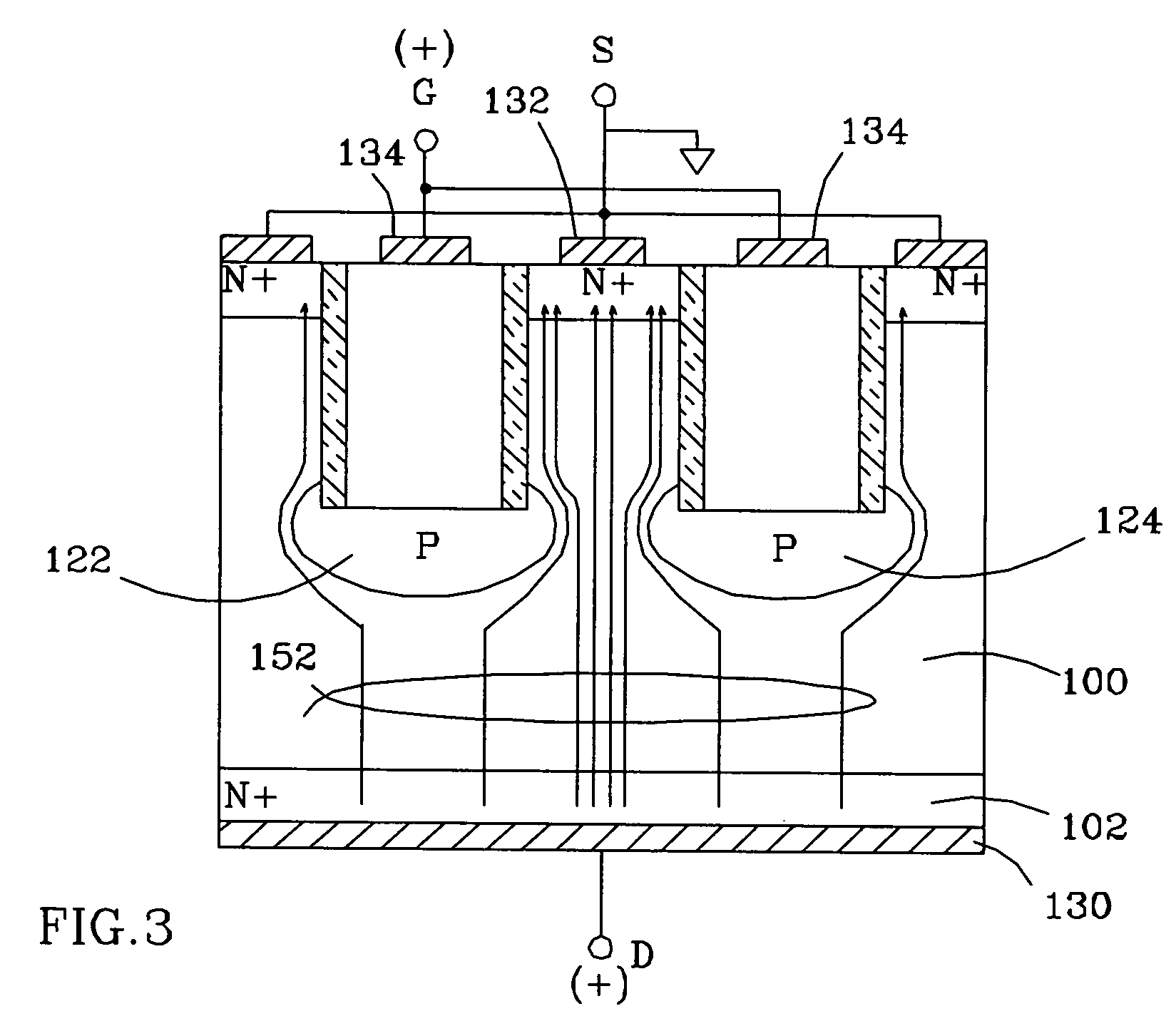

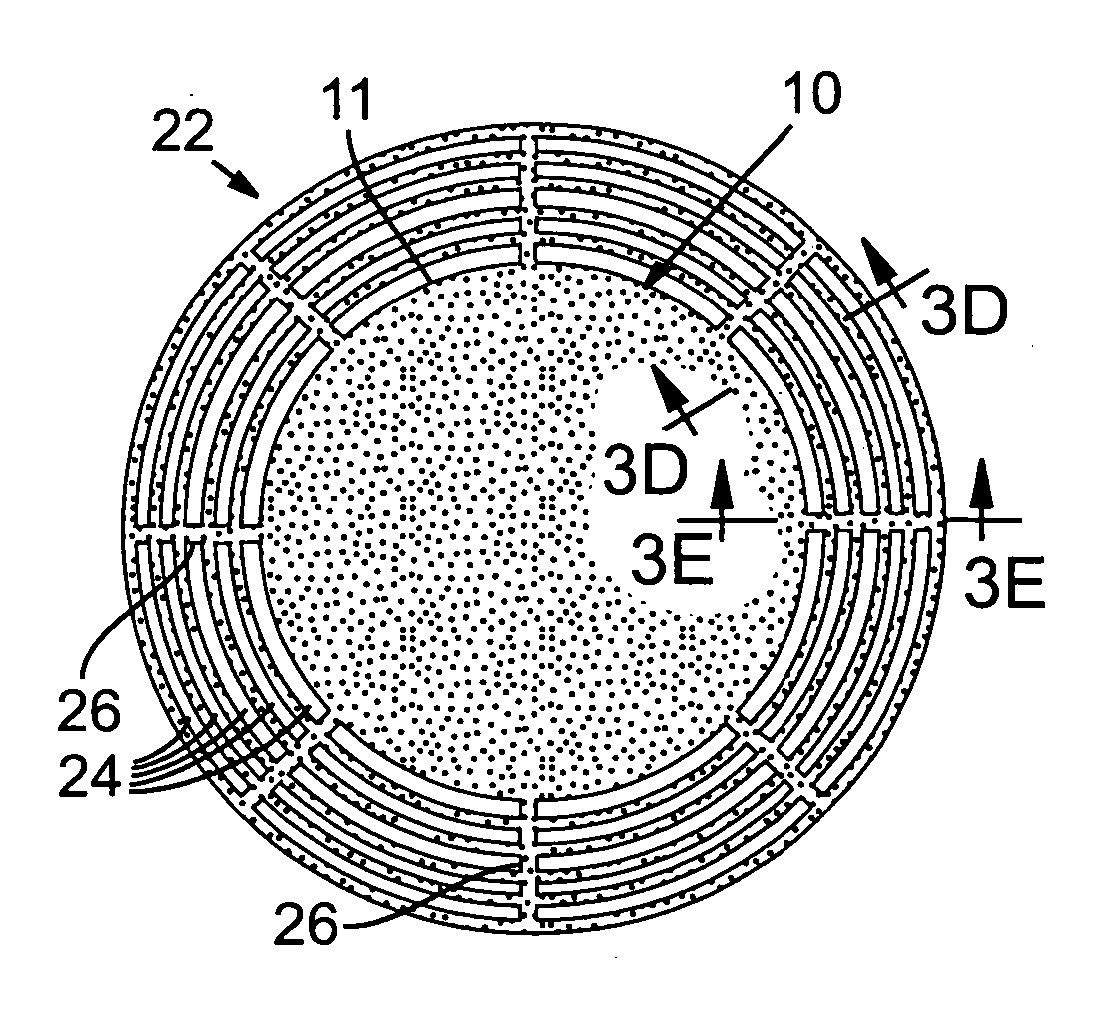

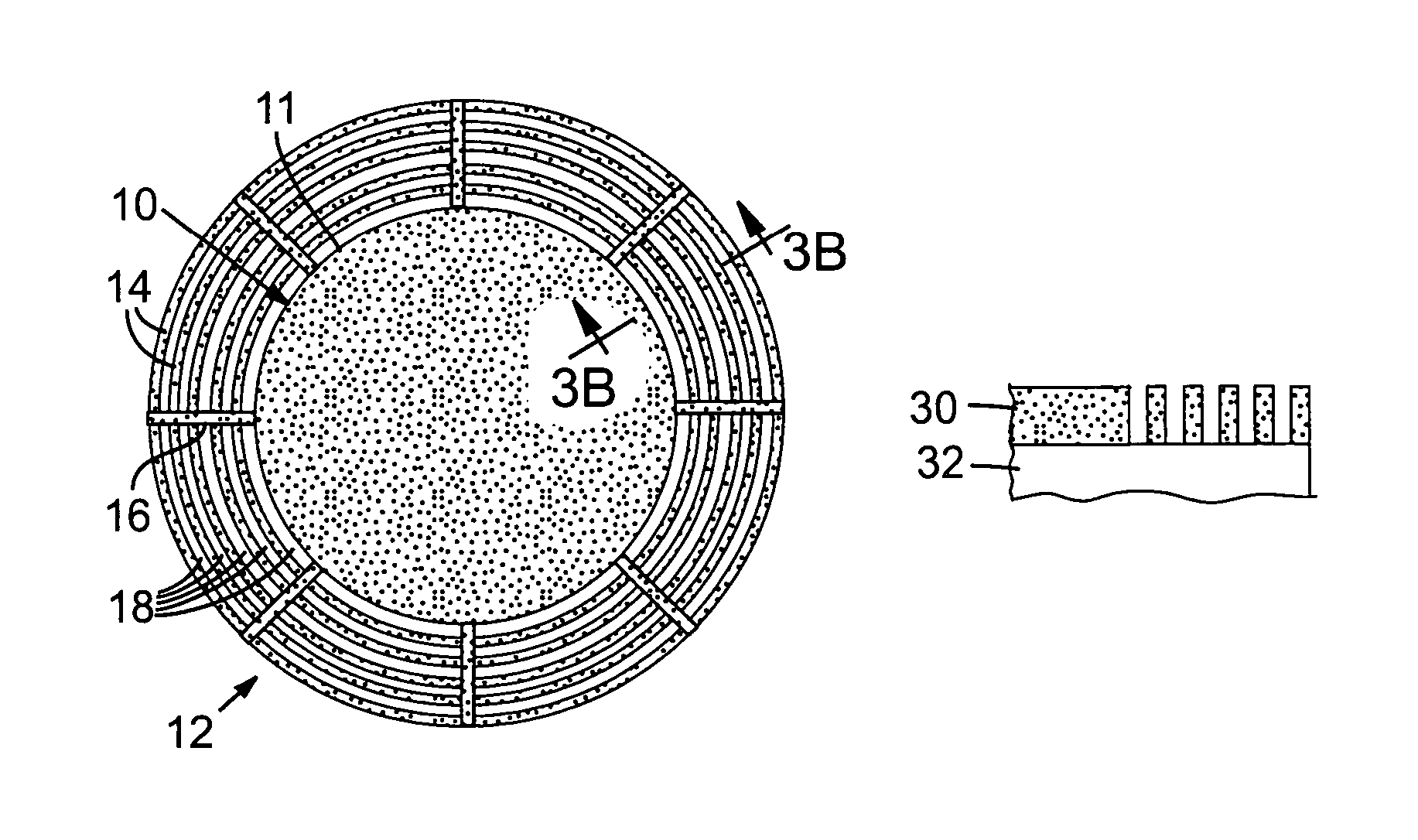

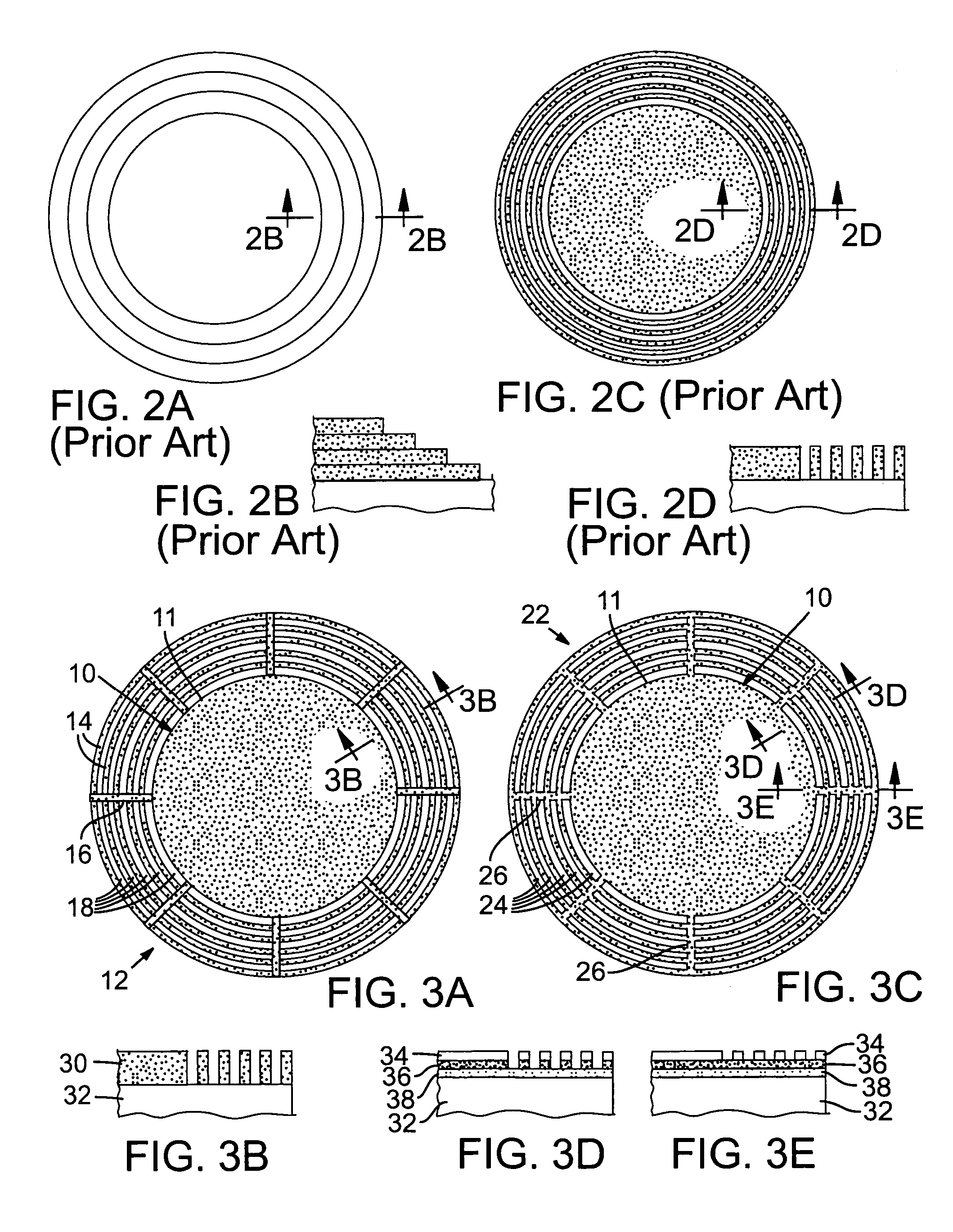

Junction termination structures for wide-bandgap power devices

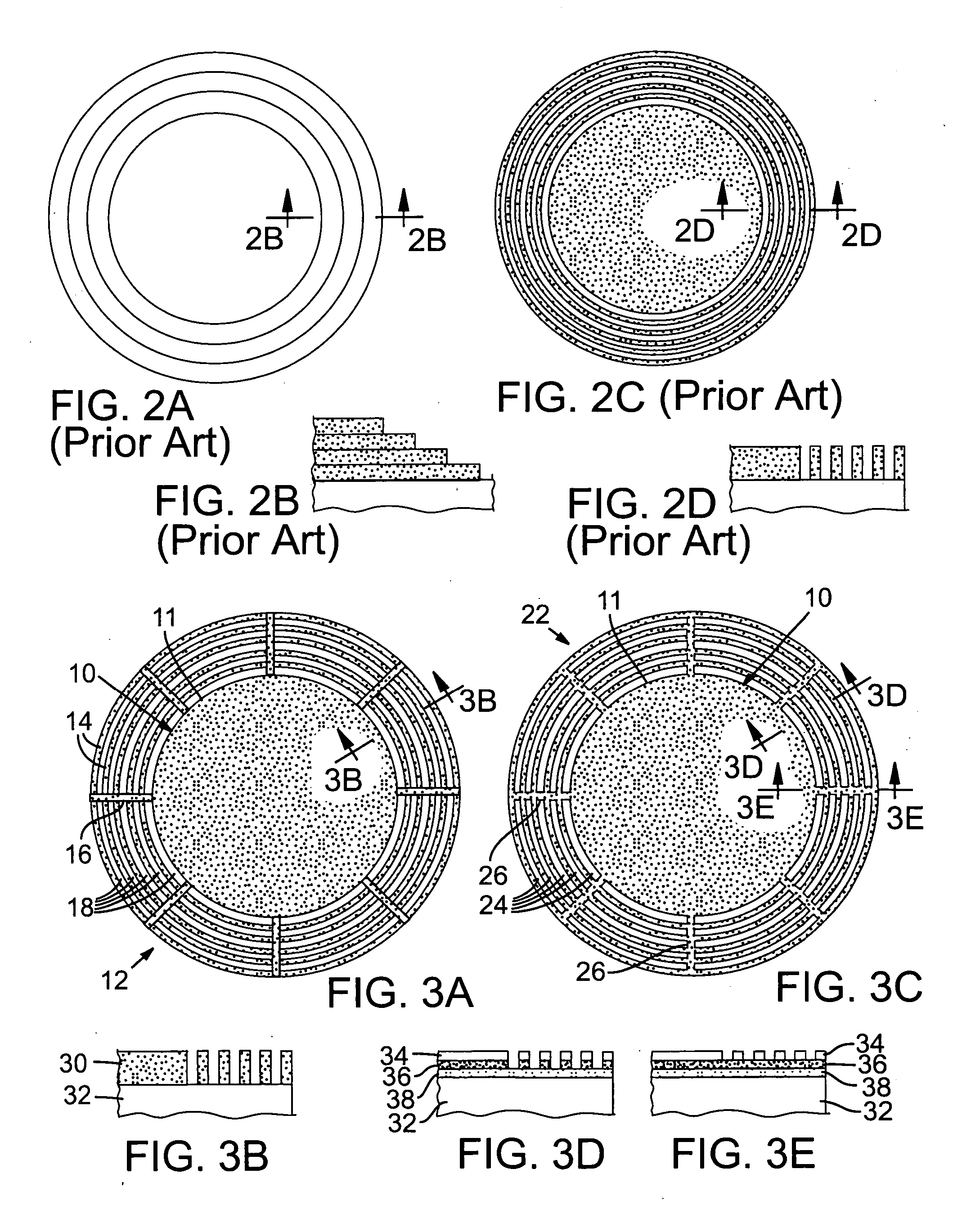

InactiveUS20060118900A1High blocking voltageSimple and controllable processTransistorRadial gradientElectrical resistivity and conductivity

Disclosed are a variety of junction termination structures for high voltage semiconductor power devices. The structures are specifically aimed at providing a high breakdown voltage while being constructed with a minimal number of process steps. The combination of an RIE etch and / or implantation and anneal process with a finely patterned mesh provides the desired radial gradient for maximum breakdown voltage. The structures provide control of both the conductivity and charge density within the region. These structures can beneficially be applied to all high voltage semiconductor device structures, but are of particular interest for wide bandgap devices as they tend to have very high breakdown fields and scaled dimensions of the depletion layer width.

Owner:MICROSEMI

Method for fabrication of iii-nitride device and the iii-nitride device thereof

ActiveUS20120326215A1Reduce leakageHigh blocking voltageSemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsEngineering

A III-nitride device is provided comprising a semiconductor substrate; a stack of active layers on the substrate, each layer comprising a III-nitride material; a gate, a source and a drain contact on the stack, wherein a gate, a source and a drain region of the substrate are projections of respectively the gate, the source and the drain contact in the substrate; and a trench in the substrate extending from a backside of the substrate (side opposite to the one in contact with the stack of active layers) to an underlayer of the stack of active layers in contact with the substrate, the trench completely surrounding the drain region, being positioned in between an edge of the gate region towards the drain and an edge of the drain region towards the gate and having a width such that the drain region of the substrate is substantially made of the semiconductor material.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

Silicon carbide mos field-effect transistor and process for producing the same

InactiveUS20090134402A1Lower on-resistanceHigh blocking voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETHigh concentration

In the SiC vertical MOSFET having a low-concentration p-type deposition film provided therein with a channel region and a base region resulting from reverse-implantation to n-type through ion implantation, dielectric breakdown of gate oxide film used to occur at the time of off, thereby preventing a further blocking voltage enhancement. This problem has been resolved by interposing of a low-concentration n-type deposition film between a low-concentration p-type deposition film and a high-concentration gate layer and selectively forming of a base region resulting from reverse-implantation to n-type through ion implantation in the low-concentration p-type deposition film so that the thickness of deposition film between the high-concentration gate layer and each of channel region and gate oxide layer is increased.

Owner:NAT INST OF ADVANCED IND SCI & TECH

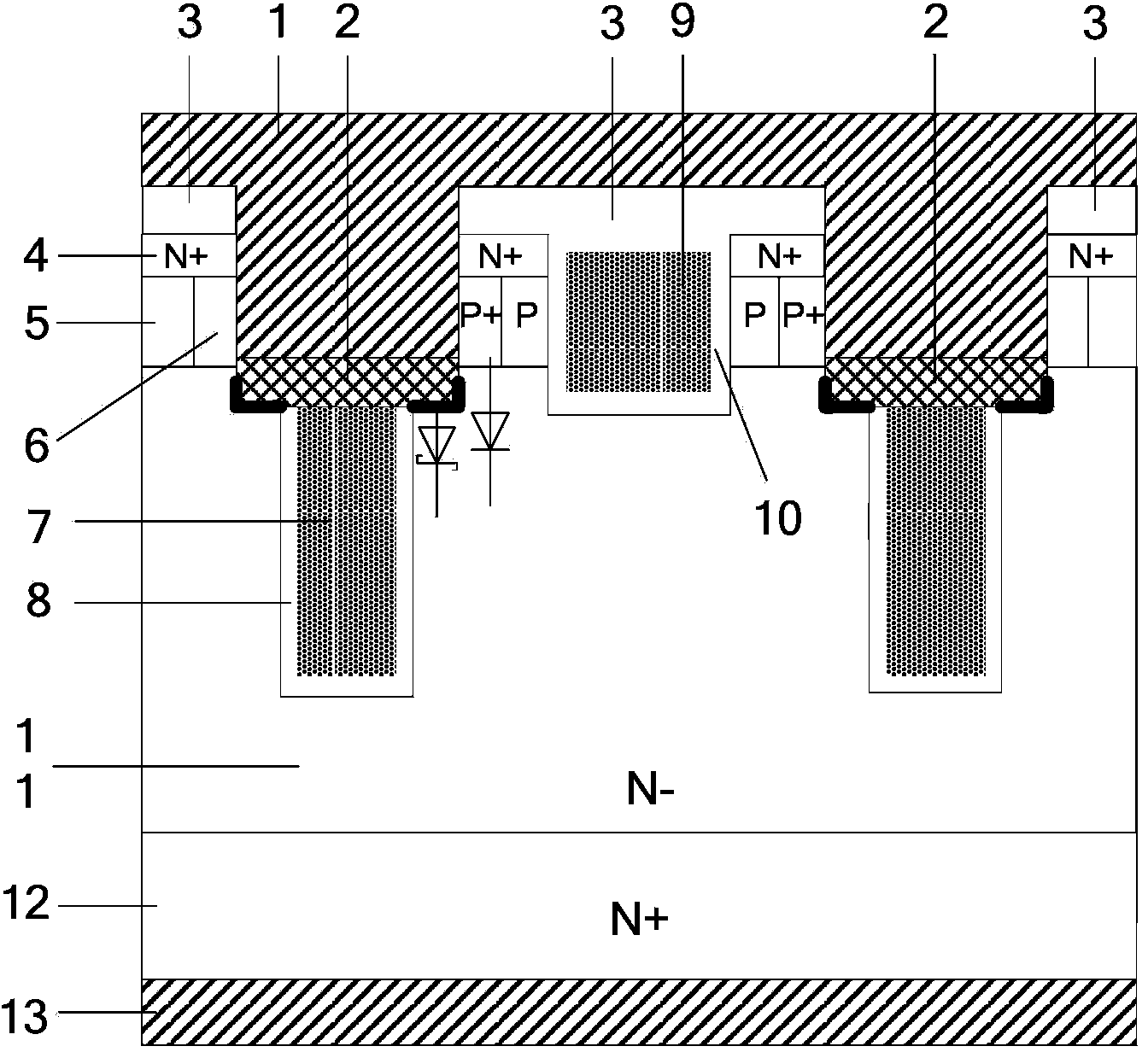

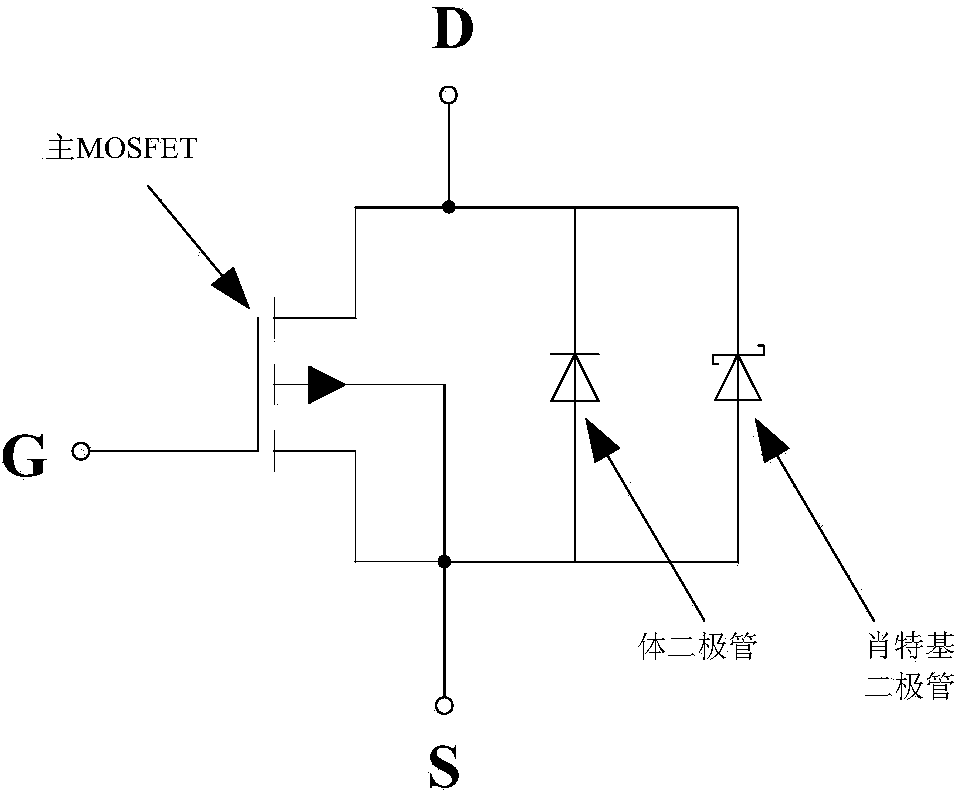

Groove gate VDMOS device integrated with Schottky diode

The invention discloses a groove gate VDMOS device integrated with a Schottky diode and belongs to the technical field of semiconductor devices. According to the groove gate VDMOS device integrated with the Schottky diode, an additional structure composed of a piece of Schottky junction metal and a body electrode conductive material is additionally arranged on each of drift regions on the two sides of a groove gate structure of a conventional groove gate VDMOS device, the upper portion of each piece of Schottky junction metal is in contact with source electrode metal, the lower portion of each piece of Schottky junction metal is in contact with a corresponding body electrode conductive material, and the lower surface and the lateral sides of the each piece Schottky junction metal are in contact with a corresponding drift region to form a Schottky junction; dielectric layers are arranged between the lateral sides of each body electrode conductive material and a corresponding drift region and between the bottom surface of each body electrode conductive material and the corresponding drift region. Compared with a traditional groove gate VDMOS device with the same size, the groove gate VDMOS device integrated with the Schottky diode has the advantages that due to the fact that higher drift region dosage concentration is adopted under the condition of same puncture voltage, turn-on resistance is reduced obviously, and the reverse recovery property of the diode is improved obviously.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

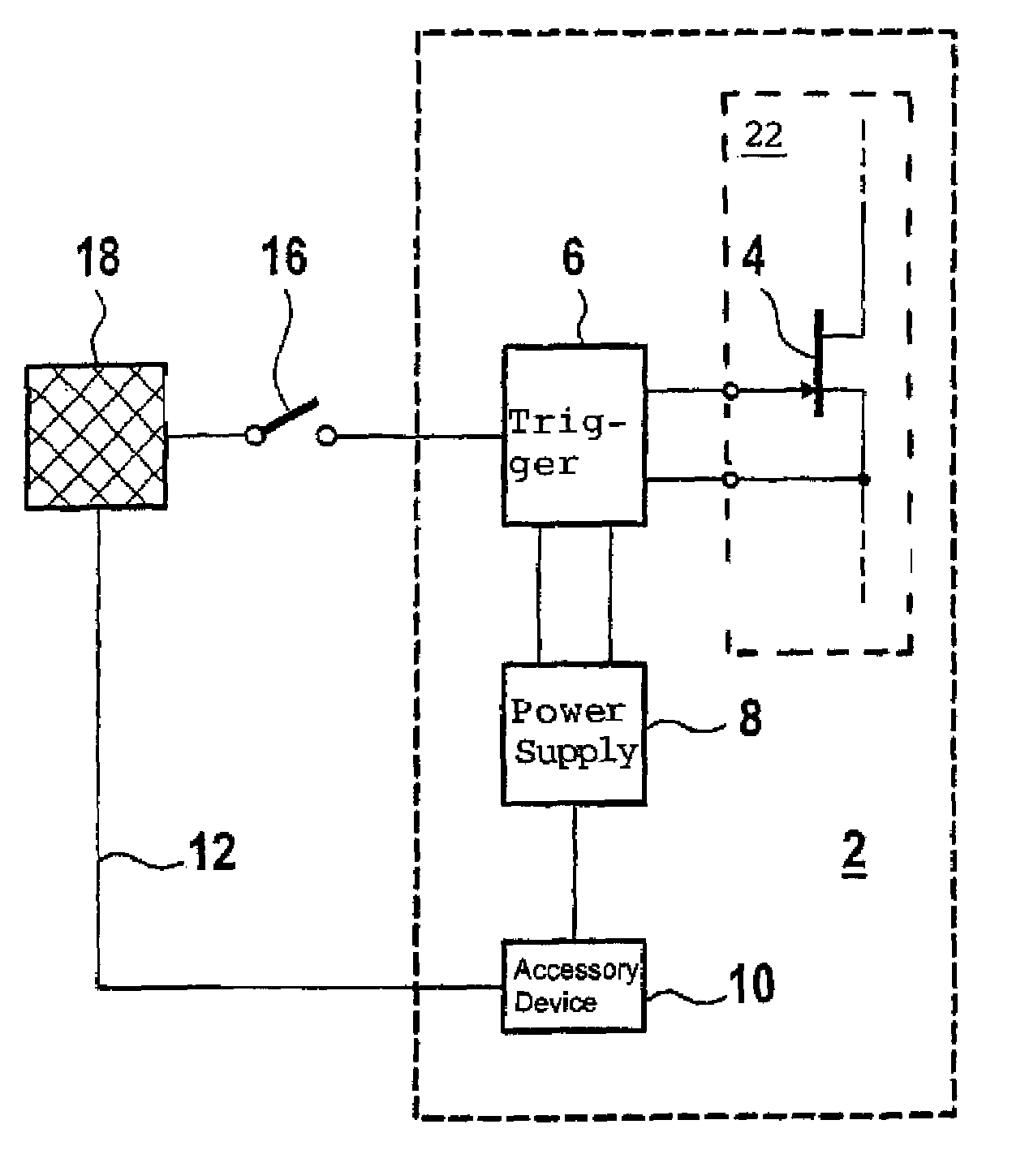

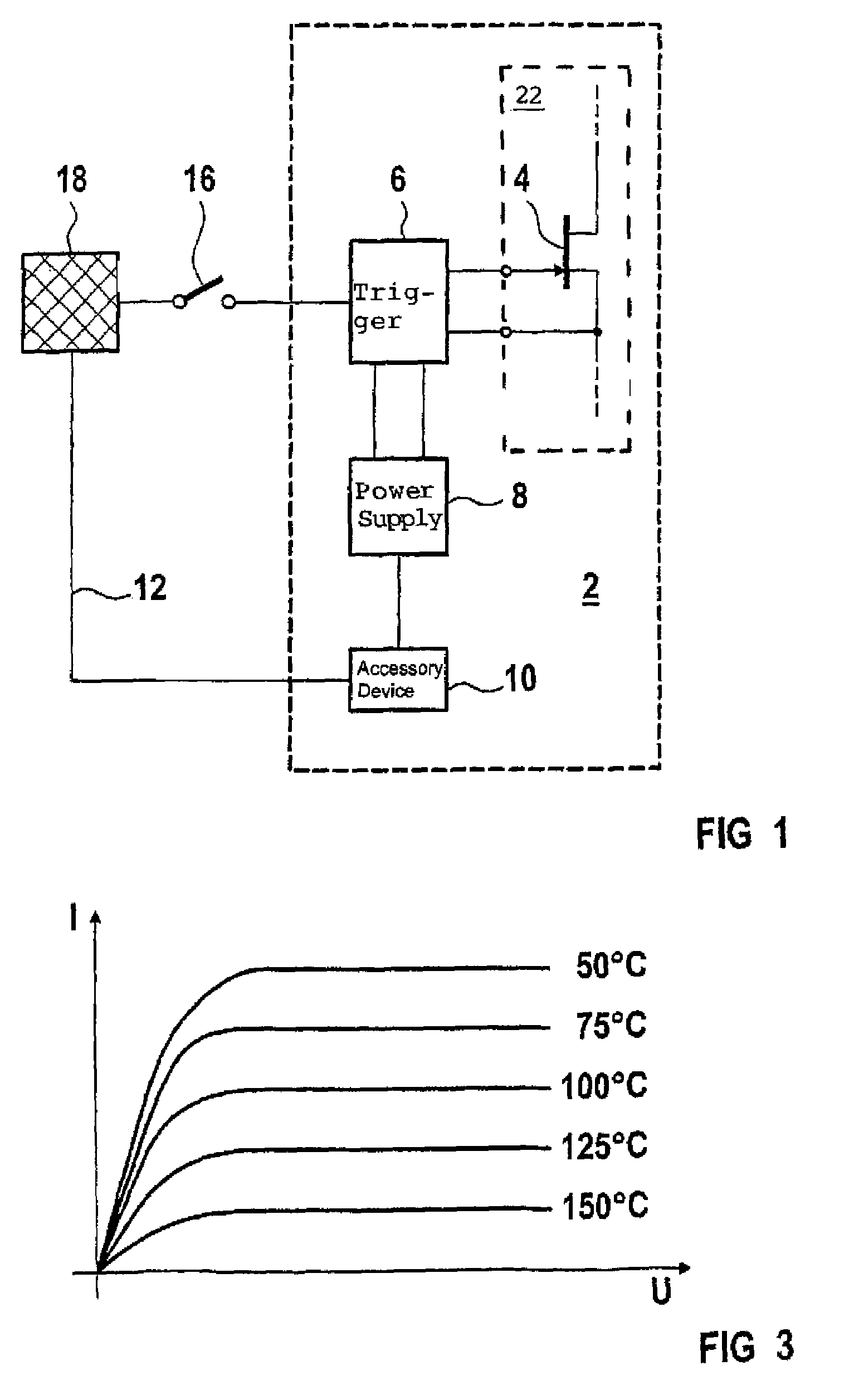

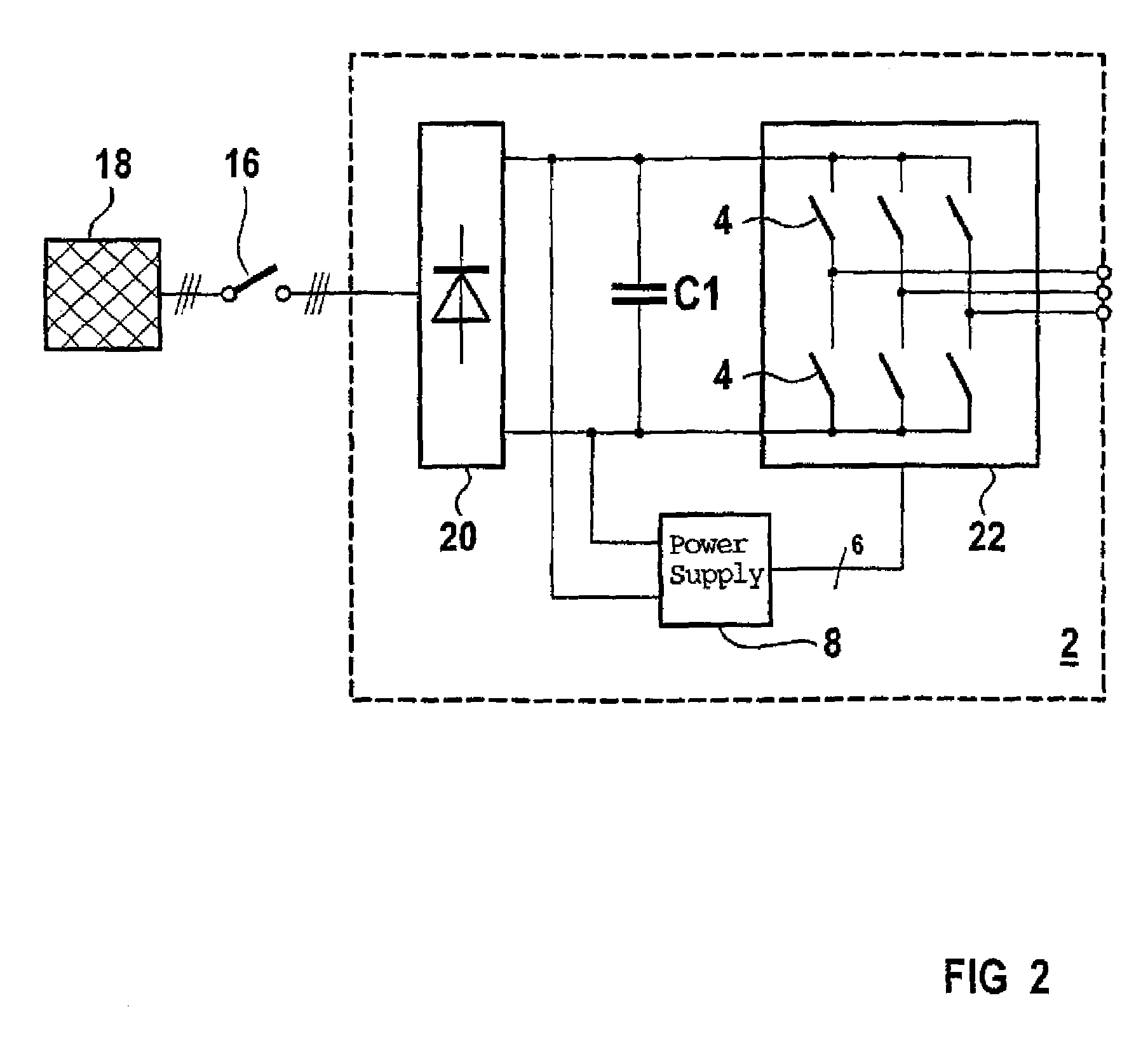

Electronic power circuit

InactiveUS7327053B2Cost-effectiveReduce numberBatteries circuit arrangementsAc-dc conversionPower semiconductor devicePower circuits

An electronic power circuit includes at least one power semiconductor whose control inputs are connected to a trigger device and a power supply which, on the output side, is connected to terminals of the trigger device and, on the input side, is connected to an accessory device to which a supply voltage is applied. The power semiconductor is implemented as a self-conducting power semiconductor, which economically reduces the forward power losses and switching losses of an electronic power circuit.

Owner:SIEMENS AG

GE Energy Power Conversion Technology Ltd

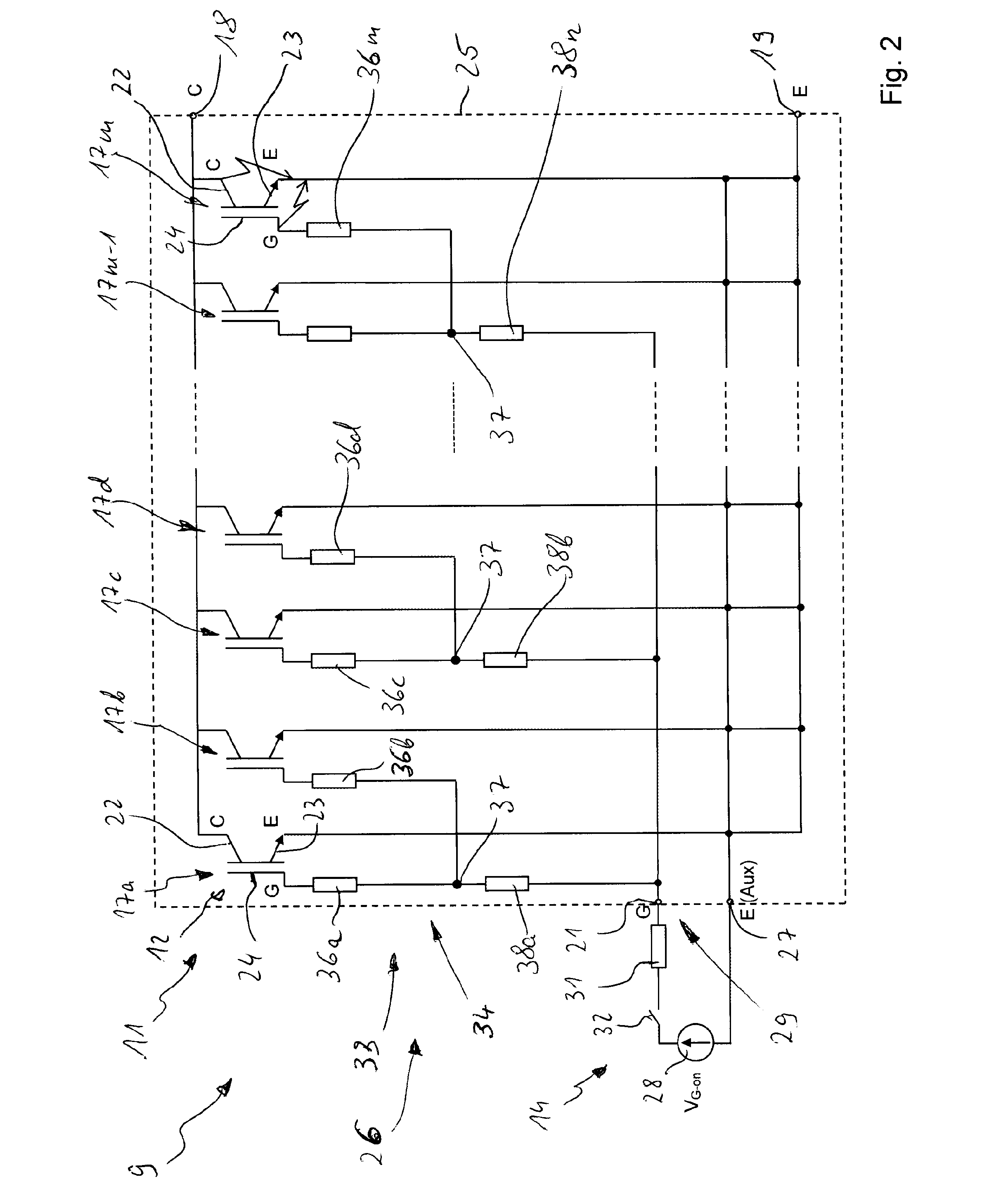

ActiveUS20160261180A1Reduce harmLower average currentTransistorAc-dc conversionElectricityComputer module

A switch module includes a collector connection, an emitter connection, and a gate connection. The switch module includes a plurality of parallel connected switching elements, e.g., insulated-gate bipolar transistors, each having a collector electrode electrically connected to the collector connection, an emitter electrode electrically connected to the emitter connection, and a gate electrode electrically connected to the gate connection. A fault protection device is operatively electrically connected between the gate connection and the switching elements and comprises passive electrical components which are selected such that in the event of a fault in at least one of the plurality of switching elements, a gate-emitter voltage is provided to the gate electrodes of non-faulty switching elements in a passive manner.

Owner:GE ENERGY POWER CONVERSION TECH

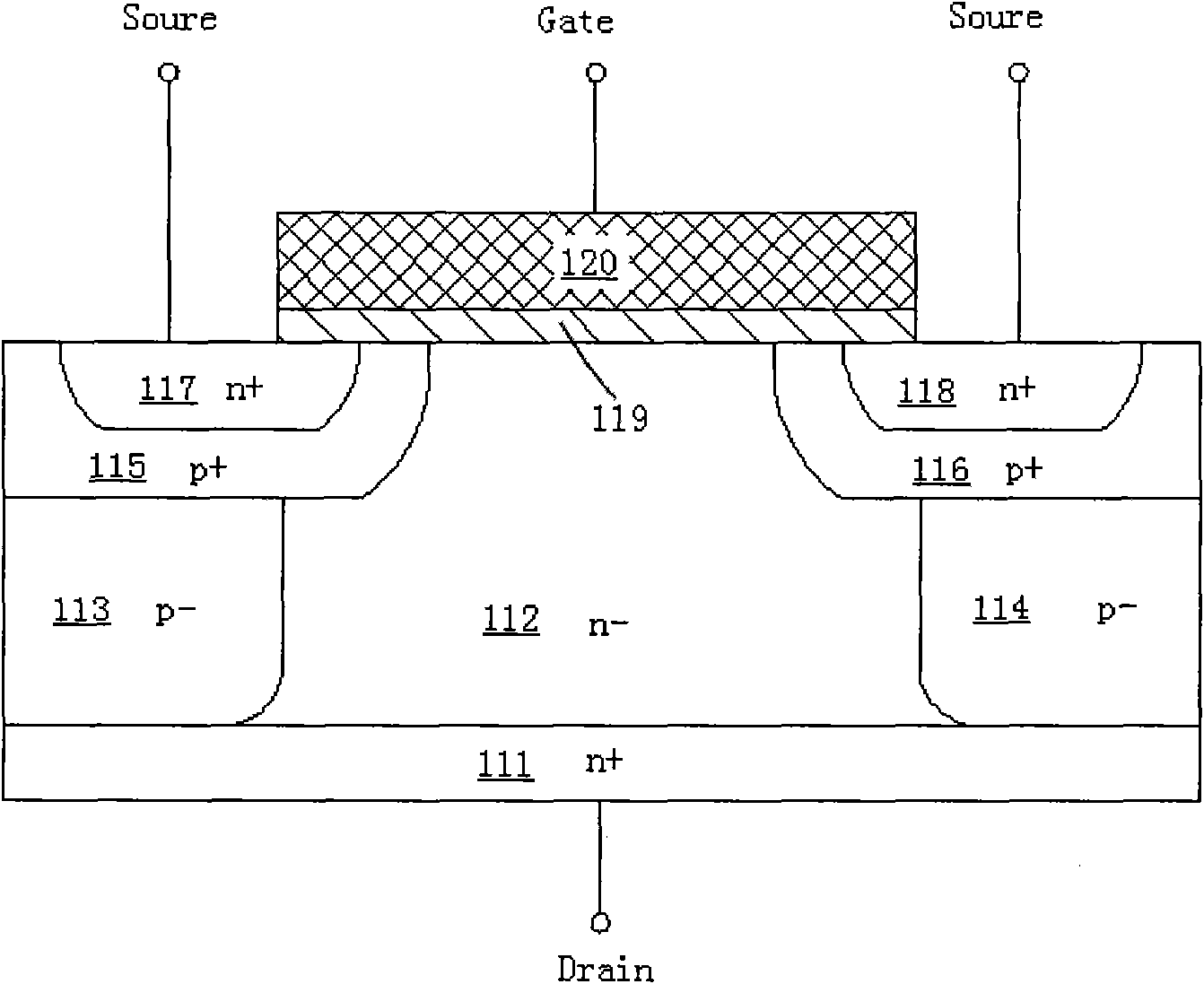

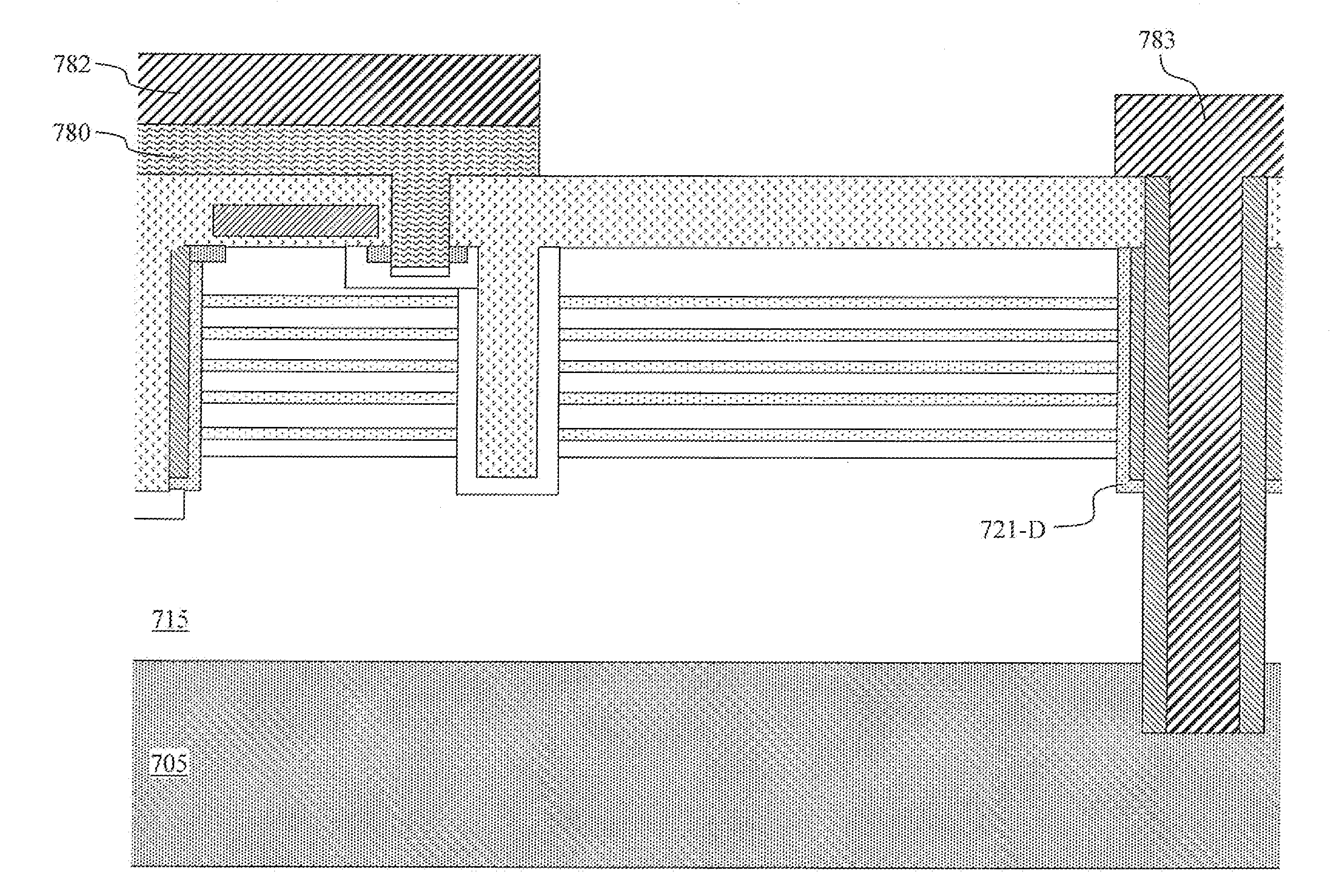

Lateral super junction device with high substrate-gate breakdown and built-in avalanche clamp diode

A lateral super junction JFET is formed from stacked alternating P type and N type semiconductor layers over a P-epi layer supported on an N+ substrate. An N+ drain column extends down through the super junction structure and the P-epi to connect to the N+ substrate to make the device a bottom drain device. N+ source column and P+ gate column extend through the super junction but stop at the P-epi layer. A gate-drain avalanche clamp diode is formed from the bottom the P+ gate column through the P-epi to the N+ drain substrate.

Owner:ALPHA & OMEGA SEMICON INC

Method of forming a trench structure having one or more diodes embedded therein adjacent a PN junction

InactiveUS20060258081A1High blocking voltageSemiconductor/solid-state device manufacturingDiodeSemiconductor structureDiode

A semiconductor structure is formed as follows. A semiconductor region is formed to have a P-type region and a N-type region forming a PN junction therebetween. A first trench is formed extending in the semiconductor region adjacent at least one of the P-type and N-type regions is formed. At least one diode is formed in the trench.

Owner:SEMICON COMPONENTS IND LLC

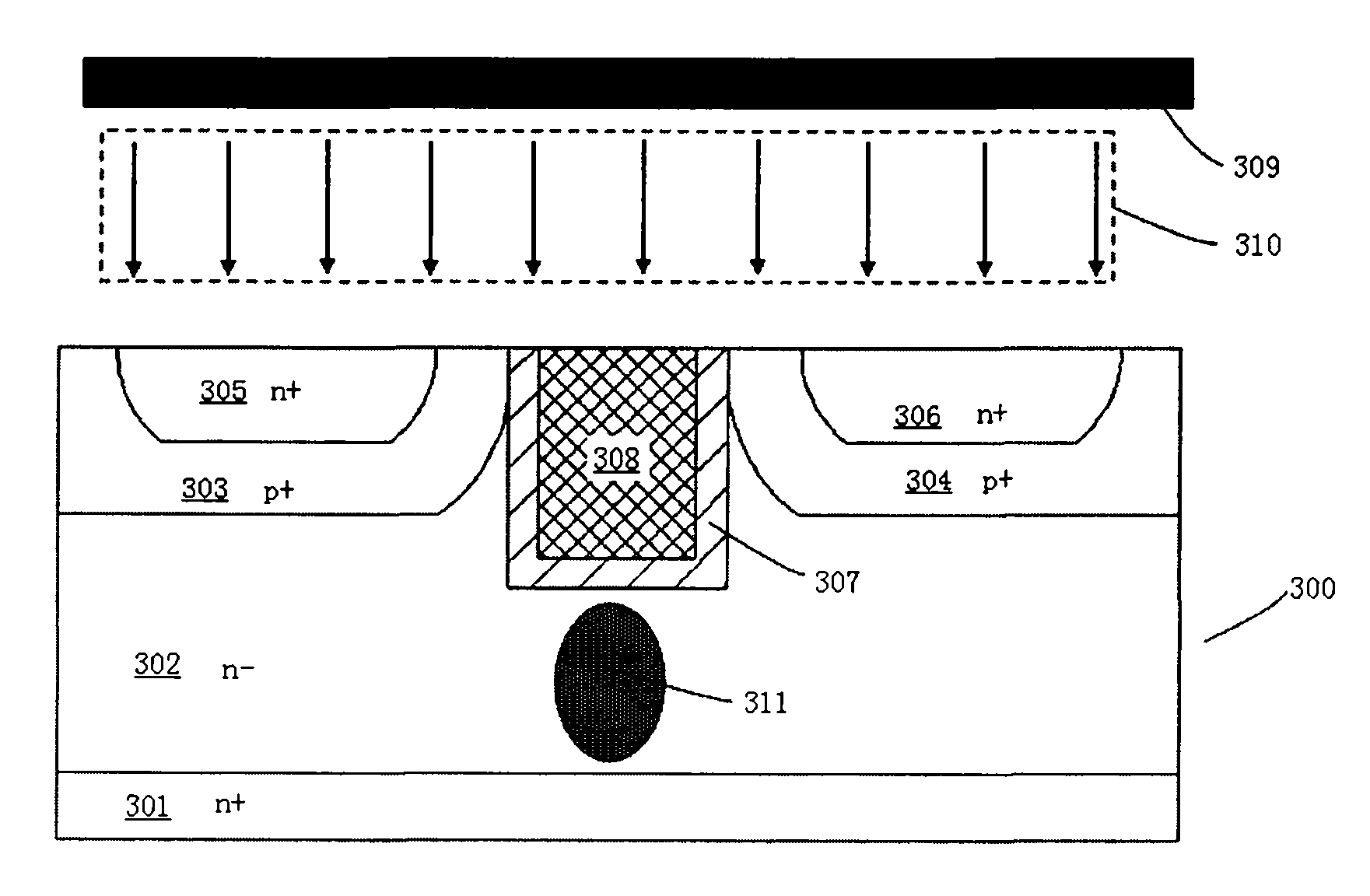

Power device and method for performing conductivity modulation by using photoelectron injection

InactiveCN101814527ALower characteristic on-resistanceImprove performanceSemiconductor devicesConductivity modulationElectron

The invention belongs to the technical filed of semiconductor devices, and in particular discloses a power device and a method for performing conductivity modulation by using photoelectron injection. The power device comprises at least one photoelectron injection light source and a power MOS transistor. By adopting a photoelectron injection method, current carriers are injected into a drift region below the gate of the power MOS transistor and the conductivity modulation is performed, so that the characteristic on-resistance of the power MOS transistor is reduced; and simultaneously the doping concentration of the drift region can be reduced and a blocking-voltage can be improved, so that the performance of the power MOS transistor is greatly improved and the application of the power MOS transistor is expanded to high-voltage fields.

Owner:FUDAN UNIV

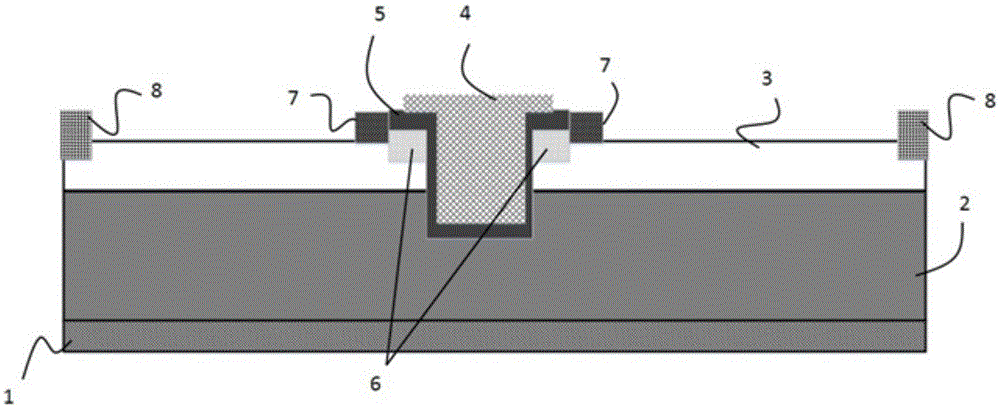

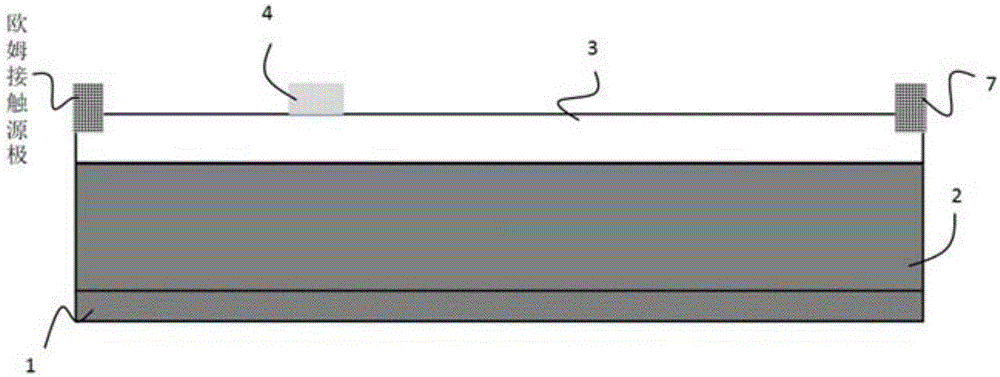

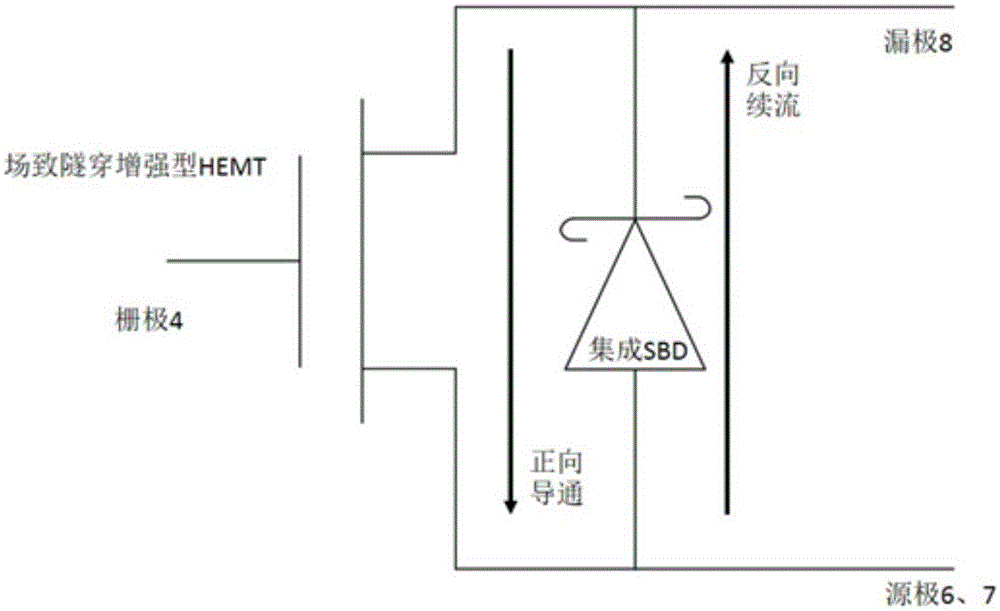

Enhanced HEMT of integrated SBD

ActiveCN105118830AWith reverse rectification performanceHigh blocking voltageSolid-state devicesSemiconductor devicesHigh voltage igbtDevice form

The invention belongs to the semiconductor technology field and especially relates to an enhanced HEMT of an integrated SBD. A source electrode is Schottky contact and is not Ohmic contact of a general device. The source electrode is divided into two portions. One portion is formed by source electrode metal and is used for providing a high voltage blocking capability. The other portion is formed by metal and is used for providing a good current transport capability and reducing a grid voltage required by an inversion layer formed by a wide bandgap semiconductor under a gate medium so that stability is increased and simultaneously realization difficulty is reduced. When a source voltage is positive and a drain voltage is negative, the device forms one SBD and a rectification capability is possessed. When the device is applied in an inductive load circuit, at a turn-off moment, a reverse current in an inductive load is discharged from an integrated SBD pathway so that safety of the device and the whole circuit is protected and stability of the device and circuit is increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Field effect transistor

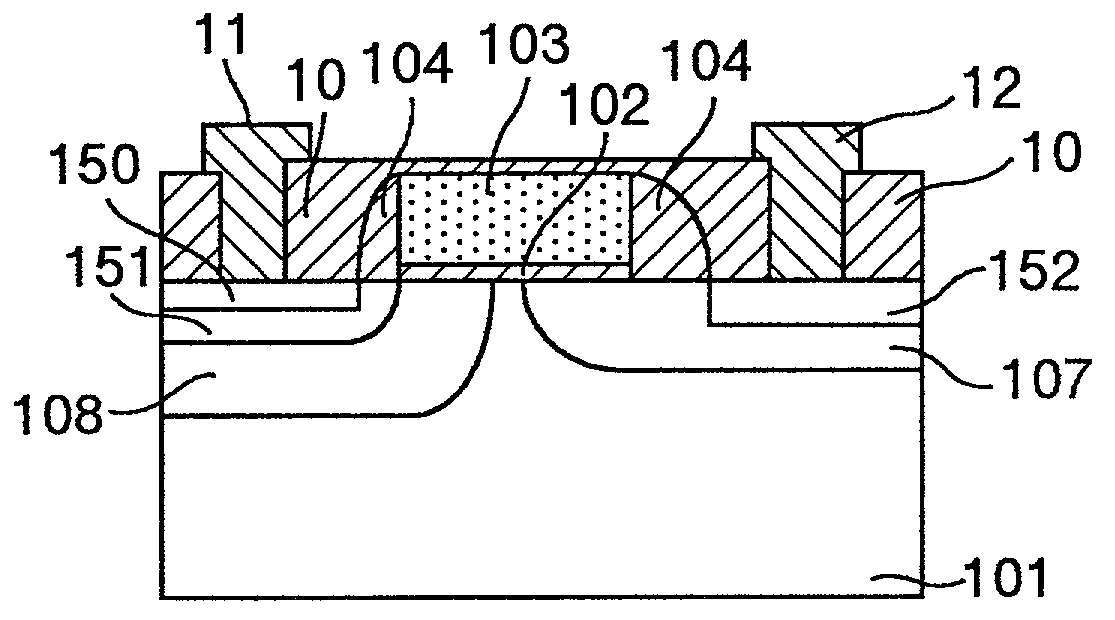

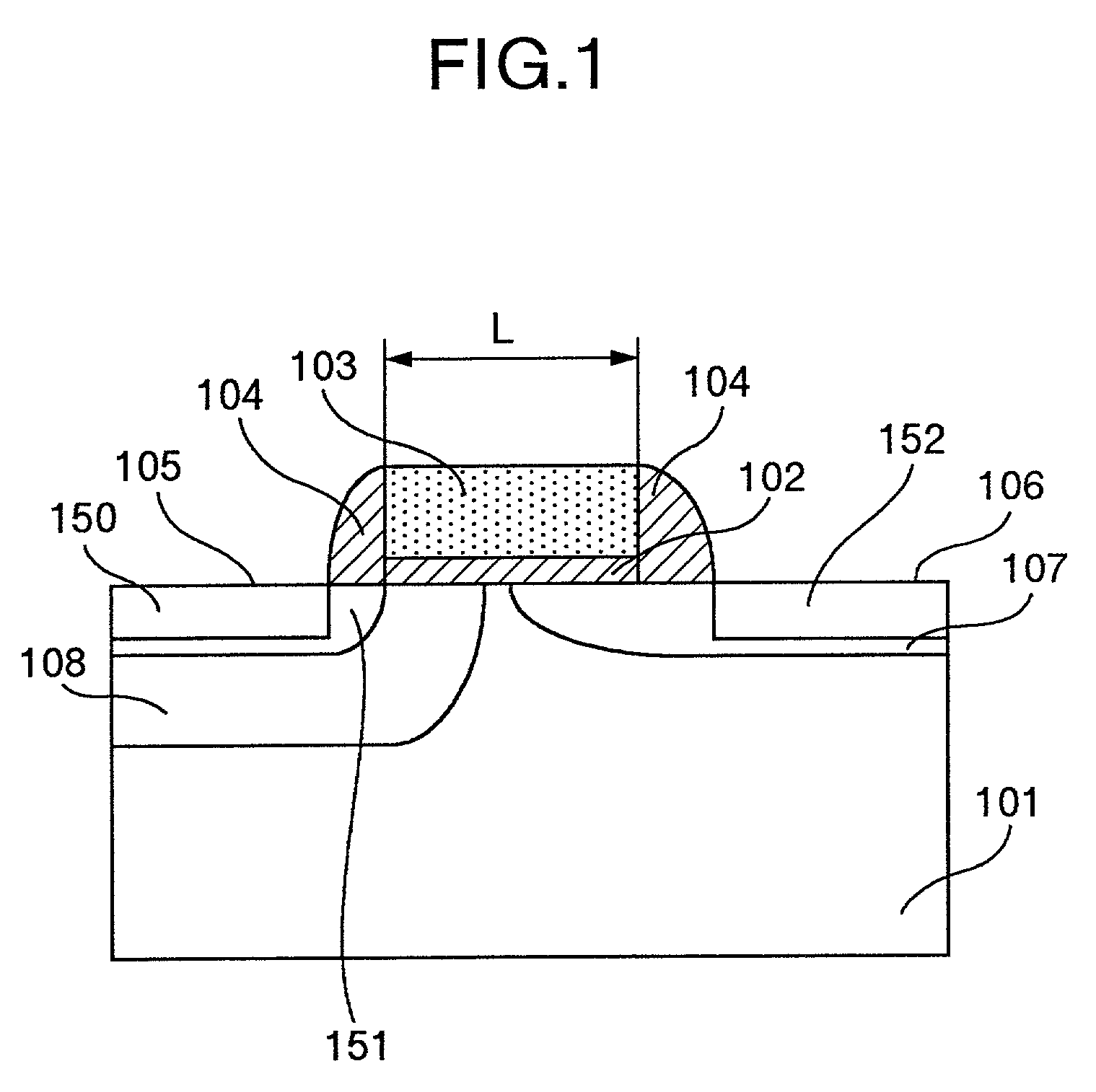

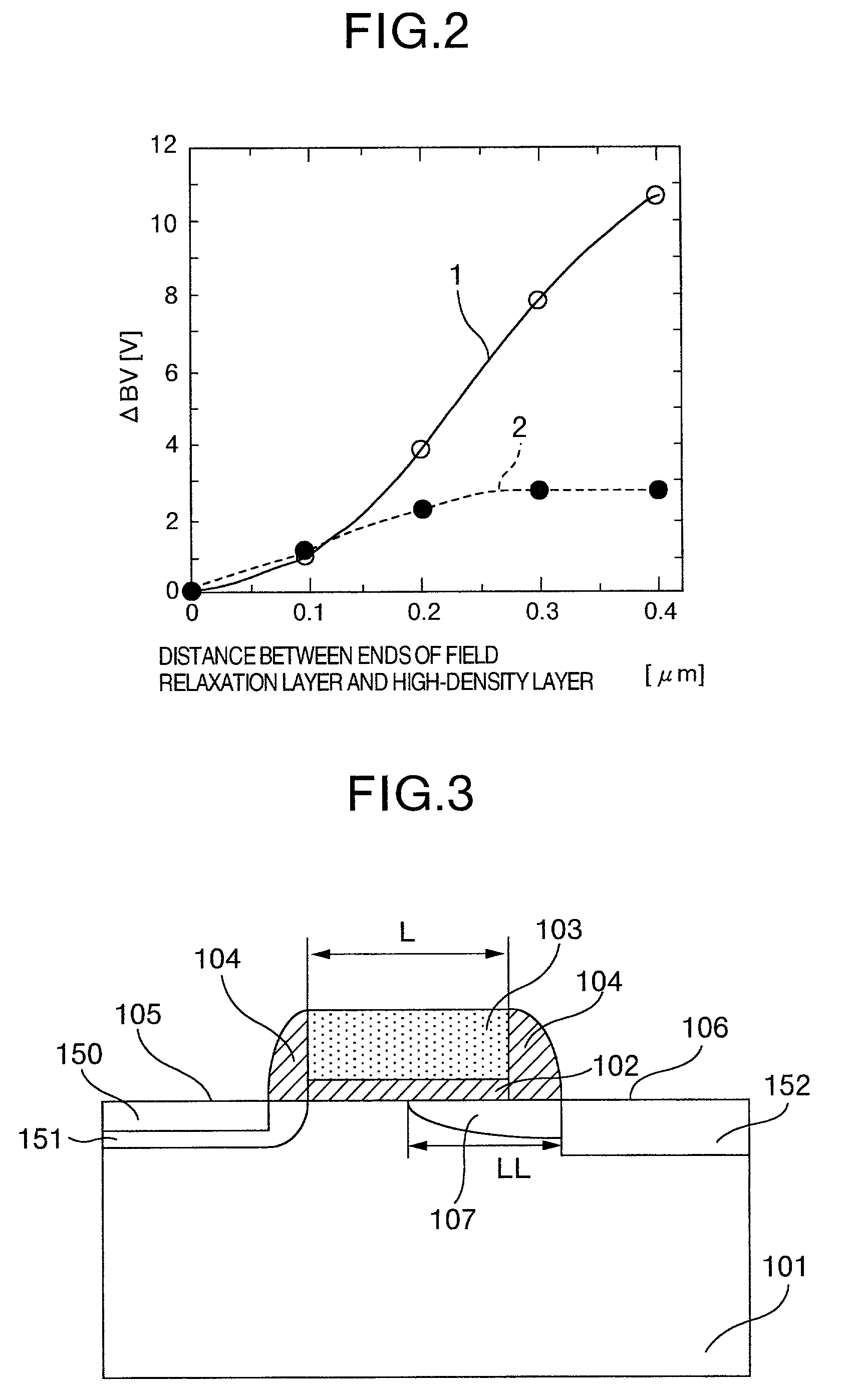

InactiveUS7067878B2High blocking voltageSignificantly miniaturized structureTransistorSemiconductor/solid-state device detailsHigh densityMiniaturization

A MOS field effect transistor. A field relaxation layer of a gate overlap structure is disposed in contact with a drain region for the purpose of relaxation of the electric field by increasing a distance between the field relaxation layer and a high-density layer. The electric field relaxation can further be promoted because the equipotential lines are bent by a gate insulation film. A punch-through stopper layer of a gate overlap structure is disposed in contact with a source region for suppressing spreading of a depletion layer toward the source region. The length of a gate electrode can be realized in a miniaturized size.

Owner:RENESAS TECH CORP

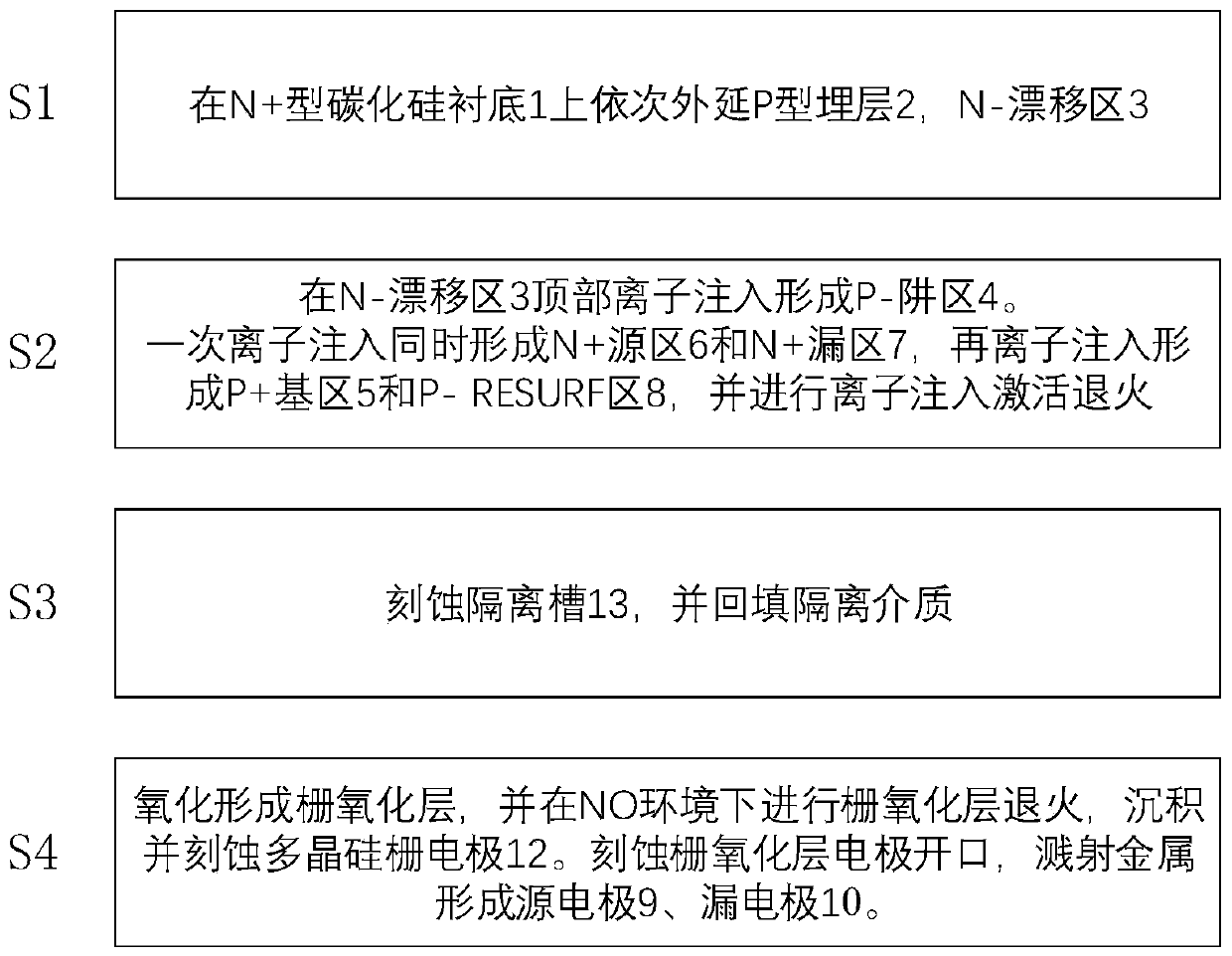

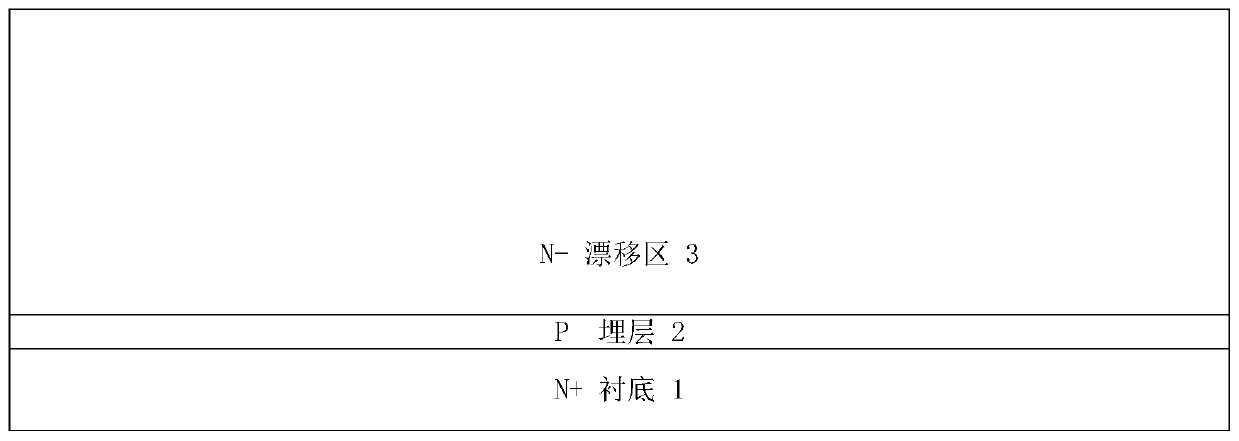

Silicon carbide LDMOS device suitable for monolithic integration and manufacturing method thereof

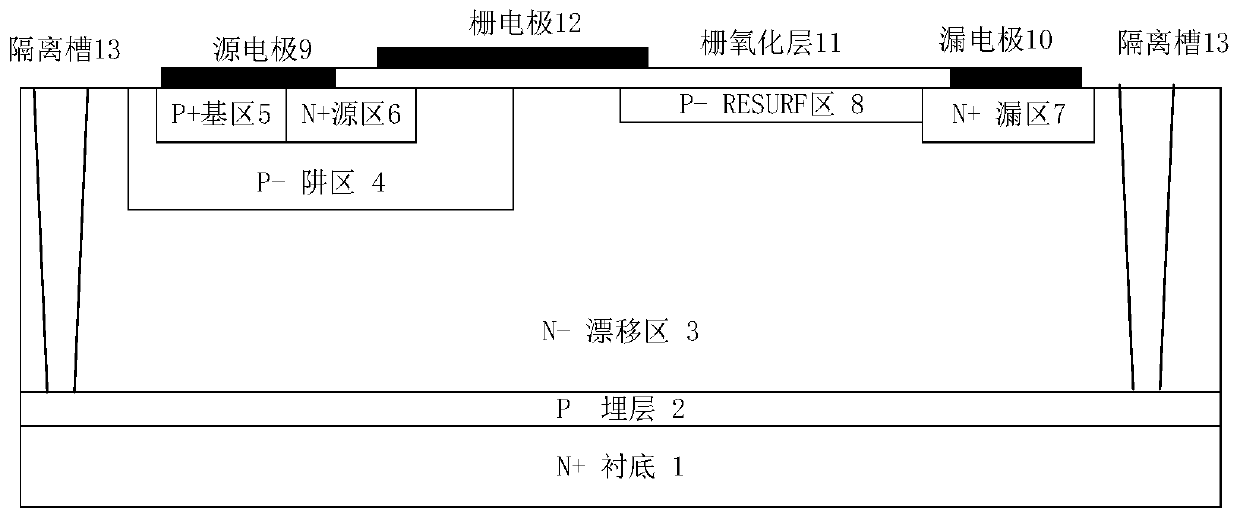

ActiveCN110518070ALower on-resistanceLow costSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETLDMOS

The invention relates to the technical field of power semiconductors, and discloses a silicon carbide LDMOS device suitable for integration and a manufacturing method thereof. The device comprises anN-type highly doped substrate on which a P-type epitaxial isolation buried layer and an N-type light doped drift region are sequentially arranged. A P- well region, a P + base region, an N + source region, a P- RESURF region and an N + drain region are distributed on the top of the drift region, wherein the P + base region and the N + source region are located in the P- well region. The P- RESURFregion is arranged between the P- well region and the N + drain region and close to N + drain region. A gate oxide layer is arranged on the drift region and covers a channel region formed by nesting the P- well region and the N + source region and the P- RESURF region. The novel silicon carbide LDMOS device has the characteristics of high blocking voltage, low conduction resistance and the like, and the process is completely compatible with the current vertical structure silicon carbide MOSFET so as to facilitate preparation of the silicon carbide power integrated circuit. Meanwhile, the RESURF technology is introduced to the device so as to increase the breakdown voltage of the device and reduce the conduction resistance of the device.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

Lateral super junction device with high substrate-gate breakdown and built-in avalanche clamp diode

ActiveUS20140227837A1Easy to spreadHigh blocking voltageSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A lateral super junction JFET is formed from stacked alternating P type and N type semiconductor layers over a P-epi layer supported on an N+ substrate. An N+ drain column extends down through the super junction structure and the P-epi to connect to the N+ substrate to make the device a bottom drain device. N+ source column and P+ gate column extend through the super junction but stop at the P-epi layer. A gate-drain avalanche clamp diode is formed from the bottom the P+ gate column through the P-epi to the N+ drain substrate.

Owner:ALPHA & OMEGA SEMICON INC

Junction termination structures for wide-bandgap power devices

InactiveUS7498651B2High blocking voltageThe process is simple and controllableTransistorEngineeringHigh pressure

Disclosed are a variety of junction termination structures for high voltage semiconductor power devices. The structures are specifically aimed at providing a high breakdown voltage while being constructed with a minimal number of process steps. The combination of an RIE etch and / or implantation and anneal process with a finely patterned mesh provides the desired radial gradient for maximum breakdown voltage. The structures provide control of both the conductivity and charge density within the region. These structures can beneficially be applied to all high voltage semiconductor device structures, but are of particular interest for wide bandgap devices as they tend to have very high breakdown fields and scaled dimensions of the depletion layer width.

Owner:MICROSEMI CORP

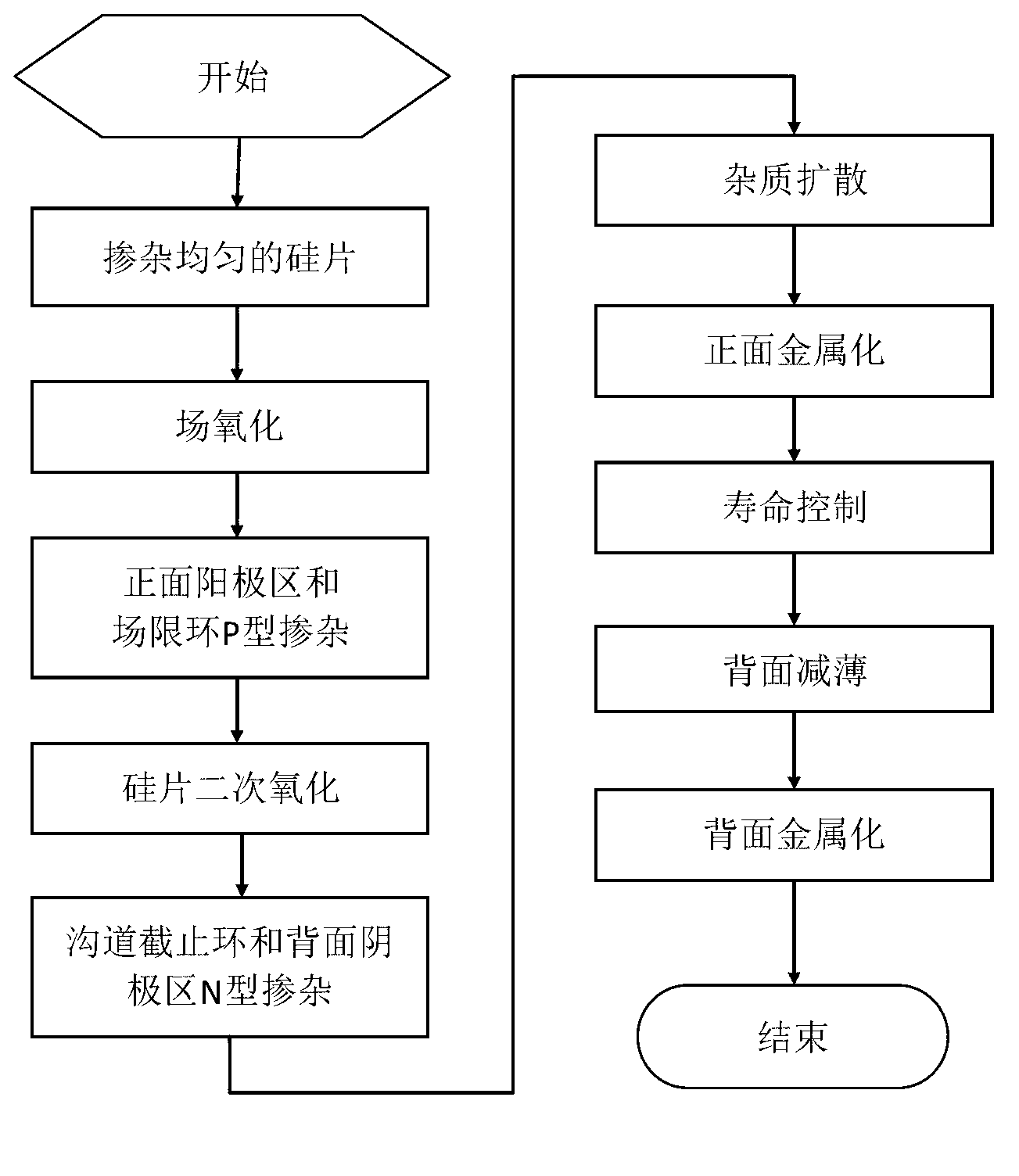

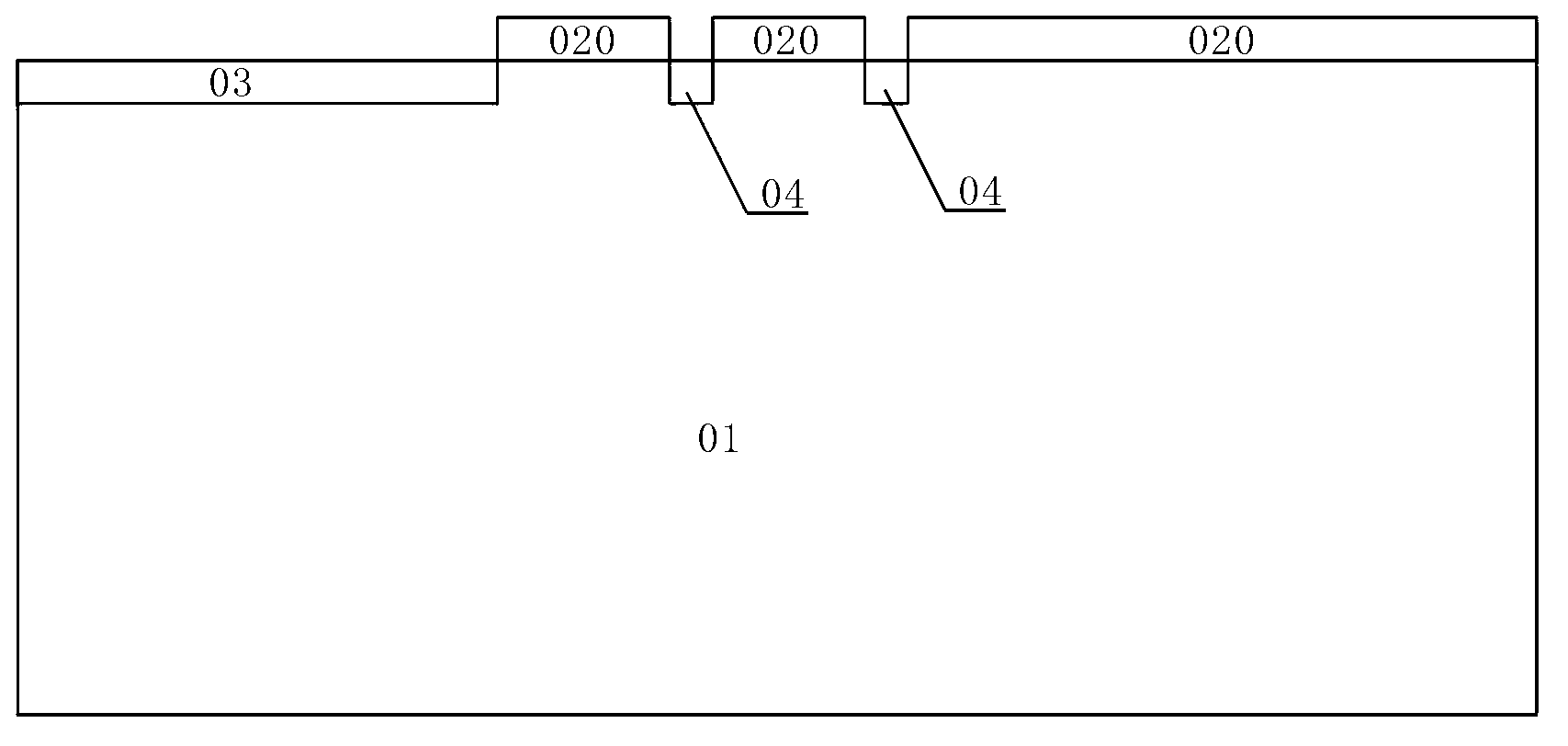

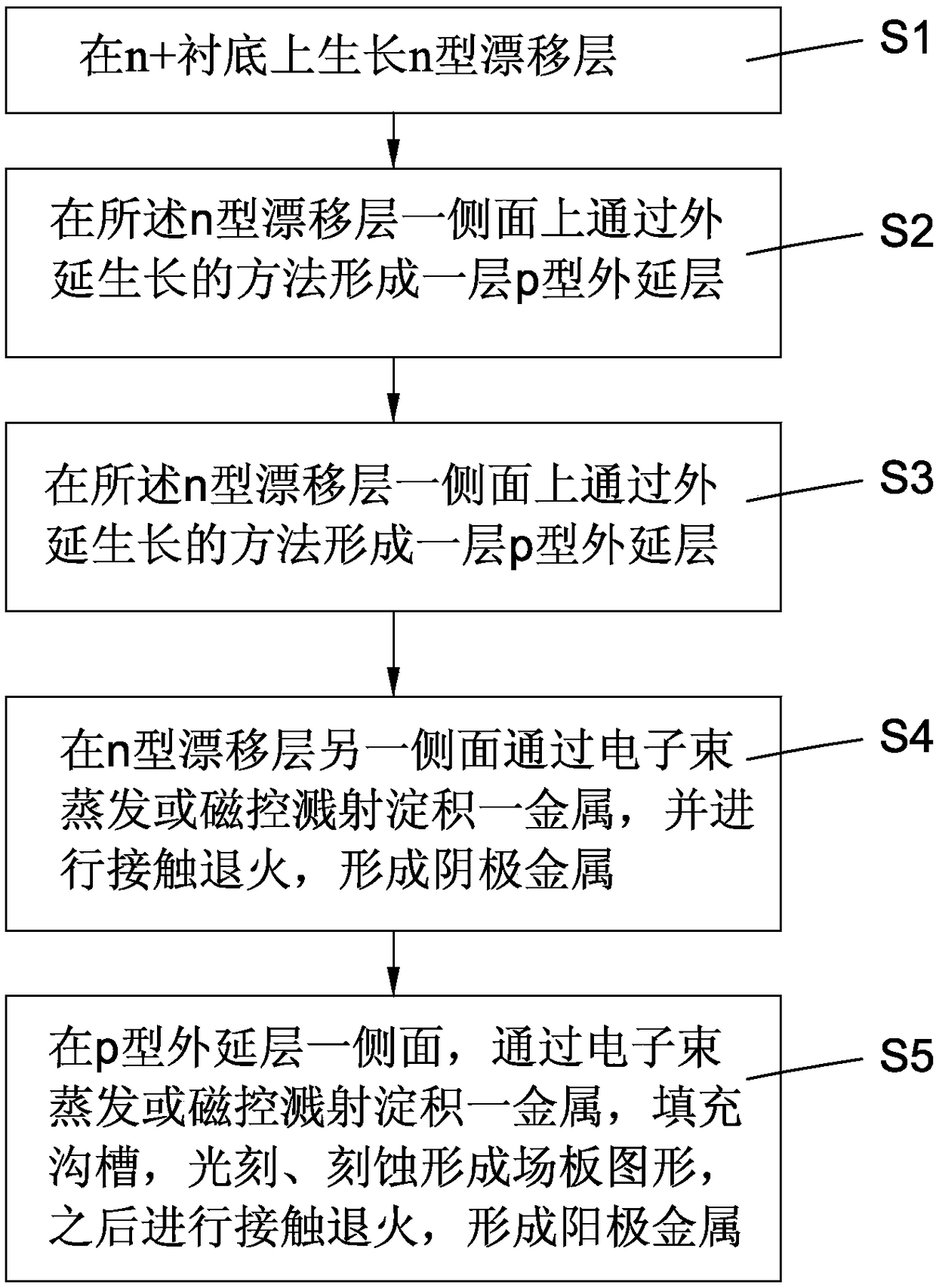

Manufacturing method of high-voltage quick-recovery diode

ActiveCN102842501ALow costReduce processing stepsSemiconductor/solid-state device manufacturingDiffusion methodsImpurity doping

The invention provides a manufacturing method of a high-voltage quick-recovery diode, and the method comprises following steps of simultaneously implementing P-type impurity doping of an anode area and a terminal field limiting ring on the front surface of an N-type monocrystalline silicon sheet which is uniformly doped through field oxidation and ion injection; adopting a diffusion method to simultaneously implement the N-type impurity doping of a silicon sheet front surface groove interception ring and a silicon-sheet back surface cathode area after the anode area and the terminal field limiting ring area are protected by an oxidation film; implementing the heat diffusion propulsion simultaneously for the P-type impurities and N-type impurities in a high-temperature diffusion furnace; and implementing the back surface metallization after completing the front surface metallization, electron radiation minority carrier lifetime control and removal of a back surface damaged layer. According to the method, the machining steps are simple, and a deep N-type doped layer on the back surface of the silicon sheet is favorable for improving the reverse recovery characteristic of the diode and improving the blocking voltage.

Owner:CHINA ELECTRIC POWER RES INST +1

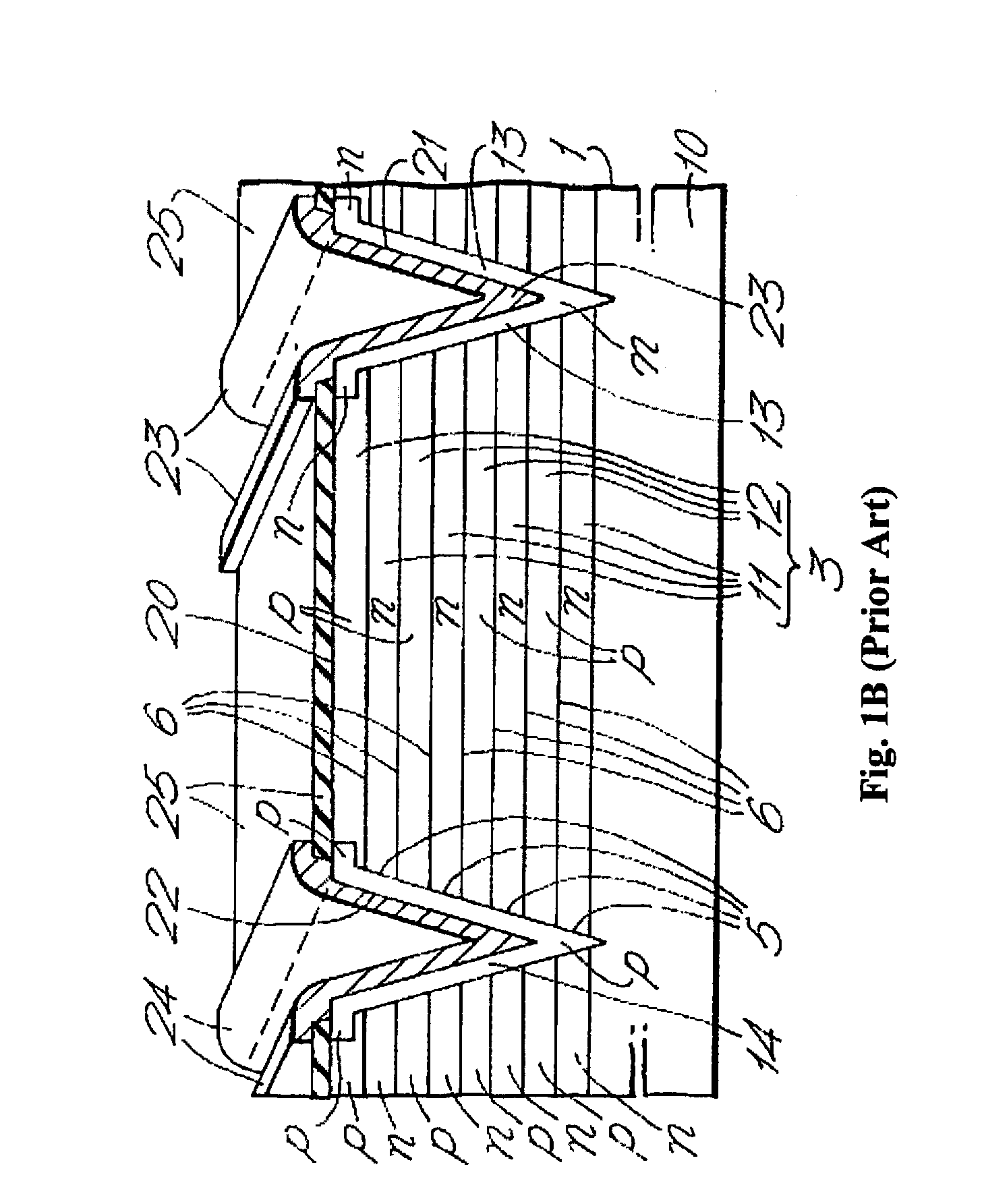

Flat gate commutated thyristor

ActiveUS20180204913A1Ensure sufficient separationIncrease contact areaThyristorPower semiconductor deviceImpurity

The invention relates to a turn-off power semiconductor device comprising a plurality of thyristor cells, each thyristor cell comprising a cathode region; a base layer; a drift layer; an anode layer; a gate electrode which is arranged lateral to the cathode region in contact with the base layer; a cathode electrode; and an anode electrode. Interfaces between the cathode regions and the cathode electrodes as well as interfaces between the base layers and the gate electrodes of the plurality of thyristor cells are flat and coplanar. In addition, the base layer includes a gate well region extending from its contact with the gate electrode to a depth, which is at least half of the depth of the cathode region, wherein, for any depth, the minimum doping concentration of the gate well region at this depth is 50% above a doping concentration of the base layer between the cathode region and the gate well region at this depth and at a lateral position, which has in an orthogonal projection onto a plane parallel to the first main side a distance of 2 μm from the cathode region. The base layer includes a compensated region of the second conductivity type, the compensated region being arranged directly adjacent to the first main side and between the cathode region and the gate well region, wherein the density of first conductivity type impurities relative to the net doping concentration in the compensated region is at least 0.4.

Owner:HITACHI ENERGY SWITZERLAND AG

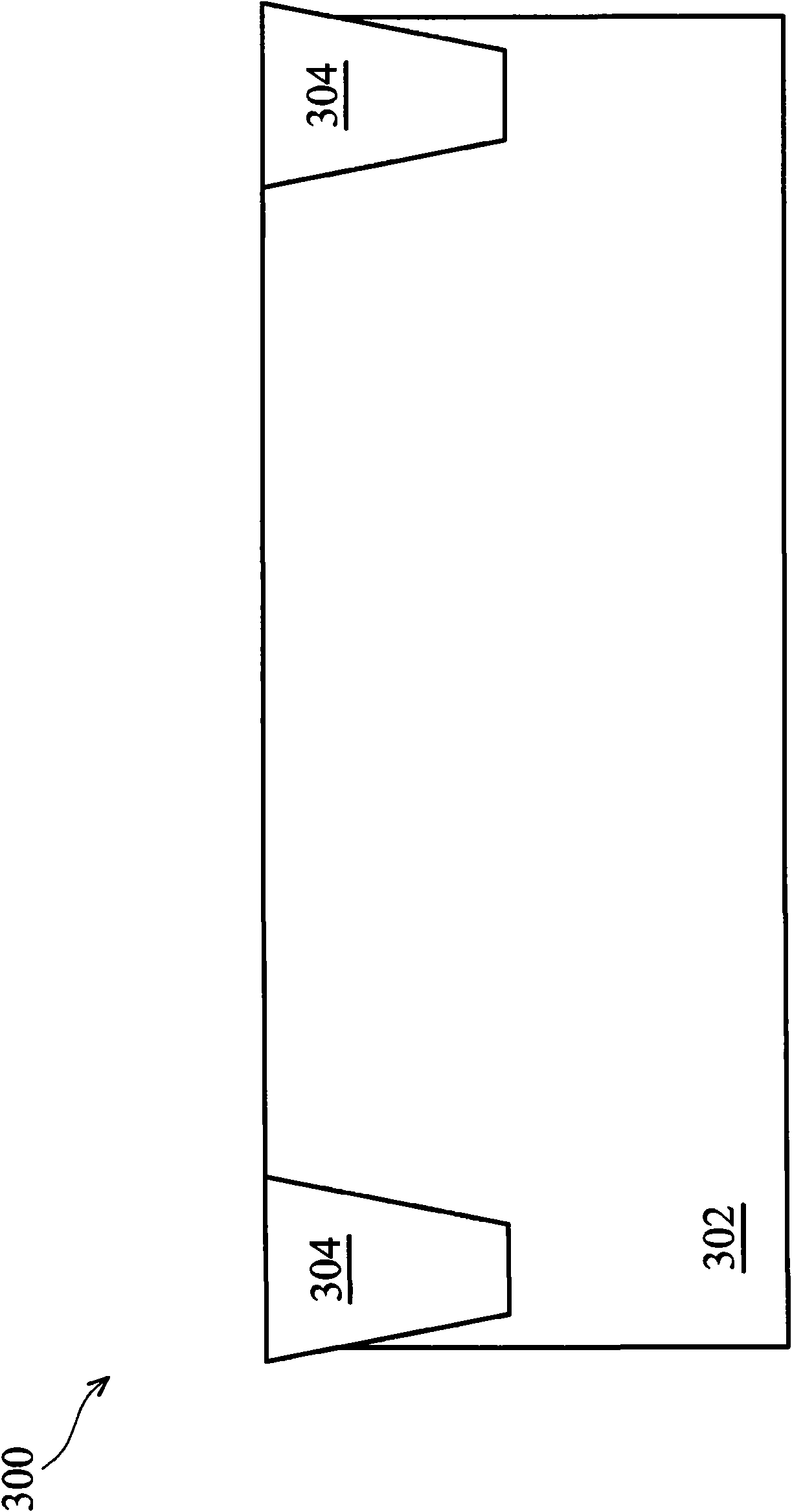

Trench Edge Termination Structure for Power Semiconductor Devices

InactiveUS20180026129A1Less to fabricateReduce technical difficultySemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEtching

Edge termination structures for power semiconductor devices (or power devices) are disclosed. The purpose of this invention is to reduce the difficulty of deep trench etching and dielectric filling by adopting an inverted trapezoidal trench. In order to save the area of edge termination and get a high blocking voltage on condition that the angle between the sidewall of the trench and horizontal is large, fixed charges are introduced at a particular location in the trench. Due to the Coulomb interaction between the ionized impurity in the drift region and the fixed charges, the depletion region of the terminal PN junction can extend fully, which relieves the concentration of electric field there. Therefore, the edge termination can exhibit a high breakdown voltage near to that of the parallel plane junction with a smaller area and the reduced technical difficulty of deep trench etching and dielectric filling.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

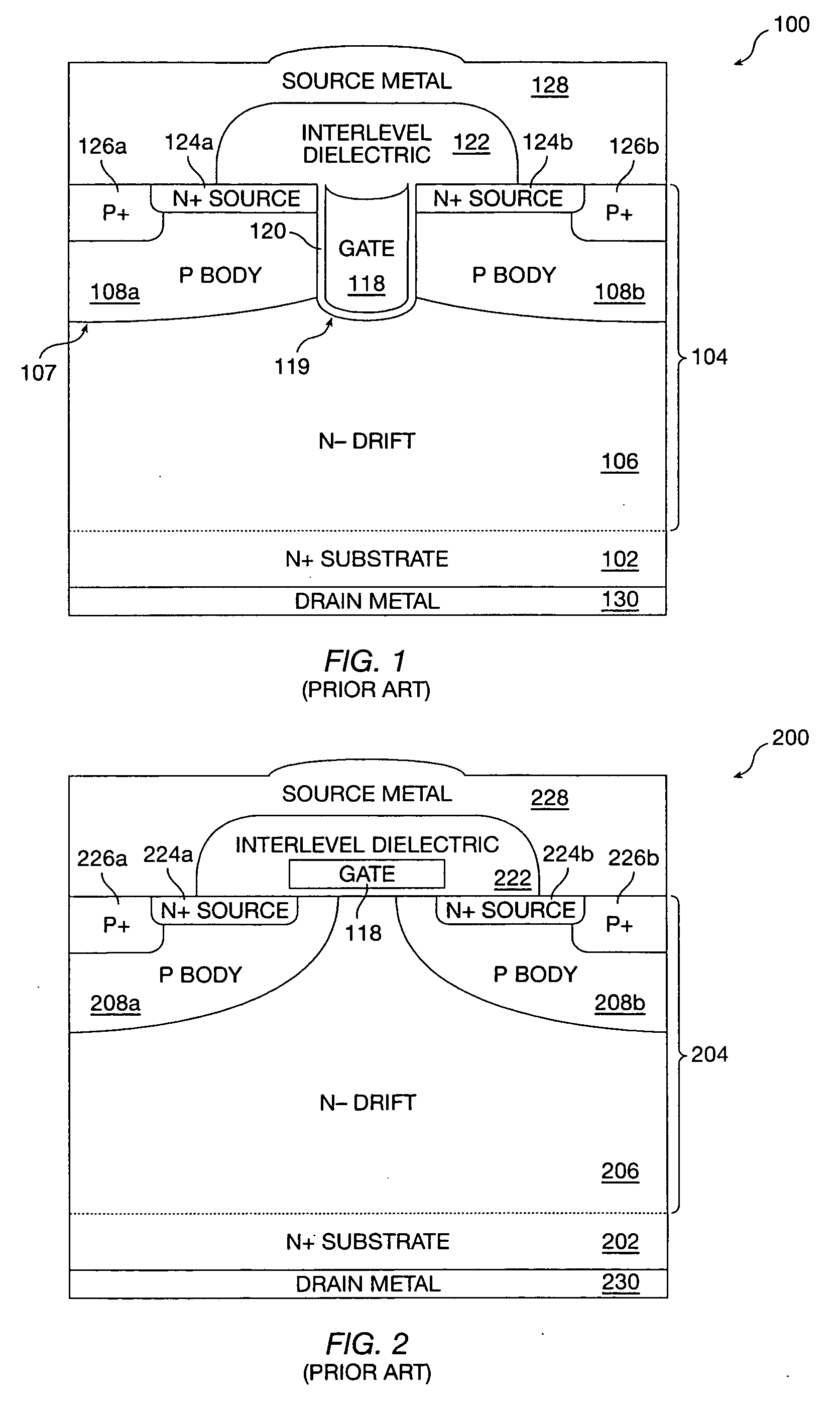

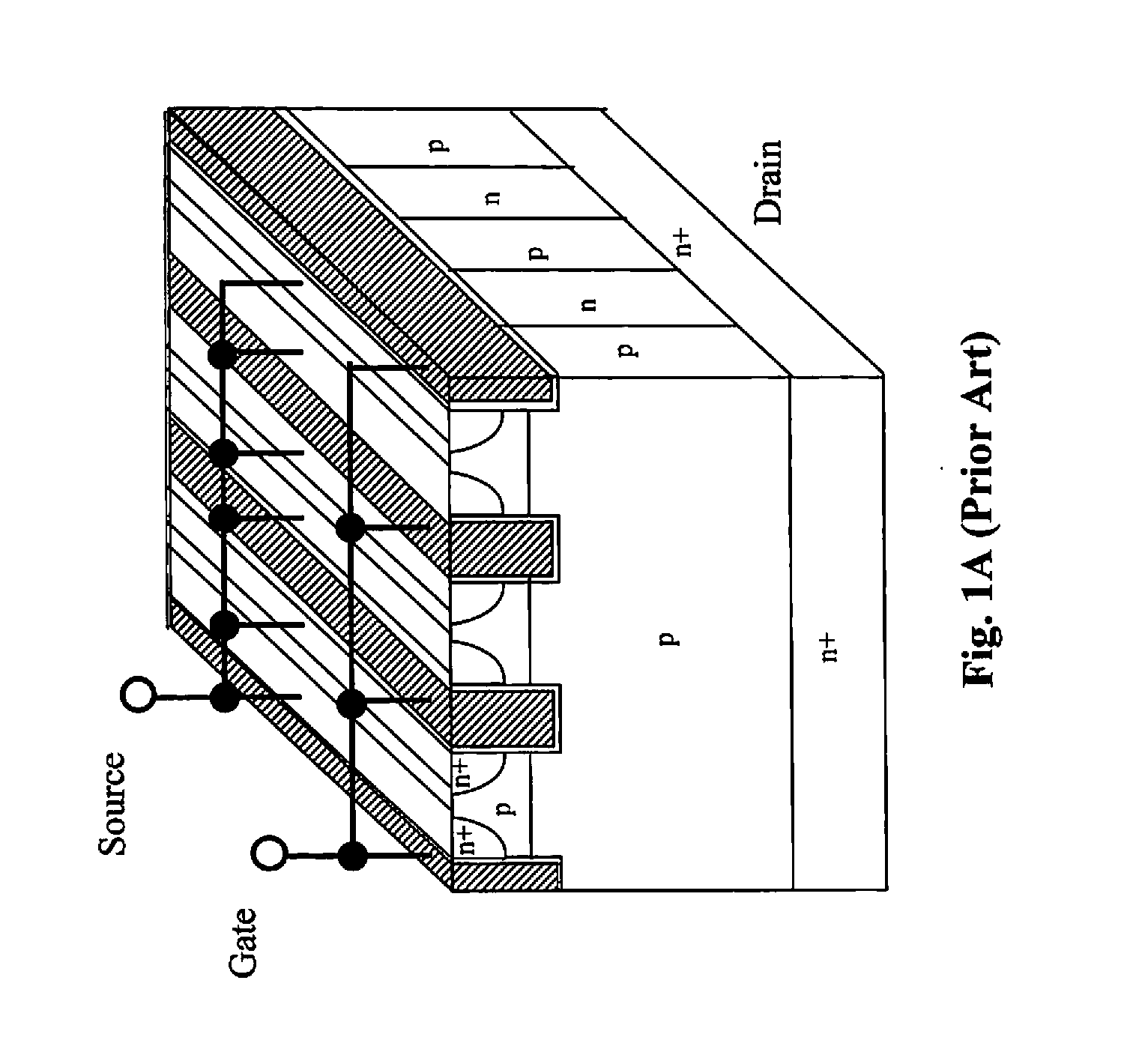

High voltage FET switch with conductivity modulation

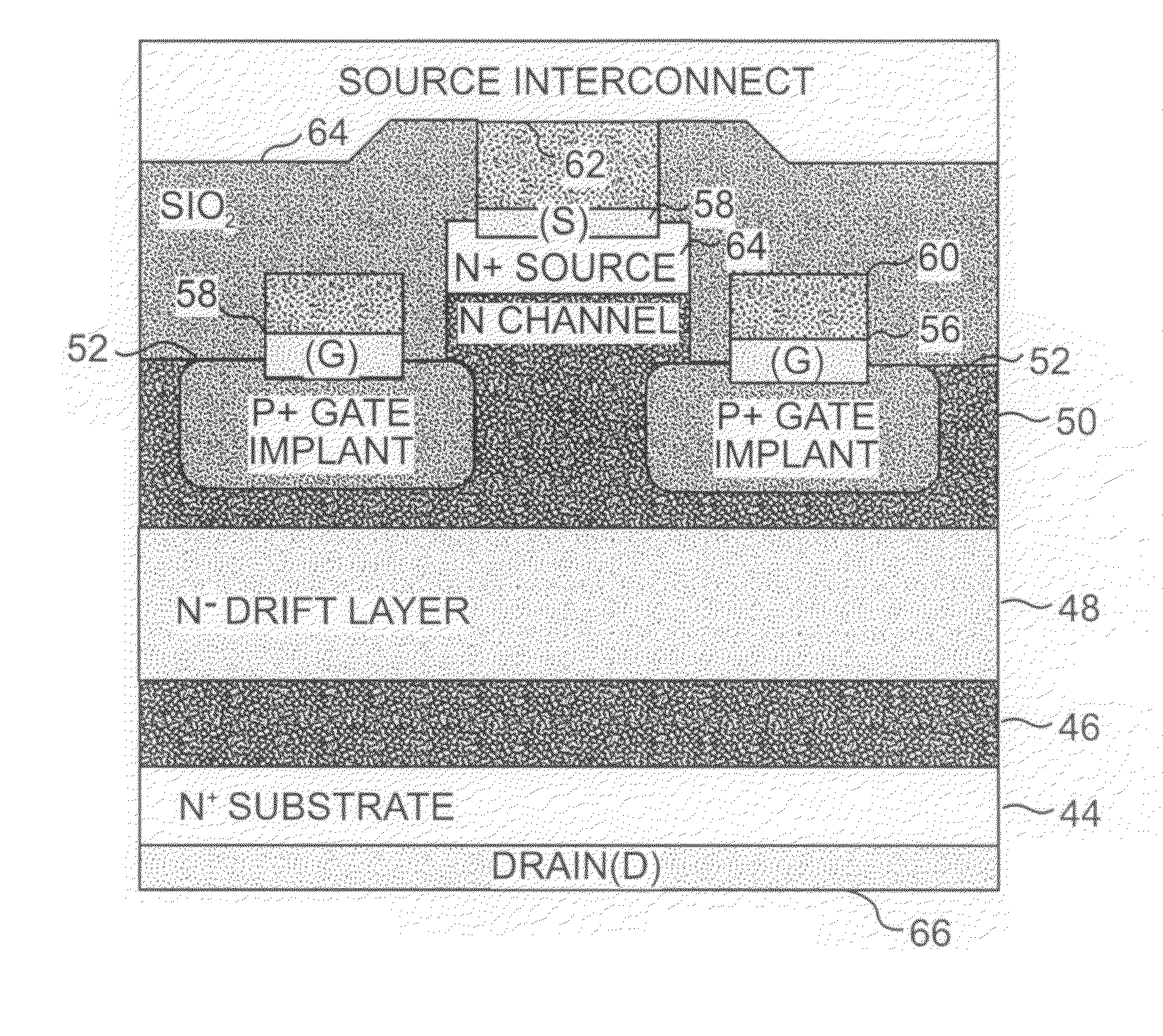

ActiveUS7135740B2Lower on-resistanceHigh blocking voltageSemiconductor/solid-state device manufacturingSemiconductor devicesConductive materialsEngineering

A high power FET switch comprises an N− drift layer, in which pairs of trenches are recessed to a predetermined depth; oxide side-walls extend to the trench bottoms, and each trench is filled with a conductive material. N+ and metal layers on opposite sides of the drift layer provide drain and source connections for the FET, and the conductive material in each trench is connected together to provide a gate connection. A shallow P region extends across the bottom and around the corners of each trench's side-walls into the drift layer. The application of a sufficient gate voltage causes holes to be injected from the shallow P regions into the N− drift layer, thereby modulating the drift layer's conductivity and lowering the device's on-resistance, and enabling current to flow between the drain and source connections.

Owner:CALLAHAN CELLULAR L L C

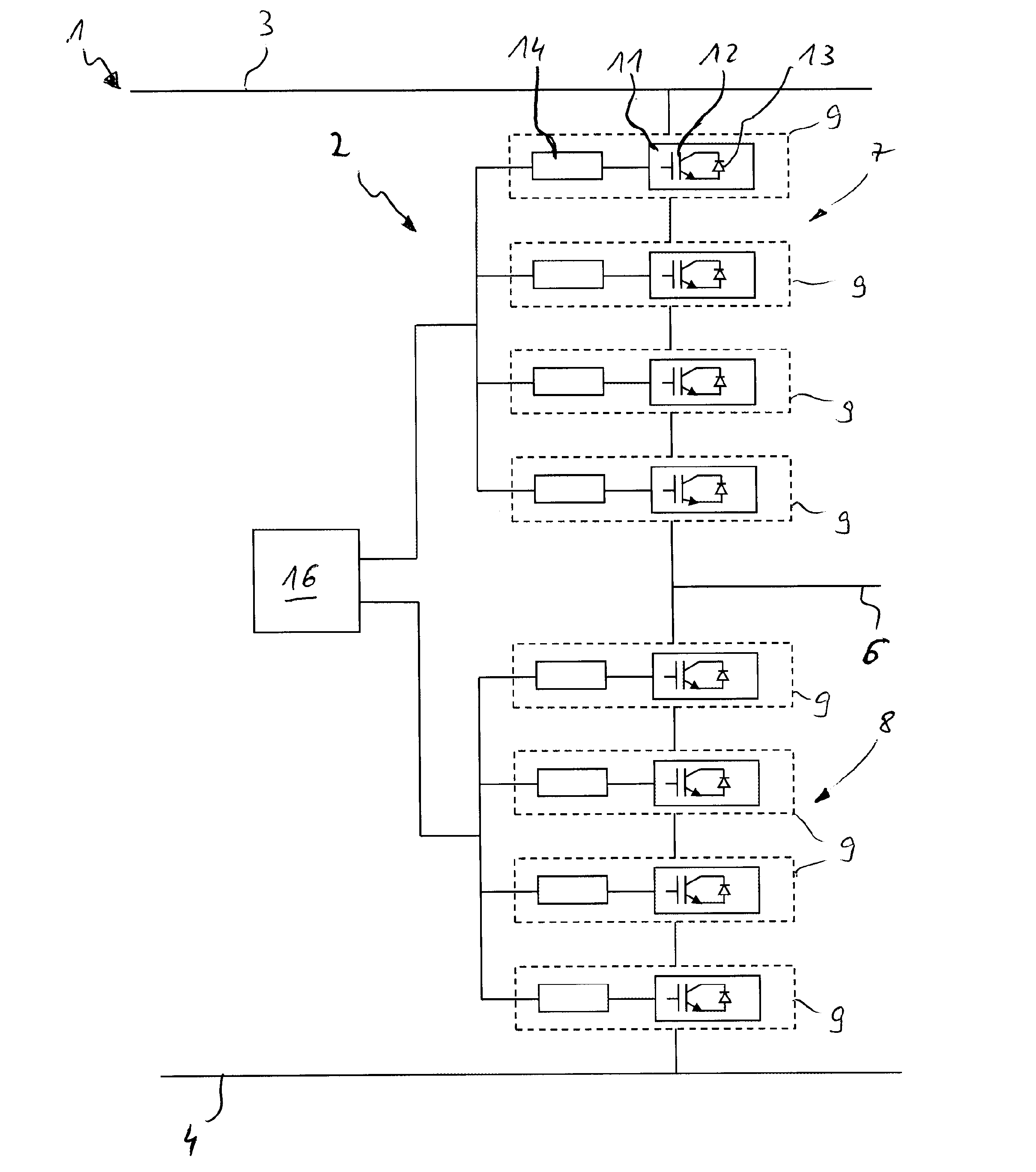

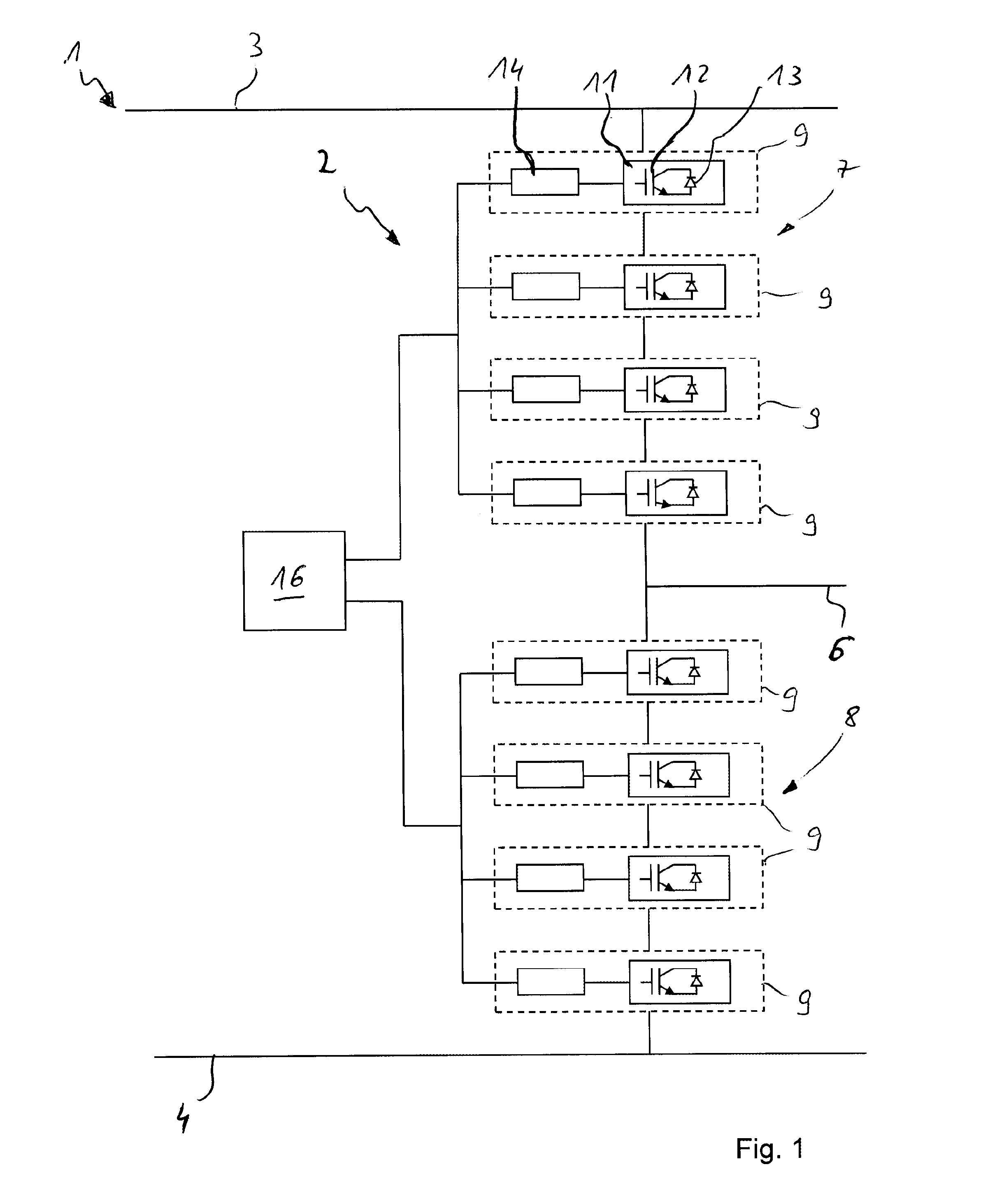

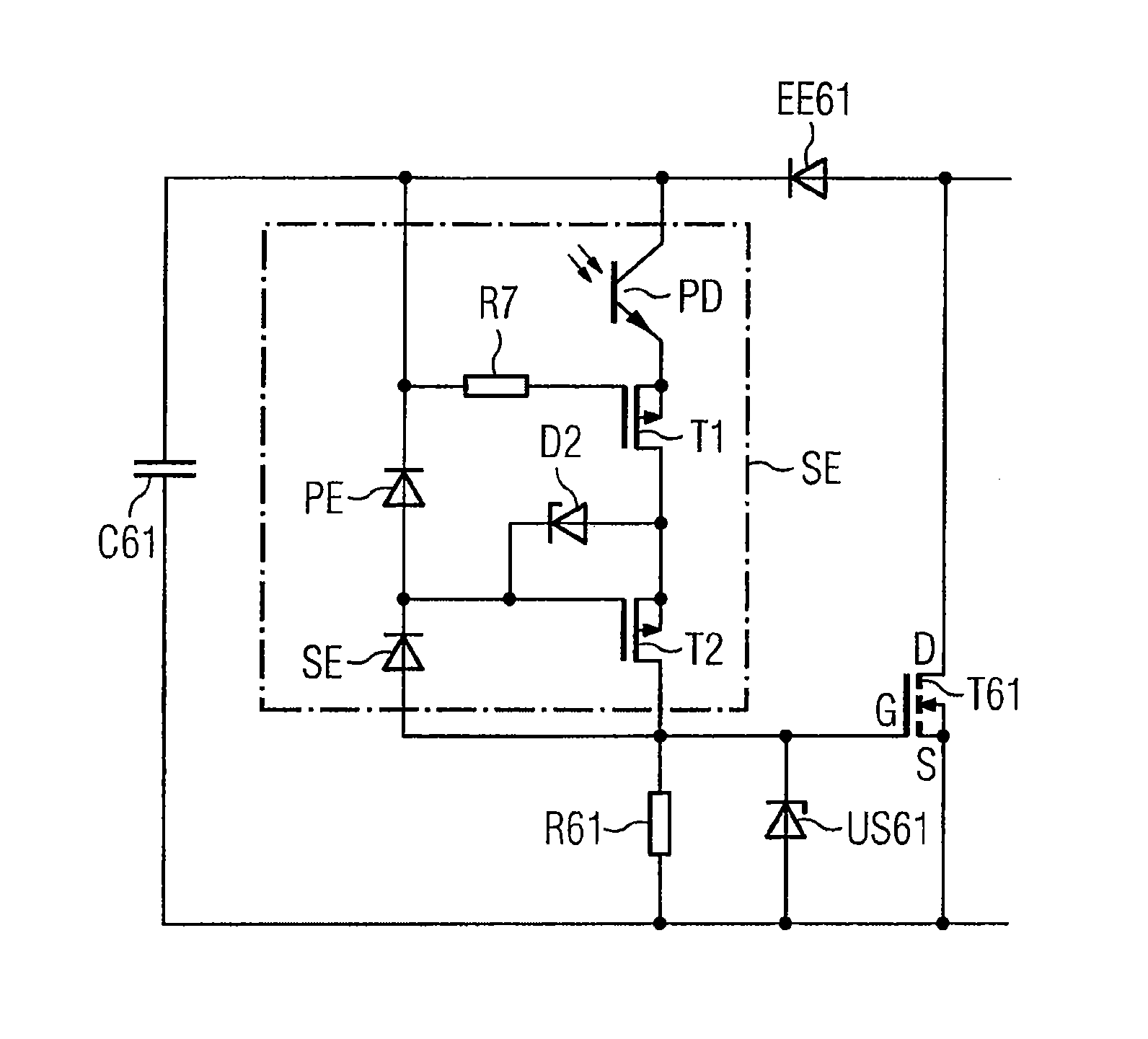

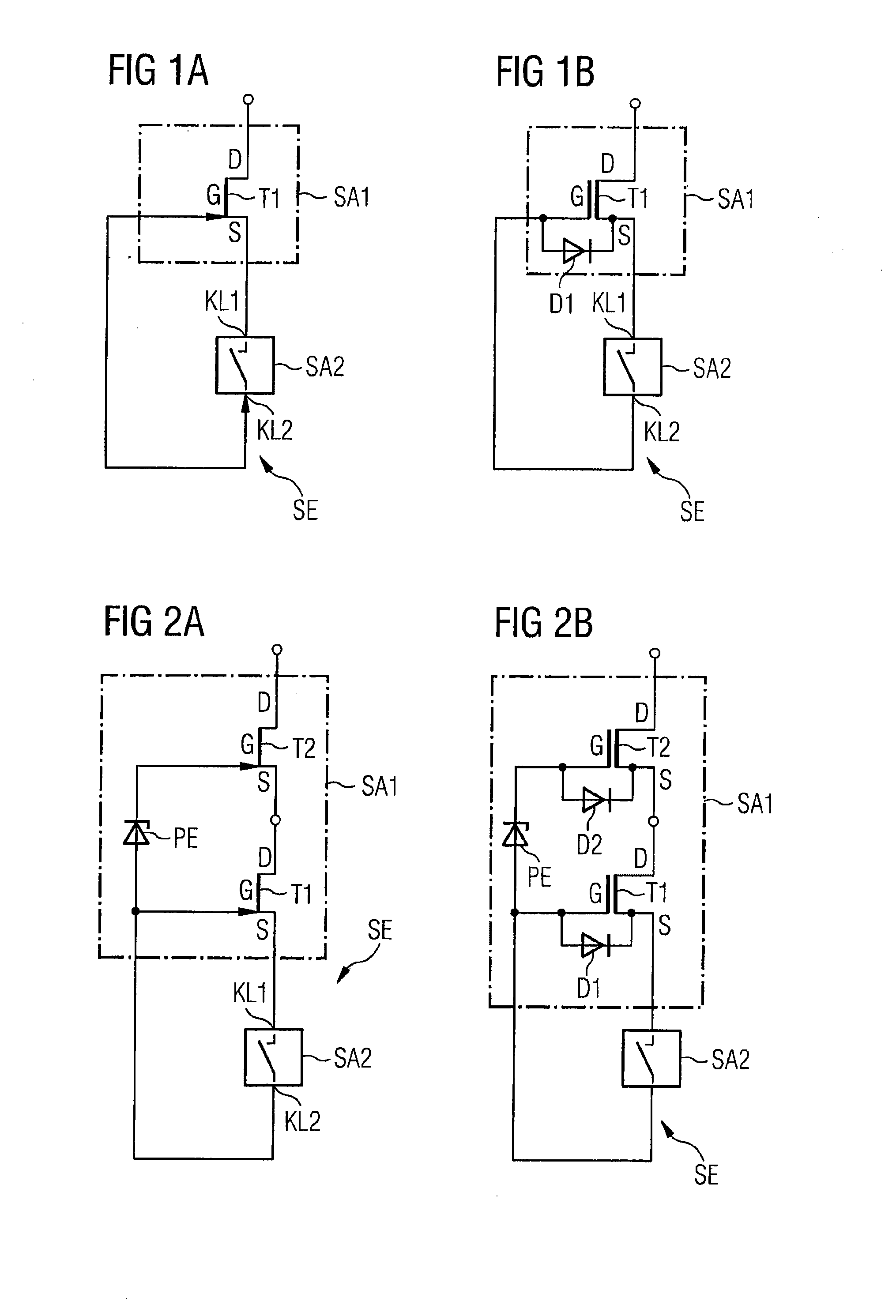

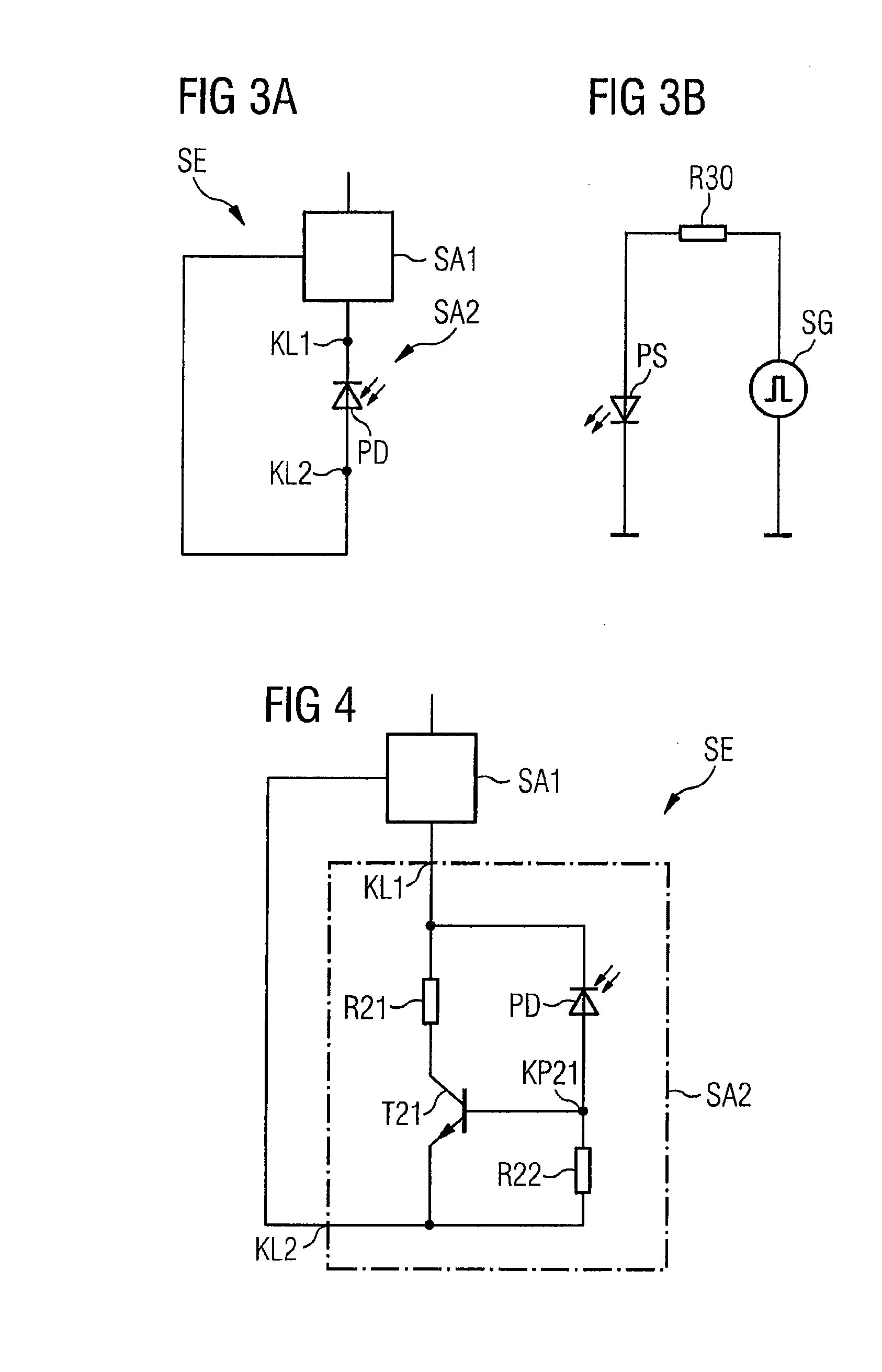

Switching device and switching arrangements for switching at high operating voltage

InactiveUS20100026371A1Reduce transmission lossIncrease working voltagePulse automatic controlElectronic switchingEngineeringOperating voltage

A switching device for switching a high operating voltage is described. The switching device-includes a first switching arrangement with a first self-conducting switching element), which has a control connector and a first and second main connector for forming a switching section. The switching device may include a second switching arrangement having a first and a second connector for forming a switching section, which is wired serially in respect to the switching section of the first switching arrangement. The second switching arrangement includes an optically triggerable switching element for switching the switching section of the second switching arrangement so it becomes conductive. The second connector of the second switching arrangement is connected with the control connector of the first self-conducting switching element.

Owner:SIEMENS HEALTHCARE GMBH

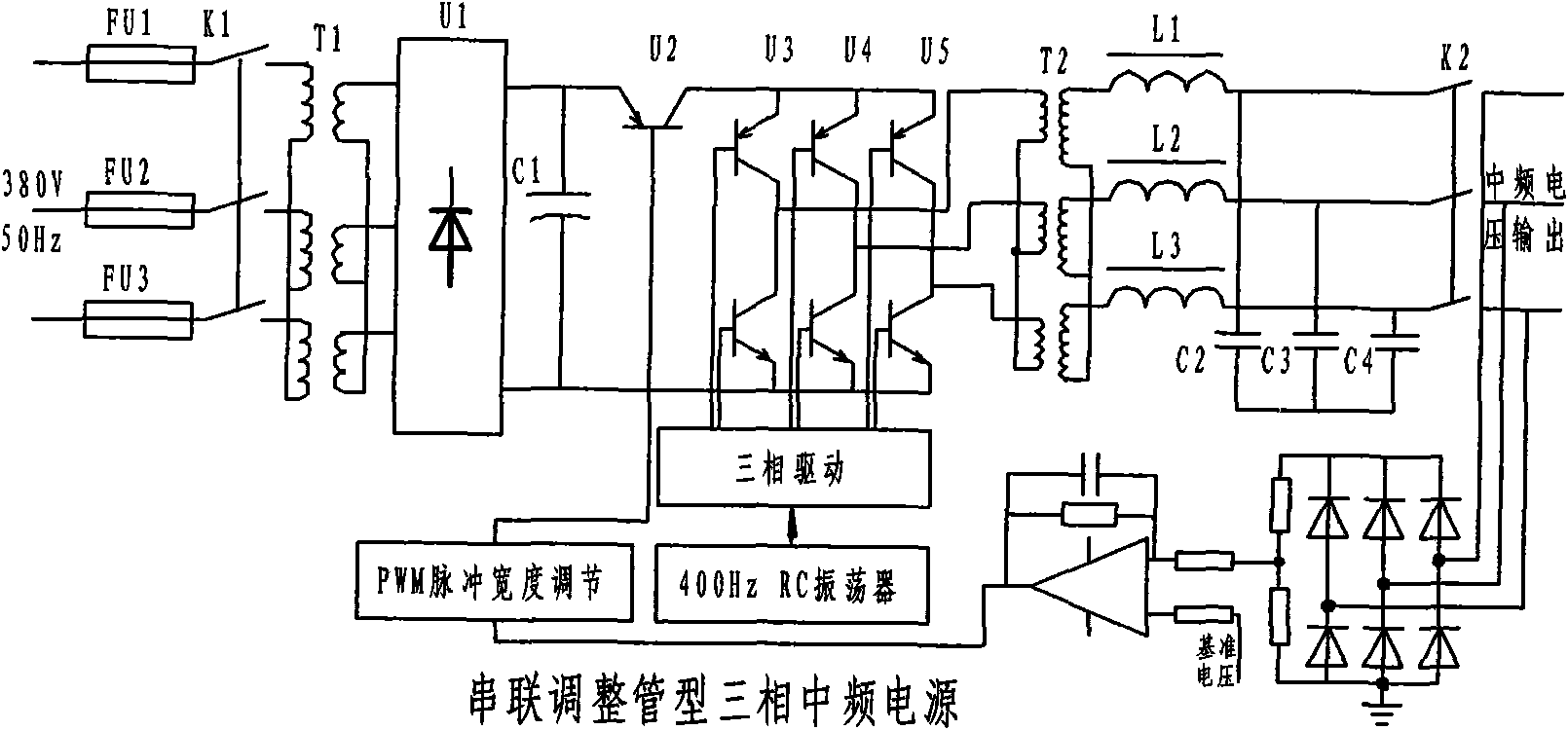

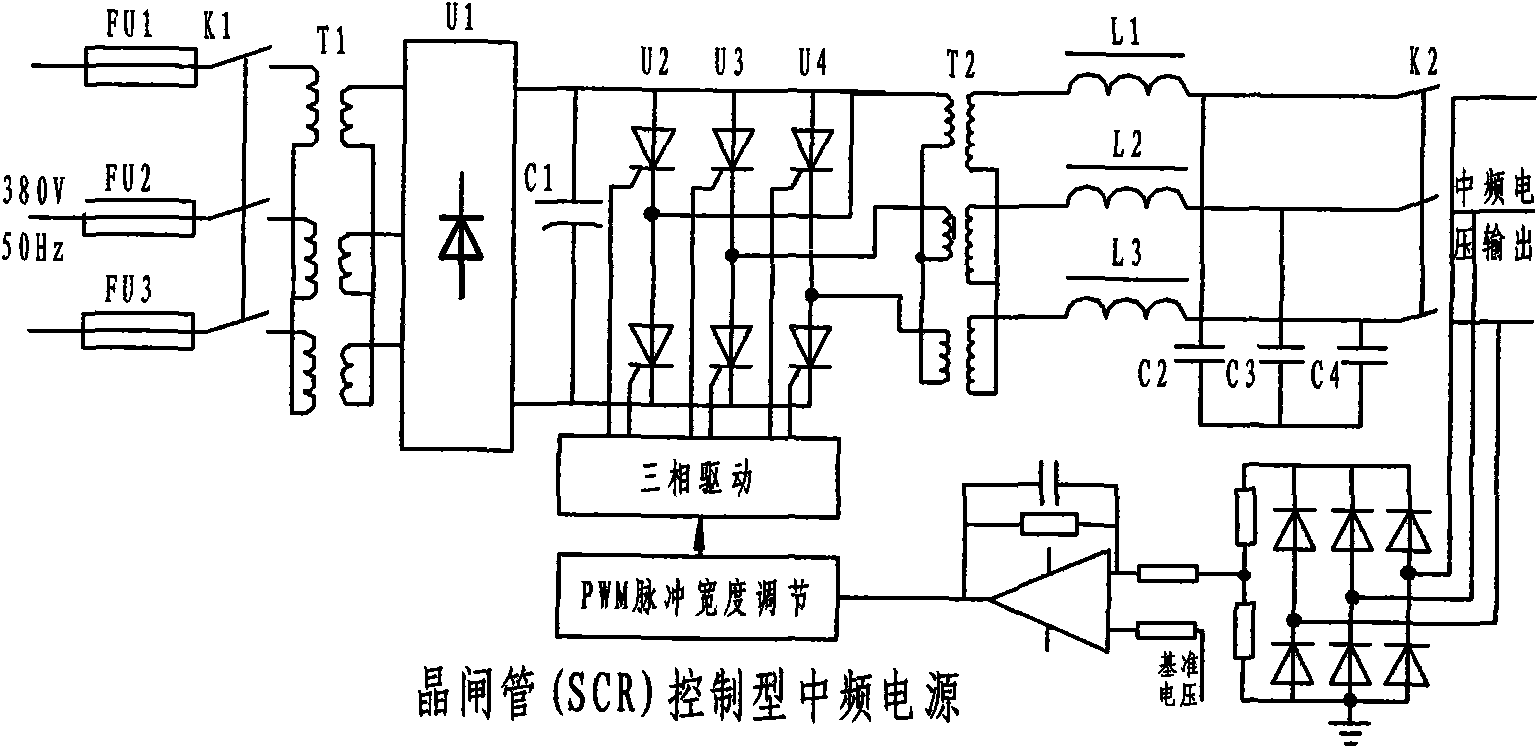

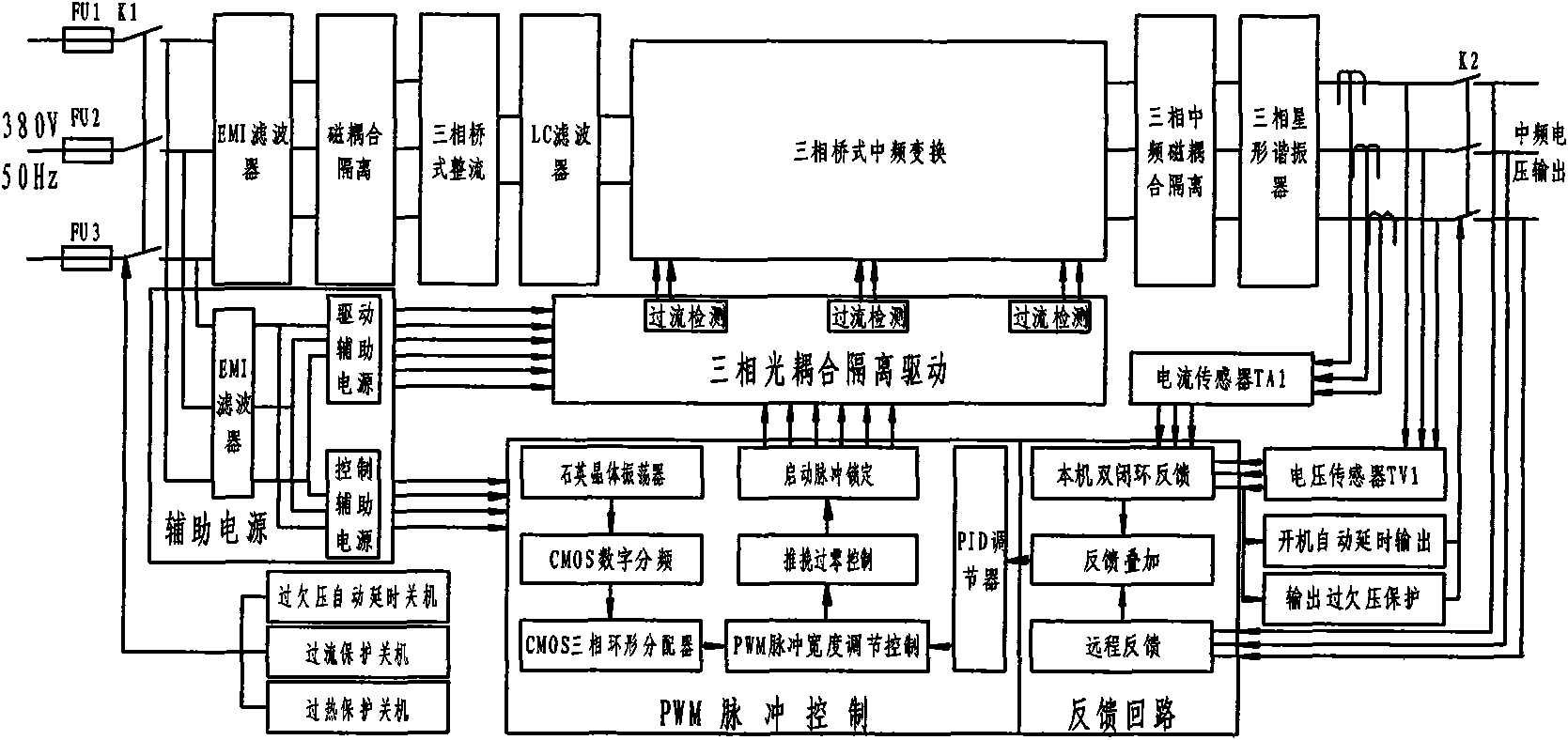

Three-phase intermediate frequency power supply

InactiveCN101562401ALow powerHigh input impedanceEmergency protective circuit arrangementsAc-ac conversionIntermediate frequencyTransformer

The invention discloses a three-phase intermediate frequency power supply. The standard voltage of a three-phase external electric network with 380V / 50Hz is input to an industrial frequency transformer after passing through a three-phase fuse, an input contactor and an anti-electromagnetic interference filter, then is input to a three-phase rectifier after isolation and voltage reduction and then is filtered through a constant K type inverted-L-shaped L second-order low-pass filter and a constant K type inverted-L-shaped C second-order low-pass filter after being rectified by a bridge rectifier to obtain the operating direct-current voltage of a major loop; and the direct-current voltage is transmitted to an IGBT switching tube in a high-power conversion module, an auxiliary power supply is used for supplying power for a control loop to generate intermediate frequency as well as an IGBT pulse width modulation control signal, the IGBT switching tube is driven, the direct-current voltage is converted into three-phase intermediate frequency voltage, isolation, integration and regulation are performed on the three-phase intermediate frequency voltage through an output intermediate frequency transformer, and filtering is performed through the second-order low-pass filter to obtain the standard three-phase intermediate frequency sinusoidal voltage output. The three-phase intermediate frequency power supply overcomes the defects of complex control and driving of intermediate frequency power, excessive high power loss, low efficiency, poor wave-shape, unstable frequency and poor reliability as the traditional intermediate frequency power supply adopts serially connected regulating transistors for voltage regulation or adopts a bipolar transistor, an SCR thyristor and a GTO thyristor as the main power tubes.

Owner:CHONGQING HUAYU ELECTRIC GRP

Semiconductor Device and a Method of Manufacturing Same

InactiveUS20160104614A1Low production costHigh blocking voltageSemiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingSilicon oxideSemiconductor

With an SiC semiconductor device, the surface of a termination region is covered with a passivation film, and the passivation film is provided with a thermal silicon oxide film which is in contact with the surface of the termination region, a CVD silicon oxide film deposited on the thermal silicon oxide film so as to be in contact with the thermal silicon oxide film, and a CVD silicon oxide film deposed on the CVD silicon oxide film so as to be in contact with the CVD silicon oxide film. By so doing, an electric field applied on the passivation film is relaxed, while production cost is reduced.

Owner:HITACHI LTD +1

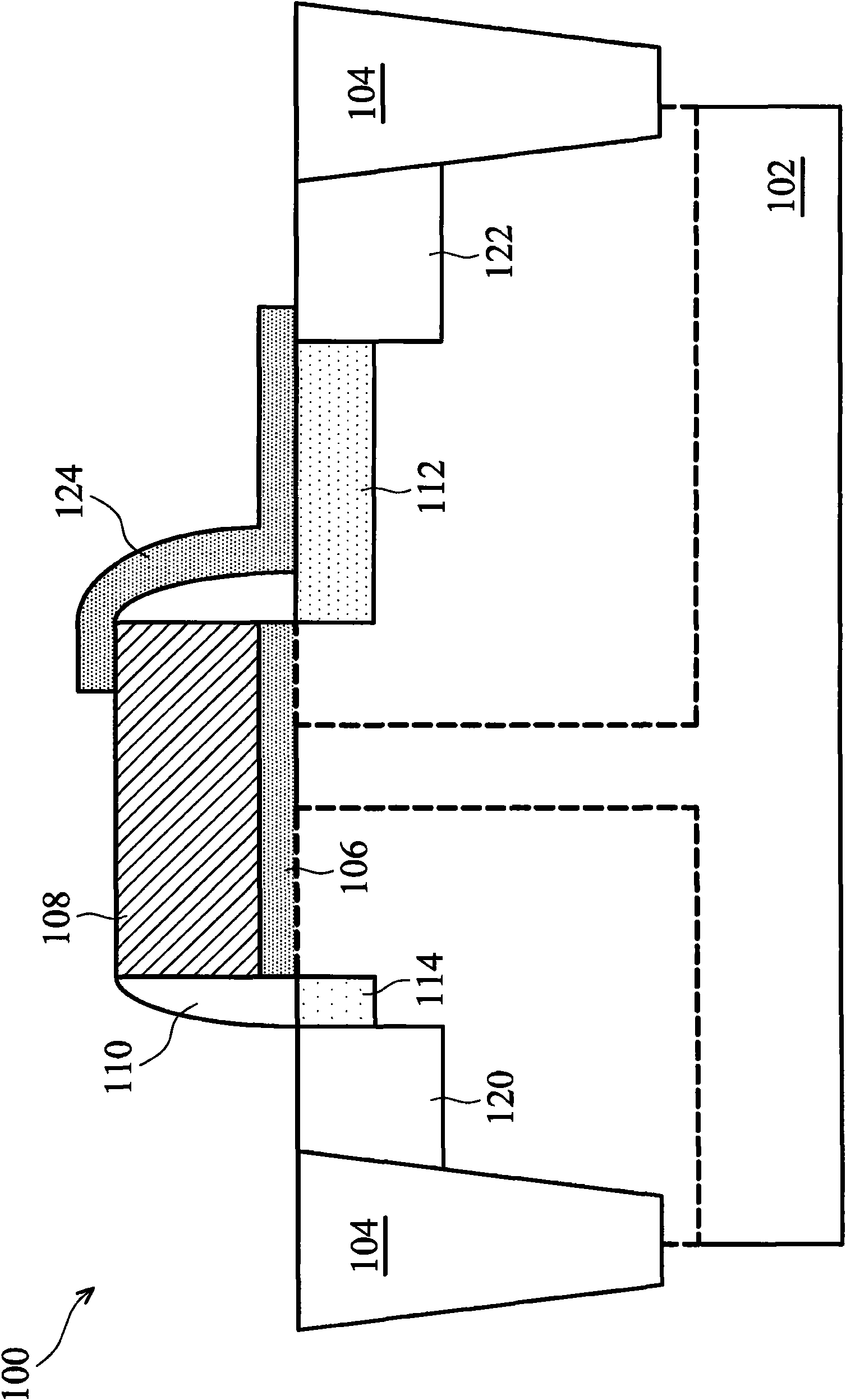

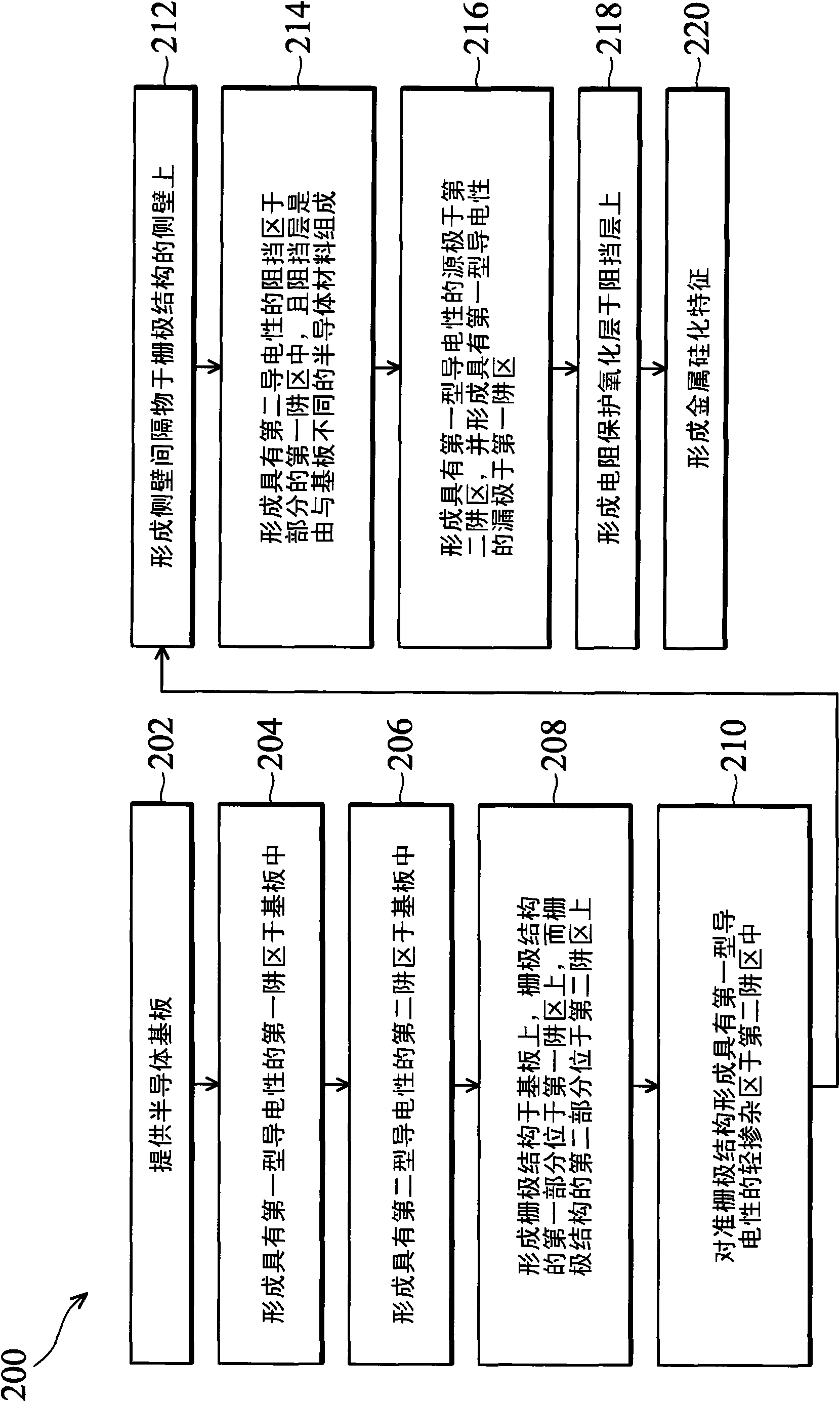

Semiconductor element and method for forming the same

ActiveCN102110714AHigh blocking voltageSemiconductor/solid-state device manufacturingSemiconductor devicesDopantSemiconductor device

The invention provides a semiconductor element and a method for forming the same. The semiconductor device includes a semiconductor substrate, a gate structure formed on the substrate, sidewall spacers formed on each side of the gate structure, a source and a drain formed in the substrate on either side of the gate structure, the source and drain having a first type of conductivity, a lightly doped region formed in the substrate and aligned with a side of the gate structure, the lightly doped region having the first type of conductivity, and a barrier region formed in the substrate and adjacent the drain. The barrier region is formed by doping a dopant of a second type of conductivity different from the first type of conductivity. The semiconductor element formed in the invention possesses high blocking voltage.

Owner:TAIWAN SEMICON MFG CO LTD

Power semiconductor device

ActiveUS7514780B2High blocking voltageEasy to operateSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceSemiconductor chip

A power semiconductor device, having a first semiconductor region, and a second semiconductor region; mounted with a first electrode pad on a semiconductor substrate main surface at the inside surrounded by the third semiconductor region, mounted in the second semiconductor region, and a multilayer substrate having first and second wiring layers, to take out an electrode of the semiconductor chip; joining the first wiring layer part for the first electrode, mounted on the multilayer substrate, in a region opposing to the semiconductor substrate main surface at the inside surrounded by the third semiconductor region, and the first electrode pad, by a conductive material; joining the first wiring layer part for the first electrode, and the second wiring layer at a conductive part; and extending the second wiring layer to the outside of a region opposing the semiconductor substrate main surface at the inside surrounded by the third semiconductor region.

Owner:HITACHI LTD

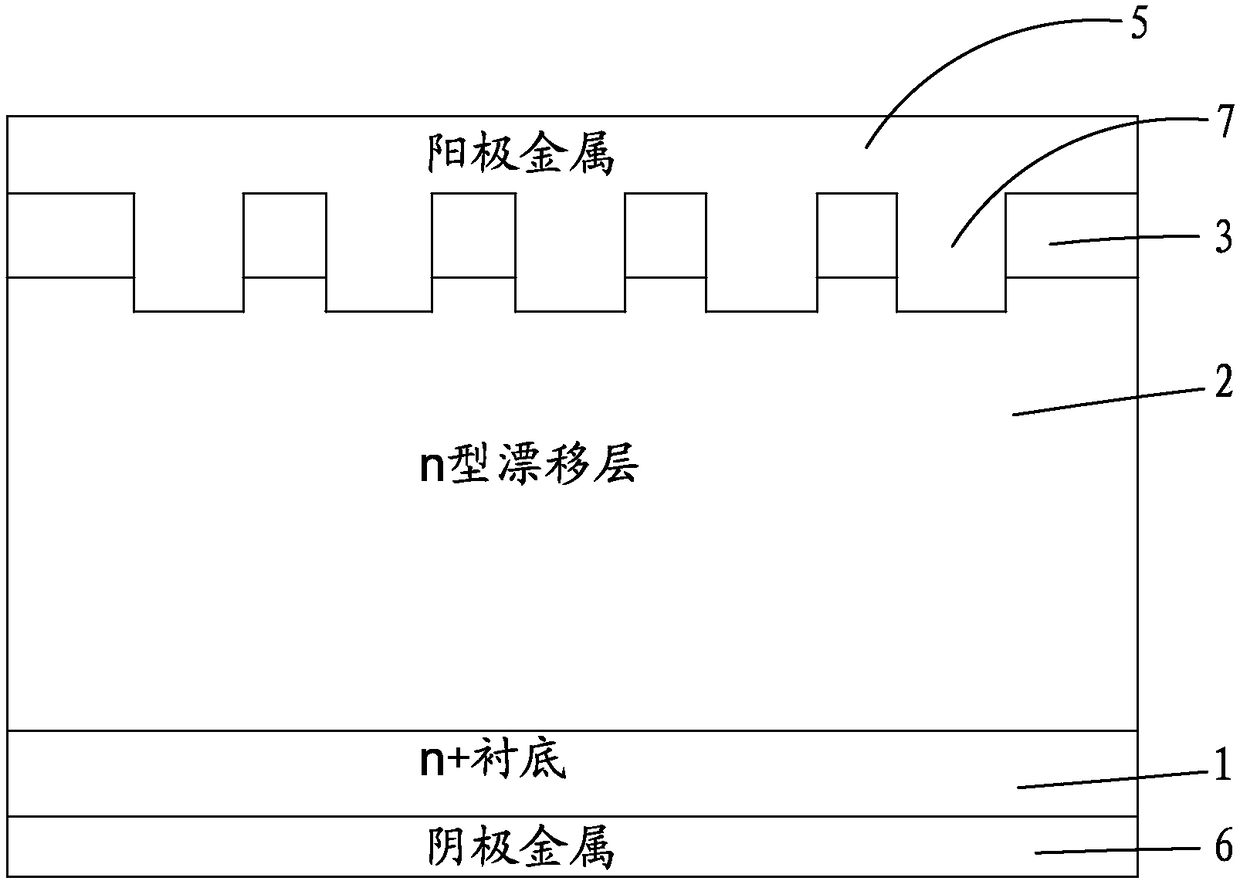

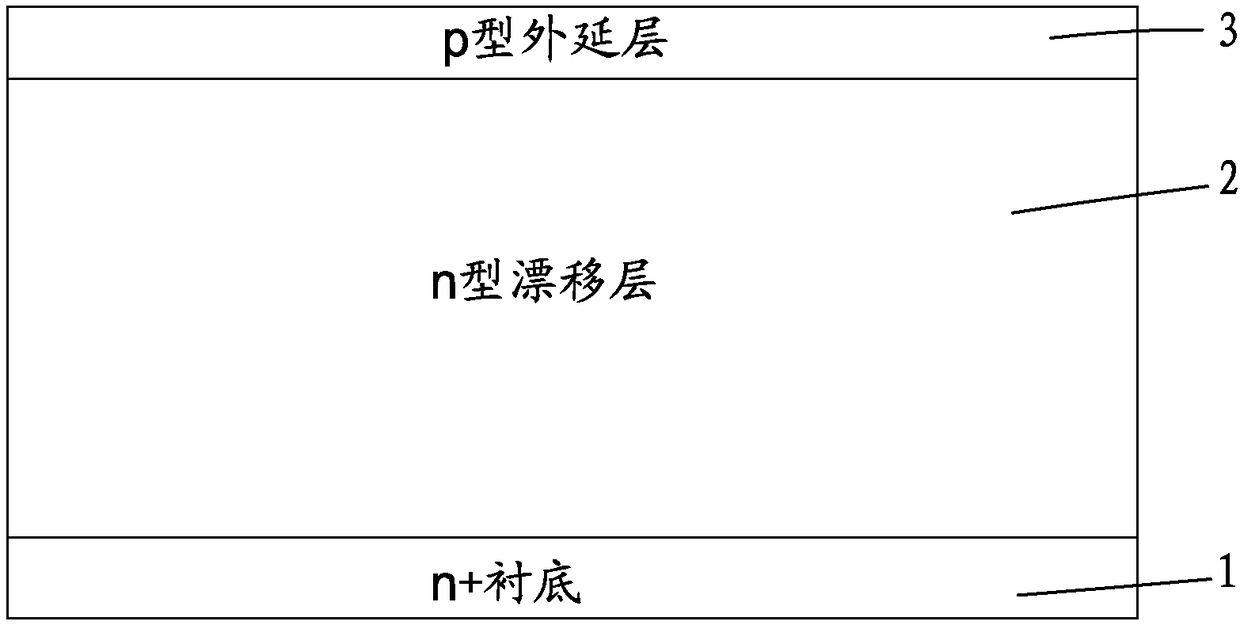

Silicon carbide Schottky diode and preparation method thereof

PendingCN108565295AImprove featuresIncreased current conduction areaSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsSchottky diode

The present invention provides a silicon carbide Schottky diode comprising anode metal, a p-type epitaxial layer, an n-type drift layer, an n+ substrate, and cathode metal which are disposed successively from top to bottom, wherein the p-type epitaxial layer is provided a plurality of trenches passing through the p-type epitaxial layer; and a side of the anode metal is provided with a plurality ofprotrusions matching the trenches. The present invention also provides a preparation method of the silicon carbide Schottky diode. The anode contact area of the Schottky diode is increased and the on-resistance of a device is reduced by using the trench structure on the basis of ensuring the blocking voltage.

Owner:GLOBAL POWER TECH CO LTD