Silicon carbide LDMOS device suitable for monolithic integration and manufacturing method thereof

A technology of monolithic integration and silicon carbide, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of high price of semi-insulating substrates and difficult preparation of P-type substrates, and achieve low cost and low cost. The effect of on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

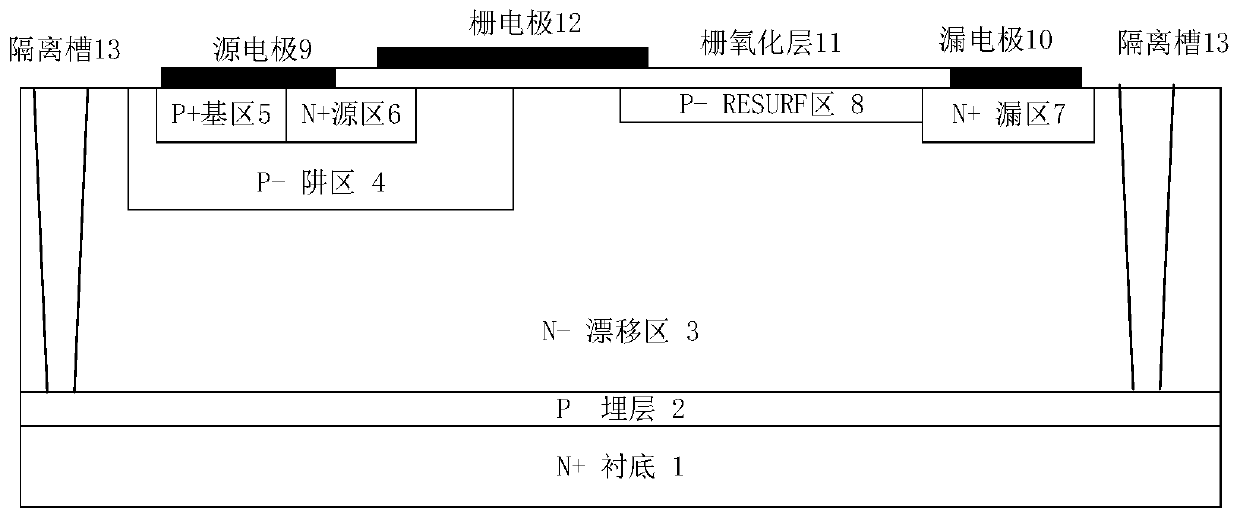

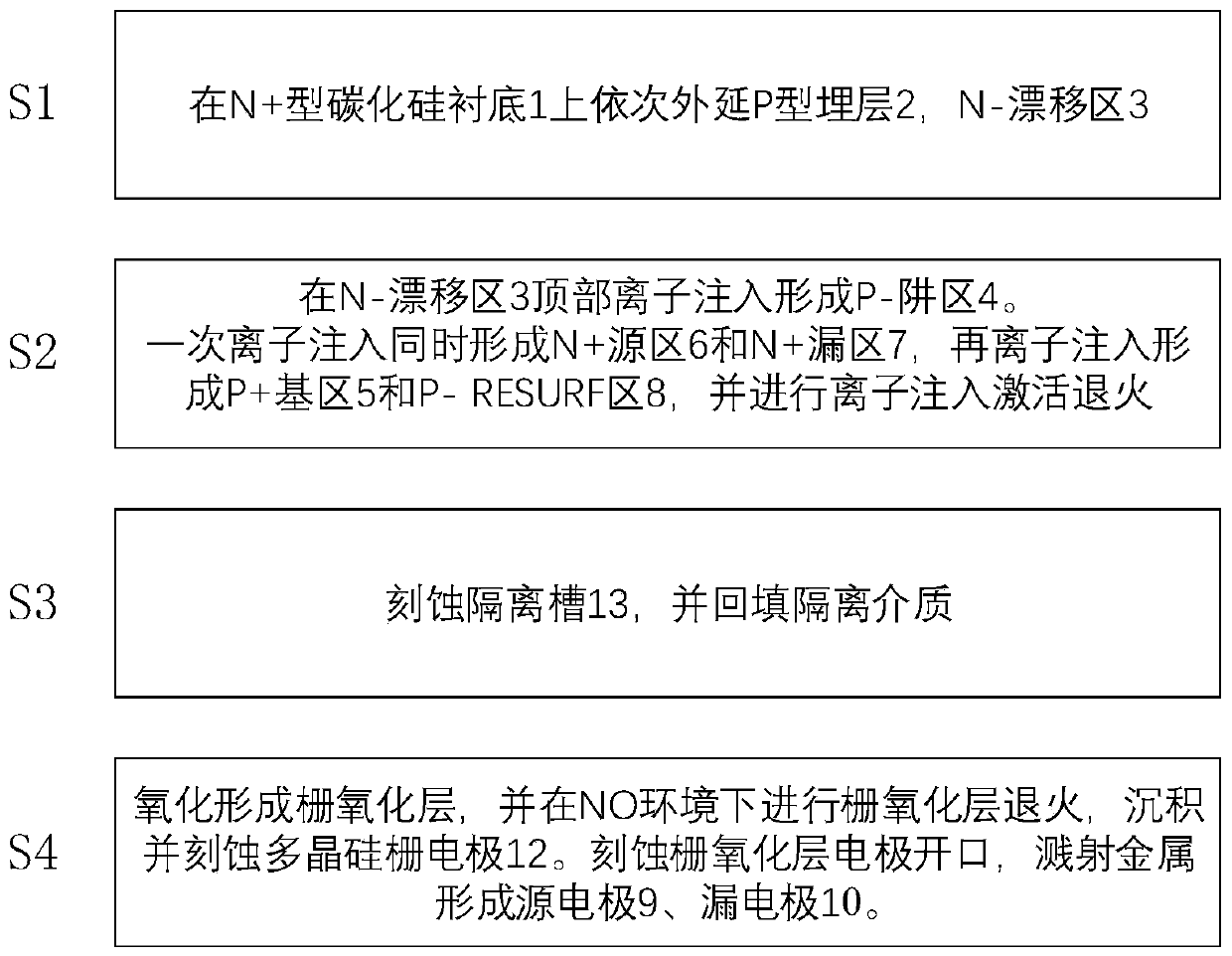

[0030] An aspect of the embodiments of the present invention provides a silicon carbide LDMOS device structure, figure 1 It is a schematic diagram of the structure of the silicon carbide LDMOS device of the present invention. Such as figure 1 As shown, the device structure includes an N-type highly doped substrate 1 , above which is a P-type epitaxial isolation buried layer 2 and an N-type lightly doped drift region 3 . On top of the drift region 3, a P-well region 4, a P+ base region 5, an N+ source region 6, a P-RESURF region 8 and an N+ drain region 7 are distributed. Wherein, the P+ base region 5 and the N+ source region 6 are located inside the P-well region 4, and there is a gap with a certain width between the N+ drain region and the P-well region, and the gap width depends on the blocking voltage set in the device design. Between the P- well region and the N+ drain region is the P-RESURF region 8 , which is close to the N+ drain region 7 . Above the drift region 3 i...

Embodiment 2

[0048] The embodiment of the present invention provides another basic structure of silicon carbide LDMOS, the basic structure of which is as follows Figure 8 shown. The difference from the structure provided in Embodiment 1 is that the P-RESURF region 8 is replaced by the segmented P-region 8, which can obtain a more uniform lateral field drop, improve the blocking capability of the device, and reduce the on-resistance of the device.

Embodiment 3

[0050] The embodiment of the present invention provides a basic structure of a silicon carbide LDMOS, the basic structure of which is as follows Figure 9 shown. The difference from the structure provided in Embodiment 1 is that the P-type buried layer is divided into two parts: a highly doped P+ buried layer 22 and a lightly doped P− buried layer 21 . The doping concentration of P-buried layer 21 is 1×10 14 cm -3 to 1×10 16 cm -3 , the doping concentration of the P+ buried layer 22 is 1×10 14 cm -3 to 1×10 16 cm -3 , which can increase the breakdown voltage of the drain liner in the blocking state.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More