Patents

Literature

61results about How to "Reduced injection efficiency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

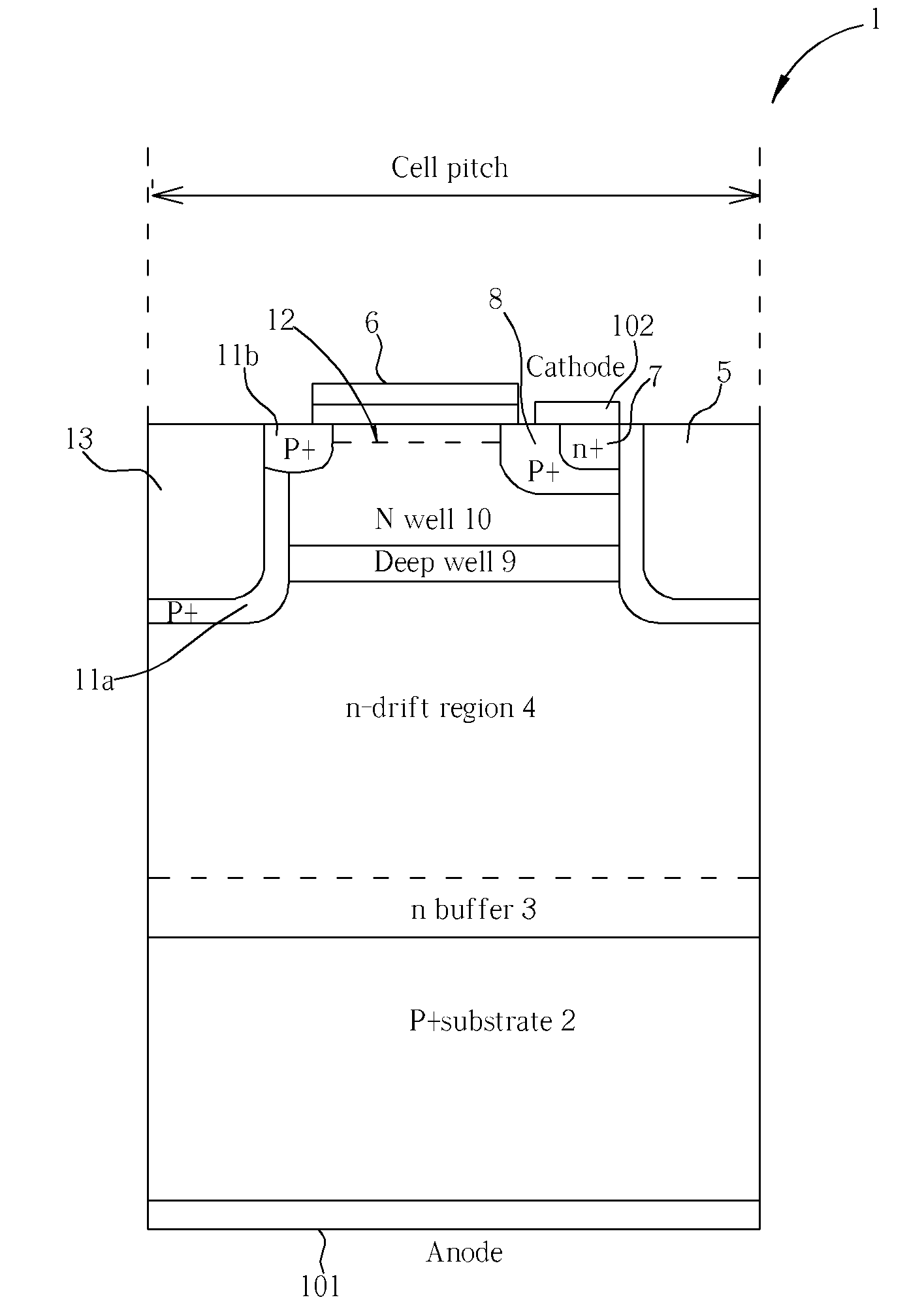

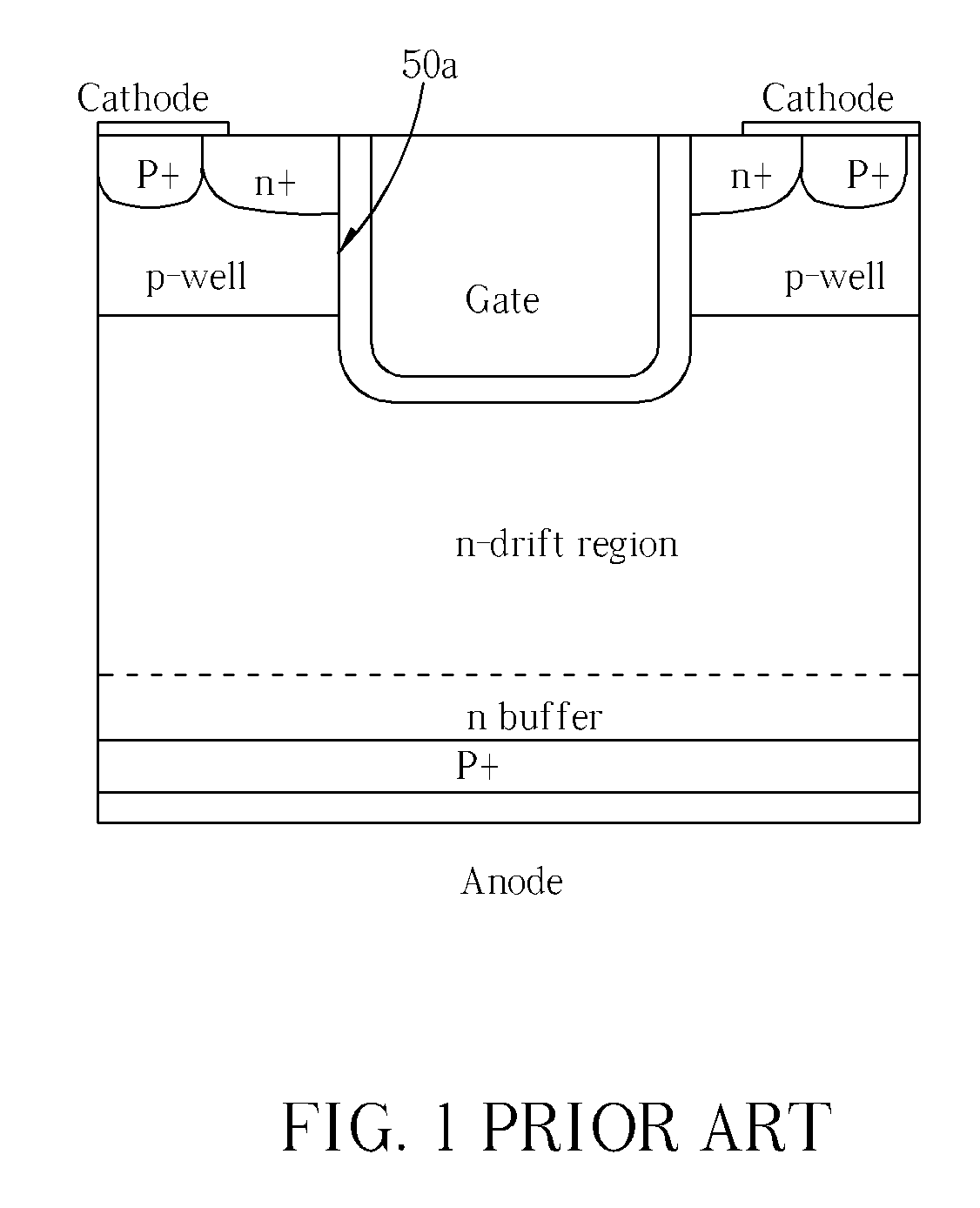

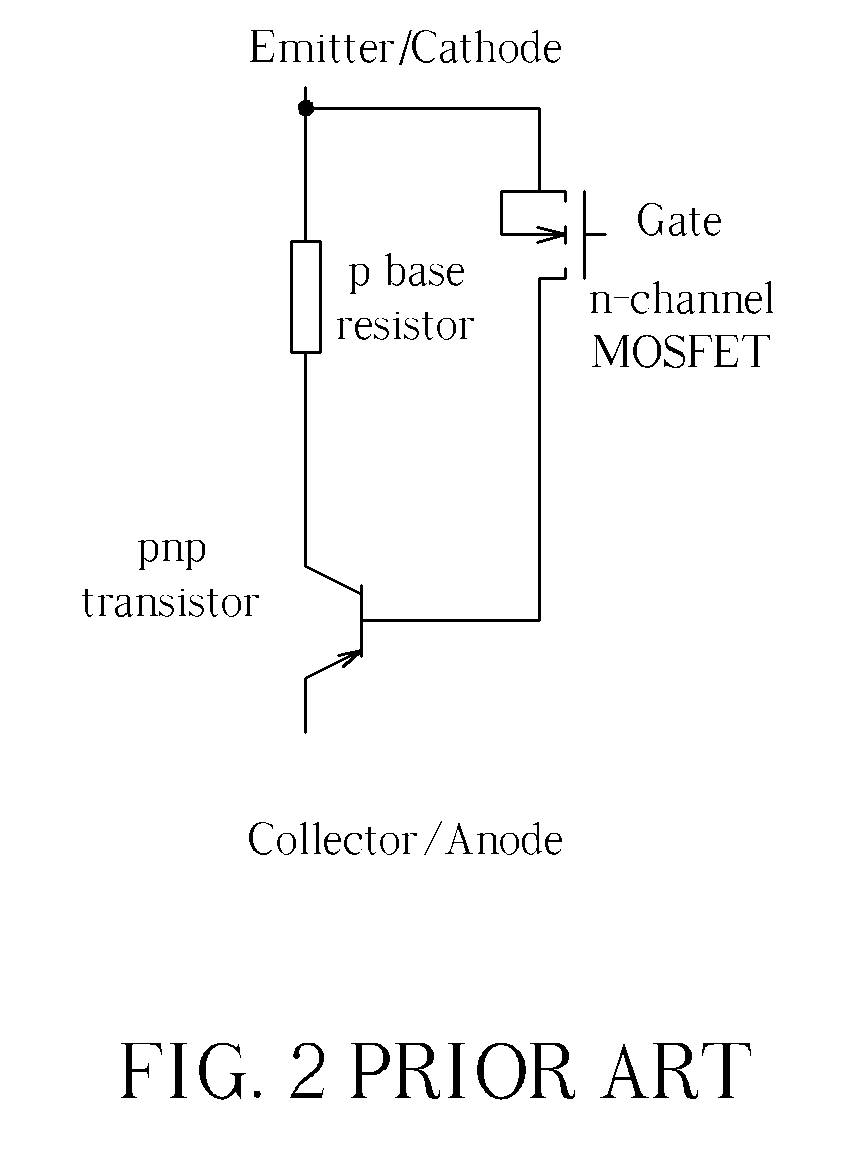

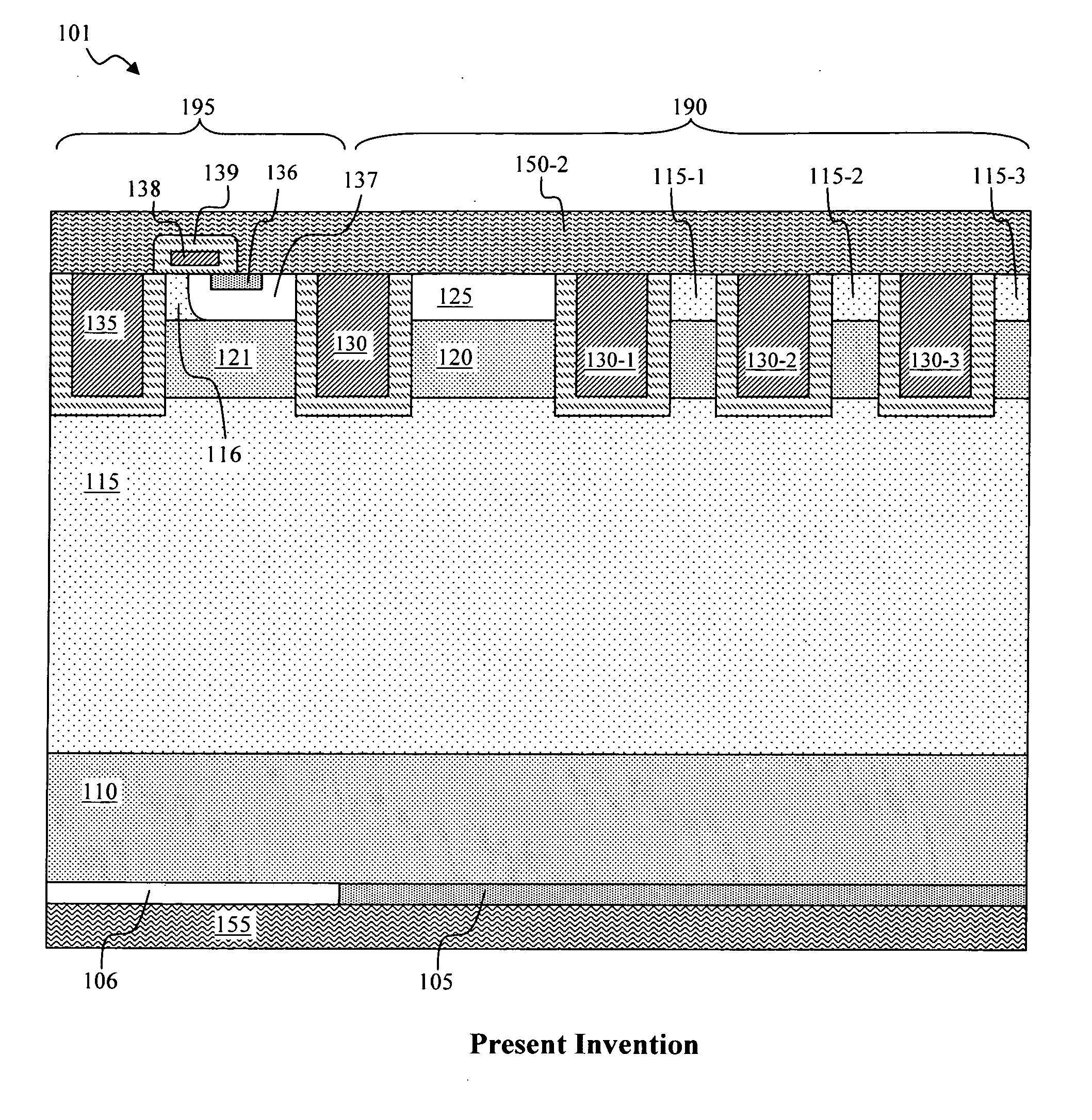

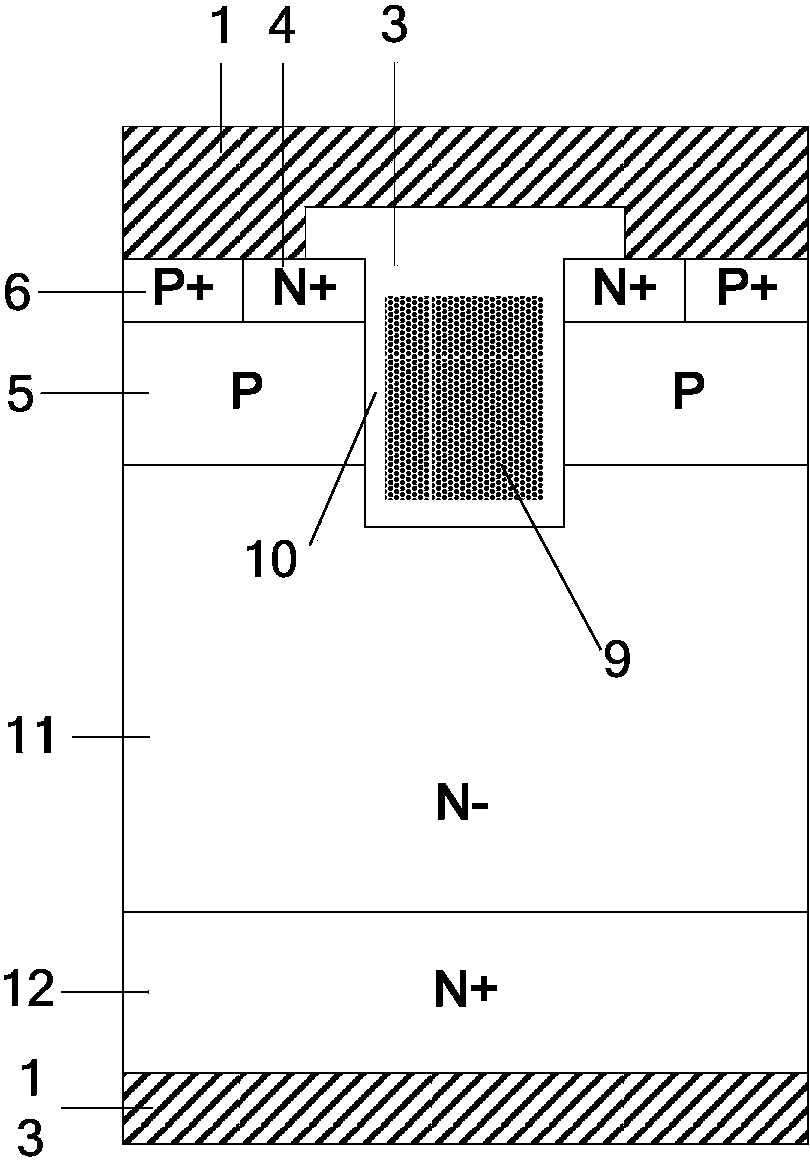

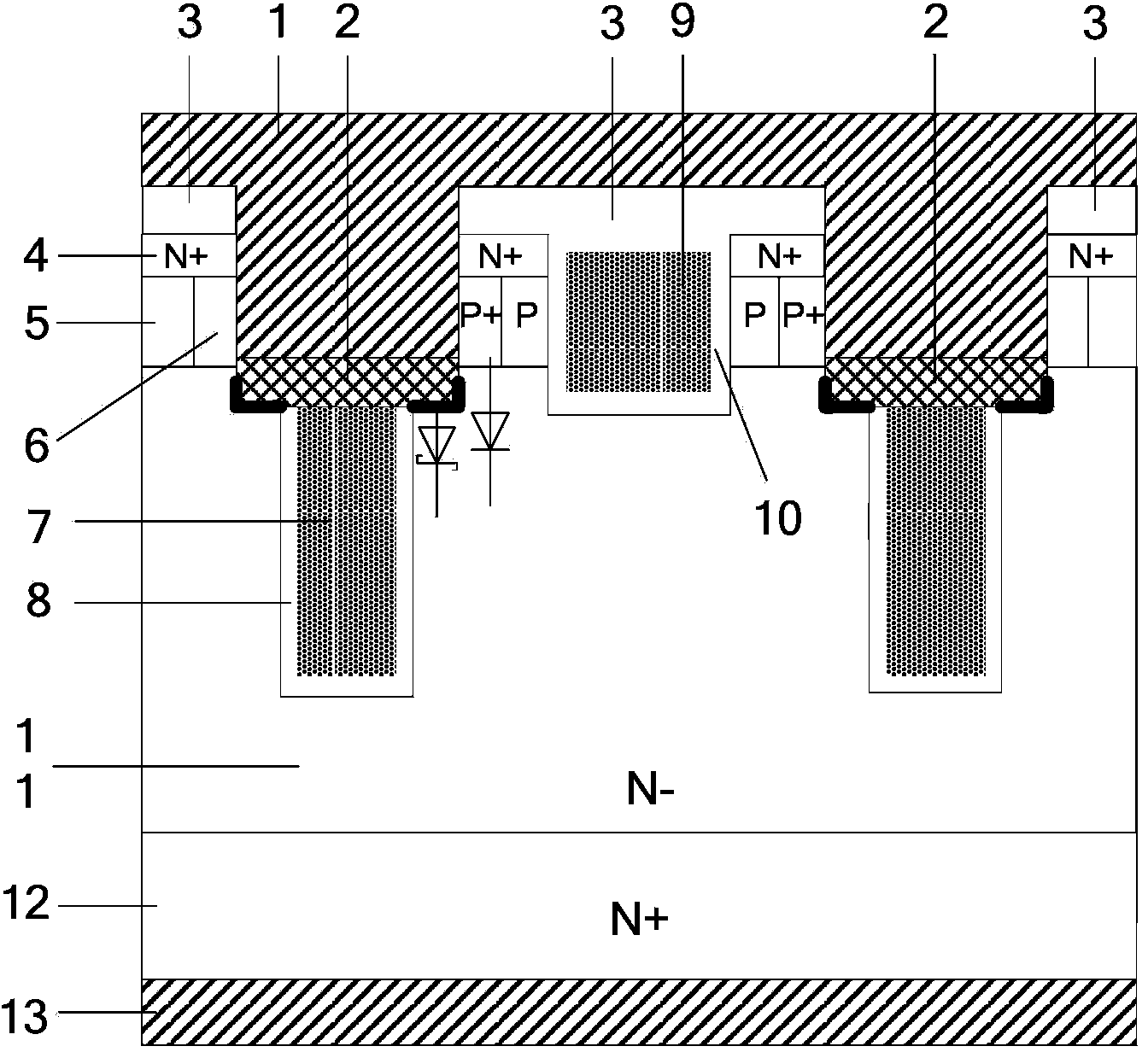

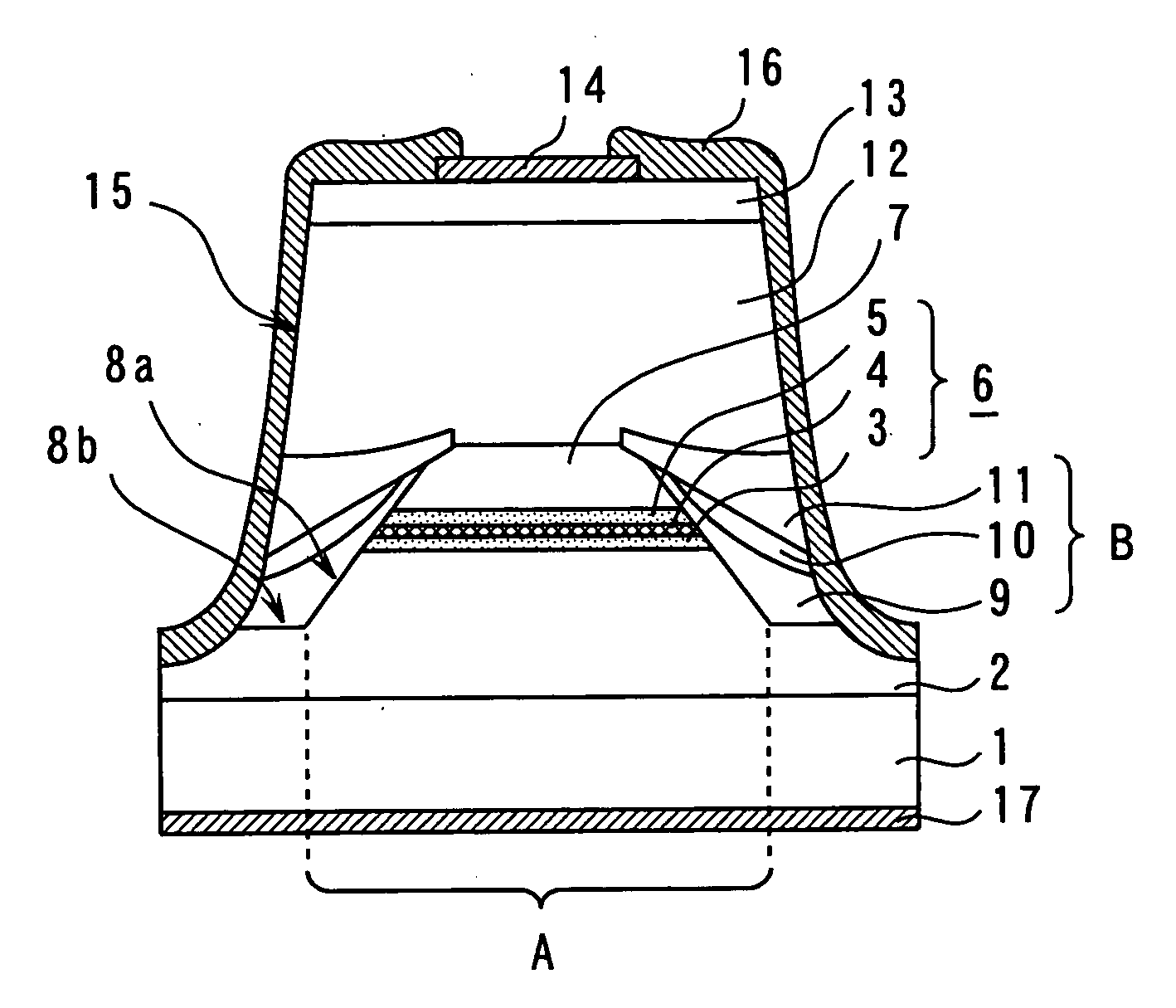

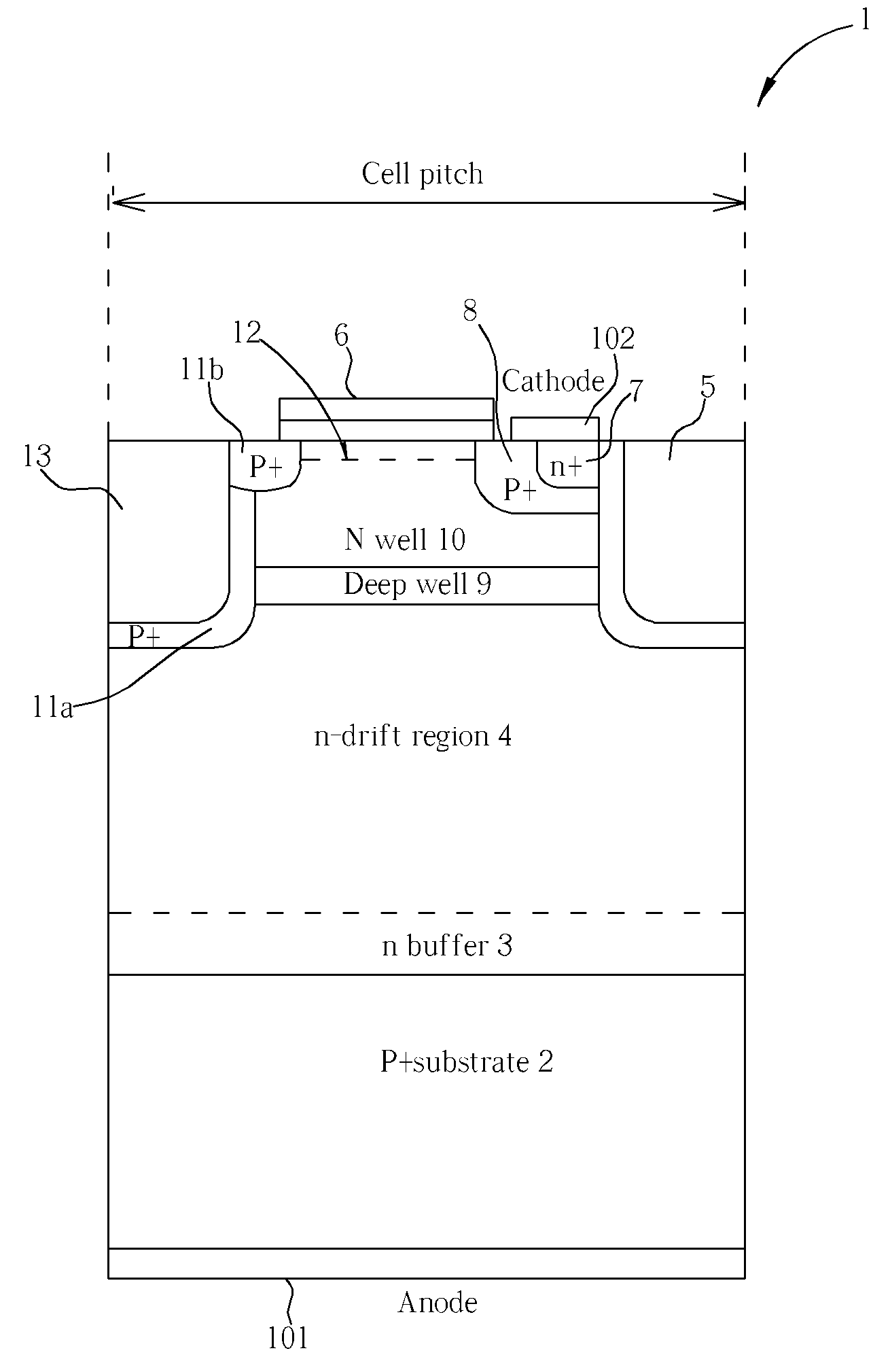

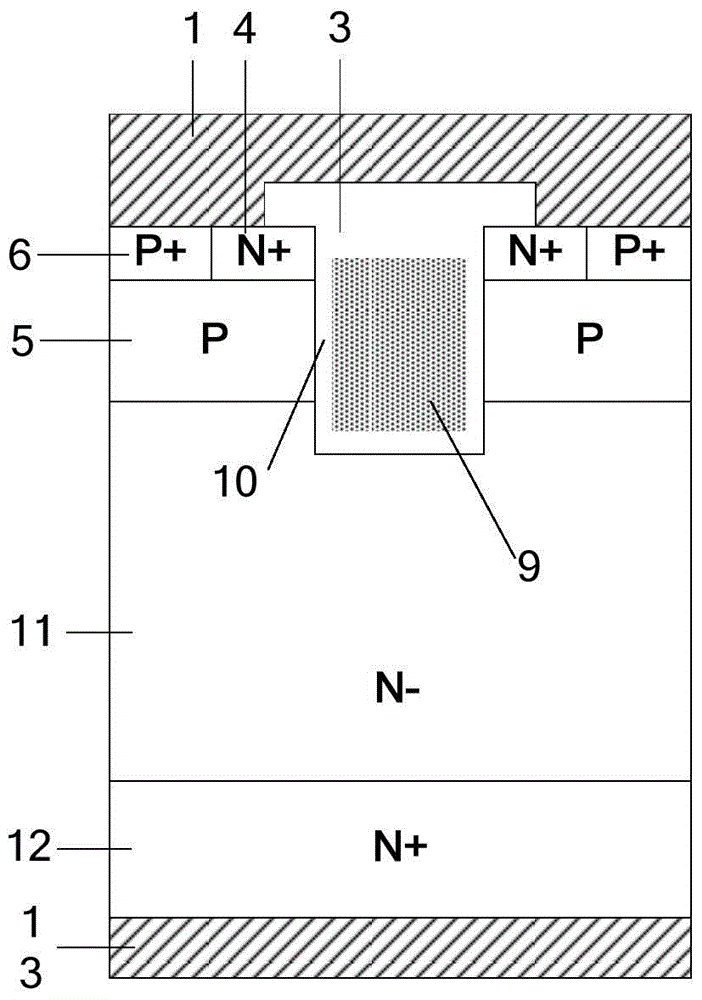

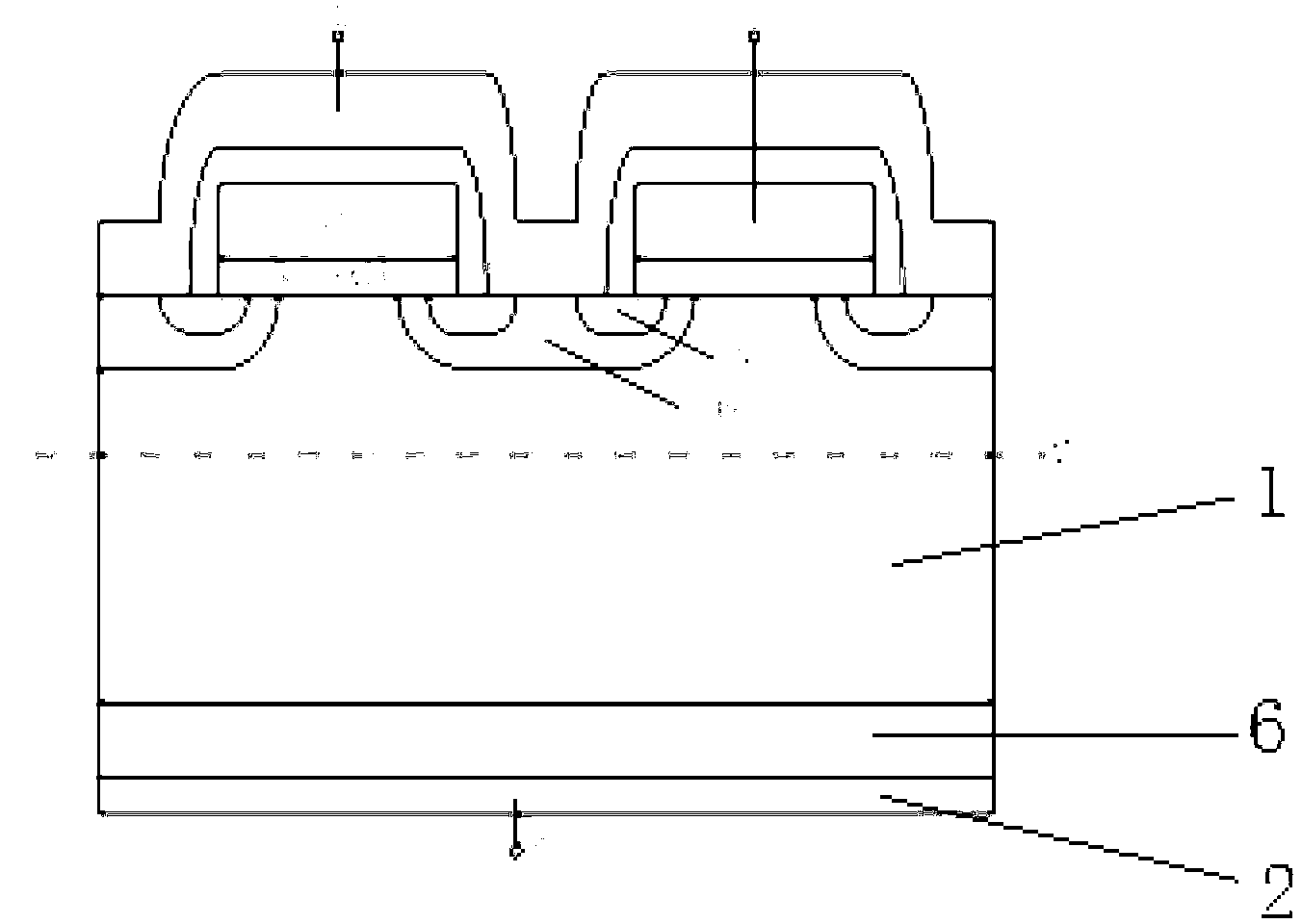

Double gate insulated gate bipolar transistor

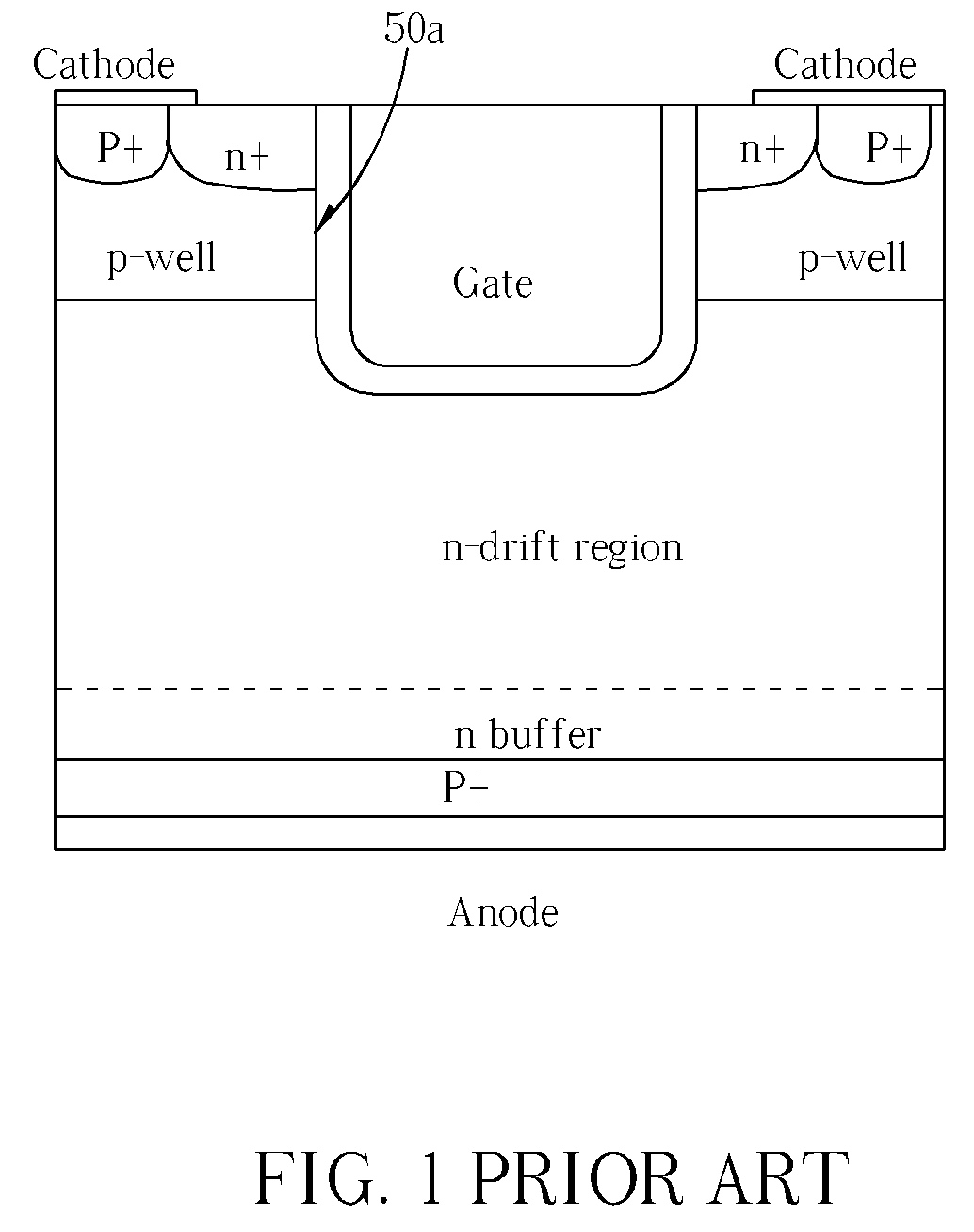

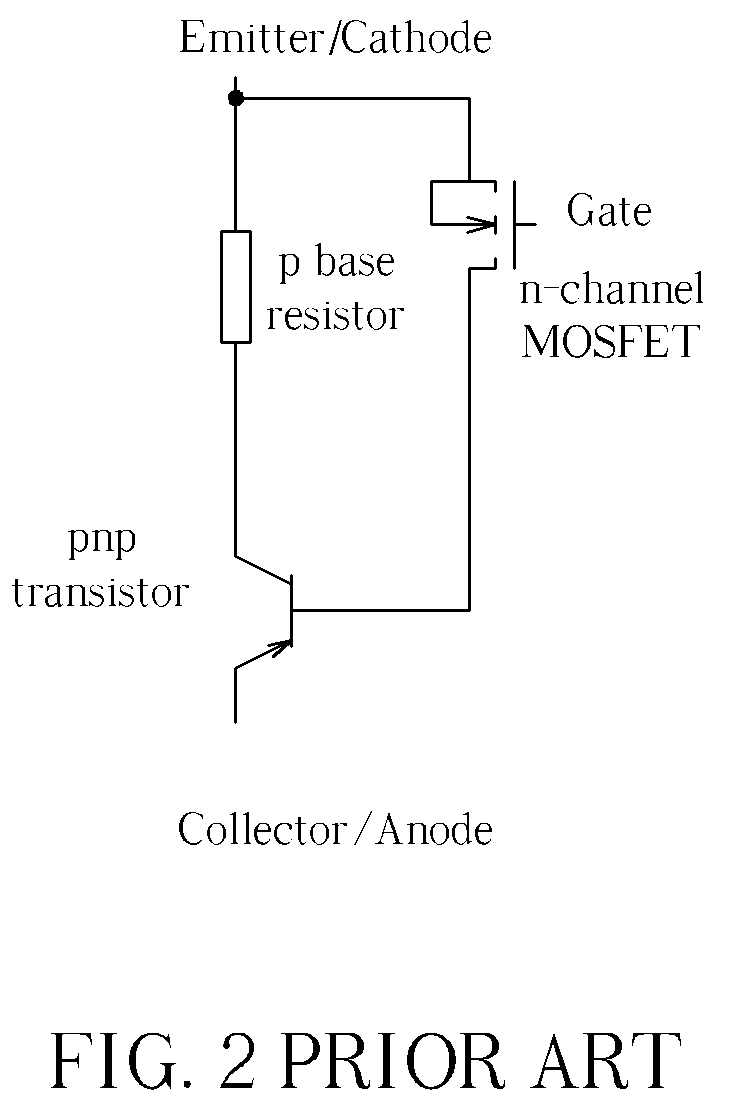

InactiveUS20090008674A1Reduce the number of holesReduce transportationTransistorSolid-state devicesParasitic bipolar transistorEngineering

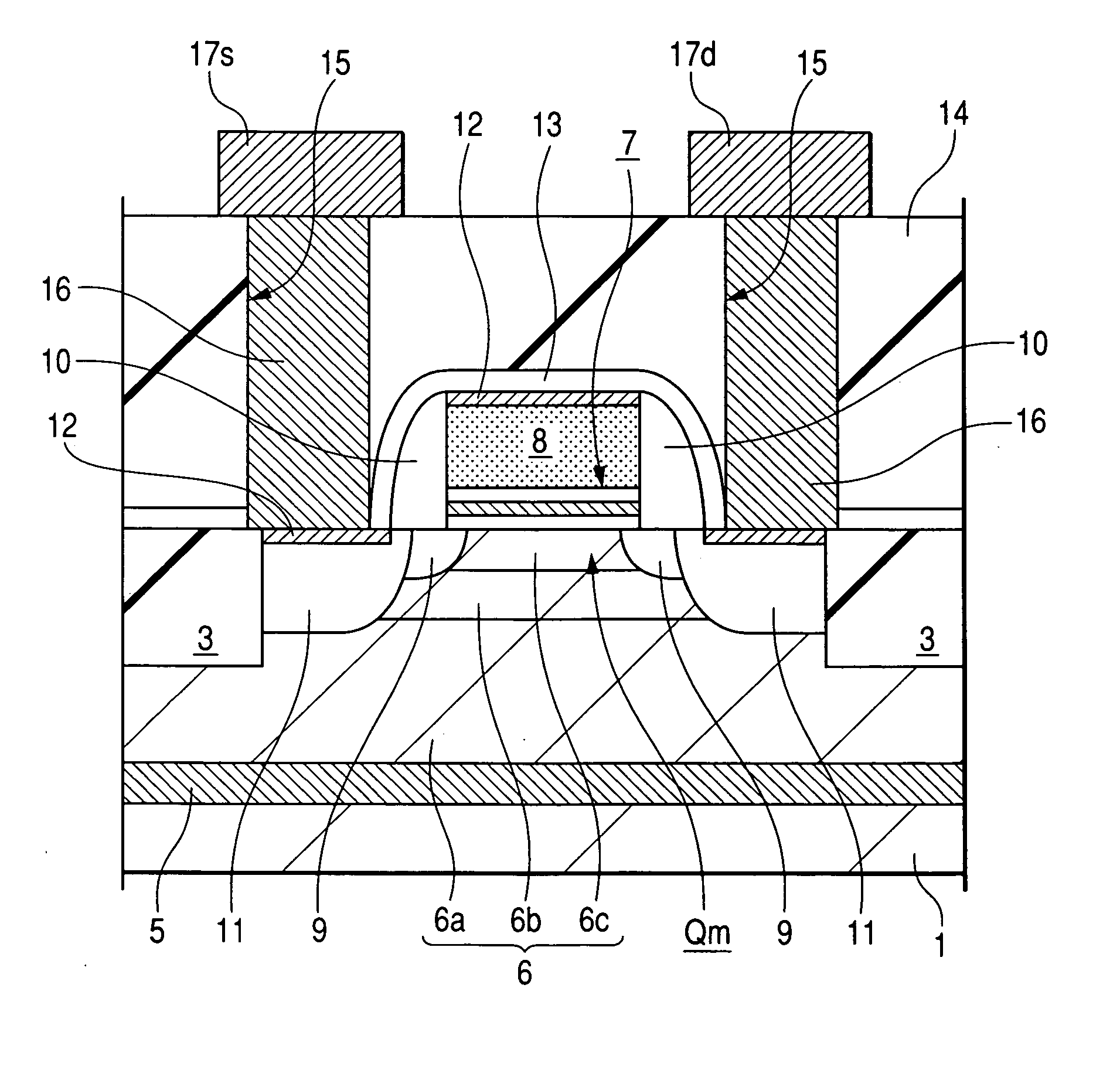

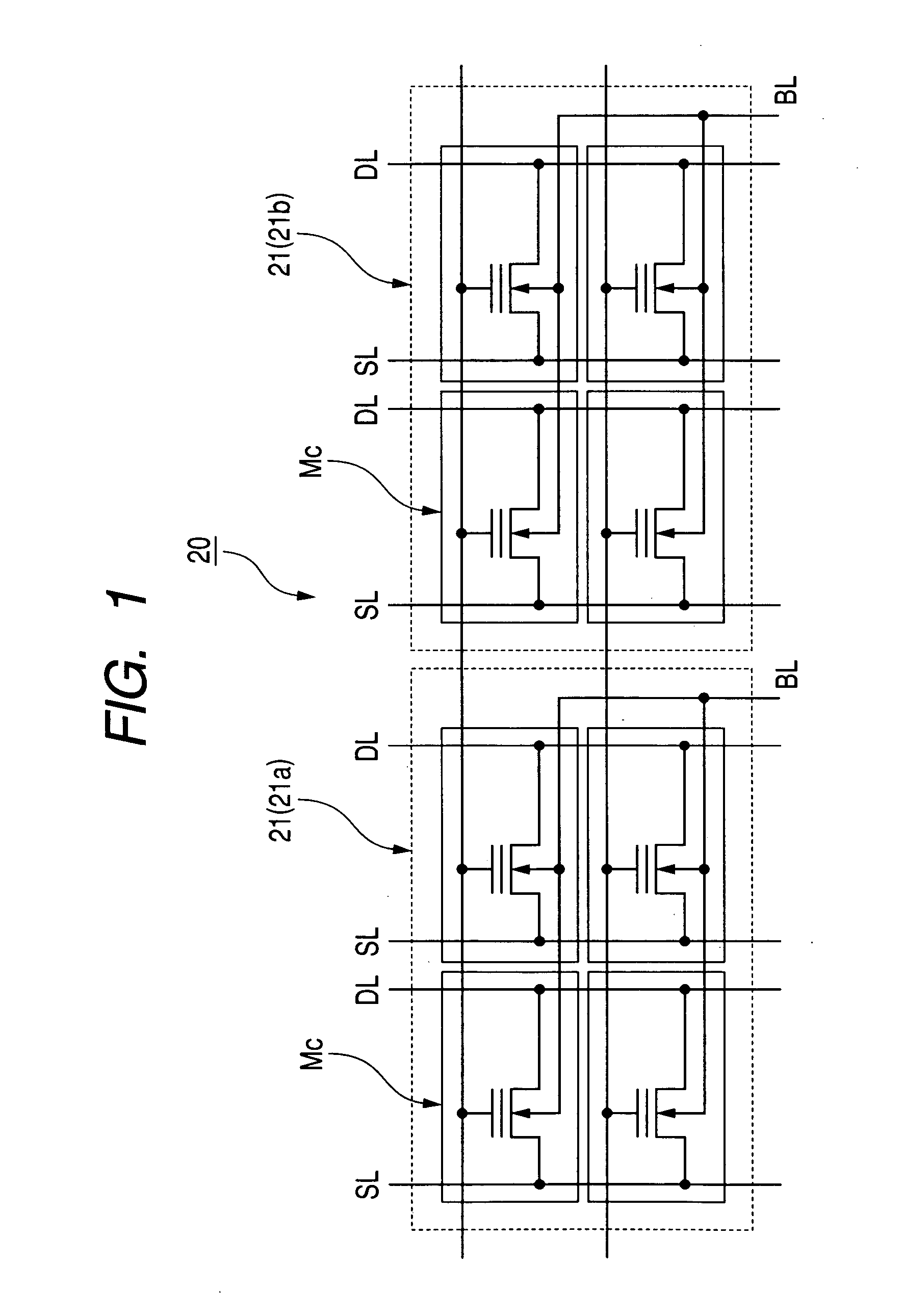

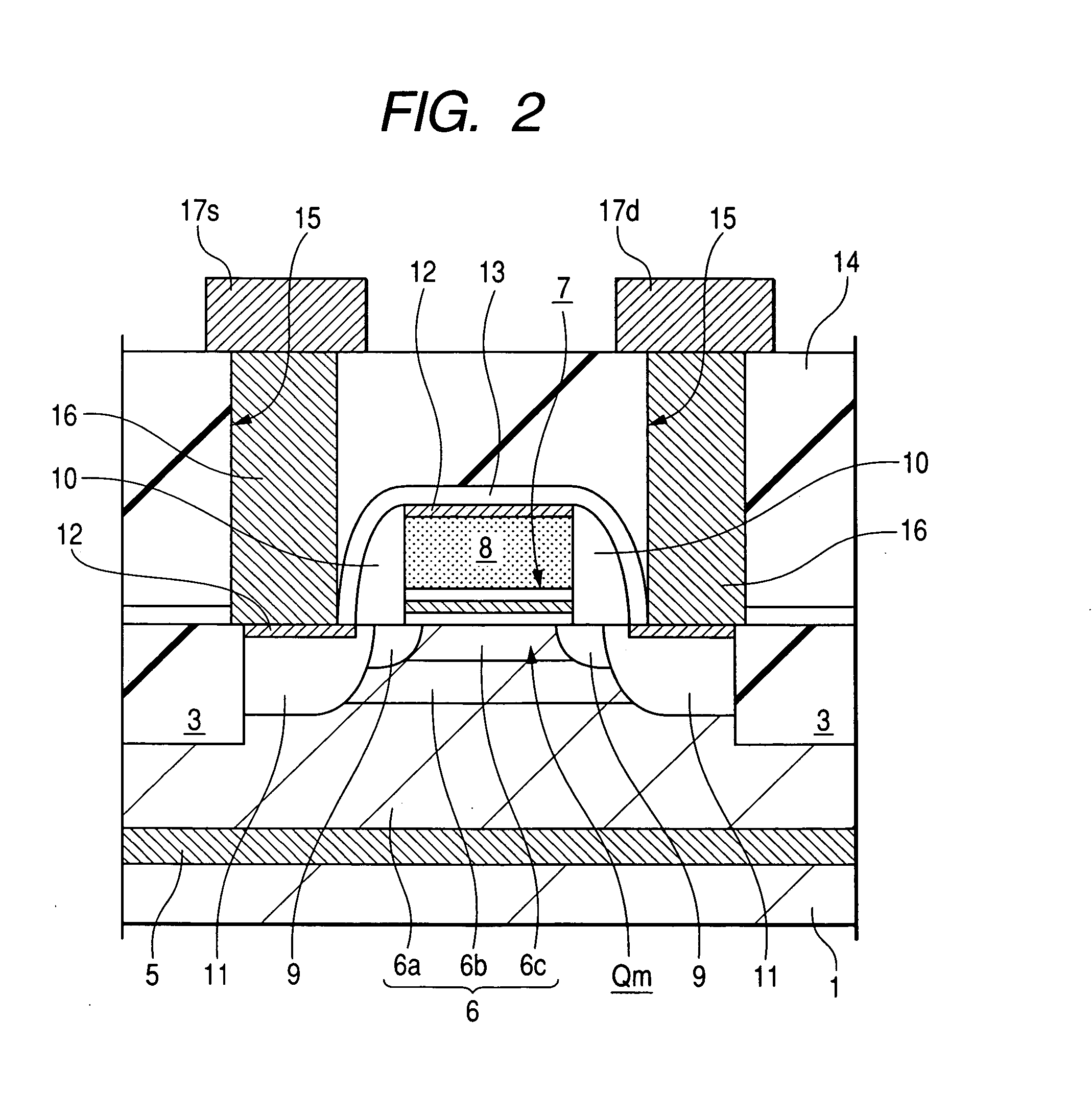

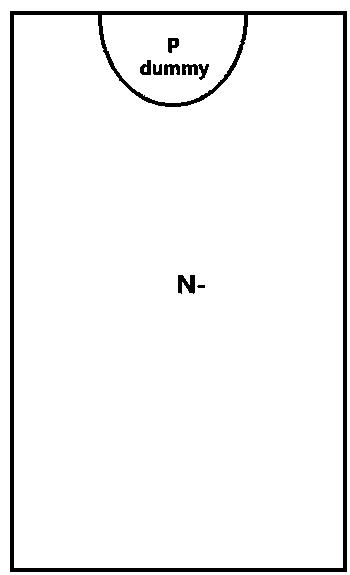

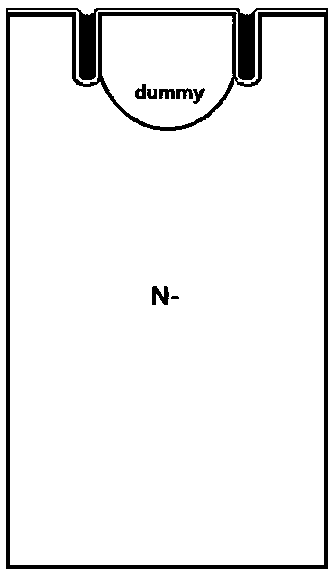

Double gate IGBT having both gates referred to a cathode in which a second gate is for controlling flow of hole current. In on-state, hole current can be largely suppressed. While during switching, hole current is allowed to flow through a second channel. Incorporating a depletion-mode p-channel MOSFET having a pre-formed hole channel that is turned ON when 0V or positive voltages below a specified threshold voltage are applied between second gate and cathode, negative voltages to the gate of p-channel are not used. Providing active control of holes amount that is collected in on-state by lowering base transport factor through increasing doping and width of n well or by reducing injection efficiency through decreasing doping of deep p well. Device includes at least anode, cathode, semiconductor substrate, n− drift region, first & second gates, n+ cathode region; p+ cathode short, deep p well, n well, and pre-formed hole channel.

Owner:ANPEC ELECTRONICS CORPORATION

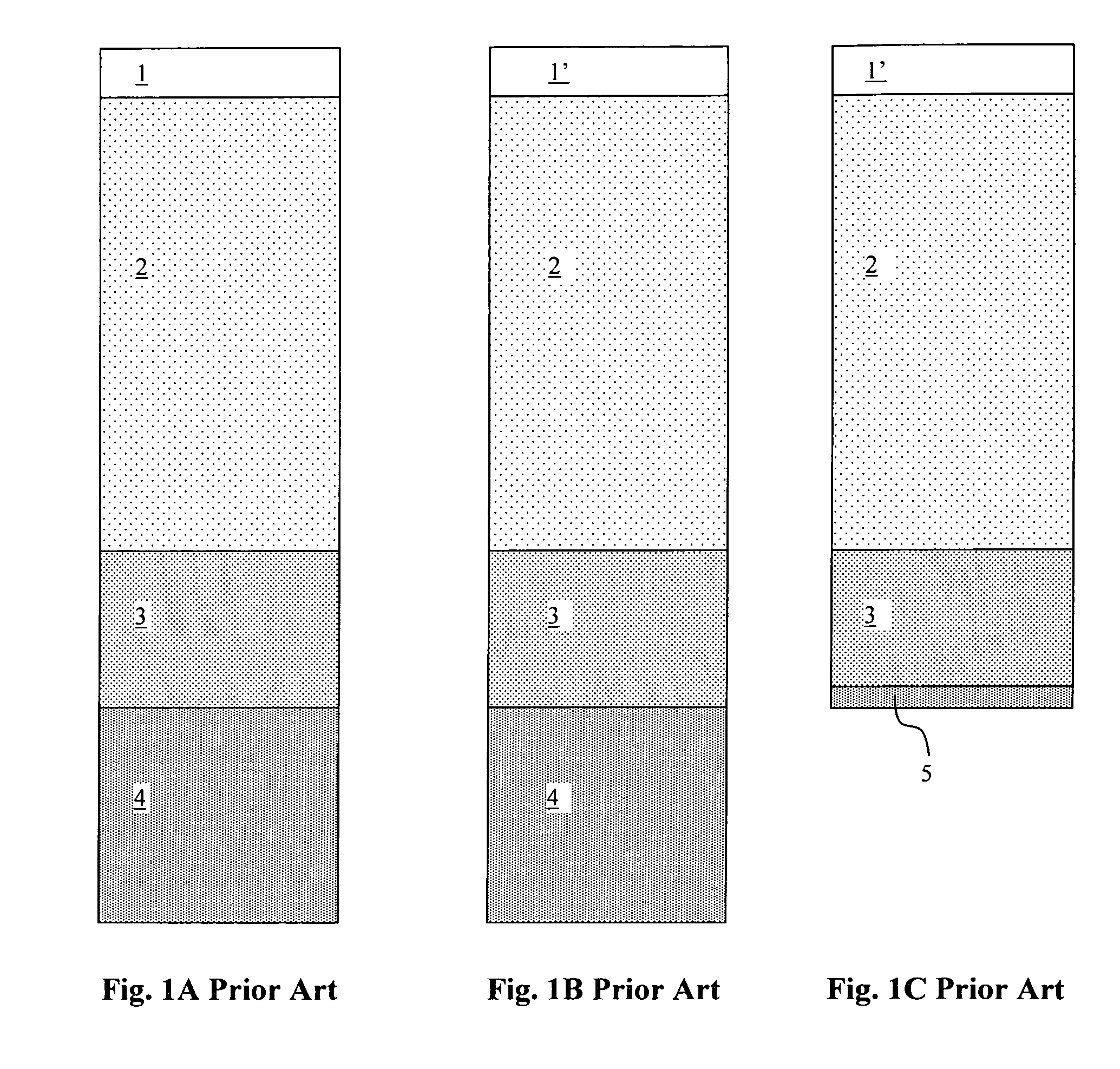

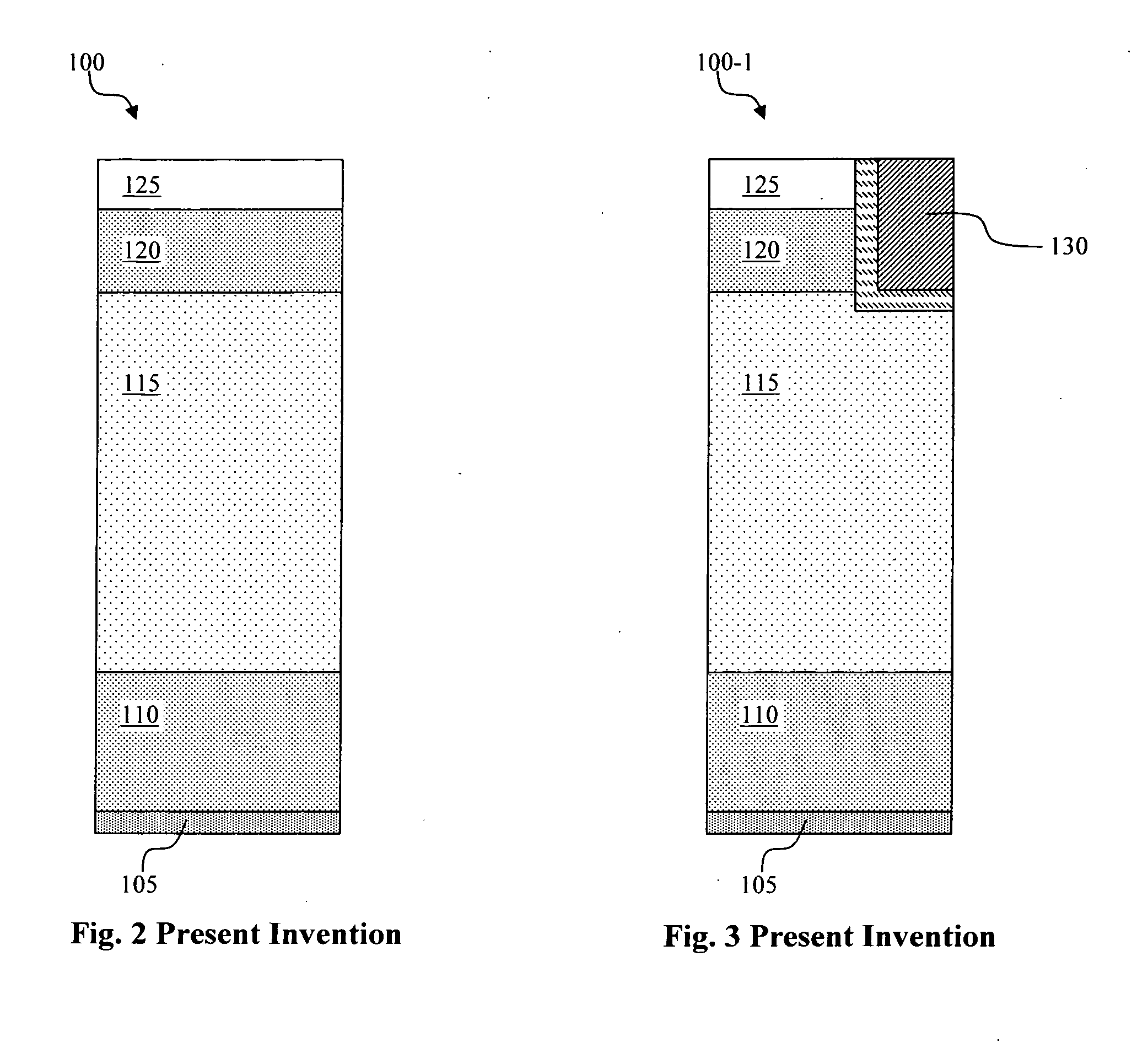

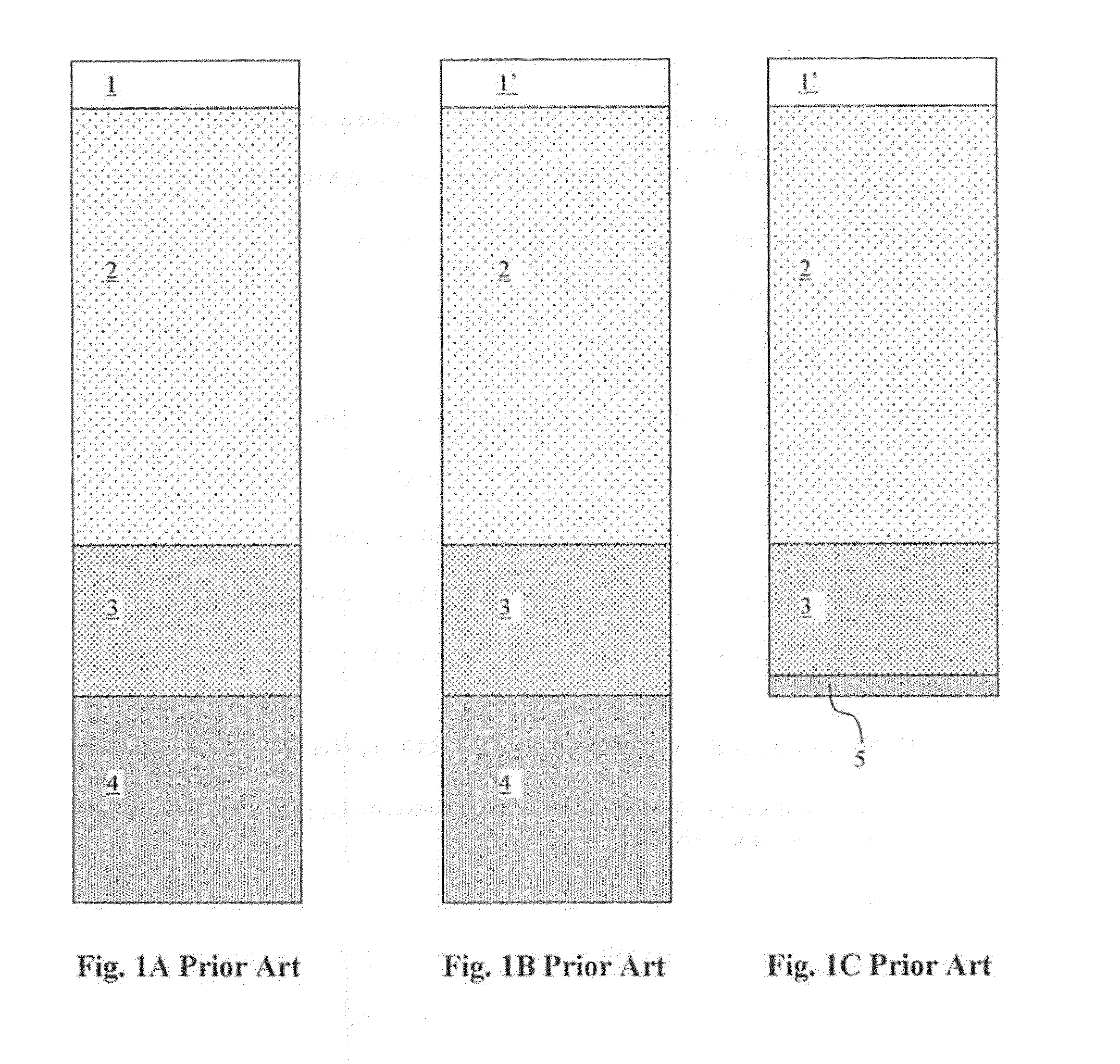

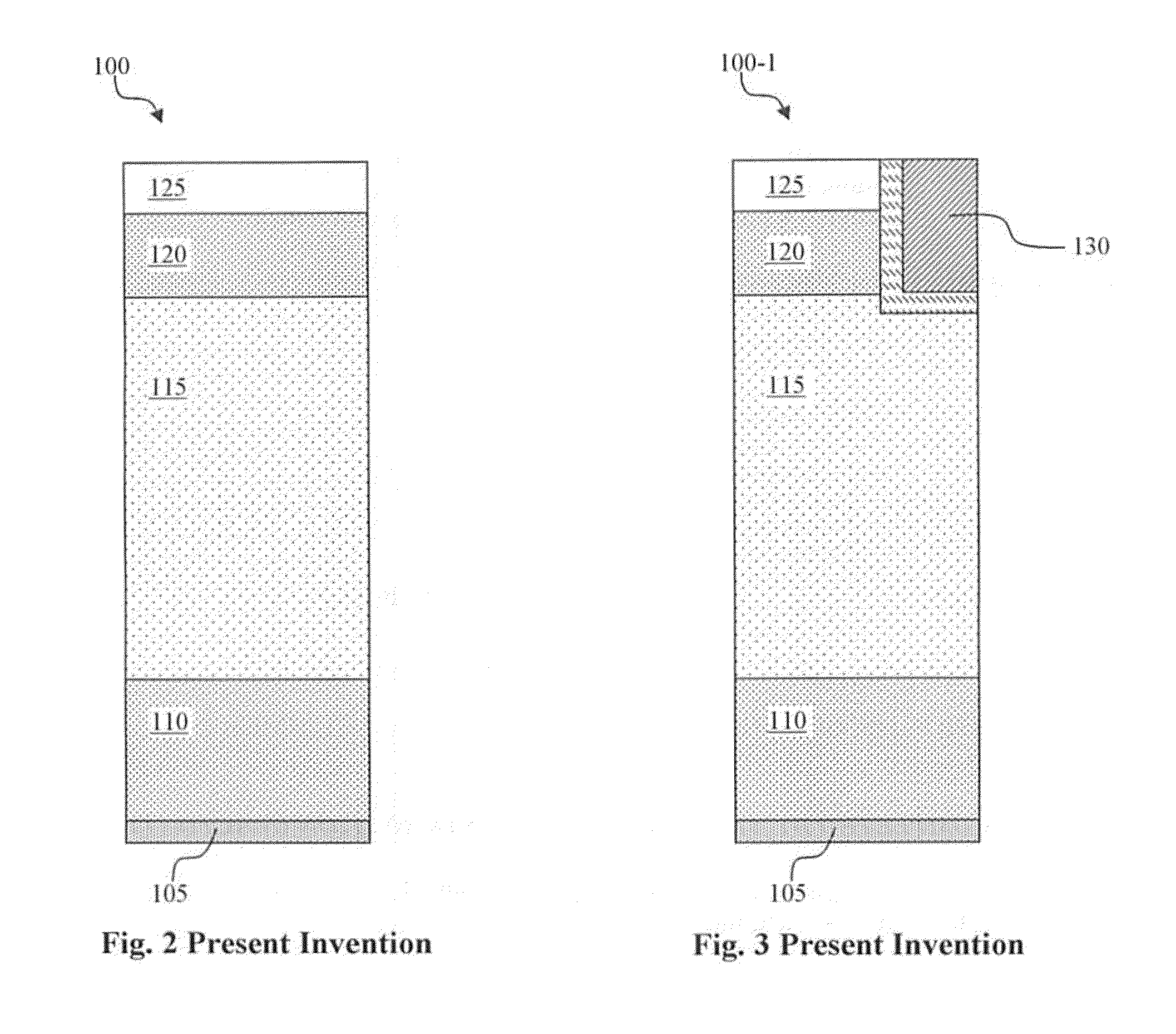

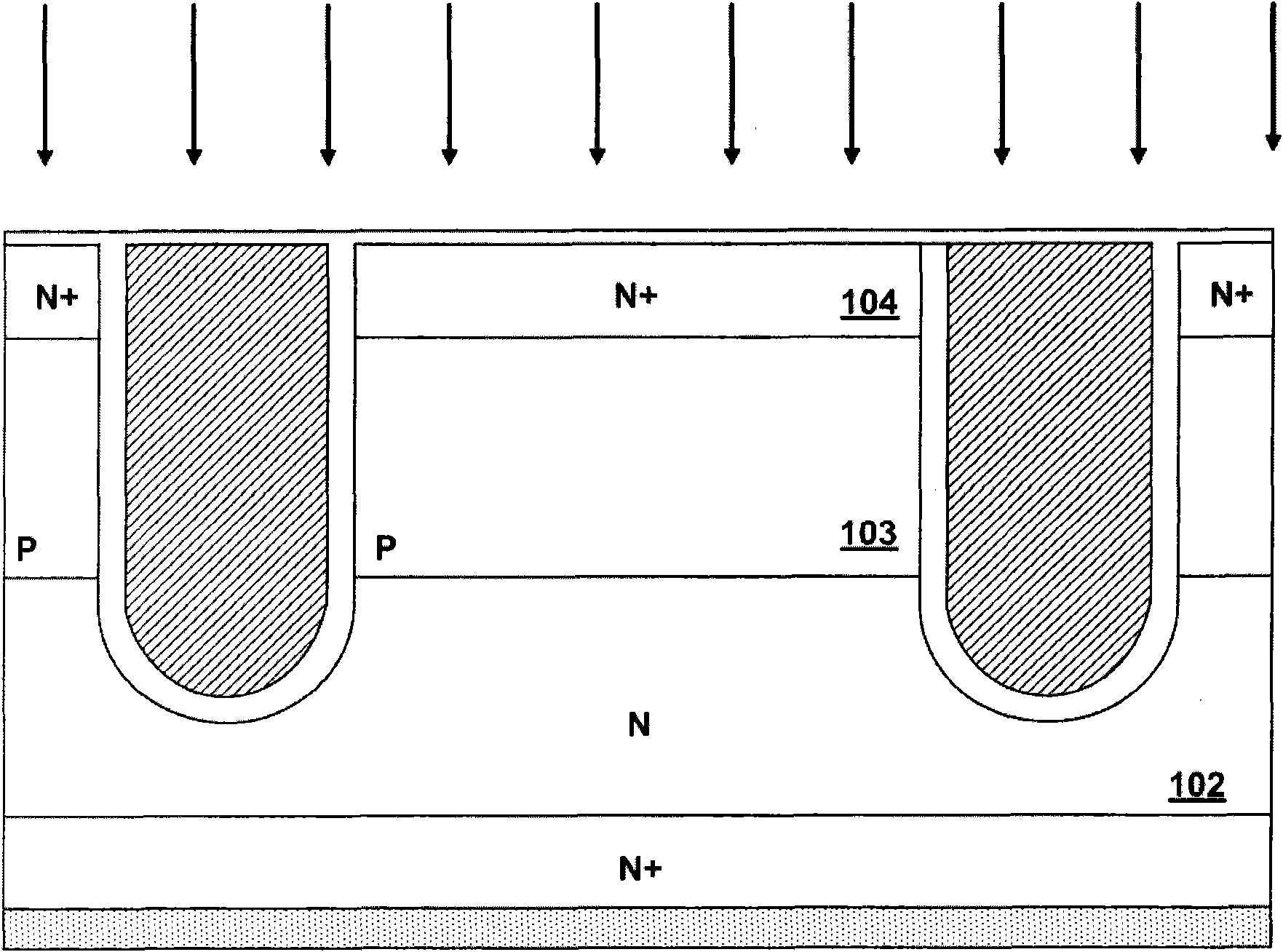

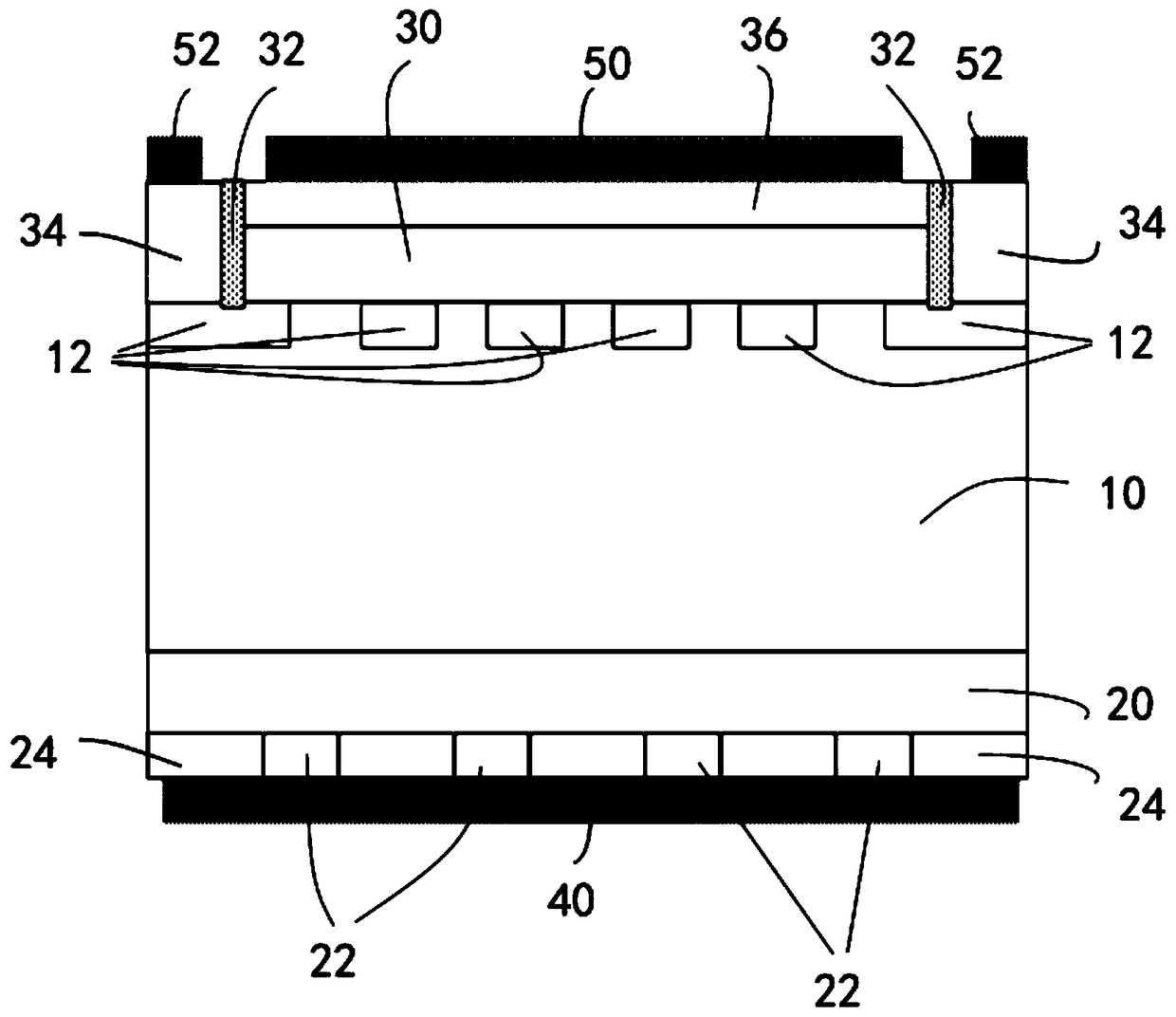

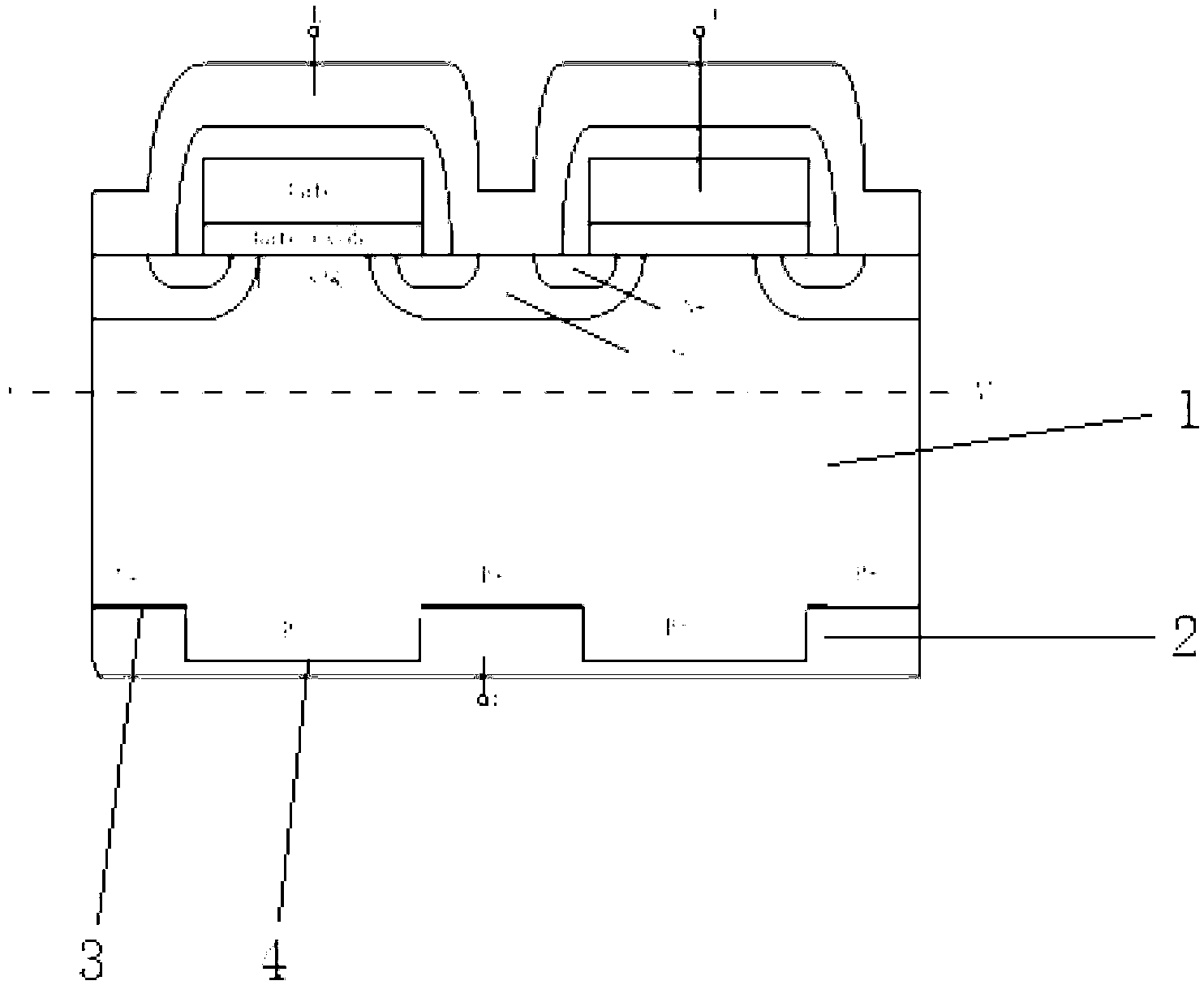

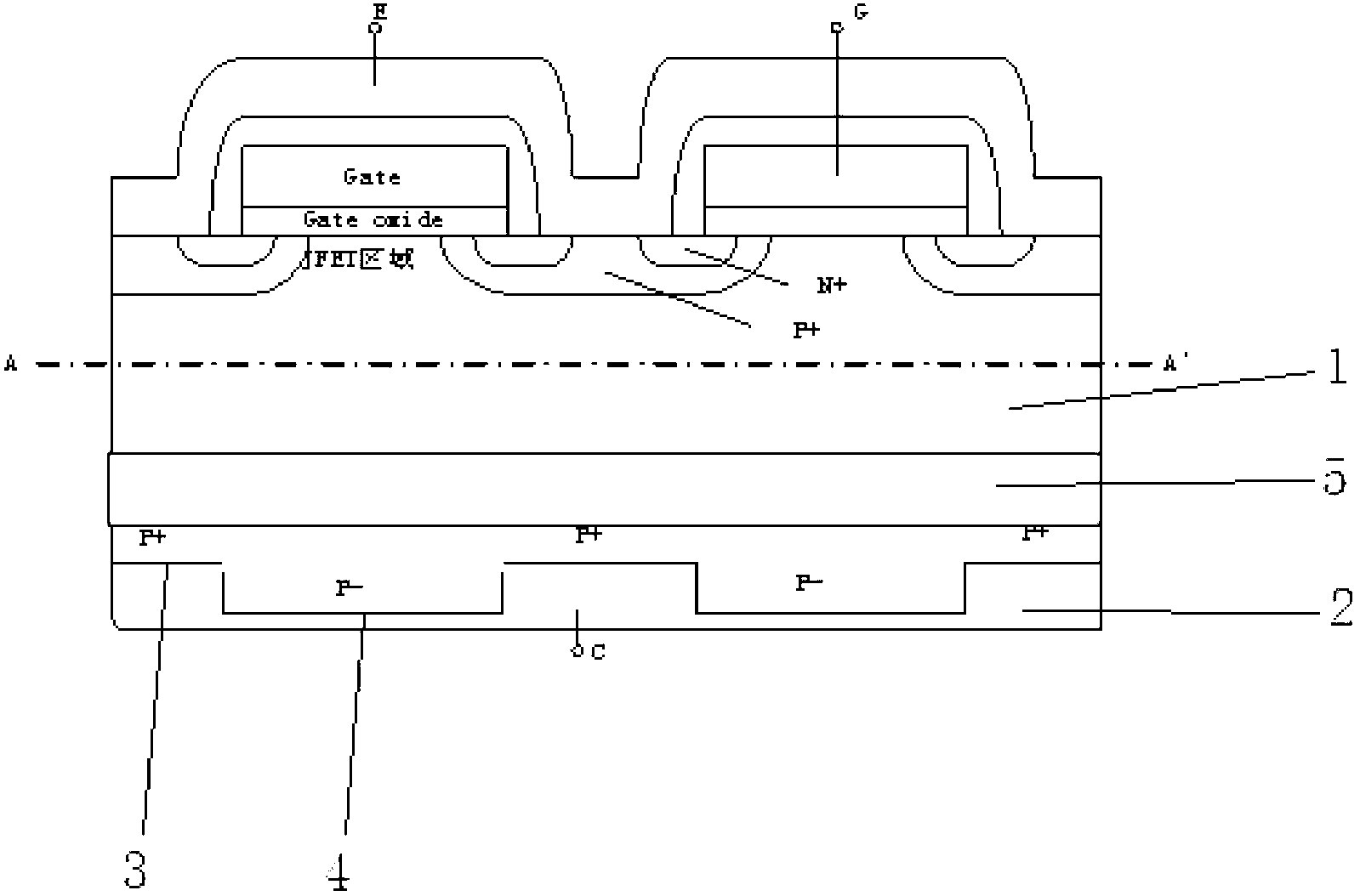

Diode structures with controlled injection efficiency for fast switching

ActiveUS20120193676A1Reduced injection efficiencyReduce chargeTransistorSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor package

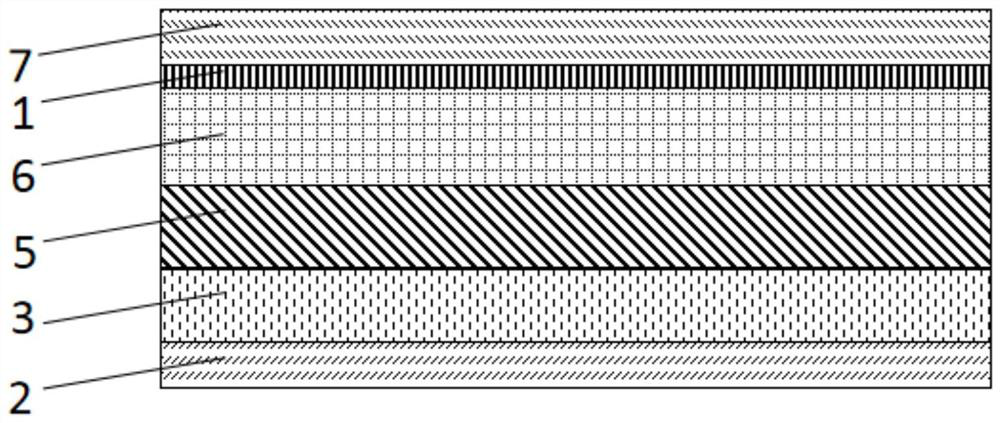

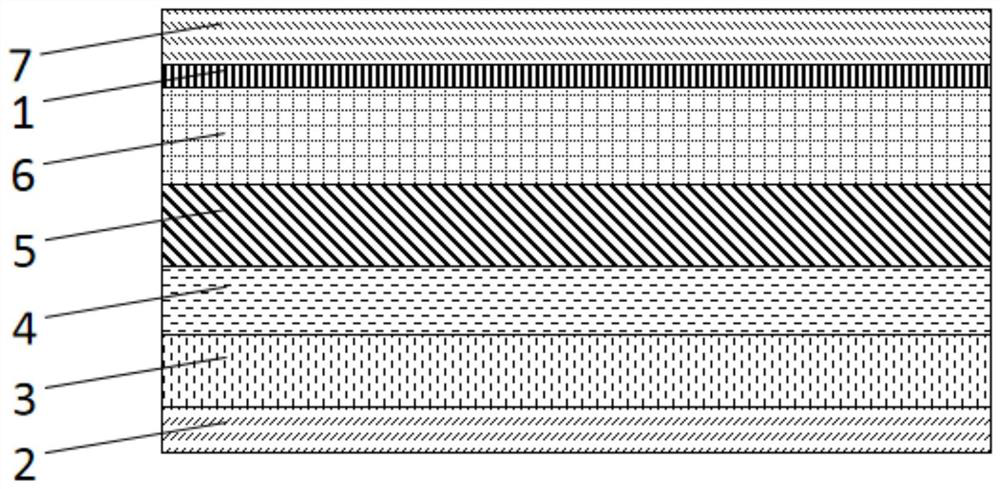

This invention discloses a semiconductor device disposed in a semiconductor substrate. The semiconductor device includes a first semiconductor layer of a first conductivity type on a first major surface. The semiconductor device further includes a second semiconductor layer of a second conductivity type on a second major surface opposite the first major surface. The semiconductor device further includes an injection efficiency controlling buffer layer of a first conductivity type disposed immediately below the second semiconductor layer to control the injection efficiency of the second semiconductor layer.

Owner:ALPHA & OMEGA SEMICON INC

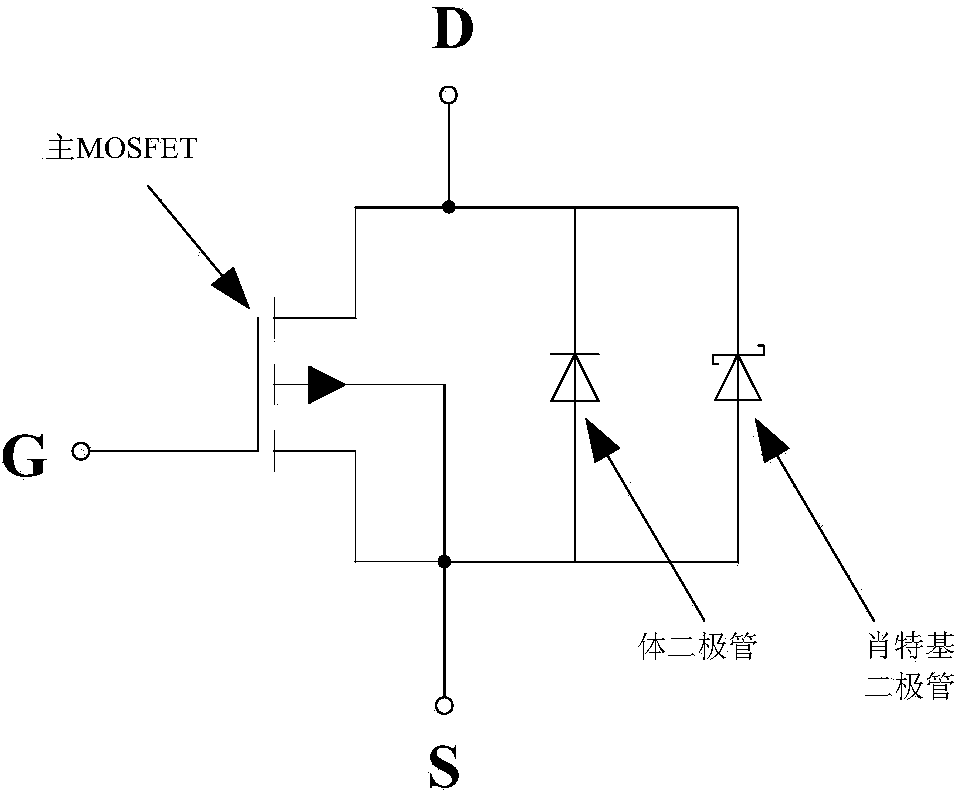

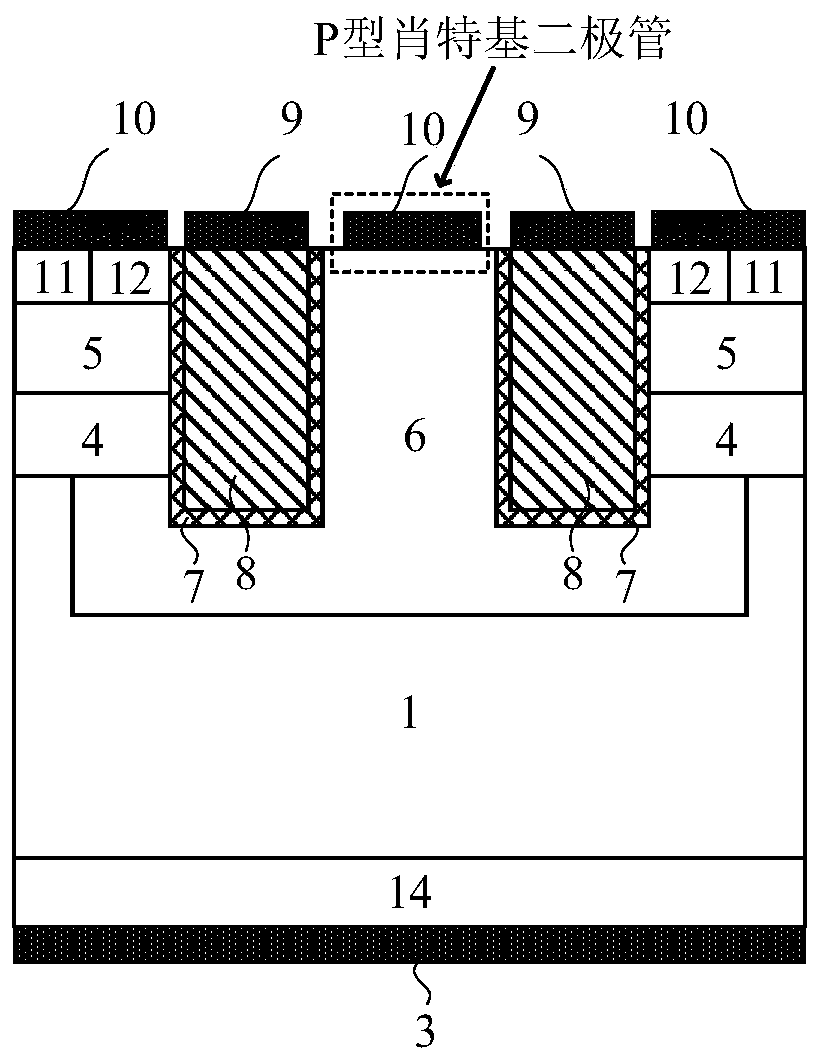

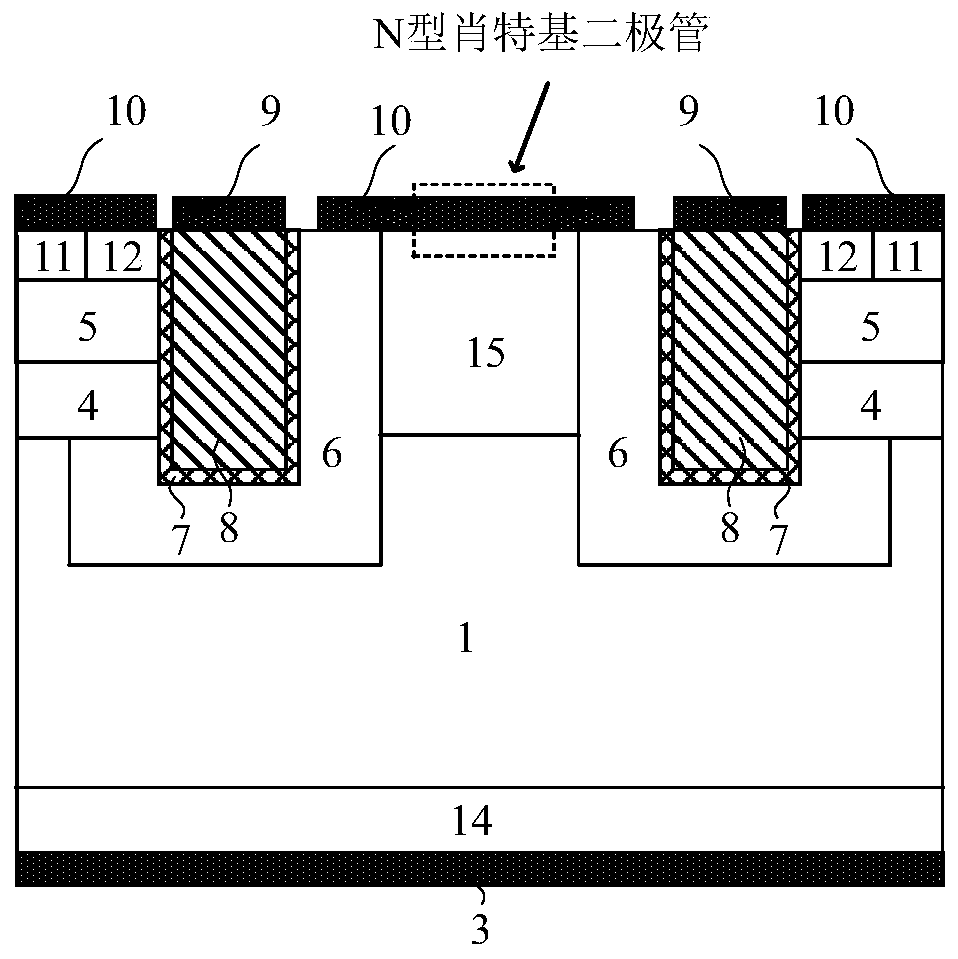

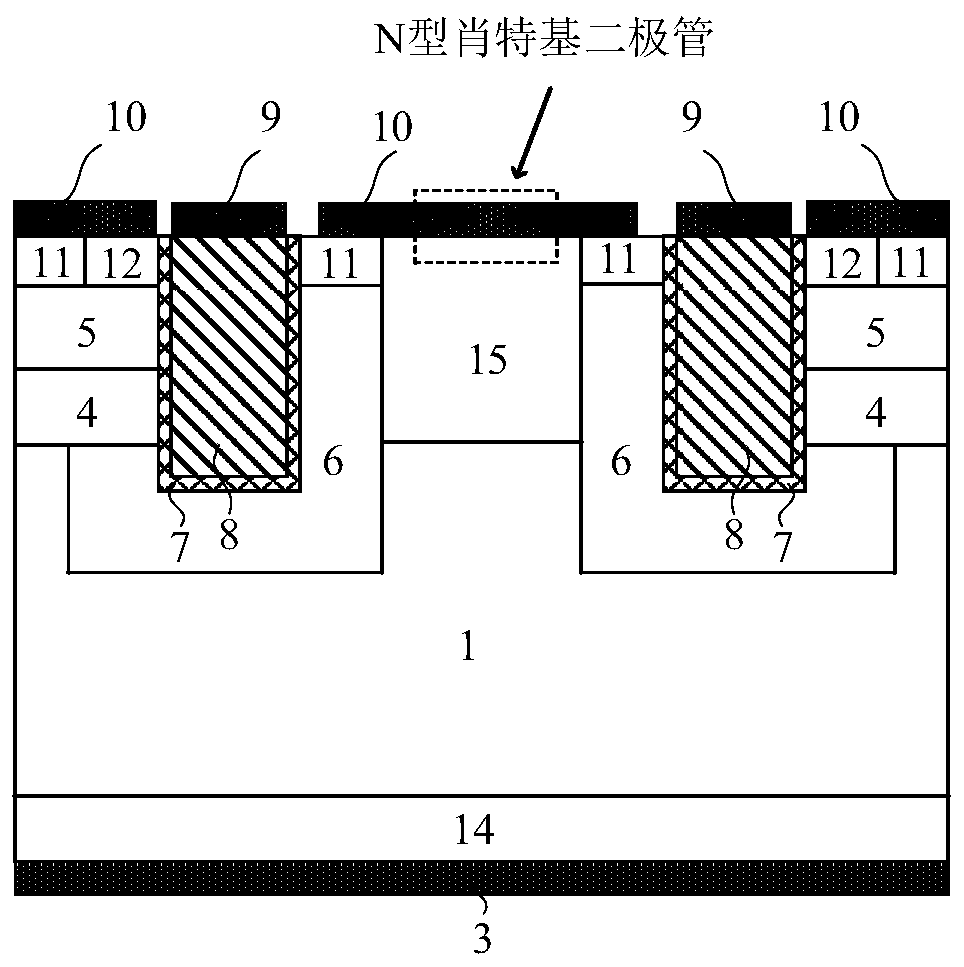

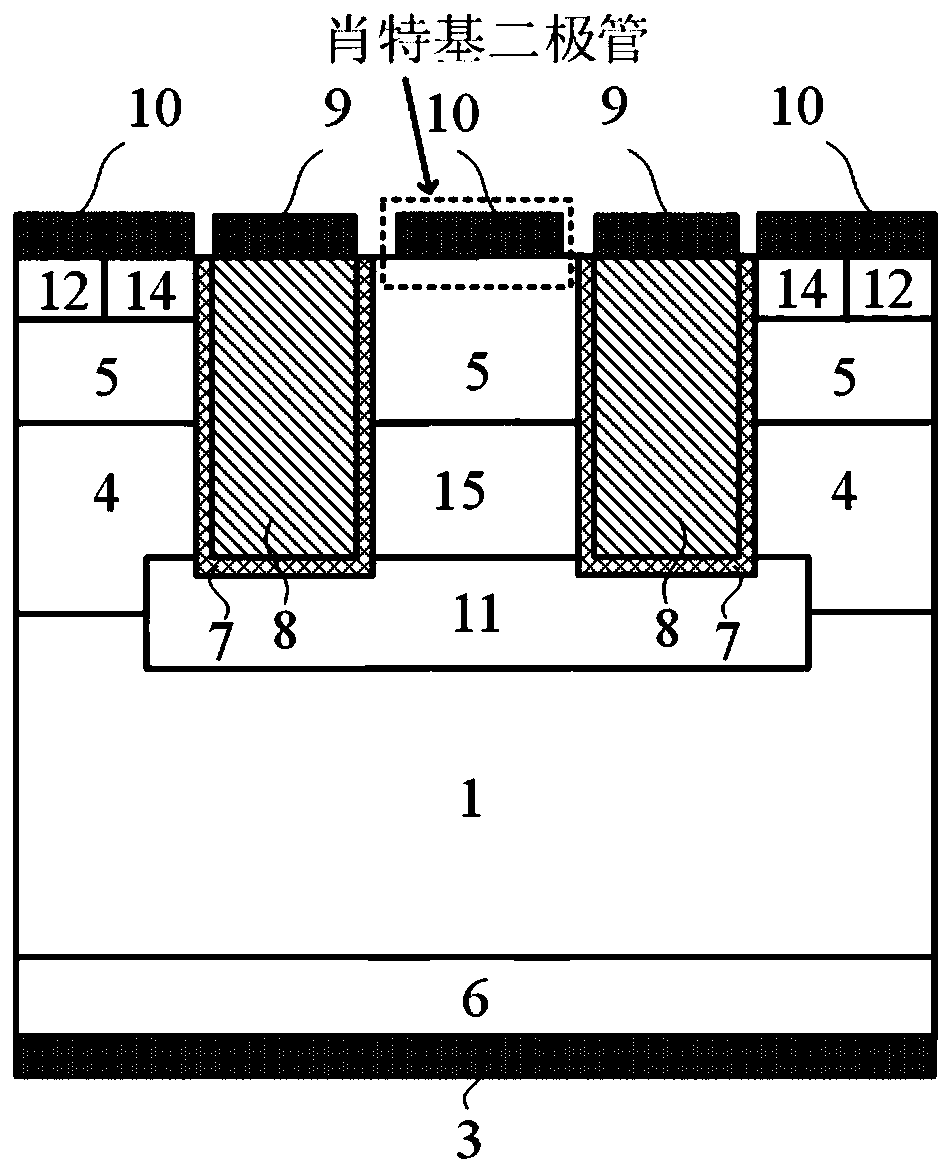

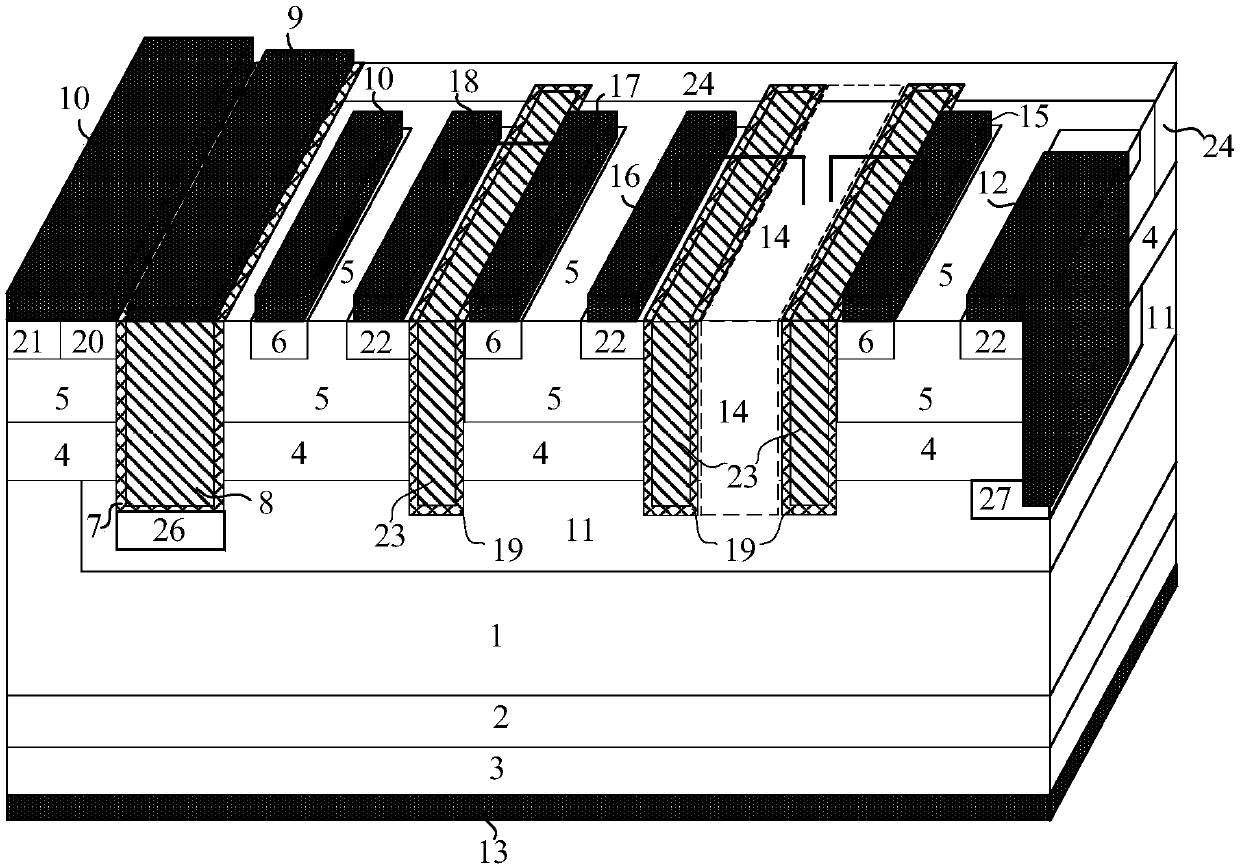

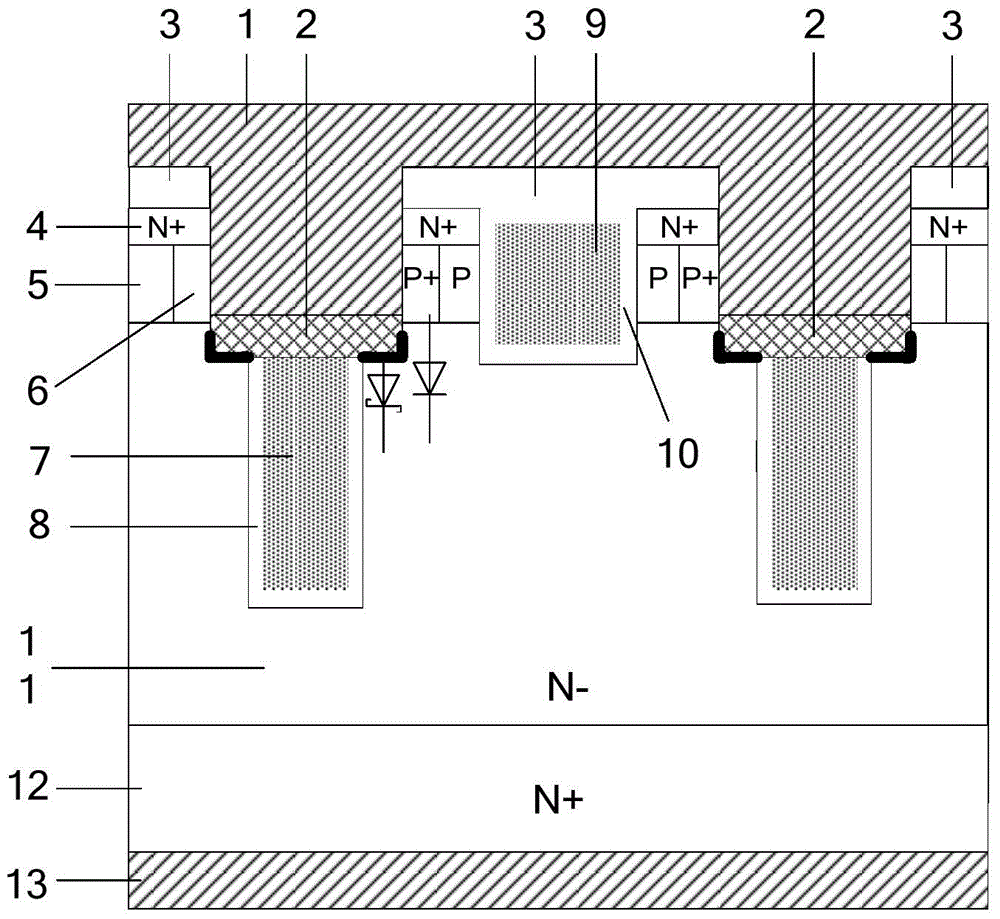

Groove gate VDMOS device integrated with Schottky diode

The invention discloses a groove gate VDMOS device integrated with a Schottky diode and belongs to the technical field of semiconductor devices. According to the groove gate VDMOS device integrated with the Schottky diode, an additional structure composed of a piece of Schottky junction metal and a body electrode conductive material is additionally arranged on each of drift regions on the two sides of a groove gate structure of a conventional groove gate VDMOS device, the upper portion of each piece of Schottky junction metal is in contact with source electrode metal, the lower portion of each piece of Schottky junction metal is in contact with a corresponding body electrode conductive material, and the lower surface and the lateral sides of the each piece Schottky junction metal are in contact with a corresponding drift region to form a Schottky junction; dielectric layers are arranged between the lateral sides of each body electrode conductive material and a corresponding drift region and between the bottom surface of each body electrode conductive material and the corresponding drift region. Compared with a traditional groove gate VDMOS device with the same size, the groove gate VDMOS device integrated with the Schottky diode has the advantages that due to the fact that higher drift region dosage concentration is adopted under the condition of same puncture voltage, turn-on resistance is reduced obviously, and the reverse recovery property of the diode is improved obviously.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

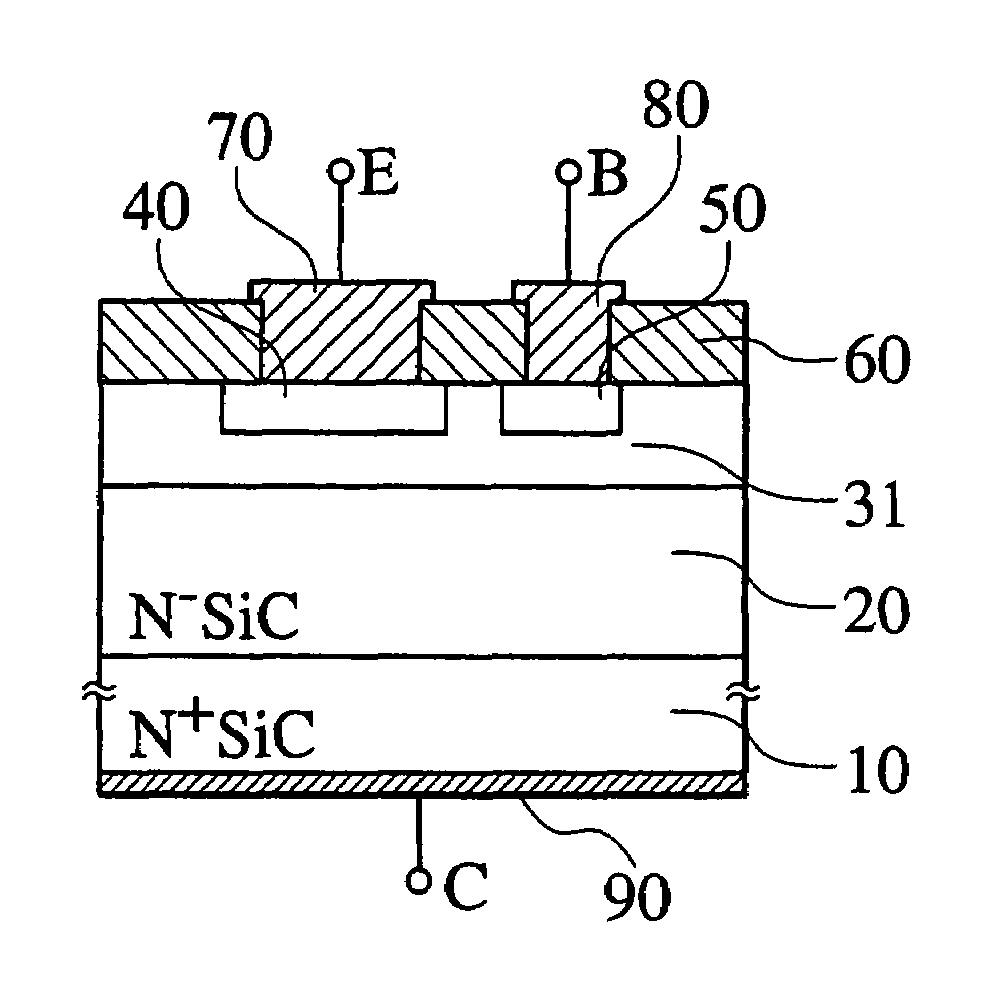

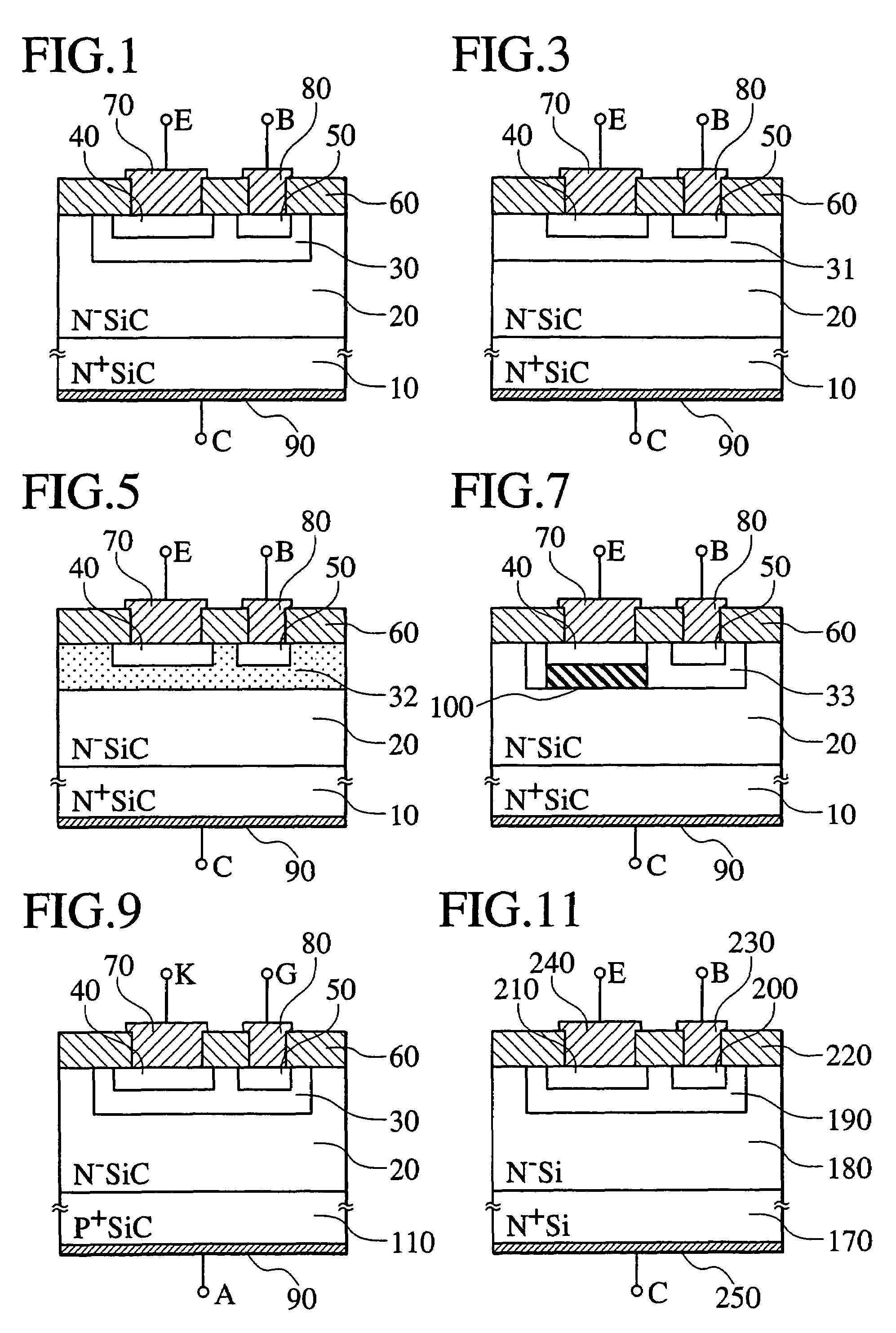

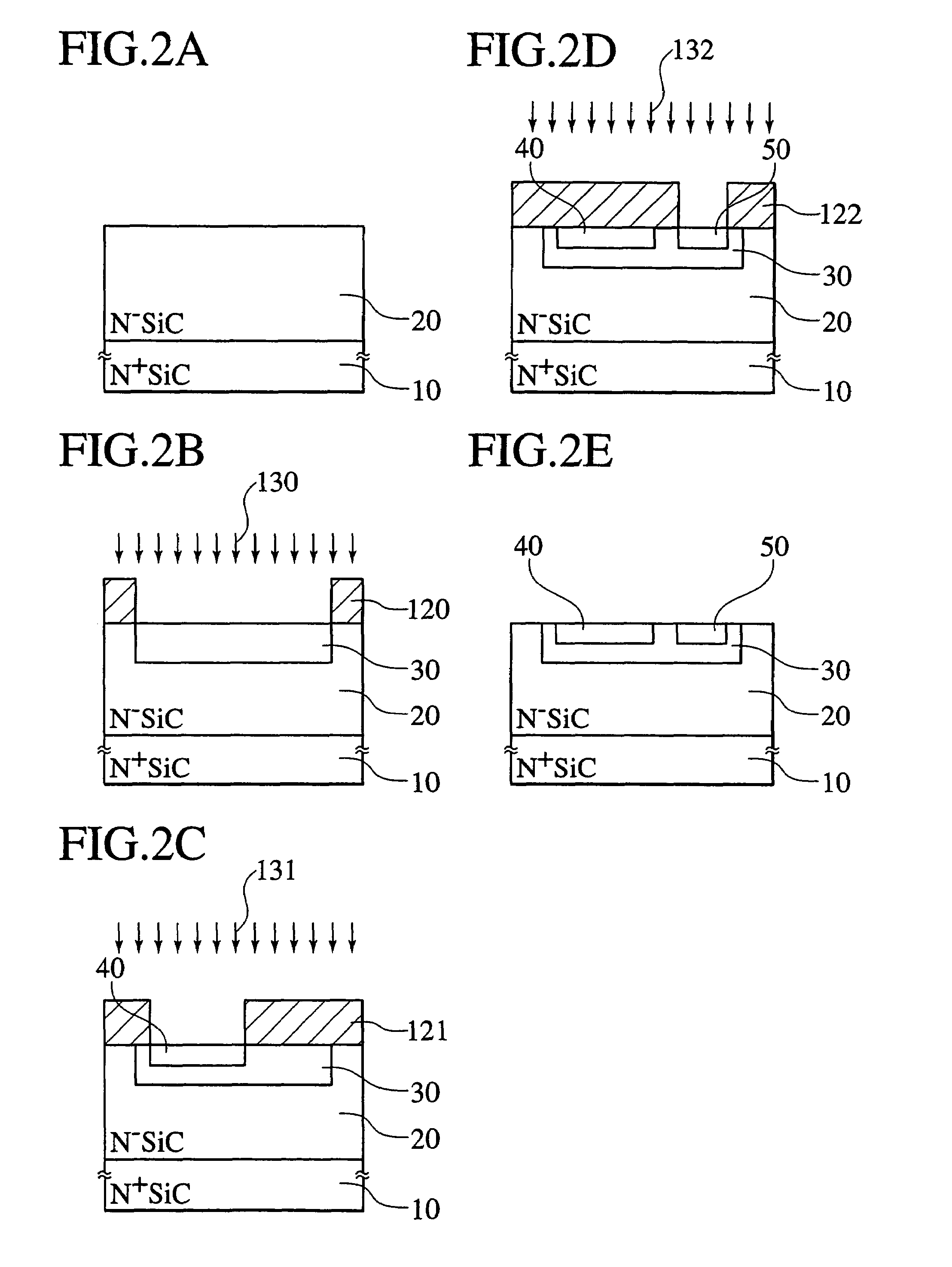

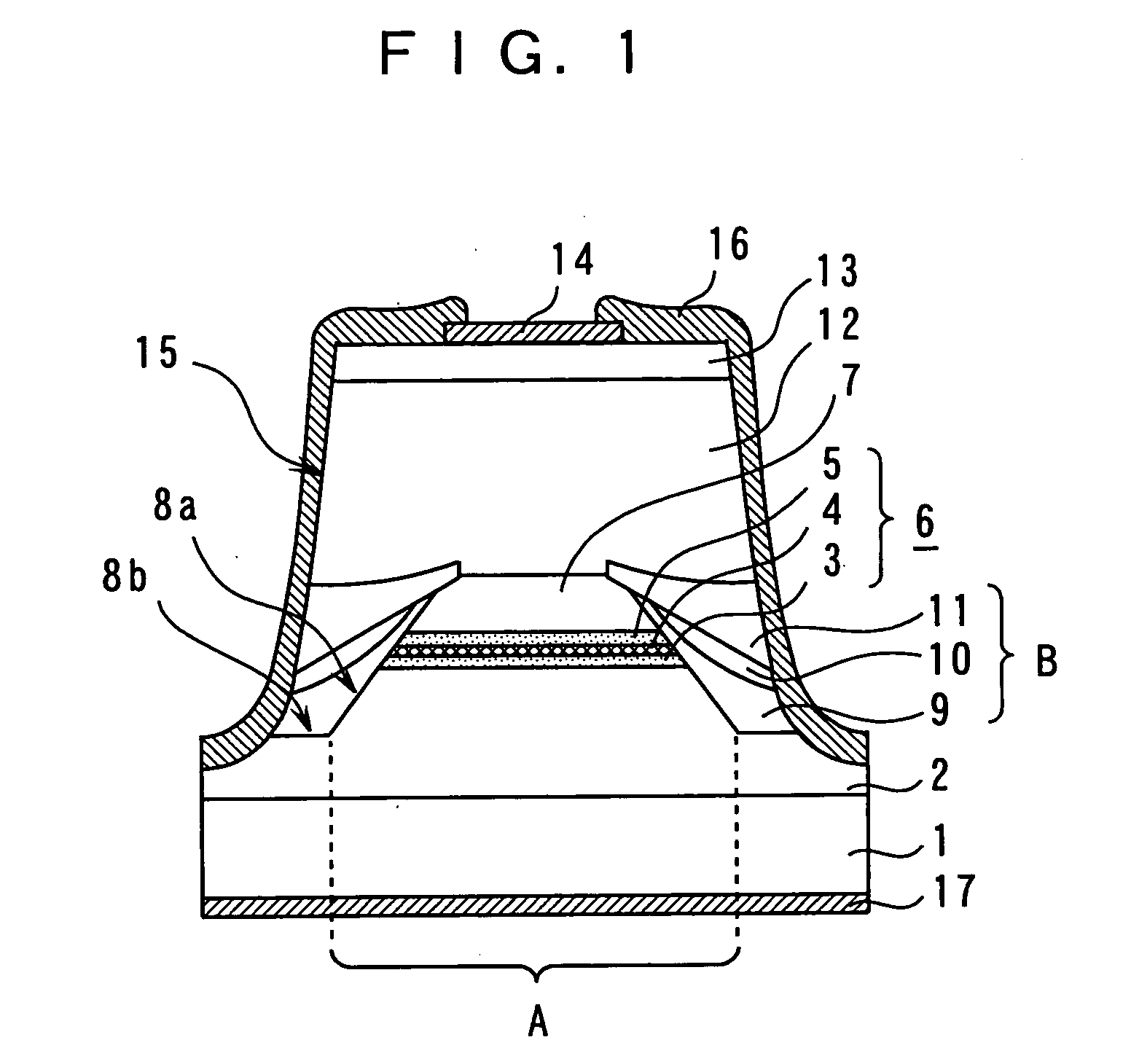

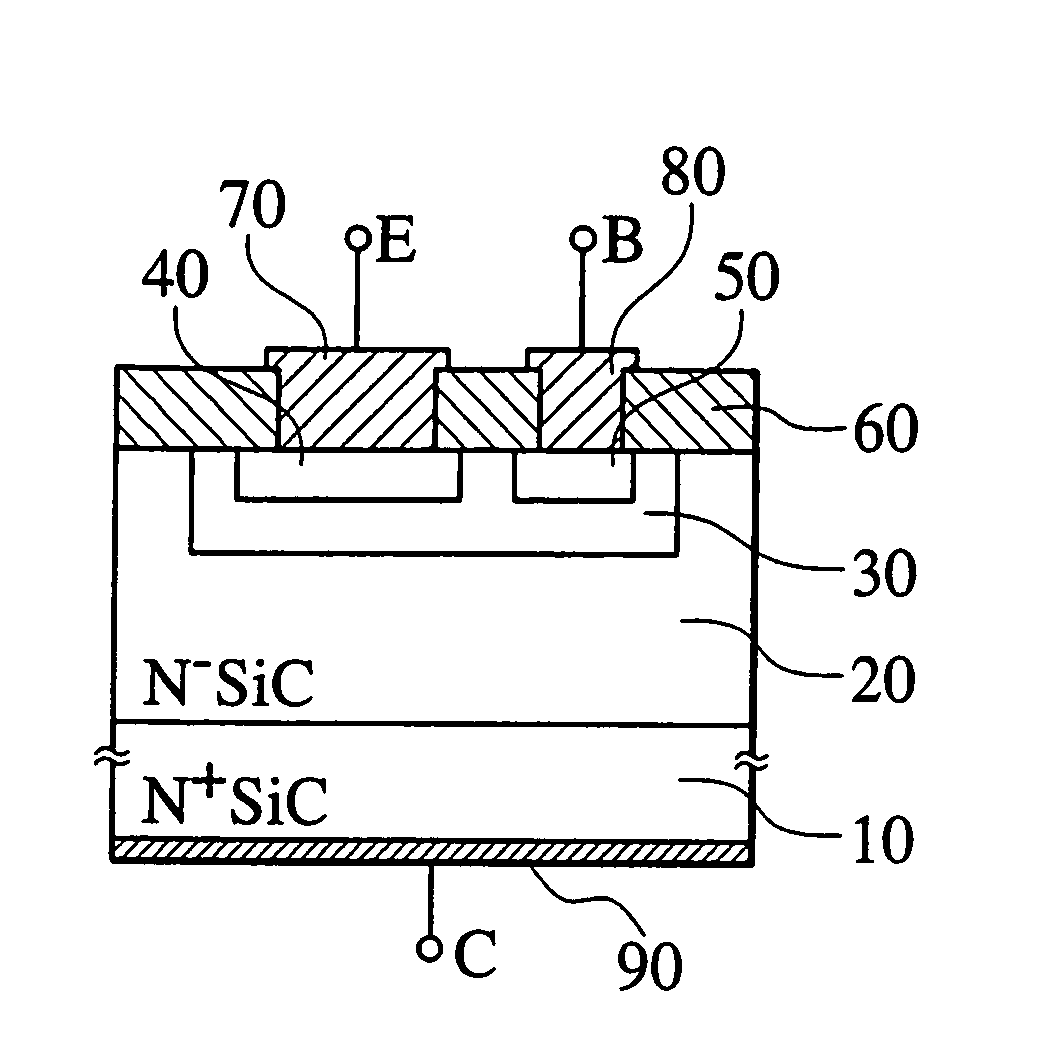

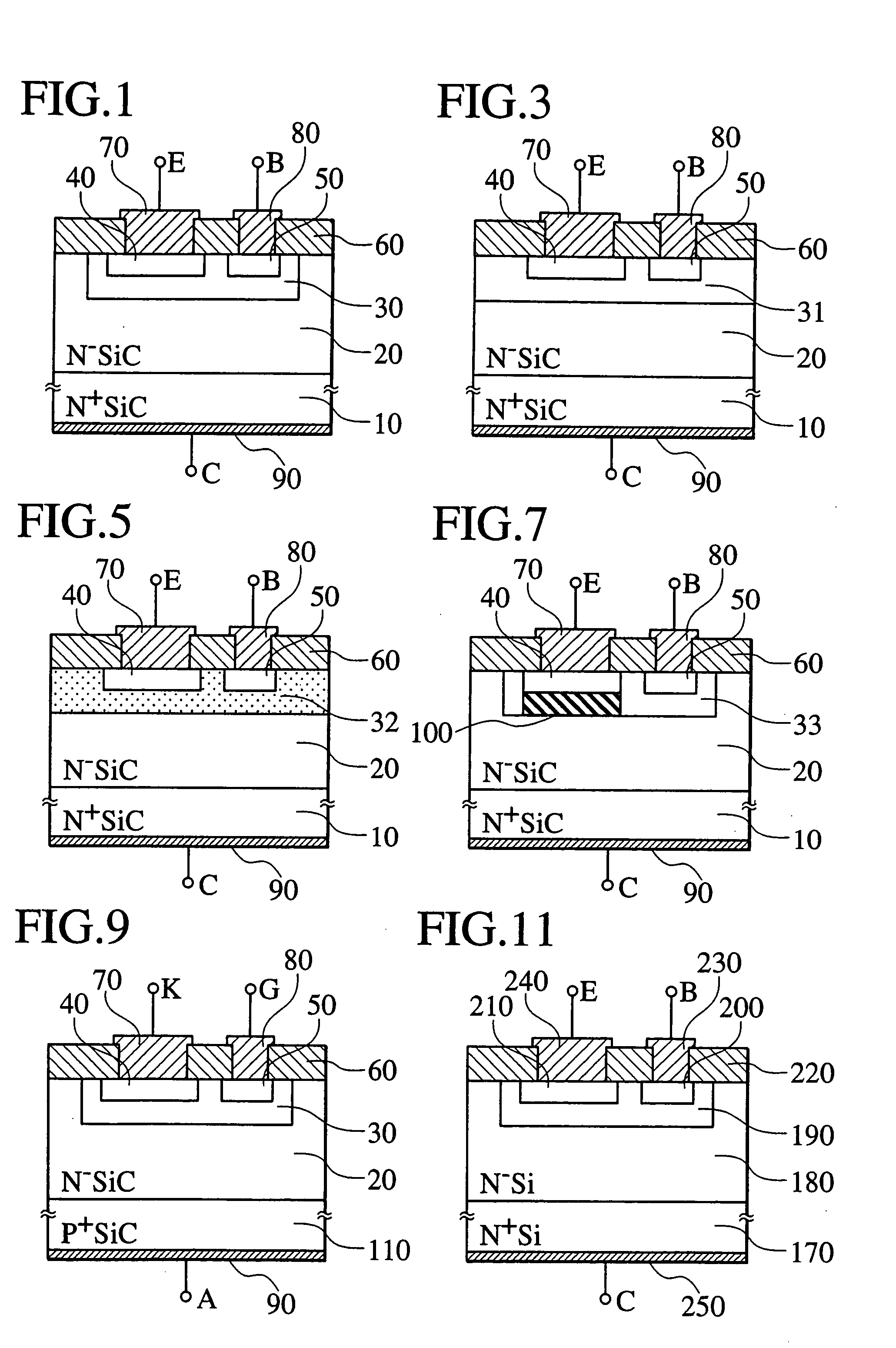

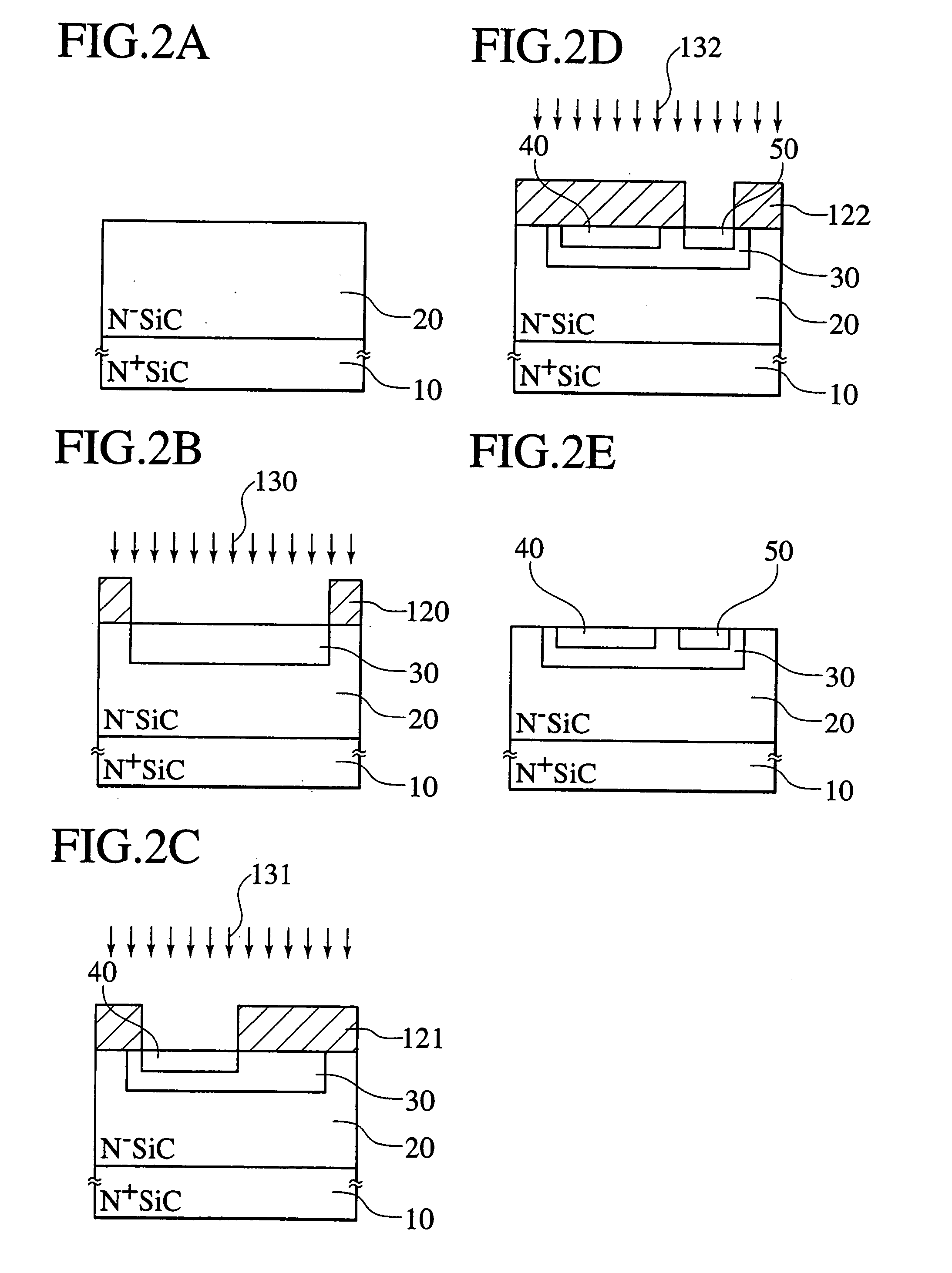

Semiconductor device and manufacturing method thereof

InactiveUS7378325B2Improve pressure resistanceReduced injection efficiencyThyristorSemiconductor/solid-state device manufacturingVolumetric Mass DensityHigh pressure

A high voltage semiconductor device having a high current gain hFE is formed with a collector region (20) of a first conduction type, an emitter region (40) of the first conduction type, and a base region (30) of a second conduction type opposite to the first conduction type located between the collector region and the emitter region. The free carrier density of the base region (30) where no depletion layer is formed is smaller than the space charge density of a depletion layer formed in the base region (30).

Owner:NISSAN MOTOR CO LTD

Semiconductor device and a method of manufacturing the same

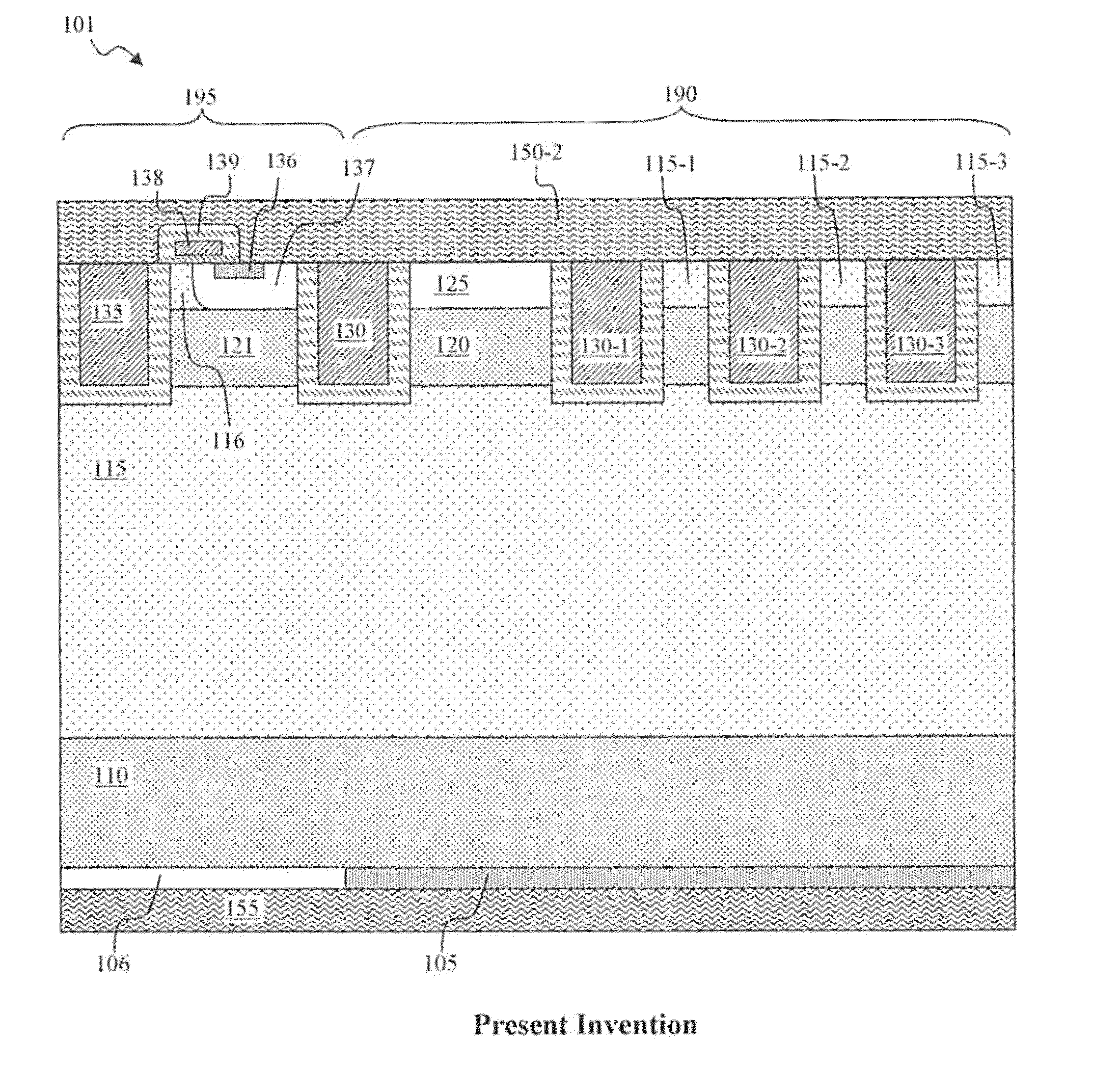

InactiveUS20060133146A1Efficient injectionImprove reliabilityRead-only memoriesDigital storageDevice materialCondensed matter physics

A semiconductor device having a well region of a first conduction type formed in a main surface of a semiconductor substrate, and a nonvolatile memory element formed at the well region is provided. The nonvolatile memory element comprises a gate electrode formed over the well region through an insulating film for charge storage, and a source region and drain region of a second conduction type which are separated from each other and are disposed in the well region. The well region includes a third semiconductor region, a second semiconductor region which is arranged at a position deeper than the third semiconductor region, and a first semiconductor region that is arranged at a position deeper than the second semiconductor region. The first and third semiconductor regions, respectively, have an impurity concentration higher than the second semiconductor region.

Owner:RENESAS TECH CORP

Diode structures with controlled injection efficiency for fast switching

ActiveUS20160181391A1Reduced injection efficiencyReduce chargeSemiconductor/solid-state device manufacturingDiodeElectrical conductorSemiconductor package

This invention discloses a semiconductor device disposed in a semiconductor substrate. The semiconductor device includes a first semiconductor layer of a first conductivity type on a first major surface. The semiconductor device further includes a second semiconductor layer of a second conductivity type on a second major surface opposite the first major surface. The semiconductor device further includes an injection efficiency controlling buffer layer of a first conductivity type disposed immediately below the second semiconductor layer to control the injection efficiency of the second semiconductor layer.

Owner:ALPHA & OMEGA SEMICON INC

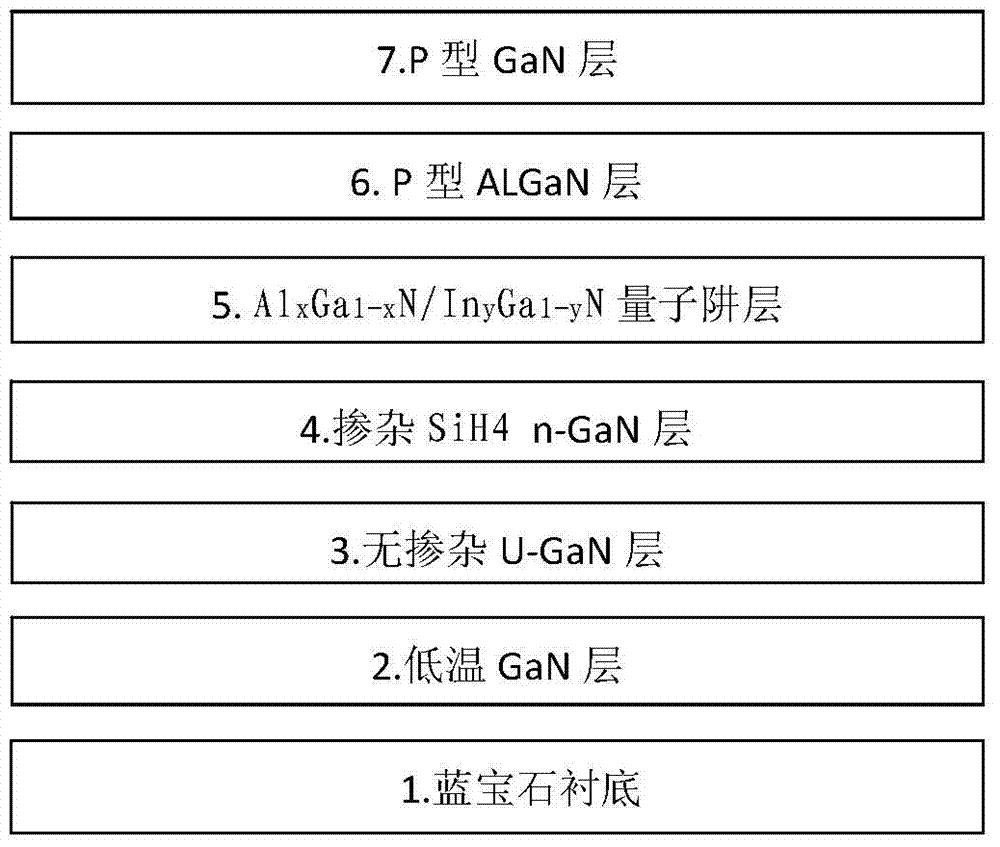

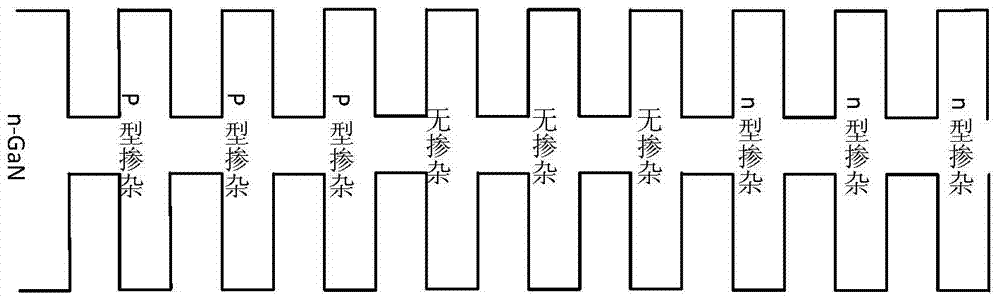

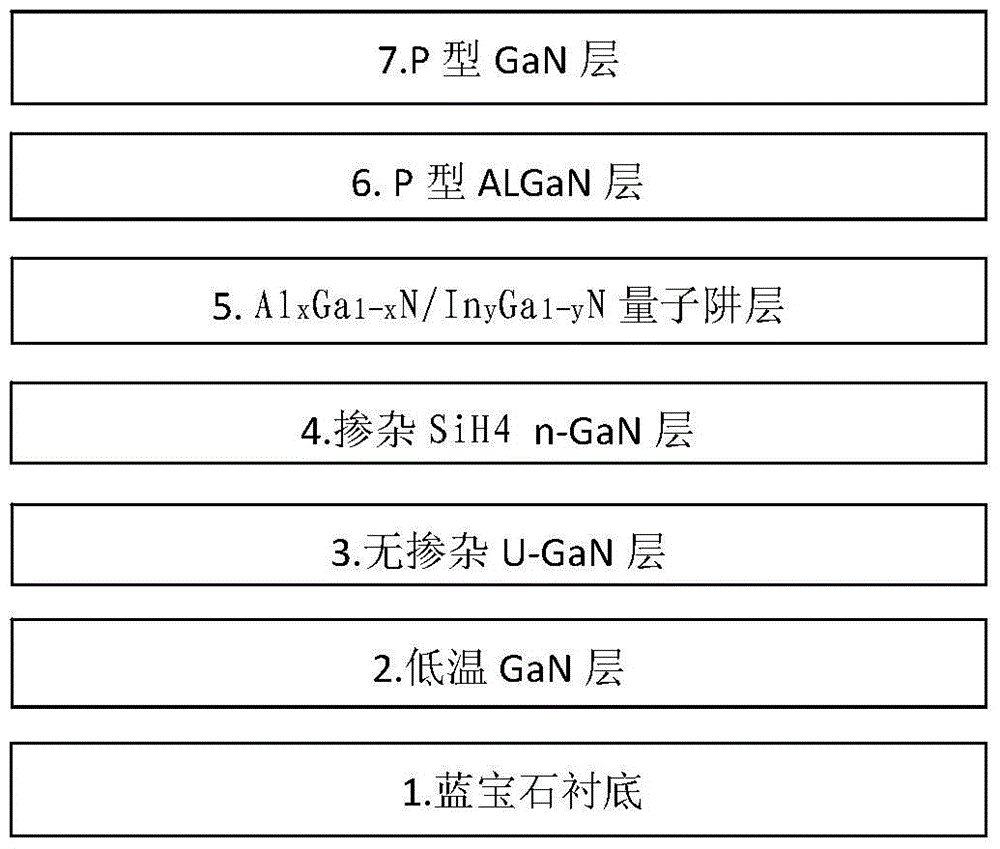

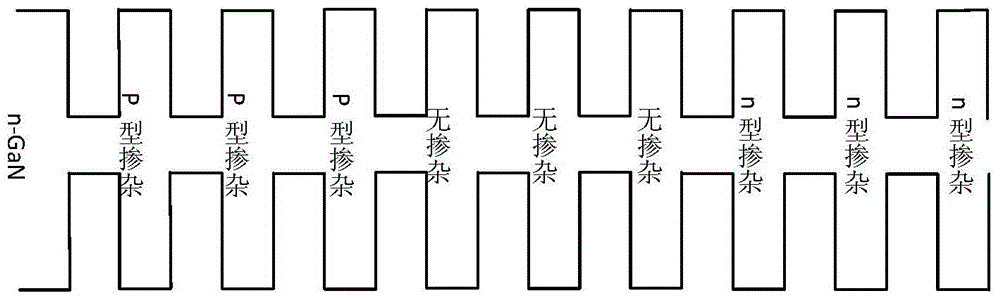

Epitaxial growth method for improving LED lighting efficiency

InactiveCN104332544AImprove luminous efficiencyComposite Luminous Efficiency DecreaseSemiconductor devicesQuantum wellP type doping

The invention provides a novel LED epitaxial growth method which can effectively improve the lighting efficiency of LED epitaxial structures. The method comprises the links of N-GaN layer growth, multi-quantum well layer growth and P-GaN layer growth, wherein the multi-quantum well layer is of a structure of a plurality of pairs of AlxGa <1-x> N / InyGa <1-y> N, wherein x is more than 0 and less than 1, and y is more than 0 and less than 1; the multi-quantum well layer growth link includes three growth stages in sequence, wherein the AlxGa1-xN quantum barrier is subjected to p type doping in the first stage, the AlxGa1-xN quantum barrier is not doped in the second stage, and the AlxGa1-xN quantum barrier is subjected to n type doping in the third stage; a p type doped AlGaN stopping layer grows, and then the P-GaN layer growth link is performed.

Owner:西安利科光电科技有限公司

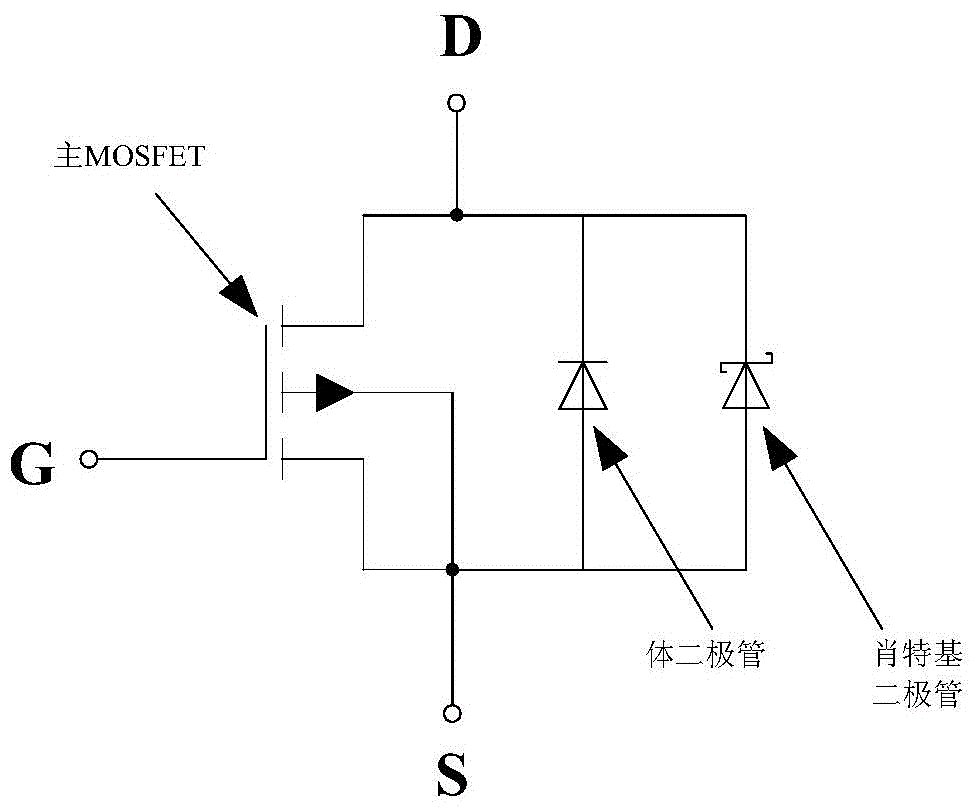

SiC power device

ActiveCN110767753ASmall pressure dropEliminate minority carrier injection effectDiodeHeterojunction diodeMinority carrier injection

The invention belongs to the field of power semiconductors, and particularly provides a SiC power device. The SiC power device comprises a SiC MOSFET and a SiC IGBT. For the SiC MOSFET device integrated with a PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak current is reduced, and the EMI noise is reduced; forthe SiC MOSFET device integrated with an N-type Schottky diode or an integrated heterojunction diode, the voltage drop during reverse conduction of the MOSFET can be reduced, and the minority carrierinjection effect is eliminated, so that the conduction loss and reverse recovery loss of the diode are reduced; for the reverse conduction type SiC IGBT device integrated with the PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak current is reduced, and the EMI noise is reduced; and moreover, for the reverse conduction type SiC IGBT device integrated with the N-type Schottky diode or the heterojunction diode, the voltage drop during reverse conduction of the reverse conduction IGBT can be reduced, the minority carrier injection effect is eliminated, and the conduction loss and reverse recovery loss of the diode are reduced.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

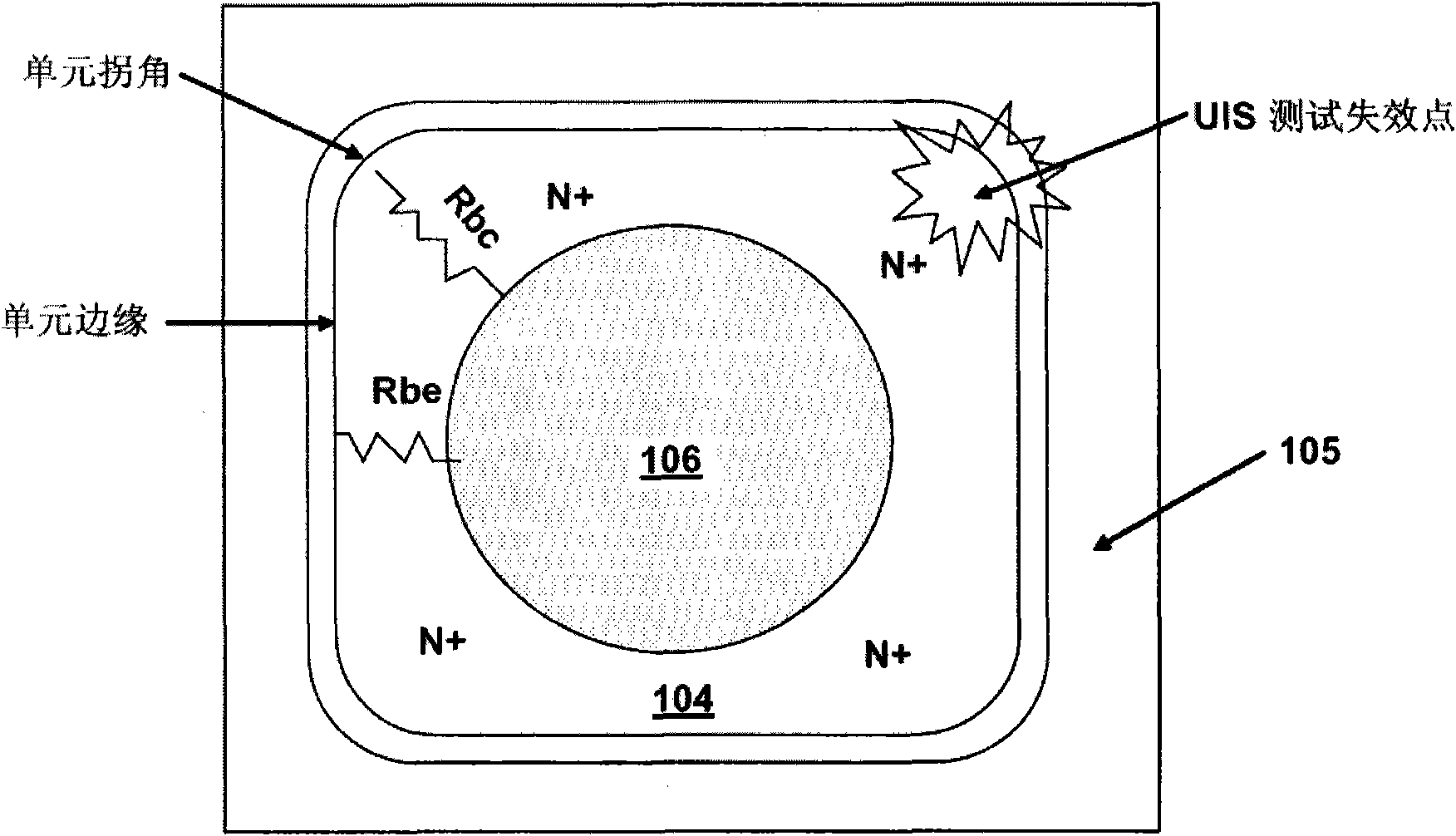

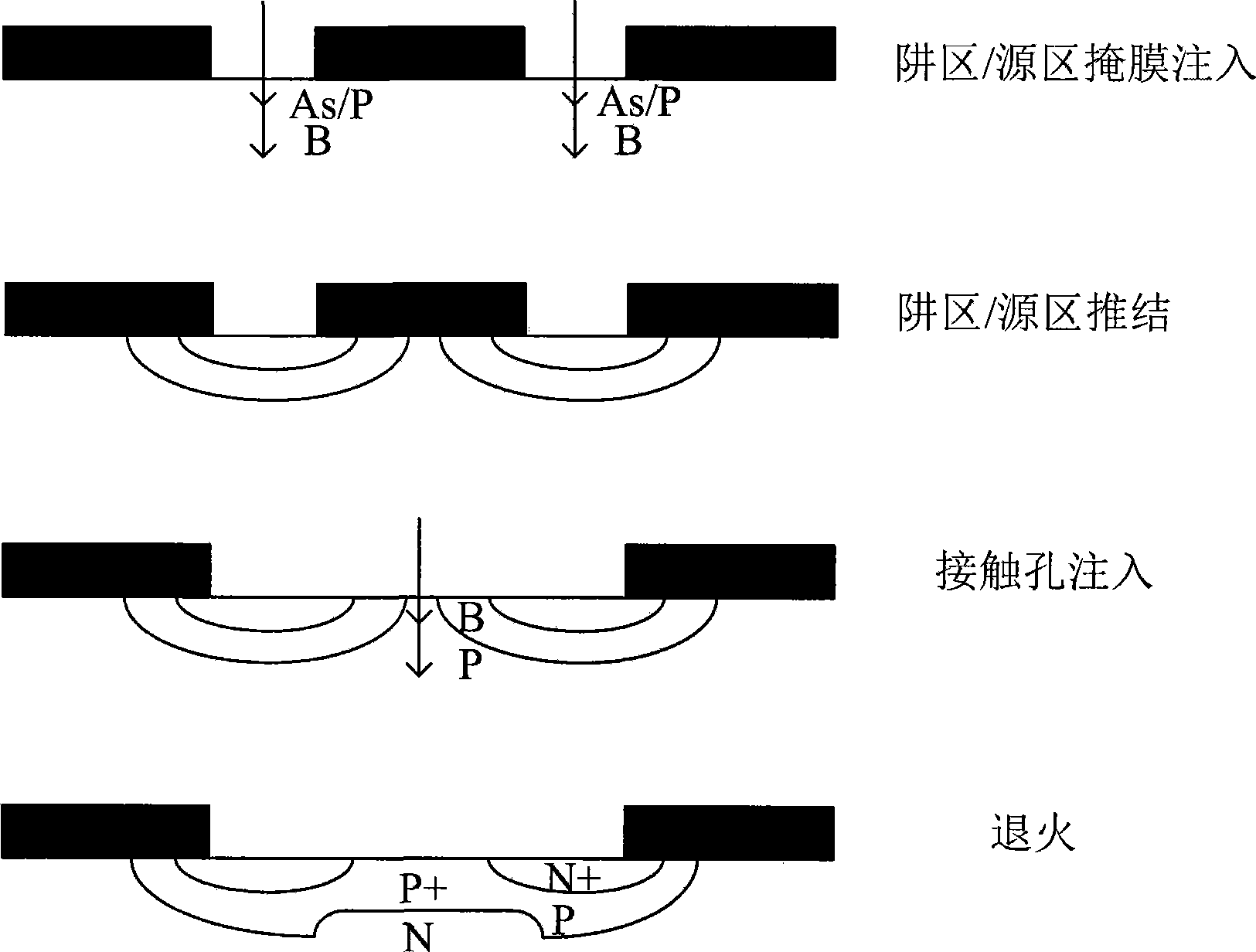

Trench MOSFET

ActiveCN101989602ASmall structural resistanceReduced injection efficiencyTransistorSemiconductor/solid-state device manufacturingTrench mosfetBody contact

The invention discloses a trench metal-oxide-semiconductor field effect transistor (MOSFET) structure and a manufacturing method thereof. Different from a source area of a trench MOSFET formed by a method in the prior art, the source area of the structure is formed by ion implantation and diffusion of majority carriers in the source area at the opening of a source body contact trench, so that the concentration distribution of the majority carriers of the source area is Gaussian distribution from the source body contact trench to a channel area along the surface of an epitaxial layer, and the junction depth of the source area is gradually reduced from the source body contact trench to the channel area. A trench MOSFET device with the structure has better avalanche breakdown property compared with the prior art. Correspondingly, in the manufacturing process, the invention discloses a manufacturing method only needing a mask plate for three times, and the production cost is greatly reduced.

Owner:FORCE MOS TECH CO LTD

Semiconductor laser device and method for manufacturing the same semiconductor laser device

InactiveUS20070091957A1Total current dropInhibit deteriorationSemiconductor lasersLaser cooling arrangementsSemiconductorBlocking layer

A current blocking structure of a semiconductor laser includes a p-type InP buried layer, an n-type InP current blocking layer, and a p-type InP current blocking layer laminated along the mesa side surface of a ridge. In the structure, an upper end part of the n-type InP current blocking layer is covered with the p-type InP buried layer and the p-type InP current blocking layer. The n-type InP current blocking layer is prevented from contacting n-type and p-type InP cladding layers. Creation of an ineffective current path from one of the n-type InP cladding layers through the n-type InP current blocking layer to a p-type InP cladding layer of the semiconductor laser is prevented.

Owner:MITSUBISHI ELECTRIC CORP

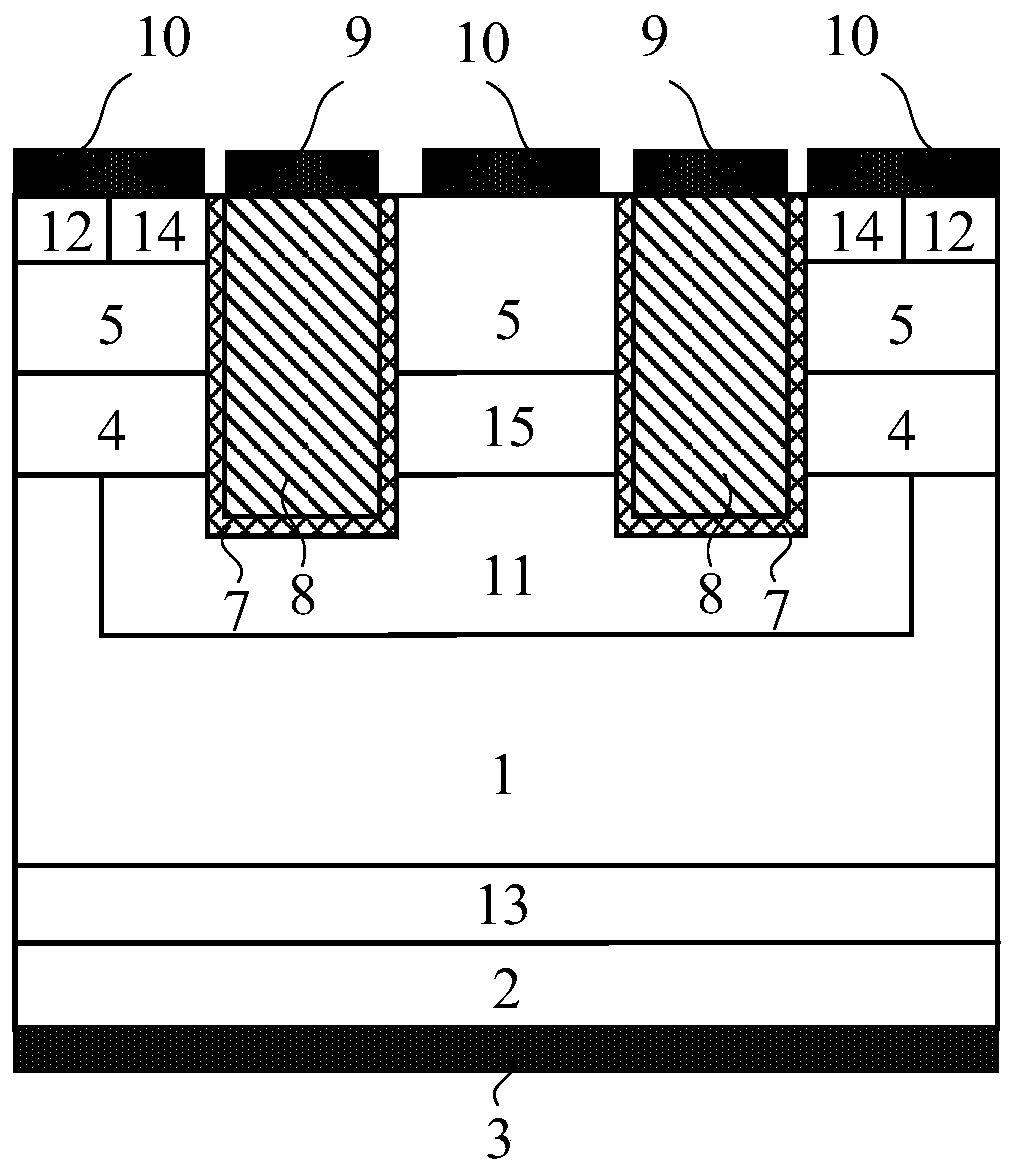

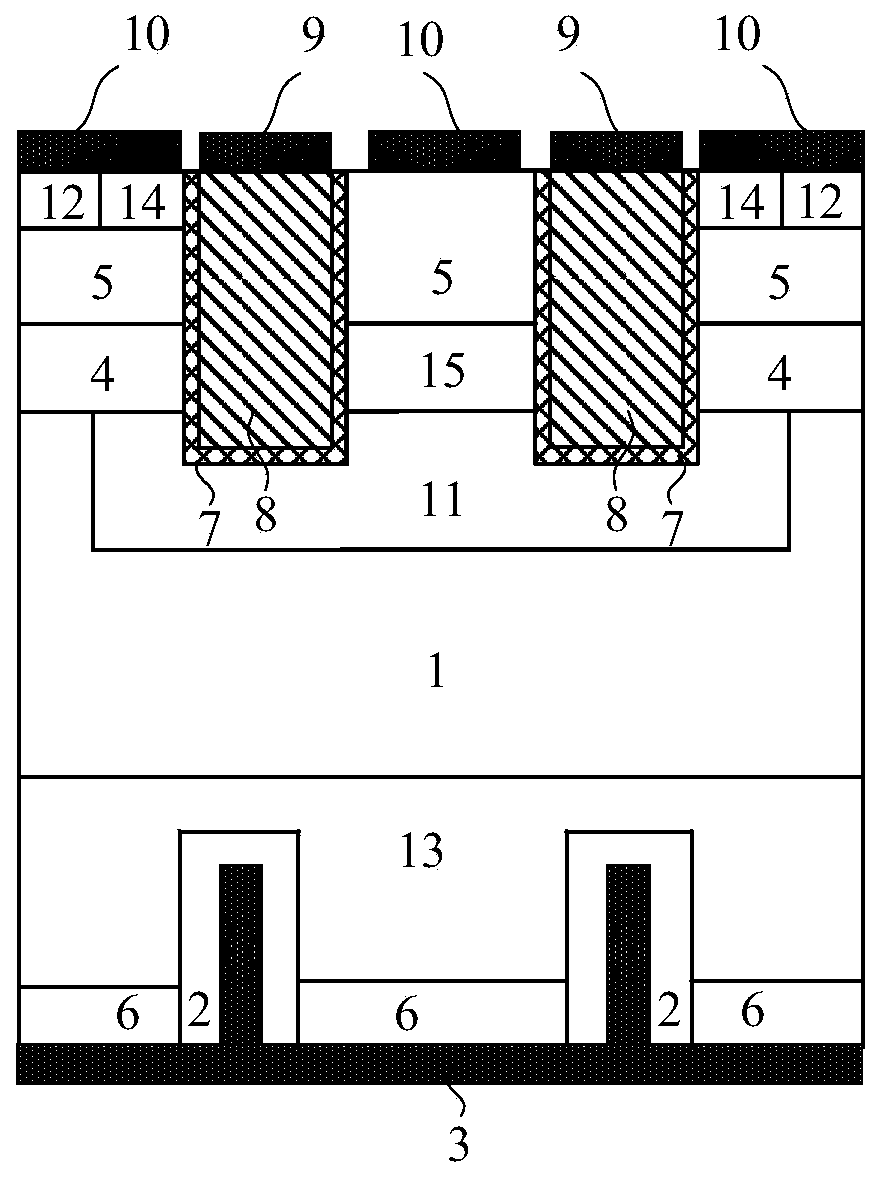

SiC power device integrated with fast recovery diode

The invention relates to the field of power semiconductors, and particularly provides a SiC power device integrated with a fast recovery diode. The SiC power device comprises a SiC MOSFET and a SiC IGBT, wherein for the SiC MOSFET device integrated with a PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak currentis reduced, and the EMI noise is reduced; for a reverse conducting SiC IGBT integrated with a PN junction body diode, the reverse recovery charge and related loss of the body diode can be greatly reduced, the reverse recovery peak current is reduced, and the EMI noise is reduced; and meanwhile, by arranging an anode deep groove at the bottom and designing the depth of the anode deep groove and the distance between the grooves, the resistance of an electron flowing path is adjusted, and the output characteristic of the reverse conducting IGBT can enter a bipolar working mode without turning ina unit cell.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Fast recovery diode with Schottky contact terminal

InactiveCN103311315AReduced turn-off lossOptimal distribution levelSemiconductor devicesPower semiconductor deviceReverse recovery

The invention discloses a fast recovery diode with a Schottky contact terminal, belonging to the technical field of power semiconductor devices. According to the fast recovery diode with the Schottky contact terminal, equipotential ring contact metal is changed into Schottky contact metal on the basis of the conventional fast recovery diode, so that the injection efficiency at a transition region is reduced, the carrier distribution of the terminal part is optimized, the turn-off loss is reduced and the reliability in a reverse recovery process is improved. The fast recovery diode is suitable for the field of semiconductor power devices and power integrated circuits from small power to high power.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Insulated gate bipolar transistor device comprising a depletion-mode MOSFET

InactiveUS7968940B2Reduce the number of holesReduce transportationTransistorSolid-state devicesEngineeringDouble gate

Double gate IGBT having both gates referred to a cathode in which a second gate is for controlling flow of hole current. In on-state, hole current can be largely suppressed. While during switching, hole current is allowed to flow through a second channel. Incorporating a depletion-mode p-channel MOSFET having a pre-formed hole channel that is turned ON when 0V or positive voltages below a specified threshold voltage are applied between second gate and cathode, negative voltages to the gate of p-channel are not used. Providing active control of holes amount that is collected in on-state by lowering base transport factor through increasing doping and width of n well or by reducing injection efficiency through decreasing doping of deep p well. Device includes at least anode, cathode, semiconductor substrate, n− drift region, first & second gates, n+ cathode region; p+ cathode short, deep p well, n well, and pre-formed hole channel.

Owner:ANPEC ELECTRONICS CORPORATION

Semiconductor device and manufacturing method thereof

InactiveUS20060208261A1Improve pressure resistanceReduced injection efficiencyThyristorSemiconductor/solid-state device manufacturingDevice materialVolumetric Mass Density

A high voltage semiconductor device having a high current gain hFE is formed with a collector region (20) of a first conduction type, an emitter region (40) of the first conduction type, and a base region (30) of a second conduction type opposite to the first conduction type located between the collector region and the emitter region. The free carrier density of the base region (30) where no depletion layer is formed is smaller than the space charge density of a depletion layer formed in the base region (30).

Owner:NISSAN MOTOR CO LTD

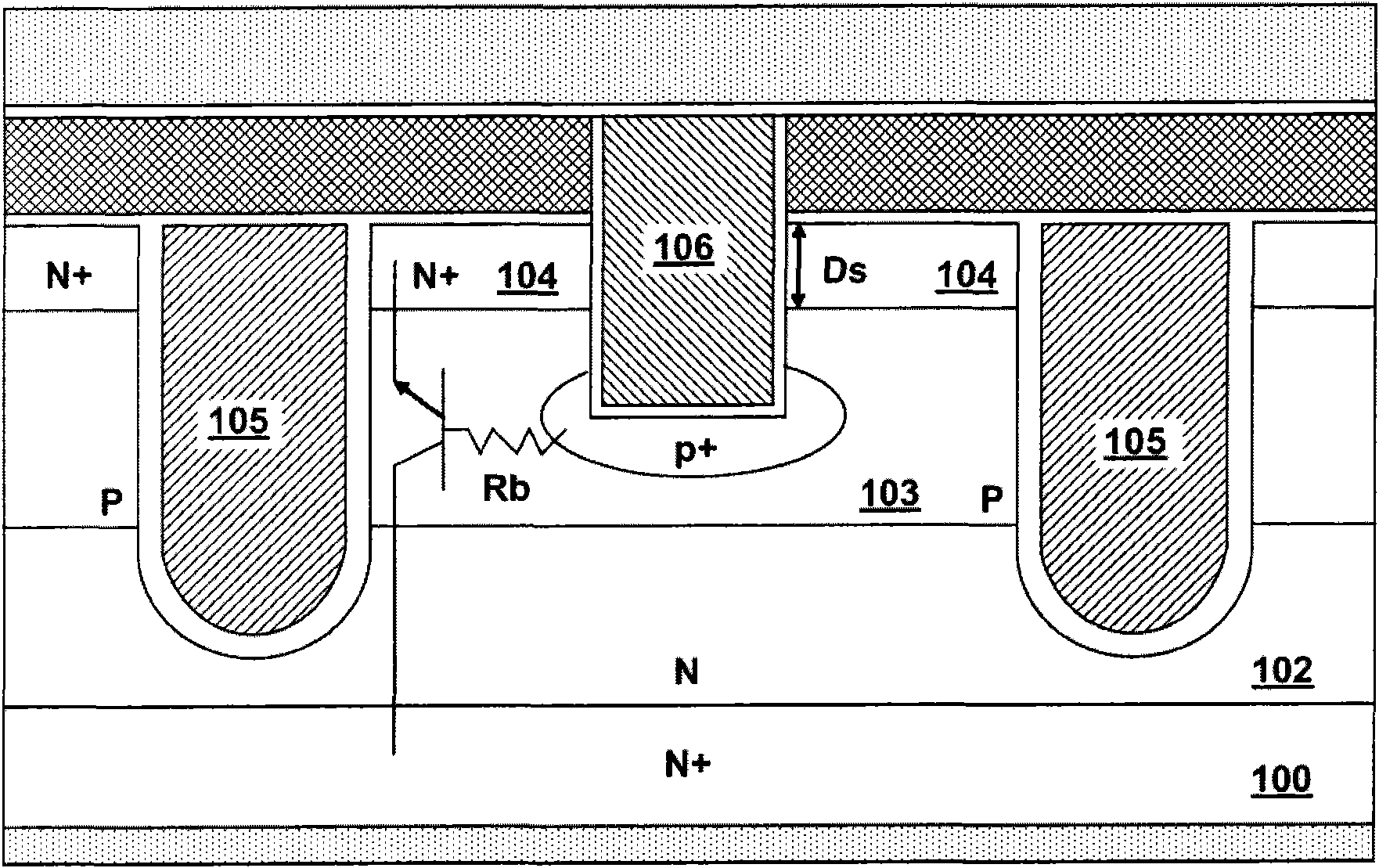

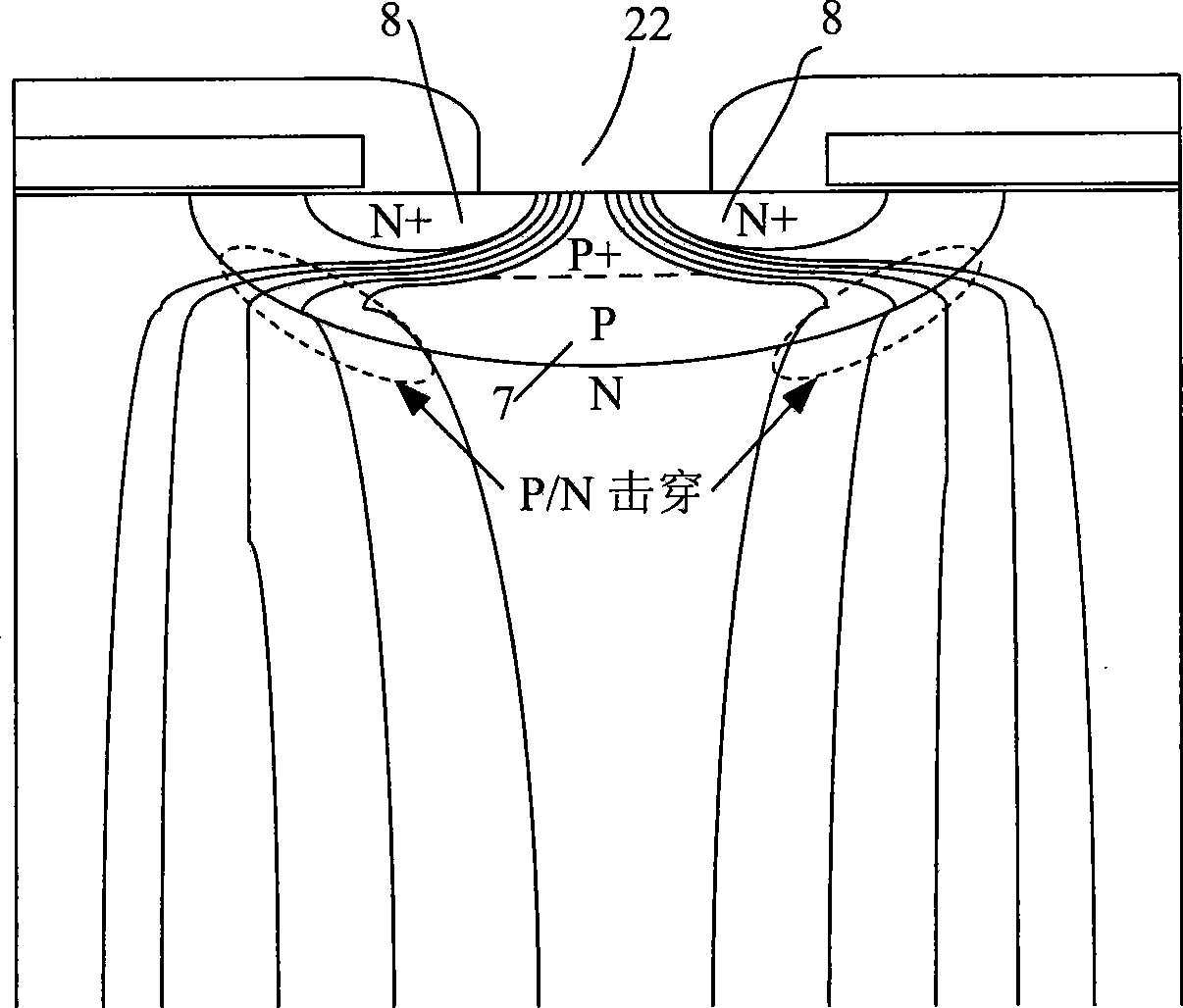

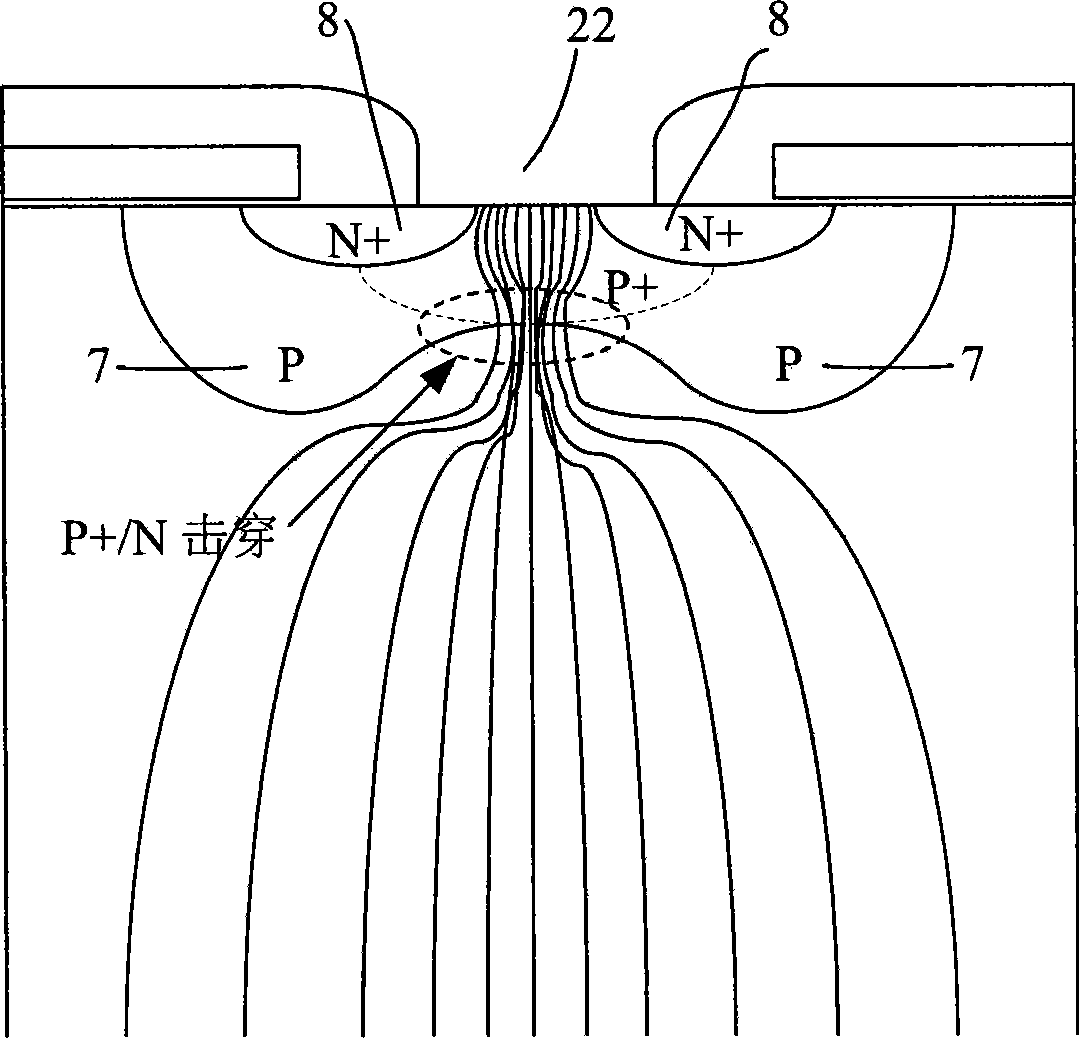

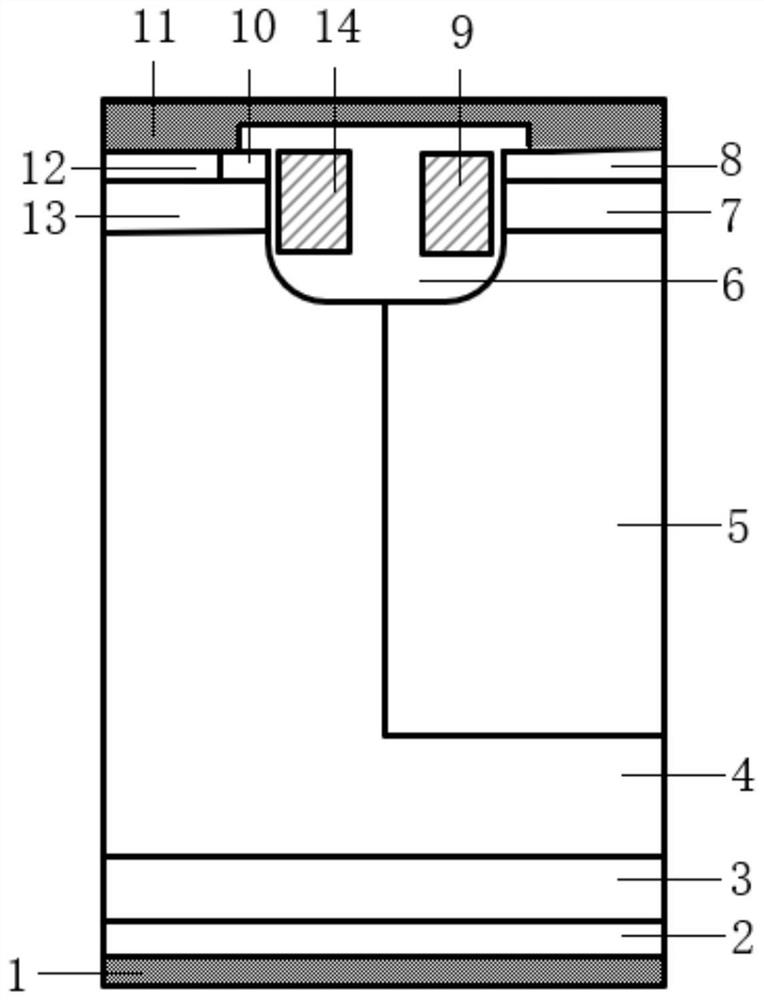

Method for implementing well division construction in super-high density slot type power device design

InactiveCN101393857AShorten the development cycleReduce R&D costsSemiconductor/solid-state device manufacturingHigh densityHigh energy

The invention relates to a novel method for achieving a Split Well structure in the design of an ultrahigh-density groove-type power device, and is effective in solving the problem that the Split Well structure (21) is incompatible with the ultrahigh-density design. Based on the impurity compensation theory, the method is characterized in that the high-energy N-type ion injection (18) and the quick annealing are carried out through a contact hole (22) so as to ensure that the Split Well structure (21) is formed at the bottom part in the middle of a well area (7). With the contact hole (22) over-etched below a silicon surface (23), the process ensures that the energy demand for sequential N-type ion injections is effectively reduced, thereby reducing the probability of injection damage to the well area (7) with less leakage sources that cause current to leak out from the device. Moreover, a higher integrated level can be attained with the Split Well structure 21 achieved in Z direction. The novel Split Well technology leads to a substantial improvement on the design of the device which ensures the long-standing reliability of the device as well as the workability of the on-resistance of the device, the firmness of the device and the reverse recovery characteristic of the body diode of the device.

Owner:成都方舟微电子有限公司

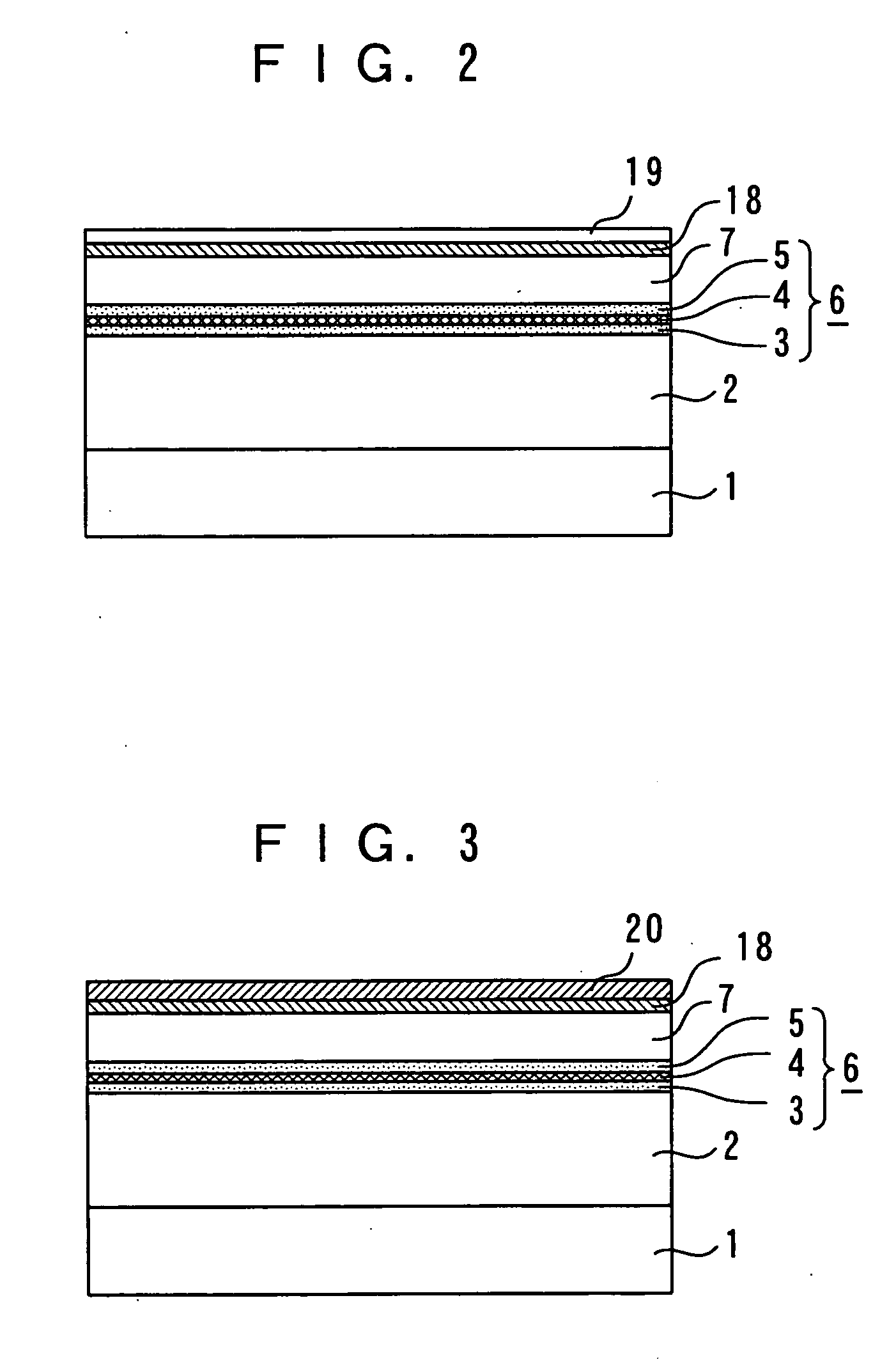

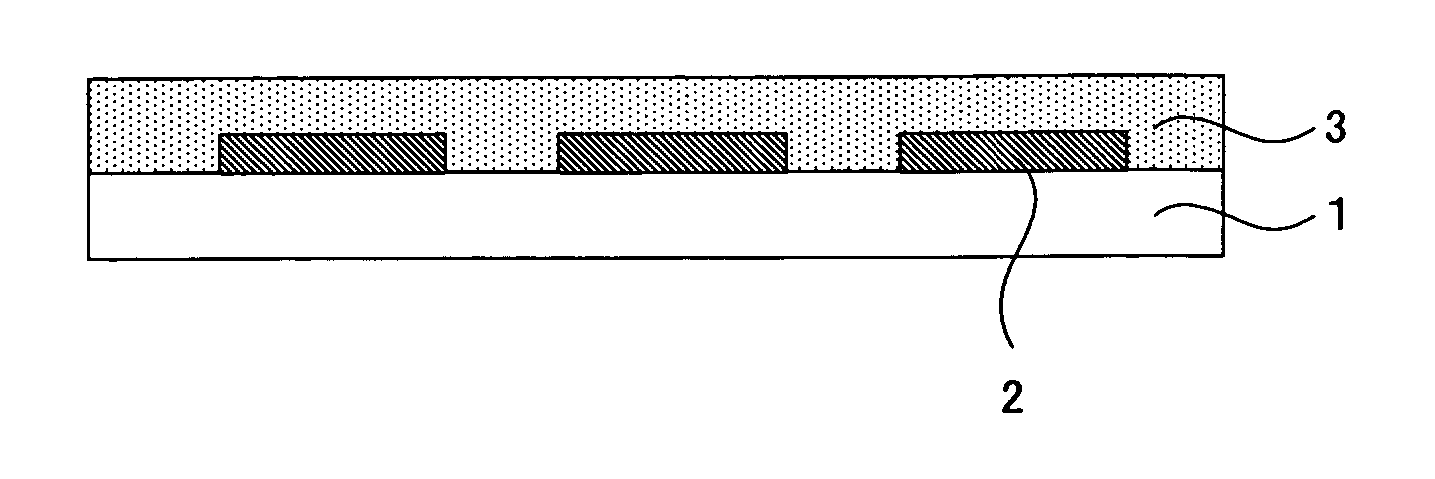

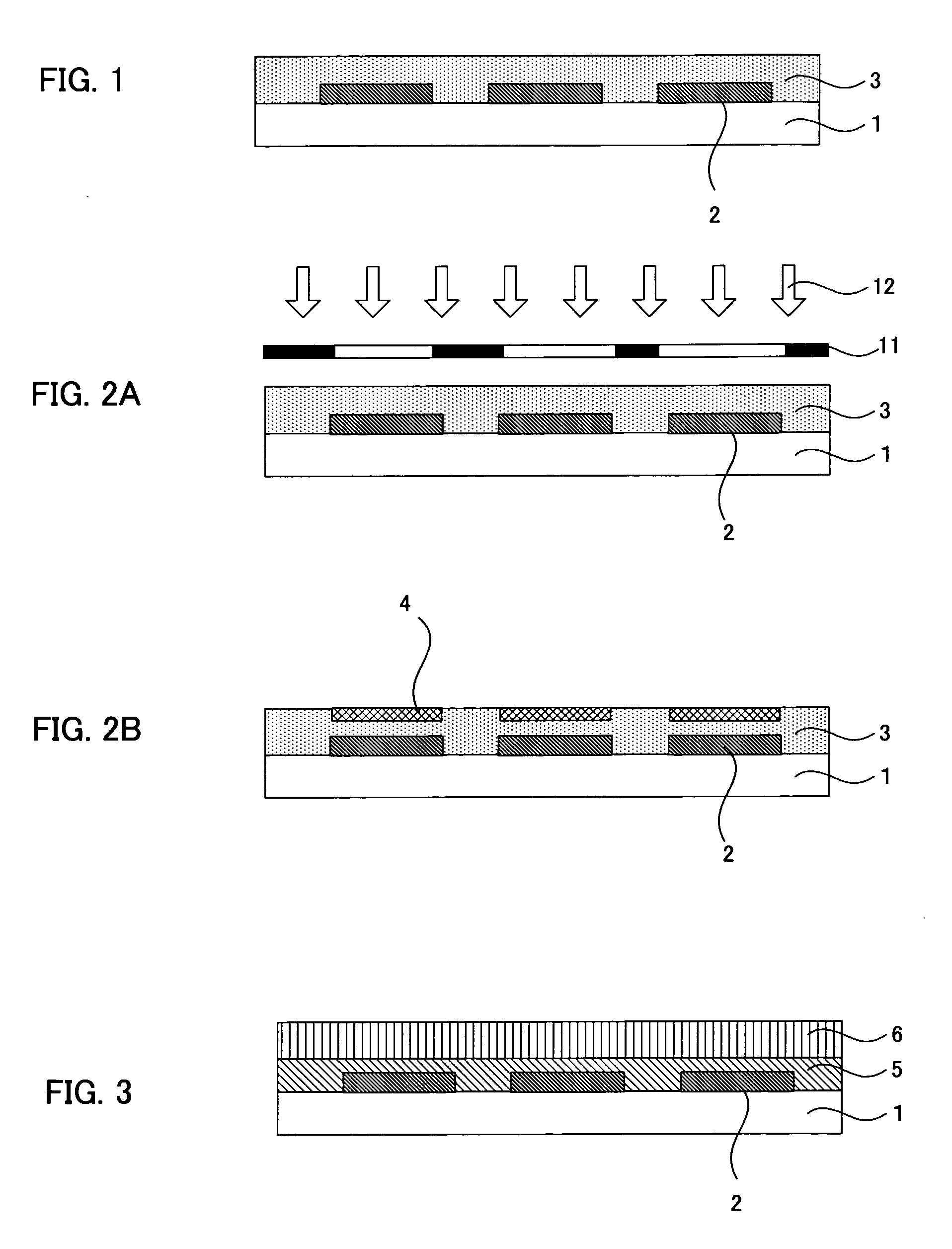

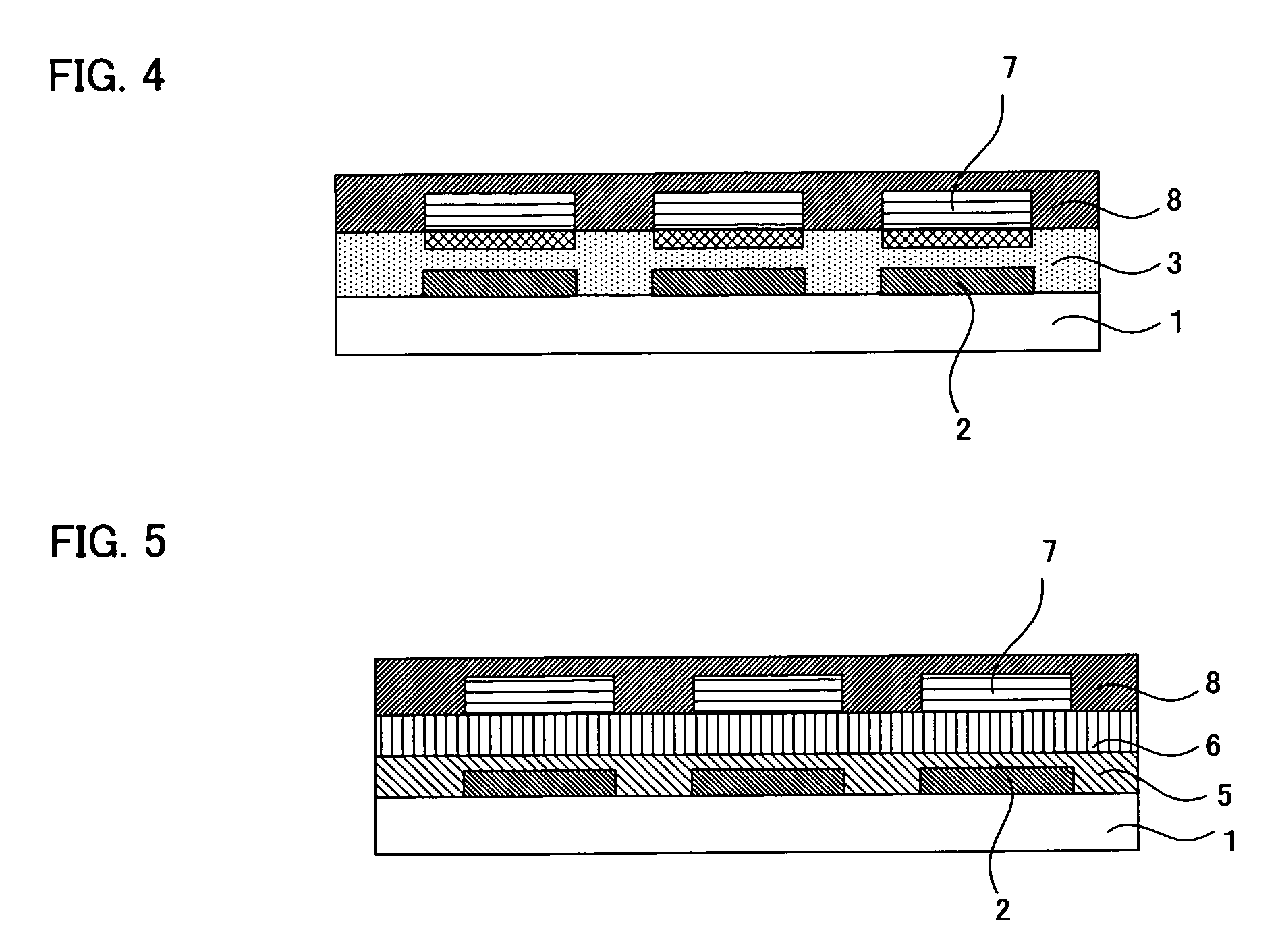

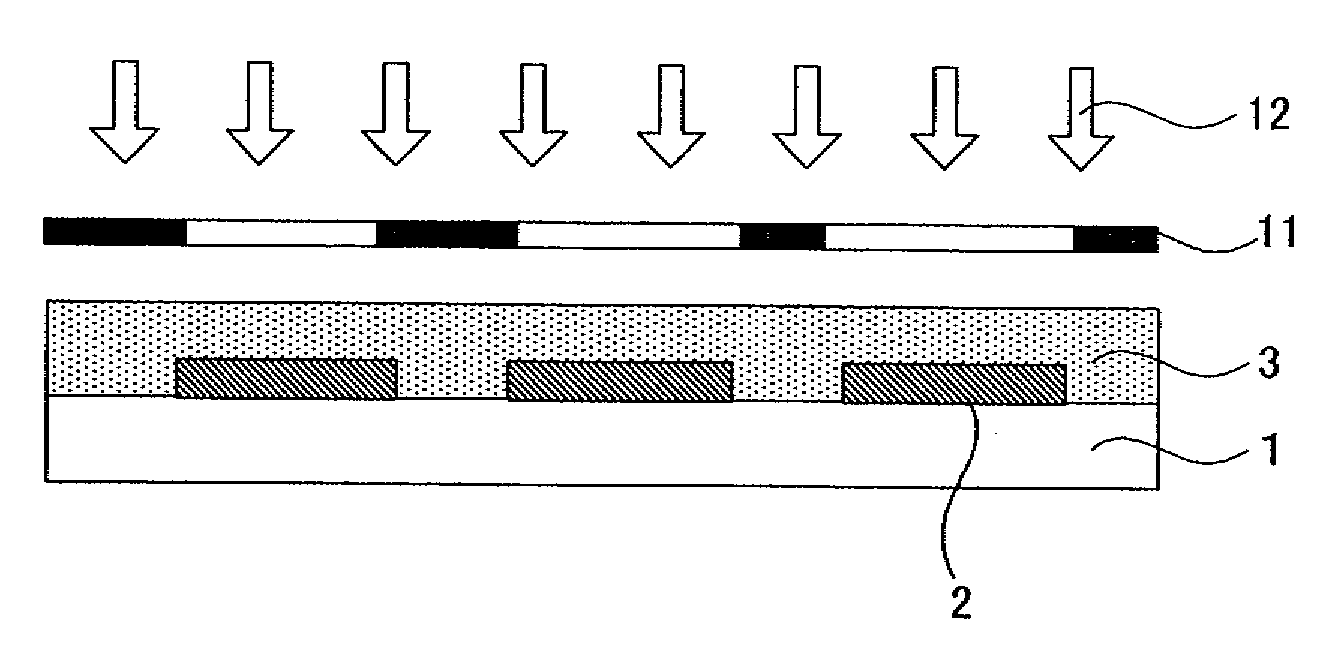

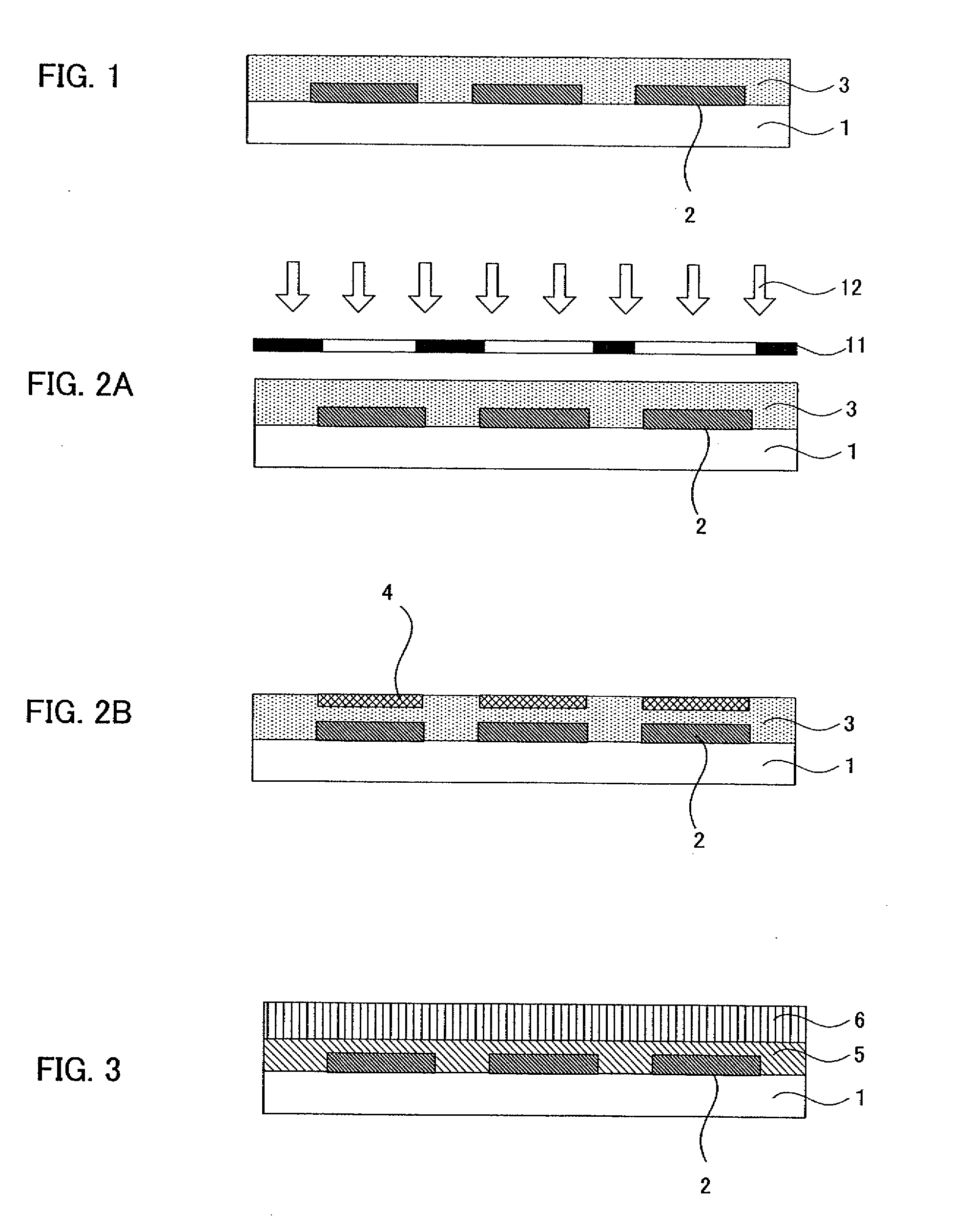

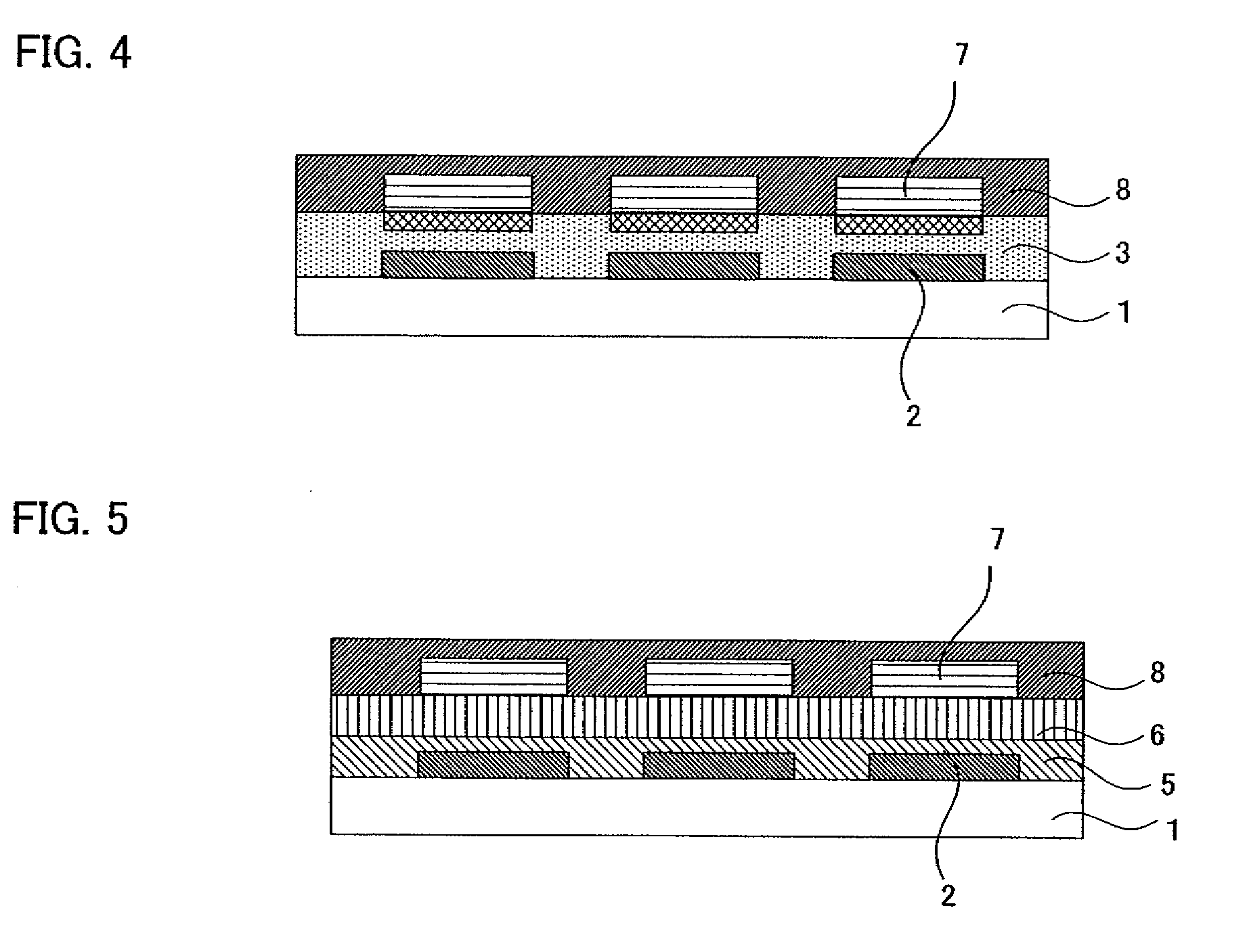

Substrate for organic electroluminescent element, and organic electroluminescent element

InactiveUS20060222890A1Simple processEfficiently formedSolid-state devicesNatural mineral layered productsUltravioletResonance spectrum

The object of the present invention is to provide a substrate for an organic EL element capable of forming an organic EL layer efficiently in a highly precise pattern in a short period of time, and an organic EL element having the preferable electric characteristics. To attain the object, the invention provides a substrate for an organic electroluminescent element comprising a base material, an electrode layer formed in a pattern on the base material, and a photocatalyst containing layer formed to cover the electrode layer and contains a photocatalyst and a binder so as to show the wettability change by the action of the photocatalyst accompanied by the energy irradiation, wherein the photocatalyst containing layer contains a portion with the signal intensity of the electron spin resonance spectrum derived from the hydroxy radical increased to 1,000 times or more in 1 second within 600 seconds of the start of the irradiation of the ultraviolet ray at the time of measuring the electron spin resonance spectrum while irradiating the ultraviolet ray.

Owner:DAI NIPPON PRINTING CO LTD

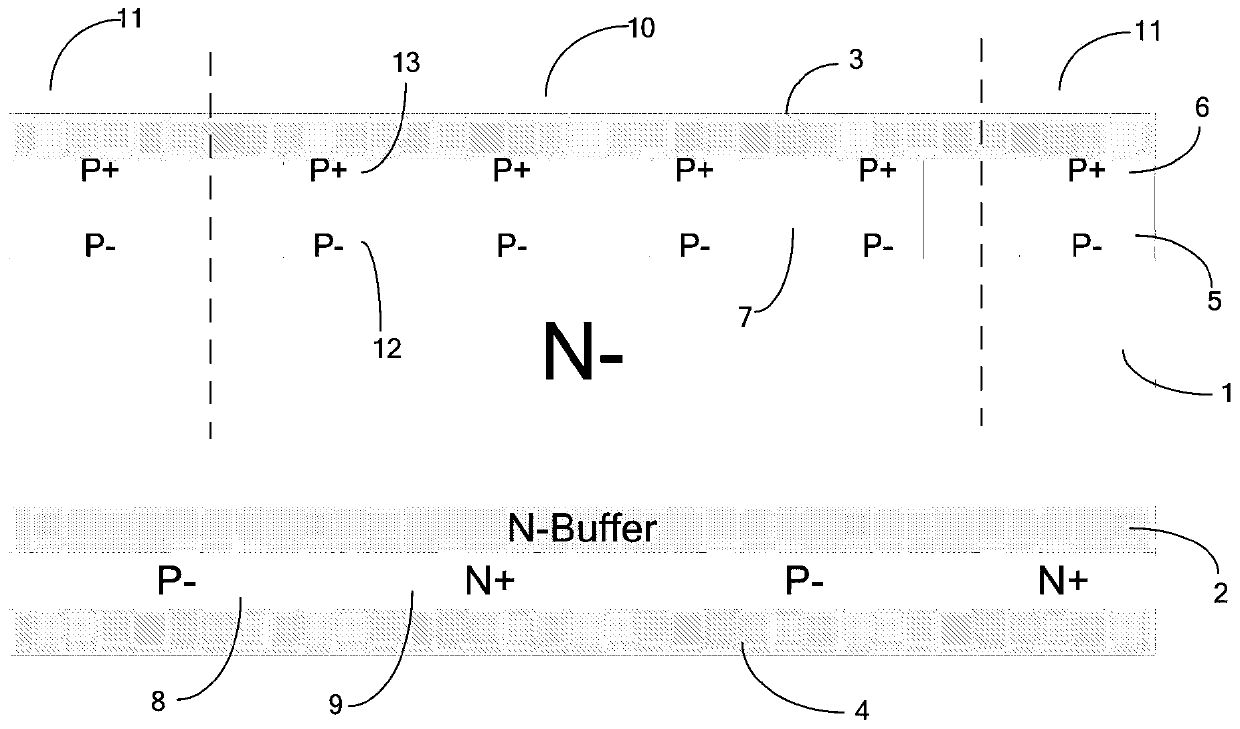

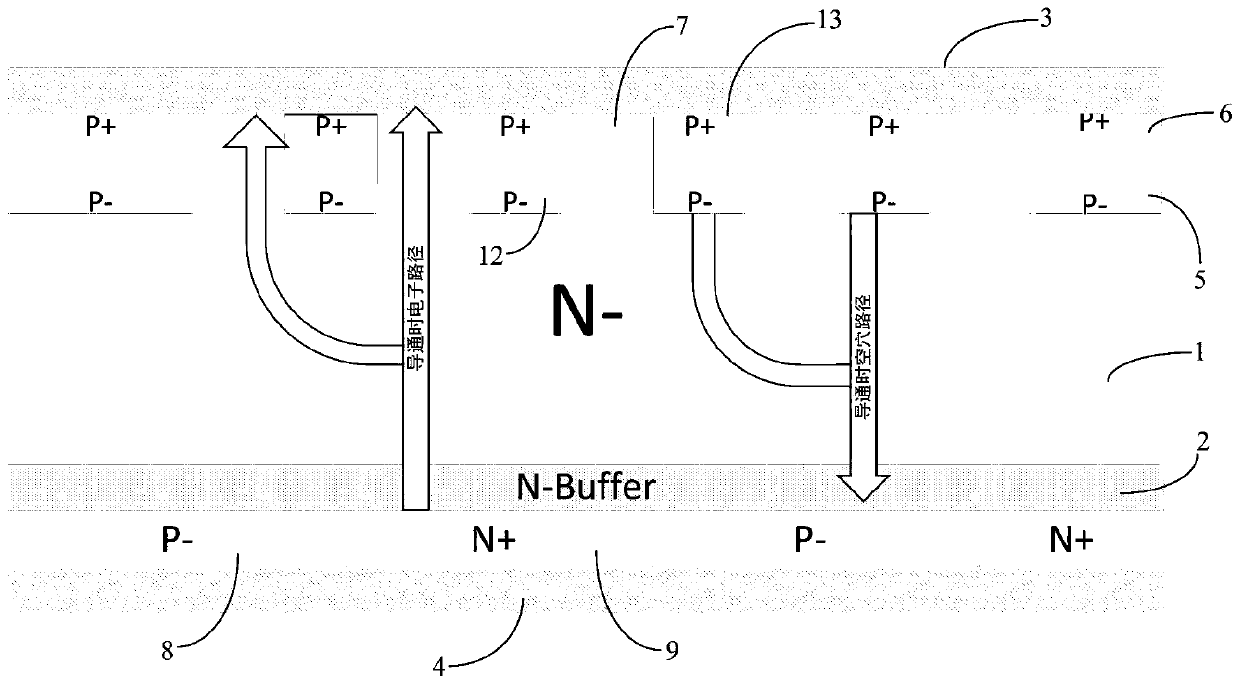

Double-sided Schottky controlled fast recovery diode device and preparation method

ActiveCN110416319ALarge speed changeHigh speedFinal product manufactureSemiconductor/solid-state device manufacturingReverse recoveryOhmic contact

The invention relates to a double-sided Schottky controlled fast recovery diode device and a preparation method. The fast recovery diode device comprises a semiconductor substrate, the semiconductor substrate comprises an N-type substrate and an N-type buffer layer, and an active region is arranged in the central area of the N-type substrate. On the cross section of the diode device, the active region comprises a number of alternately distributed active P-columns and active N-columns. Anode metal is arranged on the N-type substrate. The active P-columns are in ohmic contact with the anode metal on the N-type substrate, and the active N-columns are in Schottky contact with the anode metal on the N-type substrate. A number of alternately distributed cathode P- regions and cathode N+ regionsare arranged on the N-type buffer layer, the cathode N+ regions are in ohmic contact with cathode metal, and the cathode P- regions are in Schottky contact with the cathode metal. Fast reverse recovery can be realized, the dynamic loss can be reduced, the excellent softness can be improved, and the device has high reliability.

Owner:JIANGSU CAS IGBT TECHNOLOGY CO LTD

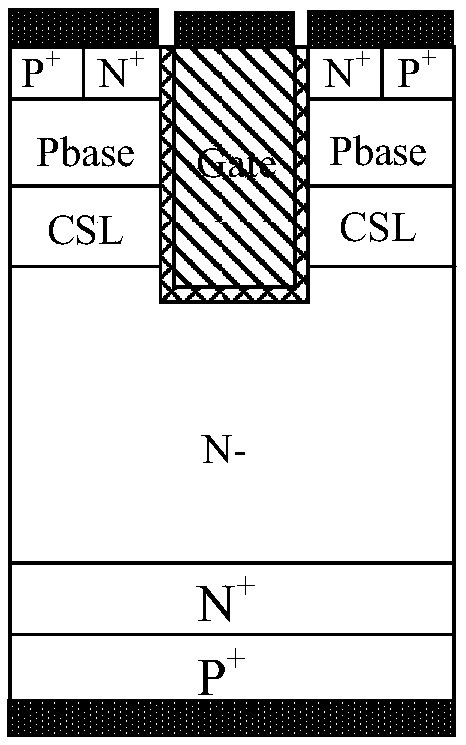

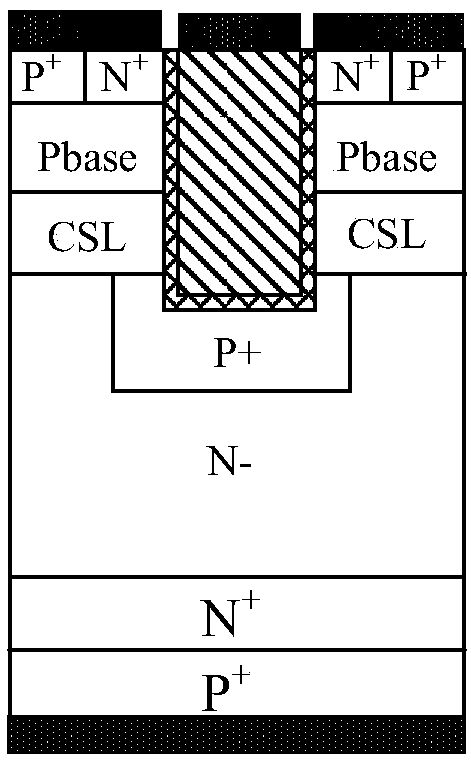

Trench gate IGBT device with carrier storage layer

This invention relates to the power semiconductor field, providing a trench gate IGBT device with carrier storage which is used for solving the problems of high saturation voltage, small short circuitsafe working area and limited concentration of the existing trench gate IGBT device with carrier storage layer, and put forward a novel trench gate IGBT device with carrier storage layer. The trenchgate IGBT device with carrier storage layer directly integrates a plurality of series diodes on the surface of silicon wafers to clamp the potential of the electric field shielding layer in the P region, thereby breaking the concentration limit of CSL on the basis of trench gate IGBT process, greatly improving the injection efficiency of IGBT emitter and greatly improving the trade-off relation between forward voltage drop and turn-off loss of IGBT. Meanwhile, due to the clamping effect of the diode, the drain near the IGBT nMOS channel is clamped at a lower voltage under high voltage and large current, thereby greatly reducing the saturation current of the novel IGBT and improving the short circuit safe working area of IGBT.

Owner:杭州朋声科技有限公司

Substrate for organic electroluminescent element, and organic electroluminescent element

InactiveUS20100127706A1High-precision patternShort timeSolid-state devicesMeasurements using electron paramagnetic resonanceUltravioletOrganic electroluminescence

The object of the present invention is to provide a substrate for an organic EL element capable of forming an organic EL layer efficiently in a highly precise pattern in a short period of time, and an organic EL element having the preferable electric characteristics.To attain the object, the invention provides a substrate for an organic electroluminescent element comprising a base material, an electrode layer formed in a pattern on the base material, and a photocatalyst containing layer formed to cover the electrode layer and contains a photocatalyst and a binder so as to show the wettability change by the action of the photocatalyst accompanied by the energy irradiation, wherein the photocatalyst containing layer contains a portion with the signal intensity of the electron spin resonance spectrum derived from the hydroxy radical increased to 1,000 times or more in 1 second within 600 seconds of the start of the irradiation of the ultraviolet ray at the time of measuring the electron spin resonance spectrum while irradiating the ultraviolet ray.

Owner:DAI NIPPON PRINTING CO LTD

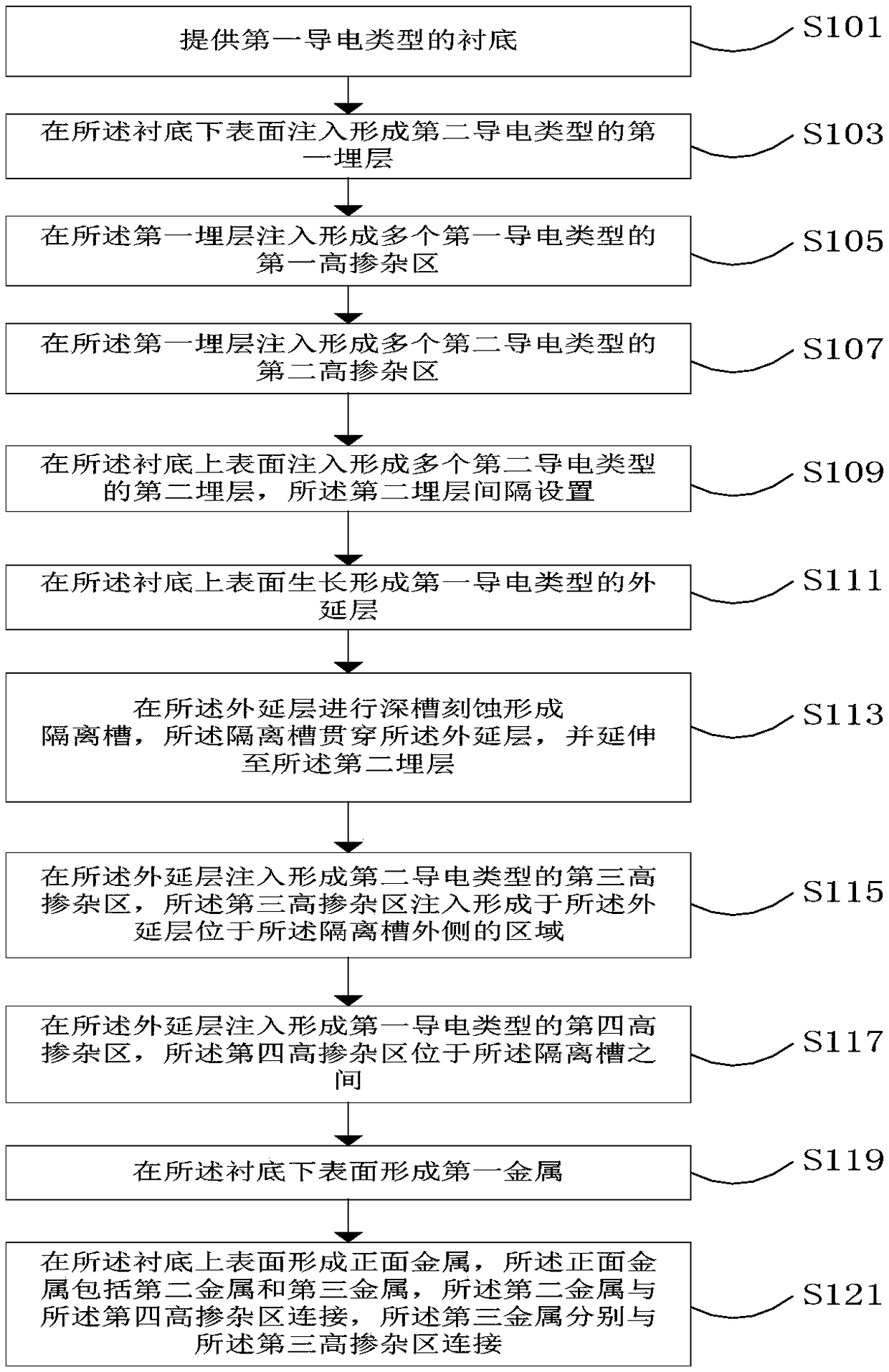

Static induction thyristor and manufacturing method thereof

InactiveCN109449205AReduce switching lossesReduce power consumptionThyristorSemiconductor/solid-state device manufacturingReverse recoveryVoltage drop

The invention provides a static induction thyristor and a manufacturing method thereof, and solves the problem that an SITH obtained in the prior art cannot meet the latest use requirements. A first highly-doped region is added to a positive electrode region of a device, so that a parasitic transistor is formed; the conduction voltage drop of the SITH is reduced, and meanwhile, the injection efficiency of a positive electrode is reduced by the first highly-doped region of the positive electrode region, so that the reverse recovery time is shortened, and the reverse recovery charge is also obviously reduced; and the final SITH device has a higher switching speed and lower switching loss. An epitaxial layer is also added between a fourth highly-doped region and a substrate, so that the effect of a buffer layer is achieved; during the reverse recovery period, the electric field intensity of the substrate and the epitaxial layer is reduced and the extraction speed of carriers is reduced, so that high-voltage oscillation is remarkably reduced, and a softer recovery characteristic is obtained; and the reverse recovery charge is less, so that the power consumption of the device is furtherreduced.

Owner:中健共创(深圳)大健康产业投资有限公司

Quantum dot light emitting diode and preparation method thereof

ActiveCN110739408AImprove hole injection efficiencyLower the barrierSolid-state devicesSemiconductor/solid-state device manufacturingQuantum dotAnode

The invention belongs to the field of display technologies, and particularly relates to a quantum dot light emitting diode and a preparation method thereof. The quantum dot light emitting diode includes an anode, a cathode, and a quantum dot light emitting layer arranged between the anode and the cathode. A first interfacial dipole layer which is used for improving the work function of the anode is arranged between the anode and the quantum dot light emitting layer, and / or a second interfacial dipole layer which is used for reducing the work function of the cathode is arranged between the cathode and the quantum dot light emitting layer. The first interface dipole layer and / or the second interface dipole layer are arranged, so as to improve the carrier injection efficiency in the quantum dot light emitting diode, and finally improve the light emitting performance thereof.

Owner:TCL CORPORATION

A trench-gate vdmos device with integrated schottky diode

InactiveCN103441148BReduced injection efficiencyShort storage timeDiodeContact formationReverse recovery

A trench gate VDMOS device integrating Schottky diodes belongs to the technical field of semiconductor devices. In the present invention, an additional structure composed of Schottky junction metal and body electrode conductive material is respectively added to the drift region on both sides of the groove gate structure of the conventional groove gate VDMOS device; It is in contact with the conductive material of the body electrode, and the rest of the lower surface and side parts are in contact with the drift region to form a Schottky junction; the side and bottom surfaces of the conductive material of the body electrode and the drift region are separated by a layer of dielectric layer. Compared with the traditional trench-gate VDMOS device with the same size, the present invention can adopt a higher doping concentration in the drift region under the same breakdown voltage, so the on-resistance is significantly reduced, and the reverse recovery characteristic of the diode is significantly improved. improvement.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Super junction IGBT device with low loss performance and production method thereof

PendingCN113964180AImprove the blocking effectLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate oxideConductivity modulation

The invention discloses a super junction IGBT device with low loss performance. The device comprises a collector electrode, a P collector electrode region, an N-buffer region, an N-pillar region, a P-pillar region, a gate oxide layer, an N-base region, a P injection region, a first grid electrode, a second grid electrode, an N + injection region, source electrode metal, a P + injection region and a P-base region. According to the invention, negative ions are injected into the oxide layer of the second grid electrode of the device, a depletion type P-channel MOS tube can be formed with a P-pillar region, an N-base region and a P injection region, the MOS tube can be used as a switch of a storage hole of the device, and when an IGBT is conducted, the MOS tube is closed and then stores the hole so that the conductivity modulation effect is improved, the on resistance of the device is reduced, and the conduction power consumption is decreased; and when the IGBT is closed, the MOS tube is opened to release holes, a low-resistance channel is provided, hole outflow is accelerated, the switching speed is increased, and the switching loss is reduced.

Owner:广州华浦电子科技有限公司

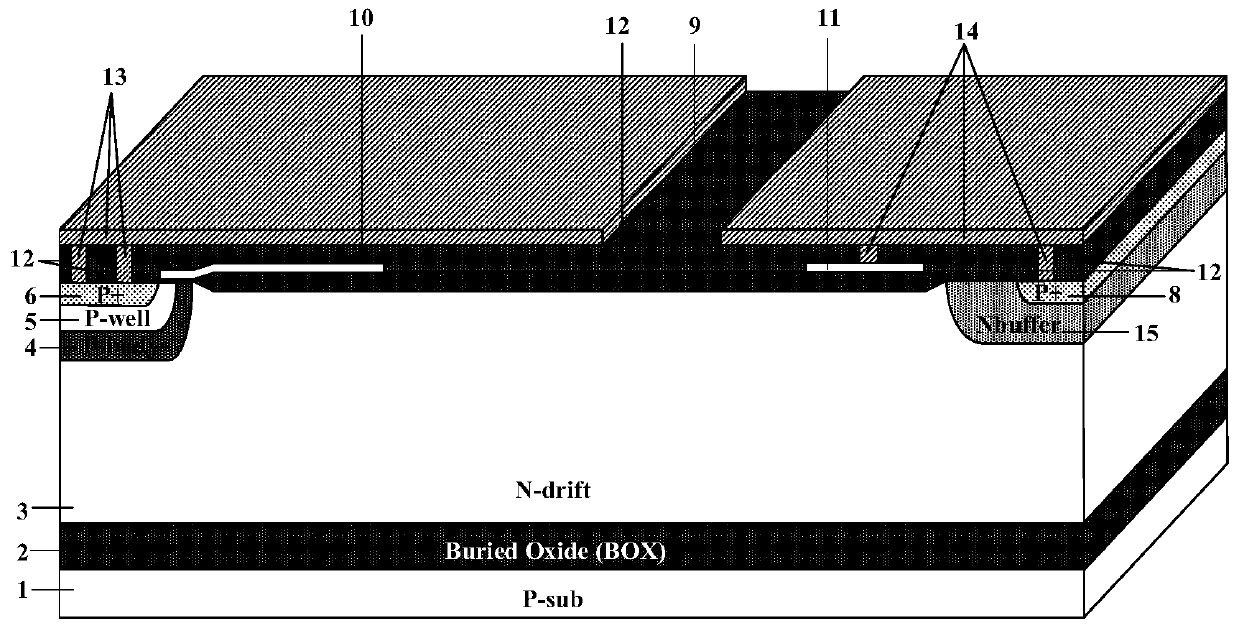

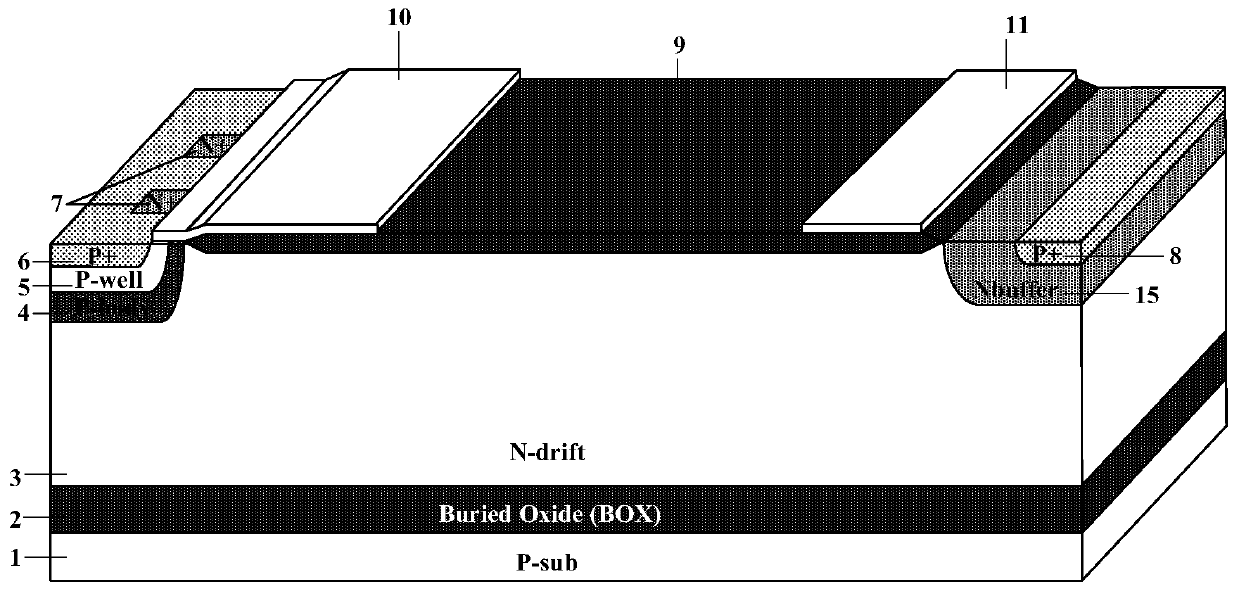

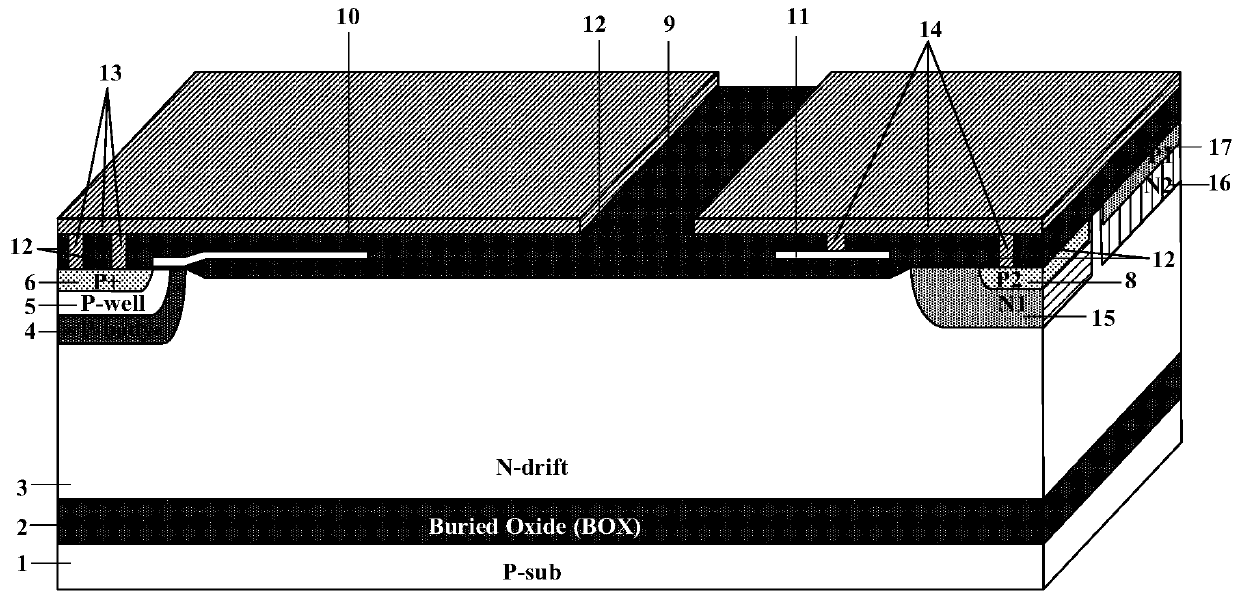

Silicon-on-insulator transverse insulated gate bipolar transistor with low saturation current

ActiveCN111430454ALarge linear currentReduced injection efficiencySemiconductor devicesPhysical chemistryEngineering

The invention discloses a silicon-on-insulator transverse insulated gate bipolar transistor with low saturation current. The According to the semiconductor is provided with:, a semiconductor substrate; wherein a buried oxide layer is arranged on the a P-type substrate; an N-type drift region is arranged above on the buried oxide layer; , wherein a P-type body region, a field oxide layer and a collector region are arranged on the N-type drift regionsubstrate; connected P traps are arranged in the P-type body region; a P-type emitter region is arranged in the P traps; an N-type emitter region isarranged on the P-type emitter region; an oxide layer is arranged above on the P-type body region, the P traps, the P-type emitter region, the field oxide layer and the collector region; a polysilicon gate is arranged between the field oxide layer and the oxide layer and extends to the upper part of the P traps; a gate oxide layer is arranged among the P traps, the P-type body region and the polysilicon gate,; wherein the collector region comprises a heavily-doped N-type collector region and a lightly-doped N-type collector region which are arranged in the N-type drift region and isolated bythe N-type drift region, a lightly-doped P-type collector region is arranged in the heavily-doped N-type collector region, and a heavily-doped P-type collector region is arranged in the lightly-dopedN-type collector region.

Owner:SOUTHEAST UNIV

Collector back side structure of insulated gate type bipolar transistor

ActiveCN103066120AReduced injection efficiencyImprove switching performanceSemiconductor devicesInsulated-gate bipolar transistorEngineering

The invention relates to a collector back side structure of an insulated gate type bipolar transistor. The collector back side structure of the insulated gate type bipolar transistor comprises a silicon base layer and a collector metal layer, a high concentration injection region and a low concentration injection region distributed in a spaced mode are arranged on the back side of the silicon base layer, and thickness of the silicon base layer at the corresponding position of the high concentration injection region is smaller than thickness of the silicon base layer at the corresponding position of the low concentration injection region. By distributing the high concentration injection region and the low concentration injection region in a spaced mode, injection efficiency of the back side collector can be effectively reduced, and switch property of components is improved. Compared with sheet and ultrathin sheet process, average thickness of chips is increased and fractional danger can be reduced.

Owner:JIANGSU CAS JUNSHINE TECH +1

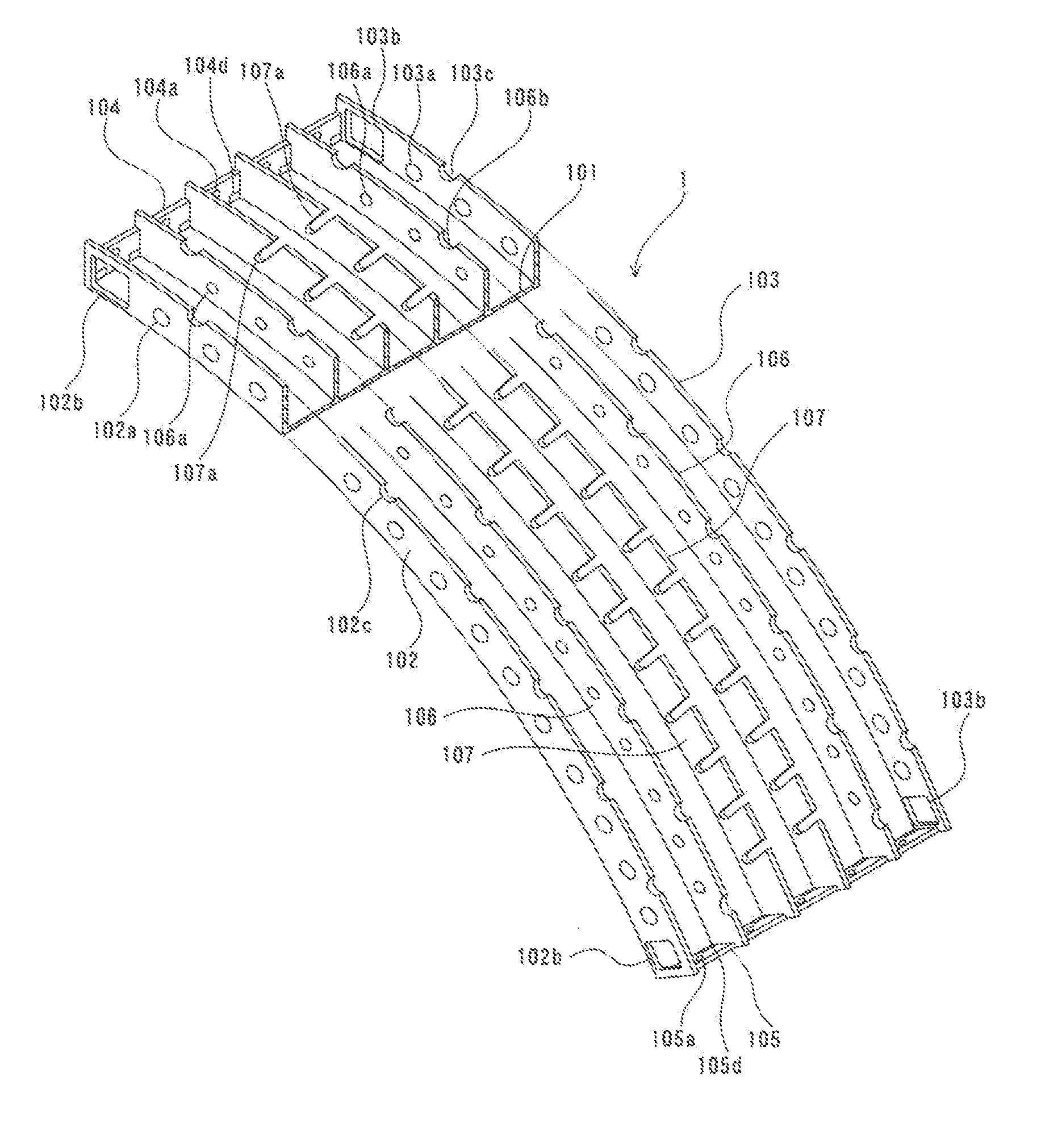

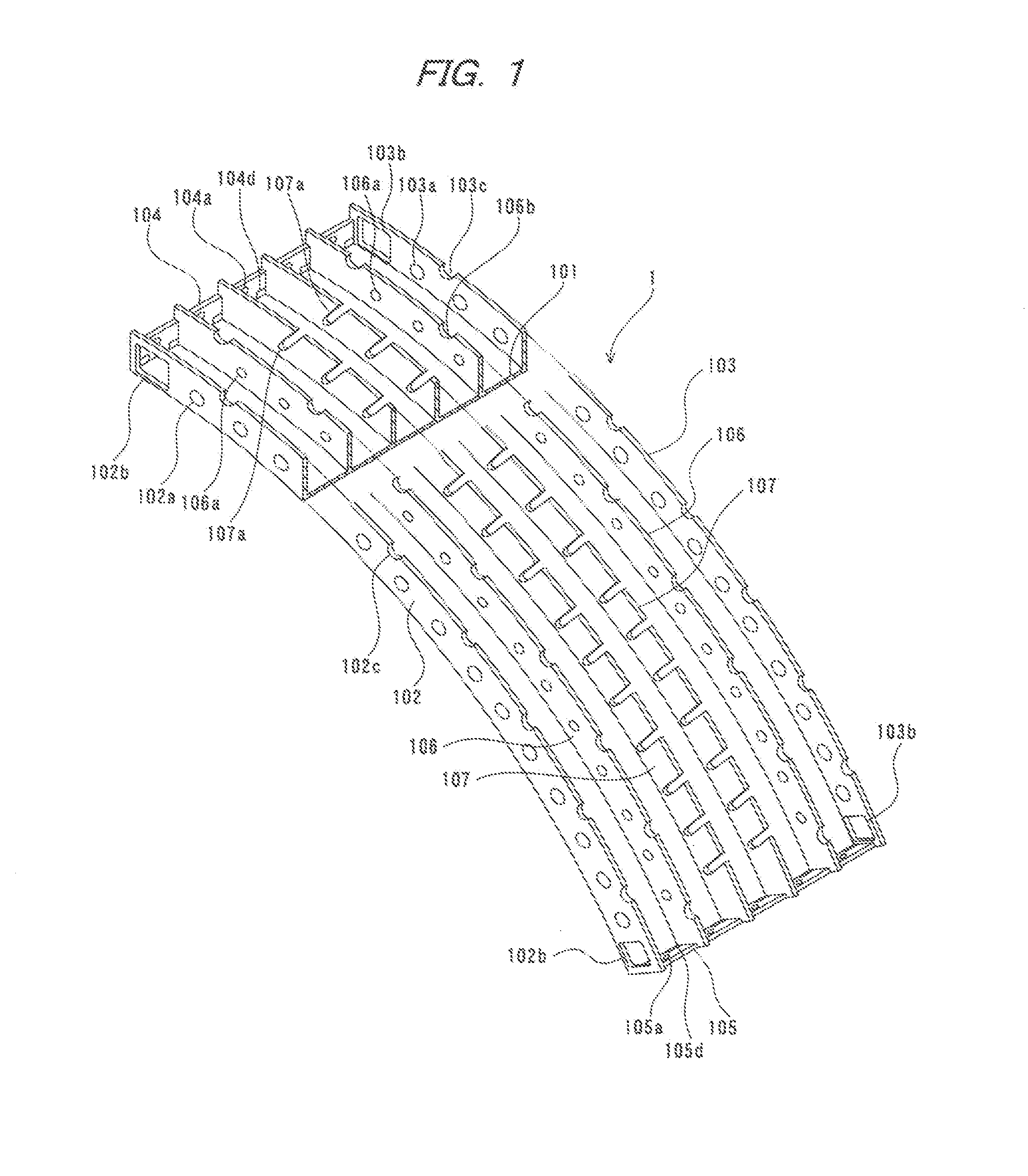

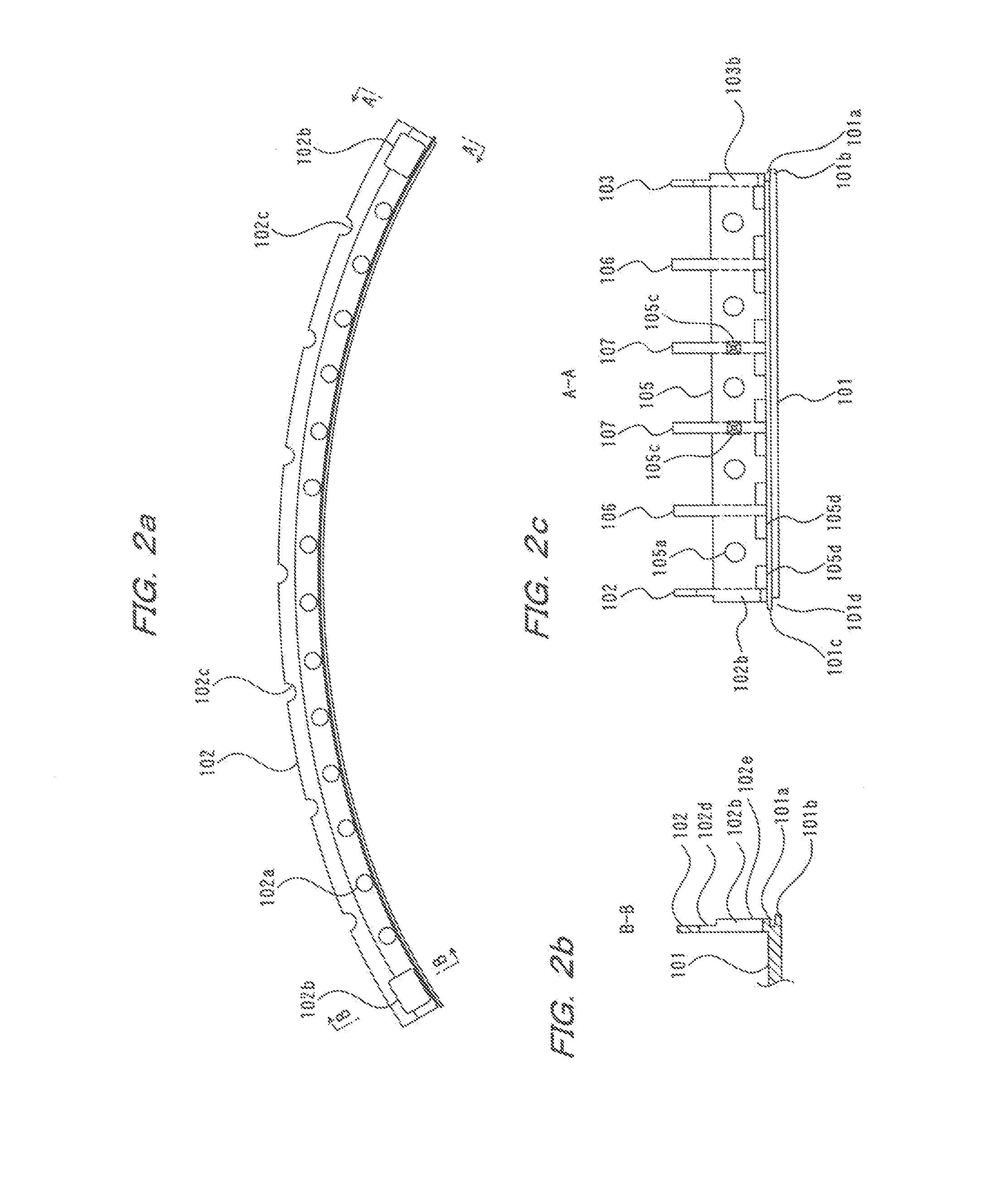

Segment for a rehabilitation pipe, and pipe rehabilitation method

ActiveUS20140096855A1Reduce the cross-sectional areaReduced injection efficiencyPipe elementsService pipe systemsFilling materialsPlastic materials

A segment for a rehabilitation pipe comprises an inner surface plate constituting an inner circumferential surface, and side plates and end plates provided upright on a peripheral edge of the inner surface plate. The plates are formed integrally from a plastic material and the segments are linked in a circumferential direction and in a pipe-length direction to install a segmental rehabilitation pipe inside an existing pipe. The end plates are provided with an insertion hole through which a linking member is inserted when the segments are linked in the circumferential direction, and provided separately from the insertion hole with an opening for passing therethrough a filler material injected into a space between the existing pipe and the rehabilitation pipe. The side plates are provided at upper edges thereof with notches for passing therethrough a filler material injected into the space between the existing pipe and the rehabilitation pipe.

Owner:SHONAN GOSEI JUSHI SEISAKUSHO KK

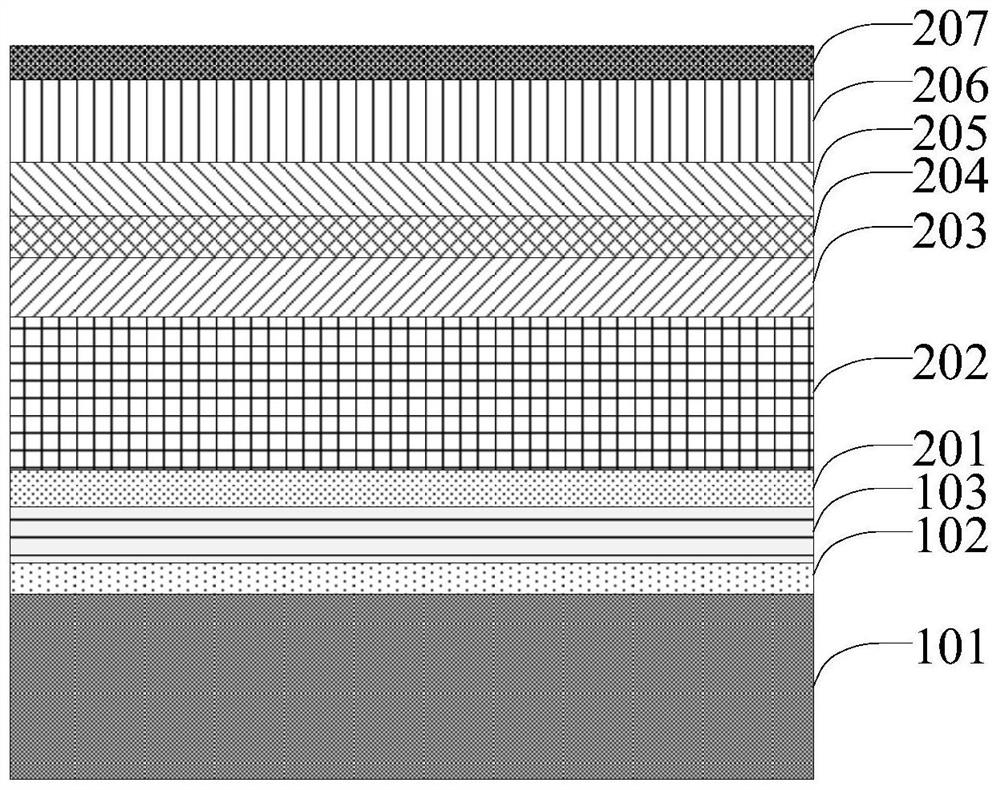

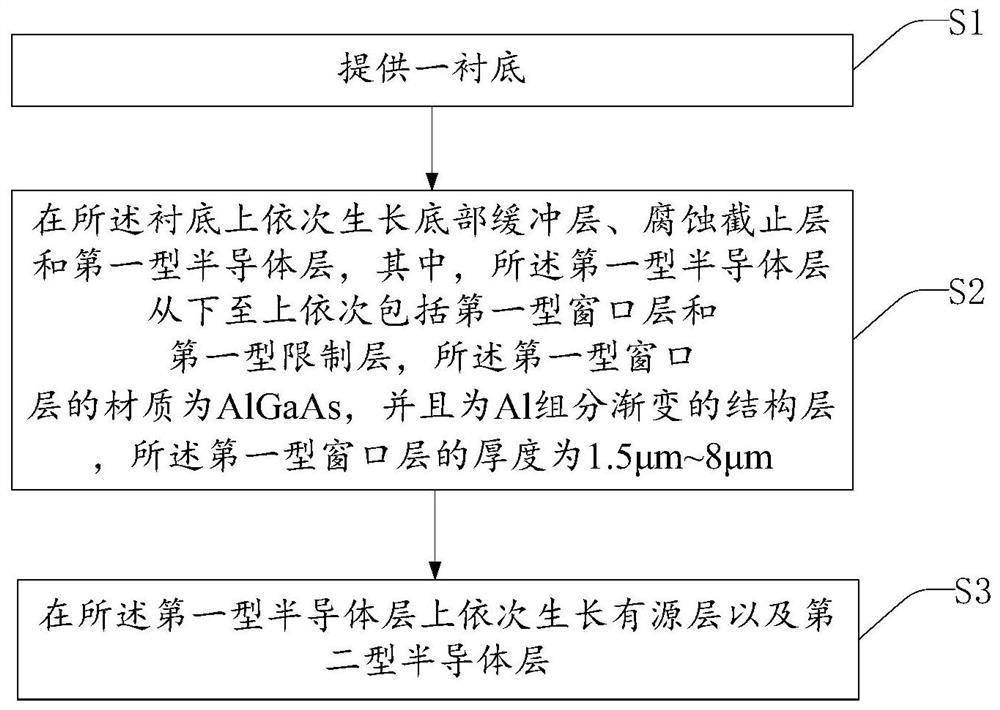

LED epitaxial structure and preparation method thereof

PendingCN114023857AReduce internal reflection lossIncrease the exit angleSemiconductor devicesActive layerMaterials science

The invention provides an LED epitaxial structure and a preparation method thereof. The LED epitaxial structure sequentially comprises a bottom buffer layer, a corrosion cut-off layer, a first type semiconductor layer, an active layer and a second type semiconductor layer from bottom to top, wherein the bottom buffer layer, the corrosion cut-off layer, the first type semiconductor layer, the active layer and the second type semiconductor layer are located on a substrate, the first type semiconductor layer sequentially comprises a first type window layer and a first type limiting layer from bottom to top, the first type window layer is made of AlGaAs and is a structural layer with an Al component being gradually changed, and the thickness of the first type window layer is 1.5 microns to 8 microns. The light emitting efficiency of the LED chip can be improved, the working voltage of the LED chip can be reduced and the high-temperature aging stability of the LED chip can be improved by forming the first type window layer with the Al component being gradually changed.

Owner:XIAMEN SILAN ADVANCED COMPOUND SEMICON CO LTD

A kind of epitaxial growth method that improves LED luminous efficiency

InactiveCN104332544BComposite Luminous Efficiency DecreaseWeaken energySemiconductor devicesQuantum wellLight emission

The invention provides a novel LED epitaxial growth method which can effectively improve the lighting efficiency of LED epitaxial structures. The method comprises the links of N-GaN layer growth, multi-quantum well layer growth and P-GaN layer growth, wherein the multi-quantum well layer is of a structure of a plurality of pairs of AlxGa <1-x> N / InyGa <1-y> N, wherein x is more than 0 and less than 1, and y is more than 0 and less than 1; the multi-quantum well layer growth link includes three growth stages in sequence, wherein the AlxGa1-xN quantum barrier is subjected to p type doping in the first stage, the AlxGa1-xN quantum barrier is not doped in the second stage, and the AlxGa1-xN quantum barrier is subjected to n type doping in the third stage; a p type doped AlGaN stopping layer grows, and then the P-GaN layer growth link is performed.

Owner:西安利科光电科技有限公司

Trench-fs type IEGT structure and manufacturing method thereof

InactiveCN110047751AReduced injection efficiencyImprove injection efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesLow voltagePeak value

The present invention relates to a Trench-fs type IEGT structure and a manufacturing method thereof. A collector is injected in two times, to form segmented collectors with different junction depths,a photoetching board adopted for forming a p++ region on the back surface and a p dummy region on the front surface adopt the same board, and a Trench-fs type IEGT structure capable of compromising switching and short circuit is obtained. According to the novel Trench-fs type IEGT structure, under a low voltage, the hole injection efficiency of the collector is lower than that of a conventional structure, under a high voltage, the hole injection efficiency of the collector is higher than that of the conventional structure, the grid voltage peak value in a short circuit period can be suppressedwithout increasing loss, and the switching and the short circuit of the IEGT can be compromised.

Owner:XIAN LONTEN RENEWABLE ENERGY TECH

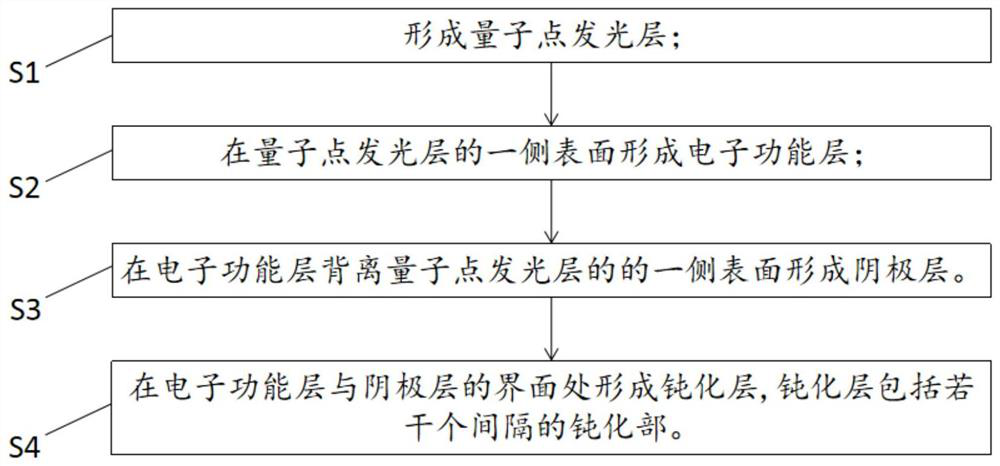

Quantum dot light-emitting diode, preparation method thereof, display panel and display device

ActiveCN112750956AReduced injection efficiencyReduce accumulationSolid-state devicesSemiconductor/solid-state device manufacturingElectron holeDisplay device

The invention discloses a quantum dot light-emitting diode, a preparation method thereof, a display panel and a display device. The quantum dot light-emitting diode comprises a quantum dot light-emitting layer, an electronic function layer, a cathode layer and a passivation layer, wherein the electronic function layer is located on one side of the quantum dot light-emitting layer; the cathode layer is positioned on one side, deviating from the quantum dot light-emitting layer, of the electronic functional layer; and the passivation layer is positioned between the electronic function layer and the cathode layer, and comprises a plurality of passivation parts which are arranged at intervals. According to the quantum dot light-emitting diode, the number difference of holes and electrons transmitted to the quantum dot light-emitting layer is reduced, the electron accumulation degree in the quantum dot light-emitting layer is finally reduced, and the device performance is improved.

Owner:义乌清越光电科技有限公司 +1