Patents

Literature

48results about How to "Inhibit on" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

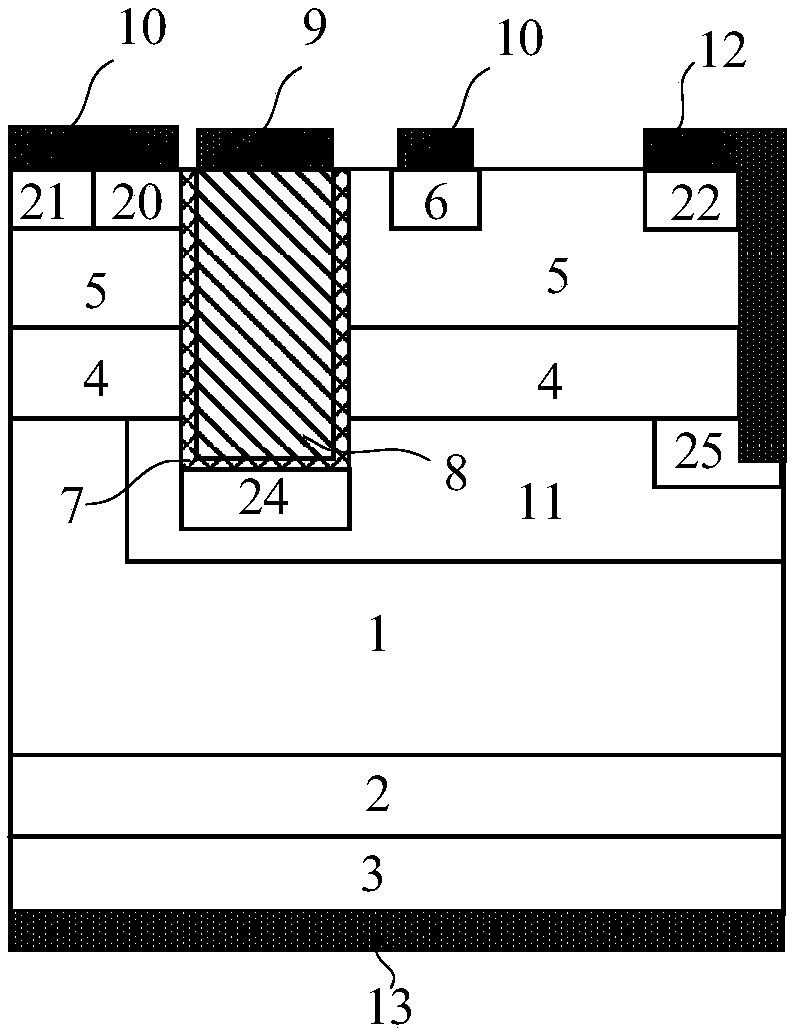

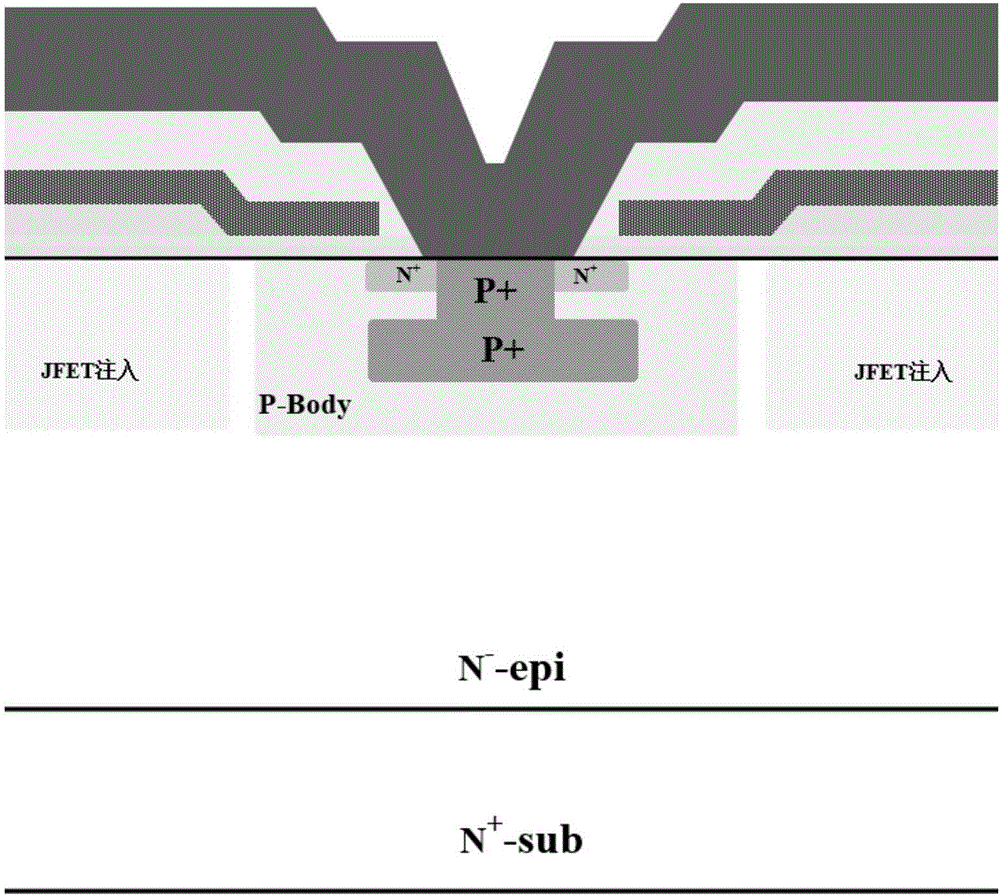

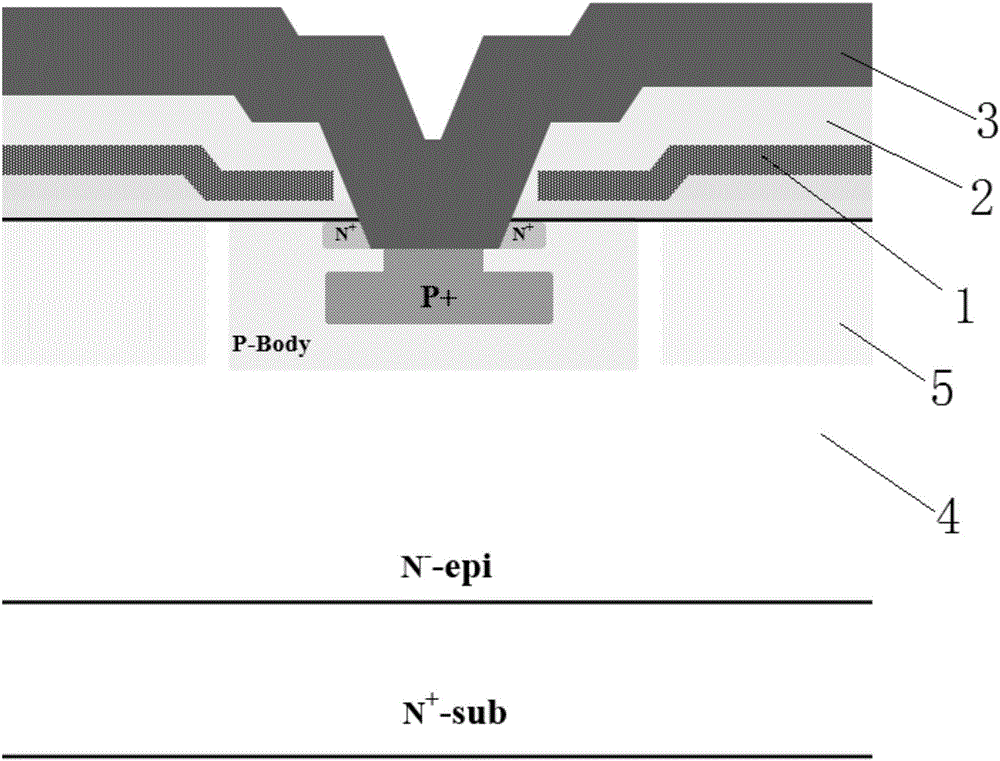

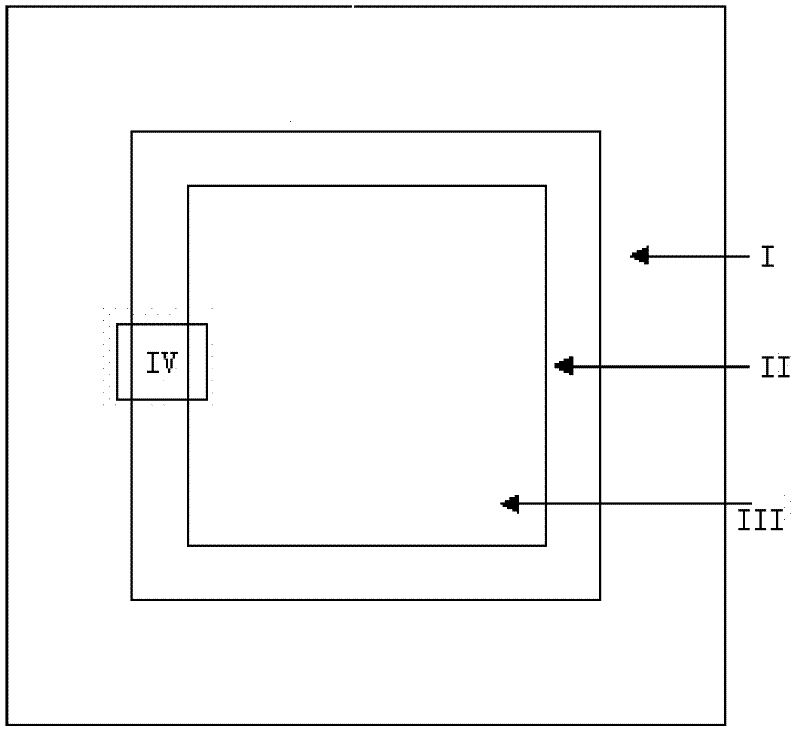

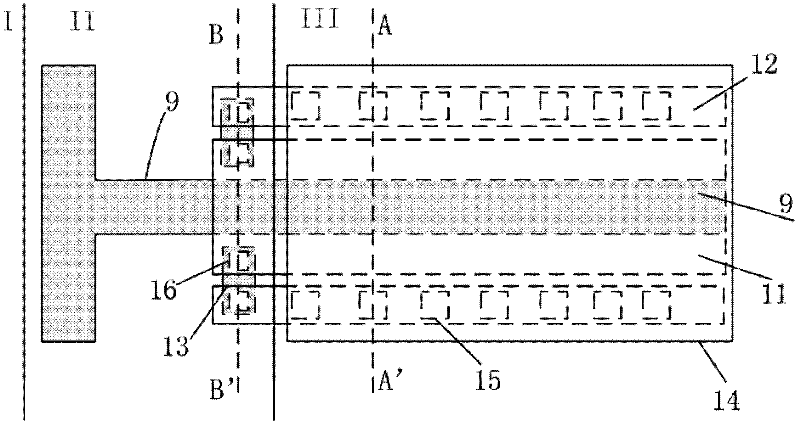

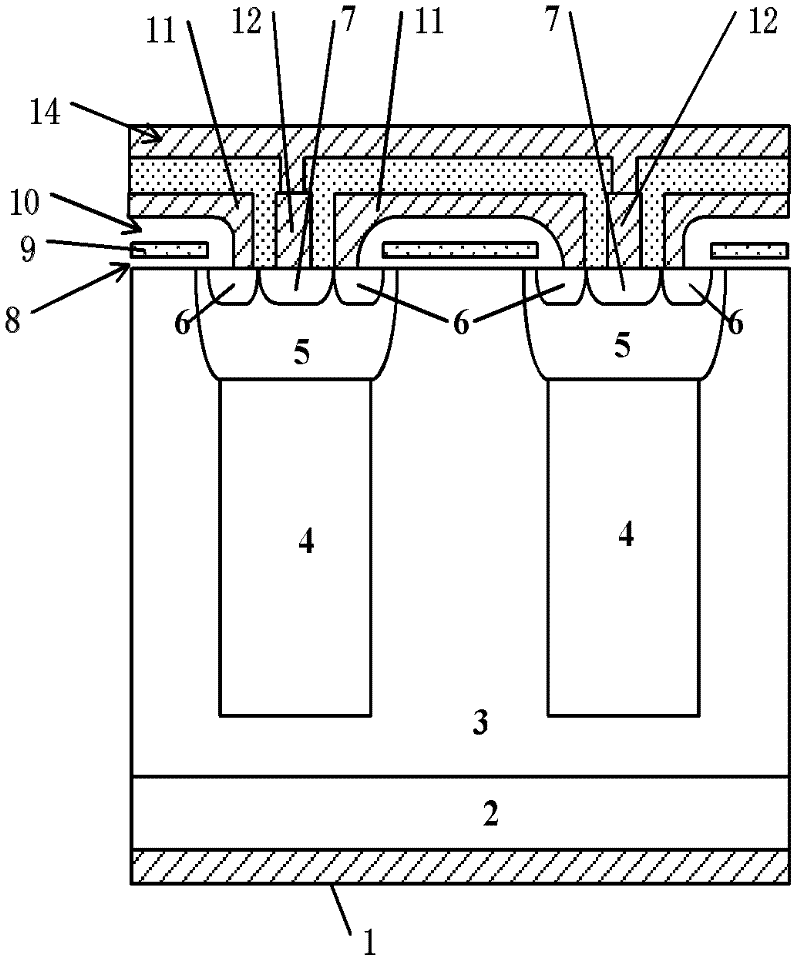

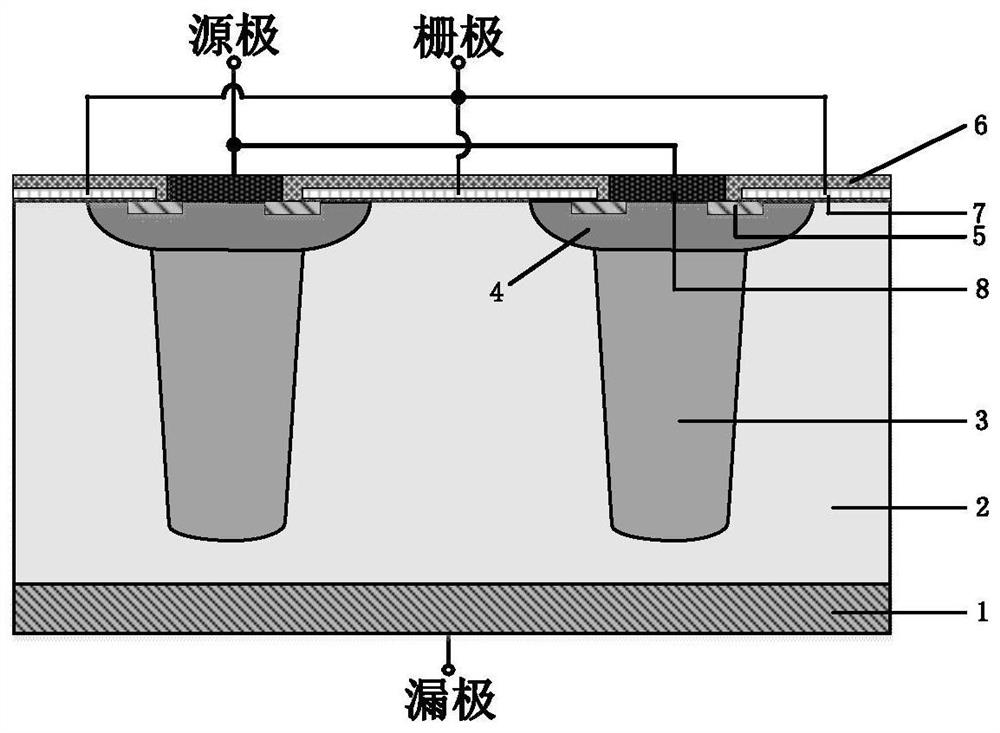

Silicon carbide MOSFET device and manufacturing method thereof

InactiveCN105762176AInhibit onImprove the ability to resist UIS failureSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEtching

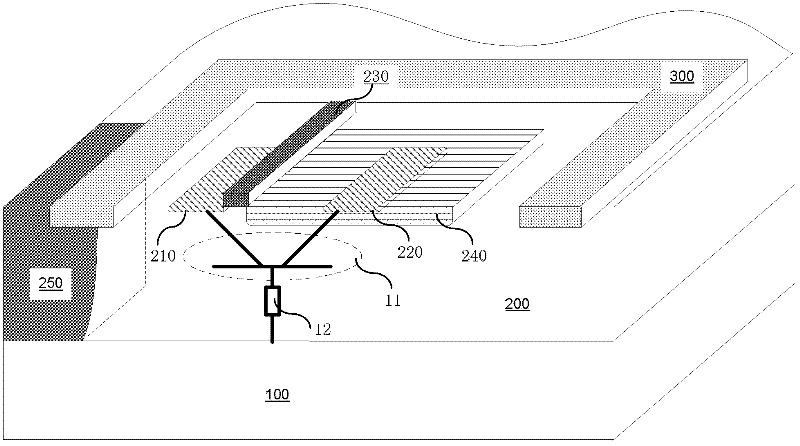

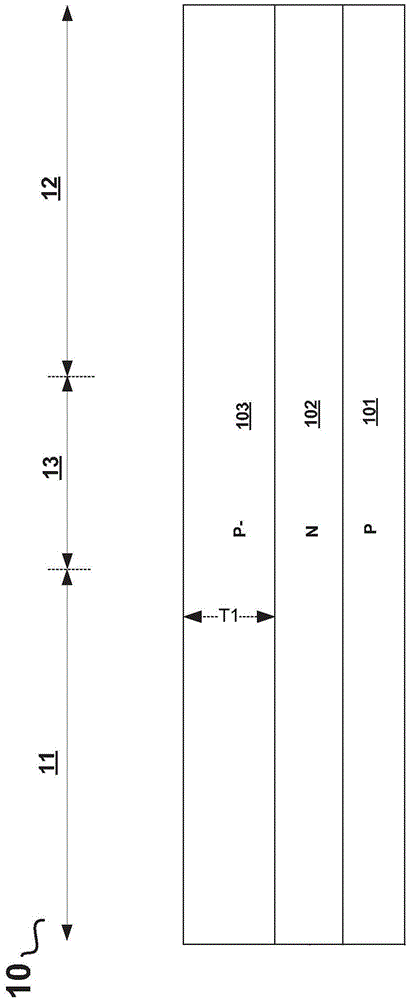

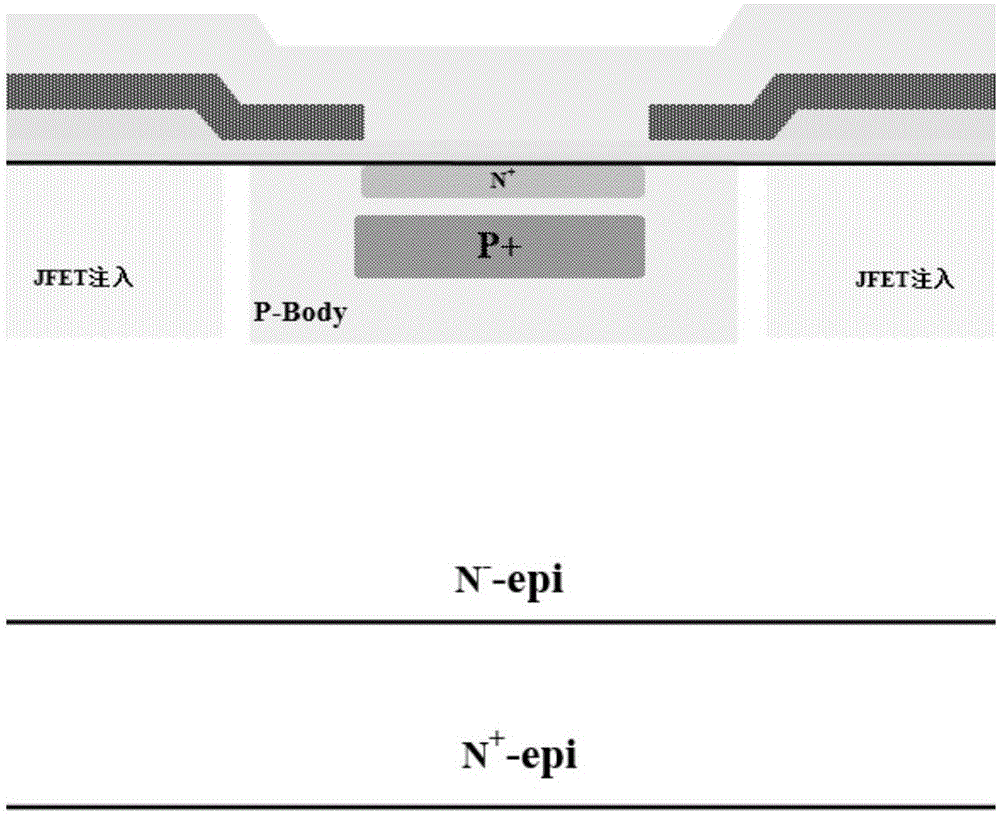

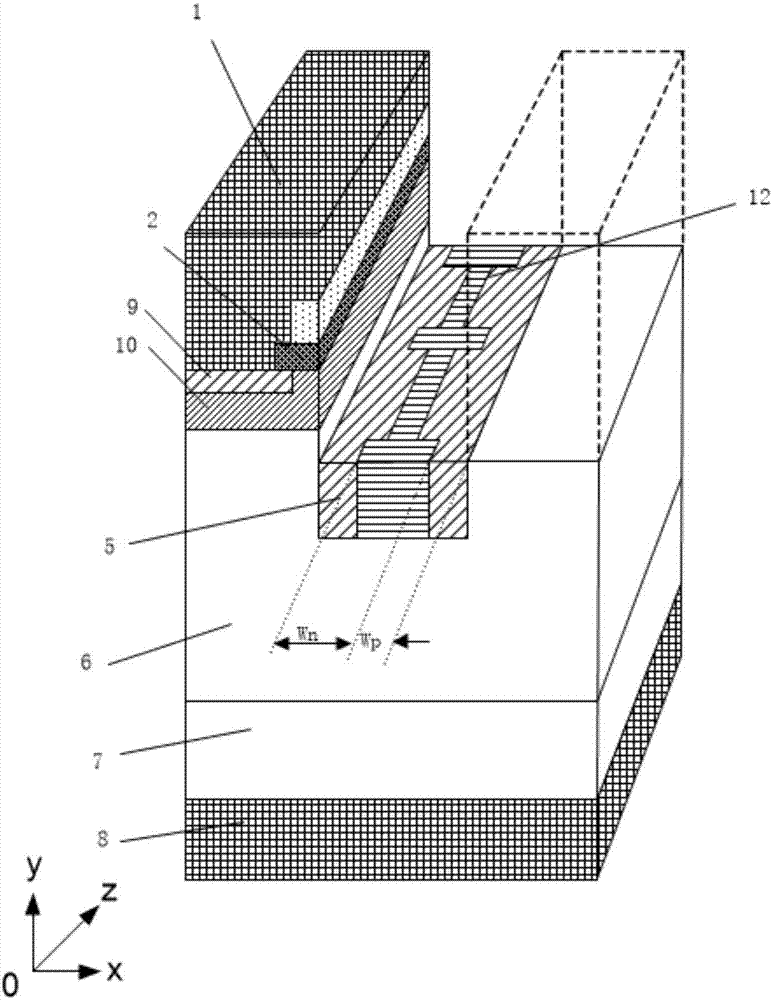

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. The device comprises a drain electrode metal unit, an N+ substrate, and an N- drift region. And a groove is formed in the N- drift region. Besides, the manufacturing method includes: a groove is etched in an epitaxial wafer, wherein the groove and a lithography aligning mark are formed simultaneously; polysilicon is deposited on an N- epitaxy unit and etching is carried out to form an ion implantation barrier layer pattern; aluminium ion implantation is carried out by using the polysilicon as a mask to form a P type base region; silicon dioxide is deposited and back etching is carried out to form a side wall, and nitrogen ion implantation is carried out by using a self-aligning technology to form an N+ source region; the polysilicon and silicon dioxide are removed, and polysilicon is deposited and an ion implantation barrier layer pattern is formed; aluminium ion implantation is carried out to form a P+ contact region; and the polysilicon is removed, ion implantation activation annealing and gate oxide oxidation are carried out. According to the invention, the channel self-aligning technology is realized and the depth of the P+ contact region is increased, so that the starting of the parasitic BJT transistor is suppressed effectively and the anti-UIS failure capability of the silicon carbide MOSFET device is enhanced to a certain extent.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

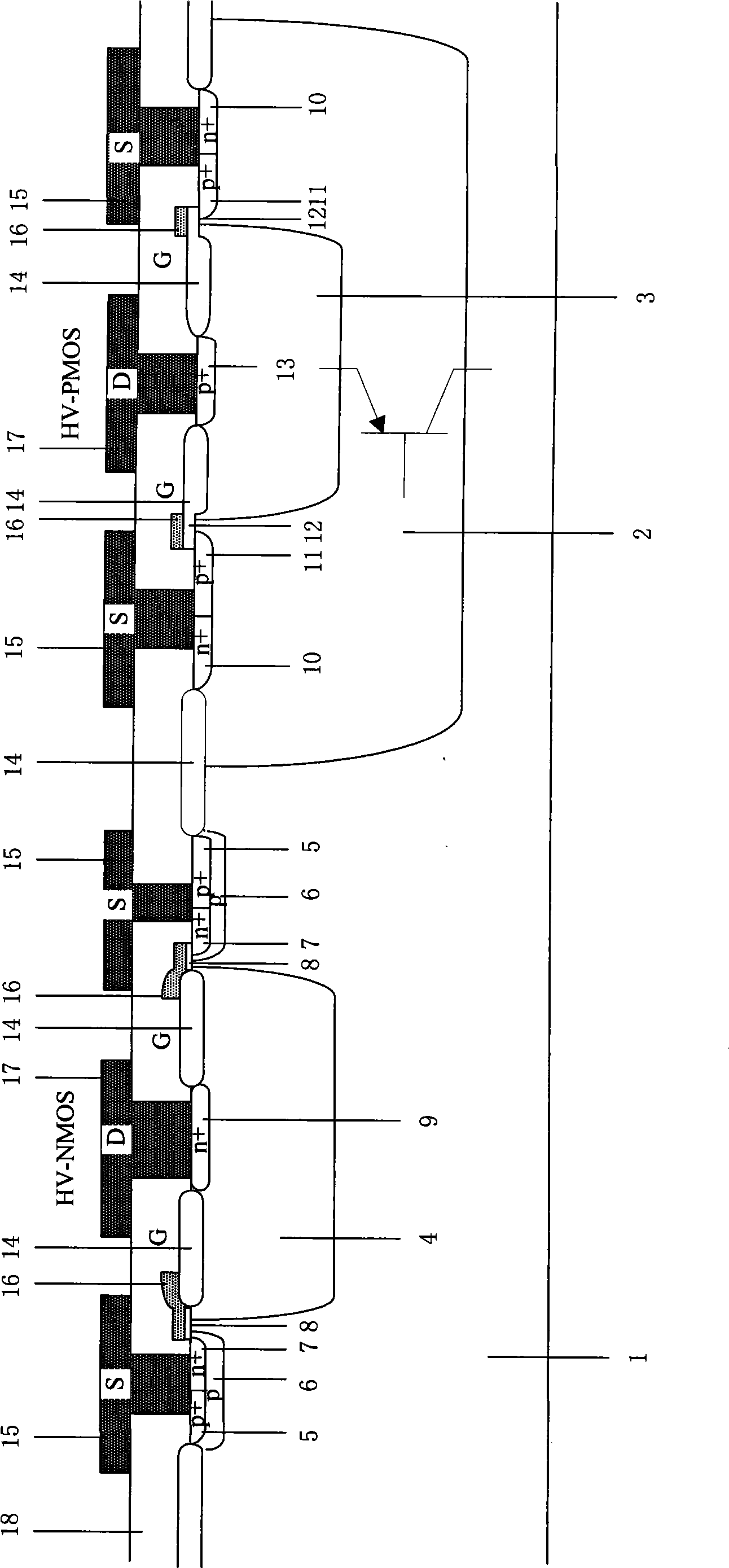

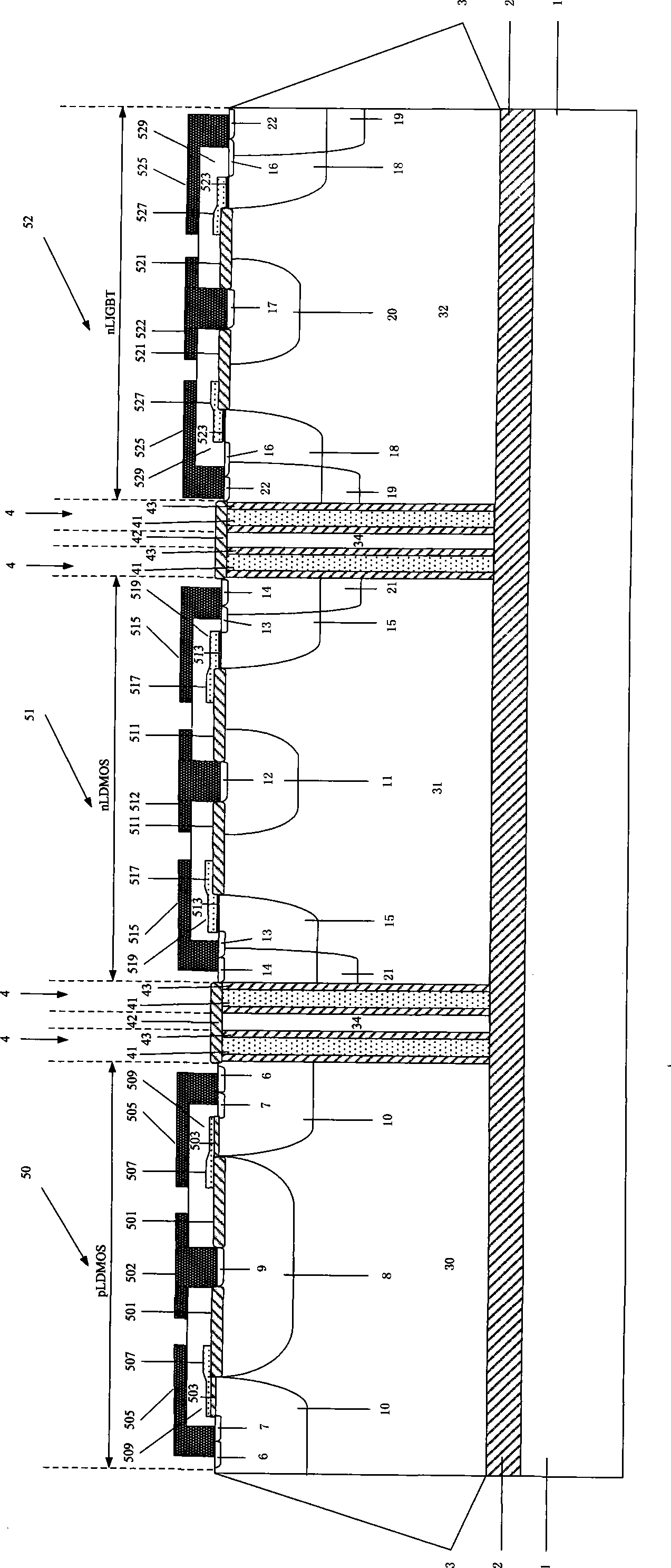

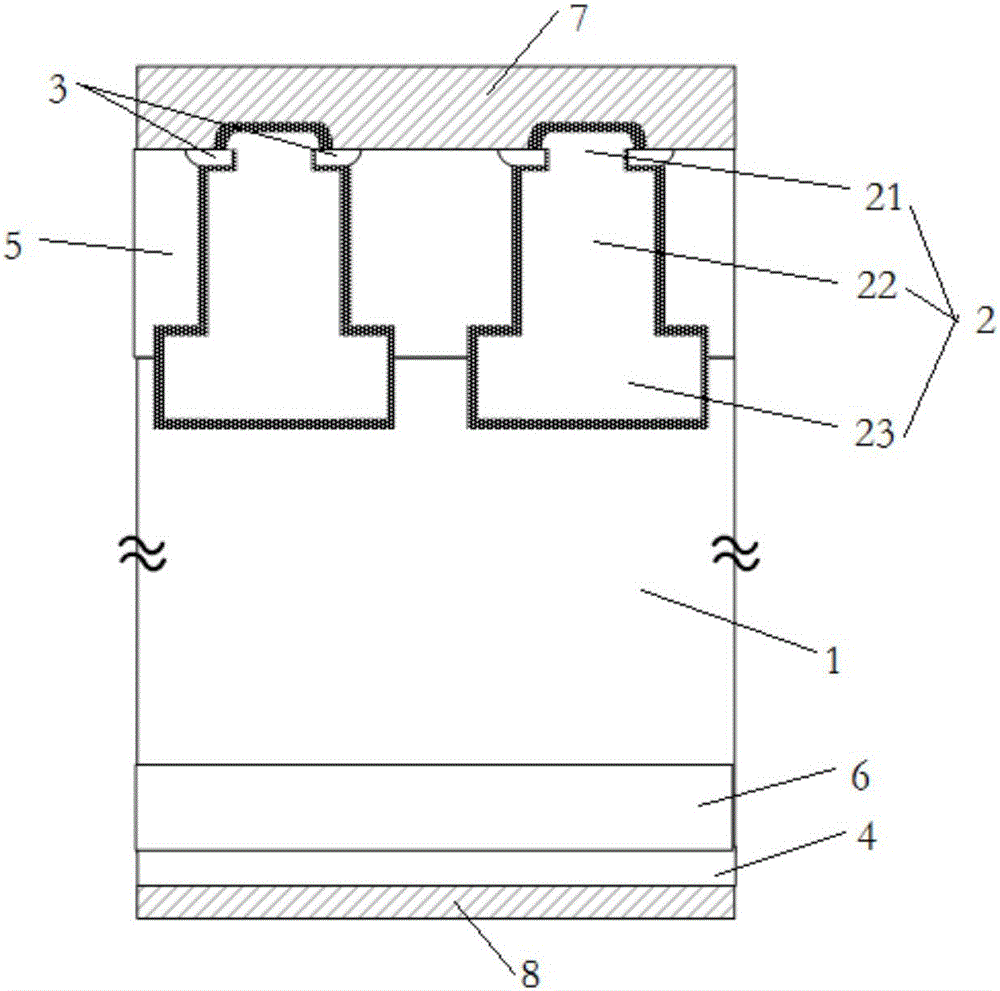

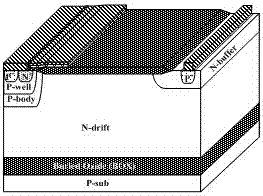

High voltage device for drive chip of plasma flat-panel display

InactiveCN101510551AIncrease load capacityImprove safe work areaSolid-state devicesSemiconductor devicesHigh densityLow voltage

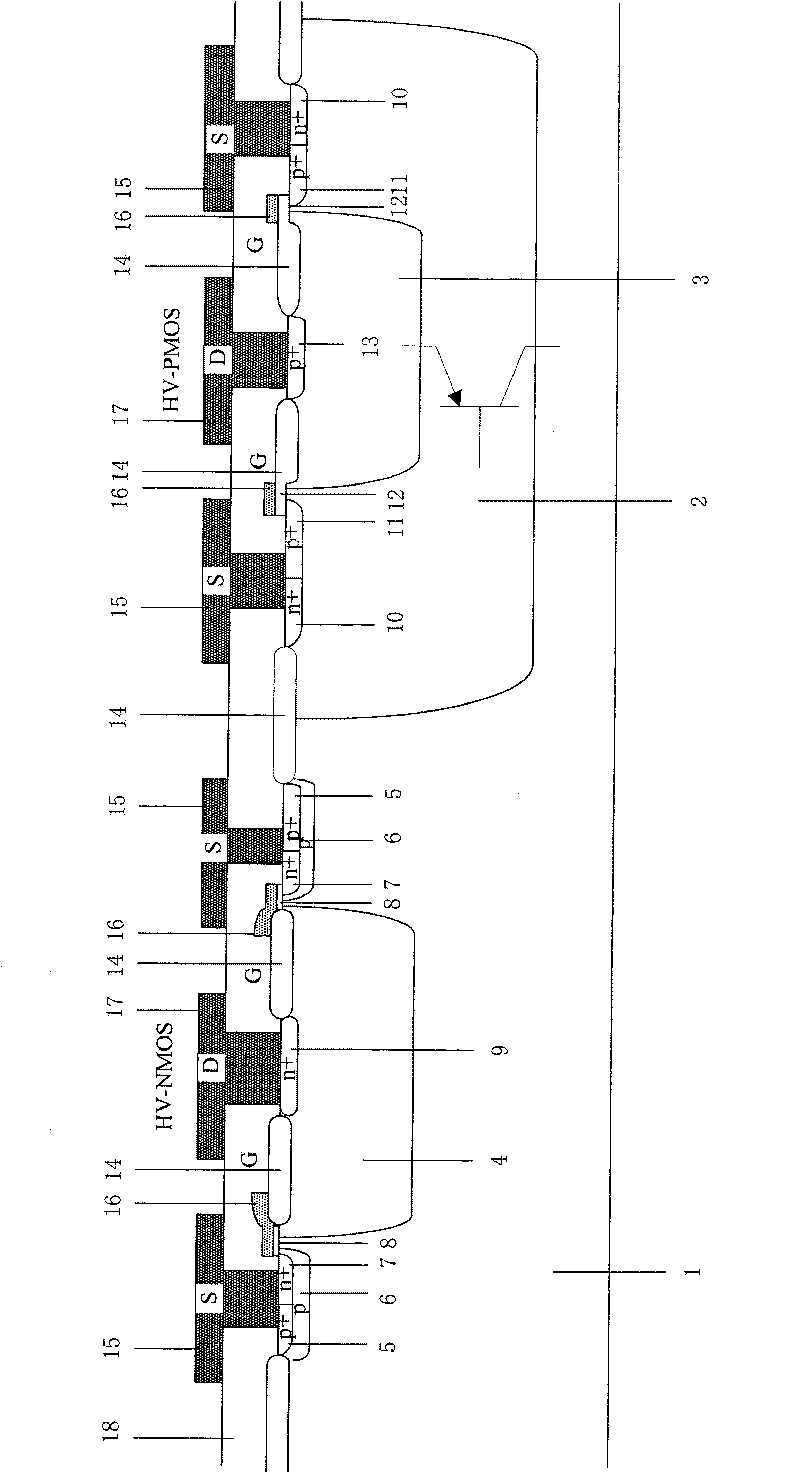

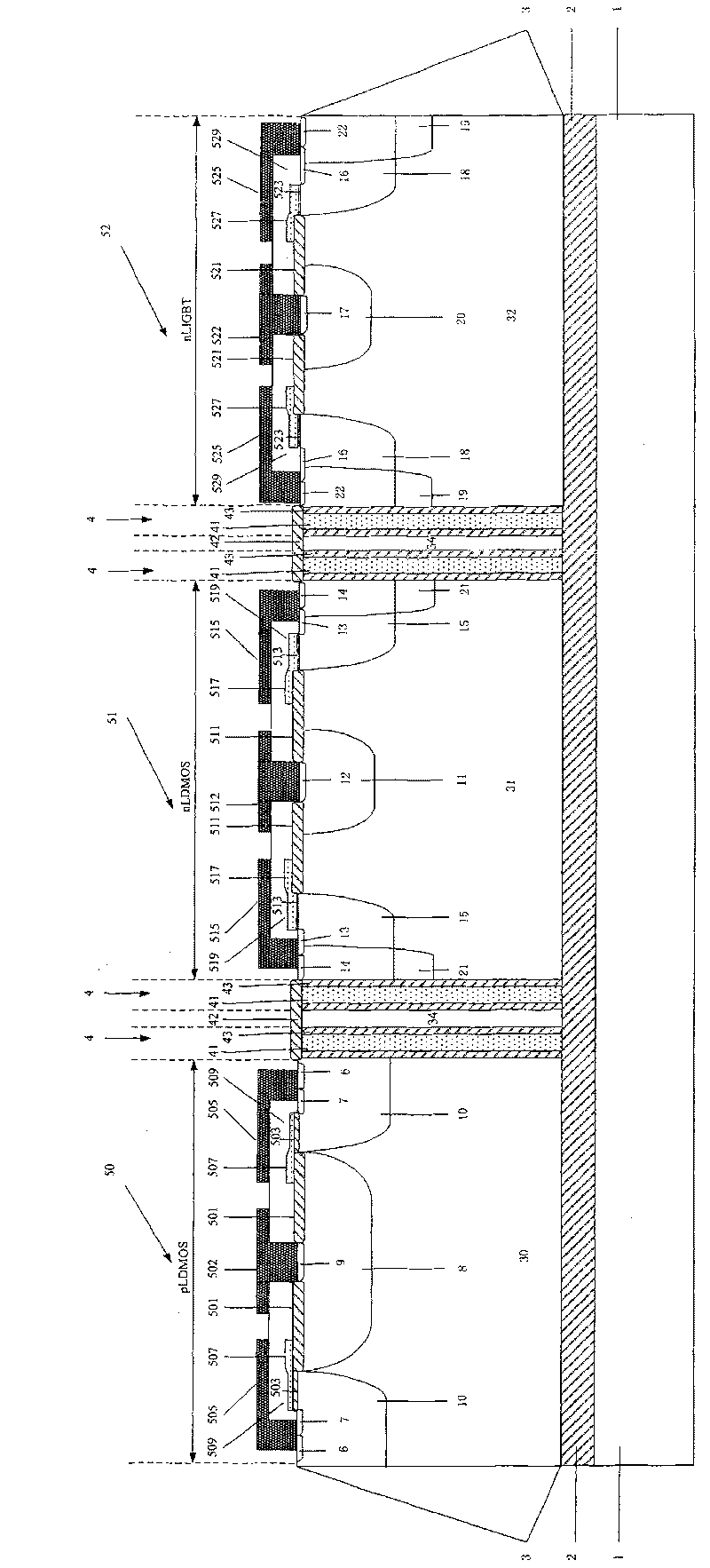

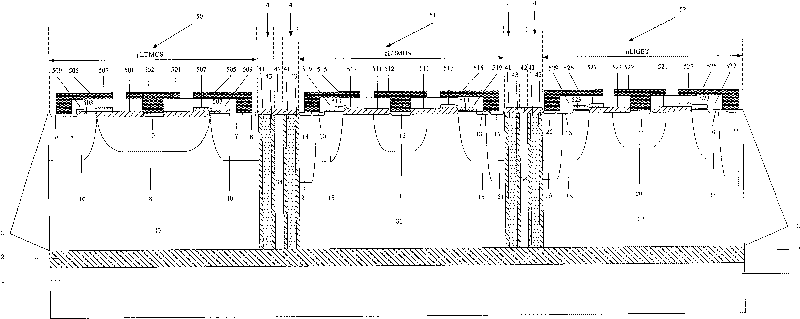

The invention provides a high-voltage device for a drive chip of a plasma flat-panel display, pertaining to the field of a semi-conductor power device. A high-voltage pLDMOS device, a high-voltage nLDMOS device and a high-voltage nLIGBT device are established on a substrate, an oxygen burying layer and an SOI layer and separated by deep-slot medium isolation areas. The oxygen burying layer and the deep-slot medium isolation areas positioned between the substrate and the SOI layer realize the full medium isolation of the device and low-voltage logic circuits. The thickness of the SOI layer is 8 micrometers and can meet the requirements of the device for high-voltage resistance. Compared with the thin SOI technology, the self-heating effect is relieved obviously and the nLIGBT device has low conduction resistance. The group of the high-voltage device for the drive chip of the plasma flat-panel display based on the thick SOI layer fully utilizes the characteristics of the SOI technology, such as low leak, small chip occupying area, high speed, high density of integration and low power consumption, thus meeting the development requirements of the large-sized plasma flat-panel display.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

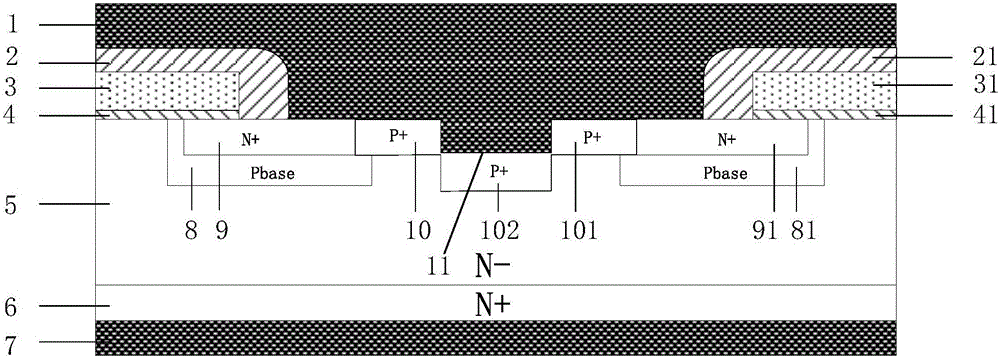

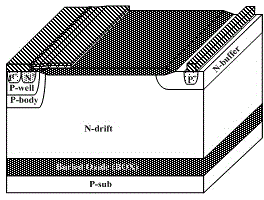

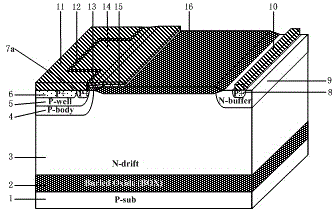

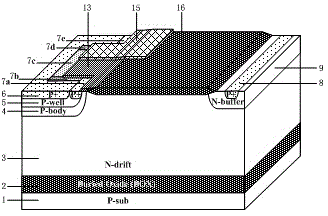

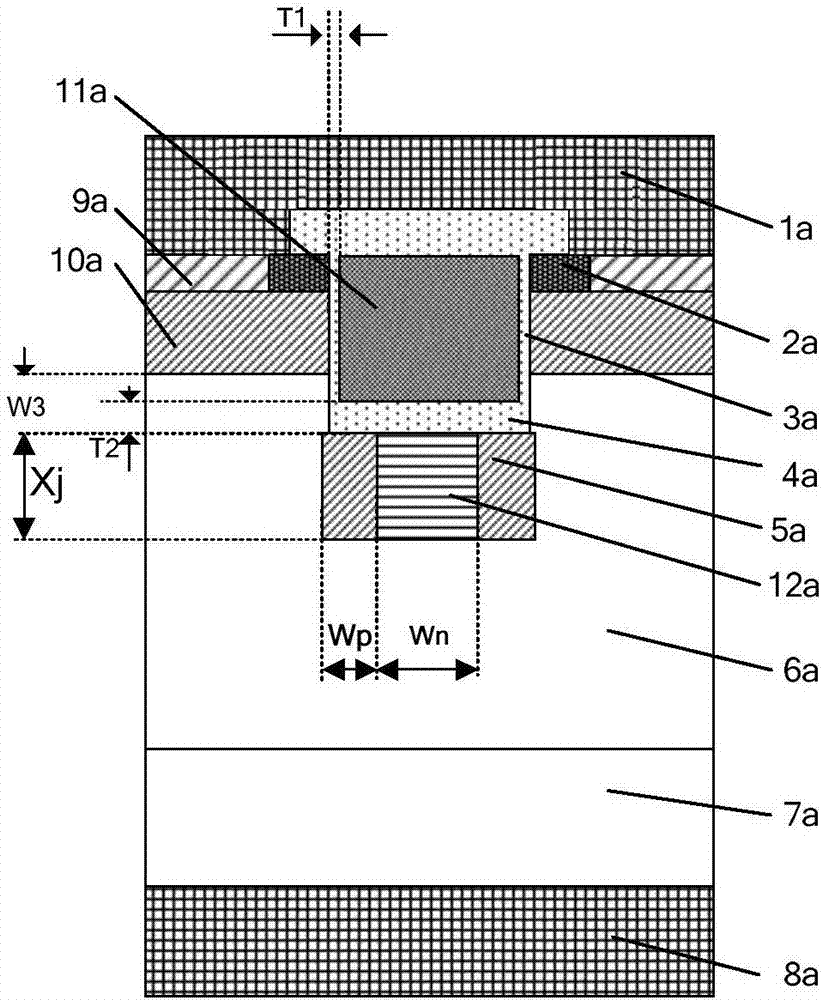

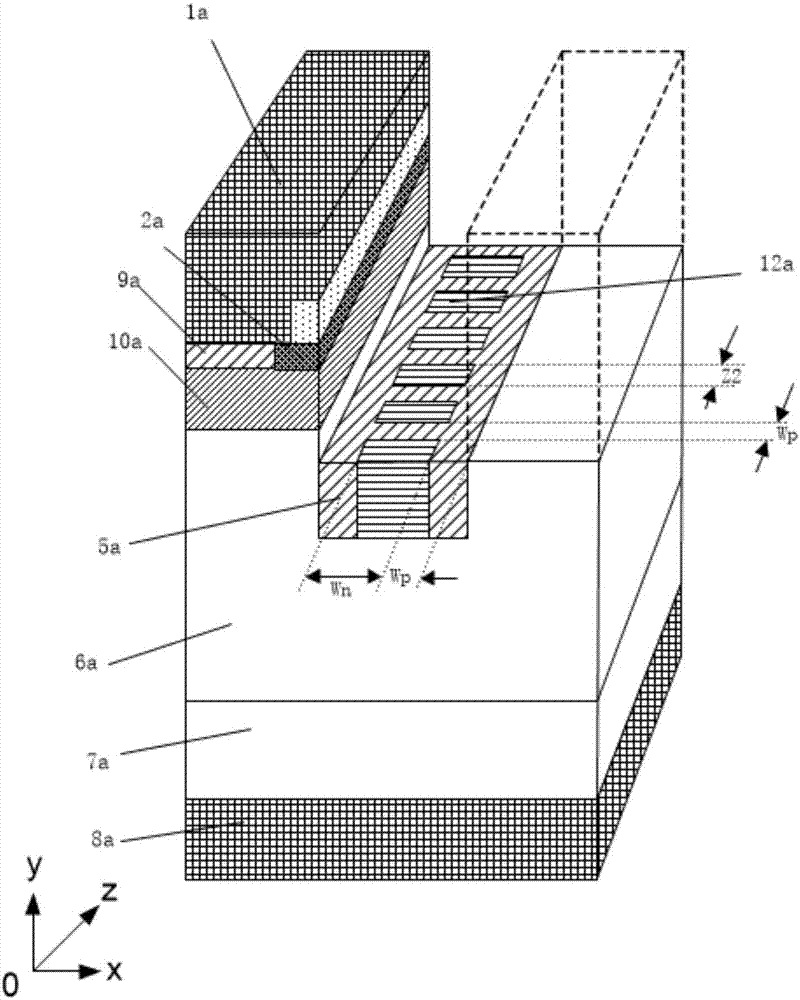

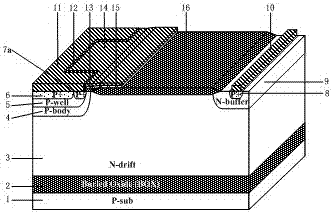

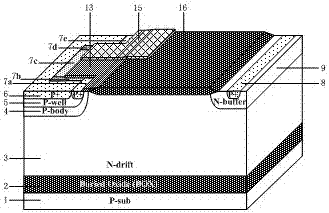

Current enhanced type lateral insulated gate bipolar transistor

ActiveCN104916674AStrong on-current capabilityImprove the conduction current capabilitySemiconductor devicesHigh current densityParasitic bipolar transistor

A current enhanced type lateral insulated gate bipolar transistor improves current density and the turn-off speed on the premise that a latching ability is maintained to be unchanged. The semiconductor is provided with buried oxide disposed on a P-type substrate and an N-drift region disposed on the buried oxide, a P-body region and an N-buffer region are disposed on the N-drift region, a P-type collecting electrode region is disposed in the N-buffer region, an anode metal is connected to the P-type collecting electrode region, a field oxide layer is disposed on the N-drift region, a P-well region is disposed in the P-body region, a P-type emitting electrode region and an emitting electrode region are disposed in the P-well region, the inner-side boundaries of the four regions, i.e., the P-body region, the P-well region, the P-type emitting electrode region and the emitting electrode region are synchronously recessed inwardly to form a square groove, the emitting electrode region surrounding the groove is successively defined as a first P-type emitting electrode region, second, third and fourth N-type emitting electrode regions and a fifth P-type emitting electrode region, the N-drift region protrudes outwardly and fills the square groove, a surface of the P-body region is provided with a gate oxide layer, a surface of the gate oxide layer is provided with a polysilicon layer, and a gate metal is connected to the polysilicon layer.

Owner:SOUTHEAST UNIV +1

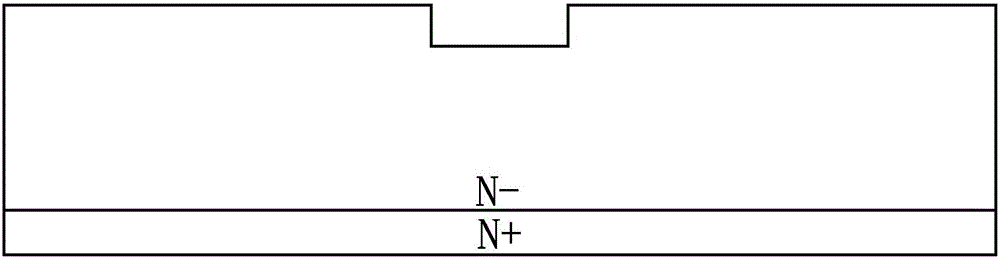

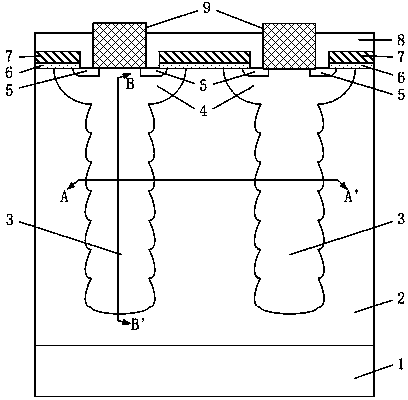

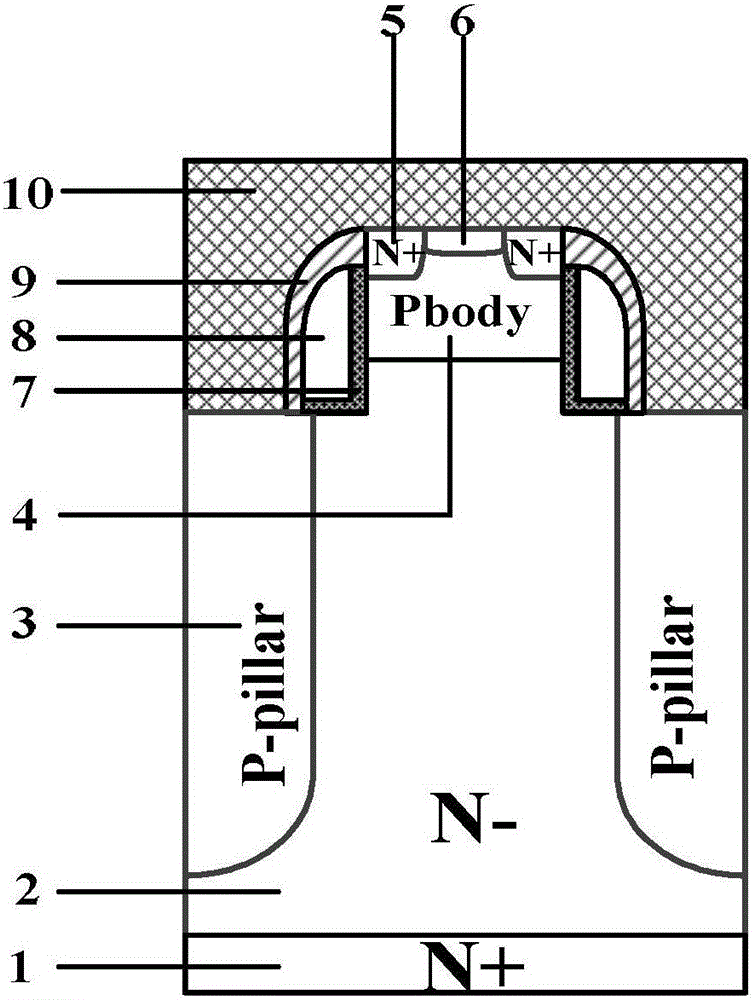

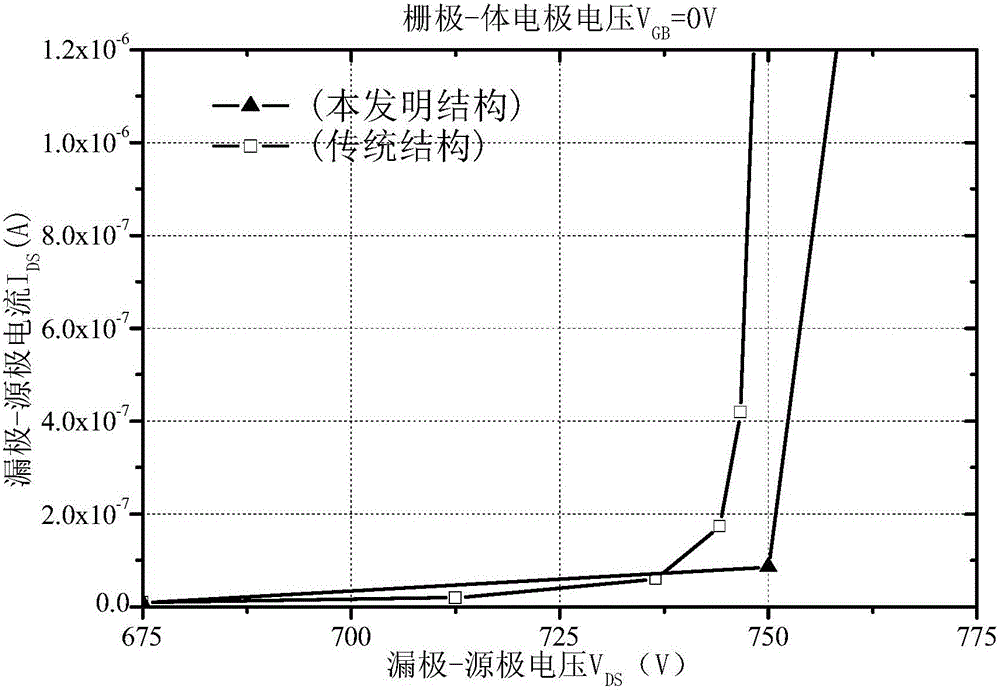

Super junction semiconductor device manufacturing method capable of improving avalanche capacity

ActiveCN103560086AImproved avalanche capabilityReduce the equivalent resistance R

<sub>B</sub>

resistance valueSemiconductor/solid-state device manufacturingSemiconductor devicesElectron avalancheHigh dosage

The invention relates to a super junction semiconductor device manufacturing method capable of improving the avalanche capacity. On-resistance is increased correspondingly due to transverse diffusion caused by the traditional high dosage concentration of a column P, and puncture voltage is reduced due to electric charge unbalance of the column P and a column N. According to the method, the epitaxy technology is utilized to form an N-type epitaxy layer; a P-type and N-type epitaxy layer is formed by injecting boron ions; the injection amount of the boron ions increases gradually, and the boron ions are pushed under the high temperature to form a P-type and N-type alternant epitaxy layer; a Pbody area is formed by injecting the boron ions; a polycrystalline silicon gate electrode is formed by etching polycrystalline silicon through the dry method; an N+ source area is formed by injecting arsenic ions; a layer of aluminum is deposited on the upper surface of a whole device, a source metal electrode is formed by etching the aluminum, and a drain electrode is formed on the back face through metallization. According to the super junction semiconductor device obtained through the method, the avalanche capacity of the super junction semiconductor device is improved, and at the same time, on-resistance is reduced.

Owner:XIAN LONTEN RENEWABLE ENERGY TECH +1

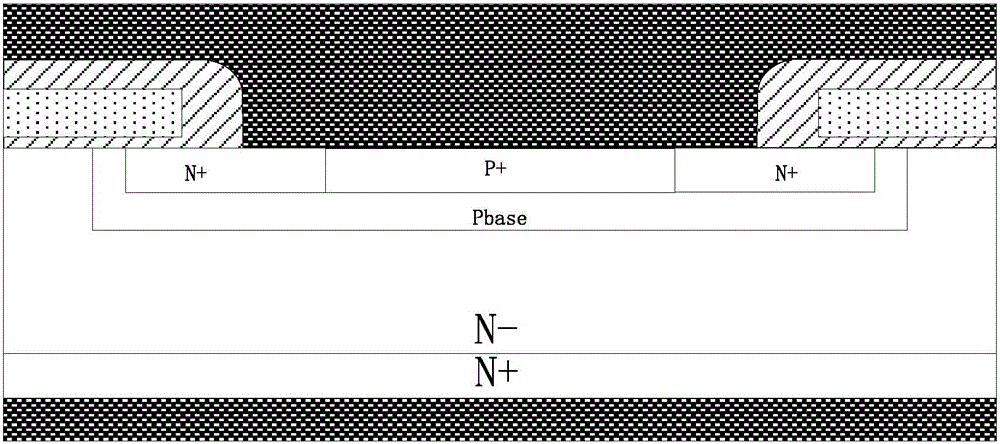

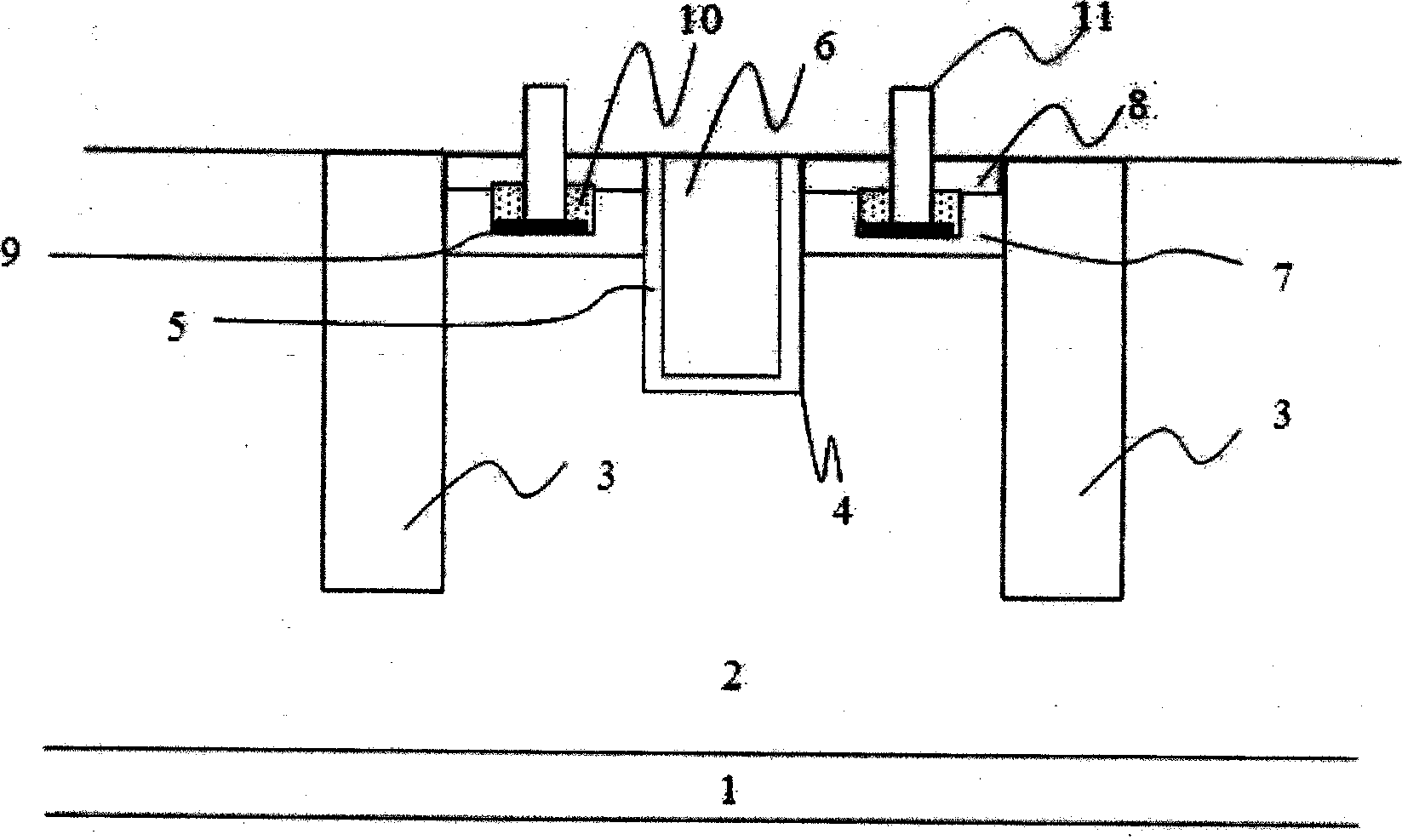

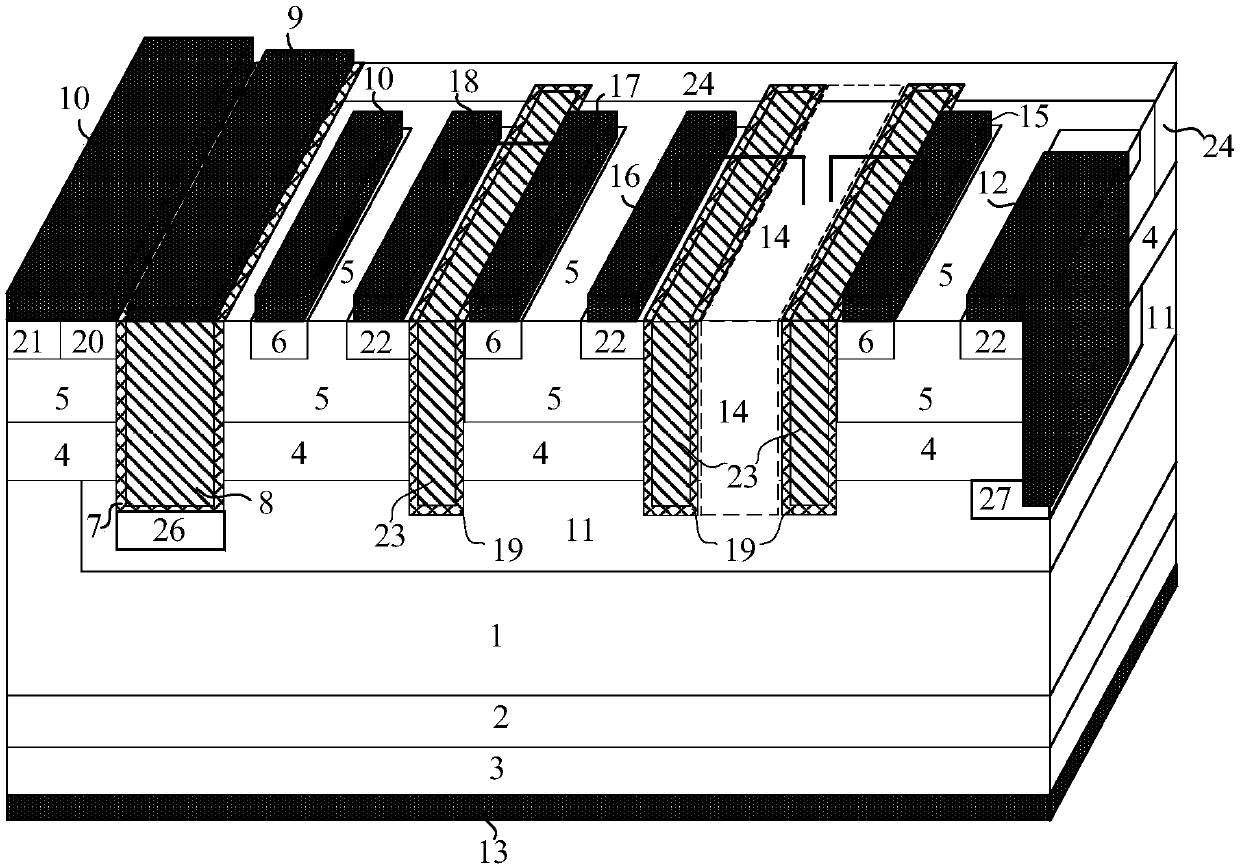

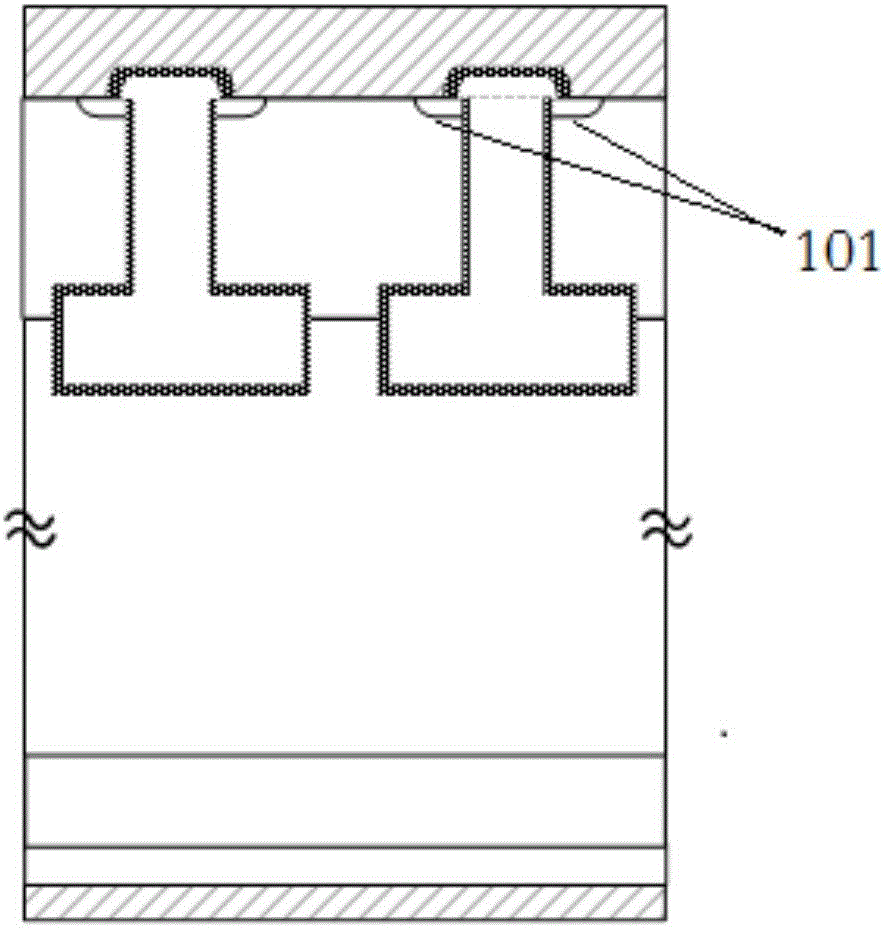

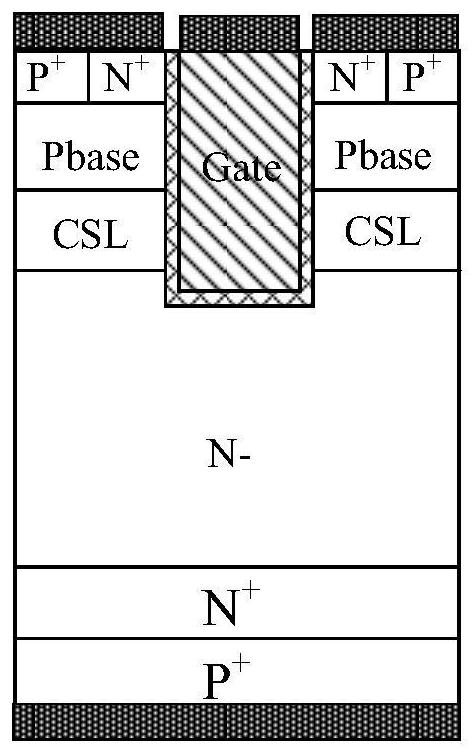

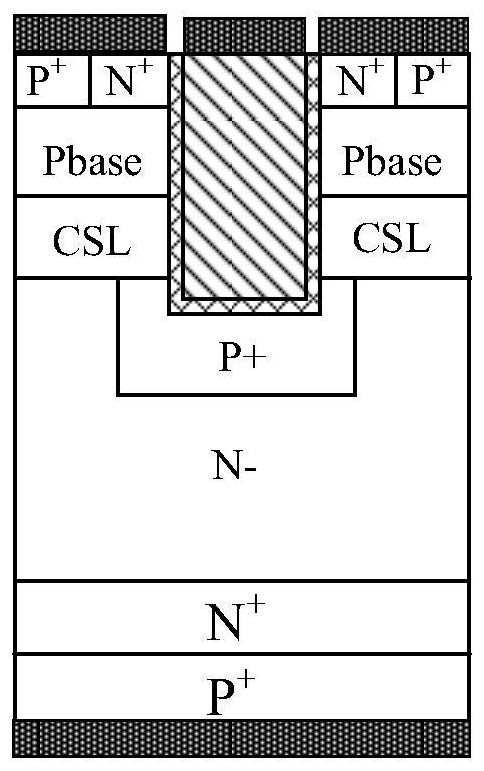

Cell structure of super junction semiconductor device and technology realizing method

InactiveCN103489785AReduced series resistanceImprove the ability to resist avalanche breakdownSemiconductor/solid-state device manufacturingSemiconductor devicesCondensed matter physicsSemiconductor device

The invention discloses a deep-groove-type cell structure of a super junction semiconductor device and a technology realizing method. The cell structure comprises a first-type heavily doped region, a first-type epitaxial drift region is arranged on the first-type heavily doped region, second-type epitaxial column regions are arranged on the two sides inside the epitaxial drift region, a grid groove is formed between the second-type epitaxial column regions, a grid polysilicon and dielectric isolation layer is arranged inside the groove, a second-type doped well region is formed between the grid groove and a semi-insulation column region, a first-type doped source region is formed on the upper portion of the well region, a second-type epitaxial region is arranged inside the second-type doped well region, and a metal buried layer is arranged under the second-type epitaxial region. The deep-groove-type cell structure can effectively reduce series resistance of the well region of the super junction product, prevent opening of parasitic transistors, and therefore the avalanche breakdown resistance capacity of the device is improved, and the related reliability of the product is improved.

Owner:上海恺创电子有限公司 +1

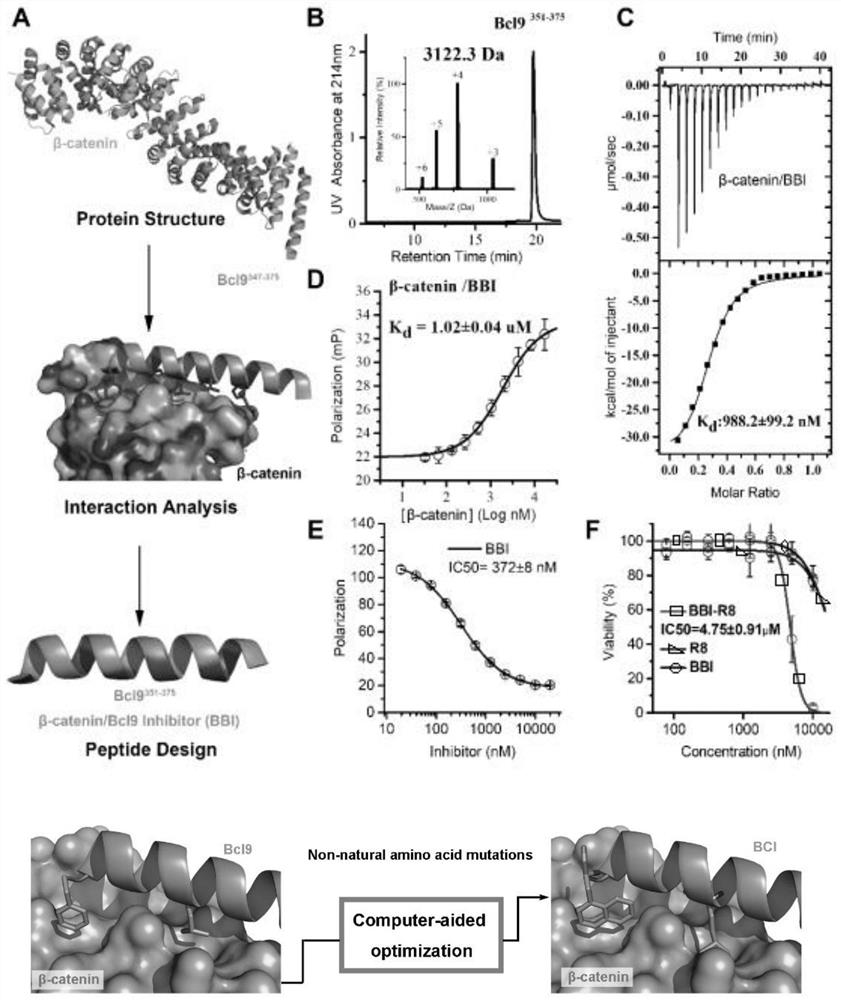

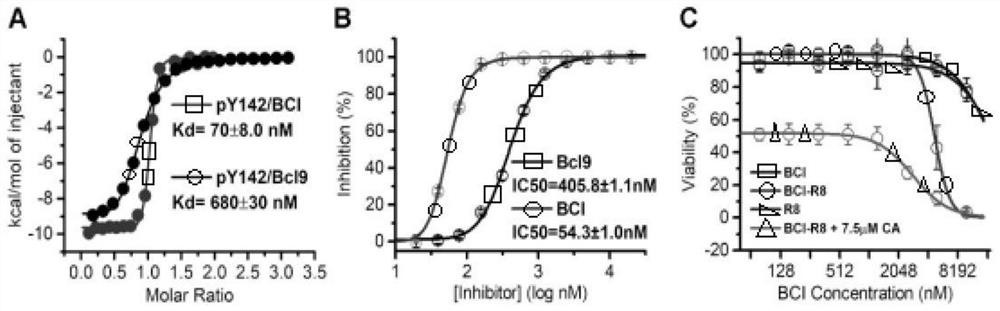

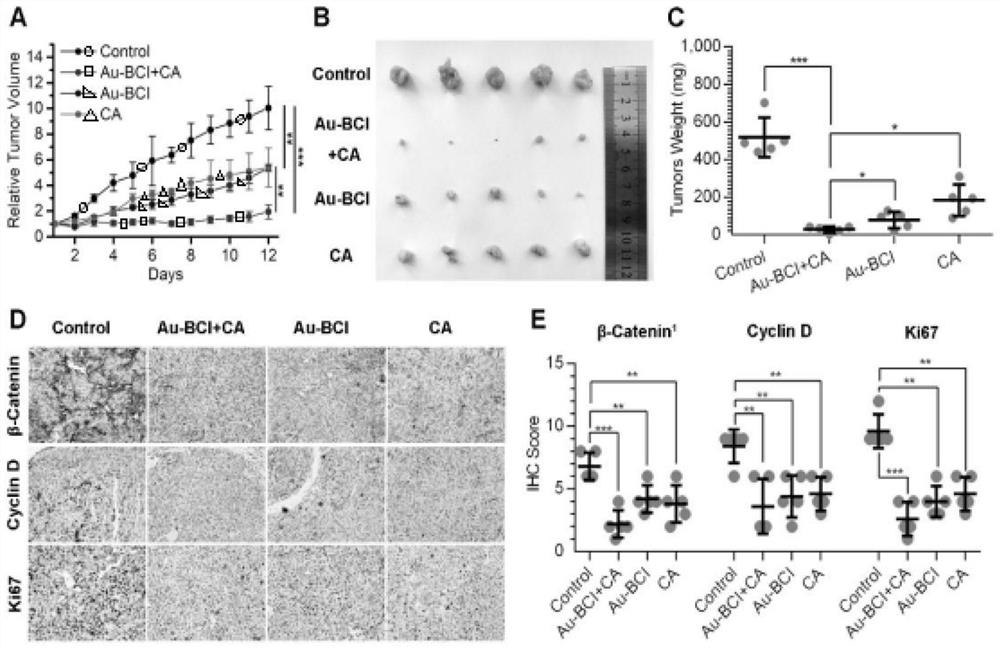

Polypeptide specifically combined with beta-catenin protein with high affinity, and application and synthesis method of polypeptide

ActiveCN111909242AThe synthesis method is simple and easy to obtainInhibit onPeptide/protein ingredientsPeptidesDiseaseCancer cell

The invention discloses a polypeptide specifically combined with beta-catenin protein with high affinity, and application and a synthesis method of the polypeptide. The amino acid sequence of the polypeptide is LEHRERSLQT(X1)RDIQRML(X2)P, wherein X1 is leucine, norleucine or homoleucine, and X2 is phenylalanine, 1-naphthyl alanine, 2-naphthyl alanine, 2-anthryl alanine or 9-anthryl alanine. The polypeptide is used for inhibiting growth of cancer cells. By the polypeptide, various tumor treatment targets can be achieved. The polypeptide inhibits opening of a beta-catenin protein-mediated Wnt signal pathway by inhibiting mutual combination of the beta-catenin protein and BCL9 in the cancer cells, so that growth of tumors is inhibited, self-apoptosis of the cells is induced, and the tumor disease treatment targets are achieved. The synthesis method of the polypeptide is simple and easy to implement, and the final product has high yield efficiency, has mass production potential, and has great drug clinical transformation potential.

Owner:THE FIRST AFFILIATED HOSPITAL OF MEDICAL COLLEGE OF XIAN JIAOTONG UNIV

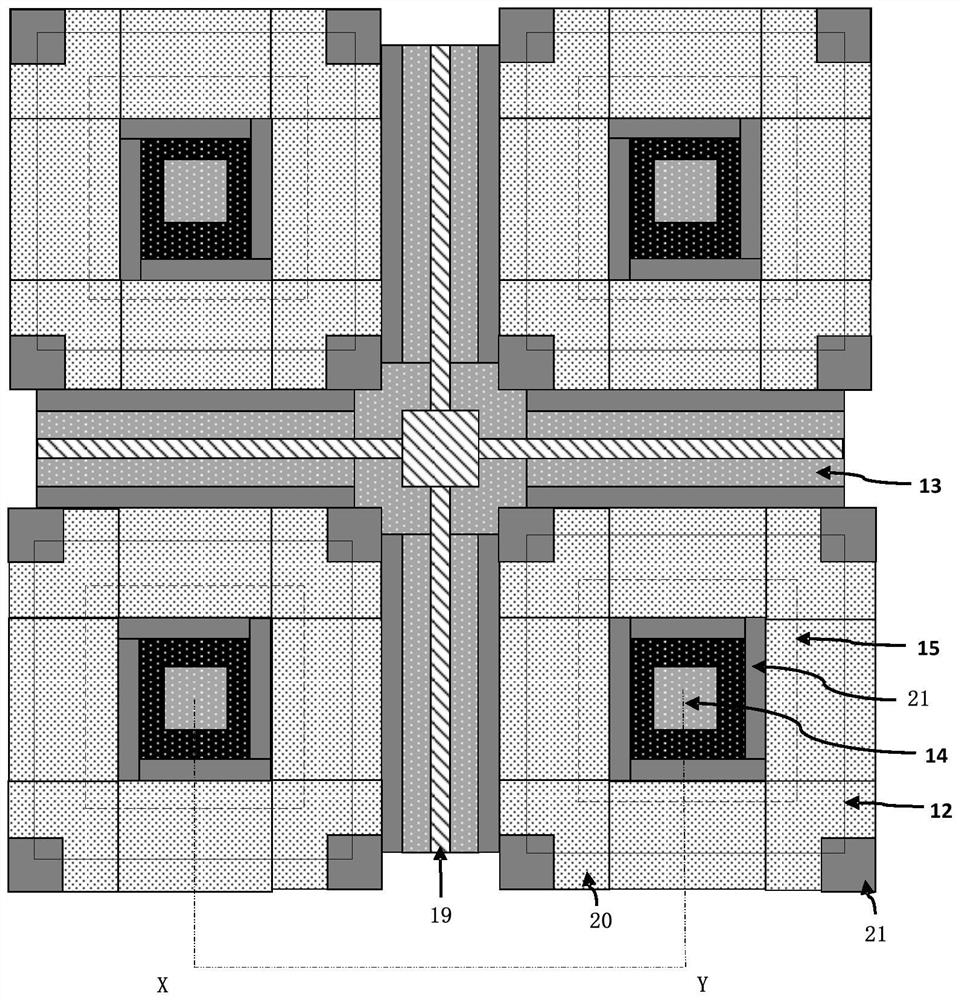

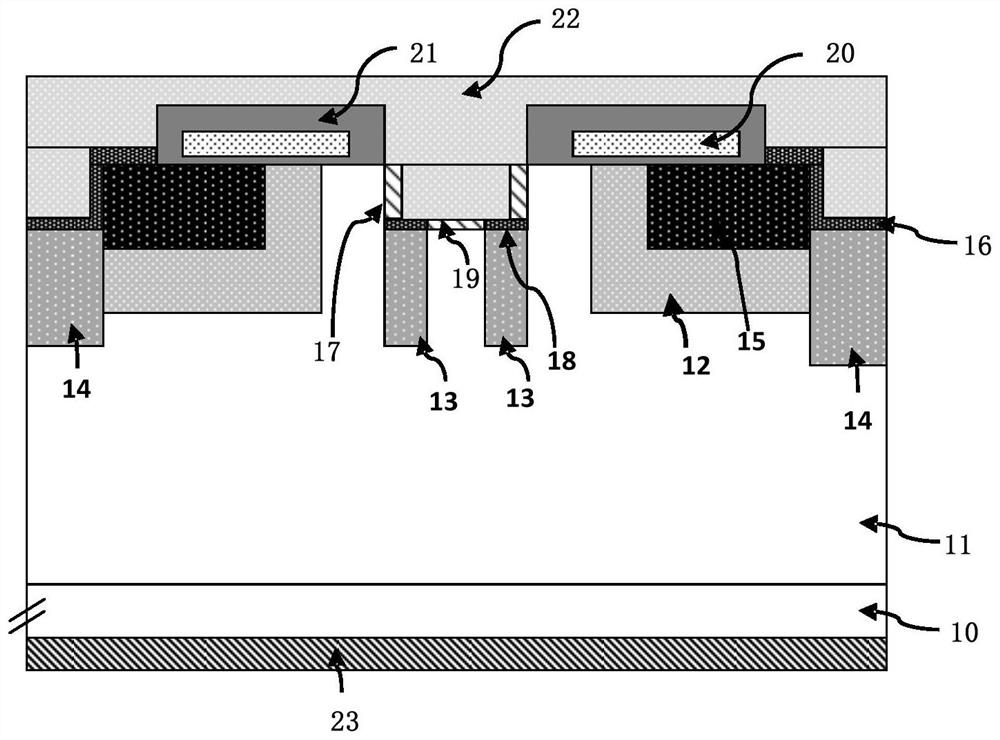

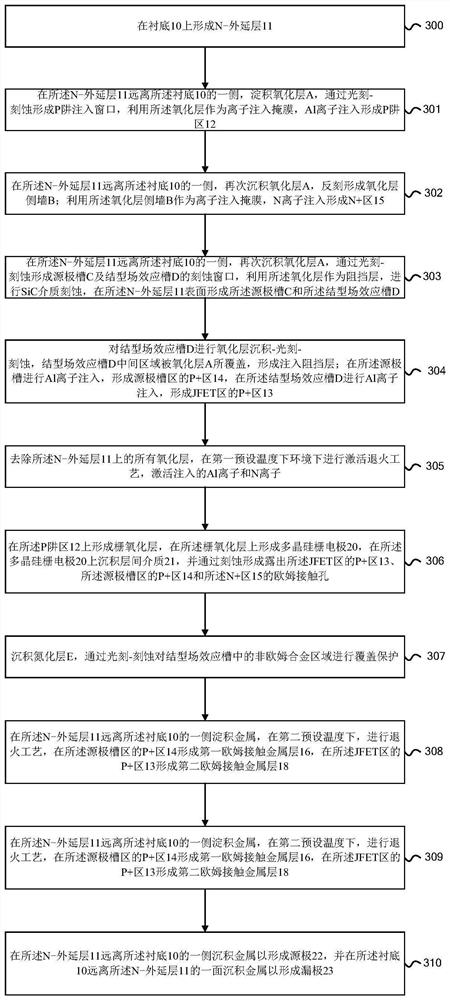

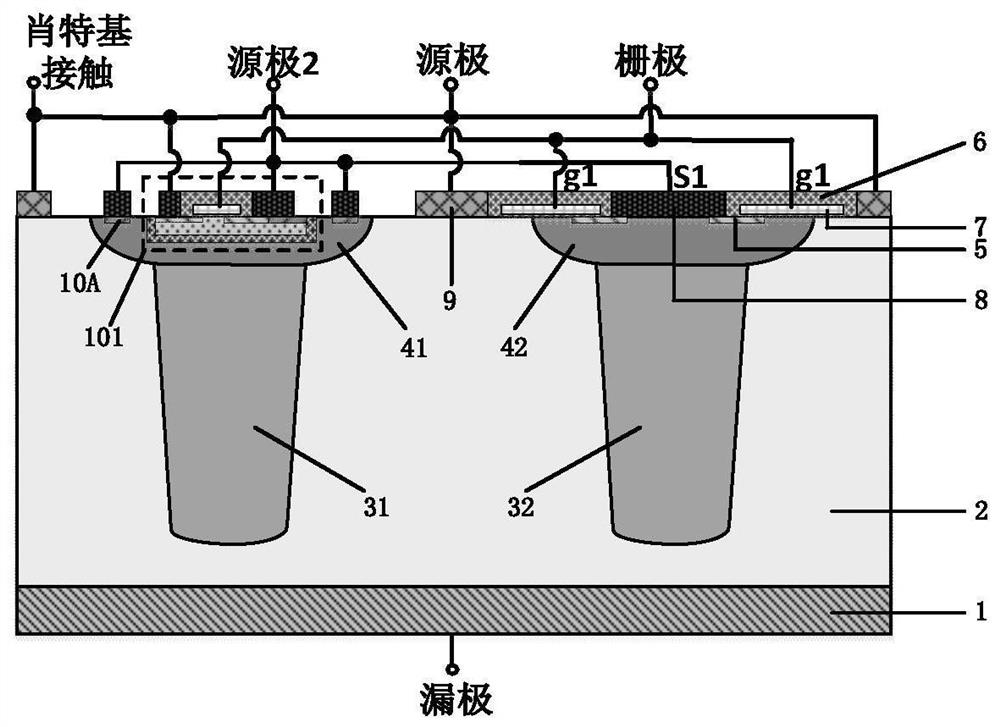

Silicon carbide MOSFET device integrated with SBD and preparation method thereof

PendingCN114220844AEliminate the effect of resistanceInhibit onSolid-state devicesSemiconductor/solid-state device manufacturingCarbide siliconMOSFET

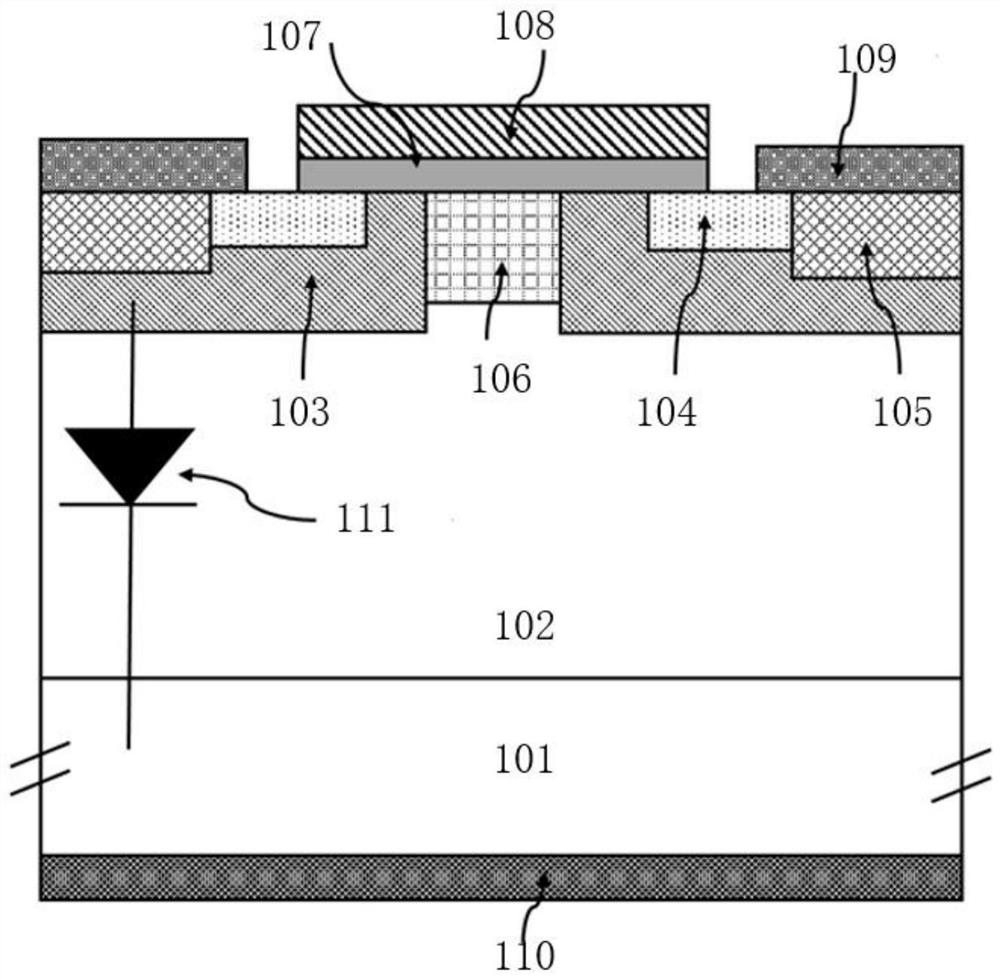

The invention discloses a silicon carbide MOSFET device integrated with an SBD and a preparation method of the silicon carbide MOSFET device. The silicon carbide MOSFET device comprises a substrate, an N-epitaxial layer, a P well region, a P + region of a junction field effect region, a P + region and an N + region of a source groove region, a first ohmic contact metal layer, a first Schottky contact metal layer, a second ohmic contact metal layer and a second Schottky contact metal layer. The P + region of the junction field effect region is positioned on one side, far away from the N + region, of the P well region; the second ohmic contact metal layer covers one surface, deviating from the N-epitaxial layer, of the P + region of the junction field effect region; the first Schottky contact metal layer is located on the side, away from the P well region, of the second ohmic contact metal layer. And the second Schottky contact metal layer is arranged on one side, deviating from the P + region of the junction field effect region, of the second ohmic contact metal layer, and is parallel to the P + region of the junction field effect region. The source contact resistance can be reduced, the through-current capability of the silicon carbide device is improved, and the reliability of the silicon carbide device is improved.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Method for preparing FinFET on germanium and III-V semiconductor material substrate

InactiveCN102832135ASmall sizeInhibit onSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsCondensed matter physics

The invention discloses a method for preparing FinFET on a germanium and III-V semiconductor material substrate, and the method mainly comprises following steps of forming a source drain and a slender graphic structure which is connected to the source drain; forming an oxidization isolation layer; forming a grid structure and a source drain structure; and forming metal contact and metal interconnection. Due to the adoption of the method, the FinFET is easily formed on the germanium and III-V semiconductor material substrate, the entire process flow is completed on the germanium and III-V semiconductor material substrate and is completely similar to the manufacturing technology of a conventional ultra-large-sized integrated structure, and the preparation process has characteristics of simpleness, convenience and short period. In addition, the minimal width of the FinFET prepared by the method can be controlled within 20 nanometers, and a multi-grid structure can provide good grid control capacity and is very suitable for preparing ultra-short-channel devices to further reduce the size of the devices. The FinFET prepared by the method has low power consumption.

Owner:PEKING UNIV

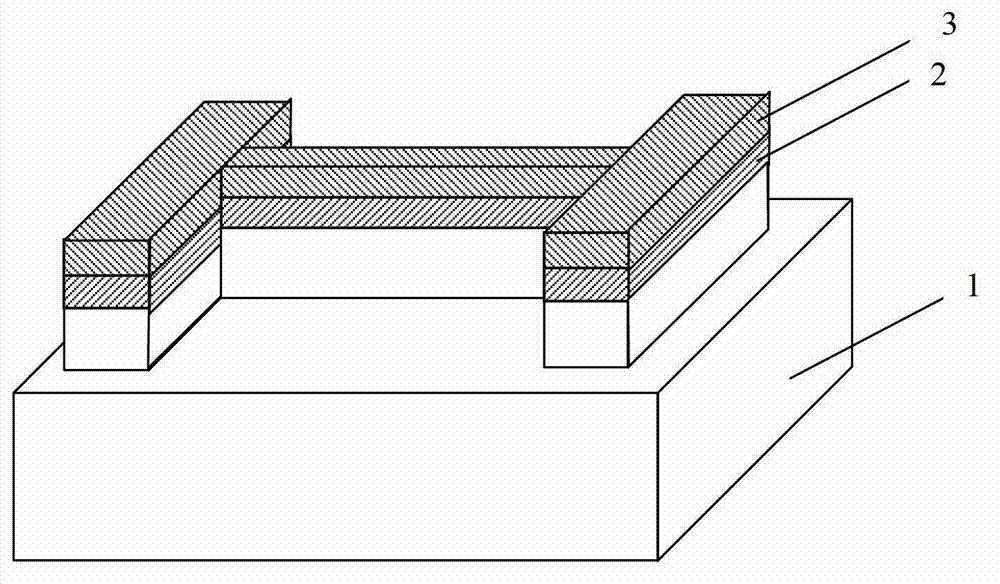

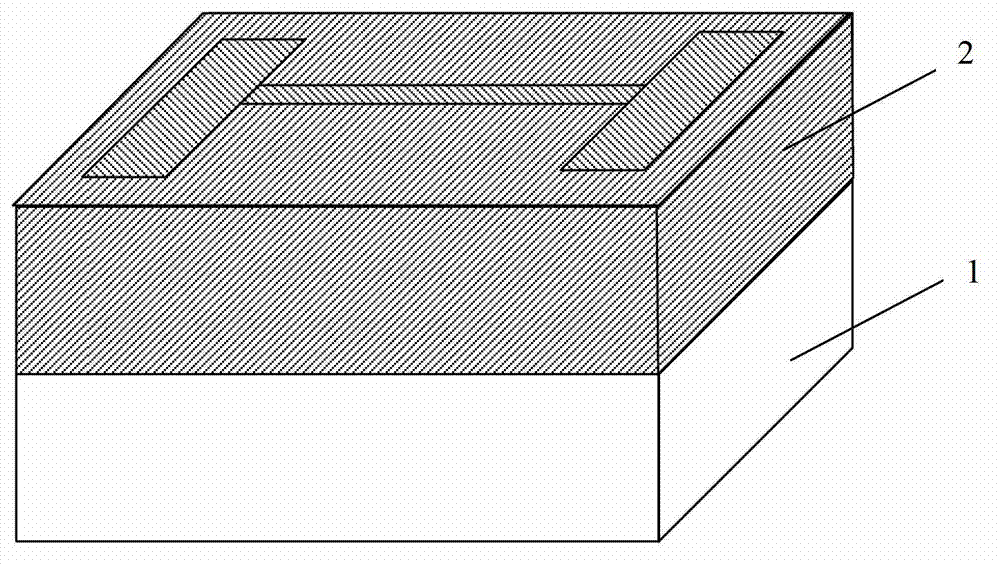

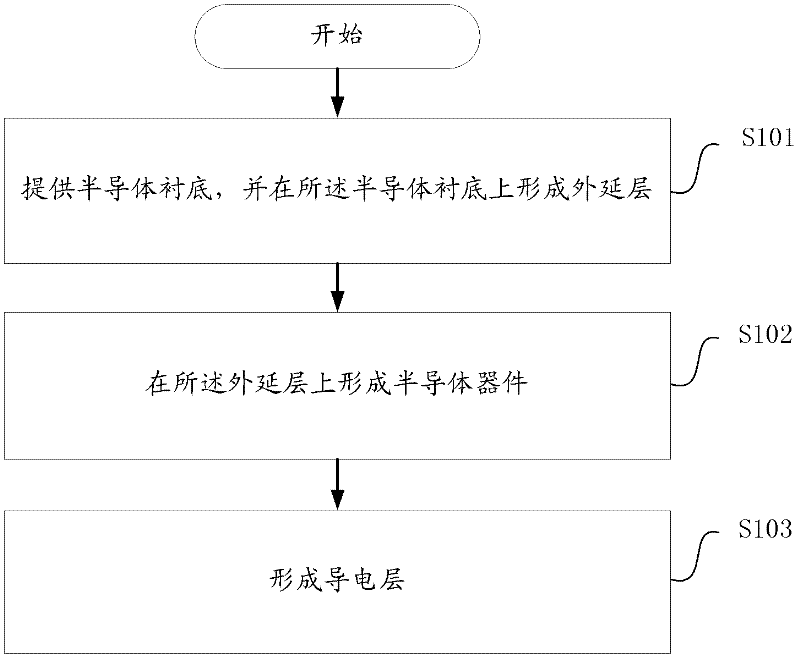

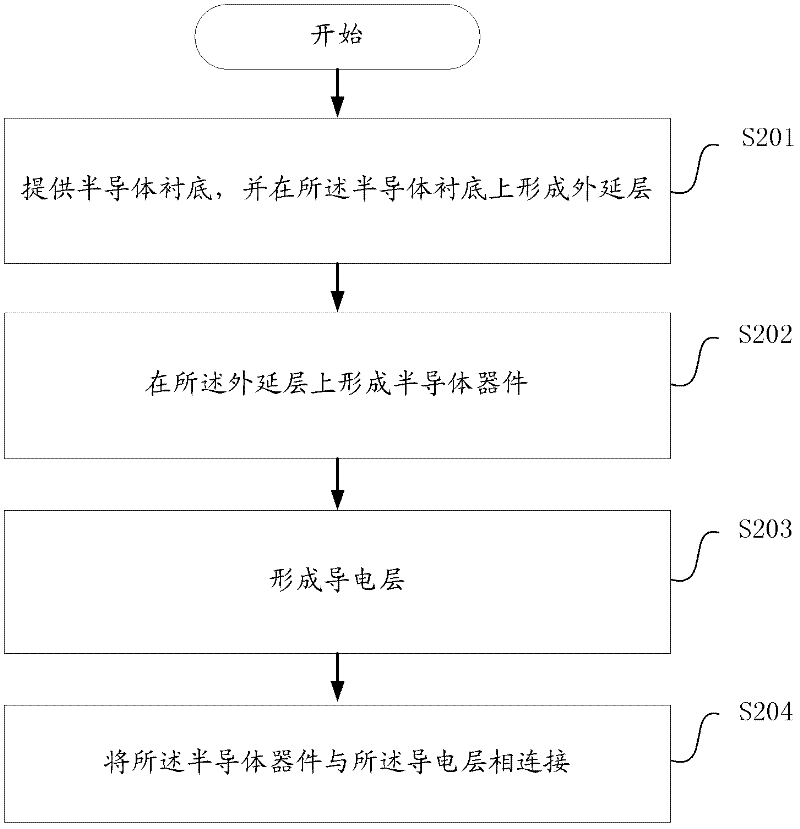

Semiconductor structure and manufacturing method thereof

InactiveCN102332403AChange the flow pathLower base resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesBipolar junction transistorPower semiconductor device

The invention provides a manufacturing method of a semiconductor structure, which is characterized by comprising the following steps of: providing a semiconductor substrate and forming an epitaxial layer on the semiconductor substrate; forming a semiconductor device on the epitaxial layer, wherein the semiconductor device comprises a source region, a drain region and a grid stack; and forming a conductive layer which is not connected with the semiconductor device at the periphery of the semiconductor device and used for reducing base resistance. Correspondingly, the invention also provides a semiconductor structure manufactured by the method. The manufacturing method and the semiconductor structure are used to restrain the parasitic effect of a BJT (bipolar junction transistor) effectively, thereby improving the overall performance of the semiconductor device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

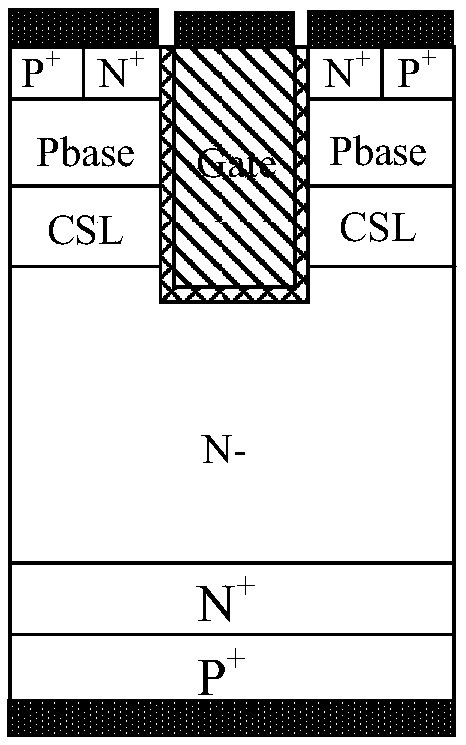

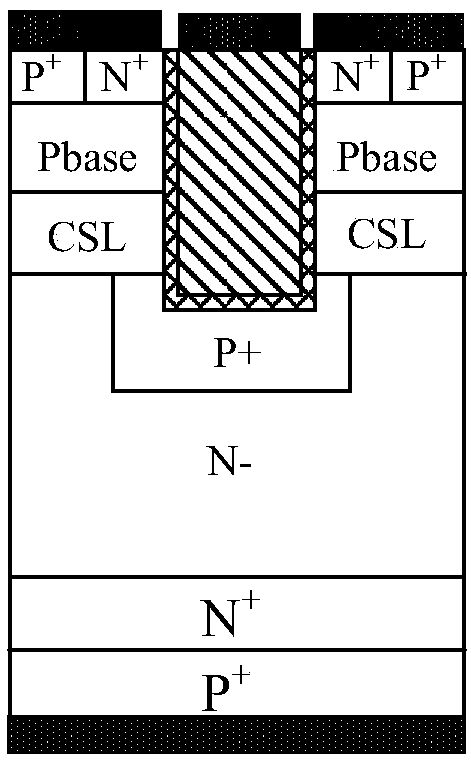

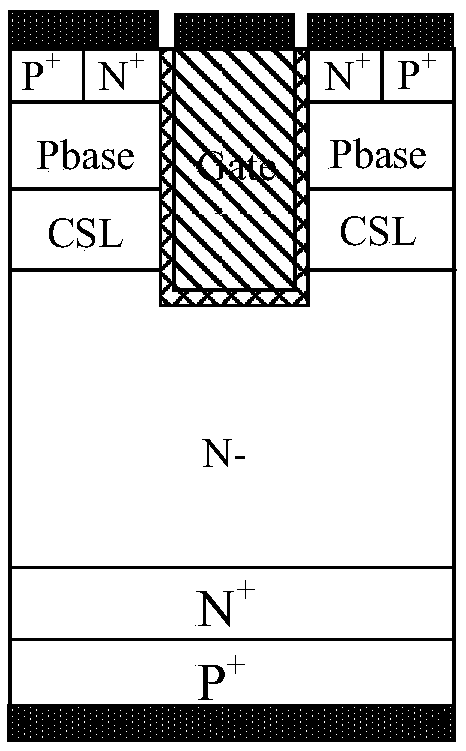

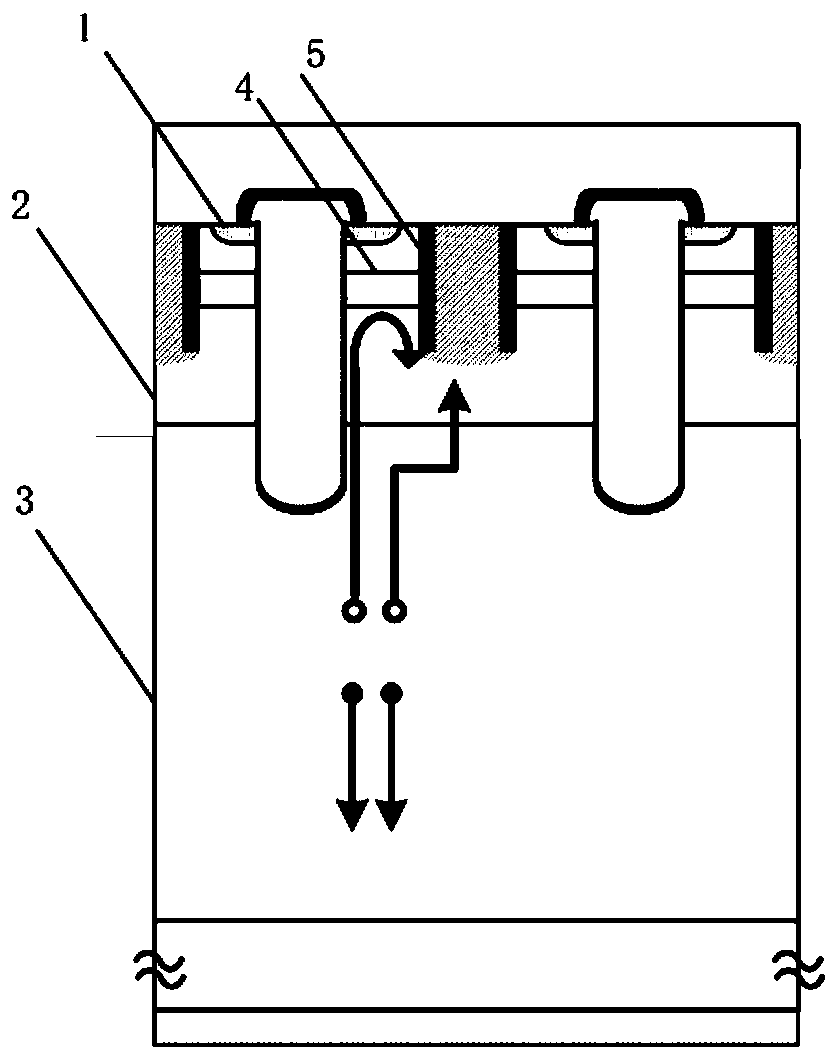

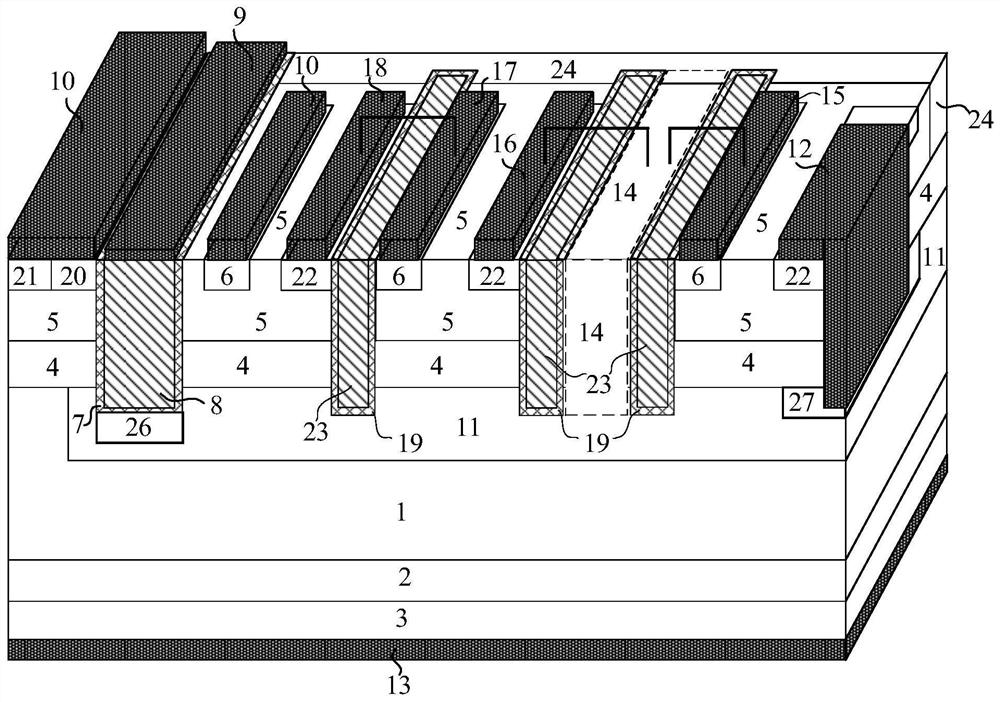

Trench gate IGBT device with carrier storage layer

This invention relates to the power semiconductor field, providing a trench gate IGBT device with carrier storage which is used for solving the problems of high saturation voltage, small short circuitsafe working area and limited concentration of the existing trench gate IGBT device with carrier storage layer, and put forward a novel trench gate IGBT device with carrier storage layer. The trenchgate IGBT device with carrier storage layer directly integrates a plurality of series diodes on the surface of silicon wafers to clamp the potential of the electric field shielding layer in the P region, thereby breaking the concentration limit of CSL on the basis of trench gate IGBT process, greatly improving the injection efficiency of IGBT emitter and greatly improving the trade-off relation between forward voltage drop and turn-off loss of IGBT. Meanwhile, due to the clamping effect of the diode, the drain near the IGBT nMOS channel is clamped at a lower voltage under high voltage and large current, thereby greatly reducing the saturation current of the novel IGBT and improving the short circuit safe working area of IGBT.

Owner:杭州朋声科技有限公司

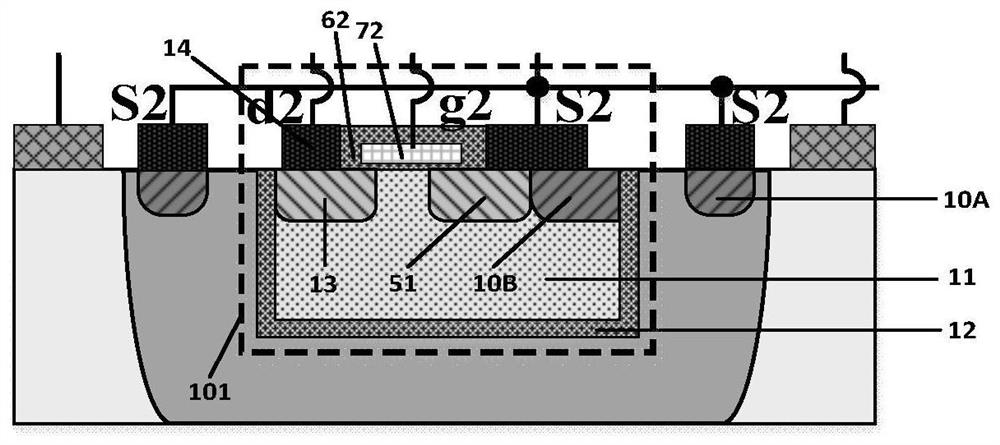

IGBT device with carrier storage layer using diode clamping

ActiveCN109686787AInhibit onPrevent breakdownTransistorSolid-state devicesSaturation voltageSemiconductor

The invention relates to the field of power semiconductors, provides an IGBT device with a carrier storage layer using diode clamping, and solves the problems that the saturation voltage of an existing groove gate IGBT with the carrier storage layer (CSL) is high, a short circuit safe working area is smaller, and the CSL concentration is limited. The IGBT device with the carrier storage layer using diode clamping has the advantages that the IGBT directly integrates one or more series diodes on the surface of a silicon wafer through a groove gate IGBT process for clamping electric potential ofan electric field shielding layer of a P region, on the basis of the groove gate IGBT process, the limitation of the CSL concentration is broken through, the injection efficiency of an IGBT emitting electrode is greatly improved, thereby greatly improving the tradeoff relationship between conduction voltage drop and turn-off loss of the IGBT; due to the clamping action of a diode, a drain electrode near an nMOS channel of the IGBT is clamped at a lower voltage under the high voltage and large current, so that saturation current of the novel IGBT is reduced to a great extent, thereby enlargingthe short circuit safe working area of the IGBT.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Fin type fast recovery super-junction power semiconductor transistor and preparation method thereof

ActiveCN106024910AInhibit onPrevent inflowFinal product manufactureSemiconductor/solid-state device manufacturingPolysilicon gateBody region

The invention discloses a fin type fast recovery super-junction power semiconductor transistor and a preparation method thereof. The fin type fast recovery super-junction power semiconductor transistor comprises an N-type substrate, wherein an N-type epitaxial layer is arranged on the N-type substrate; second columnar P-type body regions are arranged in the N-type epitaxial layer; a first P-type body region is arranged on the top of the N-type epitaxial layer, and the first P-type body region is positioned between the two second columnar P-type body regions; the surface of the N-type epitaxial layer is provided with an N-type heavily-doped source region and a P-type heavily-doped semiconductor contact region; the N-type heavily-doped source region, the P-type heavily-doped semiconductor contact region and the second P-type body region are connected with source electrode metals; polysilicon gates are arranged on two sides of the first P-type body region respectively; the second columnar P-type body regions are terminated at the lower surfaces of the polysilicon gates, and the second columnar P-type body regions are lower than the first P-type body region; gate oxide layers are arranged between the polysilicon gates and the first P-type body region, the N-type epitaxial layer and the second P-type body regions; insulated layers are arranged between the polysilicon gates and the source electrode metals; and the gate oxide layers enable the first P-type body region and the second P-type body regions to be separated from each other.

Owner:SOUTHEAST UNIV

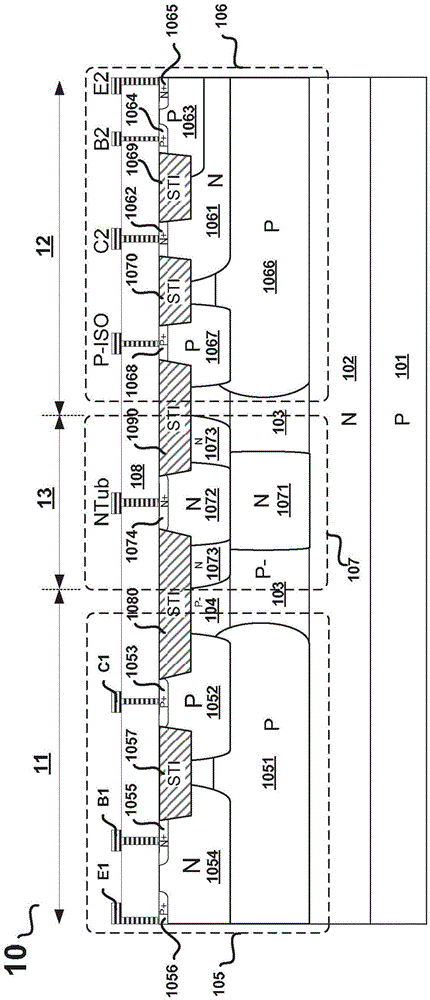

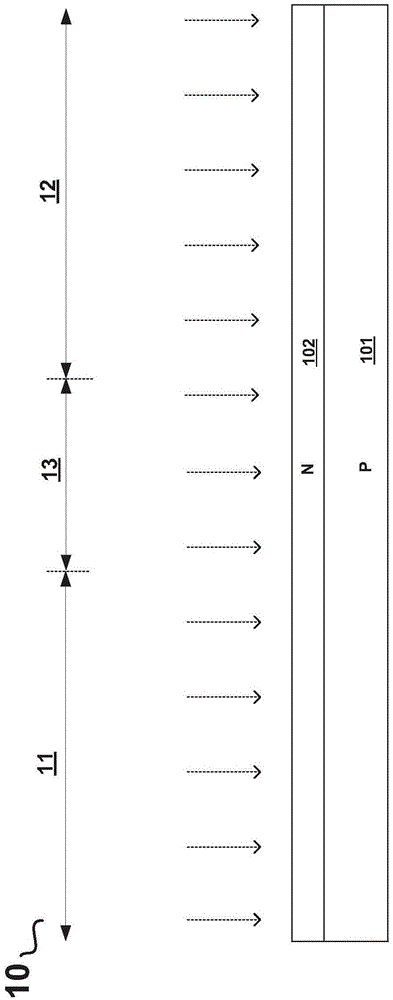

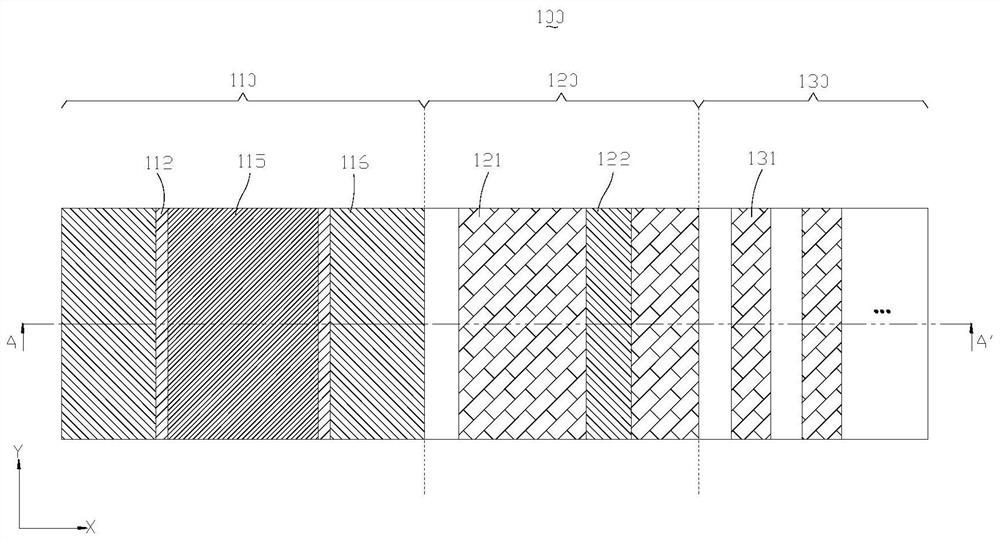

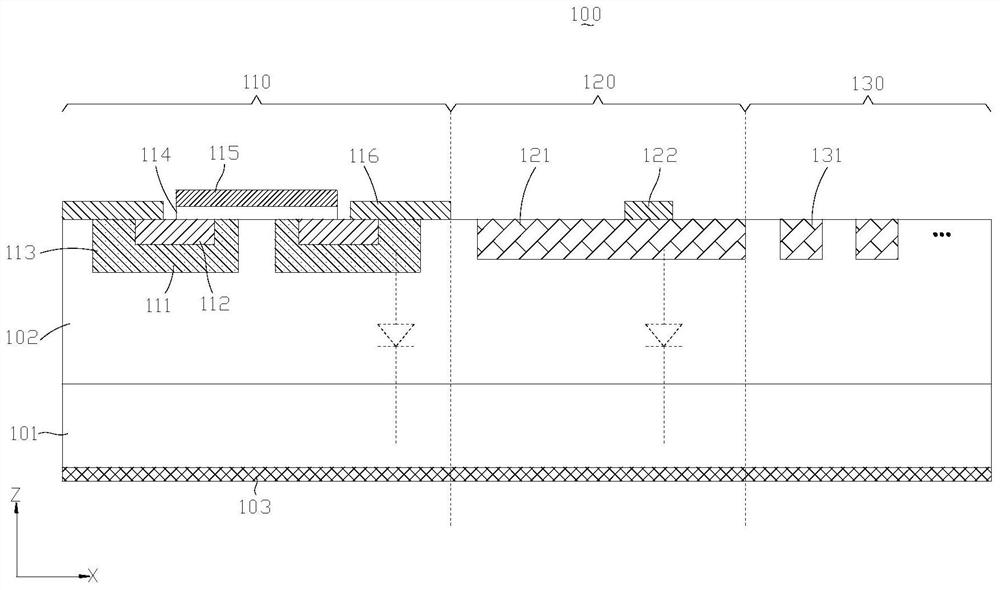

Bipolar junction transistor and related manufacturing method thereof

ActiveCN105633078AInhibit onSimplify the design processTransistorSolid-state devicesCharge carrierEngineering

The invention provides a bipolar junction transistor and a related manufacturing method thereof. According to the embodiment provided by the invention, the bipolar junction transistor comprises a first buried layer, a first epitaxial layer, a second epitaxial layer, a PNP bipolar junction transistor unit, an NPN bipolar junction transistor unit and a first isolating structure, wherein the first buried layer is formed in a semiconductor substrate; the first epitaxial layer and the second epitaxial layer are formed on the first buried layer; the PNP bipolar junction transistor unit, the NPN bipolar junction transistor unit and the first isolating structure are fabricated in the first epitaxial layer and the second epitaxial layer; the first isolating structure is located between the PNP bipolar junction transistor unit and the the NPN bipolar junction transistor unit and are connected with the first buried layer to form an isolating barrier. The isolating barrier not only can effectively isolate the PNP bipolar junction transistor unit from the NPN bipolar junction transistor unit, but also can effectively isolate the PNP bipolar junction transistor unit and the NPN bipolar junction transistor unit from the semiconductor substrate, and prevents a charge carrier from being injected into the substrate and a parasitic BJT from being formed.

Owner:CHENGDU MONOLITHIC POWER SYST

Silicon carbide MOSFET chip

ActiveCN113054015AImprove reliabilityImprove area utilization efficiencyEfficient power electronics conversionSemiconductor devicesMOSFETCarbide silicon

The invention provides a silicon carbide MOSFET (metal oxide semiconductor field effect transistor) chip. The silicon carbide MOSFET chip comprises an active region, a terminal region and a transition region which are arranged on a drift layer, wherein the active region comprises a plurality of cellular structures; the cellular structure includes a second conductivity type first enhancement region disposed side by side with a source region in the surface of a first well region and in contact with one end of the source region away from the center of the cellular structure, and a first Schottky metal layer located above the drift layer on both sides of the cellular structure and forming Schottky contact with the drift layer. The transition region comprises a second source electrode metal layer which is arranged above the second enhancement region and forms ohmic contact with the second enhancement region, and a second Schottky metal layer which forms Schottky contact with a region, which is not covered by the second enhancement region, of the drift layer is arranged on the surface of the drift layer. By simultaneously integrating the SBD in the active region and the transition region of the silicon carbide MOSFET chip, the bipolar degradation effect of the silicon carbide chip is improved, and the reliability of the chip is improved.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

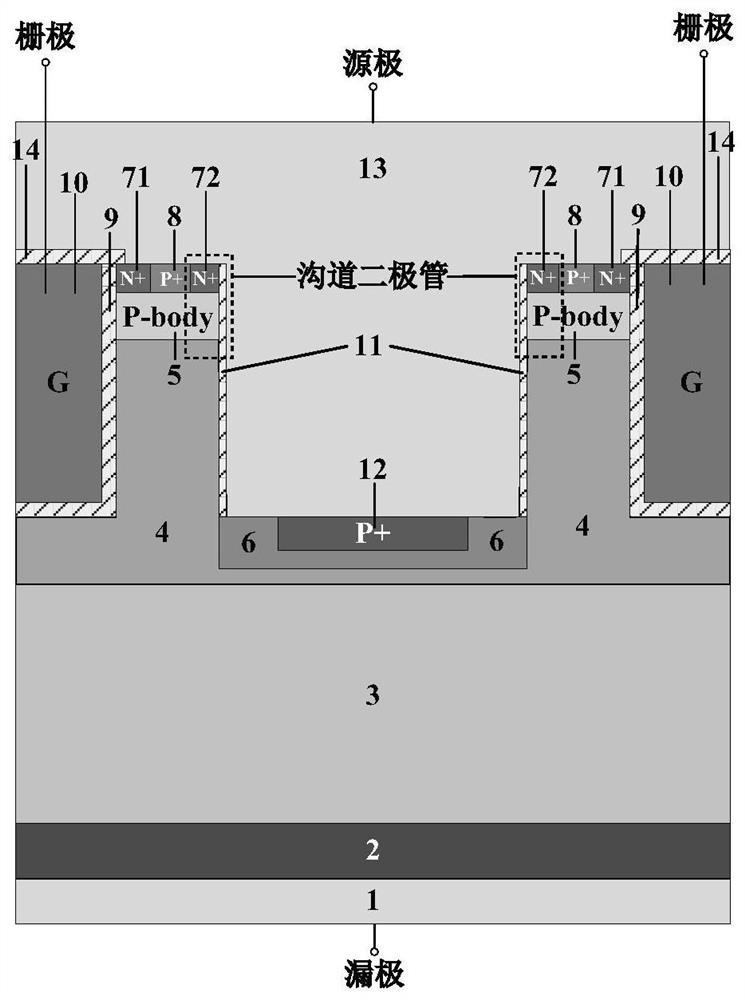

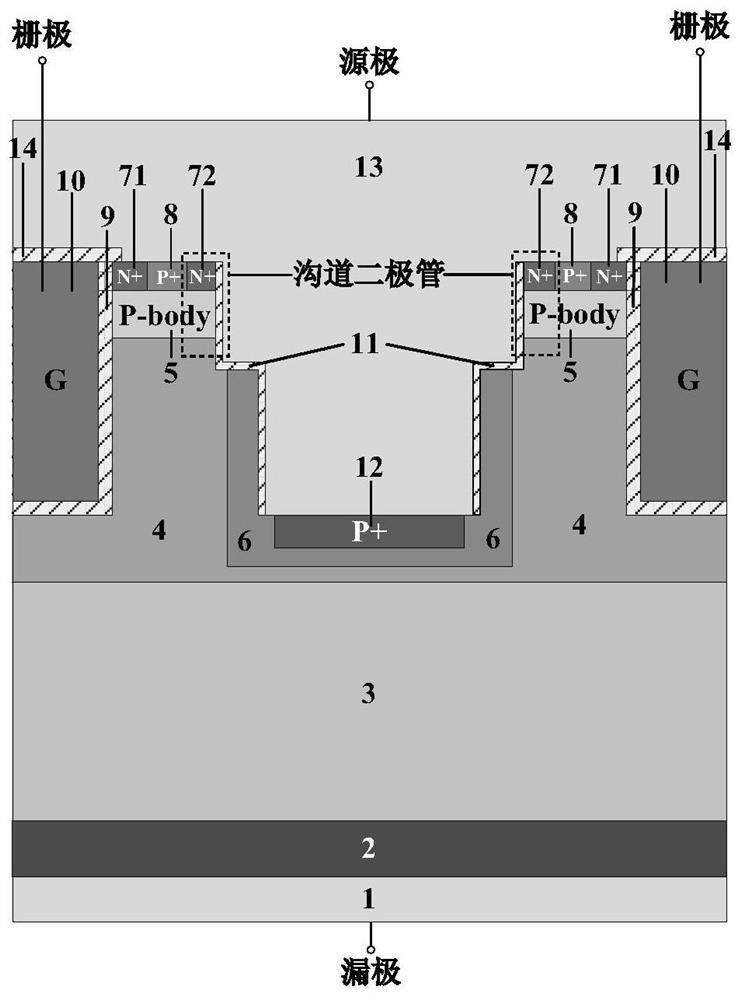

Silicon carbide double-groove MOSFET integrated with channel diode

ActiveCN113990923ASmall pressure dropImprove reliabilityEfficient power electronics conversionSolid-state devicesMOSFETCarbide silicon

The invention belongs to the technical field of power semiconductors, and particularly relates to a silicon carbide double-groove MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) integrated with an channel diode. The MOSFET is mainly characterized in that: firstly, a channel diode is integrated, when a device is in a follow current working mode, the channel diode is conducted to achieve a follow current function, conduction of a body diode is effectively restrained by reducing reverse conduction voltage drop, and meanwhile the influence caused by bipolar degradation is eliminated; and secondly, an electric field is modulated through a P-type region below the source groove, so that the peak of the electric field at the corner of silicon dioxide at the bottom of the gate groove is reduced, and the breakdown voltage and the reliability of the device in a blocking working mode are improved;.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

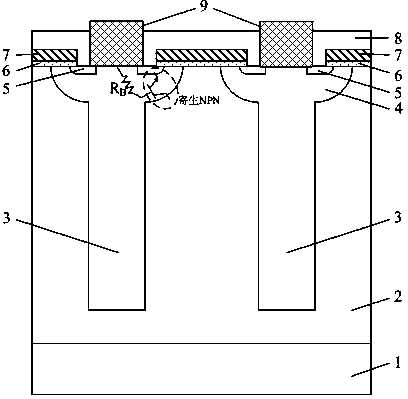

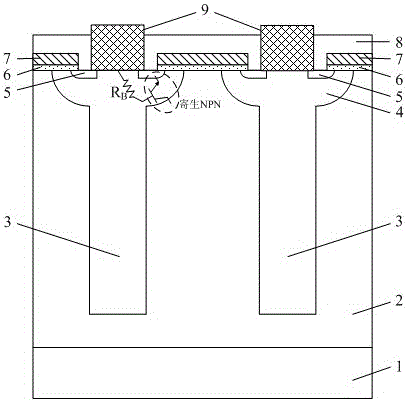

Discrete power mos field effect transistor and manufacturing method thereof

PendingCN106531810AThe production process is simpleShorten the contact pathSemiconductor/solid-state device manufacturingSemiconductor devicesLithography processLithographic artist

The invention discloses a discrete power mos field effect transistor and a manufacturing method thereof. In the process of forming the power mos field effect transistor, a source region is firstly formed in an epitaxial layer, contact hole corrosion is carried out on the formed source region, P+ injection and original P+ region connection are carried out on a contact hole region to form a P+ region, metal deposition is carried out to form a metal layer and contact of the metal layer and N+ and P+ of the source region is finally obtained. In the technical process, the lithography process of separately forming N+ and P+ through twice lithography corrosion in the original technical process is reduced, so that one-time lithography is reduced from the manufacturing process of a power MOS, and the manufacturing process is simplified and the production cost is reduced; a contact path of the P+ and the metal layer is shortened by adopting a silicon etching technology, so that parasitic P+ resistance is reduced to inhibit starting of a parasitic NPN and improvement of the avalanche breakdown tolerance is facilitated; and the source region is firstly formed and then contact hole corrosion is carried out on the formed source region, so that the trouble that P+ injection cannot be carried out after contact hole lithography due to the fact that the concentration of the N+ is much greater than that of the P+ is avoided.

Owner:西安锴威半导体有限公司

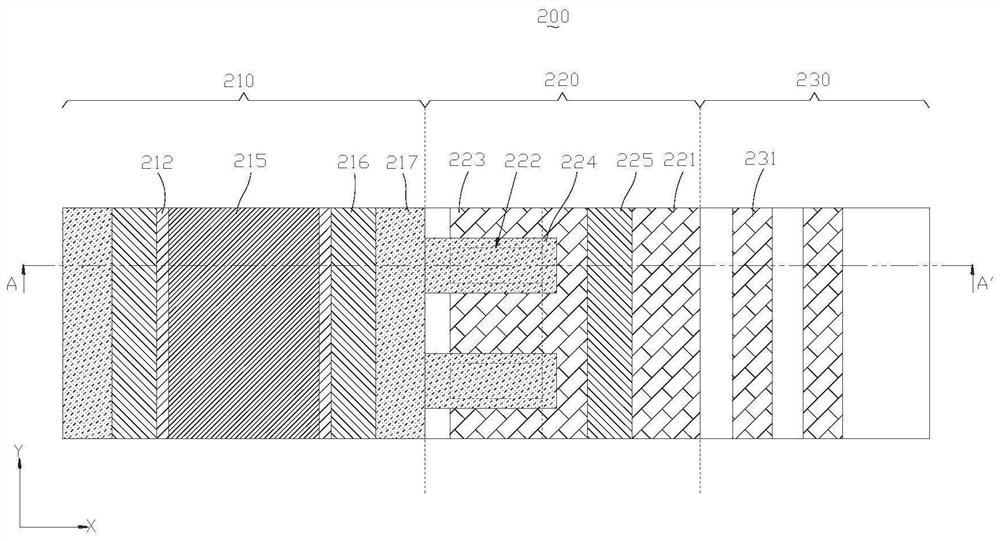

Cellular structure of silicon carbide MOSFET device, and power semiconductor device

ActiveCN113054016AImprove reliabilityInhibit onTransistorEfficient power electronics conversionMOSFETCarbide silicon

The invention discloses a cellular structure of a silicon carbide MOSFET device. The cellular structure comprises a drift region positioned on a substrate layer, a second conductive type well region and a first JFET region which are positioned in the drift region, an enhancement region positioned in the surface of the well region, a gate insulation layer located on the first conductivity type enhancement region, the well region and the first JFET region and making contact with the first conductivity type enhancement region, the well region and the first JFET region at the same time, a gate on the gate insulation layer, a source metal located on the enhancement region, Schottky metals located on the second conductivity type enhancement region and the drift region, a second JFET region located on the surface of the drift region between the Schottky metals, and a drain metal. An SBD is integrated in the silicon carbide MOSFET cellular structure, so opening of a body diode is restrained, and the reliability of the device is improved; the SBD is integrated between the second conduction type enhancement regions of the MOSFET cellular structure, so the overall power density of the chip is increased; and Schottky metal and the second JFET region are arranged at intervals, so a good compromise relationship between the on resistance and the leakage current is realized.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Insulated gate bipolar transistor

The invention discloses an insulated gate bipolar transistor comprising a substrate, gate structures, emitters and a collector. The gate structures, the emitters and the collector are arranged at the substrate; and the collector and the emitters are arranged at the two ends of the substrate. Each gate structure consists of a narrow part, a first widening part, and a second widening part; the narrow part is arranged between two emitters; the second widening part is arranged at one side, approaching the collector, of the gate structure; and the first widening part is connected between the narrow part and the second widening part. The first widening part is wider than the narrow part and thus areas that are connected with the emitter and are arranged in first directions of the emitters are filled, thereby suppressing starting of parasitic transistors at the edges of the emitters; and the second widening part is wider than the first widening part. Therefore, a technical problem of weak anti-latching capability of the existing PNM-IGBT device in the prior art can be solved; and thus a technical effect that the anti-latching capability is improved obviously while the parameter performance of the device is guaranteed is realized.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Trench gate metal oxide field effect transistor and manufacturing method thereof

PendingCN106876470AIncrease exhaustRun out fastSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSingle crystal

The invention relates to a trench gate metal oxide field effect transistor, which comprises a front metal electrode, a back metal electrode, an N-type single crystal substrate, an N-type epitaxial layer and a first P-type doping region, wherein a central part of the N-type epitaxial layer and a central part of the first P-type doping region are provided with a vertical trench, a first dielectric layer is arranged between the side wall of a grid electrode in the trench and the first P-type doping region, a second dielectric layer is arranged between the bottom of the grid electrode and the epitaxial layer, the first P-type doping region is provided with a first N-type doping region at the part close to the two sides of the trench, the first P-type doping region is further provided with a second P-type doping region at the part away from the two sides of the trench, the internal part of the epitaxial layer is further provided with a third P-type doping region and a second N-type doping region which are contacted with the lower part of the second dielectric layer, the third P-type doping region and the second N-type doping region are enabled to be mutually staggered and spaced, and a plurality of PN junction units are formed in the length direction and the thickness direction. According to the invention, parasitic capacitance between a grid electrode and a drain electrode of a low trench gate SiC MOSFET can be reduced, the electric field intensity at the bottom of the trench is reduced, and turn-on of a parasitic BJT (Bipolar Junction Transistor) is suppressed.

Owner:SHENZHEN BASIC SEMICON LTD

High voltage device for drive chip of plasma flat-panel display

InactiveCN101510551BIncrease load capacityImprove safe work areaSolid-state devicesSemiconductor devicesHigh densityLow voltage

The invention provides a high-voltage device for a drive chip of a plasma flat-panel display, pertaining to the field of a semi-conductor power device. A high-voltage pLDMOS device, a high-voltage nLDMOS device and a high-voltage nLIGBT device are established on a substrate, an oxygen burying layer and an SOI layer and separated by deep-slot medium isolation areas. The oxygen burying layer and thedeep-slot medium isolation areas positioned between the substrate and the SOI layer realize the full medium isolation of the device and low-voltage logic circuits. The thickness of the SOI layer is 8micrometers and can meet the requirements of the device for high-voltage resistance. Compared with the thin SOI technology, the self-heating effect is relieved obviously and the nLIGBT device has lowconduction resistance. The group of the high-voltage device for the drive chip of the plasma flat-panel display based on the thick SOI layer fully utilizes the characteristics of the SOI technology,such as low leak, small chip occupying area, high speed, high density of integration and low power consumption, thus meeting the development requirements of the large-sized plasma flat-panel display.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Super-junction vertical double-diffusion metal oxide semiconductor tube

ActiveCN102646710AImprove reliabilityInhibit onSemiconductor devicesDouble diffusionActive electrode

The invention provides a super-junction vertical double-diffusion metal oxide semiconductor tube, comprising an N-type heavily-doped silicon substrate which is used as a drain region, wherein drain electrode metal is arranged on the lower surface of the N-type heavily-doped silicon substrate; an N-type doped silicon epitaxial layer is arranged on the upper surface of the N-type heavily-doped silicon substrate; a discontinuous P-type doped columnar semiconductor region is arranged in the N-type doped silicon epitaxial layer; a first P-type doped semiconductor region is arranged on the P-type doped columnar semiconductor region; the first P-type doped semiconductor region is arranged in the N-type doped silicon epitaxial layer; and the first P-type doped semiconductor region is internally provided with a second P-type doped semiconductor contact region and an N-type doped semiconductor source region. The super-junction vertical double-diffusion metal oxide semiconductor tube is characterized in that: the N-type doped semiconductor source region is connected with active electrode metal; the second P-type doped semiconductor contact region is connected with substrate metal; polycrystalline silicon which is used as an resistor is arranged below the active electrode metal and the substrate metal; and the polycrystalline silicon is respectively connected with the active electrode metal and the substrate metal, and top layer metal is connected with the substrate metal.

Owner:SOUTHEAST UNIV

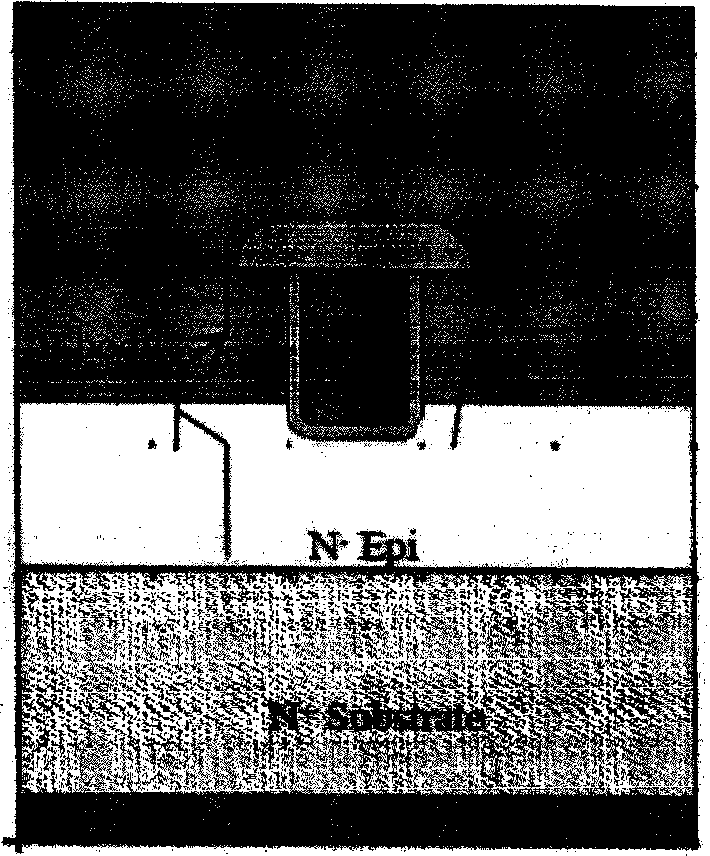

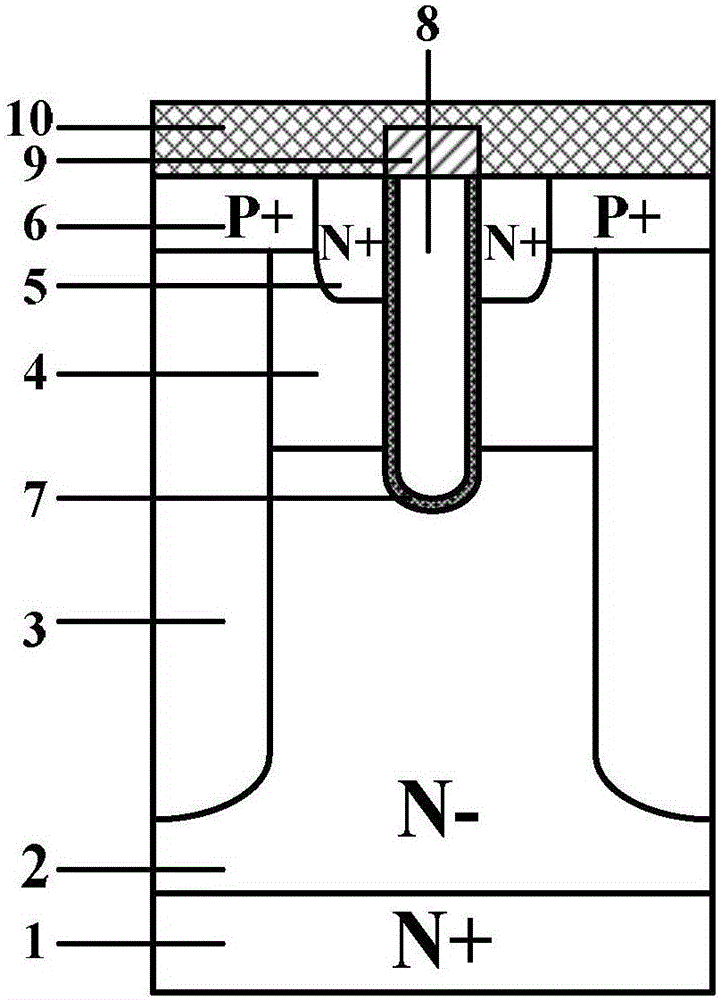

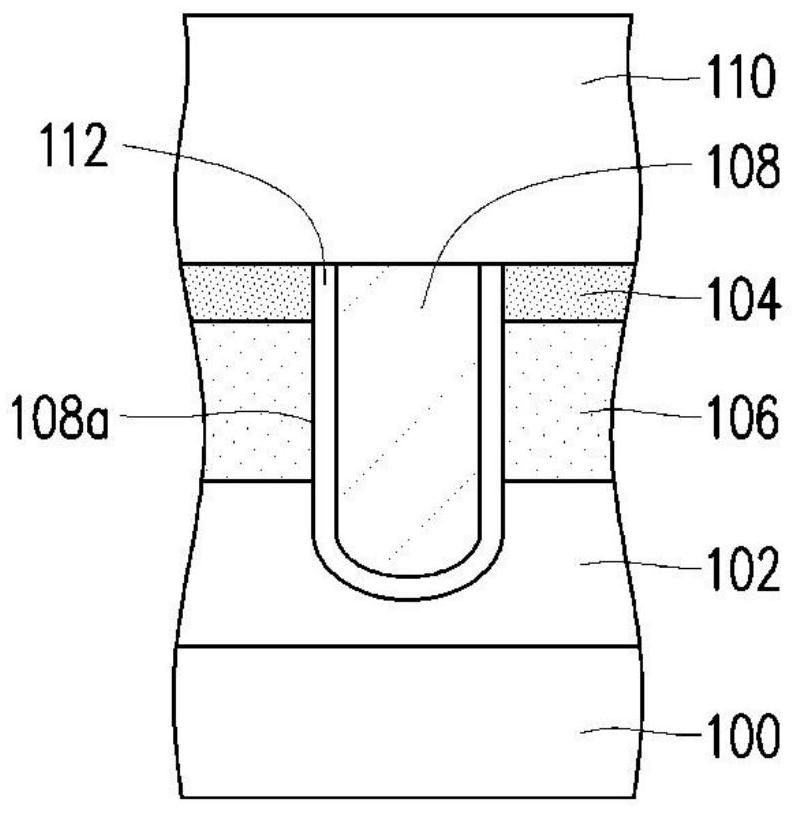

Trench mosfet and manufacturing method of the same

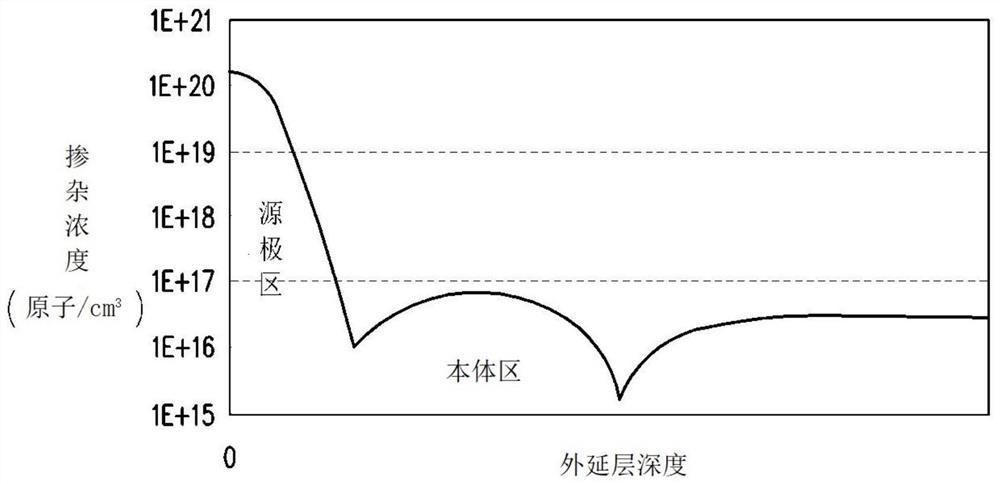

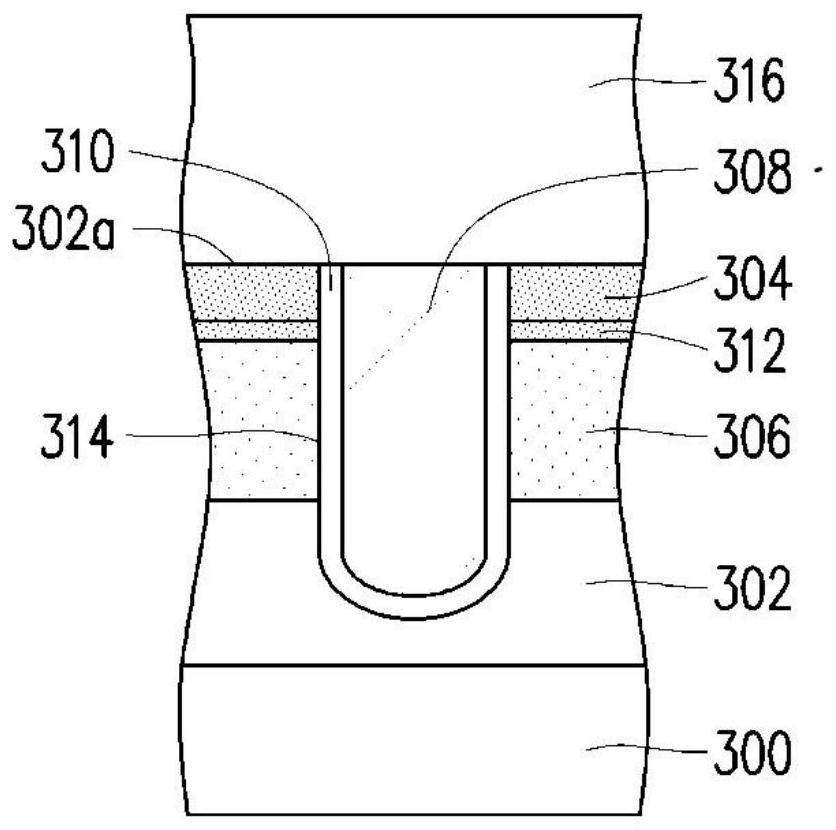

ActiveCN113035931AInhibit onImprove UIS capabilitiesSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetField-effect transistor

A trench MOSFET and a manufacturing method of the same are provided. The trench MOSFET includes a substrate, an epitaxial layer having a first conductive type, a gate in a trench in the epitaxial layer, a gate oxide layer, a source region having the first conductive type, and a body region and an anti-punch through region having a second conductive type. The anti-punch through region is located at an interface between the source region and the body region, and a doping concentration thereof is higher than that of the body region. The epitaxial layer has a first pn junction near the source region and a second pn junction near the substrate. N regions are divided into N equal portions between the two pn junctions, and N is an integer greater than 1. The closer the N regions are to the first pn junction, the greater the doping concentration thereof is. Each of the N regions has a doping concentration integral area, and the doping concentration integral area of the region closer to the first pn junction in the N regions is larger. Through the breakdown-resistant doped region, the device has steep concentration distribution, so that the UIS capability of the device is improved.

Owner:EXCELLIANCE MOS

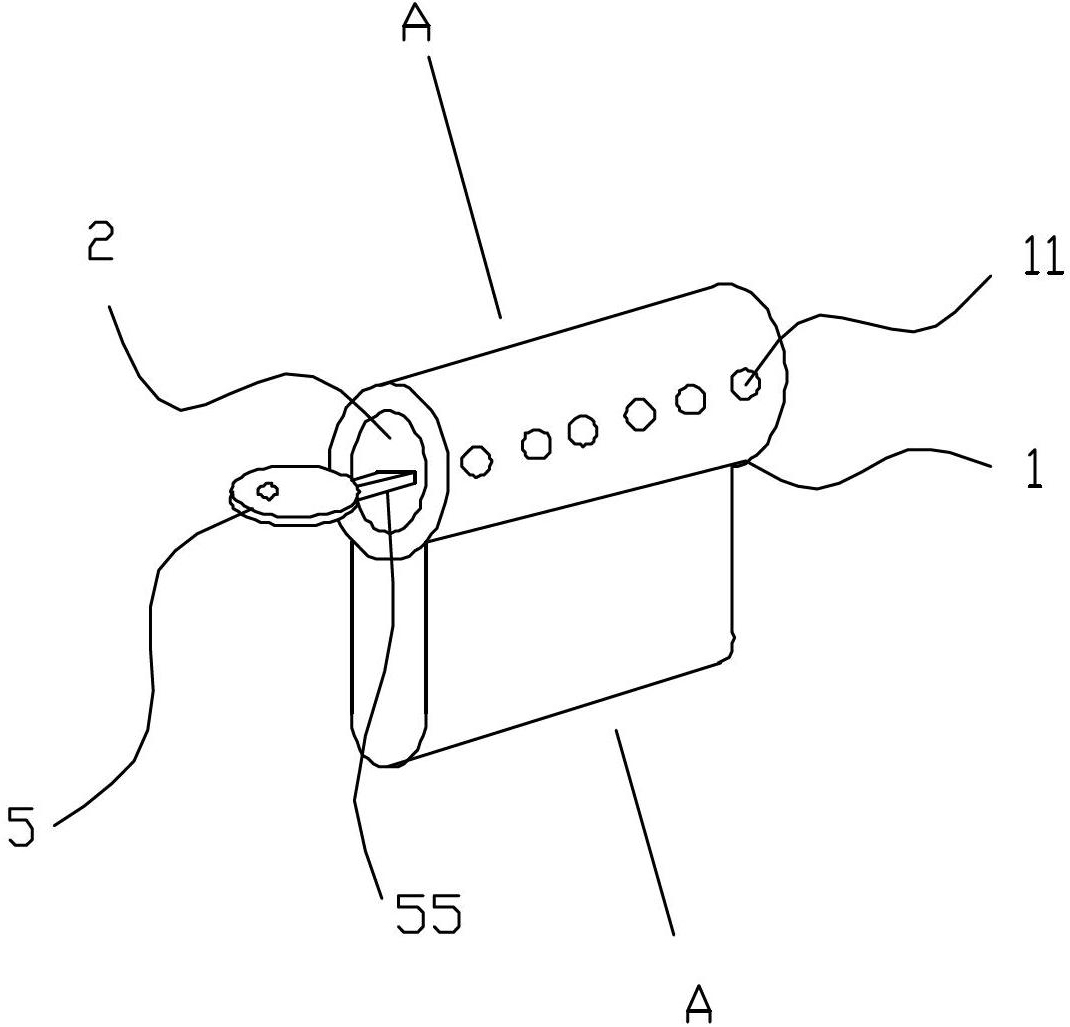

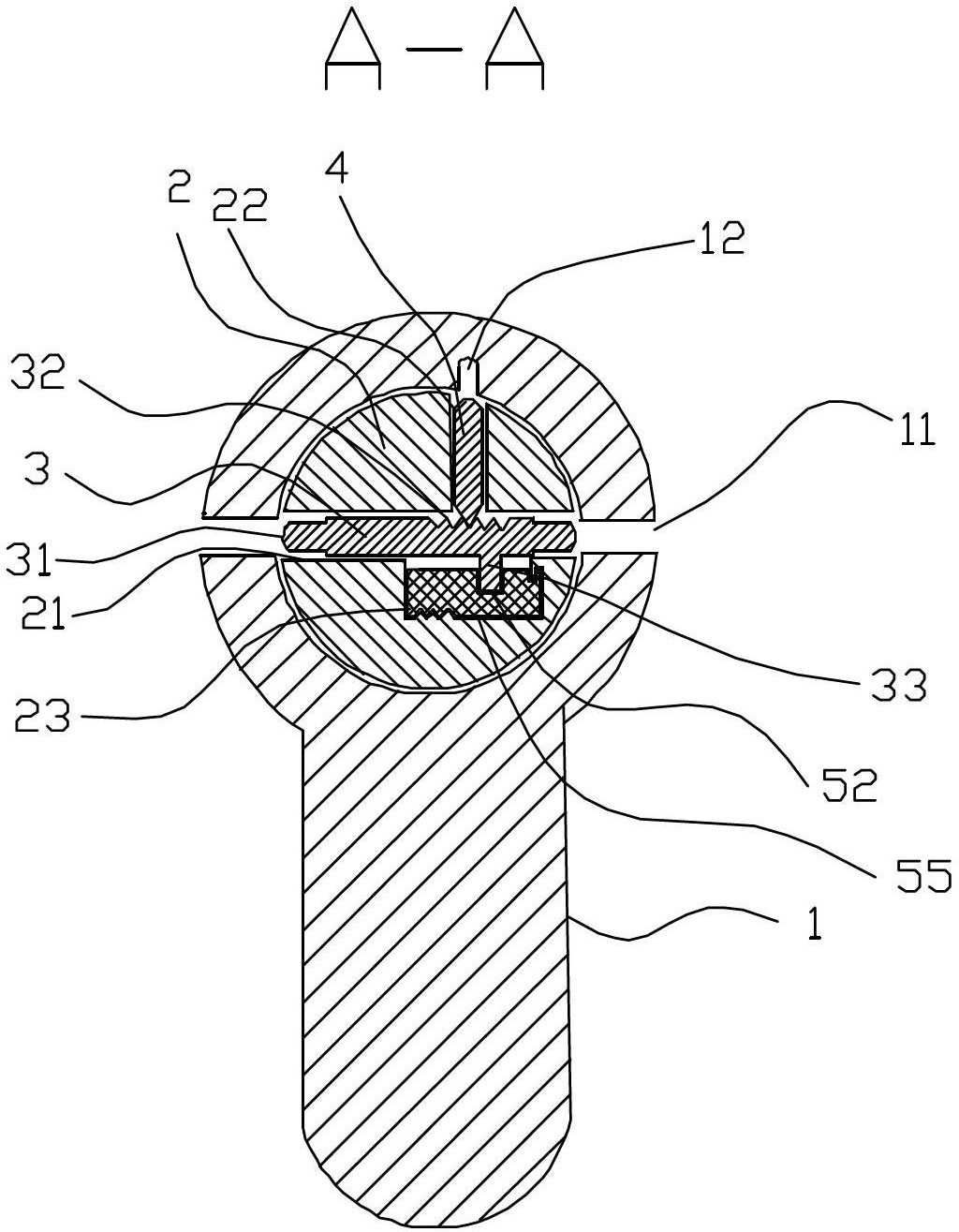

Lock and key used by matching with same

Owner:樊俊峰 +1

A Current Enhanced Lateral Insulated Gate Bipolar Transistor

ActiveCN104916674BStrong on-current capabilityImprove the conduction current capabilitySemiconductor devicesHigh current densityPower flow

A current enhanced type lateral insulated gate bipolar transistor improves current density and the turn-off speed on the premise that a latching ability is maintained to be unchanged. The semiconductor is provided with buried oxide disposed on a P-type substrate and an N-drift region disposed on the buried oxide, a P-body region and an N-buffer region are disposed on the N-drift region, a P-type collecting electrode region is disposed in the N-buffer region, an anode metal is connected to the P-type collecting electrode region, a field oxide layer is disposed on the N-drift region, a P-well region is disposed in the P-body region, a P-type emitting electrode region and an emitting electrode region are disposed in the P-well region, the inner-side boundaries of the four regions, i.e., the P-body region, the P-well region, the P-type emitting electrode region and the emitting electrode region are synchronously recessed inwardly to form a square groove, the emitting electrode region surrounding the groove is successively defined as a first P-type emitting electrode region, second, third and fourth N-type emitting electrode regions and a fifth P-type emitting electrode region, the N-drift region protrudes outwardly and fills the square groove, a surface of the P-body region is provided with a gate oxide layer, a surface of the gate oxide layer is provided with a polysilicon layer, and a gate metal is connected to the polysilicon layer.

Owner:SOUTHEAST UNIV +1

An extremely low reverse recovery charge superjunction power vdmos

ActiveCN109830524BImprove reverse recovery characteristicsReduce the total hole chargeSolid-state devicesSemiconductor devicesReverse recoverySchottky diode

The present invention relates to a super-junction power VDMOS having an extremely low reverse recovery charge, comprising an N-type substrate also serving as a drain and an N-type drift region. A first P column is provided in the N-type drift region; a first P-type body region is provided in the top of the first P column; an NMOS is provided in the first P-type body region; a SiO2 isolation layer is provided between the NMOS and the first P-type body region; and a first P-type heavily doped region is provided in the first P-type body region. Source metal of a super-junction VDMOS, source metal of the NMOS, and the first P-type heavily doped region are connected; the drain of the super-junction VDMOS serves as the drain of the super-junction power VDMOS; the gate of the super-junction VDMOS and the gate of the NMOS are connected and serve as the gate of the super-junction power VDMOS; the drain of the NMOS serves as the source of the super-junction power VDMOS; and an N-type drift region of the super-junction VDMOS is provided with a Schottky contact which is connected to the drain of the NMOS, so as to form a Schottky diode of which the cathode and anode are respectively connected to the drain and source in the structure provided by the present invention.

Owner:SOUTHEAST UNIV

Preparation method of super junction semiconductor device capable of improving avalanche capability

ActiveCN103560086BImproved avalanche capabilityLower the resistance valueSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSource area

The invention relates to a super junction semiconductor device manufacturing method capable of improving the avalanche capacity. On-resistance is increased correspondingly due to transverse diffusion caused by the traditional high dosage concentration of a column P, and puncture voltage is reduced due to electric charge unbalance of the column P and a column N. According to the method, the epitaxy technology is utilized to form an N-type epitaxy layer; a P-type and N-type epitaxy layer is formed by injecting boron ions; the injection amount of the boron ions increases gradually, and the boron ions are pushed under the high temperature to form a P-type and N-type alternant epitaxy layer; a Pbody area is formed by injecting the boron ions; a polycrystalline silicon gate electrode is formed by etching polycrystalline silicon through the dry method; an N+ source area is formed by injecting arsenic ions; a layer of aluminum is deposited on the upper surface of a whole device, a source metal electrode is formed by etching the aluminum, and a drain electrode is formed on the back face through metallization. According to the super junction semiconductor device obtained through the method, the avalanche capacity of the super junction semiconductor device is improved, and at the same time, on-resistance is reduced.

Owner:XIAN LONTEN RENEWABLE ENERGY TECH +1

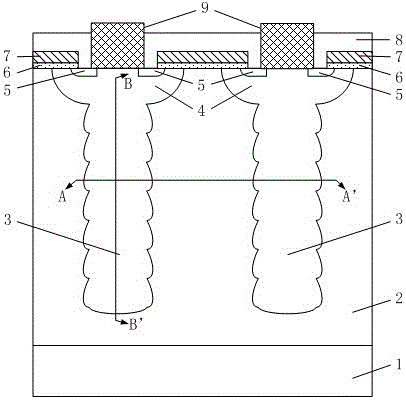

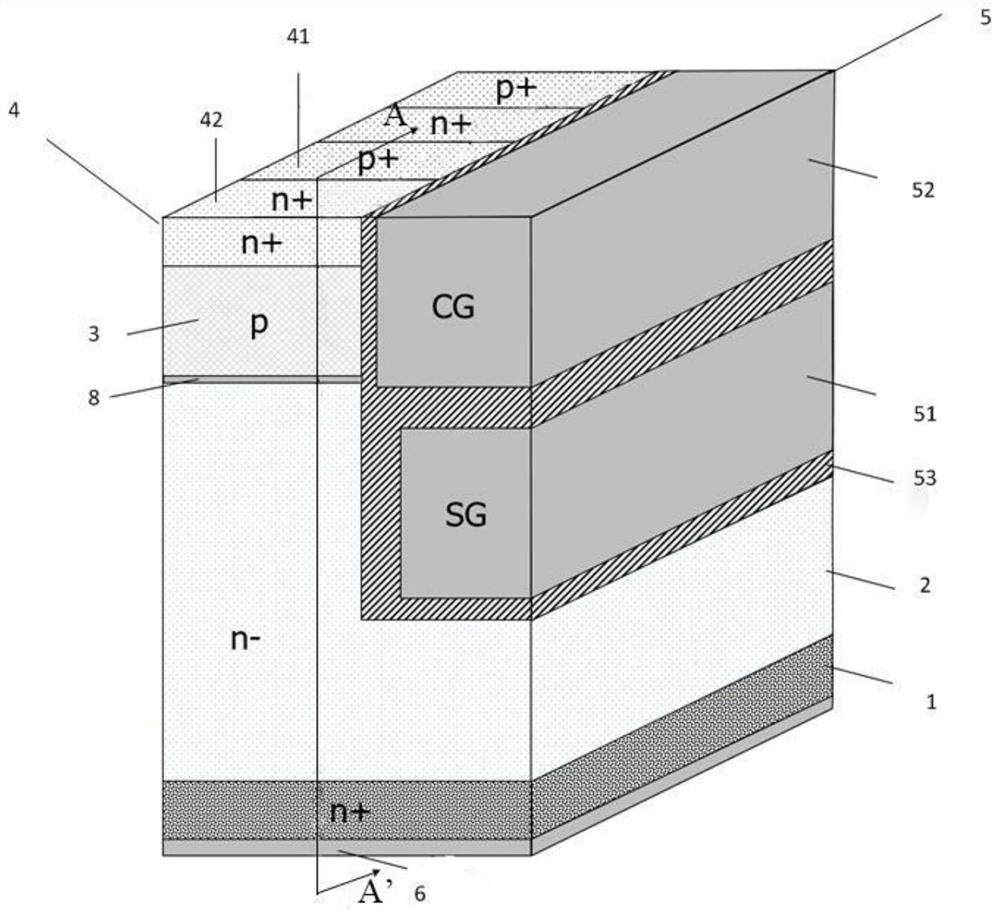

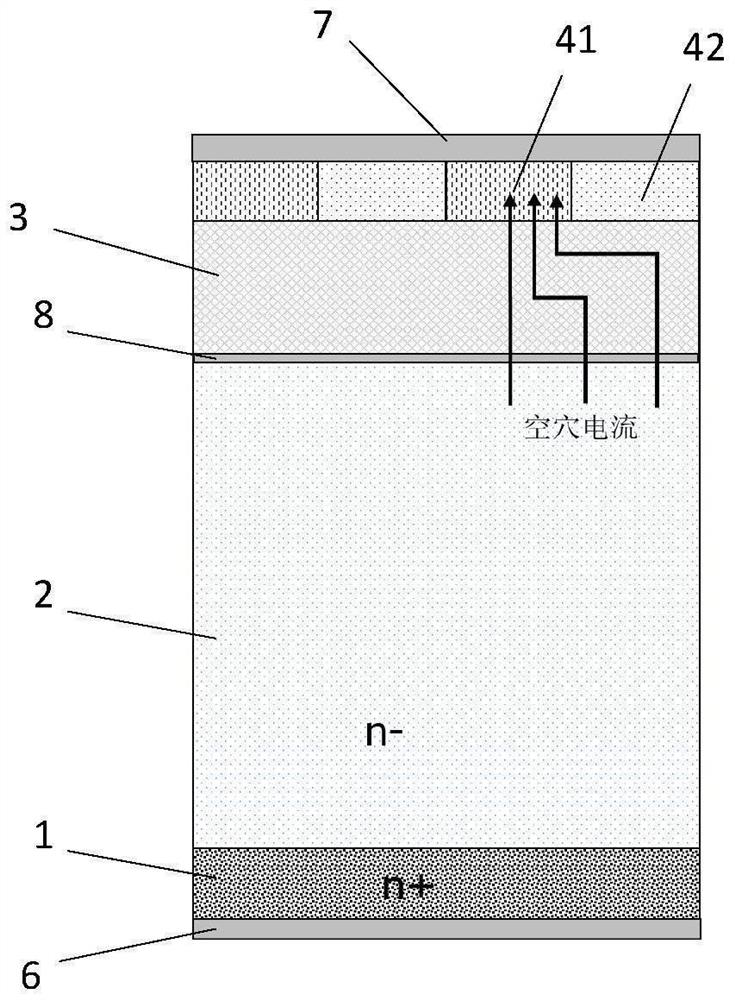

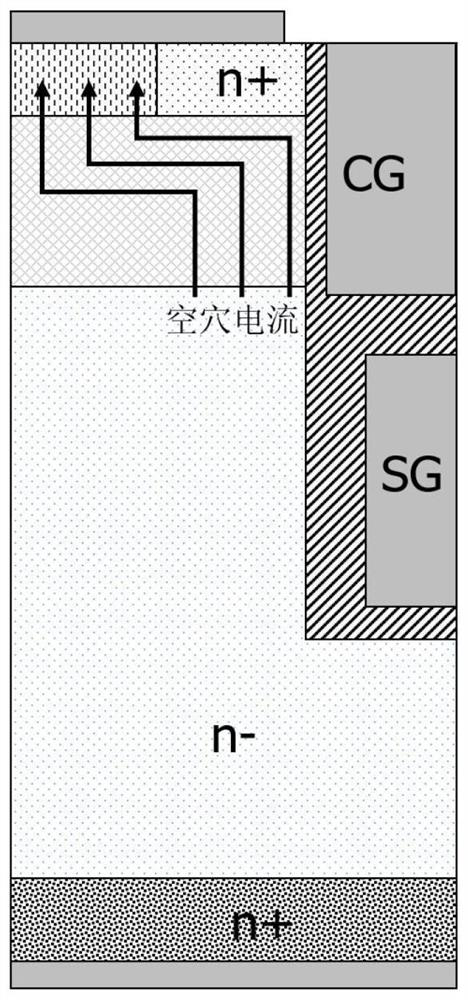

Shield gate groove type field effect transistor and preparation method thereof

PendingCN114141861AIncreased avalanche toleranceInhibit onSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringField effect

The invention relates to a shield gate trench type field effect transistor, which comprises a substrate region, a drift region, a matrix region, a source region, a trench region, a drain electrode and a source electrode, the drift region is connected with the substrate region, and the base region and the source region are sequentially arranged above the drift region by taking the direction of the substrate region pointing to the drift region as the upper part; the trench region is arranged on the side of the base body region and is connected with the drift region, the base body region and the source region respectively; the trench region comprises a shield gate, a control gate, an insulating layer and a metal gate; the source region consists of a P-type source region and an N-type source region, and the P-type source region and the N-type source region are arranged in parallel and are respectively connected to the trench region; and the shield grid is connected with the drift region. When avalanche breakdown occurs, hole current can be directly injected into the P-type source region along the side edge of the groove region, the moving path of the hole current is shortened, starting of a parasitic triode is inhibited, and avalanche tolerance is improved.

Owner:无锡先瞳半导体科技有限公司

A slotted gate power device with enhanced anti-single event capability

ActiveCN108122990BImprove reliabilityInhibit onSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceMechanical engineering

The application provides a trough type grate power device for enhancing reinforcement of resistance to a single particle, and relates to the field of semi-conductor devices. The trough type grate power device comprises an N+ source contact region, a Pwell region and an N drift region, wherein the N+ source contact region is in a deep trough structure; the Pwell region is located below an N+ source; the N drift region is located below the Pwell region; and the N+ source, the Pwell region and the N drift region form a parasitic NPN transistor structure. The device also comprises an N type hole blocking layer arranged below the N+ source and used for blocking the flow of hole carriers. According to the device, the technical problems of a method for improving the resistance to the single particle in the prior art that the application limitation is great, and the process is difficult in implementation, are solved, a hole flow path in a traditional structure is improved, and hole current flowing through a parasitic resistor region is greatly reduced, and therefore, the opening of a parasitic transistor is effectively suppressed, and the technical effect of enhancing the reliability of the resistance to the single particle is achieved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

A slot gate igbt device with carrier storage layer

The invention relates to the field of power semiconductors, and provides a slot-gate IGBT device with a carrier storage layer (CSL), which is used to solve the problem of high saturation voltage and short-circuit safe working area of the existing slot-gate IGBT with a carrier storage layer (CSL). In view of the problems of small size and limited concentration of CSL, a new trench-gate IGBT device with carrier storage layer is proposed. The IGBT of the present invention directly integrates a plurality of series diodes on the surface of the silicon chip in the trench gate IGBT process to clamp the potential of the electric field shielding layer in the P region, thereby breaking through the concentration limit of CSL on the basis of the existing trench gate IGBT process, and extremely The injection efficiency of the emitter of the IGBT is greatly improved, thereby greatly improving the trade-off relationship between the turn-on voltage drop and the turn-off loss of the IGBT; at the same time, due to the clamping effect of the diode, the drain near the nMOS channel of the IGBT is in the Under high voltage and high current, it is clamped at a lower voltage, so that the saturation current of the new IGBT is greatly reduced, thereby improving the short-circuit safe working area of the IGBT.

Owner:杭州朋声科技有限公司

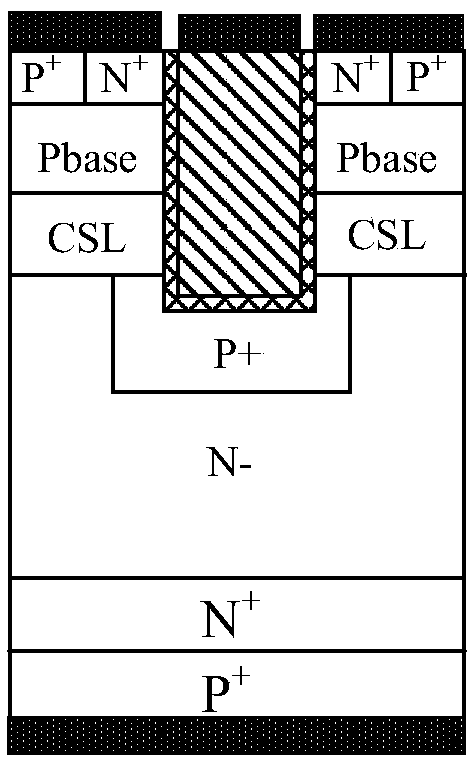

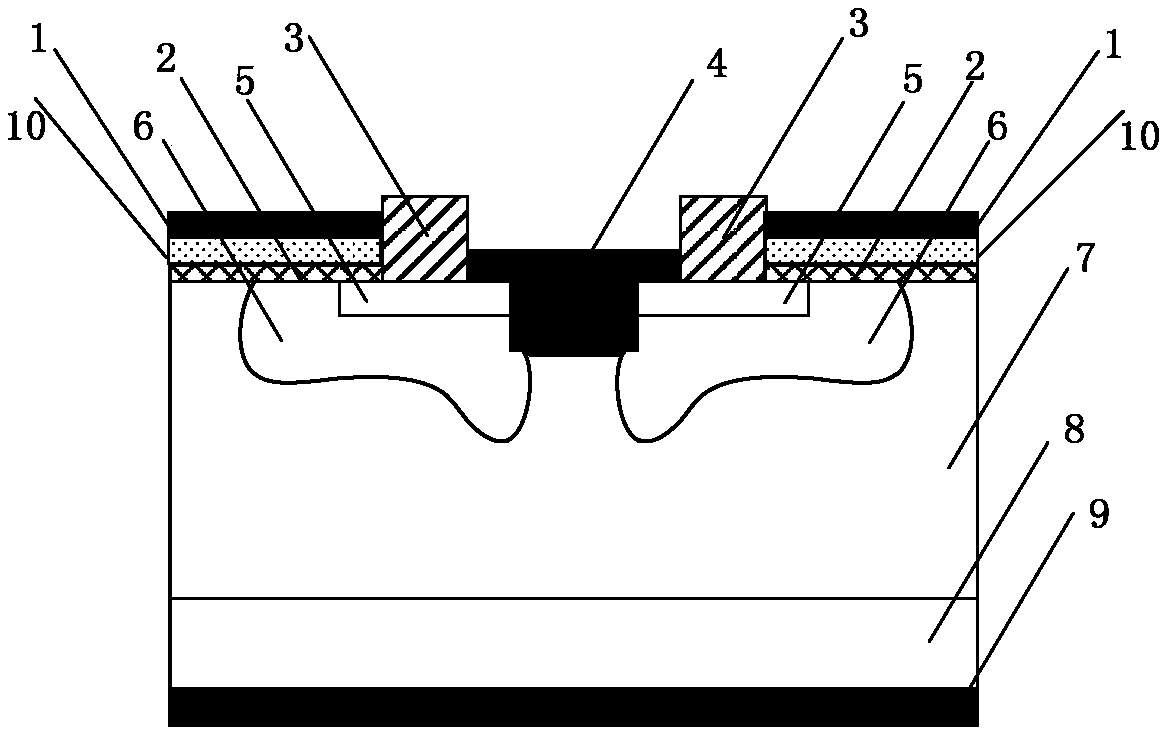

U-type source slot VDMOSFET device with Schottky diode

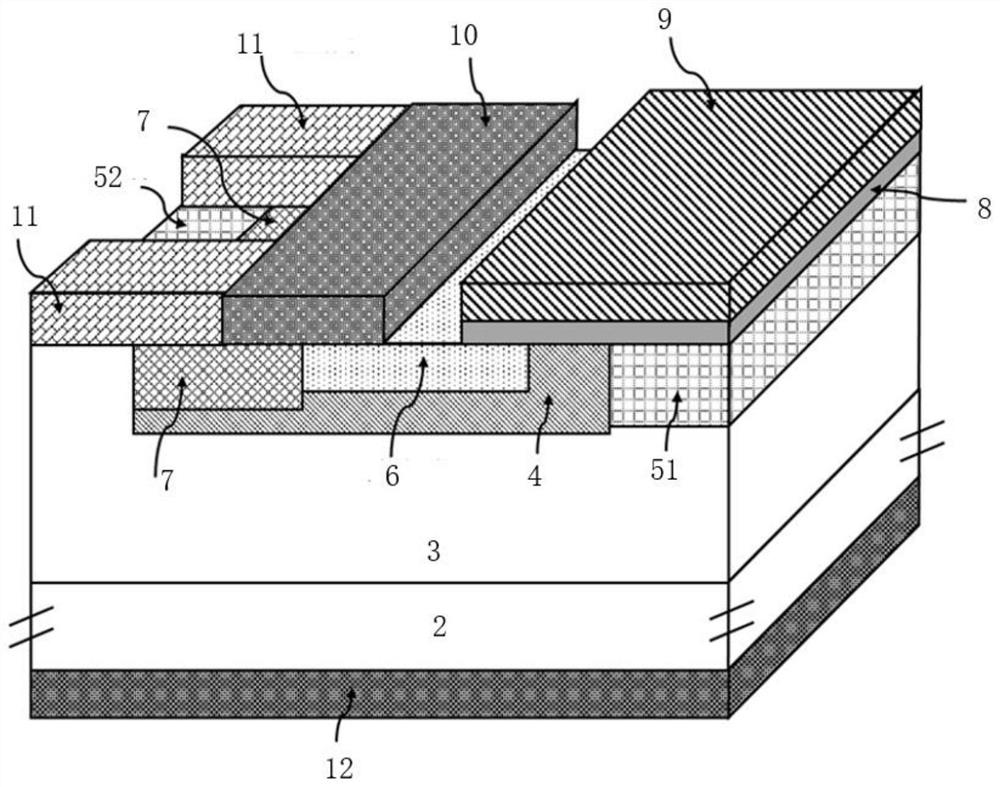

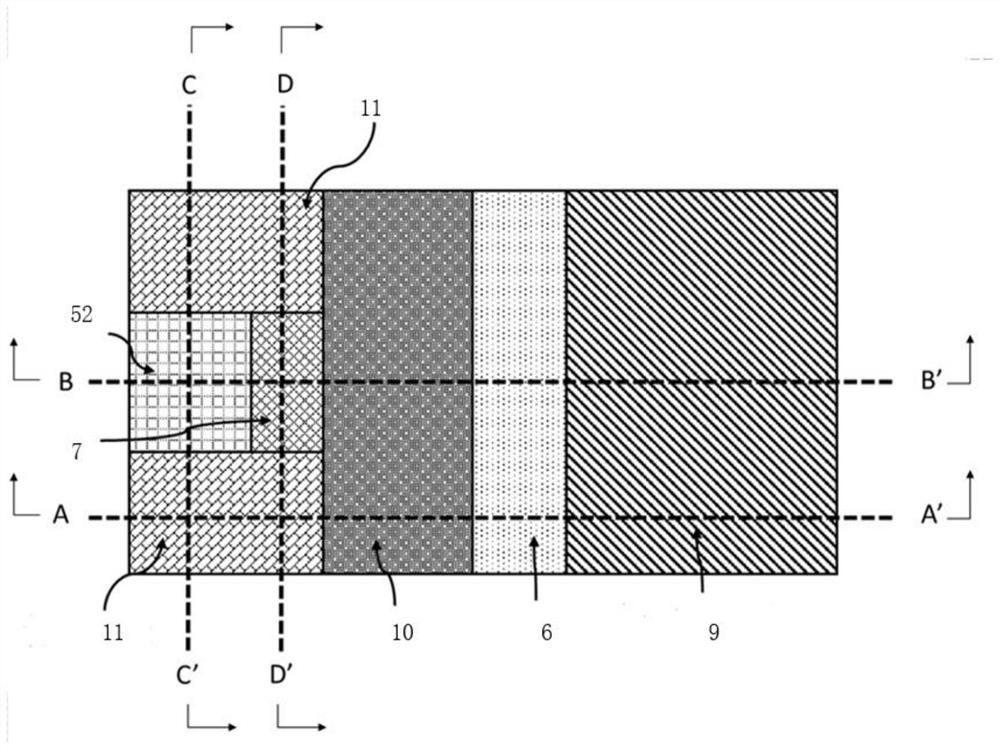

ActiveCN109192776ANo additional etch process steps requiredReduce areaDiodeGate dielectricSchottky diode

The invention relates to the field of integrated circuits and discloses a U-shaped source slot VDMOSFET device integrated with a Schottky diode, which is characterized in that the device comprises a substrate (8); a drain electrode (9) arranged below the substrate (8); N-drift region (7) arranged above the substrate (8); a source (4) arranged above the N-drift region (7); an N+ source region (5) arranged in the N-drift region on both sides of the source electrode (4); a P-type base region (6) provided in the N-drift region (7); a gate-source isolation layer (3) arranged above the N+ source region (5); a gate dielectric (2) and a gate electrode (10). The interfaces of the source (4) and the N-drift region (7) are in a Schottky contact. The device can improve the reliability of the device performance and reduce the complexity and cost of the design.

Owner:XIDIAN UNIV