Fin type fast recovery super-junction power semiconductor transistor and preparation method thereof

A technology of power semiconductors and transistors, applied in semiconductor/solid-state device manufacturing, semiconductor devices, final product manufacturing, etc., can solve the problems of increased device manufacturing cost, long time, high hardness of body diode reverse recovery, etc. The effect of the hole current path

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

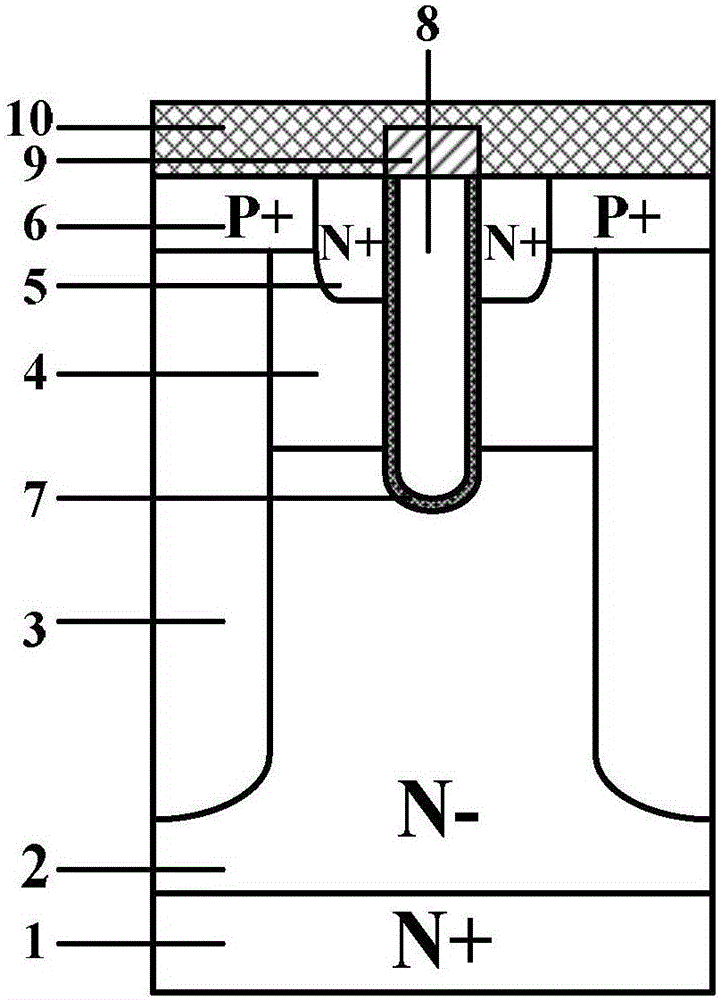

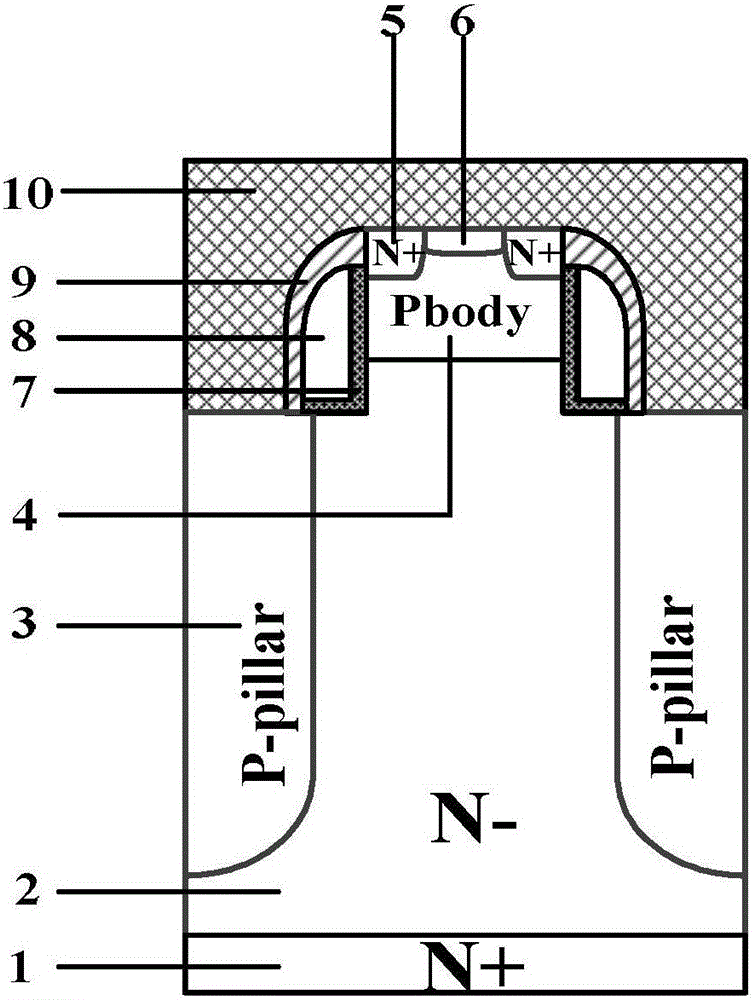

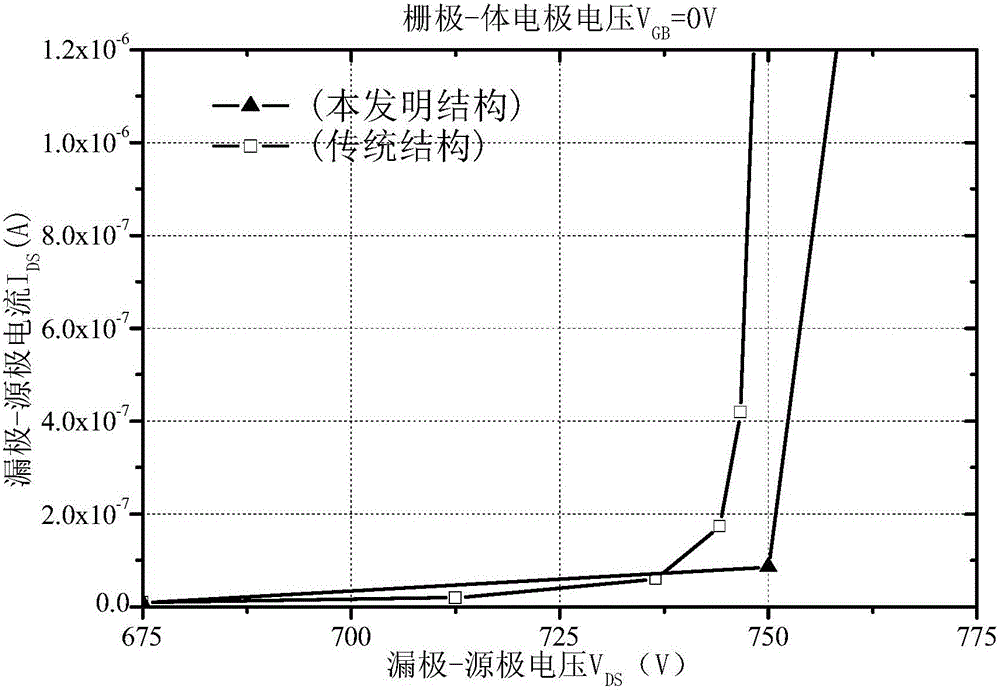

[0032] Combine below figure 2, the present invention is described in detail, a fin-type fast recovery super junction power semiconductor transistor, comprising: an N-type substrate 1, an N-type epitaxial layer 2 is arranged on the N-type substrate 1, and an inner layer of the N-type epitaxial layer 2 A columnar second P-type body region 3 is provided, and a first P-type body region 4 is provided on the top of the N-type epitaxial layer 2, and the first P-type body region 4 is located between two columnar second P-type body regions 3 An N-type heavily doped source region 5 and a P-type heavily doped semiconductor contact region 6 are provided on the surface of the first P-type body region 4, and an N-type heavily doped source region 5 and a P-type heavily doped semiconductor contact region 6 and the second P-type body region 3 are connected with a source metal 10, which is characterized in that polysilicon gates 8 are respectively arranged on both sides of the first P-type bod...

Embodiment 2

[0034] Combine below Figure 10 ~ Figure 18 , the present invention is described in detail, a method for preparing a fin-type fast recovery super-junction power semiconductor transistor, characterized in that:

[0035] The first step: first select N-type silicon material as the substrate and epitaxially grow N-type epitaxial layer;

[0036] Step 2: First, use a mask to selectively etch deep trenches in the N-type epitaxial layer, and epitaxially grow to form the second P-type body region 3;

[0037] Step 3: selectively etching the N-type epitaxial layer to form a convex epitaxial layer 2;

[0038] Step 4: Thermally grow a gate oxide layer 7 on the surface of the convex epitaxial layer 2, and then deposit polysilicon to fill the concave part of the N-type epitaxial layer 2;

[0039] Step 5: Etching the polysilicon to the surface of the raised portion of the N-type epitaxial layer 2, implanting boron ions, and annealing to form the first P-type body region 4;

[0040] Step 6:...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More