Patents

Literature

73results about How to "Increased avalanche tolerance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

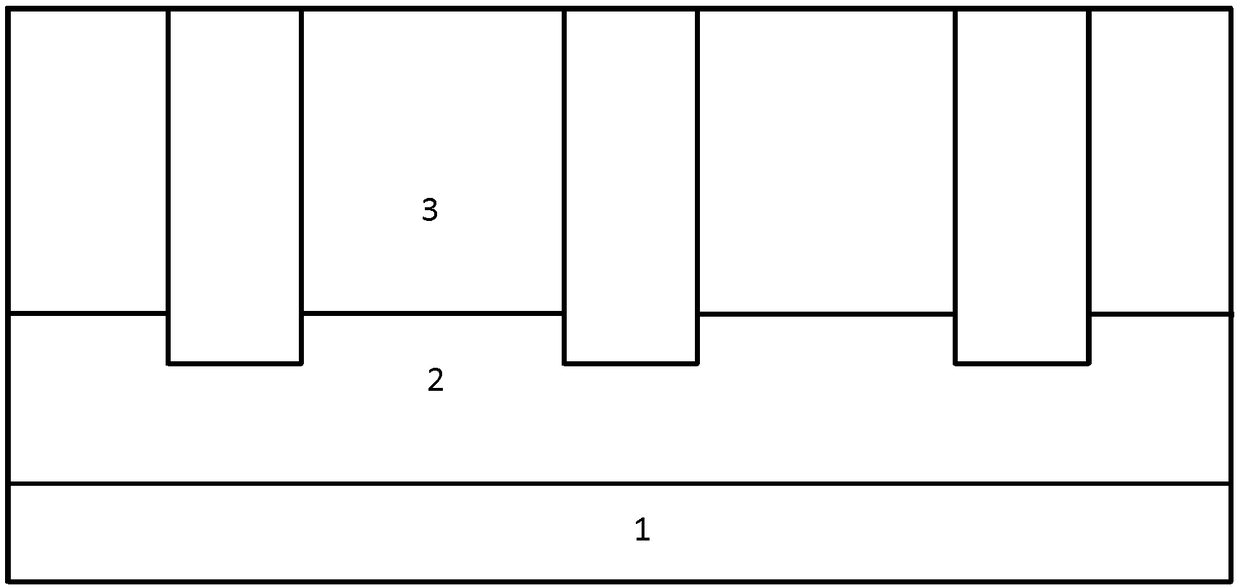

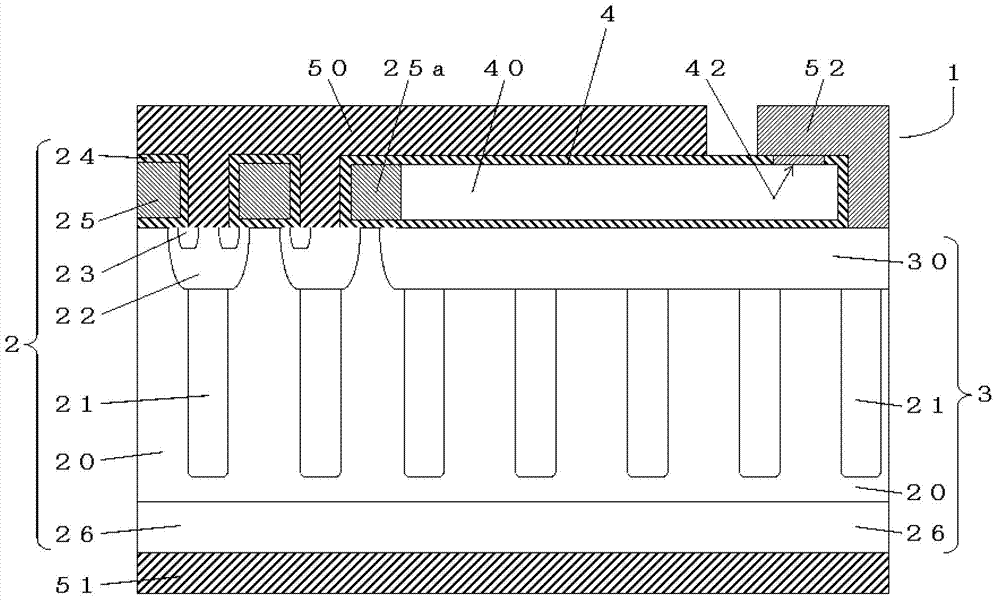

Semiconductor device

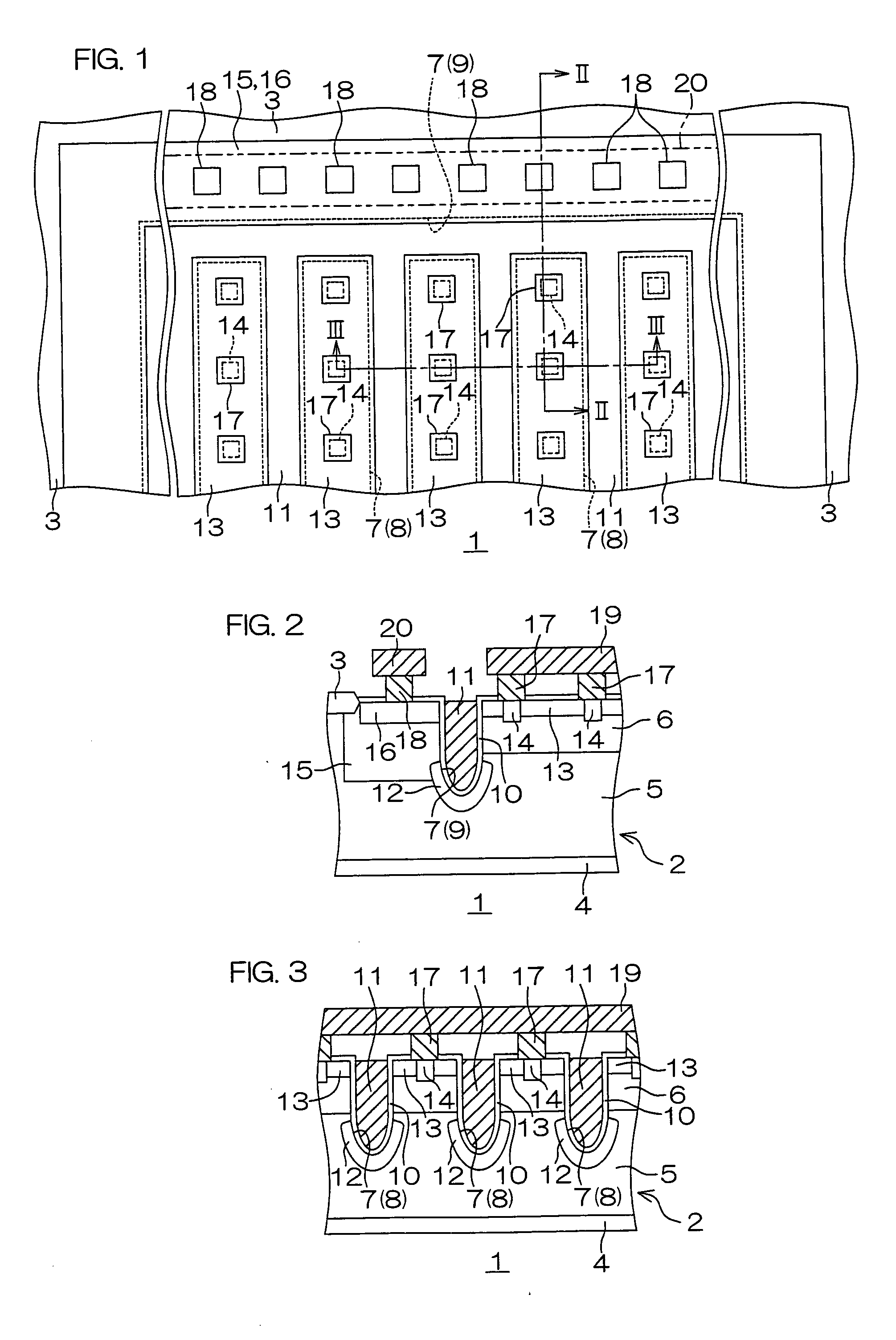

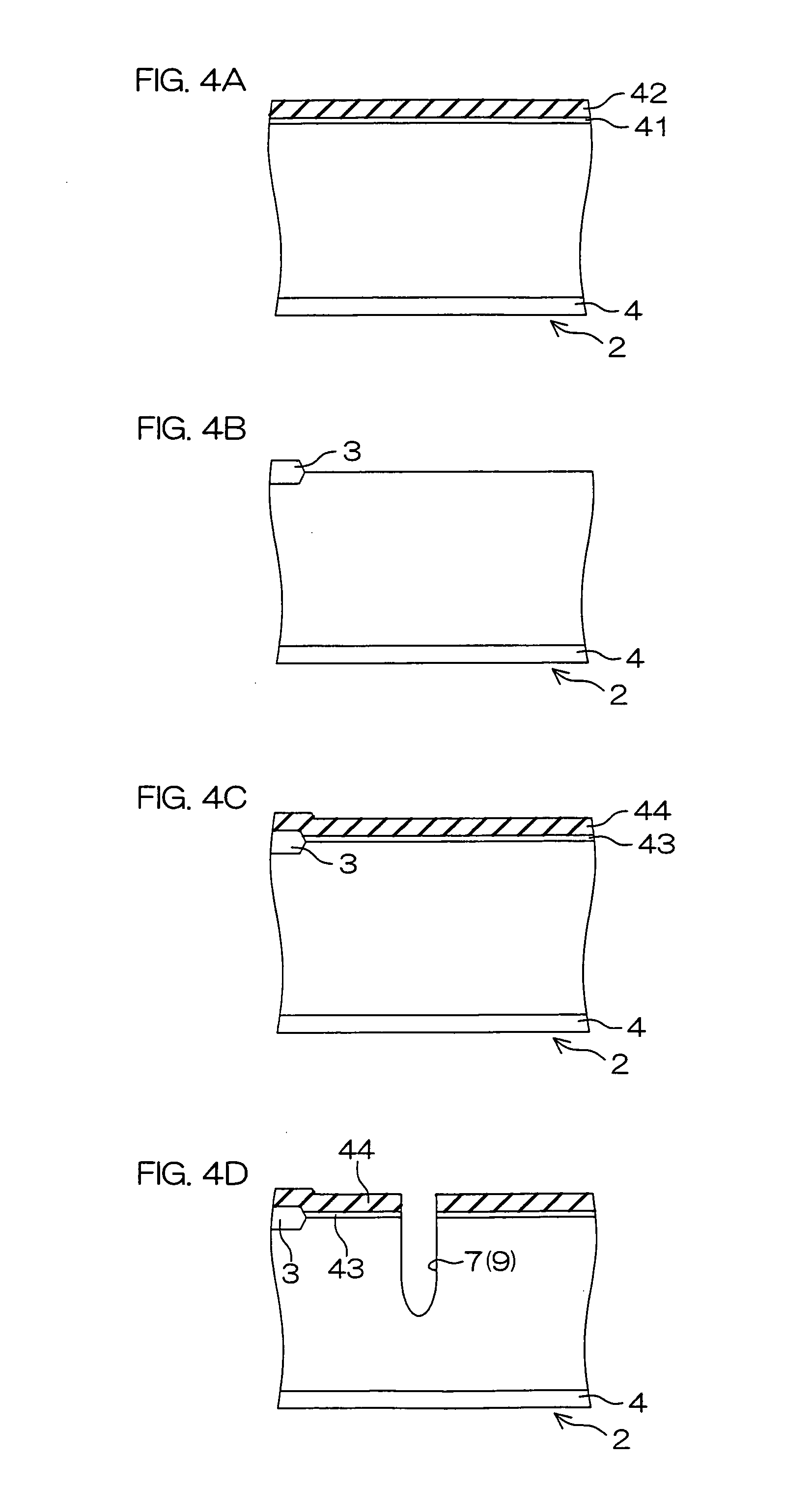

ActiveUS20100102383A1Improve avalanche toleranceIncreased avalanche toleranceThyristorSolid-state devicesBody regionSurface layer

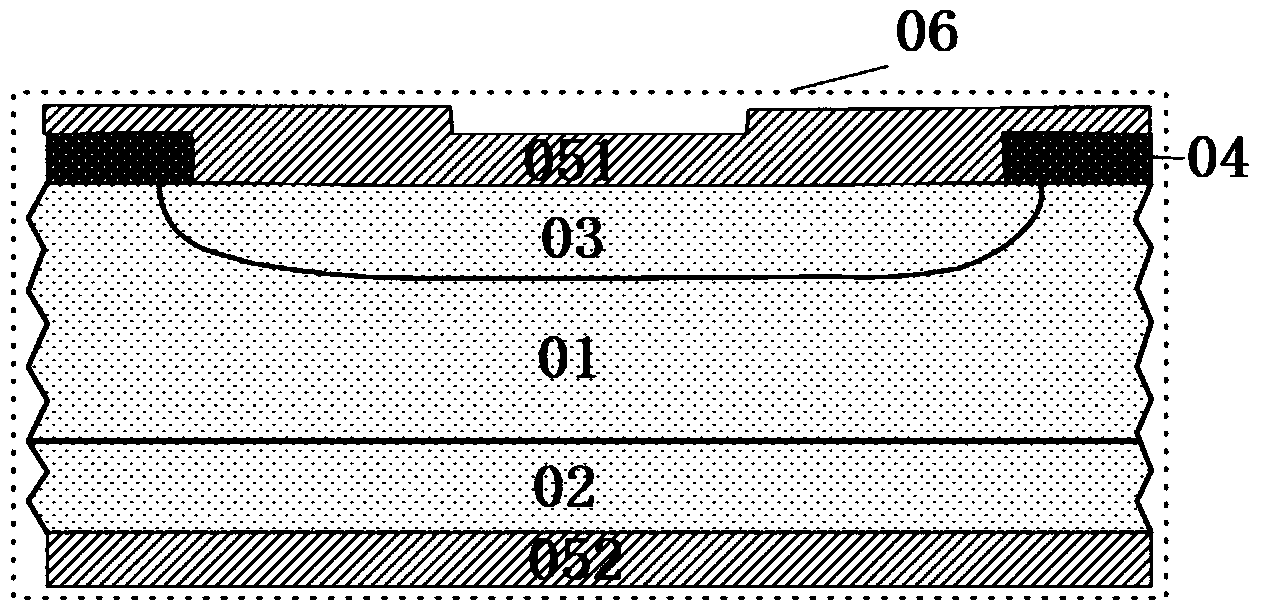

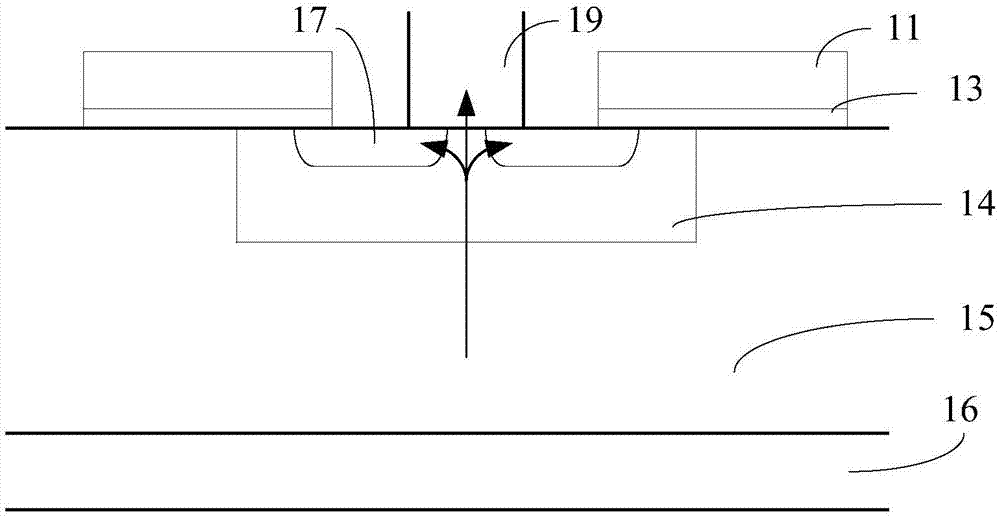

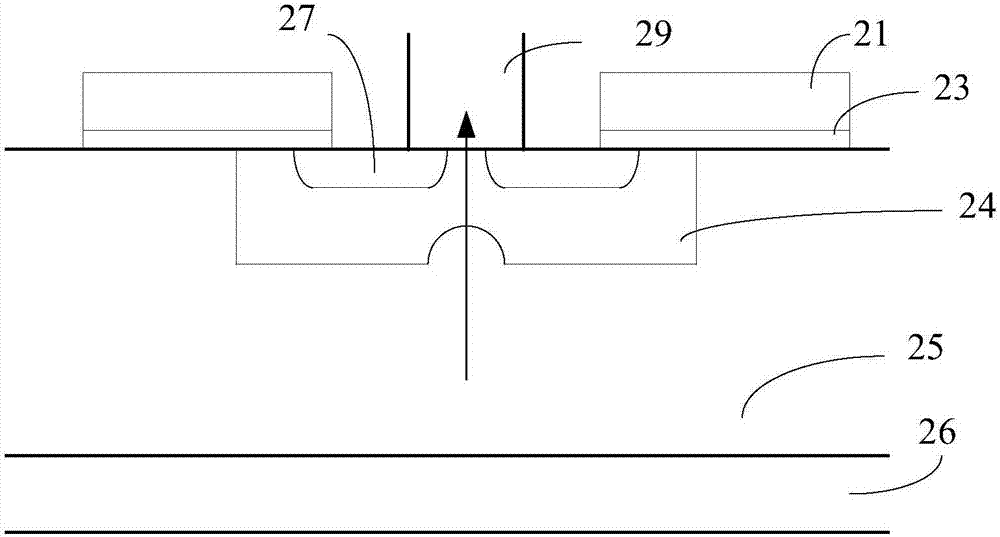

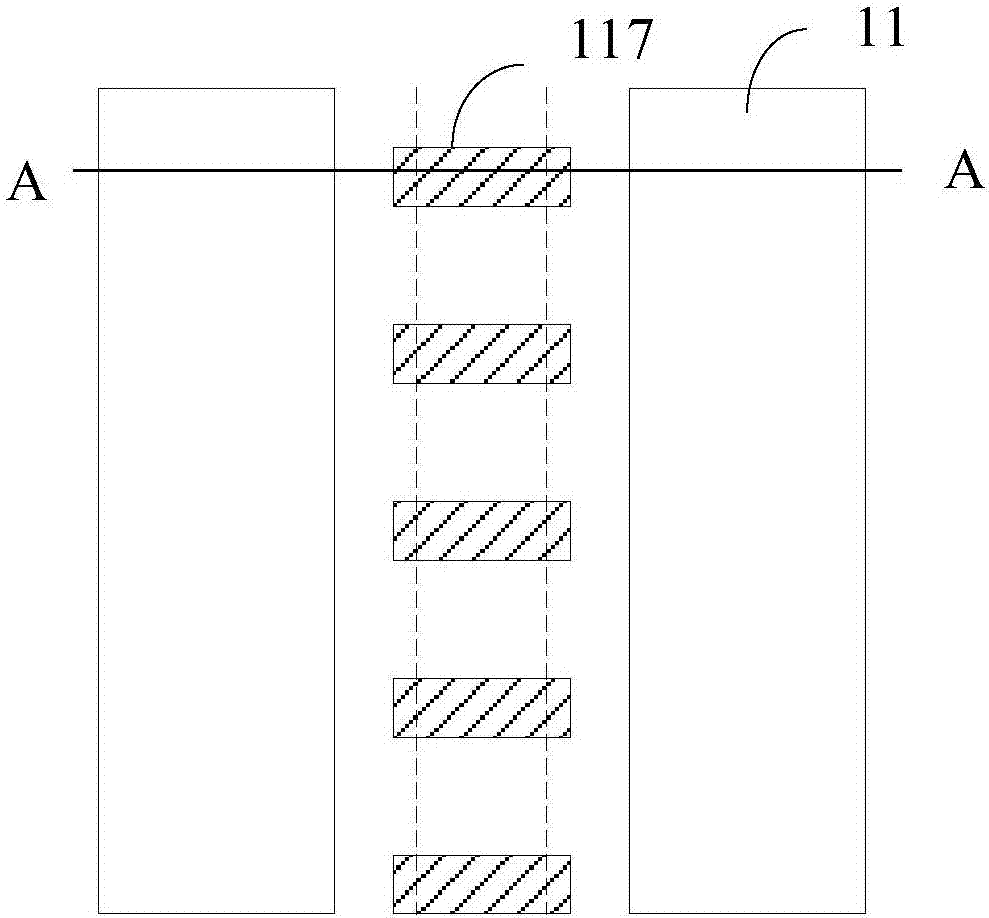

An inventive semiconductor device includes: a body region of a second conductivity type provided on the drift region of a first conductivity type in a semiconductor layer; a trench extending from a surface of the body region in the semiconductor layer with its bottom located in the drift region; a gate electrode provided in the trench with the intervention of a gate insulation film; a source region of the first conductivity type provided in a surface layer portion of the body region; a first impurity region of the second conductivity type provided around the bottom of the trench in spaced relation from the body region; and a second impurity region of the second conductivity type provided on a lateral side of the body region in the semiconductor layer, the second impurity region being isolated from the body region and electrically connected to the first impurity region.

Owner:ROHM CO LTD

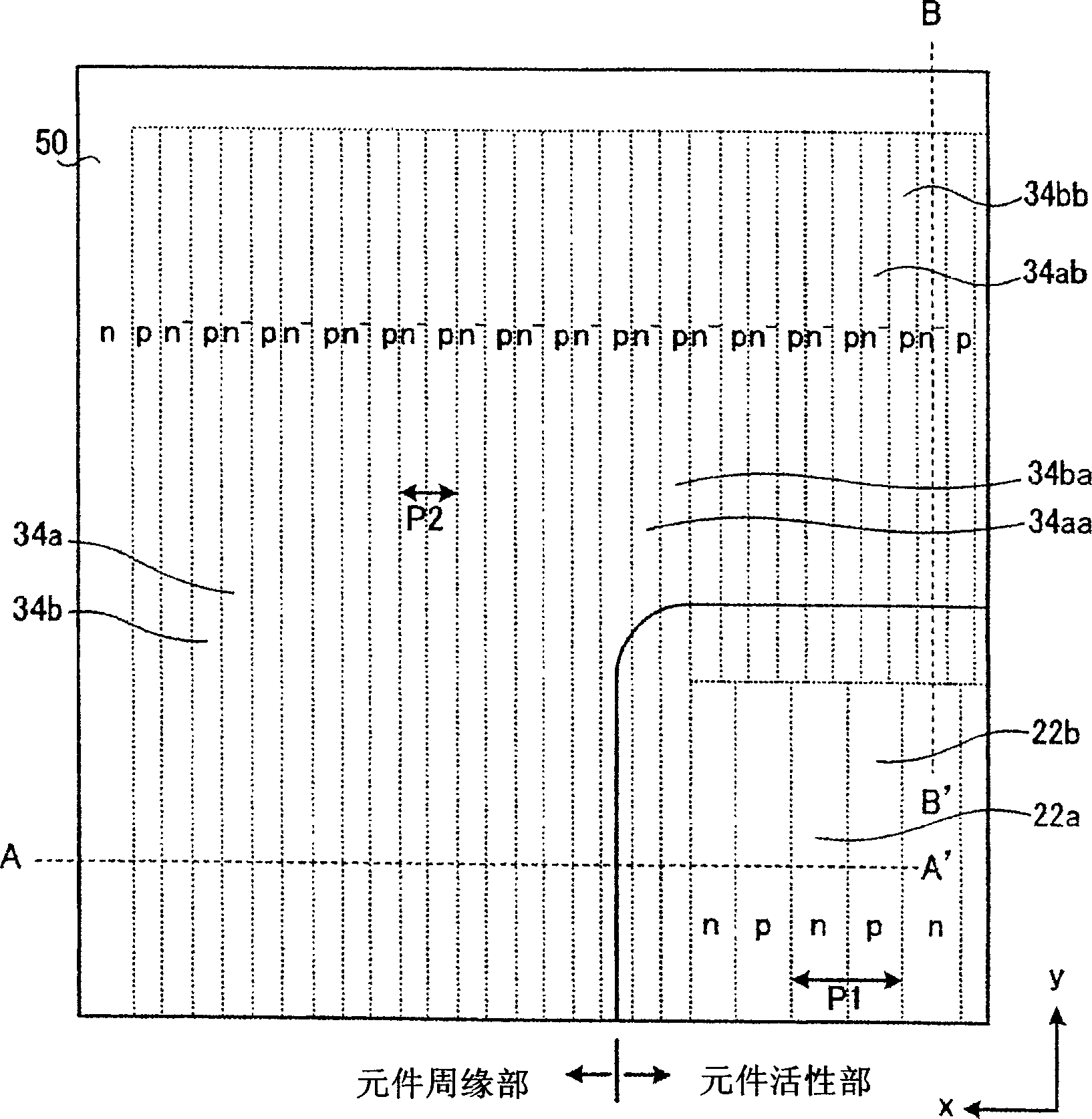

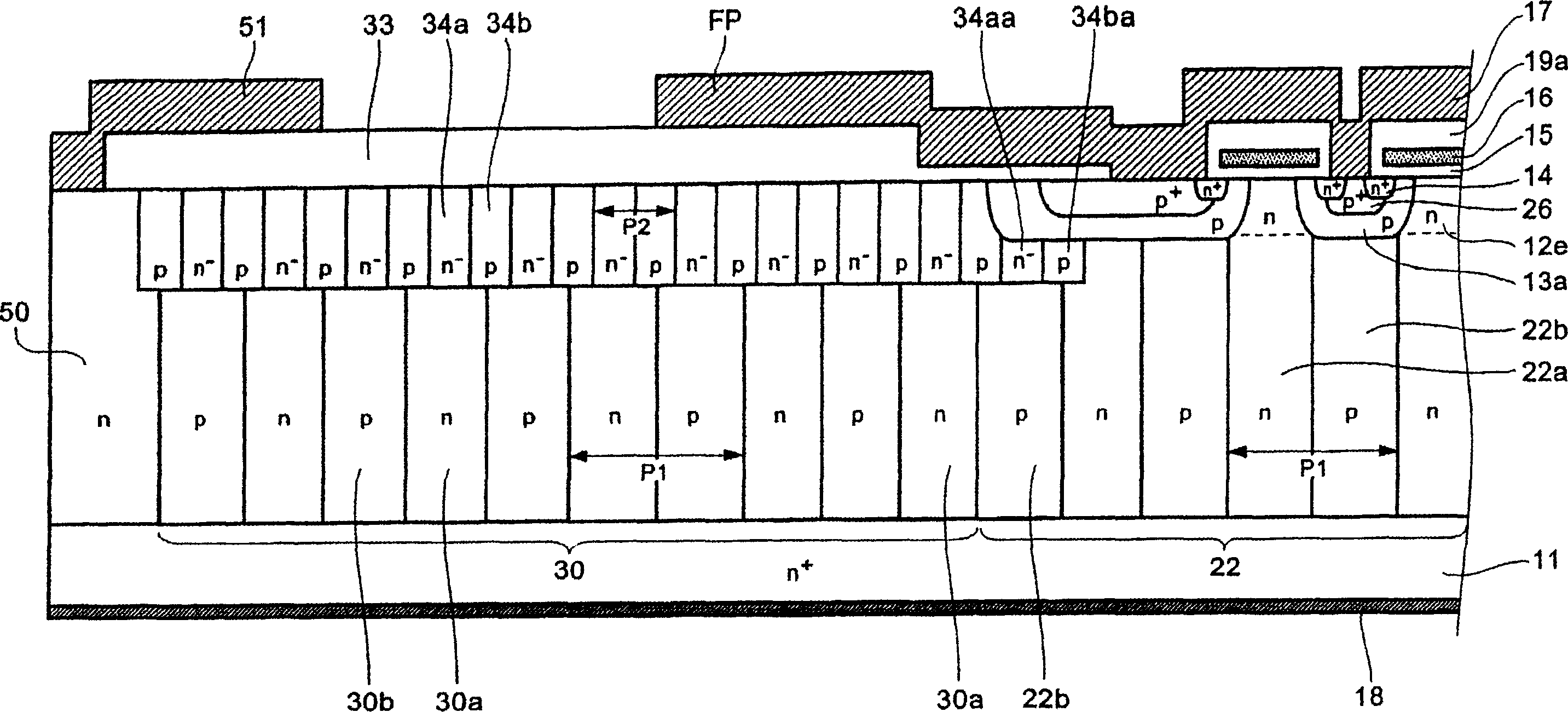

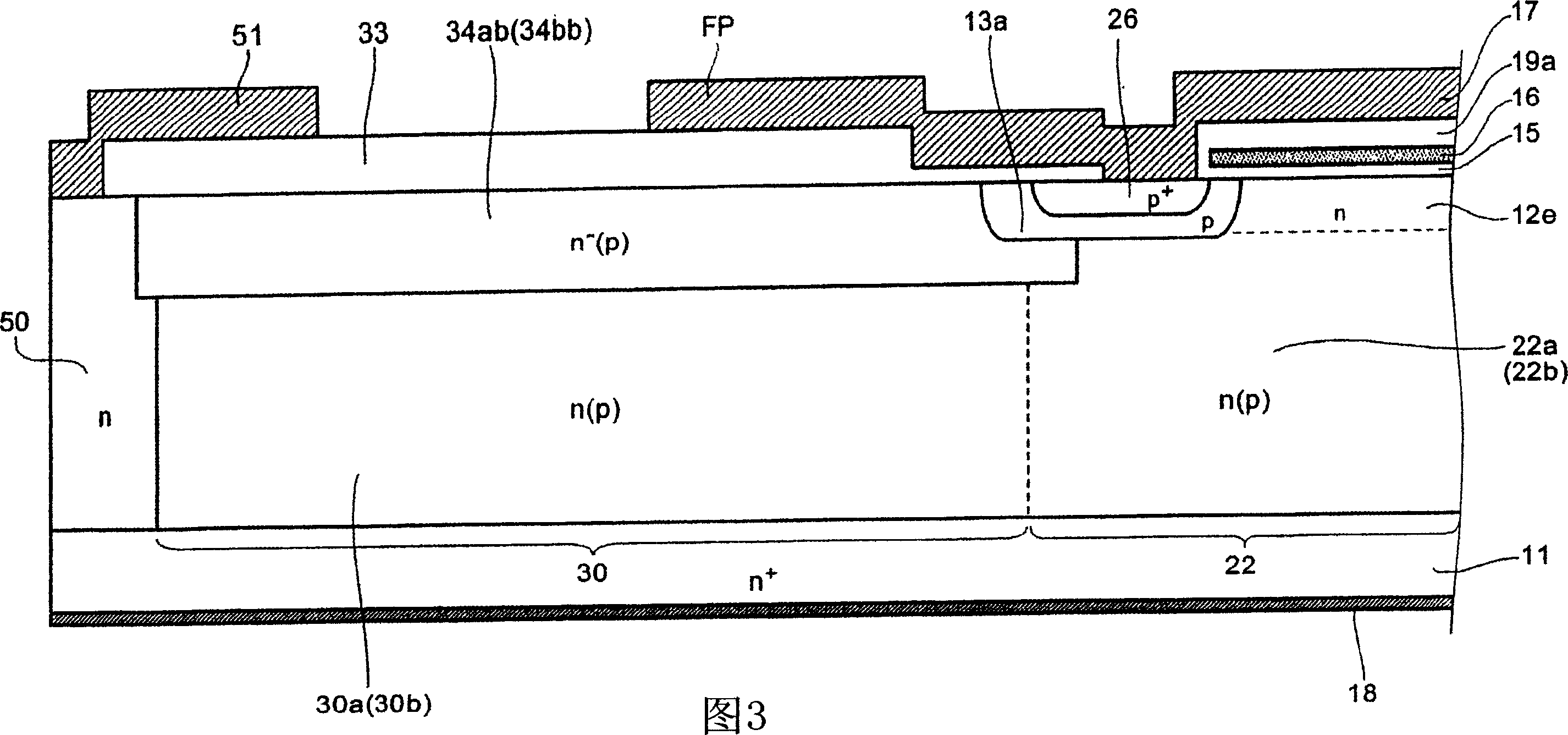

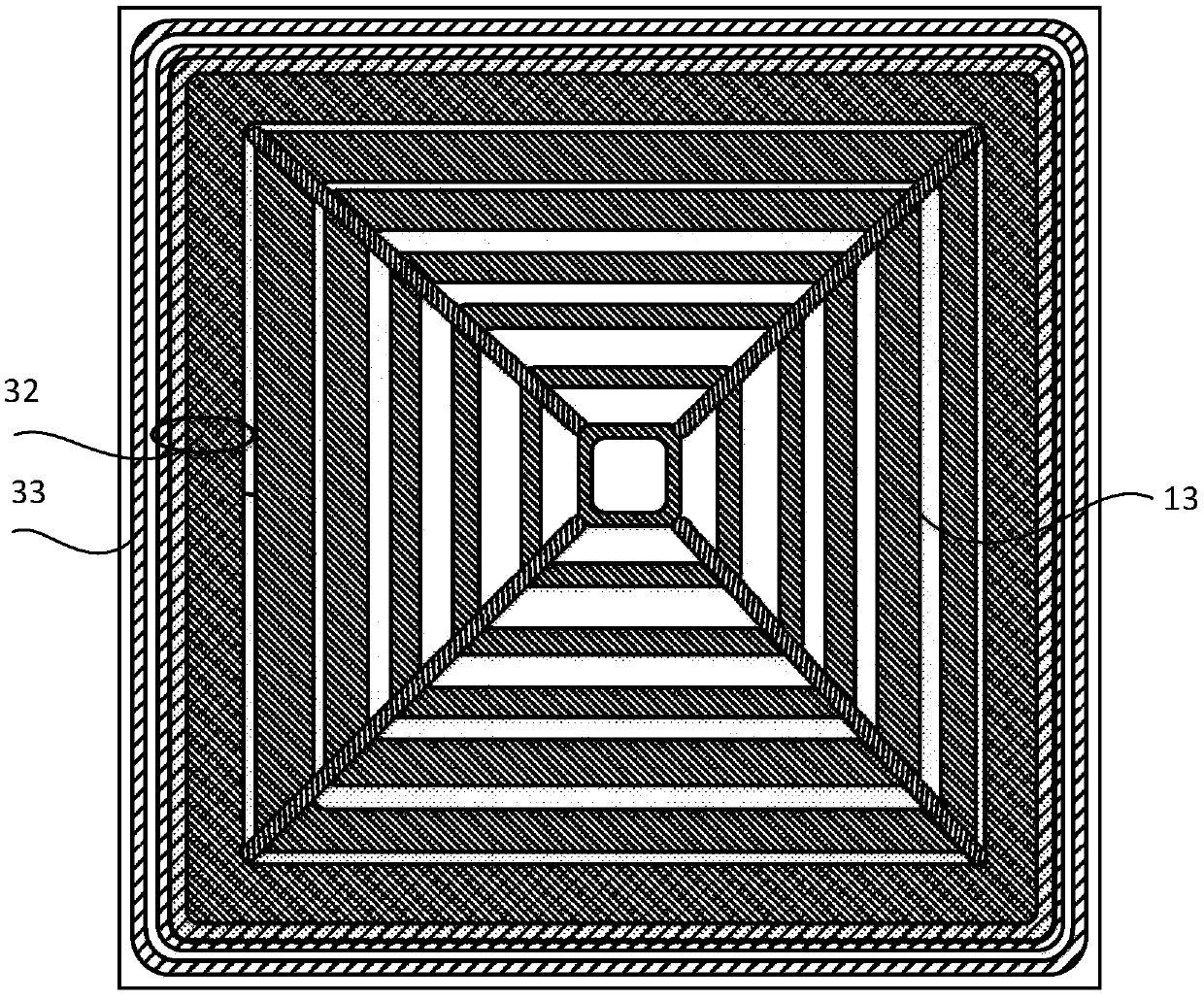

Semiconductor device with improved breakdown voltage and high current capacity

ActiveCN1734782AIncrease the avalanche voltageIncreased avalanche currentSemiconductor devicesSurface layerEngineering

To improve the avalanche resistance of an entire element by improving the avalanche resistance of the peripheral part of the element in a super junction semiconductor element. A drain drift part has a first parallel pn structure constituted by alternately and repeatedly bonding a first n-type region and a first p-type region at a pitch P1. The periphery of the drain drift part is the fringe of an element comprising a second parallel pn structure. The fringe of the element continuing to the first parallel pn structure is constituted by alternately and repeatedly bonding a second n-type region and a second p-type region at the pitch P1. Impurity concentrations of the first and the second parallel pn structures are almost equal to each other. A third parallel pn structure formed at a surface layer region of the fringe of the element is constituted by alternately and repeatedly bonding a third n-type region and a third p-type region having the higher impurity concentration than that of the third n-type region at a pitch P2 smaller than the P1. The impurity concentration of the third parallel pn structure is lower than those of the first and the second parallel pn structures.

Owner:FUJI ELECTRIC CO LTD

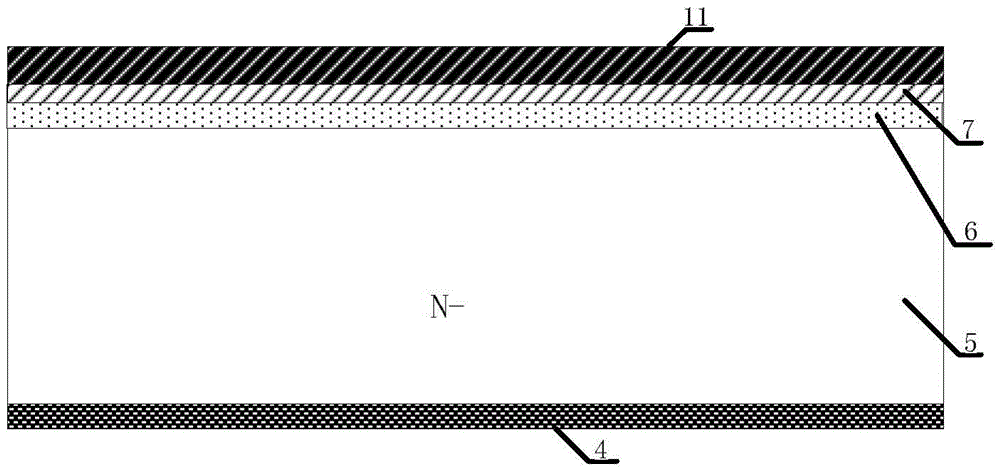

A fast recovery diode and a manufacturing method thereof

ActiveCN103618006AIncreased avalanche toleranceReduce the amount of introductionSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceEngineering

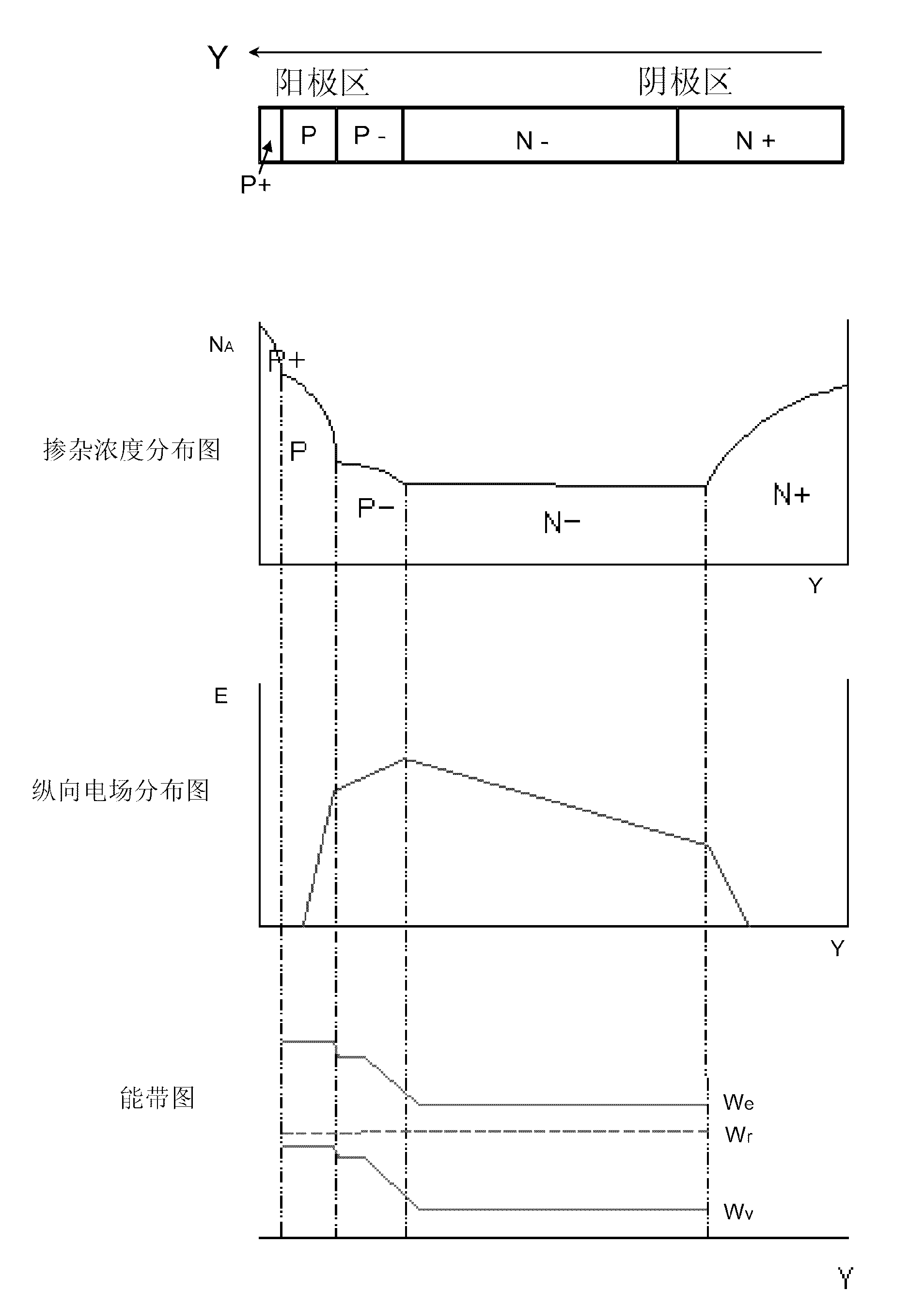

The invention relates to a power semiconductor device and a manufacturing method thereof and specifically to a fast recovery diode and a manufacturing method thereof. A junction pushing is performed in an active region in order to form a P+ region and a P region. A junction forming process comprises: firstly performing boron injection in order to push a junction one to ten [mu]m; secondly performing phosphorus compensative injection, wherein a phosphorus injection condition requires that the amount of injected phosphorus only decreases the concentration of the P region close to the silicon surface but not reverses a junction; and performing active region compensative injection to form the P region with low surface concentration. Therefore, the amount of hole injection of the P region in forward conduction is decreased while the concentration on the two sides of a PN junction is guaranteed. When minority carrier lifetime control is used, excessive recombination centers are not required to be generated. Therefore, a series of parameters are optimized. The fast recovery diode and the manufacturing method thereof perform phosphorus compensative injection on the P region so as to achieve the decrease in the surface concentration of the P region. Therefore, the decrease in the number of the hole injection in forward conduction is actually achieved.

Owner:STATE GRID CORP OF CHINA +2

Fast recovery diode and manufacturing method thereof

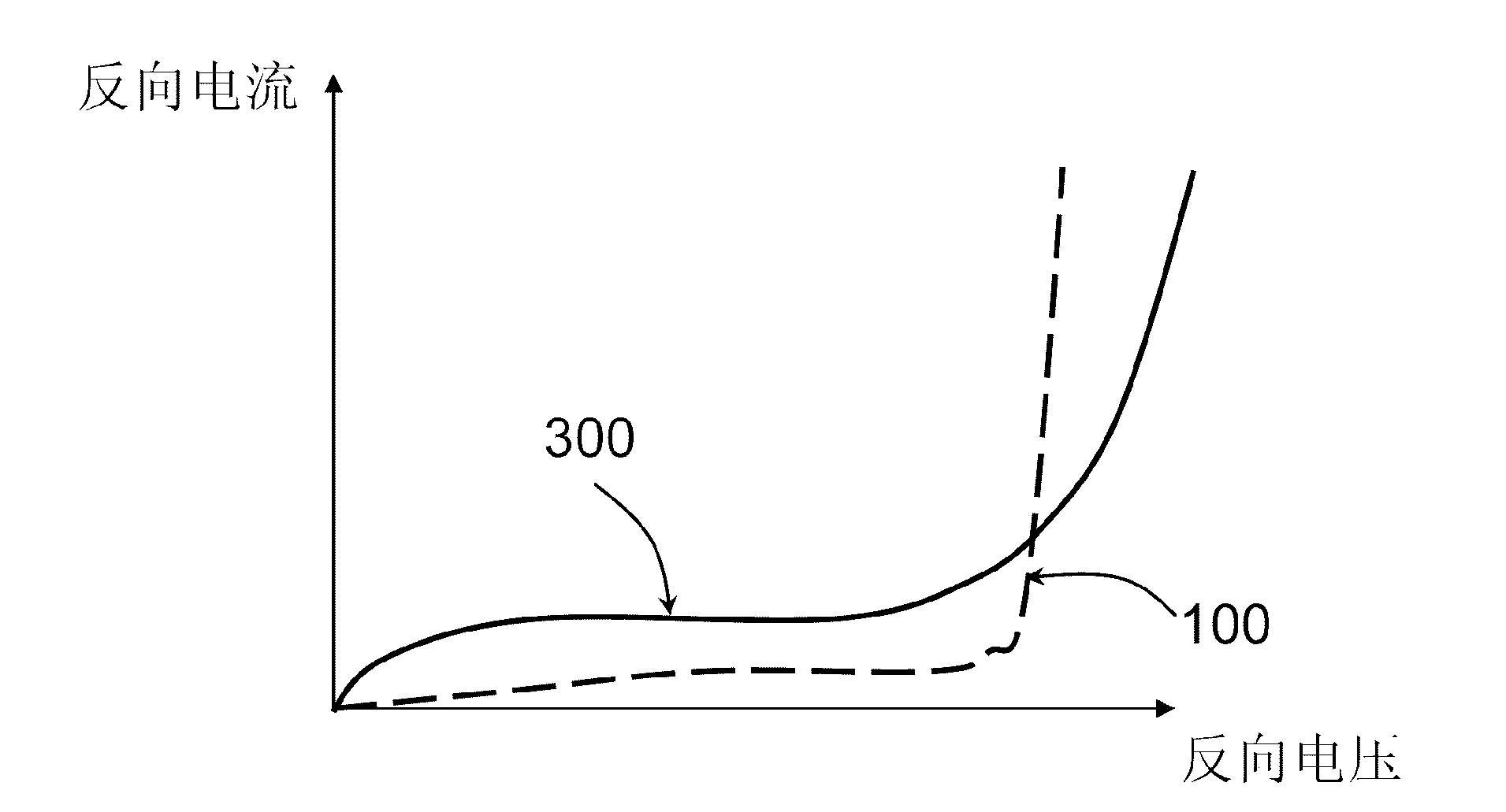

InactiveCN105702746AReduce leakageIncreased avalanche toleranceSemiconductor/solid-state device manufacturingSemiconductor devicesControl layerHydrogen

The invention relates to a fast recovery diode and a manufacturing method thereof. The diode comprises a substrate and a P+ region. The P+ region is formed on the substrate, and forms a PN junction together with the substrate, wherein the substrate is the cathode of the diode, and the P+ region is the anode of the diode. Hydrogen or helium is injected into the surface of the anode P+ region to form a local service life control layer. The fast recovery diode provided by the invention has the characteristic of fast and soft recovery. Because of existence of the local service life control layer, the fast recovery diode does not need too many global composite centers, electric leakage of the device is reduced, and the avalanche tolerance of the device is improved. Through electron irradiation and platinum doping, a device with a minor positive temperature coefficient of forward voltage drop is realized, and parallel connection is facilitated. Structures and doping of the diode anode and diode cathode can be adjusted. Forward surging and dynamic avalanche resistance are improved.

Owner:STATE GRID CORP OF CHINA +2

Soft fast recovery diode and manufacturing method thereof

ActiveCN103872144AReduce EMIReduce lossSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceControl layer

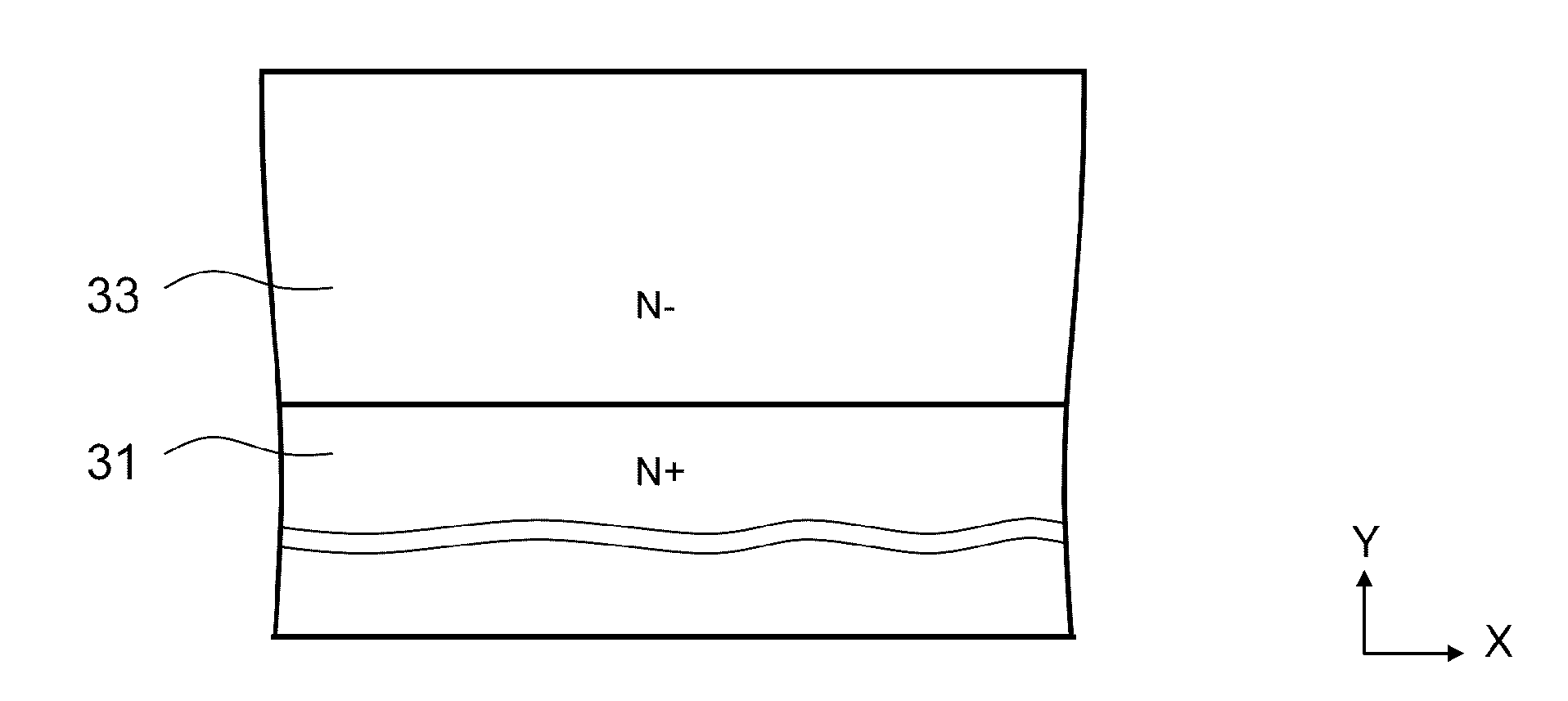

The invention relates to a soft fast recovery diode and a manufacturing method thereof. The diode comprises an N type intrinsic region, a back N<+> buffer region, an anode metal layer and a cathode metal layer, wherein the back N<+> buffer region is formed on the back face of the N type intrinsic region; a P type emitting region is formed between the front face of the N type intrinsic region and the anode metal layer; mask oxide layers are formed symmetrically at the two ends of the anode metal layer; a P type high-resistance region is formed on the boundary of an active region; a P<+> ohmic contact layer is formed in the center of the active region; an overall lifetime control region is formed on the entire diode, and covers all structural layers of the diode; a localized lifetime control layer is positioned close to the P<+> ohmic contact layer in the P type emitting region along the axial direction of the diode; the localized lifetime control layer is positioned in a plane constructed by the P type emitting region and the P type high-resistance region along a direction which is vertical to the axial direction of the diode. The soft fast recovery characteristic of a device is realized by adopting an overall-localized lifetime control way; by arranging the high-resistance region, the snow slide resistance of the device is improved.

Owner:STATE GRID CORP OF CHINA +2

Novel silicon carbide junction barrier Schottky diode and fabrication method thereof

ActiveCN109560142AIncreased avalanche toleranceSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsProtection ring

The invention provides a novel silicon carbide junction barrier Schottky diode. The novel silicon carbide junction barrier Schottky diode comprises a first conductive type of silicon carbide substrateand a first conductive type of silicon carbide epitaxial layer which are arranged in a lamination way, wherein an active region, a protection ring and a second conductive type of terminal field limitation ring are sequentially arranged on an upper surface of the first conductive type of silicon carbide epitaxial layer from center to outside, the active region comprises a plurality of second conductive types of junction barrier regions which are arranged at intervals, the distance between adjacent second conductive types of junction barrier regions is gradually increased along a direction fromthe protection ring to the center of the active region, and the widths of the second conductive types of junction barrier regions are gradually reduced. The invention also provides a fabrication method of the silicon carbide junction barrier Schottky diode.

Owner:HUNAN SANAN SEMICON CO LTD

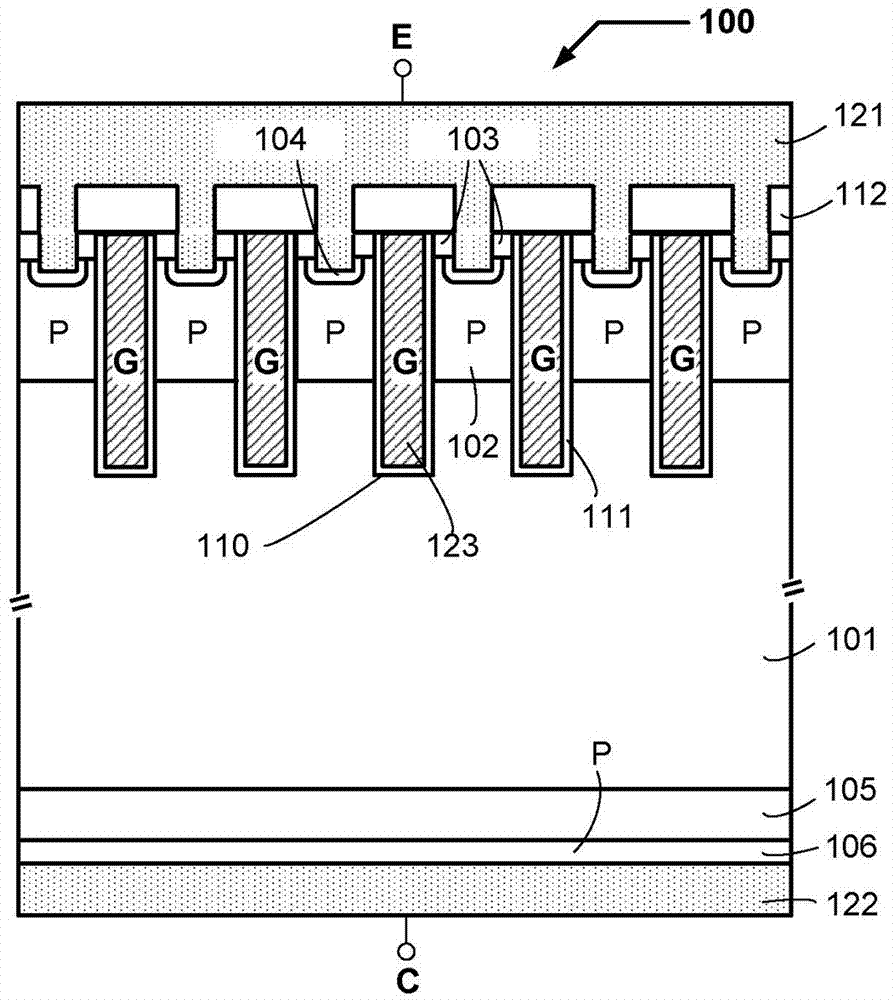

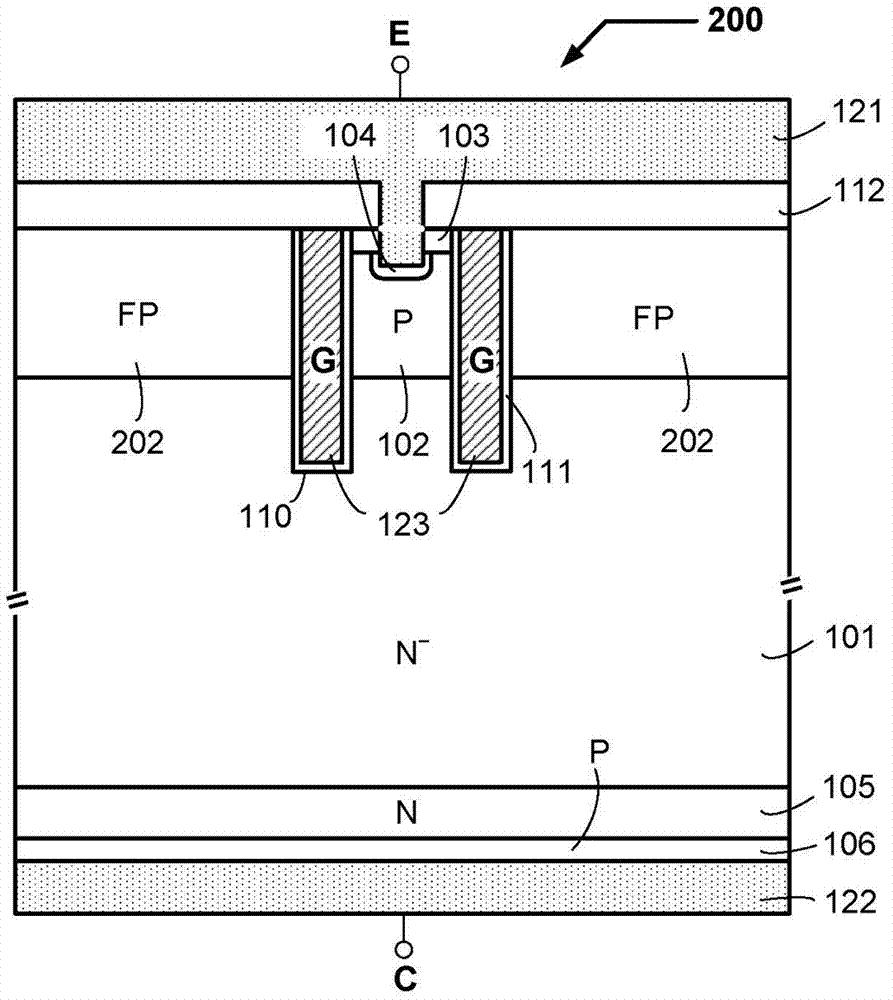

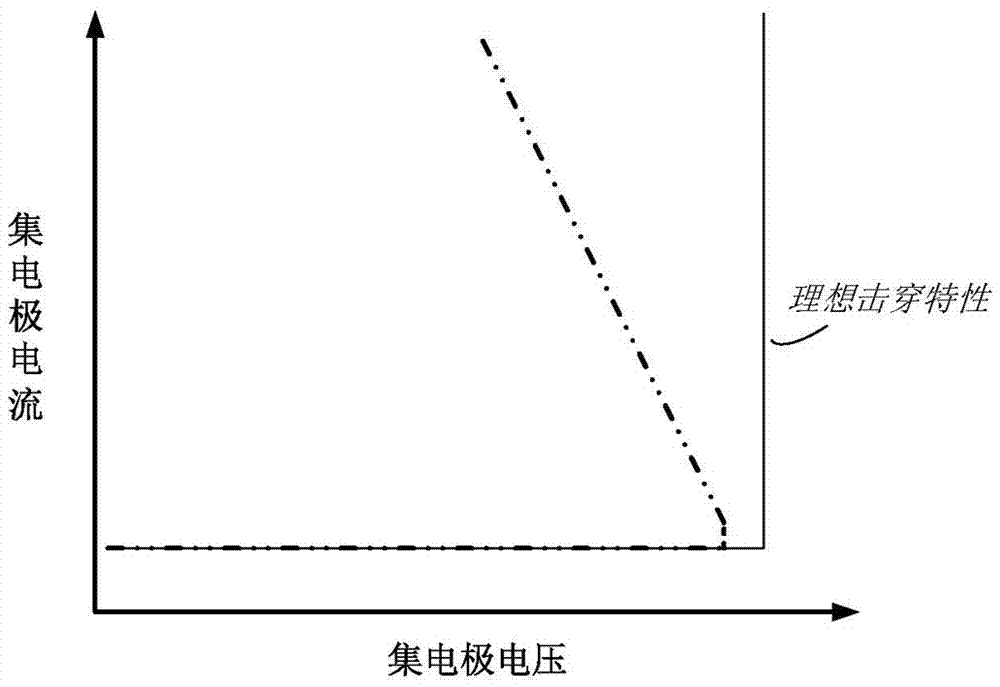

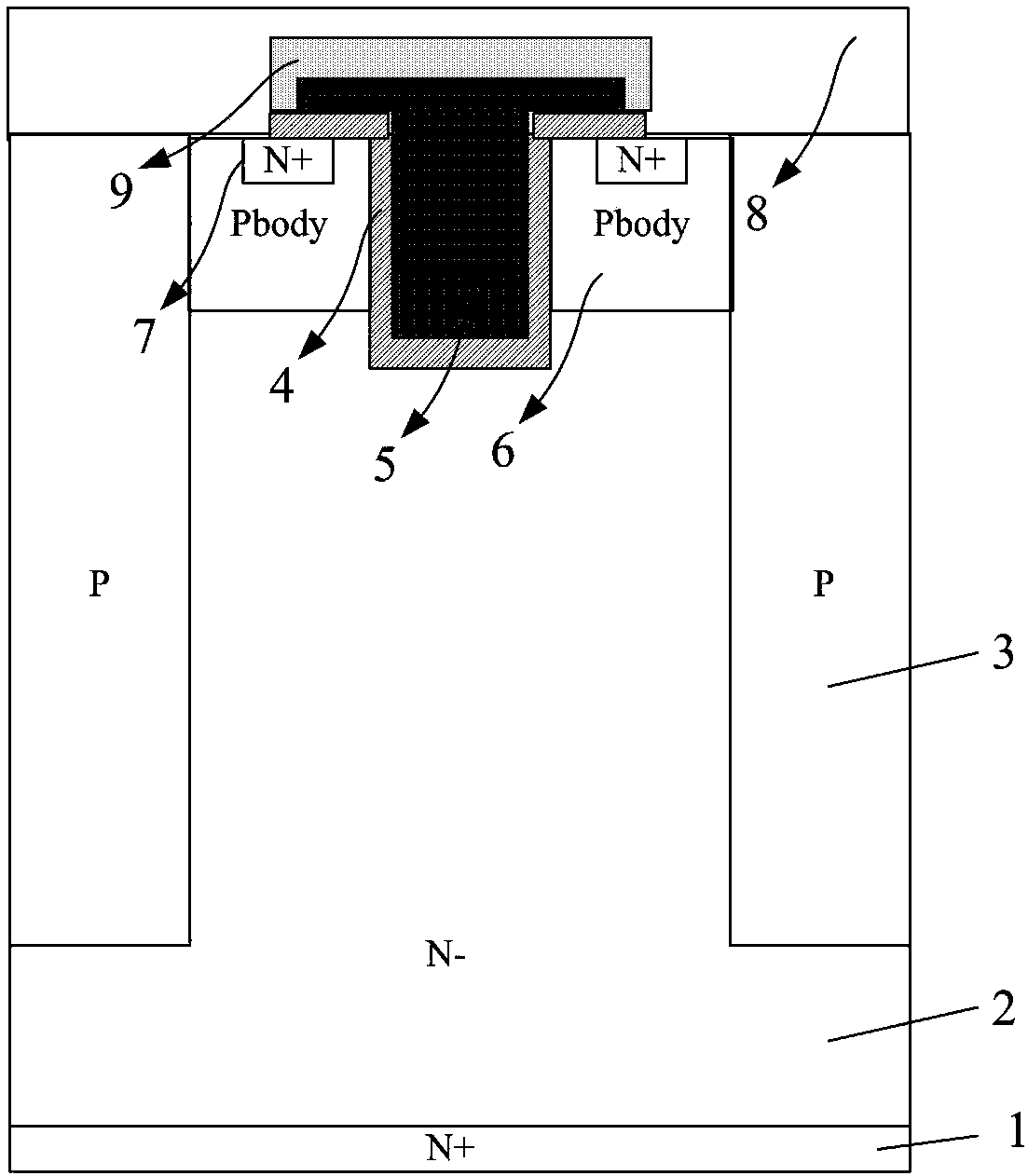

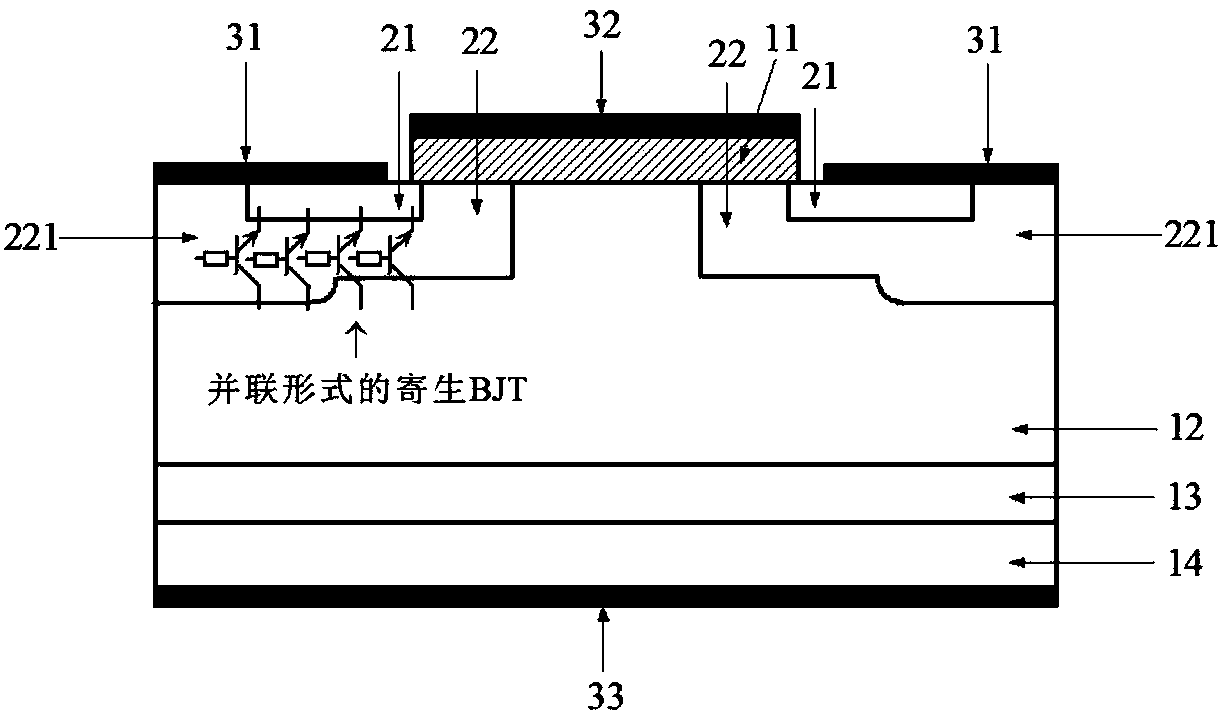

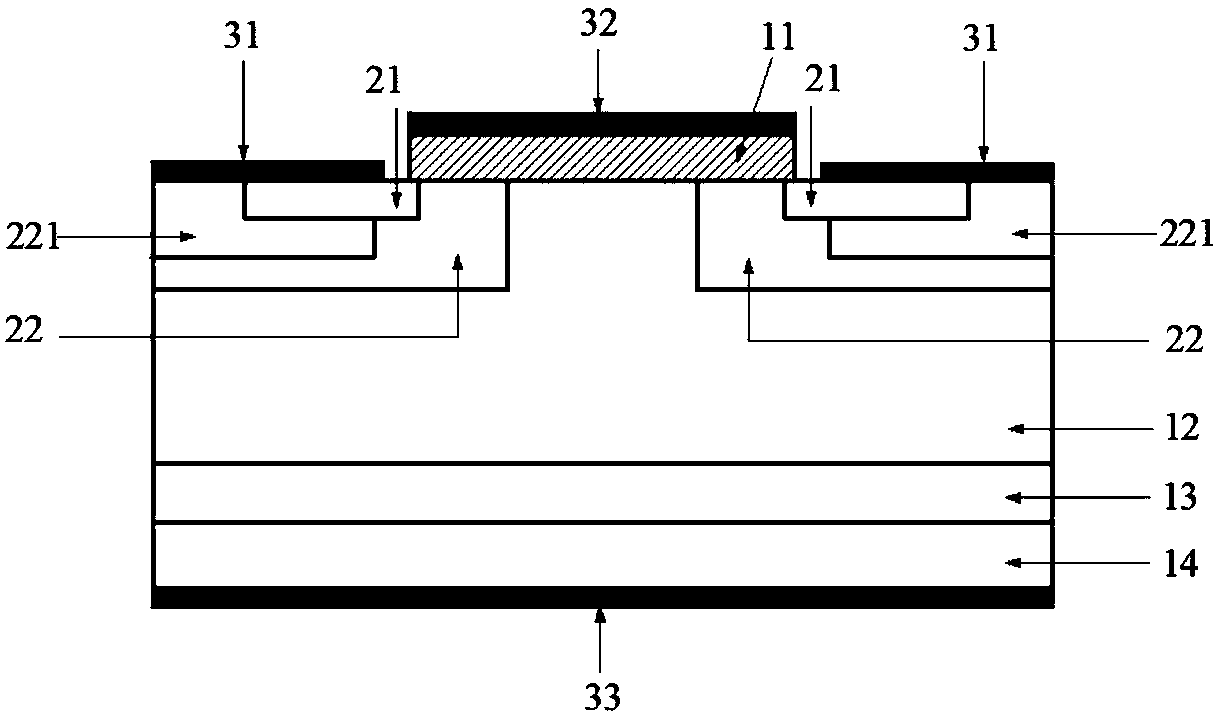

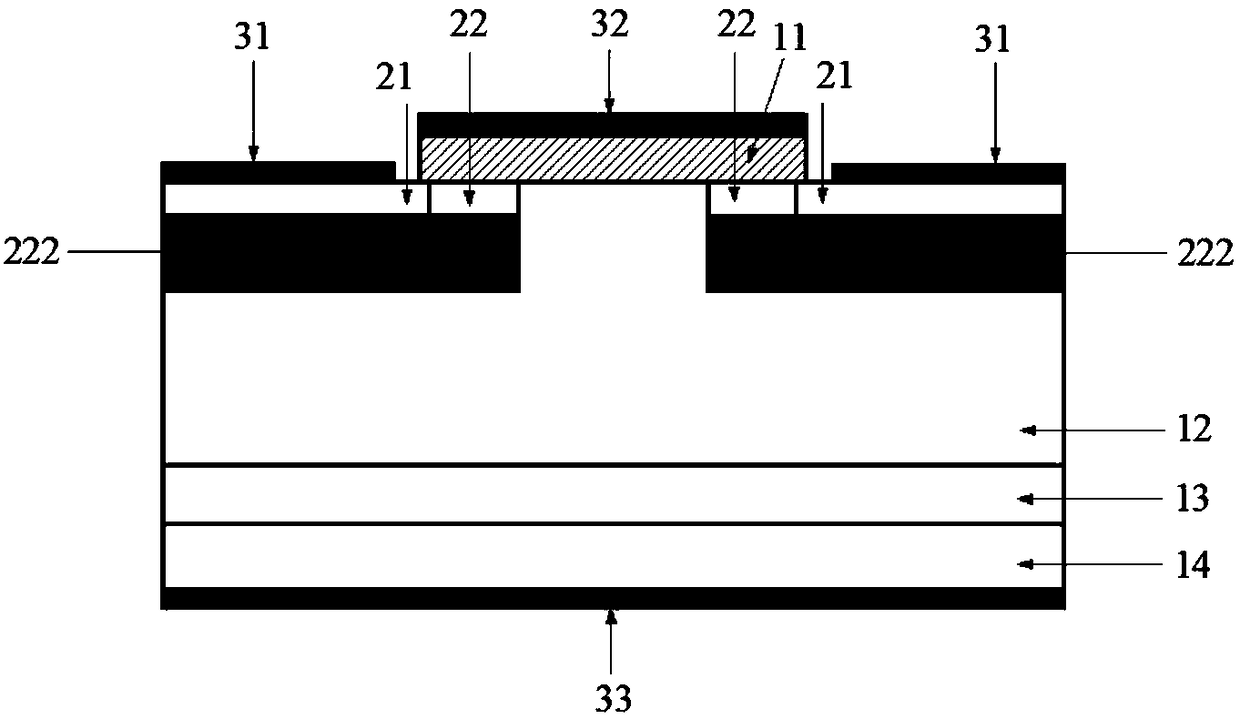

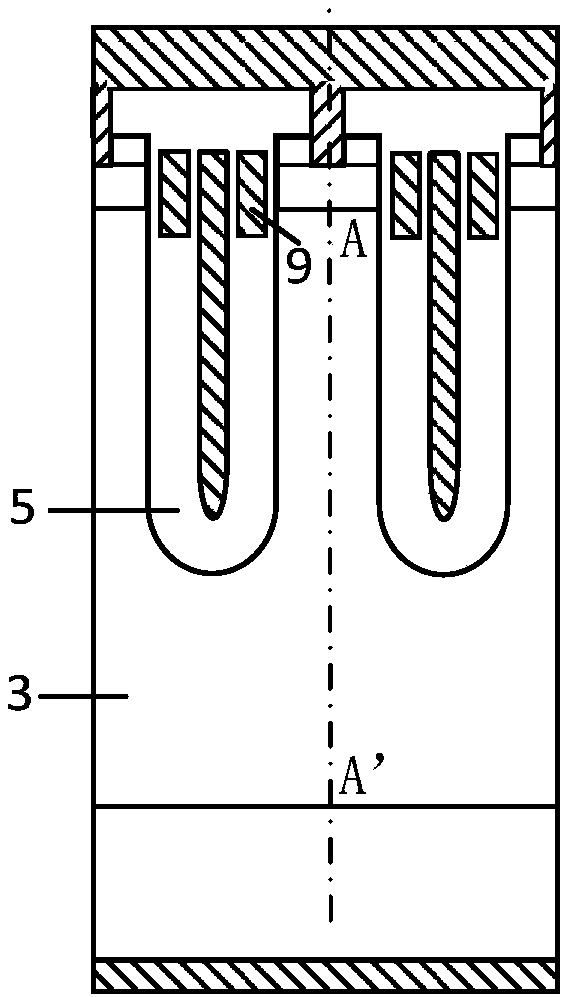

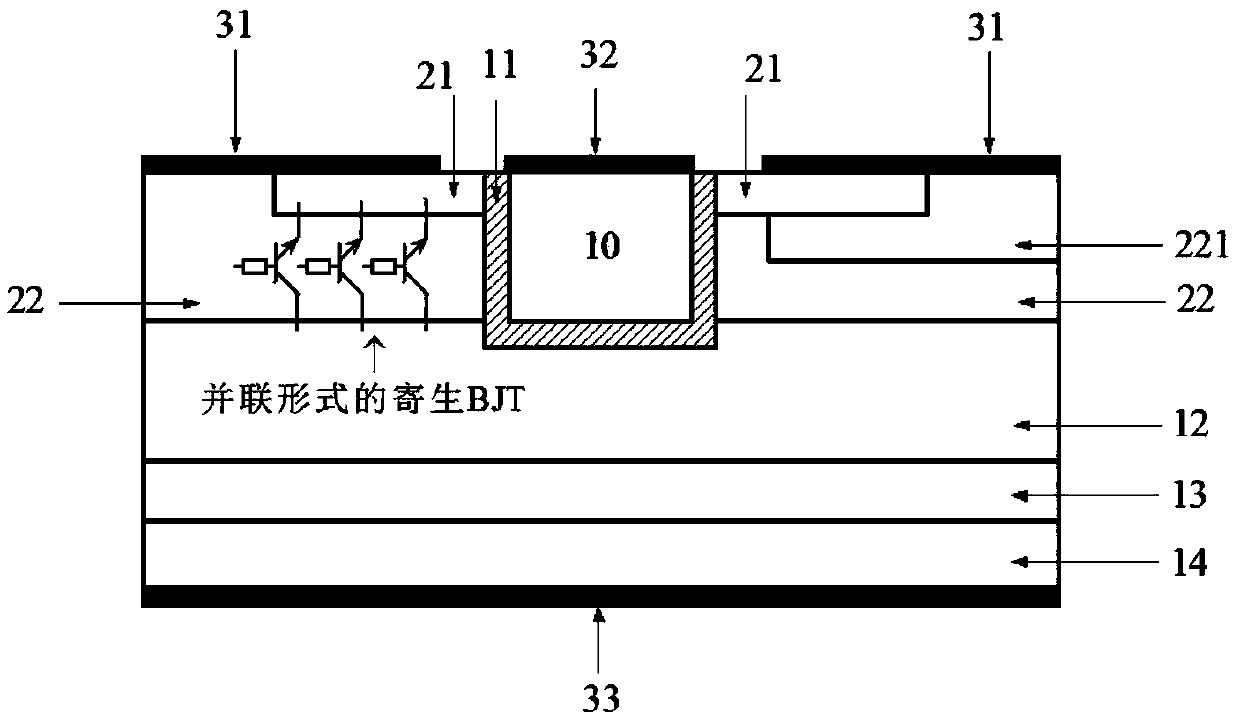

IGBT device and preparation method thereof

ActiveCN106997899ALower breakdown voltageNo adverse effects on performance parametersSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceVoltage drop

The invention discloses an IGBT device and a preparation method thereof, relates to a power semiconductor device, and provides a device structure design scheme capable of improving avalanche tolerance on the basis of not lowering other performance indexes (such as forward conduction voltage drop V<on>, switching speed, load short-circuit capacity and the like) of the IGBT. The invention provides a novel IGBT device structure and a preparation method thereof. Beneficial effects are achieved as follows: compared with the IGBT device in the prior art, the IGBT device disclosed by the invention can realize more stable breakdown characteristic, so that the avalanche tolerance of the device can be greatly improved, thereby enabling the device to the safer and more reliable in an actual high-speed high-power application.

Owner:安建科技(深圳)有限公司

Fast recovery epitaxial diode (FRED) and preparation method thereof

InactiveCN103178120AImprove avalanche resistanceIncreased avalanche toleranceSemiconductor/solid-state device manufacturingSemiconductor devicesFlyback diodeP–n junction

The invention provides an FRED and a preparation method thereof and belongs to the technical field of power apparatuses. A P-type semiconductor doping layer of an anode region for forming a PN junction of the FRED comprises a first P-type semiconductor region, a second P-type semiconductor region and a third P-type semiconductor region, and the doping concentration of the first P-type semiconductor region, the second P-type semiconductor region and the third P-type semiconductor region increases progressively successively. In a preparation method of the FRED, the first P-type semiconductor region, the second P-type semiconductor region and the third P-type semiconductor region are formed through three doping steps, and accordingly, the doping concentration of P-type semiconductor doping layers is redistributed. The FRED is high in the avalanche resistance and relatively 'soft' in the reverse breakdown characteristic and particularly suitable for being used in series or as fly-wheel diode of insulated gate bipolar translator (IGBT).

Owner:MACMIC SCIENCE & TECHNOLOGY CO LTD

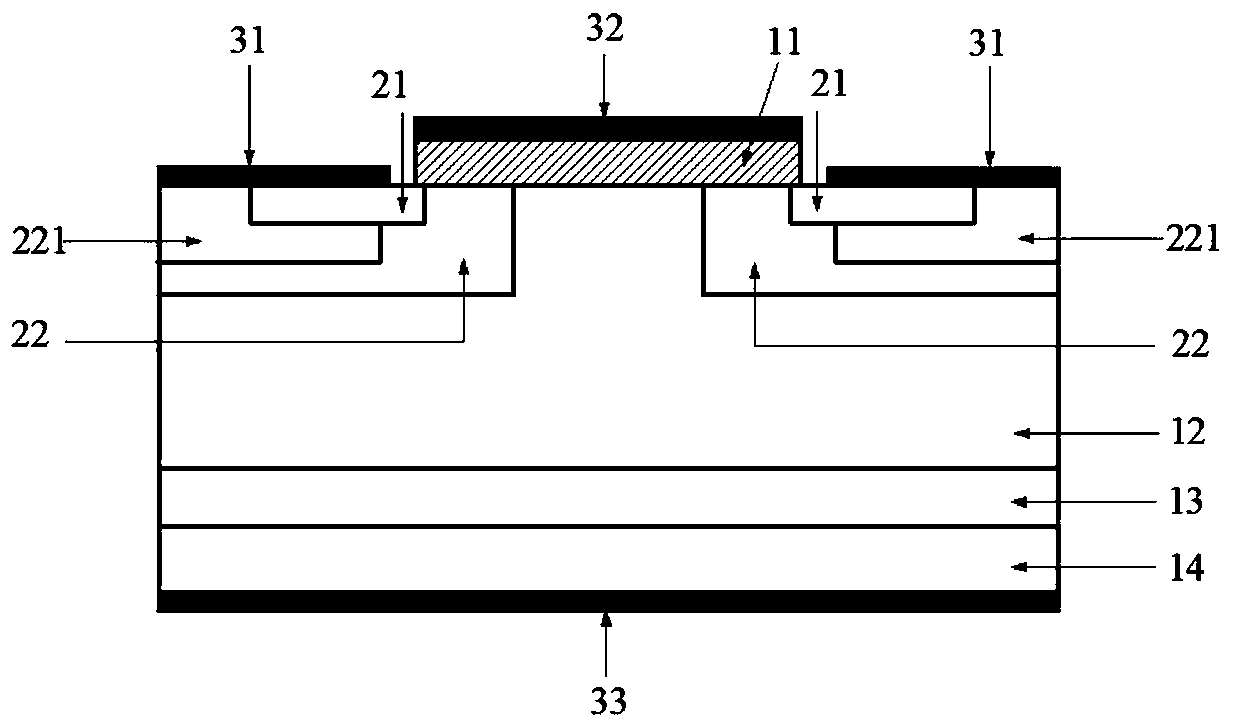

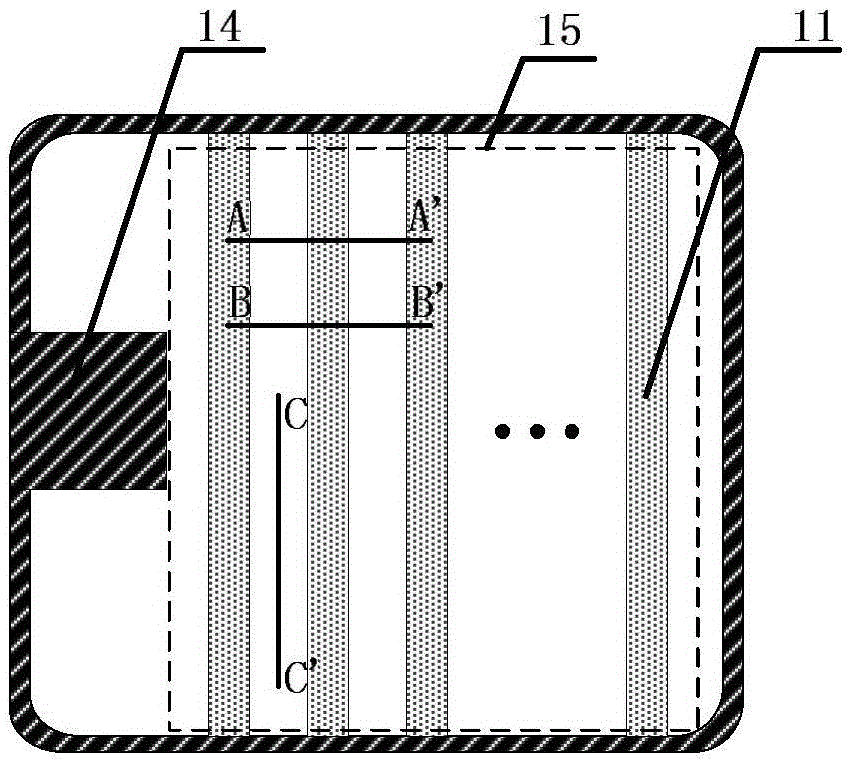

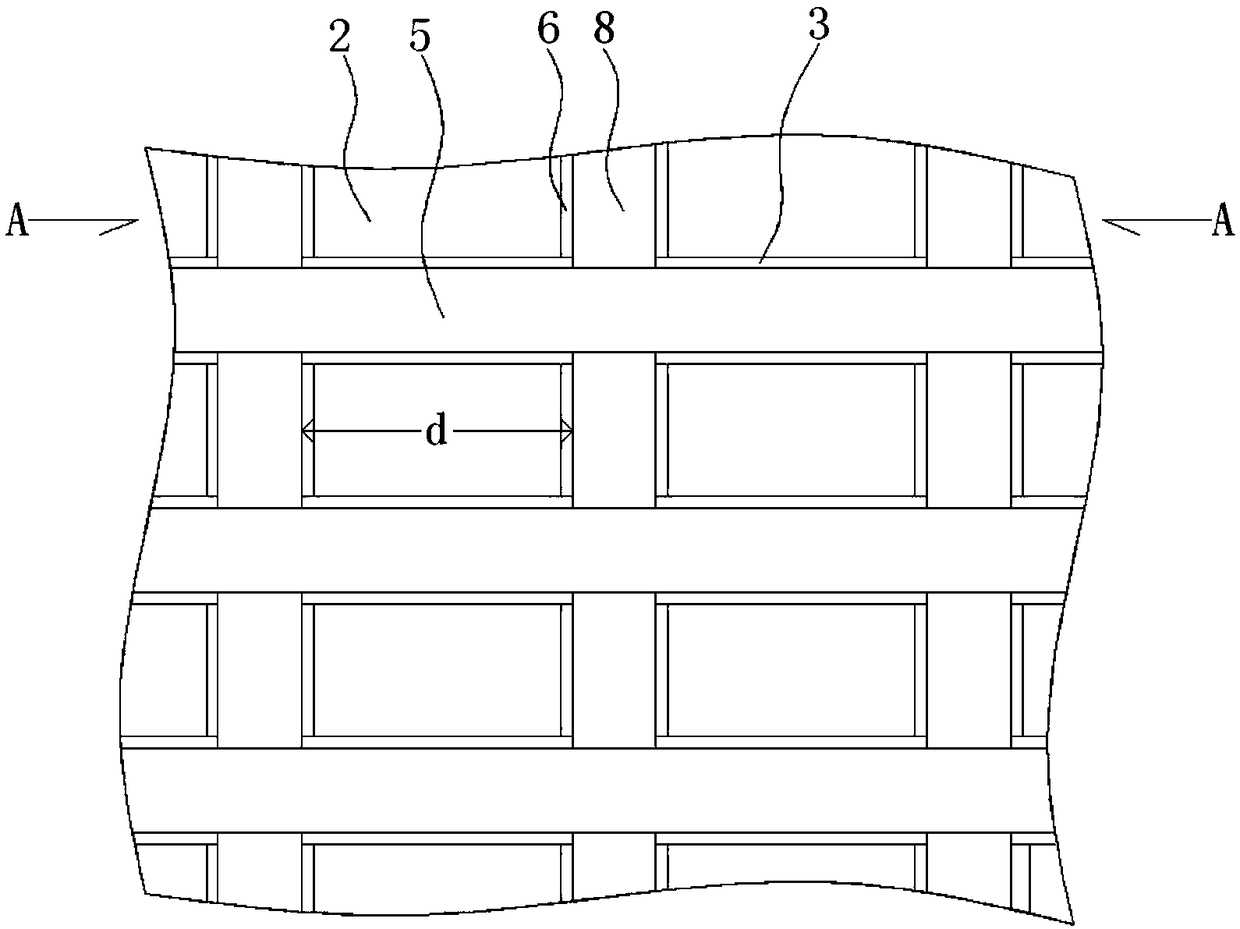

Trench gate super-junction MOSFET device and preparation method therefor

InactiveCN107591453ALower on-resistanceIncreased avalanche toleranceSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETTrench gate

The invention relates to a trench gate super-junction MOSFET device and a preparation method therefor. The device comprises a semiconductor substrate and a cellular region positioned in the central region of the semiconductor substrate; the semiconductor substrate comprises a first conductive type substrate and a first conductive type epitaxial layer positioned above the first conductive type substrate; a super-junction structure is arranged in the first conductive type epitaxial layer in the cellular region; second conductive type columns and the first conductive type epitaxial layer can formthe super-junction structure; a cellular trench is formed between the adjacent second conductive type columns; an insulating oxide layer and conductive polysilicon are arranged in each cellular trench; by virtue of the super-junction structure and the trench gate structure, on resistance can be lowered effectively; the first conductive type epitaxial layer outside the cellular trench opening is covered with the insulating oxide layer; the insulating oxide layer outside the cellular trench opening is covered with the conductive polysilicon at the same time; and by virtue of the insulating oxide layer outside the cellular trench opening and the conductive polysilicon, avalanche resistance can be improved, and compact structure and safety and reliability are realized.

Owner:江苏芯长征微电子集团股份有限公司

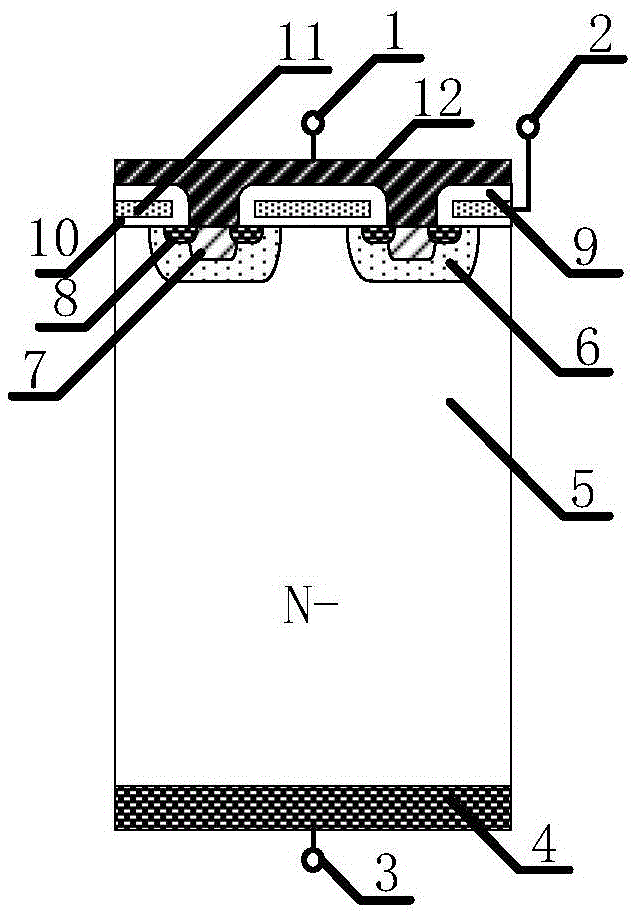

High-snow-slide-tolerance deep-groove power device

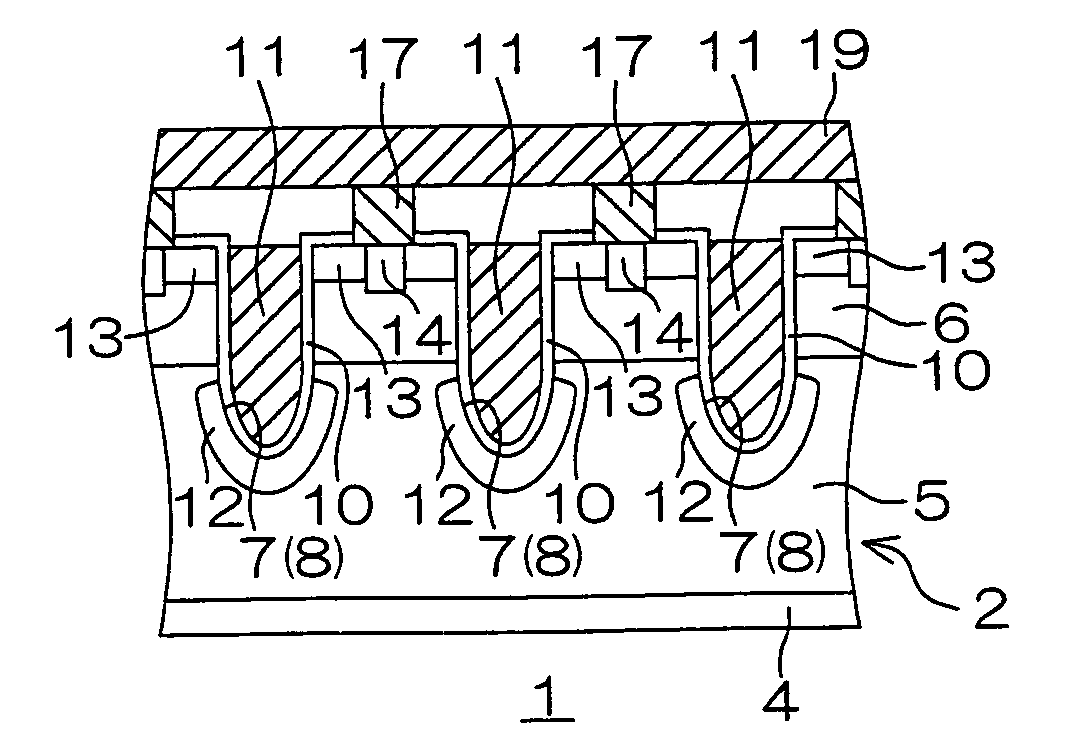

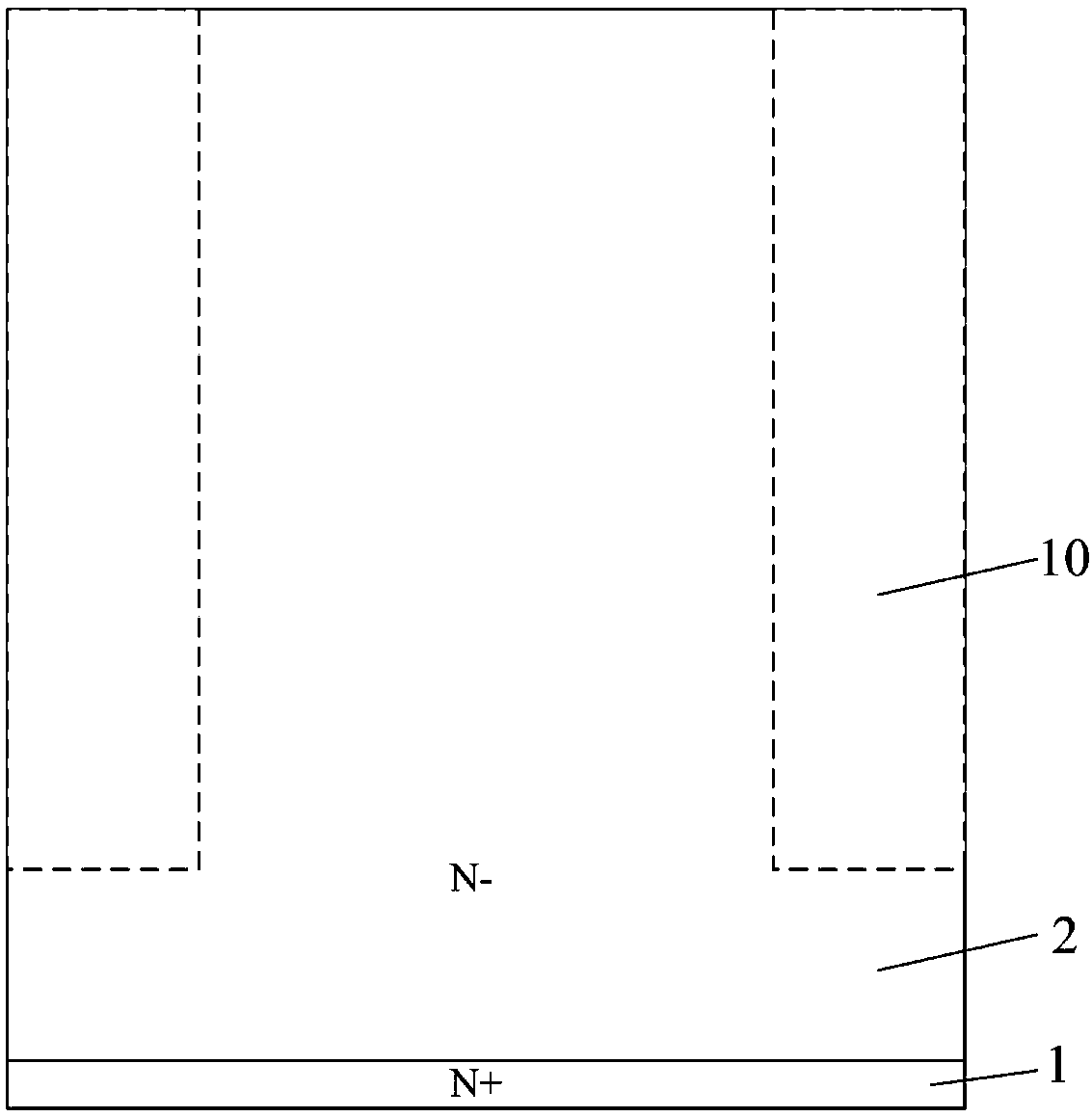

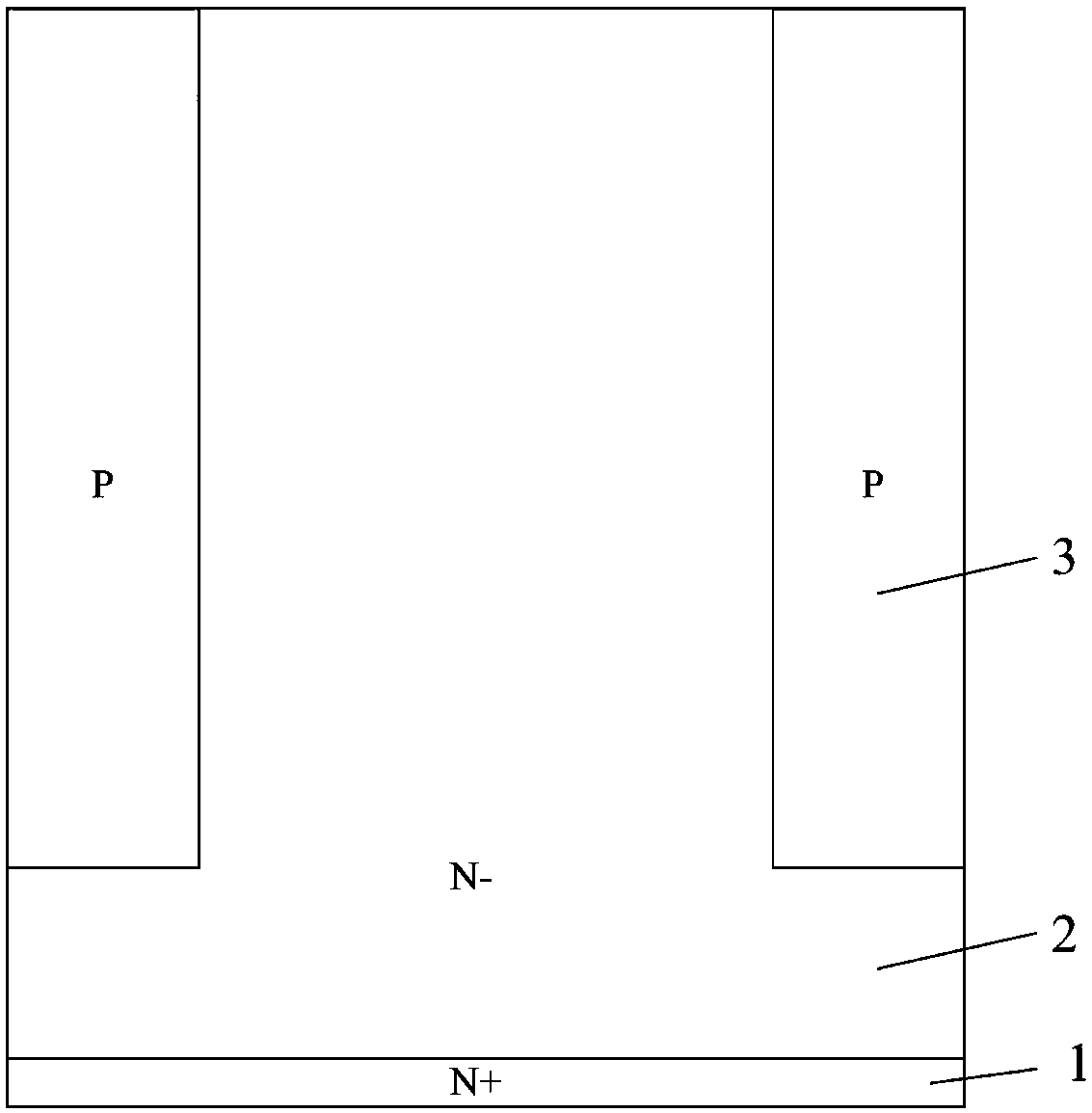

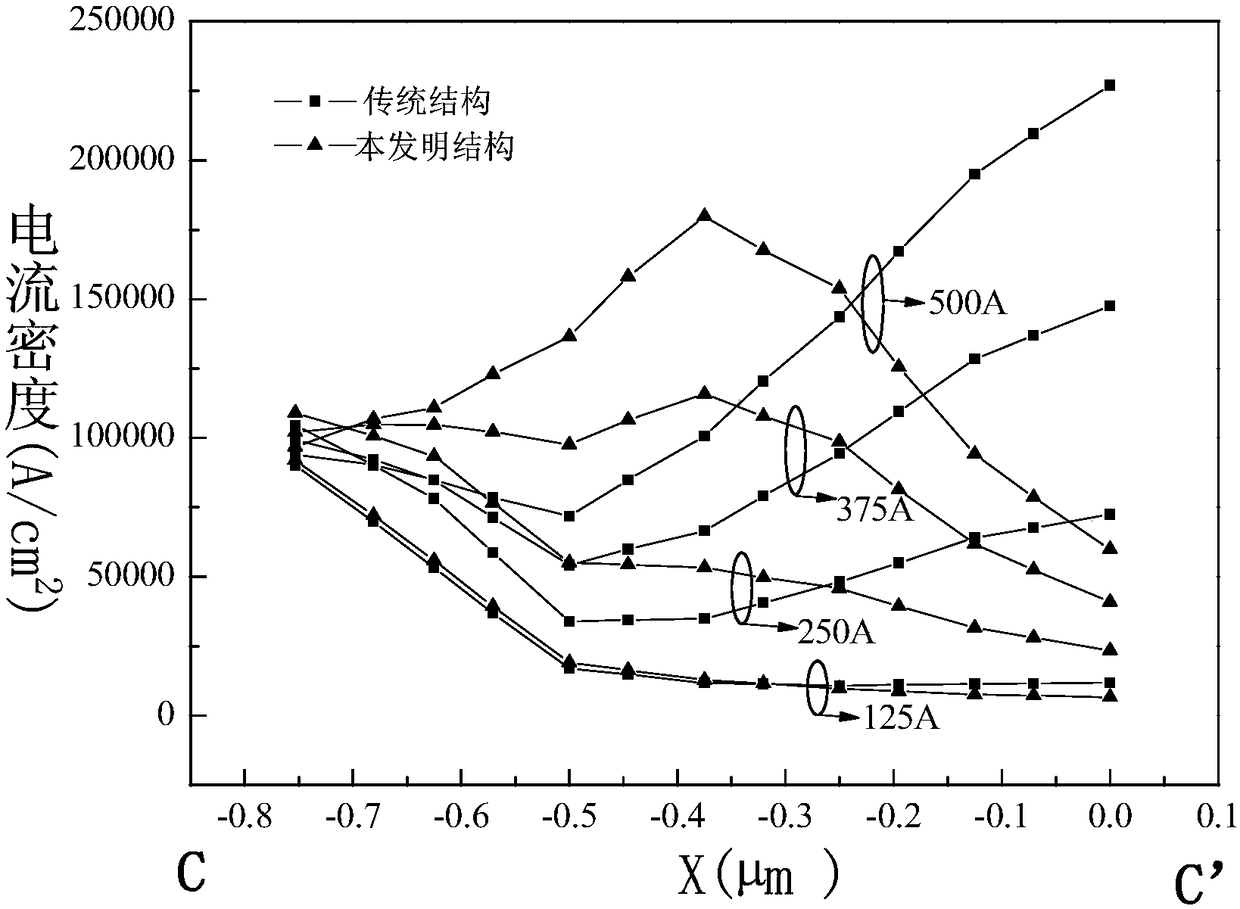

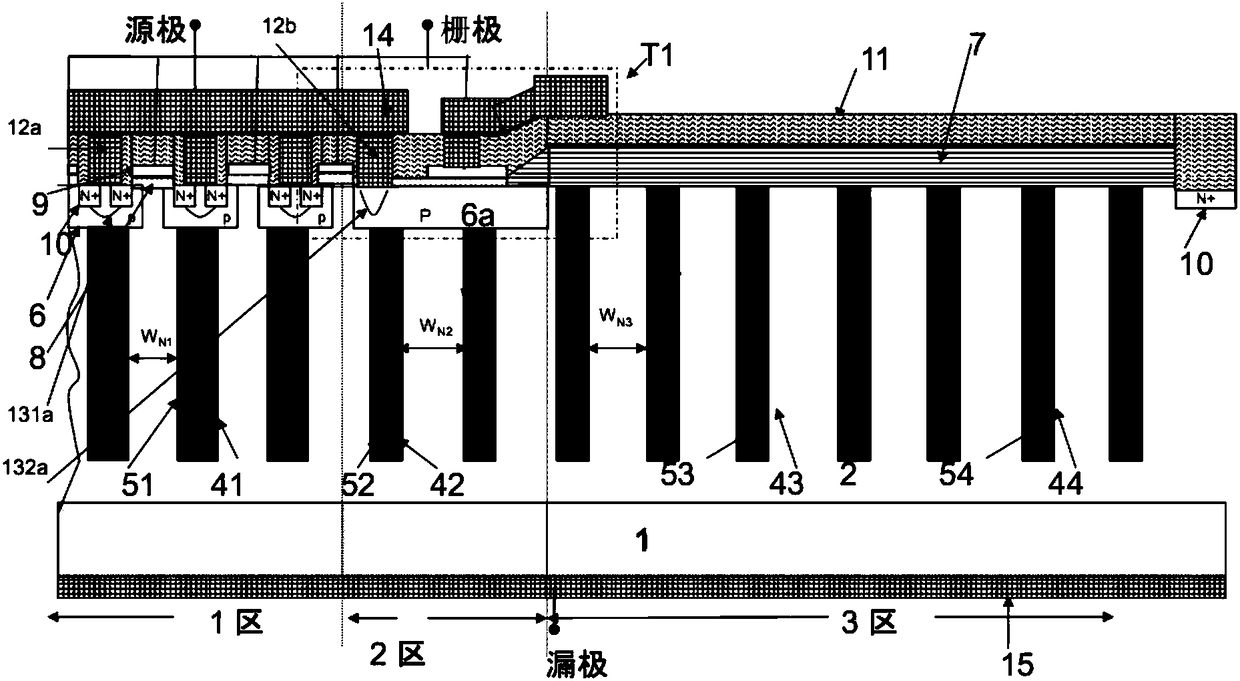

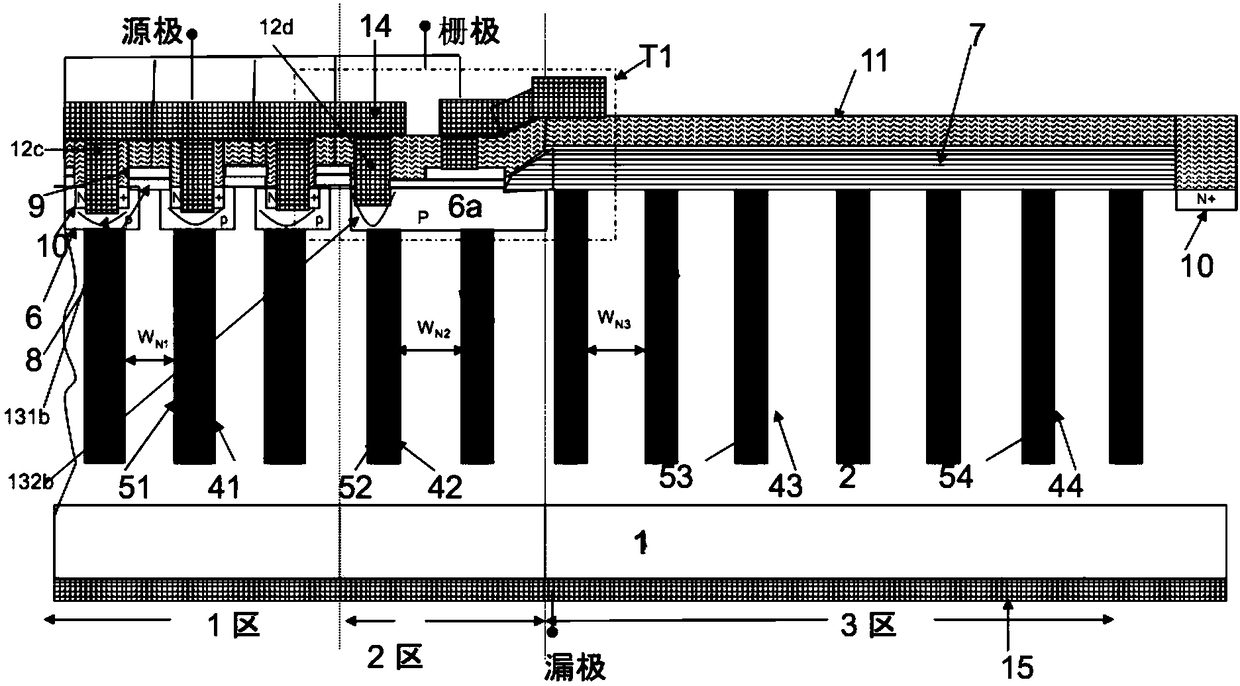

PendingCN108336139AIncreased avalanche toleranceReduce peak current densitySemiconductor devicesManufacturing technologyBody area

The invention belongs to the technical field of manufacturing of semiconductor devices and relates to a high-snow-slide-tolerance deep-groove power device. The device comprises a first electric-condition-type silicon substrate and a first electric-condition-type silicon epitaxial layer, grooves are formed in the first electric-condition-type silicon epitaxial layer, and field oxygen layers, shieldgrids, grid electrodes and grid oxygen layers are arranged in the grooves; second electric-condition-type body areas and first electric-condition-type source areas are arranged between the adjacent grooves, and insulation dielectric layers and source electrode metal are arranged in the grooves and the first electric-condition-type source areas. The device is characterized in that in a platform area between the adjacent grooves, the source electrode metal is in contact with the second electric-condition-type body areas through two through holes, and second electric-condition-type source areasare arranged below all the through holes; a traditional single through hole is improved into double through holes, current can be effectively inhibited from being gathered to the center of a platform,the generation of weak point breakdown is inhibited accordingly, the epitaxial layer with lower specific resistance and the thicker field oxygen layers can be adopted for the deep-groove device, andthen the conduction resistance of the device is lowered.

Owner:WUXI NCE POWER

Super-junction device and manufacturing method thereof

ActiveCN108428732AImprove softness factorImprove reverse recovery characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryEngineering

The invention discloses a super-junction device, which is characterized in that a protective epoxy film exposes a charge flow region, completely covers a transition region and completely or mostly covers a terminal region, a second contact hole at the top of a P-type ring of the transition region is enabled to penetrate deeper than a first contact hole at the top of a P-type well of the charge flow region by the thickness of one protective epoxy film, and thus the junction depth of a second P+ contact region at the bottom of the second contact hole is enabled to be less than the junction depthof a first P+ contact region at the bottom of the first contact hole, so that the distance between a hole collected by the P-type ring to the second P+ contact region, and a softness factor of reverse recovery of a body diode of the device is increased. The invention further discloses a manufacturing method of the super-junction device. According to the invention, the reverse recovery characteristics of device can be improved, and the avalanche tolerance of the device is enhanced at the same time.

Owner:SHENZHEN SANRISE TECH CO LTD

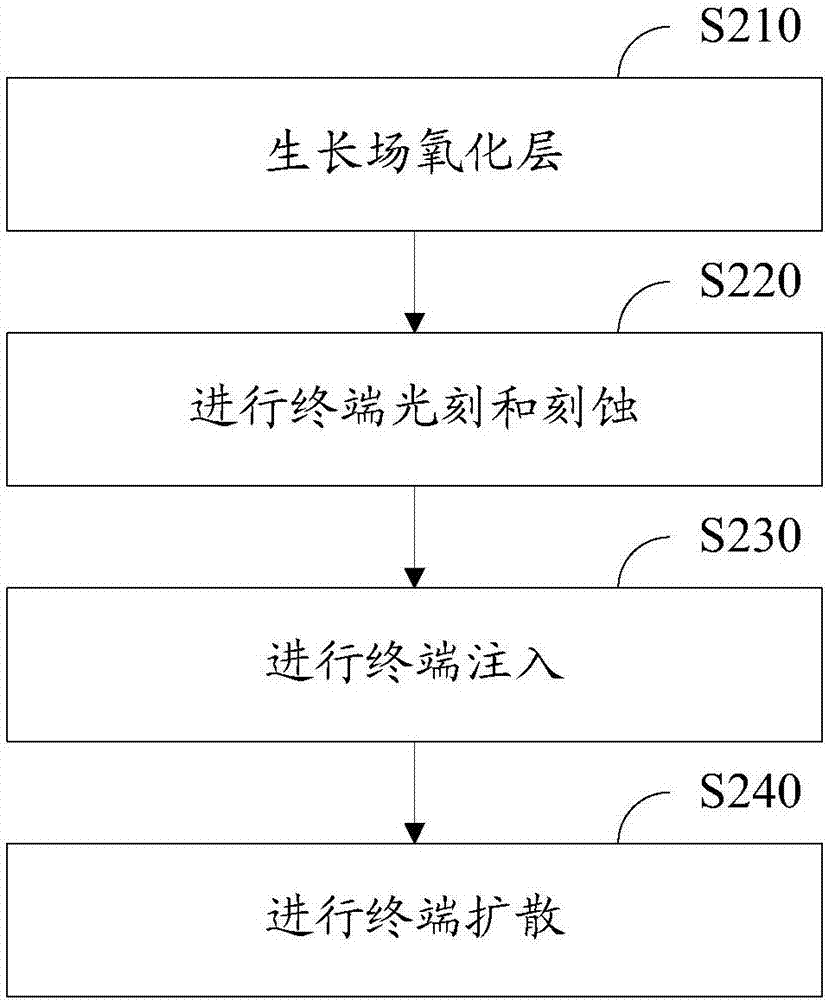

Method for manufacturing super-junction high-voltage power device

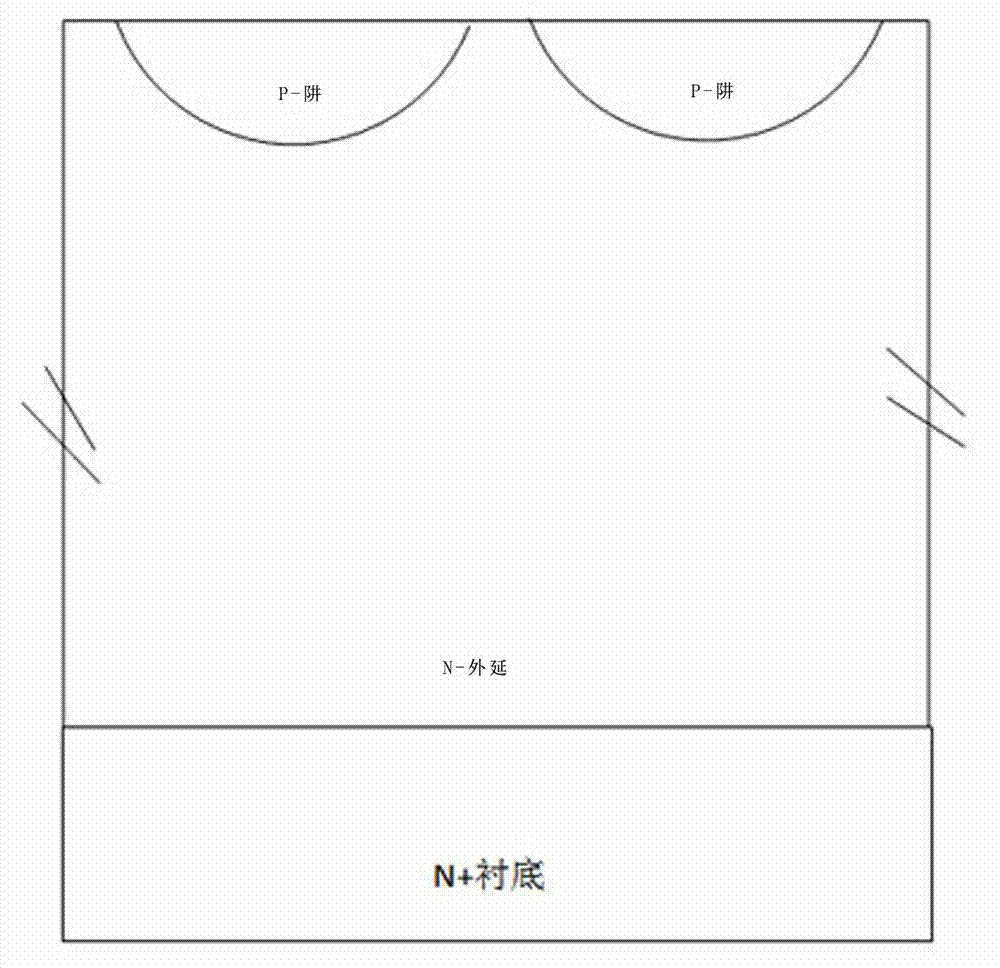

ActiveCN102881595AIncreased avalanche toleranceImprove reliabilitySemiconductor/solid-state device manufacturingEngineeringMaterials science

The invention relates to a method for manufacturing a super-junction high-voltage power device. The method comprises the following steps of: providing an n-type heavy doping n+ substrate, forming an n-type epitaxial layer on the n+ substrate, and forming a p well region and a composite buffer layer; growing a field oxide layer on a silicon chip, defining an active region of the device, growing a gate oxide layer, and defining an area etched by polycrystalline silicon at the first time; performing deep p+ implantation on the surface of the whole semiconductor silicon chip, wherein a p+ area can be defined in a polycrystalline silicon area formed by the previous process; putting the silicon chip in polycrystalline silicon etching solution, performing secondary etching on the polycrystalline silicon by controlling the etching time and the etching rate, and forming an n-type source region n+; depositing a dielectric layer on the surface of the whole semiconductor silicon chip, defining a contact hole area, and etching the oxide layer; and depositing a metal layer, defining an etching area through photoetching, and performing metal etching. By the method, the avalanche tolerance of the device is improved, the reliability of the device is improved, and the threshold voltage and on-resistance of the device are not influenced.

Owner:XIAN LONTEN RENEWABLE ENERGY TECH

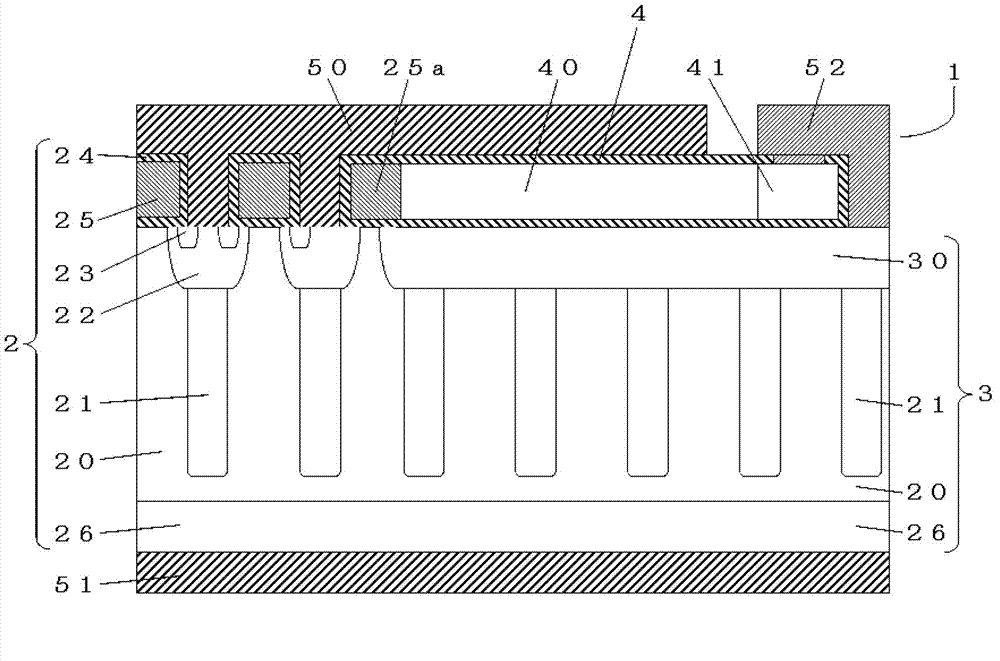

Semiconductor device and method of manufacturing semiconductor device

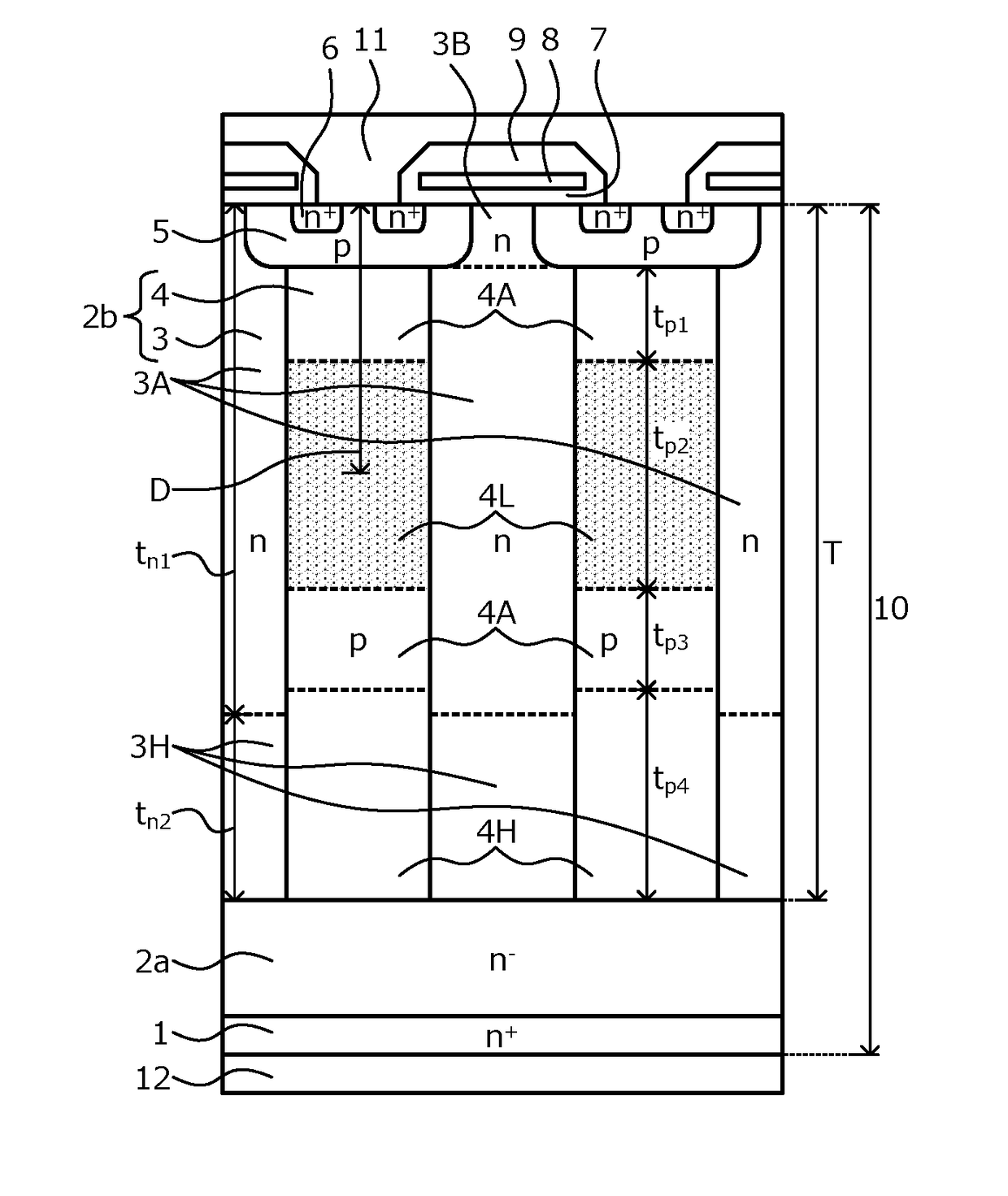

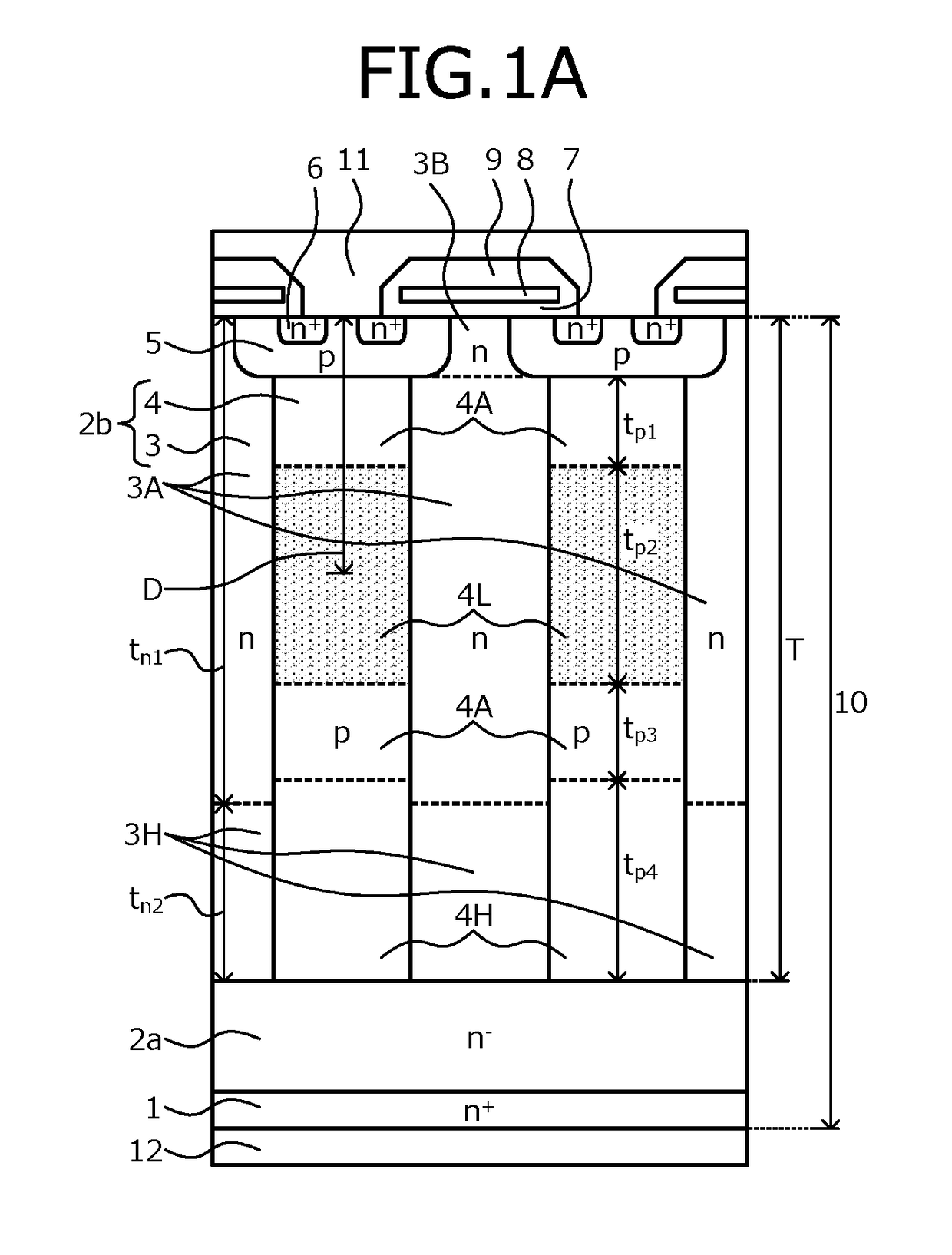

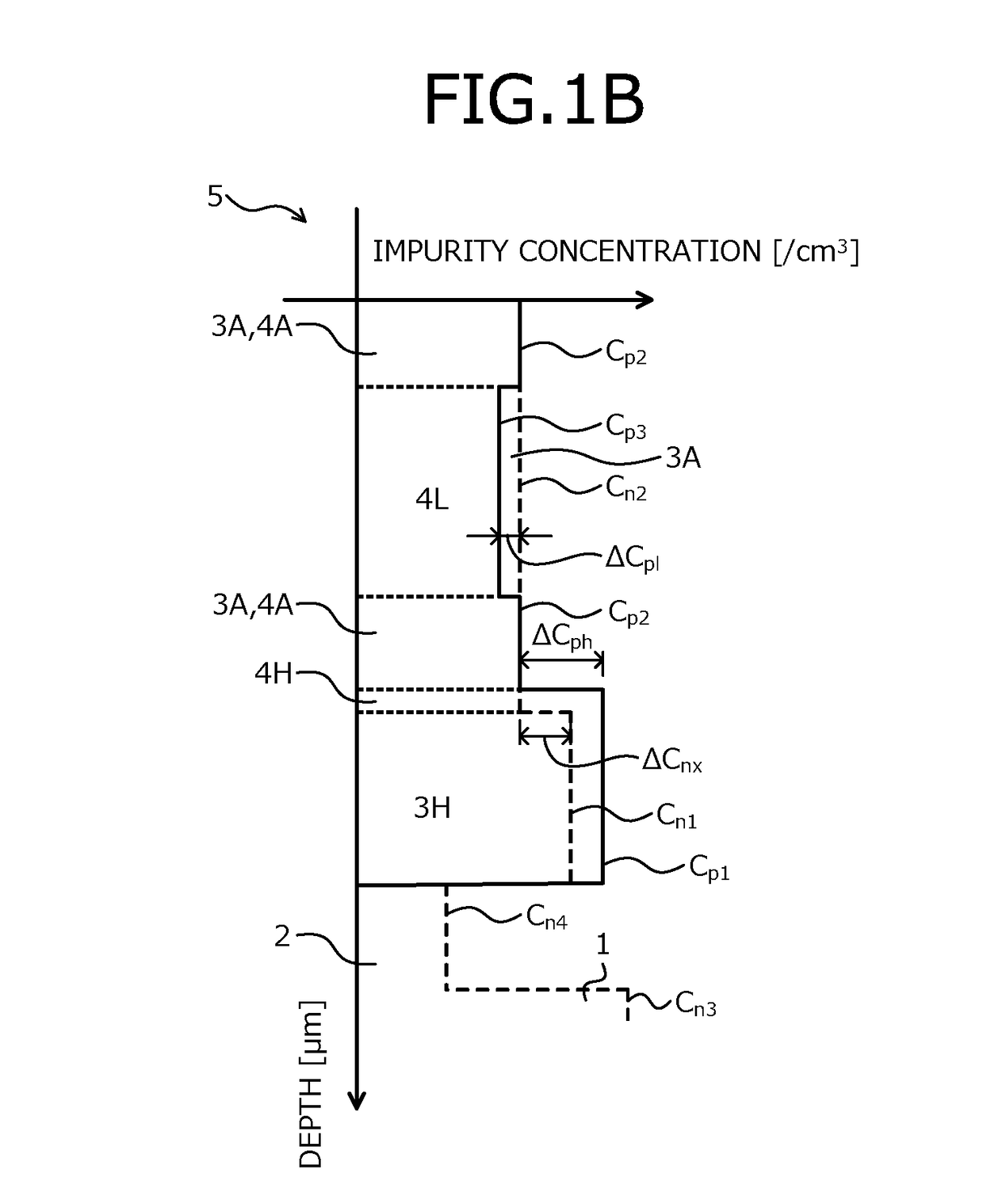

ActiveUS20180076315A1Lower on-state resistanceIncreased avalanche toleranceTransistorSemiconductor/solid-state device manufacturingMOSFETDepth direction

A SJ-MOSFET includes a parallel pn layer in which an n-type drift region and a p-type partition region are alternately arranged repeatedly along a direction parallel to a base main-surface. The n-type drift region and the p-type partition region have total impurity amounts that are roughly the same and widths that are basically constant over an entire depth direction. The n-type drift region is configured to have an n-type impurity concentration profile in which an impurity concentration of a portion on the drain-side is higher than an impurity concentration of a portion on the source-side by ΔCnx. The p-type partition region is configured to have a p-type impurity concentration profile in which an impurity concentration of a portion on the drain-side is higher than an impurity concentration of a portion on the source-side by ΔCph, and an impurity concentration of part of the portion on the source-side is relatively low.

Owner:FUJI ELECTRIC CO LTD

MOSFET (metal oxide semiconductor field effect transistor) with semi-insulating region and preparation method thereof

ActiveCN108417638AReduced areaReduce in quantitySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETField-effect transistor

The invention discloses an MOSFET (metal oxide semiconductor field effect transistor) with a semi-insulating region and a preparation method thereof and belongs to the technical field of high-voltageelectronics and power. The MOSFET with the semi-insulating region is characterized in that the semi-insulating region is positioned below a first conductive-type semiconductor-doped base region and asecond conductive-type semiconductor-doped transmitting region which are arranged side by side; both the bottom and lateral side of the semi-insulating region are in contact with a second conductive-type semiconductor-doped drift layer; the semi-insulating region is formed by: performing ion implantation on second conductive-type impurities to arrive at contra-doping so as to form an electrical neutral layer, performing ion implantation on amphoteric impurity elements to form a semi-insulating region, and performing ion implantation on first conductive-type impurities above the semi-insulatingregion to form a shallow base region. By narrowing a region of MOSFET parasitic transistors, the problem is solved that startup of conventional MOSFET parasitic transistors cause uncontrollable current under UIS condition, causing 'heat rush'; avalanche tolerance, robustness, high current resistance, breakthrough voltage and reliability can be significantly improved.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY

Power semiconductor device and preparation method thereof

PendingCN112271218AReduce generationIncrease cooling areaTransistorThyristorPower semiconductor deviceEngineering

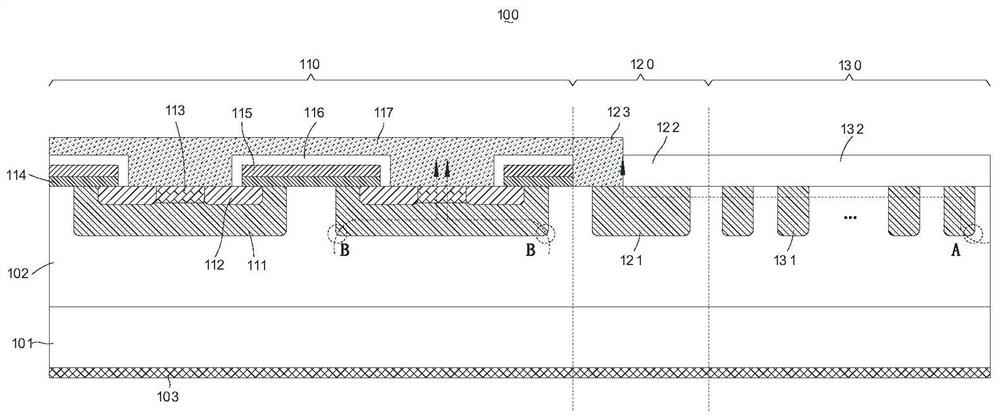

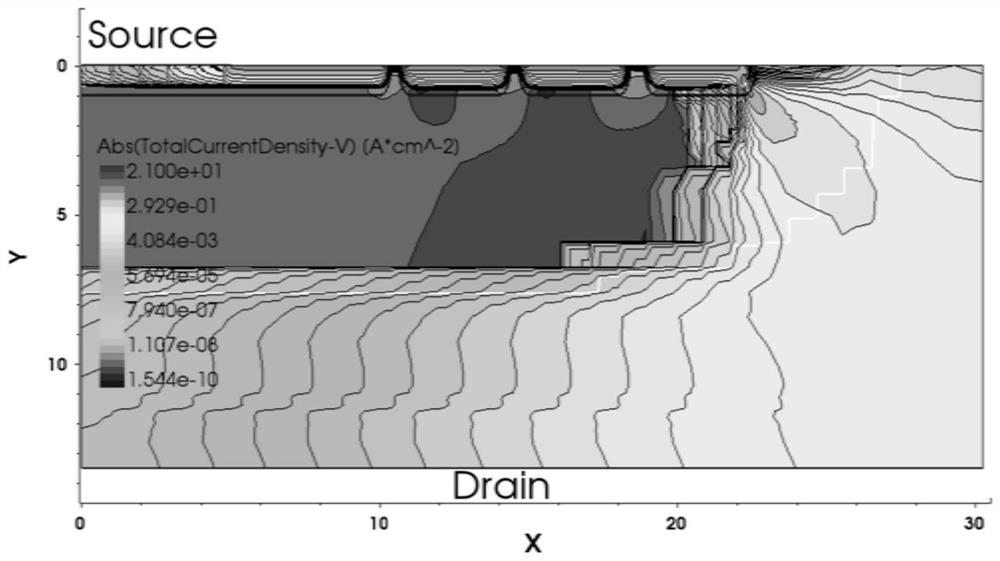

The invention provides a power semiconductor device and a preparation method thereof. The power semiconductor device comprises an active region, a terminal region and a transition region, wherein theactive region and the terminal region are arranged on an epitaxial layer; the transition region is positioned between the active region and the terminal region; and the active region comprises a plurality of second conductive type well regions arranged in the surface of the epitaxial layer at intervals, grooves formed in the surfaces of the well regions, first conductive type source regions located in the surfaces of the well regions and located on the two sides of the grooves, and second conductive type short circuit regions located in the well regions and located below the grooves, wherein the bottom of the well region is provided with a recessed structure at a position corresponding to the grooves. By forming the concave structure at the bottom of the well region at the position corresponding to the trench, the avalanche breakdown position is transferred from the terminal region to the active region with a larger area, the heat dissipation area is increased, the avalanche current path avoids the parasitic npn transistor base region, the avalanche current path is shortened, the generation of heat is reduced, and the avalanche tolerance is improved.

Owner:湖南国芯半导体科技有限公司

Power transistor and manufacturing method thereof

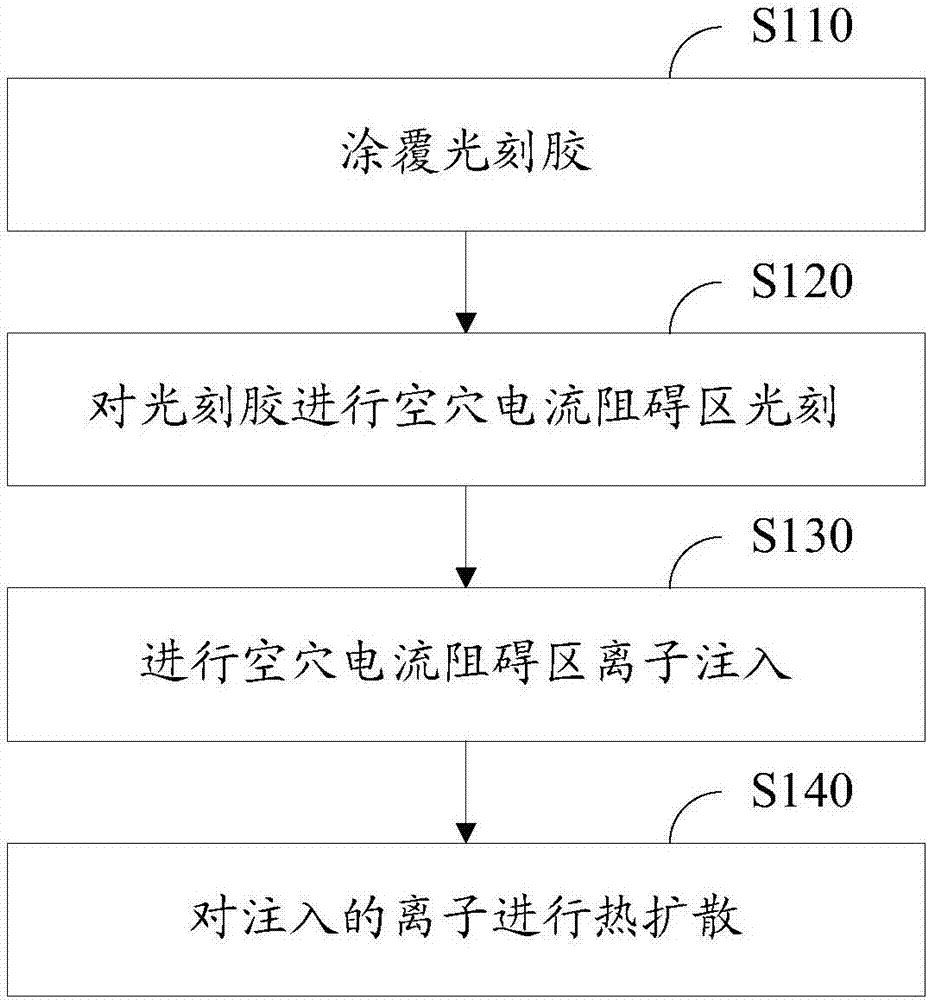

PendingCN106920846AReduce doping concentrationIncreased avalanche toleranceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringTransistor

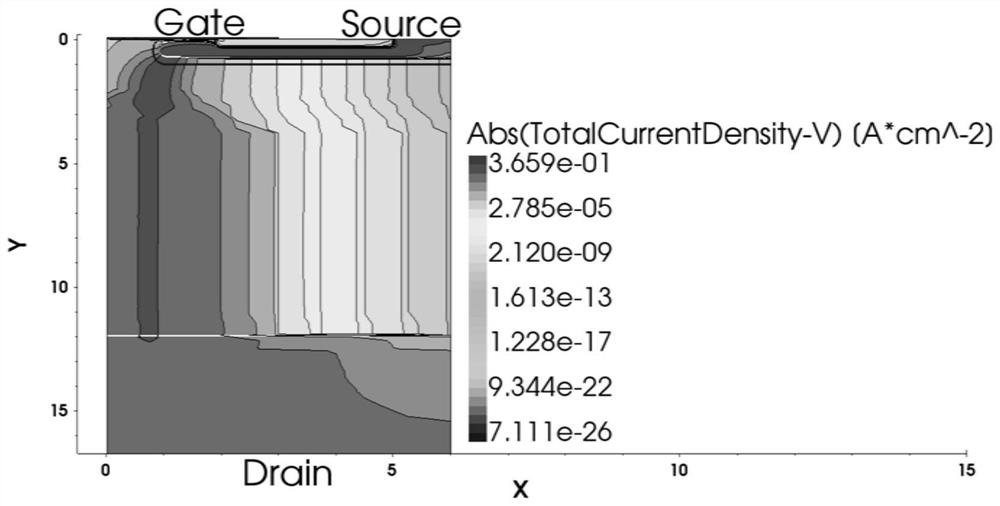

The invention relates to a power transistor and a manufacturing method thereof. A cell structure of the power transistor comprises a first conductive type of substrate, a second conductive type of well region on the substrate, a first conductive type of source region in the well region and a gate above the well region, wherein the first conductive type and the second conductive type are opposite conductive types, the power transistor is characterized in that the cell structure also comprises a hole current blocking region, the hole current blocking region wraps at least one part of the well region and is in the second conductive type, the doping concentration of the hole blocking region is smaller than the doping concentration of the well region, and the hole current blocking region extends to a part below a gate adjacent to the gate from a part below the gate. By the power transistor, the avalanche tolerance of the power transistor can be improved, the conventional parameter of a device is not affected, and meanwhile, the reliability of the device working in an inductive load environment is improved.

Owner:深圳深爱半导体股份有限公司

Power device and manufacturing method thereof

PendingCN109326653AImprove breakdown voltageIncreased avalanche toleranceTransistorSemiconductor/solid-state device manufacturingPhysics

Owner:上海昱率科技有限公司

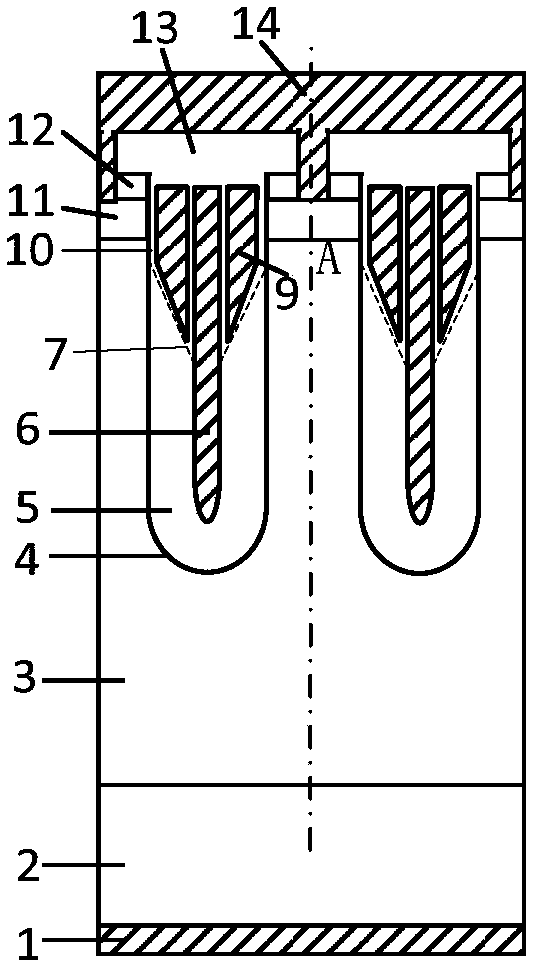

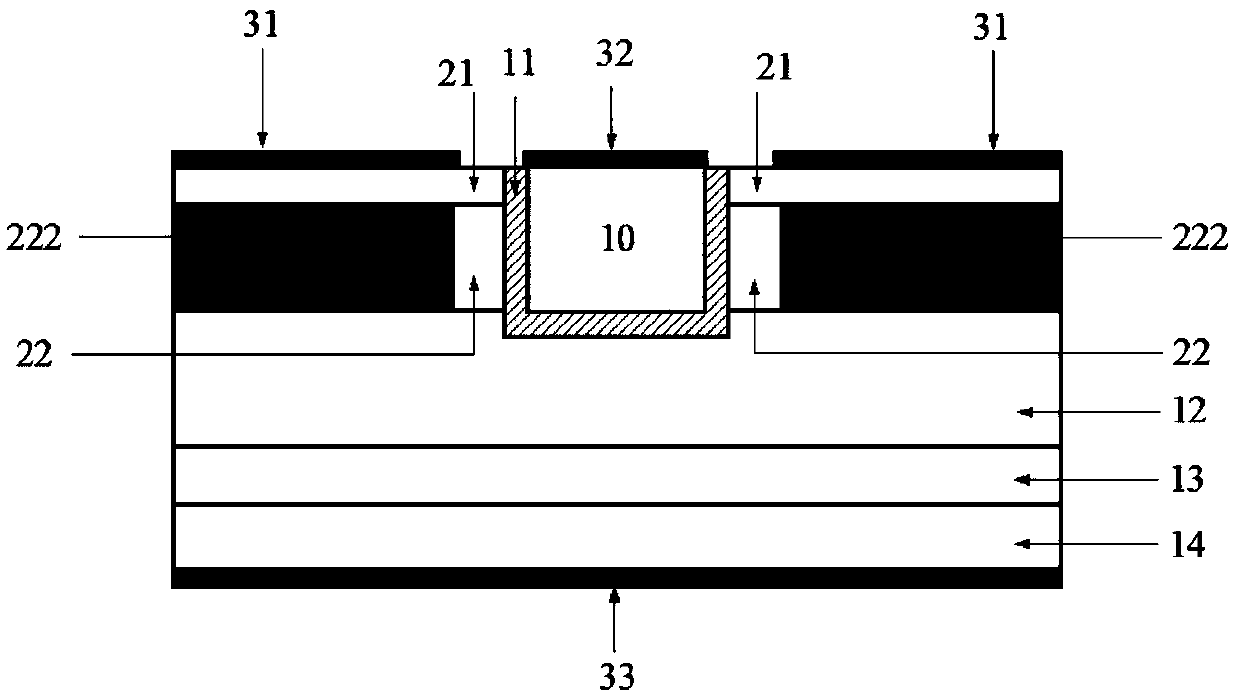

Power semiconductor device and manufacturing method thereof

PendingCN107611169AIncreased avalanche toleranceImprove reliabilitySemiconductor devicesPower semiconductor deviceAcute angle

The invention discloses a power semiconductor device, which comprises a cell area, a terminal protection area, a first type of insulating dielectric body and a first type of electric conductor, wherein the cell area comprises a substrate of a first conductivity type and an epitaxial layer of a first conductivity type; a U-shaped groove is formed in the epitaxial layer of the first conductivity type; the groove is filled with the first type of insulating dielectric body and the first type of electric conductor; the first type of insulating dielectric body is arranged in a manner of surroundingthe first type of electric conductor; inner grooves are formed between one of two sides of the upper end of the first type of electric conductor and the first type of insulating dielectric body and between the other side and the epitaxial layer of the first conductivity type separately, and the cross section of each inner groove is in a right-angled trapezoid form; an acute angle in a right-angledtrapezoid form is formed between the first type of insulating dielectric body and the first type of electric conductor; and gate-conductive polysilicon matched with the inner grooves is arranged in the inner grooves. The invention further discloses a manufacturing method of the power semiconductor device. According to the power semiconductor device, the on-resistance of the device is obviously reduced.

Owner:WUXI NCE POWER

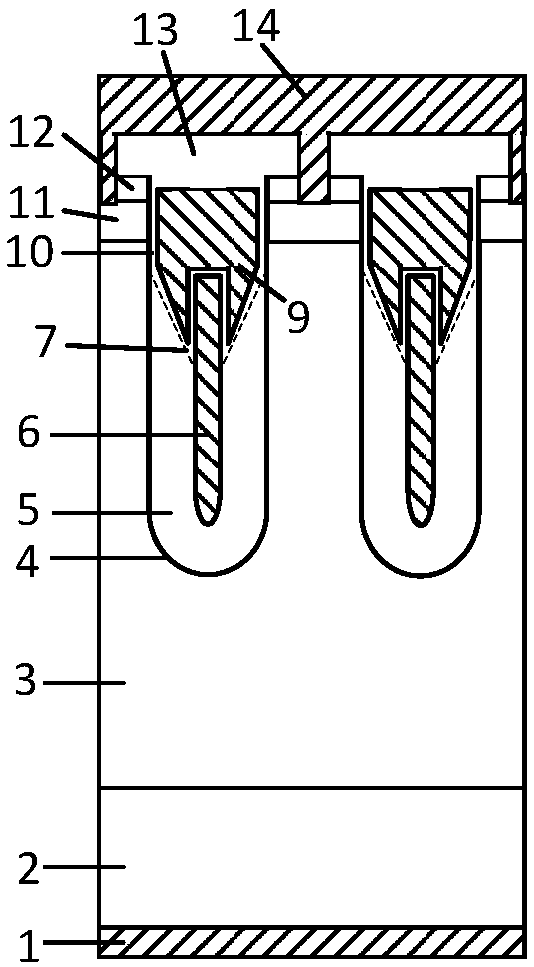

Power semiconductor device and manufacturing method thereof

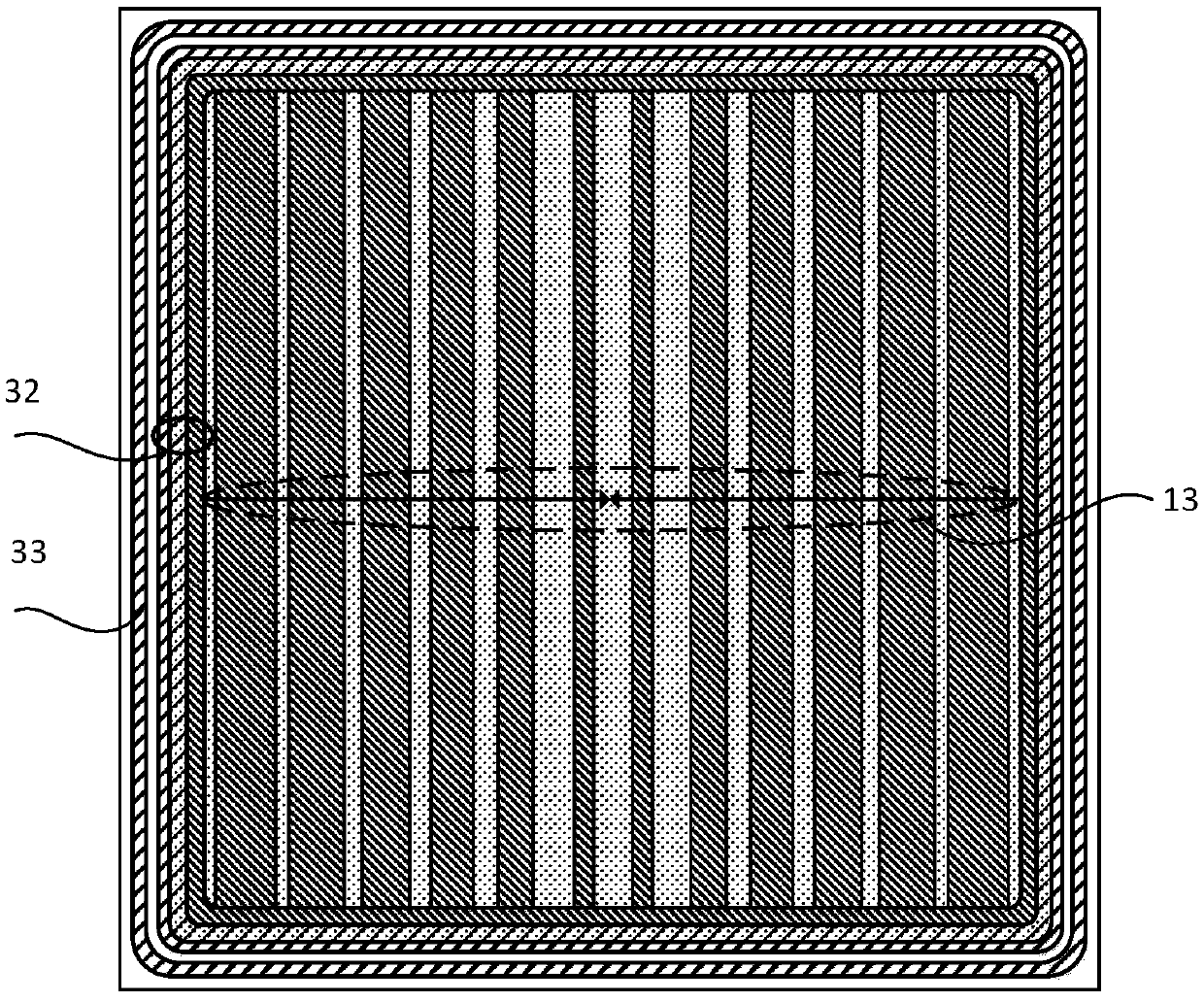

PendingCN107134478AIncreased avalanche toleranceSemiconductor/solid-state device manufacturingSemiconductor devicesLoad circuitMetal interconnect

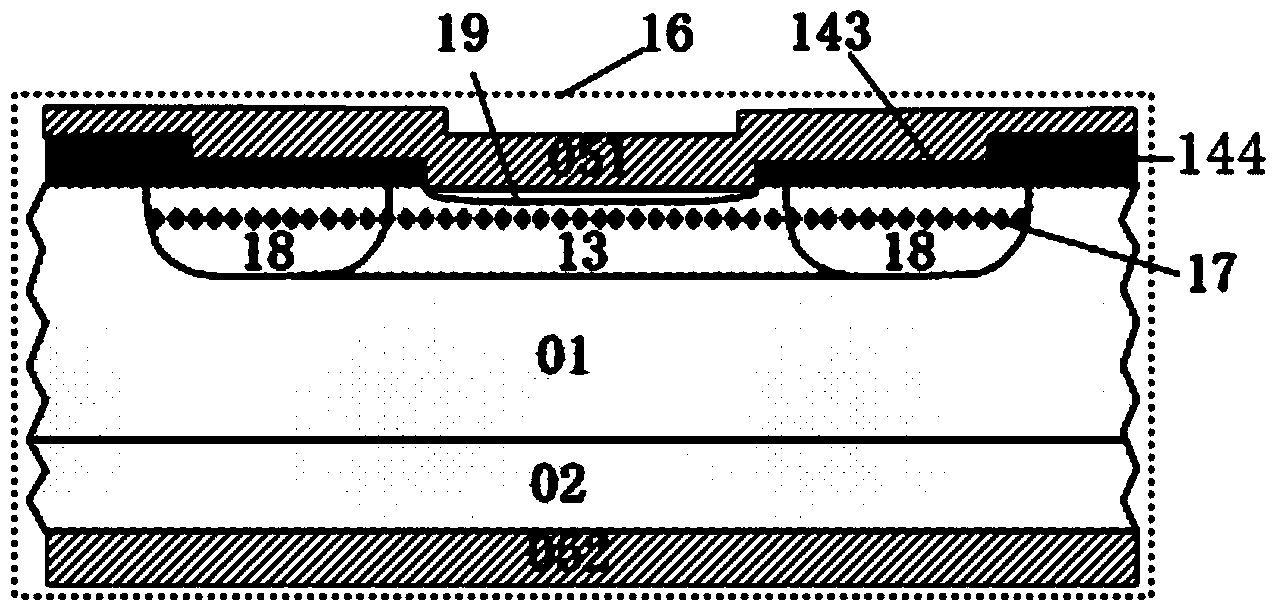

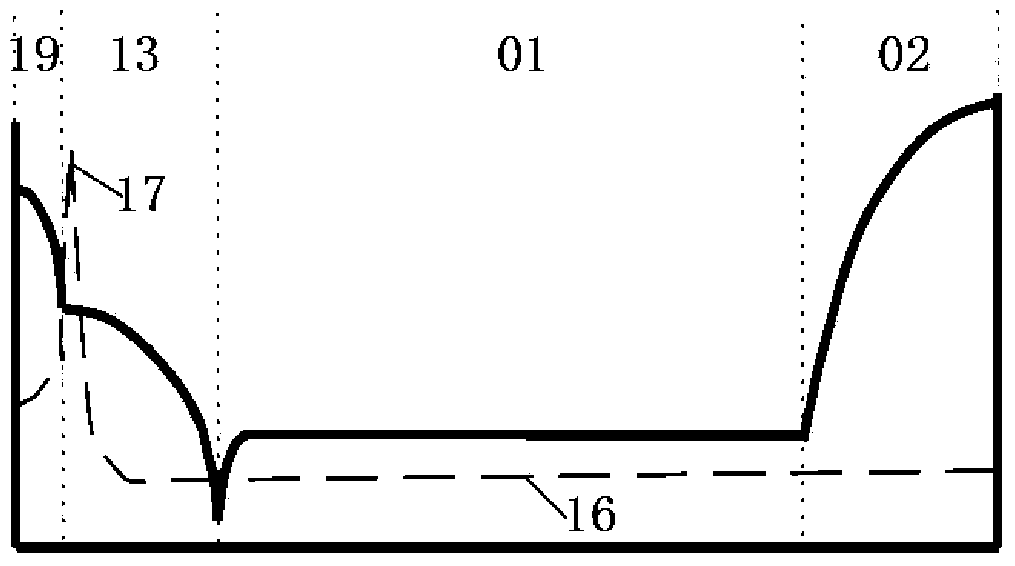

The invention relates to a power semiconductor device and a manufacturing method thereof. The manufacturing method comprises the a step of well injection, and is characterized in that an injection blocking layer in the step of well injection comprises a strip-shaped injection blocking structure located between two adjacent grid electrodes, the bottom of a well region below the injection blocking structure is enabled to form a recess sinking into the well region upward after well injection and diffusion, the extending direction of the strip-shaped injection blocking structure is perpendicular to the spacing direction of the two adjacent grid electrodes, and the width of the injection blocking structure is less than the width of a metal interconnecting wire connected with a source region at the source region connecting part. When the power semiconductor device is turned off in an inductive load circuit, hole current flowing from the recess is short in path to source metal, and the hole current can directly get into the source metal, so that the possibility of getting into the source region is reduced, a parasitic NPN transistor is enabled to be difficult to open, and thus the avalanche tolerance of the device is increased.

Owner:深圳深爱半导体股份有限公司

Trench gate power MOS transistor containing semi-insulating region and preparation method

ActiveCN108682684AReduce in quantitySmall currentSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringHigh pressure

The invention discloses a trench gate power MOS transistor containing a semi-insulating region and a preparation method, and belongs to the technical field of high voltage power electronics. The trench gate power MOS transistor containing the semi-insulating region comprises a second conduction type-doped source region, and a first conduction type-doped base region and semi-insulating region, thesecond conduction type-doped source region is located above the first conduction type-doped base region and semi-insulating region which are arranged side by side, and the bottom of the semi-insulating region is in contact with a second conduction type semiconductor-doped drifting layer. The semi-insulating region first adopts ion implantation of impurities of the second conduction type to realizecontra-doping to form an electrically neutral layer, and then the semi-insulating region is formed by ion implantation of amphoteric impurity elements. Aiming at the problem of low UIS avalanche tolerance of a trench gate power MOS transistor in the prior art, the UIS avalanche tolerance and robustness of the trench gate power MOS transistor provided by the invention can be remarkably improved, acapability of resisting large current of the trench gate power MOS transistor is improved, the reliability of the trench gate power MOS transistor is improved, and the breakdown voltage of the trenchgate power MOS transistor is appropriately improved.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY

Super-junction structure and manufacturing method thereof

ActiveCN111341830AReduce etchingReduce difficultySemiconductor/solid-state device manufacturingSemiconductor devicesElectrical field strengthEngineering

The invention discloses a super-junction structure. The super-junction structure is formed by superposing two layers of super-junction substructures, and each of the two layers of P-type sub-columns consists of a P-type sub-epitaxial layer filled in the corresponding sub-groove; each sub-groove is of a structure with the side face inclined and the top width larger than the bottom width. The position corresponding to the change range of the optimal charge balance plus + / -5% of the first super-junction sub-structure at the bottom layer is arranged at the longitudinal center position, and the position of the maximum electric field intensity of the first super-junction sub-structure tends to the longitudinal center position and has a first value; the maximum electric field intensity value in the second super-junction substructure is a second value, and the first value is greater than the second value, so the breakdown position of the whole super-junction unit structure tends to the longitudinal center position of the first super-junction substructure. The invention further discloses a manufacturing method of the super-junction structure. According to the invention, the consistency of device performances such as breakdown voltage and avalanche tolerance can be improved.

Owner:SHENZHEN SANRISE TECH CO LTD

Groove type field effect transistor structure and preparation method thereof

ActiveCN112864018ALower channel resistanceReduced characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

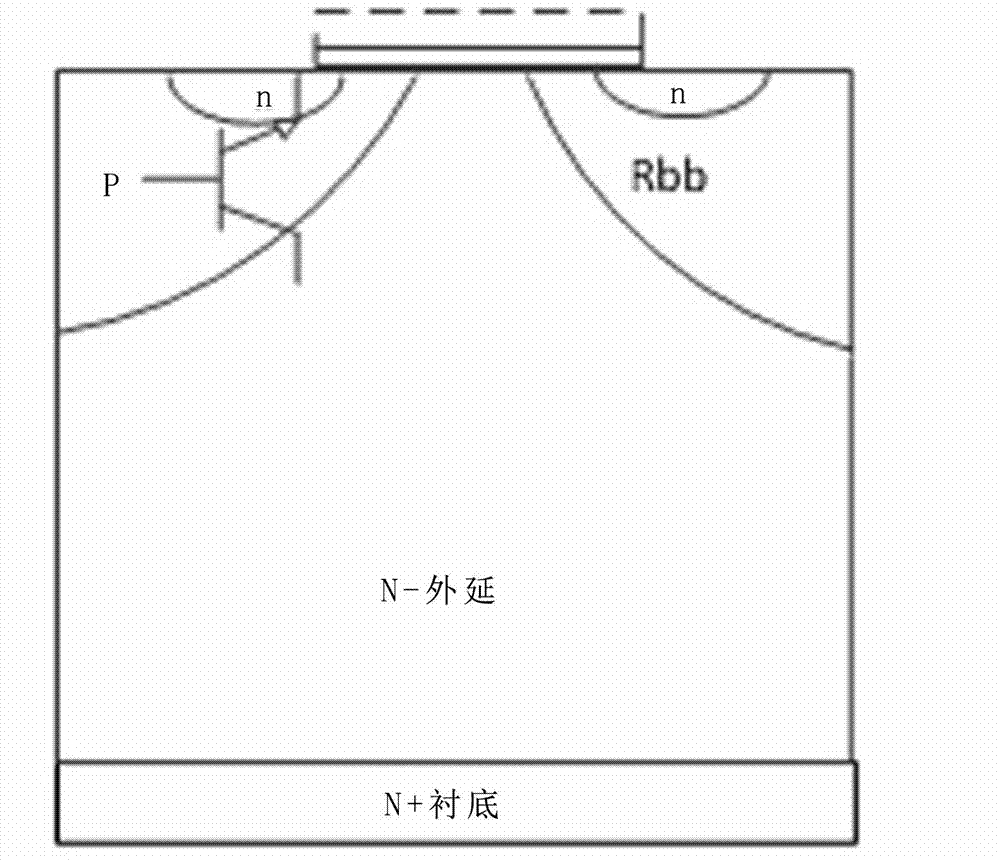

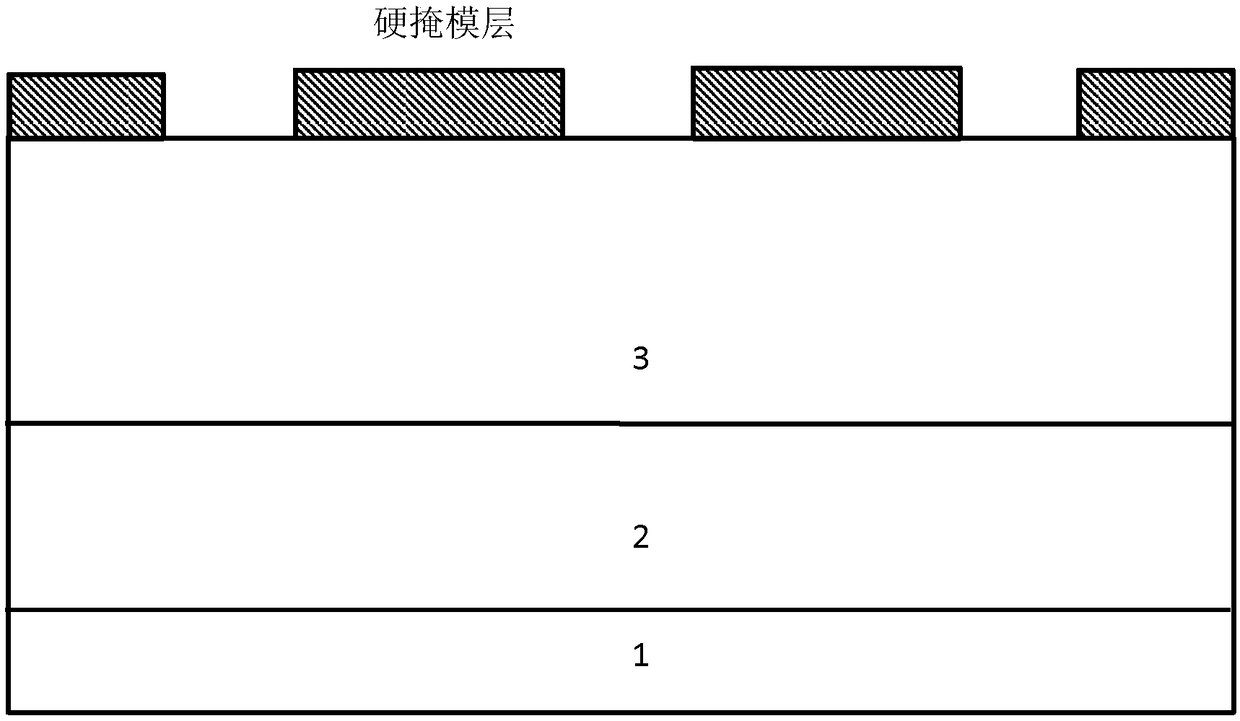

High-avalanche capability power semiconductor transistor structure and preparation method thereof

InactiveCN105552110AEvenly distributedElimination of the effects of process variabilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate oxideMedia layer

The invention provides a high-avalanche capability power semiconductor transistor structure, which comprises an N-type substrate used as a drain region, wherein an N-type epitaxial layer is arranged on the N-type substrate; P-type strip body regions are arranged on the surface of the N-type epitaxial layer; a heavily doped N-type source region and a heavily doped P-type source region are arranged on the surface of each P-type strip body region; an insulated gate oxidation layer is arranged on the N-type epitaxial layer; conductive polysilicon is arranged on the insulated gate oxidation layer, and is located at the upper part of the region between the adjacent P-type strip body regions and two sides of the conductive polysilicon respectively cover the adjacent P-type strip body regions; an insulated medium layer is arranged on the conductive polysilicon; the heavily doped N-type source regions and the heavily doped N-type source regions are connected with a source metal; the high-avalanche capability power semiconductor transistor structure is characterized in that the P-type strip body regions extend towards the N-type epitaxial layer to form a plurality of P-type arched body regions; and the P-type arched body regions are evenly distributed on the P-type strip body regions and are embedded into the N-type epitaxial layer. According to the high-avalanche capability power semiconductor transistor structure, a preparation method of a traditional power semiconductor transistor is reserved; the avalanche capability is improved; the chip area is reduced; and the cost is relatively low.

Owner:SOUTHEAST UNIV

Semiconductor device

InactiveCN103035641AIncreased avalanche toleranceLower on-resistanceTransistorSolid-state devicesElectrical conductorSemiconductor package

A semiconductor device comprising: a Metal Oxide Semiconductor Field Effect Transistor including: a semiconductor substrate including a first semiconductor layer of a first conductivity type; second semiconductor layers of a second conductivity type extending in a depth direction from one surface of the semiconductor substrate, and having space each other; a first diode including a fifth semiconductor layer of the second conductivity type contacting the second semiconductor layer in one surface side of the semiconductor substrate, the first semiconductor layer and the second semiconductor layers; and an anode of the second diode connected to an anode of the first diode.

Owner:KK TOSHIBA

Super junction structure and manufacturing method thereof

ActiveCN111341828AReduce etchingReduce difficultySemiconductor/solid-state device manufacturingSemiconductor devicesMechanical engineeringSubstructure

The invention discloses a super junction structure. The super junction structure is formed by superposing two layers of super junction substructures, each of the two layers of P-type sub-columns consists of a P-type sub-epitaxial layer filled in the corresponding sub-groove; each sub-groove is of a structure with the side face inclined and the top width larger than the bottom width. The top surface is arranged at the position corresponding to the optimal charge balance of the first super junction substructure at the bottom layer plus the change range of plus or minus 5%; the bottom surface isarranged at the position corresponding to the optimal charge balance of the second super junction substructure plus the change range of plus or minus 5%, so the breakdown position of the super junction structure is located at the contact position of the two layers of super junction substructures. The invention further discloses a manufacturing method of the super junction structure. According to the invention, the consistency of device performances such as breakdown voltage and avalanche tolerance can be improved.

Owner:SHENZHEN SANRISE TECH CO LTD

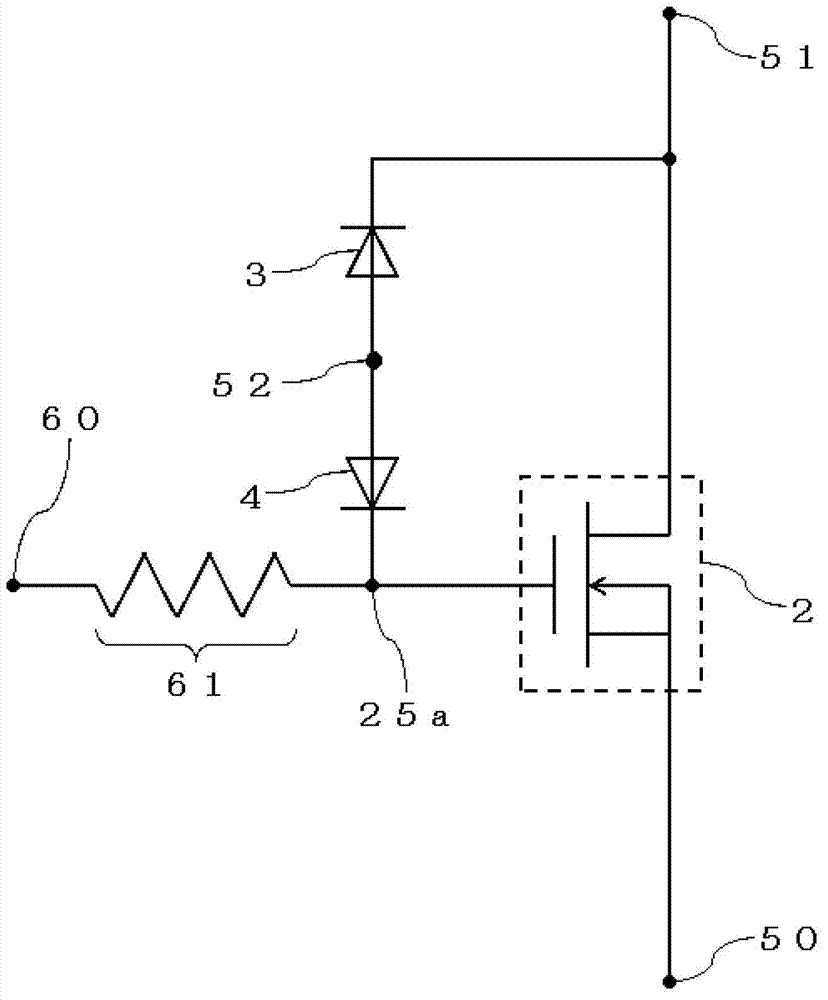

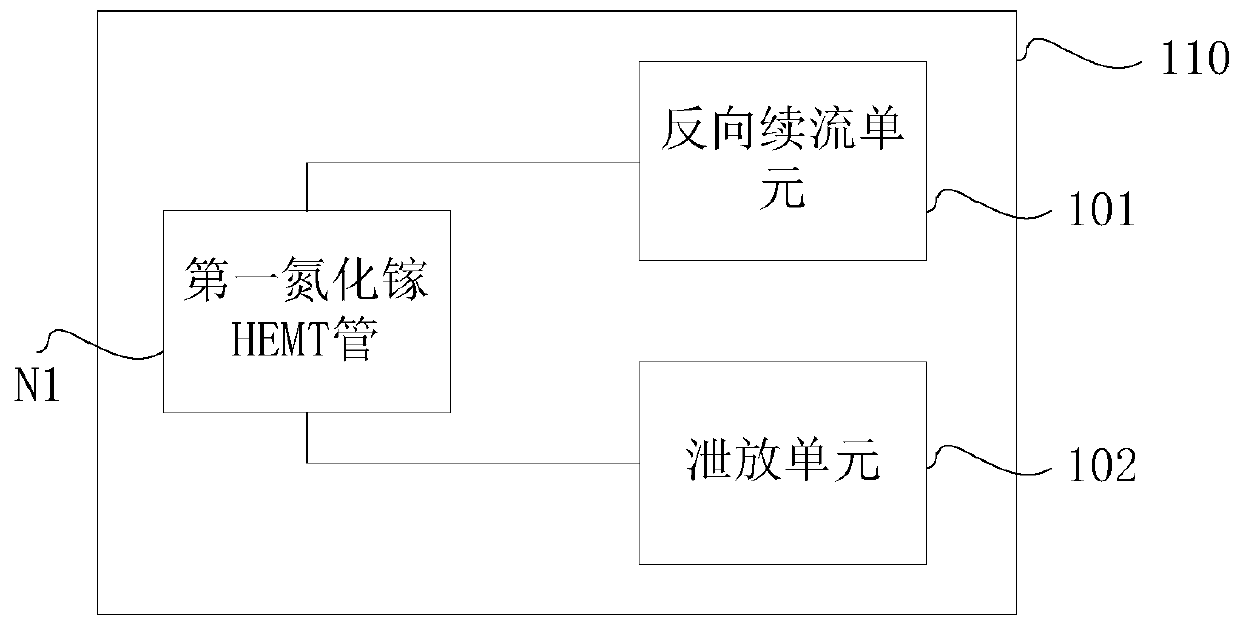

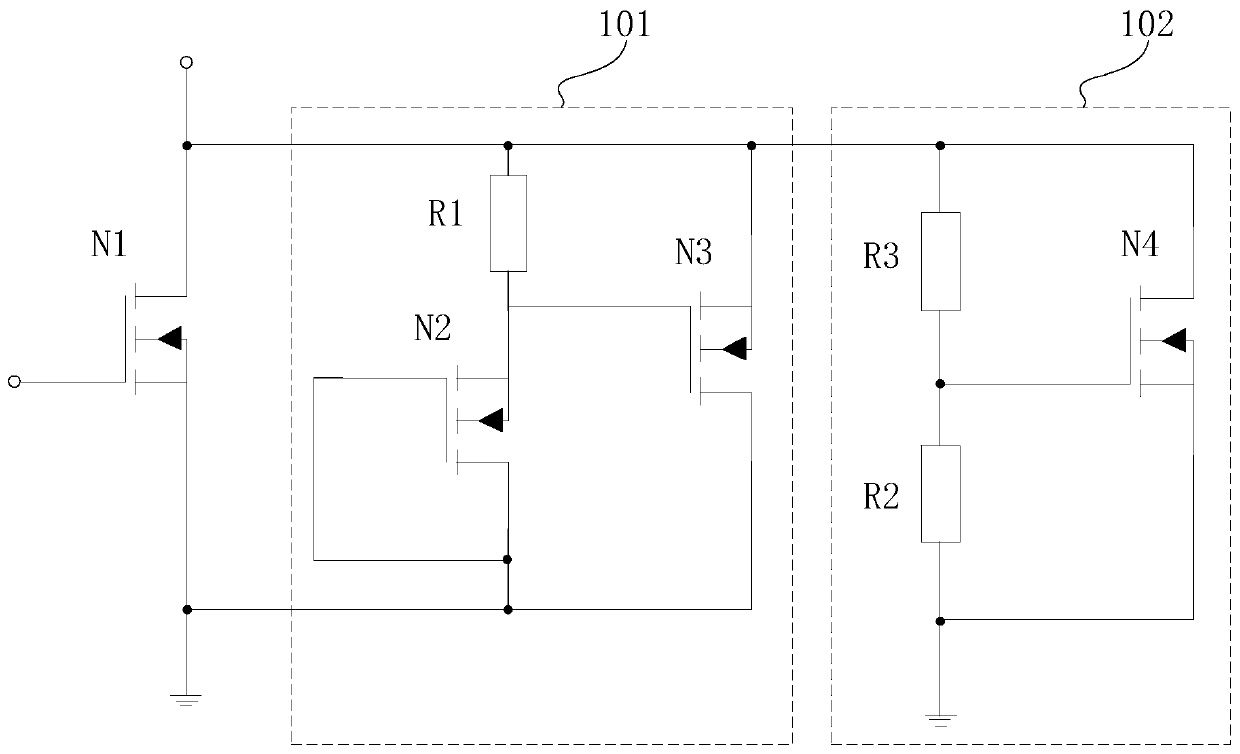

Gallium nitride HEMT tube integrated circuit, flyback circuit, bridgeless PFC circuit and laser radar

PendingCN110649914AGood reverse flow abilityIncreased avalanche toleranceWave based measurement systemsElectric pulse generator detailsMOSFETHemt circuits

The invention relates to a gallium nitride HEMT tube integrated circuit, a flyback circuit, a bridgeless PFC circuit and a laser radar. The gallium nitride HEMT tube integrated circuit comprises a first gallium nitride HEMT tube packaged in a tube shell, a reverse follow current unit and a discharge unit; the input end of the reverse freewheeling unit is connected with the source electrode of thefirst gallium nitride HEMT tube, and the output end of the reverse freewheeling unit is connected with the drain electrode of the first gallium nitride HEMT tube and used for forming a reverse freewheeling loop with the first gallium nitride HEMT tube; and the input end of the discharge unit is connected with the drain electrode of the first gallium nitride HEMT tube, and the output end of the discharge unit is used for grounding and carrying out current discharge on the first gallium nitride HEMT tube. A reverse follow current unit is configured for a first gallium nitride HEMT tube of a maintube core; the gallium nitride HEMT tube integrated circuit is enabled to have good reverse follow current capability; and the discharge unit is configured to discharge current for the first galliumnitride HEMT, so that the avalanche tolerance is improved, the tolerance range of the first gallium nitride HEMT of the main tube core is expanded, MOSFETs can be replaced in more scenes, and the performance better than that of the MOSFETs is obtained.

Owner:INNOSCIENCE (ZHUHAI) TECH CO LTD

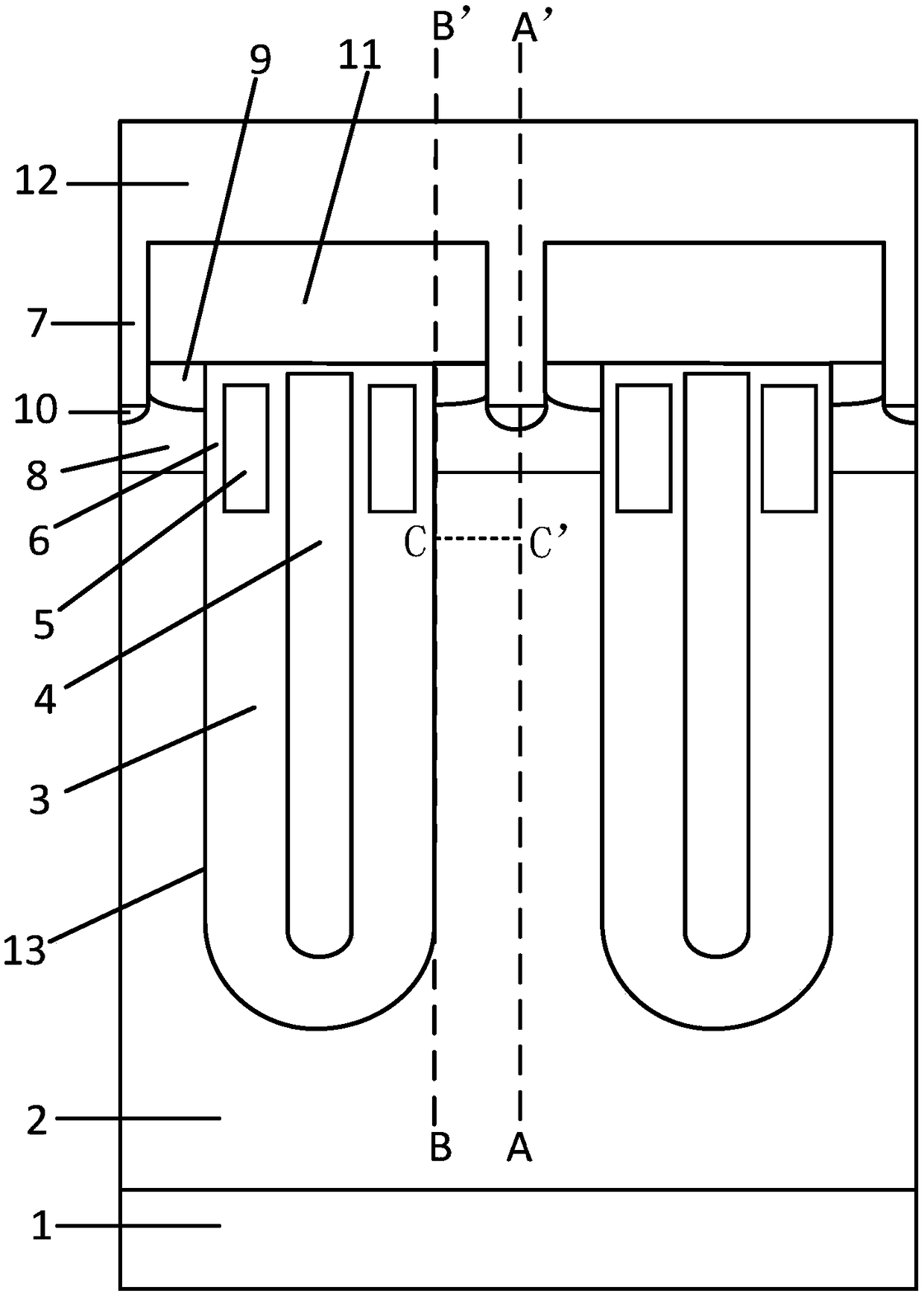

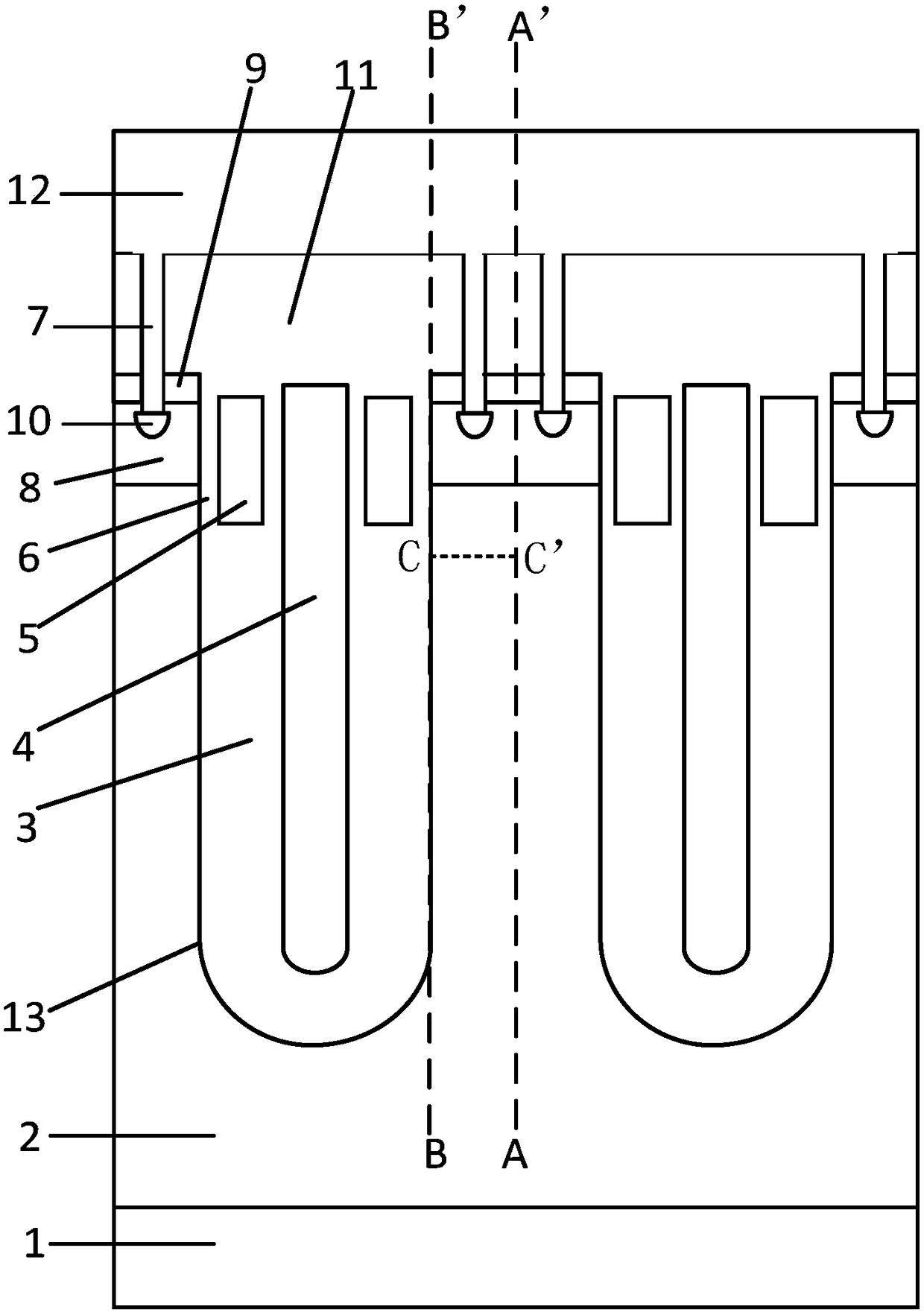

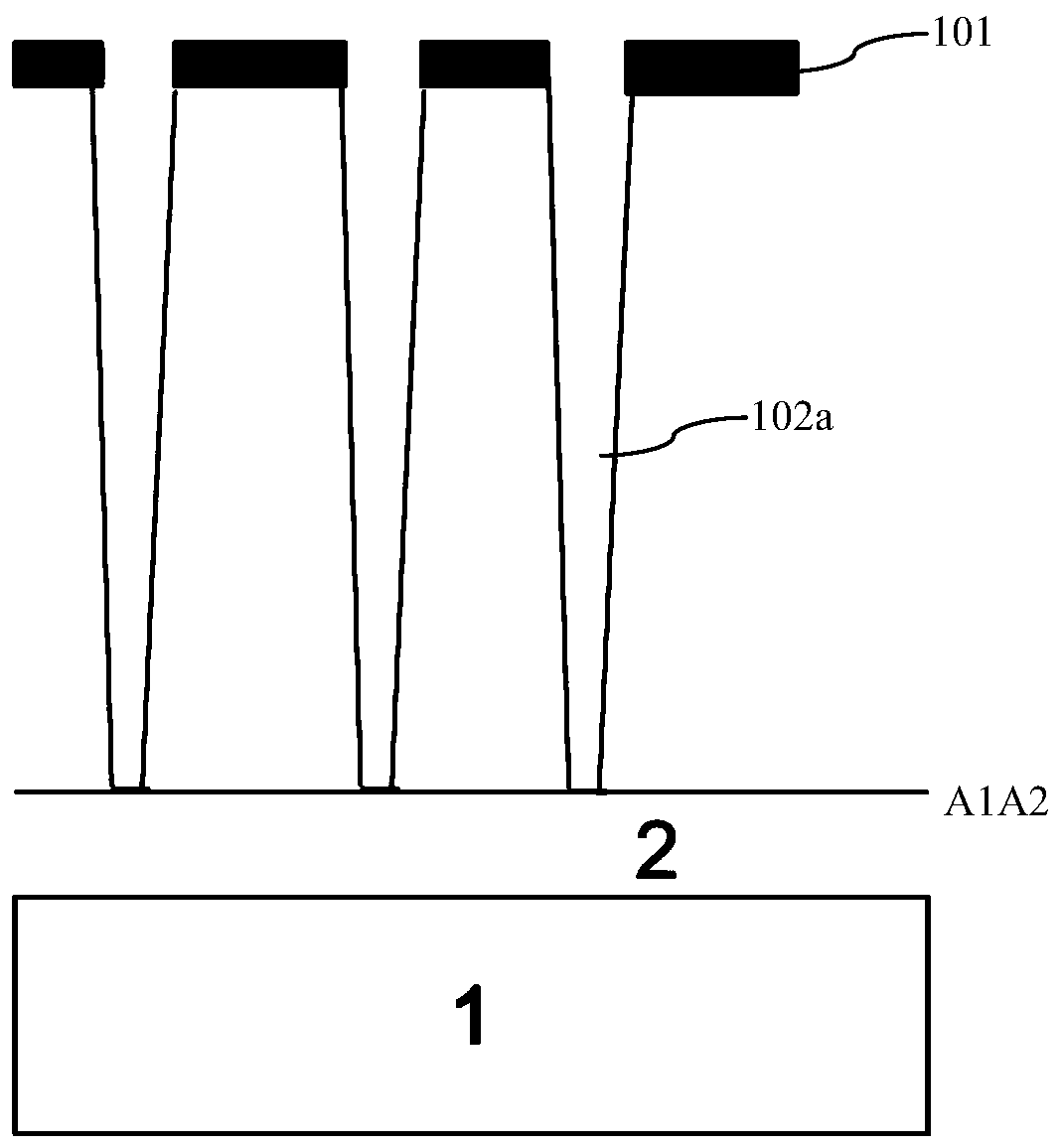

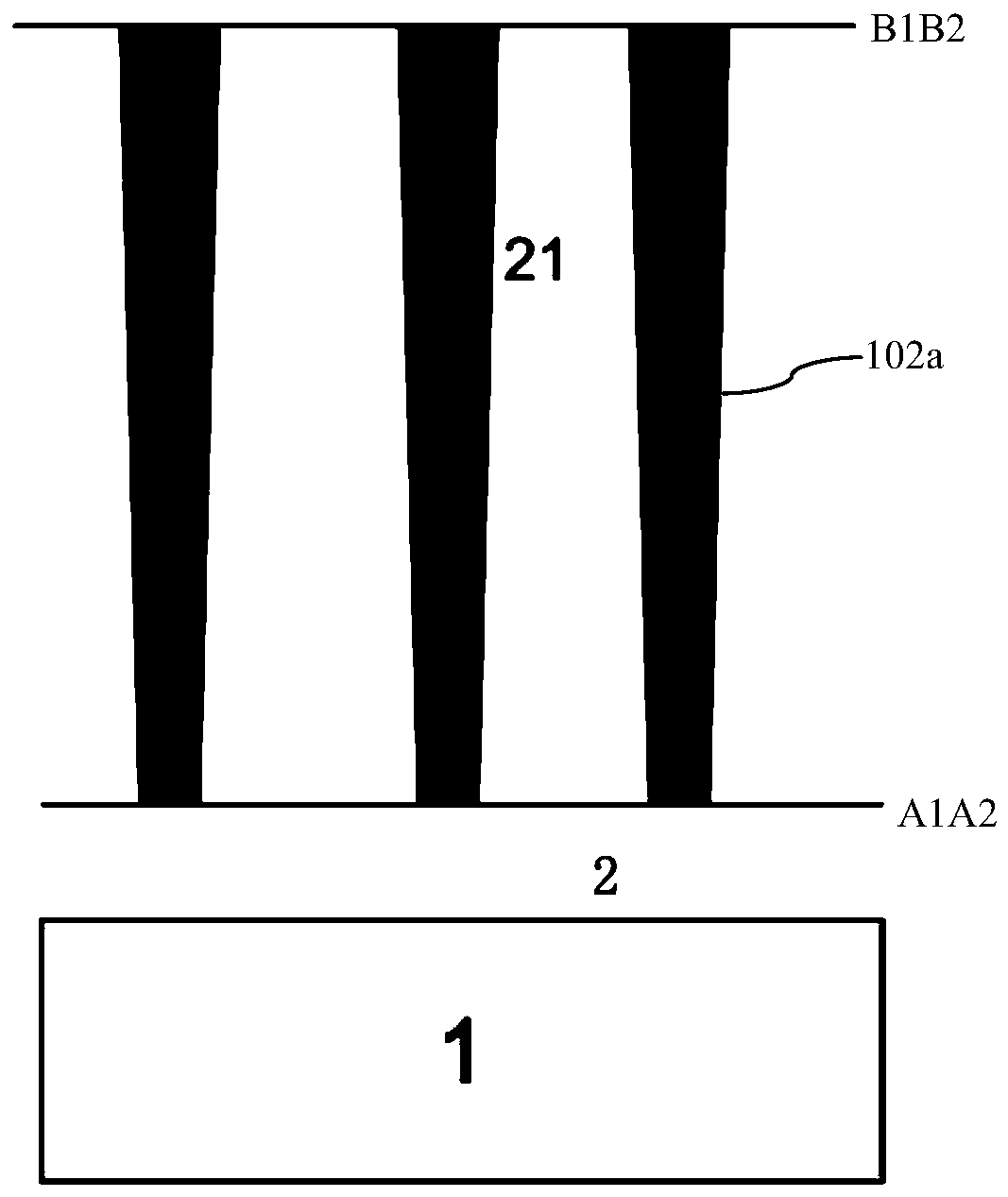

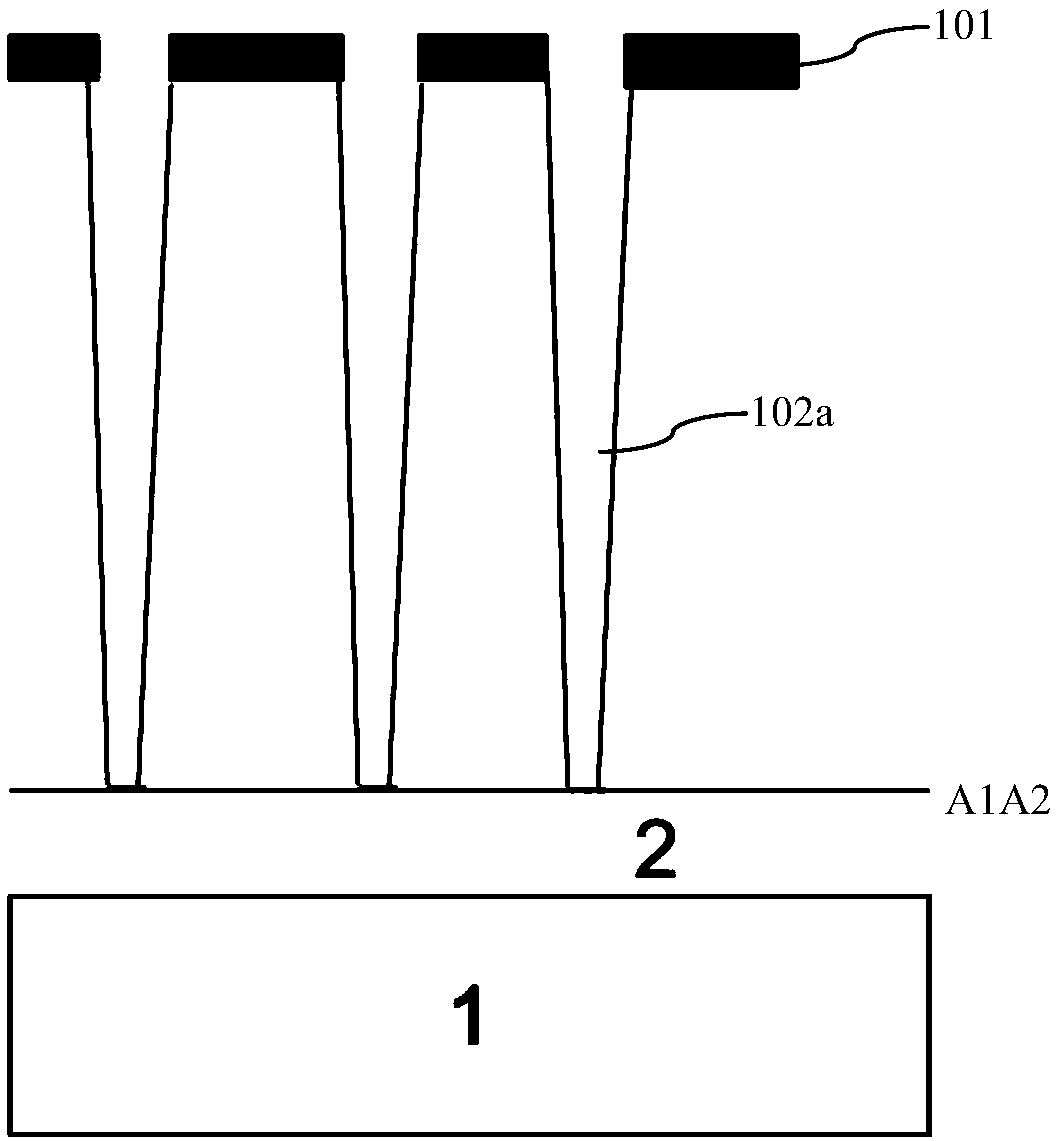

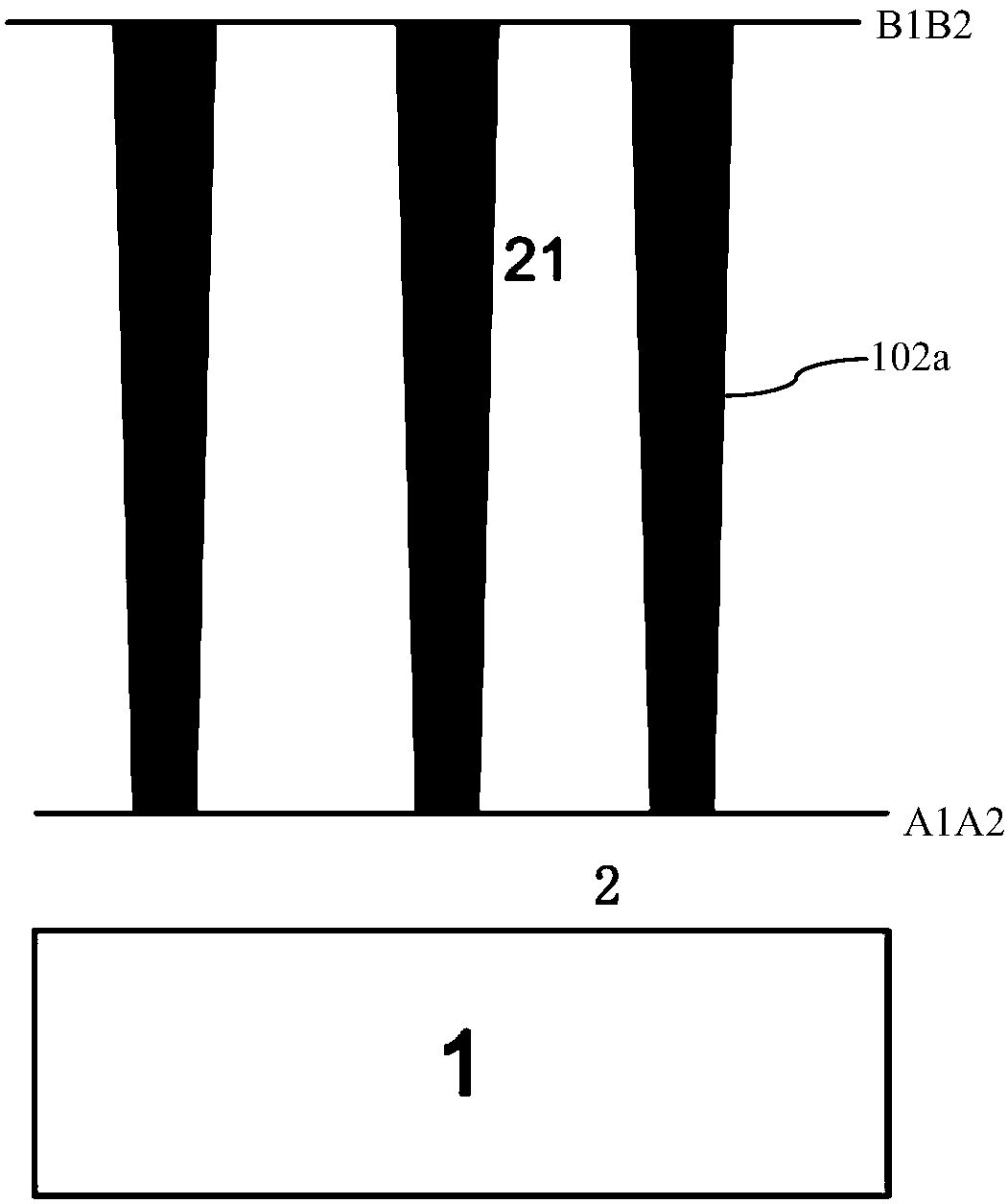

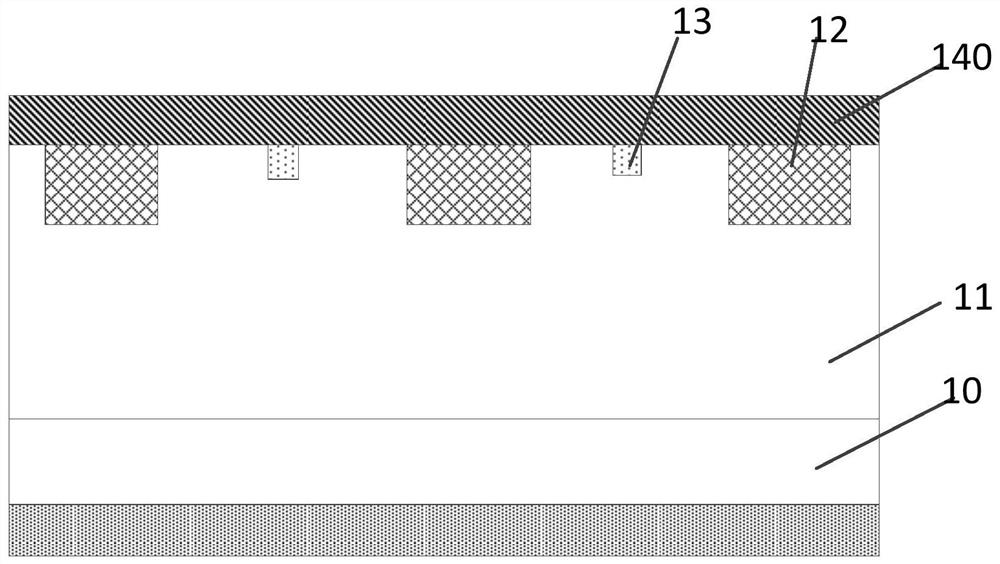

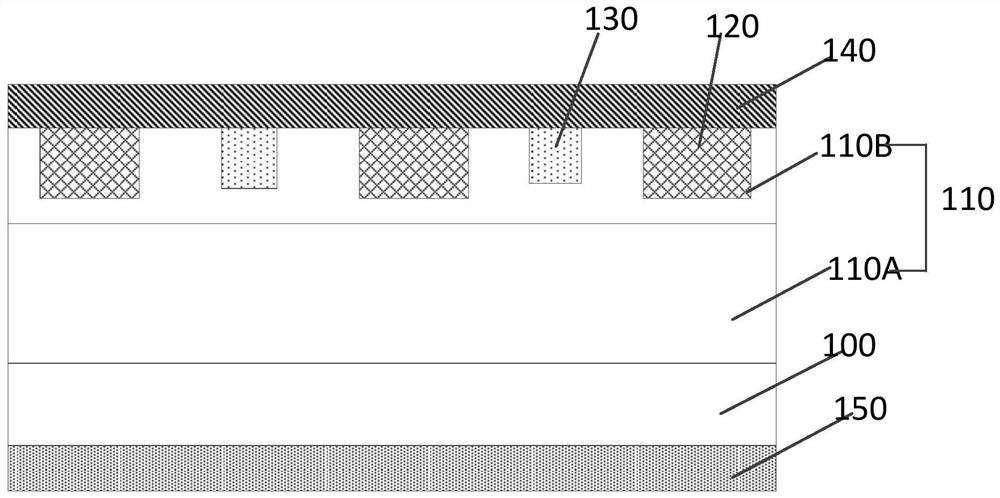

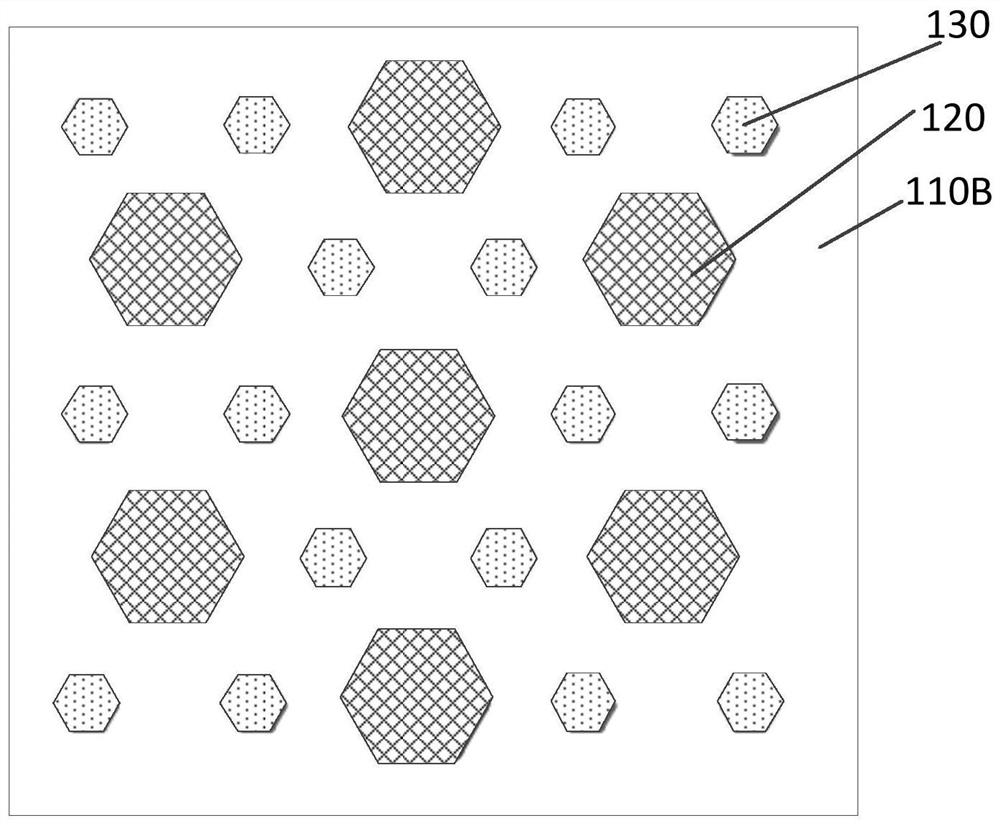

Trench field effect transistor structure and manufacturing method thereof

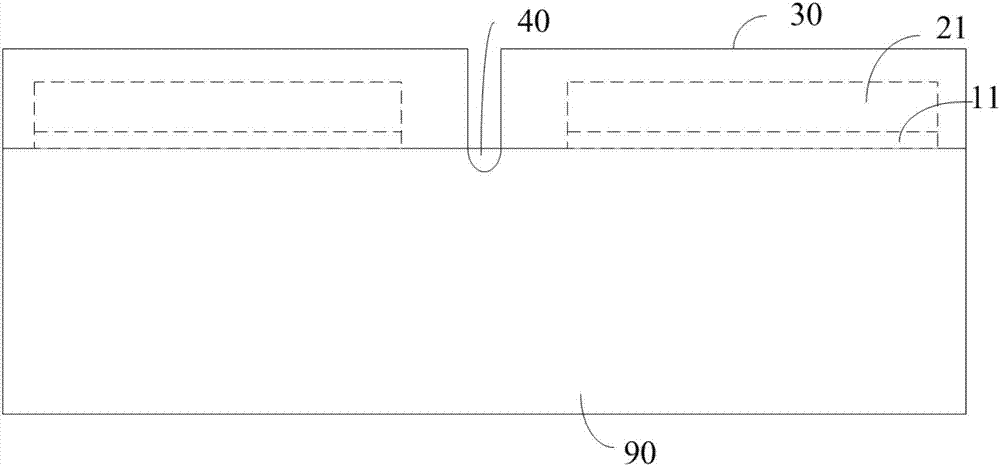

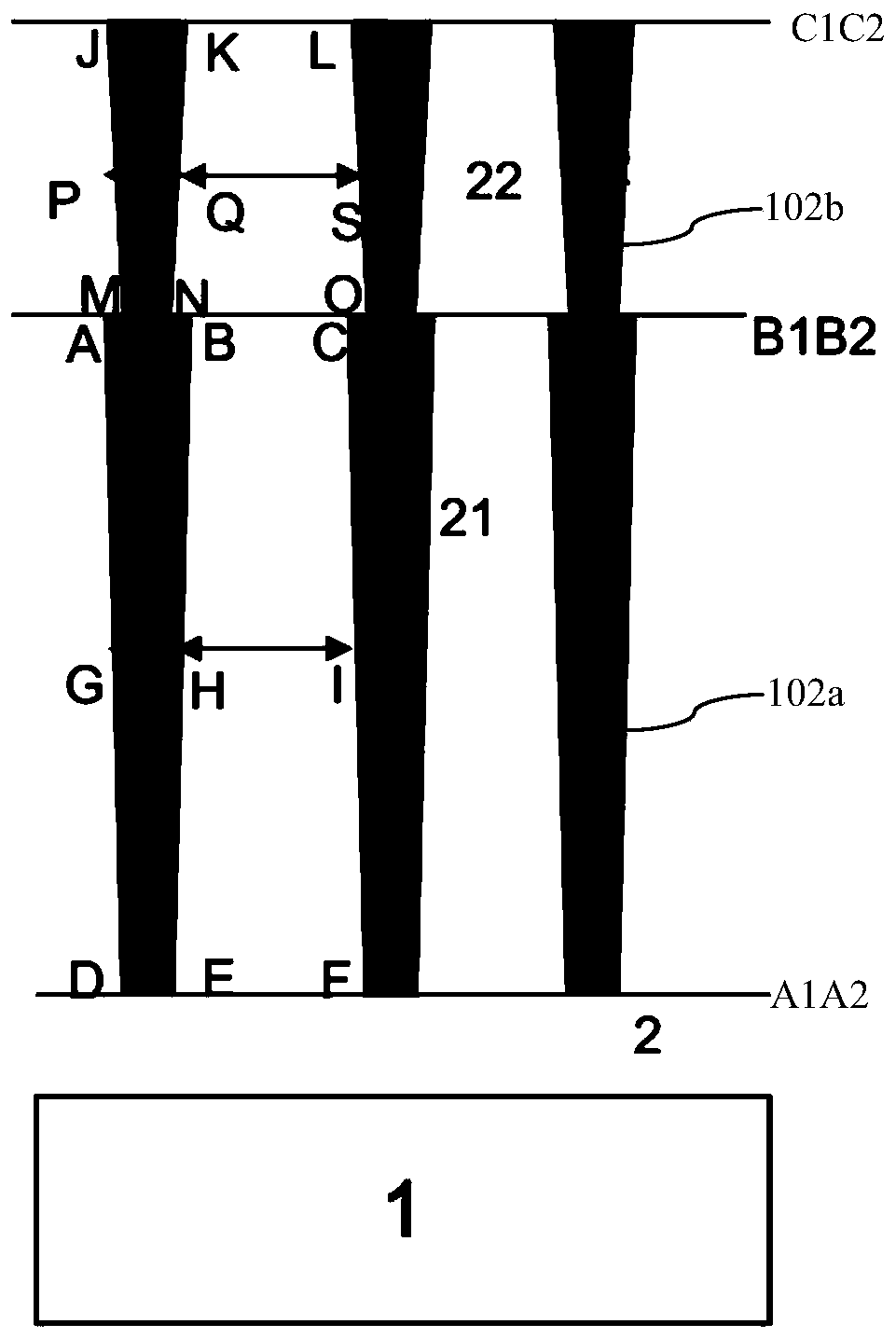

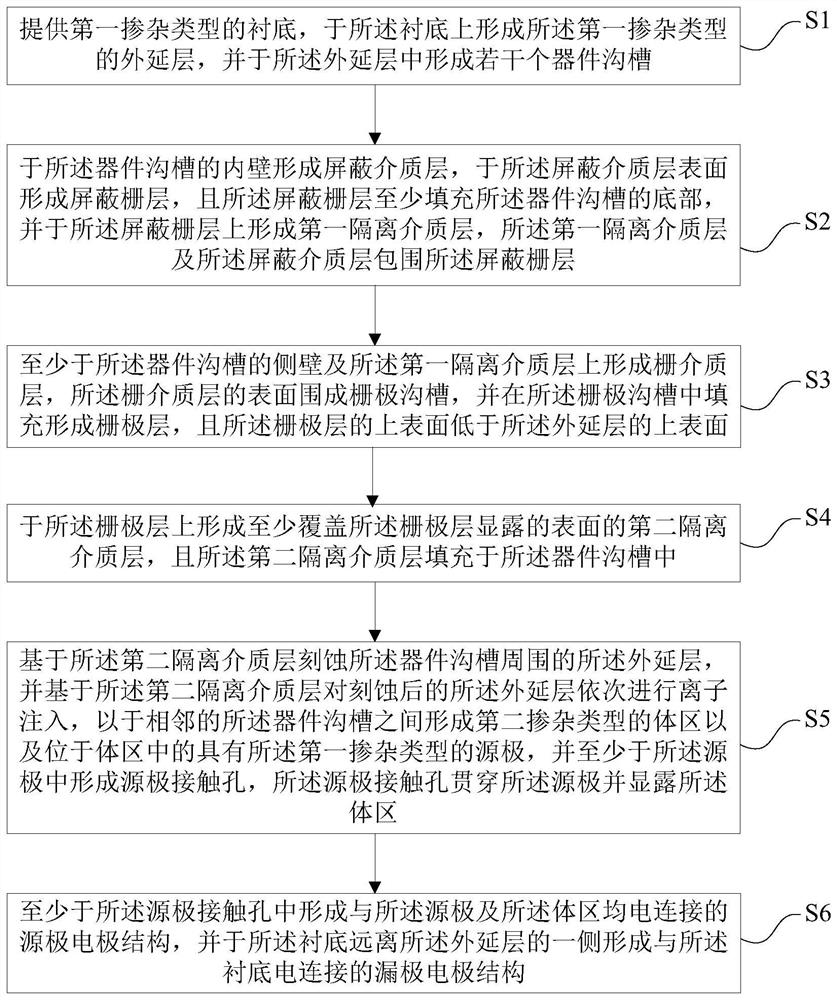

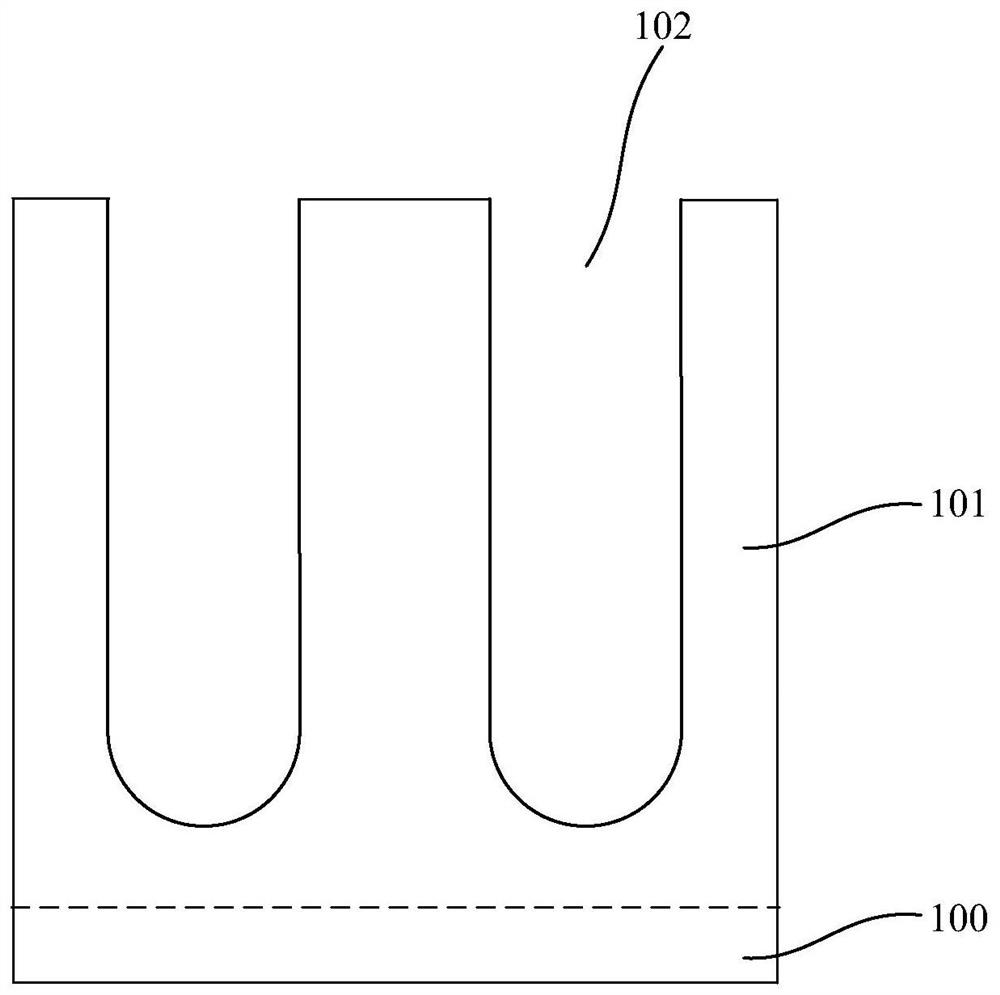

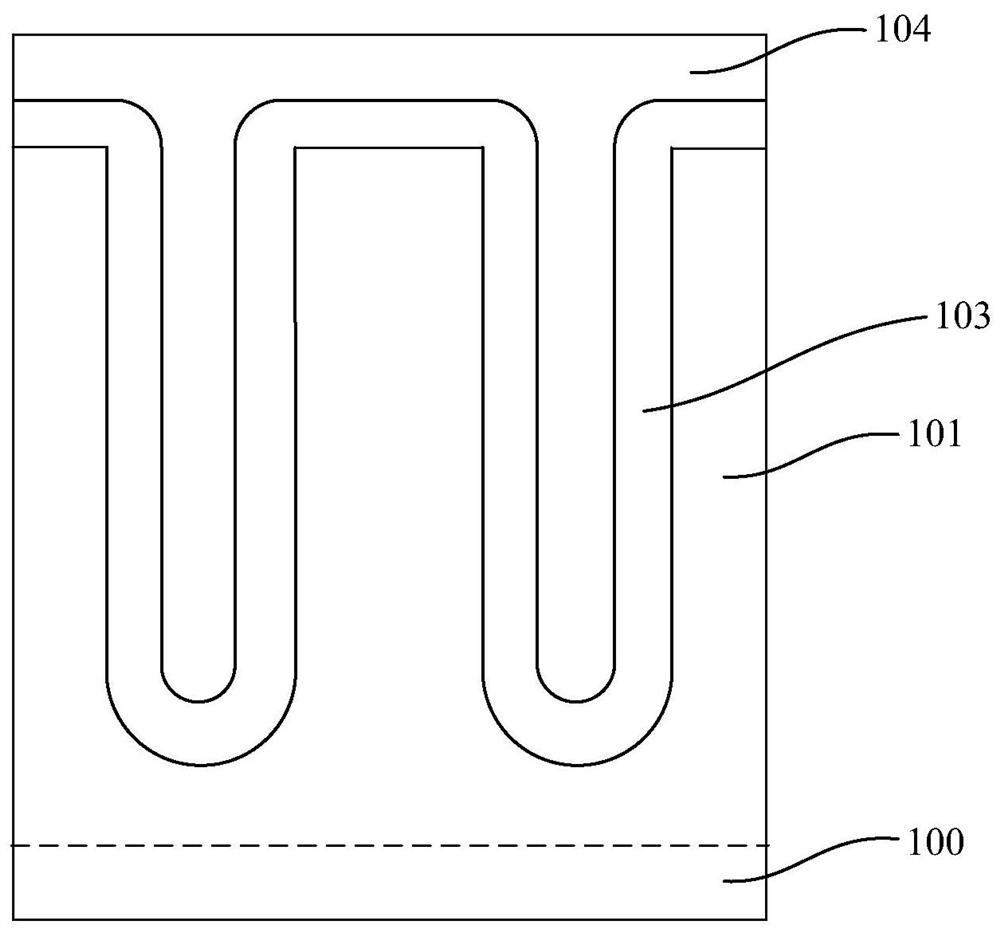

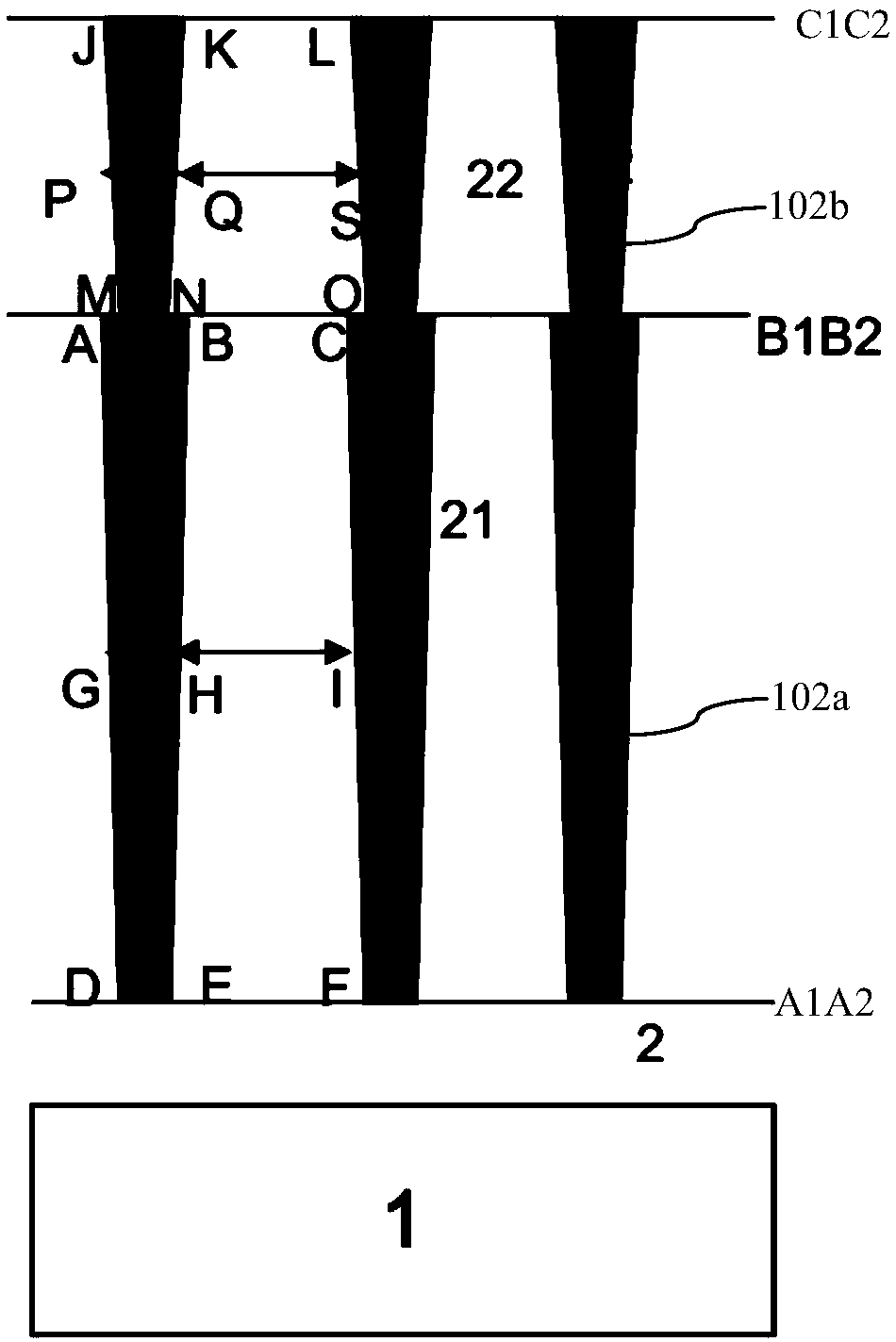

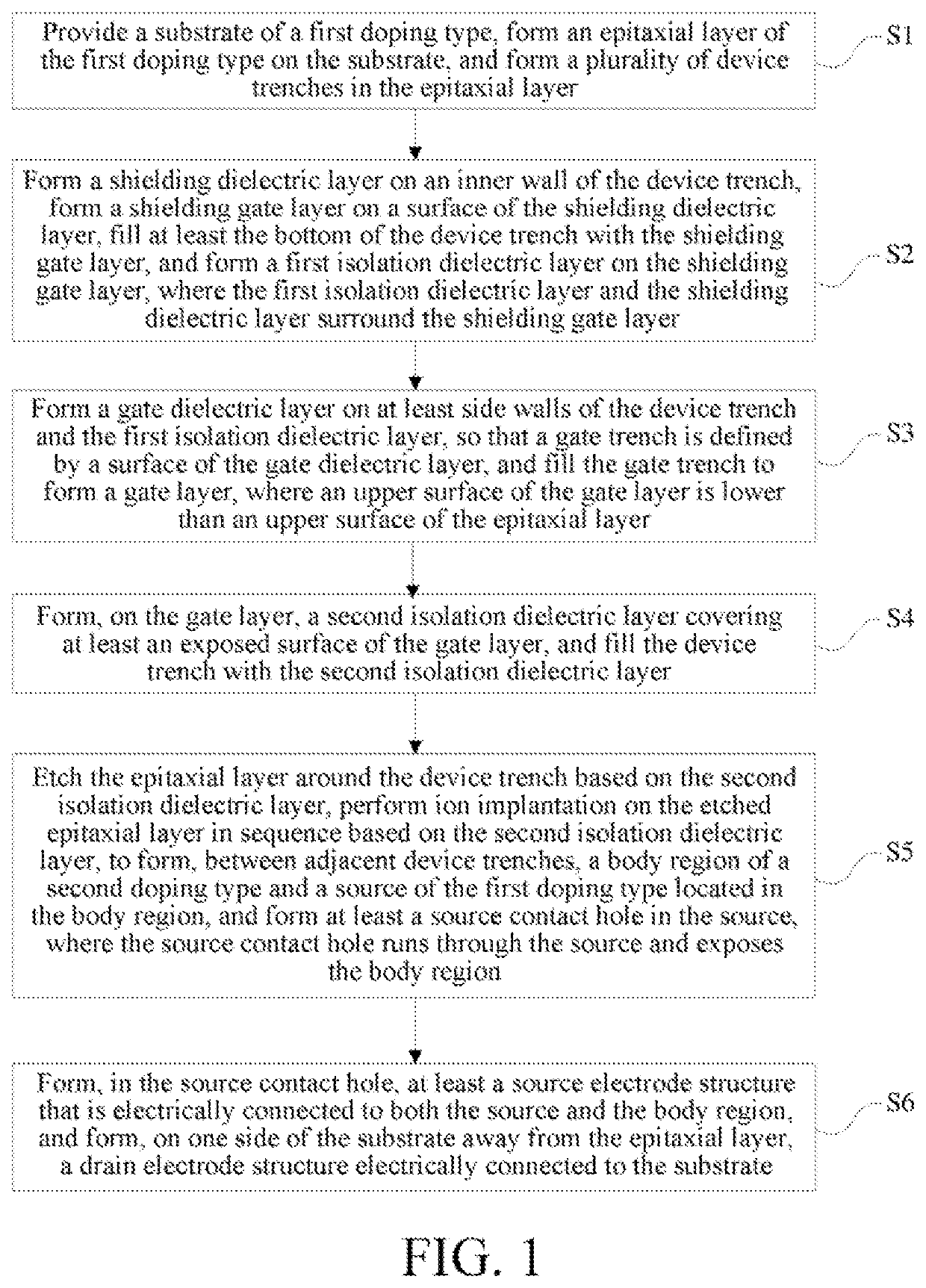

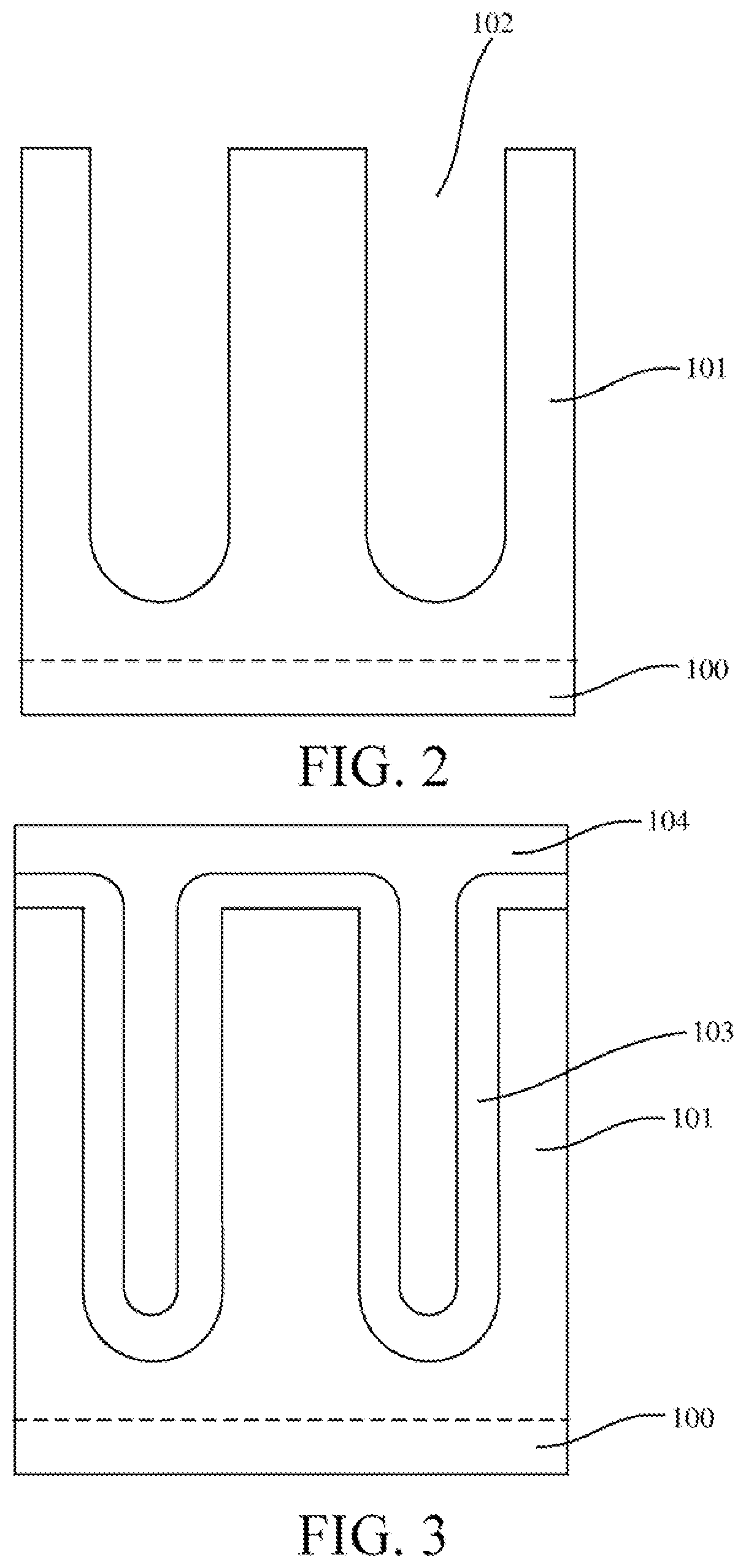

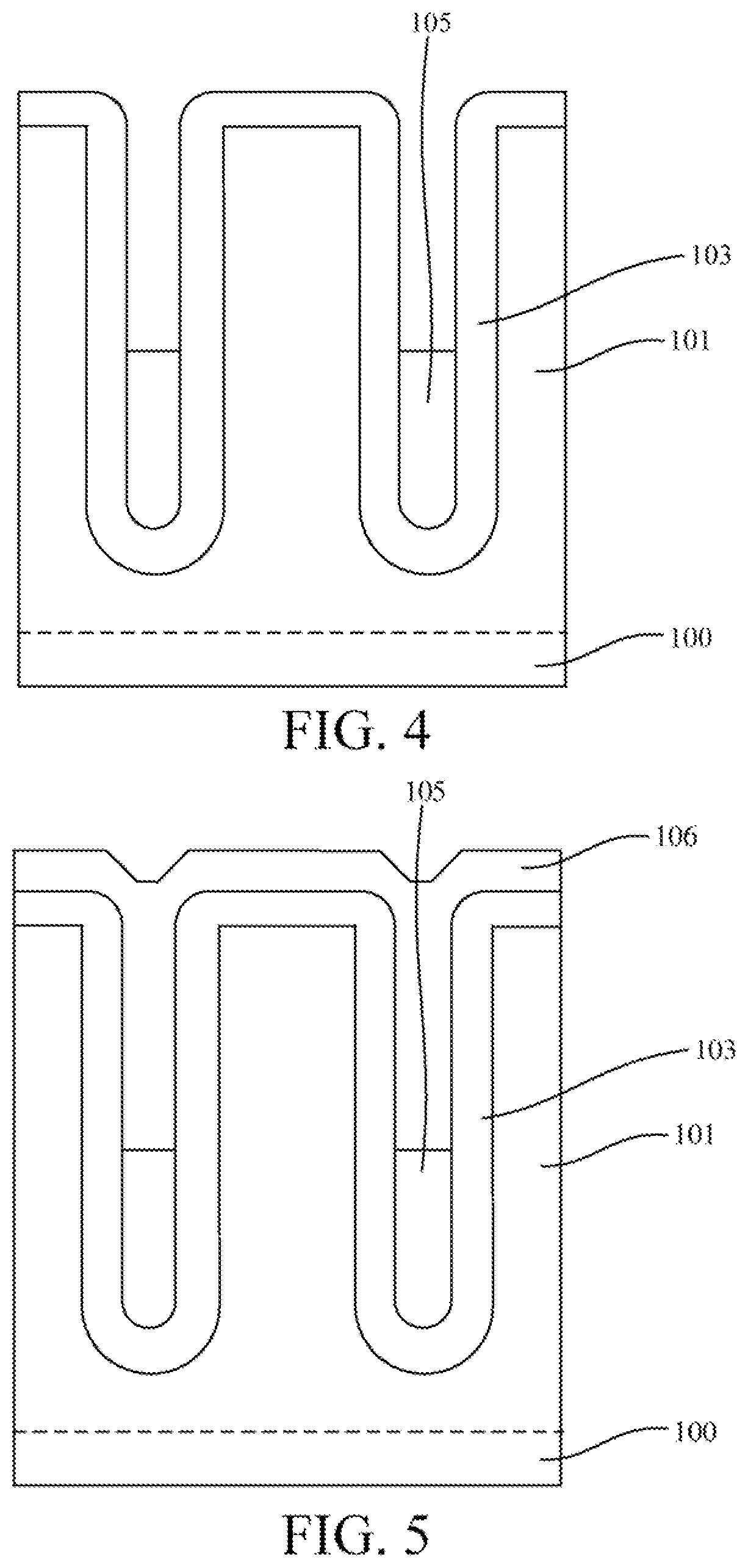

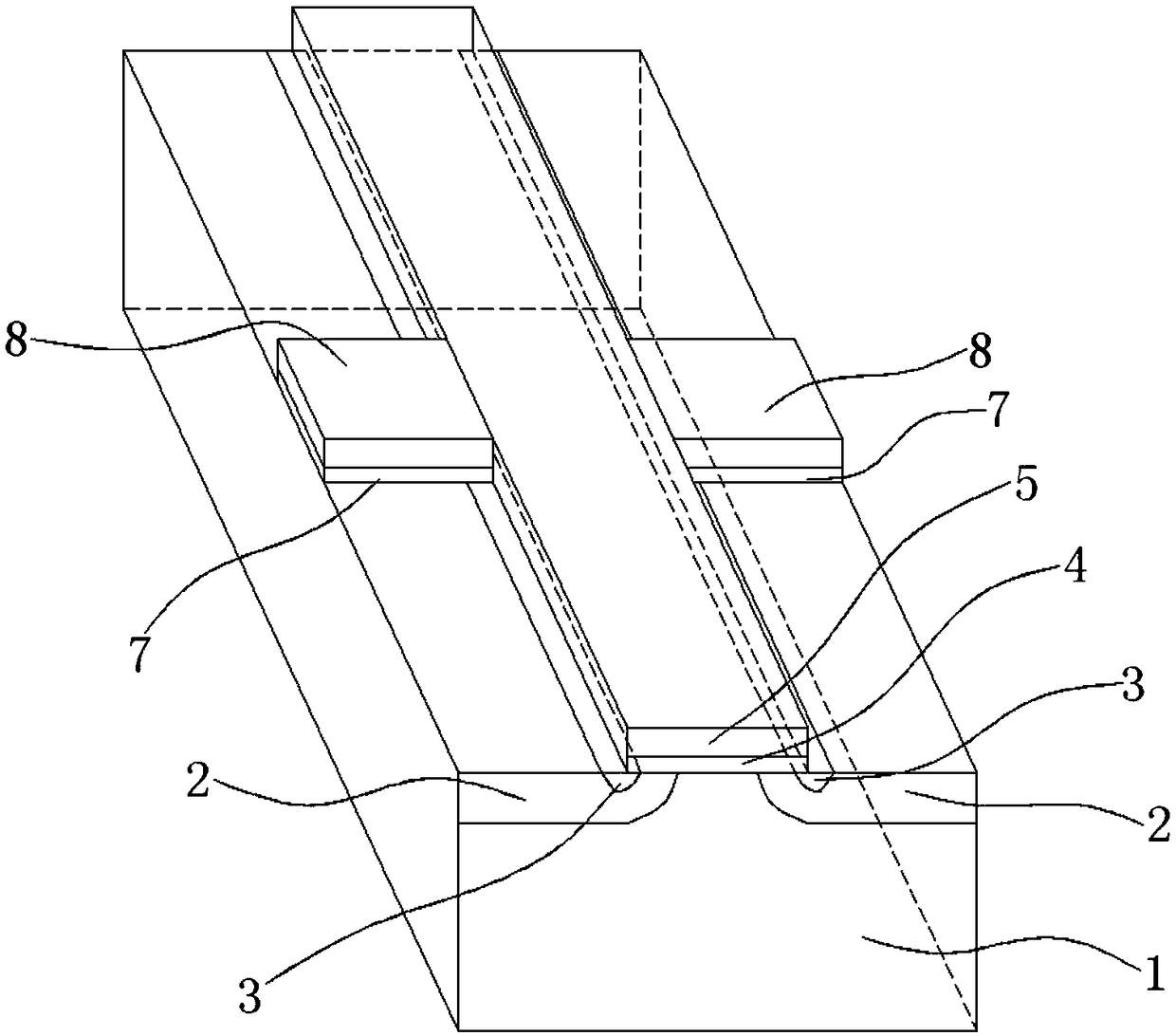

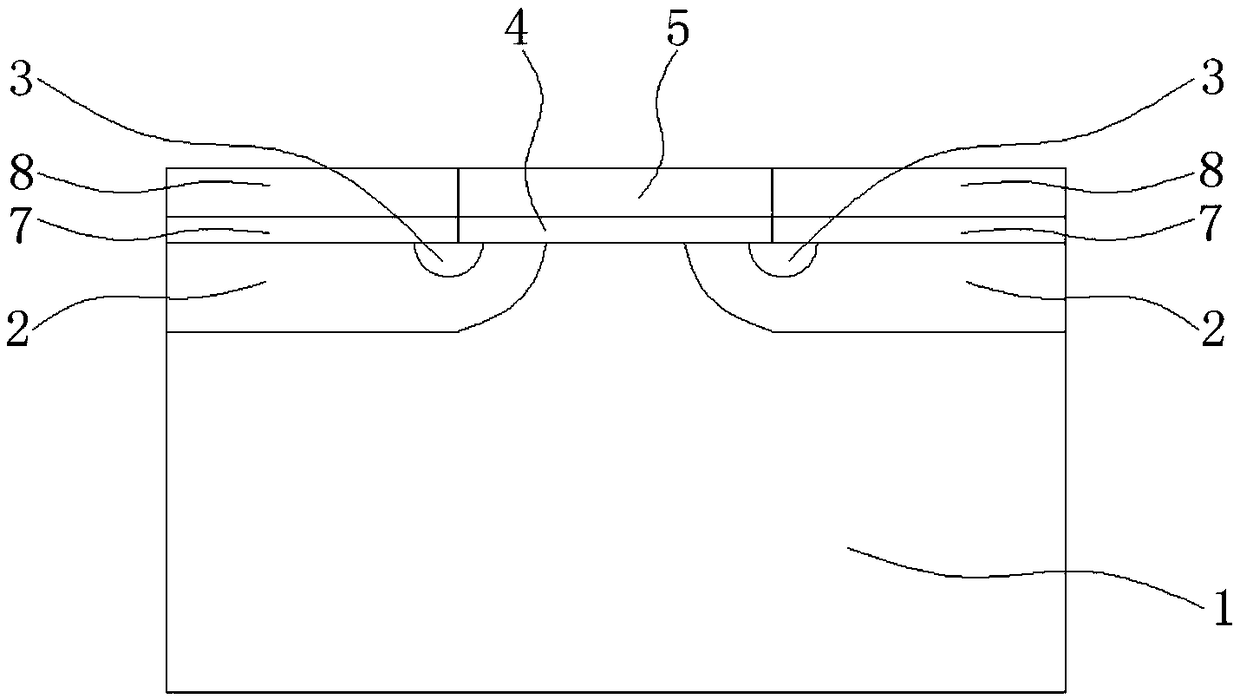

PendingUS20220328658A1Increased avalanche toleranceReduce the cell unit pitch of a deviceSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionEngineering

The present disclosure provides a trench field effect transistor structure and a manufacturing method thereof. The manufacturing method includes: providing a substrate (100), forming an epitaxial layer (101), forming a device trench (102) in the epitaxial layer, and forming a shielding dielectric layer (107), a shielding gate layer (105), a first isolation dielectric layer (108), a gate dielectric layer (109), a gate layer (110), a second isolation dielectric layer (112), a body region (114), a source (115), a source contact hole (118), a source electrode structure (122), and a drain electrode structure (123). During manufacturing of a trench field effect transistor structure, a self-alignment process is adopted in a manufacturing process, so that a cell pitch is not limited by an exposure capability and alignment accuracy of a lithography machine, to further reduce the cell pitch of the device, improve a cell density, and reduce a device channel resistance.

Owner:CHINA RESOURCES MICROELECTRONICS (CHONGQING) CO LTD

Cellular structure and power device

The invention discloses a cellular structure and a power device. A cell comprises an N-epitaxial layer and two P-traps symmetrically arranged on the upper side of the epitaxial layer at an interval, afirst N+ trap is arranged on the inner upper side of each P-trap, a first gate oxide layer covers each of the inner-end upper side of each P-trap, the inner upper side of each first N+ trap and the upper side of the N-epitaxial layer between the P-traps, a first polycrystalline strip is arranged on the upper side of each gate oxide layer, two second N+ traps are transversely arranged on the P-traps on two sides of the middle of the first polycrystalline strip at an interval, second gate oxide layers arranged on the inner upper sides of the two second N+ traps and the upper side of the P-trapbetween the two second N+ traps, and a second polycrystalline layer is arranged on the upper side of each second gate oxide layer. Through structural improvement, avalanche current orientation can beguided, so that avalanche tolerance is improved. After being improved by the scheme, the avalanche tolerance of the device can be improved by higher than 50% generally.

Owner:NANJING HRM SEMICON CO LTD

Schottky diode and preparation method thereof

PendingCN112909098AIncrease the areaLower channel resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryReverse bias

The invention discloses a Schottky diode and a preparation method thereof. The Schottky diode comprises a semiconductor substrate layer; a drift layer is located on the semiconductor substrate layer and comprises a first drift region and a second drift region, the second drift region is located on the side, opposite to the semiconductor substrate layer, of the first drift region, and the doping concentration of the second drift region is larger than that of the first drift region; an auxiliary doping layer is located in a part of the second drift region, and the conduction type of the auxiliary doping layer is opposite to that of the drift layer; a number of main doping layers are located in the drift layer and distributed around the auxiliary doping layer at intervals, and the conduction type of the main doping layers is the same as that of the auxiliary doping layer. The Schottky diode ensures that a conducting channel is completely pinched off when the reverse bias voltage is relatively small, and meanwhile, the Schottky diode can ensure that the Schottky diode has low on-resistance when the Schottky diode is in forward conduction.

Owner:GUANGHUA LINGANG ENG APPL & TECH R&D (SHANGHAI) CO LTD

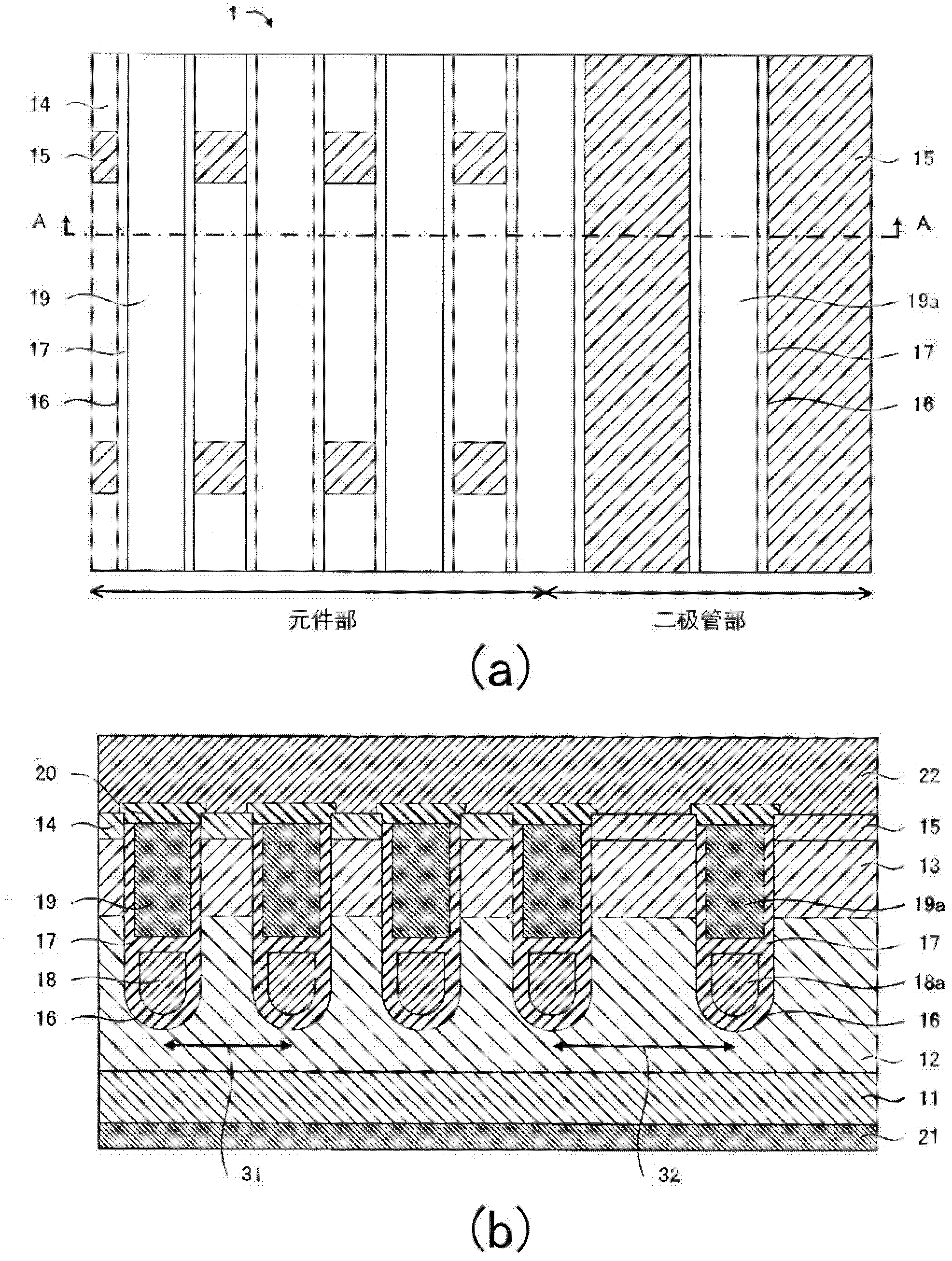

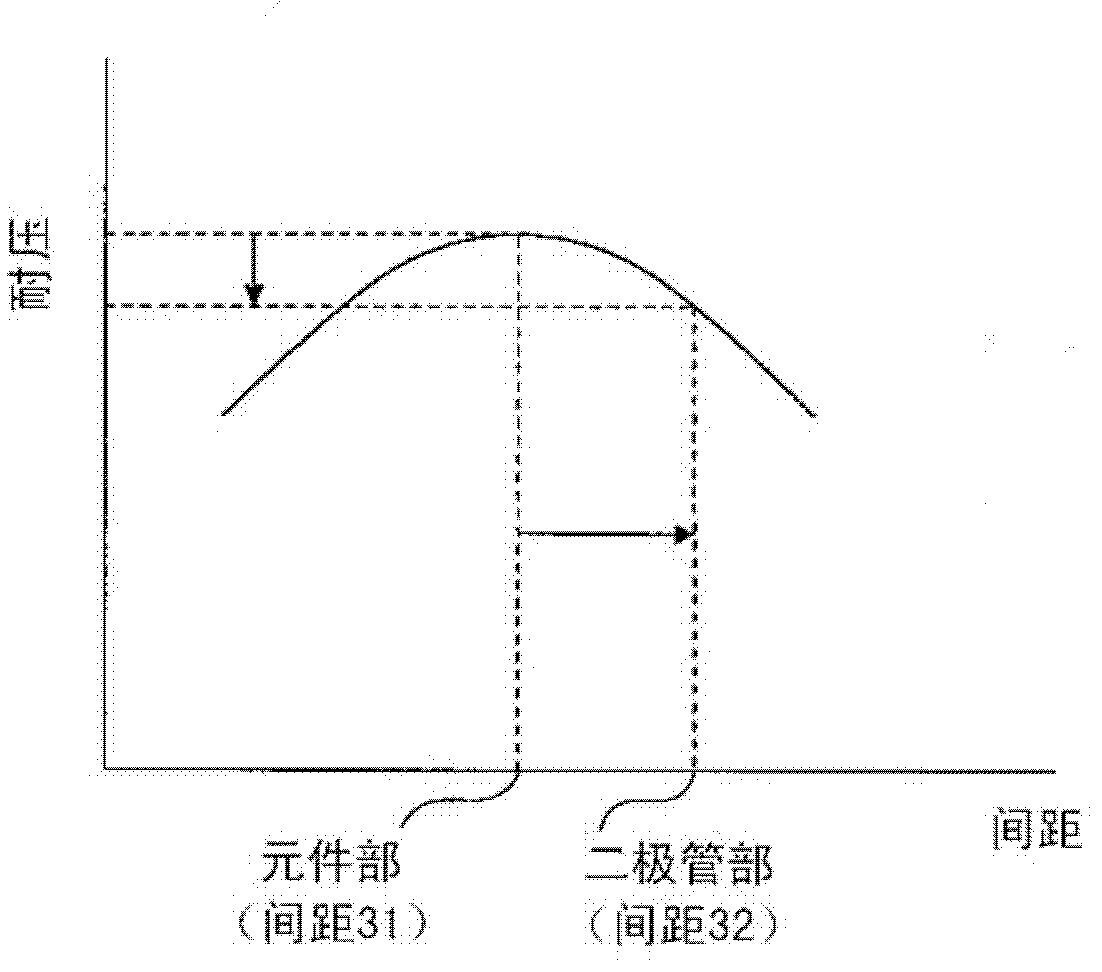

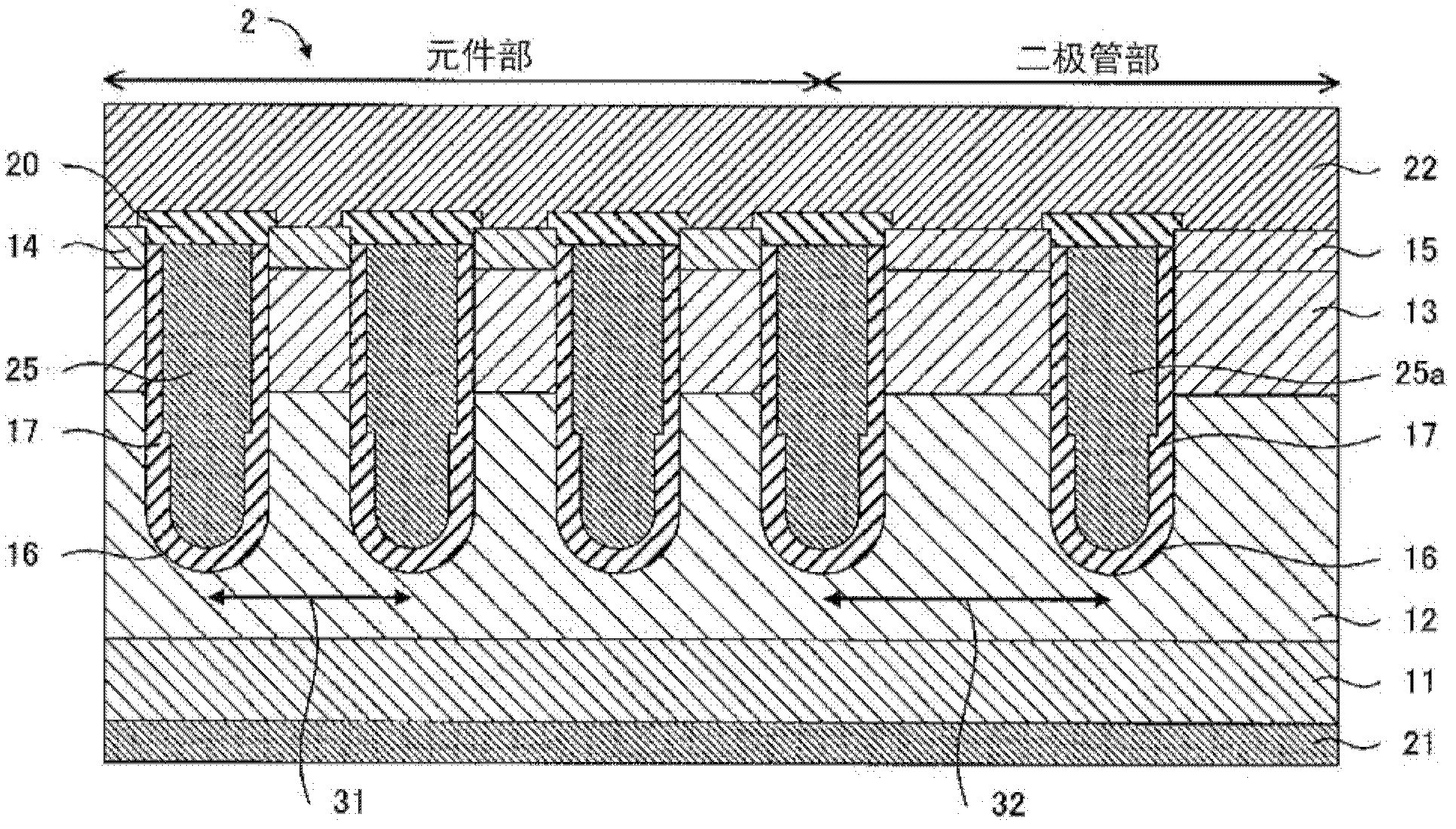

Power semiconductor device

InactiveCN102412262AIncreased avalanche toleranceInhibition steps increaseThyristorSolid-state devicesMOSFETPower semiconductor device

The invention provides a semiconductor device, which includes an element unit including a vertical-type MOSFET and a diode unit adjacent to the element unit. The vertical-type MOSFET includes a first semiconductor layer of a first conductivity type, a second semiconductor layer of a first conductivity type, a third semiconductor layer of a second conductivity type, a fourth semiconductor layer of a first conductivity type, a fifth semiconductor layer of a second conductivity type; an insulator covering inner surfaces of a plurality of trenches penetrating from the surface of the fourth semiconductor layer or the fifth semiconductor layer to the second semiconductor layer through the third semiconductor layer, the adjacent trenches being provided with a first interval in between; a first embedded conducting layer, a second embedded conducting layer, a layer insulation film, a first main electrode and a second main electrode. The diode unit includes a first semiconductor layer, a second semiconductor layer, a third semiconductor layer, a fifth semiconductor layer, an insulator, a first embedded conducting layer, a second embedded conducting layer, a layer insulation film, a first main electrode and a second main electrode, the adjacent trenches being provided with a second interval in between.

Owner:KK TOSHIBA