Patents

Literature

130results about How to "Reduce doping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

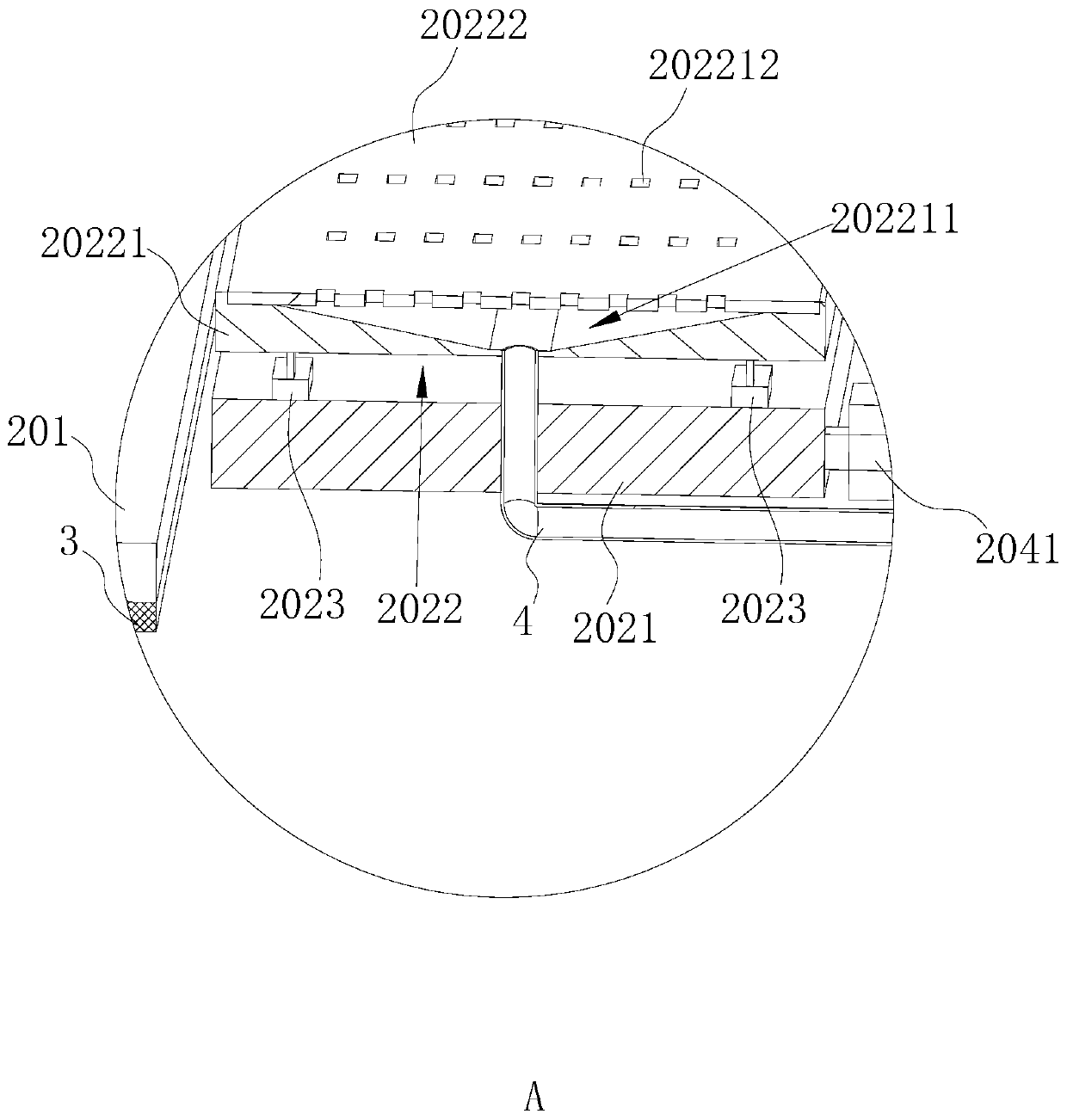

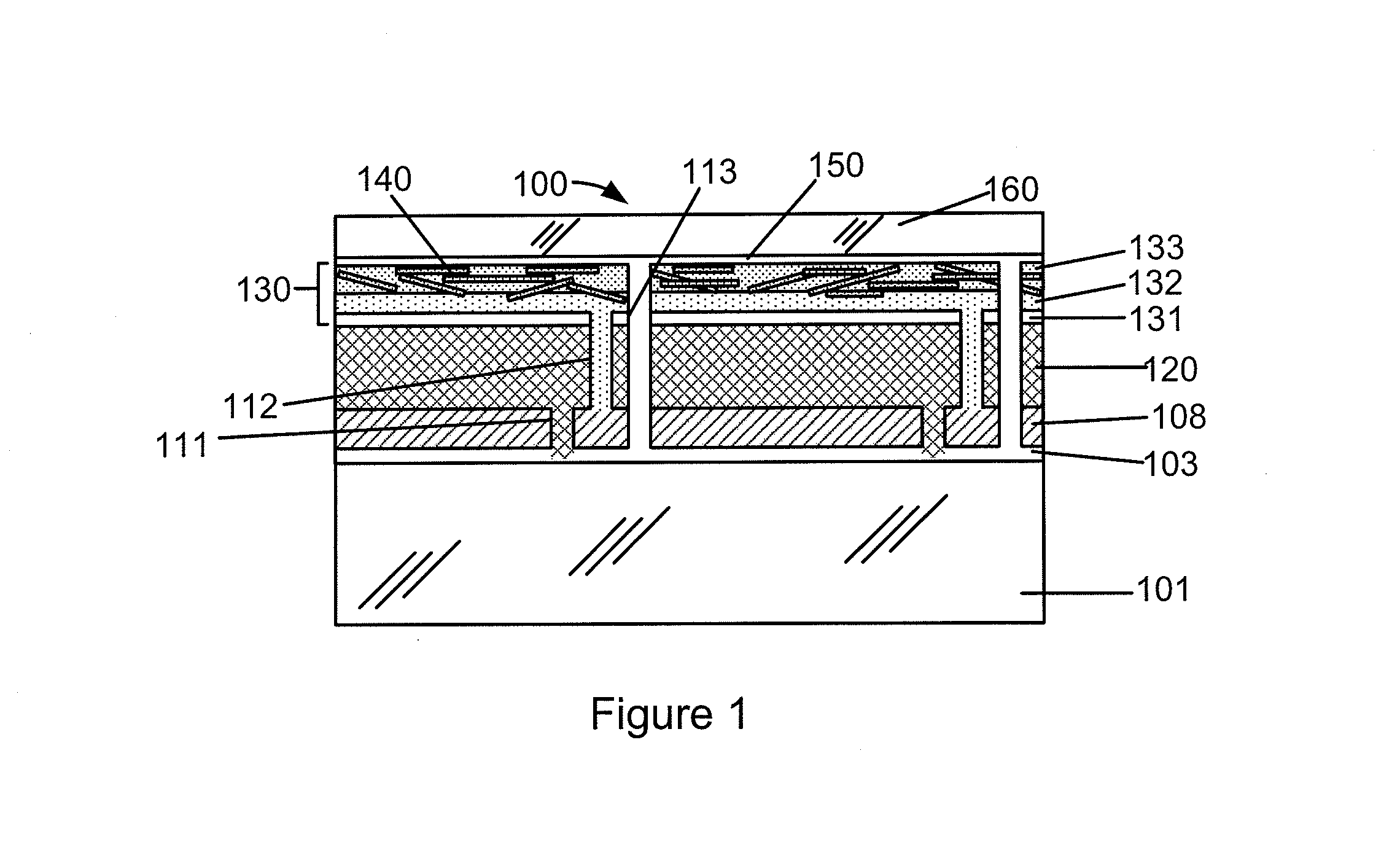

Double gate insulated gate bipolar transistor

InactiveUS20090008674A1Reduce the number of holesReduce transportationTransistorSolid-state devicesParasitic bipolar transistorEngineering

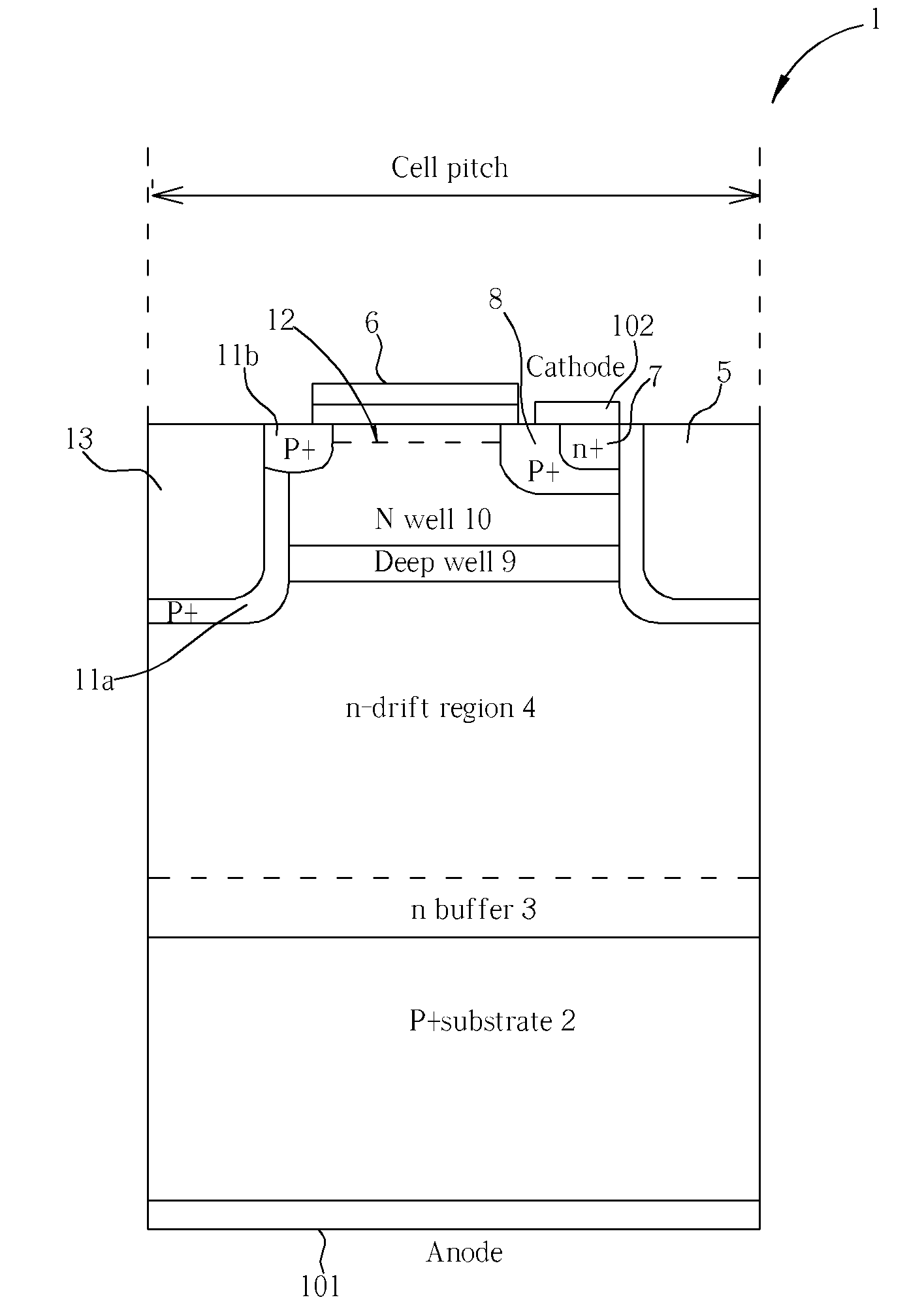

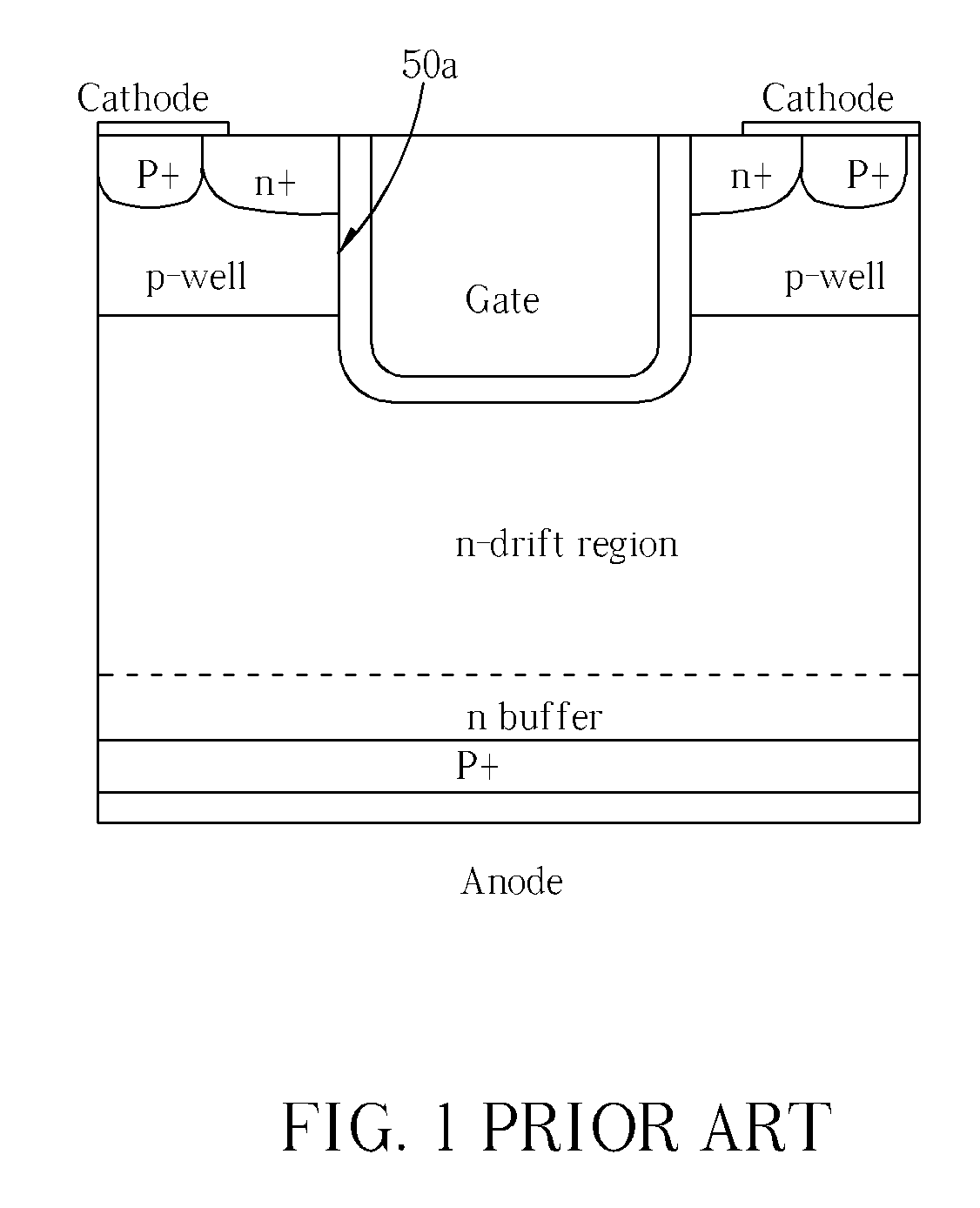

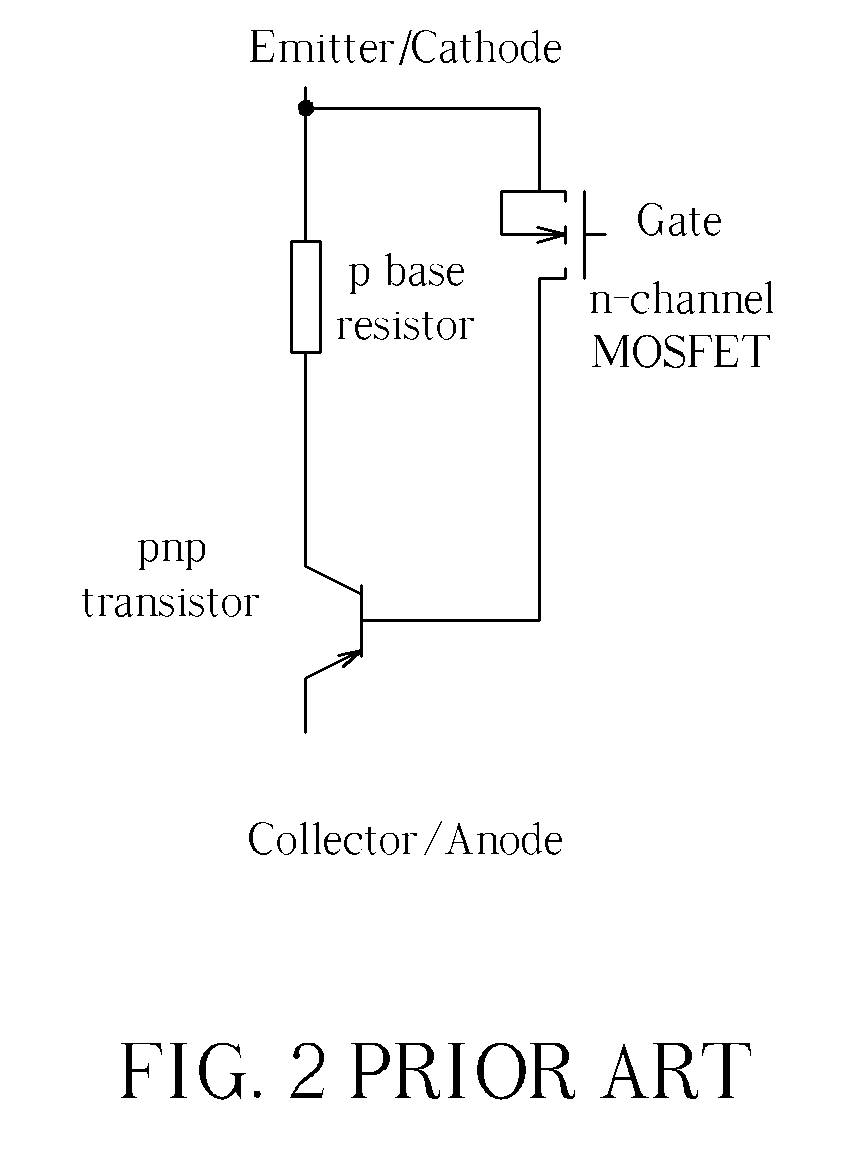

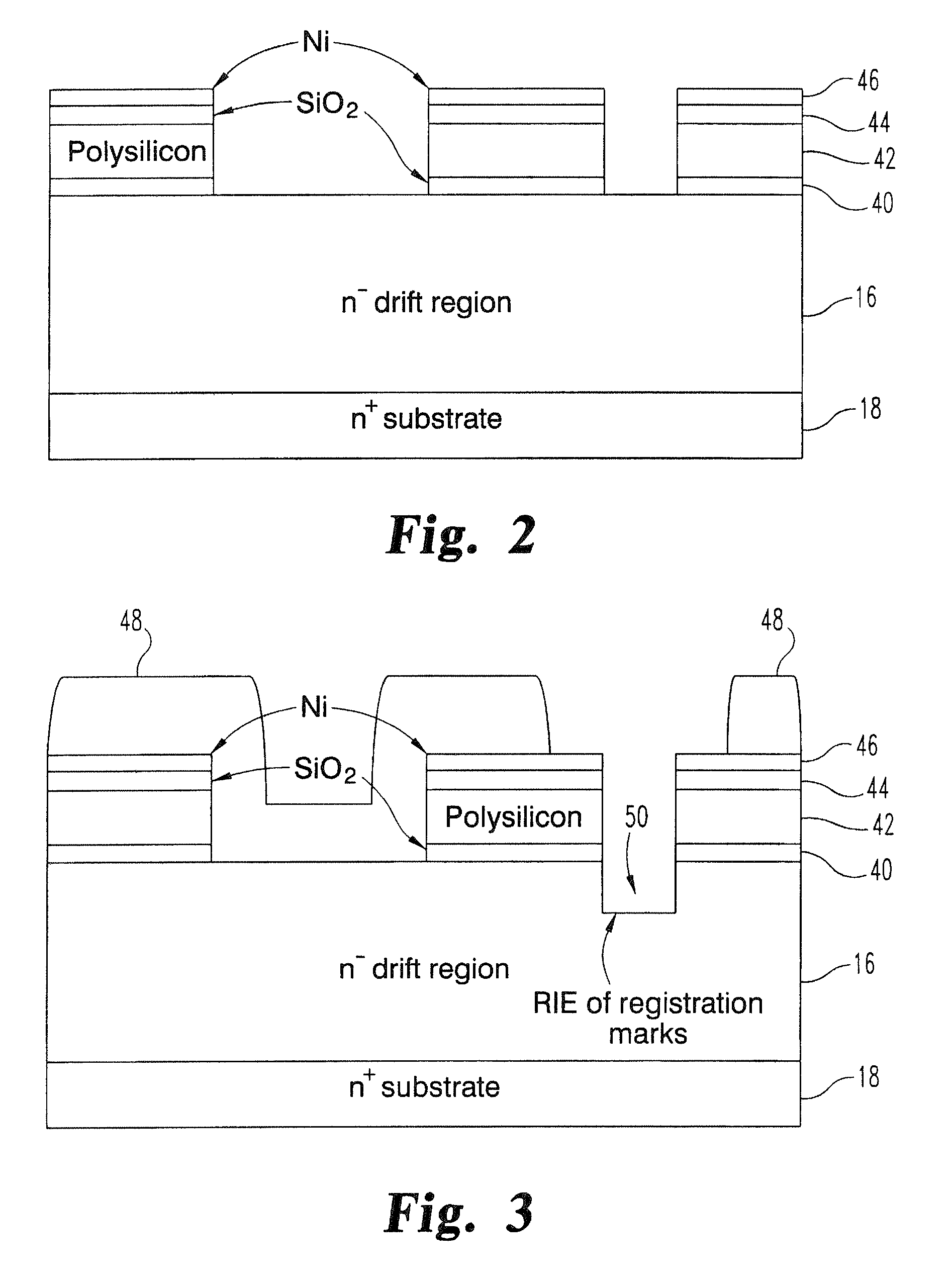

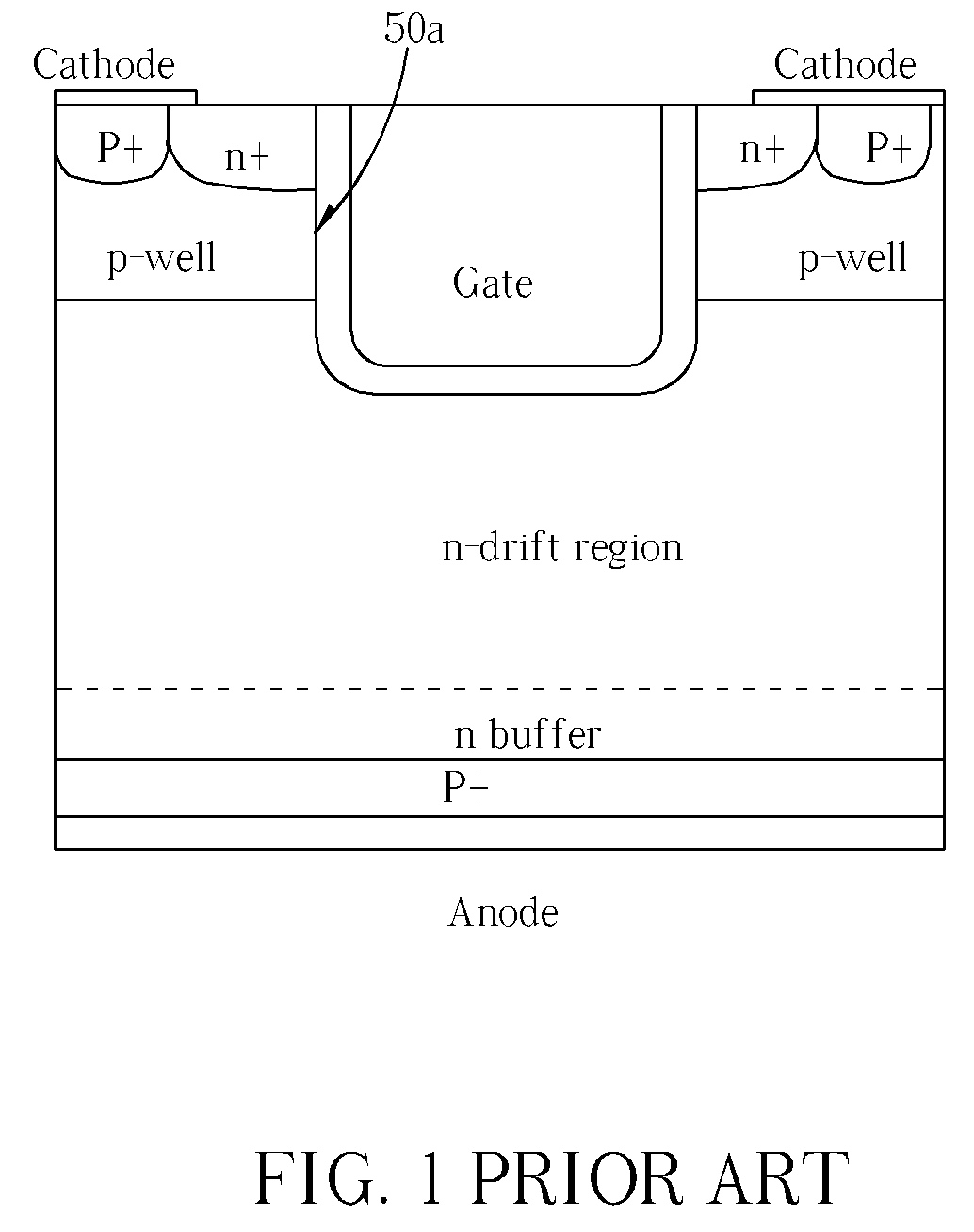

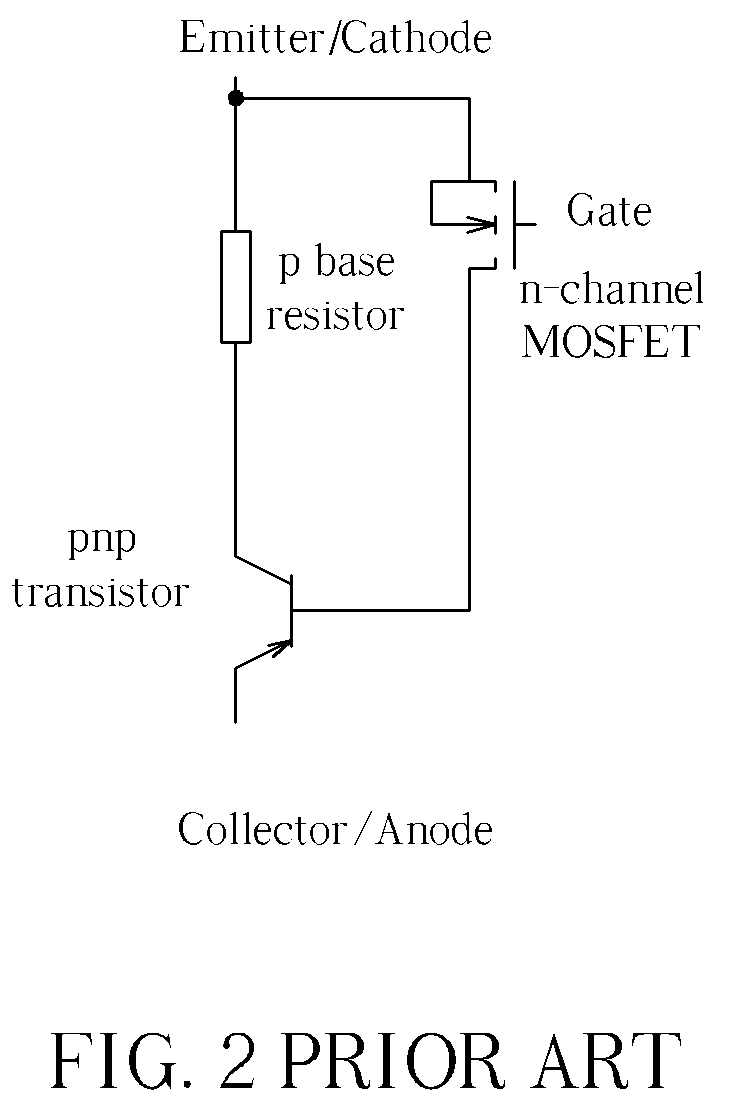

Double gate IGBT having both gates referred to a cathode in which a second gate is for controlling flow of hole current. In on-state, hole current can be largely suppressed. While during switching, hole current is allowed to flow through a second channel. Incorporating a depletion-mode p-channel MOSFET having a pre-formed hole channel that is turned ON when 0V or positive voltages below a specified threshold voltage are applied between second gate and cathode, negative voltages to the gate of p-channel are not used. Providing active control of holes amount that is collected in on-state by lowering base transport factor through increasing doping and width of n well or by reducing injection efficiency through decreasing doping of deep p well. Device includes at least anode, cathode, semiconductor substrate, n− drift region, first & second gates, n+ cathode region; p+ cathode short, deep p well, n well, and pre-formed hole channel.

Owner:ANPEC ELECTRONICS CORPORATION

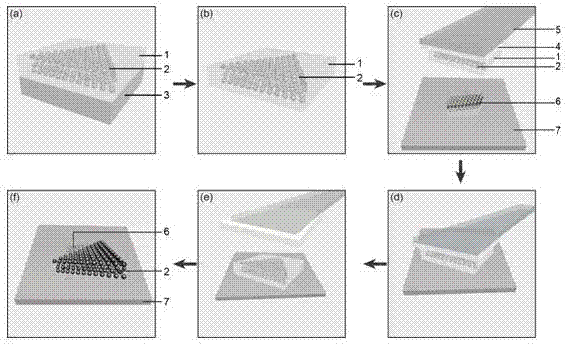

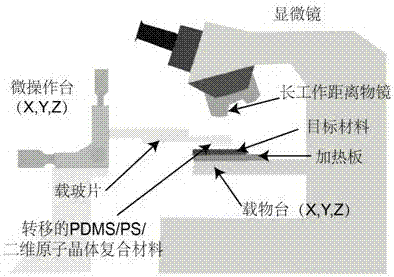

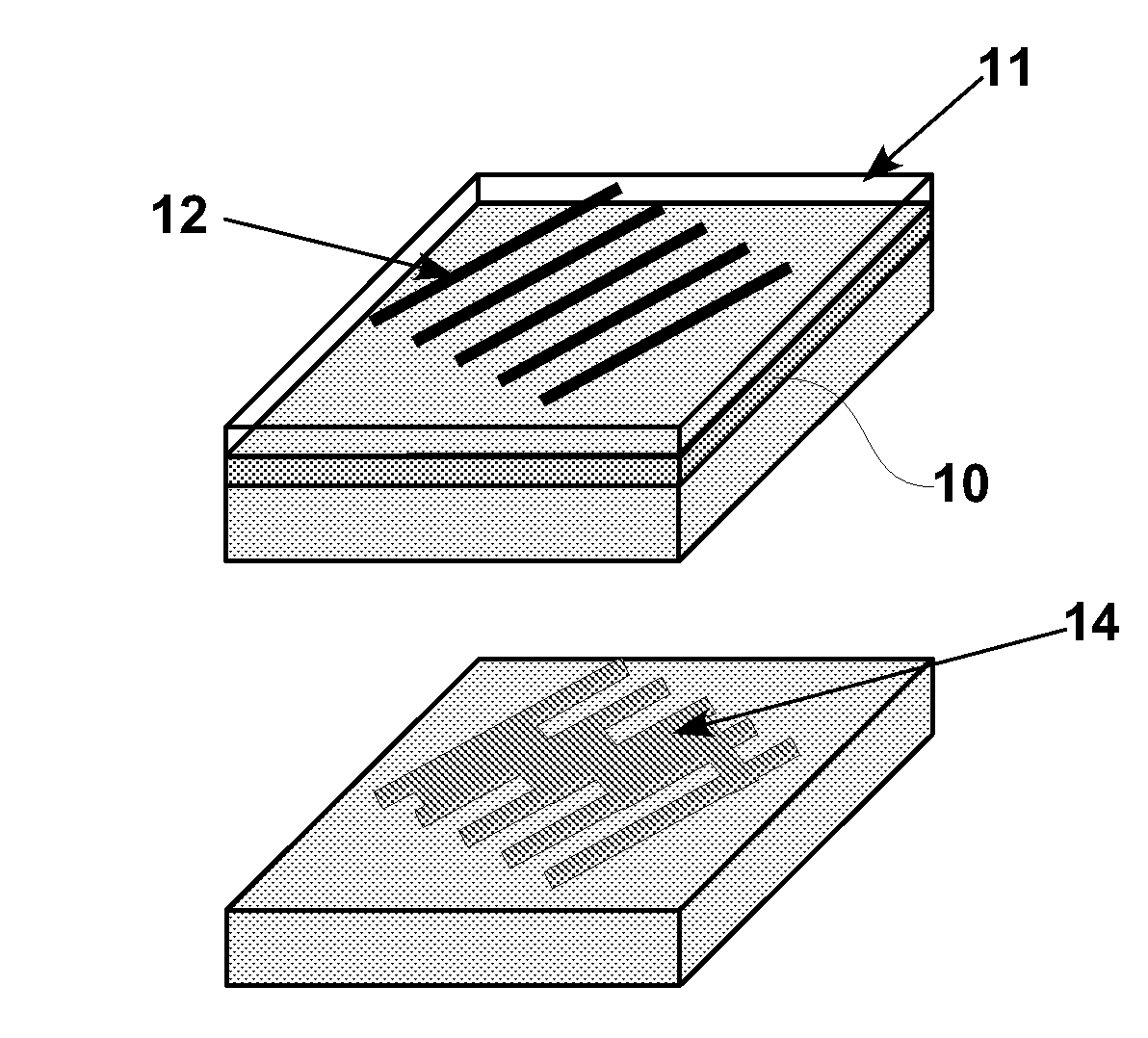

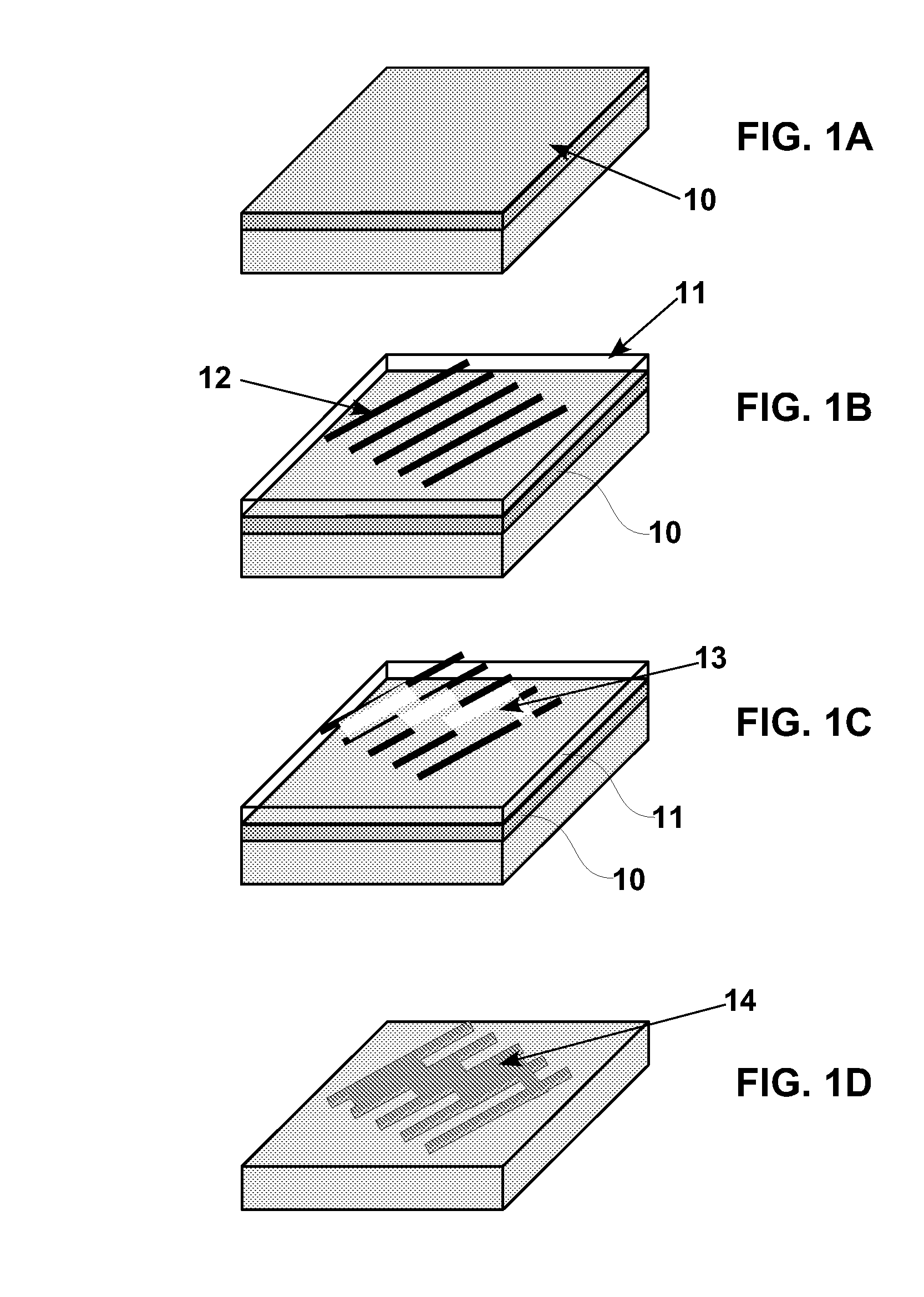

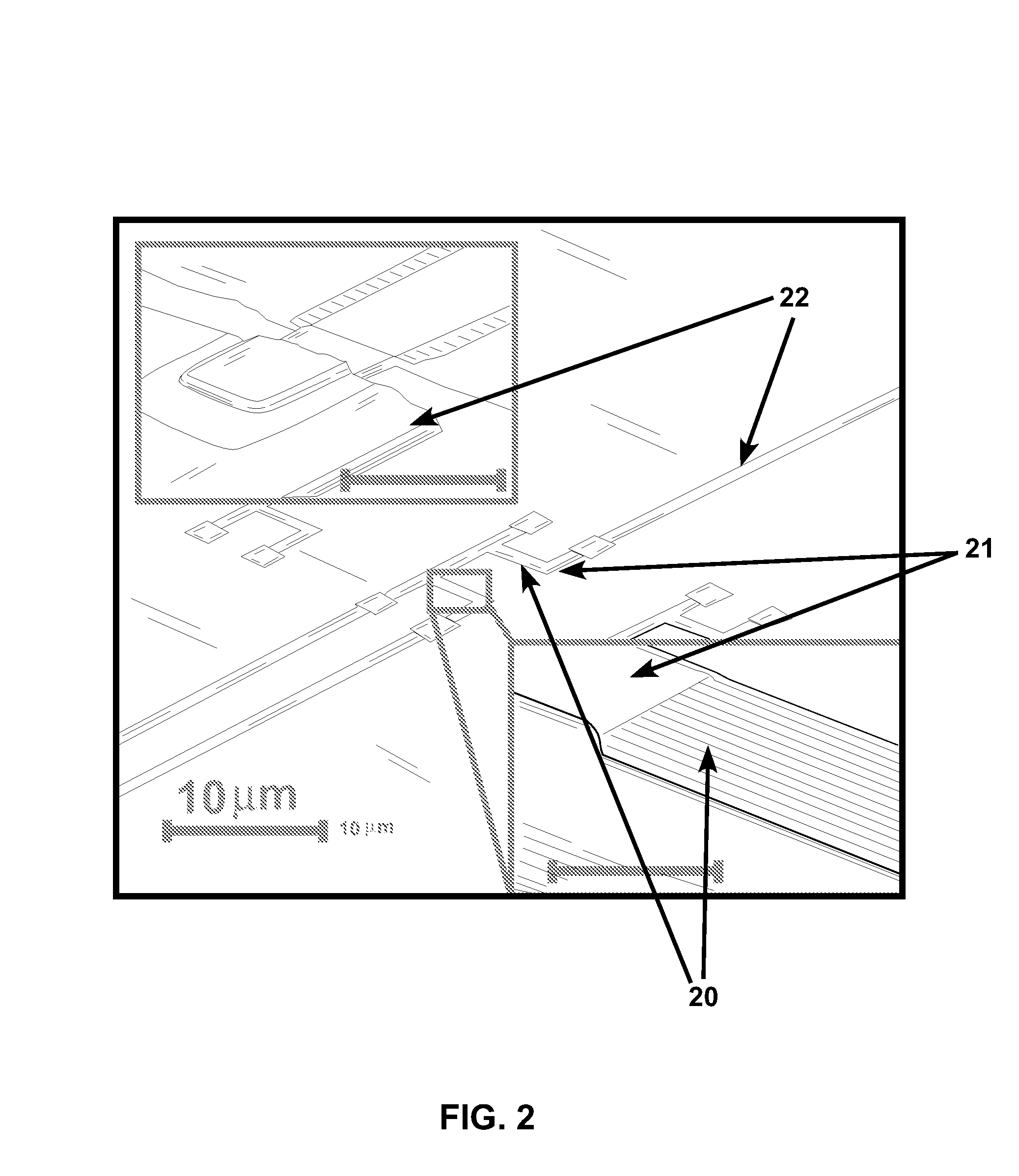

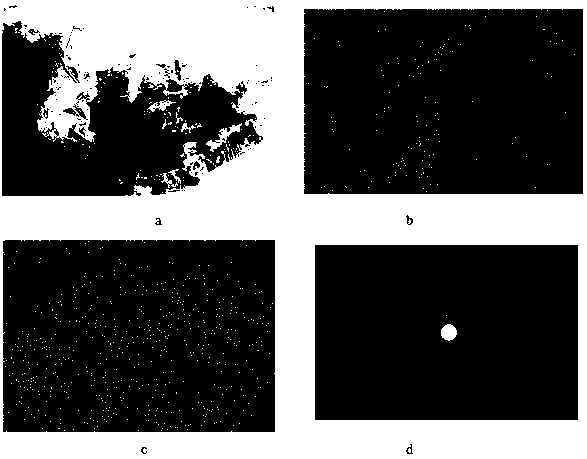

Method for transferring and preparing two-dimensional atomic crystal laminated structure

ActiveCN107170711AReduce doping and damageEasy to deal with residual glueSemiconductor/solid-state device manufacturingToluenePolystyrene

The invention discloses a method for transferring and preparing a two-dimensional atomic crystal laminated structure and relates to a stripping, positioning and transferring method for substrate-based two-dimensional atomic crystal film. The method comprises the specific steps of carrying out spin-coating on the surface of the two-dimensional atomic crystal film through utilization of polystyrene film, wherein the two-dimensional atomic crystal film is prepared based on a substrate; separating two-dimensional atomic crystals from the substrate through utilization of water tension and transferring the two-dimensional atomic crystals to dimethyl siloxane polymer; attaching the two-dimensional atomic crystals / polystyrene / dimethyl siloxane polymer on a target material through utilization of the van-der waals force; and separating the dimethyl siloxane polymer in a heating mode and removing the polystyrene through utilization of toluene solution or a vacuum annealing method, namely preparing the two-dimensional atomic crystal laminated structure. The method is simple in operation and is high in success rate, is fast and can be widely applied to the field of a large-area ultra-thin material photoelectric sensor.

Owner:SUN YAT SEN UNIV

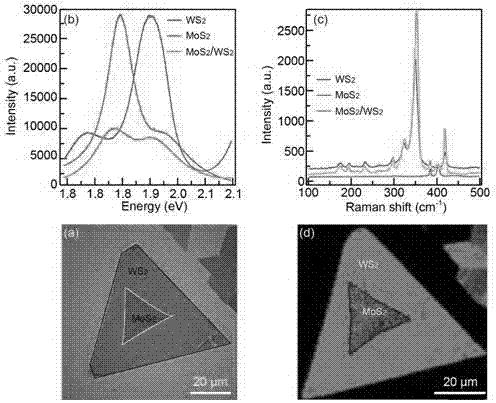

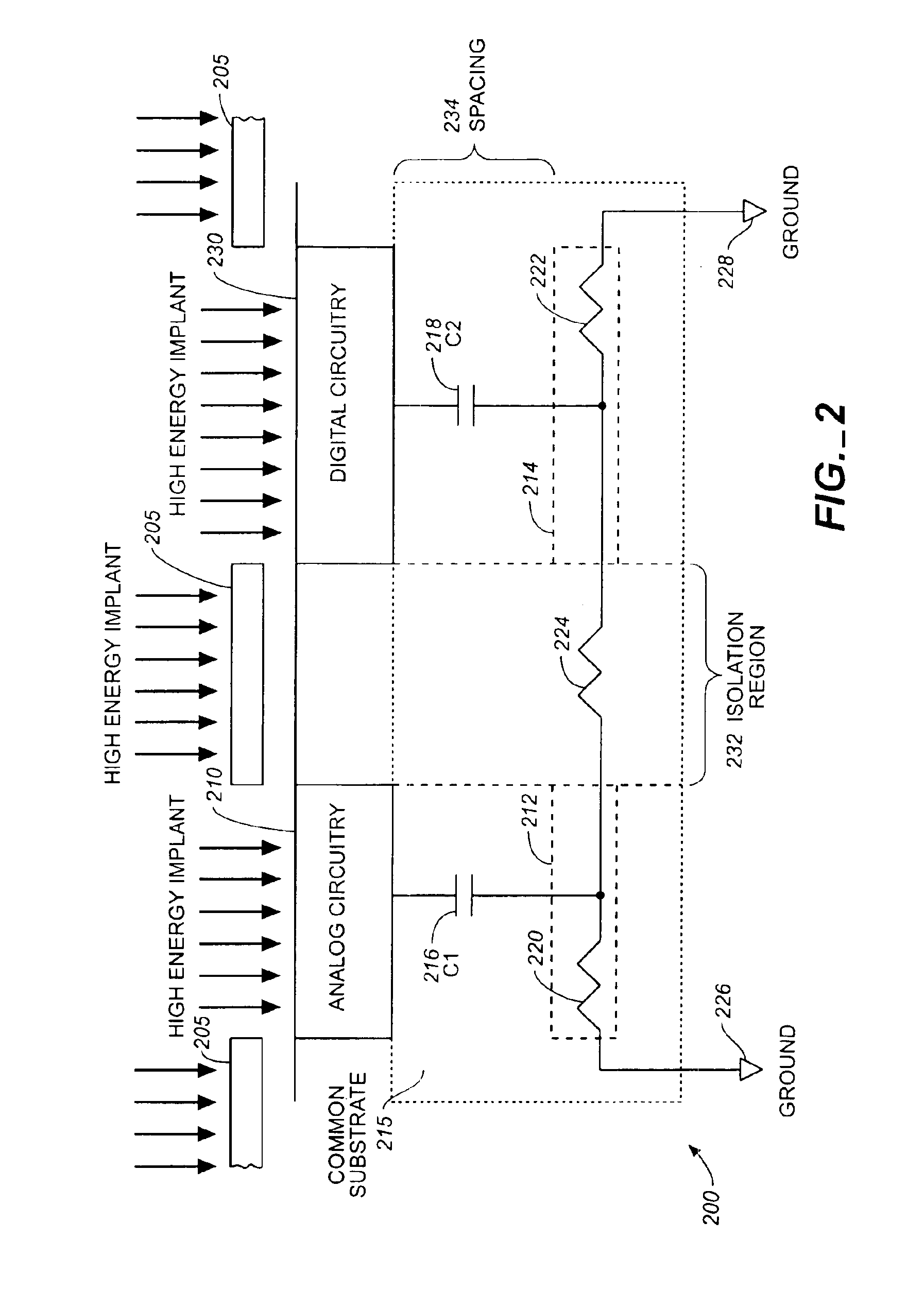

Circuit isolation utilizing MeV implantation

InactiveUS6885078B2Reduce resistanceIncrease resistanceTransistorSemiconductor/solid-state device detailsHigh energySilicon dioxide

A circuit isolation technique that uses implanted ions in embedded portions of a wafer substrate to lower the resistance of the substrate under circuits formed on the wafer or portions of circuits formed on the wafer to prevent the flow of injected currents across the substrate. The embedded ions provide low resistance regions that allow injected currents from a circuit to flow directly to a ground potential in the same circuit rather than flowing across the substrate to other circuits. High energy implantation processes on the order of 1 MeV to 3 MeVs can be used to implant the ions in embedded regions. Multiple energy levels can be used to provide thick embedded layers either prior to or after application of an epitaxial layer. Various masking materials can be used to mask the isolation regions during the implantation process, including hard masking materials such as silicon dioxide or silicon nitride, poly-silicon or an amorphous silicon layer, and a photoresist layer. Additive materials can be used in one or more of the masking layers to increase the absorption characteristics of the high energy ions. Separate physical masks can be used to block the implantation of ions.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

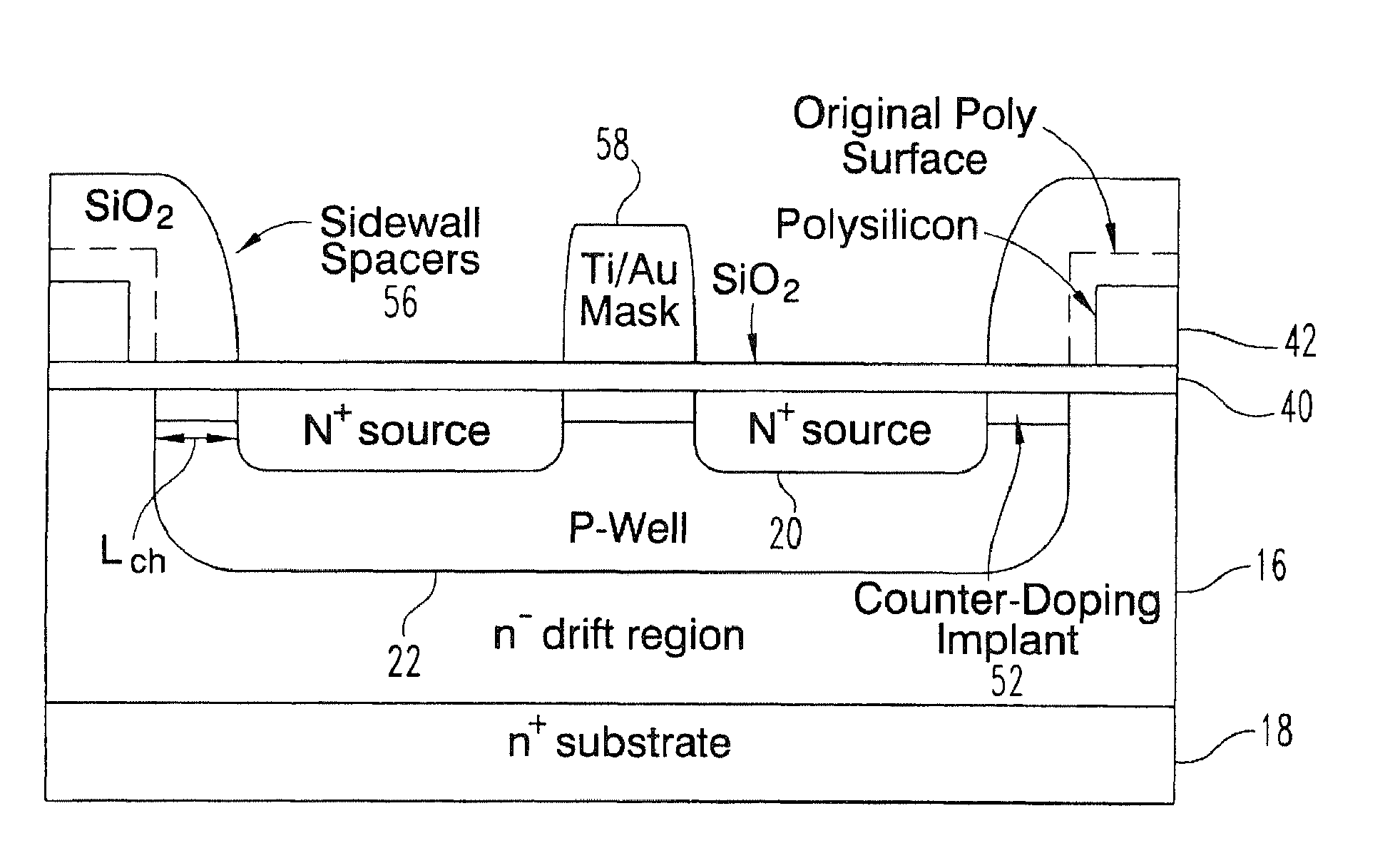

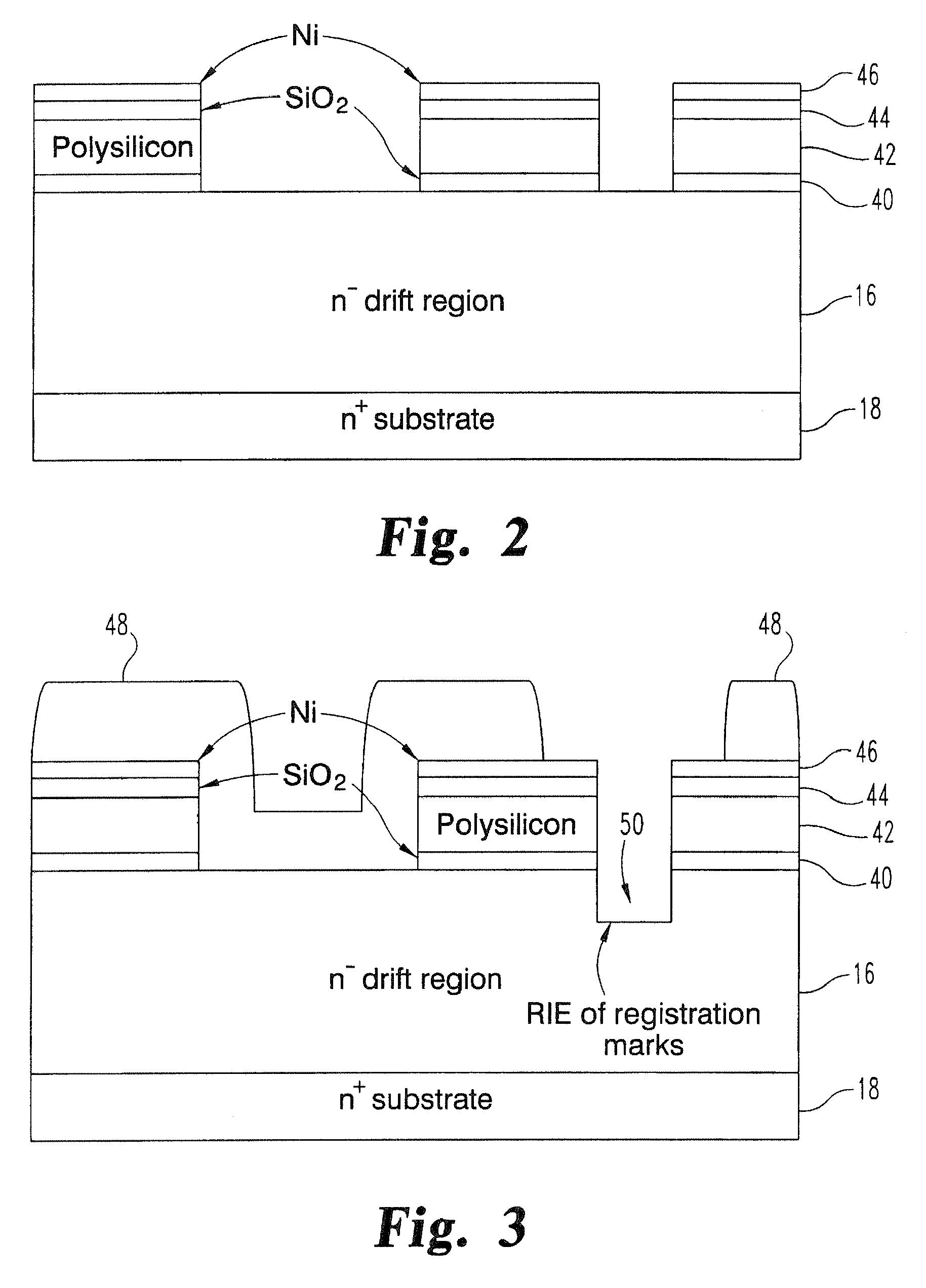

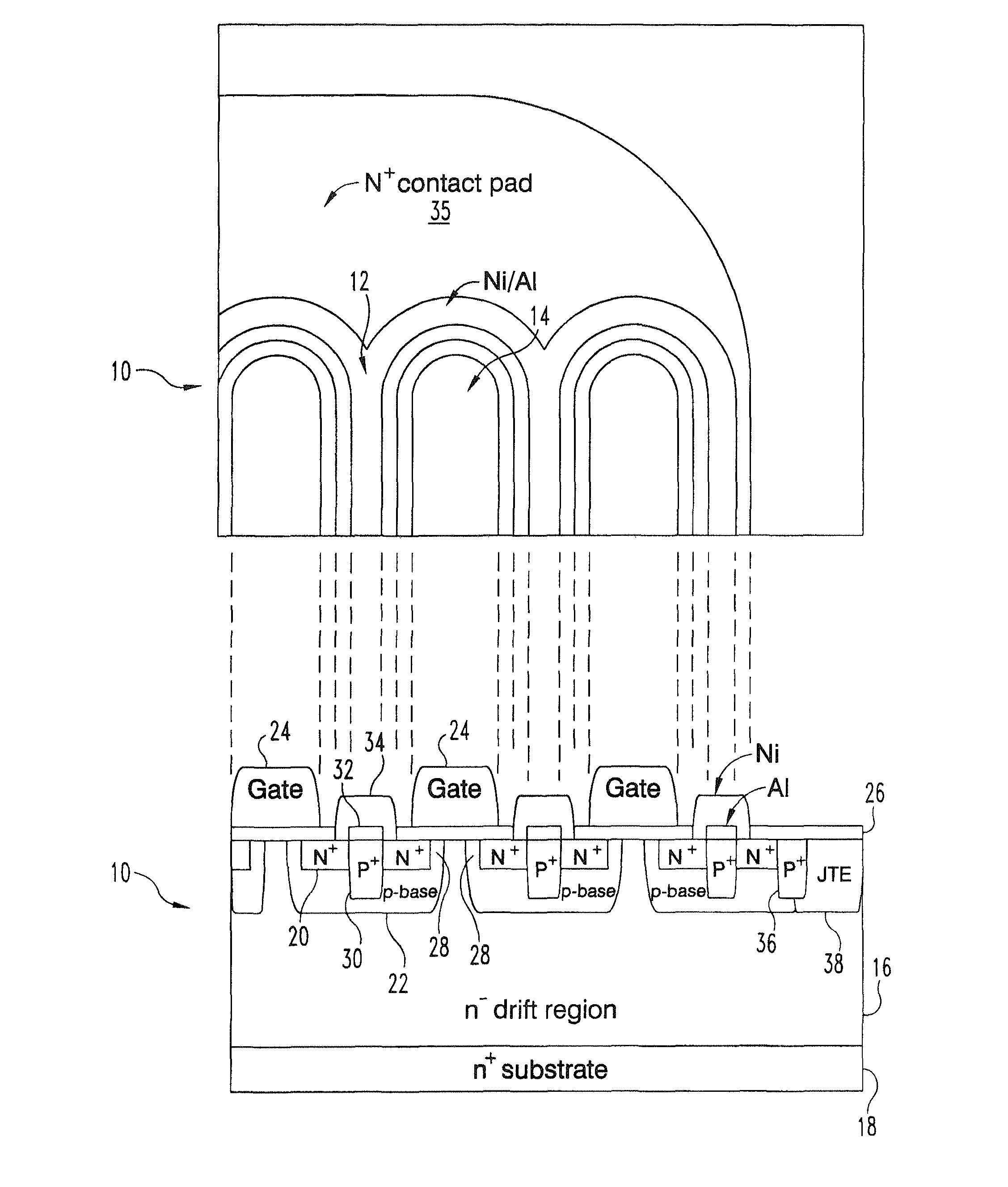

Short-channel silicon carbide power MOSFET

ActiveUS8476697B1Reduce specific on-resistanceImprove channel mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactPower MOSFET

A silicon carbide power MOSFET having a drain region of a first conductivity type, a base region of a second conductivity type above the drain region, and a source region of the first conductivity type adjacent an upper surface of the base region, the base region including a channel extending from the source region through the base region adjacent a gate interface surface thereof, the channel having a length less than approximately 0.6 μm, and the base region having a doping concentration of the second conductivity type sufficiently high that the potential barrier at the source end of the channel is not lowered by the voltage applied to the drain. The MOSFET includes self-aligned base and source regions as well as self-aligned ohmic contacts to the base and source regions.

Owner:PURDUE RES FOUND INC

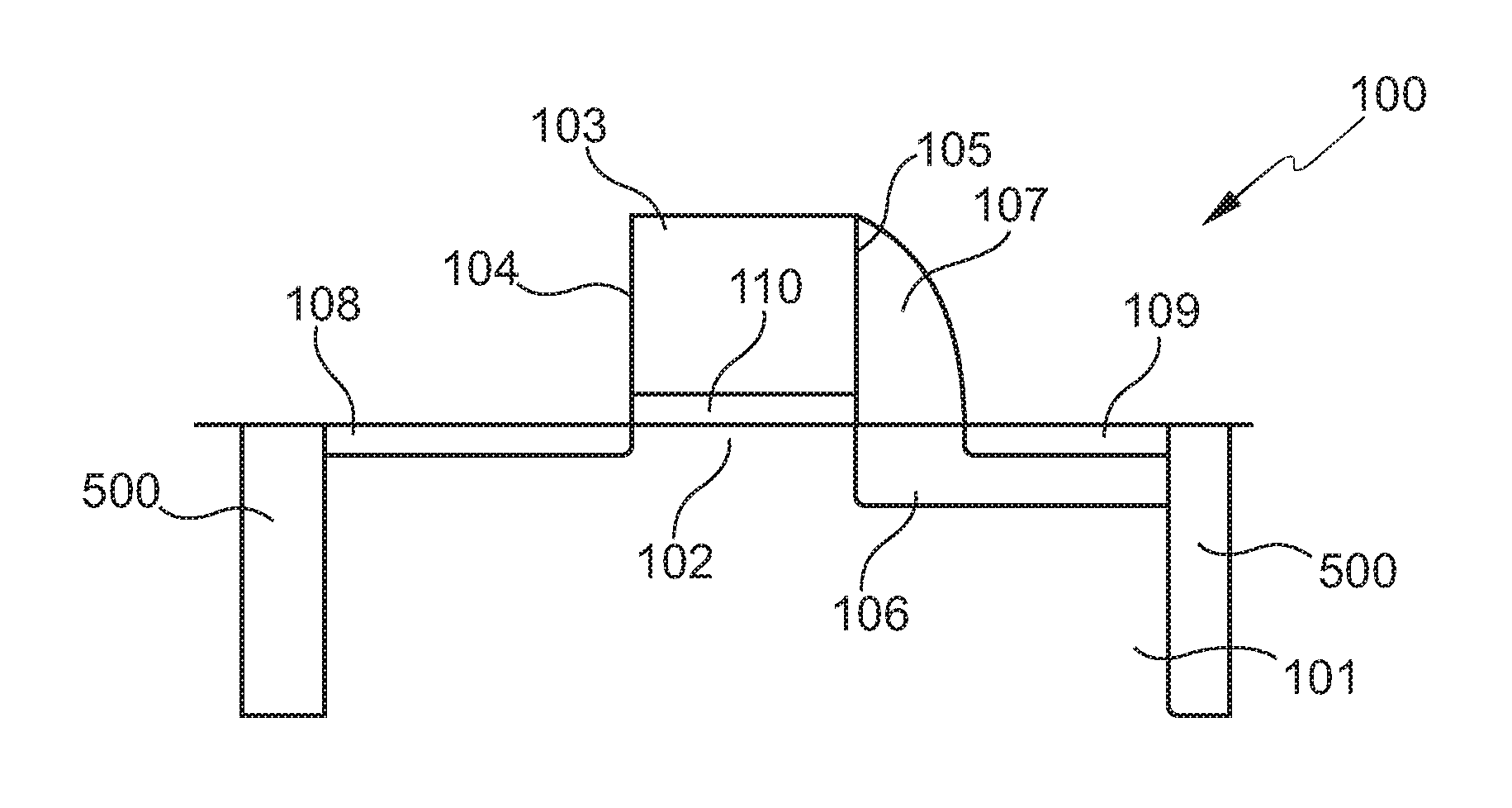

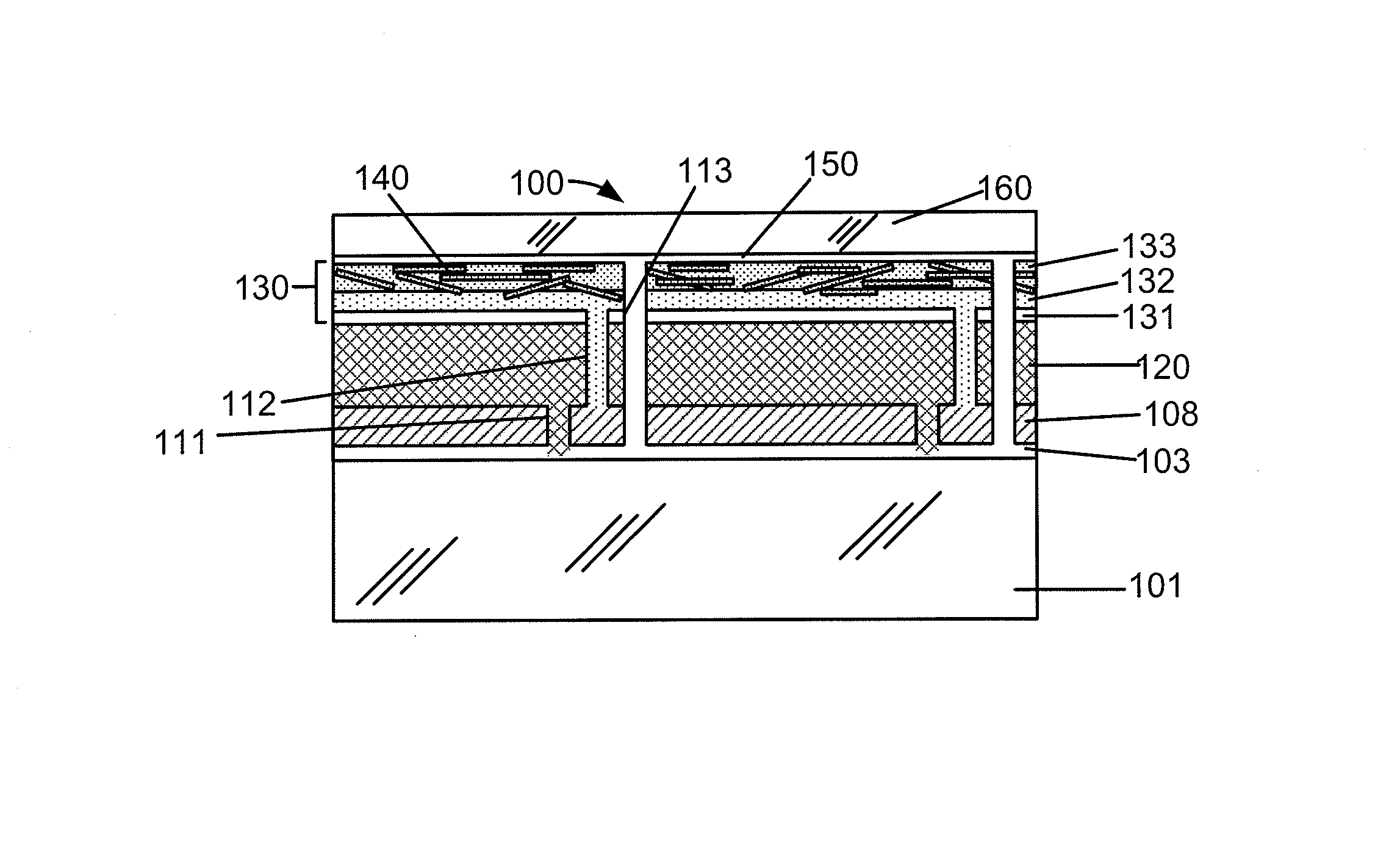

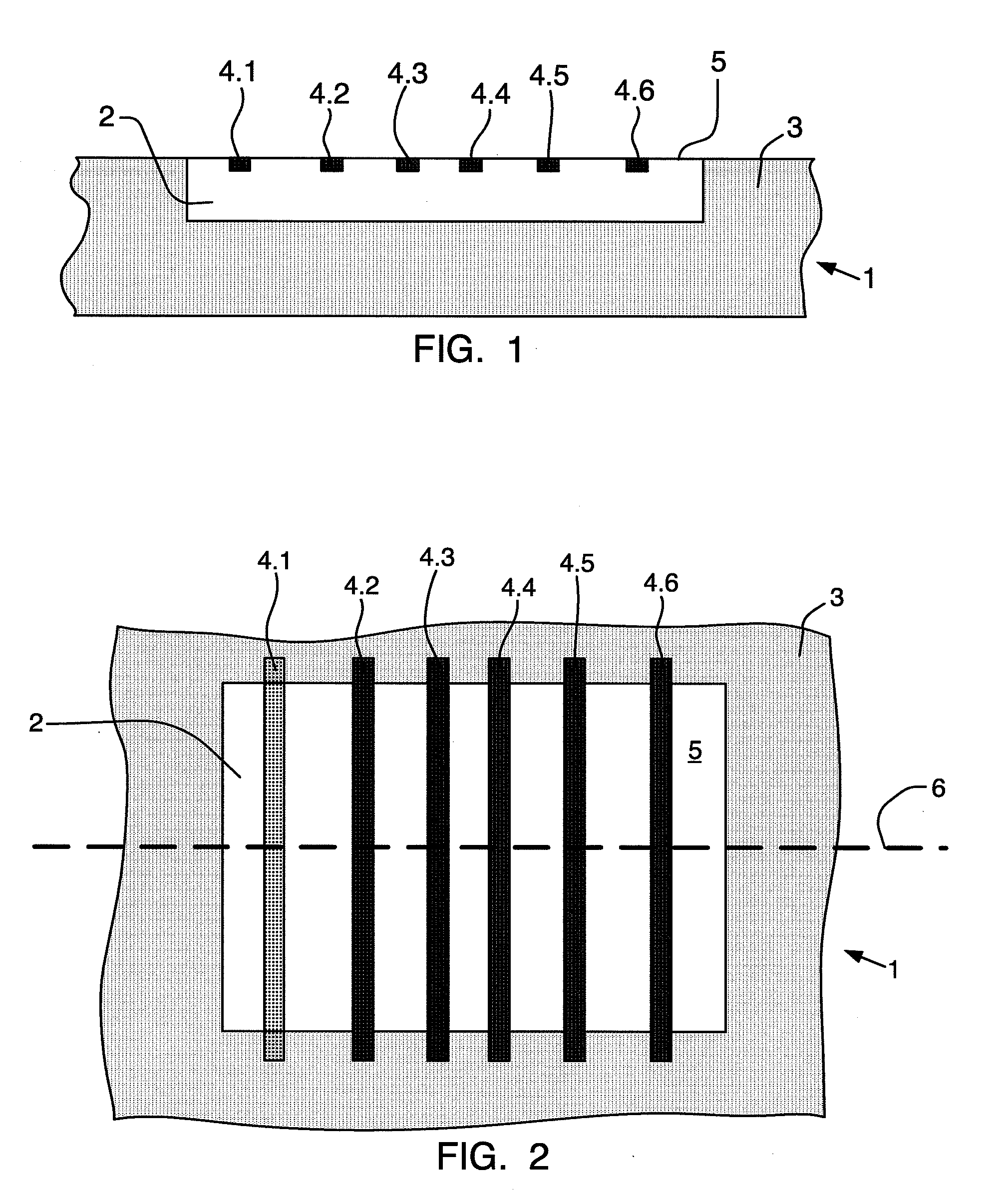

Extended drain transistor and method of manufacturing the same

ActiveUS20100181618A1Reduce dopingReduce hot carrier effectSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringTransistor

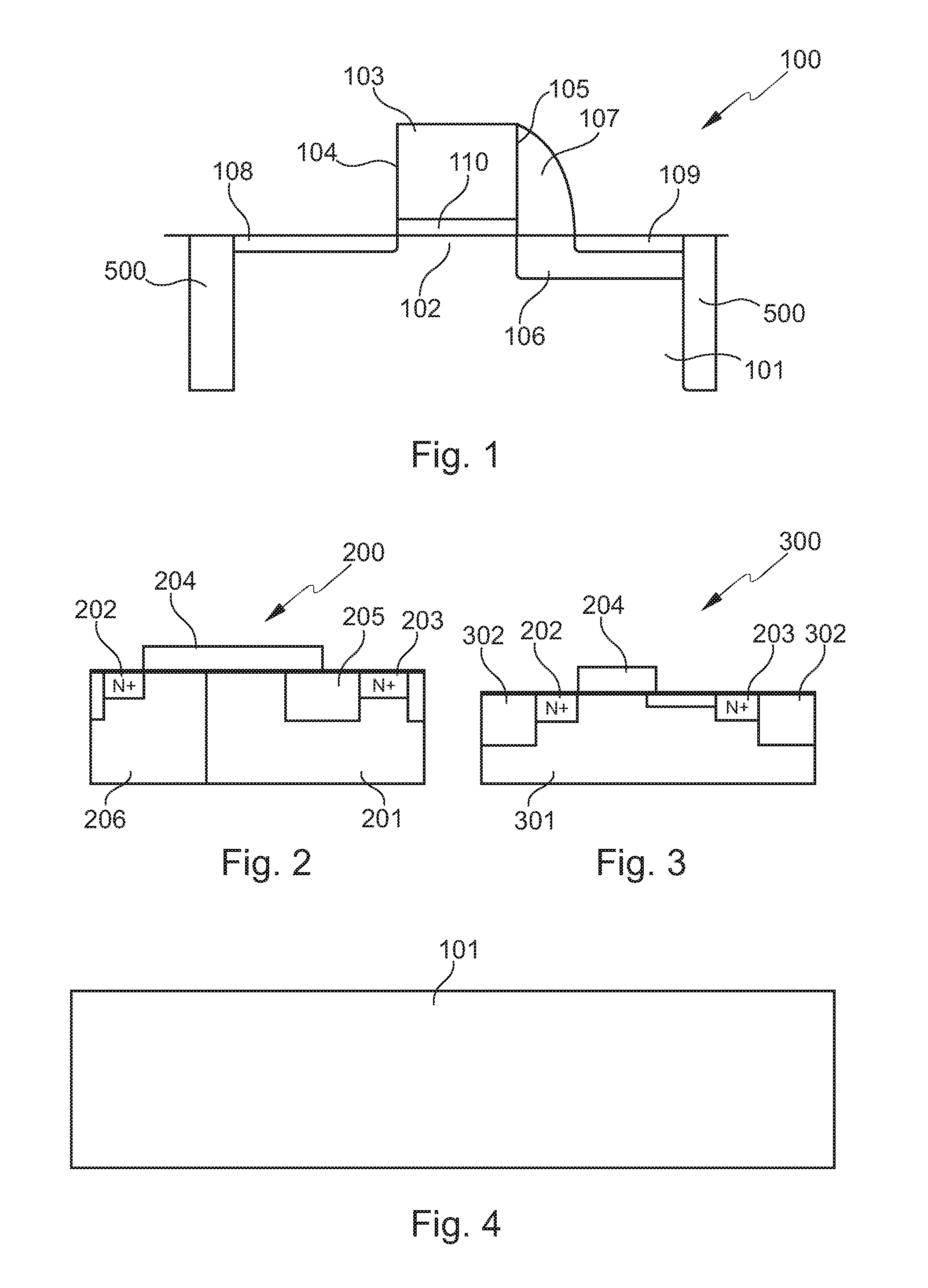

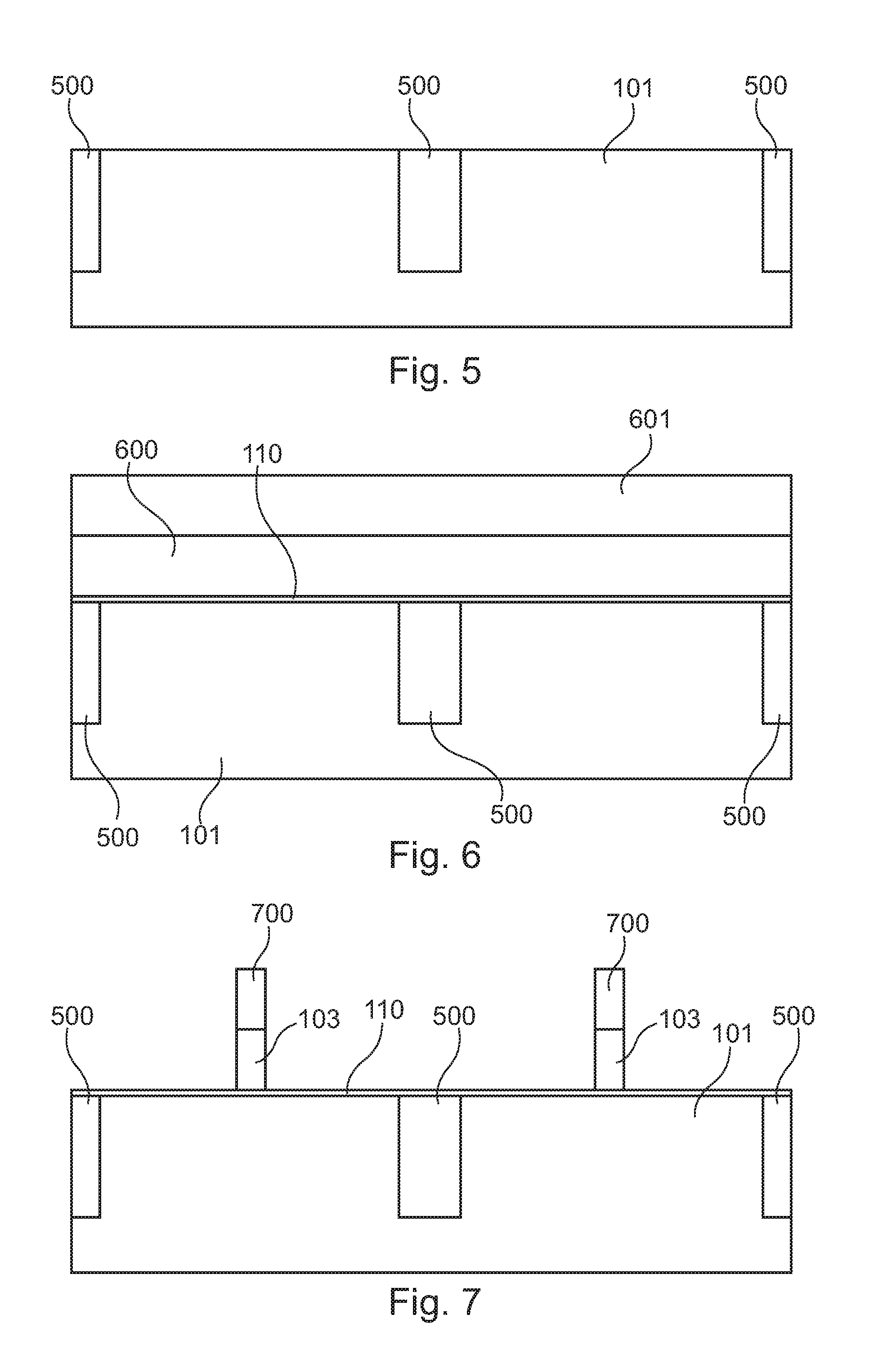

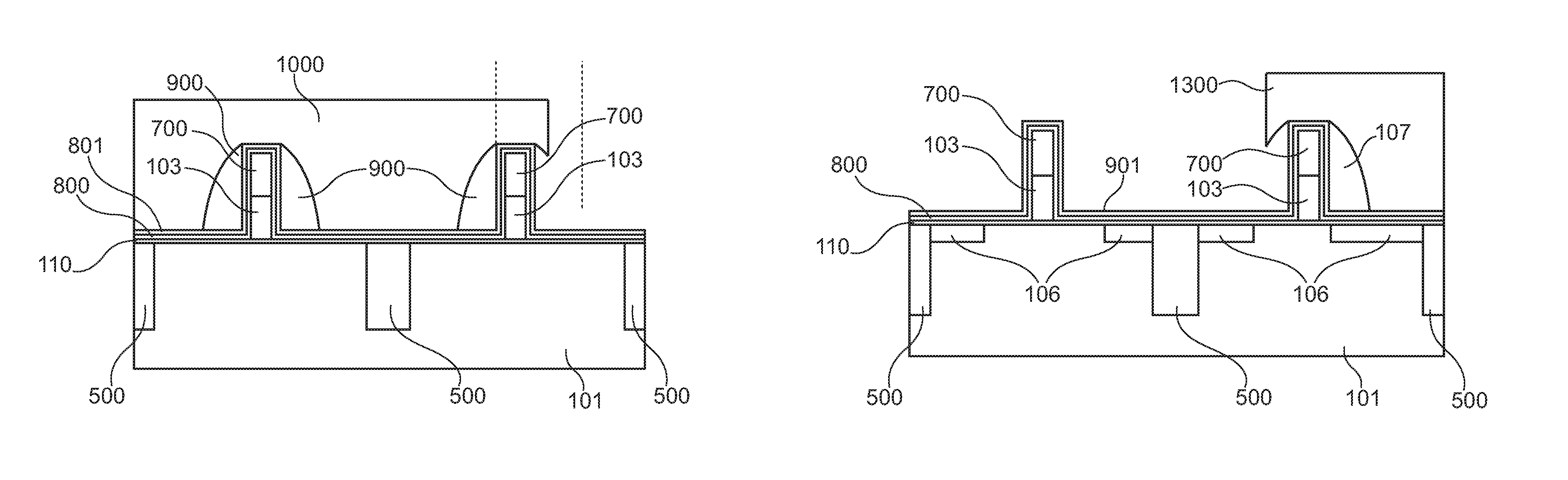

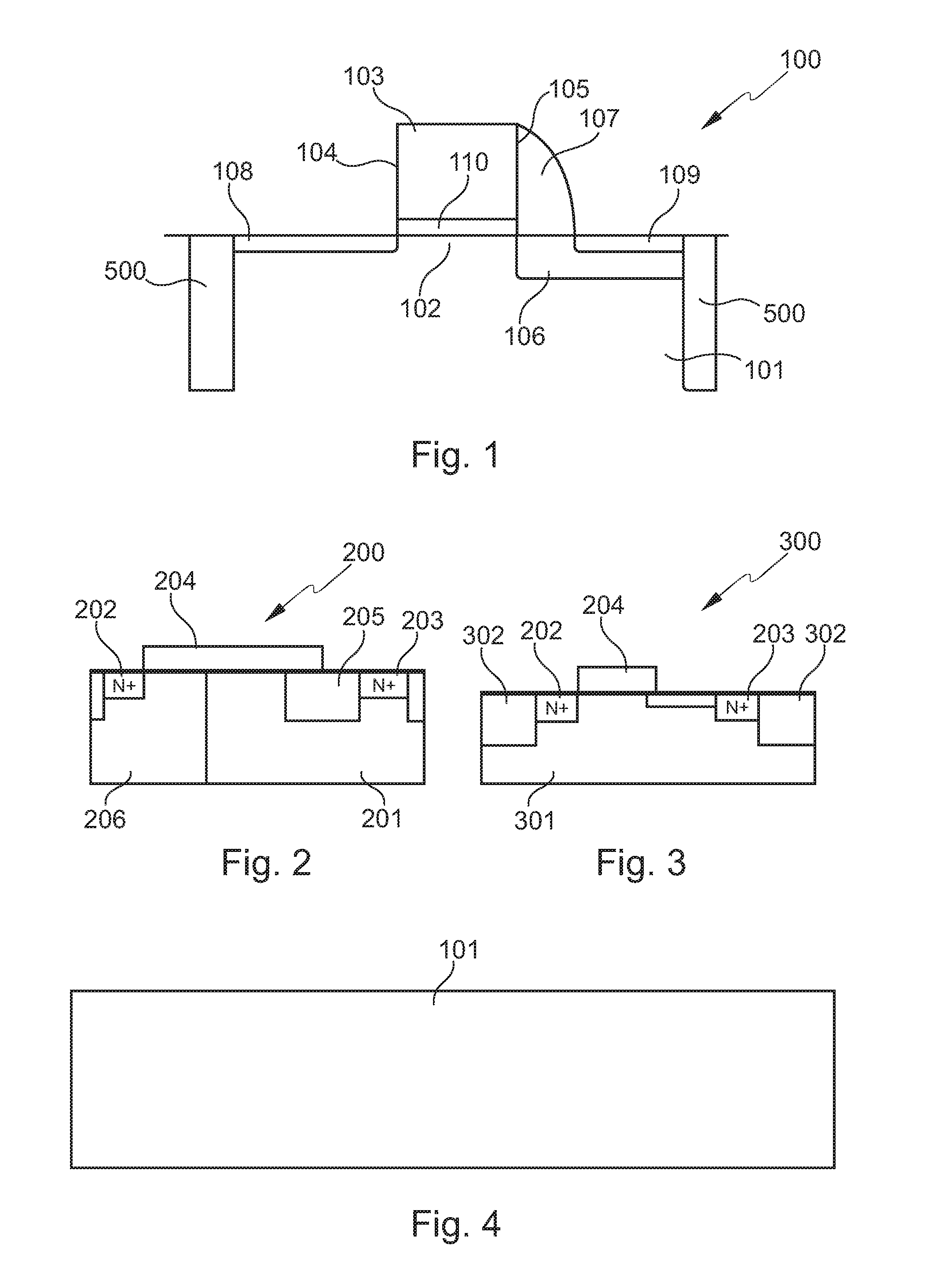

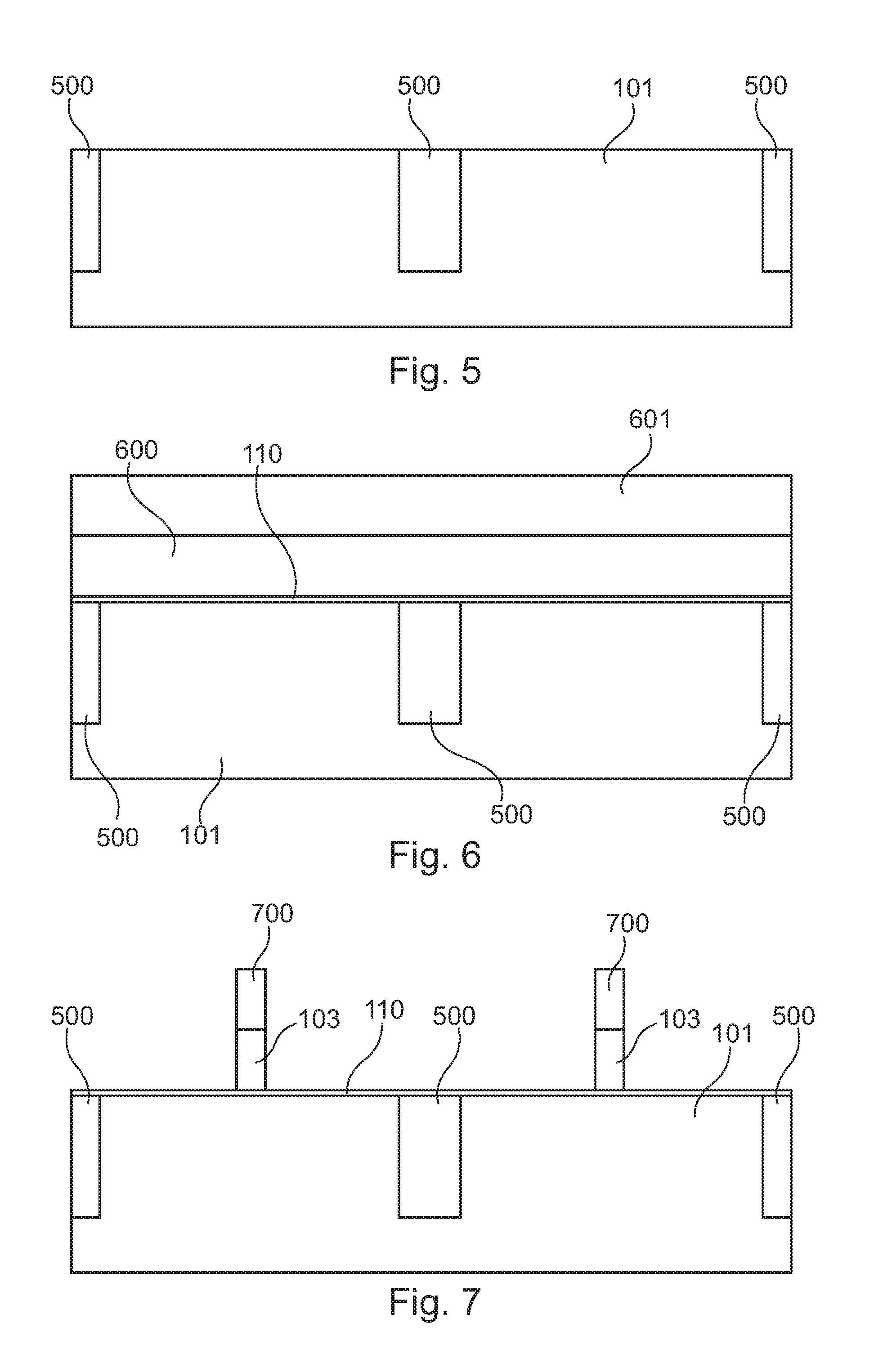

An extended drain transistor (100) comprising a substrate (101), a gate (103) formed on the substrate (100), the gate (103) having a first side wall (104) and a second side wall (105) opposing the first side wall (104), an extended drain (106) implanted in a surface portion of the substrate (101) adjacent the second side wall (105) of the gate (103), a spacer (107) on the second side wall (105) of the gate (103), a source (108) implanted in a surface portion of the substrate (101) adjacent the first side wall (104) of the gate (103), and a drain (109) implanted in a surface portion of the substrate (101) adjacent the spacer (107) in such a manner that the extended drain (106) is arranged between the gate (103) and the drain (109).

Owner:NXP BV

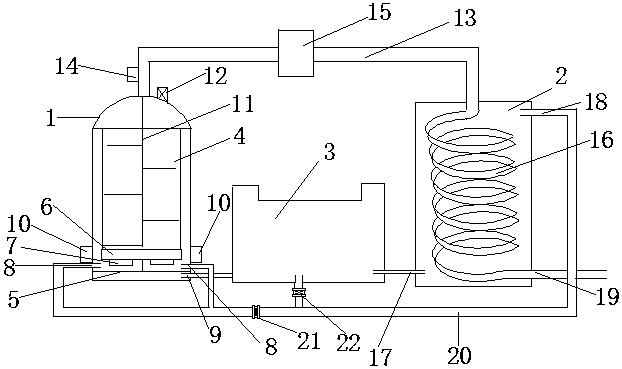

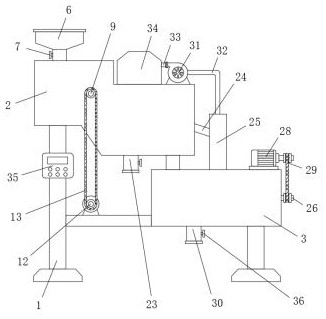

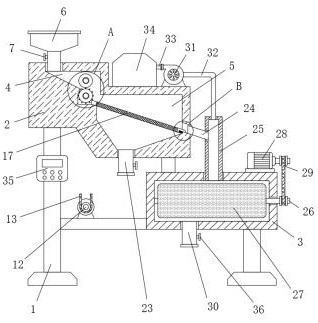

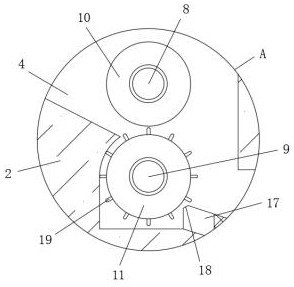

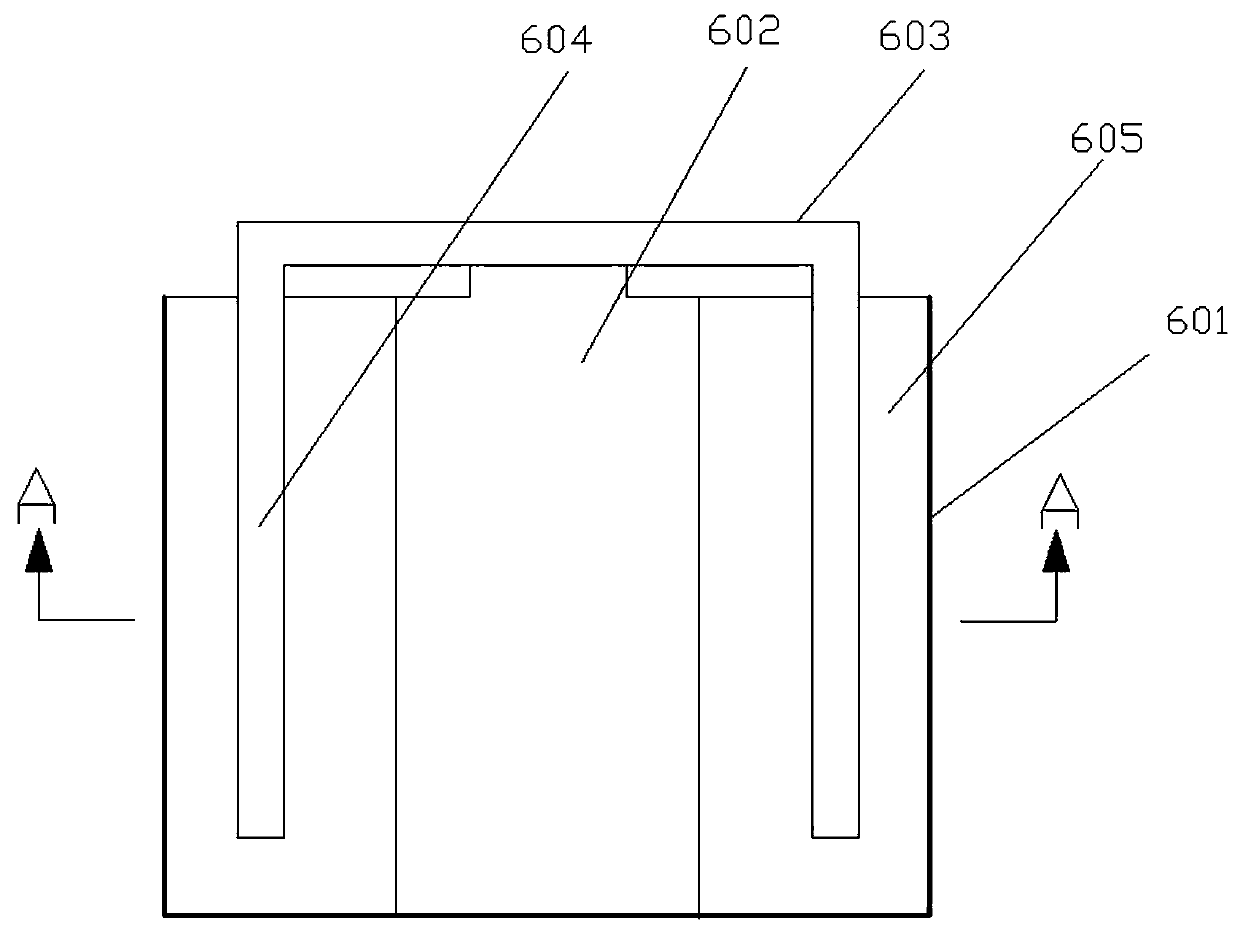

Oil separator

PendingCN110357205ABeneficial technical effectReduce the hassle of separationFatty/oily/floating substances removal devicesLiquid separationOil separationOil water

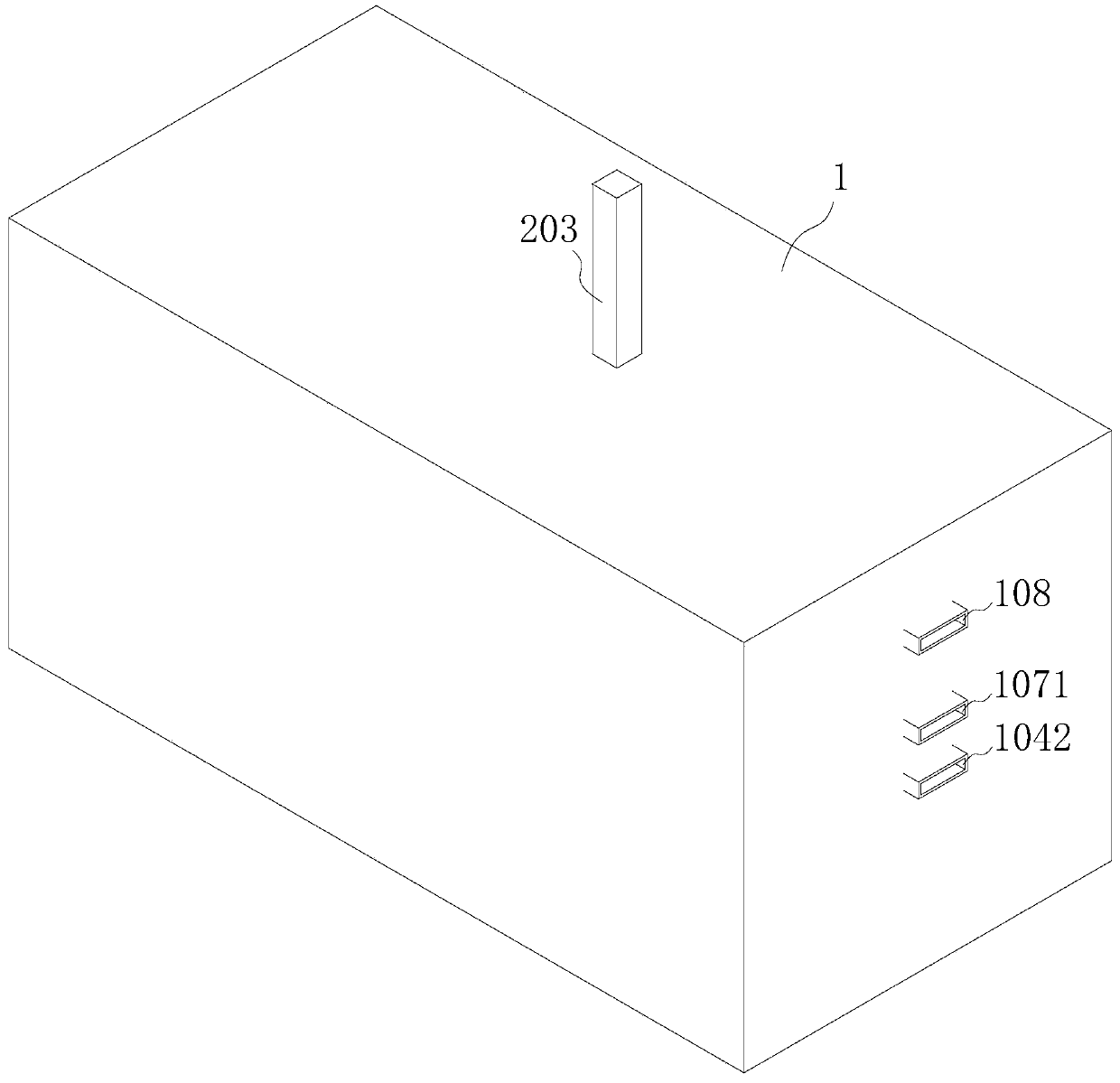

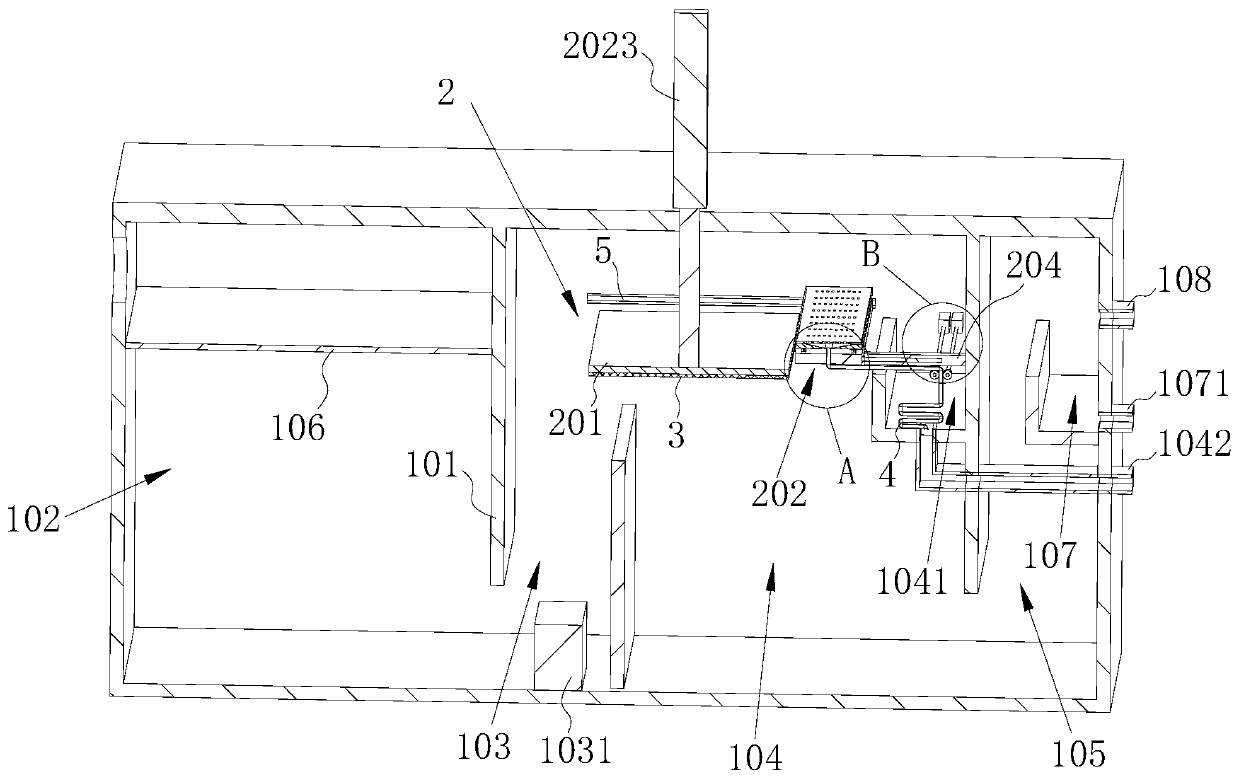

The invention discloses an oil separator. The oil separator comprises a box body, a solid-liquid separation chamber, a water-oil separation chamber and a water discharge chamber are arranged in the box body, an oil collection trough and an oil-water separation device are arranged in the oil-water separation chamber, the oil-water separation device comprises an oil adsorbing plate, an oil scrapingplate, a vertical driving assembly and a horizontal driving assembly, the lower surface of the oil adsorbing plate is provided with an oil adsorbing sponge layer, the oil-water separation device further comprises an oil guiding tube, one end of the oil guiding tube is connected with the oil scraping plate, the other end of the oil guiding tube extends to the oil collection trough, and the oil guiding tube receives oil scraped off by the oil scraping plate and guides the oil into the oil collecting trough. The vertical driving assembly drives the oil adsorbing plate to contact the liquid surface in the oil-water separation chamber, the oil adsorbing sponge layer adsorbs the oil, the vertical driving assembly drives the oil adsorbing plate to rise, the horizontal driving assembly drives theoil scraping plate to abut against the oil absorbing sponge layer, and the oil adsorbed by the oil adsorbing sponge layer is scraped by the oil scraping plate, goes through the oil guiding tube, and is collected into the oil collecting trough, so the water doped in the separated oil is reduced, and the trouble of secondary oil-water separation is reduced.

Owner:GUANGZHOU HENGDE ENVIRONMENTAL PROTECTION TECH

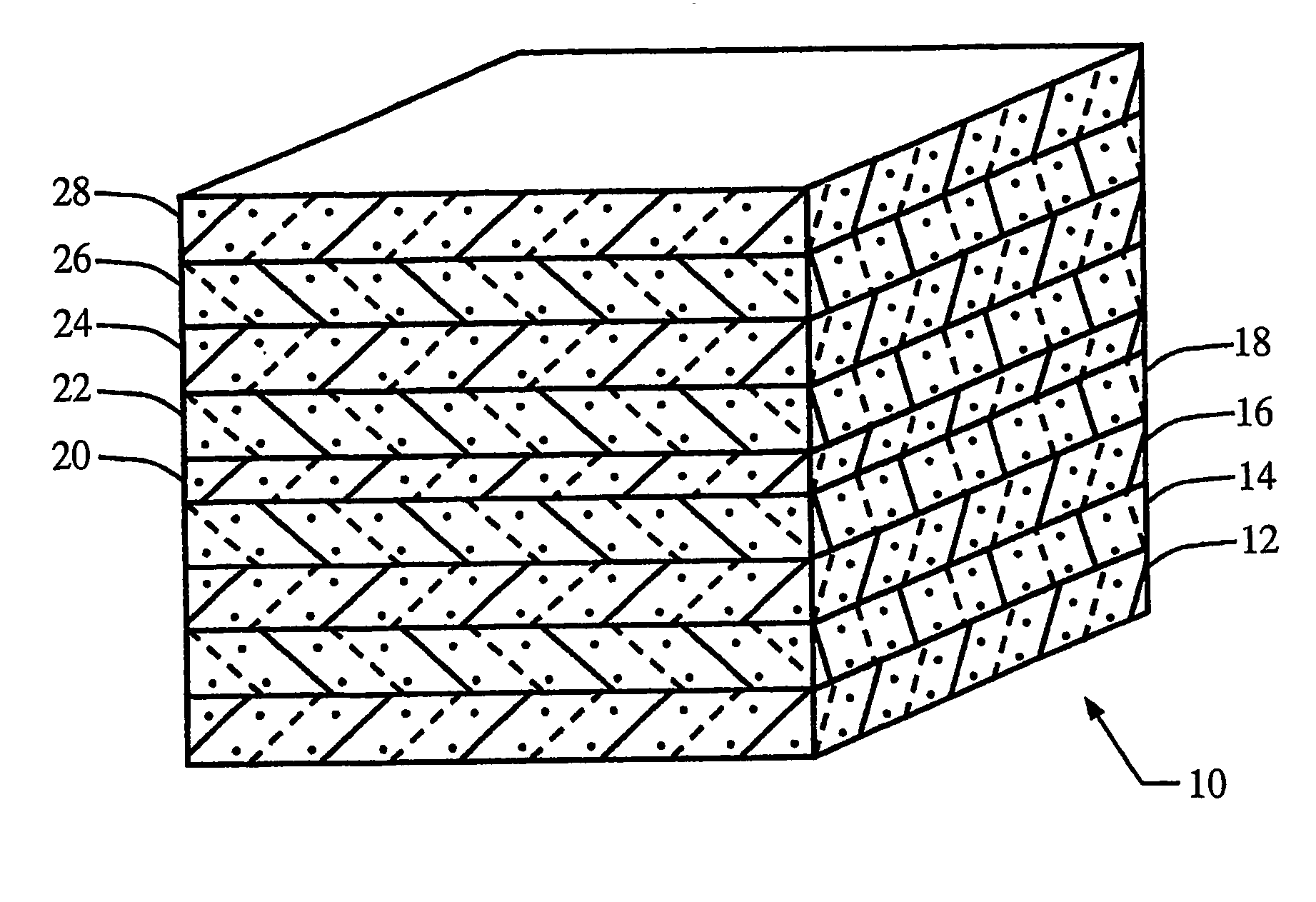

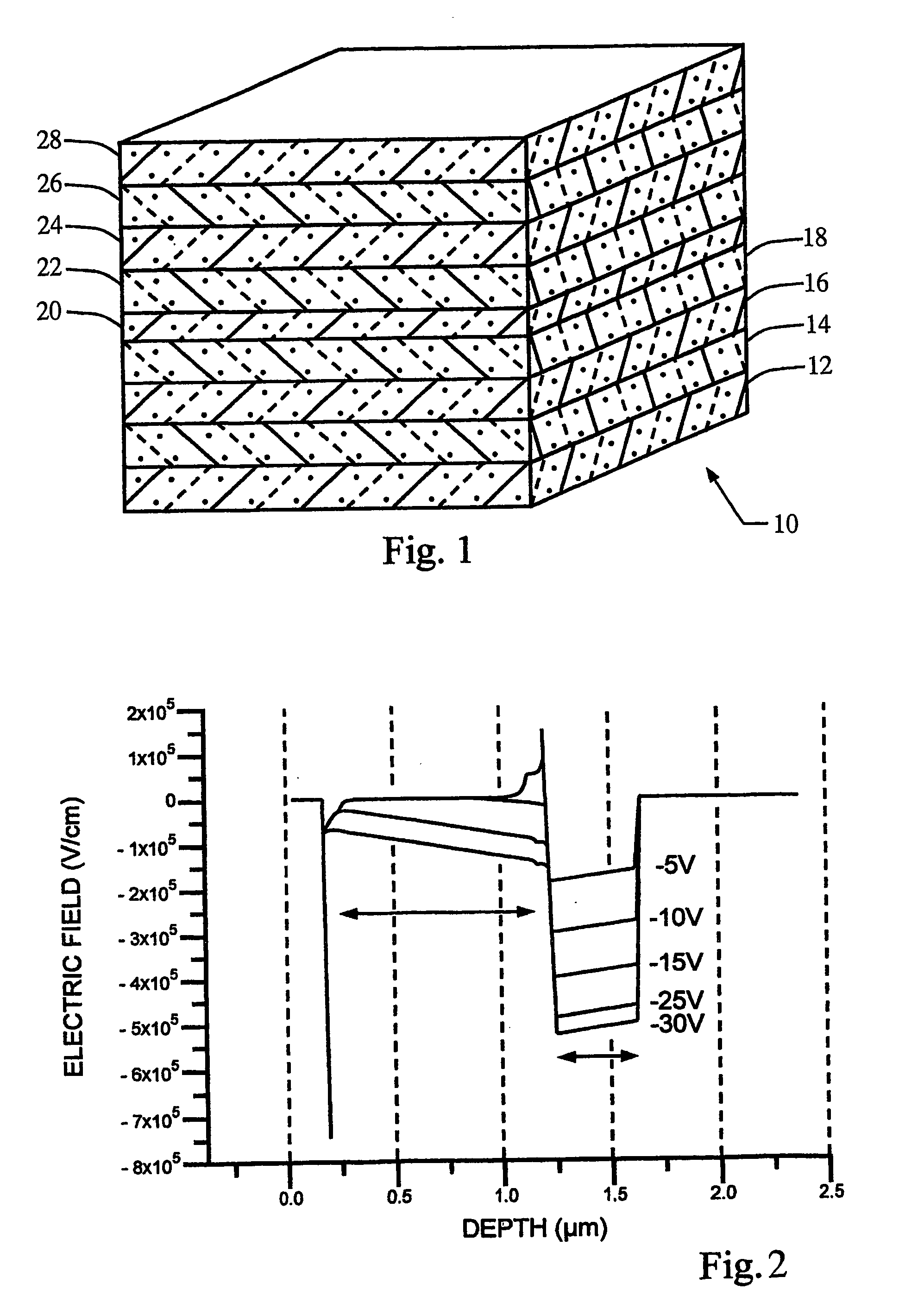

Charge controlled avalanche photodiode and method of making the same

InactiveUS20050029541A1Prevent charge carrier breakdownLarge gainSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesCharge controlContact layer

The present invention includes an epitaxial structure (16) grown on a semi-insulating InP substrate (12). First, a buffer layer (14) is grown to isolate defects originated from substrates (12). Then an n-type layer (18) is grown to serve as n-contact layer to collect electrons. Next, a multiplication layer (20) is grown to provide avalanche gain for the APD device (10). Following that, an ultra-thin charge control layer (22) is grown with carbon doping. An absorption layer (24) is grown to serve as the region for creating electronhole pairs due to a photo-excitation. Finally, a p-type layer (28) is grown to serve as p-contact layer to collect holes.

Owner:PICOMETRIX

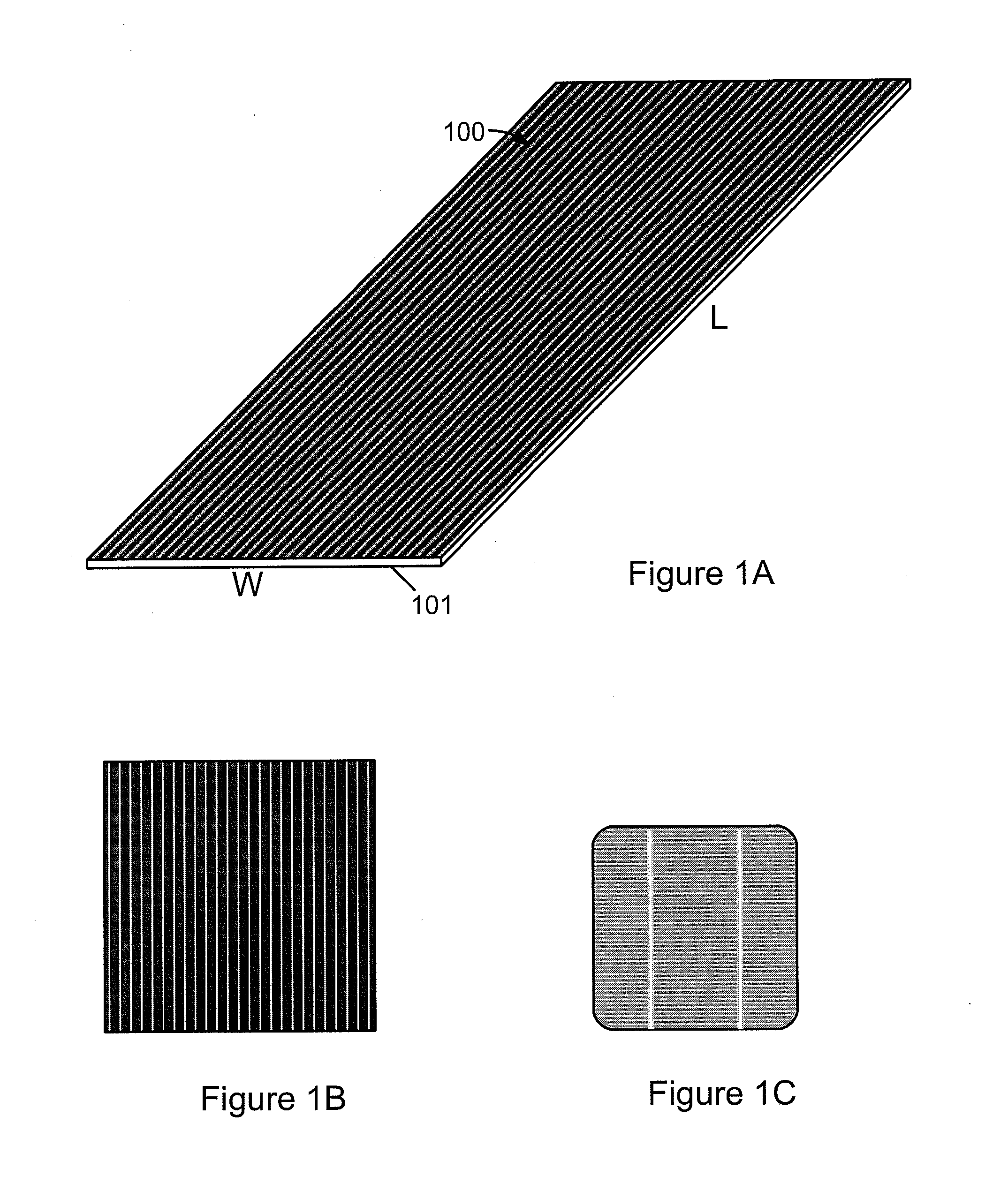

Nanowire enhanced transparent conductive oxide for thin film photovoltaic devices

InactiveUS20130174900A1Easy to scatterFacilitates off-resonance scatteringFinal product manufactureNanoinformaticsShadowingsNanowire

A thin-film photovoltaic devices includes transparent conductive oxide which has embedded within it nanowires at less than 2% nominal shadowing area. The nanowires enhance the electrical conductivity of the conductive oxide.

Owner:CM MFG

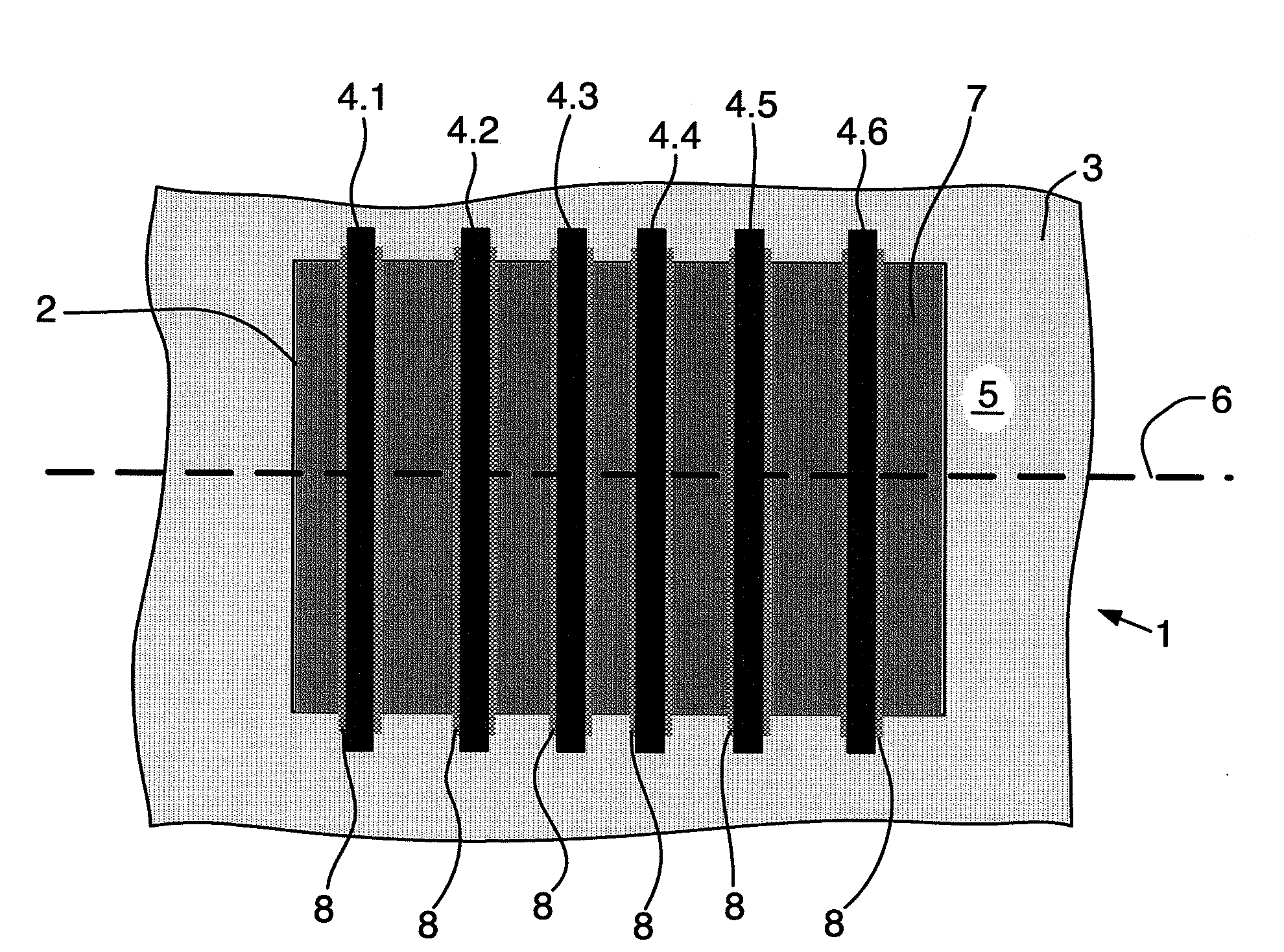

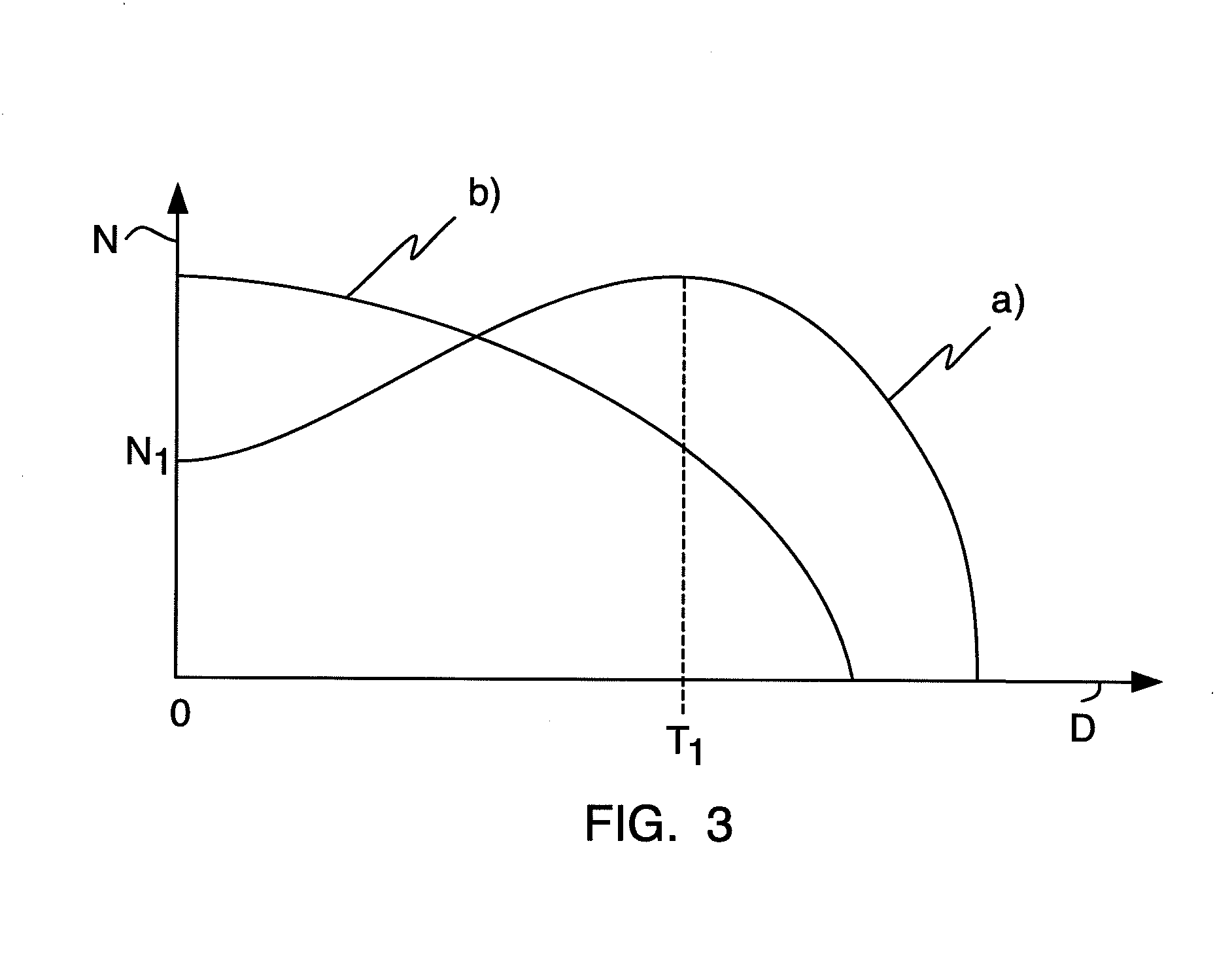

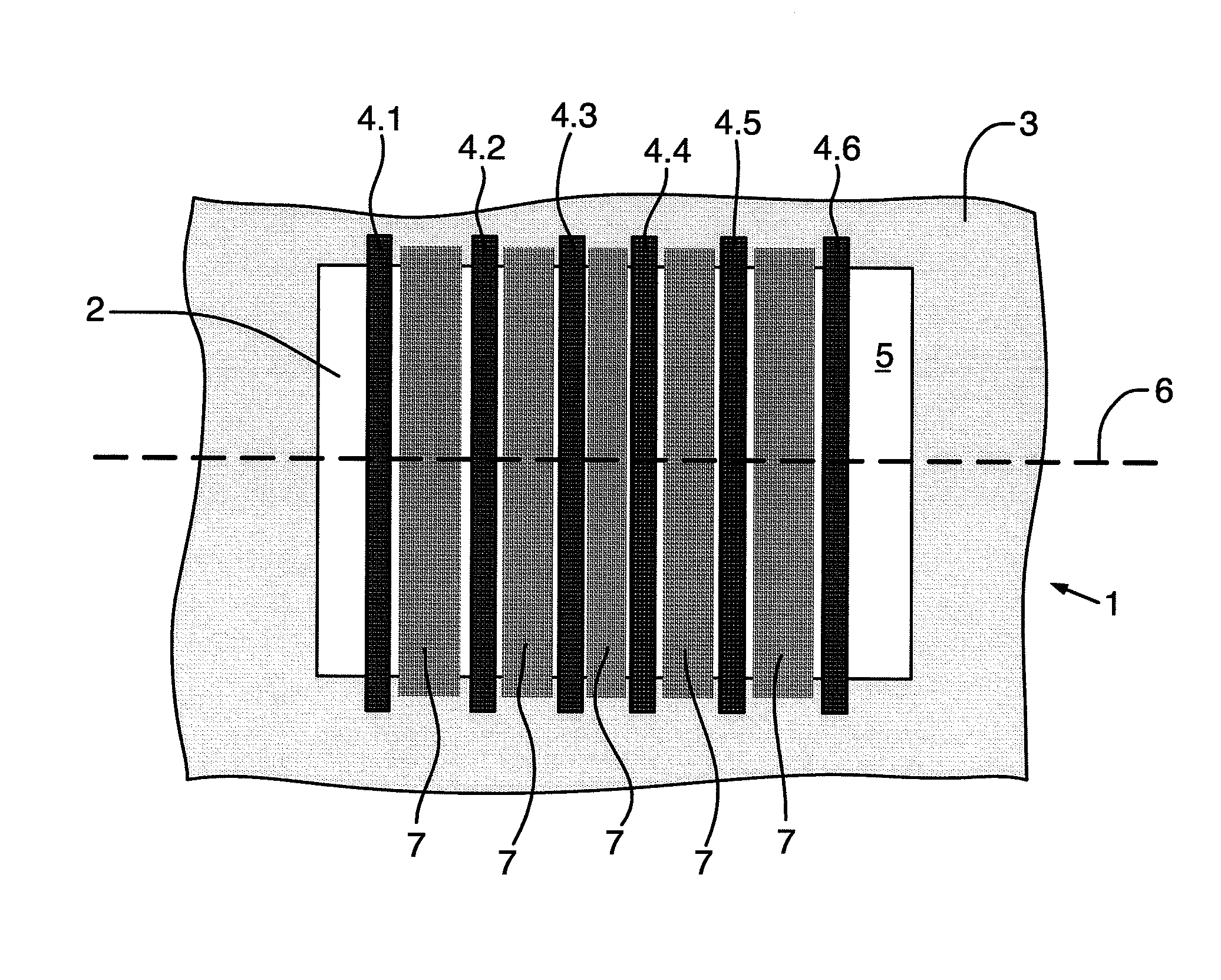

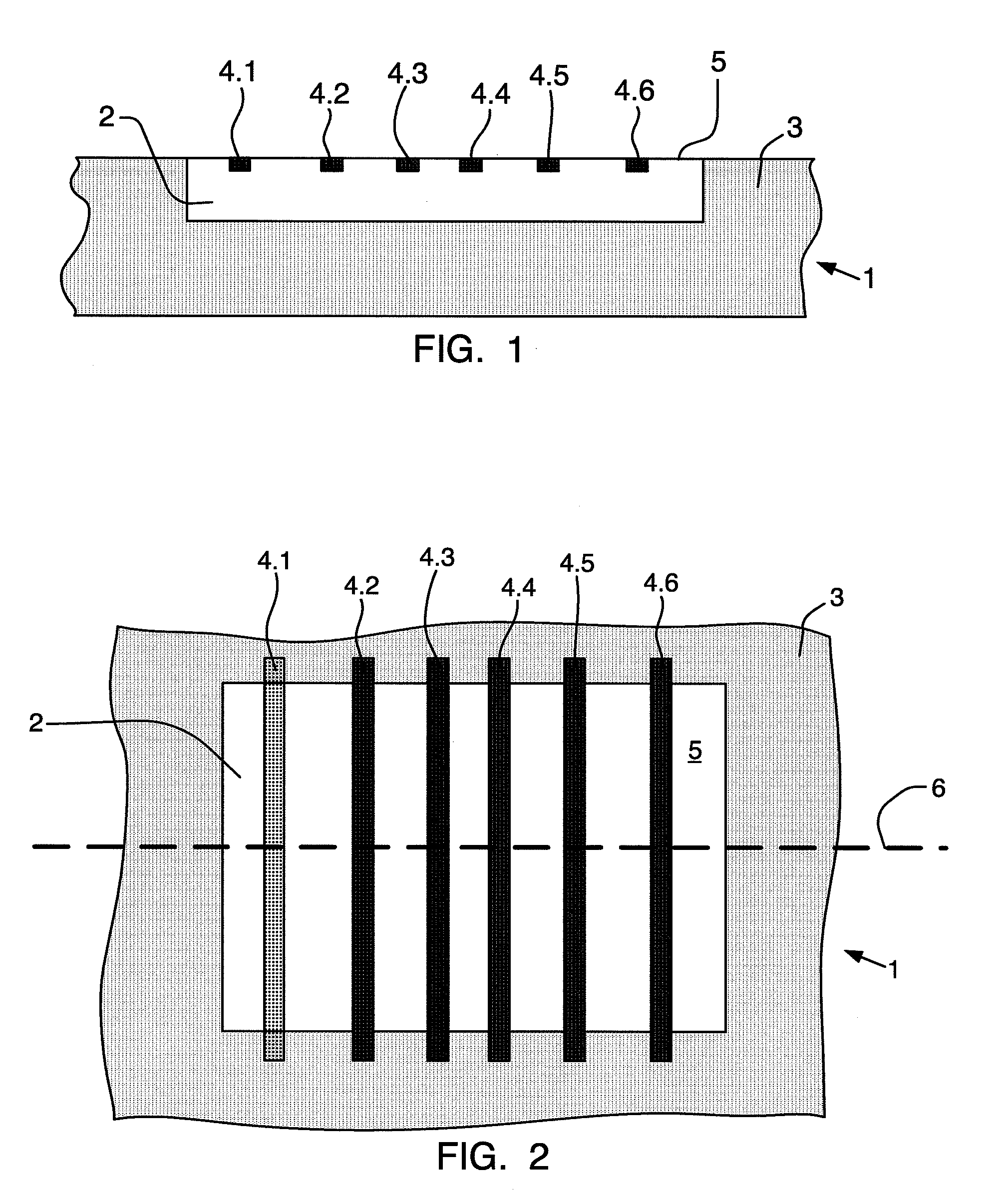

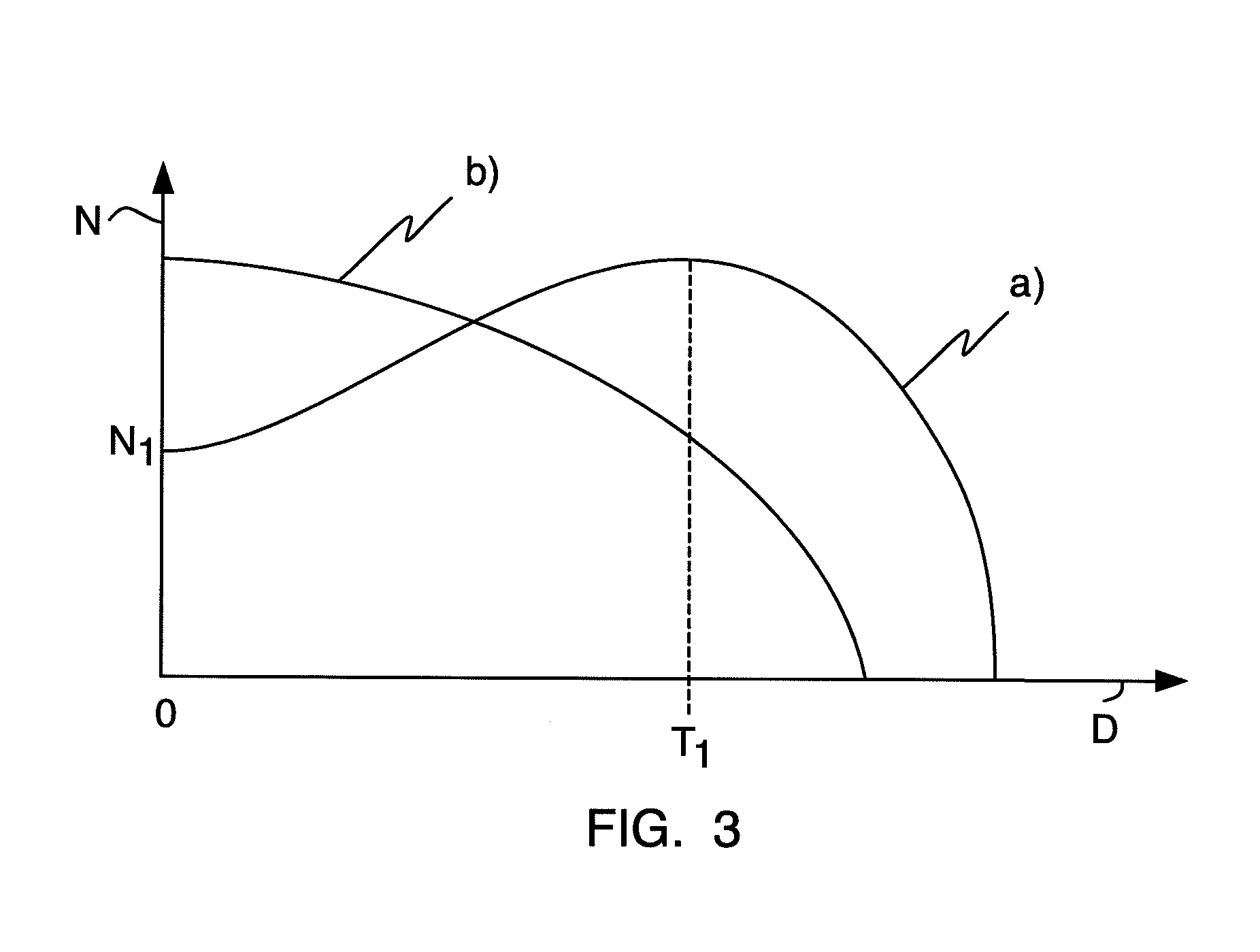

Vertical hall sensor and method for producing a vertical hall sensor

ActiveUS20120241887A1Doping being increasedReduce dopingMagnetic measurementsSolid-state devicesElectricityHigh energy

The invention relates to a vertical Hall sensor integrated in a semiconductor chip and a method for the production thereof. The vertical Hall sensor has an electrically conductive well of a first conductivity type, which is embedded in an electrically conductive region of a second conductivity type. The electrical contacts are arranged along a straight line on a planar surface of the electrically conductive well. The electrically conductive well is generated by means of high-energy ion implantation and subsequent heating, so that it has a doping profile which either has a maximum which is located at a depth T1 from the planar surface of the electrically conductive well, or is essentially constant up to a depth T2.

Owner:X FAB SEMICON FOUNDRIES +1

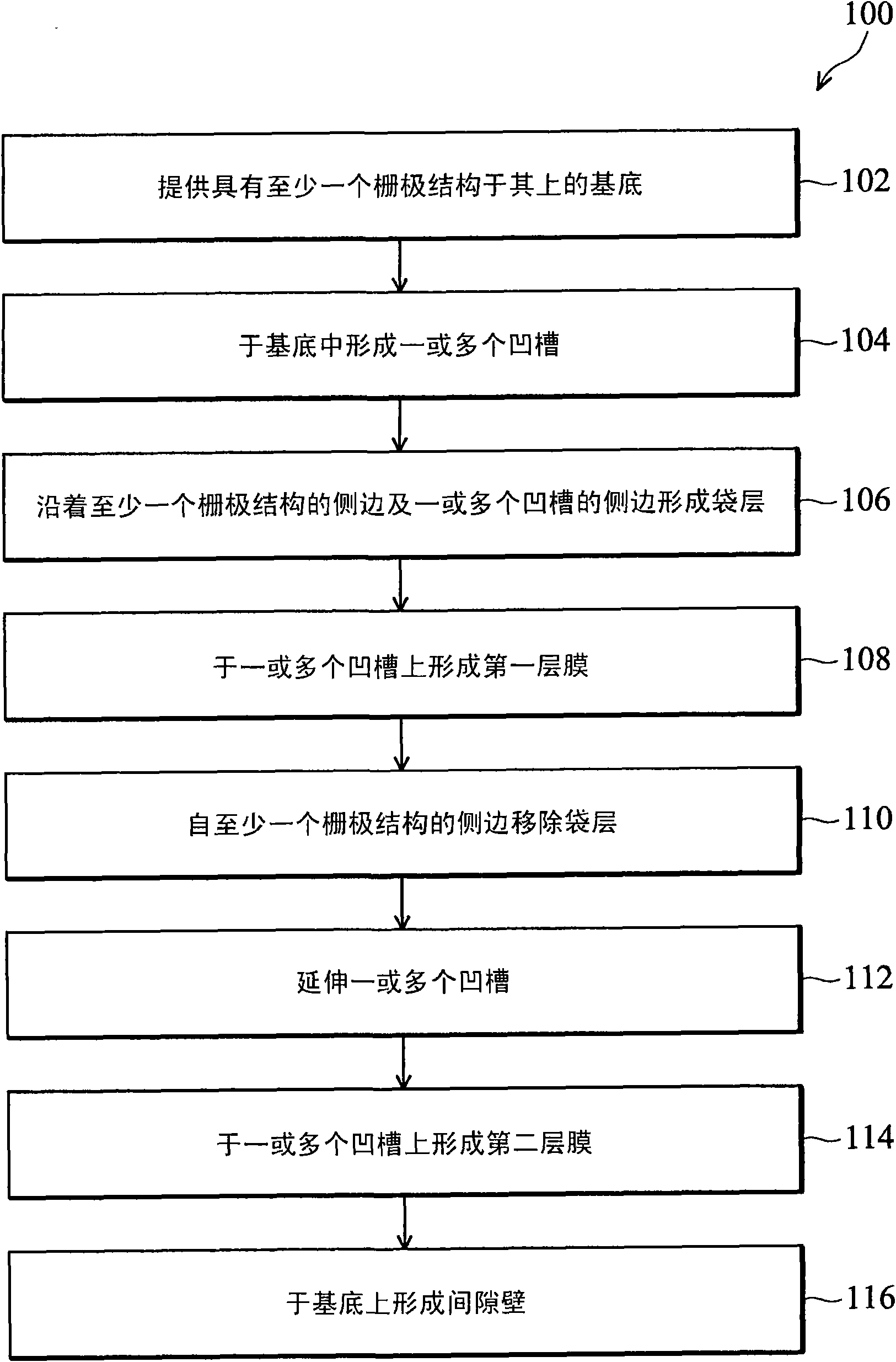

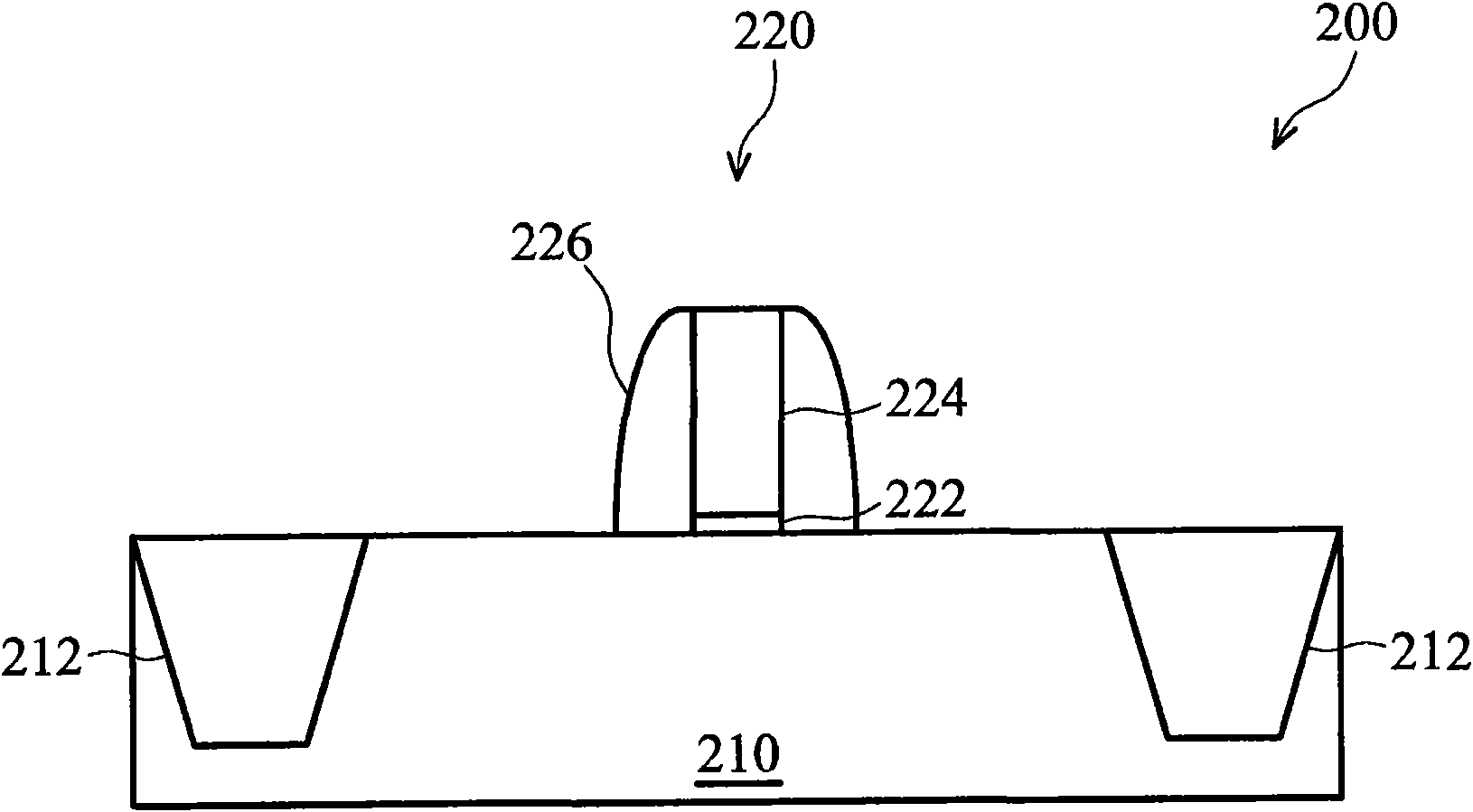

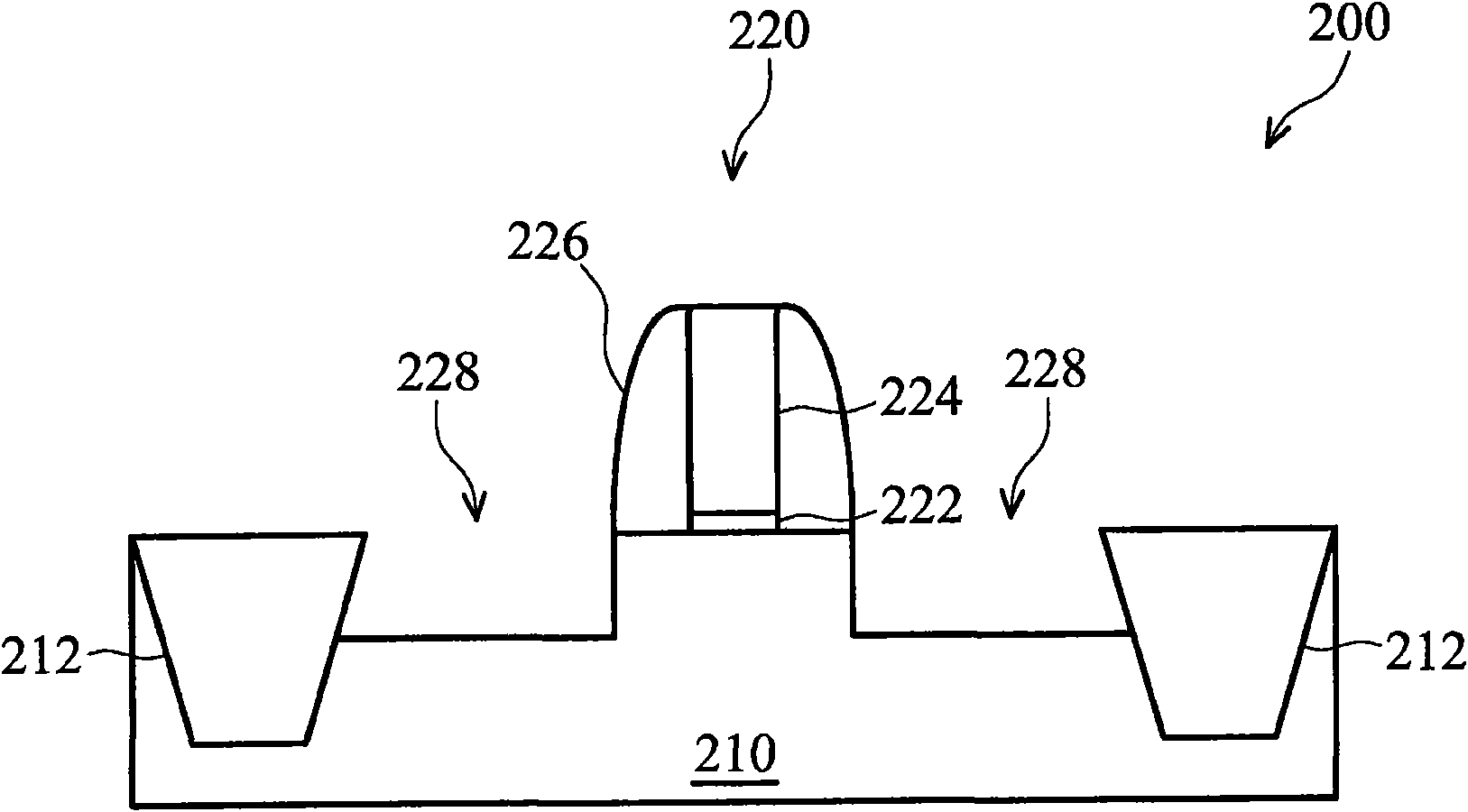

Semiconductor apparatus and method for fabricating the same

ActiveCN101908506AReduce dopingImprove short channel effectTransistorSemiconductor/solid-state device manufacturingElectrical junctionEngineering

The invention provides a semiconductor apparatus and method for fabricating the same. The method comprises providing a substrate comprising a first material; forming at least one gate stack over the substrate; forming one or more recesses in the substrate, wherein the one or more recesses define at least one source region and at least one drain region; and forming a pocket, a first layer comprising a second material, and a second layer comprising a third material in the one or more recesses, the pocket being disposed between the first layer and the substrate. The pockets 234 of the invention,essentially providing an abrupt junction between the source / drain region and substrate interface, may lead to significant improvement in SCEs (short channel effect) and / or reduce current leakage. Improvement in SCEs can allow continual semiconductor device scaling down. Further, in the present embodiment, the method may reduce strain relaxation within the SiGe portions of the source / drain regions, which can improve the performance of semiconductor device. the invention also reduces the channel doping degree.

Owner:TAIWAN SEMICON MFG CO LTD

Method for fabricating monolithic two-dimensional nanostructures

InactiveUS8641912B2Reliable electrical contactReduce dopingDecorative surface effectsNanoinformaticsResistEpoxy

A patterning method for the creation of two-dimensional nanowire structures. Nanowire patterning methods are used with lithographical patterning approaches to form patterns in a layer of epoxy and resist material. These patterns are then transferred to an underlying thin film to produce a two-dimensional structure with desired characteristics.

Owner:CALIFORNIA INST OF TECH

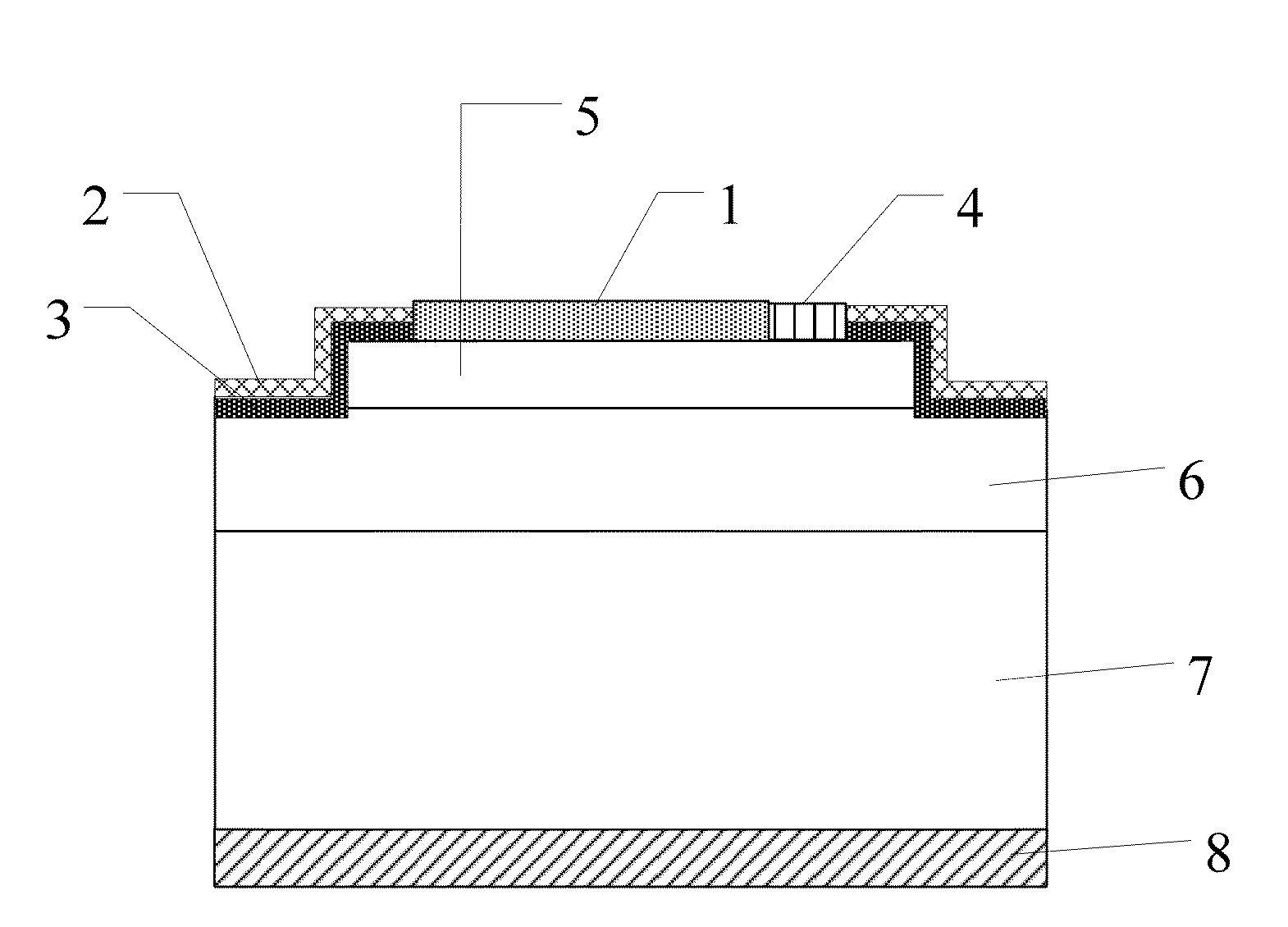

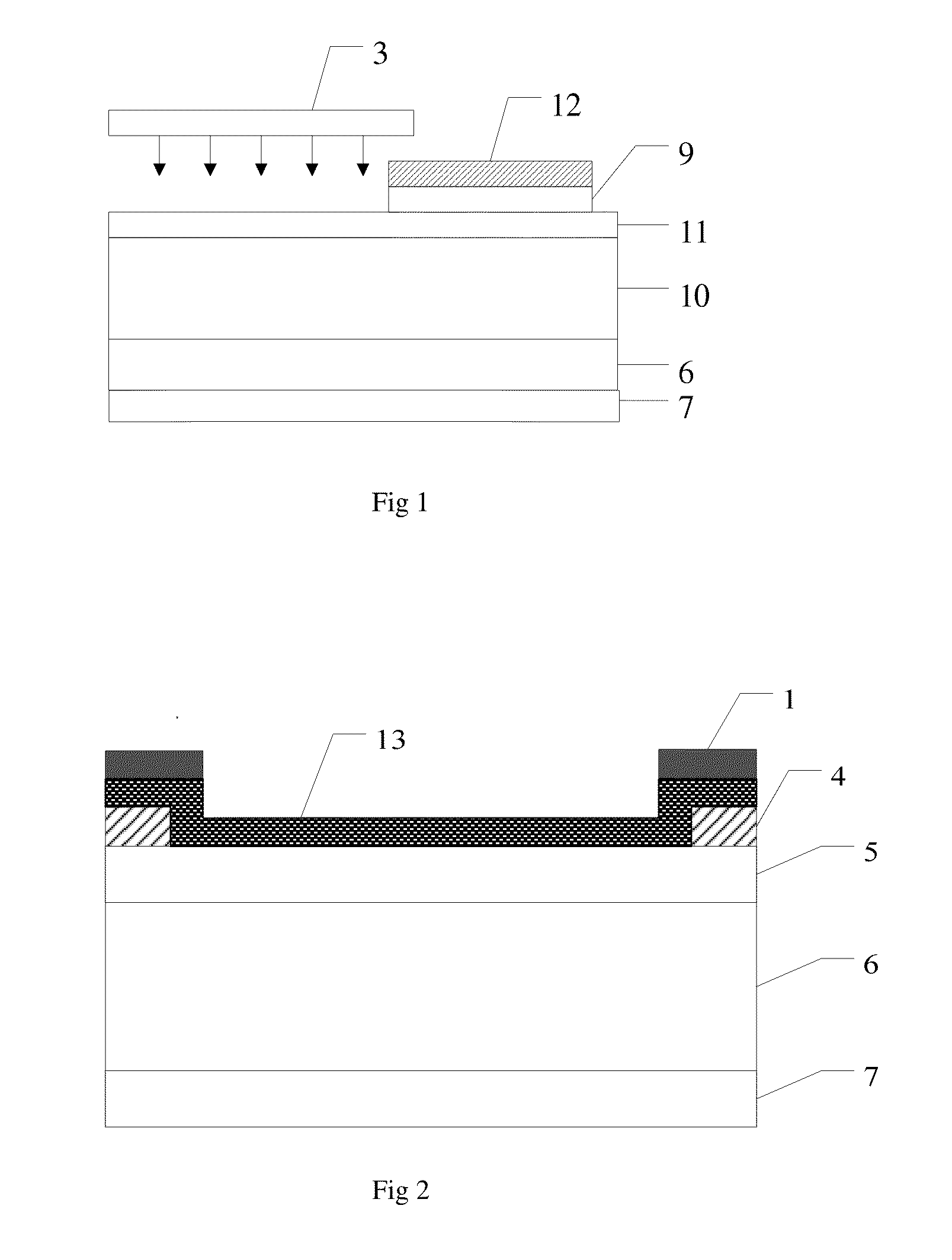

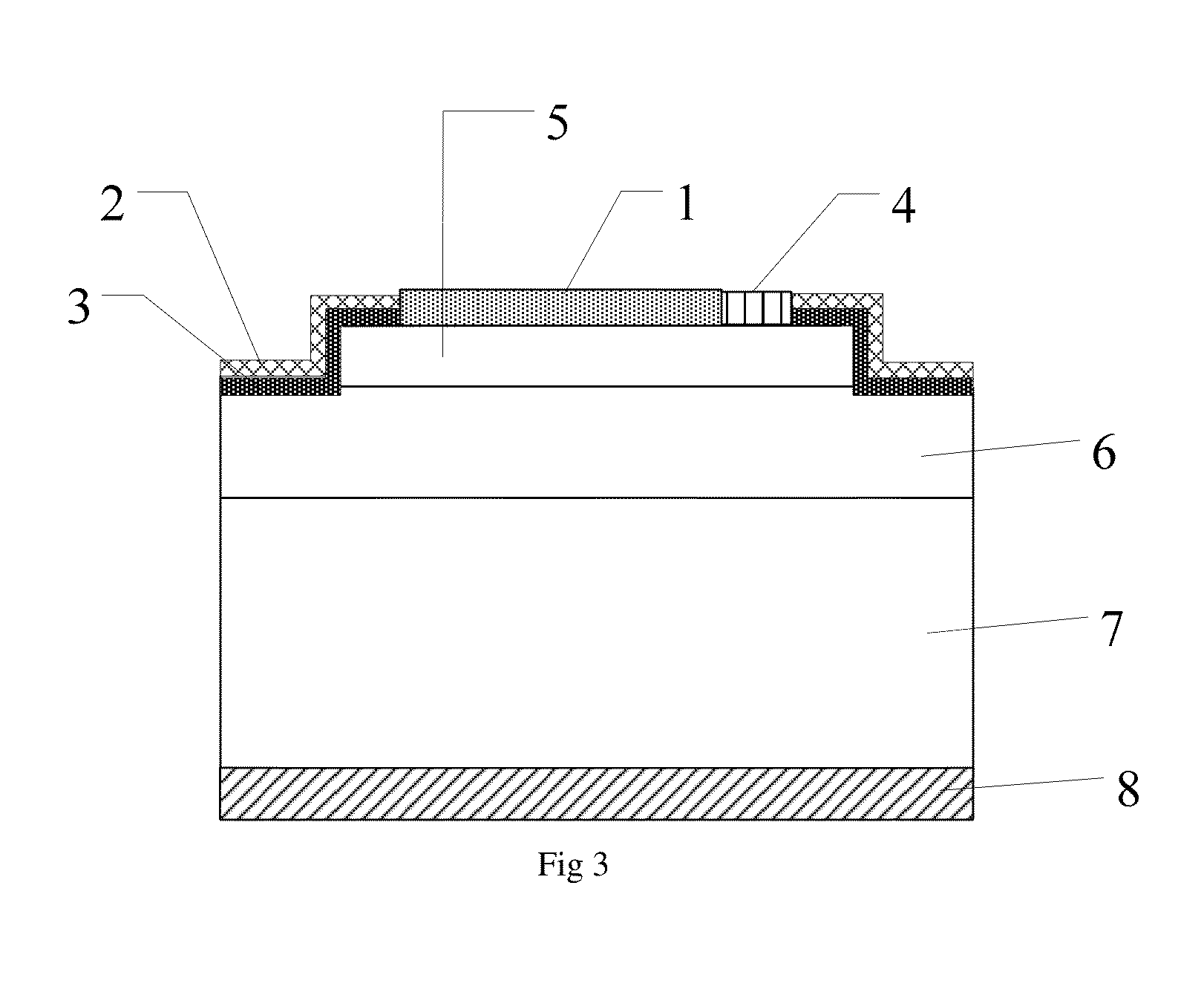

I-Layer Vanadium-Doped Pin Type Nuclear Battery and the Preparation Process Thereof

ActiveUS20140225472A1Increase widthIncrease collection rateSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerVanadium doping

A layer I vanadium-doped PIN-type nuclear battery, including from top to bottom a radioisotope source layer(1), a p-type ohm contact electrode(4), a SiO2 passivation layer(2), a SiO2 compact insulation layer(3), a p-type SiC epitaxial layer(5), an n-type SiC epitaxial layer(6), an n-type SiC substrate(7) and an n-type ohm contact electrode(8). The doping density of the p-type SiC epitaxial layer(5) is 1×1019 to 5×1019 cm3, the doping density of the n-type SiC substrate(7) is 1×1018 to 7×1018 cm3. The n-type SiC epitaxial layer(6) is a low-doped layer I formed by injecting vanadium ions, with the doping density thereof being 1×1013 to 5×1014 cm3. Also provided is a preparation method for a layer I vanadium-doped PIN-type nuclear battery. The present invention solves the problem that the doping density of layer I of the exiting SiC PIN-type nuclear battery is high.

Owner:XIDIAN UNIV

Short-channel silicon carbide power mosfet

ActiveUS8133789B1Reduced specific on-resistanceIncreased on-state current densitySemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactPower MOSFET

A silicon carbide power MOSFET having a drain region of a first conductivity type, a base region of a second conductivity type above the drain region, and a source region of the first conductivity type adjacent an upper surface of the base region, the base region including a channel extending from the source region through the base region adjacent a gate interface surface thereof, the channel having a length less than approximately 0.6 μm, and the base region having a doping concentration of the second conductivity type sufficiently high that the potential barrier at the source end of the channel is not lowered by the voltage applied to the drain. The MOSFET includes self-aligned base and source regions as well as self-aligned ohmic contacts to the base and source regions.

Owner:PURDUE RES FOUND INC

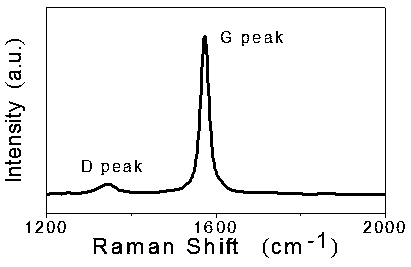

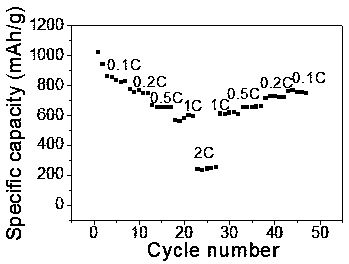

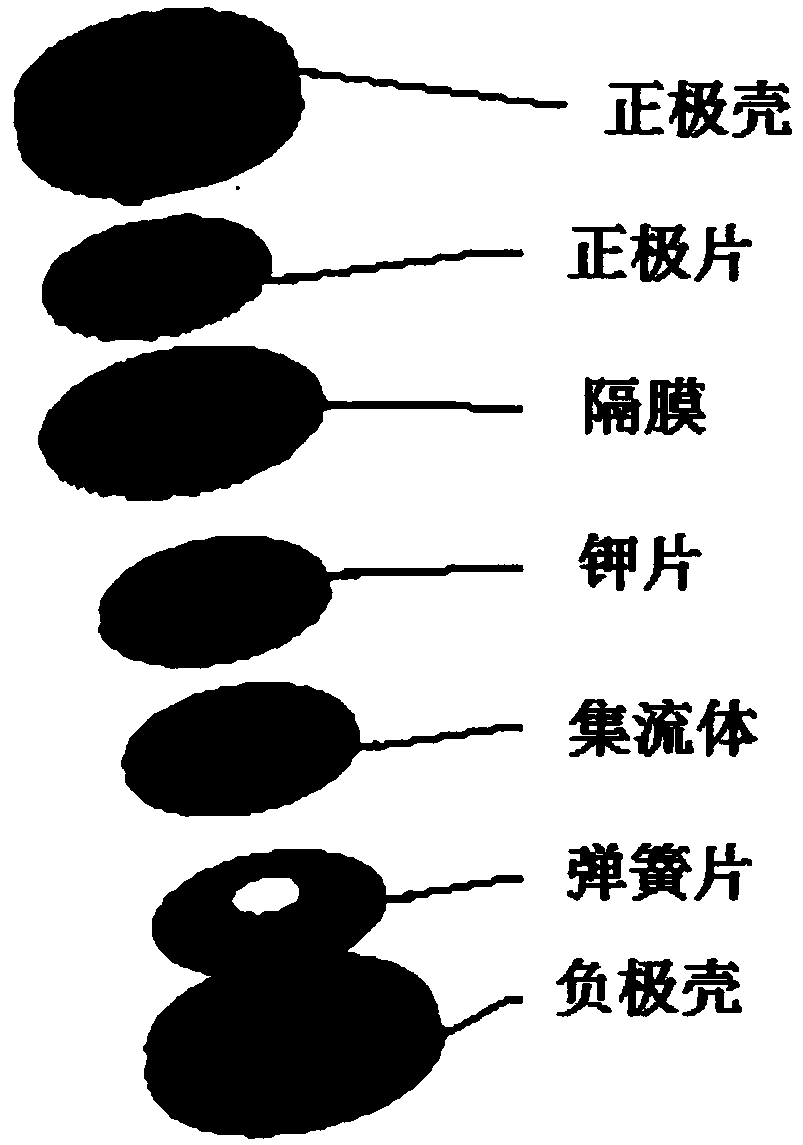

Small-size graphene positive electrode material for lithium-sulfur battery, lithium-sulfur battery prepared by small-size graphene positive electrode material and preparation method

ActiveCN107611395AImproved magnification performanceImprove wettabilityCell electrodesFinal product manufactureElectrolysisLithium sulfur

The invention discloses a small-size graphene positive electrode material for a lithium-sulfur battery, the lithium-sulfur battery prepared by the small-size graphene positive electrode material and apreparation method and belongs to the field of battery materials. The preparation method comprises the steps of preparing small-size graphene through electrolyzing microcrystalline graphite powder; compounding the small-size graphene or surface-modified small-size graphene, such as the small-size graphene-modified by sodium carboxymethyl cellulose, sulfate, silicate, metal ions, a metal oxide, anon-metallic element or a high polymer material and sulfur at the mass ratio of 2:(1-9) to prepare the positive electrode material for the lithium-sulfur battery; and then preparing the lithium-sulfurbattery by adopting metal lithium as a negative electrode. The prepared lithium-sulfur battery is a real sense of graphene lithium-sulfur battery, the graphene is only used as an additive in the other lithium-sulfur batteries, and the prepared lithium-sulfur battery is fundamentally different from the other lithium-sulfur batteries. The positive electrode material for the lithium-sulfur battery is high in specific capacity, good in cycle performance, high in security, high in conductivity and low in cost, and has a very broad market prospect.

Owner:SHANXI INST OF COAL CHEM CHINESE ACAD OF SCI

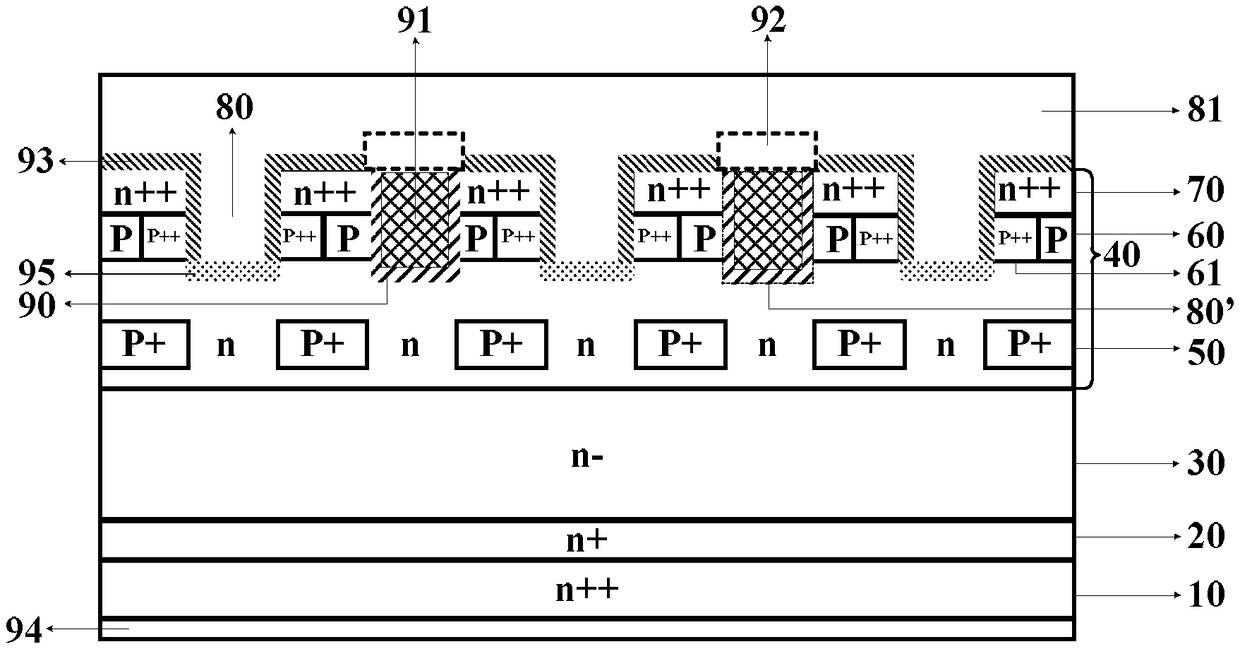

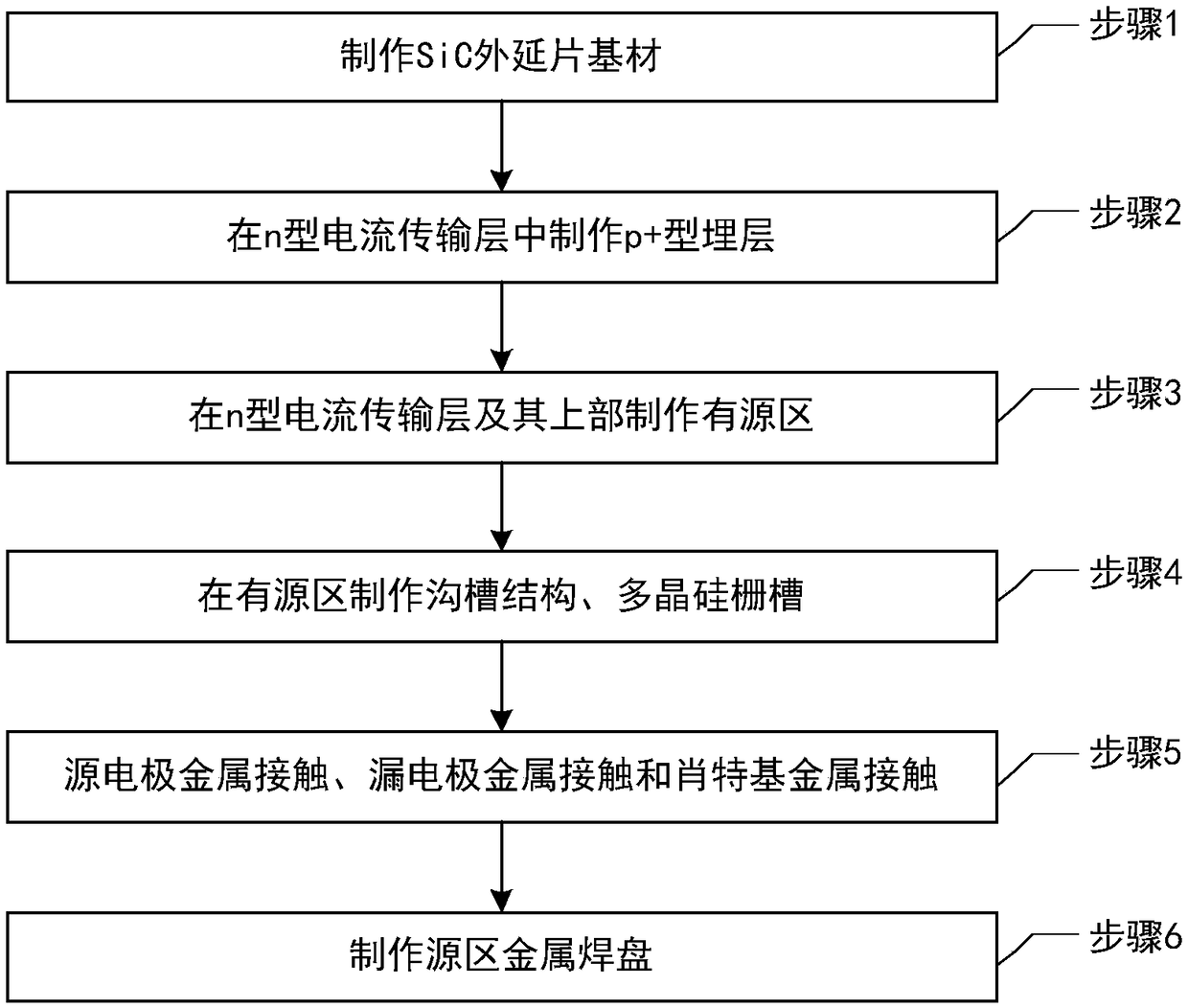

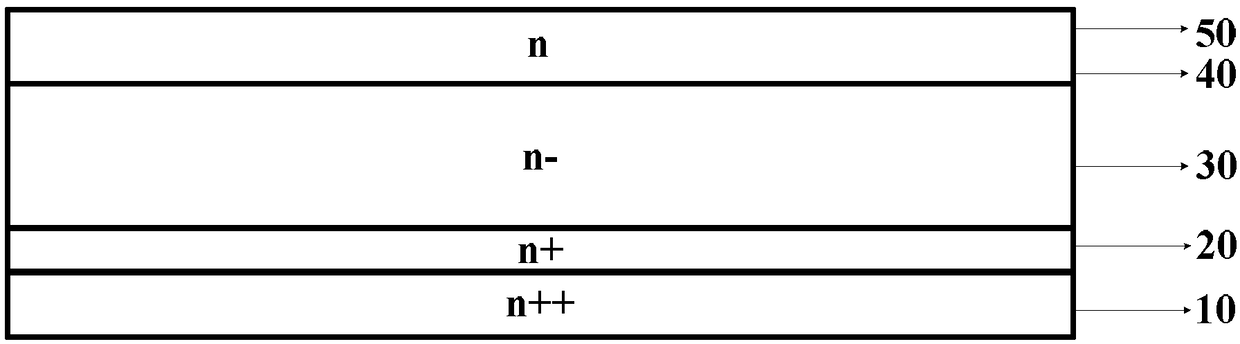

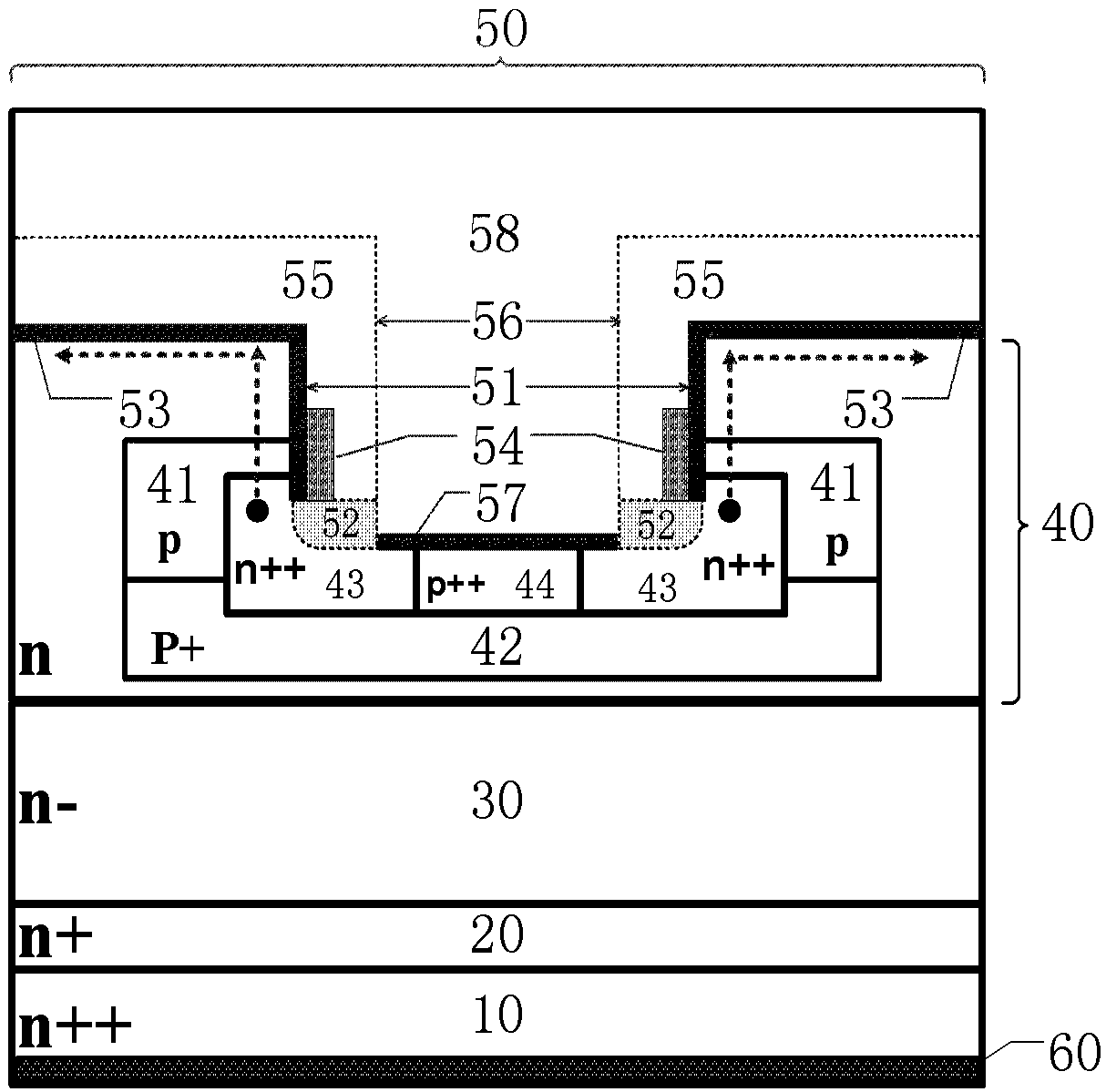

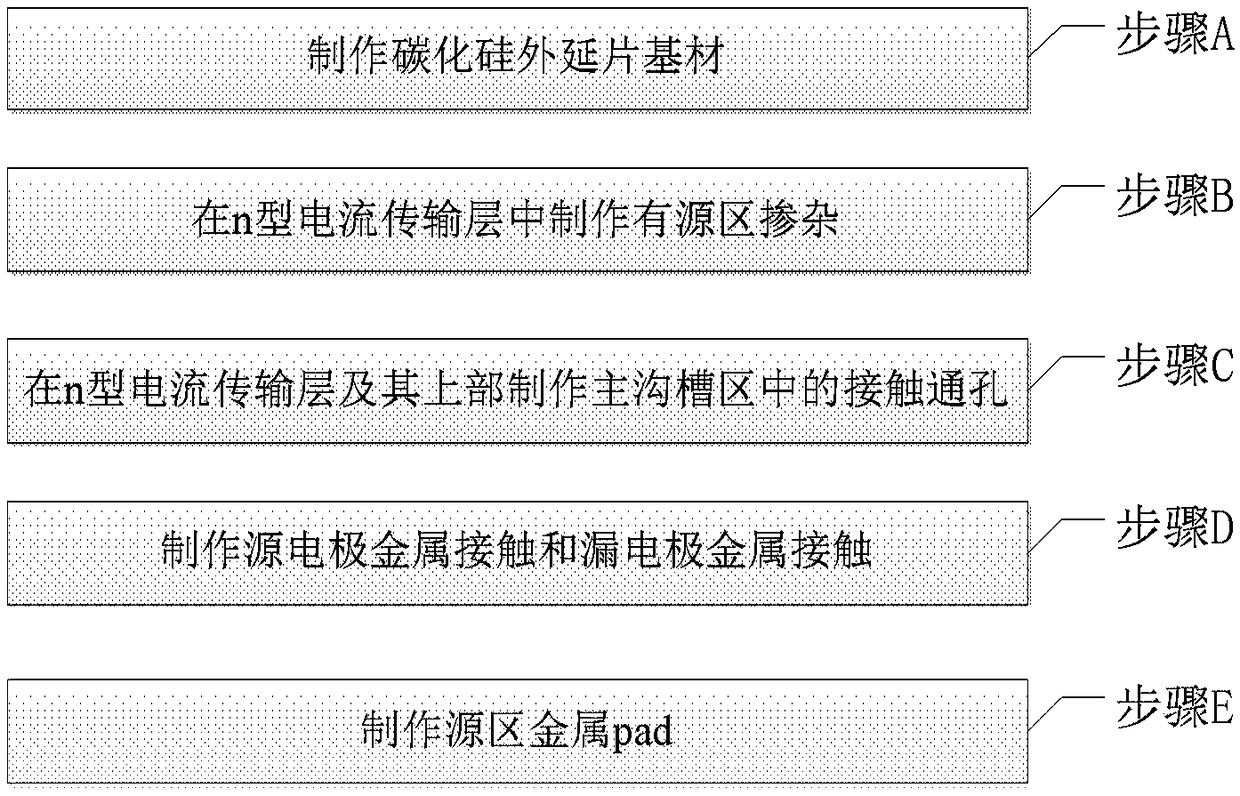

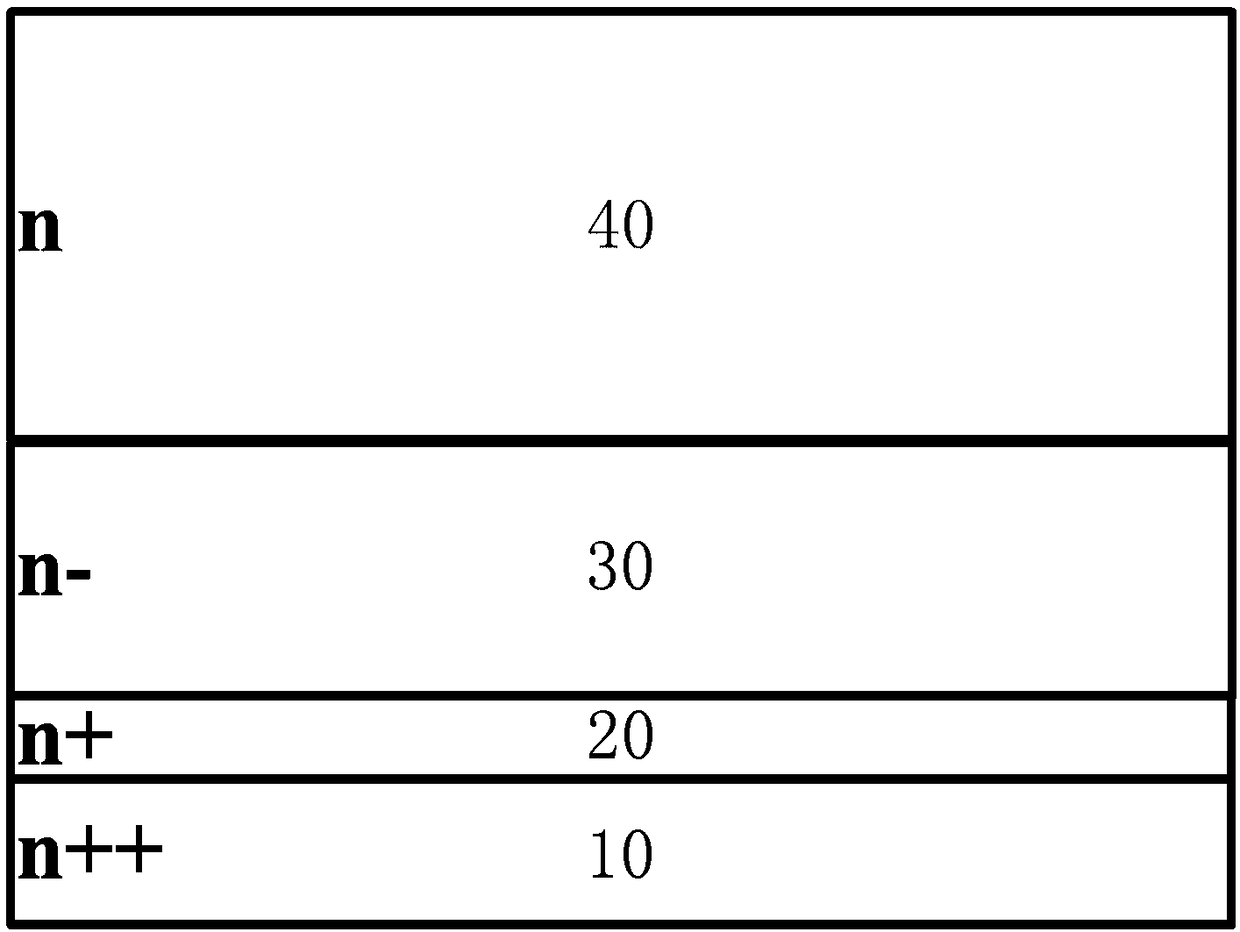

A structure of SiC UMOSFET integrated with SBD and a preparation method thereof

InactiveCN109065540AGood on-state characteristicsReduce dopingSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETField-effect transistor

The invention provides a silicon carbide trench gate metal oxide with semiconductor field effect transistor (SiC UMOSFET) structure integrated Schottky diode (SBD) and a method for manufacturing the same, The structure is characterized by, a p +-type bury layer (50) is formed on the n-type current transport layer (40) by implantation, and further an n-type current transport layer (40) is epitaxially formed so that the p +-type buried layer (50) floats, and the p +-type buried layer (50) can effectively reduce the electric field in the gate trench oxide and the electric field at the Schottky contact position in the blocking mode, so that the SBD integrated SiC UMOSFET has high blocking ability, and the high temperature and high field reliability of the device are greatly improved. At that same time, the relative position of the main trench (80), the main trench (80') and the p +-type buried layer (50) and the n-type current transport layer (40) are adjusted so that when the MOSFET is operated in the first quadrant, the conduction characteristic of the MOSFET does not degrade significantly; When the MOSFET is operated in the third quadrant, the conduction of the parasitic pn diode inthe MOSFET is effectively suppressed and the Schottky diode conduction mode is obtained. SiC UMOSFETs with integrated SBD have a lower total chip area than discrete SBD and MOSFET devices.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

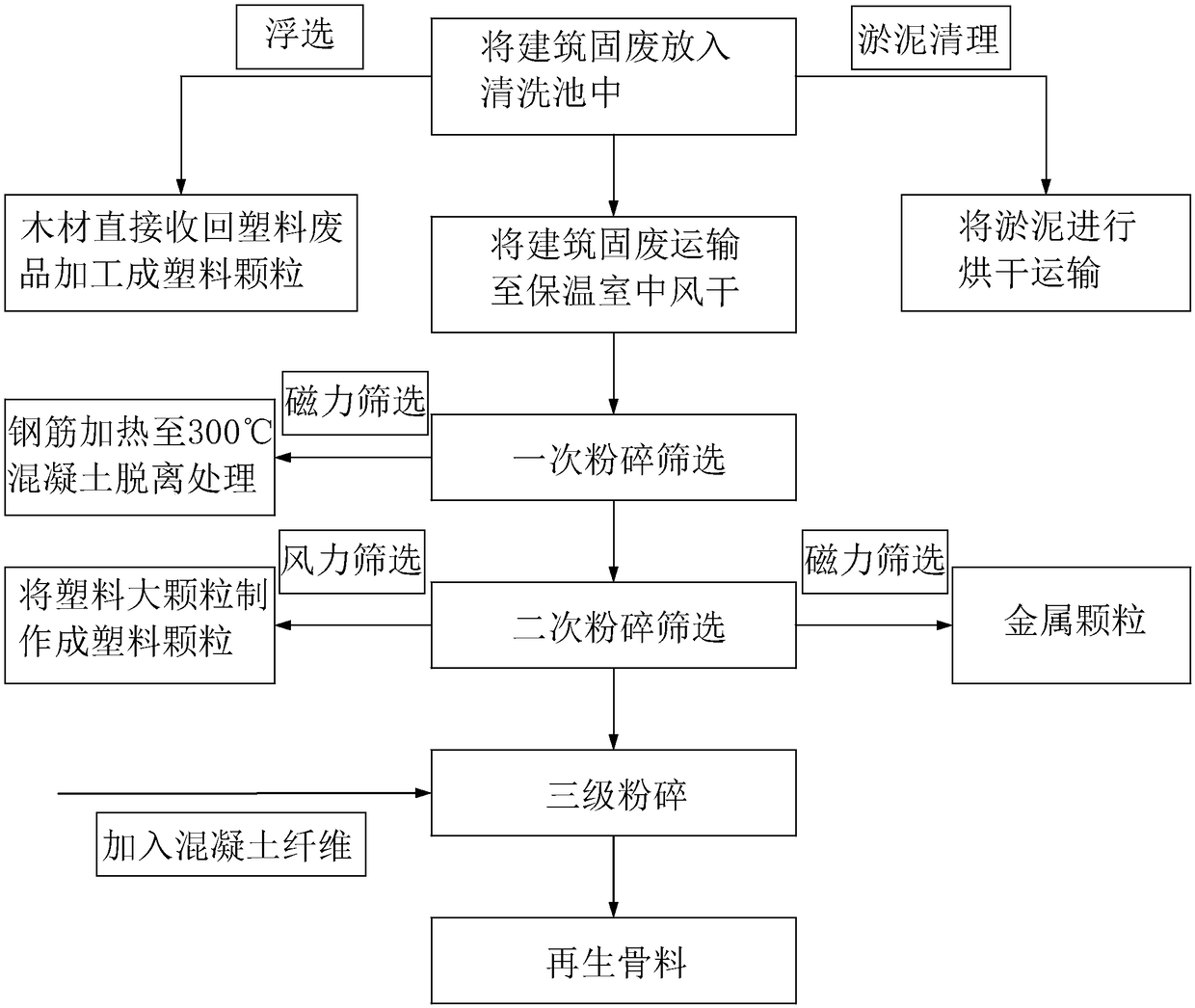

High-quality processing technology for building solid waste

InactiveCN108994040AReduce dopingEasy to separateConstruction waste recoverySolid waste disposalSludgeEngineering

The invention discloses a high-quality processing technology for building solid waste, and belongs to the field of building solid waste recycling. The key point of the technical scheme is that the building solid waste is subjected to technological steps such as washing flotation, sludge treatment, primary crushing screening, secondary crushing screening, tertiary crushing screening and the like successively, metal solids, plastic solids, wood and the like in the waste are screened, and recycled aggregate is made of a main material of the building solid waste. The problems of heavy work, laborconsumption and low work efficiency caused by manual screening of solid wastes such as plastic, wood and the like in building wastes are solved; plastics, wood and the like in the building solid wastecan be screened conveniently and efficiently.

Owner:温州市申宏建设有限公司

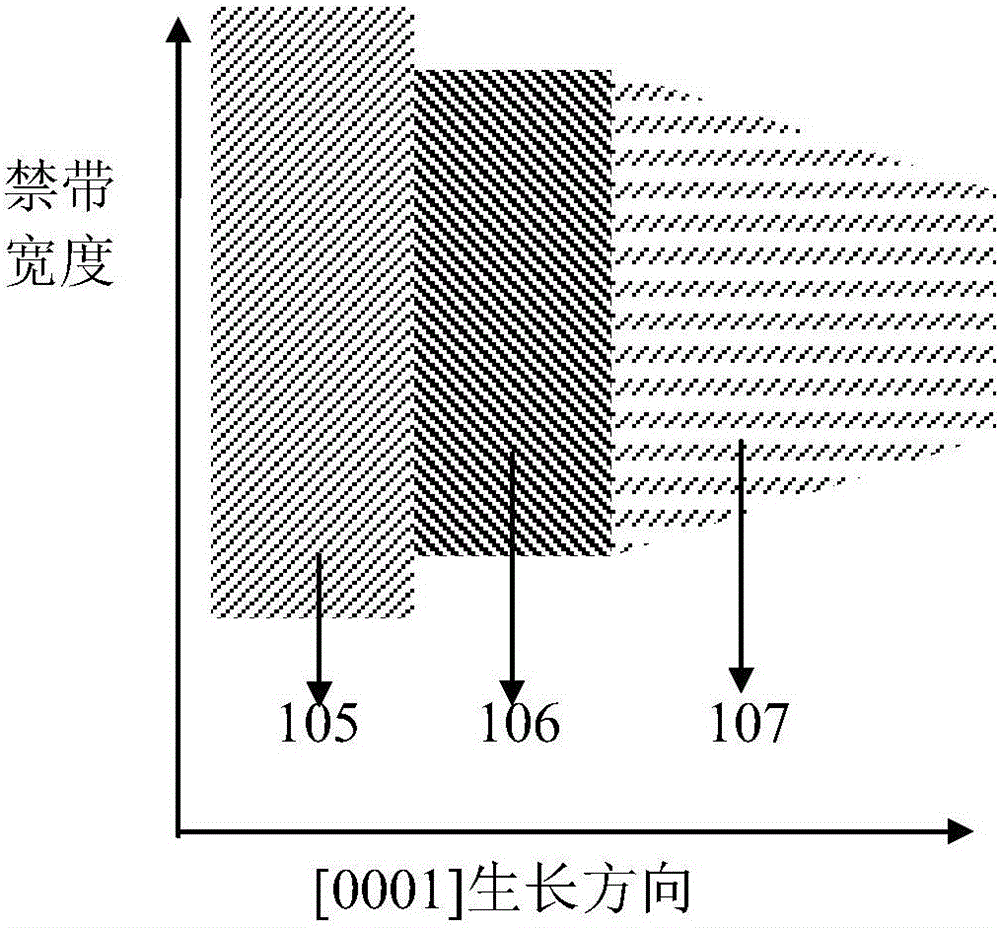

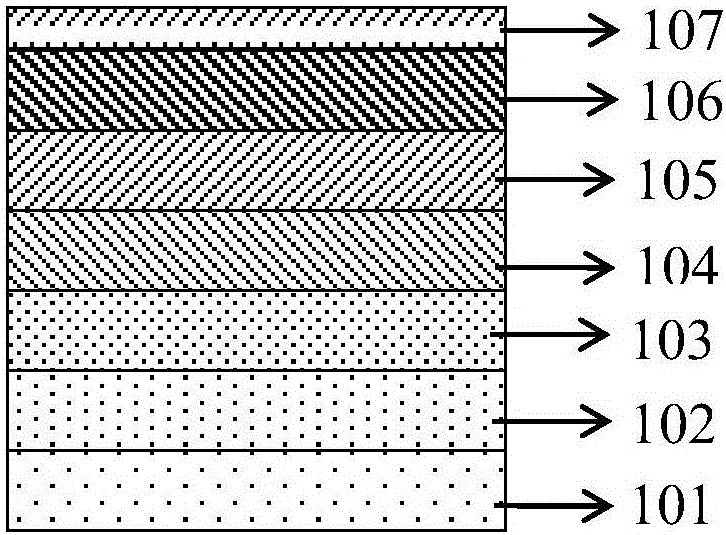

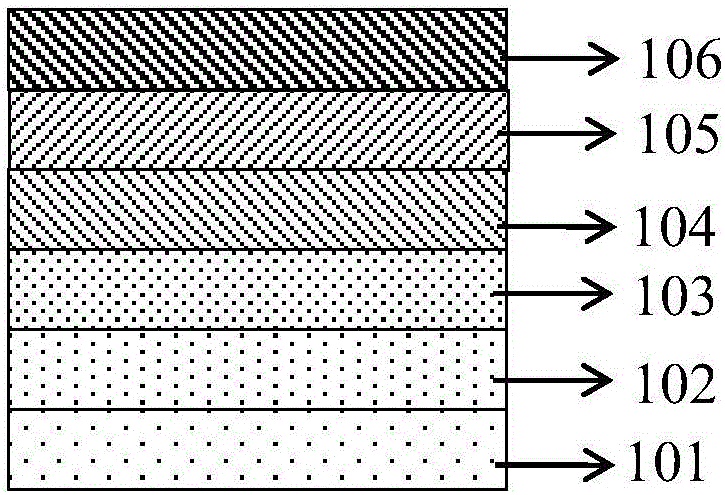

Light emitting diode epitaxy structure provided with P-type ohmic contact layer

ActiveCN105702829AImprove luminous efficiencyImproved contact characteristicsSemiconductor devicesSemiconductor materialsTransport layer

The invention discloses a light emitting diode epitaxy structure provided with a P-type ohmic contact layer and relates to a semiconductor device which is characterized by the electrode, is provided with at least one potential jump barrier or surface barrier and is special for light emission. The structure comprises a substrate, a buffer layer, an N-type semiconductor material layer, a multiple quantum well layer, a P-type electron blocking layer, a P-type semiconductor material transport layer and the P-type ohmic contact layer from top to bottom in sequence, wherein the P-type ohmic contact layer consists of AlxInyGa1-x-yN, wherein x is not less than 0 and is less than 1, y is not less than 0 and is less than 1, 1-x-y is not less than 0, the group component is gradient, the lattice constant is gradually increased along the growth direction and the forbidden bandwidth is gradually reduced. The light emitting diode epitaxy structure overcomes the defects that the wideband gap nitride semiconductor is difficult to form P-type ohmic contact and the hole supply is difficult in the prior art, and the light emitting efficiency of the LED is improved.

Owner:ZHIXIN SEMICON (HANGZHOU) CO LTD

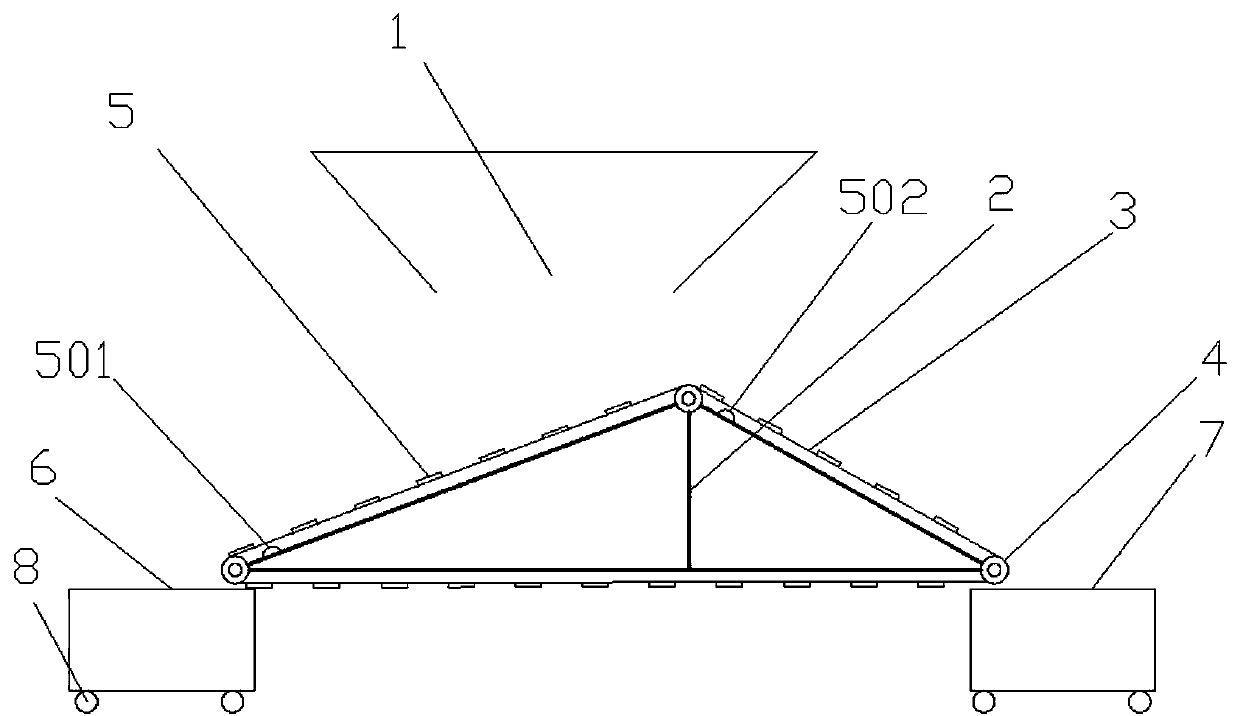

Wine distillation equipment

InactiveCN107686804AGuaranteed qualityReduce dopingAlcoholic beverage preparationDistillationEngineering

The invention provides wine distillation equipment, which comprises a distillation barrel, a condensation barrel and a cooling water tank, wherein the distillation barrel is composed of two parts of an upper barrel and a lower barrel, the lower barrel is divided into an upper layer and a lower layer, the upper layer is averagely divided into a left part and a right part, a heating motor is respectively arranged in the two parts, a water inlet is respectively formed in the left side and the right side of the upper layer, a water outlet is formed in the right side of the lower layer of the lowerbarrel, a steam circulation space is reversed between the upper barrel and a barrel wall of the distillation barrel, the water outlet is connected with the left side of the cooling water tank, a stirring rod is arranged in the upper barrel, a thermometer and a filter are connected to a distillation pipeline, a spiral condensation pipeline is arranged in the condensation barrel, the top of the condensation pipeline is connected with the distillation pipeline, the bottom end of the condensation pipeline is connected with a wine outlet, a cold water inlet is formed in a lower left part of the condensation barrel, a hot water outlet is formed in an upper right part of the condensation barrel, the water inlets are connected with the cooling water tank, a first control valve and a second control valve are arranged on a hot water pipeline, and the cold water inlet is connected with the cooling water tank.

Owner:句容市华东综合酿造厂

Dust removal type shelling and polishing equipment for rice processing

ActiveCN112206855AImprove aestheticsReduce pollutionGrain huskingGrain polishingAgricultural engineeringAgricultural science

The invention belongs to the technical field of rice processing equipment, particularly relates to dust removal type shelling and polishing equipment for rice processing. Aiming at the problem that inthe prior art, feeding and discharging conveying is inconvenient, the screening effect is poor, and dust generated during rice processing cannot be pumped away during processing, and the processing environment is influenced to a certain extent while the appearance of rice is influenced, the following scheme is currently provided. According to the scheme, the dust removal type shelling and polishing equipment comprises a mounting frame, wherein a shelling box and a polishing box are fixedly mounted on the mounting frame, and the shelling box is located above the polishing box. According to thedust removal type shelling and polishing equipment, through the cooperation of a first rubber roller, a second rubber roller, protruding blocks and a screen, the effective conveying and screening effects of the rice can be achieved, through cooperation of an inclined conveying barrel, a vertical conveying barrel and a draught fan, the dust removal effect can be achieved in the rice conveying process, dust mixed in the rice is reduced, and meanwhile, pollution to the processing environment is reduced, and the practicability is improved.

Owner:HUNAN ZHANWANG BIOTECH DEV

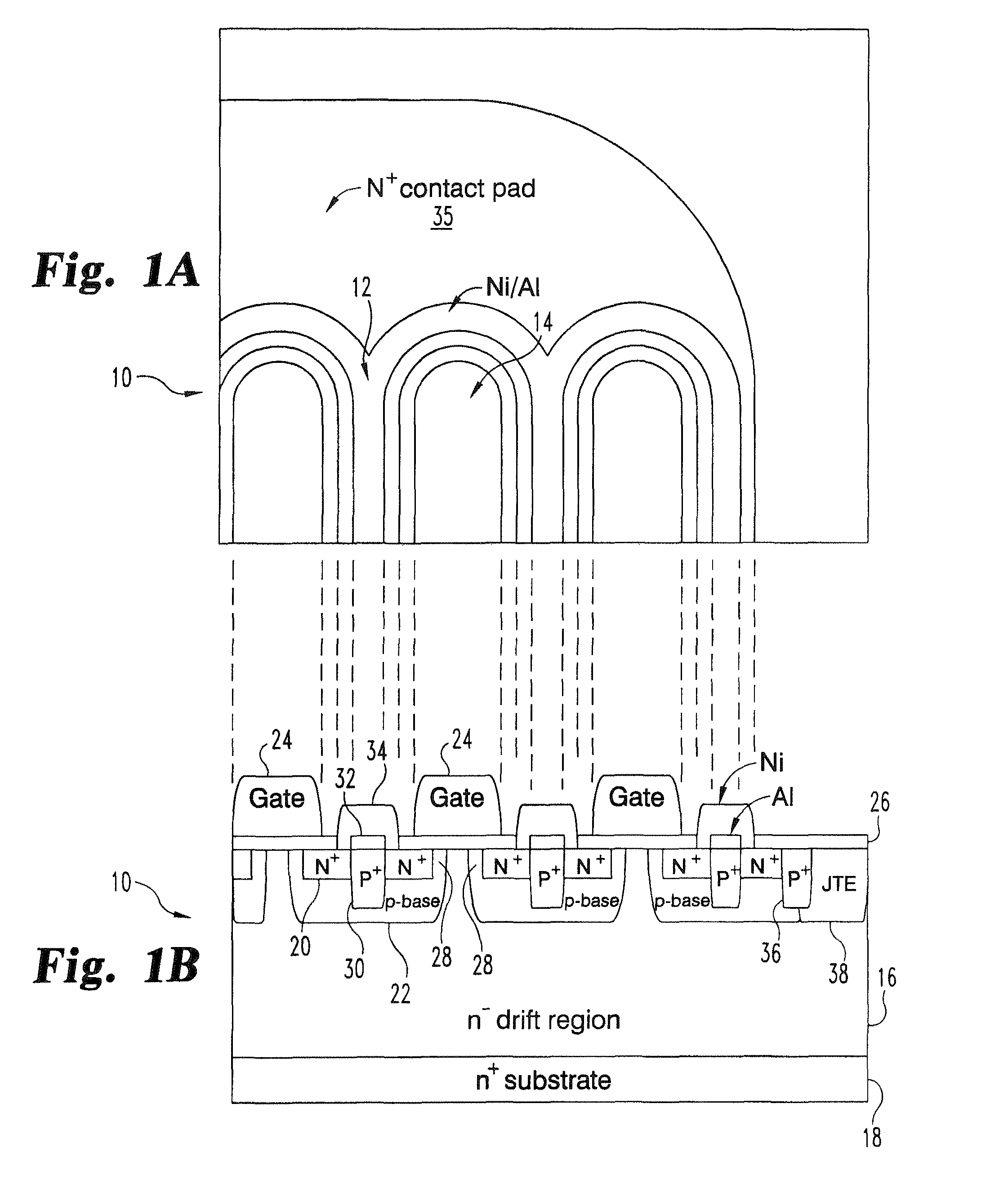

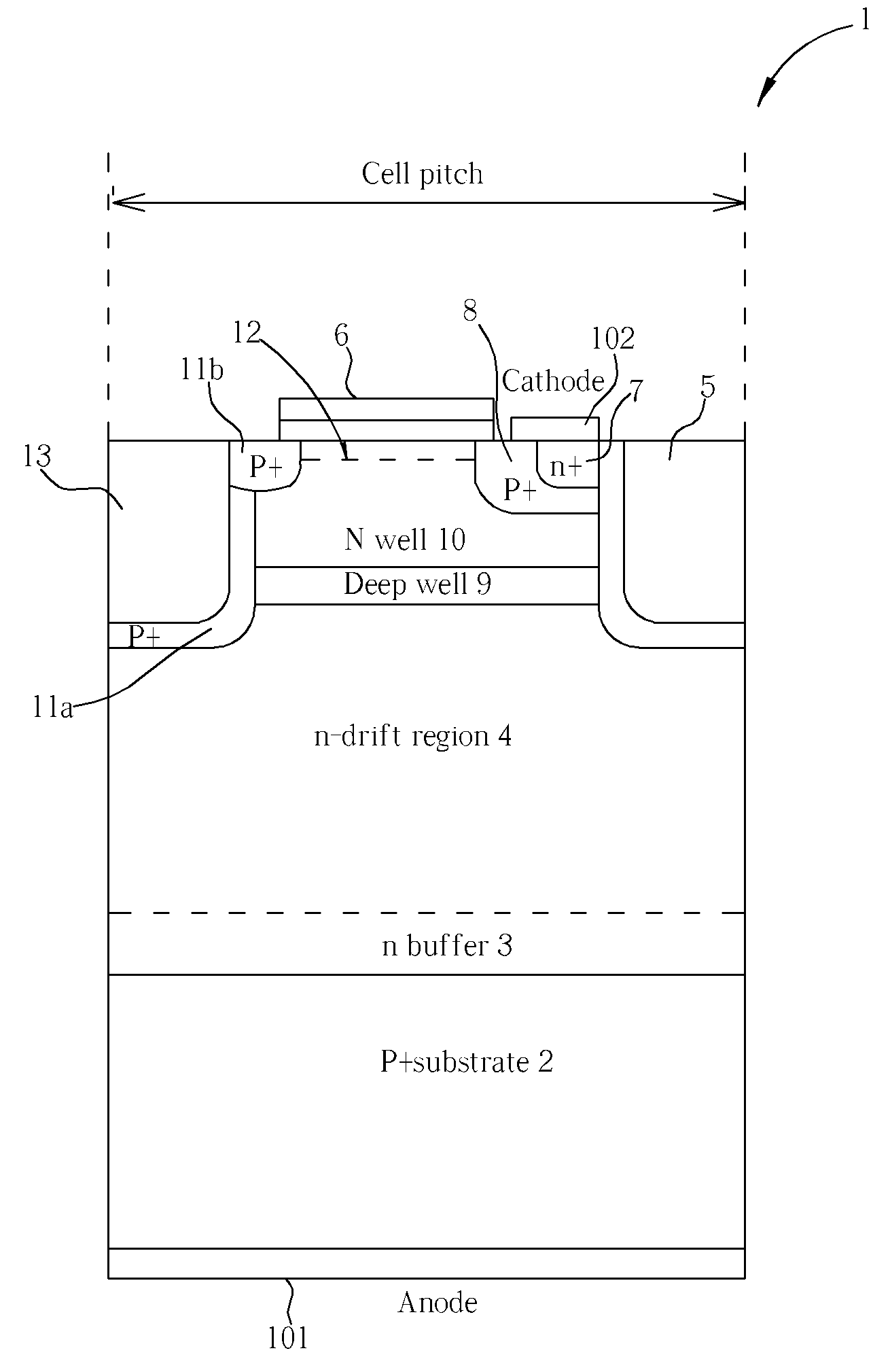

Insulated gate bipolar transistor device comprising a depletion-mode MOSFET

InactiveUS7968940B2Reduce the number of holesReduce transportationTransistorSolid-state devicesEngineeringDouble gate

Double gate IGBT having both gates referred to a cathode in which a second gate is for controlling flow of hole current. In on-state, hole current can be largely suppressed. While during switching, hole current is allowed to flow through a second channel. Incorporating a depletion-mode p-channel MOSFET having a pre-formed hole channel that is turned ON when 0V or positive voltages below a specified threshold voltage are applied between second gate and cathode, negative voltages to the gate of p-channel are not used. Providing active control of holes amount that is collected in on-state by lowering base transport factor through increasing doping and width of n well or by reducing injection efficiency through decreasing doping of deep p well. Device includes at least anode, cathode, semiconductor substrate, n− drift region, first & second gates, n+ cathode region; p+ cathode short, deep p well, n well, and pre-formed hole channel.

Owner:ANPEC ELECTRONICS CORPORATION

Vertical hall sensor and method for producing a vertical hall sensor

The invention relates to a vertical Hall sensor integrated in a semiconductor chip and a method for the production thereof. The vertical Hall sensor has an electrically conductive well of a first conductivity type, which is embedded in an electrically conductive region of a second conductivity type. The electrical contacts are arranged along a straight line on a planar surface of the electrically conductive well. The electrically conductive well is generated by means of high-energy ion implantation and subsequent heating, so that it has a doping profile which either has a maximum which is located at a depth T1 from the planar surface of the electrically conductive well, or is essentially constant up to a depth T2.

Owner:X FAB SEMICON FOUNDRIES +1

Silicon carbide groove-shaped metal-oxide-semiconductor field-effect transistors (MOSFETs) and fabrication method thereof

ActiveCN108417617AImprove mobilityReduce dopingSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETElectrical resistance and conductance

The invention provides silicon carbide groove-shaped metal-oxide-semiconductor field-effect transistors (MOSFETs) and a fabrication method thereof. Gate contact of the MOSFETs is arranged at a side wall of a main groove, source metal contact is formed at the bottom of the groove, electrons flow through an inversion layer at the side wall of the groove from bottom to top to form an inverse conduction channel different from traditional groove-shaped MOSFETs during positive conduction, a high electric field of a body region of a device is effectively shielded by the source metal contact at the bottom of the groove during reverse blocking, so that the gate dielectric field of the device is greatly reduced, and avalanche occurs at a PN junction of the body region of the device. The fabricated silicon carbide groove-shaped MOSFETs have relatively low positive conduction resistance and relatively high reverse blocking capability, and the static and dynamic working reliability of the device can be improved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Gear hobbing machine iron chip processing device

The invention discloses a gear hobbing machine iron chip processing device and belongs to the field of iron chip processing assemblies of gear hobbing machines. The gear hobbing machine iron chip processing device comprises a triangular support and a conveyer belt outside the support. V-shaped electromagnets are evenly arranged on the conveyer belt. Under the action of a left contact switch and aright contact switch, attraction and separation of iron chips are conducted, and most of the iron chips falls into a right iron chip collecting vehicle. A stirring device is arranged in a left cuttingoil collecting device. The lower side of the stirring device is provided with eight electromagnetic rods. During stirring, the iron chips in the cutting oil can be attracted, so that further separation is achieved. Compared with an existing device which only depends on a magnetic assembly on the conveyer belt to conduct attraction, the gear hobbing machine iron chip processing device obtains thecutting liquid of a higher purity, and iron chip separation treatment can be conducted on the high concentration of cutting oil.

Owner:广州席风机电设备工程有限公司

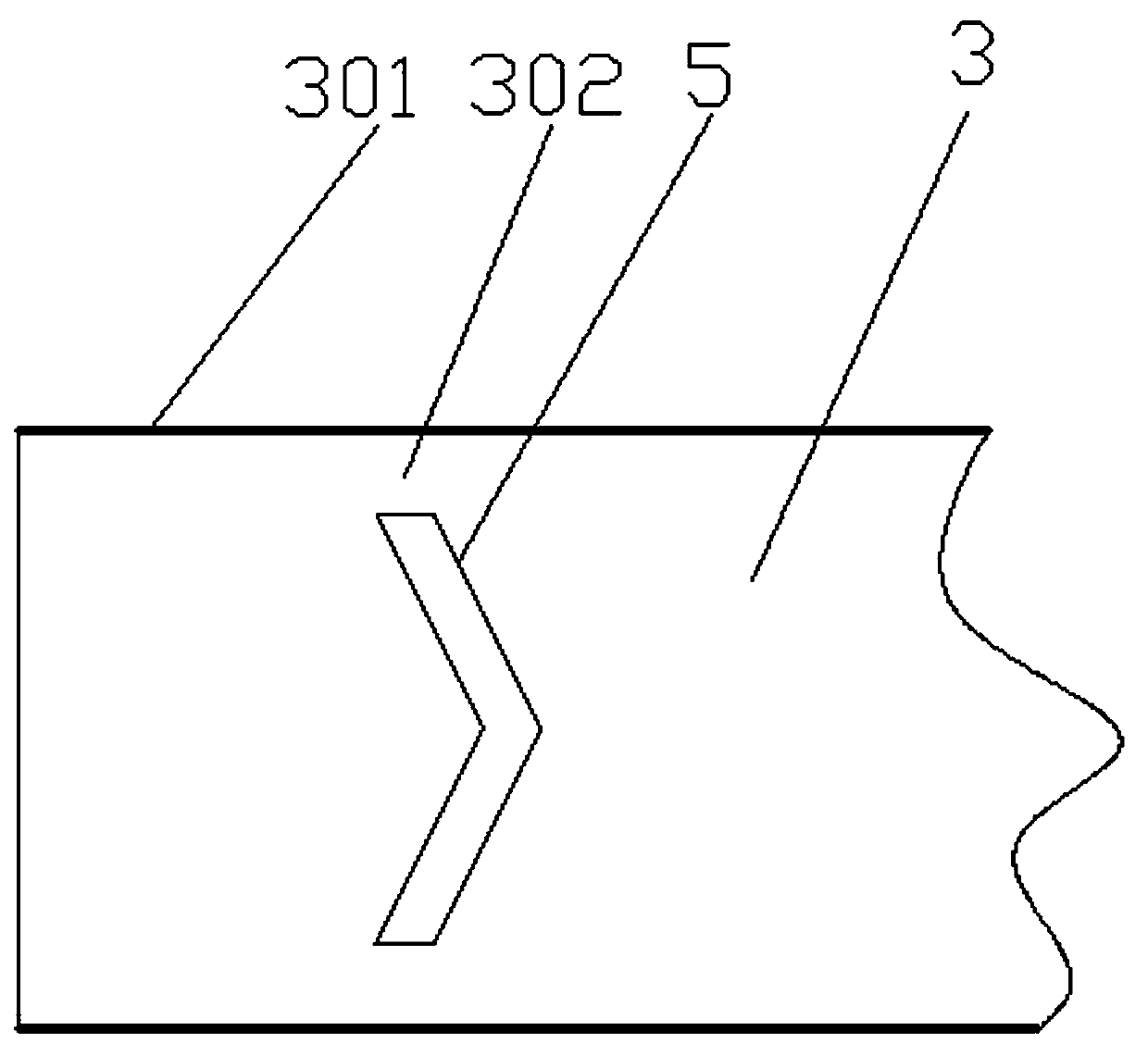

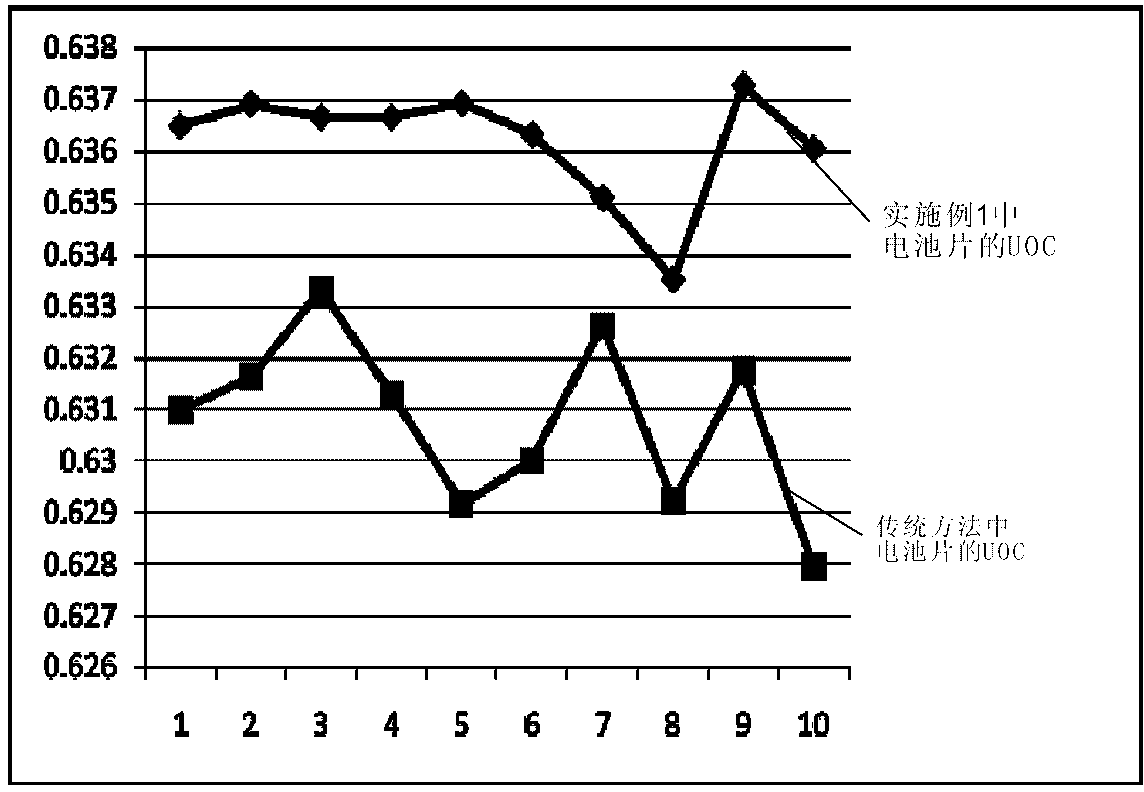

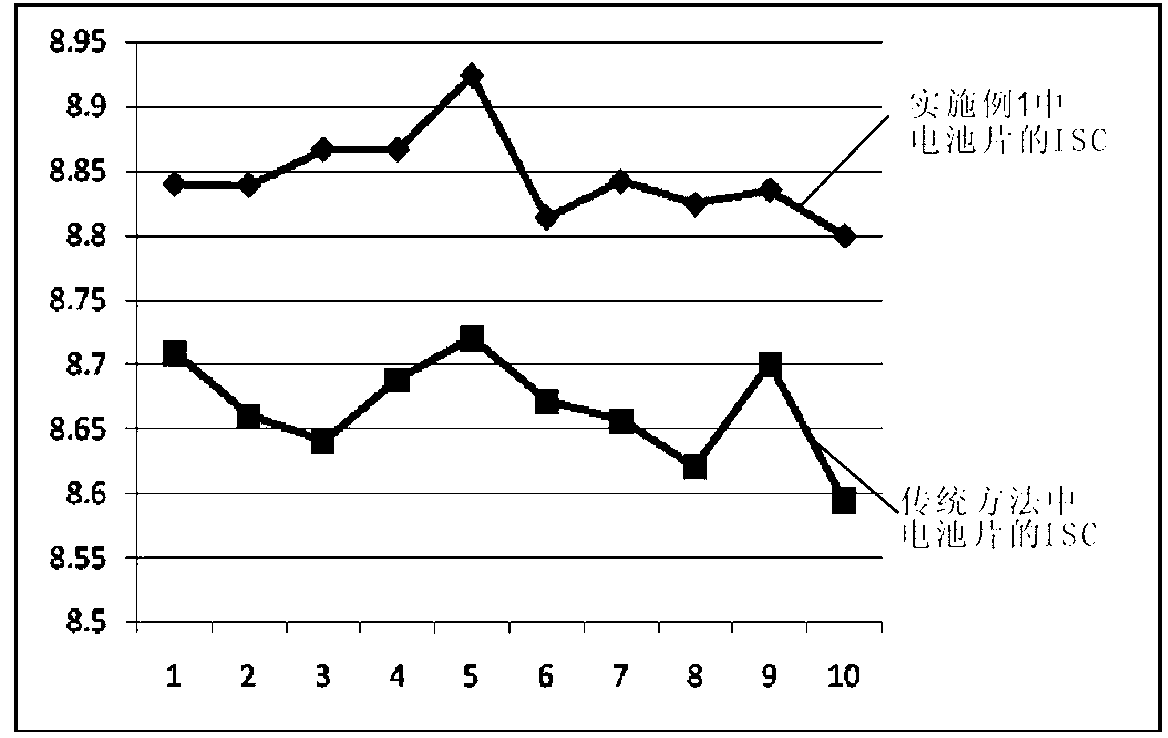

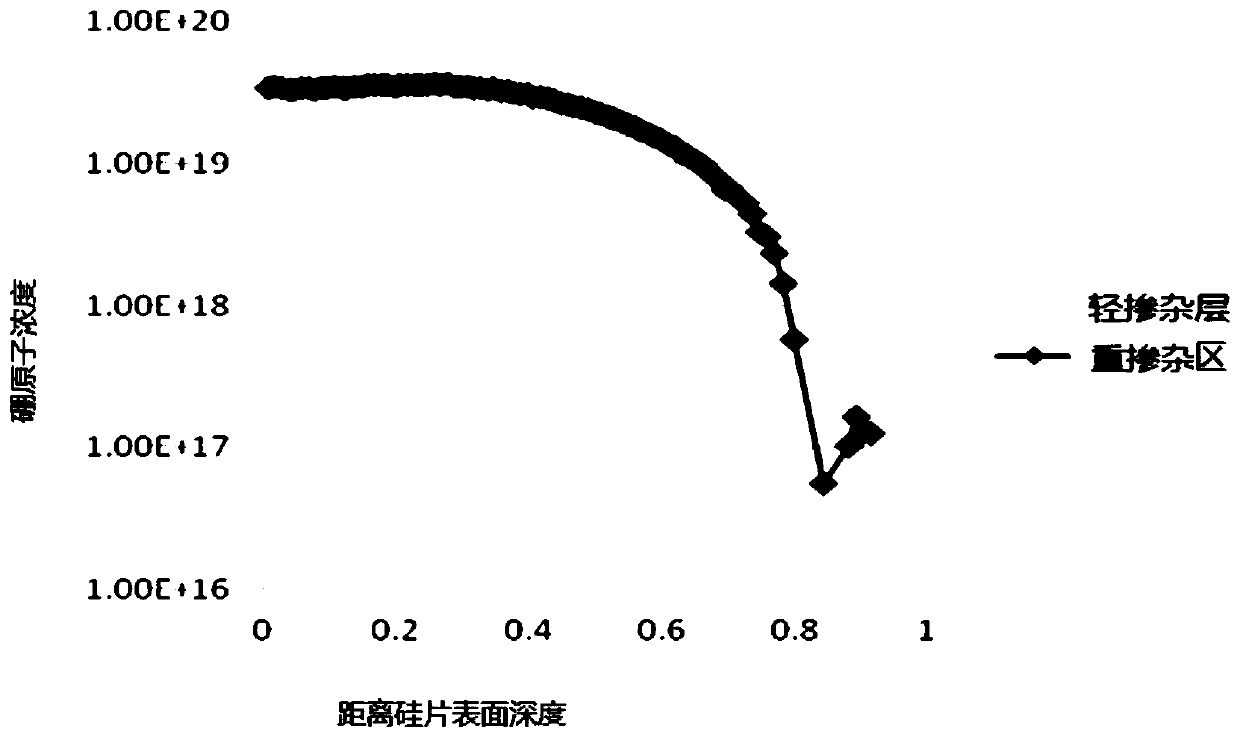

Method for preparing crystalline silicon battery pieces through multistep gradient diffusion method

ActiveCN103346074AReduce dopingExtend your lifeSemiconductor/solid-state device manufacturingMetallurgyPhysical chemistry

The invention relates to the production technology of crystalline silicon battery pieces, in particular to the filed of crystalline silicon battery piece diffusion manufacturing procedures. A method for preparing the crystalline silicon battery pieces through a multistep gradient diffusion method specifically comprises the following steps: P type crystalline silicon is placed in a furnace tube at the preset temperature of 800 DEG C, then, nitrogen is blown into the furnace tube, and the temperature is kept constant for 600-900 seconds; the temperature inside the furnace tube is raised to 860 DEG C in two steps, and oxygen and the nitrogen are blown into the furnace tube at the same time; the temperature inside the furnace tube is kept constant at 860 DEG C, and the oxygen, the nitrogen and a phosphorus source are blown into the furnace tube at the same time; the temperature inside the furnace tube is gradually and slowly lowered to 852 DEG C, the phosphorus source, the oxygen and the nitrogen are blown into the furnace tube at the same time, and the time duration is 800 seconds; the temperature inside the furnace tube is directly lowered again to 800 DEG C, the oxygen and the nitrogen are blown into the furnace tube at the same time, and annealing is conducted after 300 seconds; after the annealing, the nitrogen is blown into the furnace tube, and a finished product is taken out of the furnace tube. Compared with the traditional technique, the method for preparing the crystalline silicon battery pieces through the multistep gradient diffusion method has increased the battery conversion rate by at least 0.25 percentage point.

Owner:九州方园新能源股份有限公司

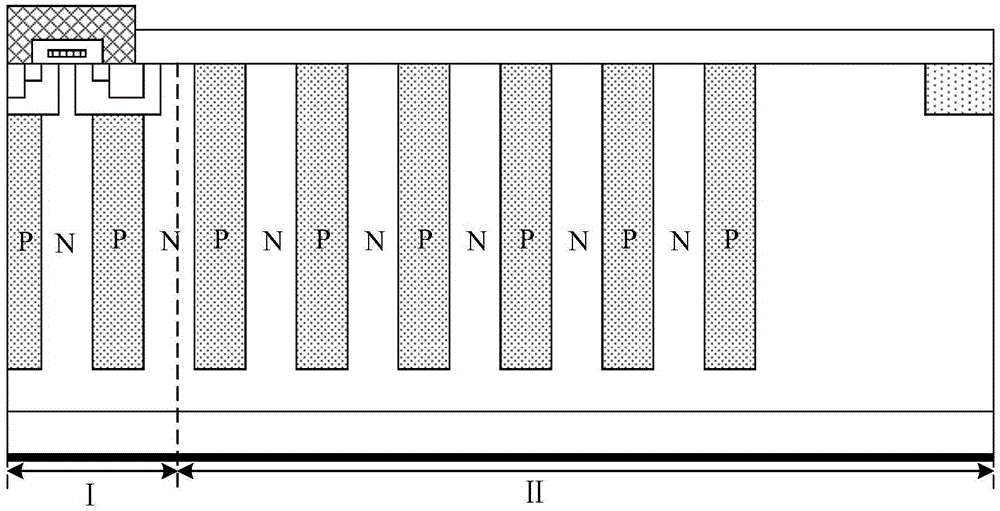

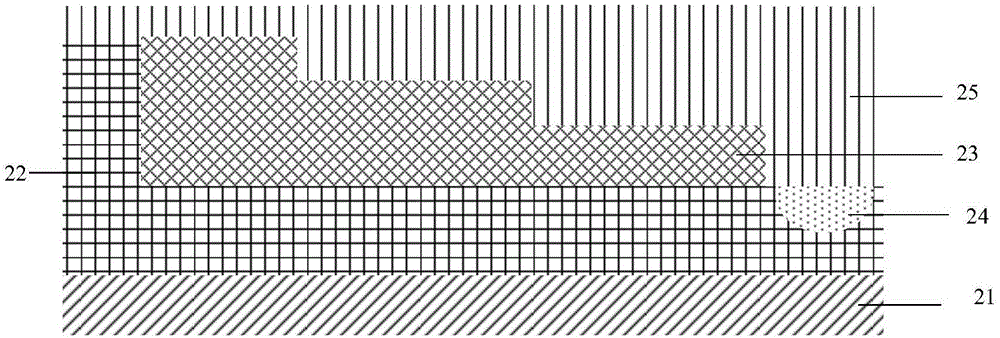

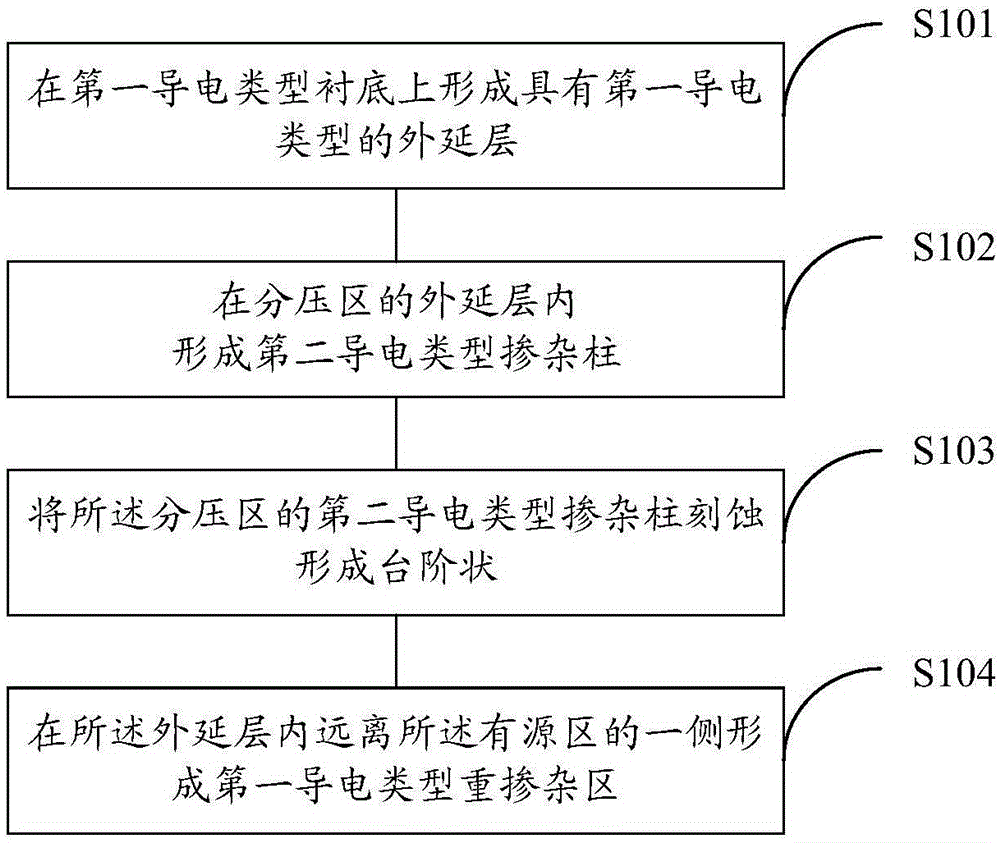

Structure and manufacturing method of terminal voltage-division region for super-junction device

ActiveCN106328688APrevent breakdownImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesTerminal voltageSemiconductor

The invention relates to a semiconductor manufacturing field, particularly to a structure and a manufacturing method of a terminal voltage-division region for a super-junction device. The structure of the terminal voltage-division region comprises a first conductive type substrate, and a first conductive type epitaxial layer which is arranged on the first conductive type substrate, wherein a second conductive type doped column in a voltage-division region is arranged in the epitaxial layer; the second conductive type doped column in the voltage-division region is not in contact with a second conductive type doped column in an active region; the second conductive type doped column in the voltage-division region is stage-shaped; the vertical heights of the stages are reduced one by one in sequence from one end close to the active region to one end far from the active region; a first conductive type heavily-doped region is arranged on one side, far from the active region, in the epitaxial layer; and the heavily-doped region is not in contact with the second conductive type doped column in the voltage-division region. By adoption of the structure and the manufacturing method of the terminal voltage-division region for the super-junction device, the problems of influence to a voltage-division effect and reduction of breakdown voltage caused by a conventional terminal structure for the super-junction device due to a large amount of generated interface charges are solved.

Owner:FOUNDER MICROELECTRONICS INT

Extended drain transistor and method of manufacturing the same

ActiveUS8216908B2Reduce dopingReduce hot carrier effectSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringTransistor

An extended drain transistor (100) comprising a substrate (101), a gate (103) formed on the substrate (100), the gate (103) having a first side wall (104) and a second side wall (105) opposing the first side wall (104), an extended drain (106) implanted in a surface portion of the substrate (101) adjacent the second side wall (105) of the gate (103), a spacer (107) on the second side wall (105) of the gate (103), a source (108) implanted in a surface portion of the substrate (101) adjacent the first side wall (104) of the gate (103), and a drain (109) implanted in a surface portion of the substrate (101) adjacent the spacer (107) in such a manner that the extended drain (106) is arranged between the gate (103) and the drain (109).

Owner:NXP BV

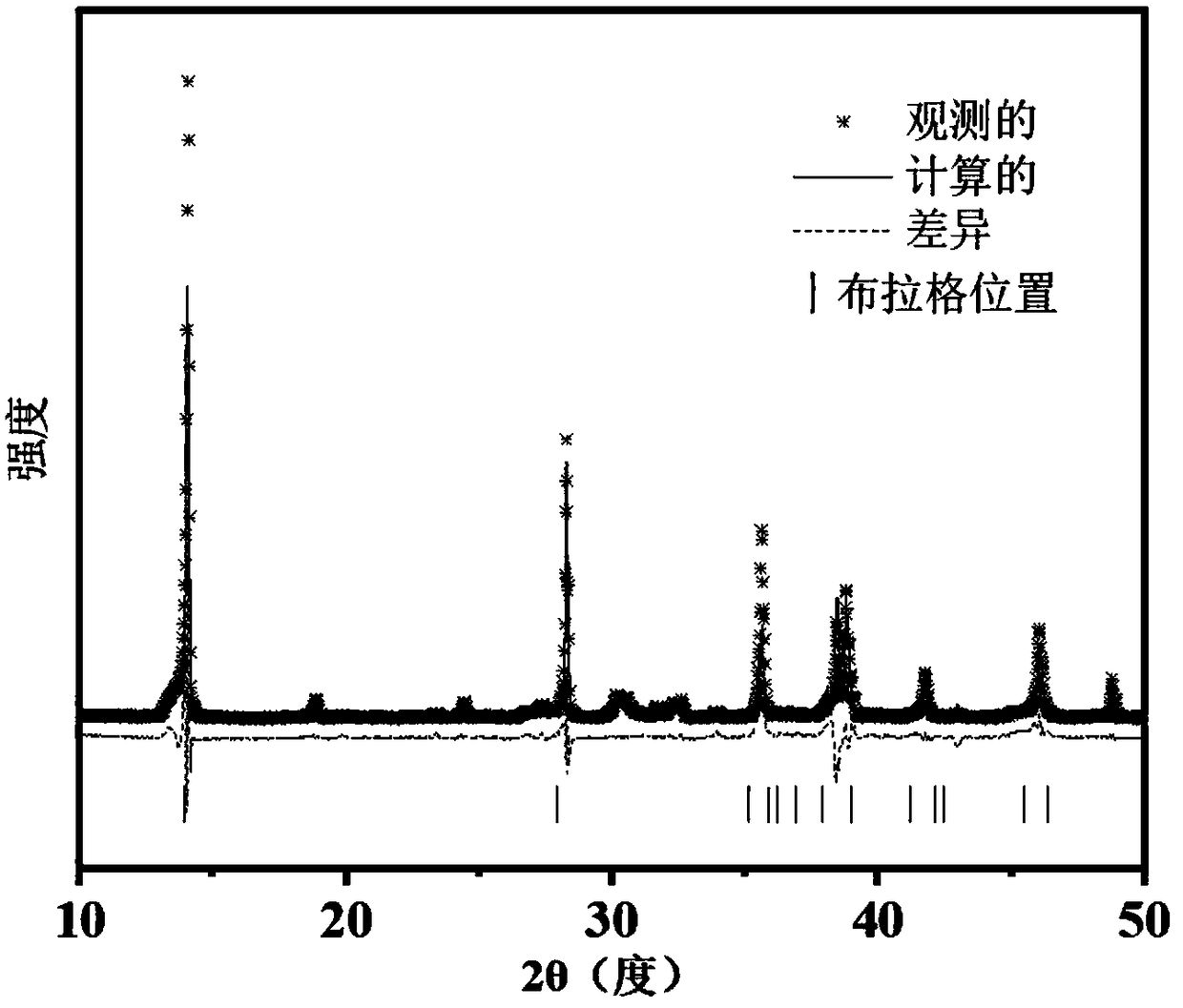

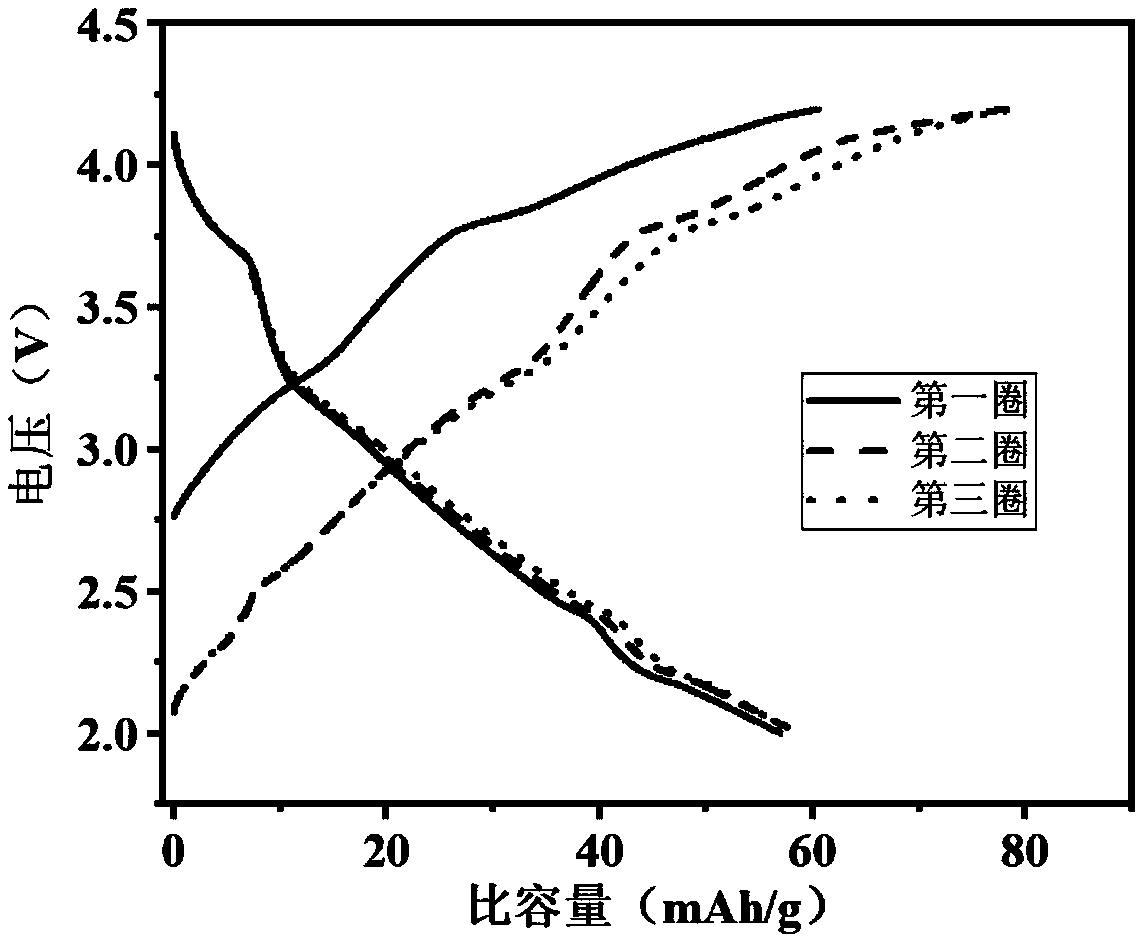

Potassium copper manganese oxide and preparation method thereof, and positive electrode as well as preparation method and application thereof

InactiveCN108565456AImprove structural stabilityReduce dopingCell electrodesPotassiumManganese oxide

The invention provides a potassium copper manganese oxide and a preparation method thereof, and a positive electrode adopting the potassium copper manganese oxide as well as a preparation method and application of the positive electrode. The potassium copper manganese oxide provided by the invention is of a layered structure, and all elements cooperate harmoniously, so that the structural stability of the potassium copper manganese oxide is improved, the ionic conductivity is better increased, and the potassium copper manganese oxide has excellent cycle stability. The results of the embodiments show that the positive electrode material prepared from the potassium copper manganese oxide provided by the invention has a charging capacity retention rate of 71.1% and a discharge capacity retention rate of 63.9% after a potassium ion battery is charged and discharged for 39 times in a using process, so that the cycle stability is good.

Owner:JILIN UNIV

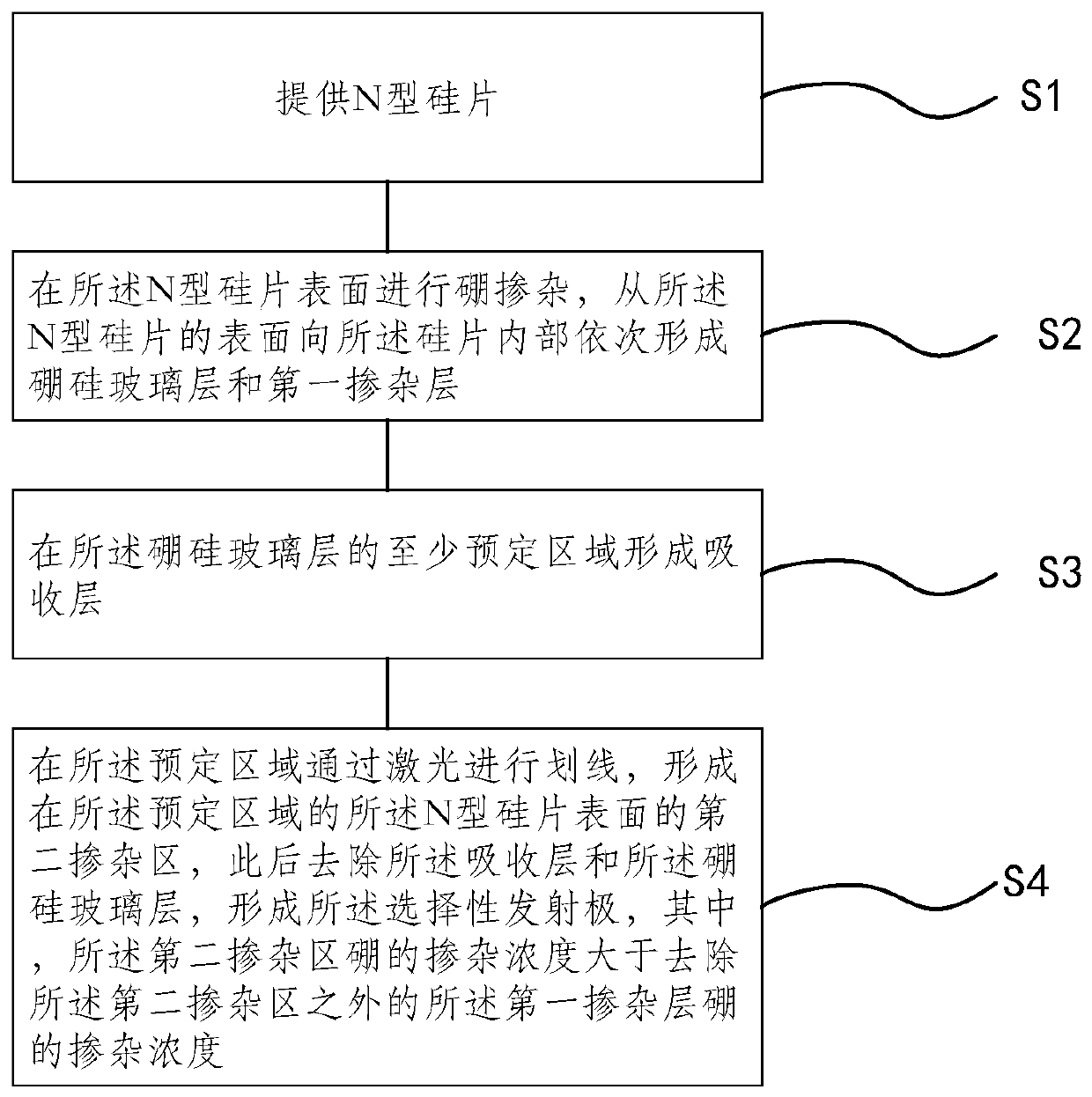

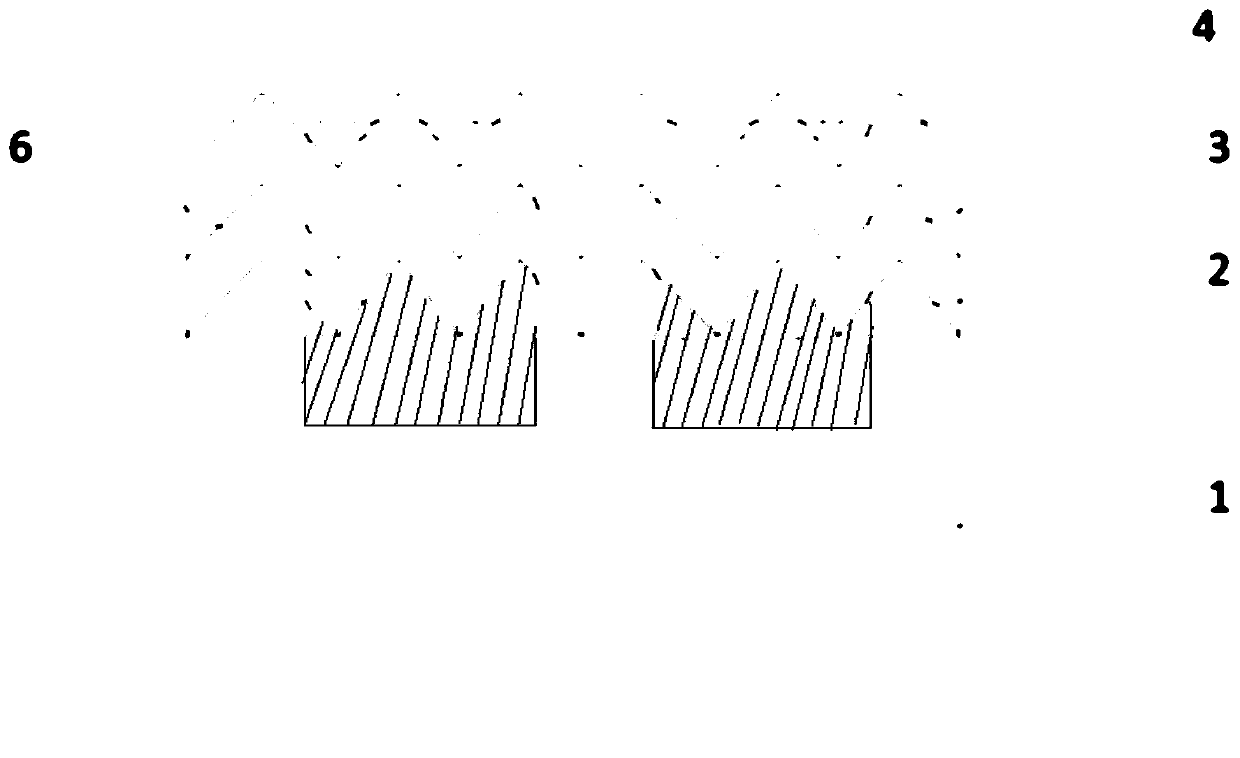

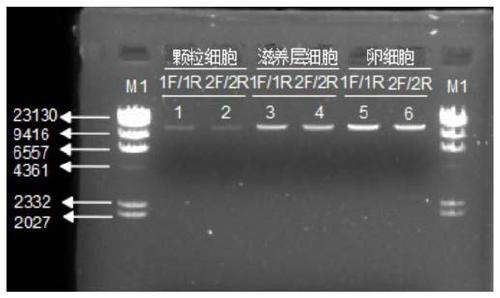

Preparation method of N-type battery and selective emitter of N-type battery, and N-type battery

ActiveCN111106188AAchieve preparationEffective absorptionPhotovoltaic energy generationSemiconductor devicesPhysical chemistryLaser scribing

The invention provides a preparation method of an N-type battery and a selective emitter of the N-type battery, and the N-type battery. The preparation method of the selective emitter of the N-type battery comprises the steps of providing an N-type silicon wafer; carrying out boron doping on the surface of the N-type silicon wafer, and sequentially forming a borosilicate glass layer and a first doping layer from the surface of the N-type silicon wafer to the interior of the silicon wafer; forming an absorption layer in at least a predetermined area of the borosilicate glass layer; and forminga second doped region on the surface of the N-type silicon wafer in the predetermined area through laser scribing in the predetermined area, and then removing the absorption layer and the borosilicateglass layer , wherein the doping concentration of boron in the second doped region is larger than the doping concentration of boron in the first doped layer except the second doped region. Accordingto the preparation method of the selective emitter of the N-type battery, the second doped region (heavily doped region) can be realized by scribing in the predetermined area through laser, so that the effective selective emitter is formed.

Owner:JA SOLAR TECH YANGZHOU +1

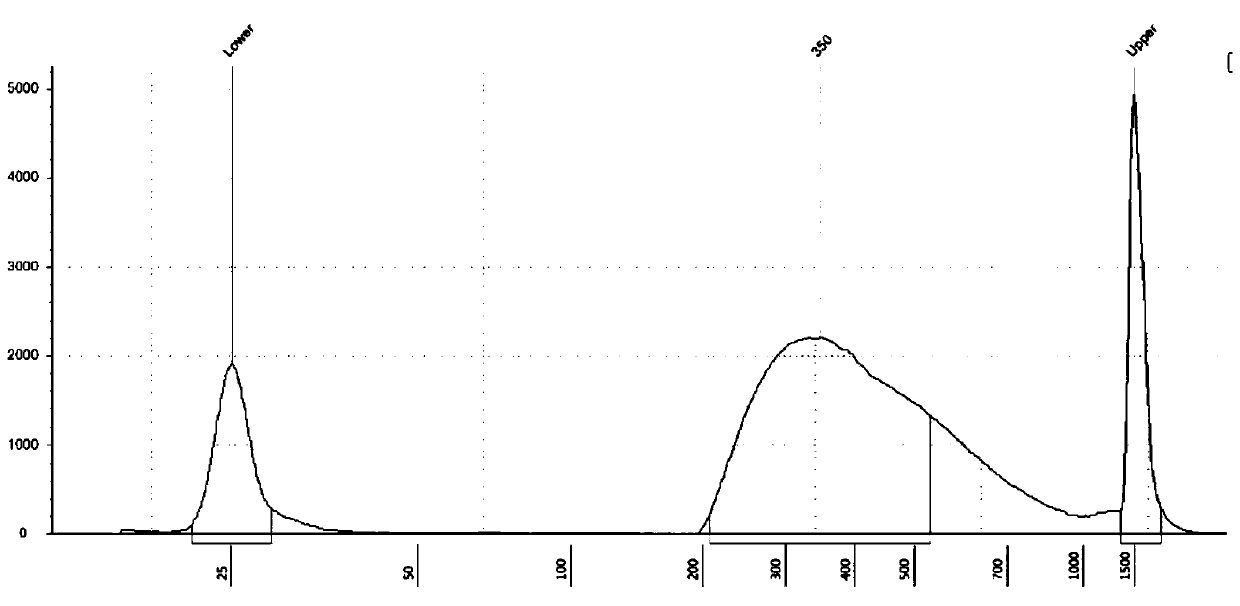

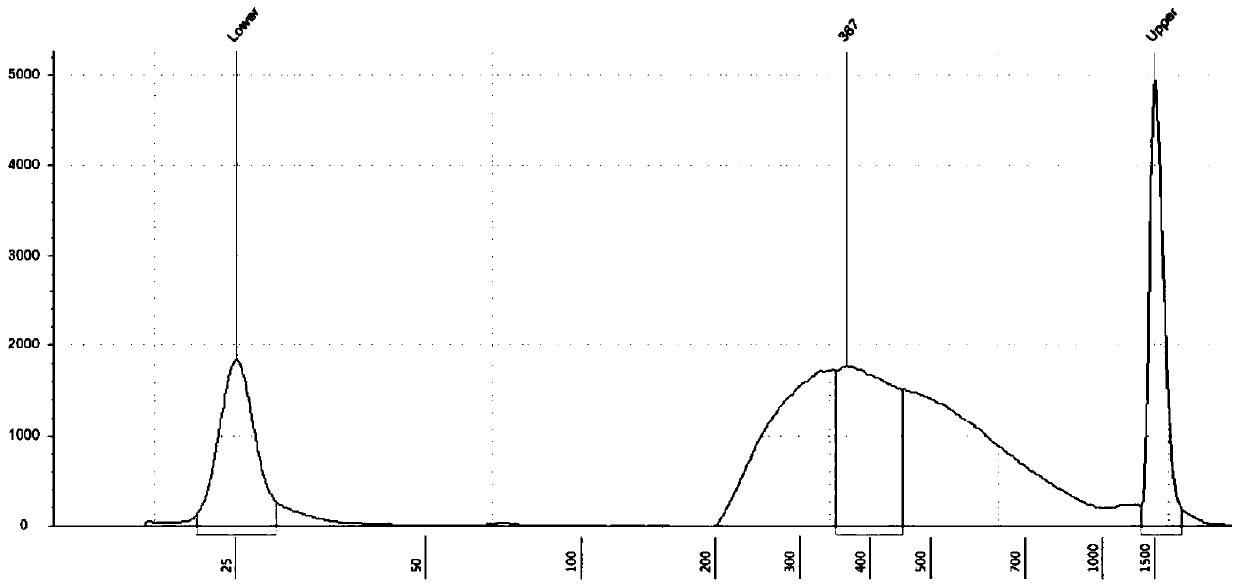

Construction method for human single cell mitochondrial high-throughput sequencing library and kit for library construction

ActiveCN111172157AEnabling ring-wide point mutationsEliminate distractionsMicrobiological testing/measurementLibrary creationPhosphorylationCell layer

The invention provides a construction method for a human single cell mitochondrial high-throughput sequencing library and a kit for library construction. The kit includes mitochondrial genome full-loop amplification primers, single cell lysate, terminal repaired, phosphorylated and 3' added adenylate components of high-throughput library construction, adaptors of high-throughput library construction and forward and reverse library amplification primers. The method realizes the high-throughput sequencing library construction of single or several cell mitochondrial genomes DNA in a mitochondrialgenome complete full-loop amplification based system, and high miss rates and high-proportion false positive site detection rates brought by conventional single cell amplification systems can be evaded, so that massive disadvantages in mitochondrial mutation detection can be got rid of at the single cell level, high sensitivity and accuracy detection can be realized; and as the method adopts themode of full-loop and full-length mitochondrial amplification, the large fragment duplication and deletion of mitochondrial DNA can be discovered while mutation sites are detected.

Owner:福州福瑞医学检验实验室有限公司

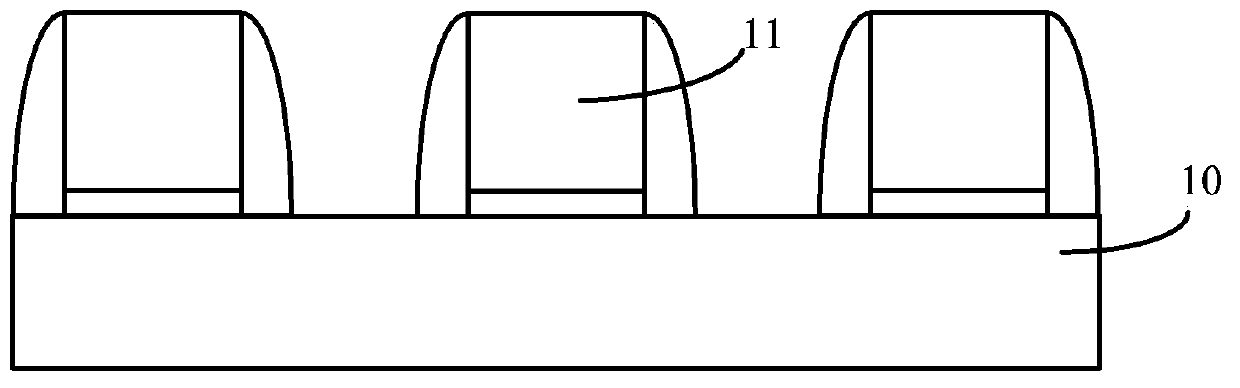

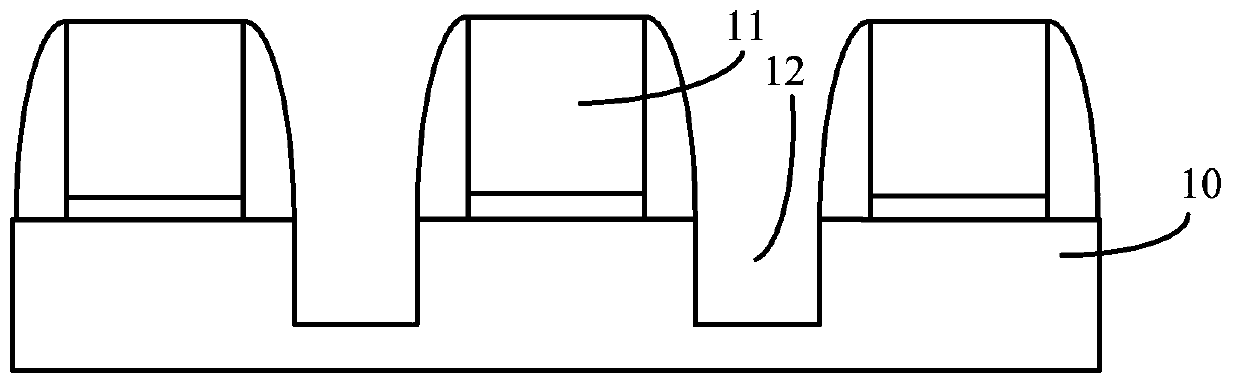

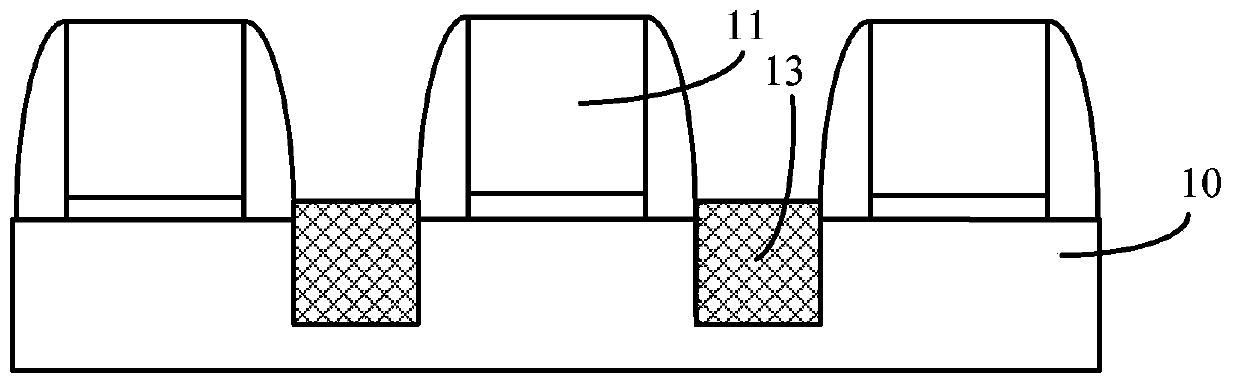

Transistor and formation method thereof

ActiveCN104217957AReduce dopingEnough stressSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsSemiconductor

Disclosed are a transistor and a formation method thereof. The transistor comprises a substrate, openings, first stress layers, dielectric layers and second stress layers. The substrate comprises an insulating layer and a semiconductor layer located on the surface of the insulating layer, and the surface of the semiconductor layer is provided with multiple gate structures; the openings of the semiconductor layer are located between the every two neighboring gate structures and exposed out of the insulating layer; the first stress layers are located on the surfaces of the side walls of the openings; the dielectric layers are located in the openings with the surfaces of the side walls provided with the first stress layers, and the surfaces of the dielectric layers are lower than the surface of the semiconductor layer; the second stress layers are located on the first stress layers and the surfaces of the dielectric layers, and the openings are filled with the second stress layers. By the transistor and the formation method thereof, leakage current of the transistor is reduced, and performance is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP