Patents

Literature

133results about How to "Improve channel mobility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Stressed semiconductor device structures having granular semiconductor material

InactiveUS20050106799A1Improve device performanceAvoid compressive stressTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsDevice material

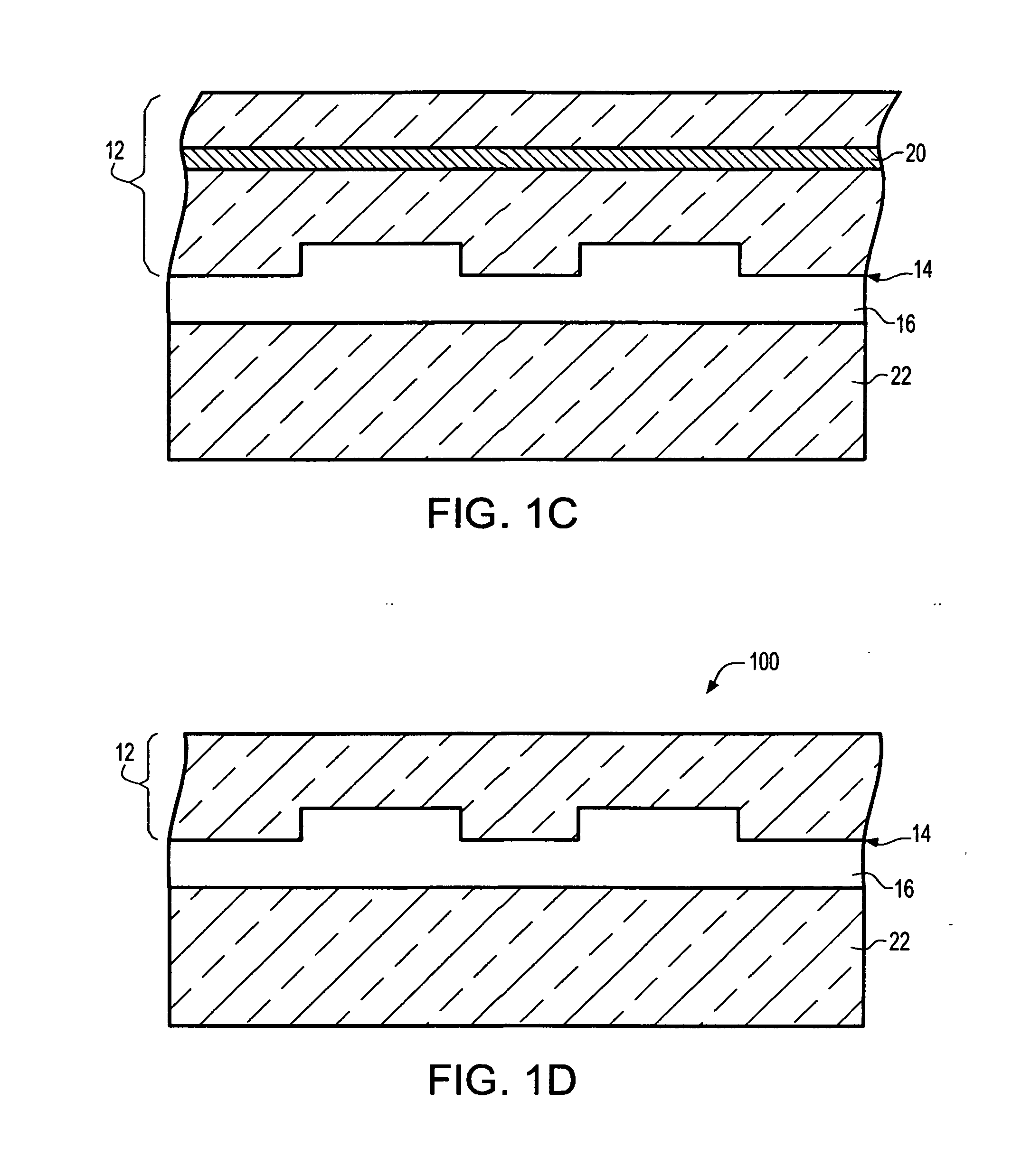

A method of fabricating a semiconductor device structure, includes: providing a substrate, providing an electrode on the substrate, forming a recess in the electrode, the recess having an opening, disposing a small grain semiconductor material within the recess, covering the opening to contain the small grain semiconductor material, within the recess, and then annealing the resultant structure.

Owner:GLOBALFOUNDRIES INC

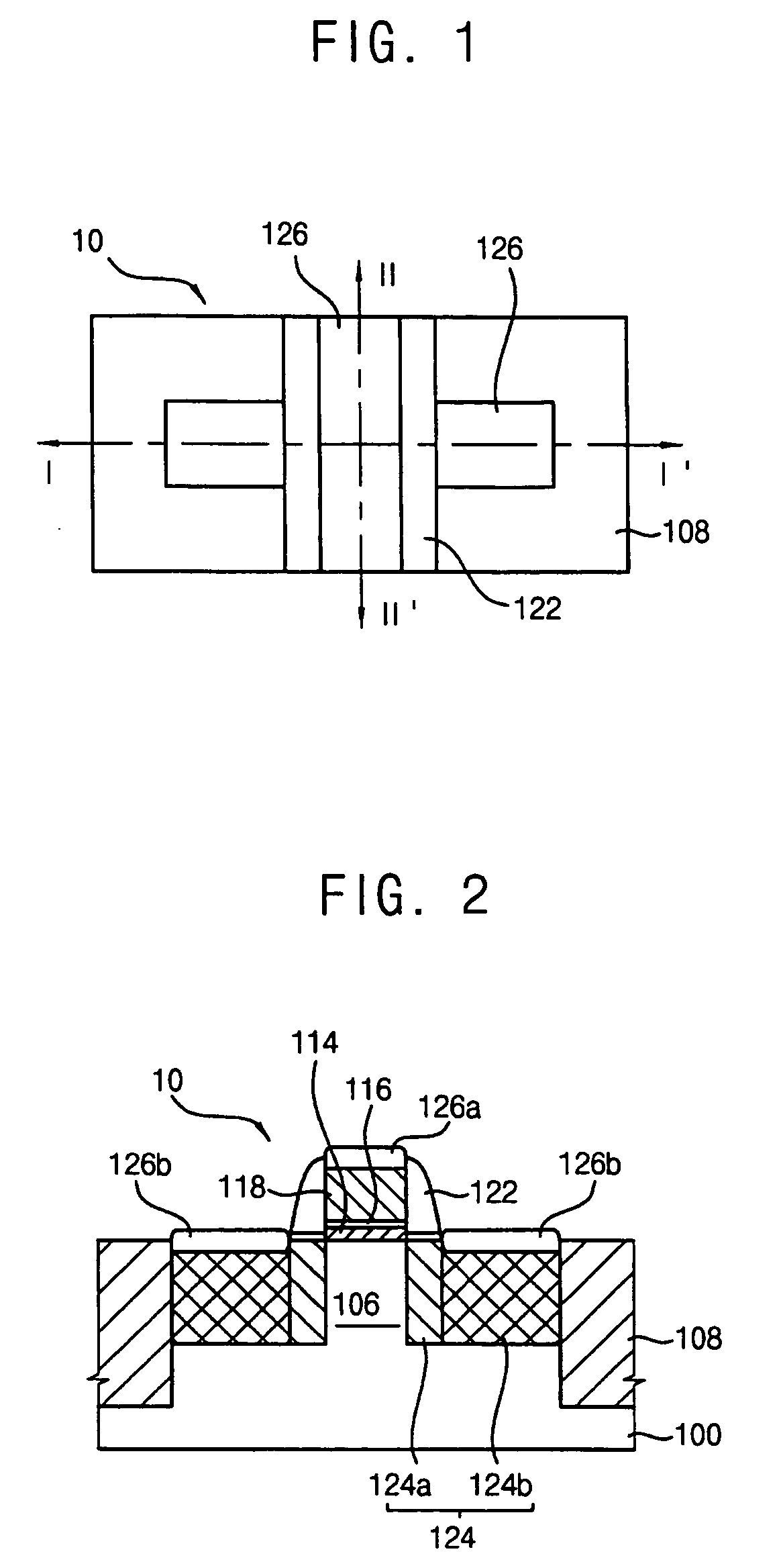

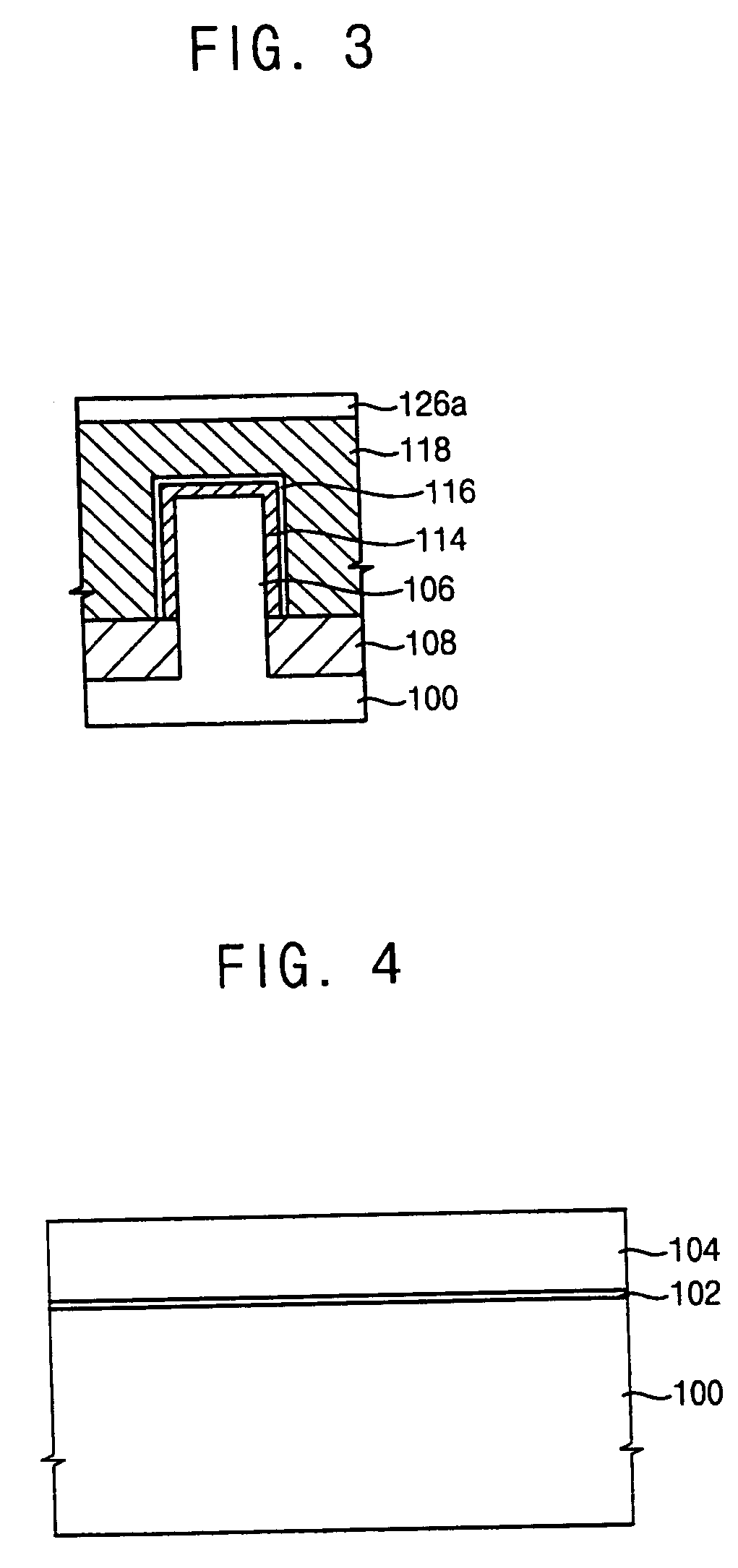

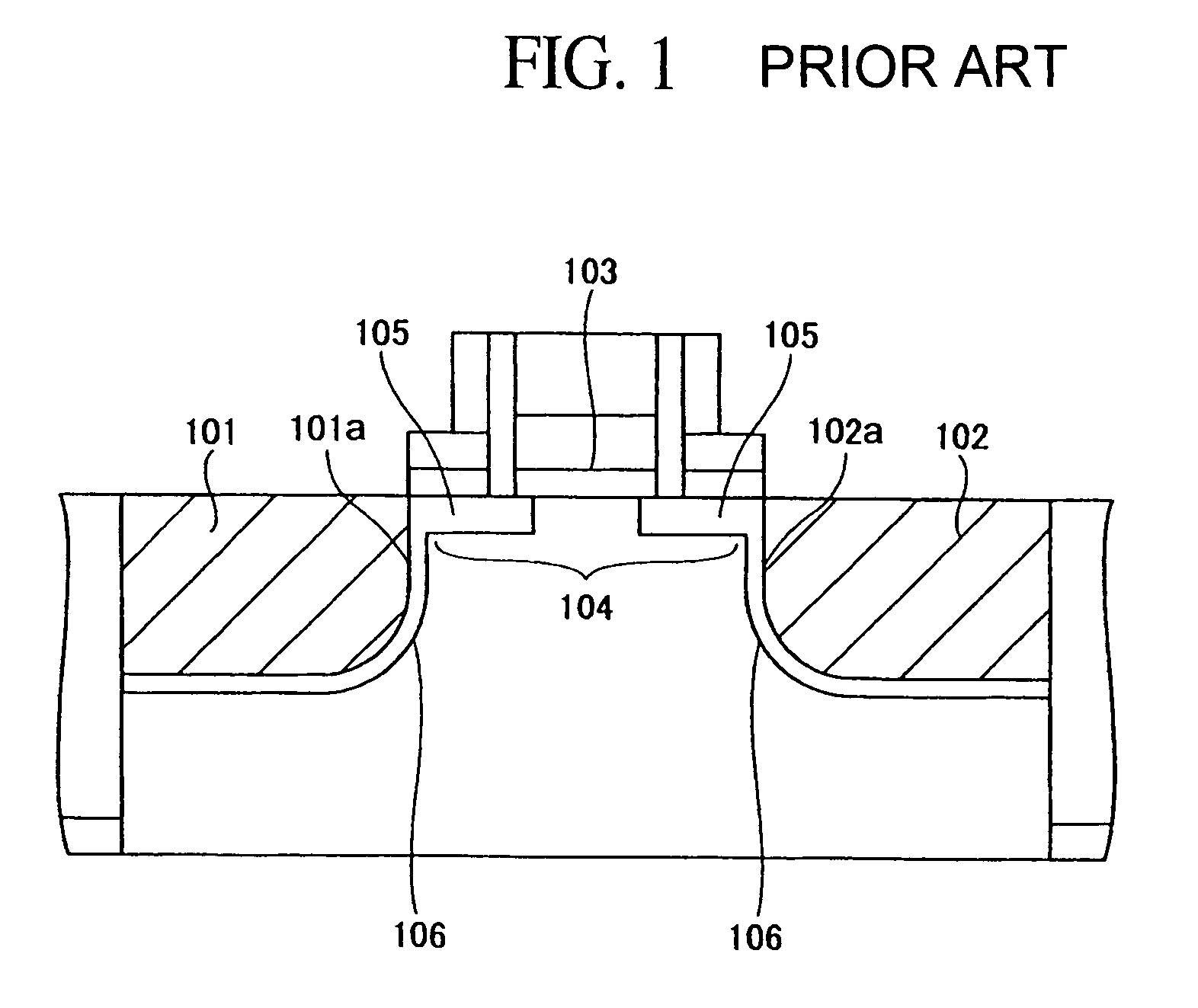

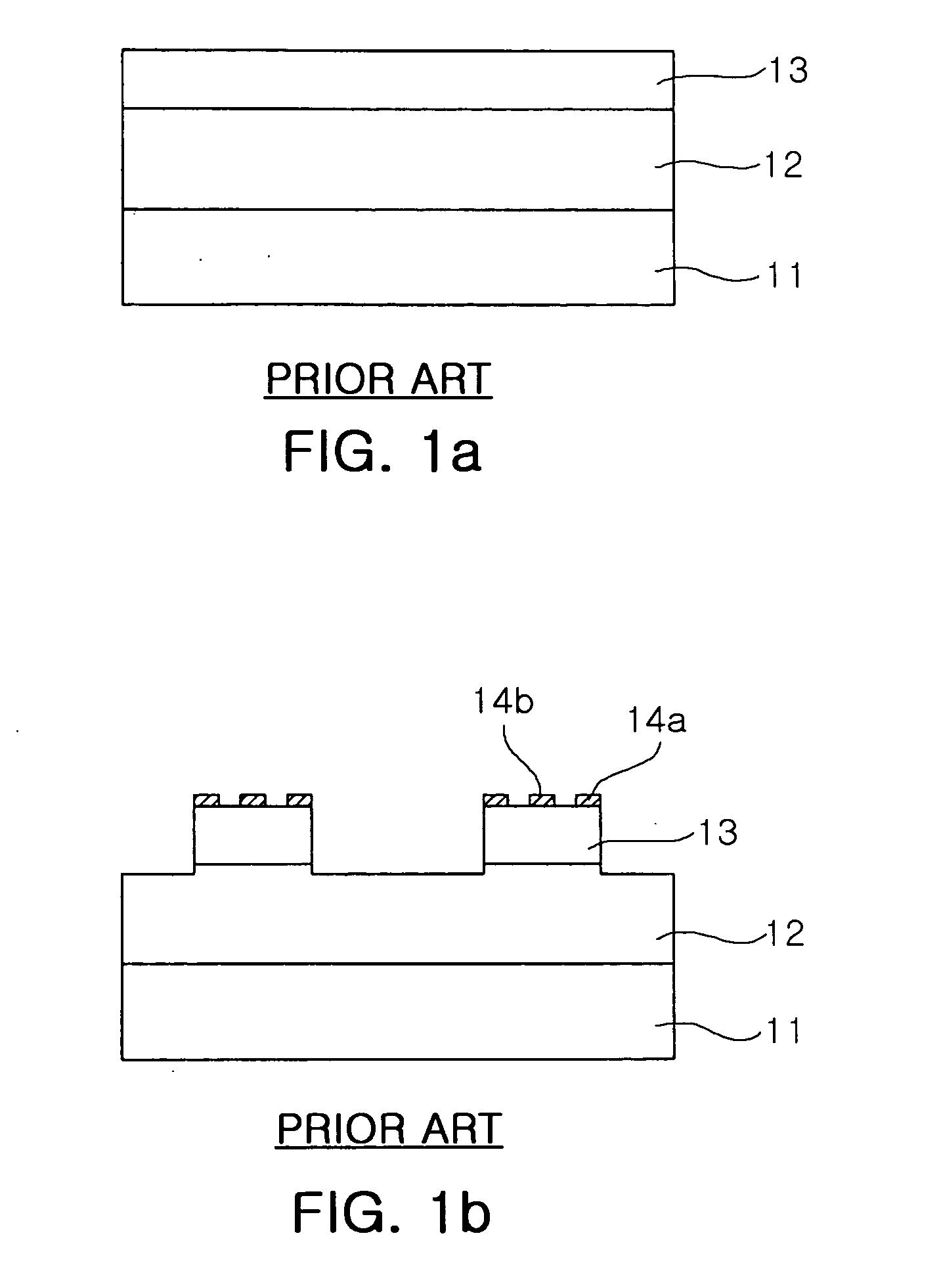

Semiconductor device having a channel layer and method of manufacturing the same

InactiveUS20050263795A1High carrier mobilityImprove channel mobilityTransistorPaper-money handling devicesDriving currentInsulation layer

In a method of forming a semiconductor device having an improved channel layer, the channel layer is formed on a surface of a semiconductor substrate and comprises a material of high carrier mobility such as silicon germanium (SiGe), germanium (Ge) and silicon carbide (SiC) using a selective epitaxial growth process. A gate insulation layer and a gate electrode are formed on the channel layer. Accordingly, a driving current of the semiconductor device increases to thereby improve operation characteristics.

Owner:SAMSUNG ELECTRONICS CO LTD

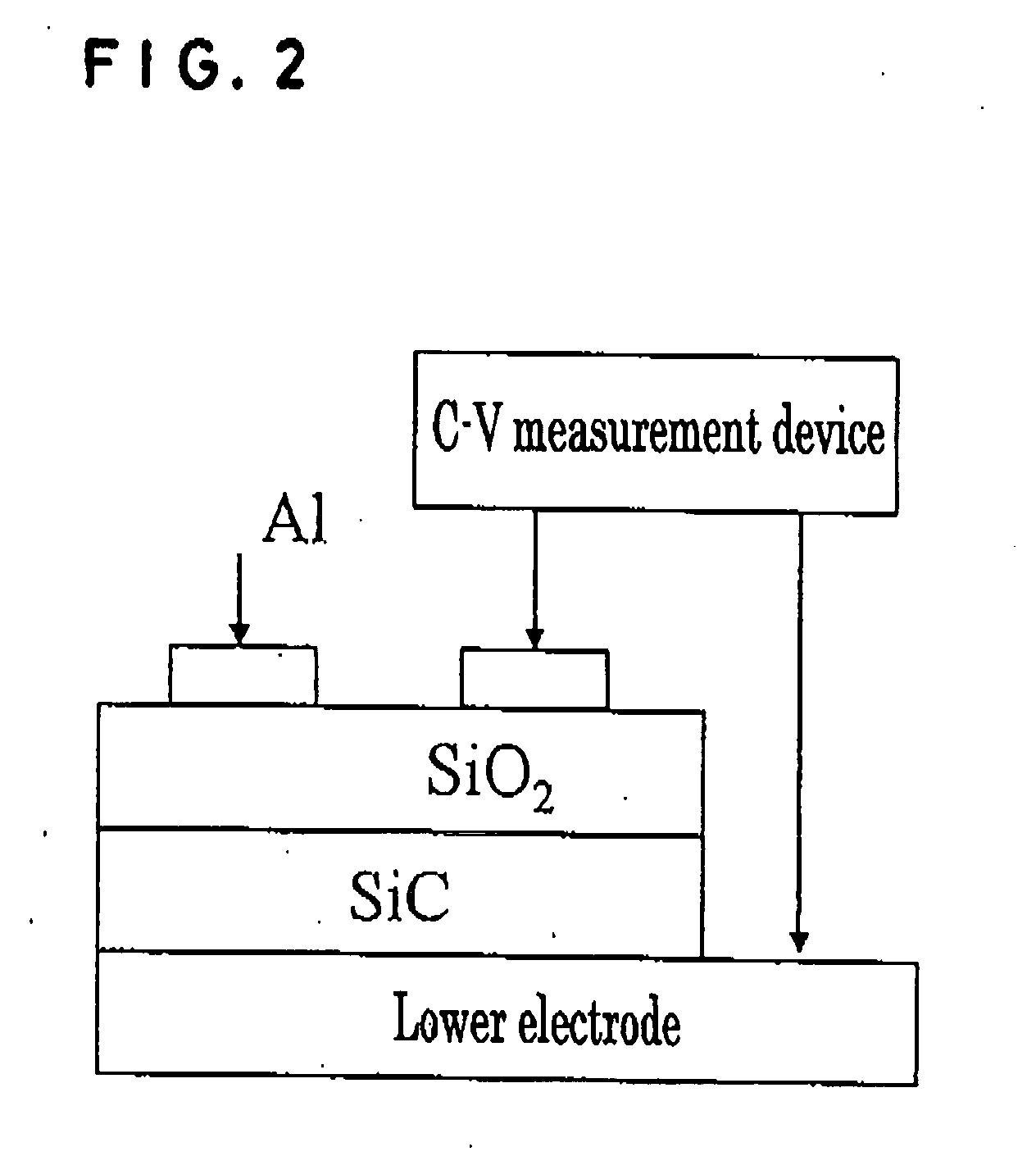

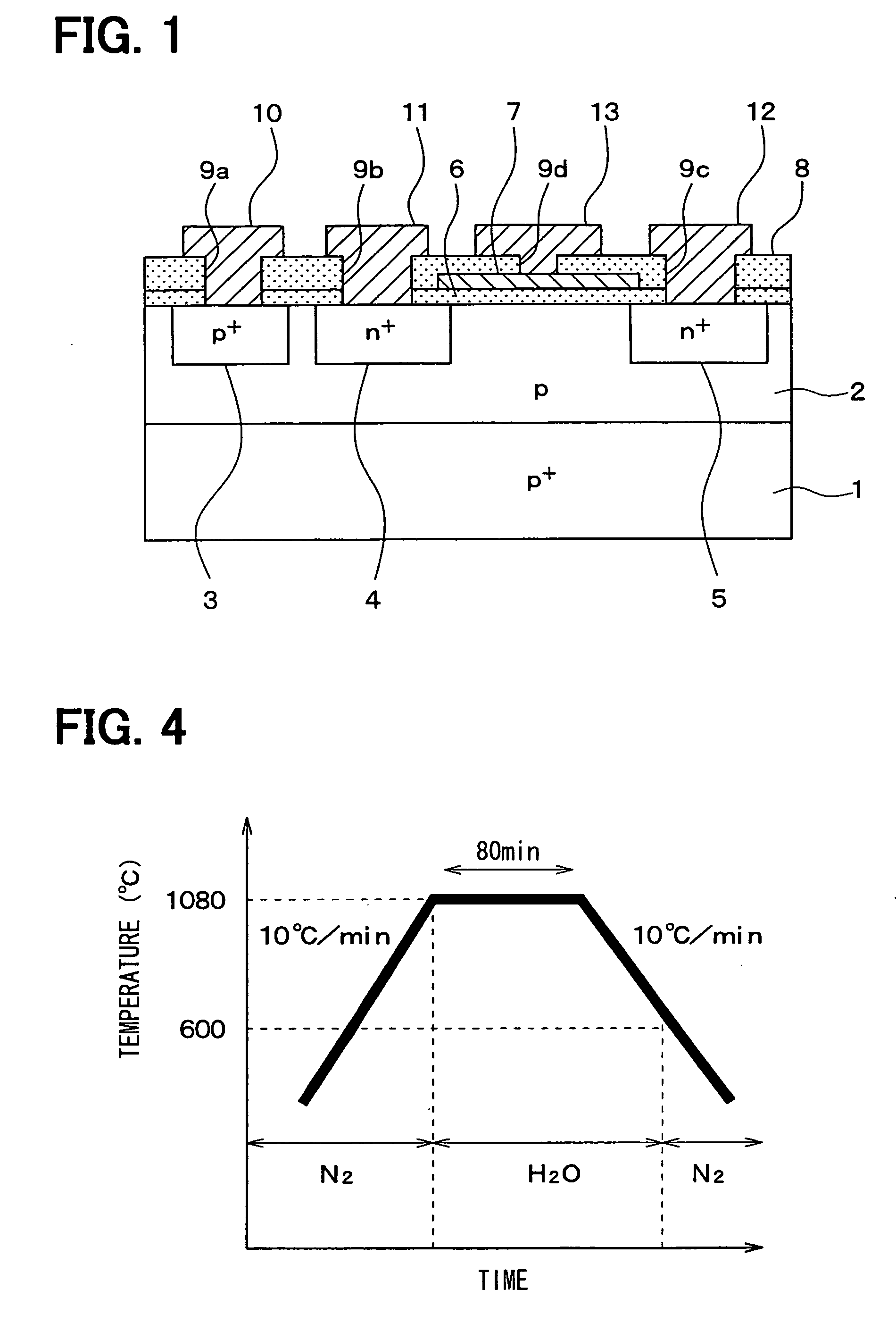

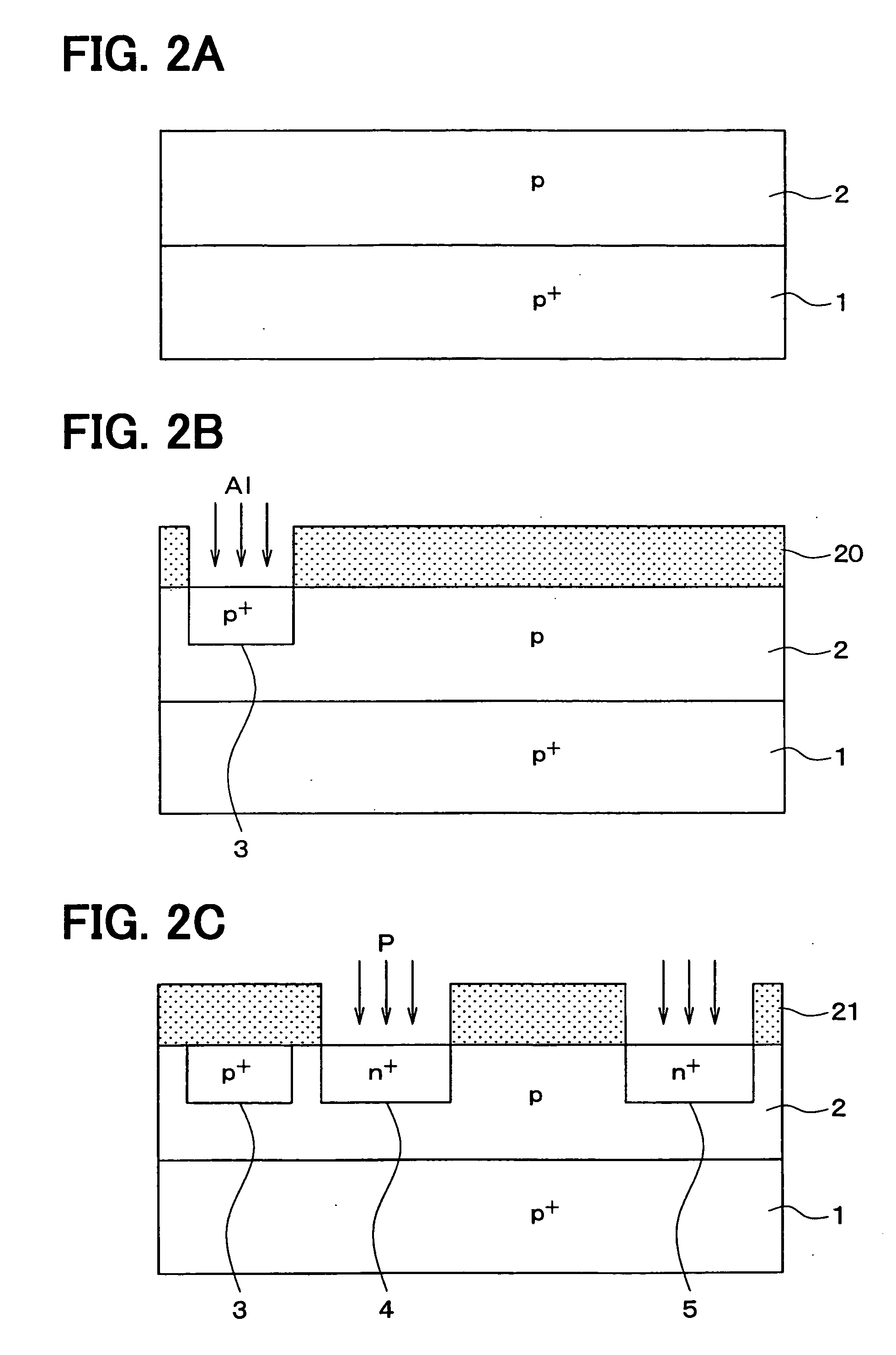

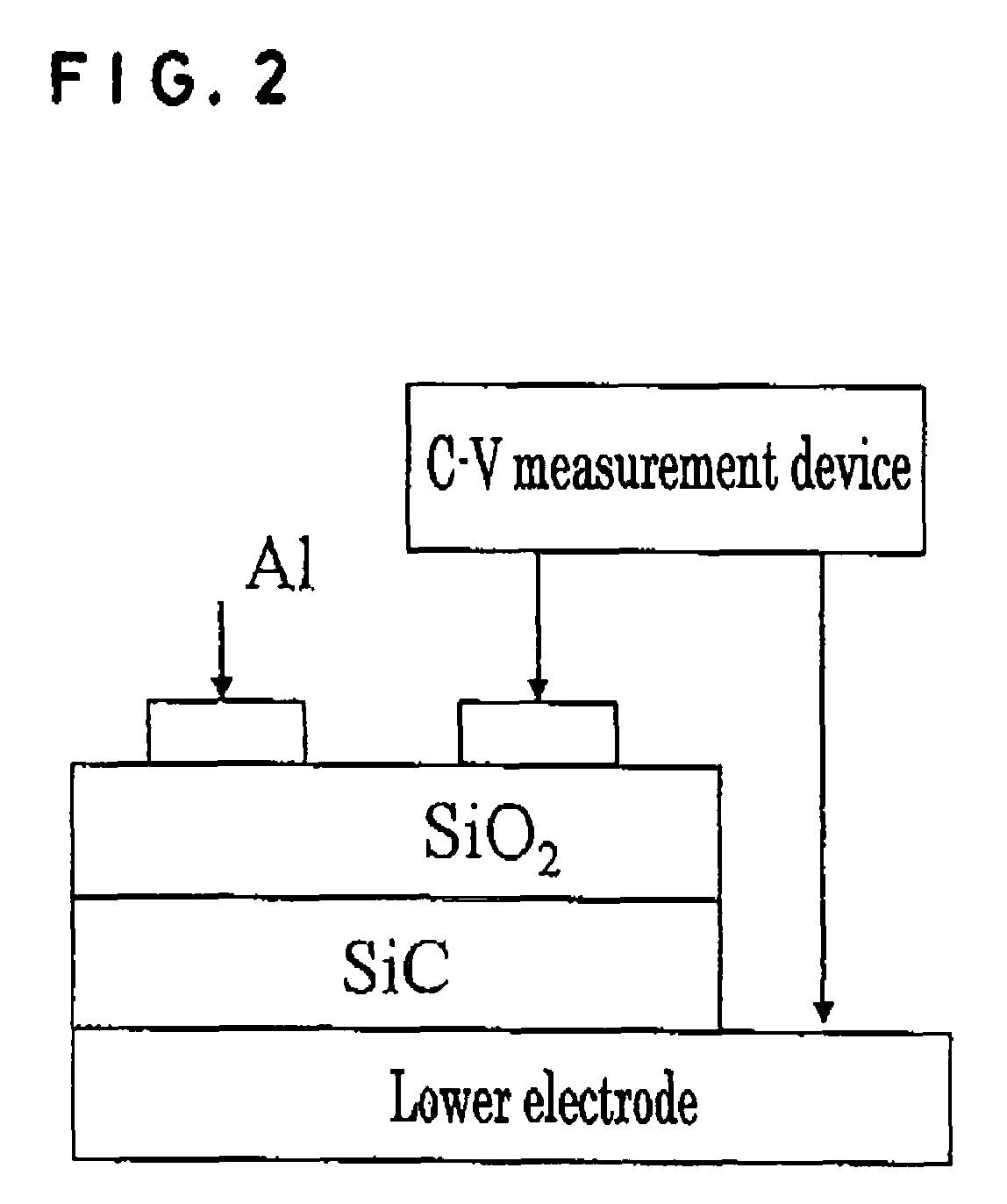

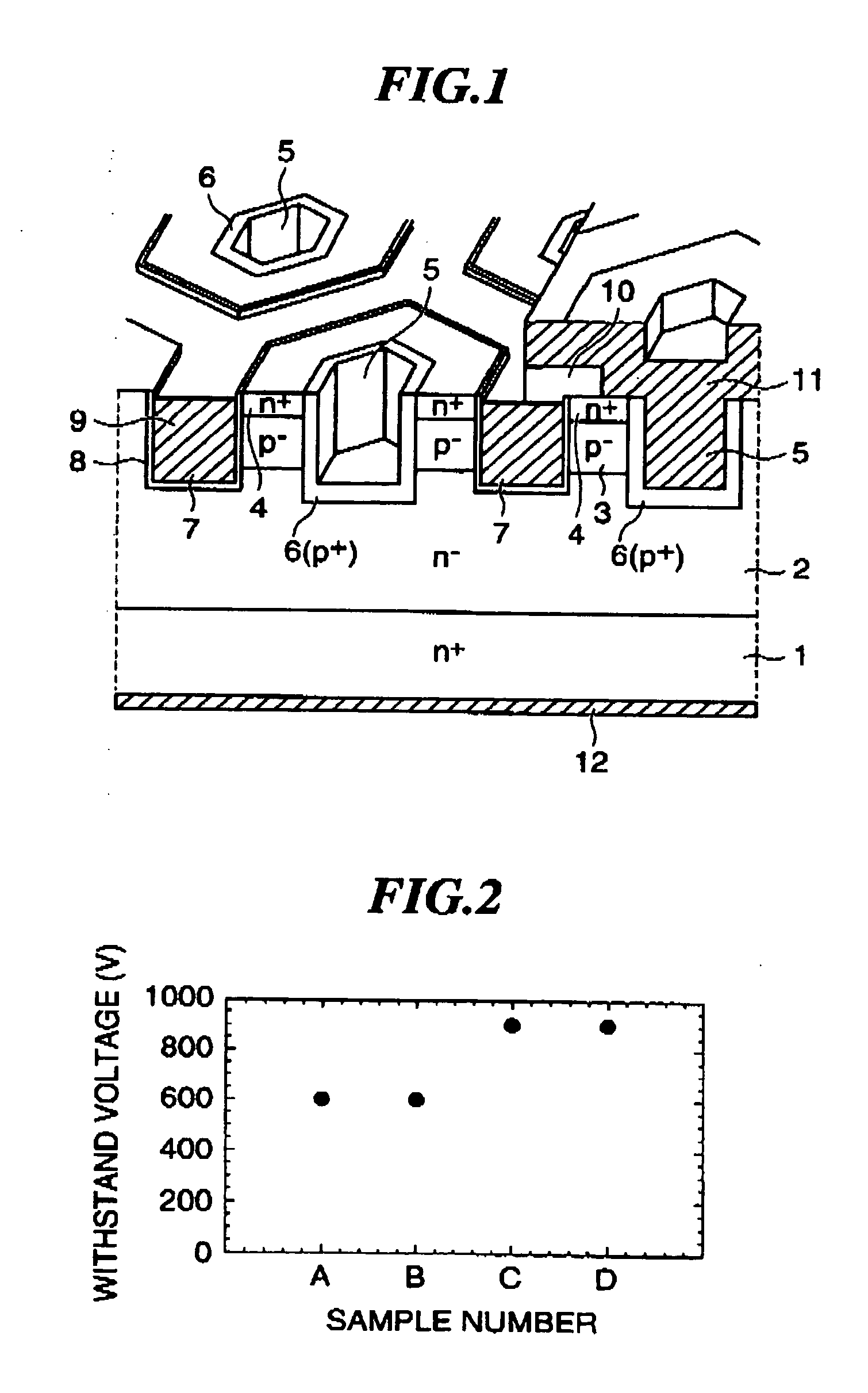

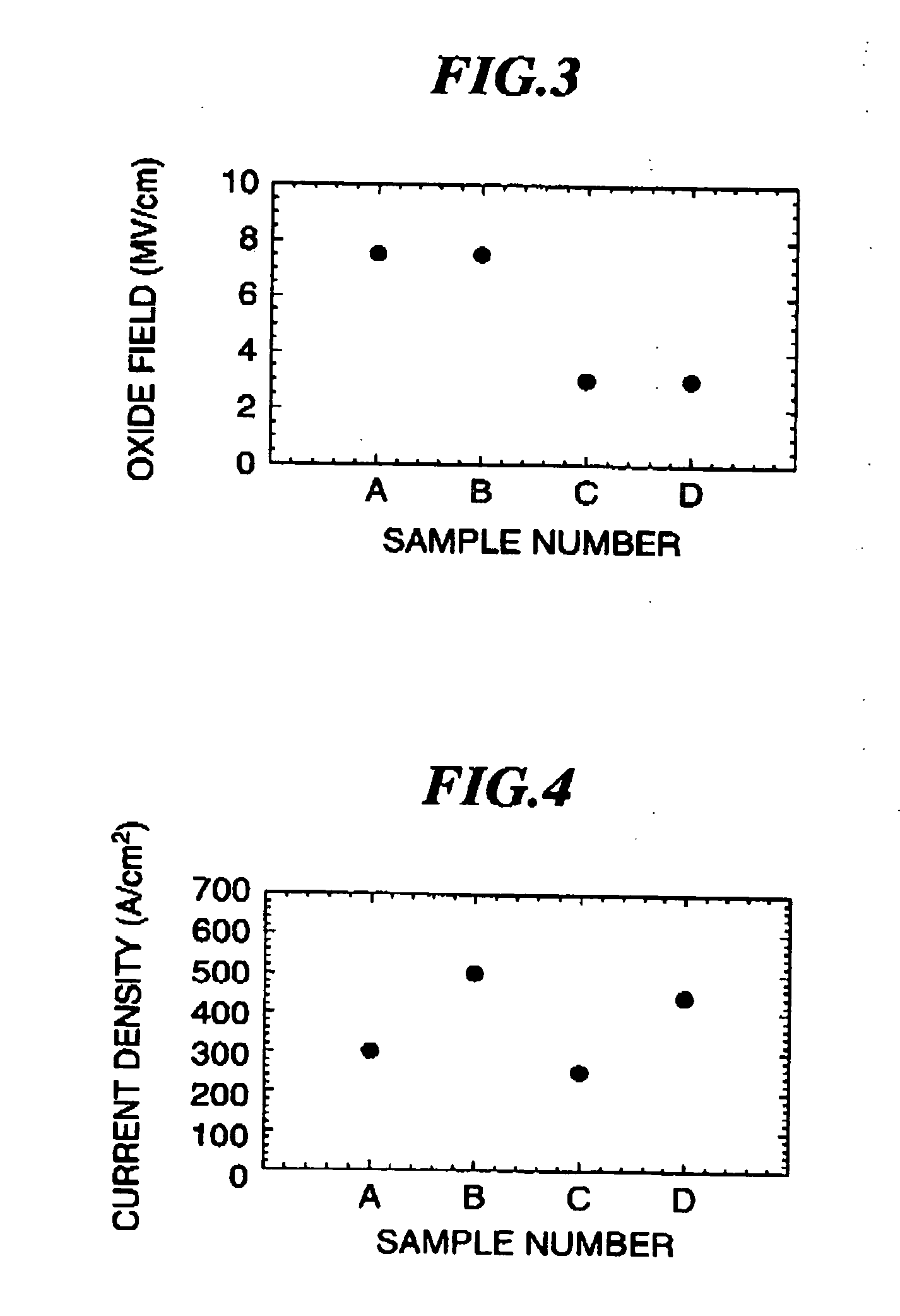

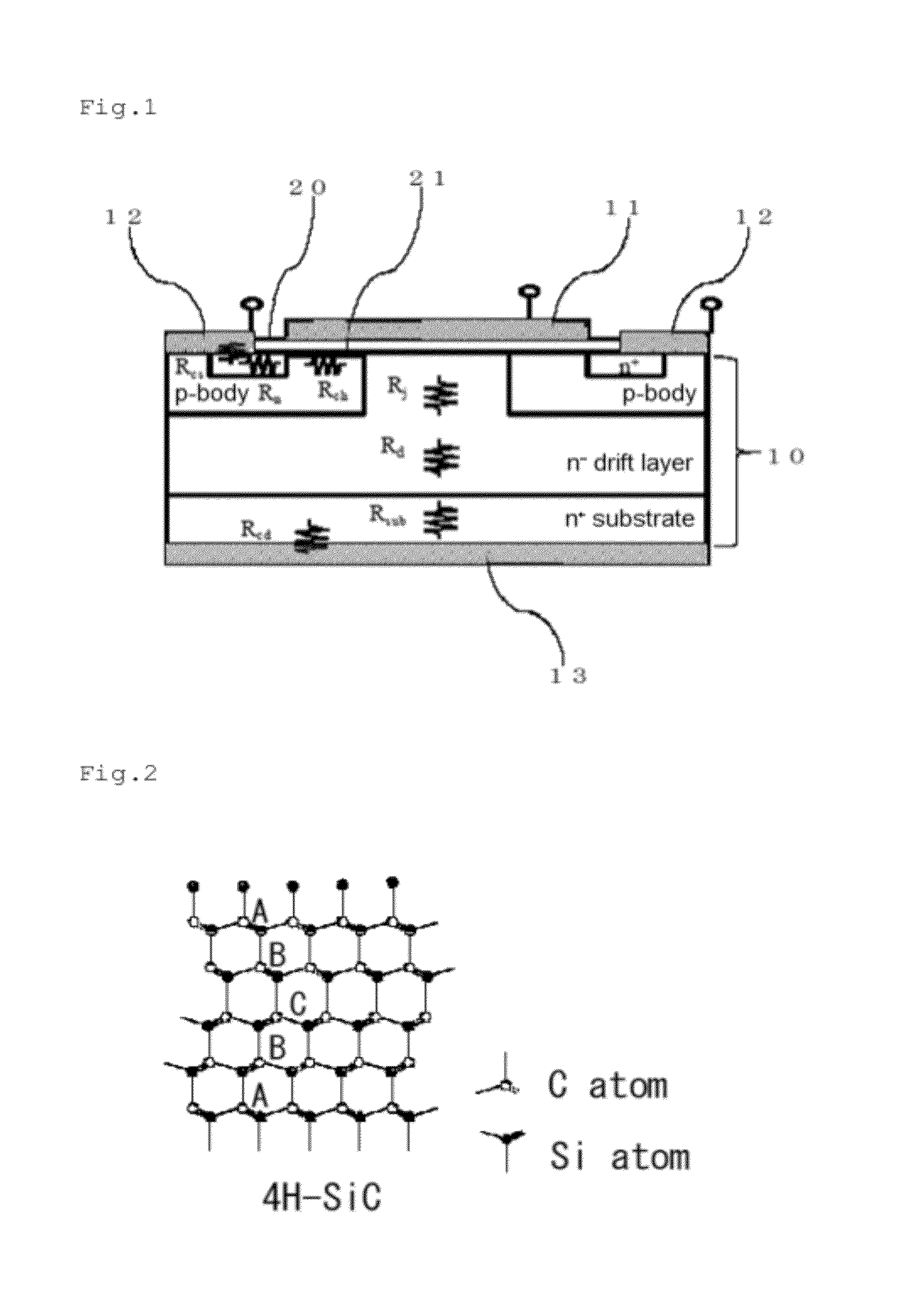

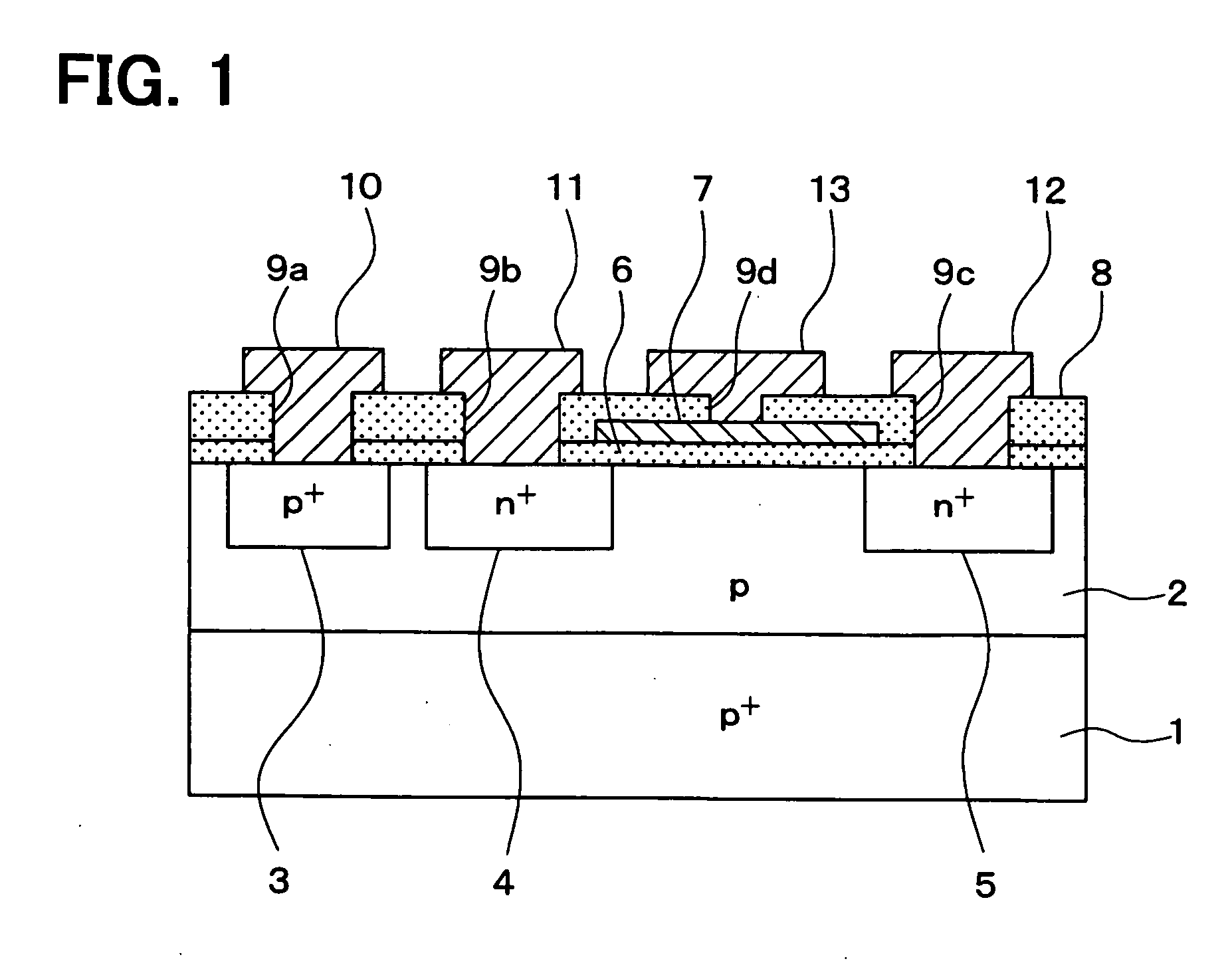

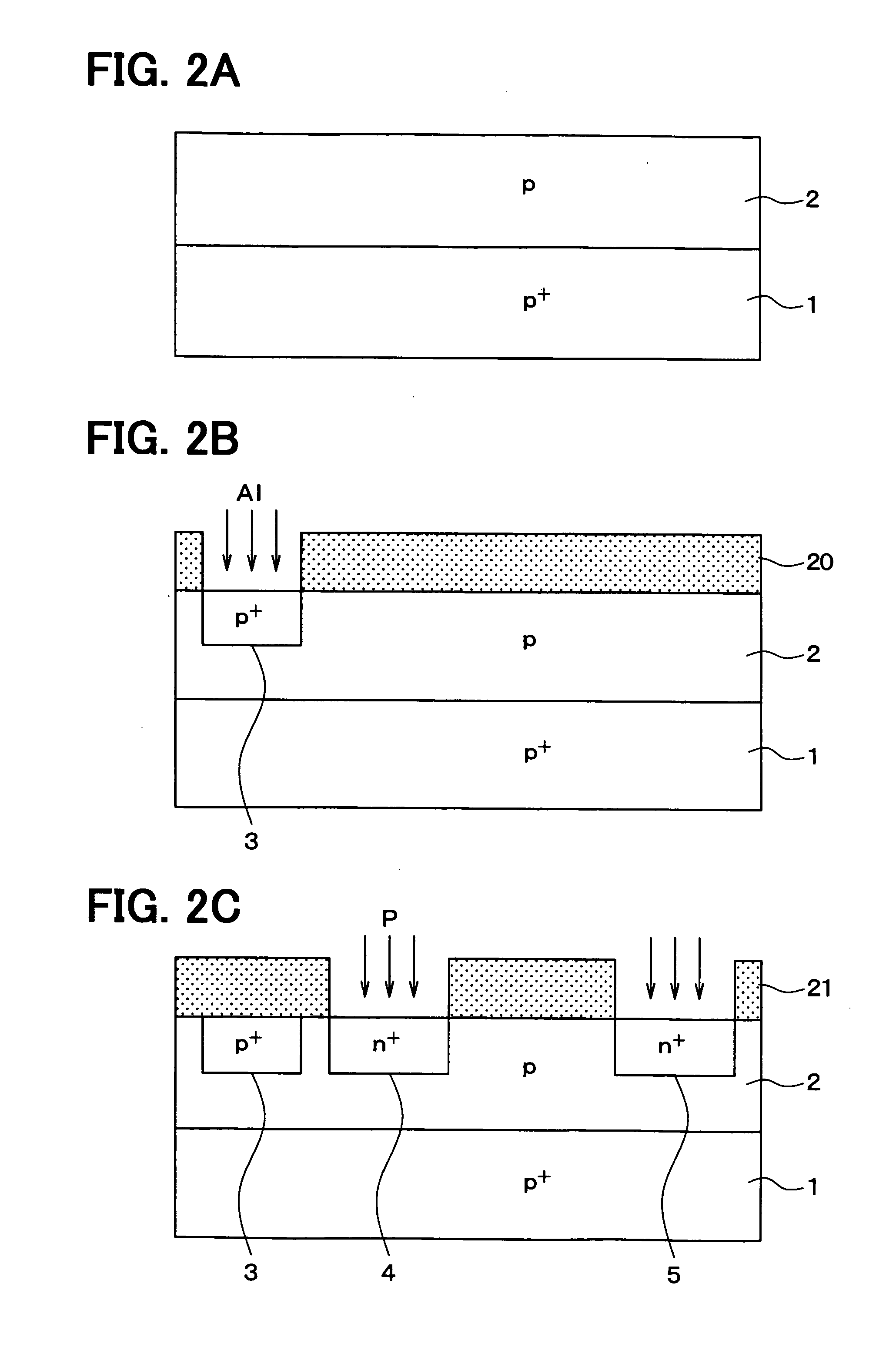

Semiconductor device and its manufacturing method

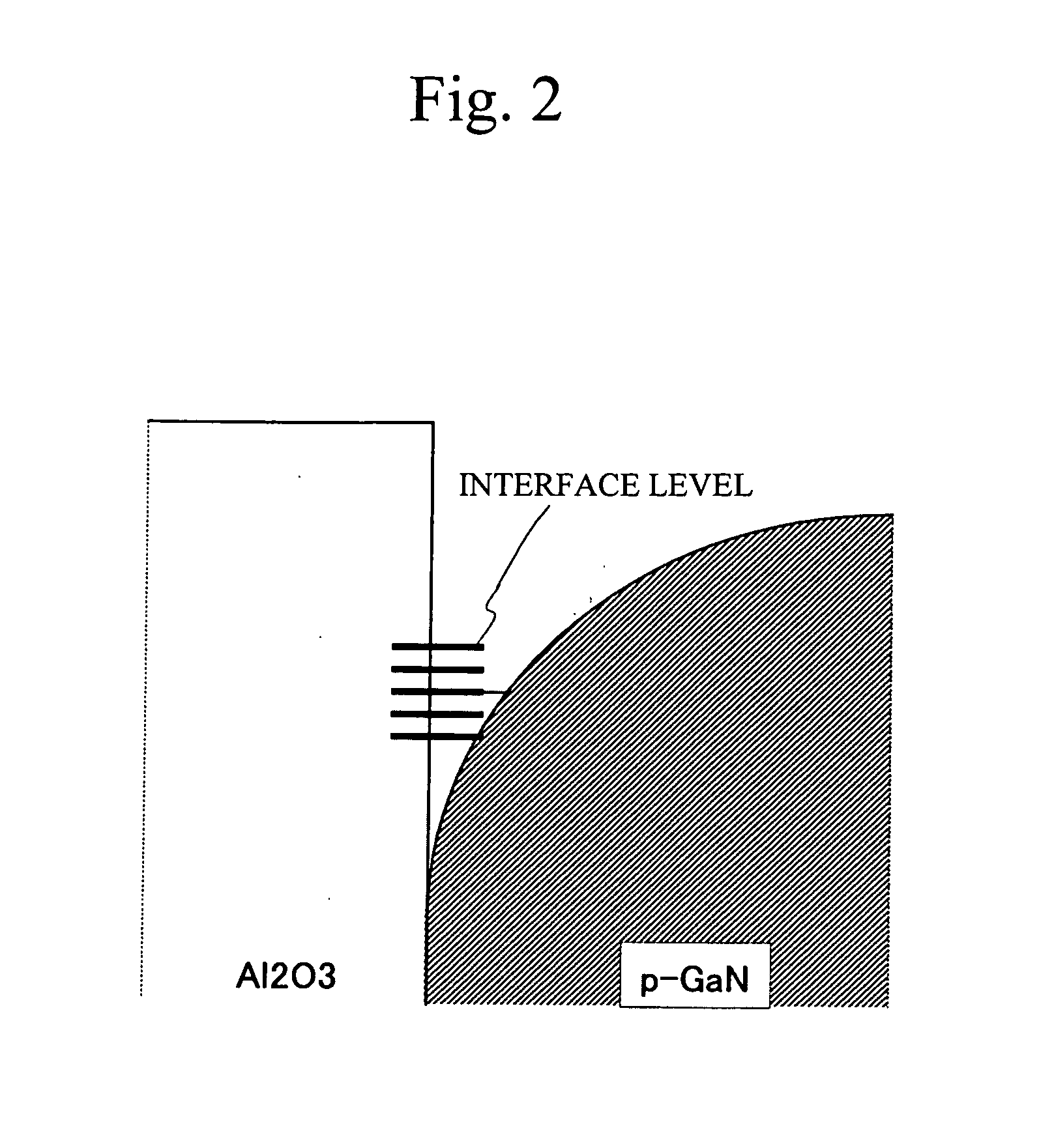

ActiveUS20050245034A1Increase temperatureLow densityTransistorSemiconductor/solid-state device manufacturingInsulation layerSemiconductor

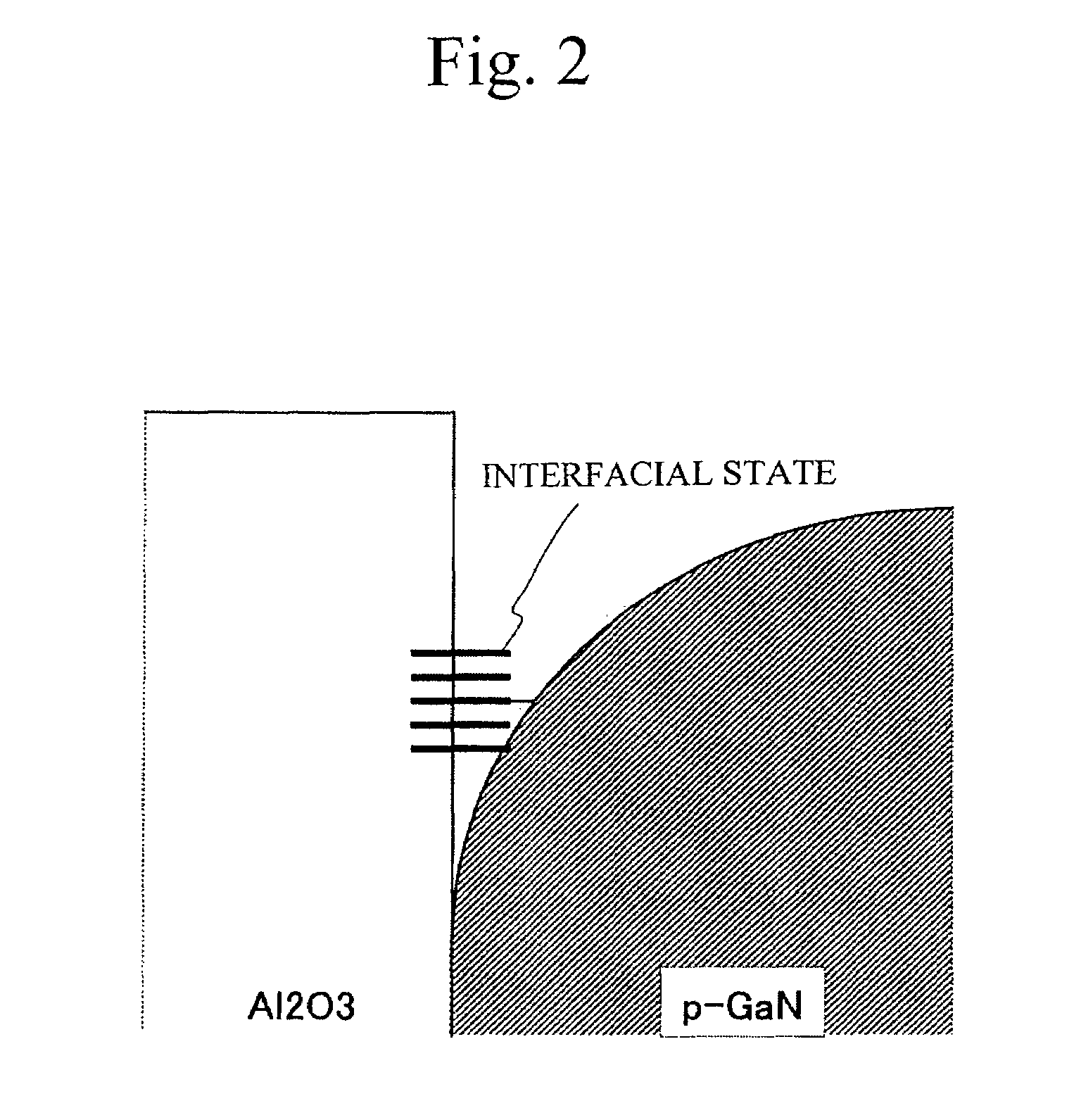

A semiconductor device and a method of manufacturing the device using a (000-1)-faced silicon carbide substrate are provided. A SiC semiconductor device having a high voltage resistancehigh blocking voltage and high channel mobility is manufactured by opting the heat treatment method used following the gate oxidation. The method of manufacturing a semiconductor device includes the steps of forming a gate insulation layer on a semiconductor region formed of silicon carbide having a (000-1) face orientation, forming a gate electrode on the gate insulation layer, forming an electrode on the semiconductor region, cleaning the semiconductor region surface. The gate insulation layer is formed in an atmosphere containing 1% or more H2O (water) vapor at a temperature of from 800° C. to 1150° C. to reduce the interface trap density of the interface between the gate insulation layer and the semiconductor region.

Owner:NAT INST OF ADVANCED IND SCI & TECH

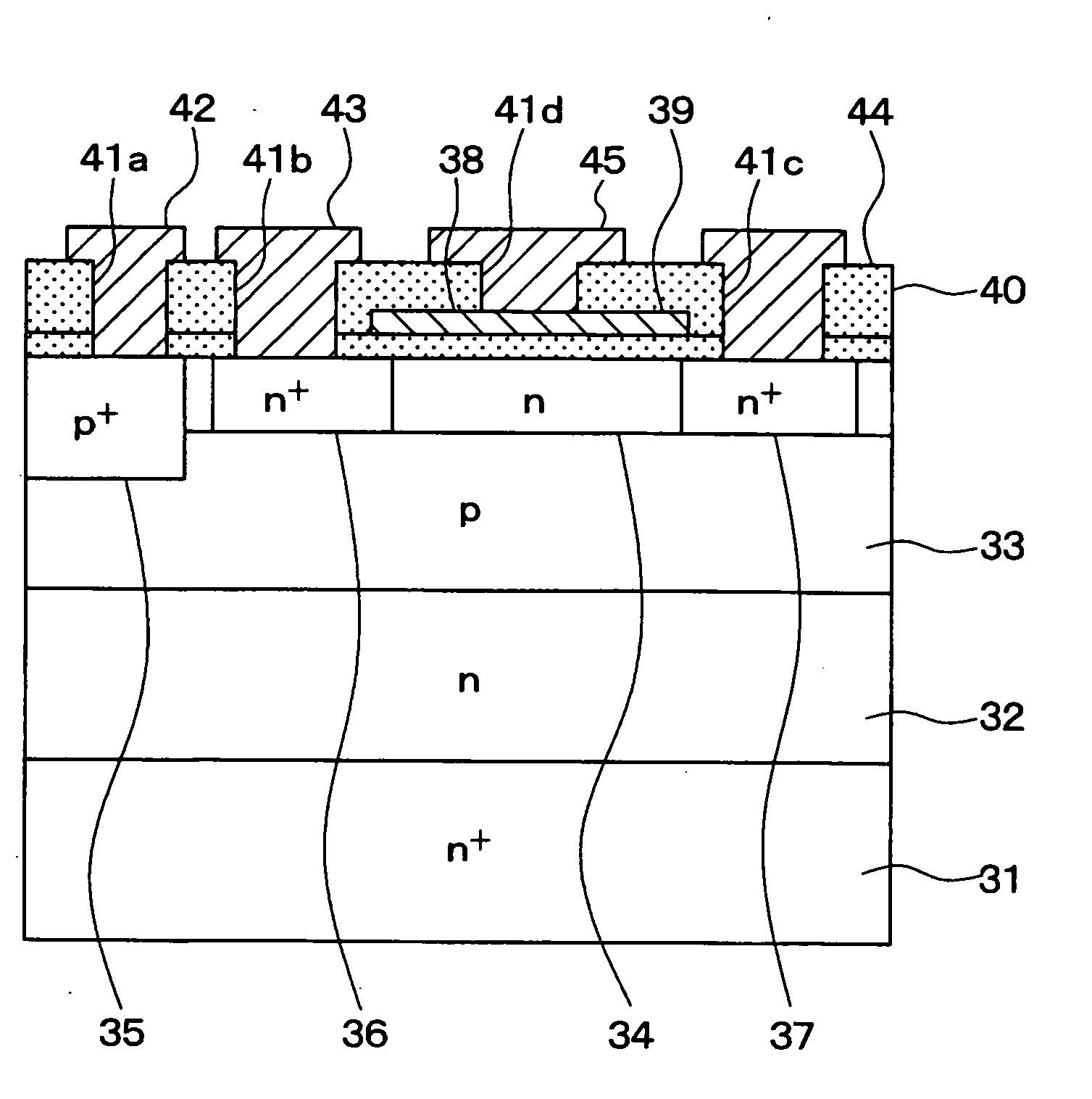

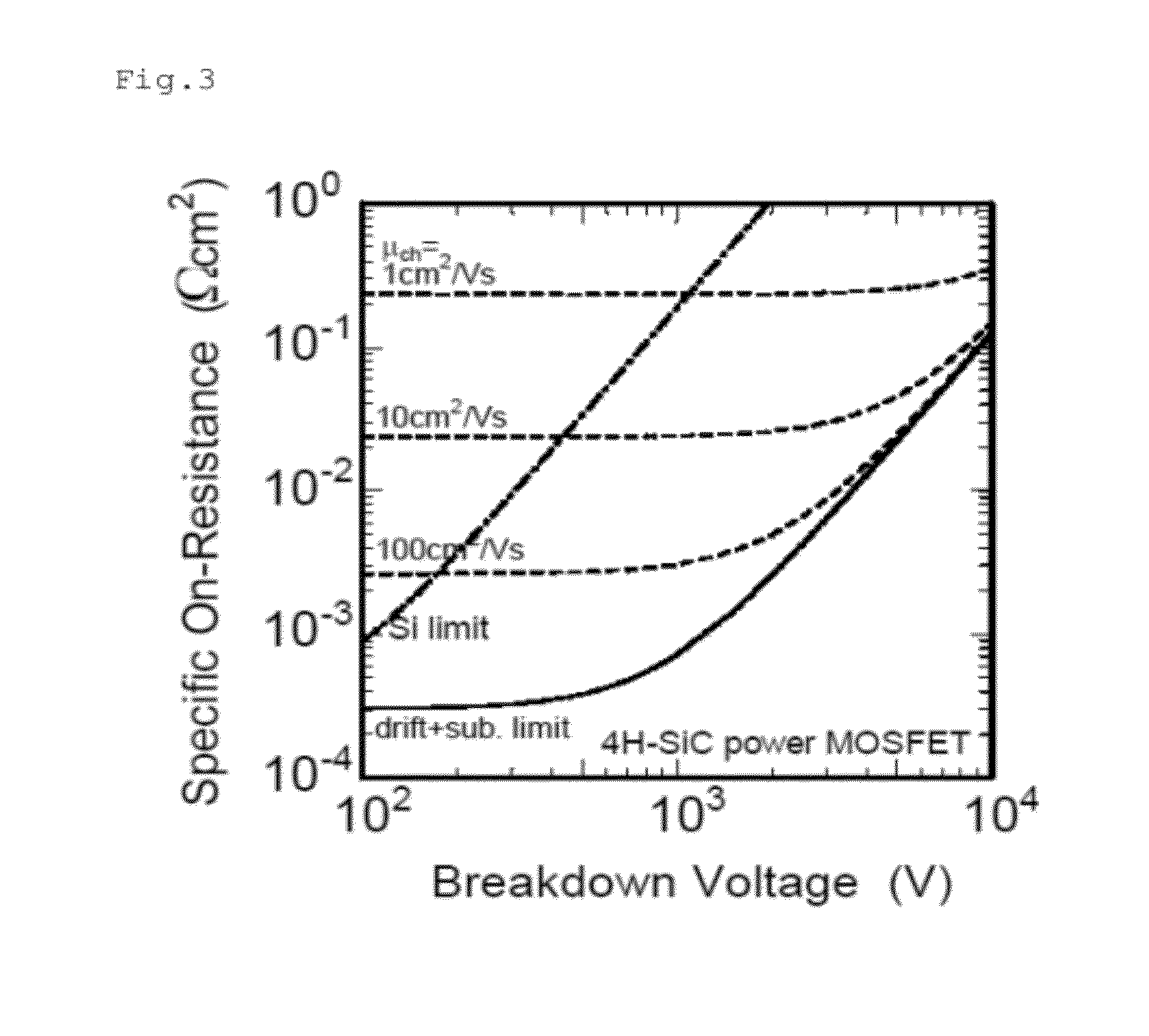

Silicon carbide semiconductor device having high channel mobility and method for manufacturing the same

ActiveUS20070045631A1Improve channel mobilityImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesHydrogen concentrationHydrogen atom

A silicon carbide semiconductor device having a MOS structure includes: a substrate; a channel area in the substrate; a first impurity area; a second impurity area; a gate insulating film on the channel area; and a gate on the gate insulating film. The channel area provides an electric current path. The channel area and the gate insulating film have an interface therebetween. The interface includes a dangling bond, which is terminated by a hydrogen atom or a hydroxyl. The interface has a hydrogen concentration equal to or larger than 2.6×1020 cm−3.

Owner:DENSO CORP

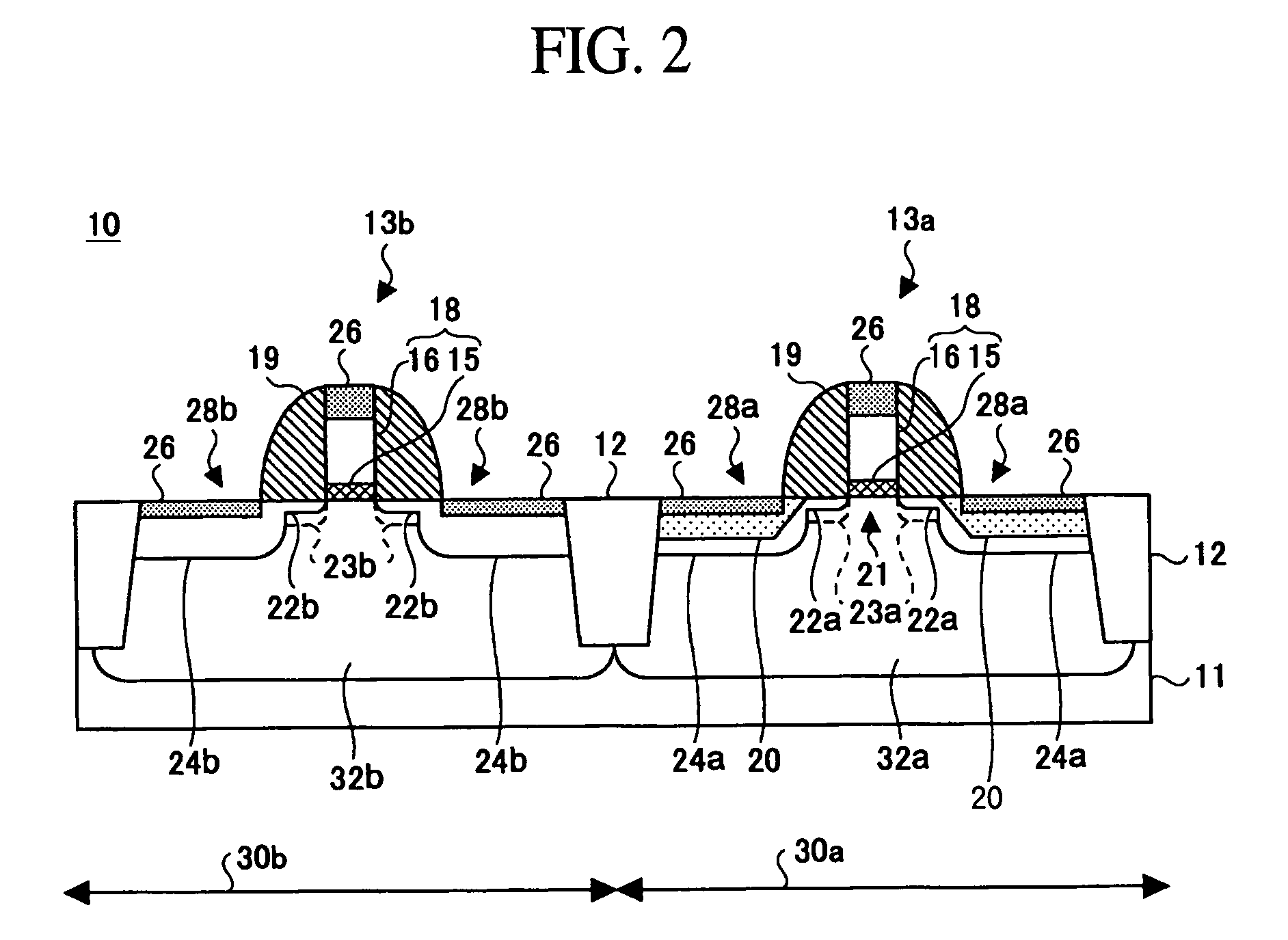

Semiconductor device fabricating method

ActiveUS20050266631A1High speedImprove channel mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

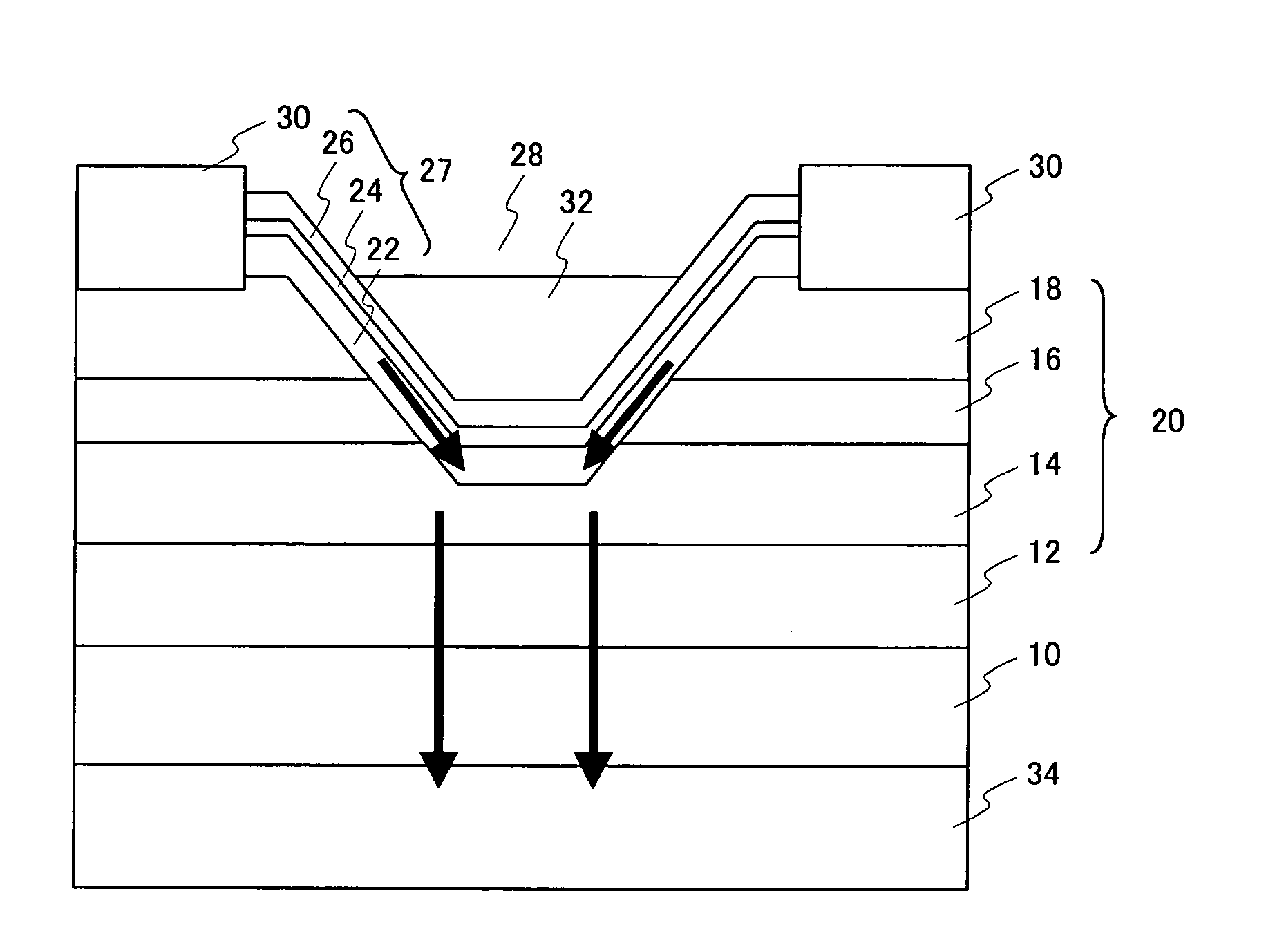

Compression stress applying portions 20 of SiGe film are formed in the source / drain regions of the p-MOSA region 30a. Then, impurities are implanted in the p-MOS region 30a and the n-MOS region 30b to form shallow junction regions 22a, 22b and deep junction regions 23a, 23b. The impurity in the shallow junction regions 22a, 22b is prevented from being diffused immediately below the gate insulation film 15 by the thermal processing in forming the SiGe film, the short channel effect is prevented, and the hole mobility of the channel region of the p-MOS transistor 14a. The operation speed of the p-MOS transistor 13a is balanced with that of the n-MOS transistor, whereby the operation speed of the complementary semiconductor device 10 can be increased. The semiconductor device fabricating method can increase and balance the operation speed of a p-transistor with that of an n-transistor.

Owner:FUJITSU SEMICON LTD

Semiconductor device and manufacturing method thereof

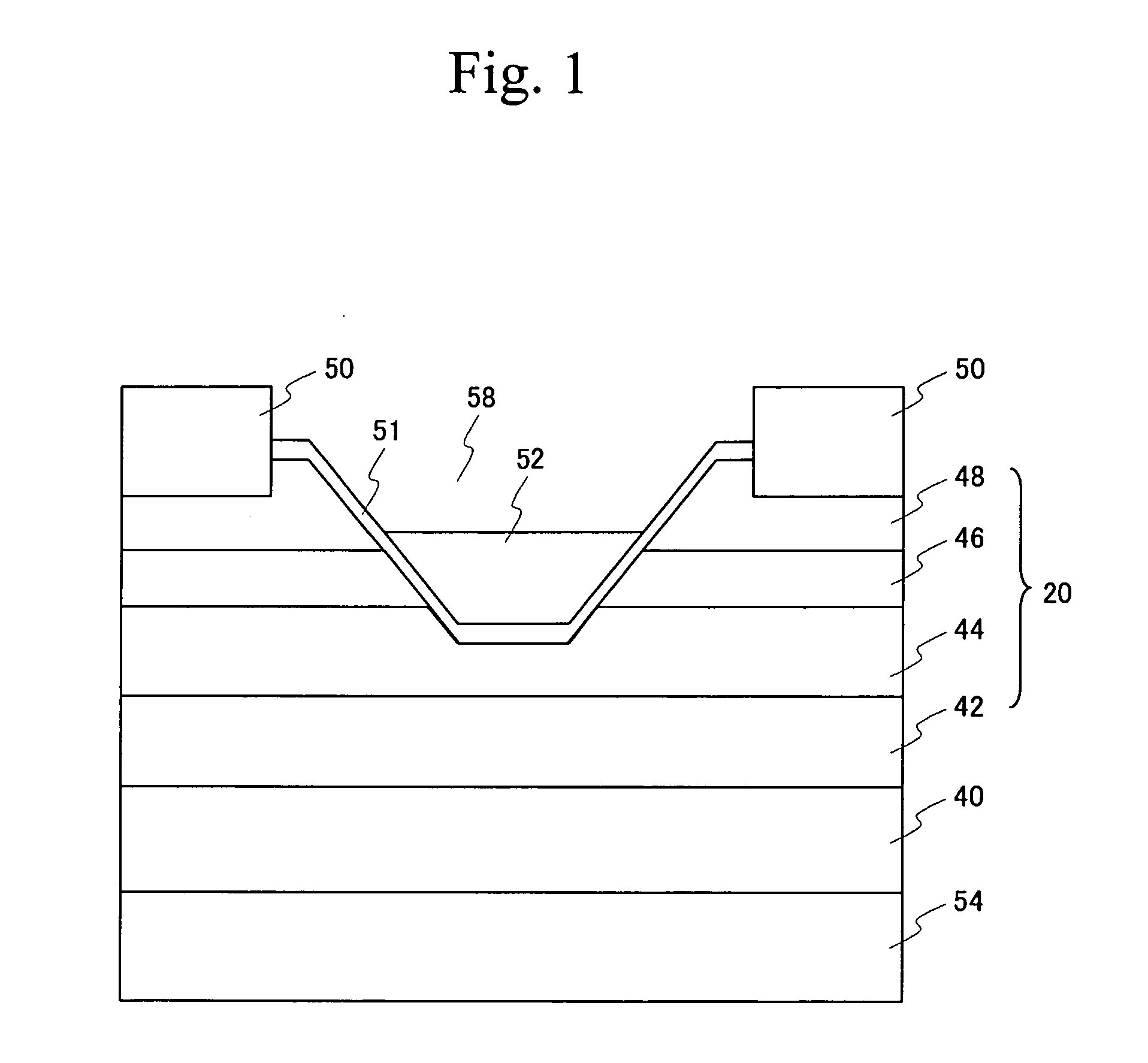

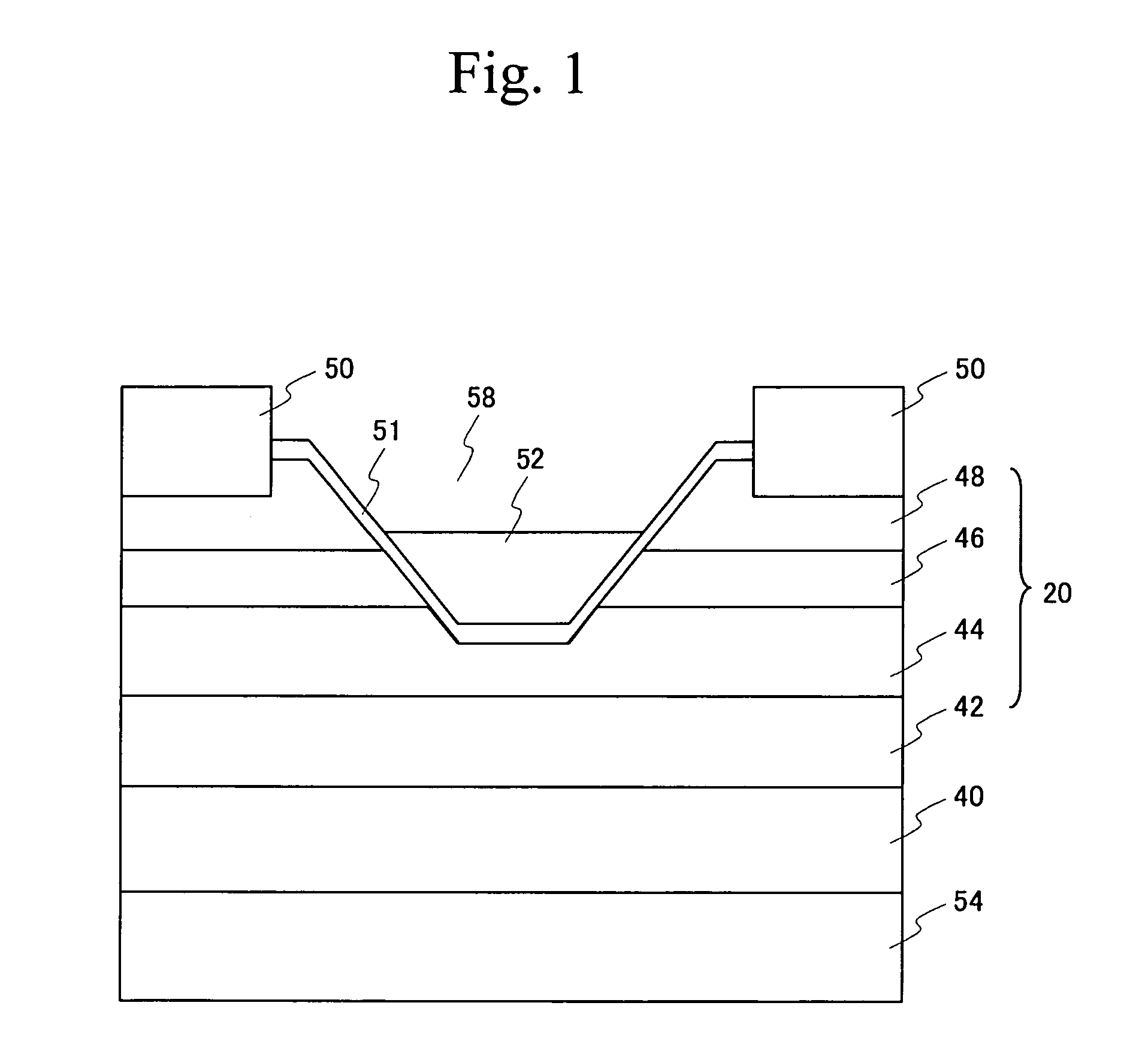

ActiveUS20060220060A1Excellent electrical propertiesImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

A semiconductor device includes a GaN-based semiconductor layer that is formed on a substrate and an opening region, an electron conduction layer formed on an inner surface of the opening region, an electron supply layer that has a larger band gap than the electron conduction layer and is formed on the electron conduction layer disposed on the inner surface of the opening region, and a gate electrode formed on a side surface of the electron supply layer in the opening region. A source electrode is formed on the GaN-based semiconductor layer. A drain electrode is connected to a surface of the GaN-based semiconductor layer opposite to the source electrode.

Owner:SUMITOMO ELECTRIC DEVICE INNOVATIONS

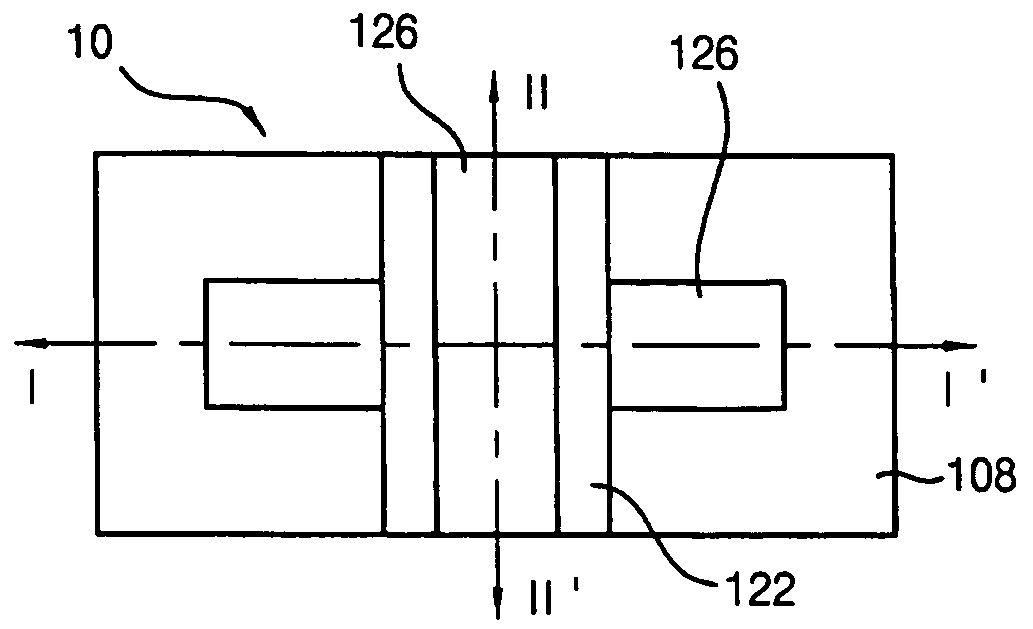

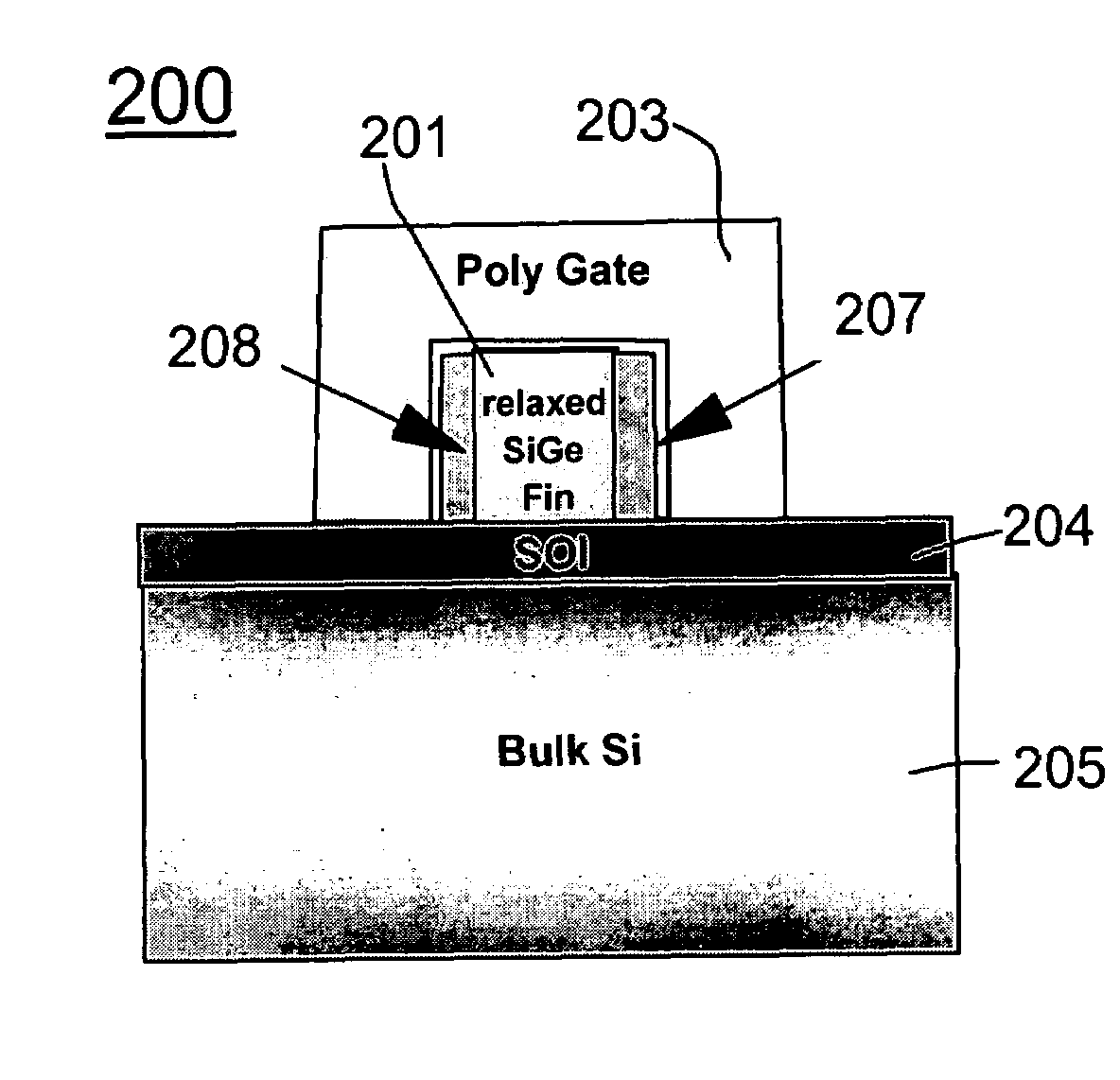

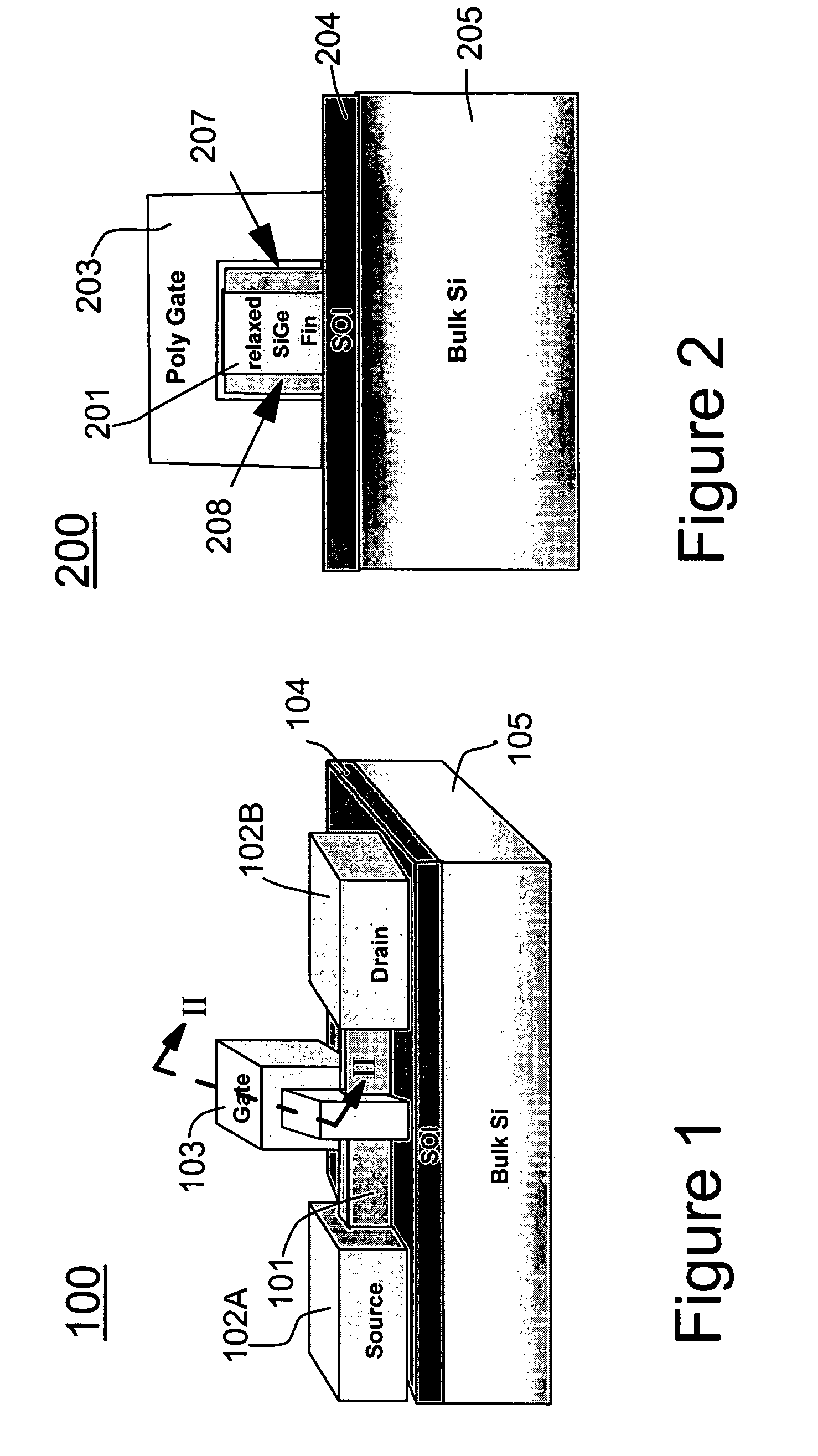

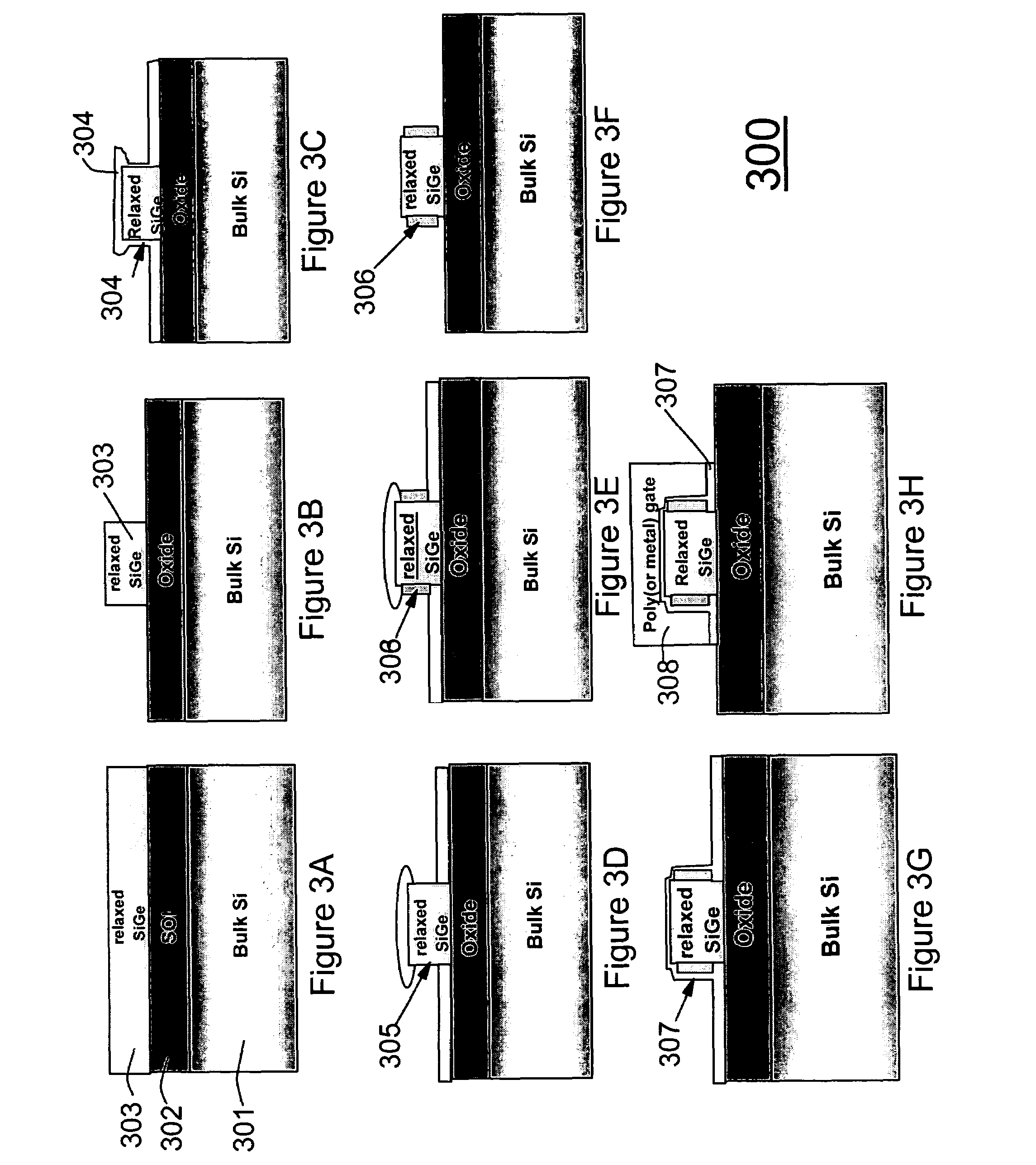

High performance strained silicon FinFETs device and method for forming same

ActiveUS7705345B2Improve channel mobilityImprove device performanceTransistorSolid-state devicesSiliconStrained silicon

A strained Fin Field Effect Transistor (FinFET) (and method for forming the same) includes a relaxed first material having a sidewall, and a strained second material formed on the sidewall of the first material. The relaxed first material and the strained second material form a fin of the FinFET.

Owner:GLOBALFOUNDRIES US INC

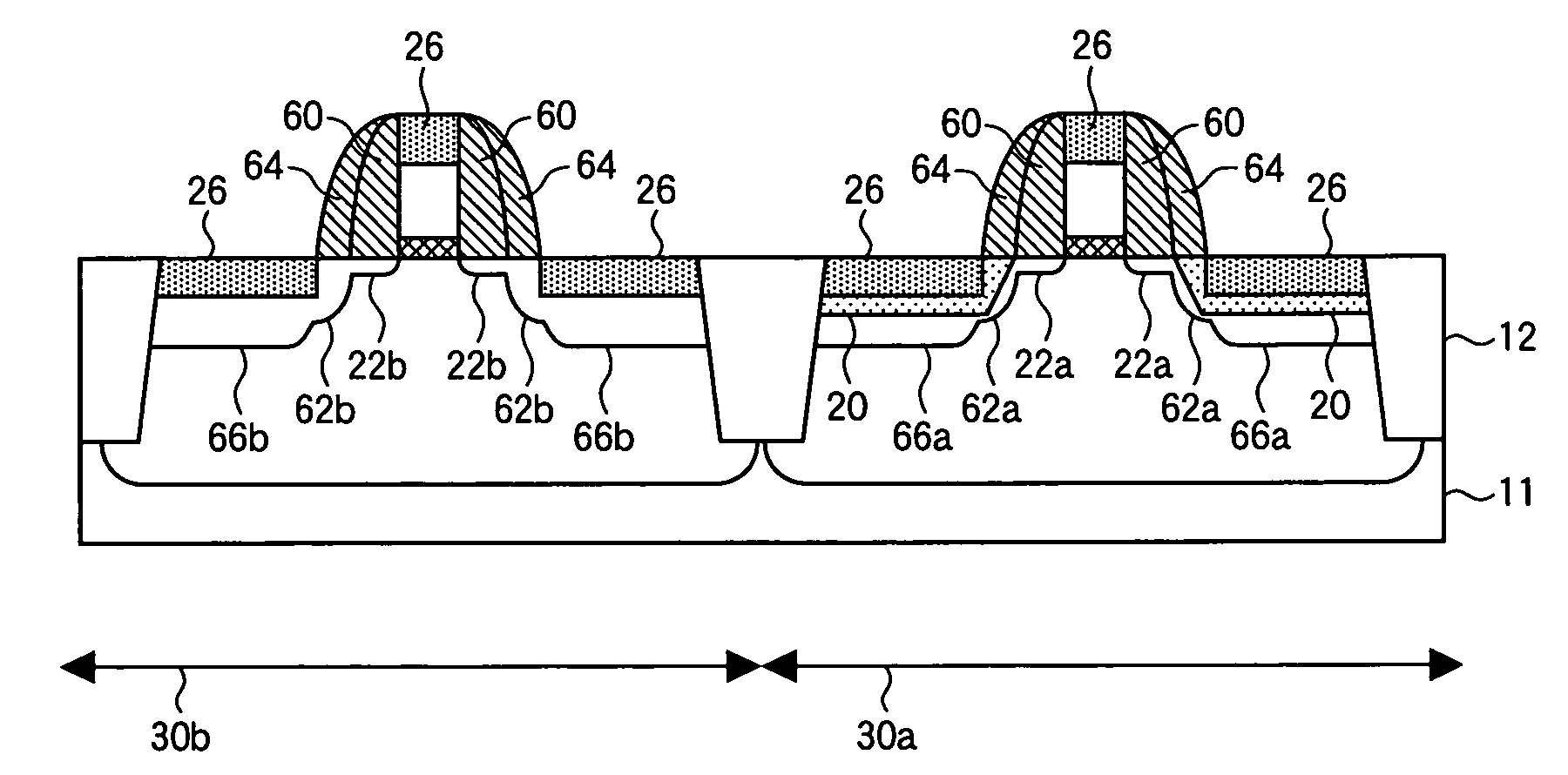

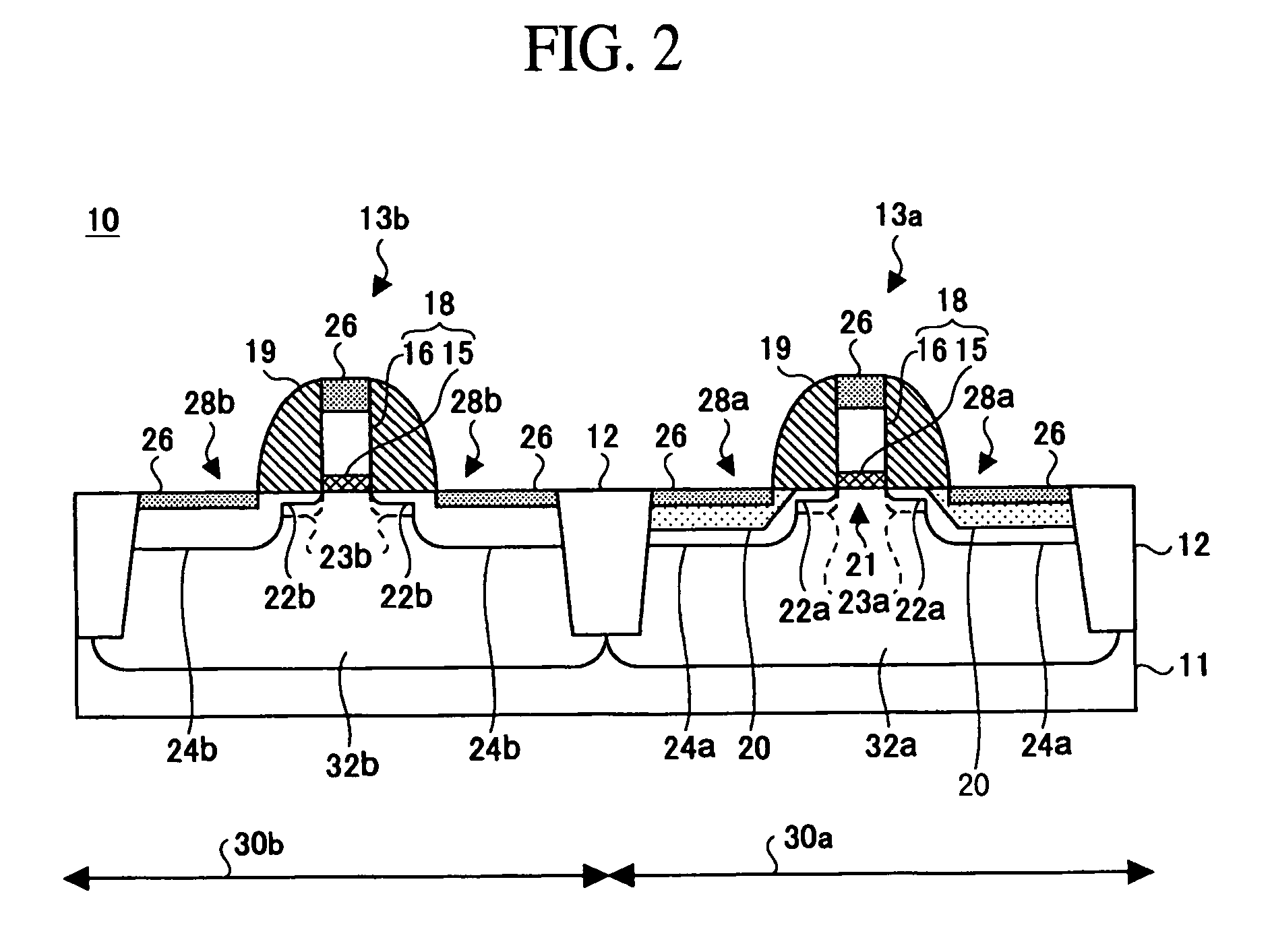

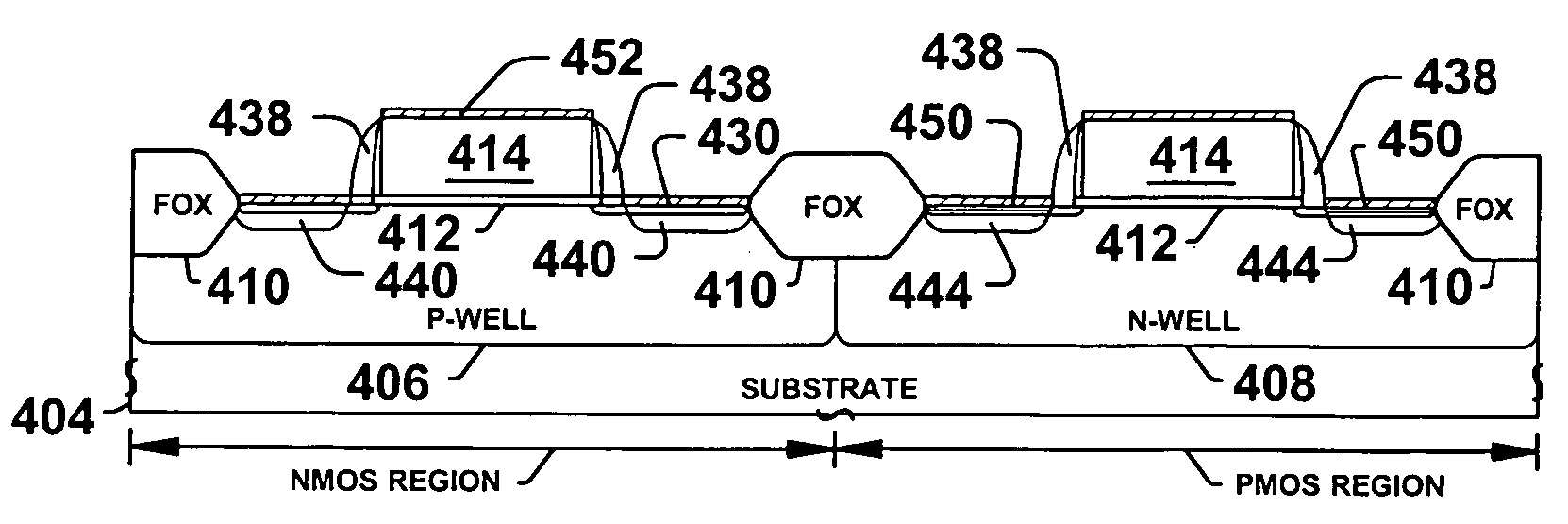

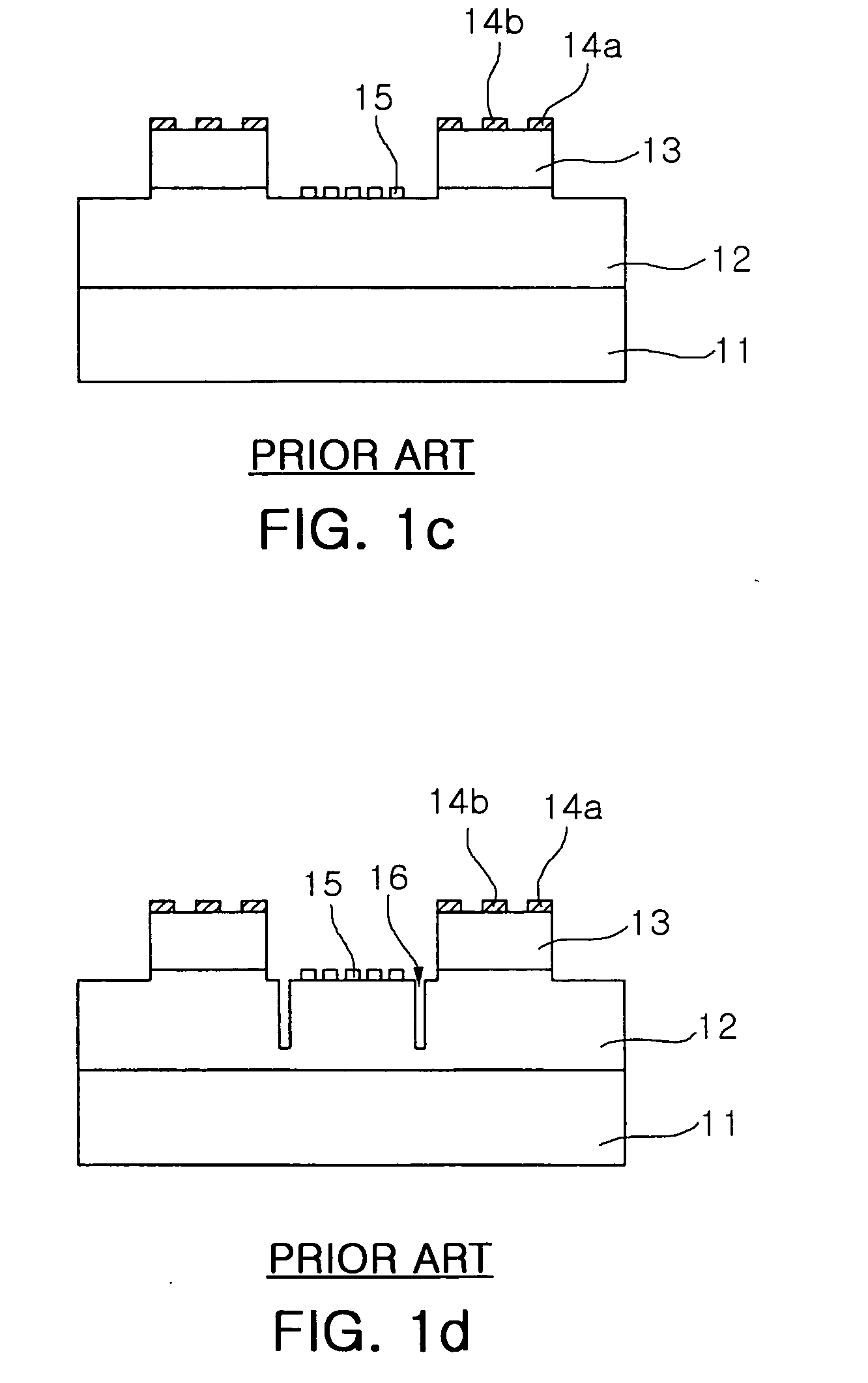

Method of fabricating a complementary semiconductor device having a strained channel p-transistor

ActiveUS7407860B2High speedImprove channel mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorImpurity

Compression stress applying portions 20 of SiGe film are formed in the source / drain regions of the p-MOSA region 30a. Then, impurities are implanted in the p-MOS region 30a and the n-MOS region 30b to form shallow junction regions 22a, 22b and deep junction regions 23a, 23b. The impurity in the shallow junction regions 22a, 22b is prevented from being diffused immediately below the gate insulation film 15 by the thermal processing in forming the SiGe film, the short channel effect is prevented, and the hole mobility of the channel region of the p-MOS transistor 14a. The operation speed of the p-MOS transistor 13a is balanced with that of the n-MOS transistor, whereby the operation speed of the complementary semiconductor device 10 can be increased. The semiconductor device fabricating method can increase and balance the operation speed of a p-transistor with that of an n-transistor.

Owner:FUJITSU SEMICON LTD

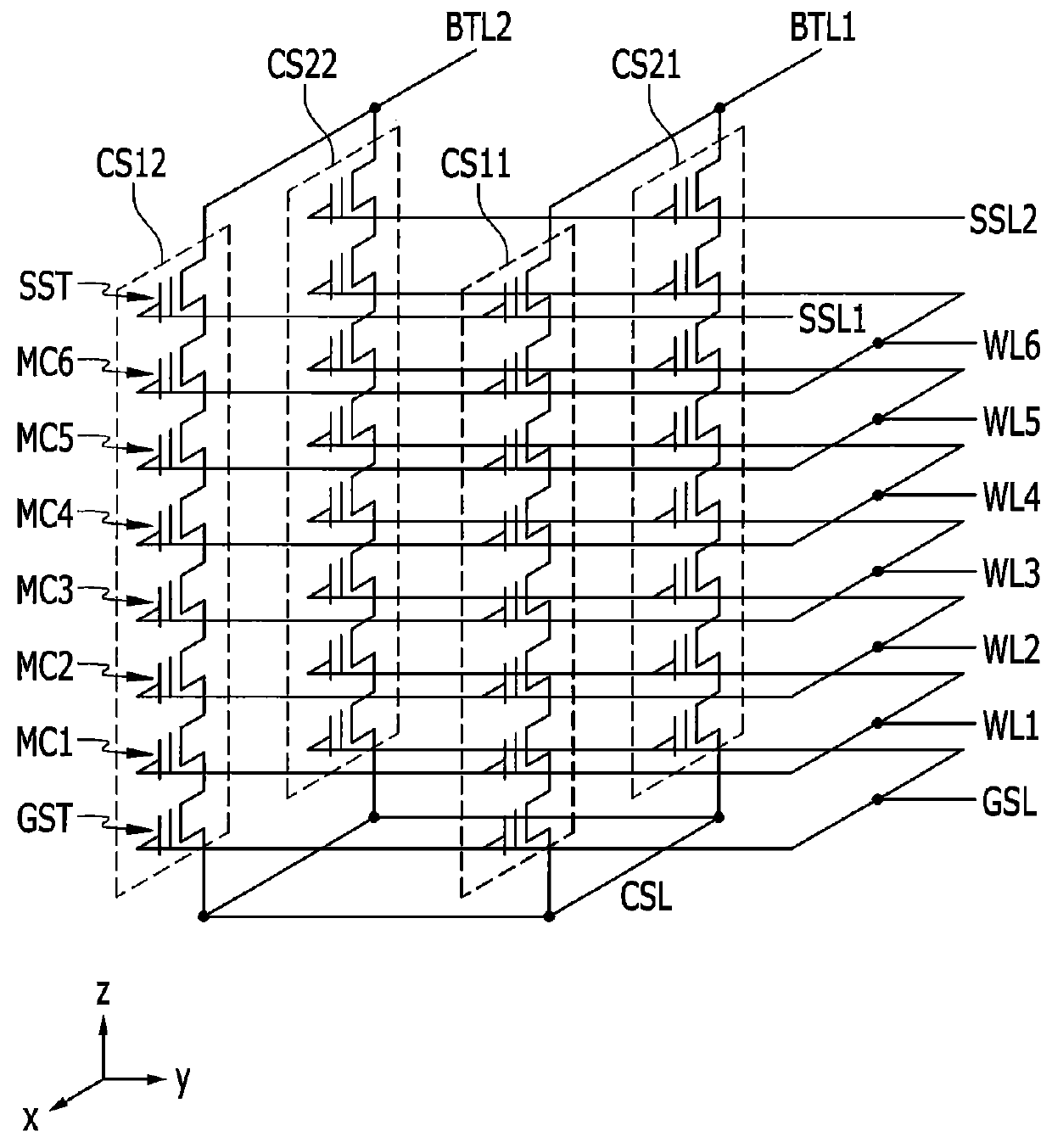

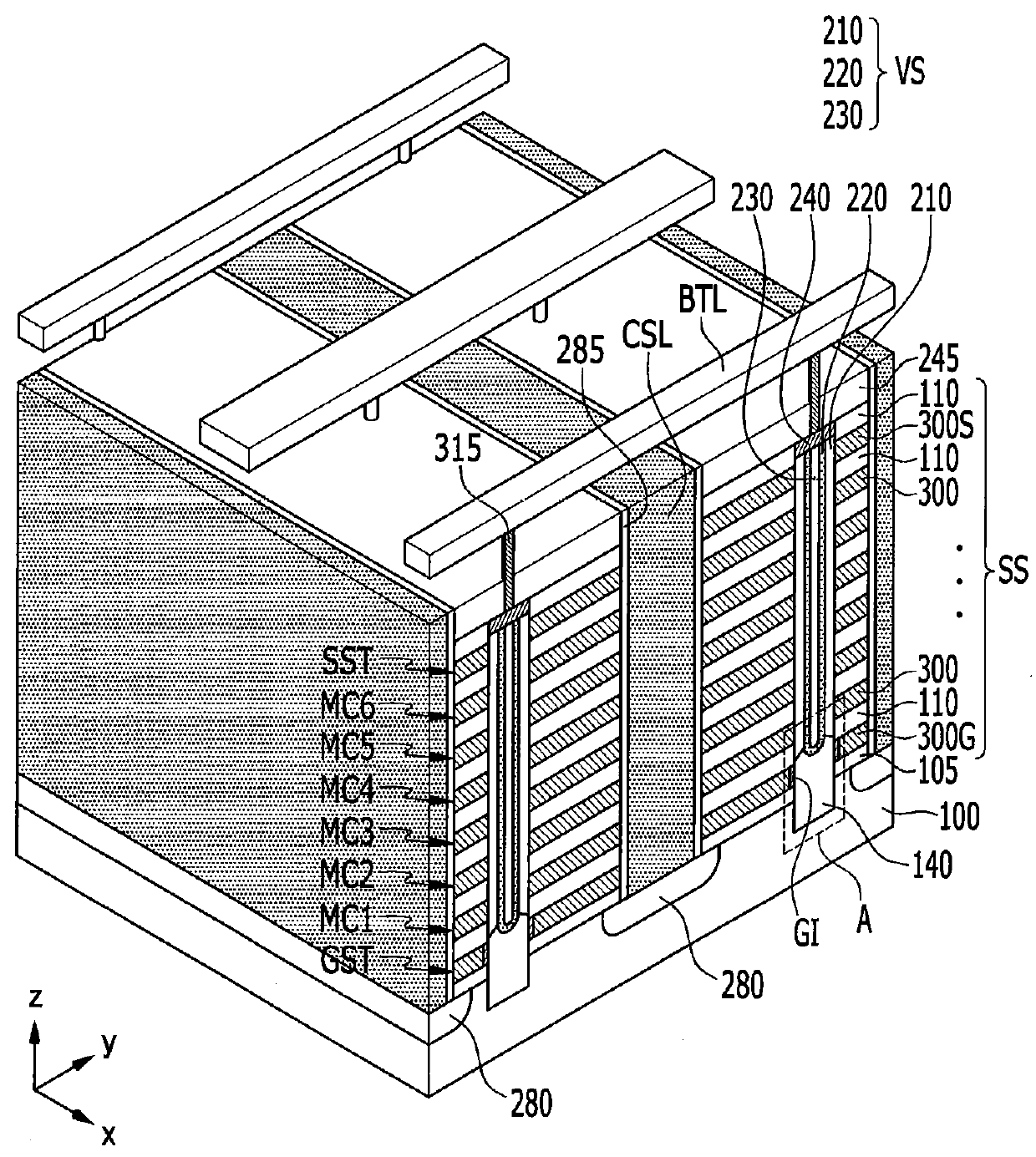

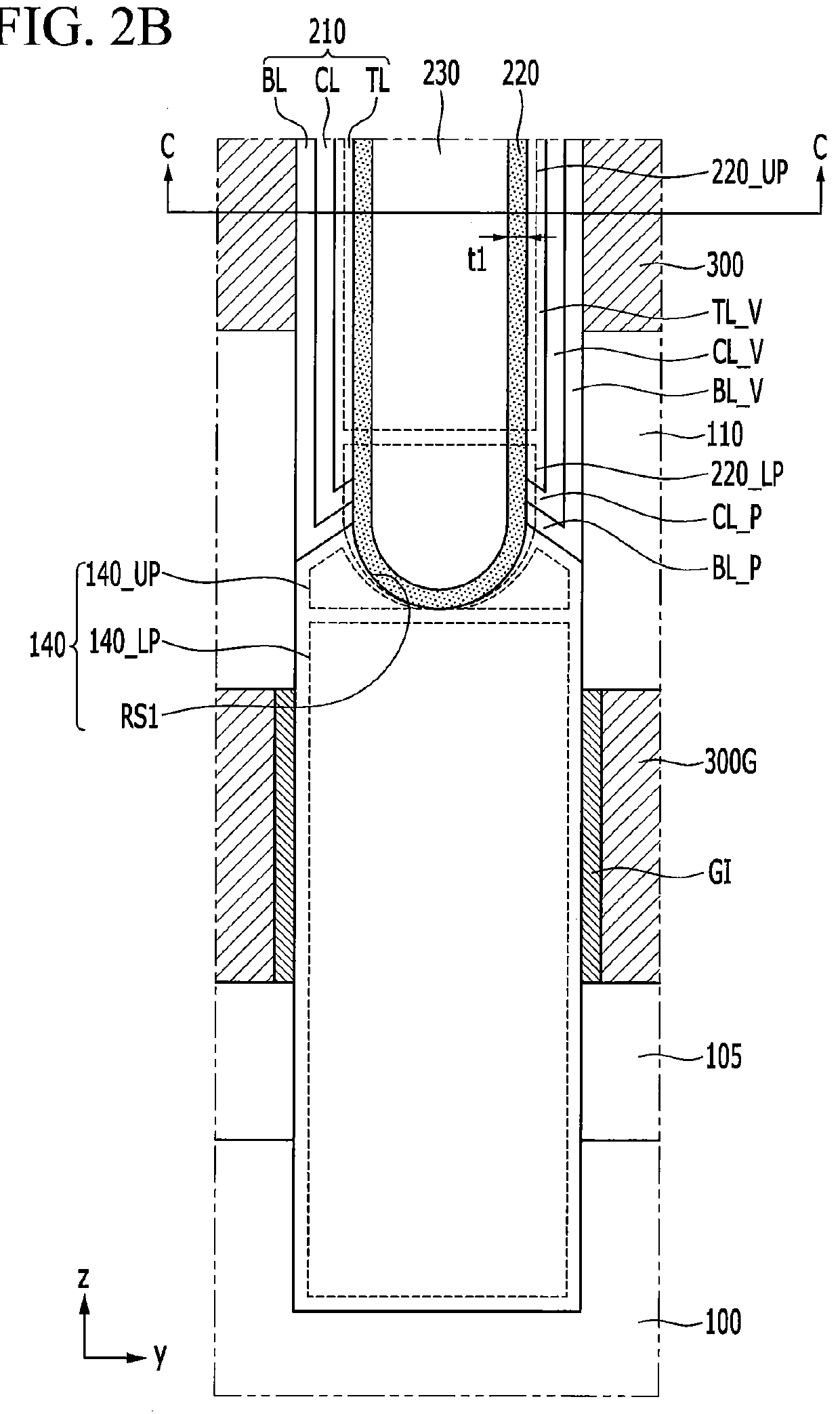

Semiconductor Memory Devices

ActiveUS20180097006A1Improve reliabilitySmall thicknessSolid-state devicesSemiconductor devicesCurve shapeEngineering

A semiconductor memory device may include: a stacking structure including a plurality of insulating layers and a plurality of gate electrodes alternately stacked on a substrate; a lower semiconductor pattern that protrudes from the top of the substrate; a vertical insulating pattern that extends in a vertical direction from the substrate and penetrates the stacking structure; and a vertical channel pattern on the inner surface of the vertical insulating pattern and contacting the lower semiconductor pattern, wherein an upper part of the lower semiconductor pattern includes a recess region including a curve-shaped profile, and in the recess region, the outer surface of a lower part of the vertical channel pattern contacts the lower semiconductor pattern along a curve of the recess region.

Owner:SAMSUNG ELECTRONICS CO LTD

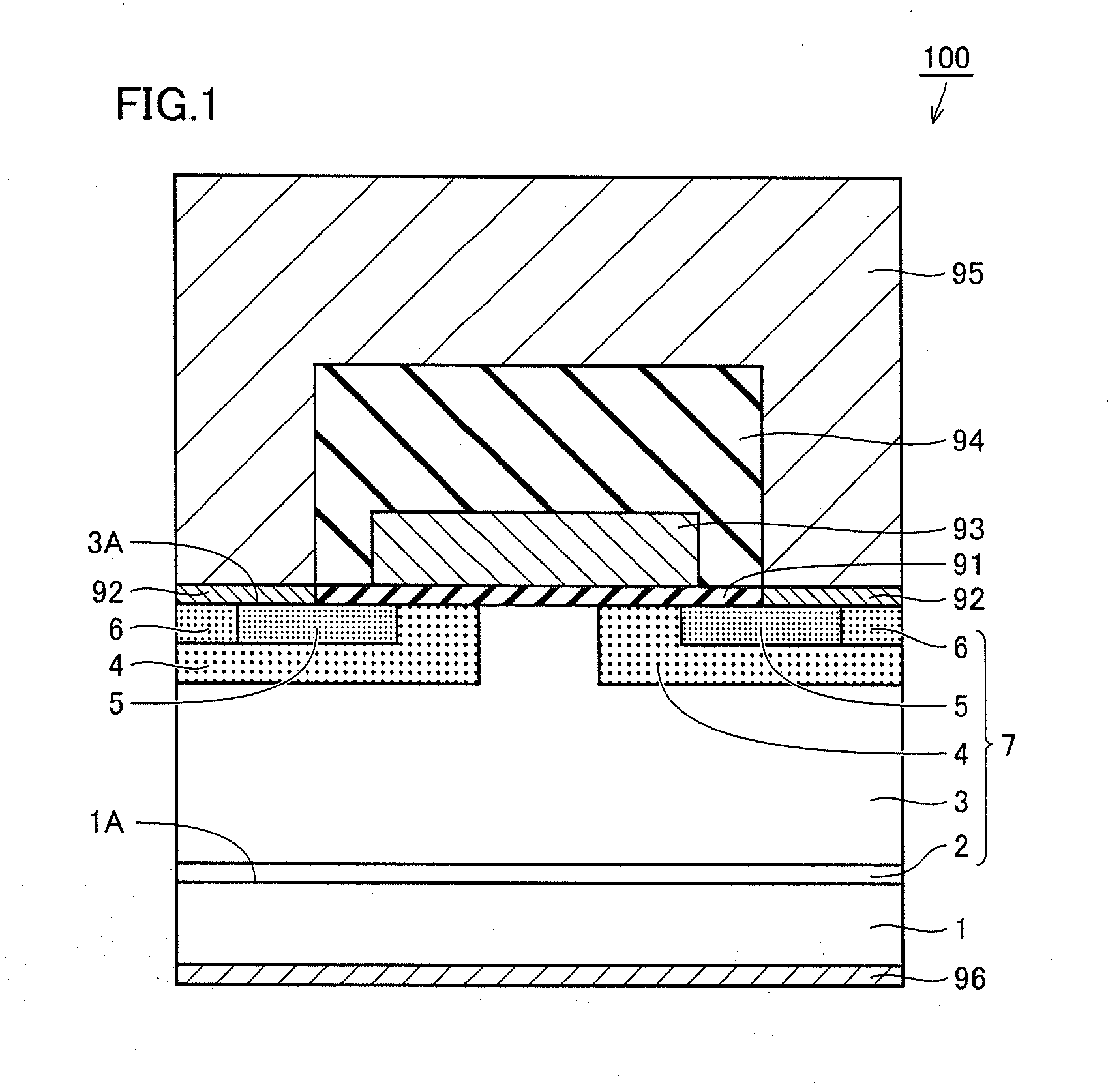

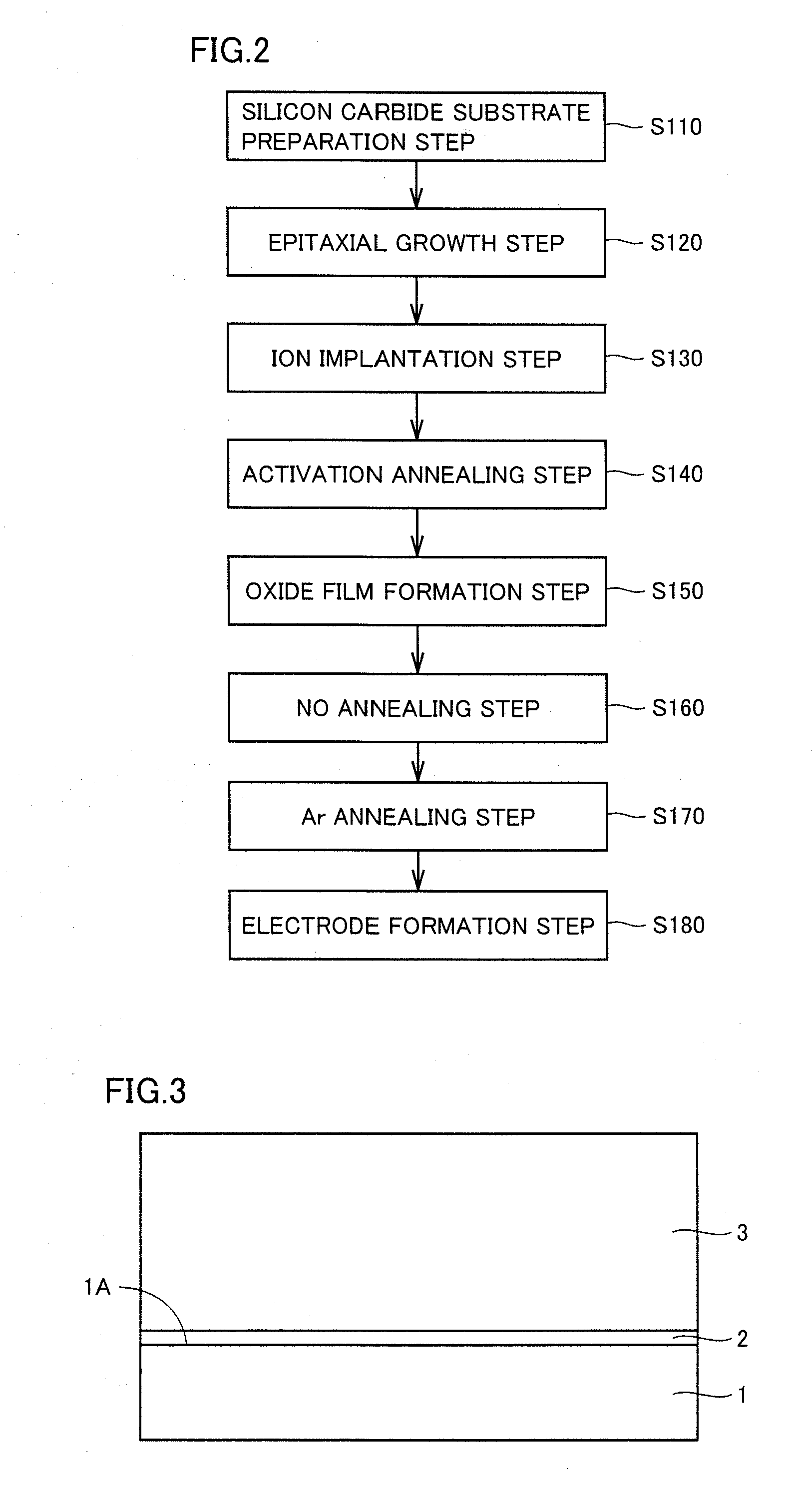

SiC semiconductor device and method for manufacturing the same

ActiveUS20080203441A1Improve channel mobilityReduce interface state densitySolid-state devicesSemiconductor/solid-state device manufacturingHydrogen concentrationEngineering

A SiC semiconductor device having a MOS structure includes: a SiC substrate; a channel region providing a current path; first and second impurity regions on upstream and downstream sides of the current path, respectively; and a gate on the channel region through the gate insulating film. The channel region for flowing current between the first and second impurity regions is controlled by a voltage applied to the gate. An interface between the channel region and the gate insulating film has a hydrogen concentration equal to or greater than 4.7×1020 cm−3. The interface provides a channel surface having a (000-1)-orientation surface.

Owner:DENSO CORP

Semiconductor device and its manufacturing method

ActiveUS7338869B2Low densityImprove channel mobilityTransistorSemiconductor/solid-state device manufacturingInsulation layerSemiconductor

Owner:NAT INST OF ADVANCED IND SCI & TECH

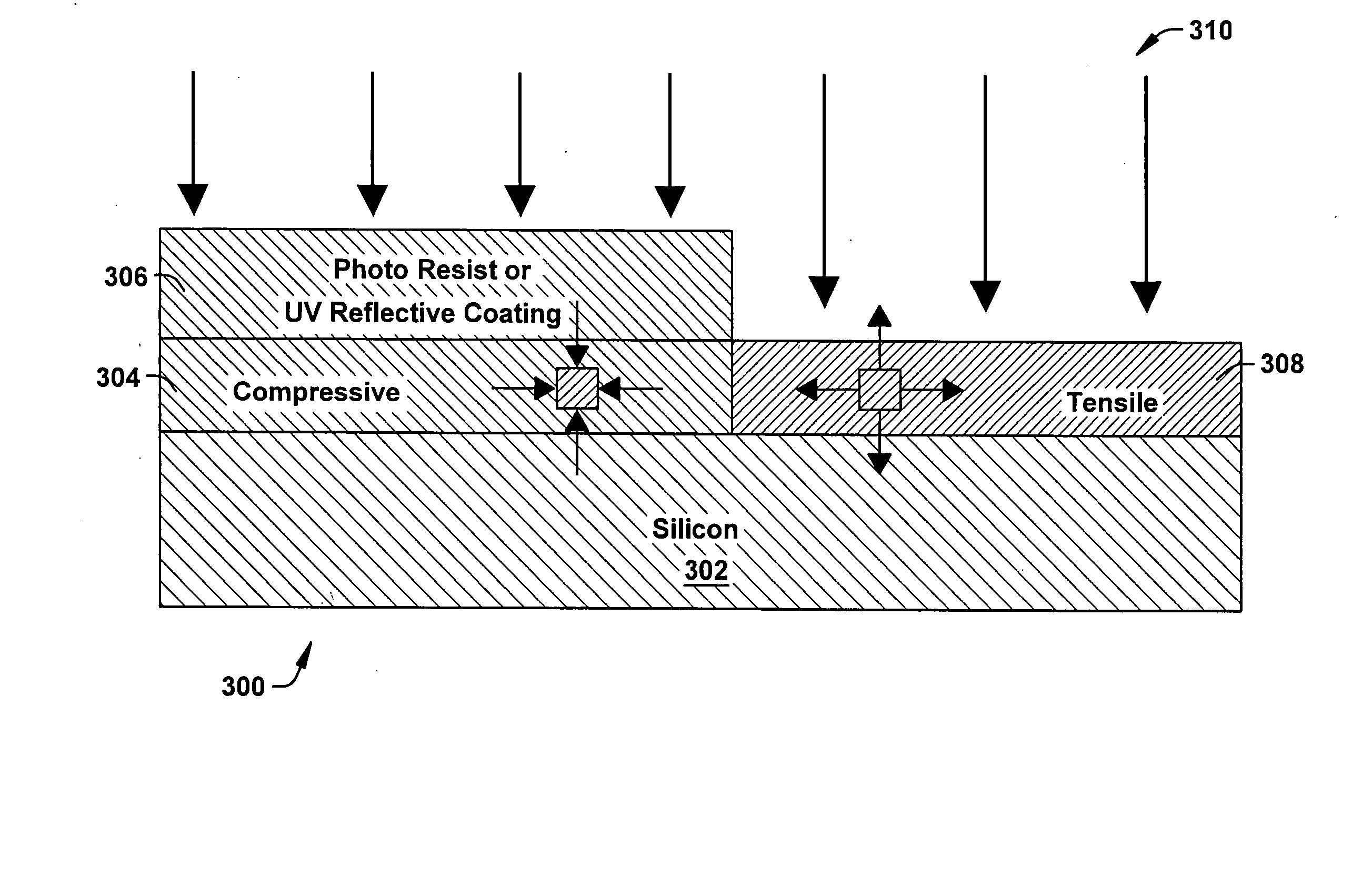

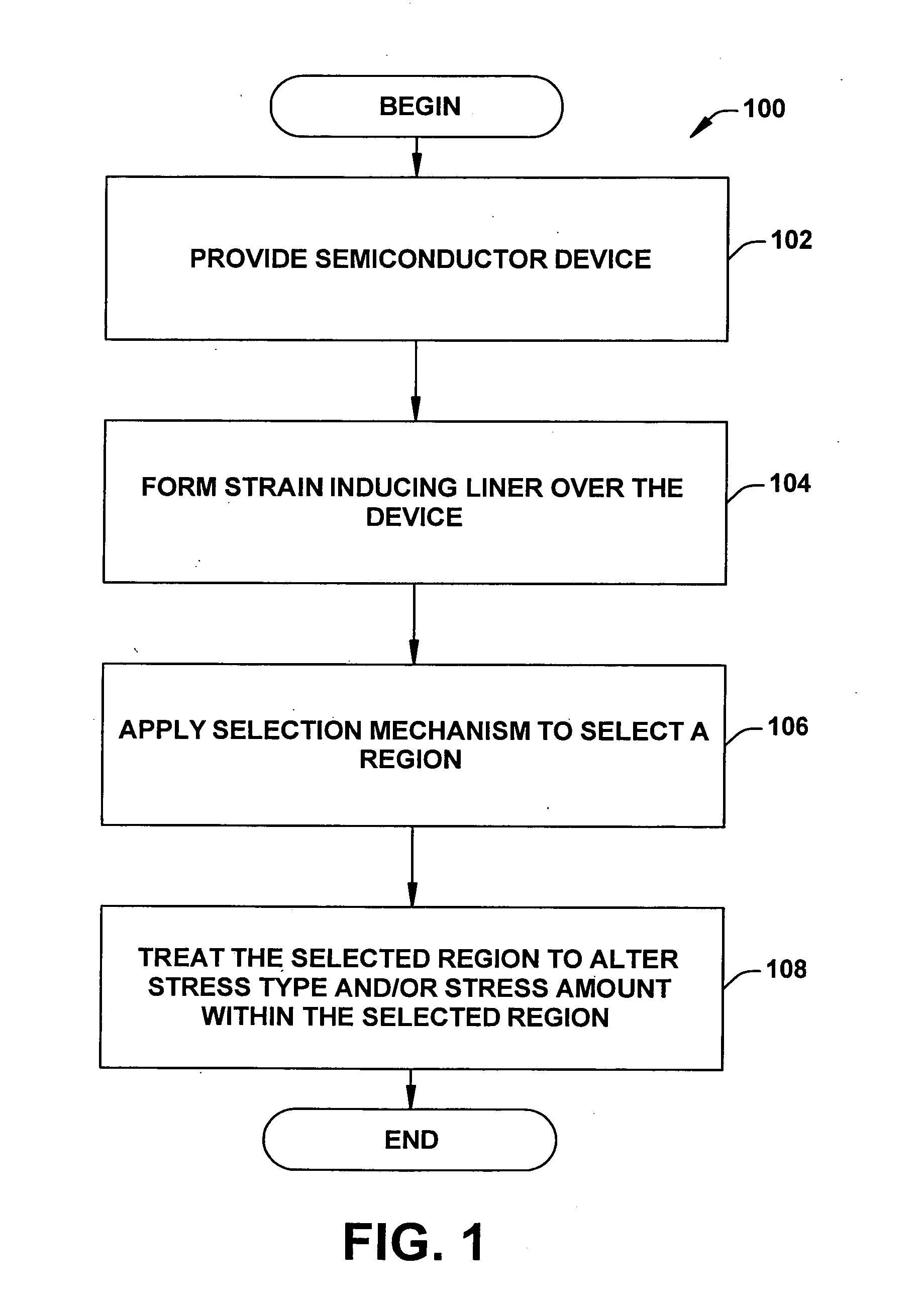

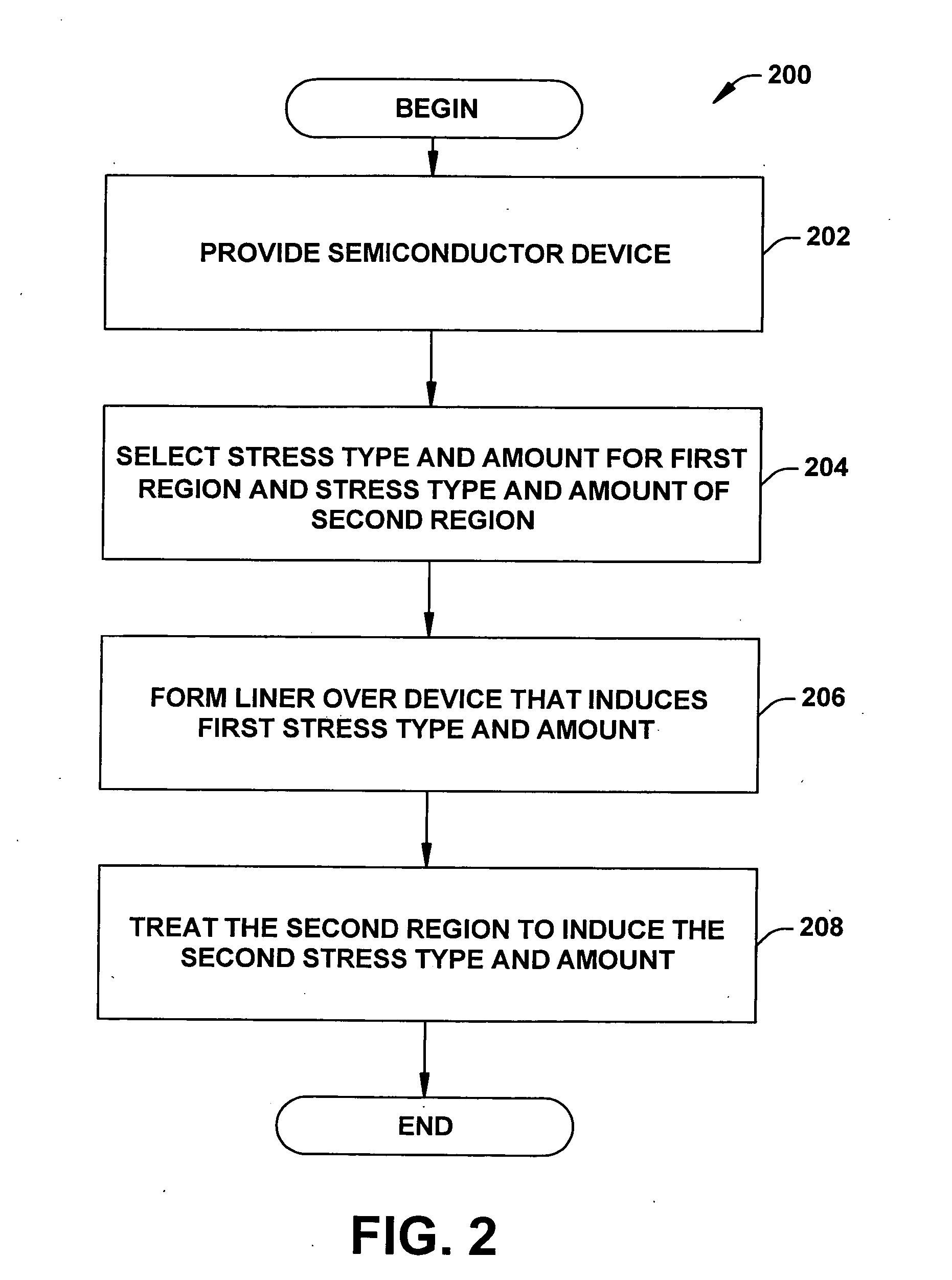

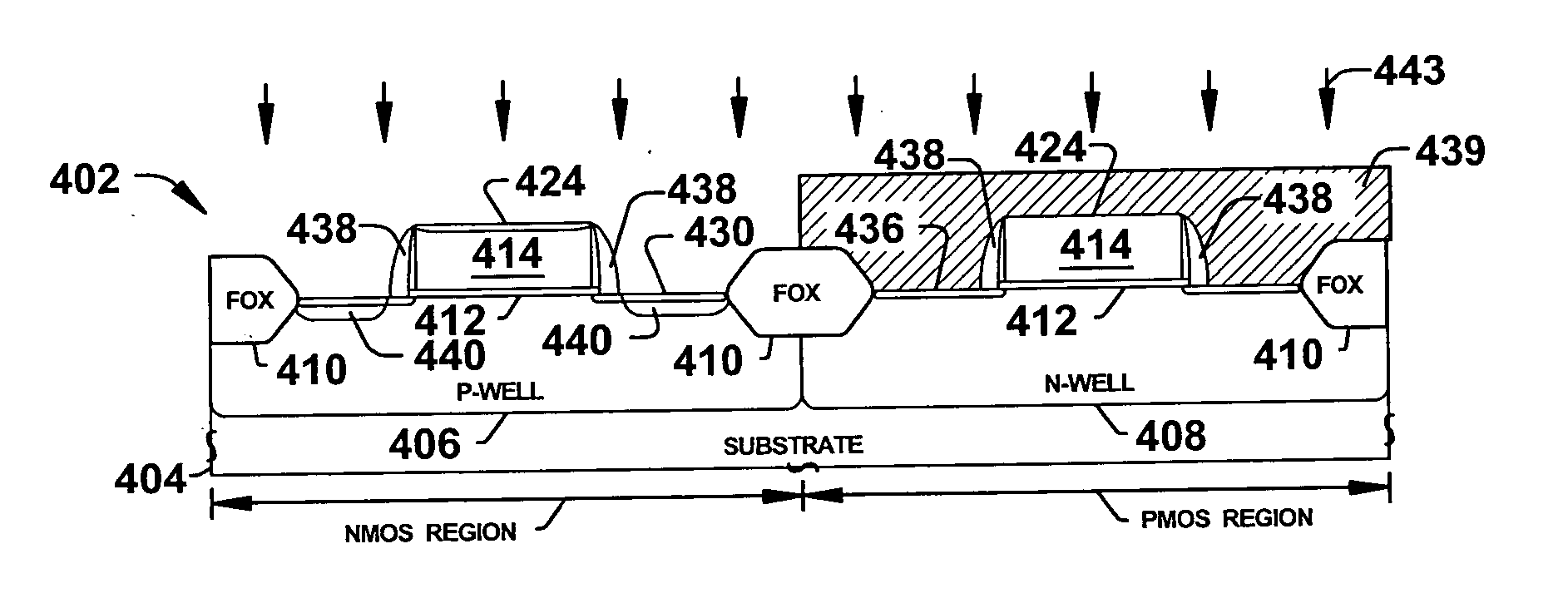

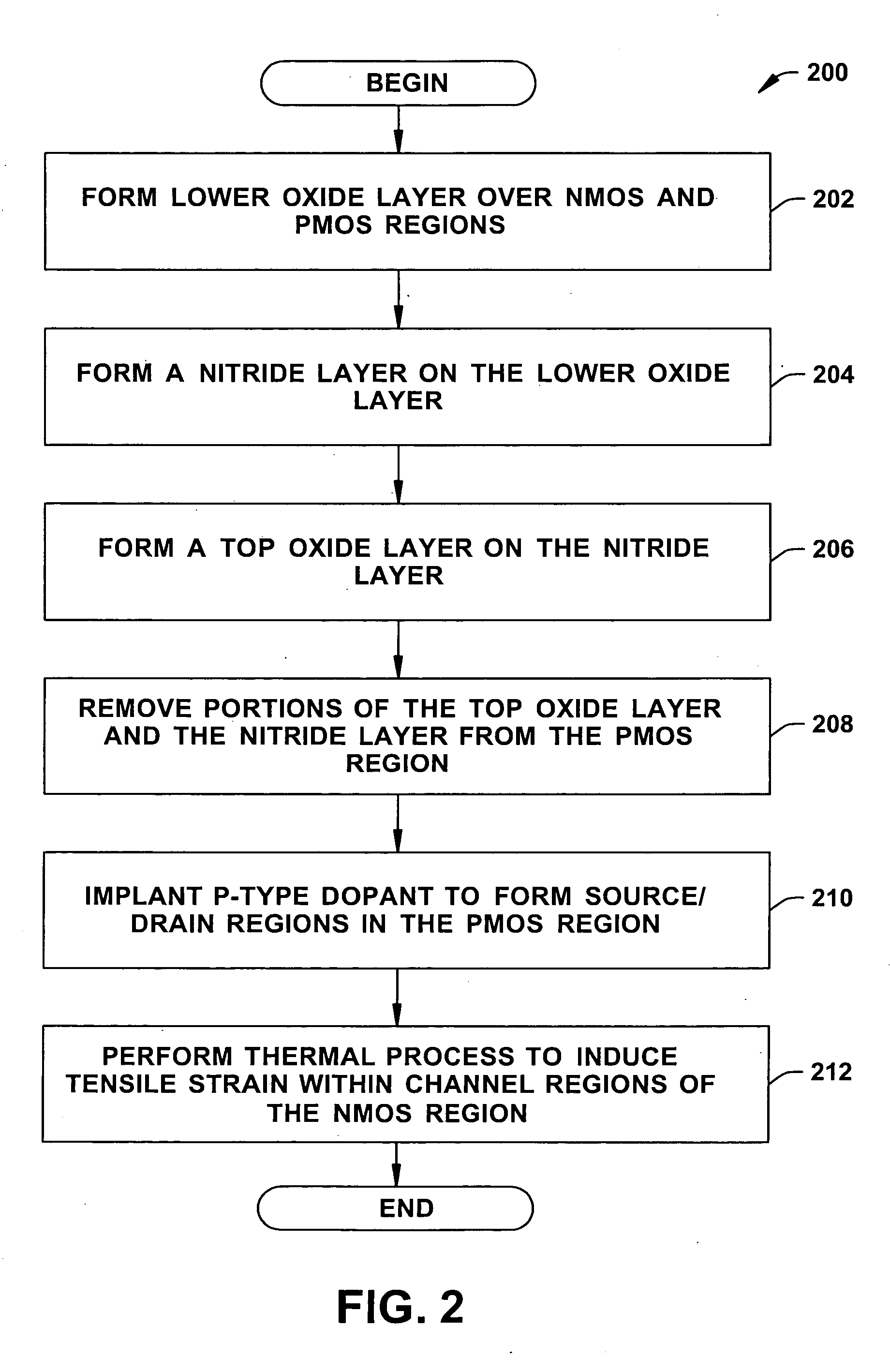

Systems and methods that selectively modify liner induced stress

ActiveUS20060172481A1Facilitates semiconductor fabricationFacilitating device operationSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialUltraviolet

The present invention facilitates semiconductor fabrication by providing methods of fabrication that selectively apply strain to multiple regions of a semiconductor device. A semiconductor device having one or more regions is provided (102). A strain inducing liner is formed over the semiconductor device (104). A selection mechanism, such as a layer of photoresist or UV reflective coating is applied to the semiconductor device to select a region (106). The selected region is treated with a stress altering treatment that alters a type and / or magnitude of stress produced by the selected region (108).

Owner:TEXAS INSTR INC

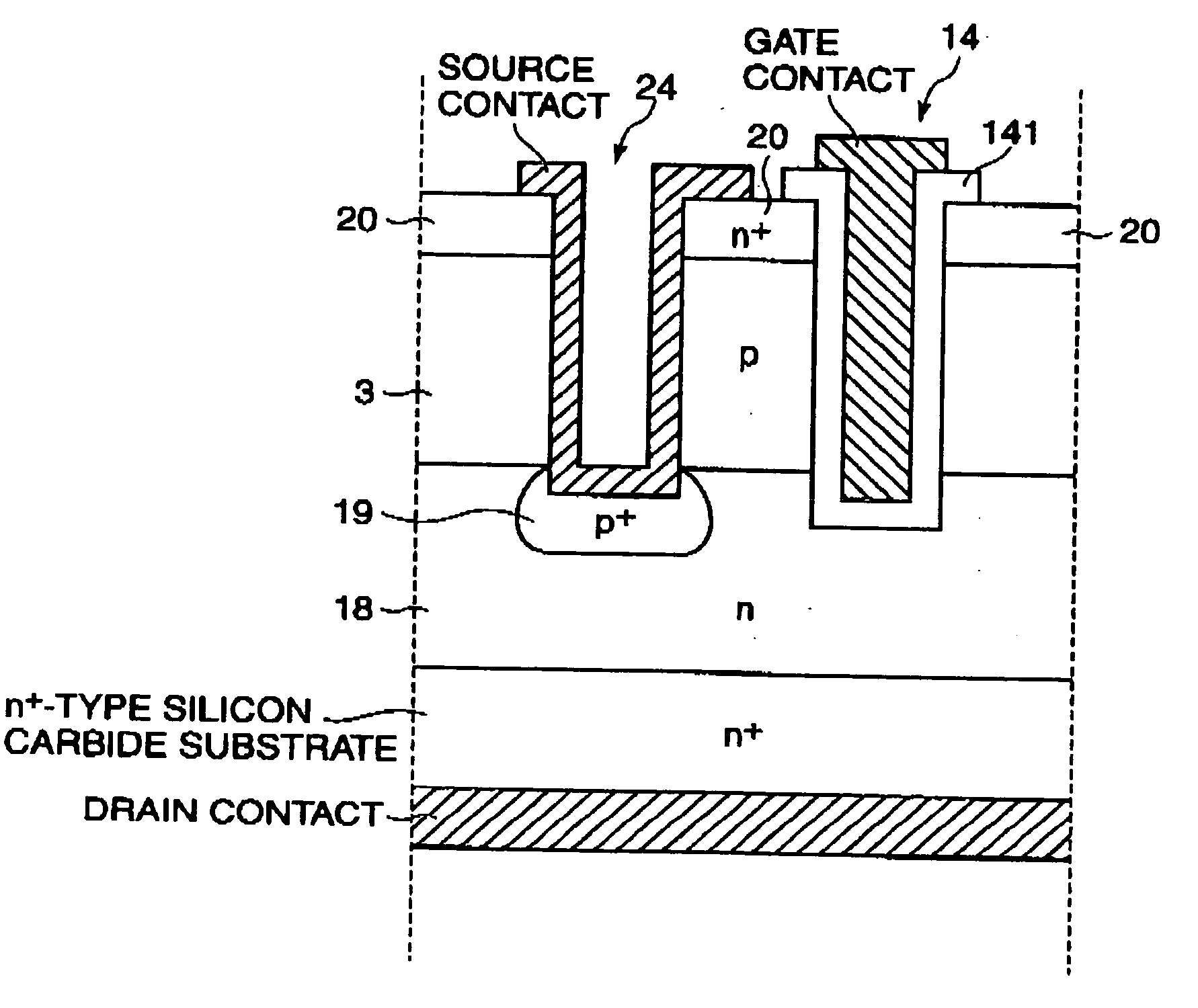

Silicon carbide semiconductor device

InactiveUS20110121316A1Improve channel mobilityArea of body is minimizedSemiconductor devicesGate oxideDeep locations

The area of each body region is minimized, and the gate oxide films at the bottoms of the trenches are more effectively protected by depletion layers extending from the body regions.According to the present invention, an n−-type drift layer and a p-type base region are stacked on an n+-type silicon carbide substrate, and an n+-type source region is formed in a predetermined region of a surface portion in the base region. A gate trench is formed in a trench groove that reaches the drift layer. A p-type body region is formed at a deeper location than the gate trench. The p-type body region is adjacent to the gate trench but is not in contact with the gate trench. When viewed from above, the gate trench having a hexagonal shape surrounds the p-type body region. The side faces of the gate trench are formed only by {11-20} planes of silicon carbide.

Owner:NAT INST OF ADVANCED IND SCI & TECH

Selective nitridation of gate oxides

ActiveUS7138691B2Reduce diffuseInvention improvedTransistorSemiconductor/solid-state device manufacturingDopantRemote plasma

Owner:GLOBALFOUNDRIES U S INC +1

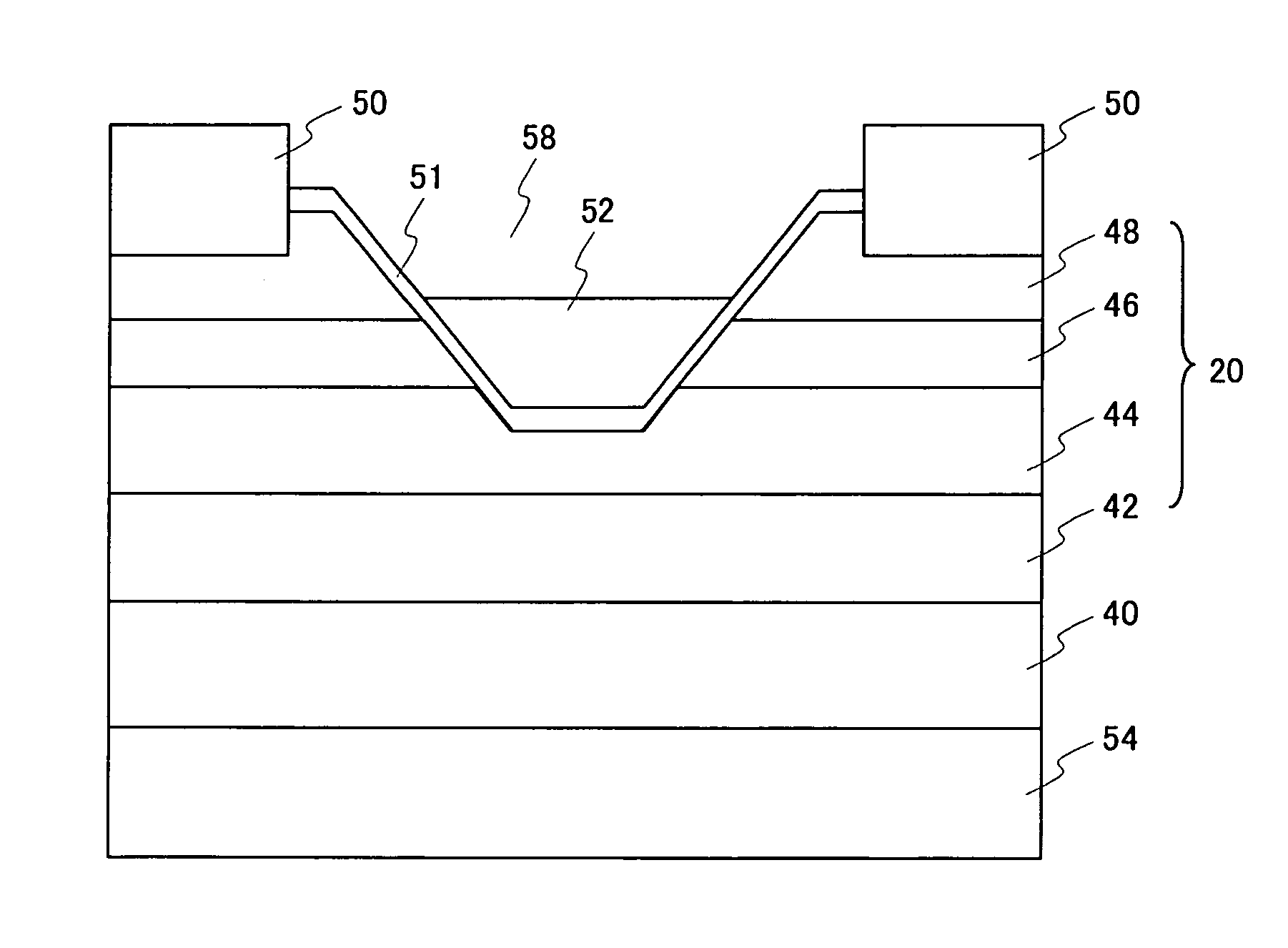

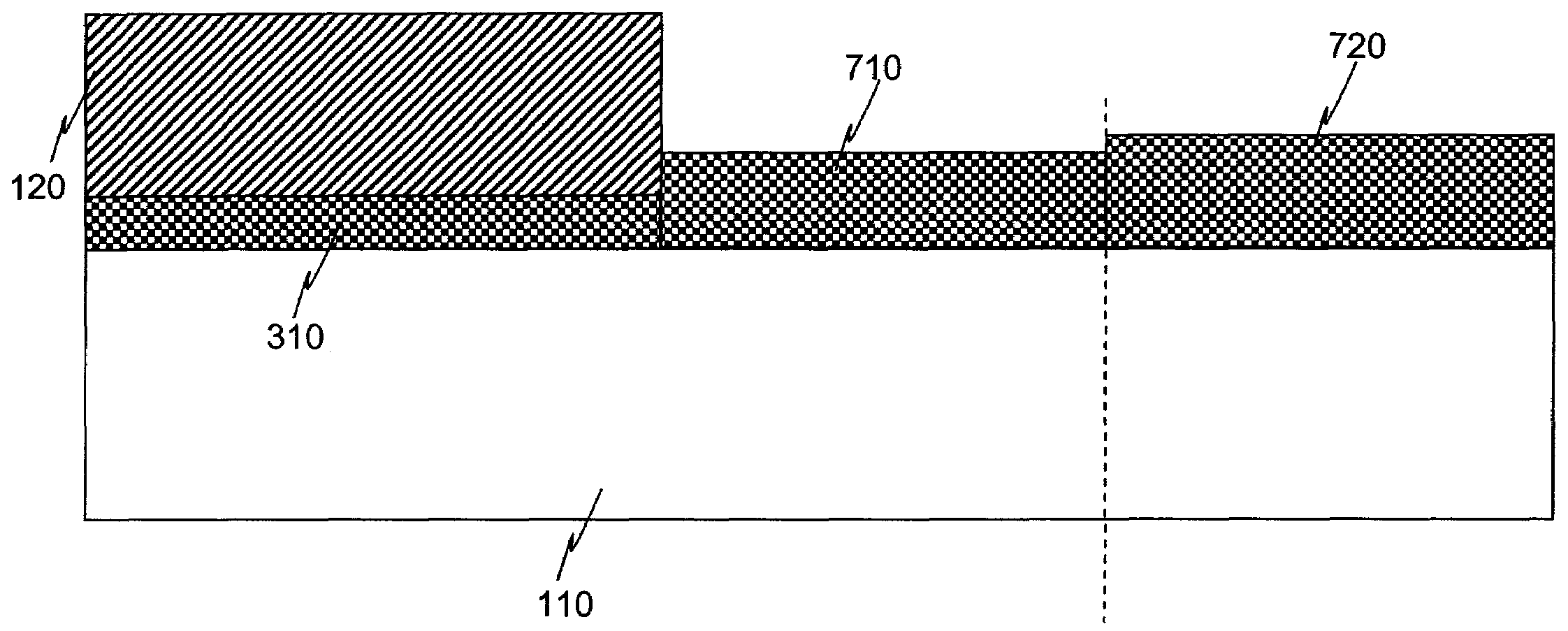

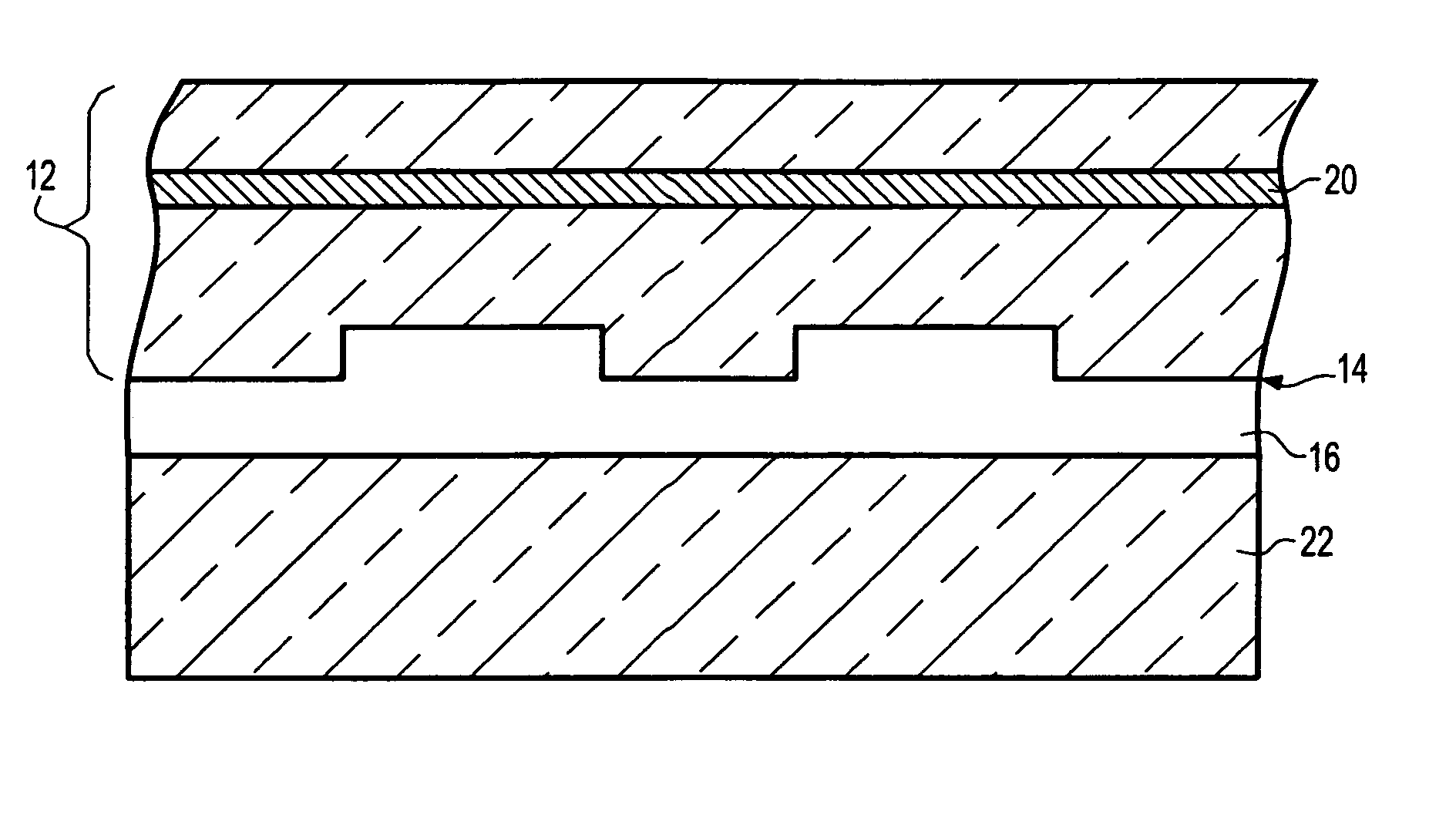

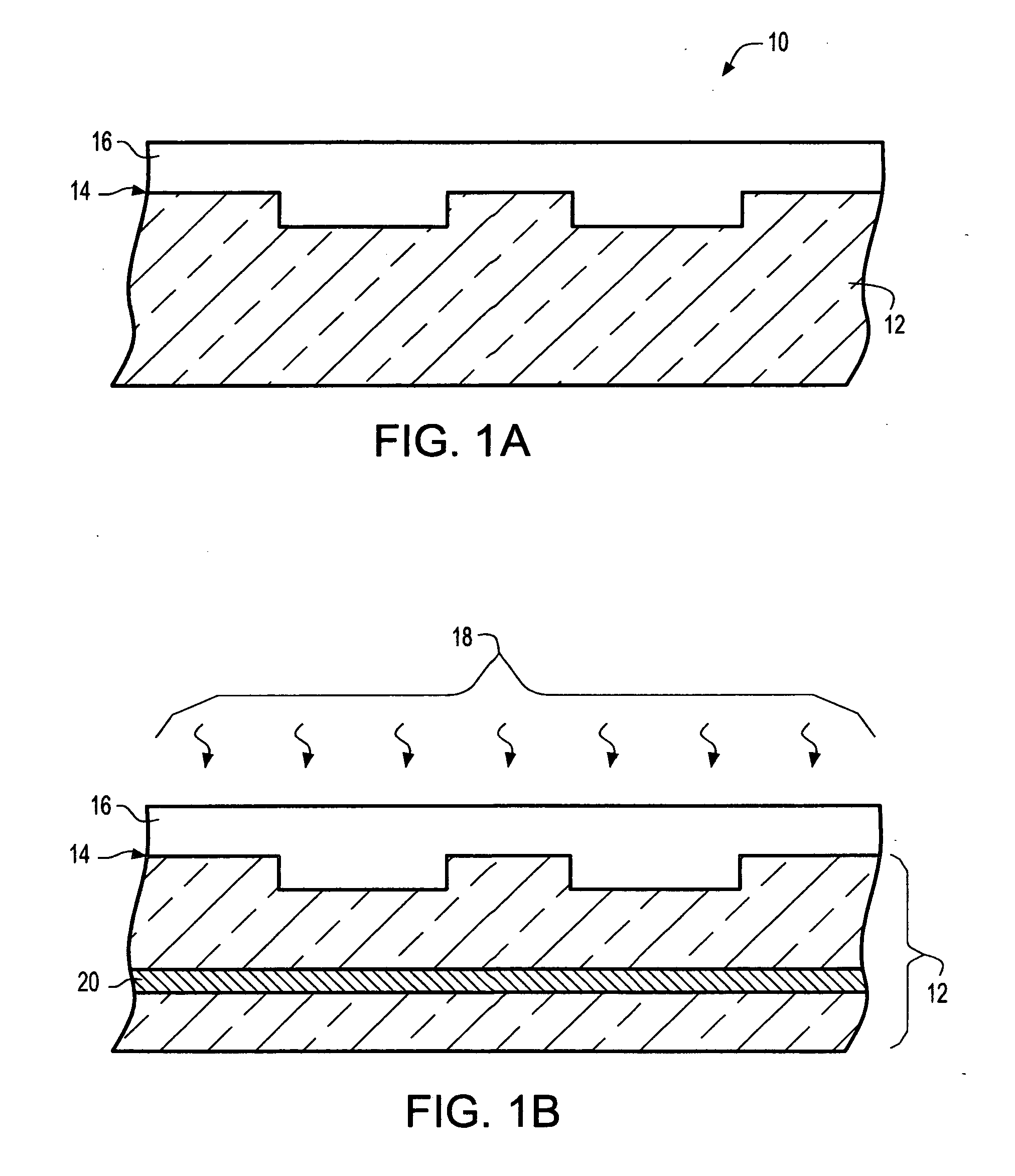

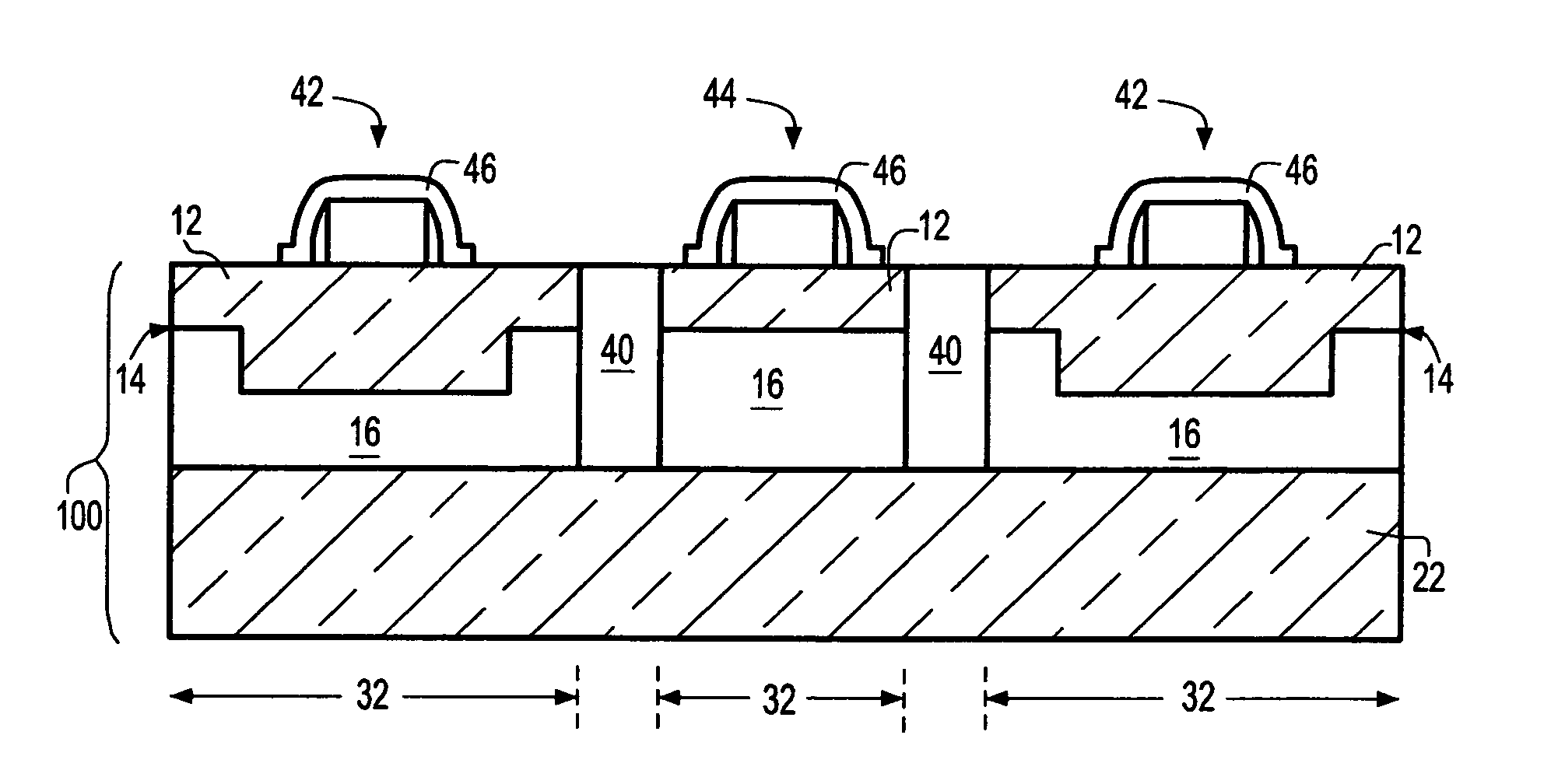

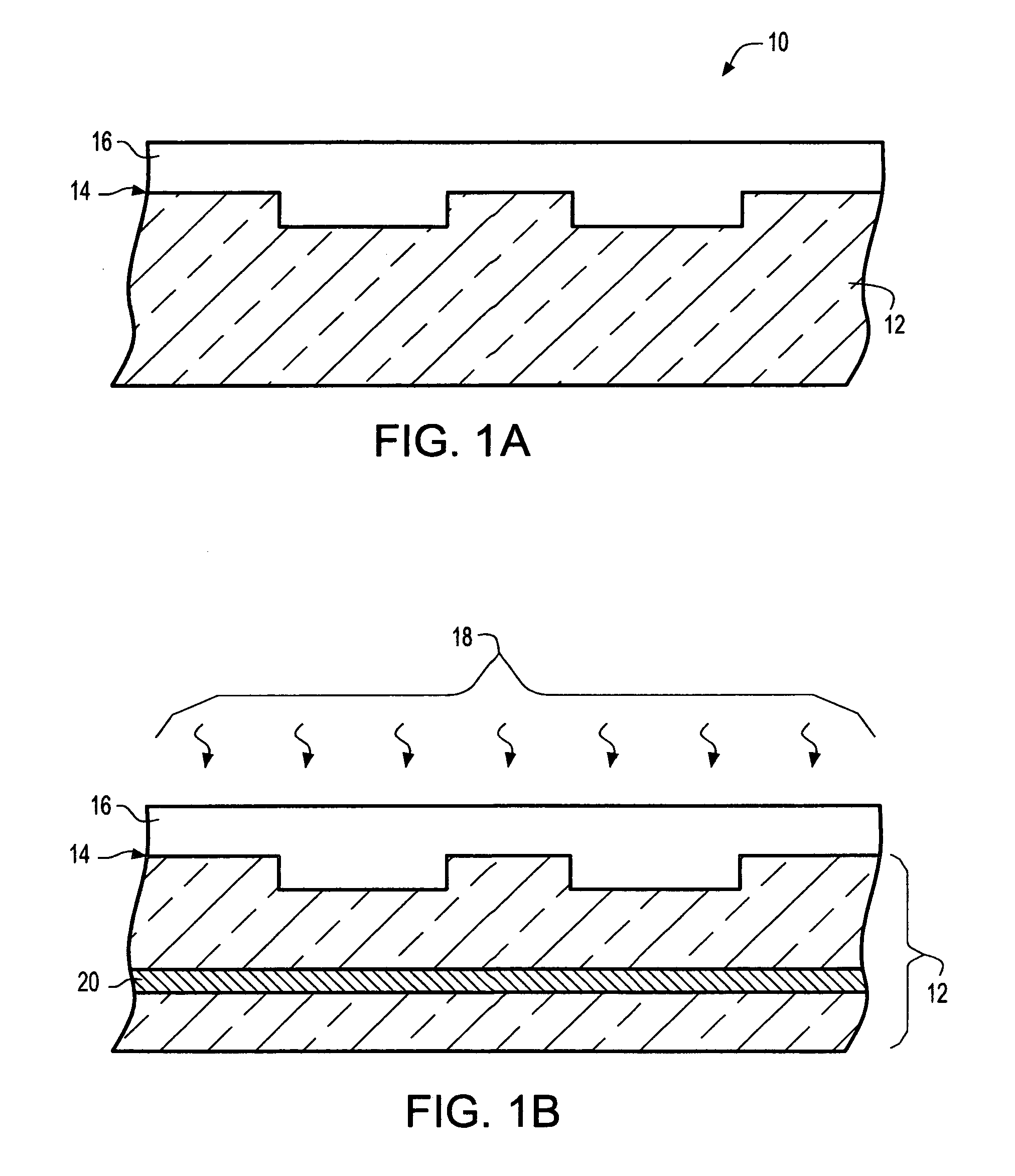

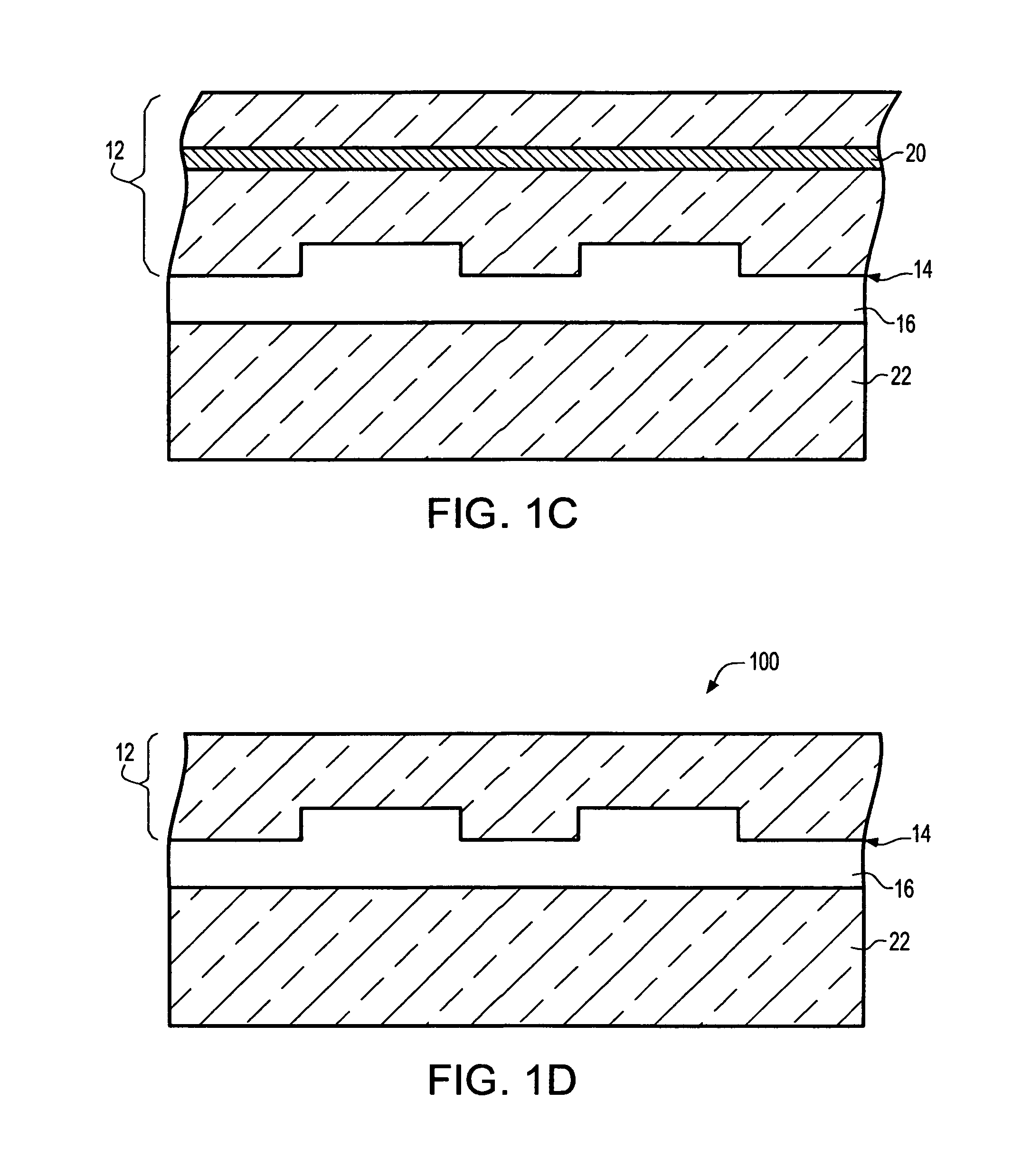

High performance field effect transistors on SOI substrate with stress-inducing material as buried insulator and methods

InactiveUS20060214225A1Enhance performanceHigh stressSemiconductor/solid-state device detailsSolid-state devicesStress inducedPerformance enhancement

The present invention provides a semiconductor structure that includes a high performance field effect transistor (FET) on a semiconductor-on-insulator (SOI) in which the insulator thereof is a stress-inducing material of a preselected geometry. Such a structure achieves performance enhancement from uniaxial stress, and the stress in the channel is not dependent on the layout design of the local contacts. In broad terms, the present invention relates to a semiconductor structure that comprises an upper semiconductor layer and a bottom semiconductor layer, wherein said upper semiconductor layer is separated from said bottom semiconductor layer in at least one region by a stress-inducing insulator having a preselected geometric shape, said stress-inducing insulator exerting a strain on the upper semiconductor layer.

Owner:GLOBALFOUNDRIES INC

Semiconductor device and manufacturing method thereof

ActiveUS7592647B2Excellent electrical propertiesImprove featuresSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A semiconductor device includes a GaN-based semiconductor layer that is formed on a substrate and an opening region, an electron conduction layer formed on an inner surface of the opening region, an electron supply layer that has a larger band gap than the electron conduction layer and is formed on the electron conduction layer disposed on the inner surface of the opening region, and a gate electrode formed on a side surface of the electron supply layer in the opening region. A source electrode is formed on the GaN-based semiconductor layer. A drain electrode is connected to a surface of the GaN-based semiconductor layer opposite to the source electrode.

Owner:SUMITOMO ELECTRIC DEVICE INNOVATIONS

High performance field effect transistors on SOI substrate with stress-inducing material as buried insulator and methods

InactiveUS7388278B2Reduce parasitic capacitanceFast switching timeSemiconductor/solid-state device detailsSolid-state devicesStress inducedPerformance enhancement

The present invention provides a semiconductor structure that includes a high performance field effect transistor (FET) on a semiconductor-on-insulator (SOI) in which the insulator thereof is a stress-inducing material of a preselected geometry. Such a structure achieves performance enhancement from uniaxial stress, and the stress in the channel is not dependent on the layout design of the local contacts. In broad terms, the present invention relates to a semiconductor structure that comprises an upper semiconductor layer and a bottom semiconductor layer, wherein said upper semiconductor layer is separated from said bottom semiconductor layer in at least one region by a stress-inducing insulator having a preselected geometric shape, said stress-inducing insulator exerting a strain on the upper semiconductor layer.

Owner:GLOBALFOUNDRIES INC

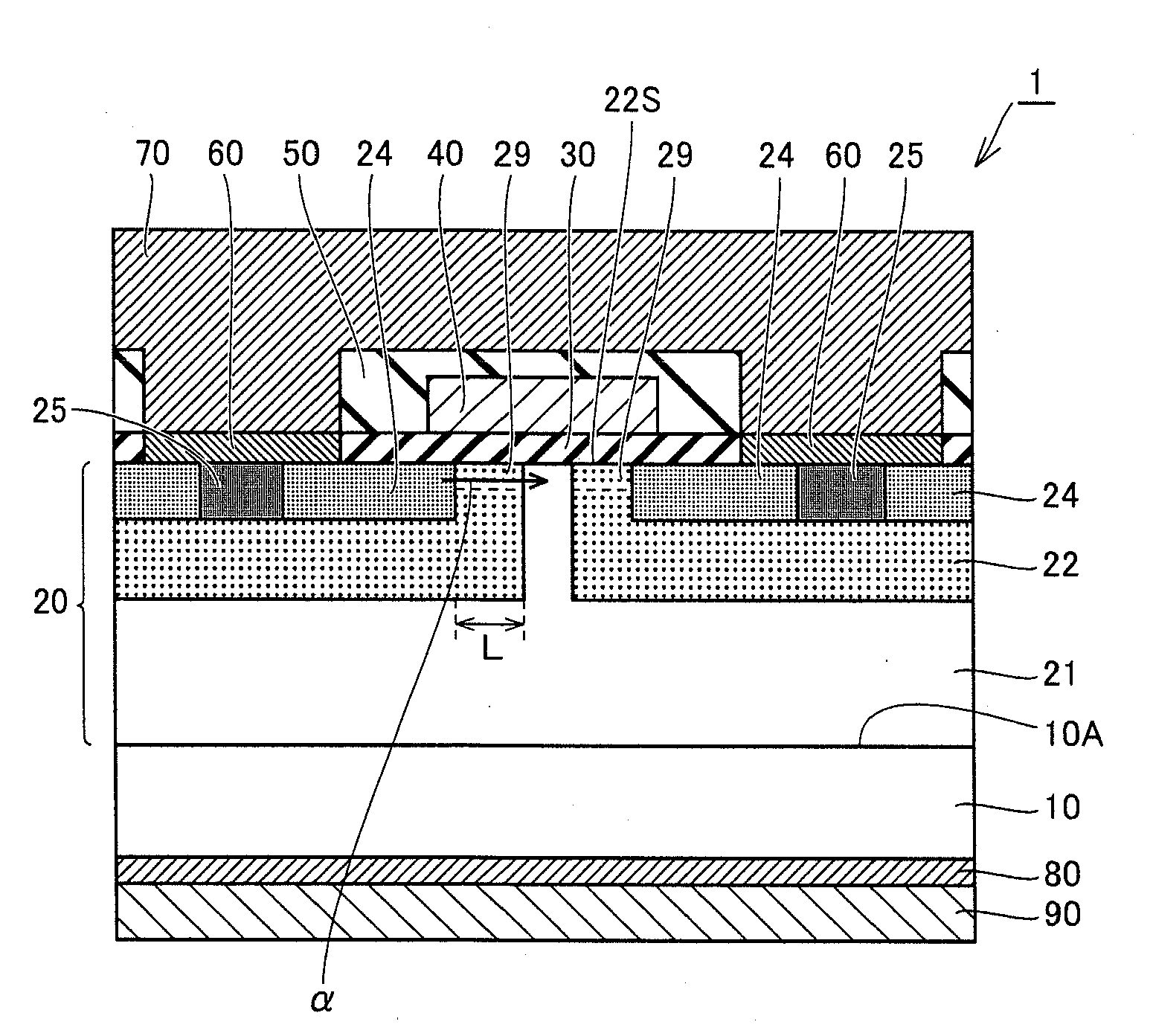

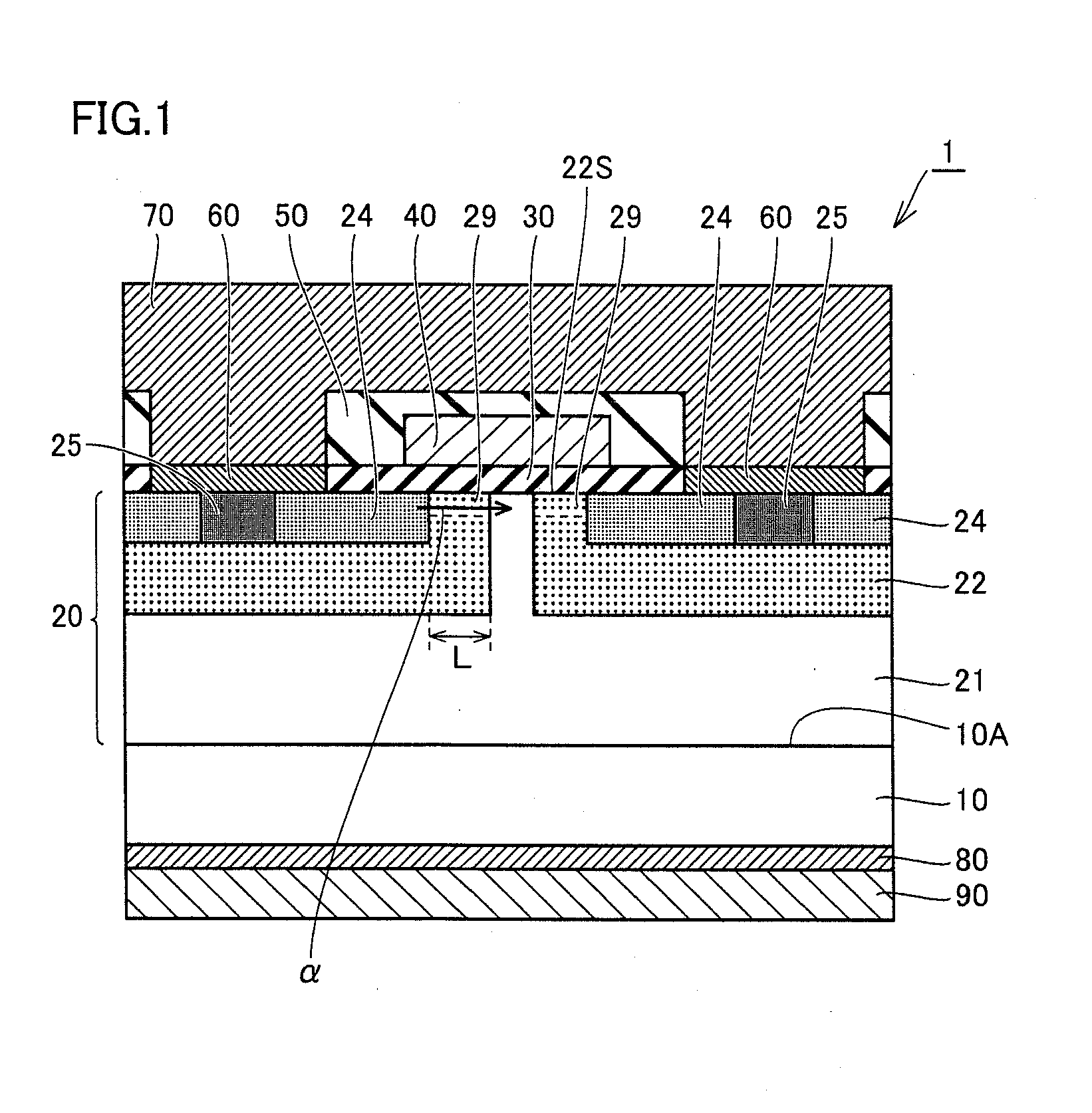

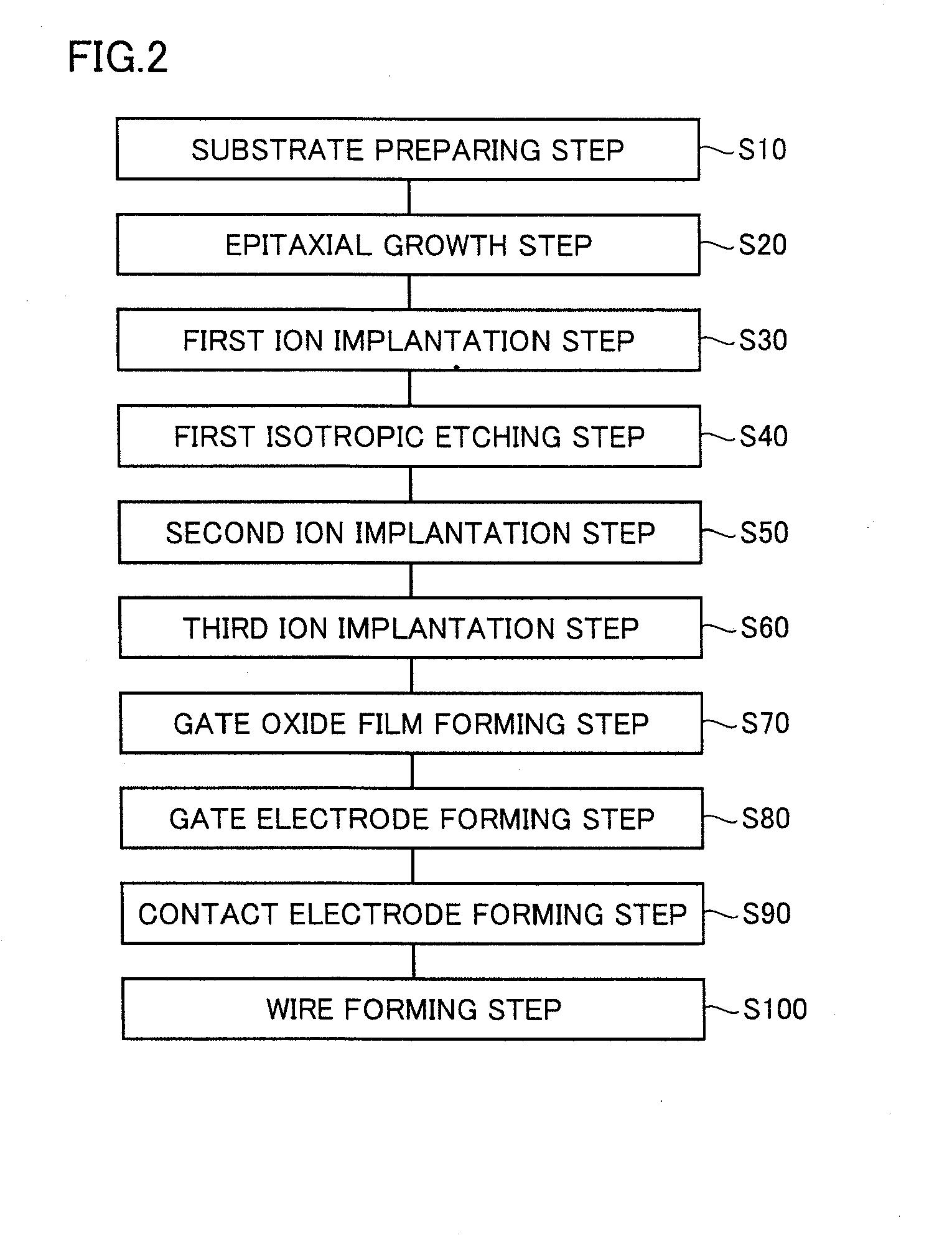

Semiconductor device

A MOSFET includes a silicon carbide substrate, an active layer, a gate oxide film, and a gate electrode. The active layer includes a p type body region in which an inversion layer is formed when the gate electrode is fed with a voltage. The inversion layer has an electron mobility μ dependent more strongly on an acceptor concentration Na of a channel region of the p type body region, as compared with a dependency of the electron mobility μ being proportional to the reciprocal of the acceptor concentration Na. The acceptor concentration Na in the channel region of the p type body region is not less than 1×1016 cm−3 and not more than 2×1018 cm3. The channel length (L) is equal to or smaller than 0.43 μm. The channel length (L) is equal to or longer than a spreading width d of a depletion layer in the channel region. The spreading width d is expressed by d=D·Na−C.

Owner:SUMITOMO ELECTRIC IND LTD

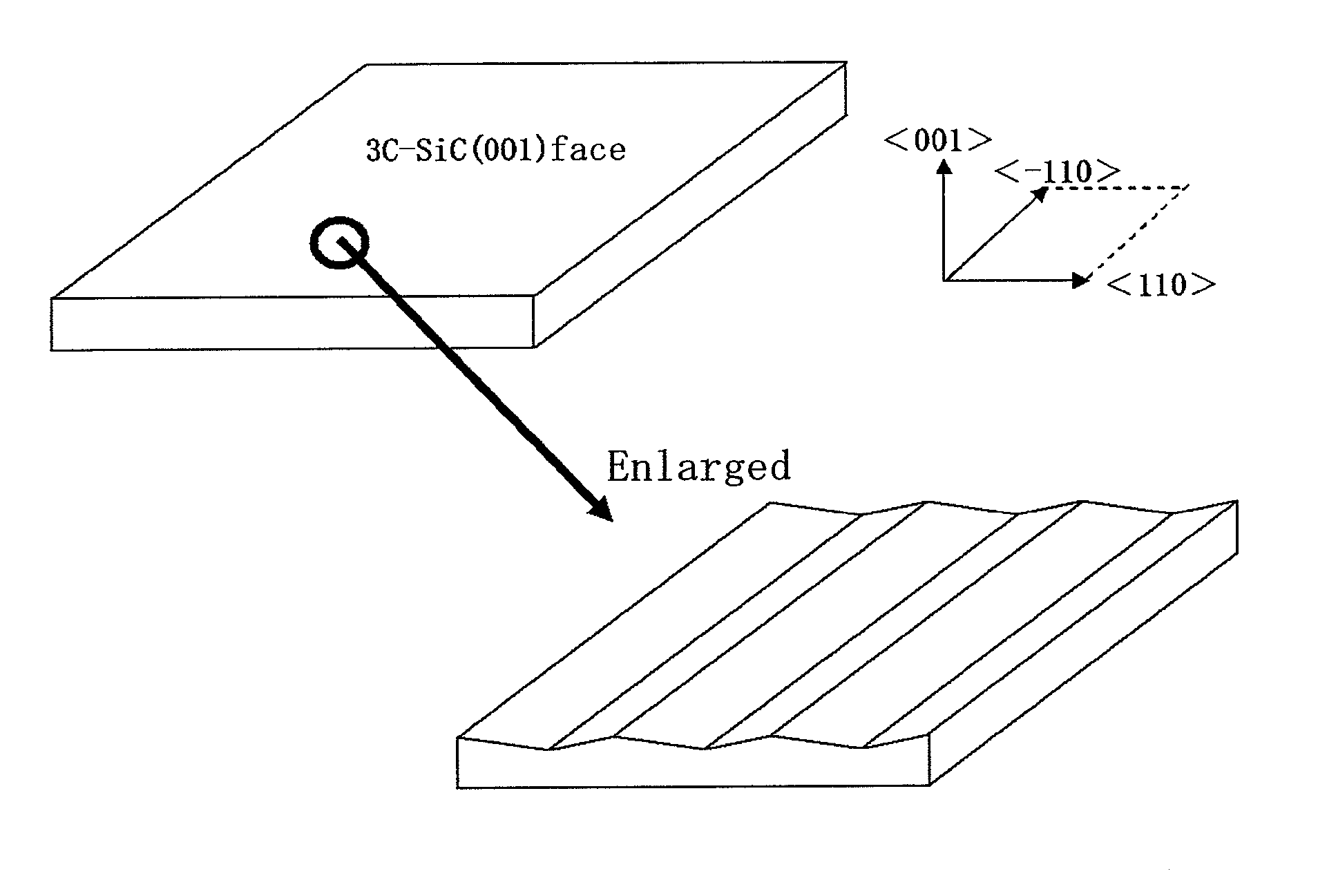

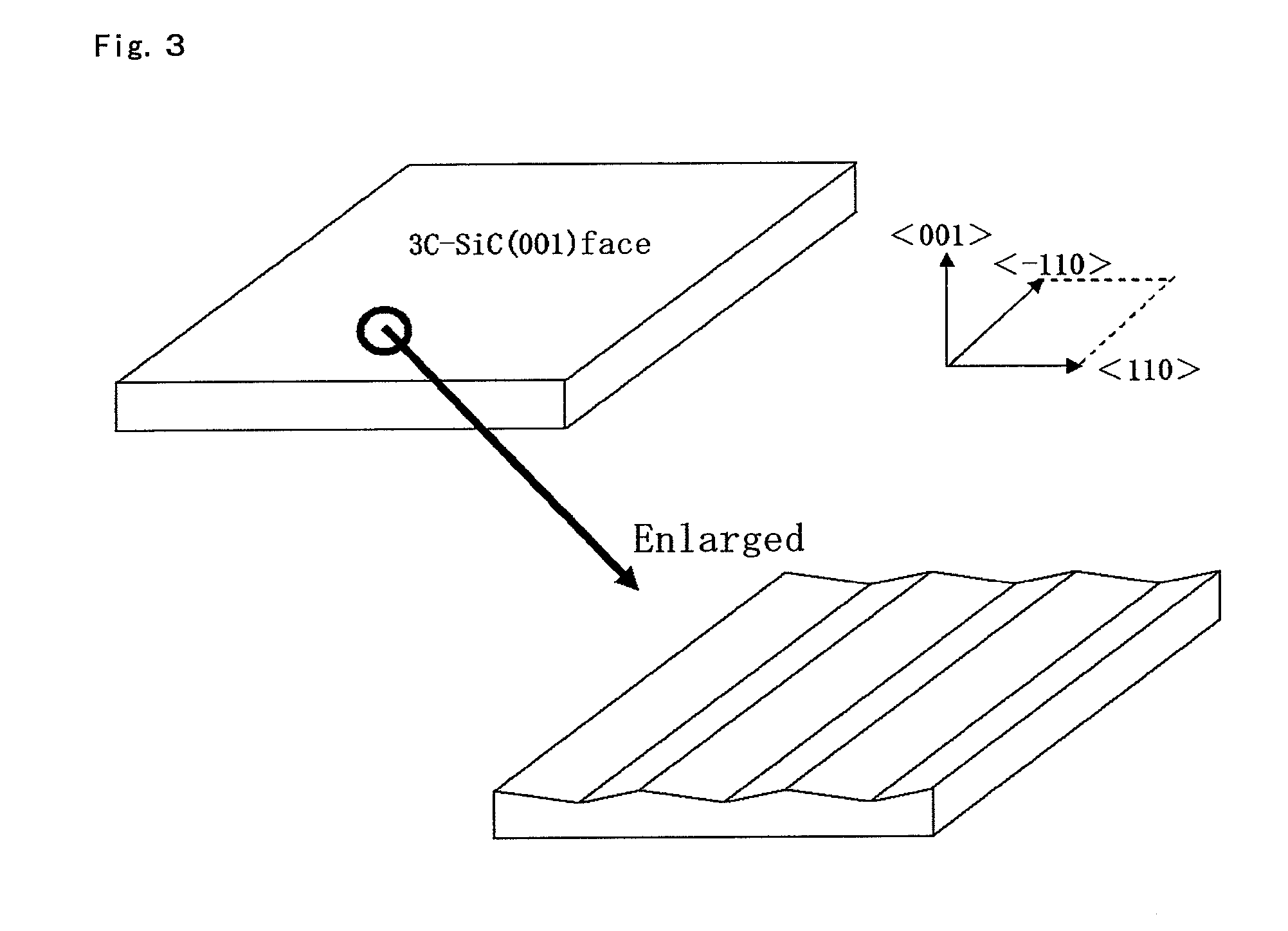

Semiconductor device and semiconductor device manufacturing method

InactiveUS20110006310A1No deterioration smoothnessUniform and stable rectifying propertySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialCarbide

A semiconductor device comprises a semiconductor substrate made of silicon carbide, a gate insulating film formed on the semiconductor substrate, and a gate electrode formed on the gate insulating film. The junction surface of the semiconductor surface joined with the gate insulating film is macroscopically parallel to a nonpolar face and microscopically comprised of the nonpolar face and a polar face. In the polar face, either a Si face or a C face is dominant. A semiconductor device comprises a semiconductor substrate comprised of silicon carbide and a gate electrode formed on the semiconductor substrate. The junction surface of the semiconductor surface joined with the electrode is macroscopically parallel to a nonpolar face and microscopically comprised of the nonpolar face and a polar face. In the polar face, either a Si face or a C face is dominant. The present invention is a semiconductor device having a silicon carbide substrate, and the electrical characteristics and the stability of the interface between the electrode and the silicon carbide or between the oxide film (insulating film) and the silicon carbide in the nonpolar face of a silicon carbide epitaxial layer can be improved.

Owner:HOYA CORP +1

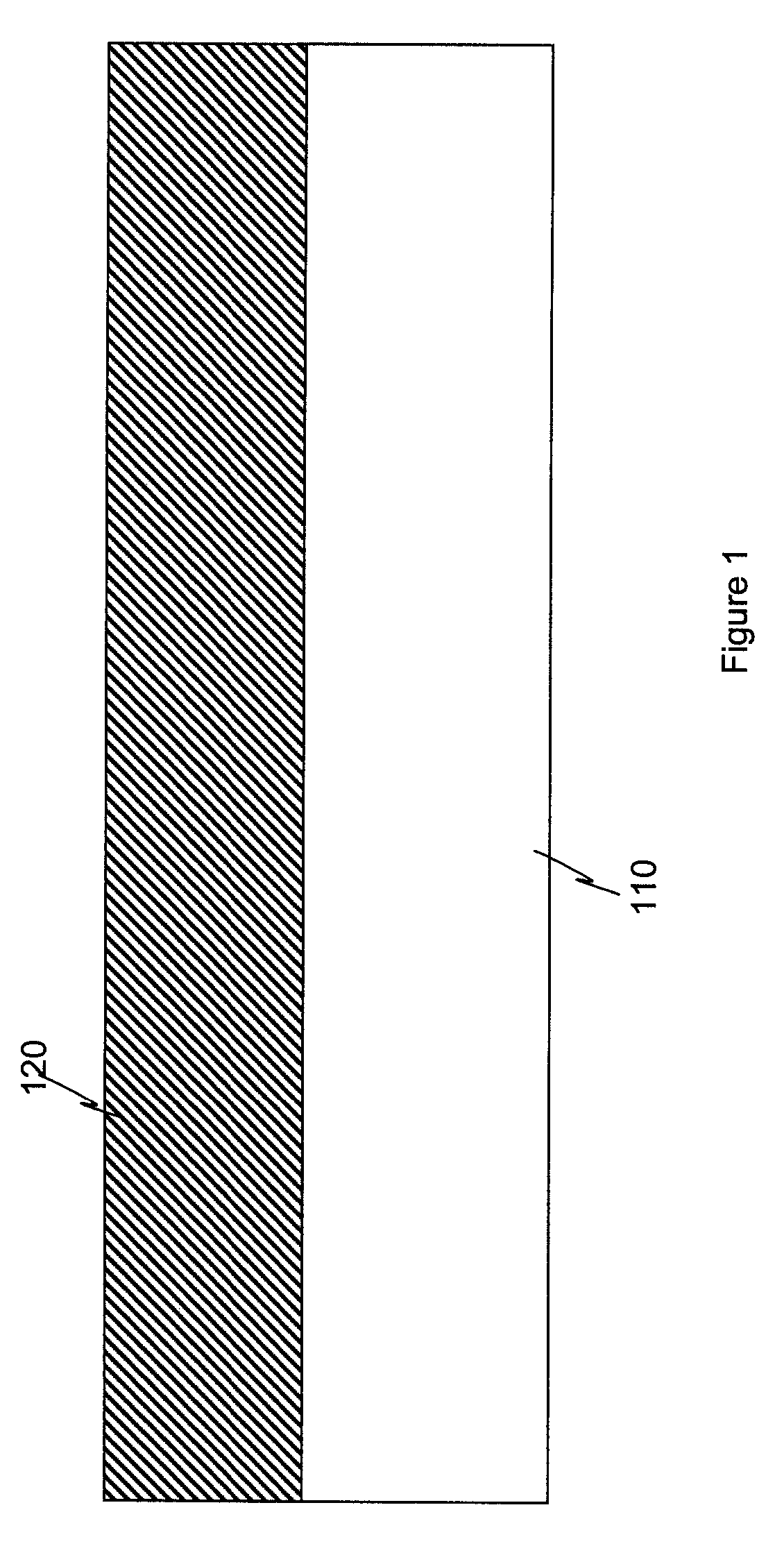

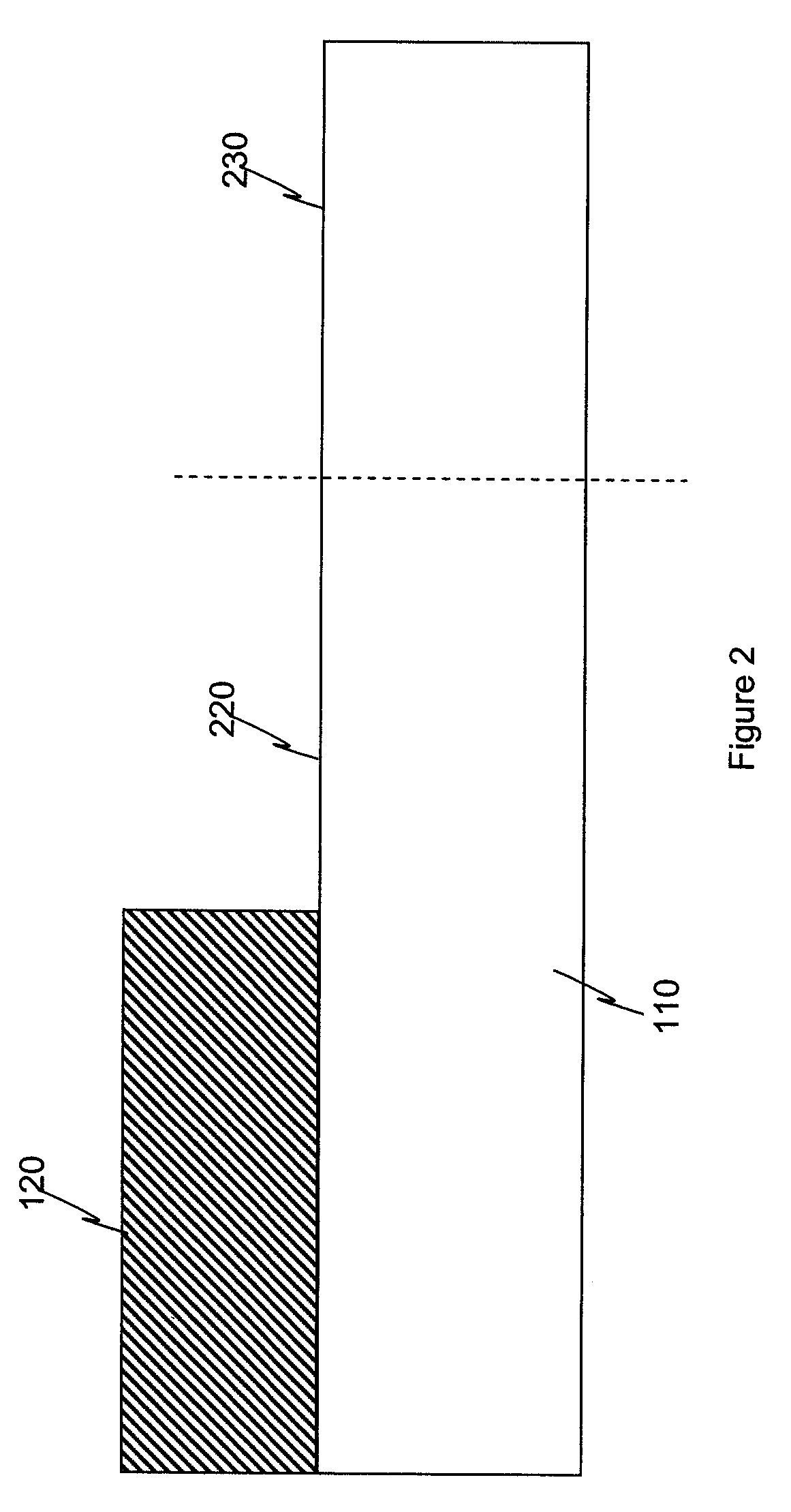

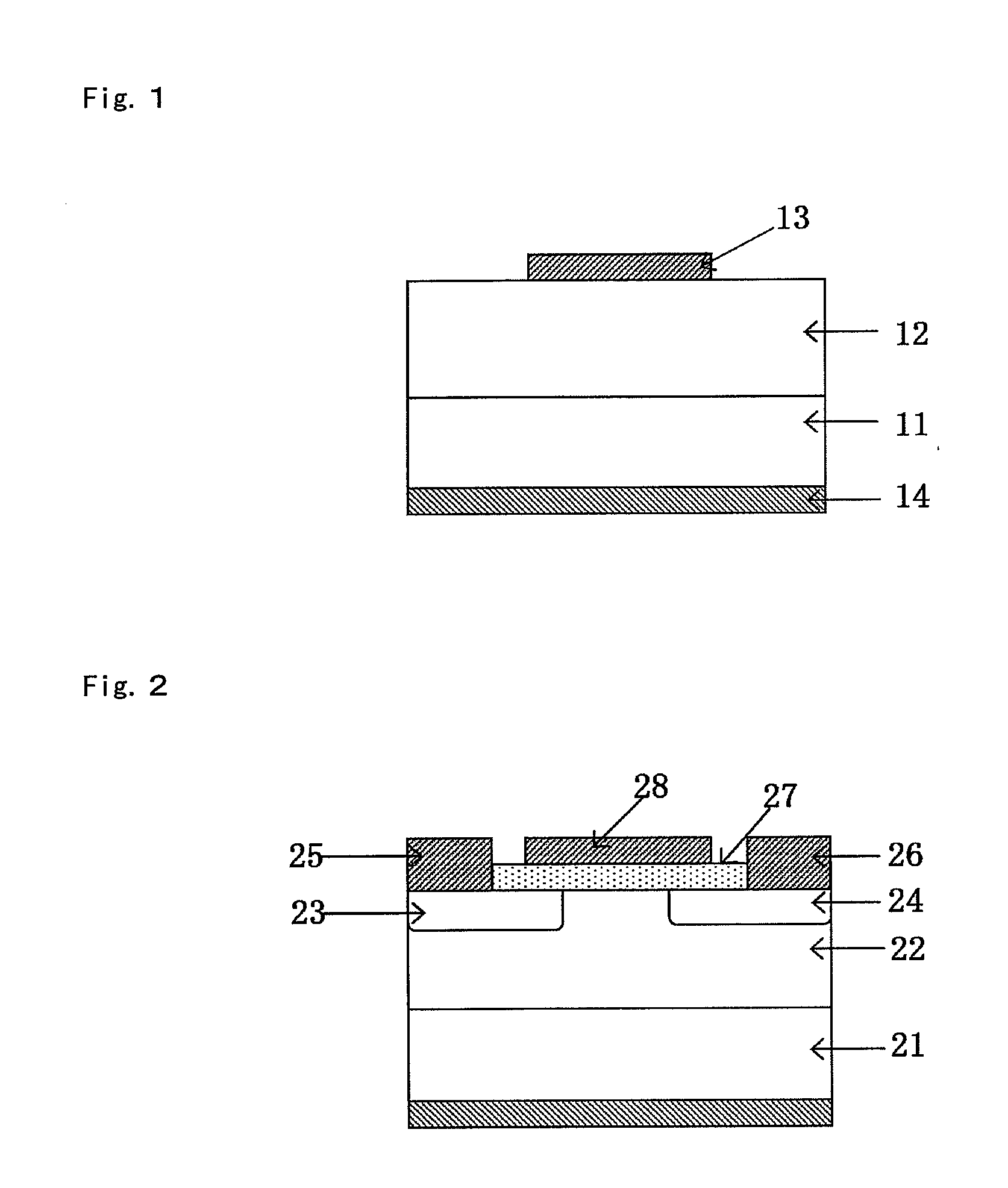

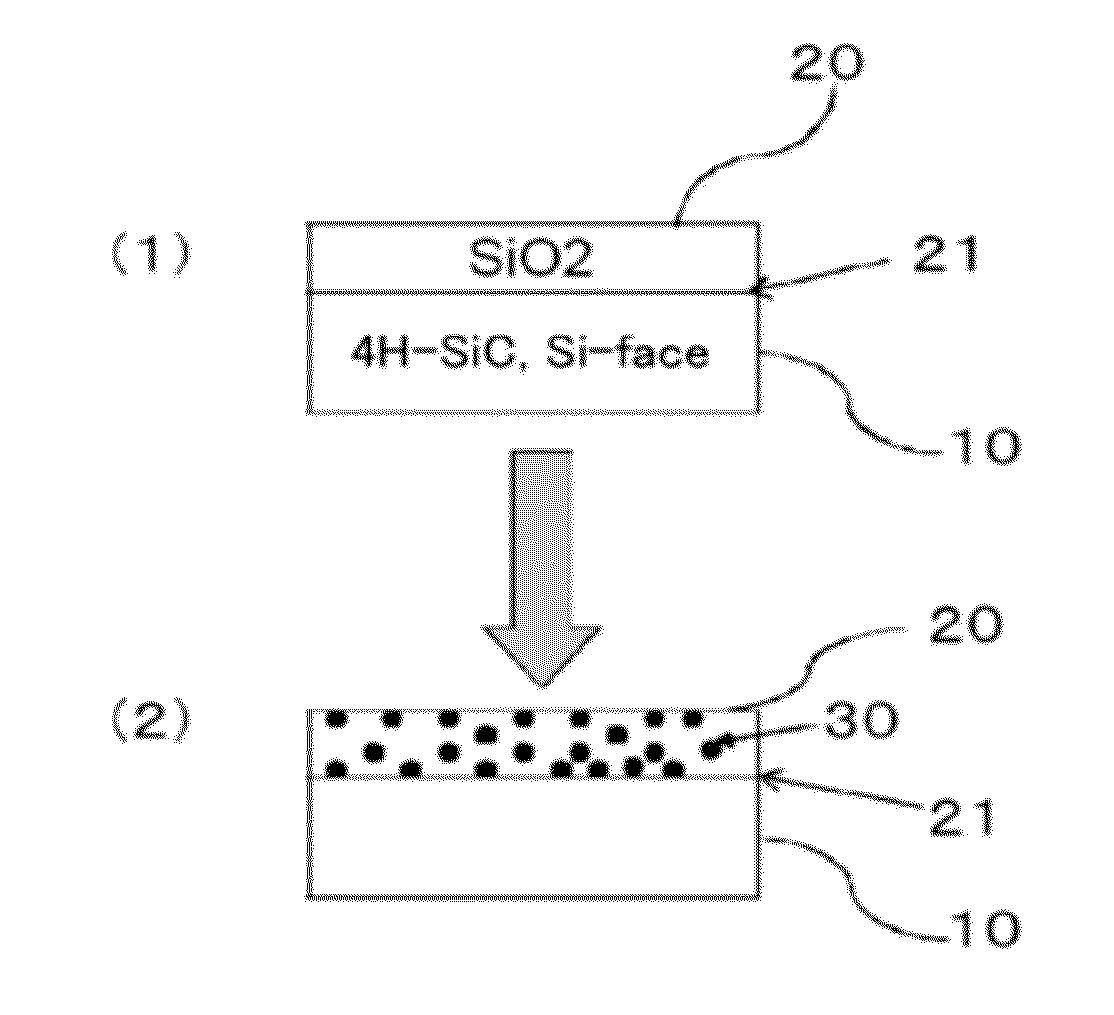

Sic semiconductor element and manufacturing method for same

ActiveUS20120241767A1Reduce interface defectsReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesState densityThreshold voltage

Disclosed are an SiC semiconductor element and manufacturing method for an SiC semiconductor element in which the interface state density of the interface of the insulating film and the SiC is reduced, and channel mobility is improved. Phosphorus (30) is added to an insulating film (20) formed on an SiC semiconductor (10) substrate in a semiconductor element. The addition of phosphorous to the insulating film makes it possible to significantly reduce the defects (interface state density) in the interface (21) of the insulating film and the SiC, and to dramatically improve the channel mobility when compared with conventional SiC semiconductor elements. The addition of phosphorus to the insulating film is carried out by heat treatment. The use of heat treatment to add phosphorous to the insulating film makes it possible to maintain the reliability of the insulating film, and to avoid variation in channel mobility and threshold voltage.

Owner:NARA INSTITUTE OF SCIENCE AND TECHNOLOGY

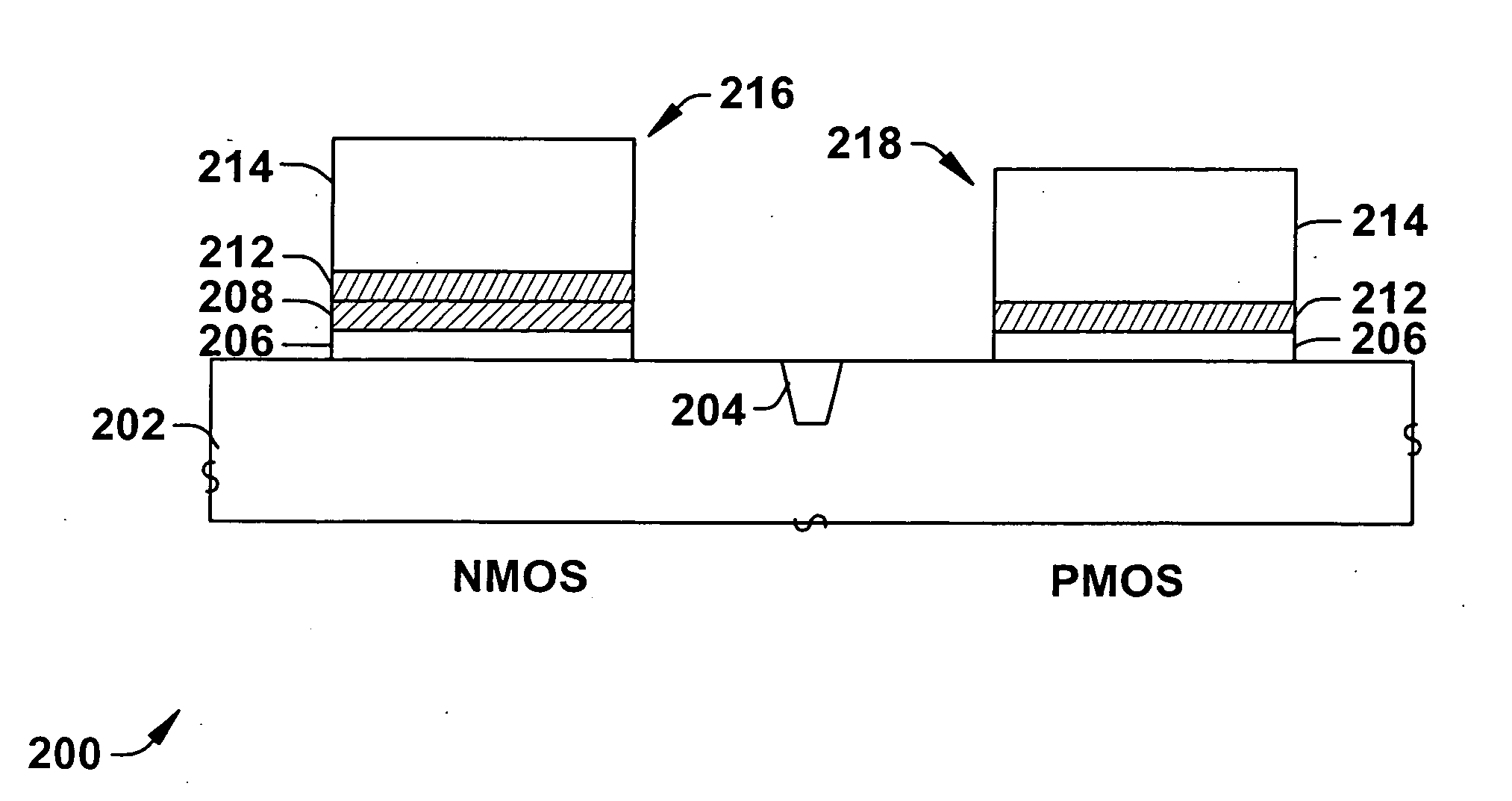

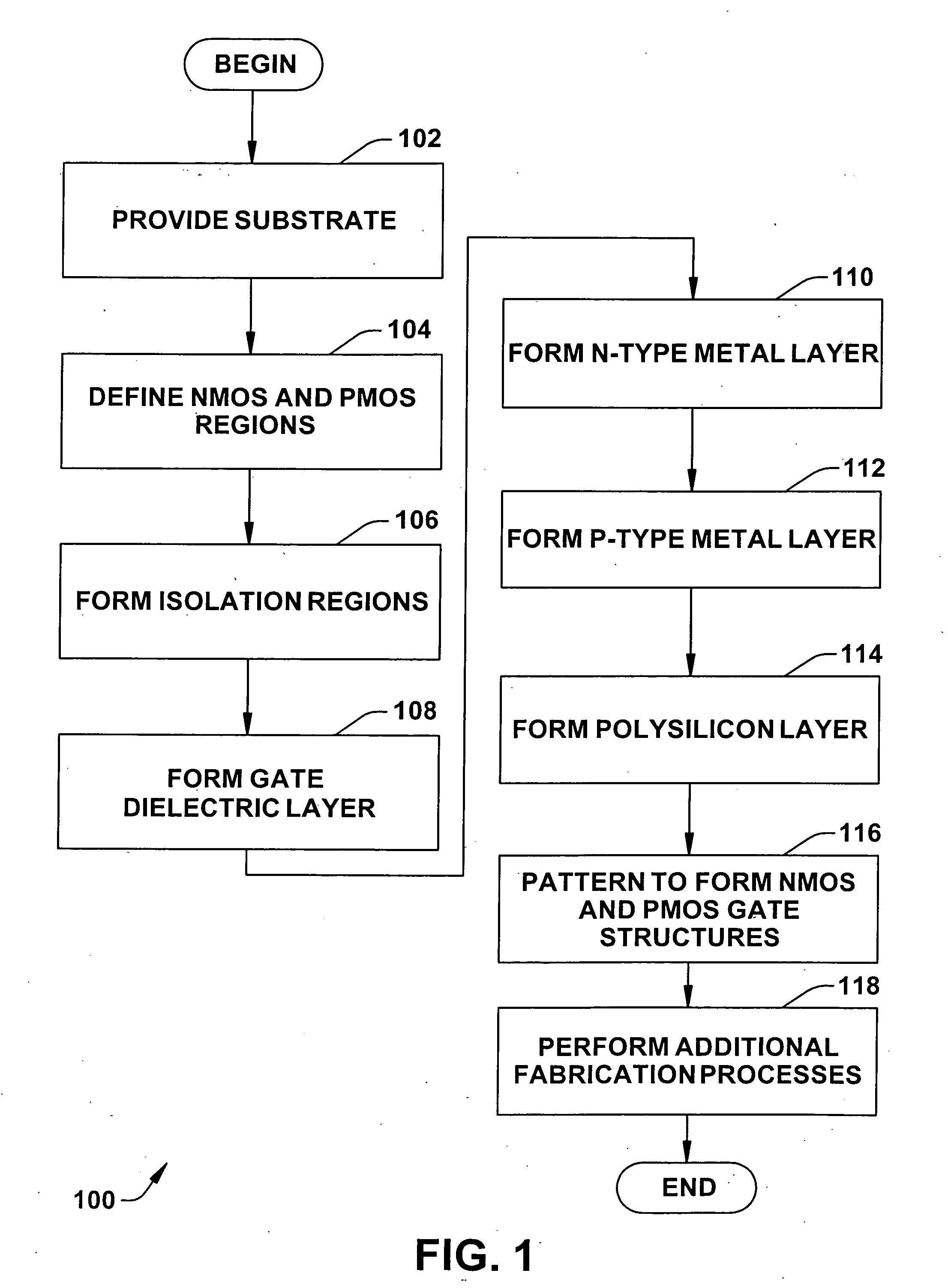

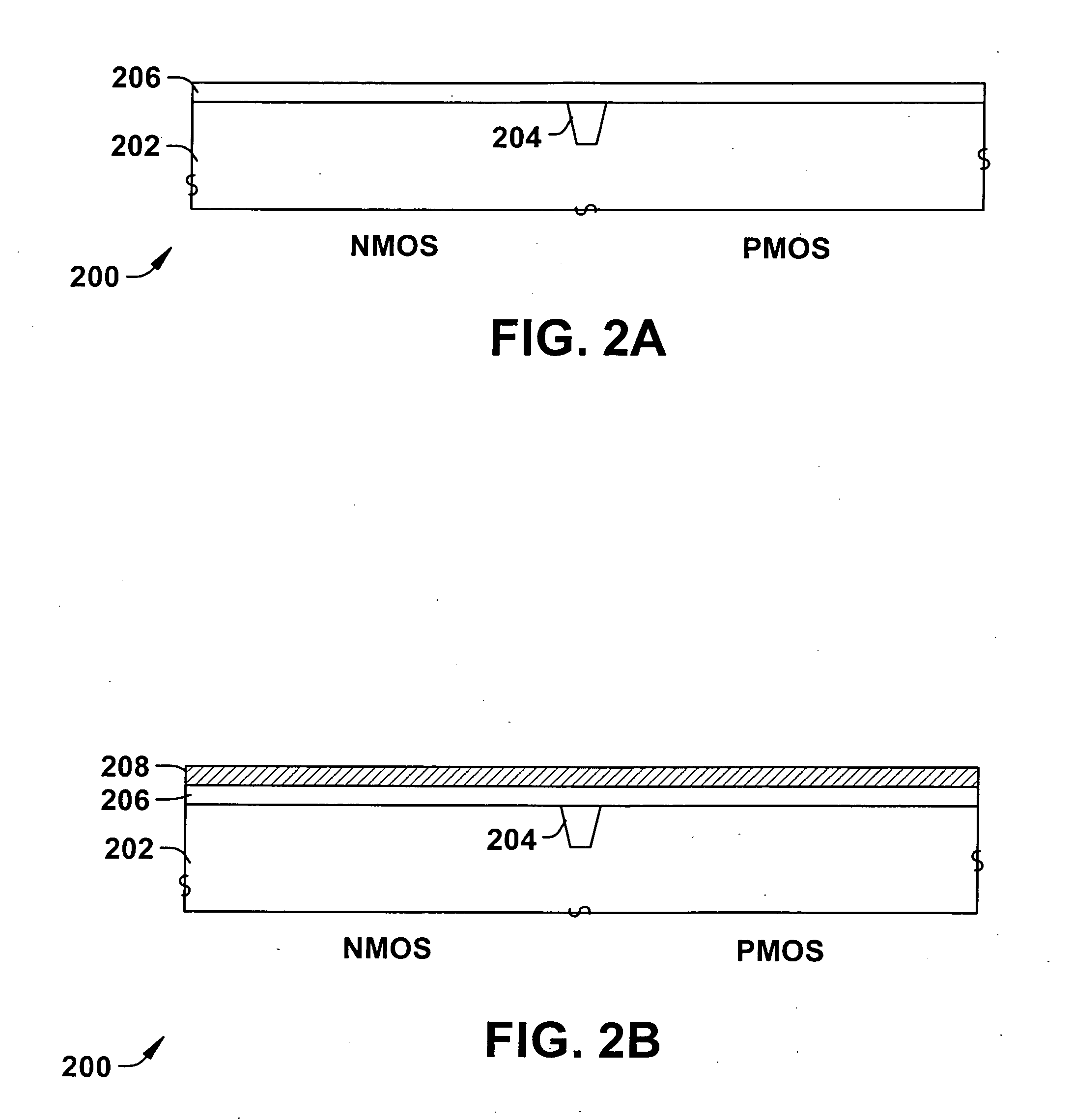

Methods and devices employing metal layers in gates to introduce channel strain

InactiveUS20080096338A1Improve channel mobilityConvenient inductionSemiconductor/solid-state device manufacturingSemiconductor devicesStress inducedGate dielectric

A semiconductor device is fabricated having a metal stress inducing layer that facilitates channel mobility. A gate dielectric layer is formed over a semiconductor substrate. The metal stress inducing layer is formed over the gate dielectric layer. The metal stress inducing layer has a selected conductivity type and is formed and composed to yield a select stress amount and type. A gate layer, such as a polysilicon layer, is formed over the metal stress inducing layer. The gate layer and the metal stress inducing layer are patterned to define gate structures.

Owner:TEXAS INSTR INC

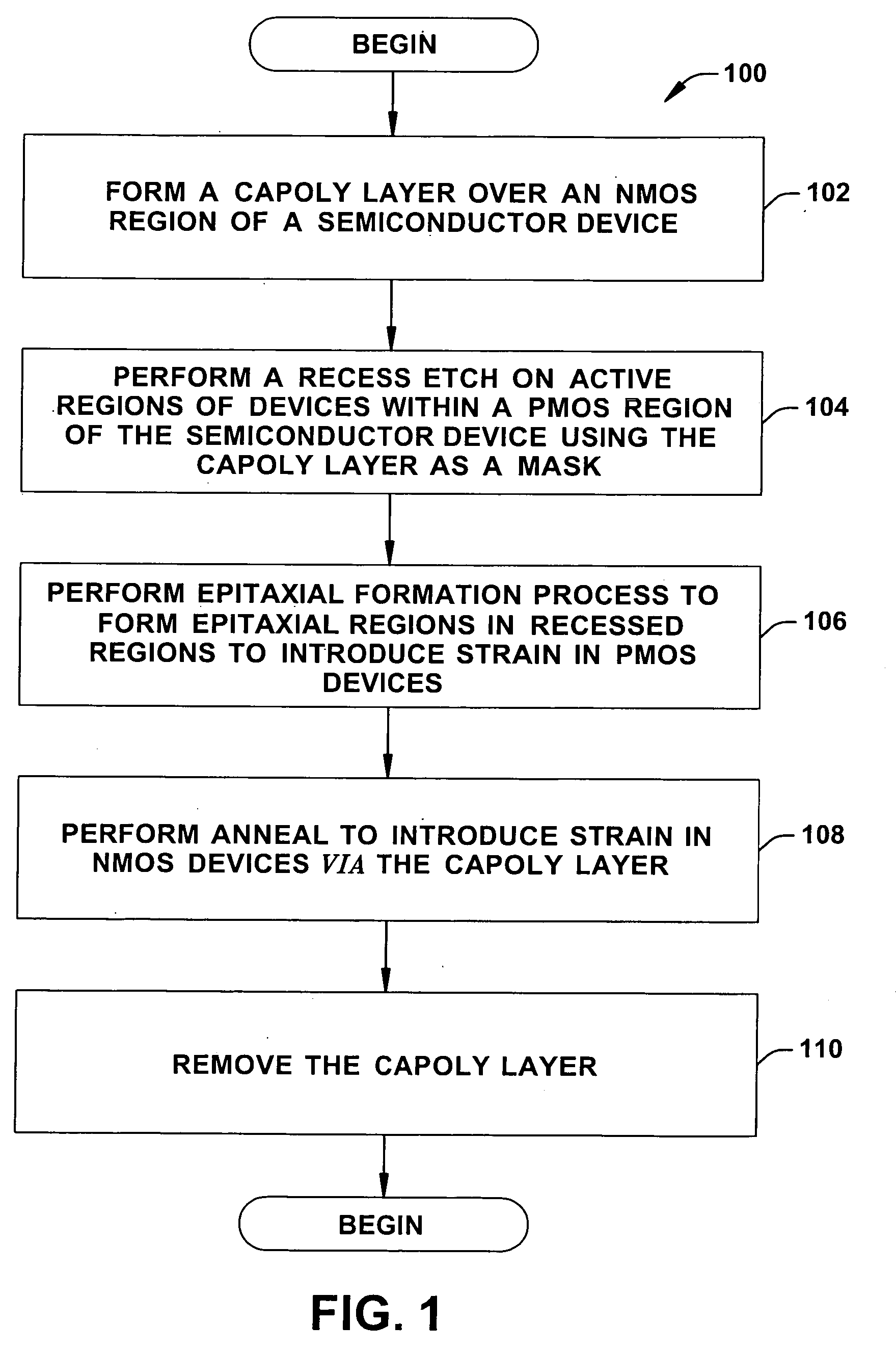

Method to selectively recess ETCH regions on a wafer surface using capoly as a mask

ActiveUS20060046367A1Avoid etchingEasy to manufactureSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

The present invention facilitates semiconductor fabrication by providing methods of fabrication that selectively apply strain to channel regions of devices while mitigating masking operations employed. A CAPOLY layer is formed over an NMOS region of a semiconductor device (102). A recess etch is performed on active regions of devices within a PMOS region of the semiconductor device (104) and the CAPOLY layer prevents etching of devices within an NMOS region of the semiconductor device. Subsequently, an epitaxial formation process (106) is performed that forms or deposits epitaxial regions and introduces a first type of strain across the channel regions in the PMOS region. Then, the semiconductor device is annealed (108) to cause the CAPOLY layer to introduce a second type of strain across the channel regions in the NMOS region. After annealing, the CAPOLY layer is removed (110).

Owner:TEXAS INSTR INC

Nitride based semiconductor device and method for manufacturing the same

InactiveUS20060065929A1Improve electrical performanceHigh crystallinityImpedence networksSolid-state devicesDevice materialSurface level

Provided is a nitride-based semiconductor device in which a SAW filter and a HFET are integrated on a single substrate, as well as a method for manufacturing the same. The nitride-based semiconductor device comprises a semi-insulating GaN layer formed on a substrate, a plurality of electrodes for a SAW filter formed on one side of the semi-insulating GaN layer, an Al-doped GaN layer formed on the other side of the semi-insulating GaN layer, an AlGaN layer formed on the Al-doped GaN layer, and a plurality of electrodes for an HFET formed on the AlGaN layer. Both sides of the semi-insulating GaN layer have the same surface level.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Semiconductor device

InactiveUS20120018743A1Improve channel mobilitySuppress leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate oxide

A MOSFET includes a silicon carbide substrate including a main surface having an off angle of not less than 50° and not more than 65° with respect to a {0001} plane, a buffer layer and a drift layer formed on the main surface, a gate oxide film formed on and in contact with the drift layer, and a p type body region of a p conductivity type formed in the drift layer to include a region in contact with the gate oxide film. The p type body region has a p type impurity density of not less than 5×1016 cm−3.

Owner:SUMITOMO ELECTRIC IND LTD

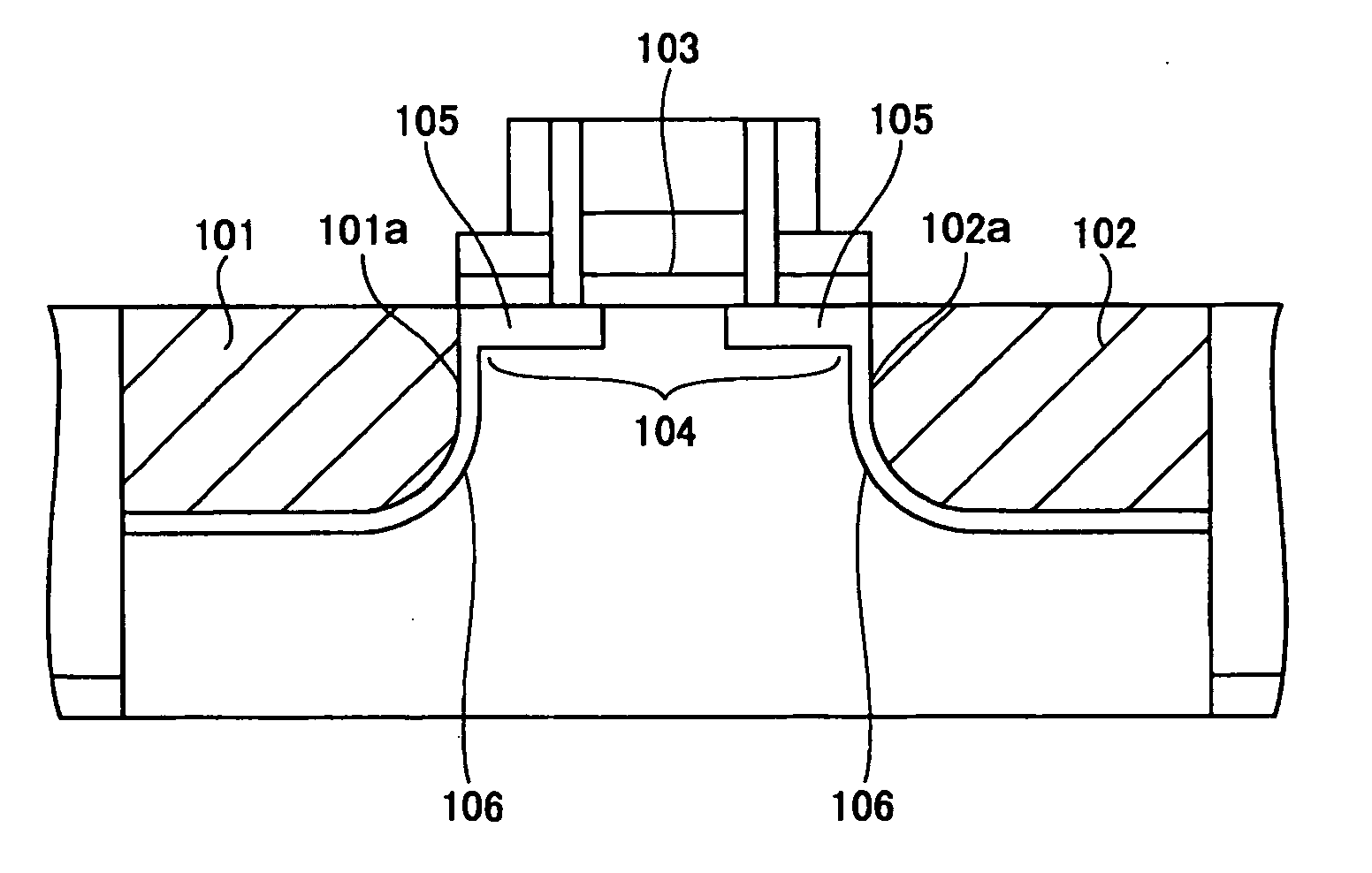

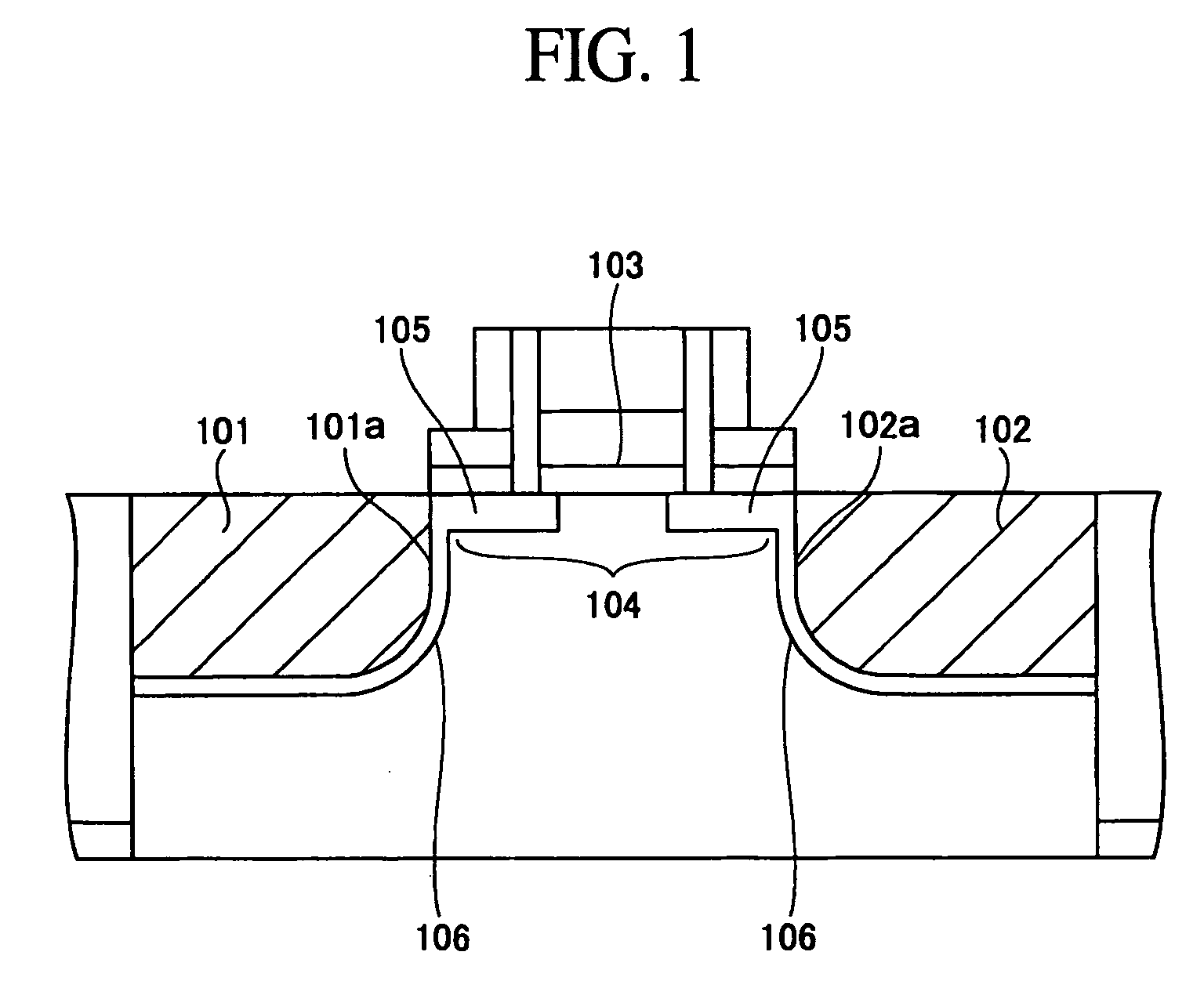

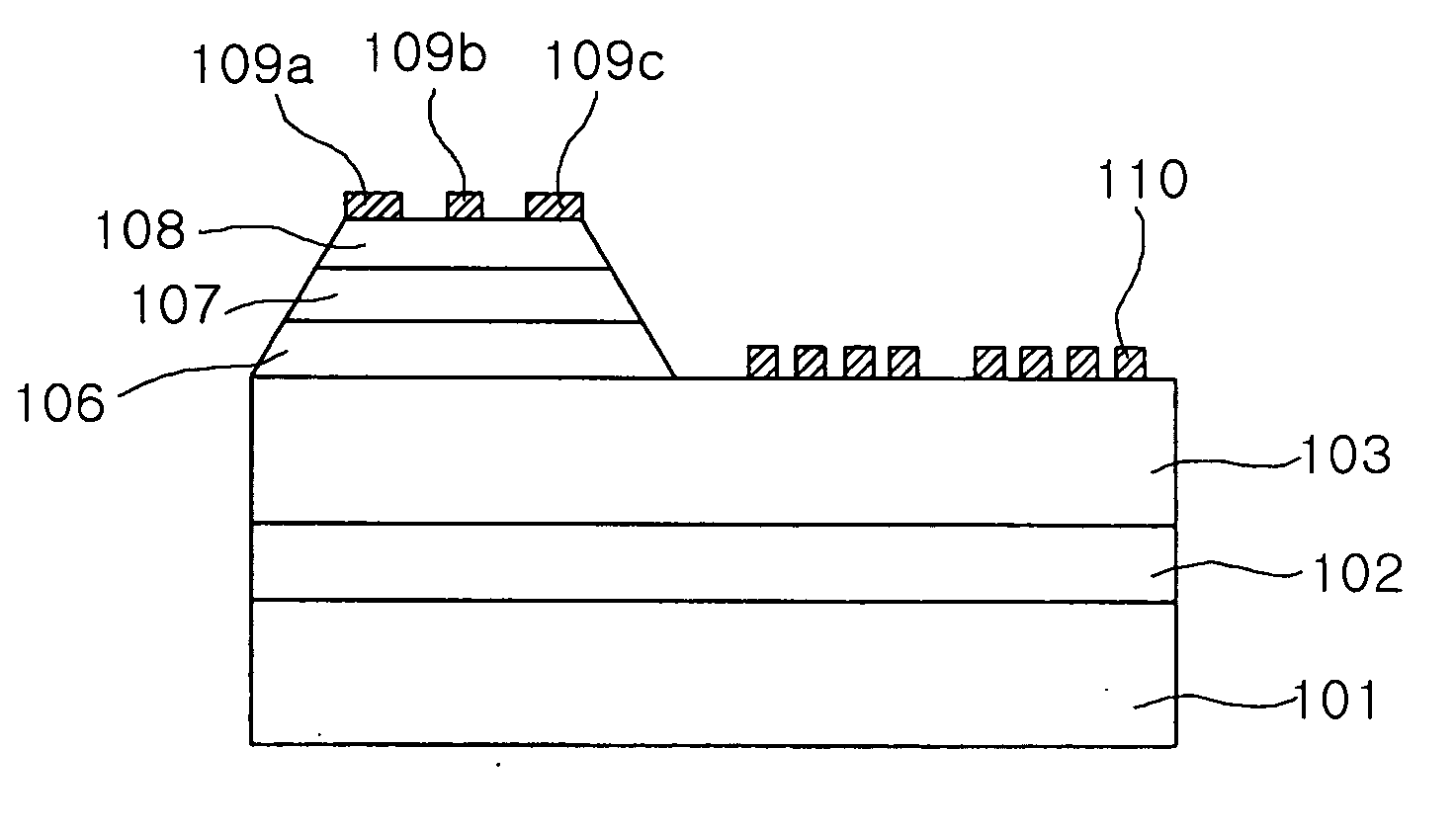

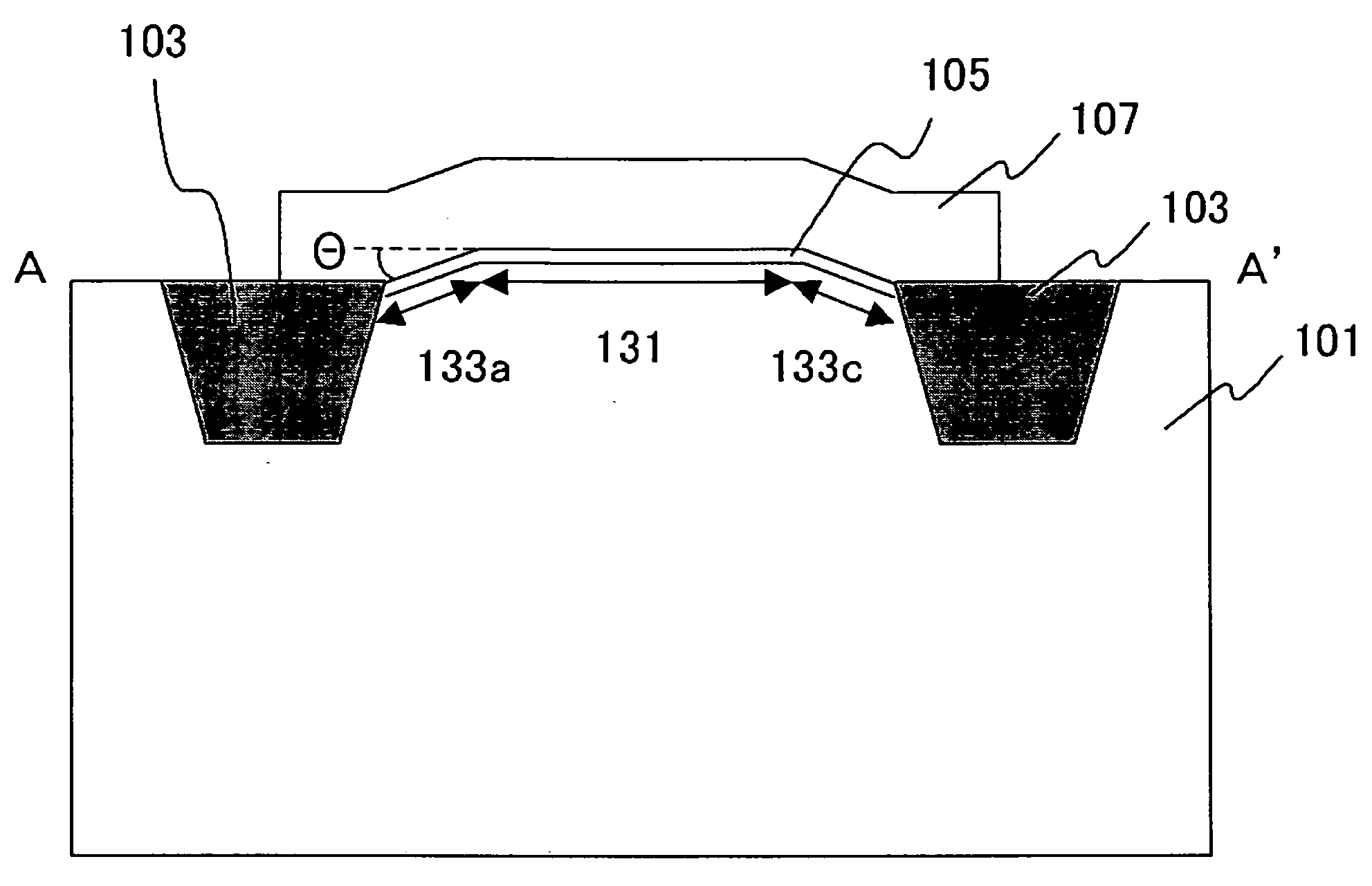

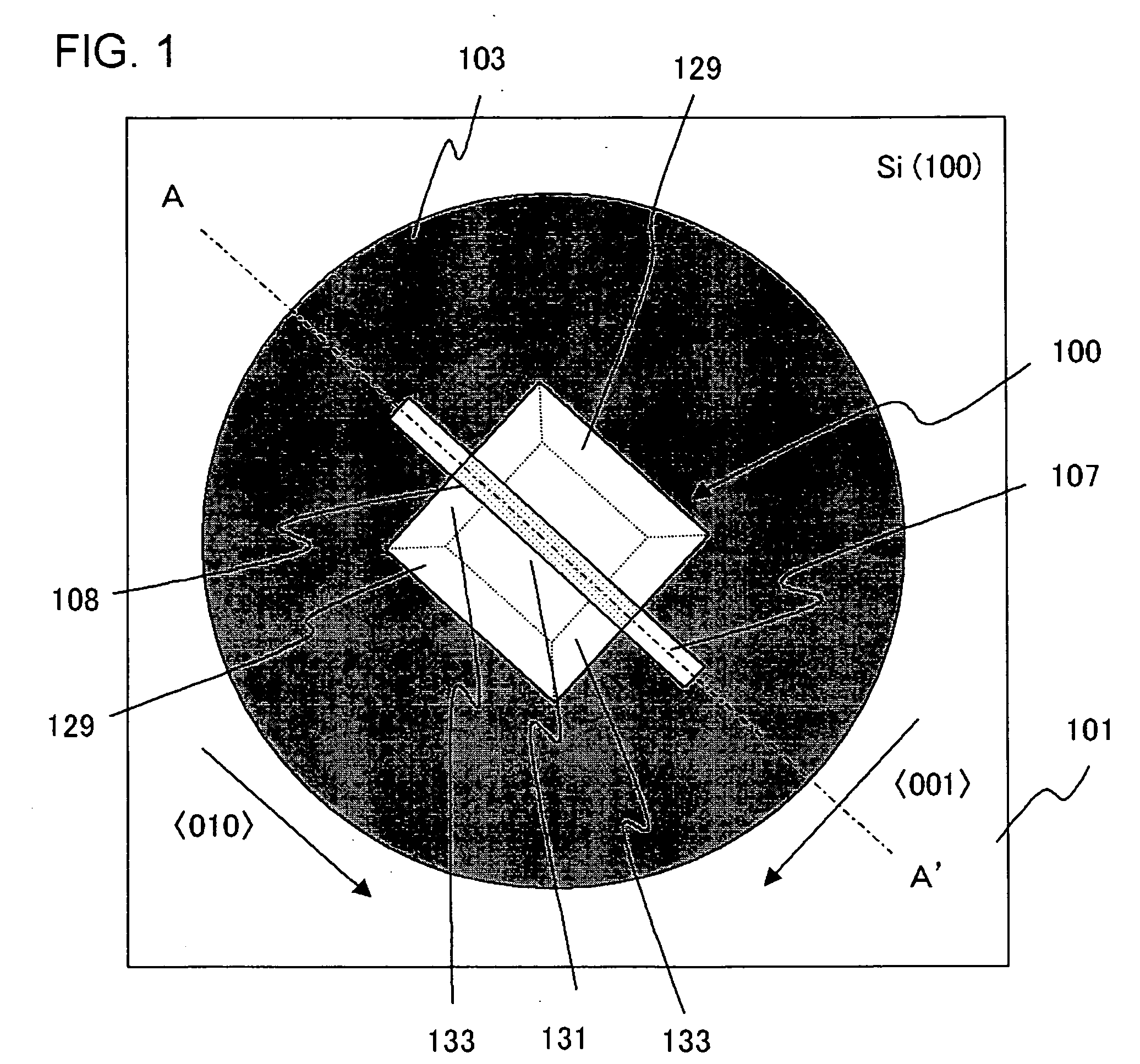

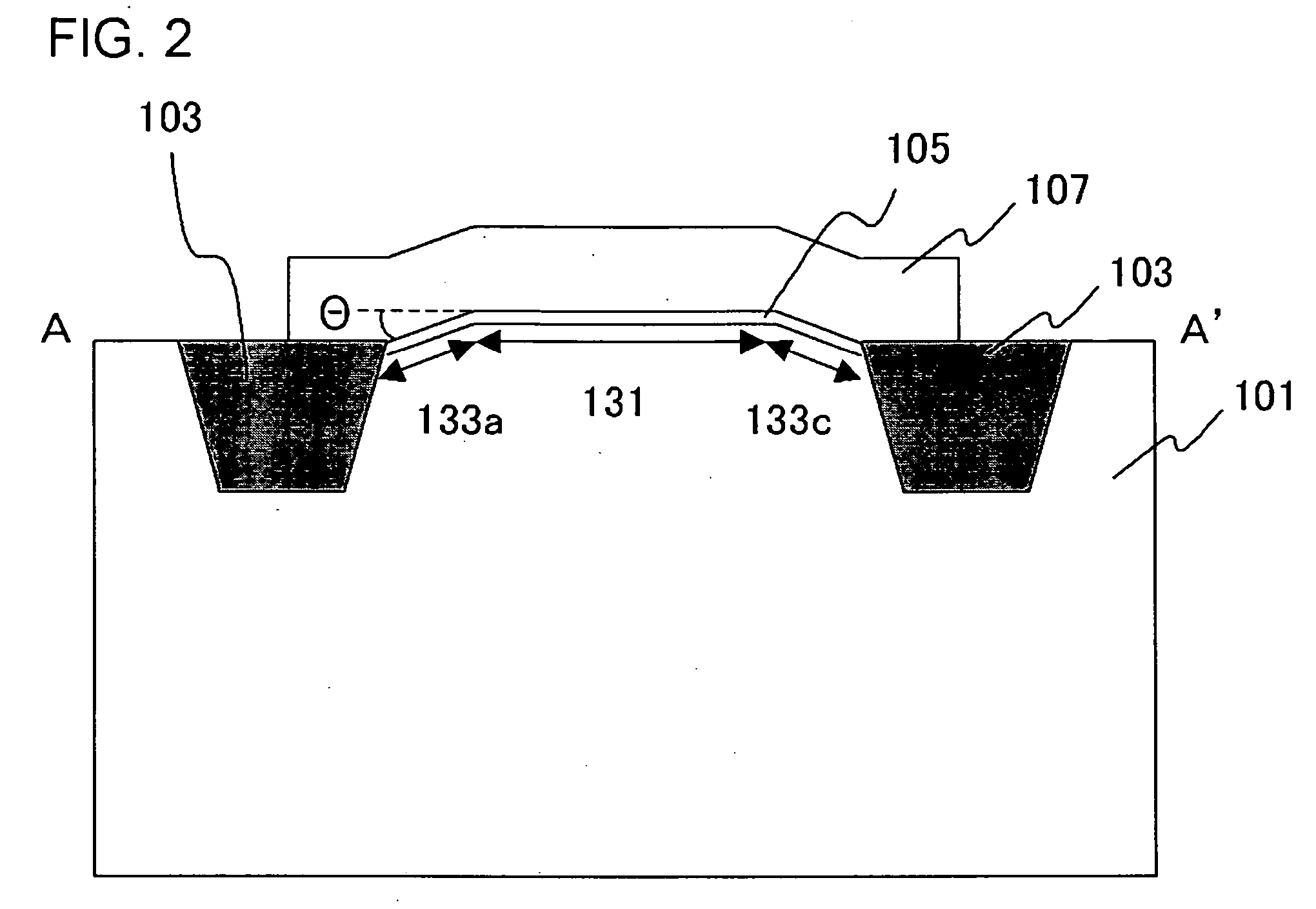

Field-effect transistor, complementary field-effect transistor, and method of manufacturing field-effect transistor

InactiveUS20060049430A1Improve channel mobilityDeterioration of ON-state can be suppressedTransistorSemiconductor/solid-state device manufacturingField-effect transistorPhysics

An objective of this invention is to improve an ON-state current of a field-effect transistor. For this purpose, on a single-crystal silicon substrate 101 having a {100} plane as a principal surface are formed a gate electrode 107 extending substantially in a <010> crystal axis direction of the single-crystal silicon or an axis direction equivalent to the <010> crystal axis direction, and in both sides of the gate electrode 107, source / drain regions 129 on the surface of the single-crystal silicon substrate 101. On the surface of the single-crystal silicon substrate 101 in a region directly below the gate electrode 107 are formed a principal surface and an inclined surface 133 oblique to the principal surface along the extension direction of the gate electrode 107.

Owner:NEC ELECTRONICS CORP +1

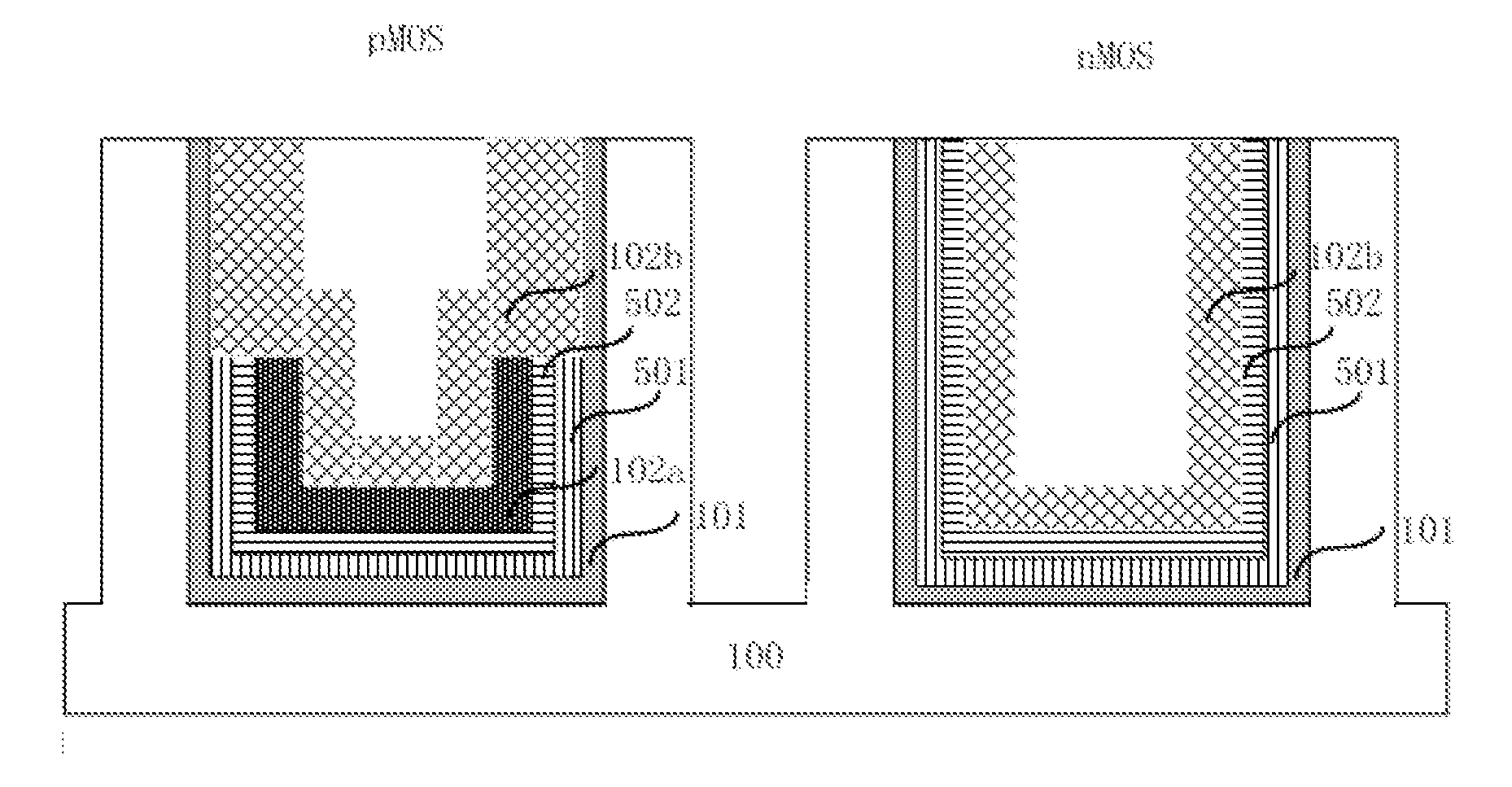

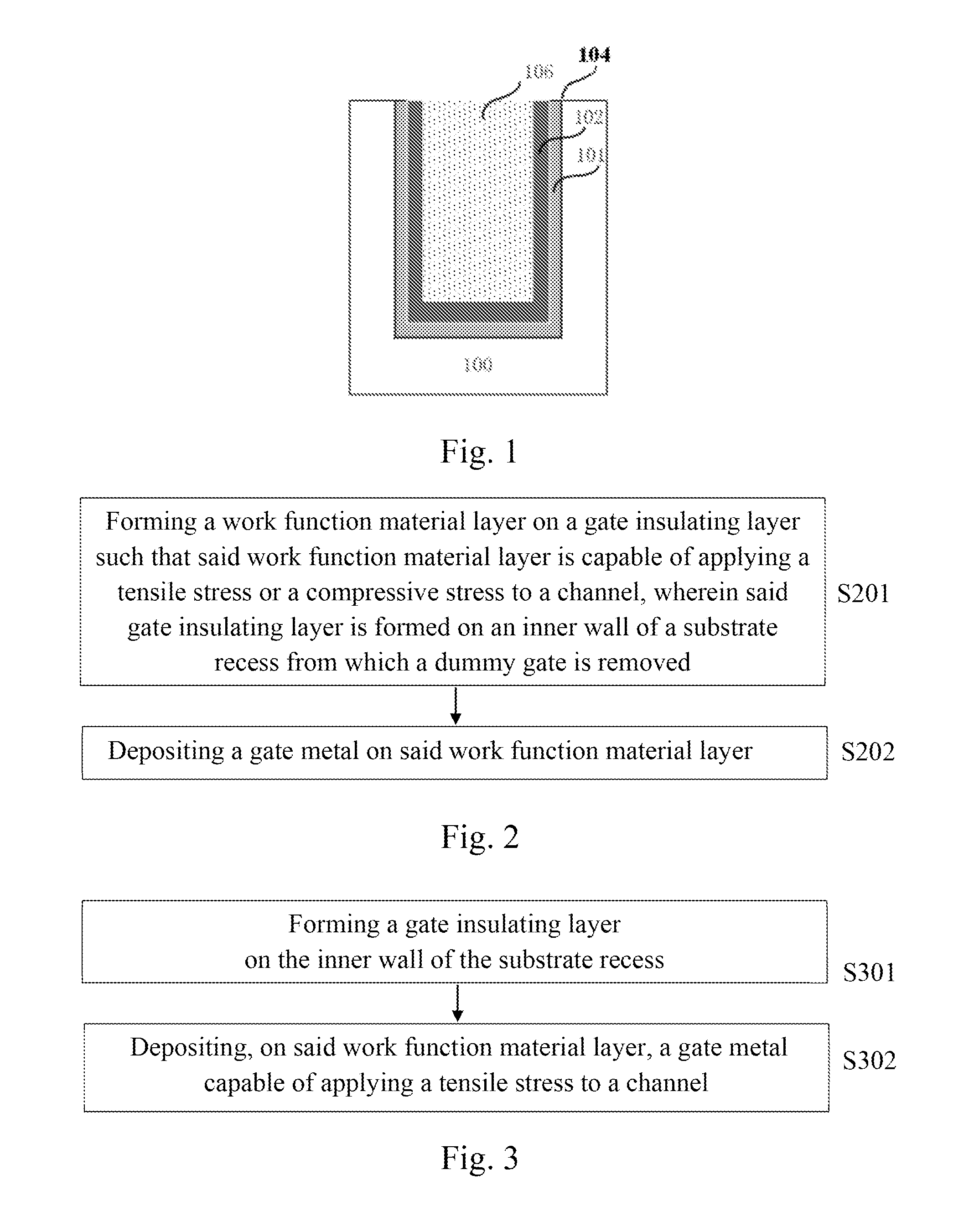

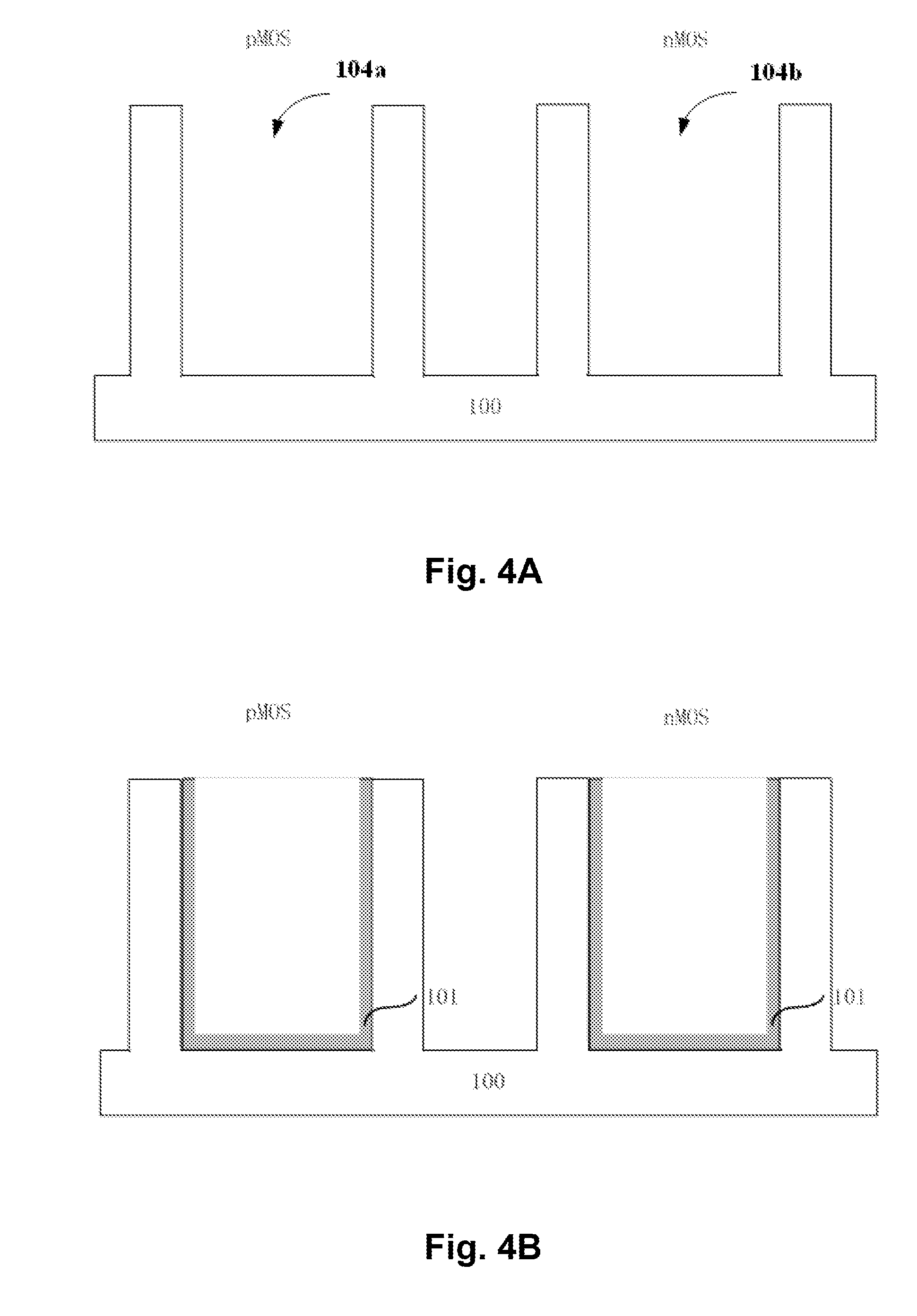

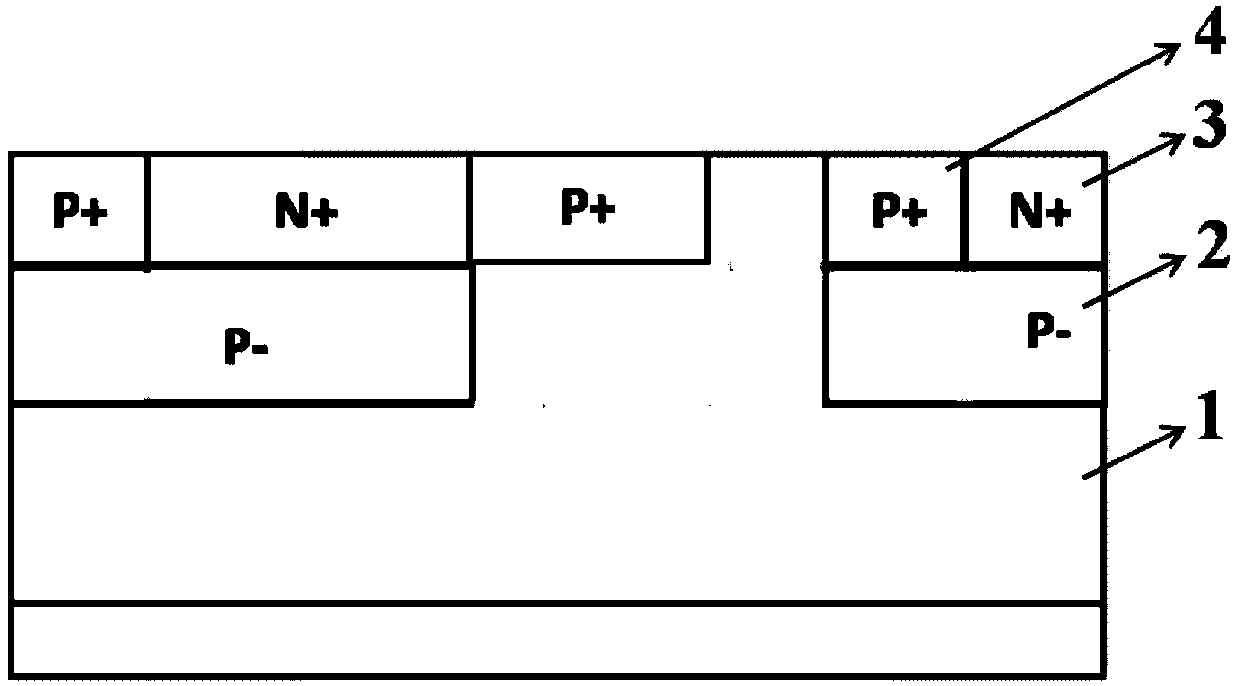

Semiconductor device and manufacturing method thereof

ActiveUS20140110778A1Reduce contact resistanceImprove channel mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesWork functionEngineering

The present invention discloses a semiconductor device and a method for manufacturing the semiconductor device. The semiconductor device includes a gate insulating layer formed on an inner wall of a substrate recess, a work function material layer formed on the gate insulating layer so as to apply a tensile stress or a compressive stress to a channel of a MOS field-effect transistor, and a gate metal formed on the work function material layer. The method for manufacturing the semiconductor device includes forming a work function material layer on a gate insulating layer so as to apply a tensile stress or a compressive stress to a channel of a MOS field-effect transistor, wherein the gate insulating layer is formed on an inner wall of a substrate recess, and depositing a gate metal on the work function material layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP

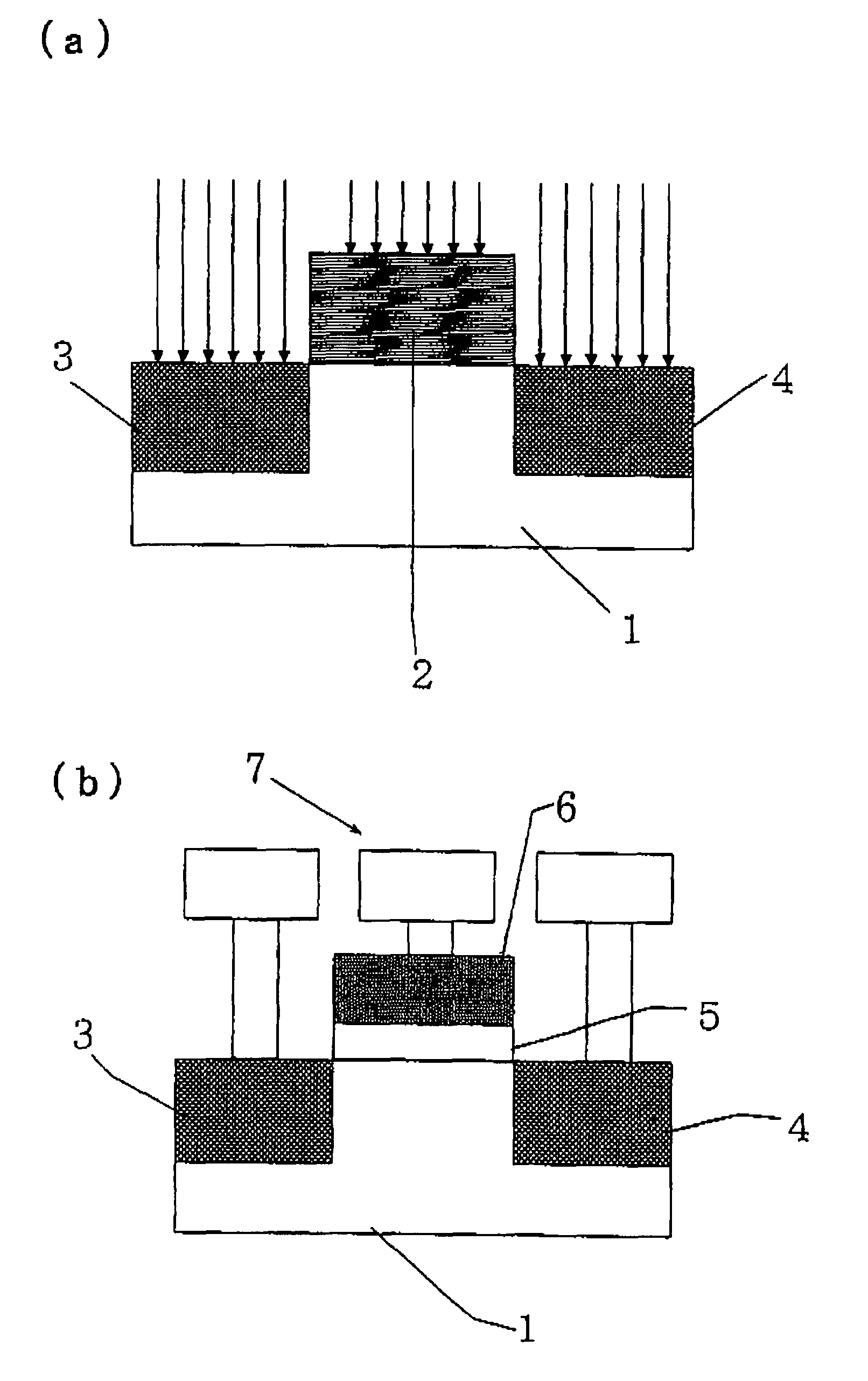

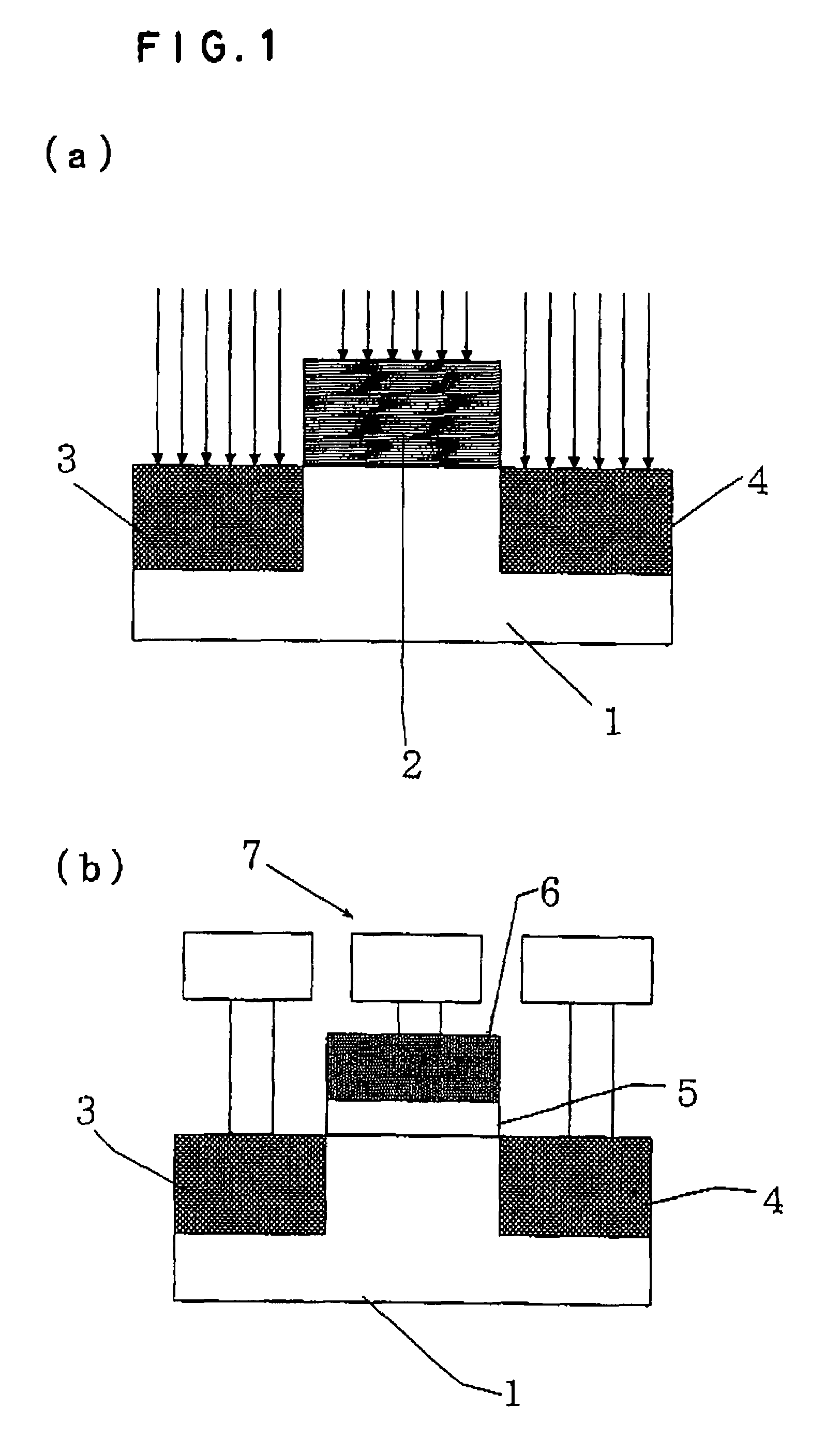

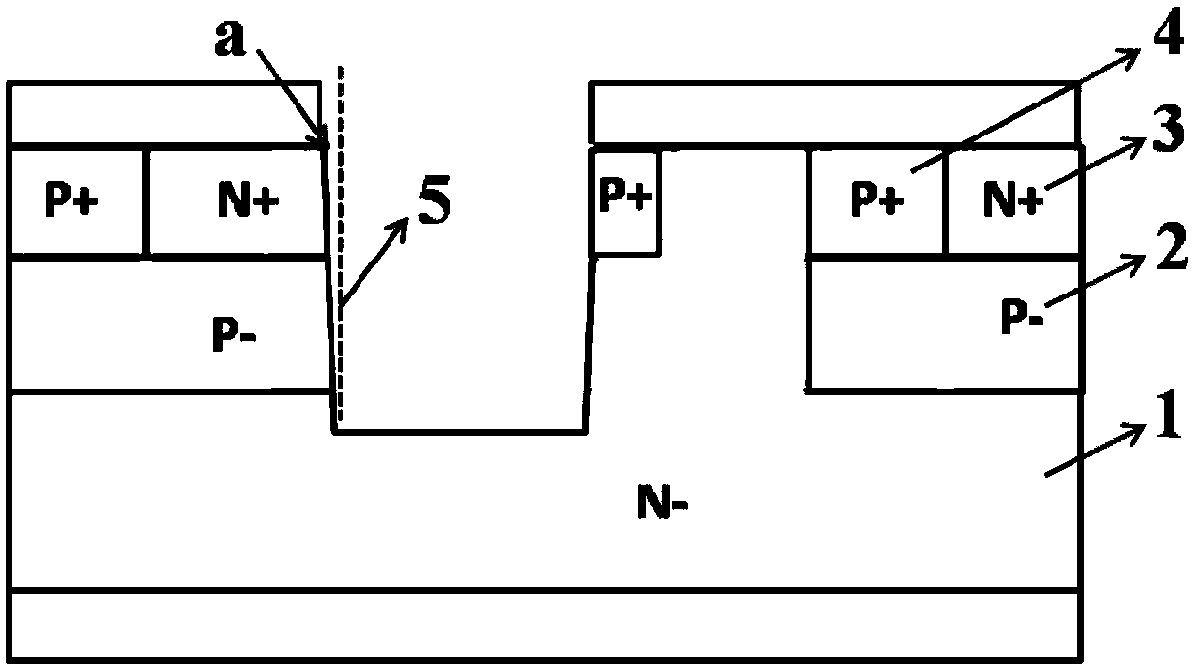

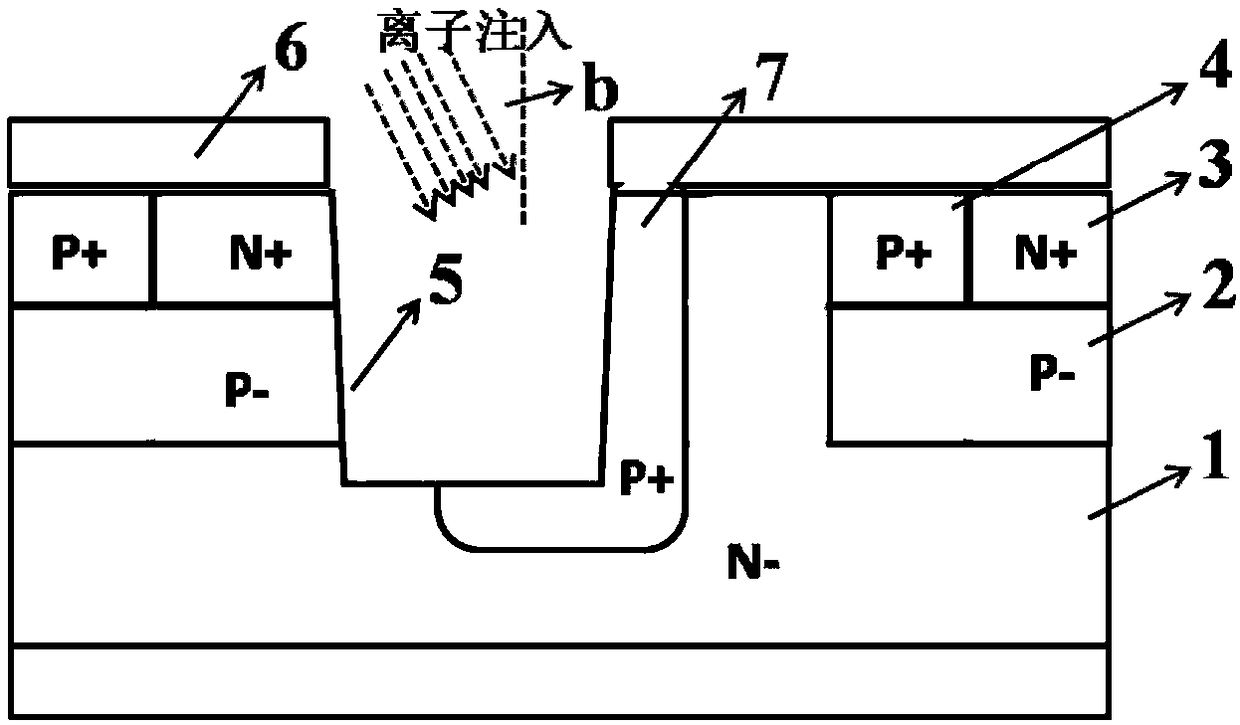

Unilateral MOS-type device manufacturing method integrated with SBD structure

InactiveCN108183131AImprove conduction performanceLow application costSemiconductor/solid-state device manufacturingDiodeMOSFETReverse recovery

The invention discloses a unilateral MOS-type device manufacturing method integrated with an SBD structure. Through introducing a special angle groove manufacturing process, an inclination angle unilateral ion implantation process and a schottky metal process compatible with an ohm process, manufacturing of an SiC groove MOSFET device integrated with an SBD structure is realized. The silicon carbide SBD structure is integrated in the silicon carbide groove-type MOSFET device, a reverse follow current function can be realized well, the reverse recovery time of the MOSFET device can be reduced,and the application cost of a silicon carbide power electronic device can be effectively reduced. In combination of a unilateral high-mobility groove structure with special crystal face etching, whilethe groove mobility is improved, the size of a primitive cell is narrowed, and the device conduction ability is improved.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

SiC semiconductor device and method for manufacturing the same

InactiveUS20080203402A1Improve channel mobilityReduce the temperatureSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogen concentrationImpurity

A SiC semiconductor device includes: a SiC substrate having a main surface; a channel region on the substrate; first and second impurity regions on upstream and downstream sides of the channel region, respectively; a gate on the channel region through a gate insulating film. The channel region for flowing current between the first and second impurity regions is controlled by a voltage applied to the gate. An interface between the channel region and the gate insulating film has a hydrogen concentration equal to or greater than 2.6×1020 cm−3. The interface provides a channel surface perpendicular to a (0001)-orientation plane.

Owner:DENSO CORP

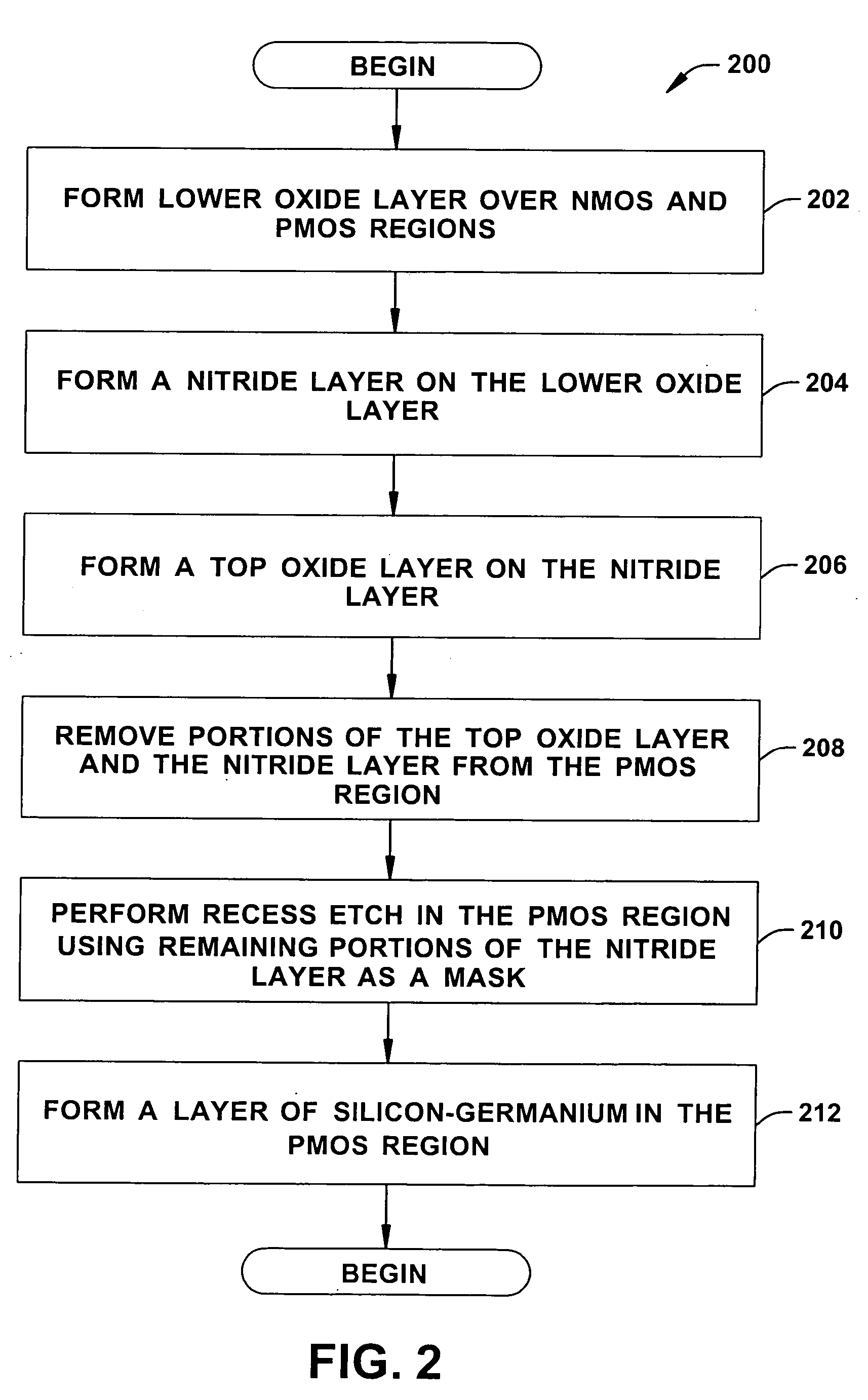

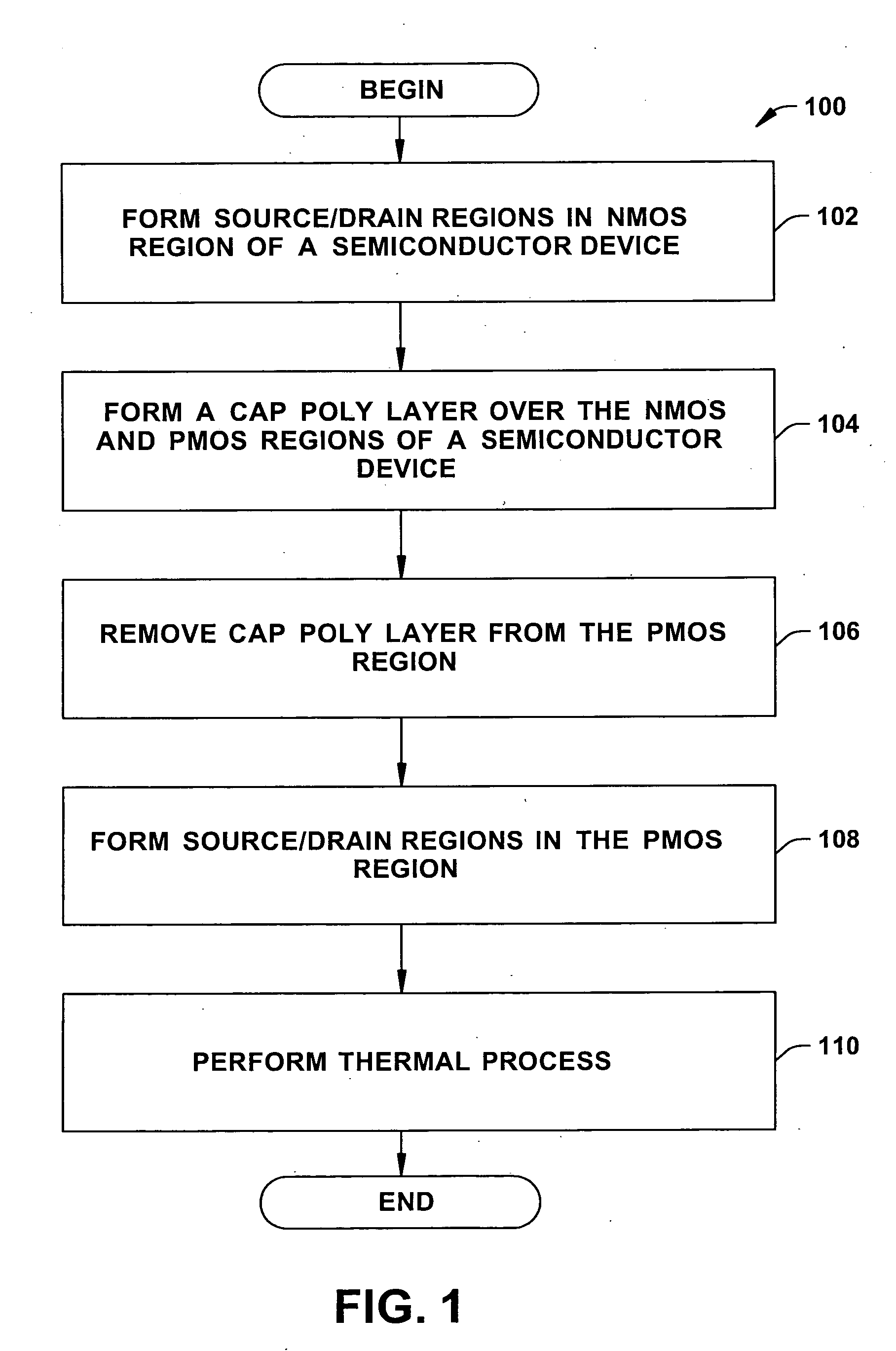

Method to selectively strain NMOS devices using a cap poly layer

ActiveUS20060073650A1Facilitates semiconductor fabricationImprove channel mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesDopantResist

The present invention facilitates semiconductor fabrication by providing methods of fabrication that selectively apply tensile strain to channel regions of devices while mitigating masking operations employed. A cap poly layer is formed over NMOS and PMOS regions of a semiconductor device. Then, a resist mask is employed to remove a portion of the cap poly layer from the PMOS region. Subsequently, the same resist mask and / or remaining portion of the cap poly layer is employed to form source / drain regions within the PMOS region by implanting a p-type dopant. Afterward, a cap poly thermal process is performed that causes tensile strain to be induced only in channel regions of devices located within the NMOS region. As a result, channel mobility and / or performance of devices located in the PMOS region is not substantially degraded.

Owner:TEXAS INSTR INC

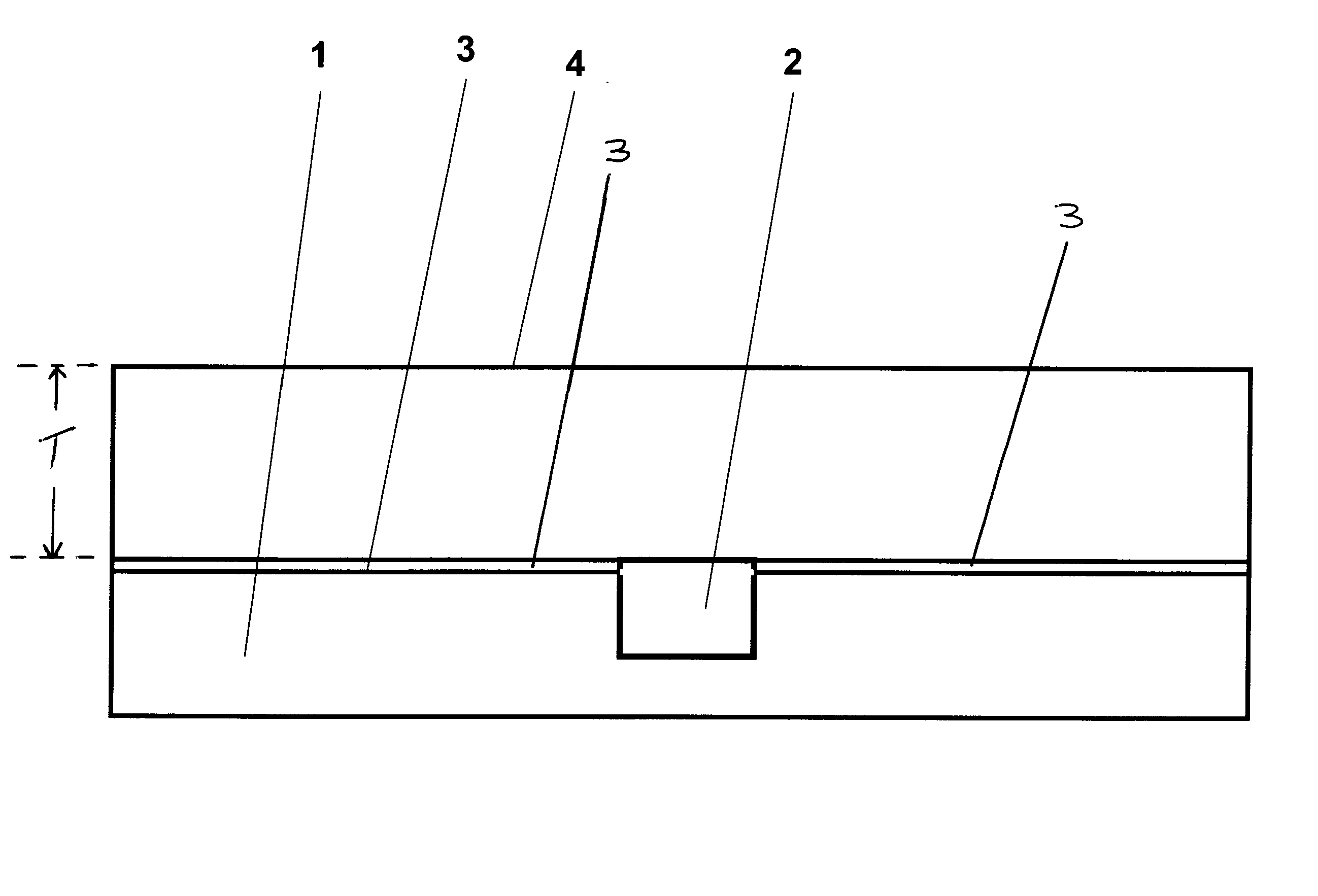

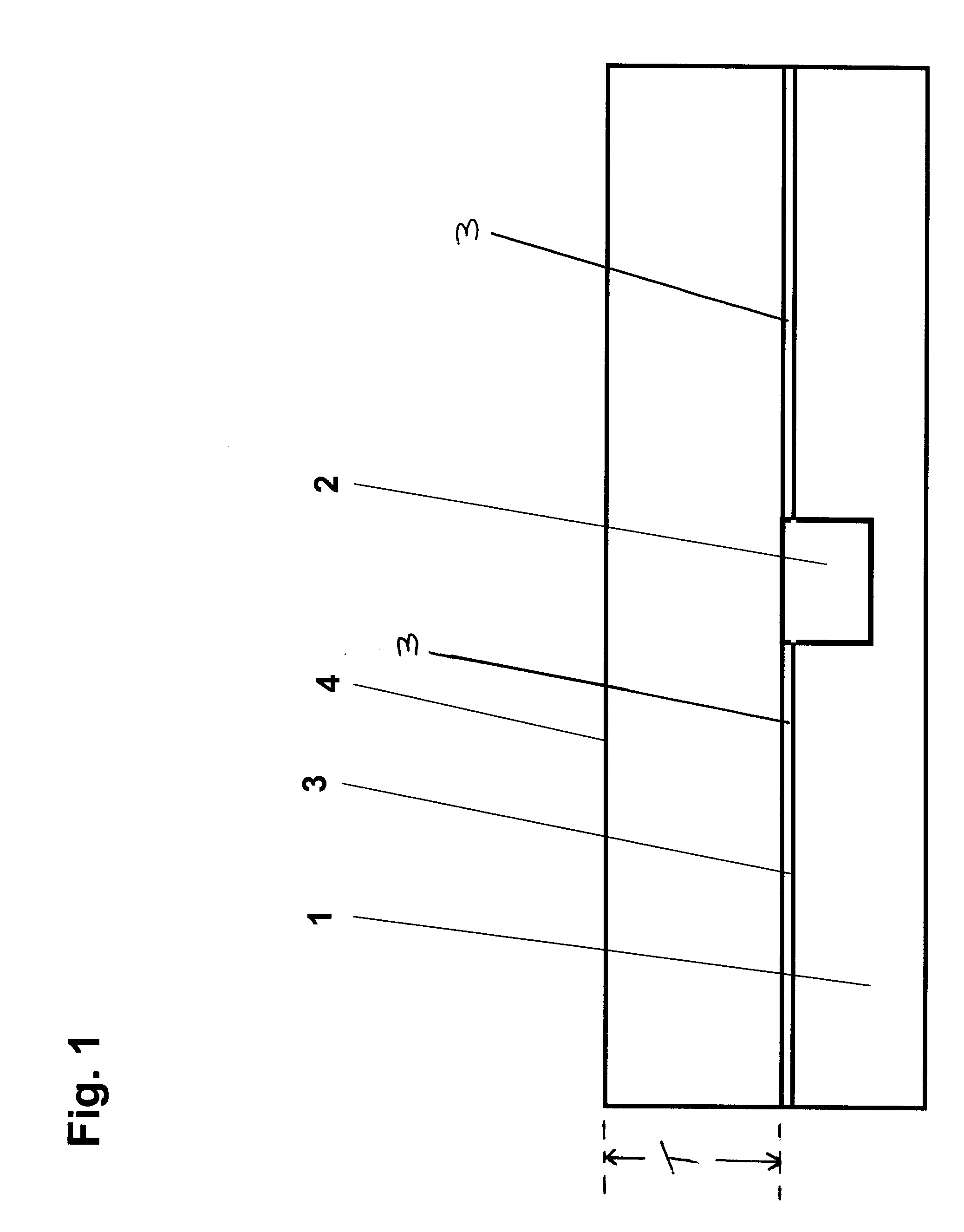

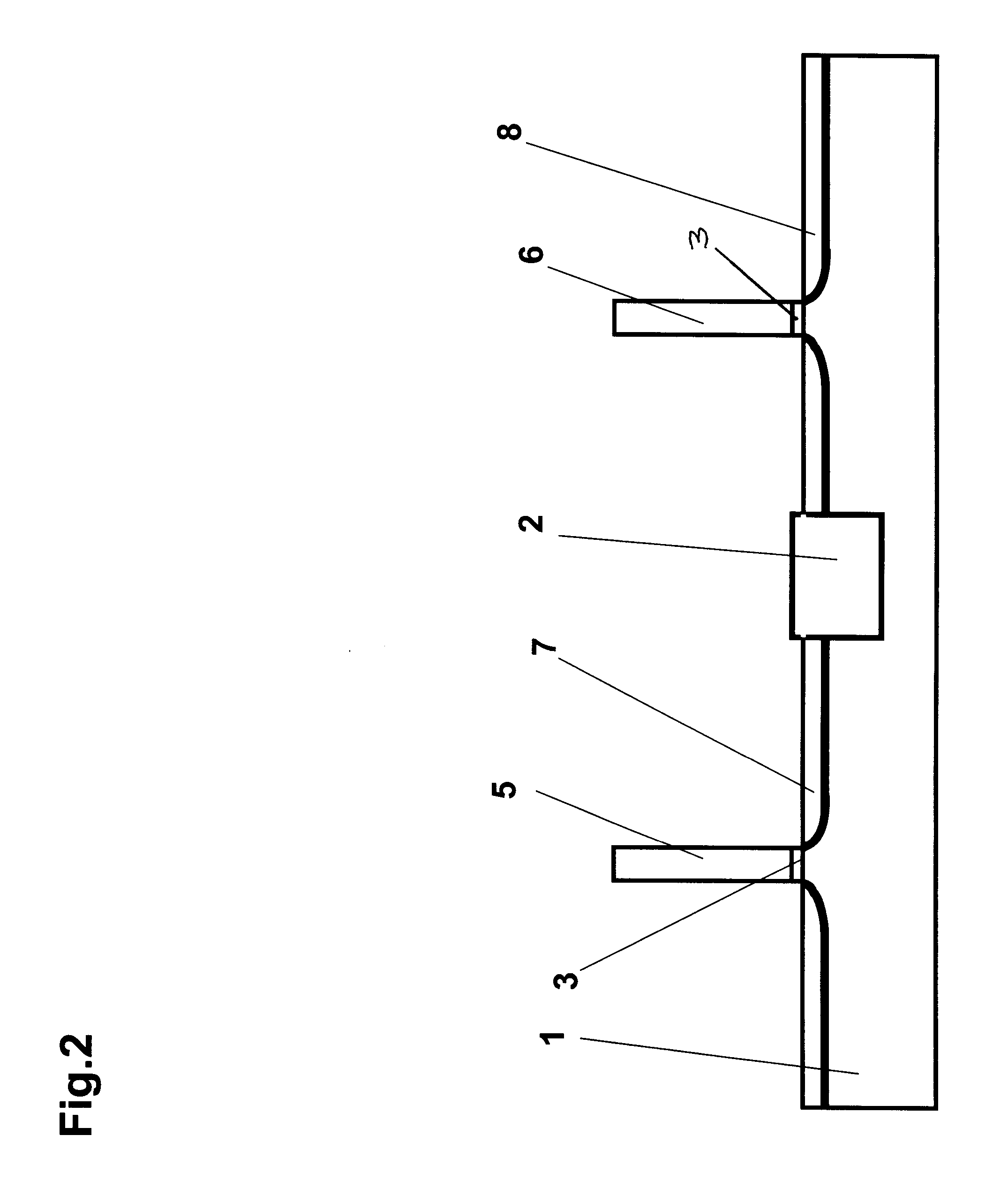

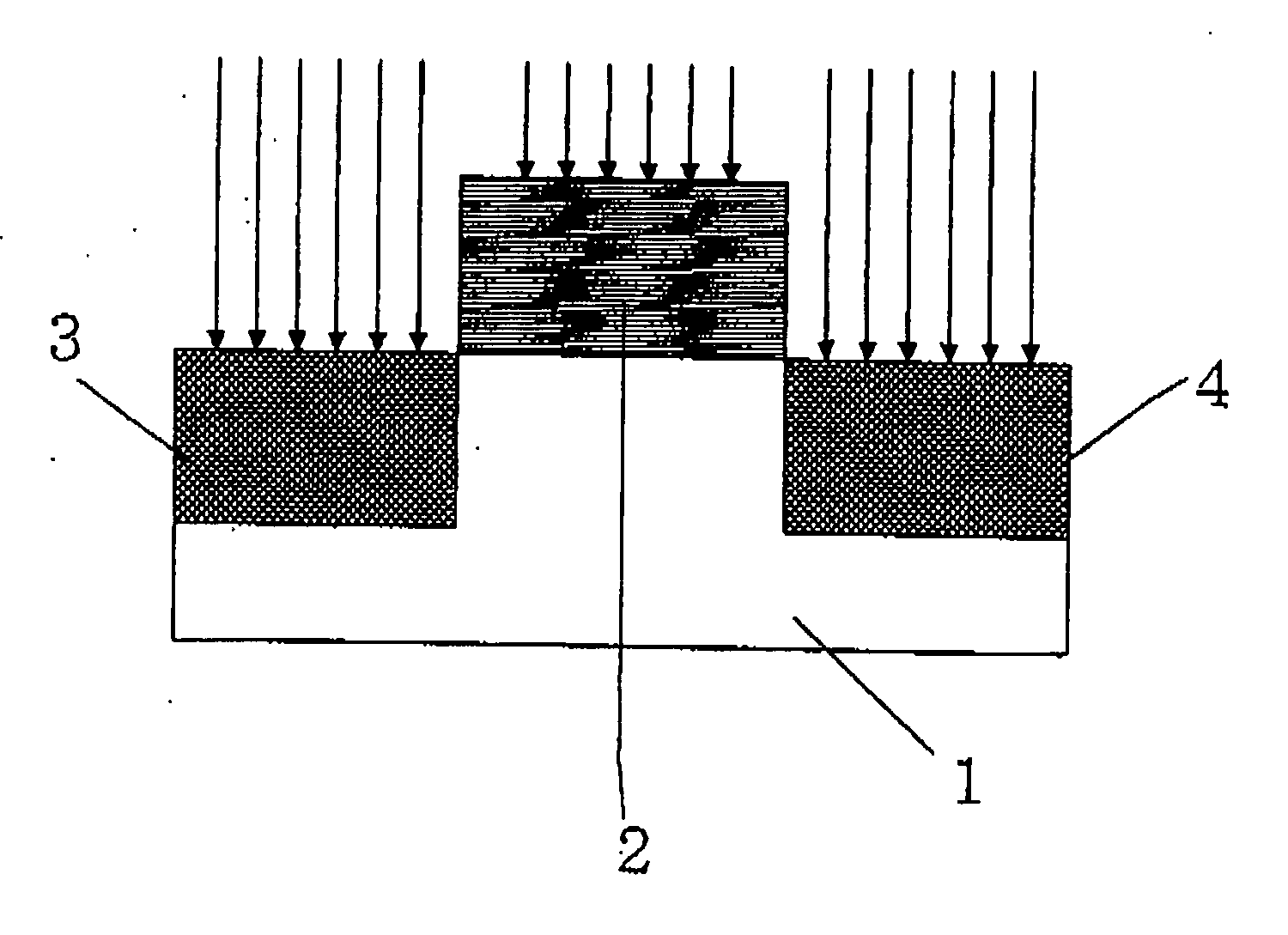

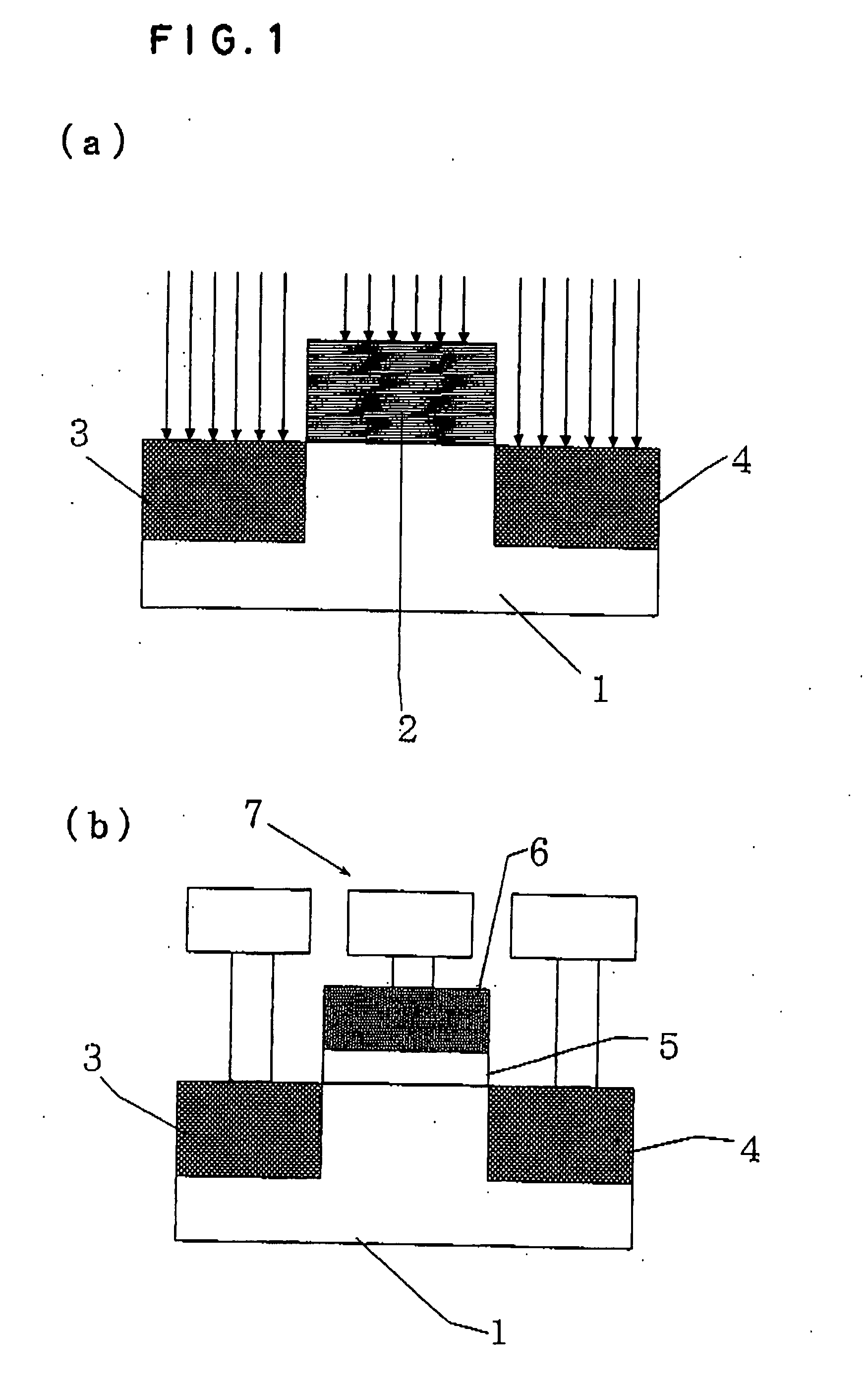

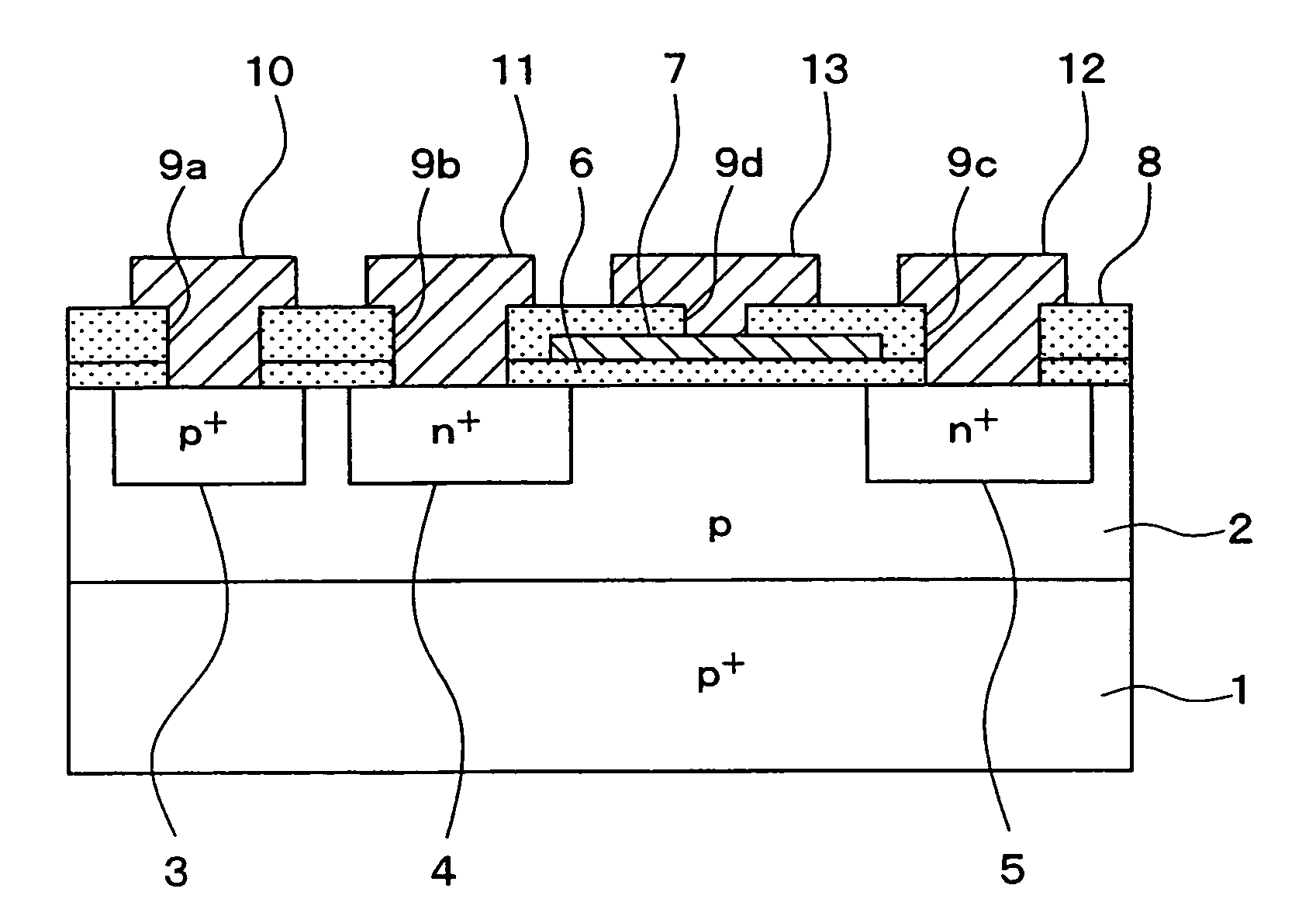

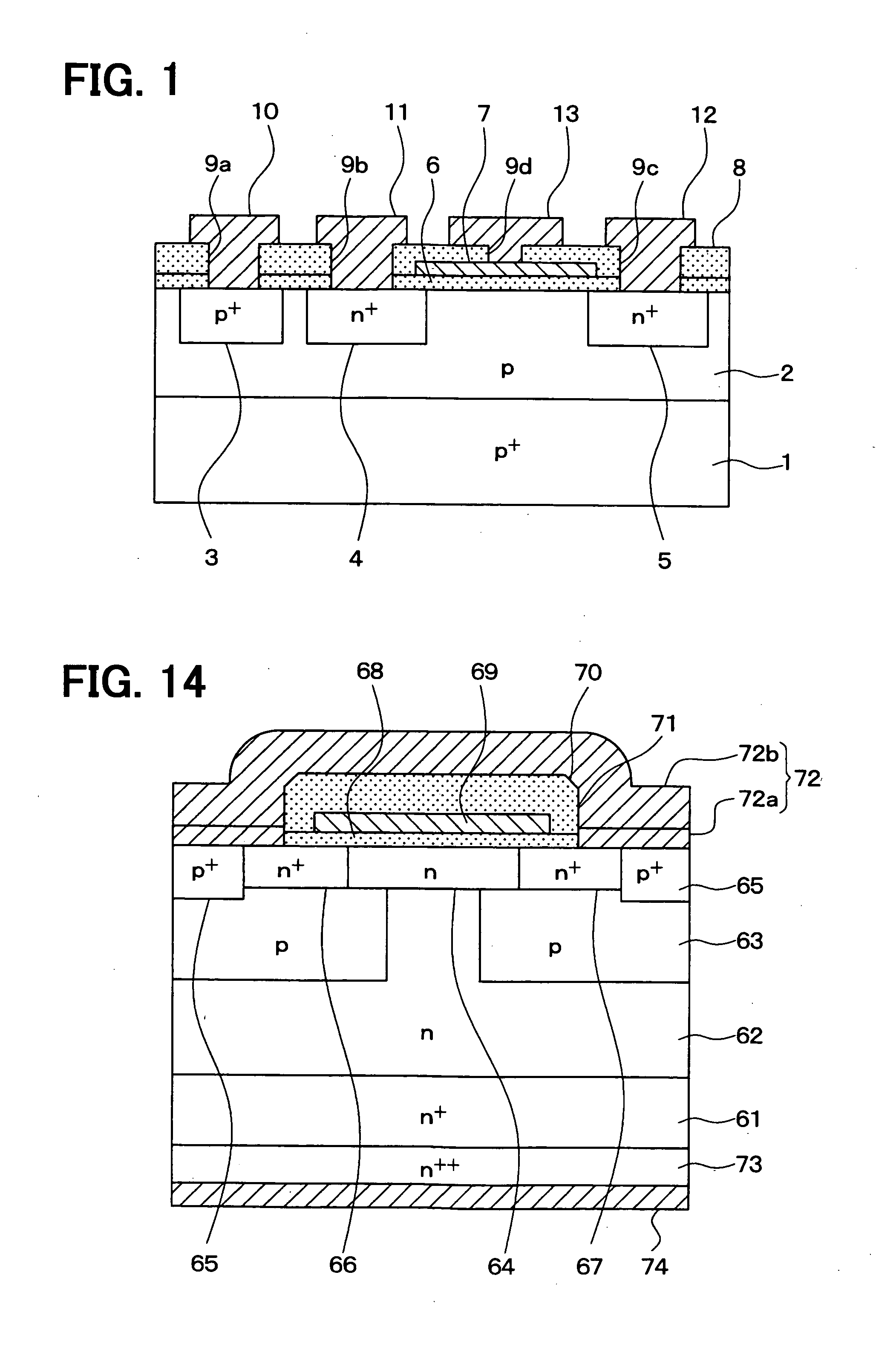

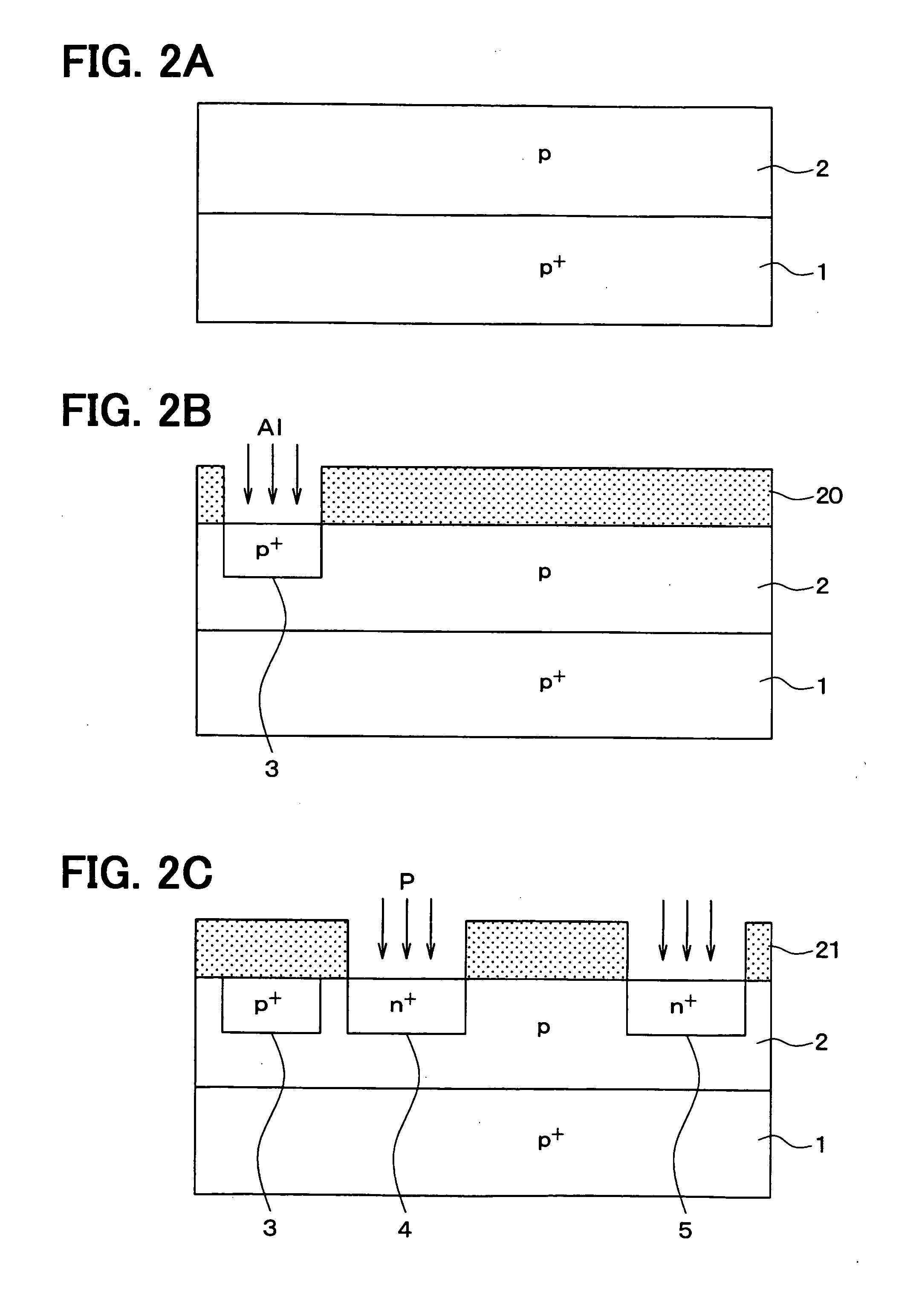

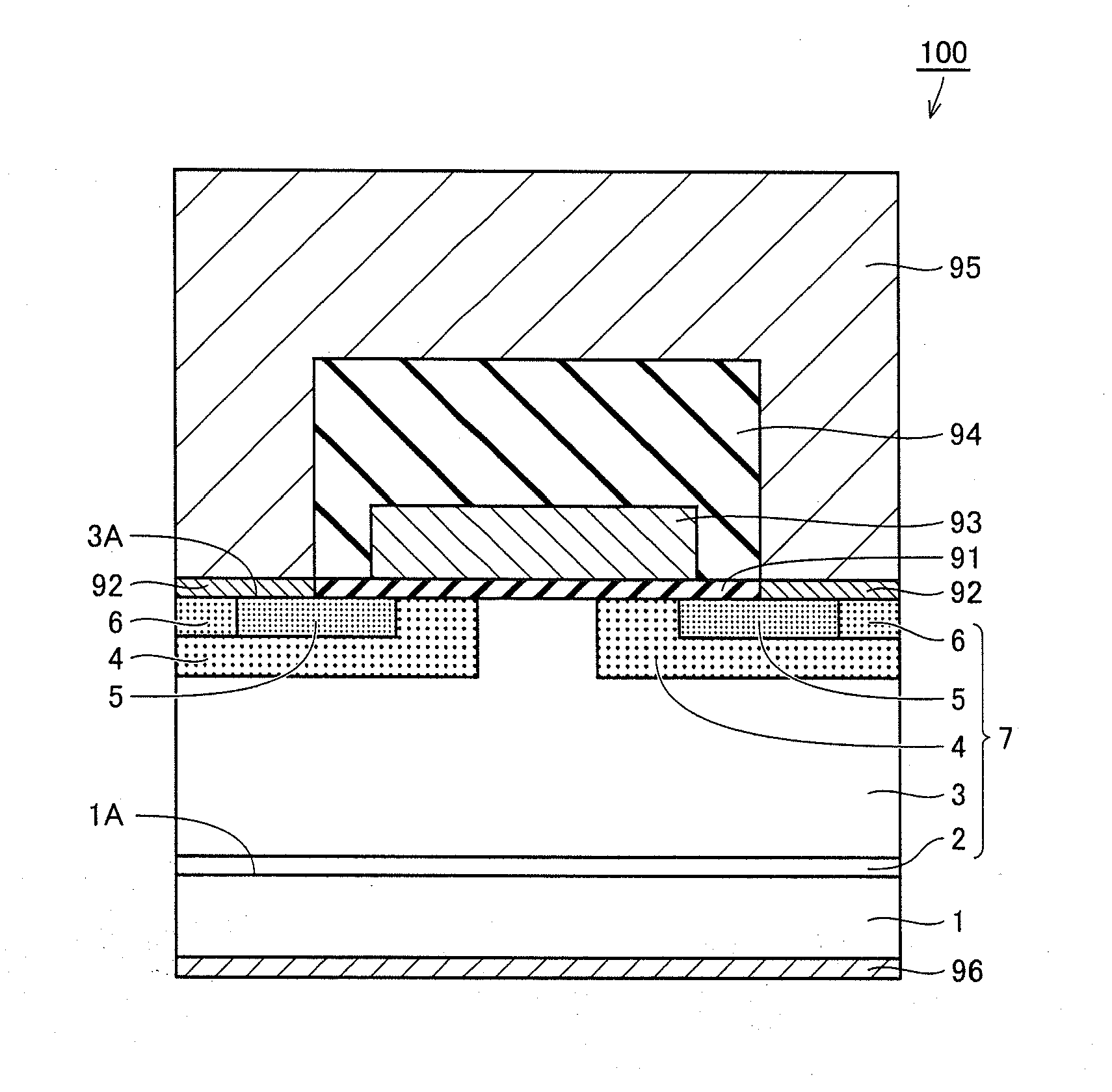

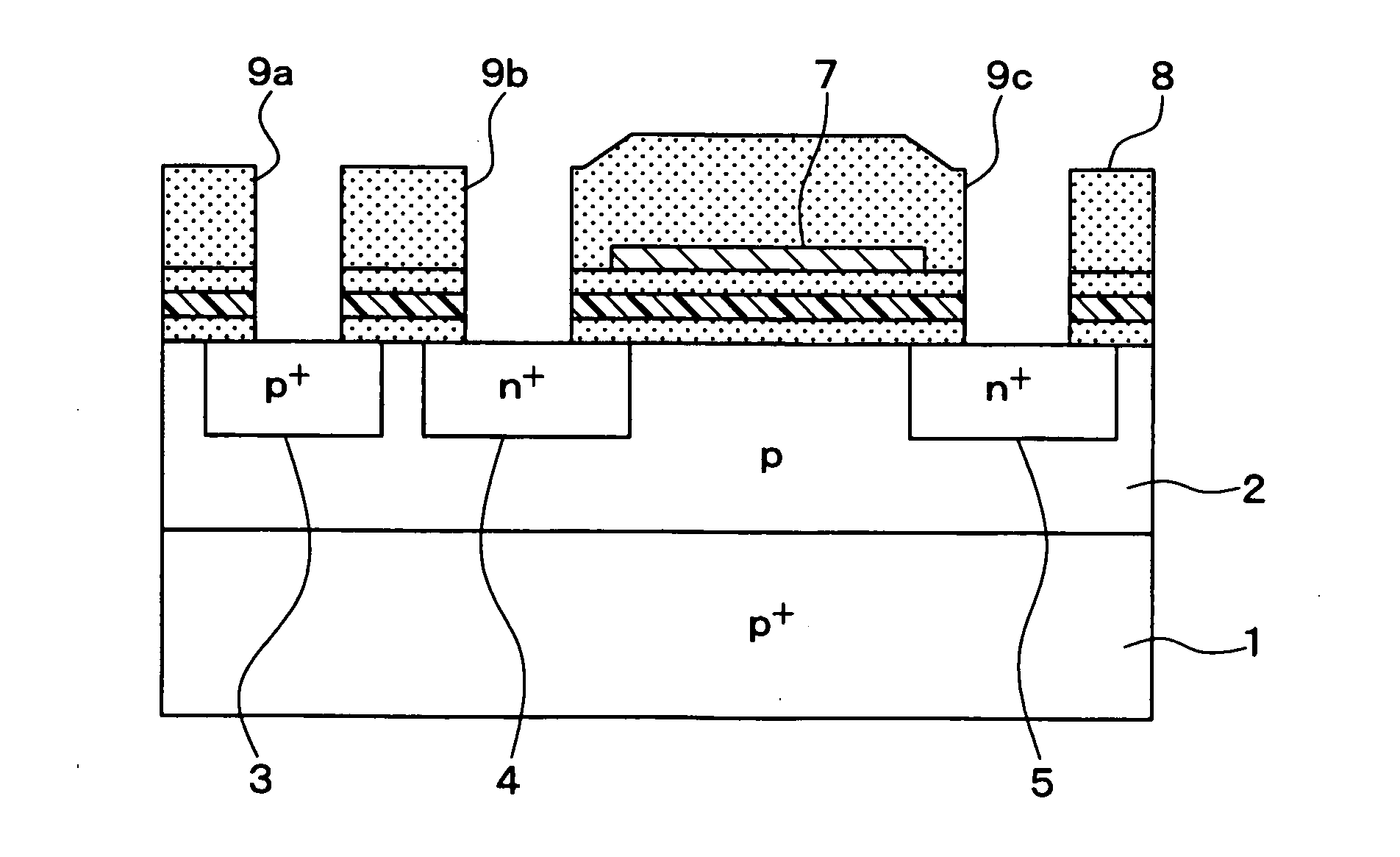

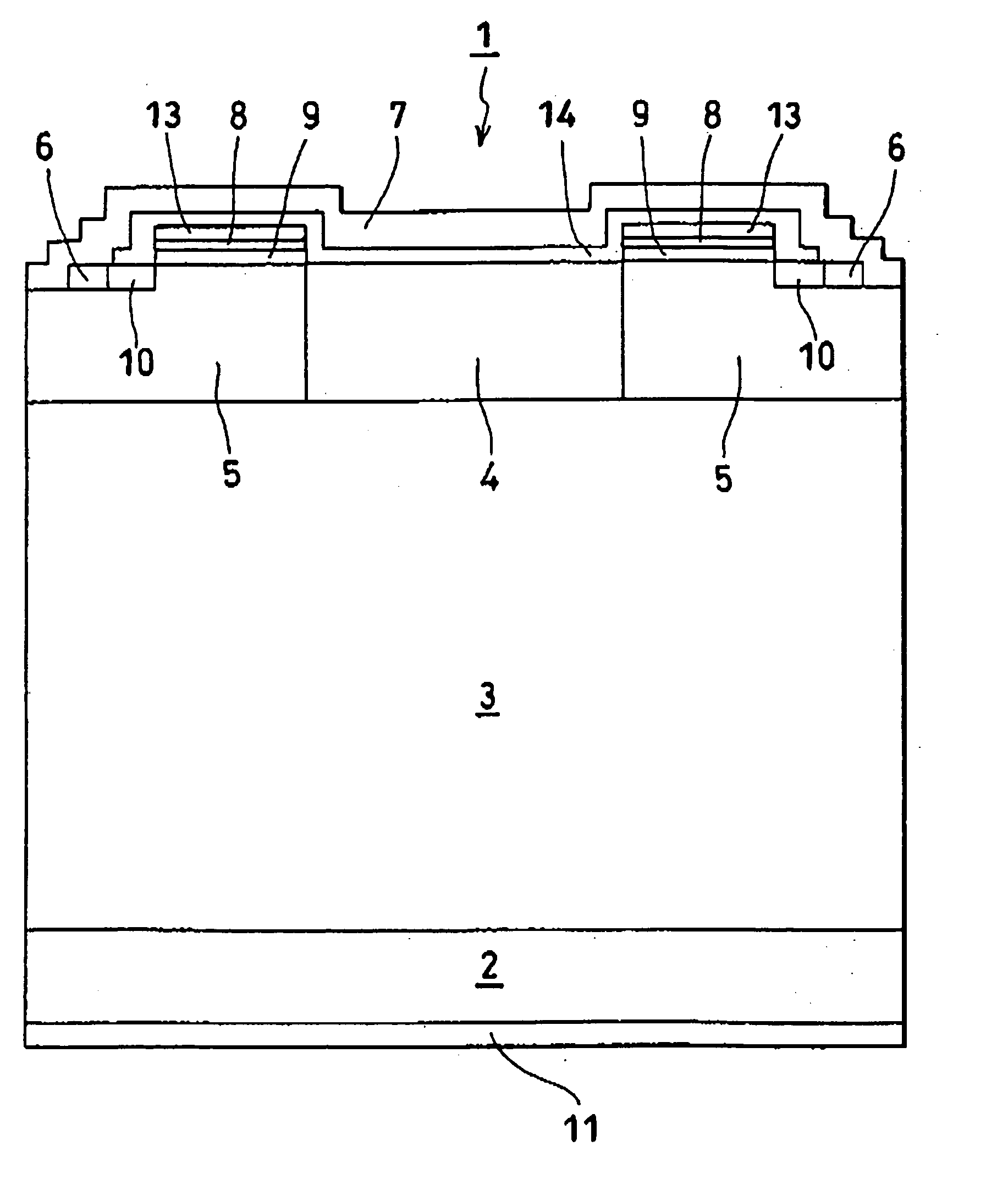

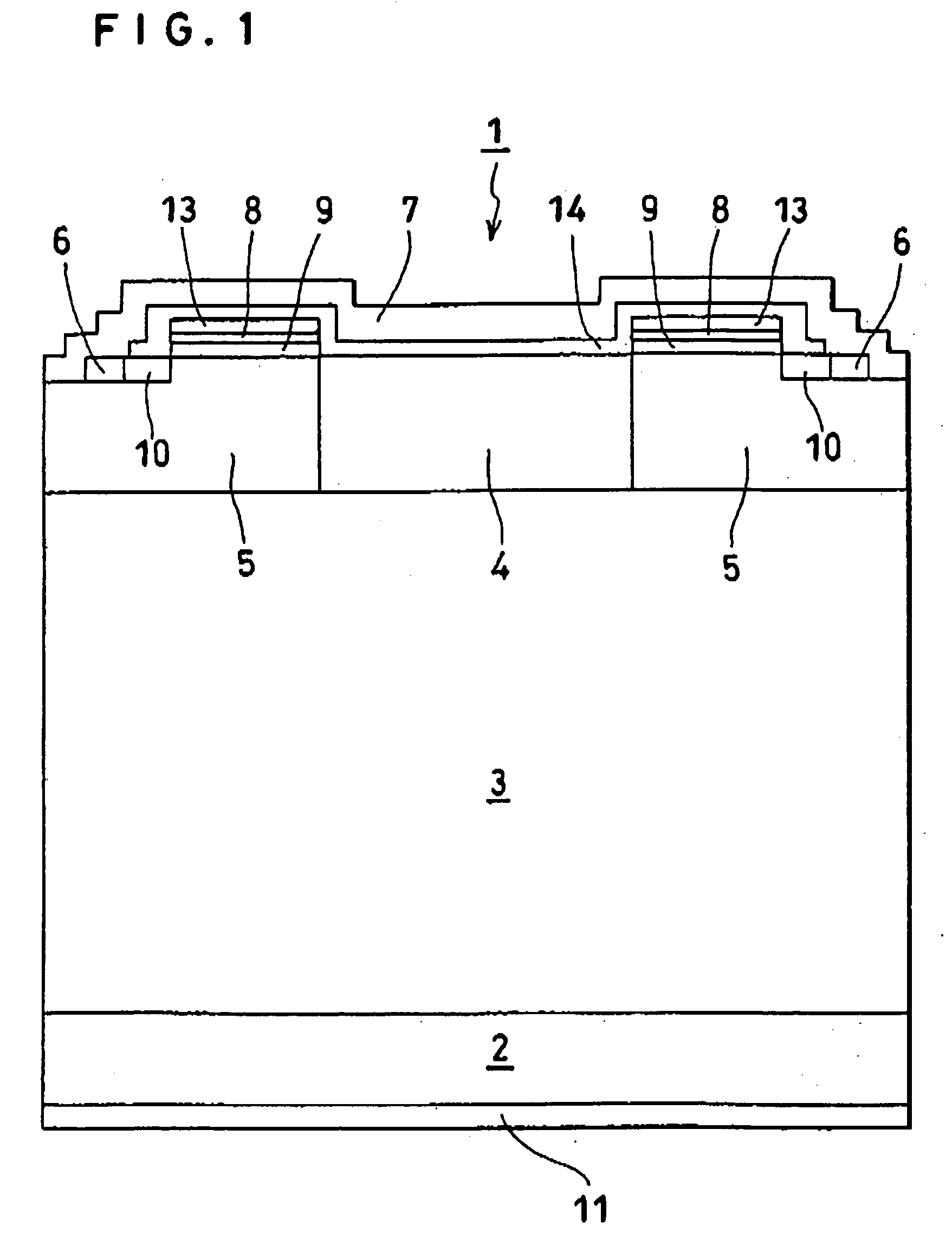

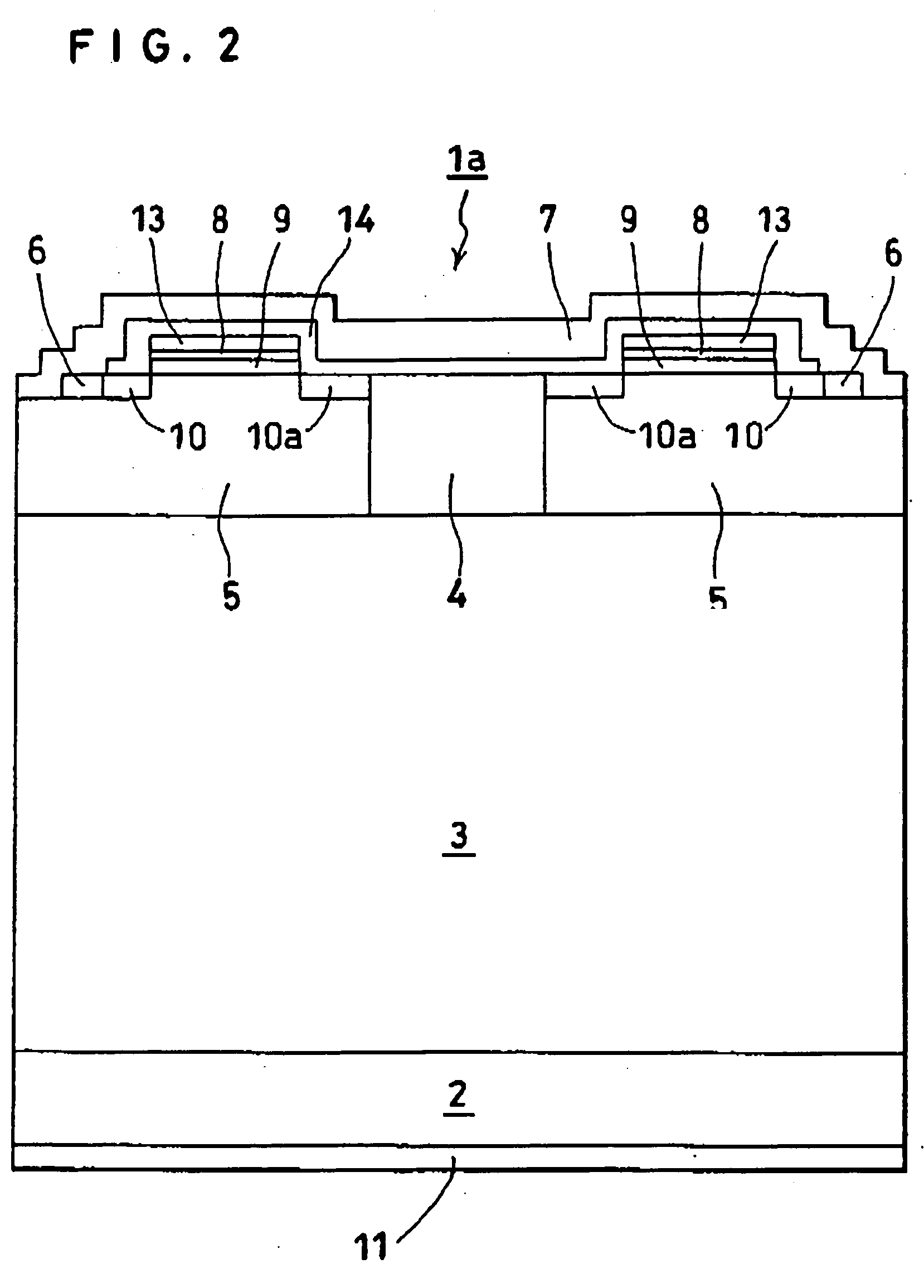

Semiconductor device

InactiveUS20060108589A1Improve channel mobilityPrevent voltageTransistorSemiconductor/solid-state device manufacturingDevice materialCarbide

A semiconductor device (1) includes an n-type silicon carbide substrate (2) of a high impurity concentration, an n-type silicon carbide layer (3) of a low impurity concentration disposed on the substrate, a first n-type silicon carbide region (4) of a first impurity concentration disposed on the surface of the n-type silicon carbide layer, first p-type silicon carbide regions (5) disposed as adjoined to the opposite sides of the first n-type silicon carbide region, a second n-type silicon carbide region (6) disposed selectively from the surface through the interior of the first p-type silicon carbide region, polycrystalline silicon (7) short-circuiting the first p-type silicon carbide region (5) to the second n-type silicon carbide region (6), a gate electrode (8) and a third n-type silicon carbide region (10), wherein the components thereof are individually constructed in a vertical DMOS structure. Since the polycrystalline silicon short-circuits the first p-type silicon carbide region to the second n-type silicon carbide region, the threshold voltage can be given a fixed value, and the device can be used as an actual MISFET.

Owner:NAT INST OF ADVANCED IND SCI & TECH