Patents

Literature

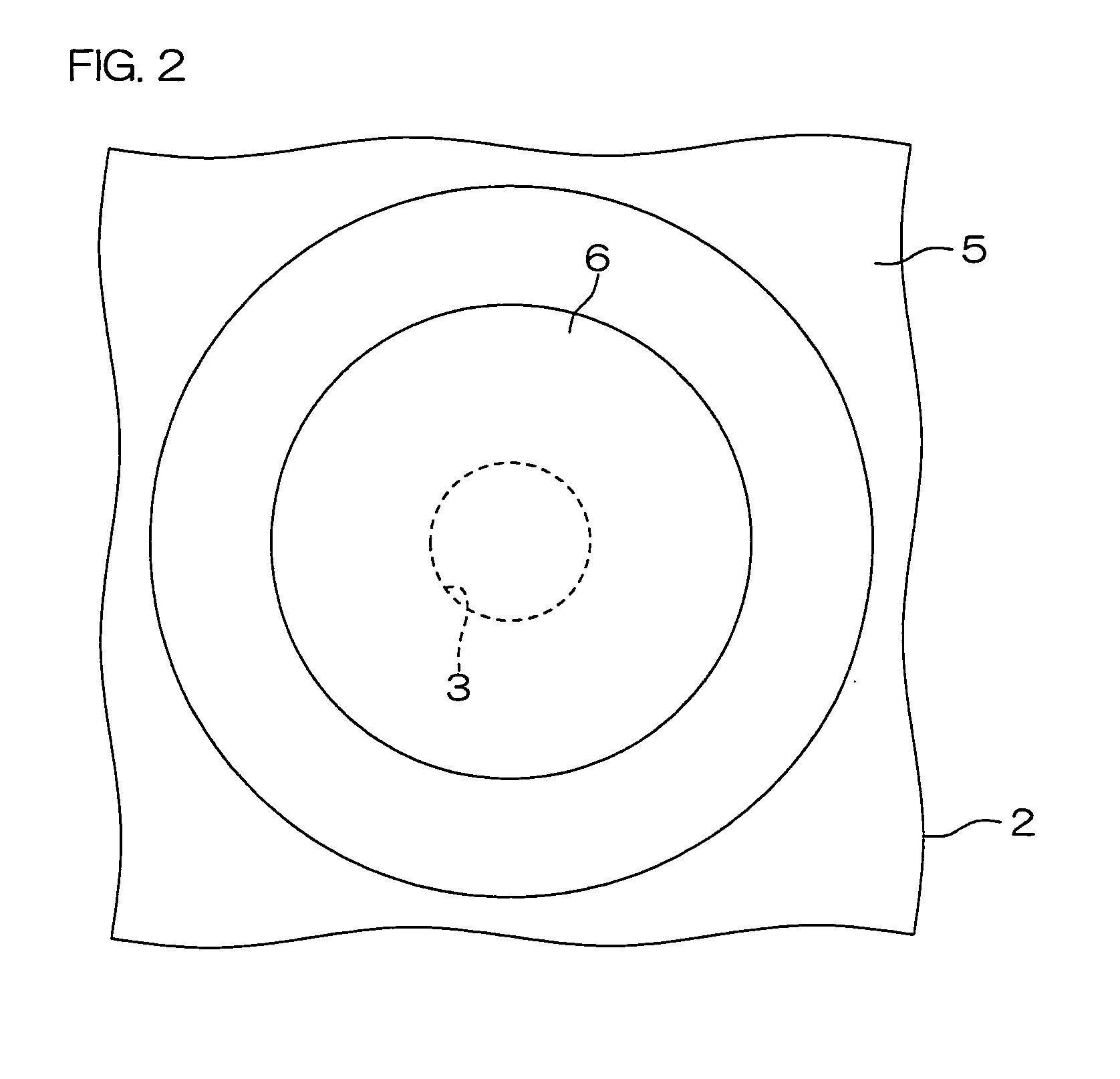

644results about How to "Avoid etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

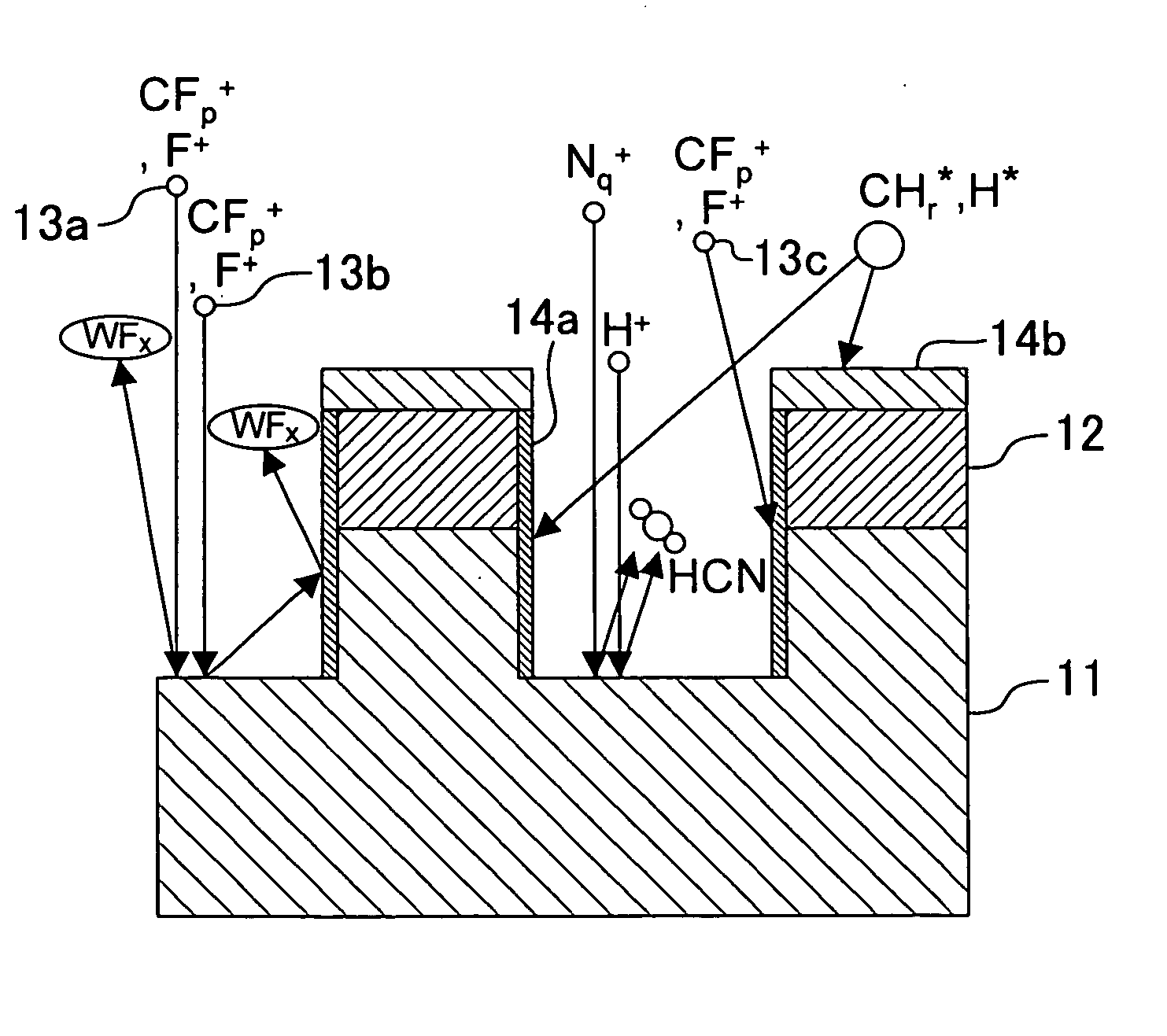

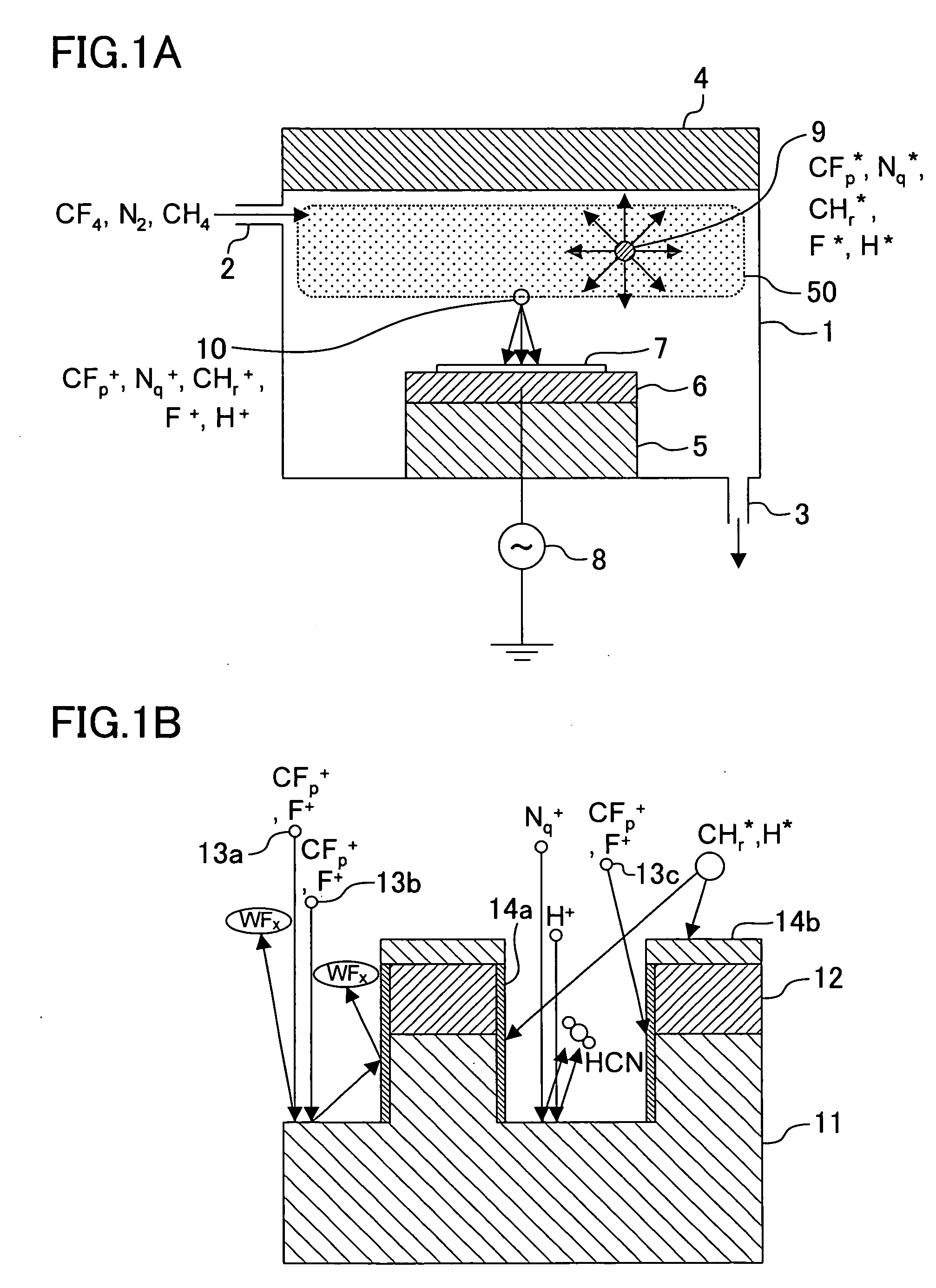

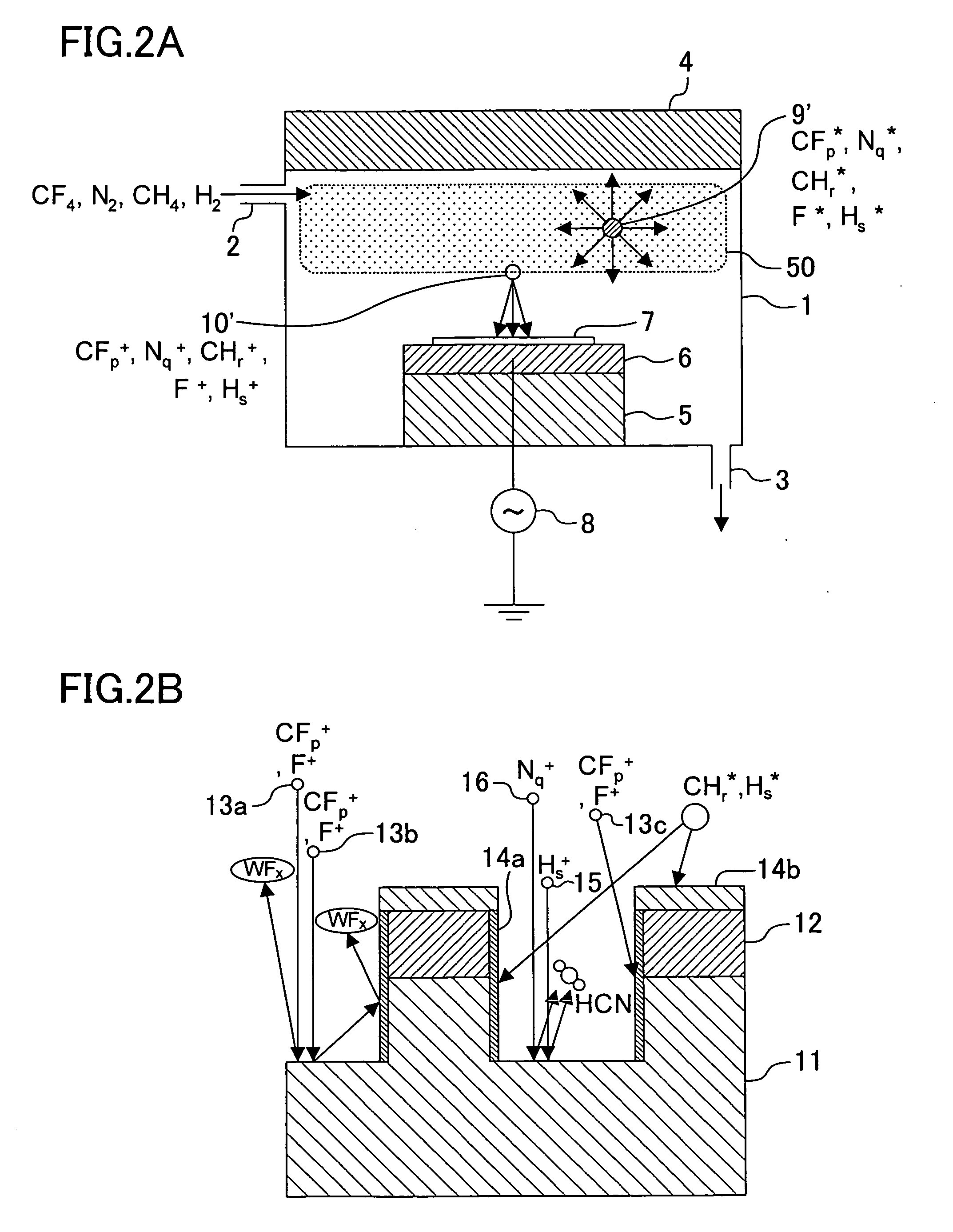

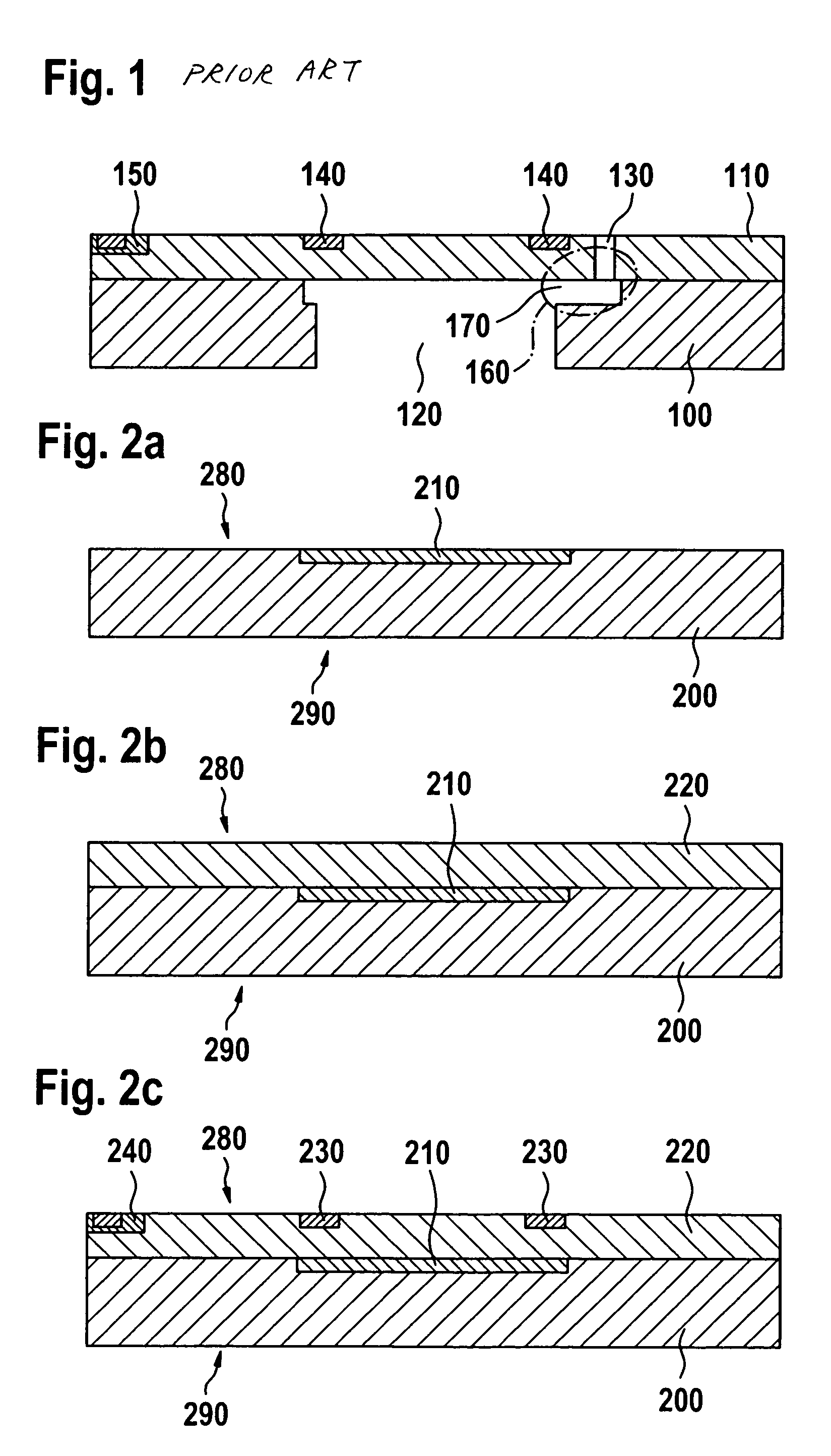

Dry etching method, fine structure formation method, mold and mold fabrication method

InactiveUS20070187362A1Increase preciseness and easinessAccurately formedDecorative surface effectsOptical light guidesNitrogen atomTungsten

Owner:PANASONIC CORP

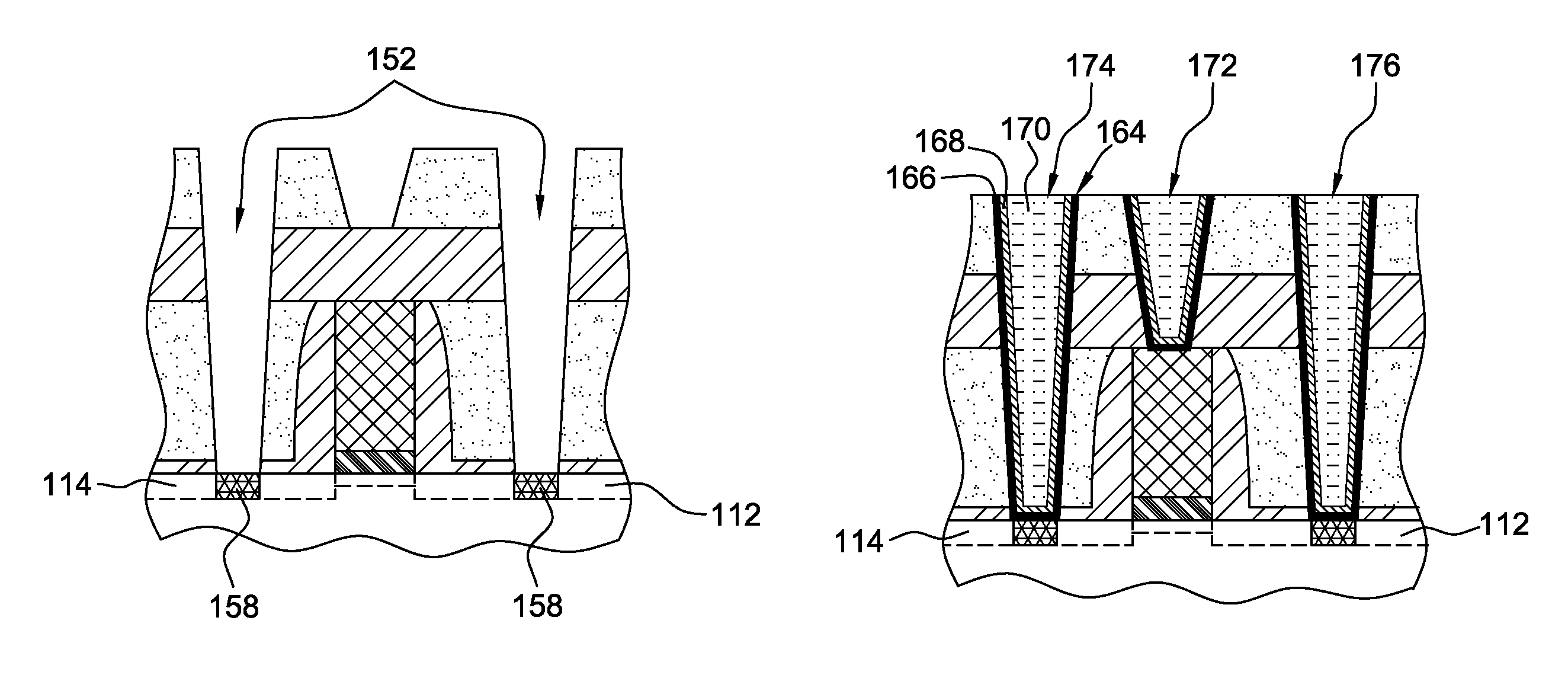

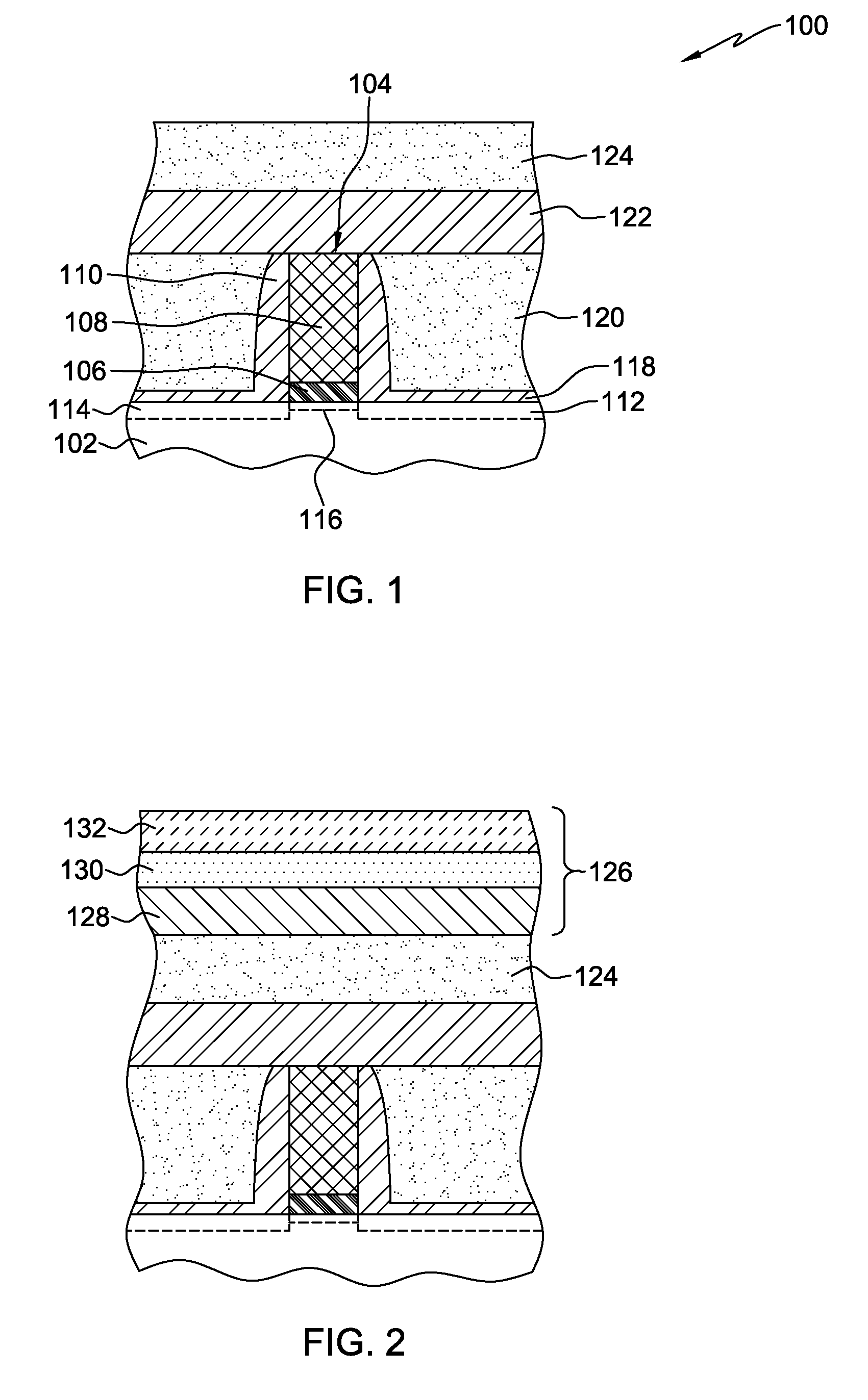

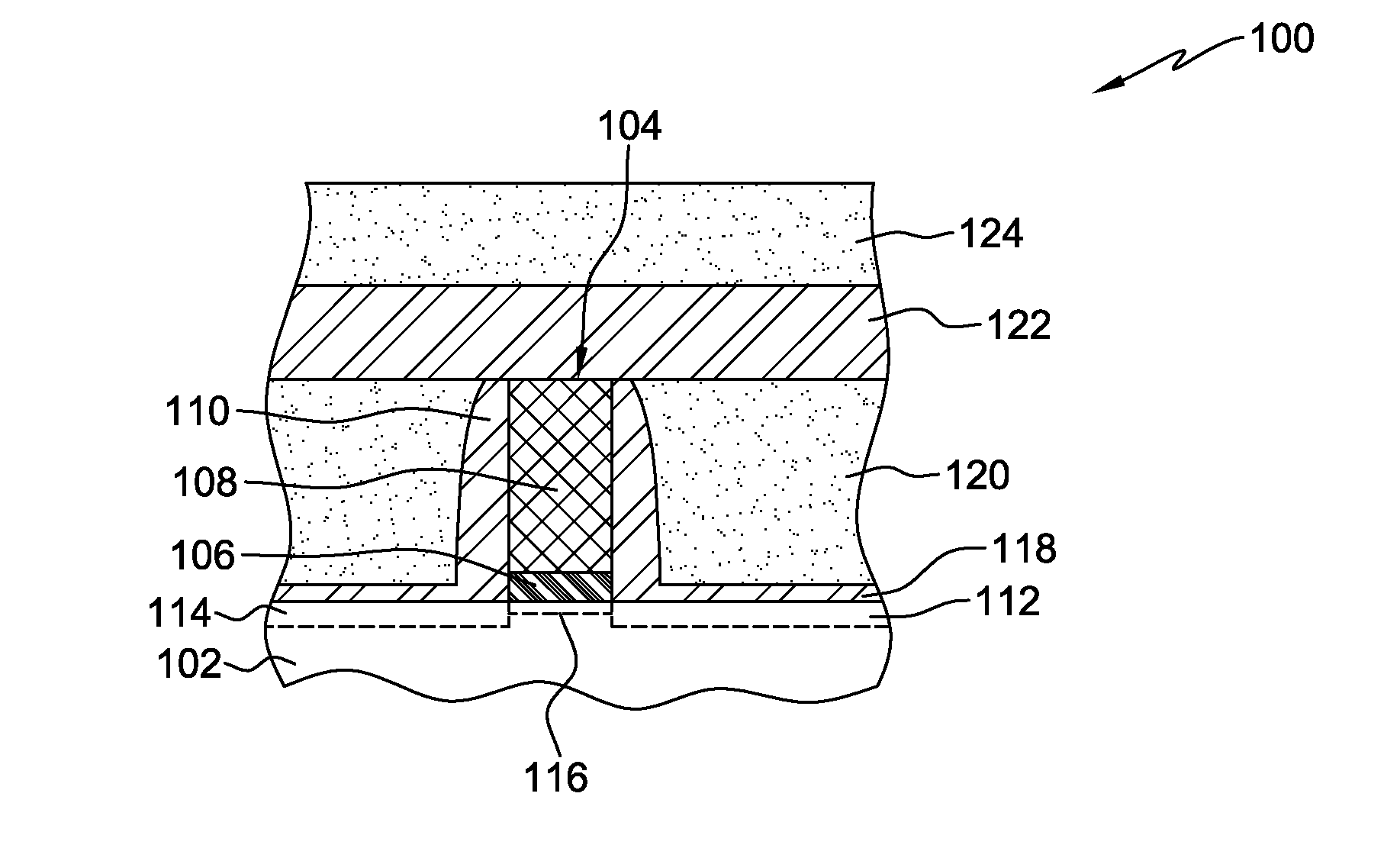

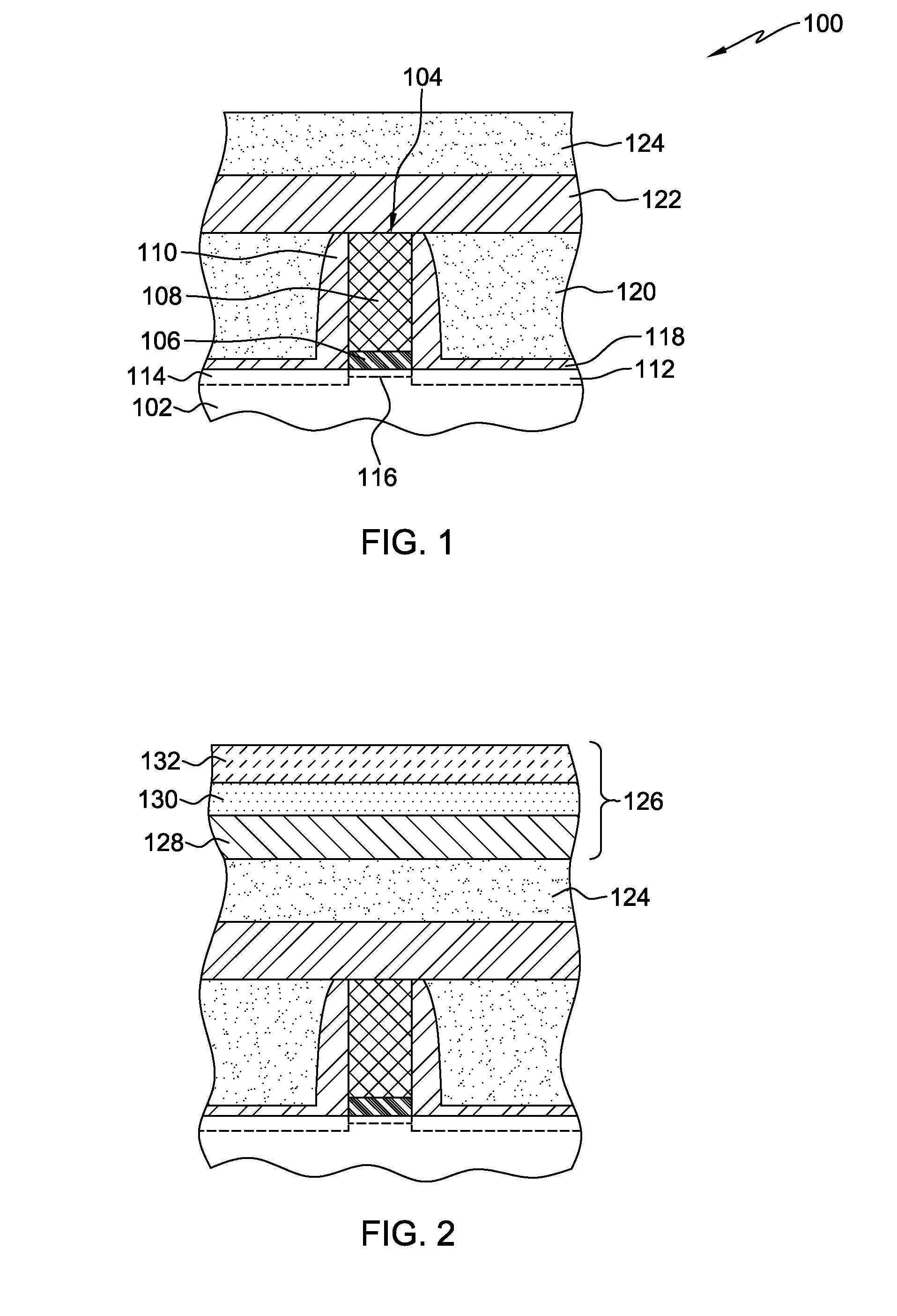

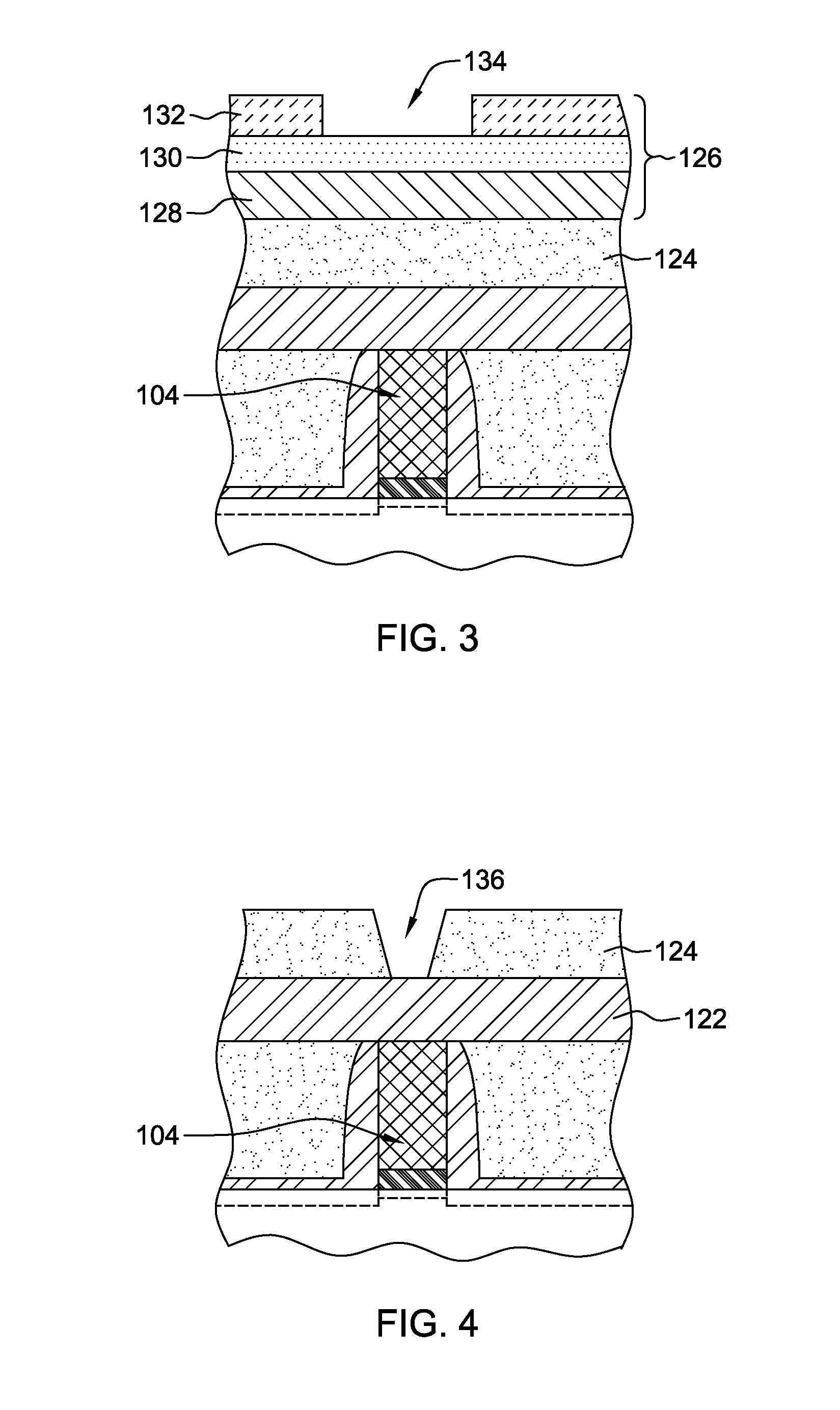

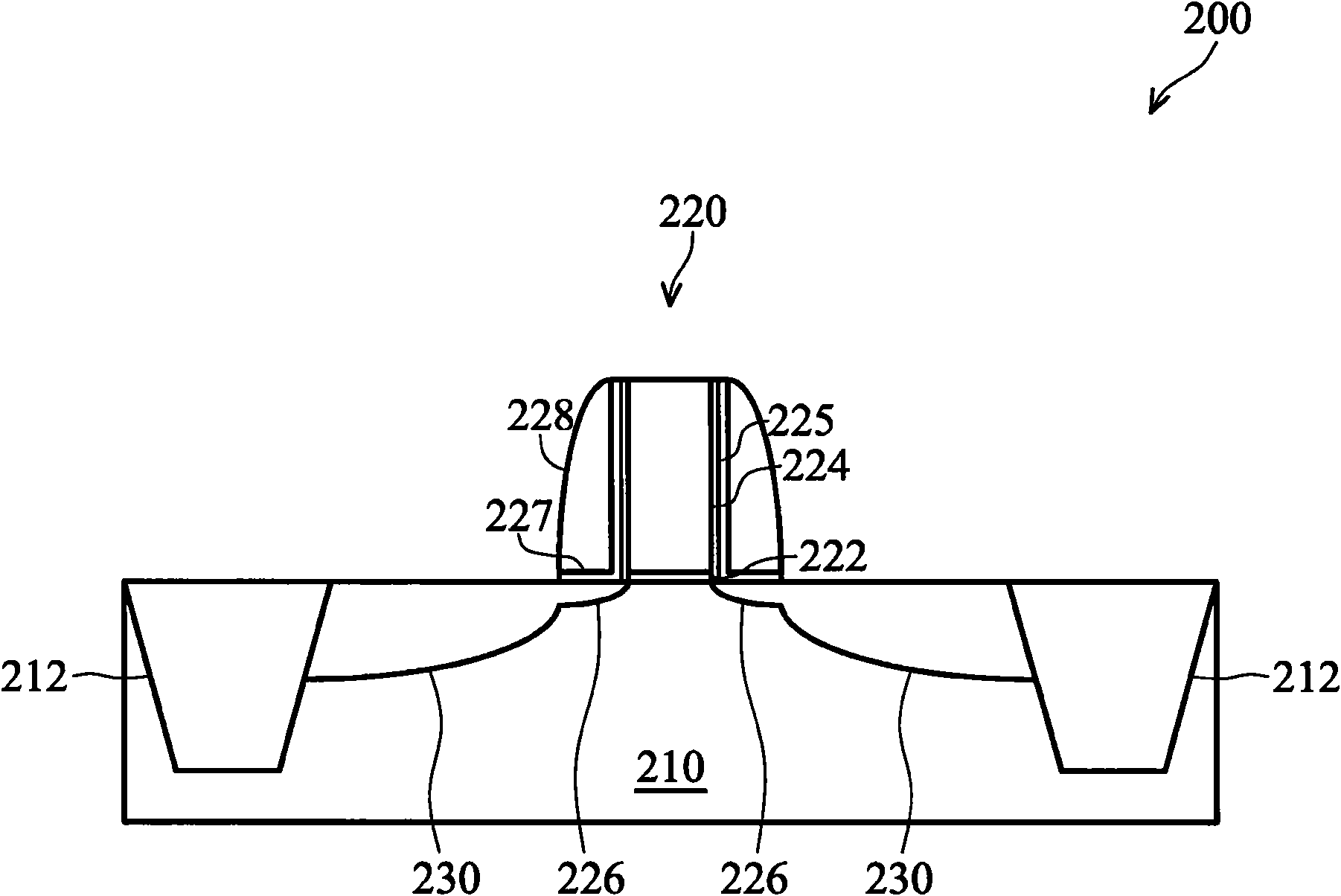

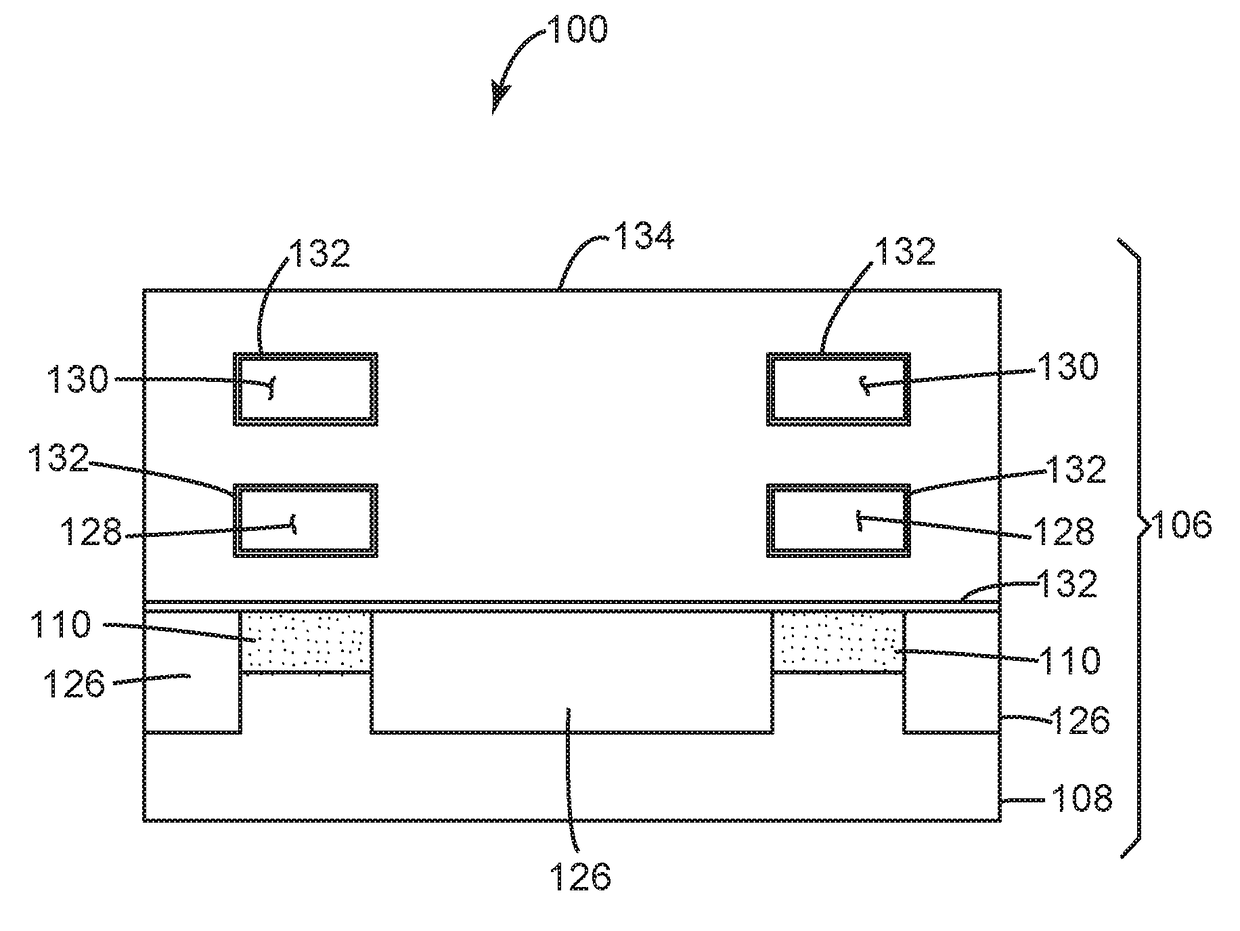

Silicide protection during contact metallization and resulting semiconductor structures

ActiveUS9111907B2Avoid damageOvercomes shortcomingSemiconductor/solid-state device detailsSolid-state devicesSalicideSemiconductor structure

Owner:GLOBALFOUNDRIES U S INC

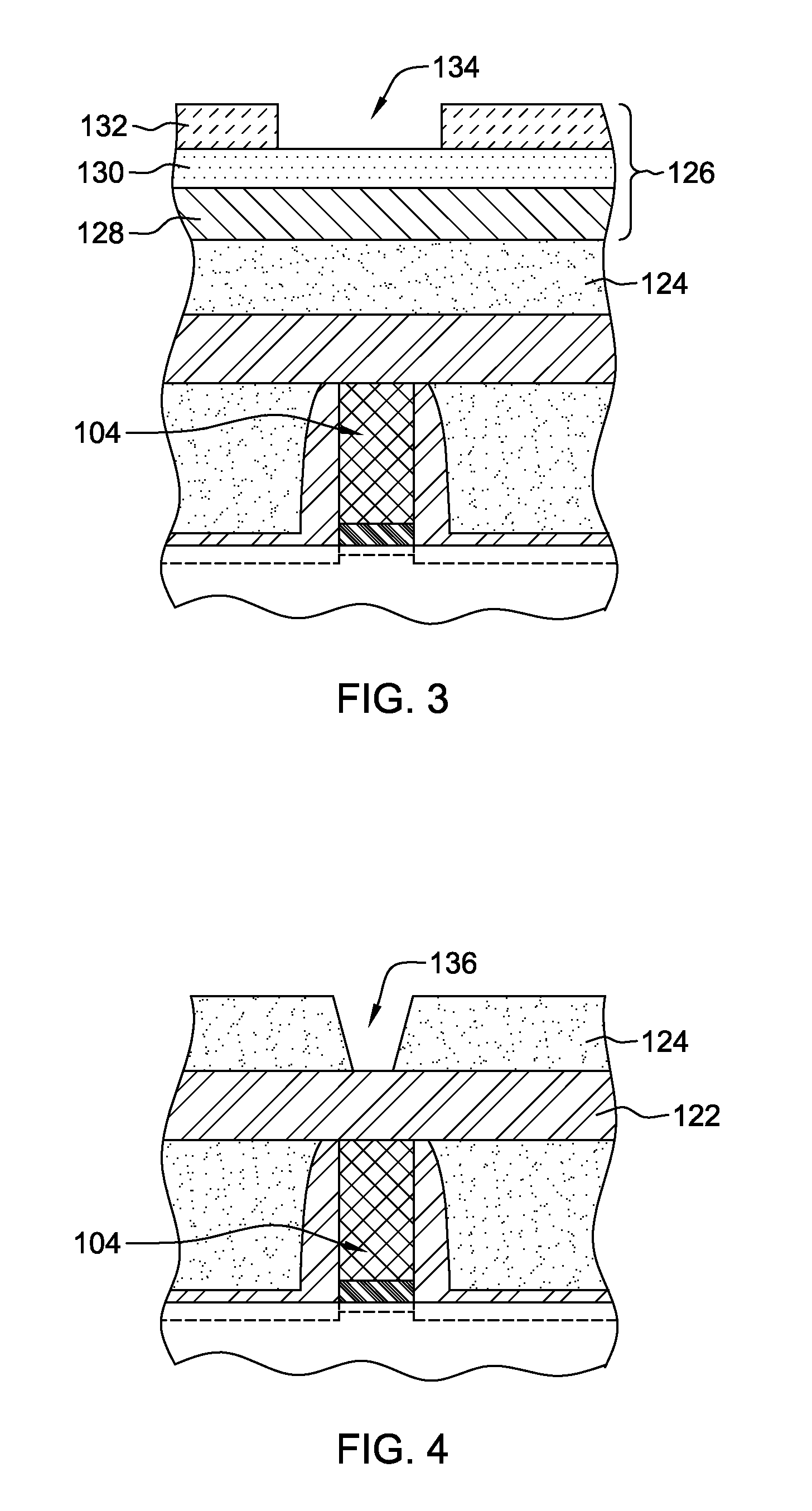

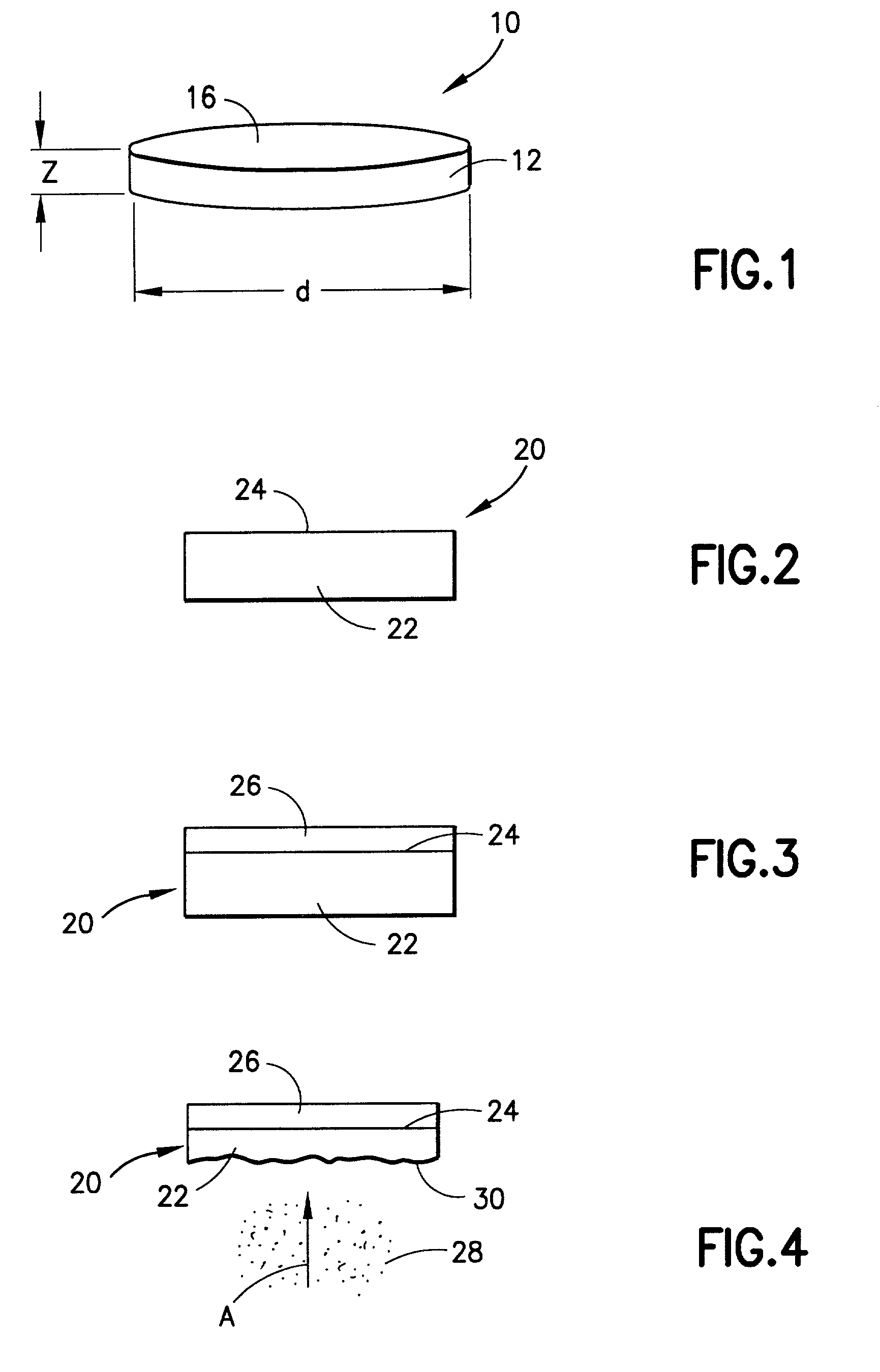

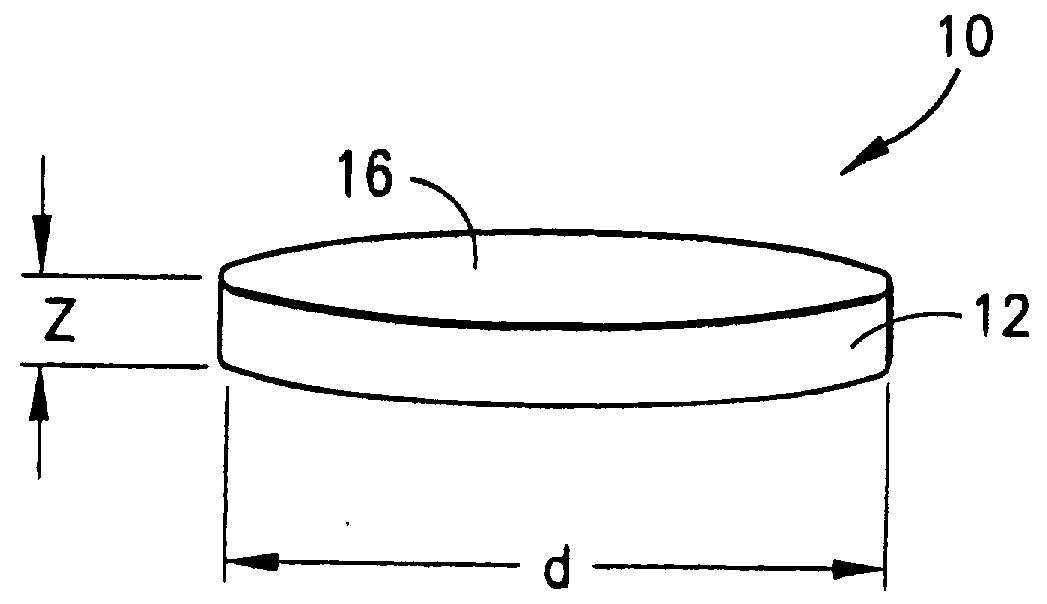

Bulk single crystal gallium nitride and method of making same

InactiveUS20010008656A1Enhance crystallinity and other characteristicAvoid etchingEnvelopes/bags making machineryLayered productsElectronic structureSingle crystal

A single crystal M*N article, which may be made by a process including the steps of: providing a substrate of material having a crystalline surface which is epitaxially compatible with M*N; depositing a layer of single crystal M*N over the surface of the substrate; and removing the substrate from the layer of single crystal M*N, e.g., with an etching agent which is applied to the substrate to remove same, to yield the layer of single crystal M*N as said single crystal M*N article. The bulk single crystal M*N article is suitable for use as a substrate for the fabrication of microelectronic structures thereon, to produce microelectronic devices comprising bulk single crystal M*N substrates, or precursor structures thereof.

Owner:ADVANCED TECH MATERIALS INC

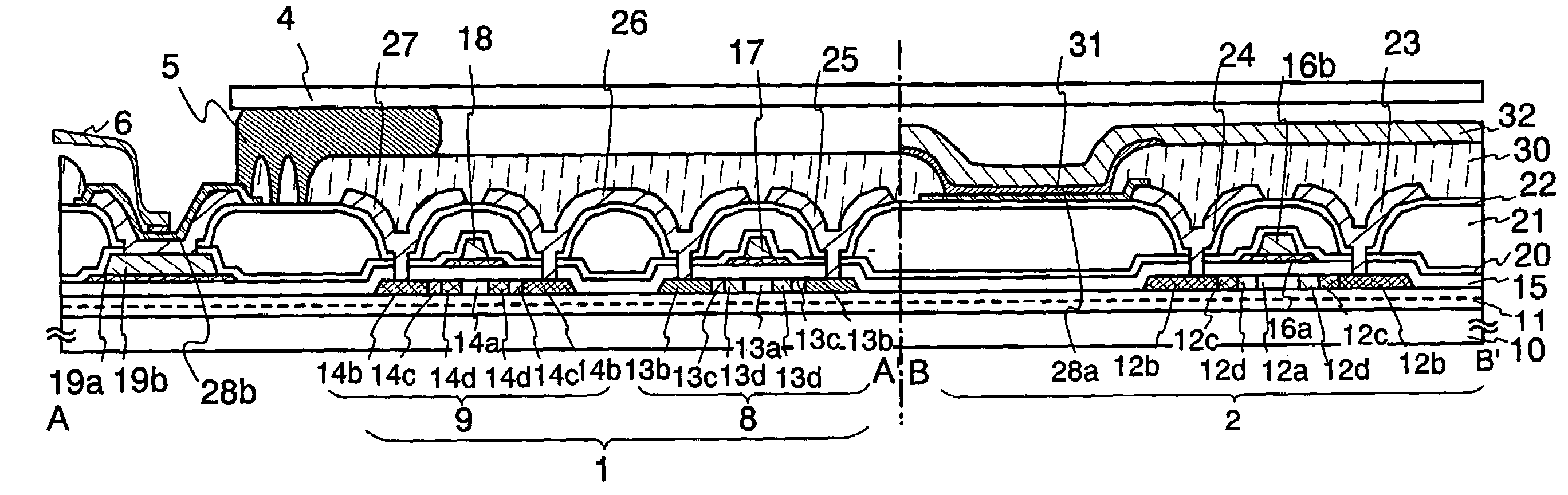

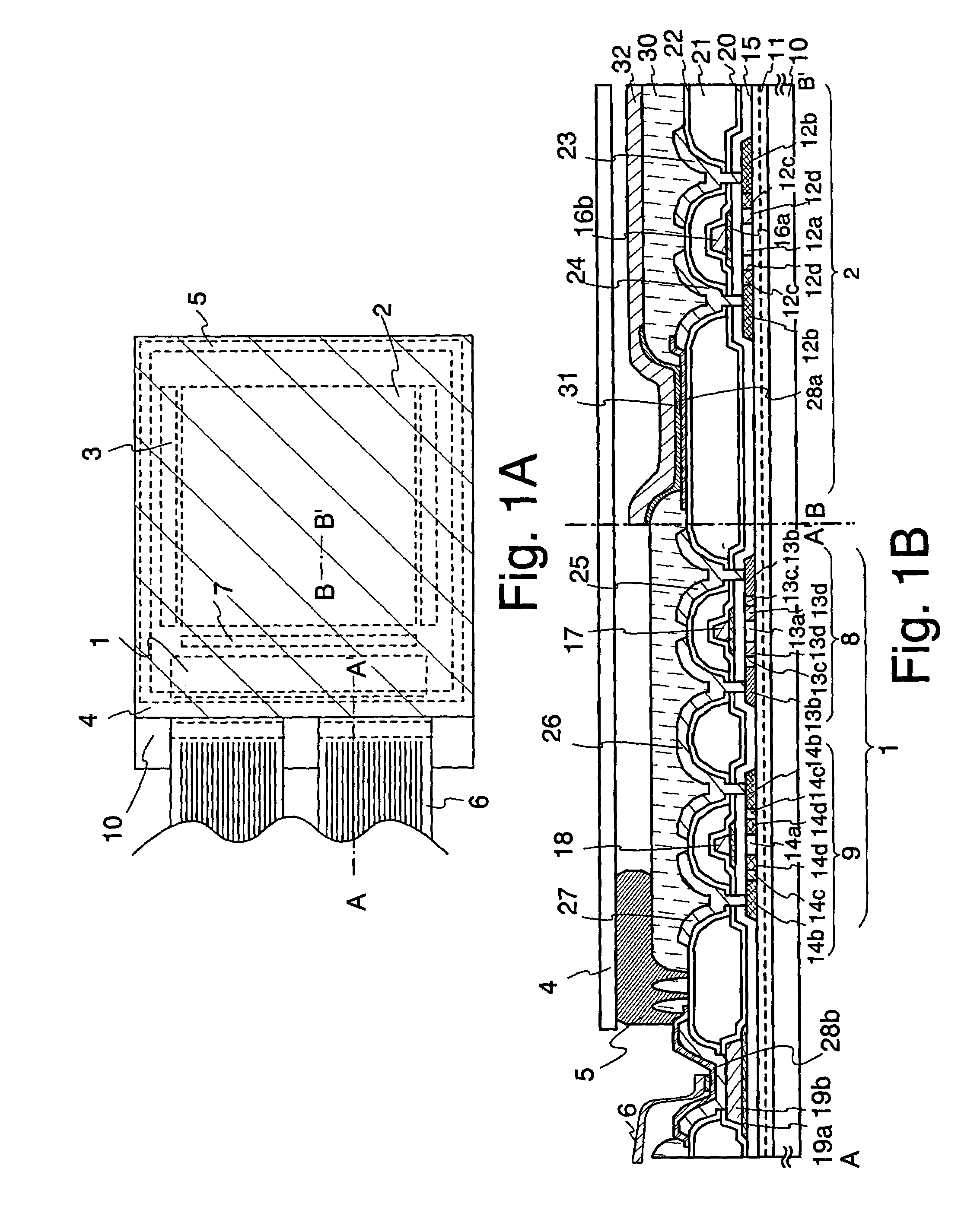

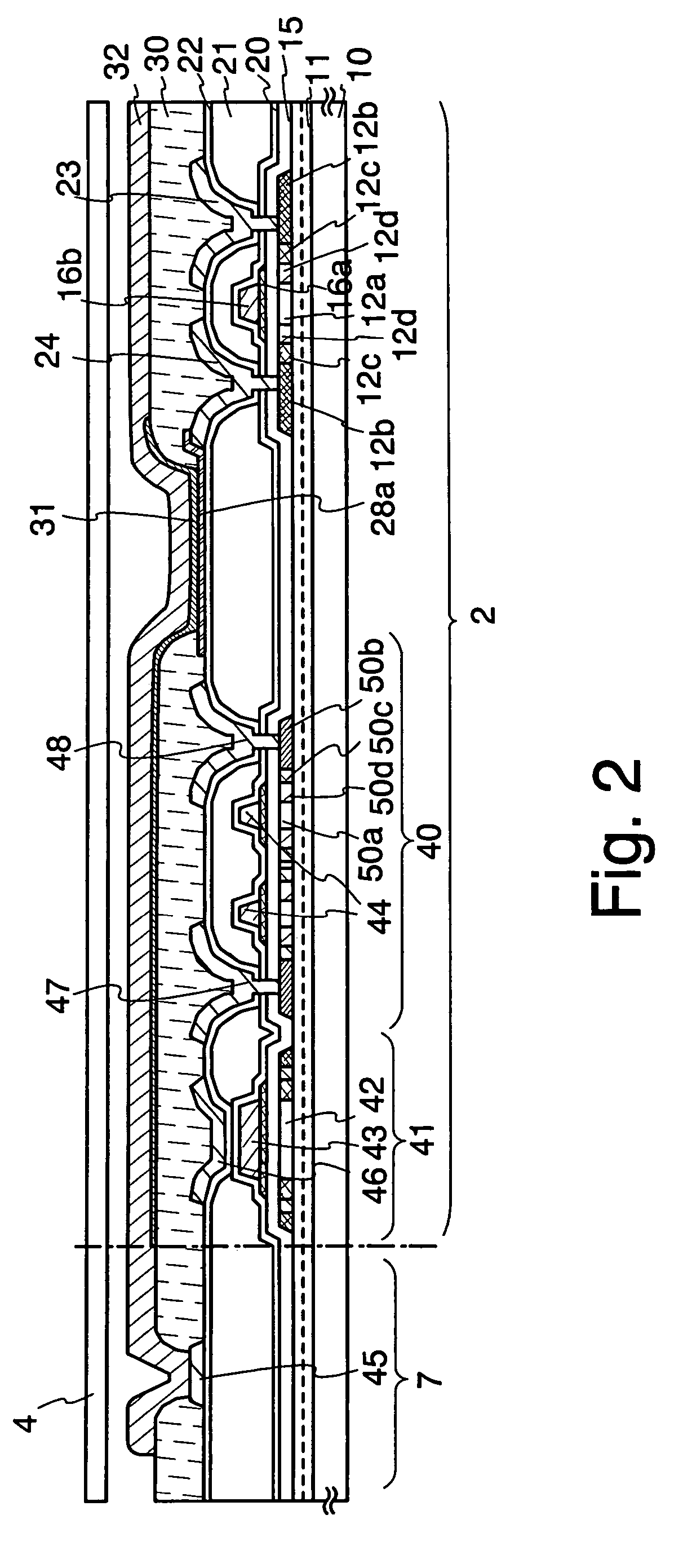

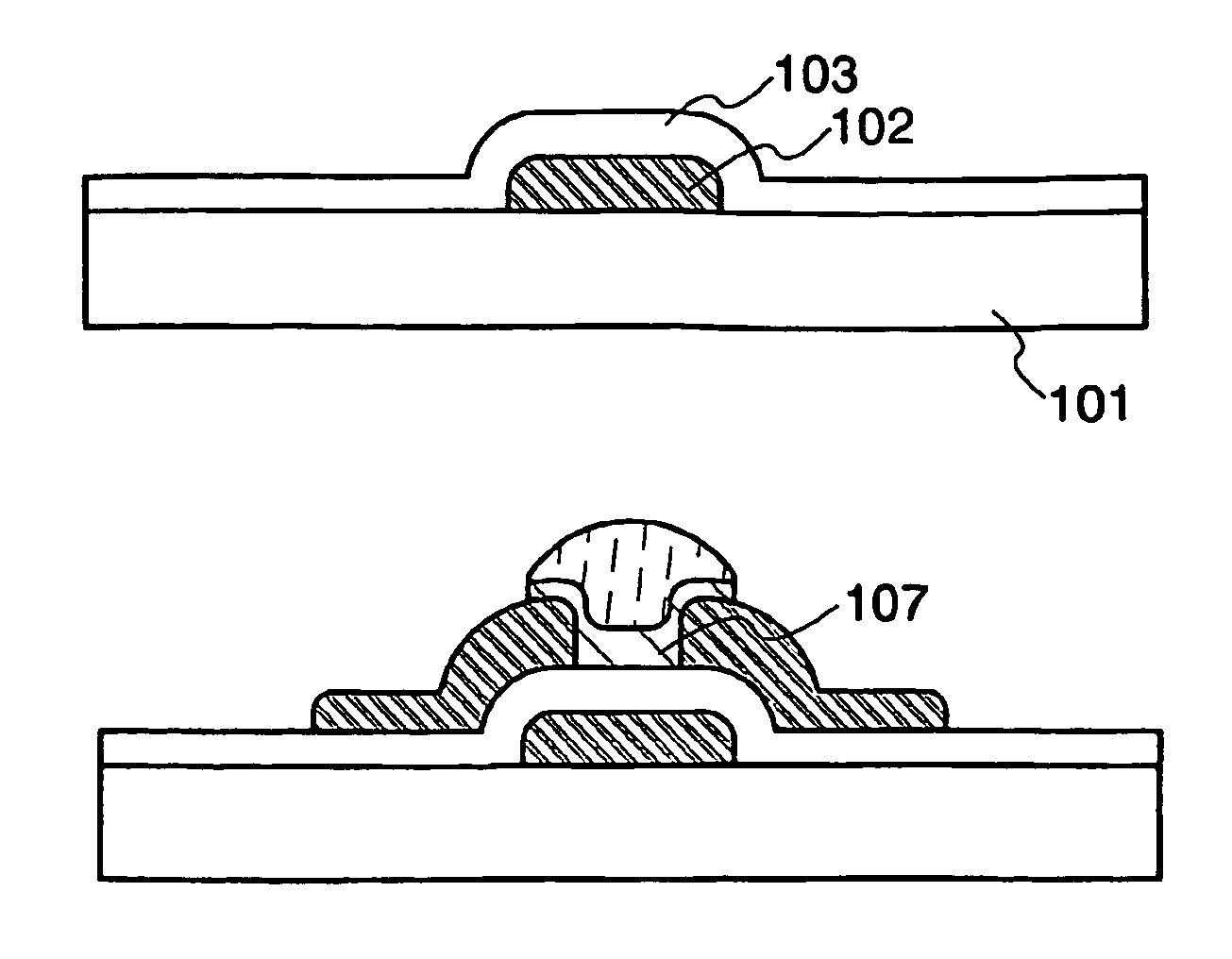

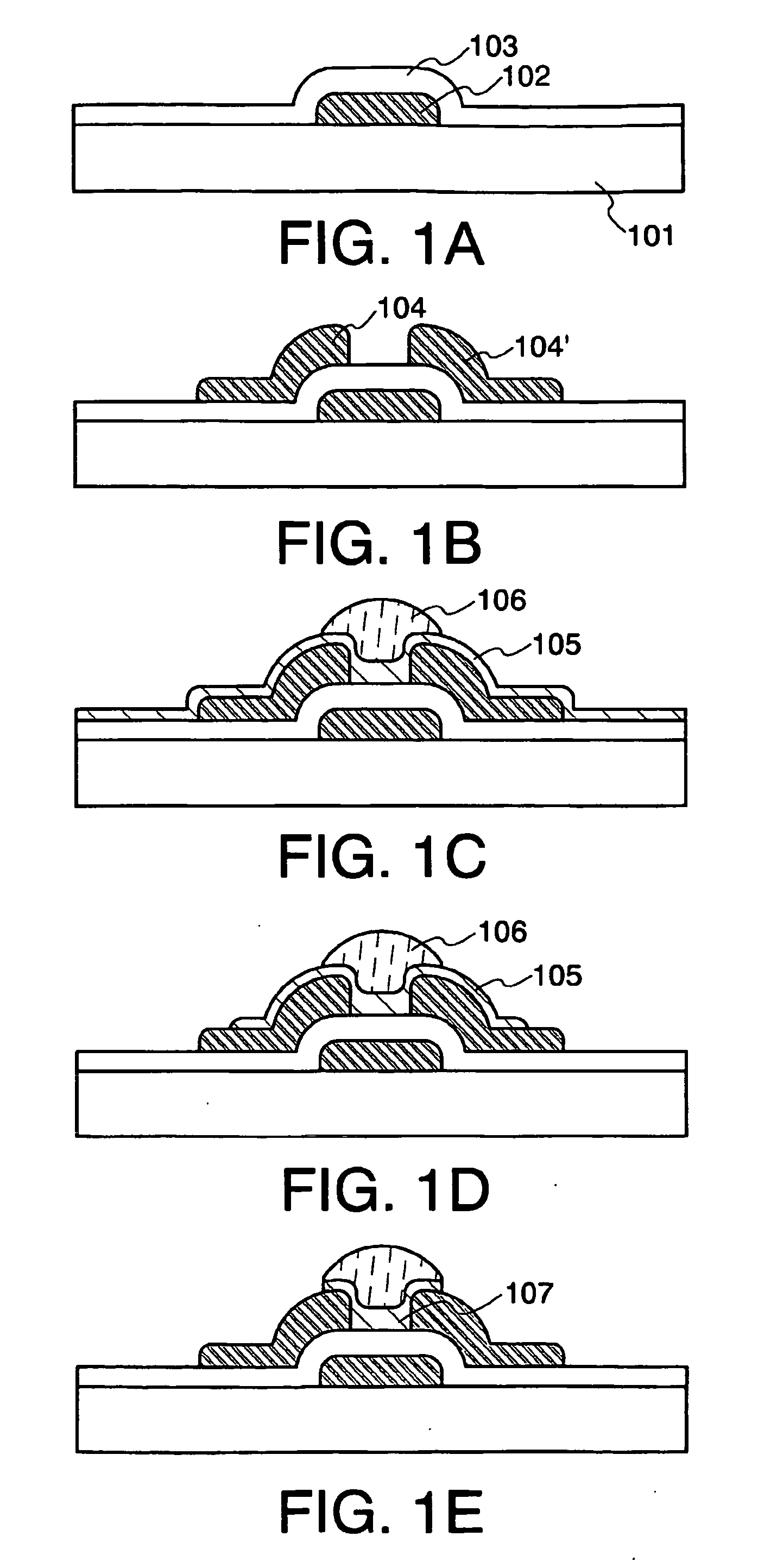

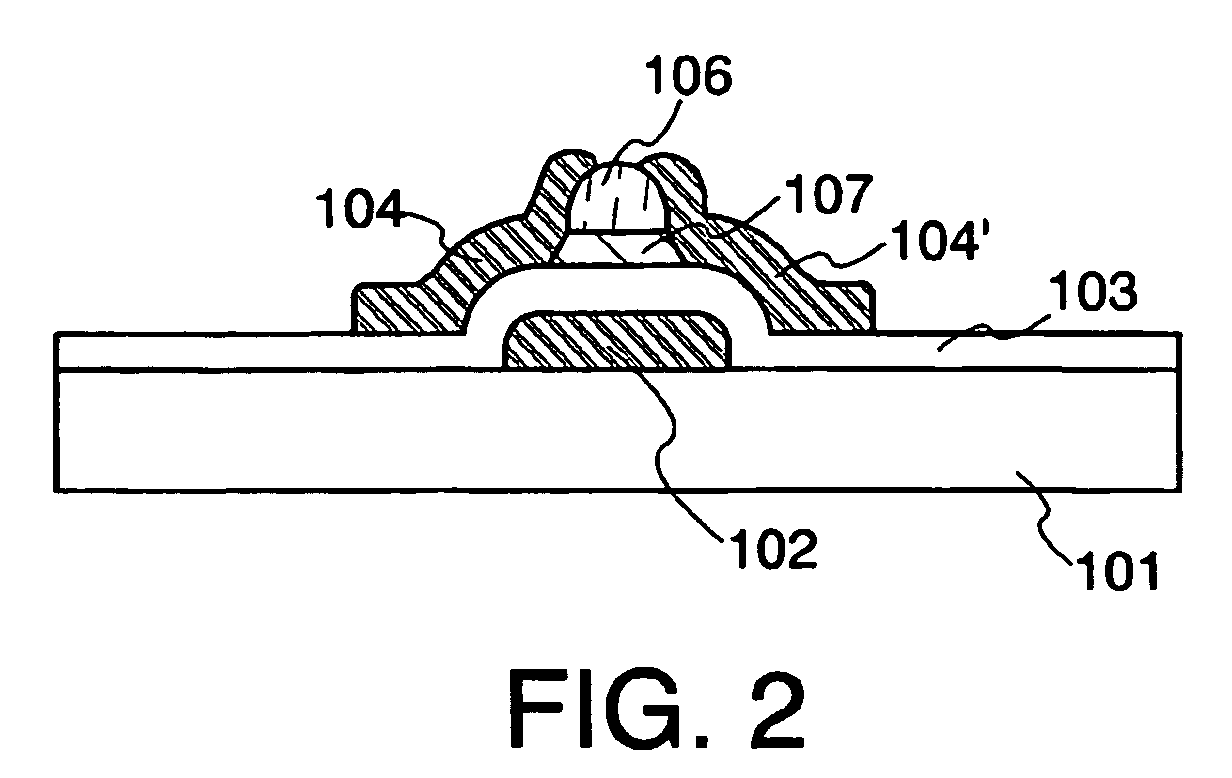

Light emitting device and method for manufacturing the same

ActiveUS6992332B2High reliabilityImprove reliabilityStatic indicating devicesElectroluminescent light sourcesSilicon nitrideOrganic compound

A light emitting element containing an organic compound has a disadvantage in that it tends to be deteriorated by various factors, so that the greatest problem thereof is to increase its reliability (make longer its life span). The present invention provides a method for manufacturing an active matrix type light emitting device and the configuration of such an active matrix type light emitting device having high reliability. In the method, a contact hole extending to a source region or a drain region is formed, and then an interlayer insulation film made of a photosensitive organic insulating material is formed on an interlayer insulation film. The interlayer insulation film has a curved surface on its upper end portion. Subsequently, an interlayer insulation film provided as a silicon nitride film having a film thickness of 20 to 50 nm is formed by a sputtering method using RF power supply.

Owner:SEMICON ENERGY LAB CO LTD

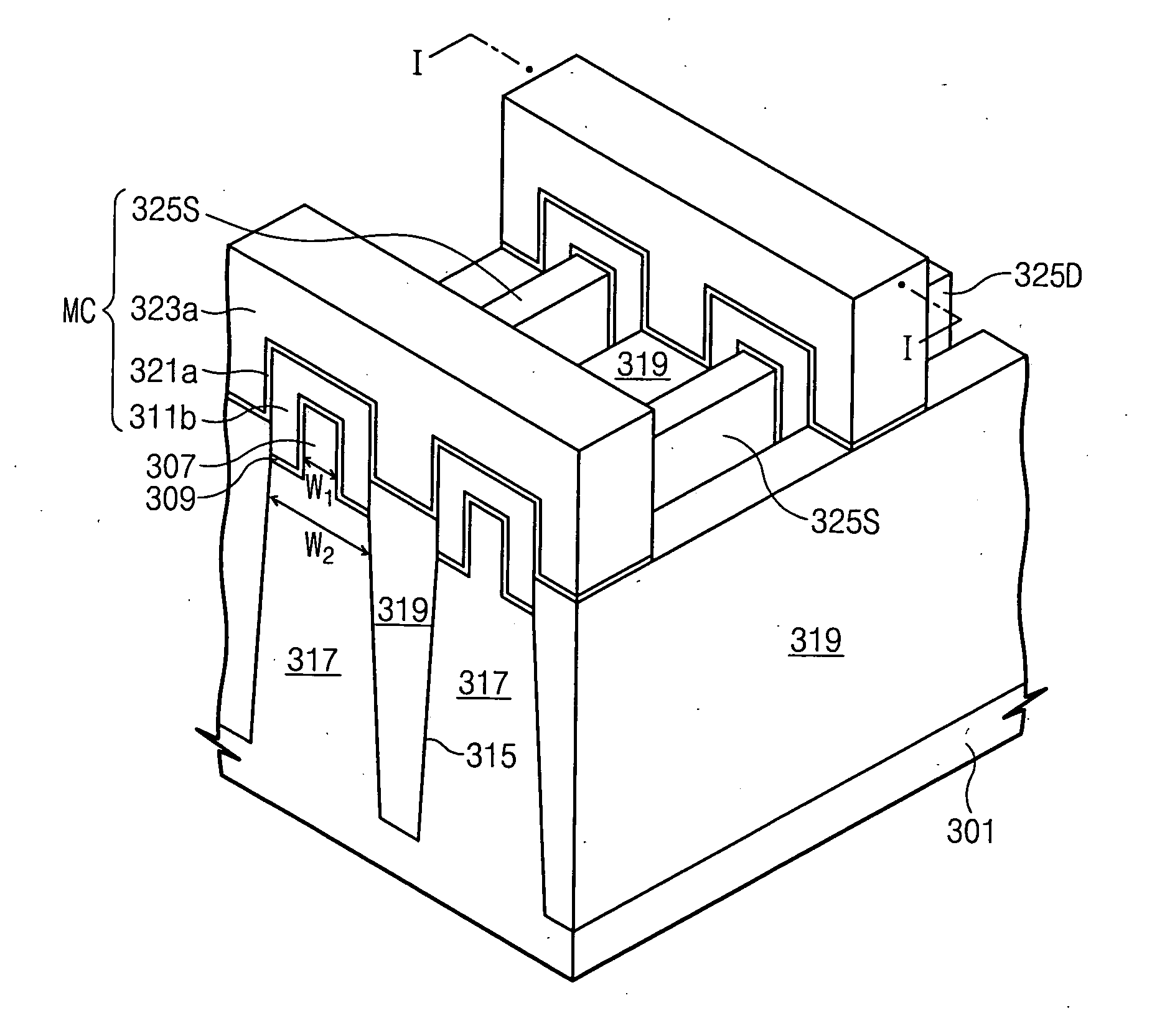

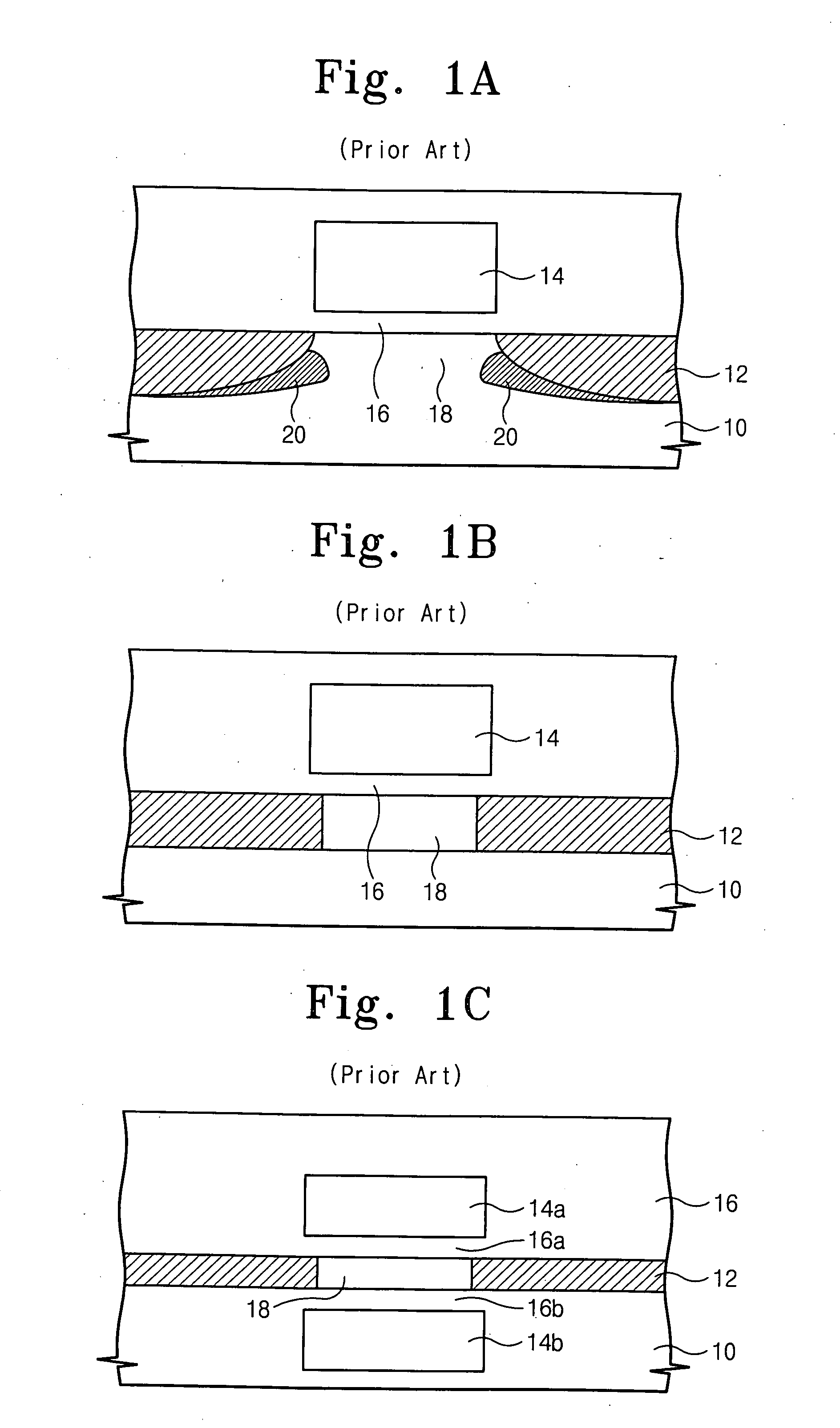

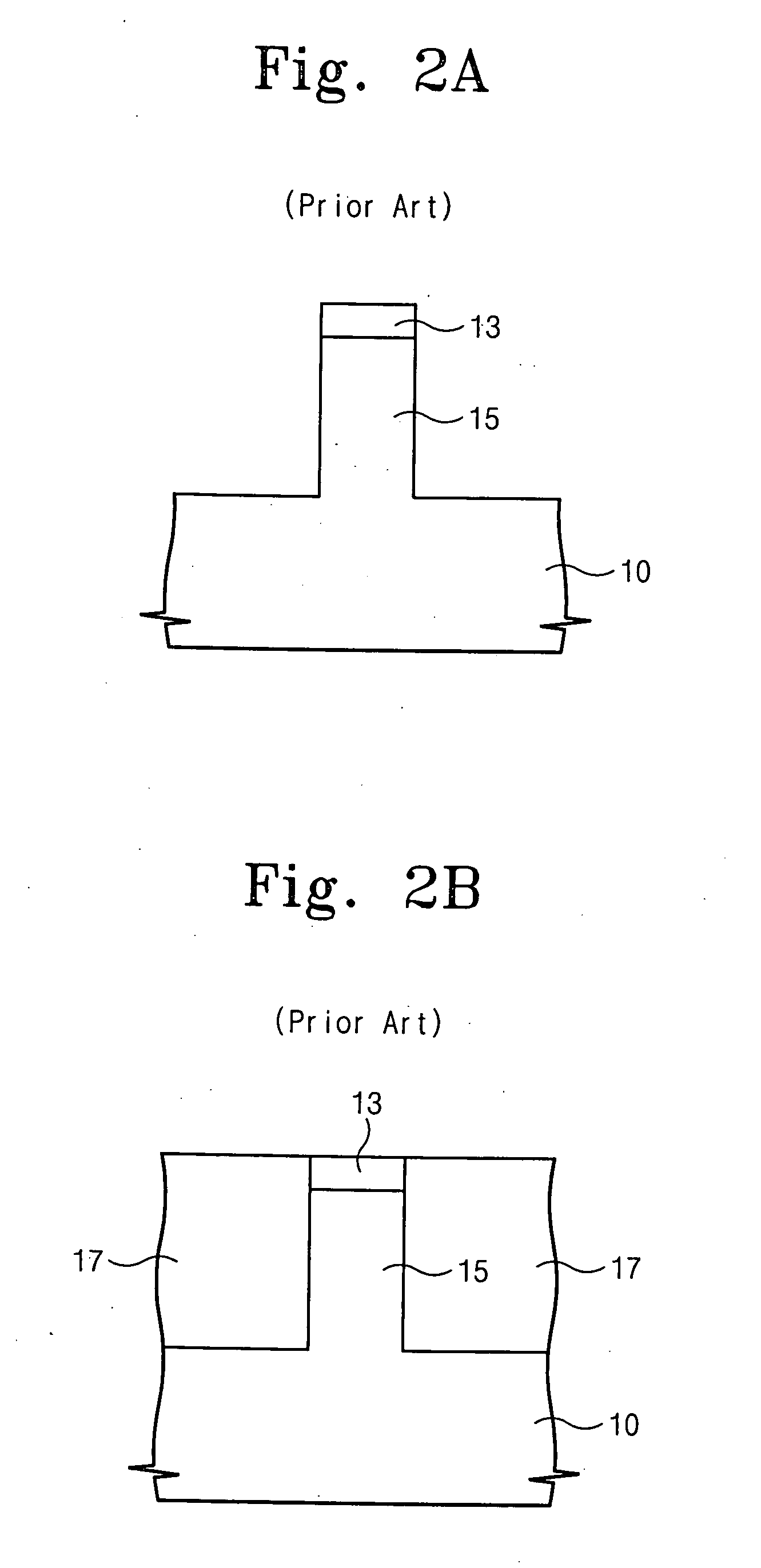

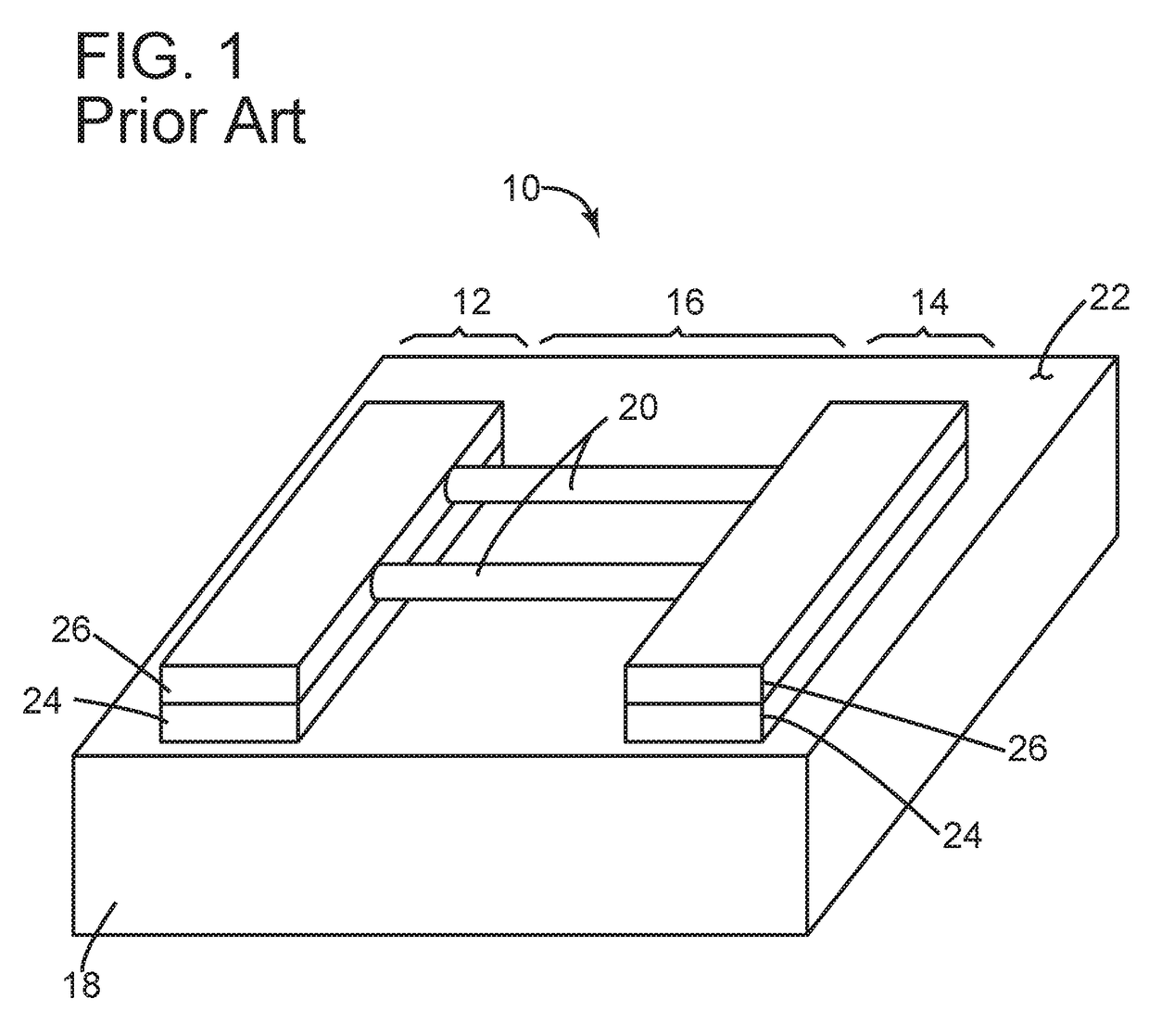

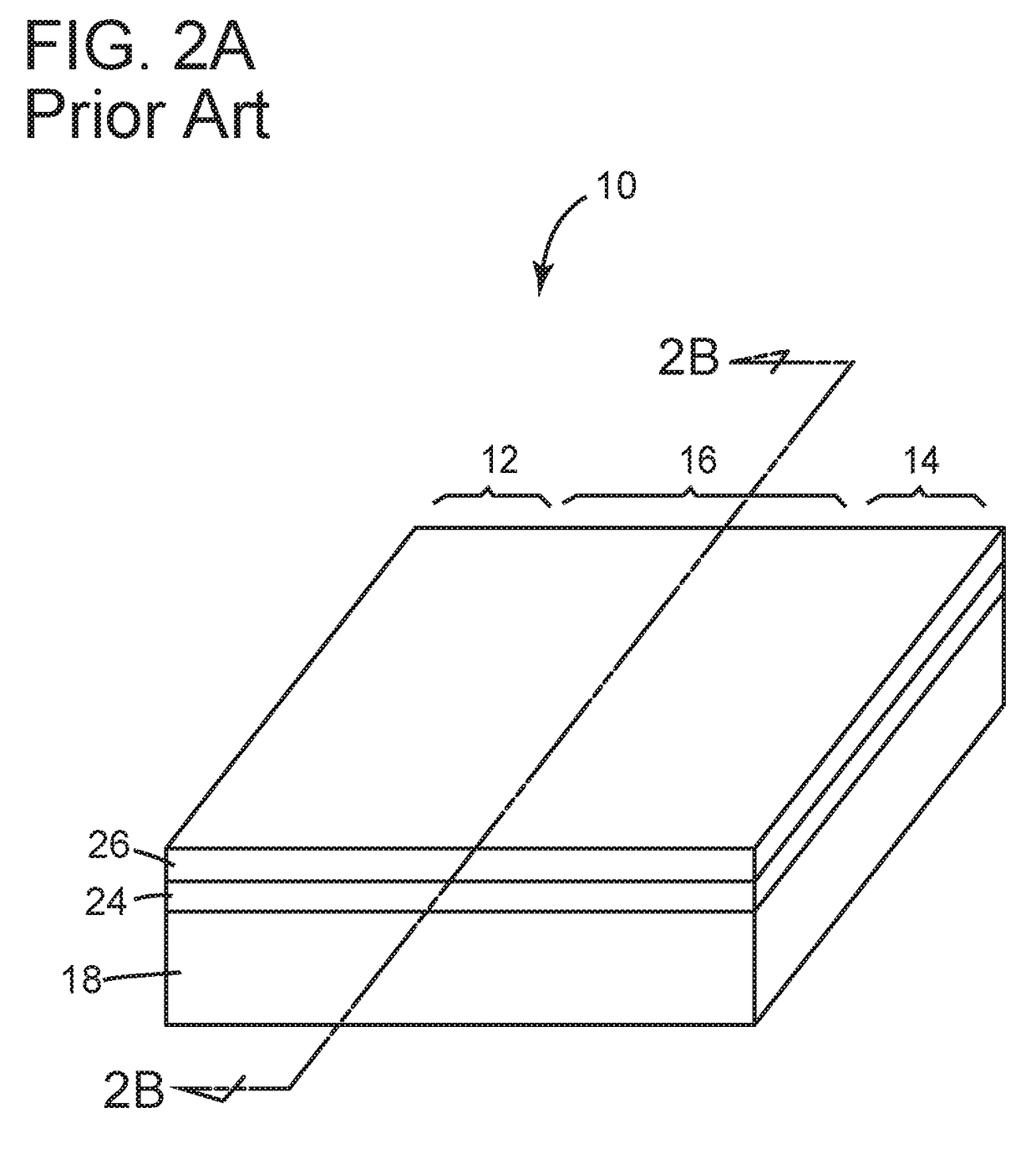

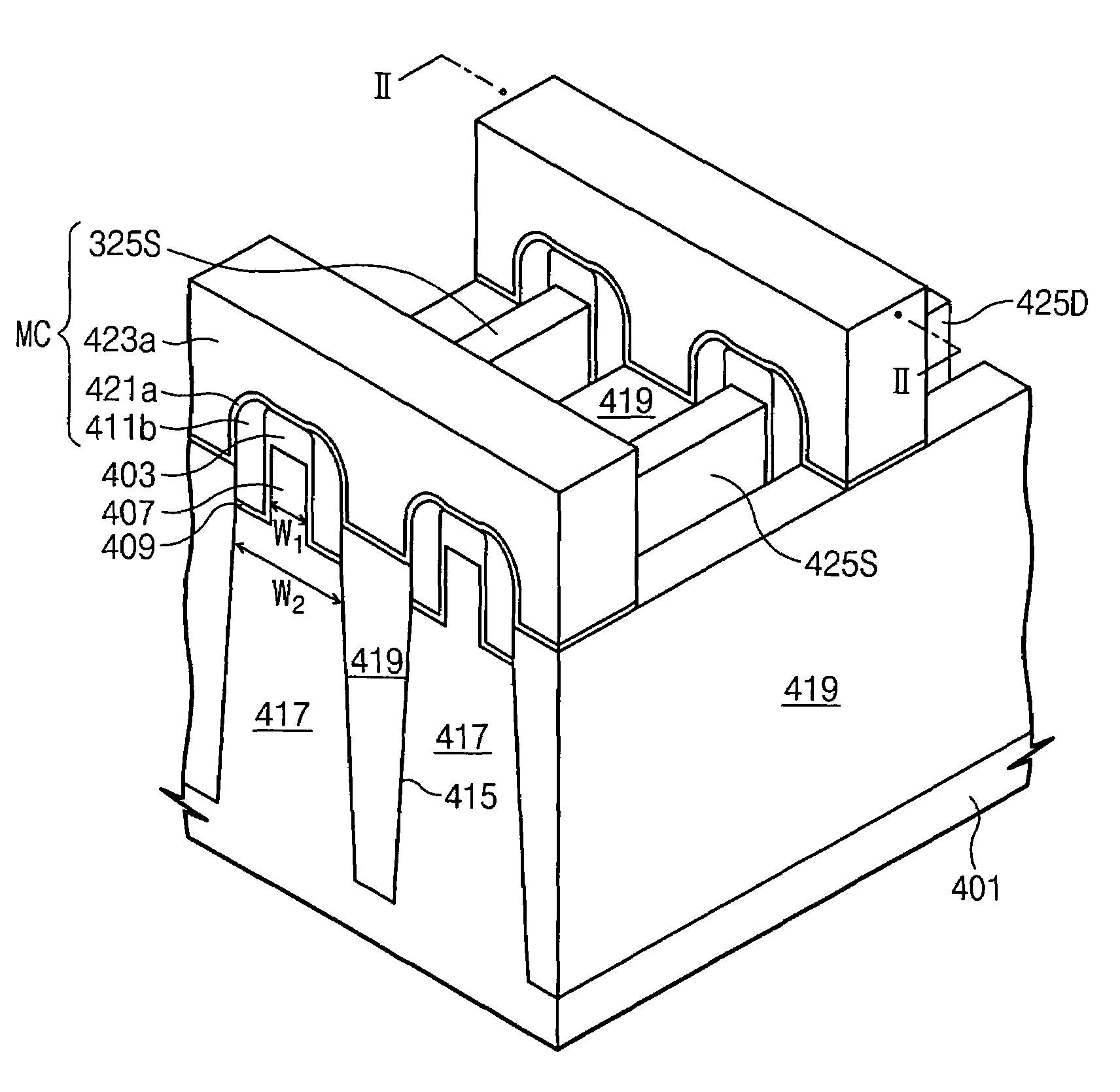

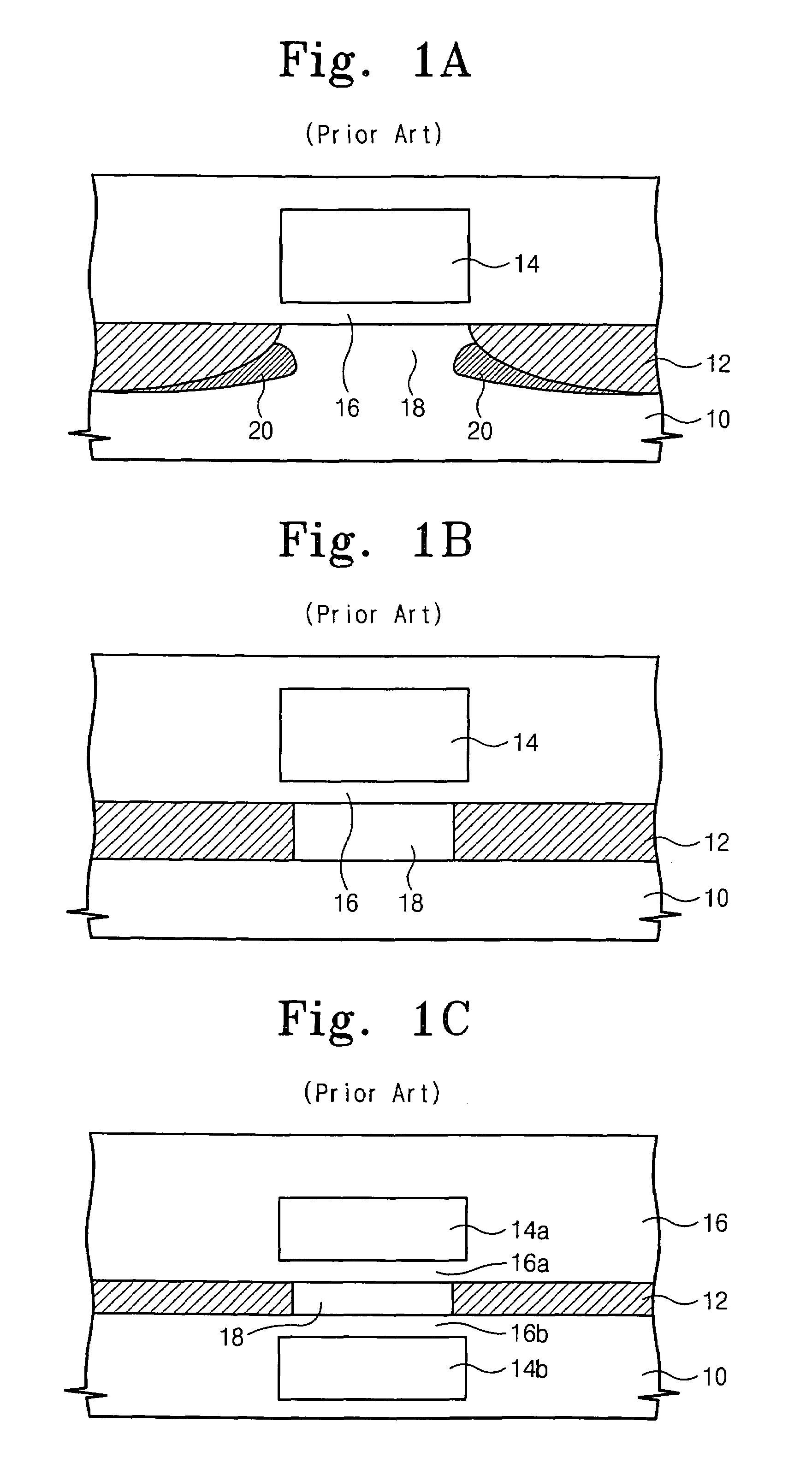

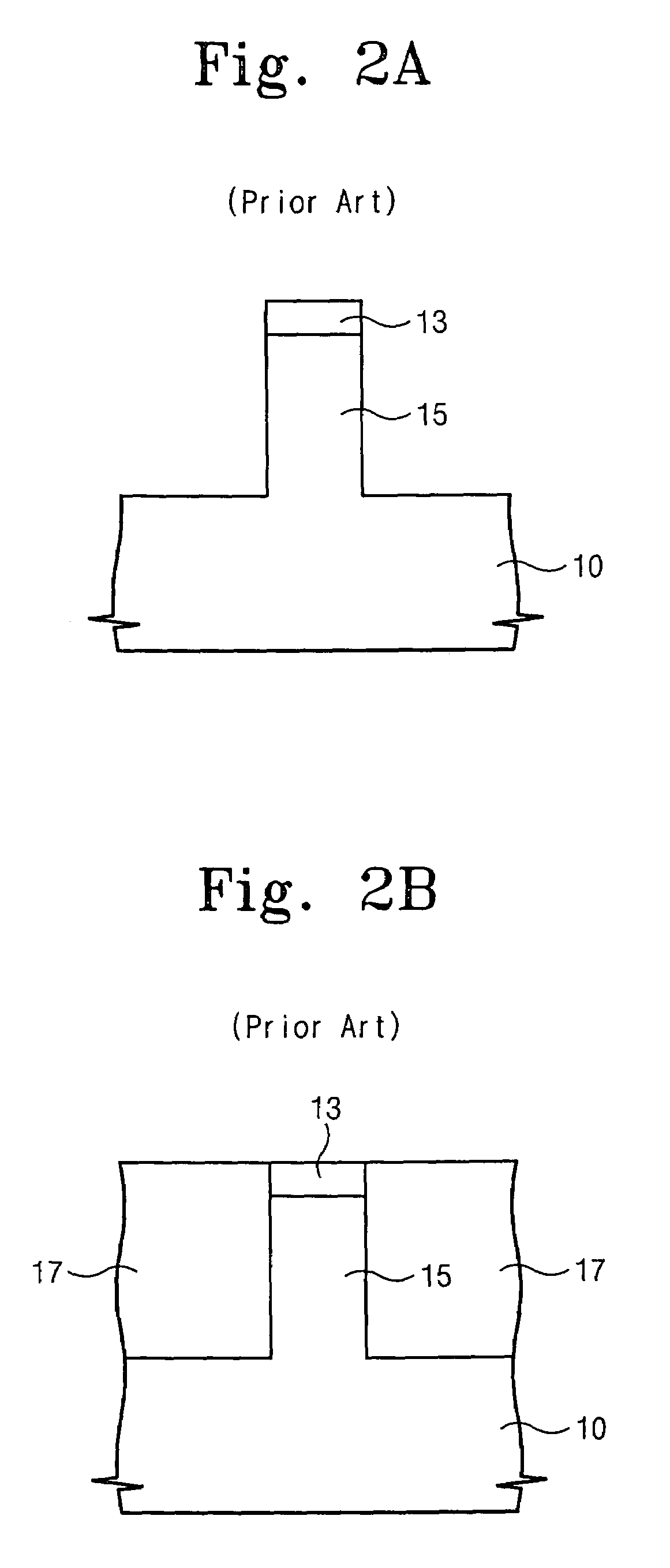

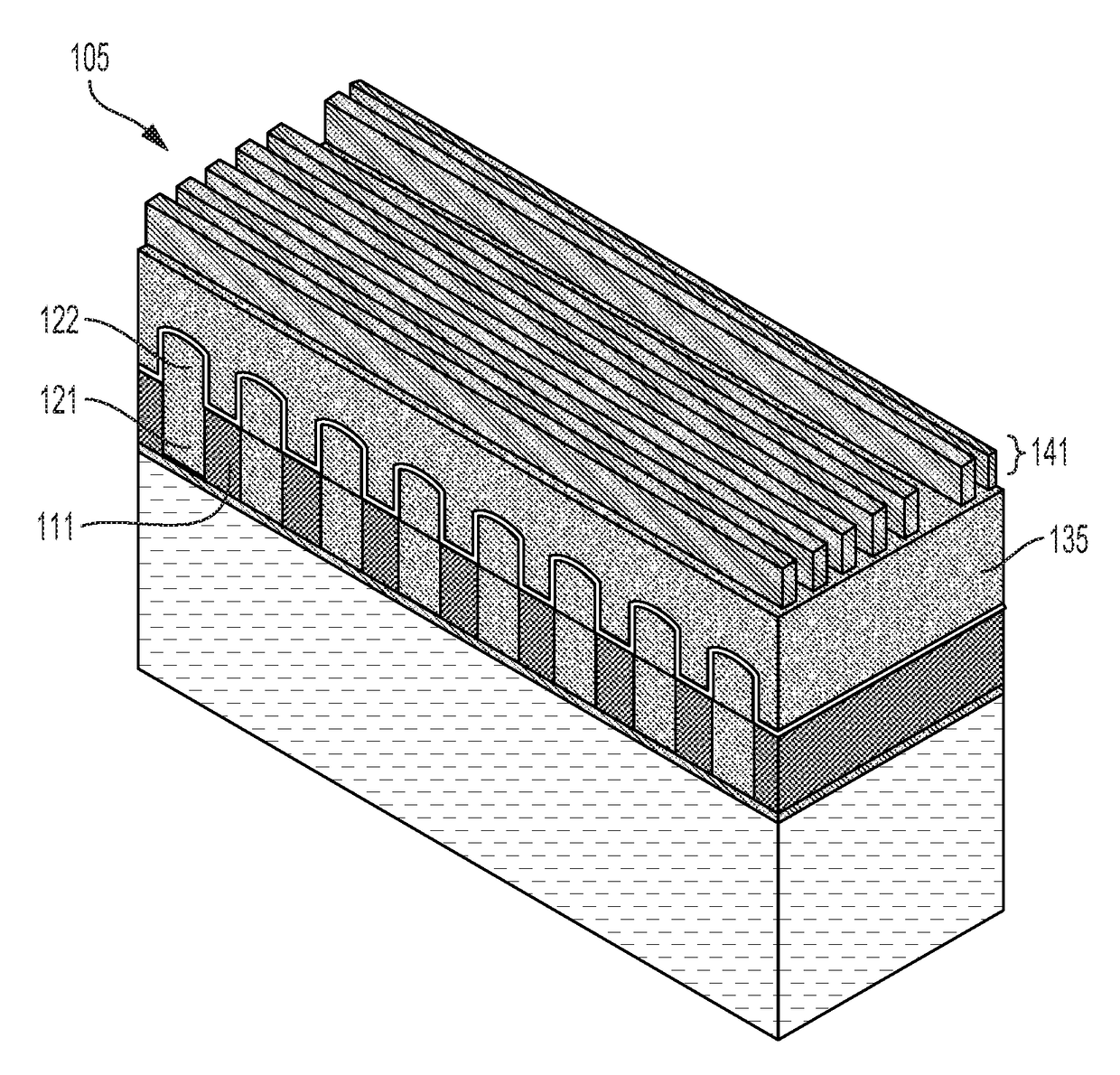

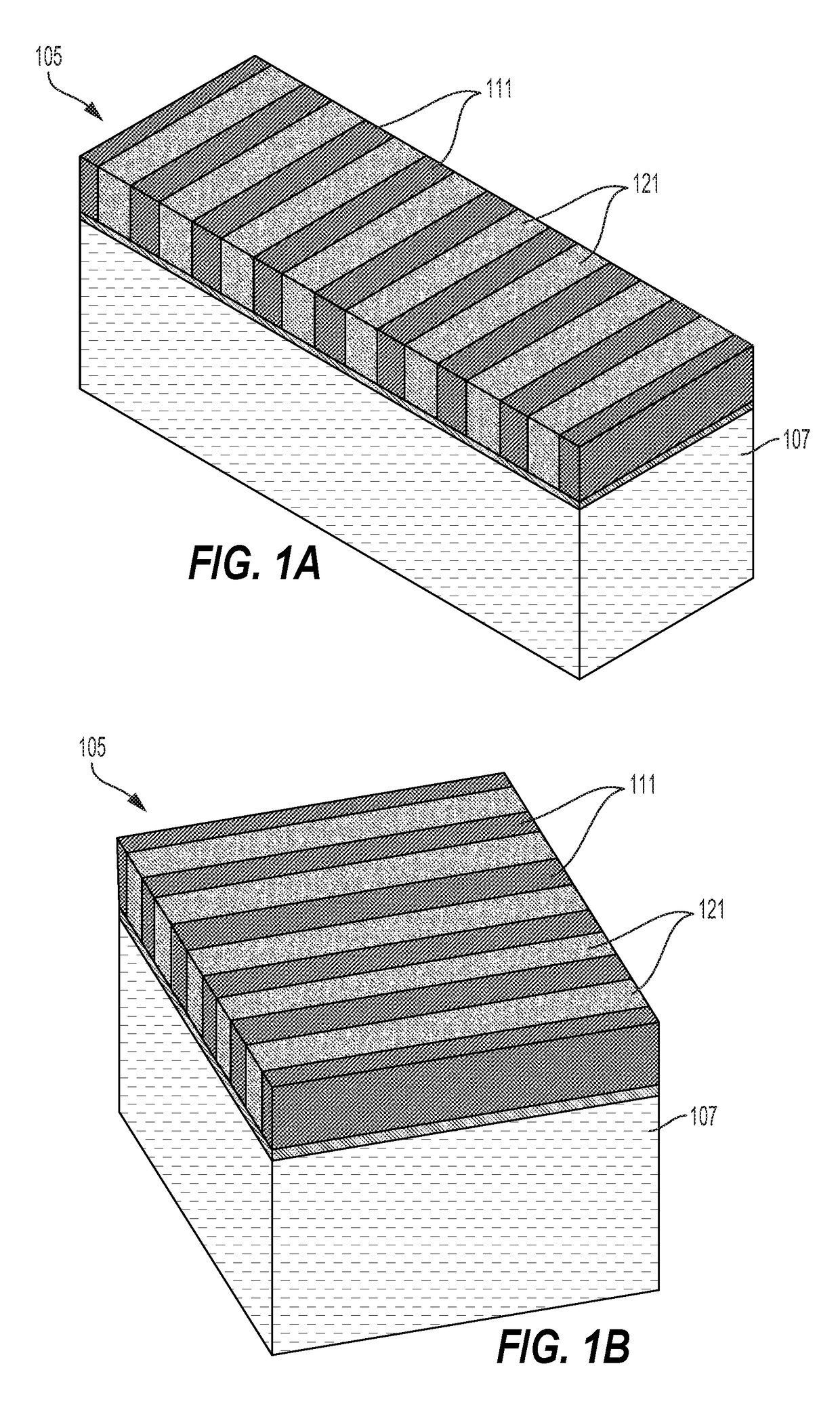

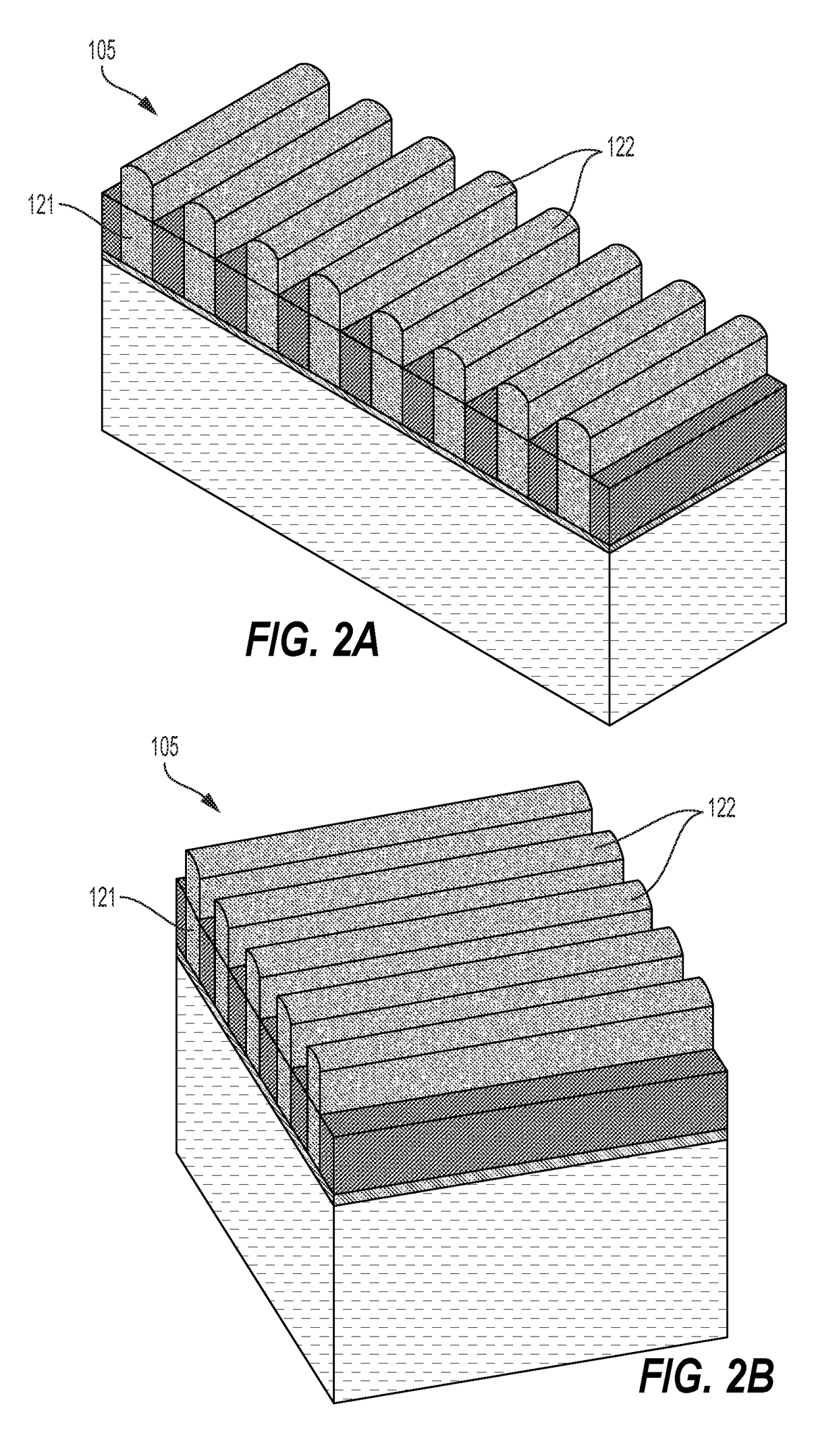

Methods of forming non-volatile semiconductor memory devices using prominences and trenches, and devices so formed

InactiveUS20060141706A1Improve equipment reliabilityDevice property can be enhancedSolid-state devicesRead-only memoriesEngineeringSemiconductor

A semiconductor substrate is patterned to form a depression and prominence. A floating gate is formed so as to cover at least both sidewalls of the prominence of the depression and prominence, and is then etched to form a trench for a device isolation self-aligned with the floating gate. Related structures are also described.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of manufacturing MEMS sensor and MEMS sensor

InactiveUS20100096714A1Prevent adhesionPreventing undesired etching of a protective filmAcceleration measurement using interia forcesTransducer detailsMetallic materialsOptoelectronics

A method of manufacturing an MEMS sensor according to the present invention includes the steps of: forming a first sacrificial layer on one surface of a substrate; forming a lower electrode on the first sacrificial layer; forming a second sacrificial layer made of a metallic material on the first sacrificial layer to cover the lower electrode; forming an upper electrode made of a metallic material on the second sacrificial layer; forming a protective film made of a nonmetallic material on the substrate to collectively cover the first sacrificial layer, the second sacrificial layer and the upper electrode; and removing at least the second sacrificial layer by forming a through-hole in the protective film and supplying an etchant to the inner side of the protective film through the through-hole.

Owner:ROHM CO LTD

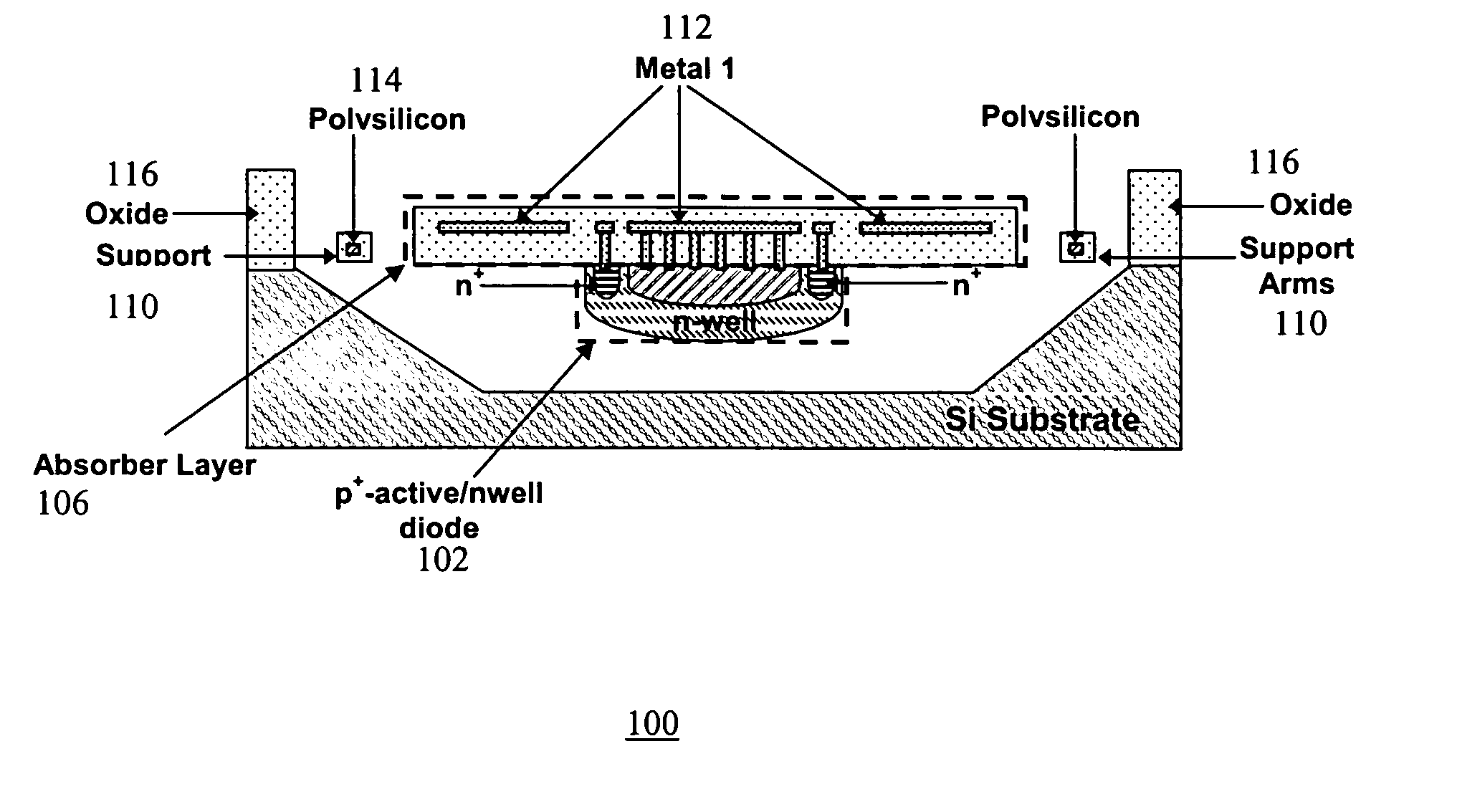

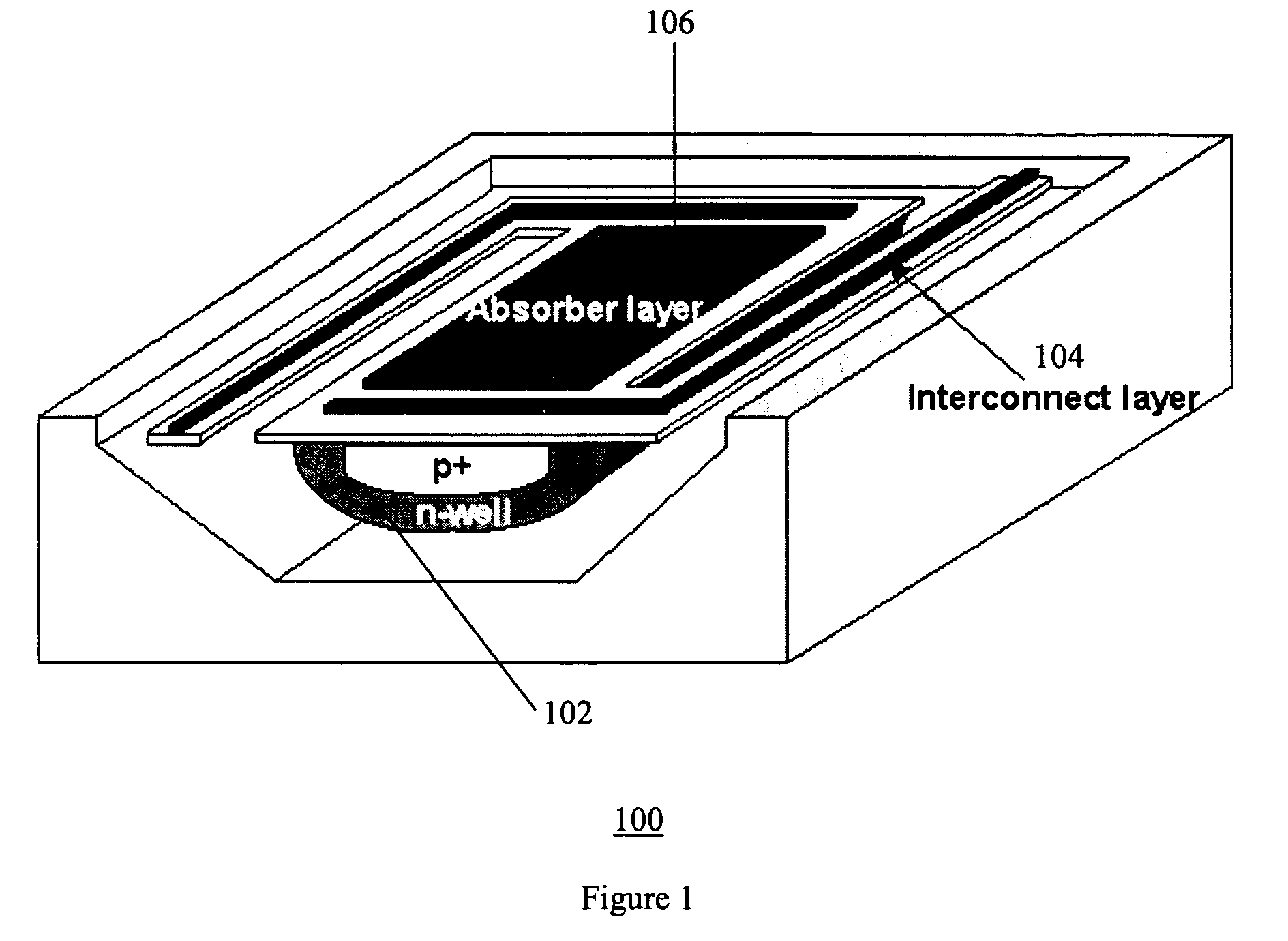

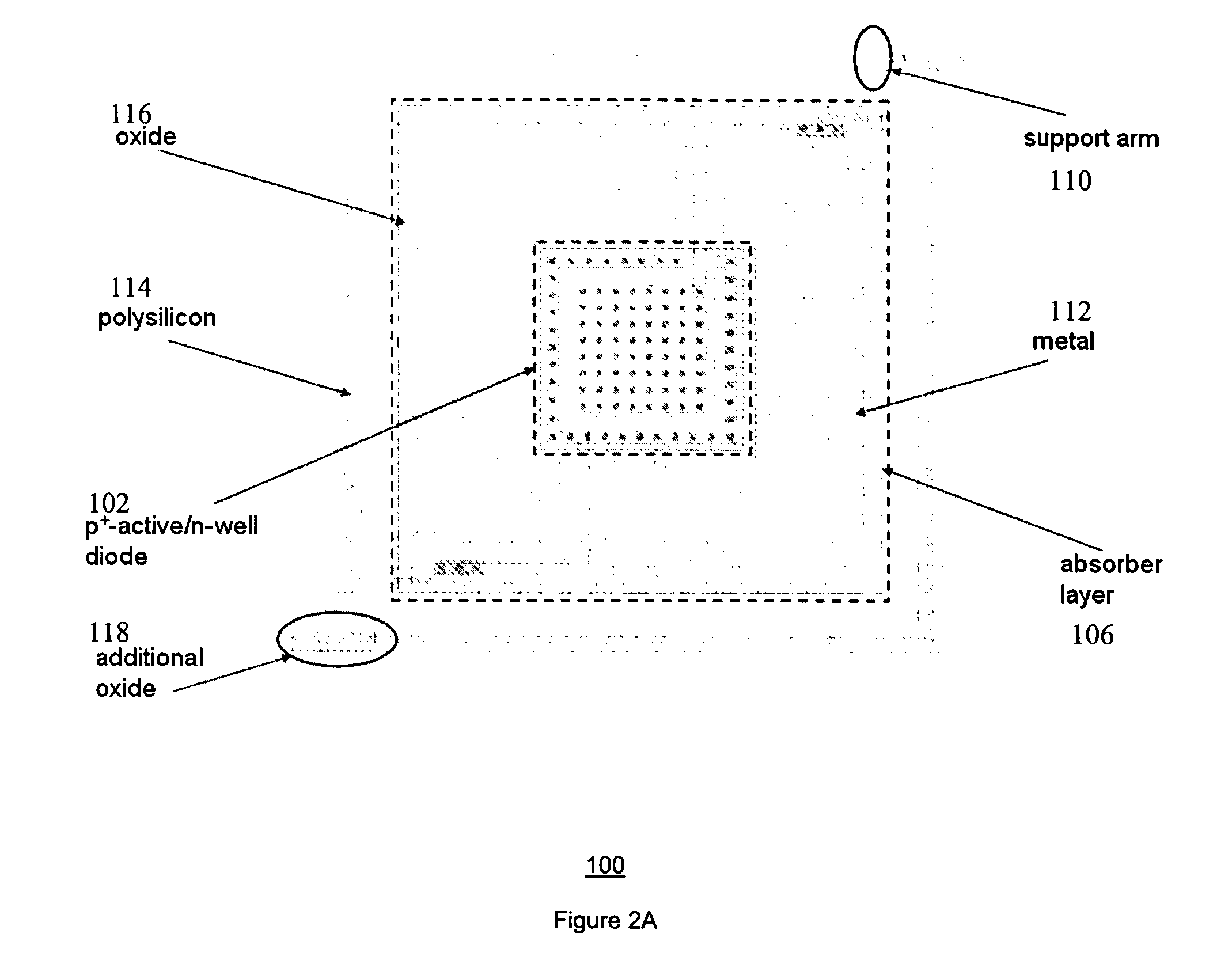

Ultra low-cost uncooled infrared detector arrays in CMOS

InactiveUS20050224714A1Low costImprove insulation performanceSolid-state devicesMaterial analysis by optical meansDetector arrayReactive-ion etching

Micromachined, CMOS p+-active / n-well diodes are used as infrared sensing elements in uncooled Focal Plane Arrays (FPA). The FPAs are fabricated using a standard CMOS process followed by post-CMOS bulk-micromachining steps without any critical lithography or complicated deposition processes. Micromachining steps include Reactive Ion Etching (RIE) to reach the bulk silicon and anisotropic silicon wet etching together with electrochemical etch-stop technique to obtain thermally isolated p+-active / n-well diodes. The FPAs are monolithically integrated with their readout circuit since they are fabricated in any standard CMOS technology.

Owner:AKIN TAYFUN

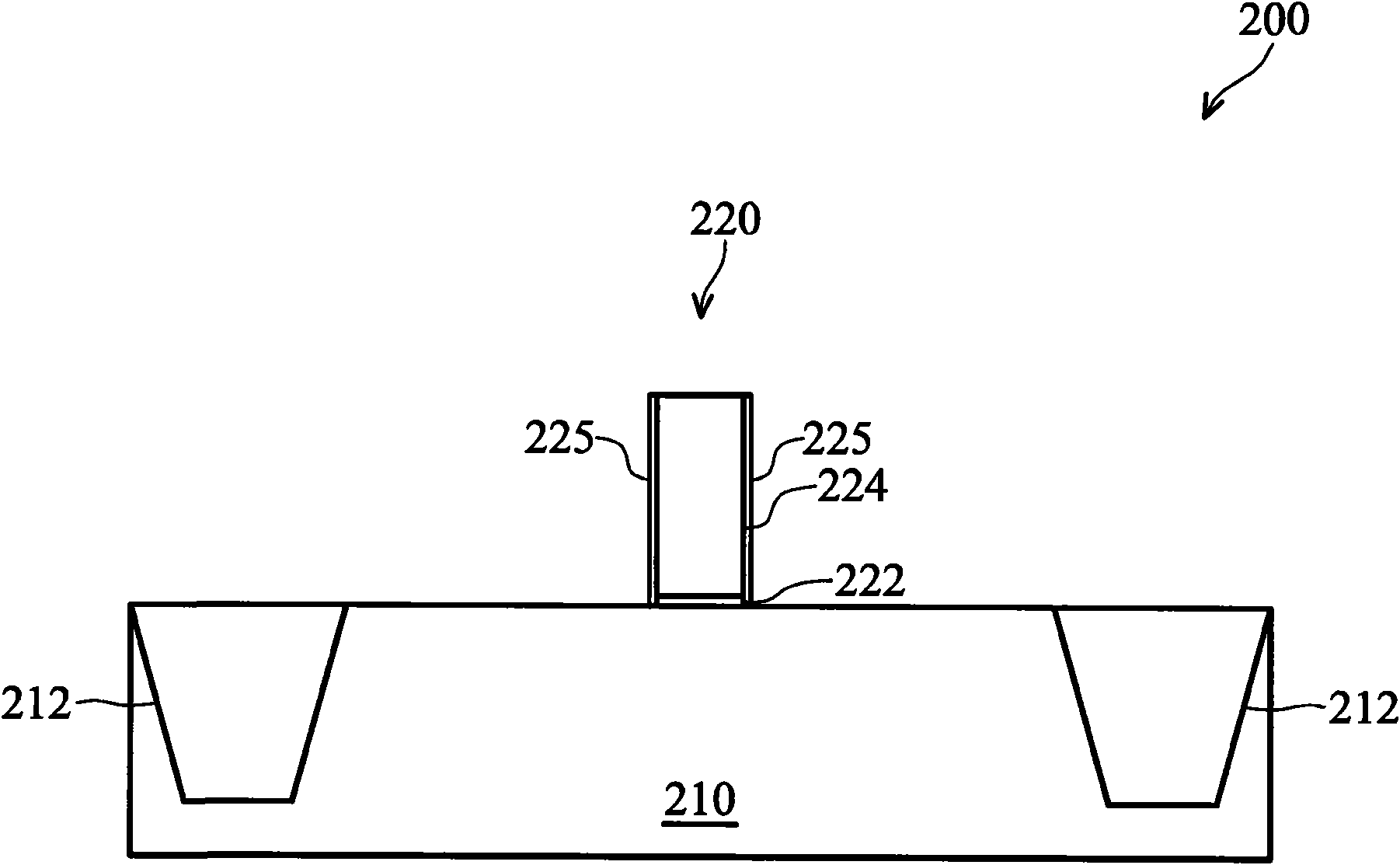

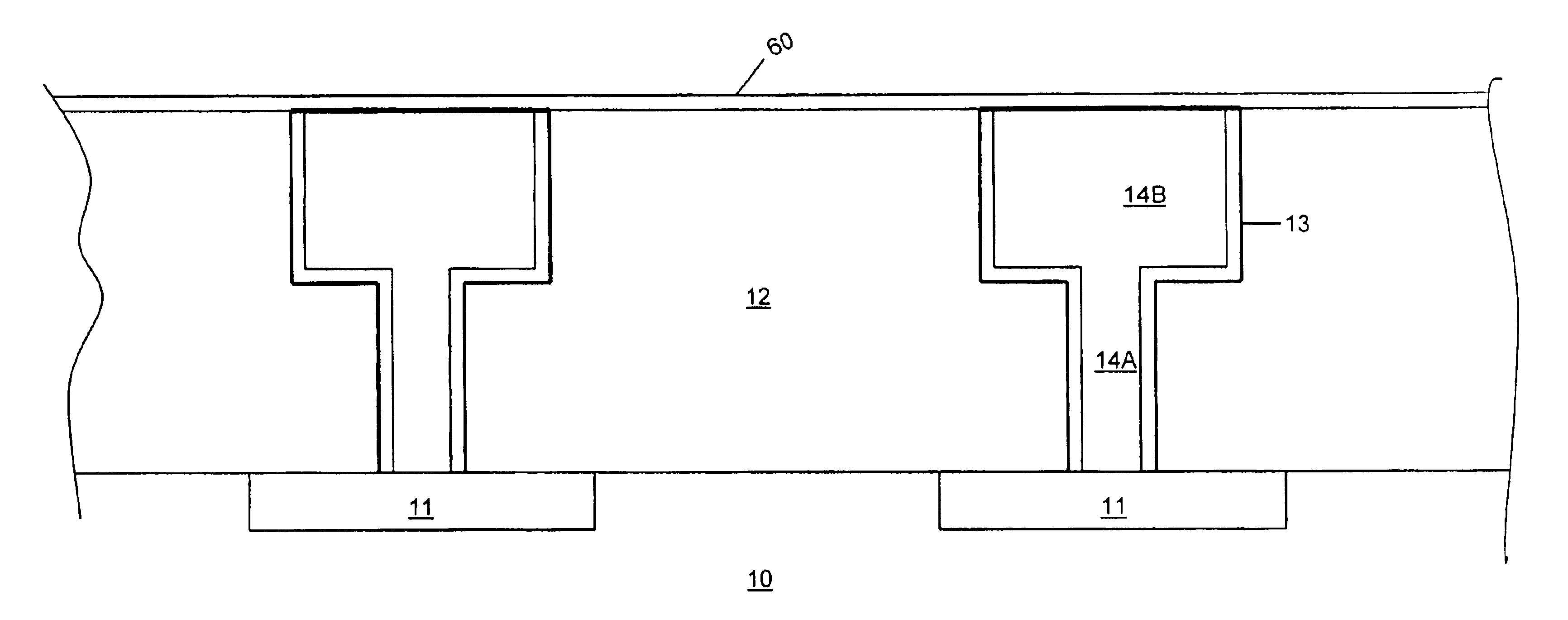

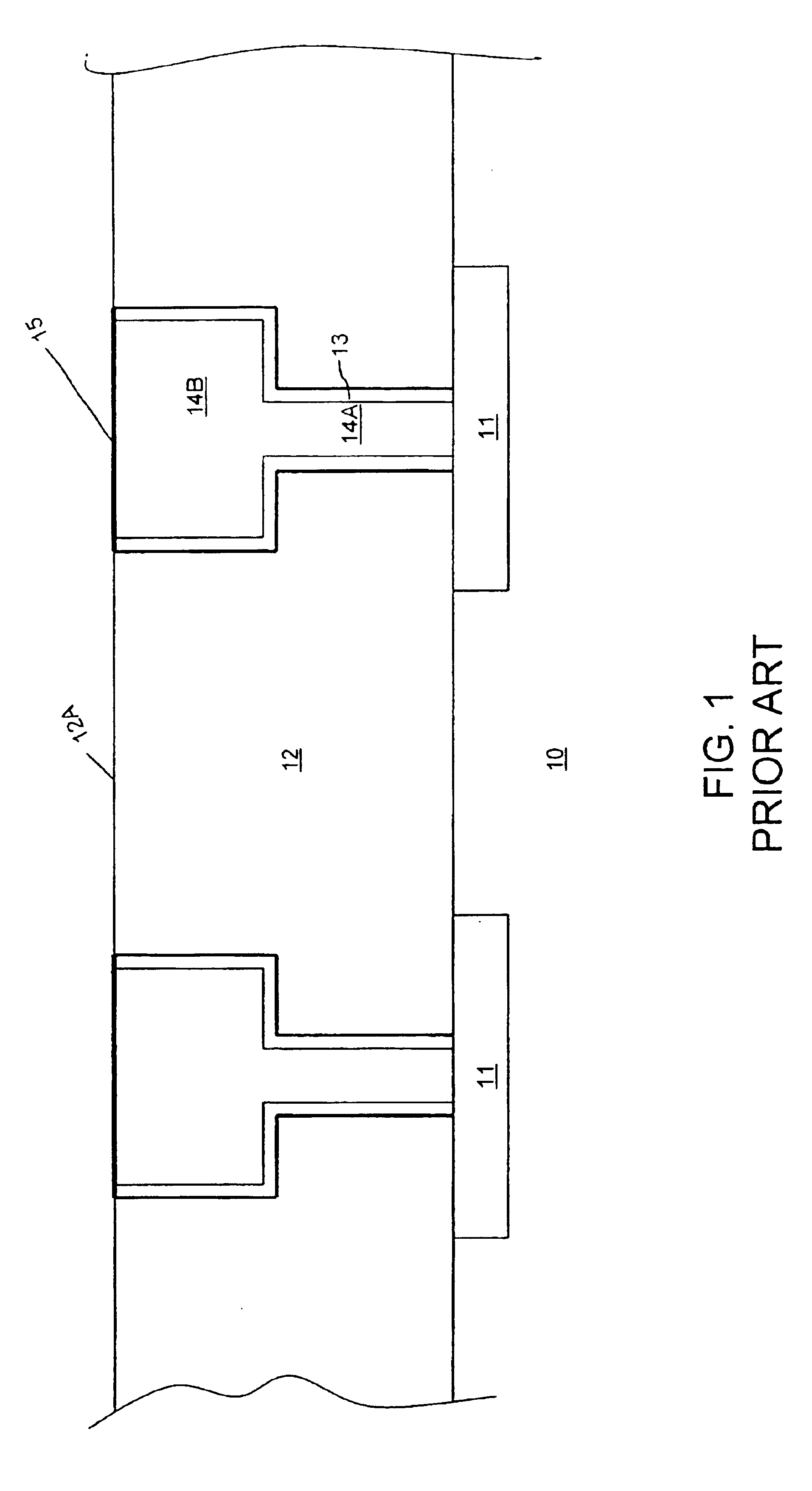

Silicide protection during contact metallization and resulting semiconductor structures

ActiveUS20150187896A1Avoid damageOvercomes shortcomingSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureCondensed matter physics

A semiconductor transistor has a structure including a semiconductor substrate, a source region, a drain region and a channel region in between the source region and the drain region. A metal gate, having a top conductive portion of tungsten is provided above the channel region. A first silicon nitride protective layer over the source region and the drain region and a second silicon nitride protective layer over the gate region are provided. The first silicon nitride protective layer and the second silicon nitride protective layer are configured to allow punch-through of the first silicon nitride protective layer while preventing etching through the second silicon nitride protective layer. Source and drain silicide is protected by avoiding fully etching a gate opening unless either the etching used would not harm the silicide, or the silicide and source and drain contacts are created prior to fully etching an opening to the gate for a gate contact.

Owner:GLOBALFOUNDRIES US INC

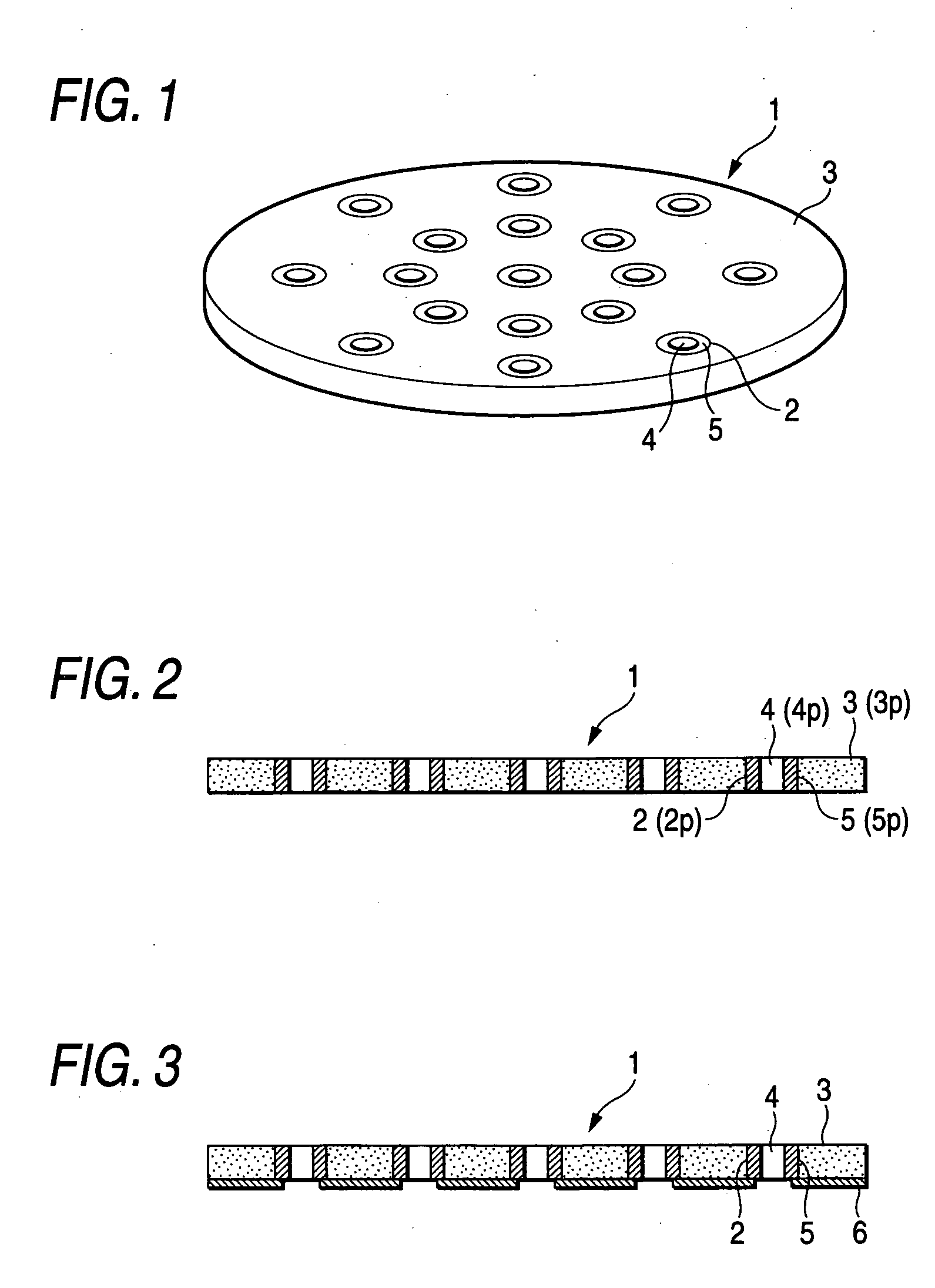

Gas diffusion plate and manufacturing method for the same

InactiveUS20060073354A1Improve manufacturing yieldPrevent generation of particleMolten spray coatingElectric discharge tubesAluminiumAluminium oxide

Owner:COVALENT MATERIALS CORP

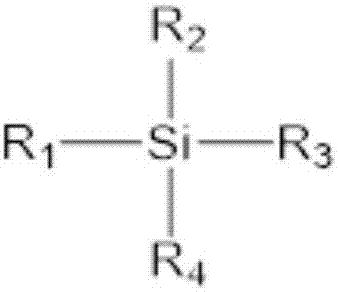

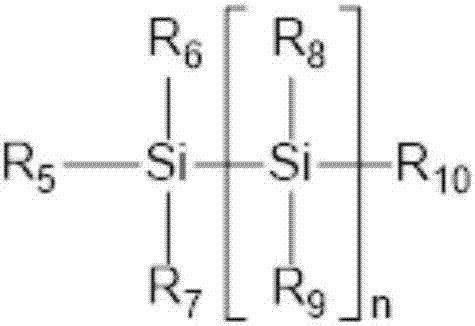

Silicon nitride film etching solution

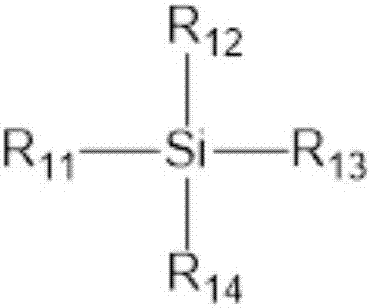

InactiveCN107573940AReduce or suppress the production ofImprove the selection ratioSurface treatment compositionsSilane compoundsSilicone oil

The invention relates to a silicon nitride film etching solution, comprising first silicone compound, whose silicone atom is dependently combined with over three hydrophilic functional groups, and second silicone compound, whose silicone atom is dependently combined with one or two hydrophilic functional groups.

Owner:OCI

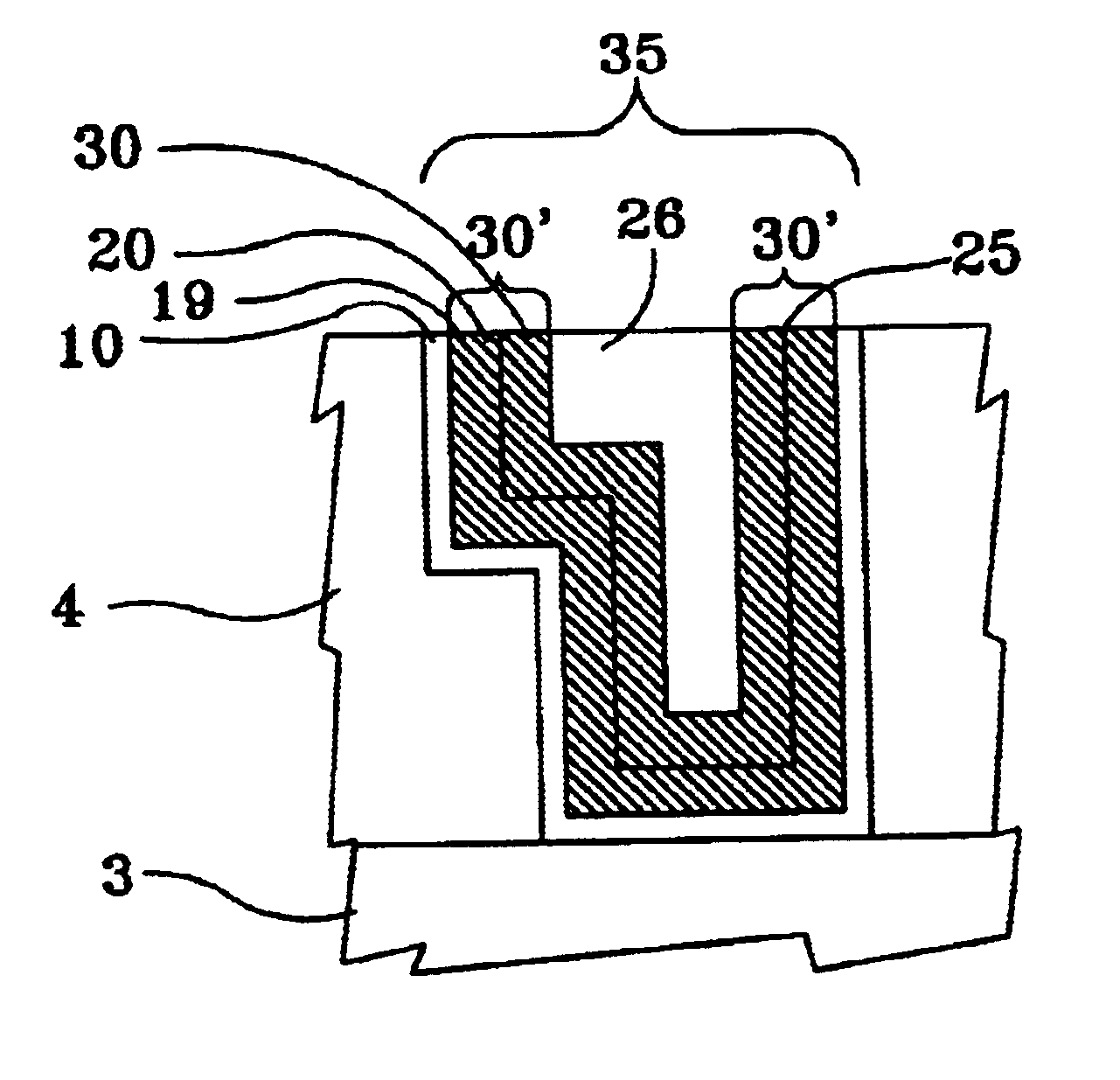

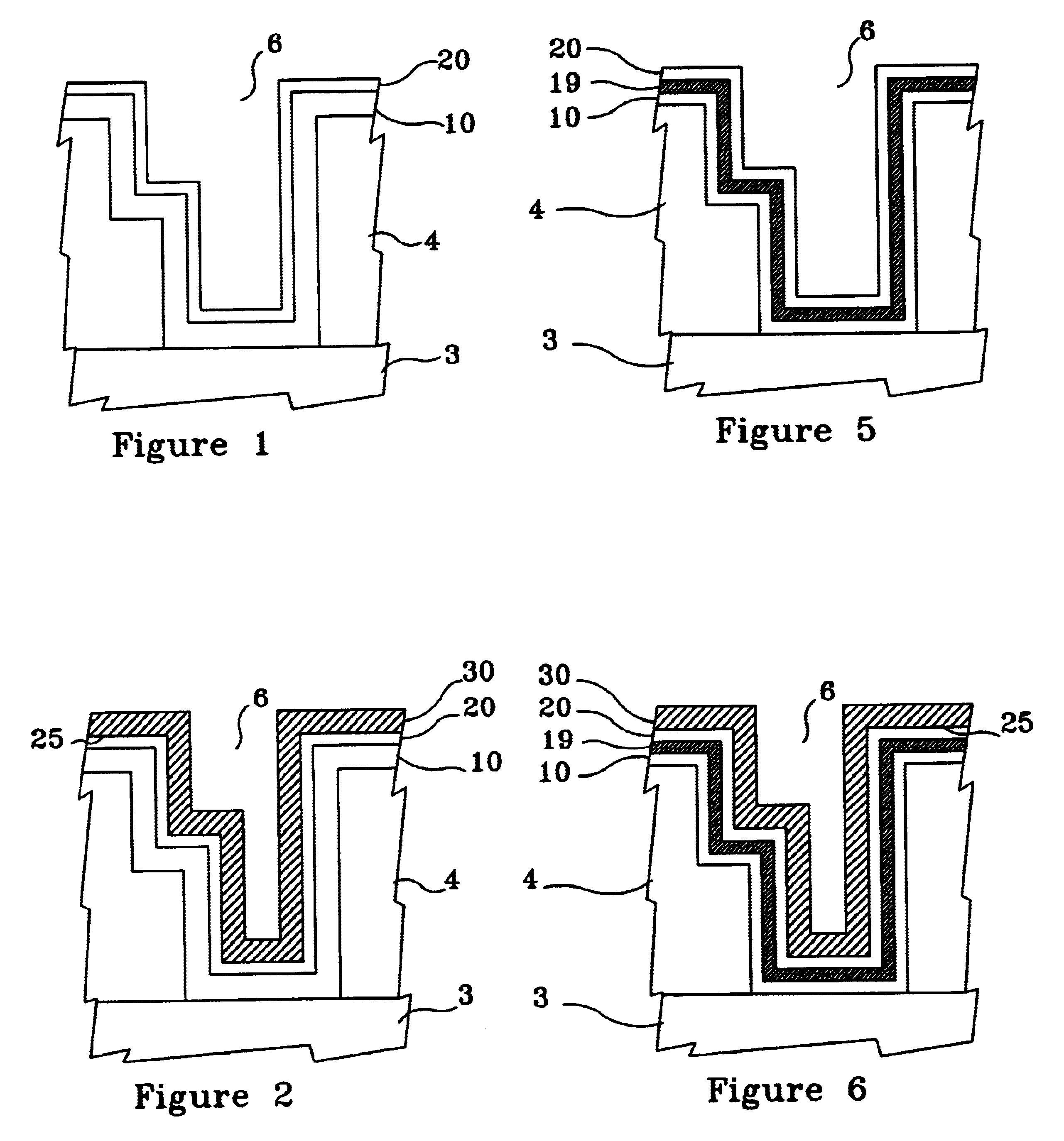

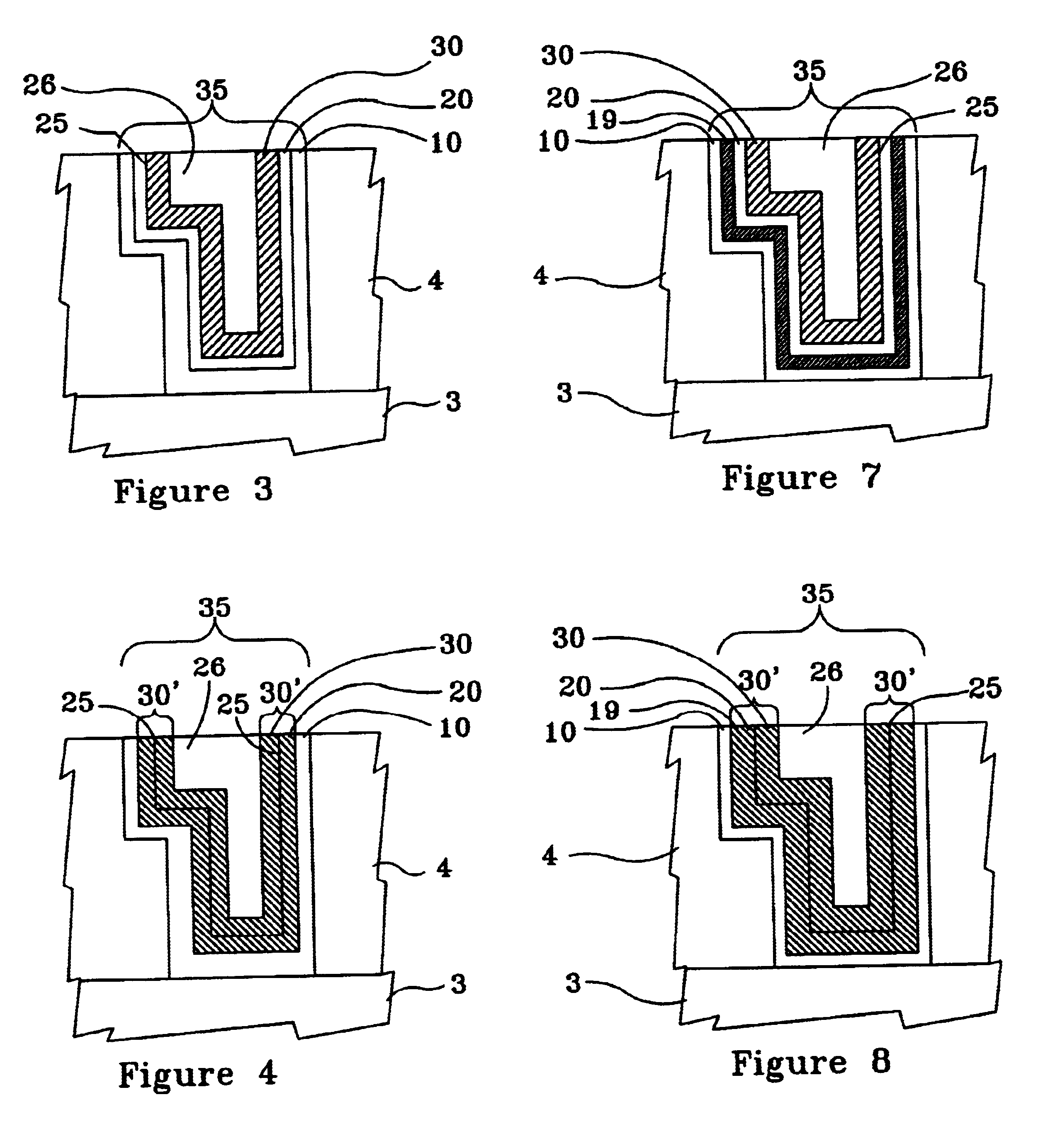

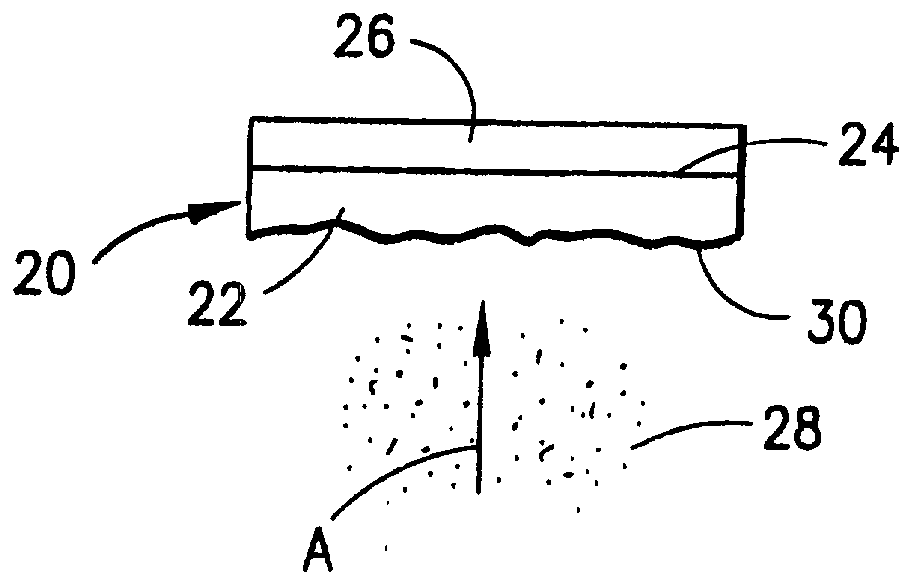

Method of reducing electromigration in a copper line by electroplating an interim copper-zinc alloy thin film on a copper surface and a semiconductor device thereby formed

InactiveUS6660633B1Improves Cu interconnect reliabilityReduce manufacturing costElectrolysis componentsSolid-state devicesCopper interconnectChemical solution

A method of fabricating a semiconductor device, having an interim reduced-oxygen Cu-Zn alloy thin film (30) electroplated on a blanket Cu surface (20) disposed in a via (6) by electroplating, using an electroplating apparatus, the Cu surface (20) in a unique chemical solution containing salts of Zn and Cu, their complexing agents, a pH adjuster, and surfactants; and annealing the interim electroplated Cu-Zn alloy thin film (30); filling the via (6) with further Cu (26); annealing and planarizing the interconnect structure (35); and a semiconductor device thereby formed. The reduction of electromigration in copper interconnect lines (35) is achieved by decreasing the drift velocity in the copper line (35) / via (6), thereby decreasing the copper migration rate as well as the void formation rate, by using an interim conformal Cu-rich Cu-Zn alloy thin film (30) electroplated on a Cu surface (20) from a stable chemical solution, and by controlling the Zn-doping thereof, which improves also interconnect reliability and corrosion resistance.

Owner:GLOBALFOUNDRIES US INC

Method for manufacturing microbridge of uncooled infrared focal plane detector and structure thereof

ActiveCN106352989AFacilitated releaseSimple supporting structurePyrometry using electric radation detectorsFistEtching

The invention relates to a method for manufacturing microbridge of uncooled infrared focal plane detector and a structure thereof.The method comprises the following steps: preparing a reflecting layer on a readout circuit-based wafer;an insulated medium layer,a first sacrificial layer and a first supporting layer;etching the first supporting layer and preparing a first through hole above the reflecting layer;preparing a fist electrode,a first medium layer,a first passivation layer, a second sacrificial layer,a second supporting layer,a thermal layer and a protective layer;etching the second supporting layer and preparing a second through hole above the first electrode;etching the protective layer and preparing a contact hole above the thermal layer;preparing a second electrode, a second medium layer, a second passivation layer,a third sacrificial layer,a third supporting layer and a third passivation layer successively;releasing respective sacrificial layers to get the detector structure.With the three-layer microbridge structure,the method for manufacturing microbridge of uncooled infrared focal plane detector increases effective filling factors and makes infrared absorption more efficient.

Owner:YANTAI RAYTRON TECH

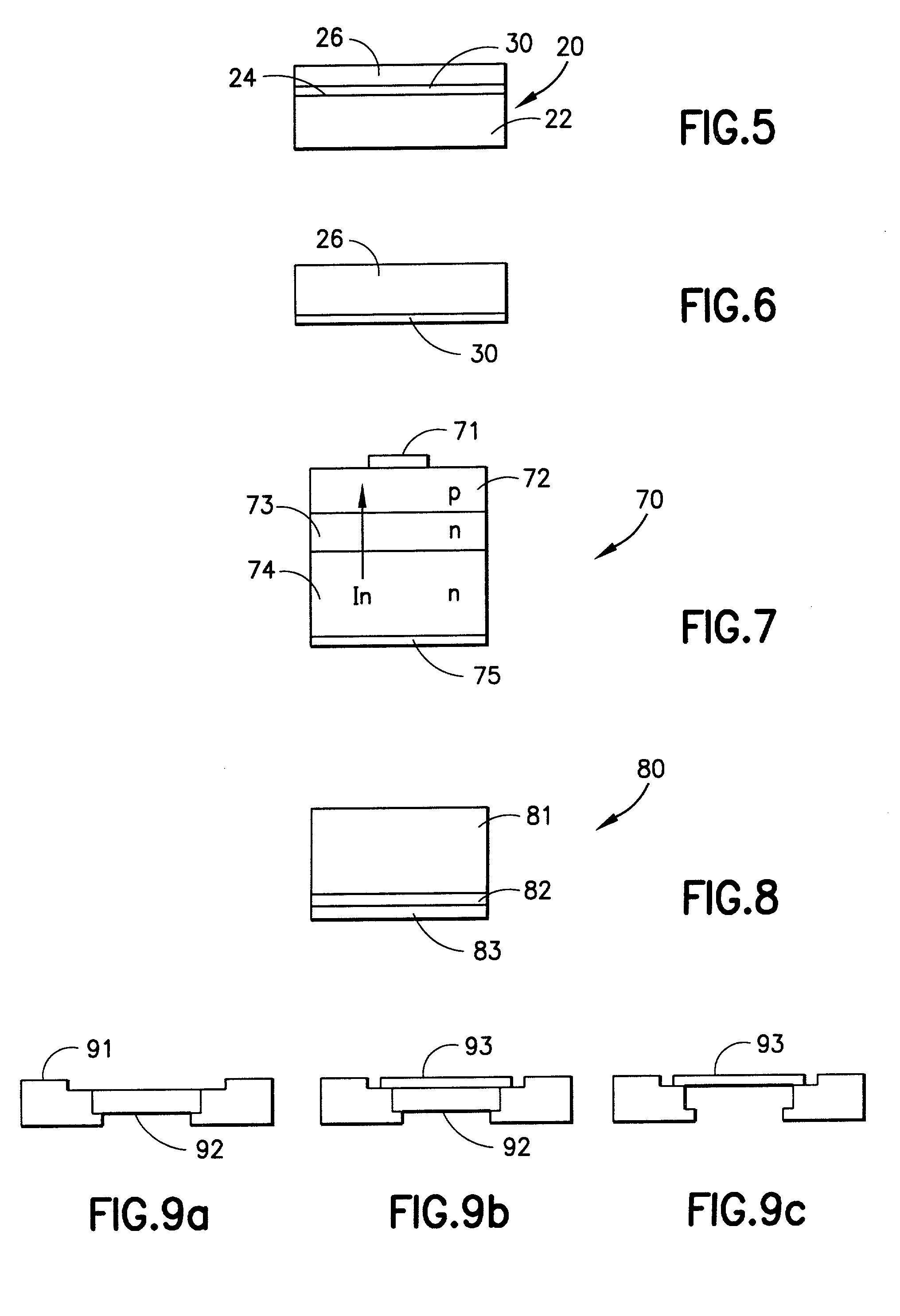

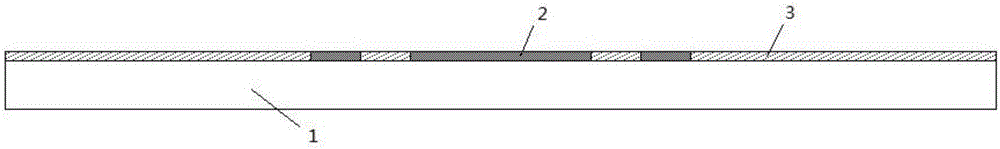

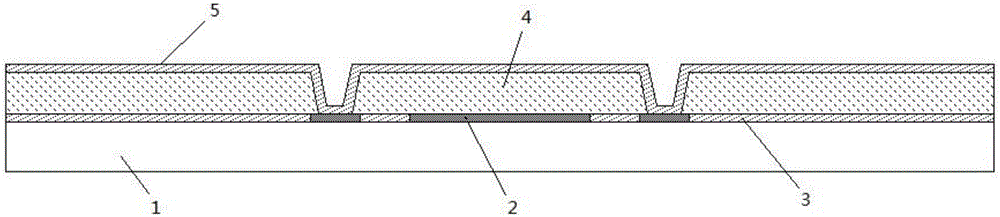

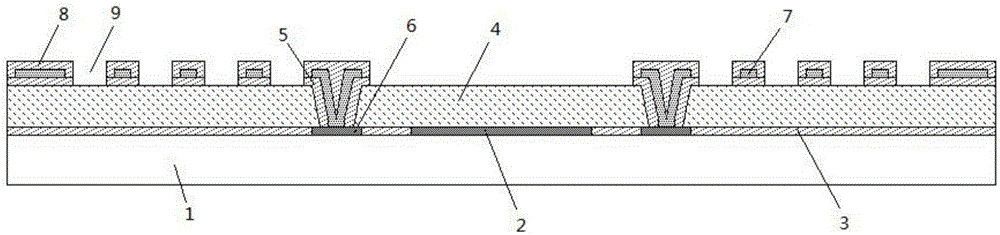

Semiconductor device and manufacturing method

ActiveCN101872742AAvoid etchingIncrease contact resistanceTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

A method for fabricating a semiconductor device is disclosed. The method includes providing a substrate; forming at least one gate structure over the substrate; forming a plurality of doped regions in the substrate; forming an etch stop layer over the substrate; removing a first portion of the etch stop layer, wherein a second portion of the etch stop layer remains over the plurality of doped regions; forming a hard mask layer over the substrate; removing a first portion of the hard mask layer, wherein a second portion of the hard mask layer remains over the at least one gate structure; and forming a first contact through the second portion of the hard mask layer to the at least one gate structure, and a second contact through the second portion of the etch stop layer to the plurality of doped regions.

Owner:TAIWAN SEMICON MFG CO LTD

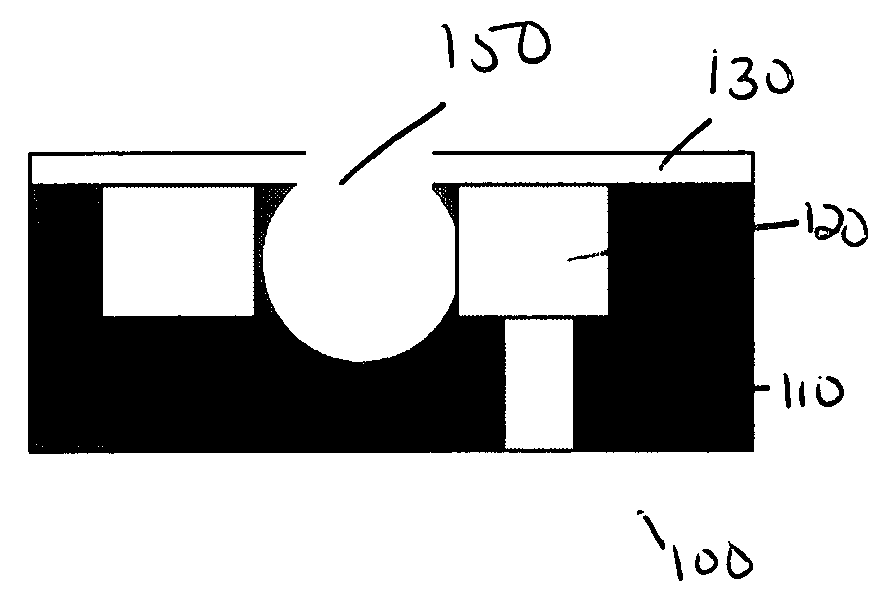

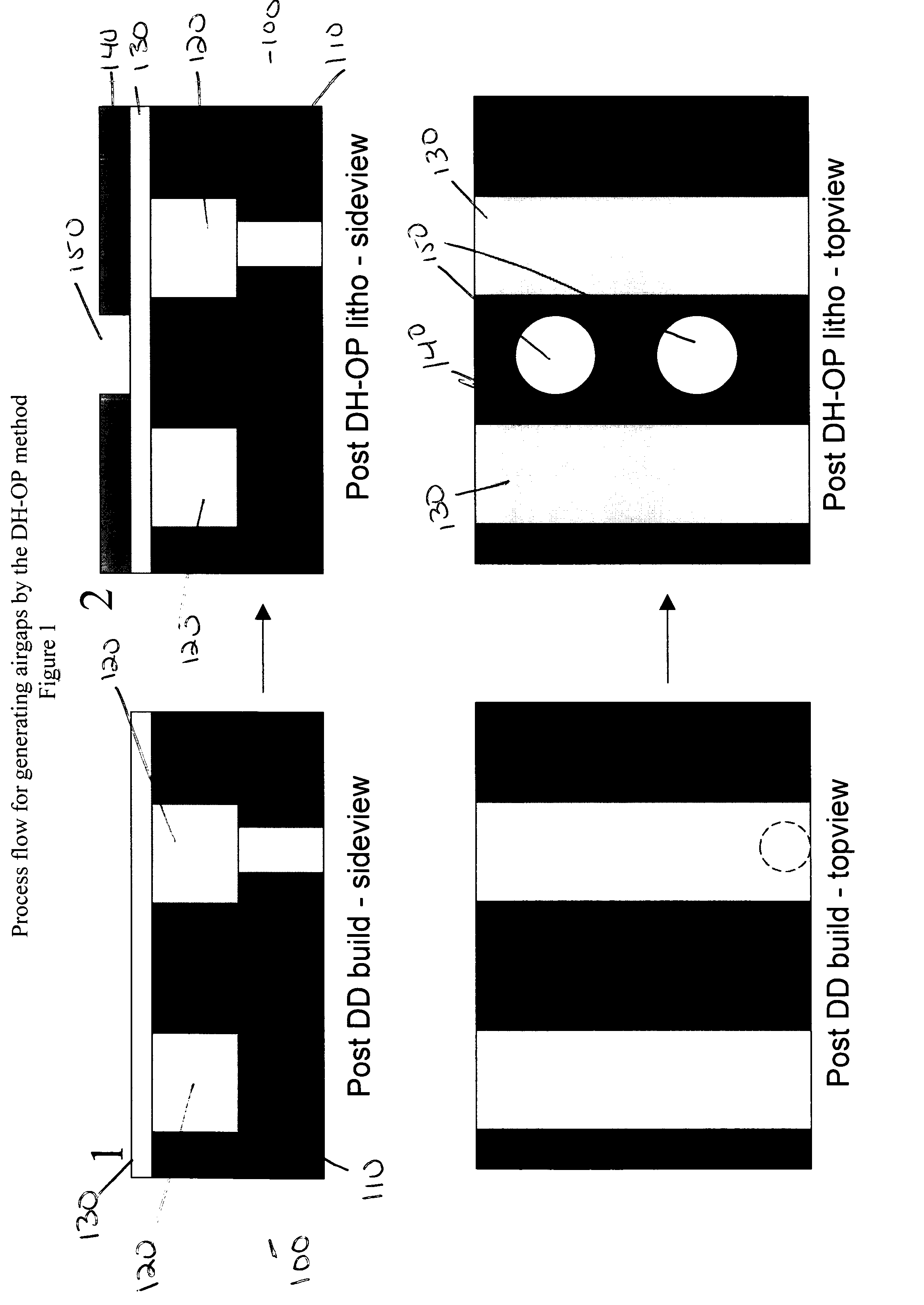

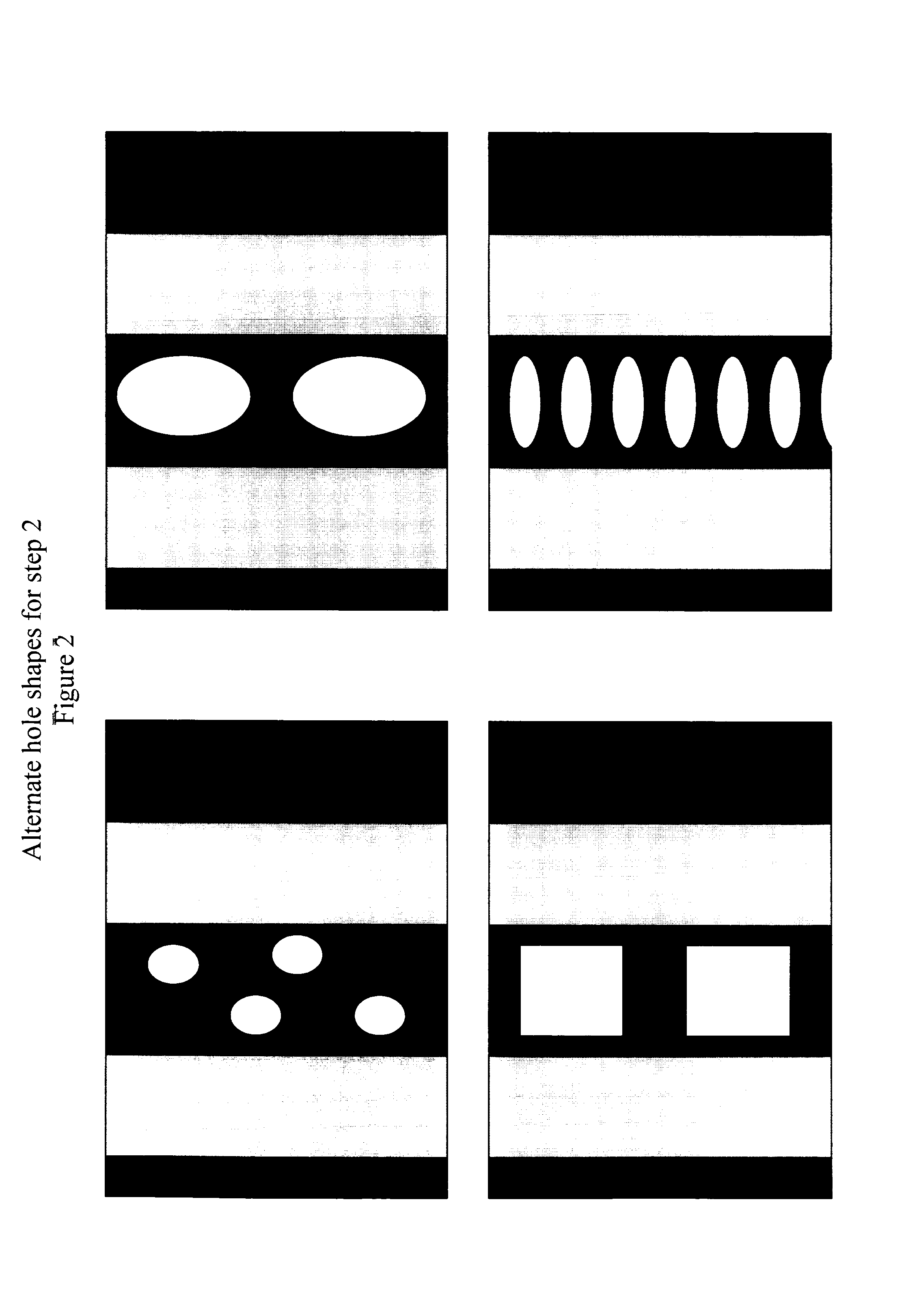

Method to generate airgaps with a template first scheme and a self aligned blockout mask

InactiveUS20080122106A1Avoid etchingSemiconductor/solid-state device detailsSolid-state devicesComputational physicsDielectric layer

A structure and method to produce an airgap on a substrate having a dielectric layer with a pattern transferred onto the dielectric layer and a self aligned block out mask transferred on the dielectric layer around the pattern.

Owner:GLOBALFOUNDRIES INC

Horizontal gate all around nanowire transistor bottom isolation

ActiveUS20170179248A1Avoid etchingNanoinformaticsSemiconductor/solid-state device manufacturingDopantMOSFET

A method of forming a GAA MOSFET includes providing a substrate having source, drain and channel regions, the substrate doped with one of a p-type and an n-type dopant. Disposing an etch stop-electric well (ESEW) layer over the substrate, the ESEW layer doped with the other of the p-type and the n-type dopant. Disposing a sacrificial layer over the ESEW layer, the sacrificial layer doped with the same type dopant as the substrate. Disposing a channel layer over the sacrificial layer. Patterning a fin out of the ESEW layer, sacrificial layer and channel layer in the channel region. Selectively etching away only the sacrificial layer of the fin to form a nanowire from the channel layer of the fin while the ESEW layer of the fin functions as an etch stop barrier to prevent etching of trenches in the substrate.

Owner:GLOBALFOUNDRIES US INC

Manufacturing method of semiconductor device

InactiveUS20070031990A1Improve reliabilitySimplify manufacturing stepsTransistorSolid-state devicesDevice materialOrganic semiconductor

In view of the problem that an organic semiconductor layer of an organic TFT is likely to deteriorate due to water, light, oxygen, or the like, it is an object of the present invention to simplify a manufacturing step and to provide a method for manufacturing a semiconductor device having an organic TFT with high reliability. According to the invention, a semiconductor layer containing an organic material is formed by patterning using a mask, and thus an organic TFT is completed in the state where the mask is not removed but to remain over the semiconductor layer. In addition, a semiconductor layer can be protected from deterioration due to water, light, oxygen, or the like by using the remaining mask.

Owner:SEMICON ENERGY LAB CO LTD

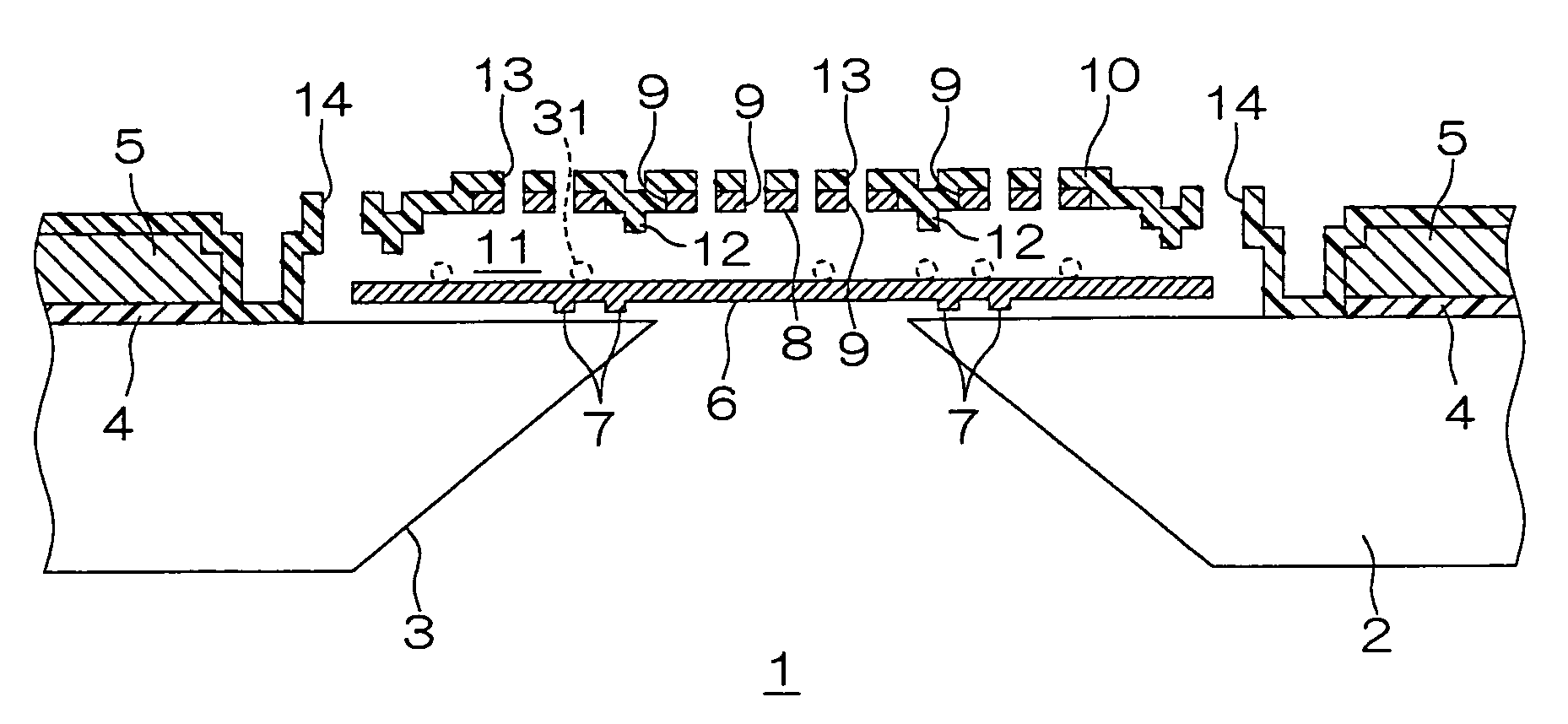

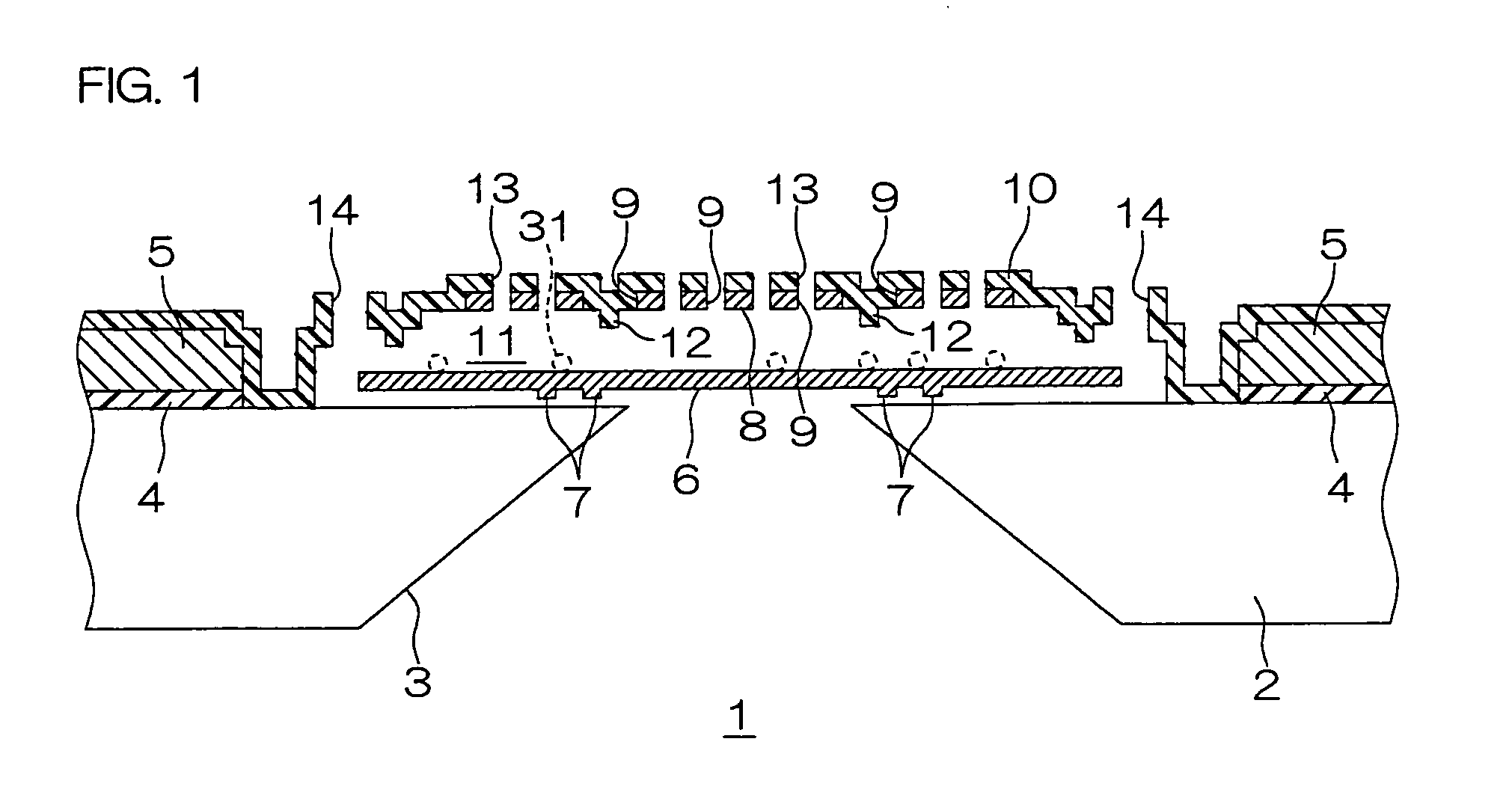

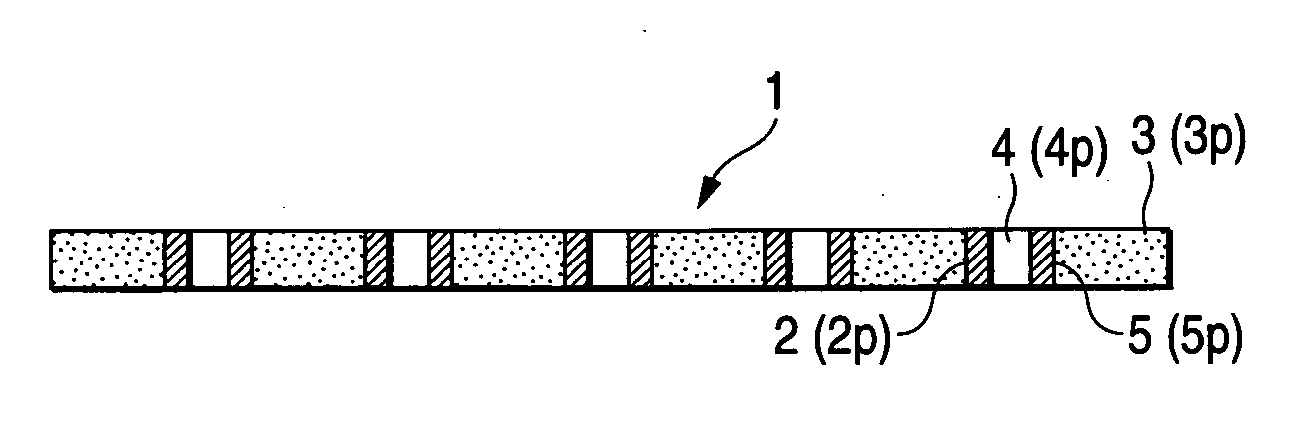

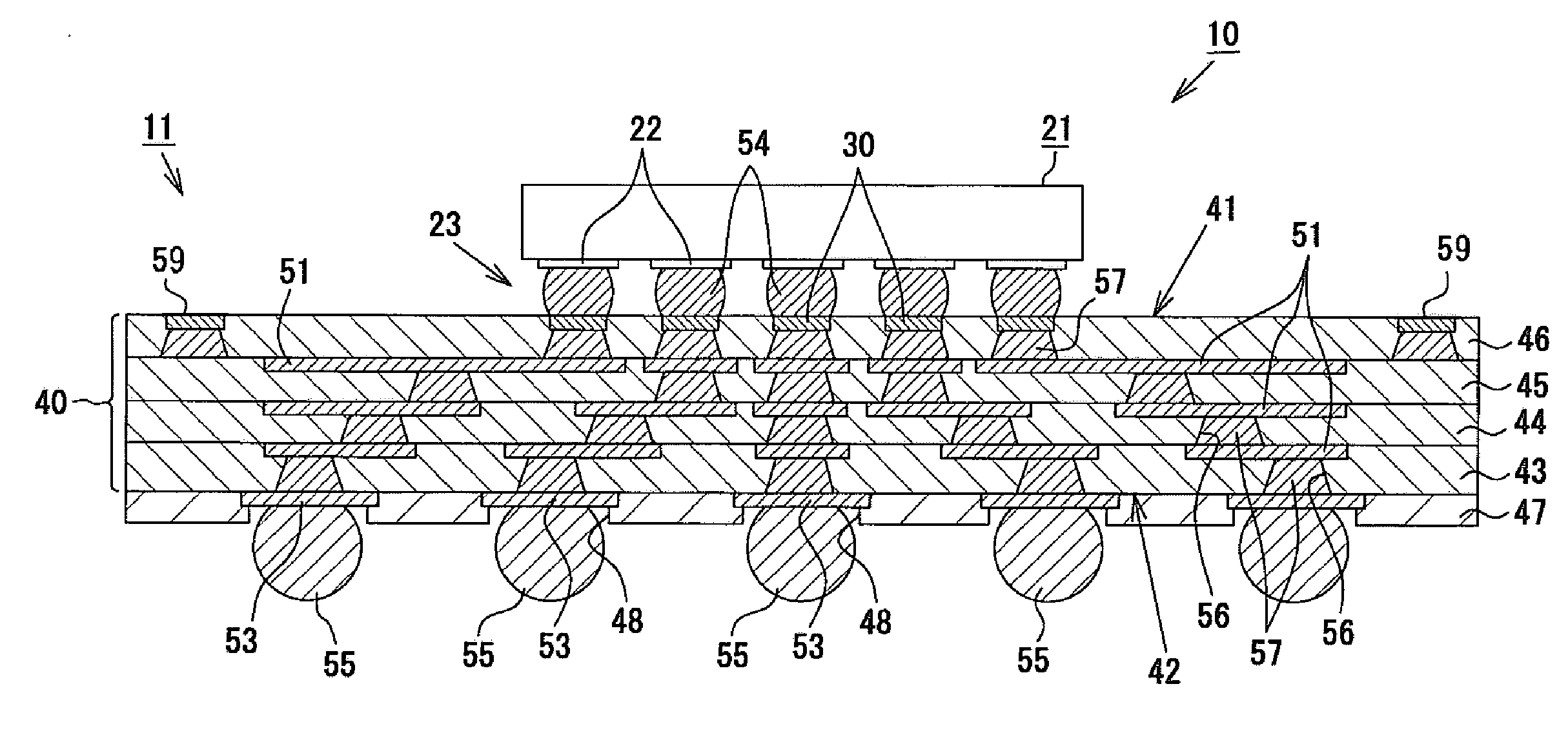

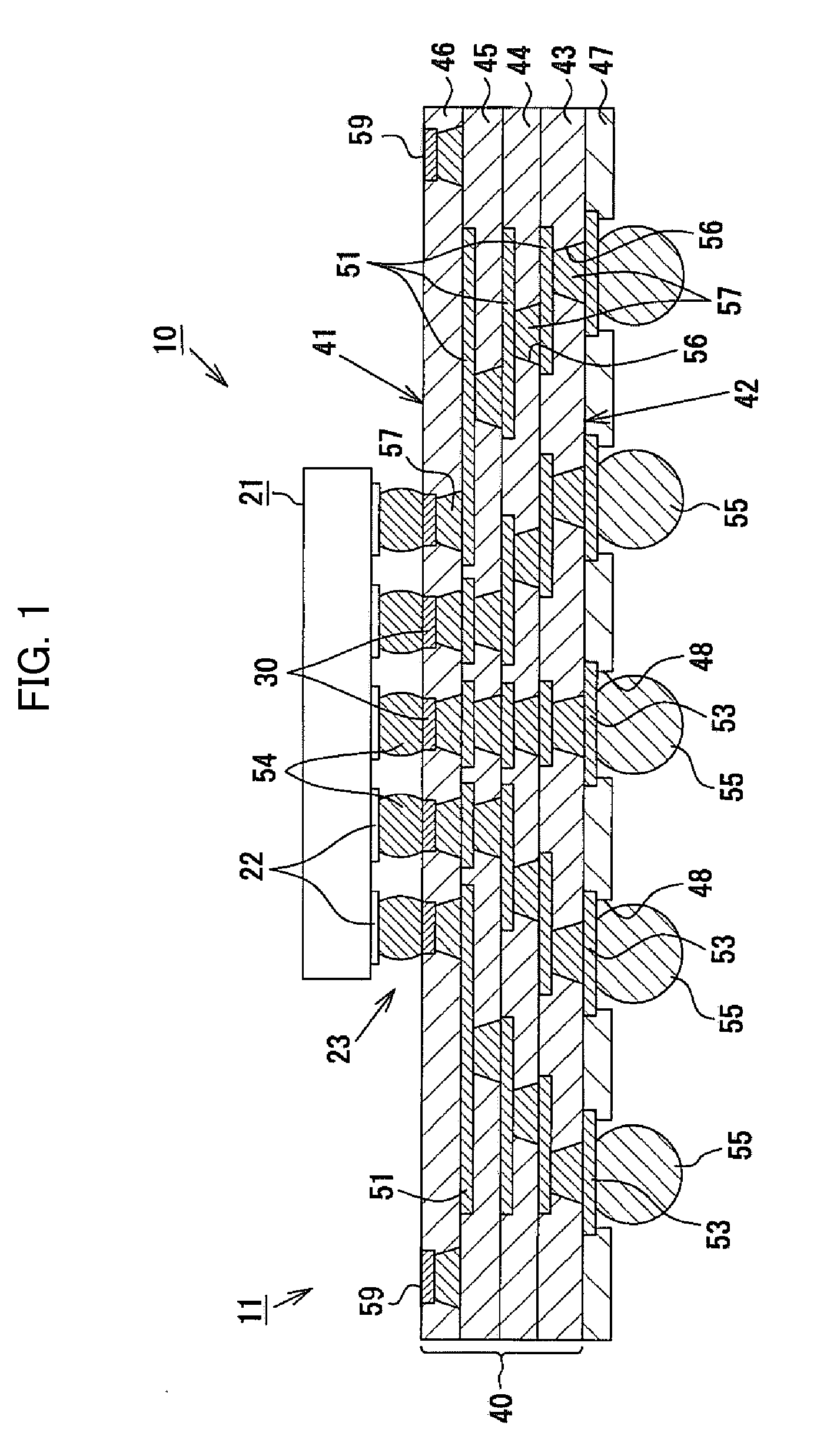

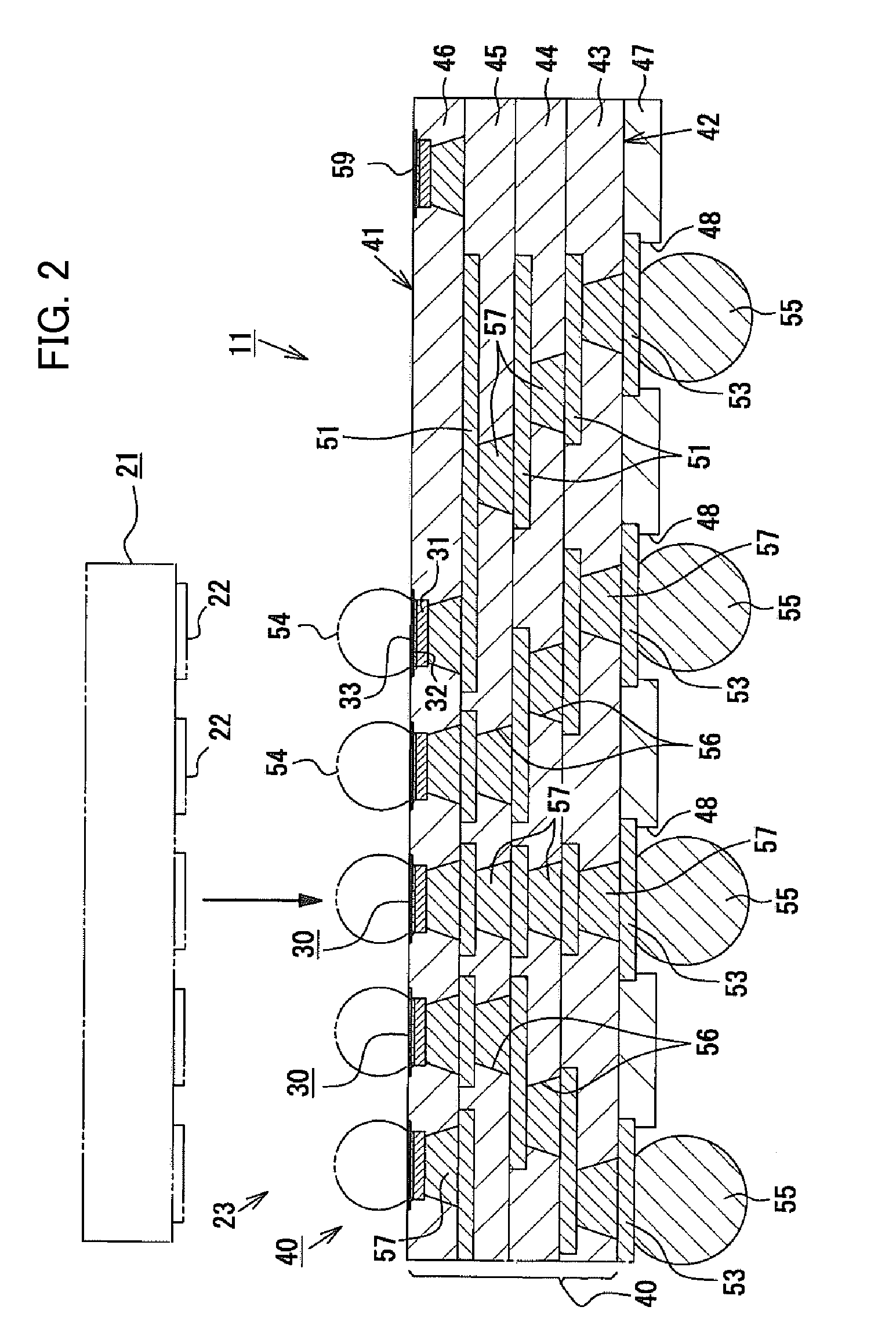

Multilayer wiring substrate and method for manufacturing the same

ActiveUS20100208437A1Low connection reliabilityDeterioration of surface shapeEarth drilling toolsDrill bitsElectrical conductorEngineering

A multilayer wiring substrate of the present invention has a laminated structure composed of conductor layers and resin insulating layers stacked alternately. A plurality of surface connection terminals to which terminals of a chip component are to be surface-connected are formed on a main face of the laminated structure. A plurality of via conductors connected to the plurality of surface connection terminals are formed in the resin insulating layers. Each of the plurality of surface connection terminals has a structure in which a copper layer, a nickel layer, and a gold layer are stacked in this sequence. The gold layer is larger in diameter than at least the copper layer. The gold layer has an overhanging portion which extends radially outward from a circumference of the copper layer.

Owner:NGK SPARK PLUG CO LTD

Bulk single crystal gallium nitride and method of making same

InactiveUS20010055660A1Enhance crystallinity and other characteristicAvoid etchingPolycrystalline material growthAfter-treatment detailsElectronic structureSingle crystal

A single crystal M*N article, which may be made by a process including the steps of: providing a substrate of material having a crystalline surface which is epitaxially compatible with M*N; depositing a layer of single crystal M*N over the surface of the substrate; and removing the substrate from the layer of single crystal M*N, e.g., with an etching agent which is applied to the substrate to remove same, to yield the layer of single crystal M*N as said single crystal M*N article. The bulk single crystal M*N article is suitable for use as a substrate for the fabrication of microelectronic structures thereon, to produce microelectronic devices comprising bulk single crystal M*N substrates, or precursor structures thereof.

Owner:WOLFSPEED INC

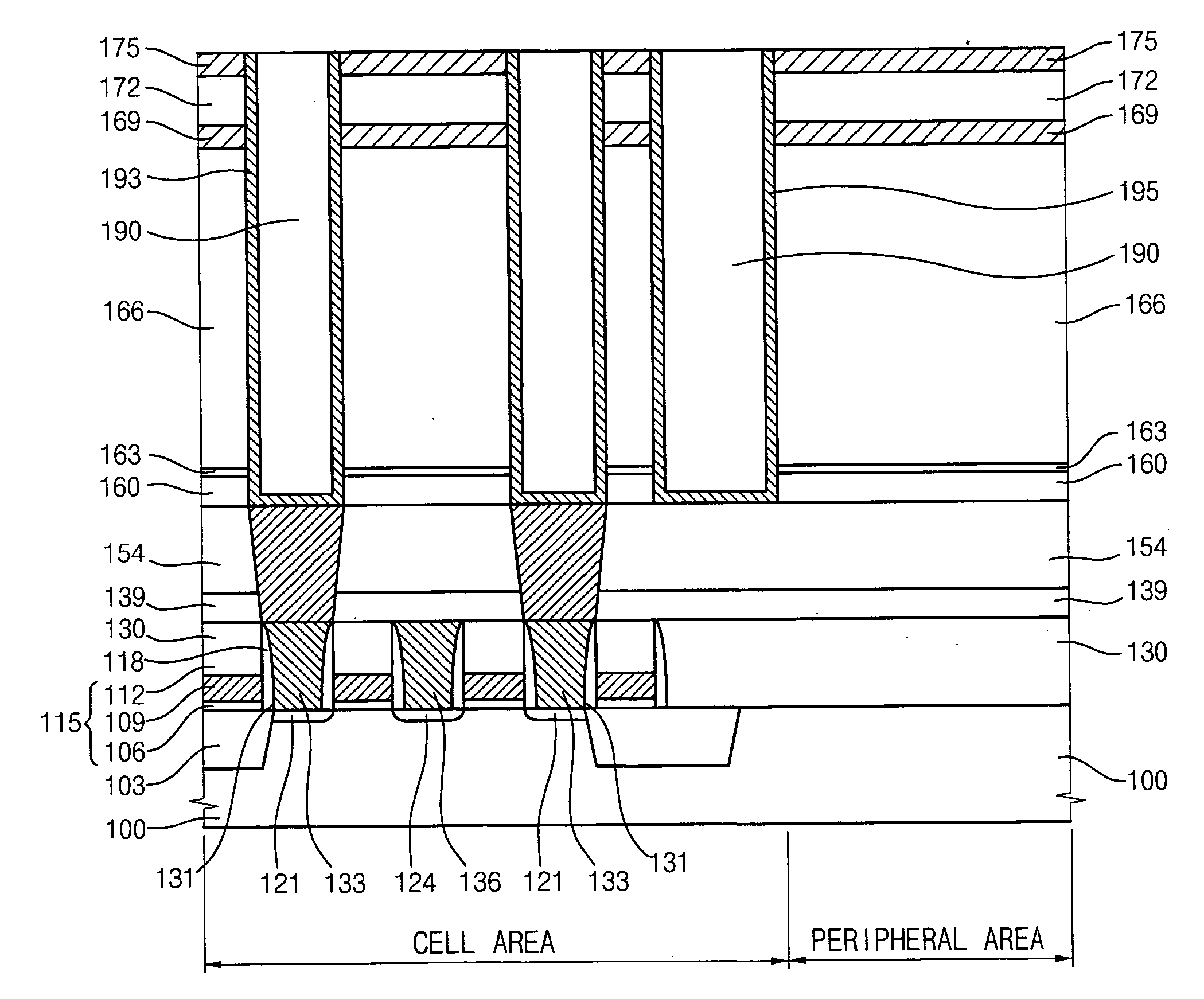

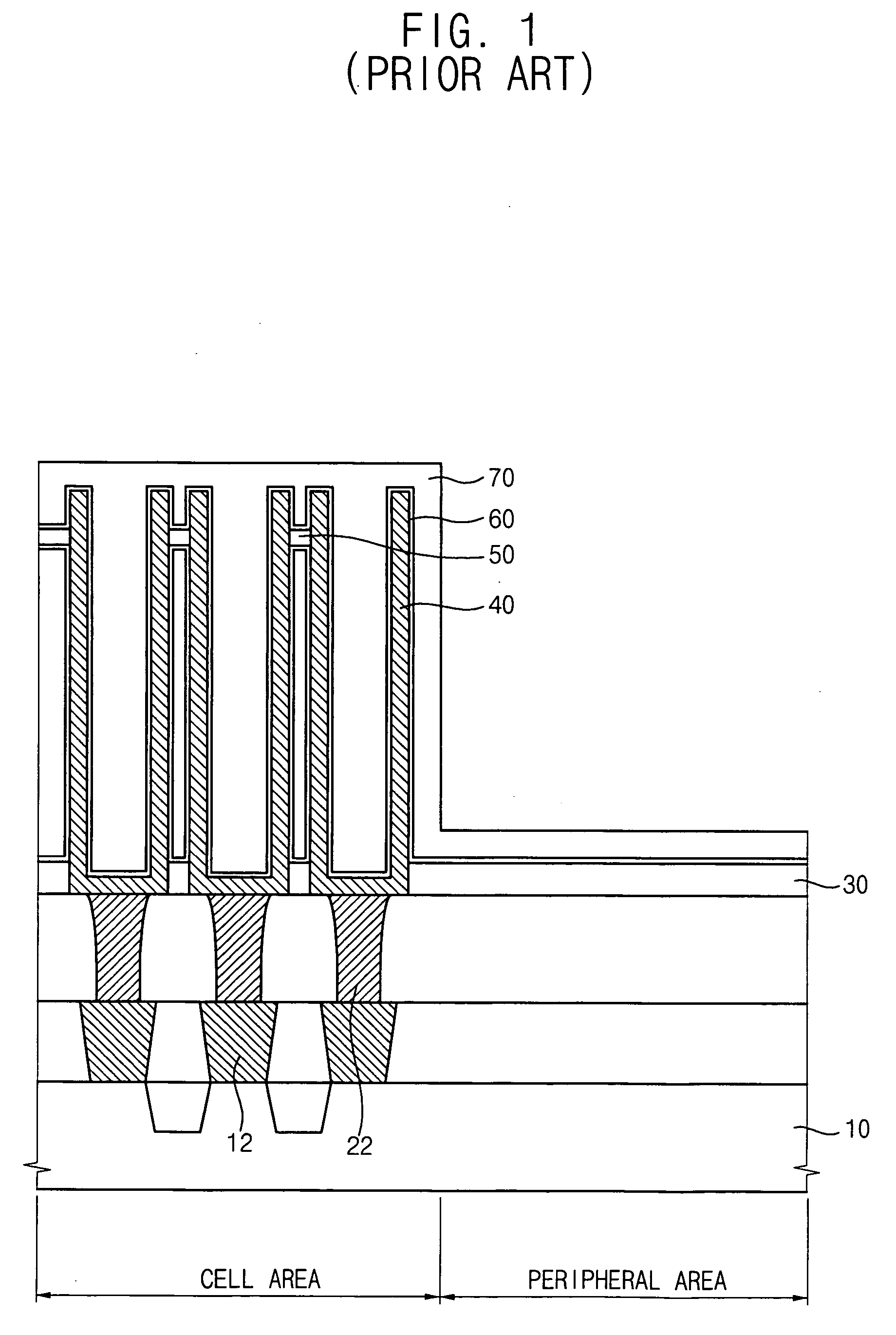

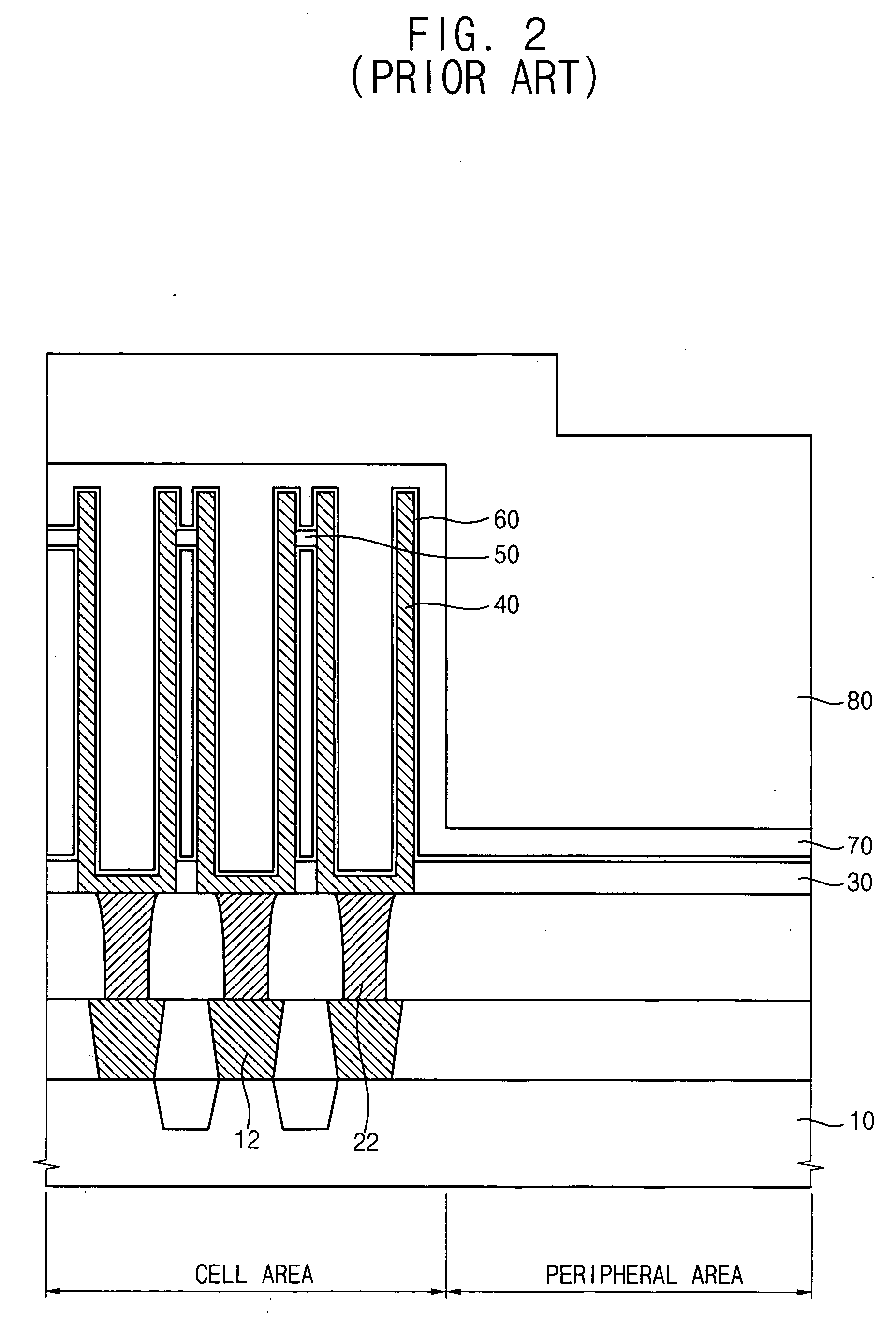

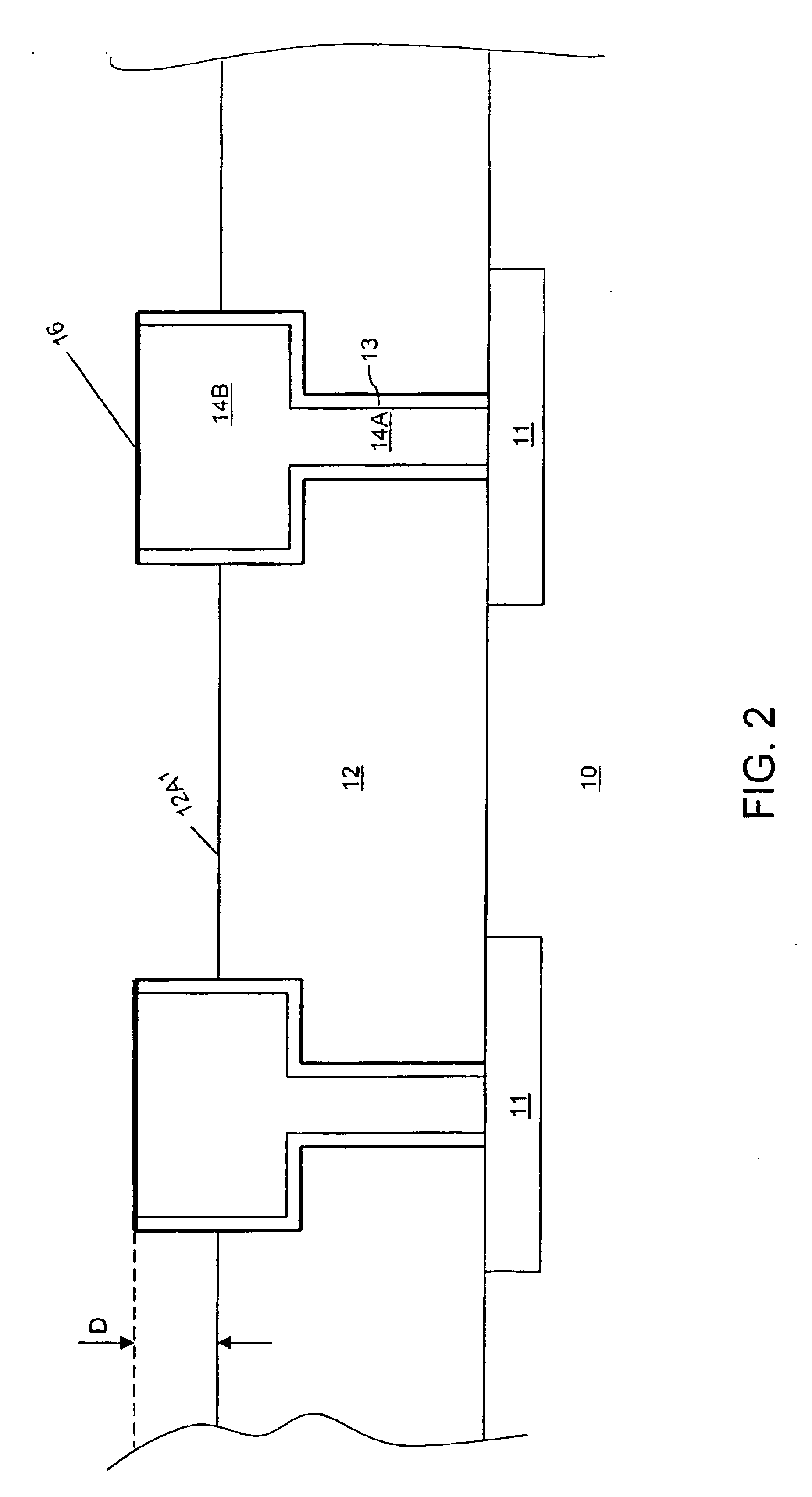

Method of manufacturing a semiconductor device

In an embodiment, a simplified method of manufacturing a semiconductor device reduces a step between cell and peripheral areas. First and second openings are formed through a plurality of thin layers including a support layer on a substrate. A storage electrode and a guide ring are formed on sidewalls and bottoms of the first and second openings, respectively. A support pattern is formed so that the support layer in the cell area is partially etched and the support layer in the peripheral area remains un-etched, thus the support pattern supports and surrounds the storage electrodes adjacent to each other in the cell area and prevents an etching of a layer underlying the support layer in the peripheral area. A dielectric layer and a plate electrode are formed on the storage electrode to complete a semiconductor device with the reduced step.

Owner:SAMSUNG ELECTRONICS CO LTD

Non-volatile semiconductor memory devices using prominences and trenches

InactiveUS7309634B2Increase widthImprove featuresSolid-state devicesRead-only memoriesSemiconductorSemiconductor memory

A semiconductor substrate is patterned to form a depression and prominence. A floating gate is formed so as to cover at least both sidewalls of the prominence of the depression and prominence, and is then etched to form a trench for a device isolation self-aligned with the floating gate. Related structures are also described.

Owner:SAMSUNG ELECTRONICS CO LTD

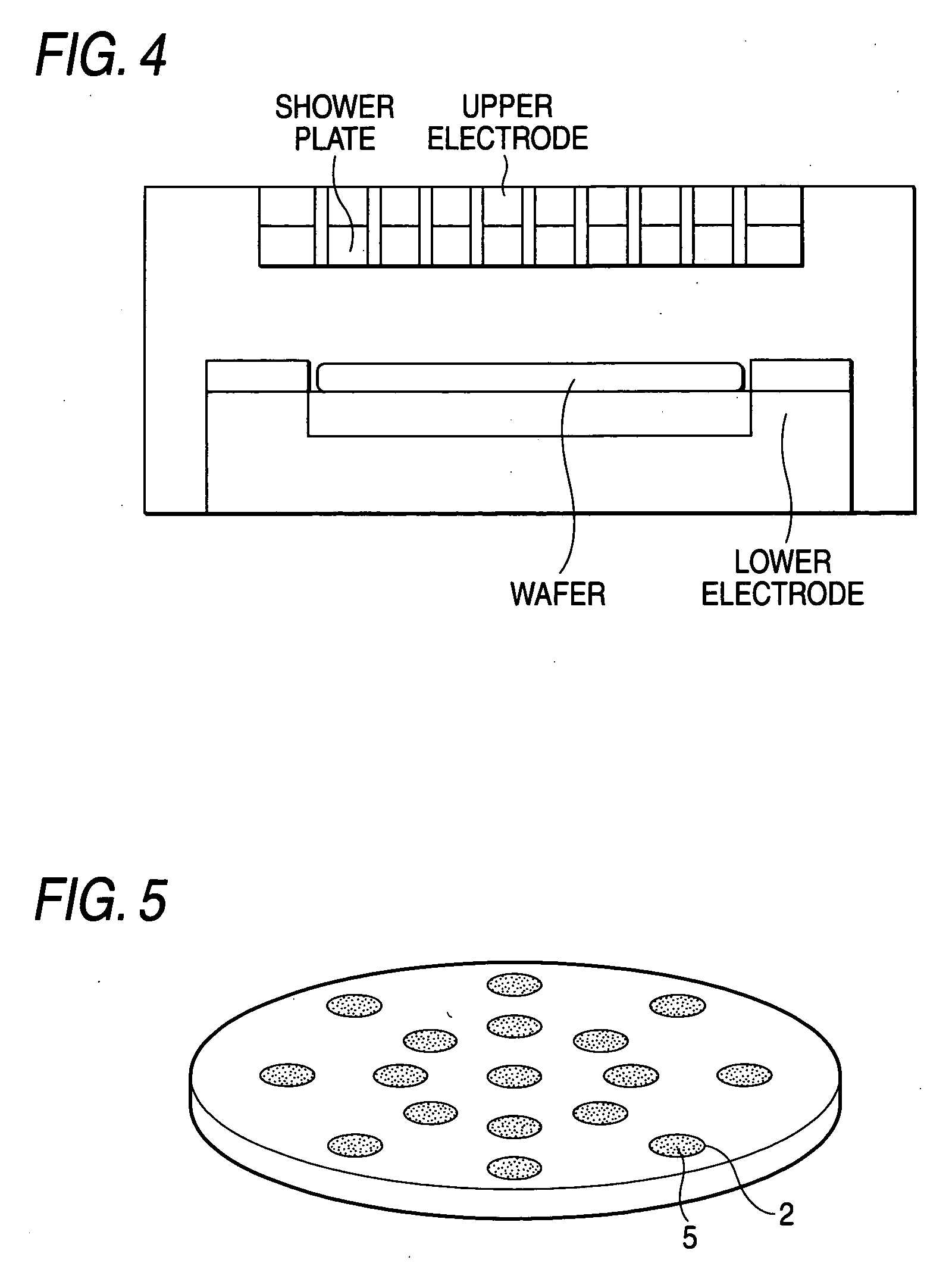

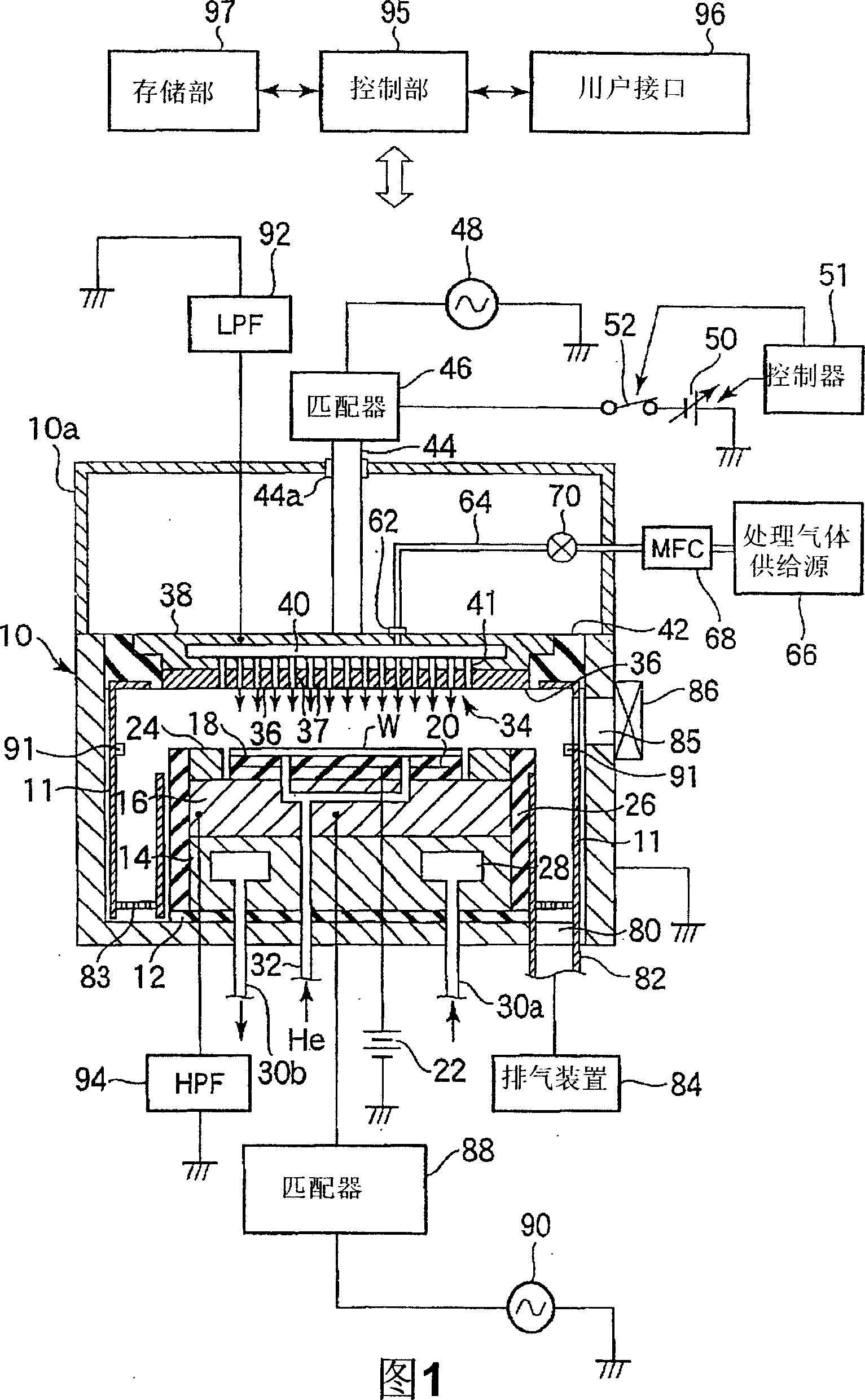

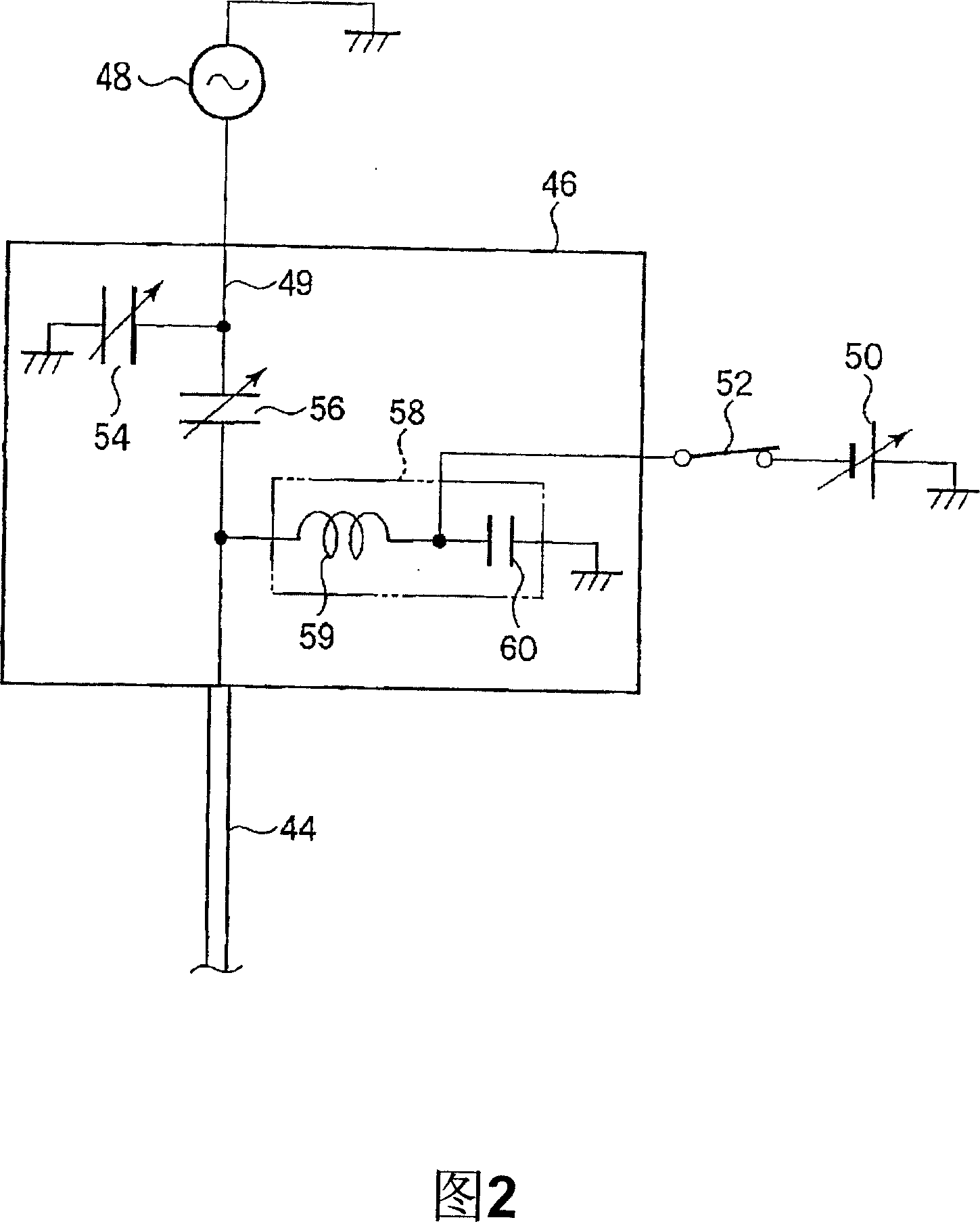

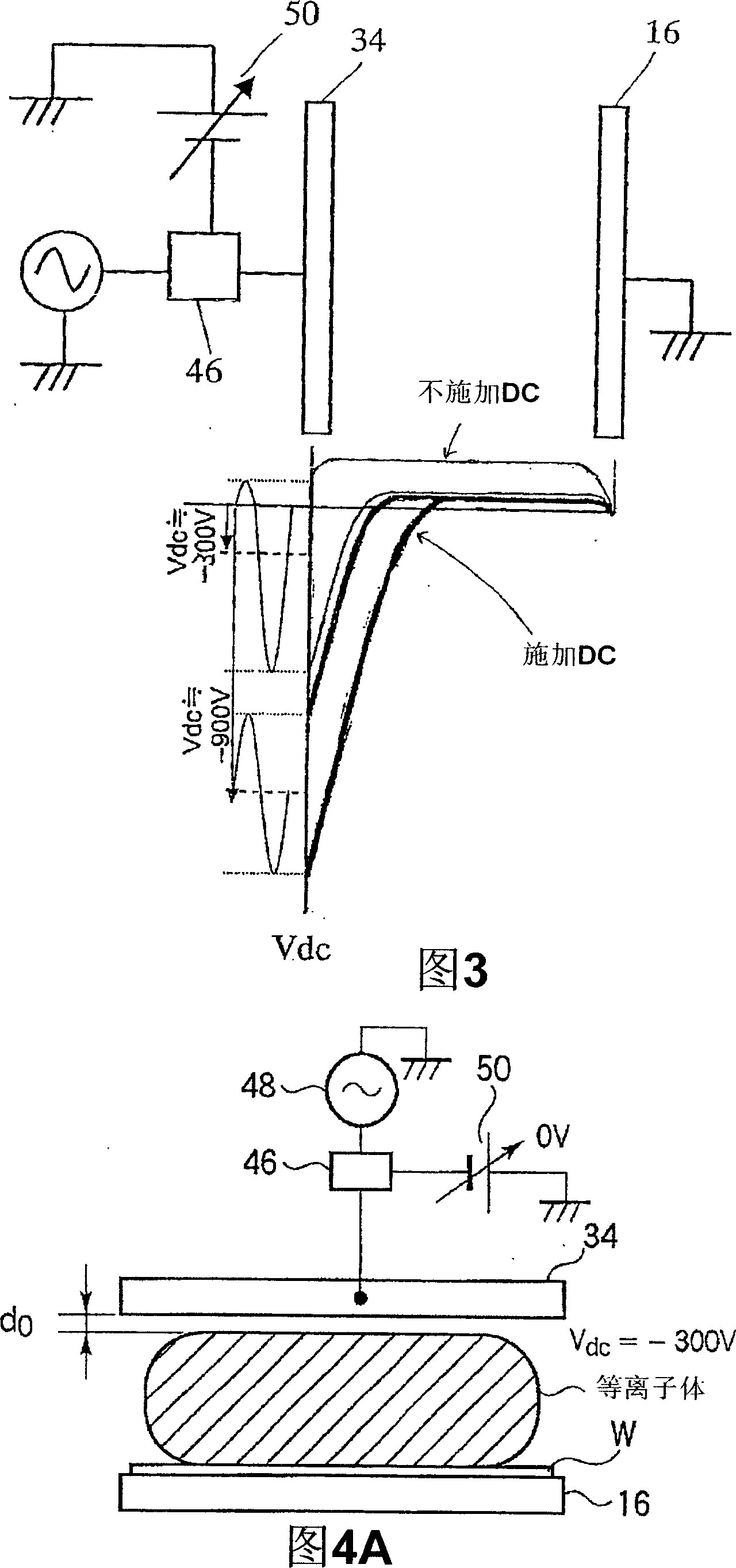

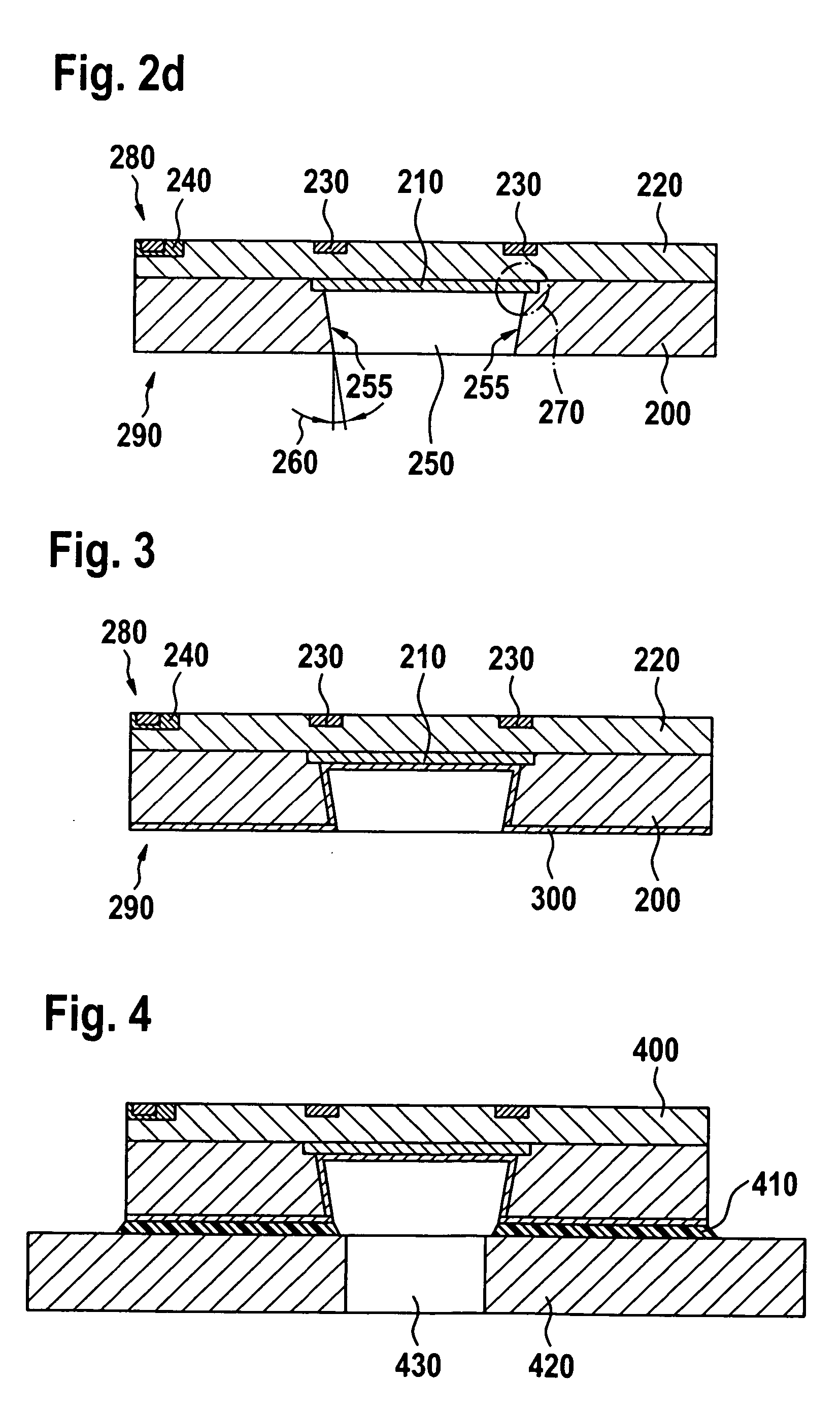

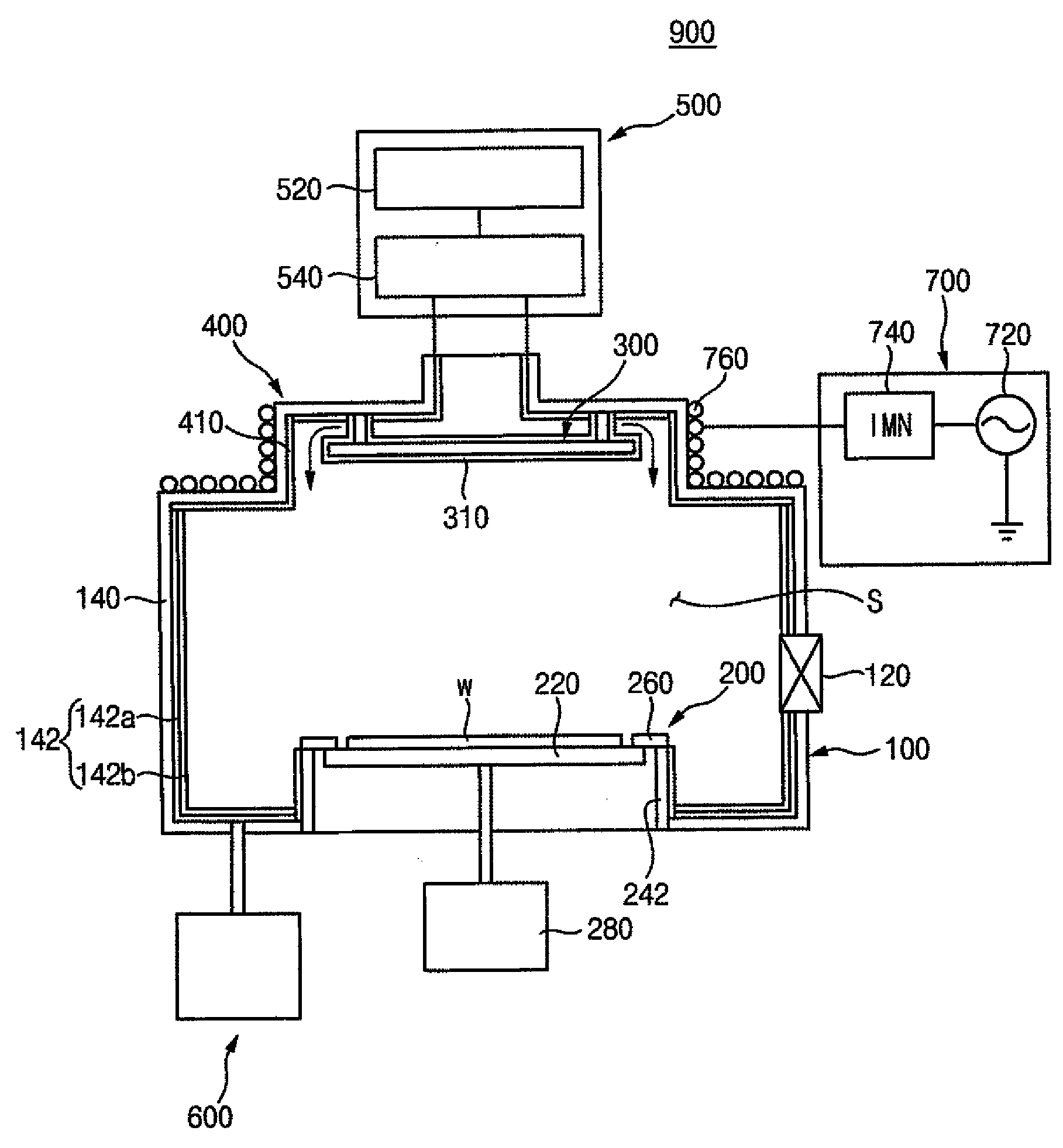

Plasma processing apparatus and method

ActiveCN1973363AEliminate attachmentEtching high speedSemiconductor/solid-state device manufacturingMiniaturizationDc voltage

There is provided a plasma etching device for generating plasma as a processing gas between an upper electrode (34) and a lower electrode (16) and subjecting a wafer (W) to plasma etching. The upper electrode (34) includes a variable DC power source (50) for applying DC voltage so that the absolute value of the self bias voltage Vdc on the surface of the upper electrode (34) becomes large enough to obtain an appropriate sputter effect to the surface and the thickness of the plasma sheath on the upper electrode (34) becomes thick enough to form a desired miniaturization plasma.

Owner:TOKYO ELECTRON LTD

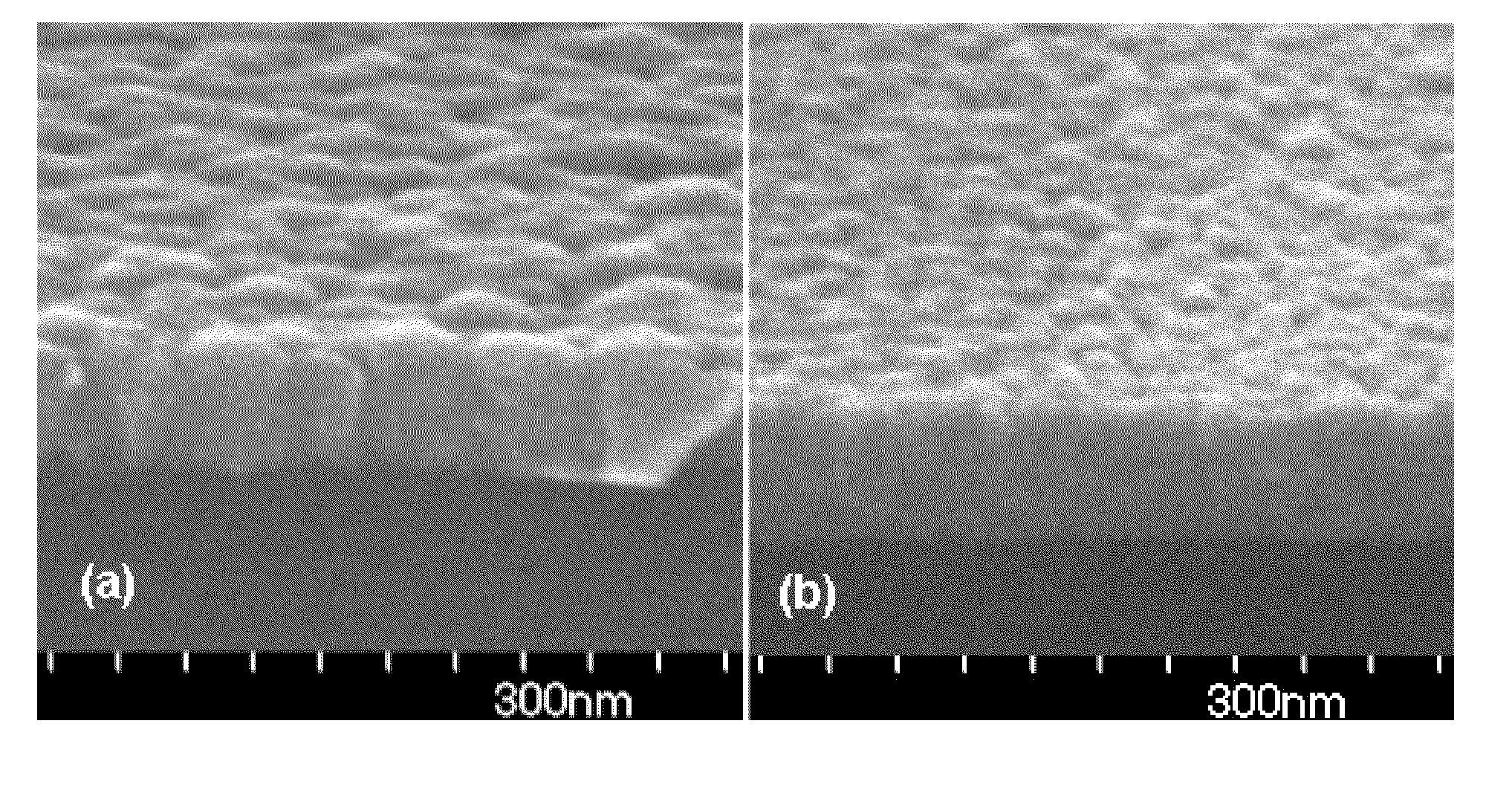

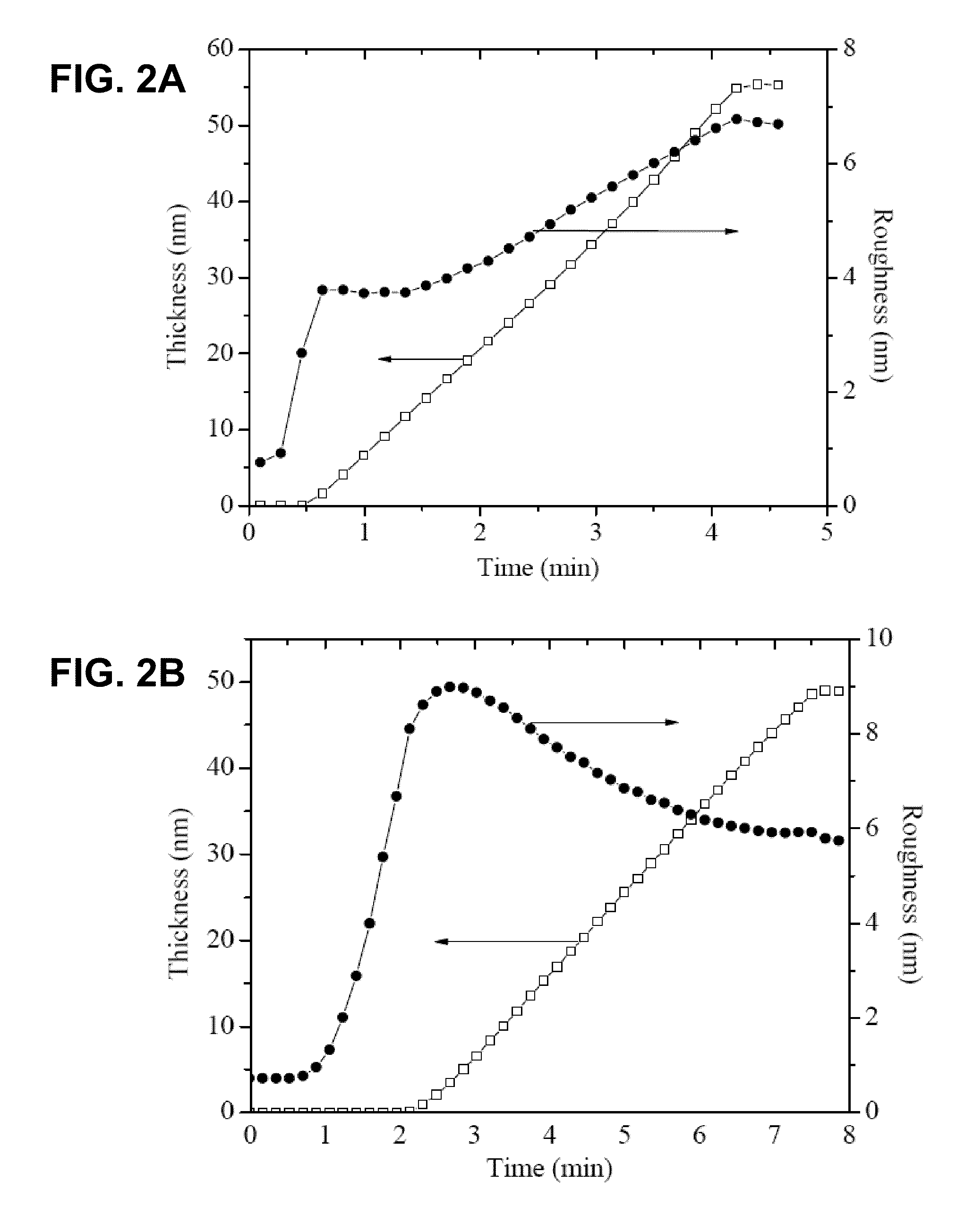

Surface preparation for thin film growth by enhanced nucleation

ActiveUS7943527B2Promote growthEnhanced nucleationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingRemote plasmaOptoelectronics

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

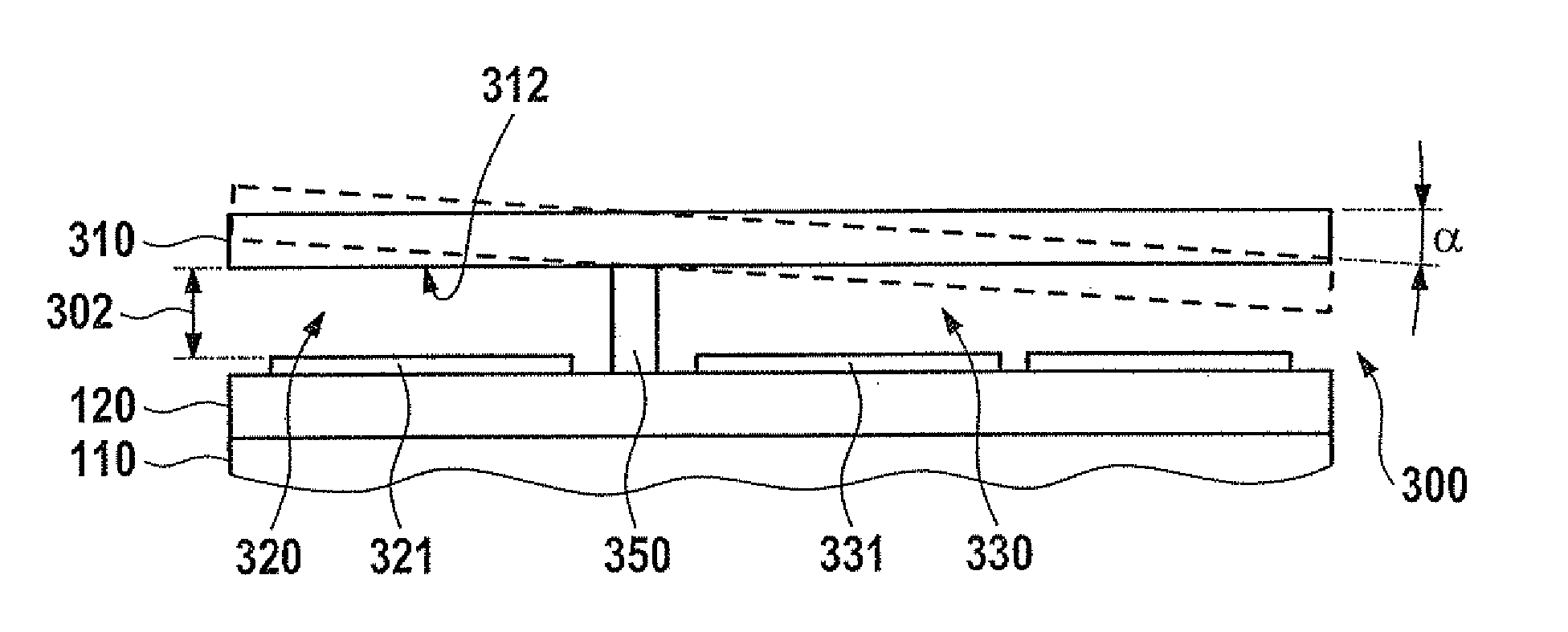

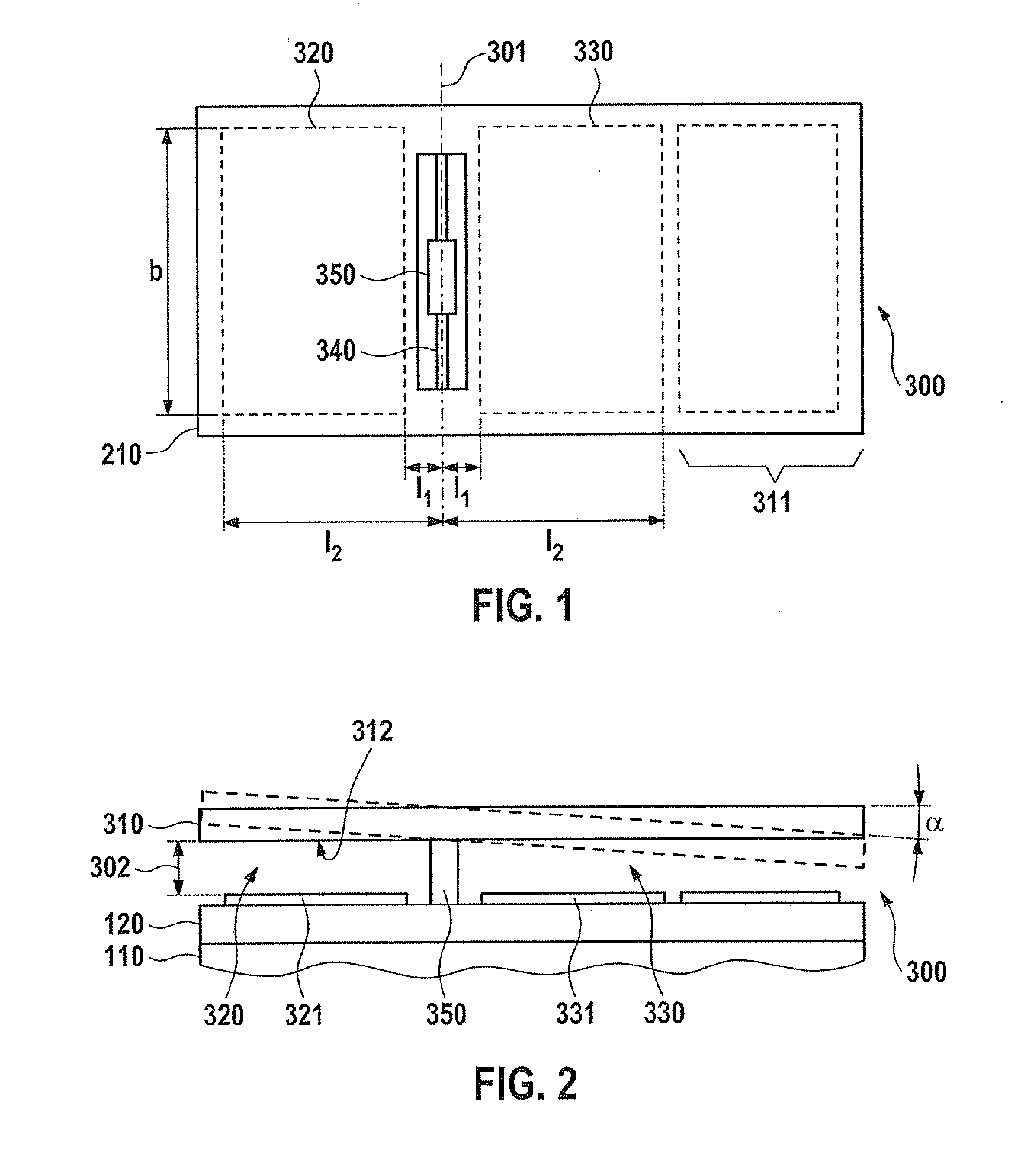

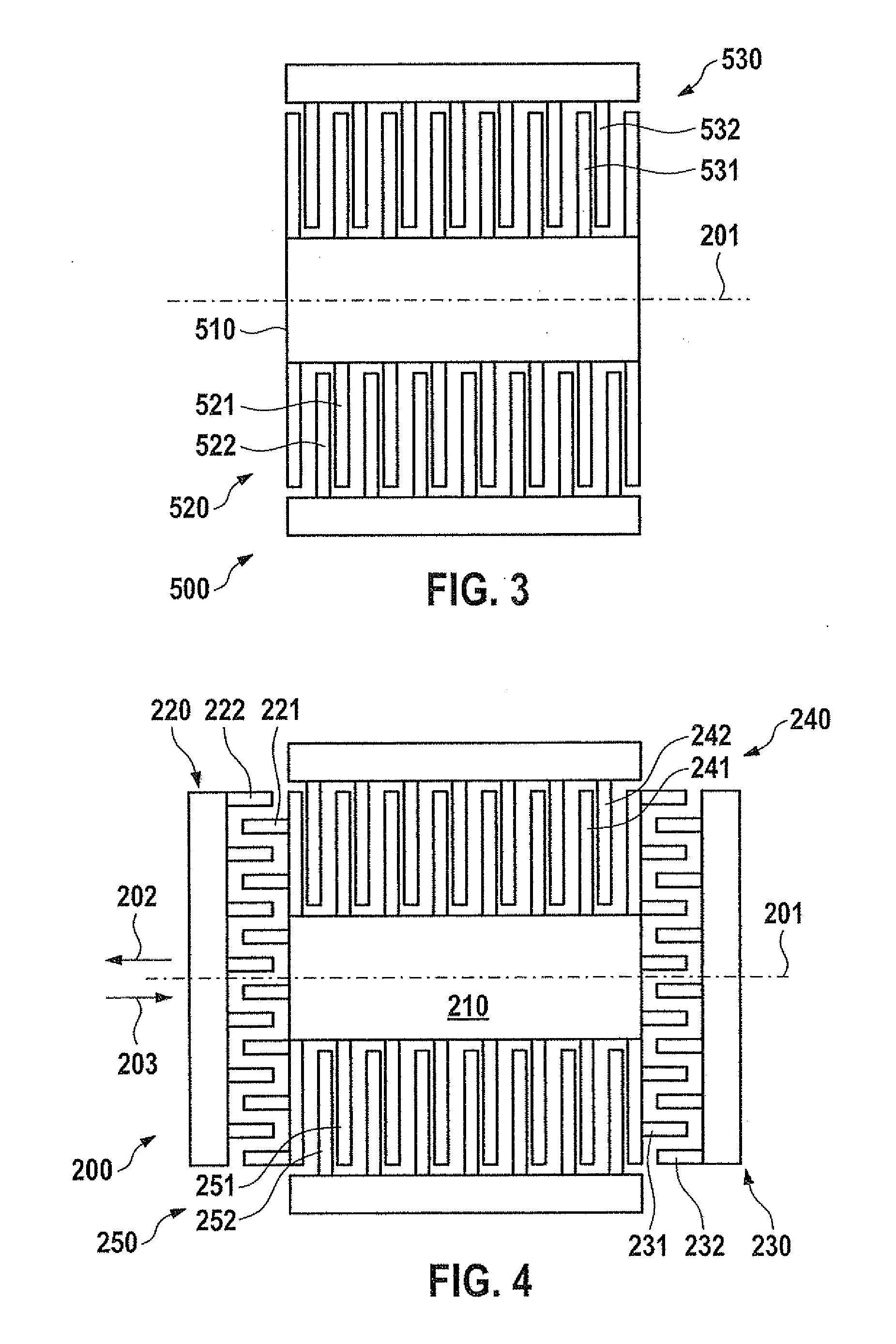

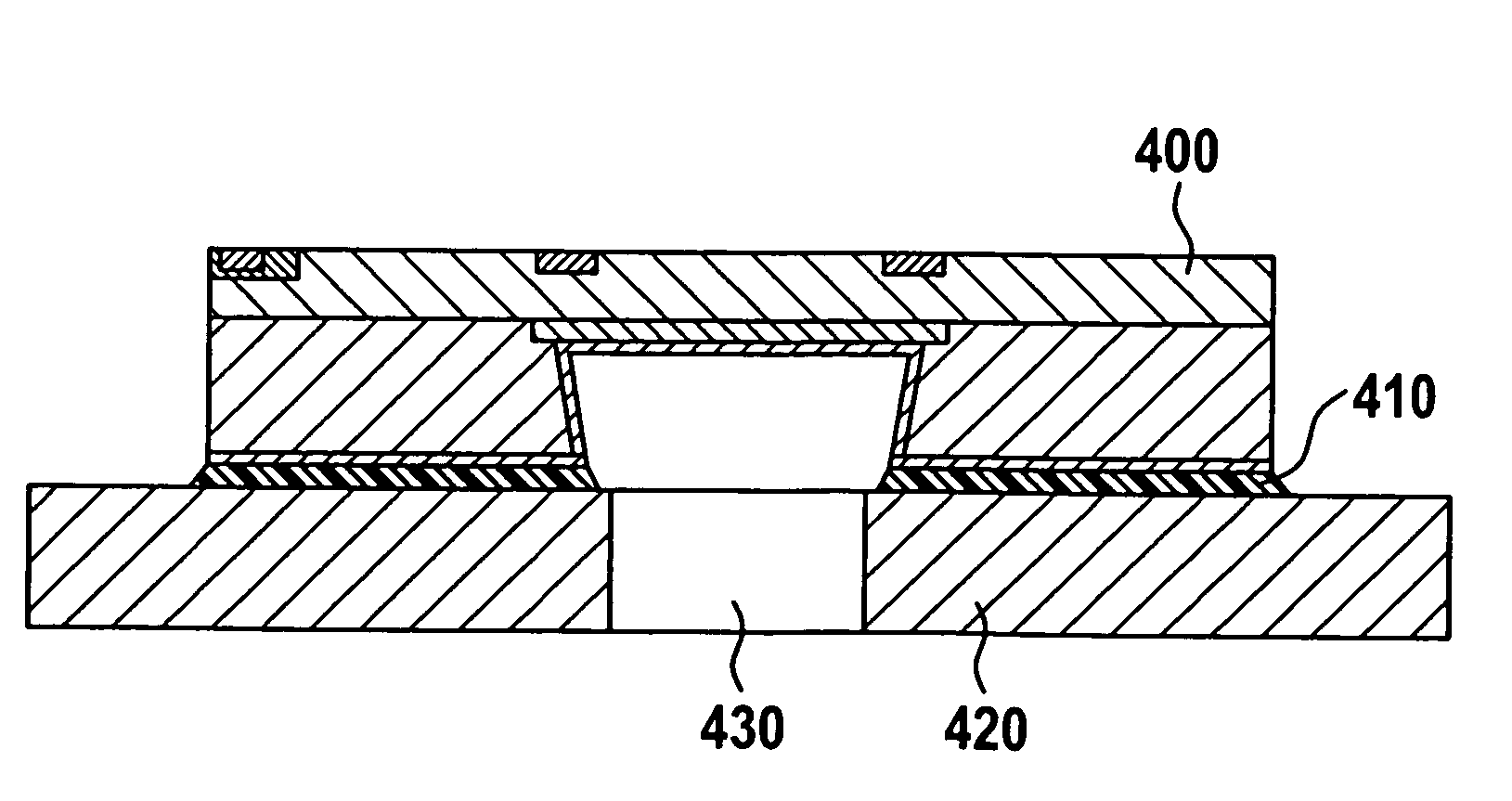

Micromechanical component having a test structure for determining the layer thickness of a spacer layer and method for manufacturing such a test structure

ActiveUS20110296917A1Reduce manufacturing costSimplified determinationResistance/reactance/impedenceAcceleration measurementSeismic massSlice thickness

A micromechanical component is described including a substrate having a spacer layer and a test structure for ascertaining the thickness of the spacer layer. The test structure includes a seismic mass, which is elastically deflectable along a measuring axis parallel to the substrate, a first electrode system and a second electrode system for deflecting the seismic mass along the measuring axis, having a mass electrode, which is produced by a part of the seismic mass, and a substrate electrode, which is situated on the substrate in each case, the first electrode system being designed to be thicker than the second electrode system by the layer thickness of the spacer layer.

Owner:ROBERT BOSCH GMBH

Differential pressure sensor

InactiveUS20050199973A1Low costSimple manufacturing processAcceleration measurement using interia forcesDecorative surface effectsPorous layerDifferential pressure

In a method for manufacturing a micromechanical semiconductor component, e.g., a pressure sensor, a locally limited, buried, and at least partially oxidized porous layer is produced in a semiconductor substrate. A cavity is subsequently produced in the semiconductor substrate from the back, directly underneath the porous first layer, using a trench etch process. The porous first layer is used as a stop layer for the trench. Thin diaphragms having a low thickness tolerance may thus be produced for differential pressure measurement.

Owner:ROBERT BOSCH GMBH

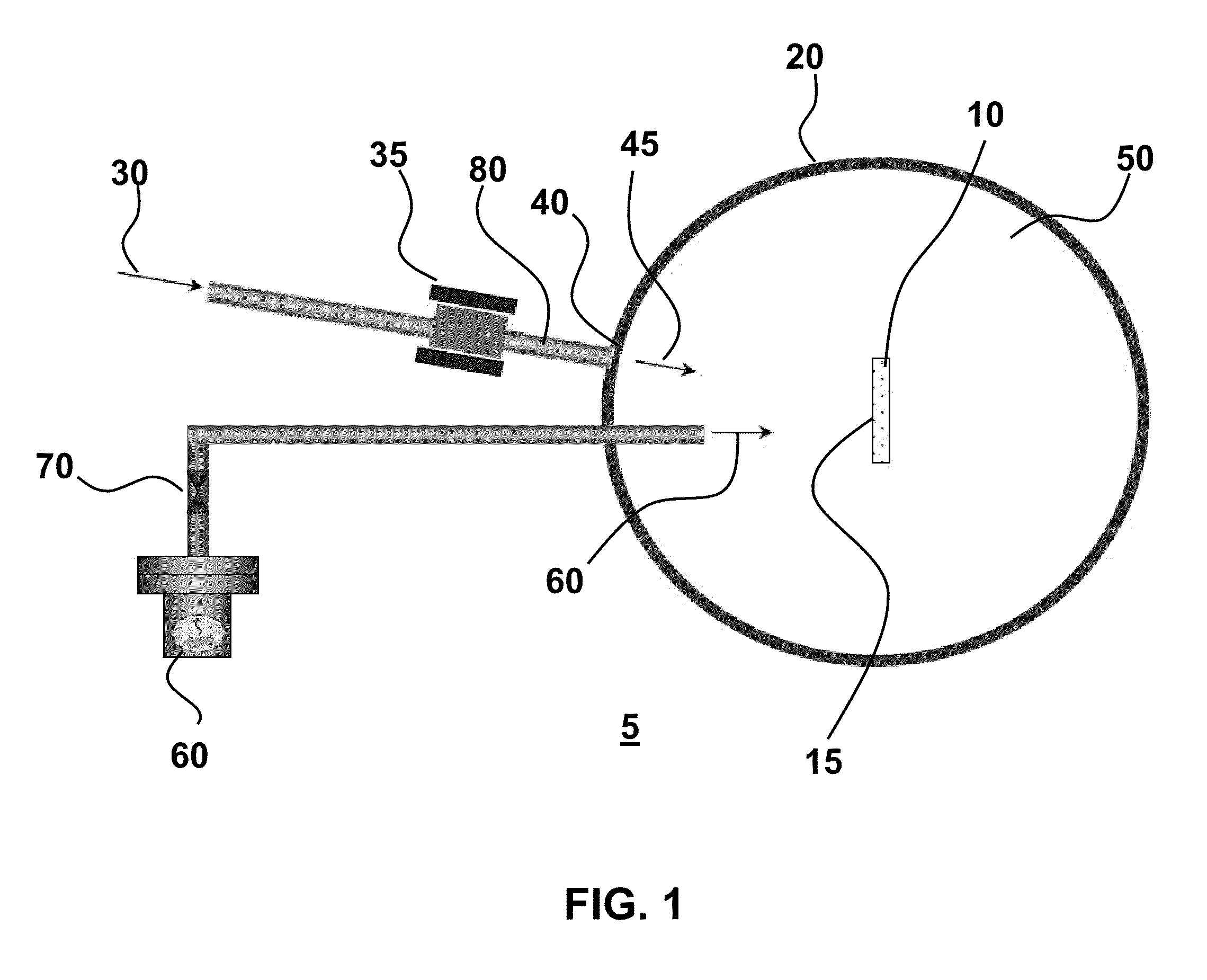

Ion implanter with etch prevention member(s)

ActiveUS20080054194A1Avoid dopingAvoid etchingElectric discharge tubesSemiconductor/solid-state device manufacturingRadio frequencyIon implantation

An apparatus and method of doping ions into a substrate are disclosed and include a process chamber having an inner space in which an ion implantation process is performed, a support unit positioned in the process chamber, supporting a substrate and being electrically connected to a first power source for generating a high frequency pulse, a conductive unit separated from the support unit in such a manner that plasma associated with the ion implantation process is generated between the support unit and the conductive unit, wherein the conductive unit comprises a first etch prevention member preventing the conductive unit from being etched by a source gas used to generate the plasma, and a power port electrically connected to a second power source and generating radio frequency (RF) power applied to the conductive unit.

Owner:SAMSUNG ELECTRONICS CO LTD

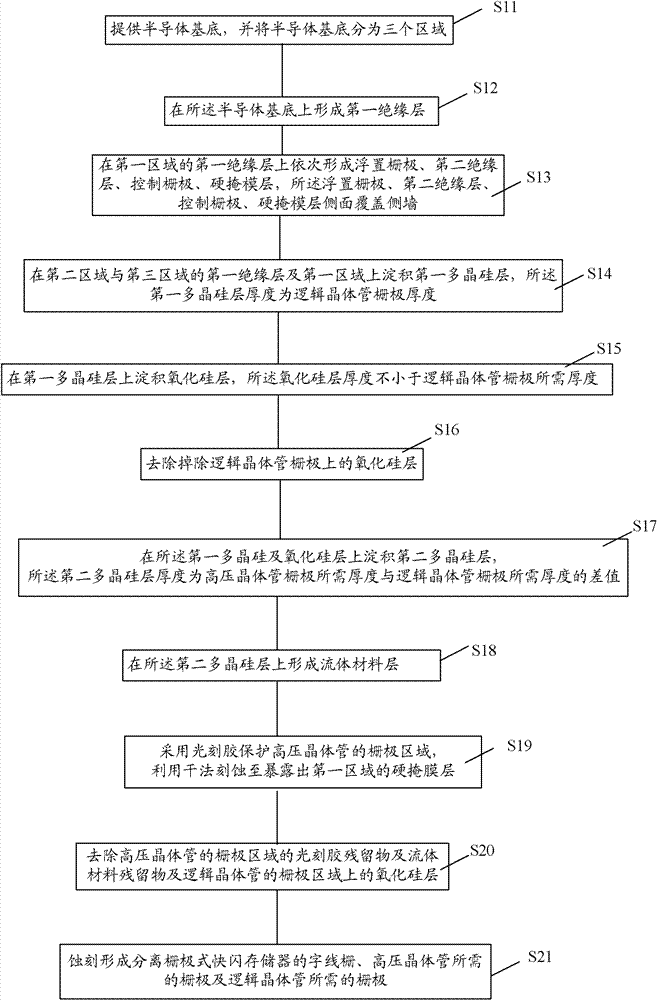

Separated gate type memory embedded into logic circuit and manufacturing method of memory group

ActiveCN102956563AHigh densityRun fastSolid-state devicesSemiconductor/solid-state device manufacturingHigh voltage transistorsSilicon oxide

The invention provides a manufacturing method of separated gate type flash memories embedded into logic circuits. Compared with a method of separately manufacturing the separated gate type flash memories, the manufacturing method includes four additional steps of once more polycrystalline deposition, once more silicon oxide deposition, once more etching and once more fluid coverage. The characteristic of good fluidity of fluid materials is utilized, grooves, especially deep grooves can be filled, and areas required to be protected can be prevented from being etched in the etching step. The separated gate type flash memories manufactured by the method are embedded into peripheral circuits of high-voltage transistors and logic transistors so that the separated gate type flash memories, the high-voltage transistors and the logic transistors can be manufactured on one integrated circuit, and the integration of the separated gate type flash memories, the high-voltage transistors and the logic transistors is high in density and quick in running. Further, integrated chips are smaller so that cost of each integrated chip is lowered.

Owner:SEMICON MFG INT (SHANGHAI) CORP

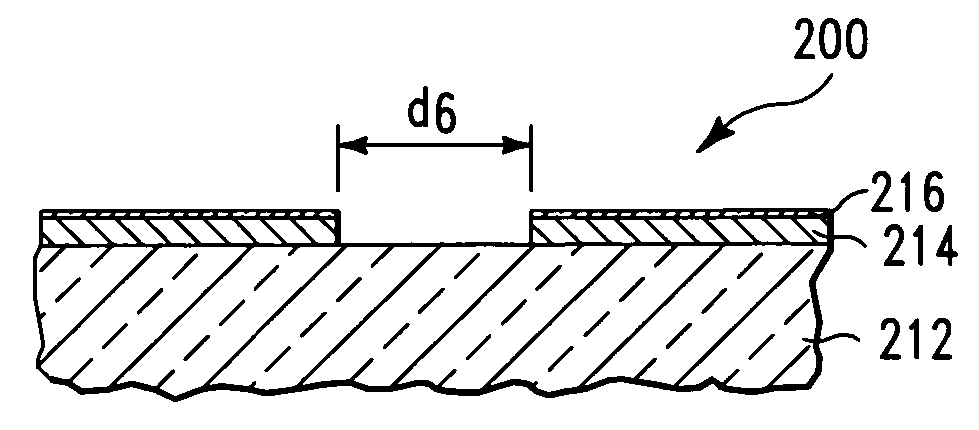

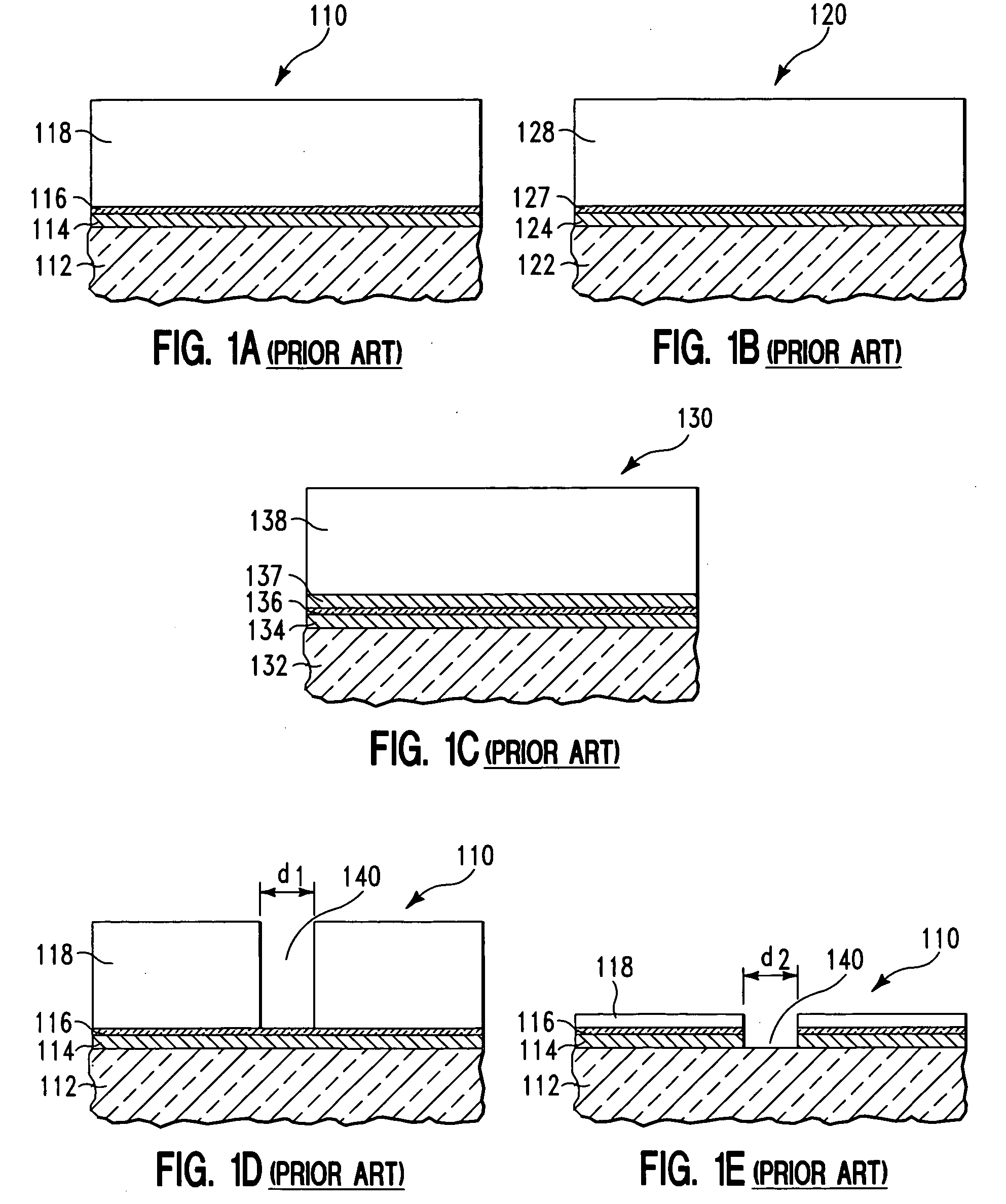

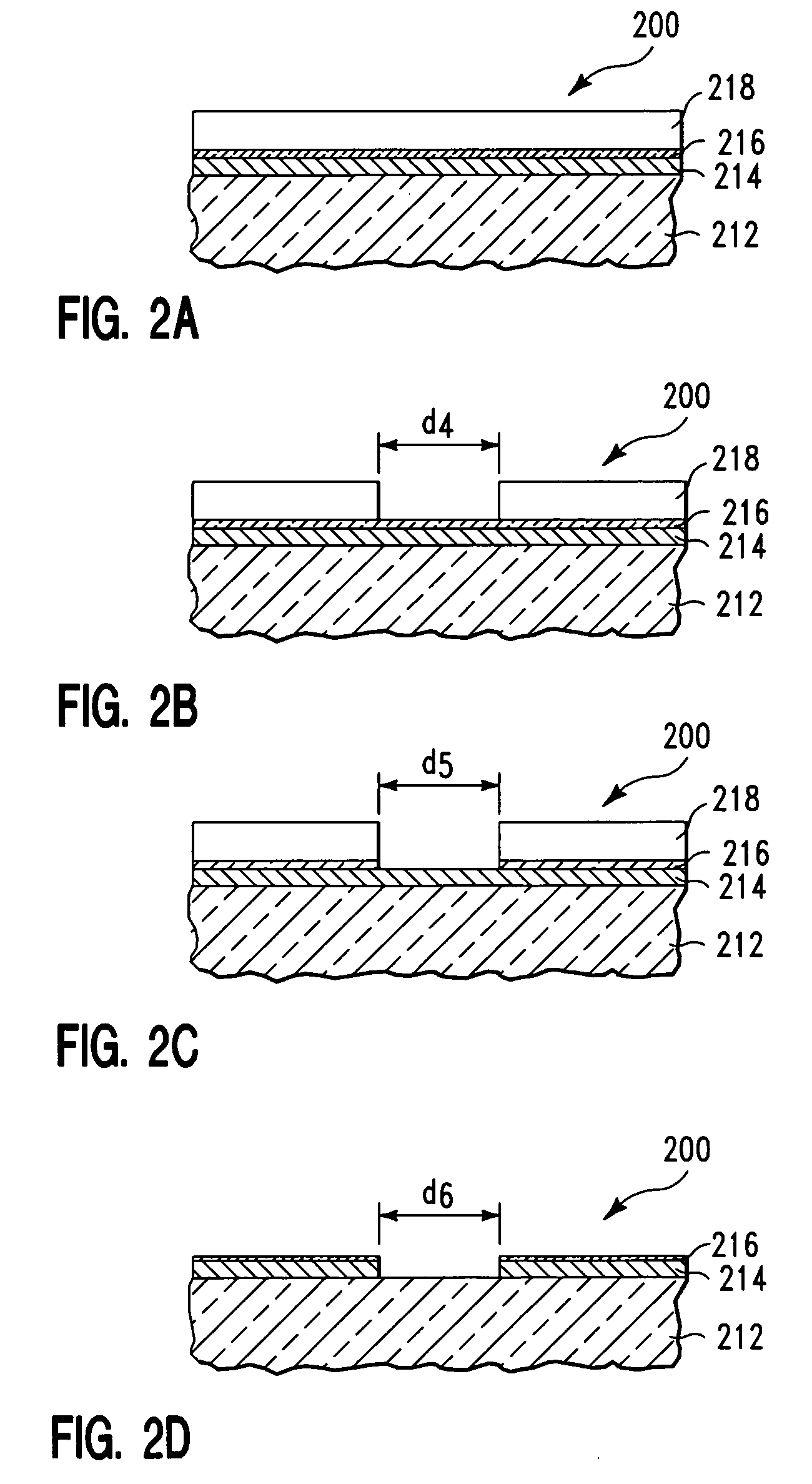

Reticle fabrication using a removable hard mask

InactiveUS20050170655A1Reduced critical dimension biasCritical dimension reductionSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingResistDevice material

We have reduced the critical dimension bias for reticle fabrication. Pattern transfer to the radiation-blocking layer of the reticle substrate essentially depends upon use of a hard mask to which the pattern is transferred from a photoresist. The photoresist pull back which occurs during pattern transfer to the hard mask is minimalized. In addition, a hard mask material having anti-reflective properties which are matched to the reflective characteristics of the radiation-blocking layer enables a reduction in critical dimension size and an improvement in the pattern feature integrity in the hard mask itself. An anti-reflective hard mask layer left on the radiation-blocking layer provides functionality when the reticle is used in a semiconductor device manufacturing process.

Owner:APPLIED MATERIALS INC

Self-alignment of metal and via using selective deposition

ActiveUS9837314B2Precise patternAvoid etchingSemiconductor/solid-state device manufacturingTectorial membraneSelective deposition

Techniques herein include methods of patterning substrates such as for back end of line (BEOL) metallization processes. Techniques herein enable fully self-aligned vias and lines. Processes herein include using selective deposition, protective films and combination etch masks for accurately patterning a substrate. In a substrate having uncovered portions of metal material and dielectric material, the dielectric material is grown upwardly without covering metal material. This raised dielectric material is conformally protected and used in subsequent patterning step to align via and line placement. Such combinations mitigate overlay errors.

Owner:TOKYO ELECTRON LTD

Method of treating inlaid copper for improved capping layer adhesion without damaging porous low-k materials

InactiveUS6875694B1Reduce time delayAvoid etchingSemiconductor/solid-state device manufacturingCopperMaterials science

An exposed surface of inlaid Cu is plasma treated for improved capping layer adhesion while controlling plasma conditions to avoid damaging porous low-k materials. Embodiments include forming a dual damascene opening in a porous dielectric material having a dielectric constant (k) of up to 2.4, e.g., 2.0 to 2.2, filling the opening with Cu, conducting CMP, plasma treating the exposed Cu surface in NH3 or H2 at a low power, e.g., 75 to 125 watts, for a short period of time, e.g., 2 to 8 seconds, without etching the porous low-k material and depositing a capping layer, e.g., silicon nitride or silicon carbide.

Owner:GLOBALFOUNDRIES INC

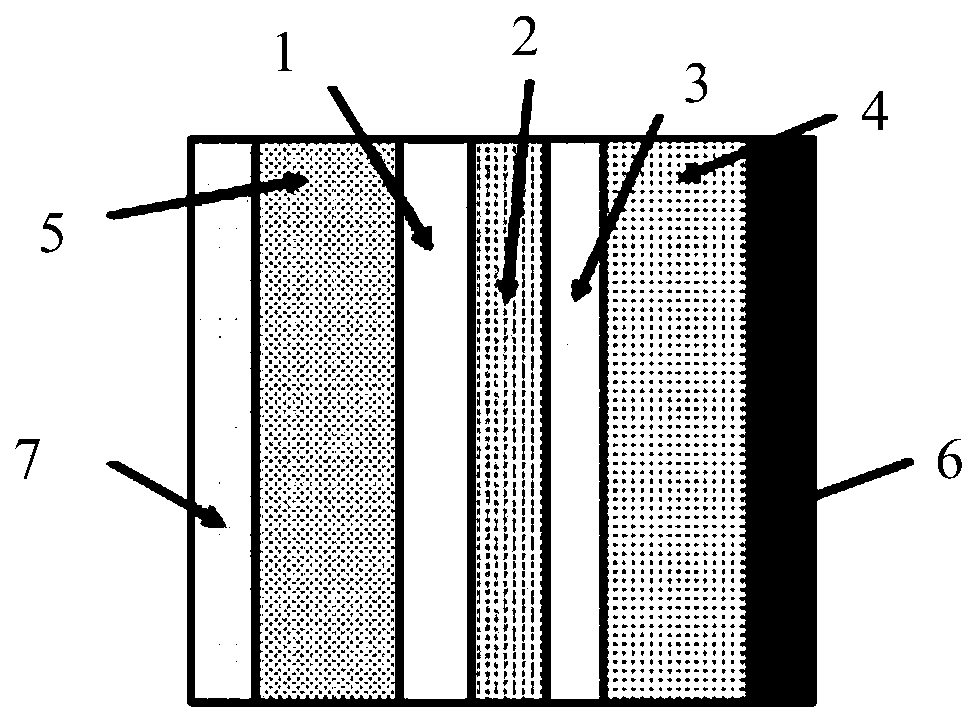

Lithium supplementing diaphragm of lithium ion battery

ActiveCN110676420AImprove the first Coulombic efficiencyImprove cycle performanceSecondary cellsCell component detailsPhysicsMetallic lithium

The invention provides a lithium supplementing diaphragm of a lithium ion battery. The lithium supplementing diaphragm comprises a plurality of diaphragm layers which are overlapped with one another;a metal lithium layer is arranged on the diaphragm layers; a protective layer is arranged on the metal lithium layer; and the diaphragm layers are polymer films. The lithium supplementing diaphragm ofthe lithium ion battery can be directly used for the pre-lithiation (lithium supplementing) of the negative electrode of the lithium ion battery, so that the first coulombic efficiency and cycle performance of the lithium ion battery are improved; the metal lithium layer is prevented from being etched by electrolyte and environment atmosphere; the metal lithium layer is prevented from irreversibly and chemically reacting with a negative electrode active layer; and the pre-lithiation or lithium supplementing efficiency of the electrode is improved.

Owner:复阳固态储能科技(溧阳)有限公司