Patents

Literature

146results about How to "Improve the selection ratio" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Silicon nitride film etching solution

InactiveCN107573940AReduce or suppress the production ofImprove the selection ratioSurface treatment compositionsSilane compoundsSilicone oil

The invention relates to a silicon nitride film etching solution, comprising first silicone compound, whose silicone atom is dependently combined with over three hydrophilic functional groups, and second silicone compound, whose silicone atom is dependently combined with one or two hydrophilic functional groups.

Owner:OCI

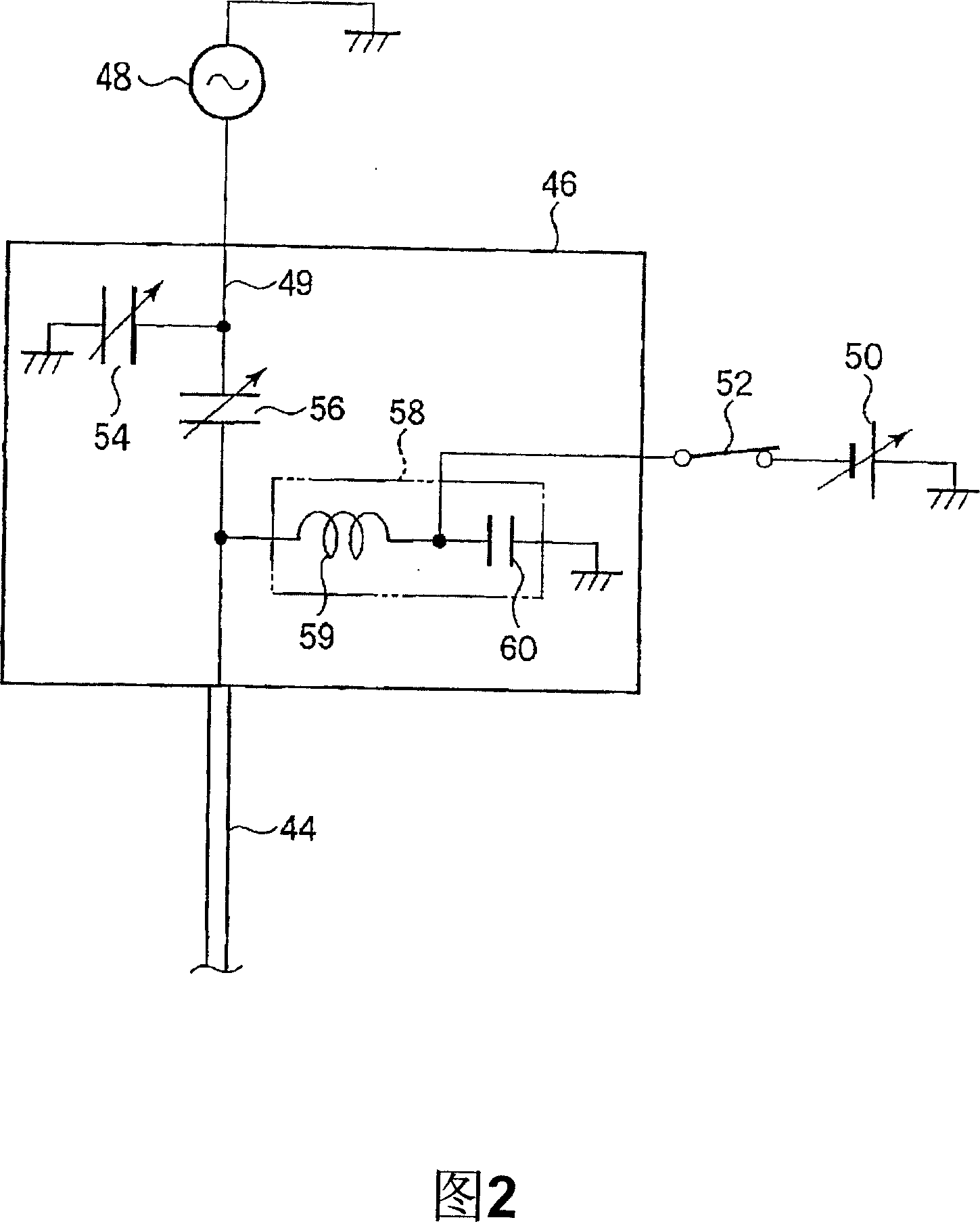

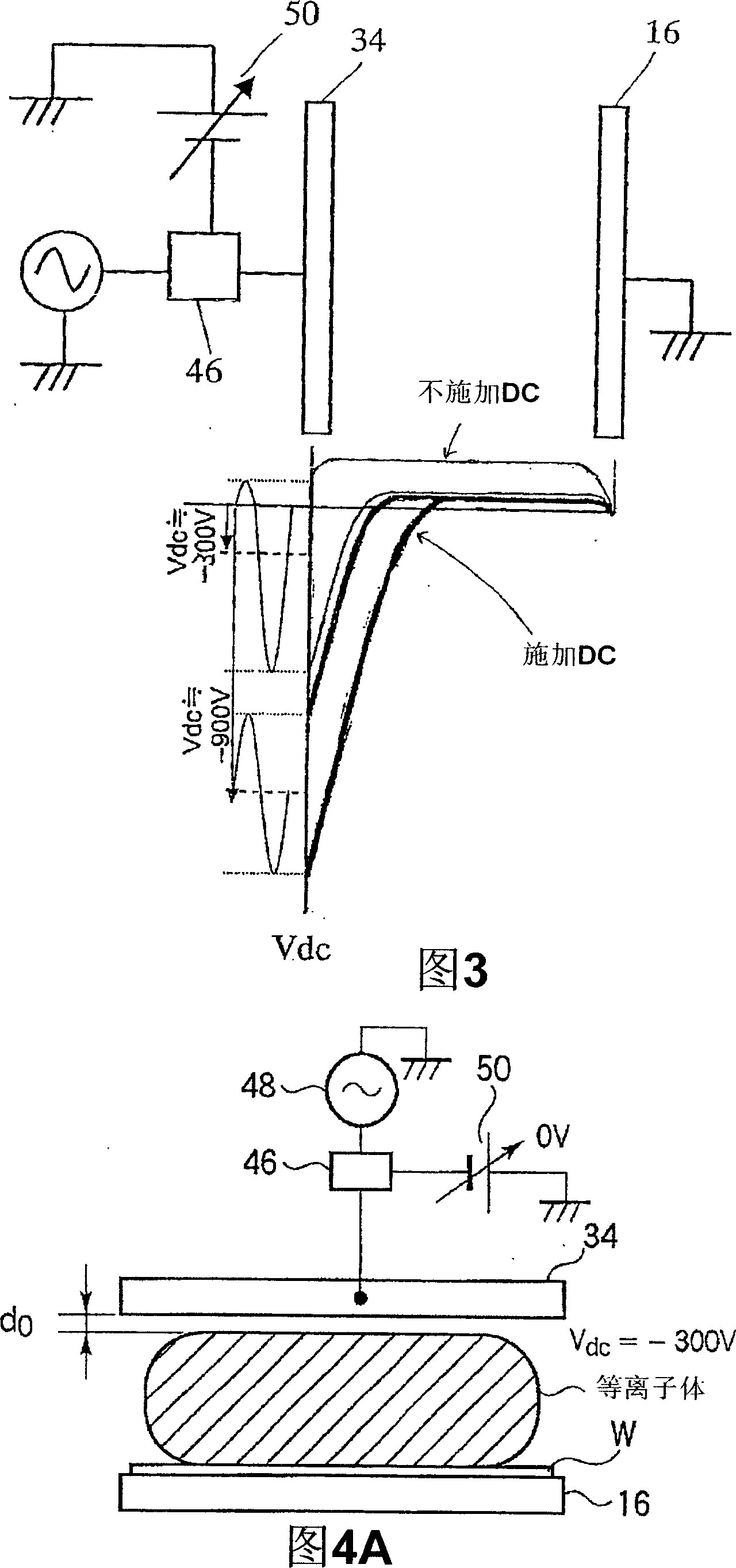

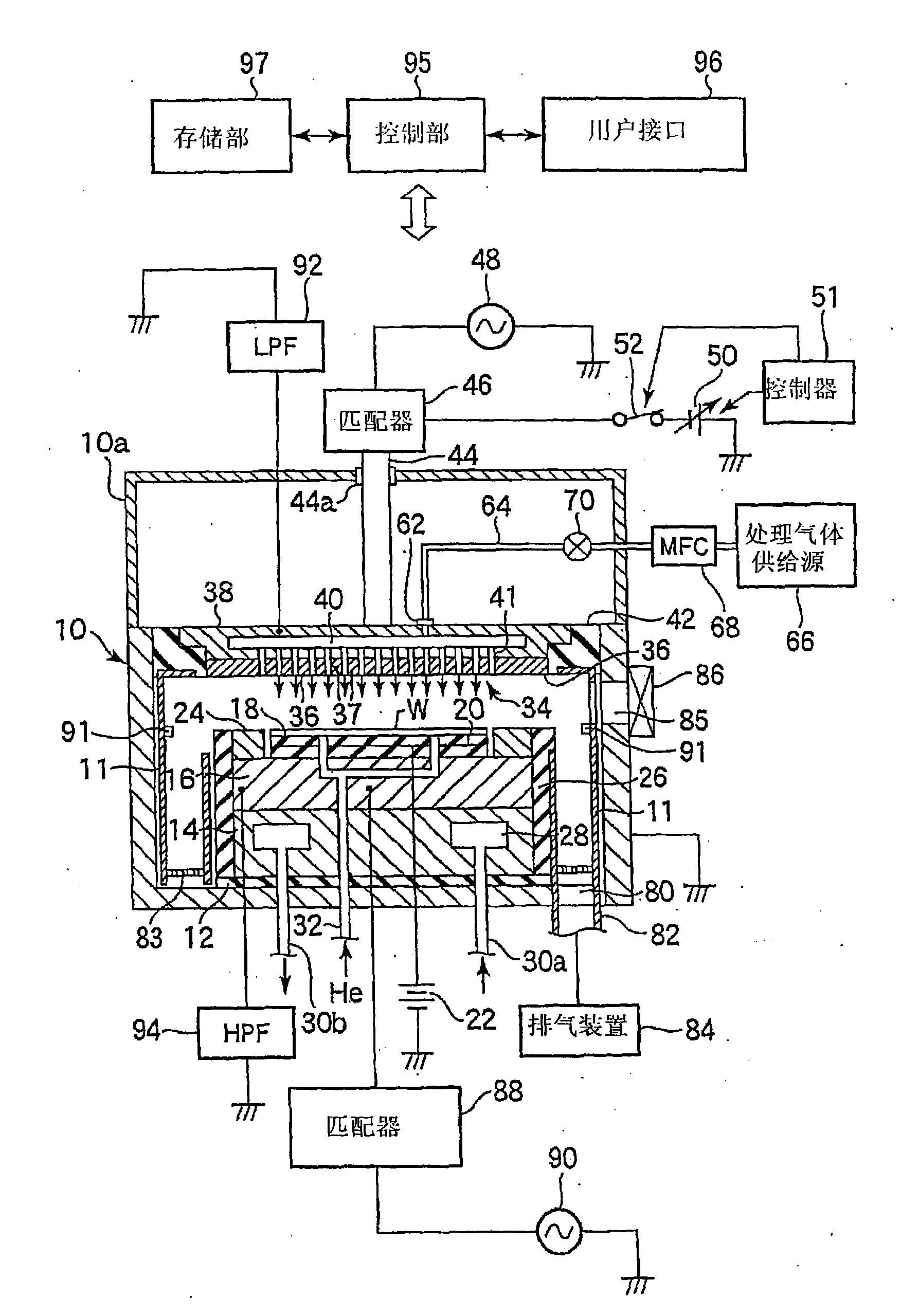

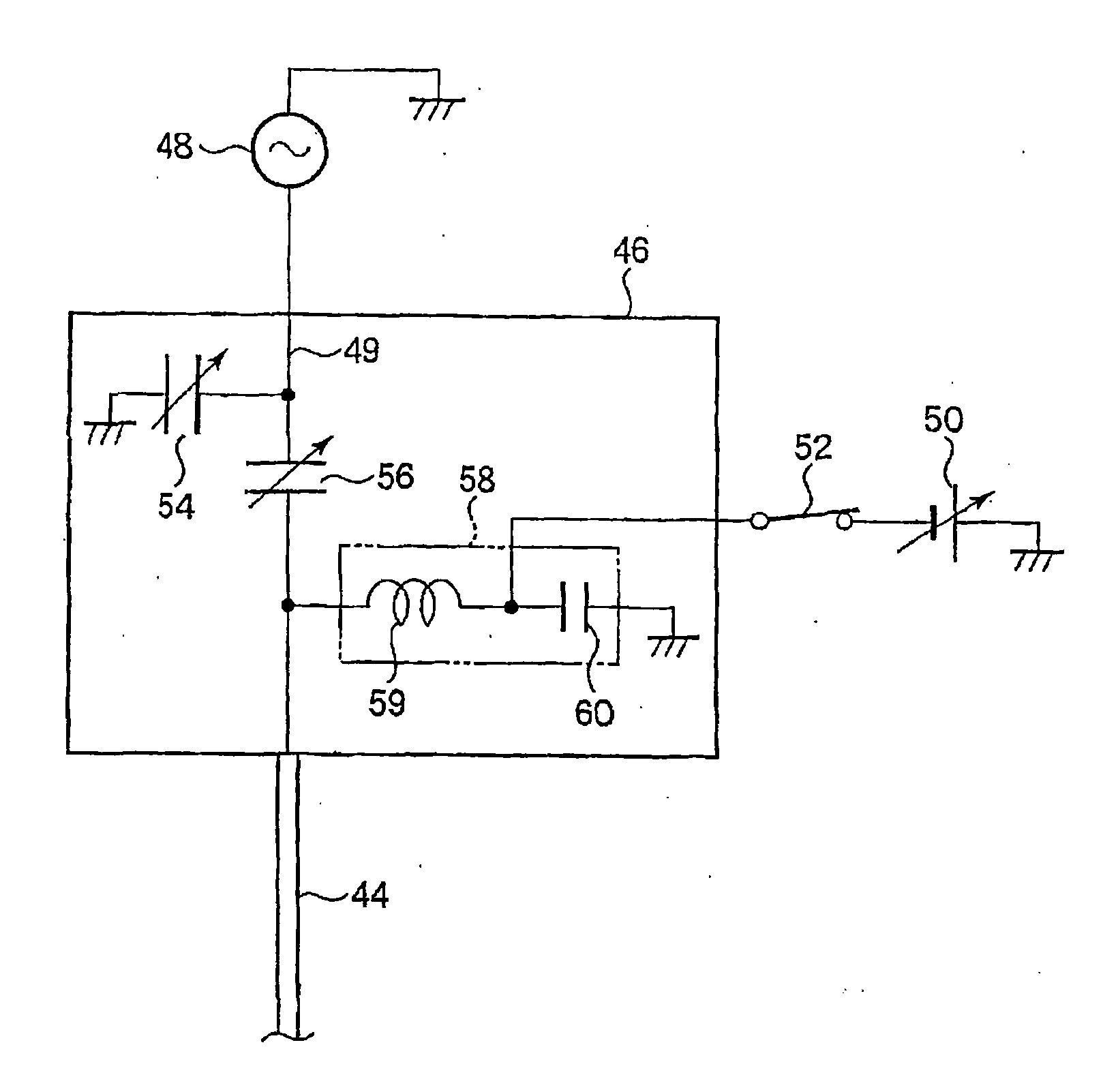

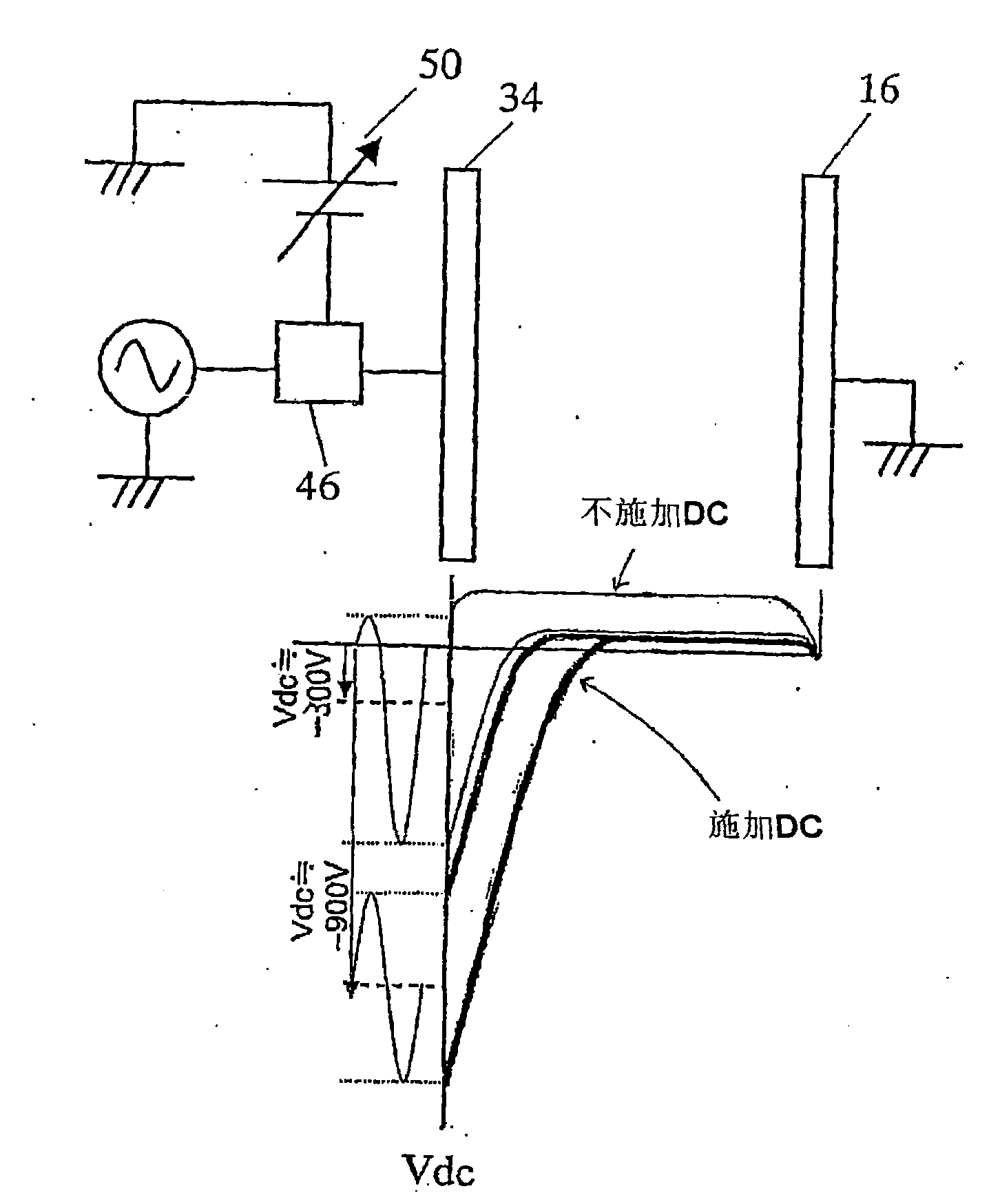

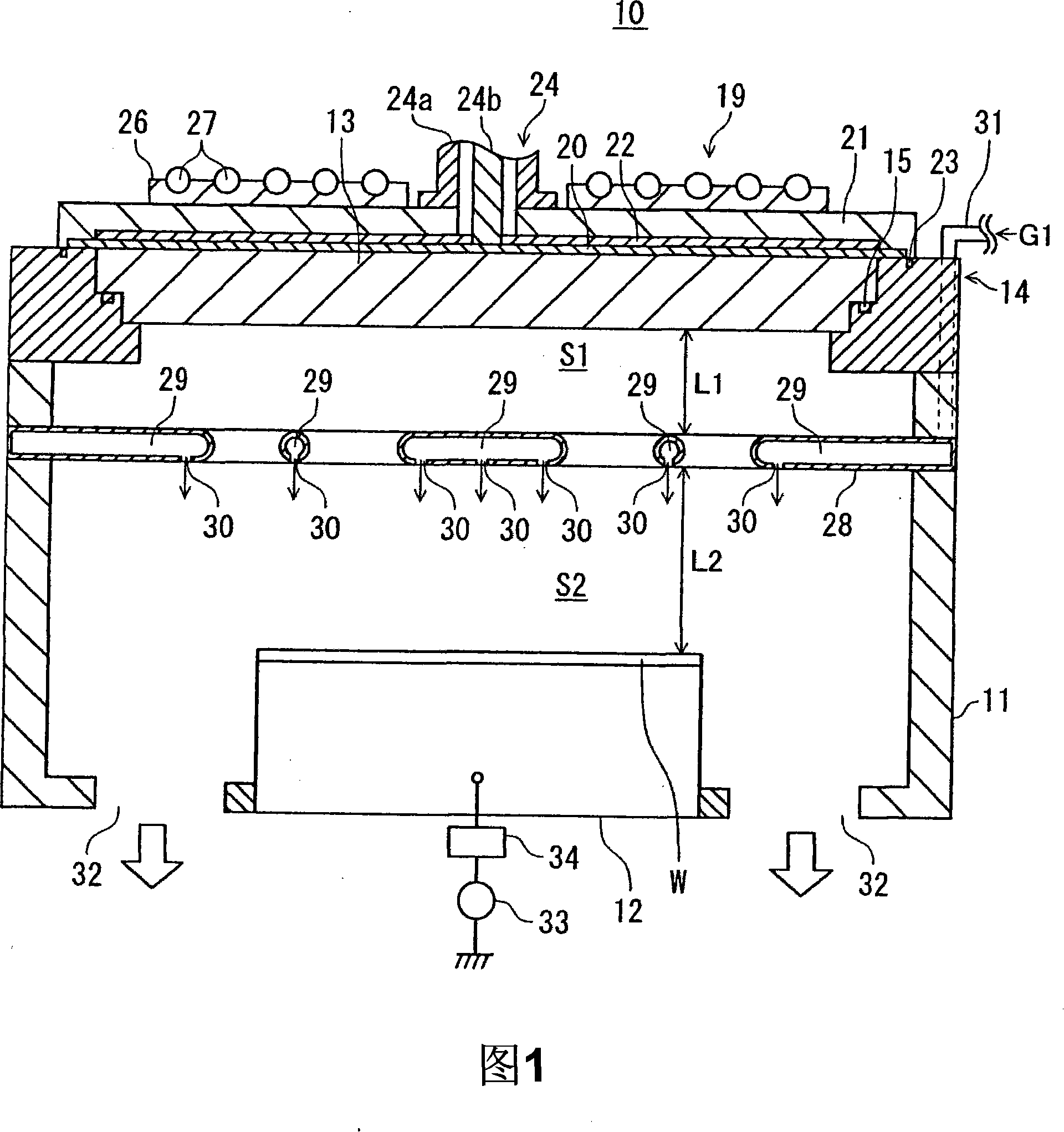

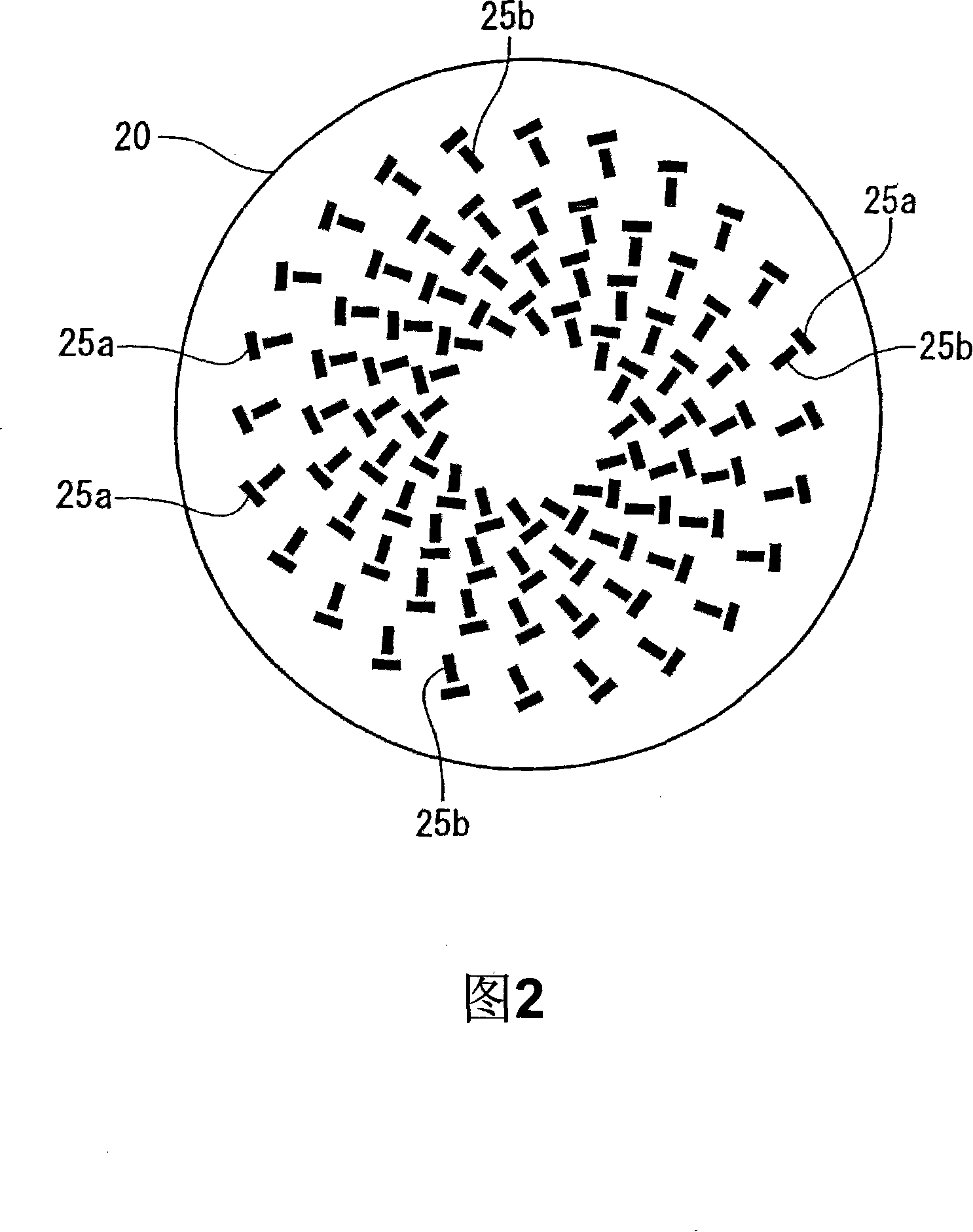

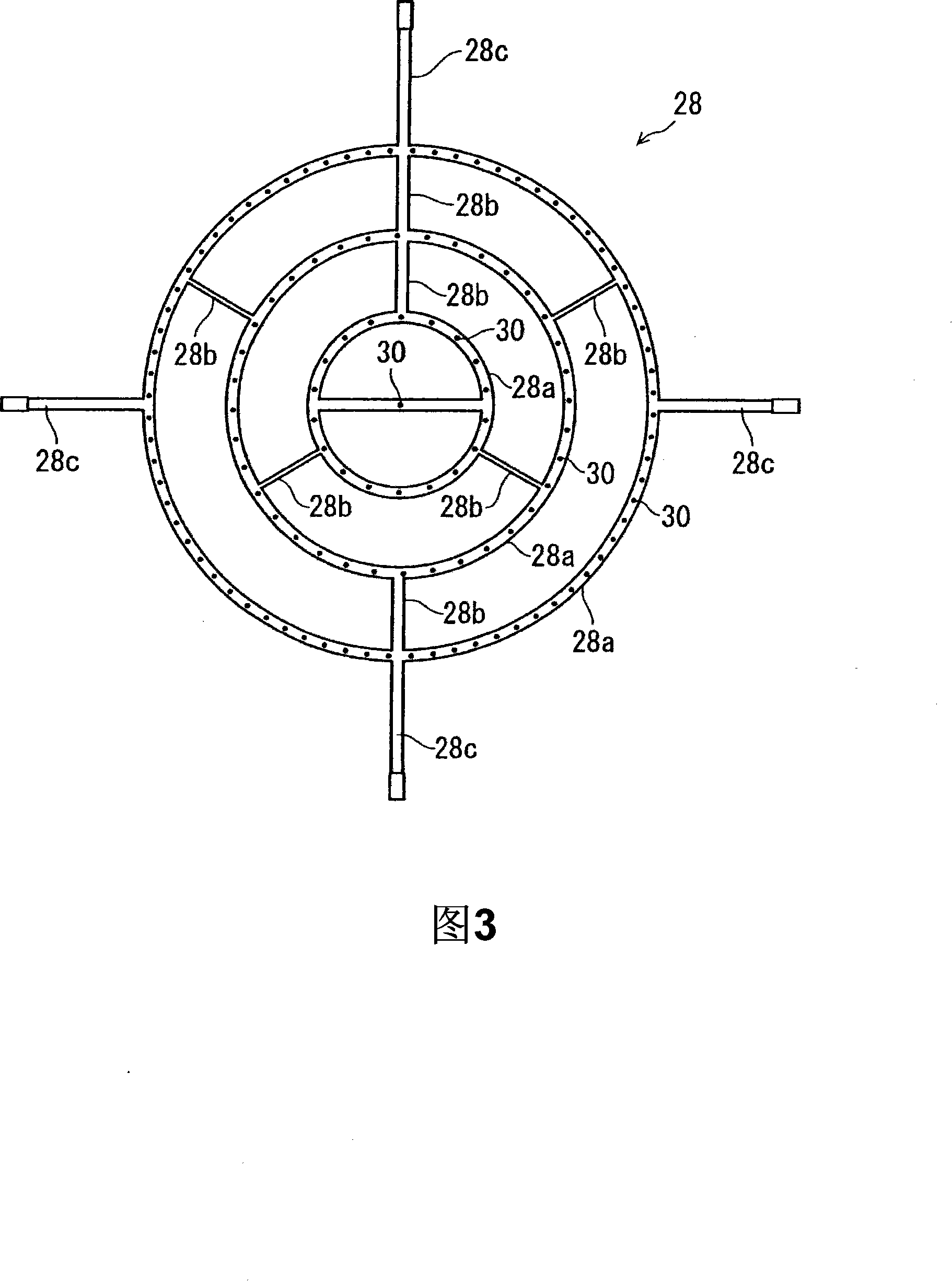

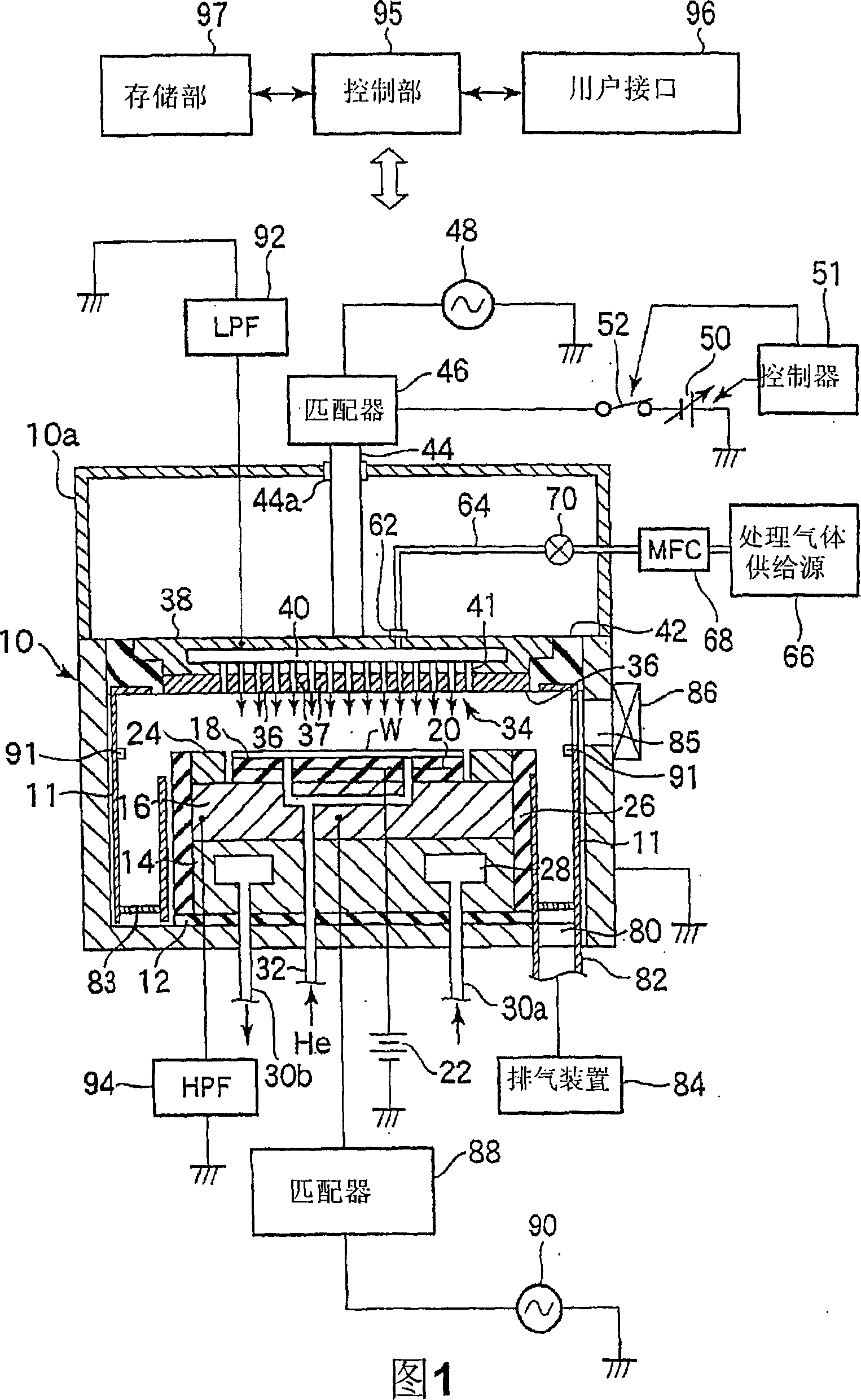

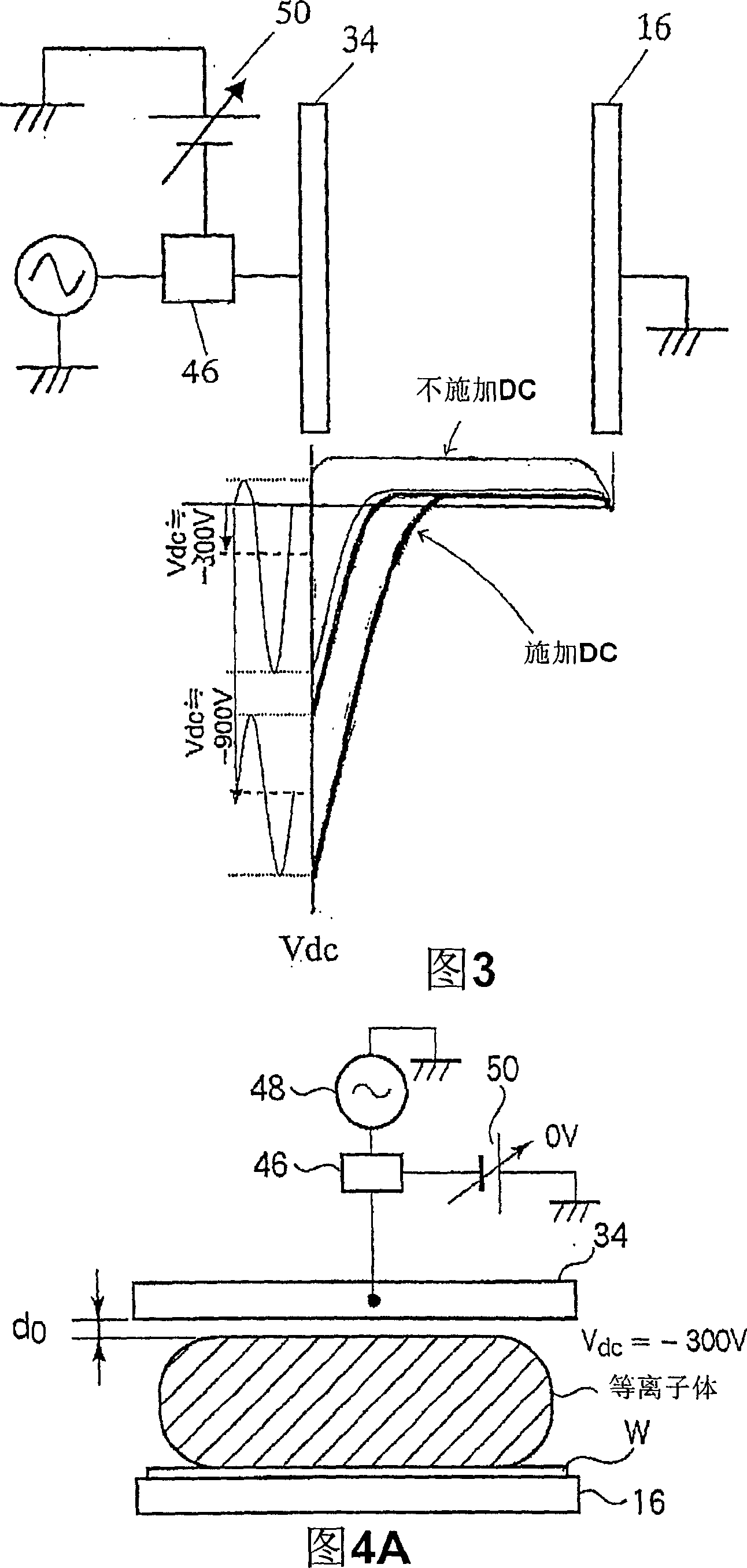

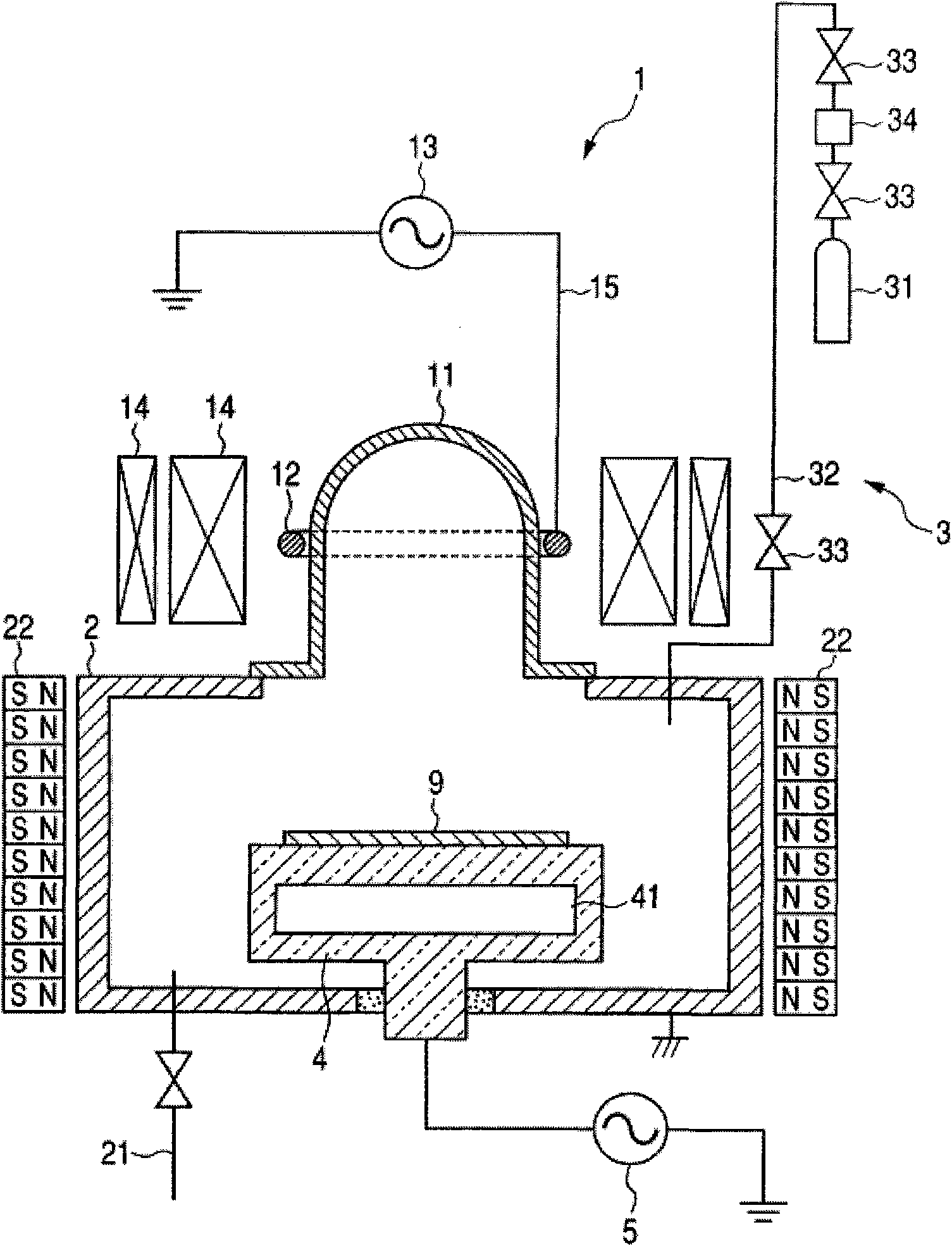

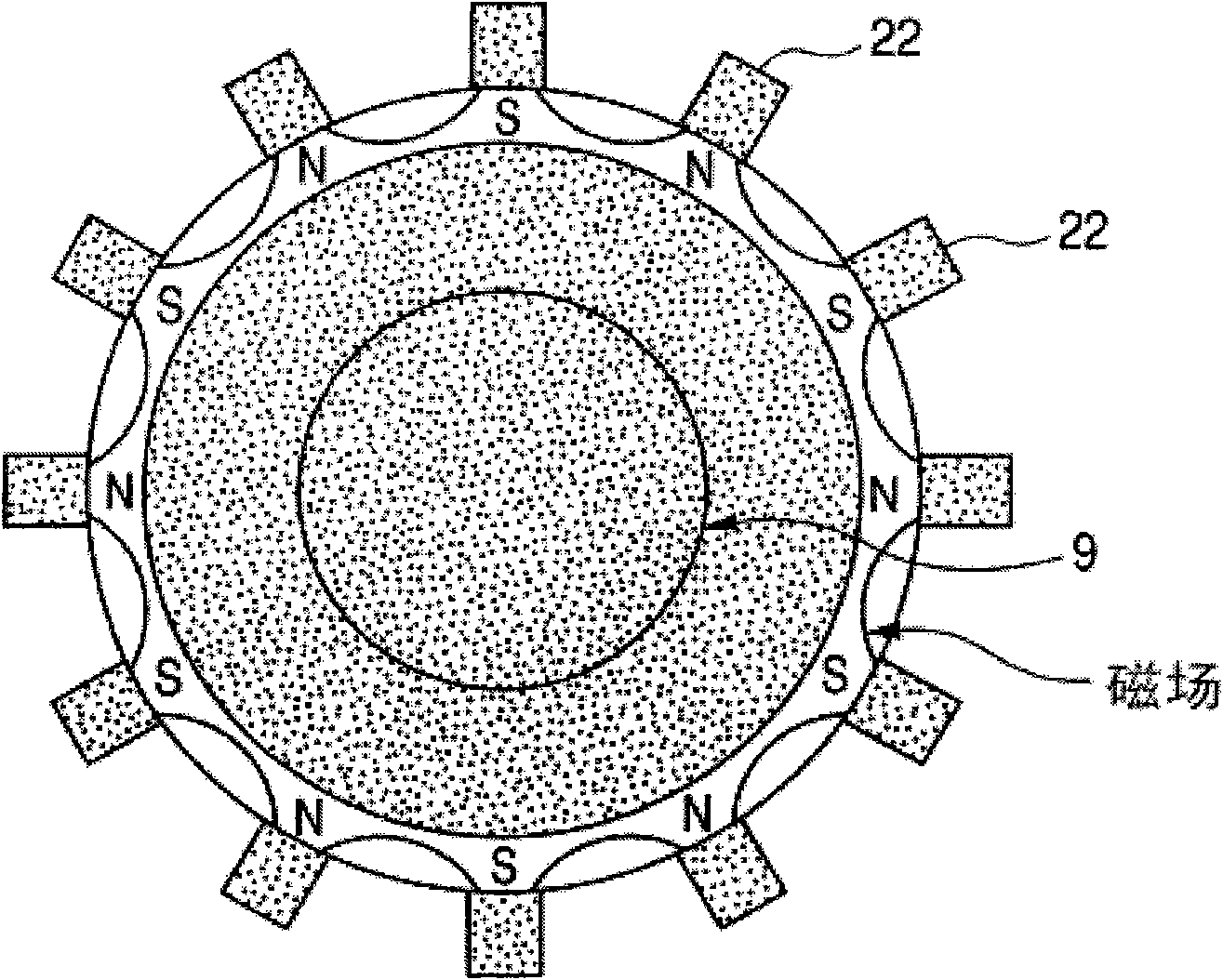

Plasma processing apparatus and method

ActiveCN1973363AEliminate attachmentEtching high speedSemiconductor/solid-state device manufacturingMiniaturizationDc voltage

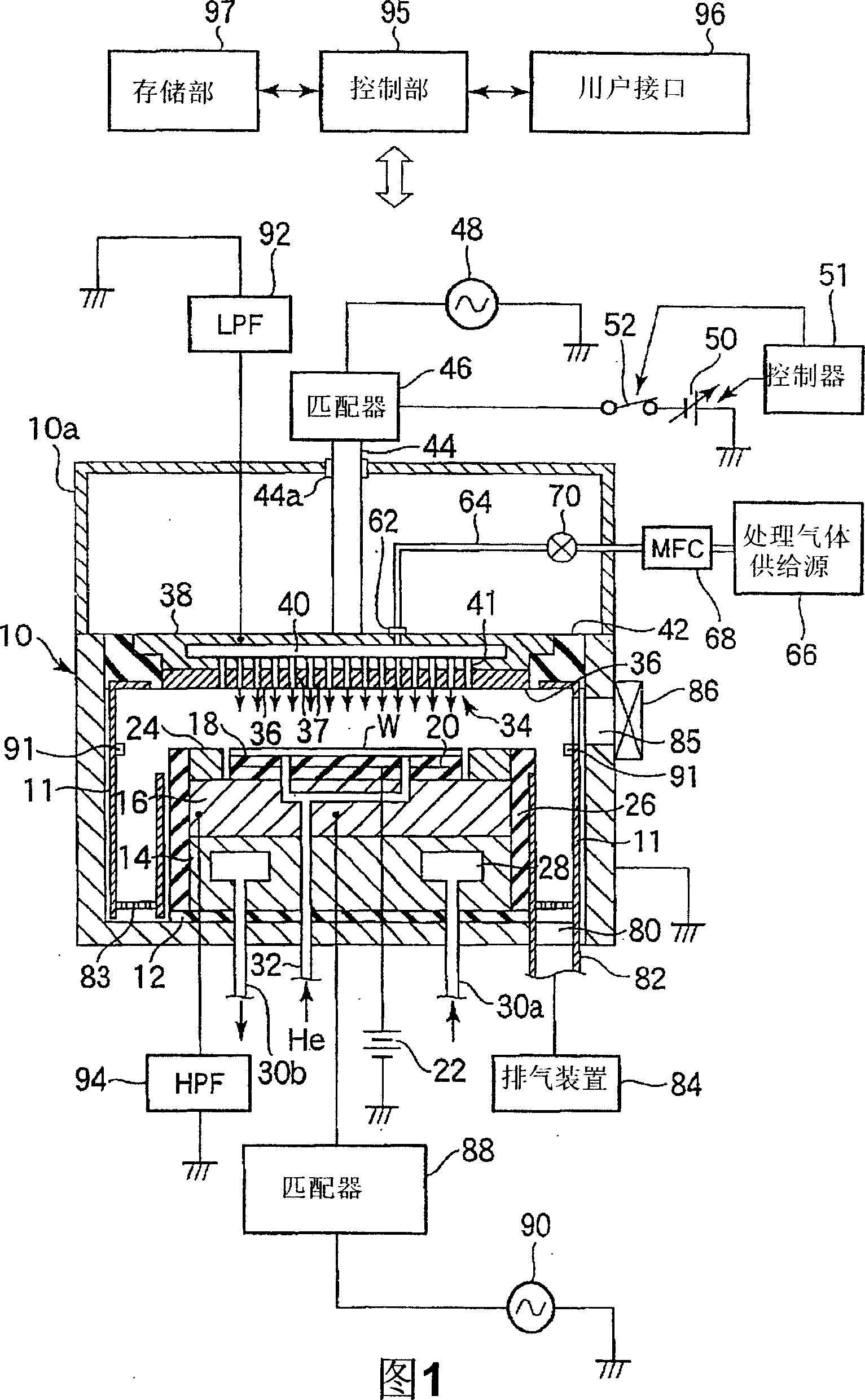

There is provided a plasma etching device for generating plasma as a processing gas between an upper electrode (34) and a lower electrode (16) and subjecting a wafer (W) to plasma etching. The upper electrode (34) includes a variable DC power source (50) for applying DC voltage so that the absolute value of the self bias voltage Vdc on the surface of the upper electrode (34) becomes large enough to obtain an appropriate sputter effect to the surface and the thickness of the plasma sheath on the upper electrode (34) becomes thick enough to form a desired miniaturization plasma.

Owner:TOKYO ELECTRON LTD

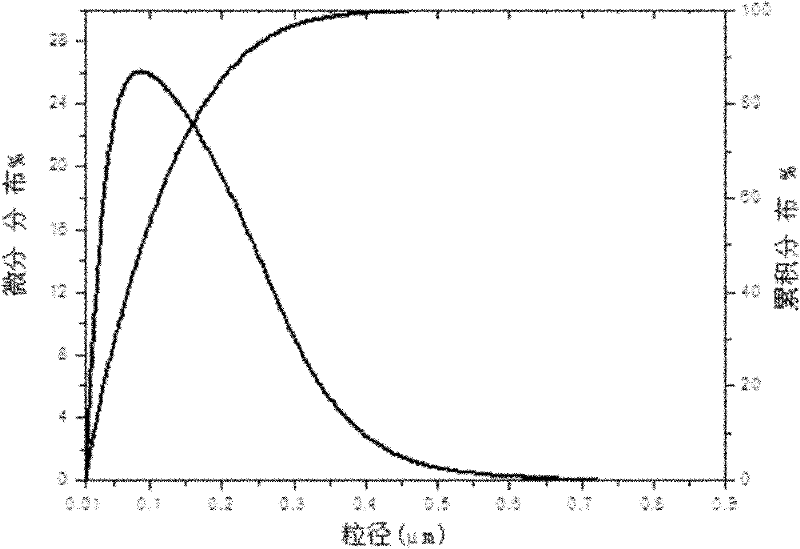

Chemical and mechanical water-free polishing liquid for lithium-cessium borate crystal and leveling method

InactiveCN1858134AGood suspensionModerate concentrationPolishing machinesAqueous dispersionsLithiumOrganic solvent

The present invention discloses a kind of chemical and mechanical water-free polishing liquid for polishing lithium-cesium borate crystal and its polishing method. The polishing liquid of the present invention consists of nanometer silica abrasive 4-8 wt%, organic solvent 72-95 wt%, organic alkali 0.5-10 wt% and surfactant 0.5-10 wt%. It is used in polishing lithium-cesium borate crystal at polishing pressure of 0.05 MPa to 0.1 MPa, polishing disc speed of 30 rpm to 60 rpm, and polishing time of 5-10 min. The water-free polishing liquid of the present invention has high flowability, no toxicity, no pollutant, no corrosion, moderate concentration and good floatability, and can obtain polished lithium-cesium borate crystal surface with high smoothness and no crack.

Owner:HEBEI UNIV OF TECH

Method for etching class-III nitride by using photo-assisted oxidation wet method

InactiveCN101625971AAvoid damageImprove the selection ratioSemiconductor/solid-state device manufacturingClass iiiPhoto assisted

The invention discloses a method for etching class-III nitride by using a photo-assisted oxidation wet method, which is characterized by comprising the following steps: step 1, preparing an ultraviolet light masking layer with patterns on the surface of the class-III nitride by using a standard photo-etching process; step 2, placing the class-III nitride of which the surface is provided with the ultraviolet light masking layer with the patterns under high-energy ultraviolet light to be exposed so as to oxidize the exposed class-III nitride with the patterns under the assistance of the ultraviolet light to generate a metal oxide; step 3, removing the masking layer; and step 4, putting a sample of the exposed class-III nitride in acid or alkali solution so that the generated metal oxide is fully eroded to form an etching step with the patterns to finish the process for etching the class-III nitride by the wet method.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

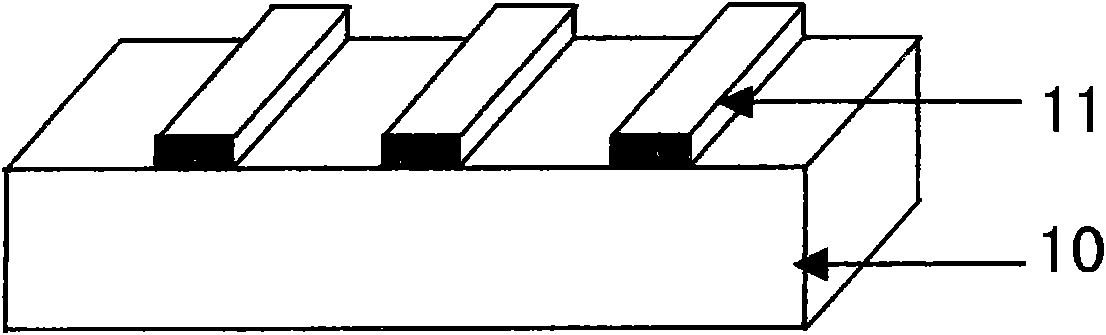

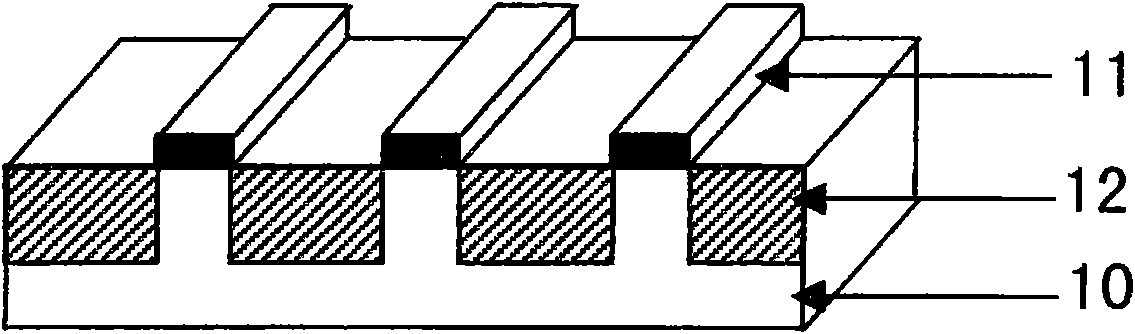

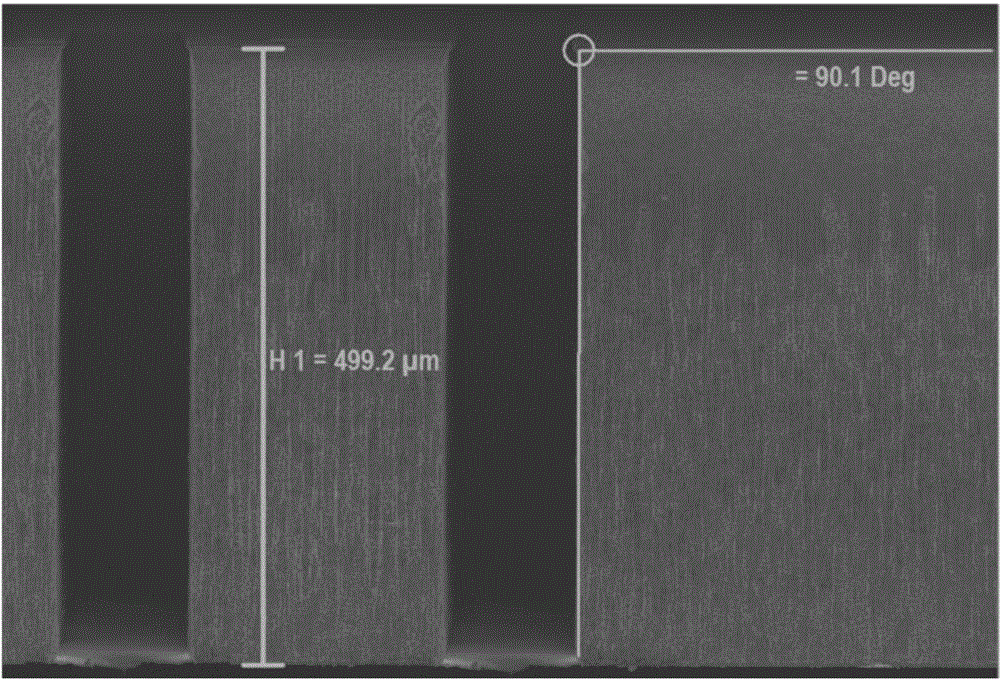

Deep silicon etching method

ActiveCN103950887AAchieve physical bombardmentReduce physical bombardmentDecorative surface effectsChemical vapor deposition coatingInductively coupled plasmaSilicon etching

The invention discloses a deep silicon etching method which comprises the following steps: (1) preparing a graphic photoresist mask on a silicon chip surface; (2) performing deep inductively coupled plasma dry etching of the silicon chip, wherein the etching is divided into several phases, each etching phase is completed in a inductively coupled plasma machine, and is completed through alternate circular processing of three steps of passivation, bombardment, and etching, and with the increase of the etching depth, the bombardment intensity in the bombardment step of each etching phase increases gradually. The method of the invention effectively solves the problems of difficult control of sidewall verticality and roughness, and difficult realization of large etching depth in the prior art, both improves the etching efficiency and increases the selection ratio or photoresist, and is high in etching groove sidewall verticality, low in roughness, and large in etching depth.

Owner:HUAZHONG UNIV OF SCI & TECH

Plasma processing apparatus and method

ActiveCN102157372AEliminate attachmentEtching high speedElectric discharge tubesSemiconductor/solid-state device manufacturingMiniaturizationDc voltage

There is provided a plasma etching device for generating plasma as a processing gas between an upper electrode (34) and a lower electrode (16) and subjecting a wafer (W) to plasma etching. The upper electrode (34) includes a variable DC power source (50) for applying DC voltage so that the absolute value of the self bias voltage Vdc on the surface of the upper electrode (34) becomes large enough to obtain an appropriate sputter effect to the surface and the thickness of the plasma sheath on the upper electrode (34) becomes thick enough to form a desired miniaturization plasma.

Owner:TOKYO ELECTRON LTD

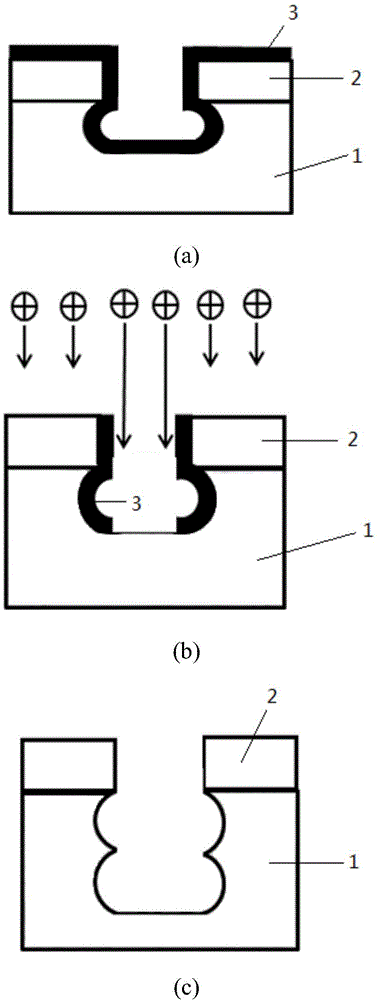

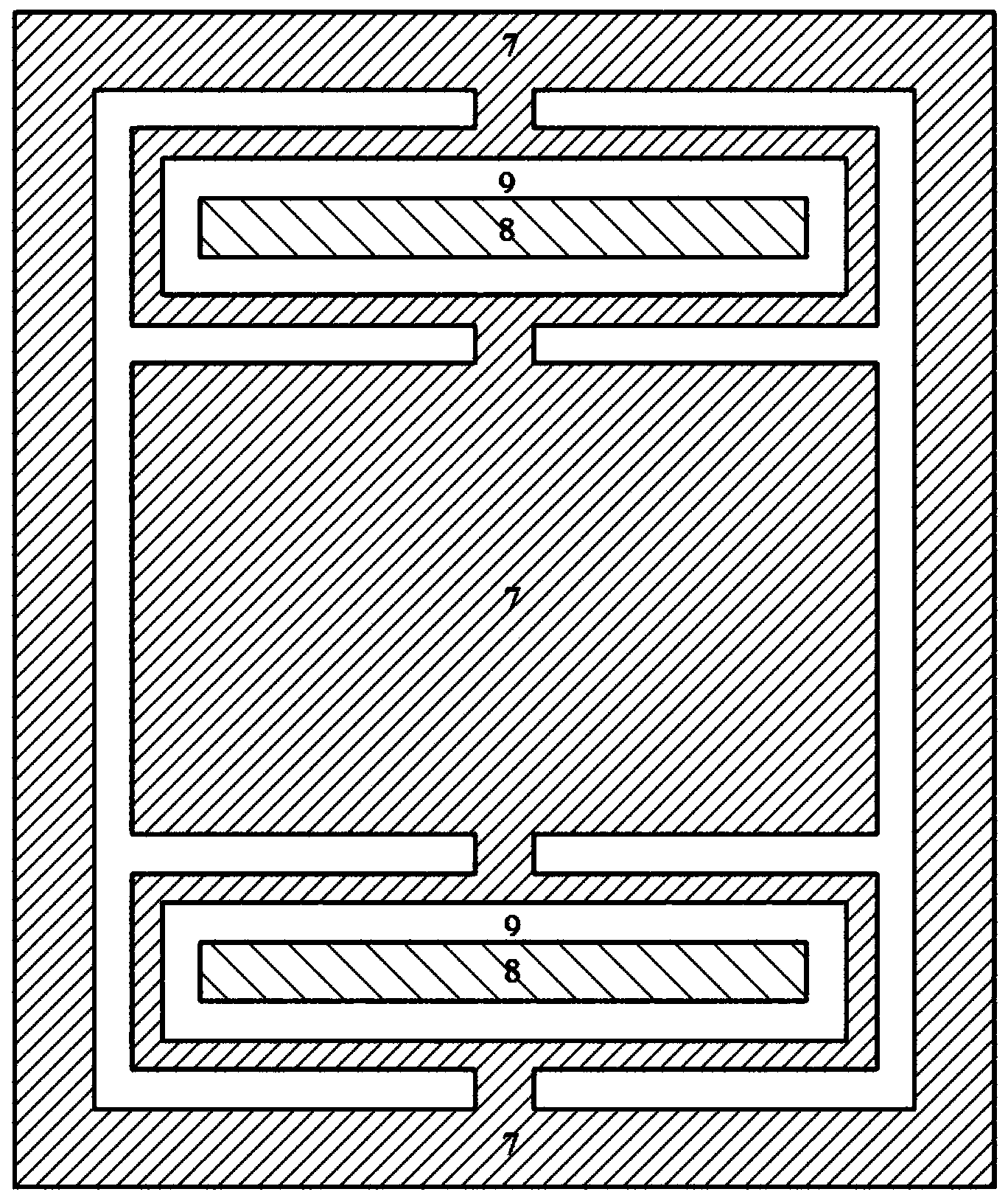

Pressure capacitance type sensor substrate cavity-forming method

InactiveCN101114591AReduce usage costsReduce processing costsDecorative surface effectsForce measurementMicro structureCapacitance

A substrate cavitation method for the pressure volume sensor has the advantages of high precision, low cost, easy operation and stable quality. The method includes the following steps: (1) forming a silica layer formed by the oxidation on one surface of the selected silicon; (2) coating a photoresist layer on the silica layer and forming a micro structure concave cavity I after exposing and developing, and the material at the bottom of the micro structure concave cavity I is silica; (3) etching the silica layer in the micro structure concave cavity I by means of ICP plasma-etching, and the photoresist layer is the mask, forming a micro structure concave cavity II, the material at the bottom of which is silicon; (4) removing the photoresist layer; (5) coating the photoresist layer again and forming a micro structure concave cavity III corresponding to the micro structure concave cavity II after exposing and developing; (6) etching the silicon wafer to a certain depth in the micro structure concave cavity III by means of ICP plasma-etching, and the photoresist layer is the mask; (7) removing the photoresist layer and obtaining the substrate provided with a micro structure concave cavity IV. The invention is suitable for making the substrate of the depressor sensor.

Owner:杭州科岛微电子有限公司 +1

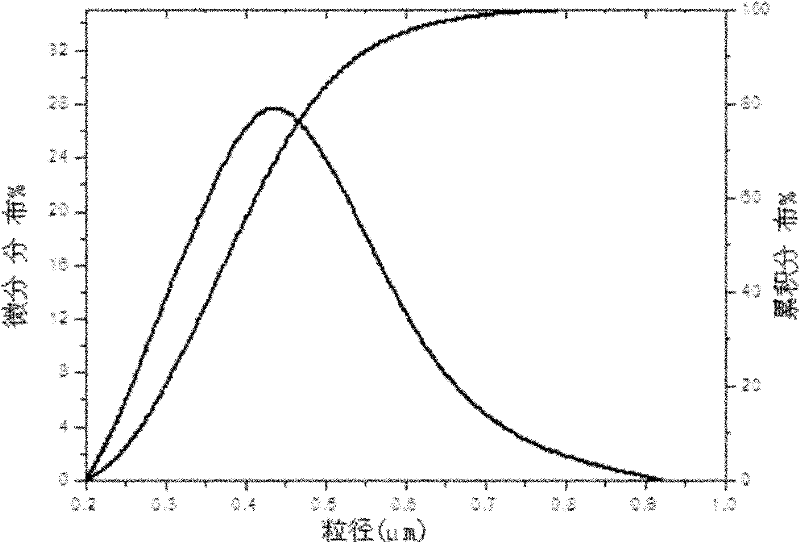

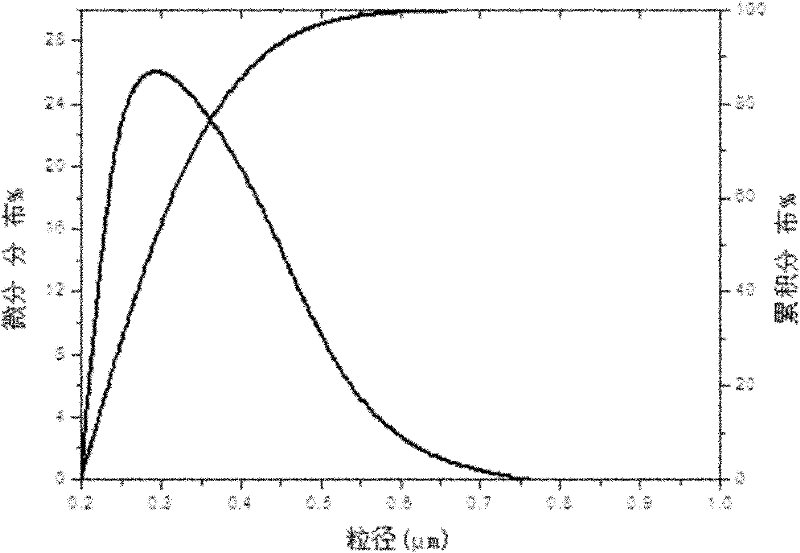

Cerium oxide composite particles, as well as preparation method and application thereof

InactiveCN103896321ACoated evenlyHigh activityOther chemical processesRare earth metal compoundsOrganic linkingInorganic particle

The invention relates to the field of chemical engineering, and specifically relates to cerium oxide composite particles, as well as a preparation method and application thereof. The preparation method of the cerium oxide composite particles, provided by the invention, comprises the steps of mixing an inorganic particle dispersion solution with an organic linking agent, then adding cerium salt and a precipitating agent, and uniformly stirring to obtain a mixed dispersion solution; transferring the dispersion solution prepared in the previous step into a closed high-pressure reaction kettle, and heating for reaction to obtain a reaction product; centrifuging the reaction product, taking a precipitate, and washing with water for a plurality of times to obtain the cerium oxide composite particles. According to the preparation method provided by the invention, inner cores of inorganic particles and cerium oxide nano-particles are combined through the organic linking agent to form the composite particles, and good crystallinity of cerium oxide is promoted by high-temperature water heat.

Owner:SHANGHAI XINANNA ELECTRONICS TECH +1

Method for generating blocking metal layer

InactiveCN1397993AImprove the selection ratioAvoid the problem of competitive adsorptionSolid-state devicesSemiconductor/solid-state device manufacturingHydrogenSilanes

This invention discloses a new forming method of embollishing metal layers containing providing a semiconductor basic material with a dielectric layer and holes then to form a barrier layer on the side wall of the dielectric layer and the holes and surface of the base to carry on at least one time of ALD to form a (continuous metal seed layer) CMSL on the barrier layer in which ALD steps including filling a mixed gas of hydrogen and silane then cleaning and vacuum, then to inlet metal reacting gas to form a CMSL of 20-40 A and to form a nucleation layer of 20-40 A on the CMSL finally.

Owner:UNITED MICROELECTRONICS CORP

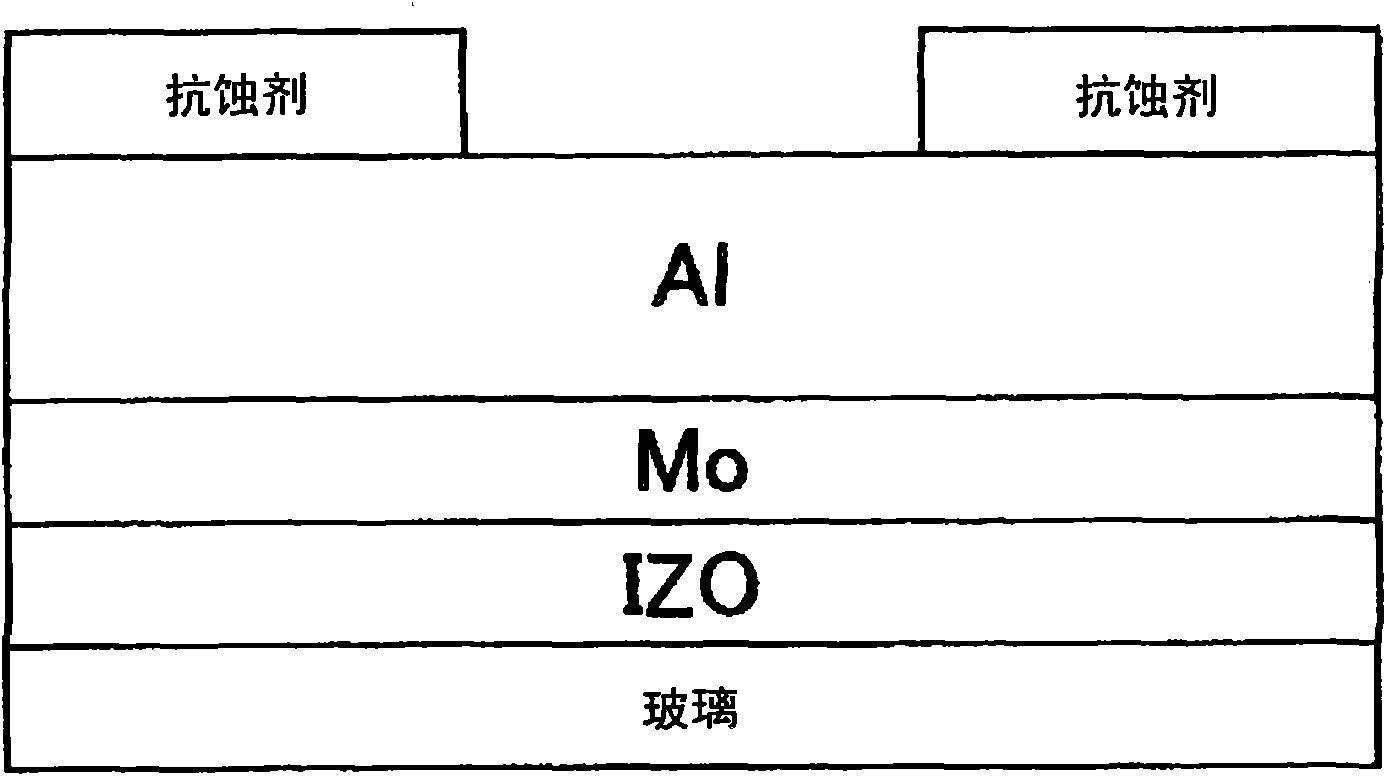

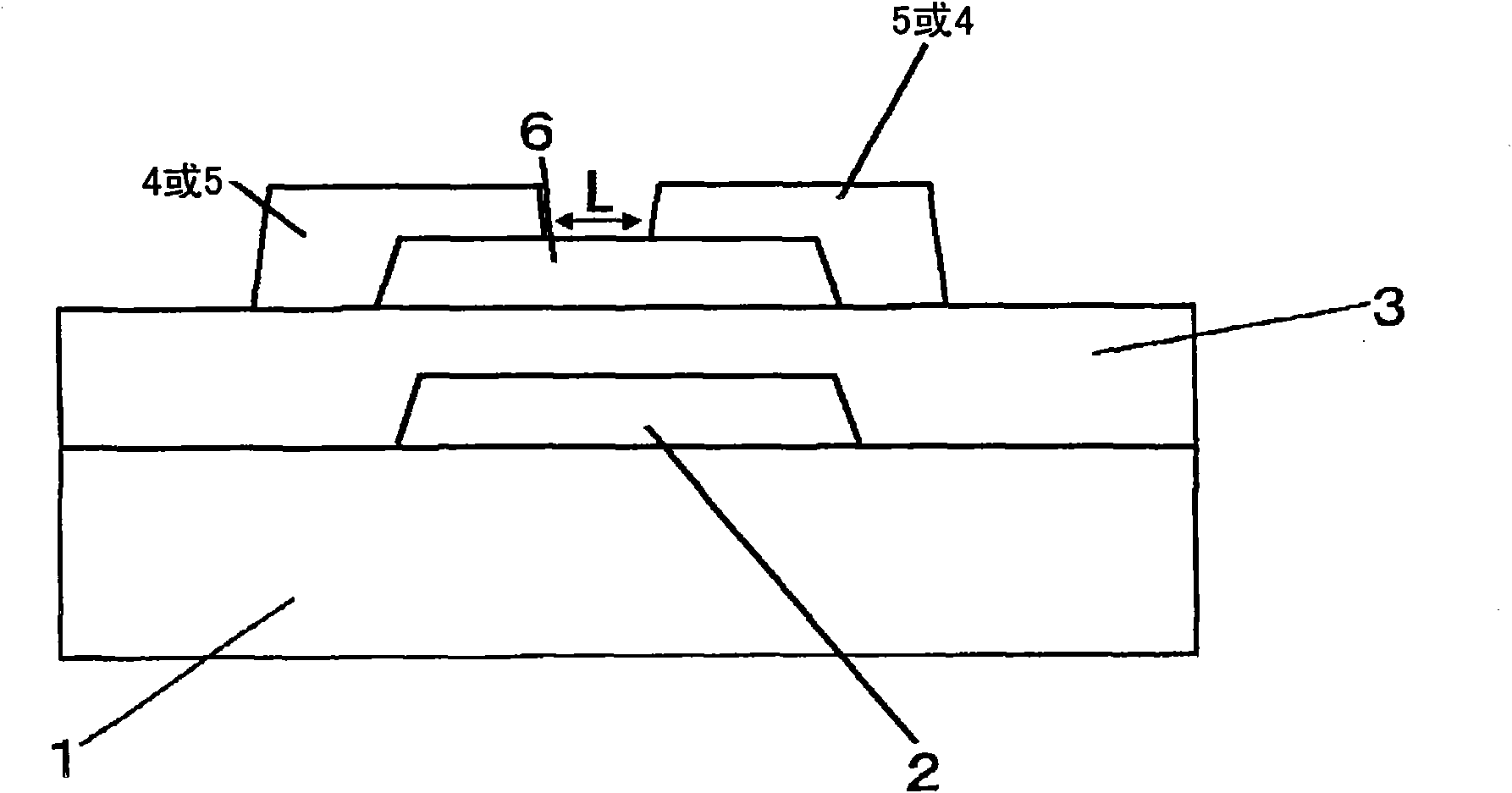

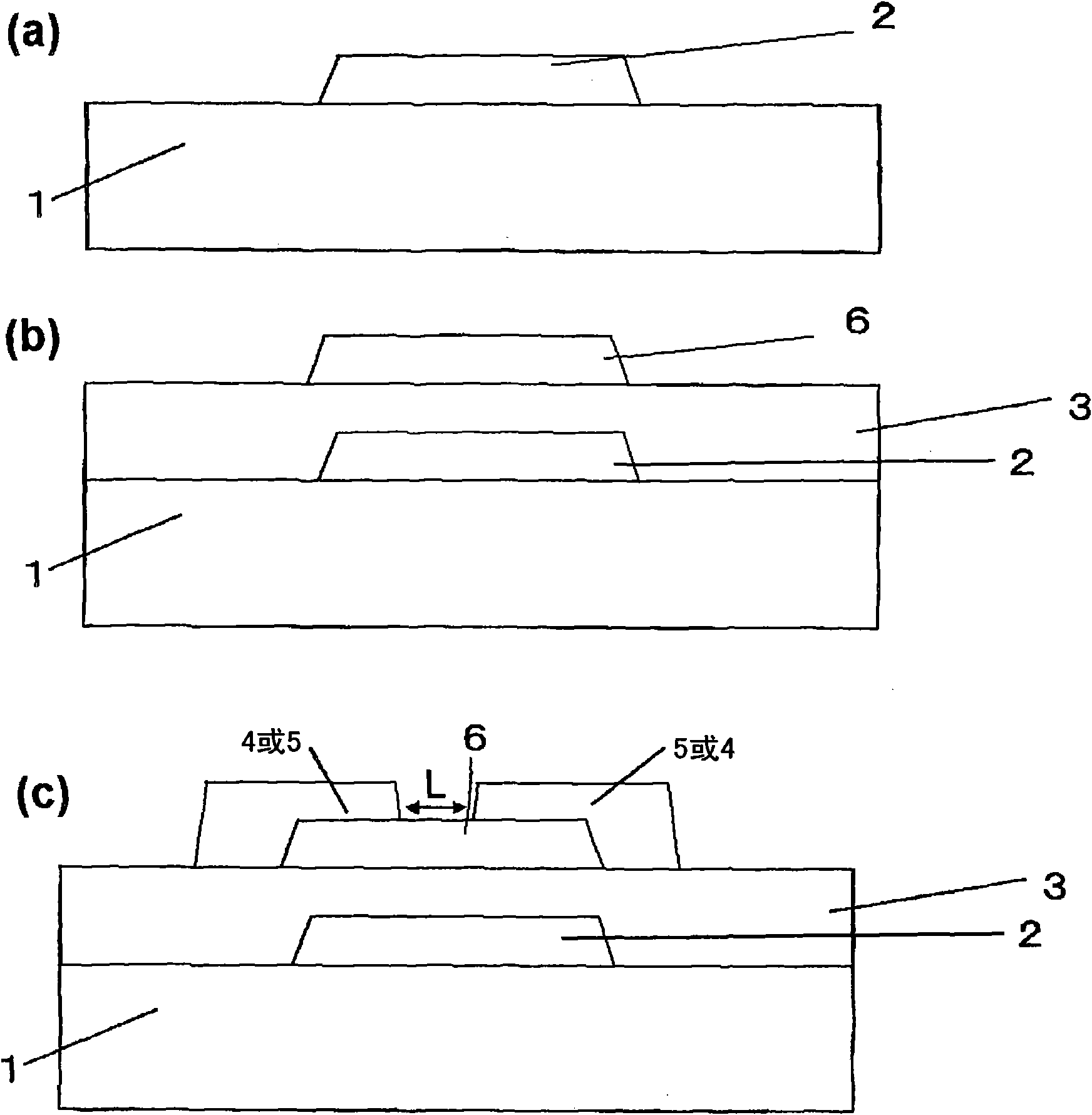

Etching solution composition

InactiveCN101952485AImprove the selection ratioSemiconductor/solid-state device manufacturingNon-linear opticsAlloyAqueous solution

Provided is an etching solution composition for selectively etching a metal film, which is composed of Al, Al alloy or the like and is arranged on an amorphous oxide film, from a laminated film including the metal film and an amorphous oxide film of various types. The etching solution composition is used for selectively etching the metal film from the laminated film which includes the amorphous oxide film and the metal film composed of Al, Al alloy, Cu, Cu alloy, Ag or Ag alloy, and is composed of an aqueous solution containing an alkali.

Owner:IDEMITSU KOSAN CO LTD +1

Etching method and semiconductor device fabrication method

InactiveCN101154582AReduce etch rateImprove the selection ratioElectric discharge tubesSemiconductor/solid-state device manufacturingResistMicrowave

Owner:TOKYO ELECTRON LTD

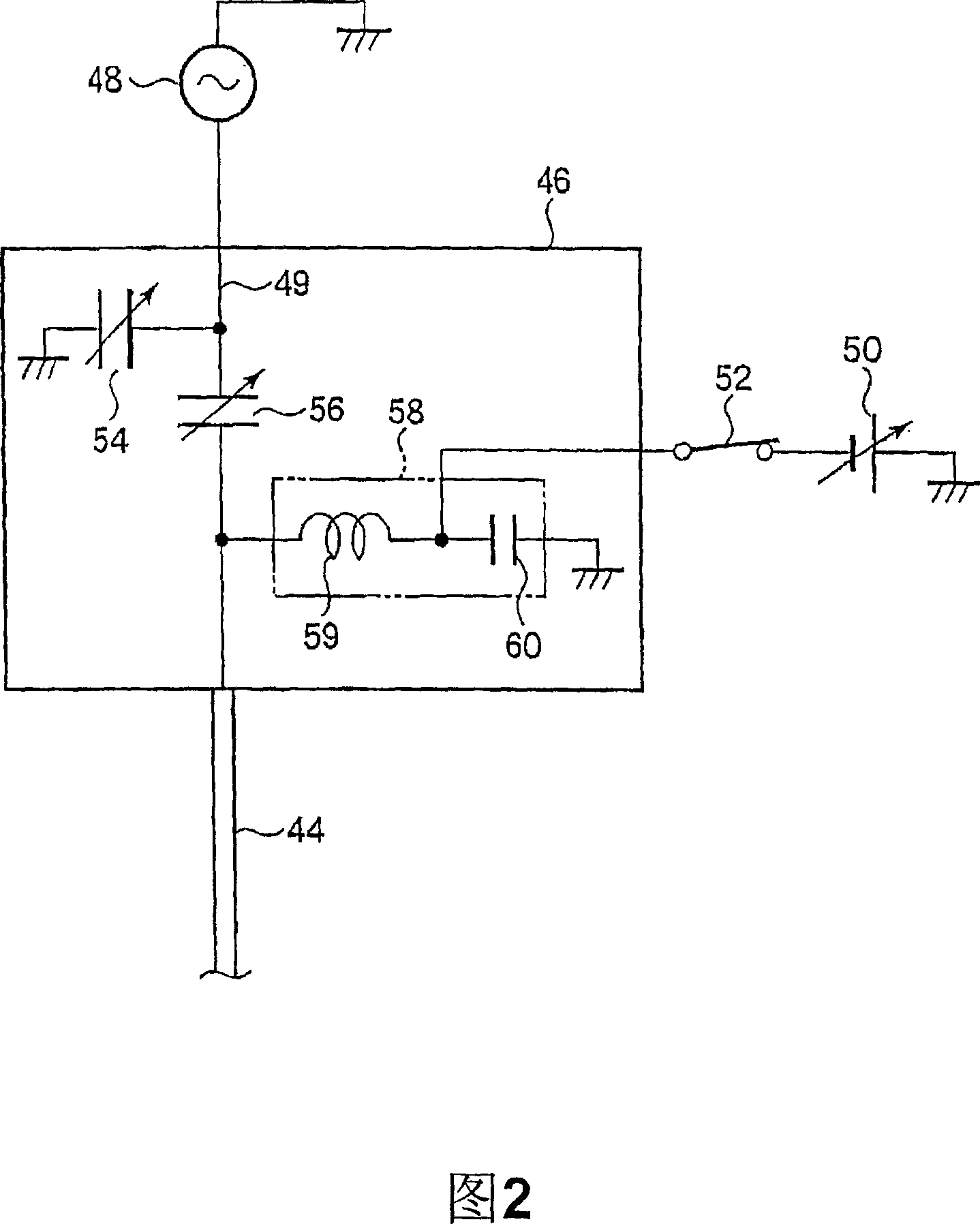

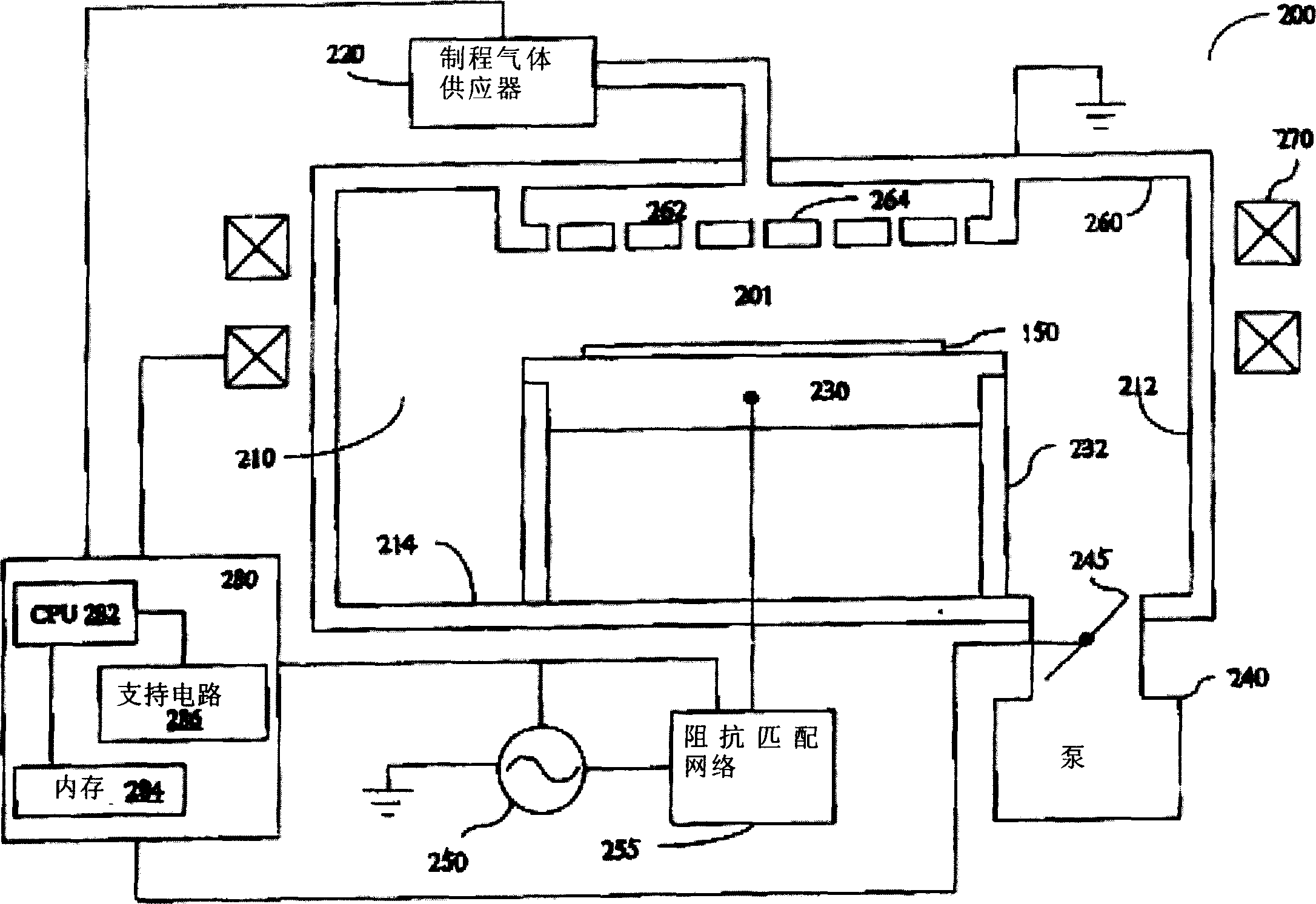

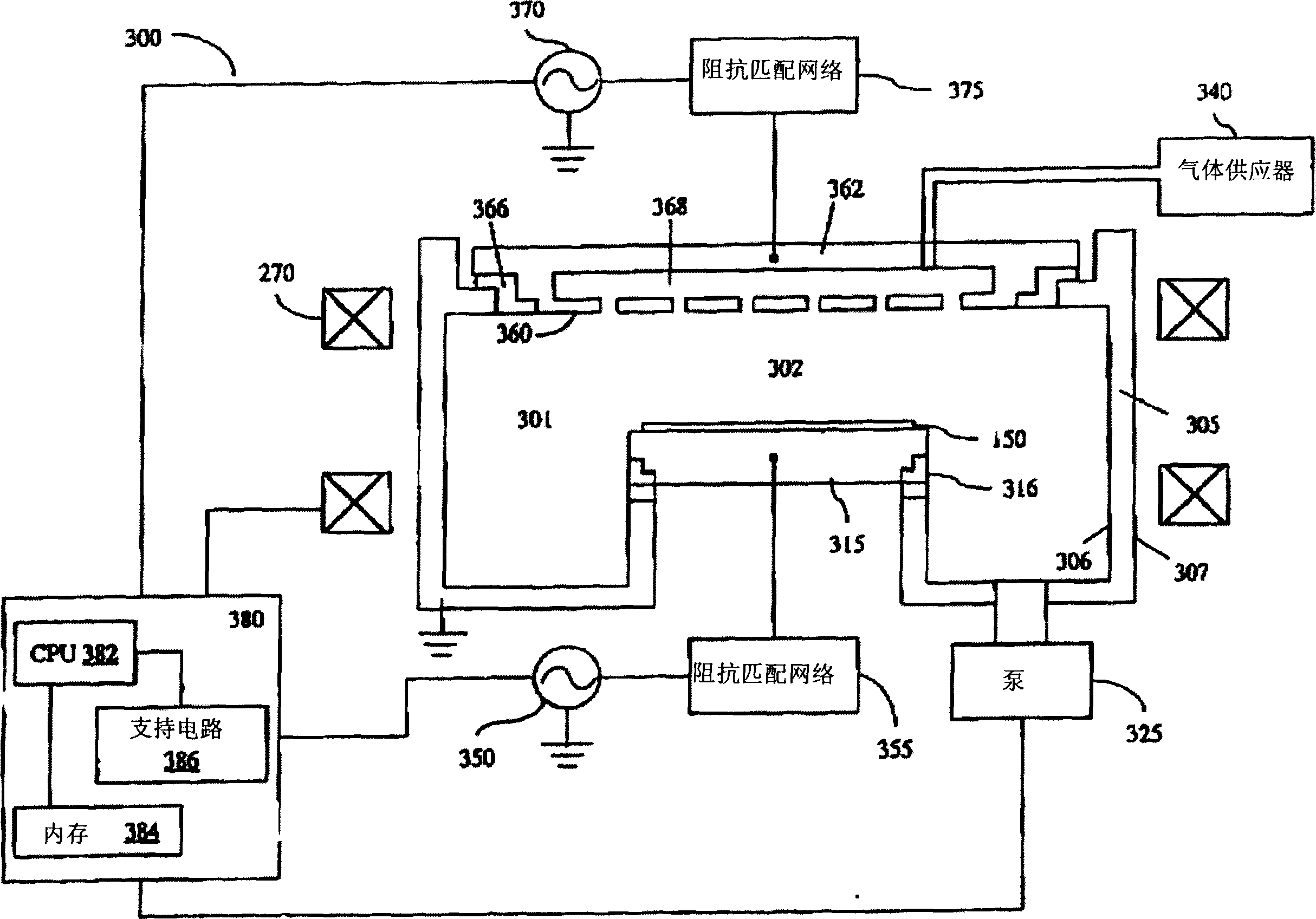

Plasma processing apparatus and method

ActiveCN1984523AEliminate attachmentEtching high speedSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHigh frequency powerEngineering

The invention provides a plasma processing system characterised in that comprises a processing container for receiving a substrate to be processed and performing vacuum exhausting air; a first electrode and a second electrode supporting the substrate to be processed arranged in the processing container oppositely; a first high-frequency power supply unit for applying a first high-frequency power of relatively high frequency to the second electrode; a second high-frequency power supply unit for applying a second high-frequency power of relatively low frequency to the second electrode; a DC power supply for applying a DC voltage to the first electrode; a gas supply unit for supplying gas which is to be processed to the processing container; and a controlling device for controlling one of the applied voltage, the applied current and the applied power from the DC power supply to the first electrode.

Owner:TOKYO ELECTRON LTD

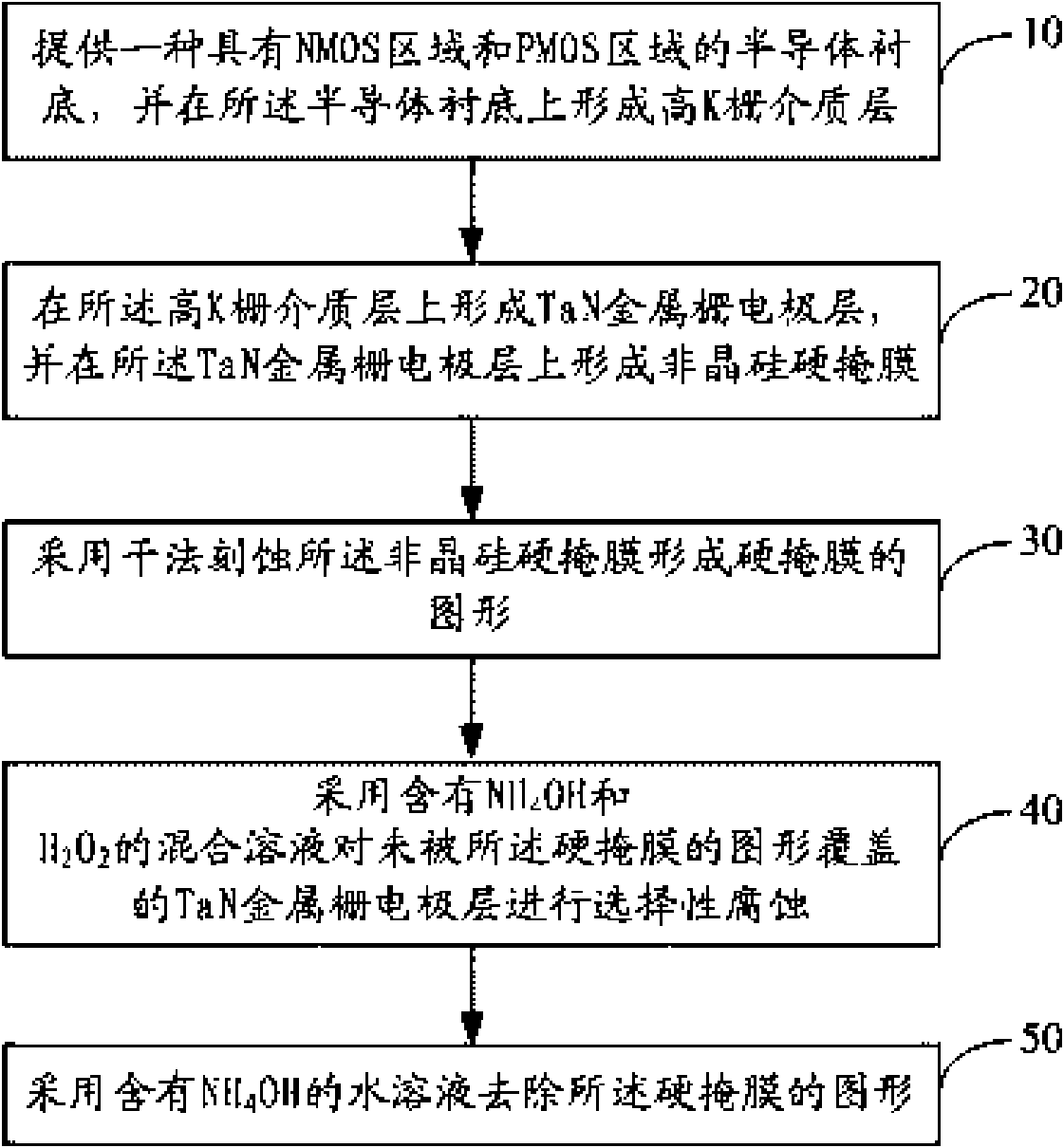

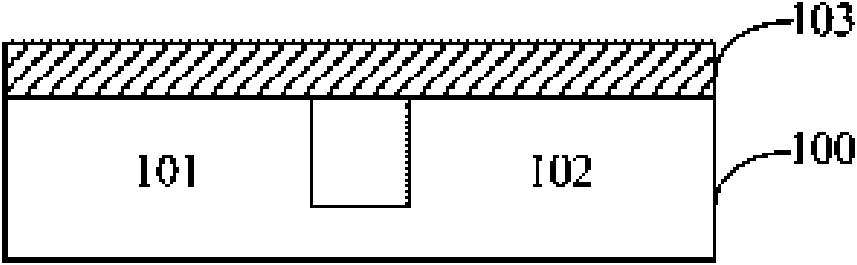

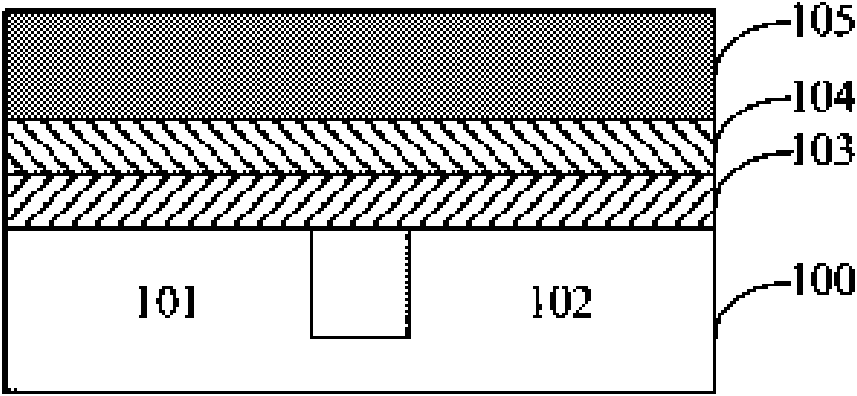

Method for selectively removing TaN metal gate electrode layer

ActiveCN101656208AAchieve removalImprove the selection ratioSemiconductor/solid-state device manufacturingSemiconductor devicesSelective leachingAmorphous silicon

The invention relates to a method for selectively removing a TaN metal gate electrode layer, belonging to the technical field of integrated circuit manufacture. The method comprises the following steps: forming a high K gate dielectric layer on a semiconductor substrate; forming a TaN metal gate electrode layer on the high K gate dielectric layer and forming an amorphous silicon hard mask on the TaN metal gate electrode layer; etching the amorphous silicon hard mask by adopting a dry method to form hard mask patterns; selectively corroding the TaN metal gate electrode layer uncovered by the hard mask patterns by adopting wet method corrosion; and removing the hard mask patterns by adopting the wet method corrosion. The method uses amorphous silicon as the hard mask and removes the TaN metal gate electrode layer with a high selection ratio by adopting the wet method corrosion of the TaN metal gate electrode layer. In addition, the method has high selection ratios to the TaN metal gate electrode layer and the high K gate dielectric layer when adopting a wet method corrosion solution to remove residential amorphous silicon hard mask and does not has compatibility problem.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

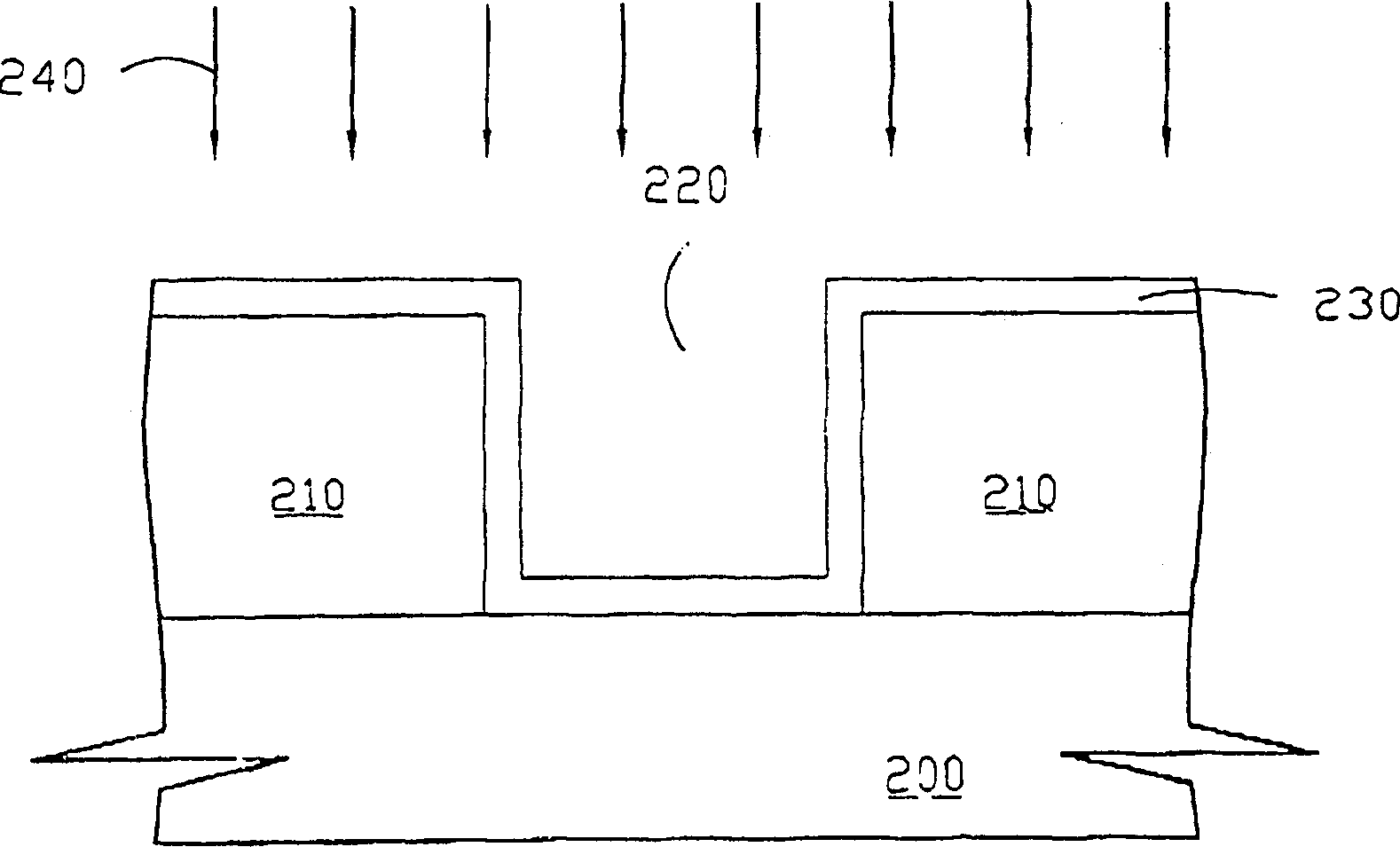

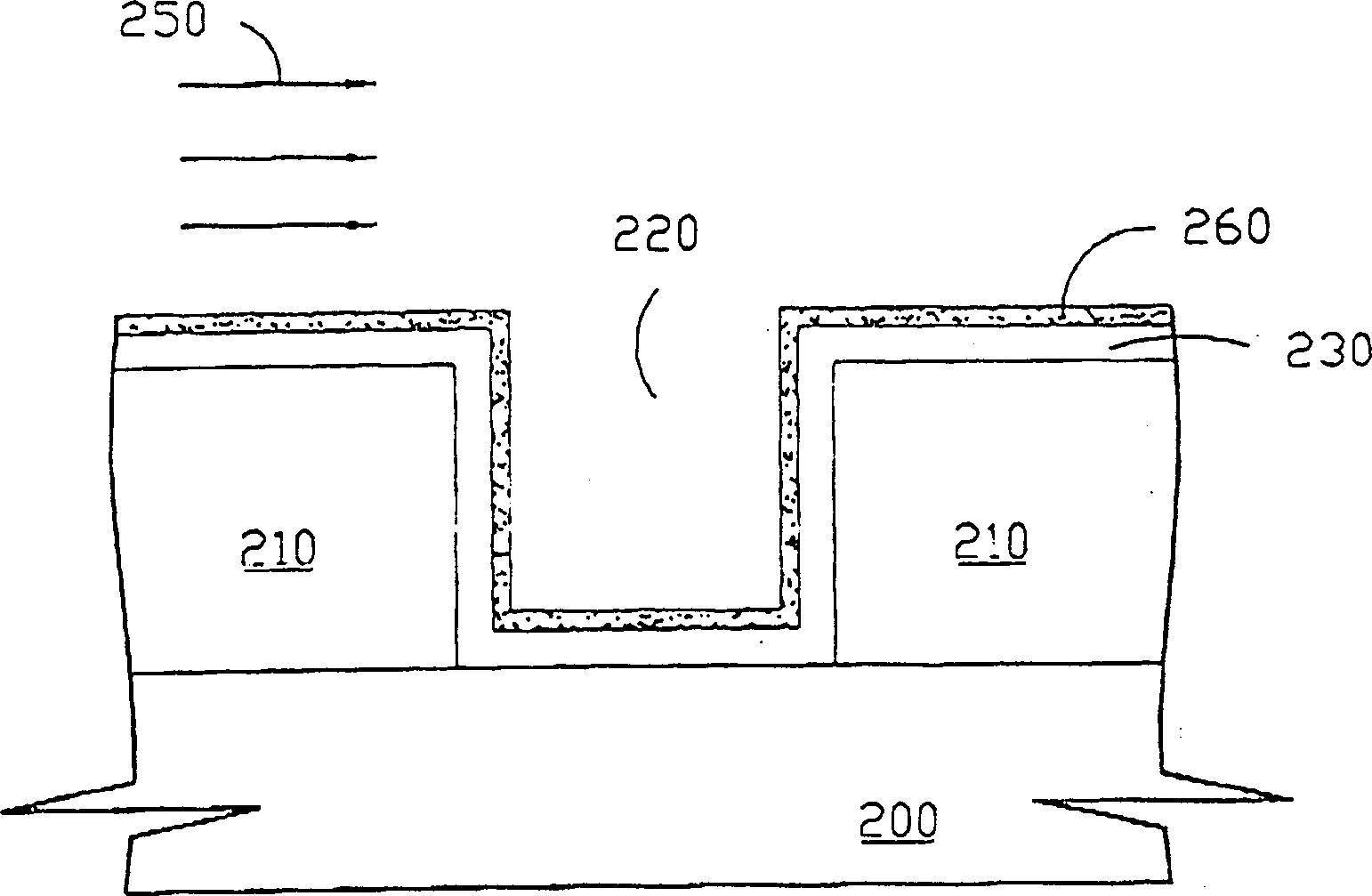

Selective etching of carbon-doped low-k dielectrics

InactiveCN1624881AImprove the selection ratioSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenNitrogen

A plasma etch process for selectively etching low dielectric constant materials on a substrate in a plasma etch chamber. The process utilizes an etching gas mixture for etching, and the etching gas mixture includes a polyfluorinated fluorocarbon or hydrofluorocarbon gas, a nitrogen-containing gas, and one or more additive gases, such as a polyfluorinated A hydrofluorocarbon gas of hydrogen, an inert gas and / or a carbon-oxygen gas. When etching the low dielectric constant material layer with this process, the etching selectivity ratio of the low dielectric constant material layer and the photoresist mask is greater than about 5:1, and the etching selectivity ratio of the low dielectric constant material layer and the barrier / liner layer The ratio is greater than 10:1, and the etch rate of the low dielectric constant material layer is greater than 4000 Angstroms / min.

Owner:APPLIED MATERIALS INC

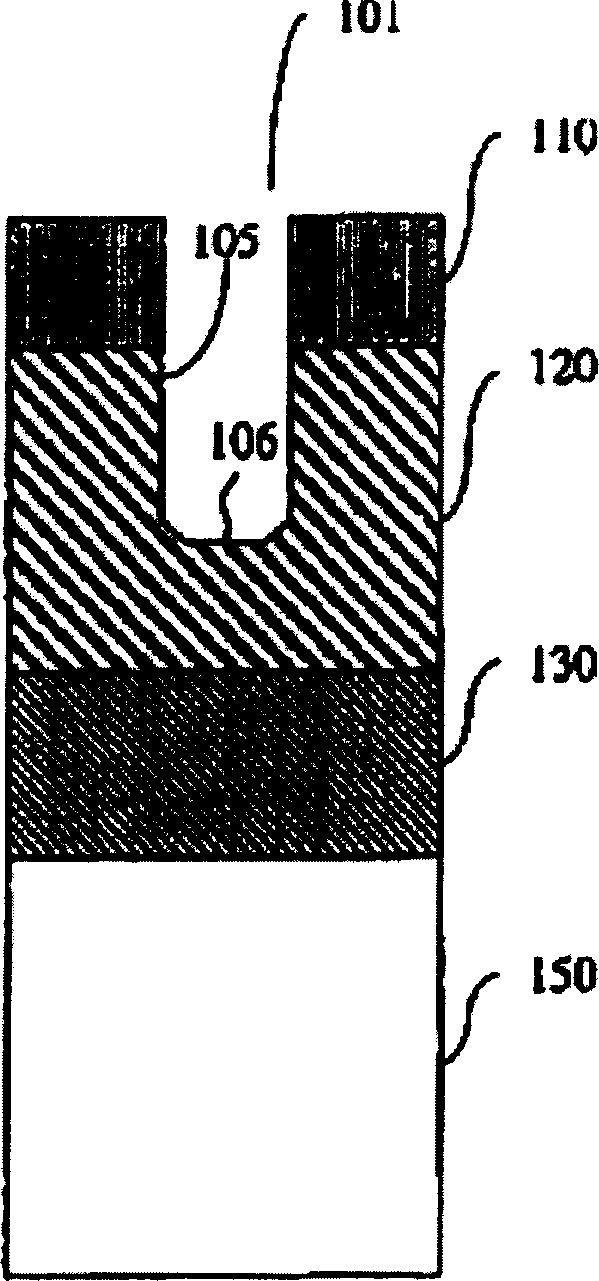

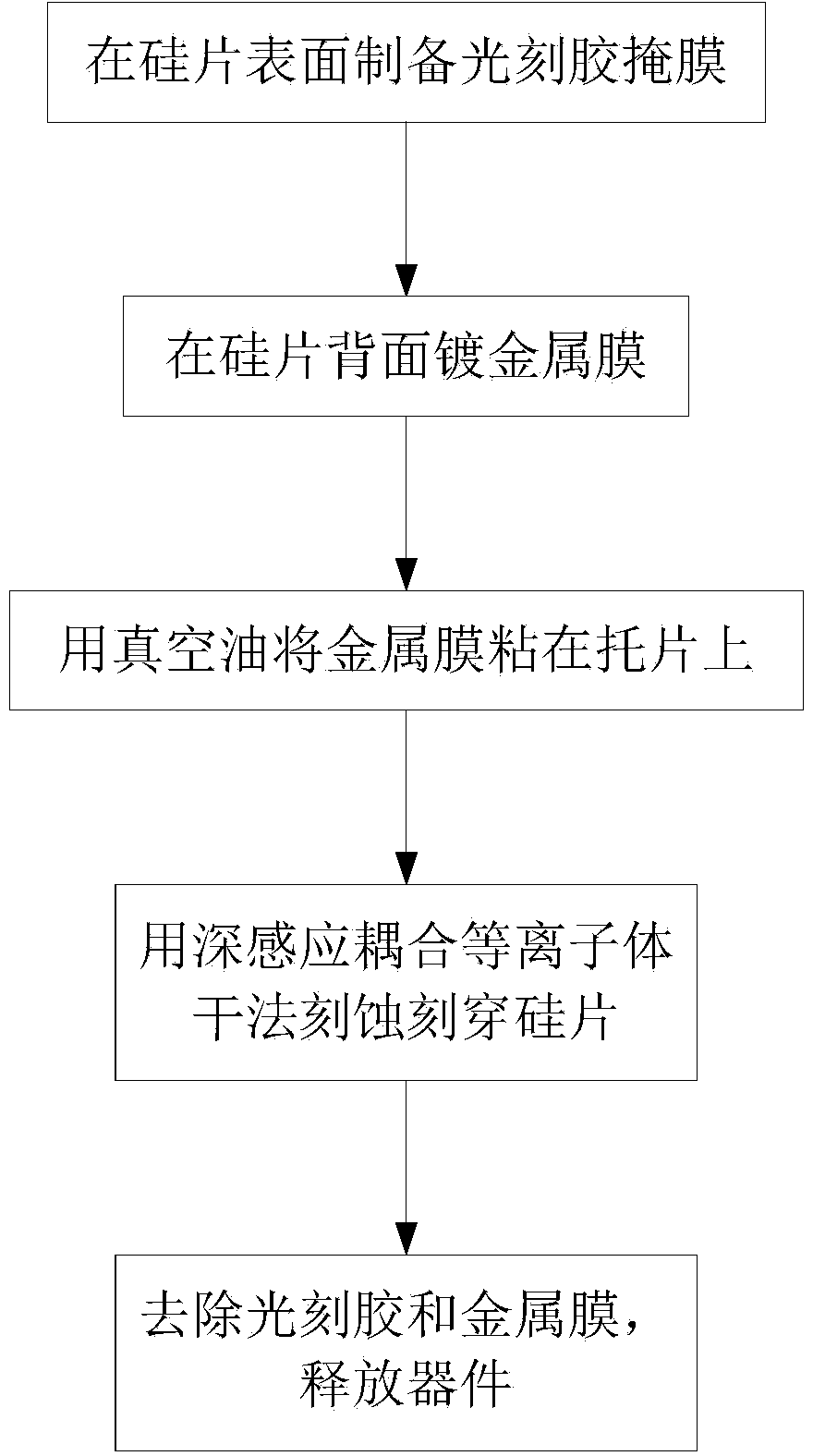

Bulk silicon machining process based on silicon chip etching and puncturing

ActiveCN103896206AAchieve physical bombardmentReduce physical bombardmentDecorative surface effectsChemical vapor deposition coatingInductively coupled plasmaMachining process

The invention discloses a bulk silicon machining process based on silicon chip etching and puncturing, which comprises the following steps of preparing a patterned photoresist mask on the surface of a silicon chip; putting a metal film on the back surface of the silicon chip; adhering the metal film to a supporting chip by using vacuum oil, wherein the supporting chip is a silicon chip with an oxide layer on the surface; etching and puncturing the silicon chip to obtain a bulk silicon microstructure by using an inductively coupled plasma dry-etching system, wherein a staged etching method is adopted for inductive coupled plasma dry-etching, and comprises a plurality of etching stages each of which is alternately and cyclically implemented by three steps of passivation, bombardment and etching in an inductive coupled plasma machine, and along with the increasing of the etching depth, the bombardment intensity of the bombardment step in each etching stage is gradually enhanced; removing the photoresist mask and the metal film, and releasing the bulk silicon microstructure. According to the process, the selection ratio of photoresist, the etching depth and the perpendicularity of the sidewall of an etching groove can be effectively increased.

Owner:HUAZHONG UNIV OF SCI & TECH

Polishing composition and polishing method for its use

InactiveCN1340583AImprove polishing effectBest chemical polishingOther chemical processesSemiconductor/solid-state device manufacturingPhysical chemistryCopper

A polishing composition comprising: (a) an abrasive, (b) a compound to form a chelate with copper ions (c) a compound to provide a protective layer-forming function to a copper layer, (d) hydrogen peroxide, and (e) water, wherein the abrasive of component (a) has a primary particle size within a range of from 50 to 120 nm. This is used for polishing a semiconductor device having at least a layer of copper and a layer of a tantalum-containing compound formed on a substrate.

Owner:FUJIMI INCORPORATED

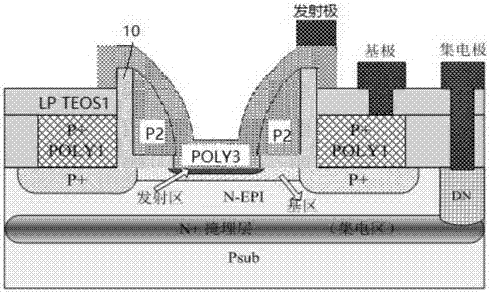

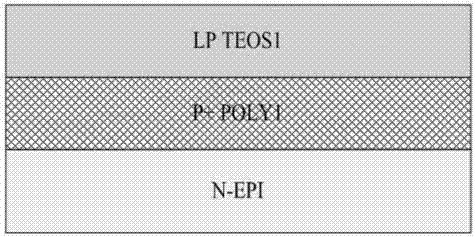

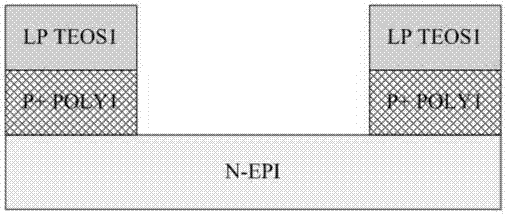

Method for making side wall between base and emitter of high frequency triode

InactiveCN107180757AWill not etchImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsPolycrystalline silicon

The invention provides a method for making a side wall between a base and an emitter of a high frequency triode. The method comprises a step of providing a substrate, forming an N epitaxial layer, a first polysilicon layer and a first TEOS layer on the surface of the substrate, a step of forming a base region trench which goes through the first polysilicon layer and the first TEOS layer, a step of forming a P type diffusion area at the N epitaxial layer under a first P polysilicon layer, and carrying out base region doping on the N epitaxial layer to form a base region, a step of orderly forming a second polysilicon layer and a second TEOS layer on the base region, in the base region trench and on the first polysilicon layer and the first TEOS layer, a step of etching the second polysilicon layer by using a dry method to form a polysilicon side wall, and a step of using a wet method to corrode the second TEOS layer to remove the second TEOS layer on the first TEOS layer and at the middle part of the base region, and retaining the second TEOS layer which is in contact with the polysilicon side wall, wherein the retained second TEOS layer is taken as the side wall between the base and the emitter.

Owner:罗灿

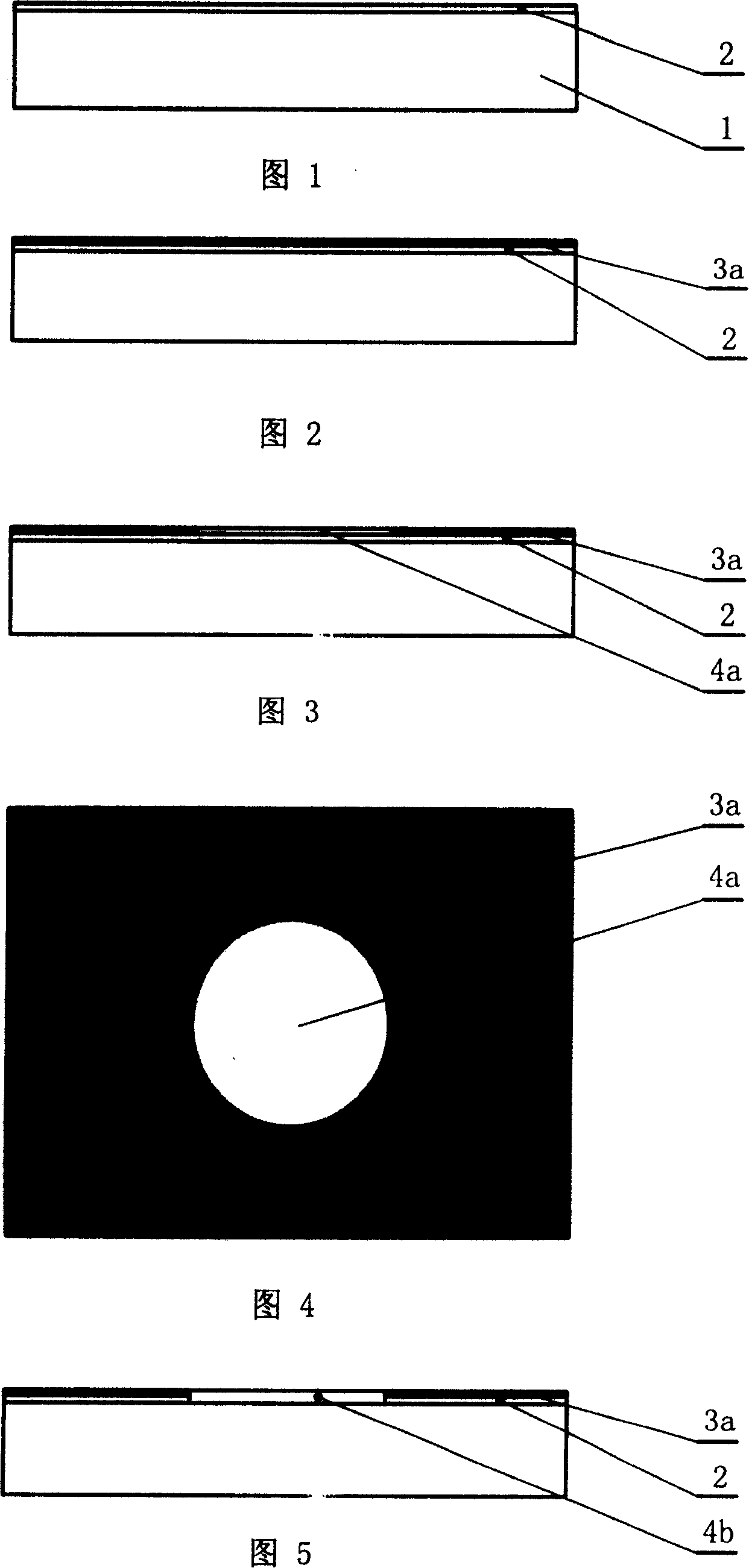

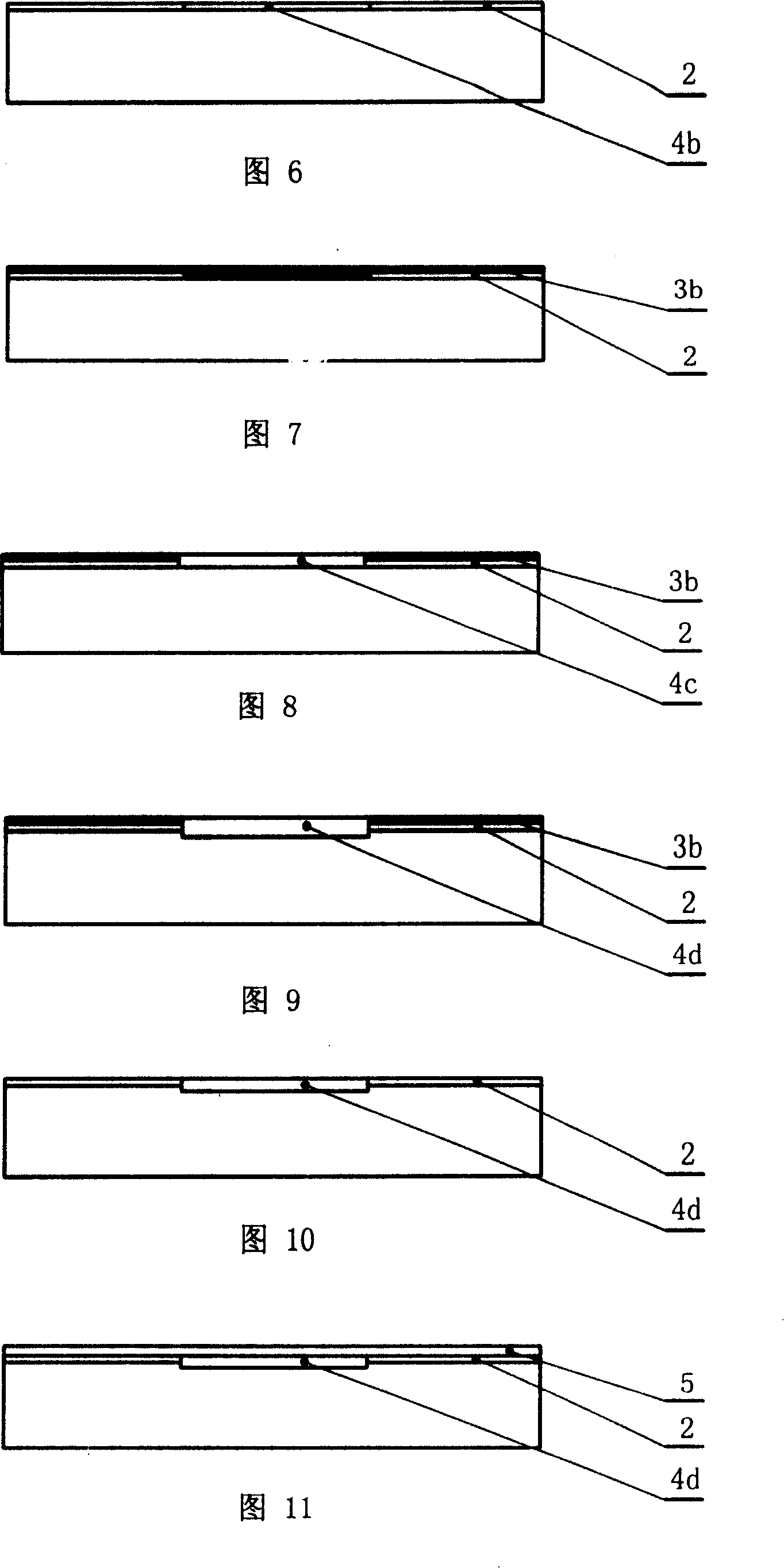

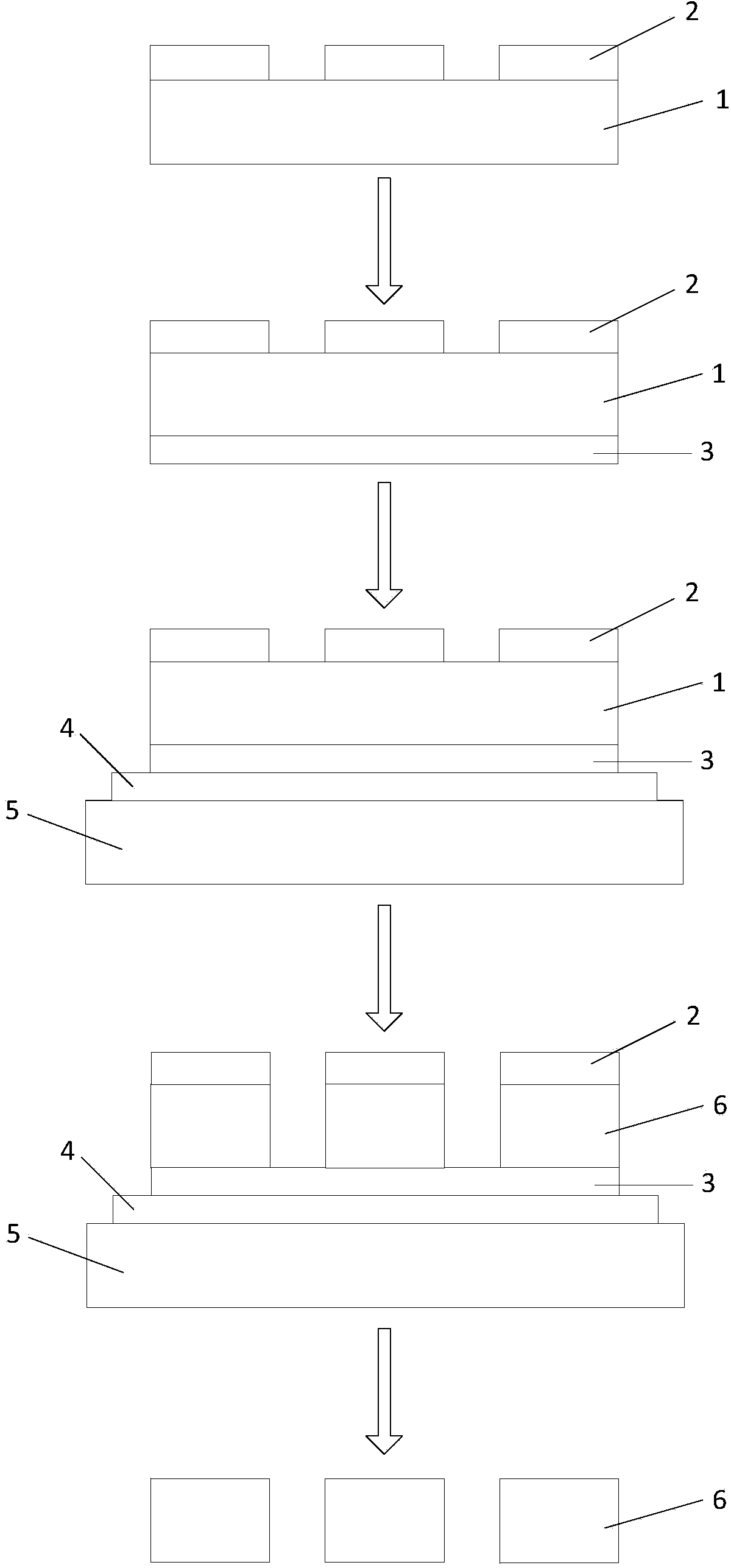

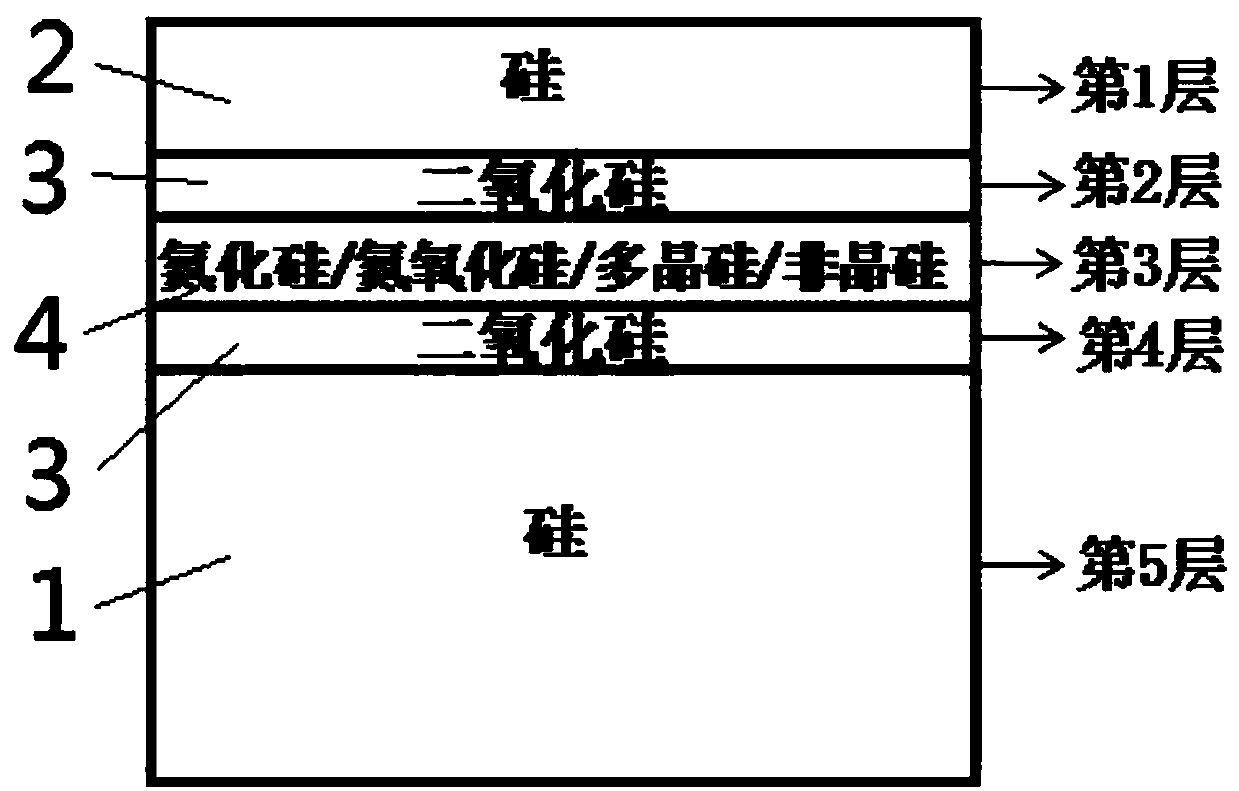

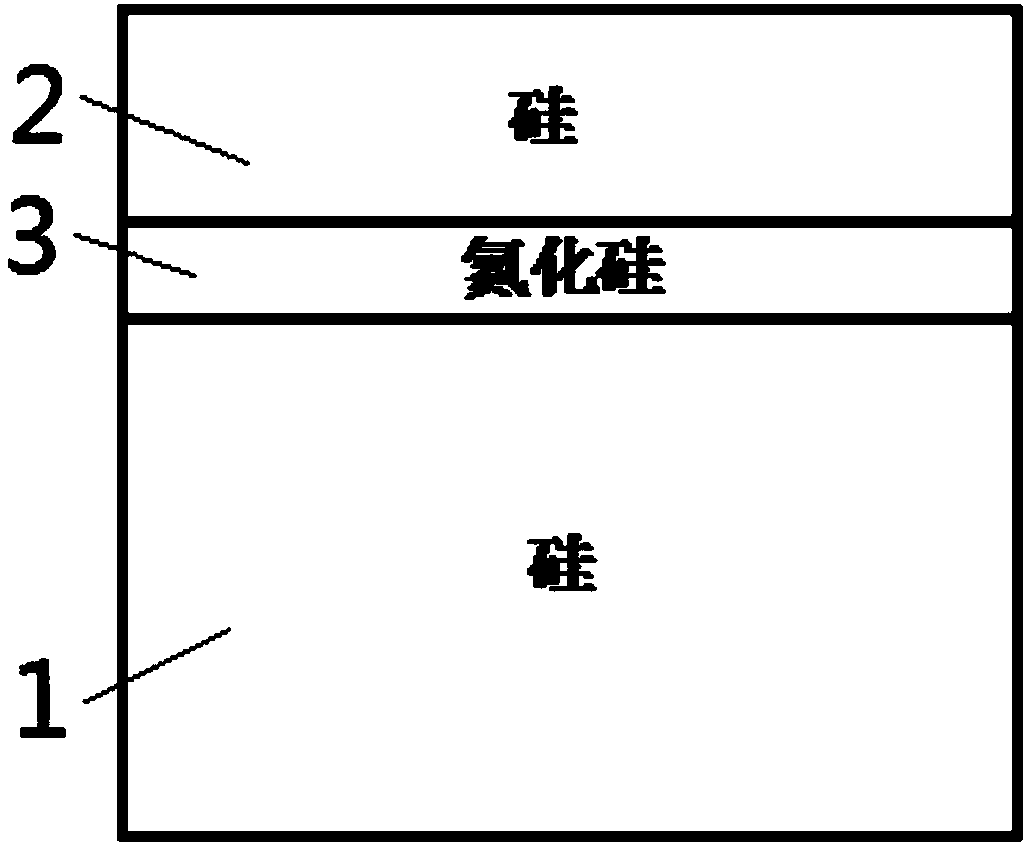

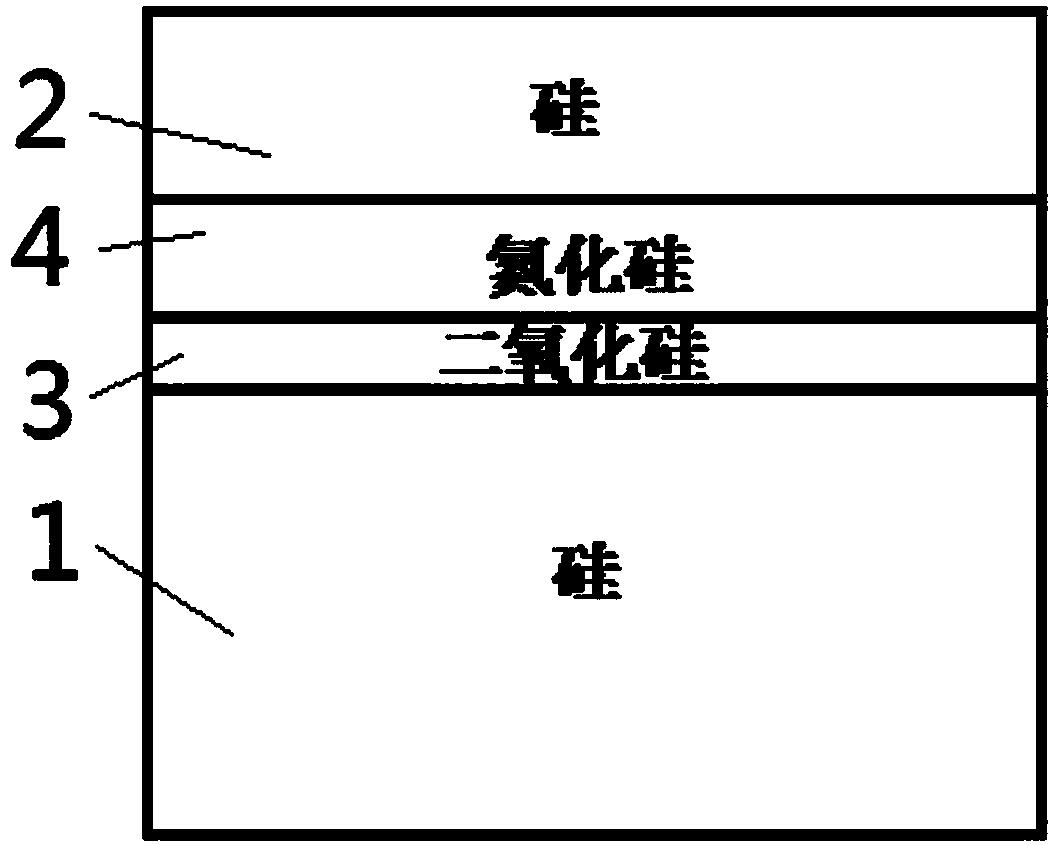

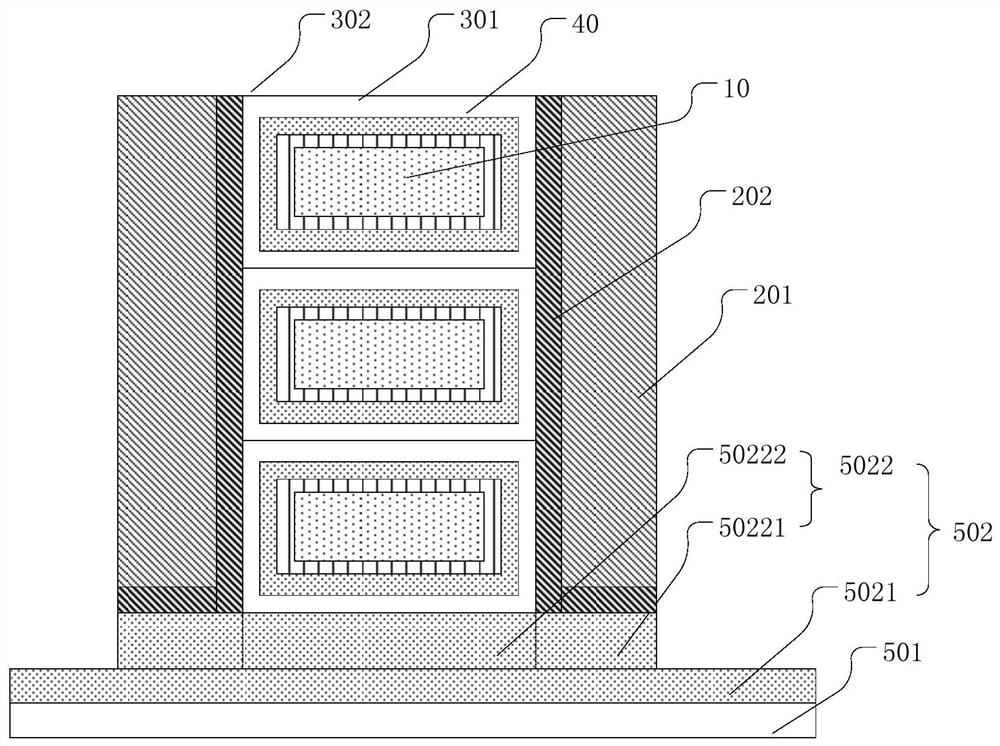

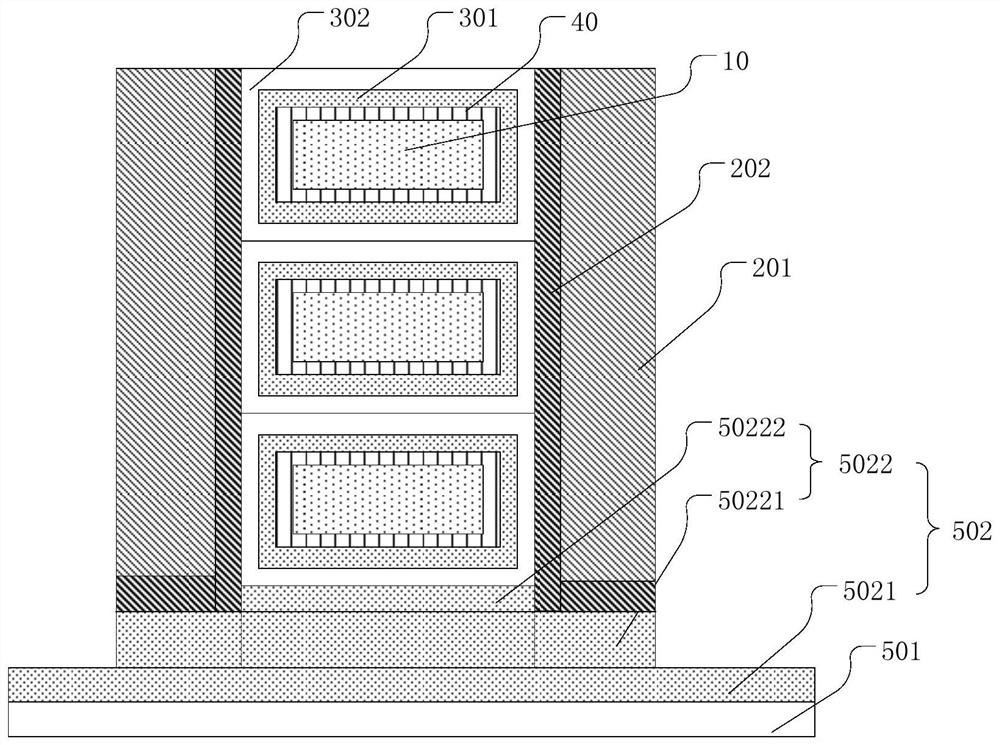

Semiconductor product insulation layer structure and preparation method thereof

InactiveCN110085550AHigh dielectric constantCompact structureSemiconductor/solid-state device detailsSolid-state devicesInsulation layerSilicon dioxide

The invention relates to a semiconductor product insulation layer structure. Both a device substrate (1) and a support substrate (2) are silicon wafers, a film layer (3) is arranged on the device substrate (1) and / or the support substrate (2), the film layer (3) is one of materials as follows, a silicon dioxide layer, a silicon oxynitride layer, a silicon nitride layer, a polysilicon layer and anamorphous silicon layer, and one of the device substrate (1) and / or the support substrate (2) and the other are bonded together through the film layer (3) disposed on at least one of the two to form an integrally multi-layer SOI structure. The invention further relates to a preparation method of the semiconductor product insulation layer structure. The special insulation layer structure is diverse, problems of serious self-heating, serious SOI warpage change caused by high-temperature annealing and poor radio frequency characteristics of an SOI device in the prior art are solved, and relatively expected large economic and social values can be achieved.

Owner:SHENYANG SILICON TECH

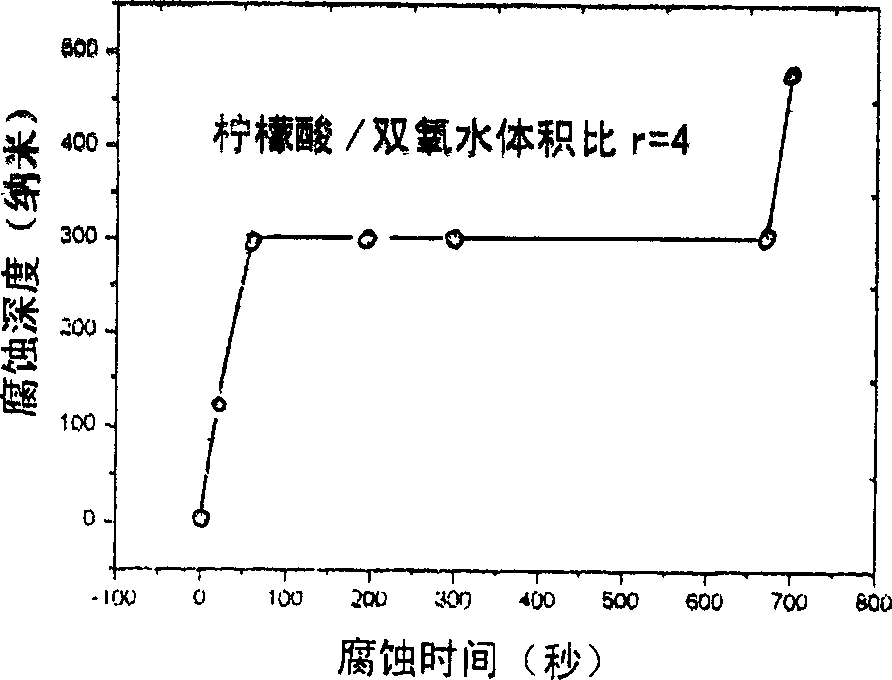

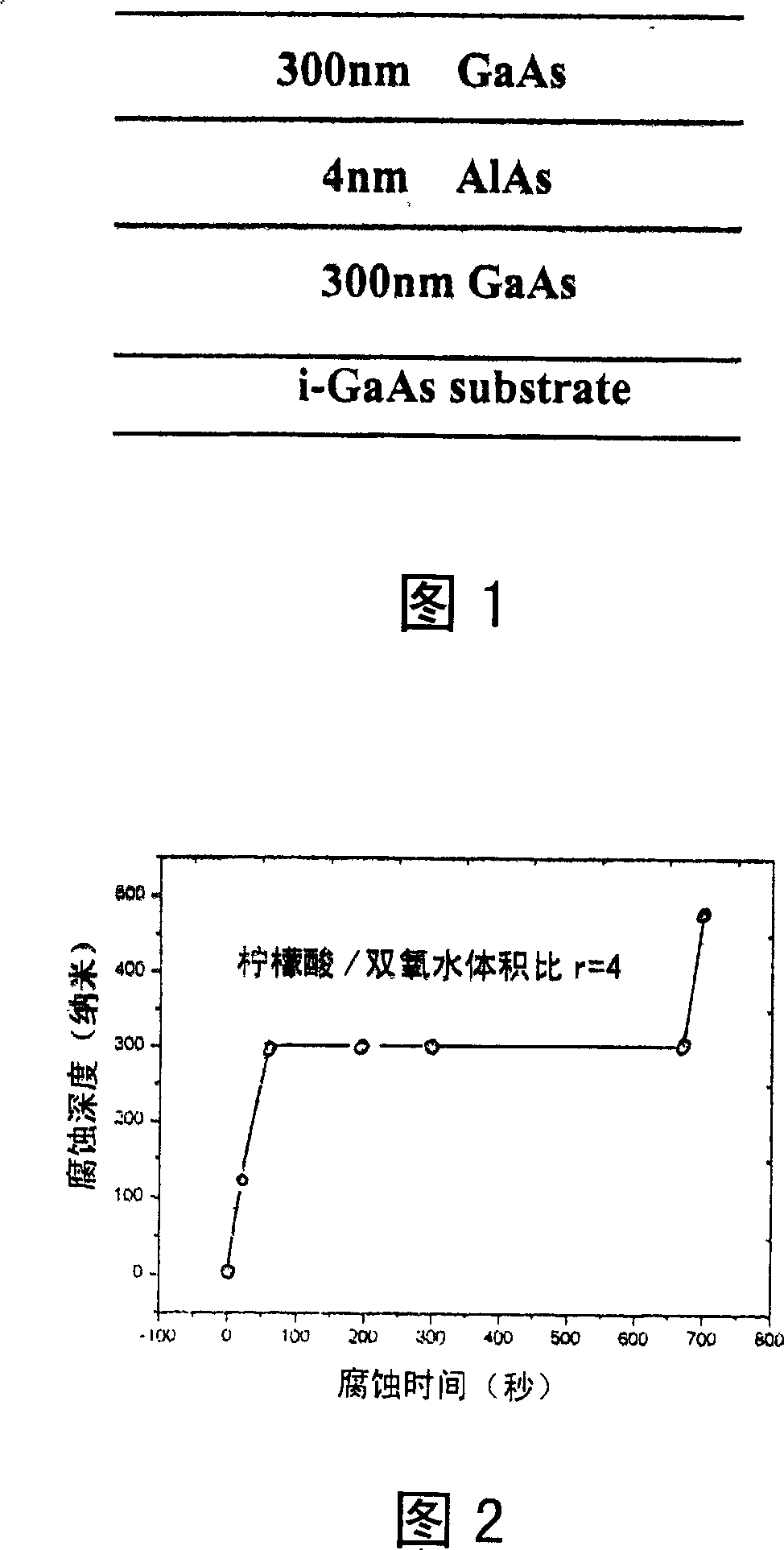

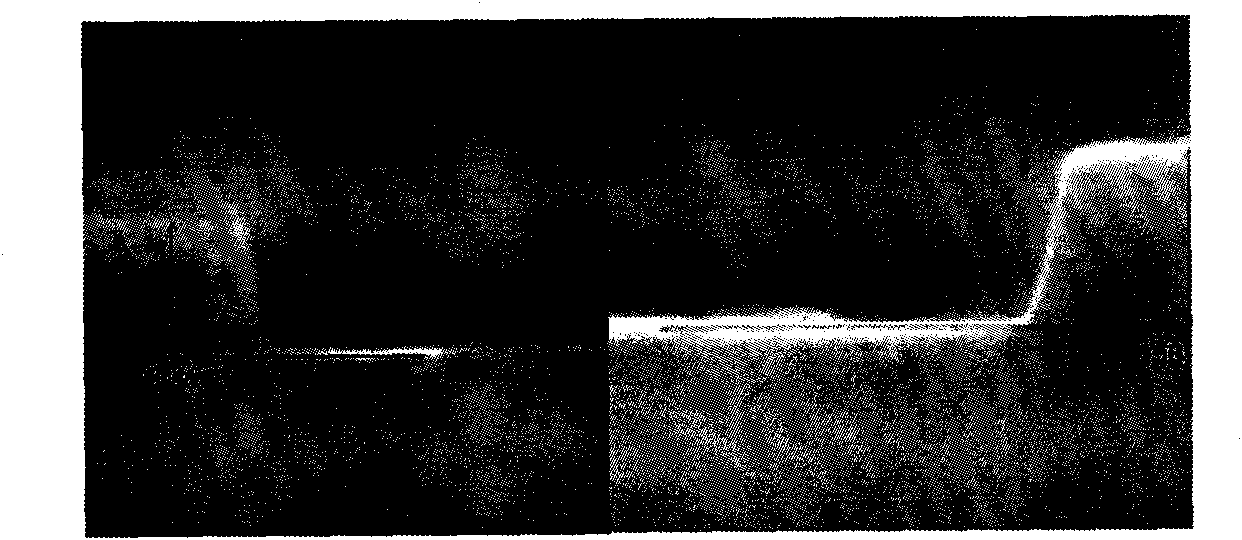

Chemical corrosion liquid in high selection ratio of gallium arsenide in aluminum arsenide / gallium arsenide

This invention relates to a chemical corrosive with high selectivity towards gallium arsenide among gallium arsenide / aluminium arsenide mixture. It uniquely contains citric acid solution and oxydol with a volume ratio of 4:1 and is compatible with gallium arsenide integration technique. Besides, it also has the advantages of nontoxic solution and simple technique.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

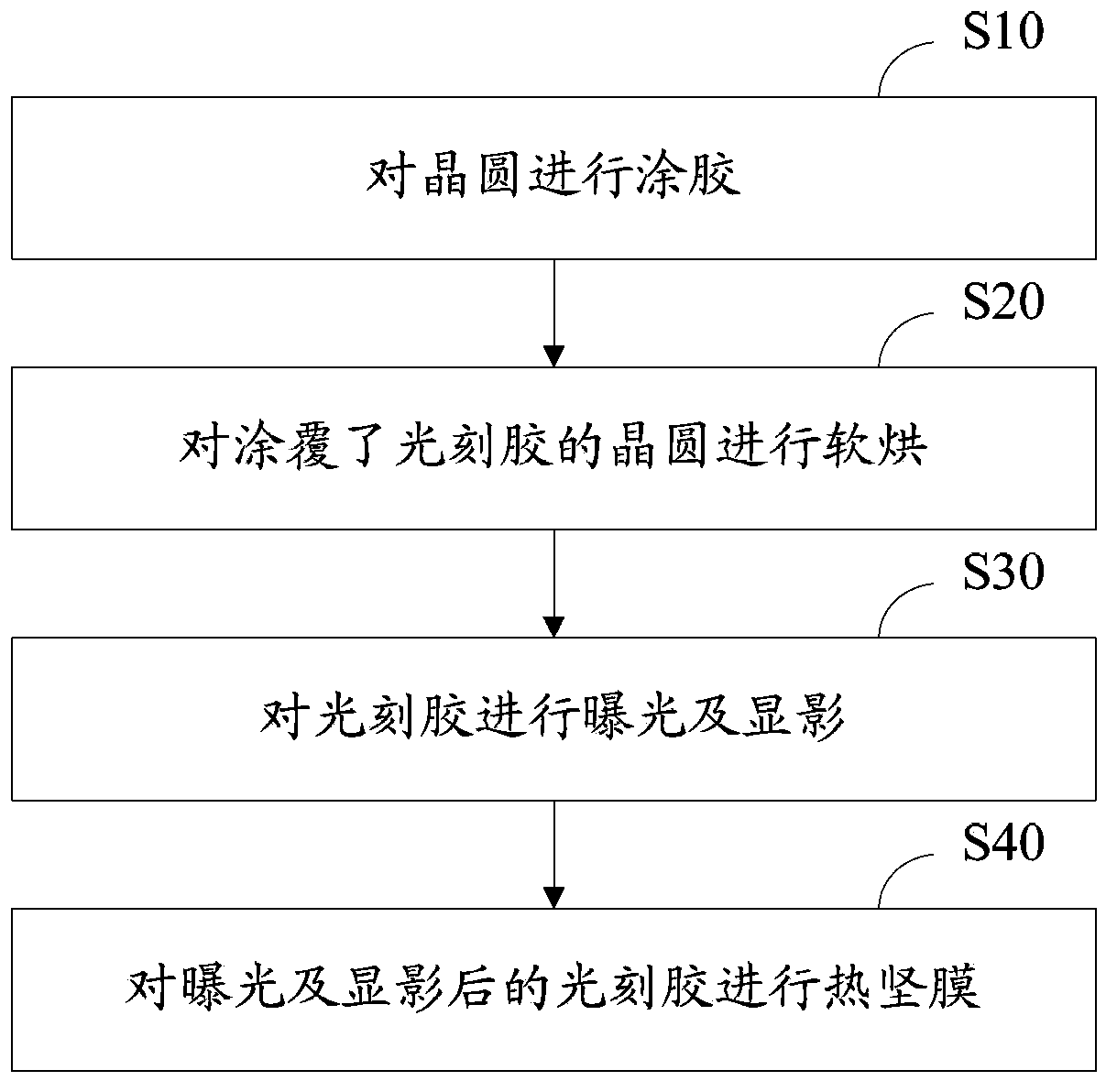

Photoetching method for photoresist as silicon groove etching mask

ActiveCN103576445AImprove the selection ratioAvoid debrisSemiconductor/solid-state device manufacturingPhotomechanical coating apparatusPhotoresistSilicon

A photoetching method for a photoresist as a silicon groove etching mask comprises the following steps: gluing a wafer; performing soft baking on the wafer coated with the photoresist; performing exposure and development on the photoresist; performing hardening on the photoresist subjected to exposure and development, wherein the thickness of the photoresist on the wafer after the hardening step is finished is 7.2-7.8 mu m; and performing etching on a silicon groove by taking the hardened photoresist as the mask. The photoetching method does not comprise the step of performing optical stabilization processing on the photoresist. By forming the thick glue with a thickness large than 7 mu m, the selectivity ratio of silicon is improved. Also because the photoetching method does not comprises the step of performing optical stabilization processing on the photoresist, a dry-process glue-removing technology can be used, and thus a spin-dry step is not needed after the glue is removed, and the problem of fragments caused by spin dry is avoided.

Owner:CSMC TECH FAB2 CO LTD

Semiconductor plasma etching technology

ActiveCN101615579AImprove the selection ratioIncrease topSemiconductor/solid-state device manufacturingSemiconductor plasmaShielding gas

The invention provides a plasma etching technology comprising a dielectric layer penetrating and etching step and a silicon main etching step, wherein, technical gas in the dielectric layer penetrating and etching step comprises fluorine-base etching gas, first light resistance protection gas and dilution gas; technical gas in the silicon main etching step comprises main etching gas, carbon-base by-product removing gas and second light resistance protection gas. In a preferable embodiment, the fluorine-base etching gas is CF4 or SF6, the first light resistance protection gas is CH2F2 or CHF3 or HBr, and the dilution gas is He, Ar or N2; the main etching gas is Cl2, the carbon-base by-product removing gas is O2, and the second light resistance protection gas is HBr. In semiconductor plasma etching, the invention can improve sidewall steepness in figure etching and prevent the upper edge and the lower edge of a line from producing fillets.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

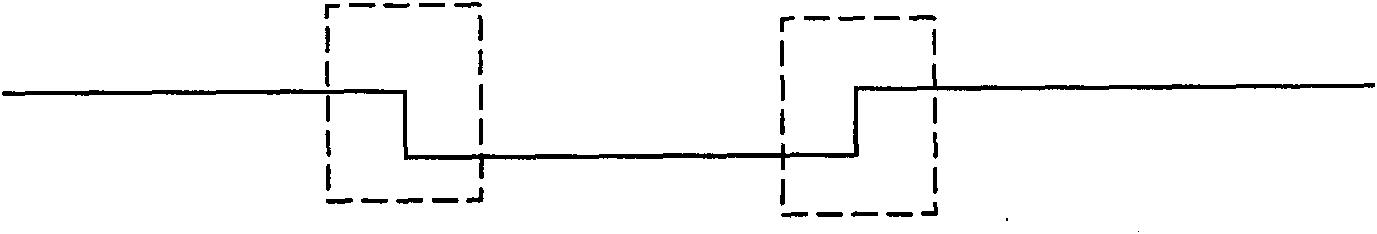

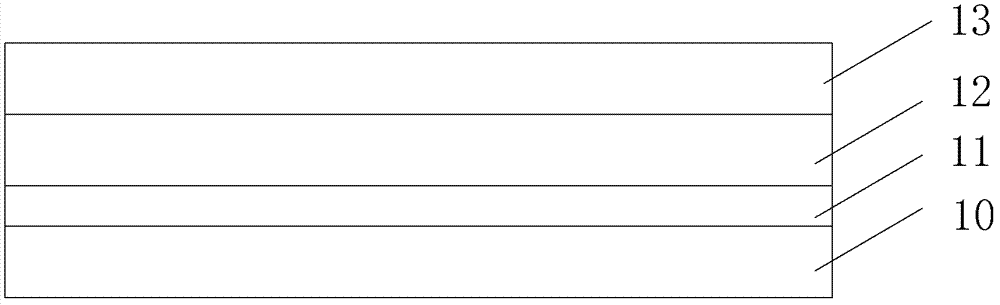

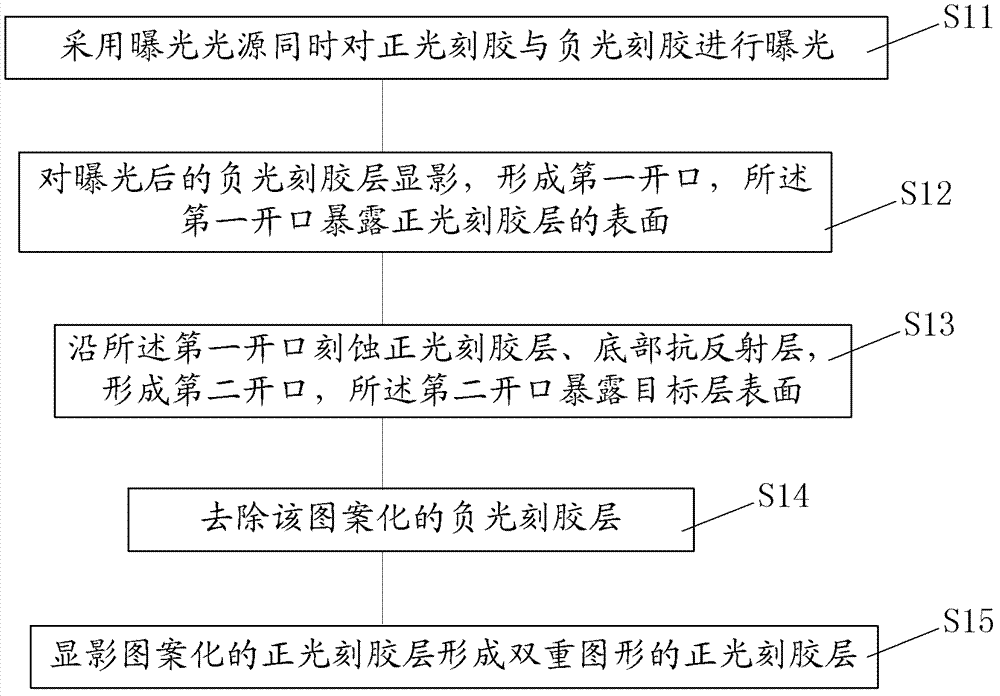

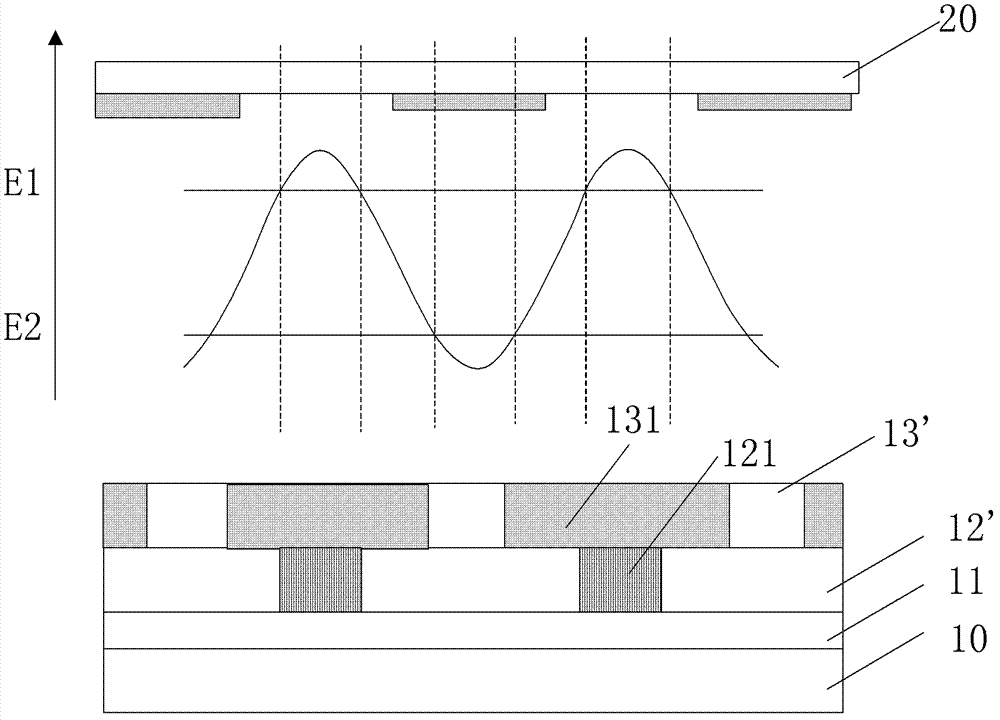

Dual-photoresist and processing method thereof

ActiveCN103365092AImprove the selection ratioReduce lossesPhotomechanical exposure apparatusMicrolithography exposure apparatusComputational physicsWater soluble

The invention discloses a dual-photoresist. The dual-photoresist comprises a first photoresist layer and a second photoresist layer which are sequentially formed on a target layer, wherein the first photoresist layer is a positive photoresist layer or a negative photoresist layer, and the polarity of the second photoresist layer is opposite to that of the first photoresist layer, and the first photoresist layer and the second photoresist layer are exposed in a same exposure process; the positive photoresist layer adopts a silicon-containing water-soluble positive photoresist. The invention further provides a processing method of the dual-photoresist. By adopting the technical scheme and adopting the fluorine-containing corrosion gas with high selection ratio to the silicon-containing water-soluble positive photoresist, the transferring between patterns of the dual photoresists is precise, and the controllability of the process is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

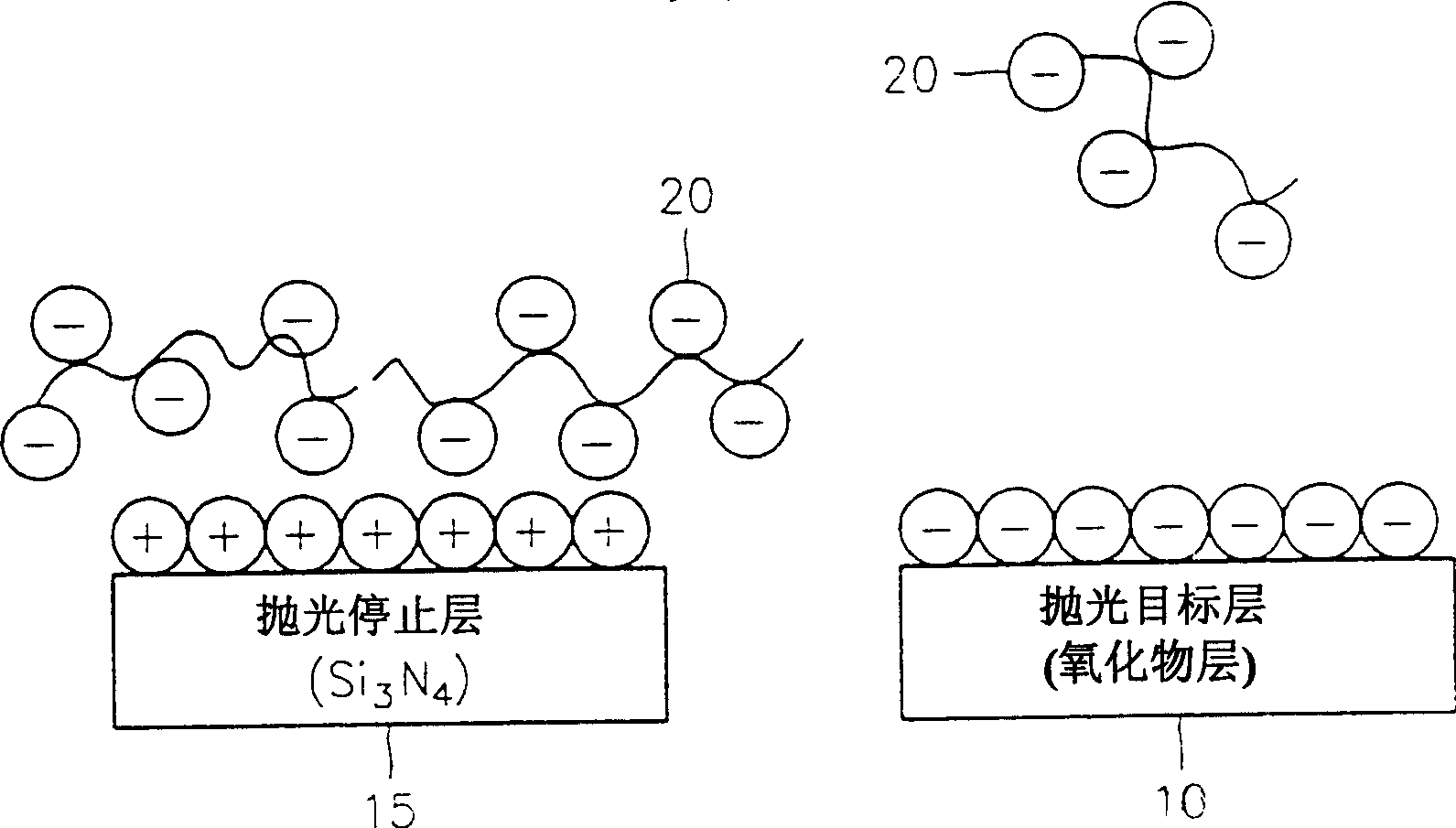

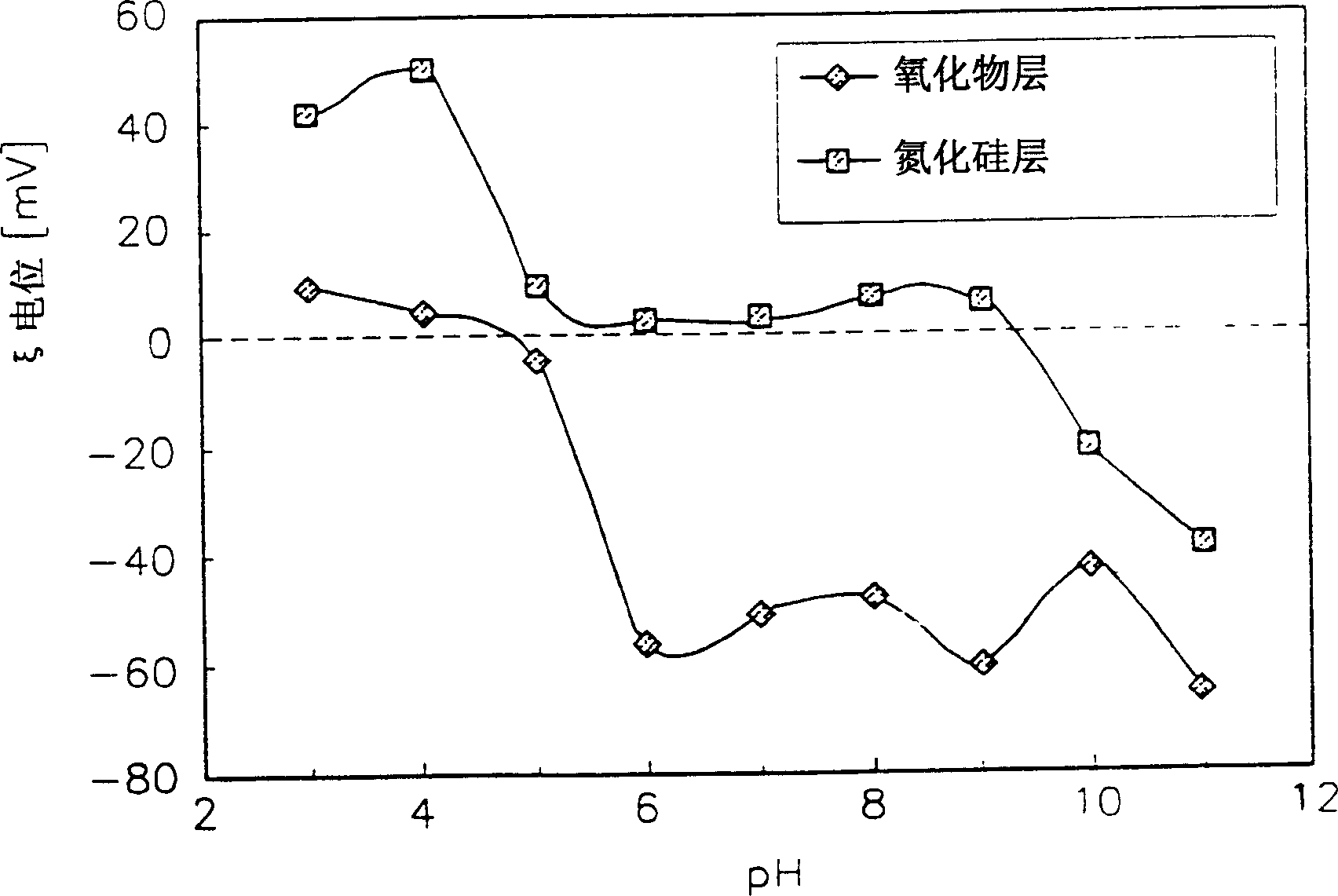

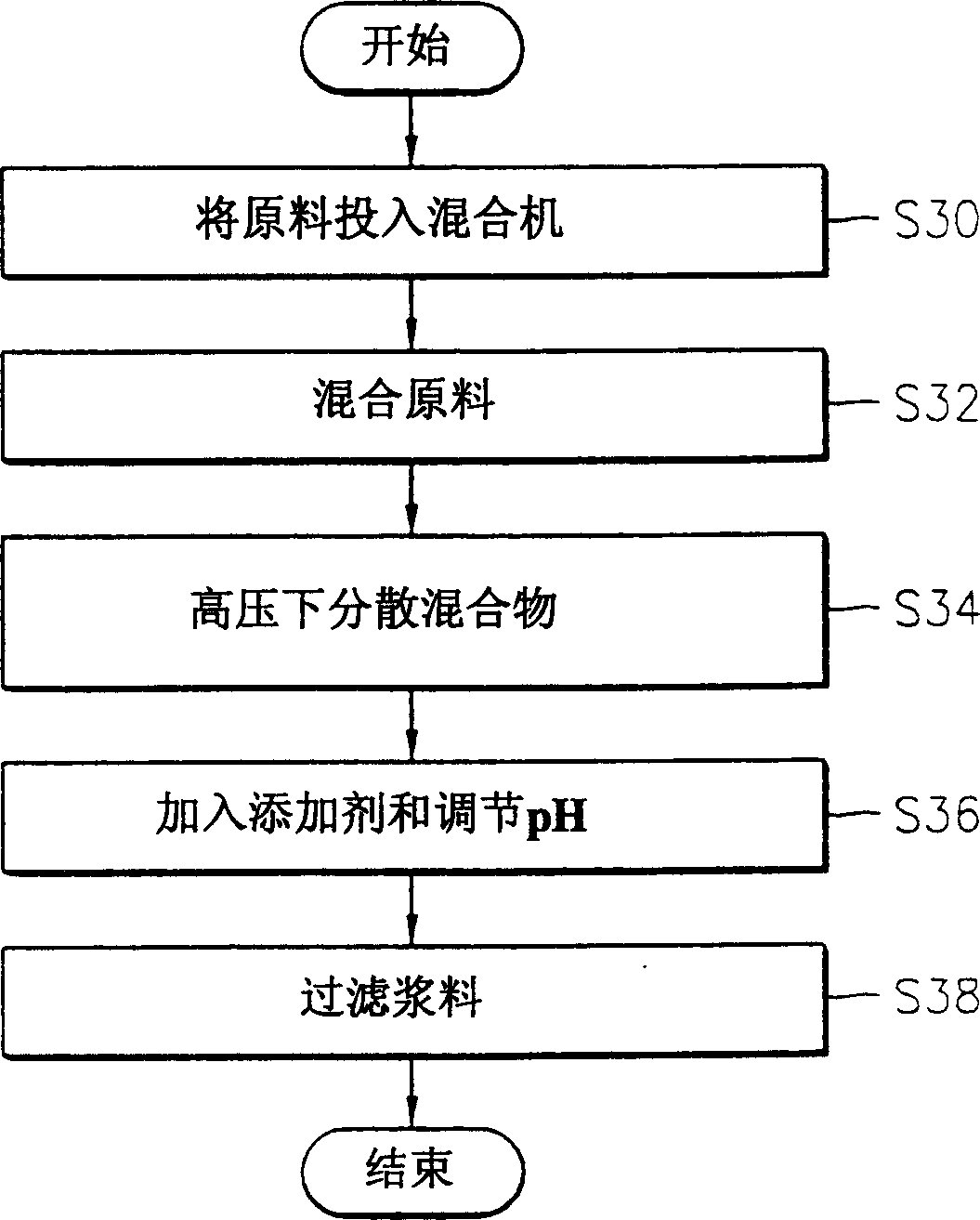

Chemical and mechanical polishing size and chemical and mechanical polishing method using said size

InactiveCN1441017AGood planarityImprove the selection ratioOther chemical processesSemiconductor/solid-state device manufacturingPh controlCompound (substance)

Owner:SAMSUNG ELECTRONICS CO LTD

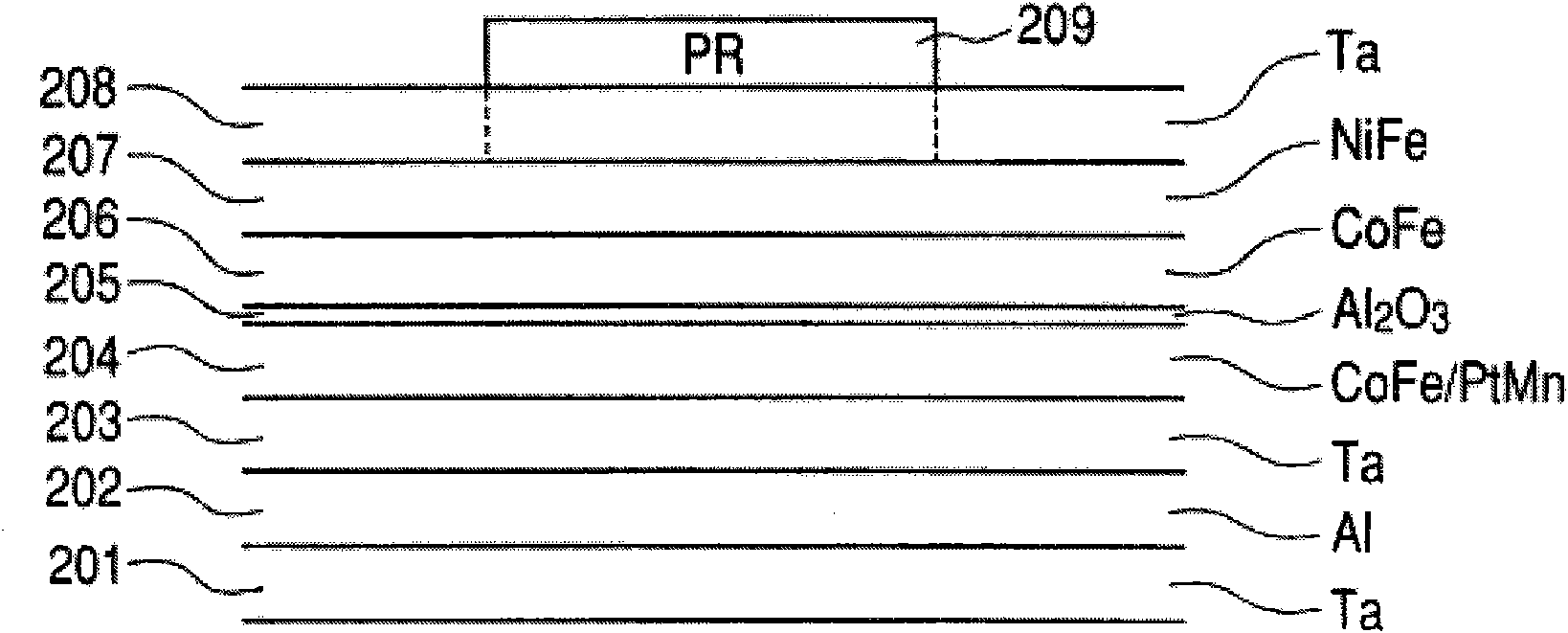

Process for producing magnetic element

InactiveCN101641807ACorrosion resistance does not need to be consideredAchieving high-level micromachiningNanomagnetismNanoinformaticsOrganic filmCarboxylic acid

A magnetic device is fabricated by etching a magnetic film in an atmosphere of plasma using a non-organic film as a mask. An atmosphere of plasma is generated by using at least one kind of gasifying compound selected from a gasifying compound group consisting of ethers, aldehydes, carboxylic acids, esters and diones; and by using a non-organic material mask, etching a magnetic film or diamagneticfilm which includes at least one kind of metal selected from a metal group consisting of VIII group, IX group and X group elements in a periodic table. As a gas in the atmosphere of plasma, at least one kind of gas selected from a gas group consisting of oxygen, ozone, nitrogen, H2O, N2O, NO2 and CO2 can be added to the gasifying compound. The etching rate and the etching ratio were favorable.

Owner:CANON ANELVA CORP

Chemical machine polishing liquor for KTP crystal

The invention discloses a chemical mechanic buffing liquid of titanium potassium oxide phosphate, which comprises the following parts: 10-90 percent nanometer SiO2 sol, 0.5-10 percent inorganic alkaline and organic alkaline, 0.5-10 percent non-ionic surfactant, 0.5-10 percent chelant and deionized water. The invention can prevent surface fish tail effectively, which improves the surface flatness.

Owner:HEBEI UNIV OF TECH

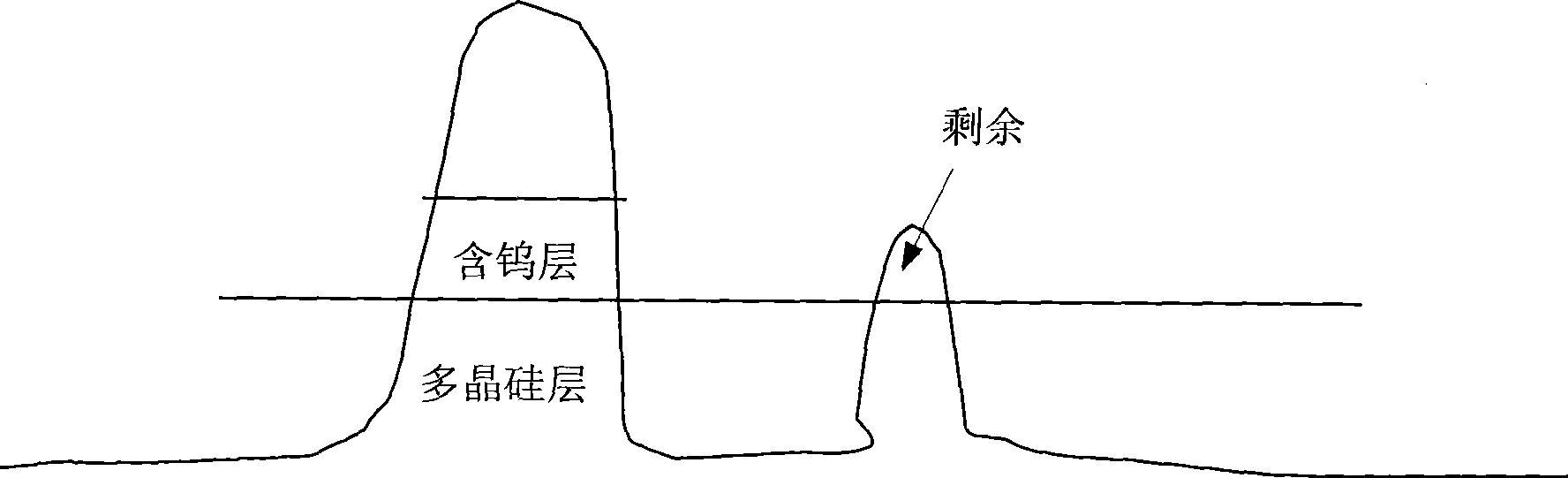

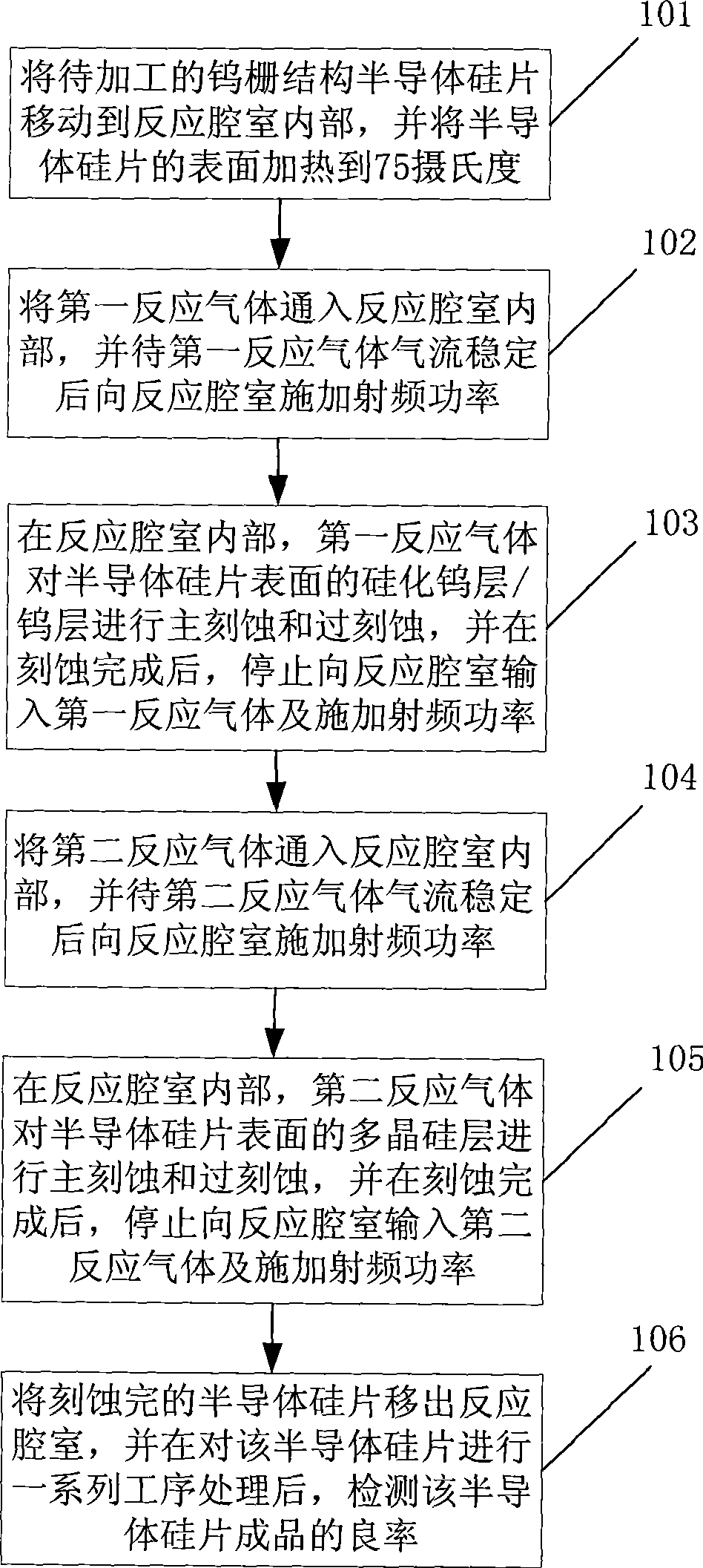

Technological method for etching tungsten gate

InactiveCN101533772AImprove the selection ratioEliminate residueSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingRadio frequency

The invention discloses a technological method for etching tungsten gate, pertaining to the field of semiconductor processing and manufacturing; the method comprises the following steps: a semiconductor silicon wafer is moved into a reaction chamber and heated to a high temperature; a first reaction gas is pumped into the reaction chamber; radio frequency power is imposed on the reaction chamber after the airflow of the first reaction gas becomes stable; and then, the first reaction gas etches the tungsten silicide layer or tungsten layer of the semiconductor silicon wafer; after the etching is finished, the pumping of the first reaction gas and the imposing of the radio frequency power are stopped; a second reaction gas is pumped into the reaction chamber; the radio frequency power is imposed on the reaction chamber after the airflow of the second reaction gas becomes stable; the second reaction gas etches the polysilicon layer of the semiconductor silicon wafer; after the etching is finished, the pumping of the second reaction gas and the imposing of the radio frequency power are stooped; and the semiconductor silicon wafer is moved out of the reaction chamber. The technological method improves the selection ratio between the tungsten silicide layer or tungsten layer and the polysilicon layer in the tungsten gate etching technology.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

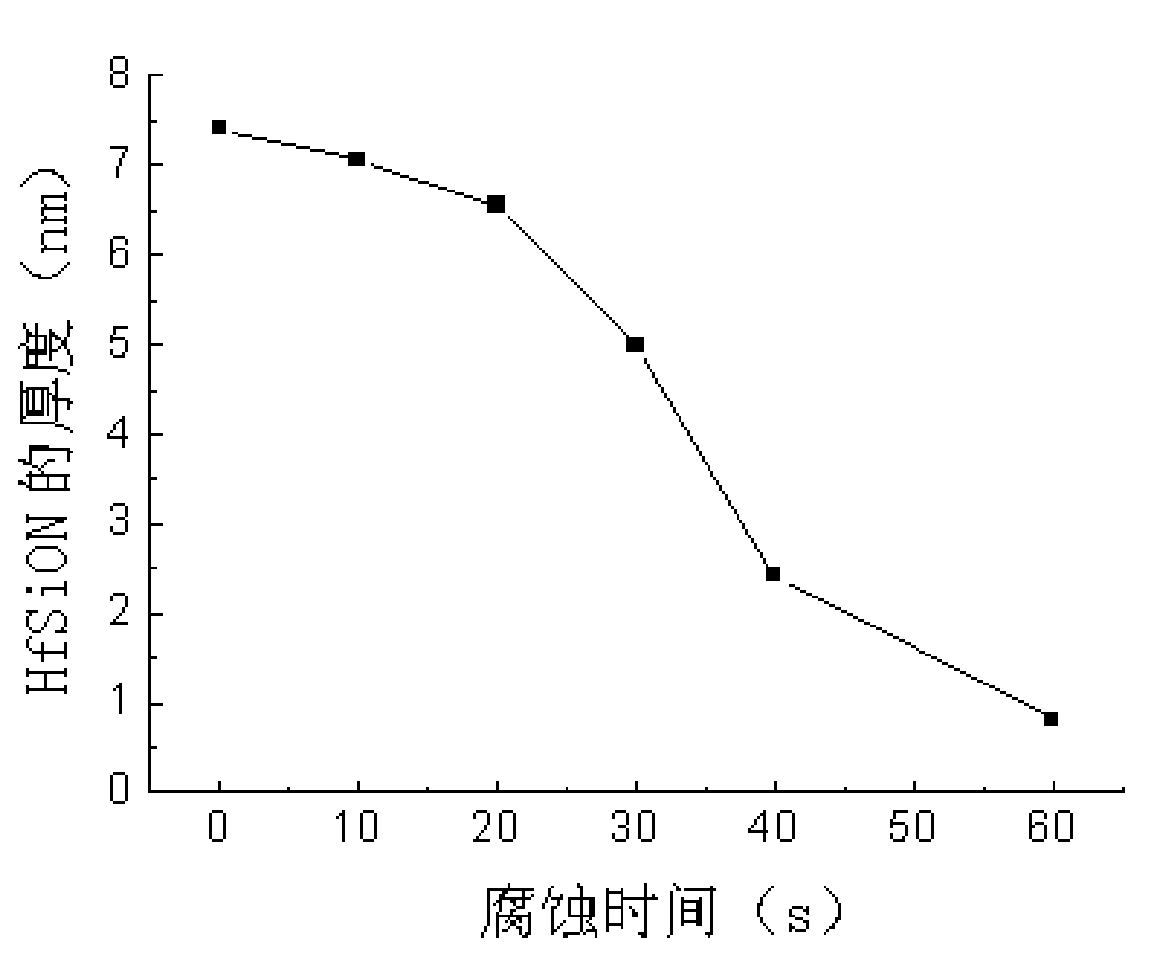

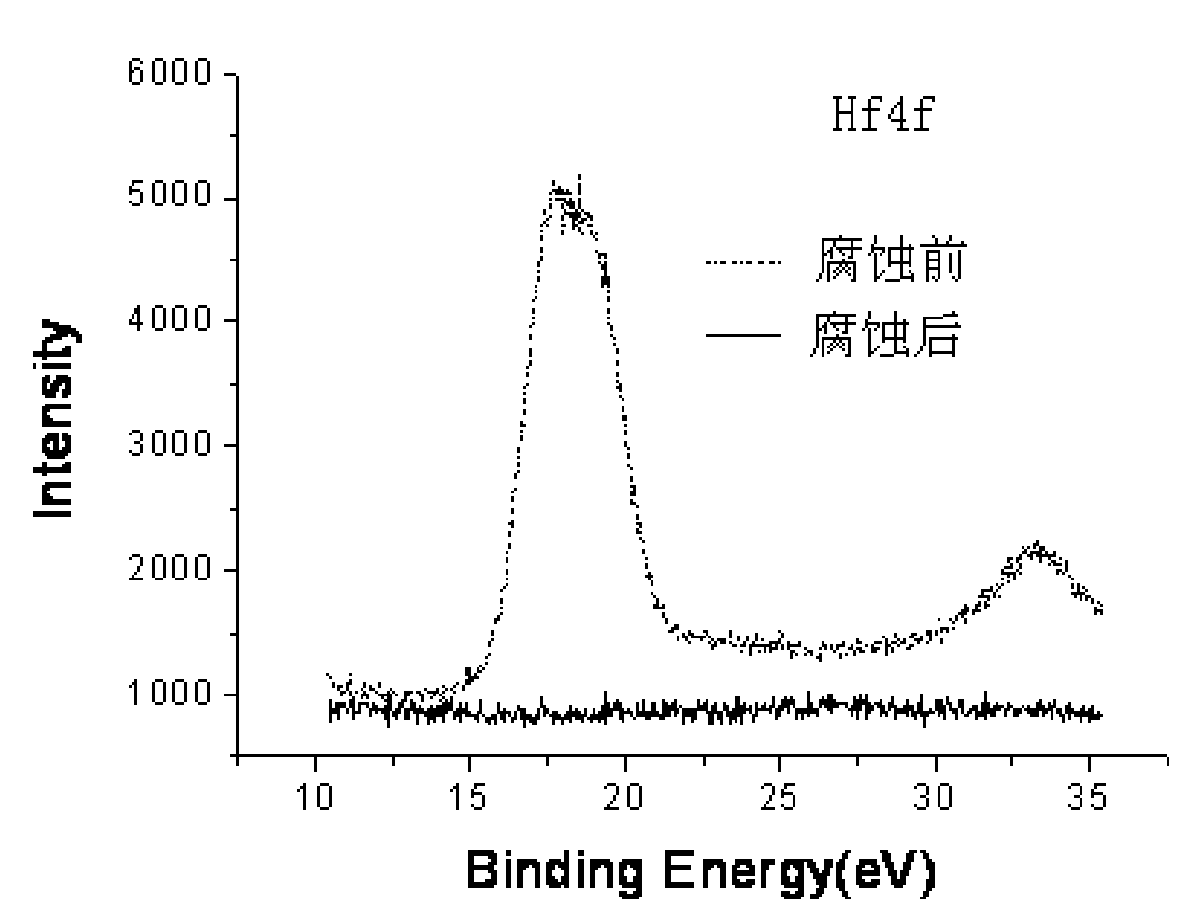

Corrosive agent and corrosion method of HfSiON high-K gate dielectric material

ActiveCN101619457ASpeed up corrosionAchieve selective removalSemiconductor/solid-state device manufacturingSemiconductor devicesHydrofluoric acidGate dielectric

The invention relates to a corrosive agent of an HfSiON high-K gate dielectric material and a corrosion method by using the corrosive agent, which belong to the technical field of integrated circuit manufacture. The corrosive agent comprises 0.19-4.83 percent by weight of hydrofluoric acid. The corrosion method by using the corrosive agent comprises the following steps: forming the HfSiON high-K gate dielectric material on an Si substrate, an Si / SiO2 interface layer or Si / SiON interface layer, and soaking the HfSiON high-K gate dielectric material in the corrosive agent for wet method corrosion. The corrosive agent is used for carrying out corrosion on the HfSiON high-K gate dielectric material and can reduce the hydrolysis of the hydrofluoric acid, thereby the corrosion speed of the HfSiON high-K gate dielectric material is improved, the corrosion speed of field oxide region SiO2 can be reduced, and the selection ratio of HfSiON to the field oxide region SiO2 can be further improved.

Owner:SOI MICRO CO LTD

Chemi-mechanical polishing fluid for polishing semiconductor wafer

ActiveCN102533123AChange the removal rateAdjust the selection ratioSemiconductor/solid-state device manufacturingPolishing compositions with abrasivesSilicon dioxideSURFACTANT BLEND

The invention provides a chemi-mechanical polishing fluid for polishing a semiconductor wafer, which is prepared from the following components in percentage by weight: 0.2-5% of acidic pH regulator, 0.01-5% of piperidine nitroxide free radical, 0.1-15% of surfactant, 0.5-20% of grinding particle and the balance of water. The polishing fluid provided by the invention can obviously change the removal rate of silicon nitride under acidic conditions, can regulate the selection ratio of silicon dioxide to silicon nitride, and has the advantages of simple preparation technique, high polishing precision and the like.

Owner:SHANGHAI HUAMING HI TECH GRP

Semiconductor device and manufacturing method thereof, integrated circuit and electronic device

PendingCN111799331AWill not corrodeSimple technologySemiconductor/solid-state device manufacturingSemiconductor devicesNanowireDevice material

The invention discloses a semiconductor device and a manufacturing method thereof, an integrated circuit and an electronic device, and relates to the technical field of semiconductors. The invention aims to provide a semiconductor device which is simple in technology, low in manufacturing difficulty, low in production cost and capable of preventing transverse corrosion to a source-drain layer whennanowires are released. The semiconductor device includes: a gate-all-around transistor; wherein the gate-all-around transistor comprises a channel layer and a source-drain structure connected with the channel layer; a source-drain structure, the source-drain structure comprising a source-drain layer and a liner layer, and the liner layer being formed between the source-drain layer and the channel layer; the material of the liner layer being the same as that of the channel layer; or the absolute value of the difference between the mass percent of the target element contained in the material of the liner layer and the mass percent of the target element contained in the channel layer is smaller than the first threshold value.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

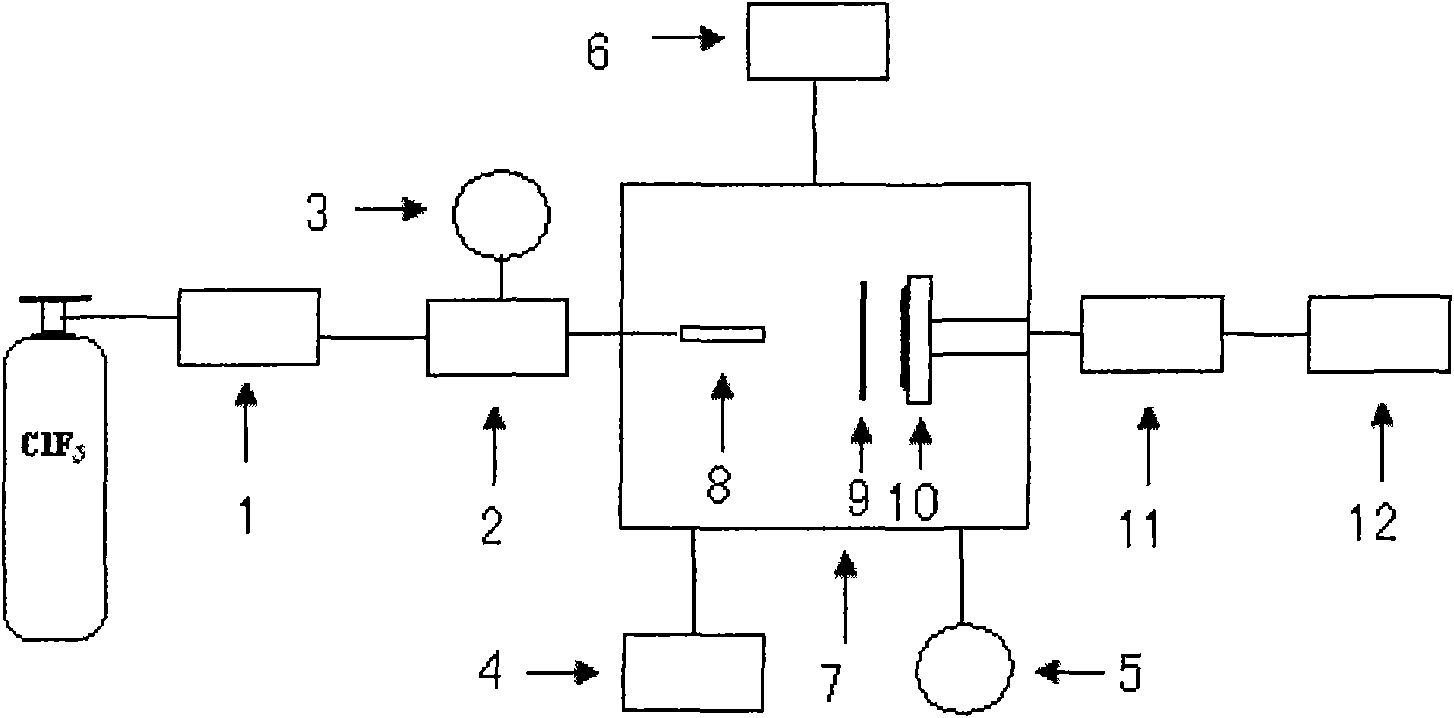

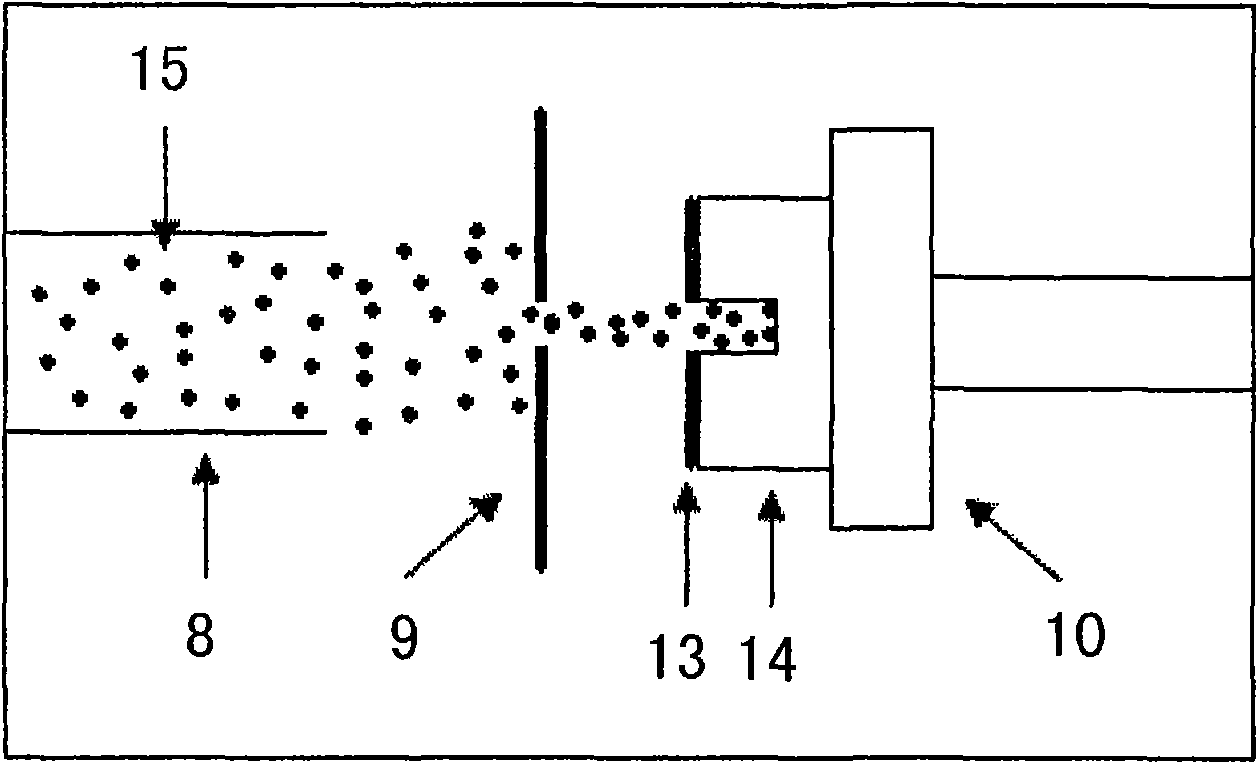

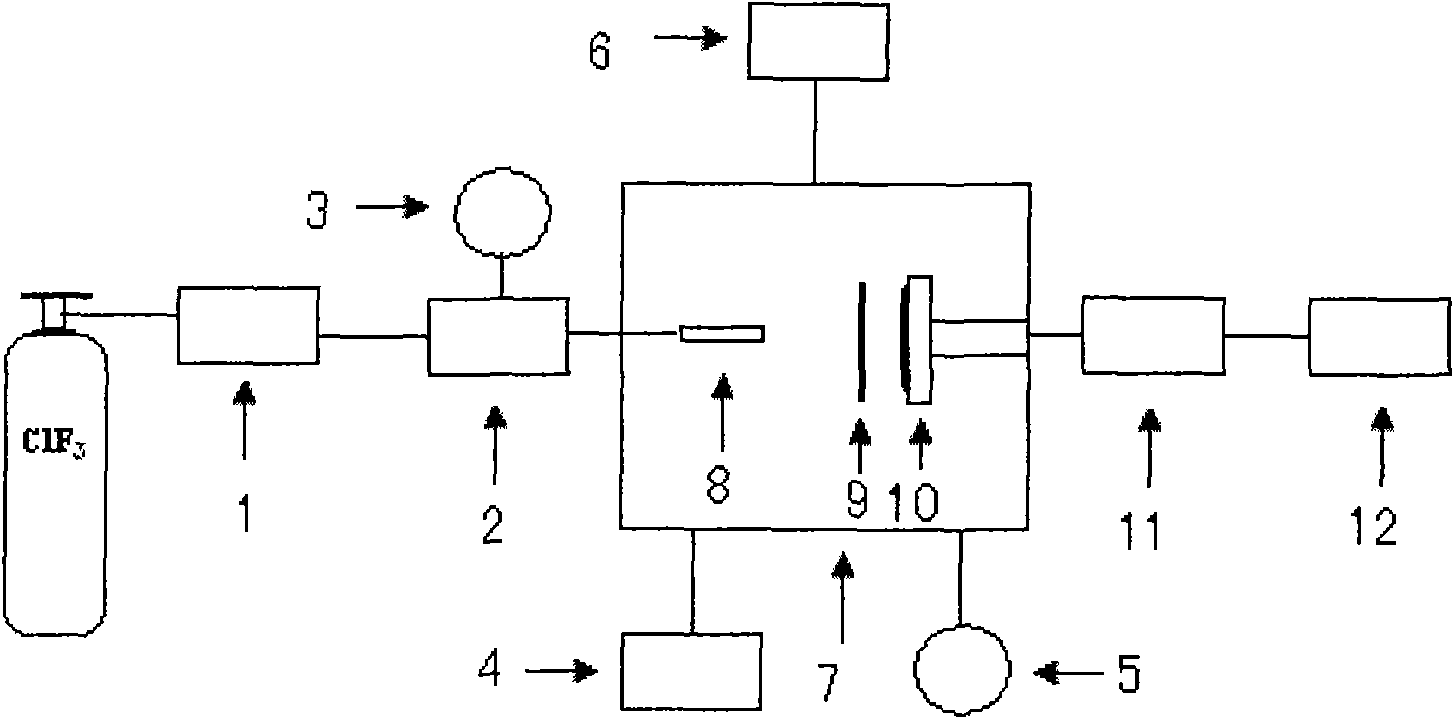

Device for gas linear cutting of silicon slice

InactiveCN101880878AFast etch rateHigh smoothness of the sectionSemi-permeable membranesSemiconductor/solid-state device manufacturingTemperature controlRoom temperature

The invention discloses a device for the gas linear cutting of a silicon slice, which comprises a flow controller, a pressure reducing valve, a pressure gauge, a vacuum pump, a vacuum-cavity pressure gauge, a vacuum-cavity temperature control device, a vacuum chamber, a spray head, a masking plate, a silicon slice frame, a post pump and a tail gas processing device, wherein the pressure reducing valve, the vacuum pump, the vacuum-cavity pressure gauge, the vacuum-cavity temperature control device and the post pump are respectively connected with the vacuum chamber, gas enters the vacuum chamber after sequentially passing through the flow controller, the pressure reducing valve and the spray head, then the silicon slice on the silicon slice frame is cut through the masking and the beam convergence and regulation of the masking plate, the temperature of the vacuum chamber is controlled to be under a room temperature environment through the vacuum-cavity temperature control device, and etched tail gas is pumped out of the vacuum chamber through the post pump and enters the tail gas processing device through the post pump. In the invention, chlorine trifluoride is used as etching reaction gas for carrying out cutting processing for the silicon slice, and the problems existing in a traditional technology can be well solved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI