Patents

Literature

217results about How to "Etching speed is fast" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Antireflective film-forming composition, method for manufacturing the same, and antireflective film and pattern formation method using the same

ActiveUS20050277058A1Improve etch selectivityEtching speed is fastSemiconductor/solid-state device manufacturingSilver halide emulsionsCross-linkResist

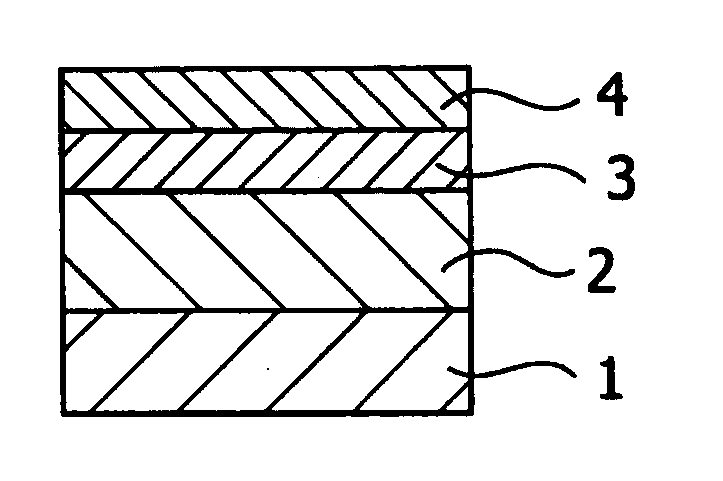

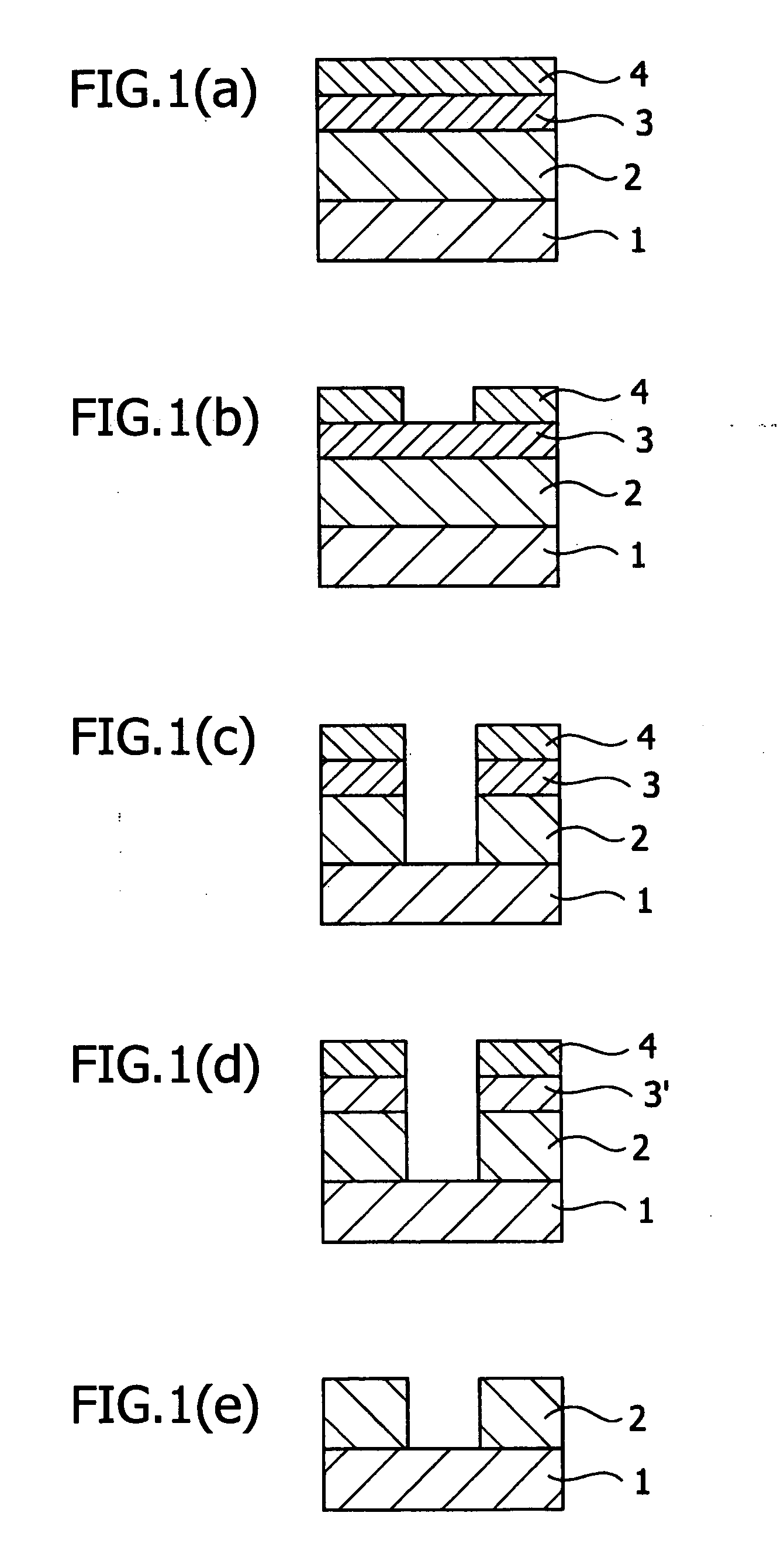

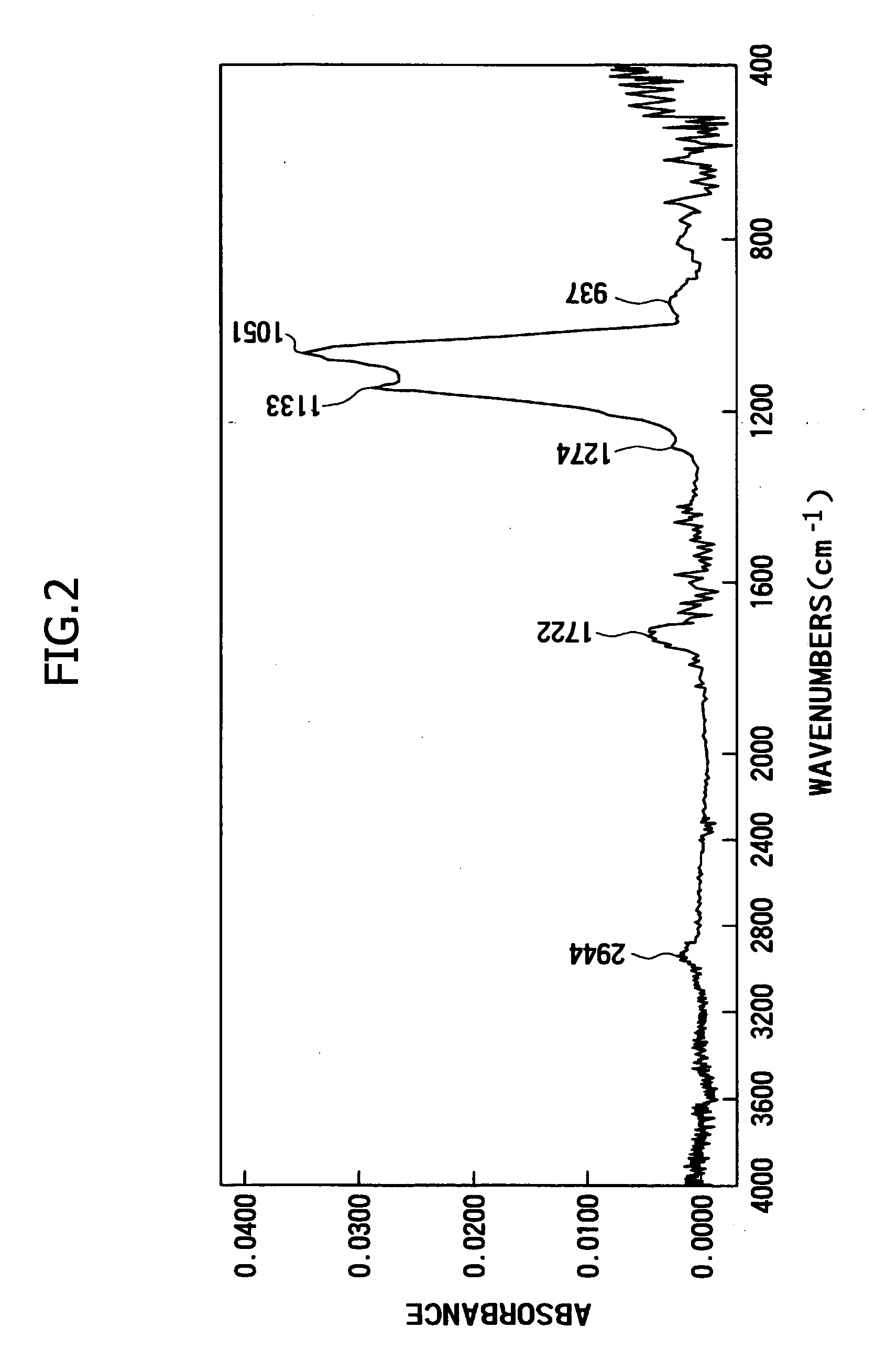

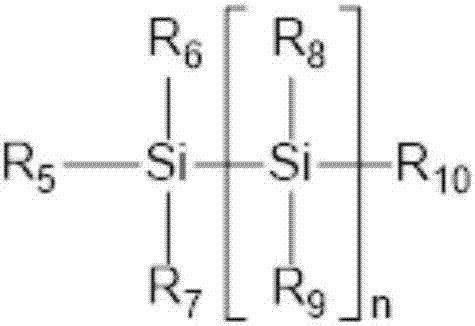

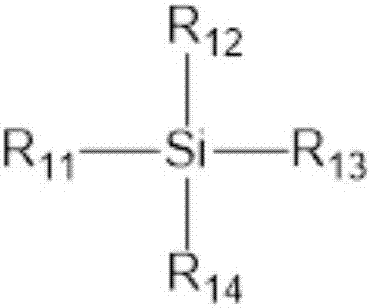

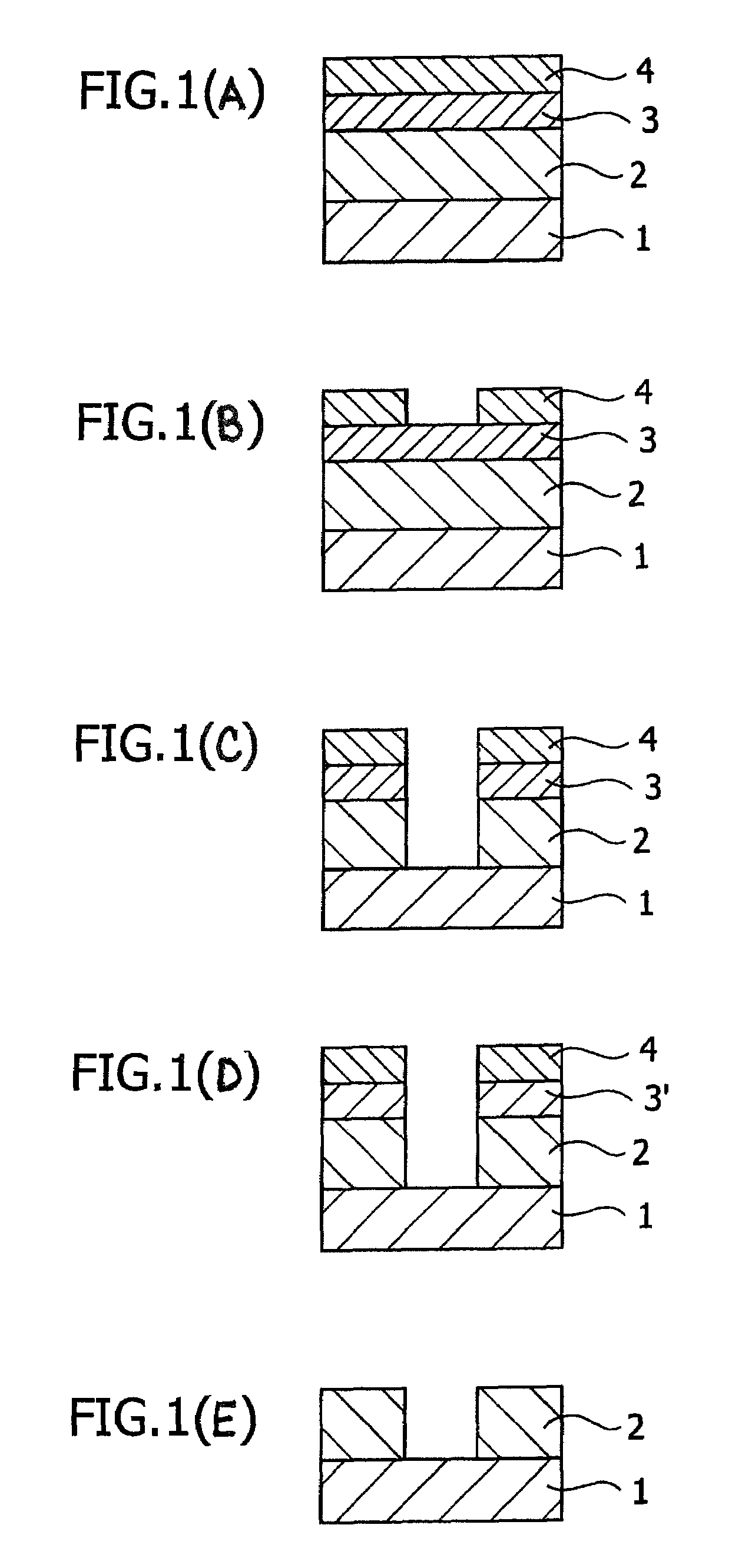

The present invention provides a material for an antireflective film characterized by high etching selectivity with respect to a resist, that is, which has a fast etching speed when compared to the resist, and in addition, can be removed without damage to a film which is to be processed. The present invention also provides a pattern formation method for forming an antireflective film layer on a substrate using this antireflective film-forming composition, and a pattern formation method that uses this antireflective film as a hard mask, and a pattern formation method that uses this antireflective film as a hard mask for processing the substrate. The present invention provides an antireflective film-forming composition comprising an organic solvent, a cross linking agent, and a polymer comprising a light absorbing group obtained by hydrolyzing and condensing more than one type of silicon compound, a crosslinking group and a non-crosslinking group.

Owner:SHIN ETSU CHEM IND CO LTD +1

Silicon nitride film etching solution

InactiveCN107573940AReduce or suppress the production ofImprove the selection ratioSurface treatment compositionsSilane compoundsSilicone oil

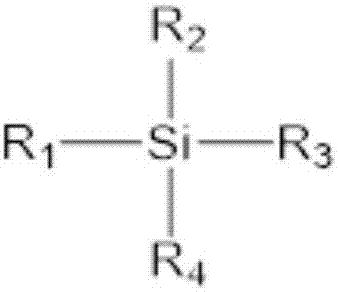

The invention relates to a silicon nitride film etching solution, comprising first silicone compound, whose silicone atom is dependently combined with over three hydrophilic functional groups, and second silicone compound, whose silicone atom is dependently combined with one or two hydrophilic functional groups.

Owner:OCI

Antireflective film-forming composition, method for manufacturing the same, and antireflective film and pattern formation method using the same

ActiveUS7541134B2Improve etch selectivityEtching speed is fastSemiconductor/solid-state device manufacturingSilver halide emulsionsResistCross-link

The present invention provides a material for an antireflective film characterized by high etching selectivity with respect to a resist, that is, which has a fast etching speed when compared to the resist, and in addition, can be removed without damage to a film which is to be processed. The present invention also provides a pattern formation method for forming an antireflective film layer on a substrate using this antireflective film-forming composition, and a pattern formation method that uses this antireflective film as a hard mask, and a pattern formation method that uses this antireflective film as a hard mask for processing the substrate. The present invention also provides an antireflective film-forming composition comprising an organic solvent, a cross linking agent, and a polymer comprising a light absorbing group obtained by hydrolyzing and condensing more than one type of silicon compound, a crosslinking group and a non-crosslinking group.

Owner:SHIN ETSU CHEM CO LTD +1

Novel PCB copper reduction etching liquid and manufacturing technology

The invention discloses novel PCB copper reduction etching liquid. The novel PCB copper reduction etching liquid comprises components including 1-100 mL / L of sulfuric acid, 1-100 mL / L of hydrogen peroxide, 1 g / L-100 g / L of hydrogen peroxide stabilizer, 1 g / L-100 g / L of a copper ion complexing agent, 0.1 g / L-10 g / L of a surface active agent, 1 g / L-100 g / L of accelerator, 0.1 g / L-10 g / L of copper surface corrosion inhibitor and 0.1 g / L-10 g / L of needle hole inhibitor. The invention further provides a method for preparing the PCB copper reduction etching liquid. The tolerance of copper ions of the prepared PCB copper reduction etching liquid is high, the etching speed is high, the copper surface is bright and not prone to oxidization, and the needle hole defect is not likely to be generatedafter abnormally-crystallized copper crystals are subjected to copper reduction etching.

Owner:湖南互连微电子材料有限公司

Glass substrate for display device and method for manufacturing same

ActiveCN103910487AInhibit or avoid melt lossInhibit devitrificationGlass productionDevitrificationMelting tank

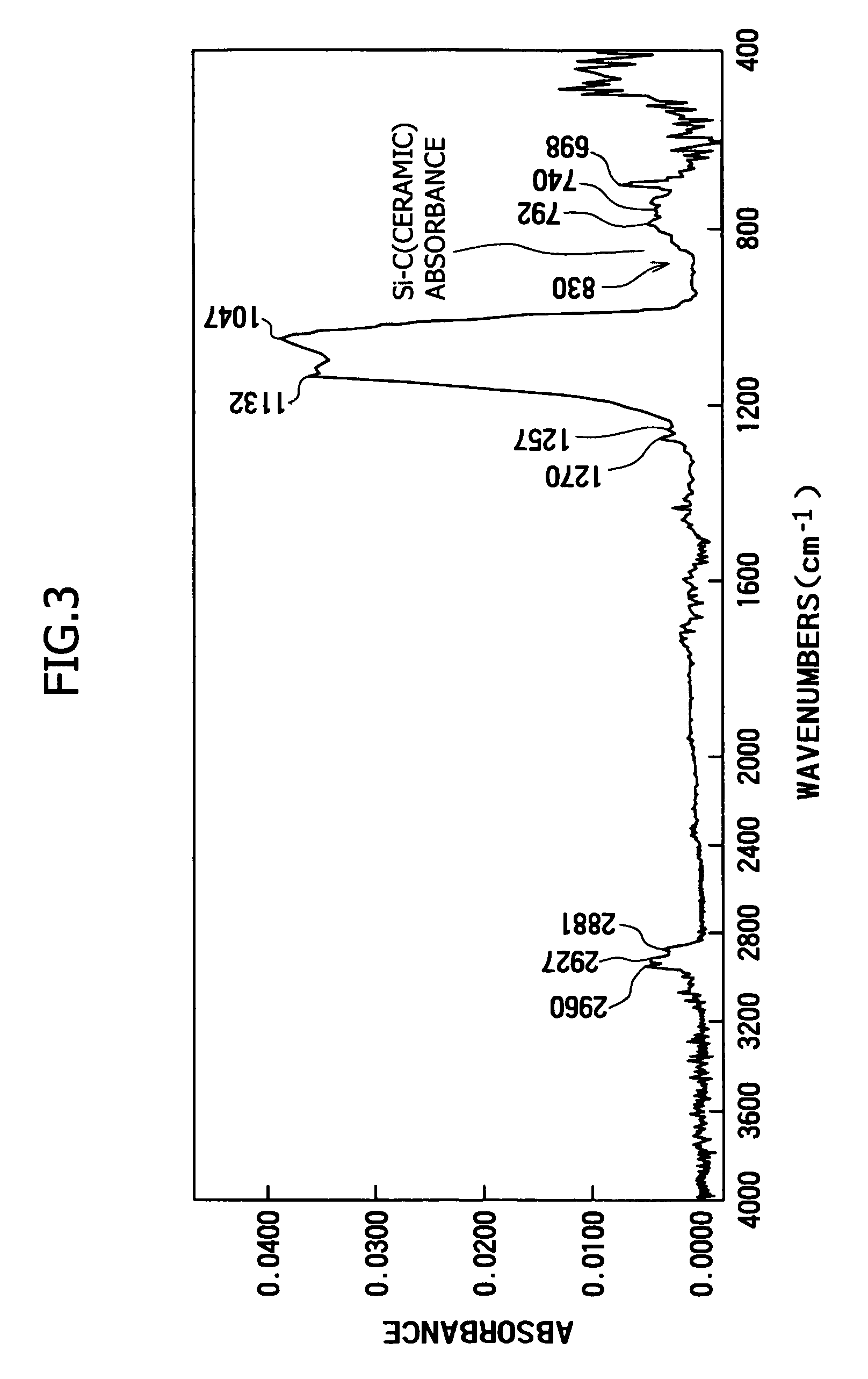

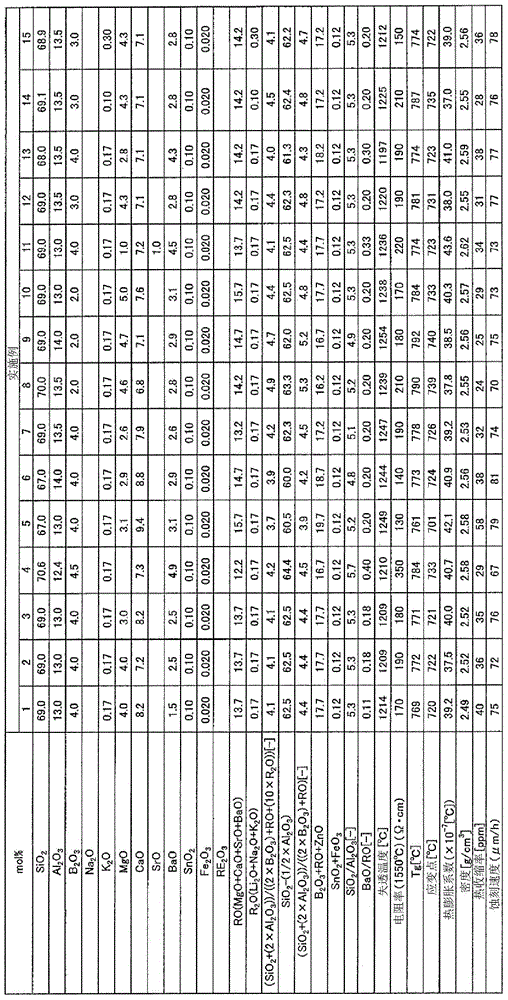

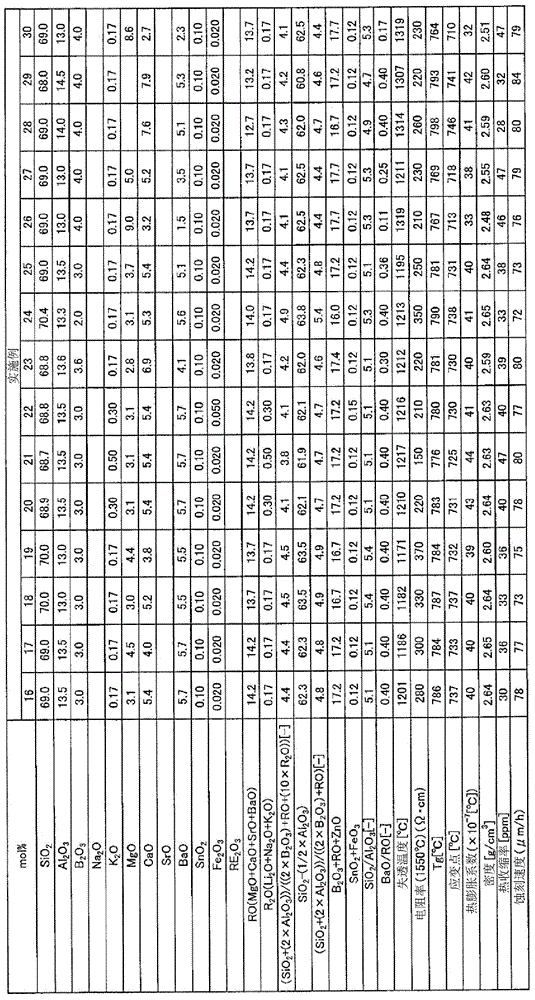

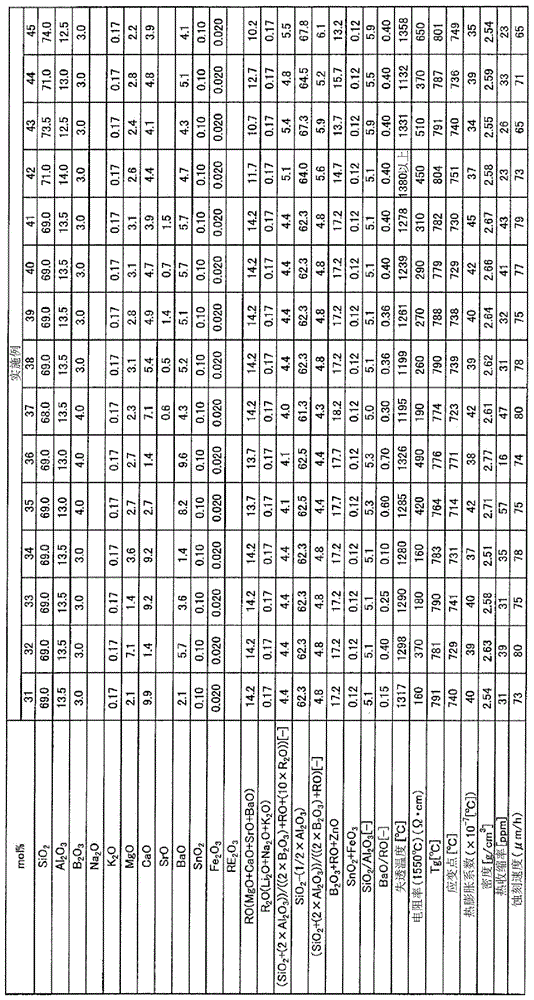

The invention relates to a glass substrate for display device and a method for manufacturing same and provides a glass substrate which is high in strain point and capable of preventing a melting tank from melting loss, a glass substrate which is high in strain point and capable of suppressing devitrification, a glass substrate which is high in strain point and etching speed, and a method for manufacturing the glass substrate. The glass substrate contains Sio2 and Al2O3, 0-8% of B2O3, 0.01-0.8 % of R2O, and 0.05-1 of BaO / RO in mol%, and the strain point is over 670 DEG C. The glass substrate may contain Sio2, Al2O3 and MgO, 0.1-0.9 of MgO / (RO+ZnO), the strain point is over 700 DEG C, and the contraction rate is 5ppm-75ppm. The glass substrate may contain Sio2, Al2O3 and BaO, 0-7% of B2O3, 1-15% of BaO, and less than 6.0 of Sio2 / Al2O3, and the strain point is over 700 DEG C. RO represents (MgO+CaO+SrO+BaO), and R2O represents (Li2O+Na2O+K2O).

Owner:AVANSTRATE INC

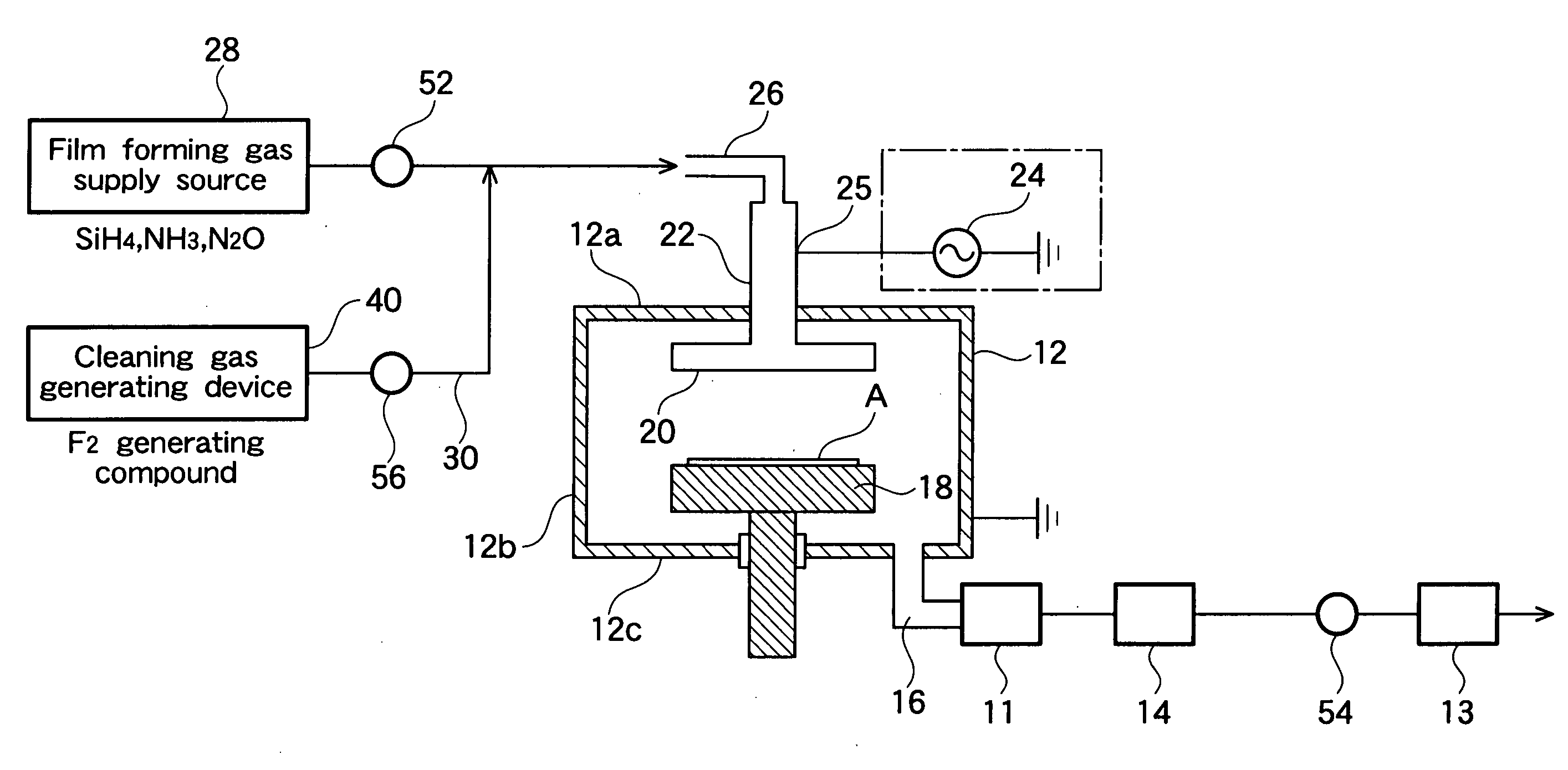

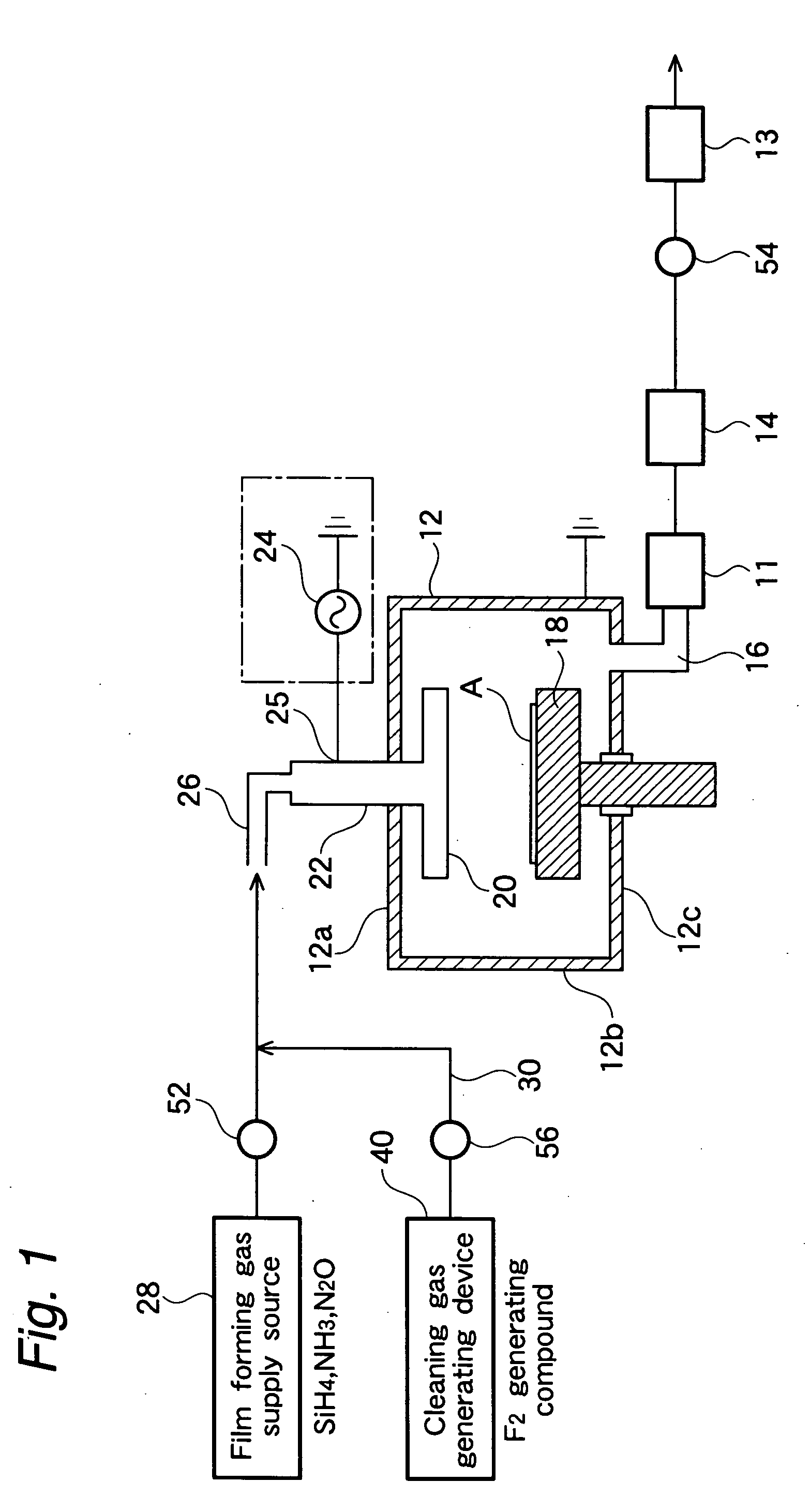

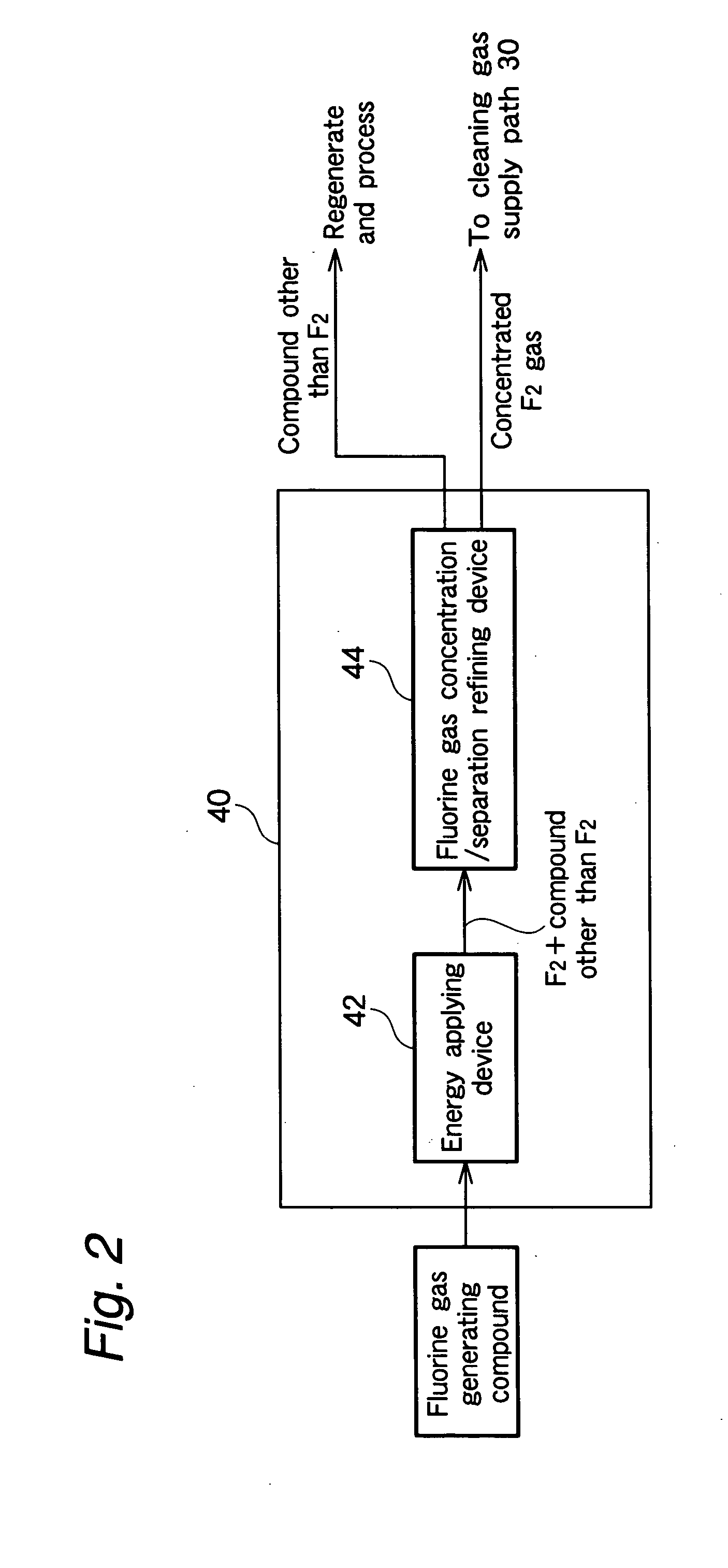

Cvd apparatus having means for cleaning with fluorine gas and method of cleaning cvd apparatus with fluorine gas

InactiveUS20050252451A1Easy to getEtching speed is fastElectric discharge tubesFinal product manufactureForming processesReaction chamber

It is an object to provide a cleaning method in a CVD apparatus capable of efficiently removing a by-product such as SiO2 or Si3N4 which is adhered to and deposited on the surfaces of an inner wall, an electrode and the like in a reaction chamber at a film forming step. Furthermore, it is an object to provide a cleaning method in which the amount of a cleaning gas to be discharged is very small, an influence on an environment such as global warming is also lessened and a cost can also be reduced. An energy is applied to a fluorine compound to react the fluorine compound, thereby generating a fluorine gas component and a component other than the fluorine gas component. Furthermore, the fluorine gas component and the component other than the fluorine gas component which are generated are separated from each other so that the fluorine gas component is separated and refined. After a film forming process for a base material is carried out by a CVD apparatus, a separated and refined fluorine gas is then converted to a plasma to remove a by-product adhered into the reaction chamber.

Owner:NAT INST OF ADVANCED IND SCI & TECH +12

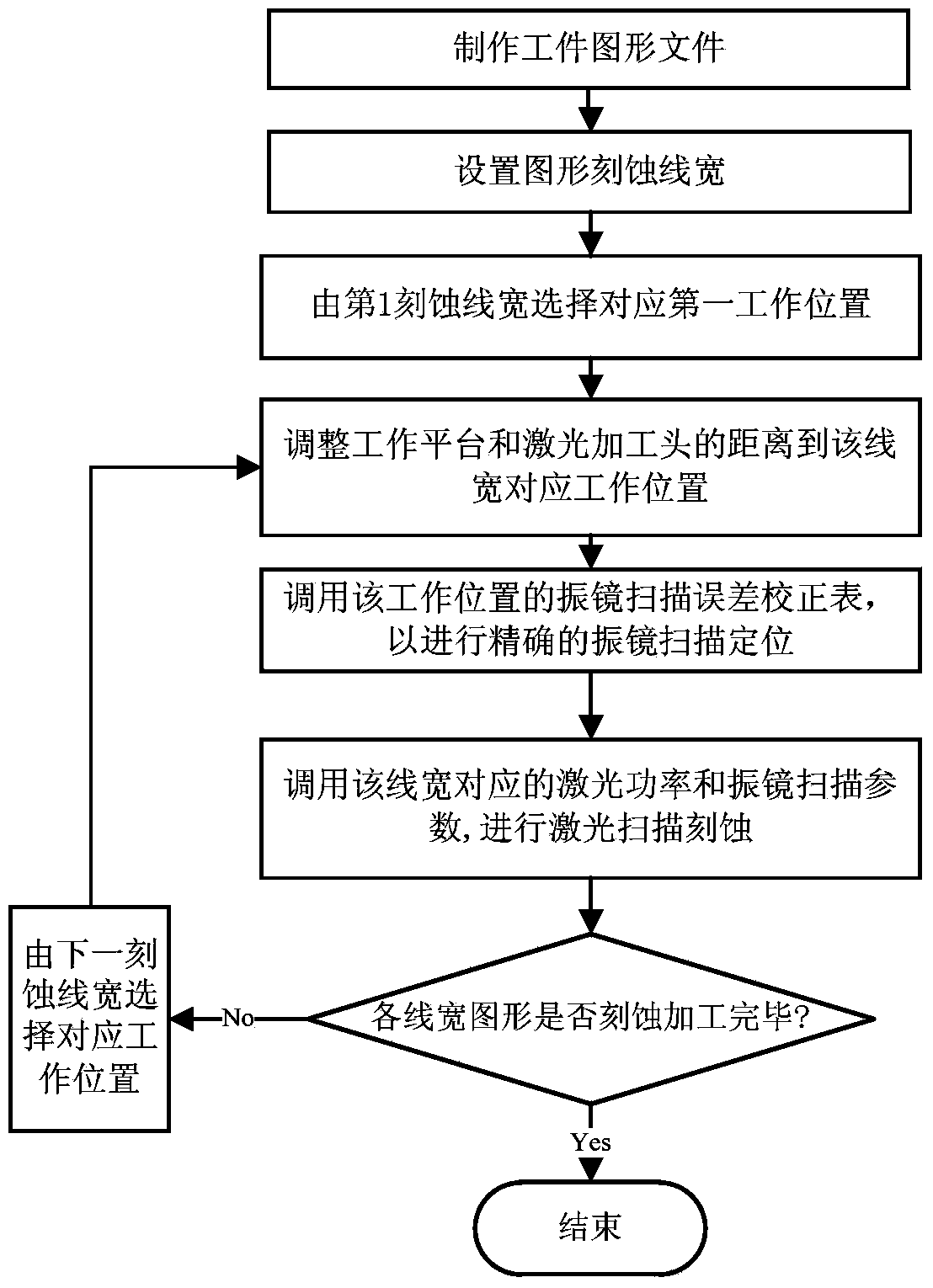

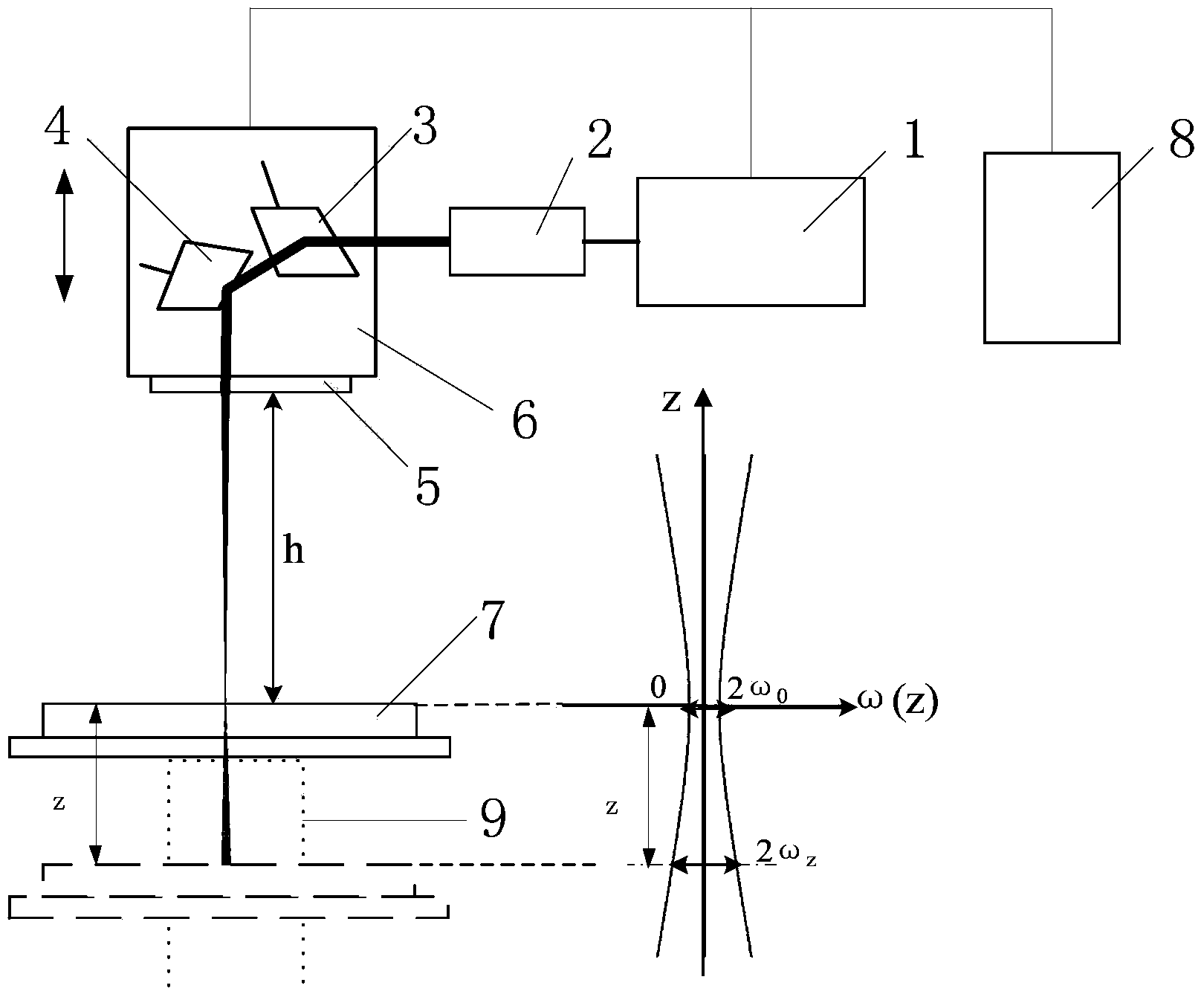

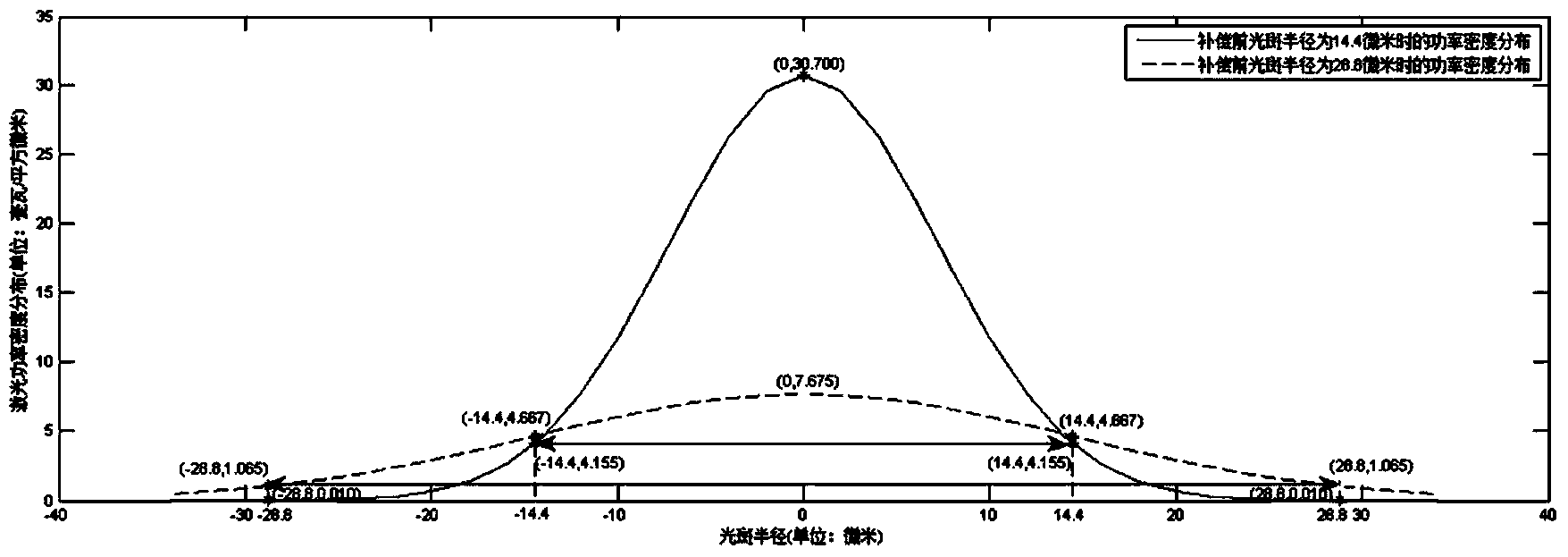

Wire-width-variable laser galvanometer scanning quick etching method and device

ActiveCN103801838AIncreased processing flexibilityImprove processing efficiencyLaser beam welding apparatusGratingLight spot

The invention discloses a wire-width-variable laser galvanometer scanning quick etching method and device. The principle that after laser beam is defocused, the power density gradient becomes small, and a light spot becomes large is used, a high-speed galvanometer scanning error accurate correcting method is used, by setting different focusing and defocusing laser processing distances and corresponding power parameters and laser galvanometer scanning parameters, the size of the laser light spot is controlled, large light spot raster scanning filling after defocusing is carried out is on an image filling zone, and then an image contour is subjected to vector scanning drawing. For different working distances, galvanometer scanning error correcting is carried out first, a high-accuracy galvanometer scanning locating table is formed, and the fact that the same high-accuracy galvanometer scanning locating effect is obtained at different laser processing distances is guaranteed. Quick accurate etching on images with different wire widths can be achieved, etching accuracy and processing speed are considered at the same time, the method and device can be widely used a plane etching system and a three-dimensional laser etching system, and the processing efficiency of equipment is improved.

Owner:武汉飞能达激光技术有限公司

Graphene capacitive touch screen metal electrode fine patterning method

InactiveCN103064574AConducive to industrialized large-scale production and processingReduce switching costsStatic indicating devicesSuperimposed coating processResistEtching

The invention relates to a graphene capacitive touch screen metal electrode fine patterning method. The method aims at a substrate transferred with graphene, and during metal film layer deposition, photo-sensitive resist is used for protecting a window touch area of a touch screen, and the touch screen is subjected to complete patterning finally after photo-sensitive resist removal. The method is beneficial to industrialized large-scale production and processing of patterned metal electrode film layers and low in equipment transformation cost, etching speed of metal electrode layers and graphene layers is increased, a yellow light fine-etching process is avoided, manufacture procedures can be simplified greatly, cost is saved, and product yield is increased.

Owner:无锡力合光电石墨烯应用研发中心有限公司 +1

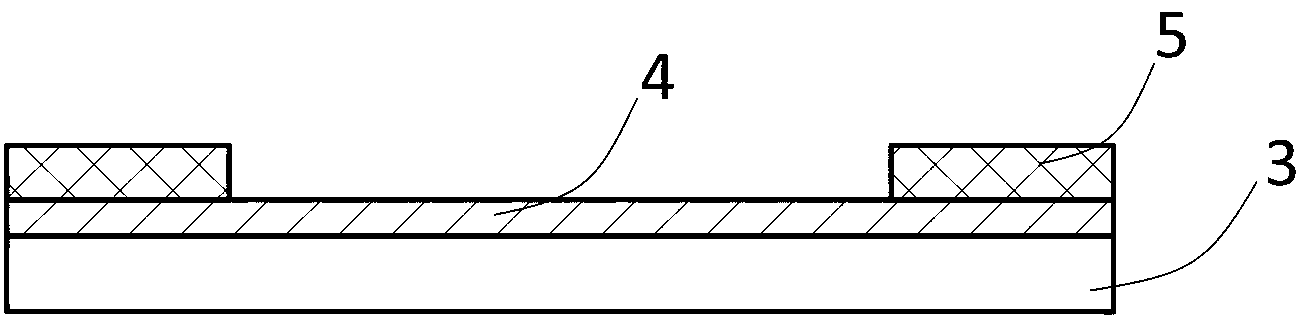

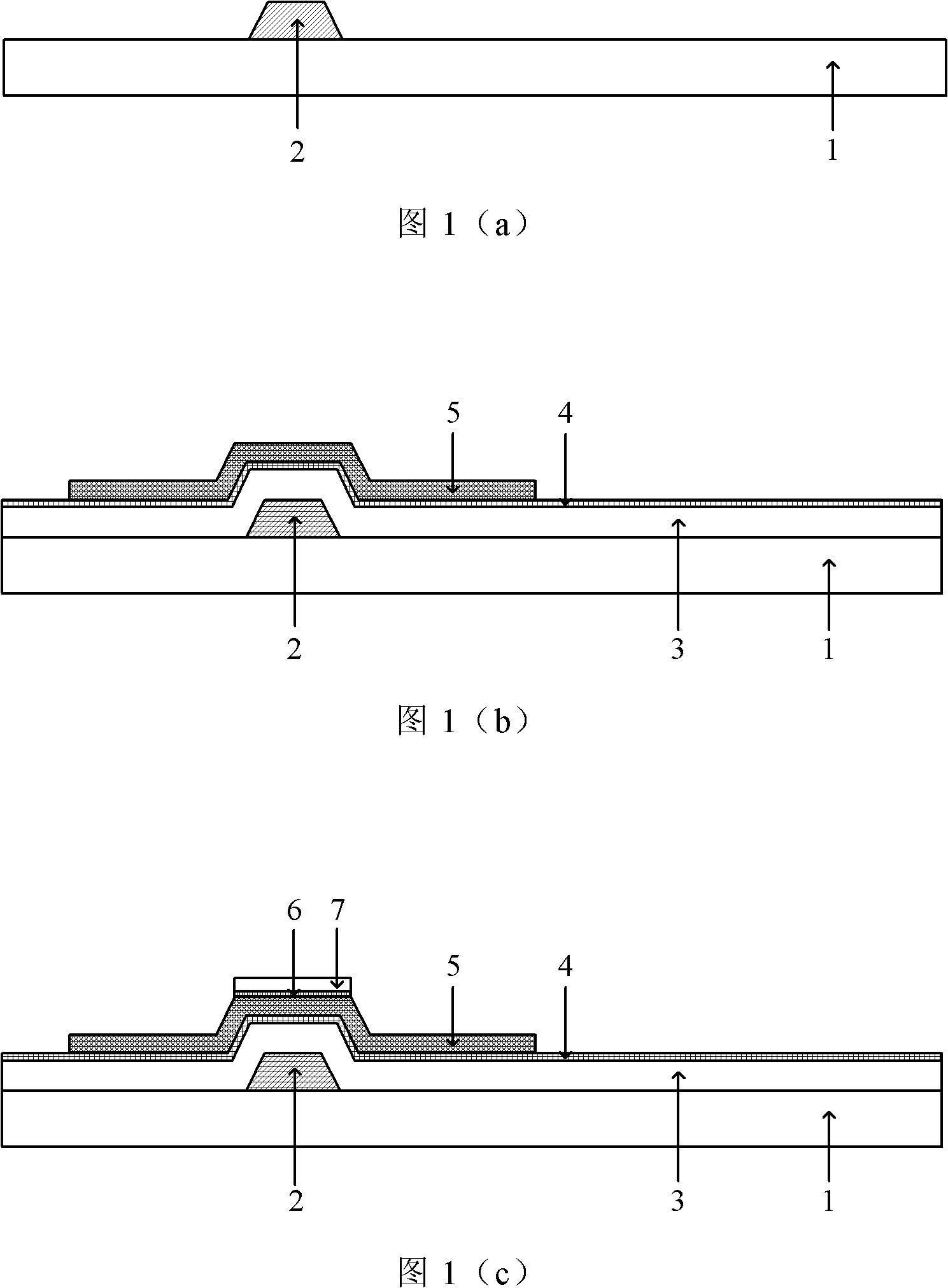

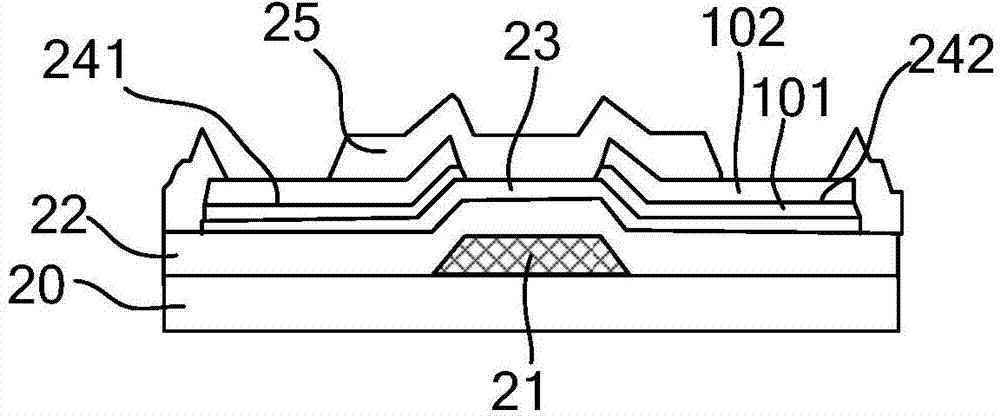

TFT (thin film transistor) array substrate

ActiveCN102646676AImprove stabilityEtching speed is fastSolid-state devicesNon-linear opticsHigh volume manufacturingOxygen

The invention provided a TFT (thin film transistor) array substrate, comprising a substrate (1) and a TFT, wherein the TFT comprises a gate electrode (2), a semiconductor layer (5), a source electrode (8) and a drain electrode (9), an adjacent layer of the semiconductor (5) is in a structure of a composite layer, the structure of the composite layer comprises a protective layer and an insulating layer, the protective layer can prevent the semiconductor layer (5) from losing oxygen, is made from an insulating material and is in contact with the semiconductor layer (5), and the insulating layer is made from an easily etching insulating material. The TFT array substrate can improve the stability of the TFT and is also suitable for large-batch production.

Owner:BOE TECH GRP CO LTD

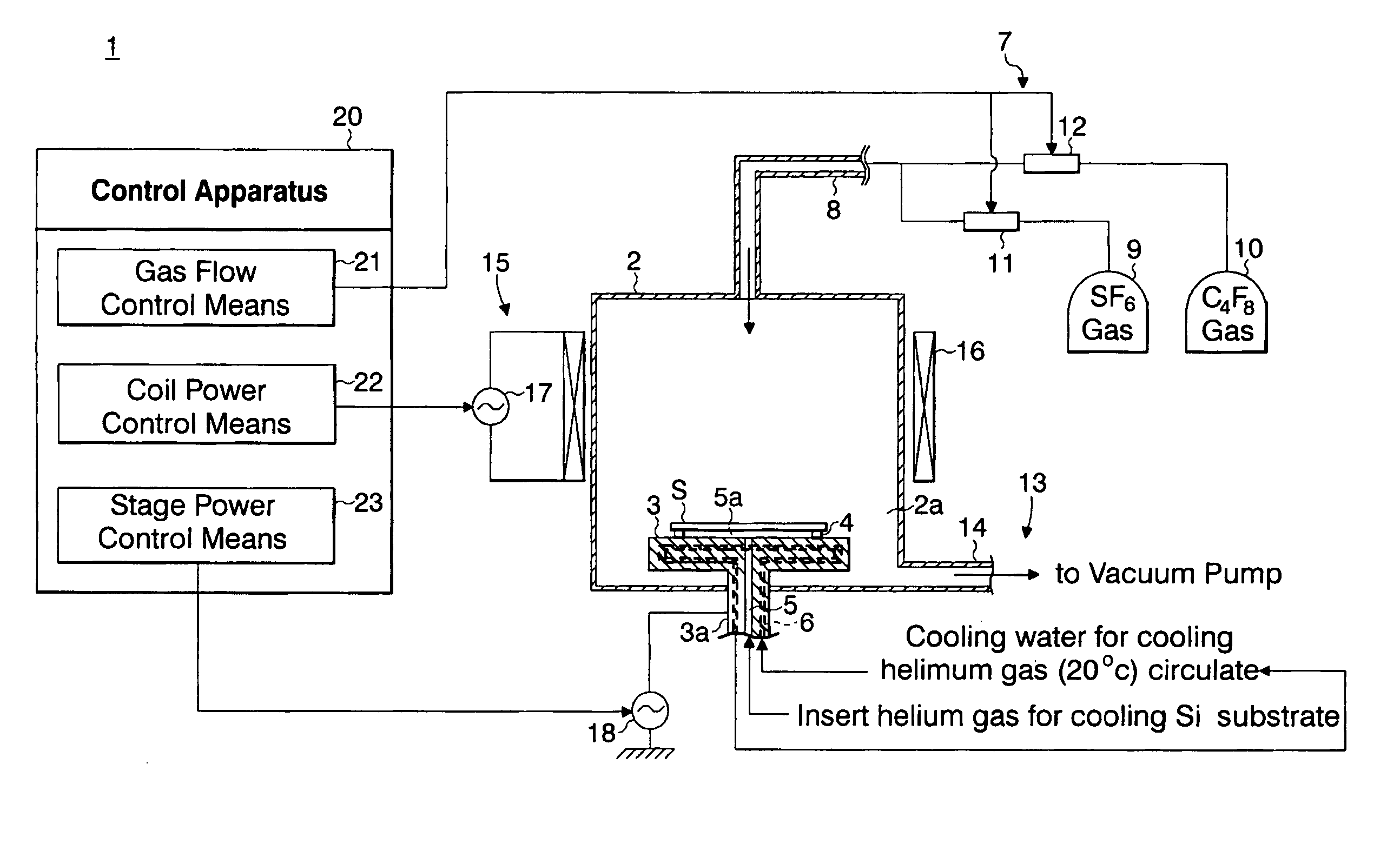

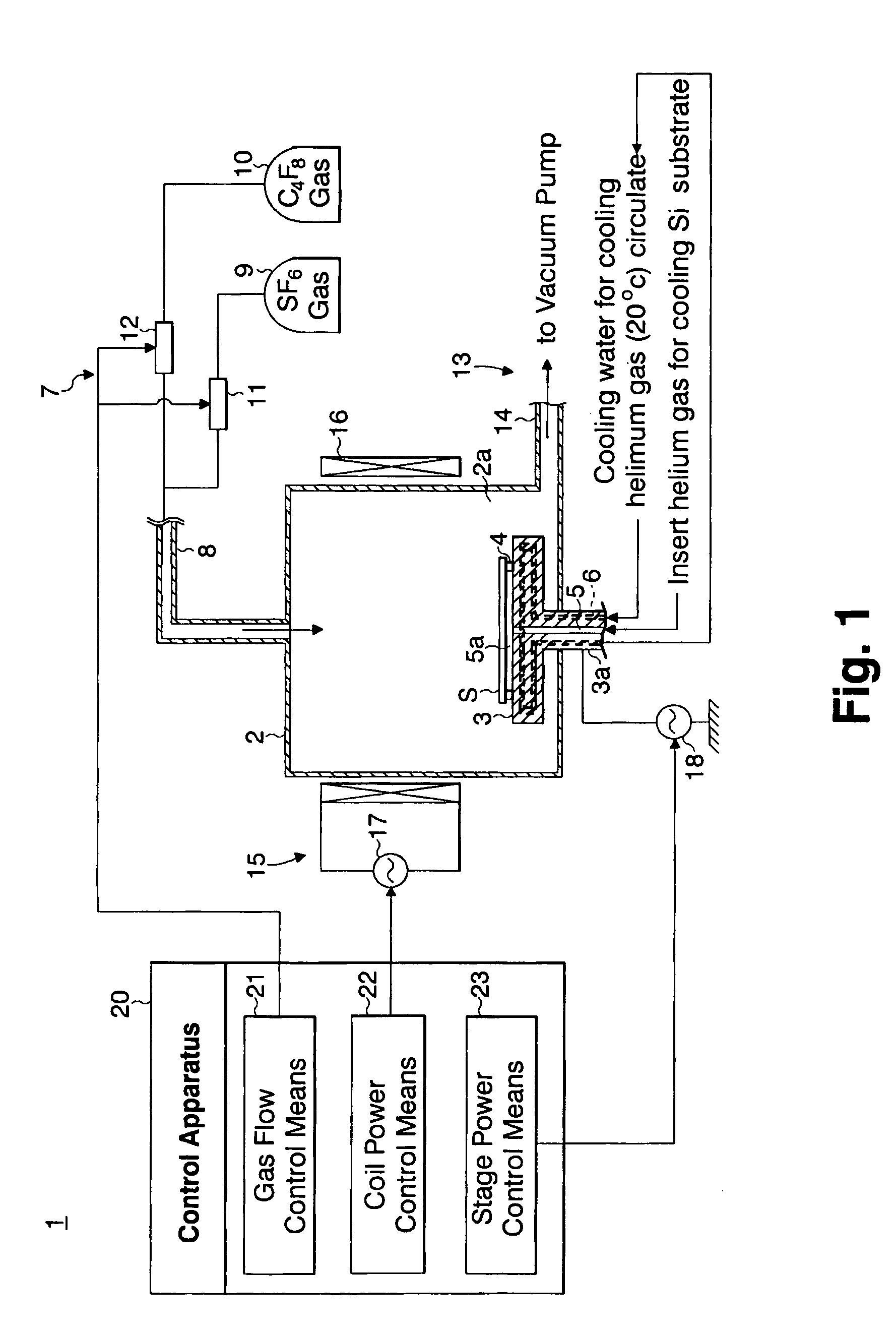

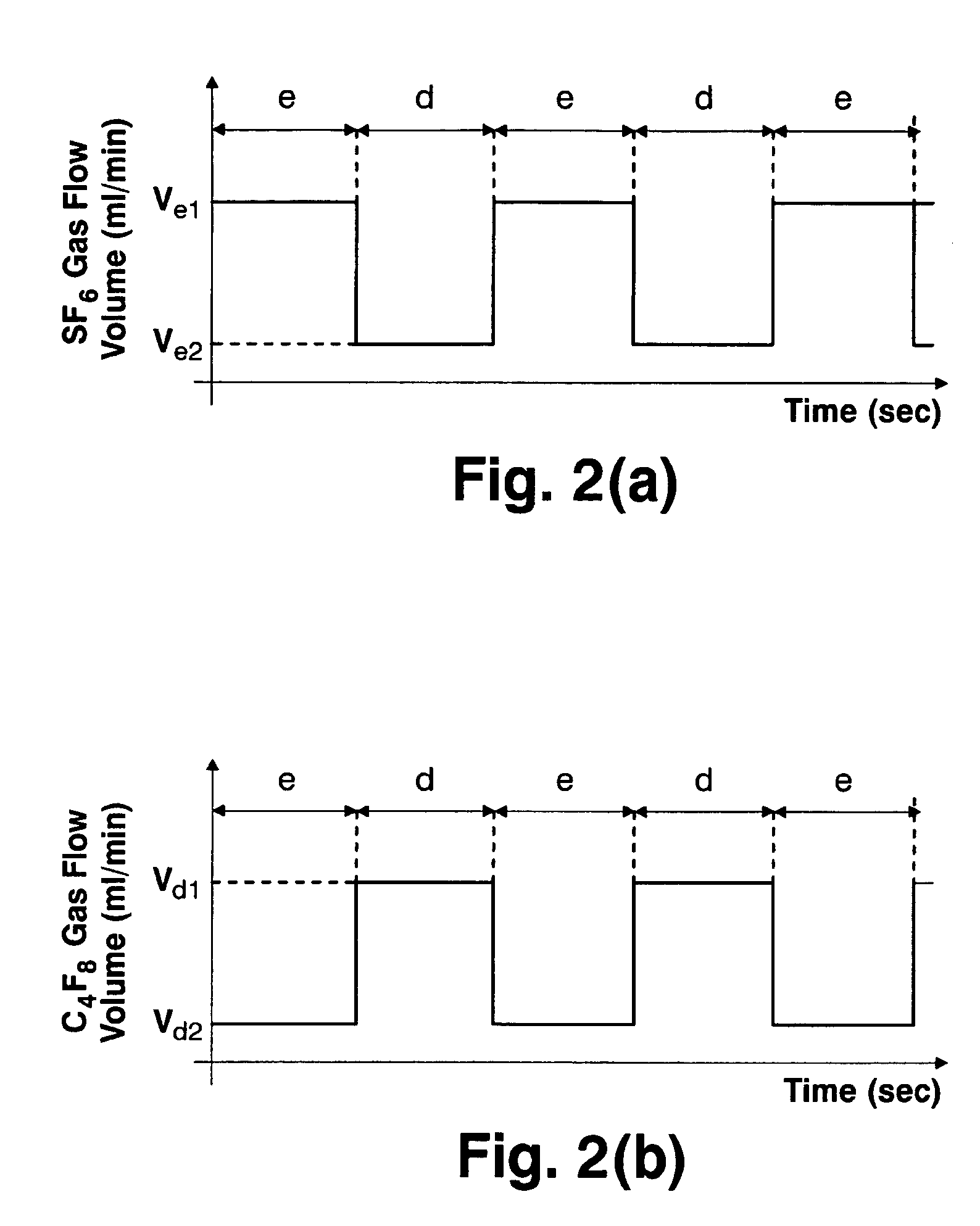

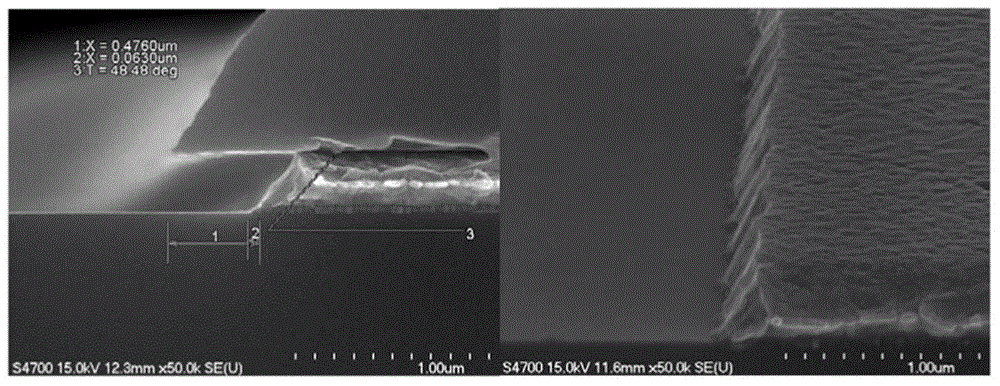

Method for etching of a silicon substrate and etching apparatus

ActiveUS20050130436A1Sufficiently smoothExcellent perpendicularity without reducing the etching speedDecorative surface effectsSemiconductor/solid-state device manufacturingCompound (substance)Fluorocarbon

A method for etching a silicon substrate is presented in which fast etching speed and etching structures with smooth and perpendicular wall surfaces are achieved. In the etching step, a constant electric power is applied to the silicon substrate to provide a bias potential. Using a mixture of SF6 gas and fluorocarbon gas, there is a step mainly for the progression of dry etching of the etching ground surface. Similarly, using a mixture gas, there is a step mainly for forming a protective layer on the structure surfaces which are perpendicular with respect to the etching ground surface. These two steps are repeated one after the other. In the step for dry etching, the mixture gas is 5-12 volume of fluorocarbon gas with respect to 100 volume SF6 gas. The mixture gas in the protective film formation step is a mixture of 2-5 volume of SF6 gas with respect to 100 volume fluorocarbon gas.

Owner:SUMITOMO PRECISION PROD CO LTD

Stainless steel electrolytic etching technique

The invention provides a stainless steel electrolytic etching process, which mainly comprises the following steps of: (a) pre-treatment: cleaning the surface of a stainless steel workpiece by washing, deoiling, etc.; (b) application: applying a photosensitive adhesive on the surface of the workpiece and carrying out exposure, developing, hardening, etc.; (c) electrolytic etching: disposing the workpiece in an electrolysis tank containing a stainless steel electrolytic etching solution and electrifying for electrolysis, wherein the stainless steel electrolytic etching solution mainly contains copper chloride 200 to 400 g / L, hydrochloric acid 20 to 80 g / L, thiourea 1 to 5 g / L and potassium sodium tartrate 10 to 20 g / L; and (d) demolding: removing the residual adhesive film on the surface after electrolysis and cleaning to obtain the product. Accordingly, the stainless steel electrolytic etching process provided by the invention can achieve very high etching speed and higher accuracy under the low pressure condition, and has the advantages of simple process, low power consumption, high etching speed and wide application prospect.

Owner:MITAC PRECISION TECH CO LTD SHUNDE DISTRICT FOSHAN CITY

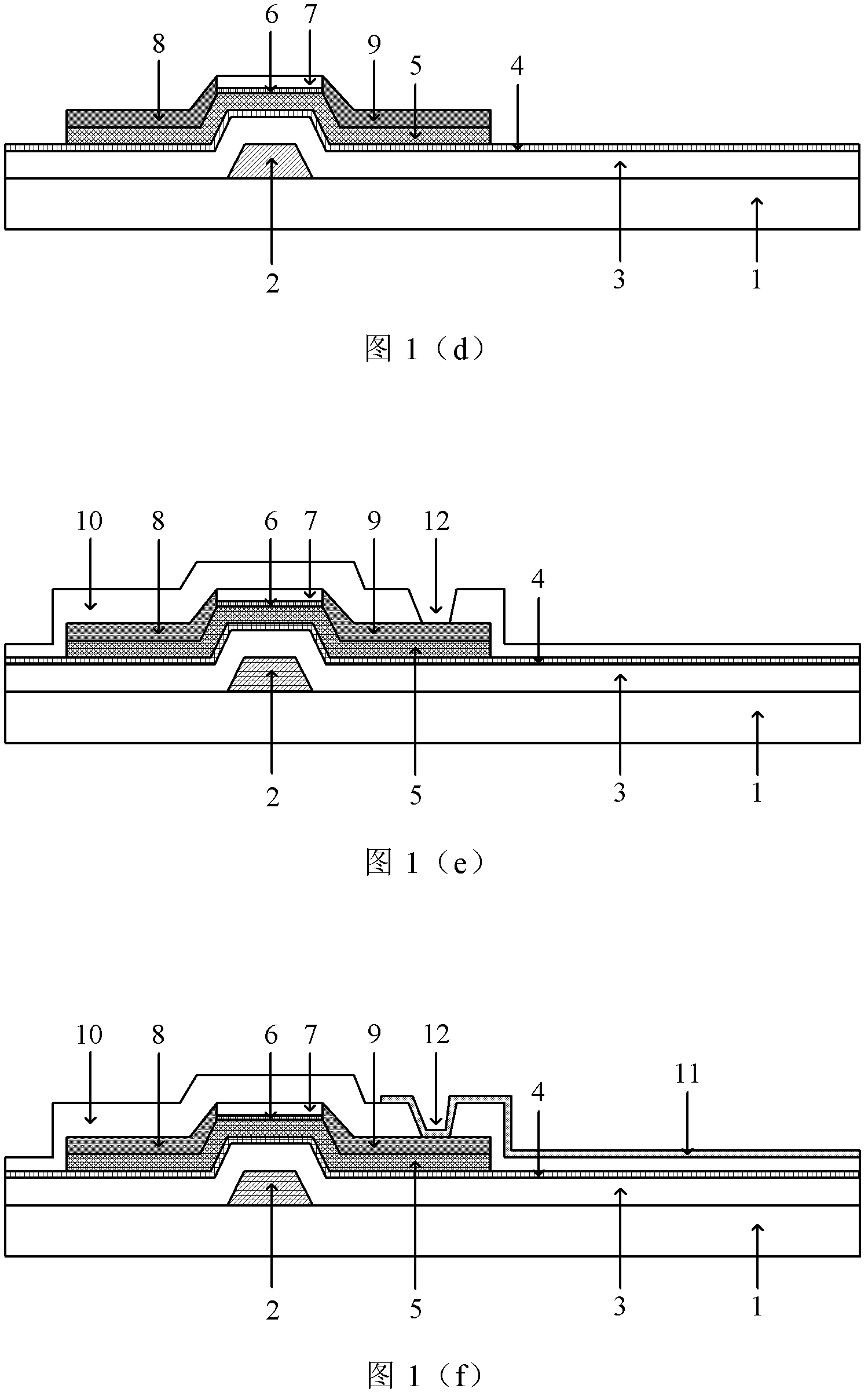

Ethicng liquid composition, and method for preparing array substrate for use in liquid crystal display device

ActiveCN104419930AAvoid it happening againEtching speed is fastSemiconductor/solid-state device manufacturingInsulation layerNiobium

The invention relates to an ethicng liquid composition, and a method for preparing an array substrate for use in a liquid crystal display device. The method comprises steps of forming grid wiring on a substrate, forming a grid insulation layer on the substrate containing the grid wiring, forming a semiconductor layer on the grid insulation layer, forming a source electrode and a drain electrode on the semiconductor layer, forming a pixel electrode connected with the drain electrode, and forming an electrode by etching films containing molybdenum metallic films or copper metallic films. A molybdenum alloy film is an alloy of niobium, tungsten or both with molybdenum. The ethicng liquid composition comprises, by weight percentage of total composition weight, 5.0%-25.0% of hydrogen peroxide, 0.01%-1.0% of fluorine compounds, 0.1%-5% of azole compounds, 0.1%-5.0% of water miscible compounds containing nitrogen atoms and carboxyl groups in a molecule, 0.1%-5.0% of phosphate compounds, 0.001%-5.0% of polyol surface active agents, and the balance of water. In addition, the ethicng liquid composition does not contain organic / inorganic acid or salt and cycloaliphatic amines

Owner:DONGWOO FINE CHEM CO LTD

Locally anti-dazzle processing process of glass and product thereof

InactiveCN104445975AEtching speed is fastReduce calcium fluoride depositsFlat panel displayStrong acids

The invention discloses a locally anti-dazzle processing process of glass. The process comprises the following steps: firstly covering the part which does not need anti-dazzle treatment on the surface of to-be-treated glass with an acid-resistant impact-resistant protective layer; then impacting silicon carbide sands which are over 2000 meshes by using compressed air to the surface of the glass which is not covered by the acid-resistant impact-resistant protective layer, wherein the sand spray time is 30-60 minutes; and after sand spray, putting the sprayed glass into a 10-25% strong acid mixed solution to etch for 25-30 minutes. The process is simple to operate and refine in step and fully satisfies the technique requirements of optical level flat panel display and subtle touch of a touch screen.

Owner:OPTON (SHUNCHANG) OPTICS CO LTD

Electrochemical etching liquid and etching method

An electrochemical etching solution is an aqueous solution containing sulfuric acid and phosphoric acid, wherein the etching solution also contains a surfactant. The electrochemical etching solution and the etching method provided by the invention can greatly increase the etching speed and reduce the occurrence of side etching phenomenon.

Owner:BYD CO LTD

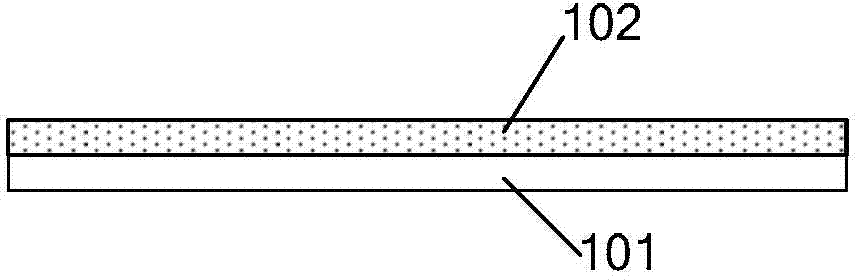

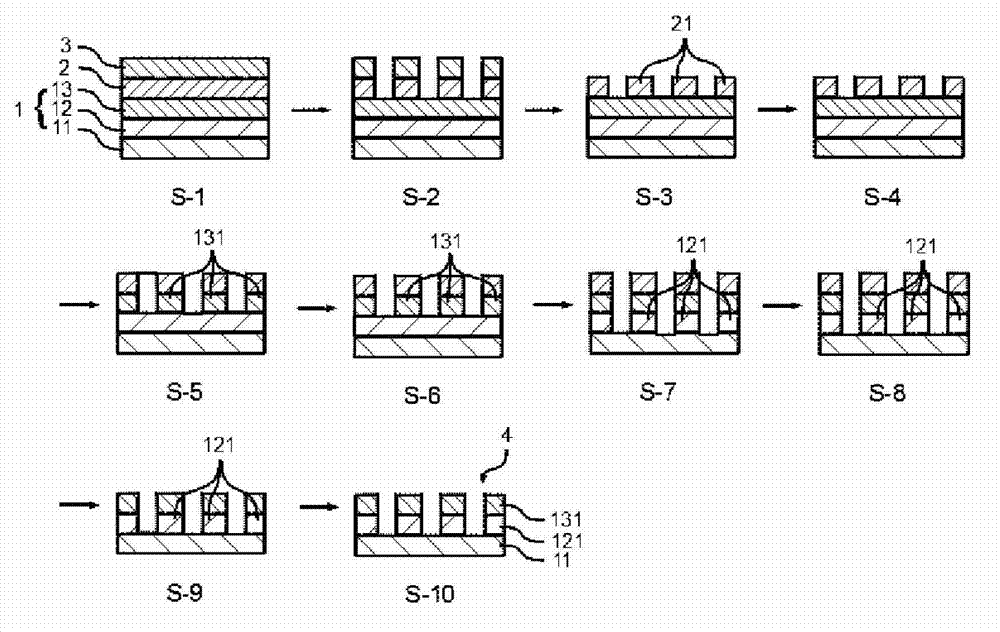

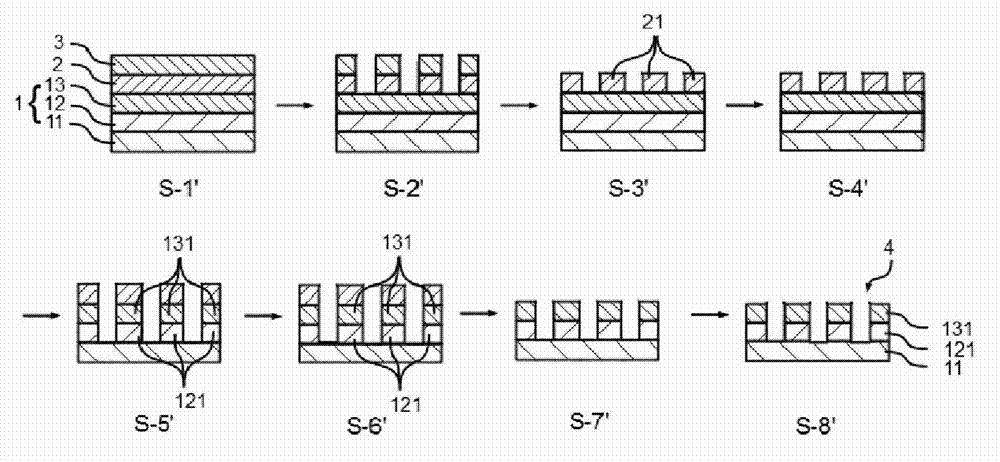

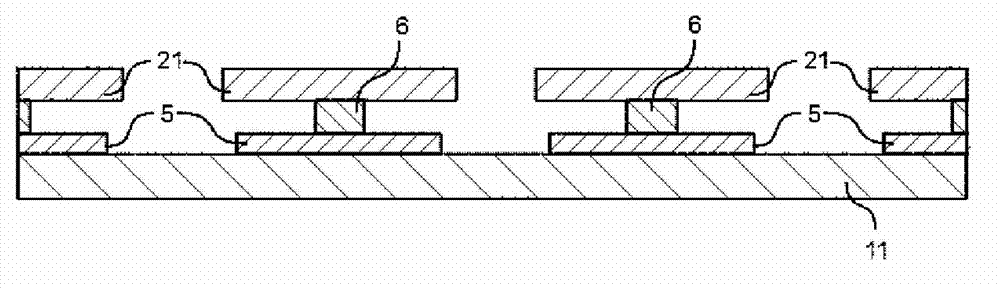

Thin film transistor and manufacturing method thereof as well as display device

ActiveCN104716198AEtching speed is fastSolve the problem of easy corrosionTransistorSemiconductor/solid-state device manufacturingEtchingDisplay device

Owner:BOE TECH GRP CO LTD

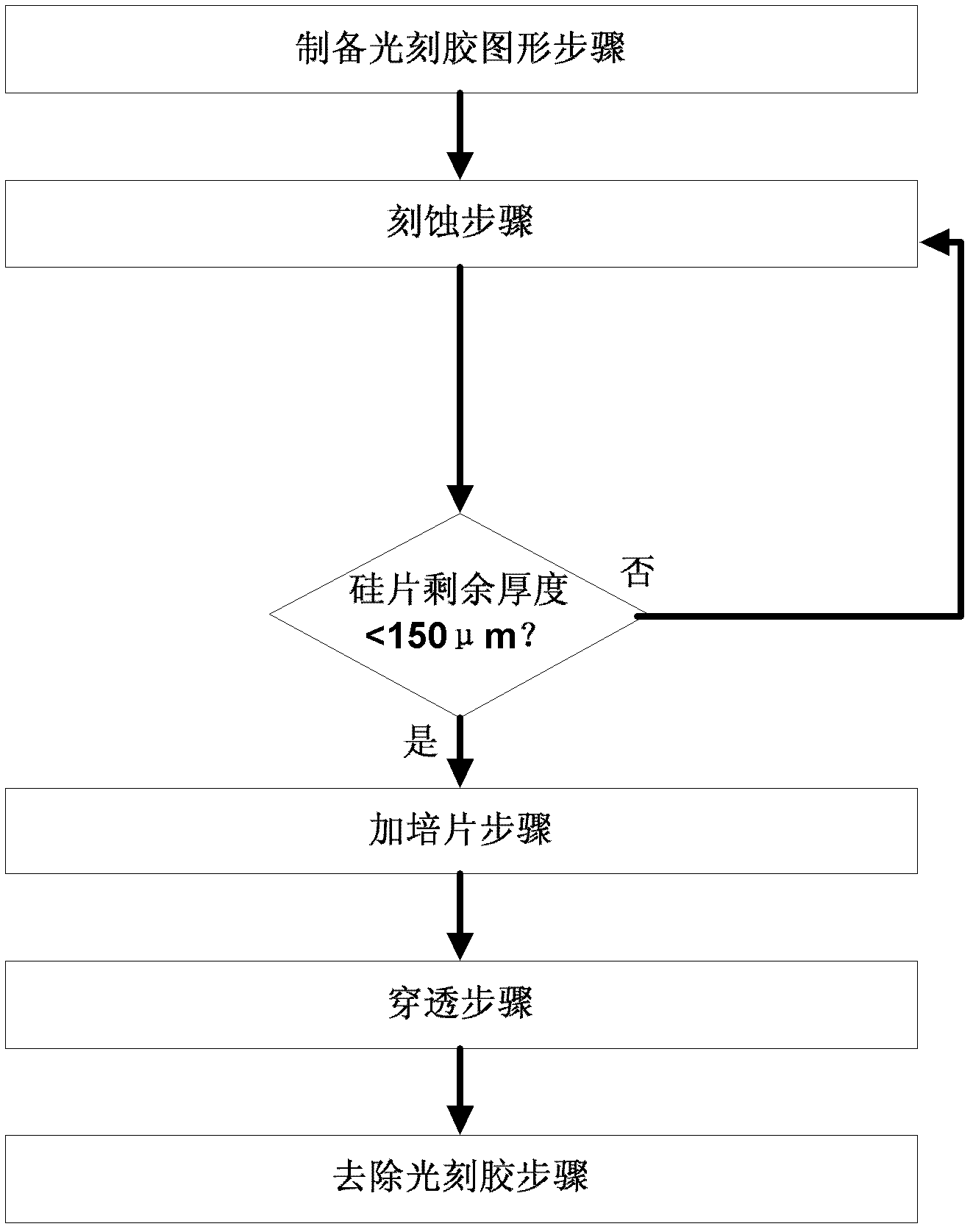

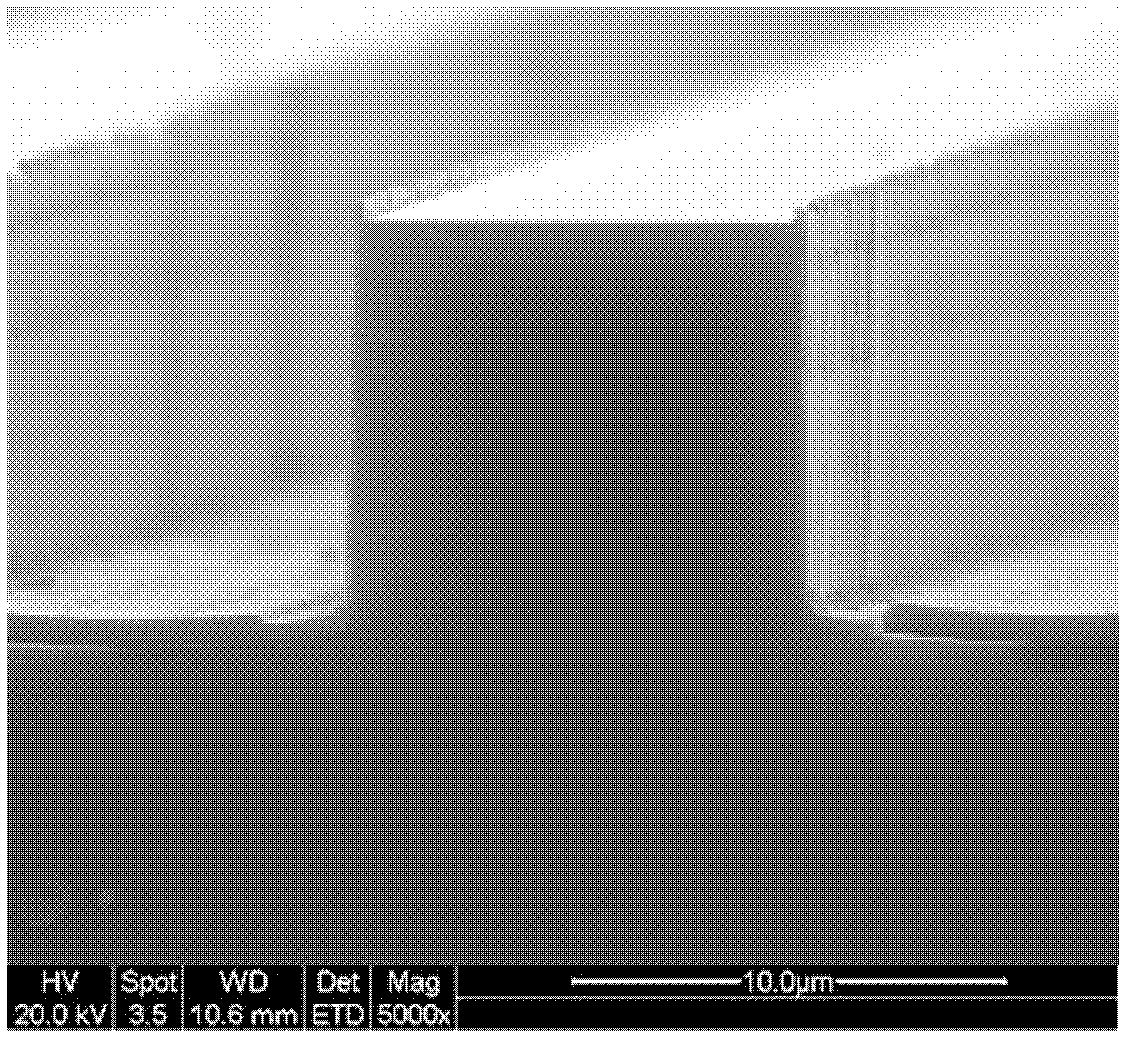

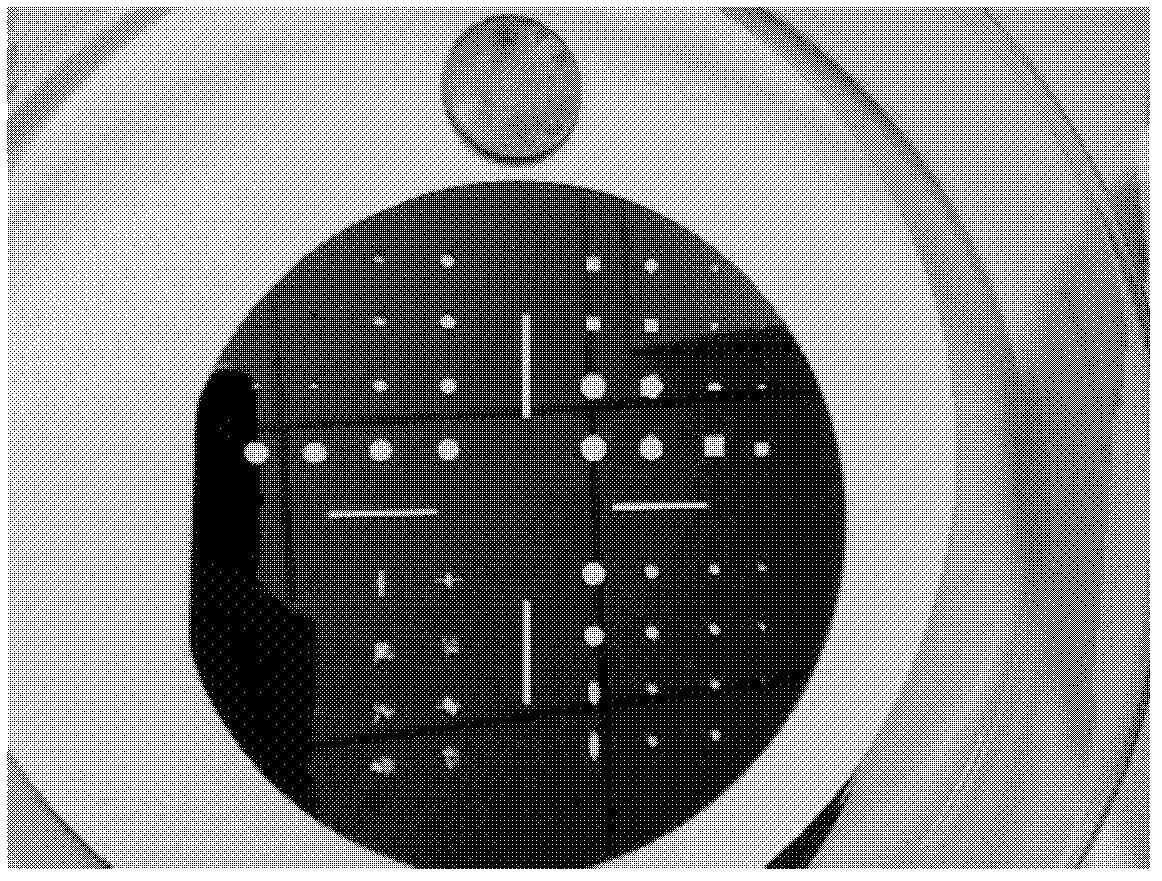

Silicon through hole etching method

InactiveCN102431960AAvoid pollutionVerticality is easy to controlDecorative surface effectsChemical vapor deposition coatingMicro nanoSilicon etching

The invention provides a silicon through hole etching method and belongs to the field of micro nano machining of micro electro mechanical systems, and the method can be used for solving the problems that the side wall of a substrate generates ripples, a photoresist can be easily damaged and metal pollution is caused when an existing Bosch process and a metal mask are utilized to carry out deep silicon etching. The method provided by the invention comprises a pattern preparation step, an etching step, a culture slice adding step, a penetrating step and a photoresist removing step. In the etching step, processing is stopped after circulative and alternative etching is finished, so that the photoresist is cooled and the protective action of the photoresist is prevented from being reduced; then circulative etching is carried out again; passivating gas is added into etching gas; and the etching gas is added into the passivating gas for improving the smoothness of the side wall. In the culture slice adding step, a silicon wafer is adhered to the upper surface of a culture slice,thus preventing silicon wafer fracture and equipment damage after etching penetration. The method provided by the invention has the advantages that the process is simple and the etching speed is quick; the photoresist utilized as the mask can be easily removed after being etched, and metal pollution is avoided; the verticality of the side wall of a through hole is easily controlled; the smoothness of the side wall is improved; and the ripples on the side wall are eliminated.

Owner:HUAZHONG UNIV OF SCI & TECH

PCB (Polychlorinated Biphenyl) acidic etching solution

The invention discloses a PCB (Polychlorinated Biphenyl) acidic etching solution which comprises the following components: 130-180 g / L of etching mother liquid copper, 120-200 g / L of hydrochloric acid (the concentration of the hydrochloric acid is 30%-38%), 150-250 g / L of oxidizing agents, 120-250 g / L of industrial salt, 0.5-15 g / L of stabilizing agents, 5-30 g / L of accelerating agents, 0.05-0.2 g / L of buffering agents and the balance of water. According to the PCB acidic etching solution, the acid value of the hydrochloric acid can be controlled to be less than 1.8 N and is greatly lower than the acid value less than 2.5 N in the prior art; the etching uniformity can reach more than 90%; and the etching factor is more than 3.5, so that the accuracy of an etching route figure and the stability of the etching solution are effectively ensured.

Owner:长沙牧泰莱电路技术有限公司

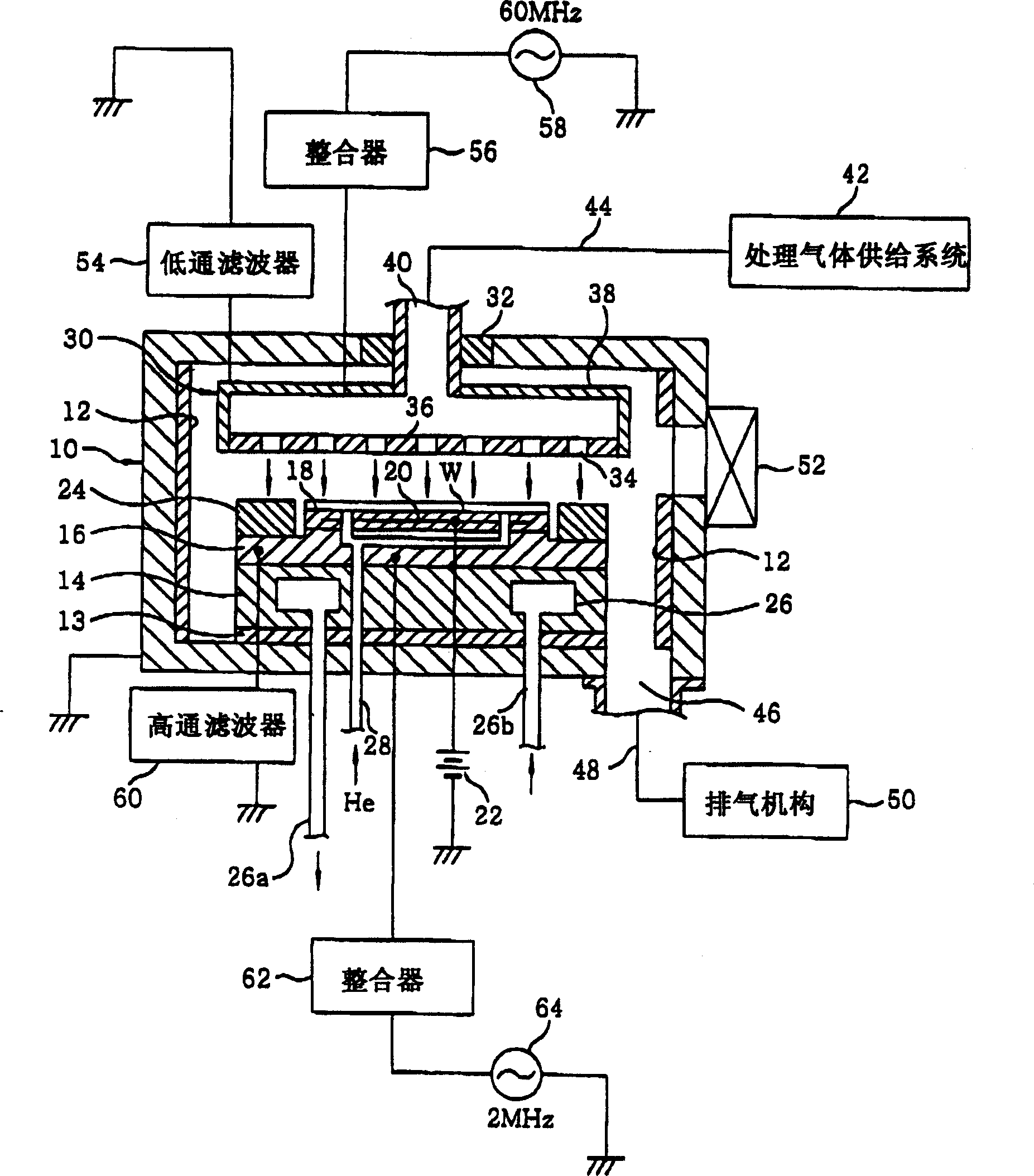

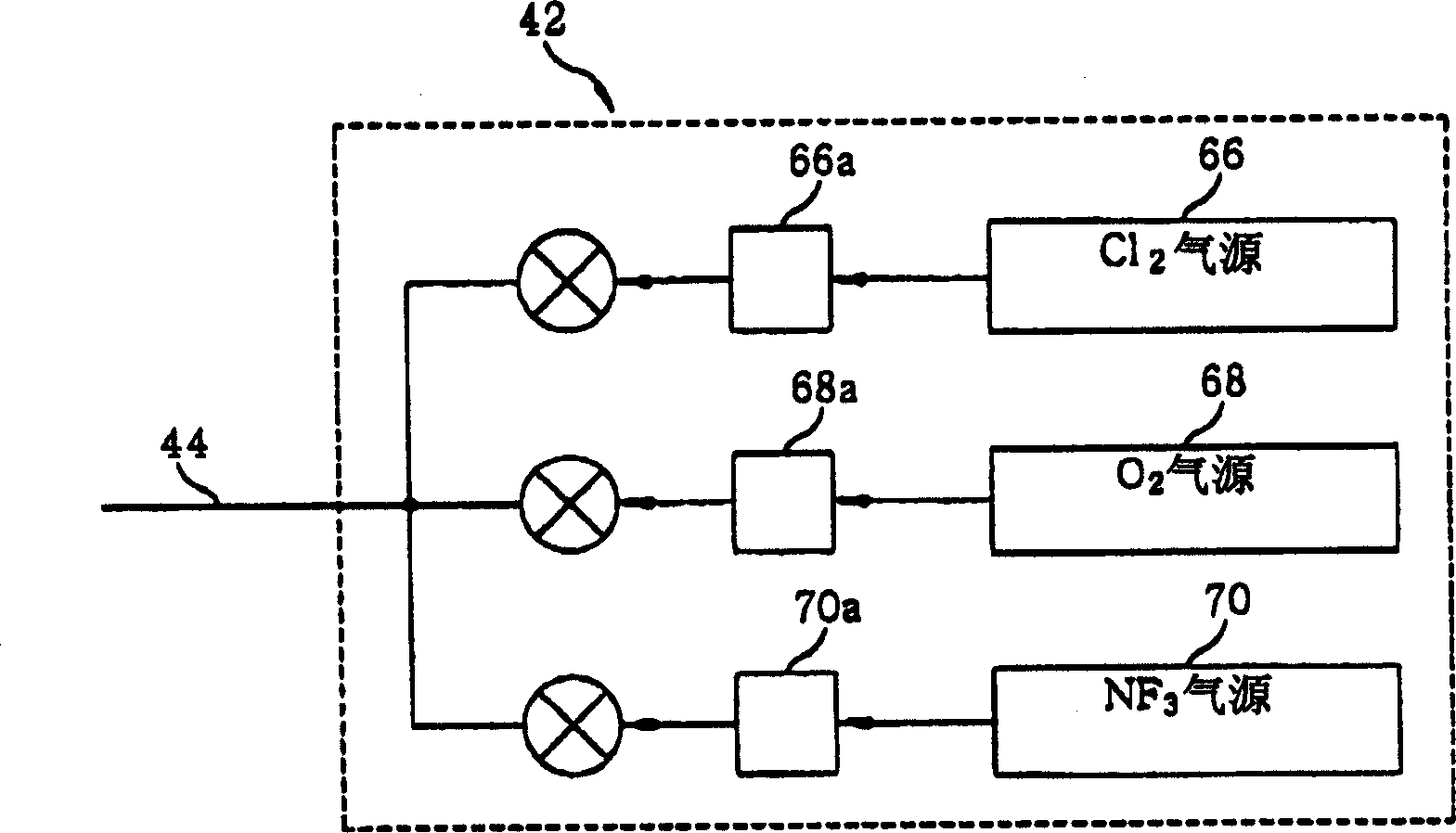

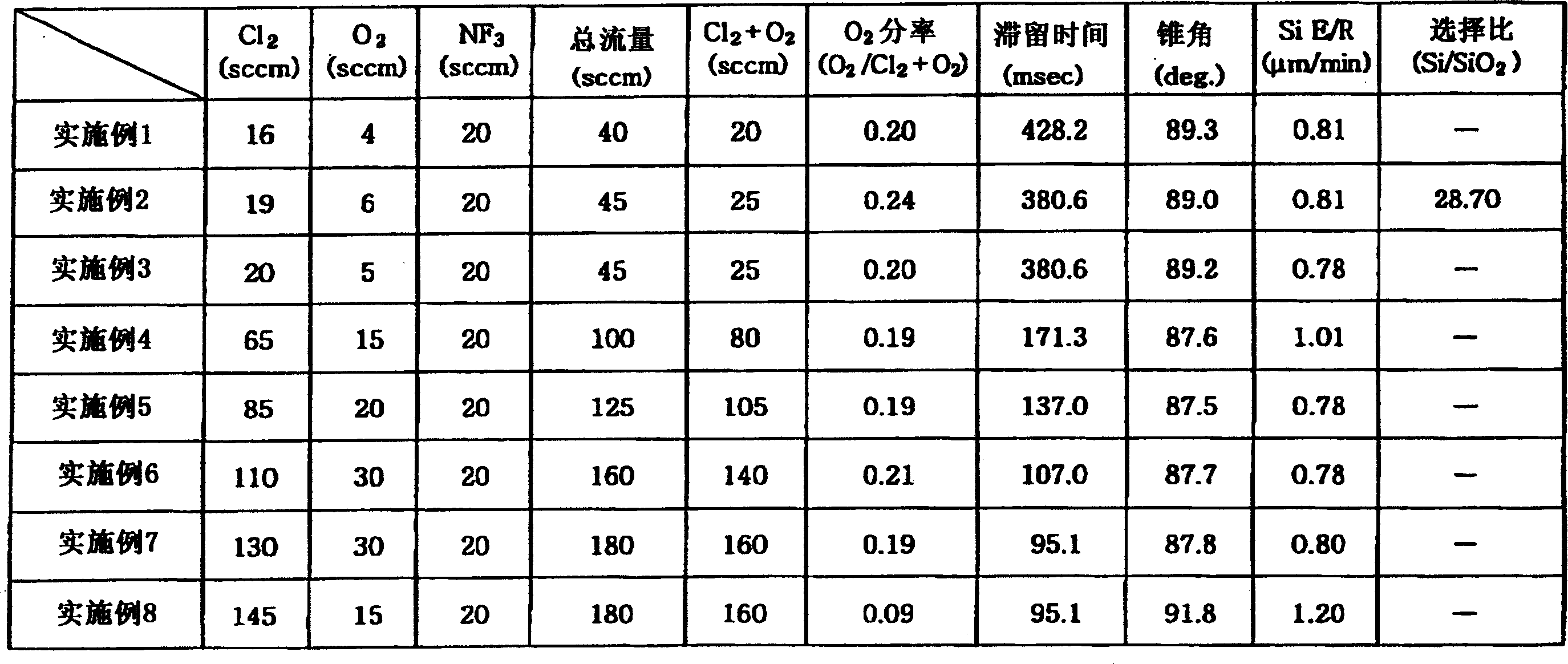

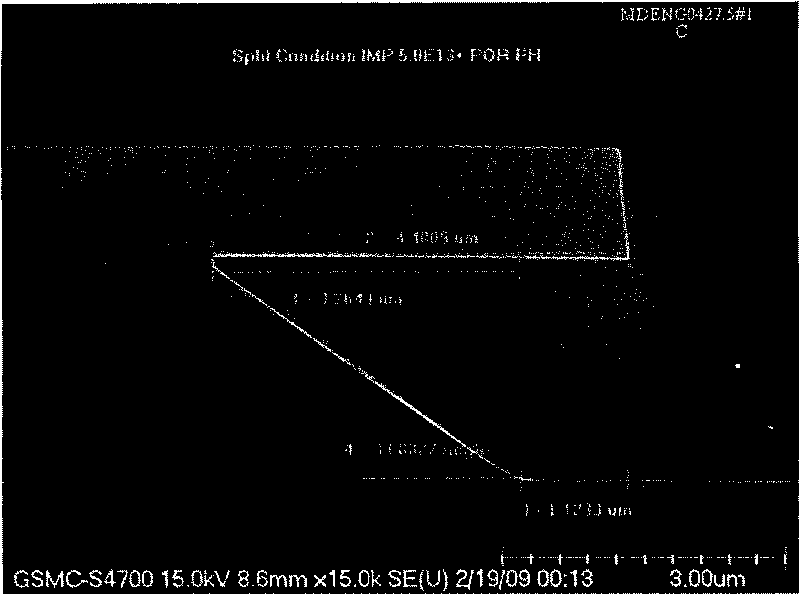

Si etching method and device

InactiveCN1490849AEtching speed is fastElectric discharge tubesSemiconductor/solid-state device manufacturingSusceptorHigh frequency power

Owner:TOKYO ELECTRON LTD

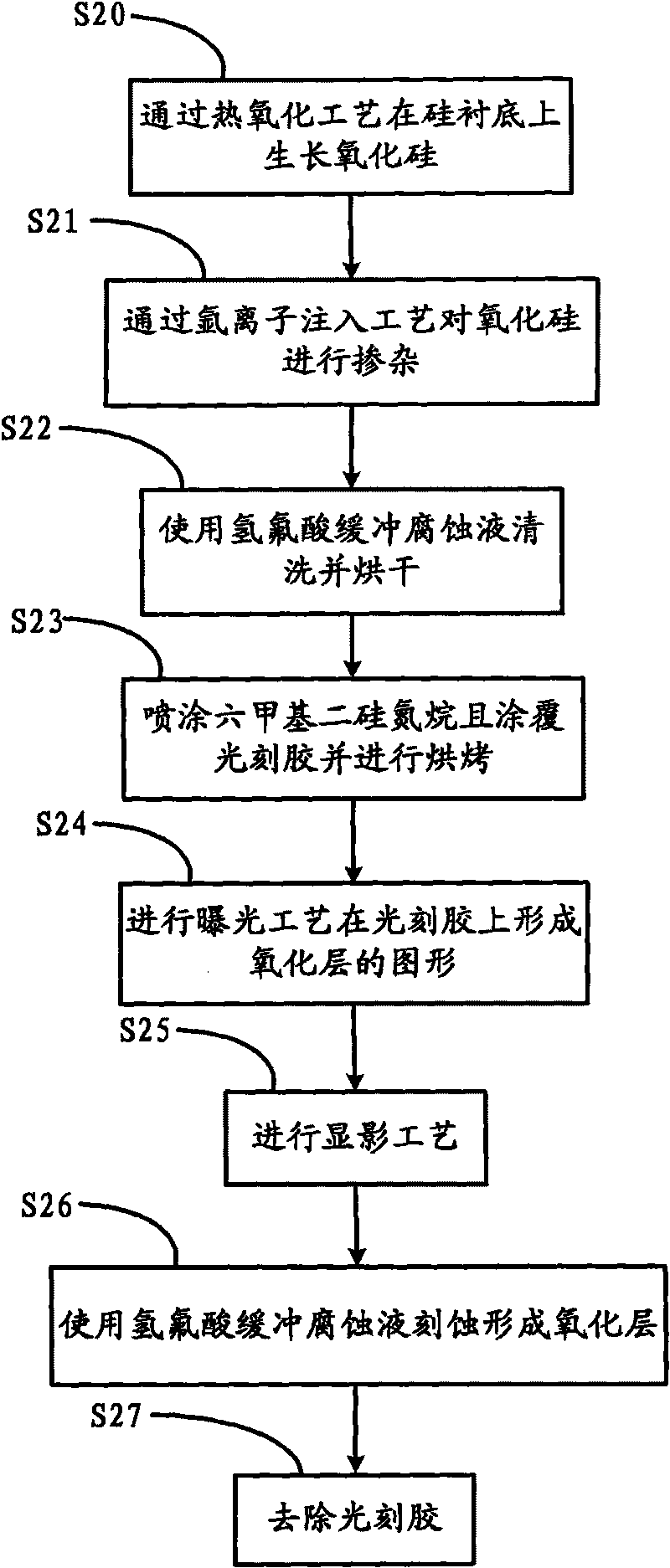

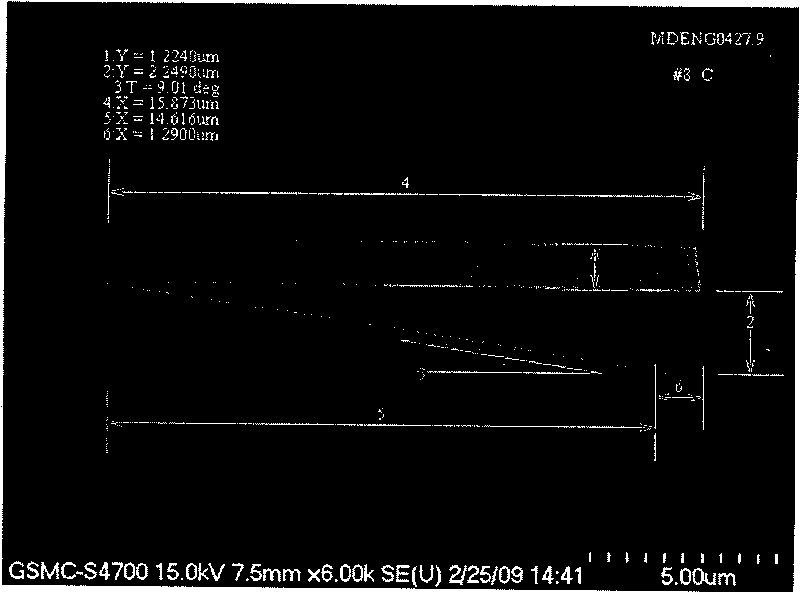

Method for manufacturing oxide layer capable of reducing gradient of side wall

ActiveCN101719468AEtching speed is fastReduce side wall slopeSemiconductor/solid-state device manufacturingPhotoresistEtching

The invention provides a method for manufacturing an oxide layer capable of reducing the gradient of a side wall. In the prior art, silicon oxide is directly subjected to photoetching and wet etching without being washed with hydrofluoric acid buffer corrosive liquid so as to result in larger gradient of the side wall. The method comprises the following steps: firstly, growing the silicon oxide on a silicon substrate through thermal oxidation process; secondly, washing the silicon oxide by using the hydrofluoric acid buffer corrosive liquid, and drying the silicon oxide; thirdly, coating photoresist on the silicon oxide, and baking the photoresist; fourthly, forming a graph of the oxide layer on the photoresist by exposure process; fifthly, developing the graph; sixthly, etching the graph by using the hydrofluoric acid buffer corrosive liquid to form the oxide layer; and finally, removing the photoresist. The method effectively reduces the compactness of the surface of the oxide layer and the adherence force of the oxide layer with the photoresist by washing the silicon oxide with the hydrofluoric acid buffer corrosive liquid before the photoetching and the wet etching processes, thereby effectively reducing the gradient of the side wall, and effectively improving the performance of a device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

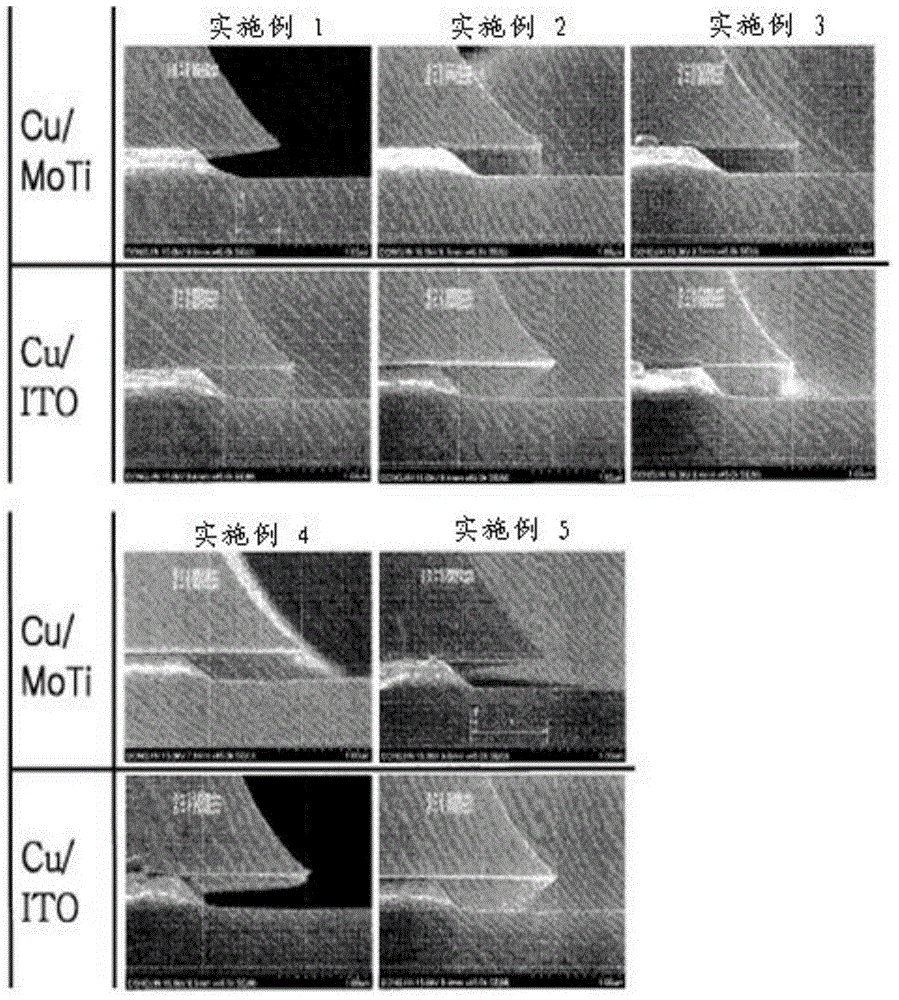

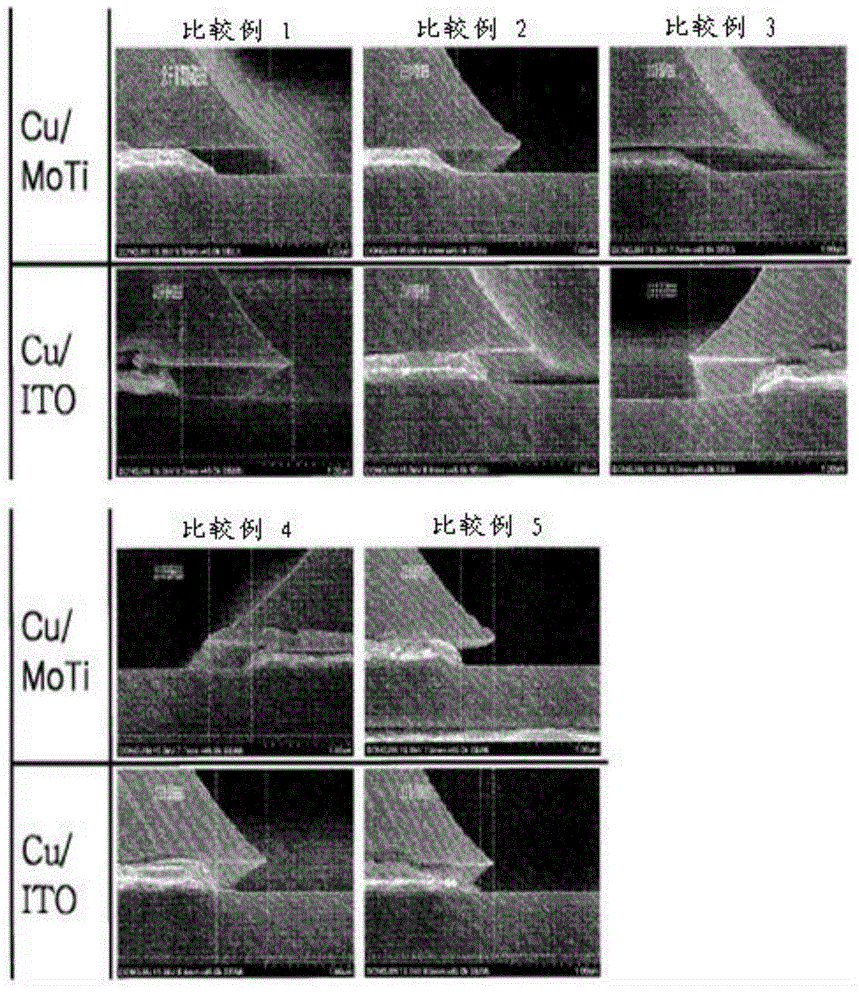

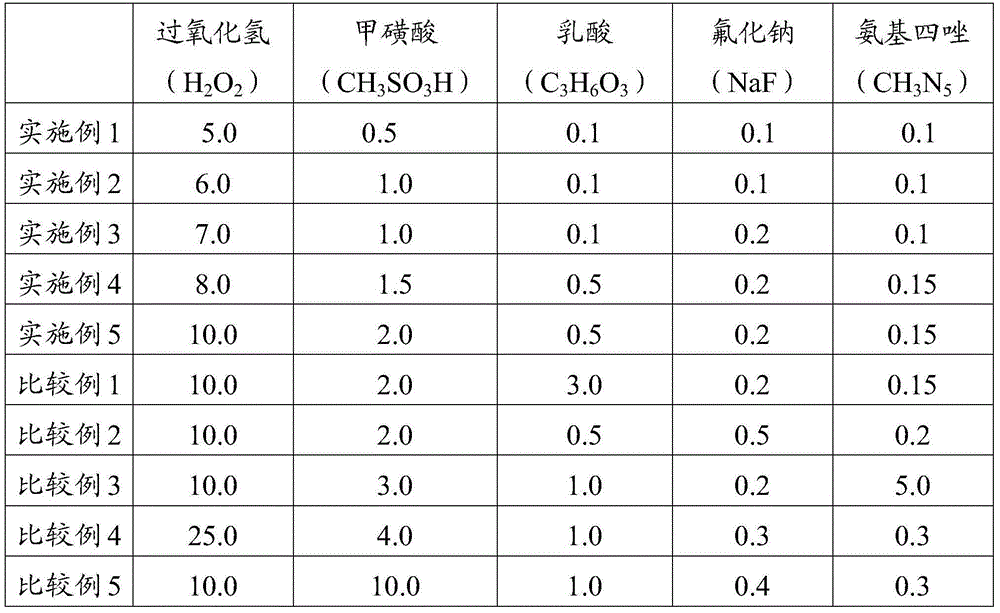

Metal-film etching-solution composition and etching method using same

ActiveCN104838040AExcellent etch profileImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesOrganic acidIndium tin oxide

Provided are: an etching-solution composition whereby it is possible to simultaneously etch a double film of a copper film and an indium tin oxide film or a double film of a copper film and a metal film; and an etching method using same. The etching-solution composition comprises between 5 and 20 wt.% of hydrogen peroxide, between 0.1 and 5 wt.% of a sulphonic acid compound, between 0.1 and 2 wt.% of a carbonyl based organic acid compound, between 0.1 and 0.4 wt.% of a fluorine compound, between 0.01 and 3 wt.% of an azole based compound, and a remainder of water.

Owner:DONGJIN SEMICHEM CO LTD

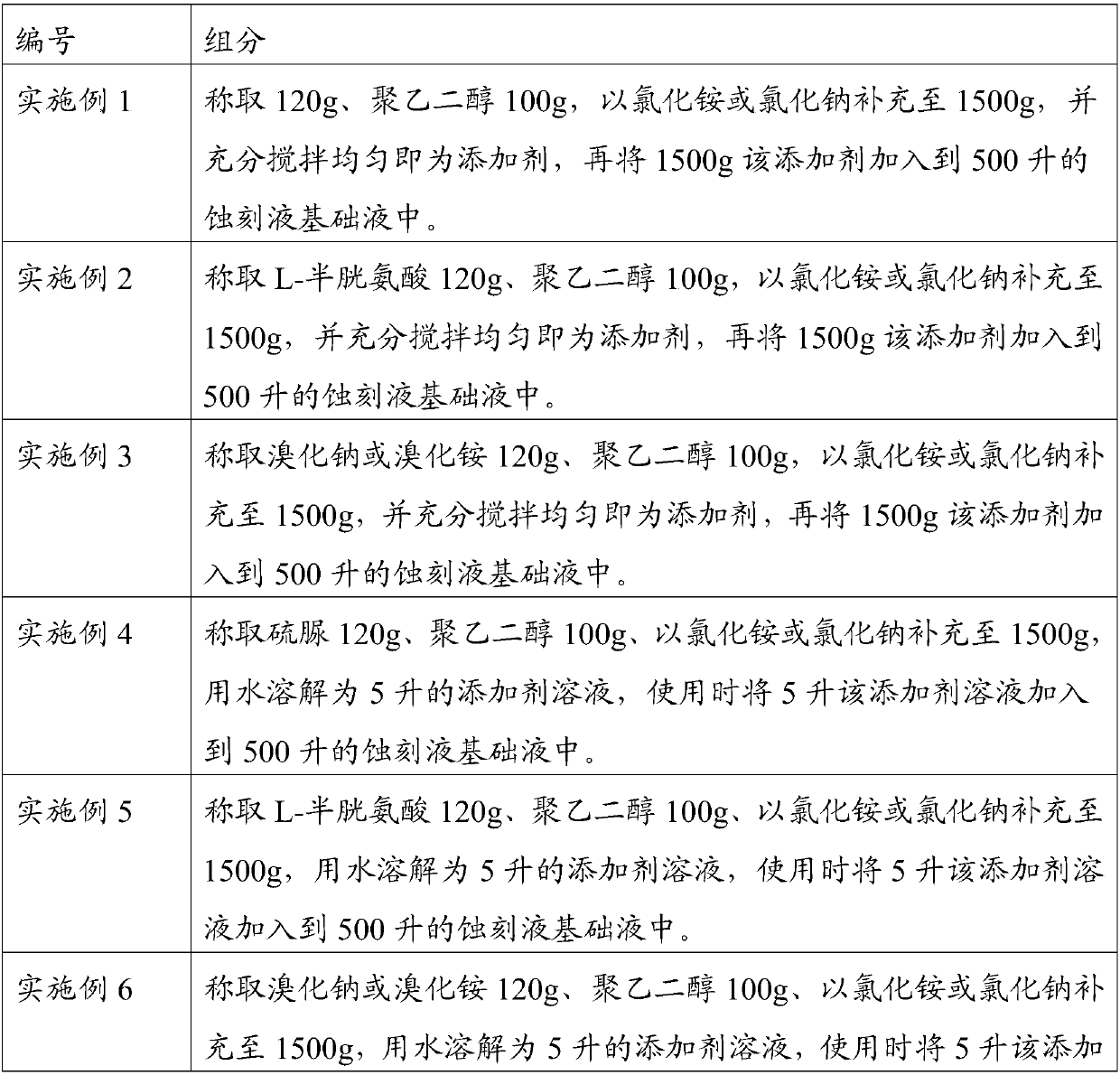

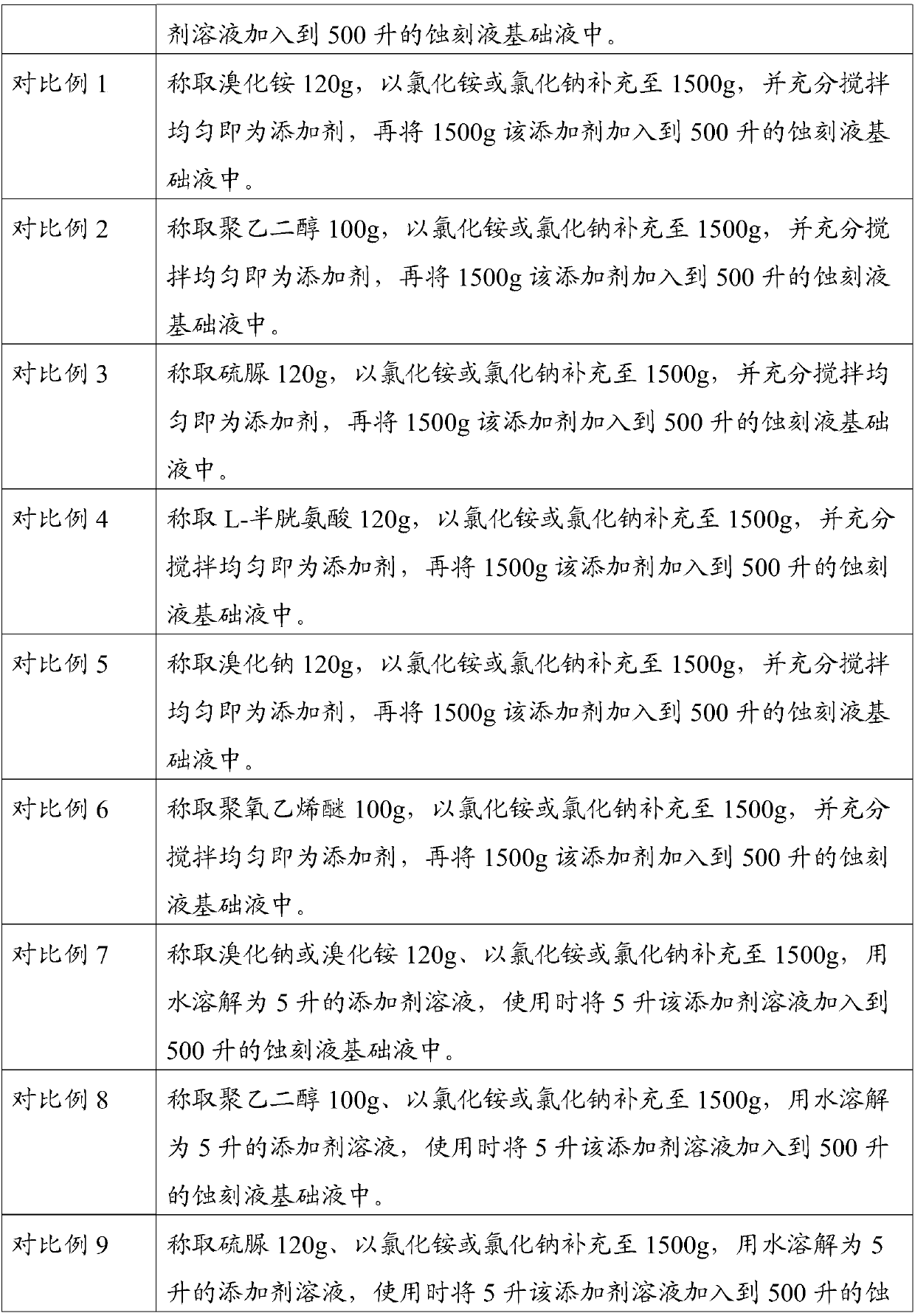

Additive for acidic etching solution and the acidic etching solution

ActiveCN107747094AOvercome the problem that the etching rate first drops and then stabilizesEtching speed is fastEtchingElectrolysis

The invention discloses an additive for acidic etching solution and the acidic etching solution. The additive includes, by mass, 1-200 parts of a nonionic surfactant and 1-200 parts of a stabilizer, wherein the stabilizer is at least one of sulfur-containing urea, mercaptan and bromides. The acidic etching solution comprises an etching basic liquid and the additive. The acidic etching solution canbe used for producing printed circuit boards, which has thick copper layer (copper thickness being 70 [mu]m or higher) or large to-be-etched area (to-be-etched area being more than 50%, especially whole-plate etching), and is free of instable or low speed during the etching. In addition, the additive can be used for directly producing bulk copper plates in a circuit board etching process withoutextra addition of an electrolysis additive.

Owner:侯延辉

Etching liquid composition and etching method

InactiveCN103046050AReduce etch rateEtching speed is fastSurface treatment compositionsCopper chlorideDisplay device

The invention relates to a display device of a flat panel display (FPD) and an etching liquid composition for the transparent conductive film used for the electrodes of a solar cell or a touch control panel, and provides an etching liquid composition for etching transparent conductive films such as copper and / or copper alloy film and indium tin oxide simultaneously, which includes hydrochloric acid, ferric chloride or copper chloride and water, wherein the concentration of hydrochloric acid is from 15.0 to 36.0 weight%, and the concentration of ferric chloride or copper chloride is from 0.05 to 2.00 weight%.

Owner:KANTO CHEM CO INC

Chemical etching liquor for aluminium and aluminum alloy

Owner:SHENZHEN FUTAIHONG PRECISION IND CO LTD

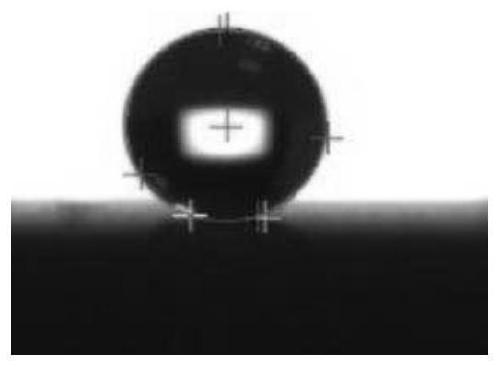

Preparation method of super-hydrophobic film on surface of steel substrate

ActiveCN110359044AEtching speed is fastSmall apertureMetallic material coating processesCorrosionOxide

The invention discloses a preparation method of a super-hydrophobic film on the surface of a steel substrate. The method includes the steps that the steel substrate is ground and subjected to deoilingpretreatment, and oil and oxides on the surface of the steel substrate are removed until the surface is smooth; the completely-treated steel substrate is soaked in a iron fluoride solution, and a rough steel substrate surface is obtained through the combination of chemical etching and electrochemical etching; and the etched steel substrate is soaked in an ethanol solution of stearic acid and perfluorooctyl trimethoxysilane to be modified for a period of time, after the steel substrate is dried at constant temperature, a modified super-hydrophobic nanosilicon dioxide solution is sprayed to thesurface of the steel substrate, and after heat treatment is completed, the super-hydrophobic composite film is obtained. The process is simple, environmentally friendly, safe and reliable, and a hydrophobic coating is high in hydrophobicity, further has the beneficial effects of being high in adsorptivity, good in abrasion resistance, high in corrosion resistance and the like, and is suitable forlarge-scale industrial production.

Owner:CHONGQING UNIV

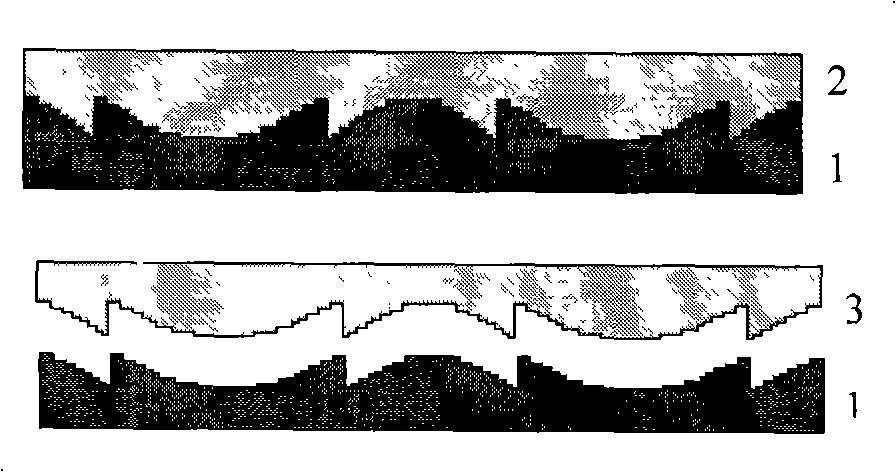

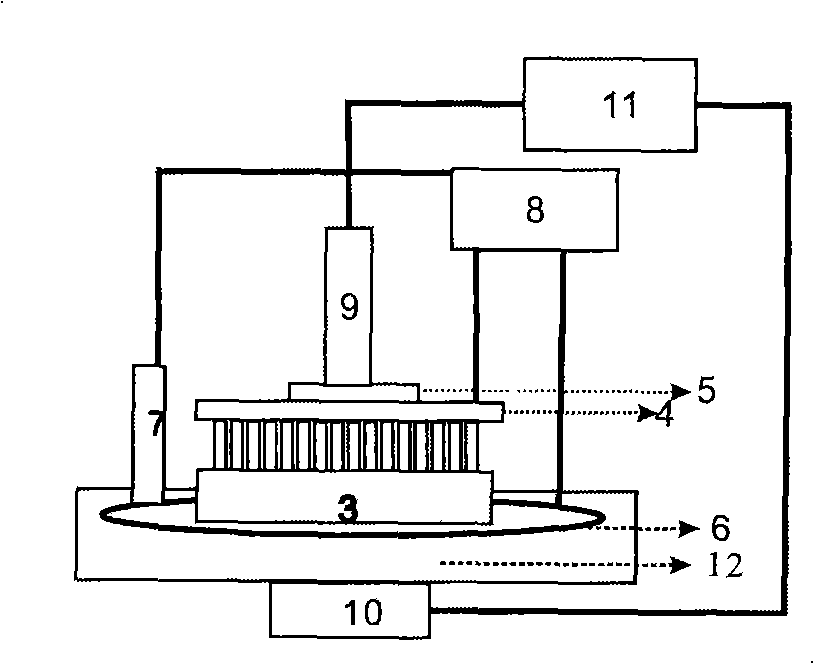

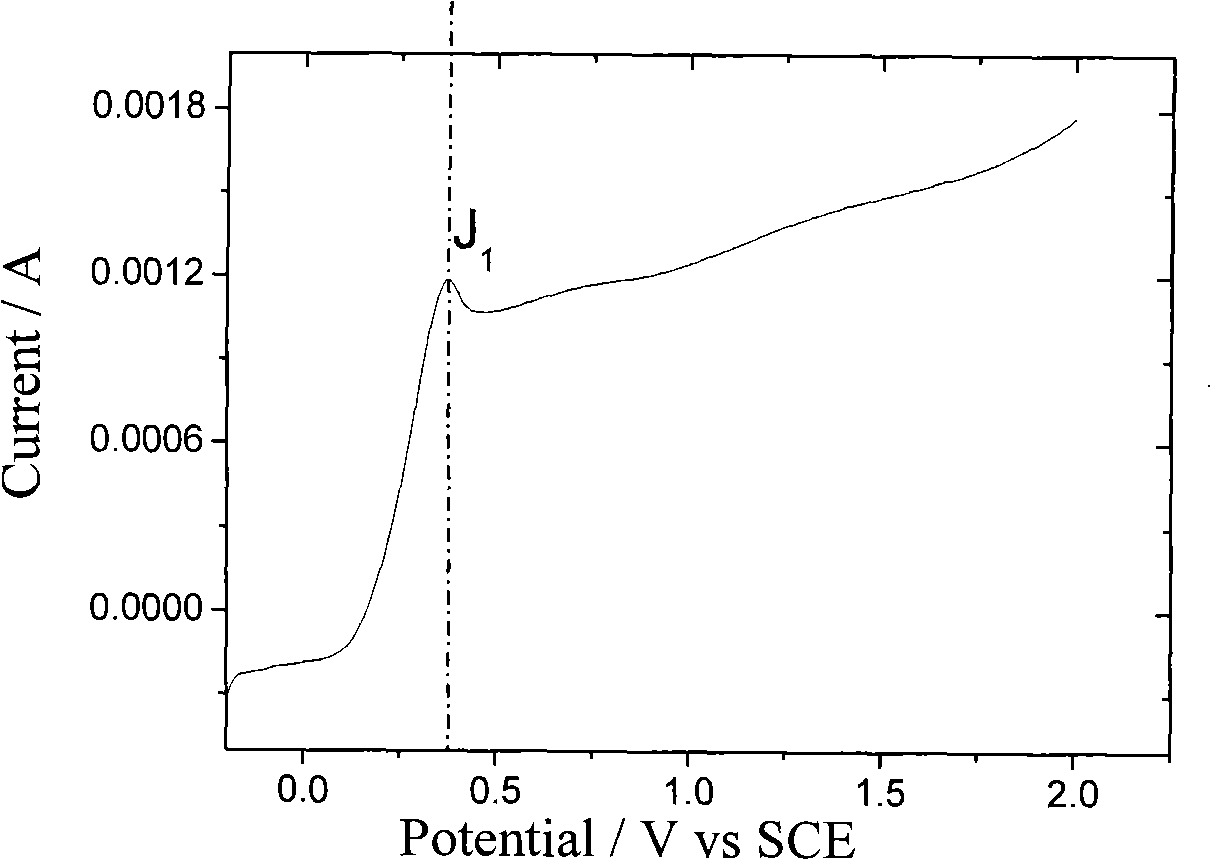

Electrochemical processing method for micro-structure of P type silicon surface

InactiveCN101271842APrecision Processing ApproachHigh copying accuracyDecorative surface effectsSemiconductor/solid-state device manufacturingMicro structureLithographic artist

The invention provides an electro-chemical processing method of a P-typed silicon surface micro-structure, relating to the processing of silicon surface. The invention provides a novel electro-chemical processing method which has low cost and simple processing steps, does not have complex processes such as mask lithography, etc., and with micro-structure etched and is processed on the surface of the P-typed silicon in one-step. The electro-chemical processing method comprises the steps that: the micro-structure on an original mother blank is transferred onto a gelose surface and then dipped in electrolyte, so as to gain the gelose gel template with the stored electrolyte; the gelose gel template is then arranged in an electrolytic cell, the micro-structure part of which is exposed on the liquid surface; a Pt layer is splashed on the back surface by the P-typed silicon through a front disposal to form an ohm contact; a polished surface is then arranged on the surface of the gelose gel template; the P-typed silicon sheet is taken as a working electrode and the electro-chemical polishing micro-processing is carried out to the P-typed silicon sheet; the micro-structure on the gelose gel template is transferred on the surface of the P-typed silicon by the electro-chemical polishing micro-processing to gain the P-typed silicon sheet with the micro-structure and the P-typed silicon sheet with the micro-structure is separated from the gelose.

Owner:XIAMEN UNIV

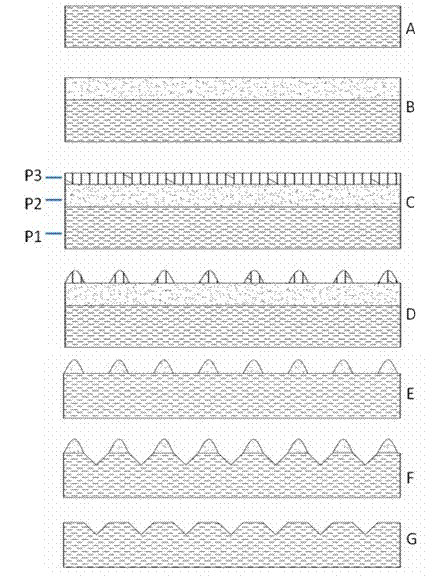

Simple and easy preparation method of nanometer-scale PPS (Patterned Sapphire Substrate)

ActiveCN102368518AImprove extraction efficiencyQuality improvementSemiconductor devicesPhosphoric acidZno nanoparticles

The invention relates to a simple and easy preparation method of a nanometer-scale PPS, comprising the following steps of: depositing an SiO2 film on a sapphire substrate; depositing an ITO (Indium Tin Oxide) or ZnO layer on the SiO2 film; carrying out high-temperature annealing to enable the ITO or ZnO film to undergo an agglomeration phenomenon, wherein the size and the distributive degree of ITO or ZnO particles on the SiO2 film are changed according to the annealing temperature; etching the SiO2 film which is blocked by the ITO or ZnO particles off through dry etching, thereby transferring a uniform ITO or ZnO nanoparticle pattern to the SiO2 film; then putting the SiO2 film to a high-temperature mixed solution containing sulfuric acid and phosphoric acid for corroding or dry etching; transferring the uniform nanometer-scale SiO2 particle pattern to the sapphire substrate again; and finally removing an SiO2 mask film with HF acid to form the nanometer-scale PSS substrate. The simple and easy preparation method disclosed by the invention has the advantages of simple and easy preparation process, low cost, high production efficiency and capability of improving the quantum effect outside an LED chip.

Owner:HC SEMITEK CORP

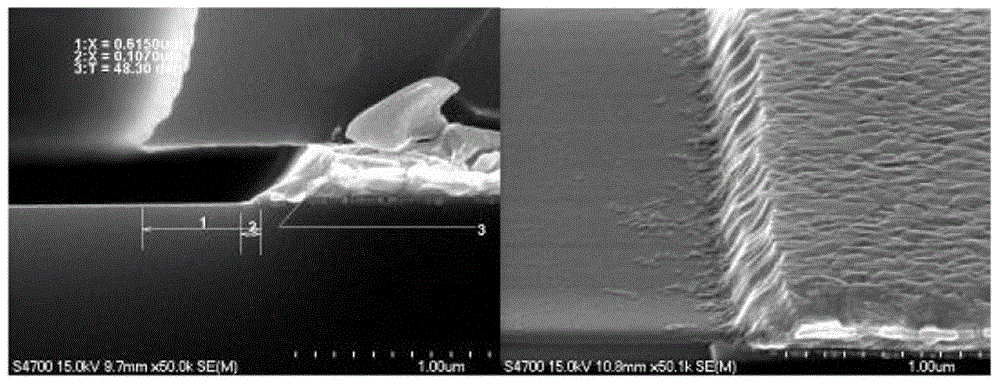

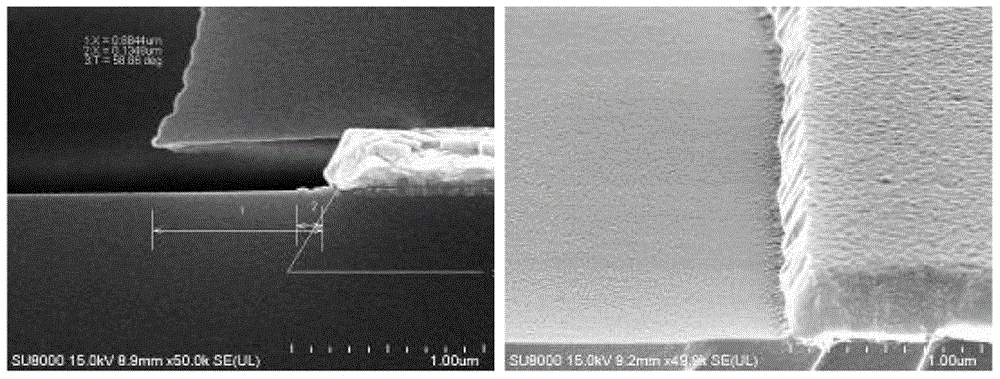

Method of preparing a sample for transmission electron microscopy

ActiveUS7649173B2Etching speedEtching speed is fastMaterial analysis using wave/particle radiationDecorative surface effectsNon dopedEnergy filtered transmission electron microscopy

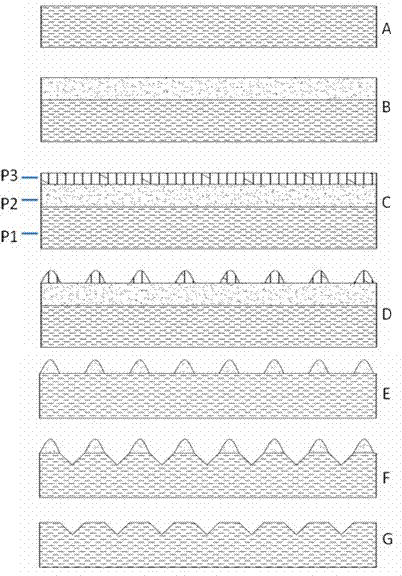

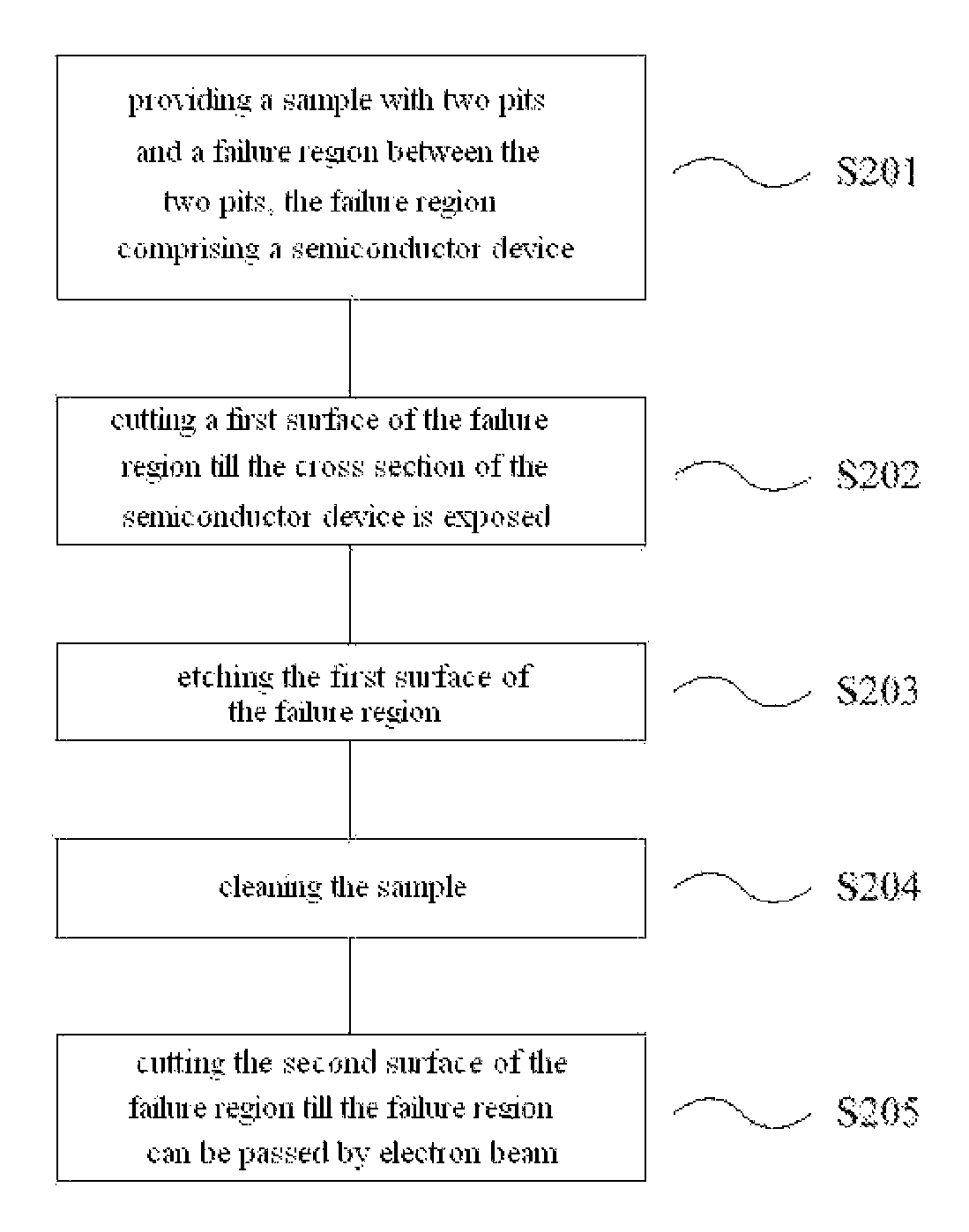

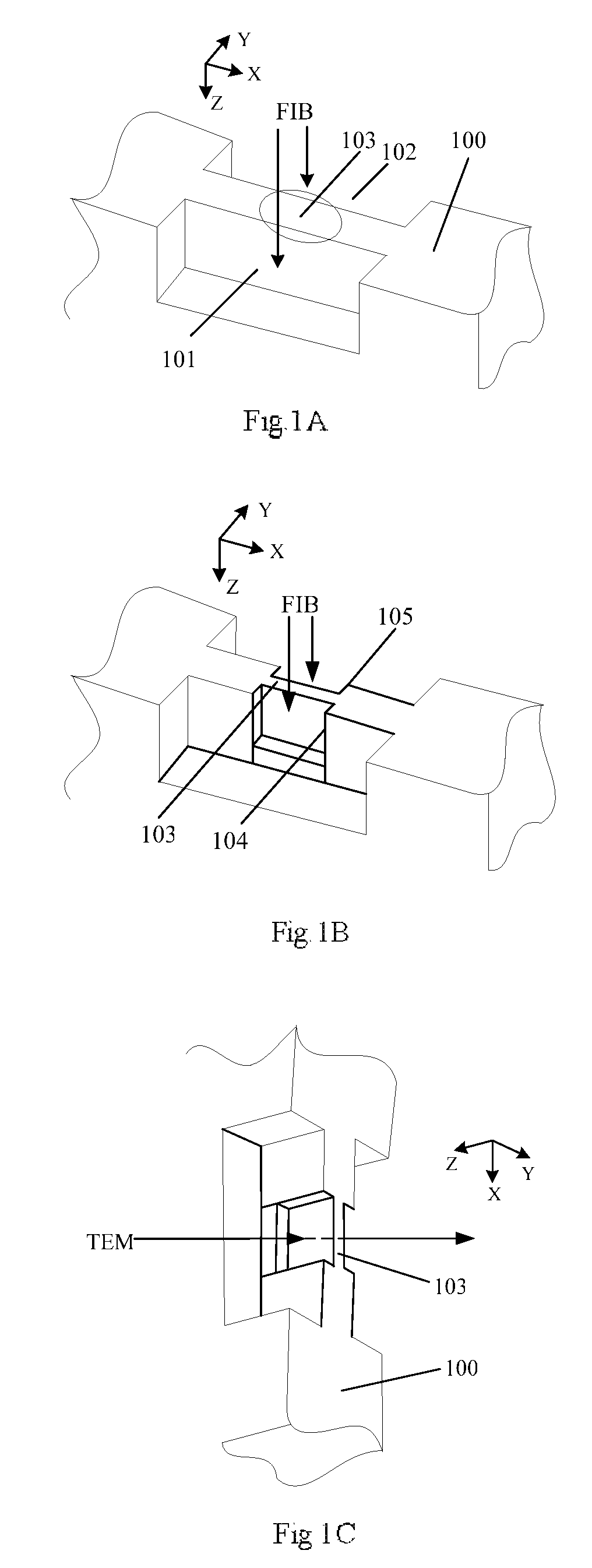

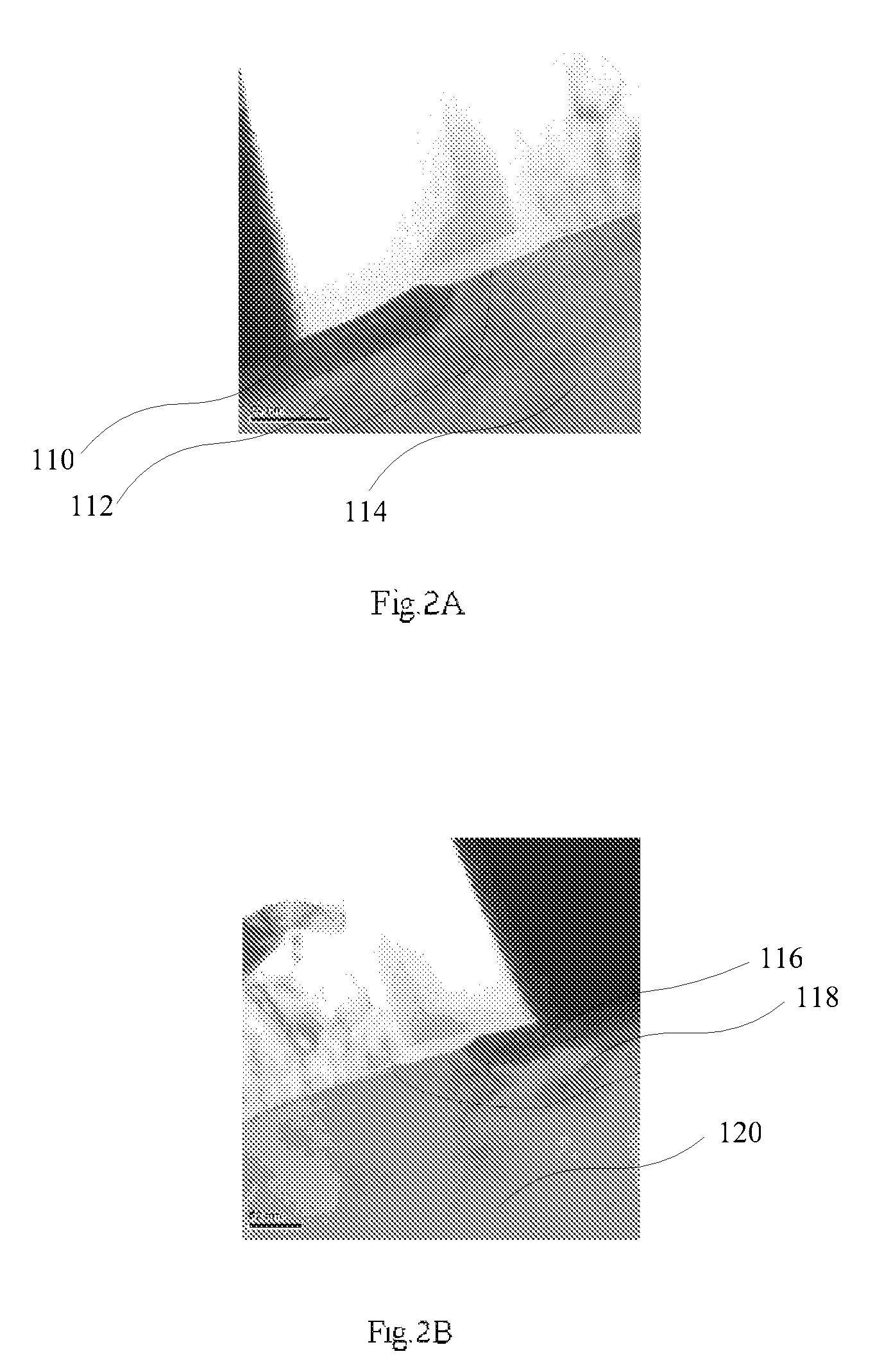

A method for preparing TEM sample, comprising the following steps: providing a sample with two pits and a failure region between the two pits, the failure region comprising a semiconductor device; milling the first surface of the failure region, till the cross section of the semiconductor device is exposed; etching the first surface of the failure region; cleaning the sample; milling the second surface of the failure region, till the failure region can be passed by electron beam. A sample can be prepared for a high resolution TEM through above steps. When the sample is observed, it is easy to distinguish the lightly doped drain, source / drain regions from the silicon substrate and observe the pattern and defects in the lightly doped drain, source / drain regions clearly; in addition, it is easy to distinguish the BPSG from the non-doped silicon dioxide in the failure region.

Owner:SEMICON MFG INT (SHANGHAI) CORP

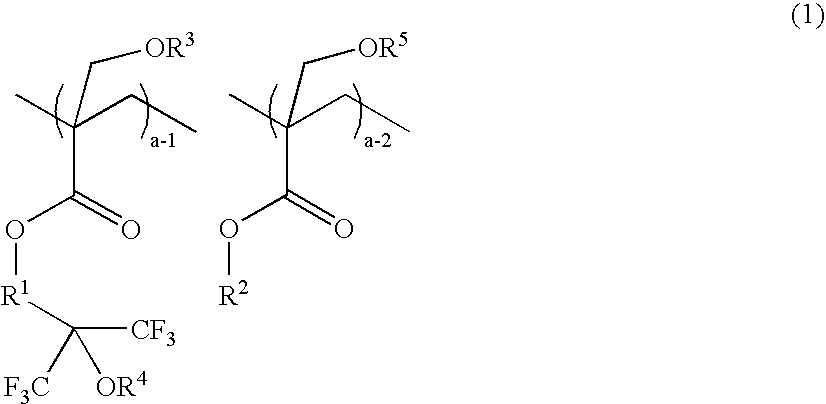

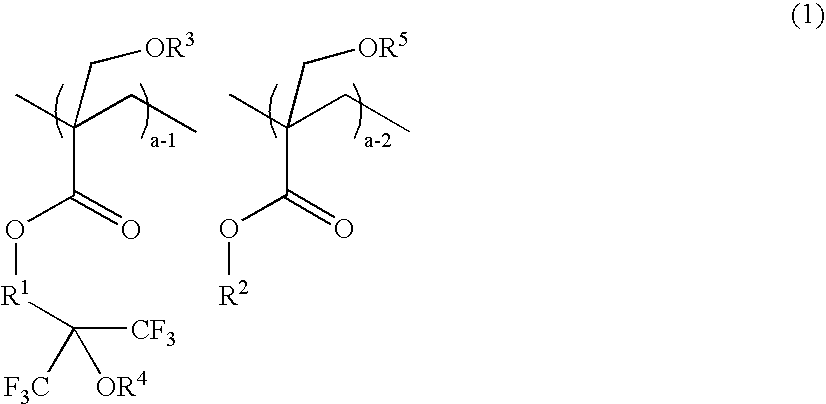

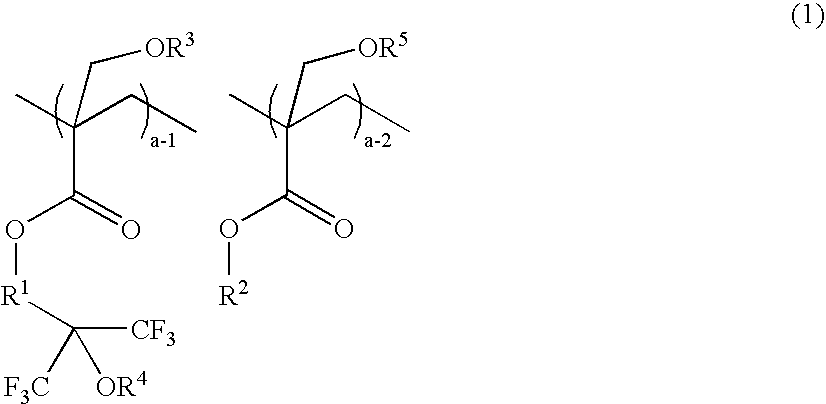

Antireflection film composition and patterning process using the same

ActiveUS20080220381A1Improve blocking propertiesEtching speed is fastPhotosensitive materialsPhotoprinting processesChemistryResist

An antireflection film composition, wherein an etching speed is fast, thus, when used as a resist lower layer, a film loss of a resist pattern and deformation of the pattern during etching can be minimized, and because of a high crosslinking density, a dense film can be formed after thermal crosslinking, thus, mixing with an upper layer resist can be prevented and the resist pattern after development is good is provided.The antireflection film composition comprising; at least a polymer having a repeating unit represented by the following general formula (1).

Owner:SHIN ETSU CHEM IND CO LTD

Etching liquor and circular use method thereof

The invention discloses etching liquor and a circular use method thereof. The etching liquor comprises copper chloride, organic amine, an oxidizing agent, an additive agent and deionized water. In each liter of etching liquor, 10 to 150 g of copper chloride, 10 to 200 g of organic amine, 1 to 100 g of the oxidizing agent, 1 to 100 g of the additive agent and the balance deionized water are included; in the use process of the etching liquor, the solution is alkaline, and the requirement for a device is not high, the use cost is low, operation is safe and environment-friendly, and a detection control system is simple; low etching is achieved, the etching speed is high, and stability is high. A membrane separation technology and a deposition reduction technology are combined, circular recycling of the etching liquor can be well achieved, a product after the reaction is nitrogen and water, other impurities are not brought in, and filter liquor obtained after copper filter and depositing can be recycled to be used for preparing new etching liquor.

Owner:长沙利洁环保科技有限公司

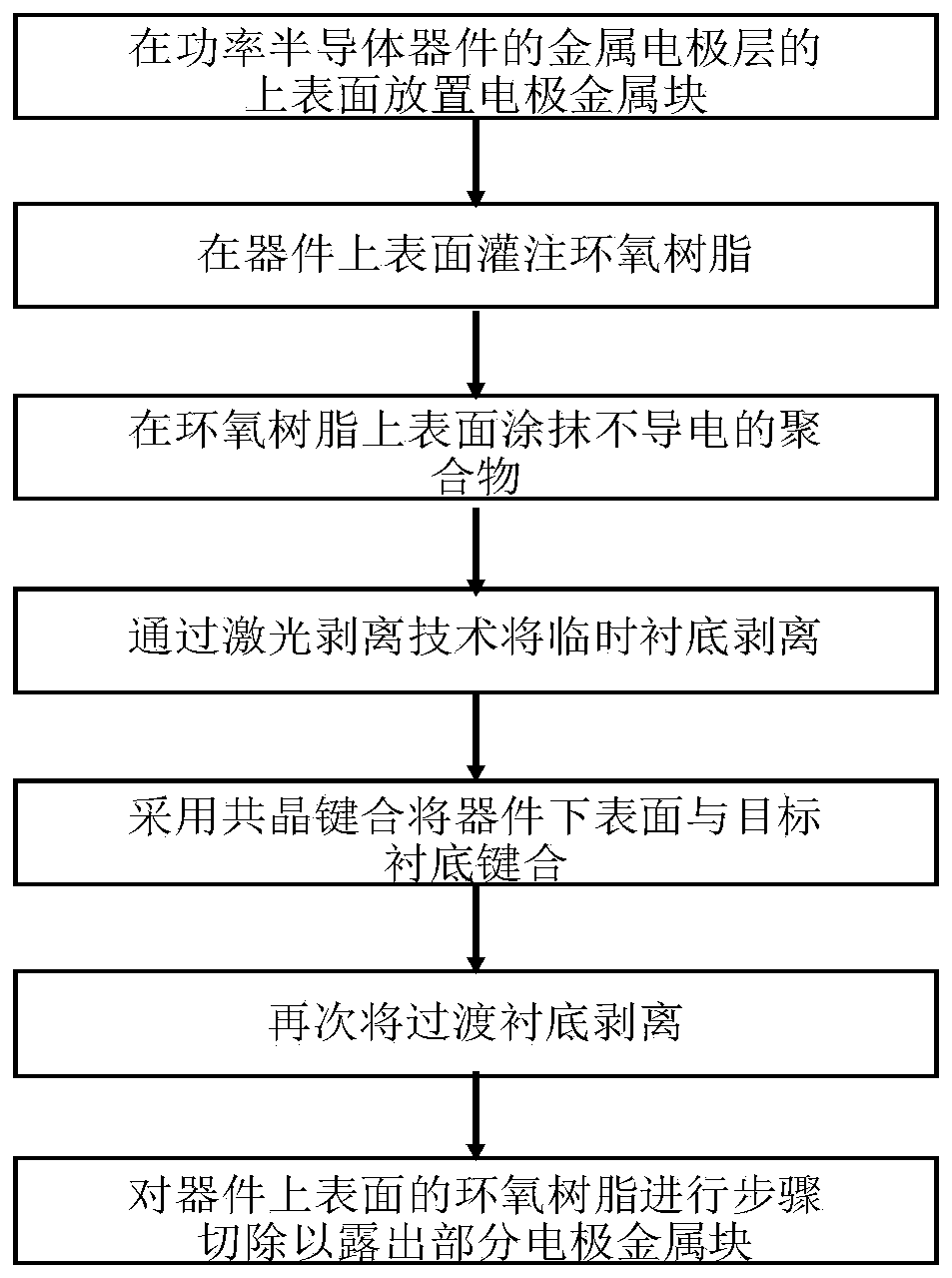

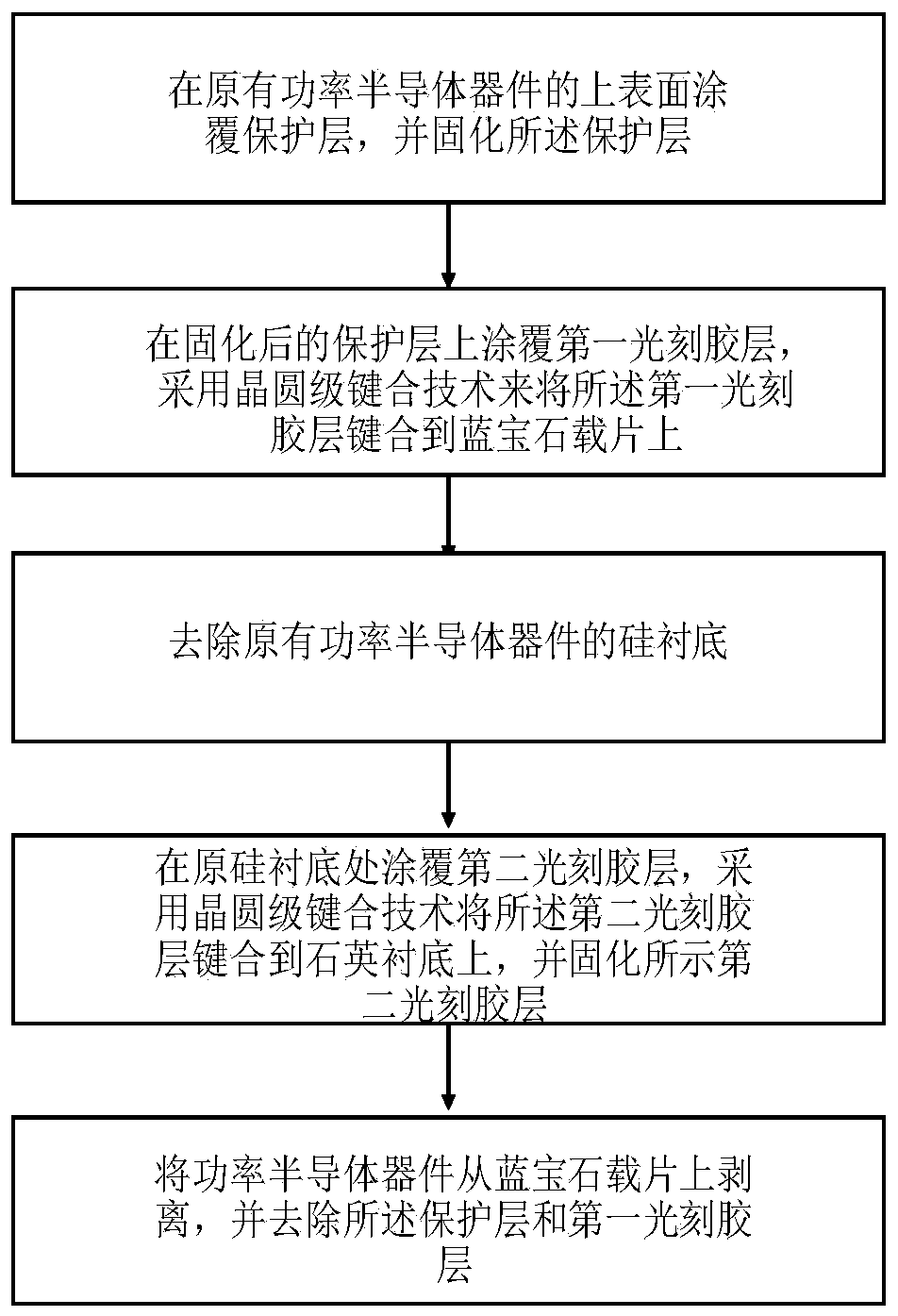

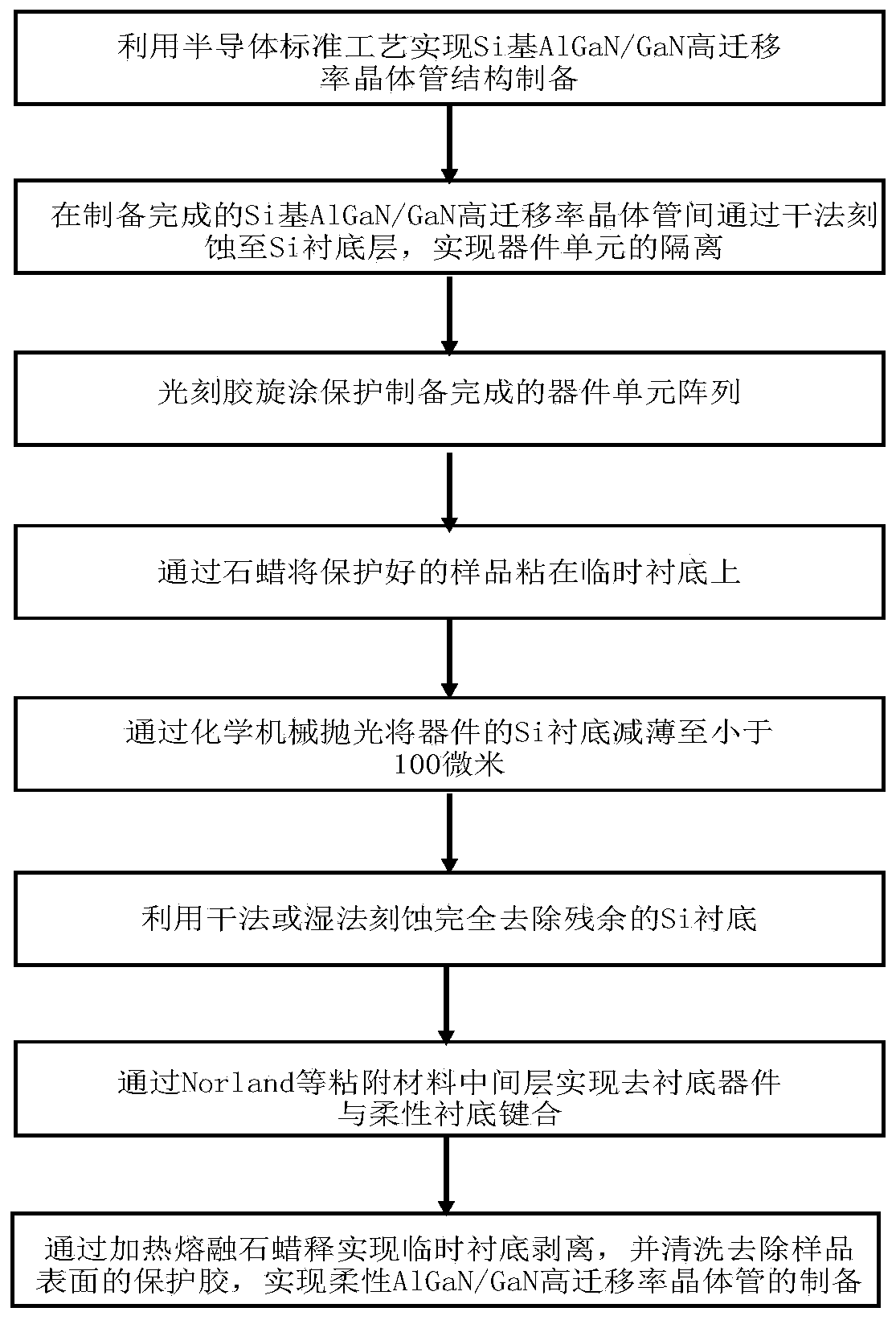

Method for transferring Si-based AlGaN/GaN high electron mobility transistor to flexible substrate

InactiveCN110148561AAchieve strippingEtching speed is fastSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingEngineering

The invention belongs to the technical field of semiconductors and particularly relates to a method for transferring a Si-based AlGaN / GaN high electron mobility transistor to a flexible substrate. Themethod of the invention comprises a step of achieving the stripping of a non-flexible Si substrate by using a mode of combining chemical mechanical polishing and dry or wet etching, and a step of transferring the high electron mobility transistor device with the removal of a substrate to the flexible substrate through an intermediate layer of an adhesive material such as Norland by using a devicebonding technique to achieve the preparation of the AlGaN / GaN high electron mobility transistor. The method has the advantages of fast etching speed, low process cost and wide application range, andthe invention includes but not limited to a hard substrate semiconductor device based on a Si substrate or a sapphire substrate.

Owner:FUDAN UNIV