TFT (thin film transistor) array substrate

An array substrate and substrate technology, applied in optics, instruments, electrical components, etc., can solve problems such as unstable performance, low rate, and oxygen loss of metal oxides of TFT array substrates, so as to improve the overall etching speed, increase productivity, The effect of improving stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

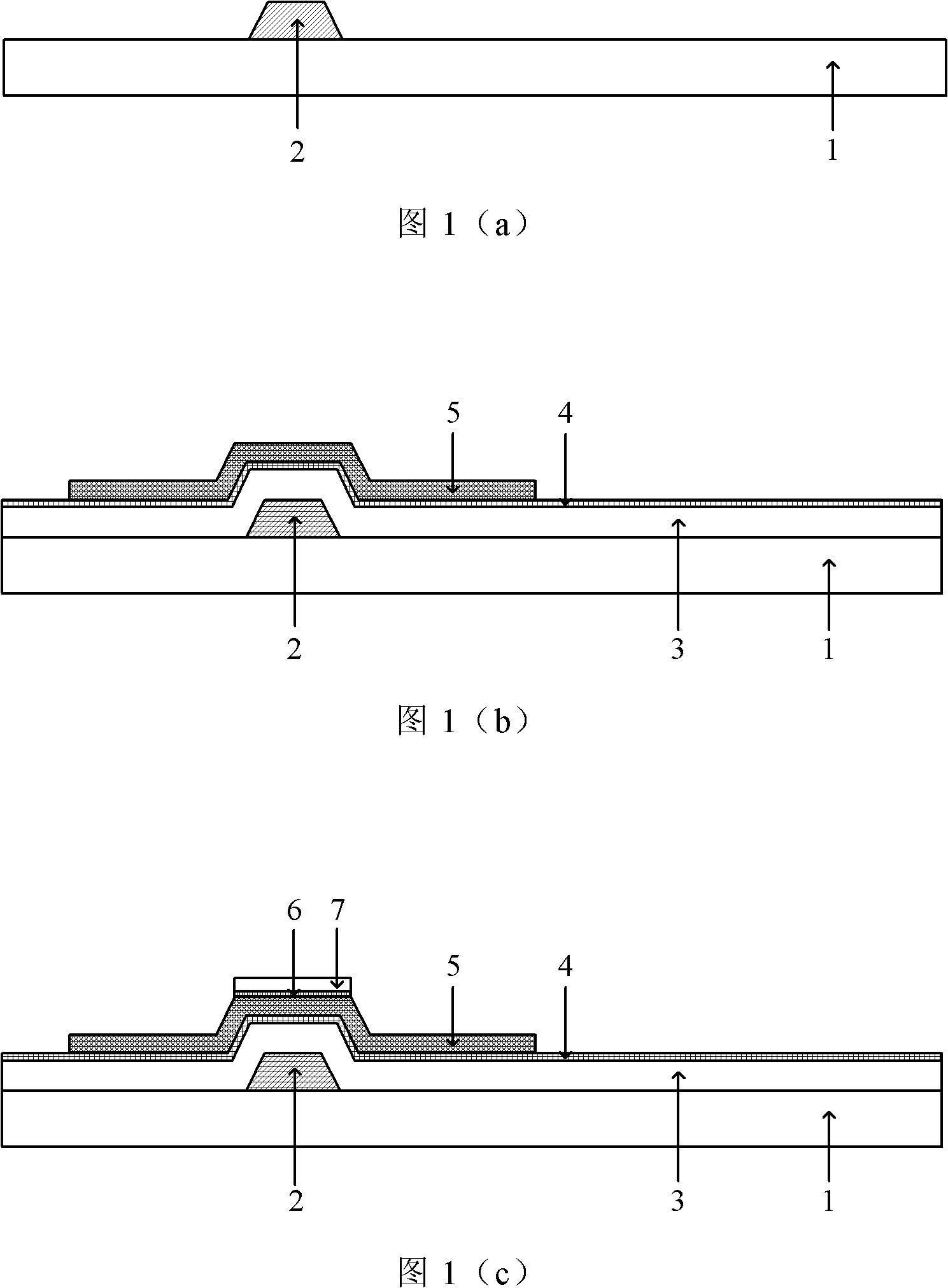

Embodiment 1

[0037] Such as figure 1As shown in (f), in this embodiment, the TFT array substrate includes: a substrate 1; a gate electrode 2 formed on the substrate; a gate insulating layer 3 covering the gate electrode 2 and extending to the substrate 1; The gate insulating protective layer 4 on the gate insulating layer 3; the semiconductor layer 5 formed on the gate insulating protective layer 4; the source electrode 8 and the drain electrode 9 formed on the semiconductor layer 5, the source electrode 8 and the drain electrode 9 A channel is provided between the drain electrodes 9; the etch stop protective layer 6 and the etch stop insulating layer 7 formed in the channel, the etch stop protective layer 6 is located under the etch stop insulating layer 7 and In contact with the semiconductor layer 5; the passivation layer 10, the passivation layer completely covers the source electrode 8, the etching stop insulating layer 7, the drain electrode 9 and the gate insulating protection layer...

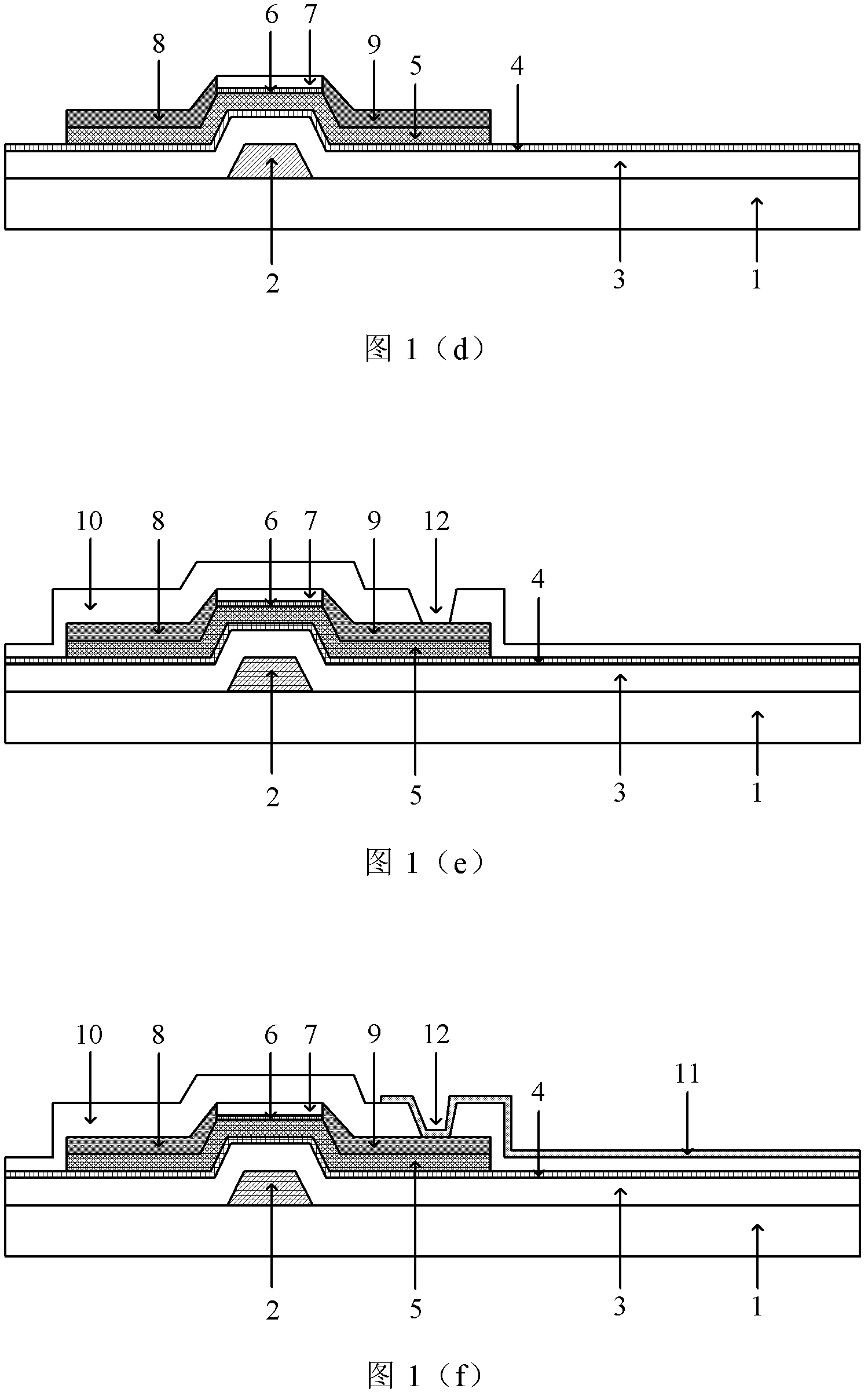

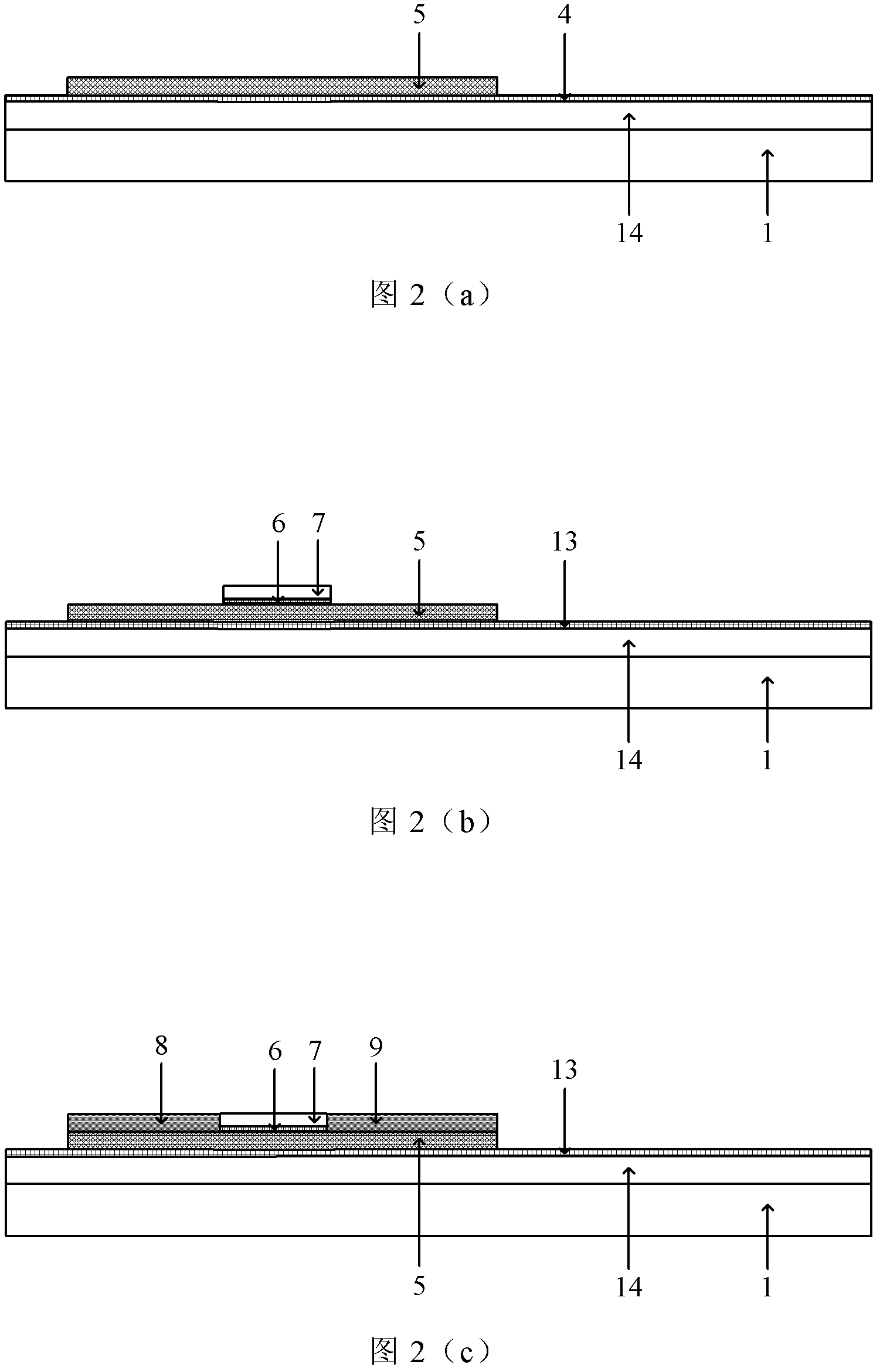

Embodiment 2

[0050] Such as figure 2 As shown in (f), in this embodiment, the TFT array substrate includes: a substrate 1; a modified insulating layer 14 covering the substrate; a modified insulating protection layer 13 covering the modified insulating layer 14; The semiconductor layer 5 on the semiconductor layer 5; the source electrode 8 and the drain electrode 9 formed on the semiconductor layer 5, and a channel is provided between the source electrode 8 and the drain electrode 9; the etching barrier protection formed in the channel layer 6 and an etch stop insulating layer 7, the etch stop protection layer 6 is located below the etch stop insulating layer 7 and is in contact with the semiconductor layer 5; a gate insulating layer 3, the gate insulating layer 3 connects the source electrode 8 , the etch stop insulating layer 7, the drain electrode 9 and the gate insulating protection layer 4 are completely covered, and the part of the gate insulating layer 3 covering the drain electrod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More