Patents

Literature

783results about How to "Improve etch selectivity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

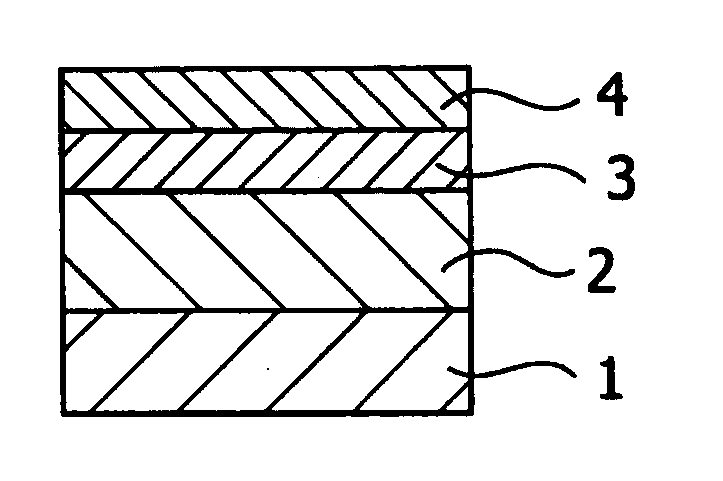

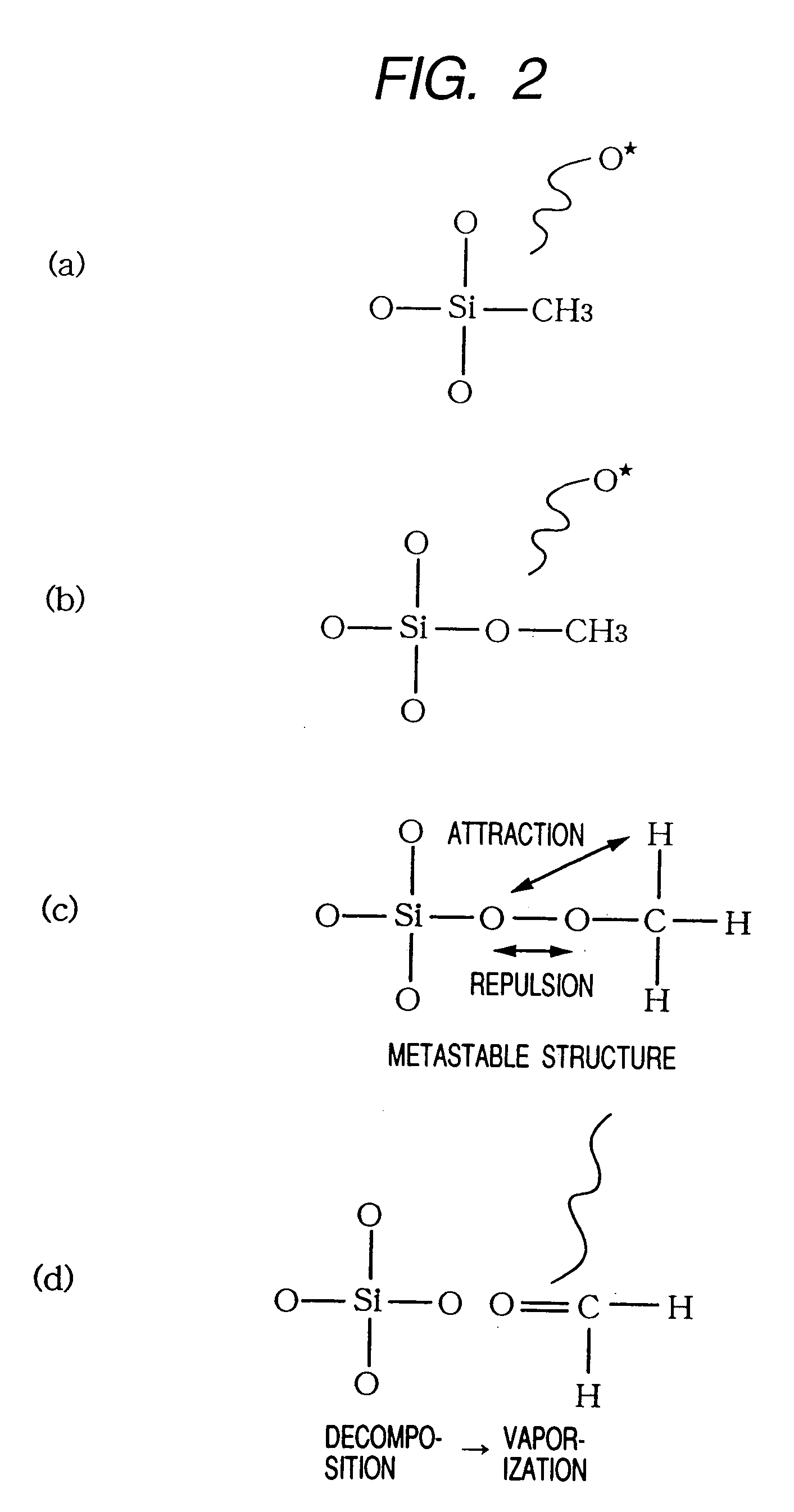

Method for forming insulation film

InactiveUS7354873B2Reduce distanceGood film densitySolid-state devicesSemiconductor/solid-state device manufacturingPlasma reactionResidence time

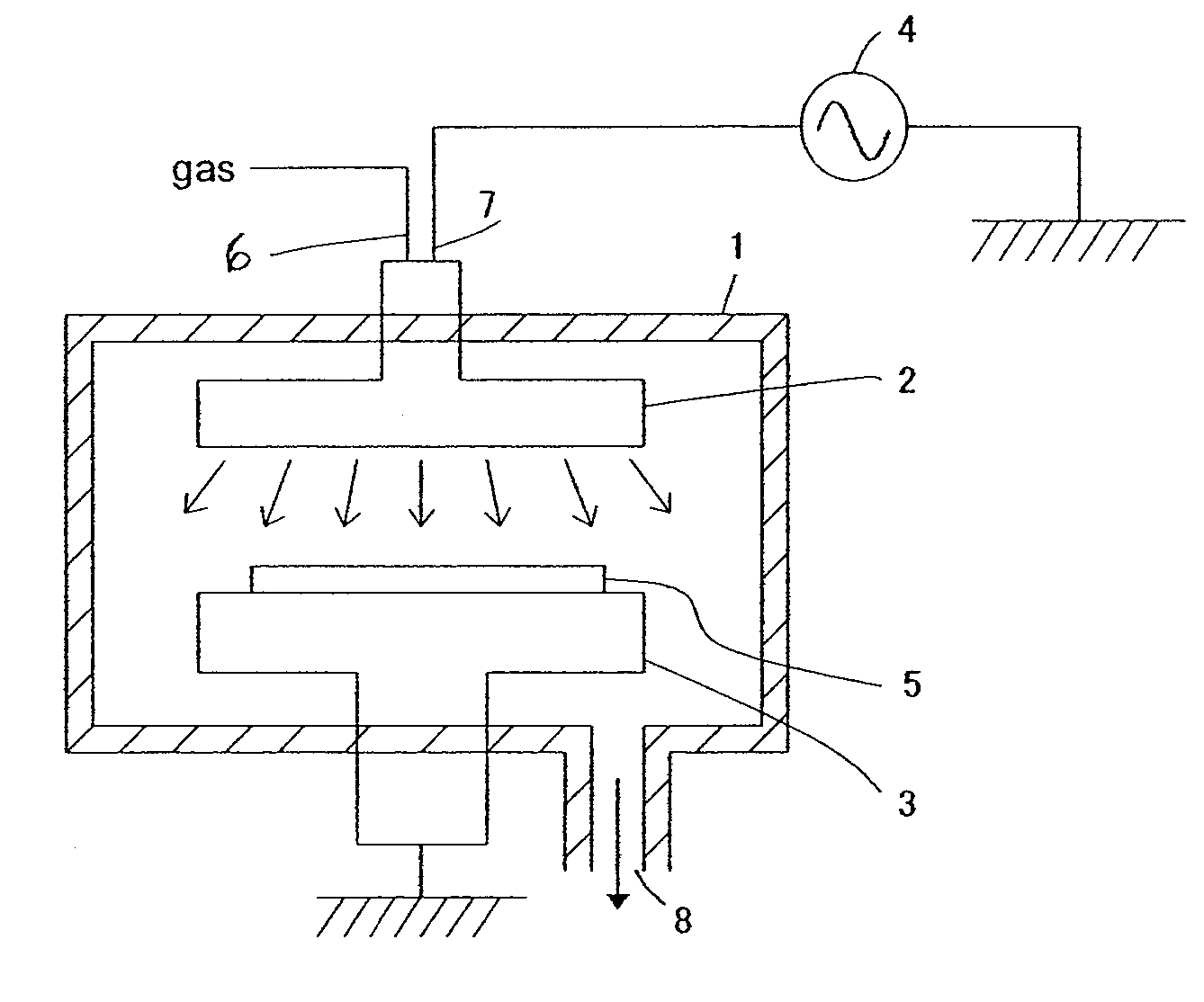

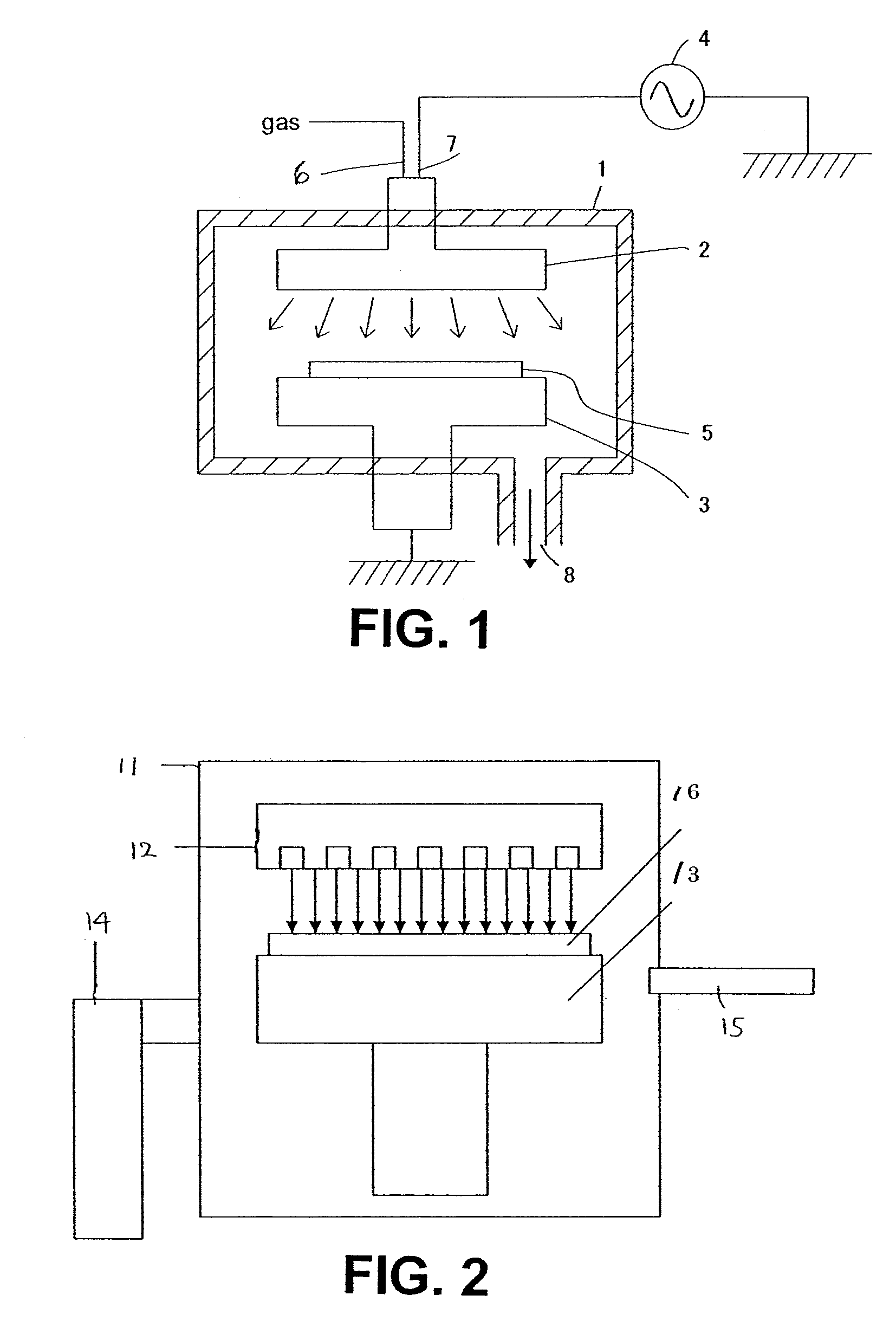

A method for forming an insulation film having filling property on a semiconductor substrate by plasma reaction includes: vaporizing a silicon-containing hydrocarbon having a Si—O bond compound to provide a source gas; introducing the source gas and a carrier gas without an oxidizing gas into a reaction space for plasma CVD processing; and forming an insulation film constituted by Si, O, H, and optionally C or N on a substrate by plasma reaction using a combination of low-frequency RF power and high-frequency RF power in the reaction space. The plasma reaction is activated while controlling the flow of the reaction gas to lengthen a residence time, Rt, of the reaction gas in the reaction space.

Owner:ASM JAPAN

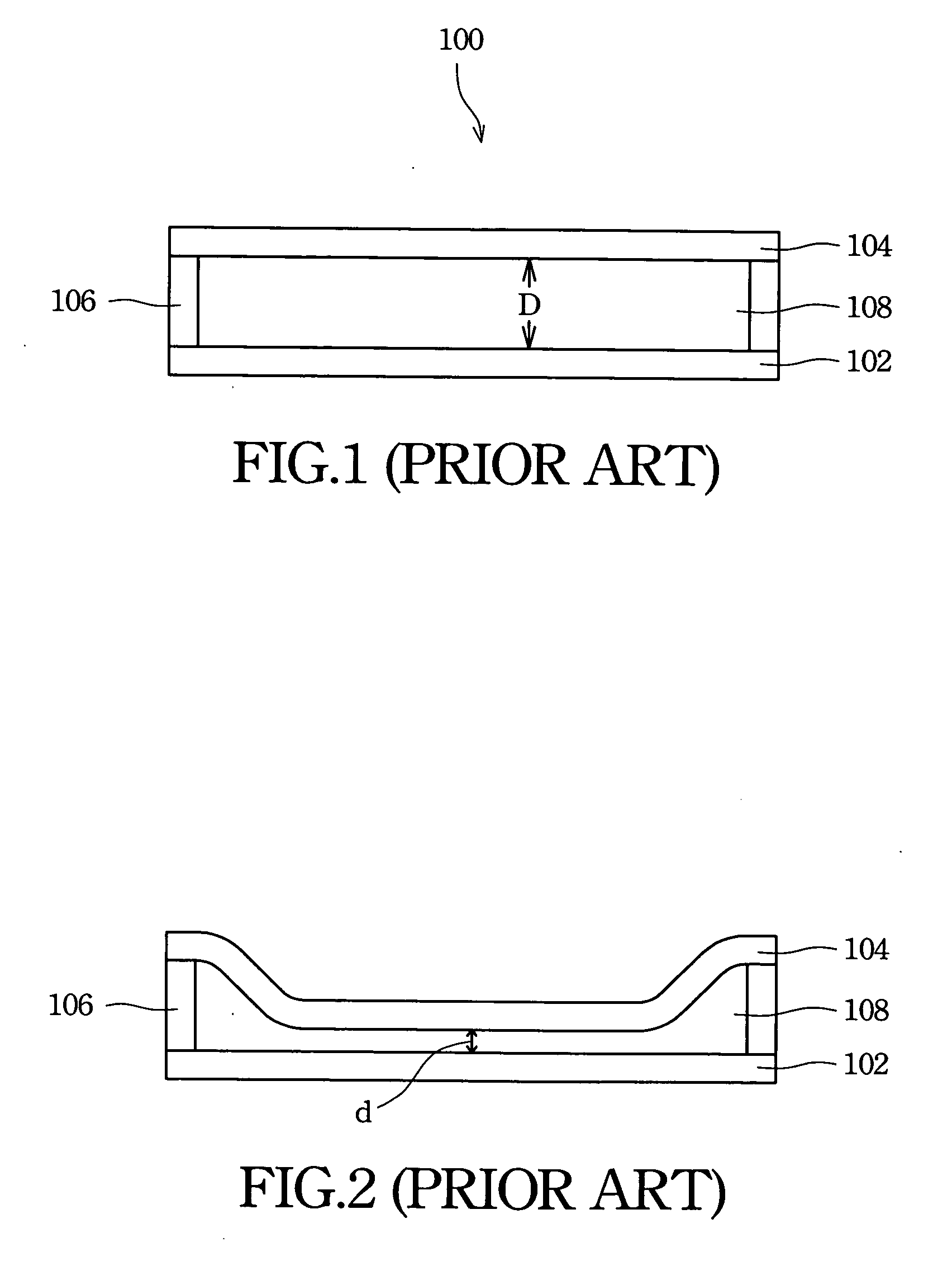

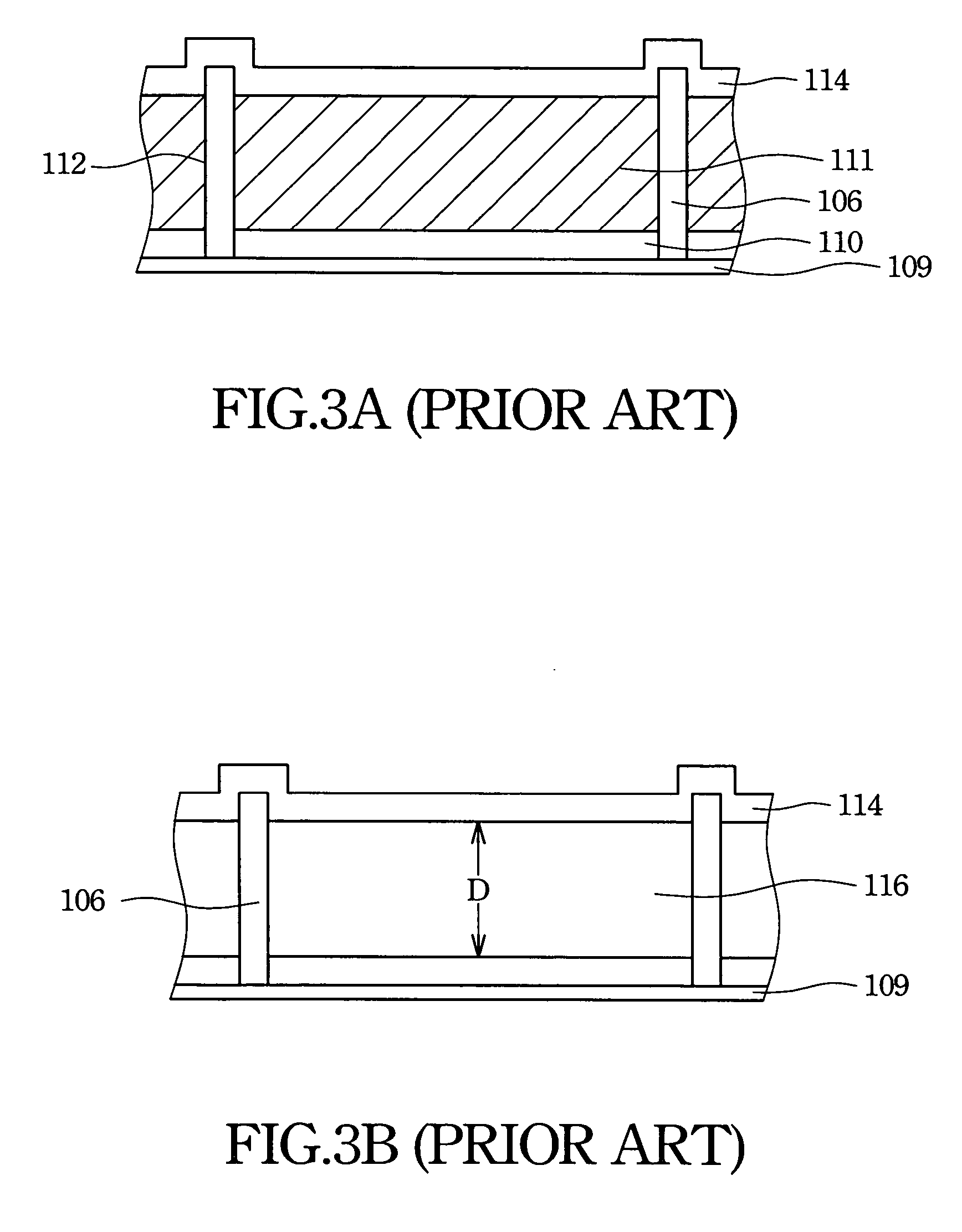

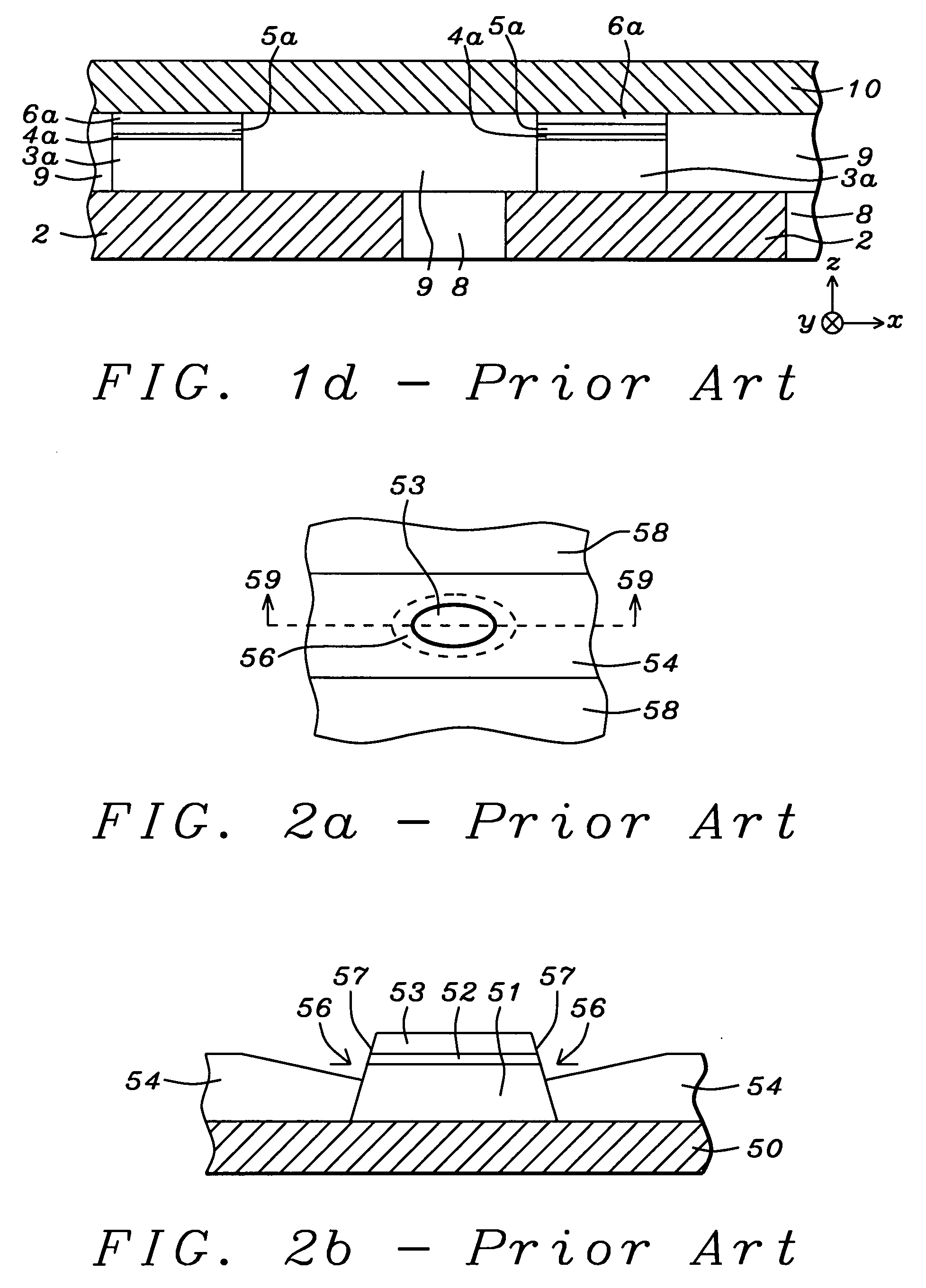

Structure of a micro electro mechanical system and the manufacturing method thereof

InactiveUS20050078348A1Improve etch selectivityHigh selectivityTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesEngineeringMechanical system

A structure of a micro electro mechanical system and a manufacturing method are provided, the structure and manufacturing method is adapted for an optical interference display cell. The structure of the optical interference display cell includes a first electrode, a second electrode and posts. The second electrode comprises a conductive layer covered by a material layer and is arranged about parallel with the first electrode. The support is located between the first plate and the second plate and a cavity is formed. In the release etch process of manufacturing the structure, the material layer protects the conductive layer from the damage by an etching reagent. The material layer also protects the conductive layer from the damage from the oxygen and moisture in the air.

Owner:SNAPTRACK

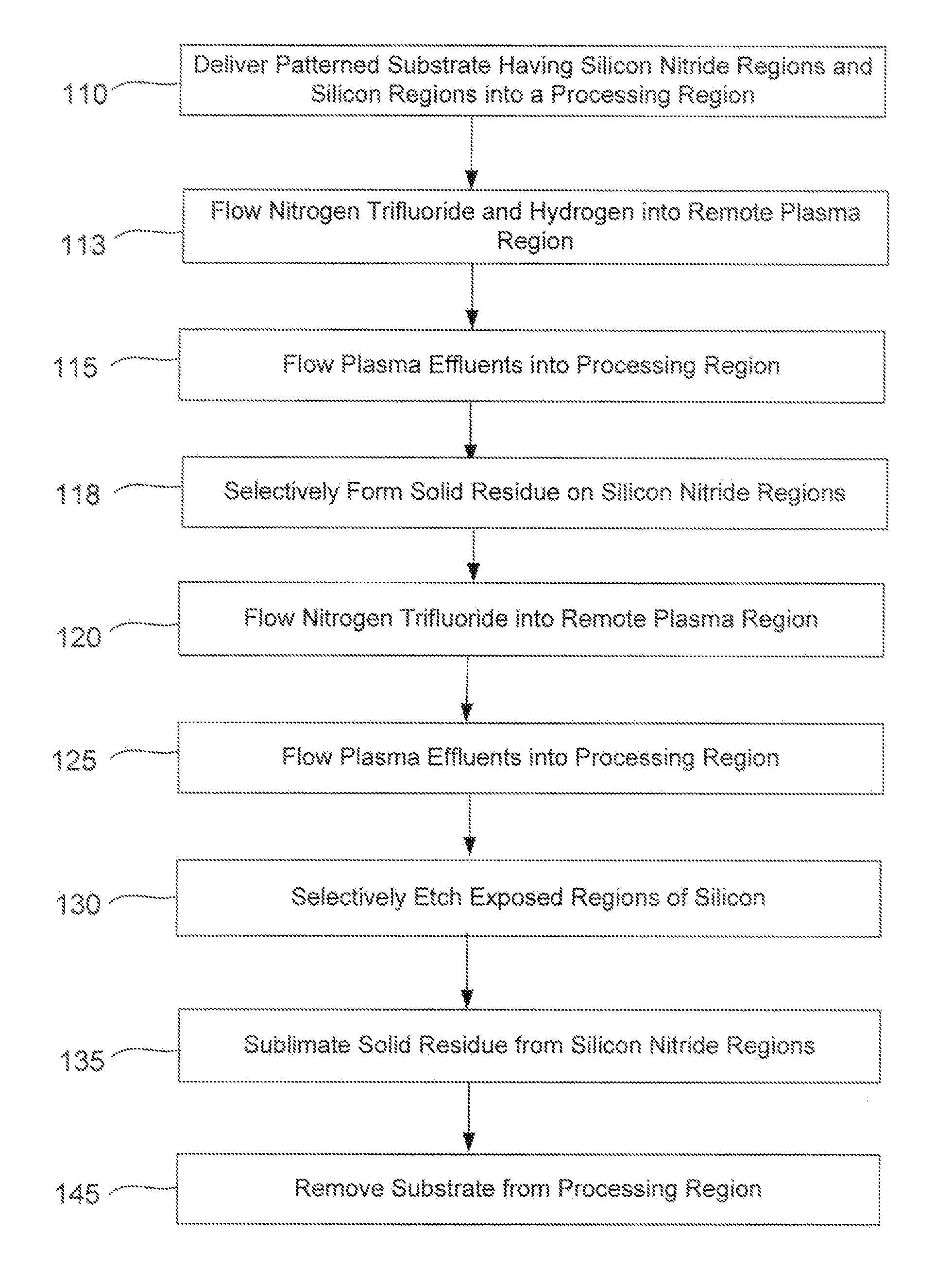

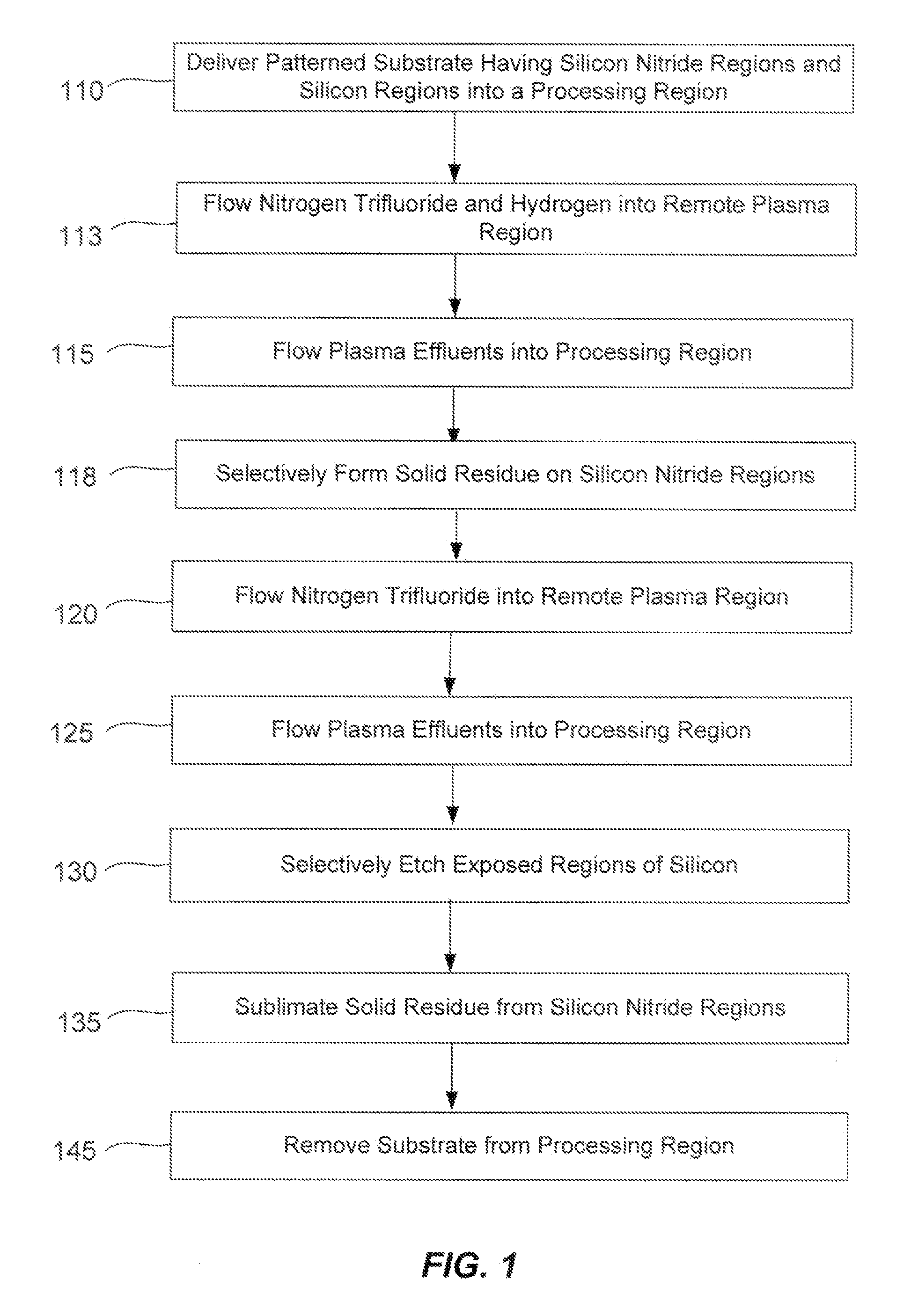

Selective suppression of dry-etch rate of materials containing both silicon and nitrogen

InactiveUS20130059440A1Inhibit etch rateImprove etch selectivityElectric discharge tubesSemiconductor/solid-state device manufacturingRemote plasmaHydrogen

A method of suppressing the etch rate for exposed silicon-and-nitrogen-containing material on patterned heterogeneous structures is described and includes a two stage remote plasma etch. The etch selectivity of silicon relative to silicon nitride and other silicon-and-nitrogen-containing material is increased using the method. The first stage of the remote plasma etch reacts plasma effluents with the patterned heterogeneous structures to form protective solid by-product on the silicon-and-nitrogen-containing material. The plasma effluents of the first stage are formed from a remote plasma of a combination of precursors, including nitrogen trifluoride and hydrogen (H2). The second stage of the remote plasma etch also reacts plasma effluents with the patterned heterogeneous structures to selectively remove material which lacks the protective solid by-product. The plasma effluents of the second stage are formed from a remote plasma of a fluorine-containing precursor.

Owner:APPLIED MATERIALS INC

Method for forming insulation film

InactiveUS20070004204A1Reduce trafficDecrease in flow volumeSolid-state devicesSemiconductor/solid-state device manufacturingProduct gasPlasma reaction

A method for forming an insulation film having filling property on a semiconductor substrate by plasma reaction includes: vaporizing a silicon-containing hydrocarbon having a Si—O bond compound to provide a source gas; introducing the source gas and a carrier gas without an oxidizing gas into a reaction space for plasma CVD processing; and forming an insulation film constituted by Si, O, H, and optionally C or N on a substrate by plasma reaction using a combination of low-frequency RF power and high-frequency RF power in the reaction space. The plasma reaction is activated while controlling the flow of the reaction gas to lengthen a residence time, Rt, of the reaction gas in the reaction space.

Owner:ASM JAPAN

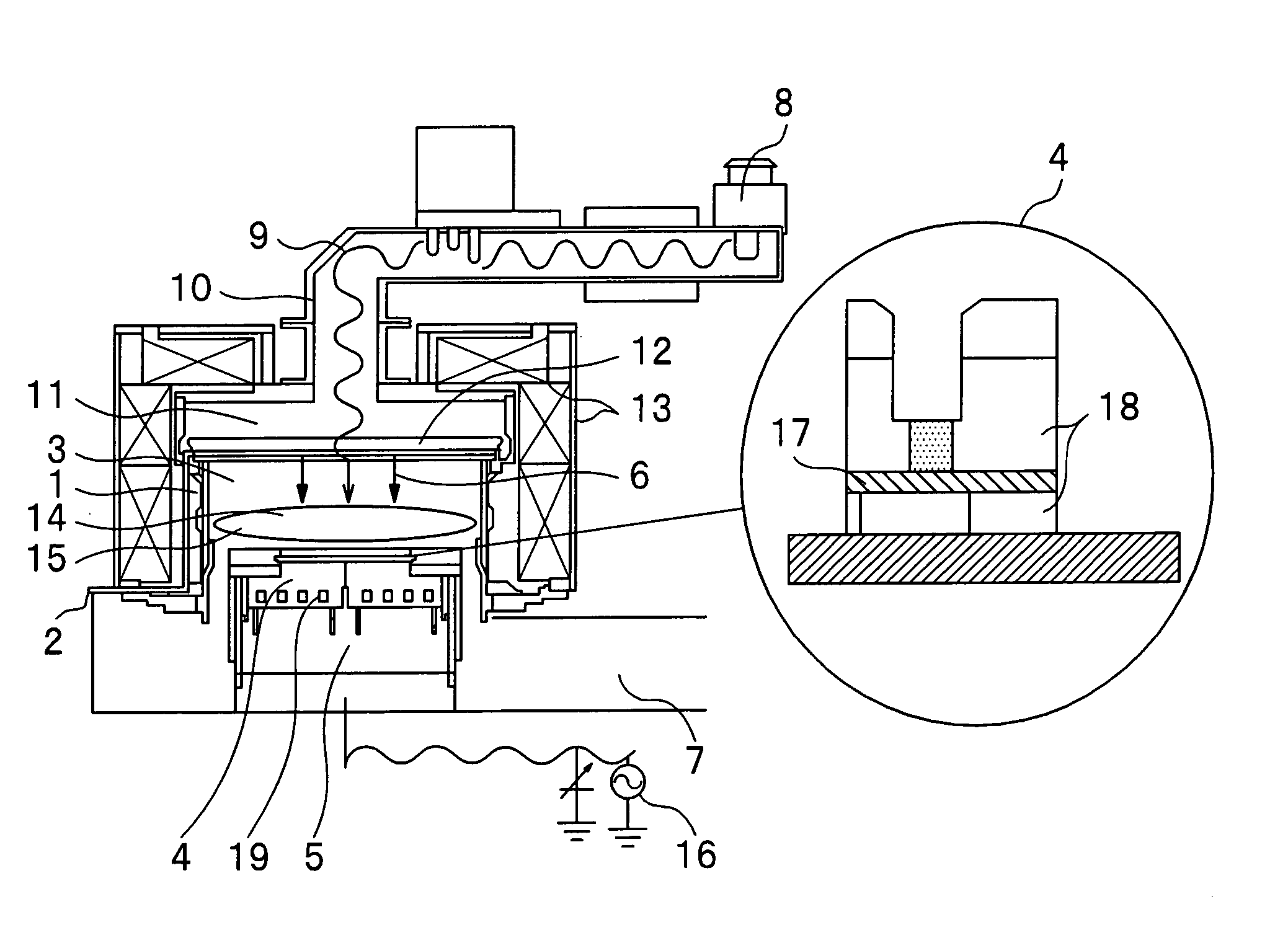

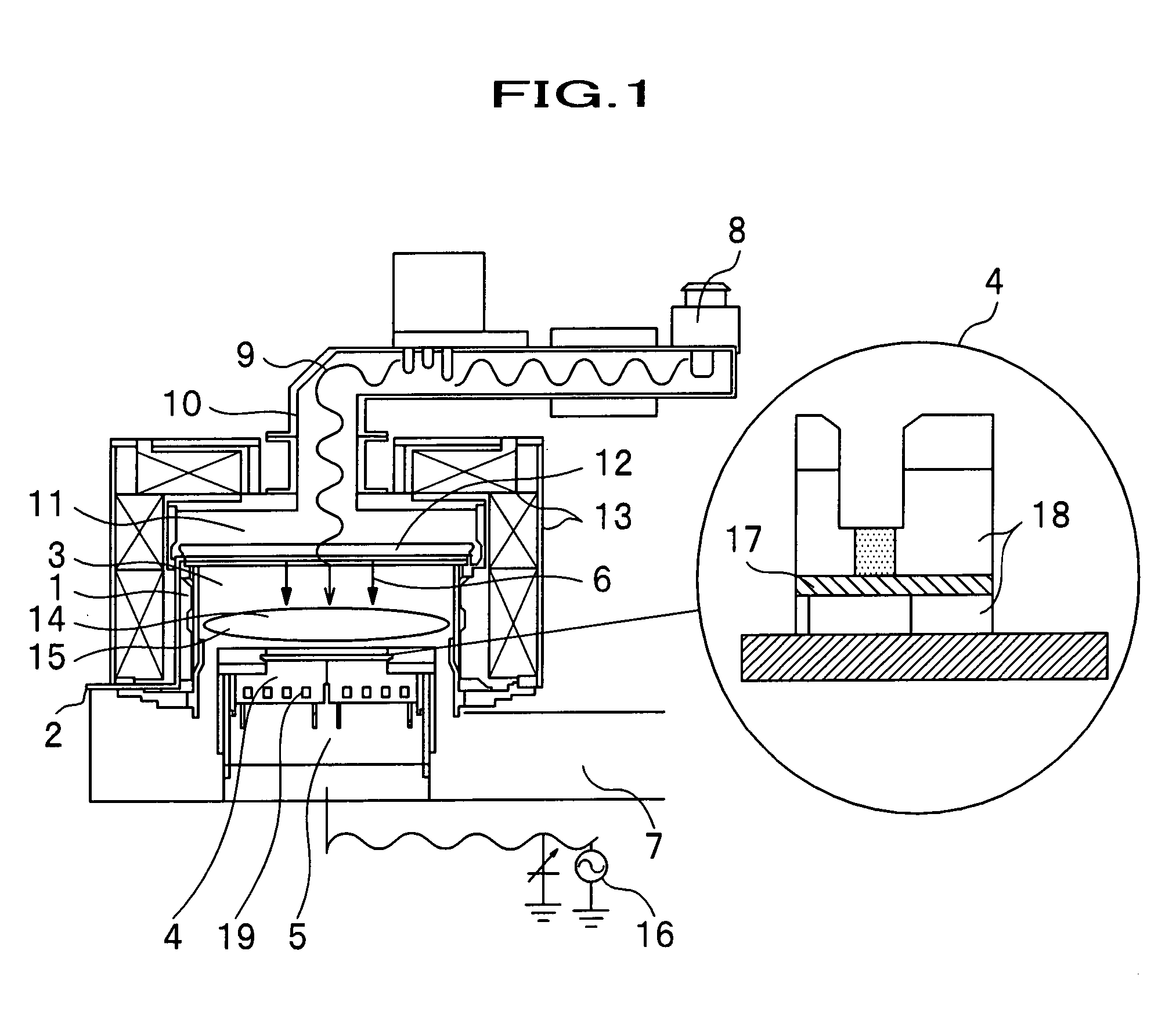

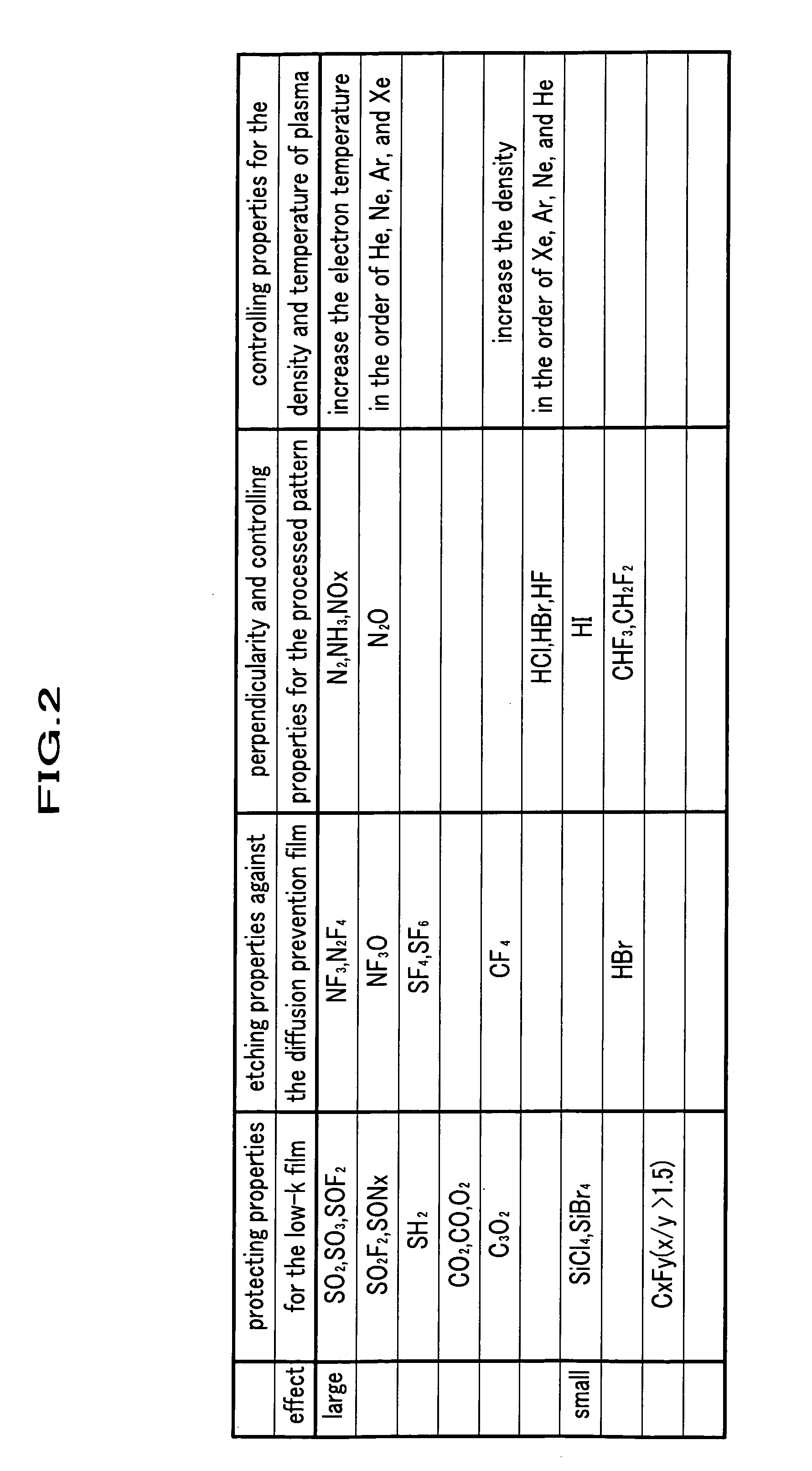

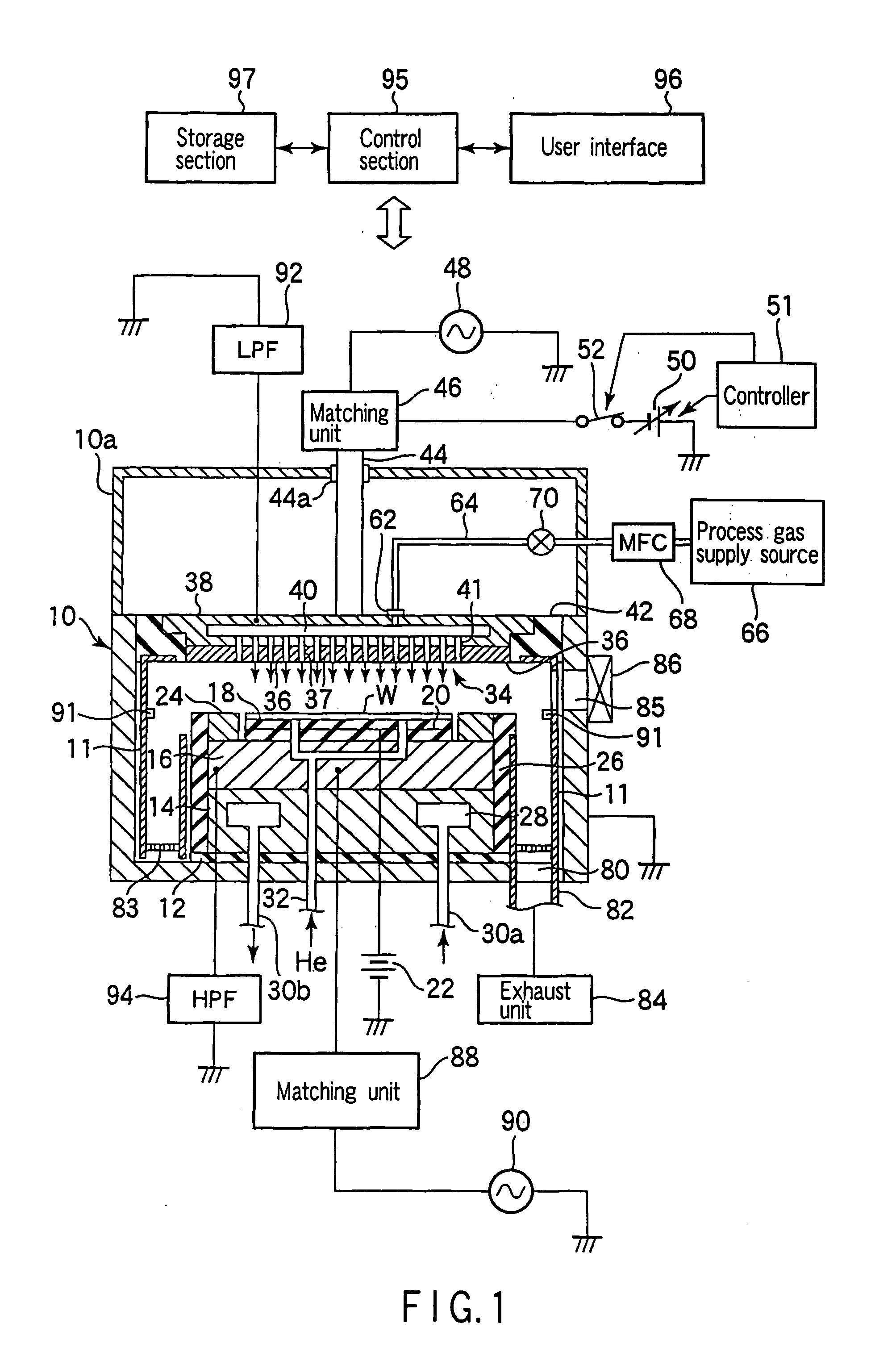

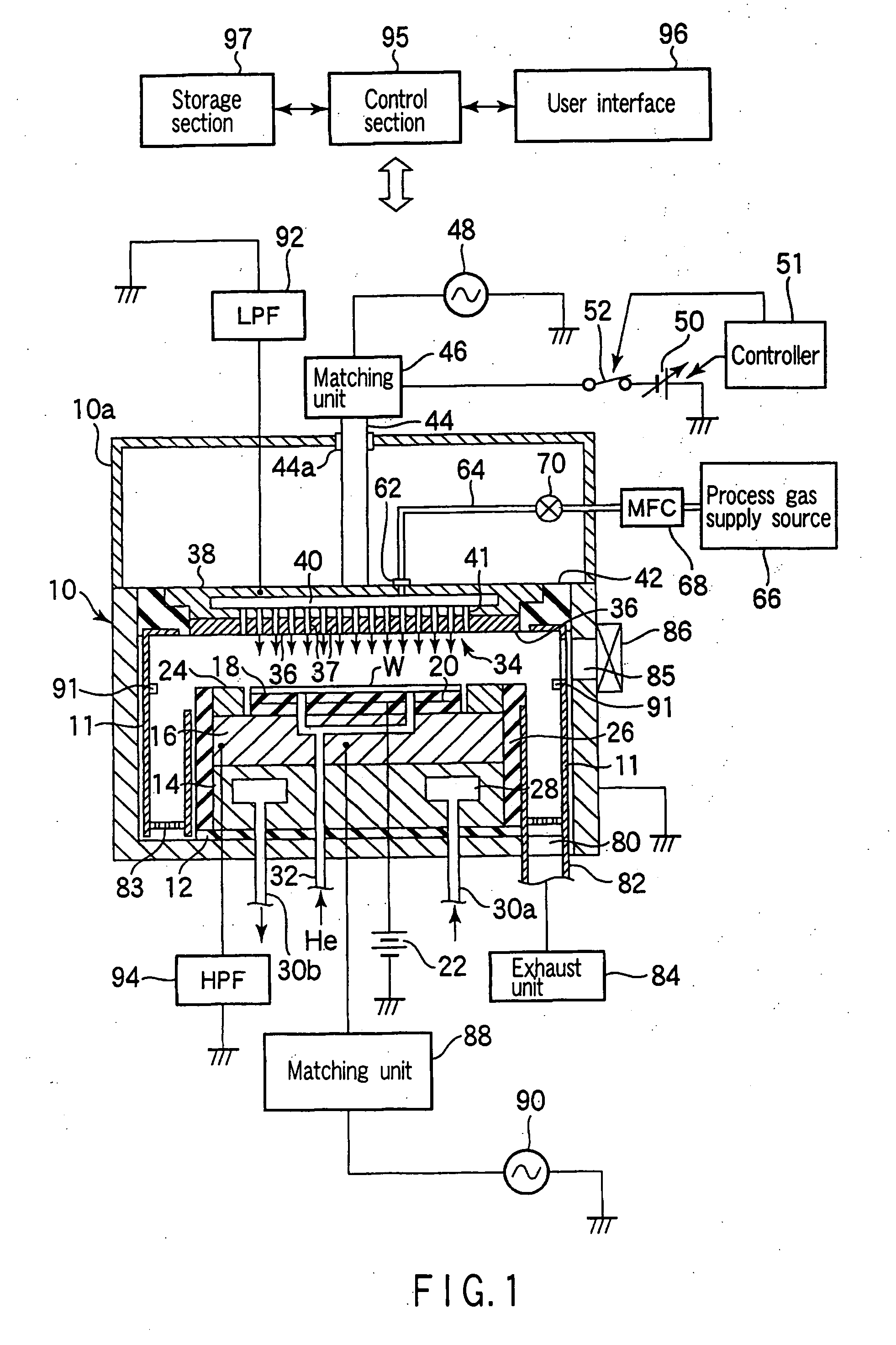

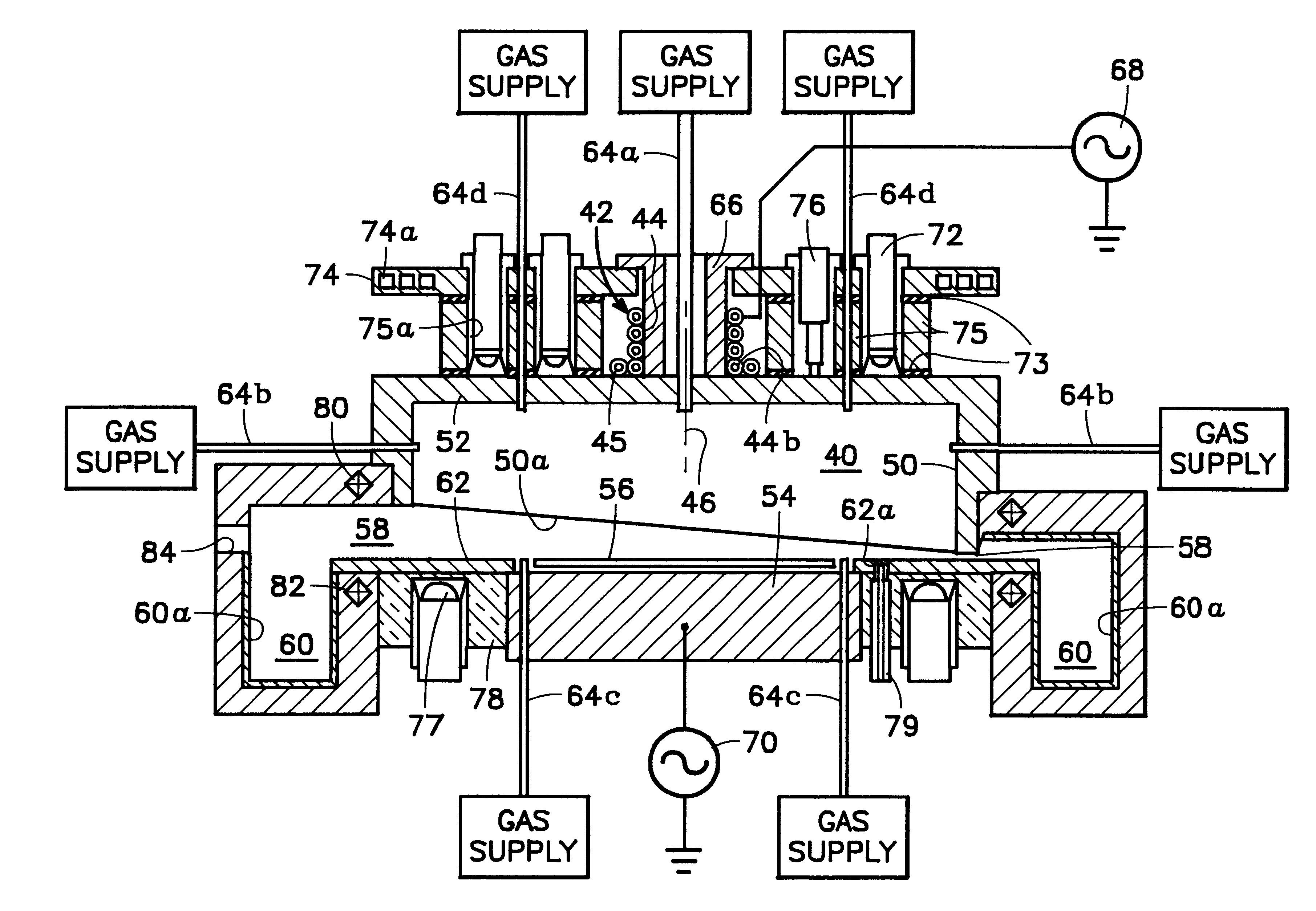

LSI device etching method and apparatus thereof

InactiveUS20050026431A1Realize processingImprove the protective effectSemiconductor/solid-state device manufacturingInterconnectionRadio frequency

An apparatus for performing a plasma-etching of a LSI device including a Cu interconnection, a low-k film, and a diffusion prevention film has a treatment chamber, into which an etching gas is introduced, and a support table which is equipped with electrodes and on which said LSI device is placed. In this apparatus, the etching gasses are turned into plasma by supplying radio frequency power to electrodes provided within the treatment chamber, so that the LSI device is etched with ions of the plasma. In this apparatus, a sulfur-containing gas and a fluorine-containing gas are mixed to the etching gasses, so that the diffusion prevention film is selectively etched against the low-k film.

Owner:HITACHI HIGH-TECH CORP

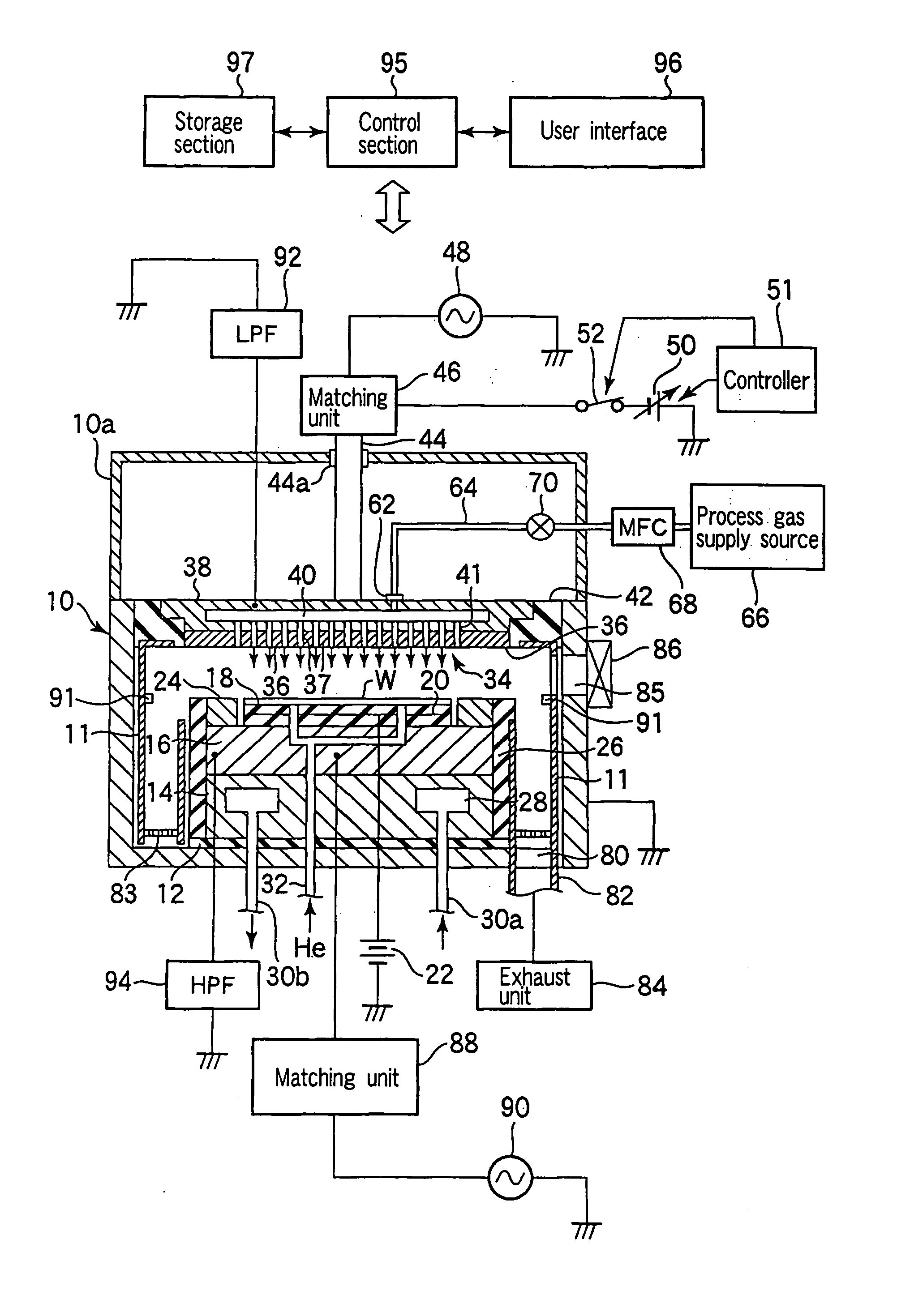

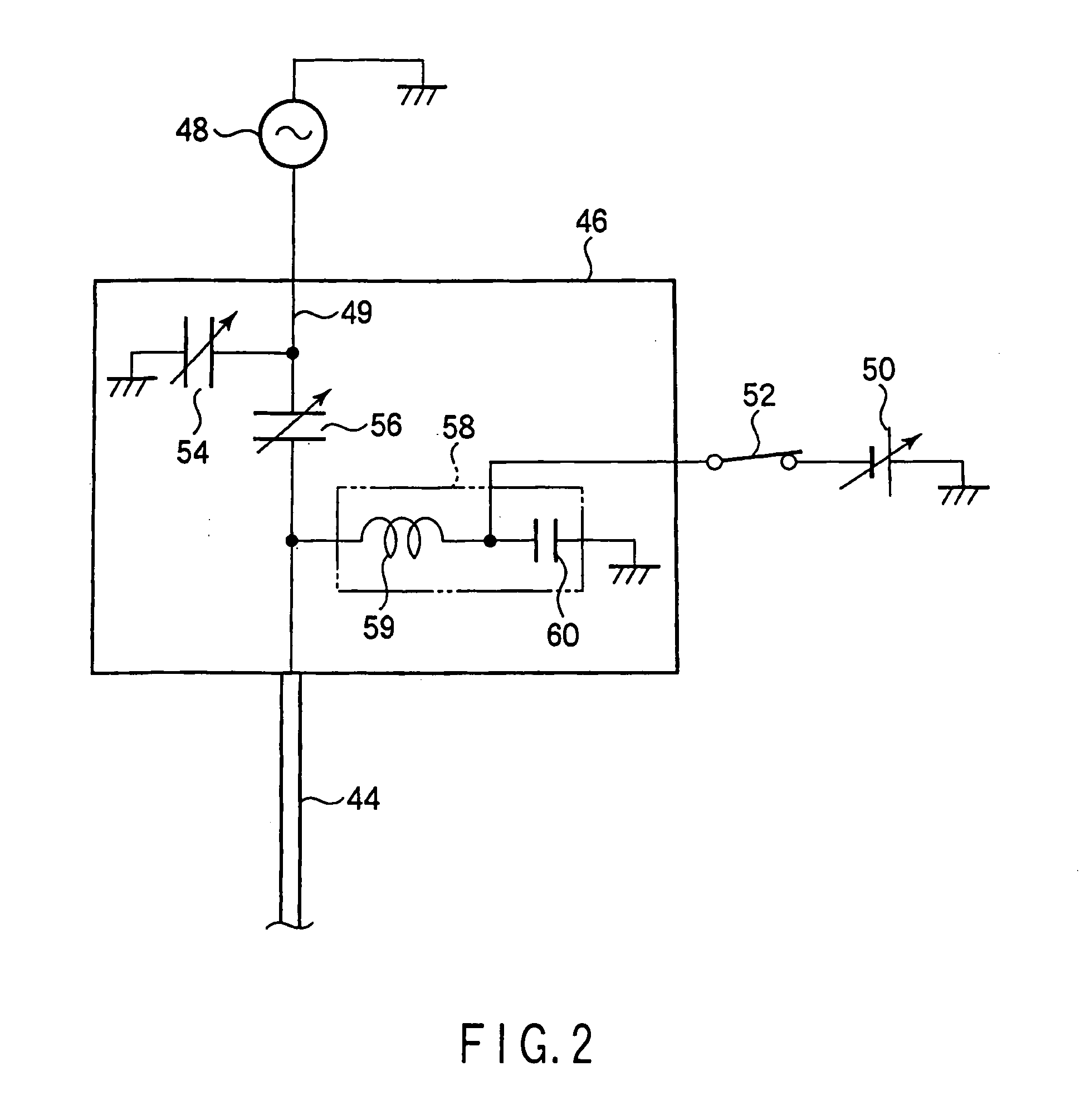

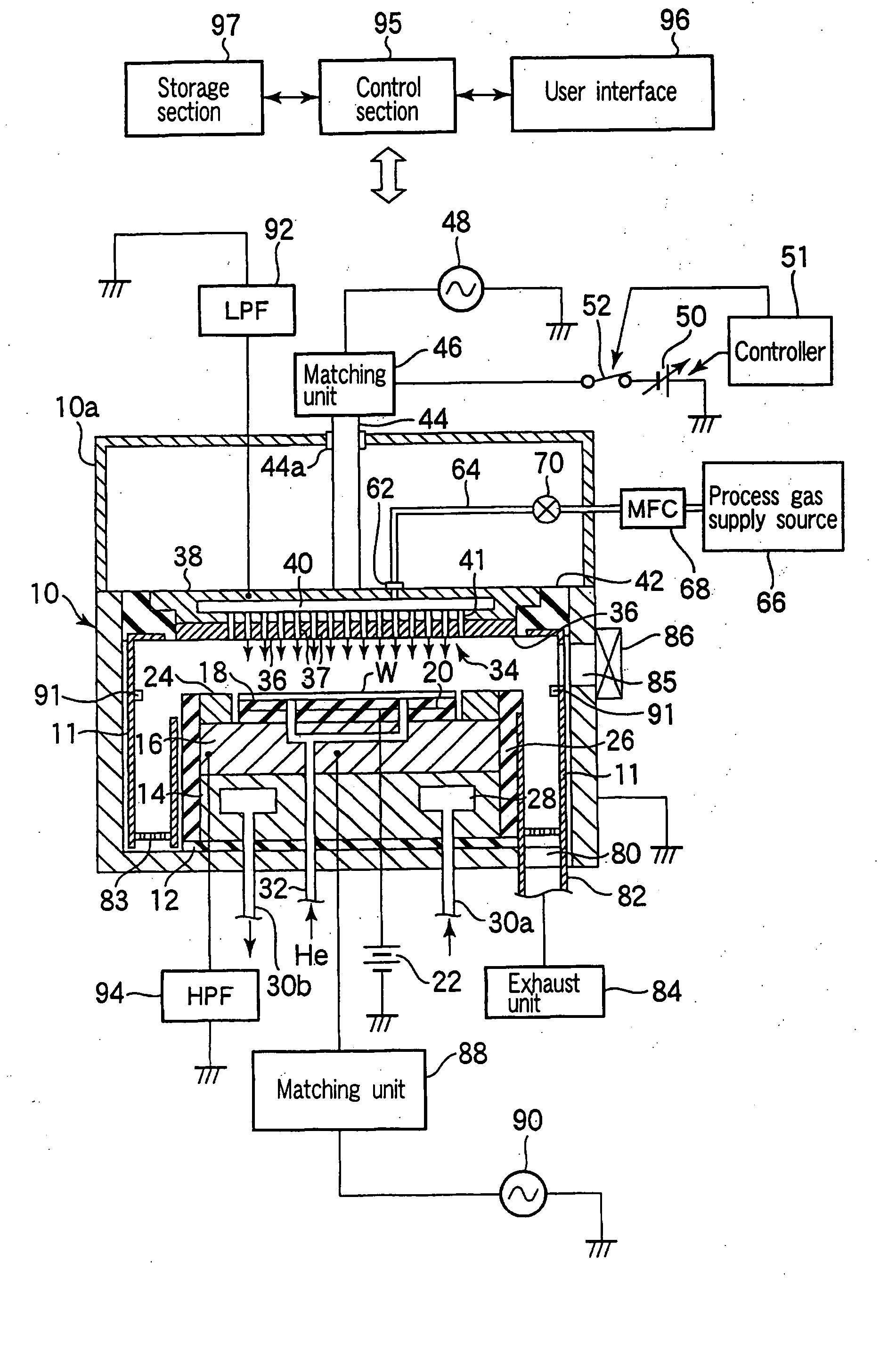

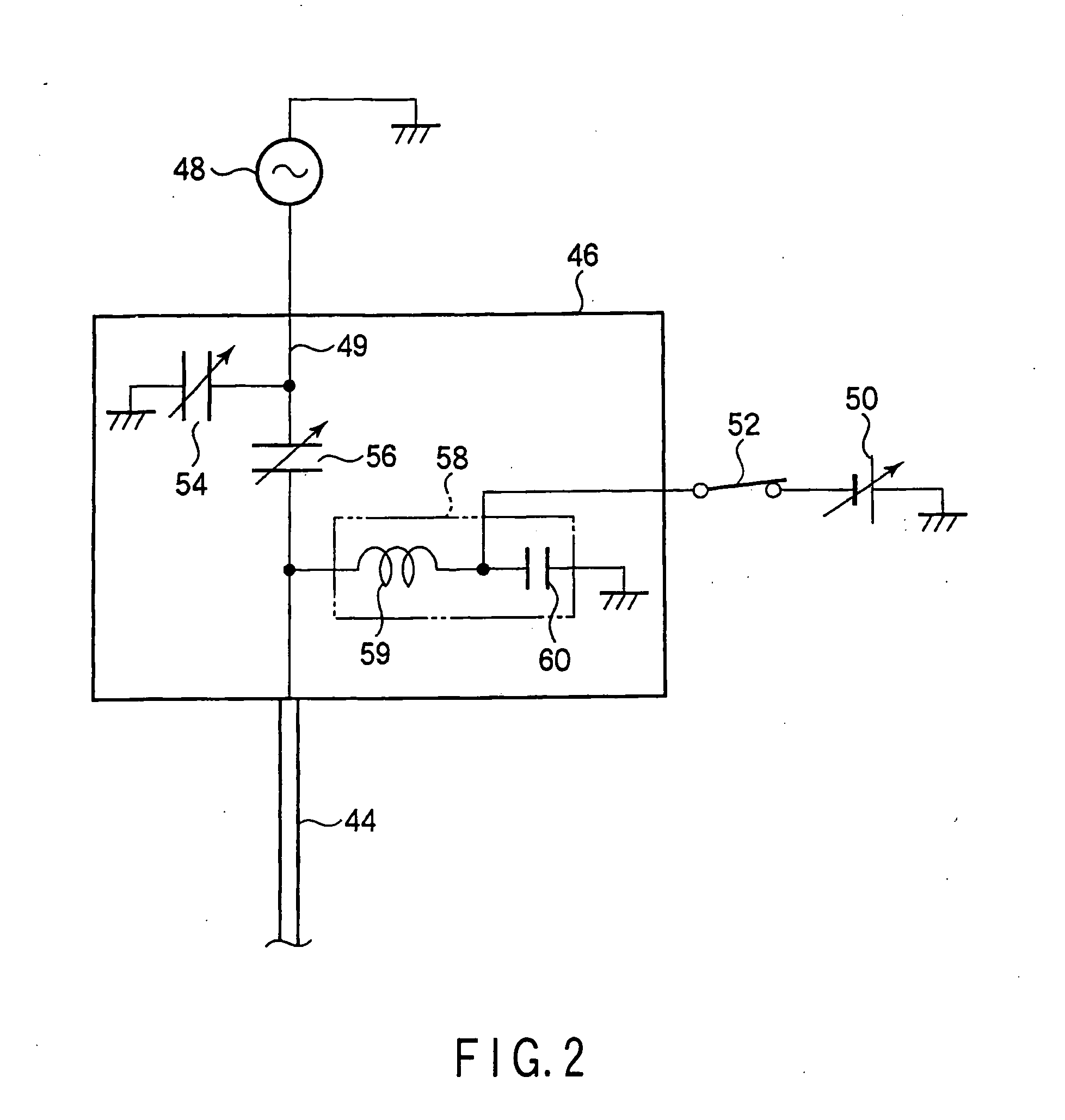

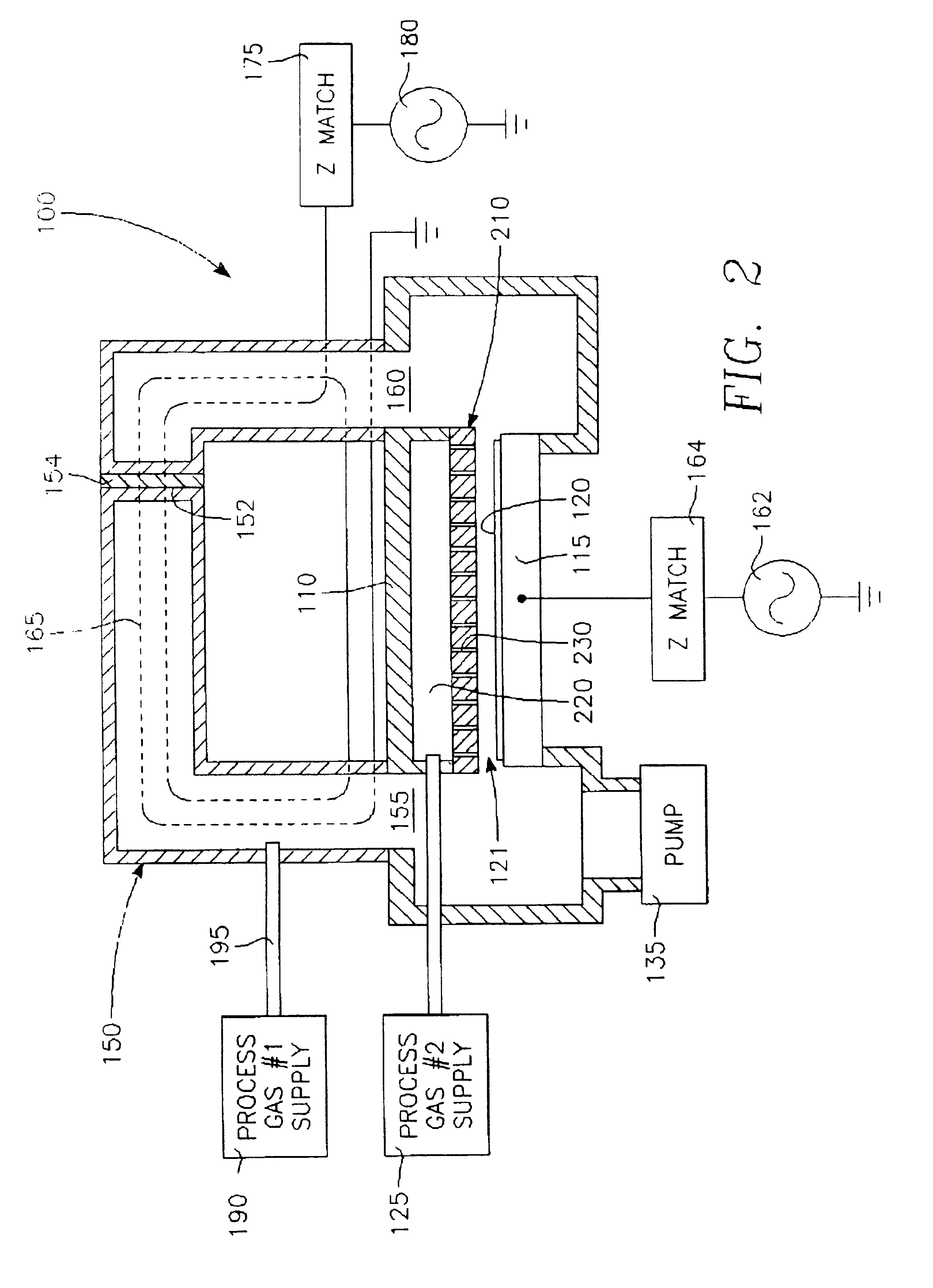

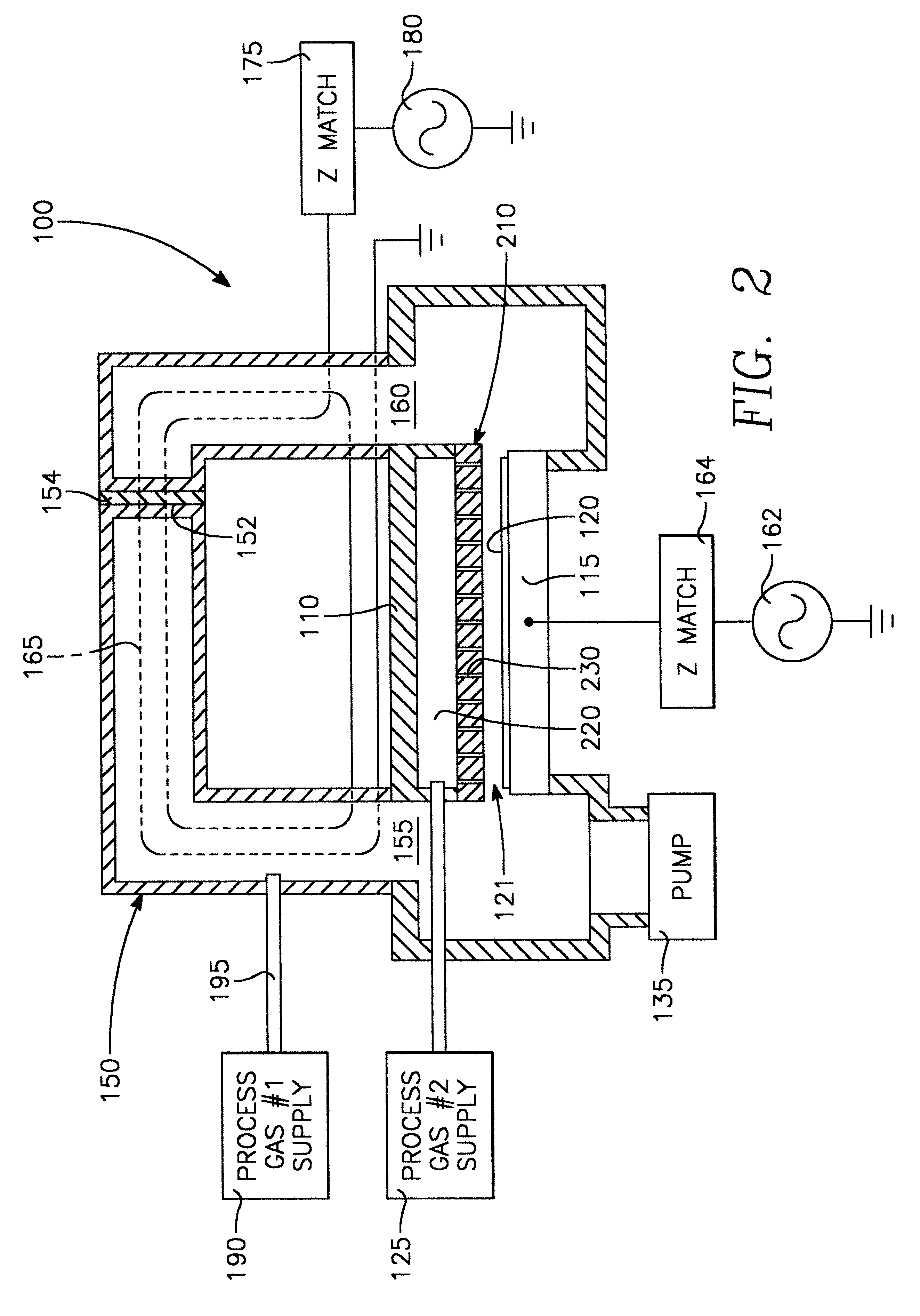

Plasma processing apparatus and method

ActiveUS20060037701A1High selectivity etchHigh rateElectric discharge tubesSemiconductor/solid-state device manufacturingPlasma processingPower flow

An apparatus includes an upper electrode and a lower electrode for supporting a wafer disposed opposite each other within a process chamber. A first RF power supply configured to apply a first RF power having a relatively higher frequency is connected to the upper electrode. A second RF power supply configured to apply a second RF power having a relatively lower frequency is connected to the lower electrode. A variable DC power supply is connected to the upper electrode. A process gas is supplied into the process chamber while any one of application voltage, application current, and application power from the variable DC power supply to the upper electrode is controlled, to generate plasma of the process gas so as to perform plasma etching.

Owner:TOKYO ELECTRON LTD

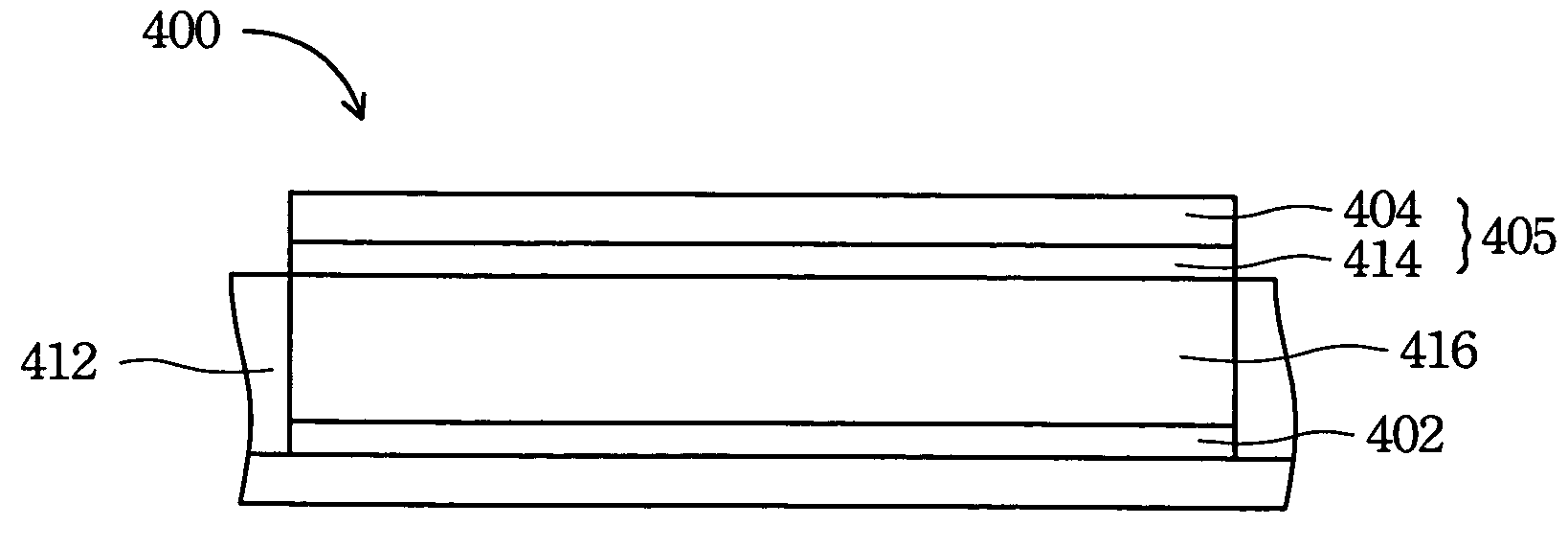

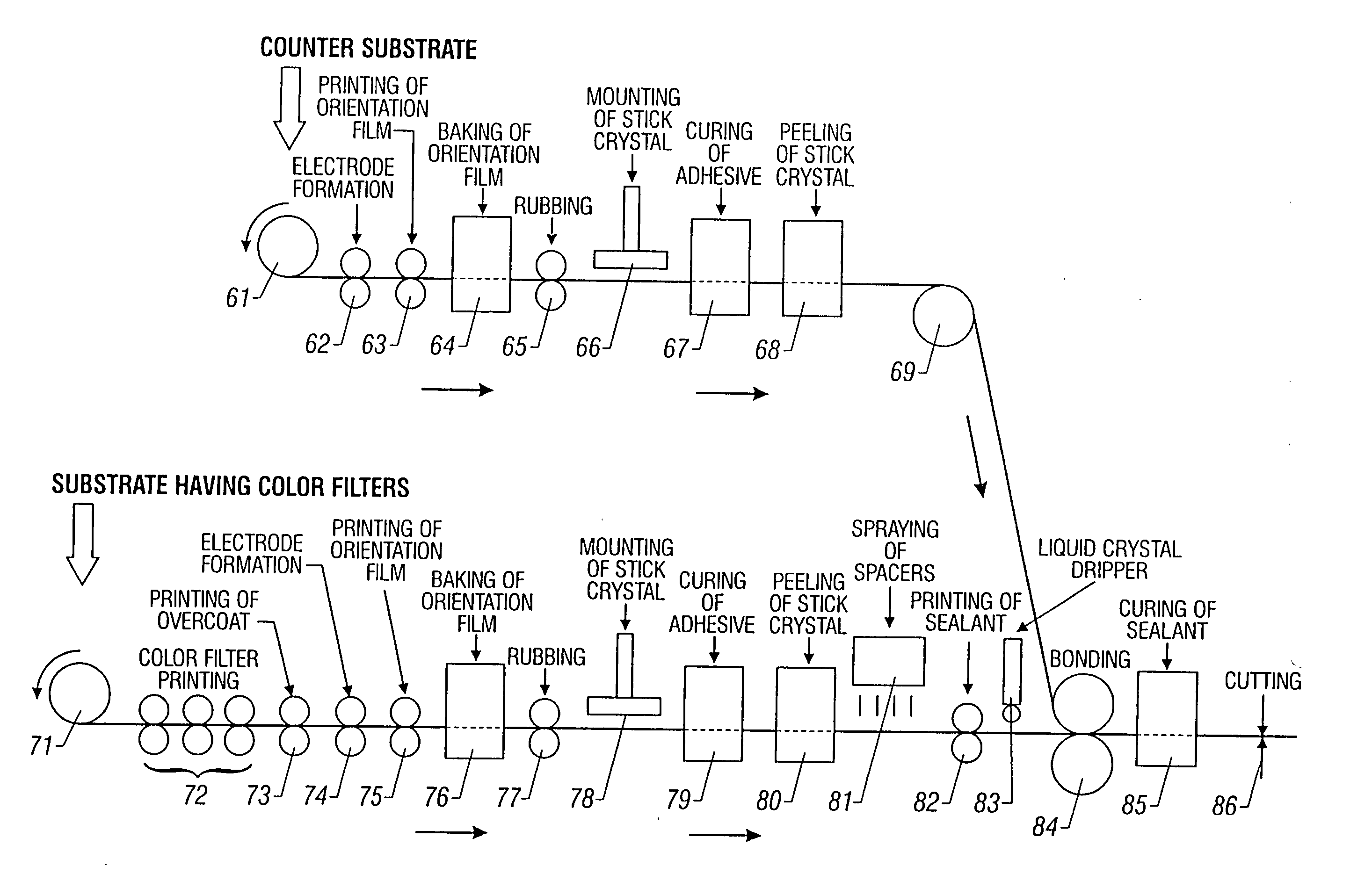

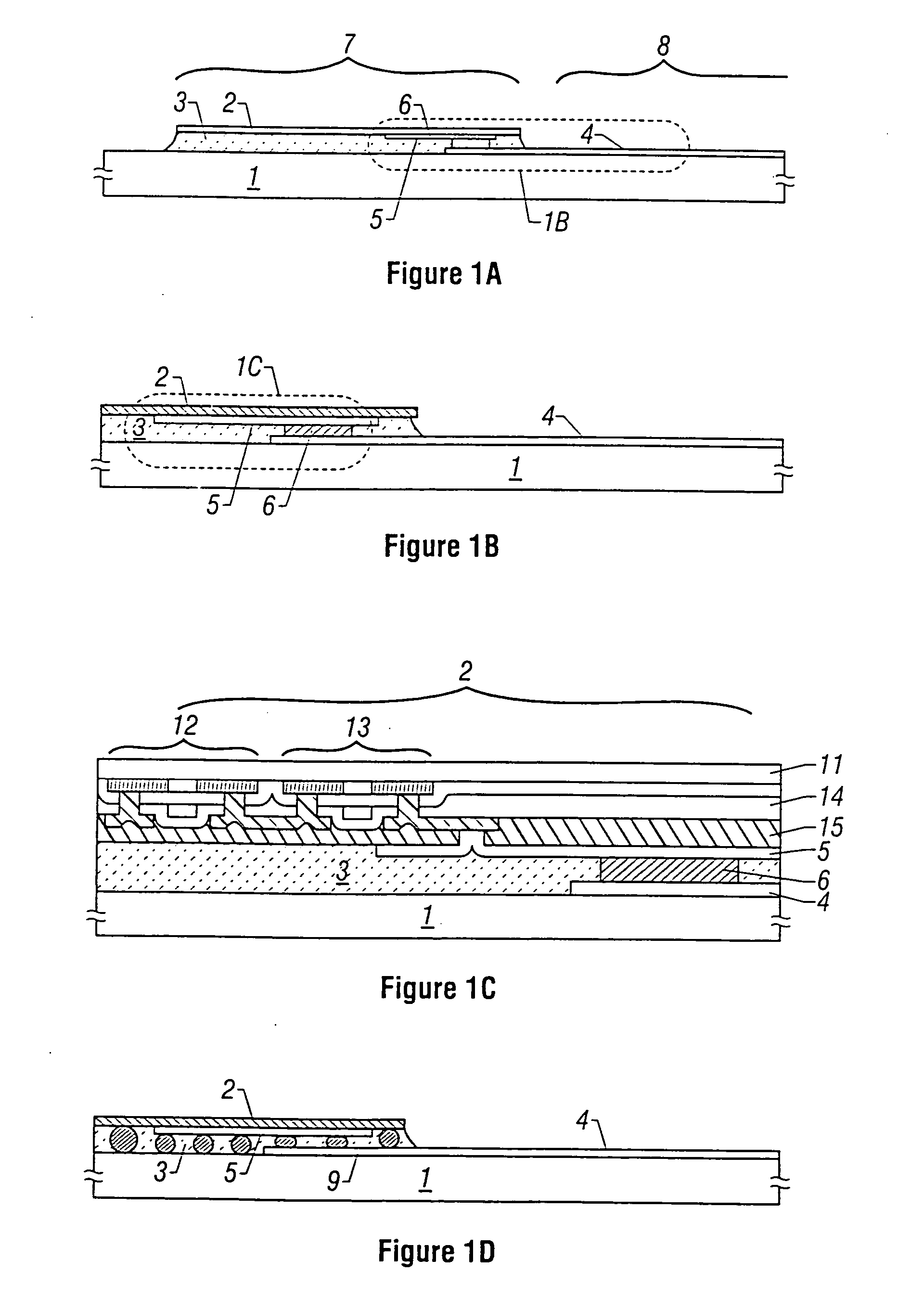

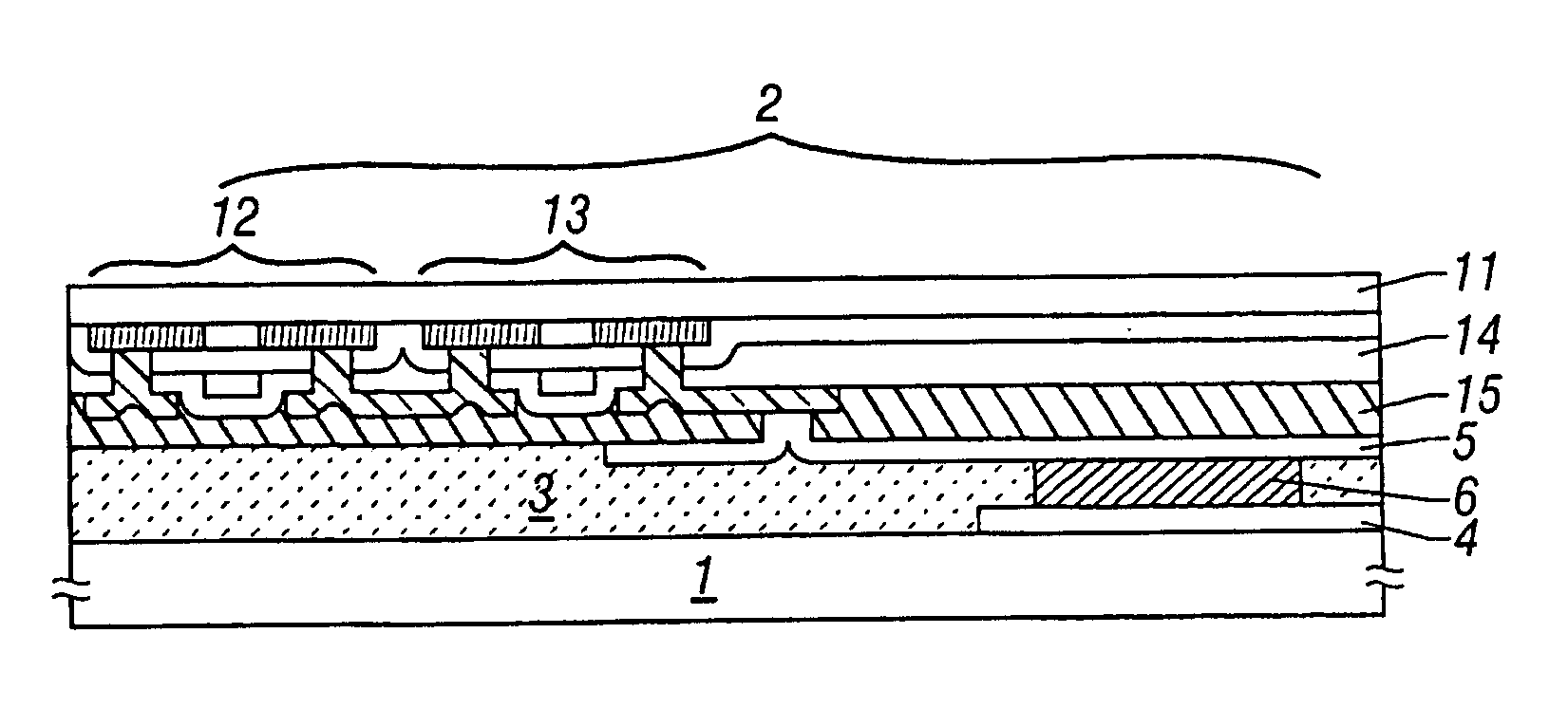

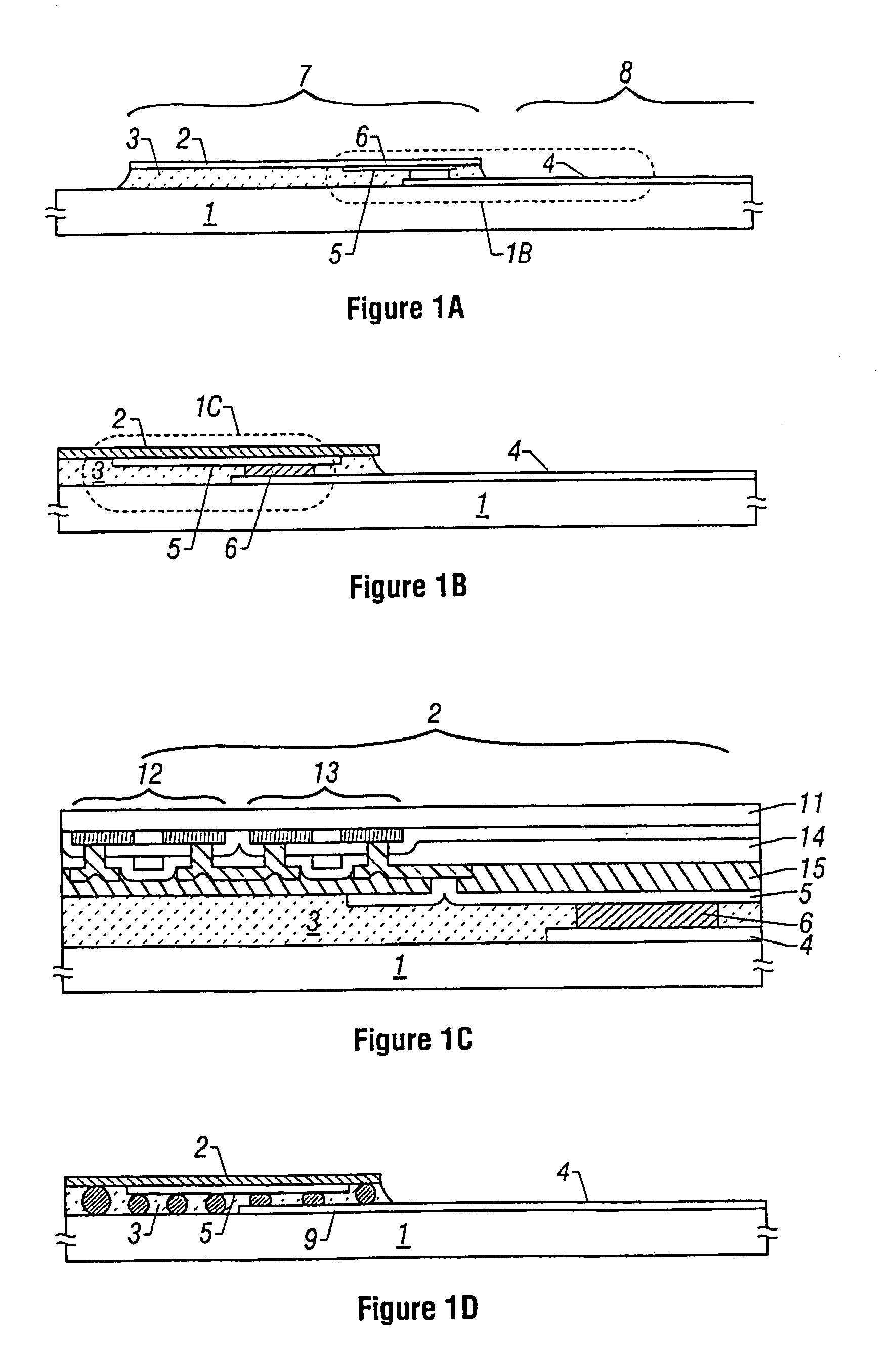

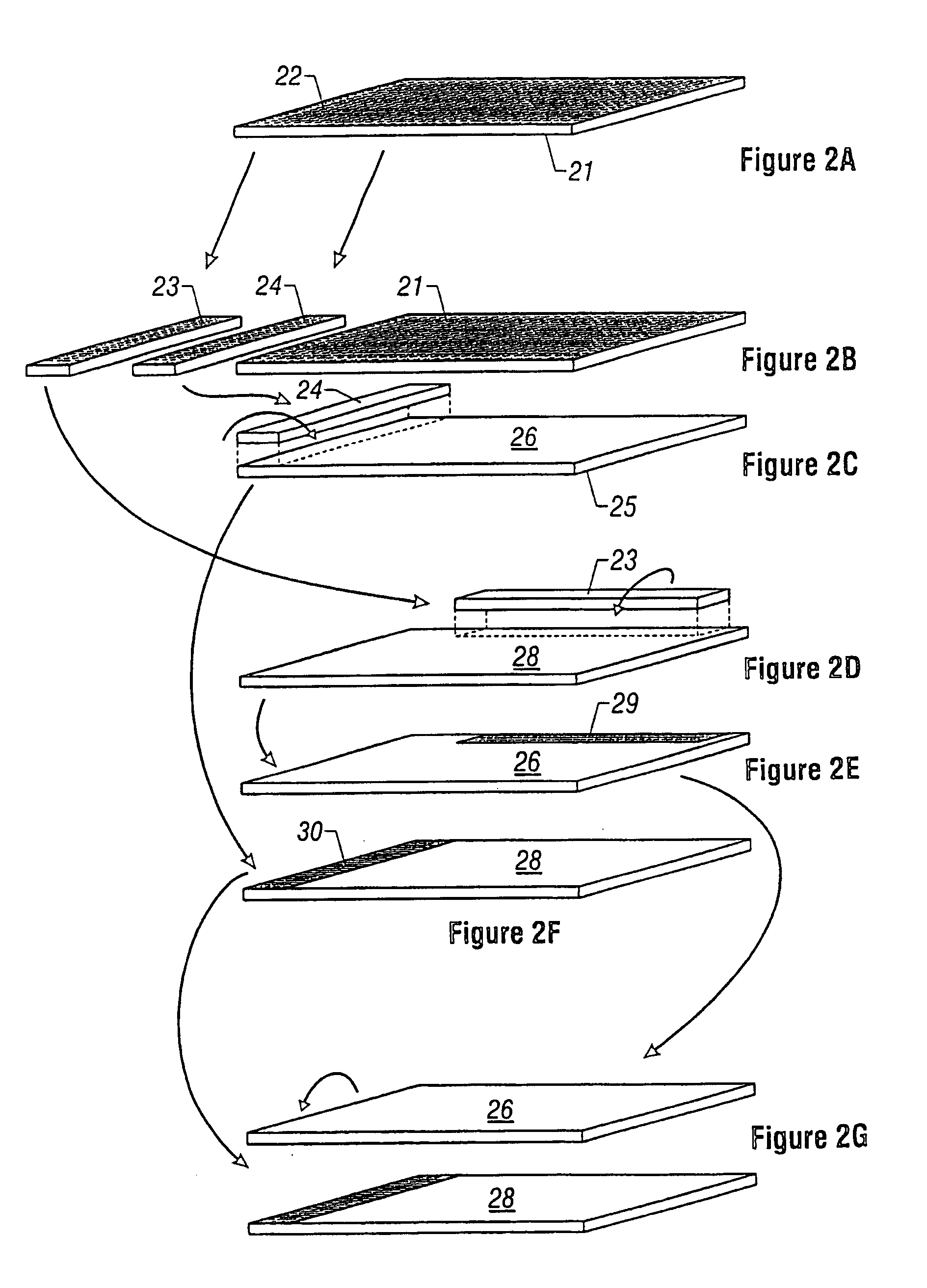

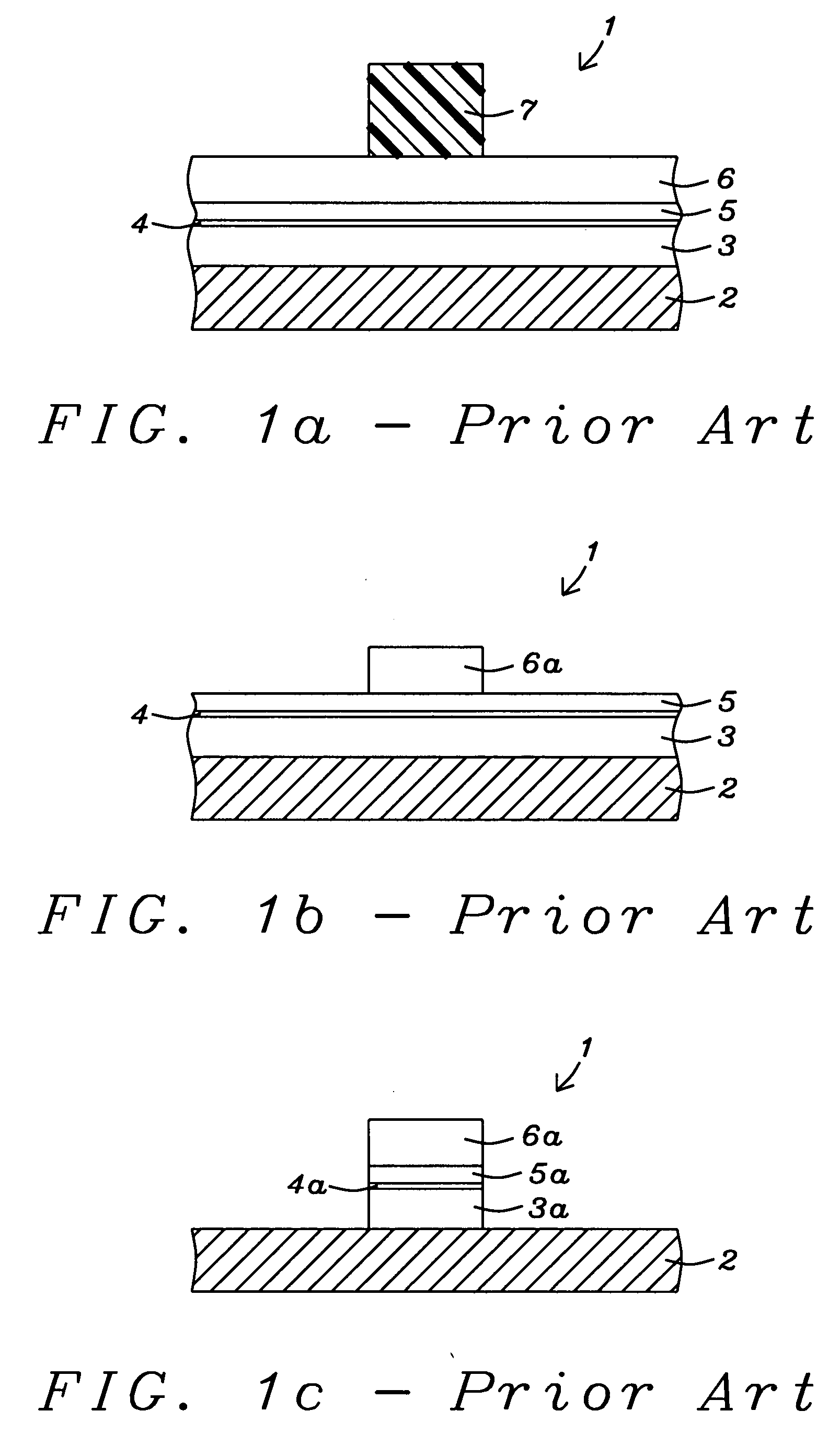

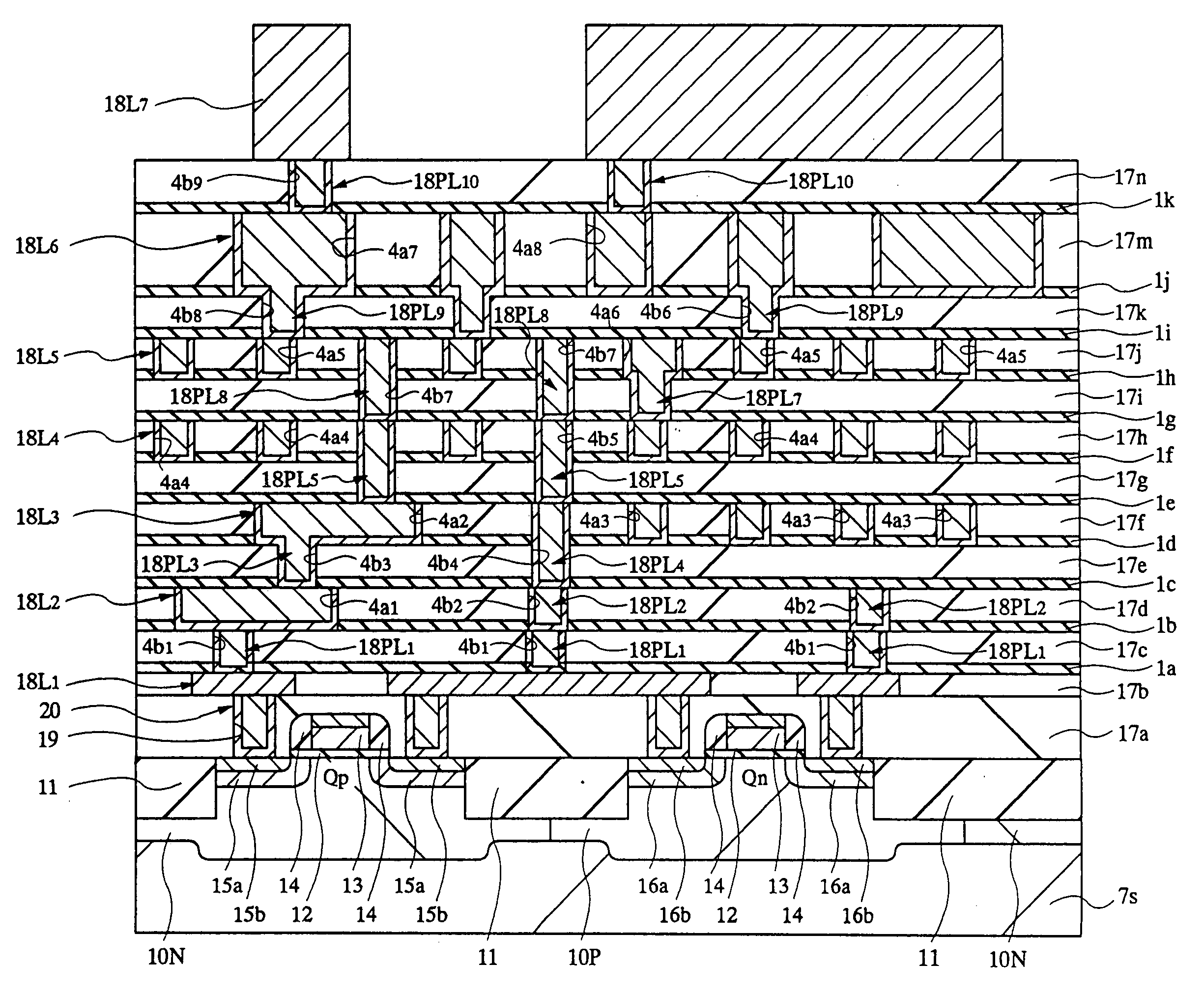

Display device and method of fabricating the same

InactiveUS20050070038A1Reduce weightAvoid stress concentrationSolid-state devicesSemiconductor/solid-state device manufacturingDriver circuitLiquid-crystal display

A method of fabricating a driver circuit for use with a passive matrix or active matrix electrooptical display device such as a liquid crystal display. The driver circuit occupies less space than heretofore. A circuit (stick crystal) having a length substantially equal to the length of one side of the matrix of the display device is used as the driver circuit. The circuit is bonded to one substrate of the display device, and then the terminals of the circuit are connected with the terminals of the display device. Subsequently, the substrate of the driver circuit is removed. This makes the configuration of the circuit much simpler than the configuration of the circuit heretofore required by the TAB method or COG method, because conducting lines are not laid in a complex manner. The driver circuit can be formed on a large-area substrate such as a glass substrate. The display device can be formed on a lightweight material having a high shock resistance such as a plastic substrate. Hence, a display device having excellent portability can be obtained.

Owner:YAMAZAKI SHUNPEI +3

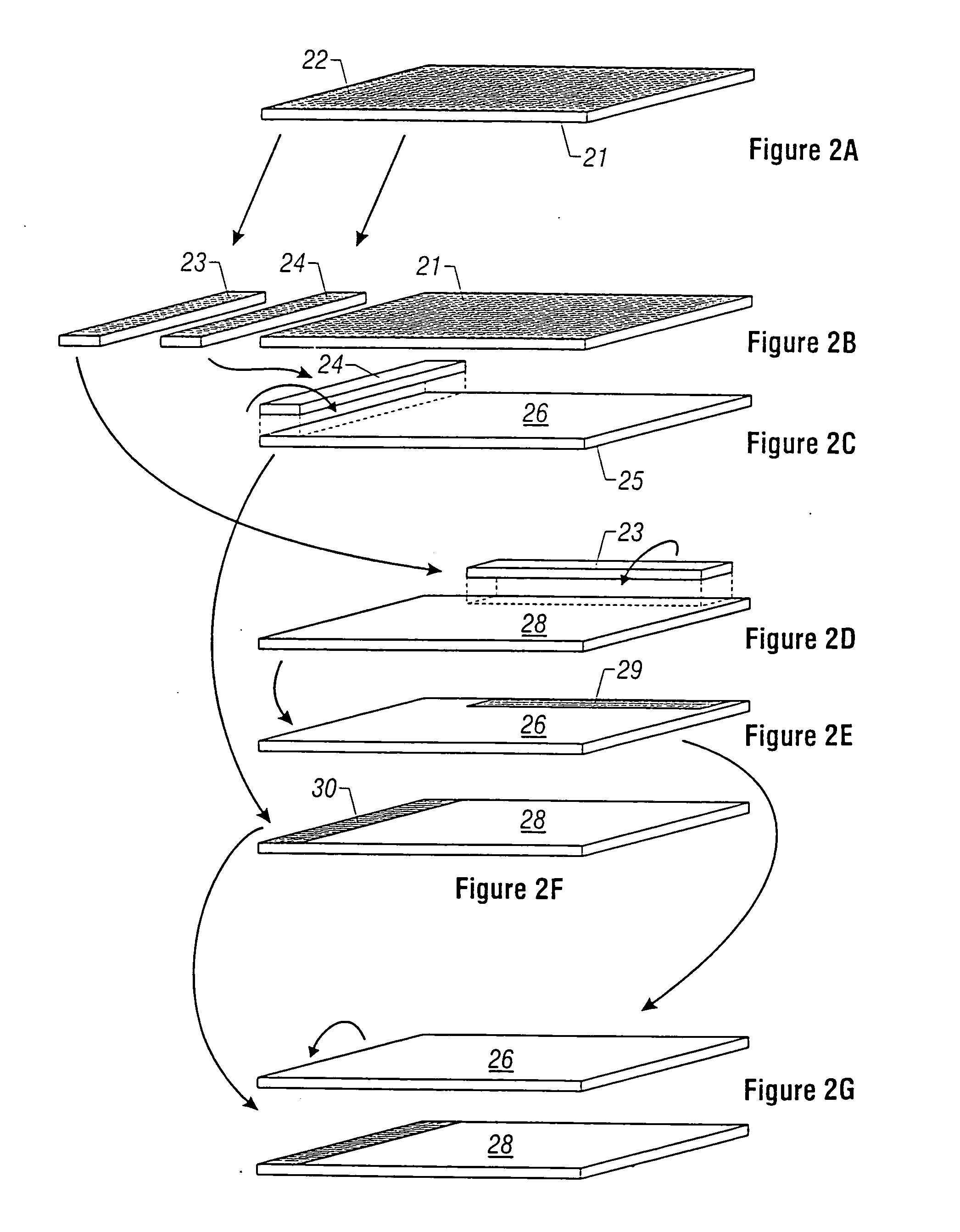

Method of manufacturing a display device having a driver circuit attached to a display substrate

InactiveUS7050138B1Reduce weightAvoid stress concentrationSolid-state devicesSemiconductor/solid-state device manufacturingDriver circuitLiquid-crystal display

Owner:SEMICON ENERGY LAB CO LTD

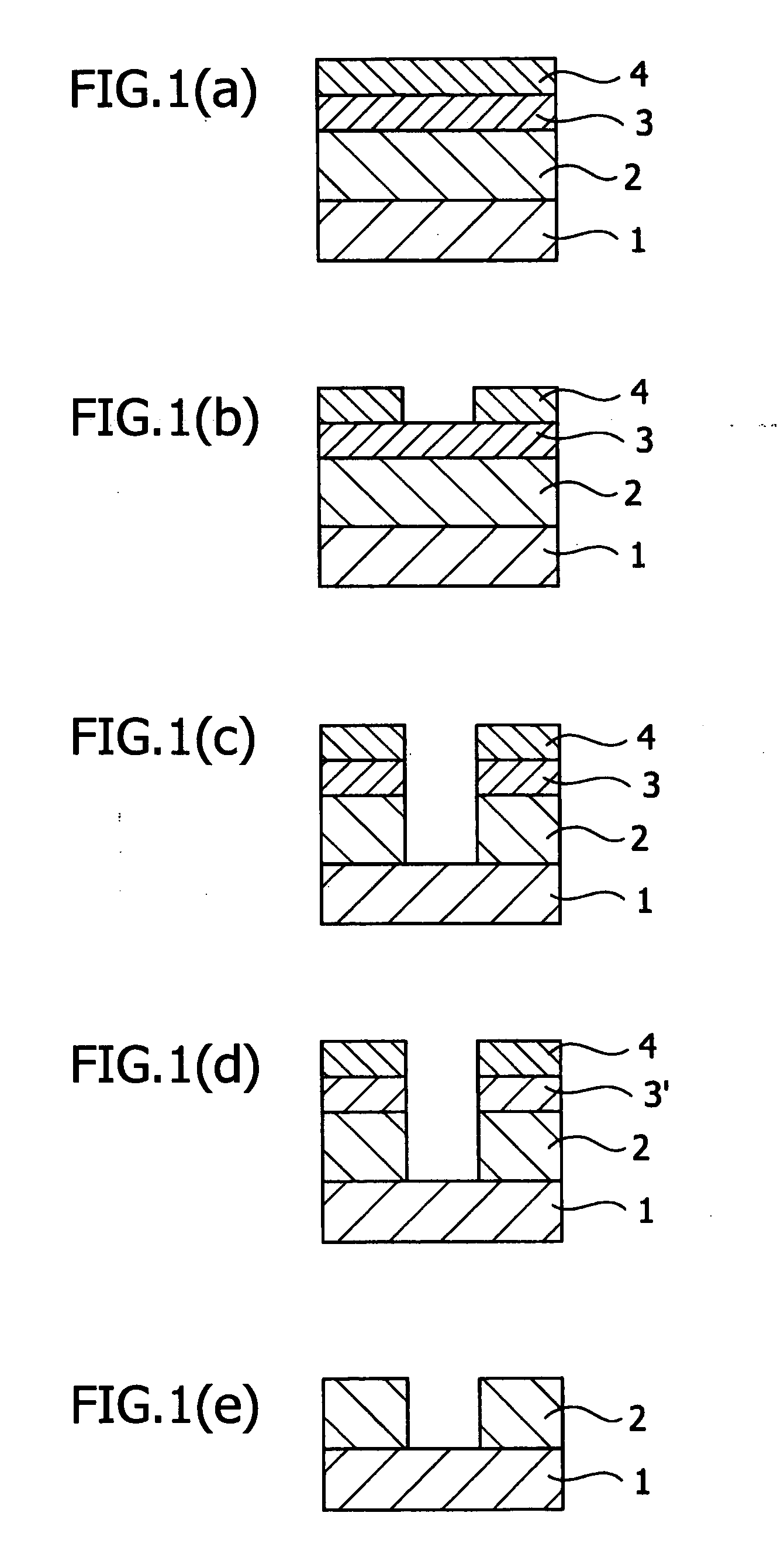

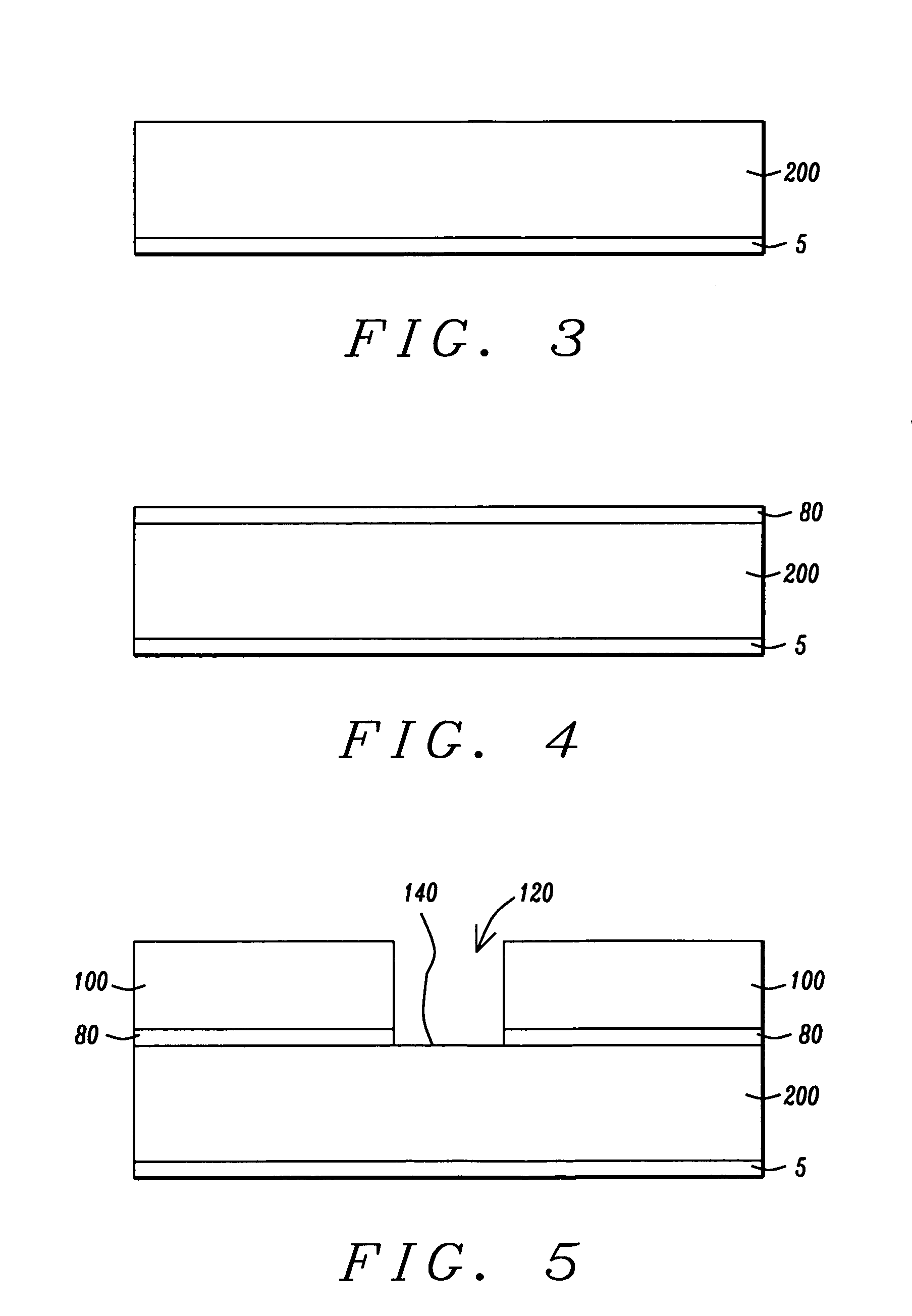

Semiconductor device manufacturing method

InactiveUS20110039407A1Appropriately and efficiently manufacturingAppropriatelySemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerDevice material

A semiconductor device manufacturing method, the method including: forming an insulation layer having a protruding portion, the insulation layer having a surface and a rising surface that protrudes upward from the surface, on a semiconductor substrate; forming a conductive layer to cover the insulation layer having the protruding portion; and removing a predetermined region of the conductive layer by patterning the predetermined region according to an etching process using microwave plasma, which uses a microwave as a plasma source, while applying bias power of 70 mW / cm2 or above on the semiconductor substrate, under a high pressure condition of 85 mTorr or above.

Owner:TOKYO ELECTRON LTD

Plasma processing apparatus and method

ActiveUS20060066247A1Improved resistance characteristicsIncrease chanceElectric discharge tubesSemiconductor/solid-state device manufacturingDc voltagePlasma processing

A plasma etching apparatus includes an upper electrode and a lower electrode, between which plasma of a process gas is generated to perform plasma etching on a wafer W. The apparatus further comprises a variable DC power supply to apply a DC voltage to the upper electrode, so as to cause the absolute value of a self-bias voltage on the surface thereof to be large enough to obtain a suitable sputtering effect on the surface, and to increase the plasma sheath length on the upper electrode side to generate predetermined pressed plasma.

Owner:TOKYO ELECTRON LTD

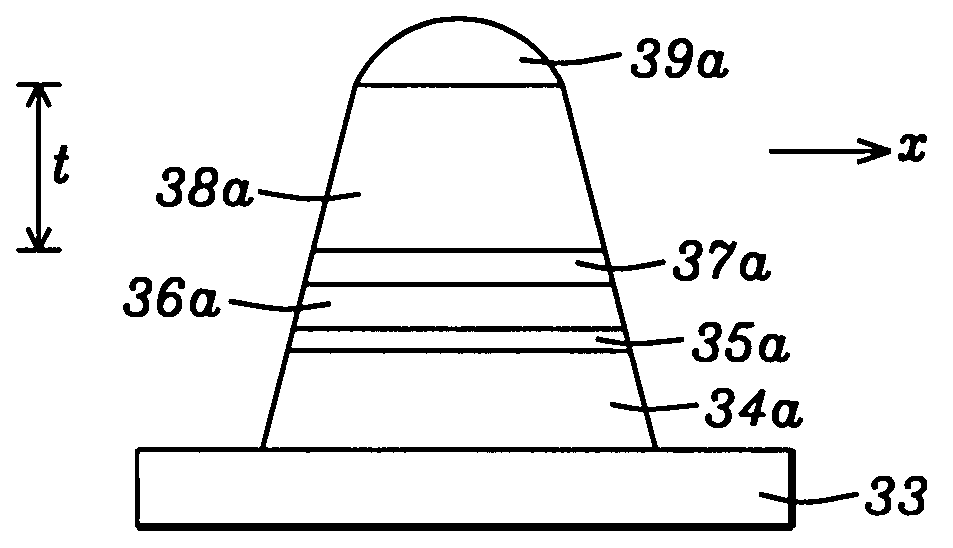

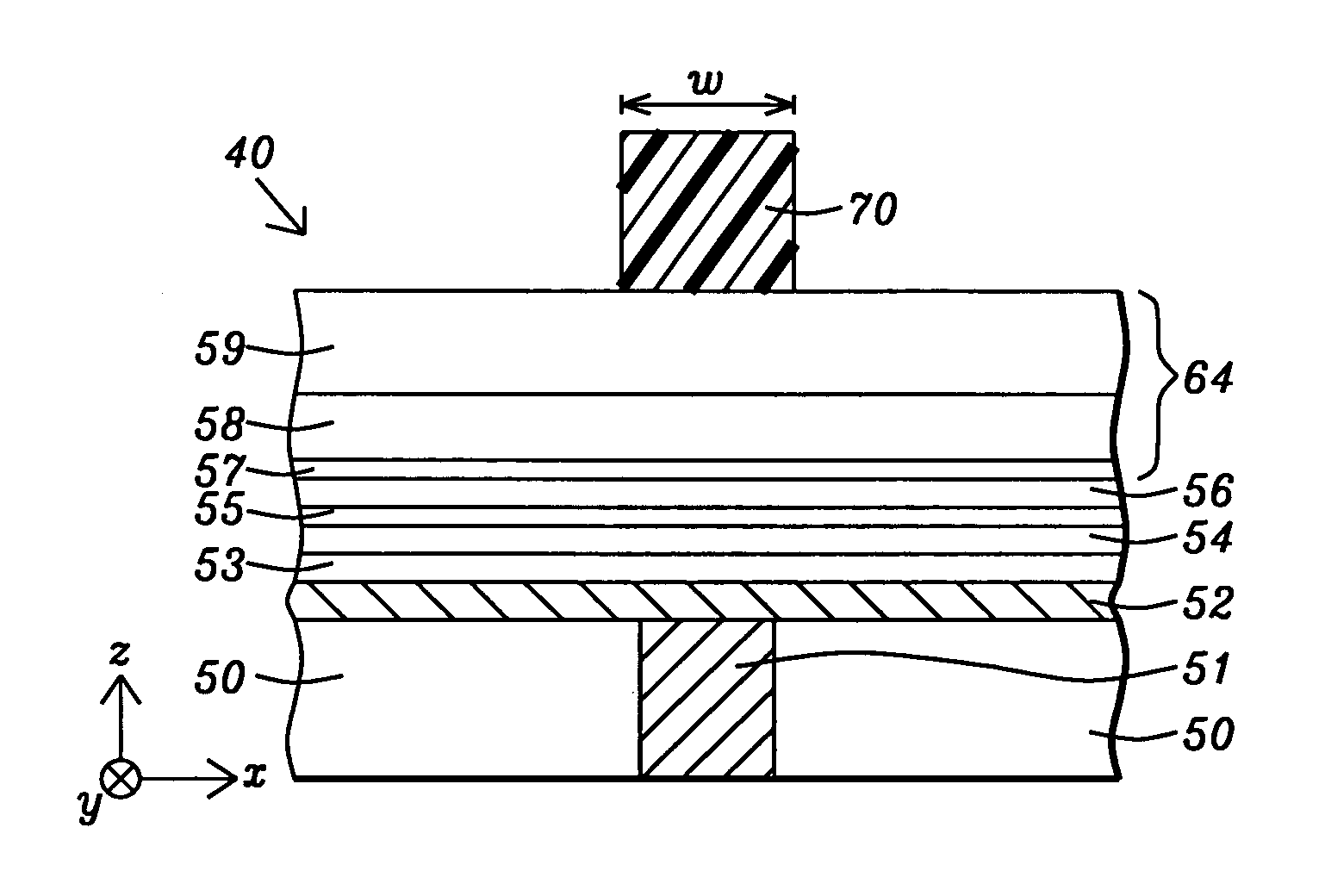

Semiconductive metal oxide thin film ferroelectric memory transistor

InactiveUS20060038242A1Simplify the manufacturing processHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate dielectric

The present invention discloses a novel transistor structure employing semiconductive metal oxide as the transistor conductive channel. By replacing the silicon conductive channel with a semiconductive metal oxide channel, the transistors can achieve simpler fabrication process and could realize 3D structure to increase circuit density. The disclosed semiconductive metal oxide transistor can have great potential in ferroelectric non volatile memory device with the further advantages of good interfacial properties with the ferroelectric materials, possible lattice matching with the ferroelectric layer, reducing or eliminating the oxygen diffusion problem to improve the reliability of the ferroelectric memory transistor. The semiconductive metal oxide film is preferably a metal oxide exhibiting semiconducting properties at the transistor operating conditions, for example, In2O3 or RuO2. The present invention ferroelectric transistor can be a metal-ferroelectric-semiconductive metal oxide FET having a gate stack of a top metal electrode disposed on a ferroelectric layer disposed on a semiconductive metal oxide channel on a substrate. Using additional layer of bottom electrode and gate dielectric, the present invention ferroelectric transistor can also be a metal-ferroelectric-metal (optional)-gate dielectric (optional)-semiconductive metal oxide FET.

Owner:SHARP KK

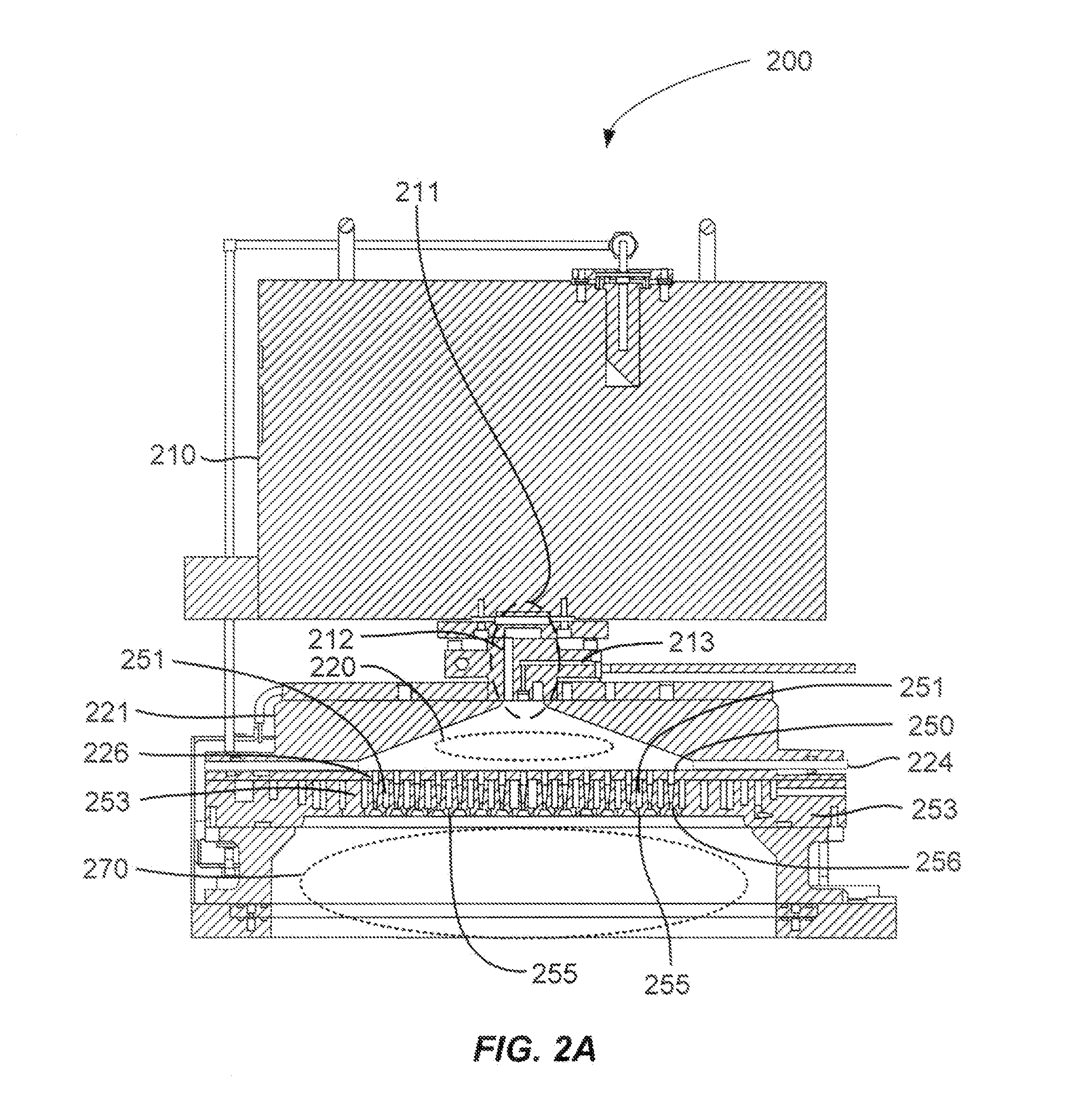

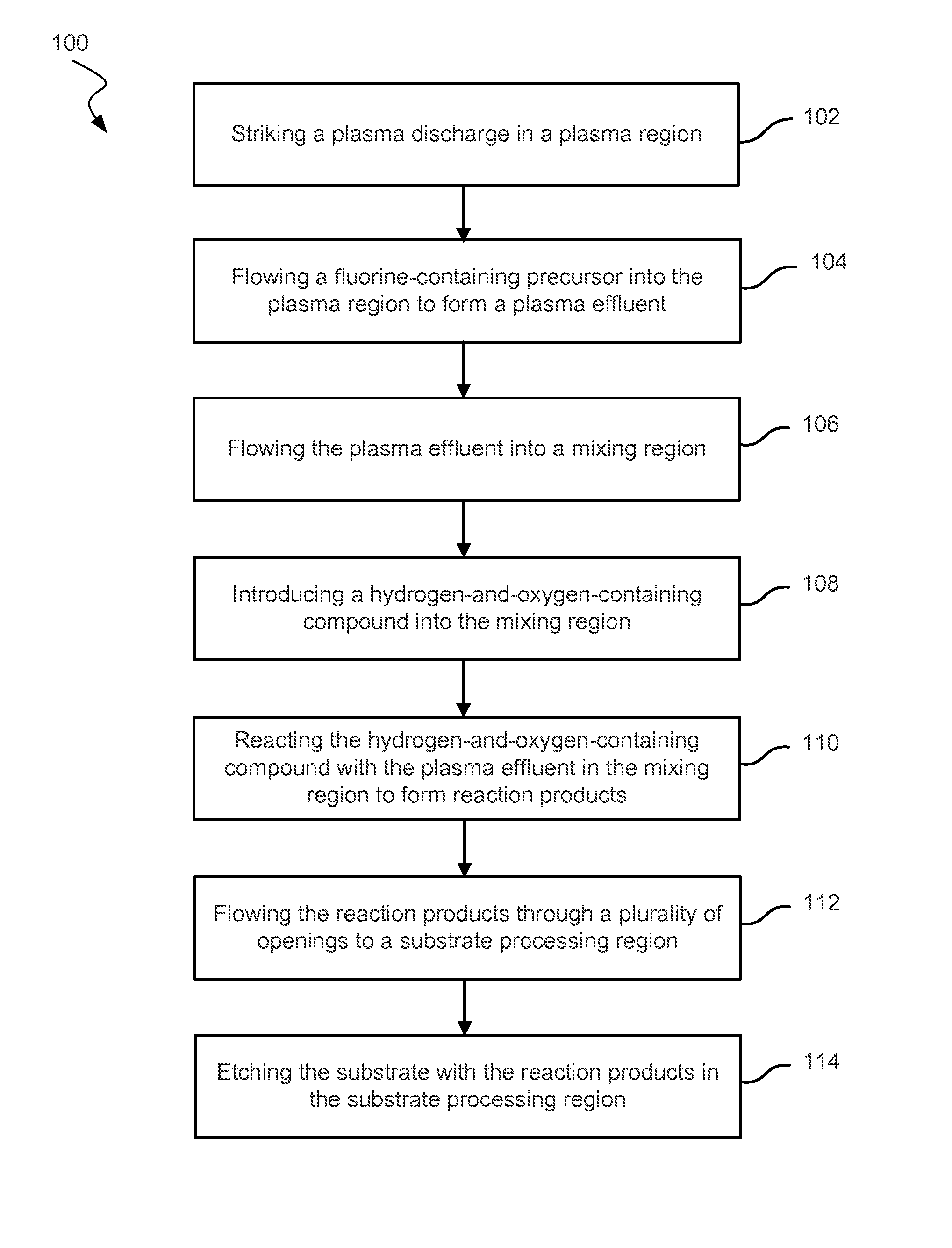

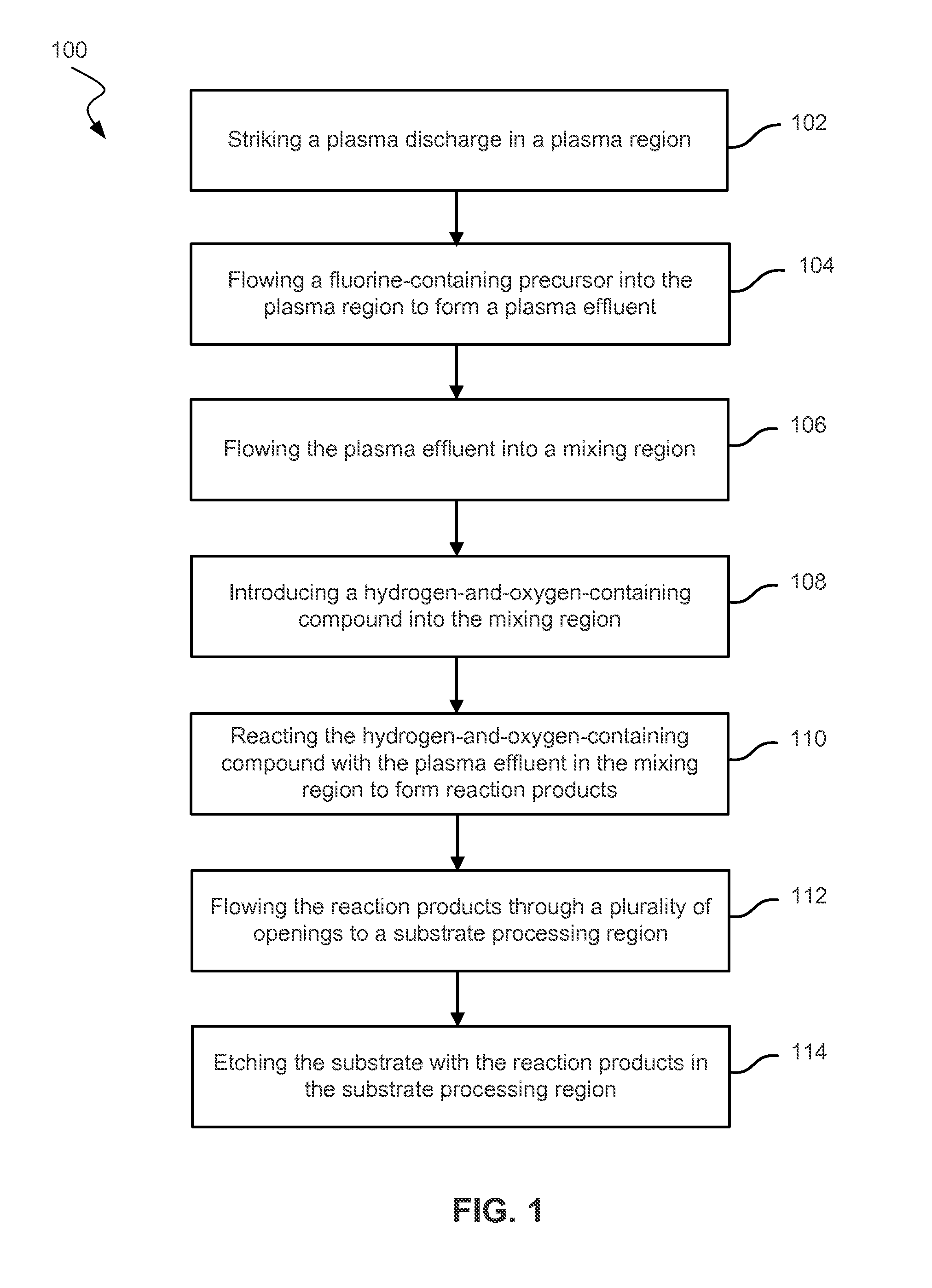

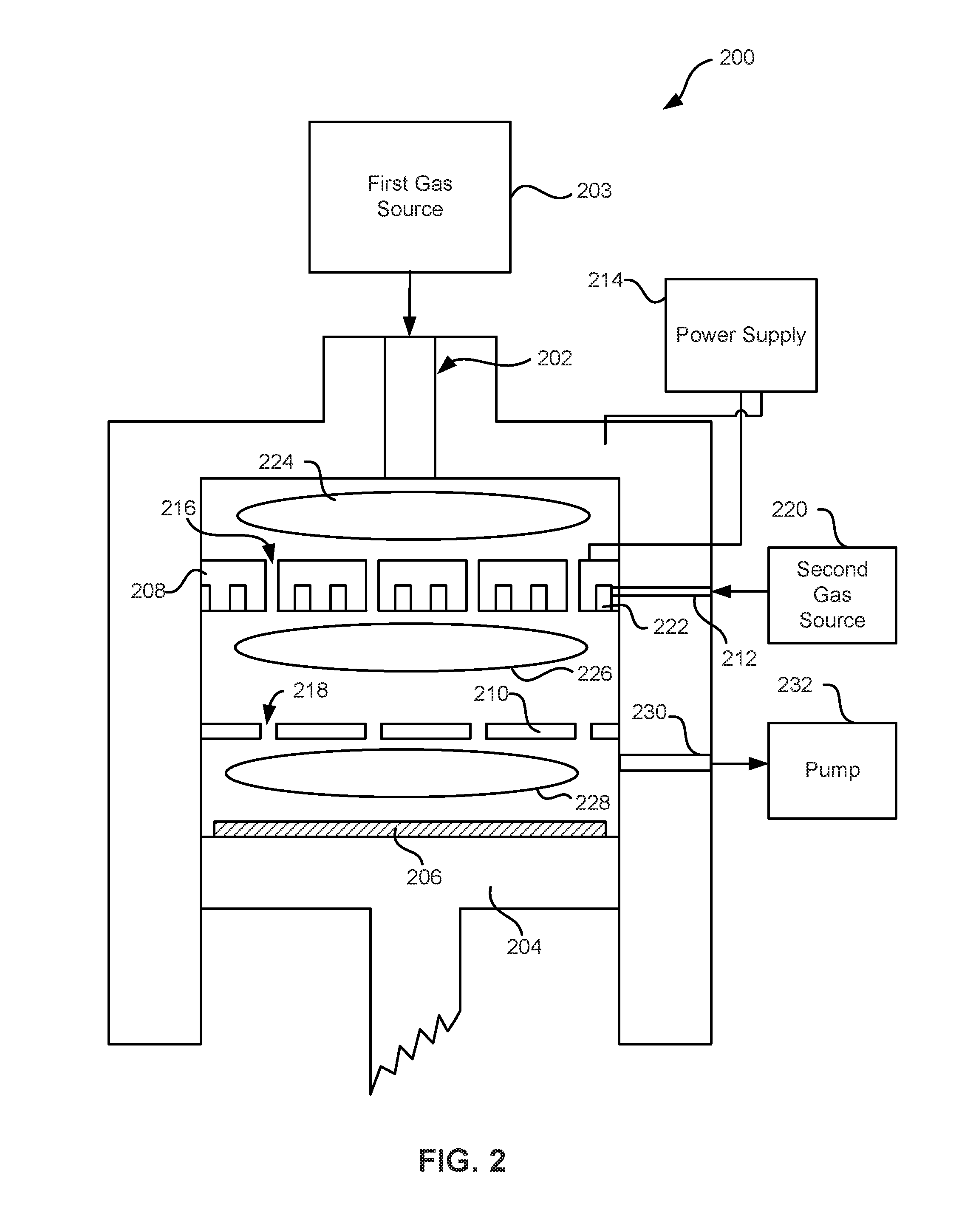

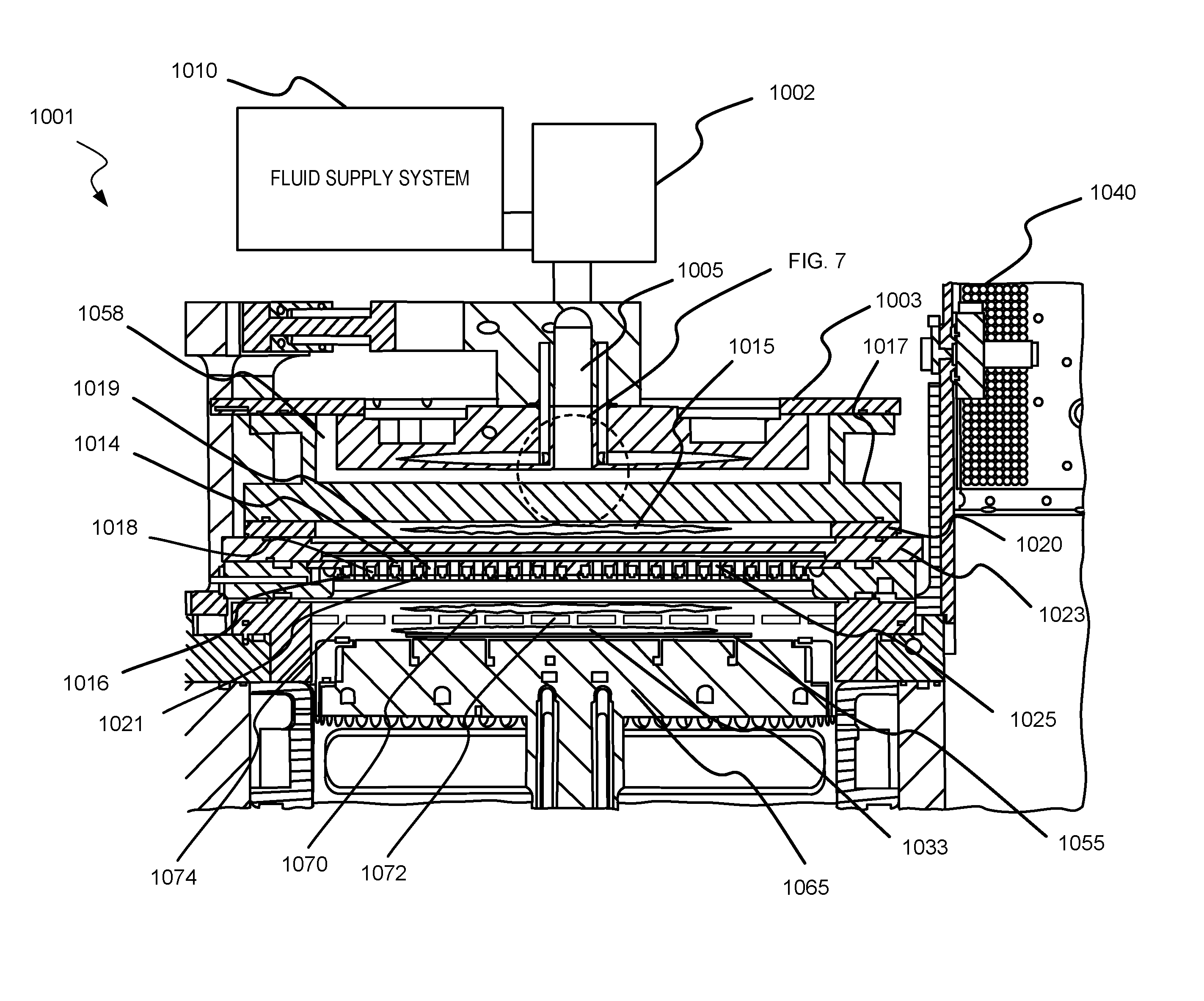

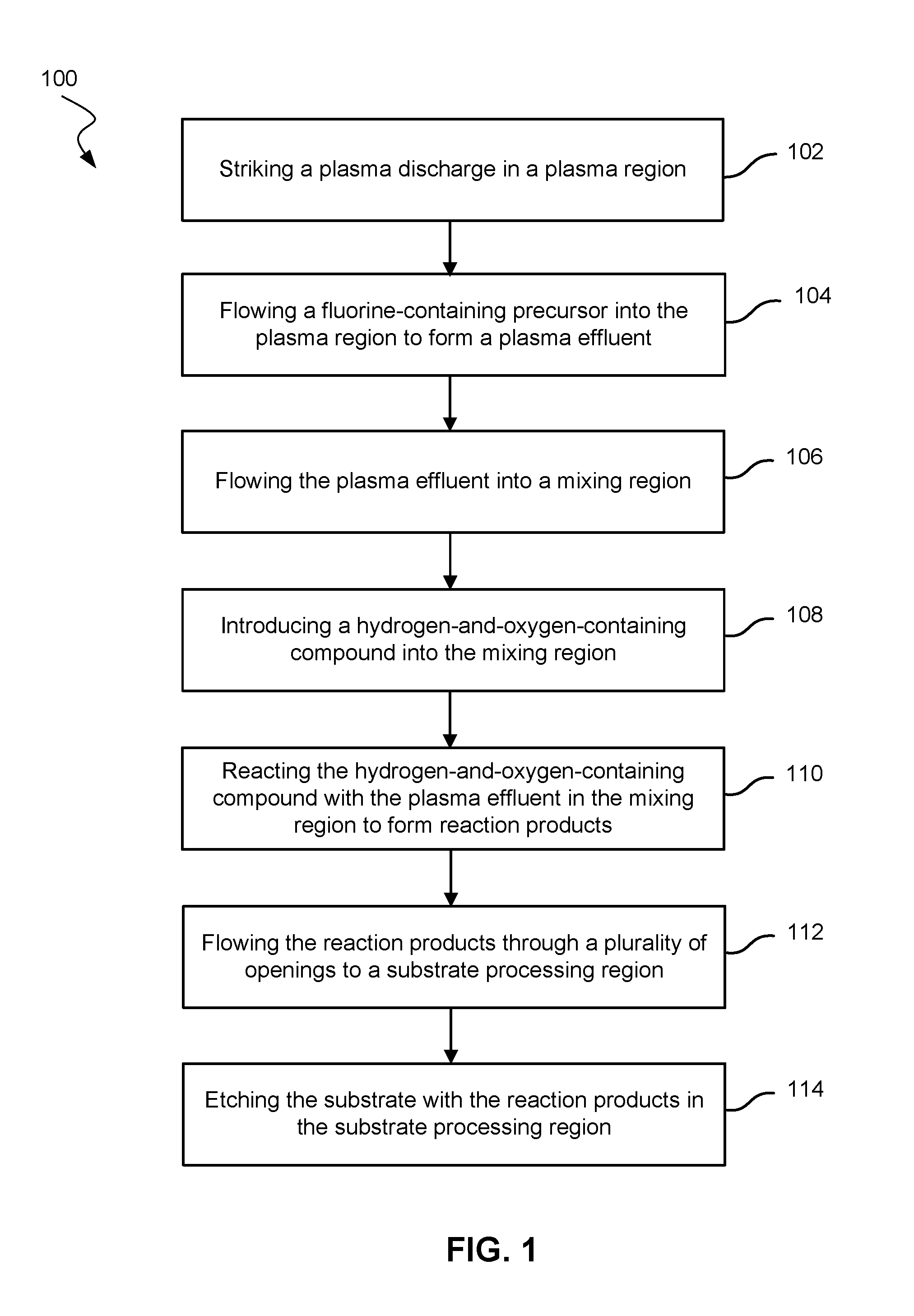

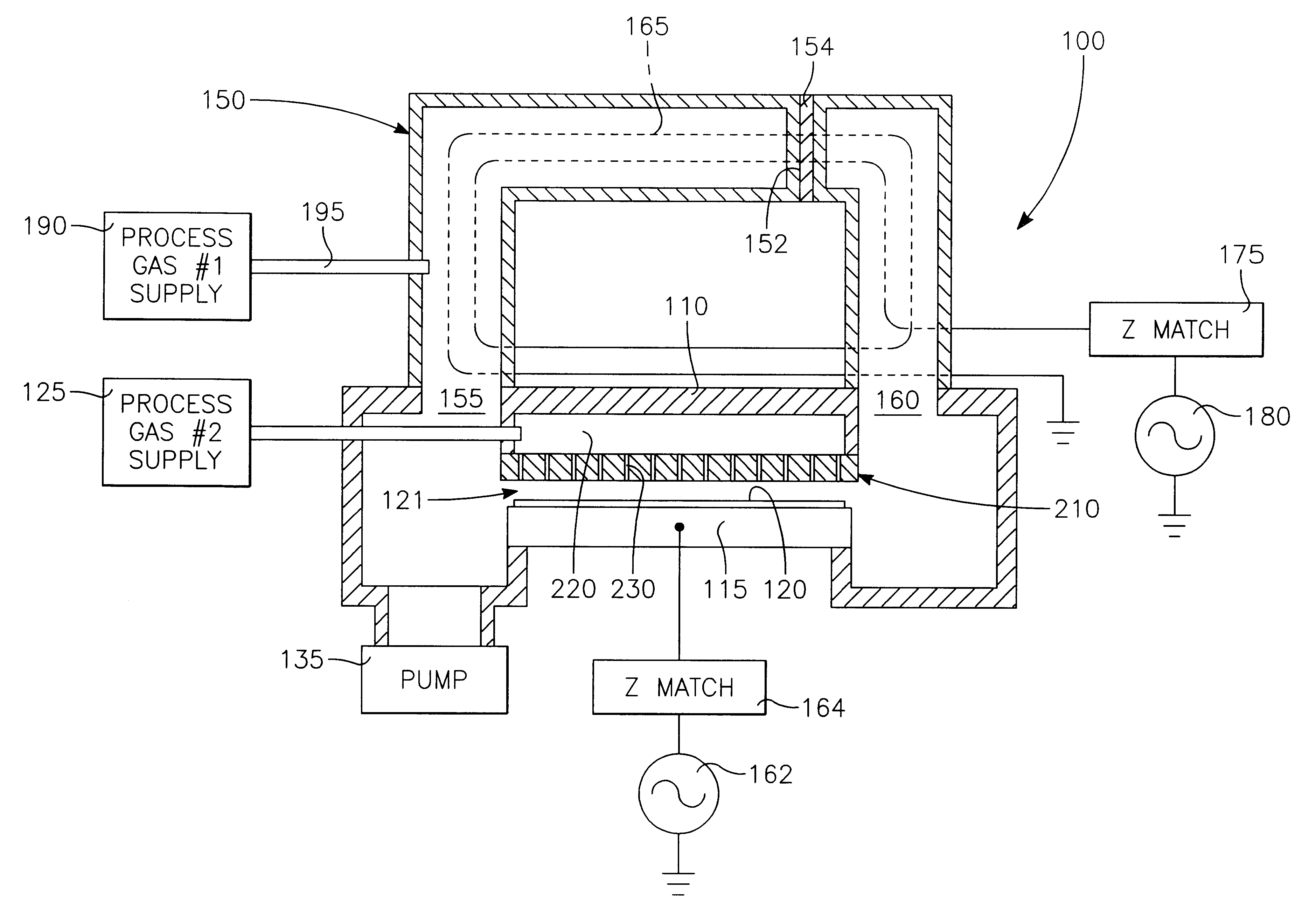

Oxide etch selectivity systems and methods

ActiveUS9349605B1Improve etch selectivityEnhance and suppress reactionElectric discharge tubesSemiconductor/solid-state device manufacturingHydrogenProcess region

Embodiments of the present technology may include a method of etching a substrate. The method may include striking a plasma discharge in a plasma region. The method may also include flowing a fluorine-containing precursor into the plasma region to form a plasma effluent. The plasma effluent may flow into a mixing region. The method may further include introducing a hydrogen-and-oxygen-containing compound into the mixing region without first passing the hydrogen-and-oxygen-containing compound into the plasma region. Additionally, the method may include reacting the hydrogen-and-oxygen-containing compound with the plasma effluent in the mixing region to form reaction products. The reaction products may flow through a plurality of openings in a partition to a substrate processing region. The method may also include etching the substrate with the reaction products in the substrate processing region.

Owner:APPLIED MATERIALS INC

Oxide etch selectivity systems and methods

ActiveUS20170040175A1Improve etch selectivityEnhance and suppress reactionElectric discharge tubesSemiconductor/solid-state device manufacturingHydrogenProcess region

Embodiments of the present technology may include a method of etching a substrate. The method may include striking a plasma discharge in a plasma region. The method may also include flowing a fluorine-containing precursor into the plasma region to form a plasma effluent. The plasma effluent may flow into a mixing region. The method may further include introducing a hydrogen-and-oxygen-containing compound into the mixing region without first passing the hydrogen-and-oxygen-containing compound into the plasma region. Additionally, the method may include reacting the hydrogen-and-oxygen-containing compound with the plasma effluent in the mixing region to form reaction products. The reaction products may flow through a plurality of openings in a partition to a substrate processing region. The method may also include etching the substrate with the reaction products in the substrate processing region.

Owner:APPLIED MATERIALS INC

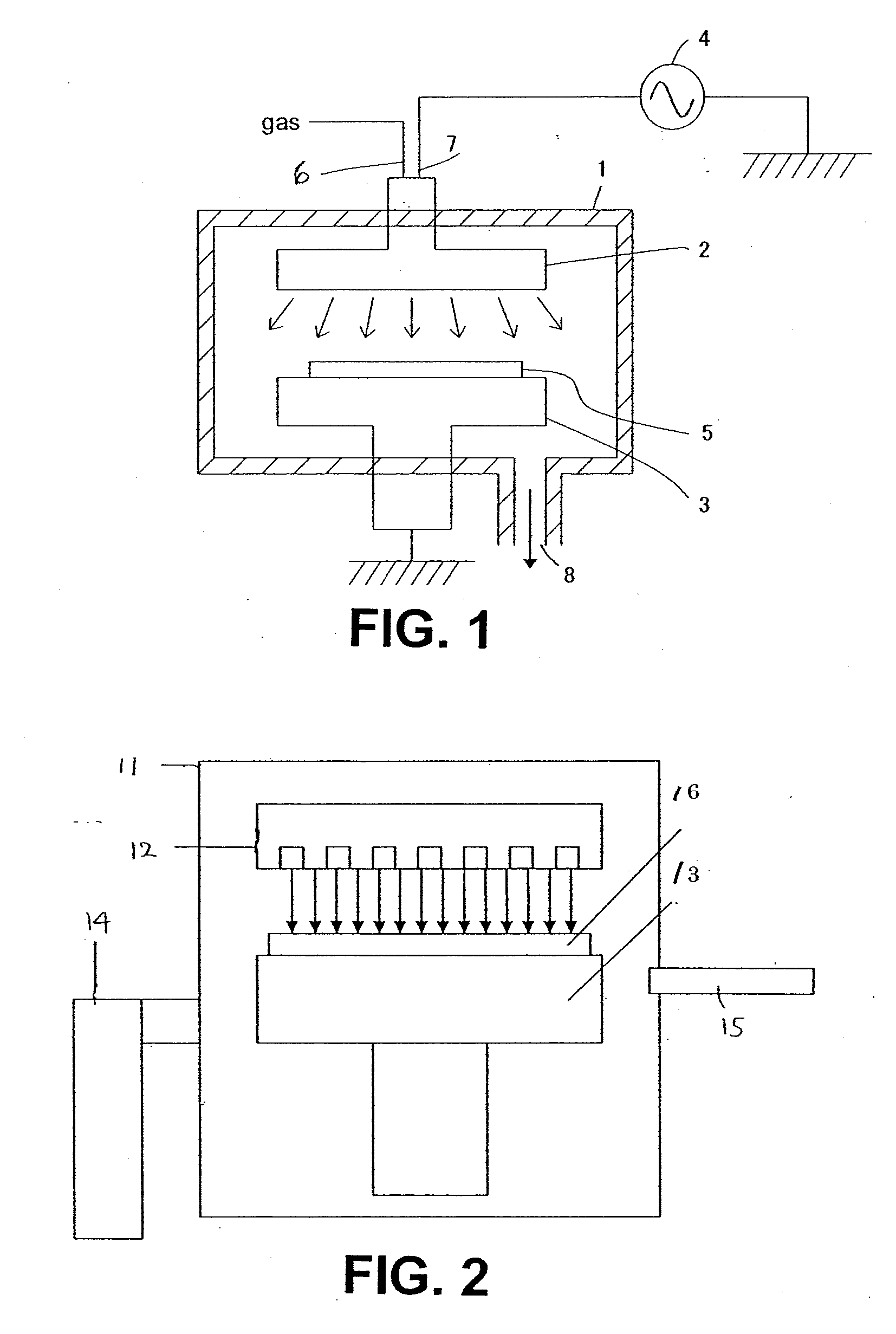

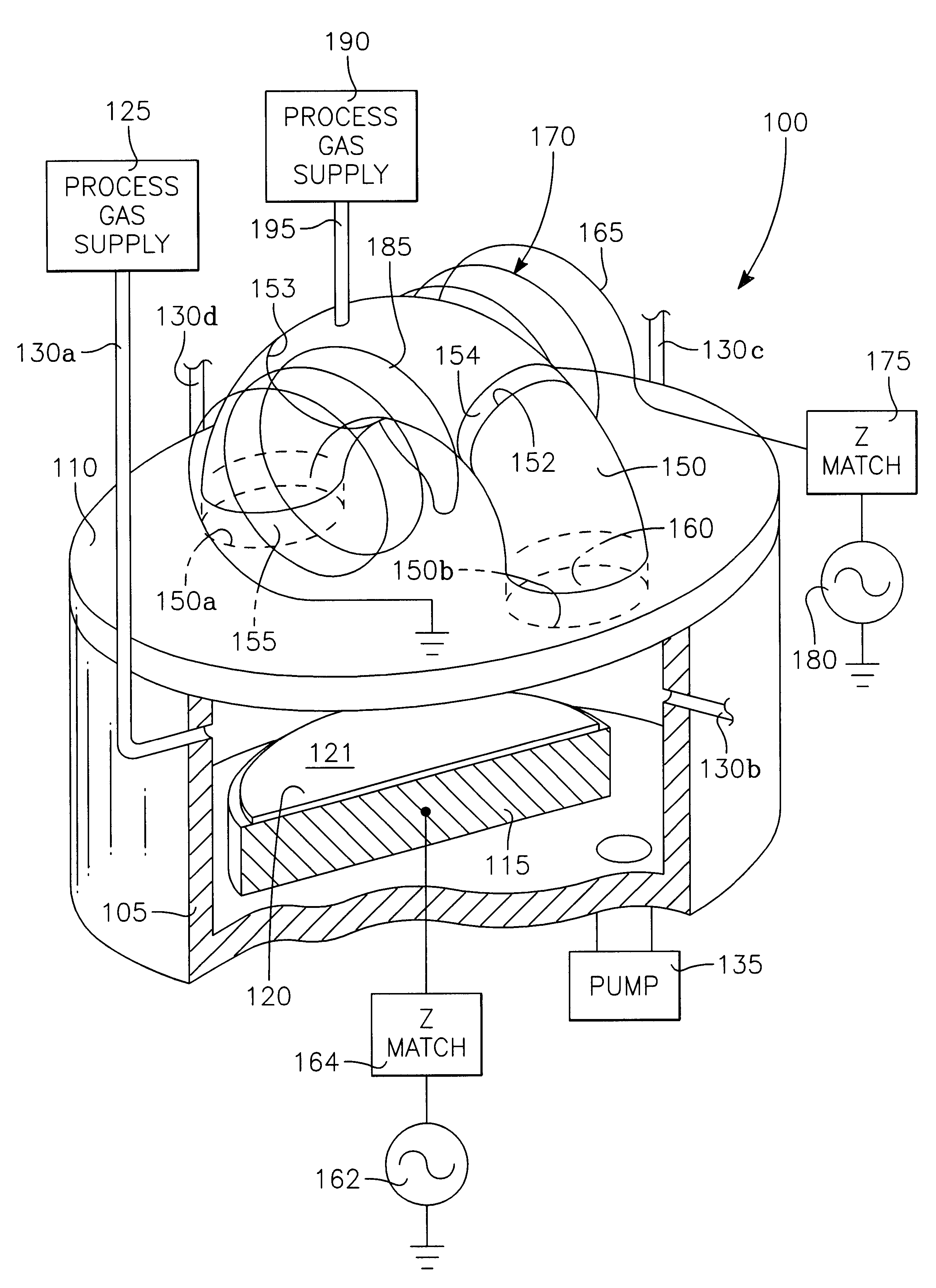

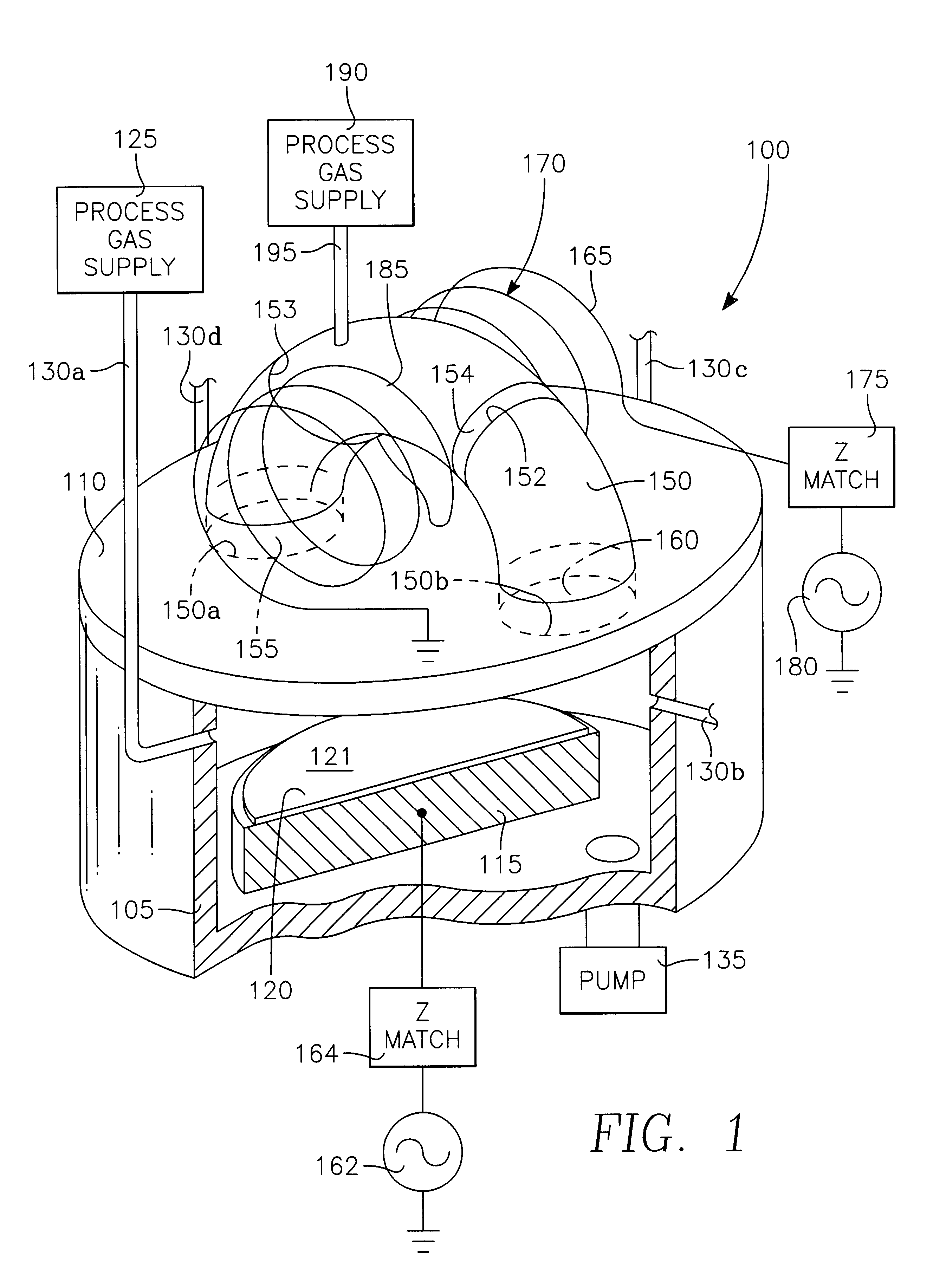

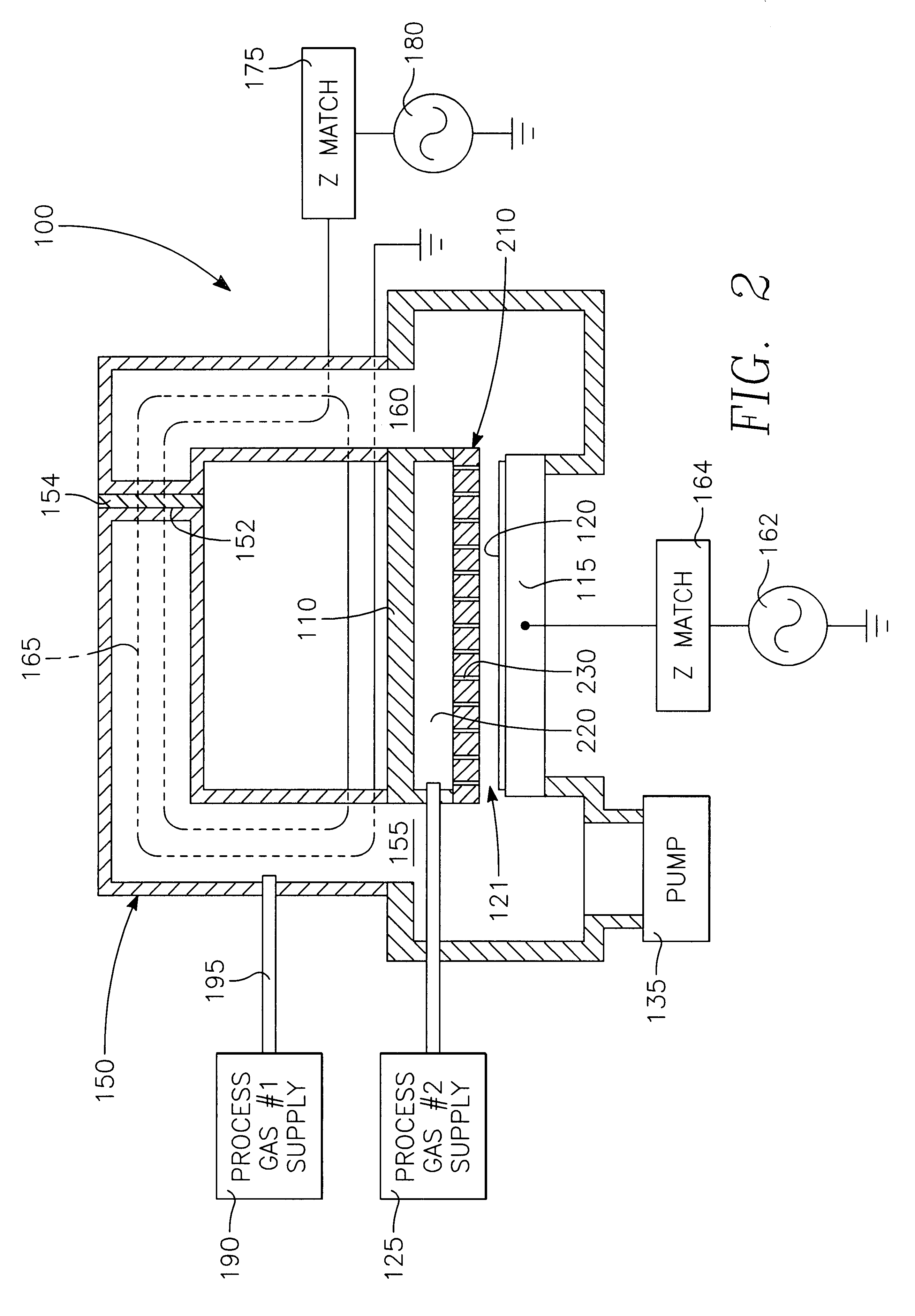

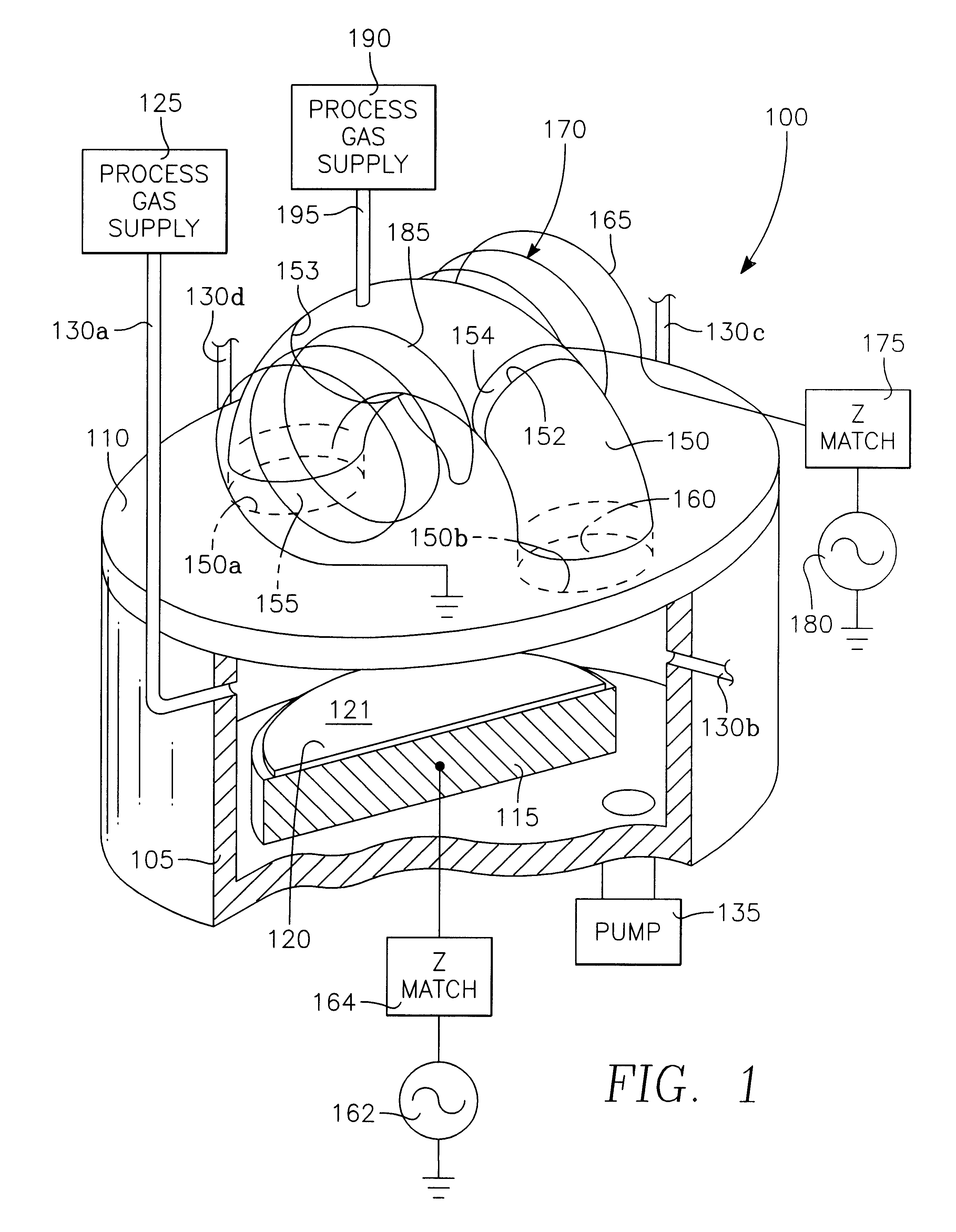

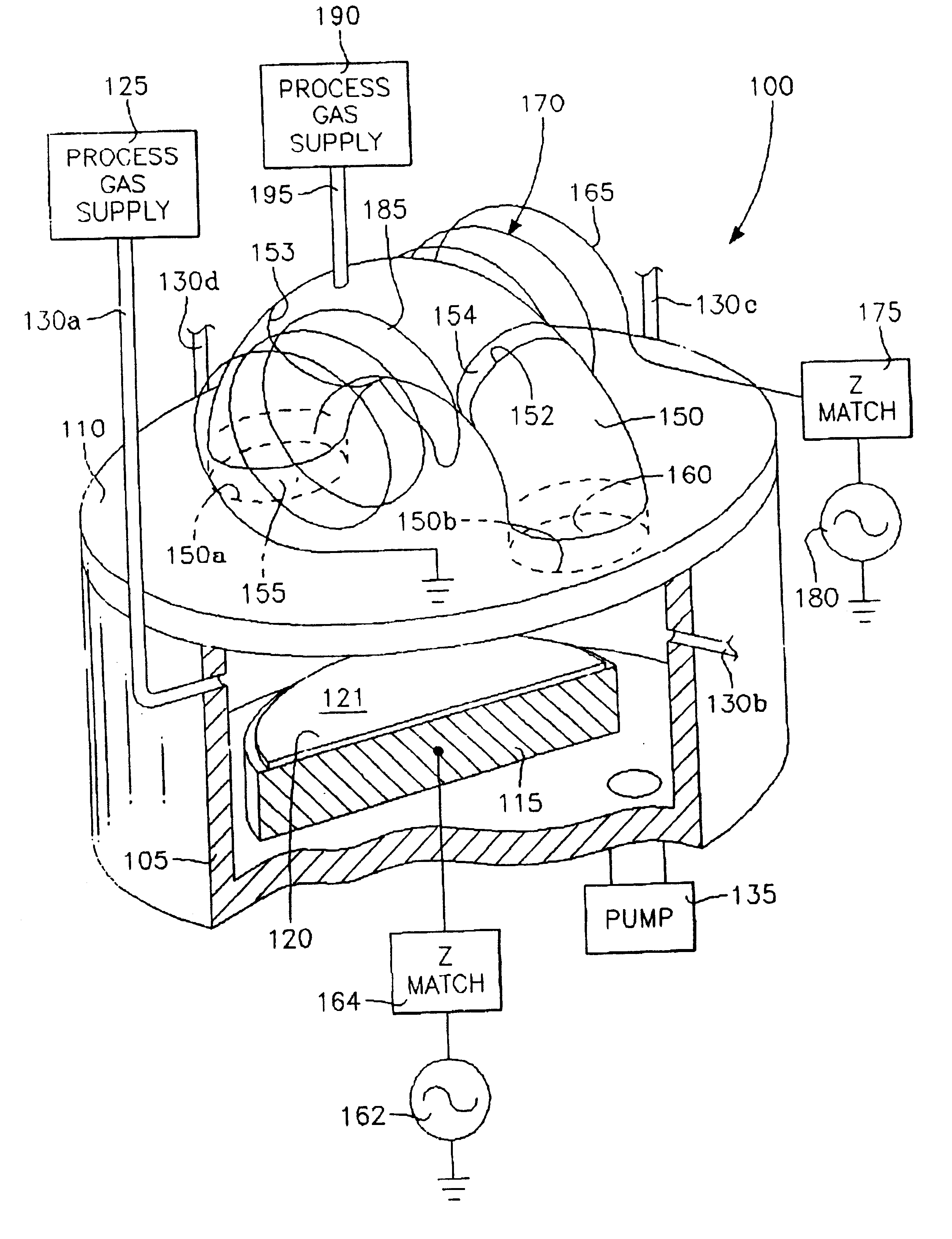

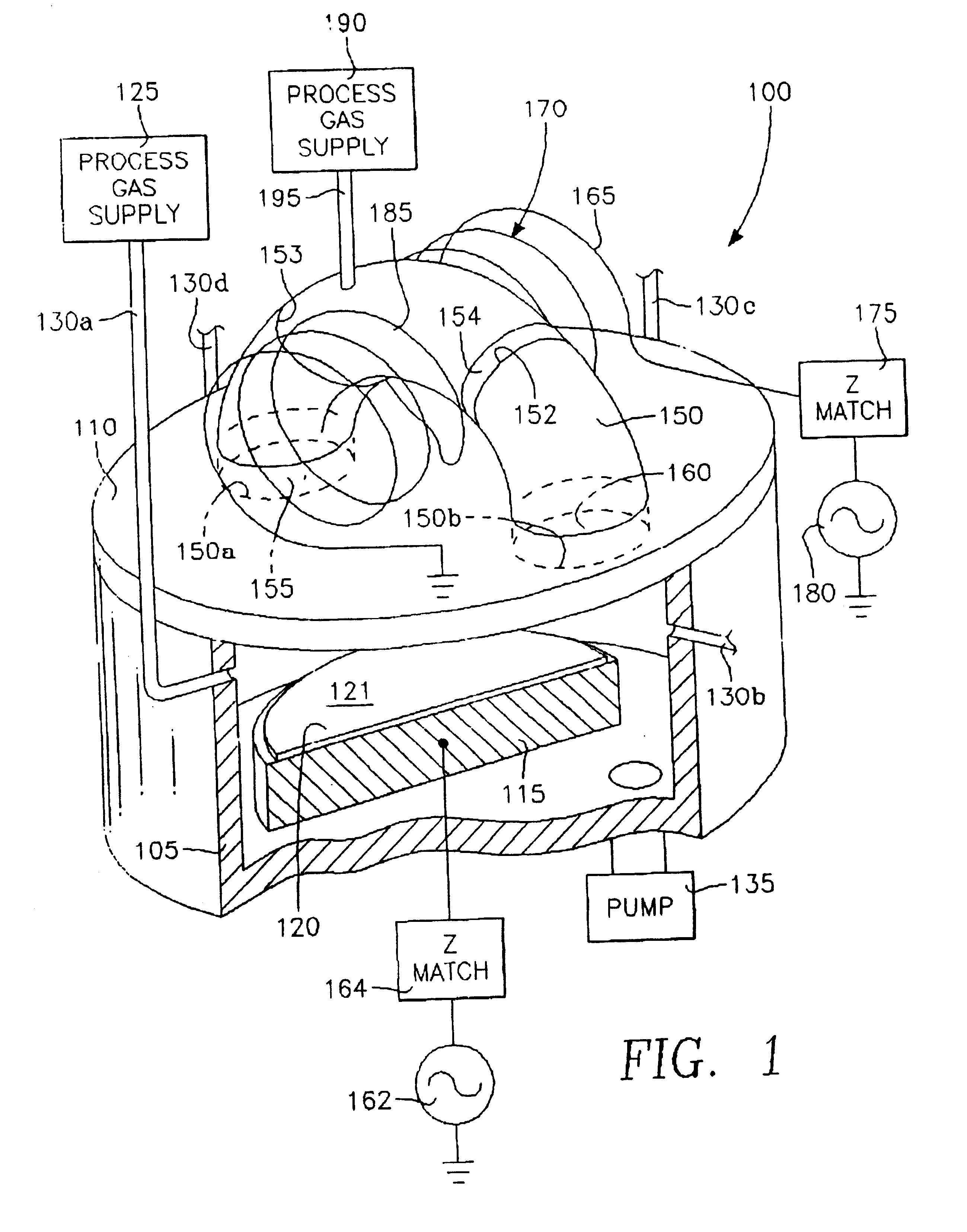

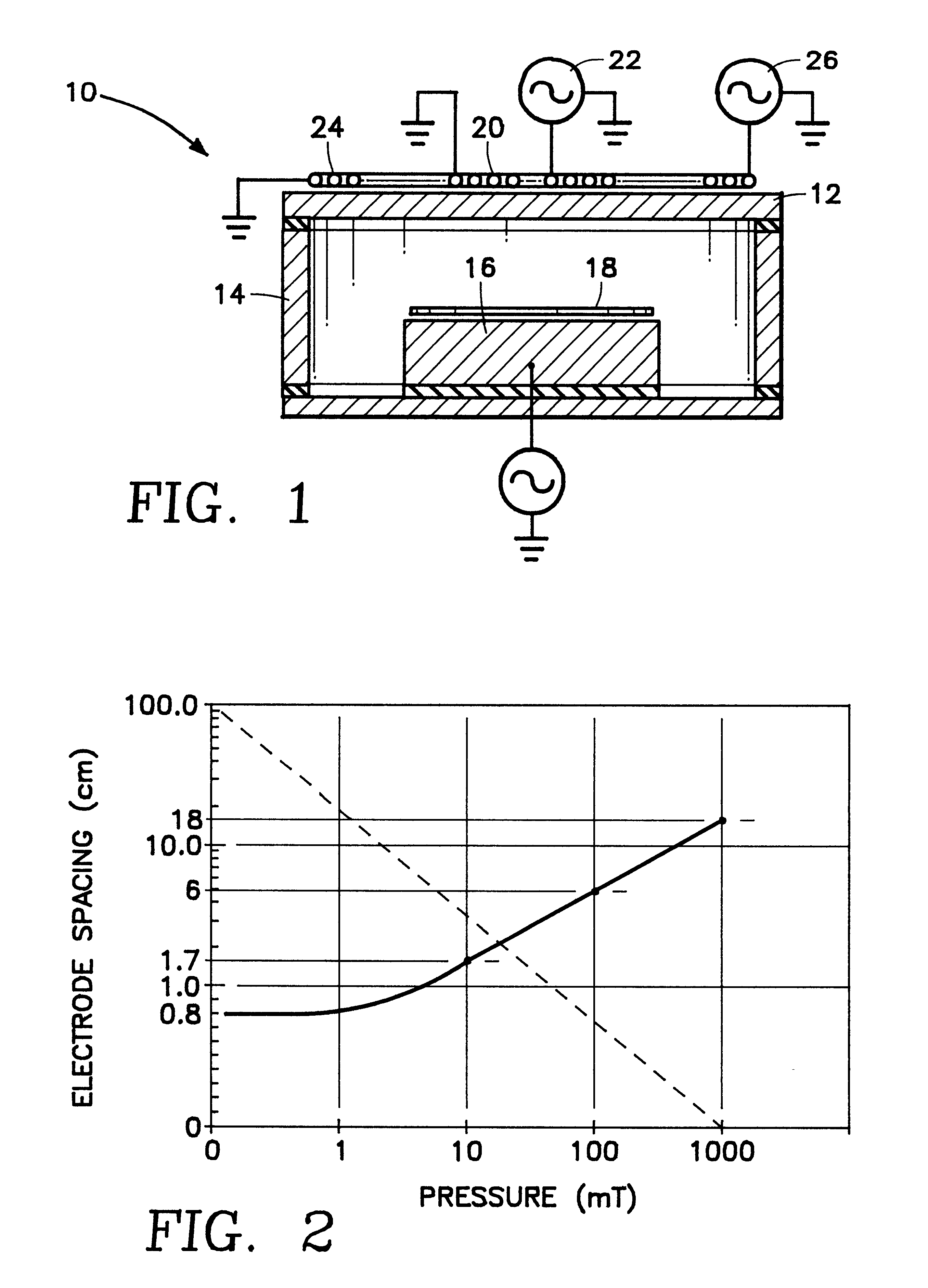

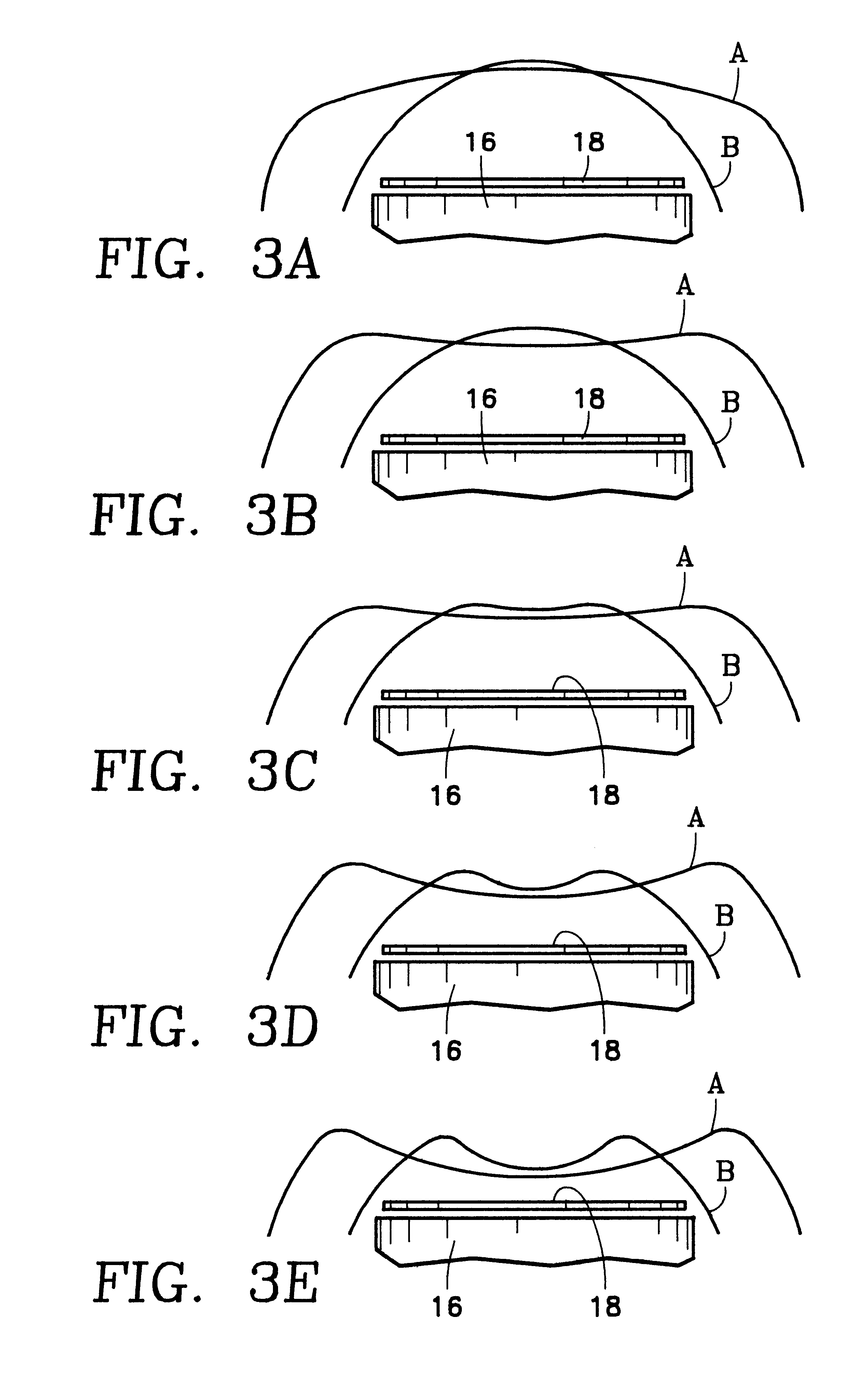

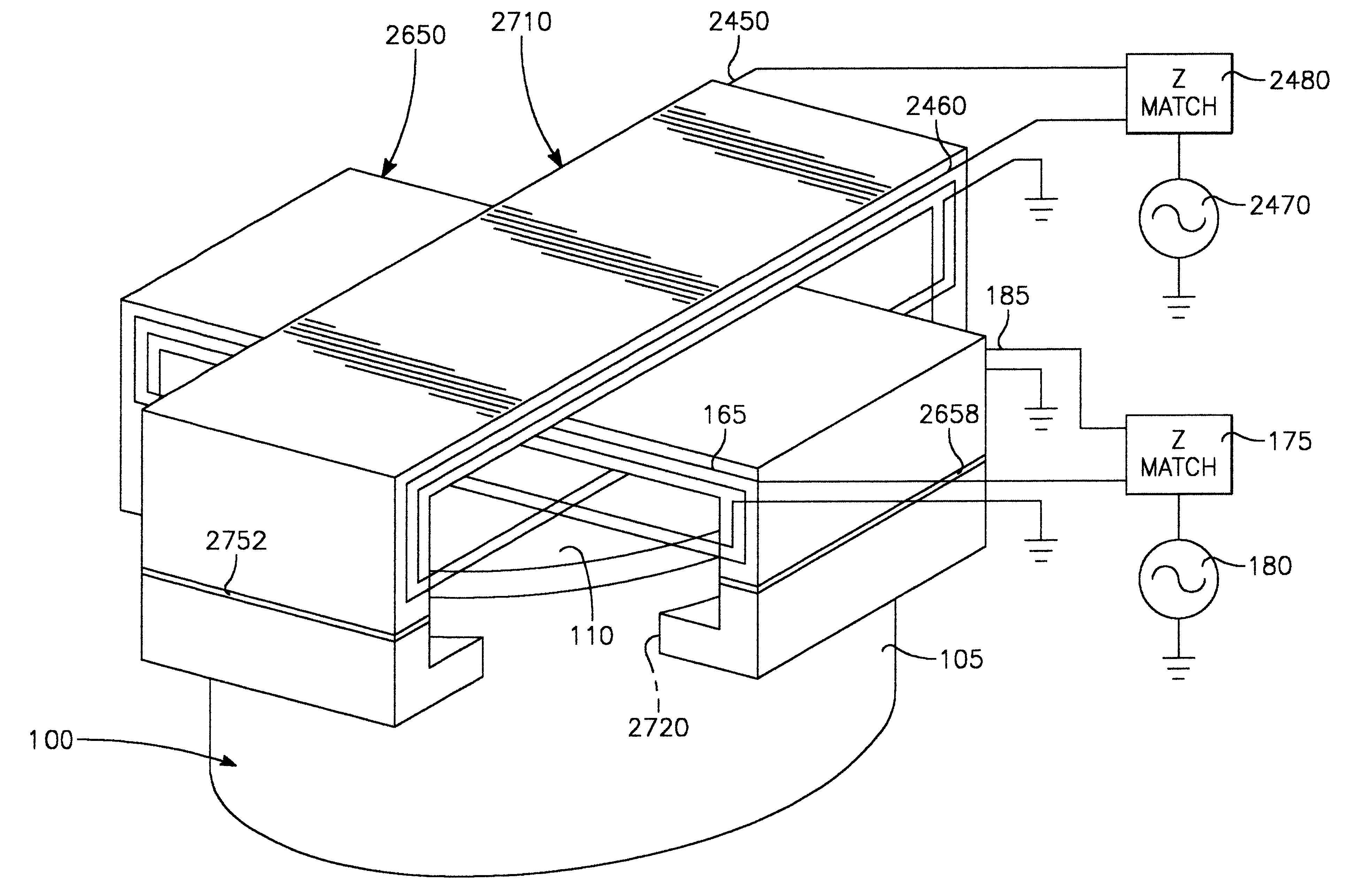

Externally excited torroidal plasma source

InactiveUS6348126B1Increase plasma densityImprove etch selectivityElectric discharge tubesSemiconductor/solid-state device manufacturingEnergy applicatorEngineering

A plasma reactor for processing a workpiece includes a chamber adapted to accept processing gases in an evacuated environment including a workpiece support, a hollow conduit defining a wall of the chamber, and having respective ends opening adjacent opposite sides of the workpiece support, and a chamber wall portion in facing relationship to the workpiece support and defining a workpiece processing zone therebetween, the processing zone and the interior of the conduit forming a torroidal interior path, and an RF energy applicator irradiating gas within the chamber to maintain a plasma within the torroidal interior path.

Owner:APPLIED MATERIALS INC

Bi-layer hard mask for the patterning and etching of nanometer size MRAM devices

ActiveUS20120028373A1Inhibition formationAvoid formingFilm/foil adhesivesSemiconductor/solid-state device manufacturingEtchingEngineering

A composite hard mask is disclosed that prevents build up of metal etch residue in a MRAM device during etch processes that define an MTJ shape. As a result, MTJ shape integrity is substantially improved. The hard mask has a lower non-magnetic spacer, a middle conductive layer, and an upper sacrificial dielectric layer. The non-magnetic spacer serves as an etch stop during a pattern transfer with fluorocarbon plasma through the conductive layer. A photoresist pattern is transferred through the dielectric layer with a first fluorocarbon etch. Then the photoresist is removed and a second fluorocarbon etch transfers the pattern through the conductive layer. The dielectric layer protects the top surface of the conductive layer during the second fluorocarbon etch and during a substantial portion of a third RIE step with a gas comprised of C, H, and O that transfers the pattern through the underlying MTJ layers.

Owner:TAIWAN SEMICON MFG CO LTD

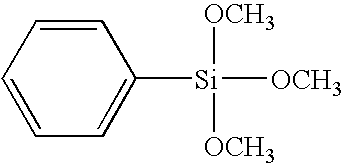

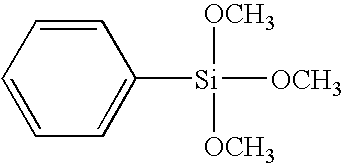

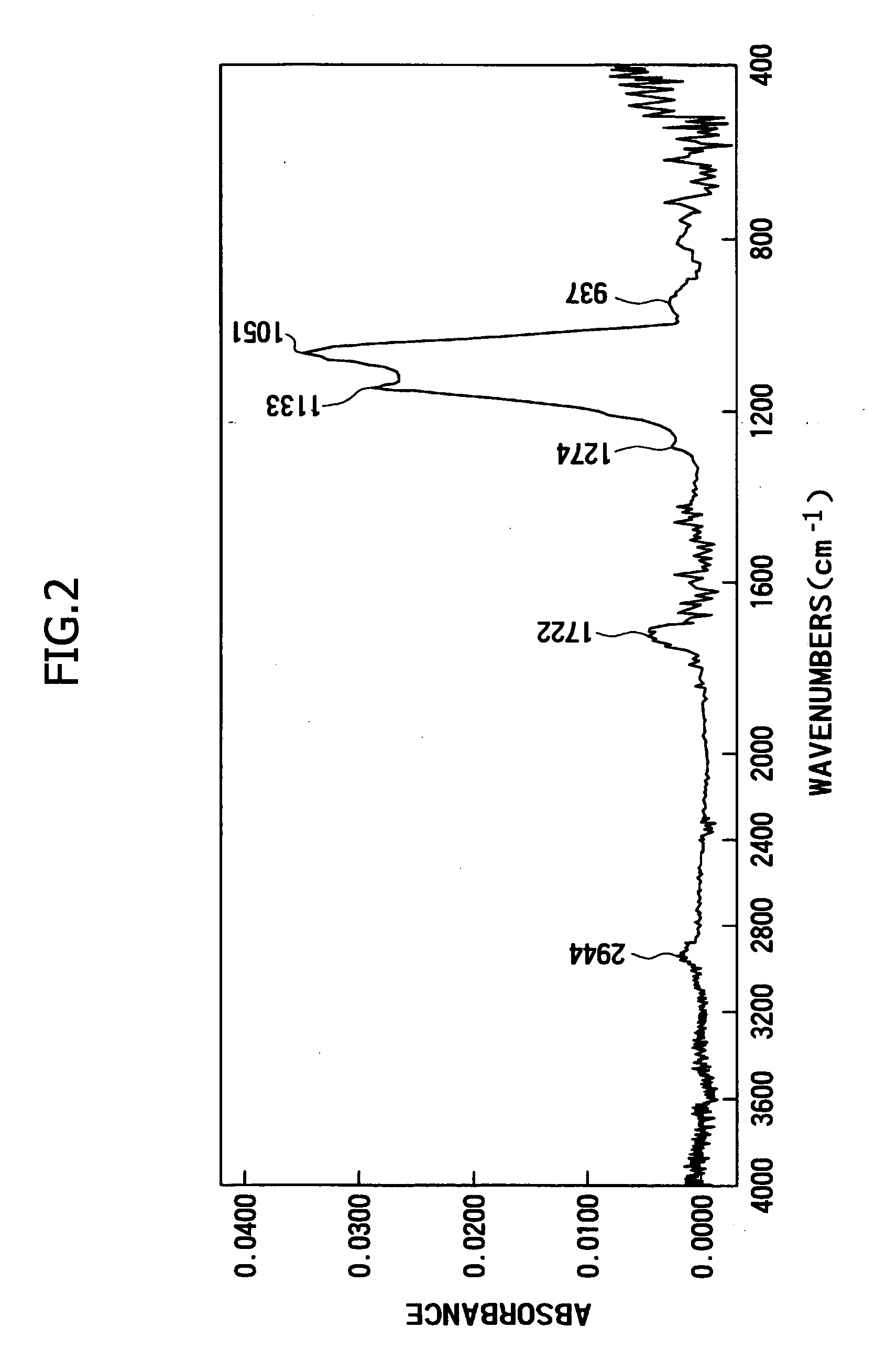

Antireflective film-forming composition, method for manufacturing the same, and antireflective film and pattern formation method using the same

ActiveUS20050277058A1Improve etch selectivityEtching speed is fastSemiconductor/solid-state device manufacturingSilver halide emulsionsCross-linkResist

The present invention provides a material for an antireflective film characterized by high etching selectivity with respect to a resist, that is, which has a fast etching speed when compared to the resist, and in addition, can be removed without damage to a film which is to be processed. The present invention also provides a pattern formation method for forming an antireflective film layer on a substrate using this antireflective film-forming composition, and a pattern formation method that uses this antireflective film as a hard mask, and a pattern formation method that uses this antireflective film as a hard mask for processing the substrate. The present invention provides an antireflective film-forming composition comprising an organic solvent, a cross linking agent, and a polymer comprising a light absorbing group obtained by hydrolyzing and condensing more than one type of silicon compound, a crosslinking group and a non-crosslinking group.

Owner:SHIN ETSU CHEM IND CO LTD +1

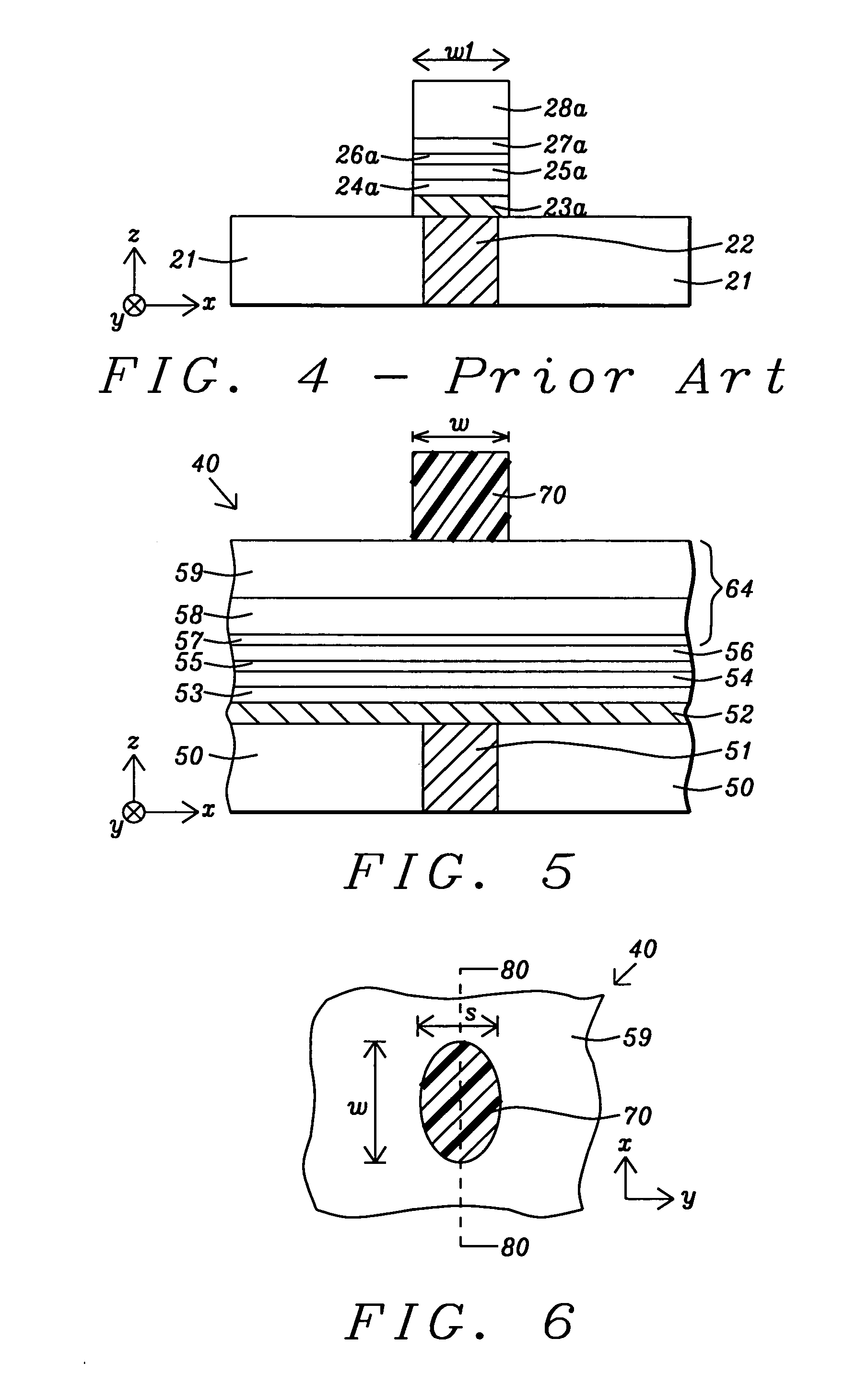

Method to make a perpendicular magnetic recording head with a side write shield

ActiveUS20070177301A1Side fringing of the magnetic field is significantly reducedImprove etch selectivityRecord information storageManufacture of flux-sensitive headsMask layerElectrical and Electronics engineering

A perpendicular magnetic recording (PMR) head is fabricated with a pole tip shielded laterally by a separated pair of side shields and shielded from above by an upper shield. The side shields are formed by a RIE process using specific gases applied to a shield layer through a masking layer formed of material that has a slower etch rate than the shield material. A masking layer of Ta, Ru / Ta, TaN or Ti, formed on a shield layer of NiFe and using RIE gases of CH3OH, CO or NH3 or their combinations, produces the desired result. The differential in etch rates maintains the opening dimension within the mask and allows the formation of a wedge-shaped trench within the shield layer that separates the layer into two shields. The pole tip is then plated within the trench and, being aligned by the trench, acquires the wedge-shaped cross-section of the trench. An upper shield is then formed above the side shields and pole.

Owner:HEADWAY TECH INC

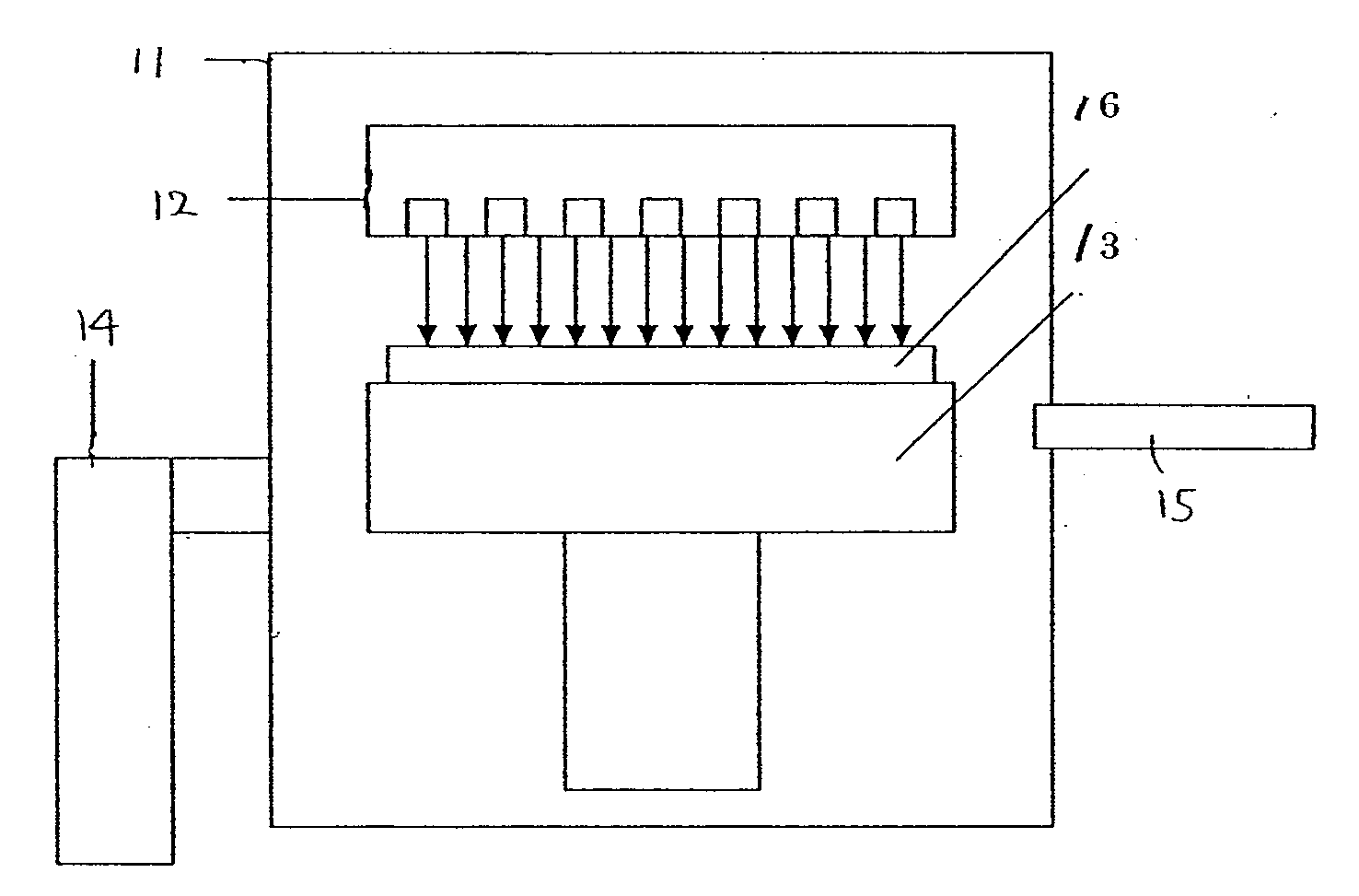

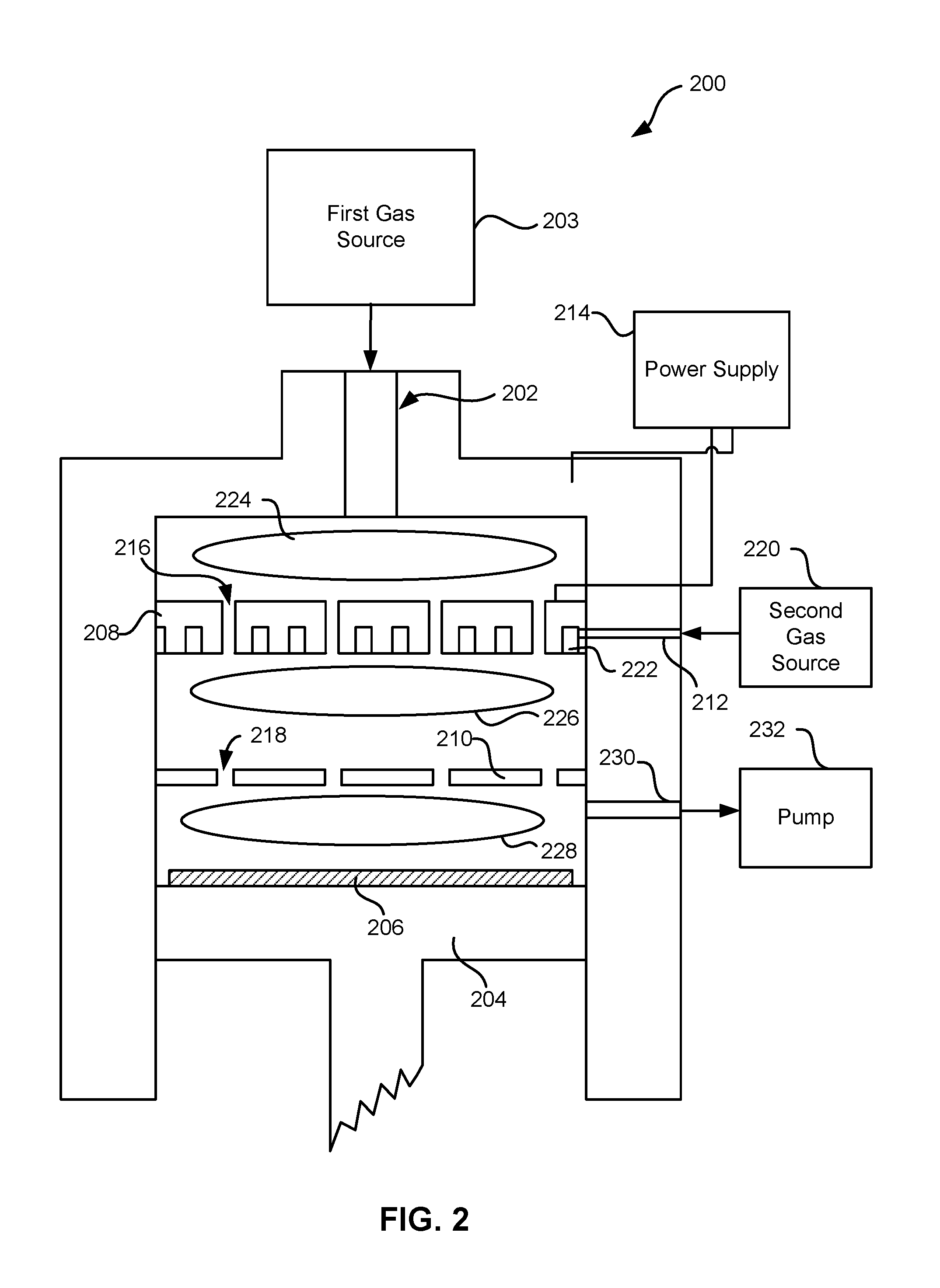

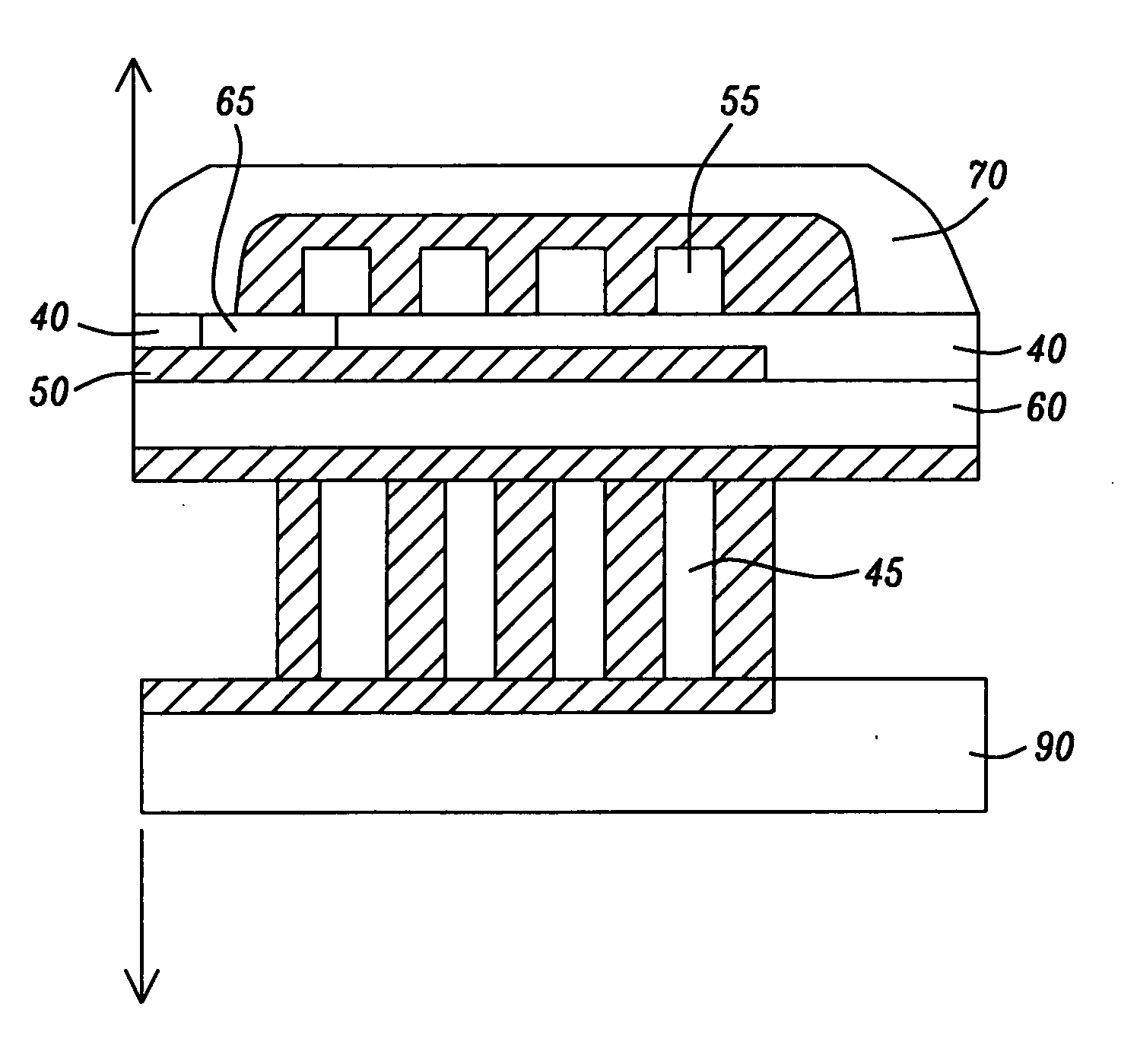

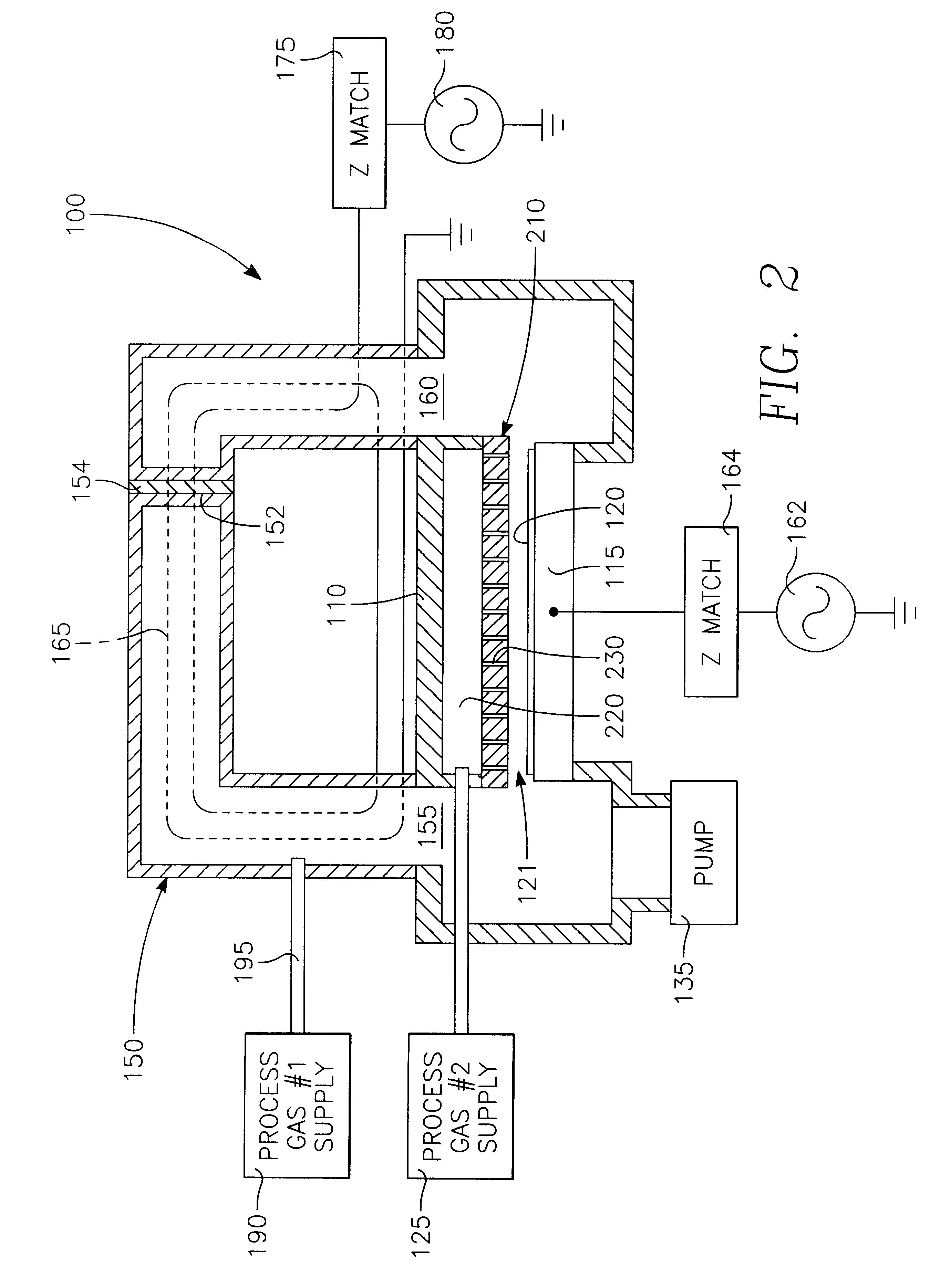

Externally excited torroidal plasma source with a gas distribution plate

InactiveUS6551446B1Increase plasma densitySimple materialElectric discharge tubesSemiconductor/solid-state device manufacturingInjection portProcess region

A plasma reactor for processing a workpiece includes a vacuum enclosure, including a wall, defining a vacuum chamber, the vacuum chamber having a main chamber portion on one side of the wall and a plenum on another side of the wall, the plenum communicating with the chamber portion through at least one opening in the wall, a workpiece support within the main chamber portion and facing the wall. A gas distribution plate is adjacent the wall and faces the workpiece support and is coupled to a reactive process gas supply for injecting reactive process gases directly into a process region adjacent the workpiece support. A gas injection port at the plenum is coupled to a diluent gas supply for injecting diluent gases into the plenum. A coil antenna adapted to accept RF power is inductively coupled to the interior of said plenum, and is capable of maintaining a plasma in a reentrant path through the plenum and across the process region.

Owner:APPLIED MATERIALS INC

Method of processing a workpiece using an externally excited torroidal plasma source

InactiveUS6410449B1Increase ion densityIncrease plasma densityElectric discharge tubesSemiconductor/solid-state device manufacturingPlasma currentIon density

A method of processing a workpiece in a plasma reactor includes establishing a torroidal path for a plasma current to flow that passes near and transverse to the surface of said workpiece, maintaining a plasma current in the torroidal path by applying RF power to a portion of the torroidal path away from the surface of the workpiece, and increasing the ion density of the plasma current in the vicinity of the workpiece by constricting the area of a portion of the torroidal path overlying the workpiece.

Owner:APPLIED MATERIALS INC

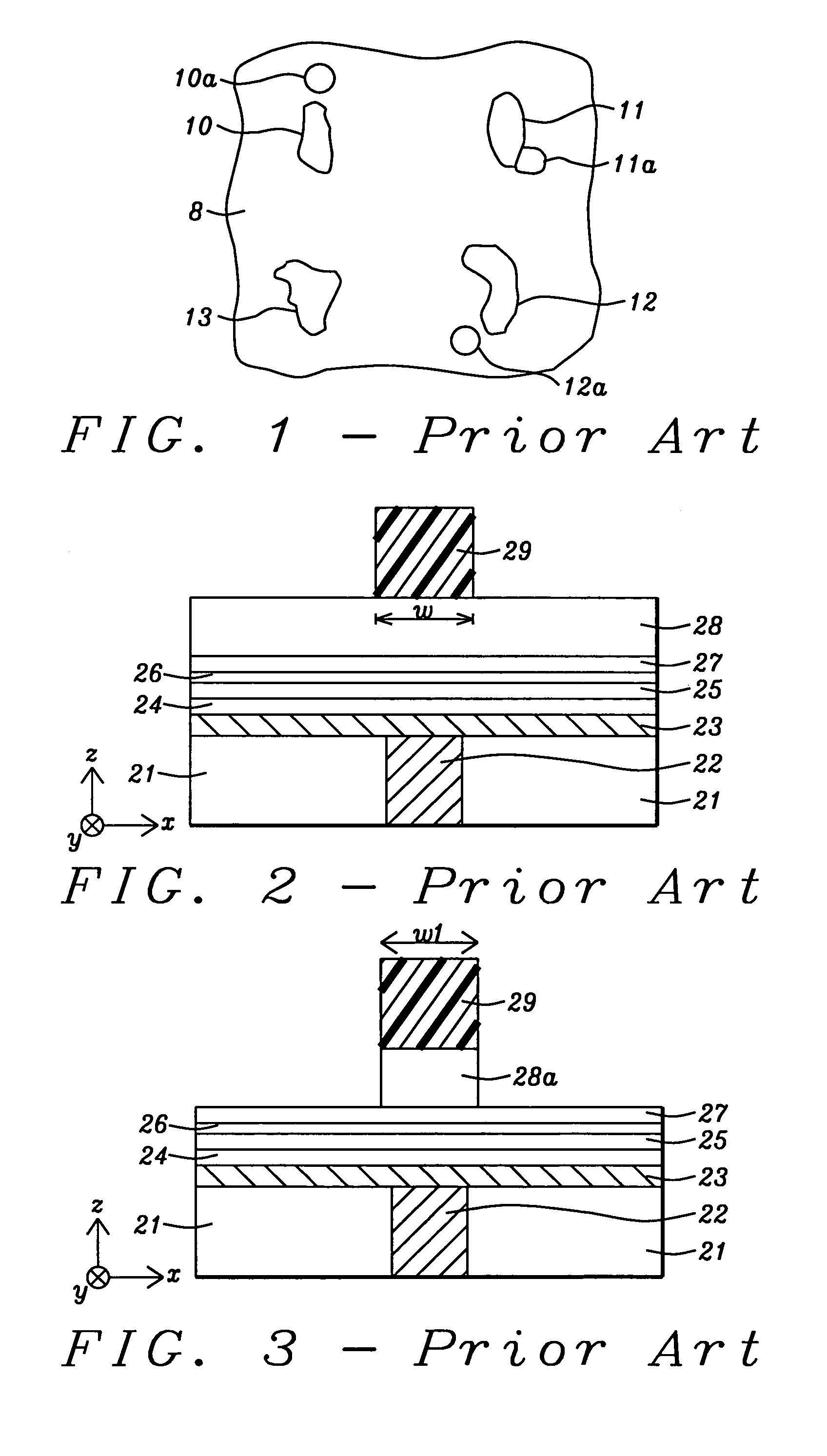

Composite hard mask for the etching of nanometer size magnetic multilayer based device

ActiveUS20090078927A1Prevent electrical shortingAvoid shortingLayered productsSemiconductor/solid-state device manufacturingBit lineEtching

A composite hard mask is disclosed that enables sub-100 nm sized MTJ cells to be formed for advanced devices such as spin torque MRAMs. The hard mask has a lower non-magnetic metallic layer such as Ru to magnetically isolate an overlying middle metallic spacer such as MnPt from an underlying free layer. The middle metallic spacer provides a height margin during subsequent processing to avoid shorting between a bit line and the MTJ cell in the final device. An upper conductive layer may be made of Ta and is thin enough to allow a MTJ pattern in a thin overlying photoresist layer to be transferred through the Ta during a fluorocarbon etch without consuming all of the photoresist. The MTJ pattern is transferred through the remaining hard mask layers and underlying MTJ stack of layers with a second etch step using a C, H, and O etch gas composition.

Owner:TAIWAN SEMICON MFG CO LTD

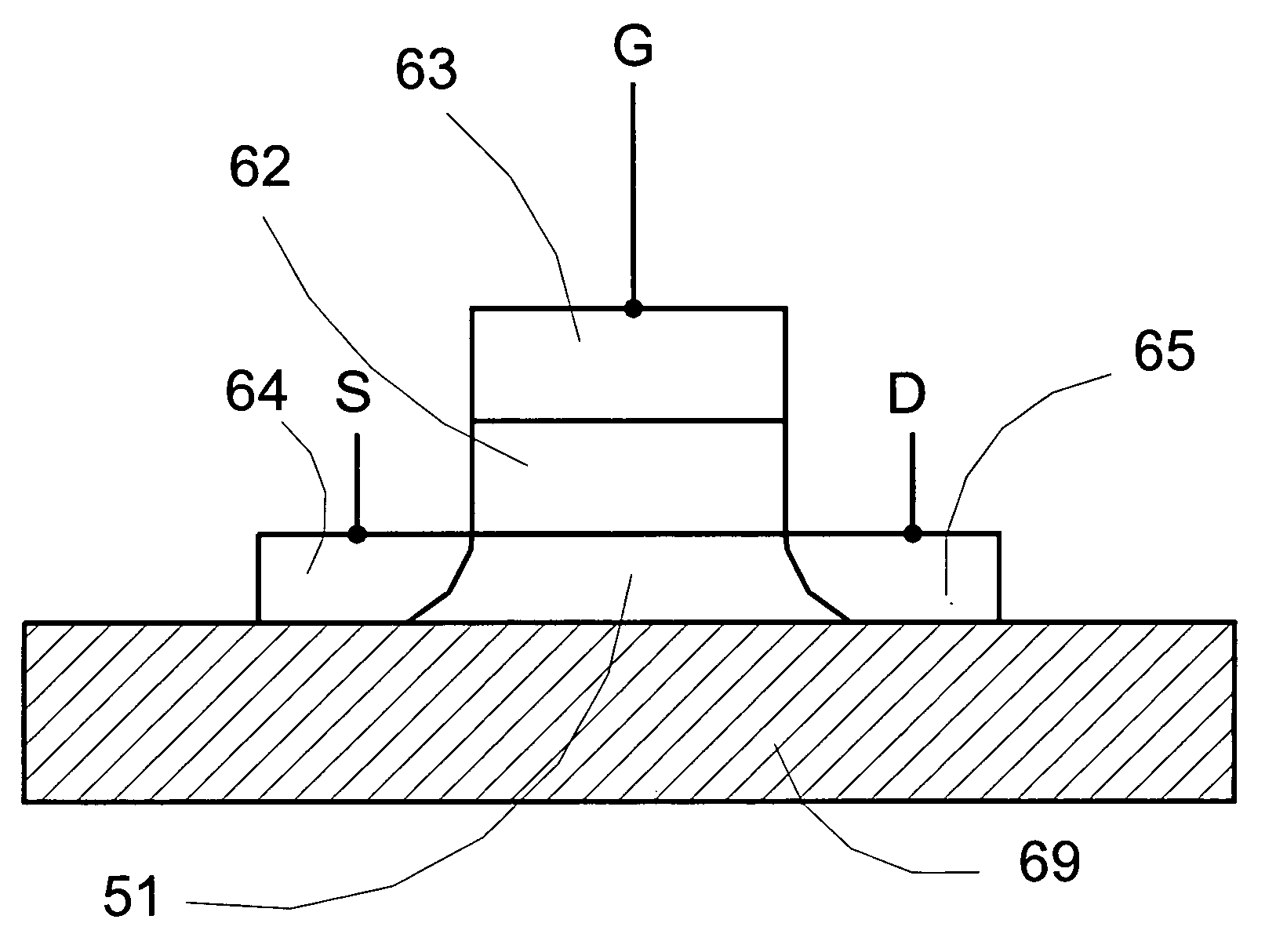

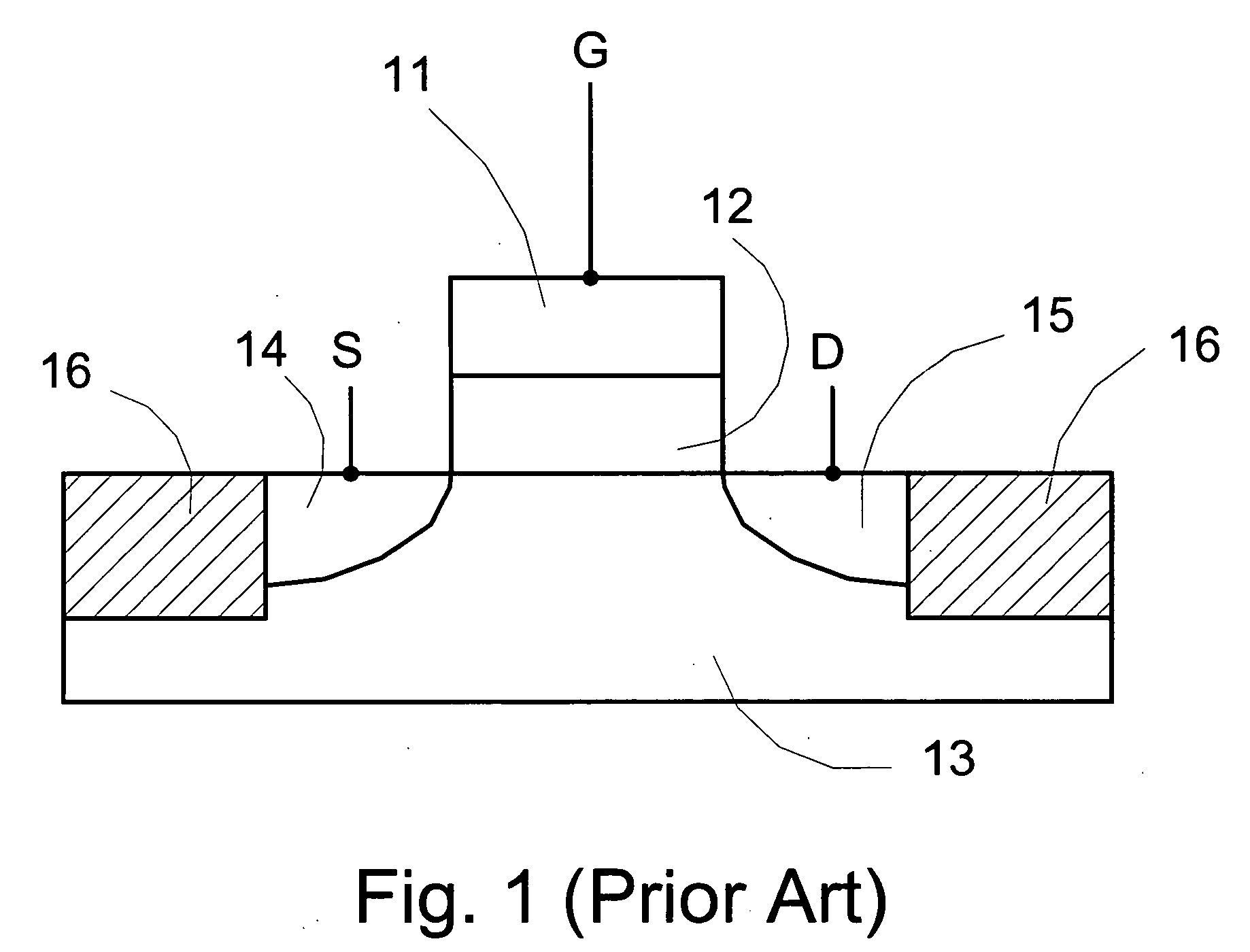

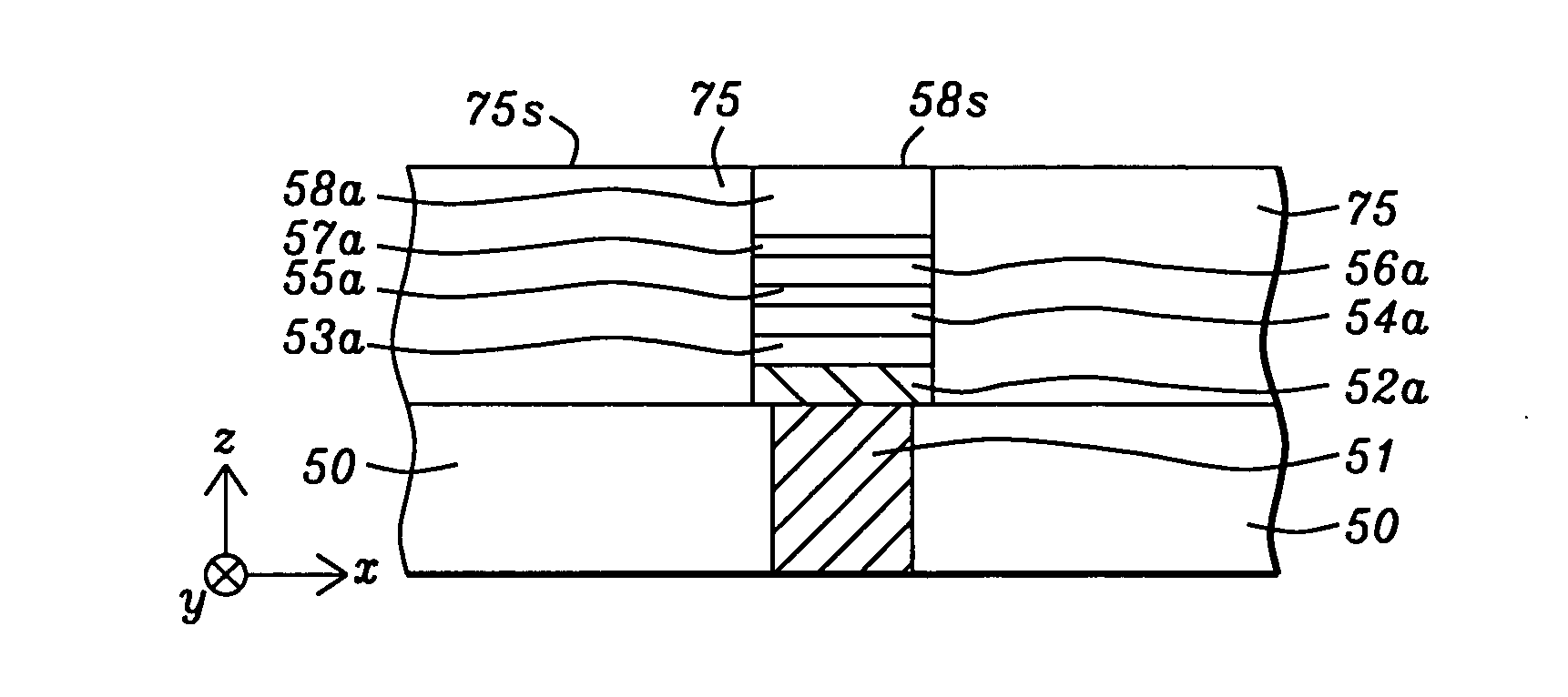

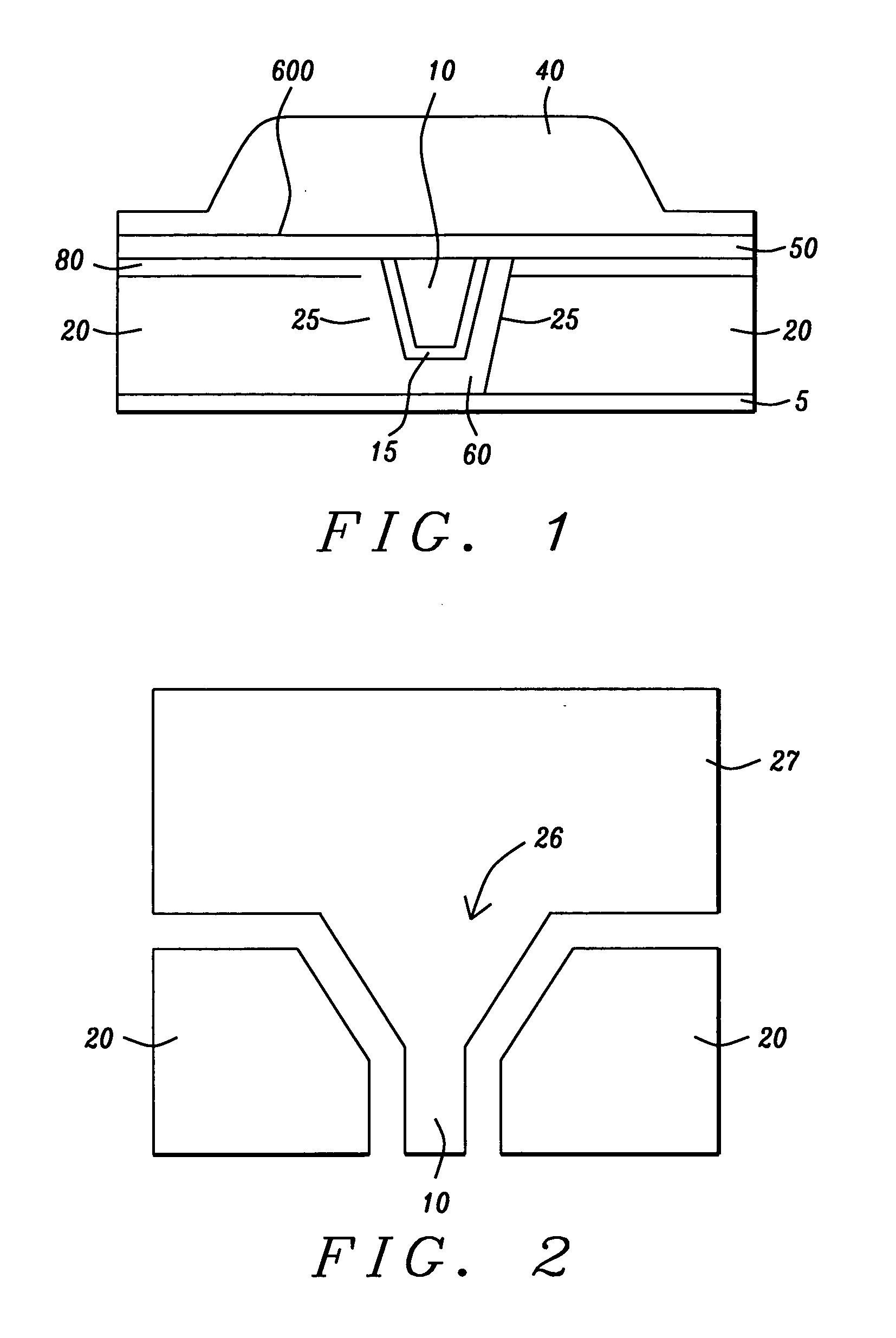

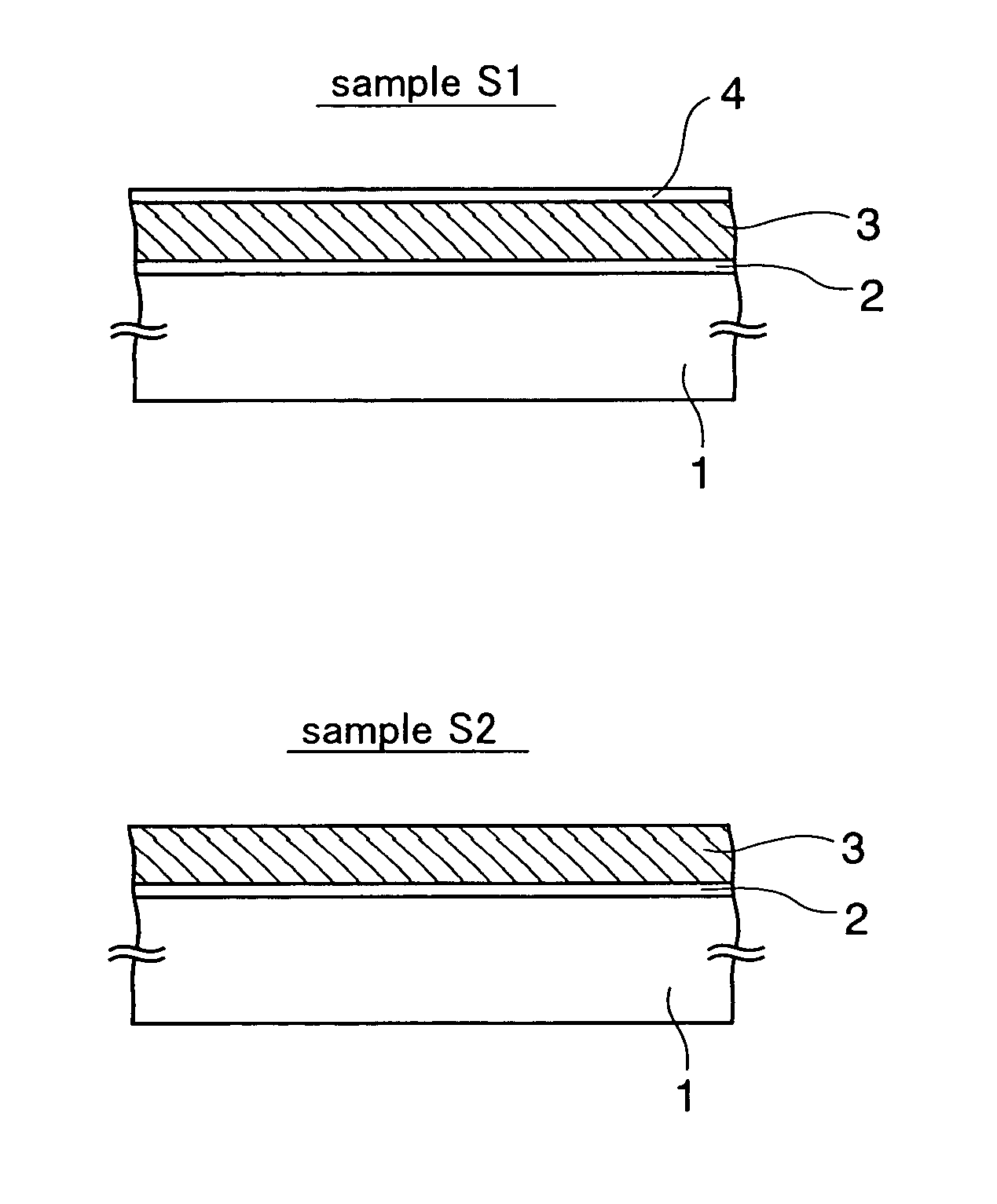

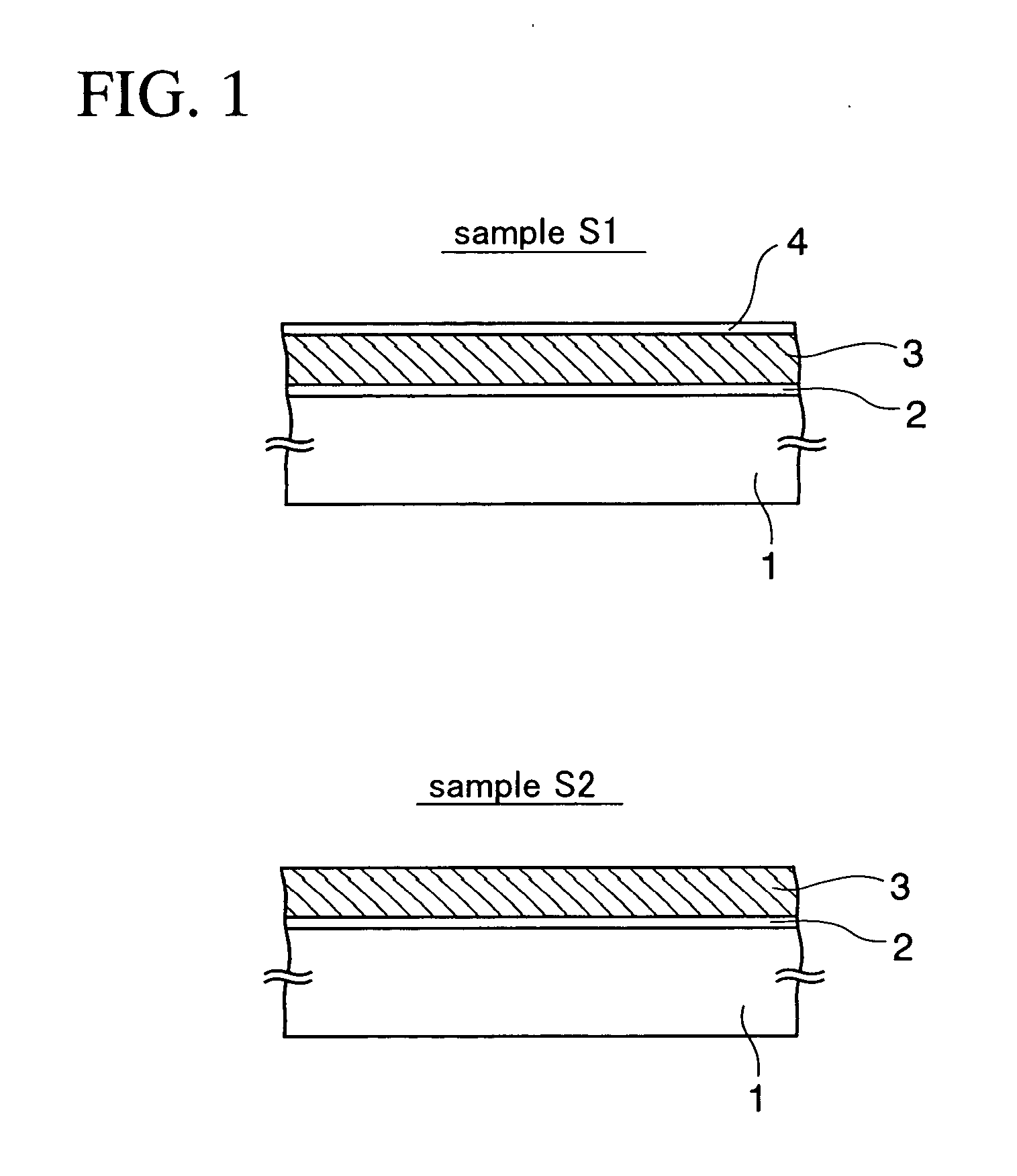

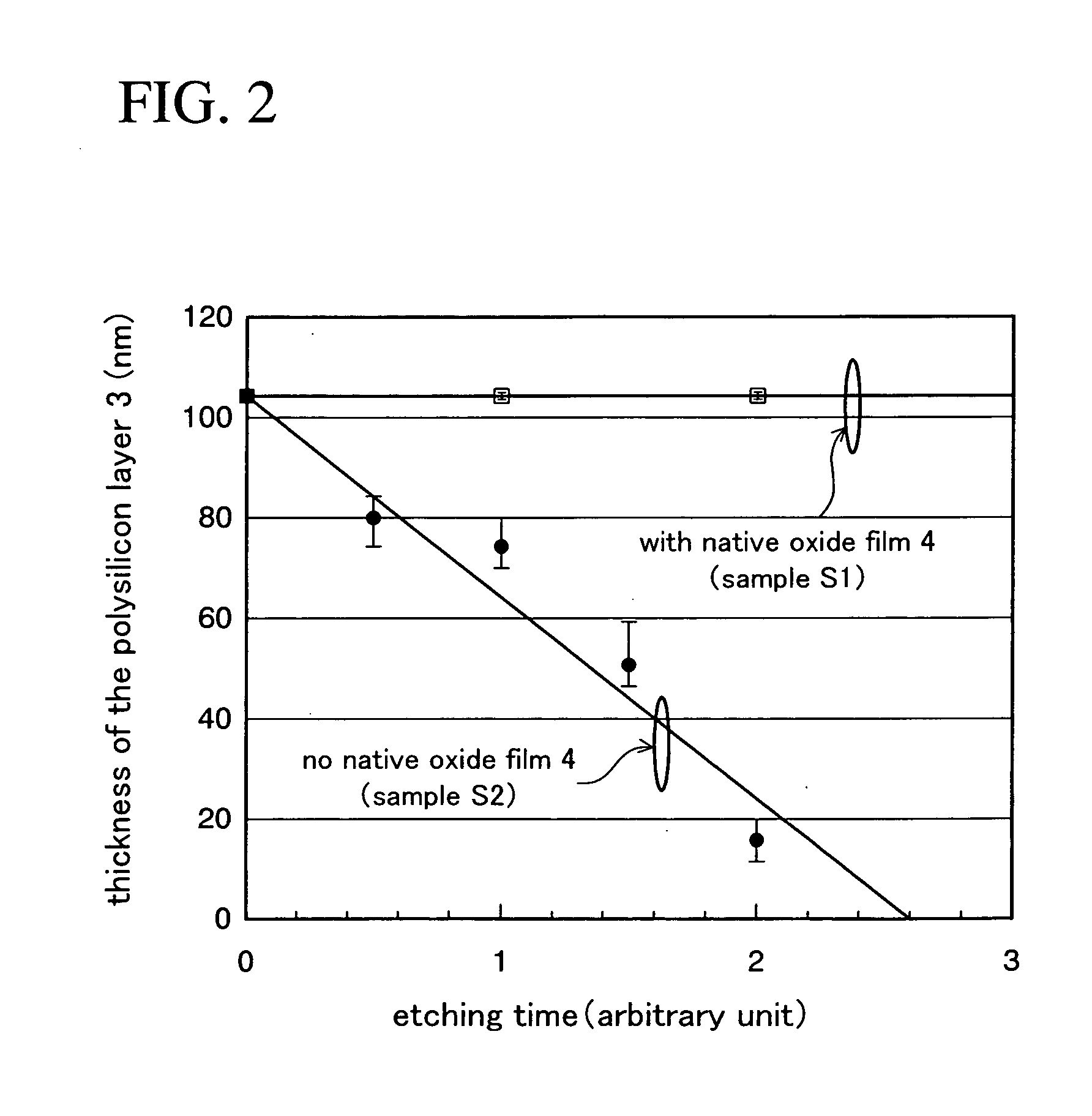

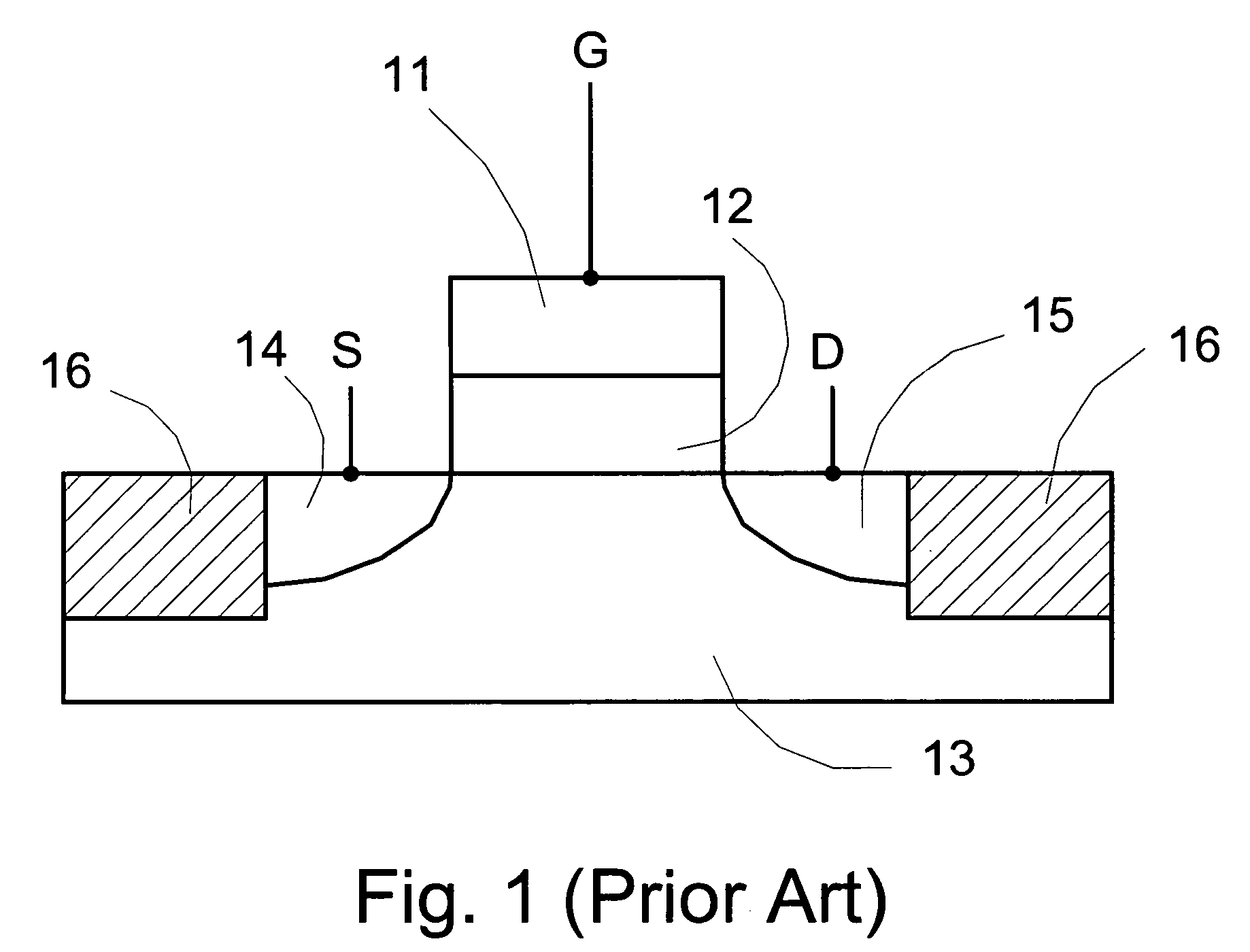

Semiconductor device, method of manufacturing the same, and method of evaluating semiconductor device

InactiveUS20050285203A1Thickness of gate be reducedReduce thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesCrystal planeSilicon

A semiconductor device has: a silicon (semiconductor) substrate; a gate insulating film and a gate electrode, which are formed on the silicon substrate in this order; and source / drain material layers formed in recesses (holes) in the silicon substrate, the recesses being located beside the gate electrode. Here, each of side surfaces of the recesses, which are closer to the gate electrode, is constituted of at least one crystal plane of the silicon substrate.

Owner:FUJITSU LTD

High pressure high non-reactive diluent gas content high plasma ion density plasma oxide etch process

InactiveUS6238588B1Increase pressureHigh strengthElectric discharge tubesDecorative surface effectsHigh plasmaOxygen

The invention is embodied in a method of processing a semiconductor workpiece in a plasma reactor chamber, including supplying a polymer and etchant precursor gas containing at least carbon and fluorine into the chamber at a first flow rate sufficient of itself to maintain a gas pressure in the chamber in a low pressure range below about 20 mT, supplying a relatively non-reactive gas into the chamber at second flow rate sufficient about one half or more of the total gas flow rate into the chamber, in combination with the first flow rate of the precursor gas, to maintain the gas pressure in the chamber in a high pressure range above 20 mT, and applying plasma source power into the chamber to form a high ion density plasma having an ion density in excess of 1010 ions per cubic centimeter. In one application of the invention, the workpiece includes an oxygen-containing overlayer to be etched by the process and a non-oxygen-containing underlayer to be protected from etching, the precursor gas dissociating in the plasma into fluorine-containing etchant species which etch the oxygen-containing layer and carbon-containing polymer species which accumulate on the non-oxygen-containing underlayer. Alternatively, the high pressure range may be defined as a pressure at which the skin depth of the inductive field exceeds {fraction (1 / 10)} of the gap between the inductive antenna and the workpiece.

Owner:APPLIED MATERIALS INC

Composite hard mask with upper sacrificial dielectric layer for the patterning and etching of nanometer size MRAM devices

ActiveUS8722543B2Avoid formingPrevent electric shortingSemiconductor/solid-state device manufacturingGalvano-magnetic device manufacture/treatmentEtchingNon magnetic

A composite hard mask is disclosed that prevents build up of metal etch residue in a MRAM device during etch processes that define an MTJ shape. As a result, MTJ shape integrity is substantially improved. The hard mask has a lower non-magnetic spacer, a middle conductive layer, and an upper sacrificial dielectric layer. The non-magnetic spacer serves as an etch stop during a pattern transfer with fluorocarbon plasma through the conductive layer. A photoresist pattern is transferred through the dielectric layer with a first fluorocarbon etch. Then the photoresist is removed and a second fluorocarbon etch transfers the pattern through the conductive layer. The dielectric layer protects the top surface of the conductive layer during the second fluorocarbon etch and during a substantial portion of a third RIE step with a gas comprised of C, H, and O that transfers the pattern through the underlying MTJ layers.

Owner:TAIWAN SEMICON MFG CO LTD

Composite hard mask for the etching of nanometer size magnetic multilayer based device

ActiveUS7696551B2Avoid shortingImprove etch selectivitySemiconductor/solid-state device manufacturingGalvano-magnetic device manufacture/treatmentBit lineEtching

A composite hard mask is disclosed that enables sub-100 nm sized MTJ cells to be formed for advanced devices such as spin torque MRAMs. The hard mask has a lower non-magnetic metallic layer such as Ru to magnetically isolate an overlying middle metallic spacer such as MnPt from an underlying free layer. The middle metallic spacer provides a height margin during subsequent processing to avoid shorting between a bit line and the MTJ cell in the final device. An upper conductive layer may be made of Ta and is thin enough to allow a MTJ pattern in a thin overlying photoresist layer to be transferred through the Ta during a fluorocarbon etch without consuming all of the photoresist. The MTJ pattern is transferred through the remaining hard mask layers and underlying MTJ stack of layers with a second etch step using a C, H, and O etch gas composition.

Owner:TAIWAN SEMICON MFG CO LTD

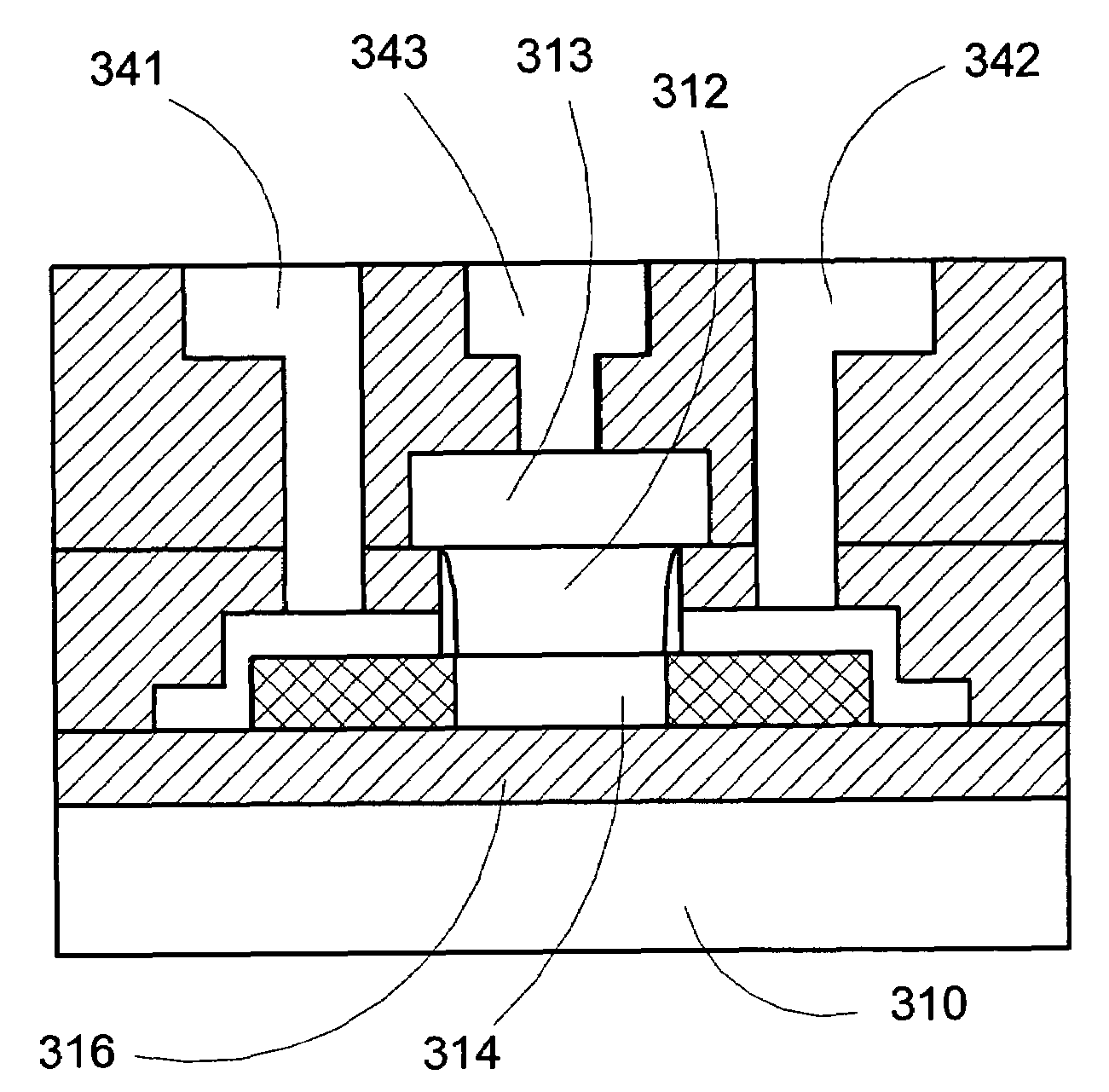

Semiconductor device having an etch stopper formed of a sin layer by low temperature ALD and method of fabricating the same

InactiveUS6858533B2Avoid damageAvoid formingTransistorSemiconductor/solid-state device manufacturingDevice materialNitride

Provided are a semiconductor device having an etch stopper formed of a nitride film by low temperature atomic layer deposition which can prevent damage to a semiconductor substrate and a method for fabricating the semiconductor device. Damage to the semiconductor substrate under the etch stopper composed of a second nitride film can be prevented by forming a first nitride film using high temperature LPCVD on the semiconductor substrate, forming the etch stopper including the second nitride film by low temperature ALD on the first nitride film, and removing the second nitride film by dry etching, thus taking advantage of the different etch selectivities of the first nitride film and the second nitride film.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductive metal oxide thin film ferroelectric memory transistor

InactiveUS7378286B2Simplify the manufacturing processHigh densityTransistorSemiconductor/solid-state device manufacturingDielectricGate dielectric

The present invention discloses a novel transistor structure employing semiconductive metal oxide as the transistor conductive channel. By replacing the silicon conductive channel with a semiconductive metal oxide channel, the transistors can achieve simpler fabrication process and could realize 3D structure to increase circuit density. The disclosed semiconductive metal oxide transistor can have great potential in ferroelectric non volatile memory device with the further advantages of good interfacial properties with the ferroelectric materials, possible lattice matching with the ferroelectric layer, reducing or eliminating the oxygen diffusion problem to improve the reliability of the ferroelectric memory transistor. The semiconductive metal oxide film is preferably a metal oxide exhibiting semiconducting properties at the transistor operating conditions, for example, In2O3 or RuO2. The present invention ferroelectric transistor can be a metal-ferroelectric-semiconductive metal oxide FET having a gate stack of a top metal electrode disposed on a ferroelectric layer disposed on a semiconductive metal oxide channel on a substrate. Using additional layer of bottom electrode and gate dielectric, the present invention ferroelectric transistor can also be a metal-ferroelectric-metal (optional)-gate dielectric (optional)-semiconductive metal oxide FET.

Owner:SHARP KK

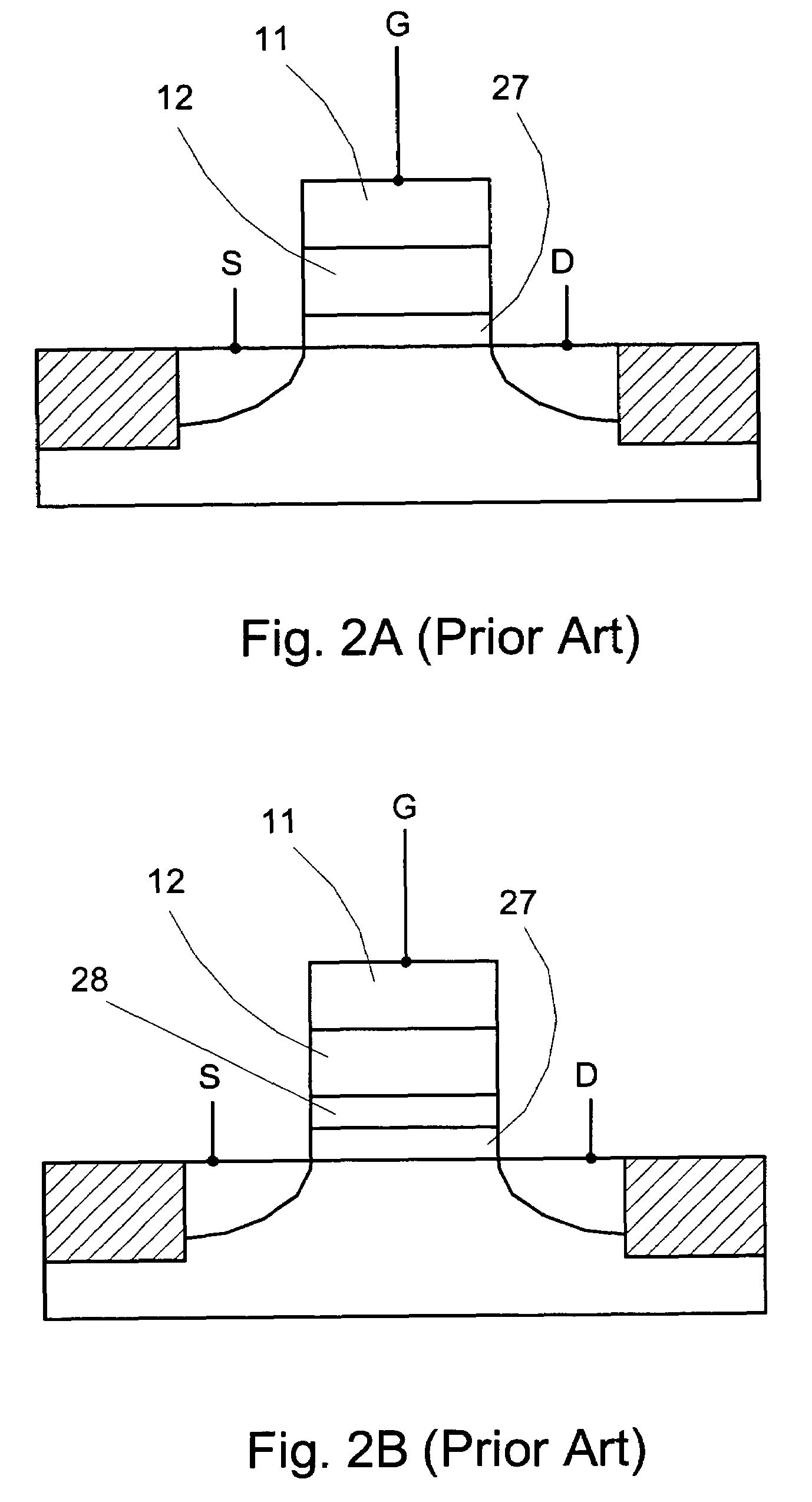

Externally excited multiple torroidal plasma source

InactiveUS6494986B1Increase plasma densityImprove etch selectivityElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringVacuum chamber

A plasma reactor for processing a workpiece, including an enclosure defining a vacuum chamber, a workpiece support within the enclosure facing an overlying portion of the enclosure, the enclosure having at least first and second pairs of openings therethrough near generally opposite sides of the workpiece support. At least first and second hollow conduits are connected to respective pairs of the openings to provide at least first and second closed torroidal paths through the respective conduits and extending between respective pairs of the openings across the wafer surface. A process gas supply is coupled to the interior of the chamber for supplying process gas to the torroidal paths. Coil antennas are coupled to RF power sources and inductively coupled to the interior of the hollow conduits and capable of maintaining a plasma in the torroidal paths.

Owner:APPLIED MATERIALS INC

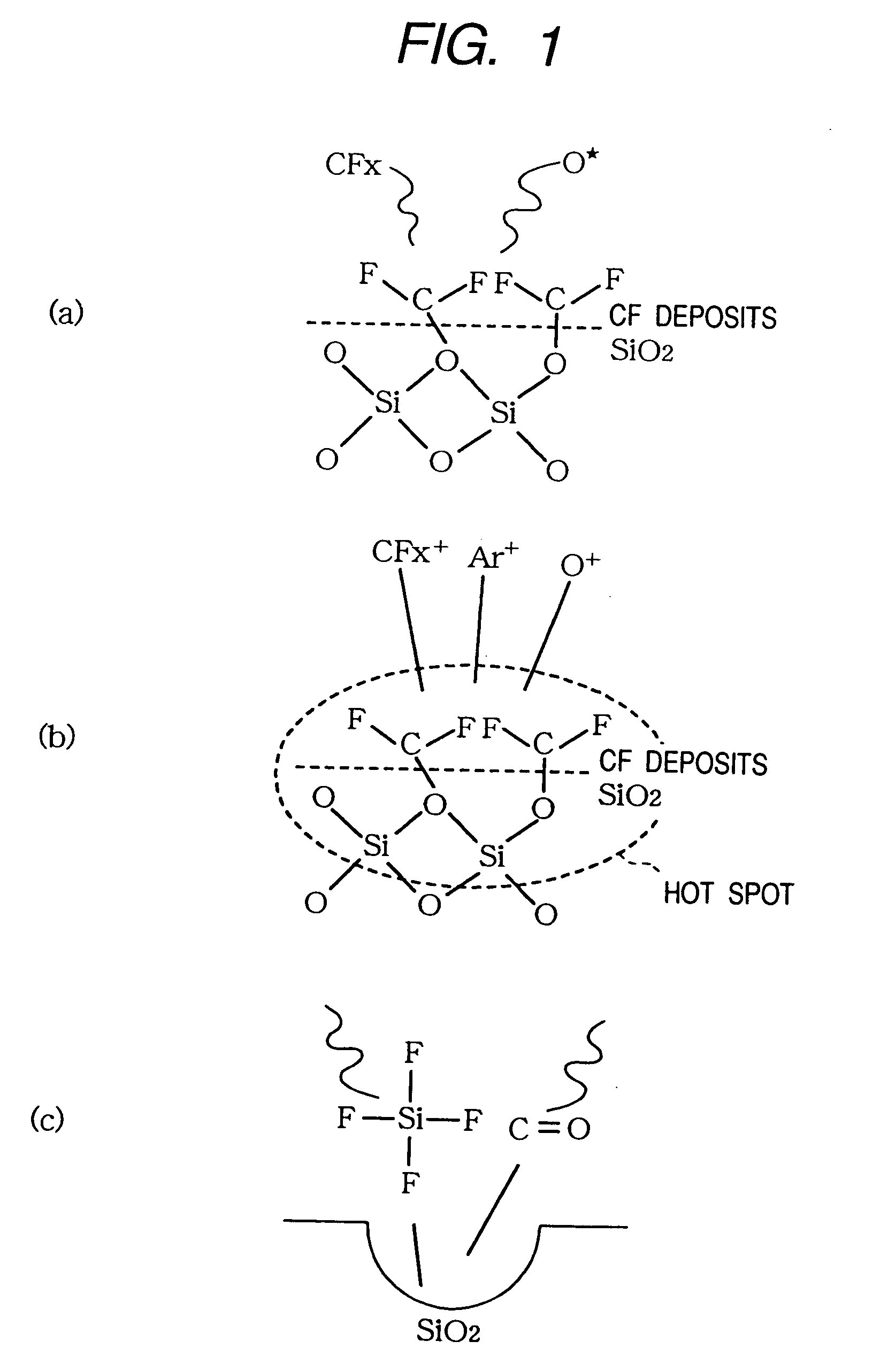

Method of manufacture of semiconductor integrated circuit

InactiveUS20050186801A1Improve etch selectivitySemiconductor/solid-state device detailsSolid-state devicesResistElectrical conductor

In a process for the manufacture of a semiconductor integrated circuit device having an inlaid interconnect structure by embedding a conductor film in a recess, such as a trench or hole, formed in an organic insulating film which constitutes an interlevel dielectric film and includes an organosiloxane as a main component, the recess, such as a trench or hole, is formed by subjecting the organic insulating film to plasma dry etching in a CF-based gas / N2 / Ar gas in order to suppress the formation of an abnormal shape on the bottom of the recess, upon formation of a photoresist film over the organic insulating film, followed by formation of the recess therein with the photoresist film as an etching mask.

Owner:RENESAS ELECTRONICS CORP

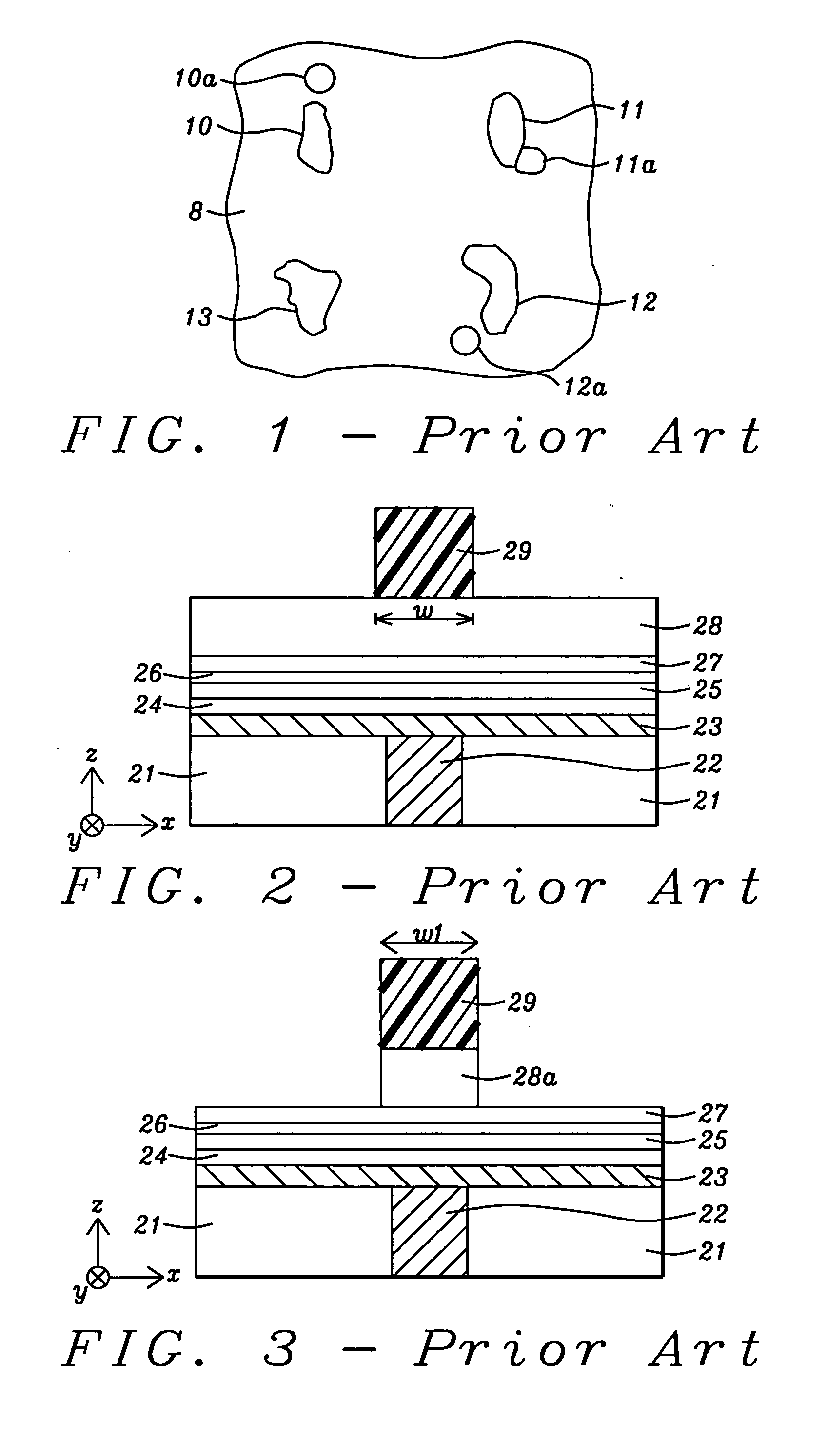

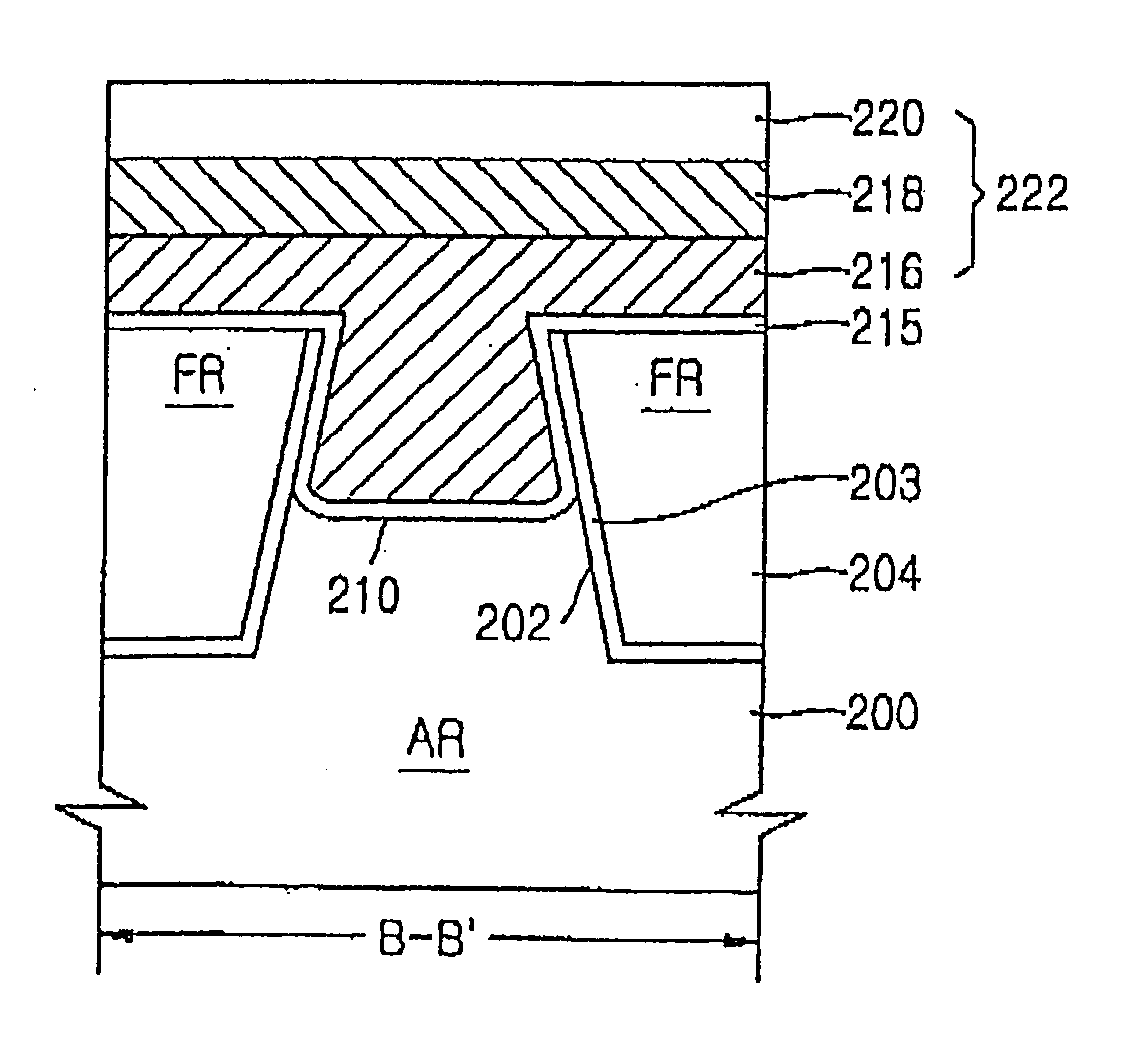

High selectivity Si-rich SiON etch-stop layer

InactiveUS6245669B1Superior light absorption qualityReduce RC delaySemiconductor/solid-state device manufacturingResistSilicon oxide

The present invention provides an anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer and two compatible oxide etch processes. The Si-Rich Silicon oxynitride (SiON) etch barrier layer can be used as a hard mask in a dual damascene structure and as a hard mask for over a polysilicon gate. The invention has the following key elements: 1) Si rich Silicon oxynitride (SiON) ARC layer, 2) Special Silicon oxide Etch process that has a high selectivity of Si-Rich SiON to silicon oxide or SiN; 3) Special Si Rich SiON spacer process for a self aligned contact (SAC).A dual damascene structure is formed by depositing a first dielectric layer. A novel anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer is deposited on top of the first dielectric layer. A first opening is etched in the first insulating layer. A second dielectric layer is deposited on the anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer. A second dual damascene opening is etched into the dielectric layers. The anti-reflective Si-Rich Silicon oxynitride (SiON) etch barrier layer can also serve as an ARC layer during these operations to reduce the amount of reflectance from conductive region to reduce distortion of the photoresist pattern.

Owner:TAIWAN SEMICON MFG CO LTD

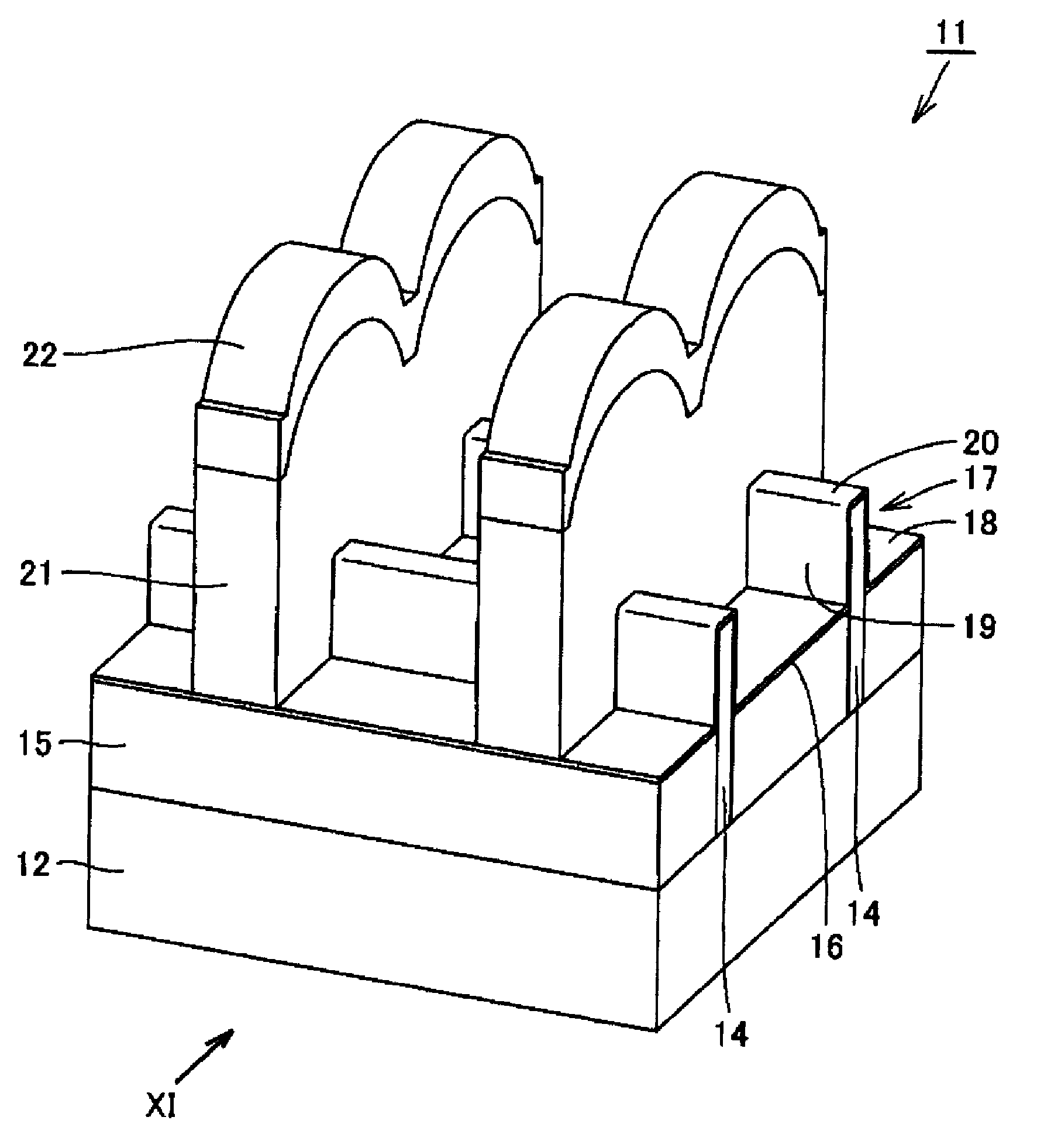

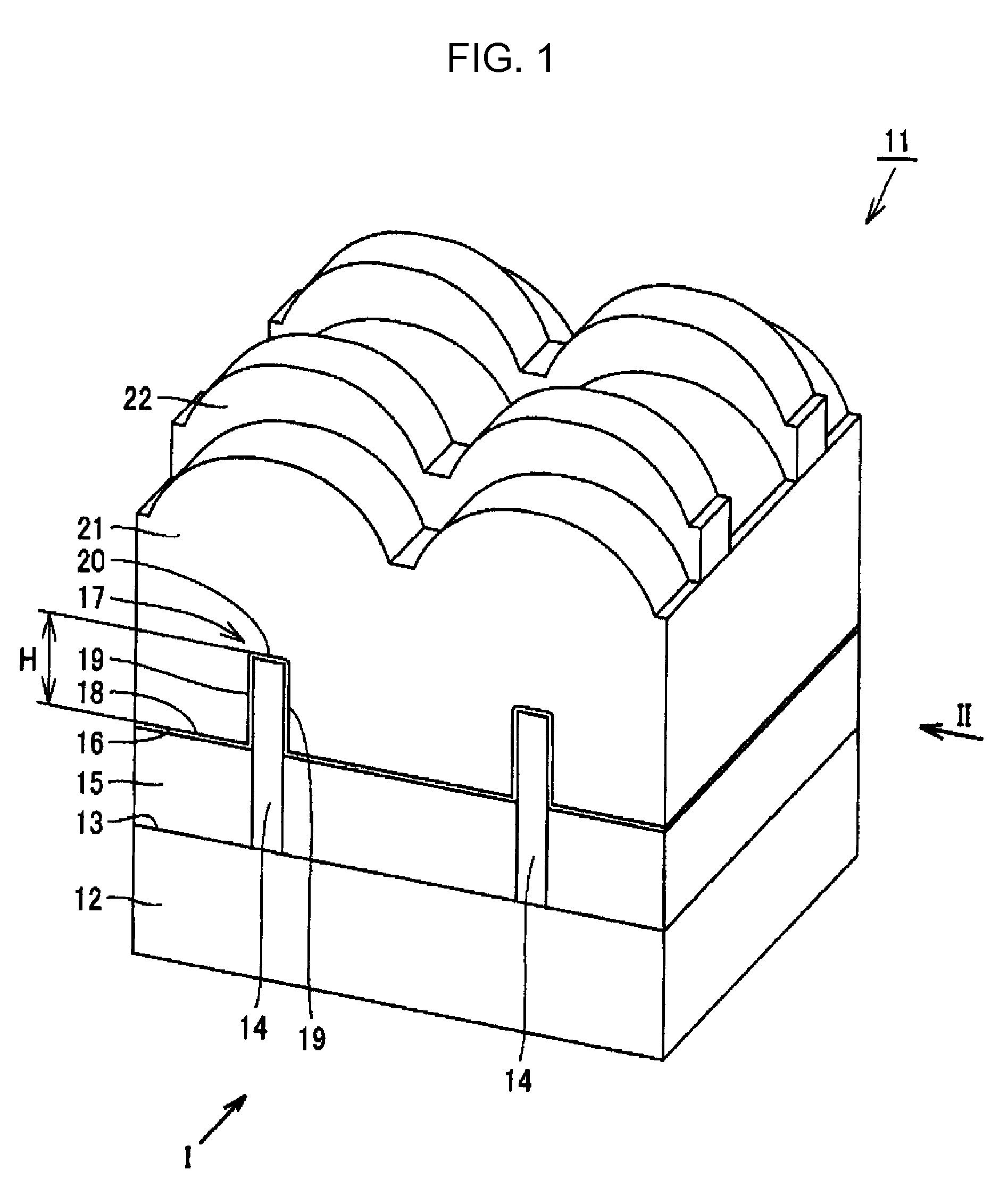

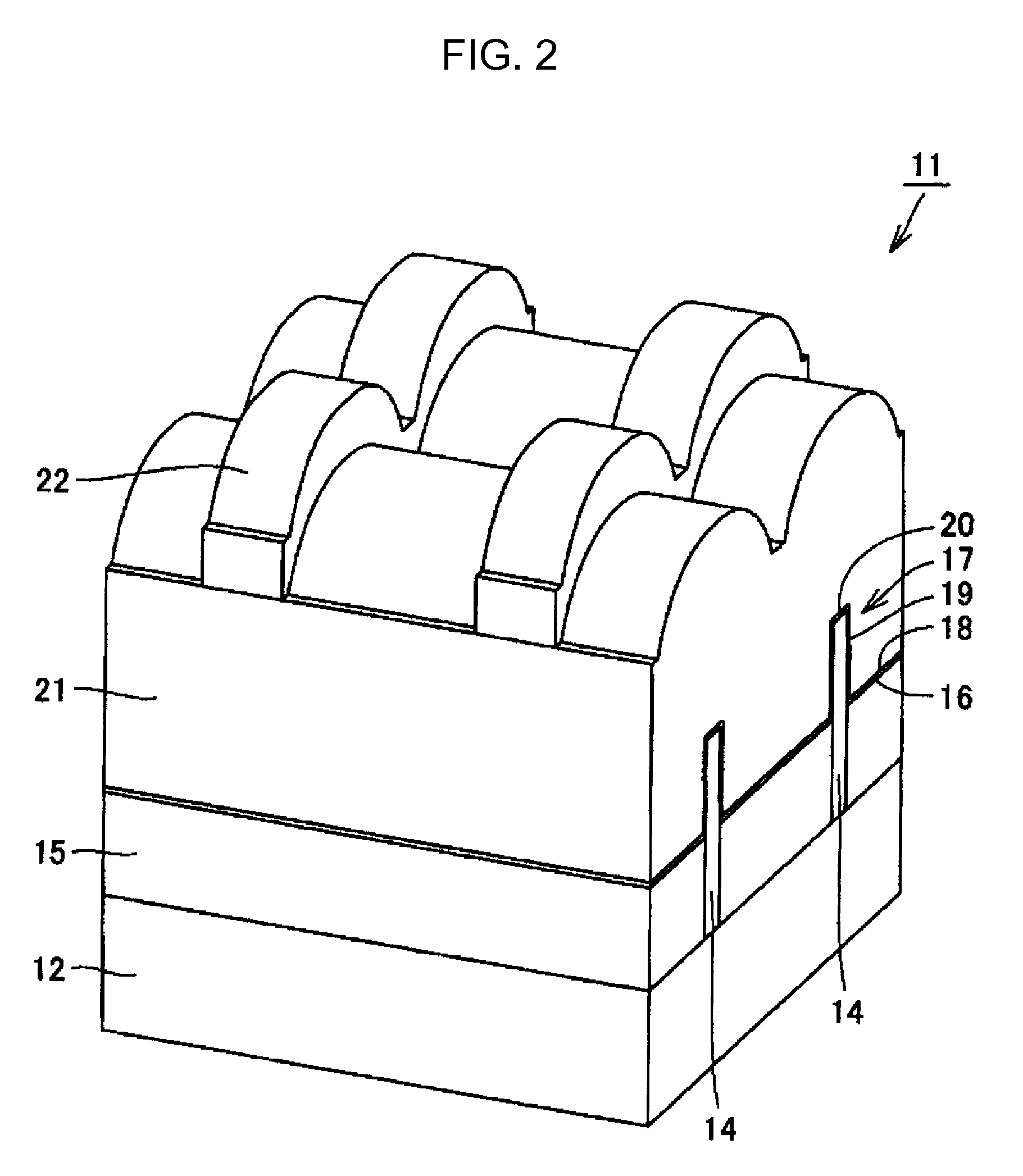

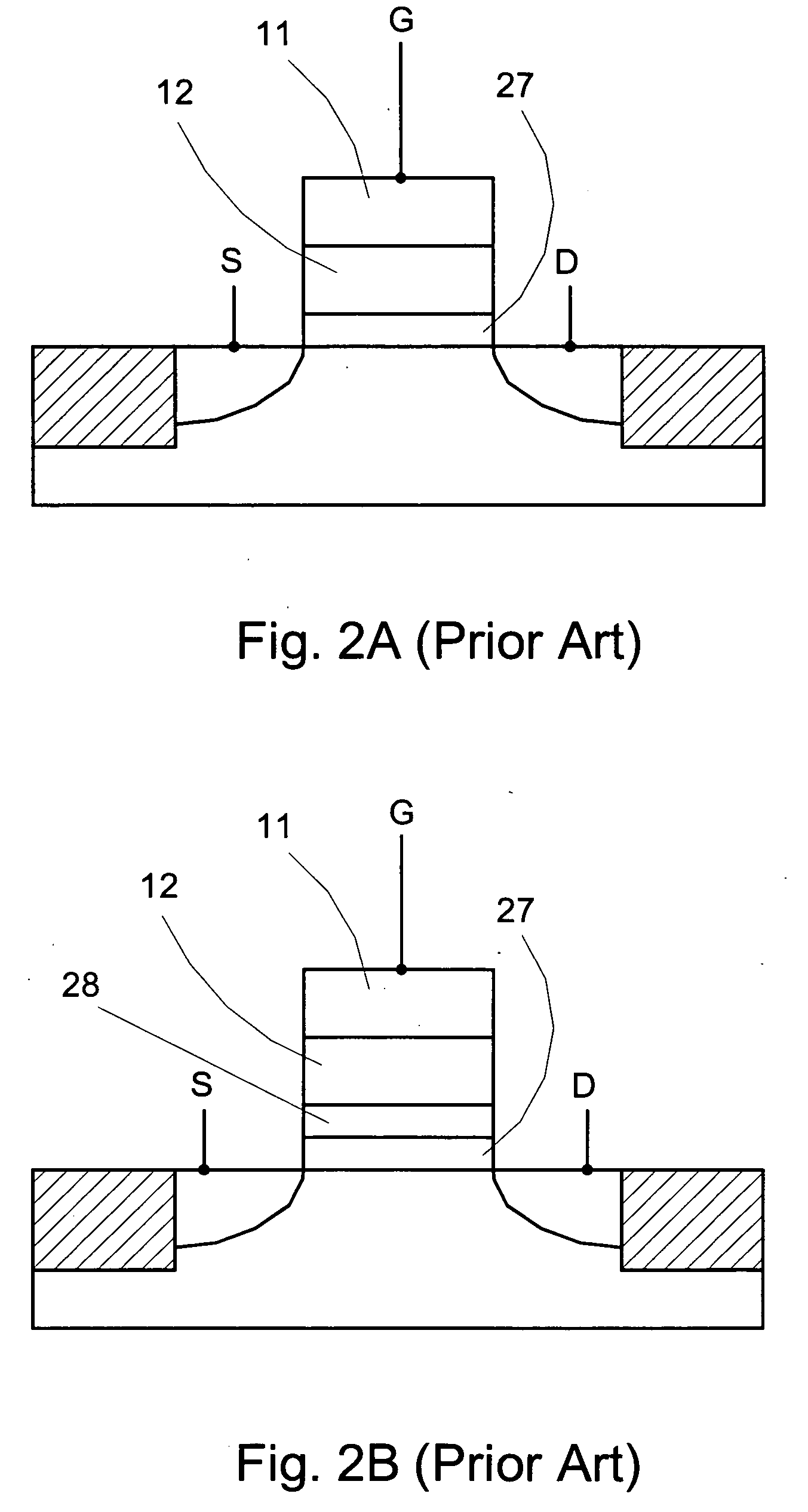

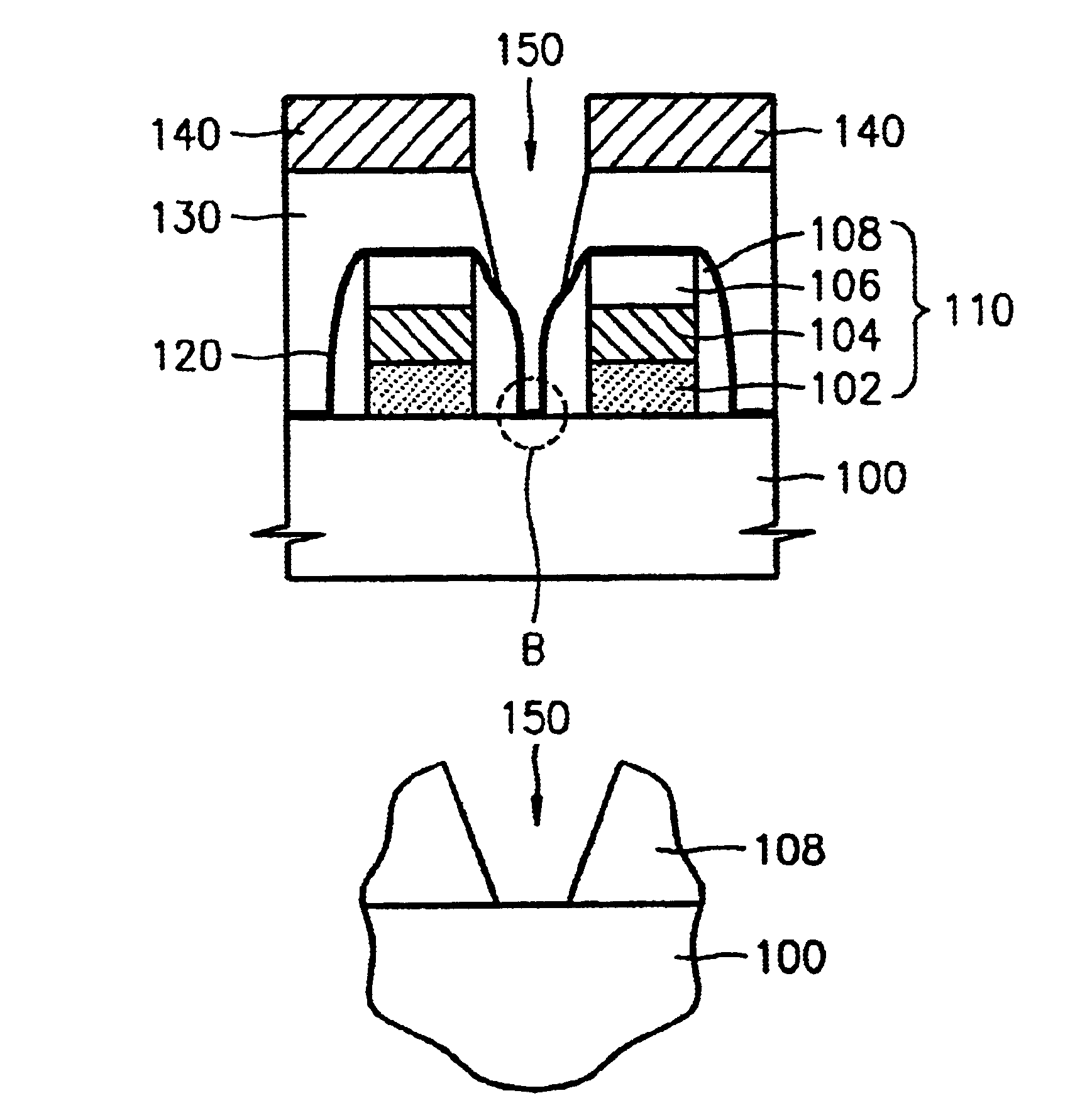

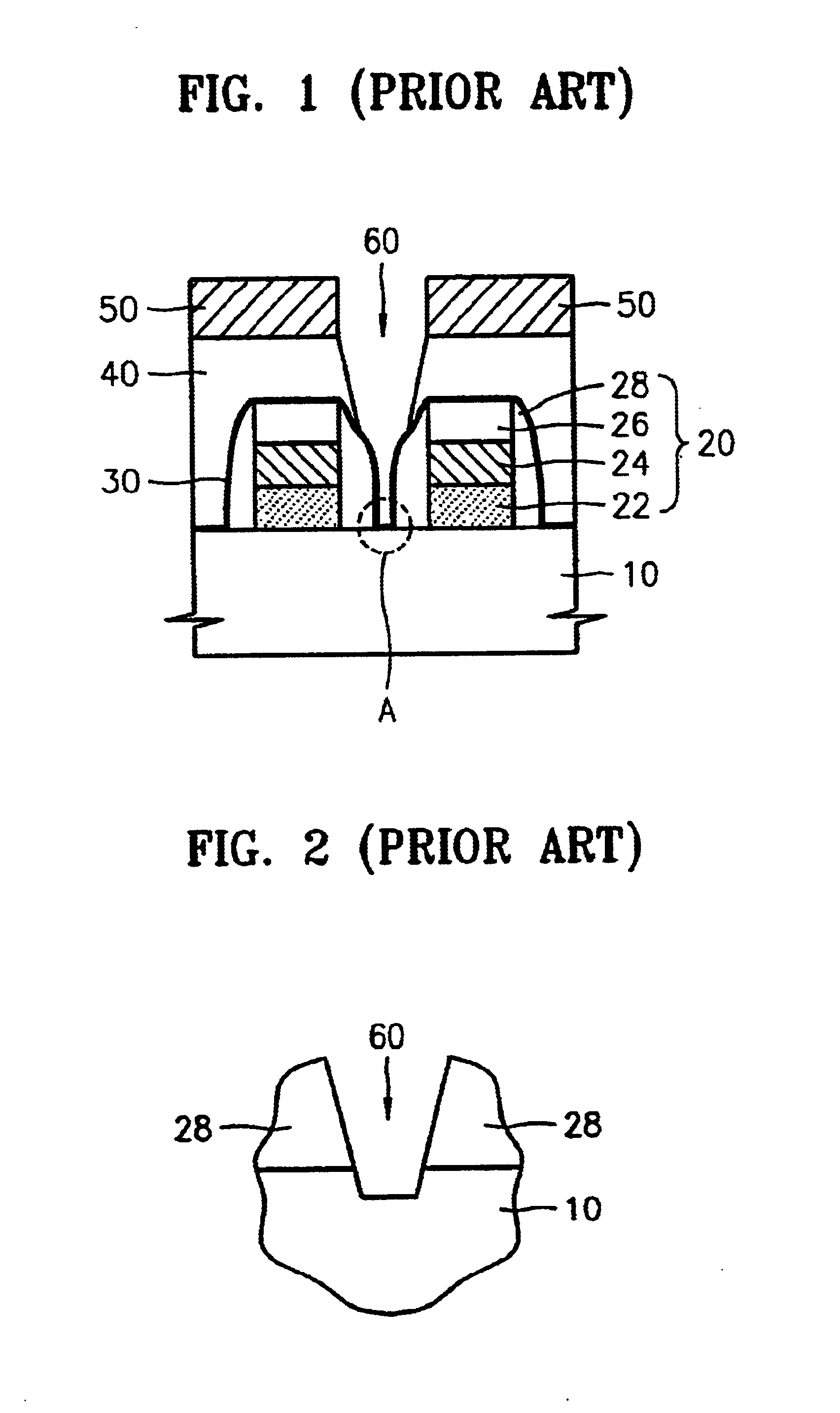

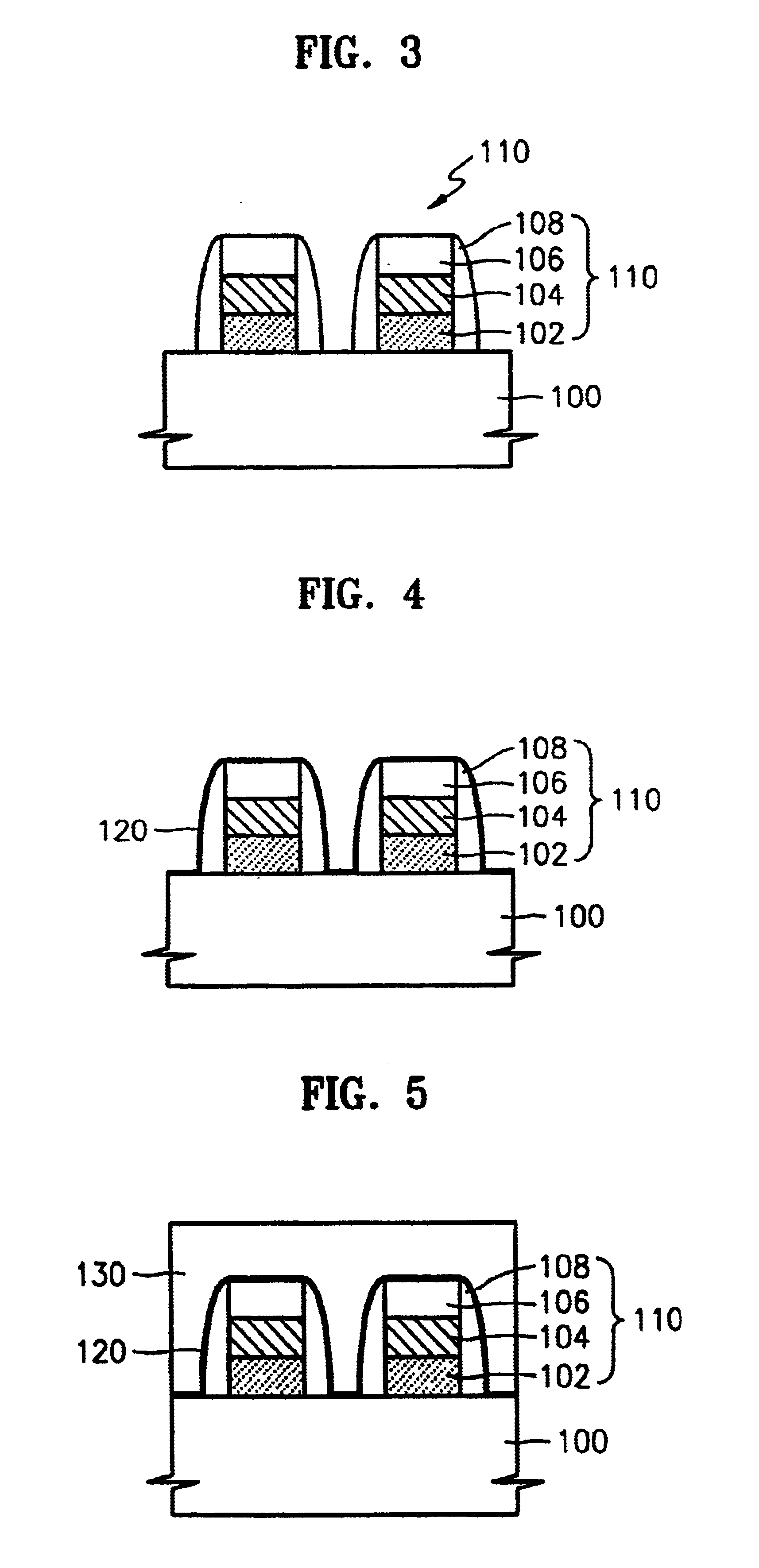

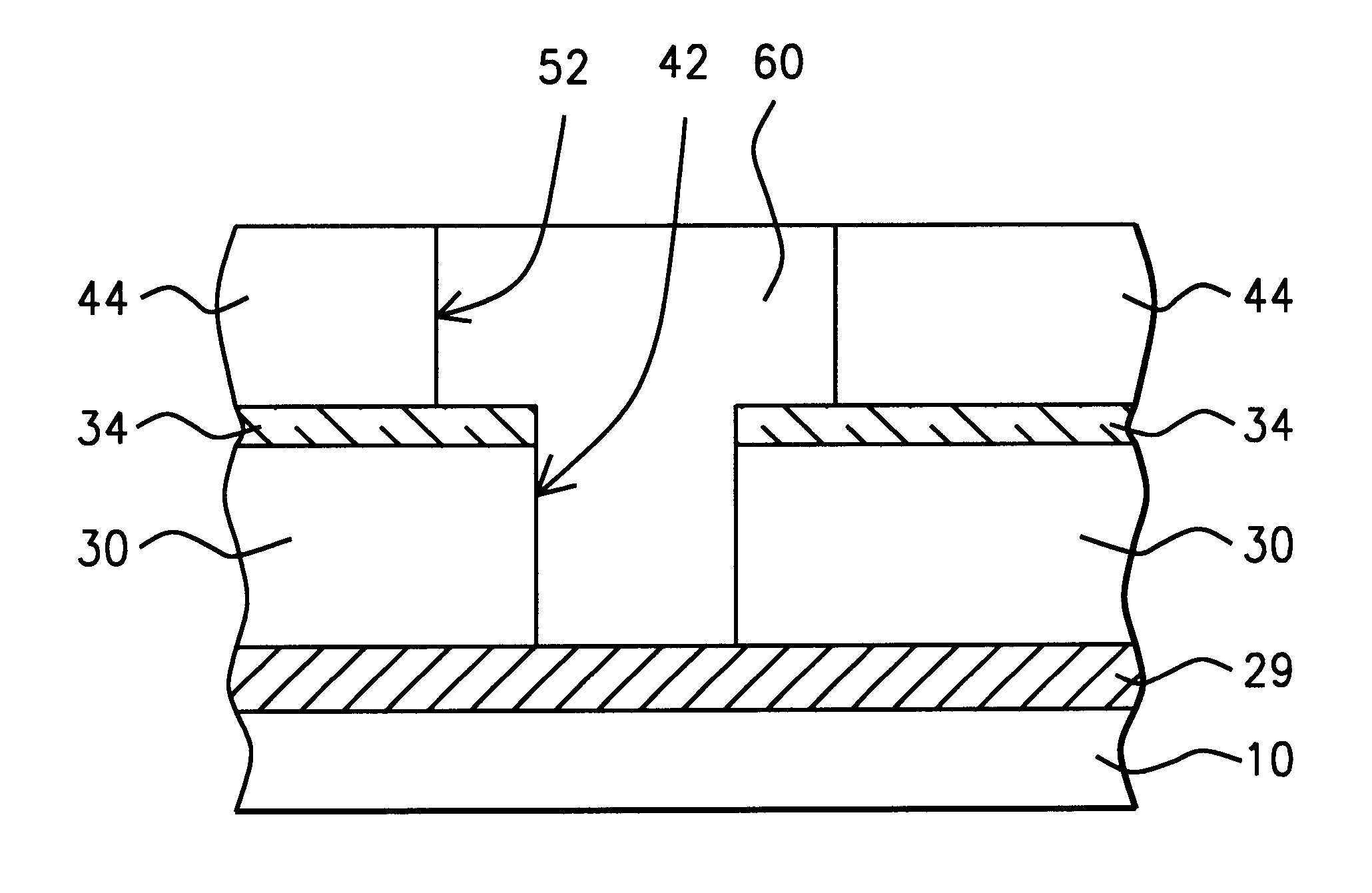

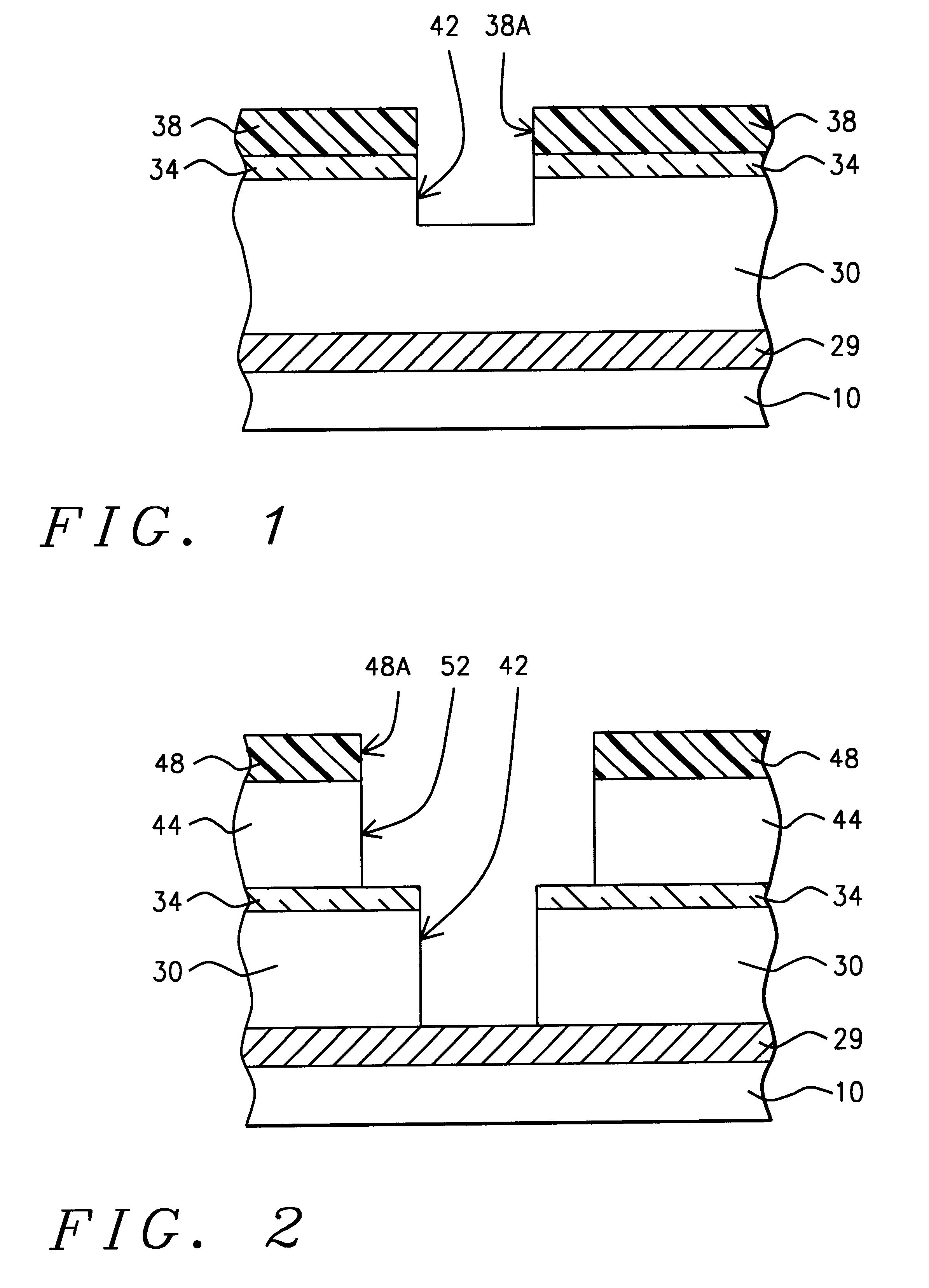

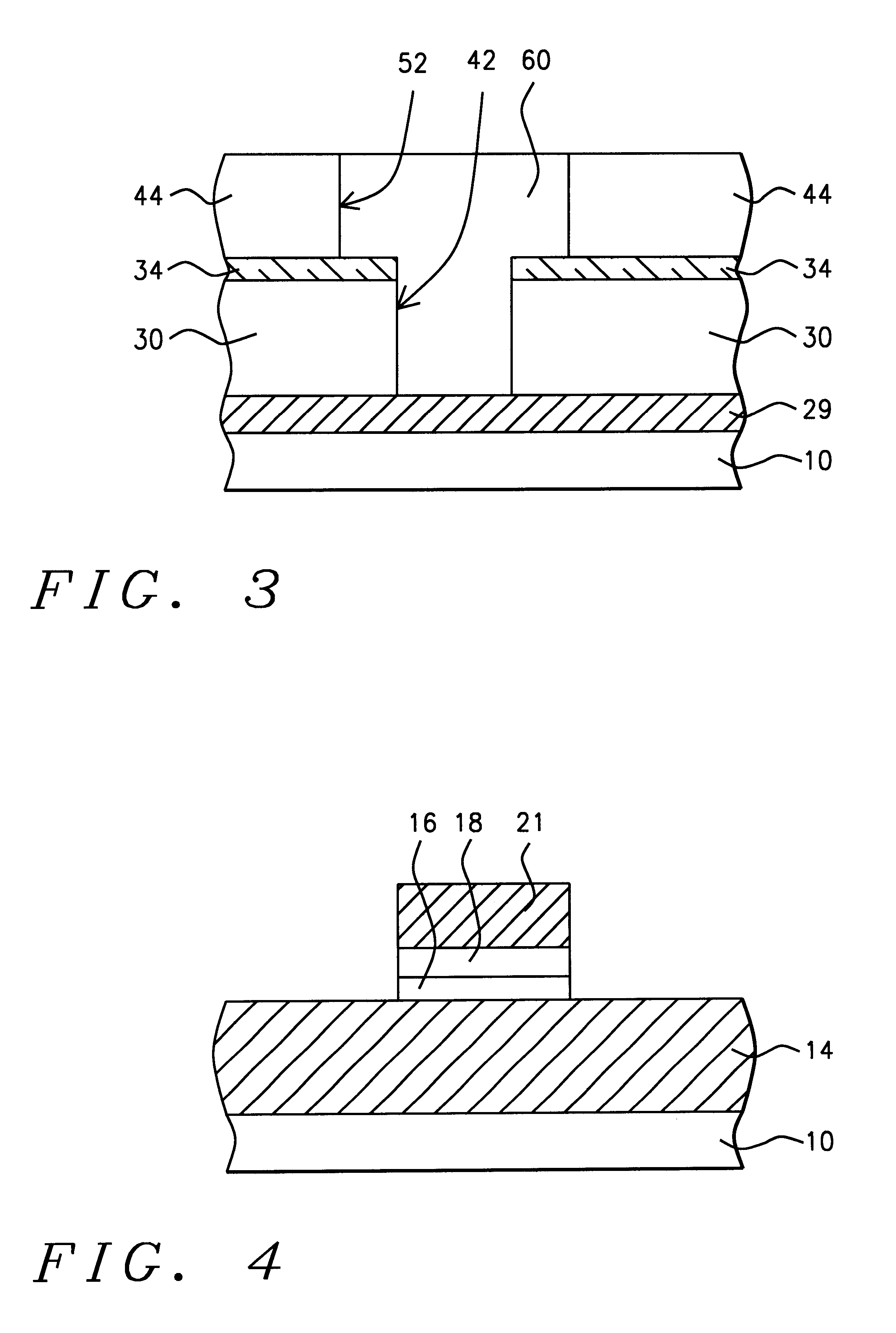

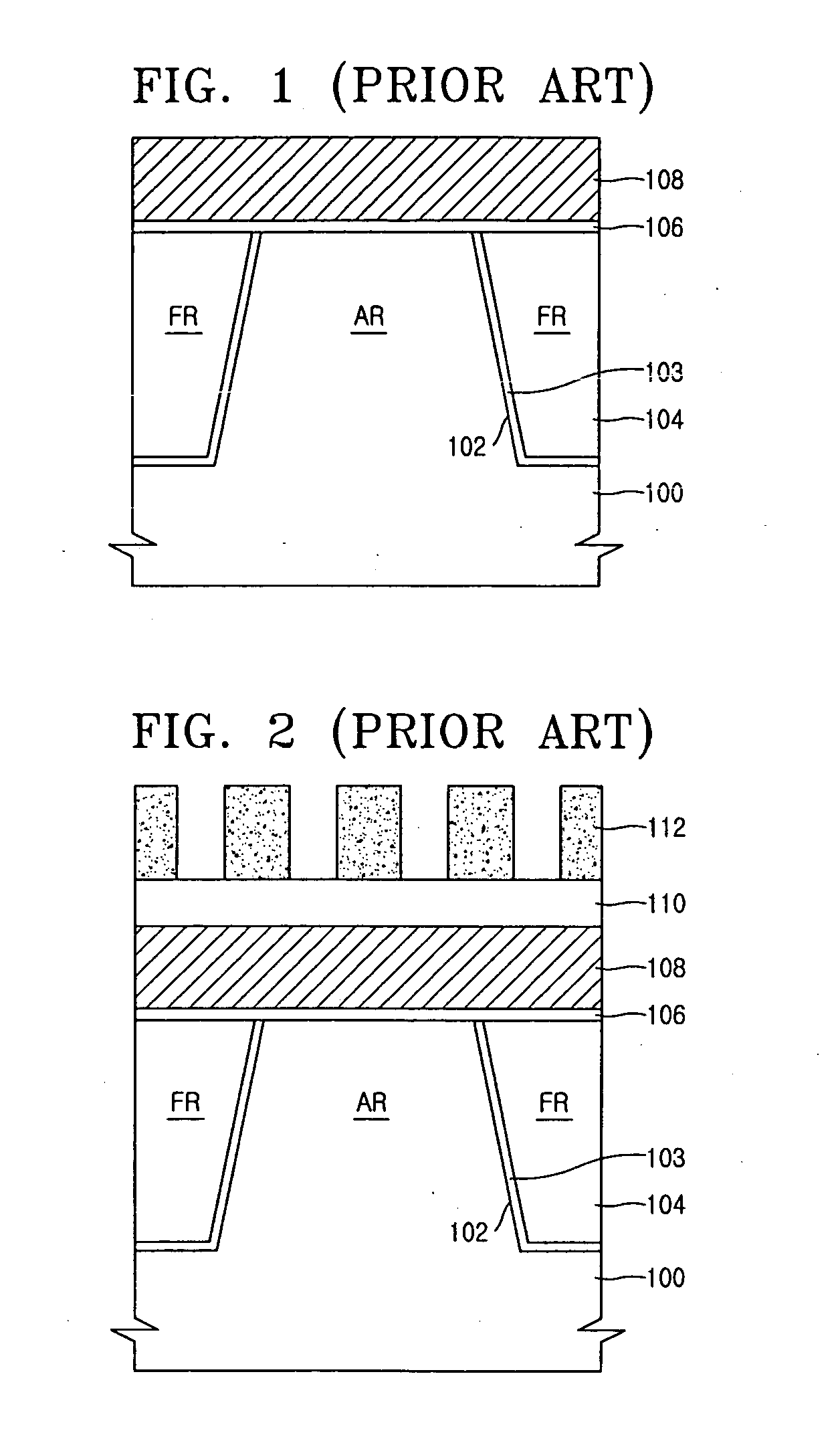

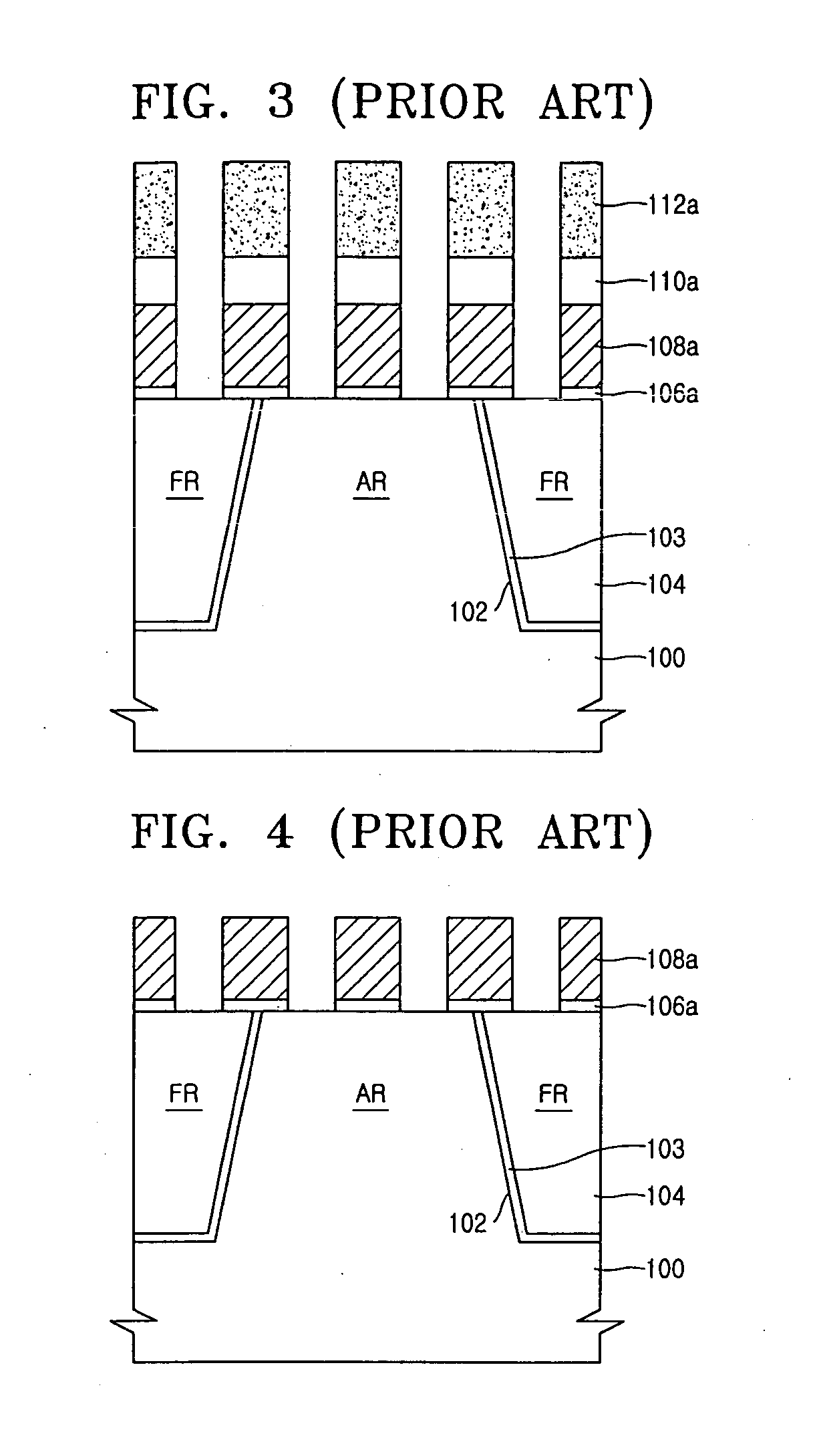

Method of fabricating a recess channel array transistor using a mask layer with a high etch selectivity with respect to a silicon substrate

ActiveUS20050136616A1Easily controlGood etch uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsEtching selectivity

A method of fabricating a recess channel array transistor. Using a mask layer pattern having a high etch selectivity with respect to a silicon substrate, the silicon substrate and an isolation insulating layer are etched to form a recess channel trench. After forming a gate insulating layer and a recess gate stack on the recess channel trench, a source and a drain are formed in the silicon substrate adjacent to both sidewalls of the recess gate stack, thereby completing the recess channel array transistor. Because the mask layer pattern having the high etch selectivity with respect to the silicon substrate is used, a depth of the recess channel trench is easily controlled while good etching uniformity of the silicon substrate is obtained.

Owner:SAMSUNG ELECTRONICS CO LTD