Patents

Literature

1173 results about "Conductive channel" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Conductive channels take topological insulators to the edge. Step edges in topological crystalline insulators can produce electrically-conducting pathways where electrons with opposite spins move in opposite directions and U-turns are prohibited.

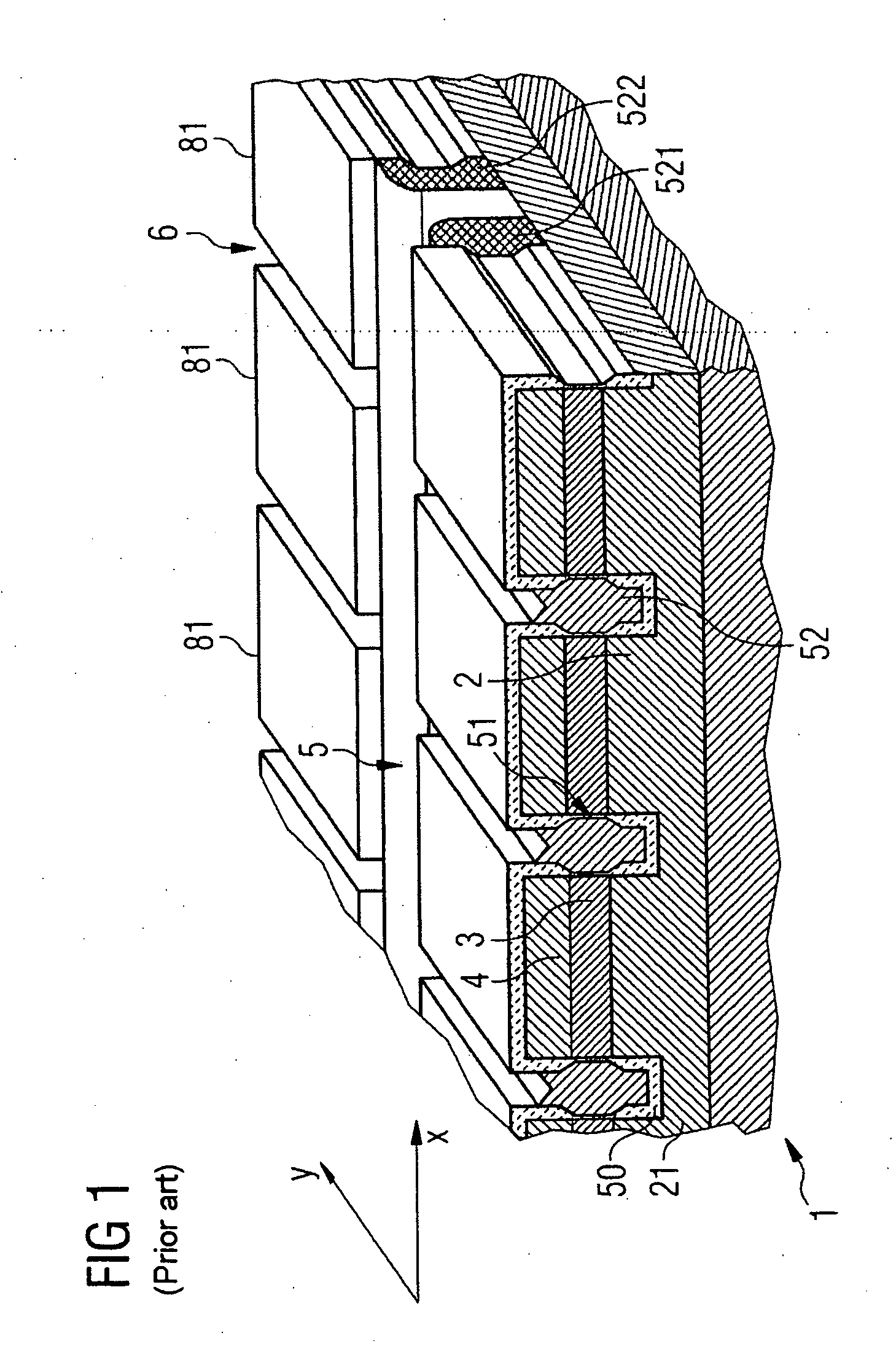

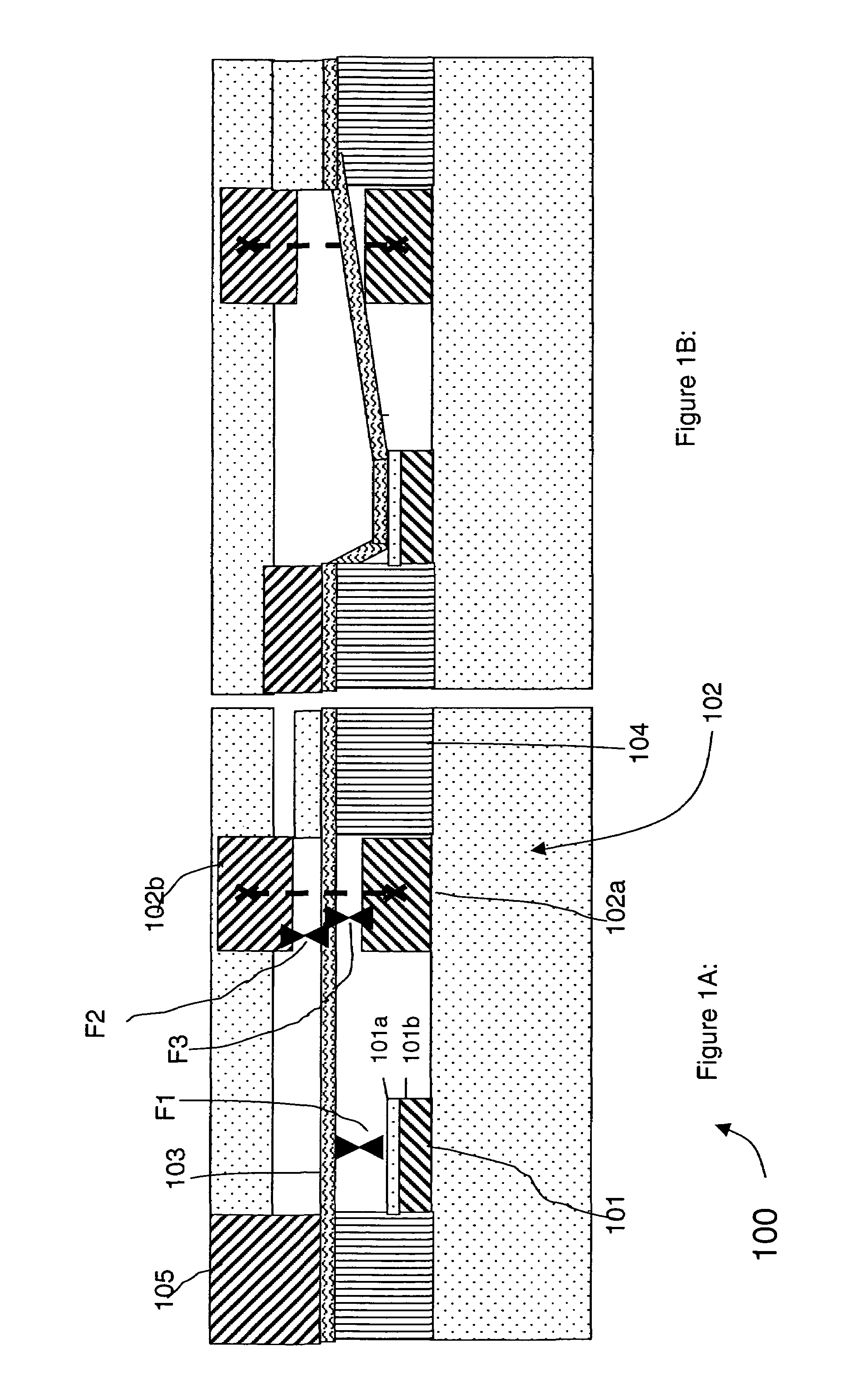

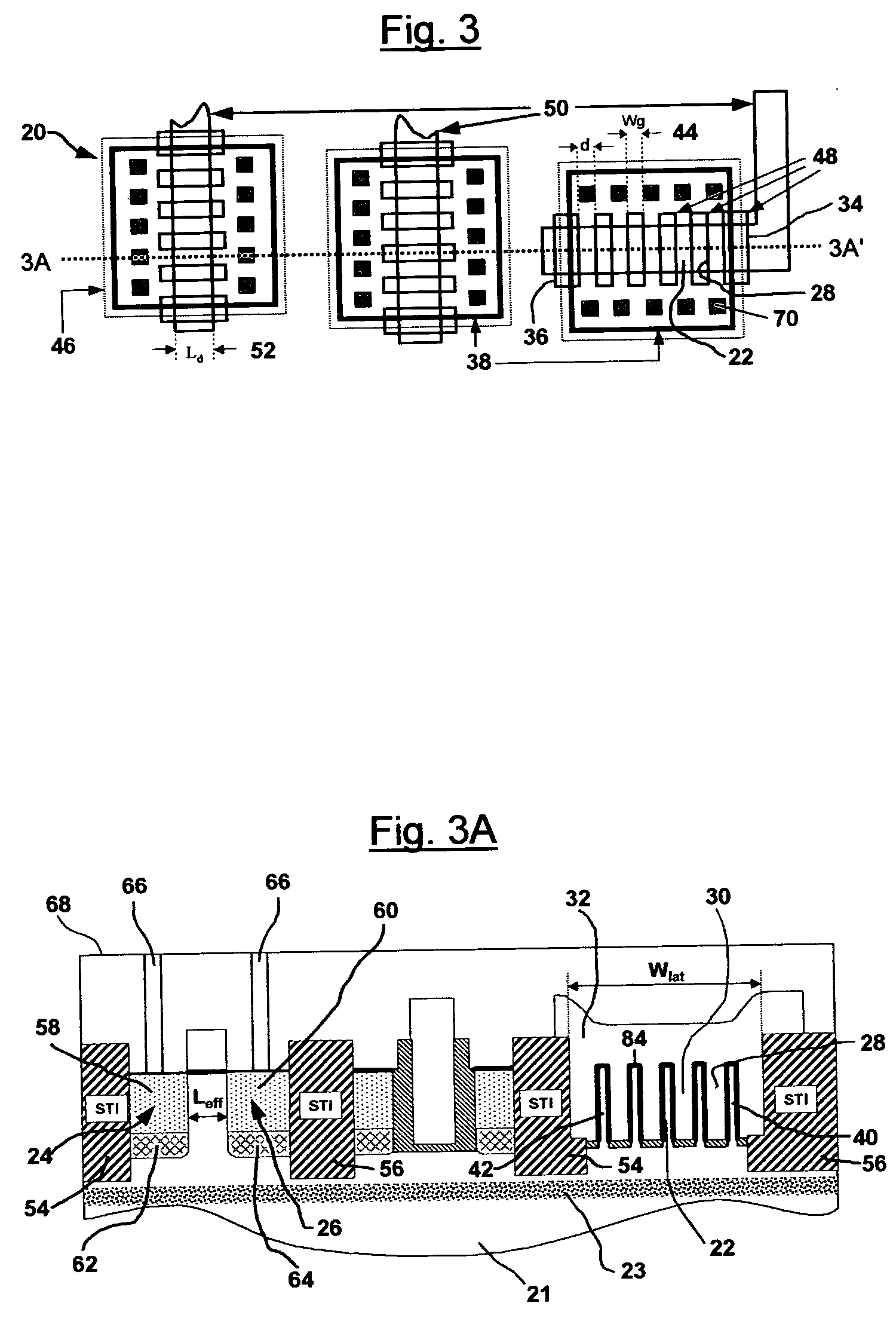

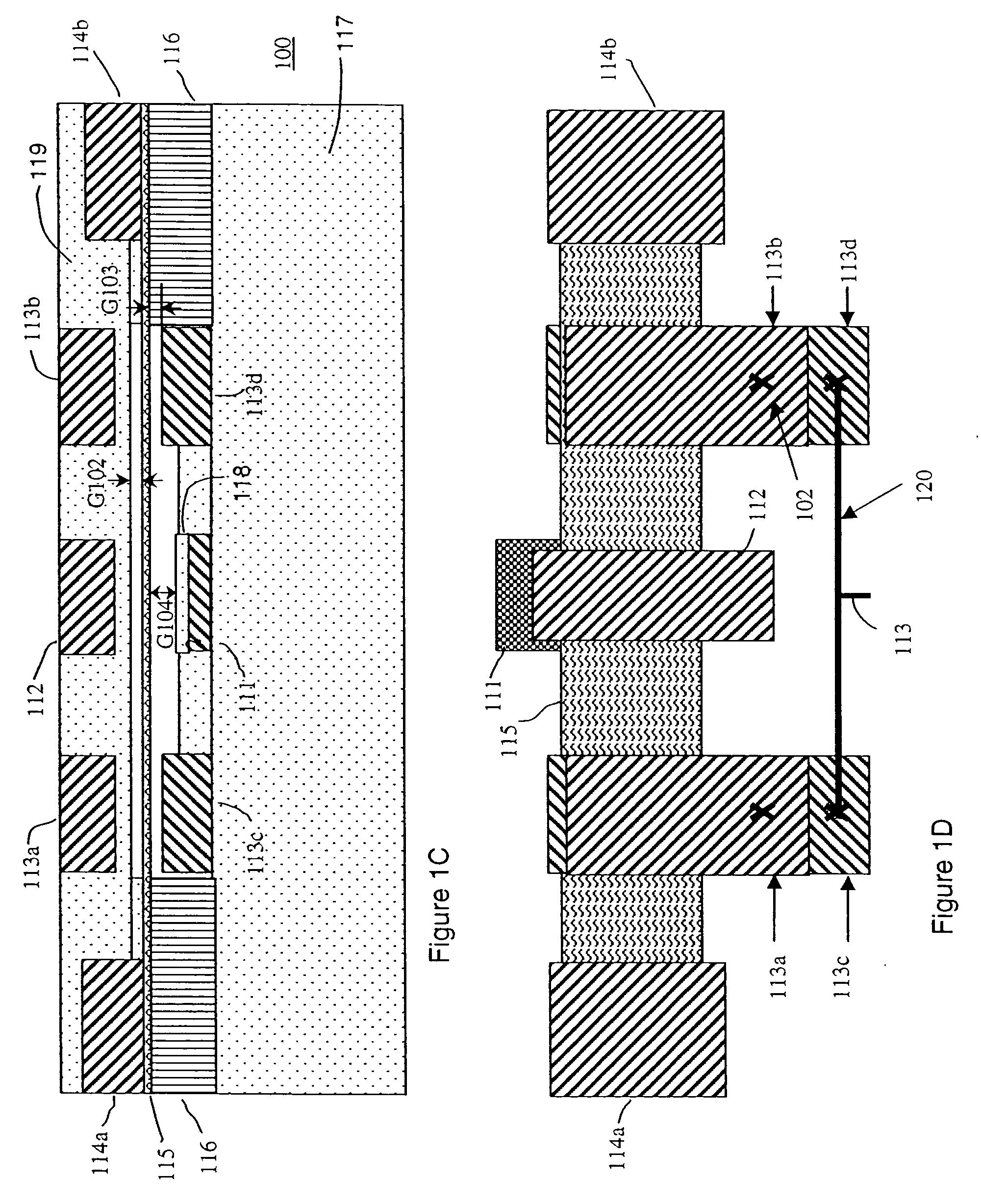

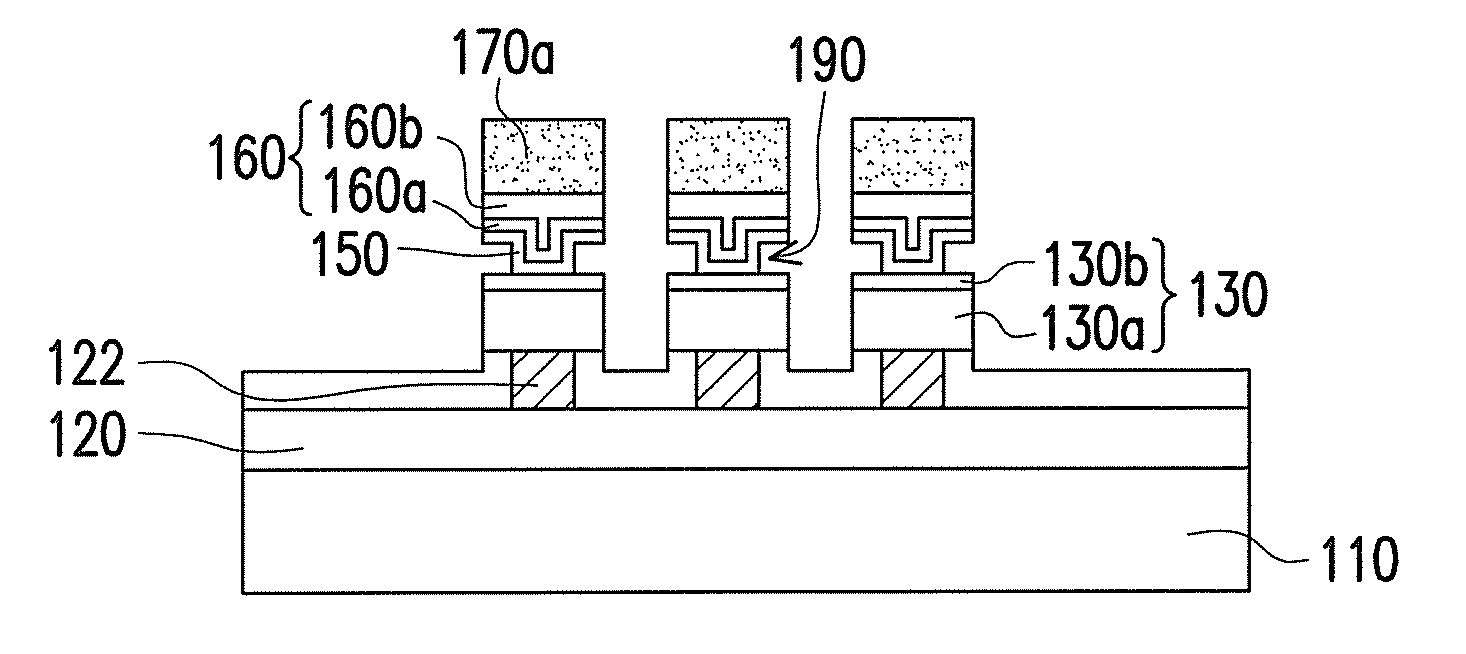

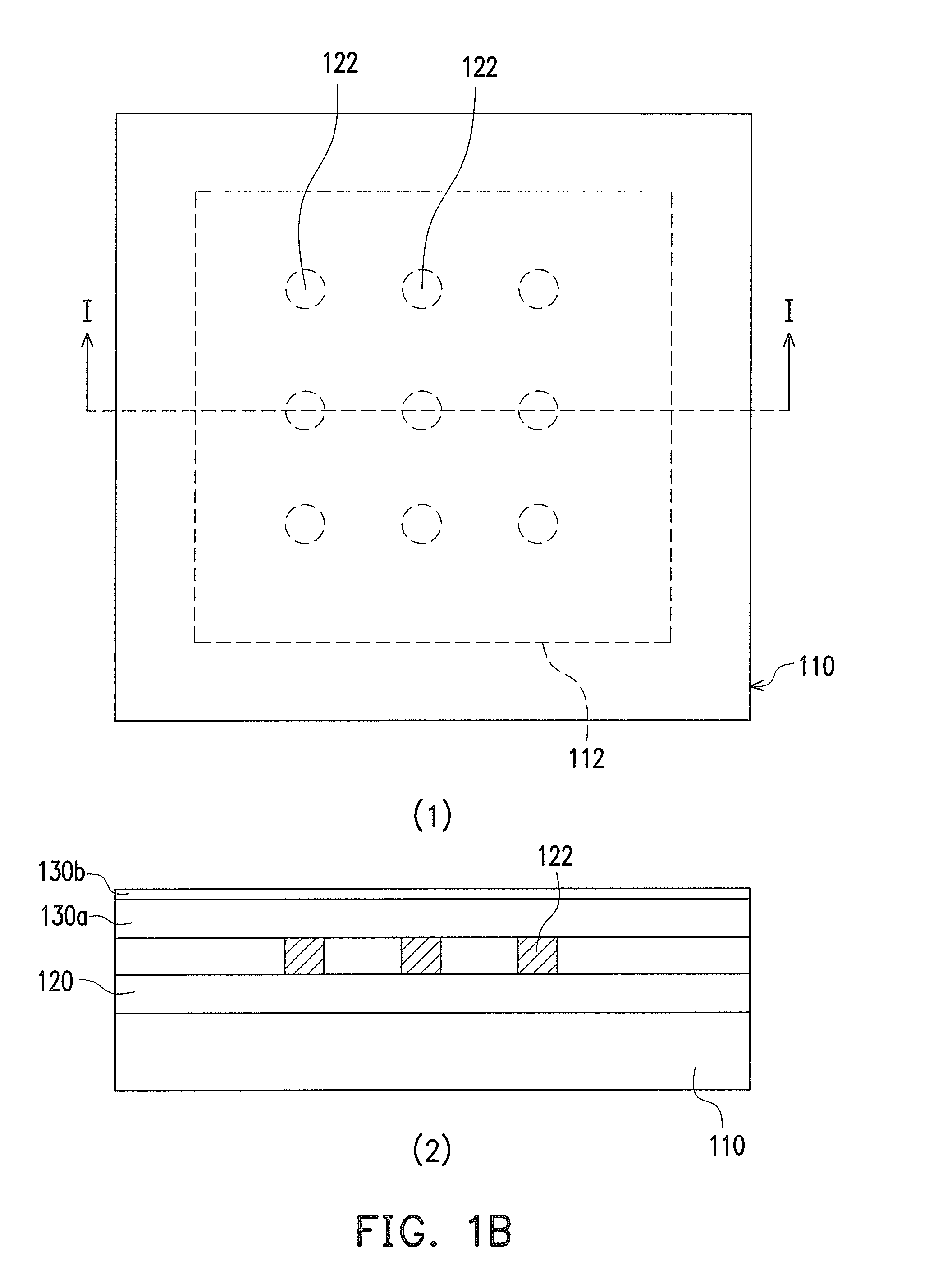

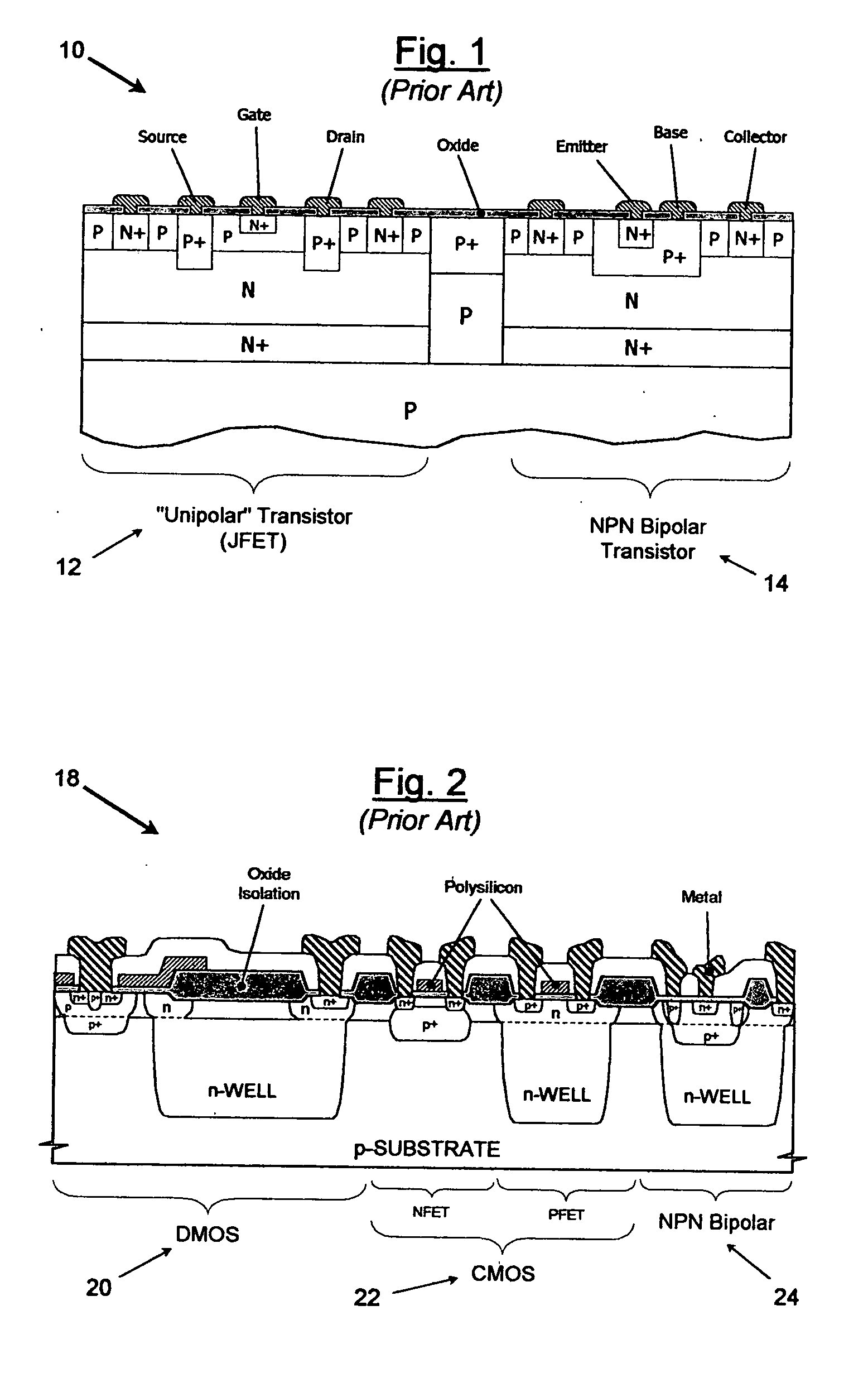

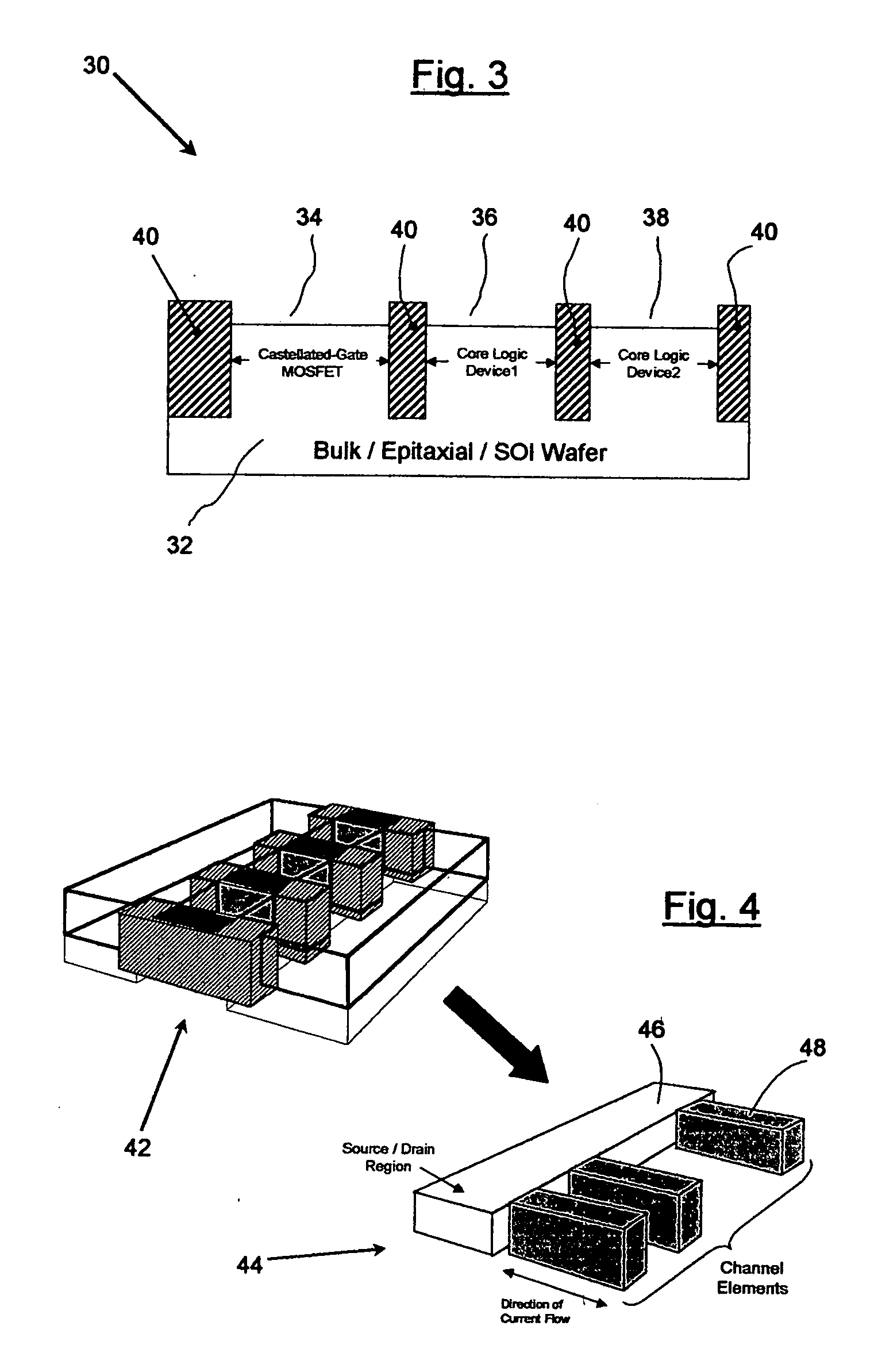

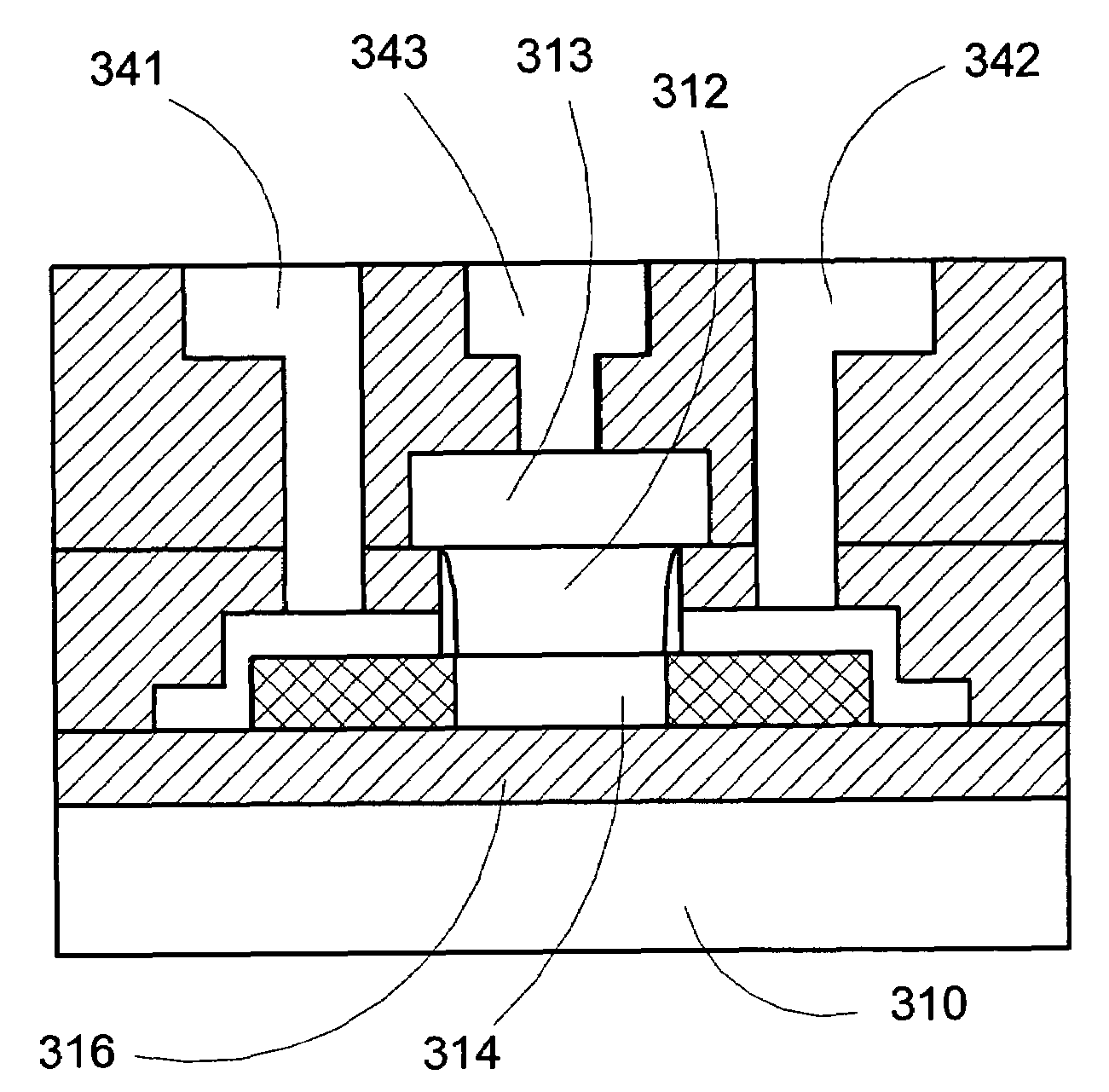

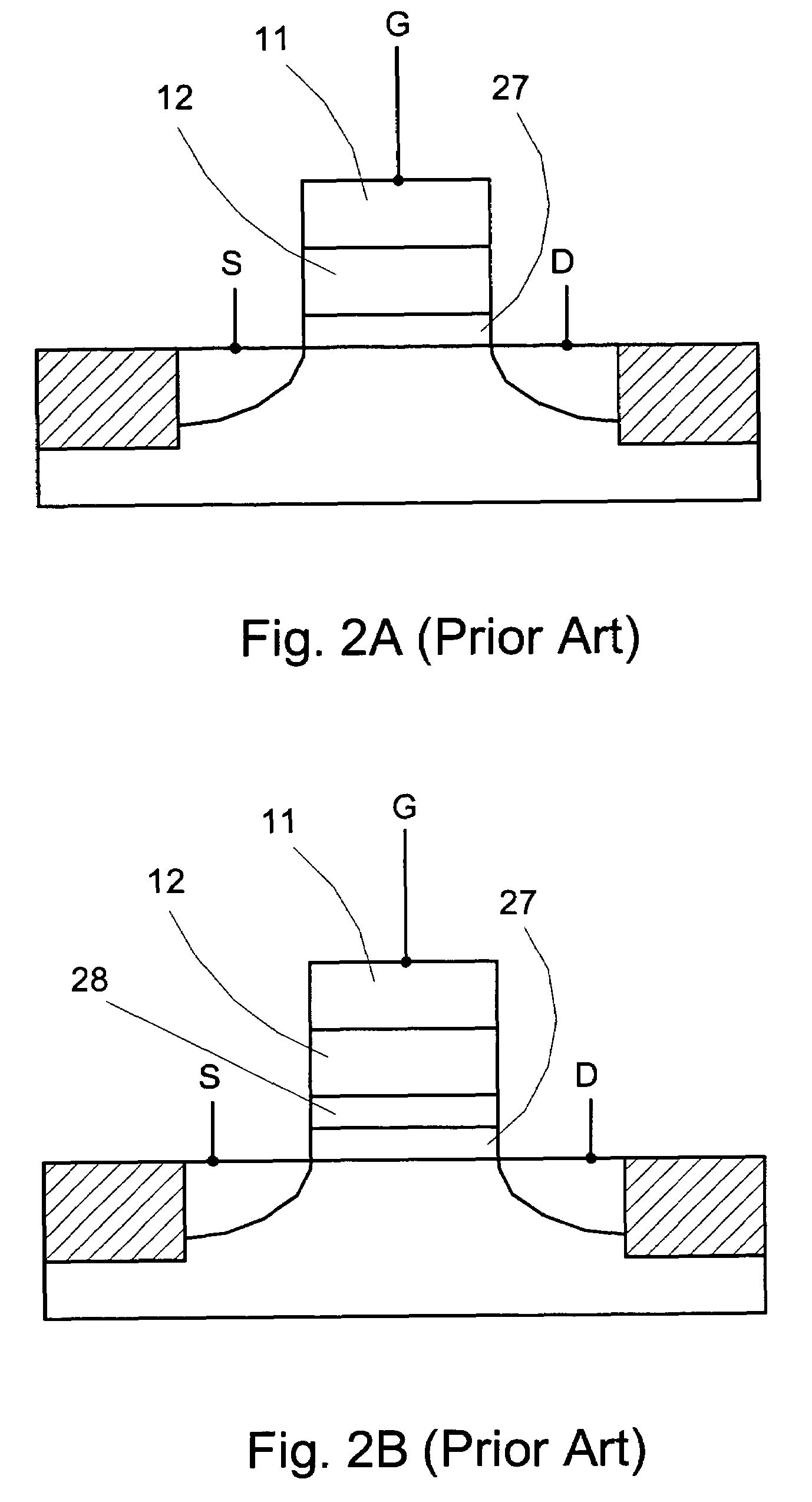

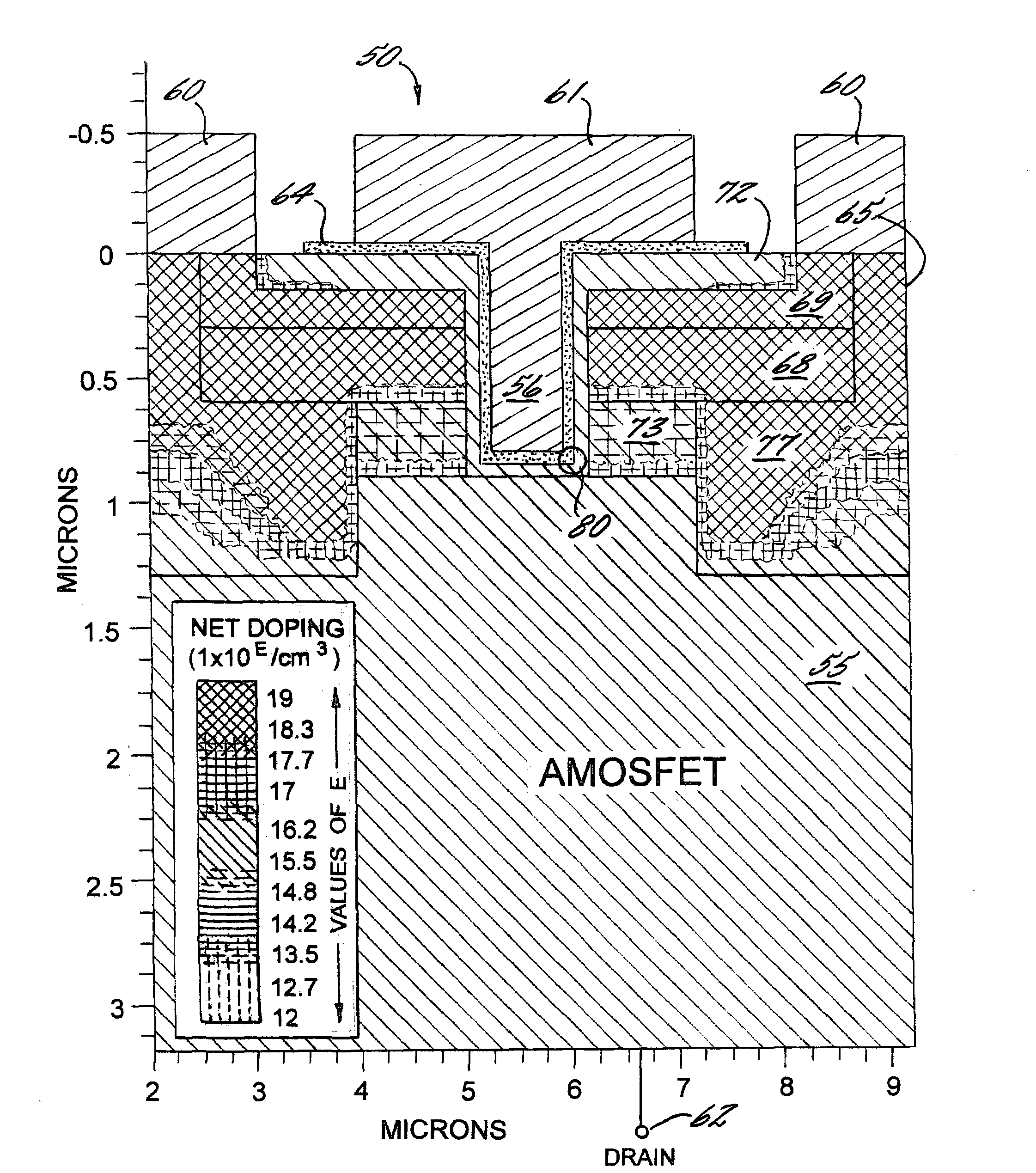

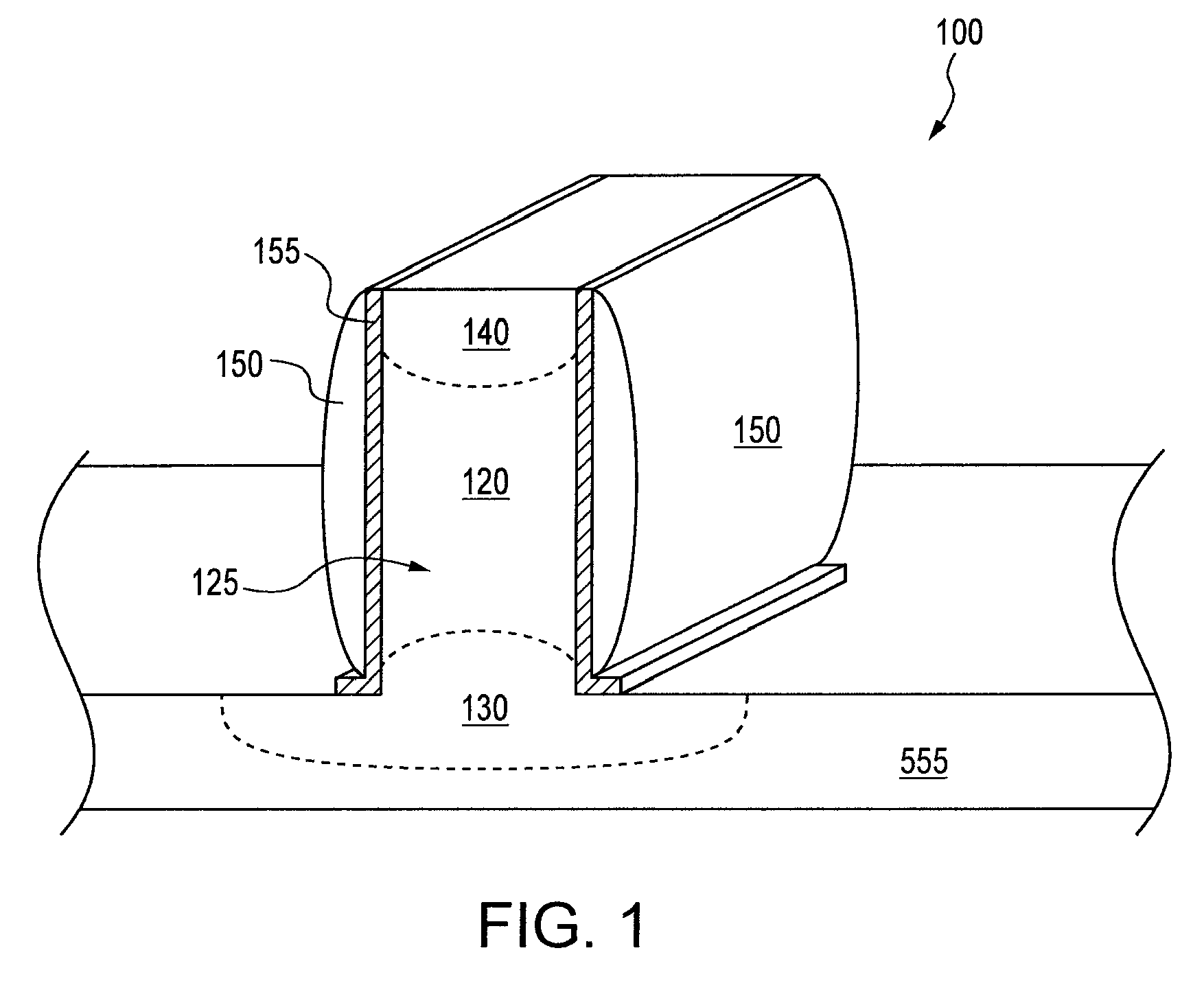

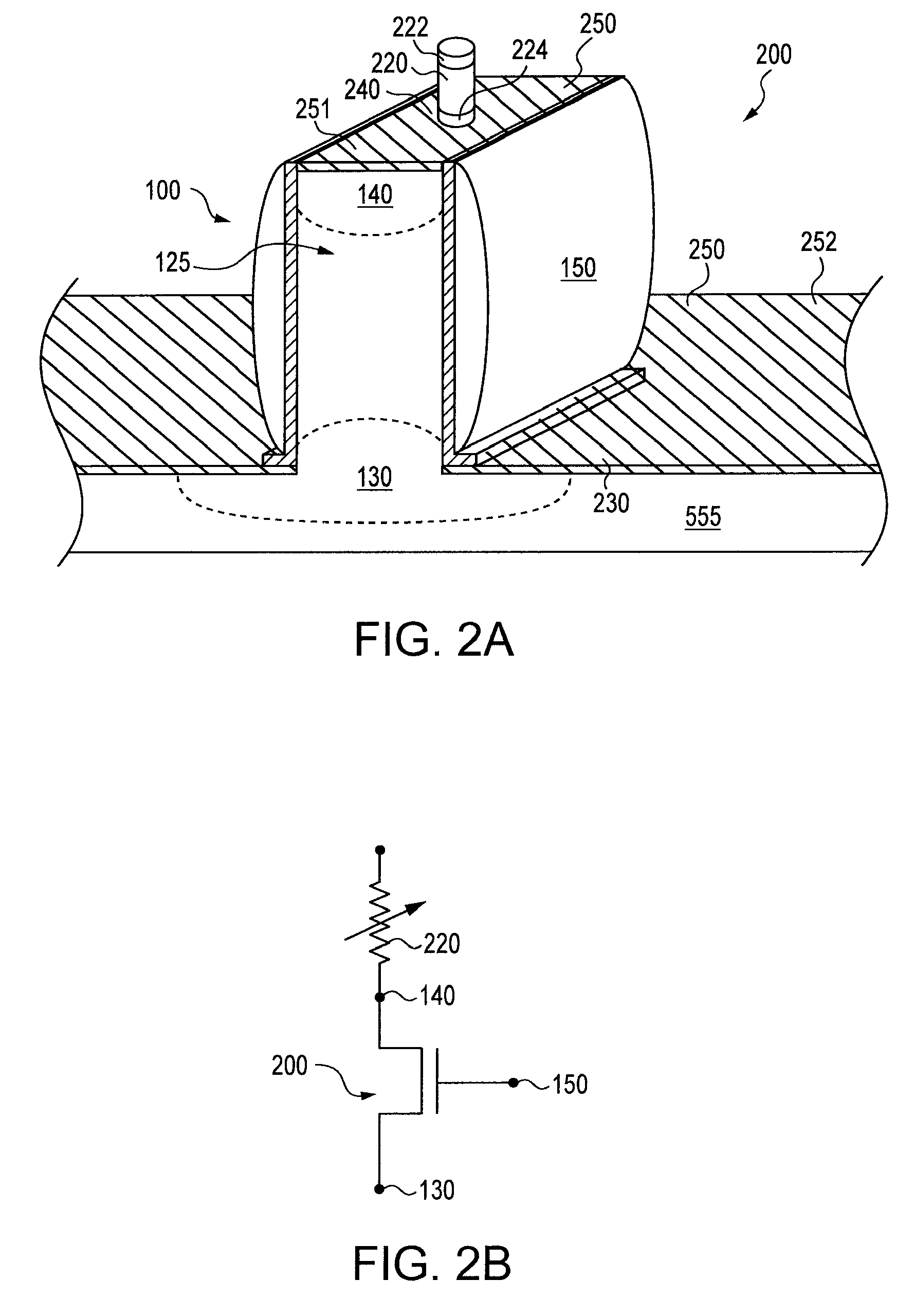

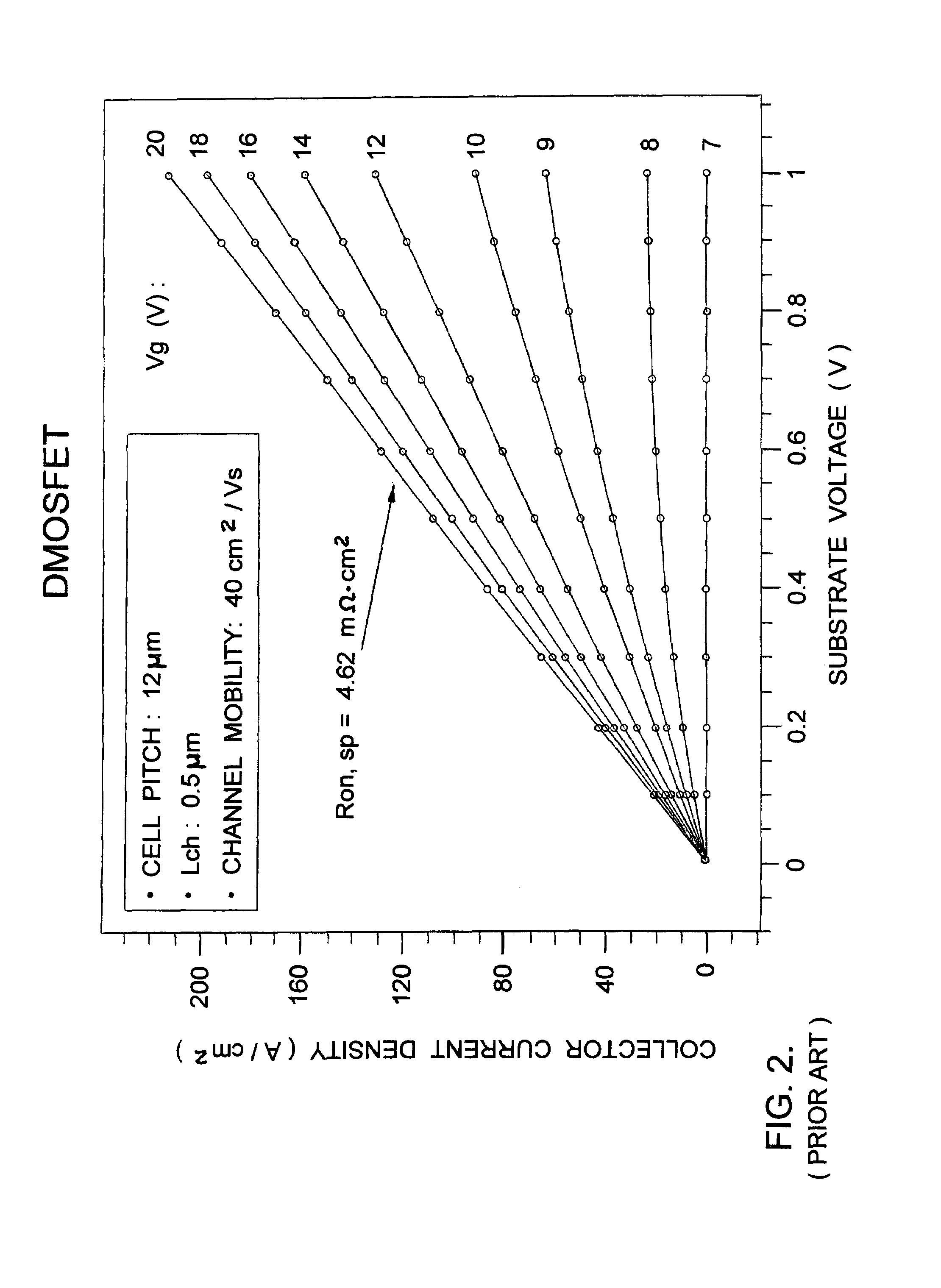

Fully-depleted castellated gate MOSFET device and method of manufacture thereof

ActiveUS20050056892A1Enhanced ESD/EOS and reliability characteristicsIncrease speedTransistorSolid-state devicesMOSFETDielectric layer

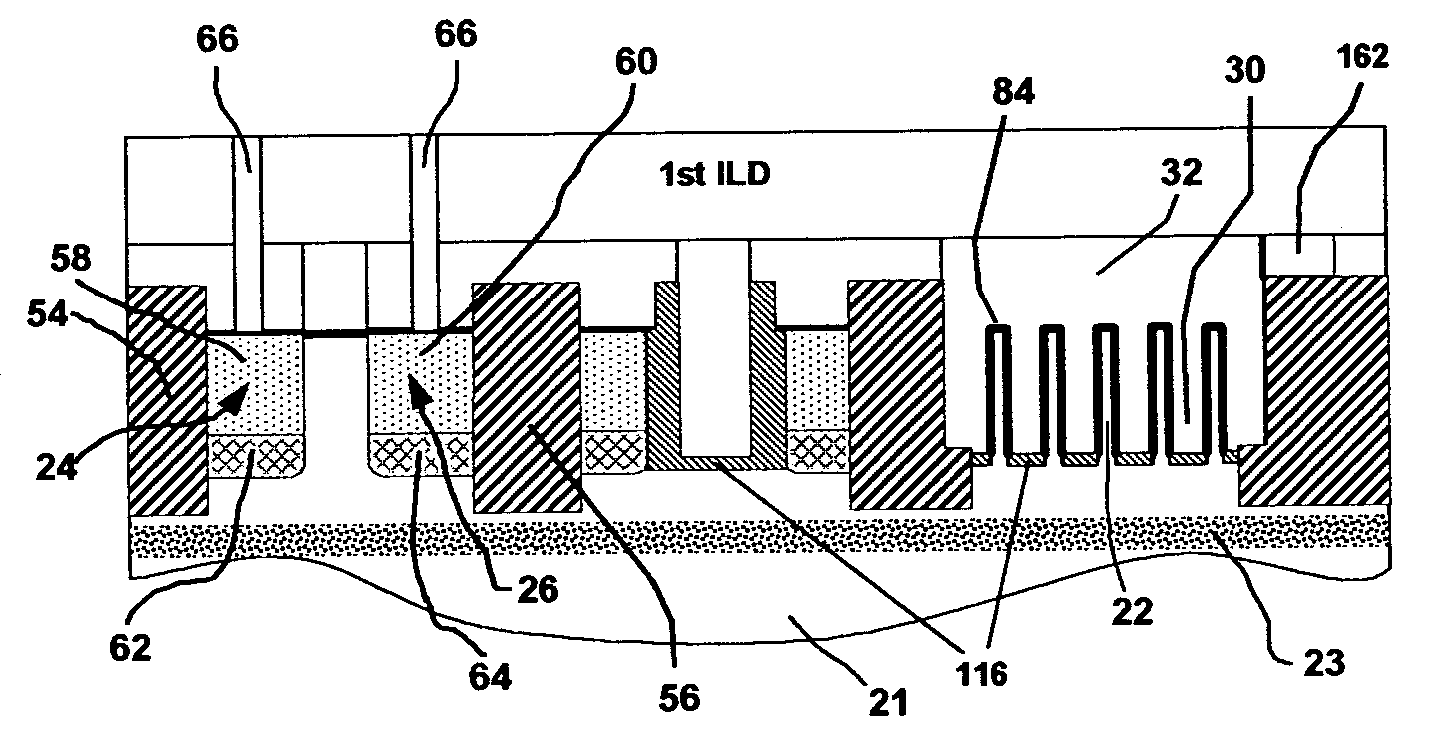

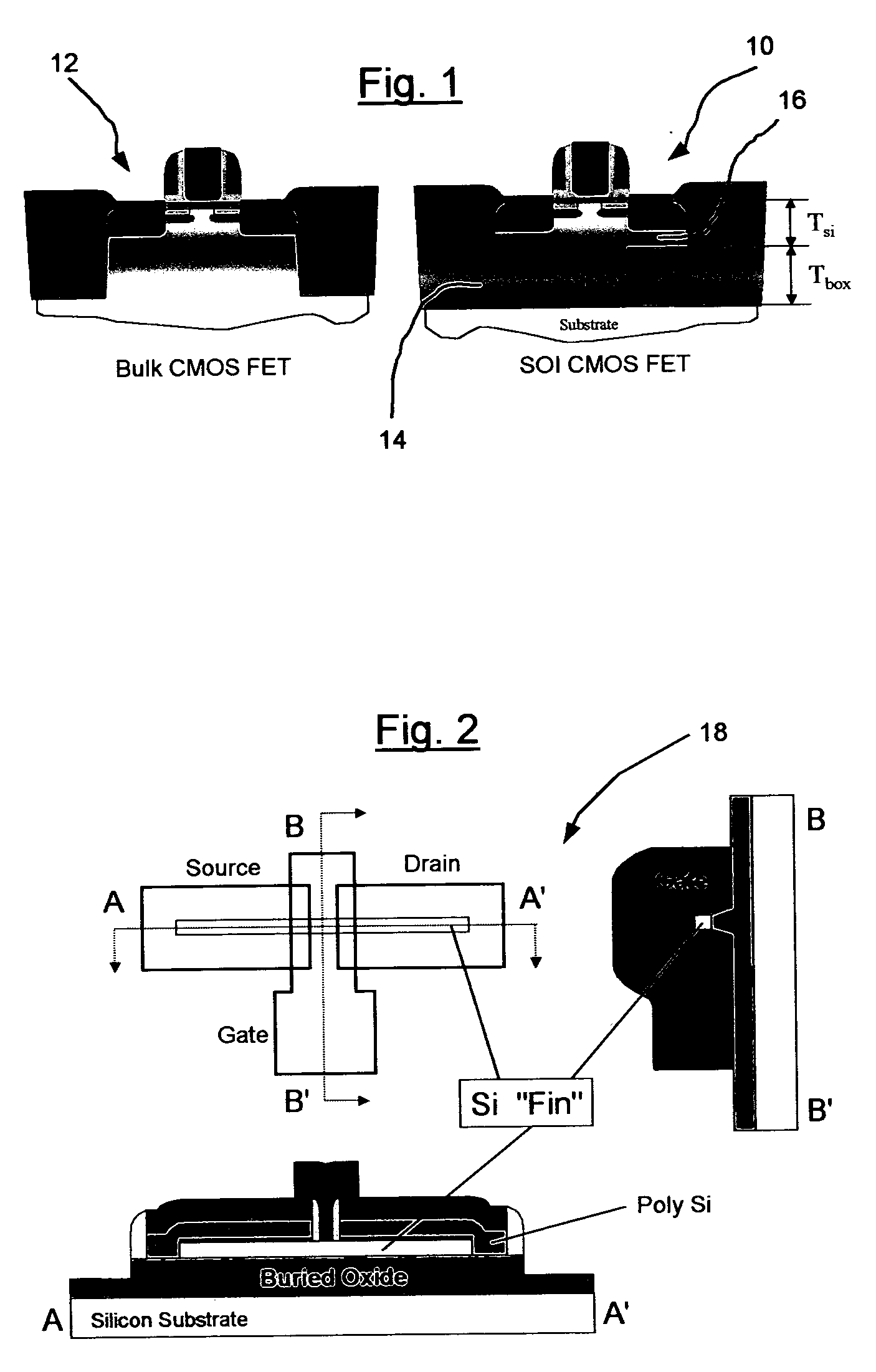

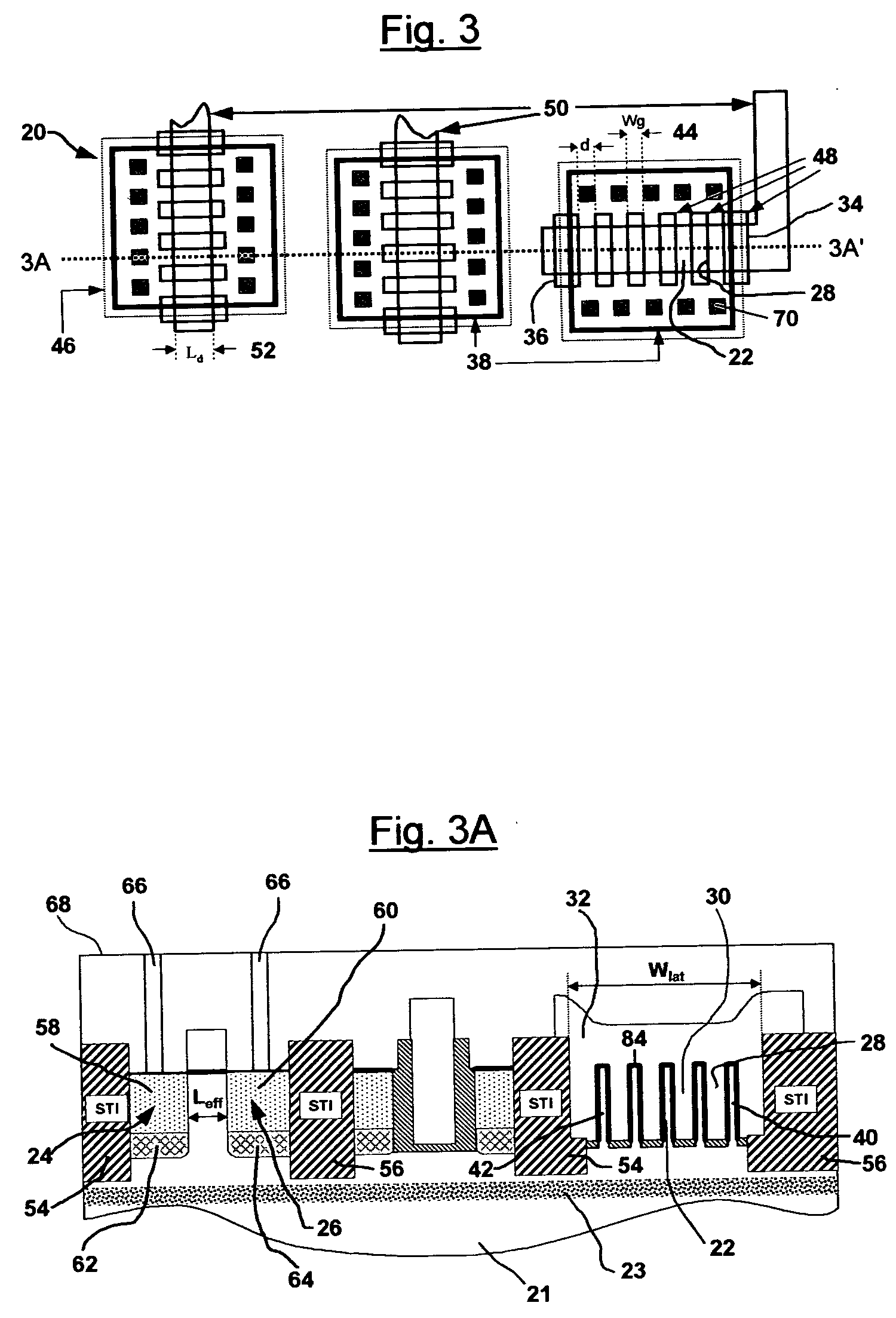

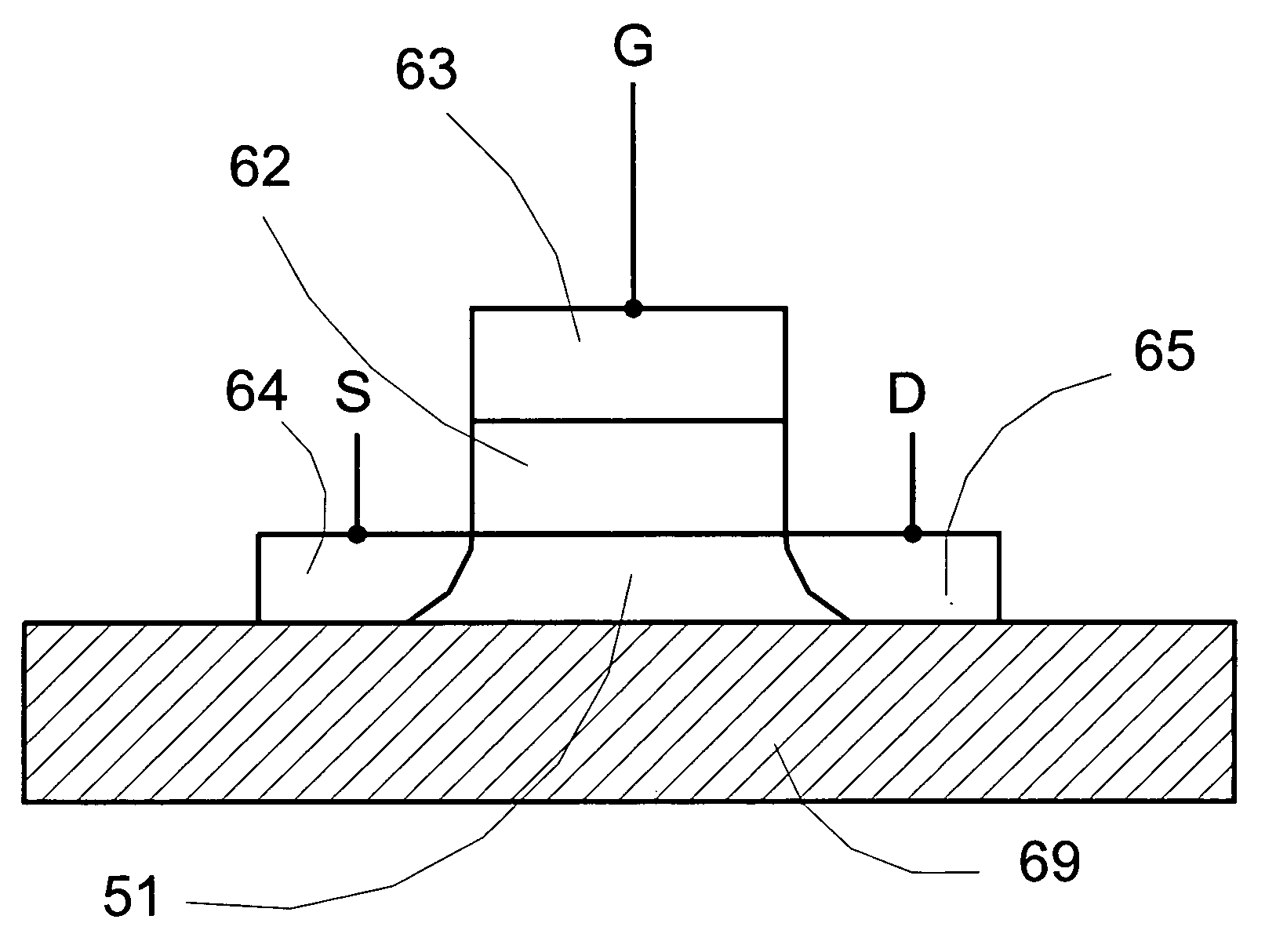

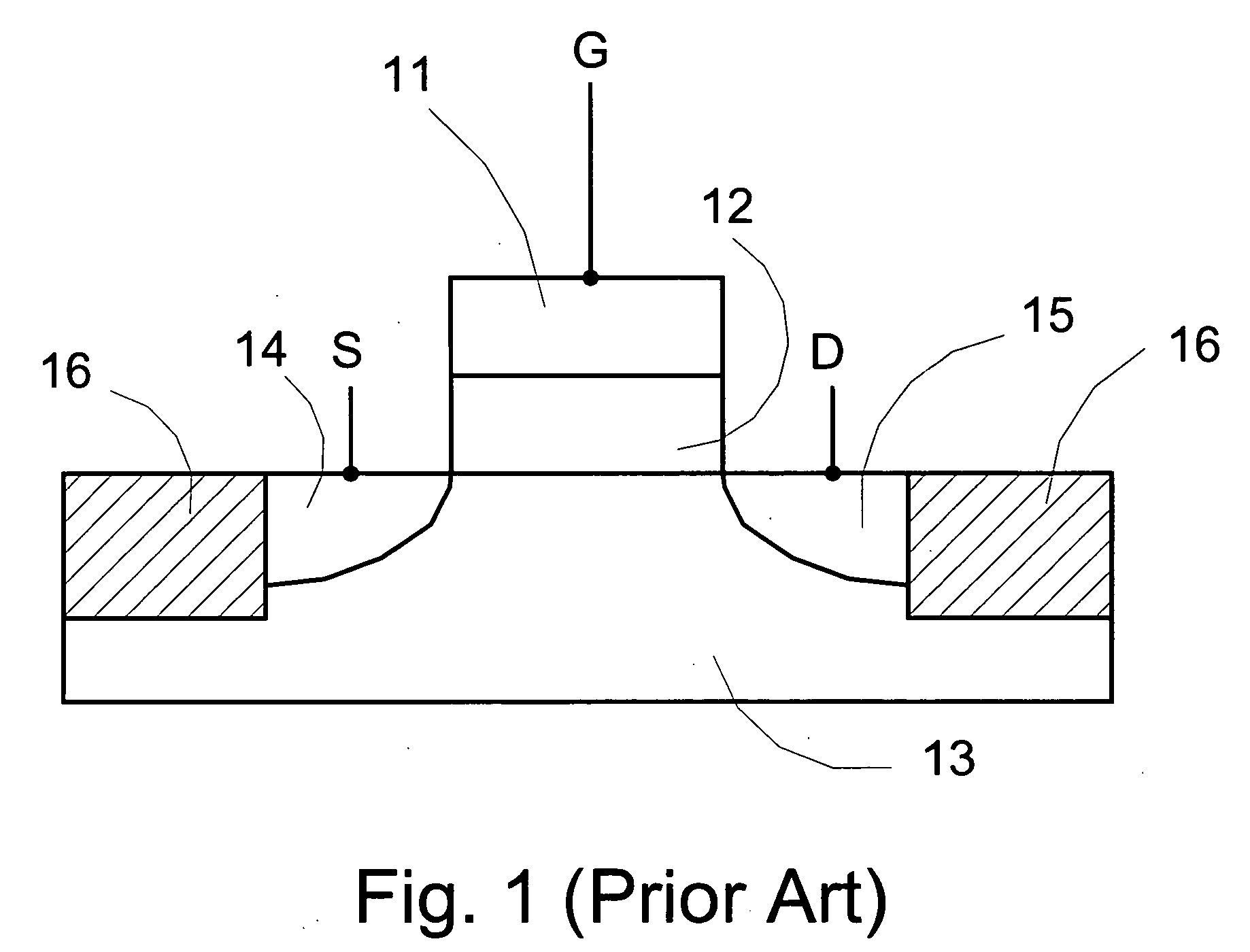

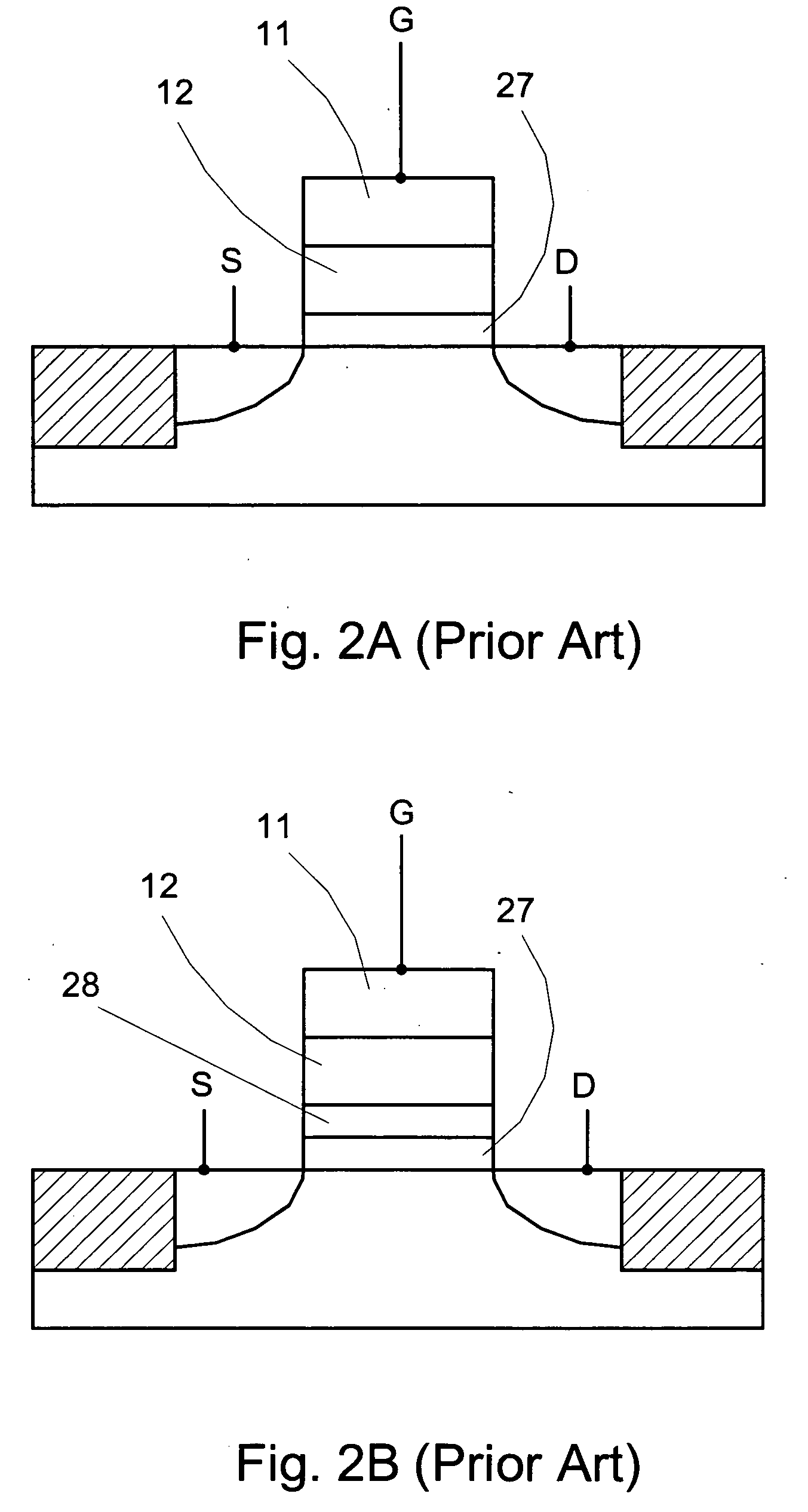

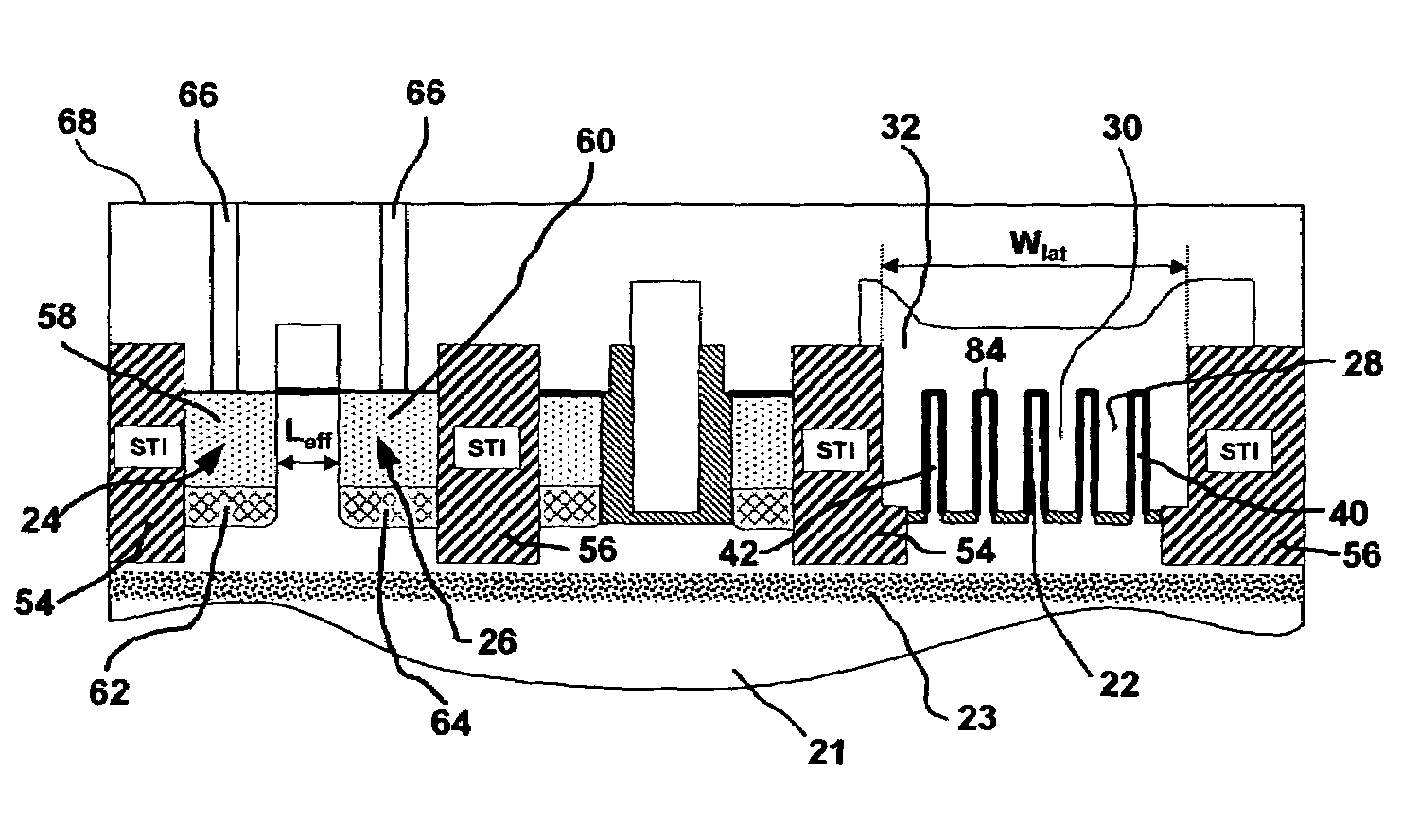

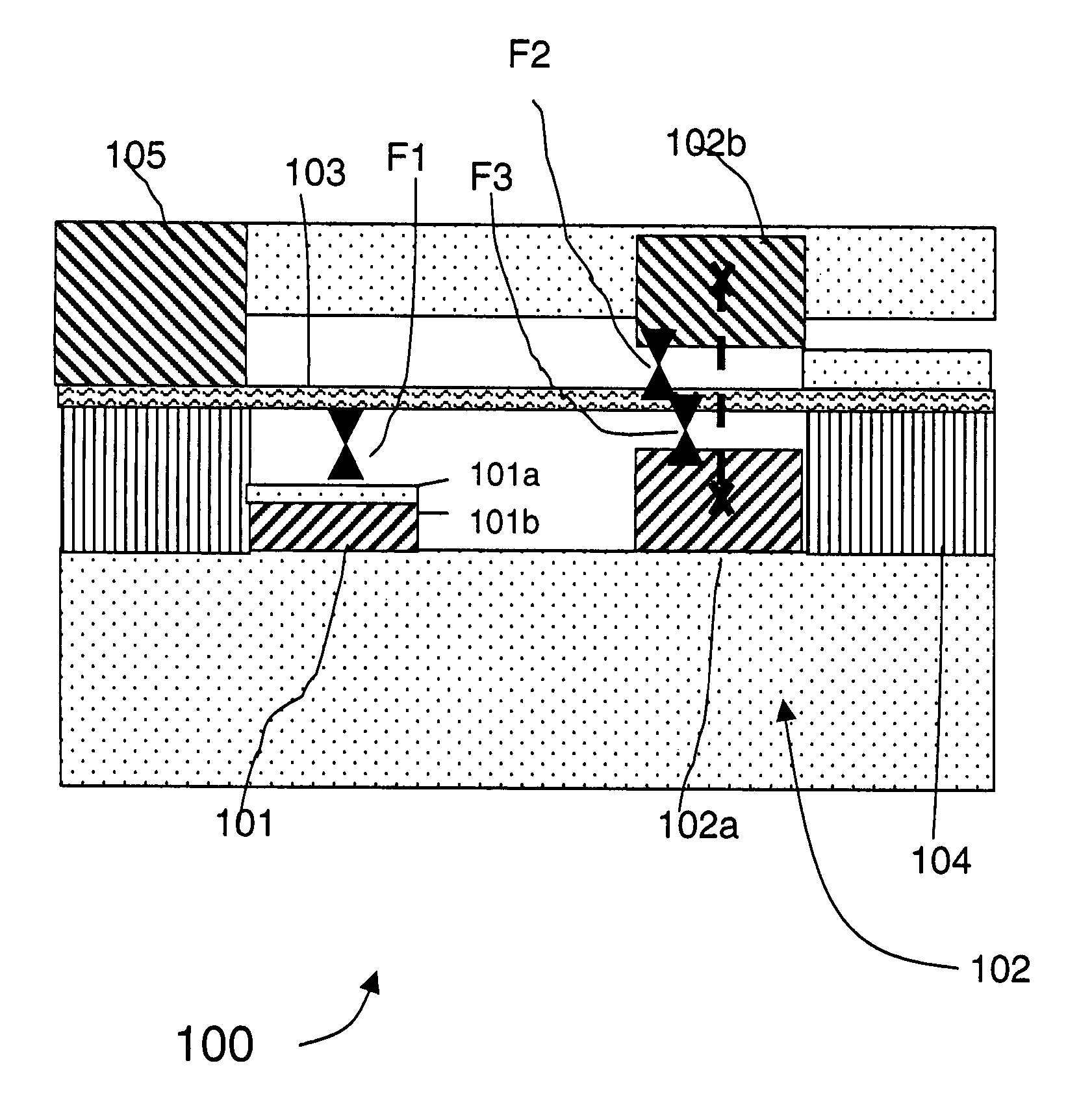

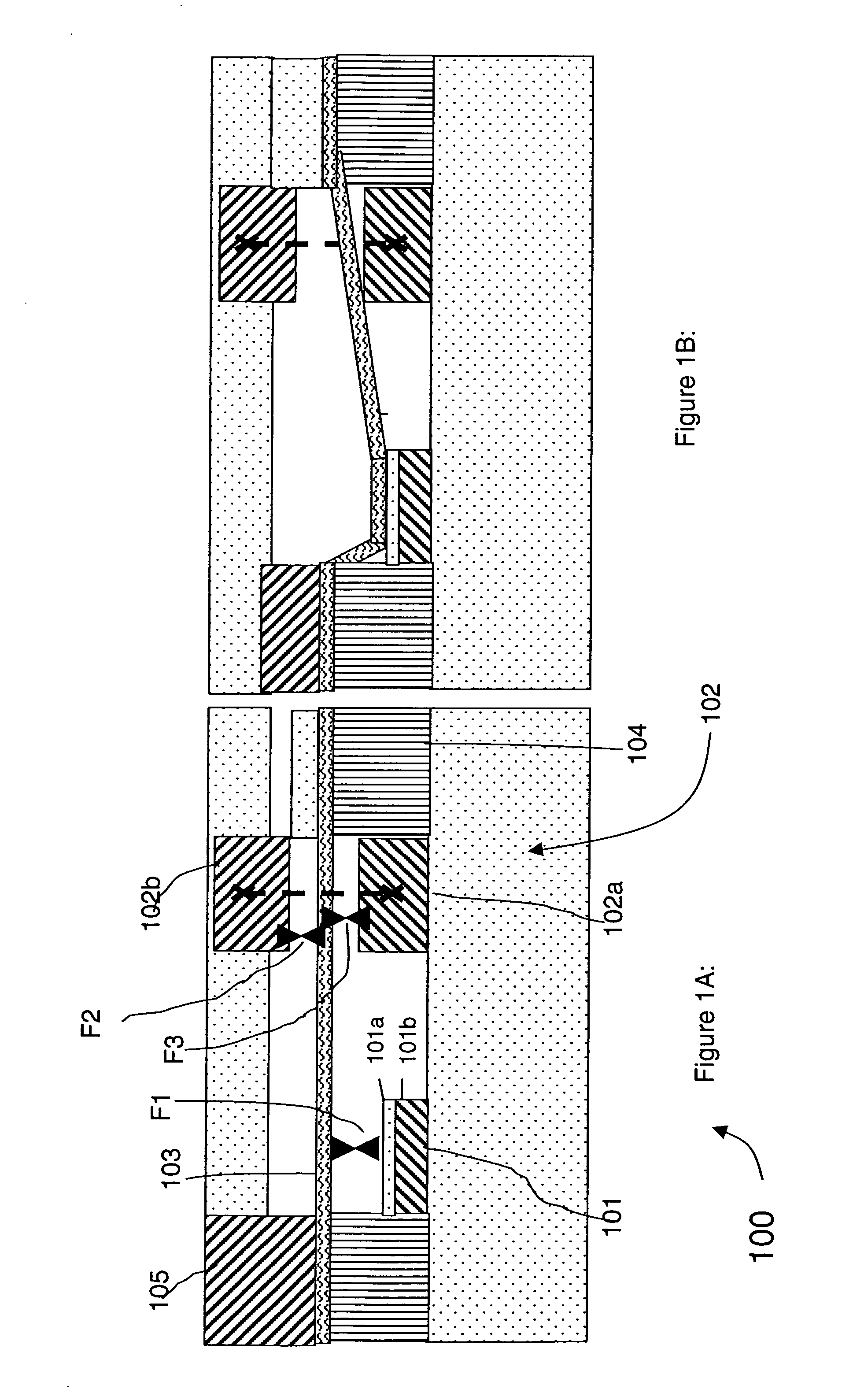

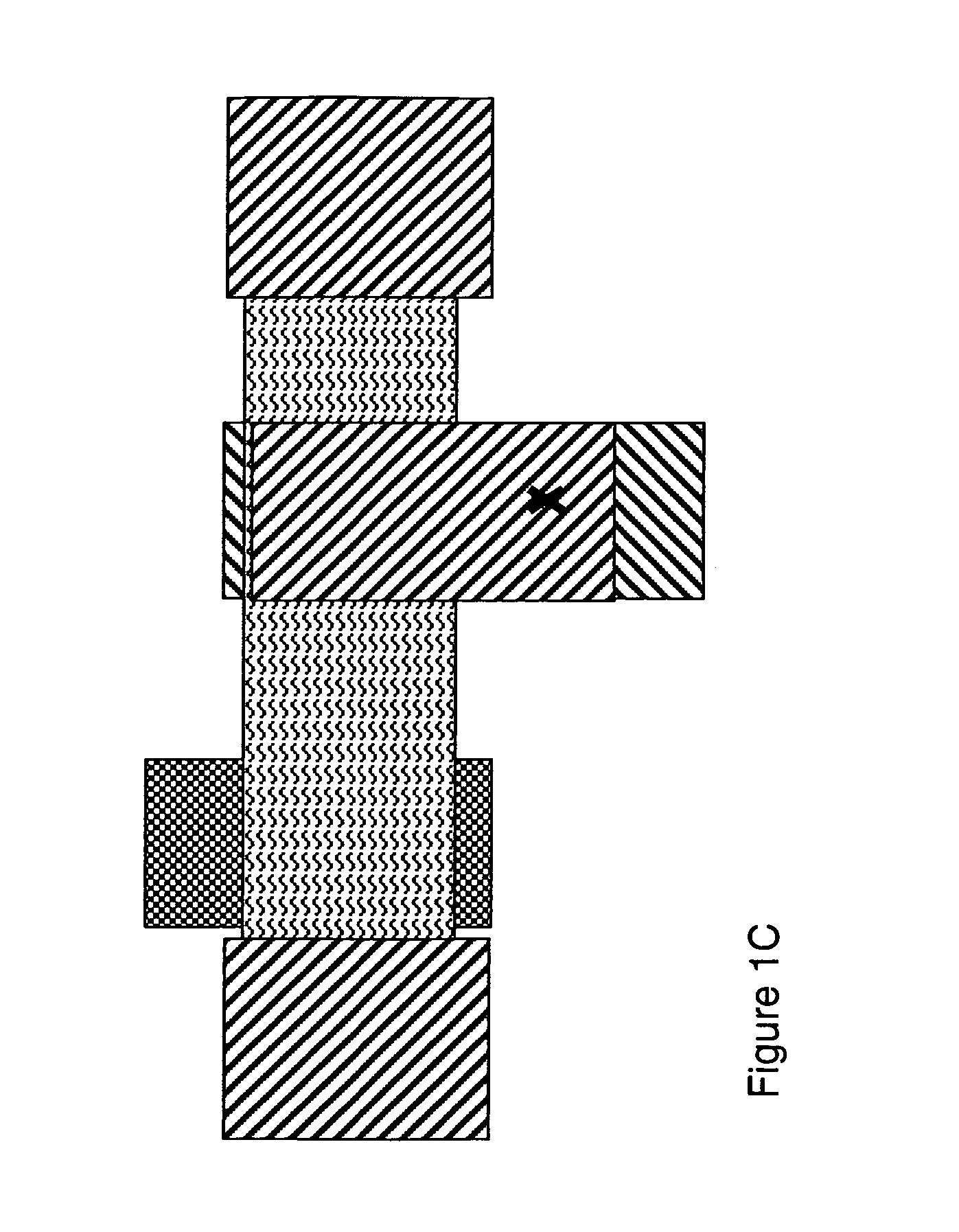

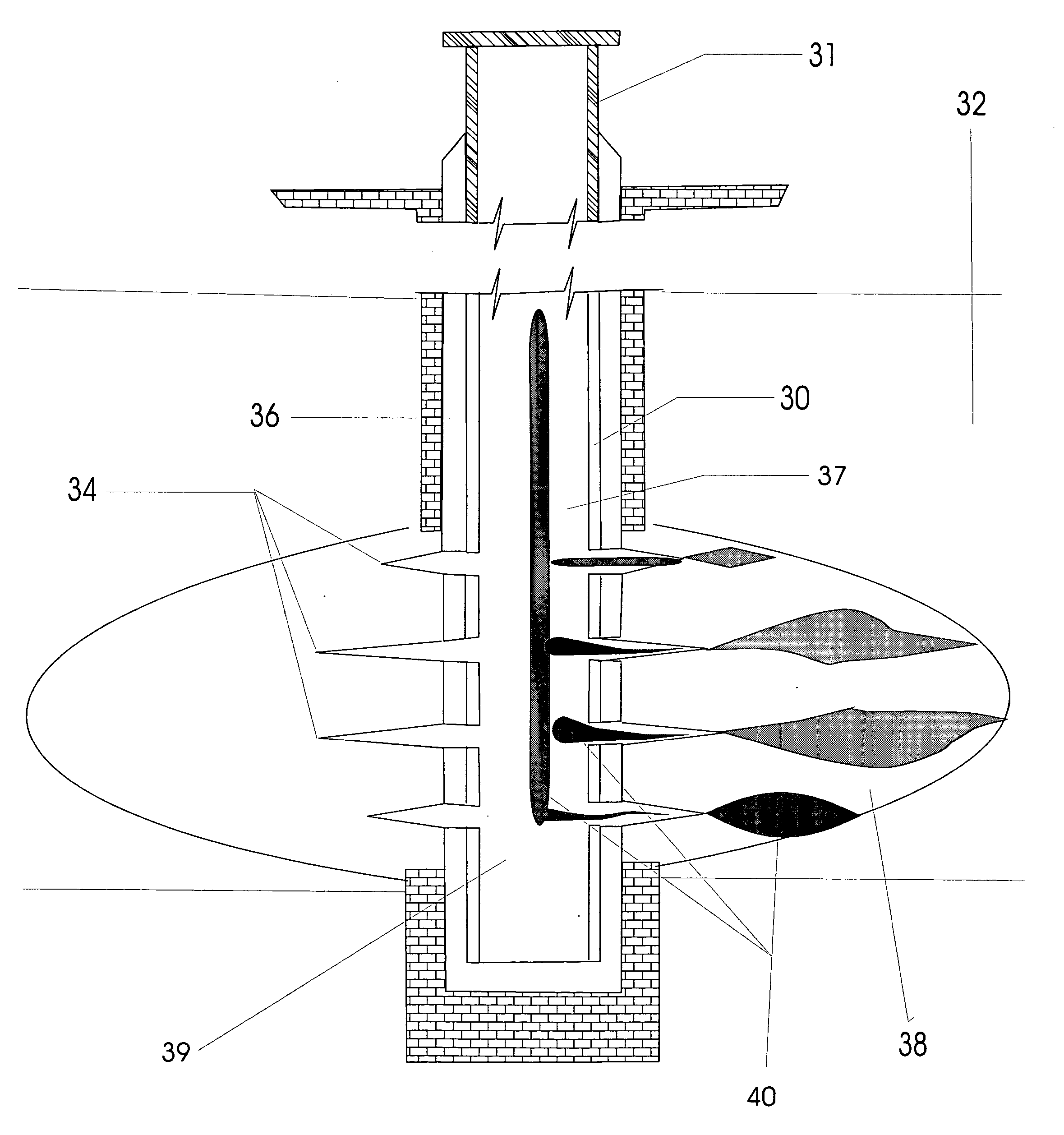

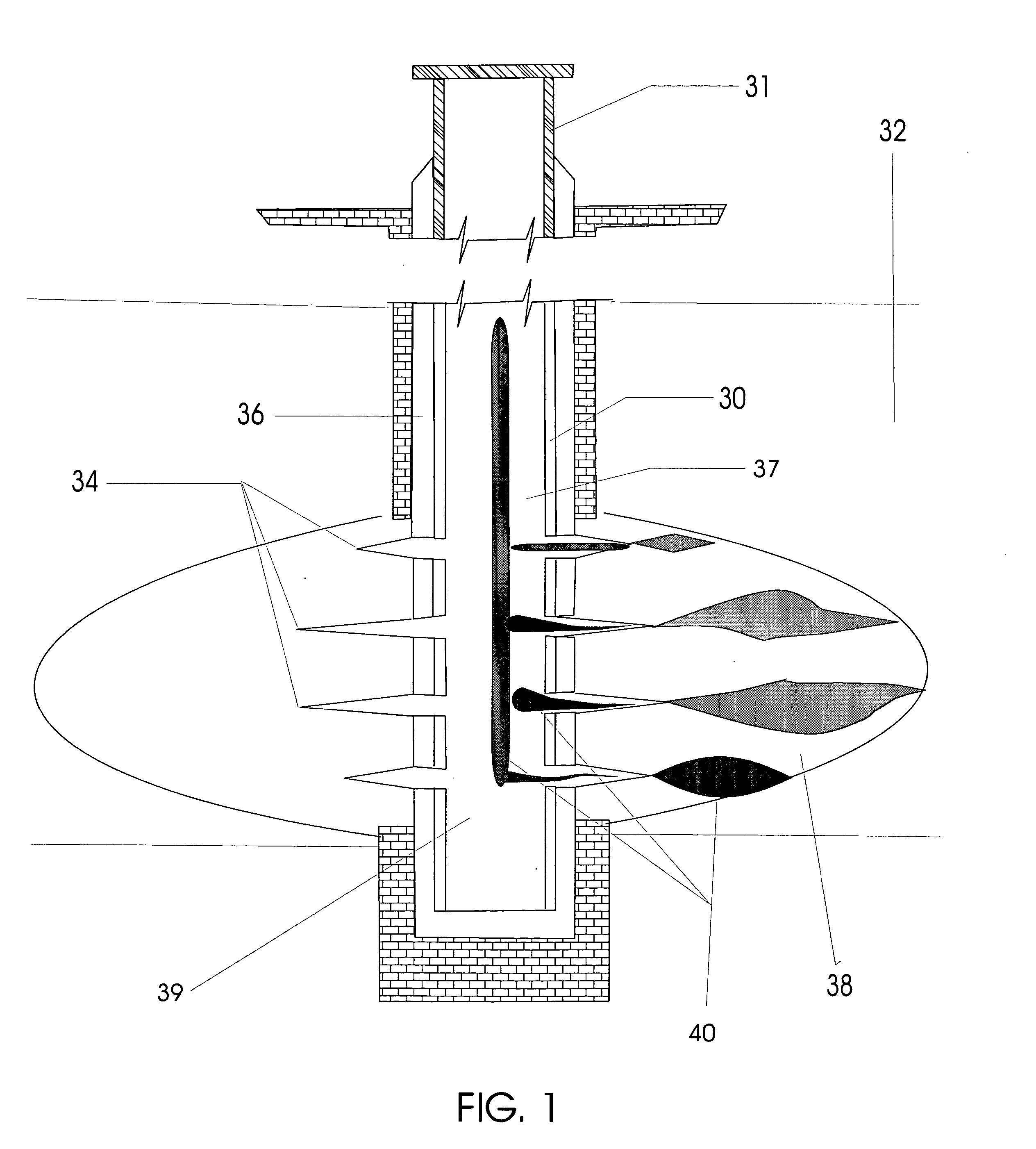

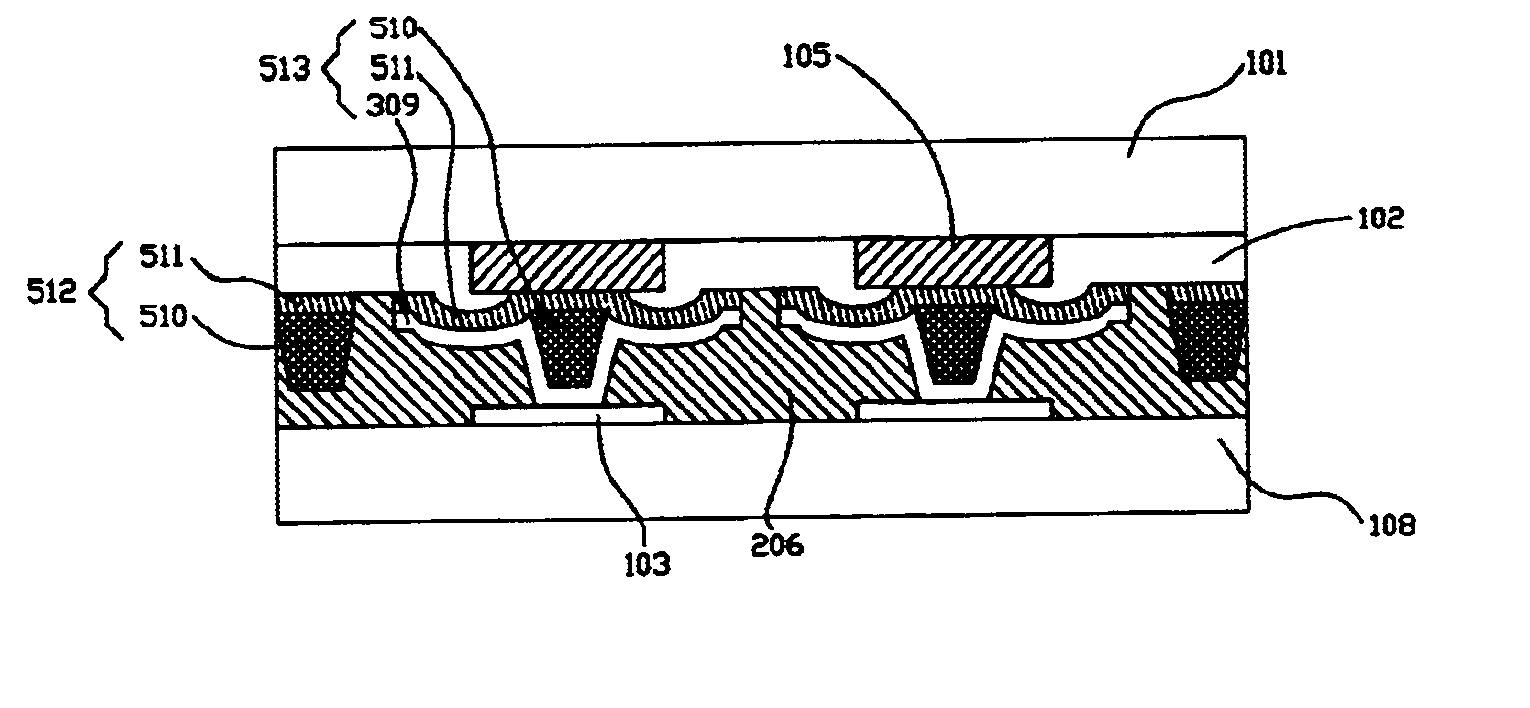

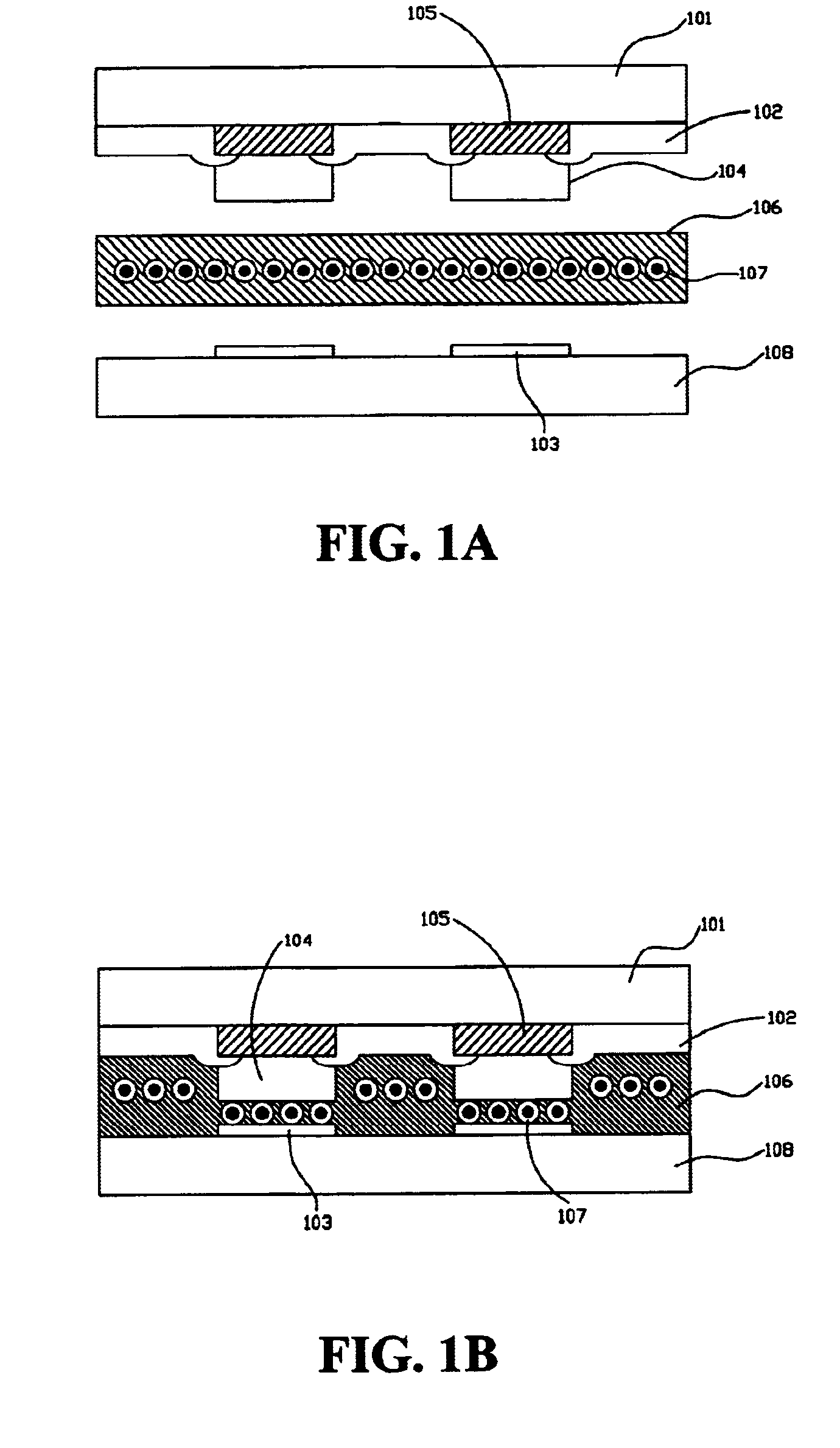

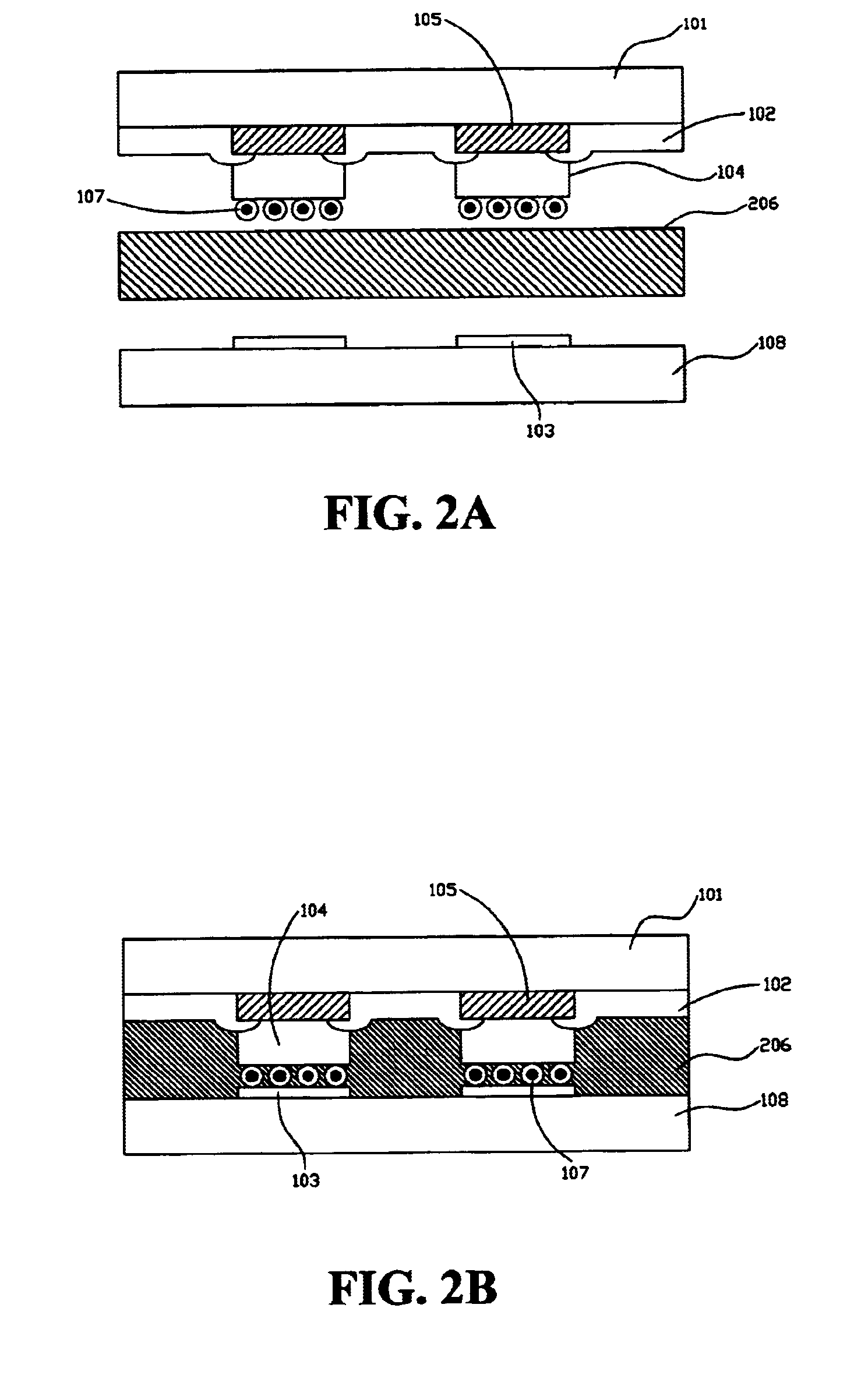

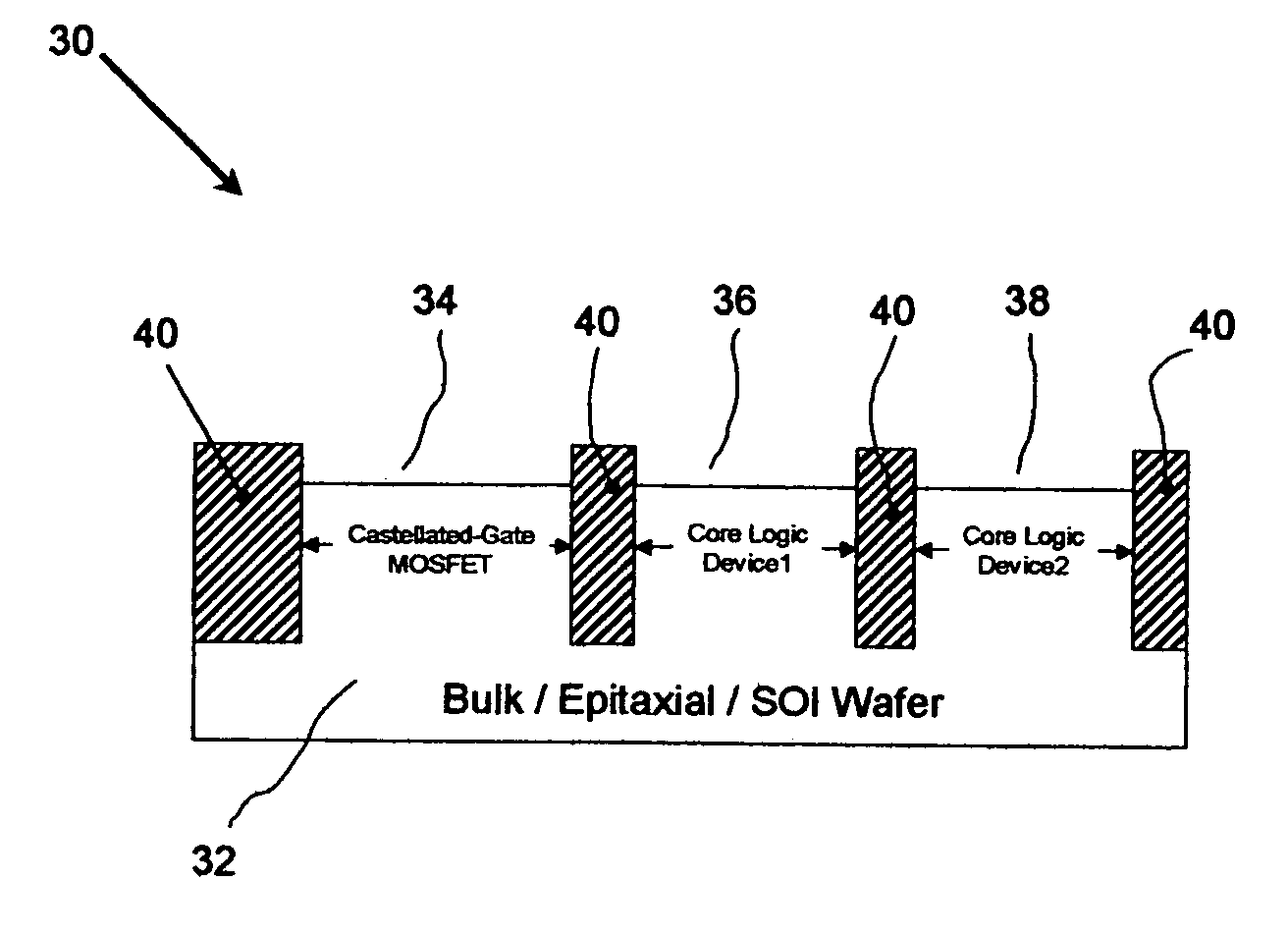

A fully depleted castellated-gate MOSFET device is disclosed along with a method of making the same. The device has robust I / O applications, and includes a semiconductor substrate body having an upper portion with an upper end surface and a lower portion with a lower end surface. A source region, a drain region, and a channel-forming region between the source and drain regions are all formed in the semiconductor substrate body. trench isolation insulator islands surround the source and drain regions as well as the channel-forming region. The channel-forming region is made up of a plurality of thin, spaced, vertically-orientated conductive channel elements that span longitudinally along the device between the source and drain regions. A gate structure is also provided in the form of a plurality of spaced, castellated gate elements interposed between the channel elements. The gate structure also includes a top gate member which interconnects the gate elements at their upper vertical ends to cover the channel elements. Finally, a dielectric layer is provided to separate the conductive channel elements from the gate structure.

Owner:IP3 2021 SERIES 600 OF ALLIED SECURITY TRUST I

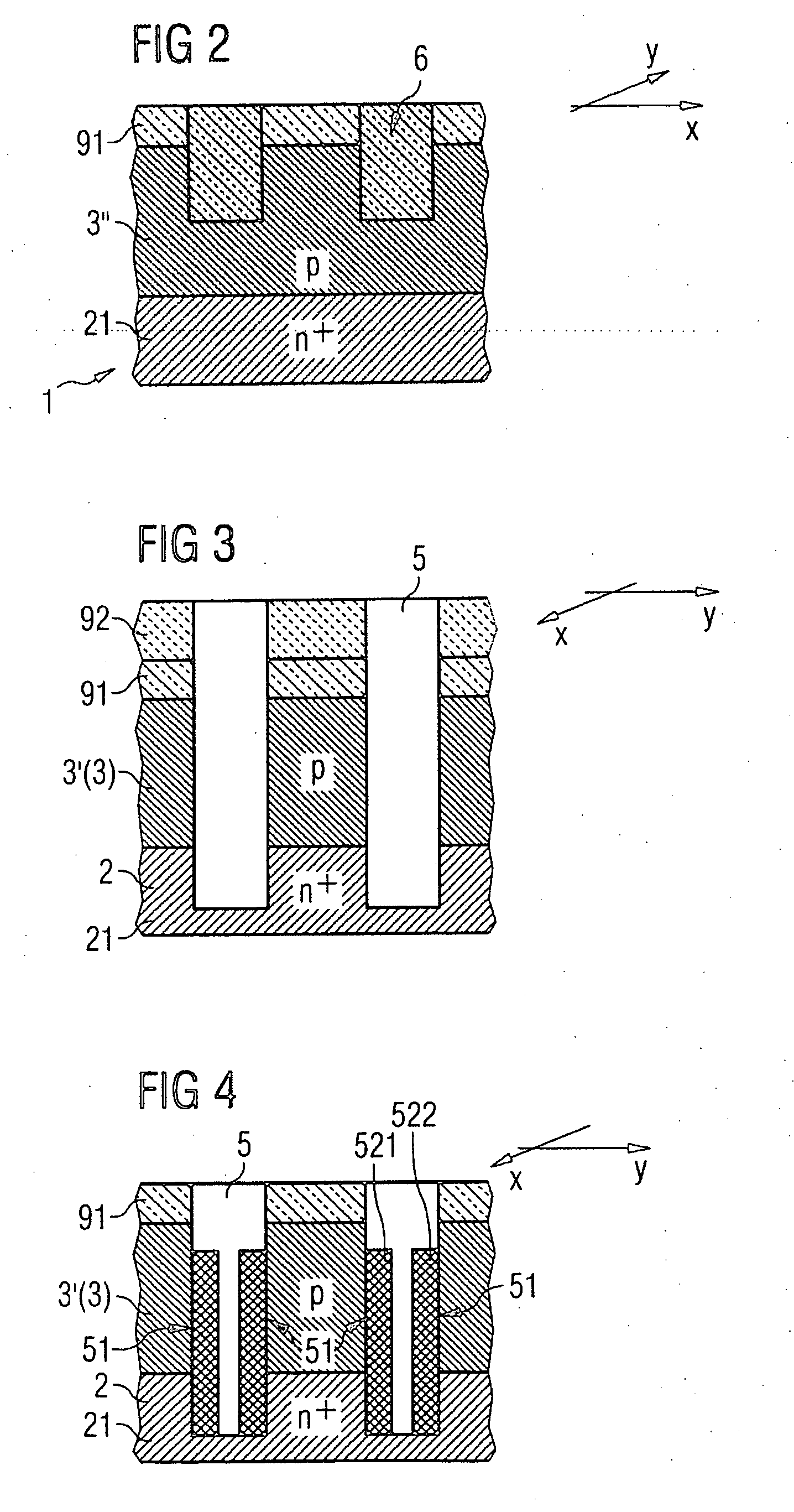

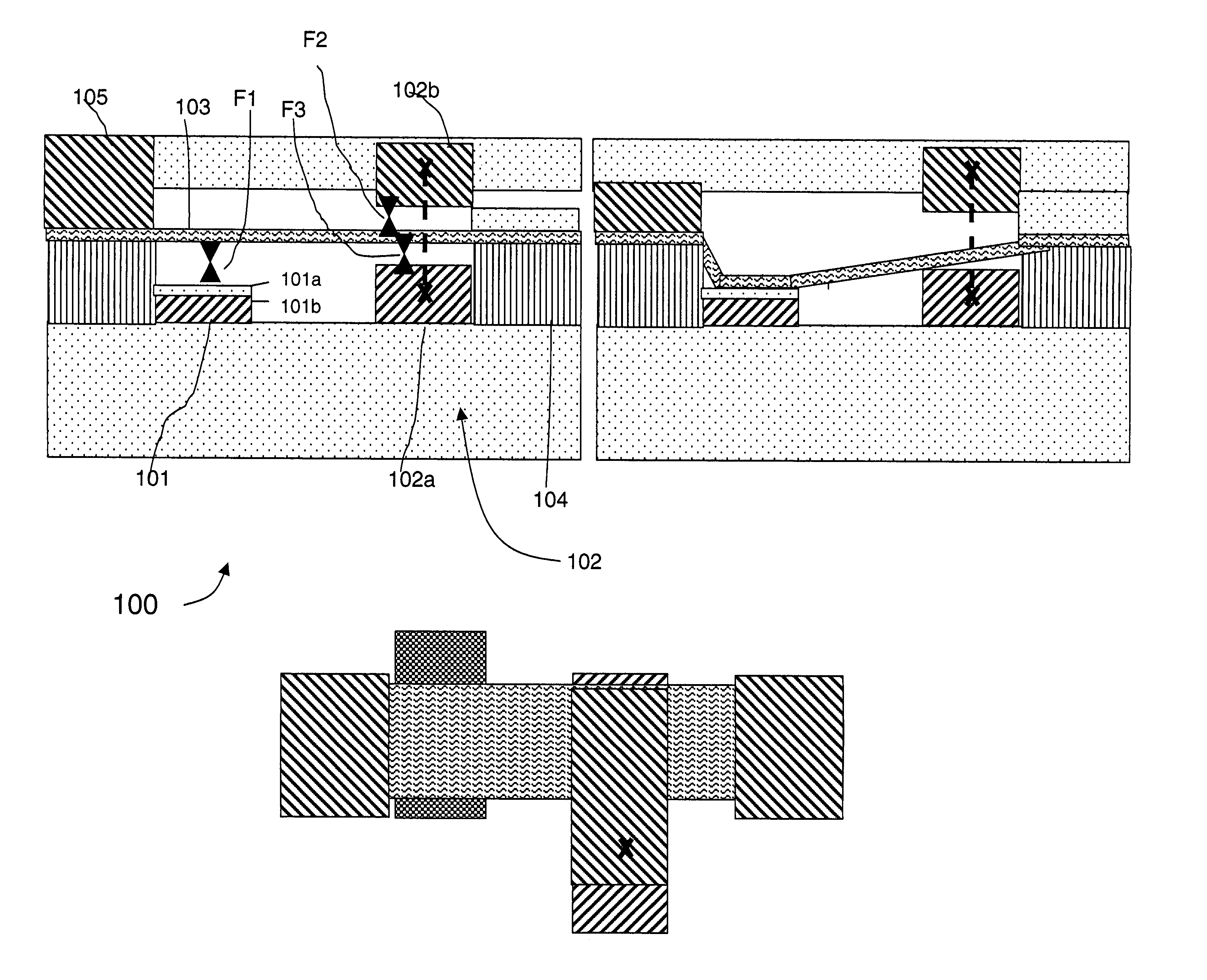

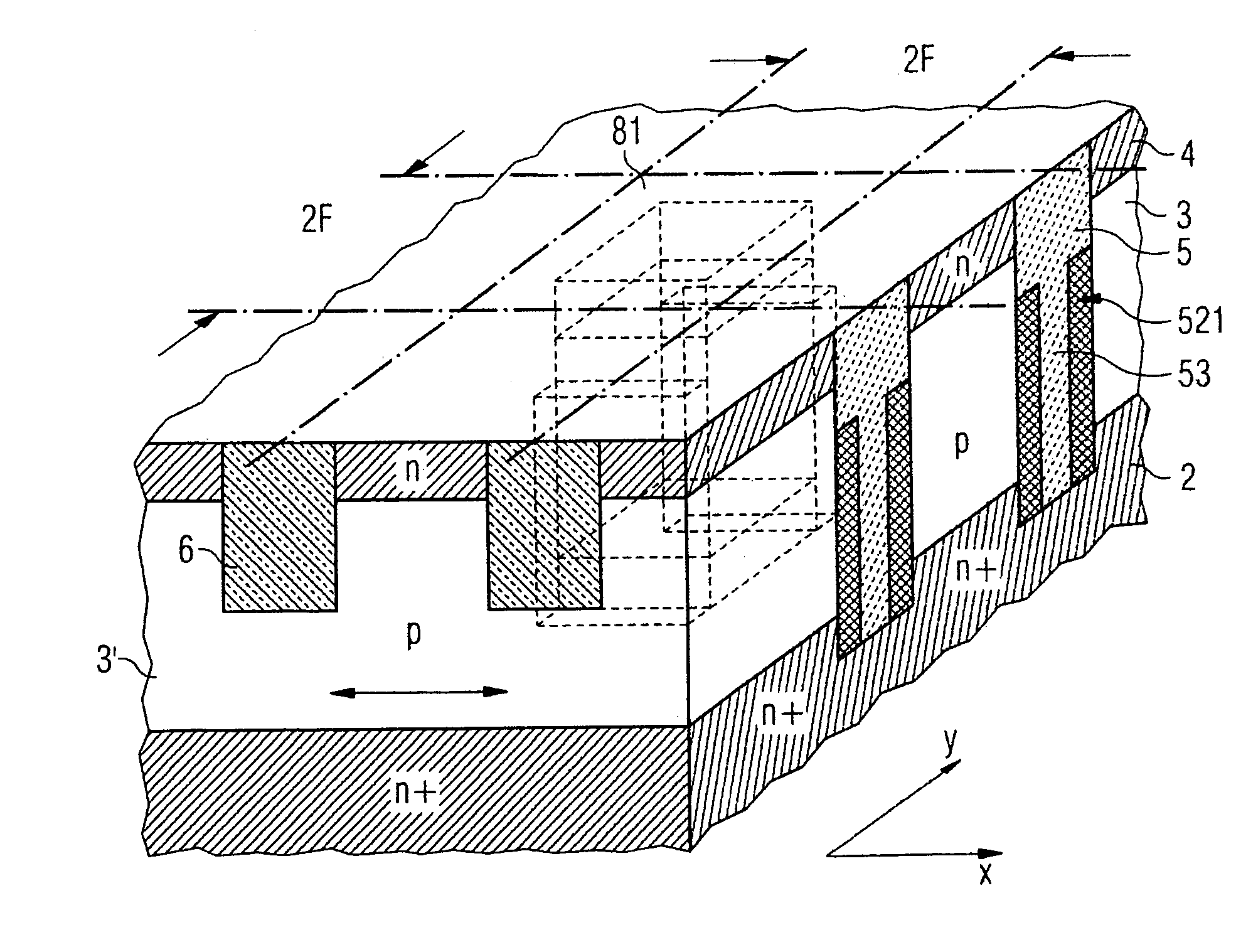

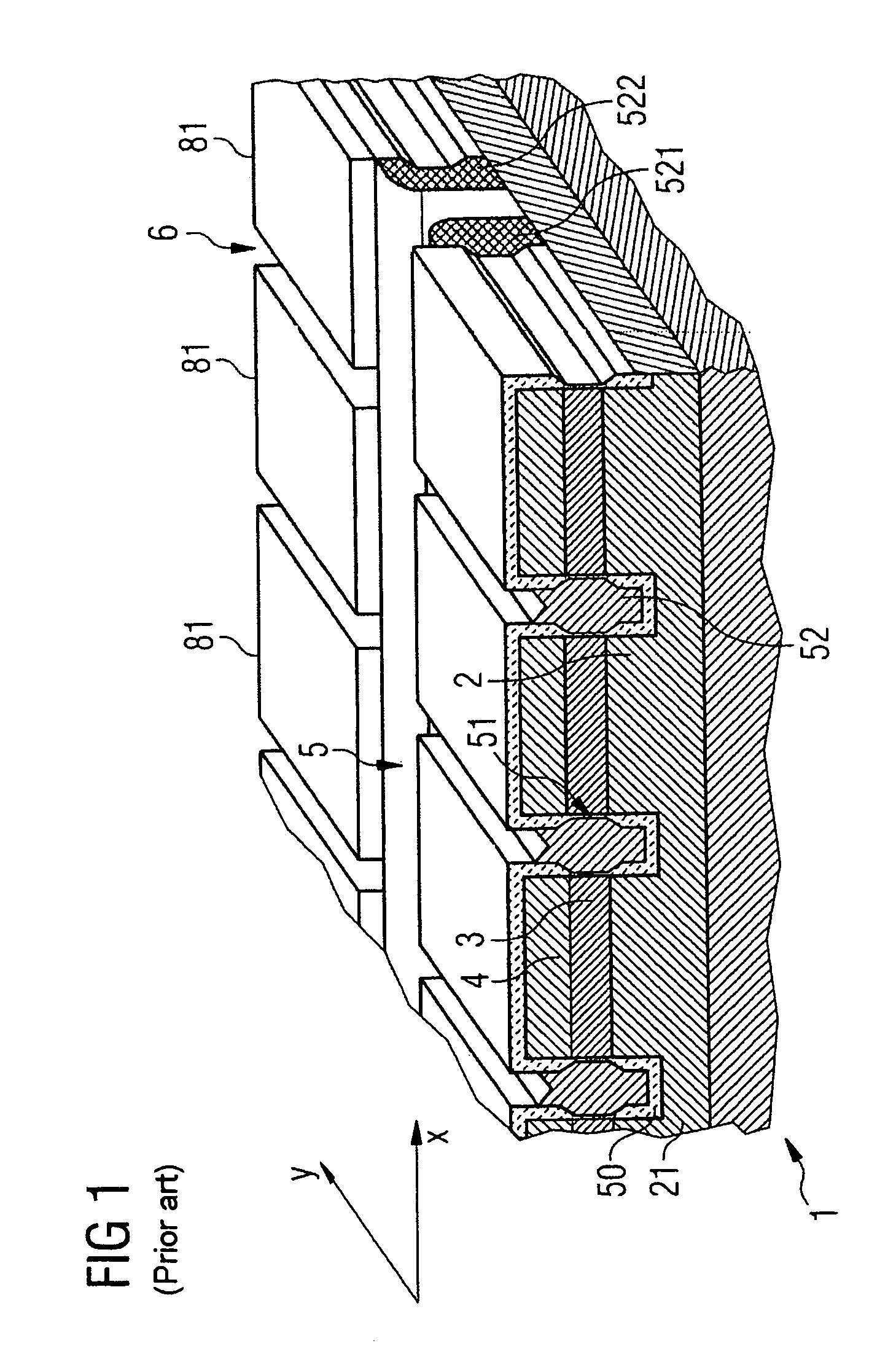

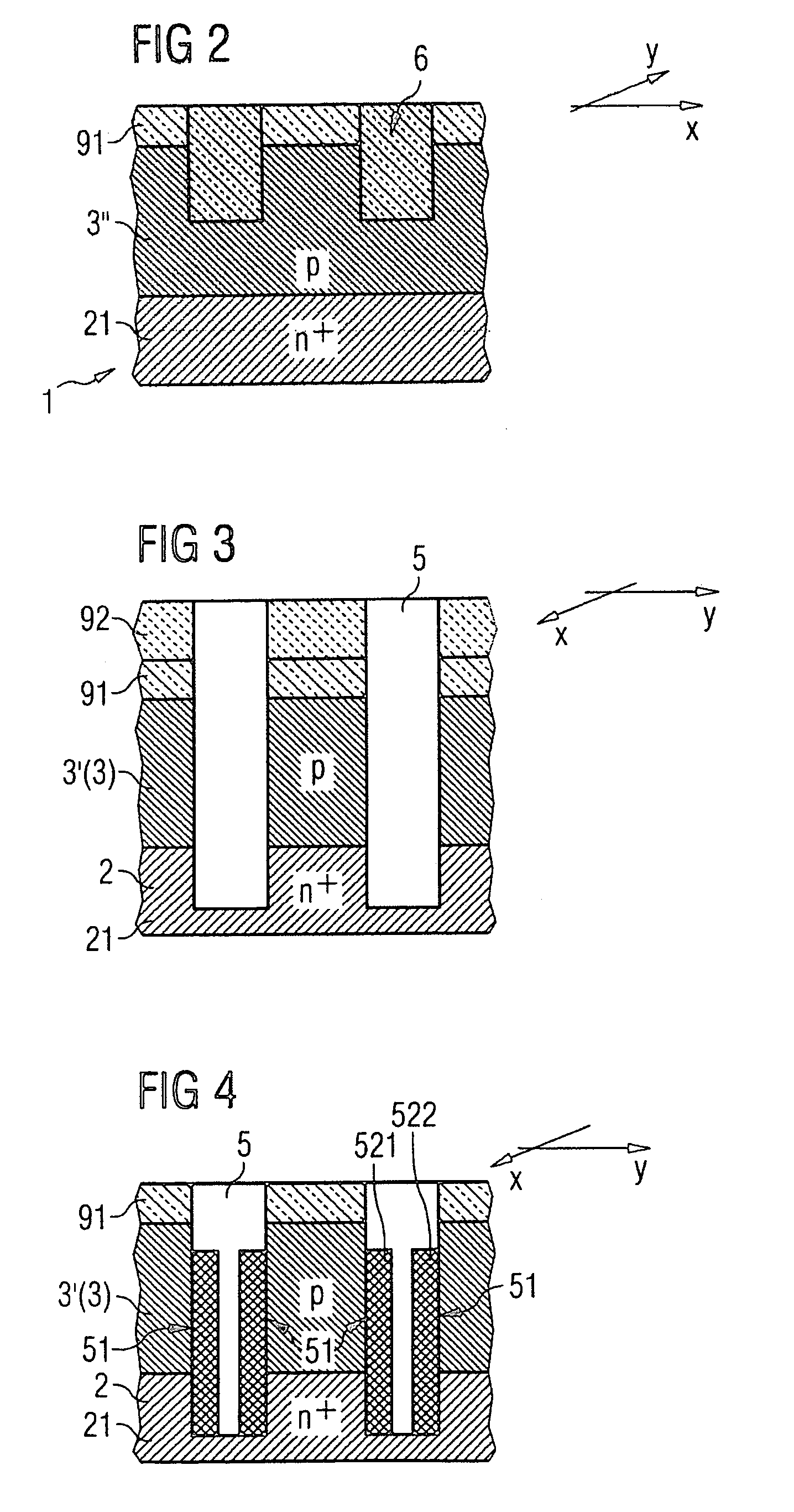

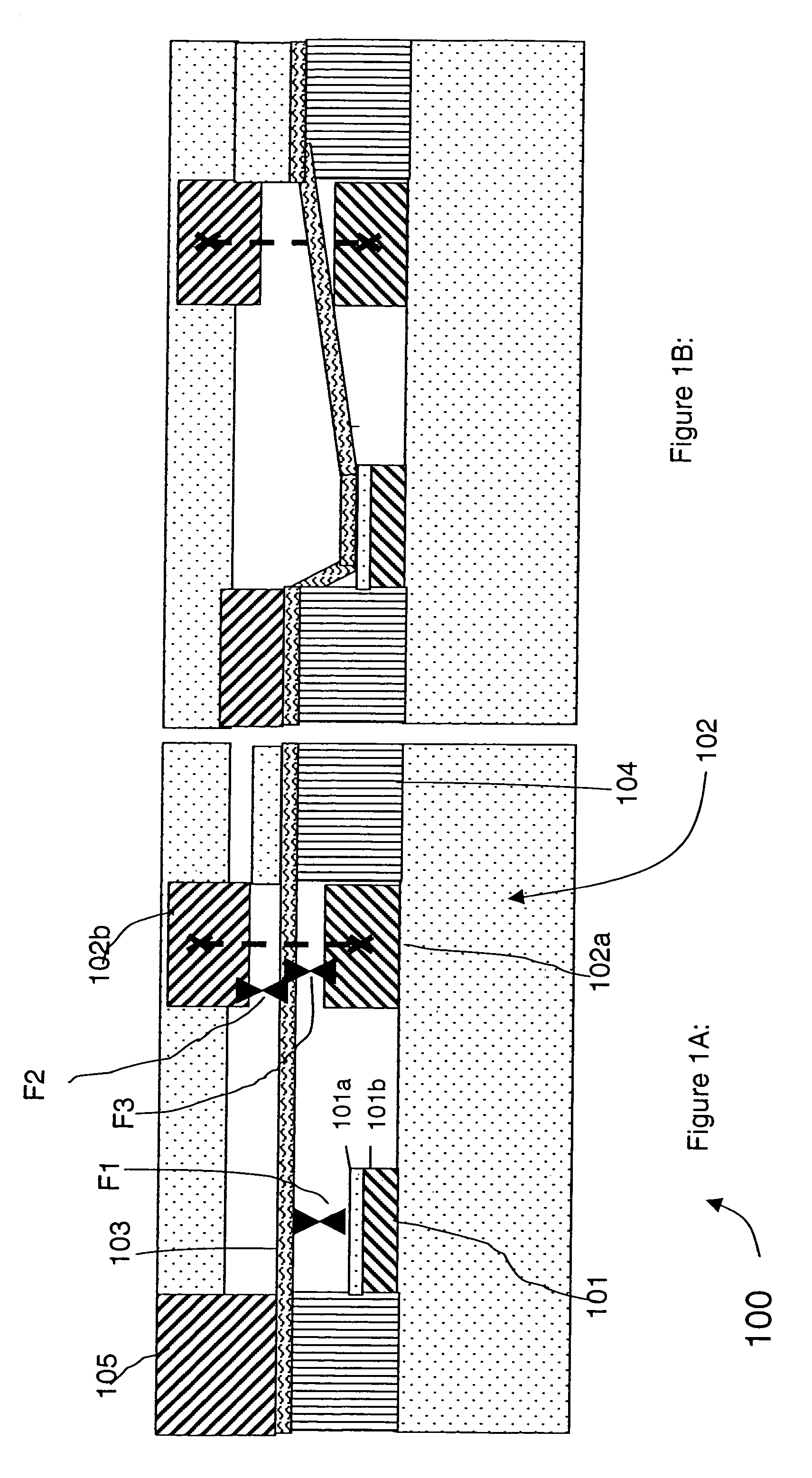

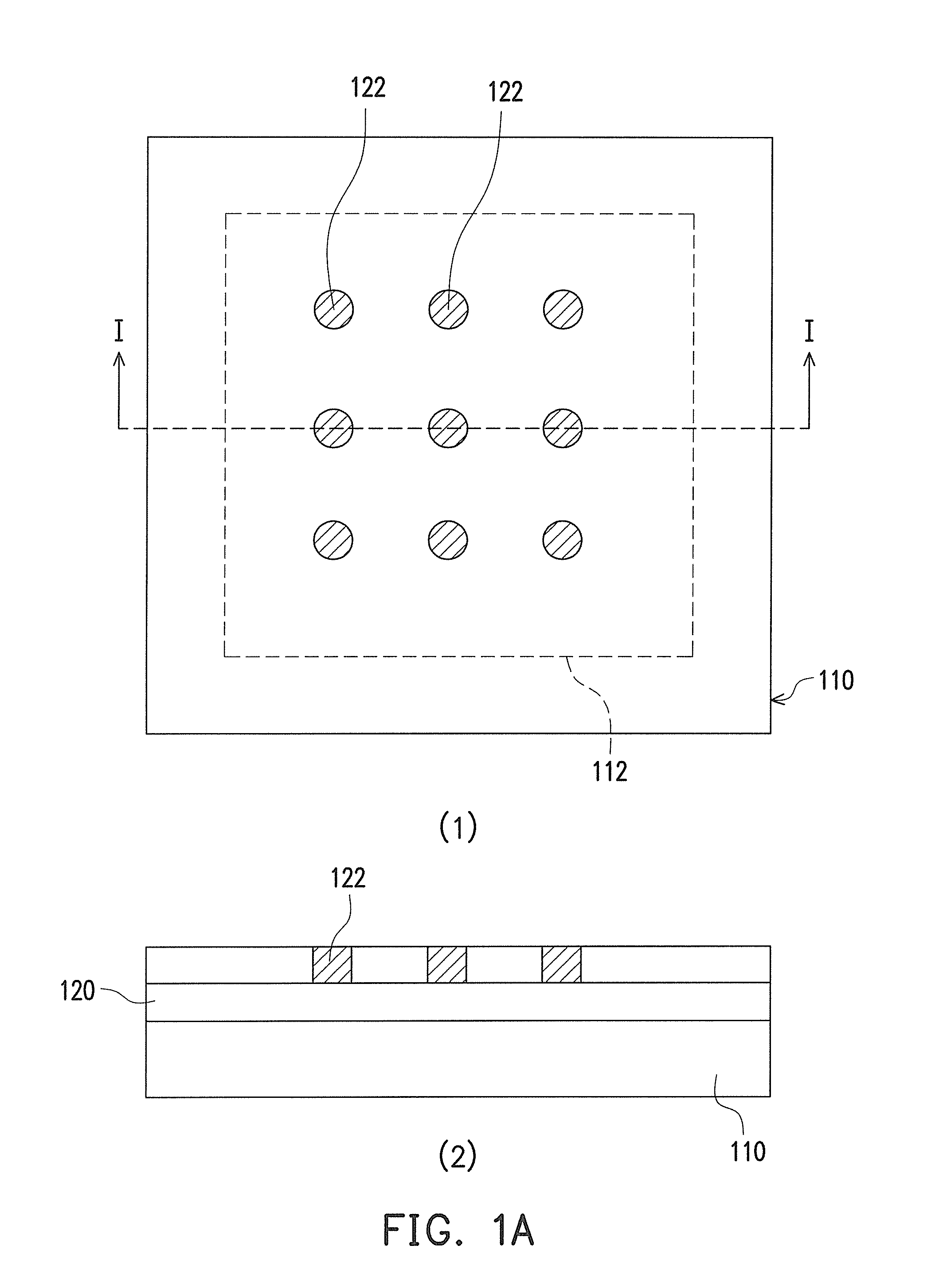

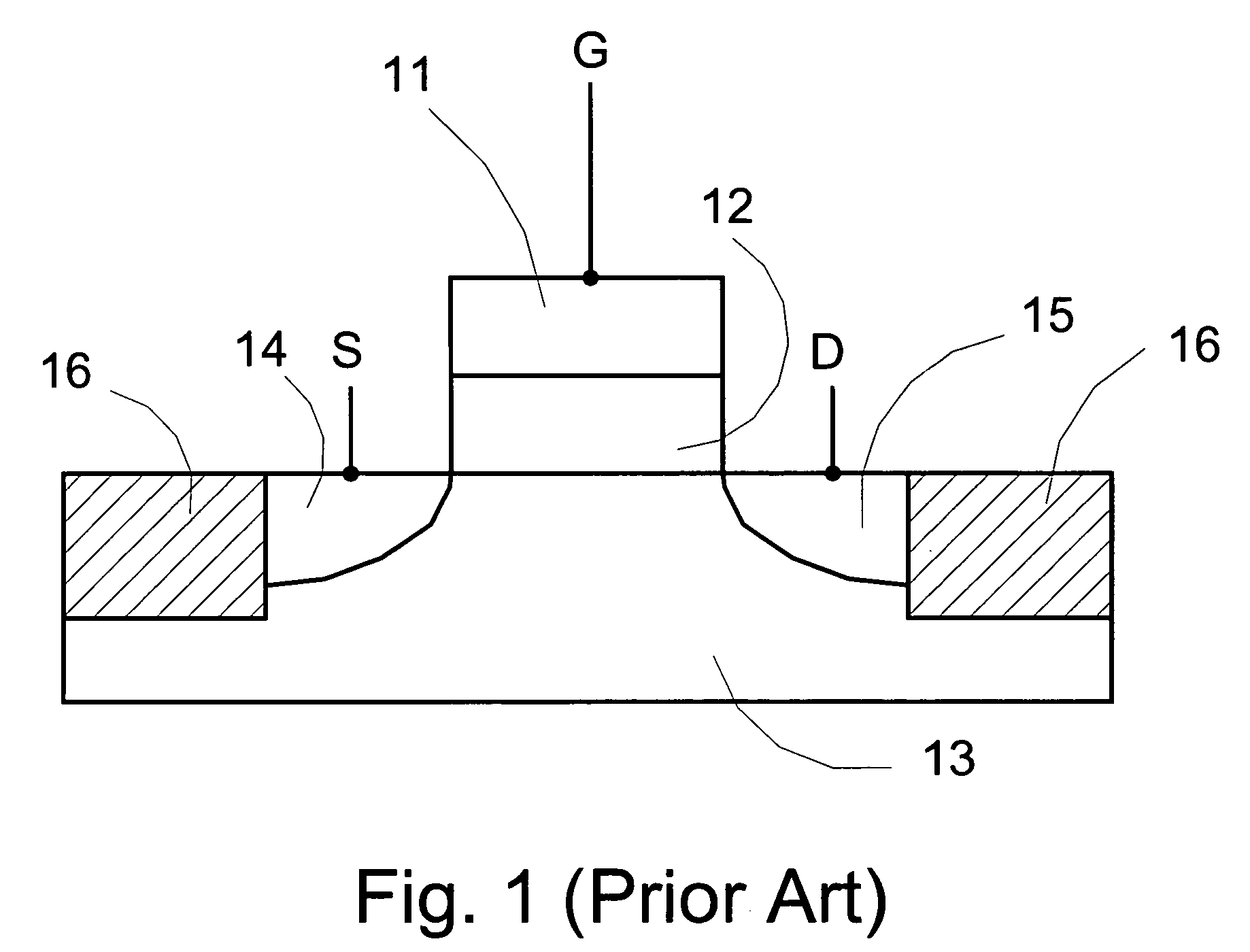

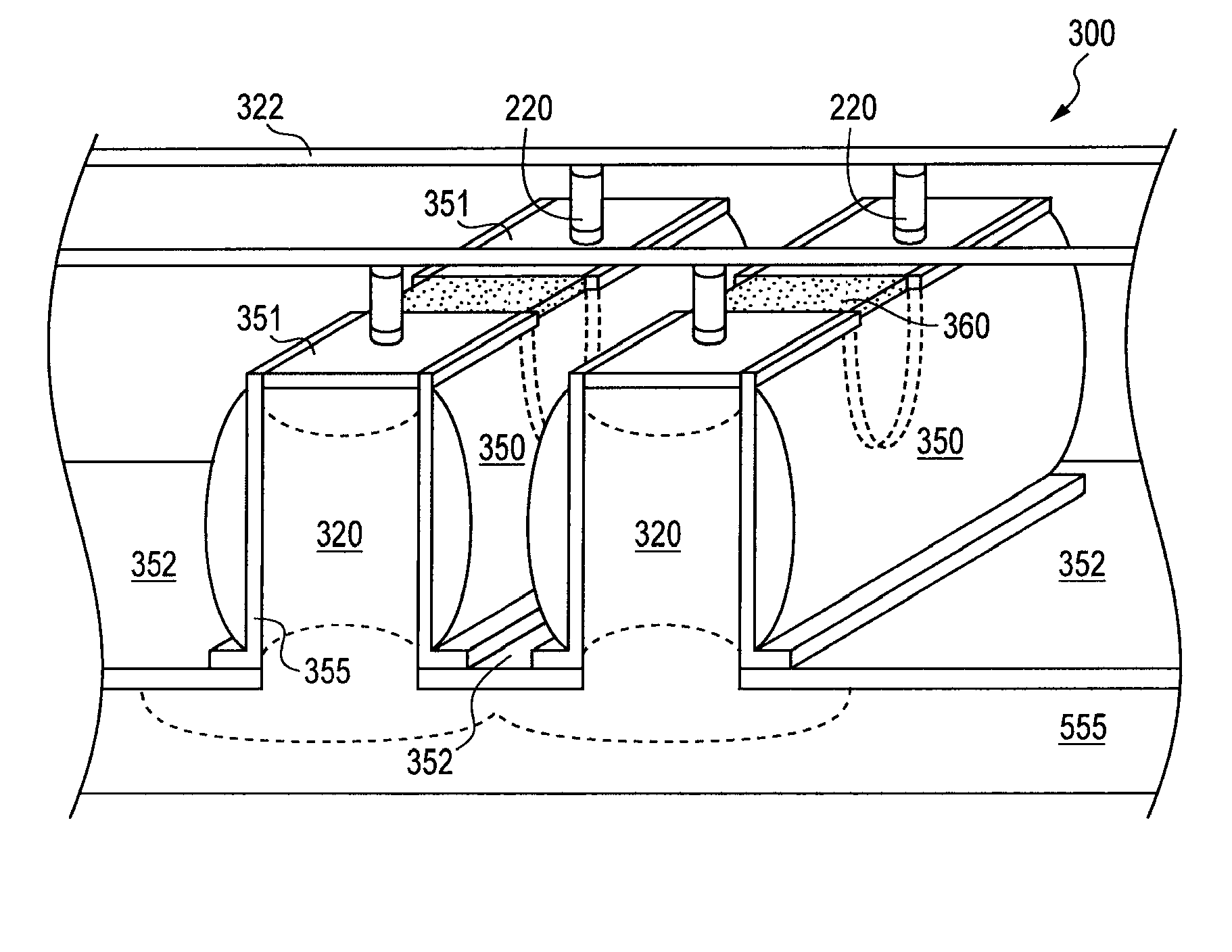

Method of fabricating and architecture for vertical transistor cells and transistor-controlled memory cells

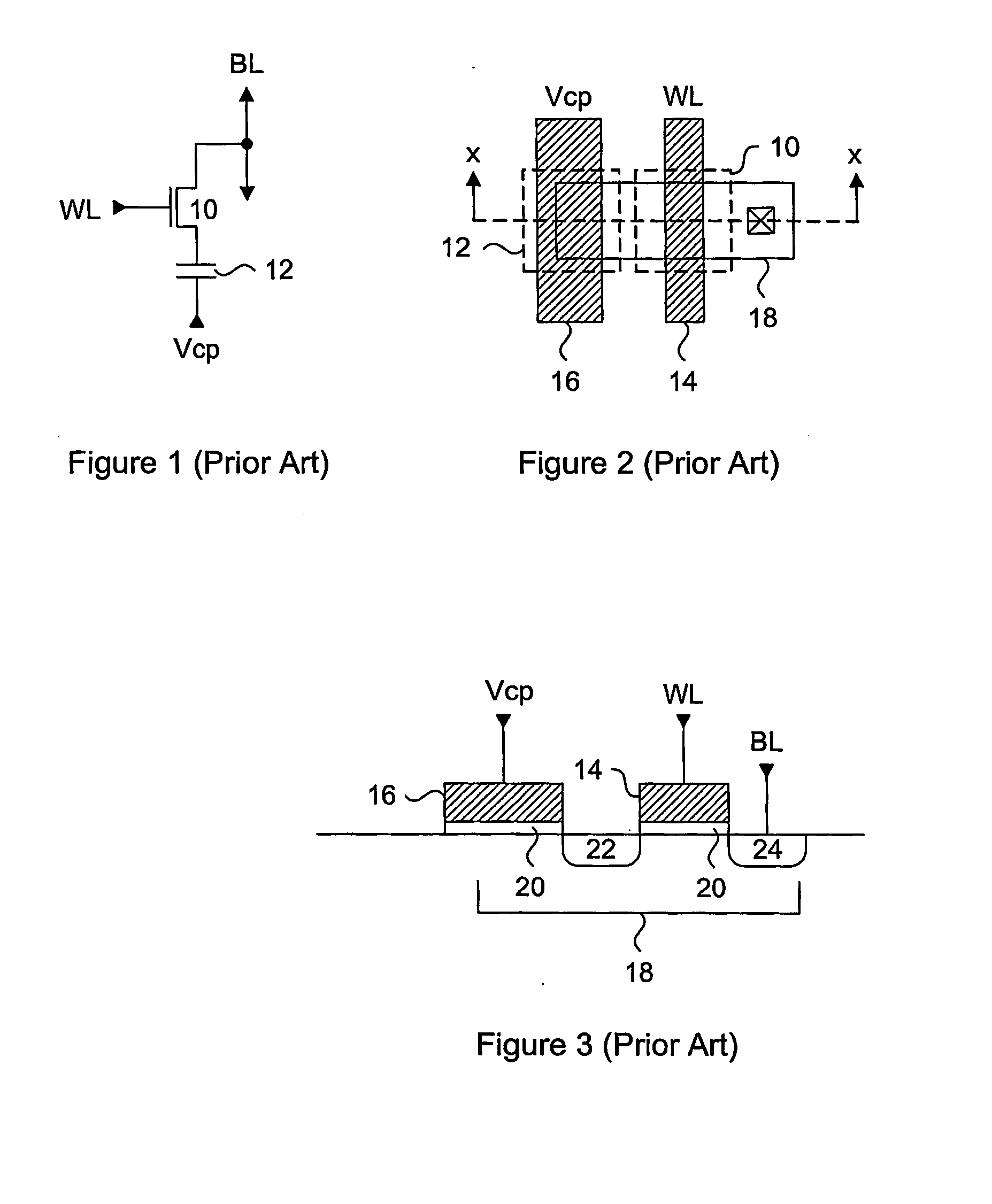

InactiveUS20050001257A1Increased area requirementLimited functionTransistorSolid-state devicesFloating body effectDram memory

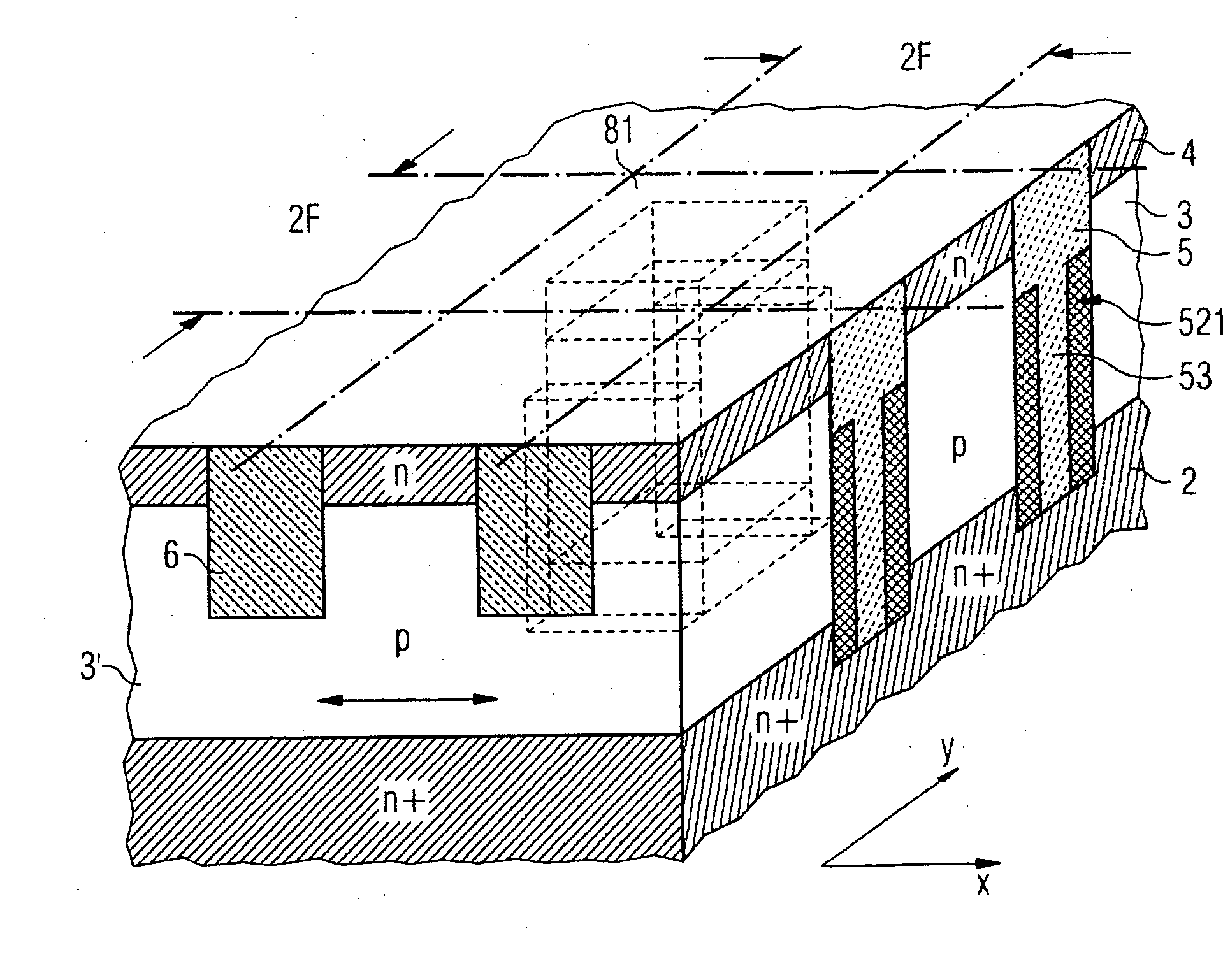

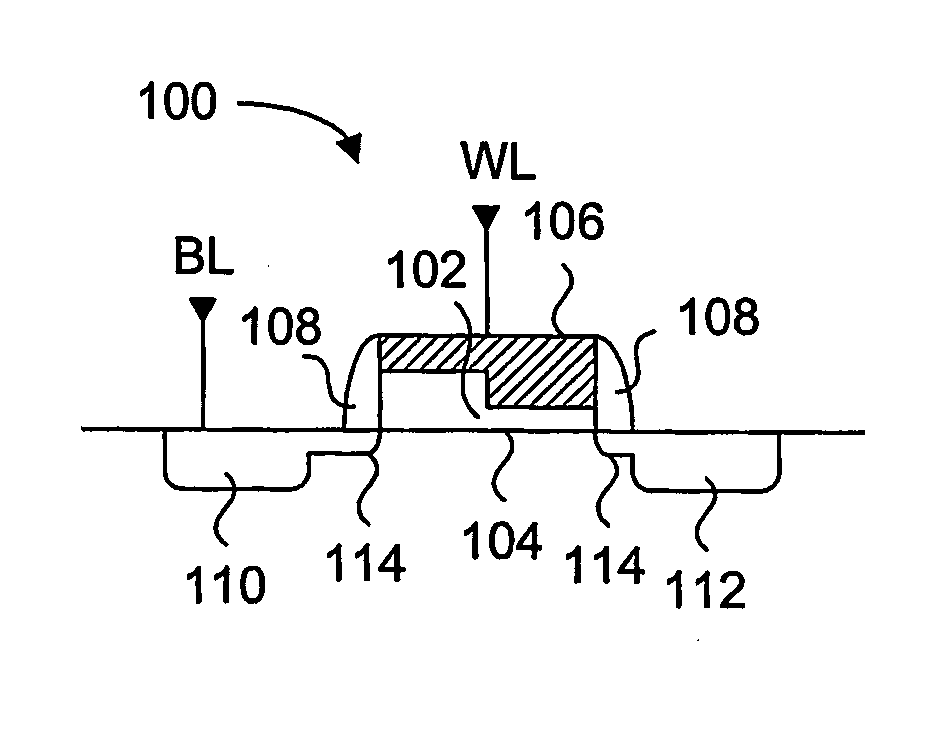

In a substrate vertical transistor cells are formed and are arranged, in a transistor cell array, row by row in an x direction and column by column in a y direction. Lower source / drain regions of the transistor cells are connected to a common connection plate. Upper source / drain regions of the transistor cells impart a contact connection for instance to a storage capacitor of a DRAM memory cell. Active trenches running between the transistor cells with word lines are formed along the x direction. The word lines form gate electrodes in sections. A potential at the gate electrode controls a conductive channel in an active region arranged in each case between the upper and the lower source / drain connection region. According to the invention, the active regions of adjacent transistor cells are sections of a contiguous layer body and are connected to one another. An accumulation of charge carriers in the active region and floating body effects are avoided without increasing the area requirement of a transistor cell.

Owner:POLARIS INNOVATIONS LTD

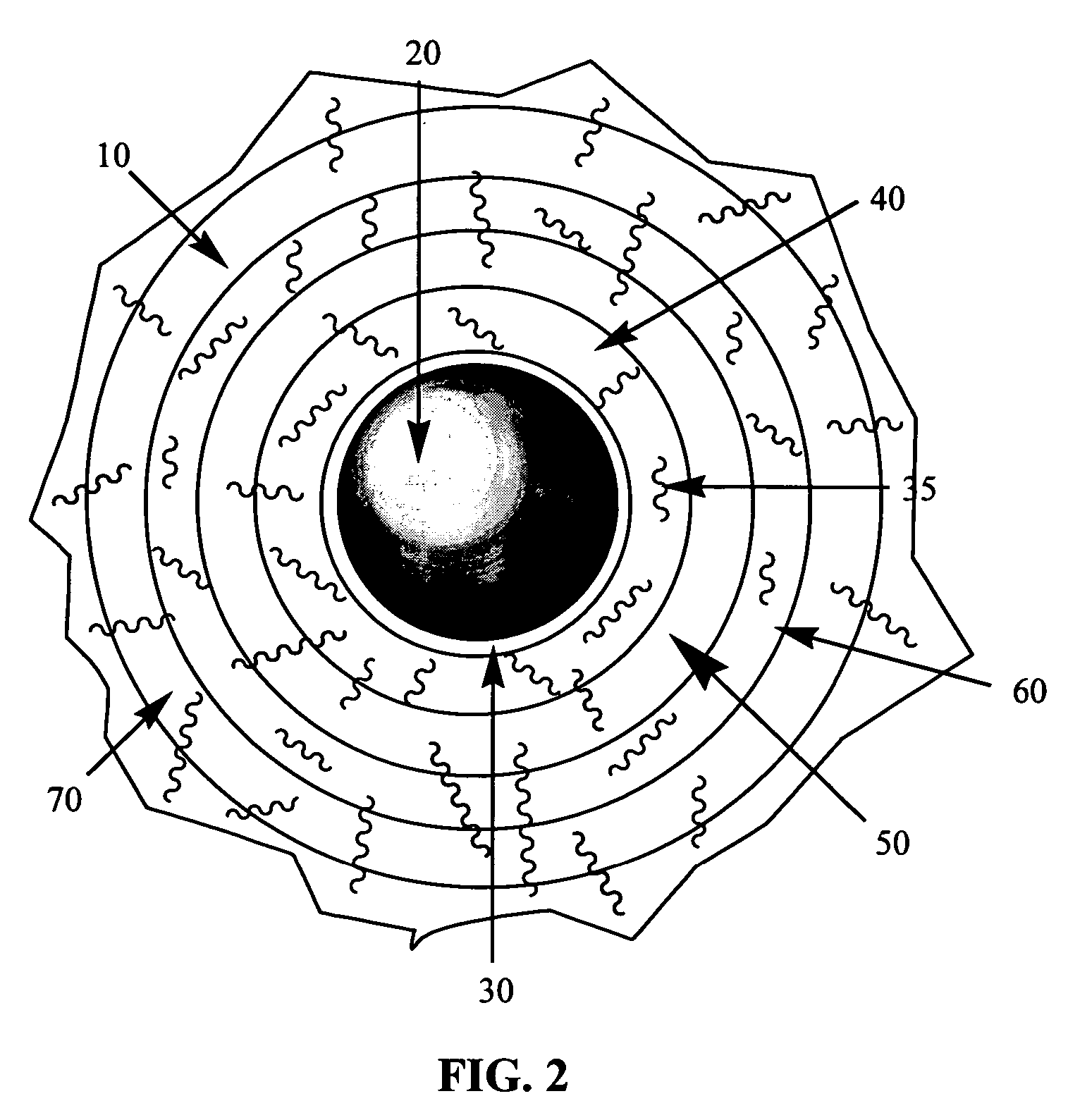

Soluble fibers for use in resin coated proppant

Coated particle substrates having a coating of resin and / or water soluble polymers and soluble, fibrous material are provided for use in subterranean formations. The coated particle substrate particles are typically proppants used to prop open subterranean hydrocarbon formations during recovery processes, such as after a hydraulic fracture, and provide both improved settling characteristics and improved hydrocarbon flow characteristics due to the conductive channels formed by the soluble fibers downhole. Methods of making the coated particles are also described.

Owner:FAIRMOUNT SANTROL

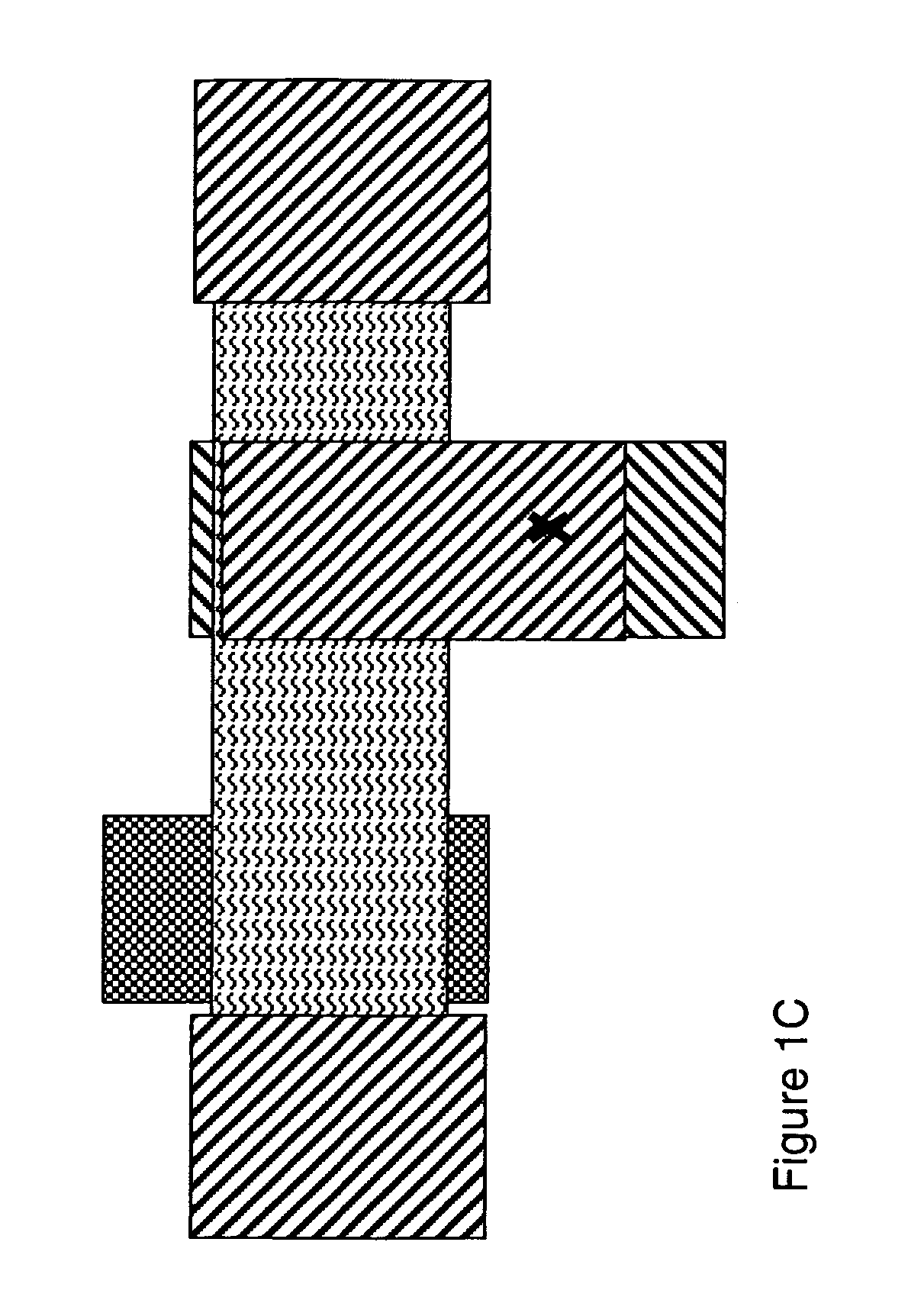

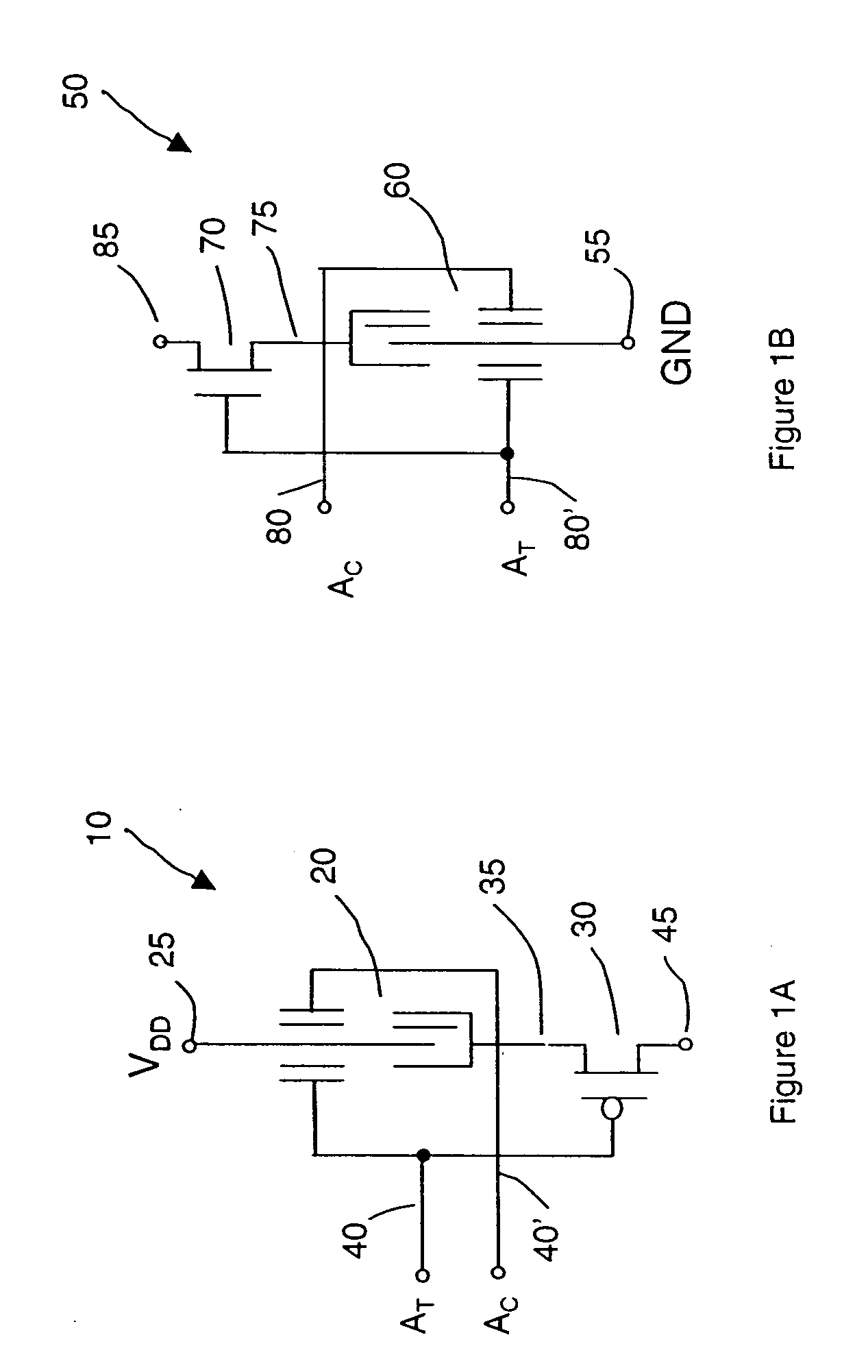

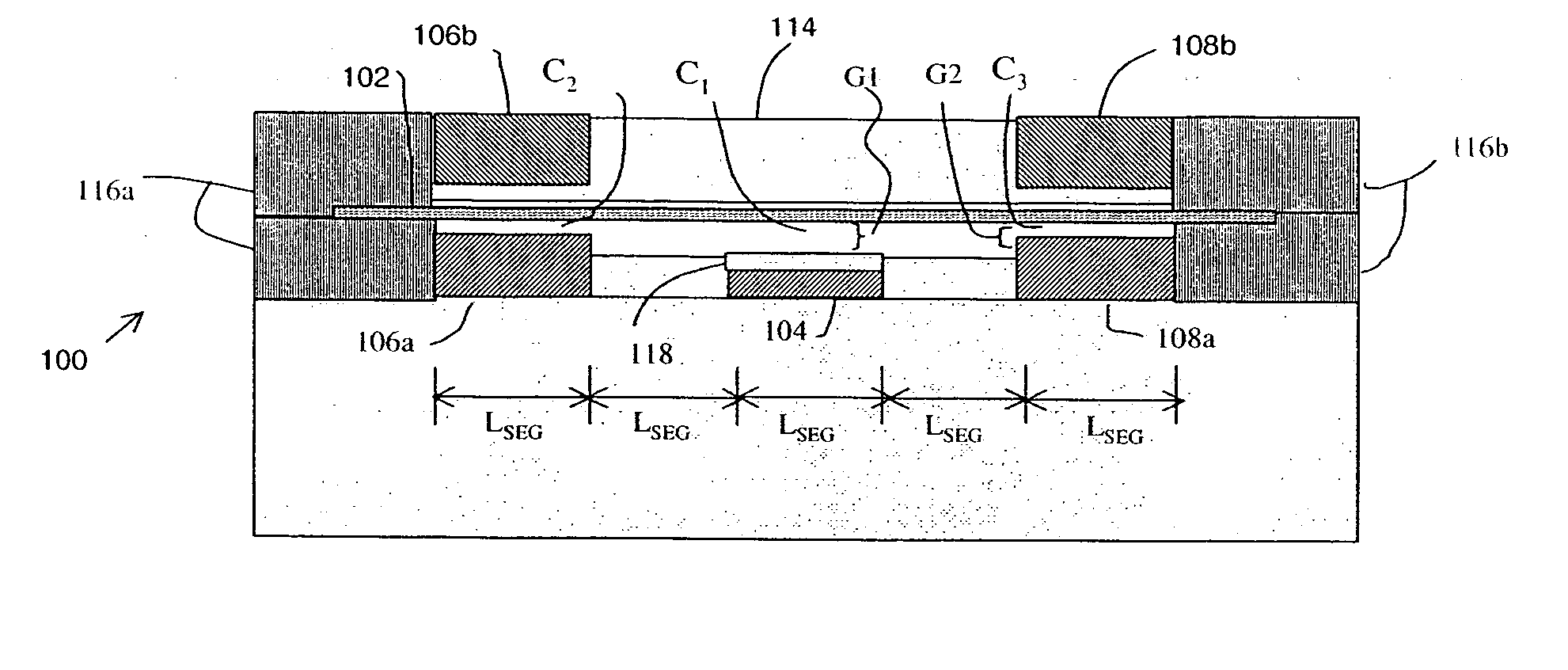

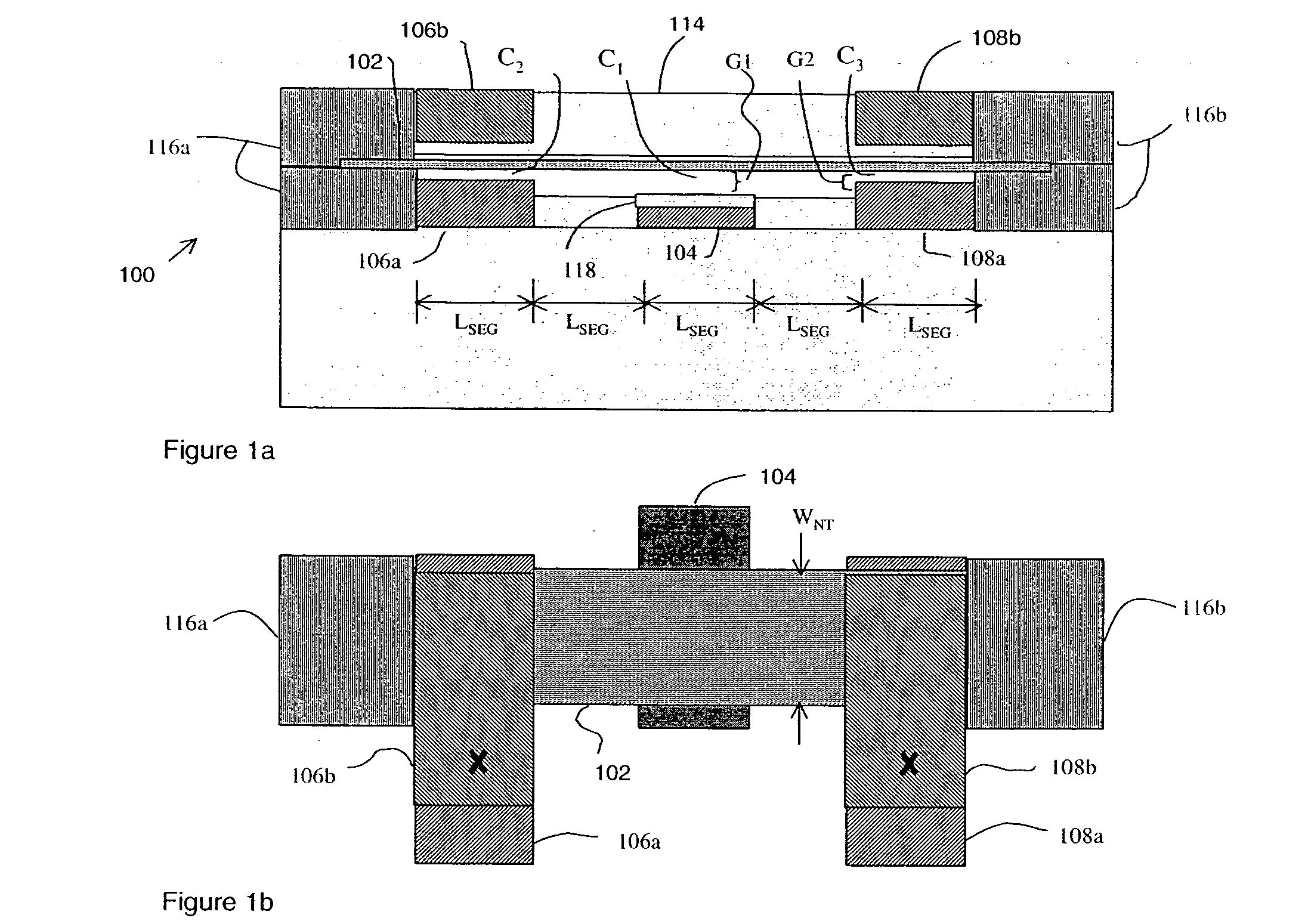

Nanotube-based switching elements

Nanotube-based switching elements and logic circuits. Under one embodiment of the invention, a switching element includes an input node, an output node, a nanotube channel element having at least one electrically conductive nanotube, and a control electrode. The control electrode is disposed in relation to the nanotube channel element to controllably form an electrically conductive channel between the input node and the output node. The channel at least includes said nanotube channel element. The output node is constructed and arranged so that channel formation is substantially unaffected by the electrical state of the output node. Under another embodiment of the invention, the control electrode is arranged in relation to the nanotube channel element to form said conductive channel by causing electromechanical deflection of said nanotube channel element. Under another embodiment of the invention, the output node includes an isolation structure disposed in relation to the nanotube channel element so that channel formation is substantially invariant from the state of the output node. Under another embodiment of the invention, the isolation structure includes electrodes disposed on opposite sides of the nanotube channel element and said electrodes produce substantially the same electric field. Under another embodiment of the invention, a Boolean logic circuit includes at least one input terminal and an output terminal, and a network of nanotube switching elements electrically disposed between said at least one input terminal and said output terminal. The network of nanotube switching elements effectuates a Boolean function transformation of Boolean signals on said at least one input terminal. The Boolean function transformation includes a Boolean inversion within the function, such as a NOT or NOR function.

Owner:NANTERO

Semiconductive metal oxide thin film ferroelectric memory transistor

InactiveUS20060038242A1Simplify the manufacturing processHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate dielectric

The present invention discloses a novel transistor structure employing semiconductive metal oxide as the transistor conductive channel. By replacing the silicon conductive channel with a semiconductive metal oxide channel, the transistors can achieve simpler fabrication process and could realize 3D structure to increase circuit density. The disclosed semiconductive metal oxide transistor can have great potential in ferroelectric non volatile memory device with the further advantages of good interfacial properties with the ferroelectric materials, possible lattice matching with the ferroelectric layer, reducing or eliminating the oxygen diffusion problem to improve the reliability of the ferroelectric memory transistor. The semiconductive metal oxide film is preferably a metal oxide exhibiting semiconducting properties at the transistor operating conditions, for example, In2O3 or RuO2. The present invention ferroelectric transistor can be a metal-ferroelectric-semiconductive metal oxide FET having a gate stack of a top metal electrode disposed on a ferroelectric layer disposed on a semiconductive metal oxide channel on a substrate. Using additional layer of bottom electrode and gate dielectric, the present invention ferroelectric transistor can also be a metal-ferroelectric-metal (optional)-gate dielectric (optional)-semiconductive metal oxide FET.

Owner:SHARP KK

Split-channel antifuse array architecture

InactiveUS20060244099A1Limited over-voltage exposureSimplify and improve and accessTransistorSemiconductor/solid-state device detailsCMOSEngineering

Generally, the present invention provides a variable thickness gate oxide anti-fuse transistor device that can be employed in a non-volatile, one-time-programmable (OTP) memory array application. The anti-fuse transistor can be fabricated with standard CMOS technology, and is configured as a standard transistor element having a source diffusion, gate oxide, polysilicon gate and optional drain diffusion. The variable gate oxide underneath the polysilicon gate consists of a thick gate oxide region and a thin gate oxide region, where the thin gate oxide region acts as a localized breakdown voltage zone. A conductive channel between the polysilicon gate and the channel region can be formed in the localized breakdown voltage zone during a programming operation. In a memory array application, a wordline read current applied to the polysilicon gate can be sensed through a bitline connected to the source diffusion, via the channel of the anti-fuse transistor. More specifically, the present invention provides an effective method for utilizing split channel MOS structures as an anti-fuse cell suitable for OTP memories.

Owner:SYNOPSYS INC

Fully-depleted castellated gate MOSFET device and method of manufacture thereof

ActiveUS7211864B2Depleted operationEnhanced ESD/EOS and reliability characteristicsTransistorSolid-state devicesMOSFETEngineering

A fully depleted castellated-gate MOSFET device is disclosed along with a method of making the same. The device has robust I / O applications, and includes a semiconductor substrate body having an upper portion with an upper end surface and a lower portion with a lower end surface. A source region, a drain region, and a channel-forming region between the source and drain regions are all formed in the semiconductor substrate body. trench isolation insulator islands surround the source and drain regions as well as the channel-forming region. The channel-forming region is made up of a plurality of thin, spaced, vertically-orientated conductive channel elements that span longitudinally along the device between the source and drain regions. A gate structure is also provided in the form of a plurality of spaced, castellated gate elements interposed between the channel elements. The gate structure also includes a top gate member which interconnects the gate elements at their upper vertical ends to cover the channel elements. Finally, a dielectric layer is provided to separate the conductive channel elements from the gate structure.

Owner:PALO ALTO NETWORKS INC

Architecture for vertical transistor cells and transistor-controlled memory cells

InactiveUS7109544B2Meet growth requirementsFunctional restriction of the transistor cells by a floating body effect is reducedTransistorSolid-state devicesTransistor arrayFloating body effect

Owner:POLARIS INNOVATIONS LTD

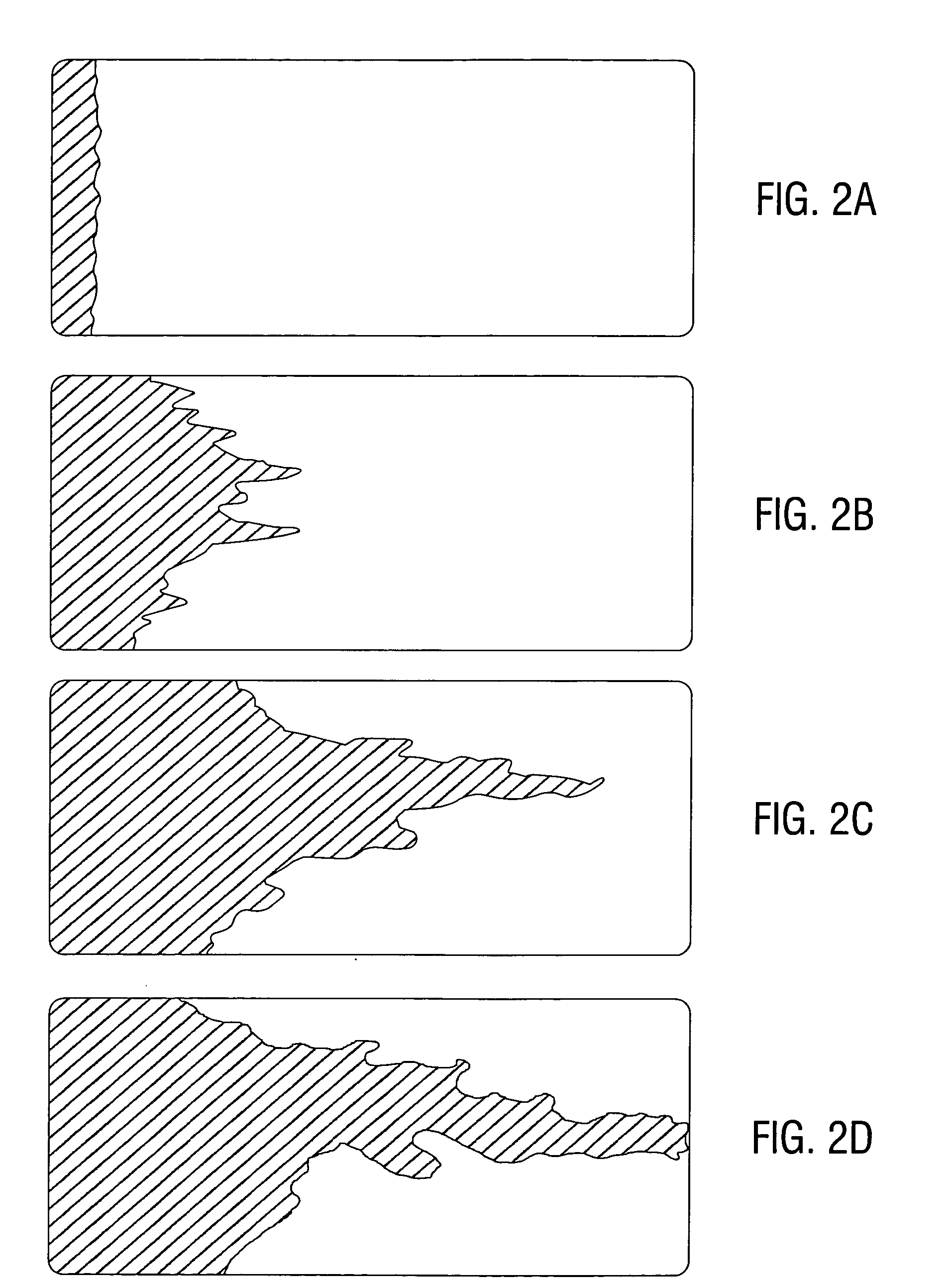

Methods for forming a permeable and stable mass in a subterranean formation

The present invention relates to increasing the permeability of a subterranean formation by forming a resinous mass having conductive channels through which fluids can be produced in the formation. Some embodiments of the present invention provide methods of creating a permeable resinous mass comprising the steps of selecting an interval along a well bore; providing a resin slurry comprising an acid curable resin, filler, and degradable material; placing the resin slurry into the selected interval; and, activating the acid curable resin using an activator wherein the activation causes the acid curable resin to substantially cure, the degradable material to substantially degrade, and forms the permeable resinous mass.

Owner:HALLIBURTON ENERGY SERVICES INC

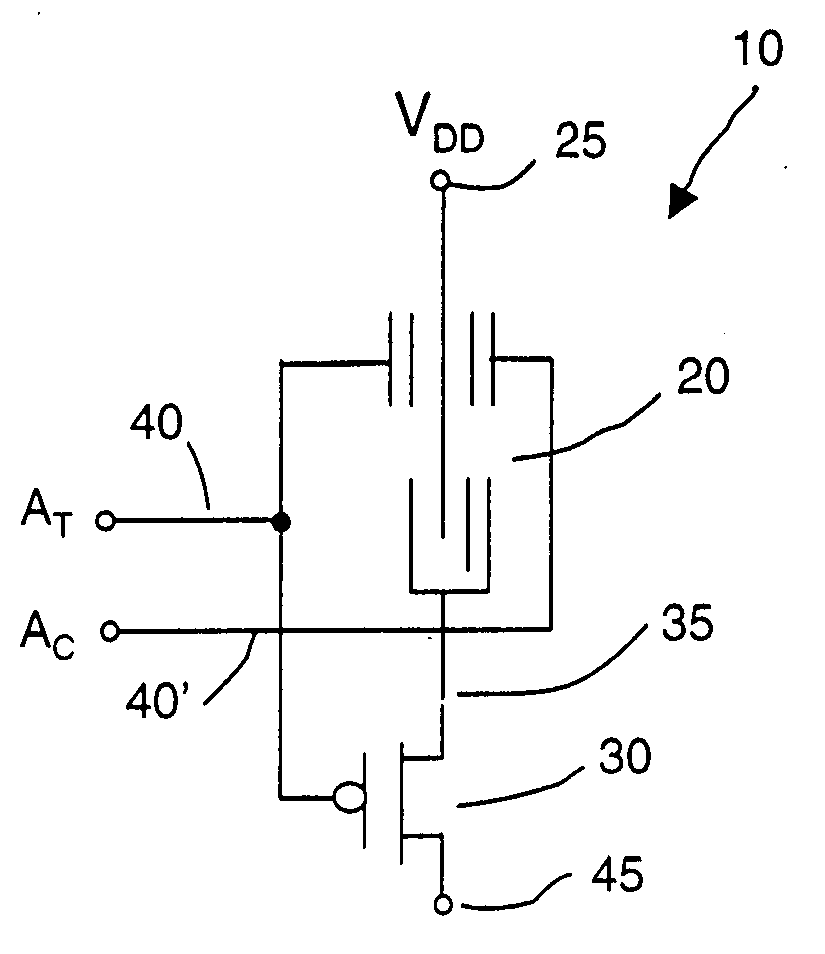

Nanotube-based switching elements

Nanotube-based switching elements and logic circuits. Under one embodiment of the invention, a switching element includes an input node, an output node, a nanotube channel element having at least one electrically conductive nanotube, and a control electrode. The control electrode is disposed in relation to the nanotube channel element to controllably form an electrically conductive channel between the input node and the output node. The channel at least includes said nanotube channel element. The output node is constructed and arranged so that channel formation is substantially unaffected by the electrical state of the output node. Under another embodiment of the invention, the control electrode is arranged in relation to the nanotube channel element to form said conductive channel by causing electromechanical deflection of said nanotube channel element. Under another embodiment of the invention, the output node includes an isolation structure disposed in relation to the nanotube channel element so that channel formation is substantially invariant from the state of the output node. Under another embodiment of the invention, the isolation structure includes electrodes disposed on opposite sides of the nanotube channel element and said electrodes produce substantially the same electric field. Under another embodiment of the invention, a Boolean logic circuit includes at least one input terminal and an output terminal, and a network of nanotube switching elements electrically disposed between said at least one input terminal and said output terminal. The network of nanotube switching elements effectuates a Boolean function transformation of Boolean signals on said at least one input terminal. The Boolean function transformation includes a Boolean inversion within the function, such as a NOT or NOR function.

Owner:NANTERO

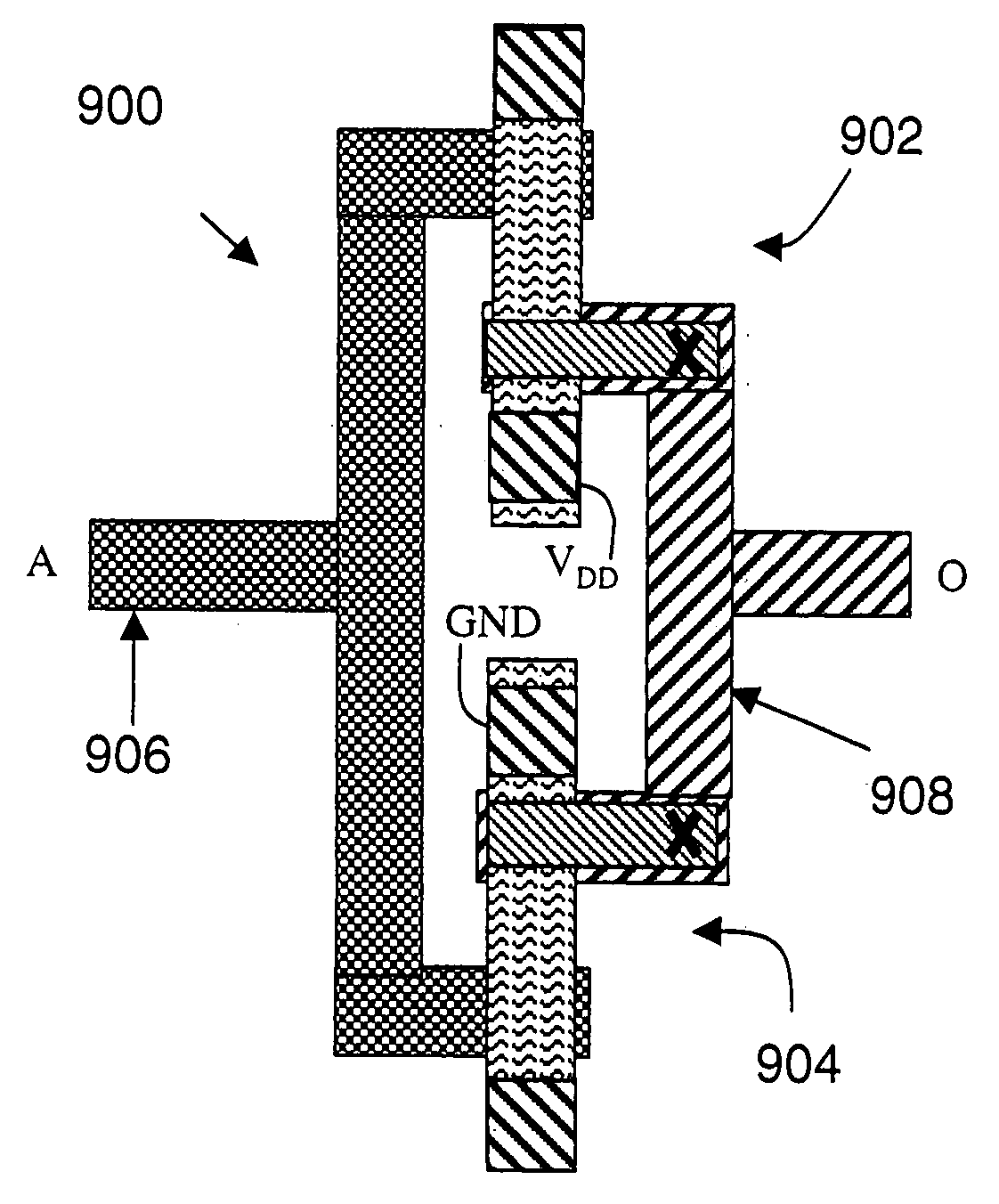

Integrated nanotube and field effect switching device

ActiveUS20060061389A1Logic circuits characterised by logic functionNanoelectromechanical switchesElectricityDevice form

Hybrid switching devices integrate nanotube switching elements with field effect devices, such as NFETs and PFETs. A switching device forms and unforms a conductive channel from the signal input to the output subject to the relative state of the control input. In embodiments of the invention, the conductive channel includes a nanotube channel element and a field modulatable semiconductor channel element. The switching device may include a nanotube switching element and a field effect device electrically disposed in series. According to one aspect of the invention, an integrated switching device is a four-terminal device with a signal input terminal, a control input terminal, a second input terminal, and an output terminal. The devices may be non-volatile. The devices can form the basis for a hybrid NT-FET logic family and can be used to implement any Boolean logic circuit.

Owner:NANTERO

Nanotube-based switching elements and logic circuits

Nanotube-based switching elements and logic circuits. Under one embodiment of the invention, a switching element includes an input node, an output node, a nanotube channel element having at least one electrically conductive nanotube, and a control electrode. The control electrode is disposed in relation to the nanotube channel element to controllably form an electrically conductive channel between the input node and the output node. The channel at least includes said nanotube channel element. The output node is constructed and arranged so that channel formation is substantially unaffected by the electrical state of the output node. Under another embodiment of the invention, the control electrode is arranged in relation to the nanotube channel element to form said conductive channel by causing electromechanical deflection of said nanotube channel element. Under another embodiment of the invention, the output node includes an isolation structure disposed in relation to the nanotube channel element so that channel formation is substantially invariant from the state of the output node. Under another embodiment of the invention, the isolation structure includes electrodes disposed on opposite sides of the nanotube channel element and said electrodes produce substantially the same electric field. Under another embodiment of the invention, a Boolean logic circuit includes at least one input terminal and an output terminal, and a network of nanotube switching elements electrically disposed between said at least one input terminal and said output terminal. The network of nanotube switching elements effectuates a Boolean function transformation of Boolean signals on said at least one input terminal. The Boolean function transformation includes a Boolean inversion within the function, such as a NOT or NOR function.

Owner:NANTERO

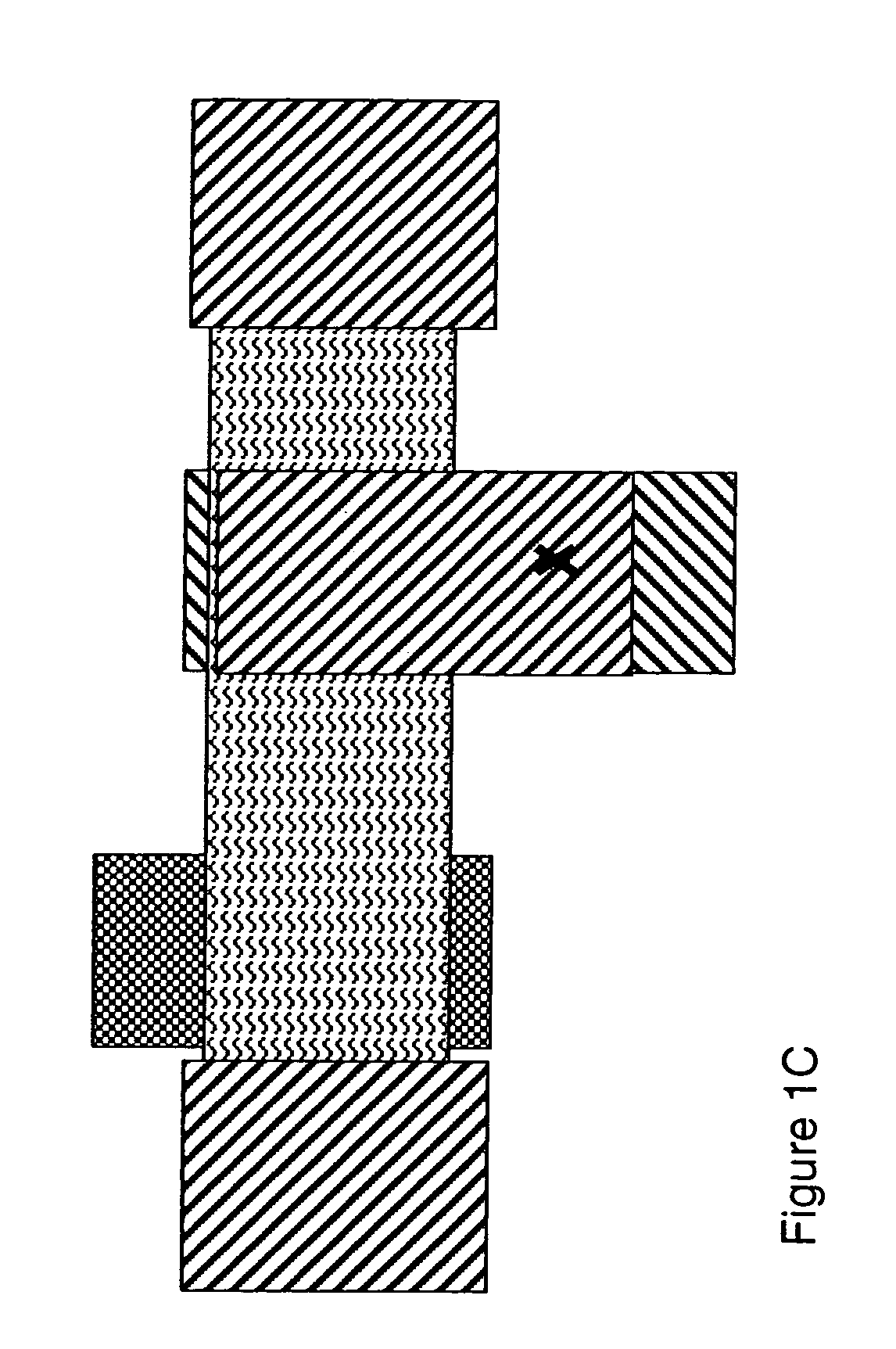

Resistive memory device and fabricating method thereof

InactiveUS20110155991A1Eliminate stray capacitanceHigh densitySolid-state devicesSemiconductor/solid-state device manufacturingInterconnectionEngineering

A resistive memory device and a fabricating method thereof are introduced herein. In resistive memory device, a plurality of bottom electrodes is disposed in active region of a substrate. Each of the bottom electrodes is disposed to correspond to each of the conductive channels; a patterned resistance switching material layer and the patterned top electrode layer are sequentially stacked on the bottom electrodes. An air dielectric layer exists between the patterned resistance switching material layer and the bottom electrodes. A plurality of patterned interconnections is disposed on the patterned top electrode.

Owner:IND TECH RES INST

Methods and compositions for introducing conductive channels into a hydraulic fracturing treatment

InactiveUS7213651B2Affecting permeabilityAvoid flowFluid removalVibration devicesFracturing fluidVolumetric Mass Density

Owner:BAKER HUGHES INC

Soluble fibers for use in resin coated proppant

Coated particle substrates having a coating of resin and / or water soluble polymers and soluble, fibrous material are provided for use in subterranean formations. The coated particle substrate particles are typically proppants used to prop open subterranean hydrocarbon formations during recovery processes, such as after a hydraulic fracture, and provide both improved settling characteristics and improved hydrocarbon flow characteristics due to the conductive channels formed by the soluble fibers downhole. Methods of making the coated particles are also described.

Owner:FAIRMOUNT SANTROL

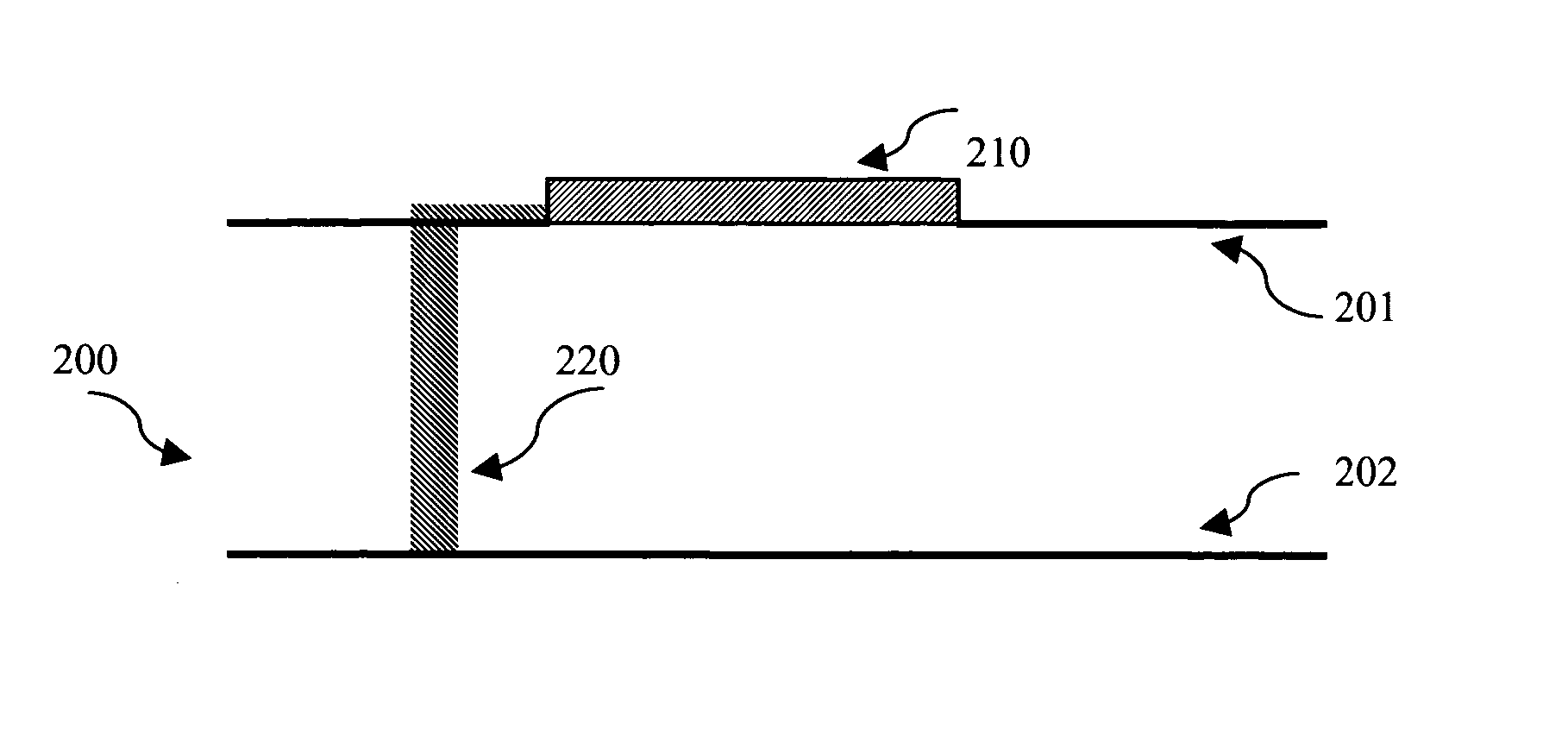

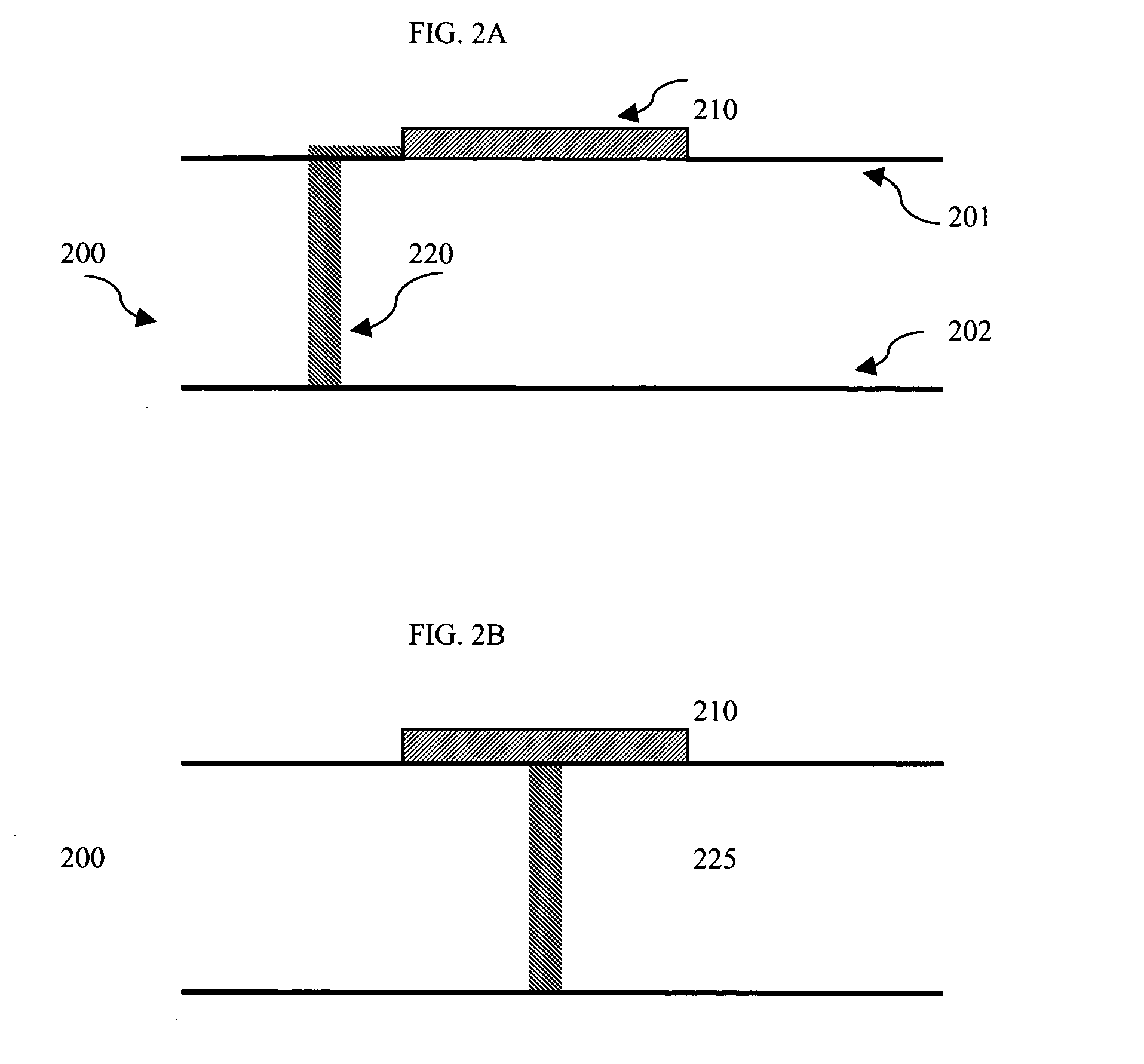

Through-wafer contact to bonding pad

InactiveUS20050156330A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringConductive materials

An integrated circuit with conductive channels connecting the bonding pads to alternative surfaces of the IC chip is disclosed. Typically the channels would be formed by reactive ion etching, passivated and then filled with copper or other conductive material. The channels may be formed at alternative points in the wafer processing flow depending on the requirements of the IC. Alternatively the channels may be used for heat sinks; in this case the channel would connect a chip “hot spot” with a conductive package member.

Owner:HARRIS JAMES M

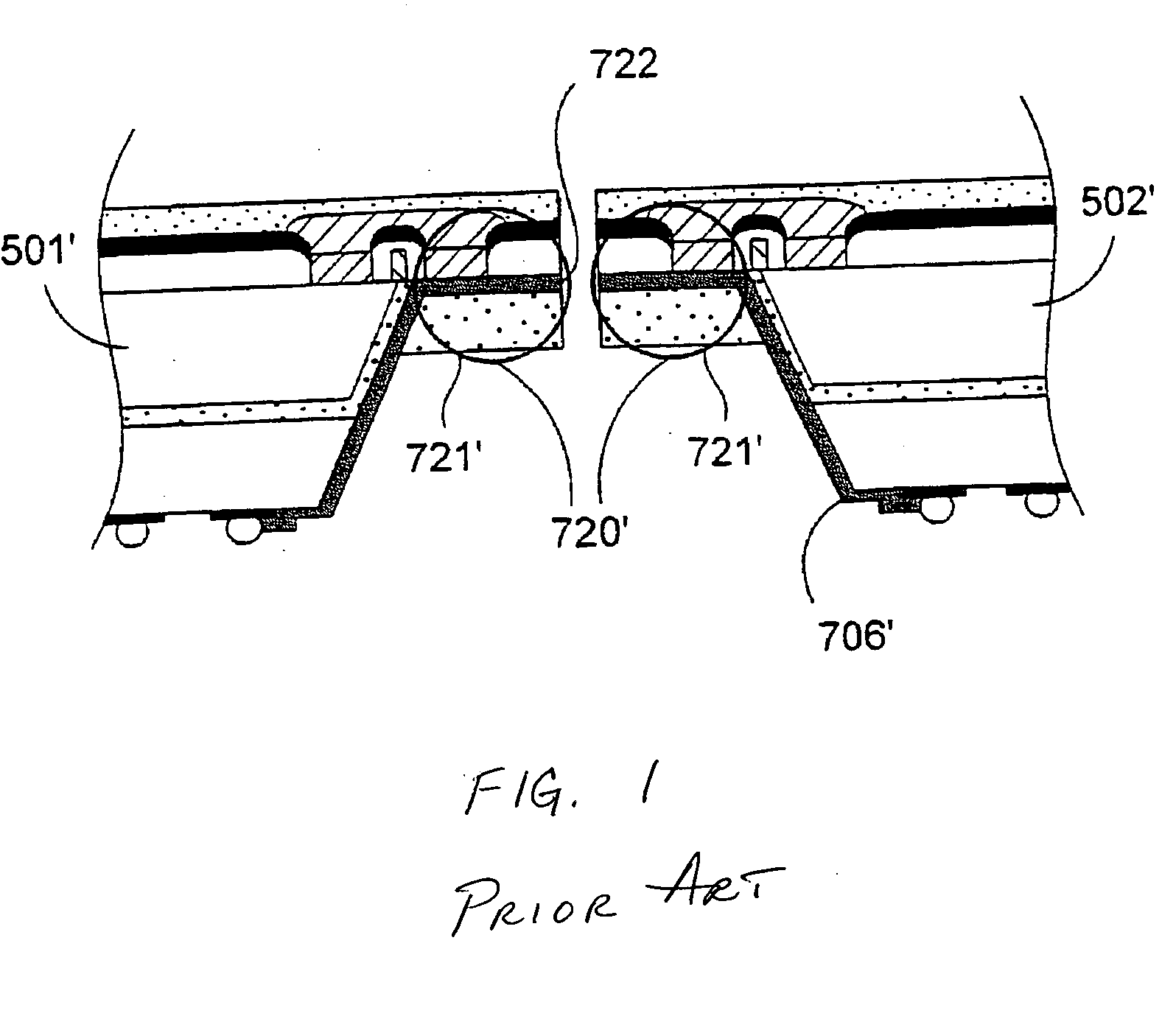

Bonding structure with compliant bumps

InactiveUS6972490B2Reduce the modulus of elasticityReduce pressurePrinted circuit assemblingSemiconductor/solid-state device detailsBonding processEngineering

A bonding structure with compliant bumps includes a stopper structure and a protection layer. Compliant bumps include at least a polymer bump, a metal layer and a surface conductive layer. Both the stopper structure and protection layer are formed with polymer bumps and metal layer. Compliant bumps provide bonding pad and conductive channel. Stoppers are used to prevent compliant bumps from crushing for overpressure in bonding process. The protection layer provides functions of grounding and shielding. The stoppers can be outside or connected with the compliant bumps. The protection layer has thickness smaller than the stopper structure and compliant bumps. It can be separated or connected with stoppers.

Owner:IND TECH RES INST

Mixed-signal semiconductor platform incorporating fully-depleted castellated-gate MOSFET device and method of manufacture thereof

Owner:IP3 2021 SERIES 600 OF ALLIED SECURITY TRUST I

Semiconductive metal oxide thin film ferroelectric memory transistor

InactiveUS7378286B2Simplify the manufacturing processHigh densityTransistorSemiconductor/solid-state device manufacturingDielectricGate dielectric

The present invention discloses a novel transistor structure employing semiconductive metal oxide as the transistor conductive channel. By replacing the silicon conductive channel with a semiconductive metal oxide channel, the transistors can achieve simpler fabrication process and could realize 3D structure to increase circuit density. The disclosed semiconductive metal oxide transistor can have great potential in ferroelectric non volatile memory device with the further advantages of good interfacial properties with the ferroelectric materials, possible lattice matching with the ferroelectric layer, reducing or eliminating the oxygen diffusion problem to improve the reliability of the ferroelectric memory transistor. The semiconductive metal oxide film is preferably a metal oxide exhibiting semiconducting properties at the transistor operating conditions, for example, In2O3 or RuO2. The present invention ferroelectric transistor can be a metal-ferroelectric-semiconductive metal oxide FET having a gate stack of a top metal electrode disposed on a ferroelectric layer disposed on a semiconductive metal oxide channel on a substrate. Using additional layer of bottom electrode and gate dielectric, the present invention ferroelectric transistor can also be a metal-ferroelectric-metal (optional)-gate dielectric (optional)-semiconductive metal oxide FET.

Owner:SHARP KK

Nanotube-based transfer devices and related circuits

InactiveUS20050279988A1Electrostatic/electro-adhesion relaysNanoinformaticsElectricityTerminal equipment

Nanotube transfer devices controllably form a nanotube-based electrically conductive channel between a first node and a second node under the control of a control structure. A control structure induces a nanotube channel element to deflect so as to form and unform the conductive channel between the nodes. The nanotube channel element is not in permanent electrical contact with either the first node or the second node. The nanotube channel element may have a floating potential in certain states of the device. Each output node may be connected to an arbitrary network of electrical components. The nanotube transfer device may be volatile or non-volatile. In preferred embodiments, the nanotube transfer device is a three-terminal device or a four-terminal device. Electrical circuits are provided that ensure proper switching of nanotube transfer devices interconnected with arbitrary circuits. The circuits may overdrive the control structure to induce the desired state of channel formation.

Owner:NANTERO

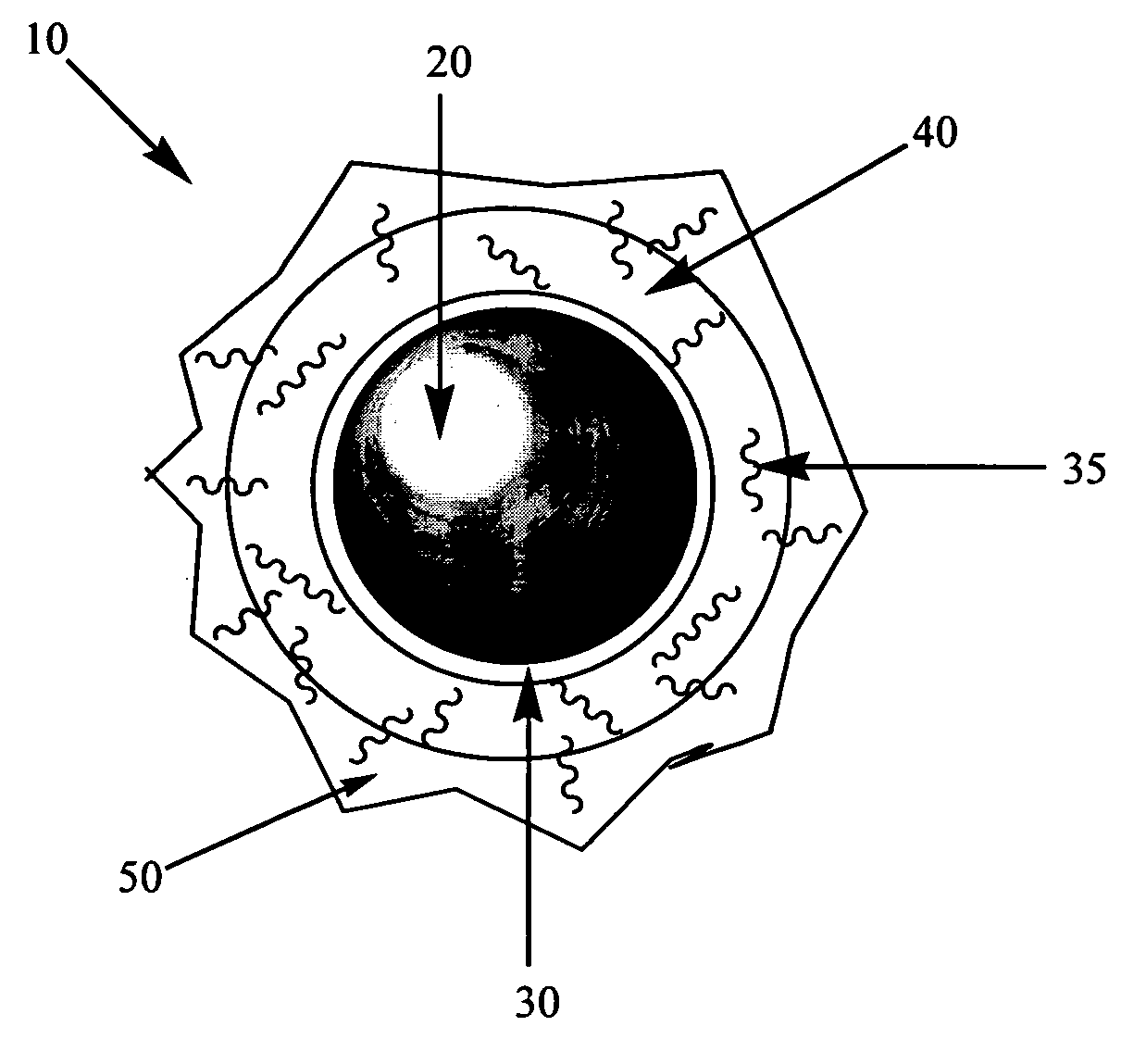

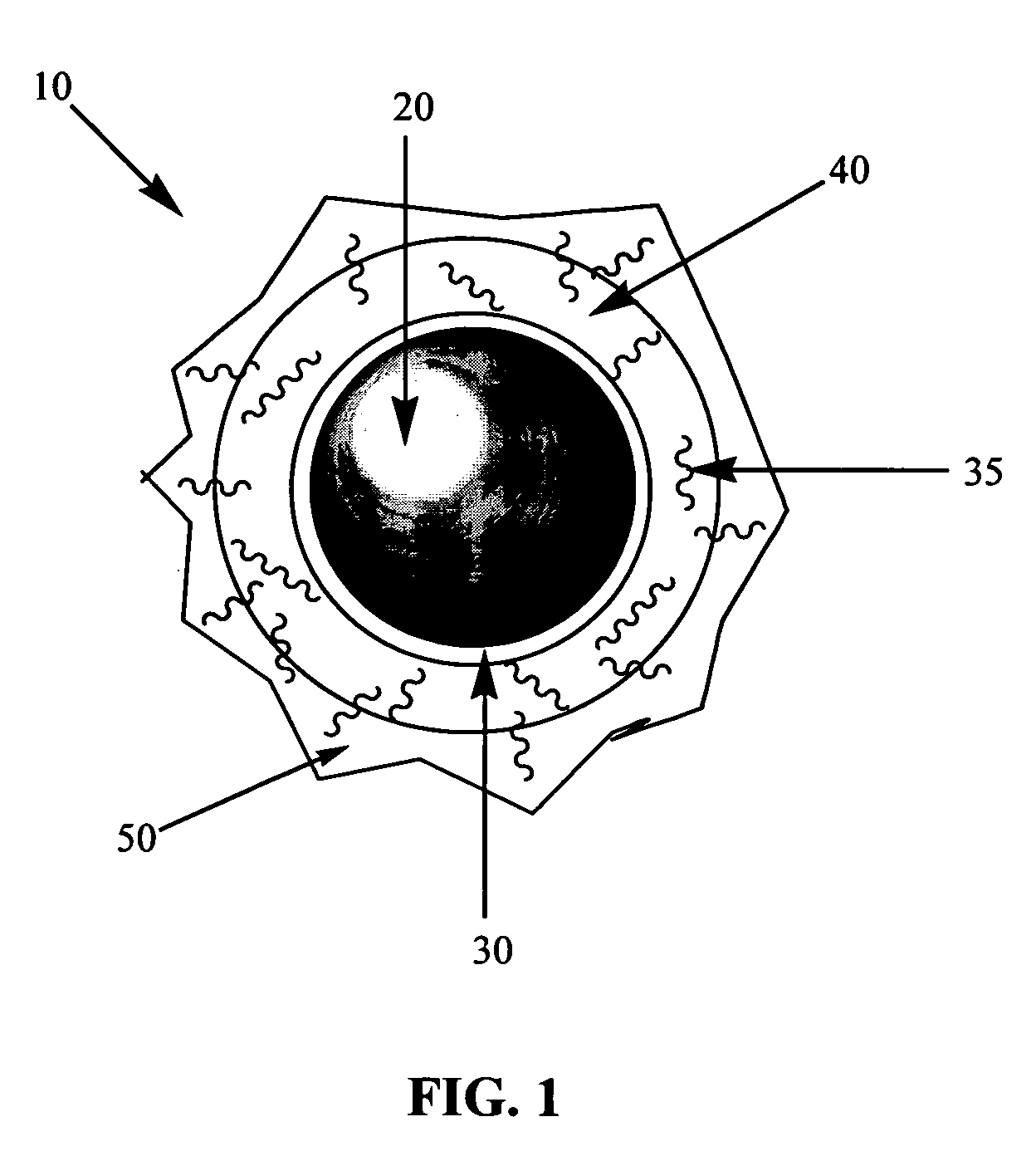

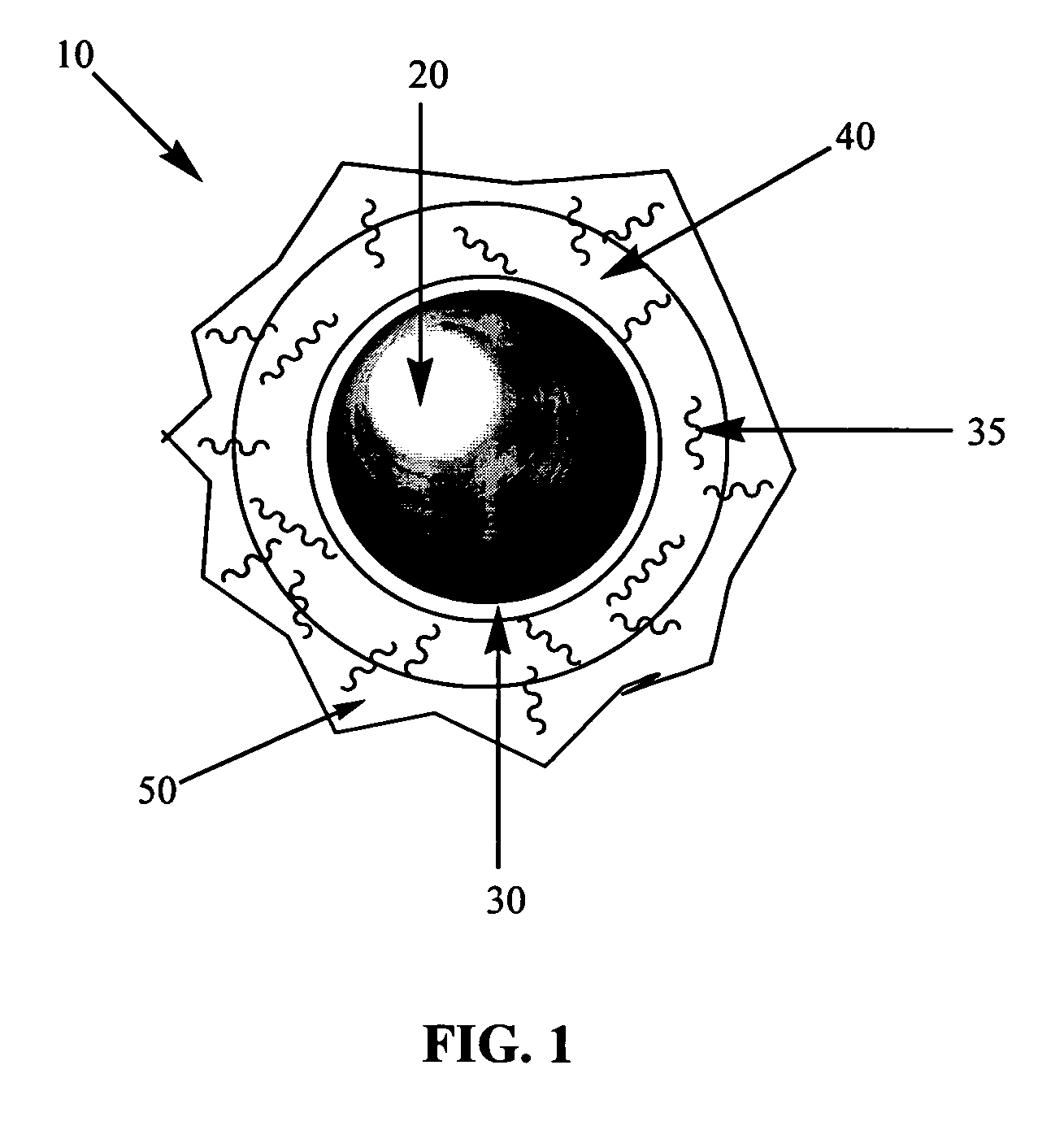

Silicon carbon composite negative electrode material for lithium ion battery as well as preparation method and applications of material

ActiveCN102903896AImprove securityImprove cycle performanceCell electrodesCarbon compositesElectrical battery

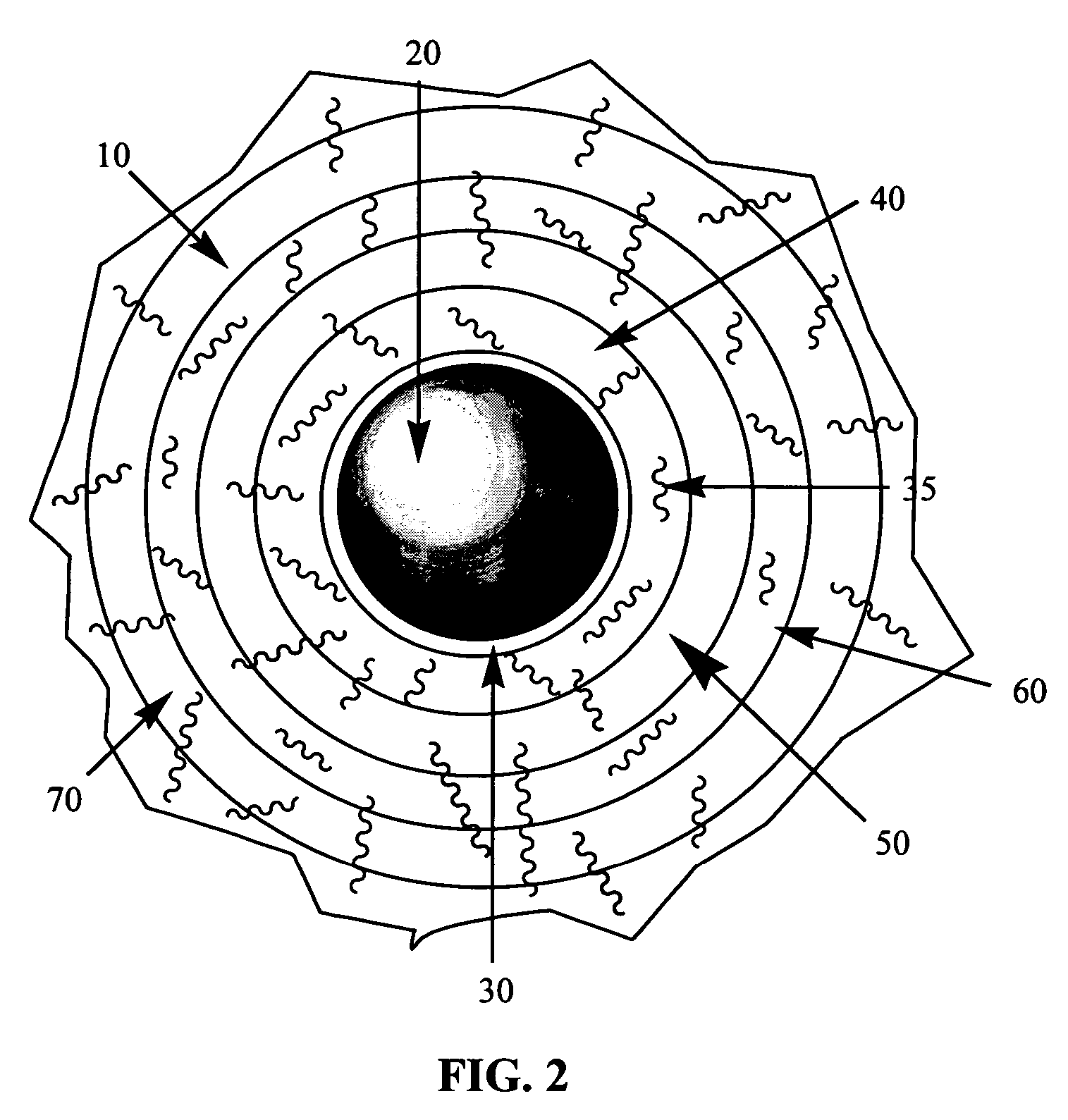

The invention is applicable to the field of novel materials, and provides a silicon carbon composite negative electrode material for a lithium ion battery, as well as a preparation method and applications of the material. The negative electrode material is of a nuclear-shell-type composite structure, and consists of nano silicon in the core, amorphous carbon at the middle layer and a one-dimensional nano carbon material at the outermost layer, wherein the amorphous carbon at the middle layer forms an elastic loose surface structure, and thus the circulating performance and multiplying performance of silicon are improved; a network structure built by the one-dimensional nano carbon material at the outermost layer not only plays a role in buffering mechanical stress, but also provides a rapid electric conducting channel for active silicon particles, and improves the circulating performance and multiplying performance of silicon further; and meanwhile, a three-dimensional electric-conducting heat-conducting network formed by the one-dimensional nano carbon material can conduct heat generated by a battery during the discharging process to the space around, and the safety performance of the battery is improved. The preparation method of the silicon carbon composite negative electrode material for the lithium ion battery is simple and feasible in process, environment-friendly and energy-saving, low in cost, and easy for industrialization.

Owner:RESEARCH INSTITUTE OF TSINGHUA UNIVERSITY IN SHENZHEN

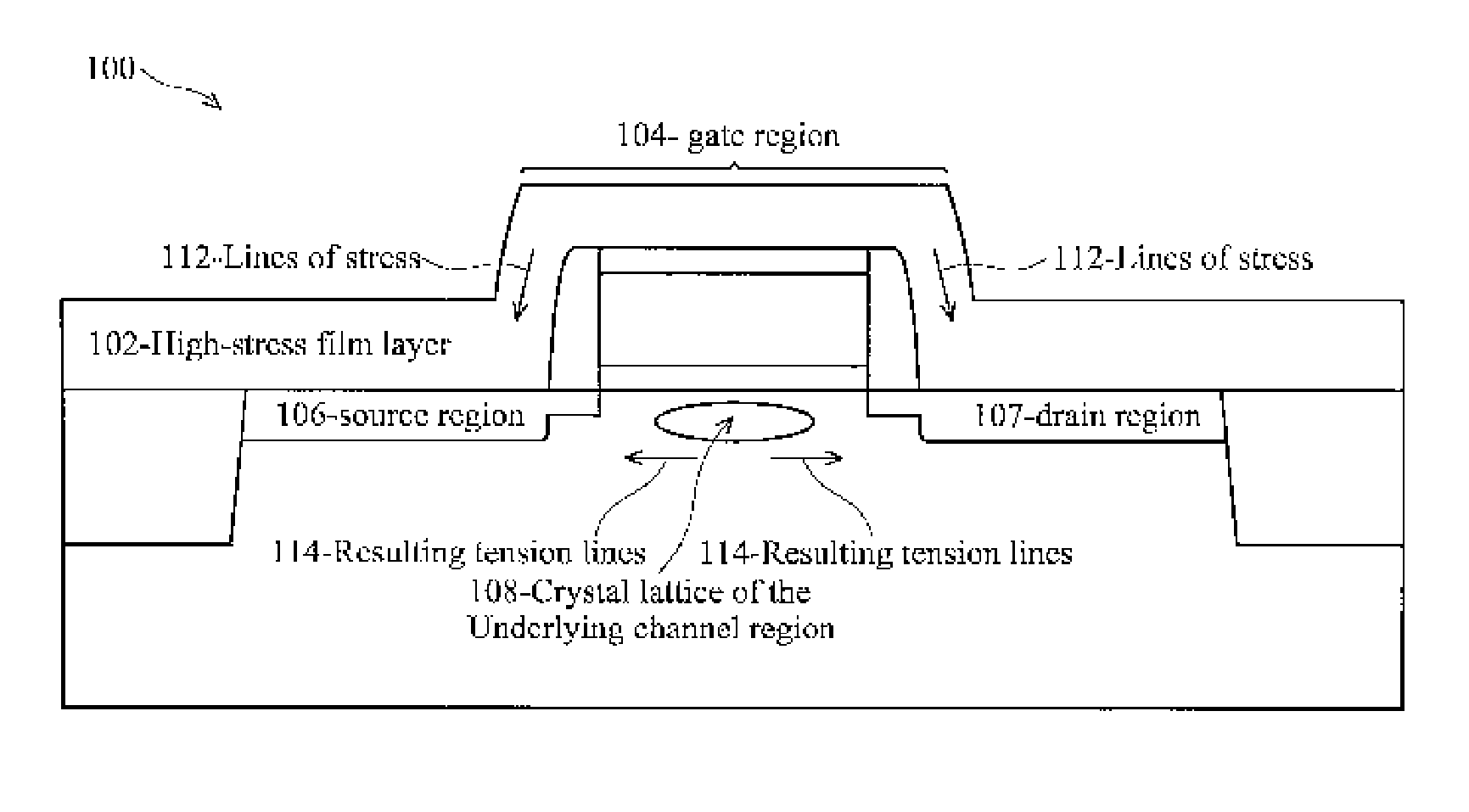

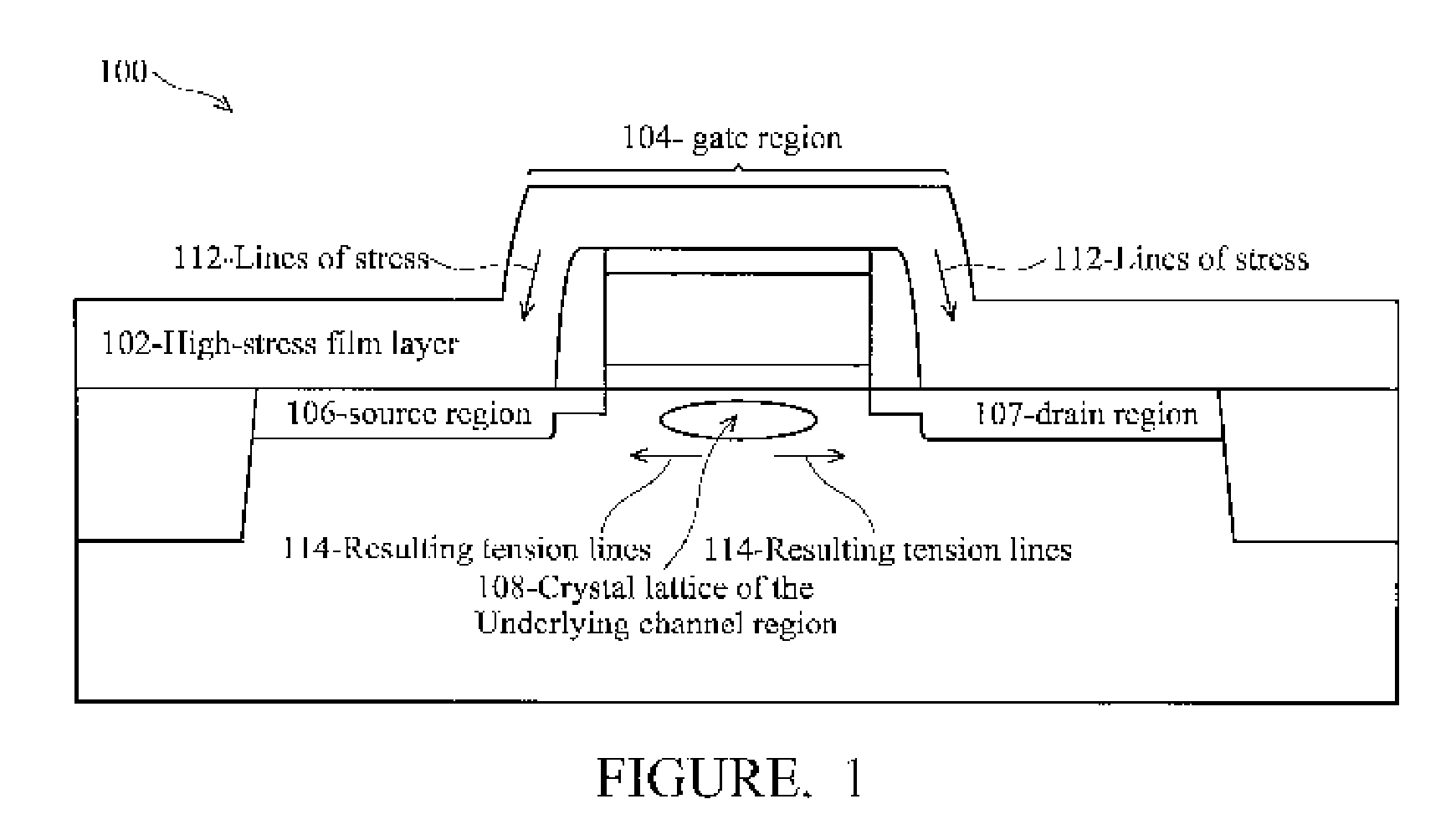

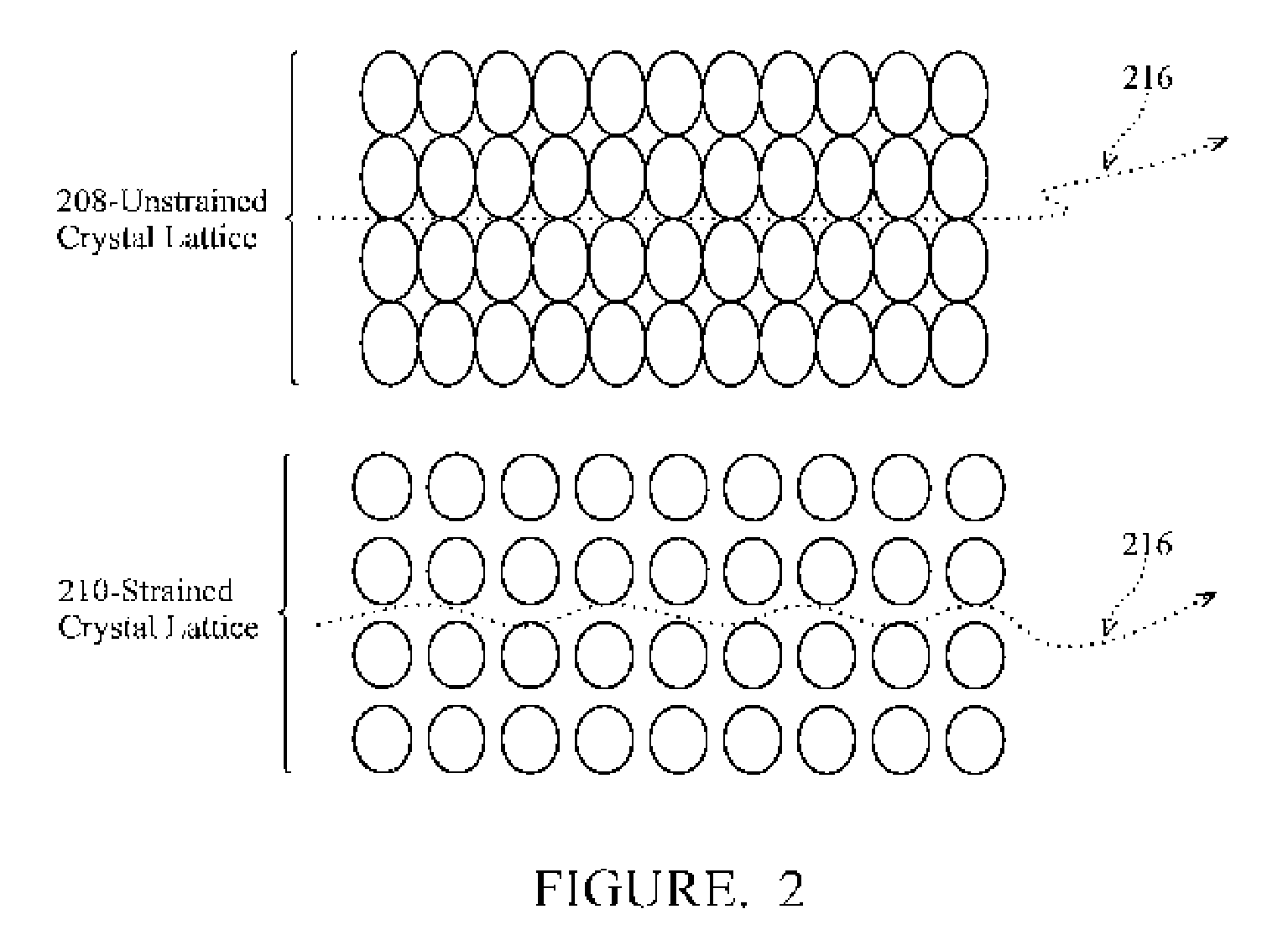

Methods and Structures to Produce a Strain-Inducing Layer in a Semiconductor Device

InactiveUS20060118892A1Increase contact resistanceIncrease pressureSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialMetal silicide

Described are methods of manufacturing a strain-inducing layer in semiconductor devices and structures formed to have such strain-inducing layers. Circuit elements are formed on a semiconductor substrate with conductive channel regions within the semiconductor substrate. Metal silicide contacts are formed on the semiconductor substrate and some are electrically connected to the channel regions. A strain-inducing layer can then be formed over the metal silicide contacts. Further, the strain-inducing layer is then treated with thermal processing, photo-thermal processing, or electron irradiation processing thereby increasing the stress of the strain-inducing layer and induce strain upon the crystal lattice structure in the conductive channel regions within the semiconductor substrate.

Owner:TAIWAN SEMICON MFG CO LTD

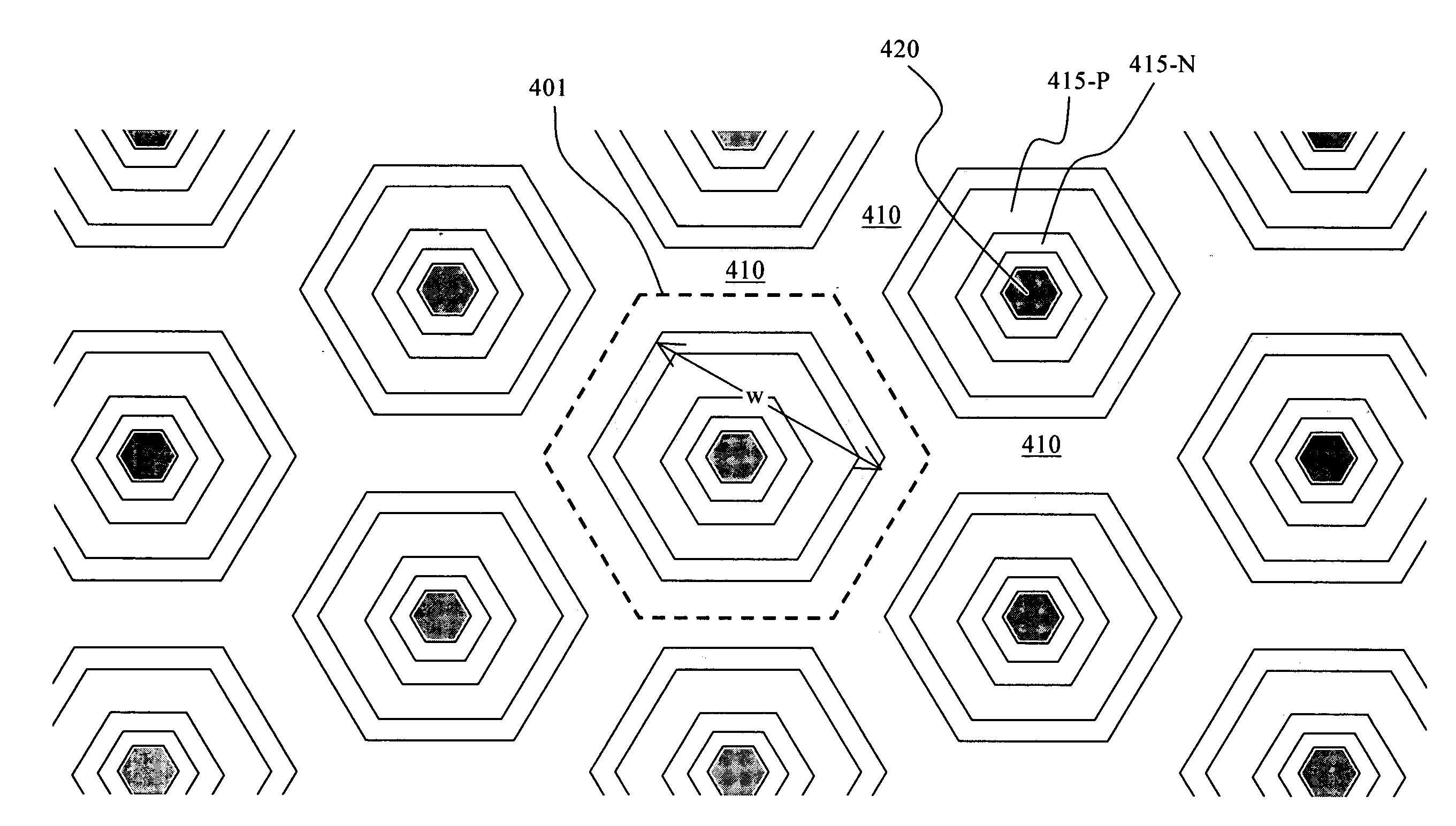

Nano-tube mosfet technology and devices

ActiveUS20100163846A1Simple and convenient processing stepEasy to carrySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETDielectric layer

This invention discloses a semiconductor power device disposed in a semiconductor substrate and the semiconductor substrate has a plurality of trenches. Each of the trenches is filled with a plurality of epitaxial layers of alternating conductivity types constituting nano tubes functioning as conducting channels stacked as layers extending along a sidewall direction with a “Gap Filler” layer filling a merging-gap between the nano tubes disposed substantially at a center of each of the trenches. The “Gap Filler” layer can be very lightly doped Silicon or grown and deposited dielectric layer. In an exemplary embodiment, the plurality of trenches are separated by pillar columns each having a width approximately half to one-third of a width of the trenches.

Owner:ALPHA & OMEGA SEMICON INC

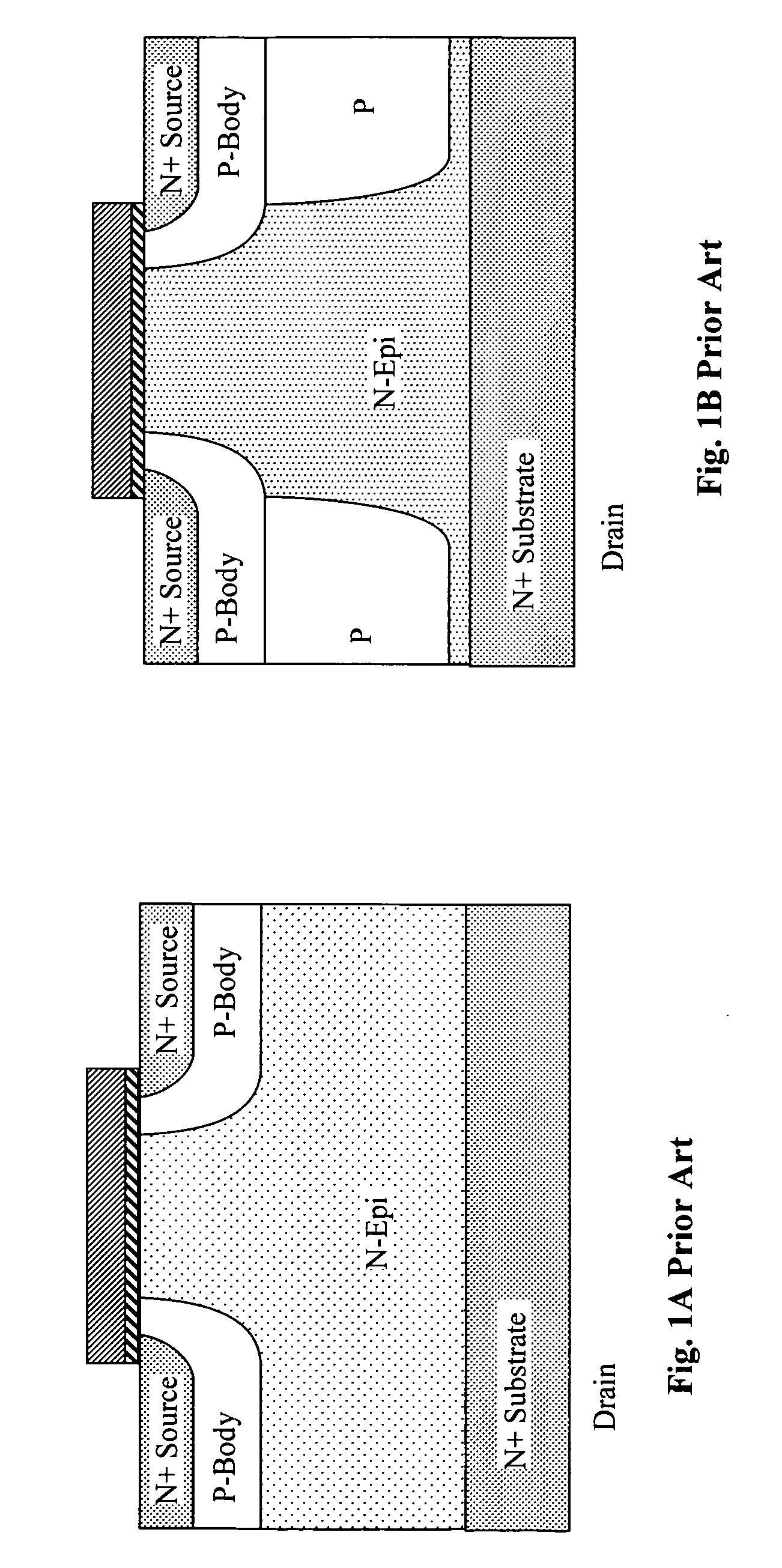

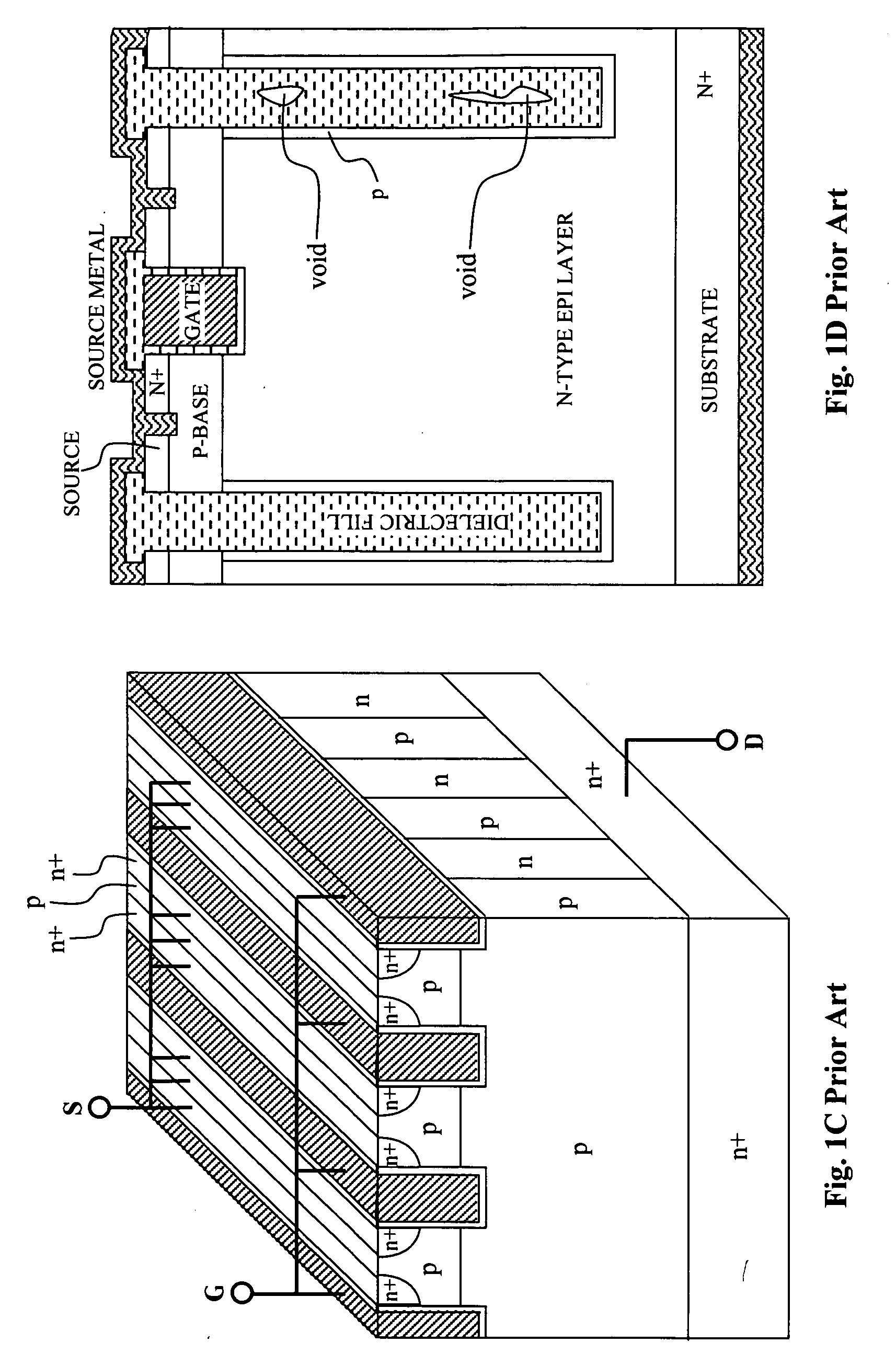

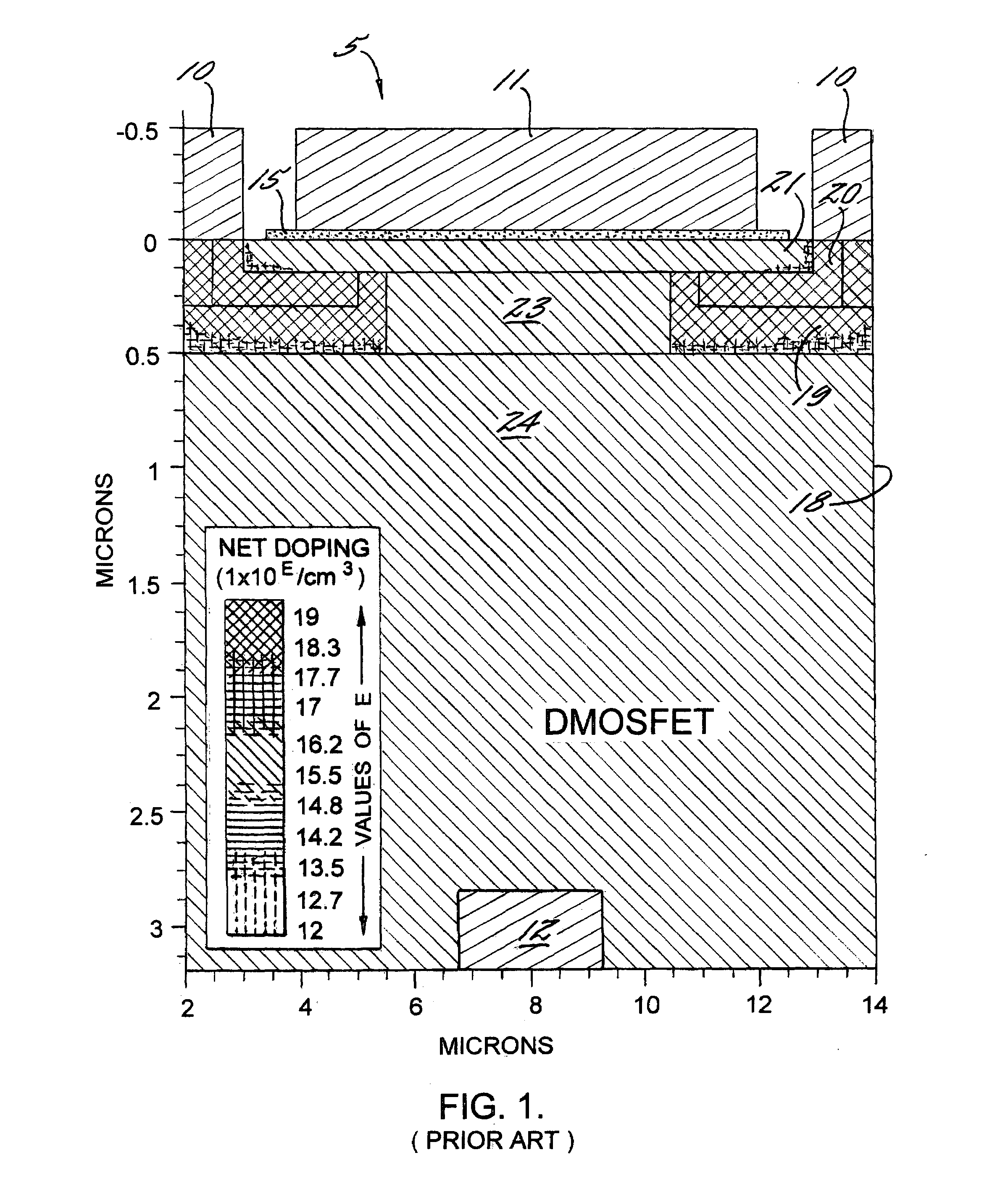

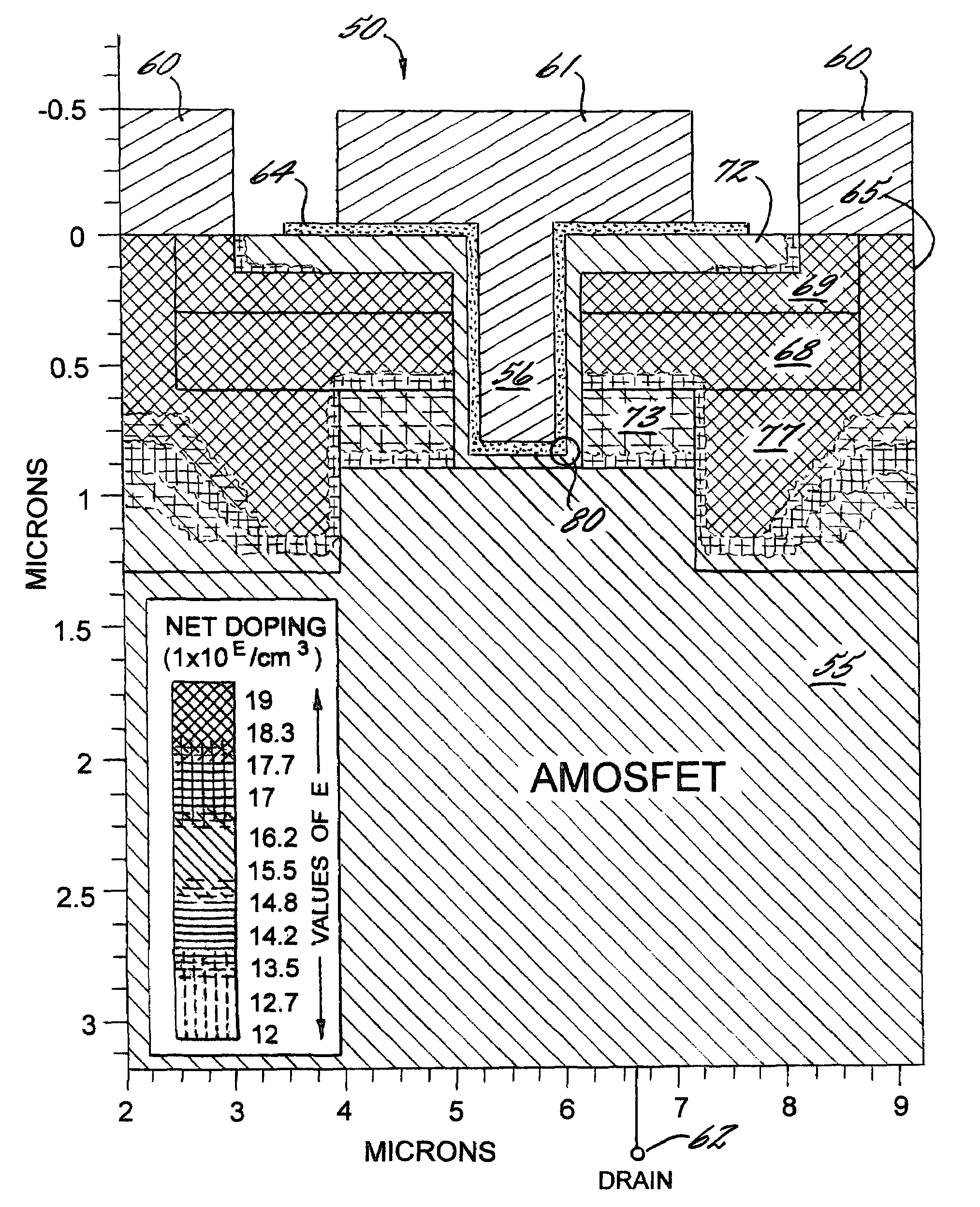

Transistor with A-Face Conductive Channel and Trench Protecting Well Region

ActiveUS20090146154A1High voltage blocking abilityMinimize JFET effectThyristorSemiconductor/solid-state device manufacturingTrench gateSemiconductor

A transistor structure optimizes current along the A-face of a silicon carbide body to form an AMOSFET that minimizes the JFET effect in the drift region during forward conduction in the on-state. The AMOSFET further shows high voltage blocking ability due to the addition of a highly doped well region that protects the gate corner region in a trench-gated device. The AMOSFET uses the A-face conduction along a trench sidewall in addition to a buried channel layer extending across portions of the semiconductor mesas defining the trench. A doped well extends from at least one of the mesas to a depth within the current spreading layer that is greater than the depth of the trench. A current spreading layer extends between the semiconductor mesas beneath the bottom of the trench to reduce junction resistance in the on-state. A buffer layer between the trench and the deep well further provides protection from field crowding at the trench corner.

Owner:WOLFSPEED INC

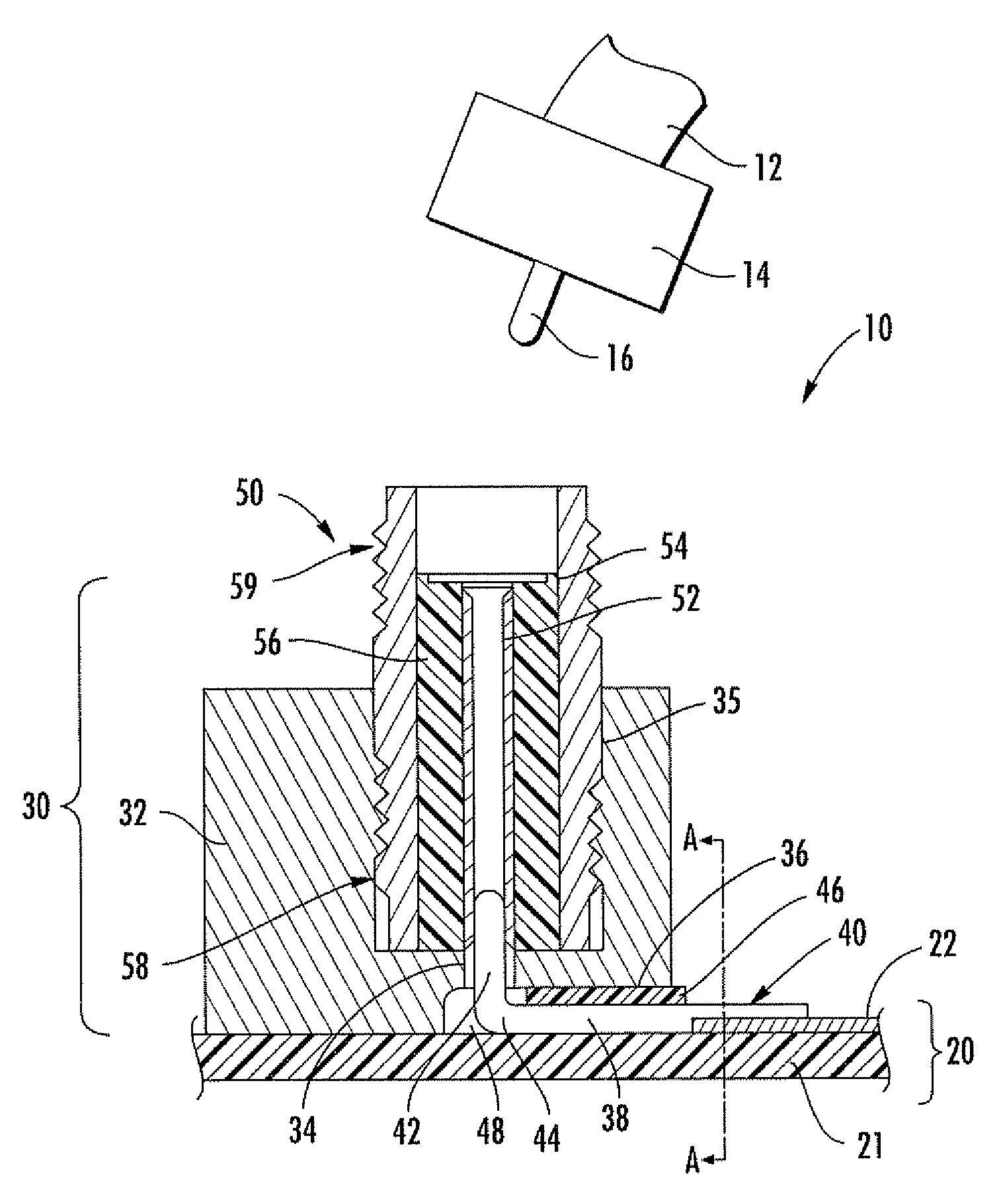

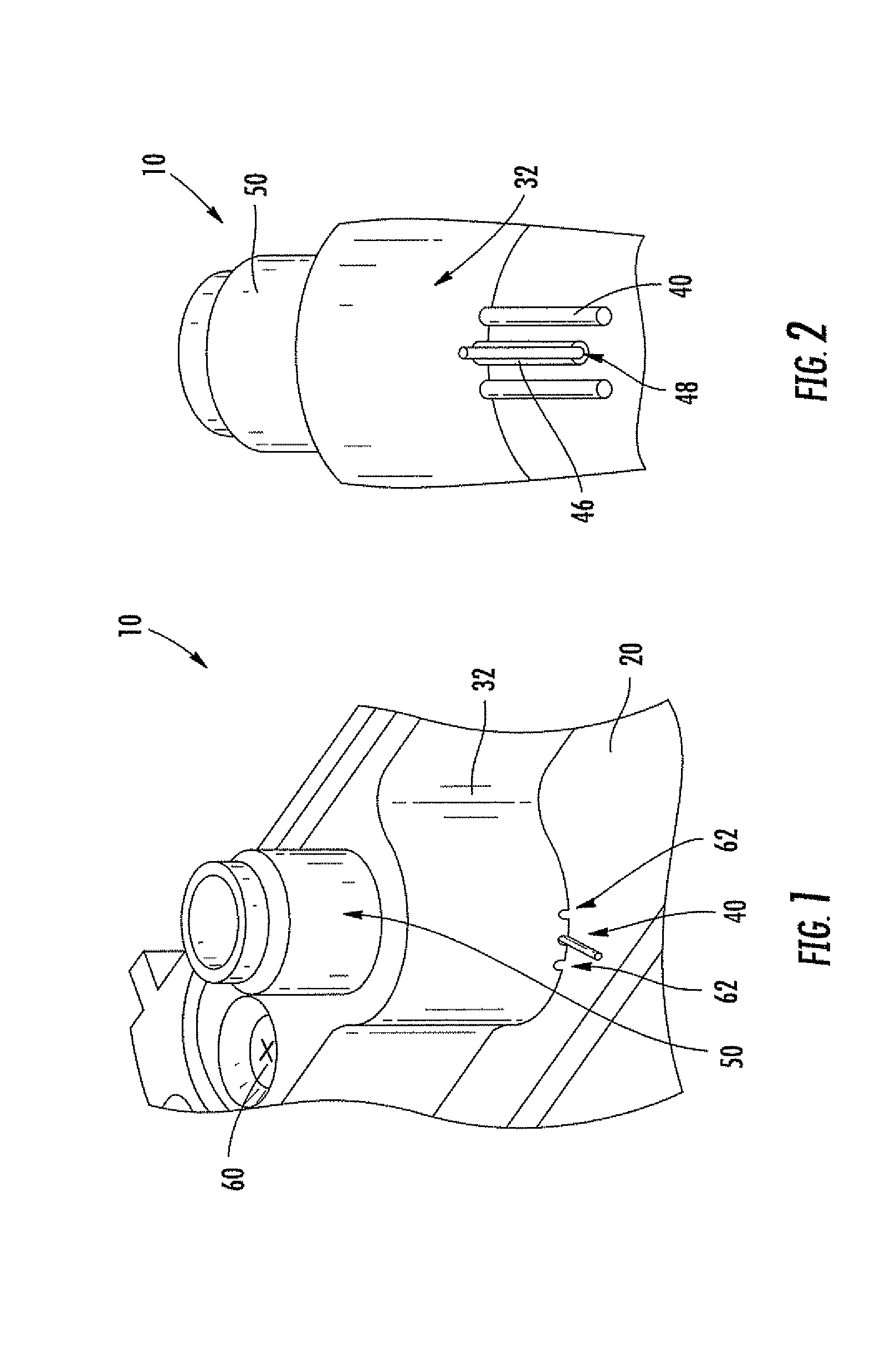

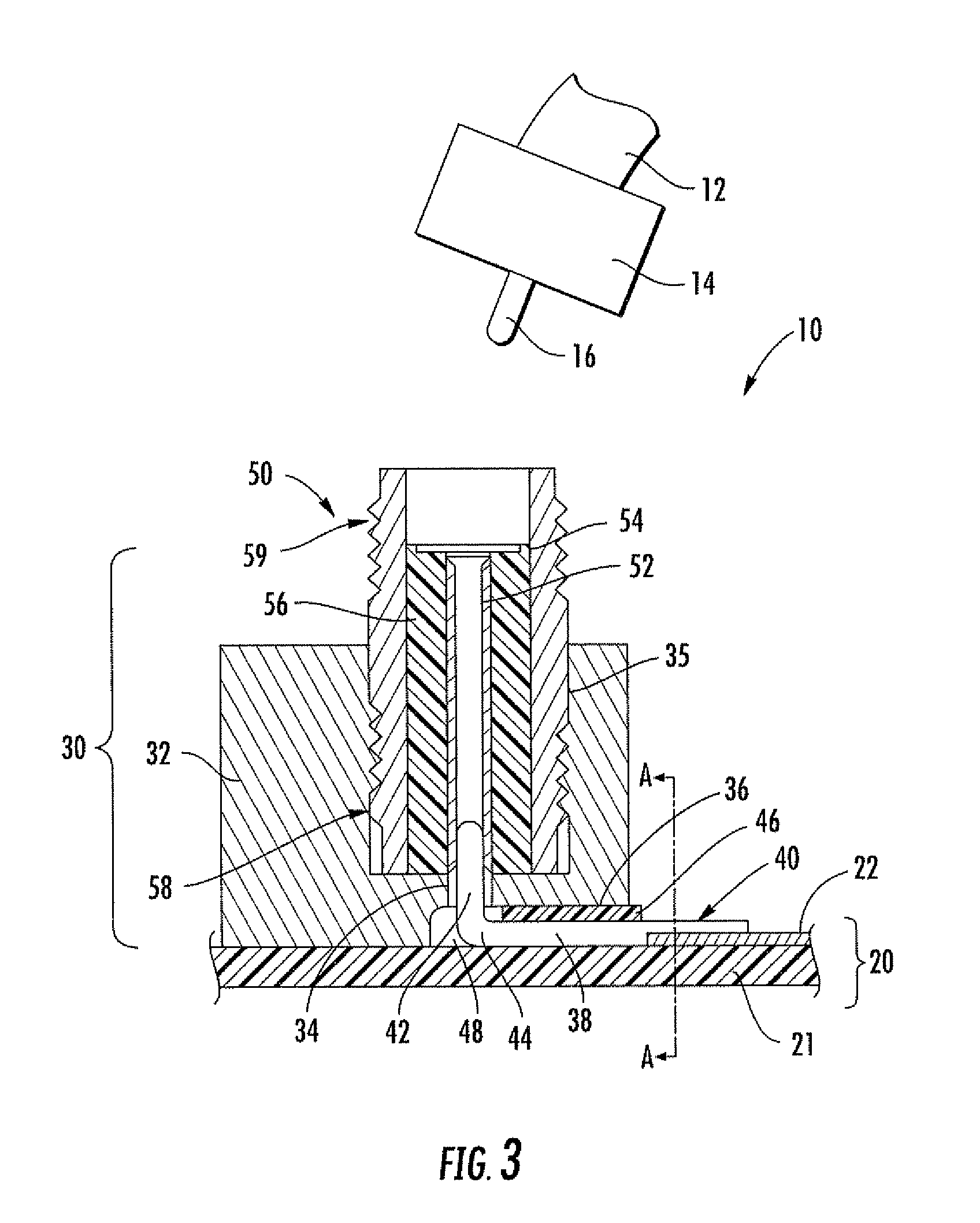

Surface mount right angle connector including strain relief and associated methods

ActiveUS7575474B1Adequate strain reliefIncrease available bandwidthElectrically conductive connectionsTwo pole connectionsDielectricSurface mounting

An electronic device includes a printed circuit board (PCB) including a planar surface conductor, e.g. such as a microstrip transmission line or coplanar transmission waveguide. A surface mount connector portion is mounted to the PCB and includes an electrically conductive header having a cylindrical bore extending therethrough and aligned normal to the PCB, the electrically conductive header also having a radially extending main recess in a bottom end thereof in communication with the cylindrical bore. An electrically conductive pin extends through the main recess and has a first end coupled to the planar surface conductor, a second end within the cylindrical bore and a bend therebetween. A dielectric is in the main recess between the pin and adjacent portions of the electrically conductive header, and an interconnect is within the cylindrical bore and includes a center conductive channel to receive the second end of the pin.

Owner:HARRIS CORP

Methods for forming a permeable and stable mass in a subterranean formation

InactiveUS20050051330A1Improve breathabilityQuality improvementFluid removalFlushingSlurryBiological activation

The present invention relates to increasing the permeability of a subterranean formation by forming a resinous mass having conductive channels through which fluids can be produced in the formation. Some embodiments of the present invention provide methods of creating a permeable resinous mass comprising the steps of selecting an interval along a well bore; providing a resin slurry comprising an acid curable resin, filler, and degradable material; placing the resin slurry into the selected interval; and, activating the acid curable resin using an activator wherein the activation causes the acid curable resin to substantially cure, the degradable material to substantially degrade, and forms the permeable resinous mass.

Owner:HALLIBURTON ENERGY SERVICES INC

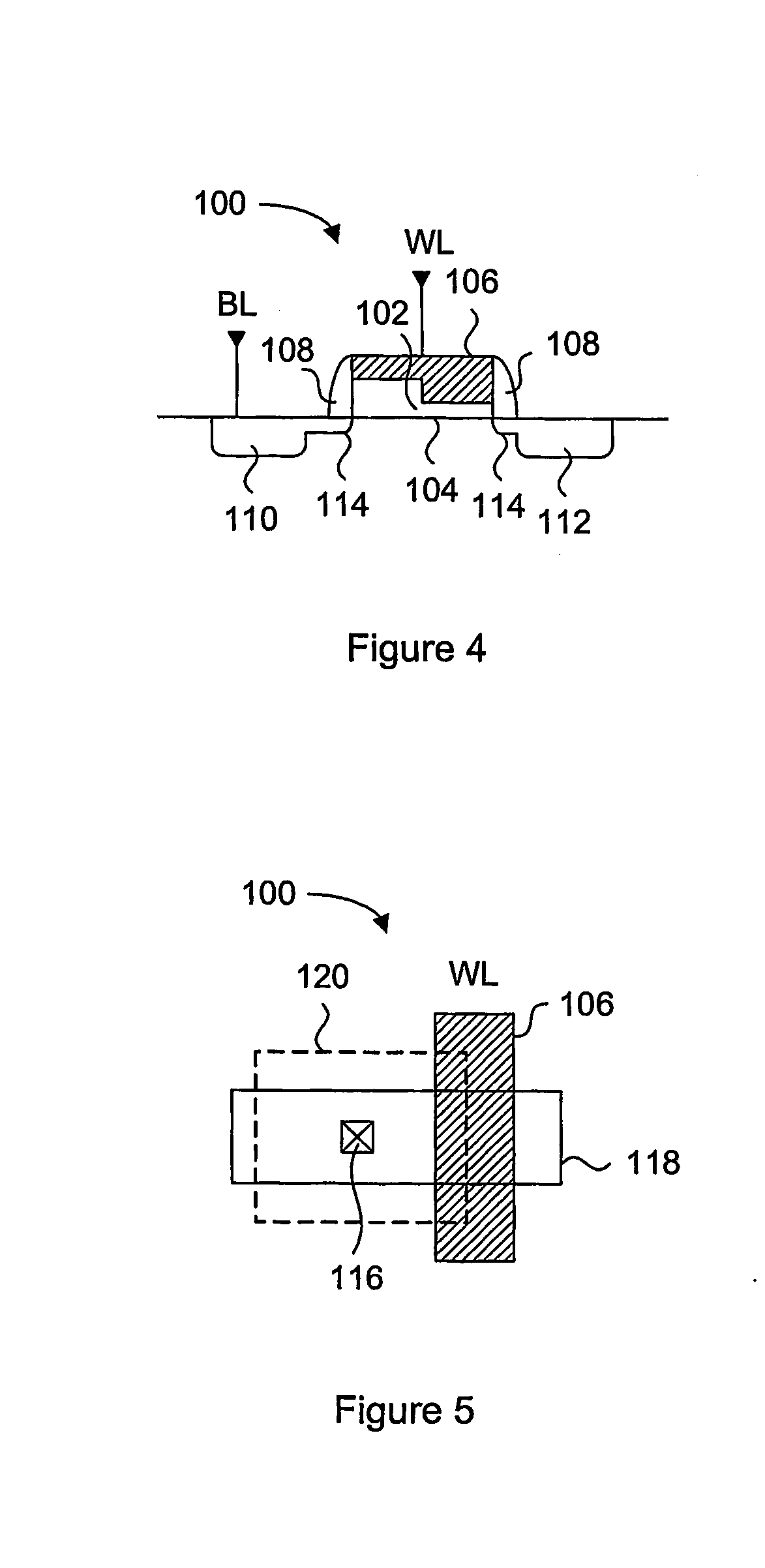

Vertically-oriented semiconductor selection device providing high drive current in cross-point array memory

A vertical semiconductor material mesa upstanding from a semiconductor base that forms a conductive channel between first and second doped regions. The first doped region is electrically coupled to one or more first silicide layers on the surface of the base. The second doped region is electrically coupled to one of a plurality of second silicide layers on the upper surface of the mesa. A gate conductor is provided on one or more sidewalls of the mesa.

Owner:MICRON TECH INC

Transistor with A-face conductive channel and trench protecting well region

ActiveUS7989882B2Improve abilitiesMinimize JFET effectSemiconductor/solid-state device manufacturingSemiconductor devicesTrench gateSemiconductor

A transistor structure optimizes current along the A-face of a silicon carbide body to form an AMOSFET that minimizes the JFET effect in the drift region during forward conduction in the on-state. The AMOSFET further shows high voltage blocking ability due to the addition of a highly doped well region that protects the gate corner region in a trench-gated device. The AMOSFET uses the A-face conduction along a trench sidewall in addition to a buried channel layer extending across portions of the semiconductor mesas defining the trench. A doped well extends from at least one of the mesas to a depth within the current spreading layer that is greater than the depth of the trench. A current spreading layer extends between the semiconductor mesas beneath the bottom of the trench to reduce junction resistance in the on-state. A buffer layer between the trench and the deep well further provides protection from field crowding at the trench corner.

Owner:WOLFSPEED INC

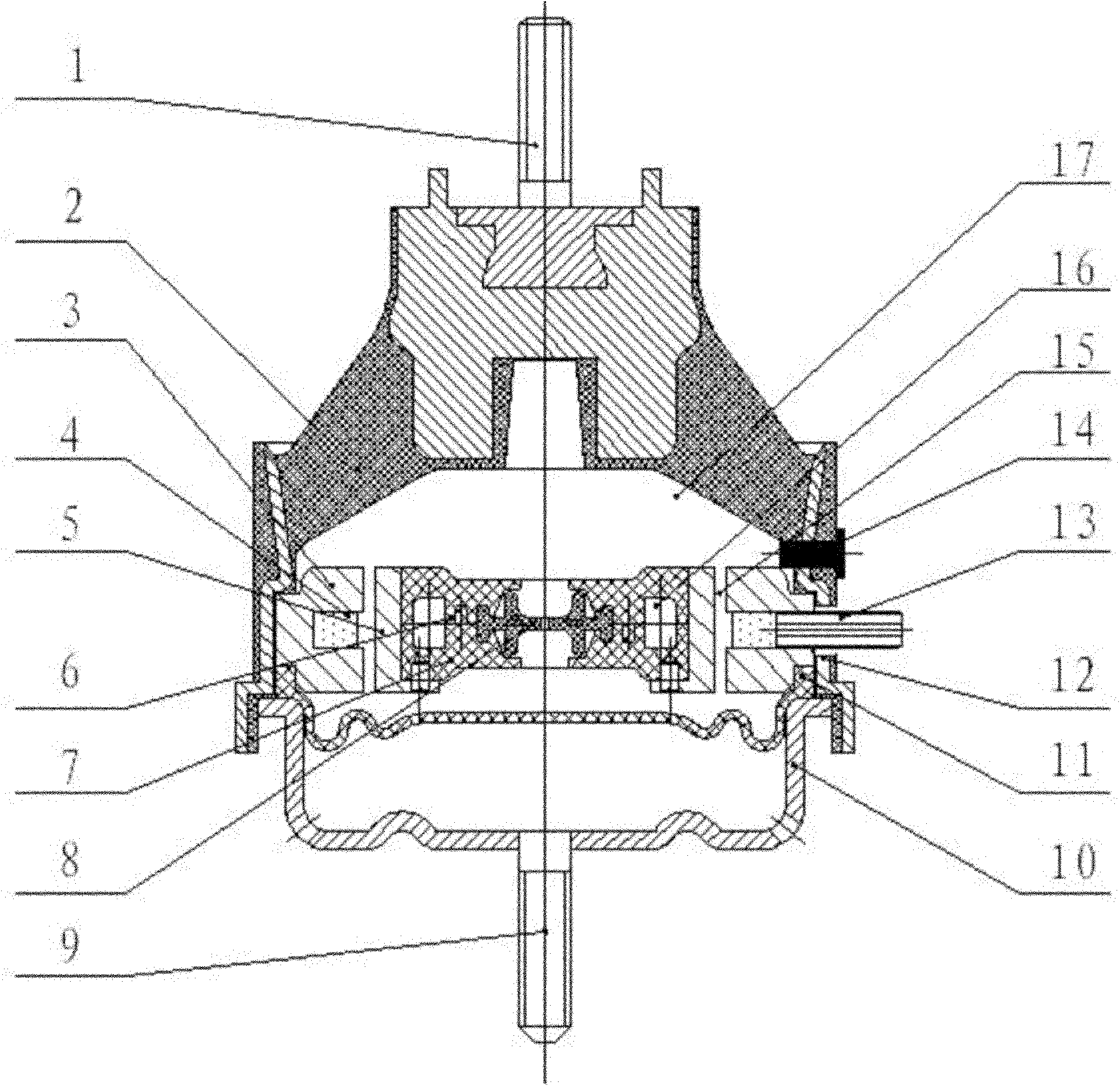

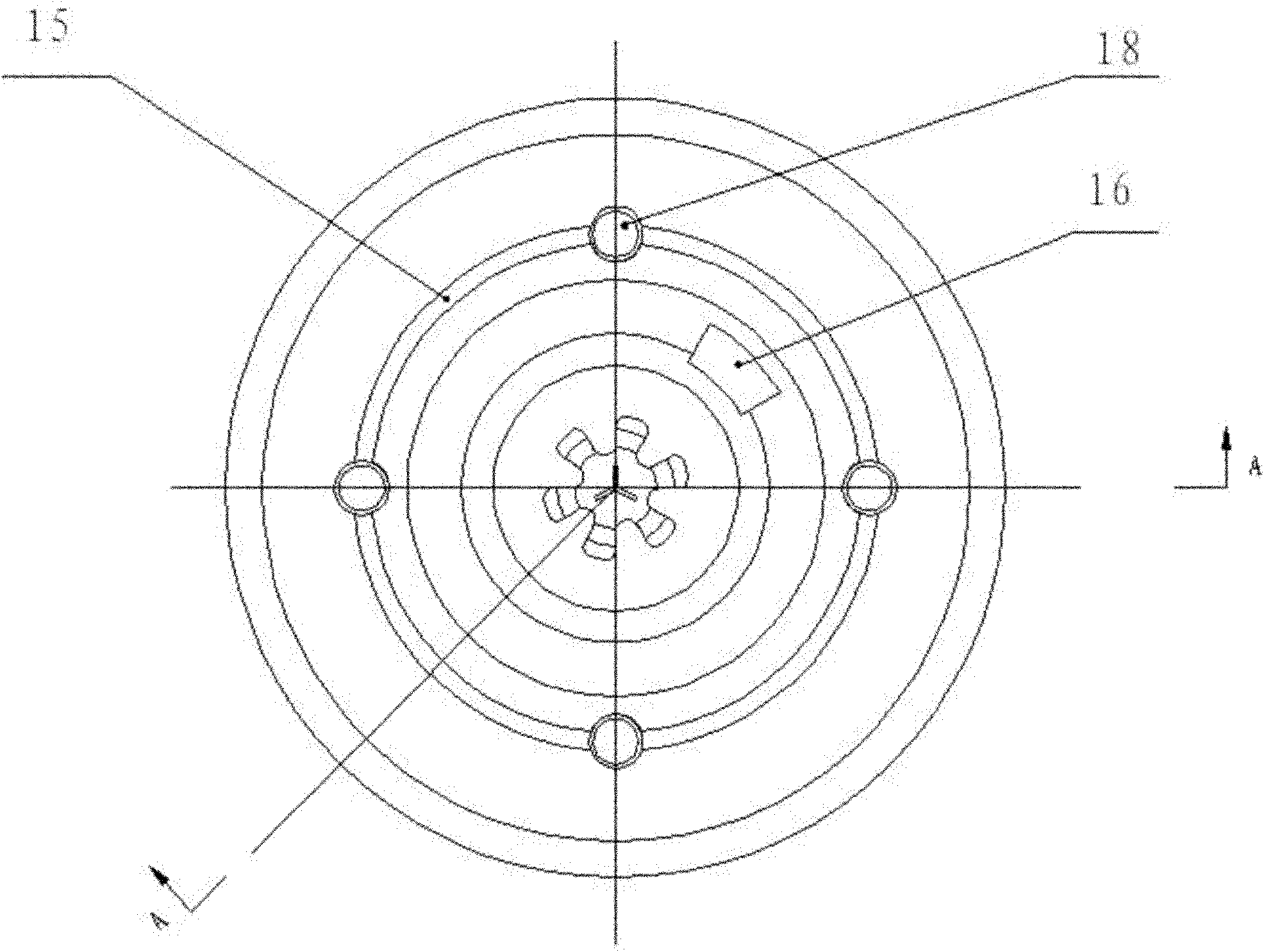

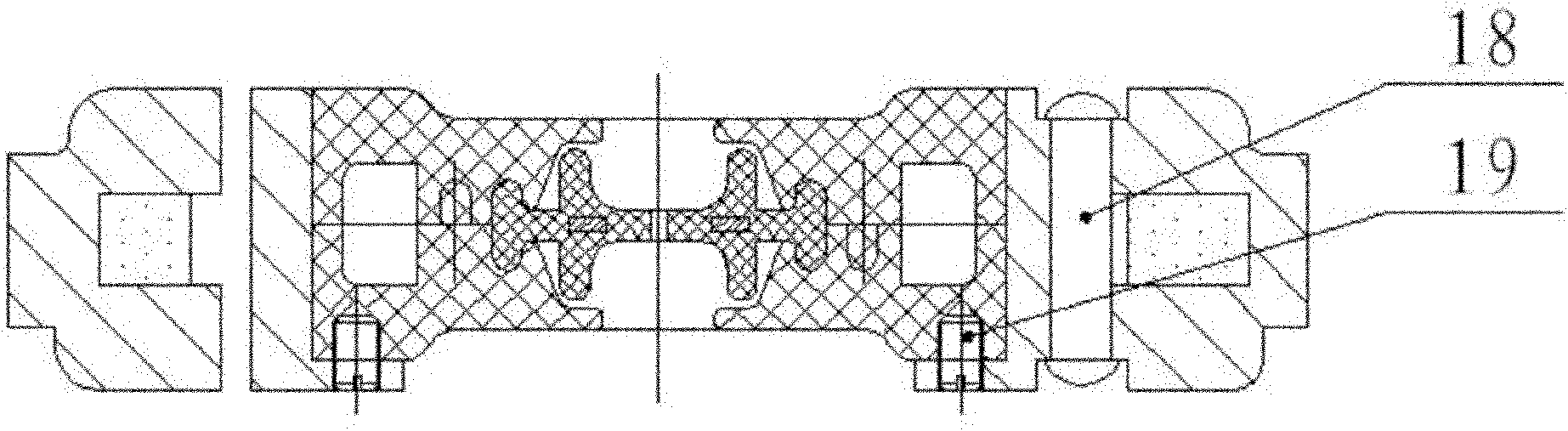

Semi-active control magnetorheological hydraulic mount for automotive powertrain

InactiveCN101936360AGood damping propertiesReduce large vibrationsSpringsNon-rotating vibration suppressionSemi activeVibration control

The invention relates to a semi-active control magnetorheological hydraulic mount for an automotive powertrain, which belongs to a semi-active control element used for vibration control of an engine and is an engine mount filled with magnetorheological fluid, wherein the viscosity of the fluid changes along with the change of the strength of a magnetic field, and the semi-active control magnetorheological hydraulic mount mainly comprises a metal framework, a rubber main spring, a coil holder, an electromagnetic coil, a magnetic conductive channel body, an inertia channel assembly, a rubber basement membrane, a bottom framework and the like, and can control the strength of applied current according to the working condition of the engine by utilizing the viscosity of the magnetorheological fluid and the following performance of the strength of the magnetic field, further change the viscosity of the fluid, lead the vibration of the engine to be well attenuated in a wider frequency band and further actively isolate the transfer of vibration noise of the engine into an automobile in the wider frequency band. A vibration damper for the magnetorheological hydraulic mount for the engine can effectively isolate the vibration of the engine, reduce the noise in the automobile and improve the NVH properties of the whole automobile, thereby having great market potential and broad prospects.

Owner:JILIN UNIV

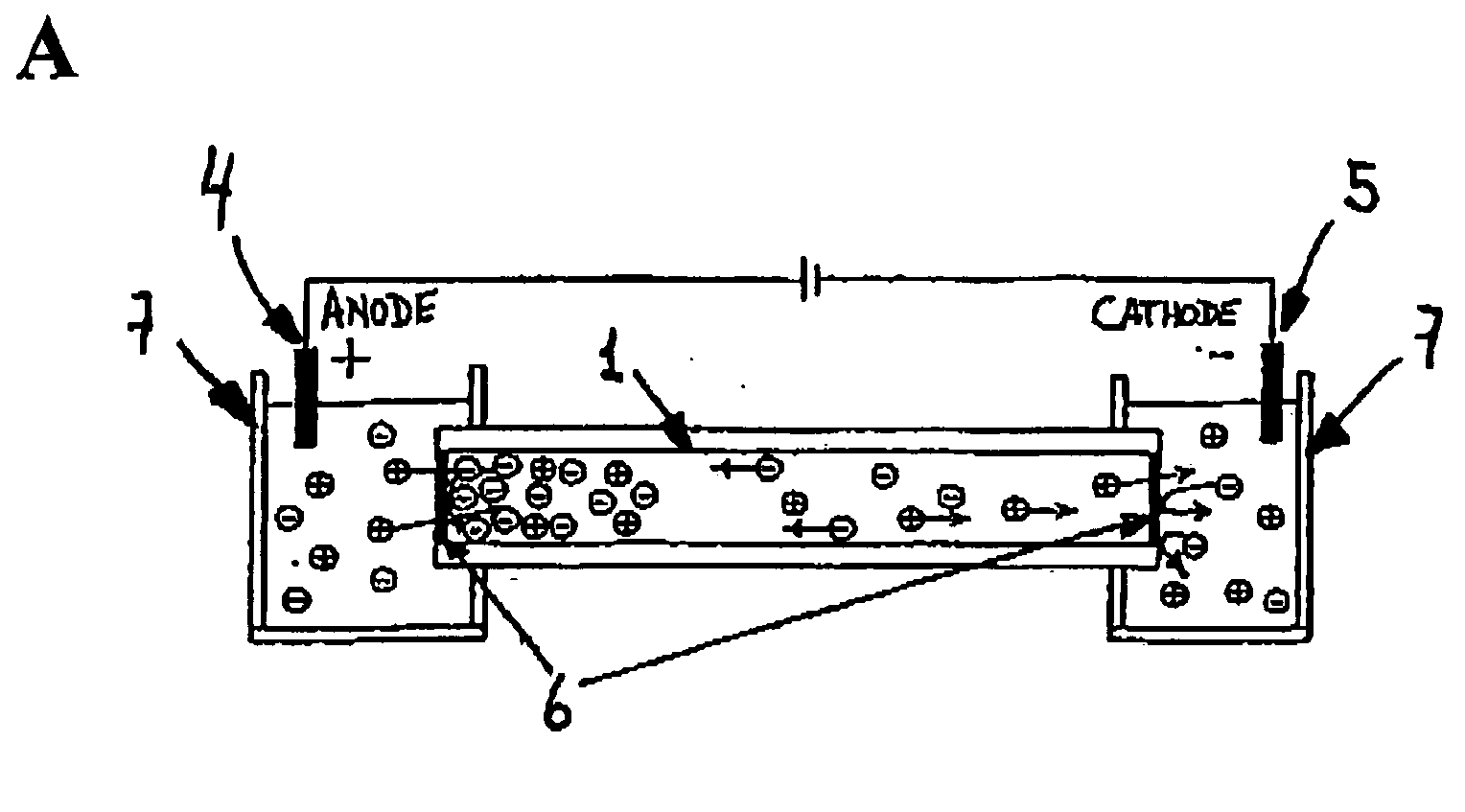

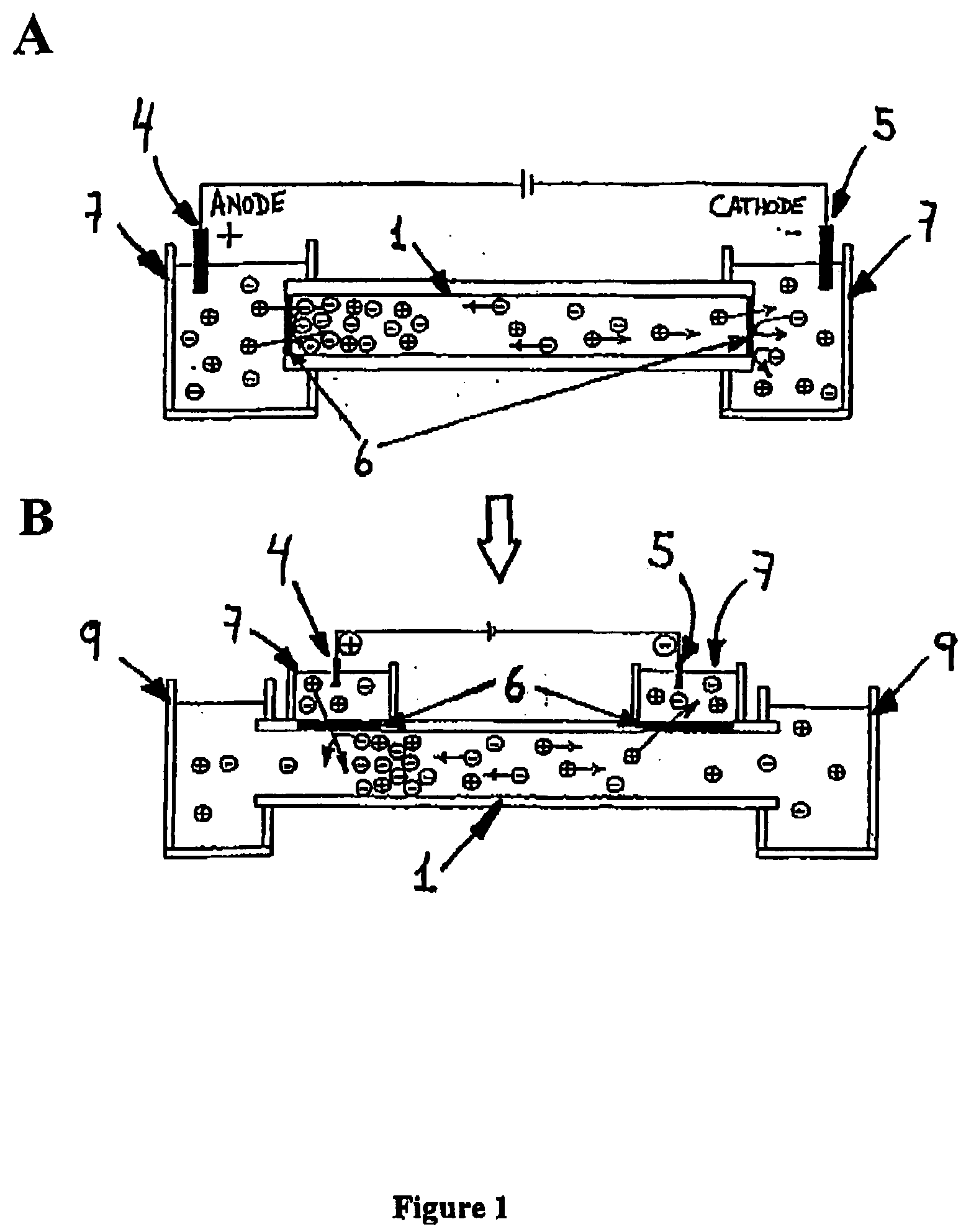

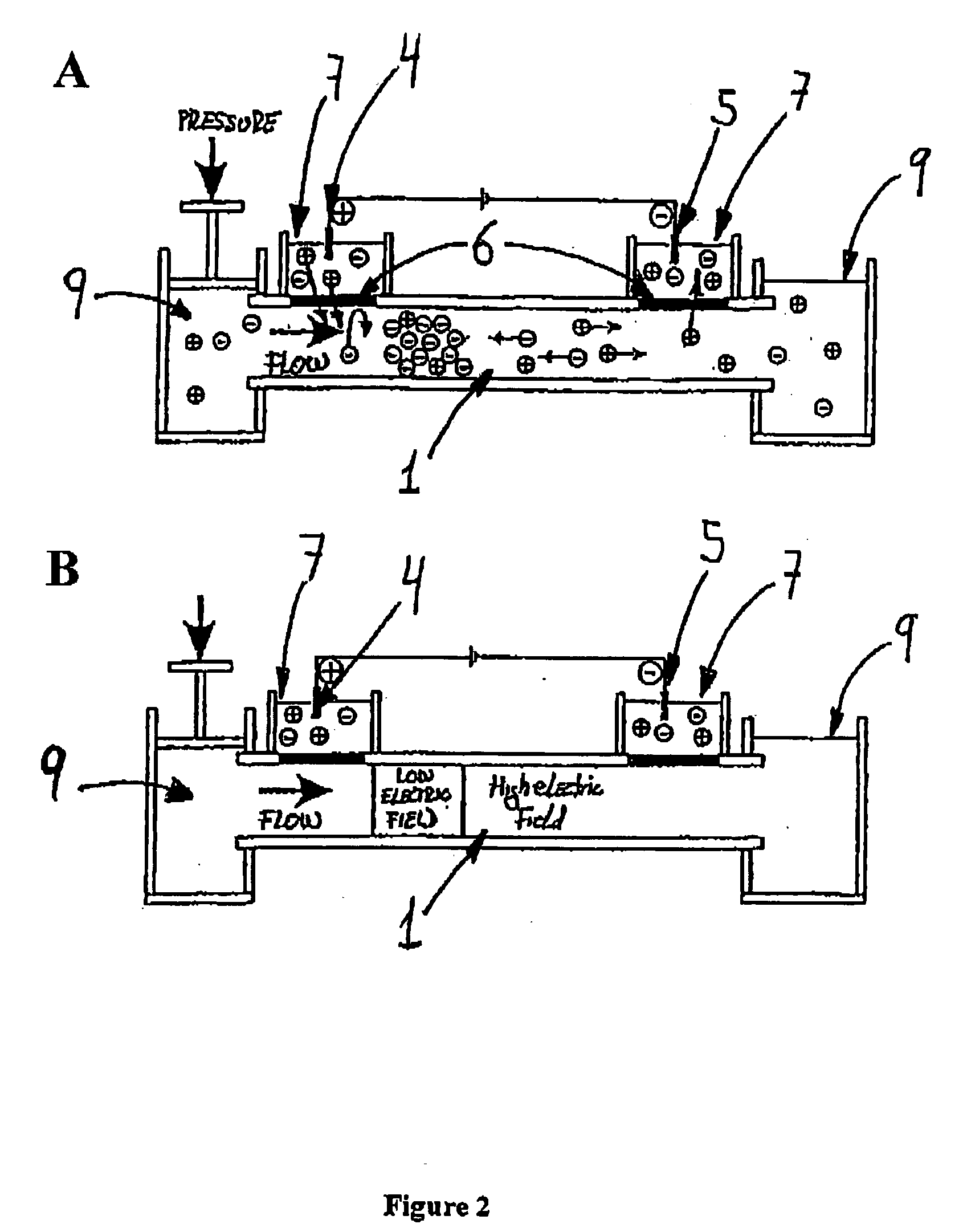

Method and device for capturing charged molecules traveling in a flow stream

ActiveUS20050284762A1Sludge treatmentVolume/mass flow measurementElectric powerMembrane configuration

The invention relates to a method for capturing charged molecules of interest traveling in an electrolyte flow stream through an electrically non-conductive channel, comprising at least one anode and at least one cathode individually separated from said channel, but in electrical contact with said flow stream, by a conductive ion selective semi-permeable membrane. Said membrane interferes with the normal migration of ions towards its respective electrode, generating at least two zones of different electric field. Balance between hydrodynamic and electrical forces captures certain ions into the flow stream. it also relates to a device for performing the method.

Owner:PERKINELMER U S LLC +2