Patents

Literature

436results about How to "Reduce etch rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

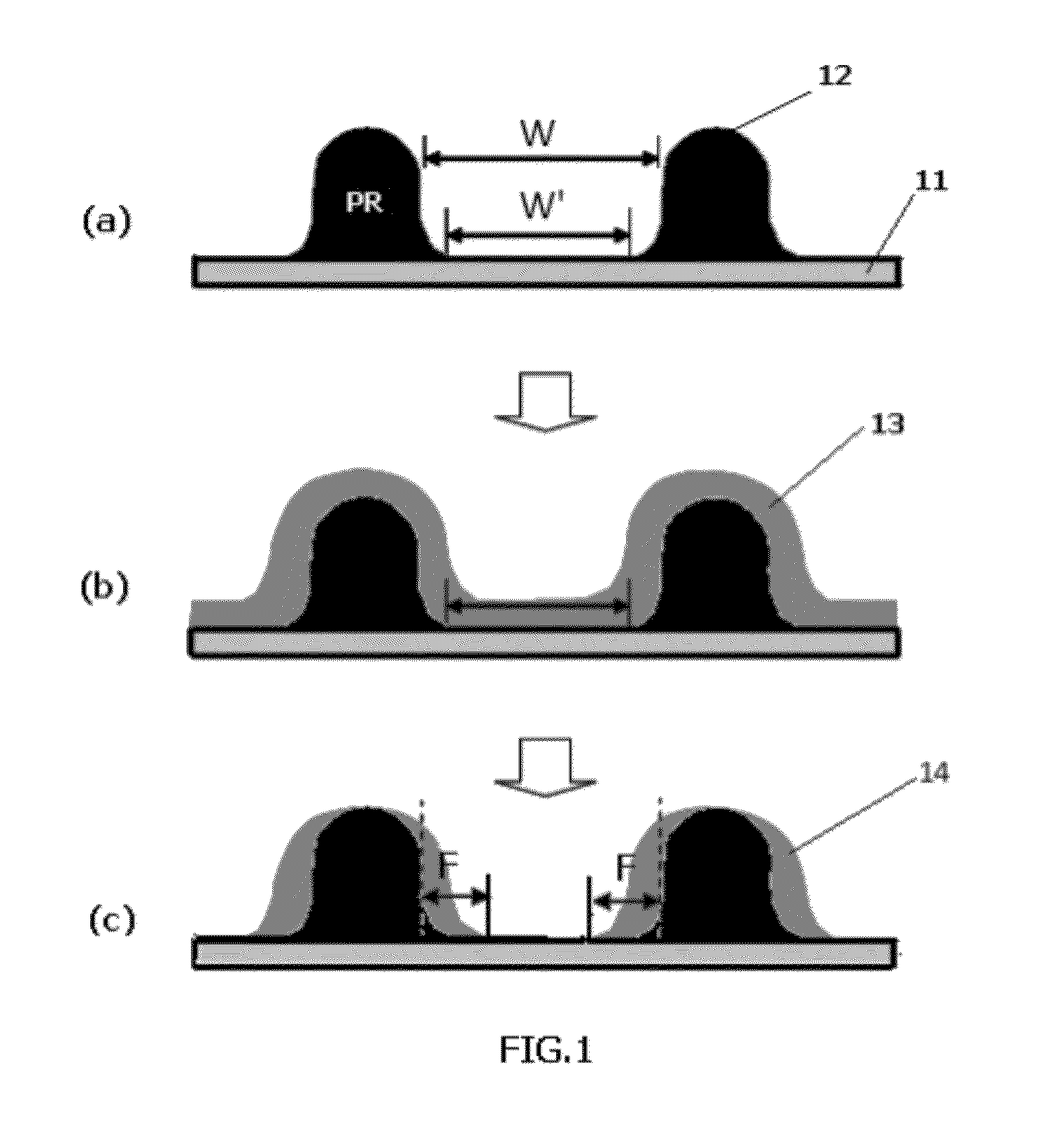

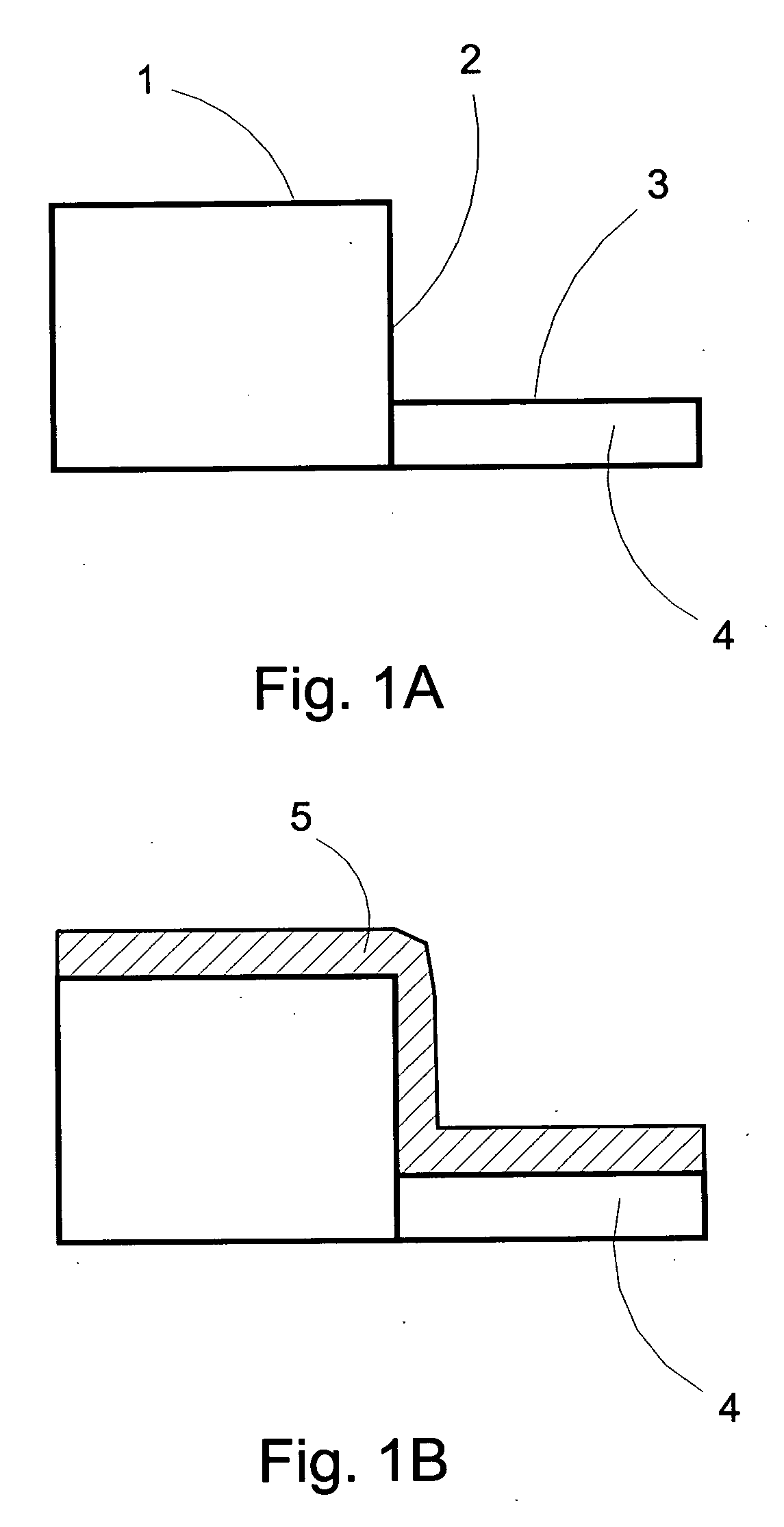

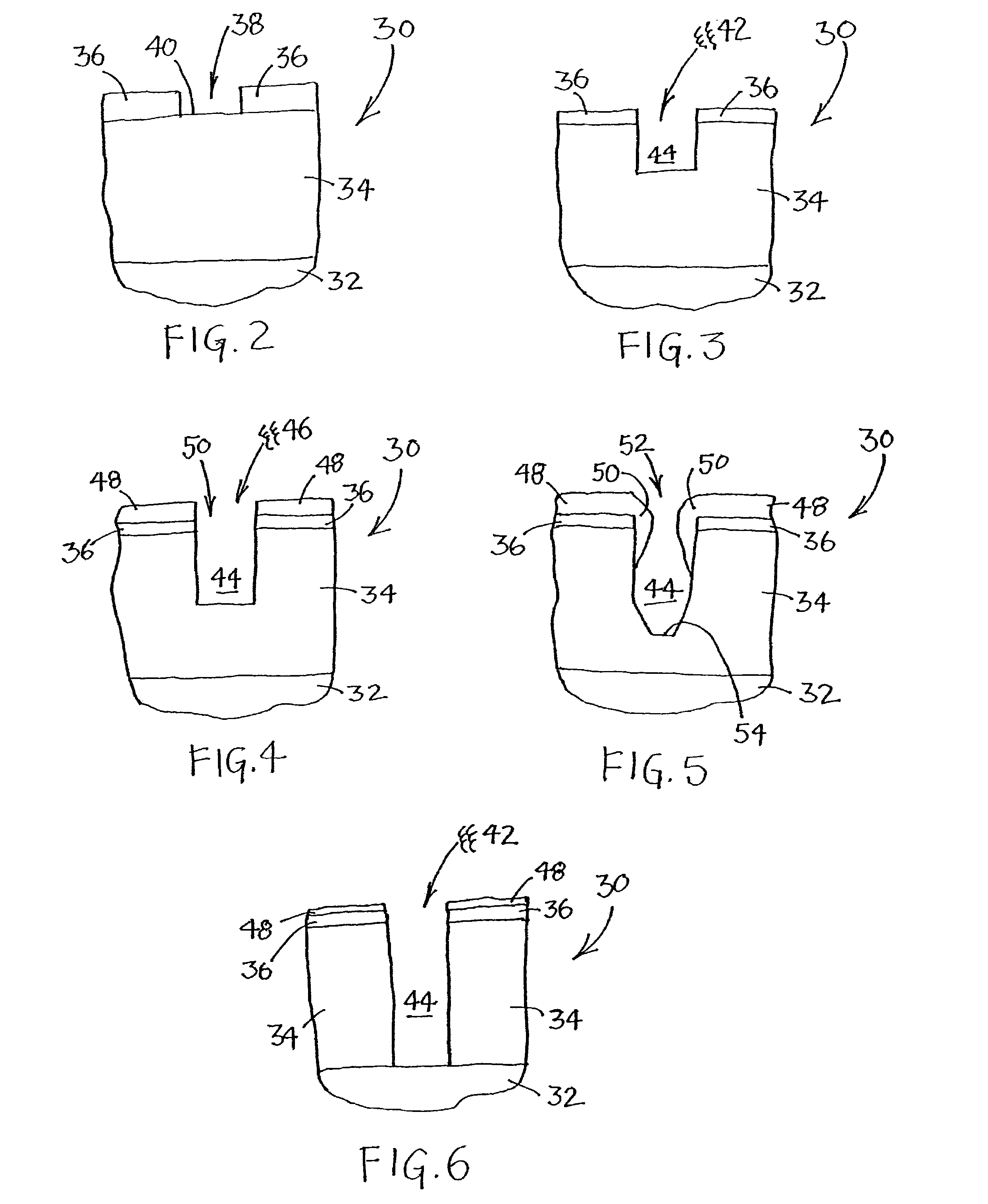

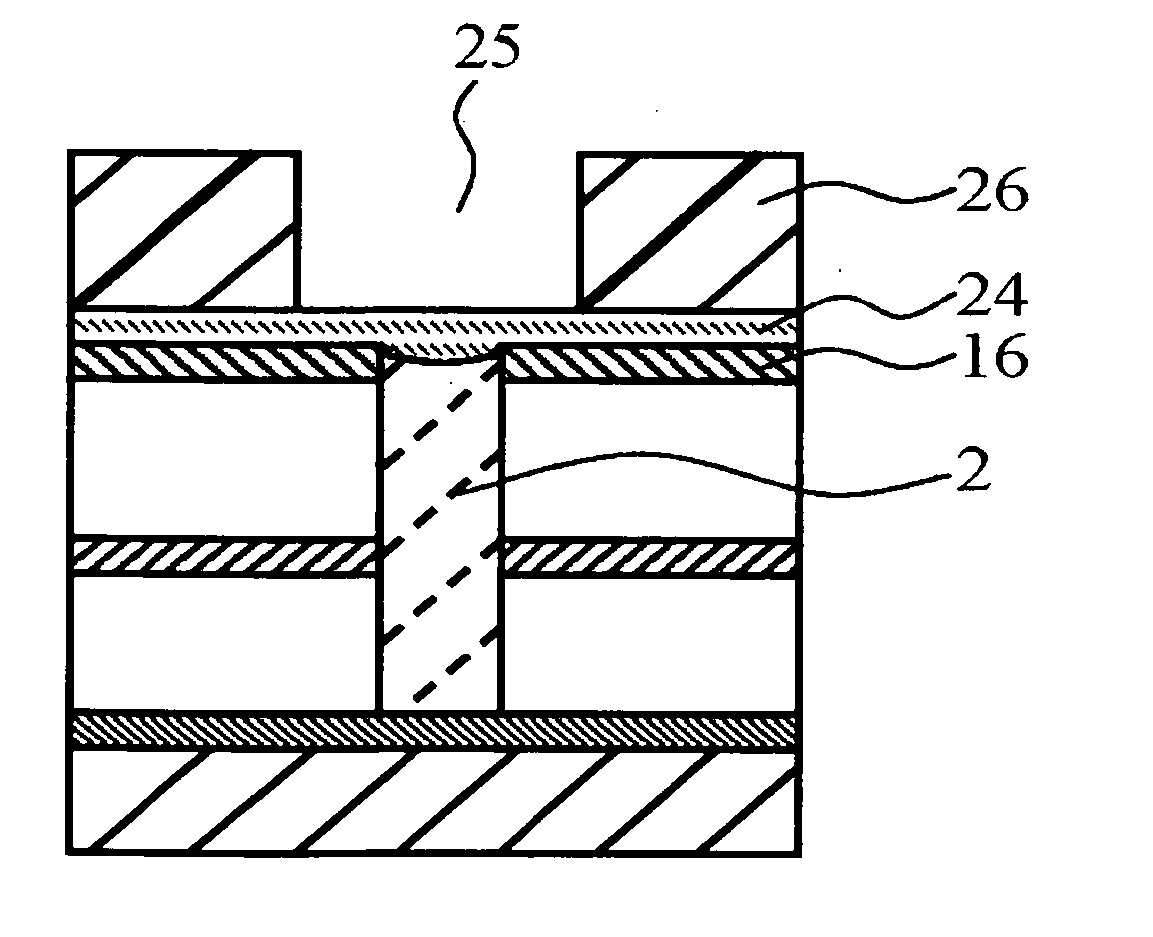

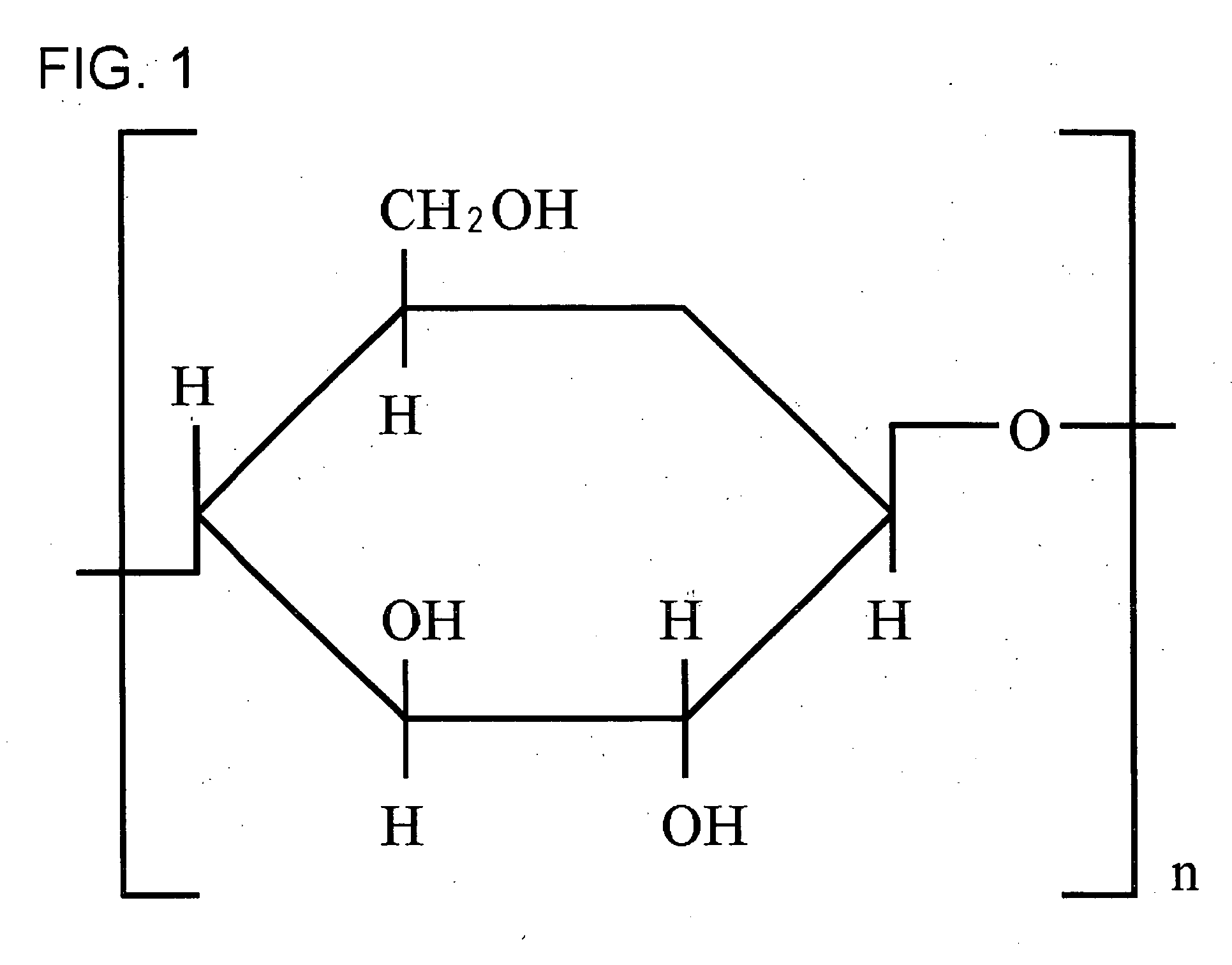

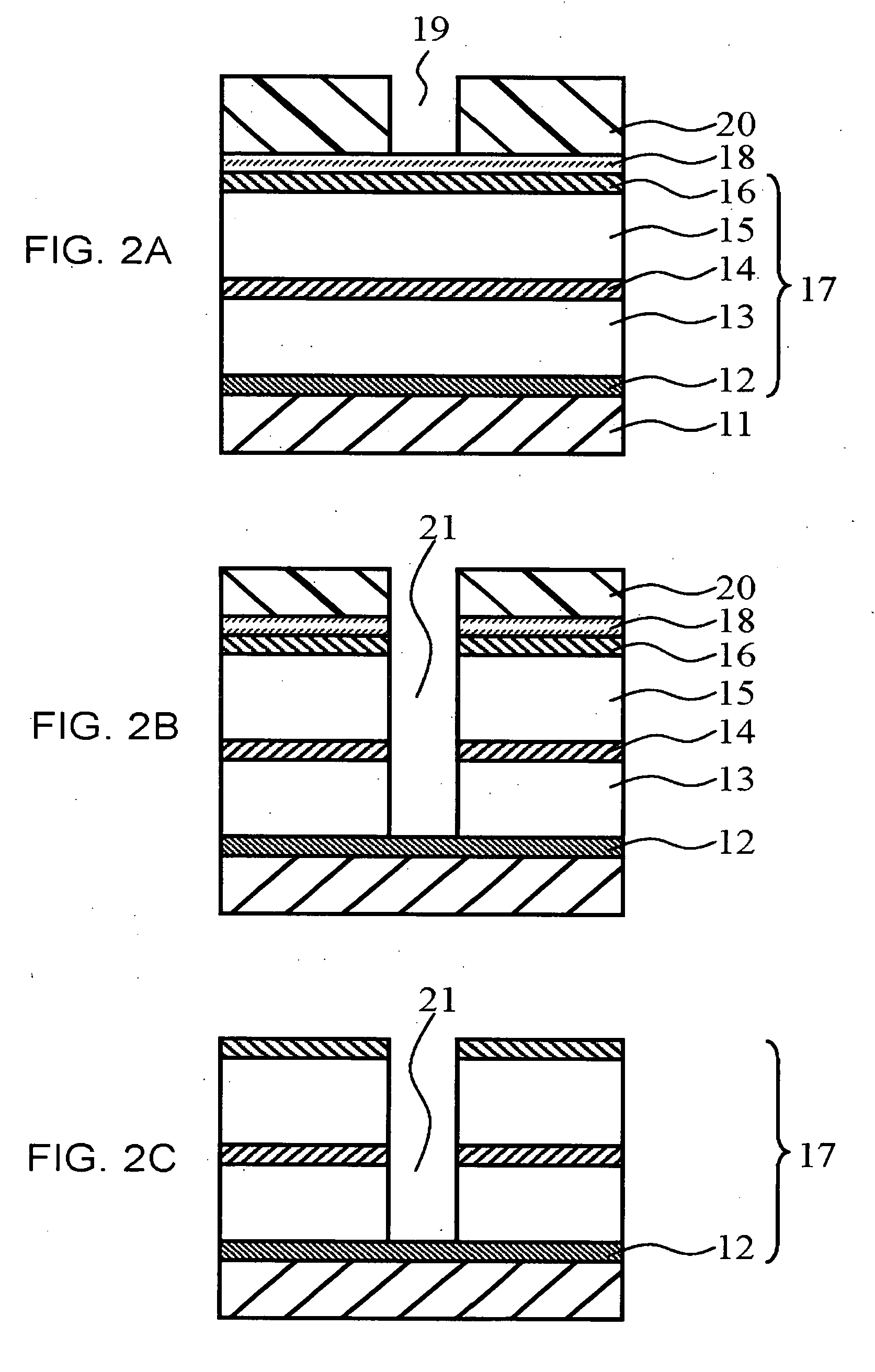

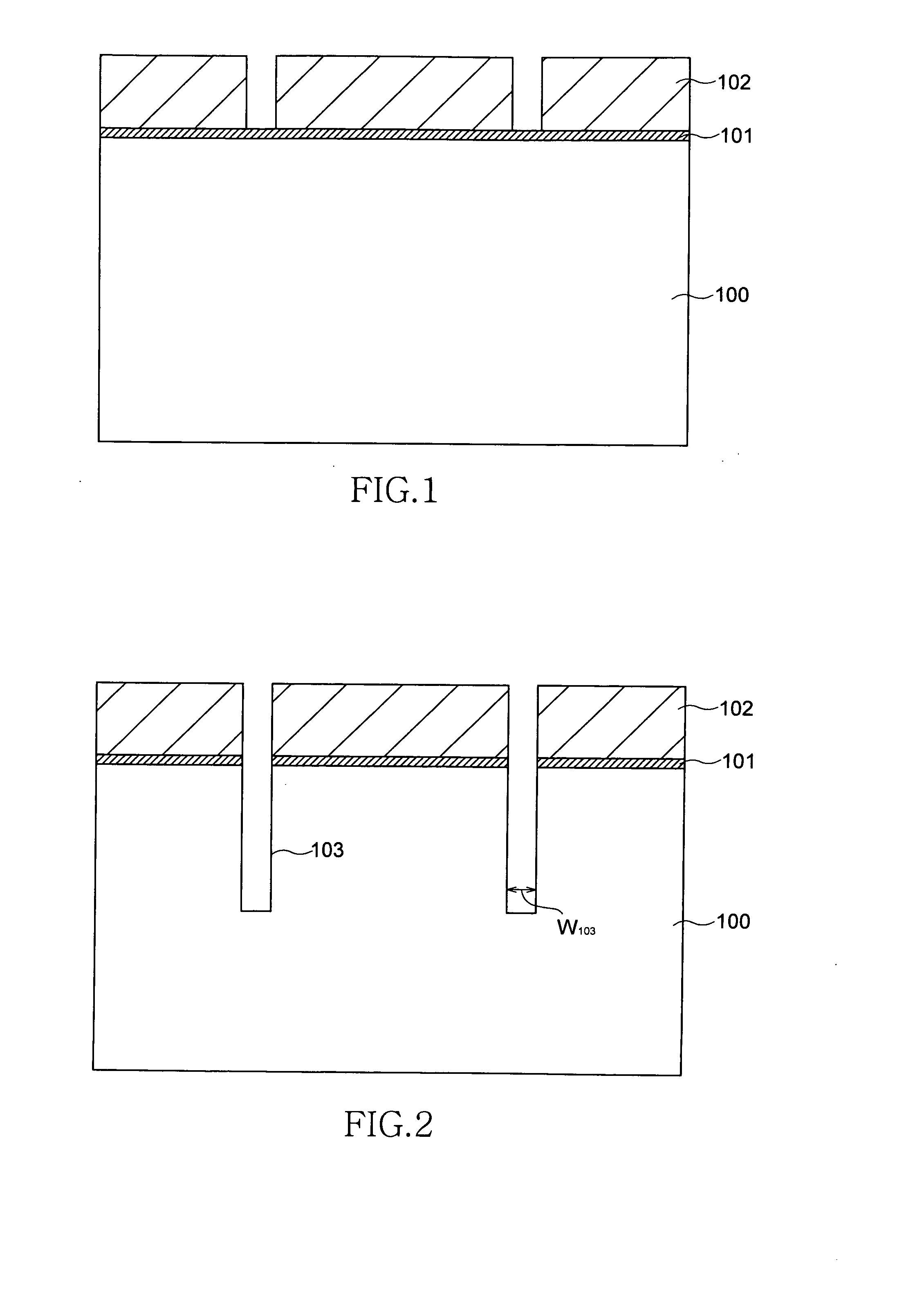

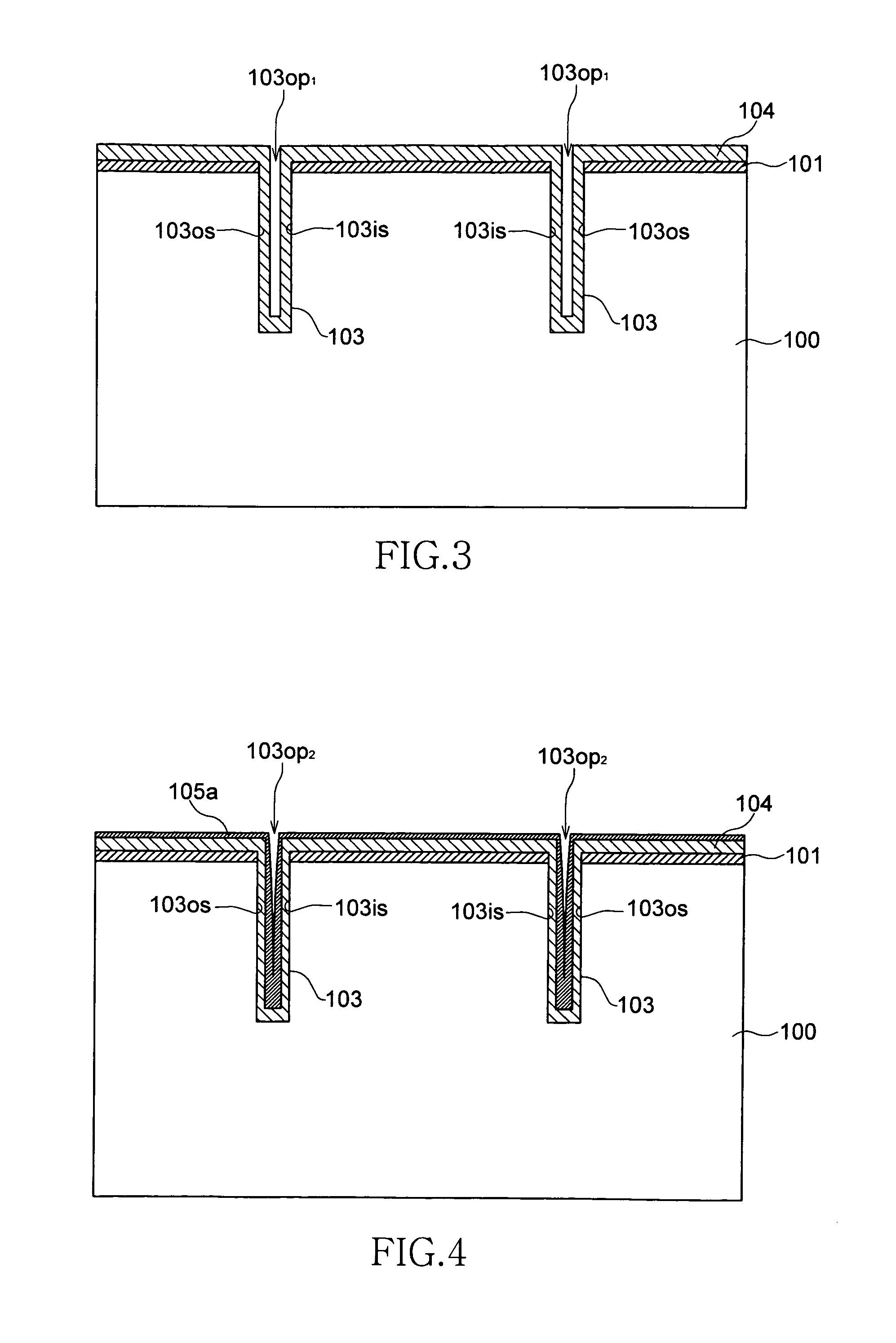

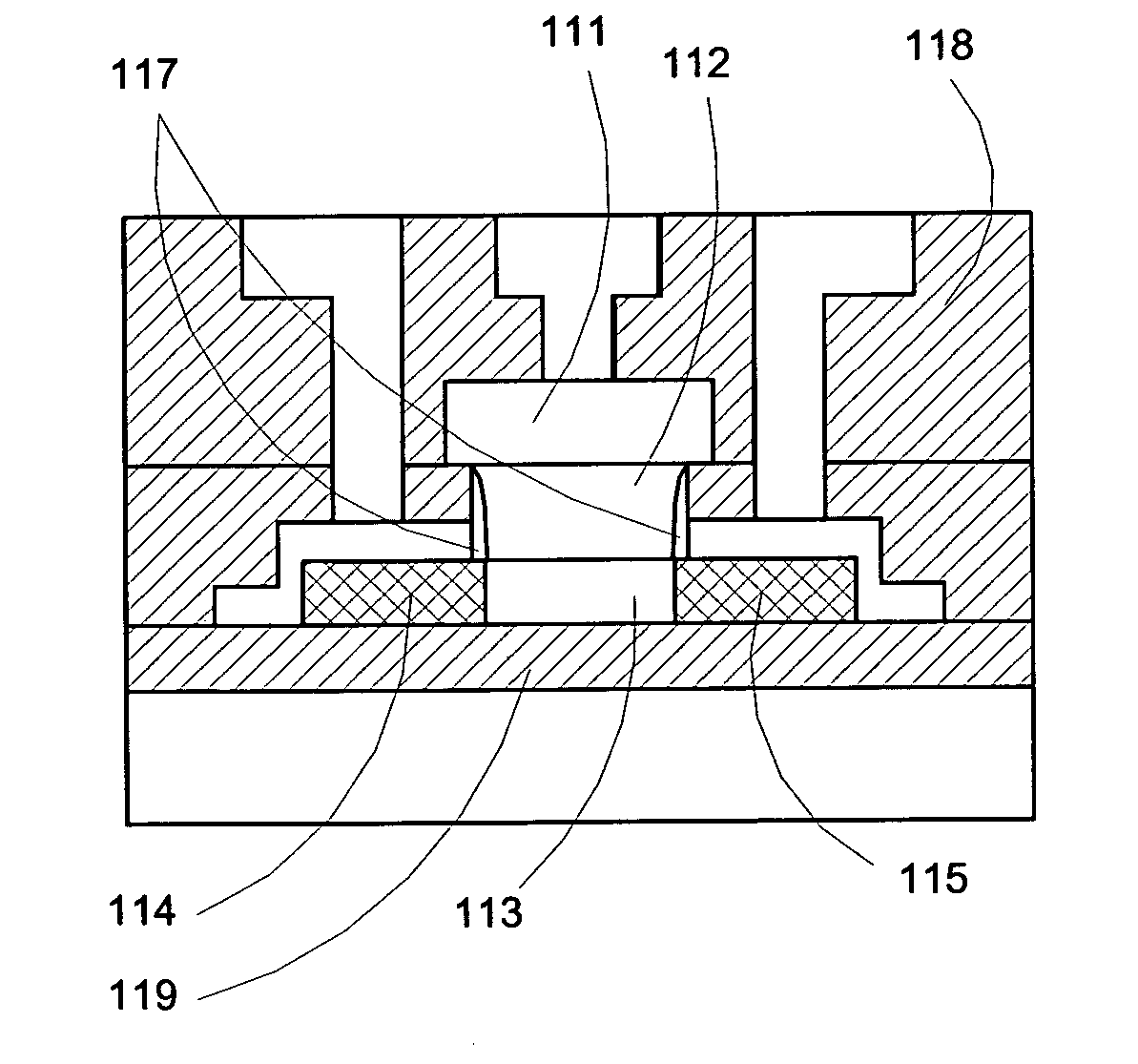

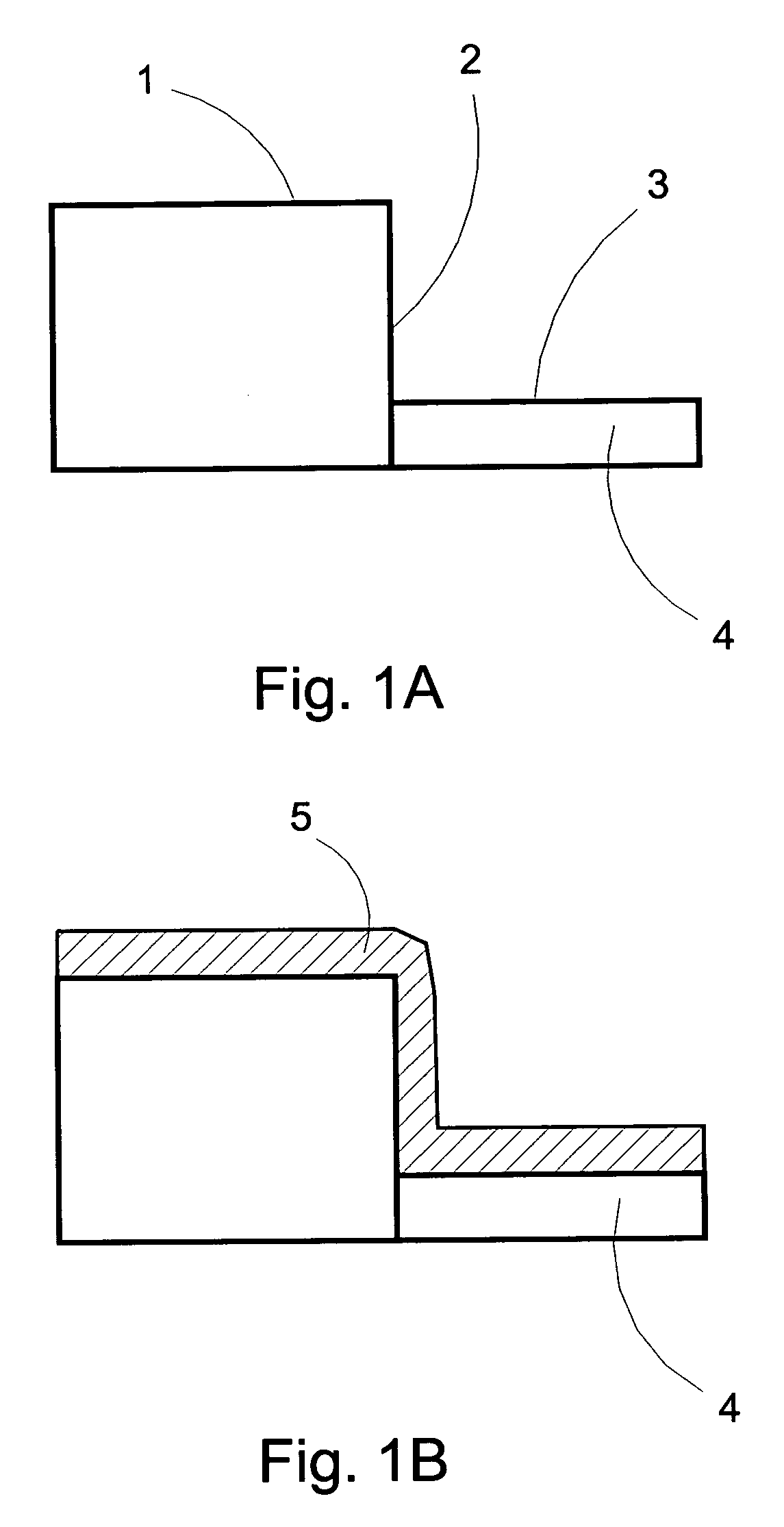

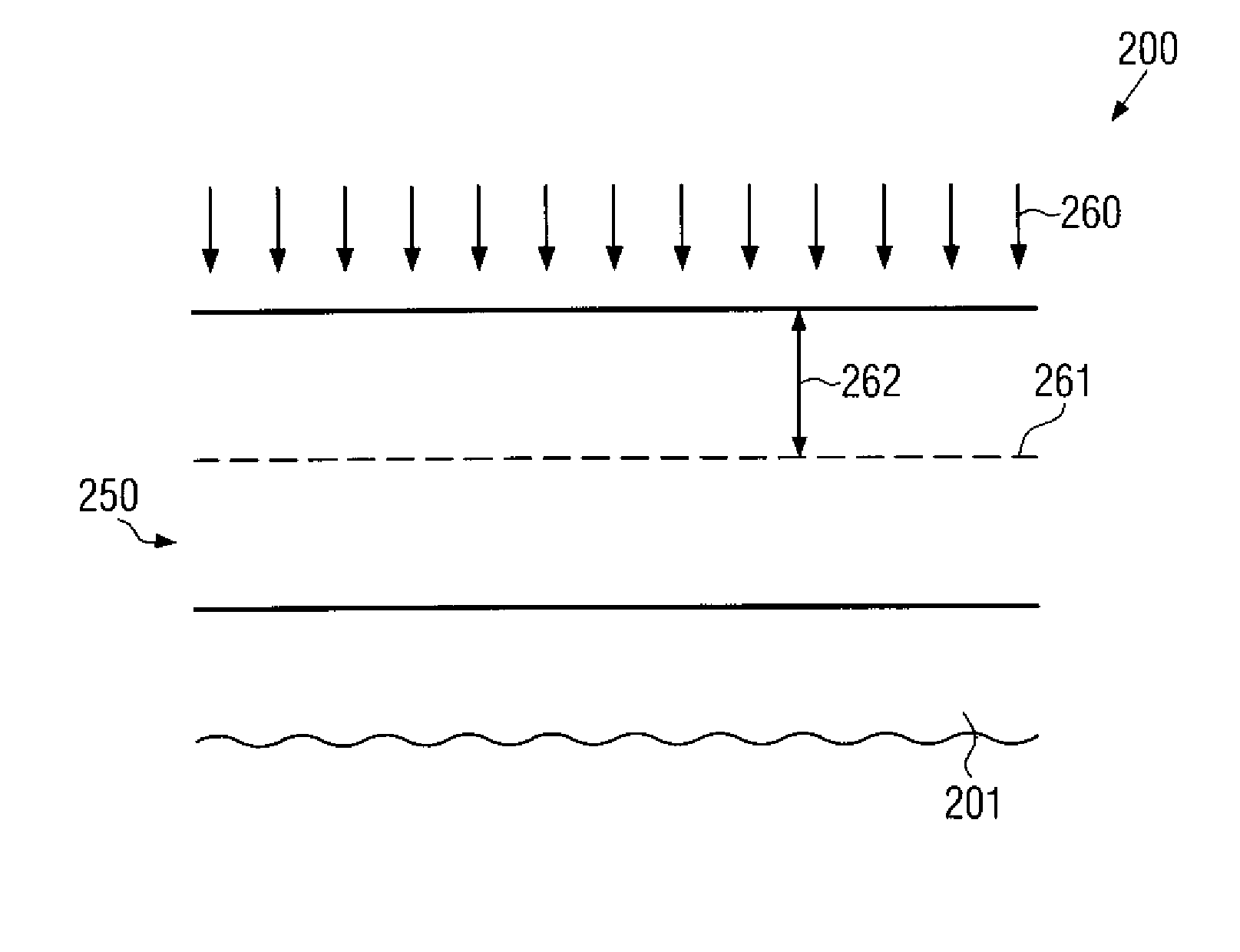

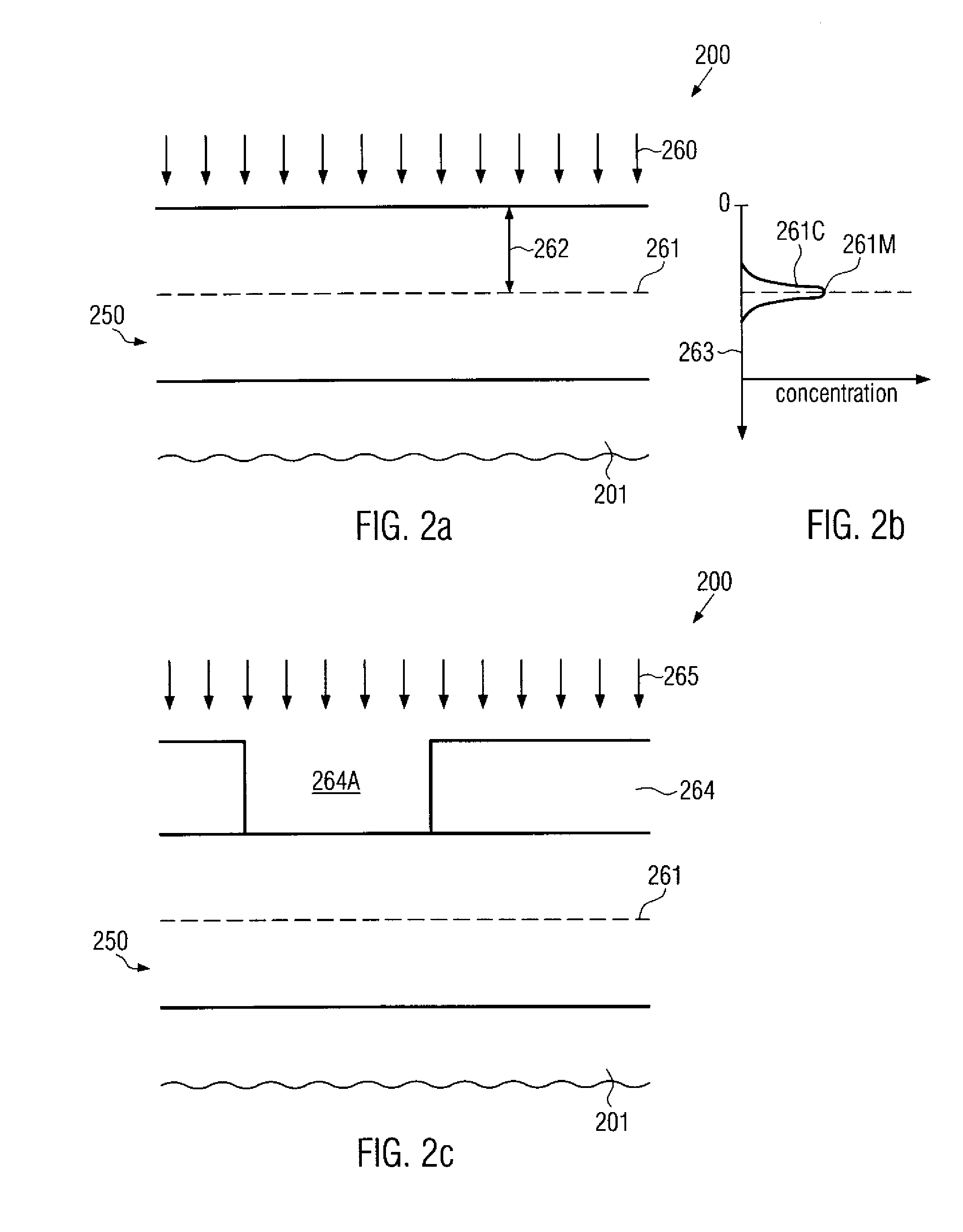

Footing reduction using etch-selective layer

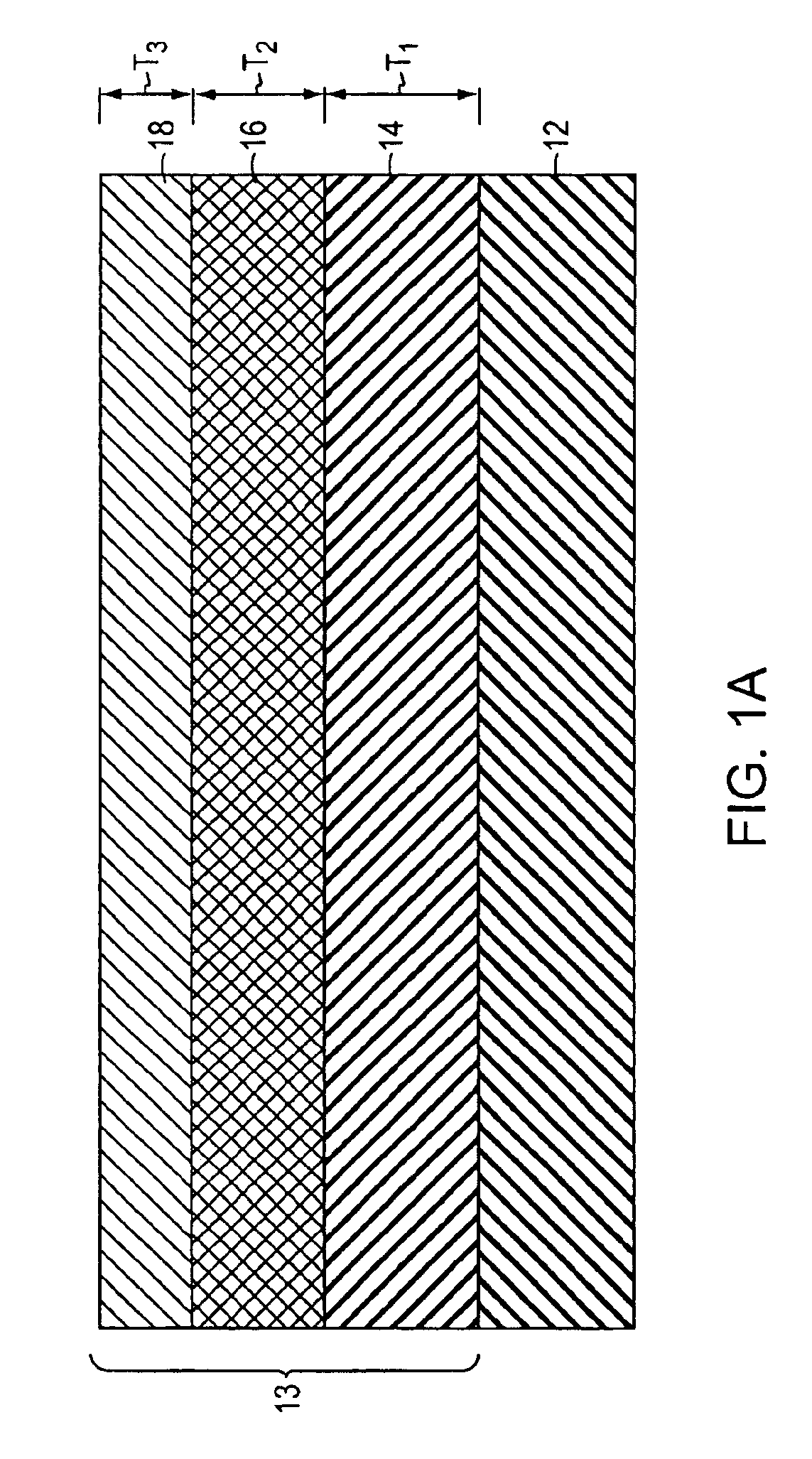

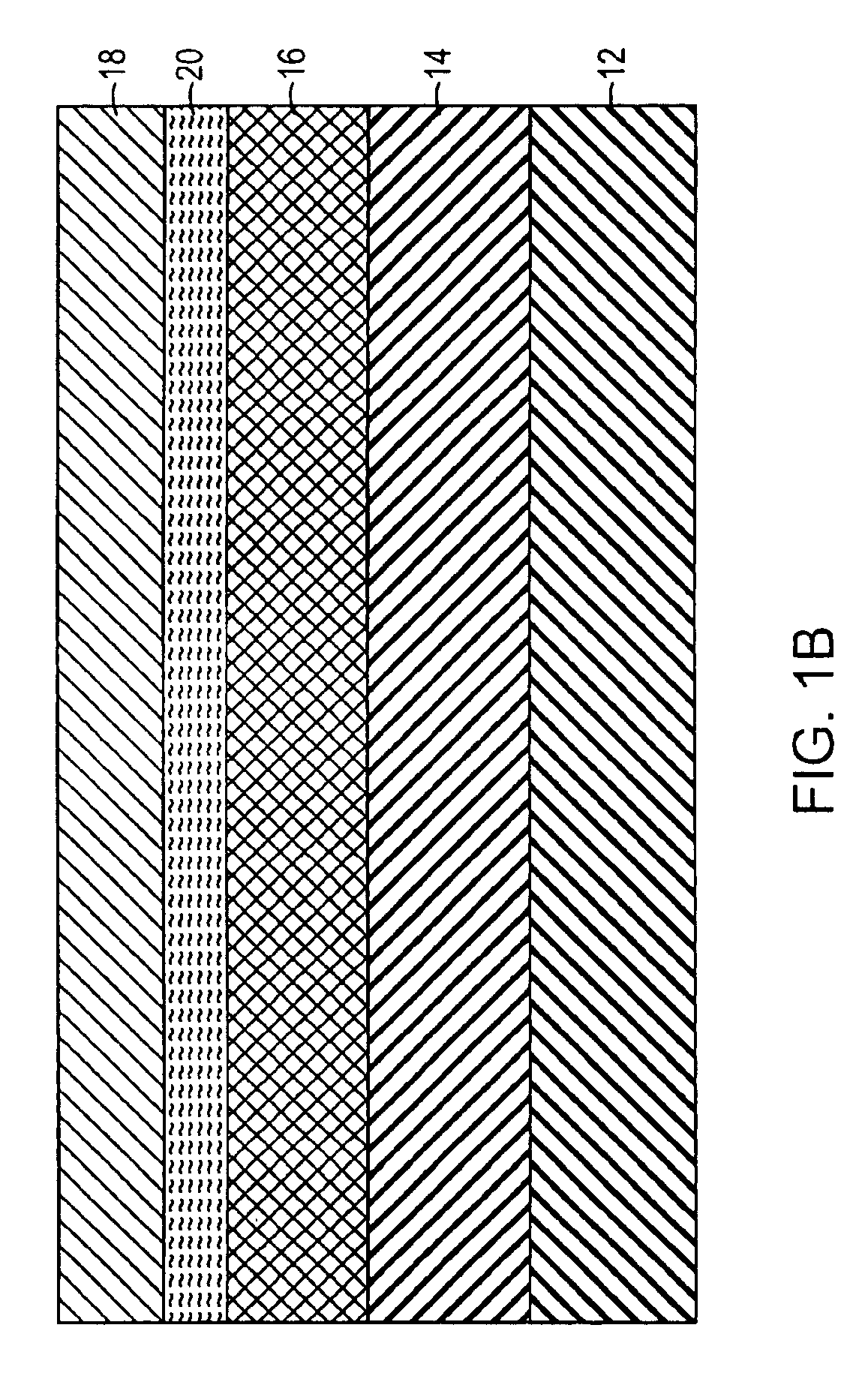

ActiveUS8298951B1Reduce etch rateReducing a widened footing of the photoresistDecorative surface effectsSemiconductor/solid-state device manufacturingEngineeringOxygen

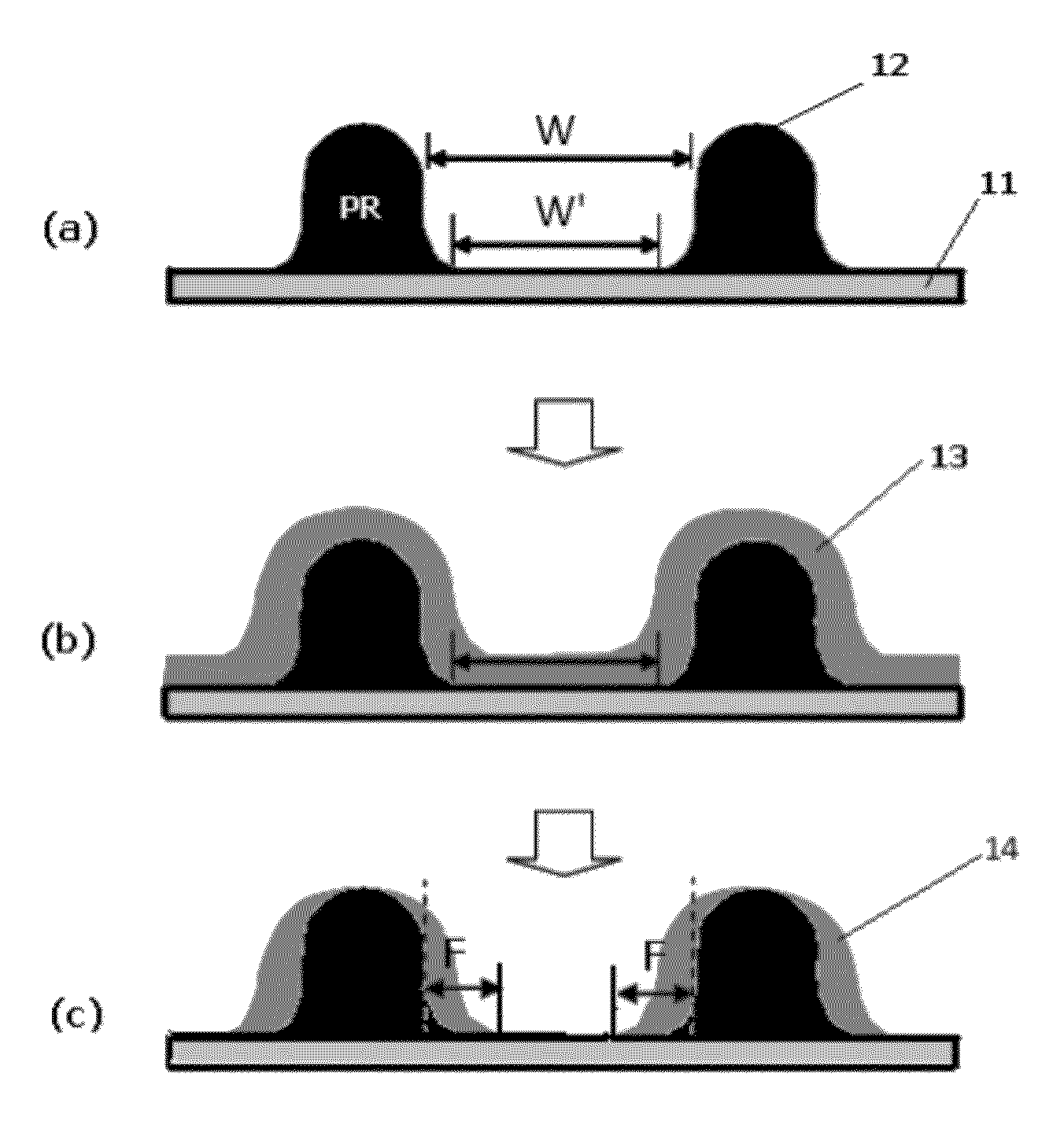

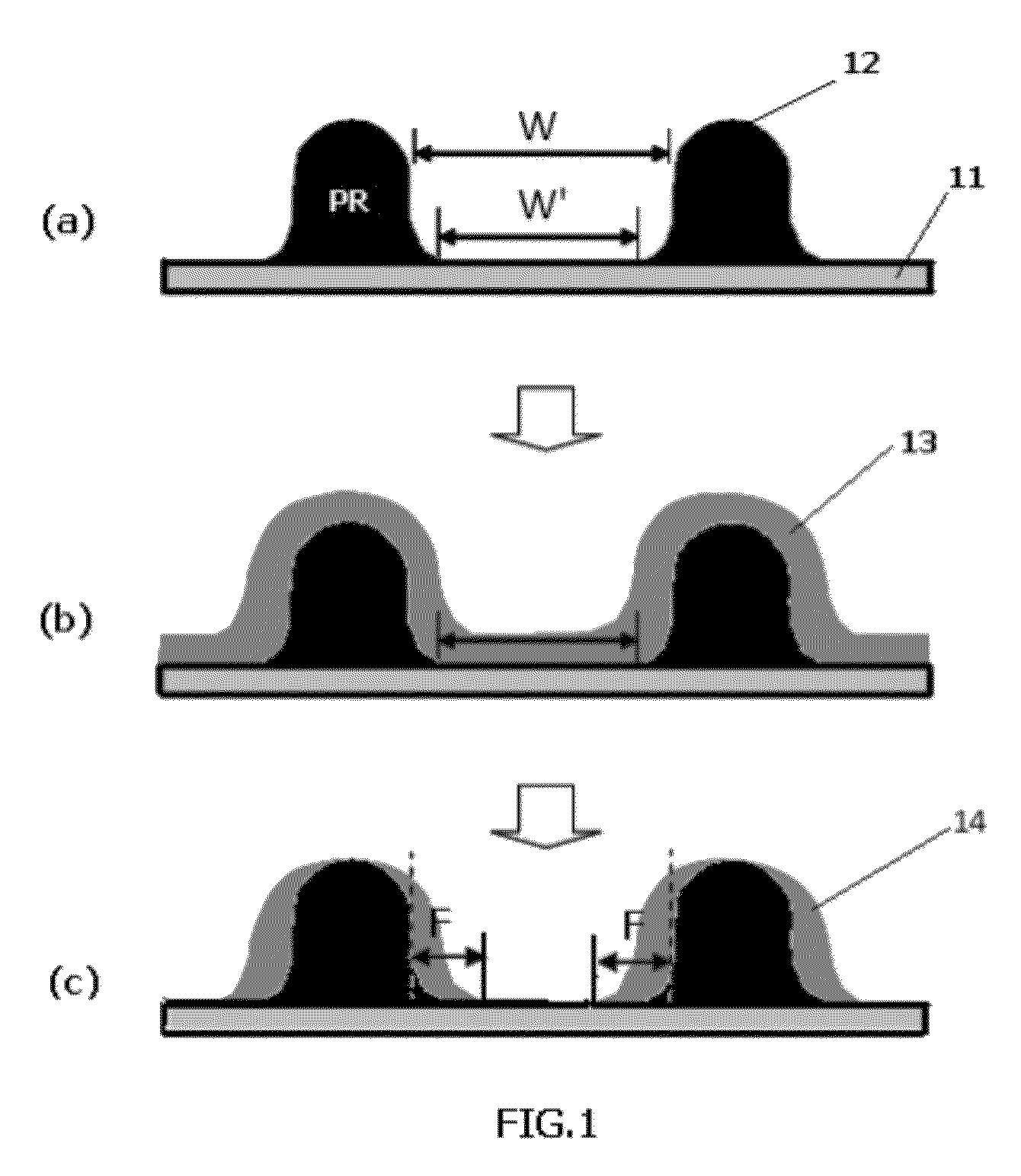

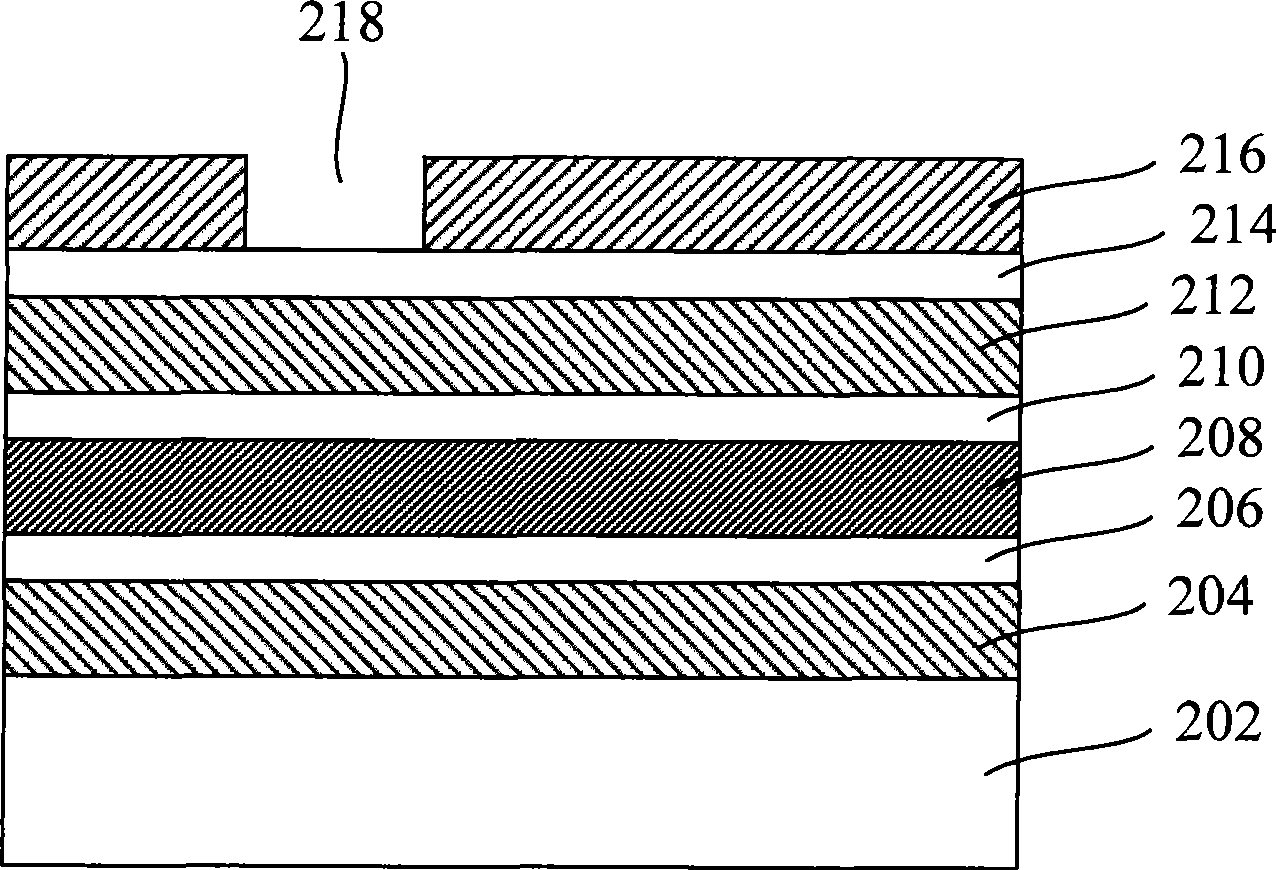

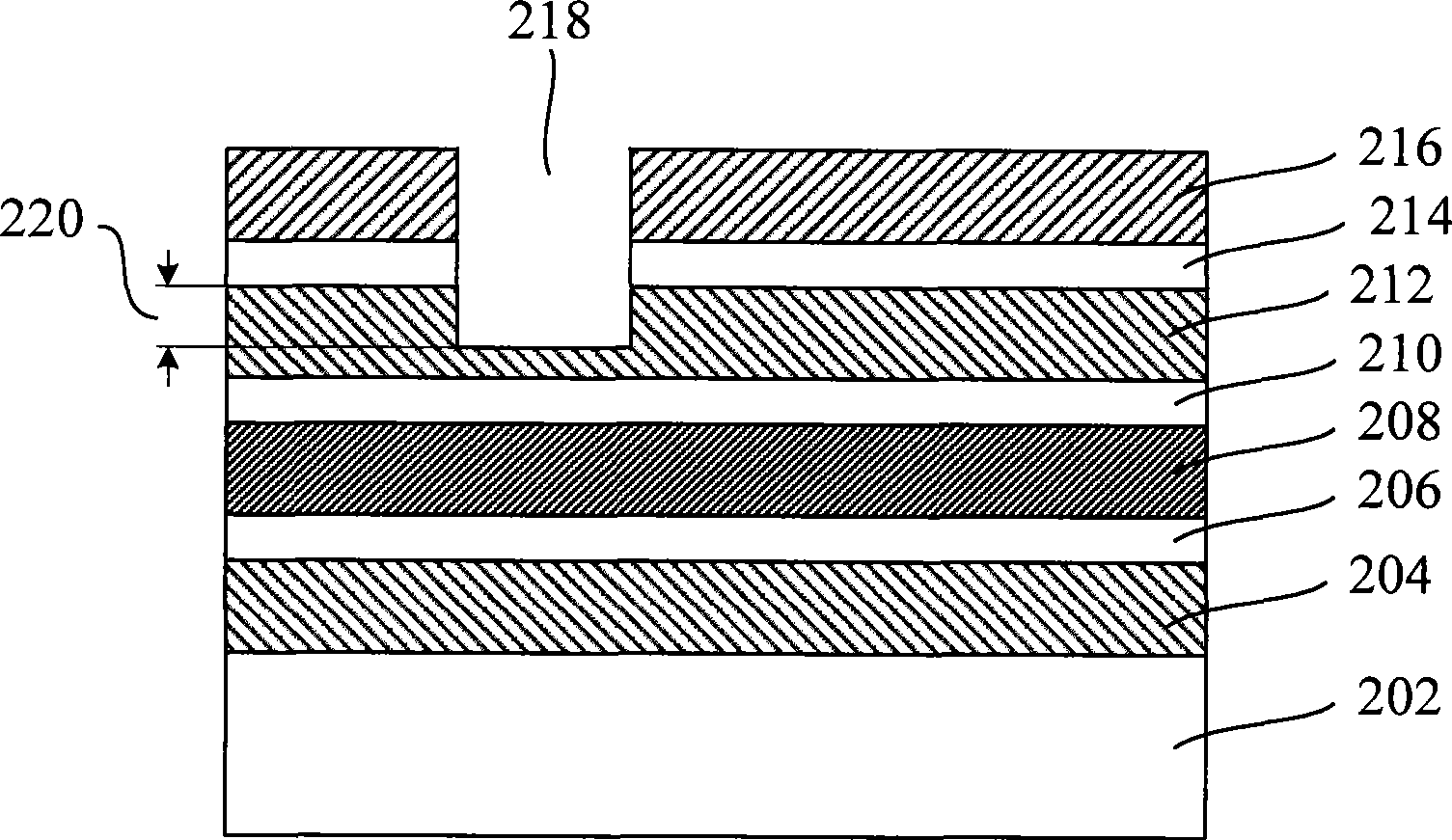

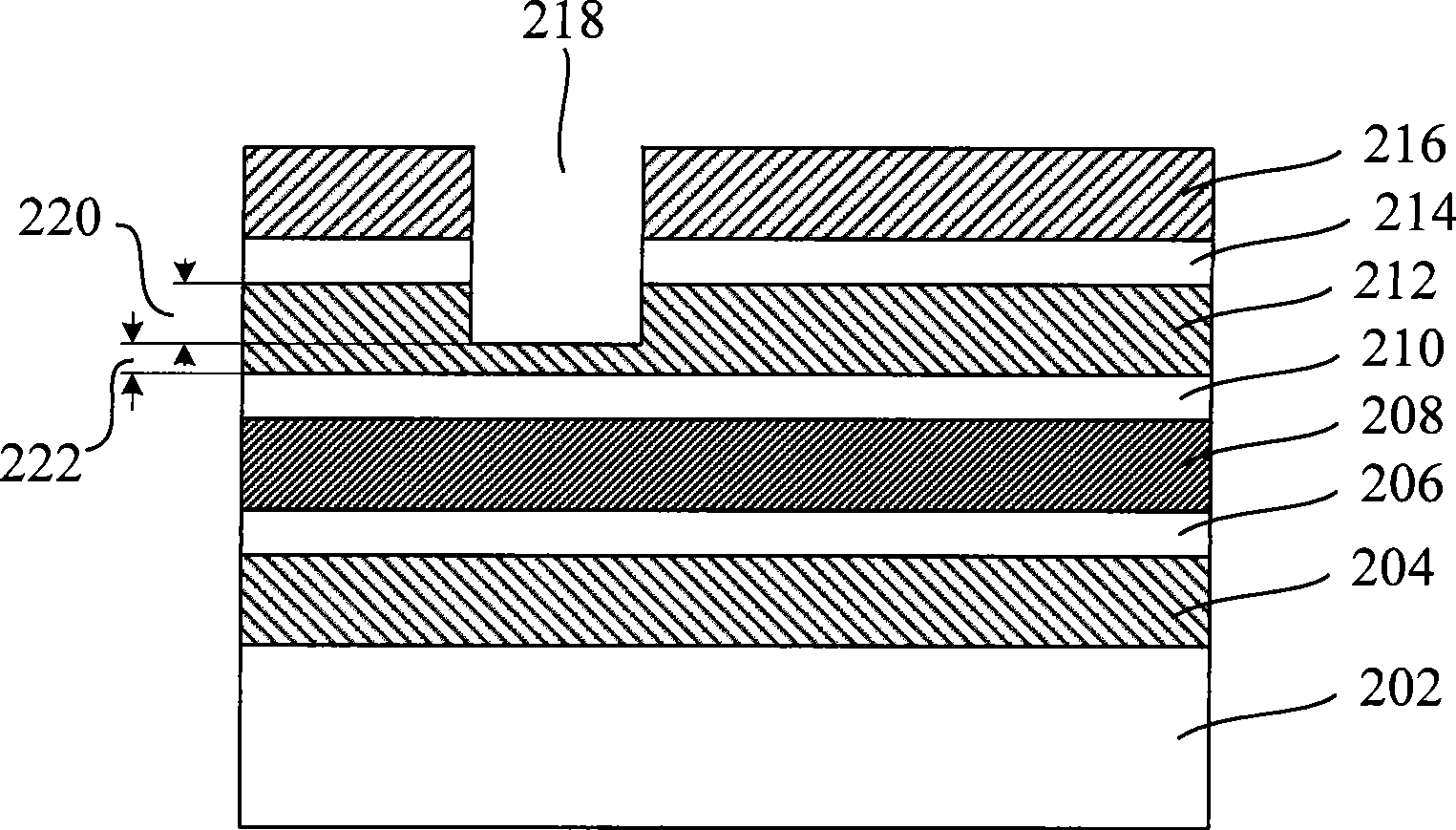

A method of forming side spacers upwardly extending from a substrate, includes: providing a template constituted by a photoresist formed on and in contact with an etch-selective layer laminated on a substrate; anisotropically etching the template in a thickness direction with an oxygen-containing plasma to remove a footing of the photoresist and an exposed portion of the underlying layer; depositing a spacer film on the template by atomic layer deposition (ALD); and forming side spacers using the spacer film by etching. The etch-selective layer has a substantially lower etch rate than that of the photoresist.

Owner:ASM JAPAN

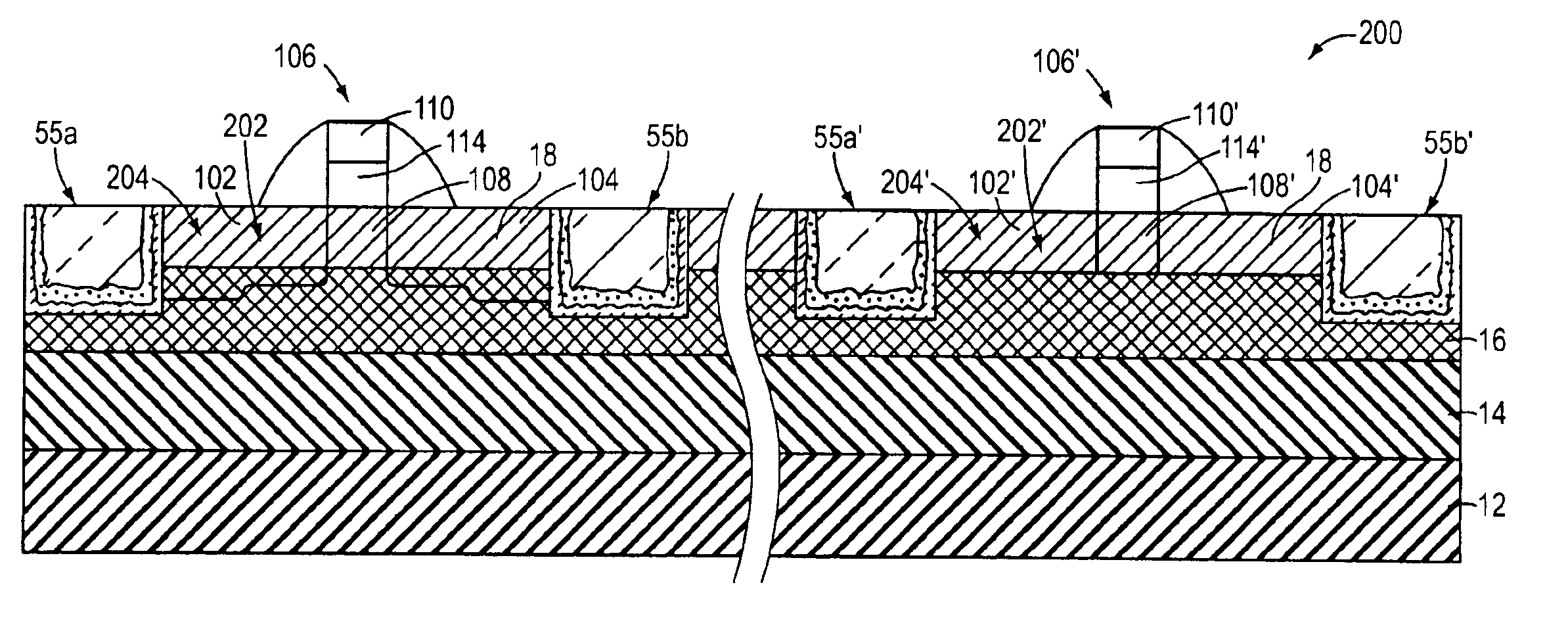

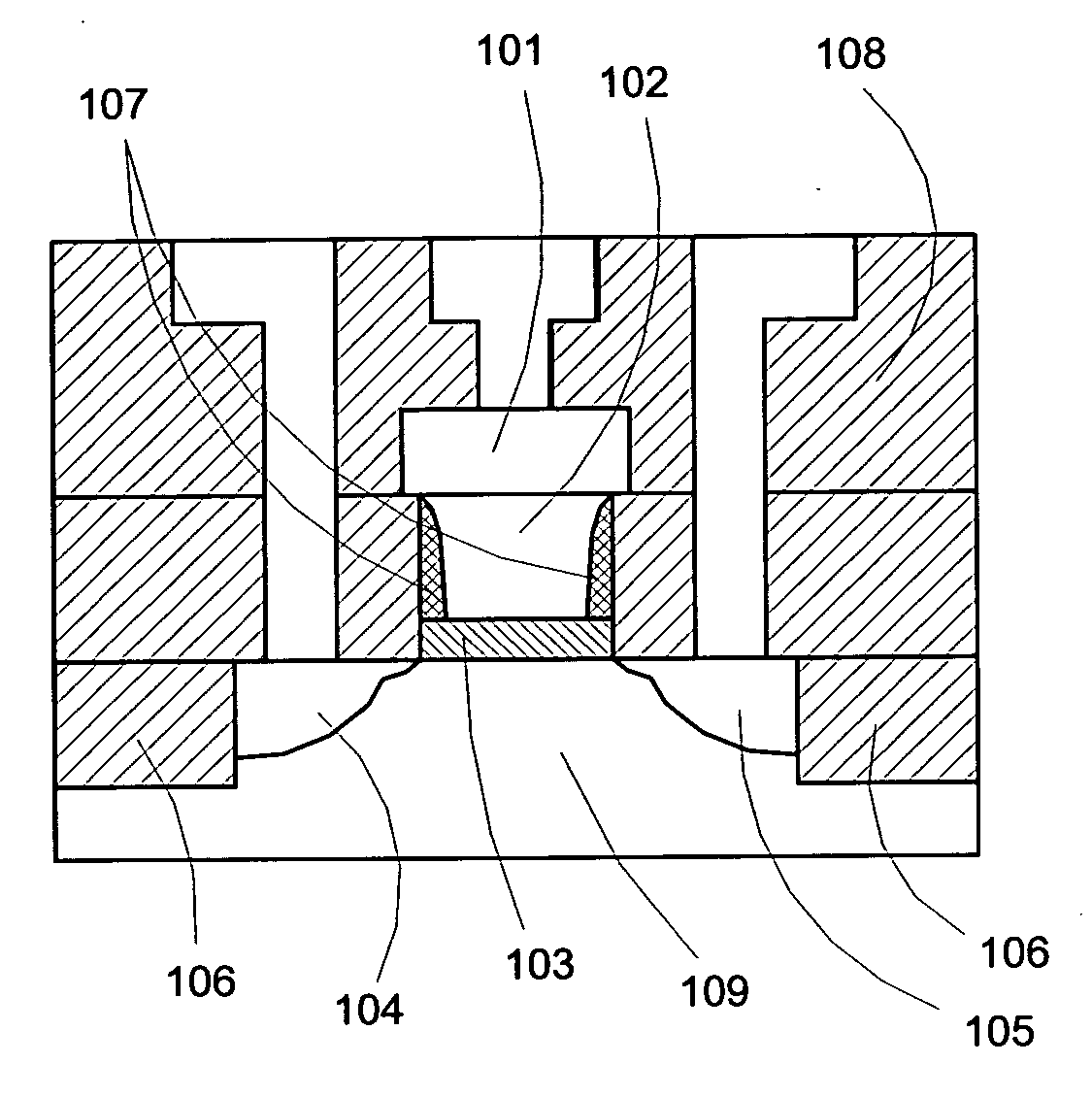

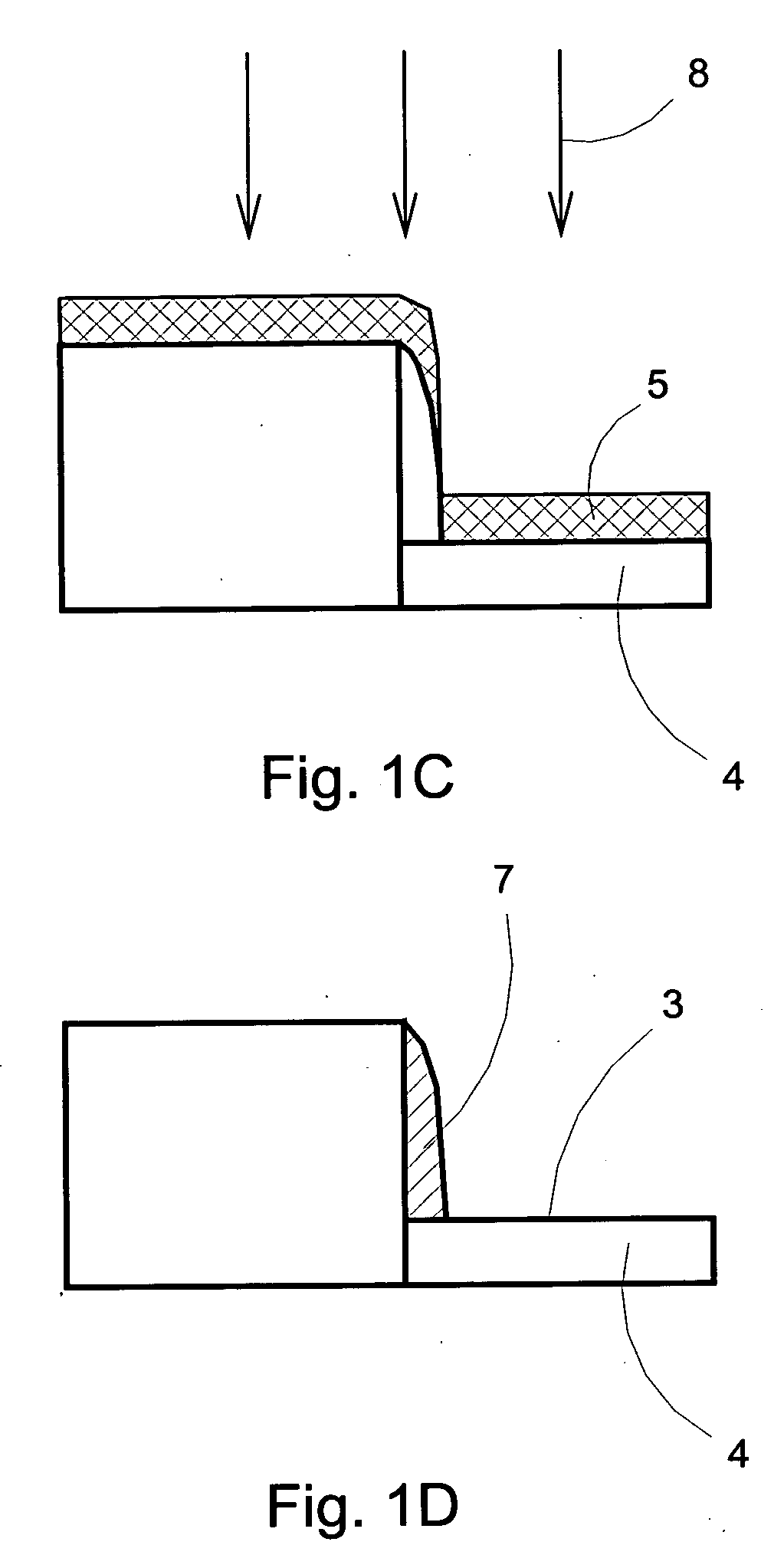

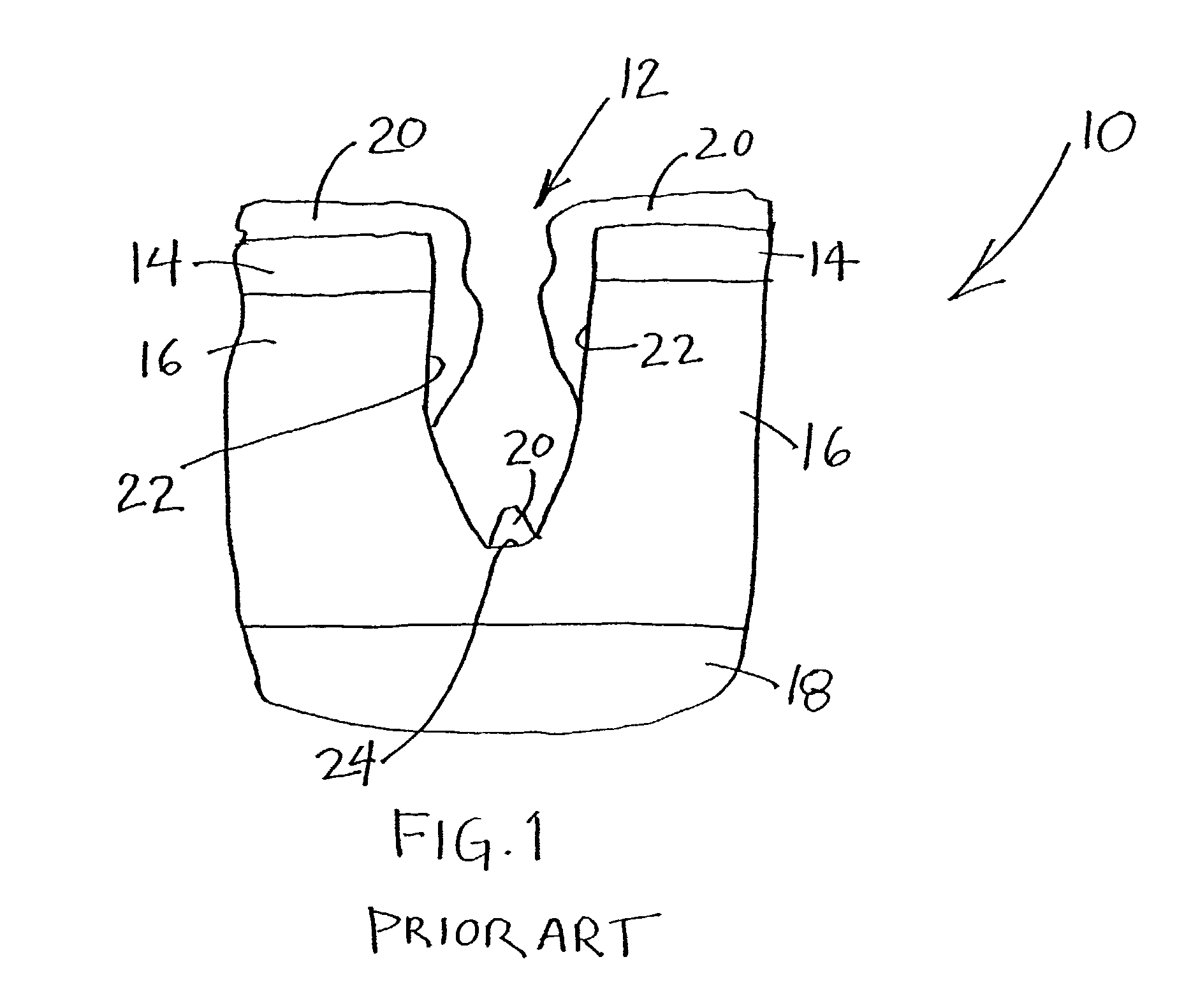

Shallow trench isolation process

ActiveUS6960781B2Improve performanceTrench sidewallTransistorSolid-state devicesEngineeringTransistor

A structure including a transistor and a trench structure, with the trench structure inducing only a portion of the strain in a channel region of the transistor.

Owner:TAIWAN SEMICON MFG CO LTD

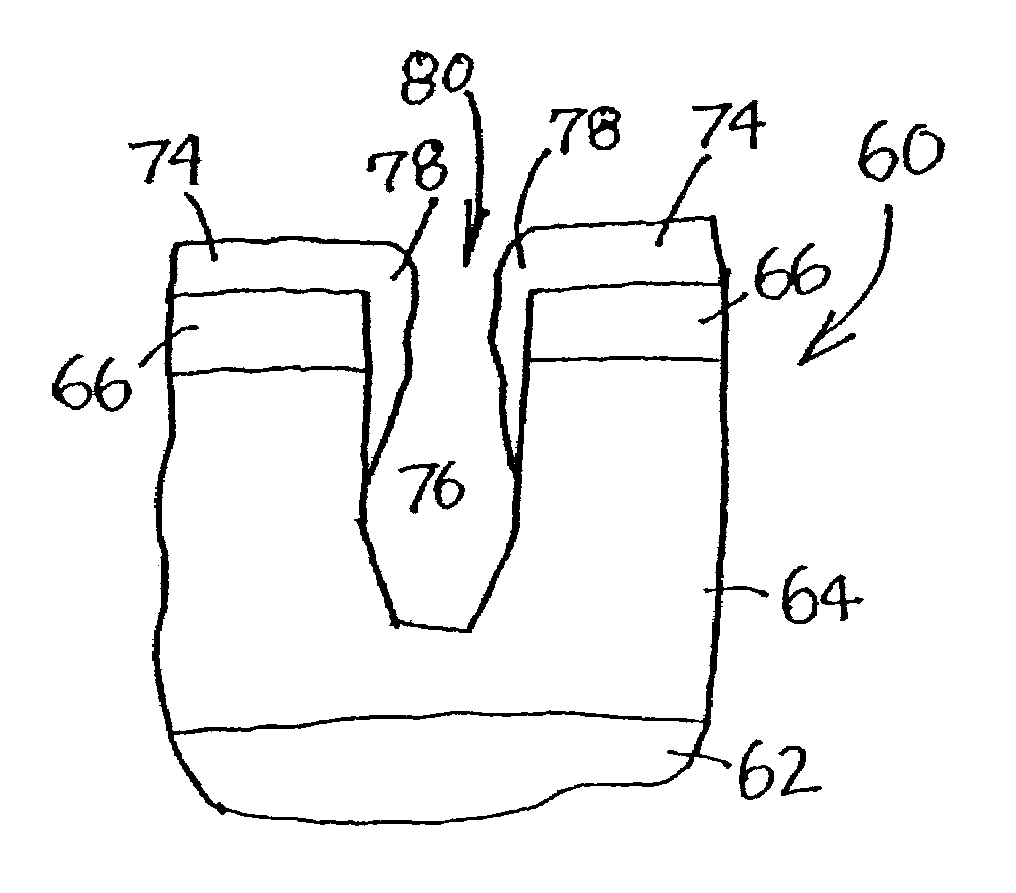

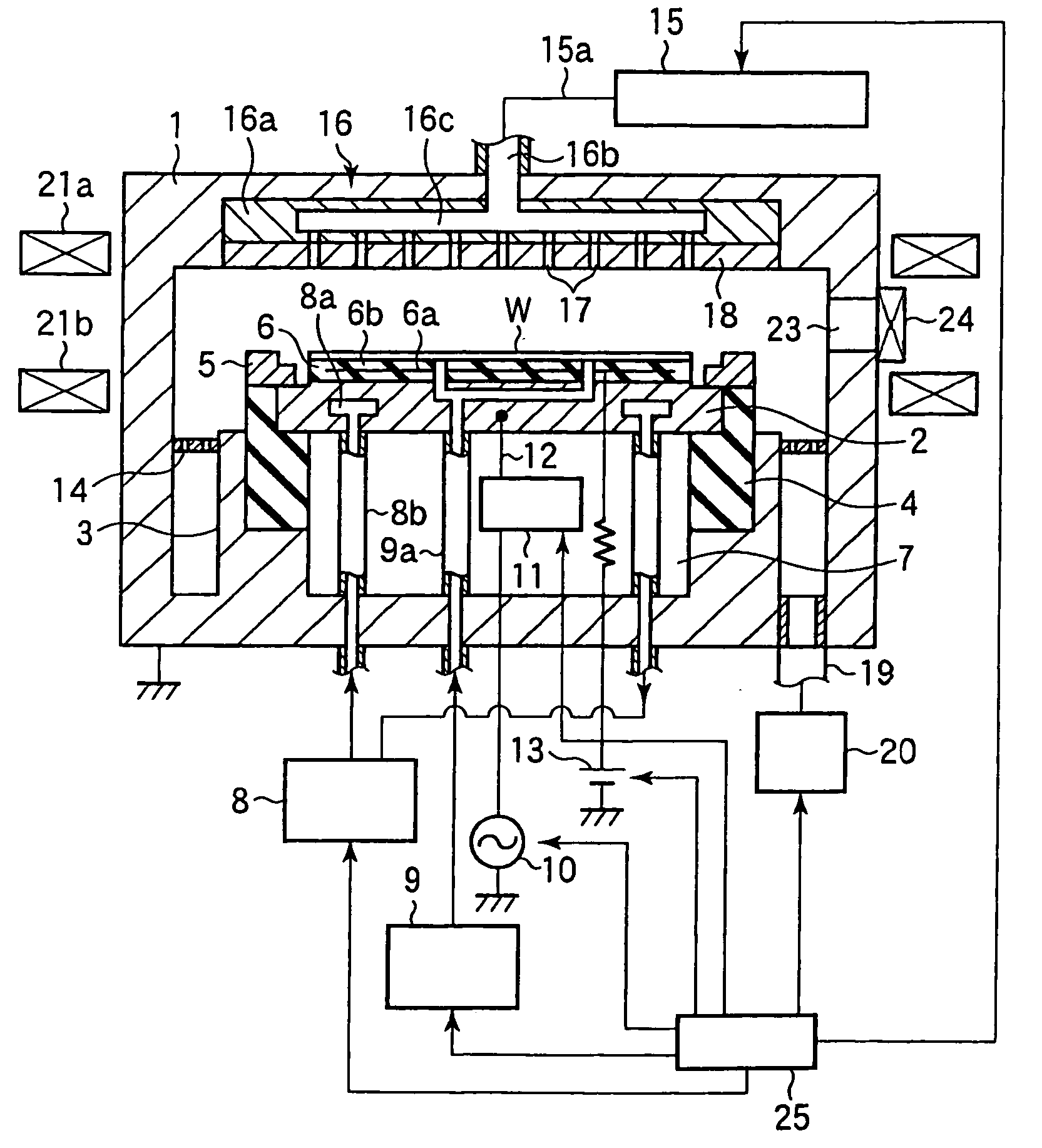

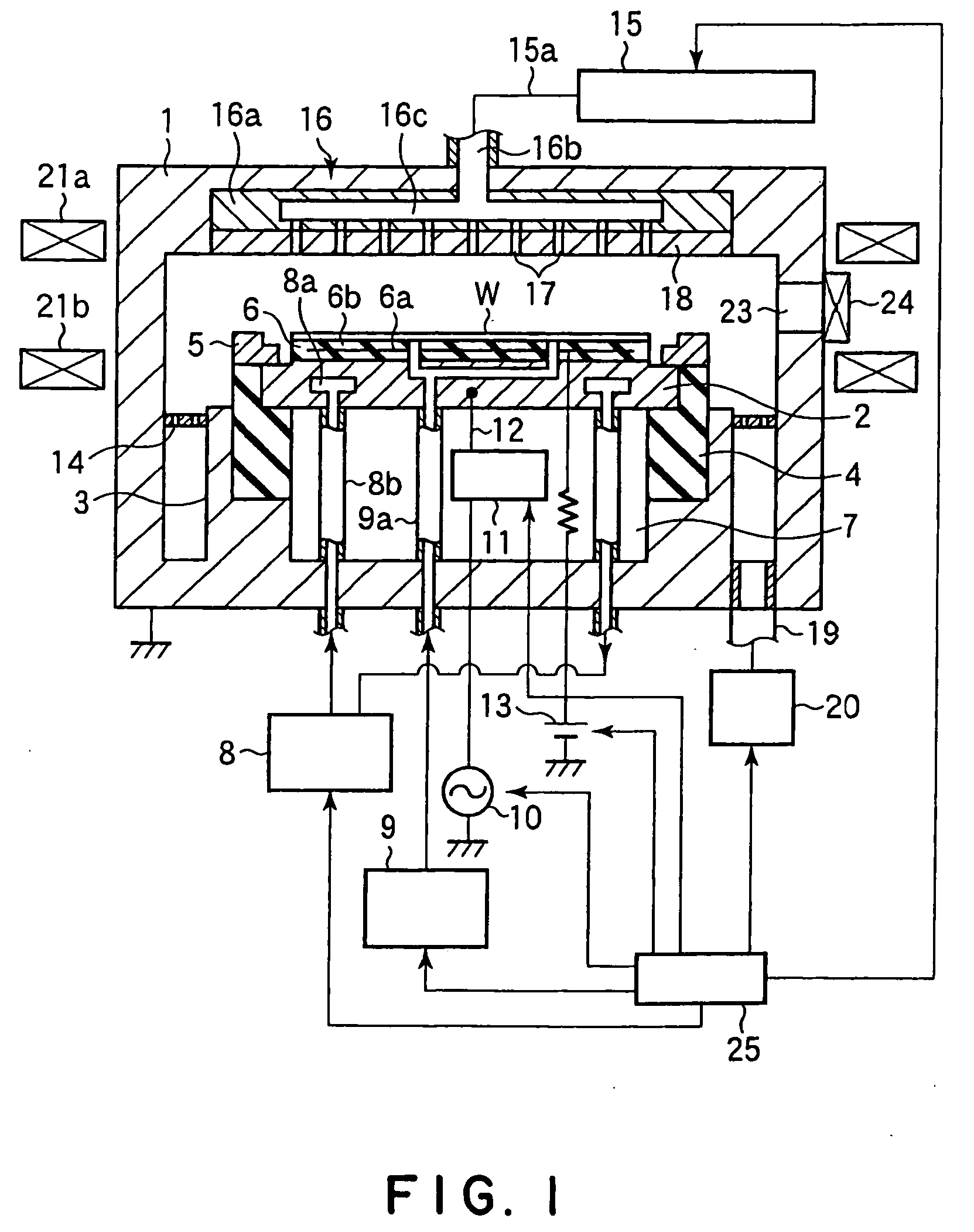

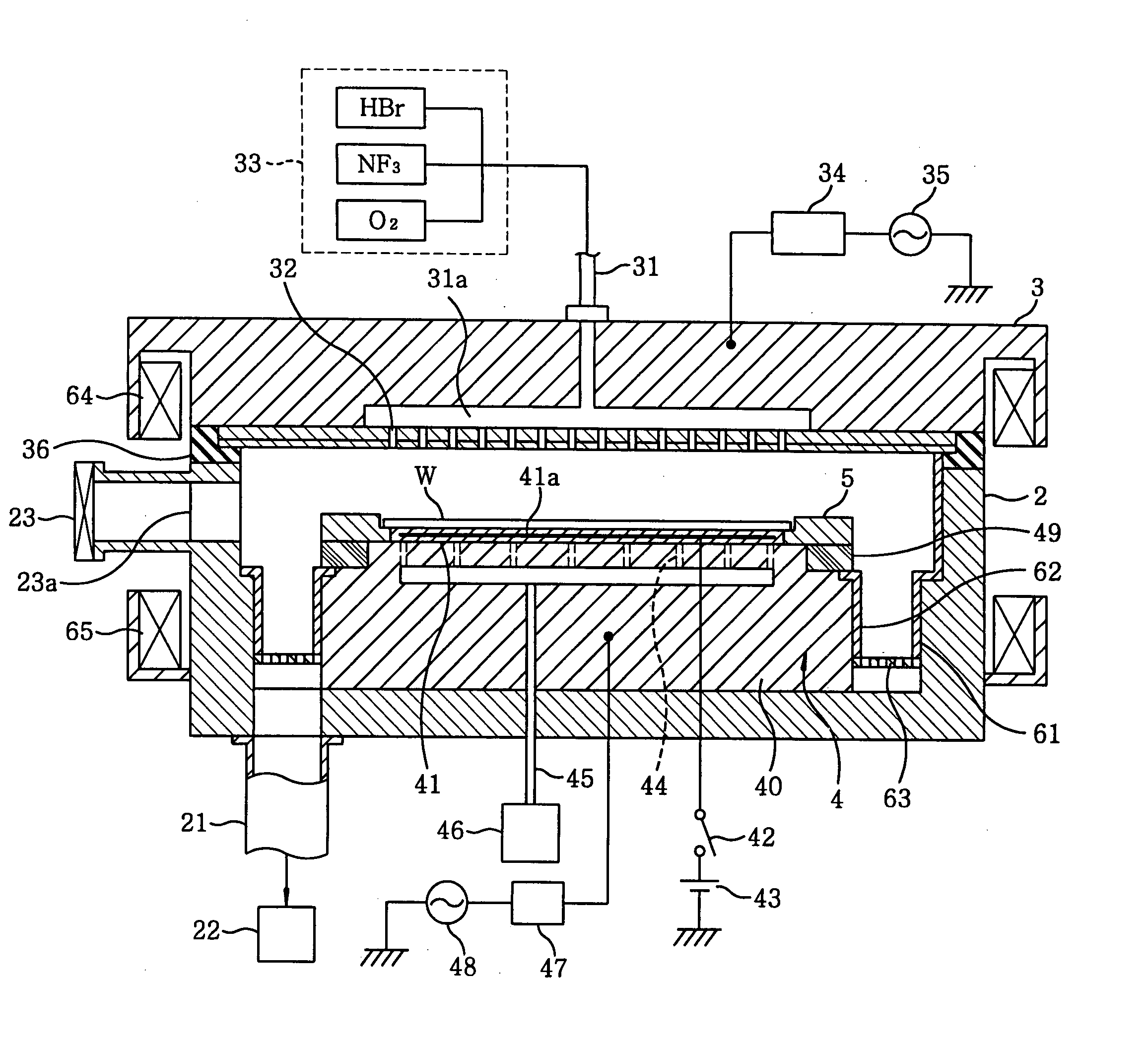

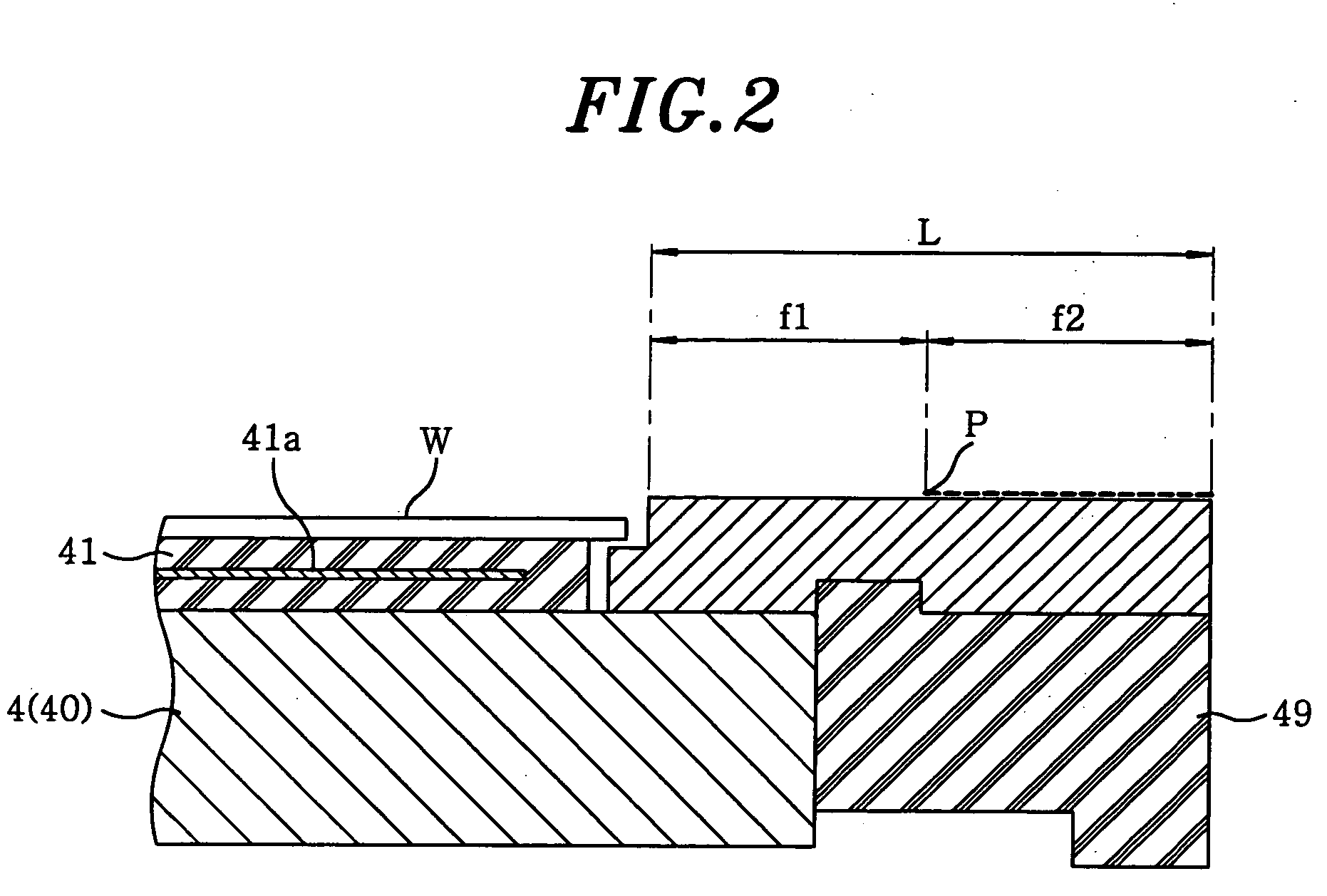

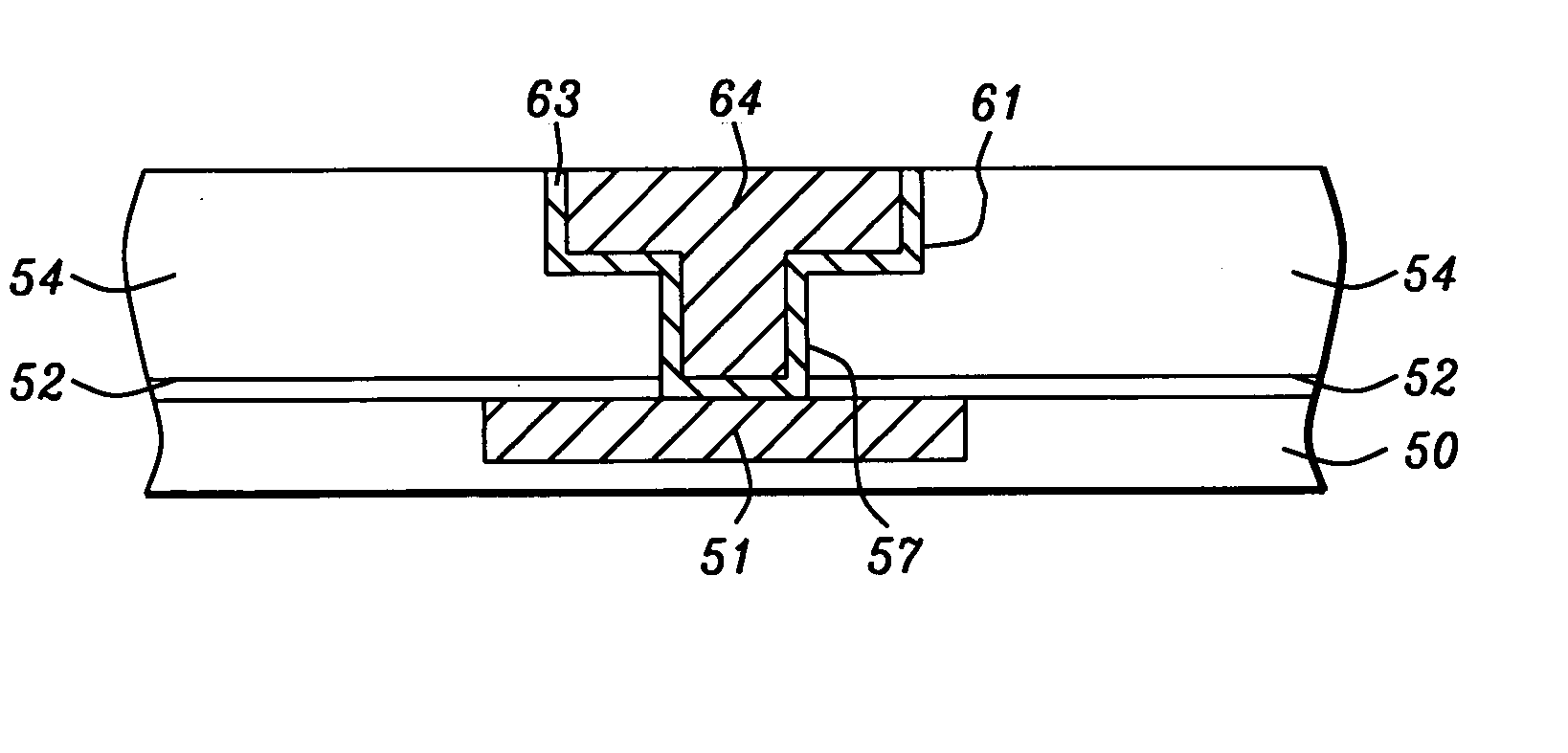

Focus ring, plasma etching apparatus and plasma etching method

ActiveUS20090255902A1Improve etching effectAccurate storageElectric discharge tubesDecorative surface effectsSusceptorSurface roughness

In a plasma etching apparatus for performing a plasma etching on a surface of a substrate mounted on a susceptor in a processing vessel, a focus ring is installed to surround the substrate and has a first region at an inner side on a surface thereof, in which an average surface roughness is small such that a reaction product produced during an etching processing is not captured to be deposited, and a second region at an outer side from the first region, in which an average surface roughness is large such that a reaction product produced during the etching process is captured to be deposited. A boundary between the first and the second region is a part where an etching amount is relatively significantly changed compared to other parts while the focus ring is equipped in the plasma etching apparatus and the plasma etching is performed on the substrate.

Owner:TOKYO ELECTRON LTD

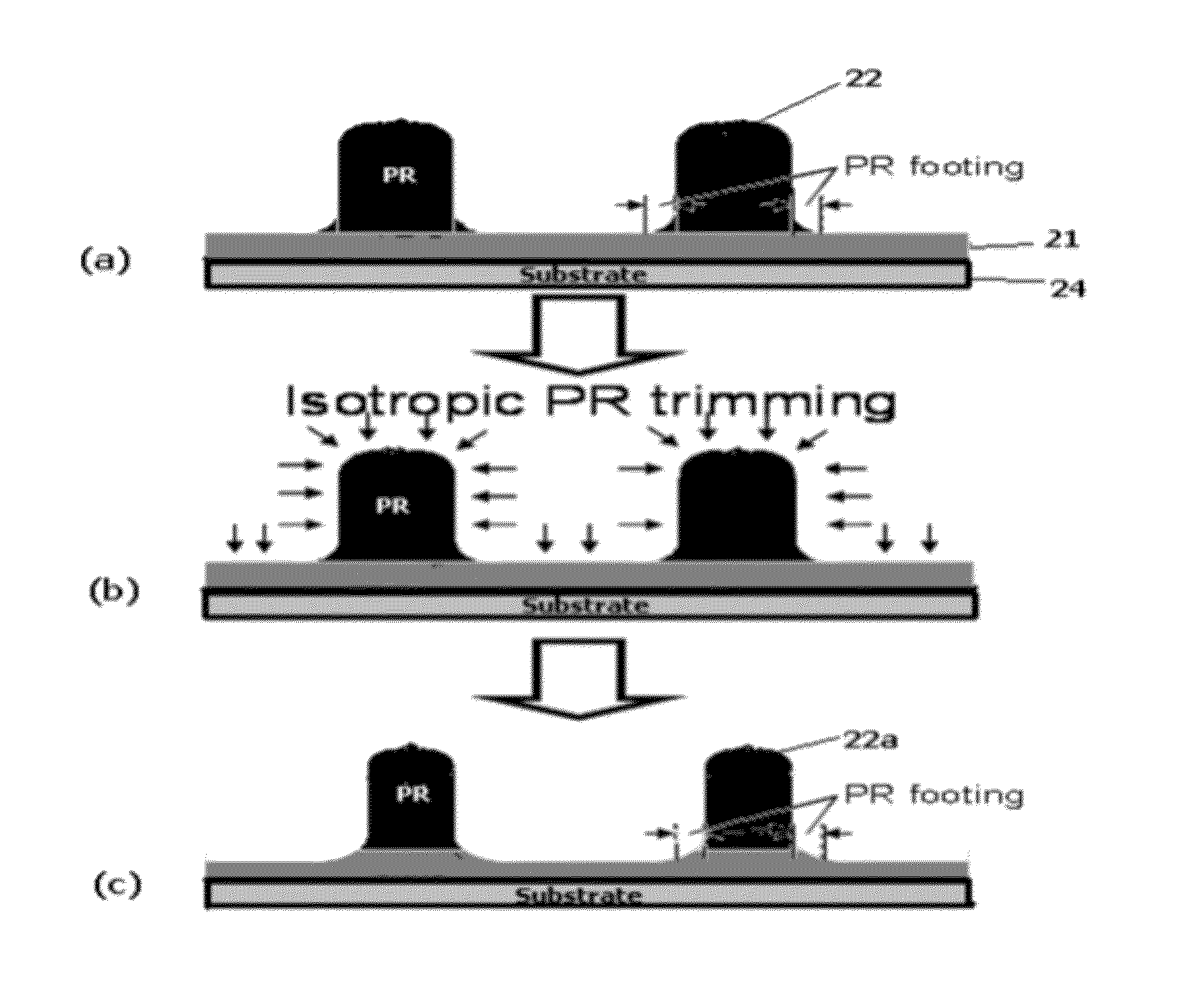

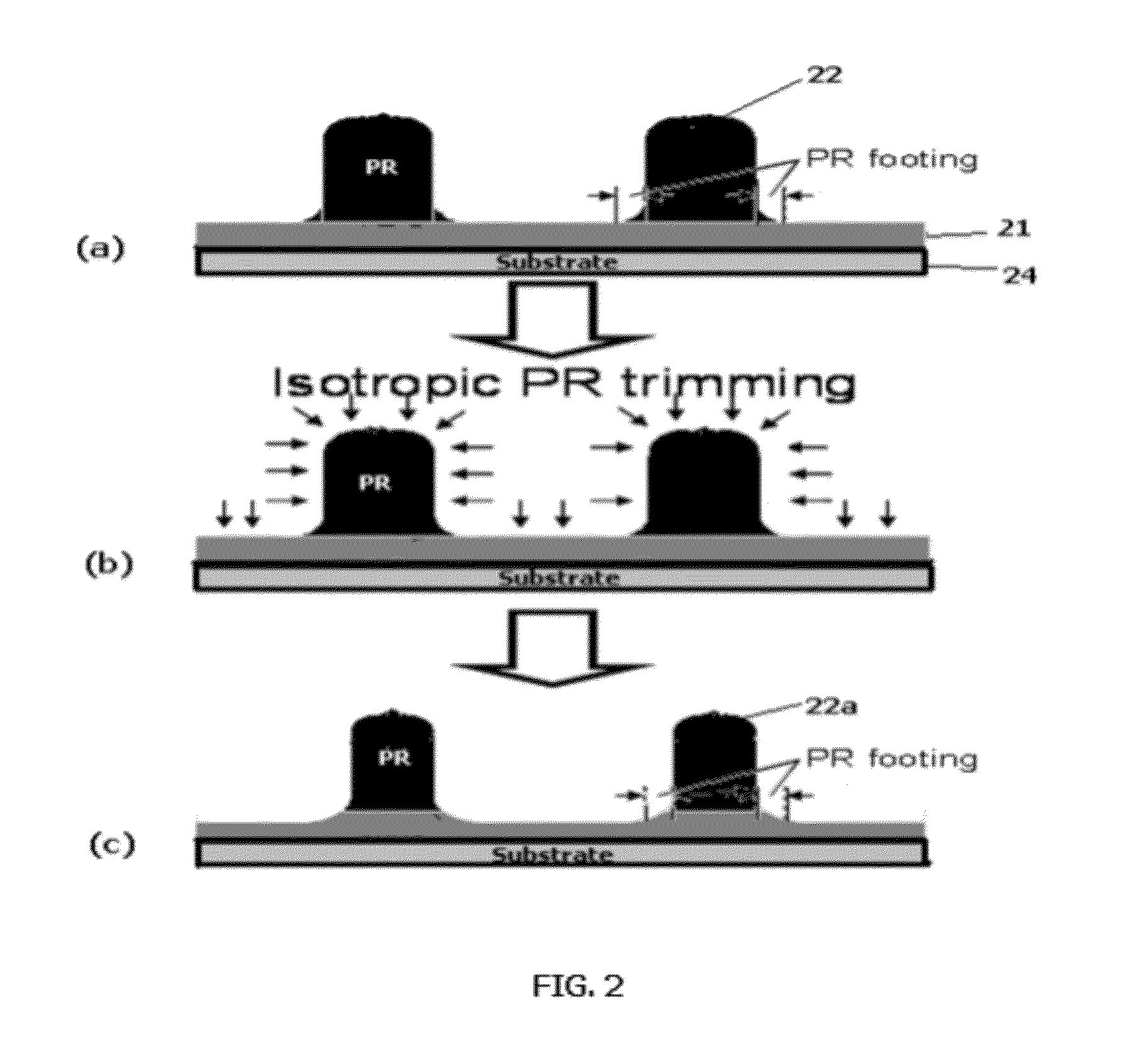

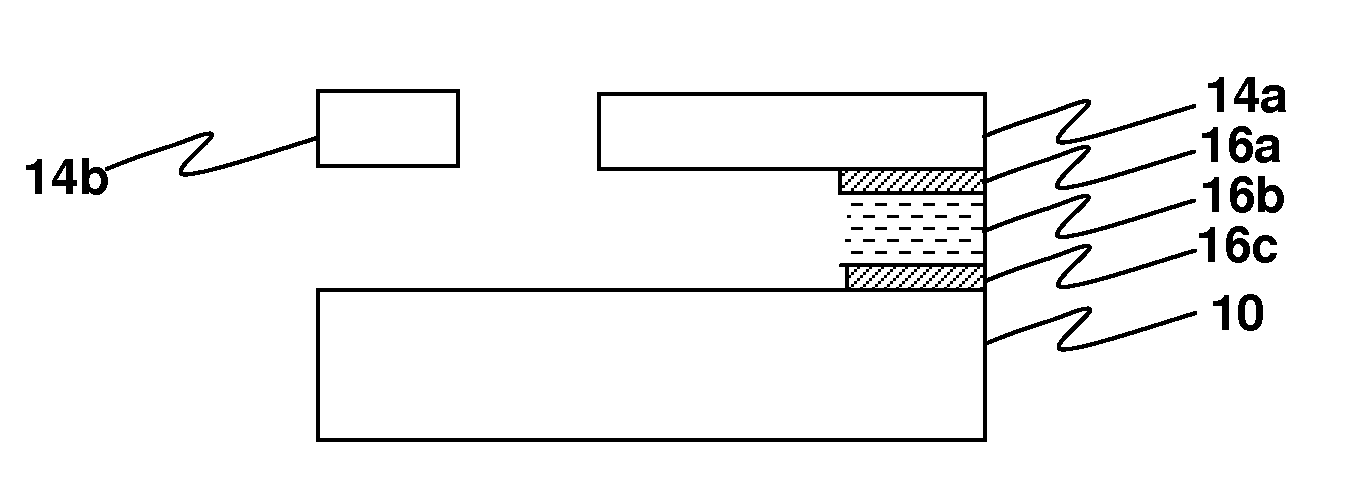

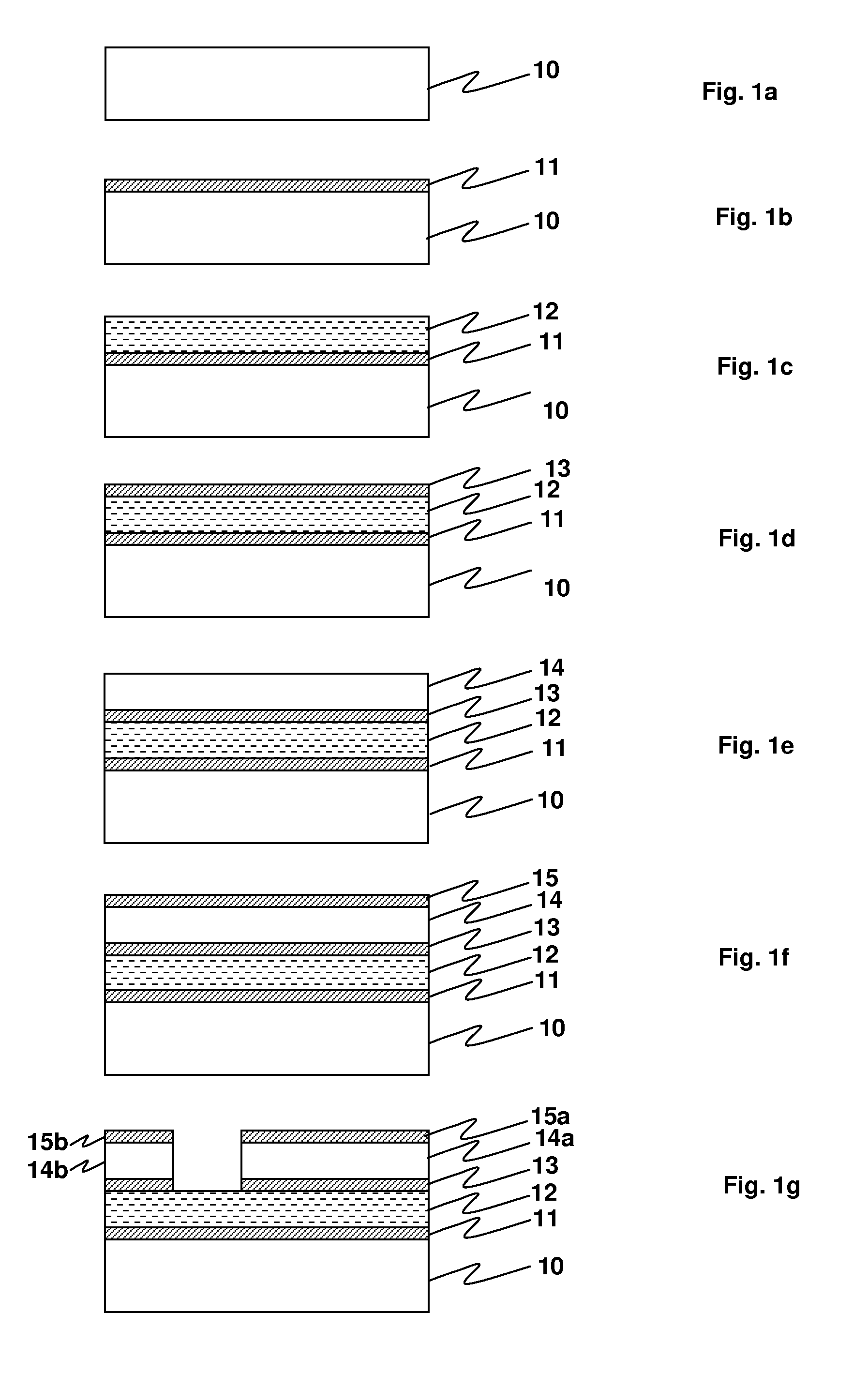

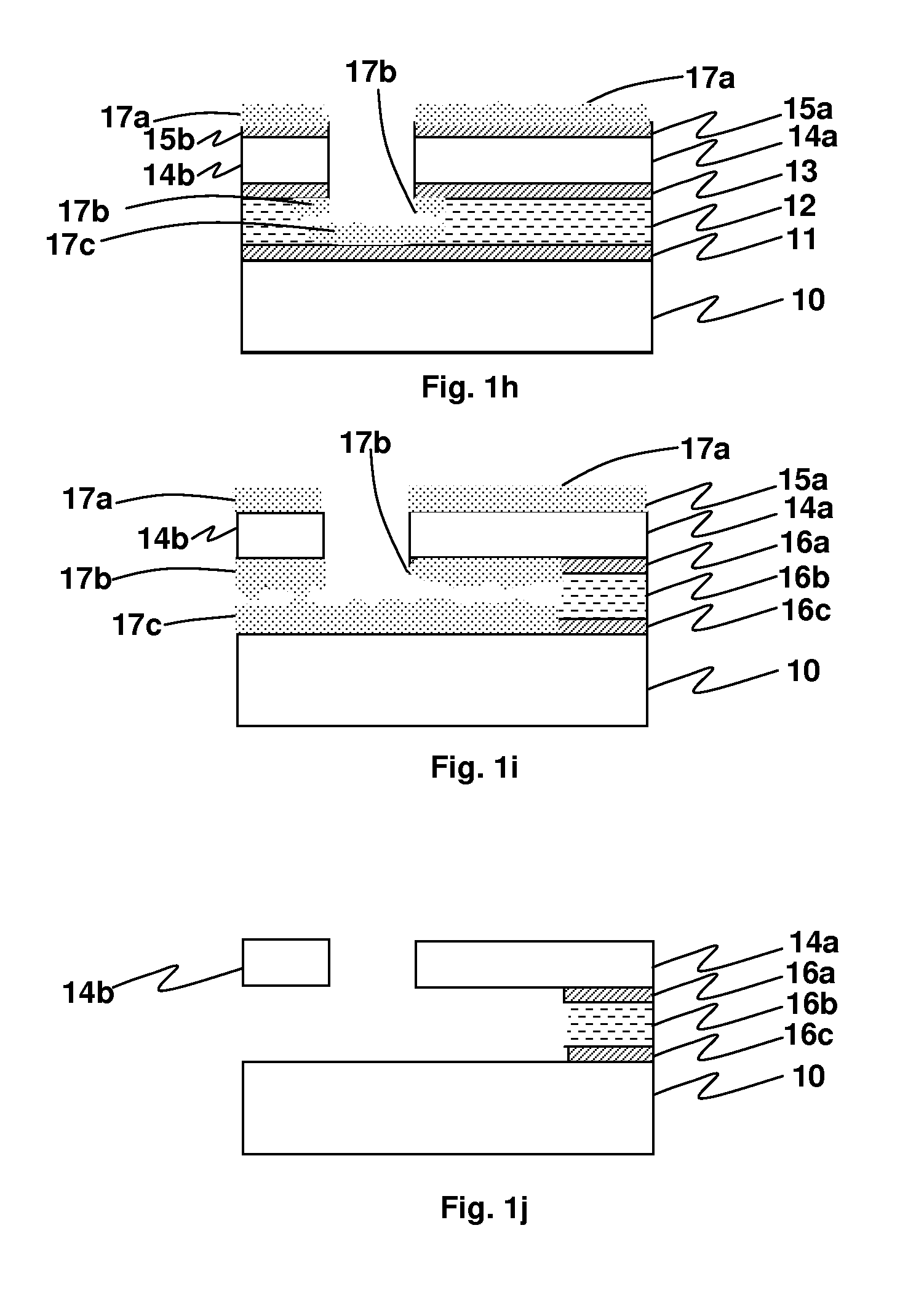

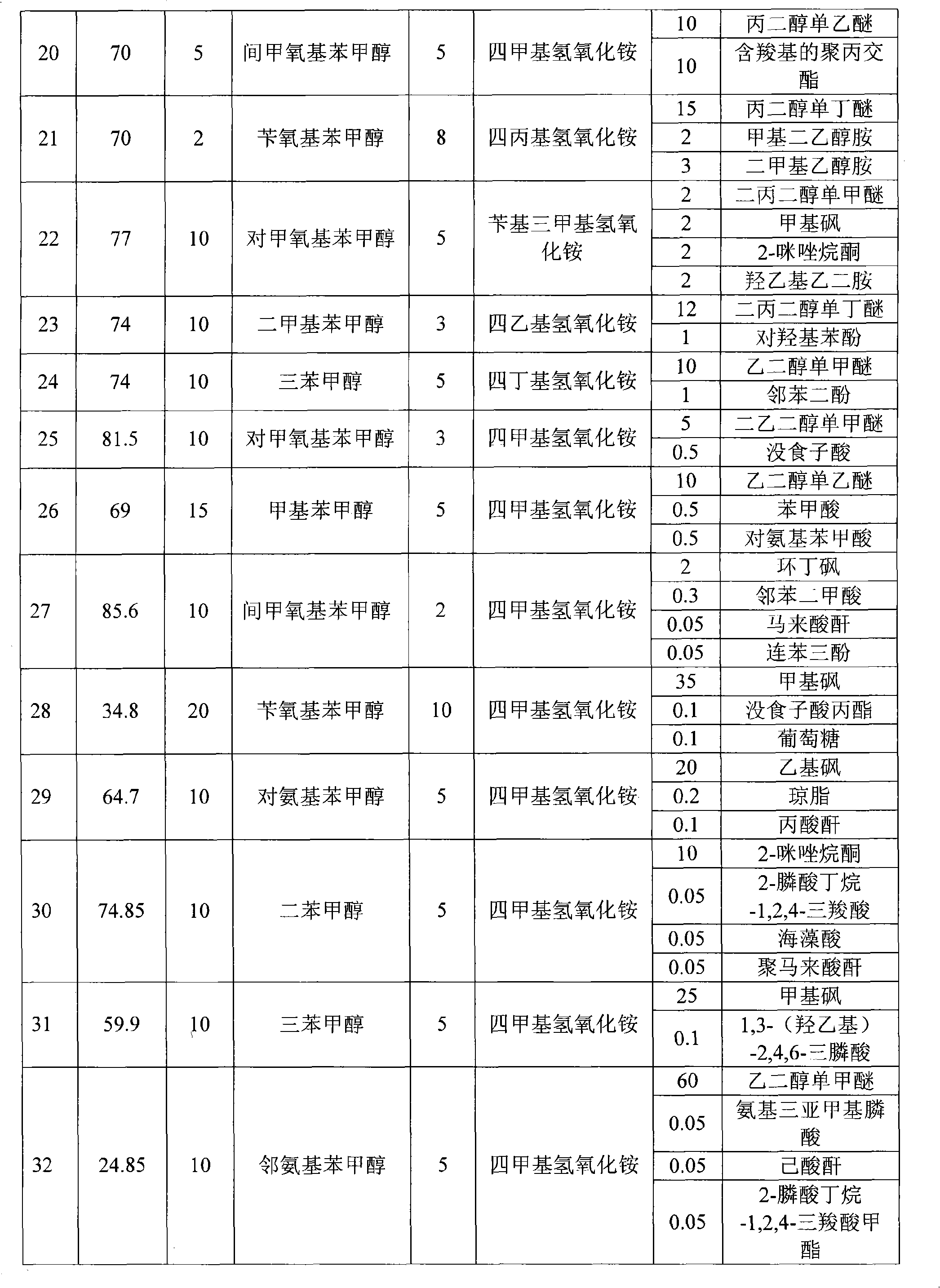

Footing Reduction Using Etch-Selective Layer

ActiveUS20120264305A1Reduce etch rateReducing a widened footing of the photoresistDecorative surface effectsSemiconductor/solid-state device manufacturingEngineeringOxygen

A method of forming side spacers upwardly extending from a substrate, includes: providing a template constituted by a photoresist formed on and in contact with an etch-selective layer laminated on a substrate; anisotropically etching the template in a thickness direction with an oxygen-containing plasma to remove a footing of the photoresist and an exposed portion of the underlying layer; depositing a spacer film on the template by atomic layer deposition (ALD); and forming side spacers using the spacer film by etching. The etch-selective layer has a substantially lower etch rate than that of the photoresist.

Owner:ASM JAPAN

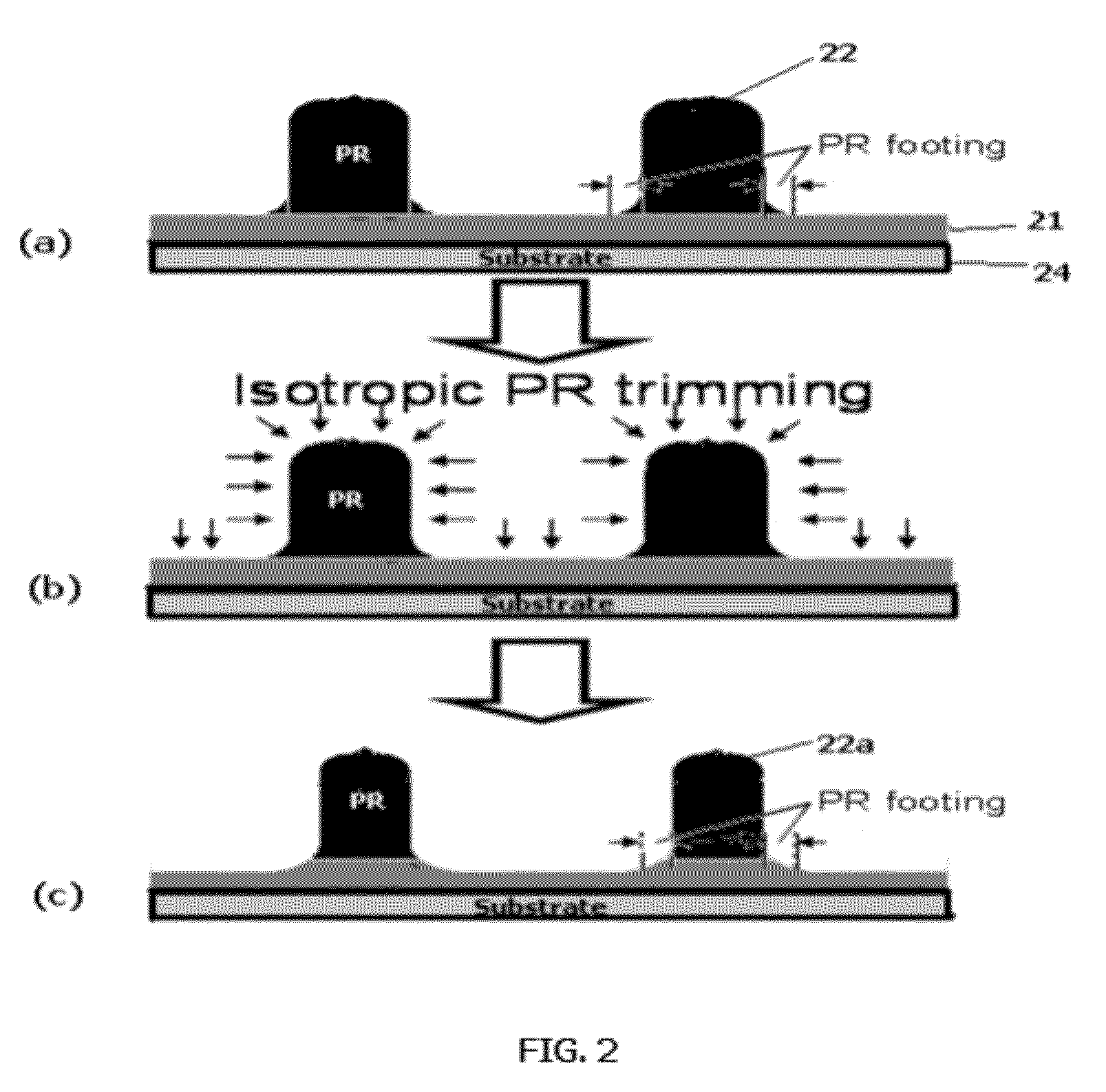

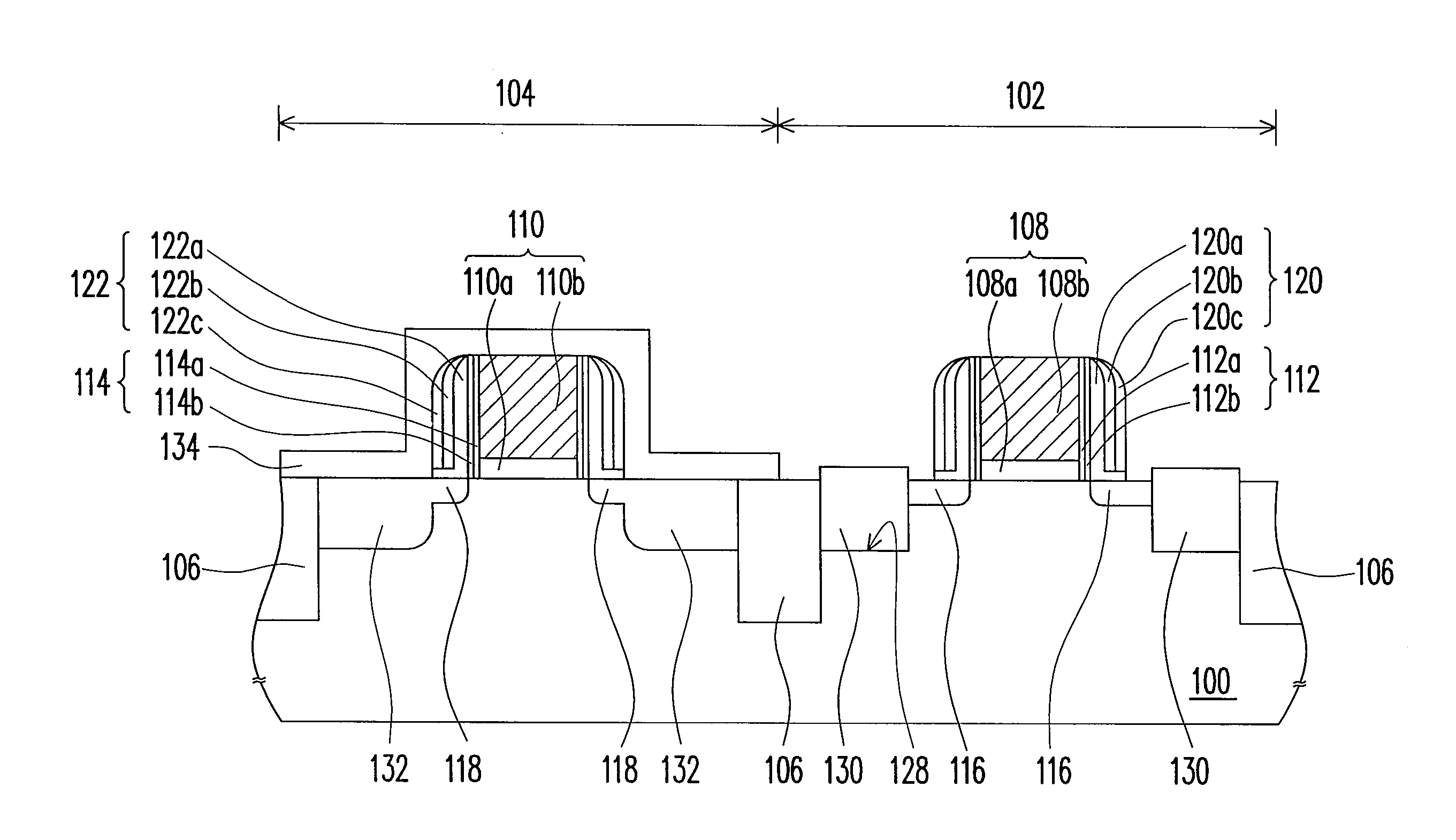

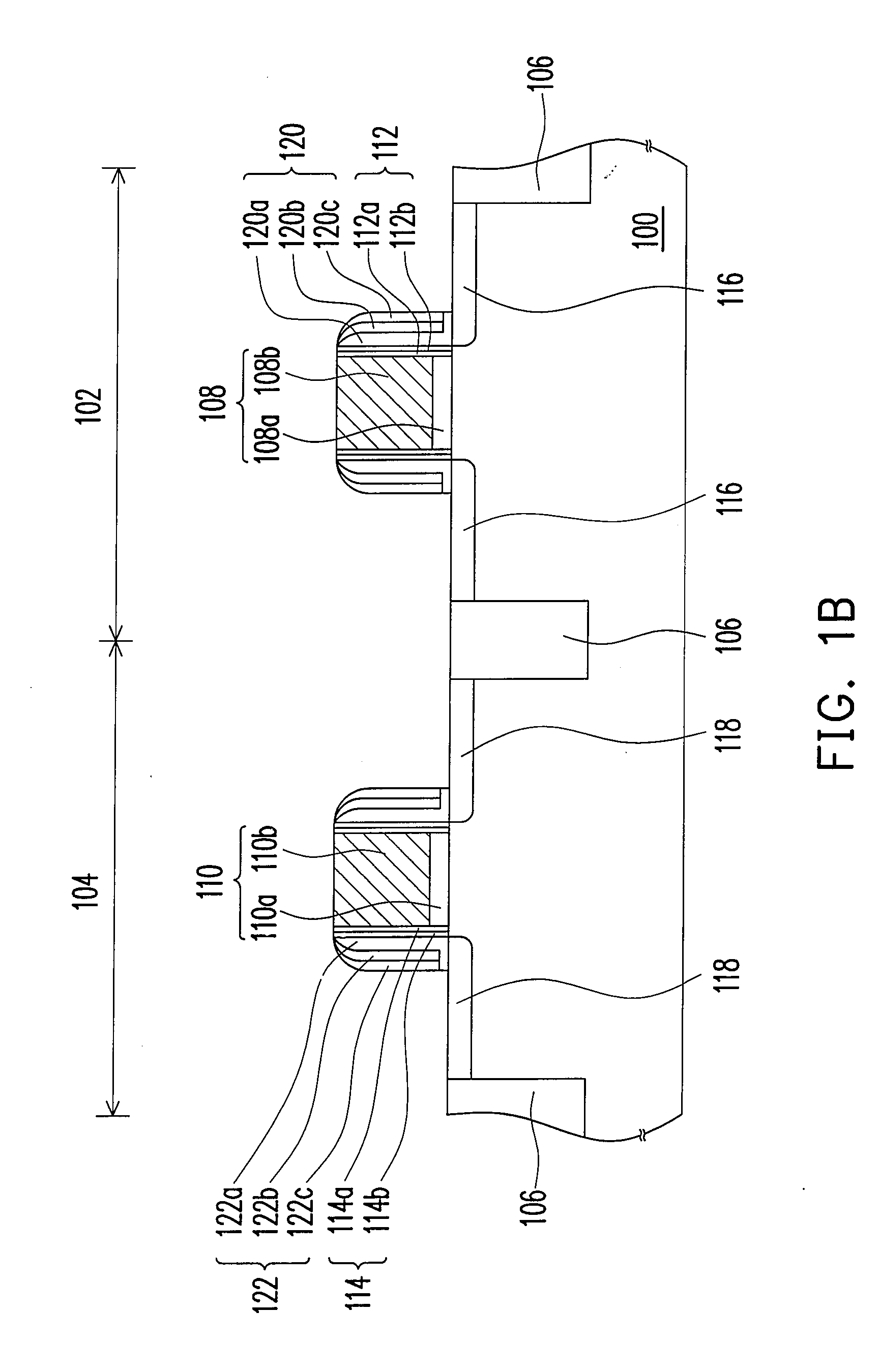

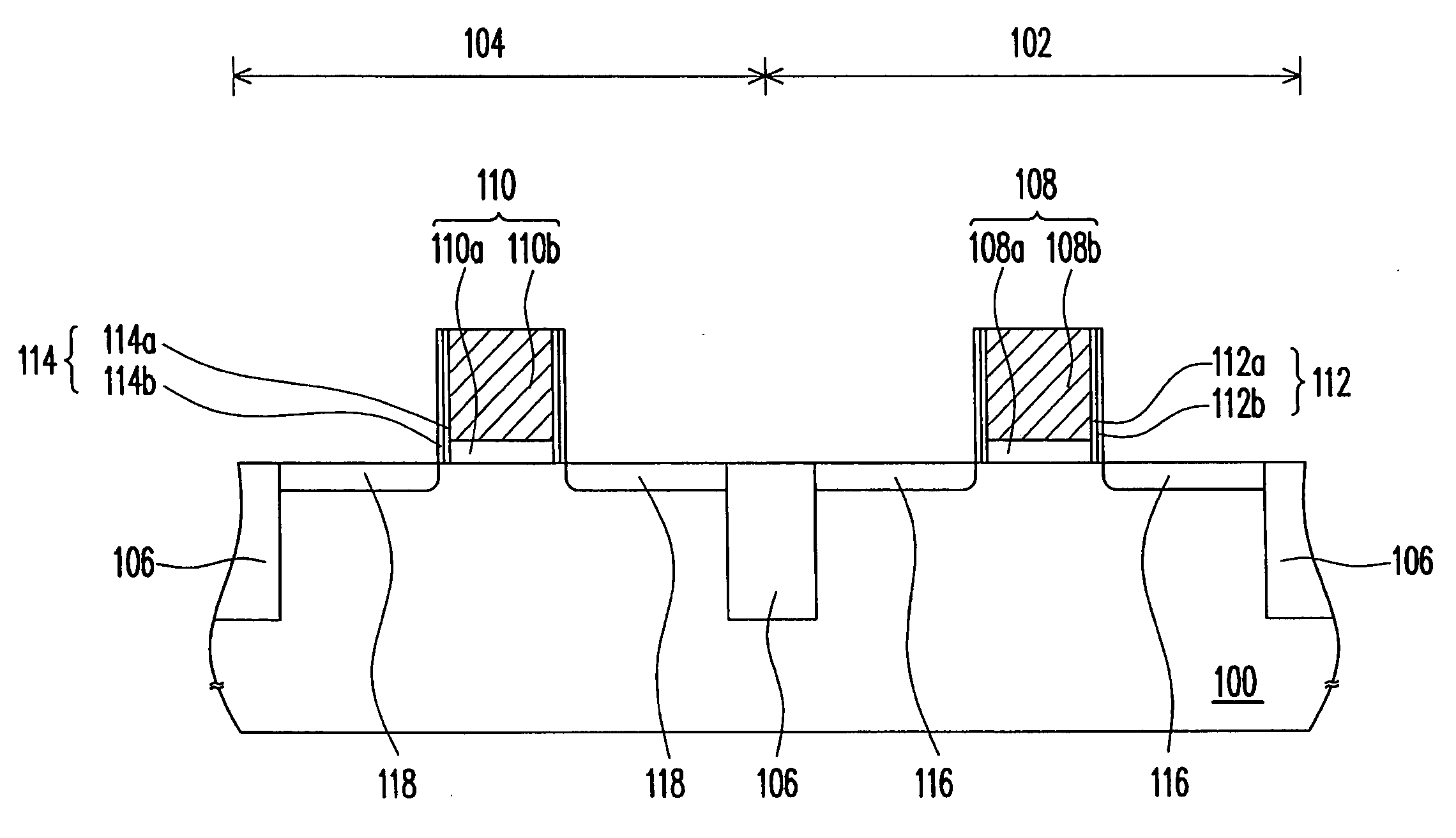

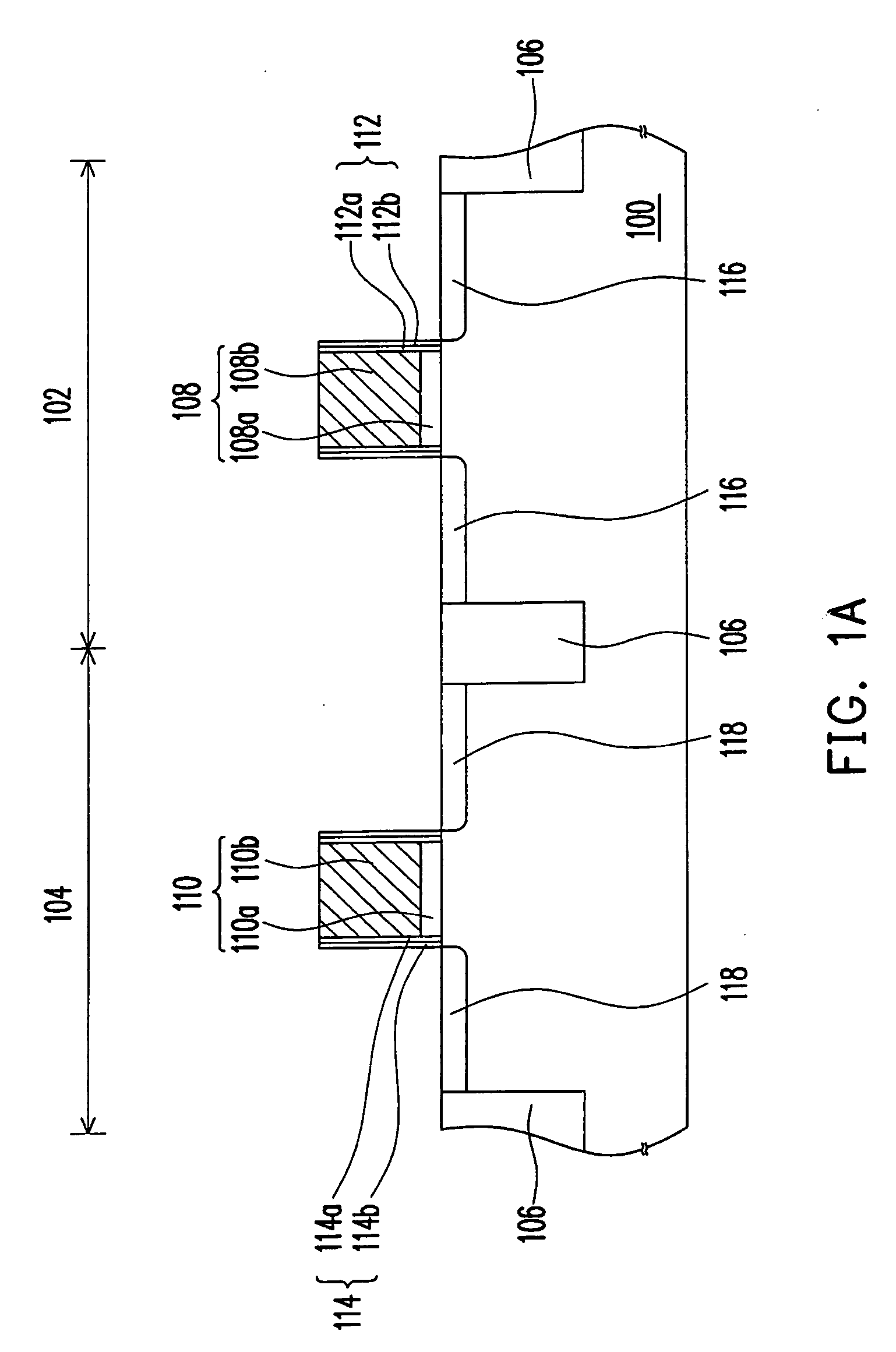

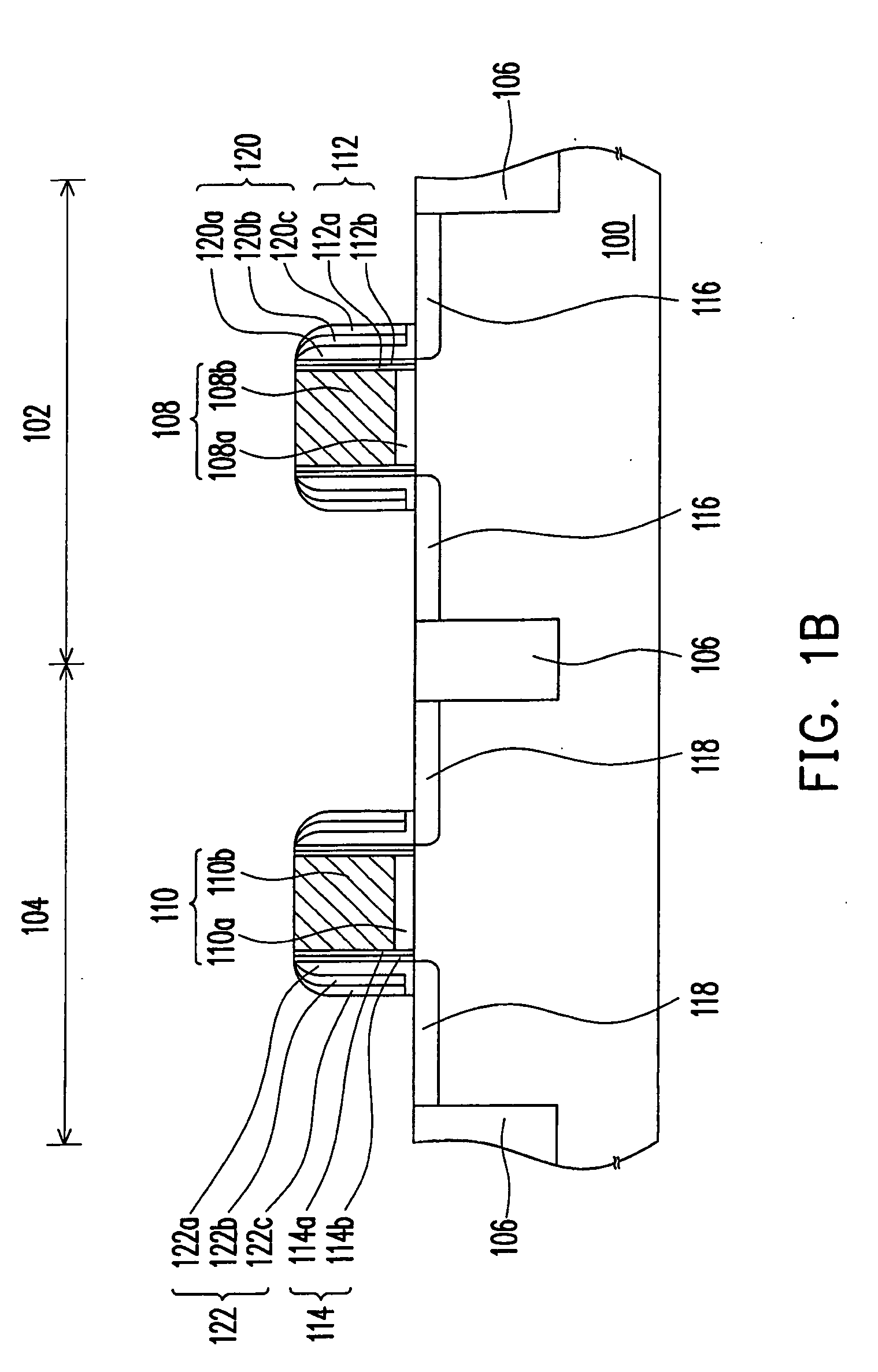

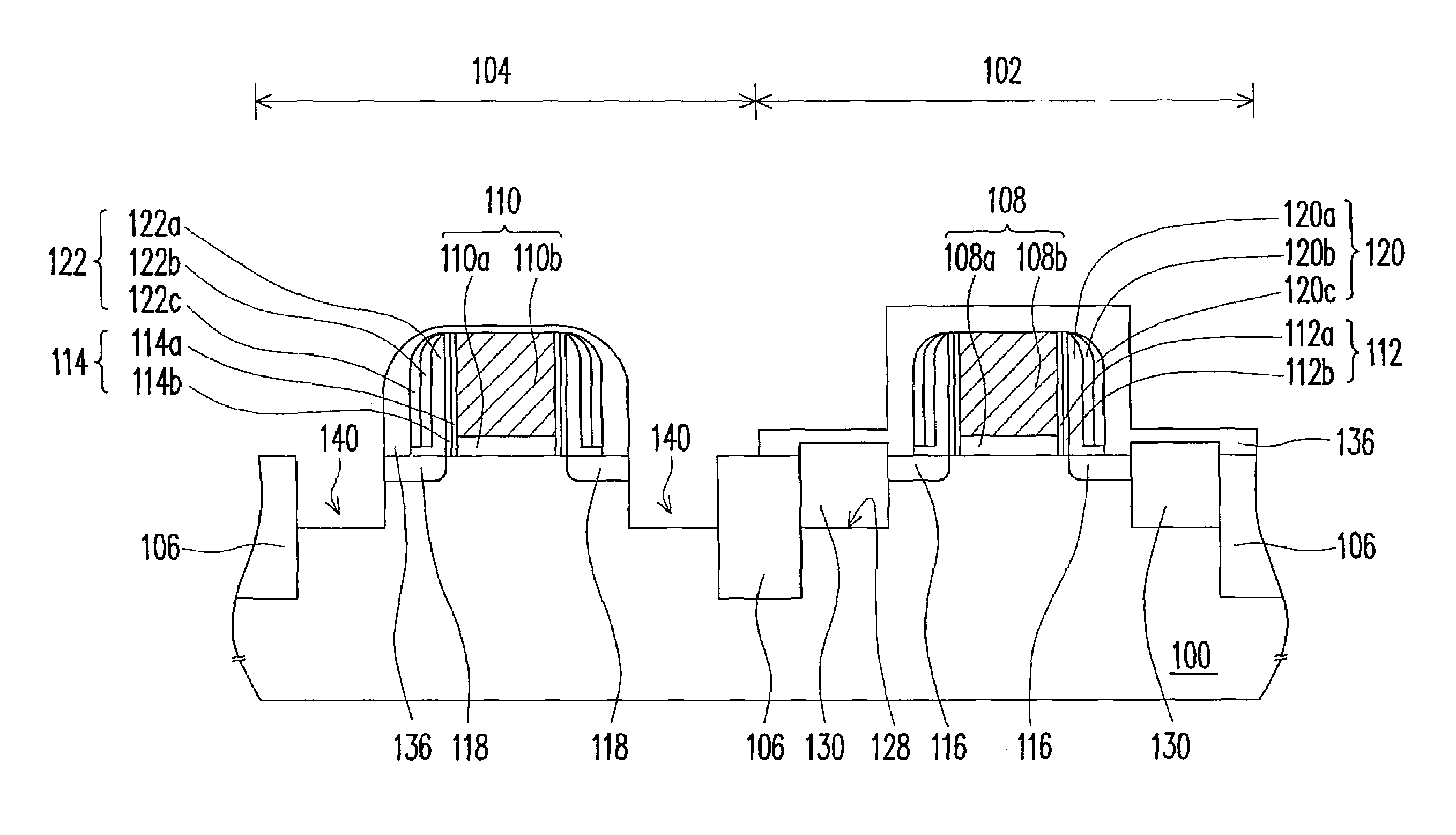

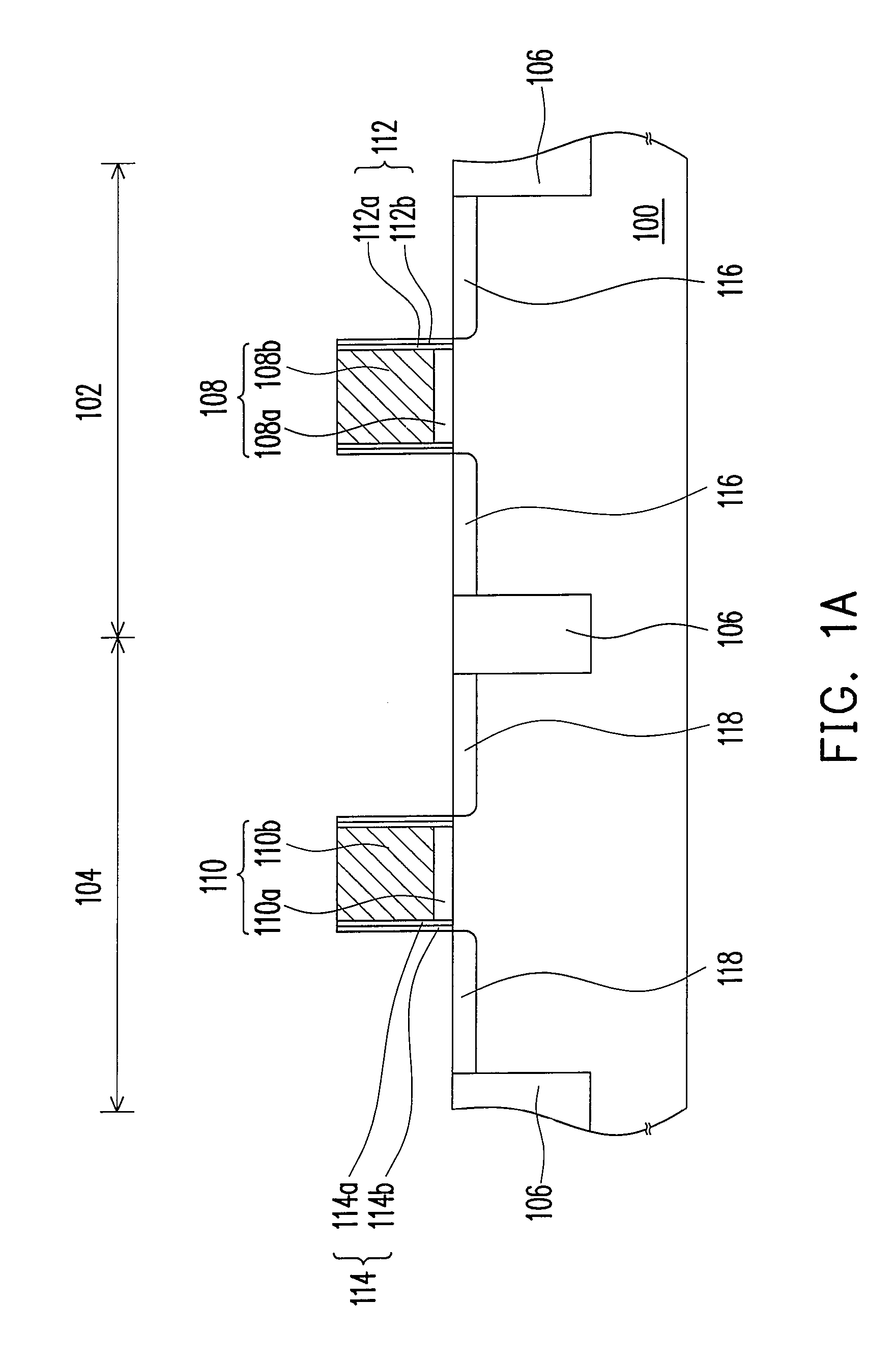

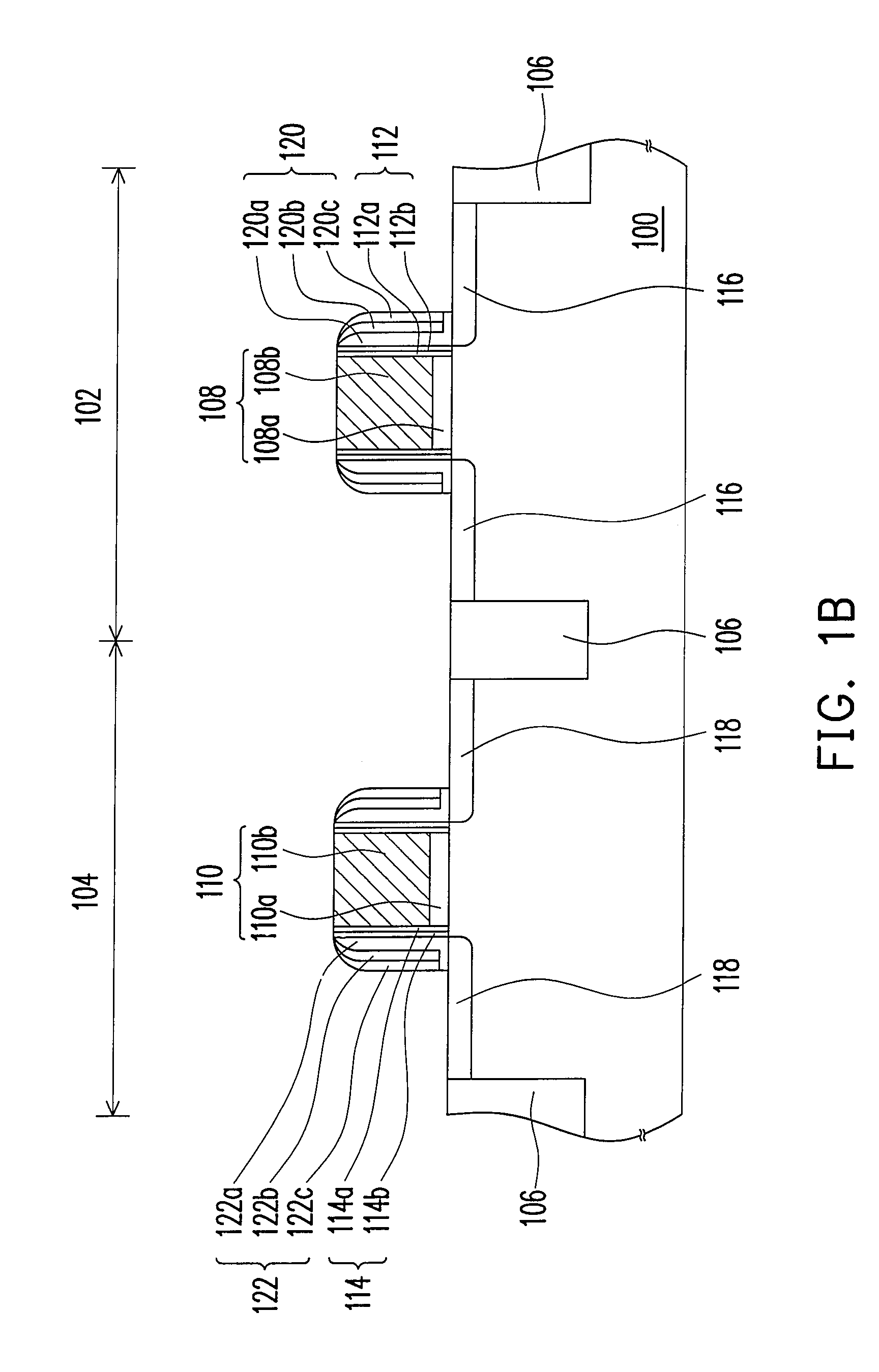

Complementary metal-oxide-semiconductor device and fabricating method thereof

ActiveUS20080061366A1Improve performanceReliability be promotedTransistorSemiconductor/solid-state device manufacturingCMOSEpitaxial material

A complementary metal-oxide-semiconductor (CMOS) device includes a substrate with a first active region and a second active region; a first gate structure and a second gate structure, respectively disposed on the first active region and the second active region; a first spacer structure and a second spacer structure respectively disposed on sidewalls of the first gate structure and the second gate structure; a first LDD and a second LDD respectively disposed in the substrate at both sides of the first gate structure and the second gate structure; an epitaxial material layer, disposed in the first active region and located on a side of the first LDD; and a passivation layer, disposed on the first gate structure, the first spacer structure, and the first LDD and covering the second active region, wherein the passivation layer comprises a carbon-containing oxynitride layer.

Owner:UNITED MICROELECTRONICS CORP

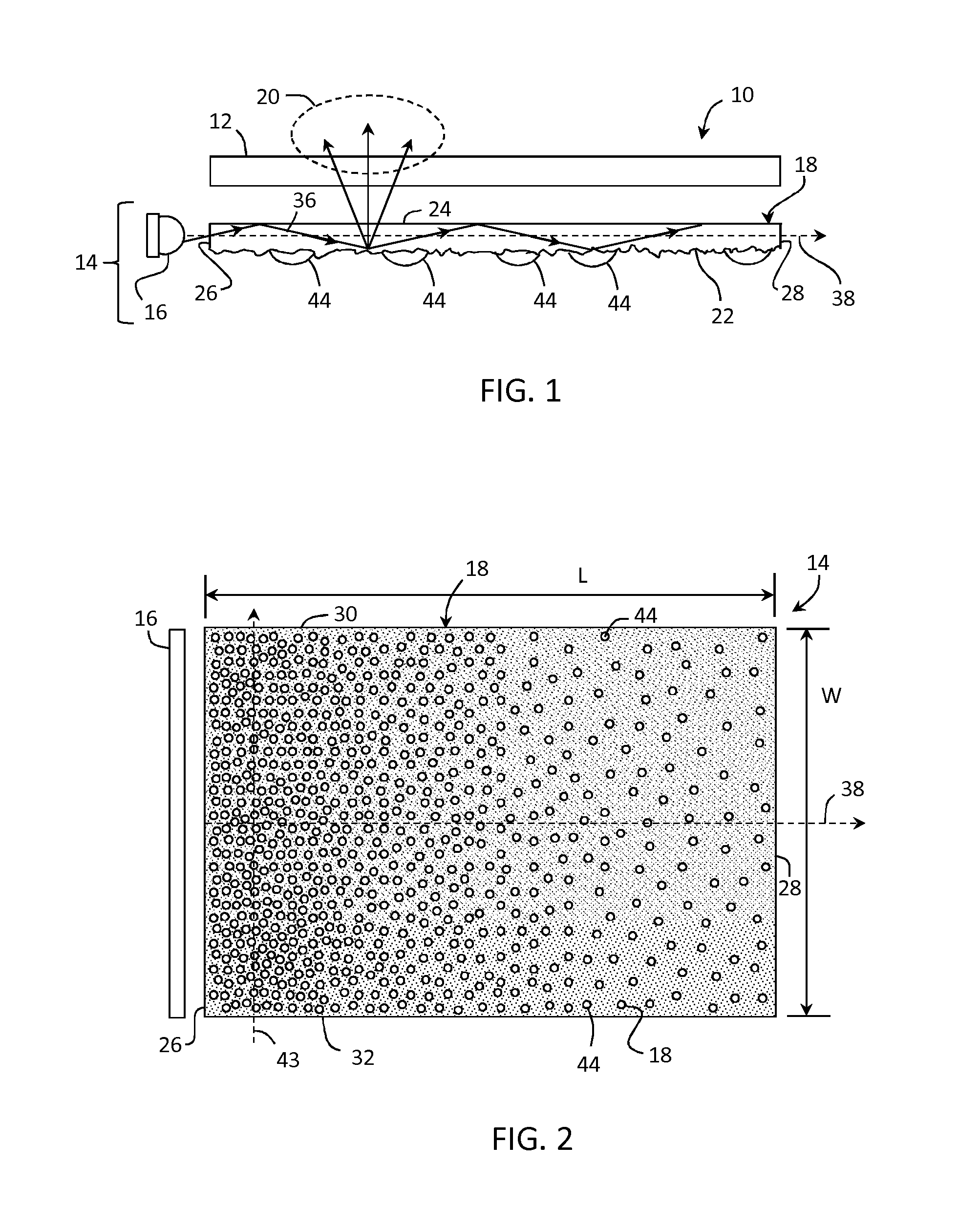

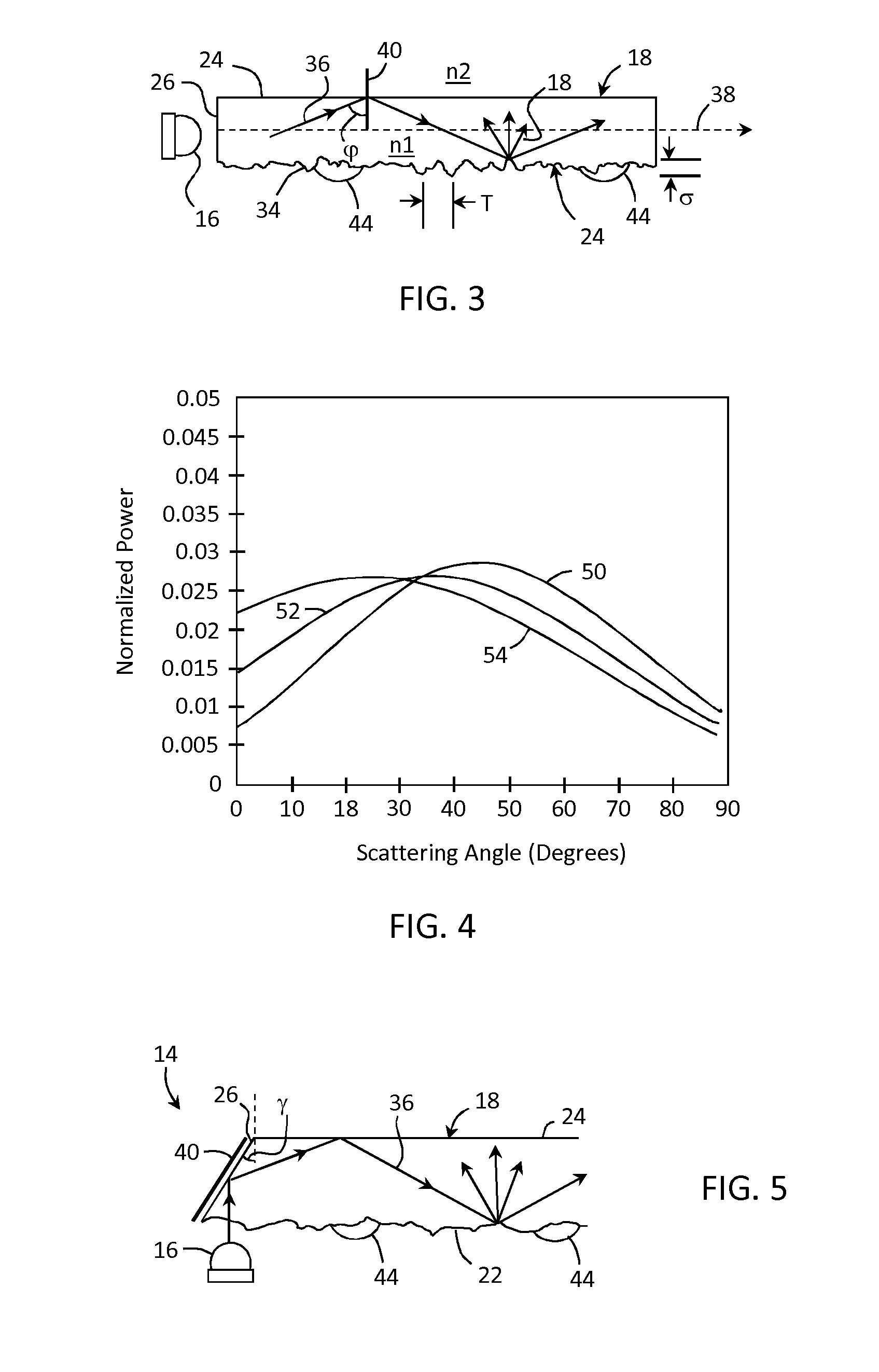

Textured surfaces for display applications

ActiveUS20160313494A1Provide protectionHigh light transmittanceMechanical apparatusDiffusing elementsLight guideDisplay device

A substrate with a textured surface is disclosed. The substrate may be, for example, a light emitter comprising a light guide, for example a backlight element for use in a display device, wherein a surface of the light guide, for example a glass substrate, is configured to have a textured surface with a predetermined RMS roughness and a predetermined correlation length of the texture. A plurality of light scatter supressing features can be provided on the textured surface. Textured surfaces disclosed herein may be effective to reduce electrostatic charging of the substrate surface. Methods of producing the textured surface are also disclosed.

Owner:CORNING INC

Process for manufacturing electro-mechanical systems

ActiveUS9139425B2Minimizing and eliminating effectReduce fluxTransducer detailsDecorative surface effectsEngineeringStiction

A method of avoiding stiction during vapor hydrofluoride (VHF) release of a microelectromechanical system (MEMS) or nanoelectromechanical system (NEMS) composed of a mechanical device and a substrate is described. A silicon nitride layer is provided between the substrate and a sacrificial oxide layer and / or between a device layer and the sacrificial oxide layer, and / or on a side of the device layer facing away from the sacrificial oxide layer, and converted to thicker ammonium hexafluorosilicate with VHF while simultaneously removing a portion of the sacrificial oxide. The ammonium hexafluorosilicate acts as a temporary support, shim, wedge, or tether which limits device movement during fabrication and is later removed by sublimation under heat and / or reduced pressure.

Owner:SPTS TECH LTD

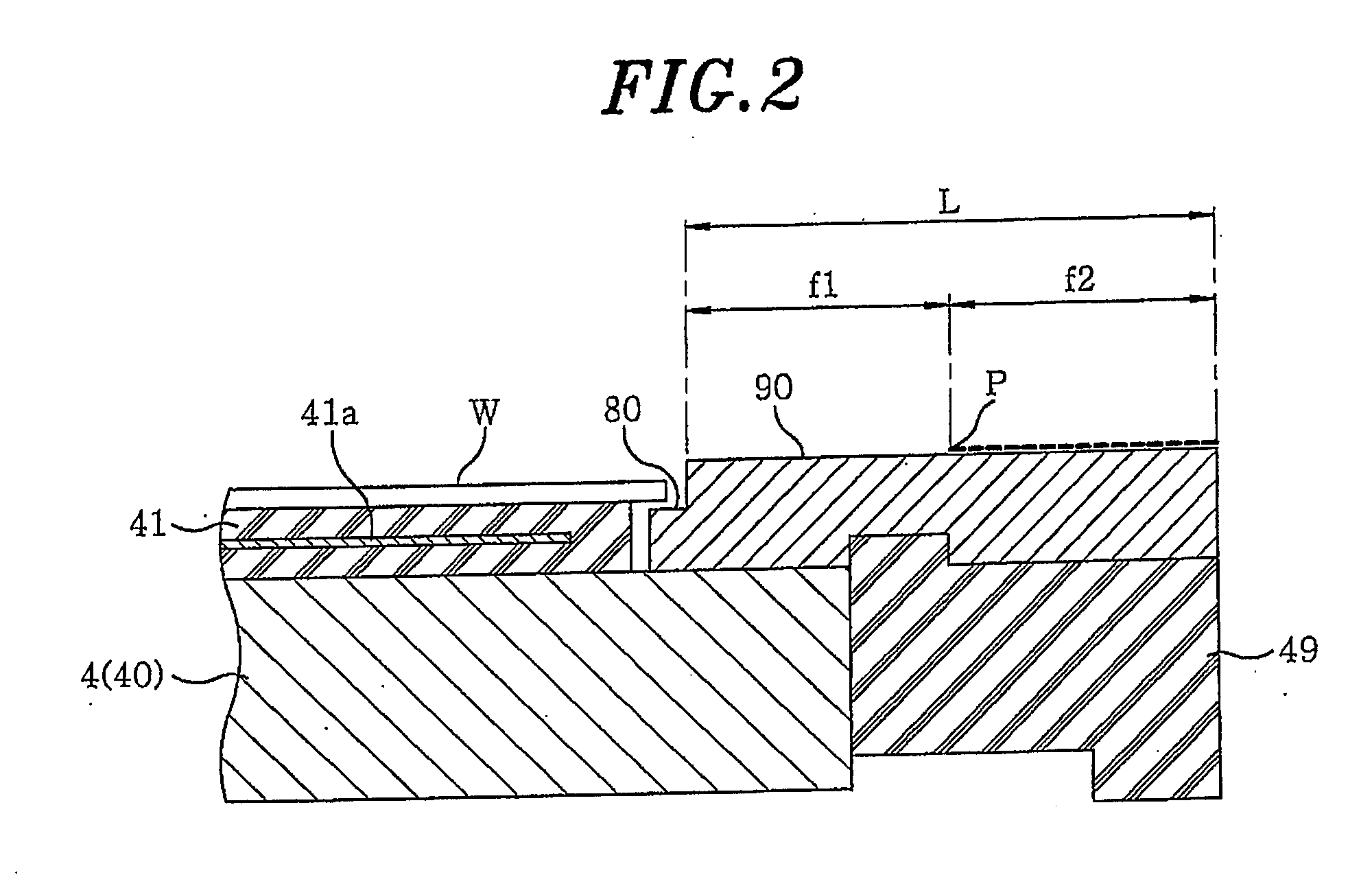

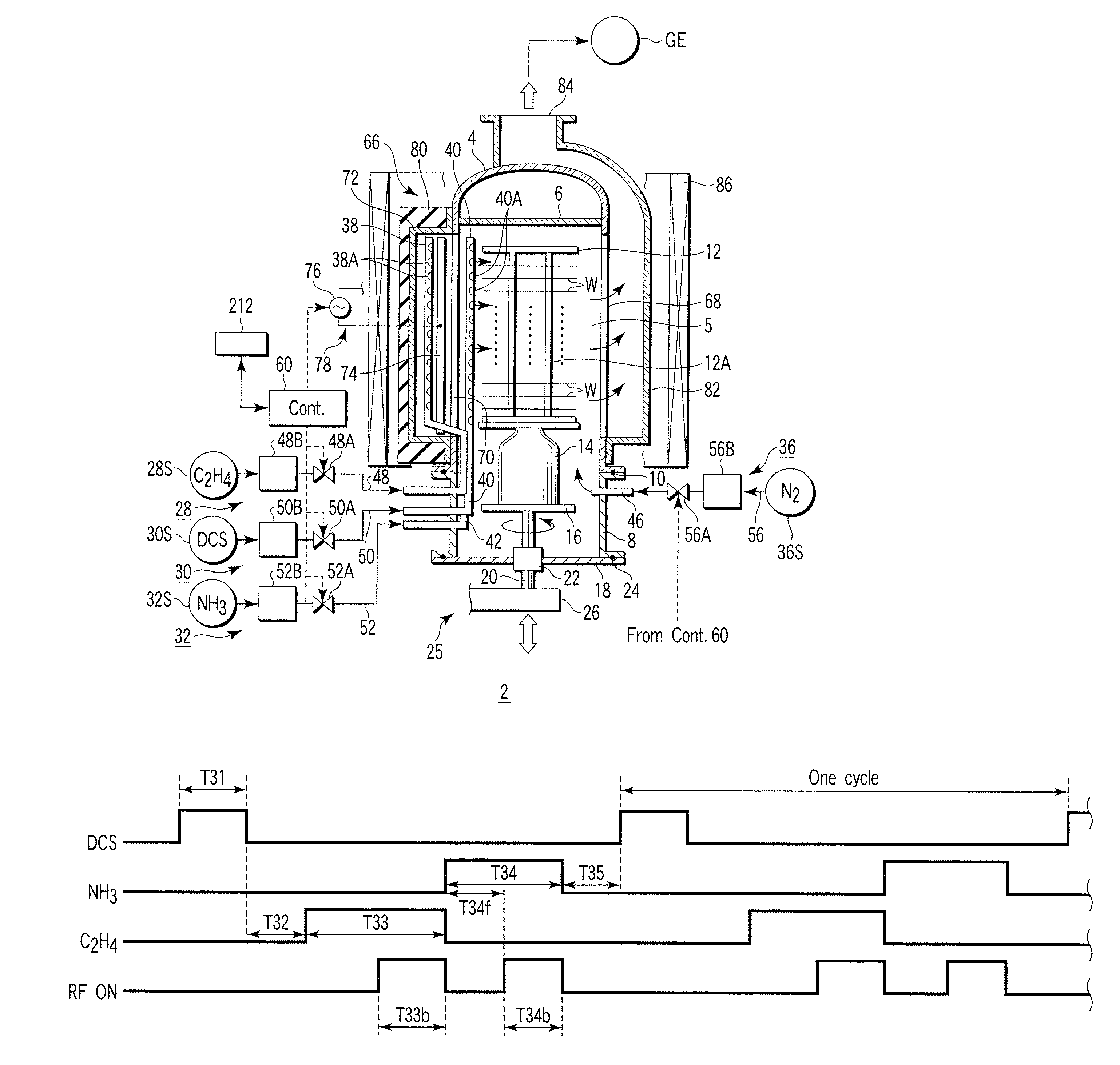

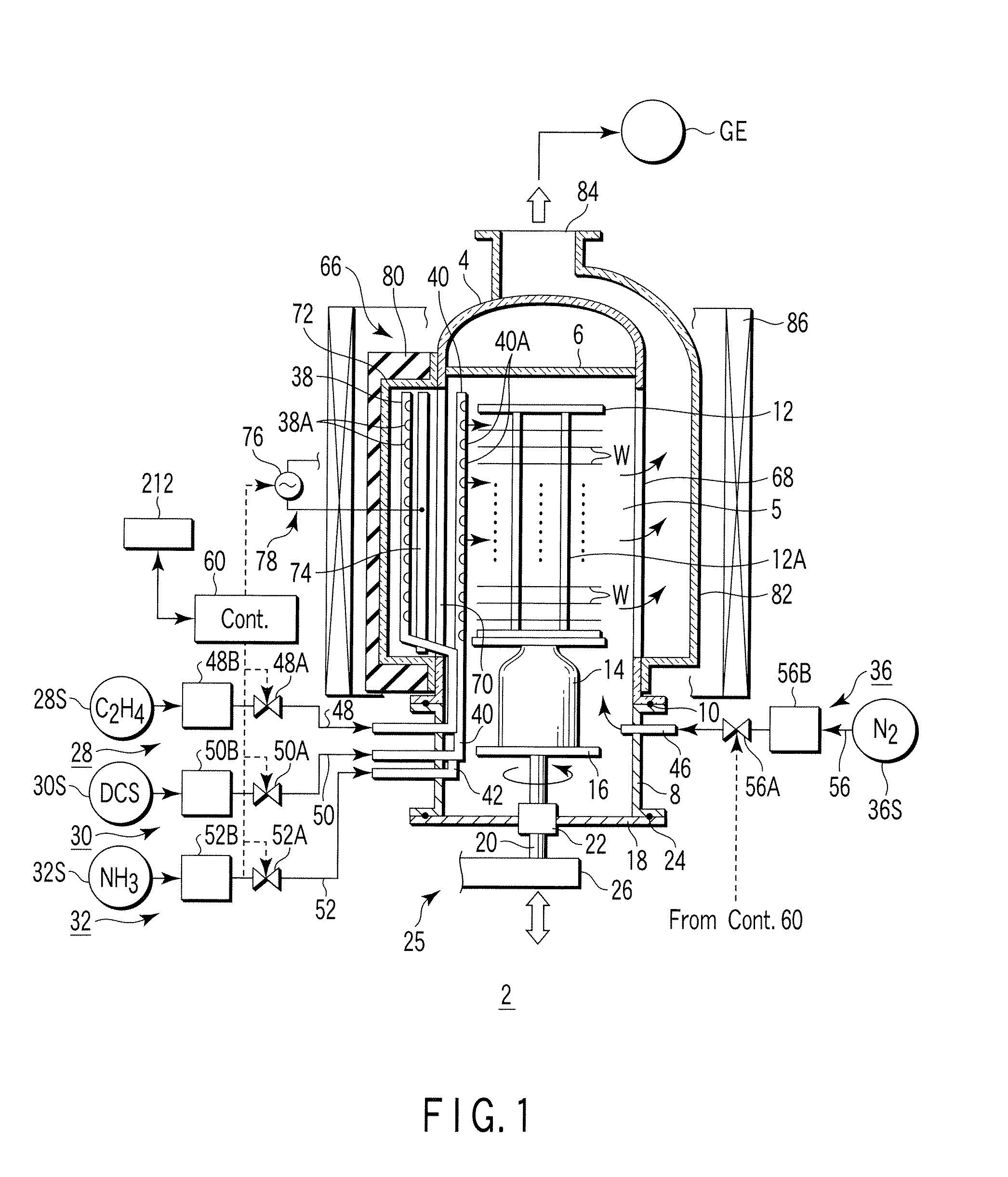

Film formation method and apparatus for semiconductor process

InactiveUS7507676B2Low process temperatureImprove controllabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingSilanesProcess region

An insulating film is formed on a target substrate by CVD, in a process field to be selectively supplied with a first process gas containing a silane family gas, a second process gas containing a nitriding gas, and a third process gas containing a carbon hydride gas. This method includes repeatedly performing supply of the first process gas to the process field, supply of the second process gas to the process field, and supply of the third process gas to the process field. The supply of the third process gas includes an excitation period of supplying the third process gas to the process field while exciting the third process gas by an exciting mechanism.

Owner:TOKYO ELECTRON LTD

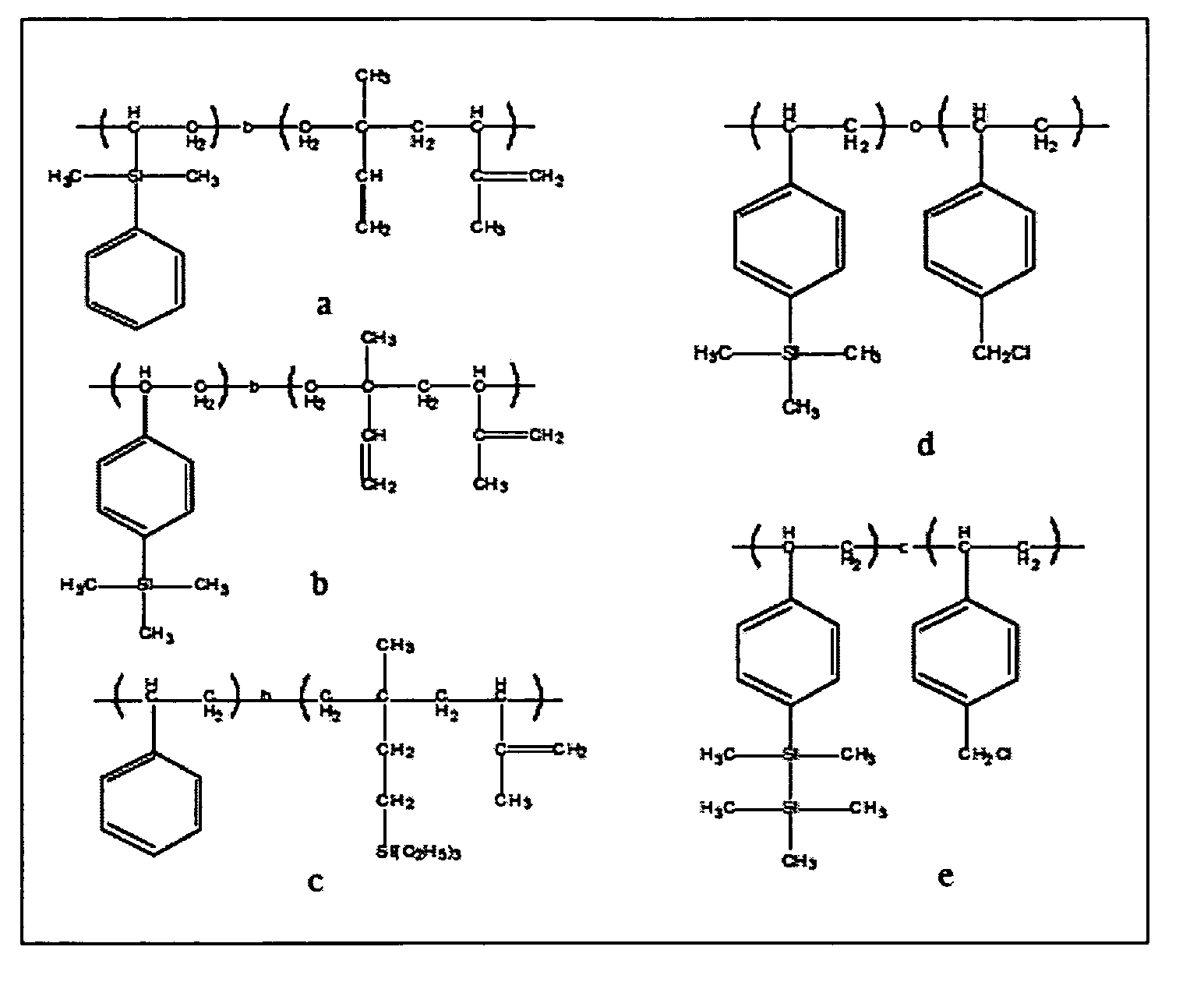

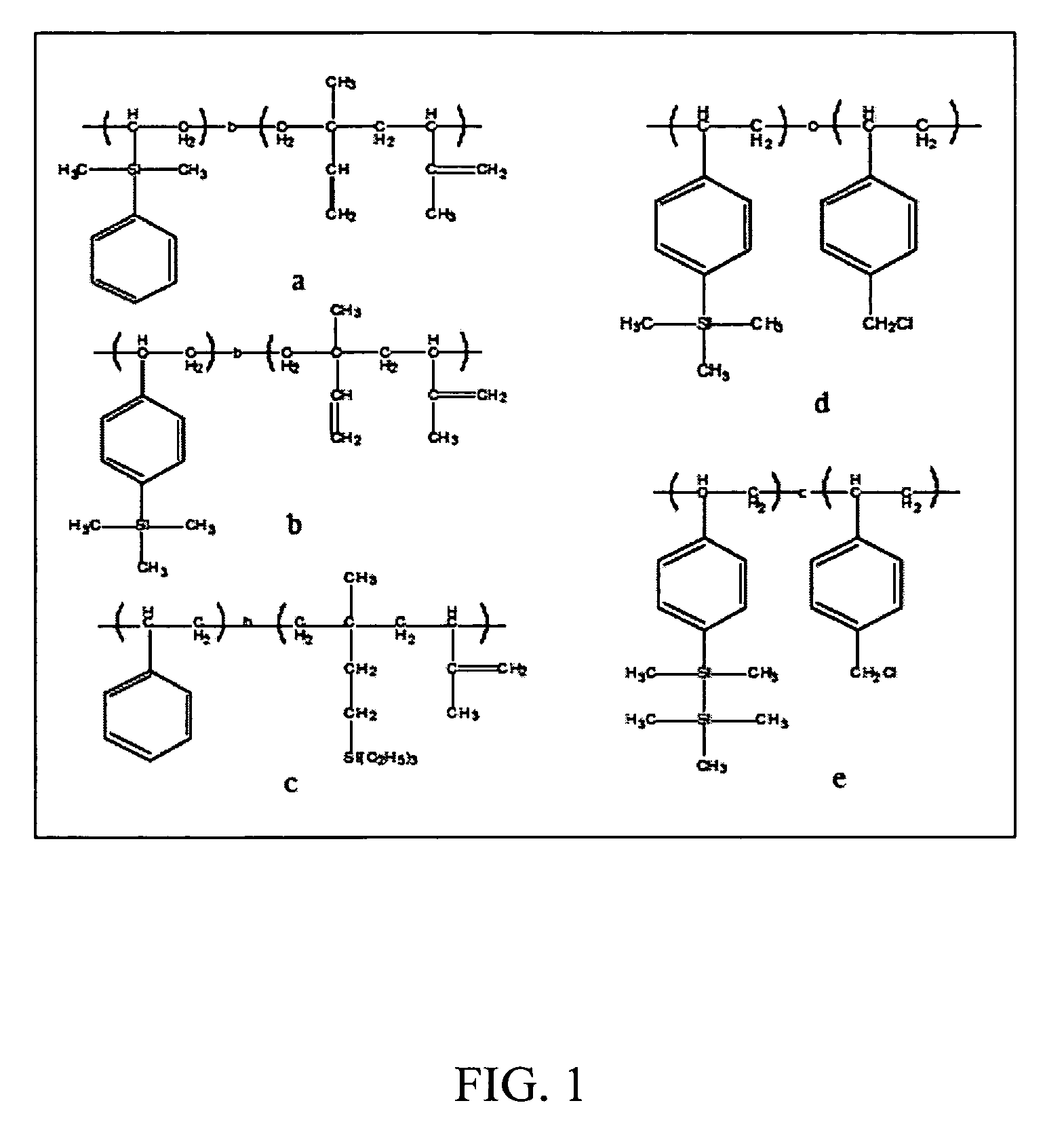

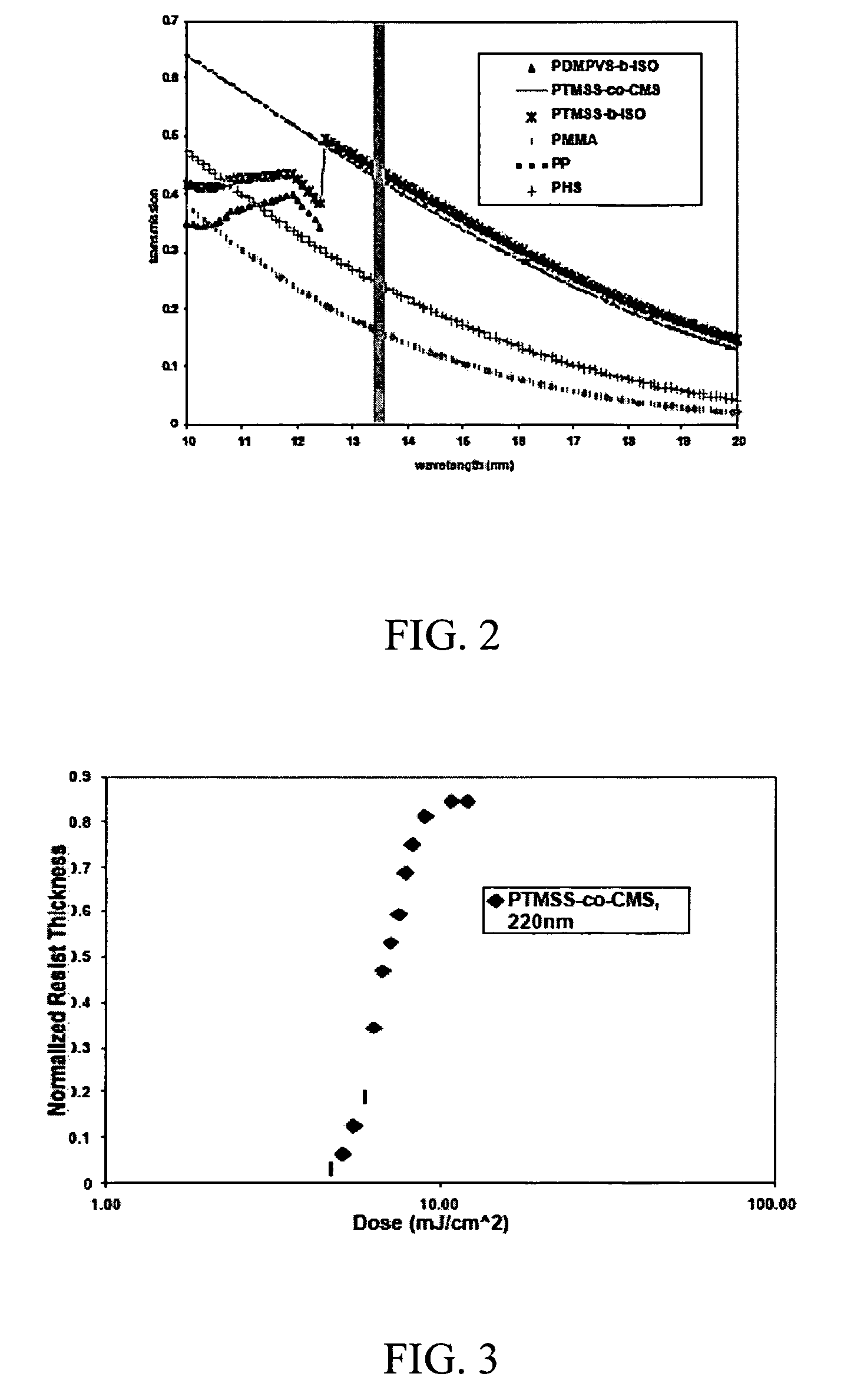

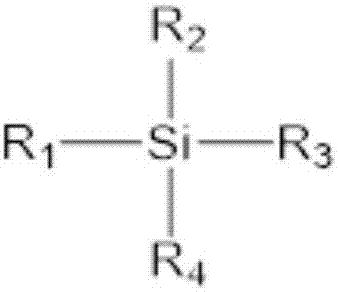

Organoelement resists for EUV lithography and methods of making the same

ActiveUS7326514B2Simple methodReduce etch ratePhotosensitive materialsRadiation applicationsLithography processUltraviolet

Resist compositions containing silicon, boron, or both silicon and boron may be used with ultra-violet lithography processes and extreme ultra-violet (EUV) lithography processes to increase the reactive ion etch resistance of the resist compositions, improve transmission of the resist materials, and to dope substrates.

Owner:WISCONSIN MADISON UNIV OF +2

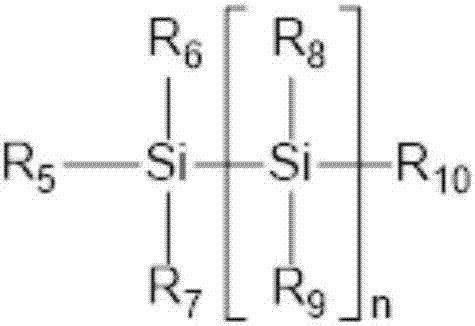

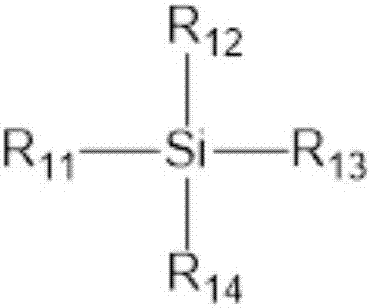

Silicon nitride film etching solution

InactiveCN107573940AReduce or suppress the production ofImprove the selection ratioSurface treatment compositionsSilane compoundsSilicone oil

The invention relates to a silicon nitride film etching solution, comprising first silicone compound, whose silicone atom is dependently combined with over three hydrophilic functional groups, and second silicone compound, whose silicone atom is dependently combined with one or two hydrophilic functional groups.

Owner:OCI

Complementary metal-oxide-semiconductor device

InactiveUS20080116525A1Improve device performanceReliability performance be promotedTransistorSemiconductor/solid-state device manufacturingCMOSEpitaxial material

A complementary metal-oxide-semiconductor (CMOS) device includes a substrate with a first active region and a second active region; a first gate structure and a second gate structure, respectively disposed on the first active region and the second active region; a first spacer structure and a second spacer structure respectively disposed on sidewalls of the first gate structure and the second gate structure; a first LDD and a second LDD respectively disposed in the substrate at both sides of the first gate structure and the second gate structure; an epitaxial material layer, disposed in the first active region and located on a side of the first LDD; and a passivation layer, disposed on the first gate structure, the first spacer structure, and the first LDD and covering the second active region, wherein the passivation layer comprises a carbon-containing oxynitride layer.

Owner:UNITED MICROELECTRONICS CORP

Selective etching processes of silicon nitride and indium oxide thin films for FeRAM device applications

InactiveUS20060073706A1Minimize overetched damagePrevent degradationTransistorDecorative surface effectsOxidizing agentSemiconductor

A dry etch process is described for selectively etching silicon nitride from conductive oxide material for use in a semiconductor fabrication process. Adding an oxidant in the etch gas mixture could increase the etch rate for the silicon nitride while reducing the etch rate for the conductive oxide, resulting in improving etch selectivity. The disclosed selective etch process is well suited for ferroelectric memory device fabrication using conductive oxide / ferroelectric interface having silicon nitride as the encapsulated material for the ferroelectric.

Owner:SHARP KK

Method to eliminate striations and surface roughness caused by dry etch

InactiveUS7153779B2Reduce resist etch rateAvoid erosionDecorative surface effectsSemiconductor/solid-state device manufacturingMetallurgyNitrogen

A plasma etch process for forming a high aspect ratio contact opening through a silicon oxide layer is disclosed. The silicon oxide layer is plasma etched using etch gases that include at least one organic fluorocarbon gas. At least one etch gas is used that includes one or more nitrogen-comprising gases to deposit a surface polymeric material during the etching for maintaining a masking layer over the silicon oxide layer. The method of the invention achieves a complete and anistropic etching of a contact opening having a high aspect ratio and the desired dimensions.

Owner:MICRON TECH INC

Method for manufacturing electonic device

InactiveUS20060094234A1Well formedSimple structureSemiconductor/solid-state device manufacturingResistEngineering

A method for manufacturing an electronic device, in which a via hole and a trench for an interconnect are integrally provided in an interlayer insulating film formed on a substrate, and the via hole and the trench for the interconnect are plugged with an electric conductor film is provided. The method includes: forming a via hole in the interlayer insulating film; forming a resin film, plugging the via hole, on the interlayer insulating film; forming a resist mask having an opening for an interconnect on the interlayer insulating film; and etching the interlayer insulating film through an etching mask of the resist mask to form a trench for the interconnect connected with the via hole. The resin film is being capable of trapping a basic substance.

Owner:RENESAS ELECTRONICS CORP

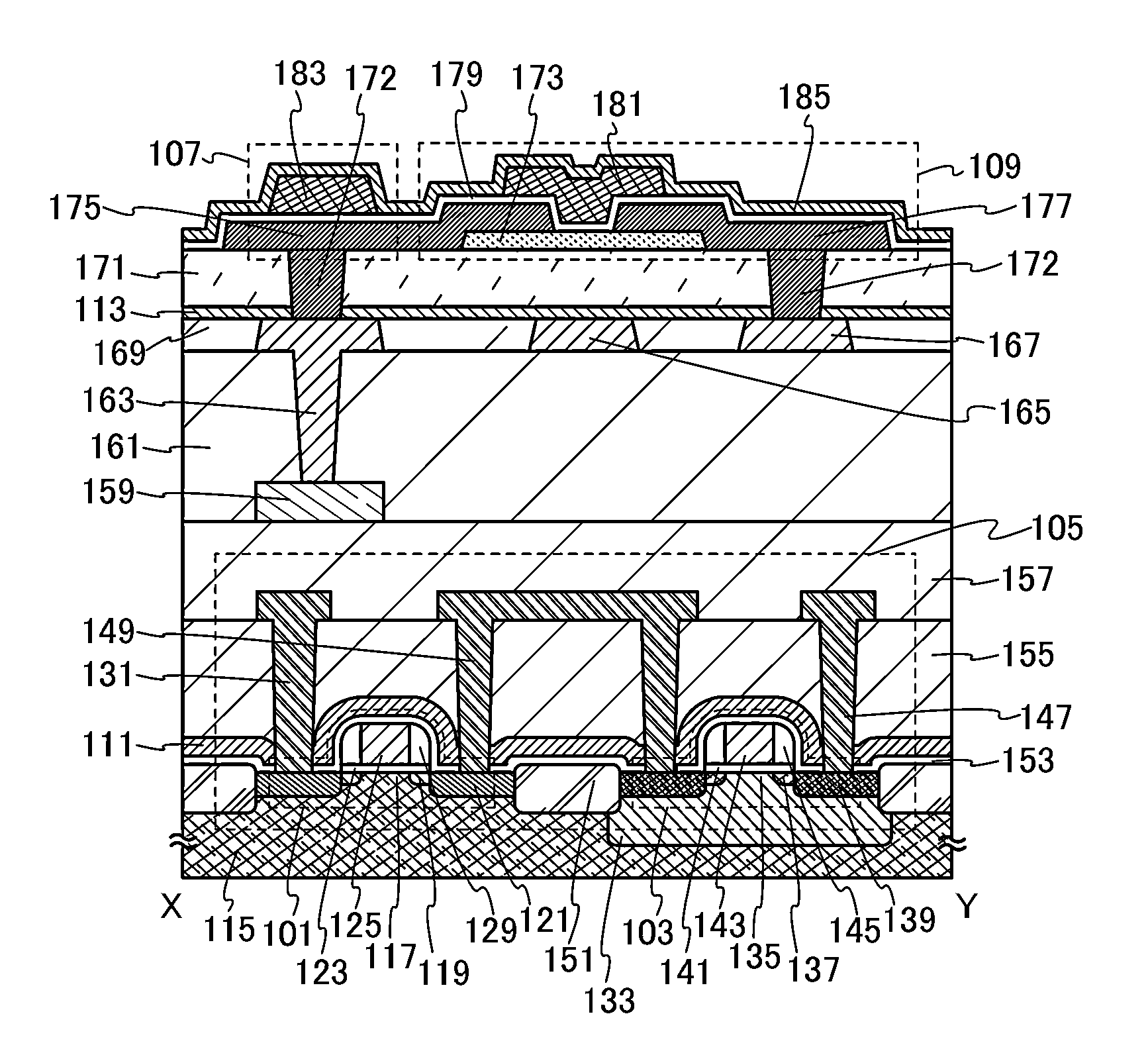

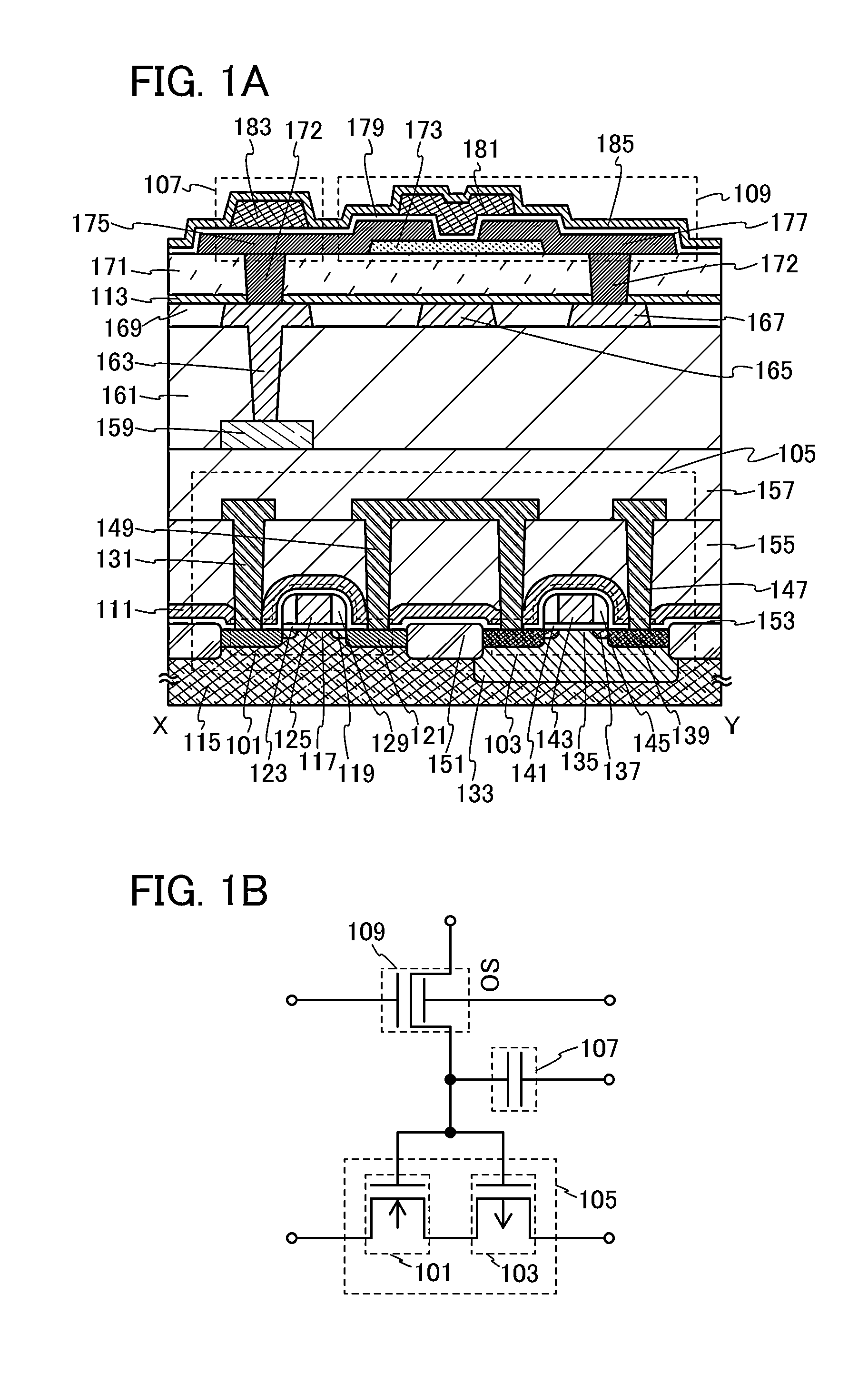

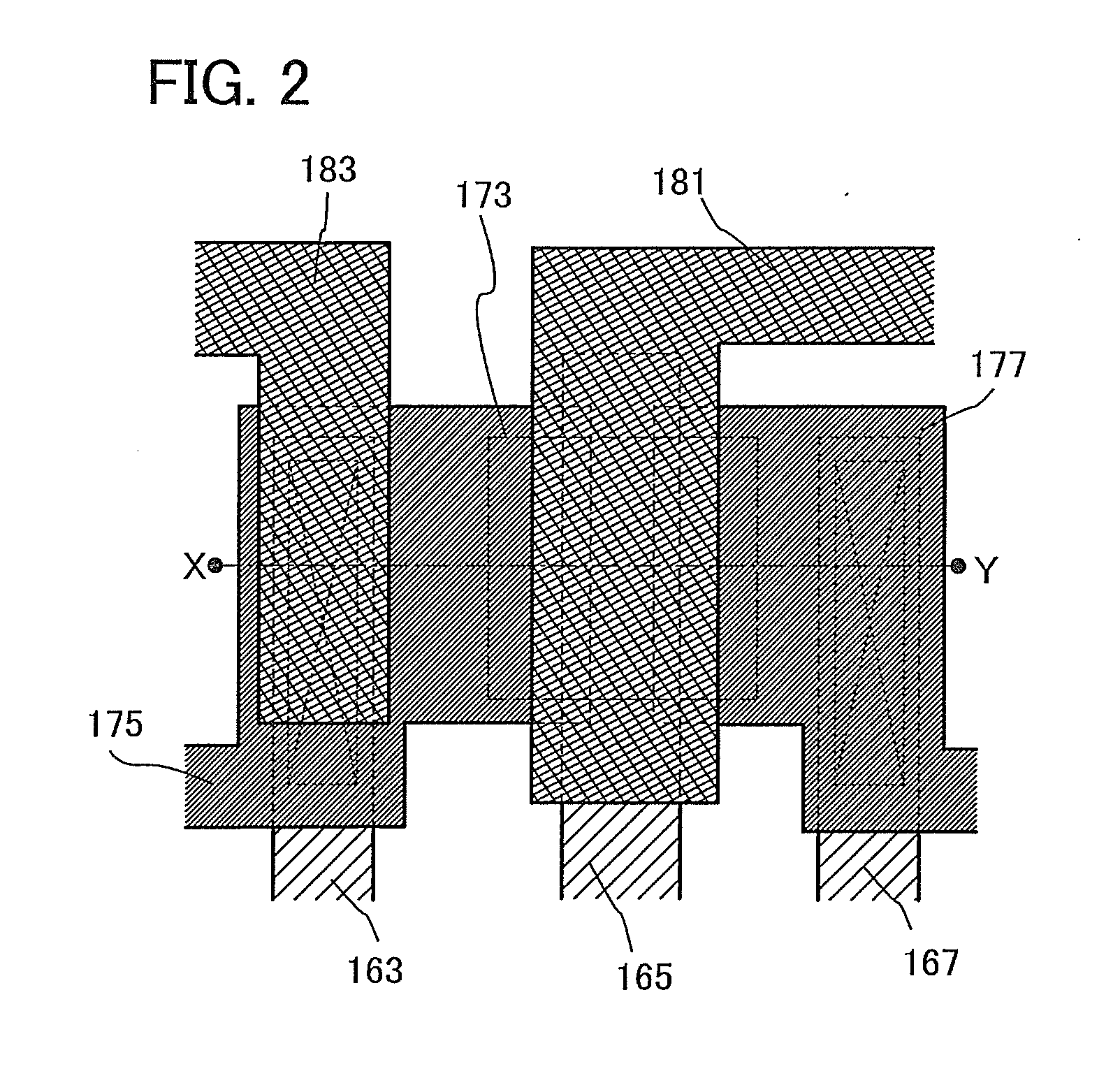

Semiconductor device

ActiveUS20140027764A1High refractive indexReduce etch rateTransistorSolid-state devicesPower semiconductor deviceHydrogen content

A nitride insulating film which prevents diffusion of hydrogen into an oxide semiconductor film in a transistor including an oxide semiconductor is provided. Further, a semiconductor device which has favorable electrical characteristics by using a transistor including a silicon semiconductor and a transistor including an oxide semiconductor is provided. Two nitride insulating films having different functions are provided between the transistor including a silicon semiconductor and the transistor including an oxide semiconductor. Specifically, a first nitride insulating film which contains hydrogen is provided over the transistor including a silicon semiconductor, and a second nitride insulating film which has a lower hydrogen content than the first nitride insulating film and functions as a barrier film against hydrogen is provided between the first nitride insulating film and the transistor including an oxide semiconductor.

Owner:SEMICON ENERGY LAB CO LTD

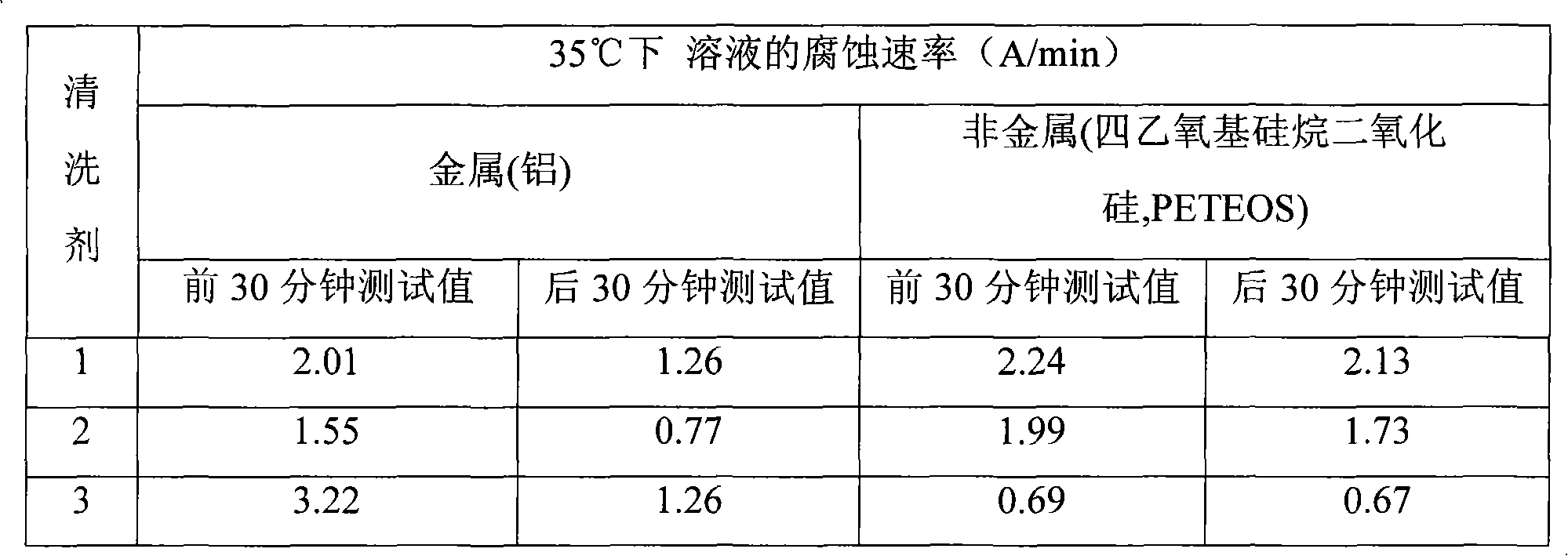

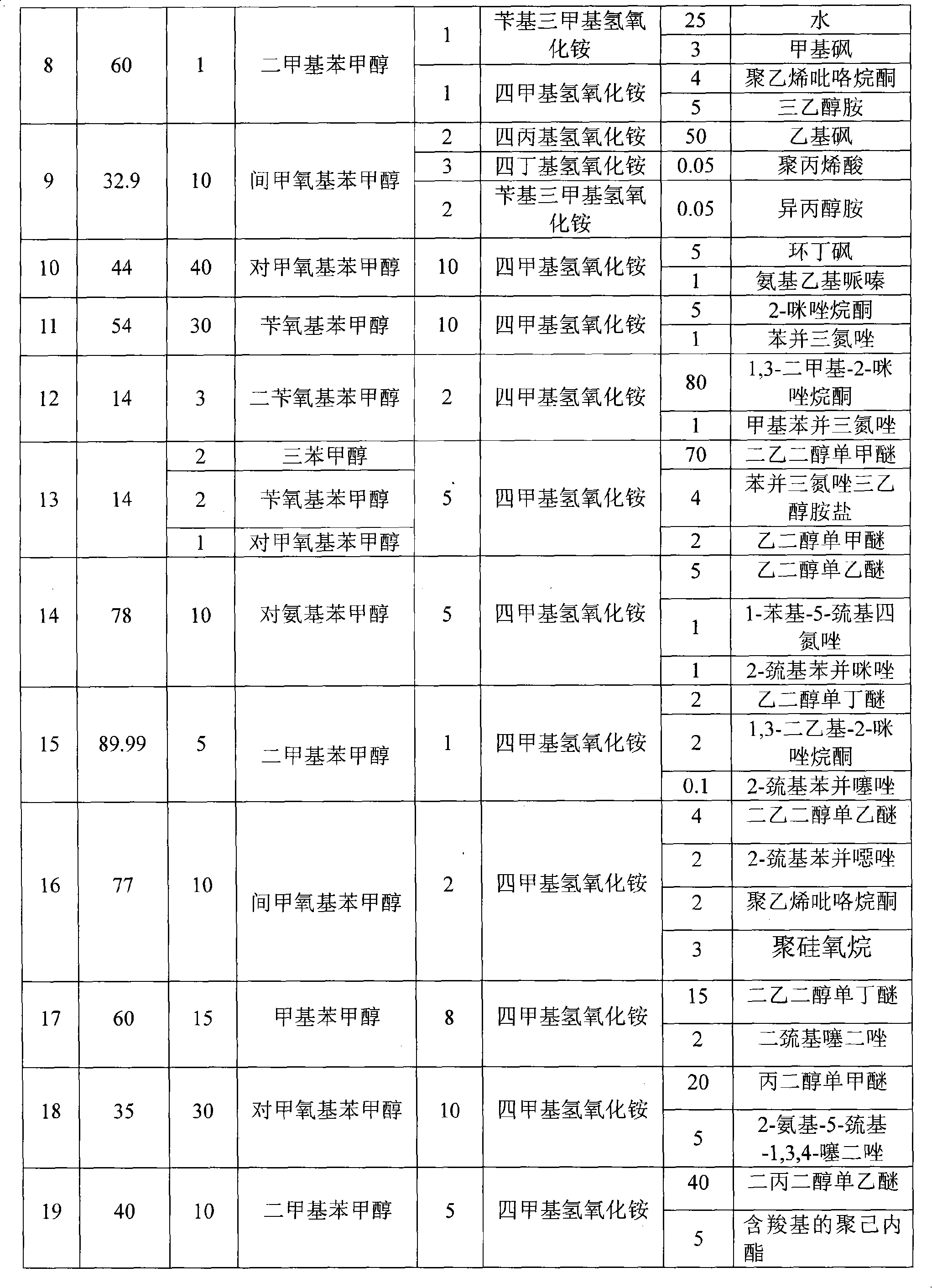

Cleaning fluid for cleaning plasma etching residue

InactiveCN101290482AImprove cleaning efficiencyEfficient and stable cleaning effectNon-surface-active detergent compositionsDetergent mixture composition preparationSilanesSolvent

The invention discloses washing liquid used in the semiconductor industry to wash plasma etching residues. The washing liquid contains citric acid / citrate buffer solution, fluorides, macromoledular corrosion inhibitor, anti-freeze agent and solvent. The washing liquid can effectively wash the plasma etching residues during the process of manufacturing a semiconductor, have low etching velocity on nonmetals and metal substrates such as Si, SiO2, tetraethoxy silane silicon dioxides (PETEOS), low-medium materials, Ti, Al, Cu and so on, is safe and harmless to the environment and the human body, and has good application prospect in the microelectronic field such as washing of semiconductor wafers and so on.

Owner:ANJI MICROELECTRONICS (SHANGHAI) CO LTD

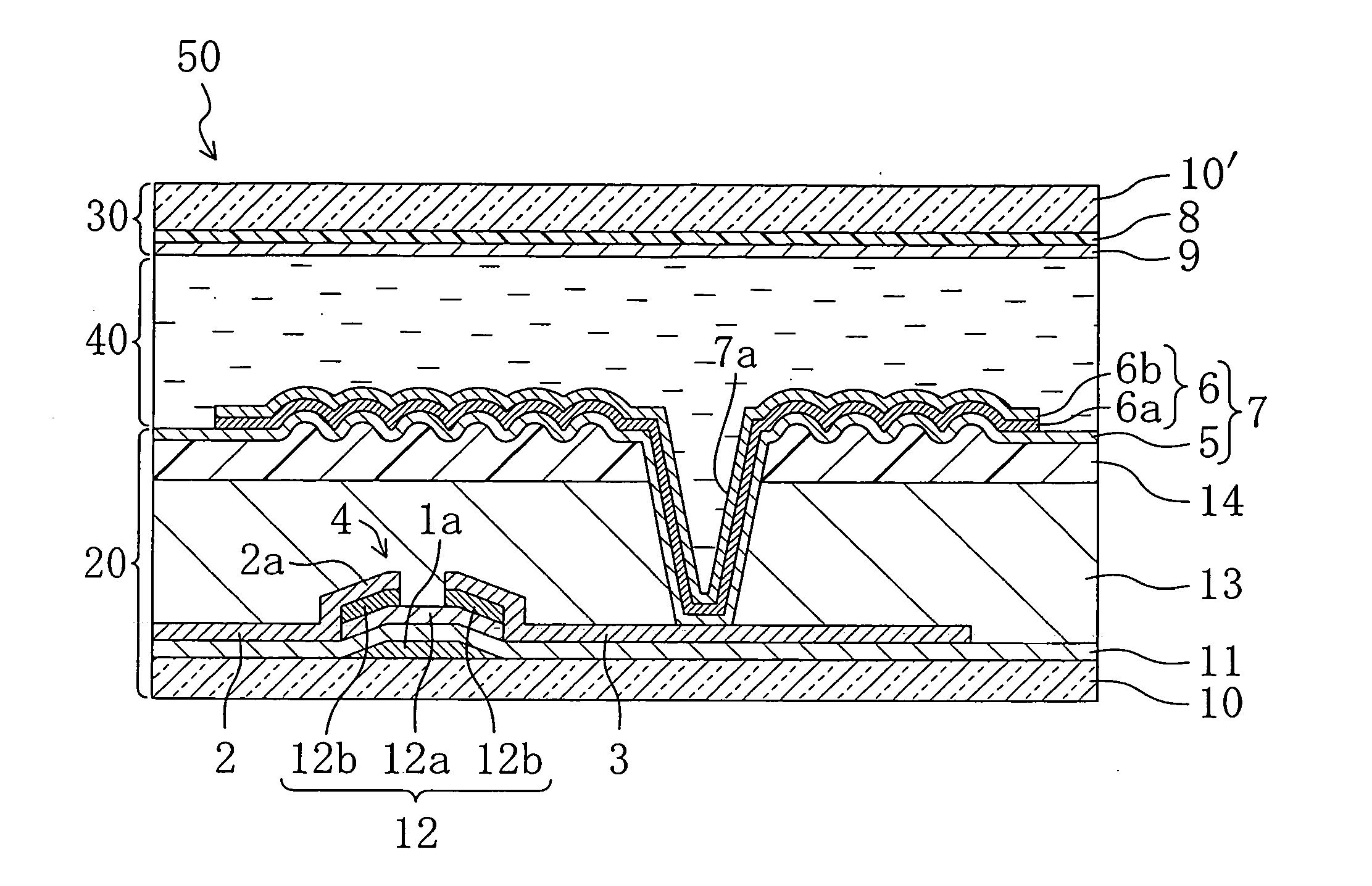

Method for manufacturing conductive element substrate, conductive element substrate, method for manufacturing liquid crystal display, liquid crystal display and electronic information equipment

InactiveUS20050186359A1High film strengthReduce etch rateLiquid crystal compositionsAdjusting/maintaining mechanical tensionLiquid-crystal displayActive matrix

A method for manufacturing a liquid crystal display which employs an active matrix substrate including a plurality of pixels arranged in matrix on a substrate and reflecting electrodes formed in the pixels, respectively. The method comprises (a) a laminated conductive film formation step of sequentially forming a conductive metal film and an amorphous transparent conductive film on a substrate to form a laminated conductive film and (b) a reflecting electrode formation step of patterning the laminated conductive film into a reflecting electrode, wherein the step (b) includes a first etching step of etching the conductive metal film and the amorphous transparent conductive film simultaneously and a second etching step of etching the amorphous transparent conductive film only.

Owner:SHARP KK

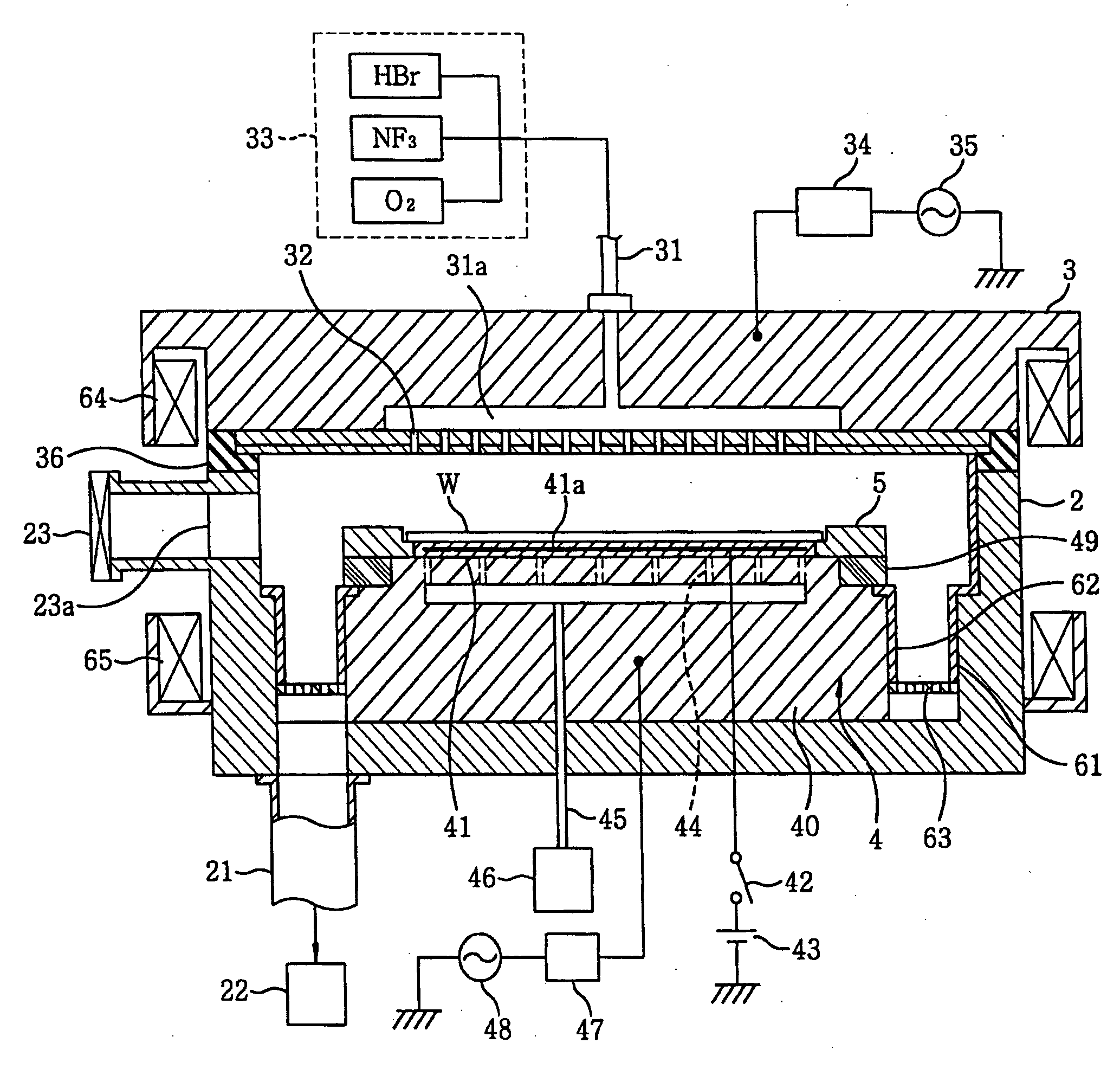

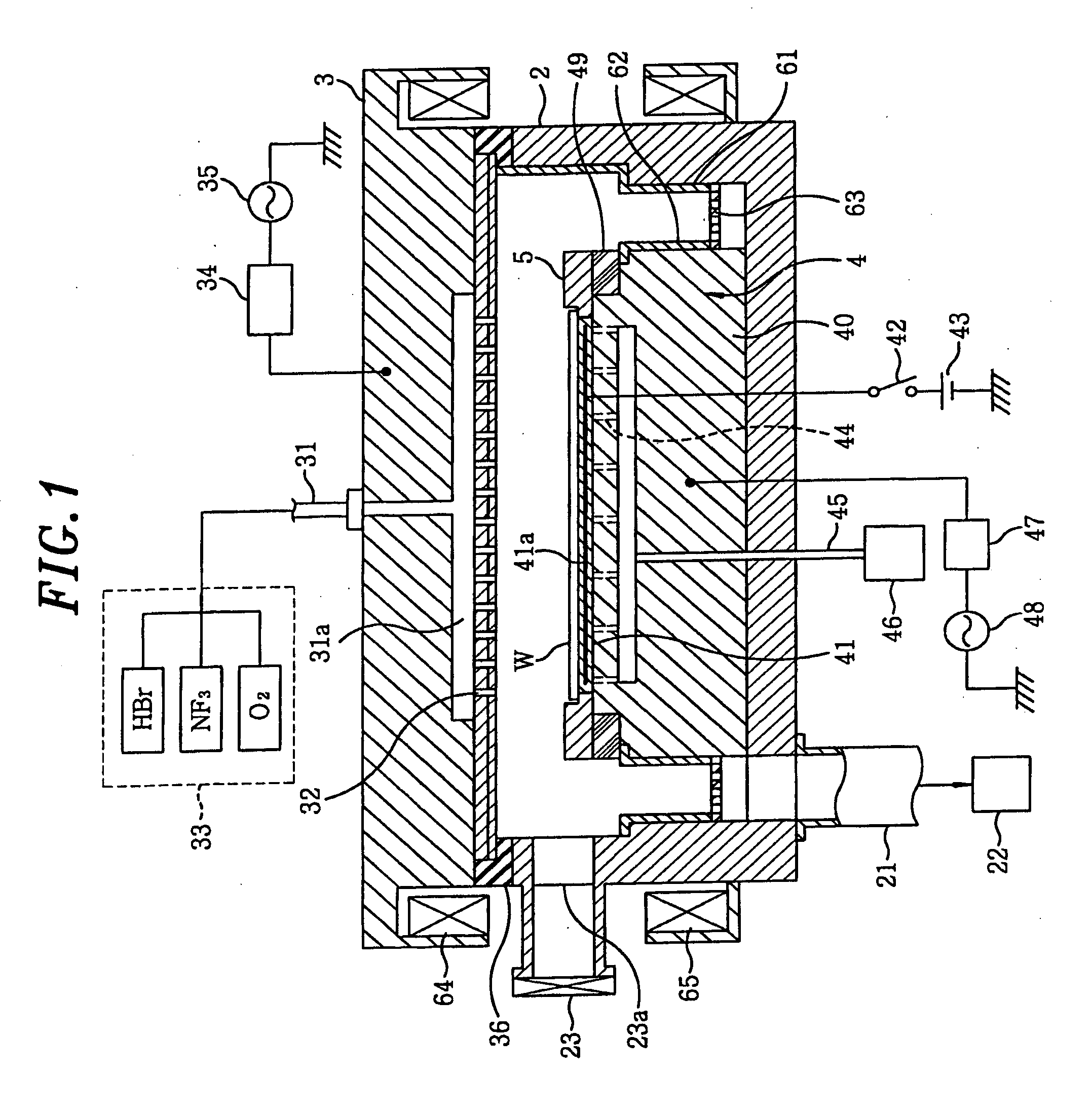

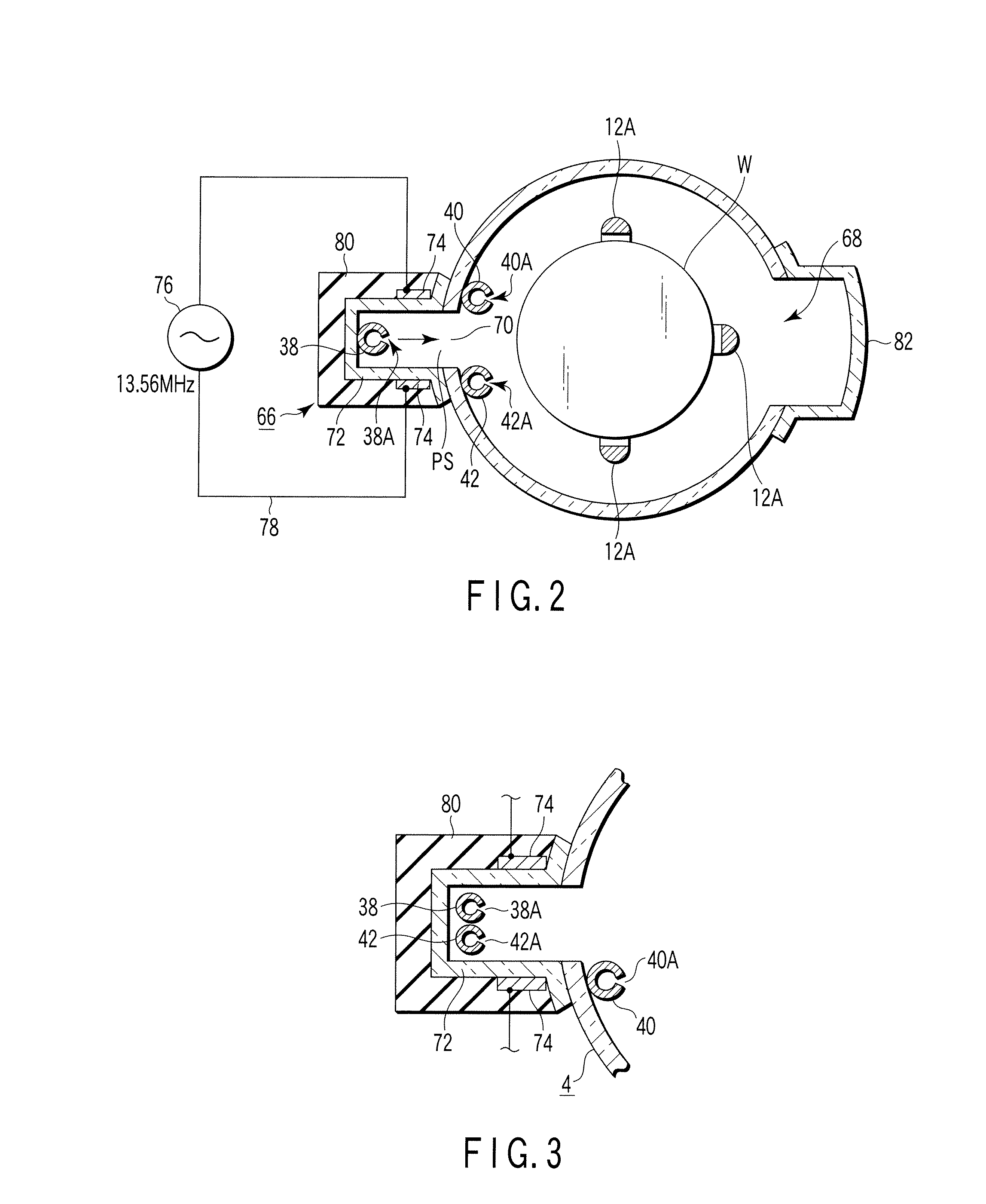

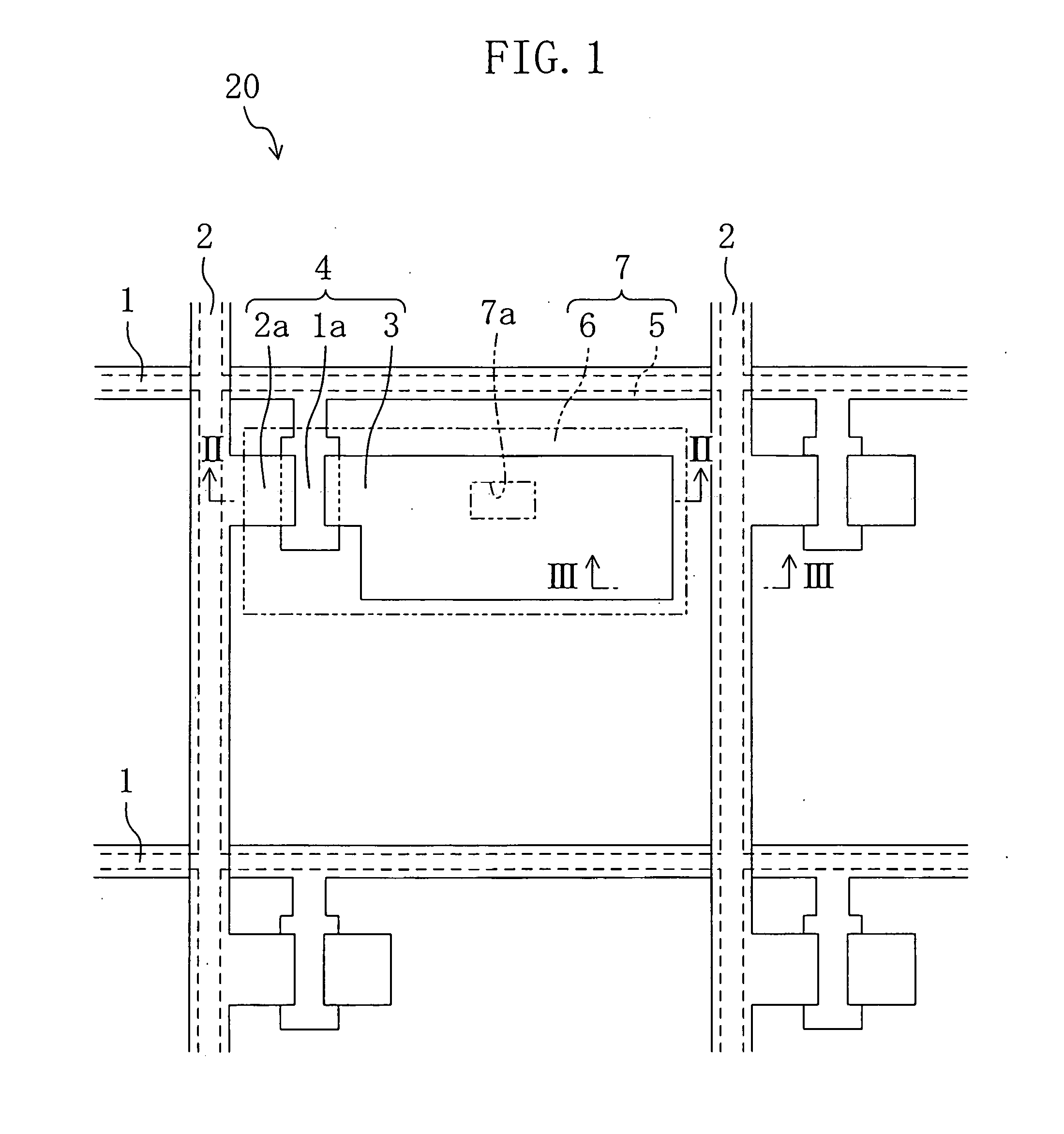

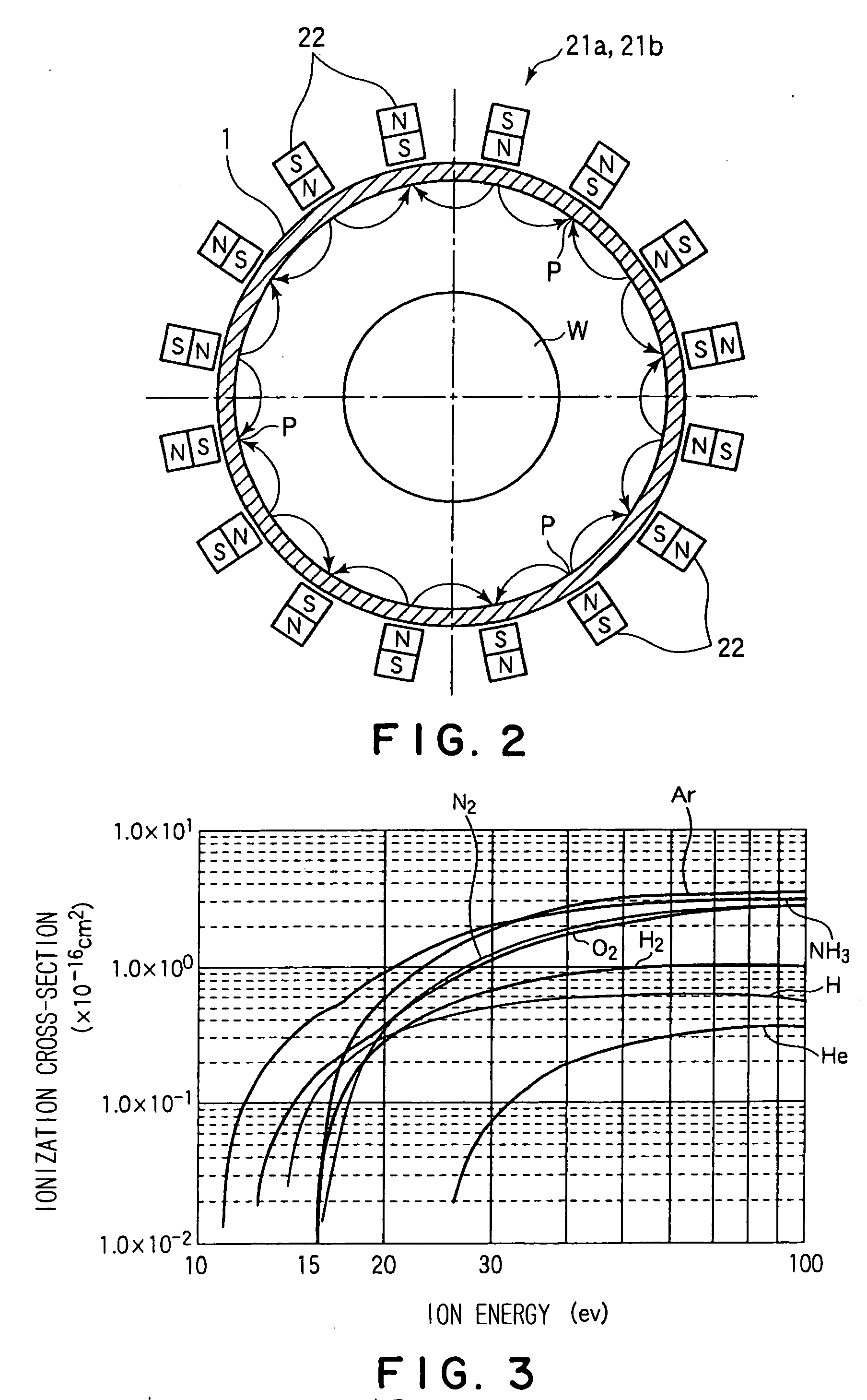

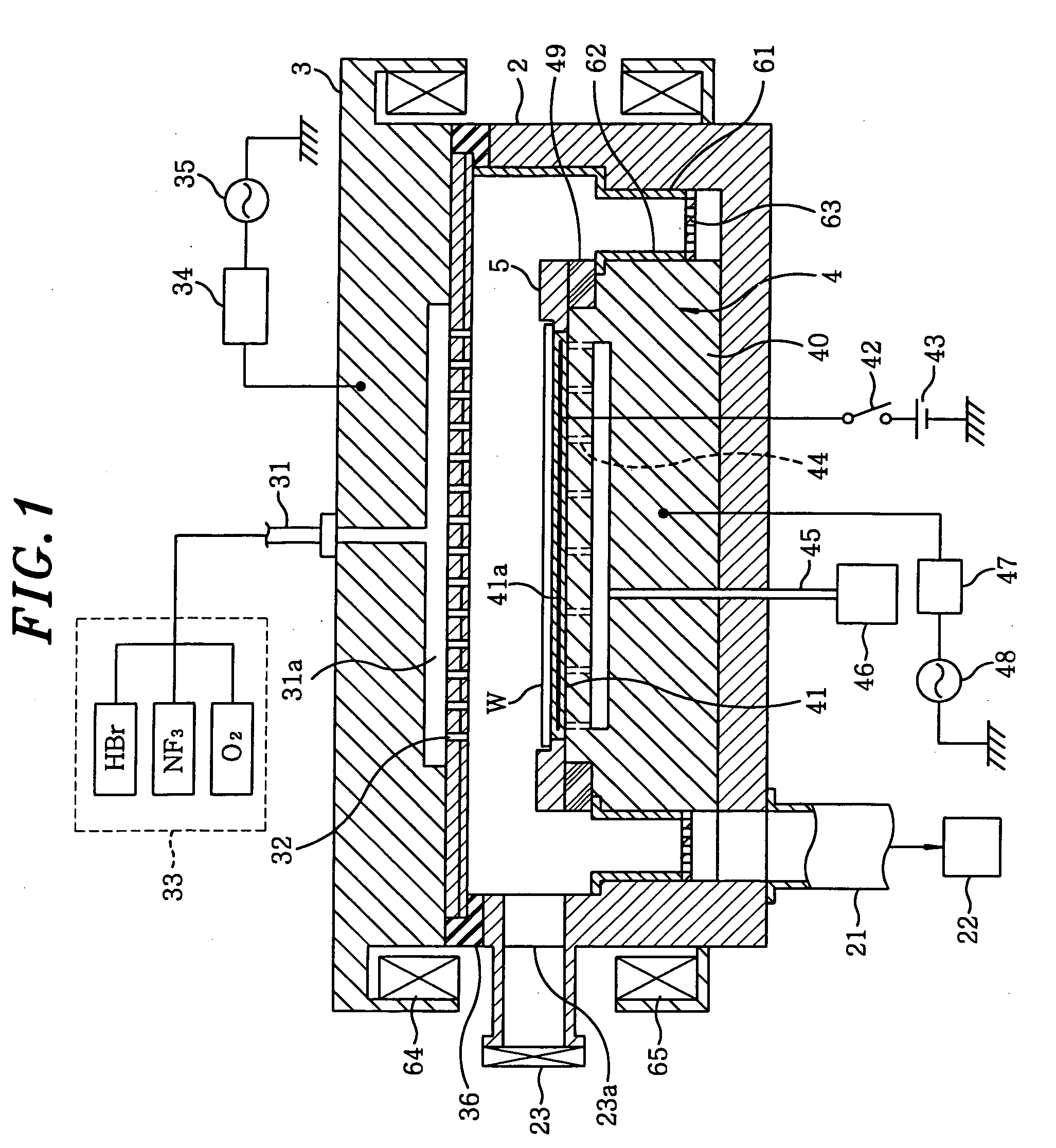

Method and device for plasma-etching organic material film

ActiveUS20060213865A1High selectivityUniform electron densityElectric discharge tubesDecorative surface effectsHigh frequency powerParallel plate

A support electrode (2) and a counter electrode (16) constituting parallel plate electrodes are disposed in a process vessel (1). A substrate (W) with an organic material film formed thereon is supported by the support electrode (2). A high-frequency power of a frequency of 40 MHz or above for generating the plasma is applied to the support electrode (2), so that a high-frequency electric field is formed between the support electrode (2) and the counter electrode (16). A process gas is supplied into the process vessel (1) to generate plasma of the process gas by the high-frequency electric field. The organic material film on the substrate (W) is etched with the plasma, with an organic material film serving as a mask. The process gas includes an ionization accelerating gas, such as Ar, that is ionized from a ground state or metastable state with an ionization energy of 10 eV or below and has a maximum ionization cross-section of 2×1016 cm2 or above.

Owner:KIOXIA CORP +1

Complementary metal-oxide-semiconductor device and fabricating method thereof

ActiveUS7402496B2Improve performanceReliability be promotedTransistorSemiconductor/solid-state device manufacturingCMOSEpitaxial material

Owner:UNITED MICROELECTRONICS CORP

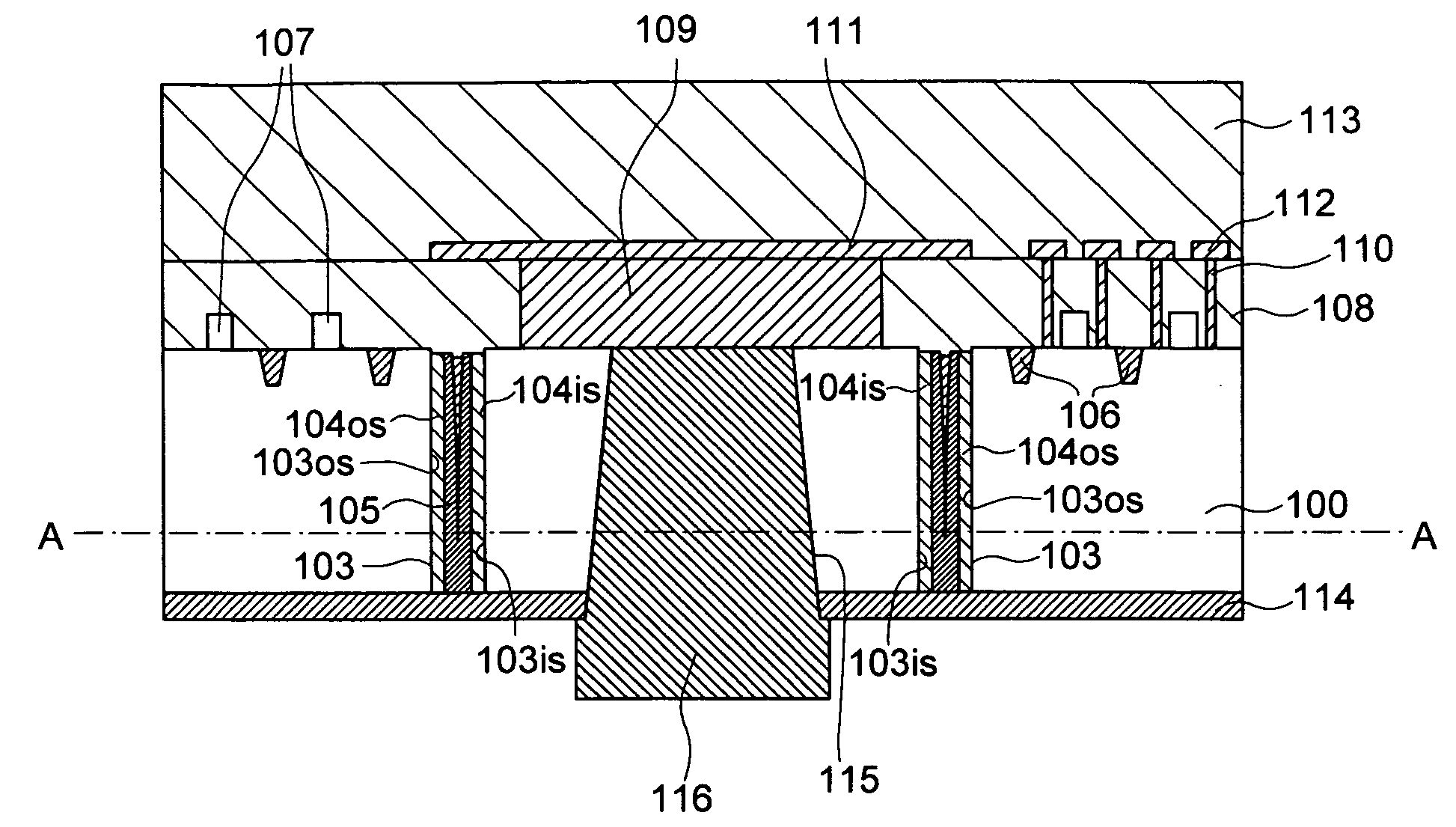

Chip-stacked semiconductor device and manufacturing method thereof

InactiveUS20080237781A1Increase etch rateSmall widthSemiconductor/solid-state device detailsSolid-state devicesChip stackingSemiconductor

The semiconductor device according to the present invention includes a through electrode that penetrates through a silicon substrate, an isolation trench provided to penetrate through the silicon substrate to surround the through electrode, a silicon film in contact with an inner surface of the isolation trench, a silicon film in contact with an outer surface of the isolation trench, and an insulation film provided between the silicon films. According to the present invention, the silicon film within the isolation trench can be substantially regarded as a part of the silicon substrate. Therefore, even when the width of the isolation trench is increased to increase the etching rate, the width of the insulation film becoming a dead space can be made sufficiently small. Consequently, the chip area can be decreased.

Owner:LONGITUDE LICENSING LTD

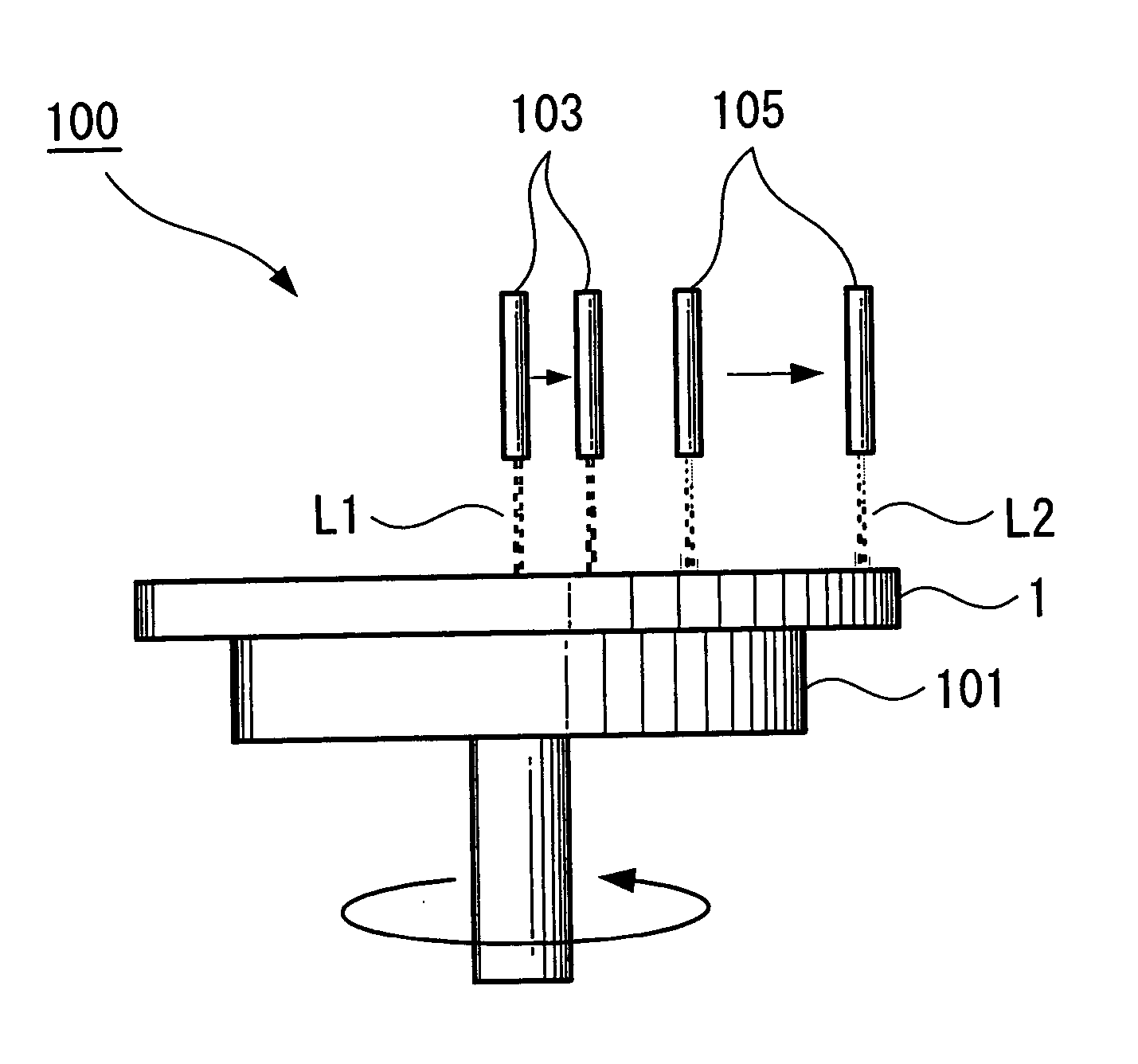

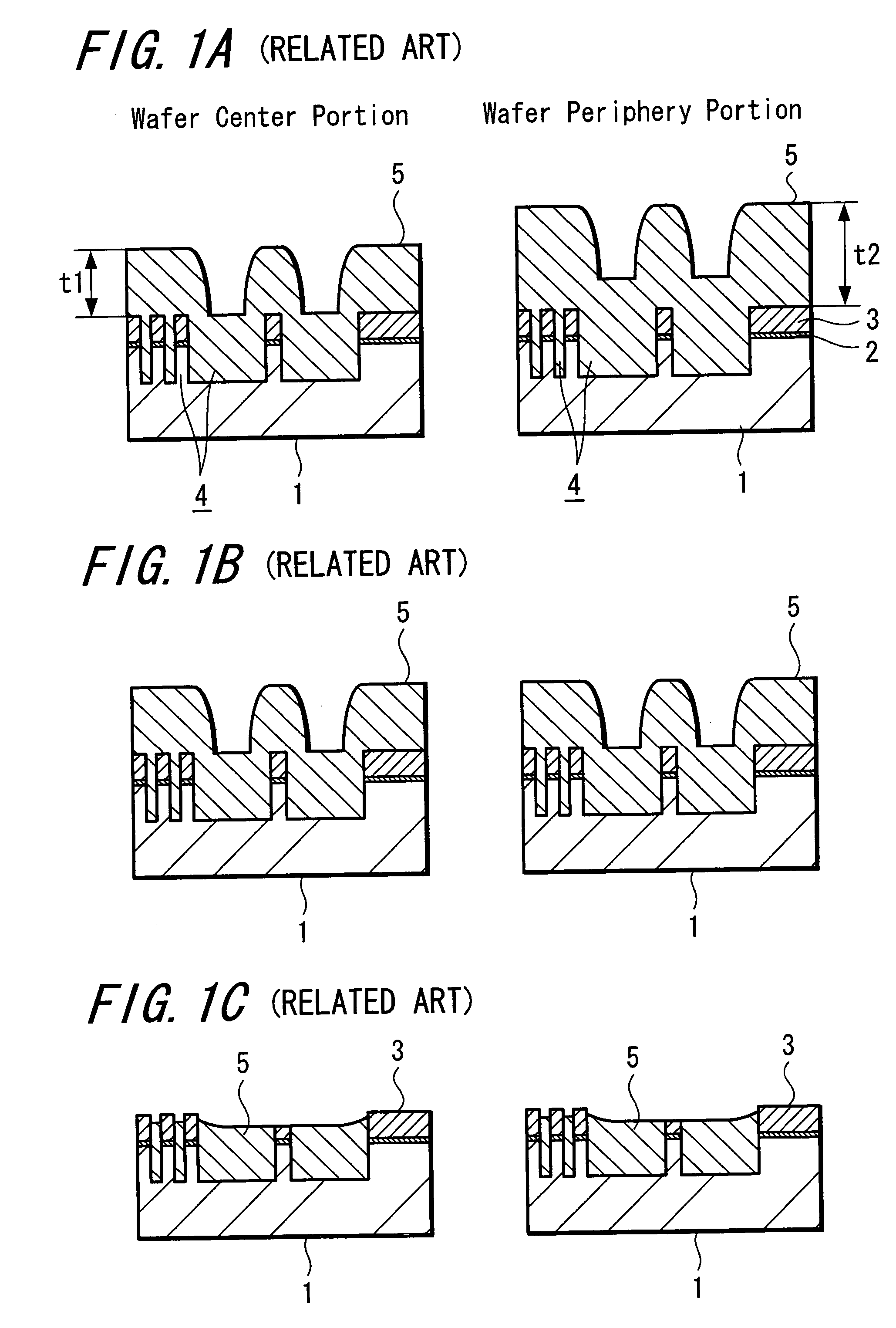

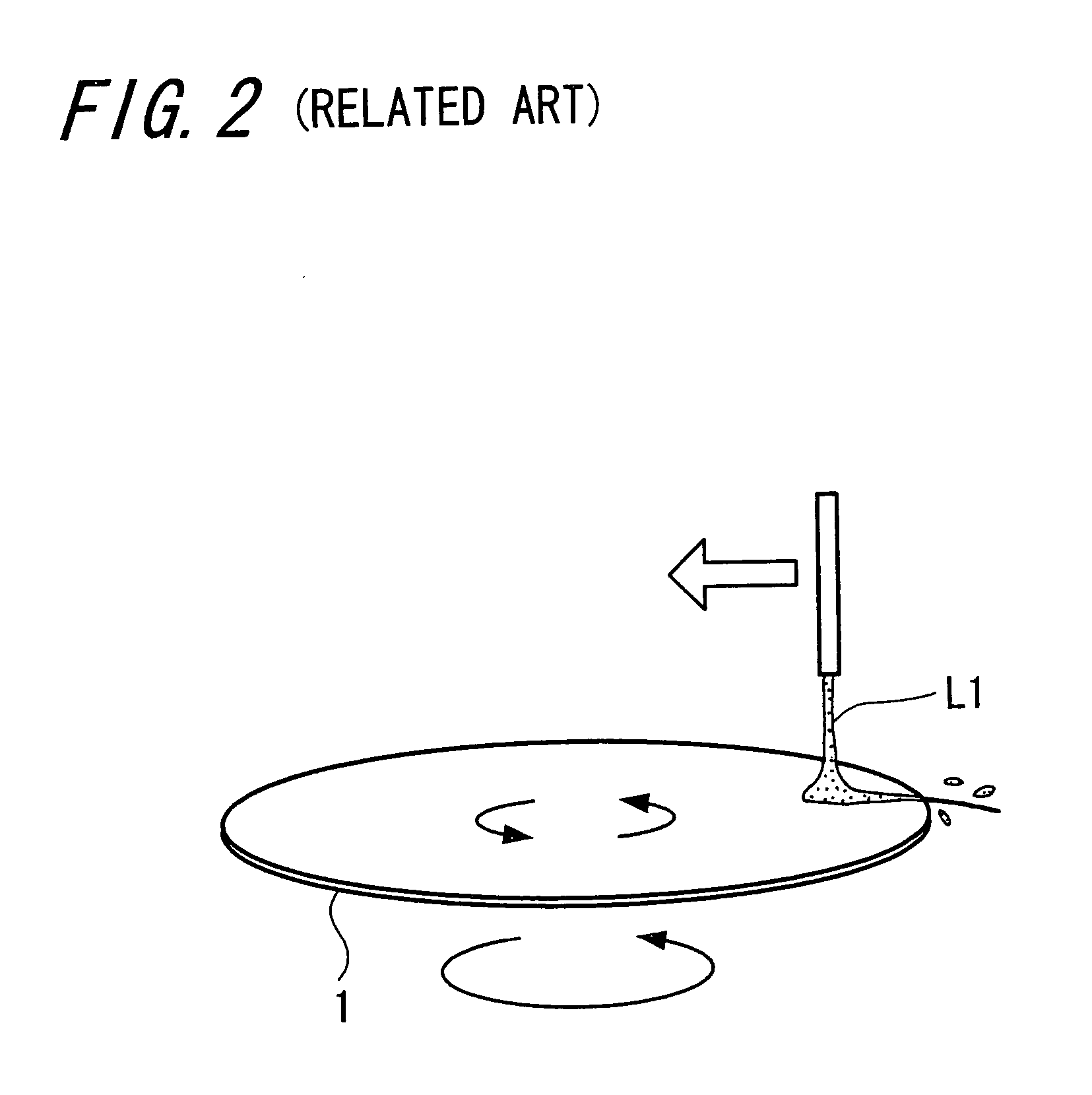

Etching method and etching device

InactiveUS20050000940A1Reduce etch rateReduce probabilityDecorative surface effectsSemiconductor/solid-state device manufacturingEtchingPhysics

An etching method and etching device are provided, enabling uniform rendering of the thickness of a film for processing on a wafer regardless of the film thickness profile thereof, and thereby enabling global planarizing of the wafer surface. In an etching method, the film thickness profile of the film for processing formed on the wafer is ascertained in advance, and wet etching is performed by discharging an etchant liquid L1 at a thick portion of the film for processing; simultaneously with the discharge of the etchant liquid L1, a diluting liquid L2 for the etchant liquid L1 is discharged at a thin portion of the film for processing.

Owner:SONY CORP +1

Selective etching processes of silicon nitride and indium oxide thin films for FeRAM device applications

InactiveUS7338907B2Increase etch rateReduce etch rateTransistorDecorative surface effectsSemiconductorOxidizing agent

A dry etch process is described for selectively etching silicon nitride from conductive oxide material for use in a semiconductor fabrication process. Adding an oxidant in the etch gas mixture could increase the etch rate for the silicon nitride while reducing the etch rate for the conductive oxide, resulting in improving etch selectivity. The disclosed selective etch process is well suited for ferroelectric memory device fabrication using conductive oxide / ferroelectric interface having silicon nitride as the encapsulated material for the ferroelectric.

Owner:SHARP KK

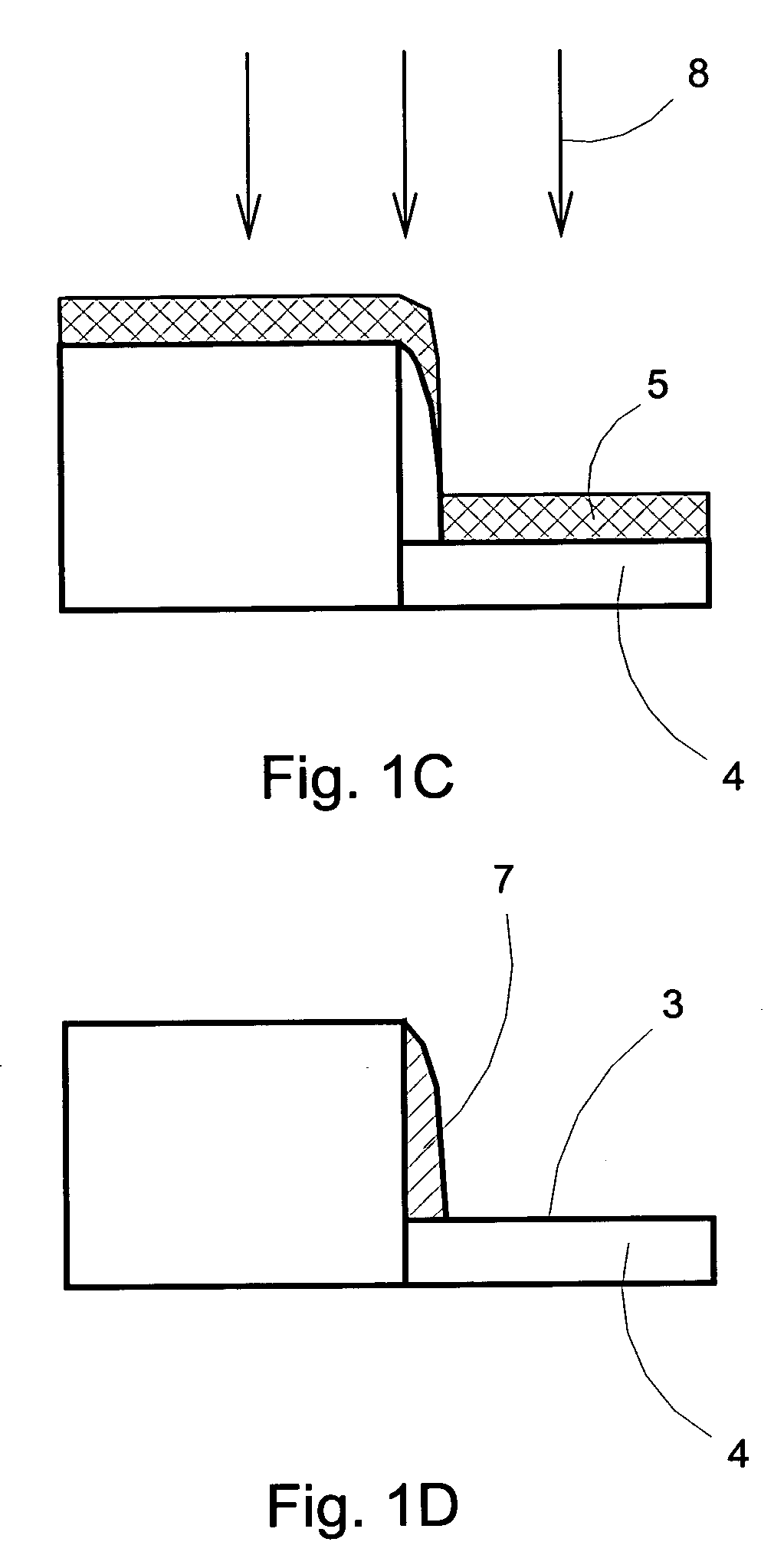

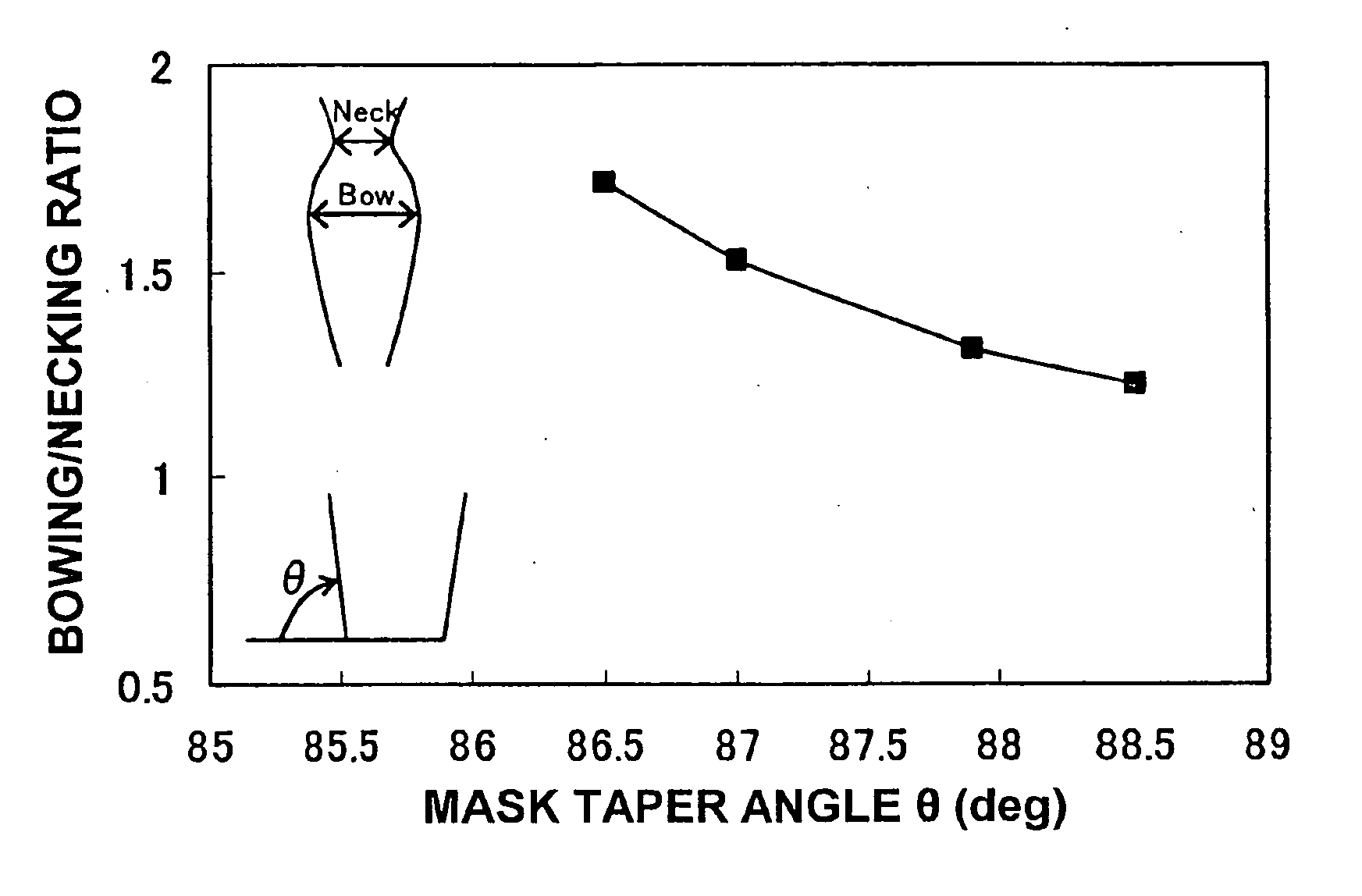

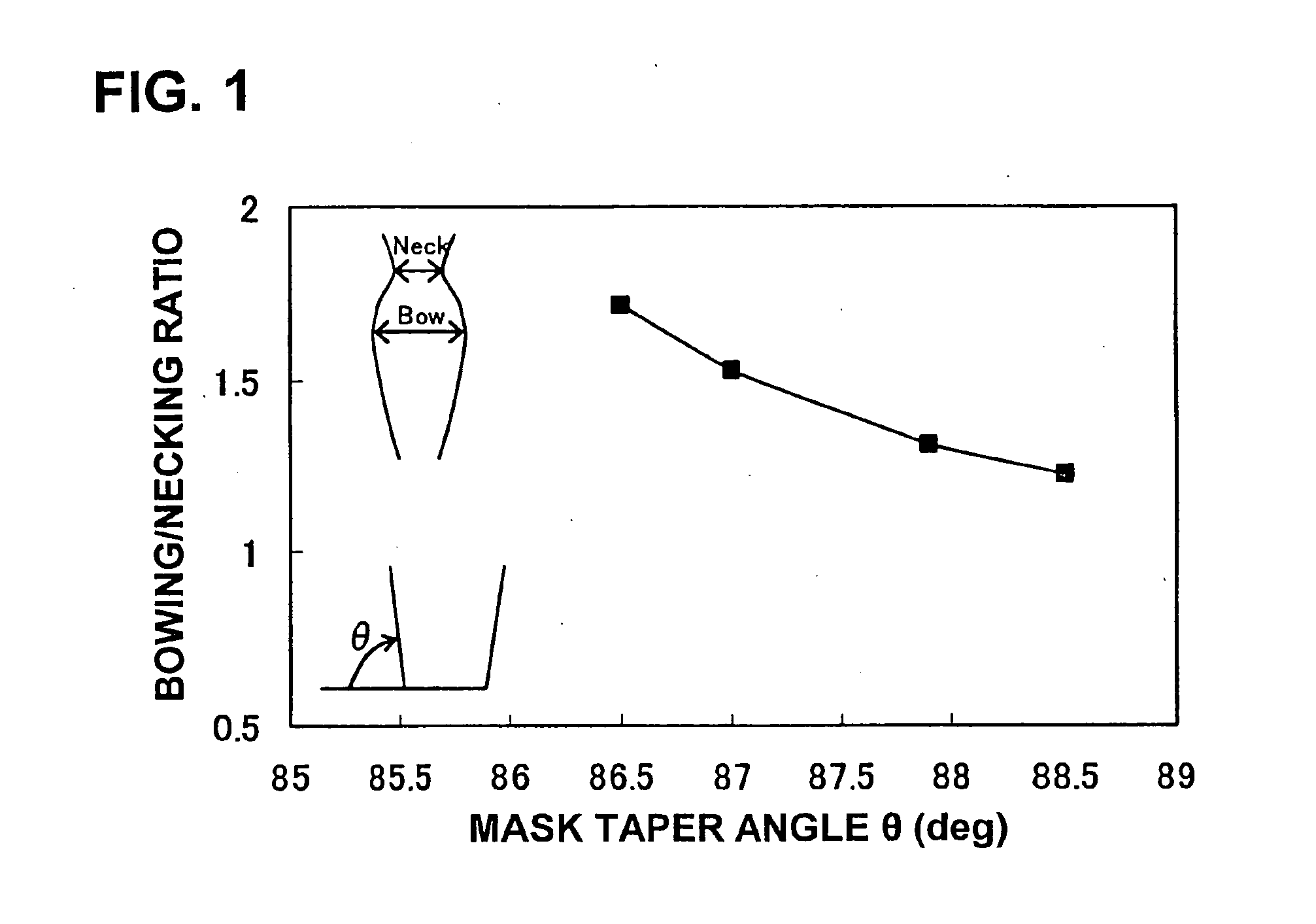

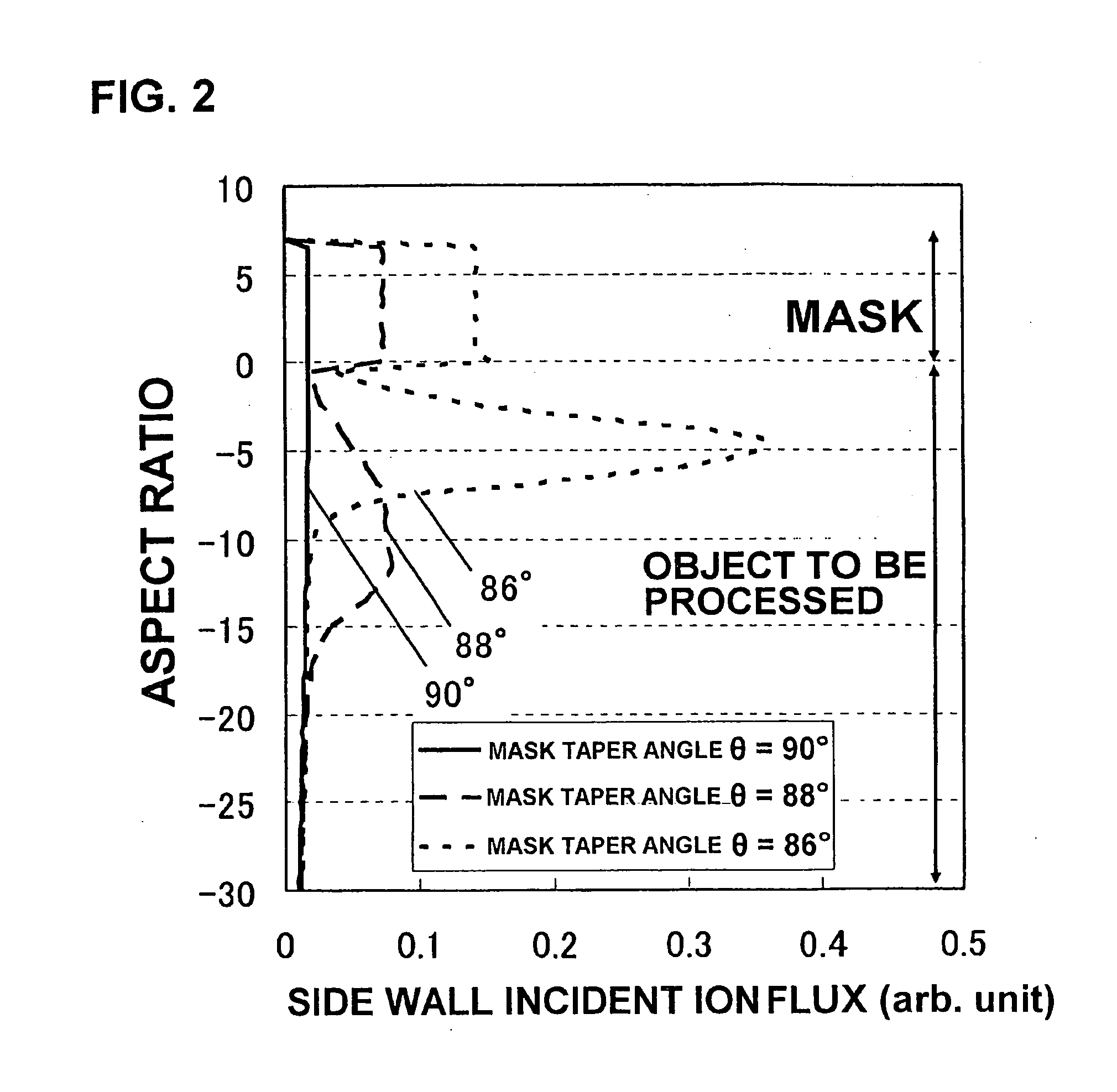

Plasma etching method for etching an object

InactiveUS20100297849A1Suppress bowingHigh selectivitySemiconductor/solid-state device manufacturingFluorocarbonDeep hole

The invention provides a plasma etching method capable of suppressing bowing of an opening of the object to be etched, and solving the lack of opening at a high aspect ratio portion in deep hole processing having a high aspect ratio. A plasma etching method for etching an object to be etched in a plasma etching apparatus using a mask patterned and formed on the object to be etched comprises sequentially performing a first step for etching the mask while attaching deposits on a side wall of an opening close to a surface of the mask pattern of the mask using fluorocarbon gas CxFy (x=1, 2, 3, 4, 5, 6, y=4, 5, 6, 8), and a second step for etching the object to be etched while removing the deposits attached to the side wall of the opening close to the surface of the mask pattern of the mask using fluorocarbon gas.

Owner:HITACHI HIGH-TECH CORP

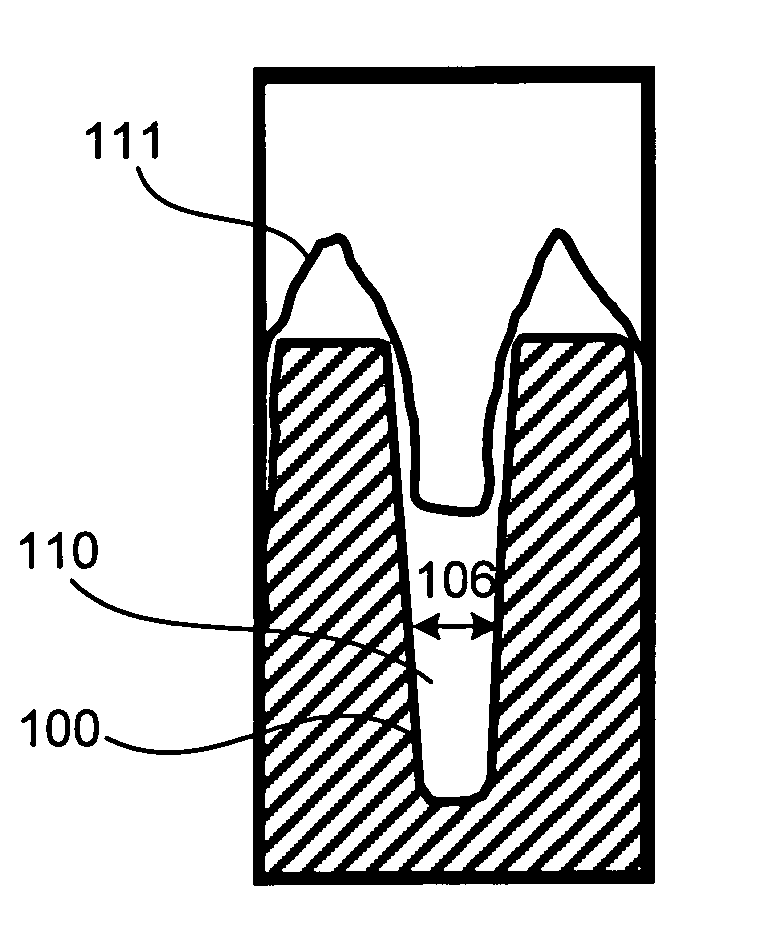

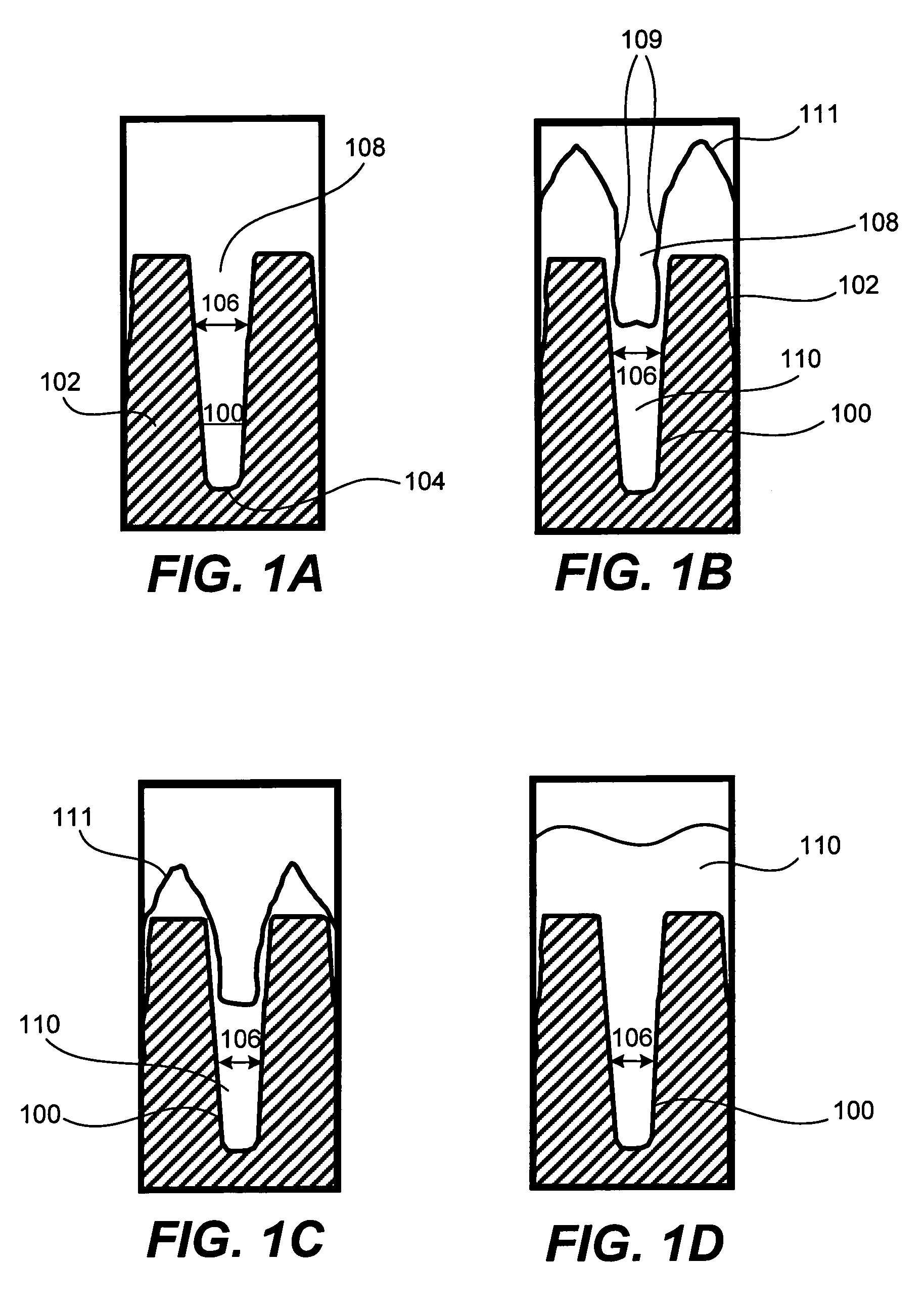

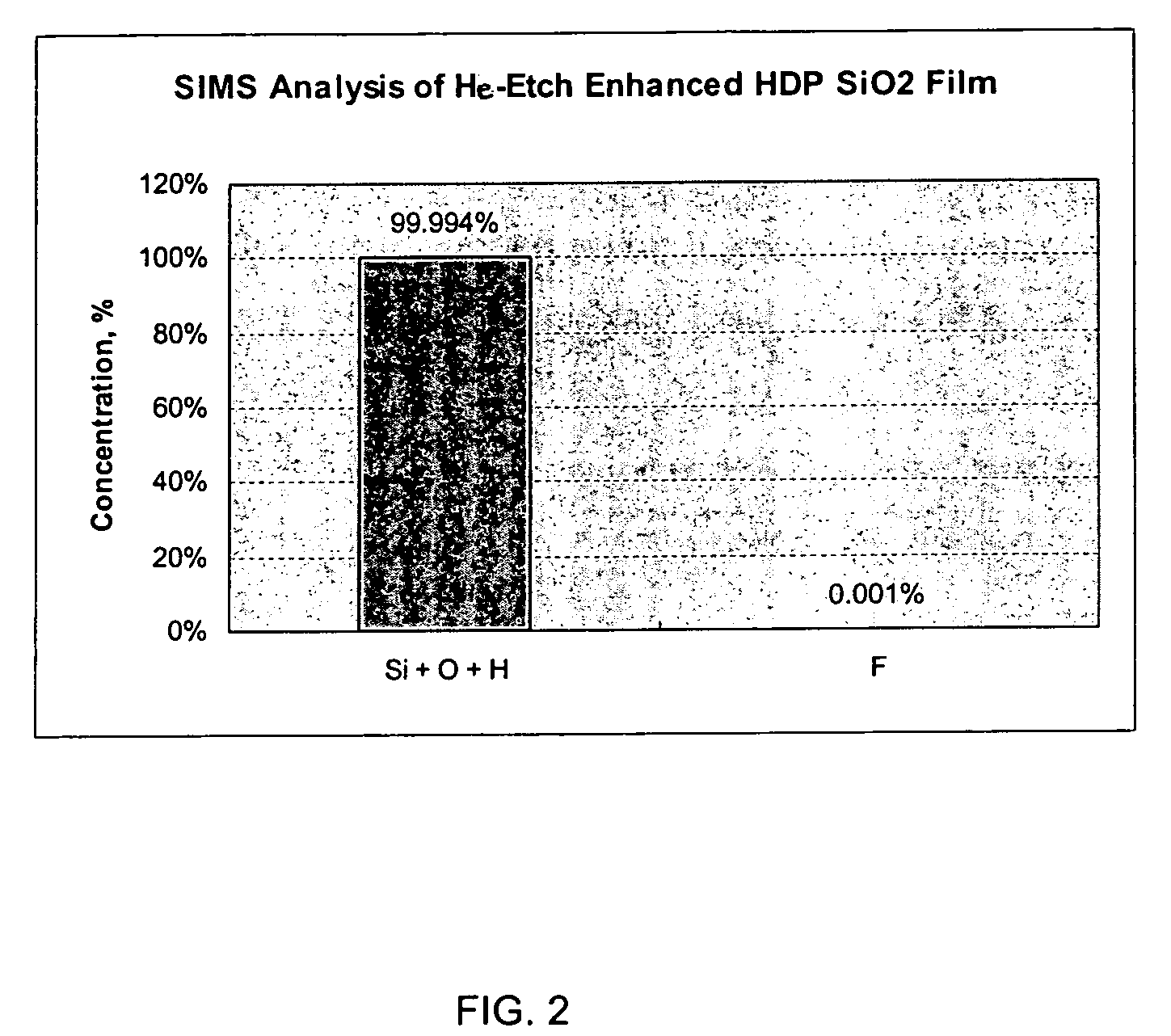

Helium-based etch process in deposition-etch-deposition gap fill

ActiveUS7344996B1Alter characterReduce etch rateLiquid surface applicatorsDecorative surface effectsHigh densityChemical species

Plasma etch processes incorporating helium-based etch chemistries can remove dielectric a semiconductor applications. In particular, high density plasma chemical vapor etch-enhanced (deposition-etch-deposition) gap fill processes incorporating etch chemistries which incorporate helium as the etchant that can effectively fill high aspect ratio gaps while reducing or eliminating dielectric contamination by etchant chemical species.

Owner:NOVELLUS SYSTEMS

Focus ring, plasma etching apparatus and plasma etching method

ActiveUS20060102288A1Improve etching effectAccurate storageElectric discharge tubesDecorative surface effectsPlasma etchingMaterials science

In a plasma etching apparatus for performing a plasma etching on a surface of a substrate mounted on a susceptor in a processing vessel, a focus ring is installed to surround the substrate and has a first region at an inner side on a surface thereof, in which an average surface roughness is small such that a reaction product produced during an etching processing is not captured to be deposited, and a second region at an outer side from the first region, in which an average surface roughness is large such that a reaction product produced during the etching process is captured to be deposited. A boundary between the first and the second region is a part where an etching amount is relatively significantly changed compared to other parts while the focus ring is equipped in the plasma etching apparatus and the plasma etching is performed on the substrate.

Owner:TOKYO ELECTRON LTD

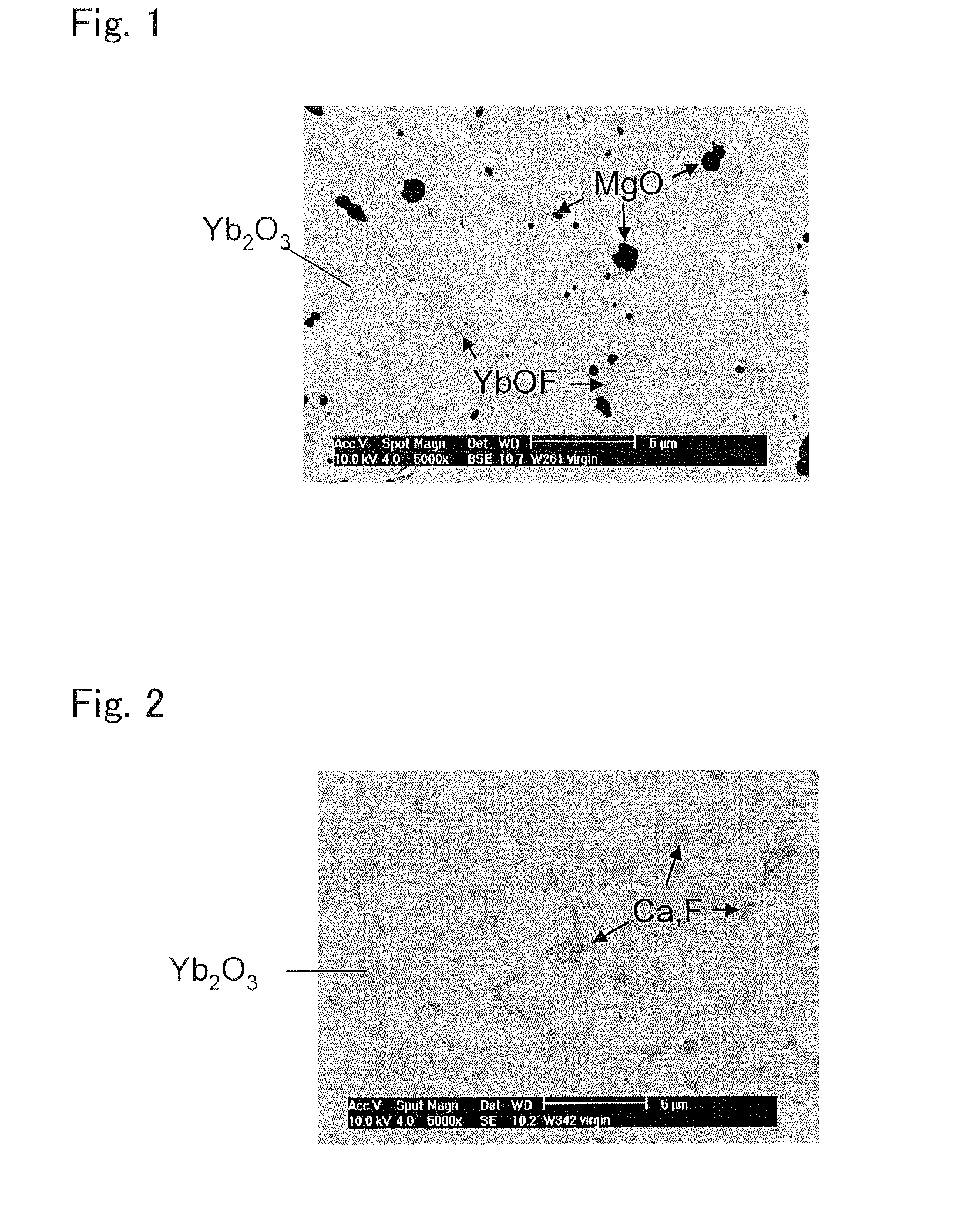

Corrosion-resistant member for semiconductor manufacturing apparatus and method for manufacturing the same

ActiveUS20130023401A1Reduce etch rateReduce the amount requiredSemiconductor/solid-state device manufacturingCeramic shaping apparatusManufactured apparatusManufactured material

Initially, an Yb2O3 raw material was subjected to uniaxial pressure forming at a pressure of 200 kgf / cm2, so that a disc-shaped compact having a diameter of about 35 mm and a thickness of about 10 mm was produced, and was stored into a graphite mold for firing. Subsequently, firing was performed by using a hot-press method at a predetermined firing temperature (1,500° C.), so as to obtain a corrosion-resistant member for semiconductor manufacturing apparatus. The press pressure during firing was specified to be 200 kgf / cm2 and an Ar atmosphere was kept until the firing was finished. The retention time at the firing temperature (maximum temperature) was specified to be 4 hours. In this manner, the corrosion-resistant member for semiconductor manufacturing apparatus made from an Yb2O3 sintered body having an open porosity of 0.2% was obtained.

Owner:NGK INSULATORS LTD

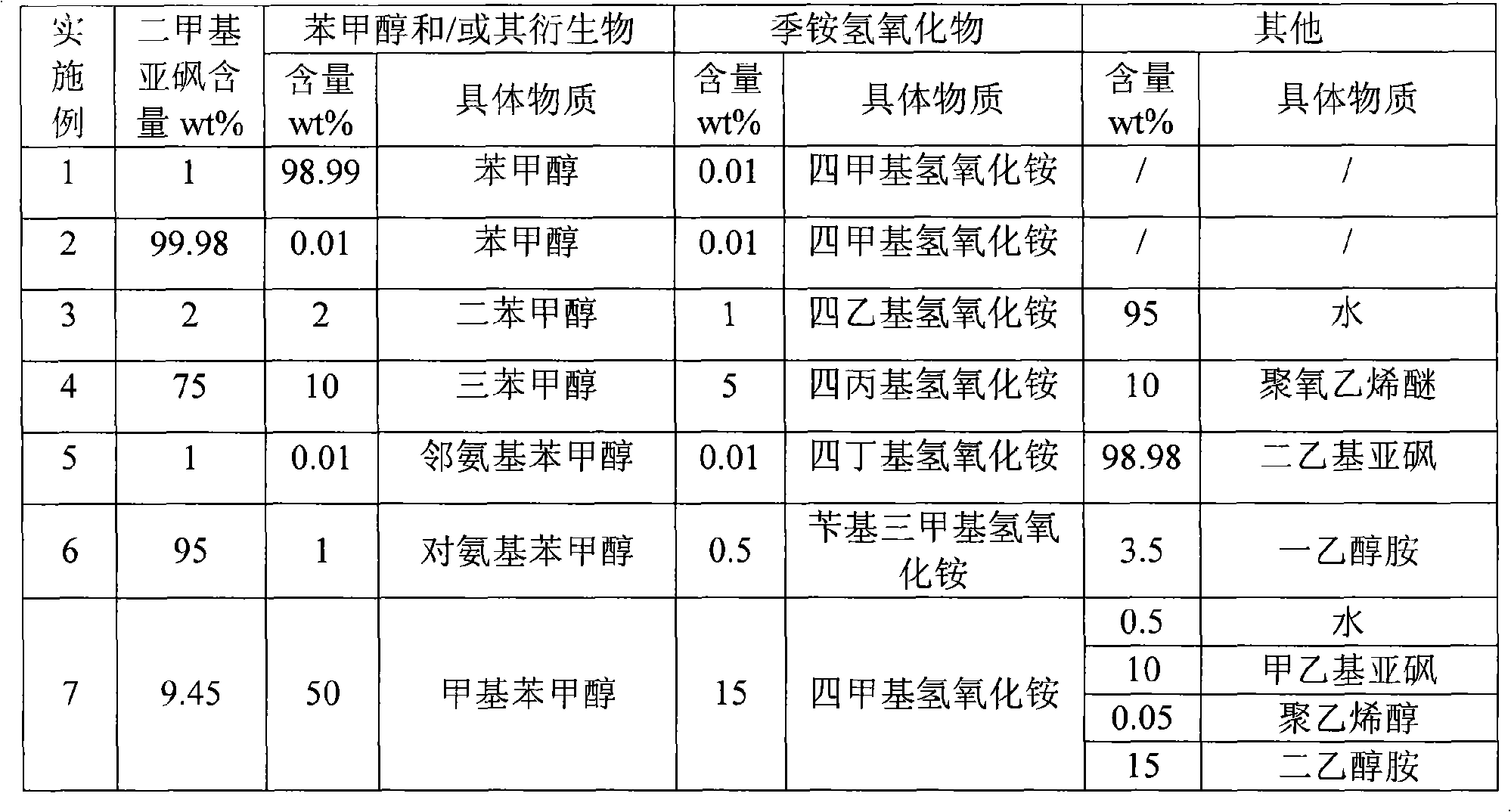

Low etching photoresist cleaning agent

InactiveCN101286016AGood application prospectExtended operating temperature rangeNon-surface-active detergent compositionsPhotosensitive material processingDielectric substrateAmmonium hydroxide

The invention discloses a low etching photoresist cleaning agent, comprising benzyl alcohol and / or ramification of the benzyl alcohol, quaternary ammonium hydroxide and dimethyl sulfoxide. The cleaning agent of the invention can be used for removing photoresist (light resistance) and other residues on metals, metal alloys or dielectric substrates, has low etching speed on metals such as SiO2, copper, etc. and low-k material, and has excellent application prospect in micro-electron fields such as semiconductor wafer cleaning, etc.

Owner:ANJI MICROELECTRONICS (SHANGHAI) CO LTD

Method of forming an etch indicator layer for reducing etch non-uniformities

InactiveUS20080026487A1Improve controllabilityReduce etch rateSemiconductor/solid-state device testing/measurementSolid-state devicesLength waveIon implantation

By incorporating an etch control material after the formation of a material layer to be patterned, an appropriate material having a highly distinctive radiation wavelength may be used for generating a distinctive endpoint detection signal during an etch process. Advantageously, the material may be incorporated by ion implantation which provides reduced non-uniformity compared to etch non-uniformities, while the implantation process provides the potential for introducing even very “exotic” implantation species. In some embodiments, the substrate-to-substrate uniformity of the patterning of dual damascene structures may be increased.

Owner:ALSEPHINA INNOVATIONS INC

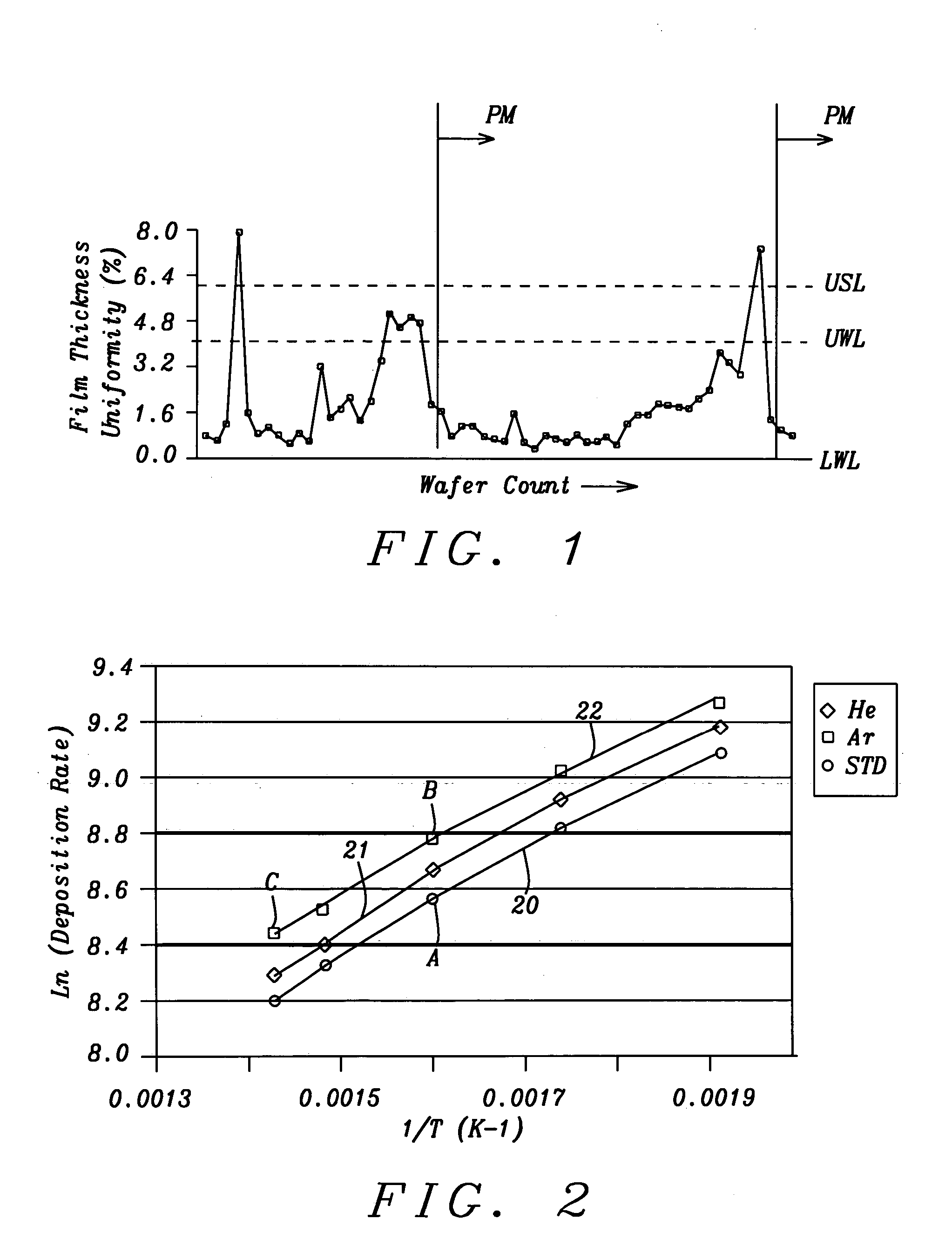

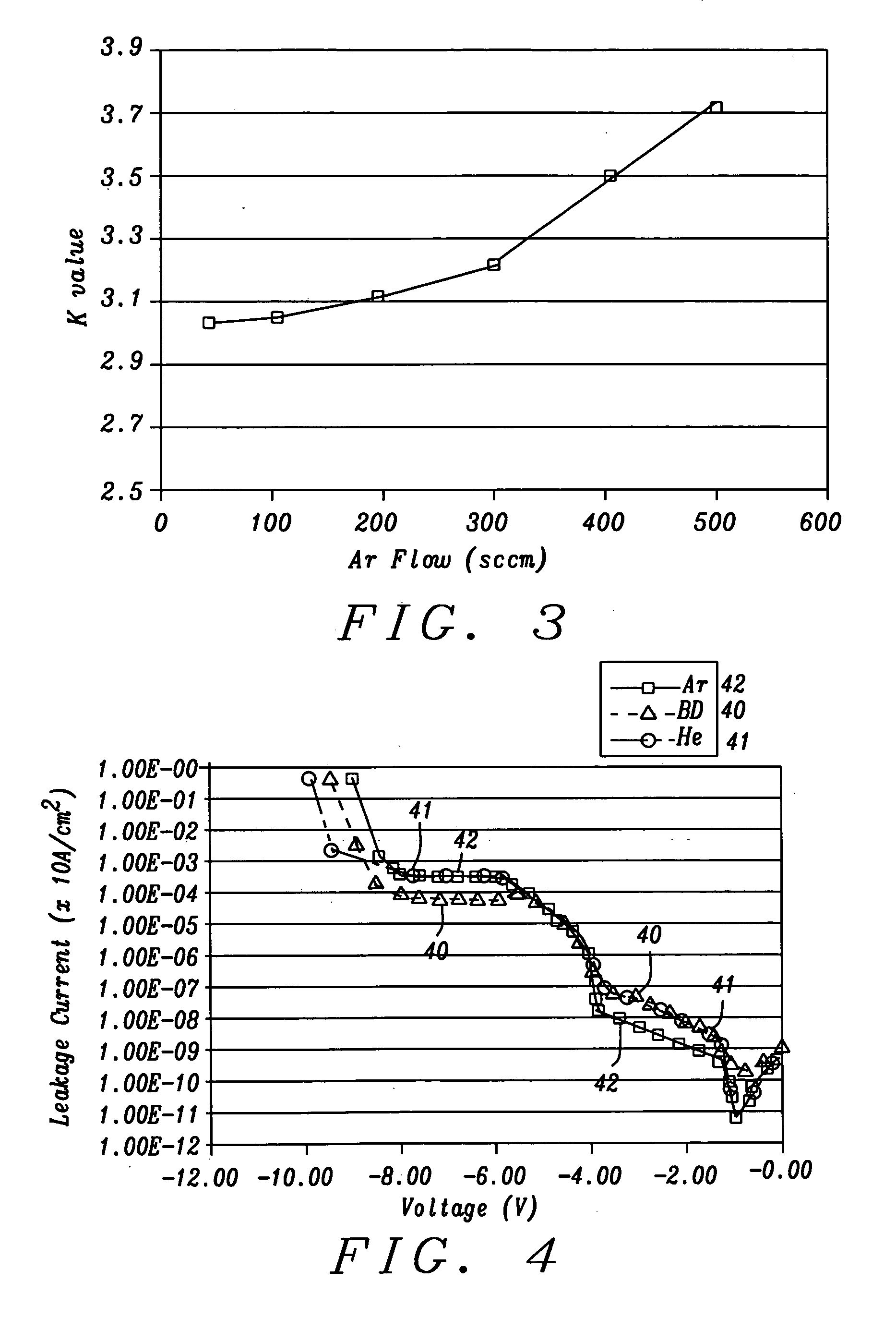

Novel method to deposit carbon doped SiO2 films with improved film quality

InactiveUS20050124151A1Increase deposition rateImprove film thickness uniformitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingMetal interconnectLow leakage

A method is disclosed for depositing a Black Diamond layer in a CVD chamber. Trimethylsilane, O2, and Ar are flowed into the chamber at 300° C. to 400° C. with an O2:Ar:trimethylsilane flow rate ratio that is preferably 1:1.5:6. The resulting low k dielectric layer is formed with a higher deposition rate than when Ar is omitted and has a k value of about 3 that increases only slightly in O2 plasma. A higher density, hardness, and tensile strength are achieved in the Black Diamond layer when Ar is included in the deposition process. The addition of Ar in the deposition maintains film thickness uniformity below 2% for a longer period so that PM cleaning operations are less frequent and affords a lower fluorocarbon plasma etch rate to enable improved trench depth control in a damascene scheme. A lower leakage current and higher breakdown voltage in achieved in the resulting metal interconnect.

Owner:TAIWAN SEMICON MFG CO LTD

Connection pore forming method

ActiveCN101459125AGuaranteed PenetrationAvoid etch-throughSemiconductor/solid-state device manufacturingSemiconductor structureDielectric layer

A method of forming connecting holes comprises steps of providing a semiconductor structure with an etch stop layer, wherein the etch stop layer is equipped with an intermetallic dielectric layer, forming a photoresist layer on the intermetallic dielectric layer, patterning the photoresist layer to form a connecting hole pattern, executing the major etching process to etch part of thickness of the intermetallic dielectric layer at the bottom portion of the connecting hole pattern, after the major etching process is finished, executing the first step of the over-etching process to etch residual thickness of the intermetallic dielectric layer and form an opening in the intermetallic dielectric layer, wherein the bottom of the opening exposes out of the etch stop layer, then executing the second step of the over-etching process to etch the bottom of the opening, and finally removing the etch stop layer at the bottom of the opening. The invention can avoid the defect that the bottom of the connecting hole is not opened.

Owner:SEMICON MFG INT (SHANGHAI) CORP