Patents

Literature

98results about How to "Fast etch rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

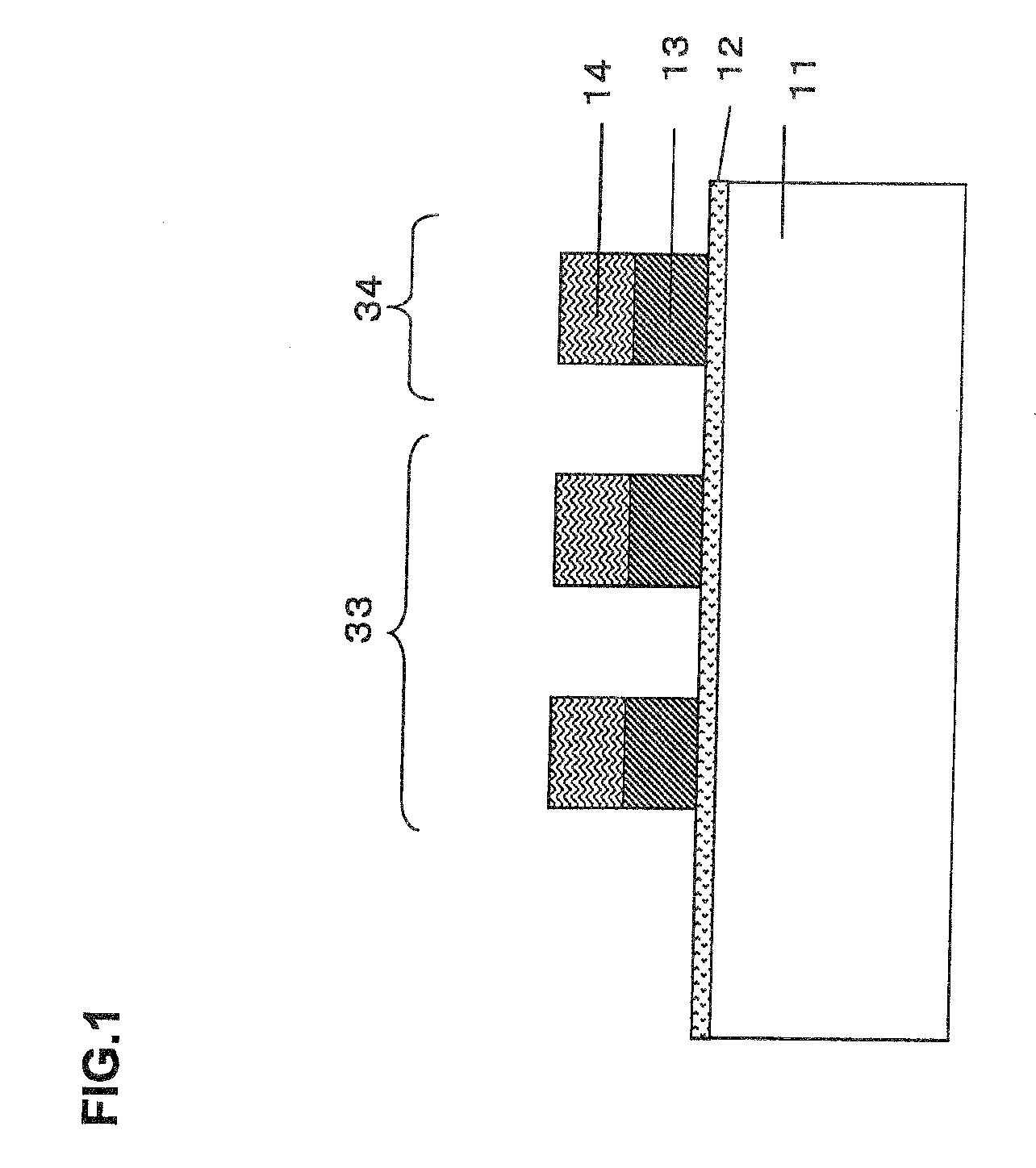

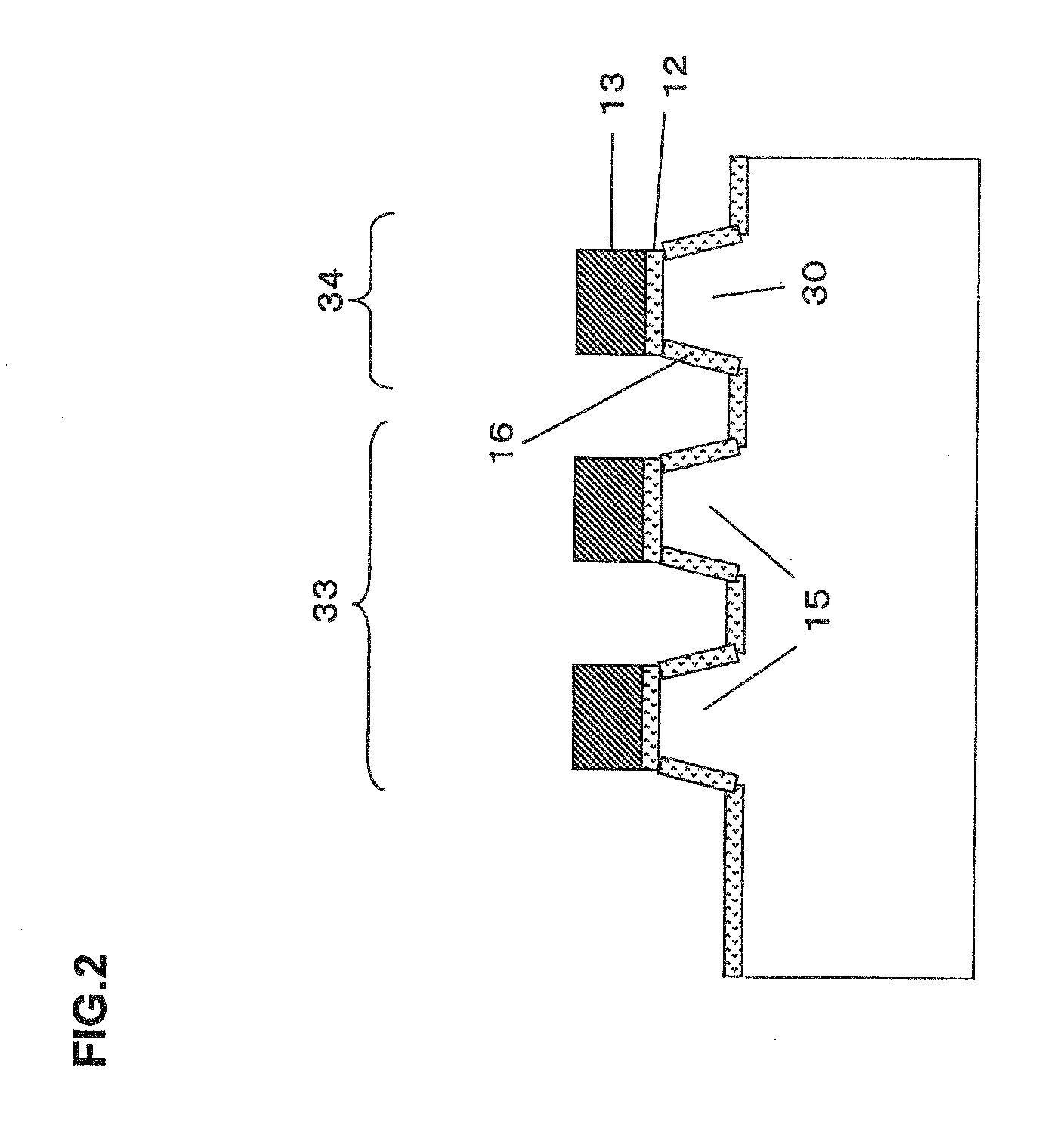

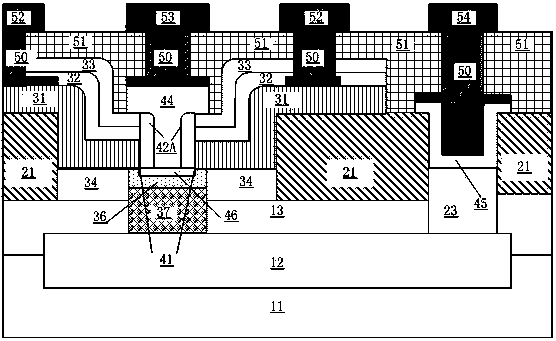

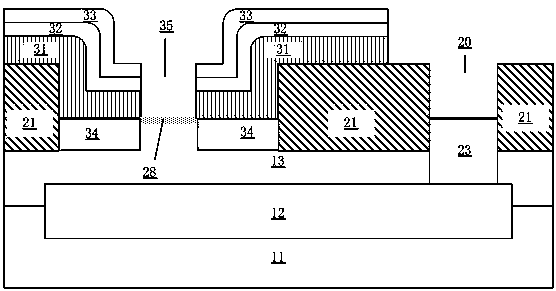

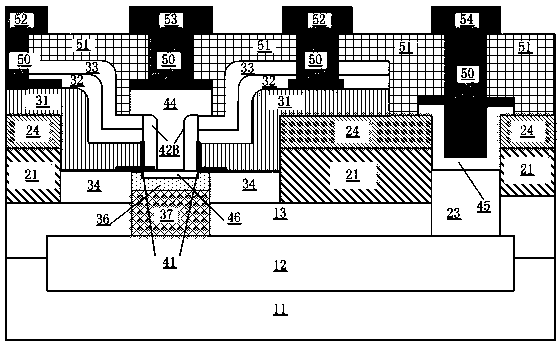

Semiconductor device and method for manufacturing the same

InactiveUS20090152611A1Fast etch rateReduce thicknessTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device

A semiconductor device comprises a first contact plug, a first structure and a second insulating layer, or comprises a first contact plug, a first structure, a protruding region and a second insulating layer. The first contact plug extends in a predetermined direction and including a step converting a cross section area of the first contact plug perpendicular to the predetermined direction discontinuously via the step in one end side. The second insulating layer is formed on side surface of a part of the first contact plug closer to the first structure than the step, or on side surfaces of the protruding region and a part of the first contact plug closer to the first structure than the step.

Owner:LONGITUDE SEMICON S A R L

Anisotropic etching agent composition used for manufacturing of micro-structures of silicon and etching method

InactiveUS20070175862A1Reduce processing timeIncrease etch rateDecorative surface effectsSemiconductor/solid-state device manufacturingMicro structureTetramethylammonium hydroxide

An anisotropic etching agent composition for manufacturing of micro-structures of silicon comprising an alkali compound and hydroxylamines; an anisotropic etching method with the use of the etching agent composition. The alkali compound is preferably tetramethylammonium hydroxide, and the hydroxylamines is preferably at least one kind selected from the group consisting of hydroxylamine, hydroxylamine sulfate, hydroxylamine chloride, hydroxylamine oxalate, dimethyl hydroxylamine hydrochloride and hydroxylamine phosphate. An anisotropic etching property whose etching rate is different in crystal face orientation especially relating with etching technology with the use of manufacturing of micro-structures of silicon used as Micro Electro Mechanical Systems (MEMS) parts, semiconductor materials, etc is provided.

Owner:MITSUBISHI GAS CHEM CO INC

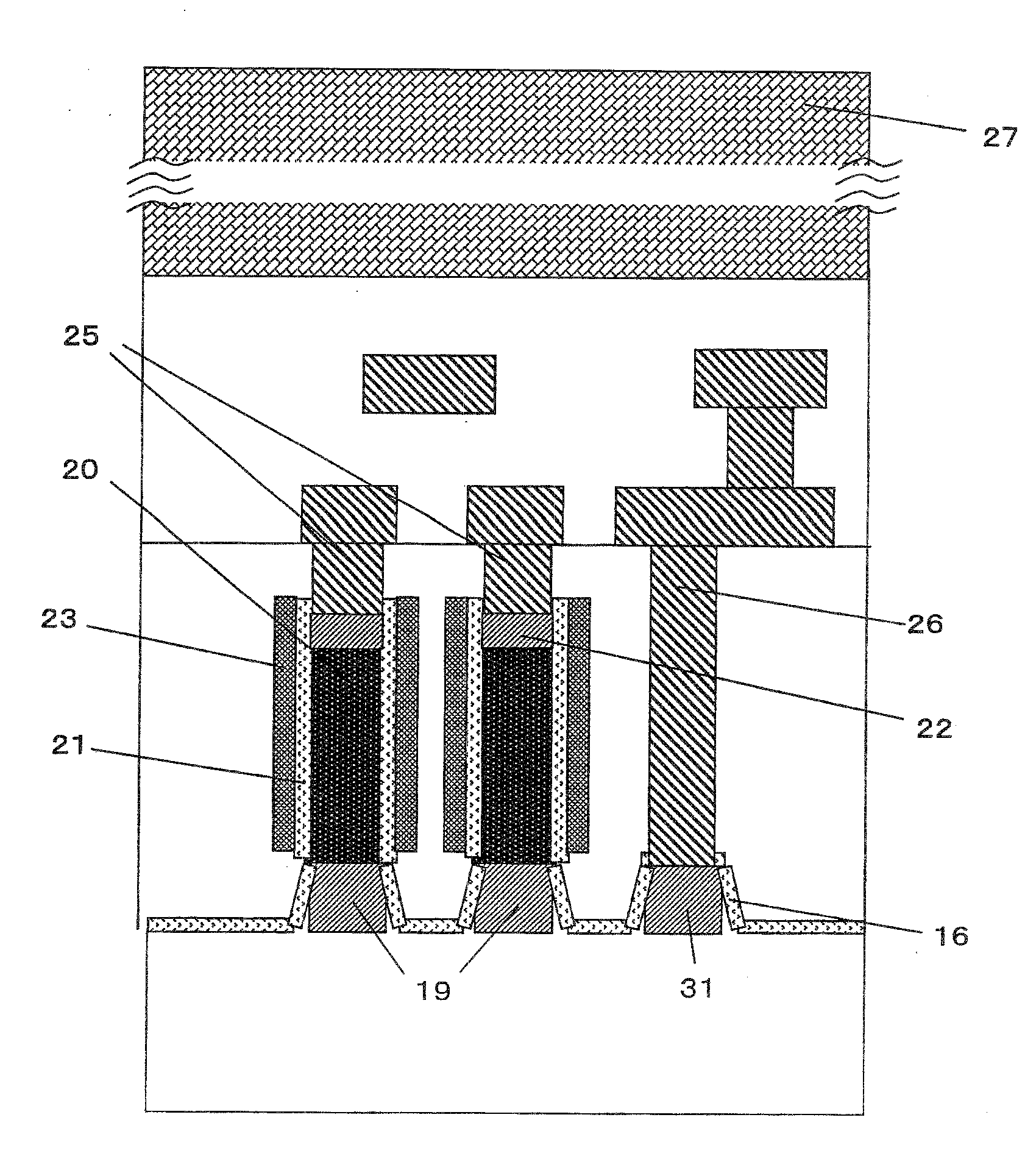

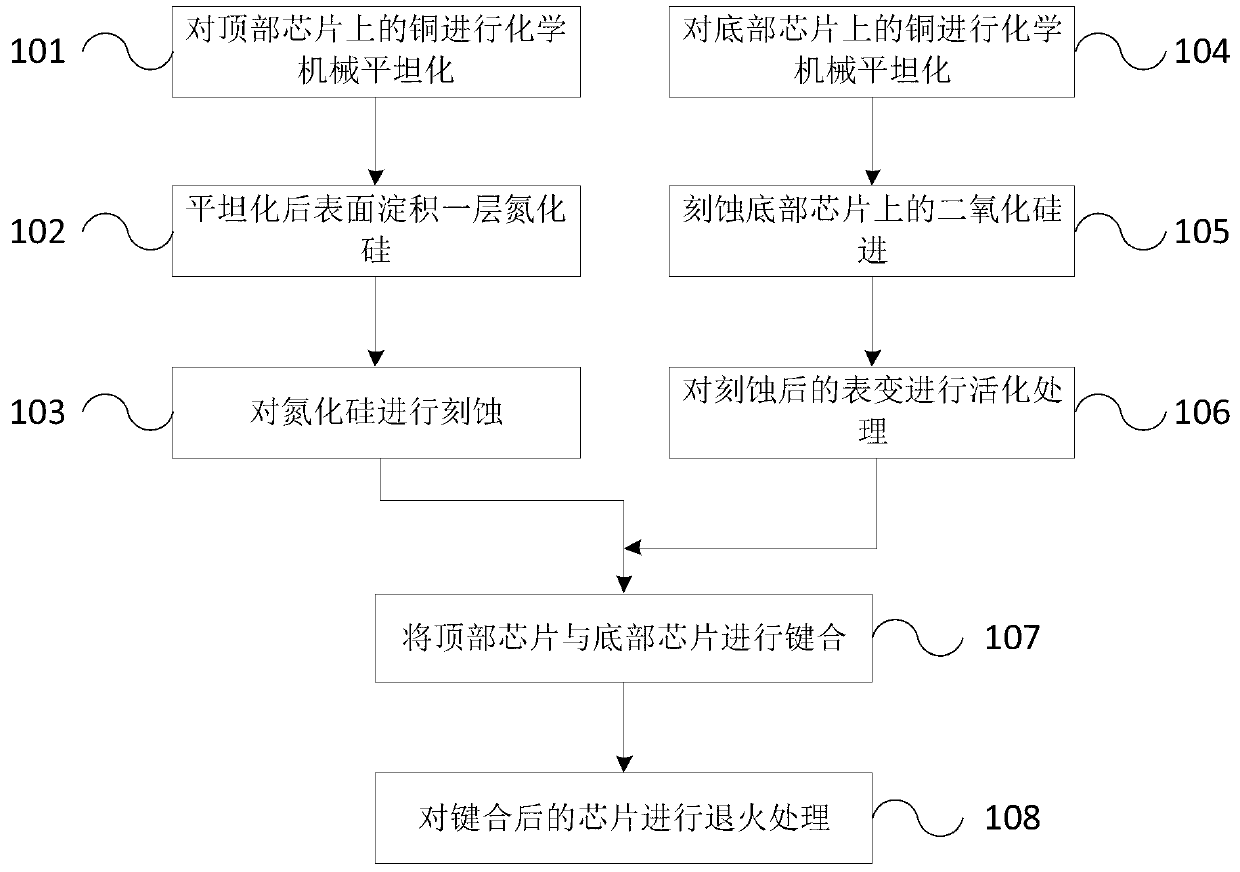

Metal bonding method of three-dimensional chip structure and bonding structure

ActiveCN103107128AStop the spreadImprove bonding qualitySemiconductor/solid-state device detailsSolid-state devicesBond qualityThin layer

The invention relates to the field of semiconductor fabrication, in particular to a metal bonding method of a three-dimensional chip structure and a bonding structure. The method comprises that copper of a top chip is processed in a chemical machinery planarization mode, a silicon nitride layer is deposited on the surface after being processed in a chemical machinery planarization mode, the silicon nitride layer attached to the copper of the top chip is etched, a groove is formed, the bottom of the groove is the copper of the top chip, copper of a bottom chip is processed in a chemical machinery planarization mode, a bottom silica layer is etched, the copper is enabled to be protruded, activating treatment is carried out to the surface after etch of the copper of the bottom chip is achieved, the copper of the top chip and the copper of the bottom chip are aligned and bonded, and annealing treatment is carried out to the chips after being bonded. According to the metal bonding method of the three-dimensional chip structure and the bonding structure, silicon oxide and silicon nitride are used for being matched with metal and metal bonding, bonding quality is enabled to be better, a silicon nitride layer thin layer can prevent the metal from diffusing into around materials, and goals that a technology process is simplified, temperature needed by bonding is reduced, bonding reliability is improved, bonding efficiency is improved, and bonding cost is reduced can be achieved.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

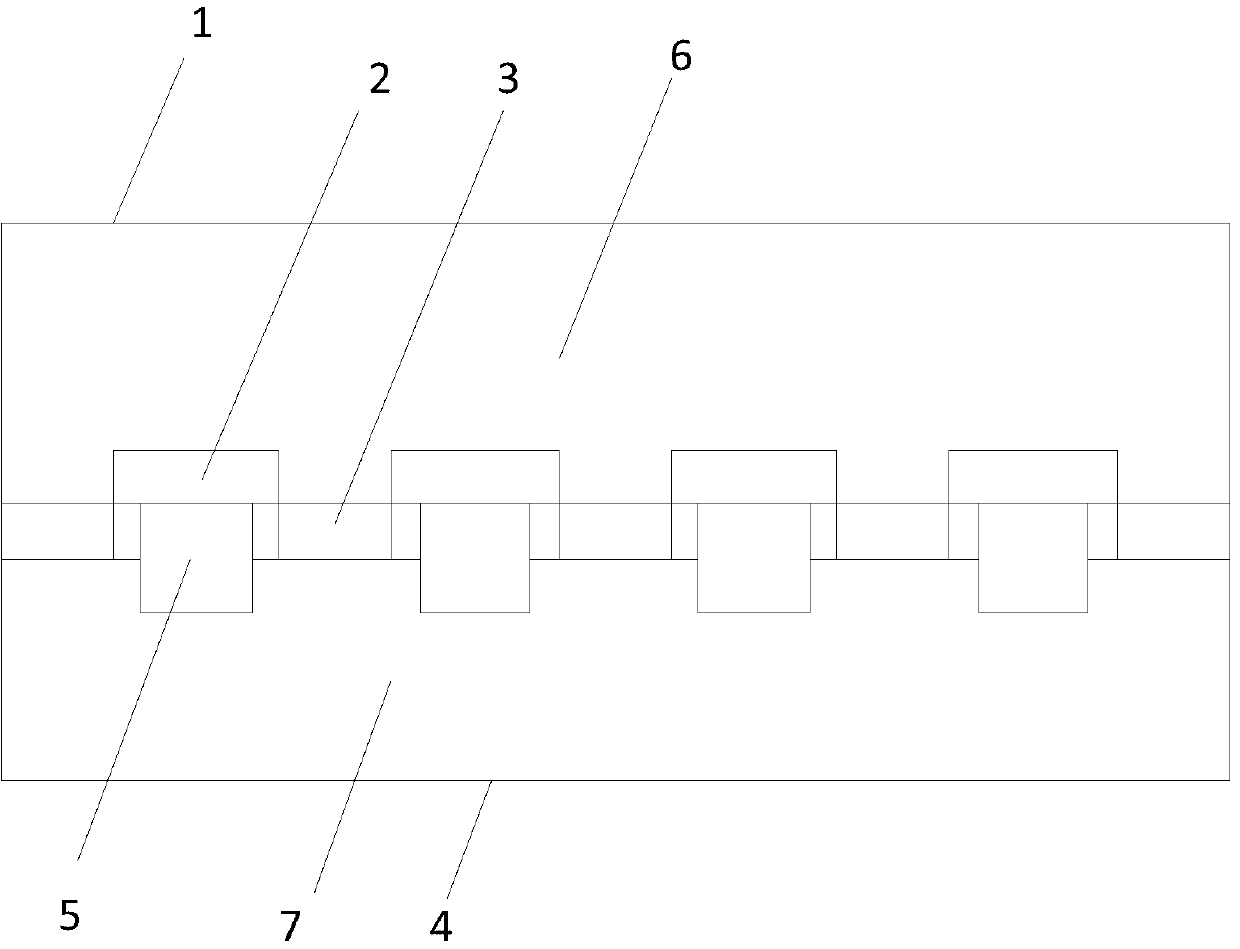

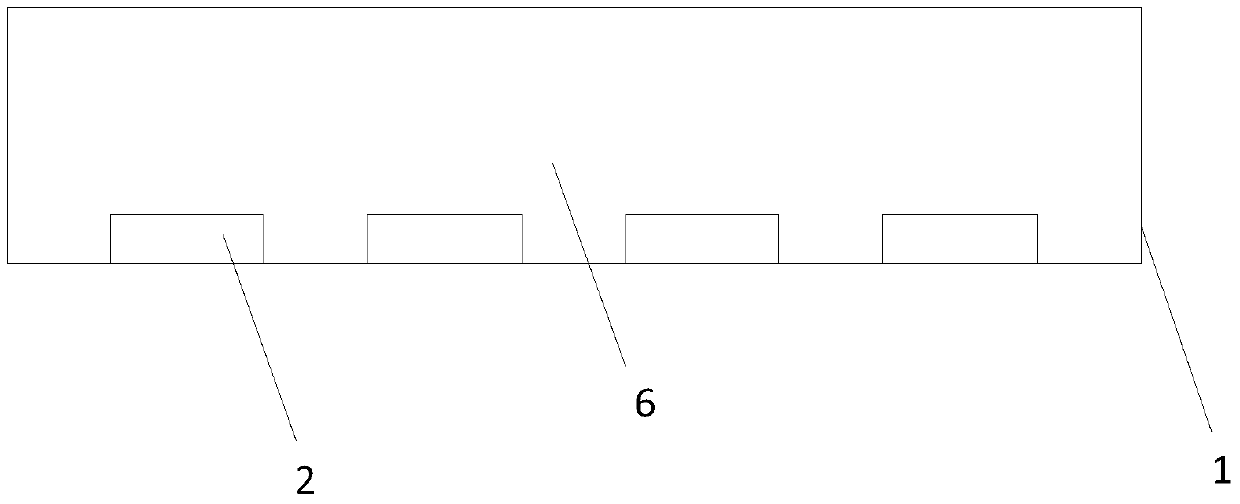

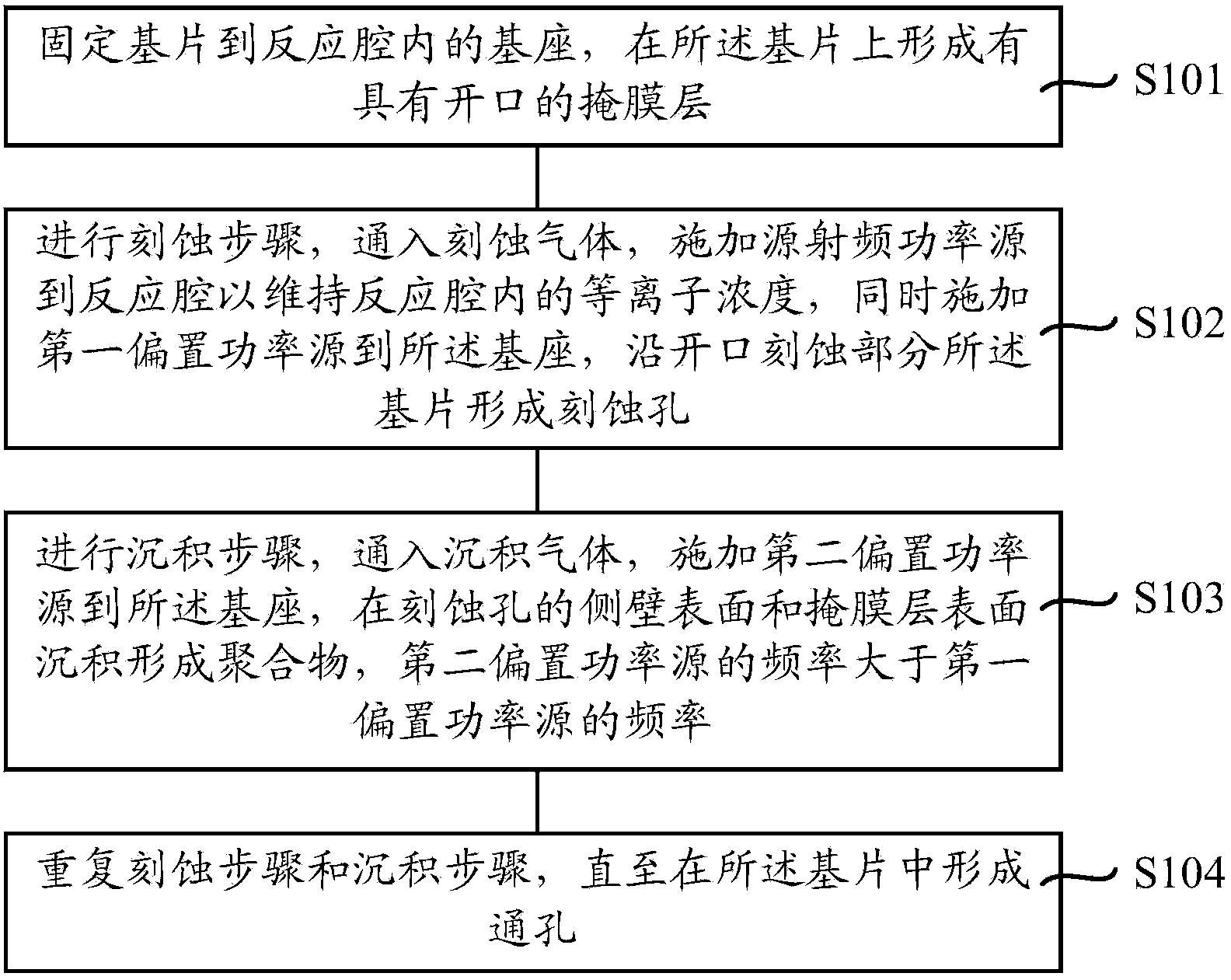

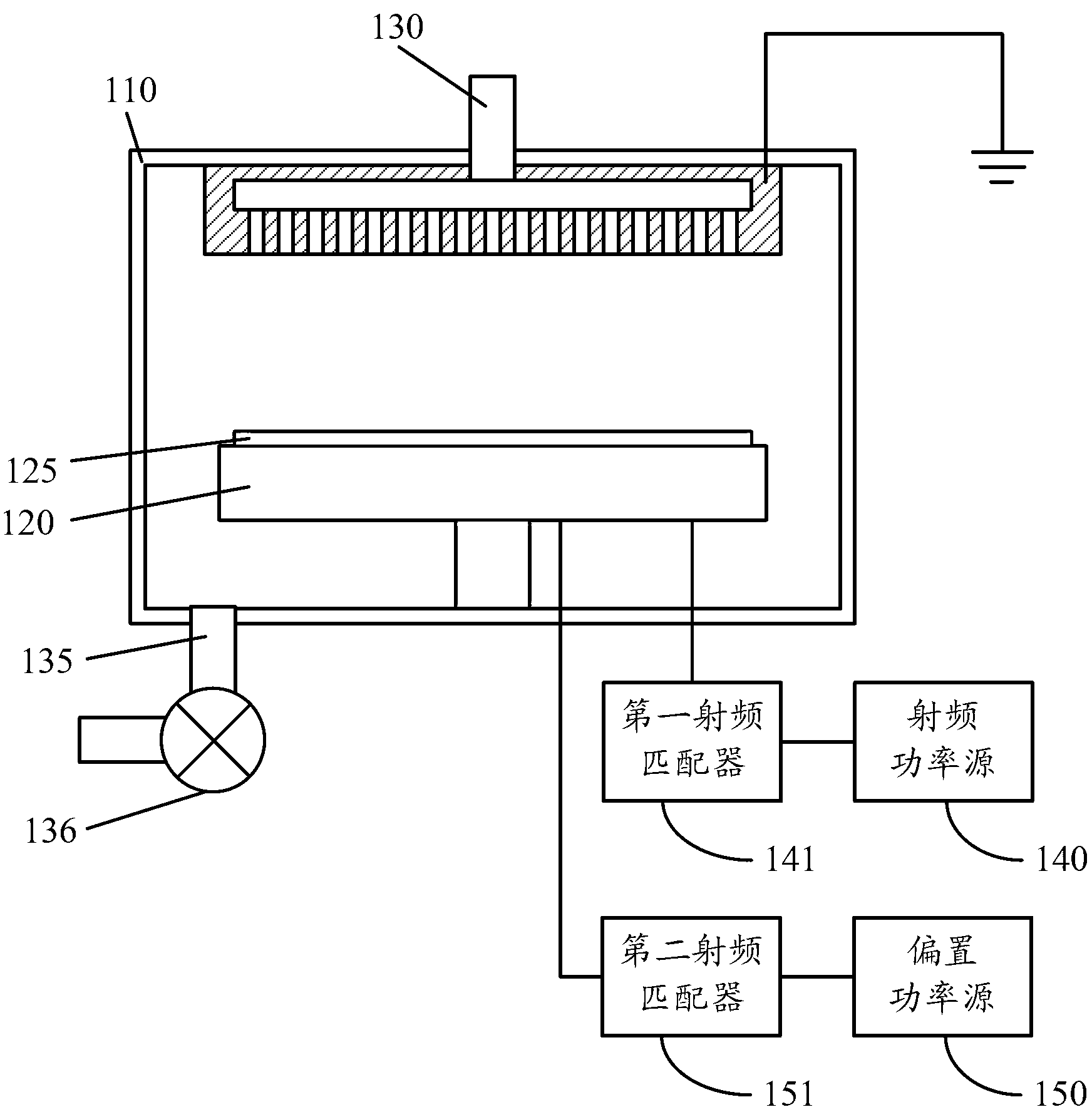

Bosch etching method

ActiveCN103400800AHigh bombardment energyLow bombardment energySemiconductor/solid-state device manufacturingRadio frequencyPolymer

The invention provides a Bosch etching method. The method comprises the following steps: a substrate is fixed on a base in a reaction chamber, and a mask layer with an opening is formed on the substrate; etching is performed: etching gas is piped in, a source radio frequency power source is applied to the reaction chamber so as to maintain plasma concentration in the reaction chamber, meanwhile, a first bias power source is applied to the base, and partial substrate is etched along the opening so as to form an etching hole; deposition is performed: deposition gas is piped in, a second bias power source is applied to the base, deposition is performed on the side wall surface of the etching hole and the surface of the mask layer so as to form a polymer, wherein the frequency of the second bias power source is larger than that of the first bias power source; etching and deposition are performed repeatedly until a through hole is formed in the substrate. The Bosch etching method provided by the invention can guarantee the etching rate, and meanwhile has higher stability.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

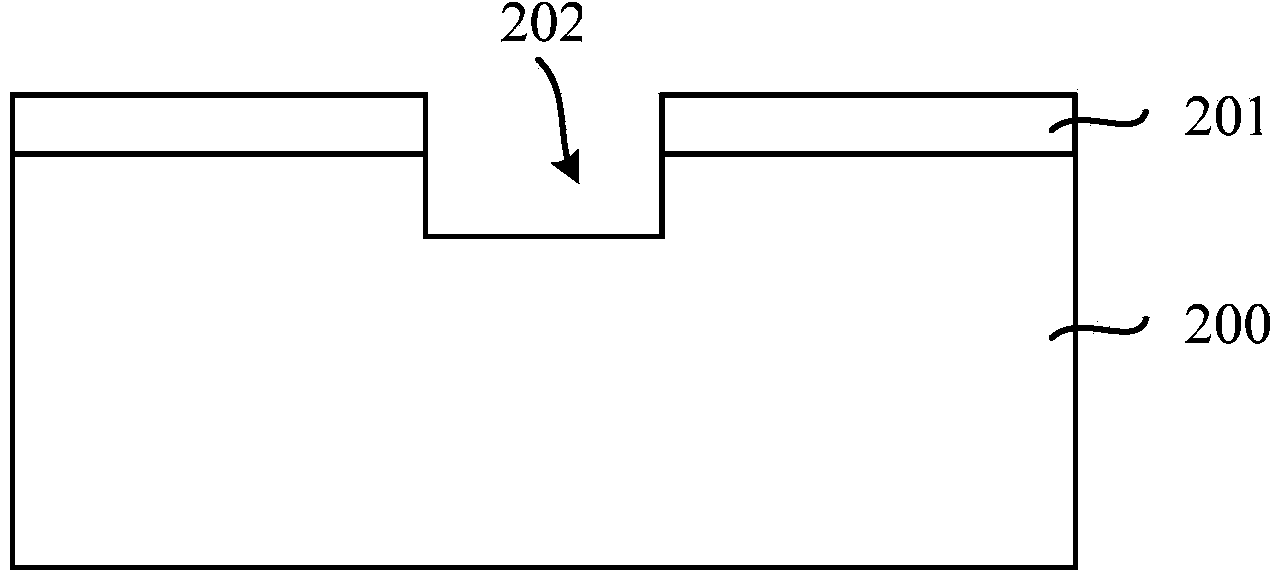

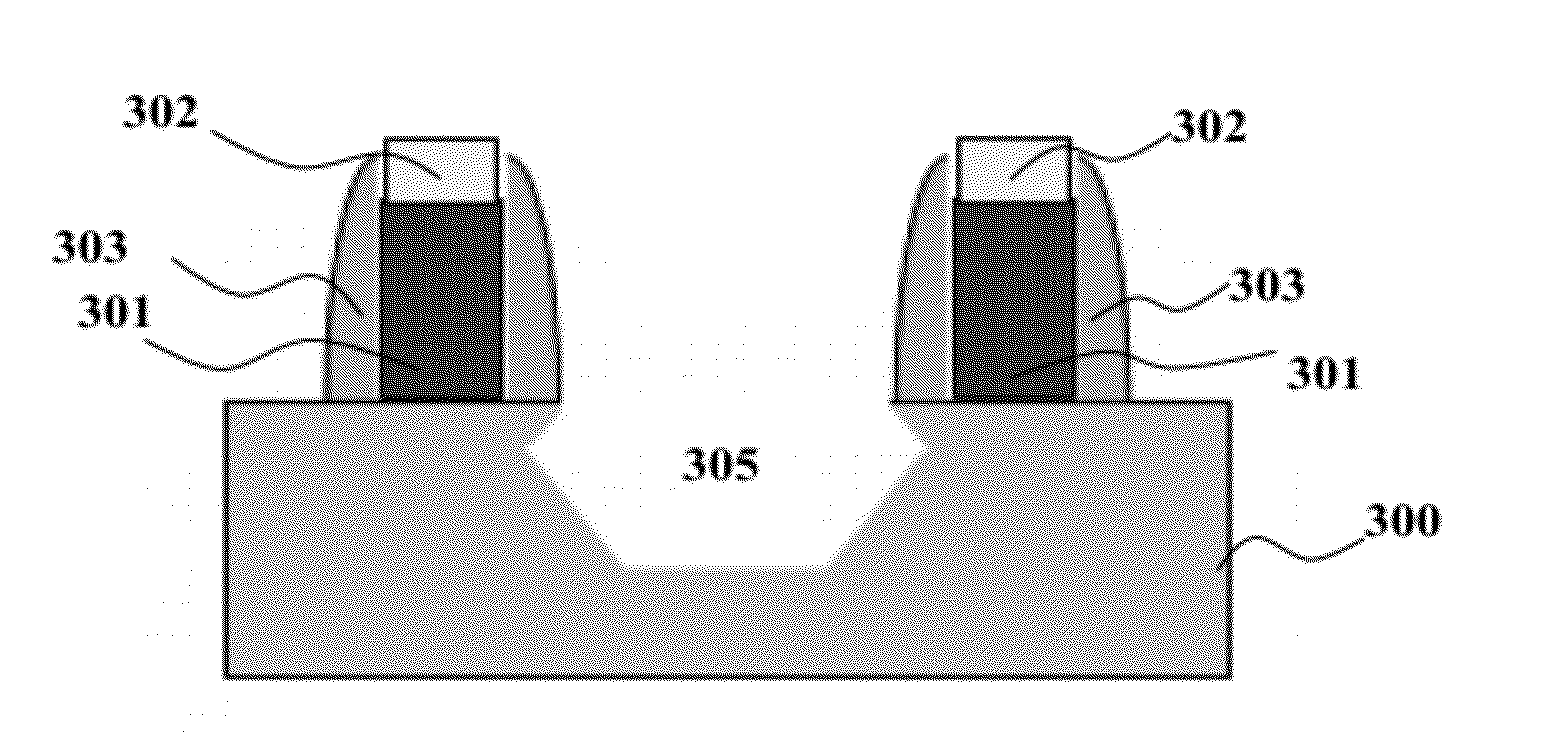

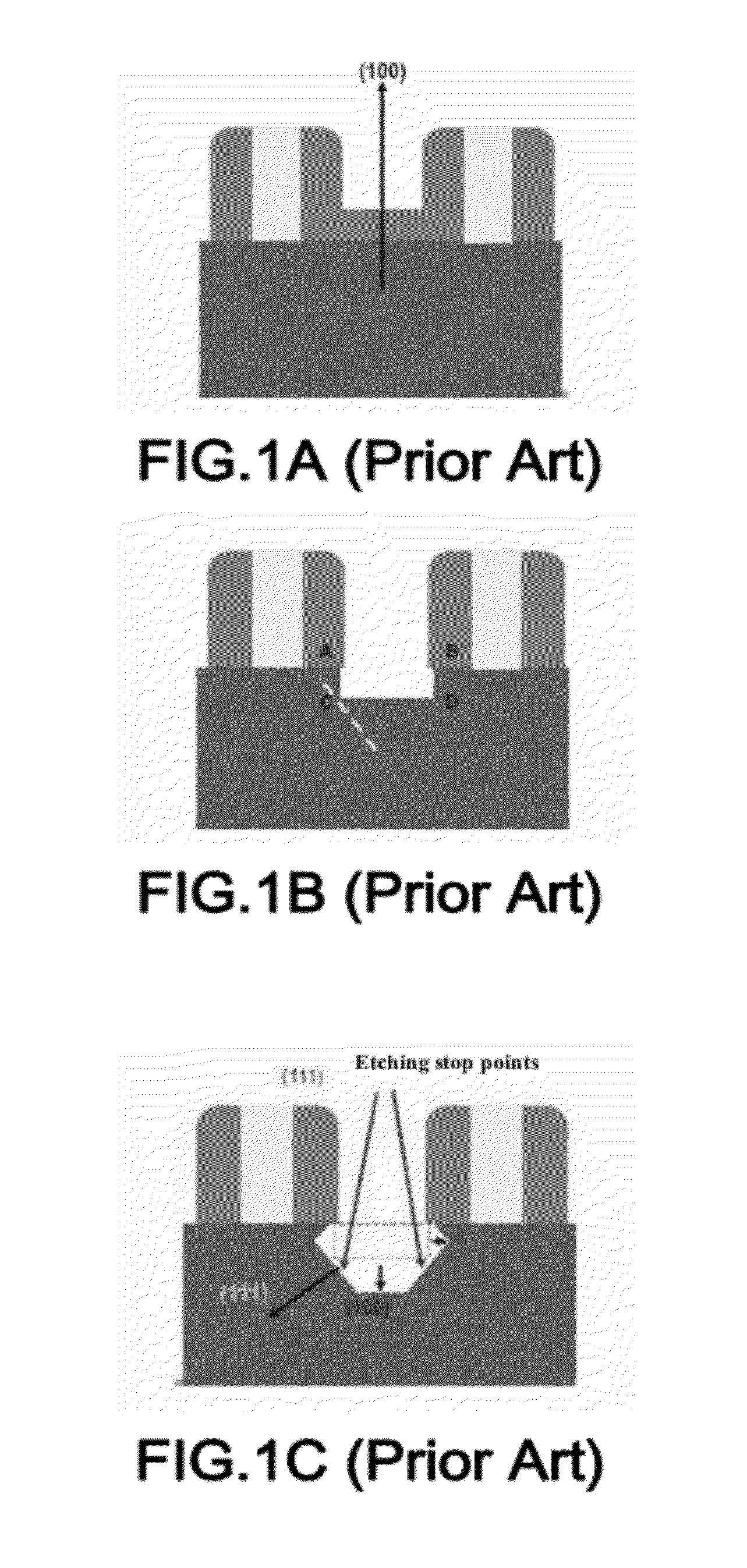

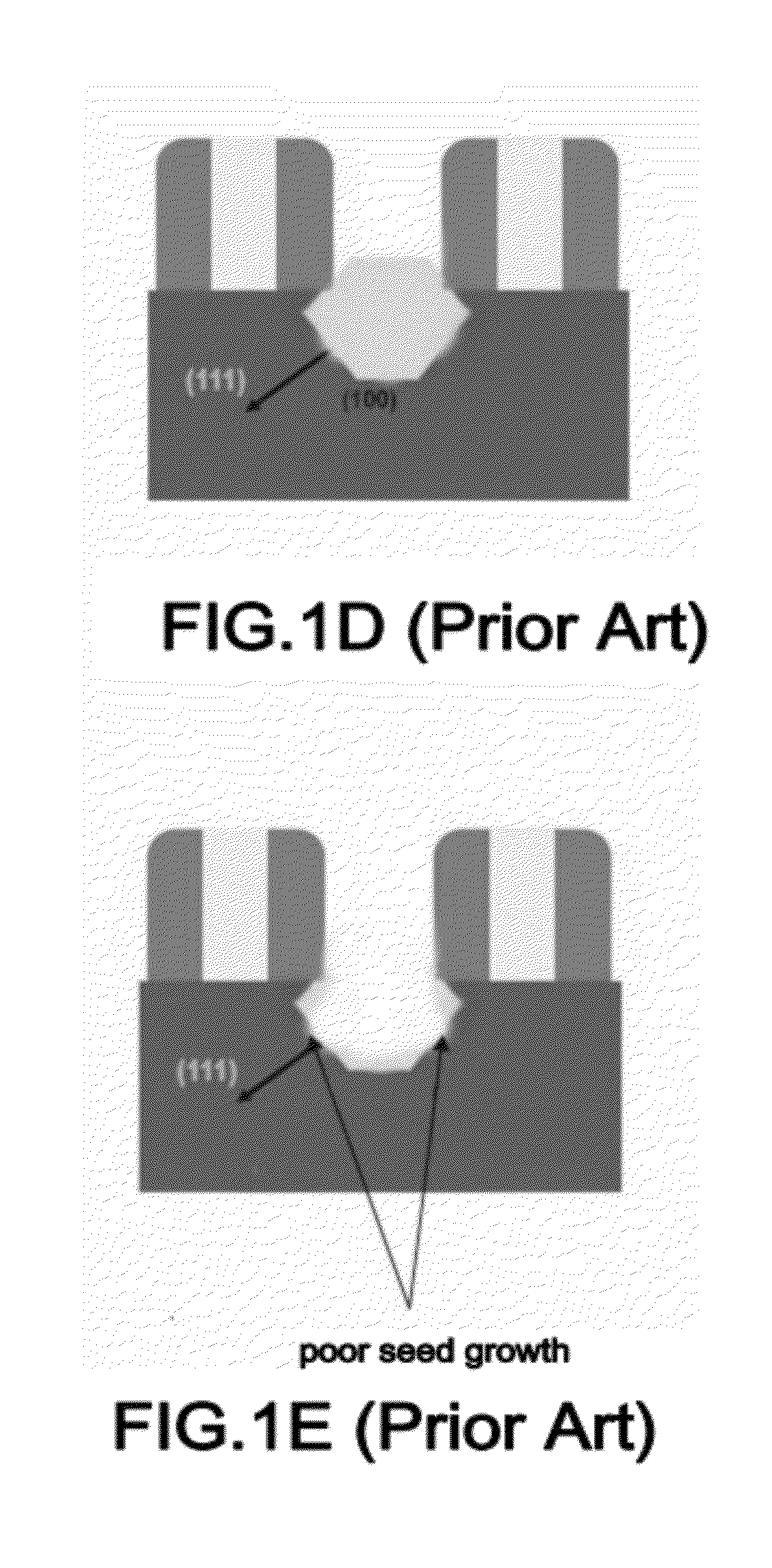

Method of fabricating semiconductor devices

ActiveUS20120309150A1Fast etch rateSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingEngineering

A method of fabricating a semiconductor device is provided. The method includes forming a gate having a first material on a substrate and a layer of a second material overlaying the gate. Sidewall spacers are formed on opposite sides of the gate. A characteristic of a portion of the substrate between adjacent sidewall spacers is changed using the layer of second material and the sidewall spacers as a mask. An isotropic wet etch process is performed to remove the substrate portion with a changed characteristic to form a recess in the substrate. An orientation selective wet etching process is performed on the recess to shape the inner walls of the recess into sigma-shape. Changing a substrate characteristic in conjunction with isotropic wet etching prevents the substrate from being damaged, and therefore can obtain defect free epitaxial SiGe growth performance.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

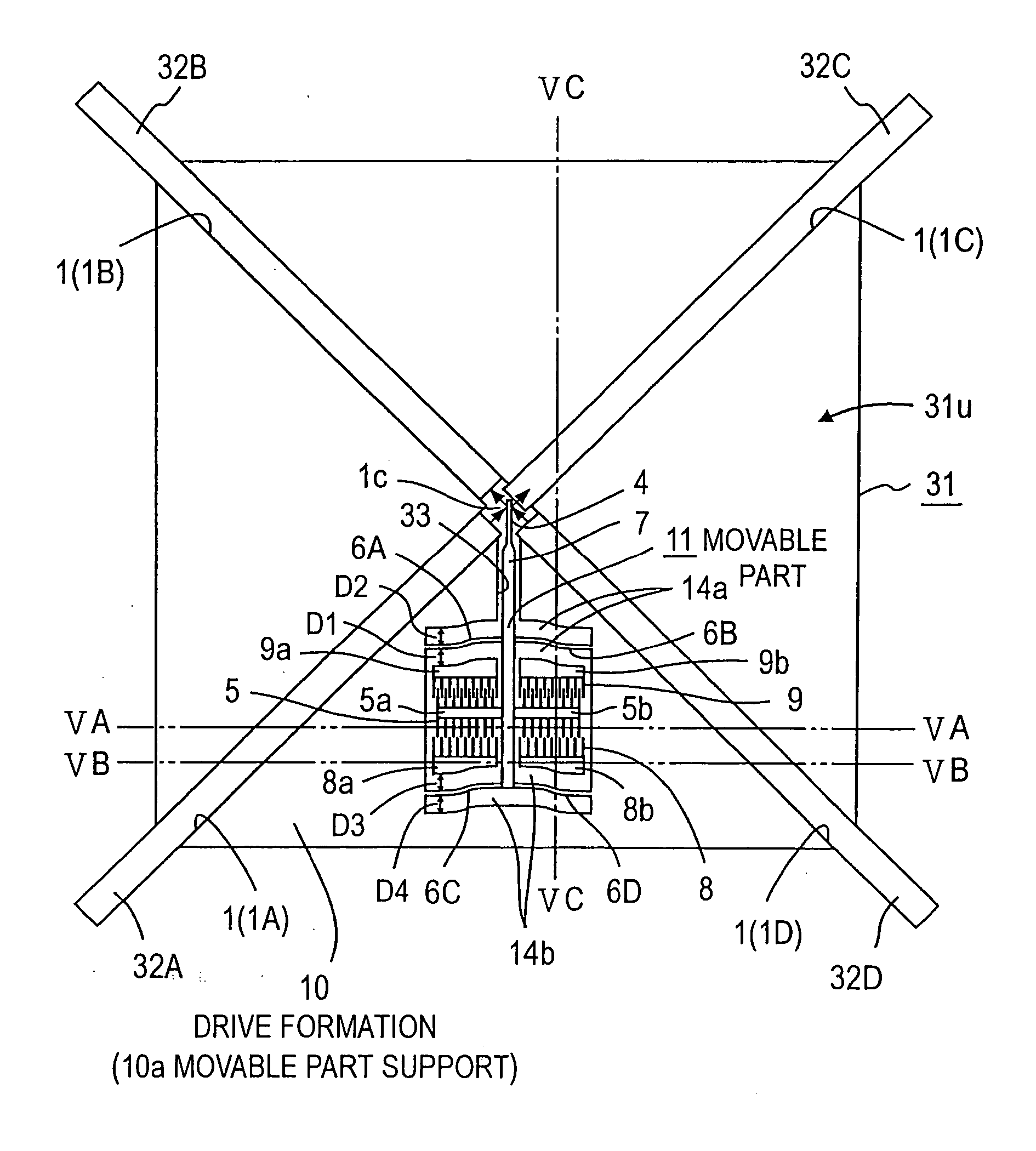

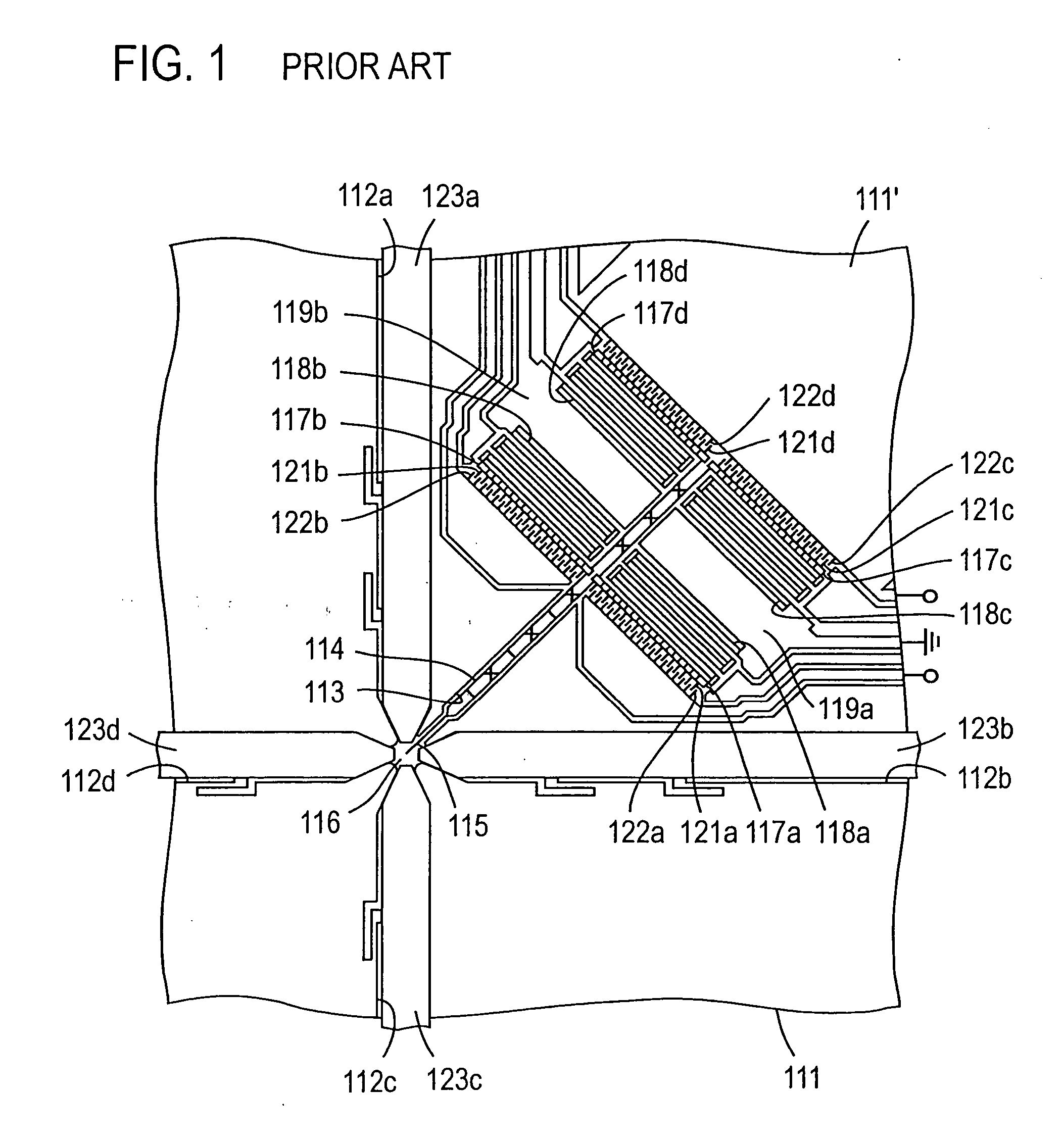

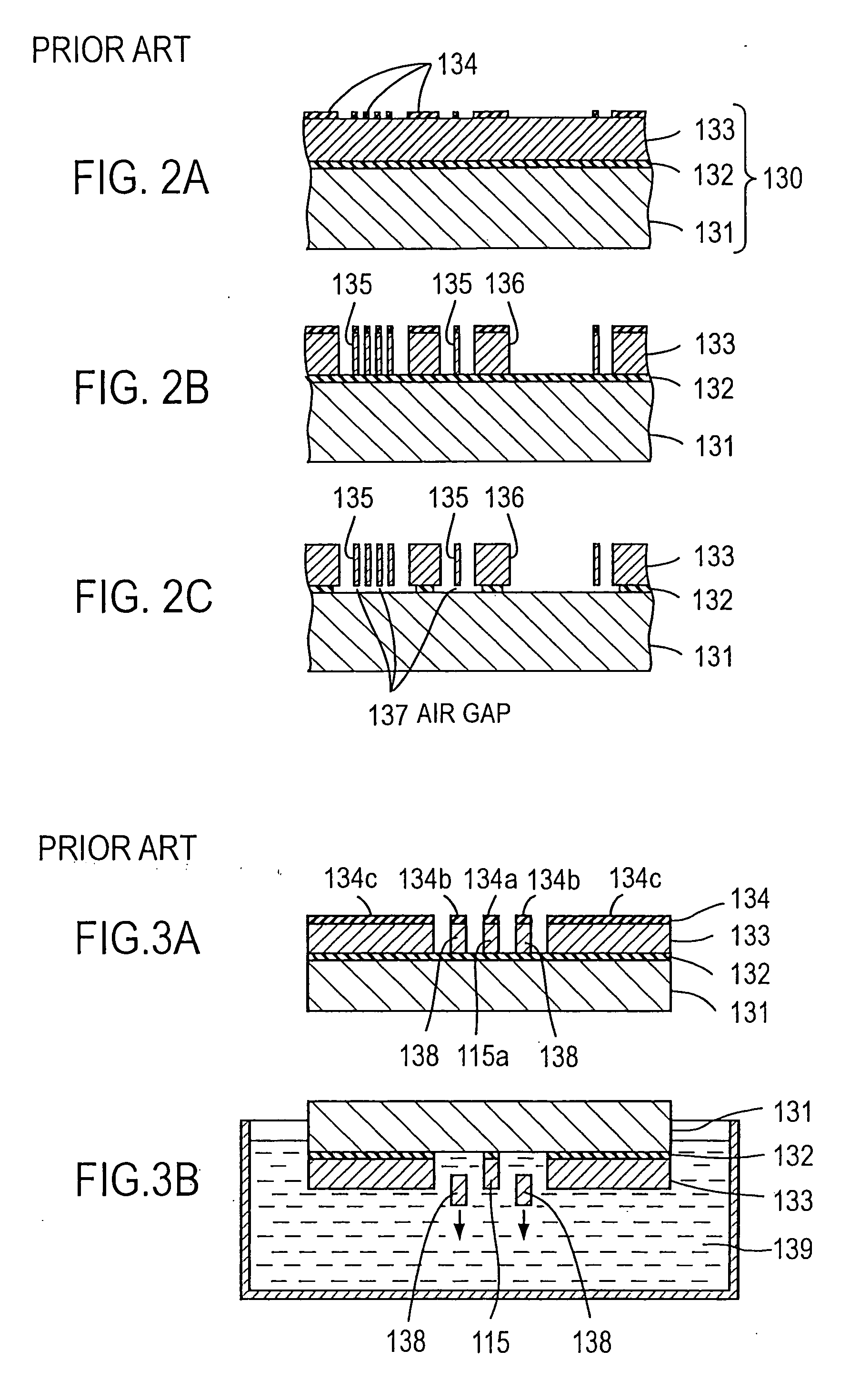

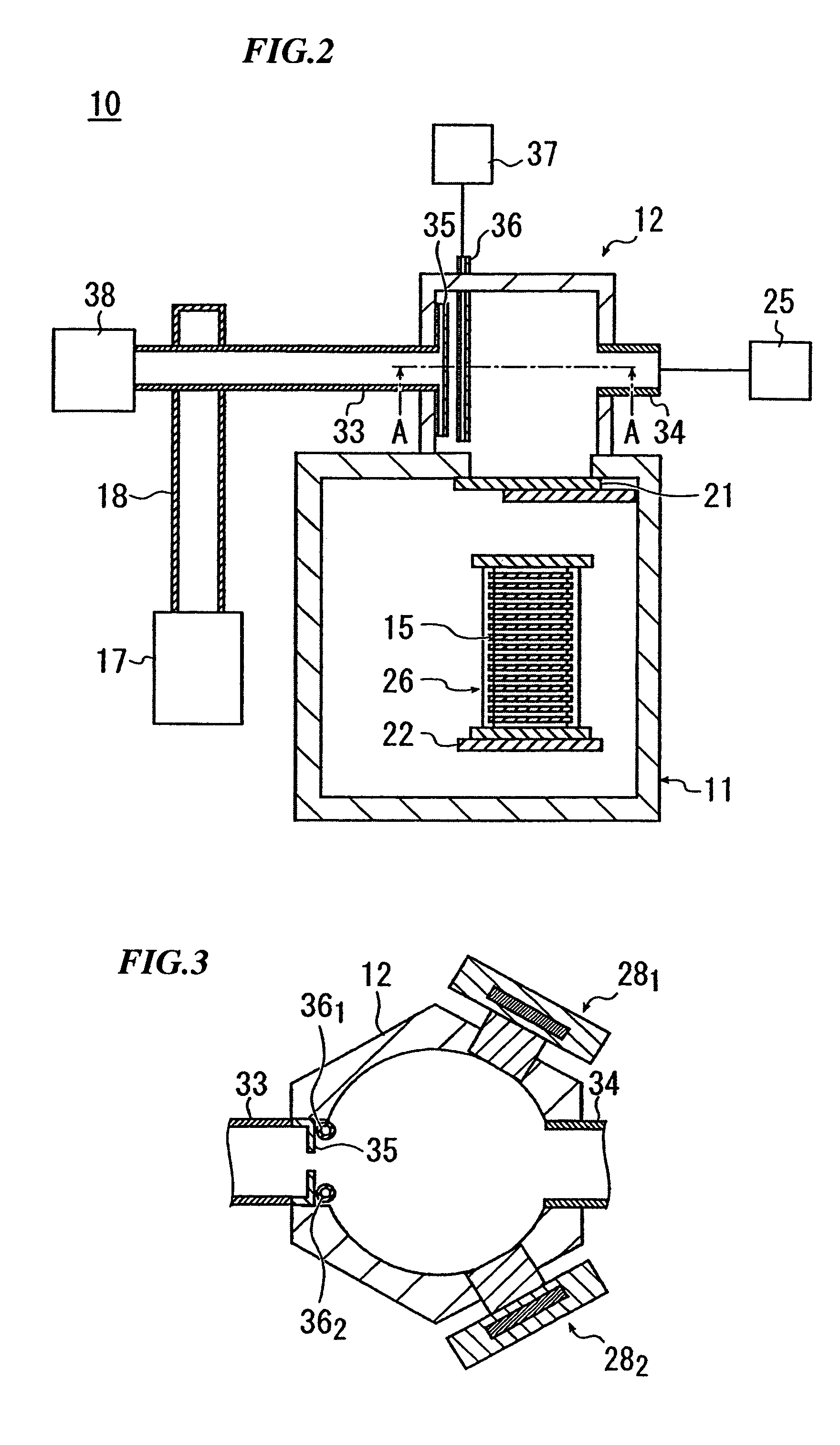

Micro-optic device and method of manufacturing same

InactiveUS20050069246A1Shorten the length of timeHigh yieldDecorative surface effectsCoupling light guidesSilicon dioxideDry etching

A micro-optic device including a complicate structure and a movable mirror is made to be manufactured in a reduced length of time. A silicon substrate and a single crystal silicon device layer with an intermediate layer of silicon dioxide interposed therebetween defines a substrate on which a layer of mask material is formed and is patterned to form a mask having the same pattern as the configuration of the intended optical device as viewed in plan view. A surface which is to be constructed as a mirror surface is chosen to be in a plane of the silicon crystal. Using the mask, the device layer is vertically etched by a reactive ion dry etching until the intermediate layer is exposed. Subsequently, using KOH solution, a wet etching which is anisotropic to the crystallographic orientation is performed with an etching rate which is on the order of 0.1 μm / min for a time interval on the order of ten minutes is performed to convert the sidewall surface of the mirror into a smooth crystallographic surface. Subsequently, the intermediate layer is selectively subject to a wet etching to remove the intermediate layer only in an area located below the movable part of the optical device.

Owner:JAPAN AVIATION ELECTRONICS IND LTD

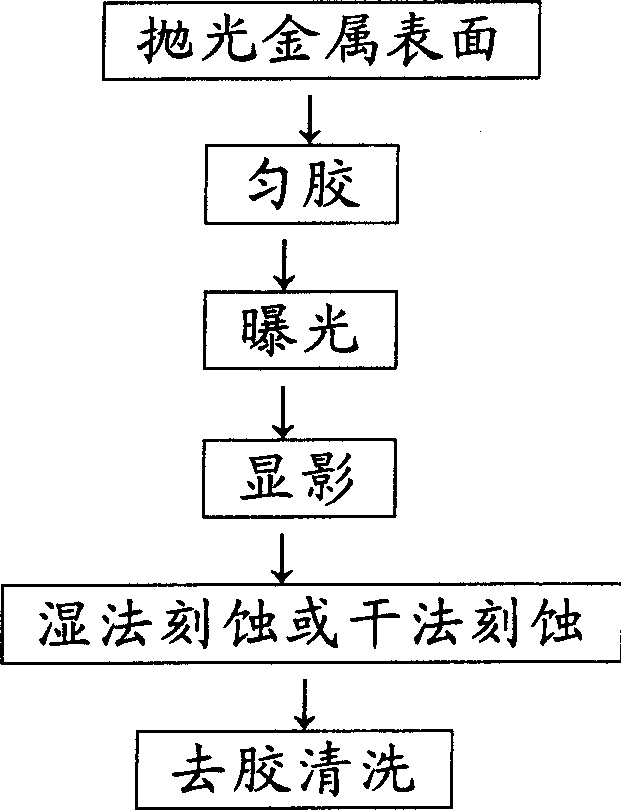

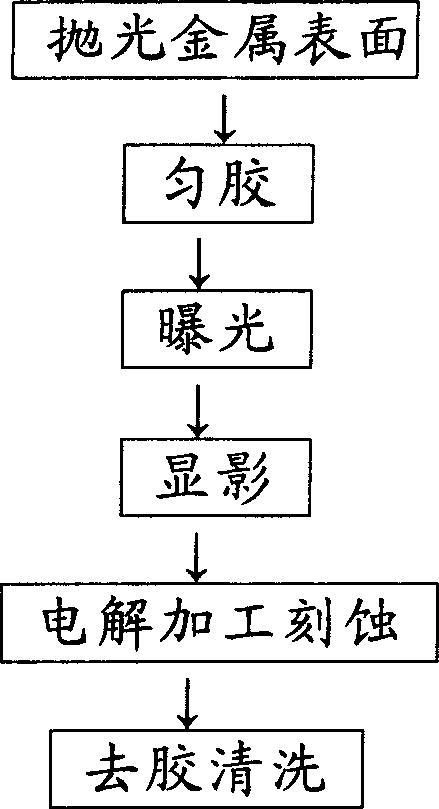

Metal grating template making process

The metal grating template making process includes photoetching comprising homogenizing photoresist, exposure, developing and other steps to form photoresist grating pattern; electrolytic etching via setting metal workpiece as positive electrode inside the electrolyte with the grating pattern side set opposite to the negative electrode to etch out the exposed the grating pattern to form grooves while protecting the photoresist masked metal surface; and taking out the metal template after reaching the required etching depth, eliminating photoresist and cleaning to obtain the metal grating template. The metal grating template making process of the present invention is simple, low in cost and fast, and etched pattern is smooth and precise.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

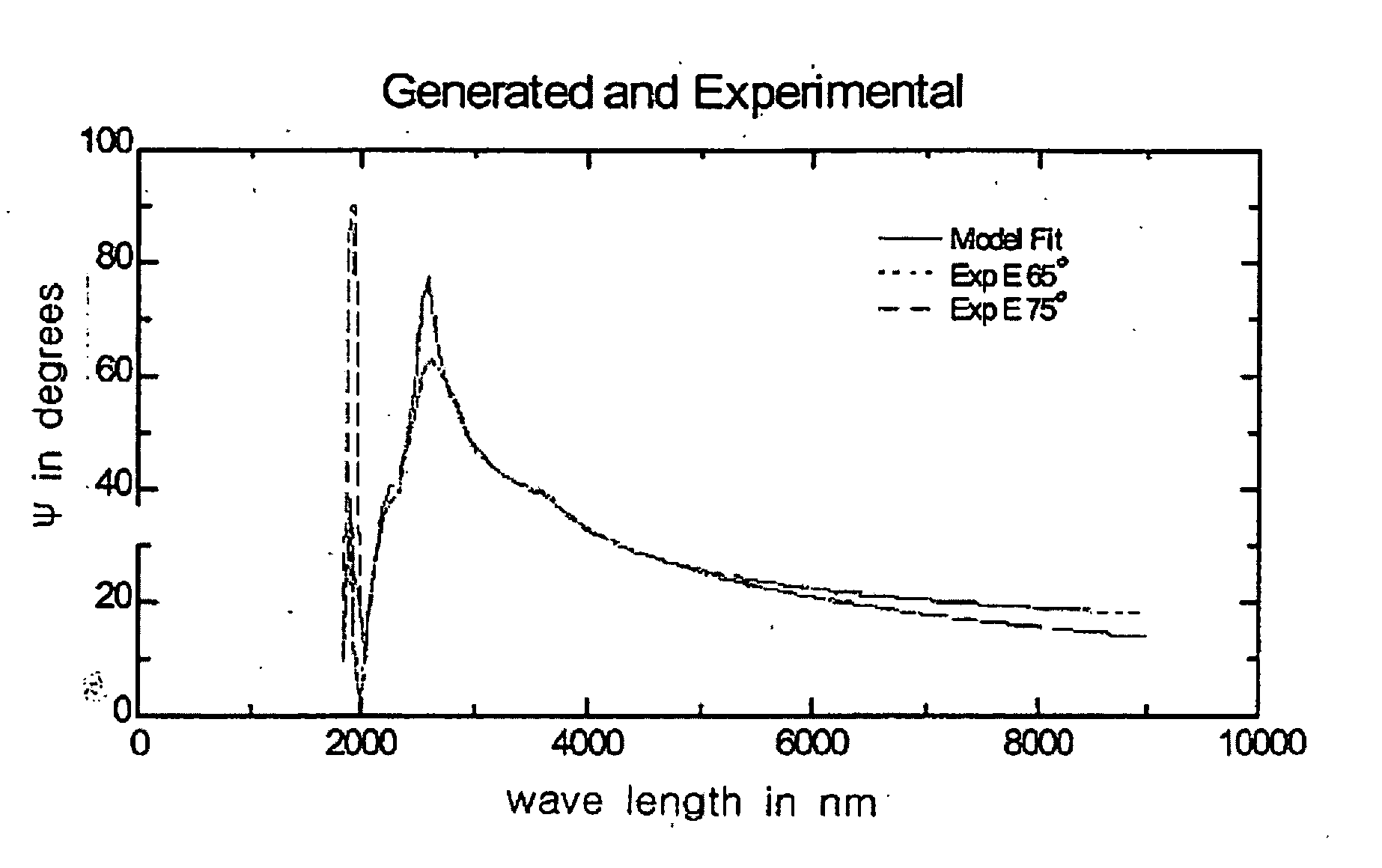

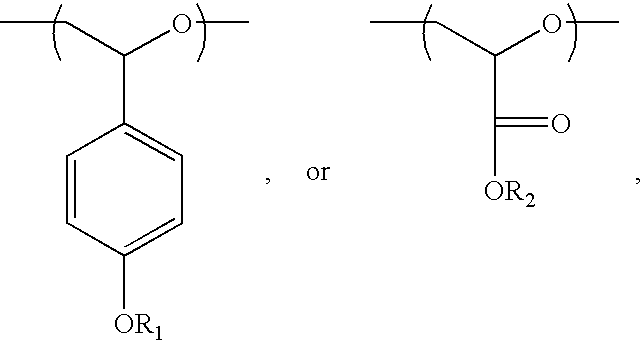

Polymer for forming anti-reflective coating layer

InactiveUS20060134558A1Improve adhesionFast etch ratePhotosensitive materialsPhotomechanical apparatusAnti-reflective coatingHydrogen

A polymer for forming an organic anti-reflective coating layer between an etching layer and a photoresist layer to absorb an exposure light in a photolithography process and a composition comprising the same are disclosed. The polymer for forming an organic anti-reflective coating layer has a repeating unit represented by wherein, R1 is hydrogen or methyl group, and R2 is a substituted or non-substituted alky group of C1 to C5. The composition for forming the organic anti-reflective coating layer includes the polymer having the repeating unit represented by above Formulas; a light absorber; and a solvent.

Owner:DONGJIN SEMICHEM CO LTD

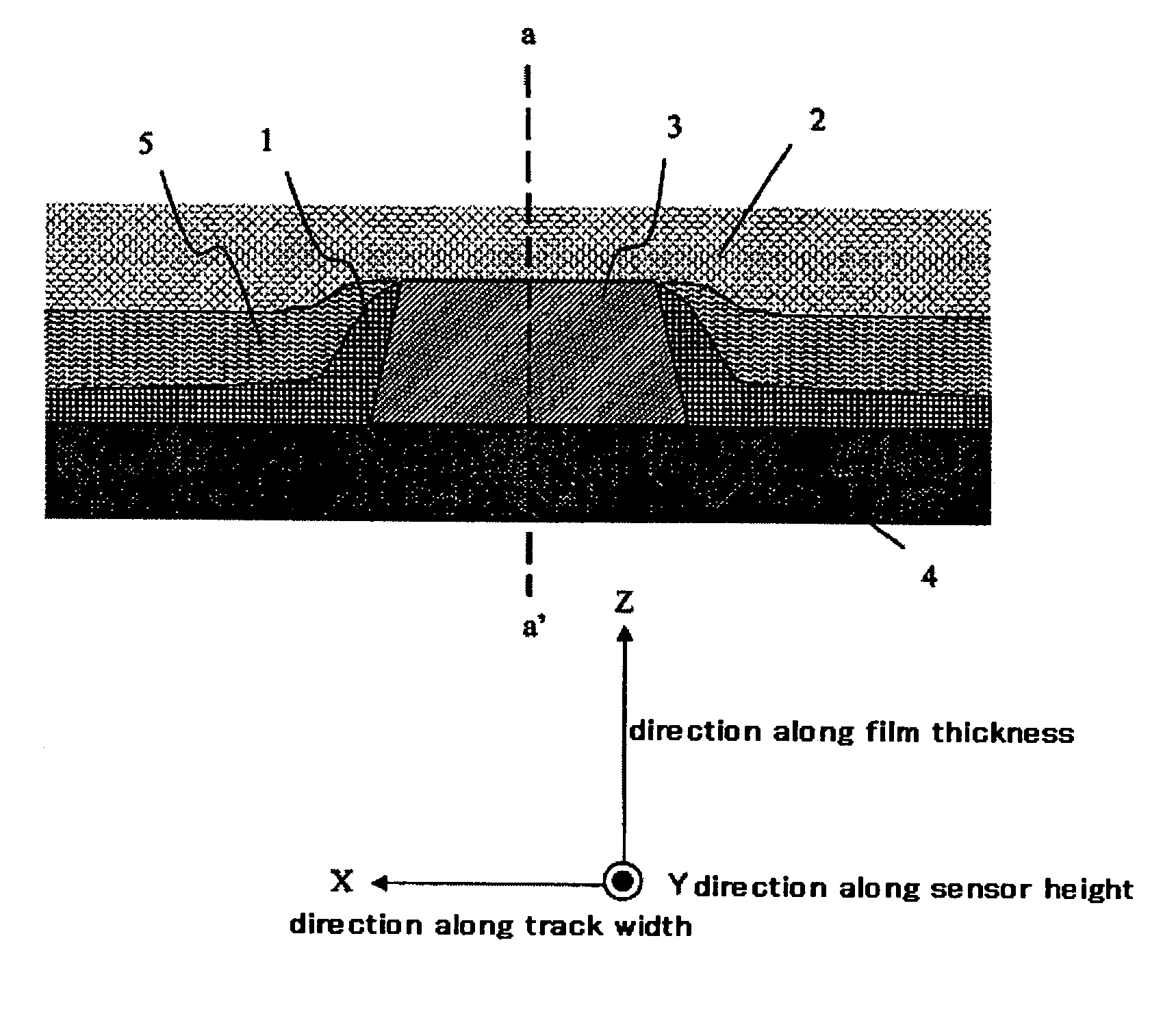

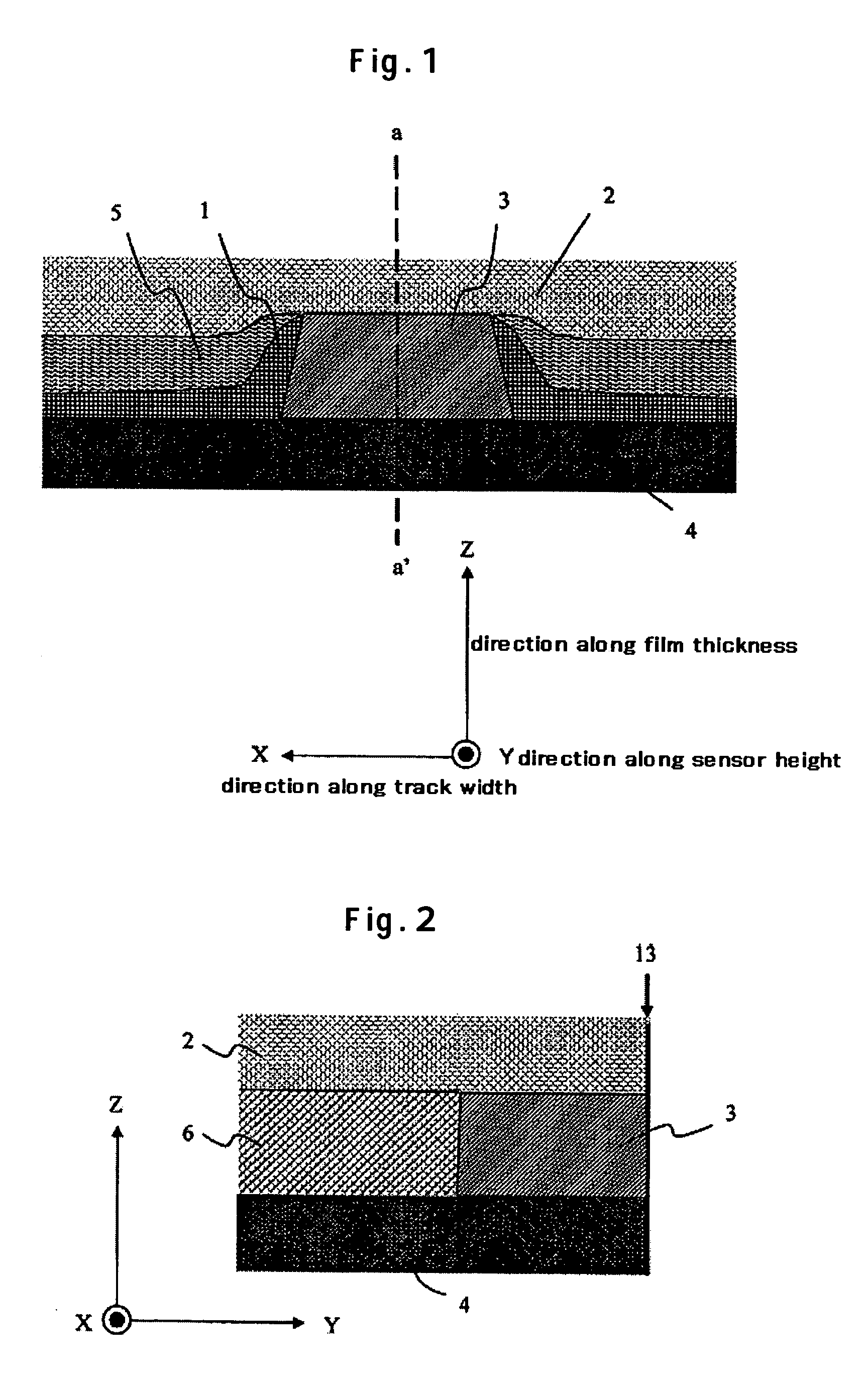

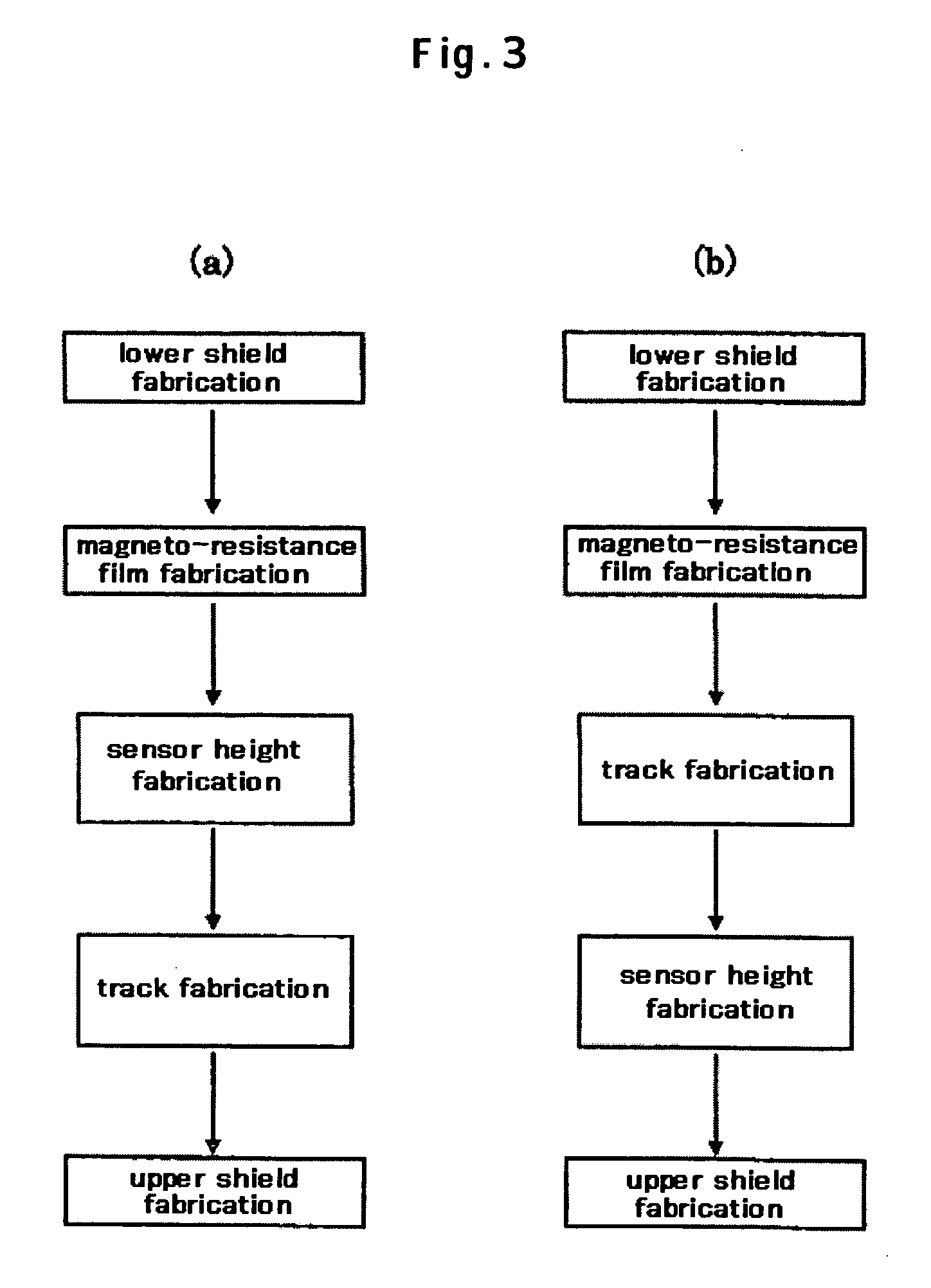

Magnetoresistive sensor with refill film, fabrication process, and magnetic disk storage apparatus mounting magnetoresistive sensor

InactiveUS20060007603A1Etching rate is slowMinimizing deteriorationNanomagnetismNanoinformaticsMagnetic reluctanceEngineering

Embodiments of the invention provide a high-output magnetic reading head by making it easy to remove a re-deposited substance that deposits on the side wall surface in the track width direction or the side wall surface in the sensor height direction of a magneto-resistance film in a fabrication process of the magnetic reading head. In one embodiment, a refill film that is fabricated first of a refill film along track width direction or a refill film along sensor height direction is fabricated such that a layer in contact with the magneto-resistance film is formed of a material that is slow in etching rate but possible to minimize deterioration of characteristics due to thermal treatment and a layer(s) other than the layer in contact with the magneto-resistance film is formed of a material(s) that is fast in etching rate.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

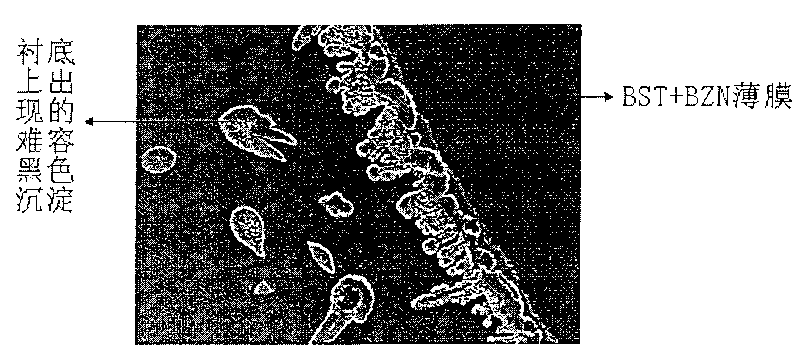

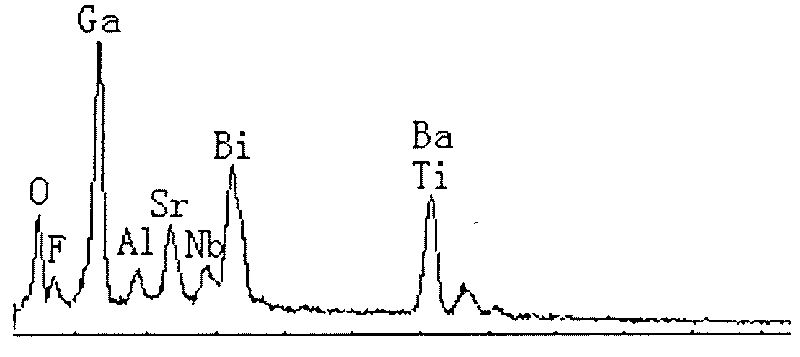

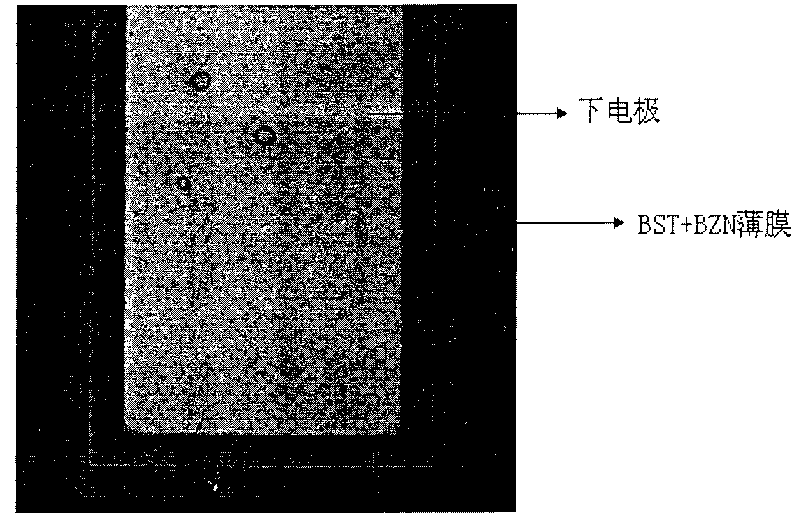

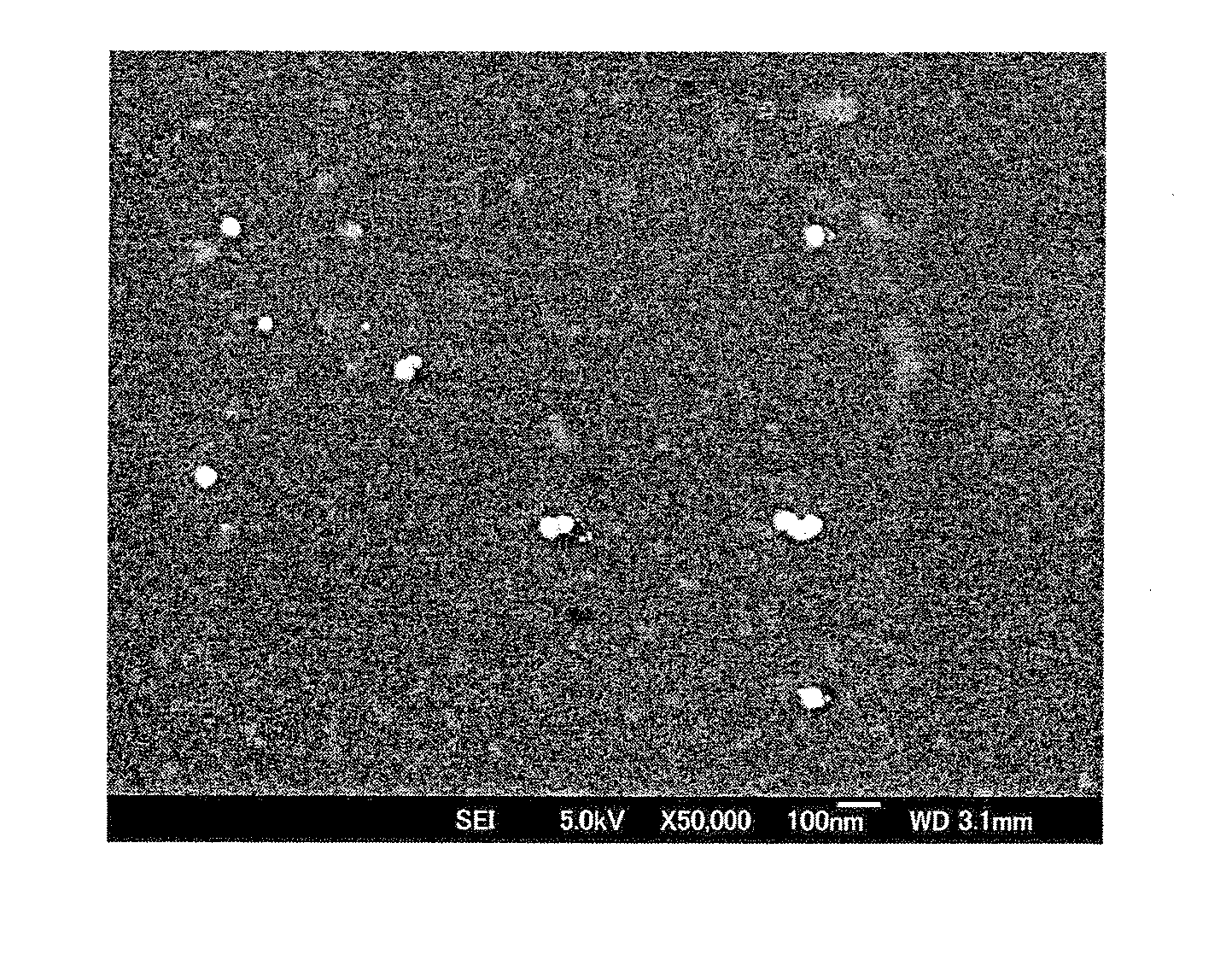

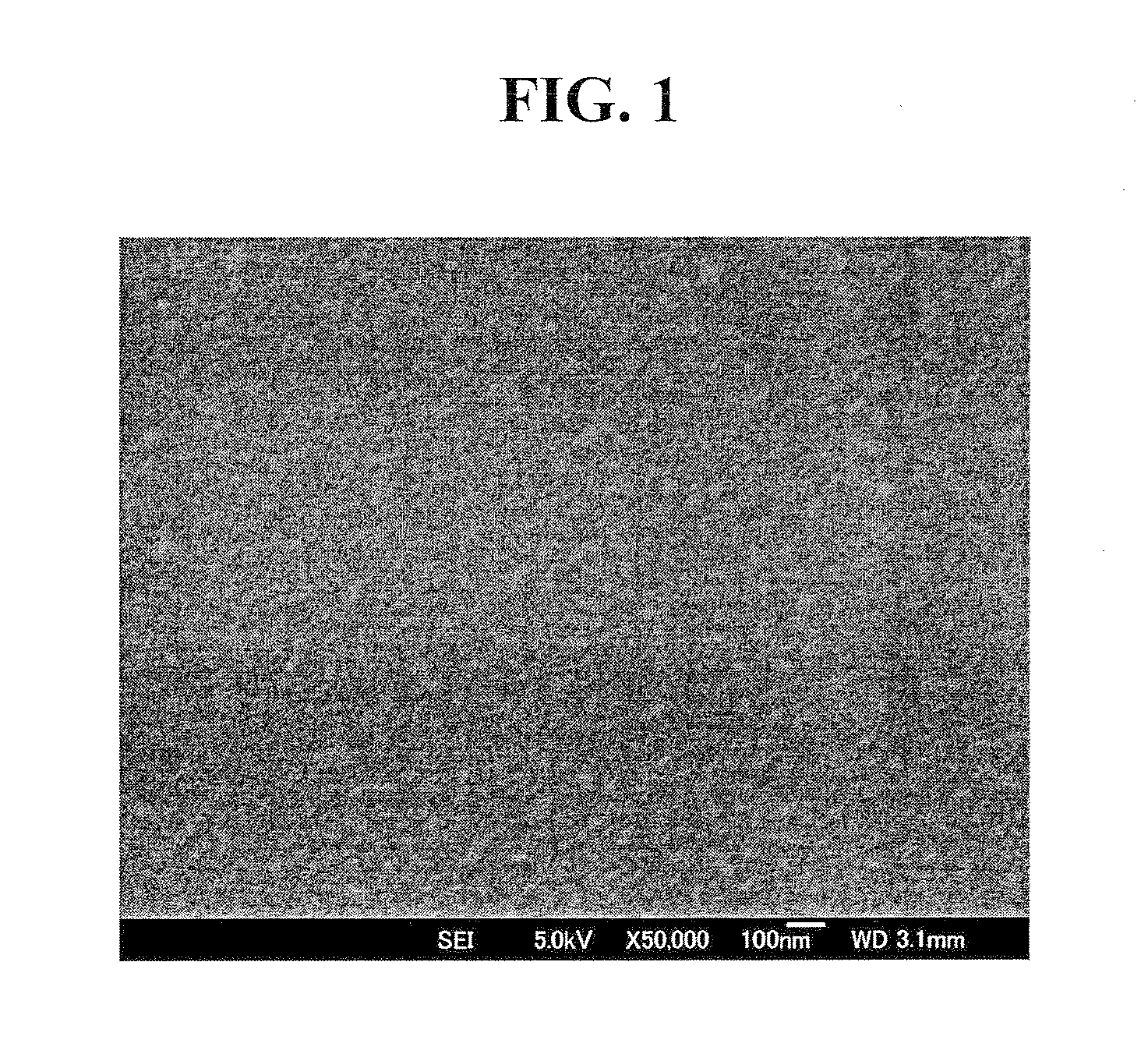

Wet etching method of barium-strontium titanate and bismuth zinc niobate composite films

InactiveCN101694012AUniform etch rateIncrease etch ratePolycrystalline material growthAfter-treatment detailsPolymer scienceComposite film

A processing method of barium-strontium titanate and bismuth zinc niotate composite films is characterized by 1, preparing a photoresist mask graphic on the surface of a BST+BZN composite film sample, 2, preparing etching: A is water solution prepared by nitricacid (HNO3), hydrofluoric acid (HF) and citrate (CA), and B is water prepared by hydrochloric acid (HC1) and hydrofluoric acid (HF), 3, sequentially etching the BST+BZN composite film sample in etching solutions A,B, and determining etching time according to respective thicknesses of BST and BZN, 4, removing a photoresist mask by aid of acetone / alcohol, and preparing the photoresist mask again, 5, performing low-power ultrasonic processing on the BST+BZN composite film sample in the etching A, and 6, utilizing the acetone / alcohol to remove the photoresist mask, cleaning the sample, and drying the sample by nitrogen (N2). Surfaces of positions etched by the processing method do not have residue, and then the processing method is complete in etching and high in graphic transforming precision.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

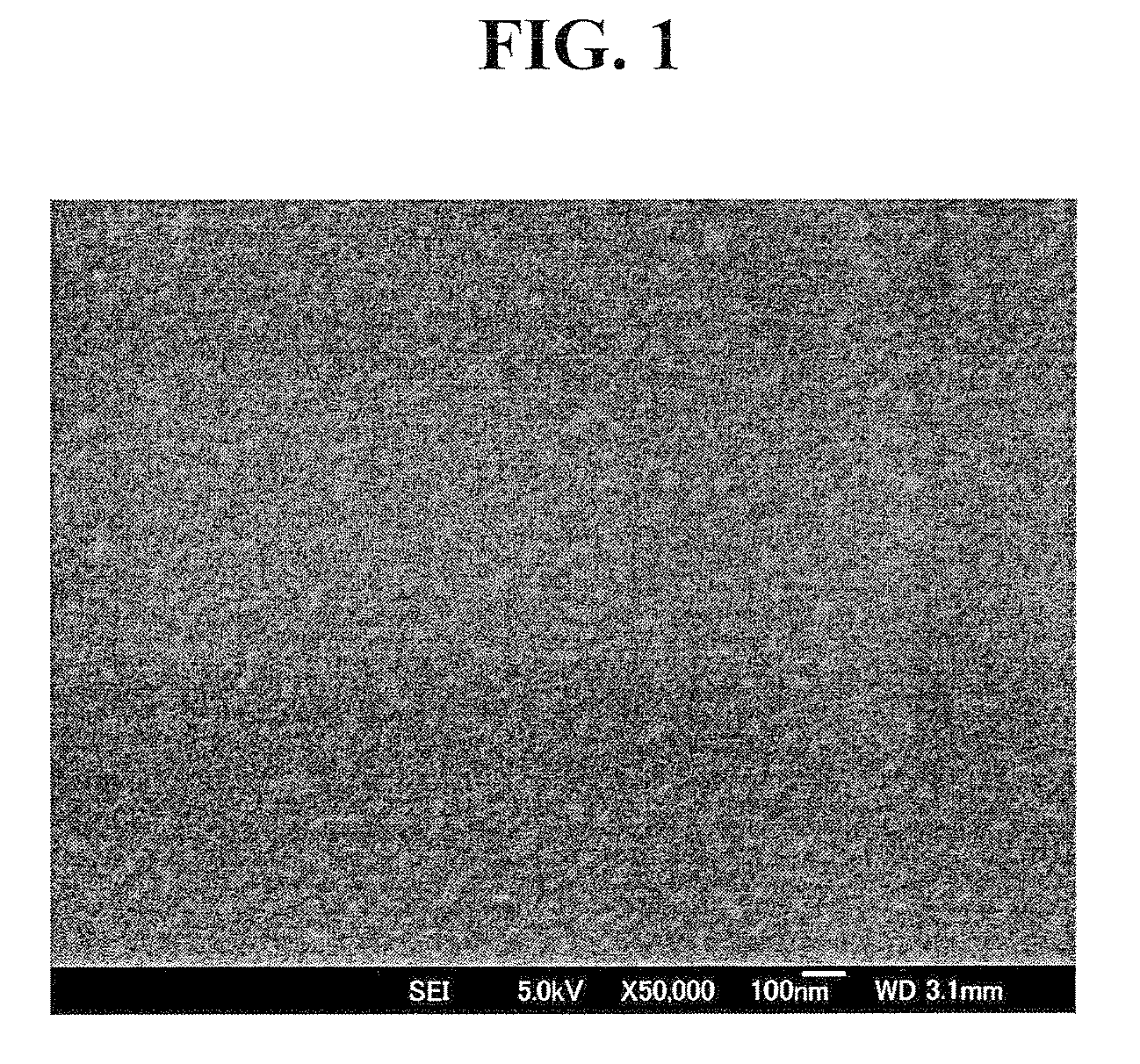

Sintered Compact of Composite Oxide, Amorphous Film of Composite Oxide, Process for Producing said Film, Crystalline Film of Composite Oxide and Process for Producing said Film

ActiveUS20100140570A1Low resistivity of filmGood effectConductive layers on insulating-supportsCell electrodesIndiumDisplay device

Provided is an amorphous film substantially comprised of indium, tin, calcium and oxygen, wherein tin is contained at a ratio of 5 to 15% based on an atomicity ratio of Sn / (In+Sn+Ca) and calcium is contained at a ratio of 0.1 to 2.0% based on an atomicity ratio of Ca / (In+Sn+Ca), and remnant is indium and oxygen. The film can be further crystallized by annealing at a temperature of 260° C. or lower in which resistivity of the film will be 0.4 mΩcm or less. An ITO thin film for use as a display electrode or the like in a flat panel display can be made into an amorphous ITO film by way of sputter deposition without heating the substrate or adding water during deposition. This ITO film is characterized in that it will crystallize by annealing at a temperature of 260° C. or less, which is not such a high temperature, and have low resistivity after being crystallized. Thus, the present invention aims to provide a method of producing such a film and a sintered compact for producing such a film.

Owner:JX NIPPON MINING& METALS CORP

Layered polyimide/metal product

InactiveUS20060127685A1Improve heat resistanceSuppressing expansionSynthetic resin layered productsInsulating layers/substrates workingMetal foilHeat resistance

A polyimide metal laminate comprising a polyimide resin formed on a metal foil, wherein the polyimide resin does not cause the peeling of not less than 100 μm in the polyimide resin and / or at an interface between the polyimide resin and the metal foil when the polyimide resin is heated in an oven at an atmospheric temperature of from 340 to 360° C. for 5 to 10 minutes, the coefficient of humidity expansion at 320 is from 1 to 20 ppm / % RH, and an average value of the etching rate by a 50 wt % aqueous solution of potassium hydroxide at 80° C. is not less than 1.0 μm / min. The polyimide metal laminate can provide good heat resistance, superior dimensional stability and can be etching processed by an aqueous alkaline solution.

Owner:MITSUI CHEM INC

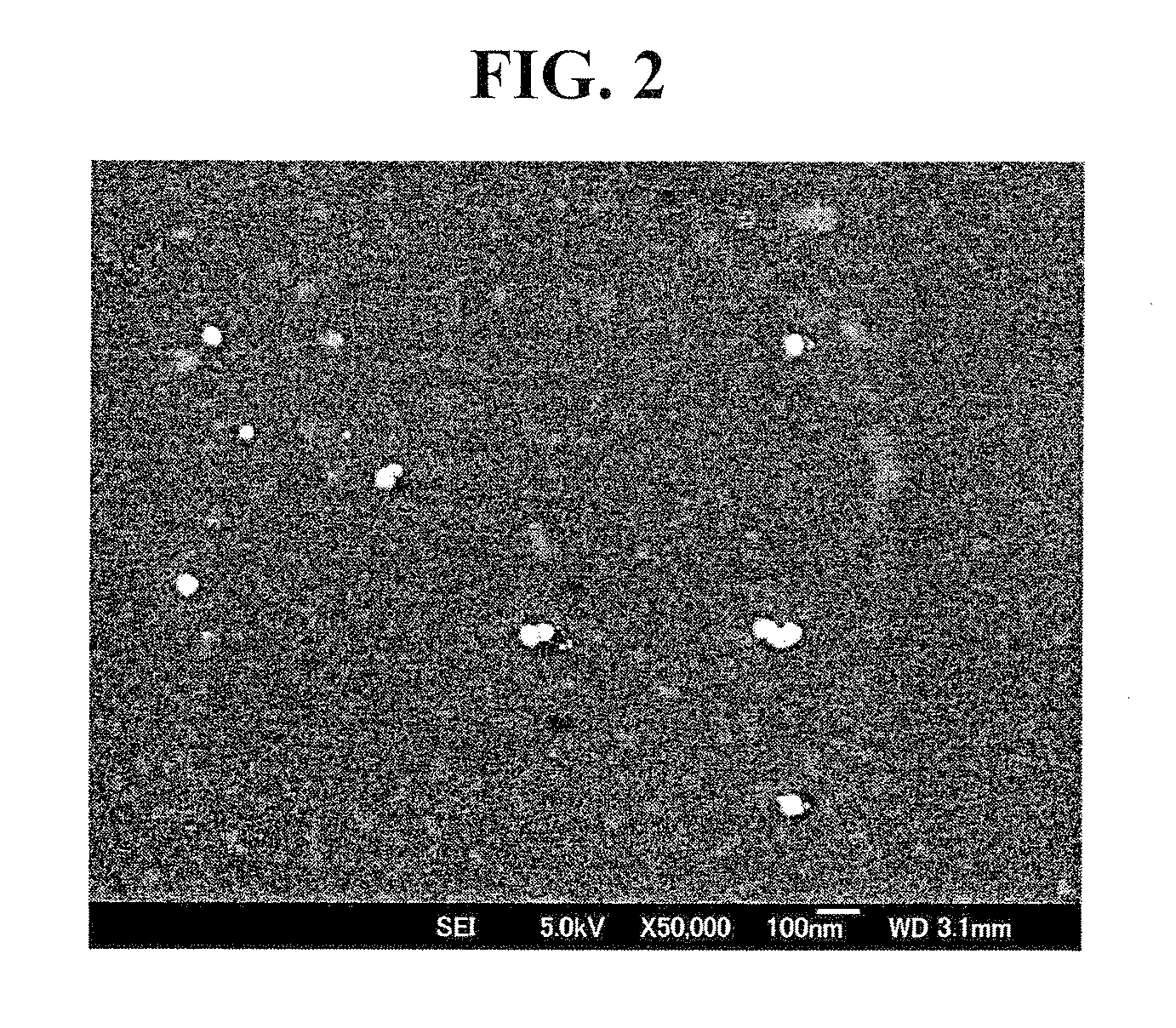

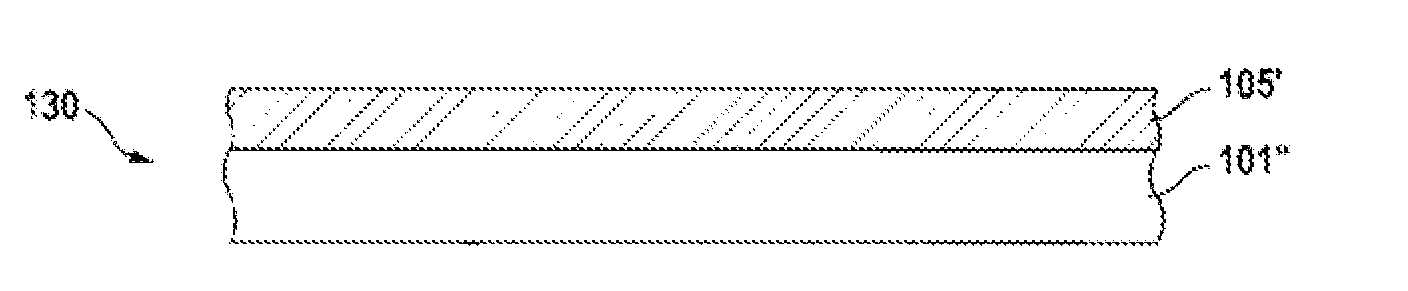

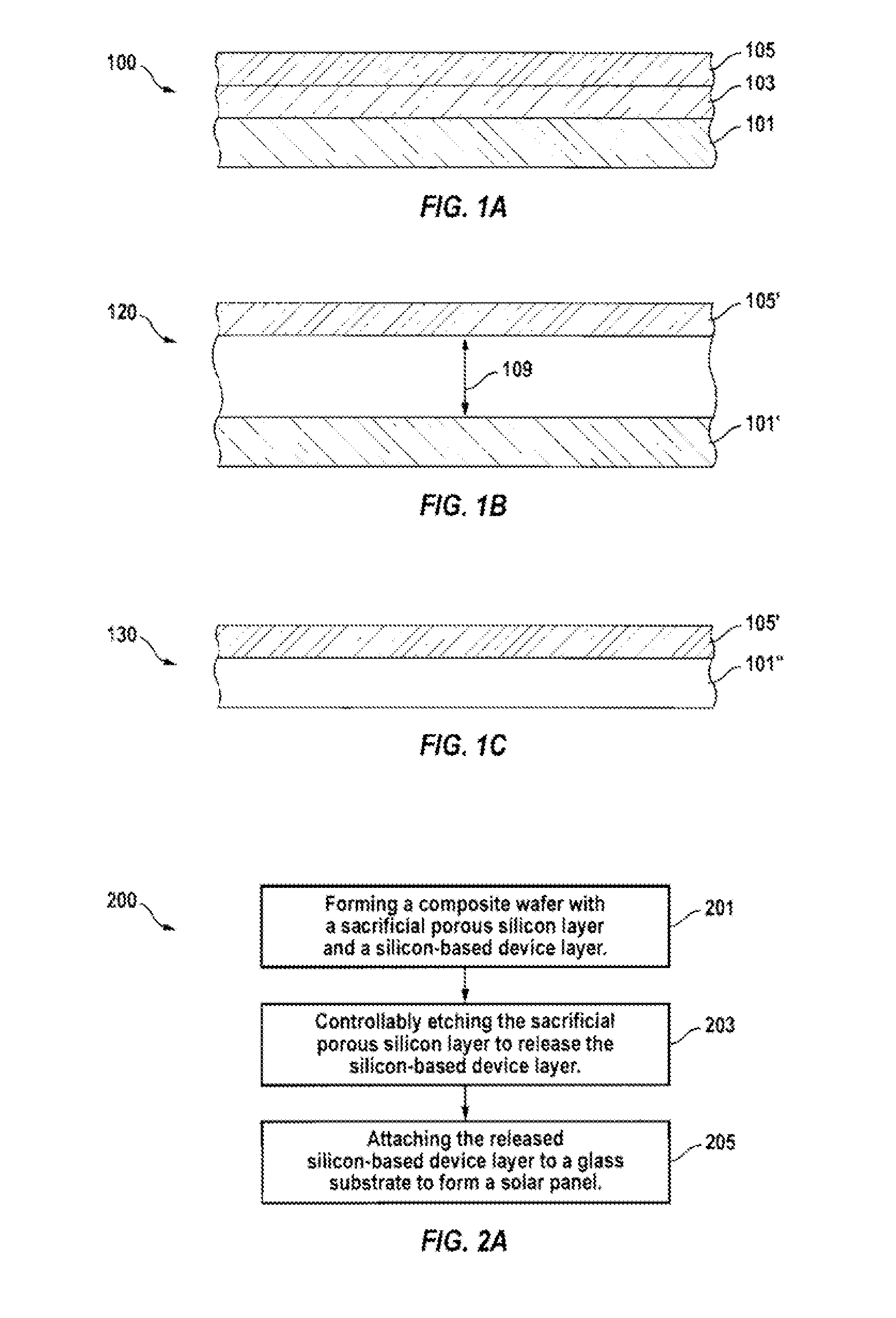

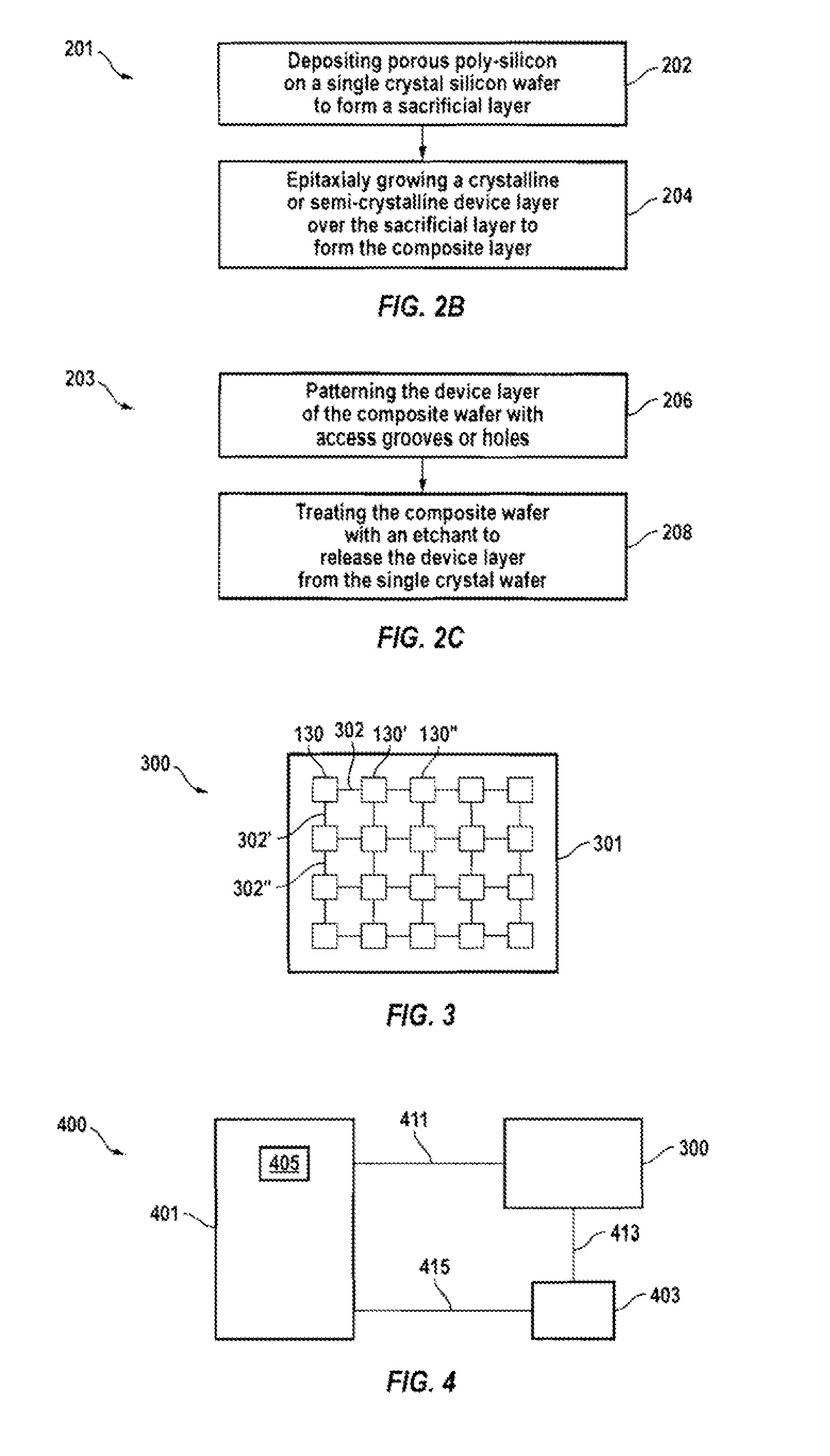

Method for selective under-etching of porous silicon

ActiveUS20100227432A1Fast etch rateFinal product manufactureSemiconductor/solid-state device manufacturingWaferingSolar cell

A method for making a solar cell is disclosed. In accordance with the method of the present invention a composite wafer is formed. The composite layer includes a single crystal silicon wafer, a silicon-based device layer and sacrificial porous silicon sandwiched therebetween. The composite wafer is treated to an aqueous etchant maintained below ambient temperatures to selectively etch the sacrificial porous silicon and release or undercut the silicon-based layer from the single crystal silicon wafer. The released silicon device layer is attached to a substrate to make a solar cell and the released single crystal silicon wafer is reused to make additional silicon device layer.

Owner:AKRION TECH

Method for manufacturing high-performance double-layer polysilicon bipolar transistor

ActiveCN103915334AReduce doping upamplificationReduce high temperature process timeTransistorSemiconductor/solid-state device manufacturingIsolation effectElectrical resistance and conductance

The invention discloses a method for manufacturing a high-performance double-layer polysilicon bipolar transistor. The method comprises the following steps that 1), LOCOS and CVD are adopted to deposit SiO2 to form a composite isolation structure, and high-temperature process time is reduced; 2), the SiO2 is used as an etching stopping layer of base polysilicon, and etching damage is avoided; 3), a composite side wall structure is formed through SiO2 and N+polysilicon, and emitter resistance is reduced. The method has the advantages that on the premise of not lowering the isolation effect, the high-temperature process time is reduced, therefore, a relatively thin epitaxial layer can be adopted, the better microwave performance is obtained, SiO2 is adopted as the etching stopping layer, the etching damage to the silicon epitaxial layer is eliminated, breakdown characteristics are improved, current amplifying coefficients are increased, and noise coefficients are reduced. The composite side wall structure with SiO2 and N+polysilicon is adopted, it can be guaranteed that emitter-base electric isolation is carried out, and meanwhile the emitter resistance is lowered, the current amplifying coefficients are increased, and the noise coefficients are reduced.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

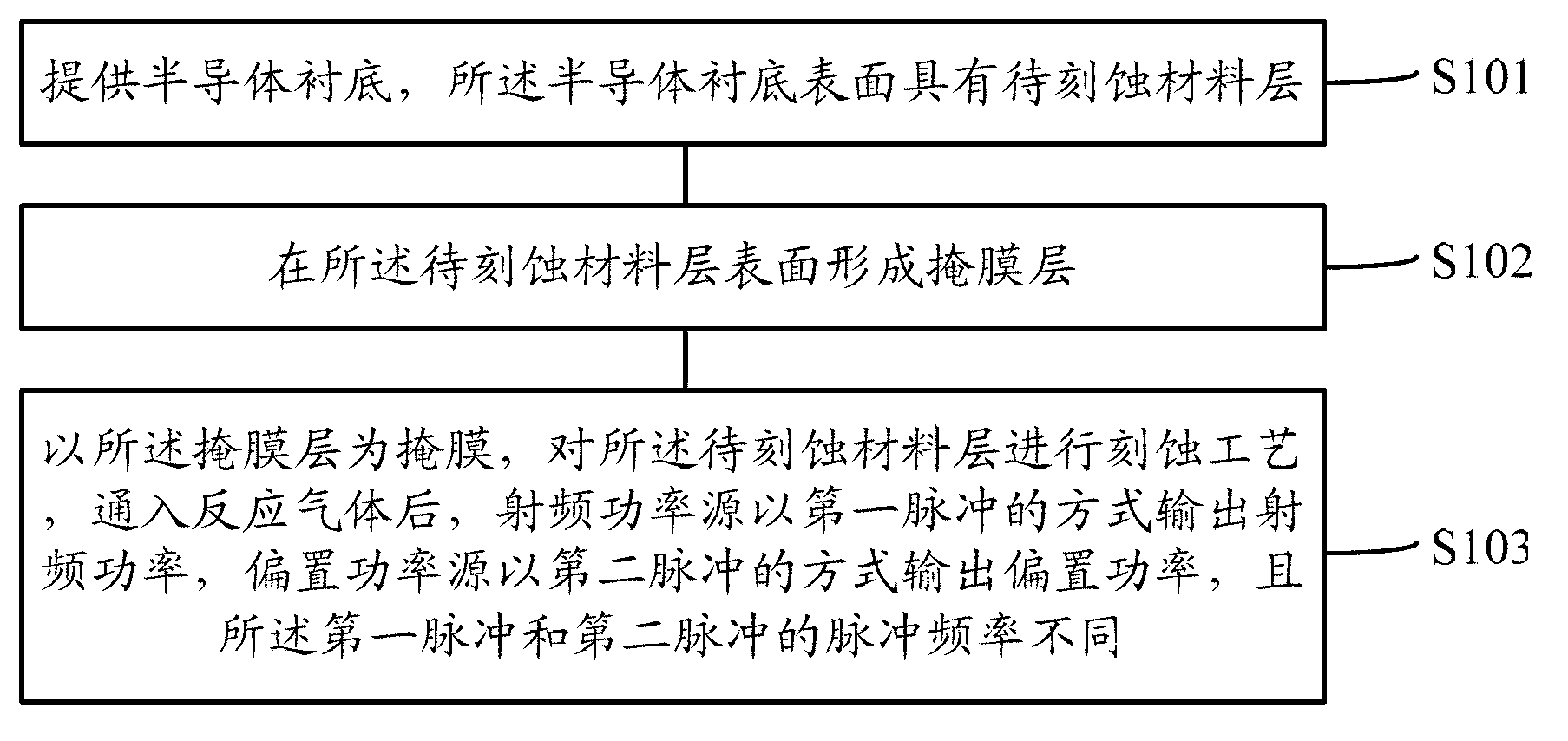

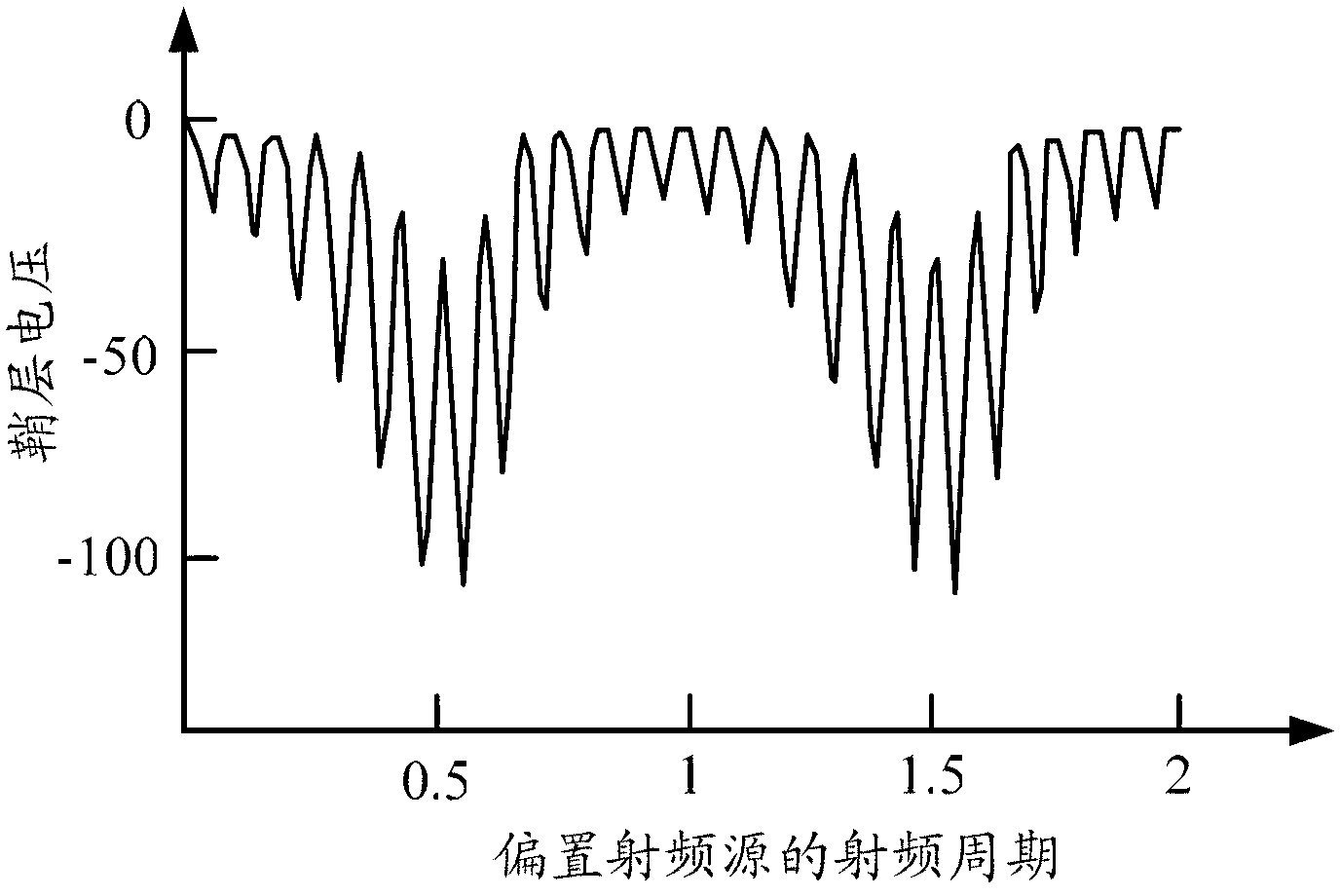

Etching method of semiconductor structure

ActiveCN103021783AAdjustable sizeEtching will not affectElectric discharge tubesSemiconductor/solid-state device manufacturingSemiconductor structureProcess window

An etching method of a semiconductor structure includes: providing a semiconductor substrate with a to-be-etched material layer on the surface; forming a mask layer on the surface of the to-be-etched material layer; using the mask layer as a mask to etch the to-be-etched material layer, and allowing a radio-frequency power source to output radio-frequency power in a first pulse manner and a bias power source to output bias power in a second pulse manner after introducing reactant gas, wherein first pulse and second pulse are different in pulse frequency. Etching is fast. In addition, the size of an etching process window and the time-varying distribution of the etching speed can be regulated by controlling pulse frequency ratio of the radio-frequency power source to the bias power source.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

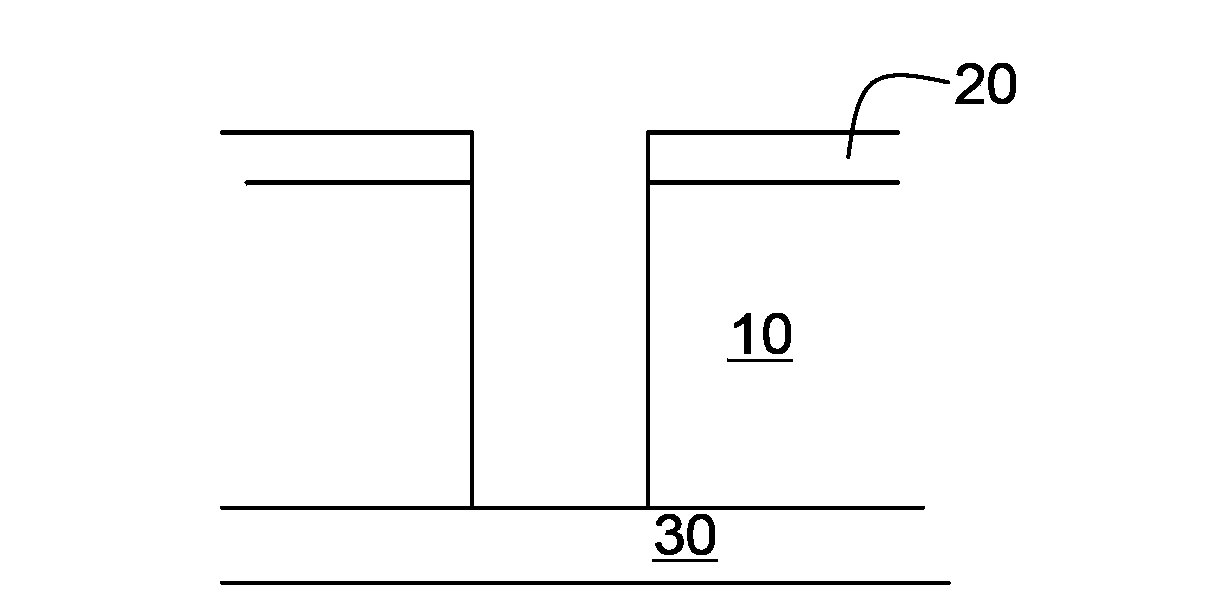

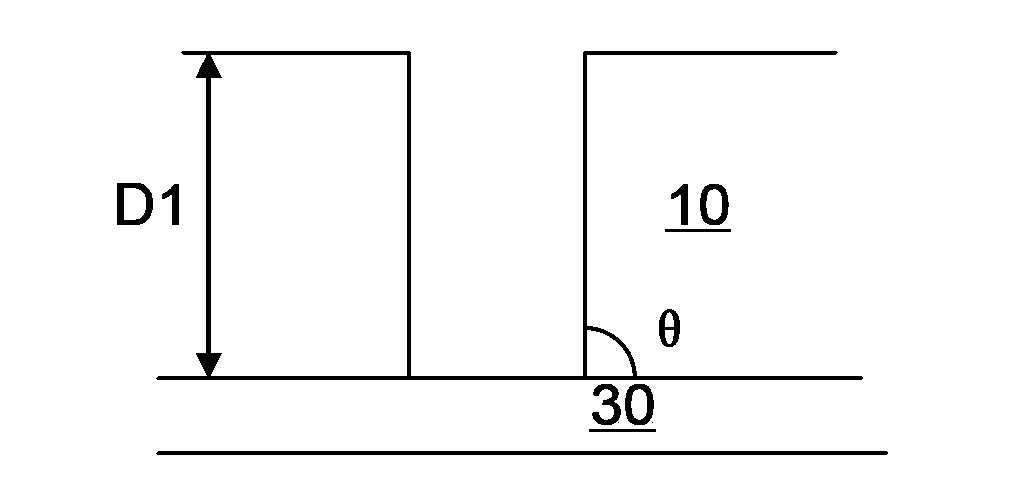

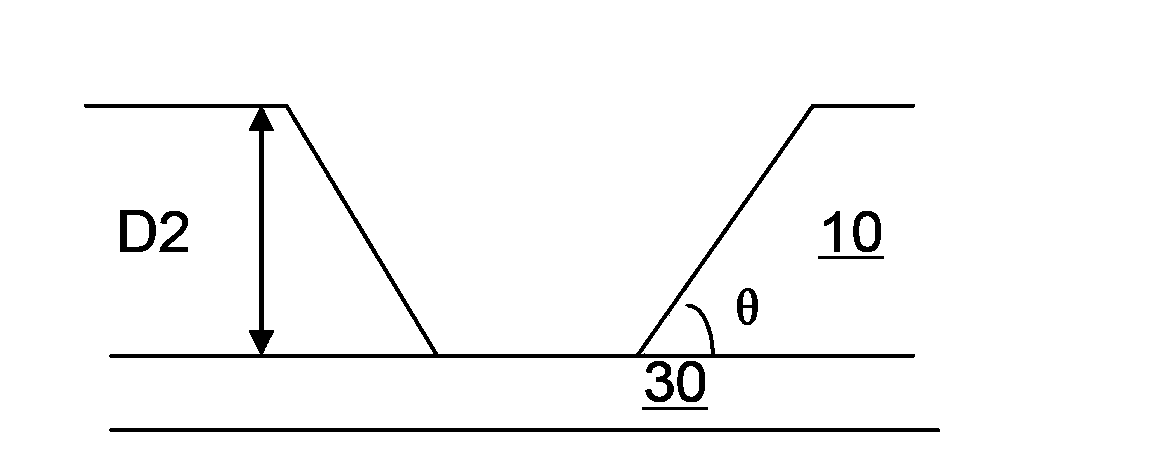

Etching method of etching hole having inclined side wall

ActiveCN103811331AFast etch rateSimple control methodSemiconductor/solid-state device manufacturingMaterials scienceAnalytical chemistry

The invention provides an etching method of an etching hole having an inclined side wall. In the etching method, an etching stopping layer, an etching target layer and a mask layer are formed in sequence on a substrate used for being etched, after the substrate to be etched is put in a plasma reaction chamber, the mask layer is used as a mask, and the target material layer is etched by a first etching process, thereby forming an etching hole vertical to the etching stopping layer at the lower side; the mask layer is etched and removed by a second etching process; the target material layer after removing the mask layer is etched by a third etching process, till a corrected etching hole is formed, and an included angle formed by the side wall of the corrected etching hole and a plane of the etching stopping layer at the lower side is smaller than 80 degrees.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

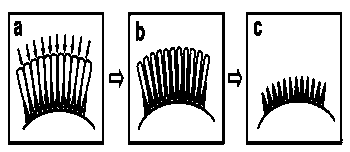

Preparation method for suede of monocrystalline silicon solar battery

InactiveCN102185032AReduce reflection lossReduce pollutionAfter-treatment detailsPhotovoltaic energy generationReflection lossCapacitive coupling

The invention discloses a preparation method for a suede of a monocrystalline silicon solar battery, and the method comprises the following steps: (1) cleaning a silicon slice; (2) etching the cleaned silicon slice by virtue of double-frequency capacitive coupling plasma equipment, thereby obtaining a suede structure in a nano column shape; and (3) cooling and taking out the silicon slice, wherein in the step (2), the etching gas is the mixed gas of C2F6 and Ar2; the flows are respectively 5-10sccm and 0.4-0.5sccm; the background vacuum is 2-3*10<-3>Pa; the working air pressure is 20-30Pa; the high-frequency frequency and the power are 60MHz and 300w; the low-frequency frequency and the power are 2MHz and 250w; and the etching time is 10-15 minutes. According to the preparation method disclosed by the invention, the suede structure, which is in a nano column shape, of the monocrystalline silicon solar battery is obtained, and the suede structure can enable the reflection loss of lightrays to be lower than 9%, thereby achieving unexpected effects.

Owner:SUZHOU UNIV

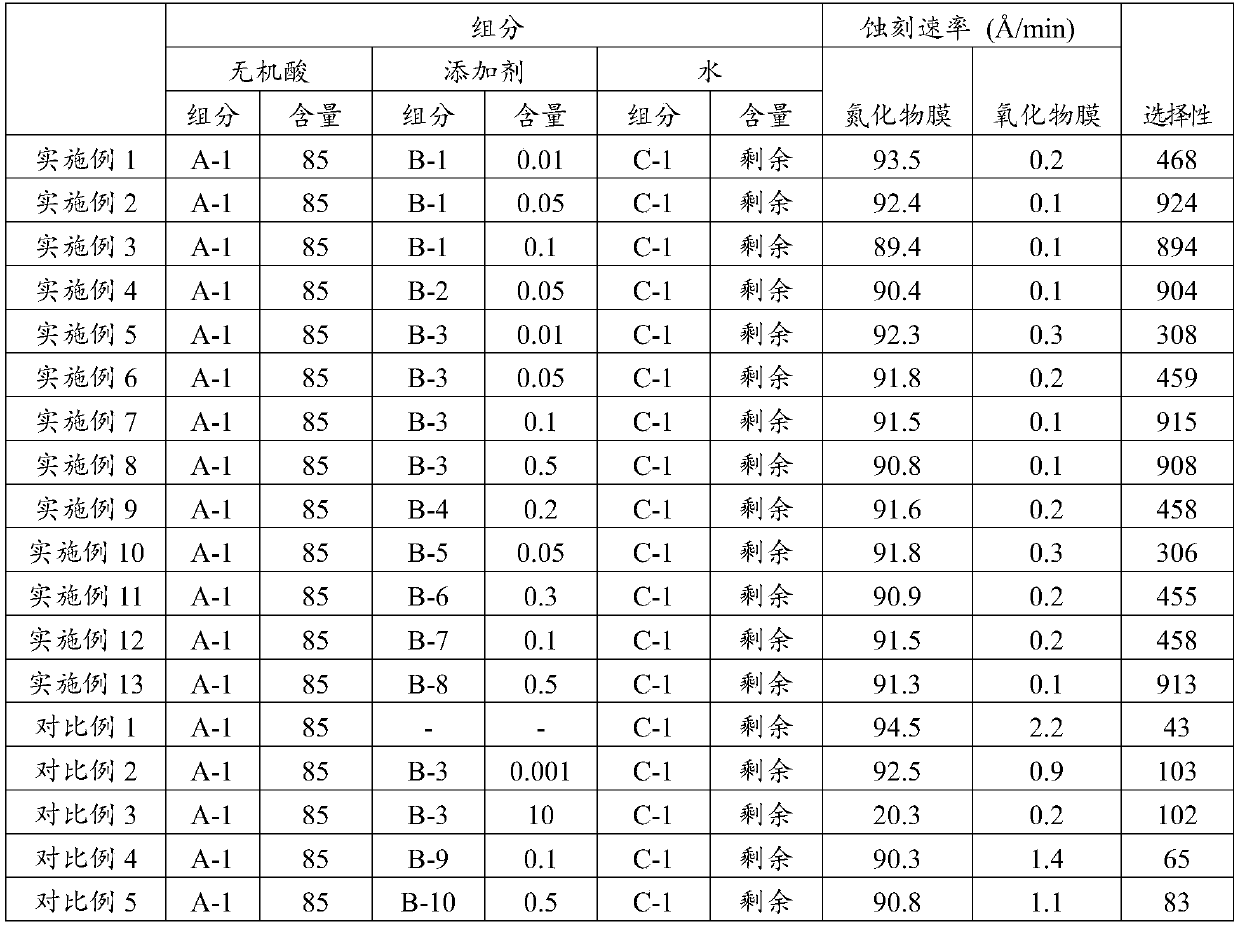

Composition for wet etching to silicon nitride

ActiveCN110551503AAvoid etchingFast etch rateSemiconductor/solid-state device manufacturingSurface treatment compositionsSilicon oxideMaterials science

The present invention relates to a composition for etching a silicon nitride layer, wherein the silicon nitride layer is composed of inorganic acid, a silicon-based compound and water, does not contain fluorine, and can selectively remove the silicon nitride layer while minimizing damage to an underlying metal layer and an etching rate of a silicon oxide layer.

Owner:LTCAM

Method for preparing one-dimensional silicon nanostructure array on surface of optical fiber

InactiveCN103708413ASimple processLow costDecorative surface effectsChemical vapor deposition coatingMicrostructureSilicon nanowires

The invention relates to a method for preparing a one-dimensional silicon nanostructure on the surface of an optical fiber. A polycrystalline silicon thin film with columnar microstructures is chemically etched to obtain a one-dimensional silicon nanostructure array on the surface of the optical fiber. The method comprises the following steps of depositing an amorphous silicon thin film on the surface of a fiber core of a clean quartz optical fiber; annealing the amorphous silicon thin film at a high temperature to obtain the polycrystalline silicon thin film with the columnar microstructures, and separating a part of columnar crystals; chemically etching the polycrystalline silicon thin film by using HF acid in which an H2O2 etchant solution is added so that porous interface layers between the columnar crystals are preferentially etched off to further separate the columnar crystals and reduce the sizes of the columnar crystals, thereby obtaining a silicon nanowire array; performing further etching to separate the columnar crystals from the surface of the optical fiber with a lower-layer tapered nanostructure array left. The preparation method is simple and low in cost; a layered one-dimensional silicon nanostructure array can be prepared, the lengths, diameters, doping types, levels and the like of nanowires can be effectively controlled, the one-dimensional silicon nanostructure array can be prepared on a long-distance optical fiber by coiling the optical fiber or through tubular deposition equipment, and even a roll-to-roll preparation process is allowed.

Owner:ANHUI NORMAL UNIV

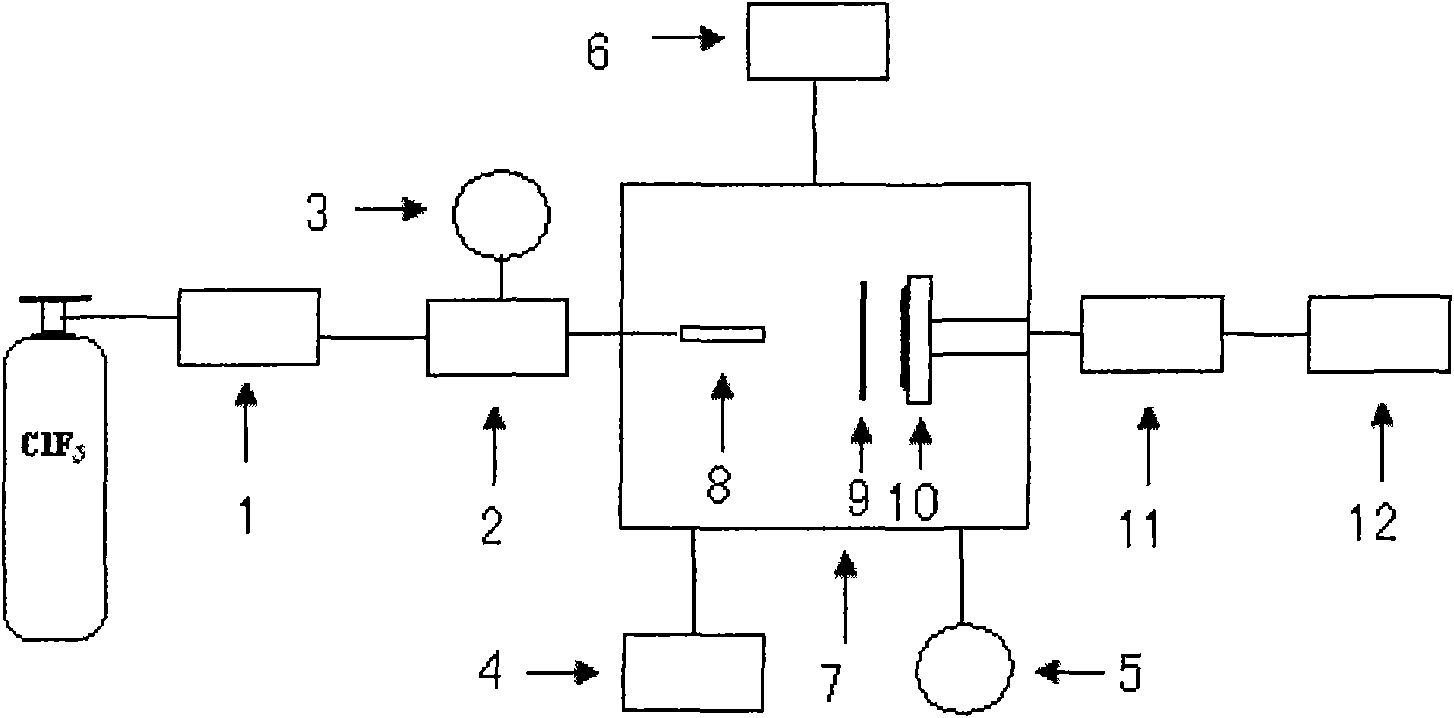

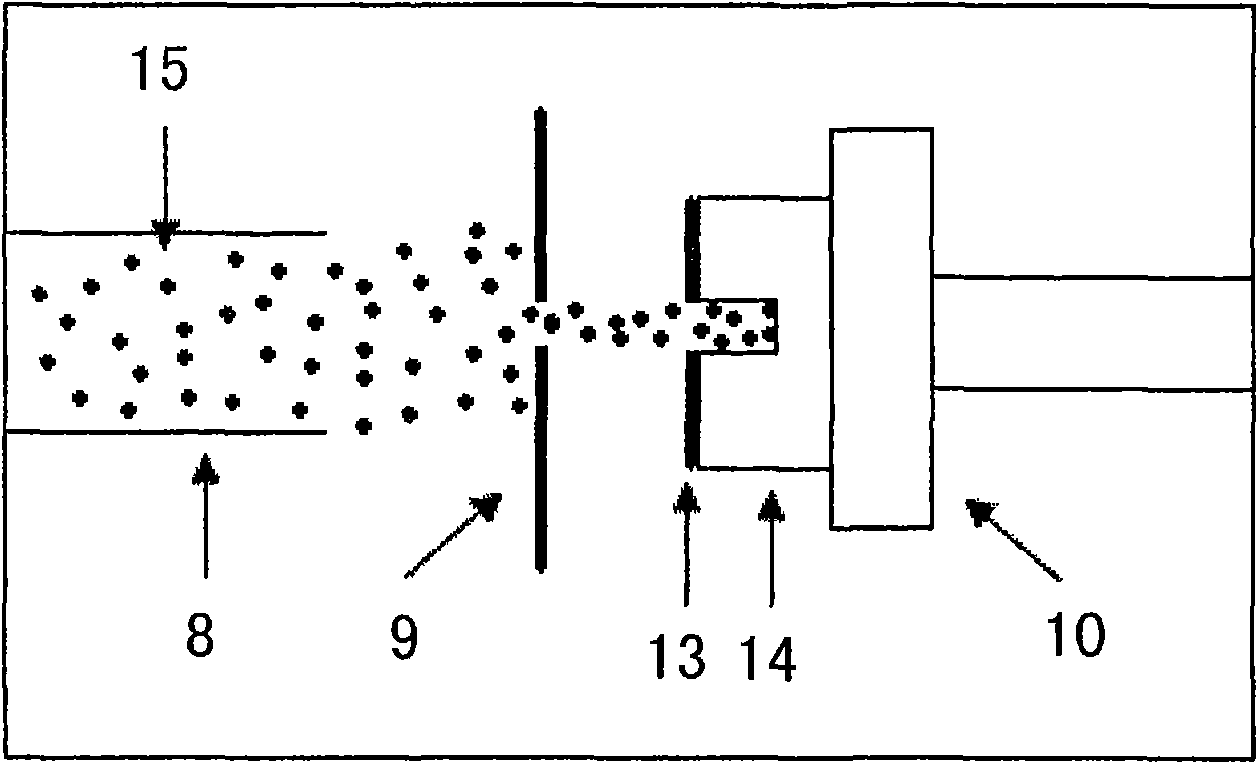

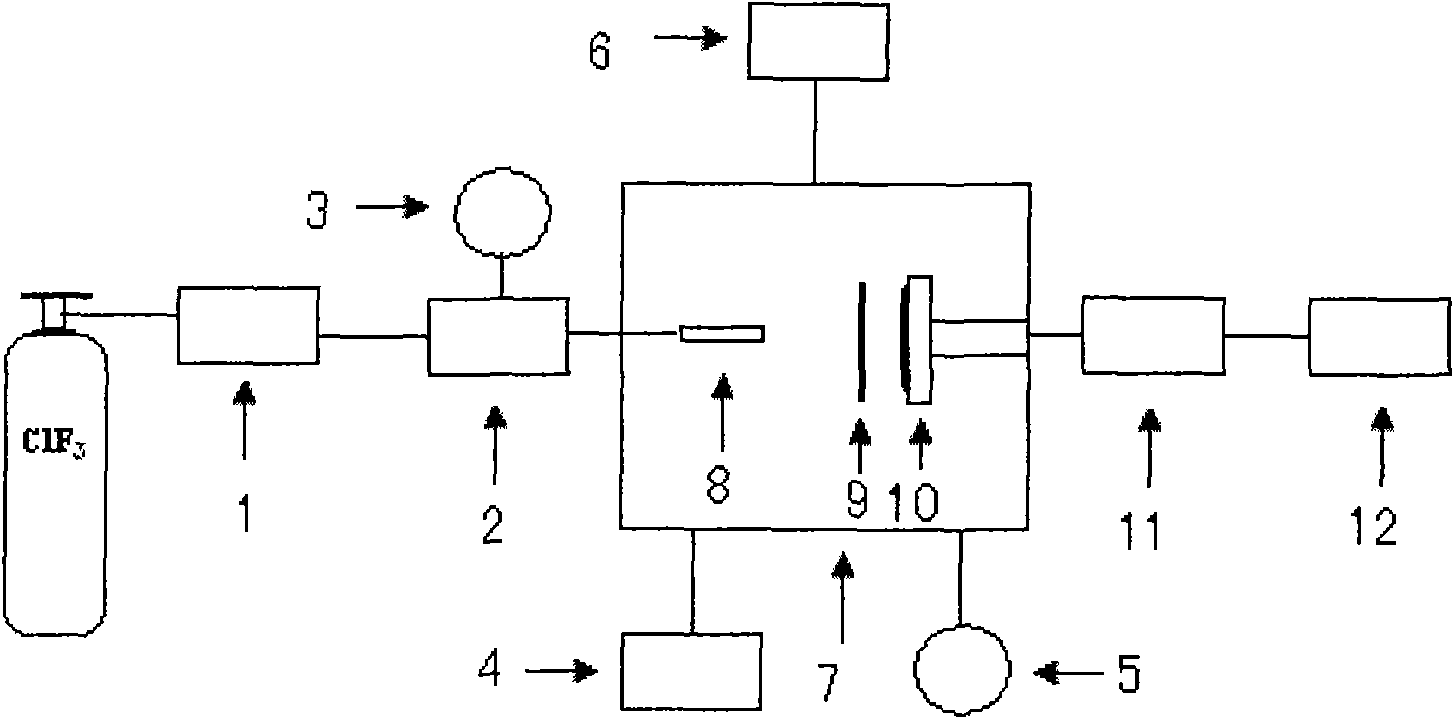

Device for gas linear cutting of silicon slice

InactiveCN101880878AFast etch rateHigh smoothness of the sectionSemi-permeable membranesSemiconductor/solid-state device manufacturingTemperature controlRoom temperature

The invention discloses a device for the gas linear cutting of a silicon slice, which comprises a flow controller, a pressure reducing valve, a pressure gauge, a vacuum pump, a vacuum-cavity pressure gauge, a vacuum-cavity temperature control device, a vacuum chamber, a spray head, a masking plate, a silicon slice frame, a post pump and a tail gas processing device, wherein the pressure reducing valve, the vacuum pump, the vacuum-cavity pressure gauge, the vacuum-cavity temperature control device and the post pump are respectively connected with the vacuum chamber, gas enters the vacuum chamber after sequentially passing through the flow controller, the pressure reducing valve and the spray head, then the silicon slice on the silicon slice frame is cut through the masking and the beam convergence and regulation of the masking plate, the temperature of the vacuum chamber is controlled to be under a room temperature environment through the vacuum-cavity temperature control device, and etched tail gas is pumped out of the vacuum chamber through the post pump and enters the tail gas processing device through the post pump. In the invention, chlorine trifluoride is used as etching reaction gas for carrying out cutting processing for the silicon slice, and the problems existing in a traditional technology can be well solved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

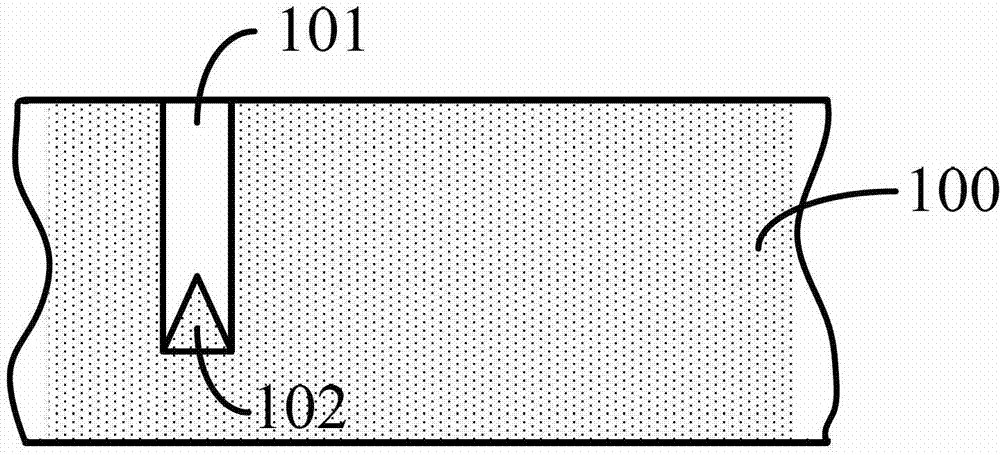

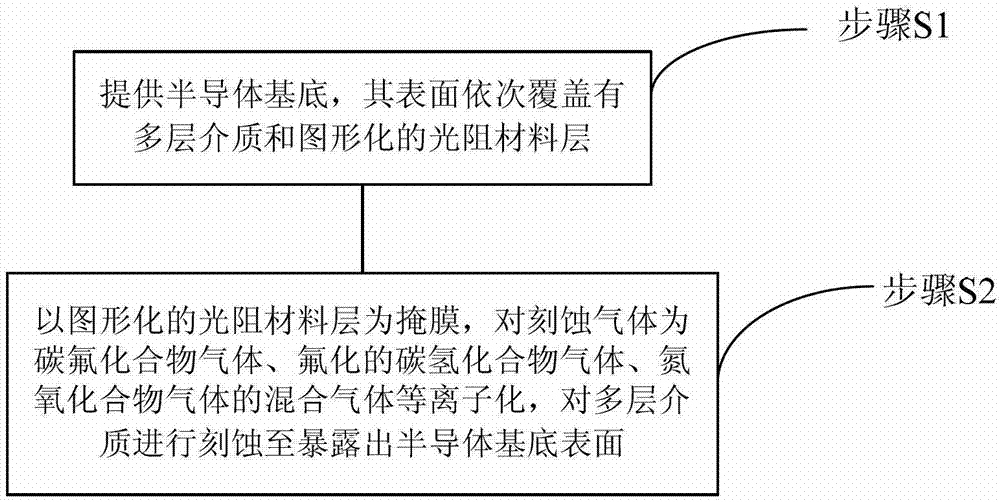

Multilayered medium etching method

ActiveCN103050396AIncrease etch rateAdjust densitySemiconductor/solid-state device manufacturingHydrogenNitrogen oxide

The invention relates to the technical field of a semiconductor, and discloses a multilayered medium etching method. The method comprises the following steps of: providing a semiconductor substrate, wherein the surface of the semiconductor substrate is sequentially coated with the multilayered medium and a graphic photoresist layer; and ionizing the etching gas which is the mixed gas such as fluorocarbon gas, fluorinated carbureted hydrogen gas and nitrogen oxide gas by taking the graphic photoresist layer as a mask, and etching the multilayered medium by the etching gas until the multilayered medium is exposed to the surface of the semiconductor substrate. The method takes the fluorocarbon gas and the fluorinated carbureted hydrogen gas with high C / F ratio as the main etching gas; and the nitrogen oxide gas in a certain flow is added, so that a purpose of etching the multilayered medium formed by different materials through one-step plasma etching primary is achieved, and the etching is not performed by many steps of layering the materials. The photoresist layer as the mask has a low etching rate.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

Etching method

ActiveUS7497963B2Fast etch rateUniform adsorptionDecorative surface effectsSemiconductor/solid-state device detailsIn planePhotochemistry

In this etching method, since an etching gas is introduced before introduction of free radicals into a processing chamber, the etching gas has been adsorbed on the surface of substrates when the free radicals are introduced. Accordingly, the free radicals react with the etching gas adsorbed on the surface of the substrates, and the reaction proceeds uniformly on the surface of the substrate. As a result, nonuniform etching does not occur on the surface of the substrate. Moreover, since the reaction between the etching gas and the free radicals occurs on the surface of the substrate, an intermediate product produced according to the reaction between the etching gas and the free radicals reacts with an etching object promptly. Therefore, the intermediate product is not exhausted from the processing chamber 12 excessively, and hence the etching efficiency is high. As a result, according to this etching method, not only the in-plane distribution of the etching amount becomes more uniform, but also the etching rate is increased more than in the conventional etching method.

Owner:SAMSUNG ELECTRONICS CO LTD

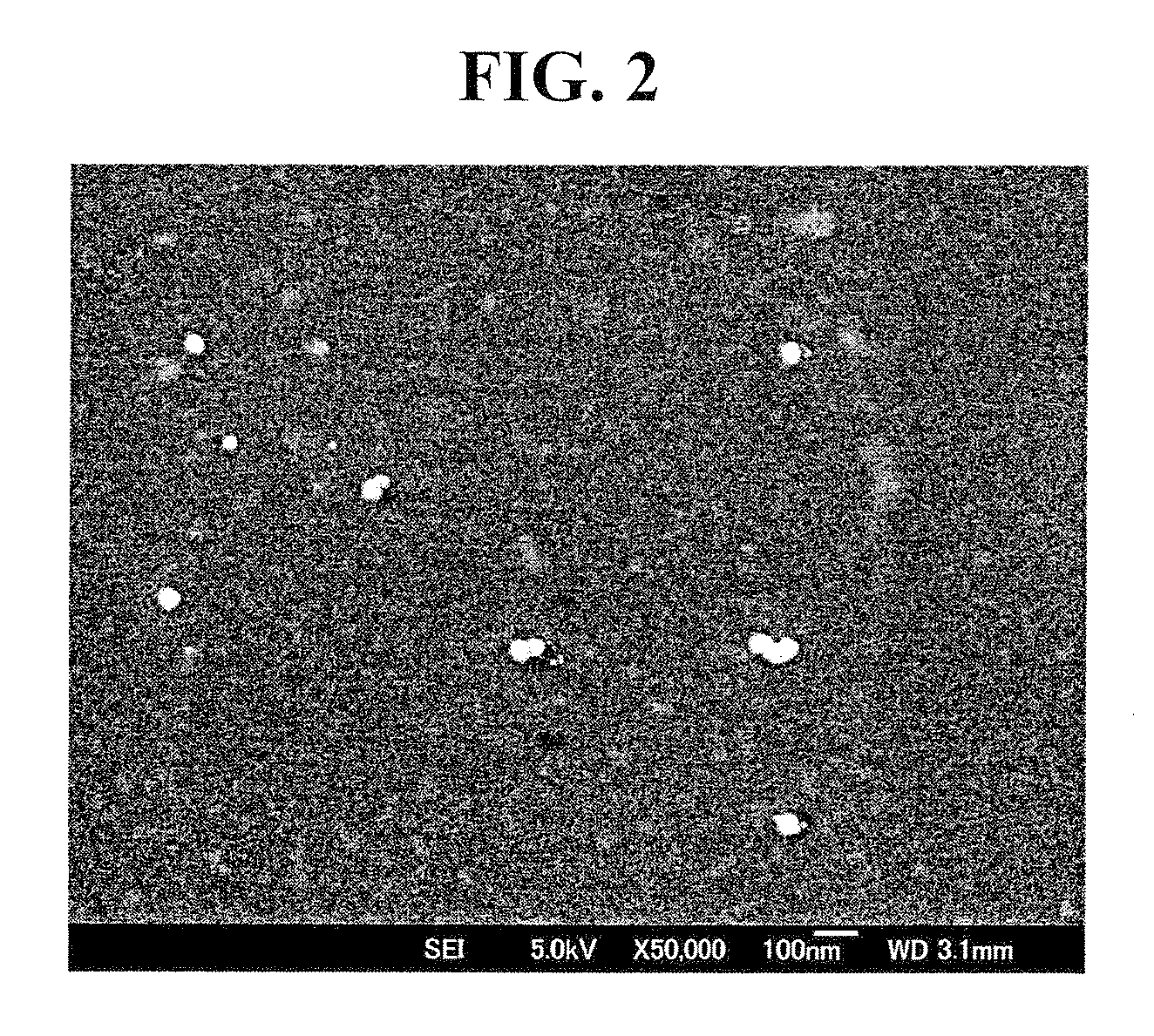

Sintered compact of composite oxide, amorphous film of composite oxide, process for producing said film, crystalline film of composite oxide and process for producing said film

ActiveUS8277694B2Improve etching effectFast etch rateConductive layers on insulating-supportsConductive materialIndiumDisplay device

Owner:JX NIPPON MINING & METALS CORP

Narrow trench manufacturing method

InactiveCN103972147ASmall amplification effectIncrease etch rateSemiconductor/solid-state device manufacturingPhotoresistSemiconductor

The invention provides a narrow trench manufacturing method. The method includes the steps that (1) a silicon nitride layer and a hard mask are arranged on a semiconductor substrate in sequence; (2) photoresist is arranged on the hard mask; (3) the photoresist is exposed and developed to form a phototresist pattern with a first size; (4) after the phototresist pattern is formed, ion injection is conducted on a wafer so as to conduct non-crystallizing processing on the exposed area of the phototresist pattern; (5) after ion injection is conducted, dry etching processing is conducted by using the phototresist with the phototresist pattern so as to form a trench with a second size in the substrate.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Alkaline etching process of printed circuit board

InactiveCN102808181AFast etch rateSlight side erosionConductive material chemical/electrolytical removalIonChemistry

The invention relates to an alkaline etching process of a printed circuit board, belonging to the technical field of production of the circuit board. The alkaline etching process of the printed circuit board comprises the steps of: firstly, controlling the temperature of an alkaline etching solution within a range from 40 DEG C to 60 DEG C and controlling the PH value within 8.0-8.8; then adding chloride ions with the content of 130-170 g / l in the alkaline etching solution; then adding bivalent copper ions with the content of 120-170 g / l in the alkaline etching solution; then adding thiourea with the content of 0.04-0.07 g / l into the alkaline etching solution; then removing a mask image from the to-be-etched PCB (Printed Circuit Board); then cleaning the to-be-etched PCB with pure water for twice and then drying the PCB in an absorbing manner by using a clean cloth material; then blow-drying the PCB by using a blower; then detecting whether the PCB is damaged; then alkaline-etching the PCB which is qualified through check by using the alkaline etching solution to remove the unused copper surface portion so as to form wiring; then scrubbing and washing the alkaline-etched PCB with ammonia water for twice; then scrubbing and washing the PCB with pure water for twice; after finishing washing, drying the PCB in an absorbing manner by using the clean cloth material; then blow-drying the PCB with the blower; and then checking whether the PCB is damaged.

Owner:PUTIAN JIAYI ELECTRONICS

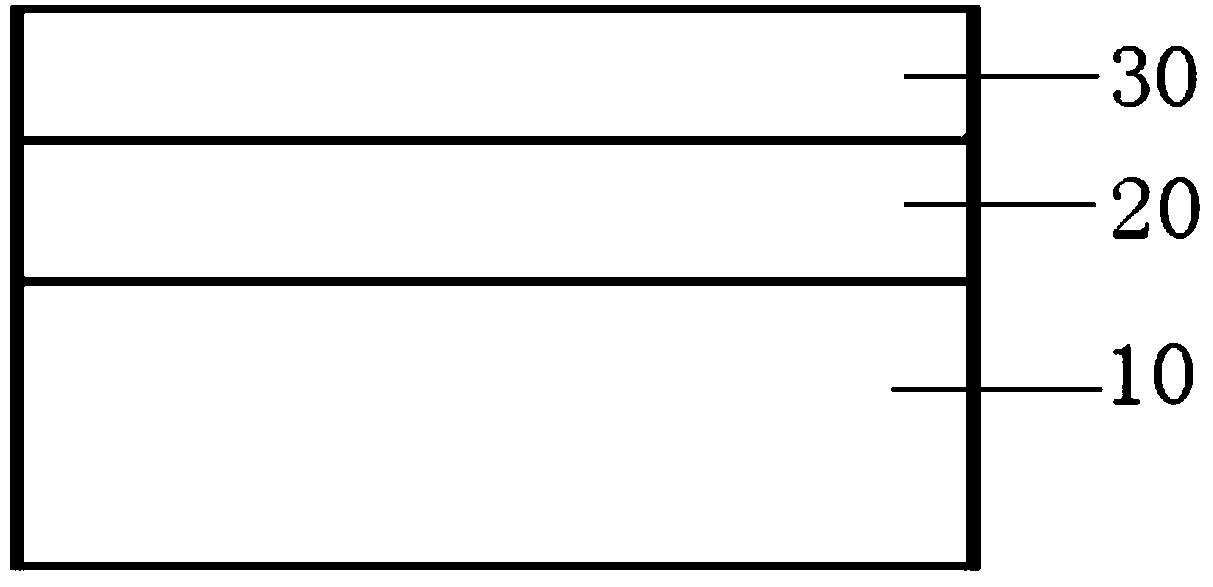

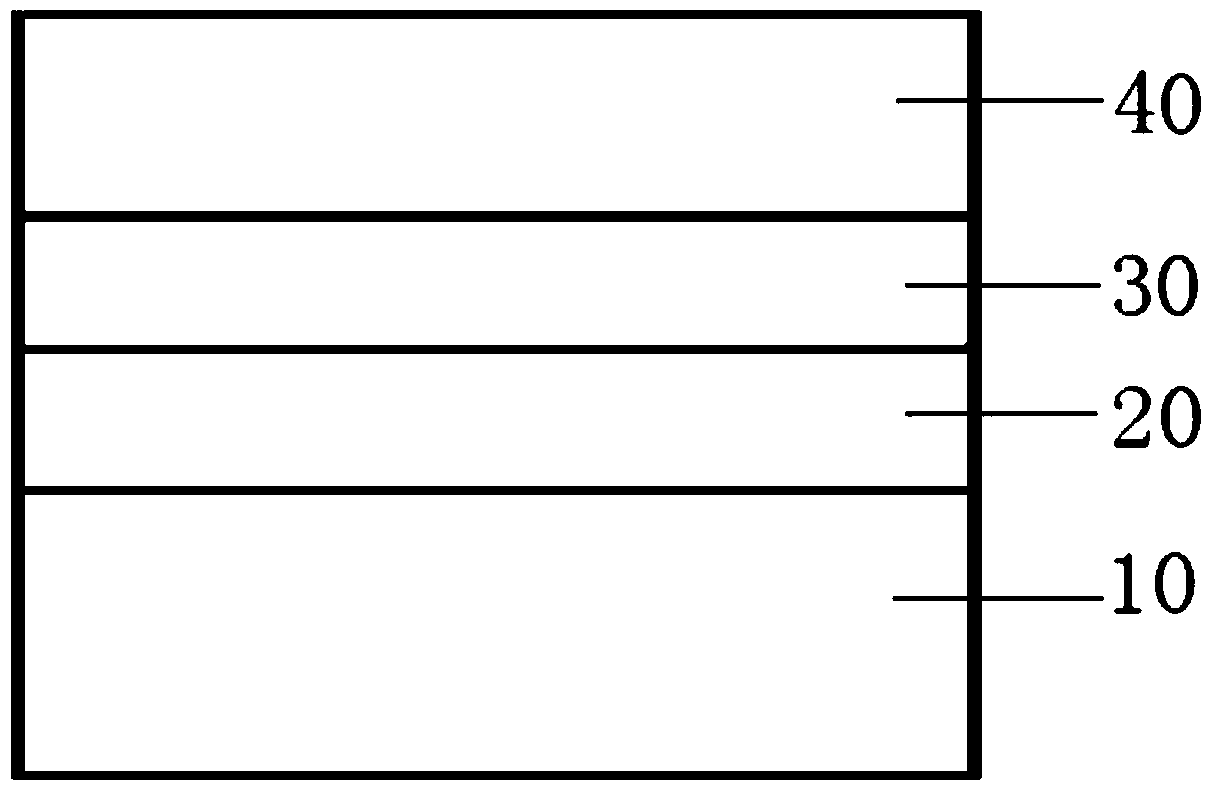

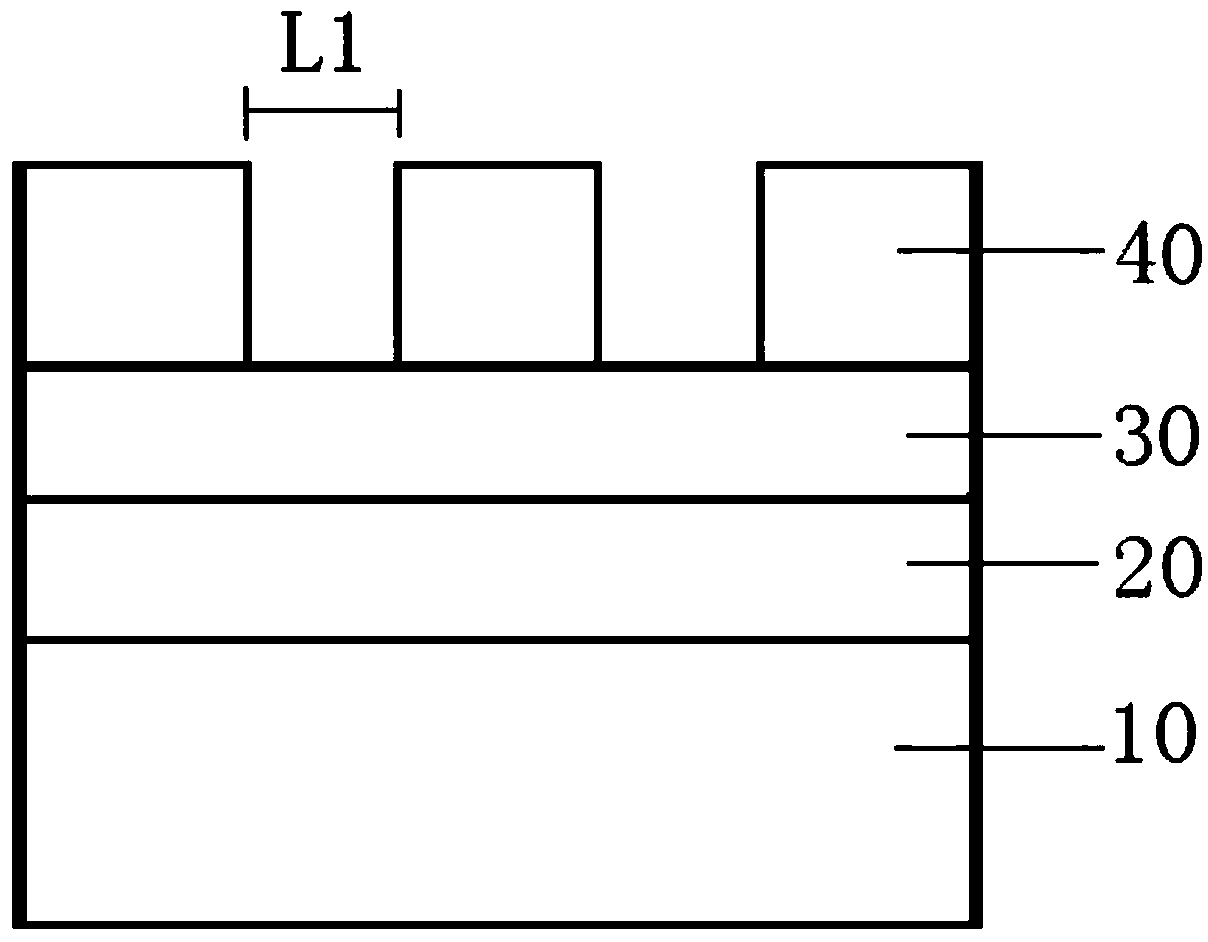

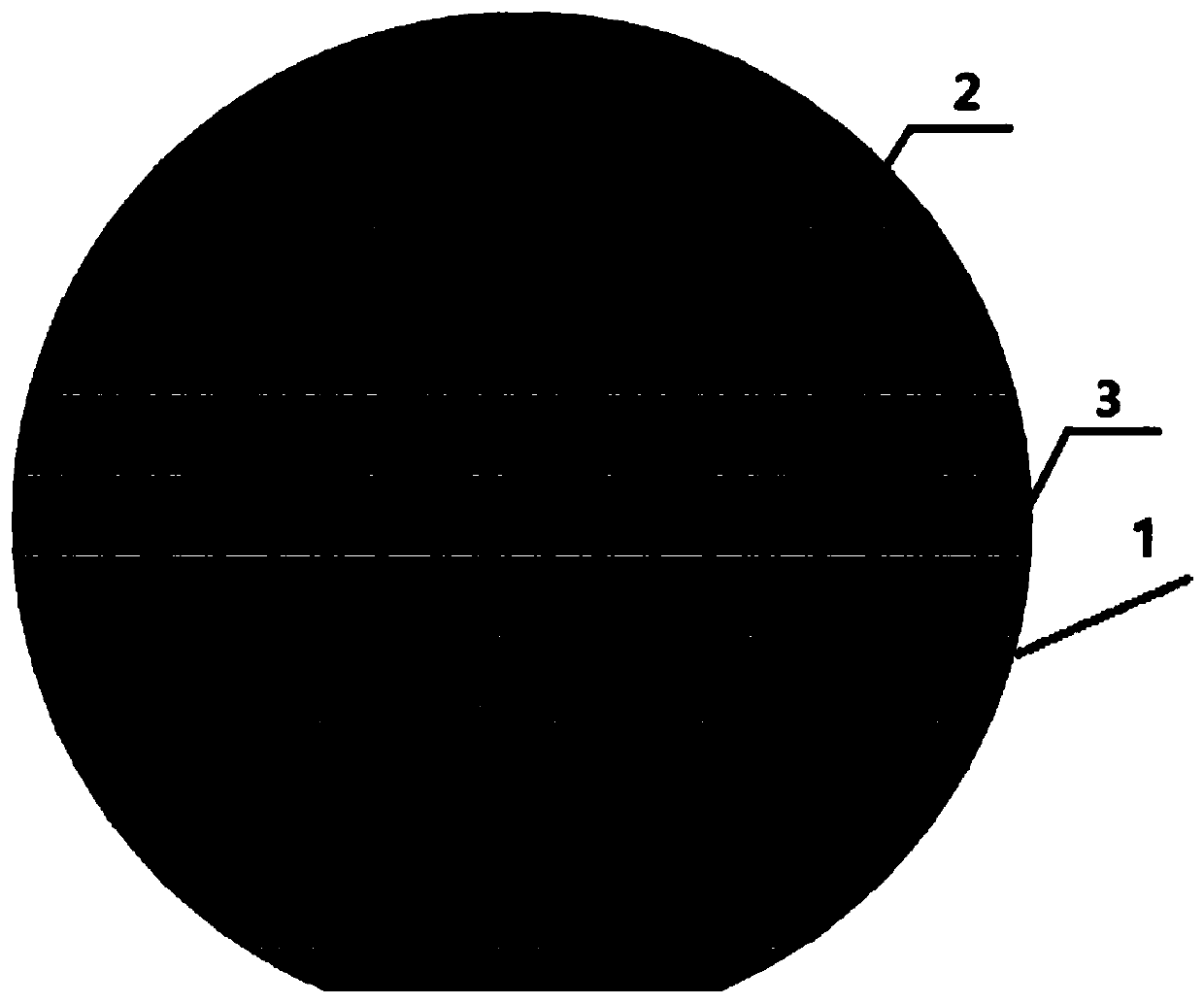

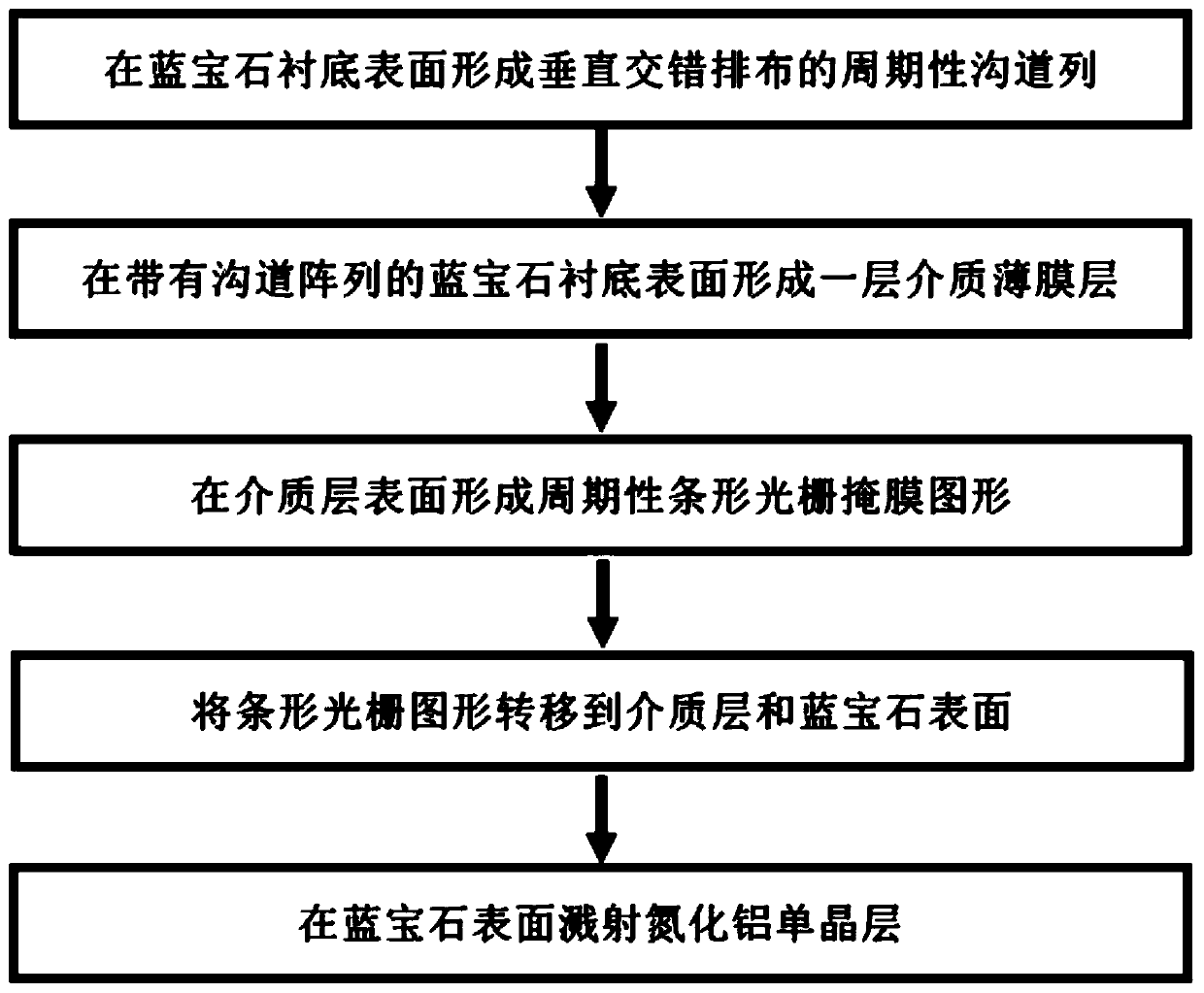

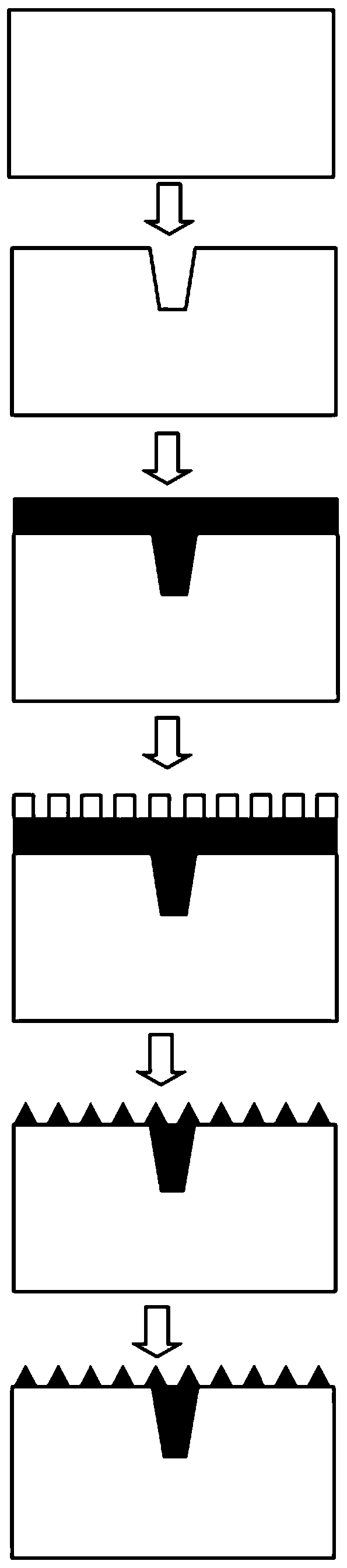

Preparation method of patterned composite substrate

InactiveCN109841709AImprove crystal qualityImprove quantum efficiencySemiconductor devicesGratingComposite substrate

The invention provides a preparation method of a patterned composite substrate. The preparation method comprises the steps of: step 1, placing a sapphire substrate on a laser cutting machine for cutting, and forming a plurality of periodic channel arrays which are arranged in a vertically staggered manner on the surface of the sapphire substrate; step 2, realizing a dielectric thin film layer on the surface of the cleaned sapphire substrate; step 3, forming a periodic strip grating mask pattern on the sapphire substrate provided with the dielectric thin film layer; step 4, and transferring themask pattern onto the dielectric thin film layer and the sapphire substrate, wherein a strip-shaped grating microstructure pattern is formed on the surface of the sapphire substrate, forming a aluminum nitride single crystal thin film layer on the surface after cleaning the sapphire substrate, and finally realizing the patterned composite substrate. The preparation method effectively avoids the problem of photoelectric performance damage of an LED chip, greatly improves the luminous efficiency of the LED chip, improves the process yield and reduces the production cost.

Owner:江苏澳洋顺昌集成电路有限公司

Micro-fluorine glass etching and polishing method

The invention discloses a micro-fluorine glass etching and polishing method comprising the following steps: respectively grinding sodium fluoride and sodium sulfate, and then, mixing sodium fluoride, sodium sulfate, sodium dihydrogen phosphate, water and an active agent at a weight ratio of 10:(7-8):1:(5-6):5 to prepare an etching solution, and etching. Compared with the prior art, the micro-fluorine glass etching and polishing method has the advantages that firstly, a great deal of hydrofluoric acid is prevented from being directly used, and the used medicines are simple in recovery and can be completely recycled; secondly, the micro-fluorine glass etching and polishing method is high in etching speed, large in etching depth, good in etching uniformity, high in safety and capable of meeting the production and application requirements; thirdly, the environment protection and sustainable development concepts are achieved, the requirement for clean production is met, and the wastewater treatment method designed for the technology is used for ensuring that the treated wastewater can be up to the natural discharge standard.

Owner:陈锋

Selective silicon etching solution

ActiveCN111019659AReduce mass transfer resistanceGuaranteed uniformitySurface treatment compositionsPhysical chemistrySilicon dioxide

The invention belongs to the field of integrated circuit electronic chemicals, and particularly relates to a selective silicon etching solution and a use method thereof. The selective silicon etchingsolution is used for selectively removing undoped silicon on a p-type silicon substrate and comprises nitric acid (or a mixture of nitric acid and a nitrate), nitrite, hydrofluoric acid or a hydrofluoride, a silicon additive, a boron additive and a solvent. According to the etching solution, the nitrate and the nitrite are used for oxidizing silicon into silicon dioxide; etching and removing of silicon dioxide are realized by utilizing hydrofluoric acid; the silicon additive is used for adjusting the etching rate of silicon; the boron additive can inhibit the etching of the p-type silicon by the etching solution, so that the etching solution has a faster etching rate for the undoped silicon than the p-type silicon.

Owner:湖北兴福电子材料股份有限公司

Etching solution

PendingCN113981447AFinely craftedSlow etch rateConductive material chemical/electrolytical removalBenzeneIntegrated circuit manufacturing

The invention discloses an etching solution formula, and relates to the field of printed circuit board manufacturing and the field of integrated circuit manufacturing. According to the invention, the etching solution can be provided for reducing the copper thickness and forming the circuit, can improve the poor pinholes in the copper surface and optimize the rectangular circuit section, and meanwhile, improves the etching speed and improves the efficiency. The etching solution is characterized by being composed of sulfuric acid, hydrogen peroxide, an alcohol accelerant and a benzene ring stabilizer, the mass ratio of hydrogen peroxide to sulfuric acid in unit volume is larger than 8: 1, the hydrogen peroxide accounts for 8-30% by mass, the sulfuric acid accounts for 0.3-15% by mass, the alcohol accelerant accounts for 5-20% by mass, and the benzene ring stabilizer accounts for 0-2% by mass.

Owner:纳然电子技术(苏州)有限公司

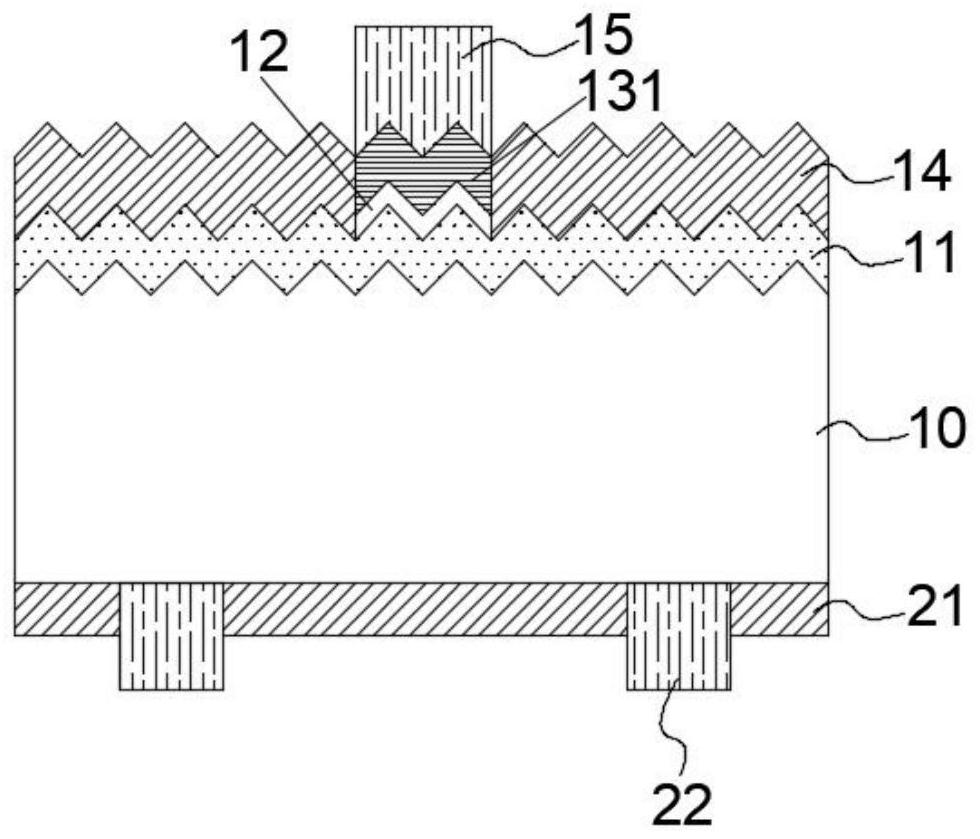

Solar cell and manufacturing method thereof

PendingCN112885924AReduce manufacturing difficultyImprove production efficiencyFinal product manufacturePhotovoltaic energy generationAmorphous siliconEngineering

The invention discloses a solar cell and a manufacturing method thereof, relates to the technical field of photovoltaics, and aims to reduce the manufacturing difficulty of a local passivation contact structure and improve the manufacturing efficiency. The manufacturing method of the solar cell comprises the following steps of: providing a silicon substrate; forming a tunneling layer on the front surface of the silicon substrate; forming an amorphous silicon layer on the tunneling layer; processing the target part of the amorphous silicon layer to form a doped polycrystalline silicon region and an amorphous silicon region; and removing the amorphous silicon region to obtain a local passivation contact structure on the front surface of the silicon substrate. The solar cell is manufactured by adopting the manufacturing method of the solar cell. The solar cell and the manufacturing method thereof provided by the invention are used for solar cell manufacturing.

Owner:LONGI SOLAR TECH (TAIZHOU) CO LTD