Method for manufacturing high-performance double-layer polysilicon bipolar transistor

A technology of bipolar transistor and manufacturing method, applied in transistor, semiconductor/solid-state device manufacturing, semiconductor device and other directions, can solve the problem of increasing base-emitter distance, reducing current amplification factor, reducing emitter current conduction area, etc. The problem is to reduce the high temperature process time, increase the current amplification factor, and reduce the buried layer doping and the expansion effect.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

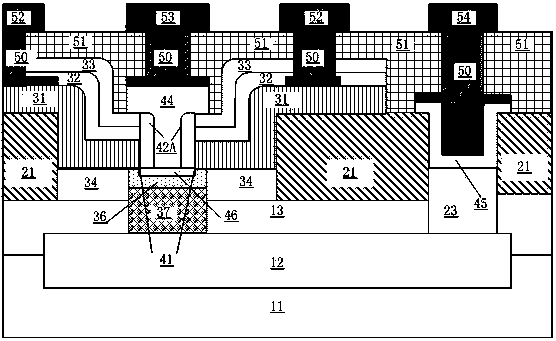

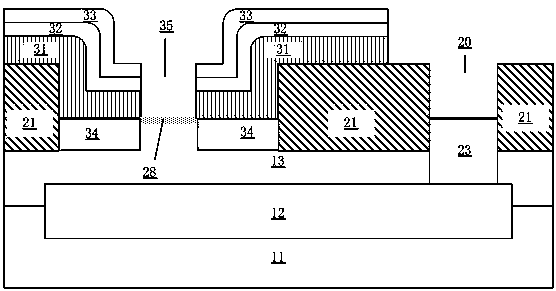

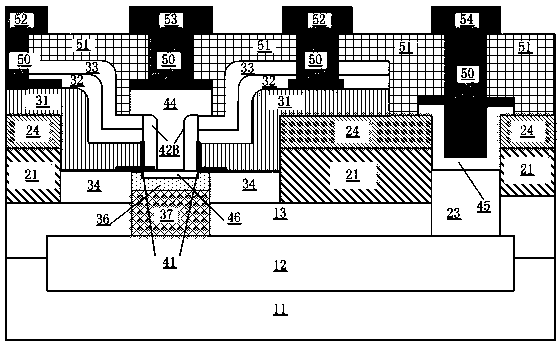

[0067] 1) Select the silicon substrate material 11, its doping is P-type, and the resistivity is 30Ω. cm; Sb atoms are selectively implanted on the substrate to form an N+ buried layer 12, followed by N-type silicon epitaxy 13, with a resistivity of 8Ω. cm, and the thickness of the epitaxial layer is 1.5 μm. ( Figure 2.2 )

[0068] 2) Oxidation to form thin SiO 2 layer 14, thickness 300?, after which deposited Si 3 N4 15, thickness 1000?, photolithography and dry etching of Si 3 N 4 , forming a local oxidation window, high temperature oxidation after degumming, to obtain LOCOS 21, thickness 5000?, oxidation temperature 1050 ℃, time 45 minutes, peel off Si after oxidation 3 N 4 . ( Figure 2.3 , Figure 2.4 )

[0069] 3) Lithograph the collector region 22, and implant phosphorus (P) atoms into the collector region with a dose of 5×10 15 / cm 2 , the energy is 150KeV, forming a low-resistance channel 23 . ( Figure 2.5 )

[0070] 4) CVD deposited SiO 2 , with a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More