Patents

Literature

149results about How to "Avoid etch damage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

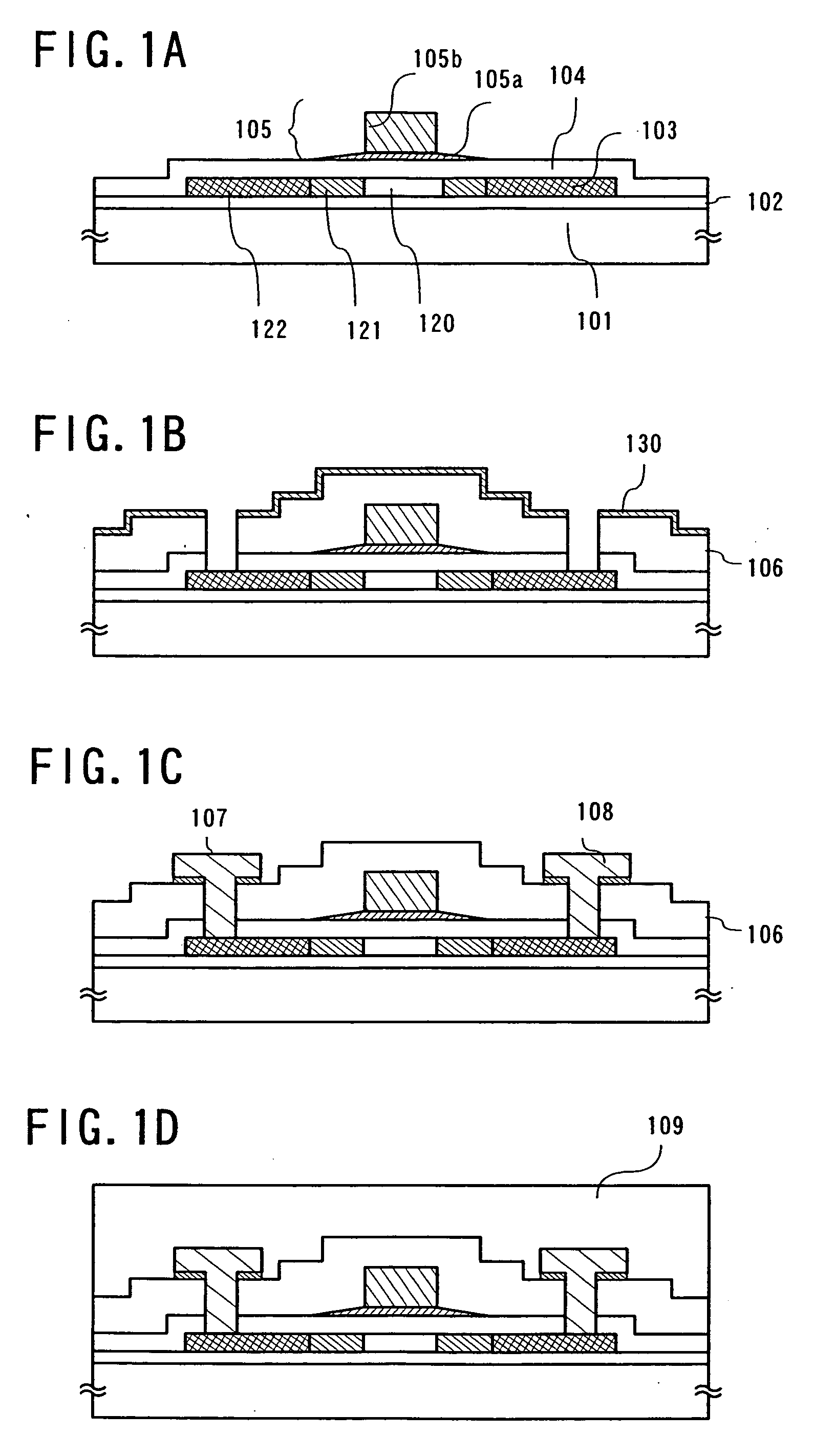

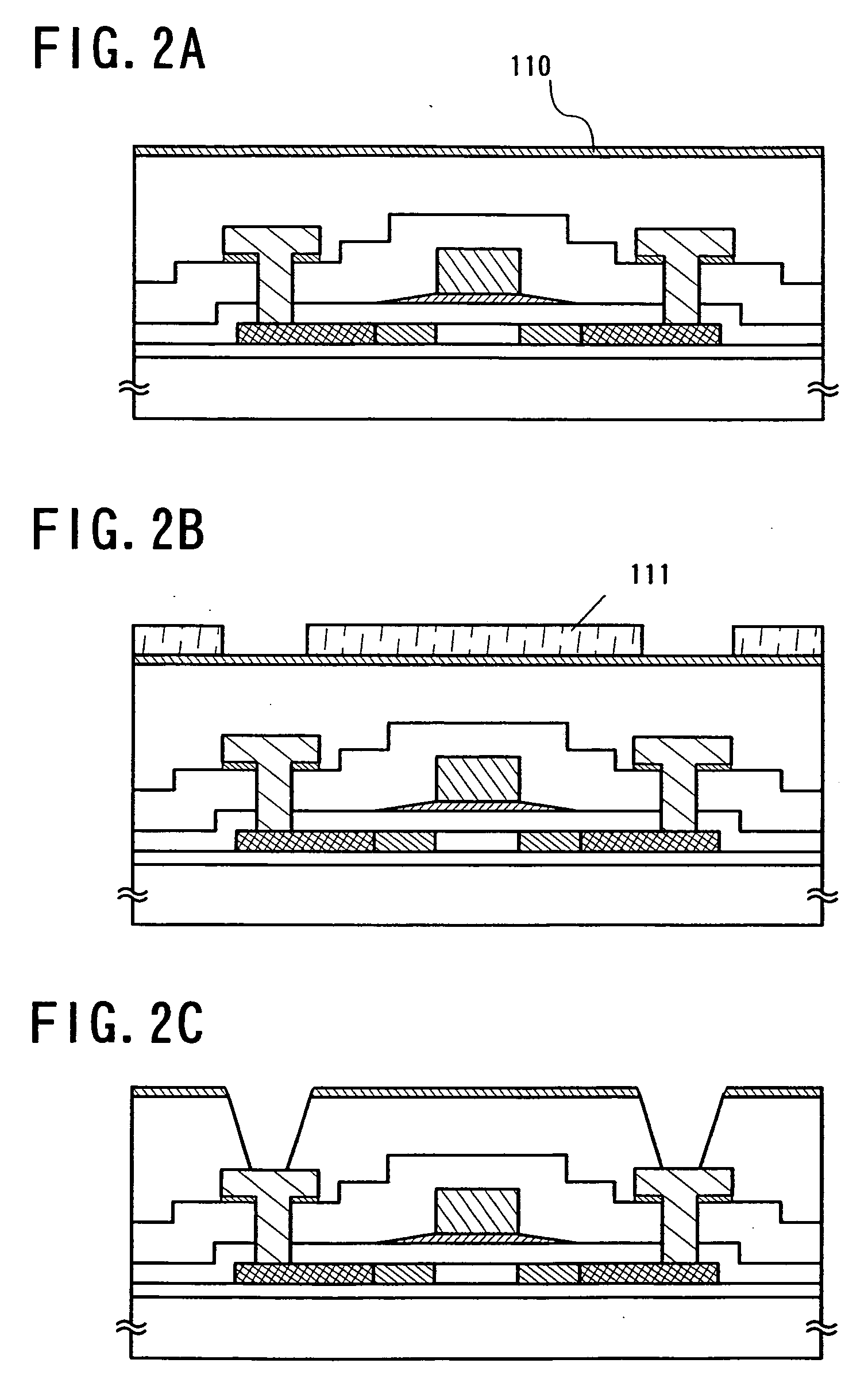

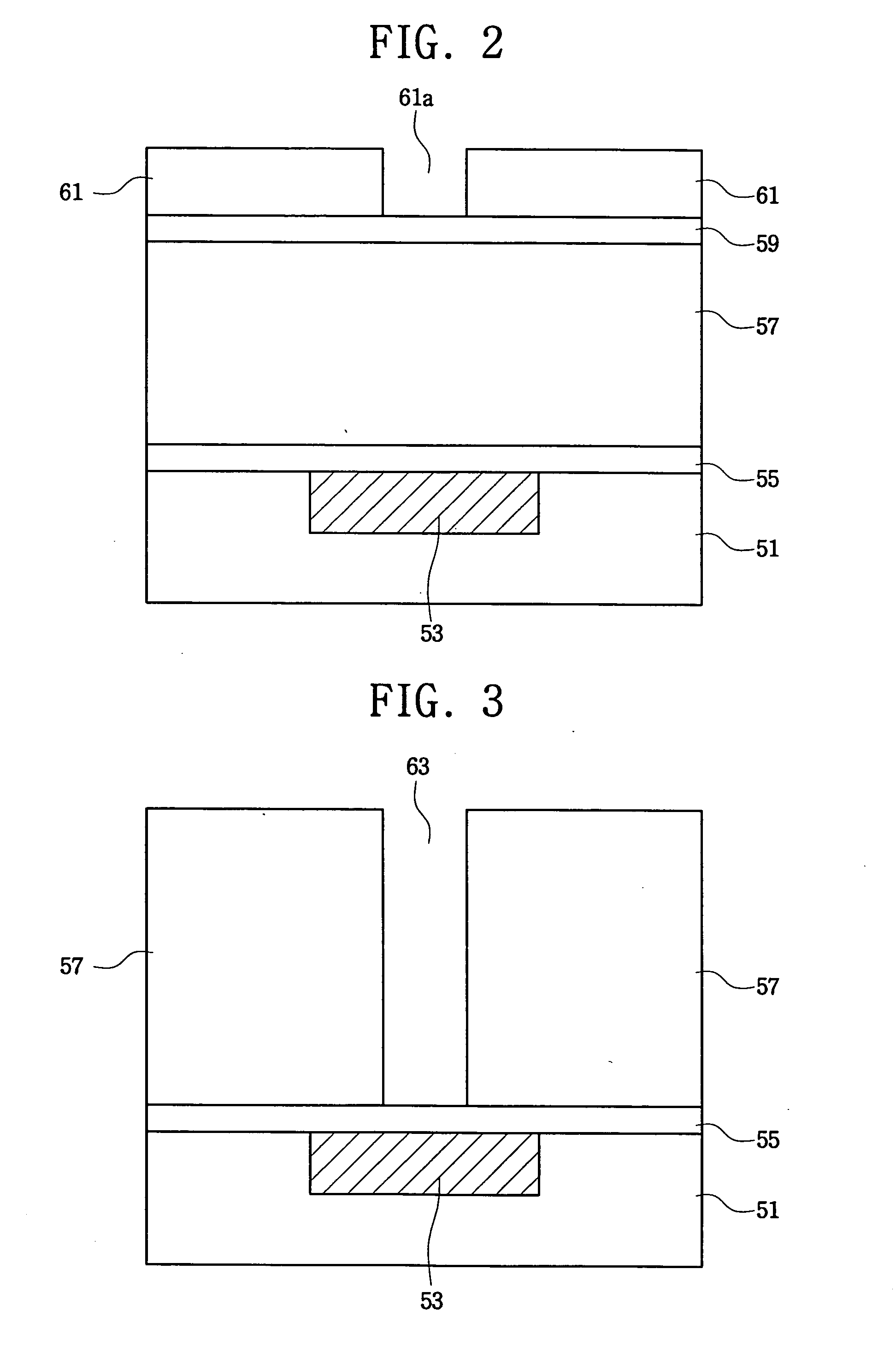

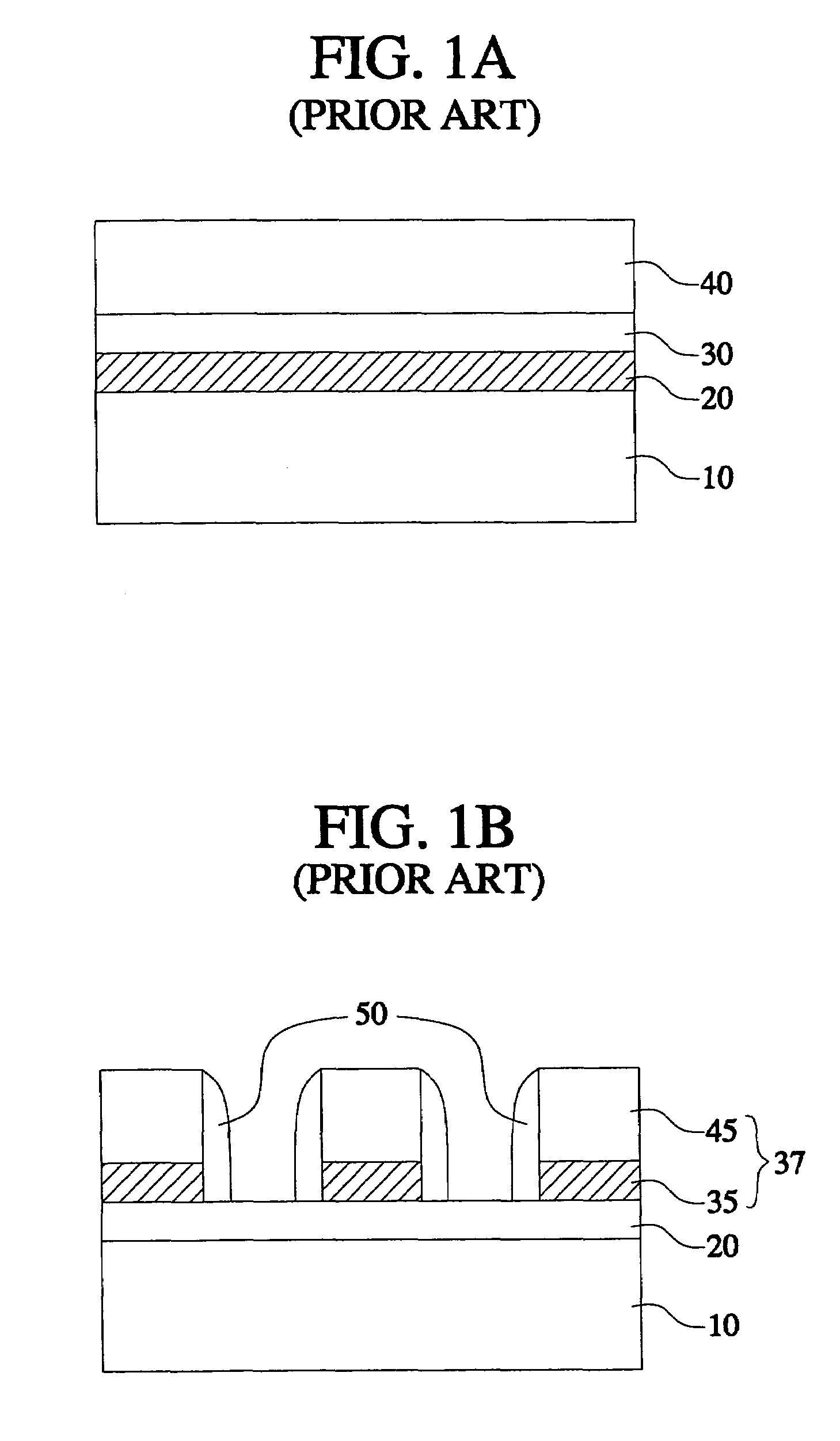

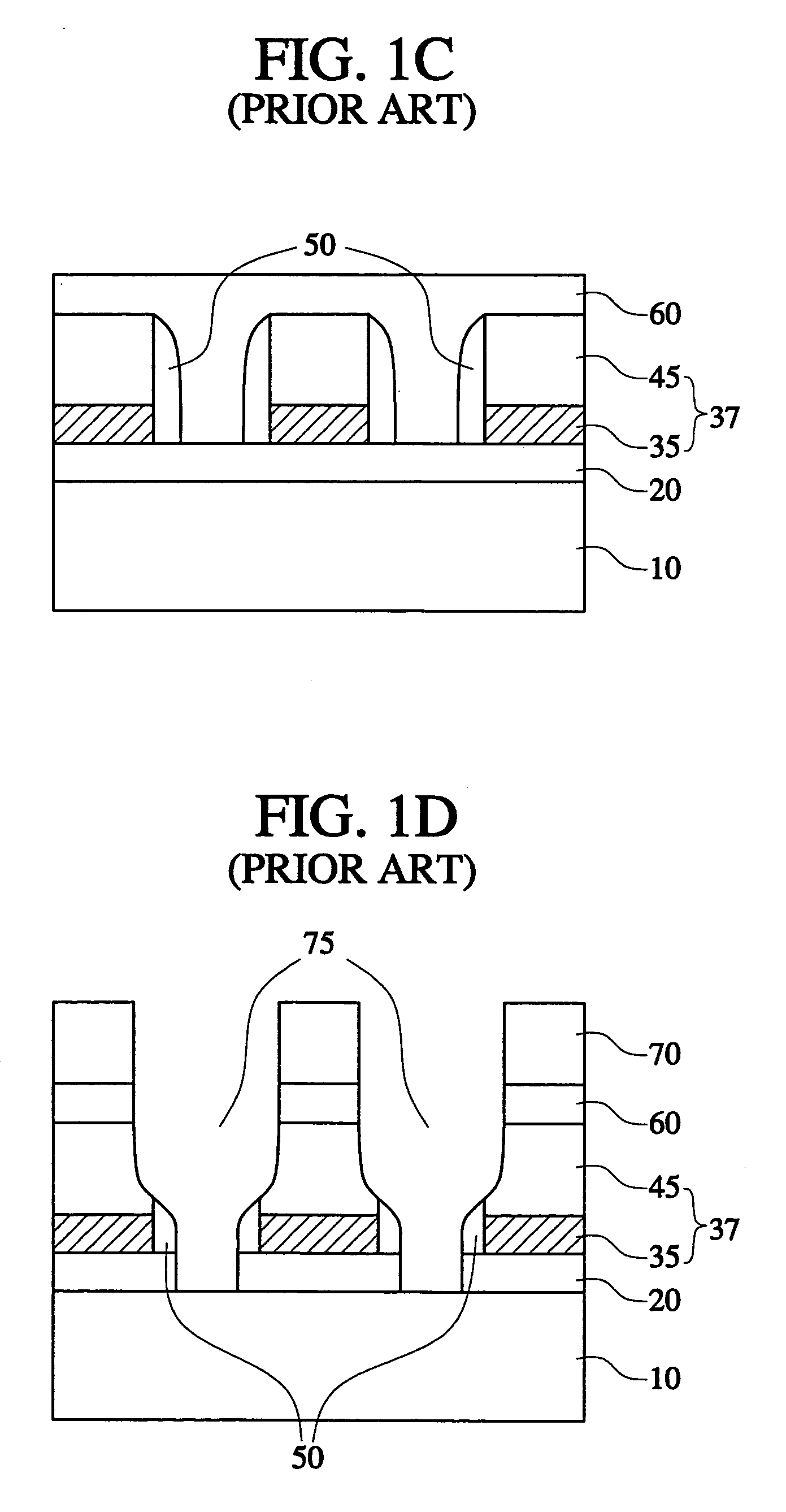

Method for manufacturing semiconductor device

InactiveUS20050250308A1Reliable and reliableNot deterioratingSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialOptoelectronics

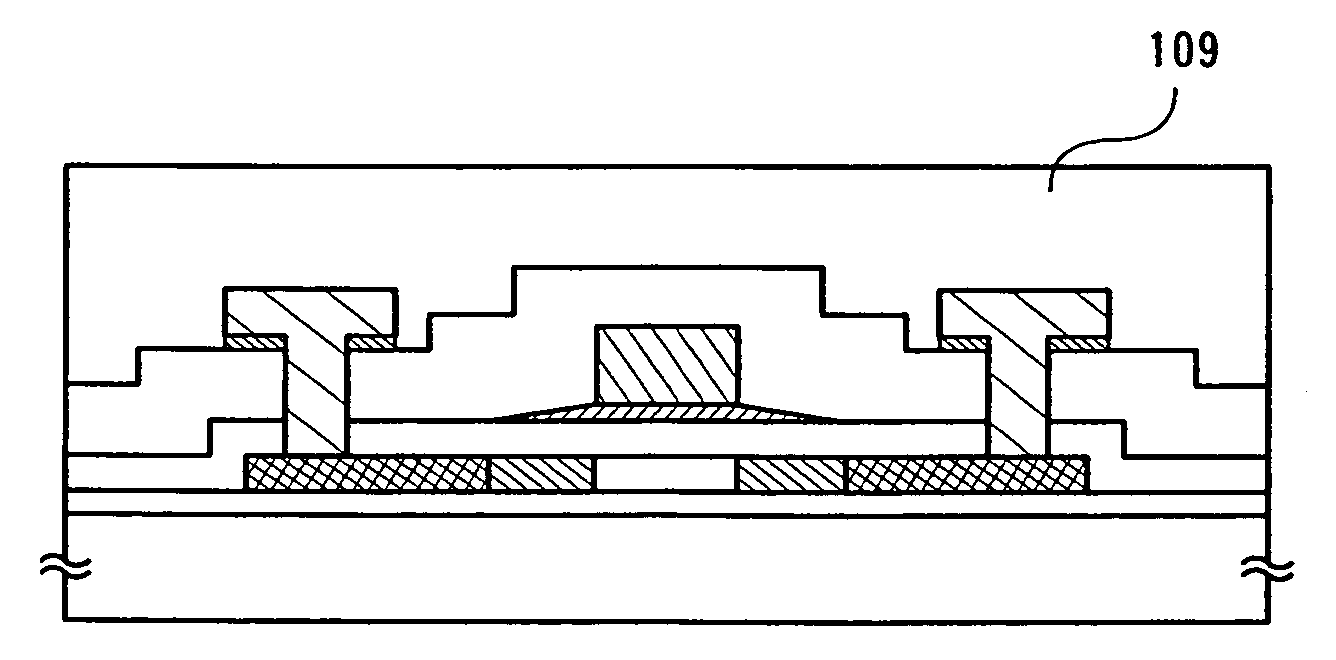

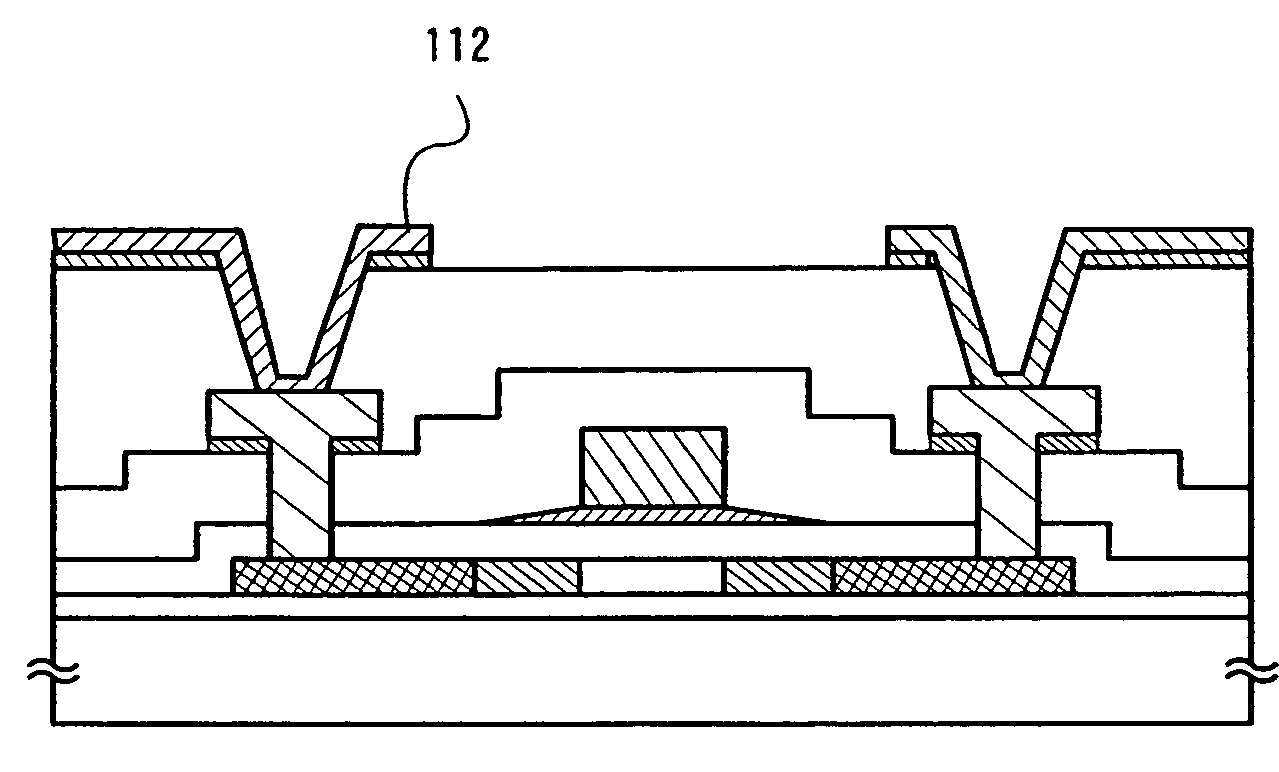

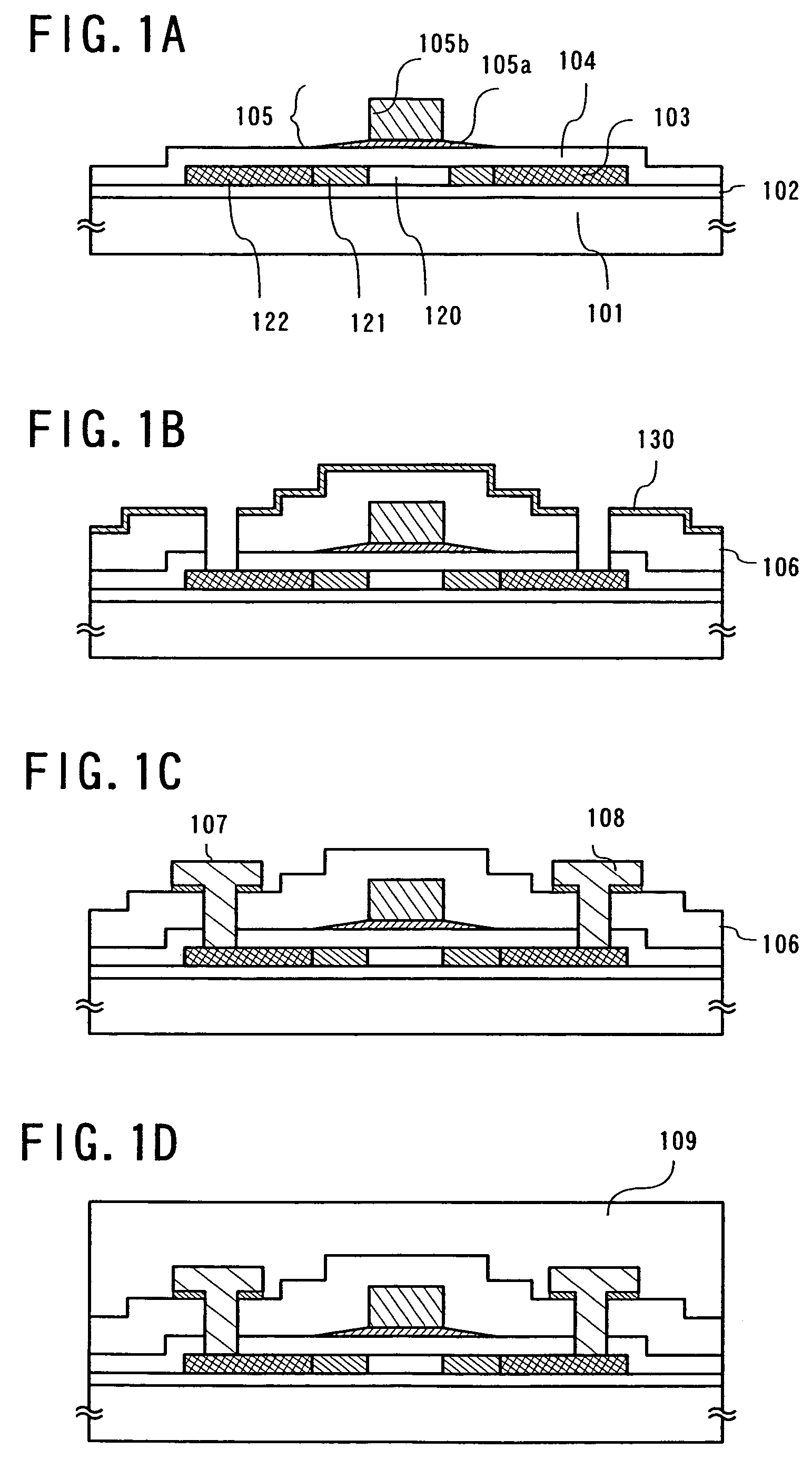

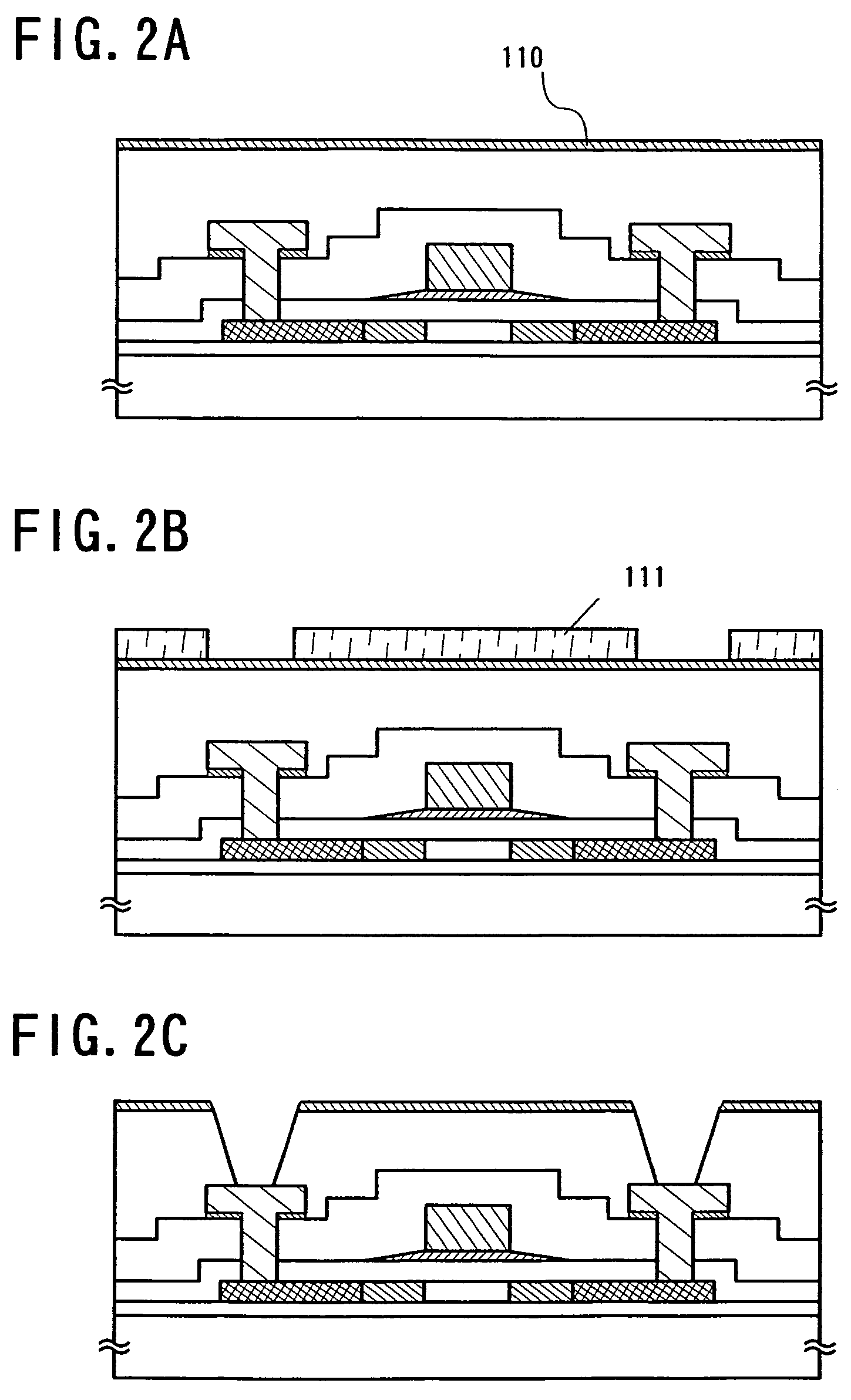

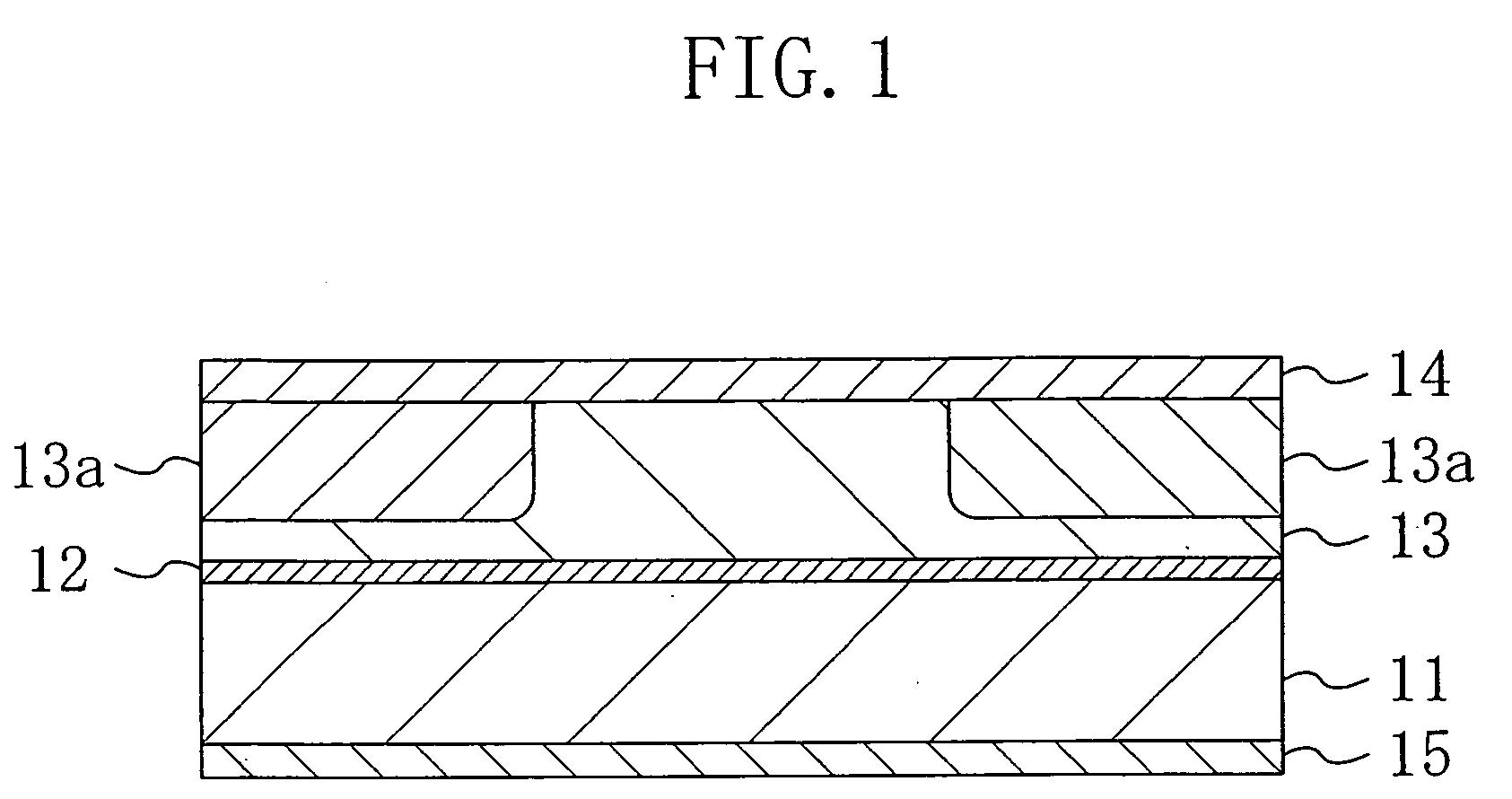

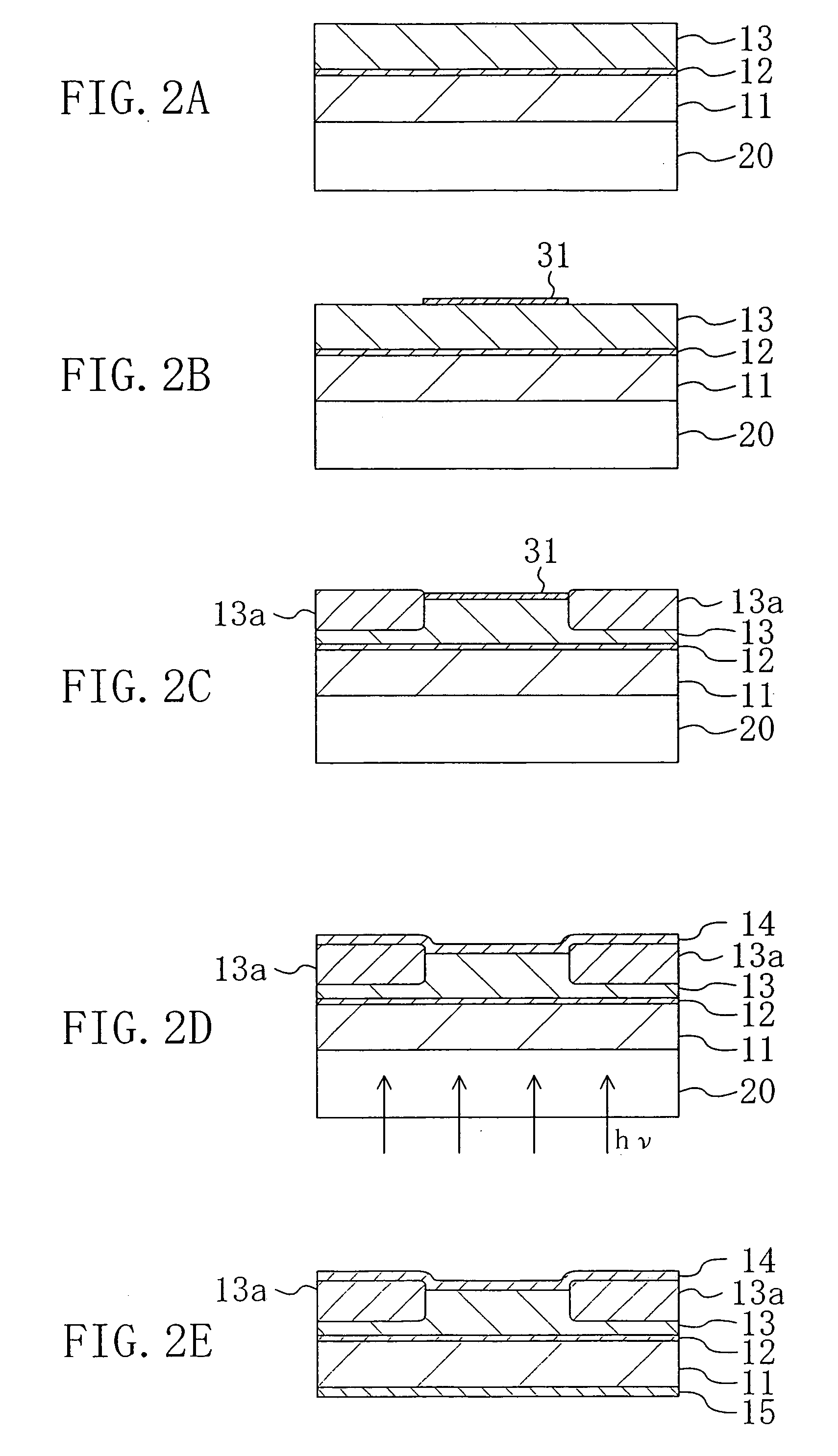

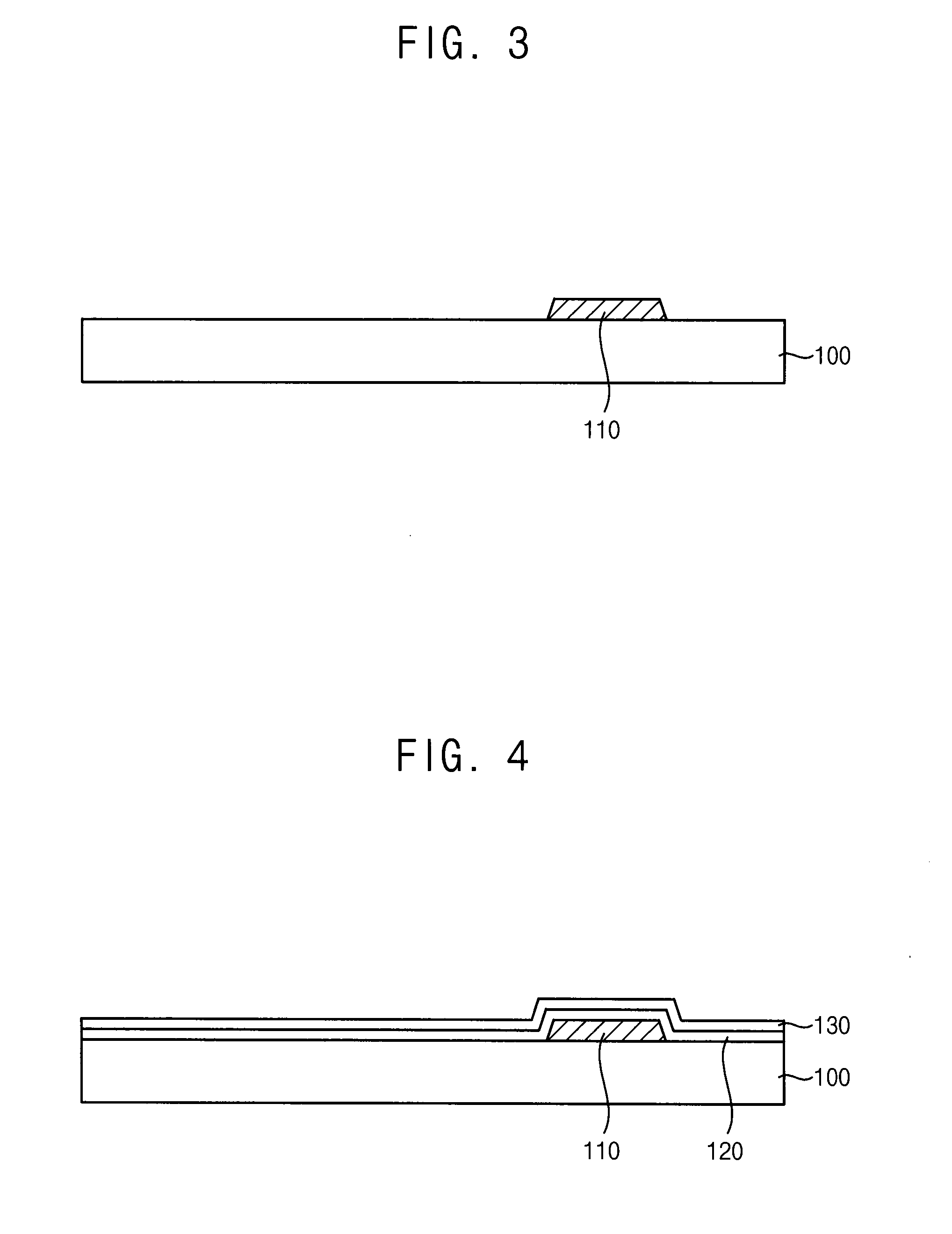

The present invention provides a method for manufacturing a semiconductor device having high characteristic and reliability. The etching damage during dry etching after forming an electrode or a wiring over an insulating film is prevented. The damage is suppressed by forming a conductive layer so that charged particles due to plasma during dry etching are not generated in a semiconductor layer. Accordingly, it is an object of the invention to provide a method not for generating the deterioration of the transistor characteristic especially in a thin film transistor having a minute structure.

Owner:SEMICON ENERGY LAB CO LTD

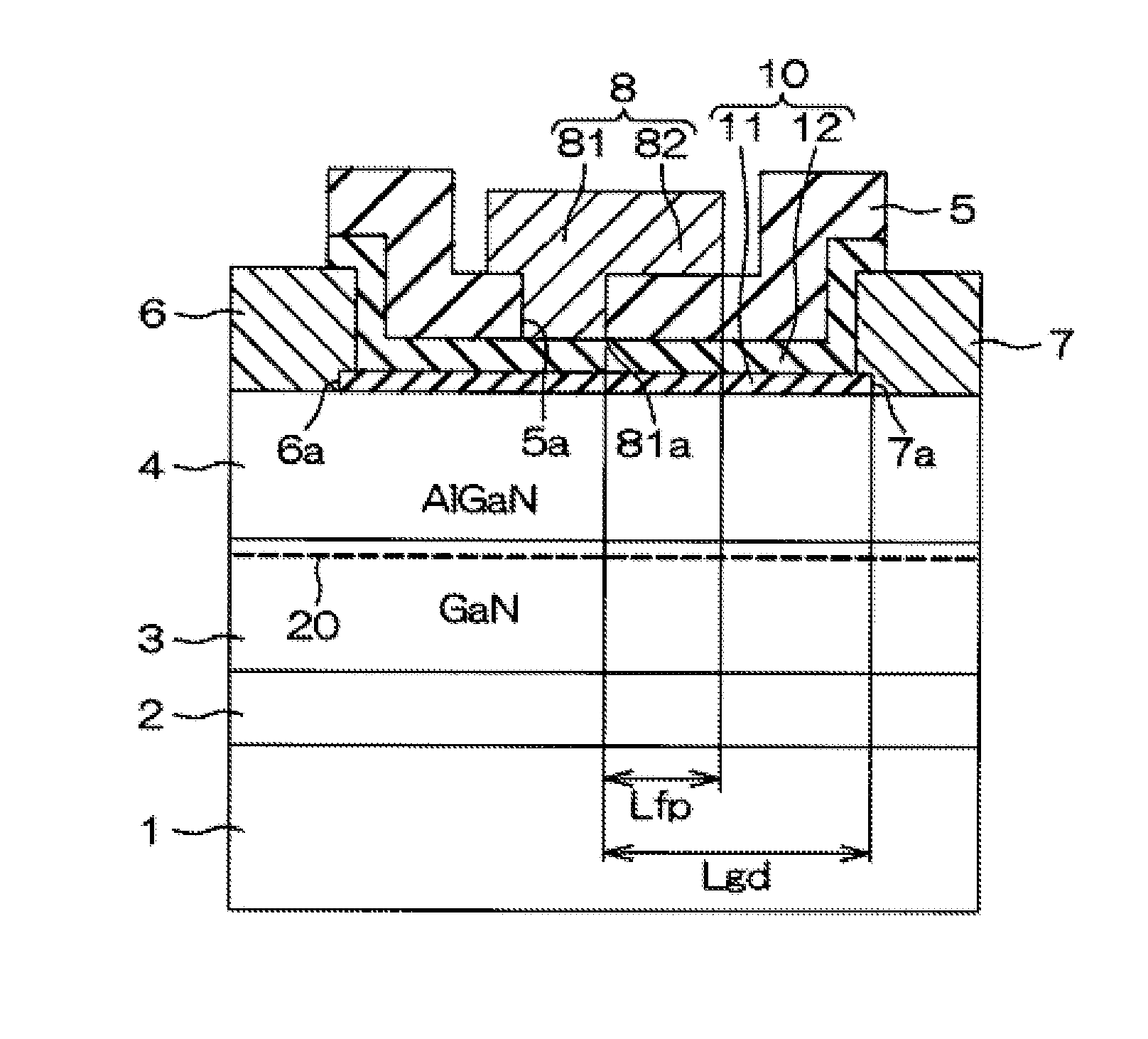

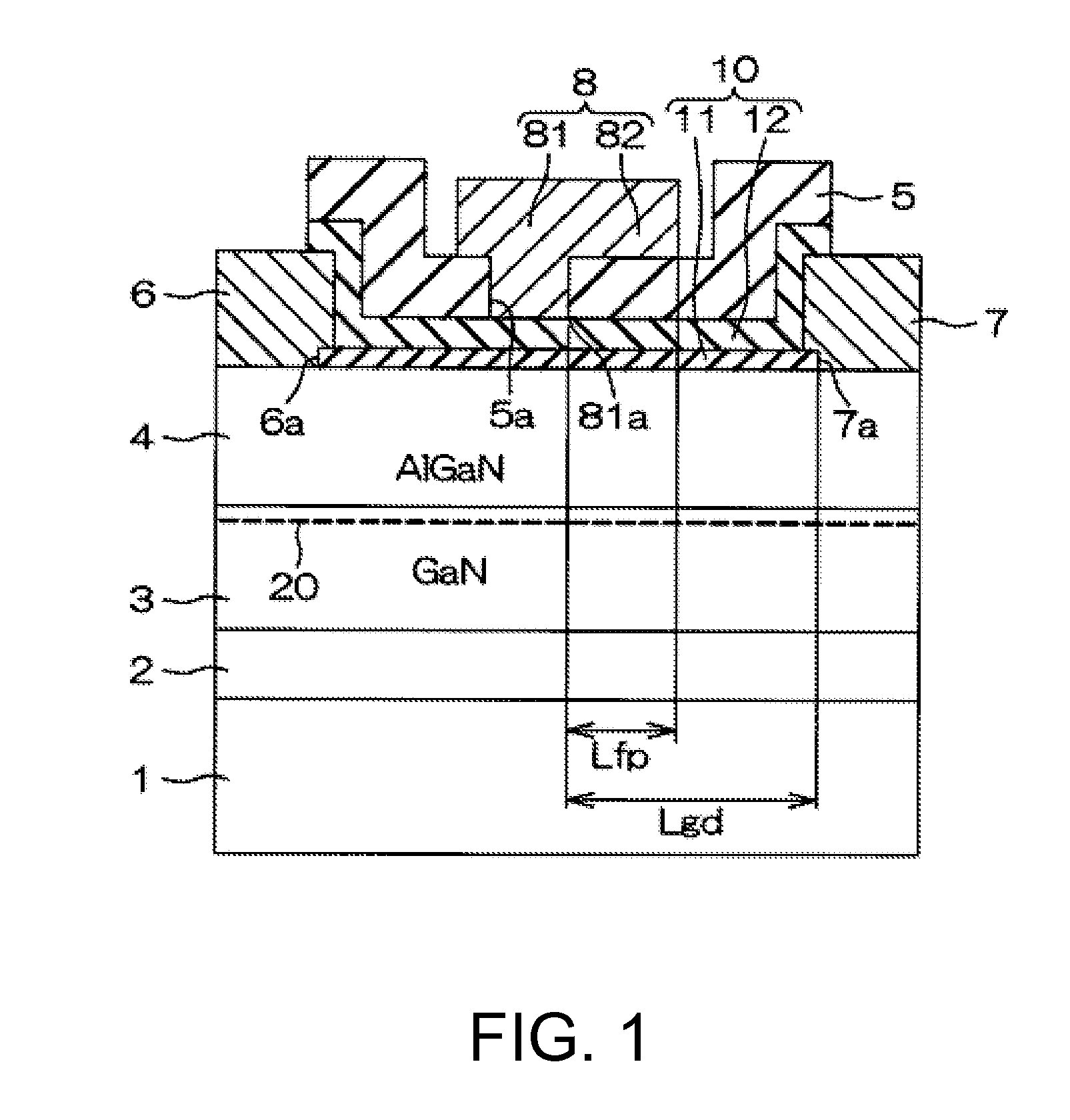

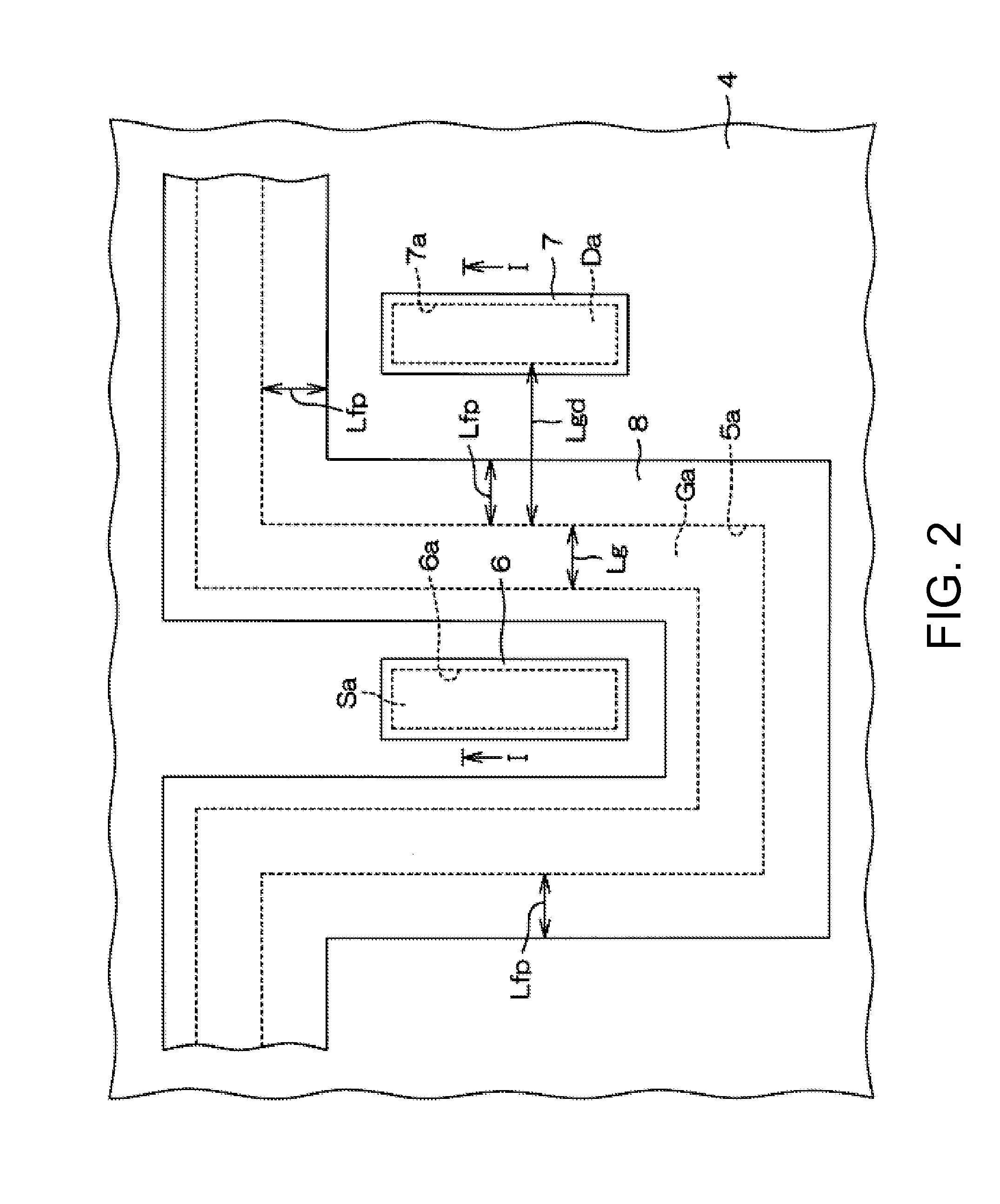

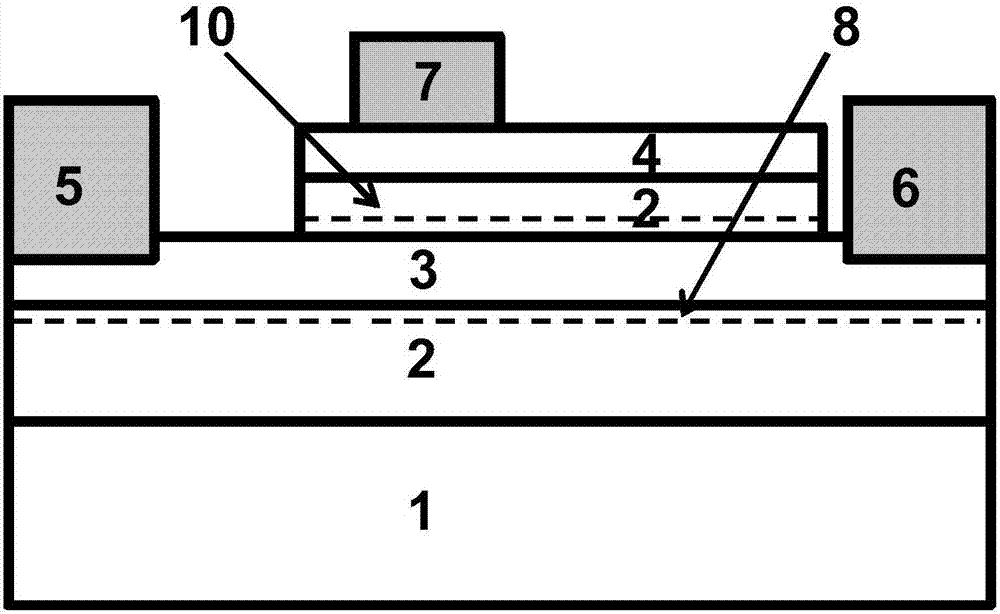

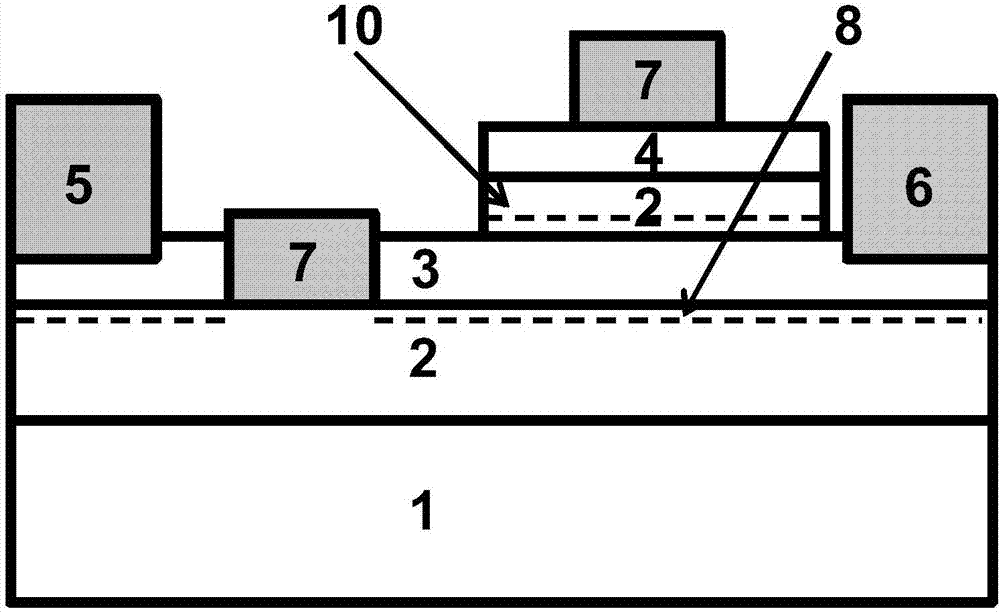

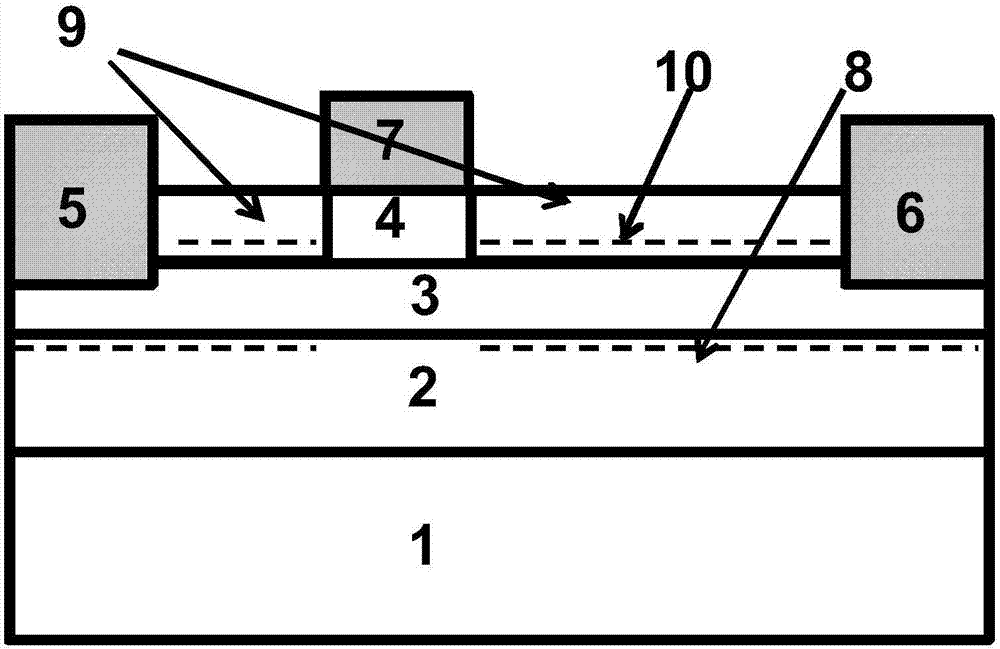

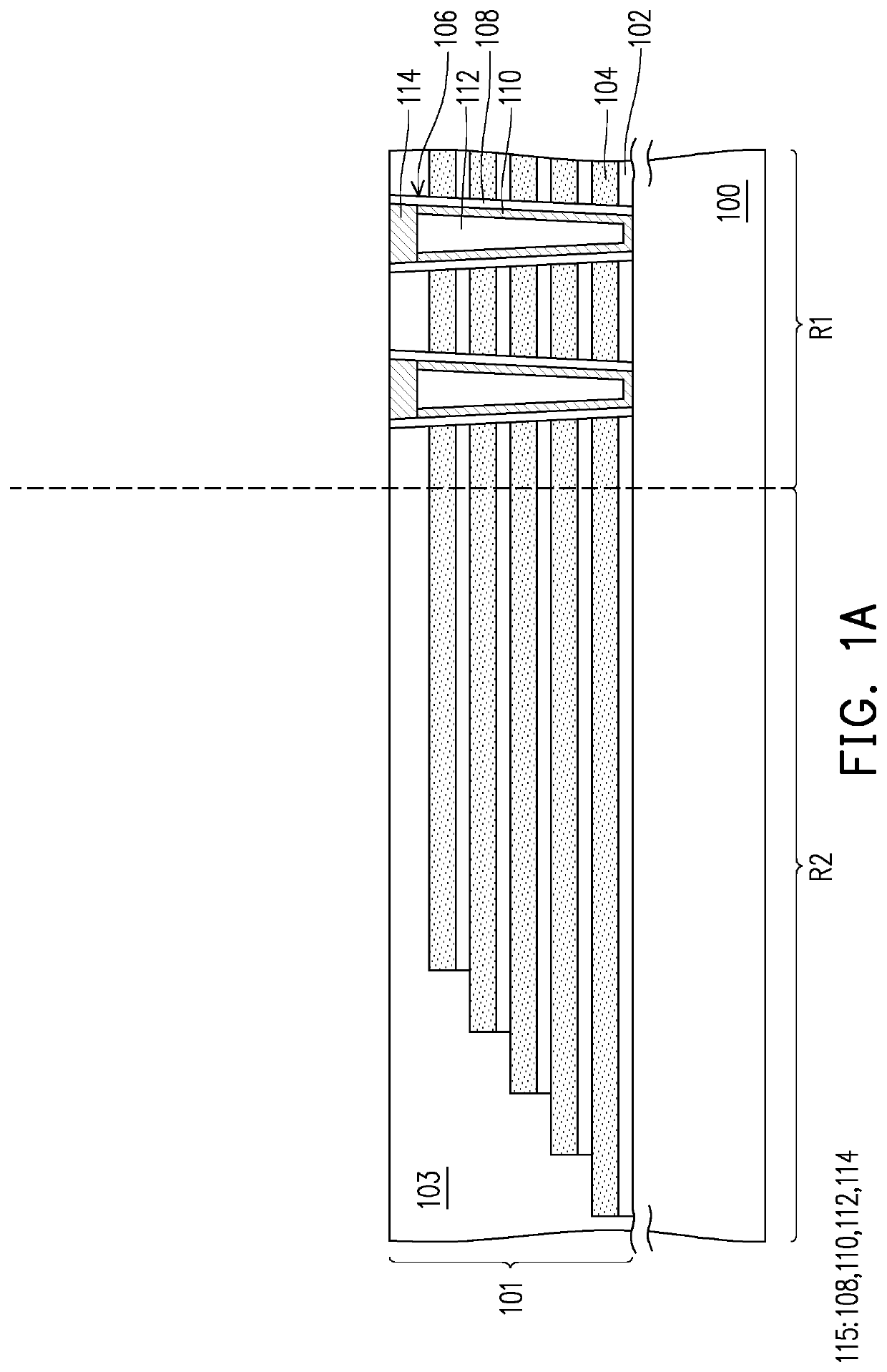

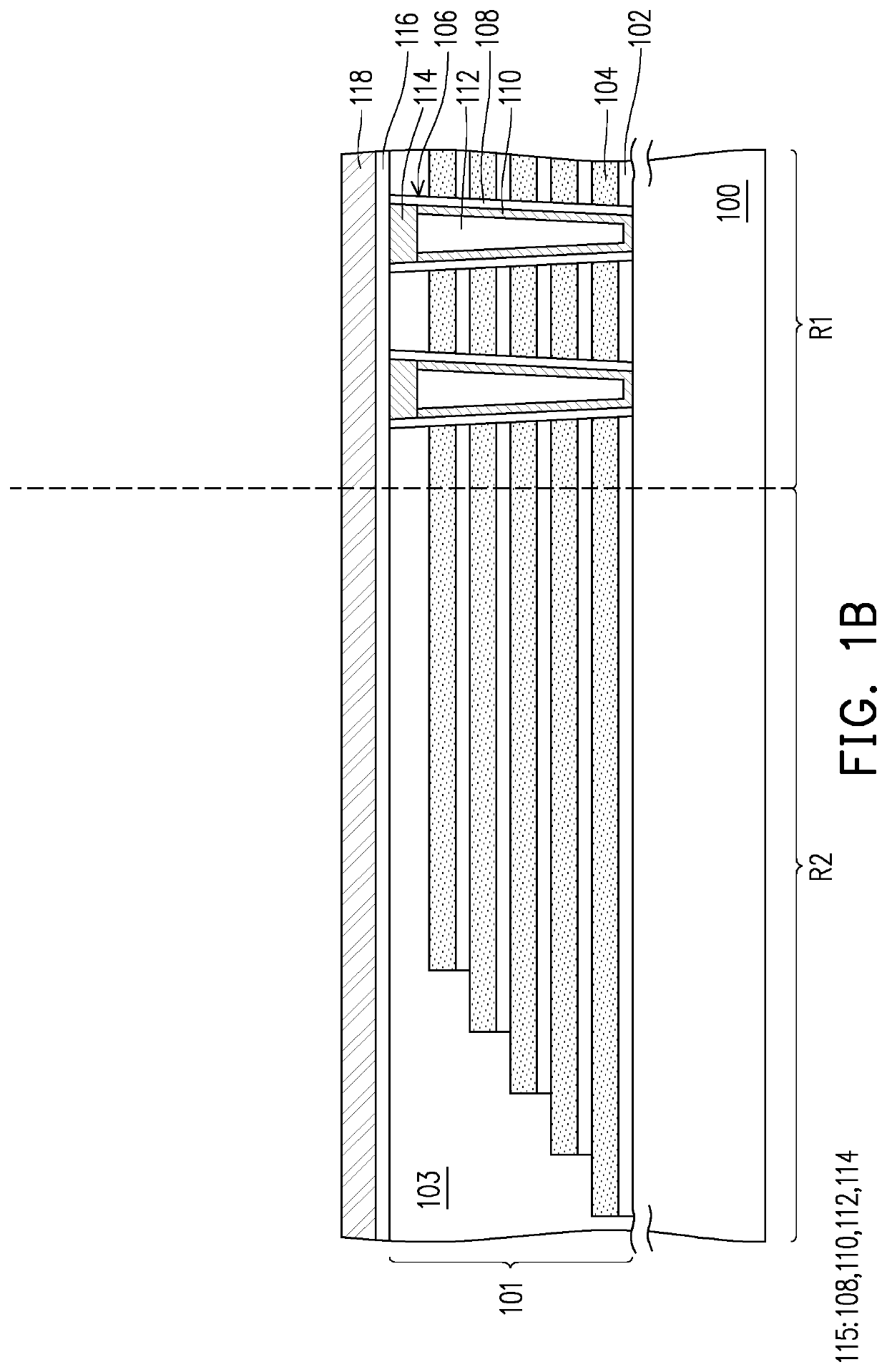

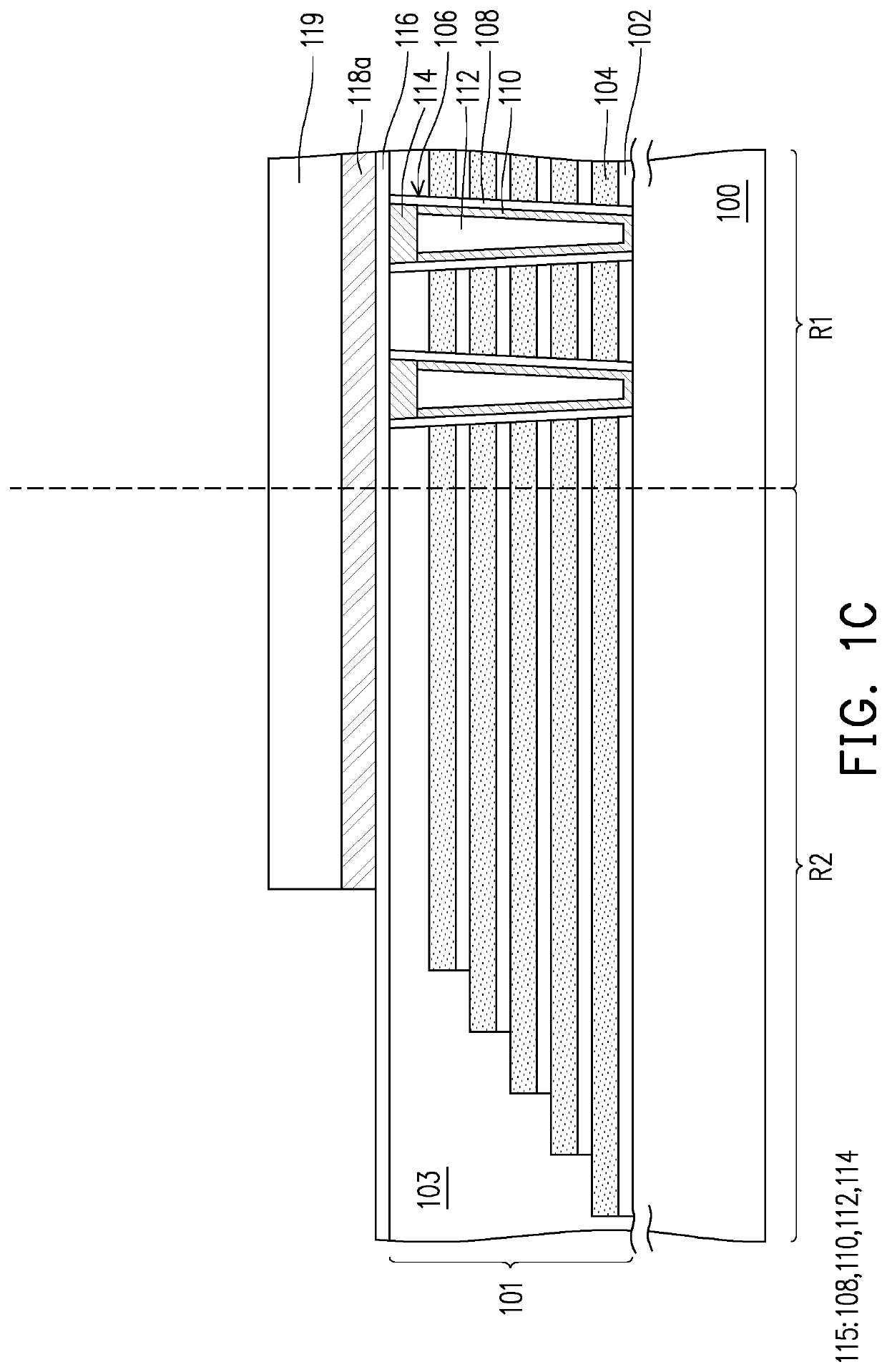

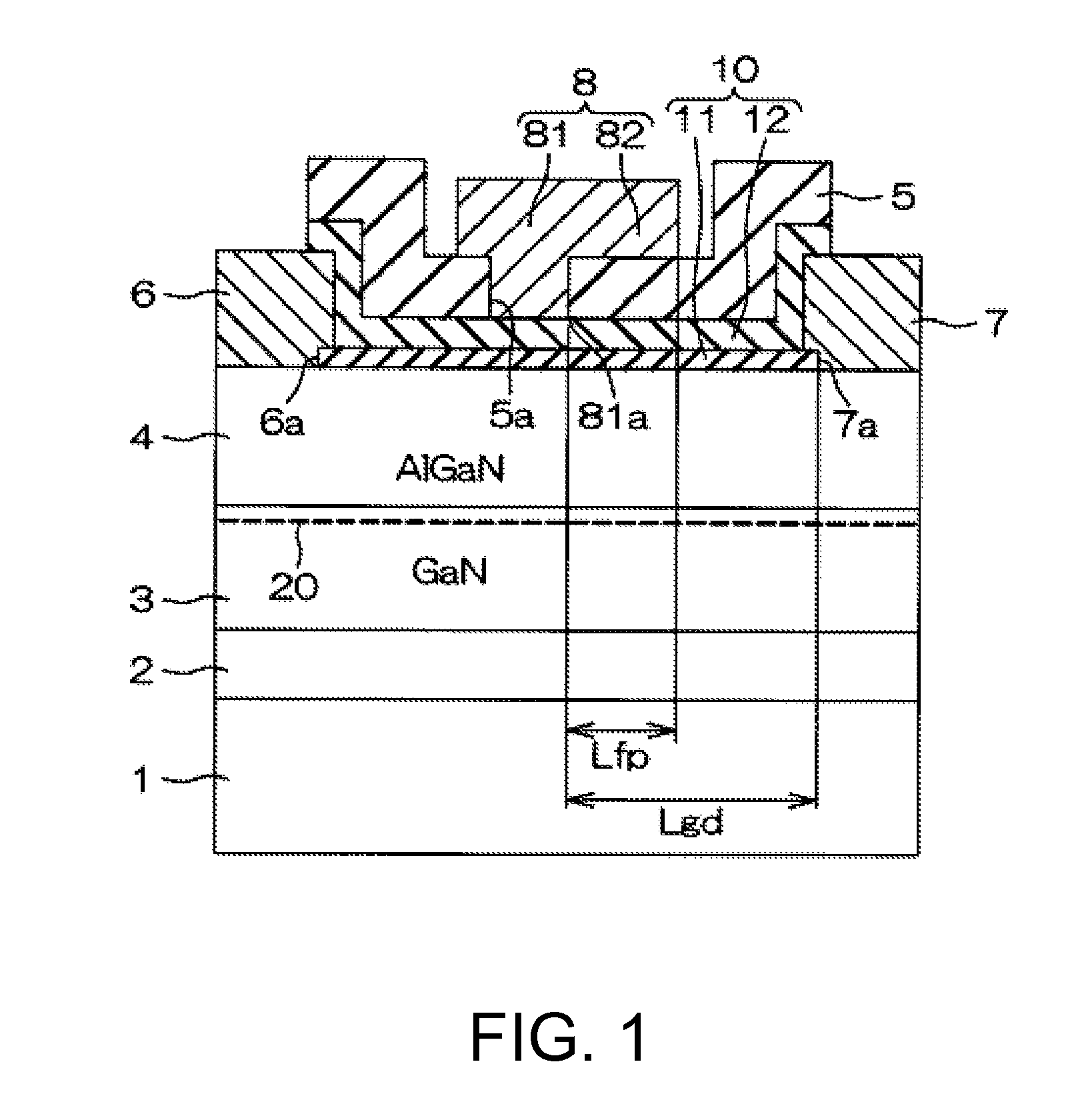

Nitride semiconductor device and manufacturing method thereof

ActiveUS20130313609A1Improve morphologyStable characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesElectron transport layerElectron

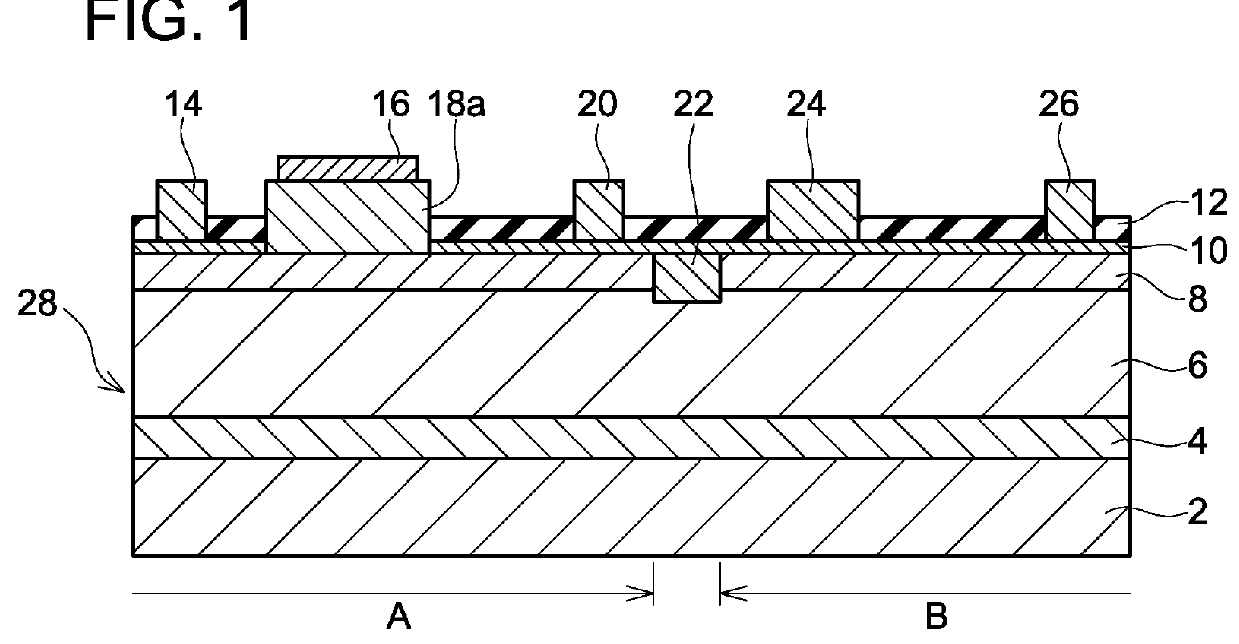

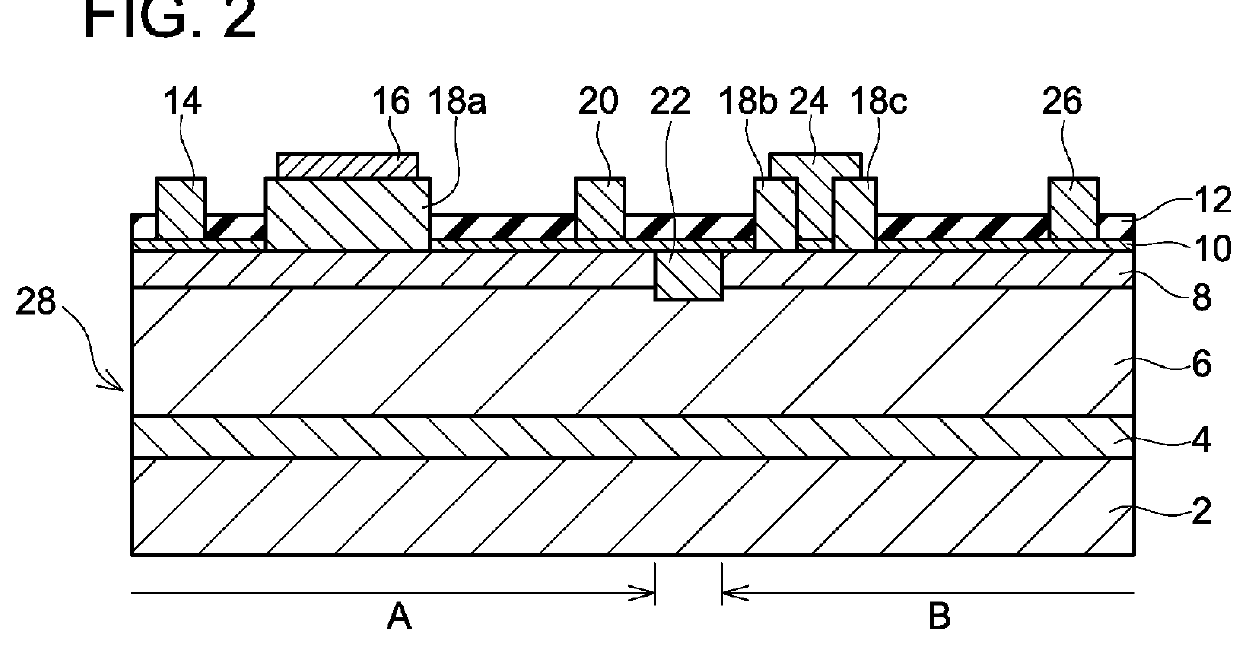

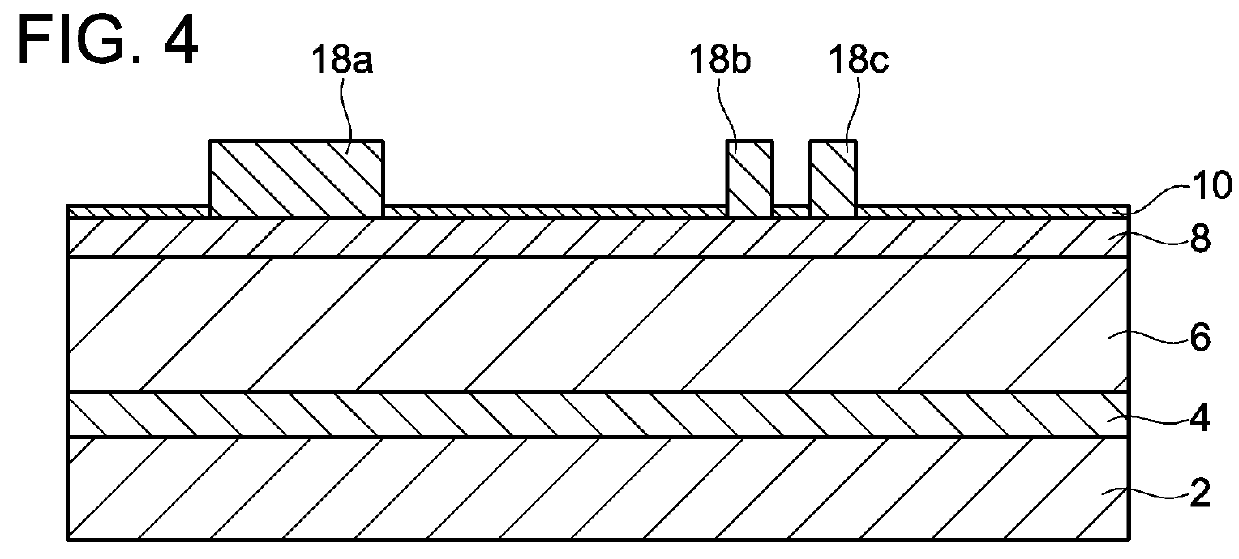

Provided are a nitride semiconductor device having an excellent boundary between a nitride semiconductor and a gate insulating film, resulting in improved device characteristics, and a manufacturing method therefor. The nitride semiconductor device includes: an electron transport layer made of a nitride semiconductor; an electron supply layer layered on the electron transport layer, the electron supply layer being made of a nitride semiconductor including Al and having an Al composition different from that of the electron transport layer; a source electrode and a drain electrode formed on the electron supply layer with a gap therebetween; a gate insulating film covering the surface of the electron supply layer between the source electrode and the drain electrode; a passivation film covering a surface of the gate insulating film and having an opening between the source electrode and the drain electrode; and a gate electrode having a main gate body in the opening facing the electron supply layer through the gate insulating film.

Owner:ROHM CO LTD

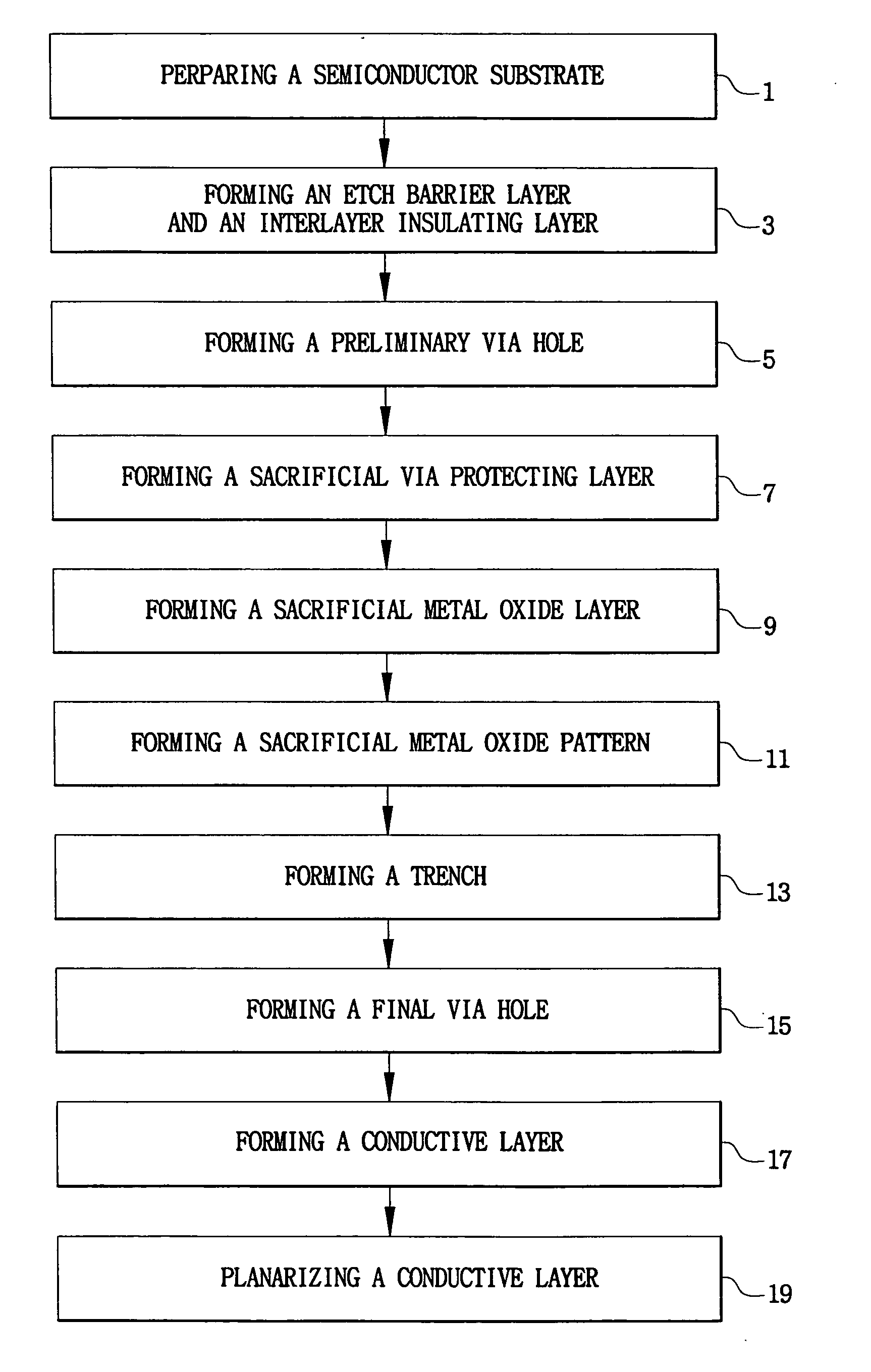

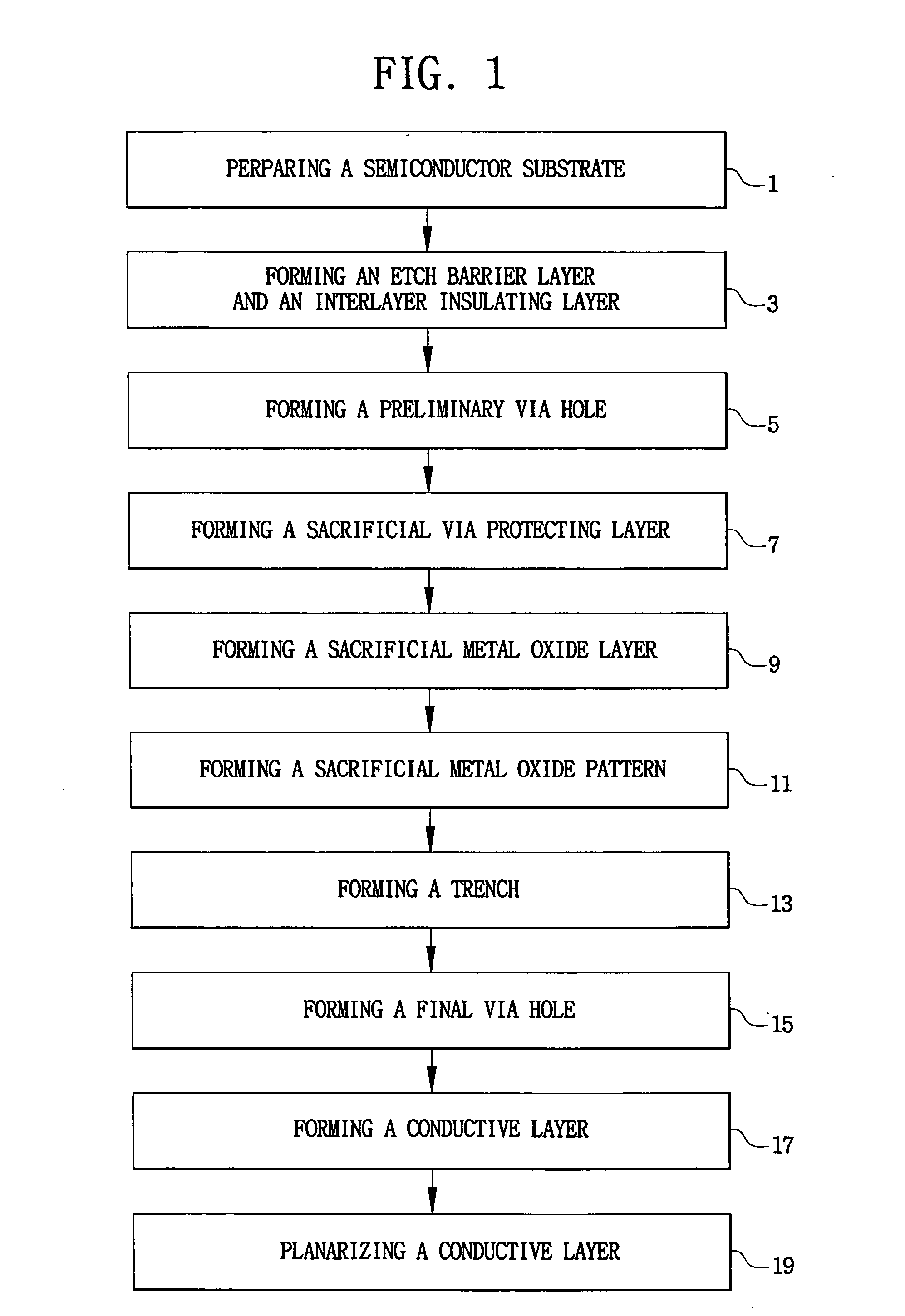

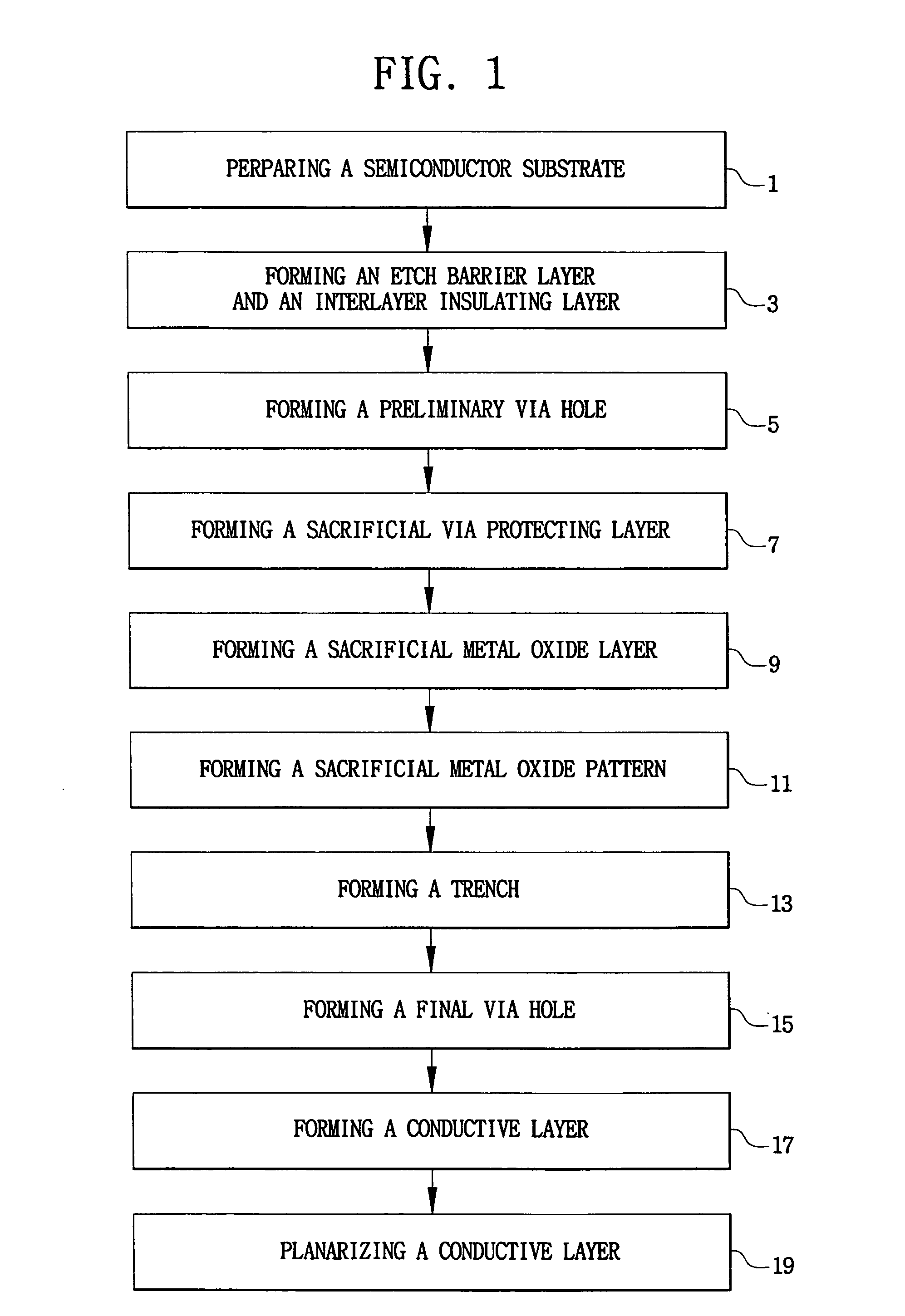

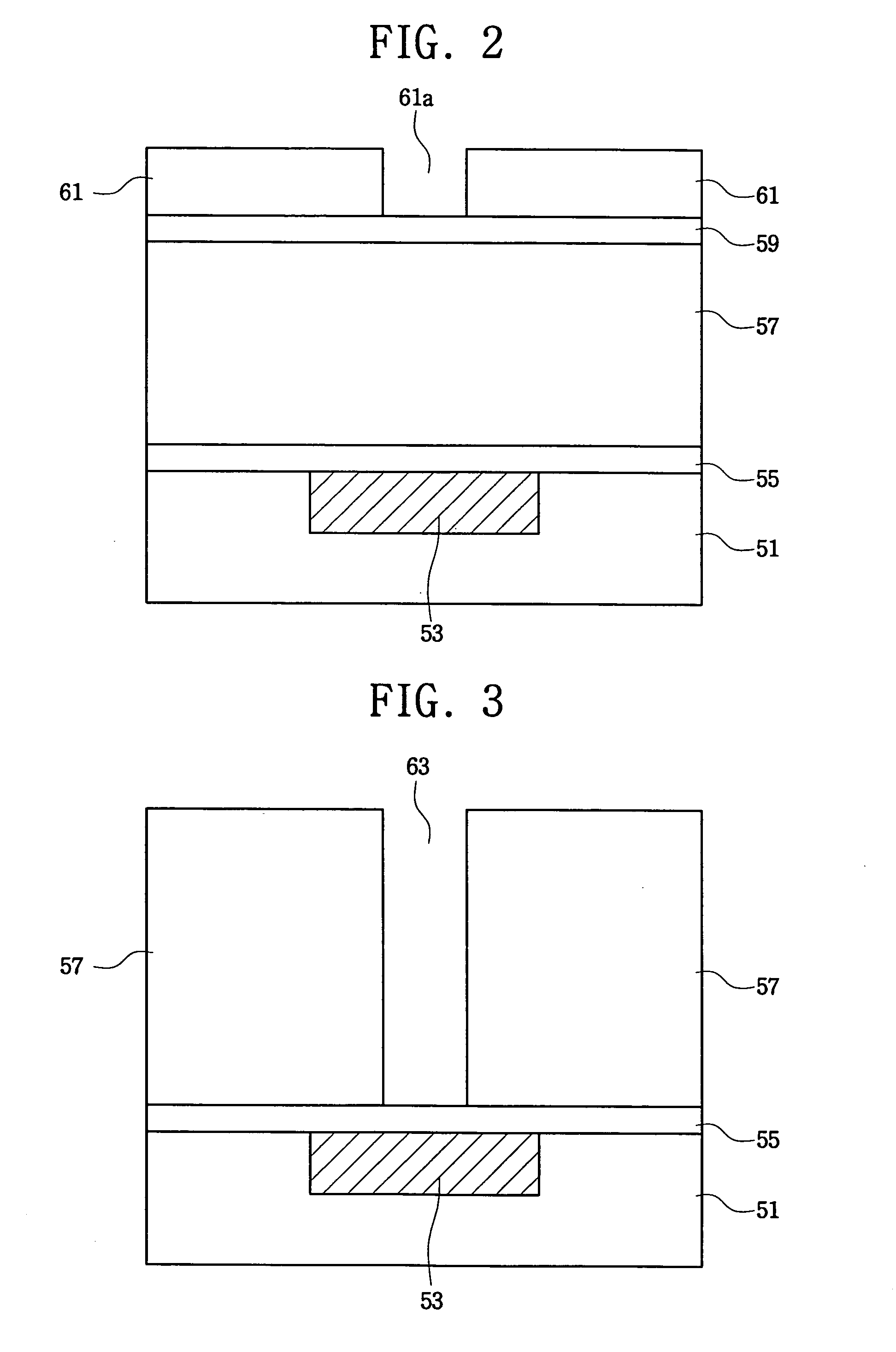

Method of forming dual damascene metal interconnection employing sacrificial metal oxide layer

ActiveUS20050124149A1Increase process marginReduce reflectivitySemiconductor/solid-state device manufacturingSemiconductor devicesInterconnectionSacrificial metal

There is provided a method of forming a dual damascene metal interconnection by employing a sacrificial metal oxide layer. The method includes preparing a semiconductor substrate. An interlayer insulating layer is formed on the semiconductor substrate, and a preliminary via hole is formed by patterning the interlayer insulating layer. A sacrificial via protecting layer is formed on the semiconductor substrate having the preliminary via hole to fill the preliminary via hole, and cover an upper surface of the interlayer insulating layer. A sacrificial metal oxide layer is formed on the sacrificial via protecting layer, the sacrificial metal oxide layer is patterned to form a sacrificial metal oxide pattern having an opening crossing over the preliminary via hole, and exposing the sacrificial via protecting layer. The sacrificial via protecting layer and the interlayer insulating layer are etched using the sacrificial metal oxide pattern as an etch mask to form a trench located inside the interlayer insulating layer.

Owner:SAMSUNG ELECTRONICS CO LTD

High-resistance cap layer-based III-nitride polarization super-junction high electron mobility transistor (HEMT) device and fabrication method thereof

InactiveCN106981513ASimple structureAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceHeterojunction

The invention discloses a high-resistance cap layer-based III-nitride polarization super-junction high electron mobility transistor (HEMT) device and a fabrication method thereof. The device comprises a first heterojunction, a second heterojunction, a p-type doping fourth semiconductor, a source, a drain and a gate, wherein the first heterojunction comprises a first semiconductor and a second semiconductor, the second semiconductor is formed on the first semiconductor and is provided with a band gap wider than the first semiconductor, a two-dimensional electron gas is formed in a first heterojunction structure, the second heterojunction comprises the second semiconductor and a third semiconductor, the third semiconductor is formed on the second semiconductor and is provided with a band gap narrower than the second semiconductor, a two-dimensional electron gas is formed in a second heterojunction structure, the fourth semiconductor is formed on the second semiconductor, the fourth semiconductor and the third semiconductor are closely connected in a horizontal direction, the source and the drain are connected with the first heterojunction and can be electrically connected through the two-dimensional electron gases, and the gate is arranged between the source and the drain and is connected with the fourth semiconductor.

Owner:SUZHOU NENGWU ELECTRONICS TECH

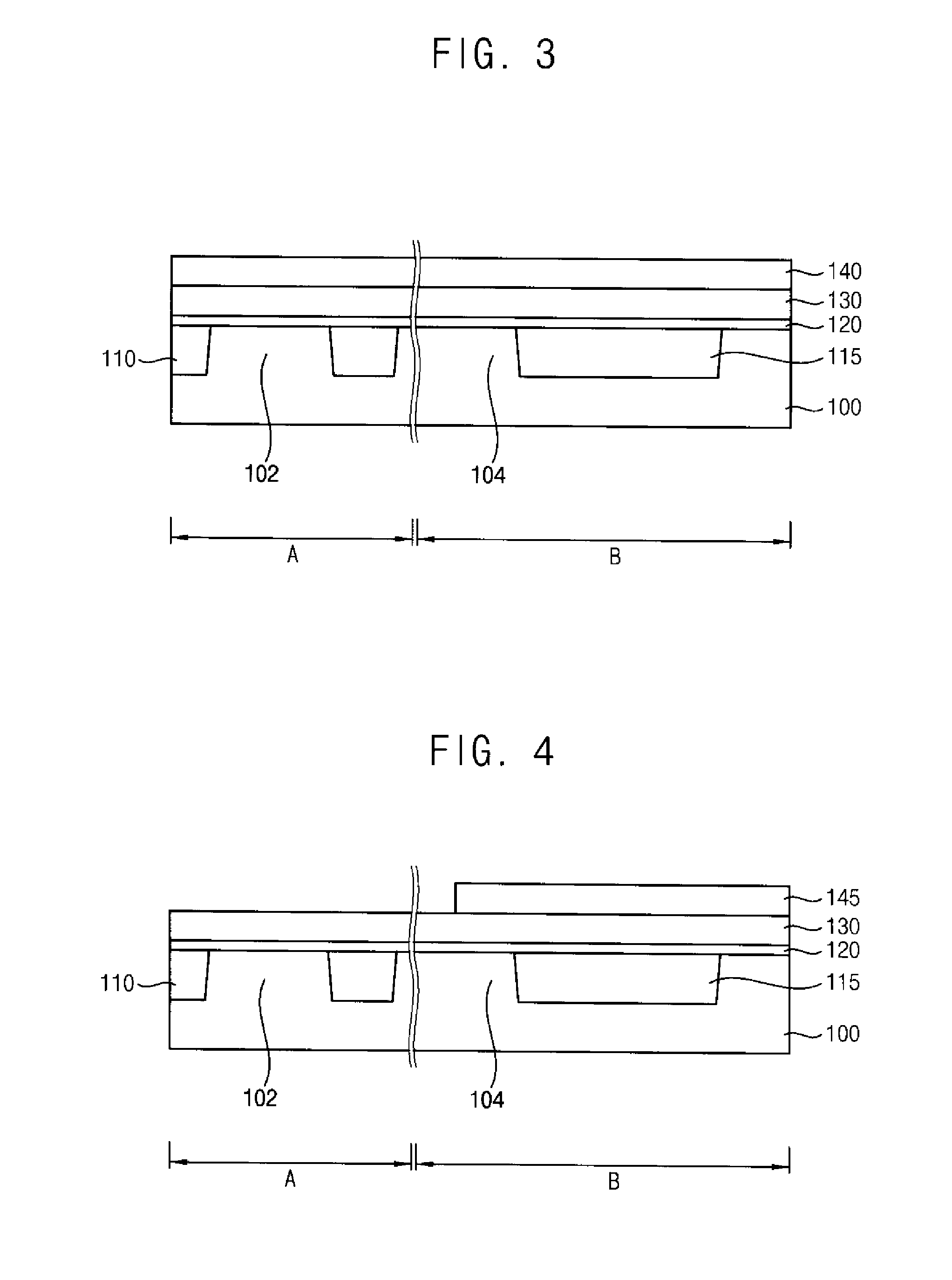

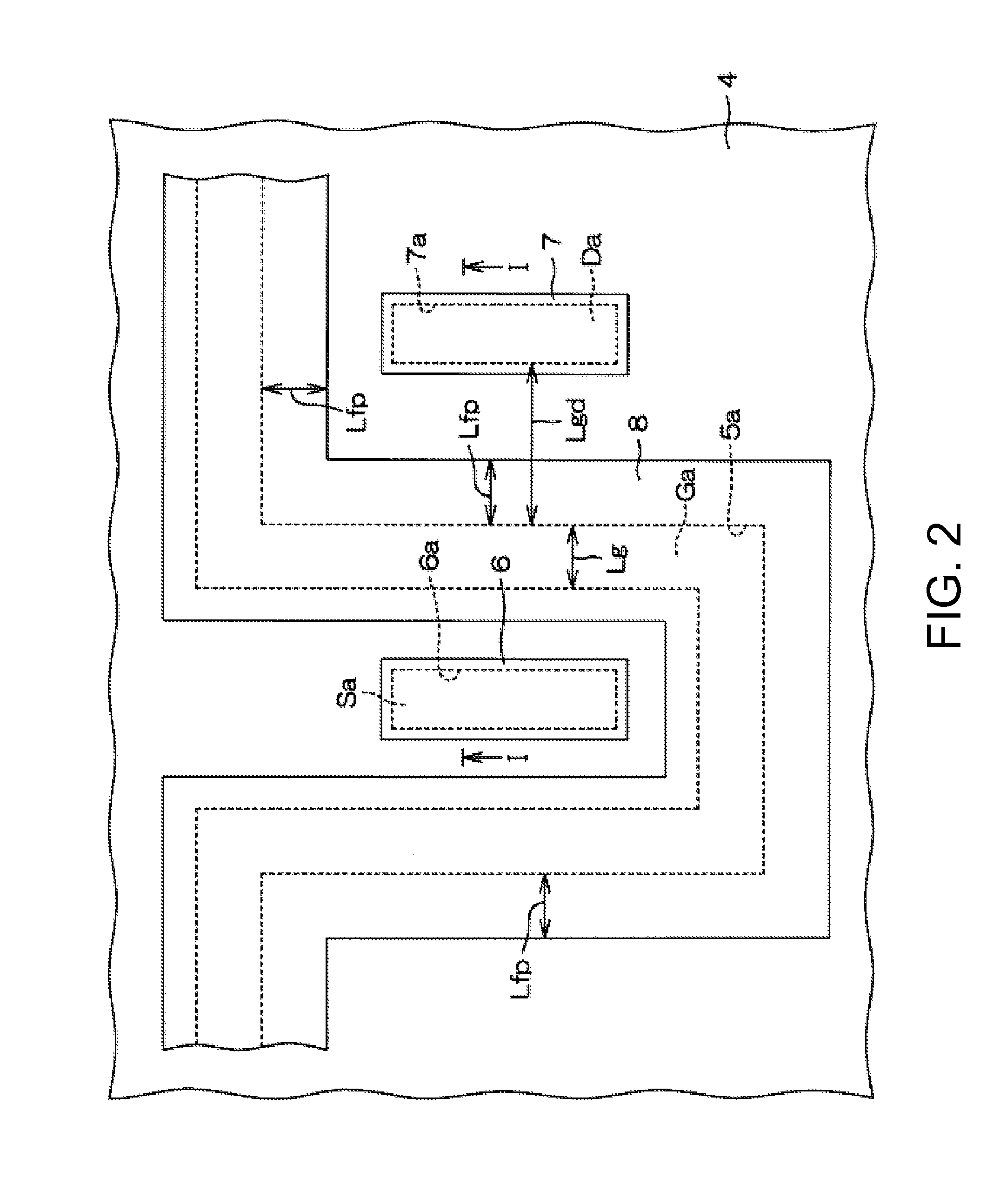

Method for manufacturing semiconductor device

InactiveUS7521368B2Not deterioratingAvoid etch damageSolid-state devicesSemiconductor/solid-state device manufacturingDry etchingSemiconductor

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method for manufacturing the same

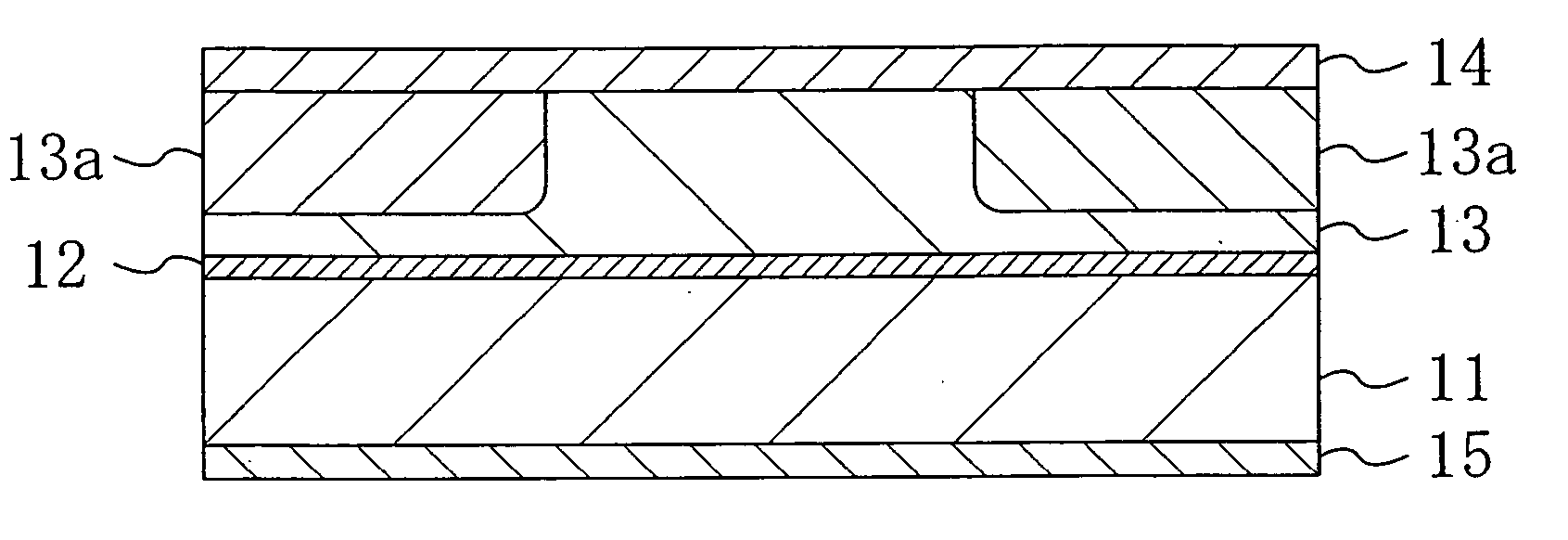

InactiveUS20050042788A1Reduce the valueImprove propertiesOptical wave guidanceLaser detailsElectrical conductorDevice material

A light emitting layer made of a group III-V nitride semiconductor is formed between a first semiconductor layer made of an n-type group III-V nitride semiconductor and a second semiconductor layer made of a p-type group III-V nitride semiconductor. In side portions of the second semiconductor layer, oxidized regions are formed through the oxidization of the second semiconductor layer itself so as to be spaced apart from each other in the direction parallel to the plane of the light emitting layer. A p-side electrode is formed across the entire upper surface of the second semiconductor layer including the oxidized regions, and an n-side electrode is formed on one surface of the first semiconductor layer that is away from the second semiconductor layer.

Owner:PANASONIC CORP

Display substrates, methods of manufacturing the same and display devices including the same

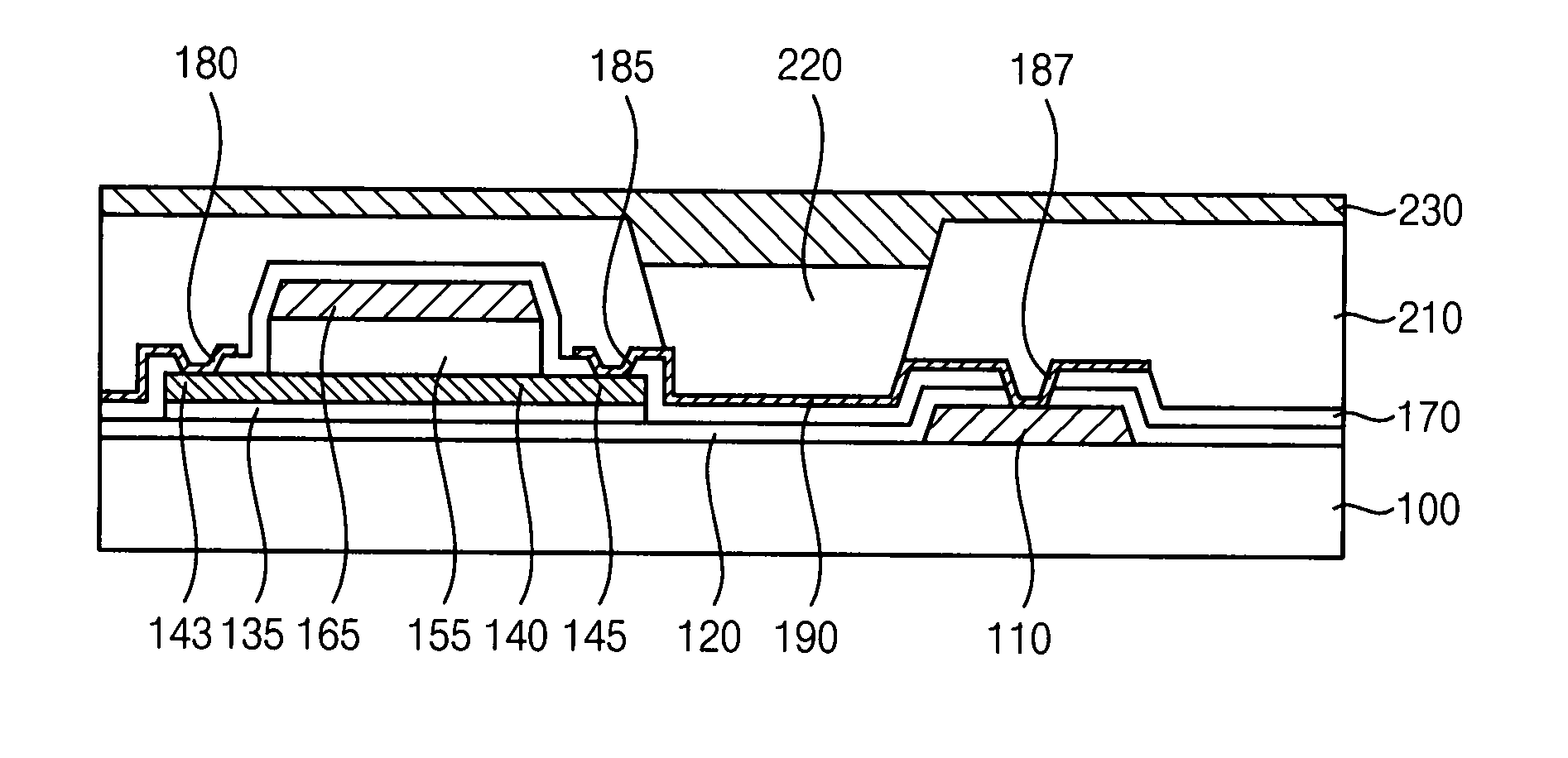

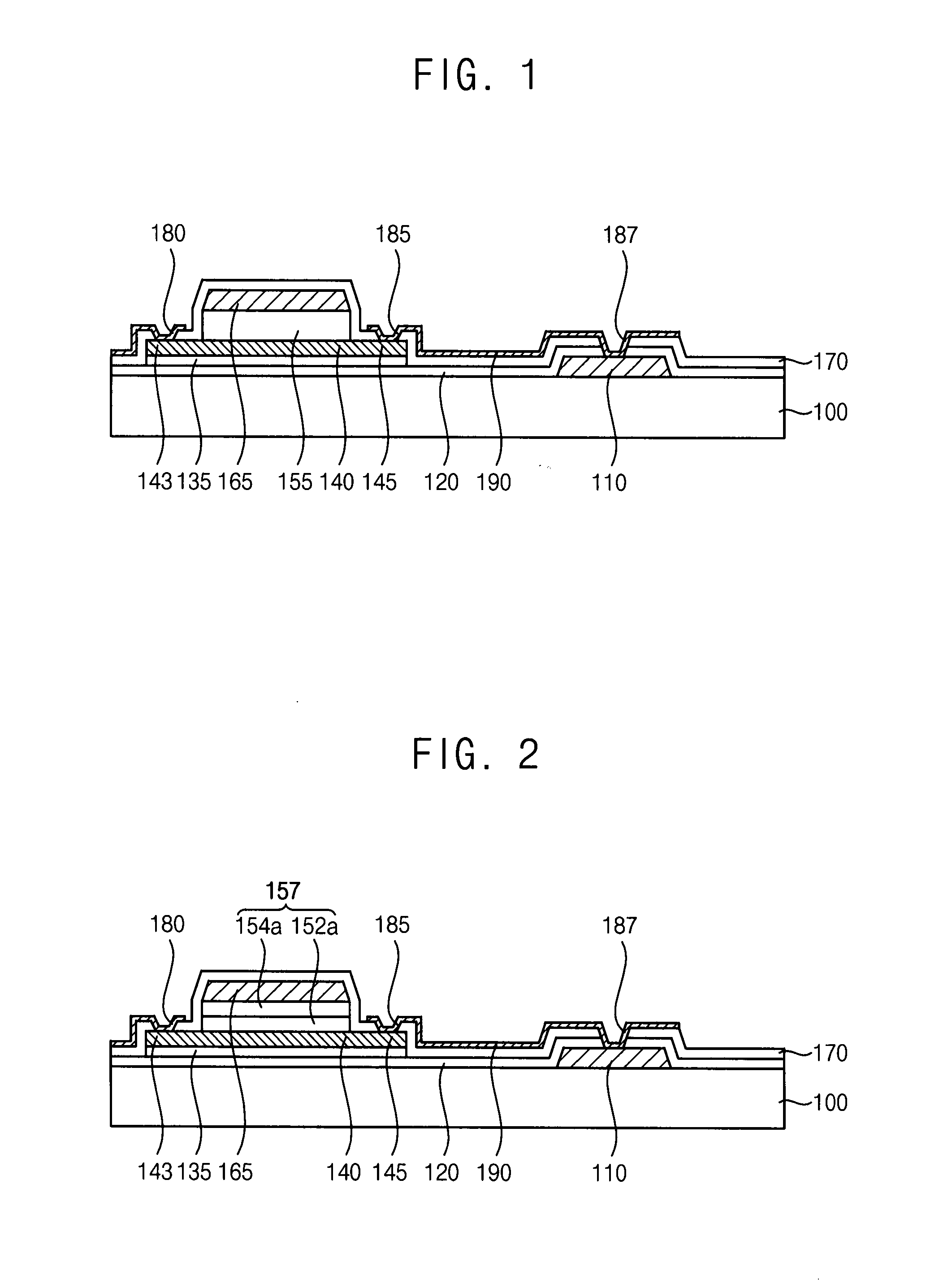

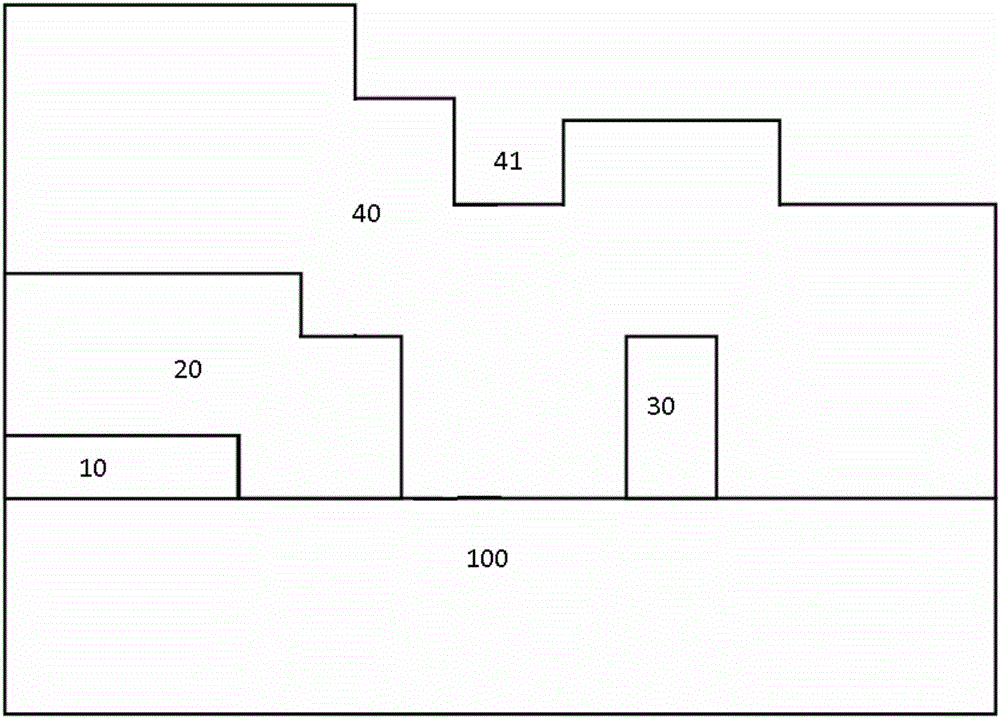

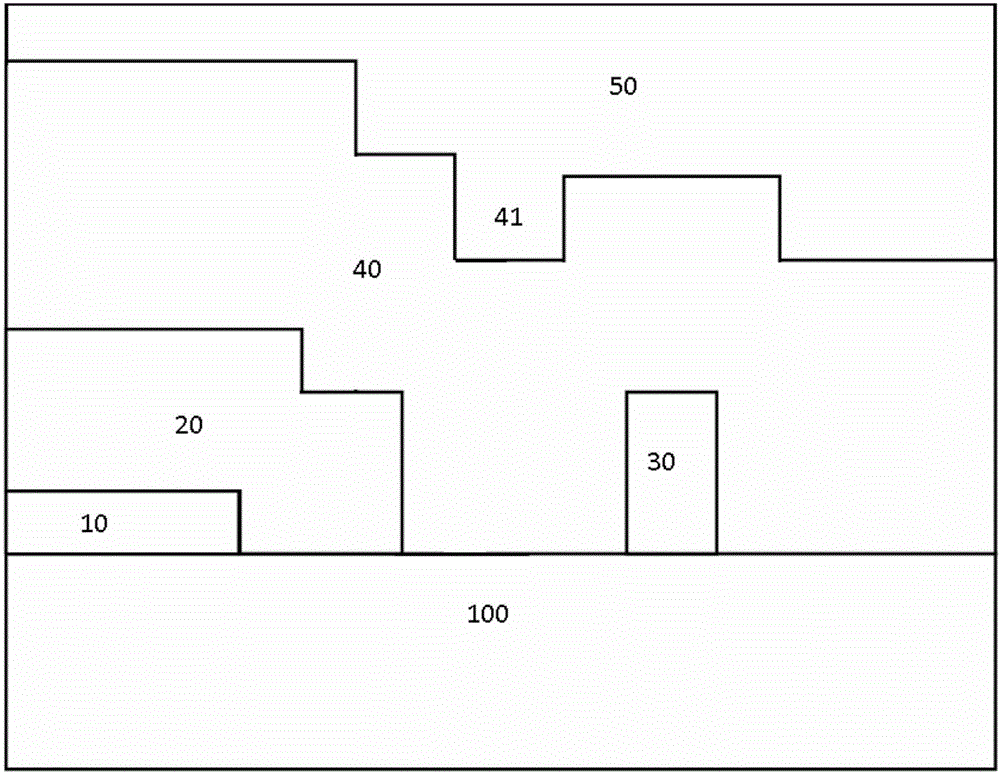

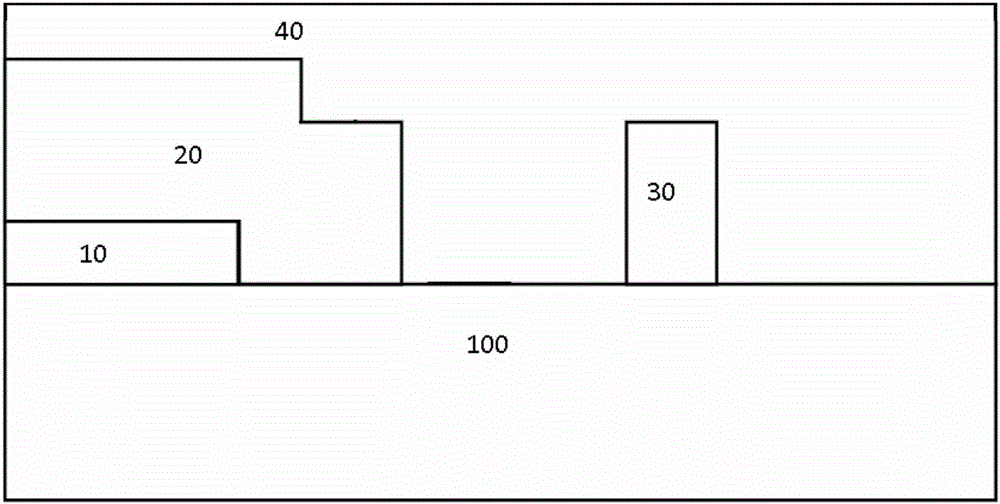

InactiveUS20150162363A1Layer thicknessReduce the amount of etchingTransistorSolid-state devicesInsulation layerDisplay device

A display substrate includes a data pad on a base substrate, a first buffer layer which covers the data pad, a second buffer layer pattern which is disposed on the first buffer layer and separated from the data pad in a plan view, an active layer on the second buffer layer pattern, a gate insulation layer pattern on the active layer, both ends of the active layer exposed by the gate insulation layer pattern, and a gate electrode on the gate insulation layer pattern.

Owner:SAMSUNG DISPLAY CO LTD

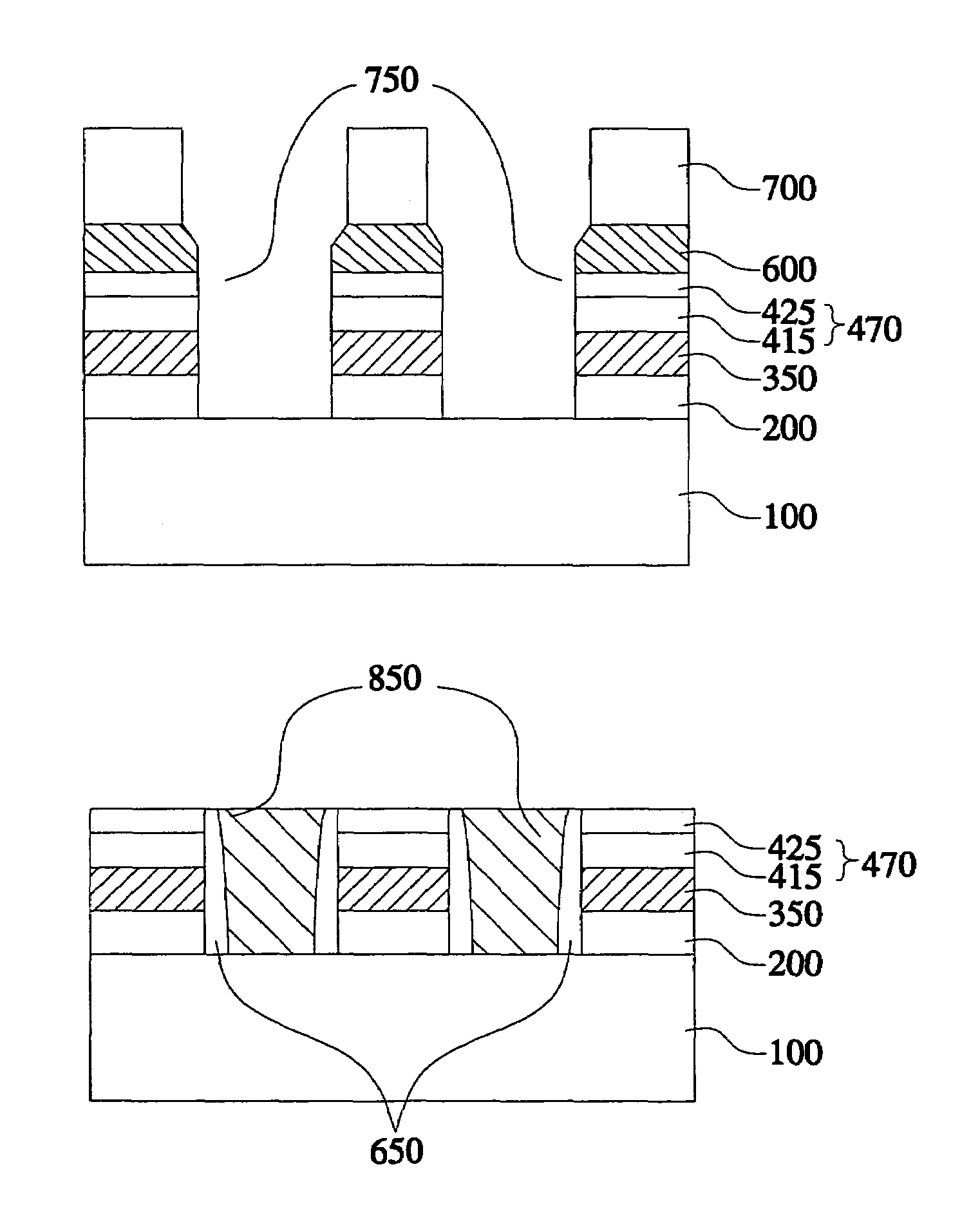

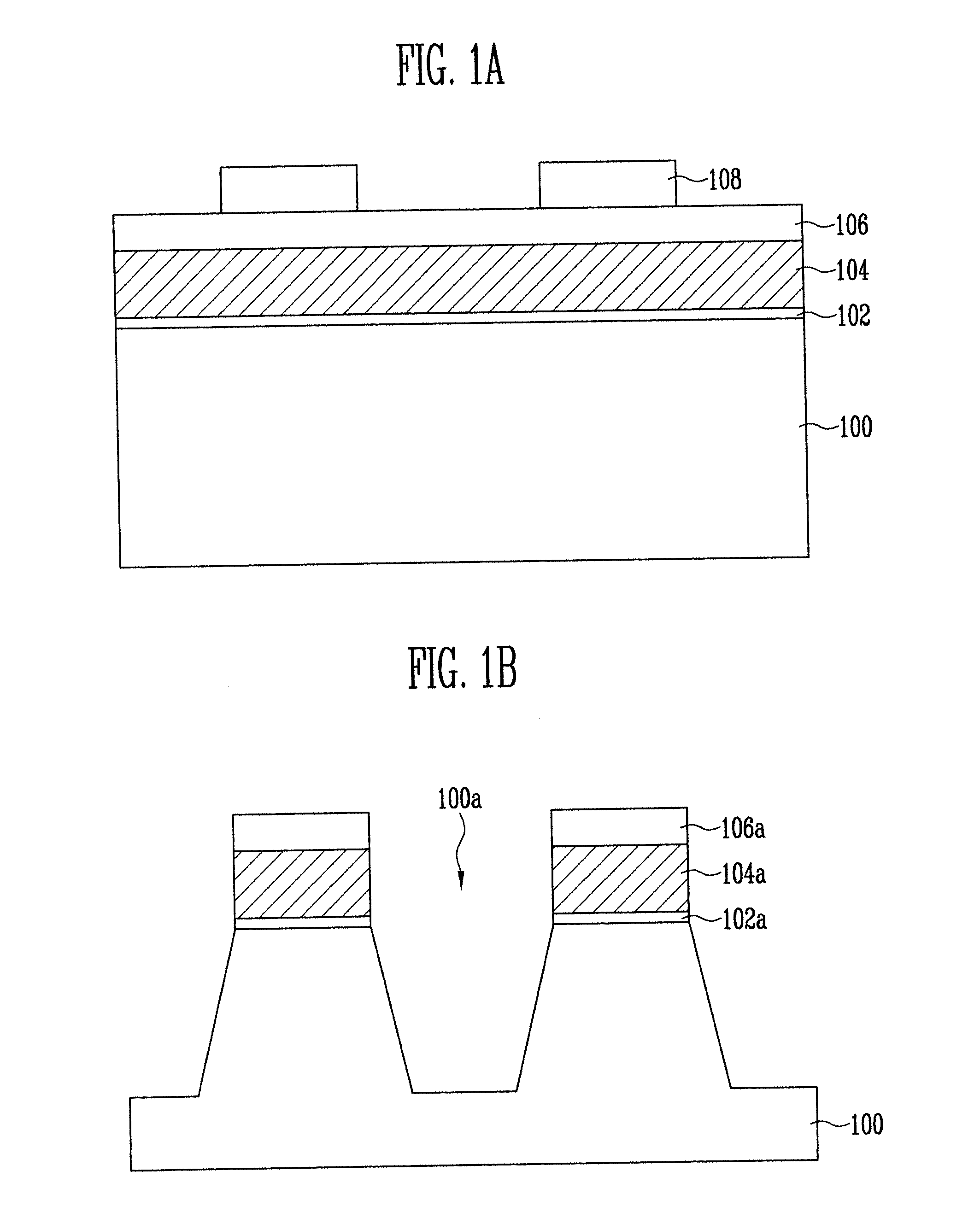

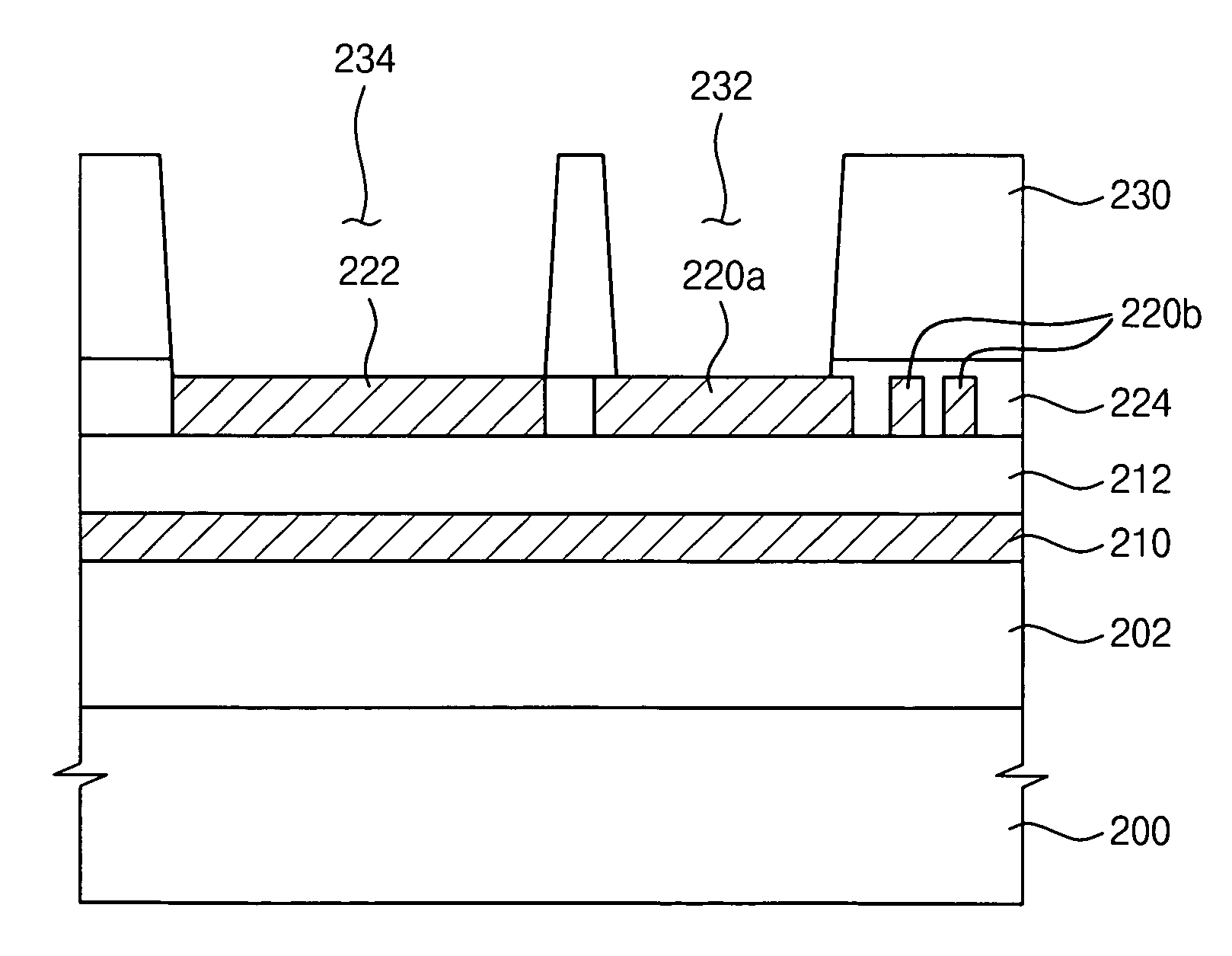

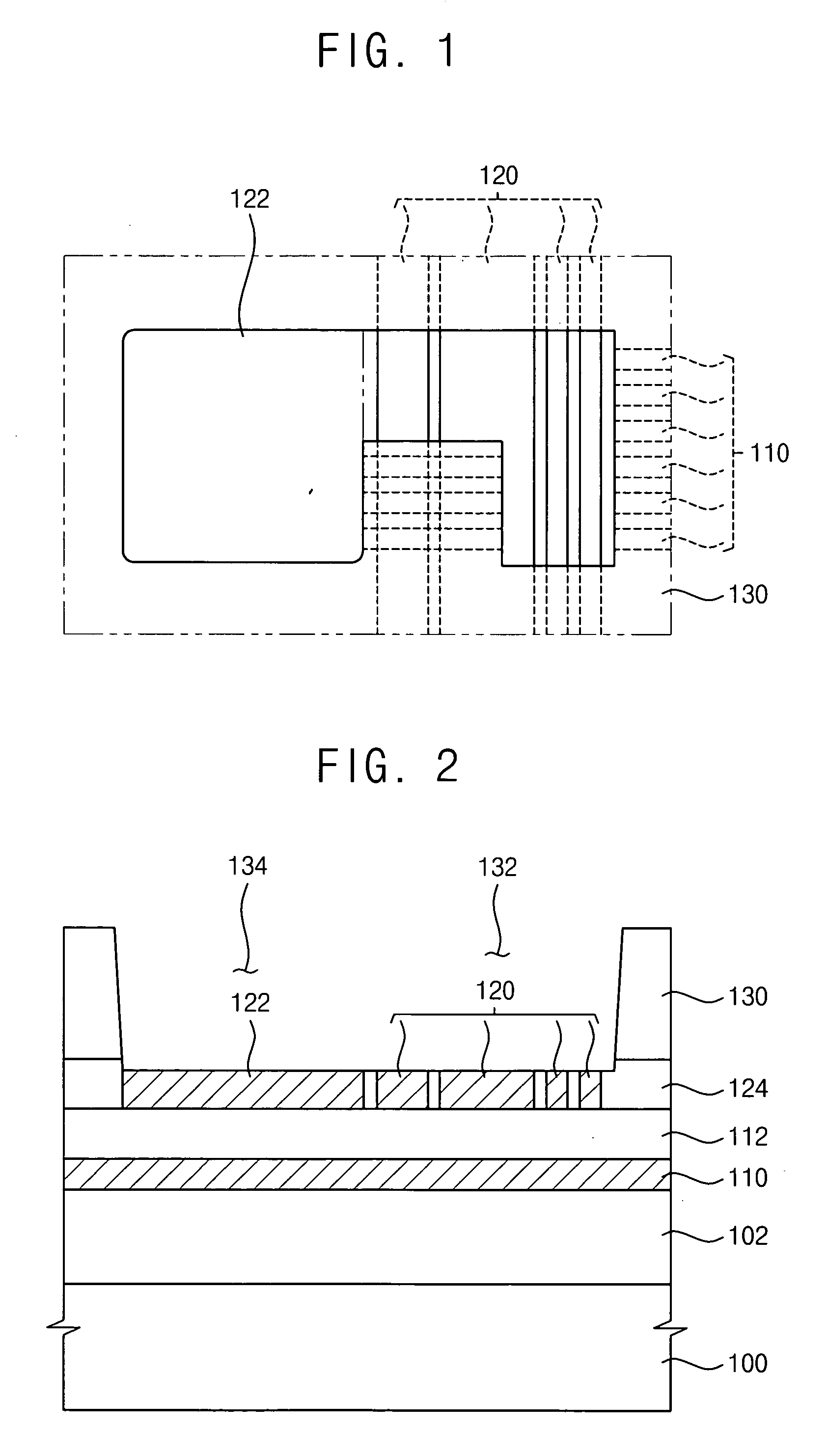

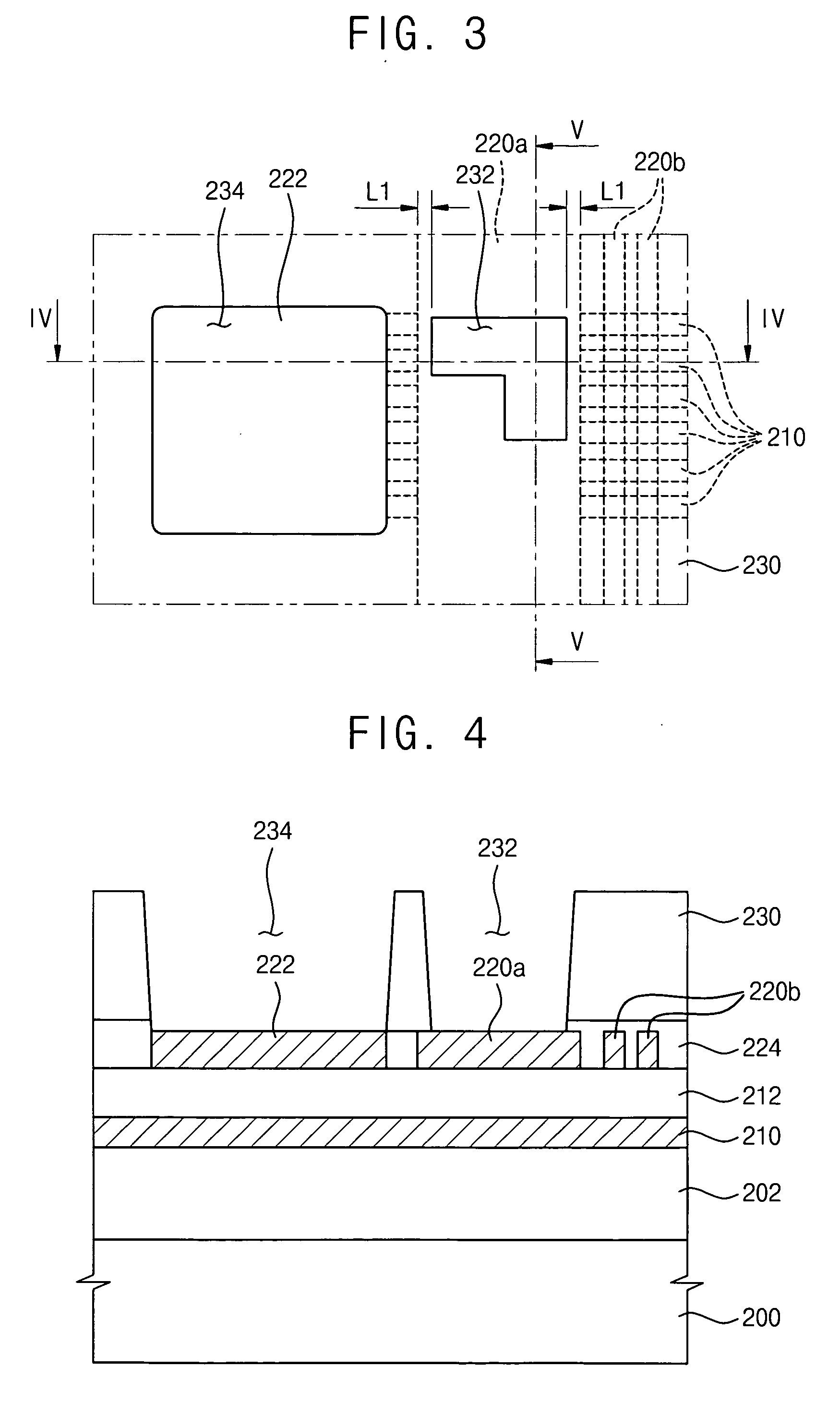

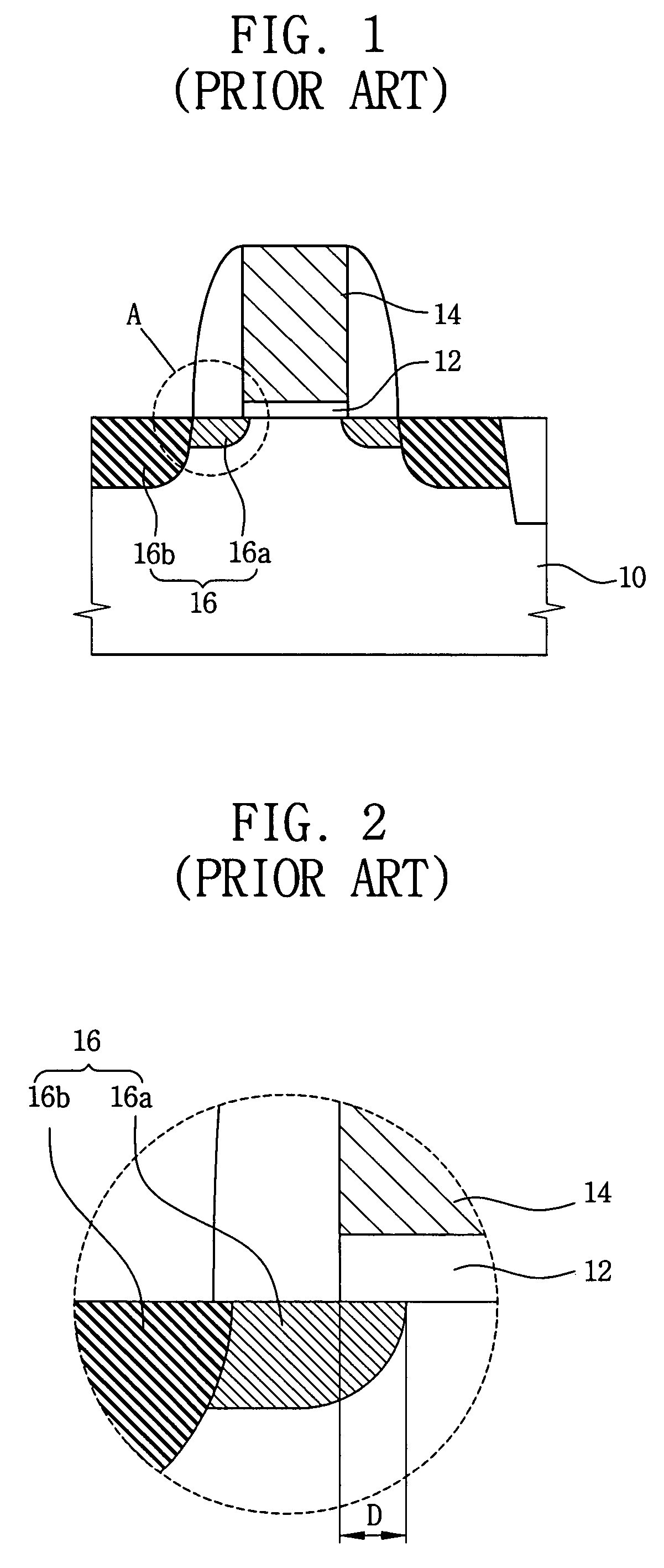

Method of forming a self-aligned contact structure using a sacrificial mask layer

ActiveUS7205232B2Reduce the overall heightAvoid etch damageSemiconductor/solid-state device detailsSolid-state devicesInterconnectionEngineering

Disclosed is a method of forming a self-aligned contact structure using a sacrificial mask layer. The method includes forming a plurality of parallel interconnection patterns on a semiconductor substrate. Each of the interconnection patterns has an interconnection and a mask pattern, which are sequentially stacked. Interlayer insulating layer patterns are formed to fill gap regions between the interconnection patterns. The mask patterns are partially etched to form recessed mask patterns that define grooves between the interlayer insulating layer patterns. Then, sacrificial mask patterns filling the grooves are formed. A predetermined region of the interlayer insulating layer patterns is etched using the sacrificial mask patterns as etching masks to form a self-aligned contact hole that exposes a predetermined region of the semiconductor substrate. A spacer is formed of a sidewall of the self-aligned contact hole, and a plug surrounded by the spacer is formed in the self-aligned contact hole.

Owner:SAMSUNG ELECTRONICS CO LTD

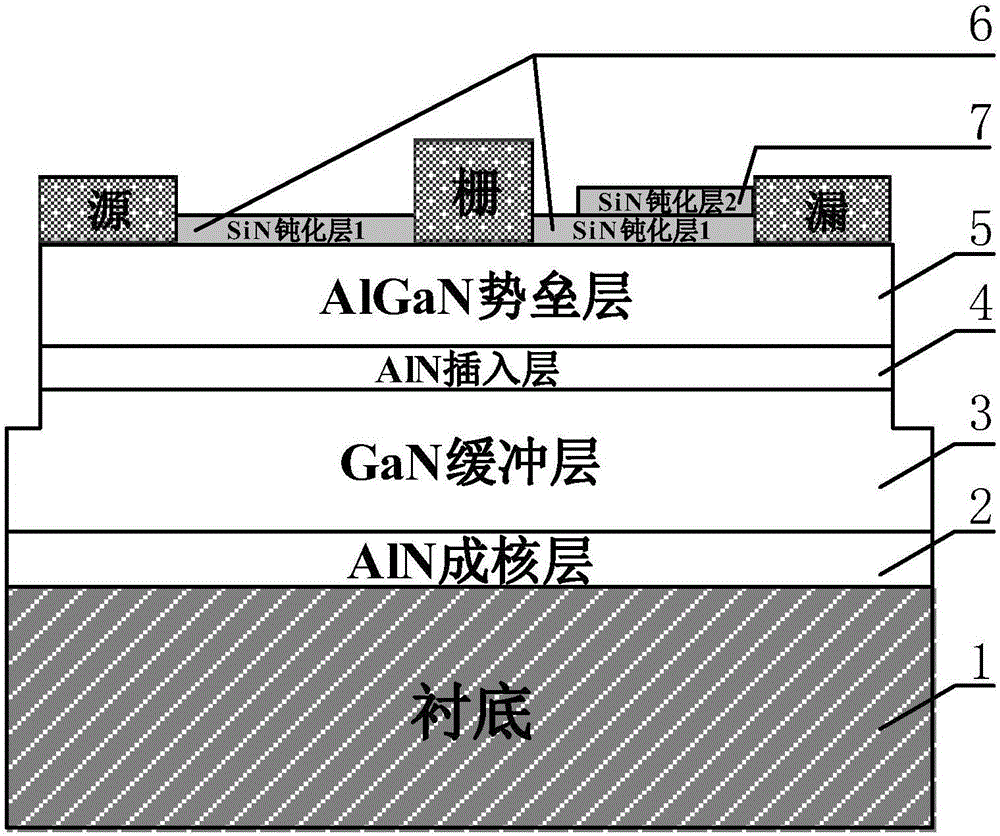

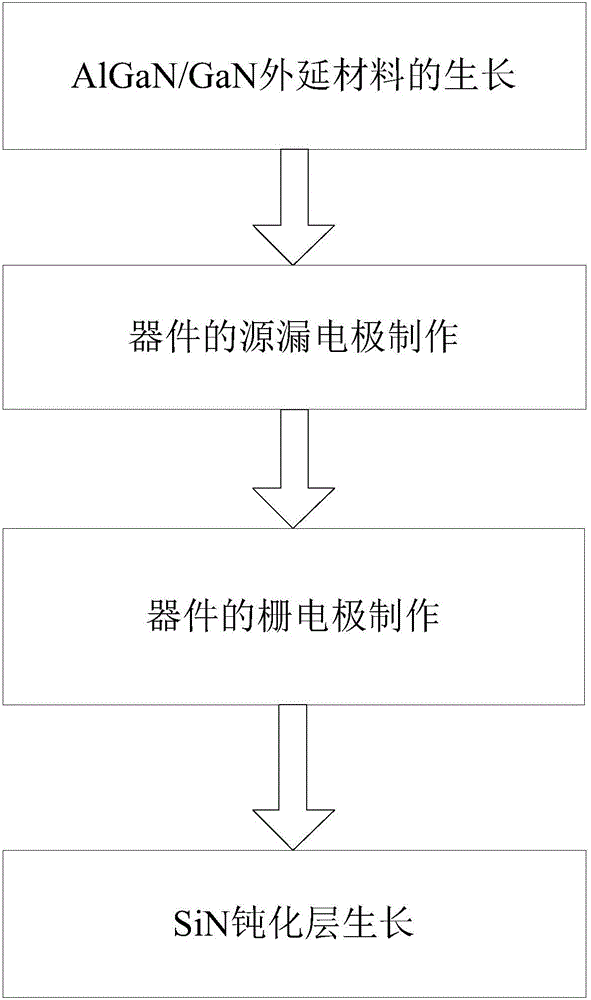

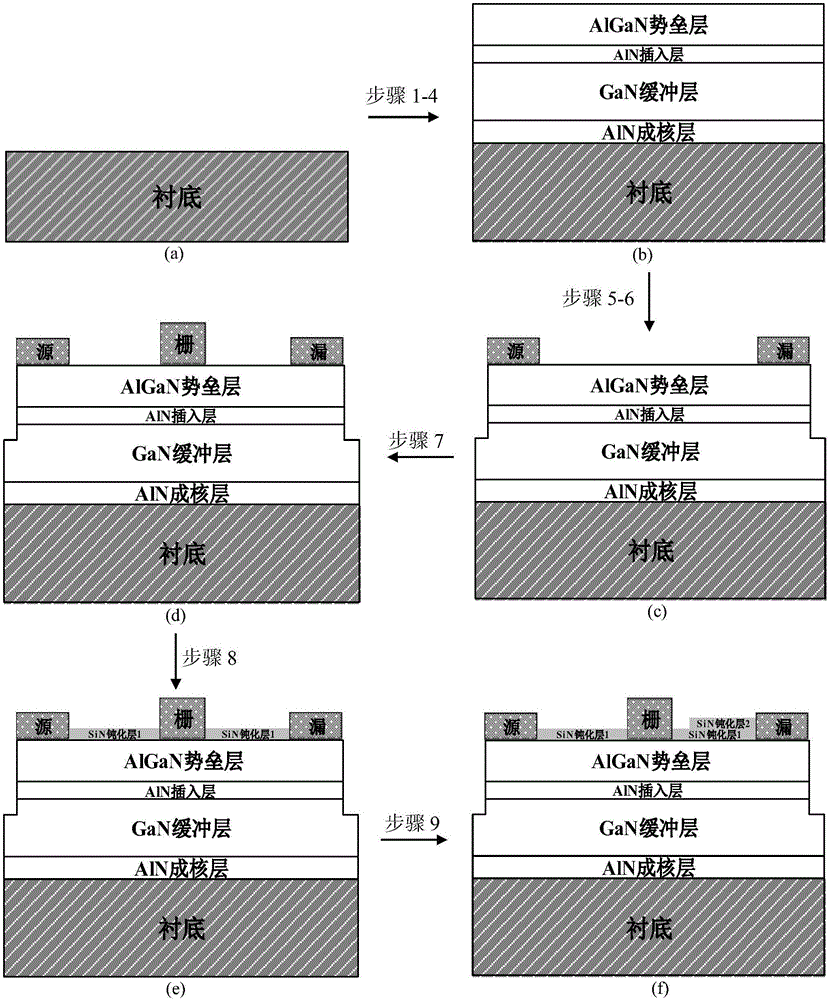

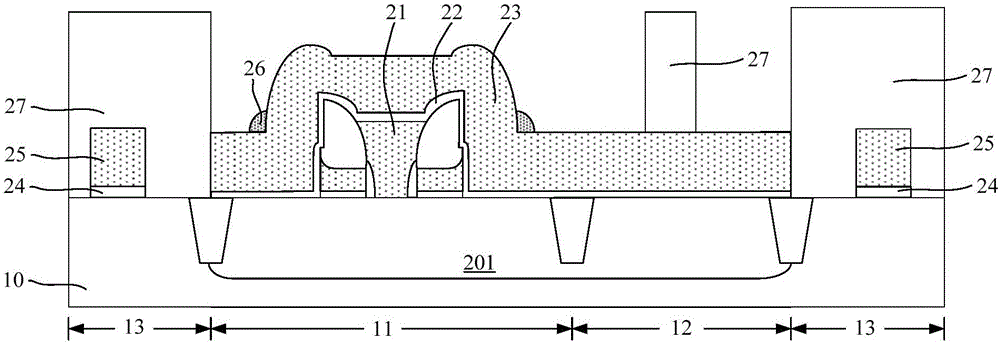

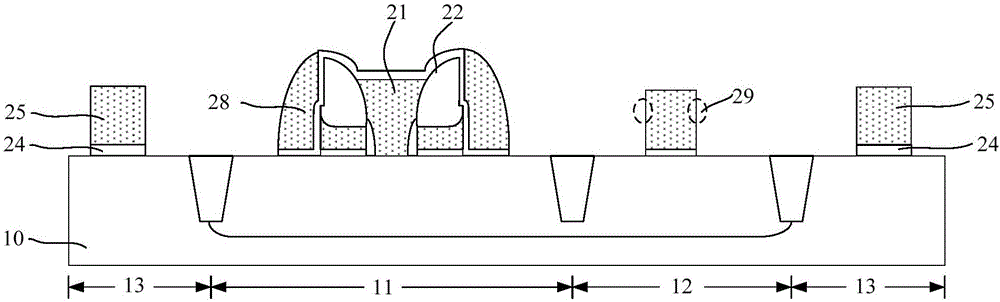

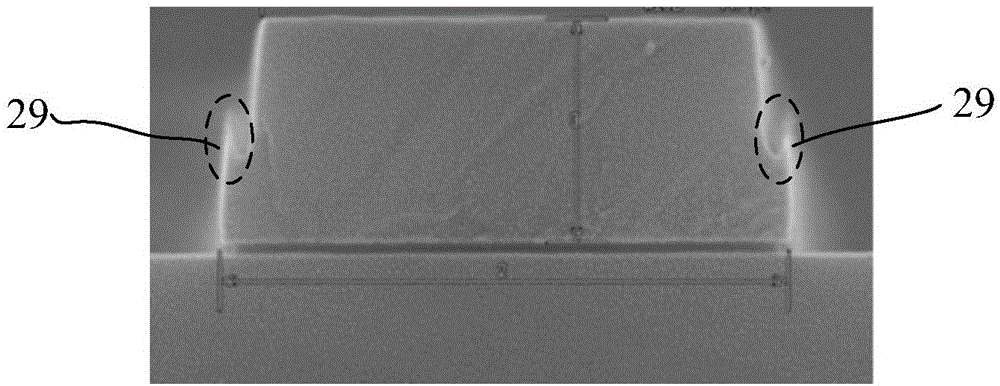

Thin barrier enhanced AlGaN/GaN high-electron-mobility transistor and manufacturing method thereof

ActiveCN105931999AImprove manufacturing precisionAvoid etch damageSemiconductor/solid-state device detailsSolid-state devicesElectron mobilityModulation effect

The invention discloses a thin barrier enhanced AlGaN / GaN high-electron-mobility transistor device and a manufacturing method thereof, and mainly solves the problems of poor breakdown performance and low output current of the existing similar devices. The technical scheme is that a self-aligned technology is introduced in the SiN passivation layer growth process of the device, and an aligned LDD-HEMT is formed by utilizing the modulation effect of thin and thick SiN passivation layers on channels. The device comprises a substrate, an AlN nucleating layer, a GaN buffer layer, an AlN inserting layer, an AlGaN barrier layer, SiN passivation layers and gate, source and drain electrodes which are arranged from the bottom to the top. There are two SiN passivation layers. After completion of manufacturing of the gate electrode, the first SiN passivation layer is deposited by utilizing the self-aligned effect of the gate electrode, and then the second SiN passivation layer is deposited close to the drain electrode region between the gate electrode and the drain electrode so that the aligned LDD structure is formed. Breakdown voltage and saturation output current of the device are high, and damage introduced in the manufacturing process is low.

Owner:西安电子科技大学重庆集成电路创新研究院

Method of forming dual damascene metal interconnection employing sacrificial metal oxide layer

ActiveUS7064059B2Increase process marginReduce reflectivitySemiconductor/solid-state device manufacturingSemiconductor devicesInterconnectionSacrificial metal

There is provided a method of forming a dual damascene metal interconnection by employing a sacrificial metal oxide layer. The method includes preparing a semiconductor substrate. An interlayer insulating layer is formed on the semiconductor substrate, and a preliminary via hole is formed by patterning the interlayer insulating layer. A sacrificial via protecting layer is formed on the semiconductor substrate having the preliminary via hole to fill the preliminary via hole, and cover an upper surface of the interlayer insulating layer. A sacrificial metal oxide layer is formed on the sacrificial via protecting layer, the sacrificial metal oxide layer is patterned to form a sacrificial metal oxide pattern having an opening crossing over the preliminary via hole, and exposing the sacrificial via protecting layer. The sacrificial via protecting layer and the interlayer insulating layer are etched using the sacrificial metal oxide pattern as an etch mask to form a trench located inside the interlayer insulating layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor apparatus including an optical device and an electronic device, and method of manufacturing the same

InactiveUS20140212087A1Reduce harmAvoid etch damageSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A method of manufacturing a semiconductor apparatus includes forming a gate structure and an etch stop layer structure on a substrate including first and second regions. The gate structure is formed in the first region, and the etch stop layer structure is formed in the second region. A first insulating interlayer is formed on the substrate to cover the gate structure and the etch stop layer structure. The first insulating interlayer is partially removed to expose the etch stop layer structure. The exposed etch stop layer is removed to expose the substrate. An optical device is formed on the exposed substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

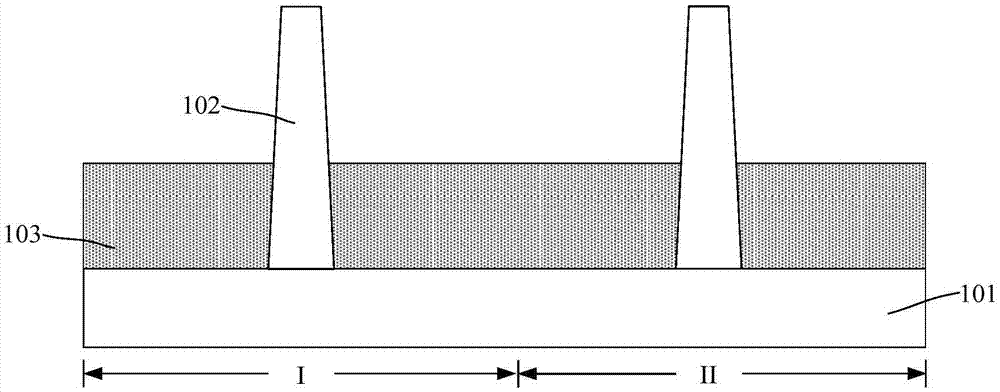

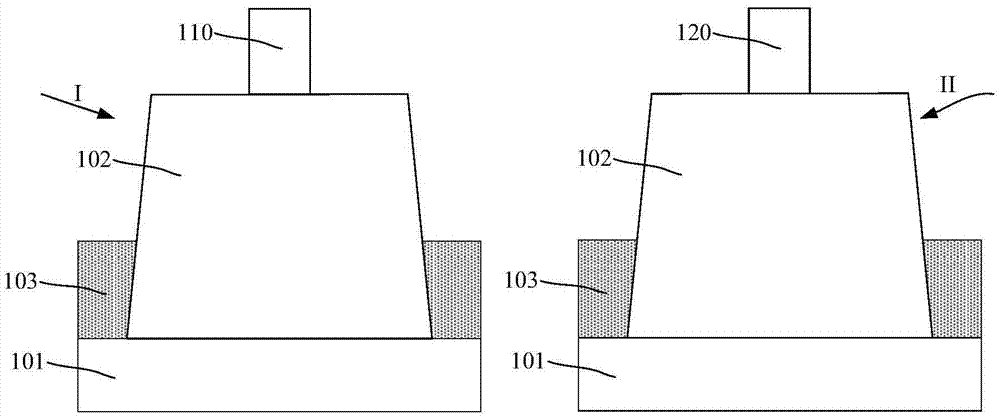

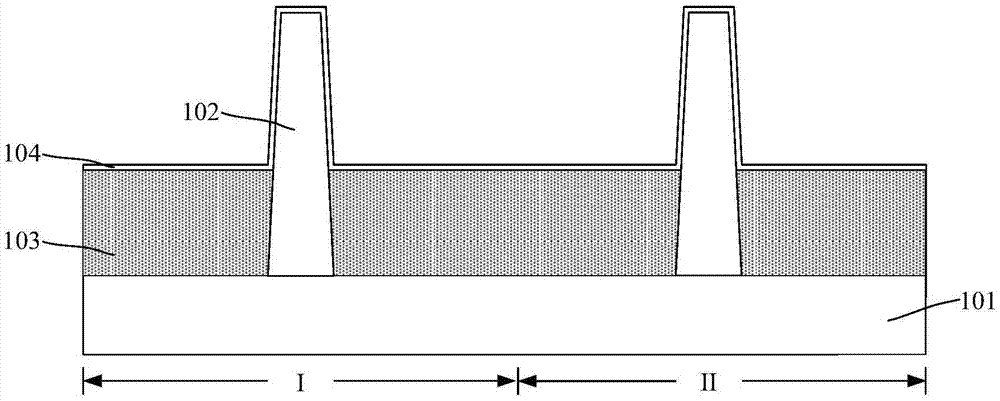

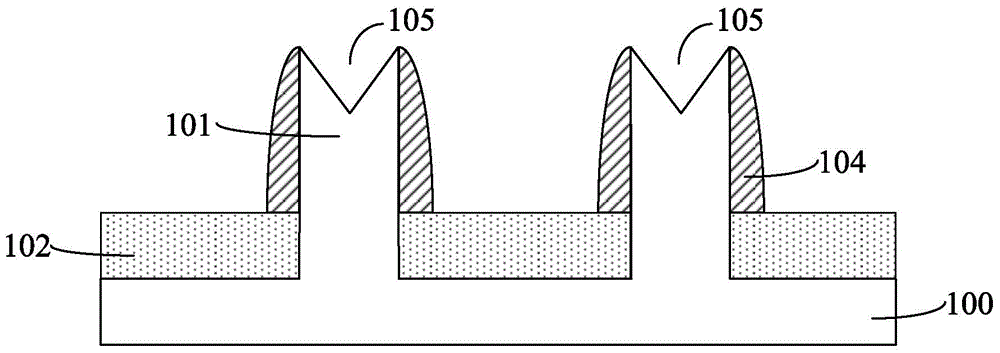

Method for improving performance of fin field-effect transistor

InactiveCN106952806AImprove protectionWeak diffusion barrierSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerEngineering

A method for improving performance of a fin field-effect transistor comprises the steps of providing a substrate, wherein discrete fin parts are formed on a surface of the substrate, an isolation layer is also formed on the surface of the substrate and covers surfaces of a part of side walls of the fin parts, and the top of the isolation layer is lower than the tops of the fin parts; forming a gate structure bridging the fin parts on a surface of the isolation layer, wherein the gate structure covers the surfaces of a part of tops and the side walls of the fin parts; forming an amorphous material layer covering the surfaces of a part of tops and the side walls of the fin parts and the surface of the isolation layer; forming an oxide doping layer on a surface of the amorphous material layer; annealing the oxide doping layer so that doping ions are diffused and enter the fin parts, and forming doping regions in the fin parts at two sides of the gate structure; and removing the oxide doping layer. During the process of removing the oxide doping layer, the amorphous material layer has a protection effect on the isolation layer, the etching loss caused by the technology of removing the oxide doping layer on the isolation layer is prevented, so that the thickness of the isolation layer is maintained unchanged, and the electrical property of the formed fin field-effect transistor is further improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

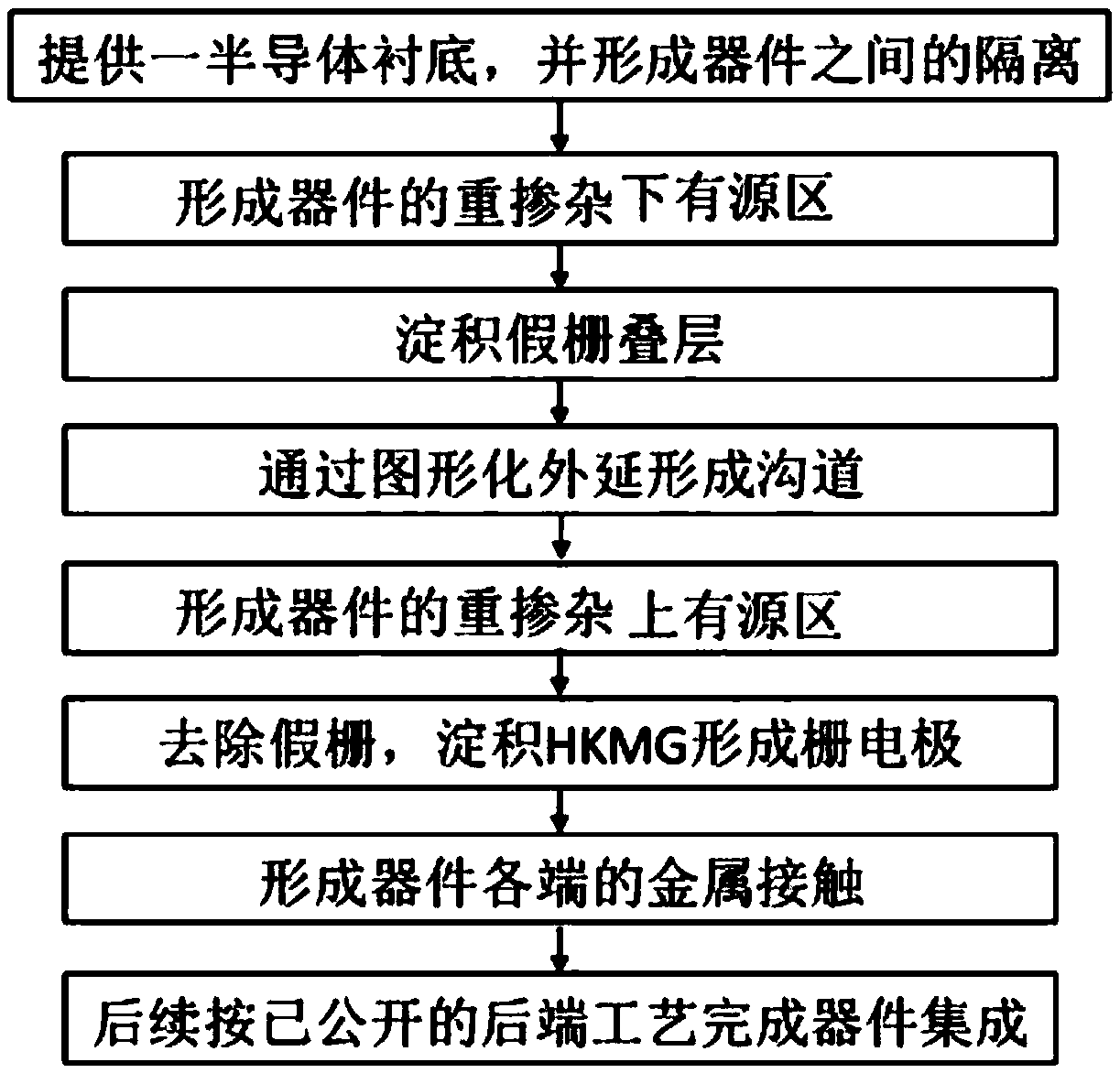

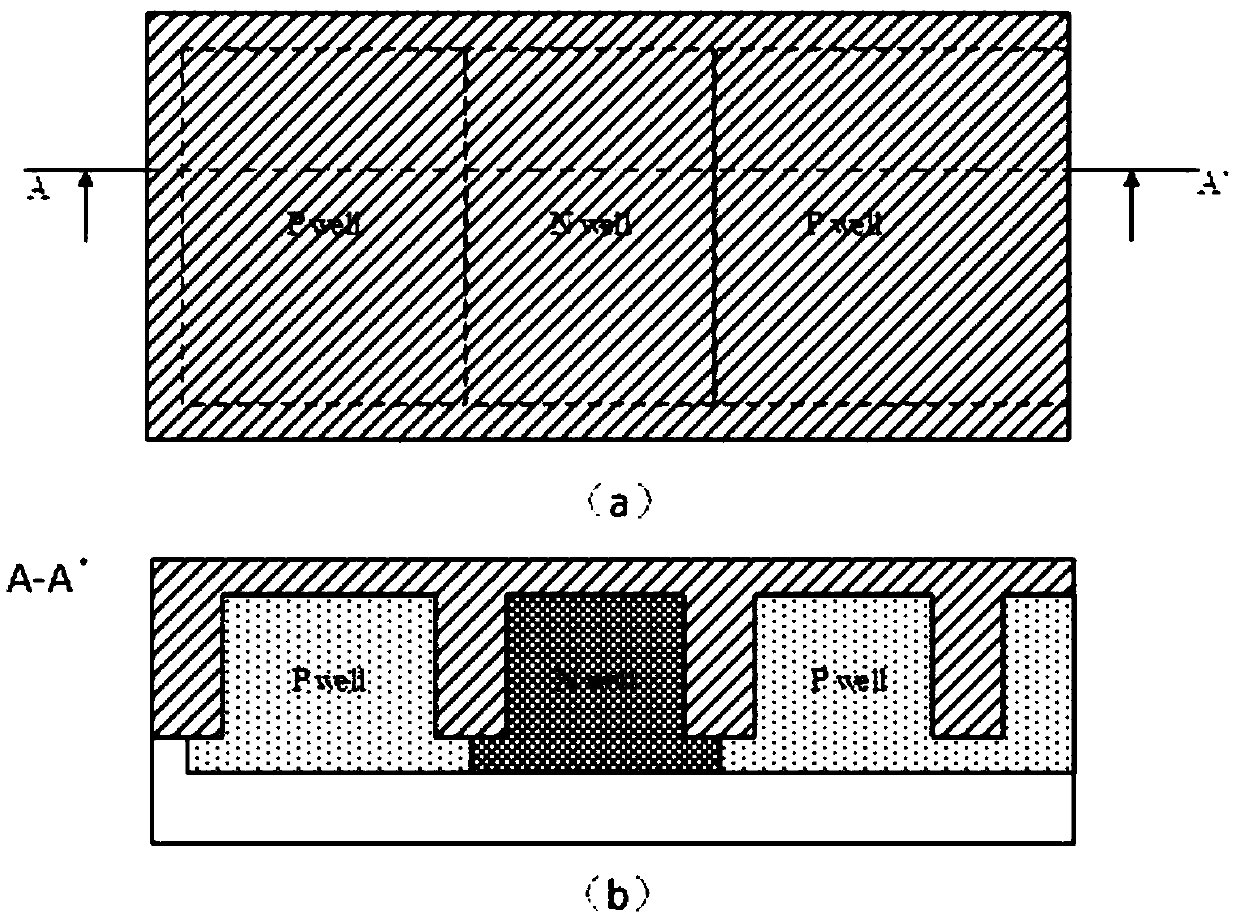

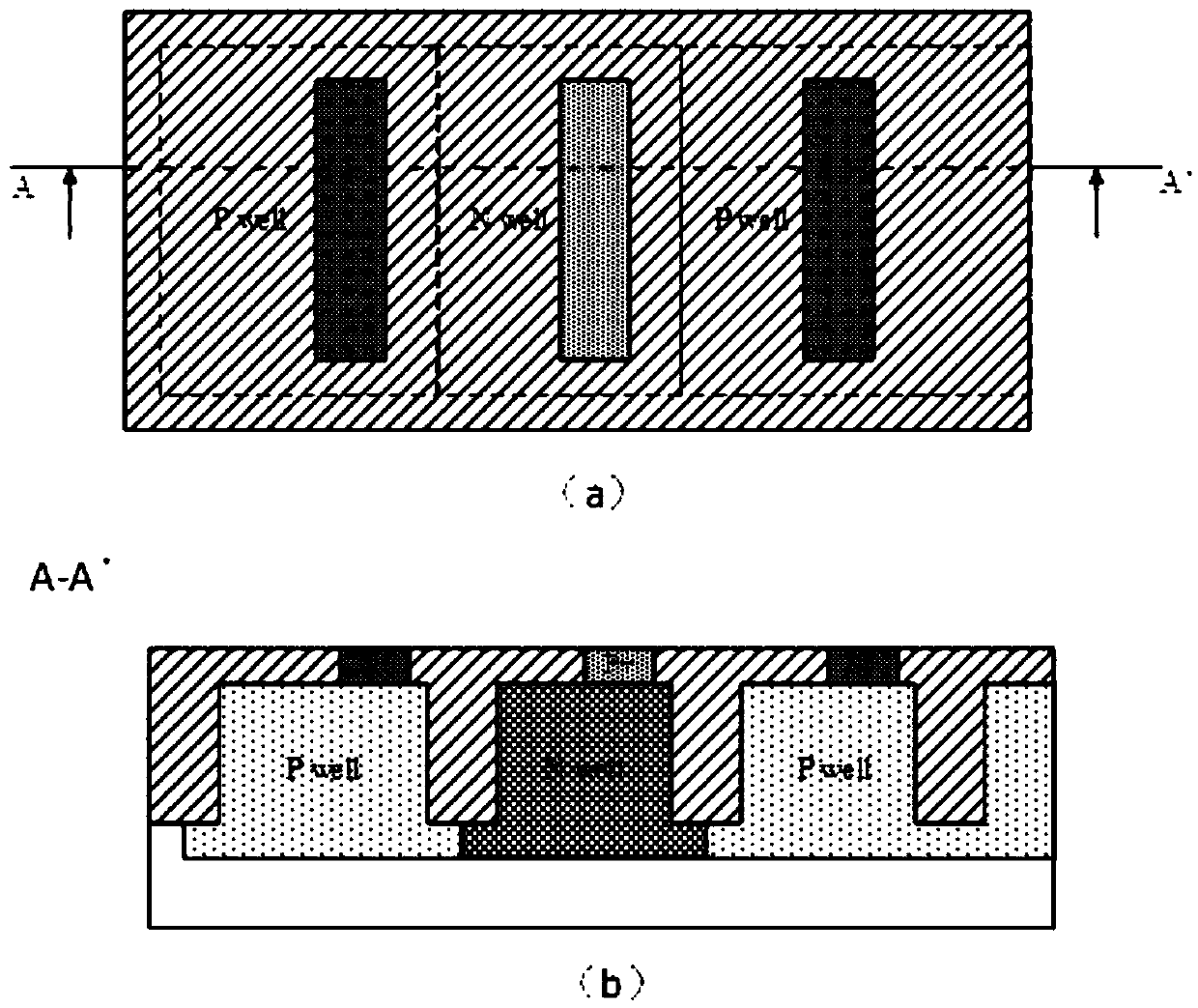

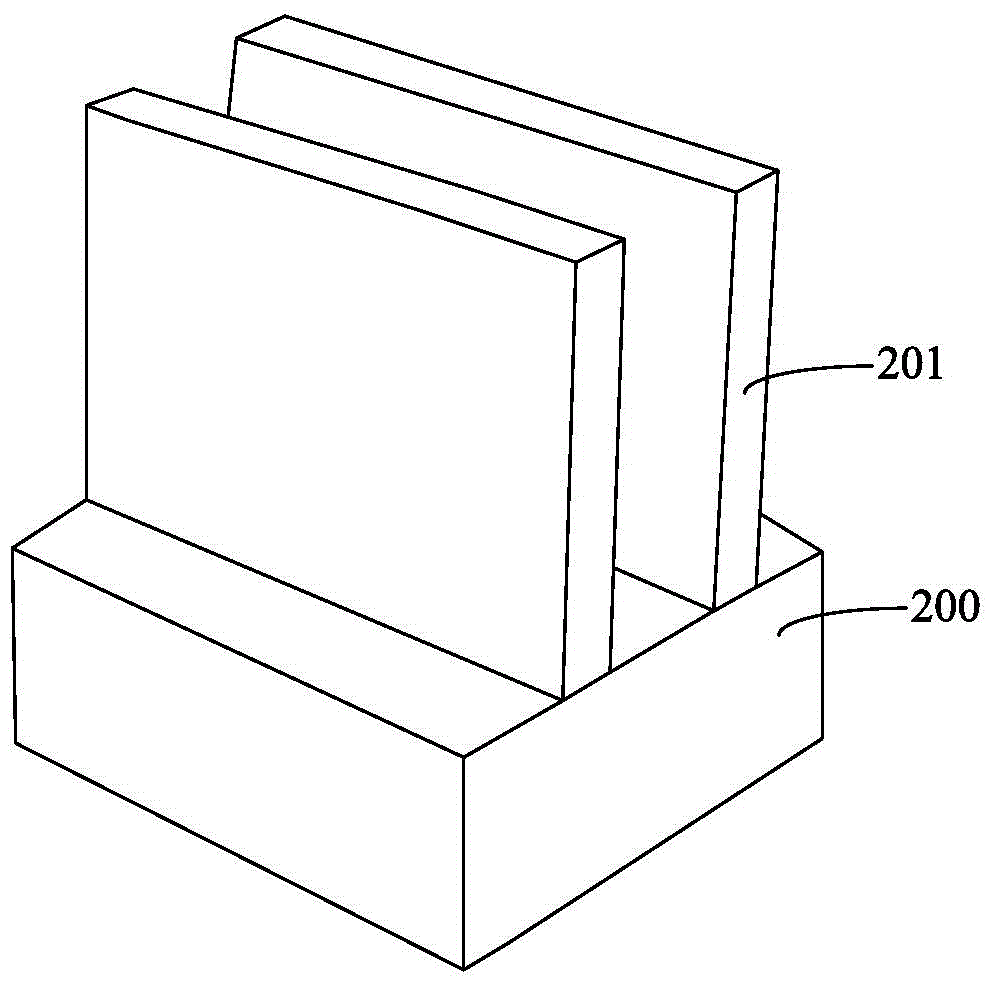

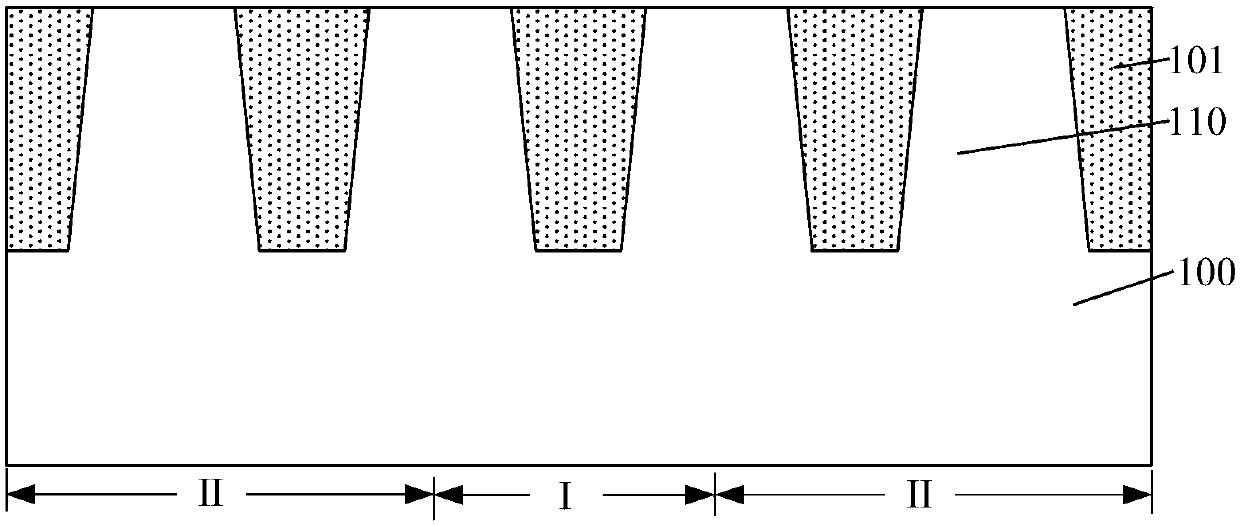

Integration method of vertical nano-wire transistor

ActiveCN105374752AControl areaControl shapeNanoinformaticsSemiconductor/solid-state device manufacturingCMOSPresent method

The invention discloses an integration method of a vertical nano-wire transistor, and belongs to the field of field effect transistor logic devices in CMOS ULSI. According to the method, graphical extension is combined with a sidewall alternative gate to realize integration of the vertical nano-wire transistor. Compared with a present method in which vertical nano wire channels are formed by etching, the sectional area and morphology of the channel of the control device can be accurately controlled, the characteristic consistency of the device is improved, damage caused by etching in the channel formation process is avoided, and the device performance is improved.

Owner:PEKING UNIV

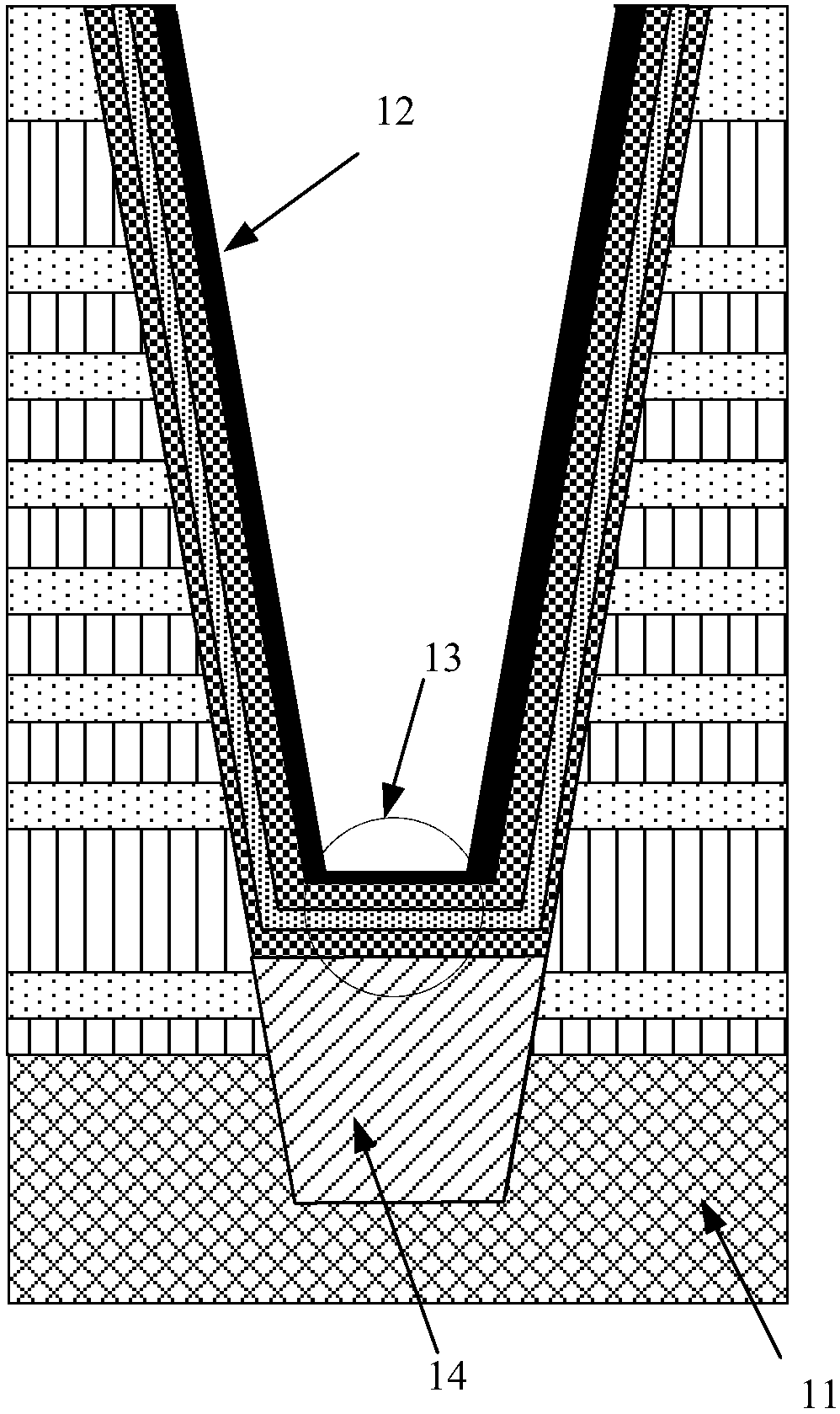

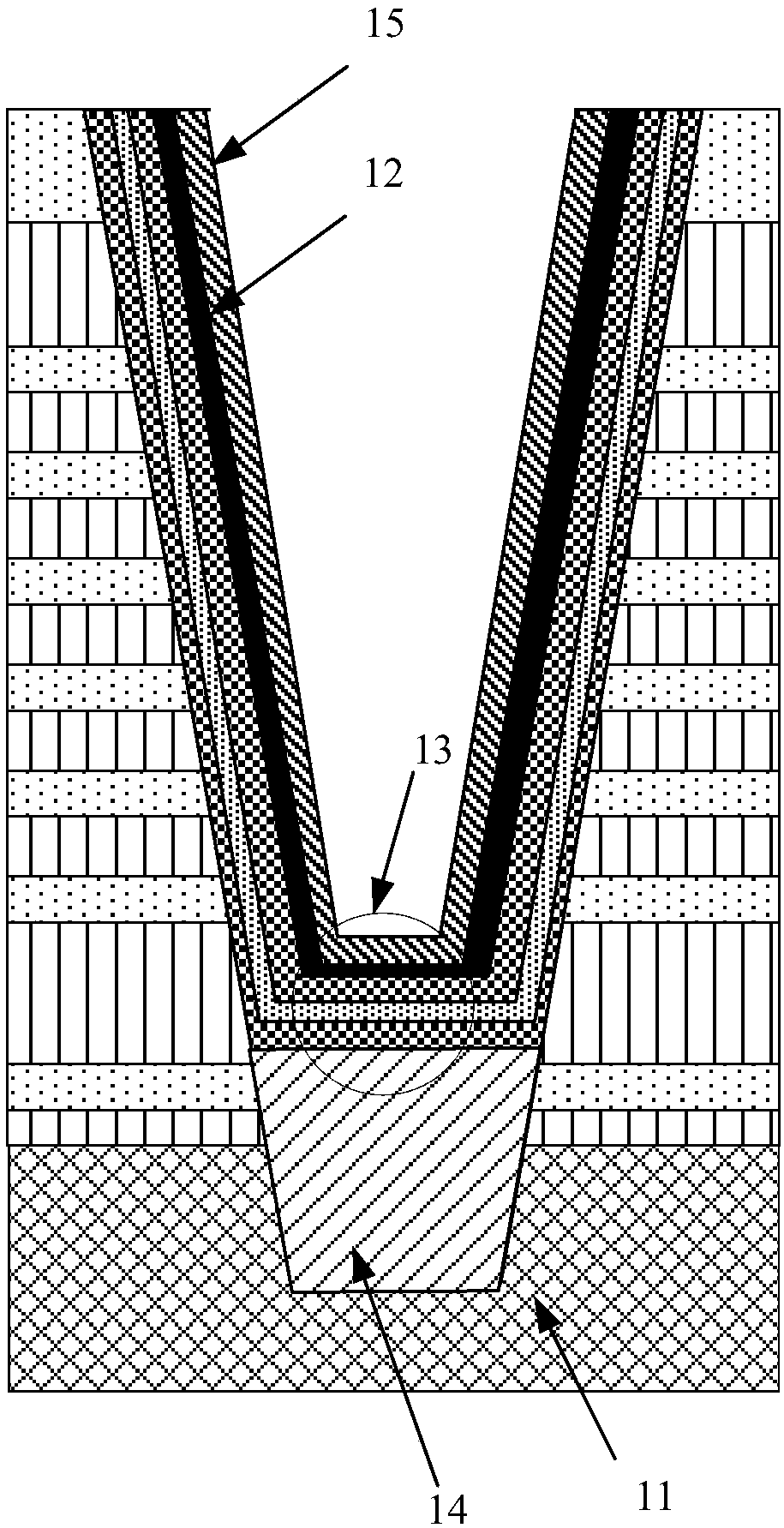

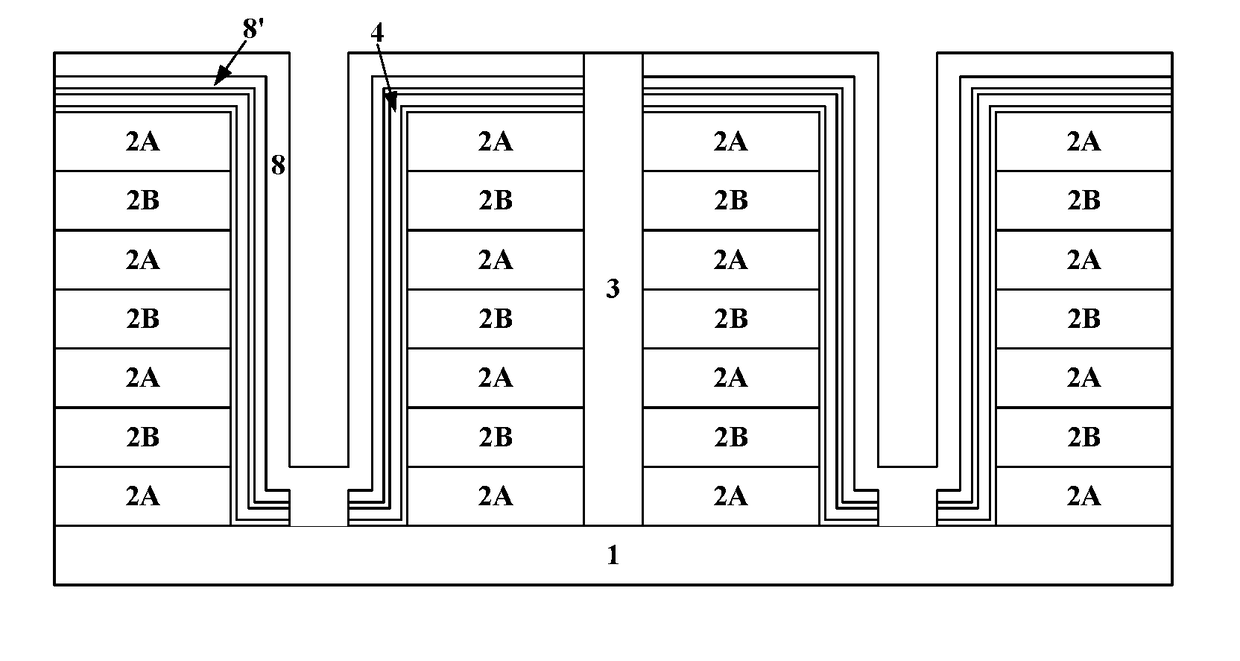

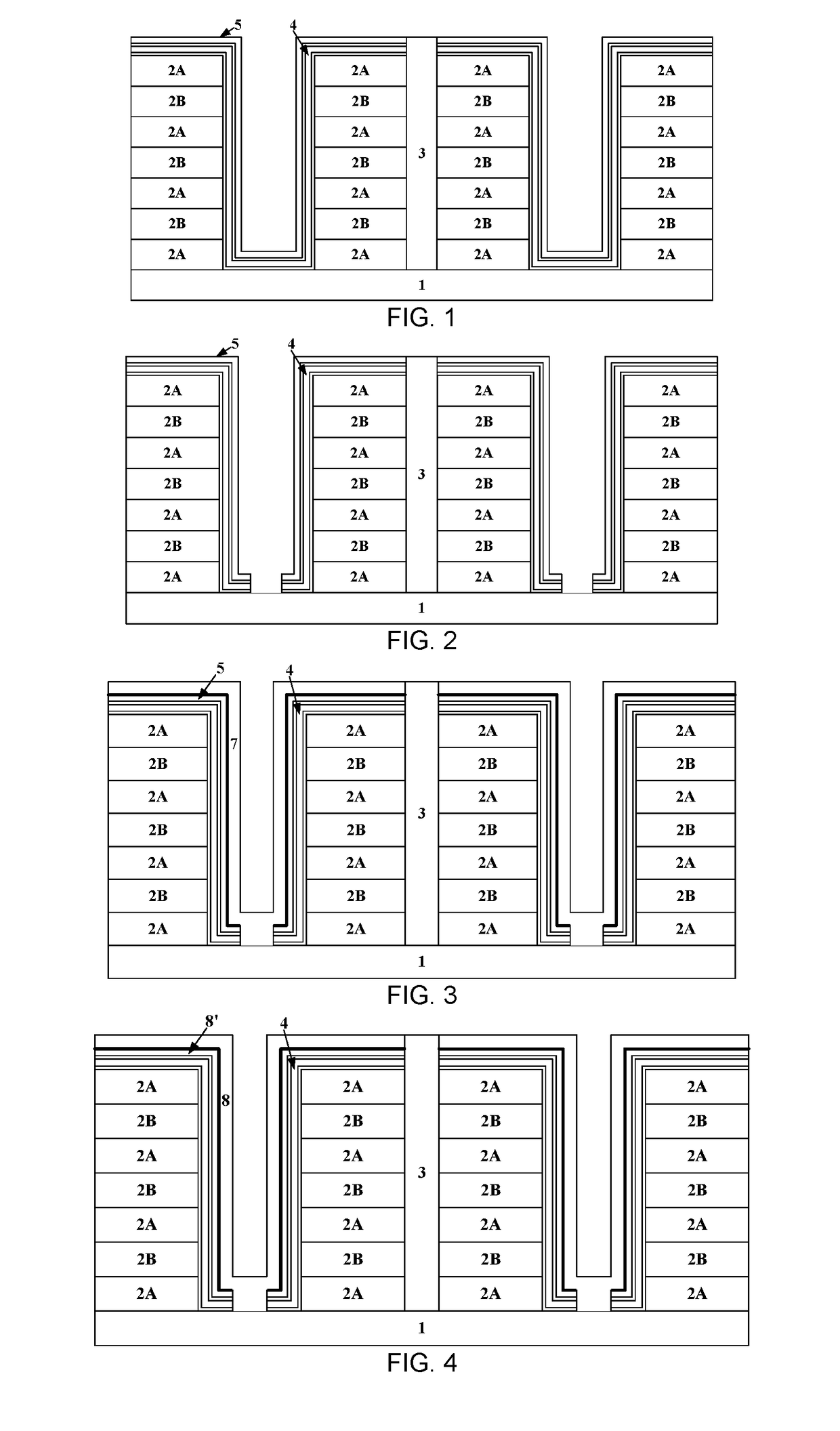

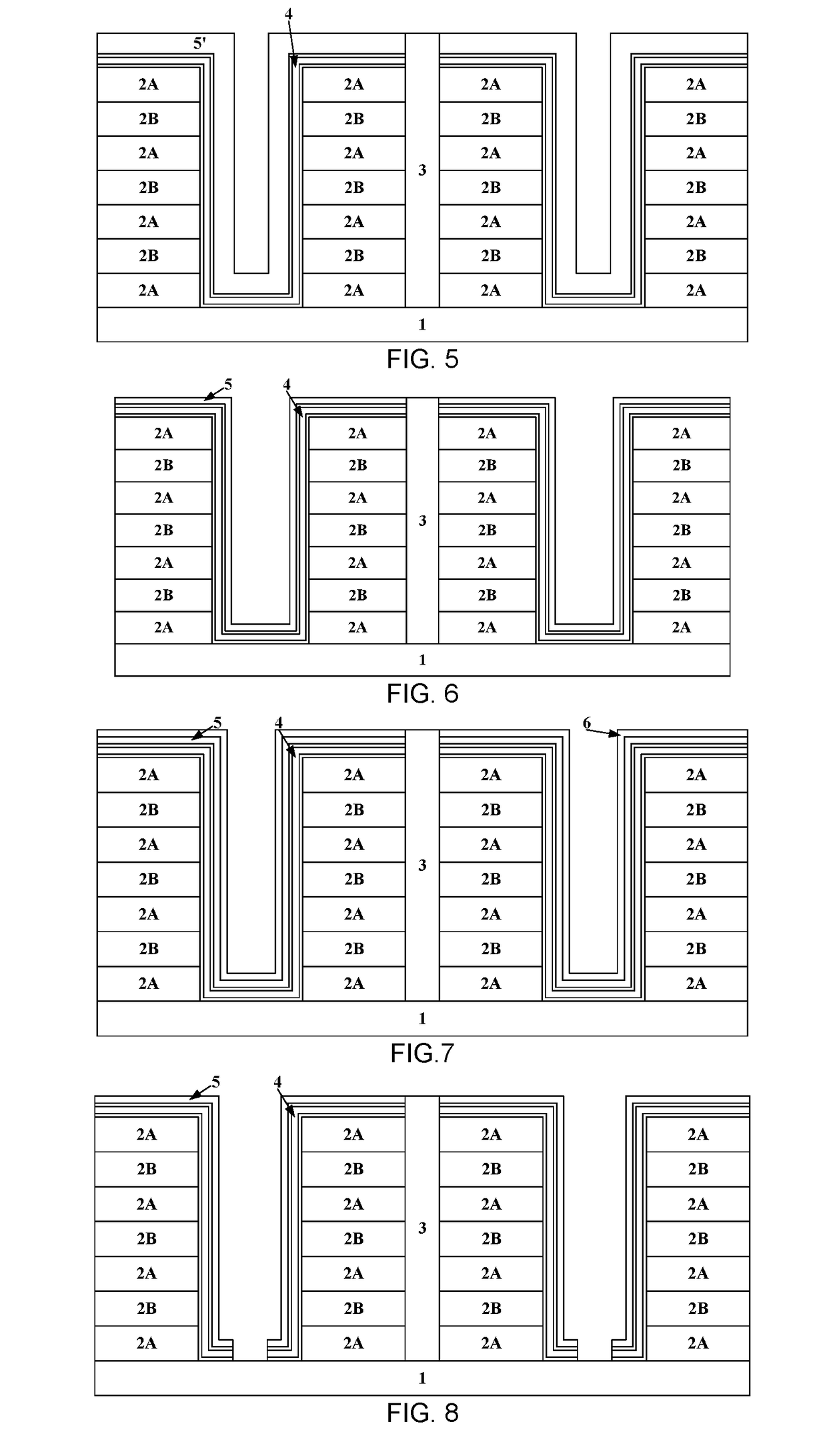

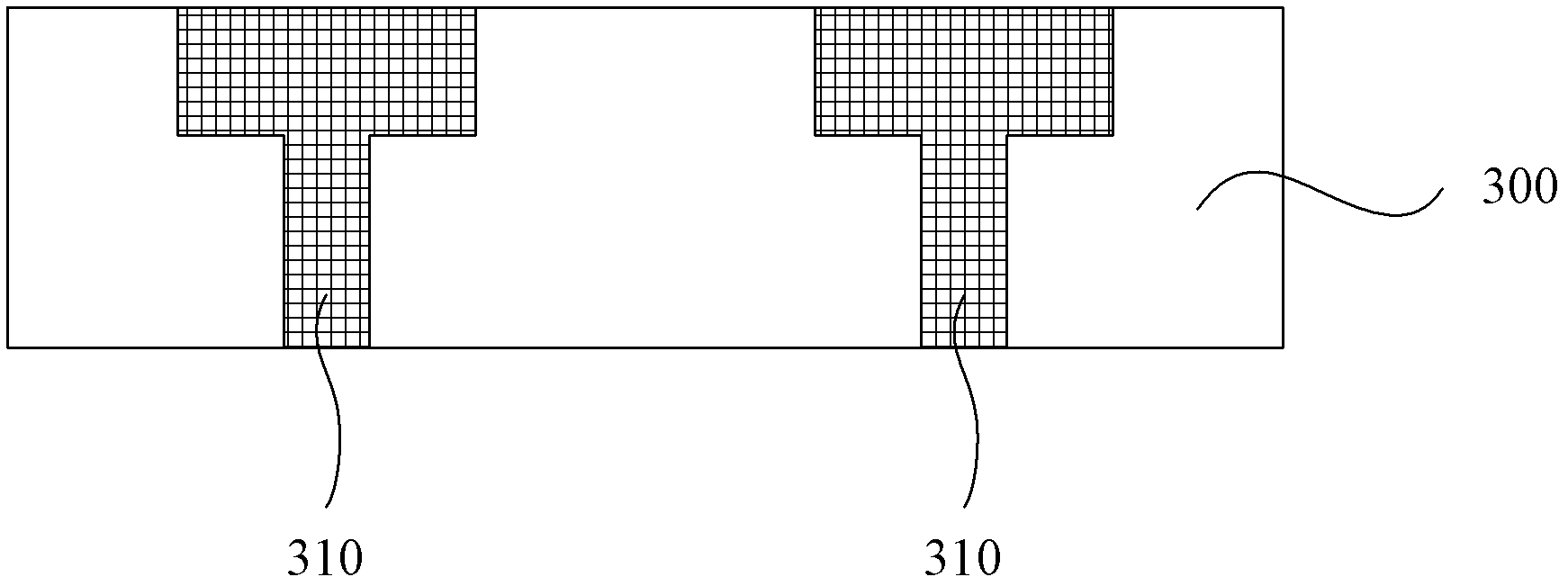

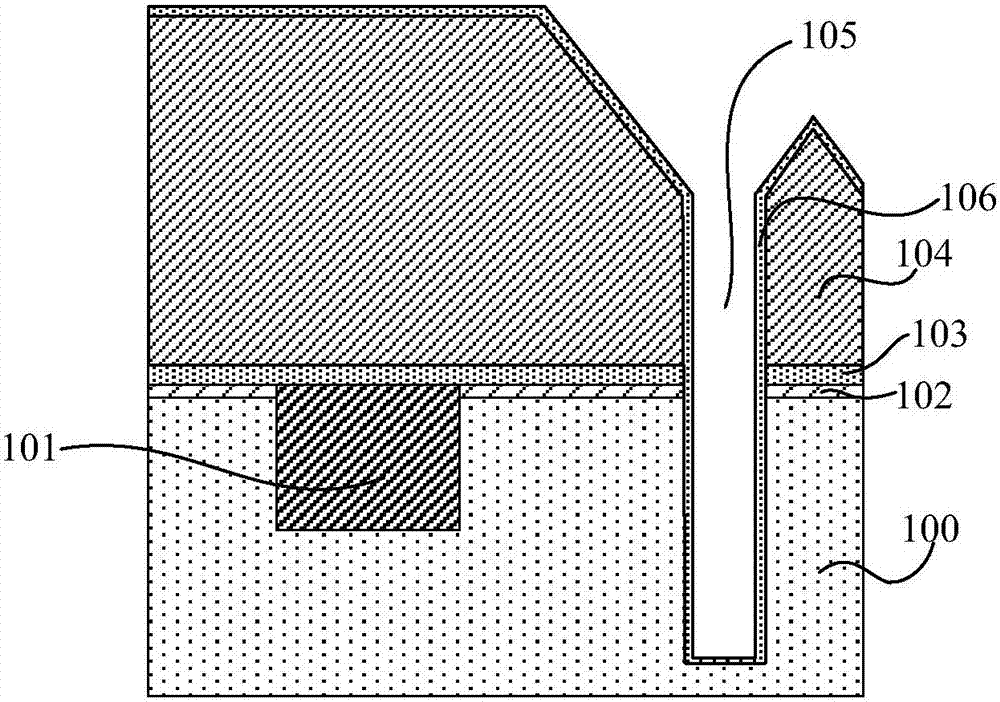

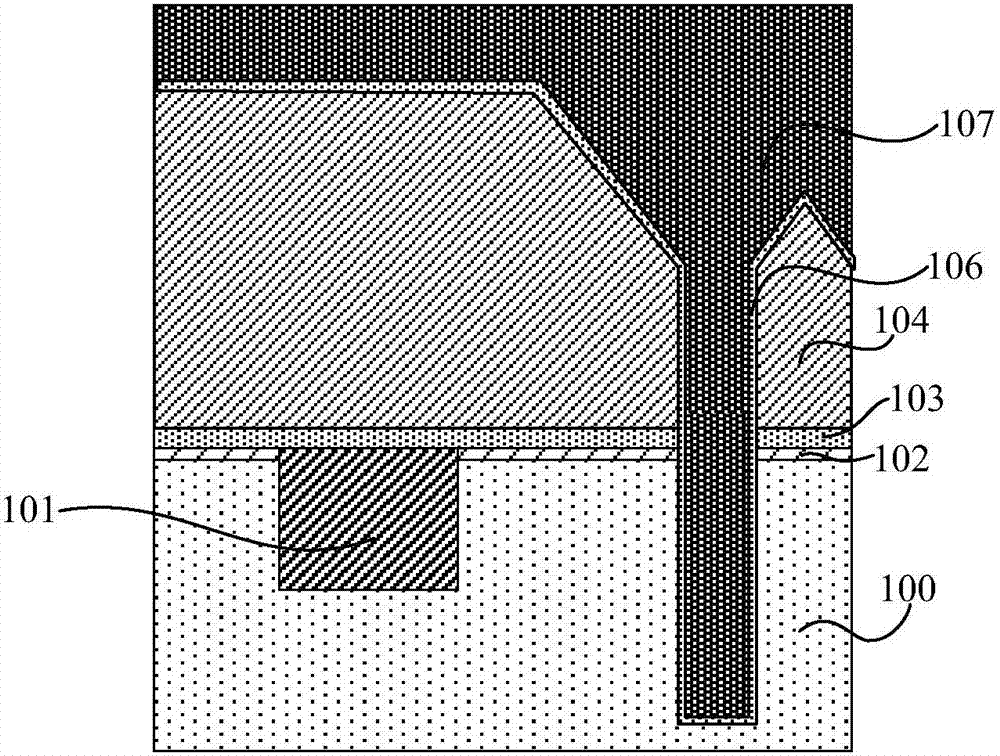

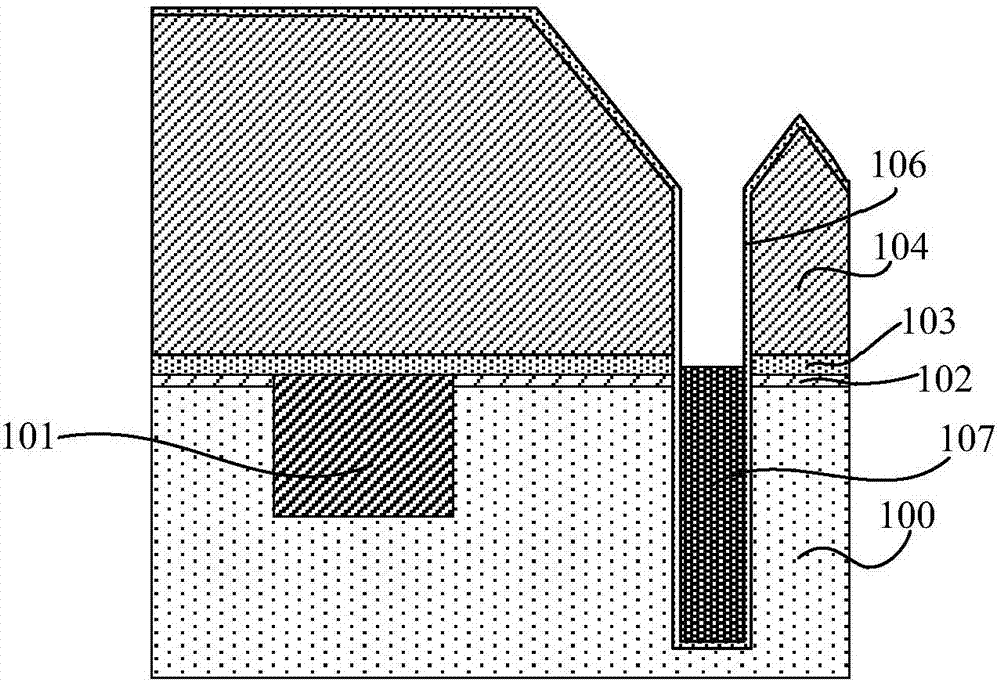

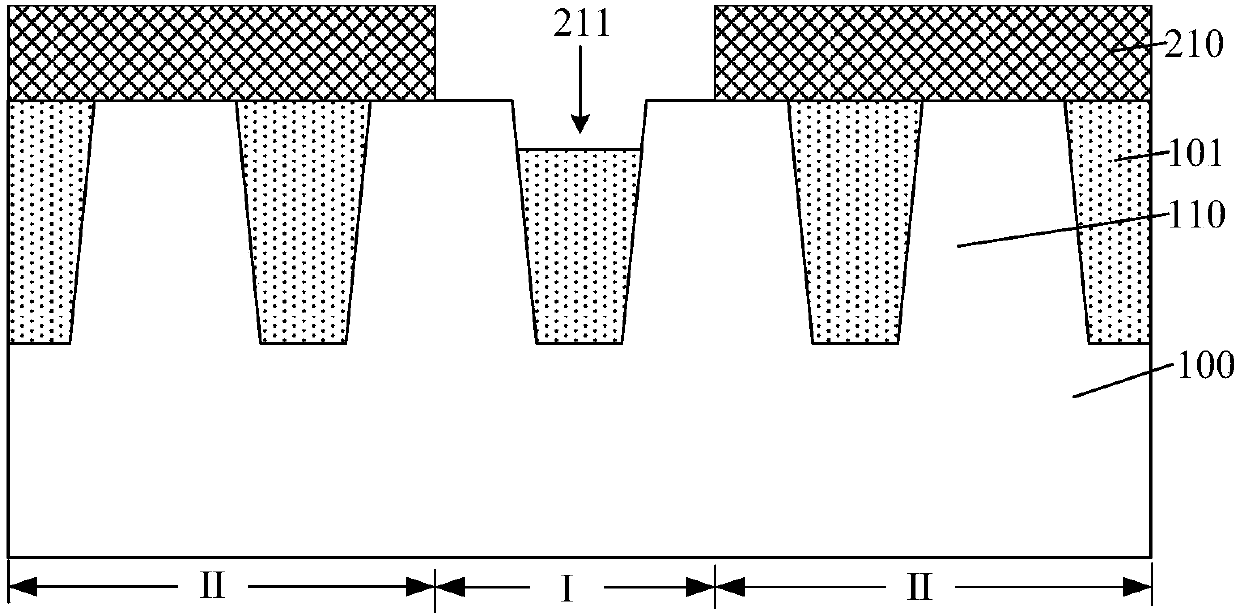

3D computer flash memory device and manufacturing method thereof, and buffer layer manufacturing method

ActiveCN107611128AAvoid etch damageImprove reliabilitySolid-state devicesSemiconductor devicesNitrideCorrosion

The invention discloses a 3D computer flash memory device and a manufacturing method thereof, and a buffer layer manufacturing method. The manufacturing method includes the following steps: providinga substrate; forming a stacked structure on the surface of the substrate, wherein the stacked structure includes multilayer oxide layers and multilayer nitride layers, and the oxide layers and the nitride layers are alternately arranged; forming a first channel through hole penetrating the stacked structure and extending into the surface of the substrate, wherein the width of the first channel through hole gradually increases from bottom to top; forming a channel structure on the surface of the substrate exposed by the first channel through hole; forming a function layer on the sidewall of thefirst channel through hole and on the surface of the channel structure; forming a buffer layer on the surface of the function layer, wherein the buffer layer has the minimum thickness at the bottom,and the sidewall thickness gradually increases from bottom to top; and forming a second channel through hole penetrating the bottom of the buffer layer and the bottom of the function layer, and exposing part of the channel structure. According to the technical scheme of the invention, corrosion damage to the function layer can be completely avoided, and the reliability of the device is improved.

Owner:YANGTZE MEMORY TECH CO LTD

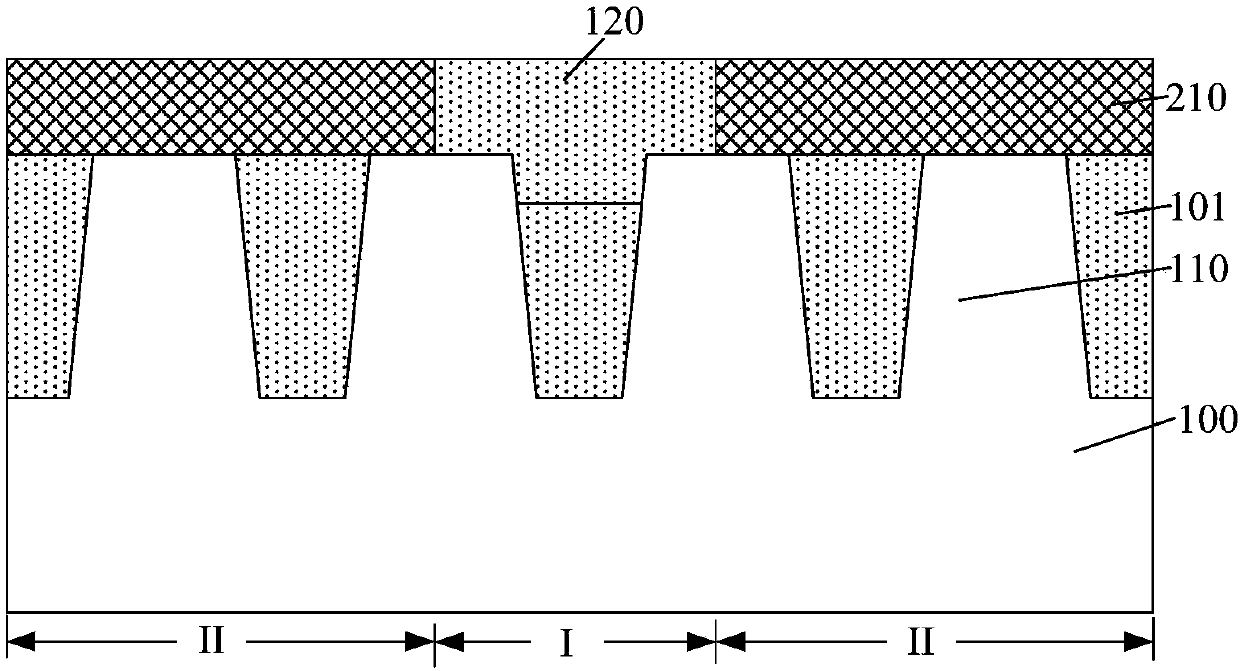

3D NAND memory array common source forming method

InactiveCN109860037ACause etch damageSimple manufacturing processSolid-state devicesSemiconductor devicesContact layerPartial thickness

The invention discloses a 3D NAND memory array common source forming method. The method comprises steps: a substrate is provided, wherein a stacked structure is formed on the substrate, and a gate separation slot exposing the surface of the substrate is formed in the stacked structure; metal contact layers are formed on the surface of the side wall and the bottom of the gate separation slot and the surface of the stacked structure; a polysilicon layer covering the metal contact layer is formed, wherein the polysilicon layer fills the gate separation slot; the polysilicon layer with a partial thickness in the gate separation slot is etched back and removed, and the metal contact layer is used as an etching stop layer; and a metal plug is formed on the etched polysilicon layer. The array common source forming process is simplified.

Owner:YANGTZE MEMORY TECH CO LTD

Method of Manufacturing a Semiconductor Device

ActiveUS20180240809A1Reduced stateImprove equipment reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor

A method of manufacturing a semiconductor device, comprising the steps of: forming a gate dielectric layer and a first amorphous channel layer on a substrate; thinning the first amorphous channel layer; etching the first amorphous channel layer and the gate dielectric layer until the substrate is exposed; forming a second amorphous channel layer on the first amorphous channel layer and the substrate; annealing such that the first amorphous channel layer and the second amorphous channel layer are converted into a polycrystalline channel layer; and thinning the polycrystalline channel layer. According to the method of manufacturing semiconductor device of the present invention, the grain size of the polycrystalline thin film is increased by depositing a thick amorphous film and then annealing and thinning it. An additional protective layer is used to avoid etching damage on the sidewalls, effectively reducing the interface state and damage defects of the polycrystalline channel layer, thereby enhancing the reliability of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

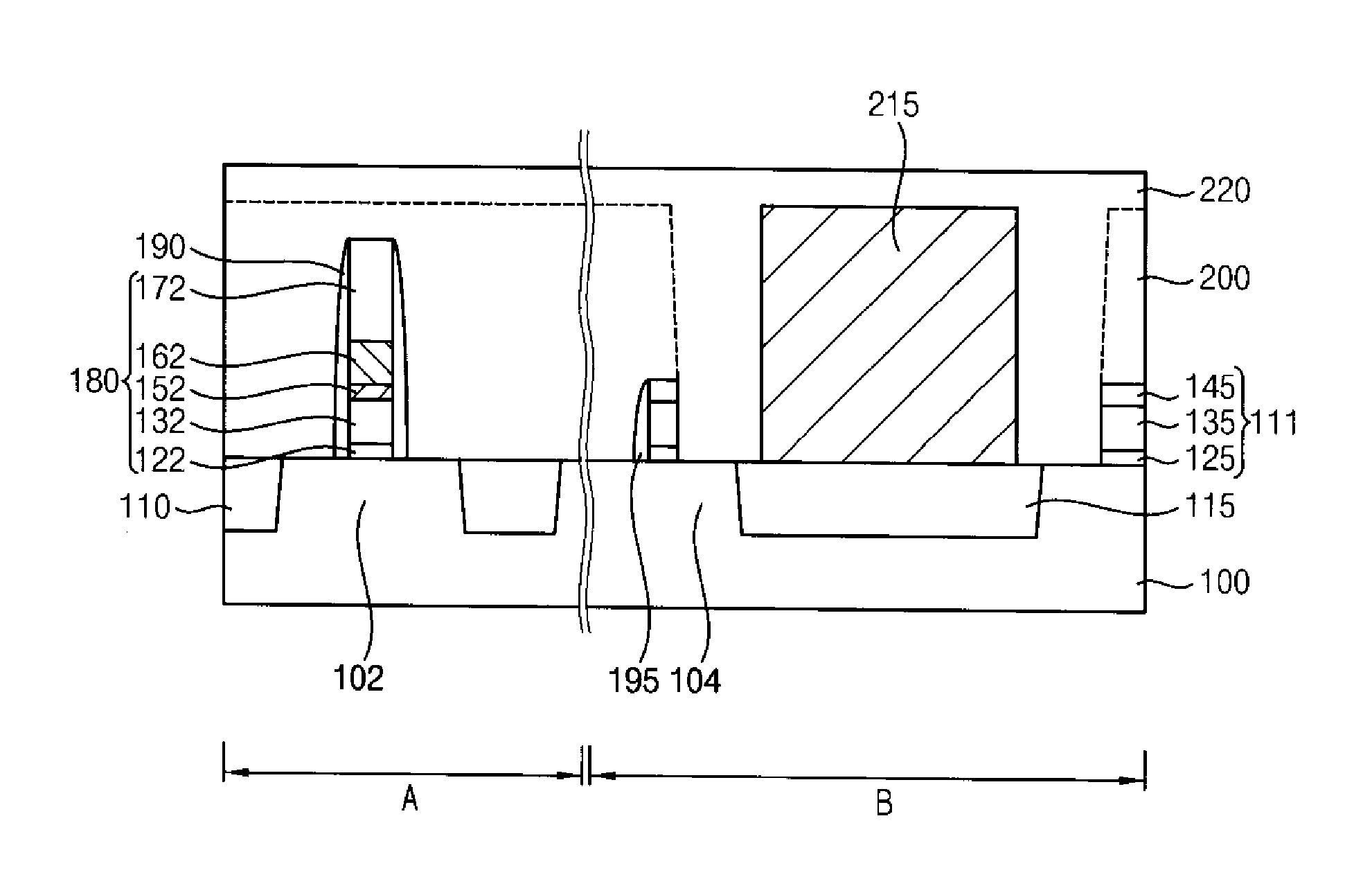

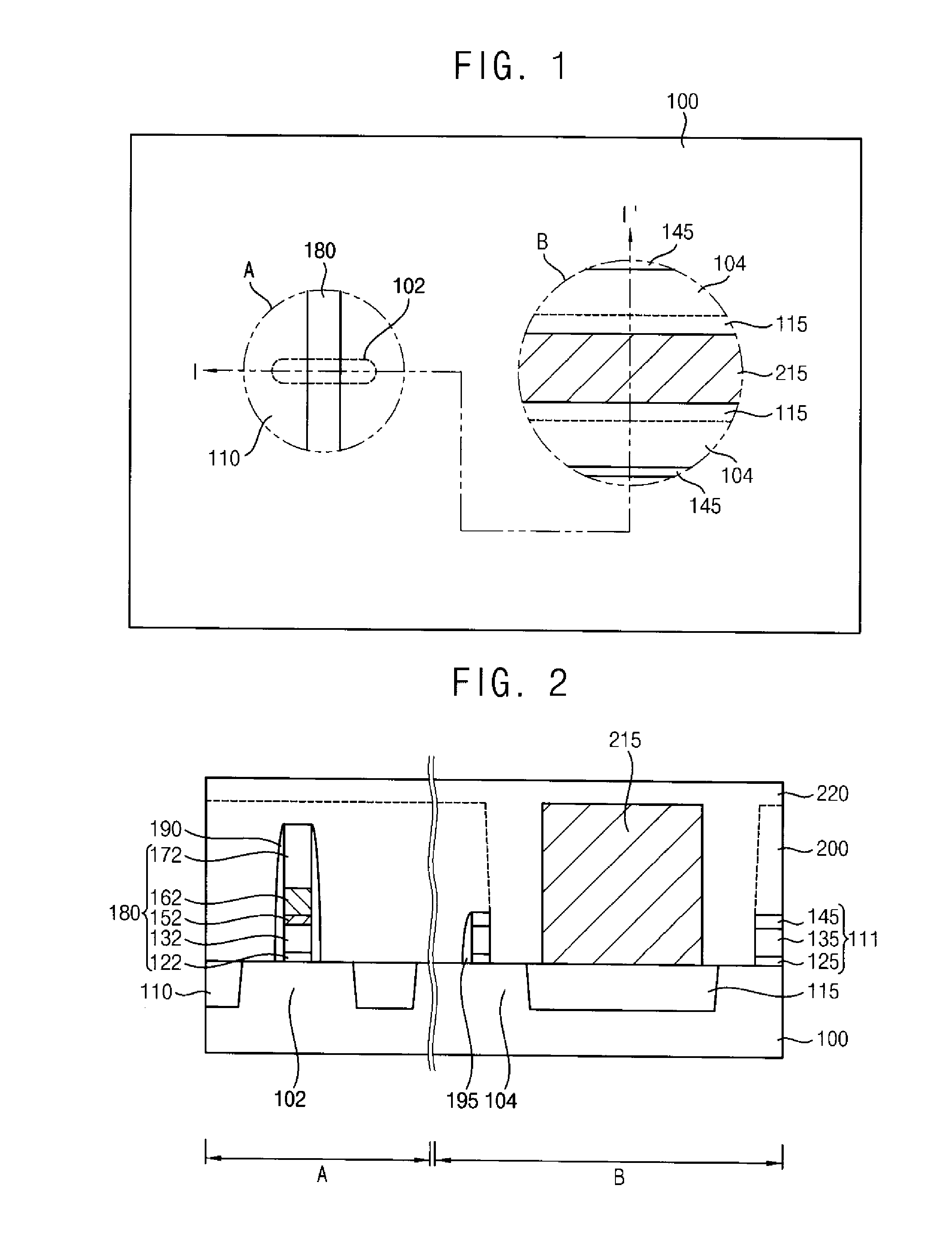

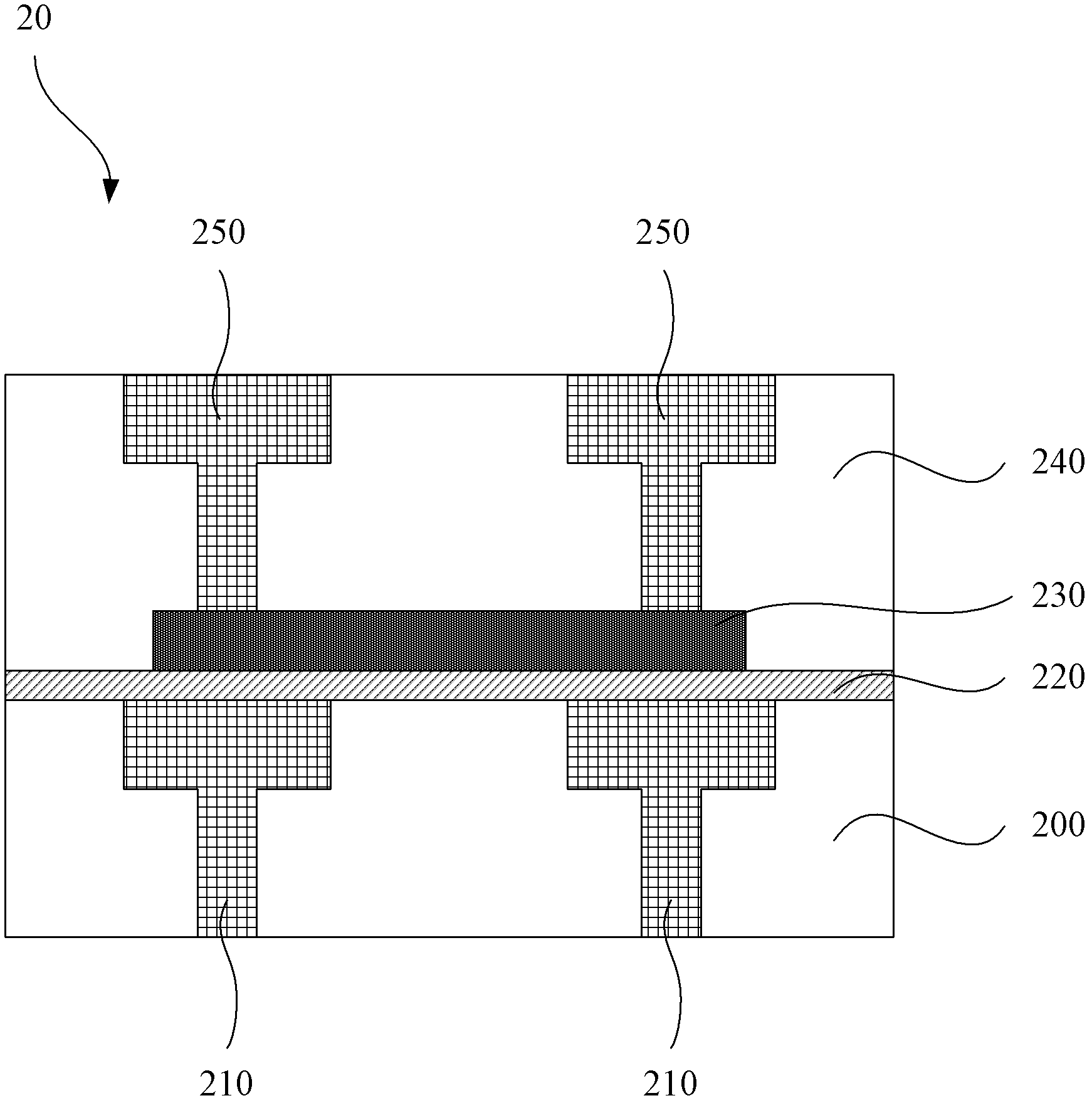

Semiconductor device and method of manufacturing the same

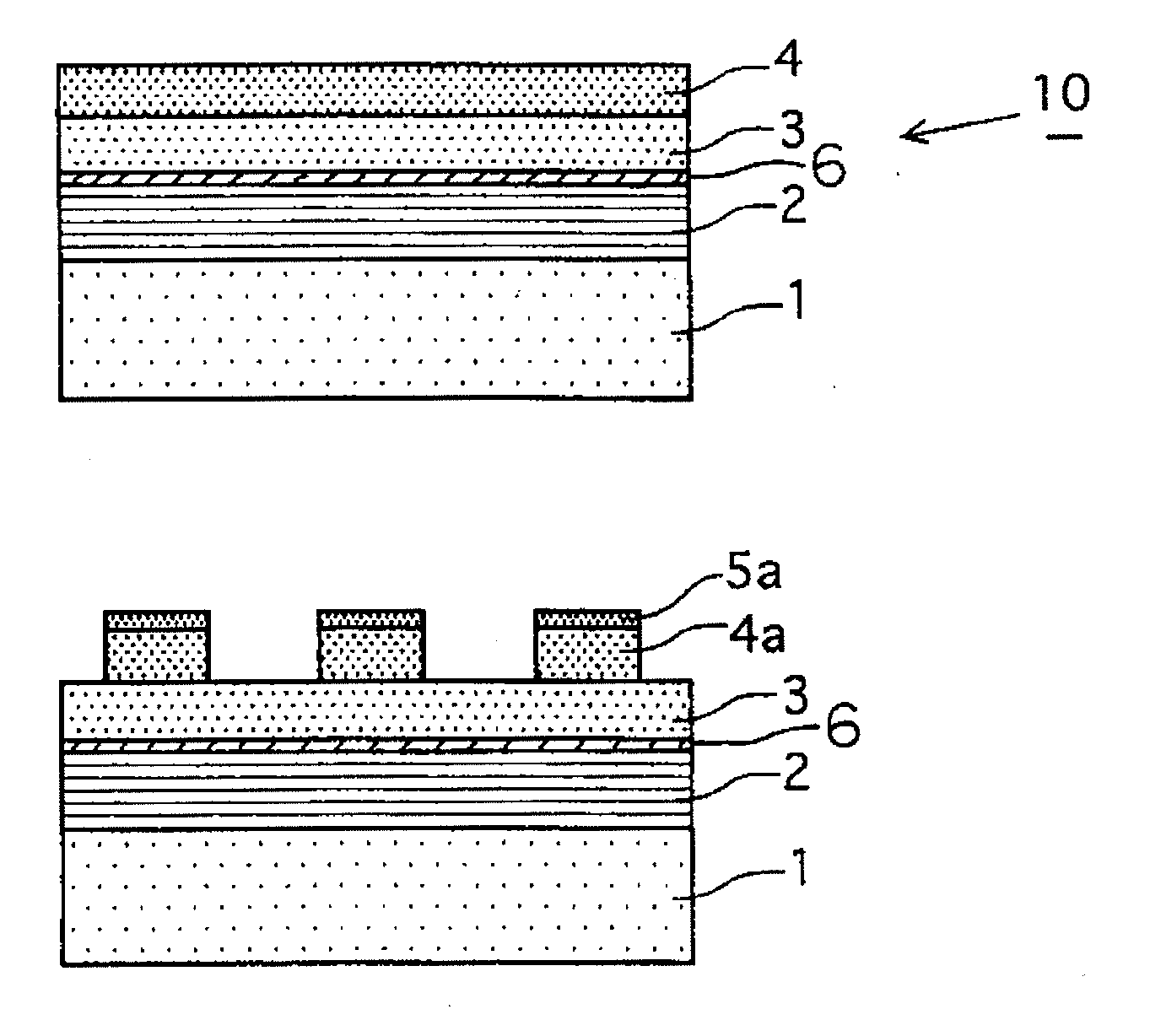

ActiveUS20160035719A1Avoid damageAvoid etch damageTransistorSolid-state devicesDevice materialElectrode Contact

Both a HEMT and a SBD are formed on a nitride semiconductor substrate. The nitride semiconductor substrate comprises a HEMT gate structure region and an anode electrode region. A first laminated structure is formed at least in the HEMT gate structure region, and includes first to third nitride semiconductor layers. A second laminated structure is formed at least in a part of the anode electrode region, and includes first and second nitride semiconductor layers. The anode electrode contacts the front surface of the second nitride semiconductor layer. At least in a contact region in which the front surface of the second nitride semiconductor layer contacts the anode electrode, the front surface of the second nitride semiconductor layer is finished to be a surface by which the second nitride semiconductor layer forms a Schottky junction with the anode electrode.

Owner:TOYOTA CENT RES & DEV LAB INC +1

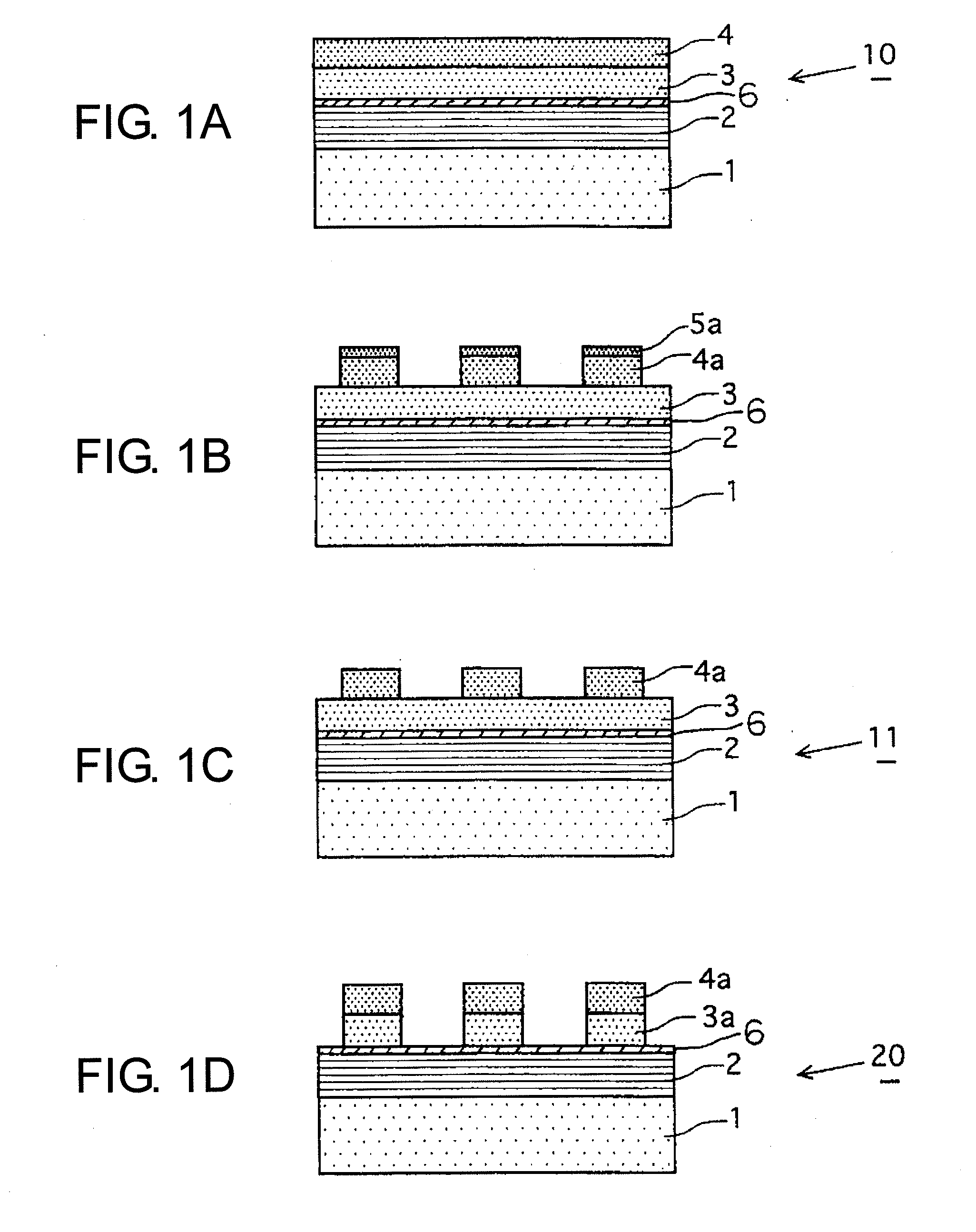

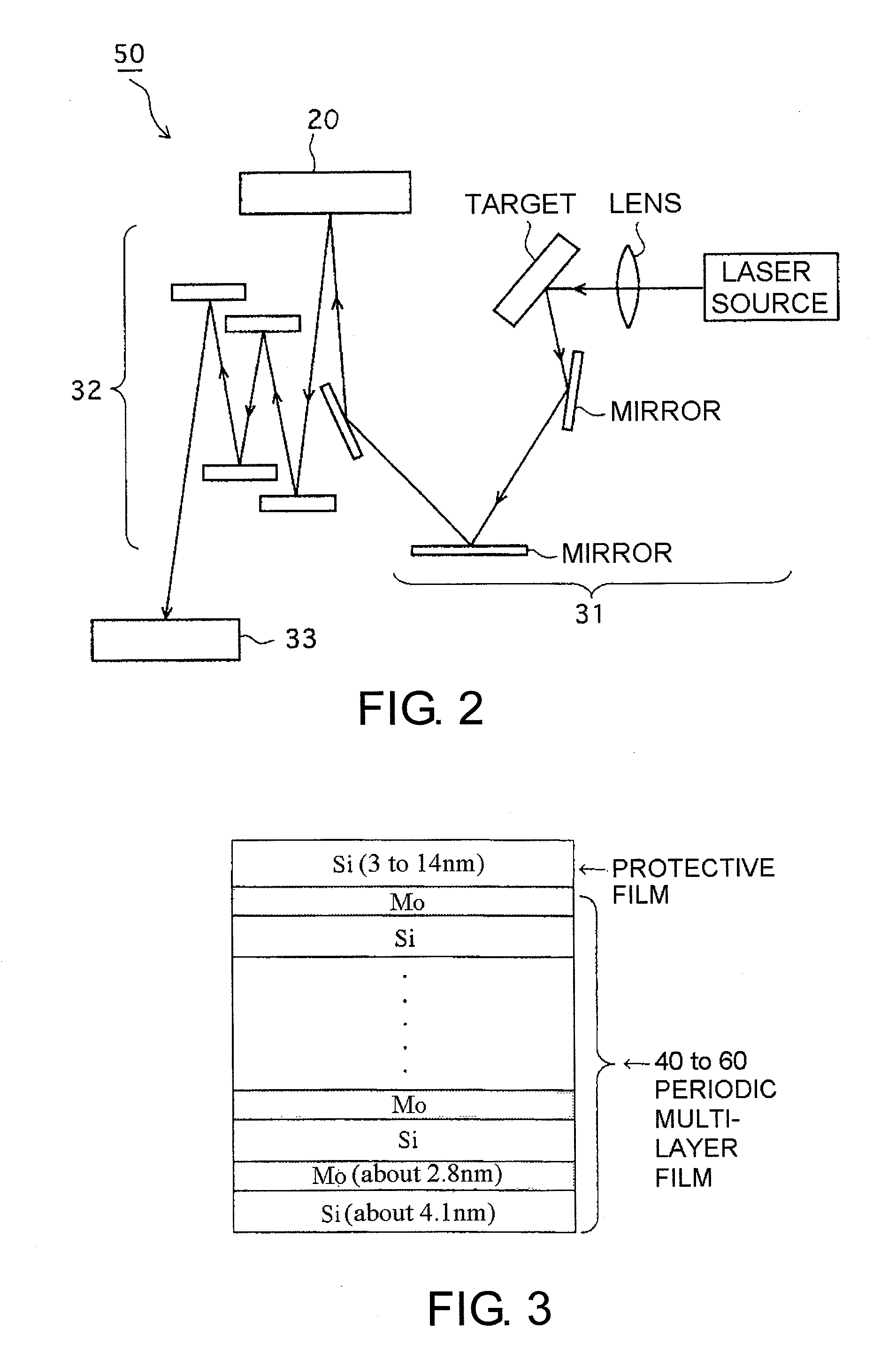

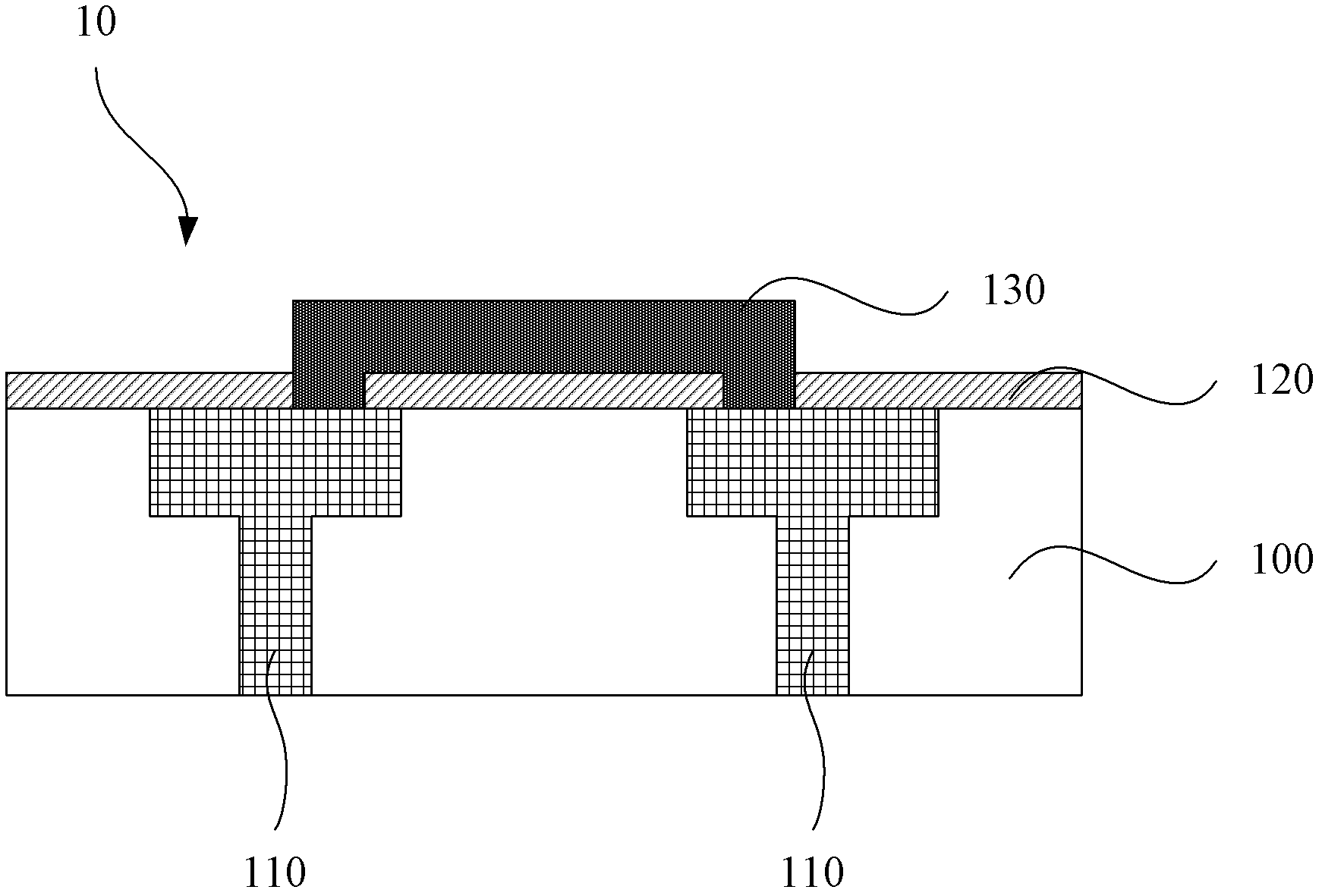

Method of producing a reflective mask

InactiveUS20100084375A1Increase resistanceGood chemical resistanceDecorative surface effectsSemiconductor/solid-state device manufacturingTectorial membraneOxygen

A method of producing a reflective mask is carried out by the use of a reflective mask blank which has a substrate, a multilayer reflective film formed on the substrate to reflect exposure light, a protective film formed on the multilayer reflective film, a buffer film formed on the protective film, and an absorber film formed on the buffer film to absorb the exposure light. The protective film is made of a ruthenium compound containing Ru and Nb. The method includes a step of patterning the buffer film by dry etching performed by the use of an etching gas containing oxygen.

Owner:HOYA CORP

Metal film resistor structure and manufacturing method thereof

ActiveCN102324427AAvoid etch damageImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesCopperMetal

The invention provides a metal film resistor structure and a manufacturing method thereof. The metal film resistor structure can be formed by adding a photoetching mask plate, wherein a metal film resistor is connected with a lower layer metallic copper interconnecting wire. The metal film resistor structure solves the problem of etch damage to the metal film resistor during the formation of an upper layer metallic copper interconnecting wire in the prior art, and then improves the reliability of the formed metal film resistor.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

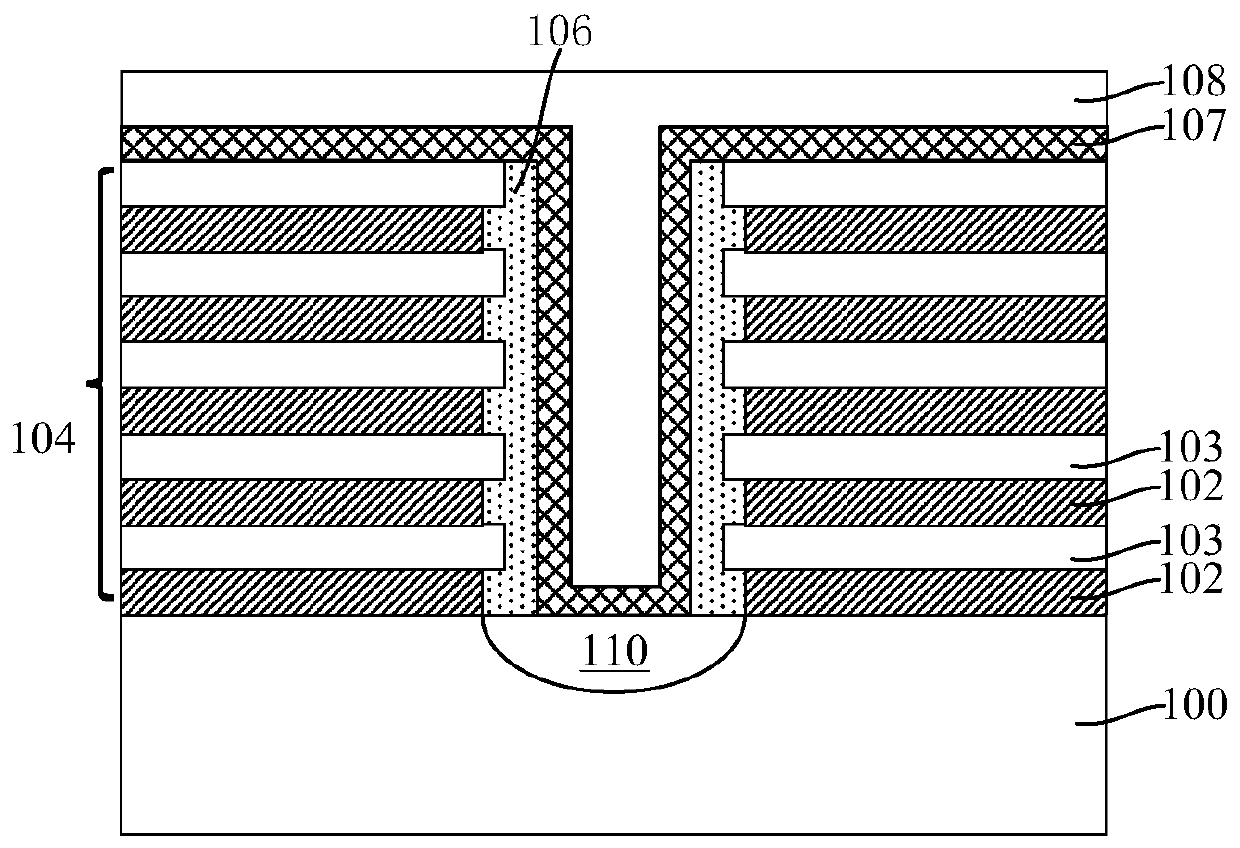

Three-dimensional memory device and manufacturing method thereof

ActiveUS20210020650A1Increased process windowHigh aspect ratioSolid-state devicesSemiconductor/solid-state device manufacturingCell regionElectrical connection

Provided is a three-dimensional memory device including a substrate, first and second stacked structures and an etching stop layer. The substrate has a cell region and a periphery region. The first stacked structure is disposed on the cell region and the periphery region, and has a first vertical channel pillar on the cell region that penetrates through the first stacked structure. The second stacked structure is located on the first stacked structure, is disposed on the cell region and the periphery region, and has a second vertical channel pillar on the cell region that penetrates through the second stacked structure. The second vertical channel pillar is electrically connected to the first vertical channel pillar. The etching stop layer is located between the first and second stacked structures, is disposed on the cell region and extends onto the periphery region, and surrounds the lower portion of the second vertical channel pillar.

Owner:MACRONIX INT CO LTD

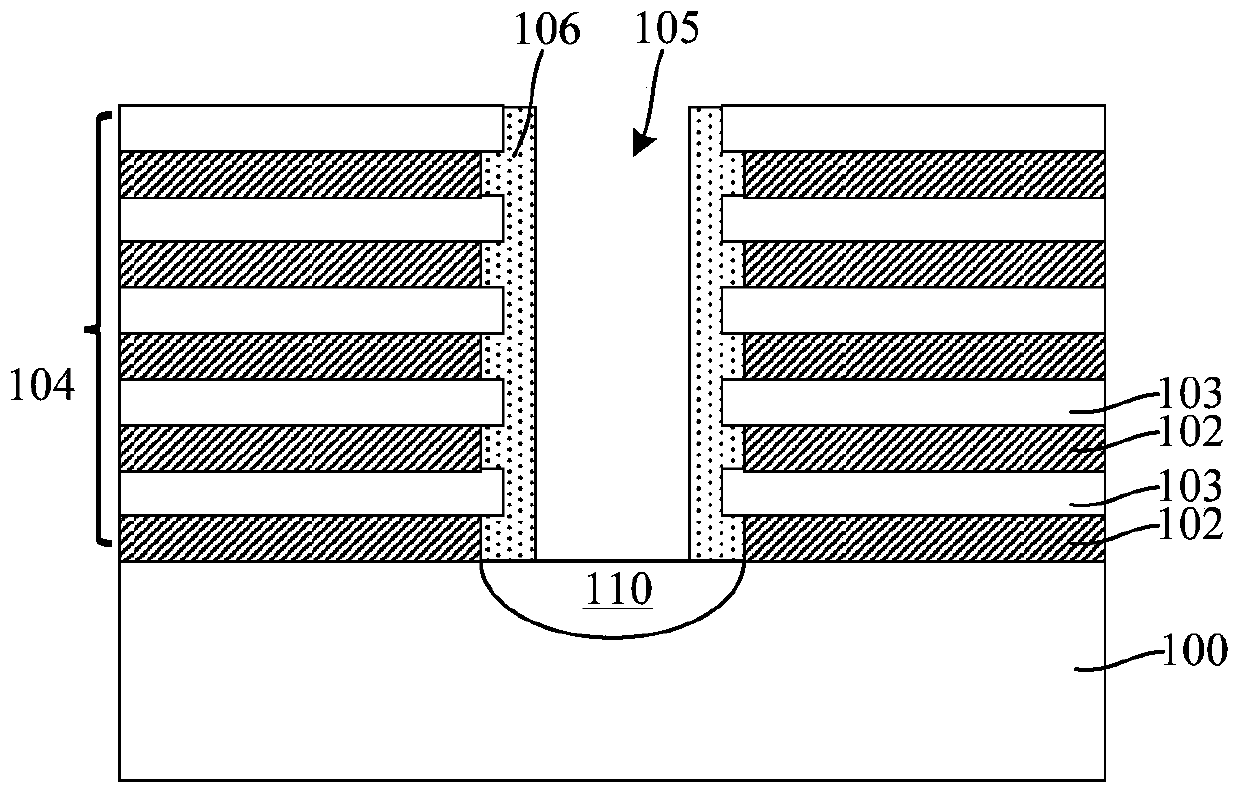

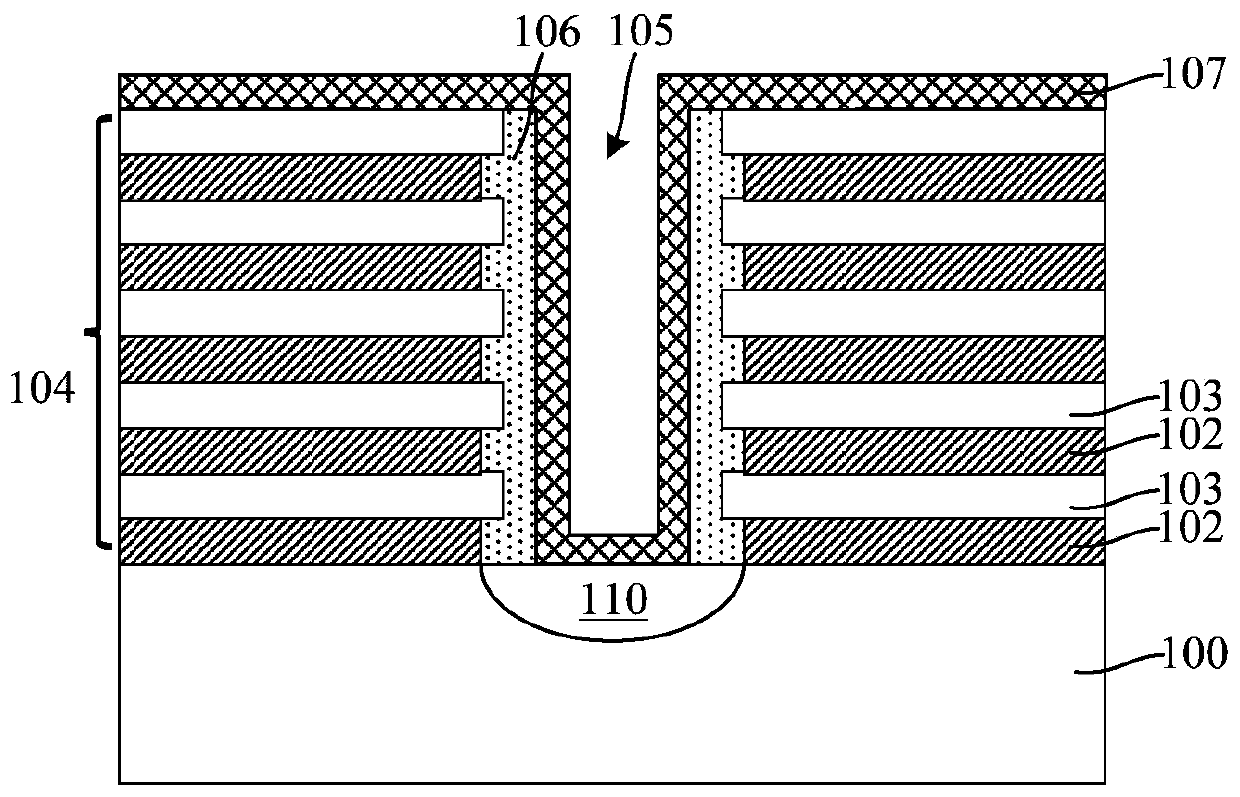

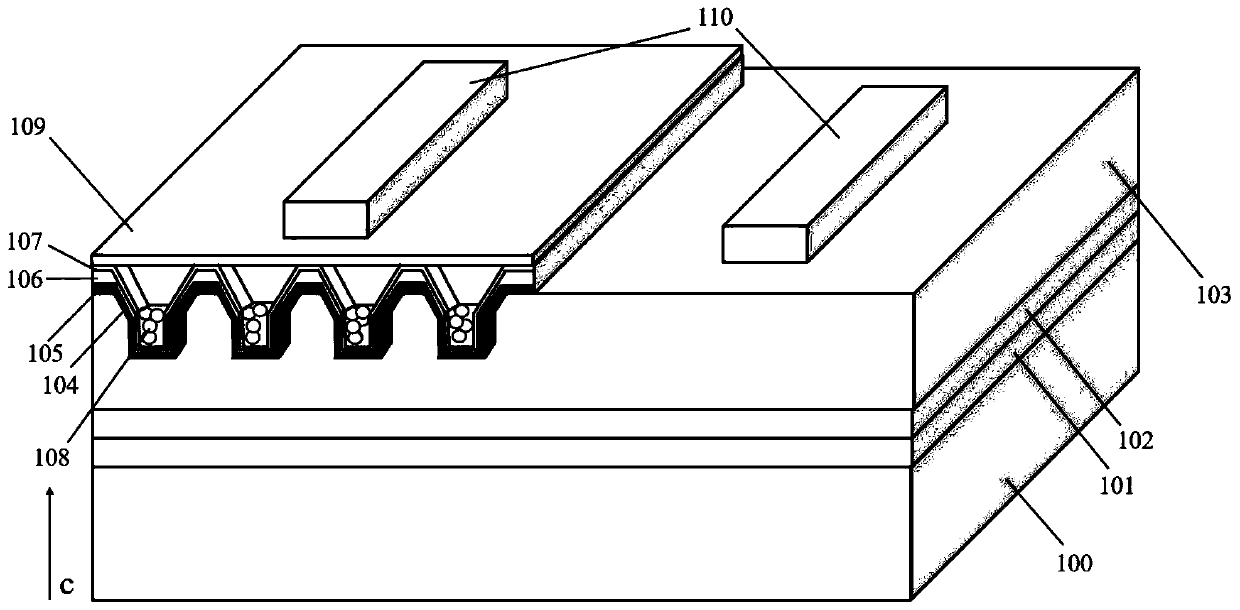

Manufacturing method of semiconductor device

ActiveCN107425018AExpanding the removal process windowIncrease windowSolid-state devicesRadiation controlled devicesCapacitanceDielectric layer

The invention provides a manufacturing method of a semiconductor device, and relates to the technical field of semiconductors. The method comprises the steps that a semiconductor substrate is provided, a first dielectric layer is formed on the surface of the semiconductor substrate, and a patterned mask layer is formed on the first dielectric layer; a deep trench arranged in the semiconductor substrate is formed; a second dielectric layer is formed on the bottom part and the side wall of the deep trench; a first polysilicon layer is formed through deposition to fill in the deep trench; the first time of etching is performed to etch and remove partial first polysilicon layer, wherein the top surface of the remaining first polysilicon layer is higher than the top surface of the first dielectric layer and lower than the top surface of the mask layer; the mask layer is removed; the second time of etching is performed to etch and remove the first polysilicon layer; and the top polar plate of the deep trench capacitor is formed. According to the method, etching damage to other film layers or materials which are arranged at the external side of the deep trench and have the same material with that of the mask layer in the removing process of the mask layer can be effectively avoided and the window of the mask layer removing process can be expanded.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

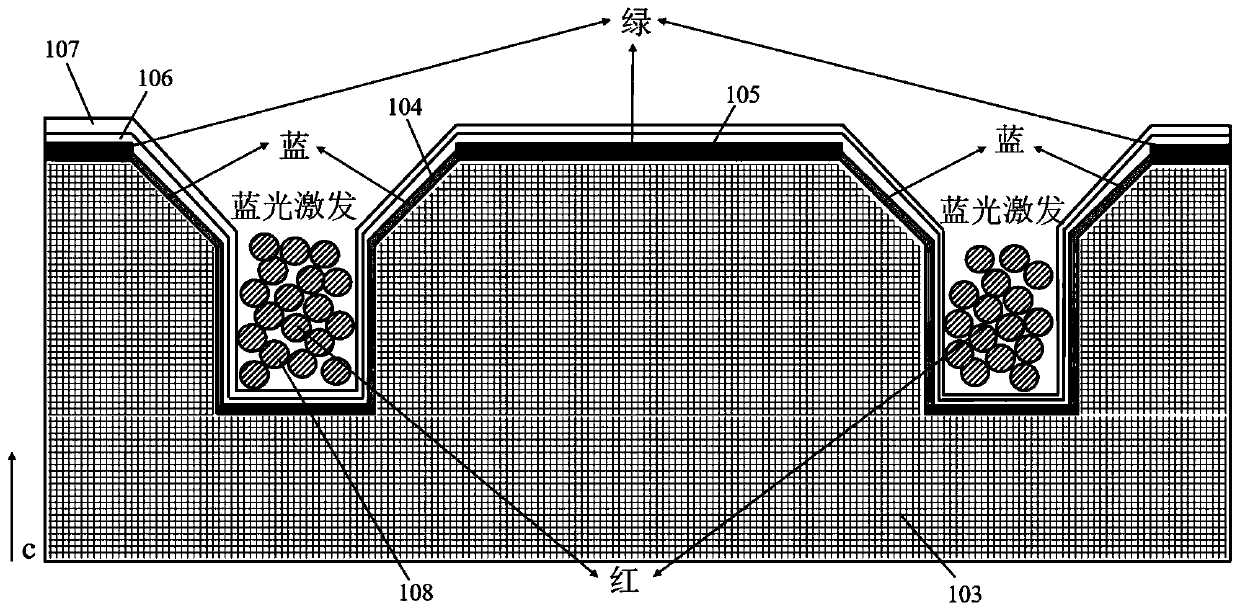

Single-chip white light emitting diode and preparation method thereof

ActiveCN111048641AImprove luminous efficiencyIncrease growth rateSemiconductor devicesGreen-lightBlocking layer

The invention discloses a single-chip white light emitting diode, which comprises a substrate, a buffer layer, a non-doped GaN layer, a patterned n-type GaN layer, a multi-quantum well active layer, an electron blocking layer, a p-type GaN layer, a red light wavelength conversion material, a current expansion layer, and n-type and p-type ohmic contact electrodes, wherein the n-type GaN layer is etched through a dry etching technology and a wet etching technology to form a hexagonal hole array with a semi-polar surface, a non-polar surface and a polar surface, the InGaN multi-quantum well active layer, the electron blocking layer and the p-type GaN layer are epitaxially grown on the patterned n-type GaN layer, and a wide spectrum from blue light to a yellow-green light waveband is emitted;and the hexagonal holes are filled with the red light wavelength conversion material, and a red light spectrum is excited by blue / green light emitted by the quantum well active region, so that a fullspectrum is formed, and the single-chip white light emitting diode with a high color rendering index is obtained.

Owner:XIAMEN UNIV

Formation method of semiconductor device

ActiveCN106340520AImprove electrical performanceGood lookingSolid-state devicesSemiconductor devicesUnit deviceElectrical performance

The invention discloses a formation method of a semiconductor device. The method comprises the following steps: forming a tunneling dielectric layer on a substrate of a flash memory area, a reference unit zone and a logic zone, wherein the tunneling dielectric layer is also disposed on a flash memory grid and a source grid; forming a word line layer on the tunneling dielectric layer; forming a first photoresist layer on the word line layer of the flash memory zone and a part of the word line layer of the reference unit zone; by taking the first photoresist layer as a mask layer, removing the word line layer disposed on the logic zone through etching, and also removing the word line layer exposed on the reference unit zone through etching, wherein the residual word line layer on the reference unit zone is used for forming a reference unit grid; after the reference unit grid is formed, forming a logic grid on the substrate of the logic zone; forming a second photoresist layer on the logic grid and the reference unit grid; and after the second photoresist layer is formed, etching the word line layer of the flash memory zone, and forming a word line on the substrate of the flash memory zone. According to the invention, the morphology of the reference unit grid of a reference unit device is improved, and electrical performance of the formed semiconductor device is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Photoetching and etching method for preventing shaped wafer surface from etching damage

ActiveCN105845564ASave timeSave costSemiconductor/solid-state device manufacturingFilling materialsPhotoresist

The invention provides a photoetching and etching method for preventing shaped wafer surface from etching damage. The method comprises following steps of forming a floating gate layer and a storage unit control gate layer on a substrate in a storage unit region; forming a gate polysilicon layer on the substrate in a periphery region; depositing advanced patterned film on the substrate; forming a gap filling material layer on the advanced patterned film, thus filling the concave and convex parts of the advanced patterned film; carrying out shape planarization on the advanced patterned film by using a planarization back processing technology; depositing anti-reflection coating film; coating photoresist; forming photoresist patterns; and executing etching processing by using the photoresist patterns, thus etching the floating gate layer and the storage unit control gate layer.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Fin field-effect transistor formation method

ActiveCN105470132AUniform etch rateReduce etch damageSolid-state devicesSemiconductor/solid-state device manufacturingEtchingEngineering

Provided is a fin field-effect transistor formation method which comprises the following steps: providing a substrate, and forming a plurality of independent fin portions on the surface of the substrate; forming an isolating layer on the surface of the substrate, the top surface of the isolating layer being lower than the top surface of each fin portion and the isolating layer covering a part of the surfaces of the side walls of the fin portions; forming a barrier layer covering the surface of the isolating layer and the top and side wall surfaces of the fin portions; converting a part of the barrier layer of a certain thickness into a passivation layer through oxidation treatment; etching back the passivation layer to form passivated side walls covering on the surface of the barrier layer on the side wall surfaces of the fin portions; and with the passivated side walls being as a mask, removing the barrier layer on the top surfaces of the fin portions by utilizing a wet etching process, and retaining the barrier layer on the side wall surfaces of the fin portions as barrier side walls. According to the fin field-effect transistor formation method, the quality of a formed stress layer is improved, and meanwhile, growth of the stress layer on the side wall surfaces of the fin portions can be prevented, and performance of a fin field-effect transistor is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

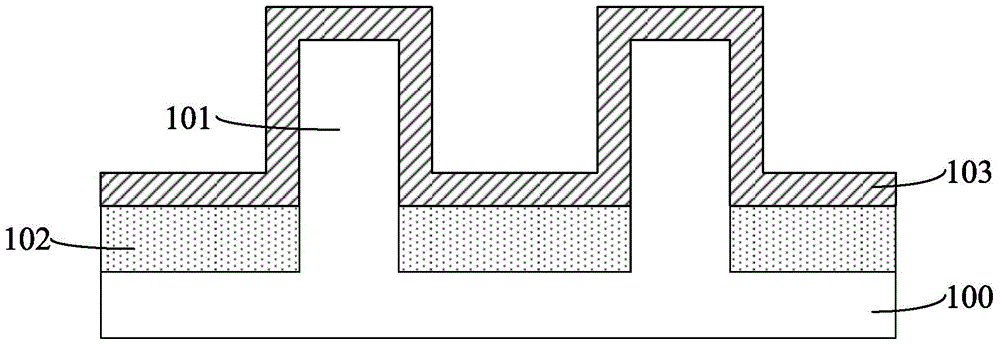

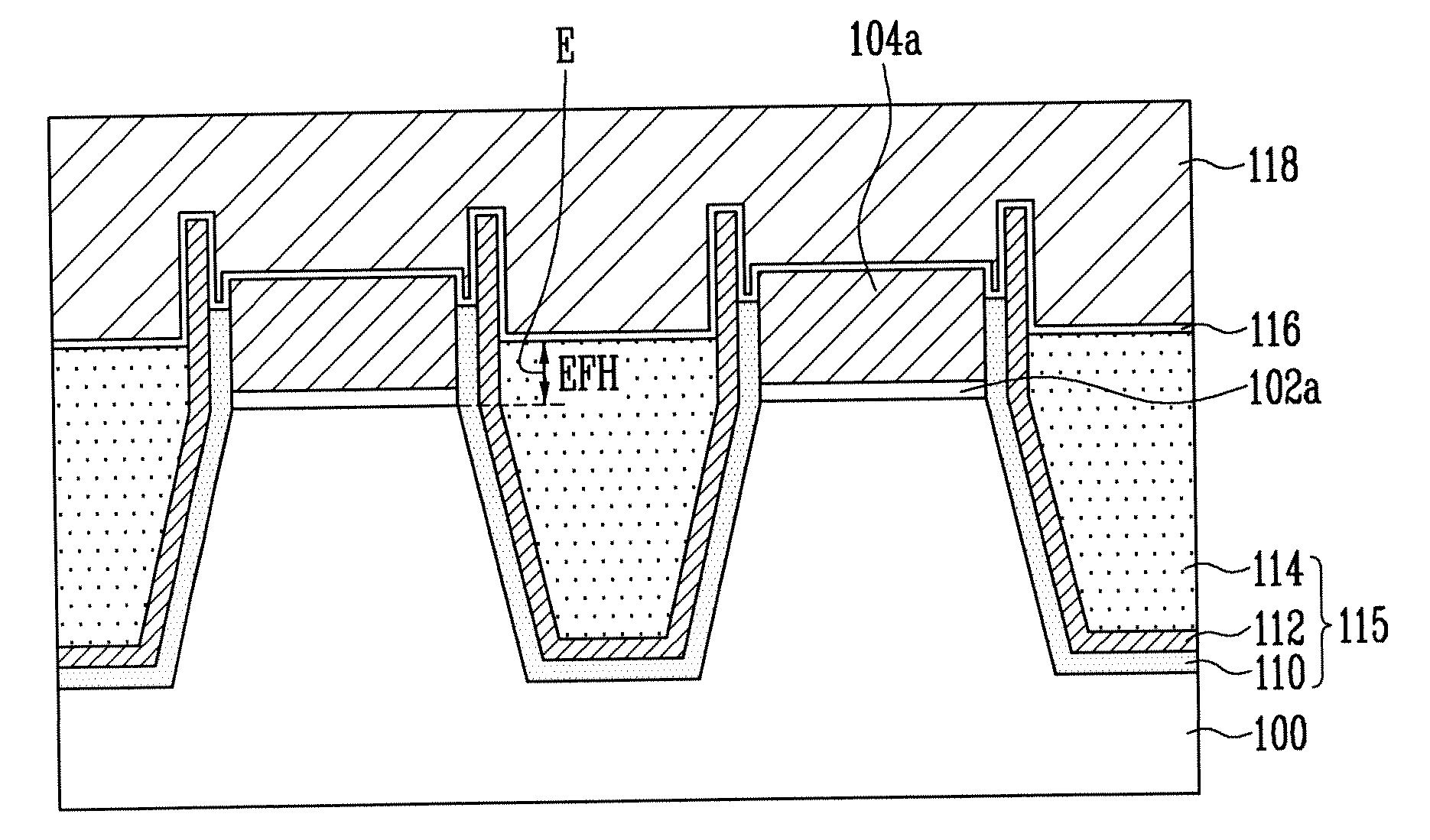

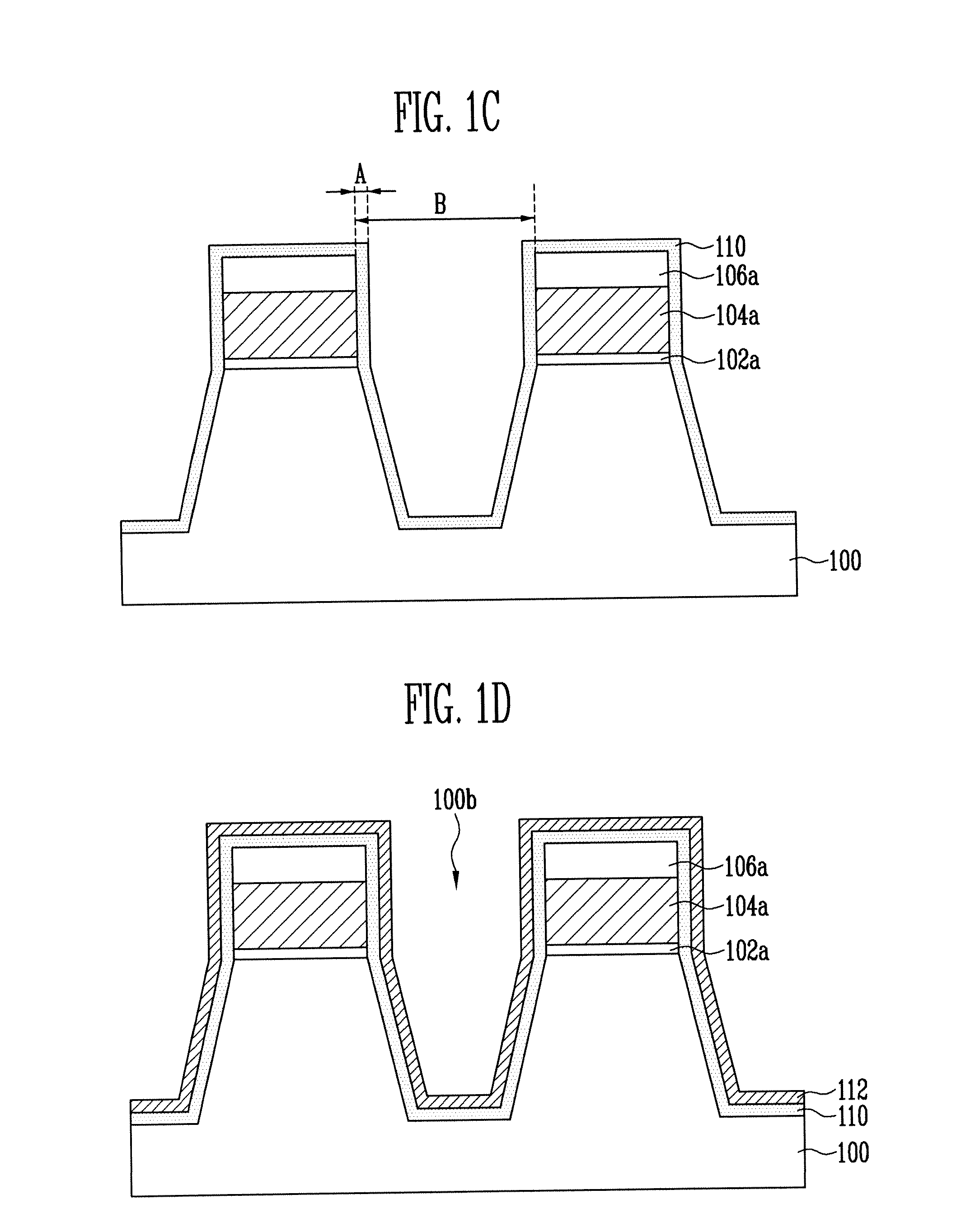

Semiconductor Memory Device and Method of Fabricating the Same

InactiveUS20080203458A1Prevent etch damageAvoid etch damageSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor memory

This patent relates to a semiconductor memory device and a method of fabricating the same. The semiconductor memory device may include a semiconductor substrate in which a tunnel insulating layer, and a first conductive layer. At least a portion of the semiconductor substrate is removed to form a trench. A first insulating layer may be formed on an internal surface of the trench. A shield layer may be made of a conductive material is formed on the first insulating layer. A second insulating layer may be formed on the shield layer and is configured to gap fill the trench.

Owner:SK HYNIX INC

Alignment key structure in a semiconductor device and method of forming the same

ActiveUS20060246648A1Improve reliabilityImprove productivitySemiconductor/solid-state device detailsSolid-state devicesInsulation layerDevice material

An alignment key structure in a semiconductor device is provided. The alignment key structure includes an insulation layer formed on a substrate, and a passivation layer pattern formed on the insulation layer. The insulation layer includes a plurality of metal wirings. The passivation layer pattern includes a first opening that exposes at least one of the metal wirings. Moreover, the first opening has a width which is narrower than a width of the exposed metal wiring.

Owner:SAMSUNG ELECTRONICS CO LTD +1

Manufacturing method of semiconductor structure

ActiveCN107785318AAvoid lateral etchingAvoiding problems with raised defect formationSemiconductor/solid-state device manufacturingEtchingSemiconductor structure

The invention relates to a manufacturing method of a semiconductor structure. The method includes the following steps that: a substrate and discrete fins on the substrate are provided, the extending direction of the fins is a first direction, and a direction perpendicular to the first direction is a second direction; an initial isolation layer between the fins is formed on the substrate and includes a first initial isolation layer for achieving the isolation of the fins in the first direction; part of the first initial isolation layer is removed by a certain thickness, so that a first isolation layer is formed, and the top of the first isolation layer is lower than the tops of the fins, and a trench is formed between the fins; a second isolation layer filling the trench is formed; protective sidewalls are formed on the sidewalls of the second isolation layer which are higher than the tops of the fins; and part of a second initial isolation layer and the second isolation layer are removed by a certain thickness. According to the manufacturing method of the semiconductor structure of the invention, the protective sidewalls are formed on the sidewalls of the second isolation layer which are higher than the tops of the fins, and therefore, when part of the second isolation layer is removed by a certain thickness, the protective sidewalls can protect the sidewalls of the second isolation layer, and therefore, the problem of the formation of protrusion defects of the second isolation layer because of insufficient lateral etching can be avoided.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

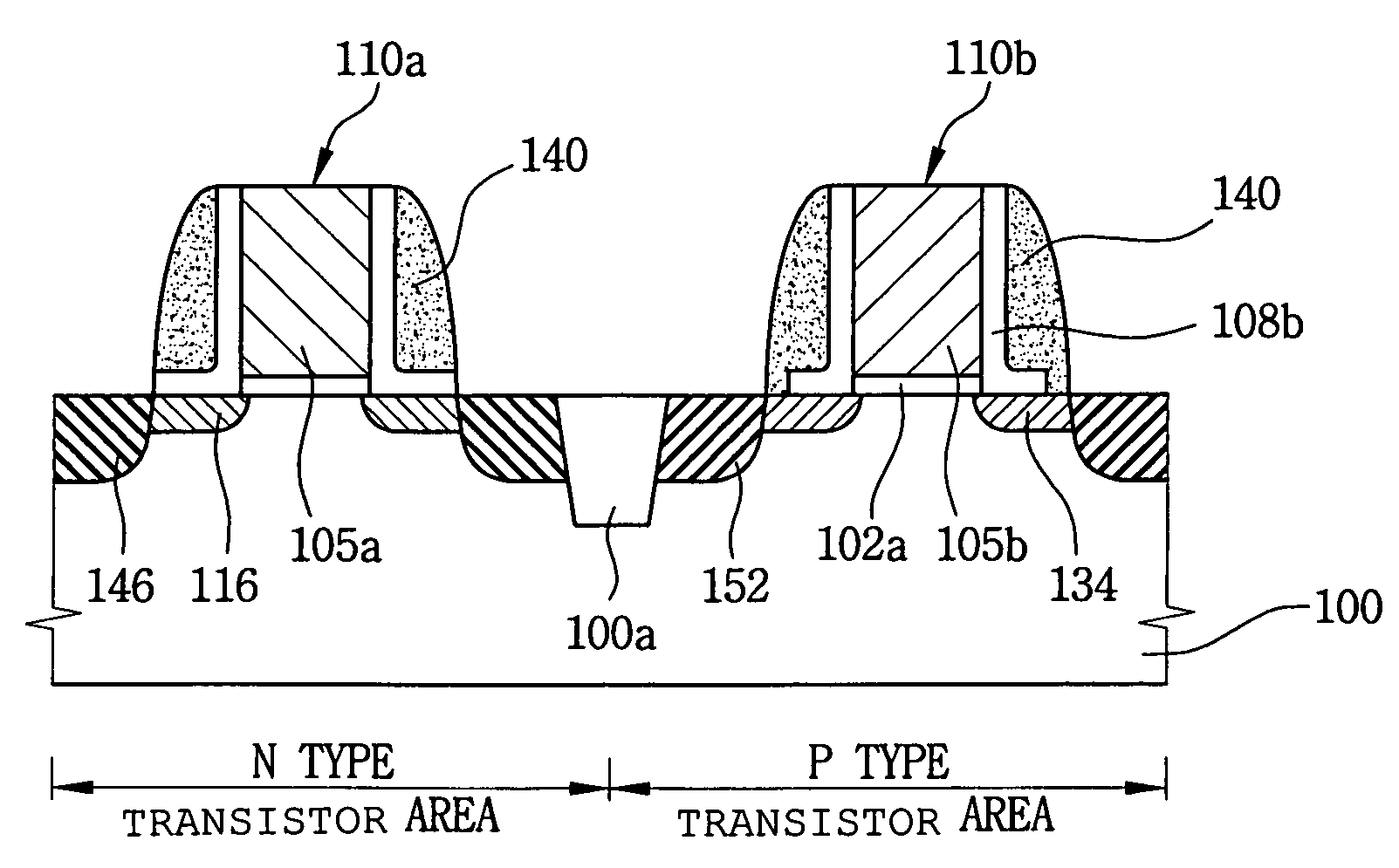

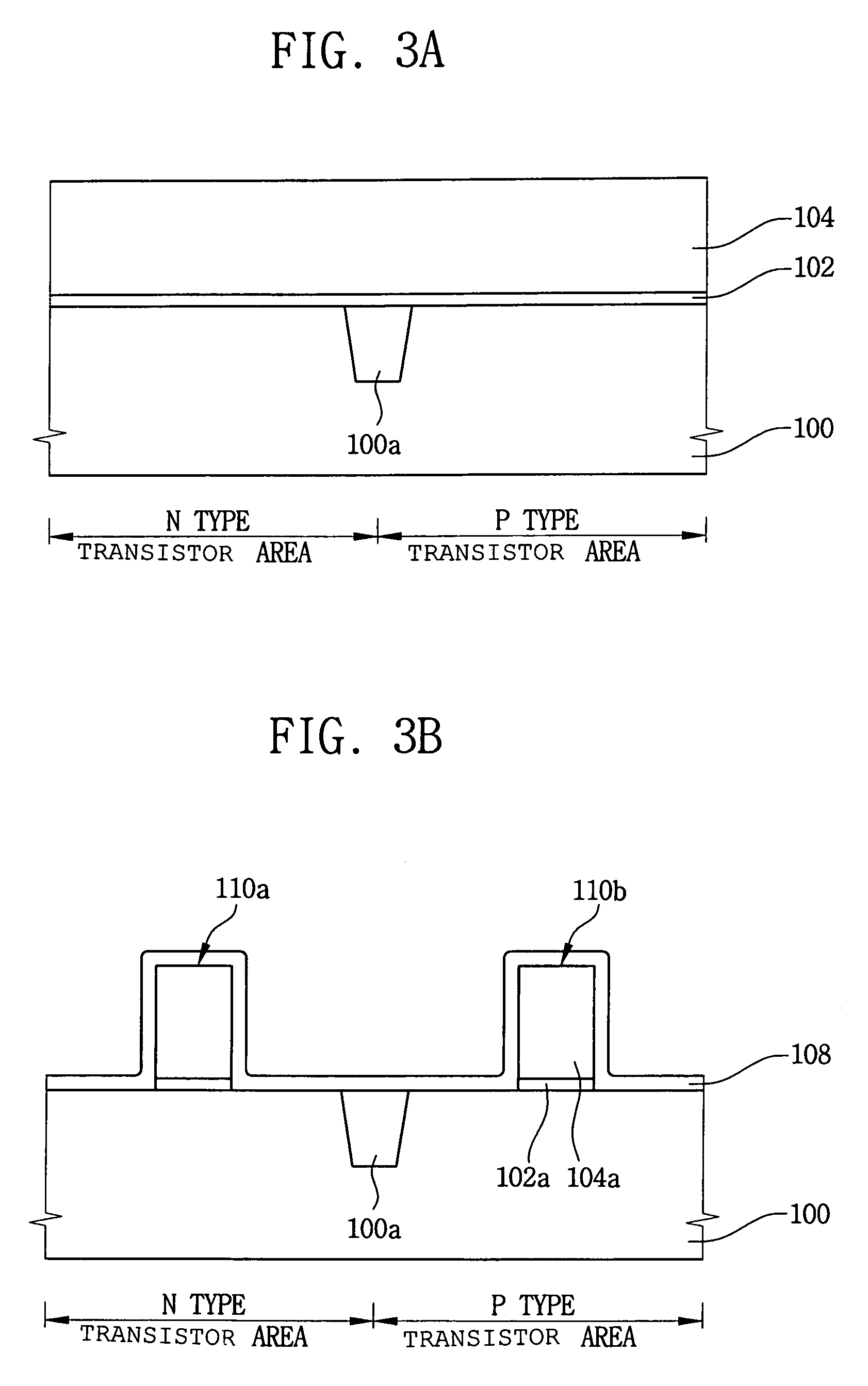

Method of manufacturing a MOS transistor of a semiconductor device

InactiveUS7067370B2Excellent electrical propertiesAvoid etch damageTransistorSemiconductor/solid-state device manufacturingCMOSInsulation layer

Owner:SAMSUNG ELECTRONICS CO LTD

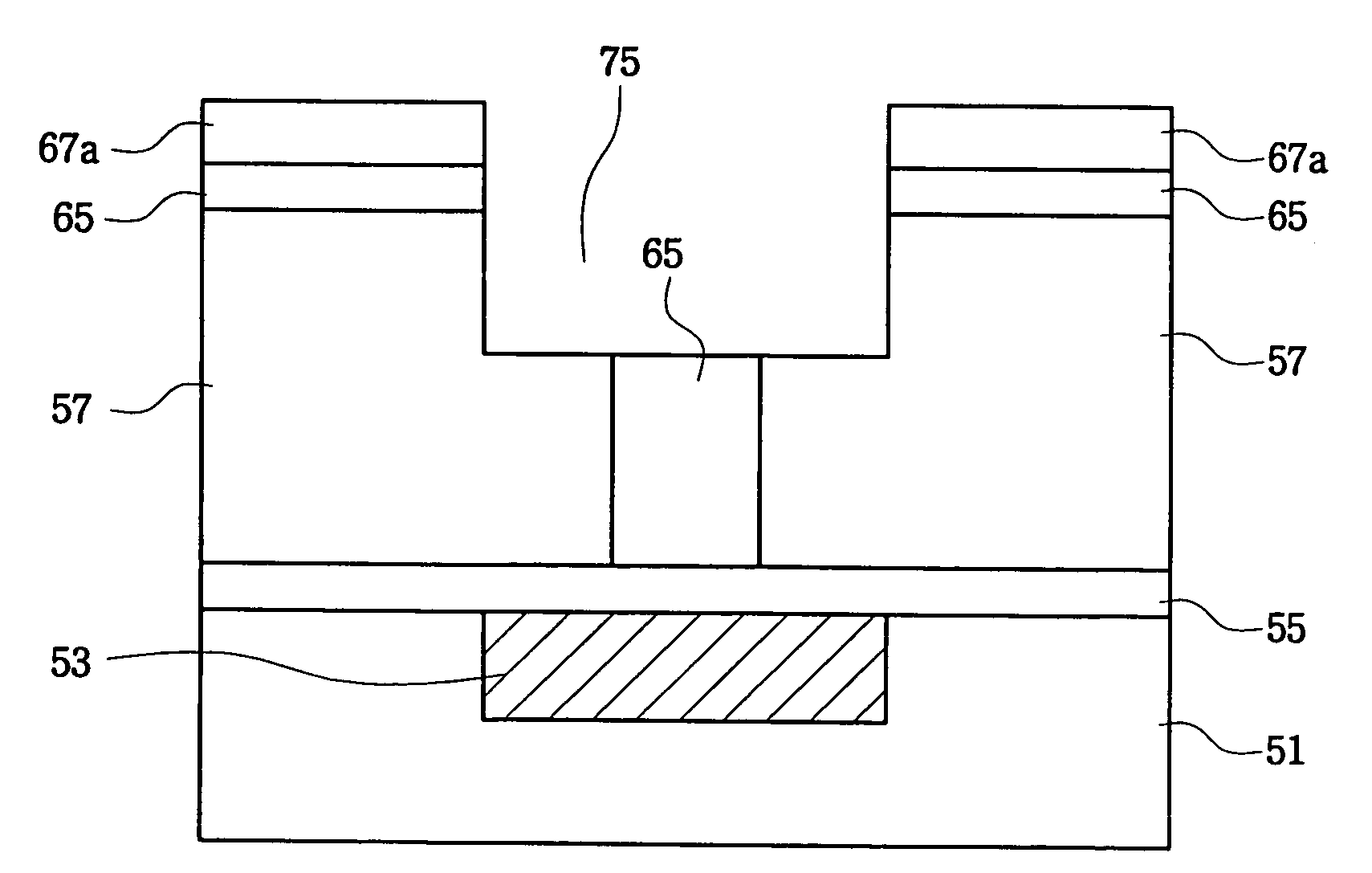

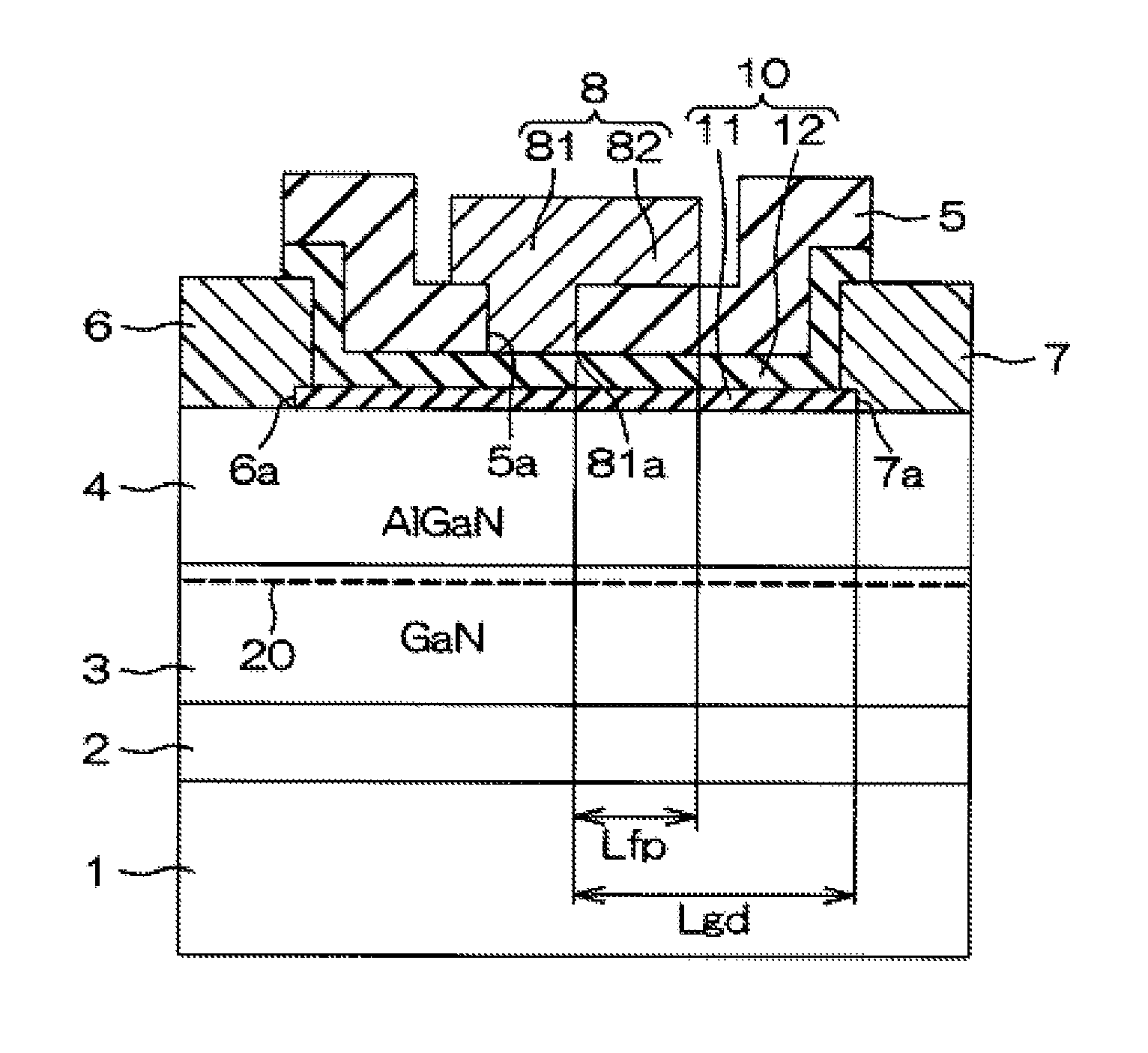

Nitride semiconductor device and manufacturing method thereof

ActiveUS9293573B2Improve featuresAvoid etch damageSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceElectron transport layer

Provided are a nitride semiconductor device having an excellent boundary between a nitride semiconductor and a gate insulating film, resulting in improved device characteristics, and a manufacturing method therefor. The nitride semiconductor device includes: an electron transport layer made of a nitride semiconductor; an electron supply layer layered on the electron transport layer, the electron supply layer being made of a nitride semiconductor including Al and having an Al composition different from that of the electron transport layer; a source electrode and a drain electrode formed on the electron supply layer with a gap therebetween; a gate insulating film covering the surface of the electron supply layer between the source electrode and the drain electrode; a passivation film covering a surface of the gate insulating film and having an opening between the source electrode and the drain electrode; and a gate electrode having a main gate body in the opening facing the electron supply layer through the gate insulating film.

Owner:ROHM CO LTD