Patents

Literature

106results about How to "Increase window" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

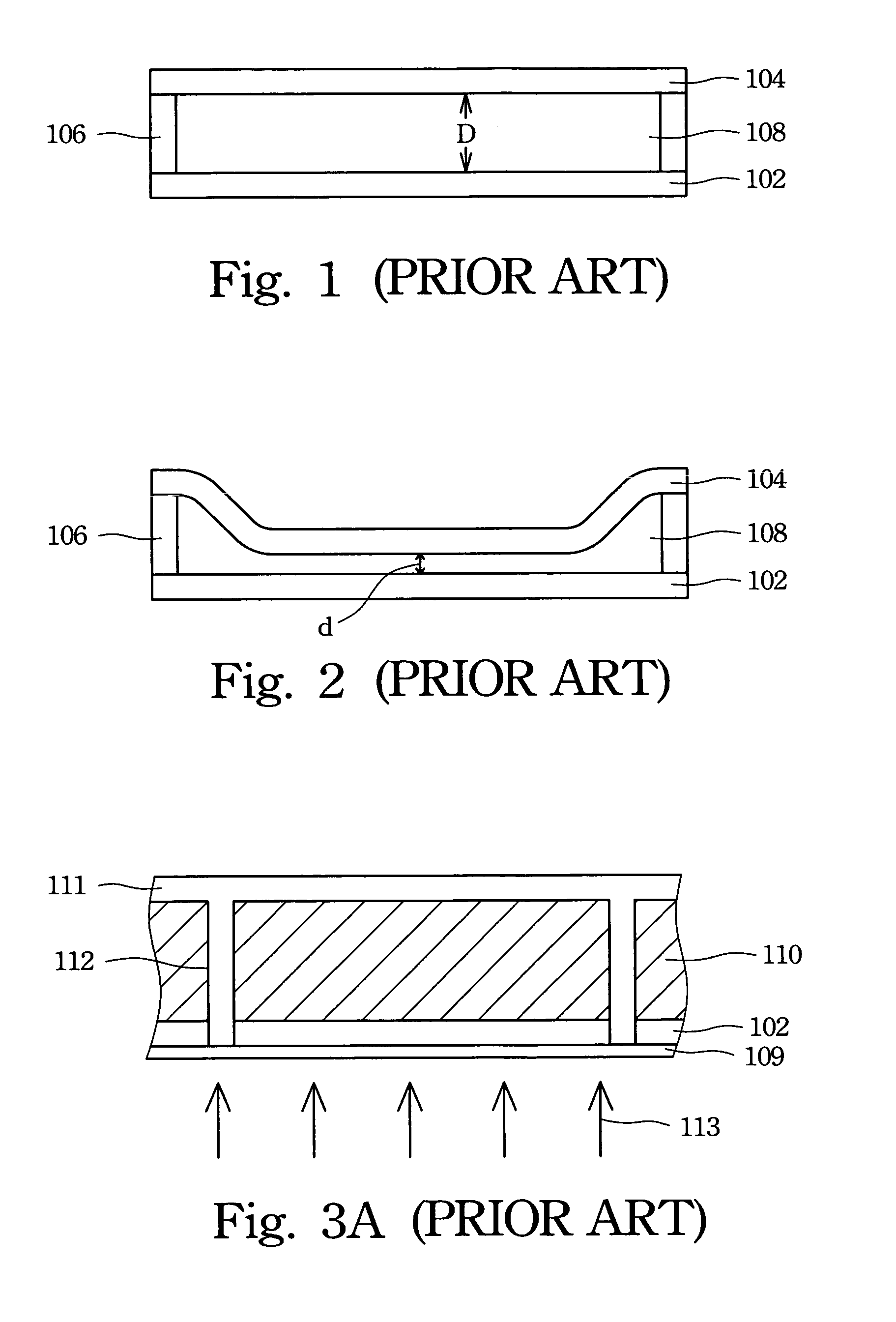

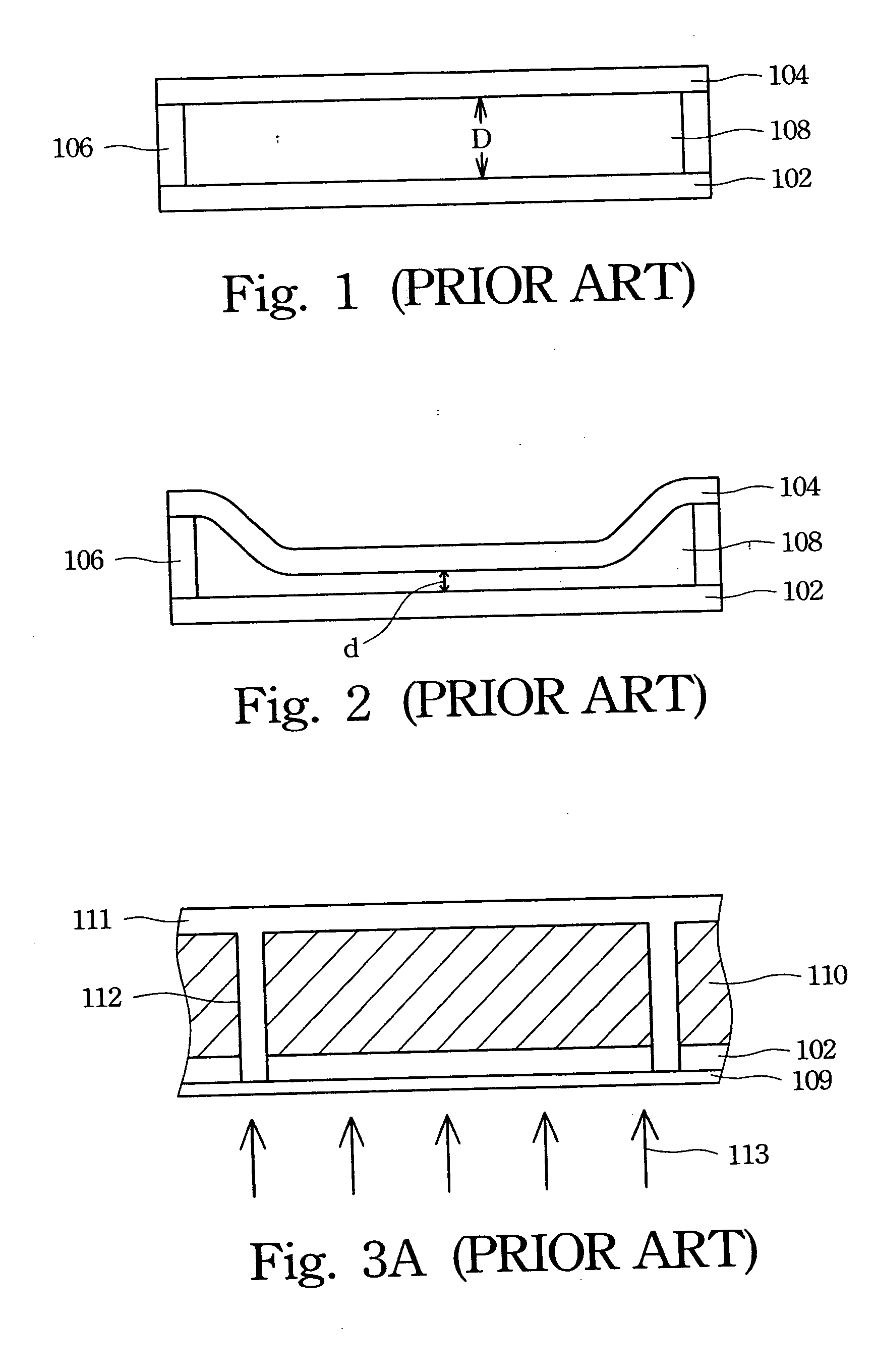

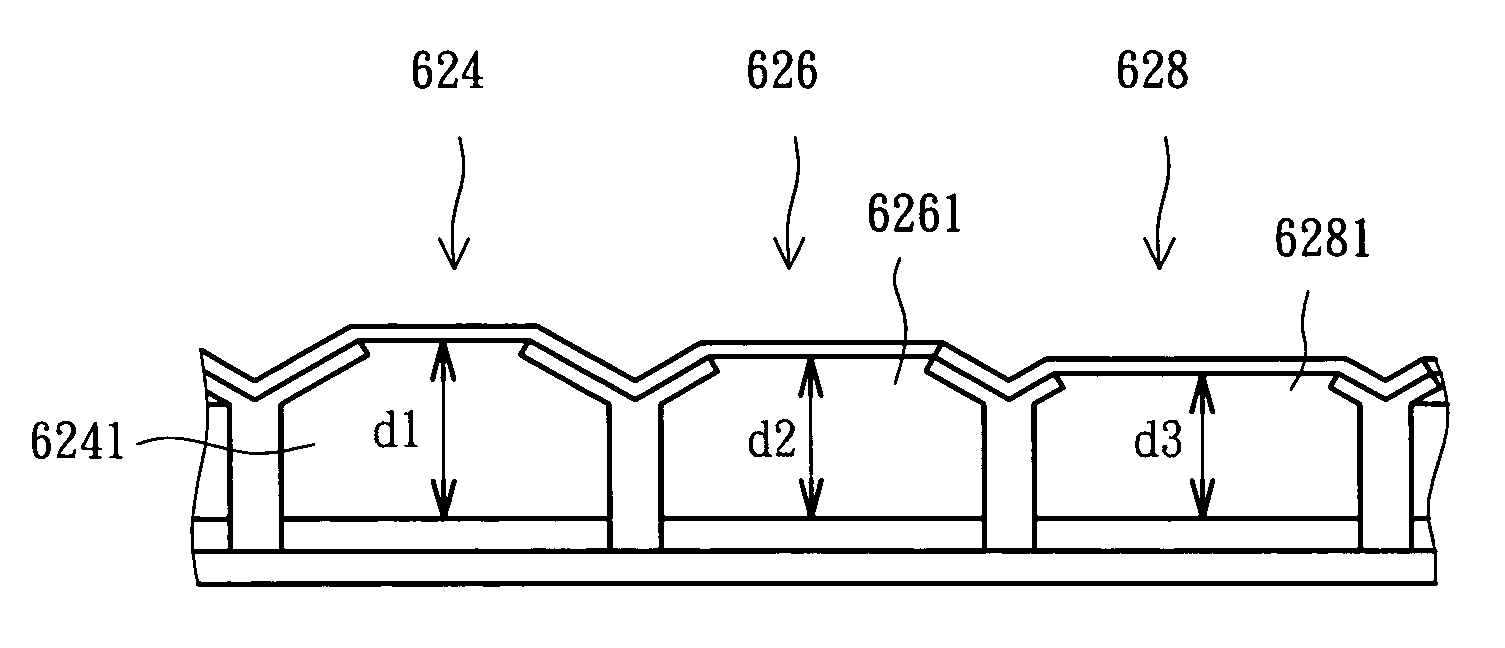

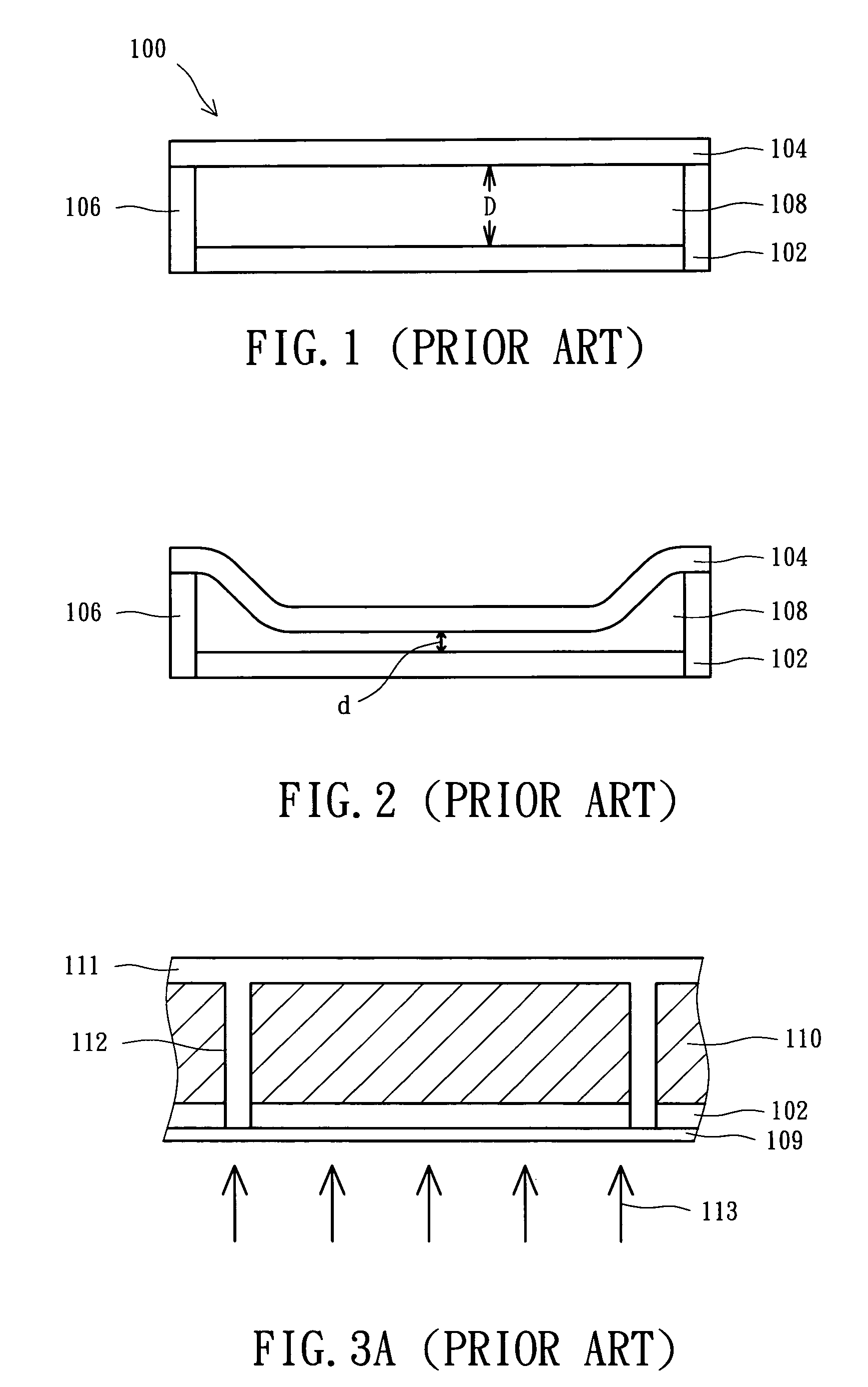

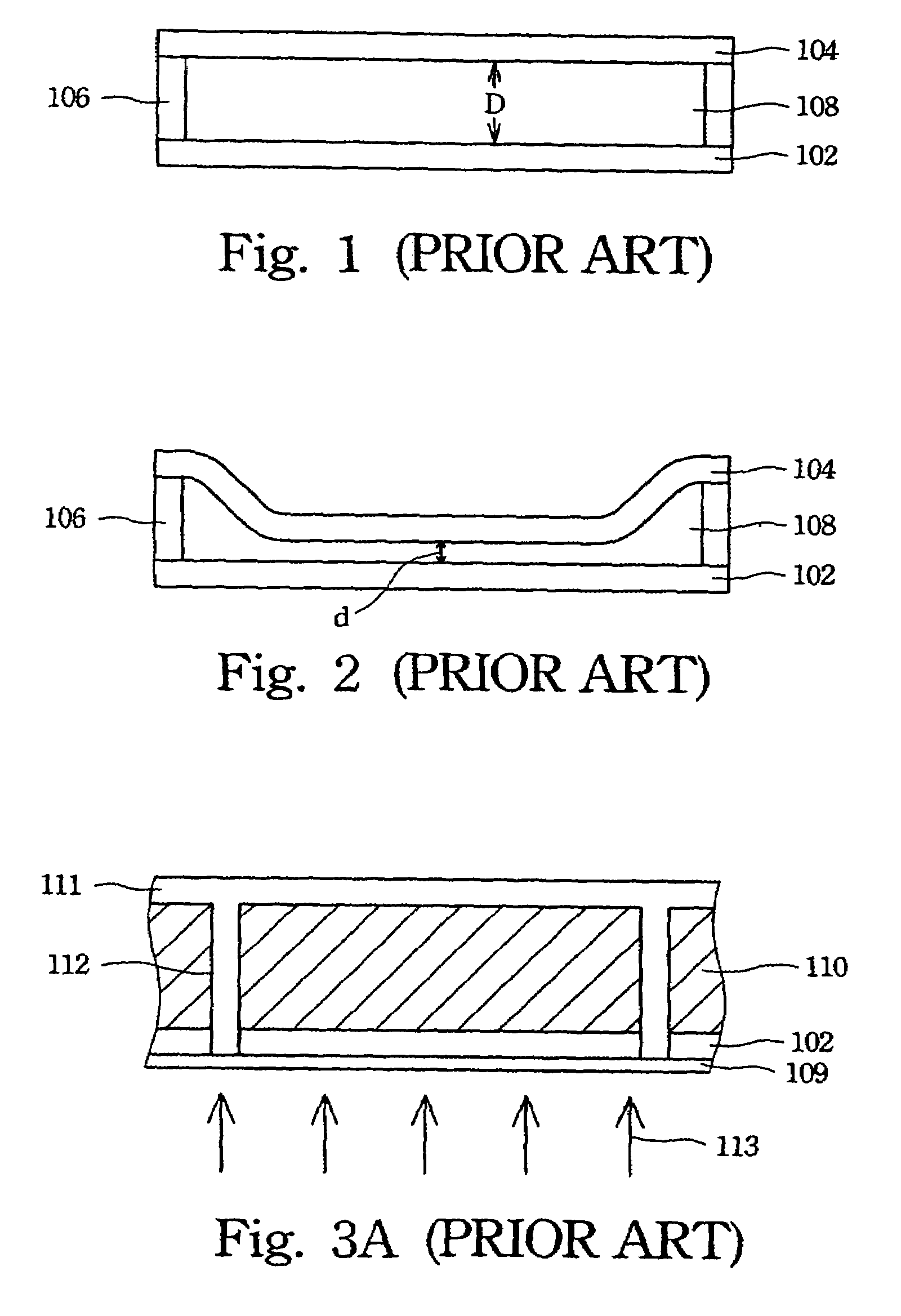

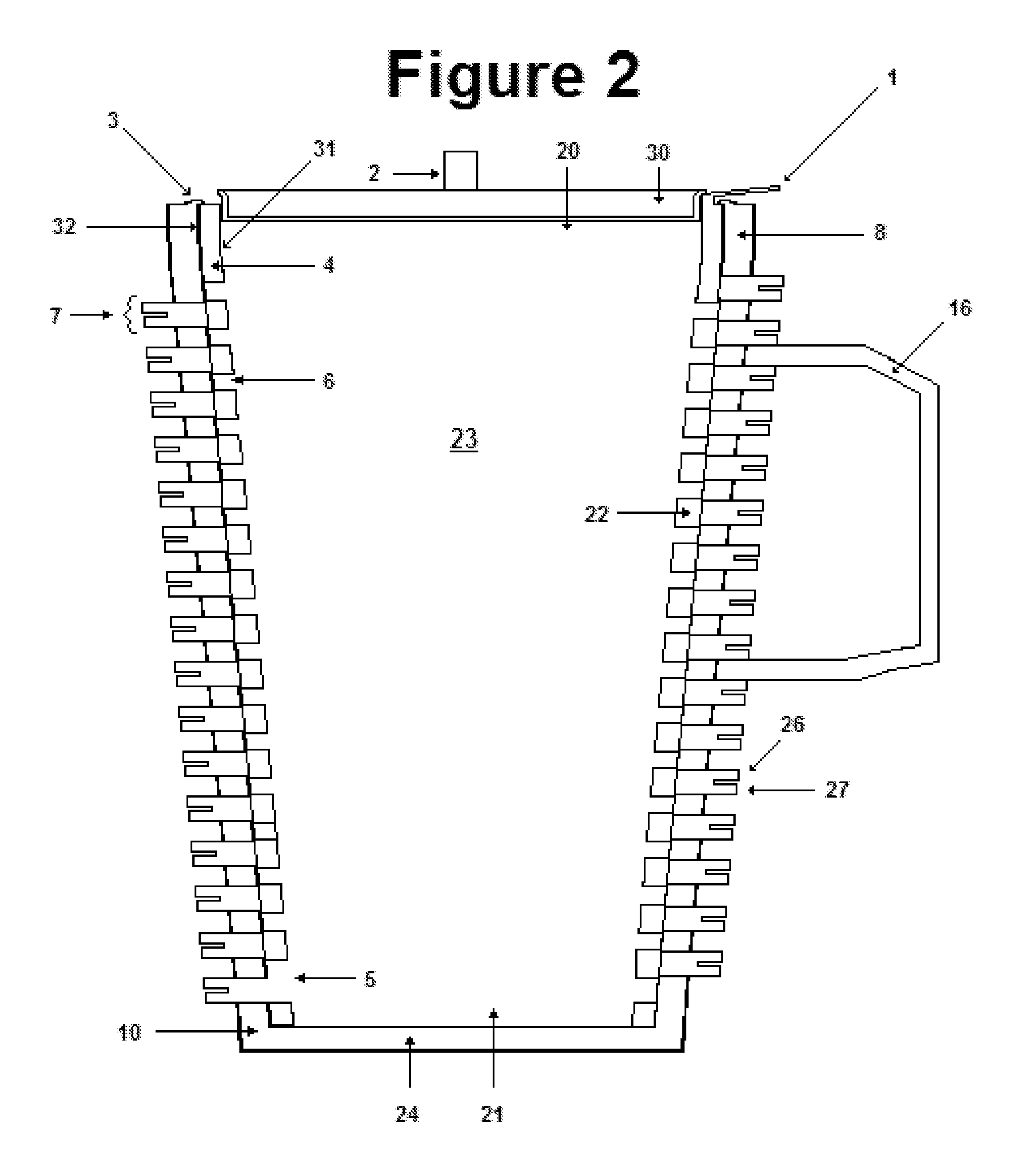

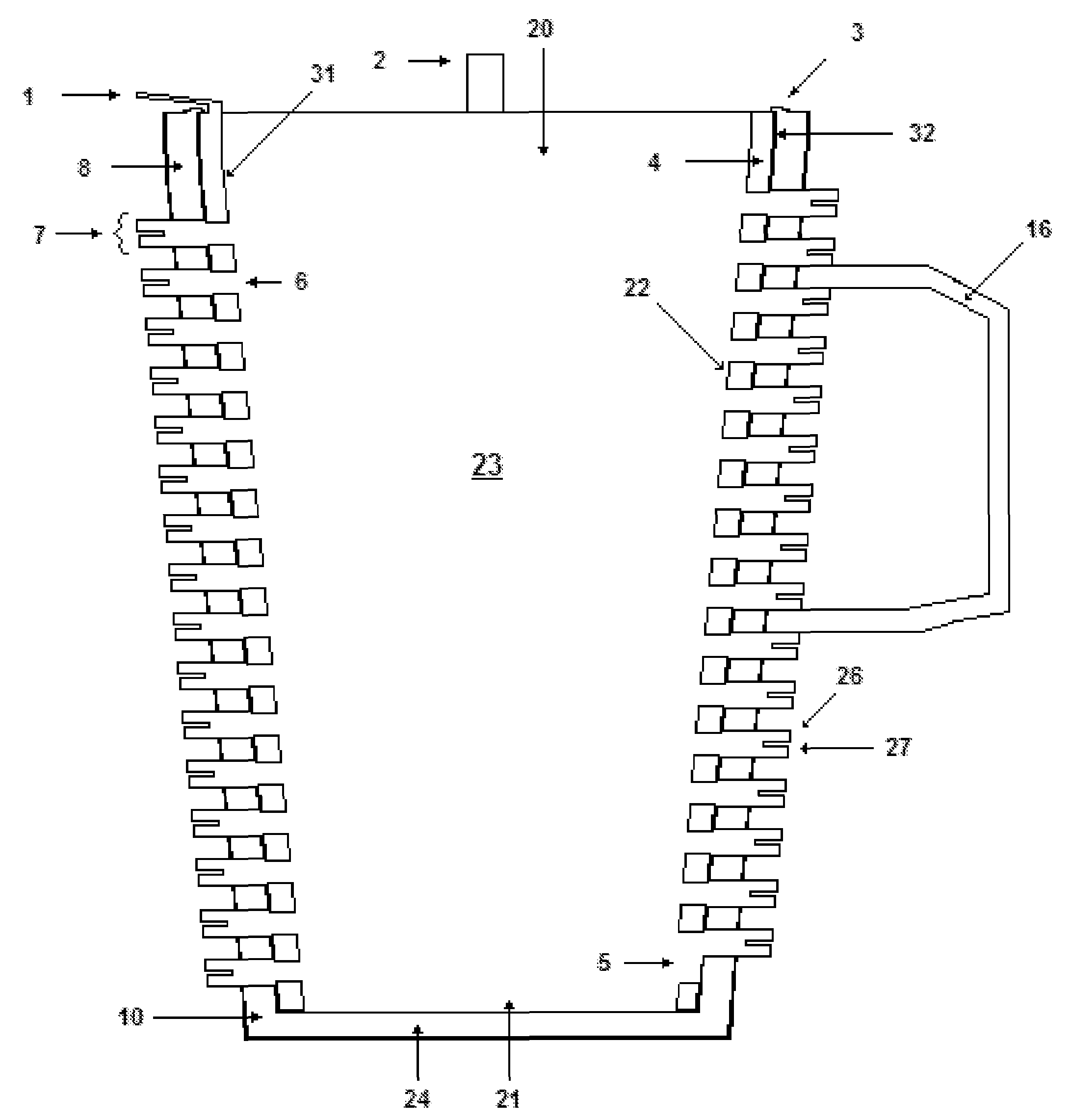

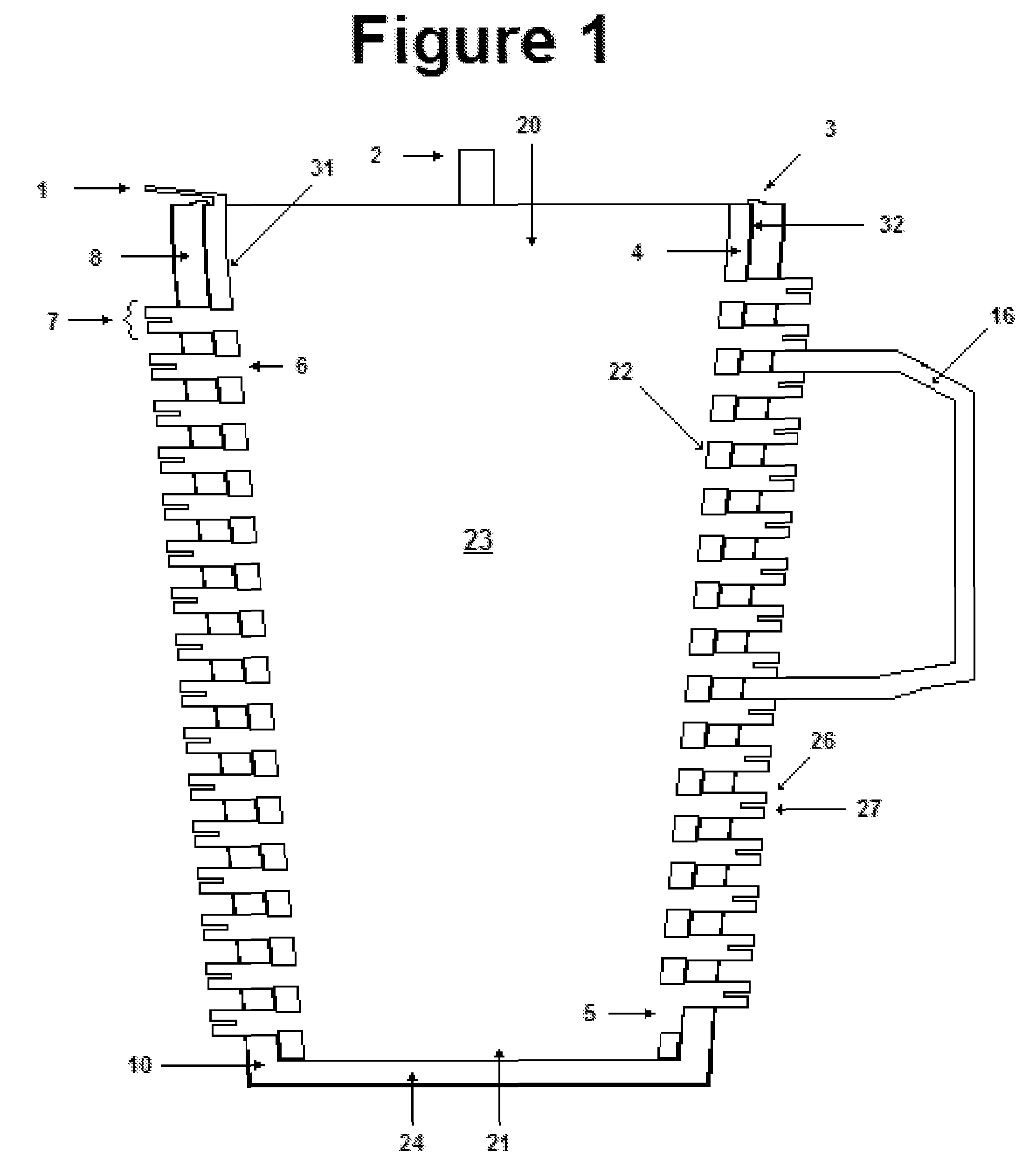

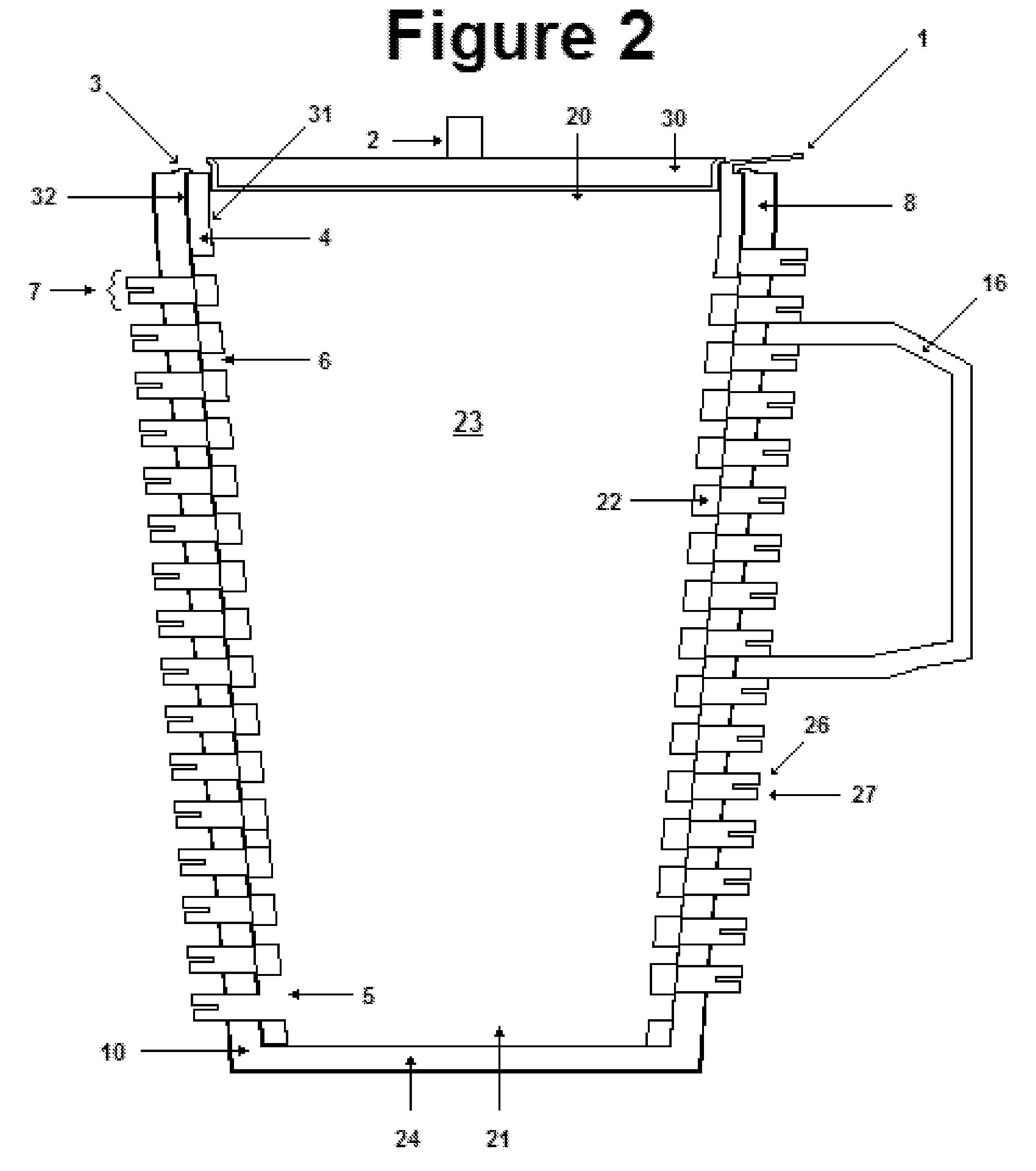

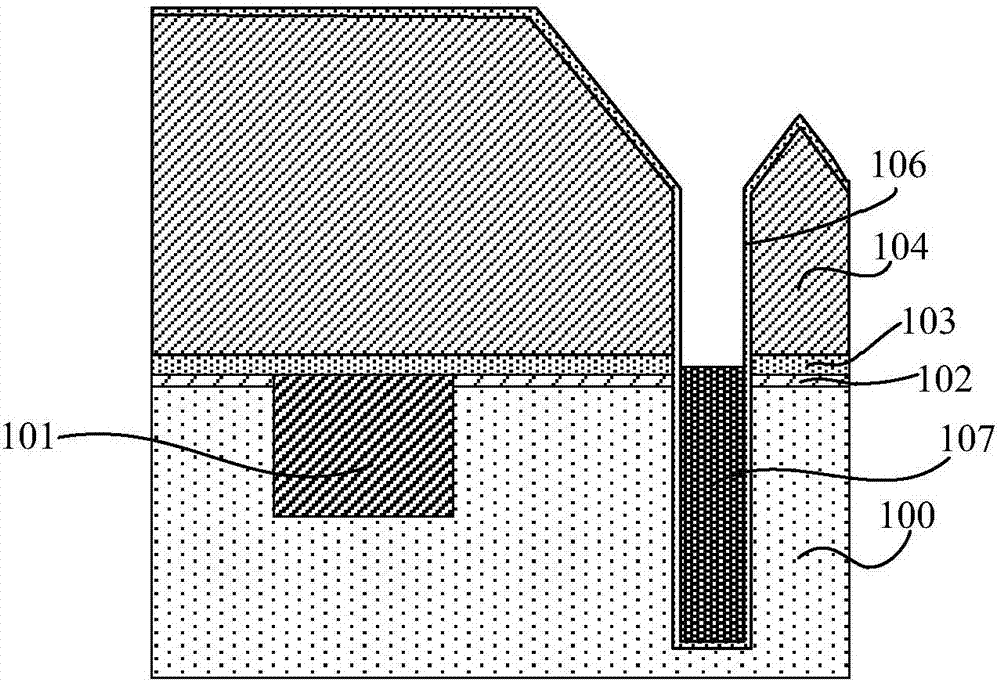

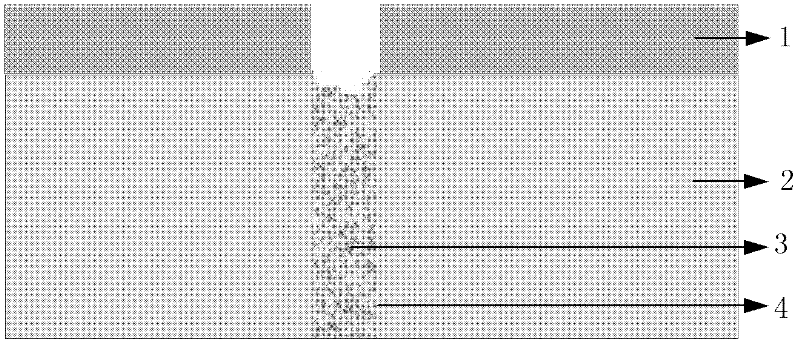

Structure of an optical interference display cell

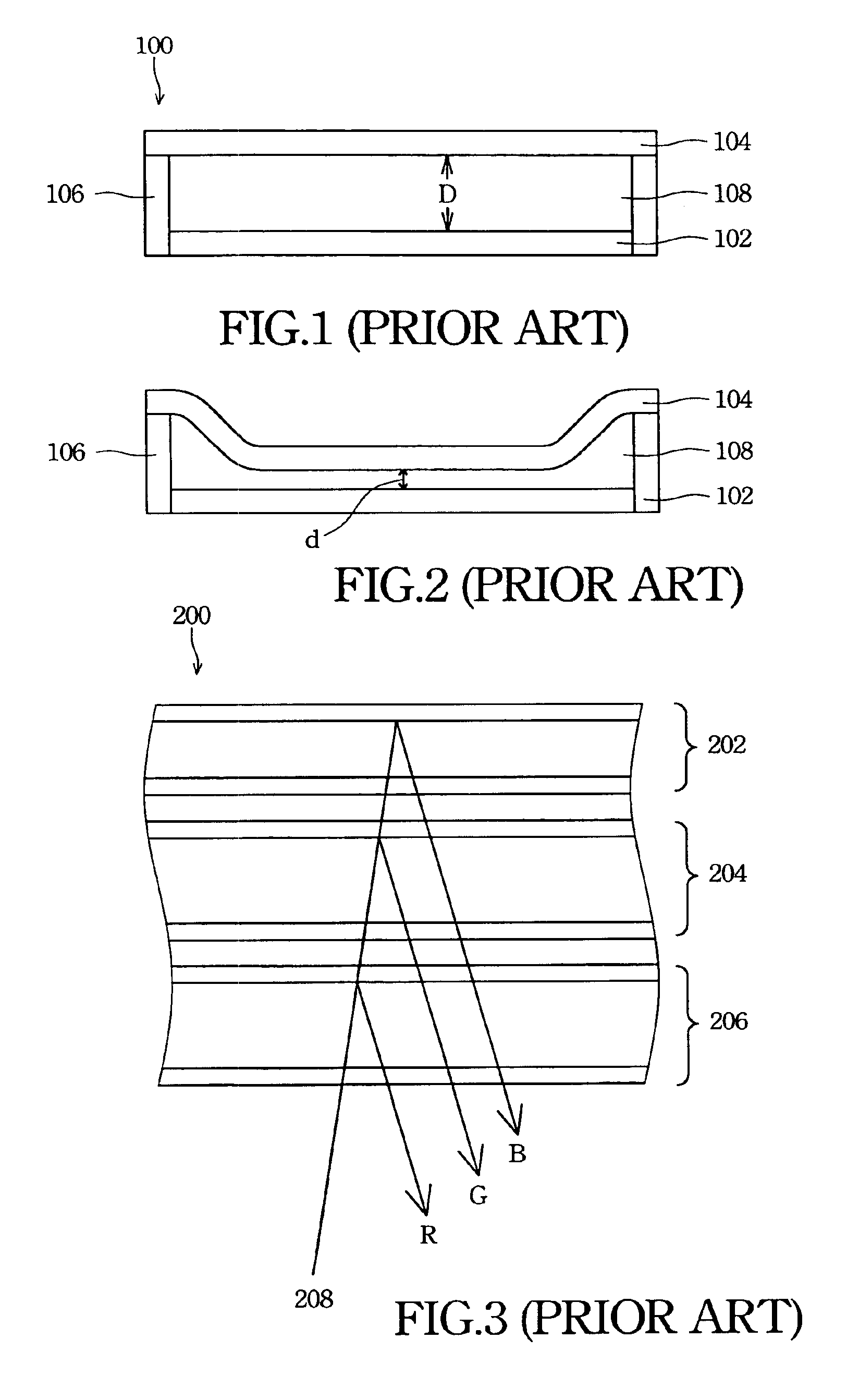

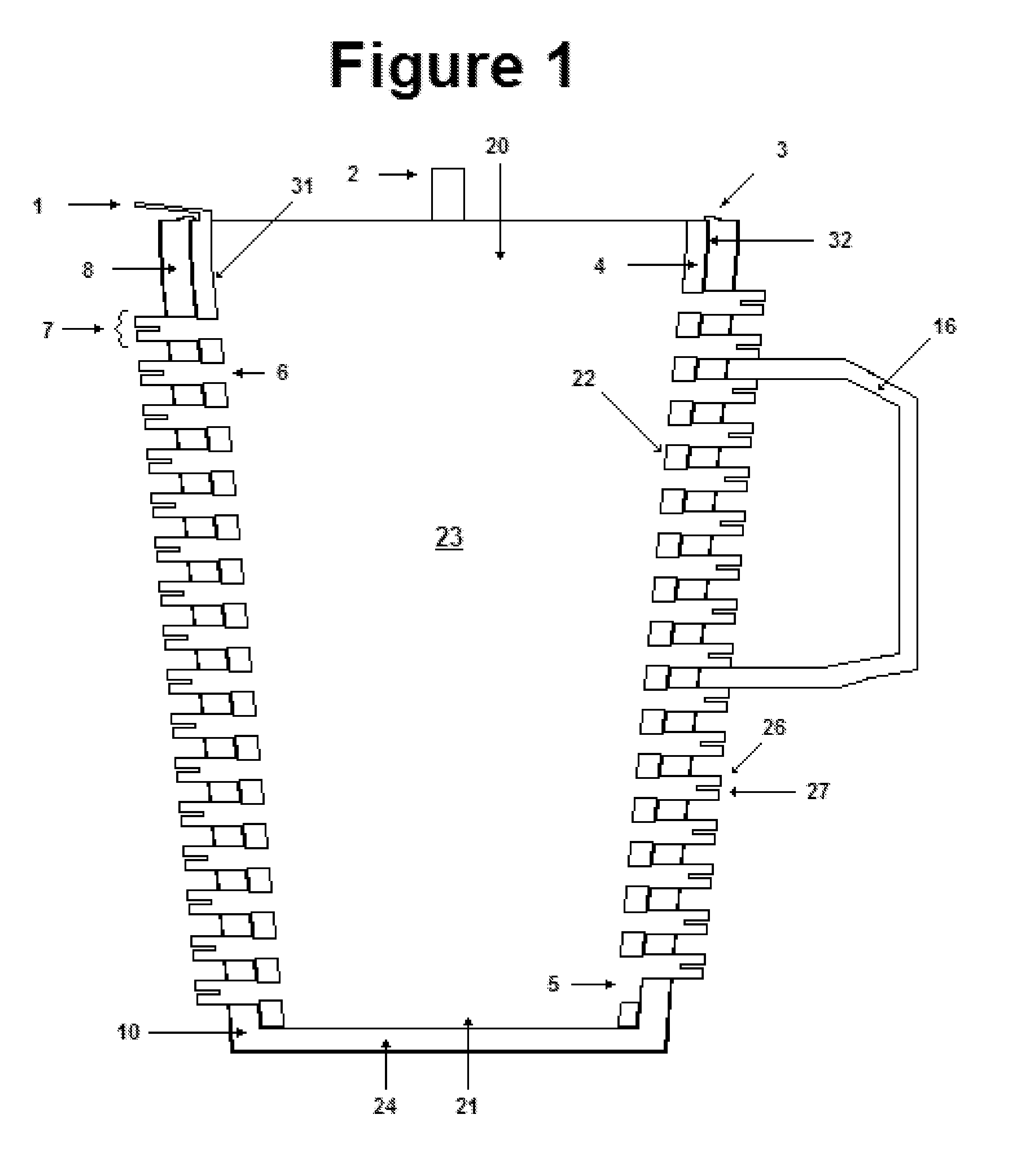

A structure of an interference display cell is provided. The cell comprises a first plate and a second plate, wherein a support is located between the first plate and the second plate. The second plate is a deformable and reflective plate. An incident light from one side of the first plate is modulated and only specific frequency light reflects by the second plate. The frequency of the reflected light is related to the distance between the first plate and the second plate. The support has at least one arm. The arm's stress makes the arm hiking upward or downward. The distance between the first plate and the second plate is also changed. Therefore, the frequency of the reflected light is altered.

Owner:SNAPTRACK

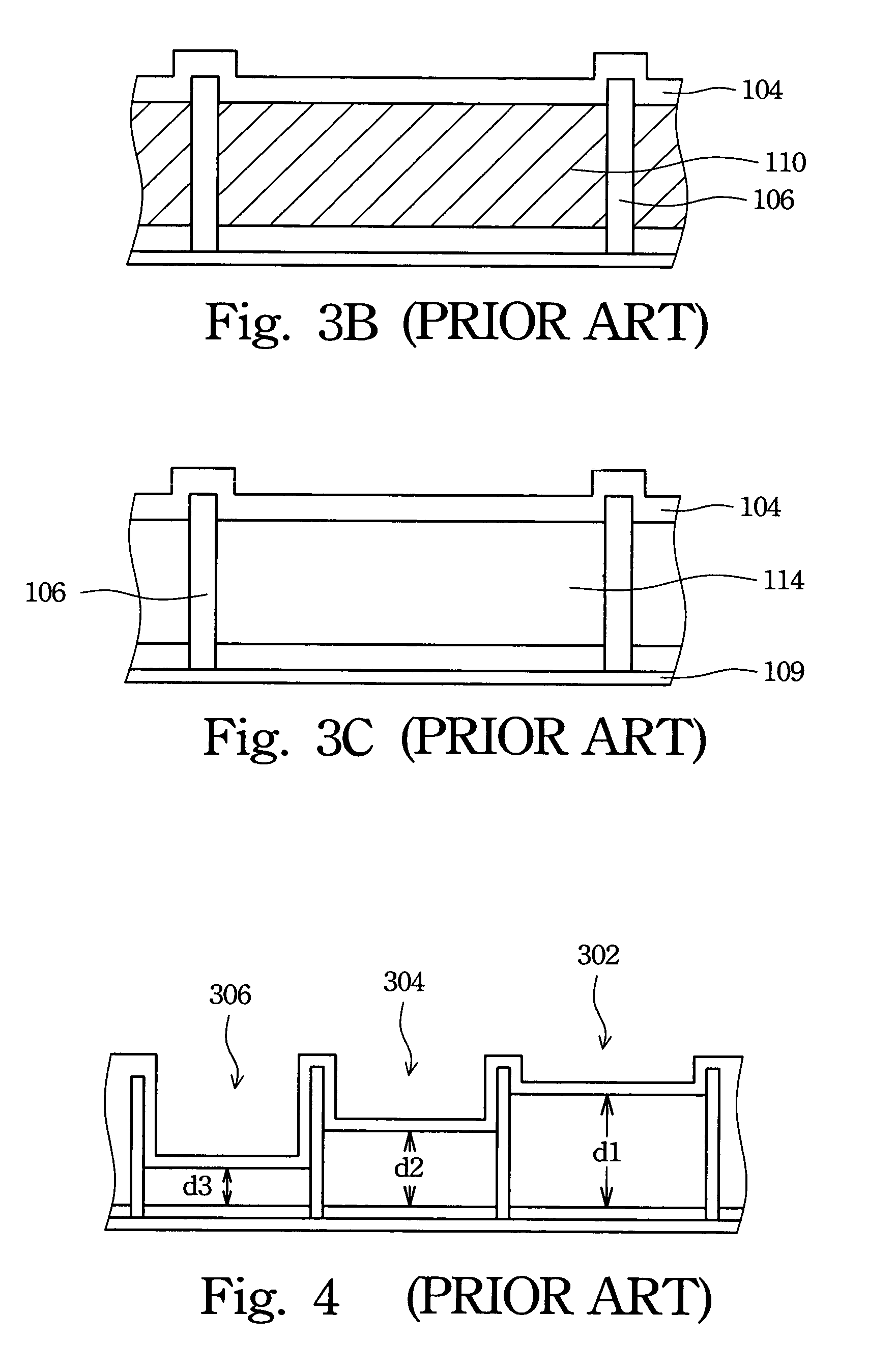

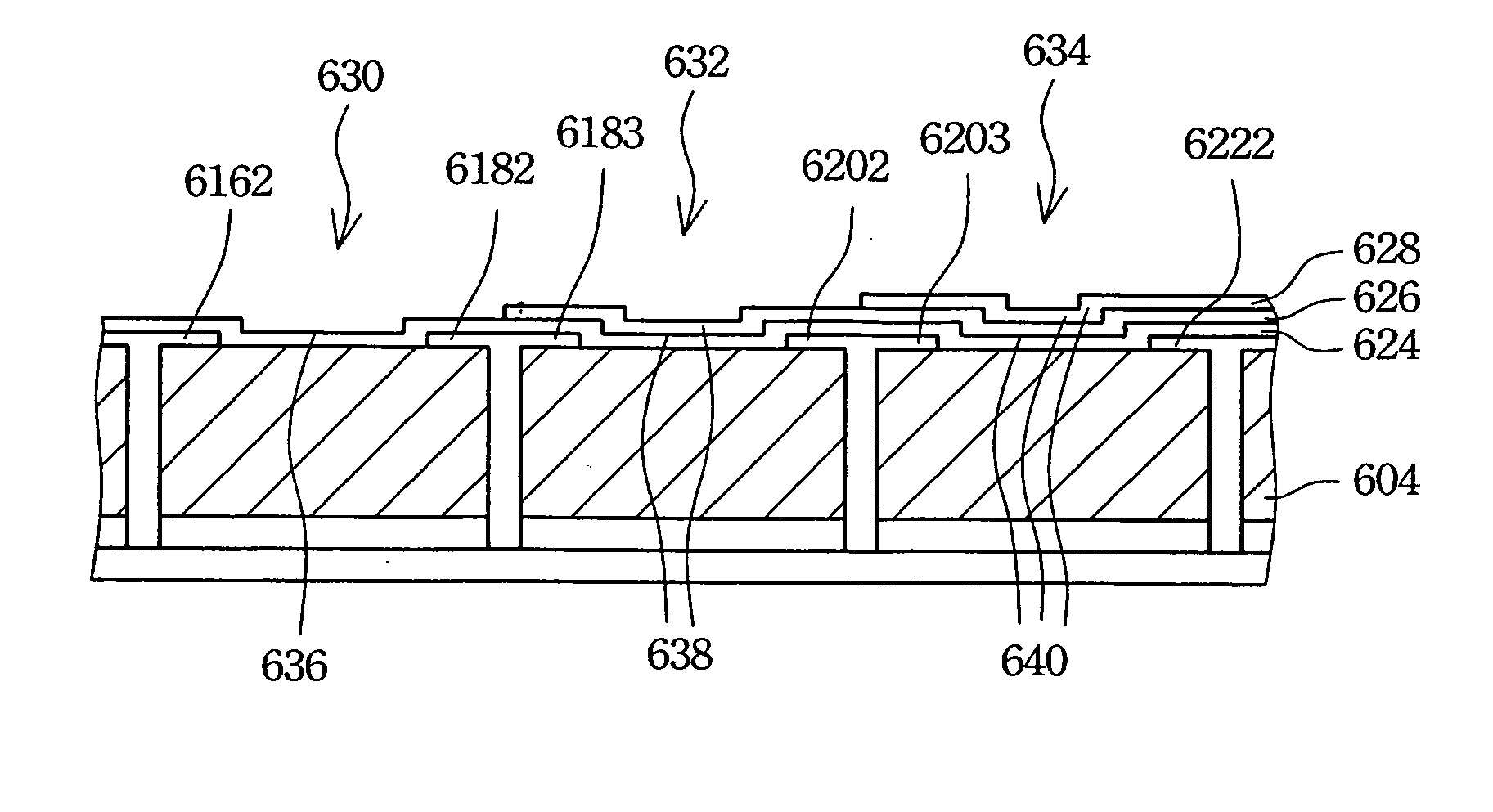

Interference display unit

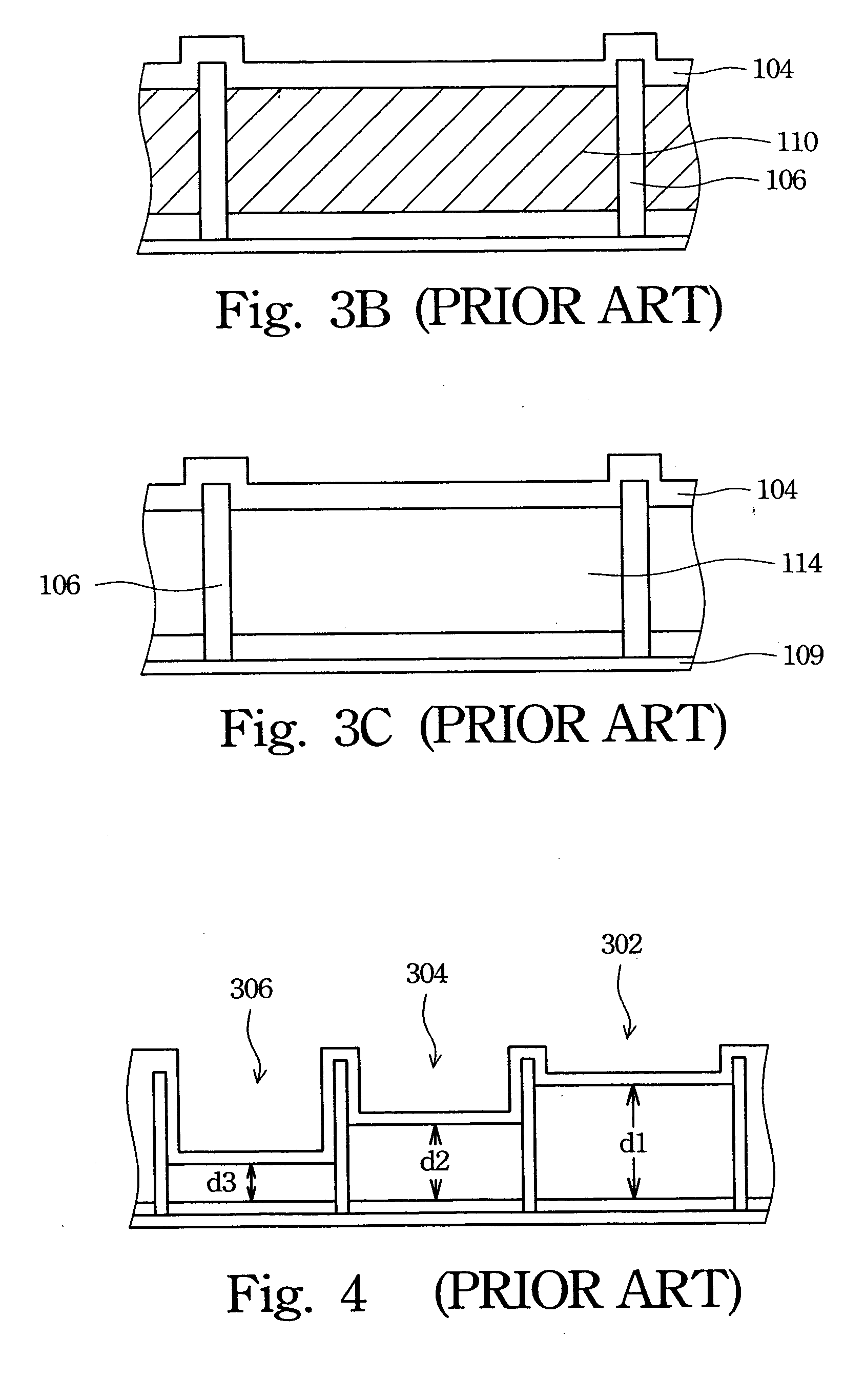

InactiveUS6995890B2Increase brightnessSimple and easy manufacturing processDecorative surface effectsOptical filtersEngineeringHeat treated

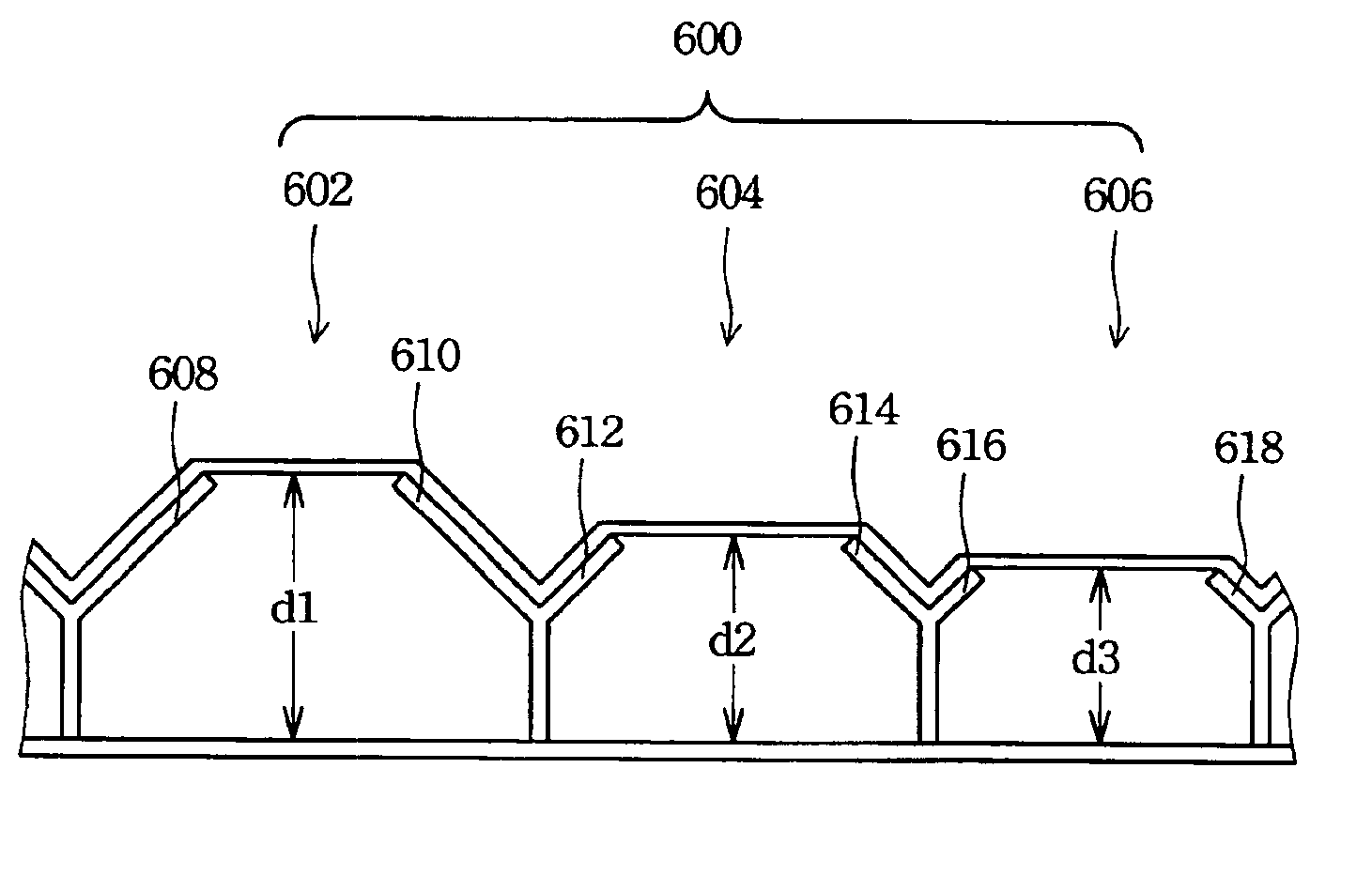

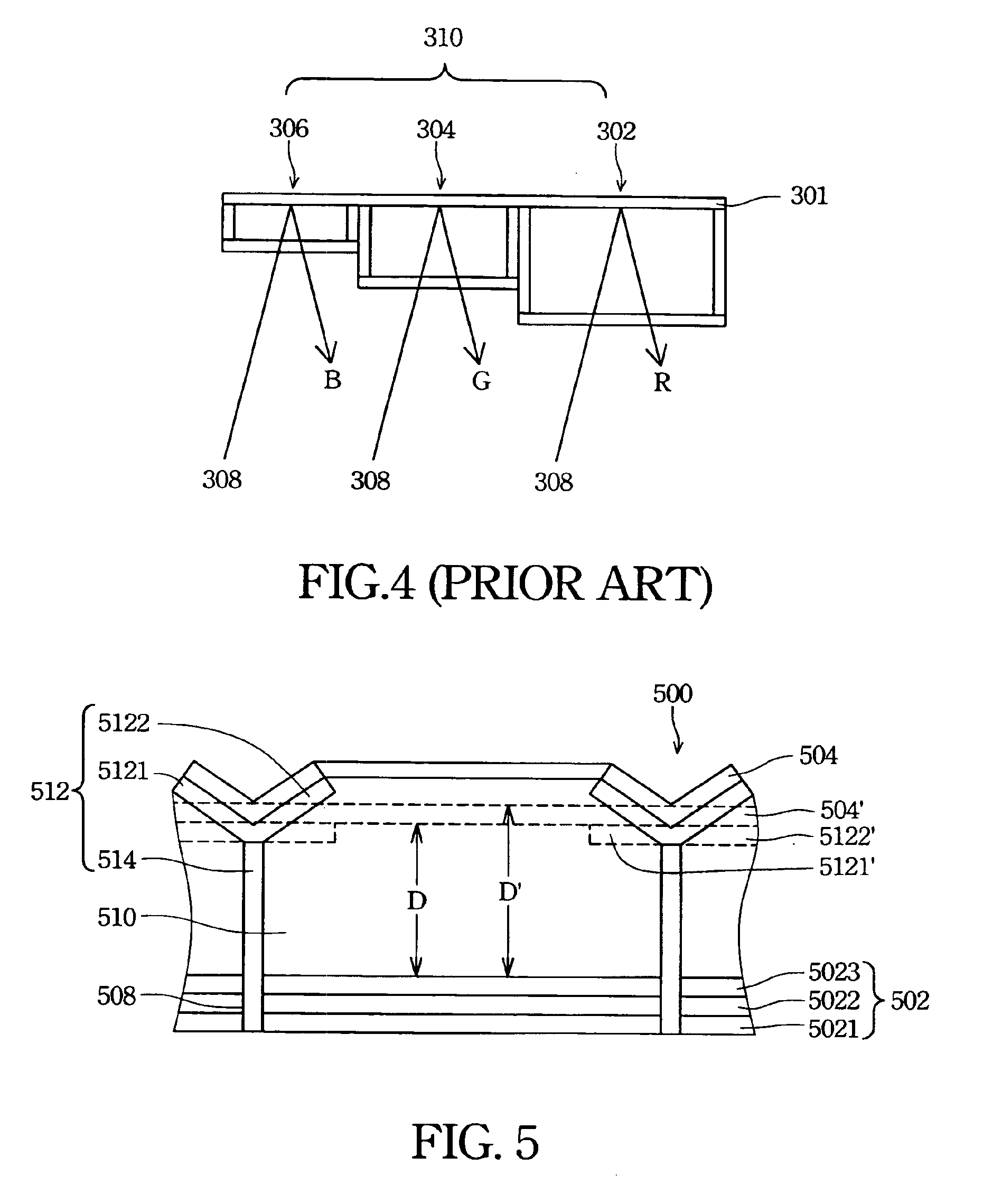

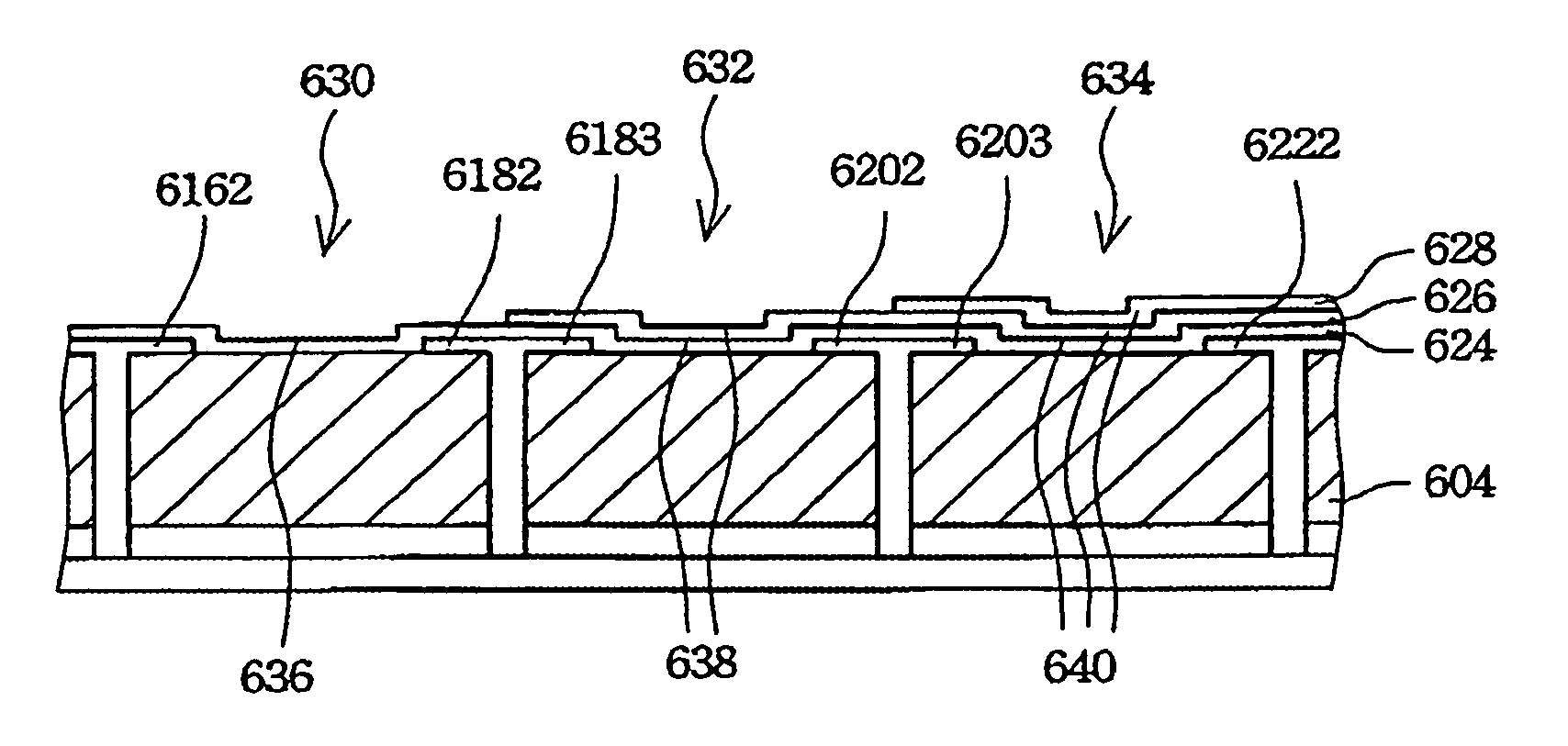

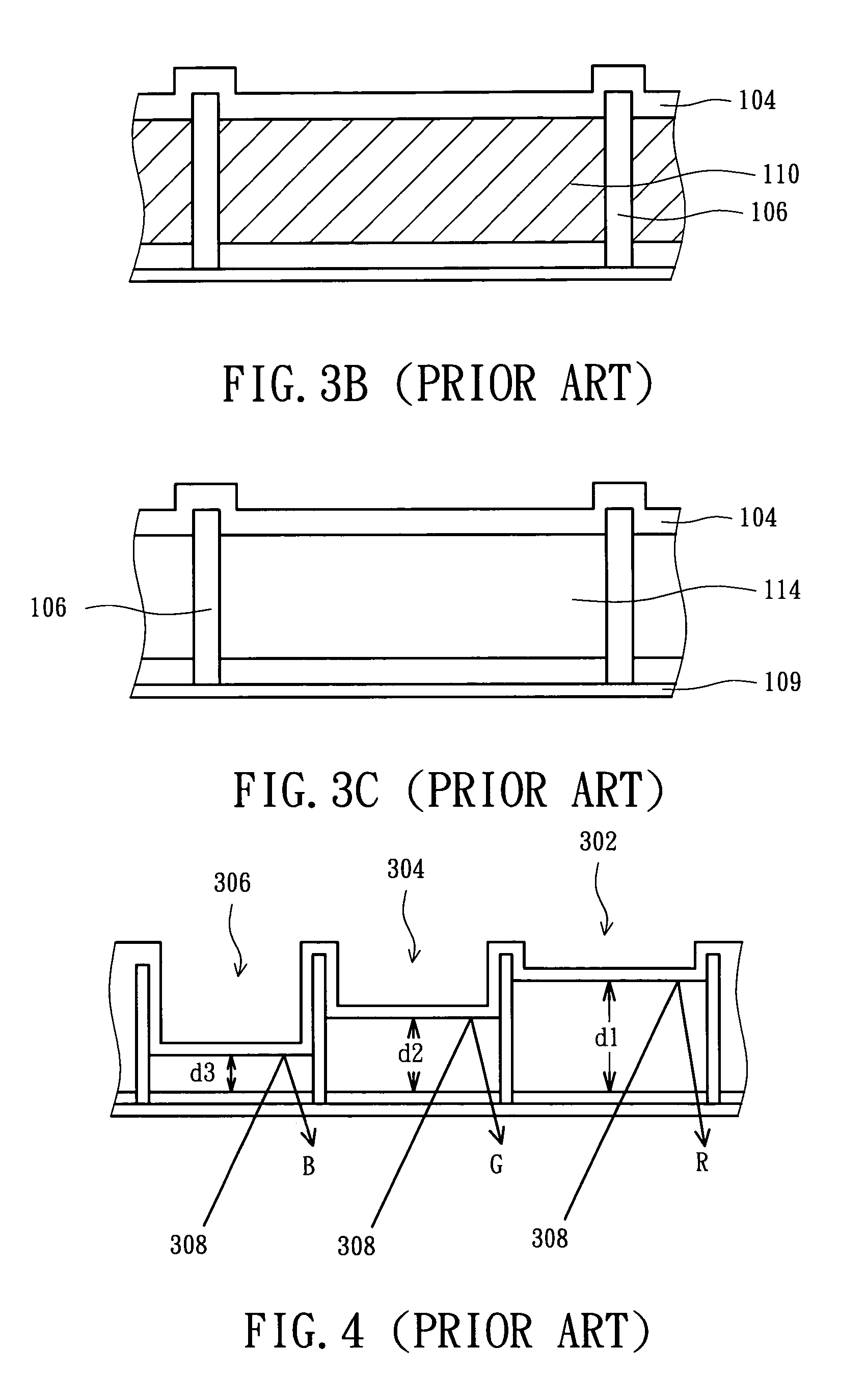

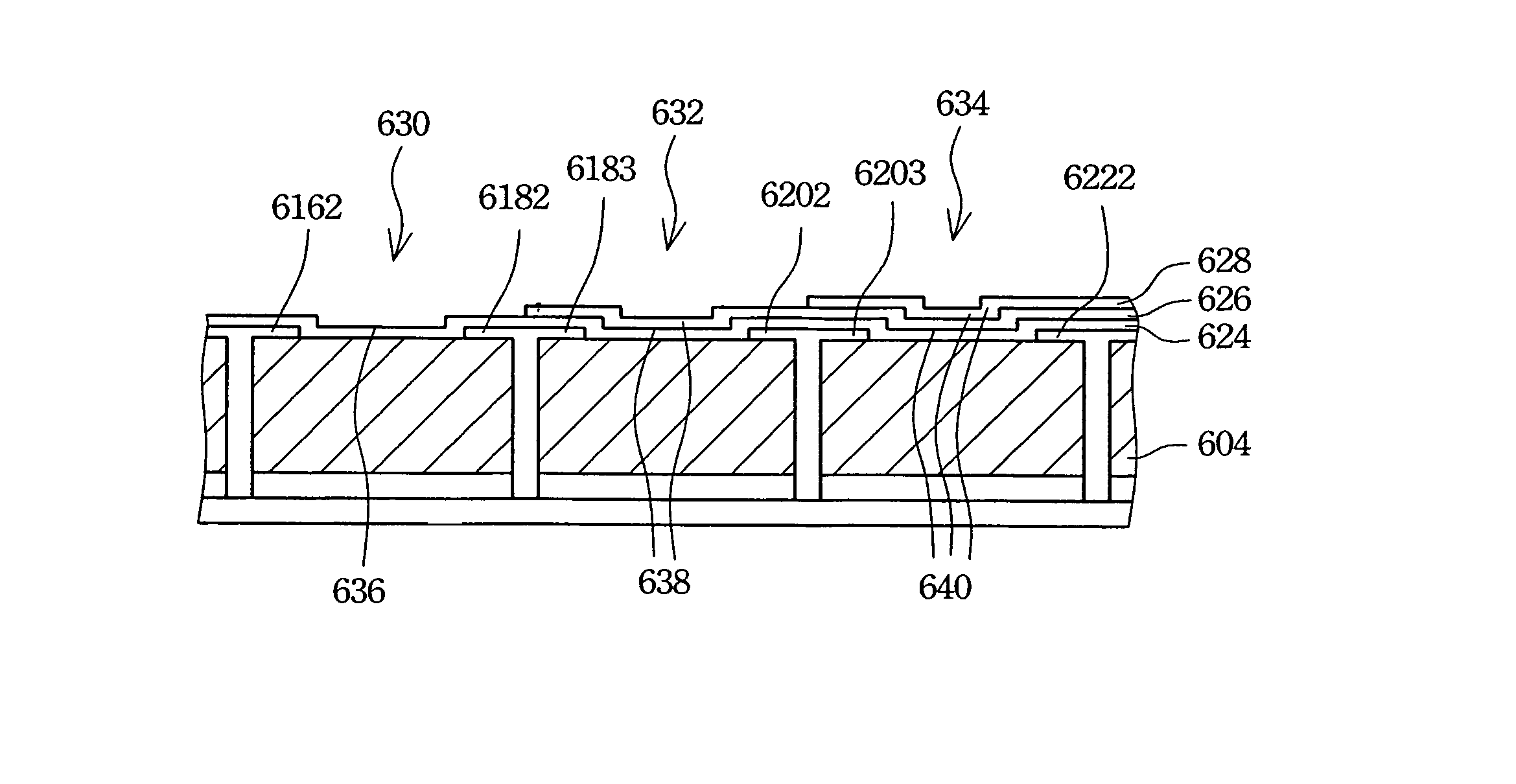

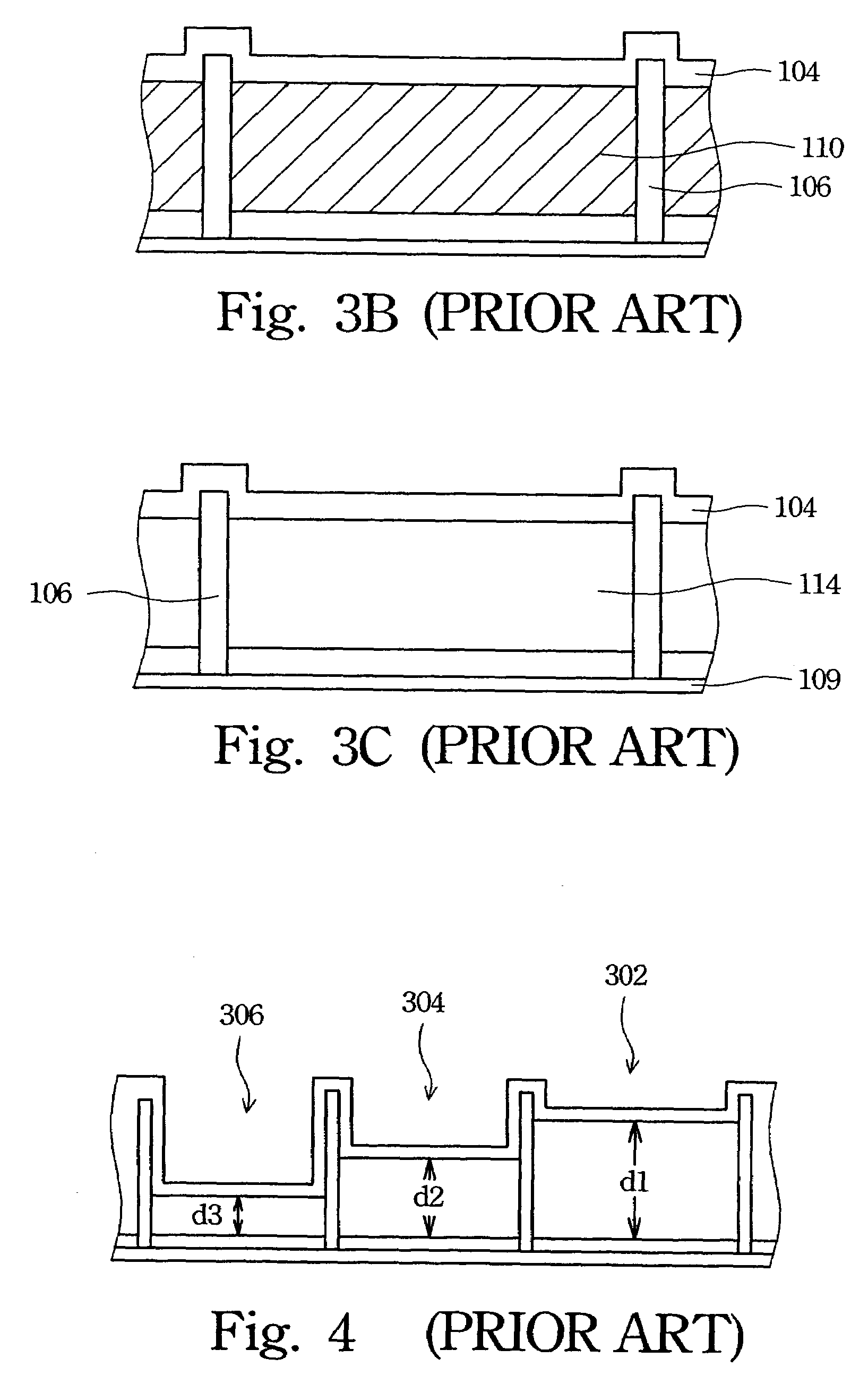

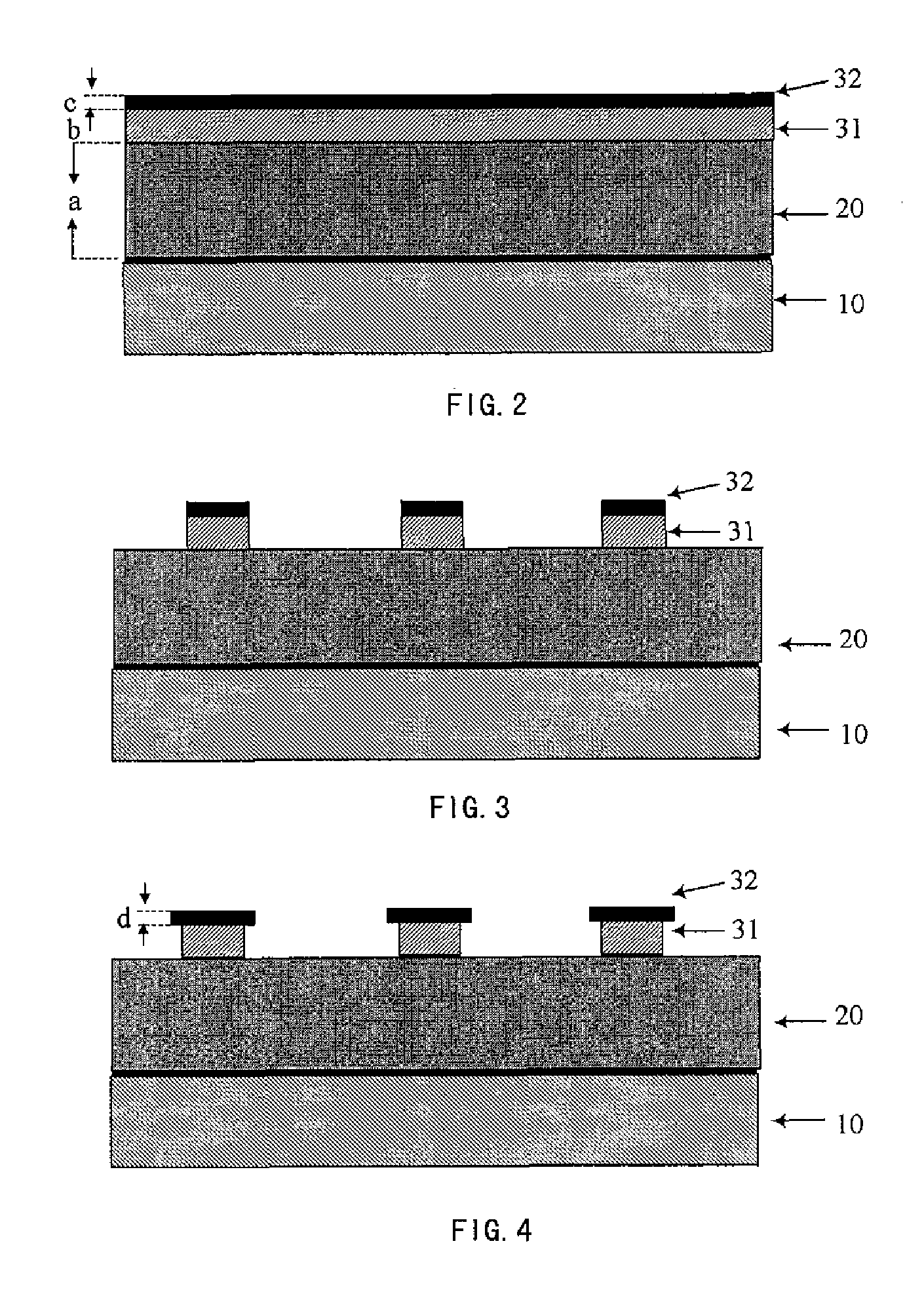

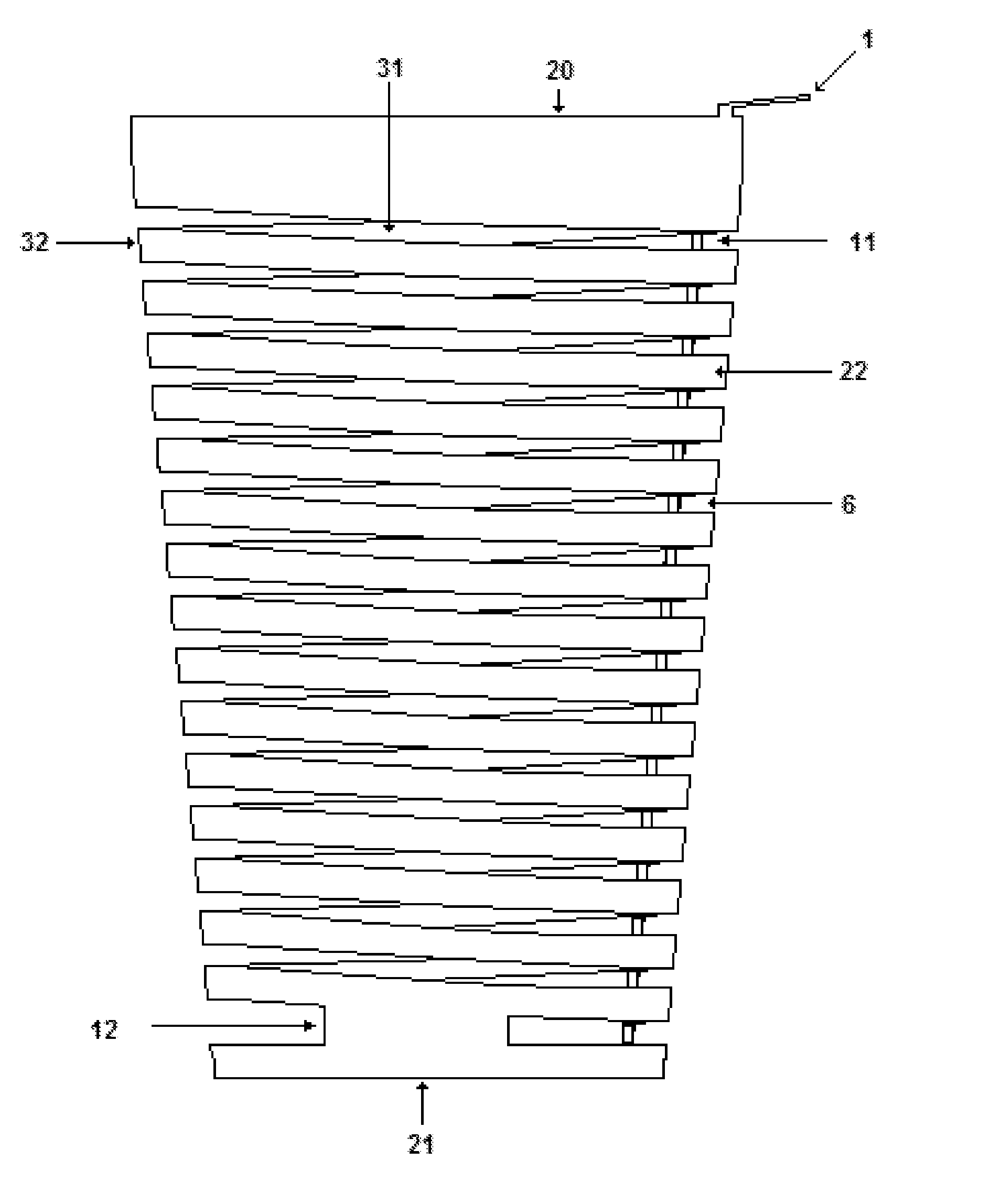

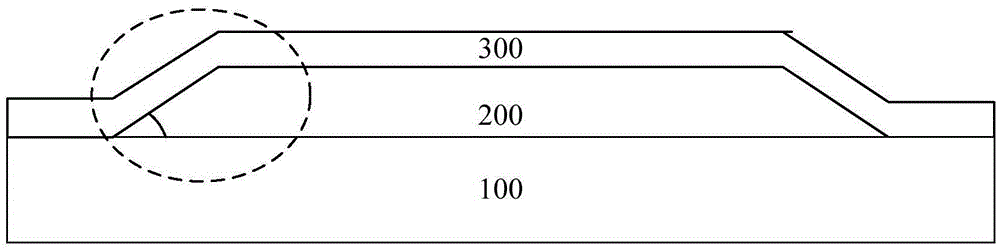

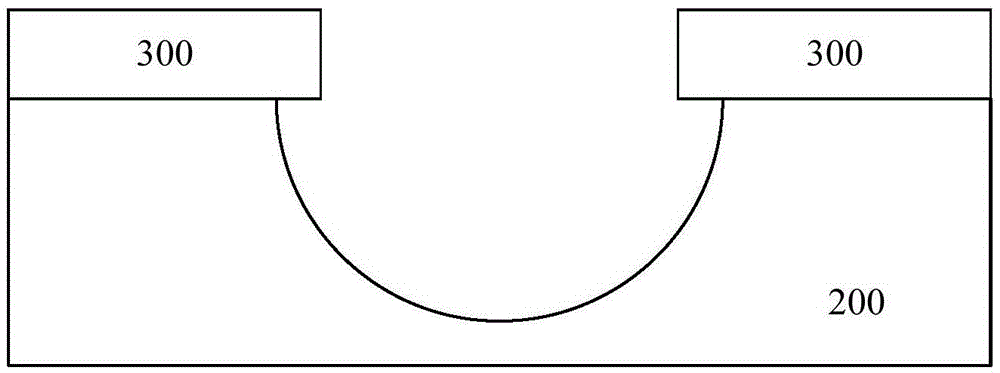

An interference display unit with a first electrode, a second electrode and posts located between the two electrodes is provided. The characteristic of the interference display unit is that the second electrode's stress is released through a thermal process. The position of the second electrode is shifted and the distance between the first electrode and the second electrode is therefore defined. A method for fabricating the structure described as follow. A first electrode and a sacrificial layer are sequentially formed on a substrate and at least two openings are formed in the first electrode and the sacrificial layer. A supporter is formed in the opening and the supporter may have at least one arm on the top portion of the supporter. A second electrode is formed on the sacrificial layer and the supporter and a thermal process is performed. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

Method for fabricating an interference display unit

InactiveUS20050168849A1Increase brightnessSimple and easy manufacturing processMirrorsDecorative surface effectsEngineeringHeat treated

An interference display unit with a first electrode, a second electrode and posts located between the two electrodes is provided. The characteristic of the interference display unit is that the second electrode's stress is released through a thermal process. The position of the second electrode is shifted and the distance between the first electrode and the second electrode is therefore defined. A method for fabricating the structure described as follow. A first electrode and a sacrificial layer are sequentially formed on a substrate and at least two openings are formed in the first electrode and the sacrificial layer. A supporter is formed in the opening and the supporter may have at least one arm on the top portion of the supporter. A second electrode is formed on the sacrificial layer and the supporter and a thermal process is performed. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

Method for fabricating an interference display unit

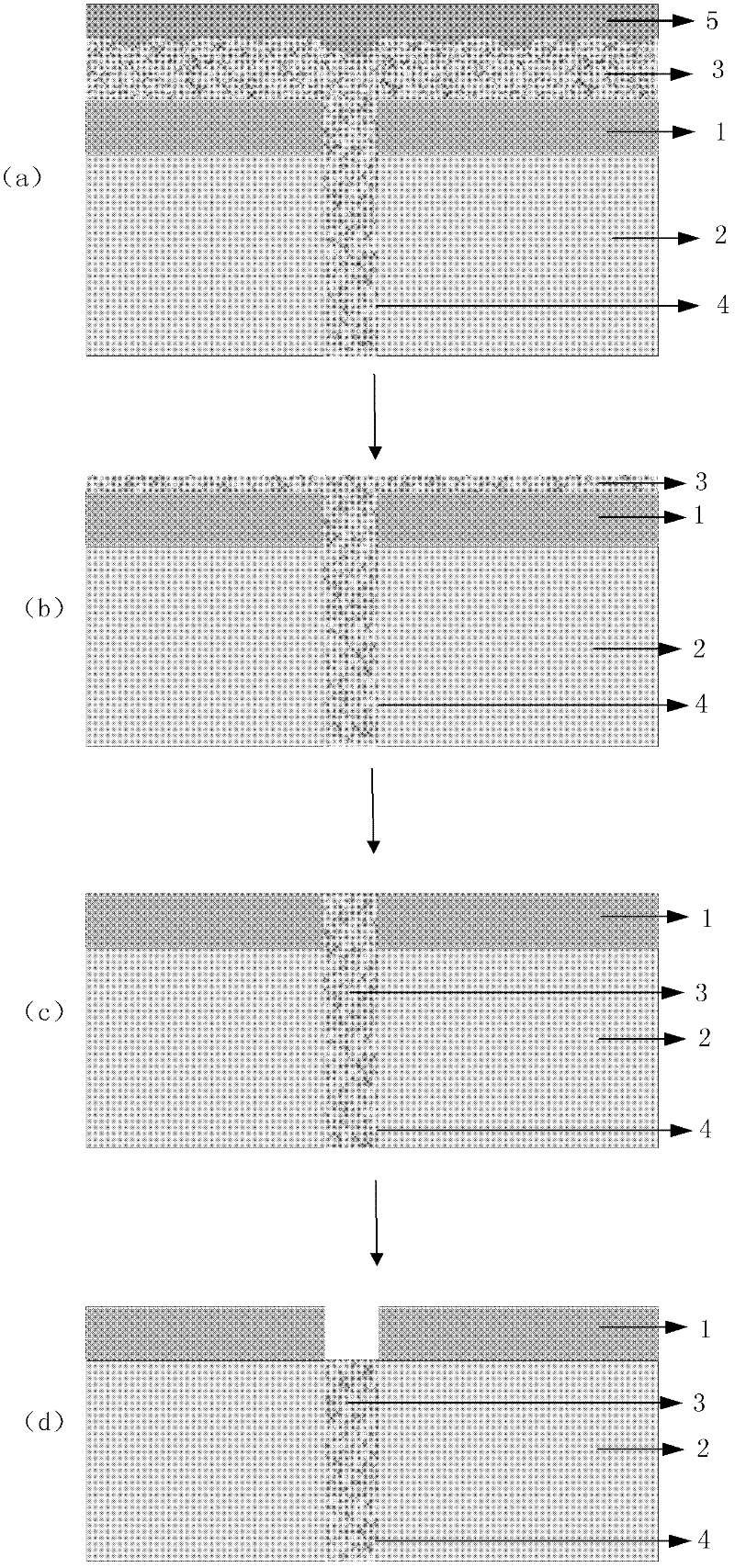

InactiveUS7198973B2Increase brightnessSimple and easy manufacturing processPhotomechanical apparatusSemiconductor/solid-state device manufacturingProcess patternsEngineering

A method for fabricating an interference display unit is provided. A first plate and a sacrificial layer are formed in order on a substrate and at least two openings are formed in the first plate and the sacrificial layer. A photoresist layer is spin-coated on the sacrificial layer and fills the openings. A photolithographic process patterns the photoresist layer to define a support with an arm. A second plate is formed on the sacrificial layer and posts. The arm's stress is released through a thermal process. The position of the arm is shifted and the distance between the first plate and the second plate is therefore defined. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

Method for fabricating an interference display unit

InactiveUS7016095B2Increase brightnessSimple and easy manufacturing processMirrorsDecorative surface effectsEngineeringPosition shift

An interference display unit with a first electrode, a second electrode and posts located between the two electrodes is provided. The characteristic of the interference display unit is that the second electrode's stress is released through a thermal process. The position of the second electrode is shifted and the distance between the first electrode and the second electrode is therefore defined. A method for fabricating the structure described as follow. A first electrode and a sacrificial layer are sequentially formed on a substrate and at least two openings are formed in the first electrode and the sacrificial layer. A supporter is formed in the opening and the supporter may have at least one arm on the top portion of the supporter. A second electrode is formed on the sacrificial layer and the supporter and a thermal process is performed. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

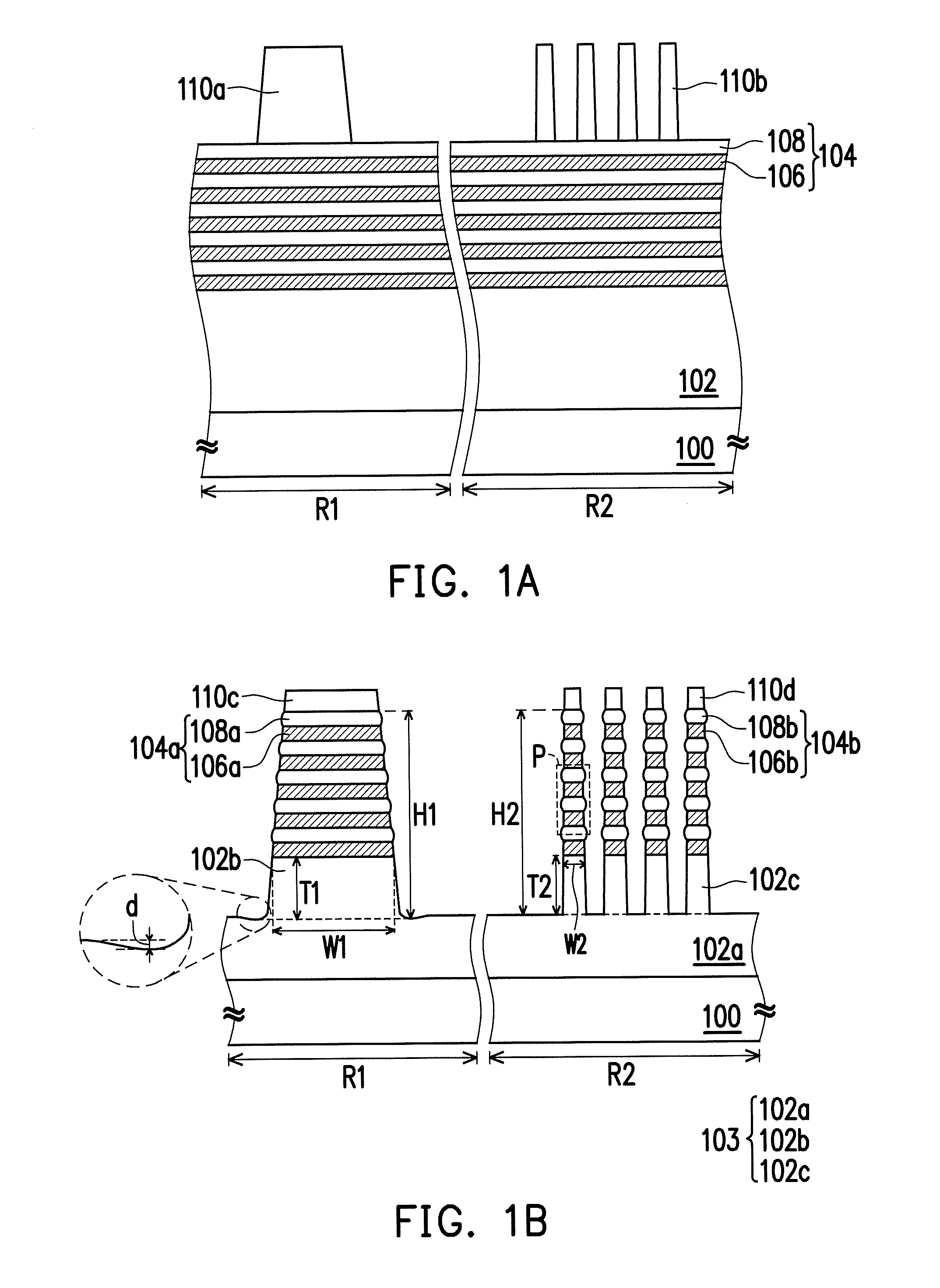

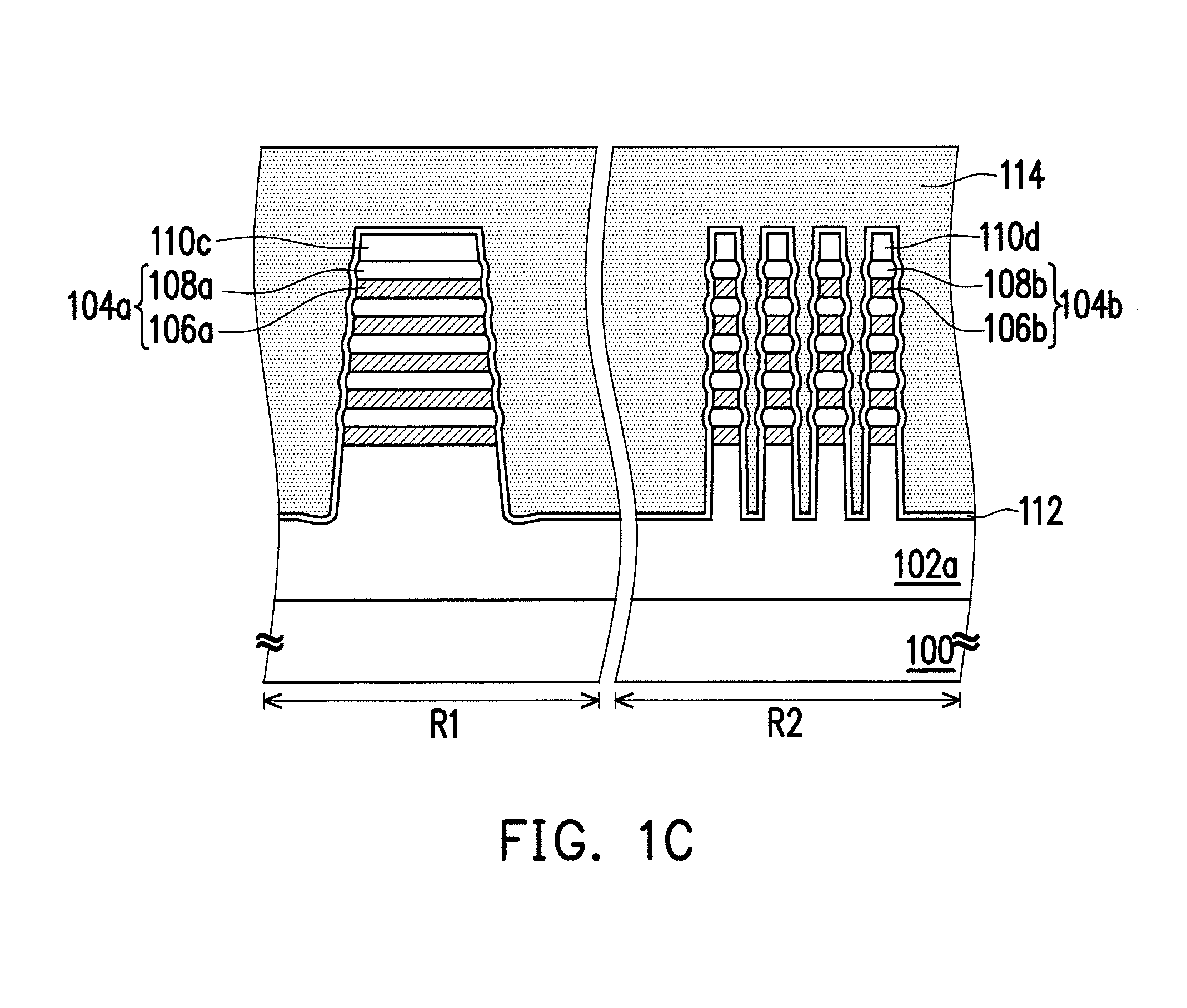

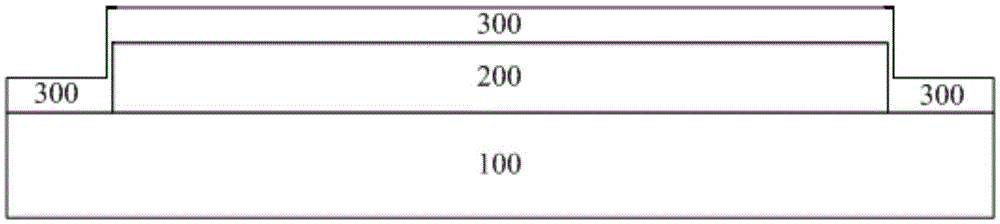

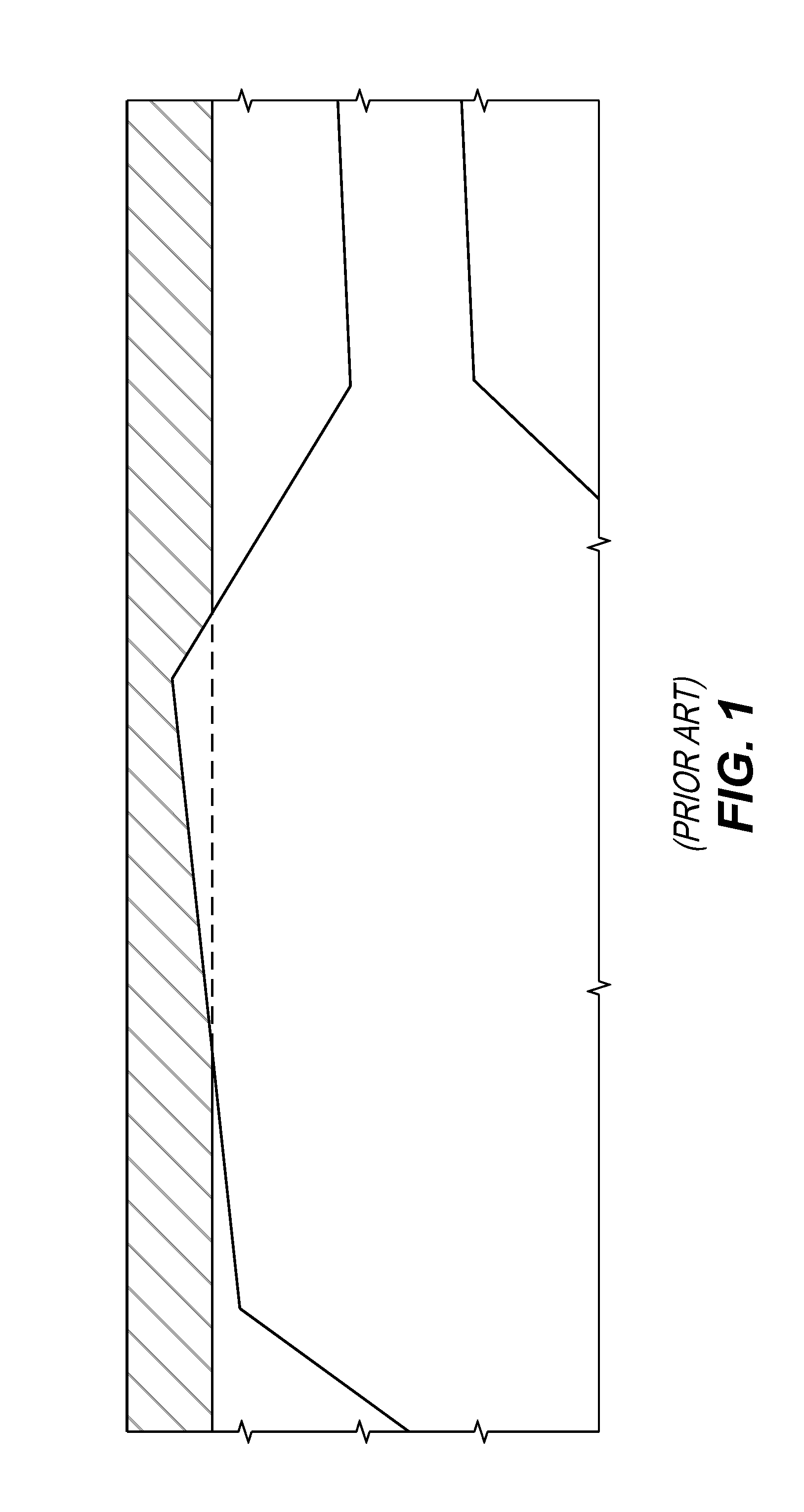

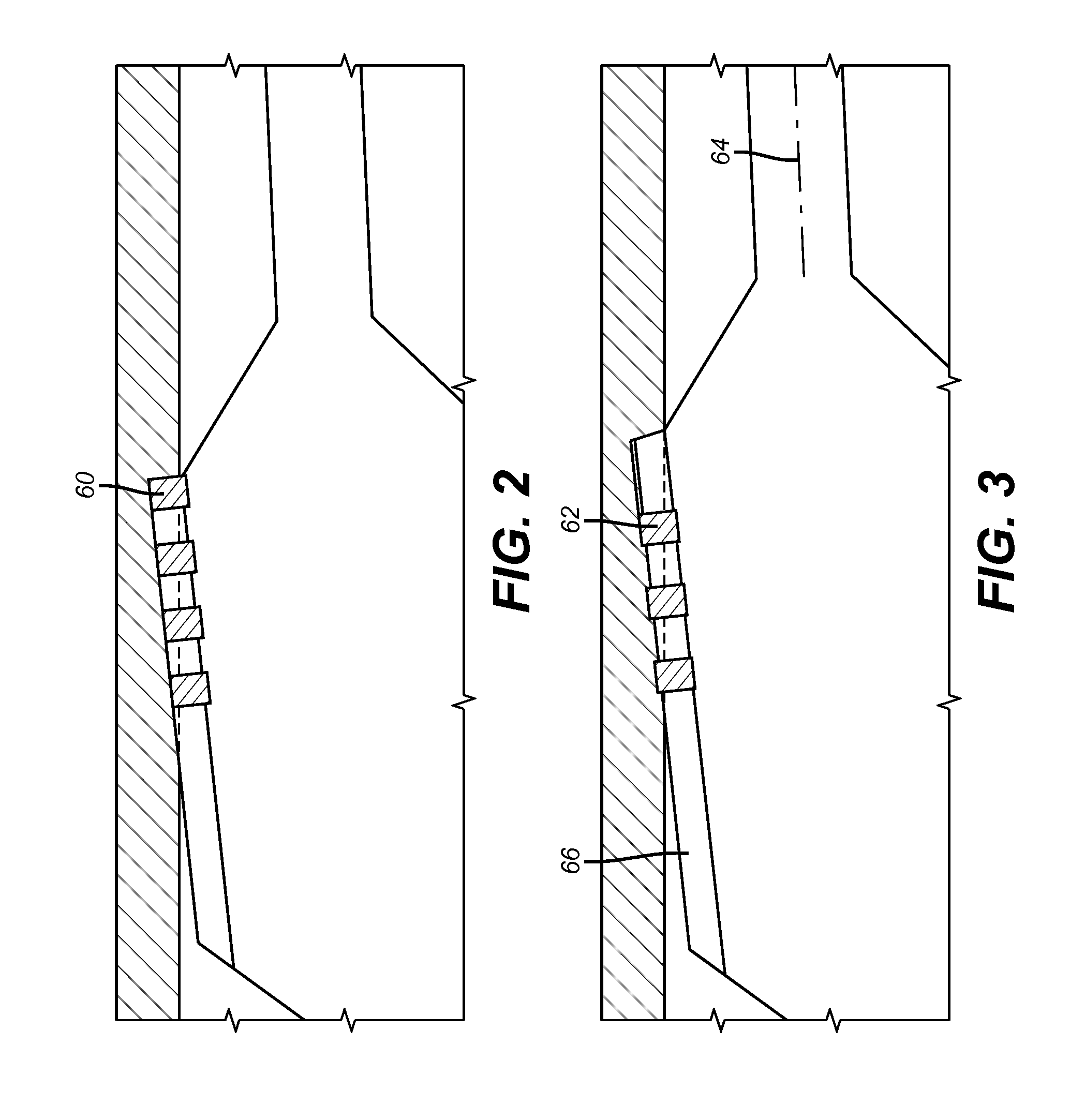

Method of Manufacturing Dummy Gates in Gate Last Process

ActiveUS20130059435A1Filled effectively and uniformlyFacilitates subsequent fillingSemiconductor/solid-state device manufacturingSemiconductor devicesDry etchingMetal

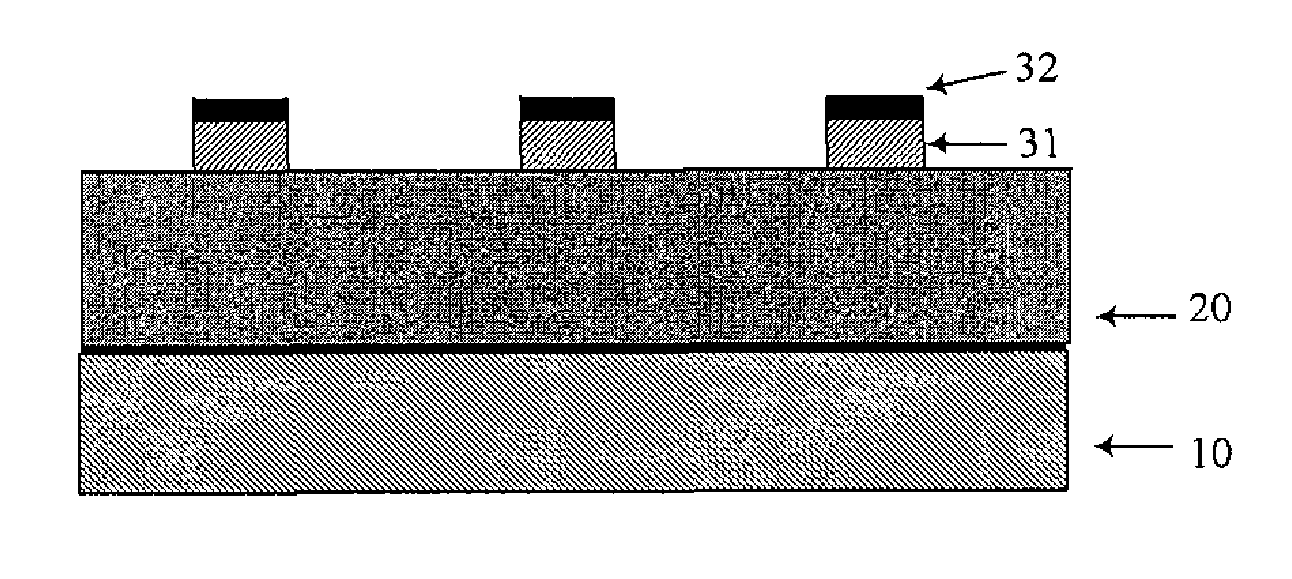

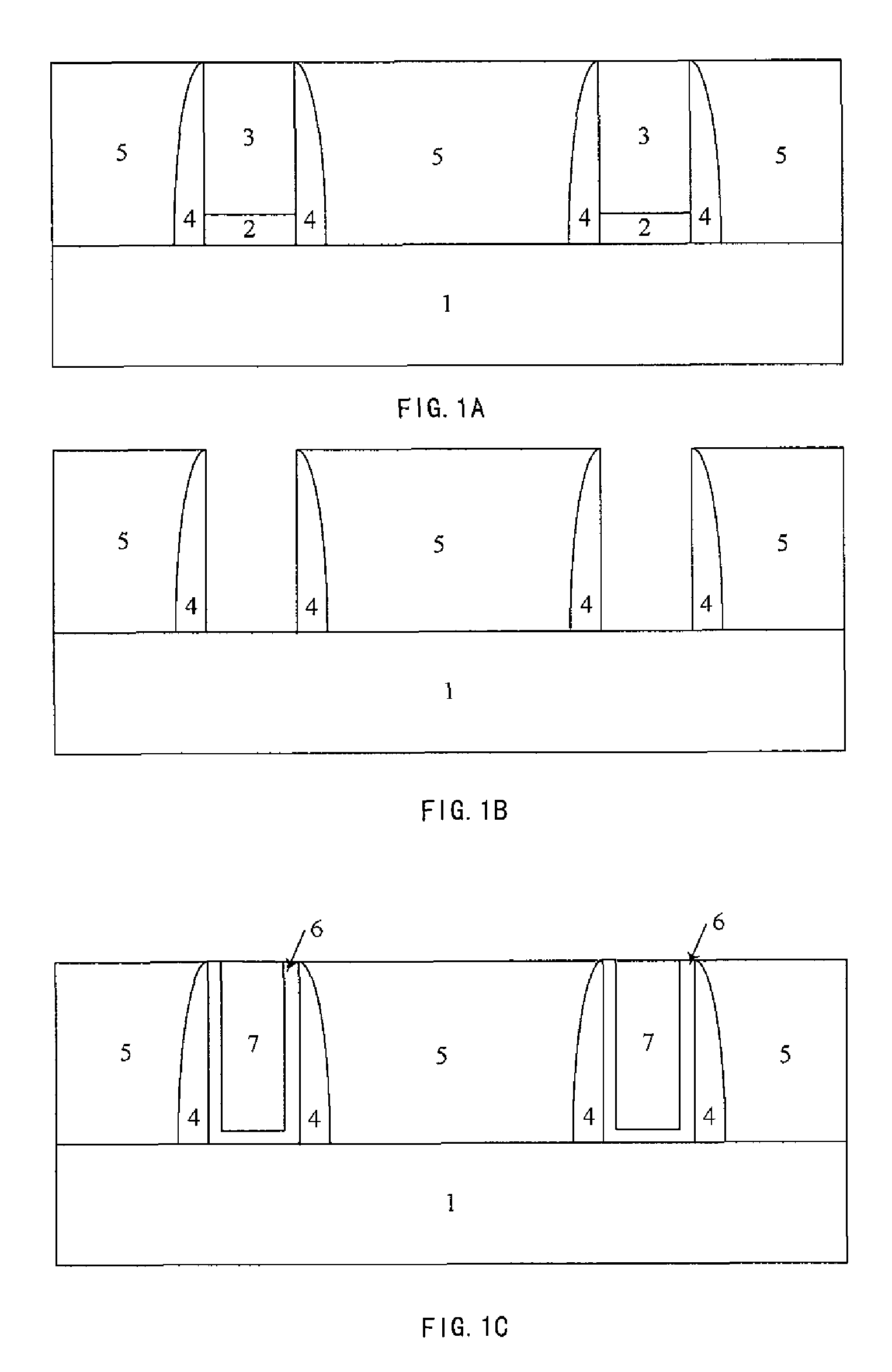

The present invention provides a method of manufacturing a dummy gate in a gate last process, which comprises the steps of forming a dummy gate material layer and a hard mask material layer sequentially on a substrate; etching the hard mask material layer to form a top-wide-bottom-narrow hard mask pattern; dry etching the dummy gate material layer using the hard mask pattern as a mask to form a top-wide-bottom-narrow dummy gate. According to the dummy gate manufacturing method of the present invention, instead of vertical dummy gates used conventionally, top-wide-bottom-narrow trapezoidal dummy gates are formed, and after removing the dummy gates, trapezoidal trenches can be formed. It facilitates the subsequent filling of the high-k or metal gate material and enlarges the window for the filling process; as a result, the device reliability will be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Hot Beverage Container

InactiveUS20070187418A1Easy to cleanIncrease temperatureDomestic cooling apparatusLighting and heating apparatusCooling pipeFlange

Owner:HANSEN DAVID SCOTT

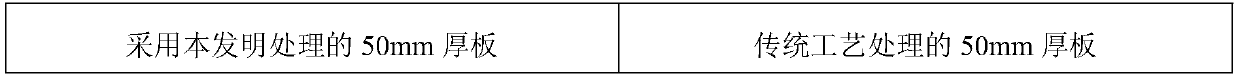

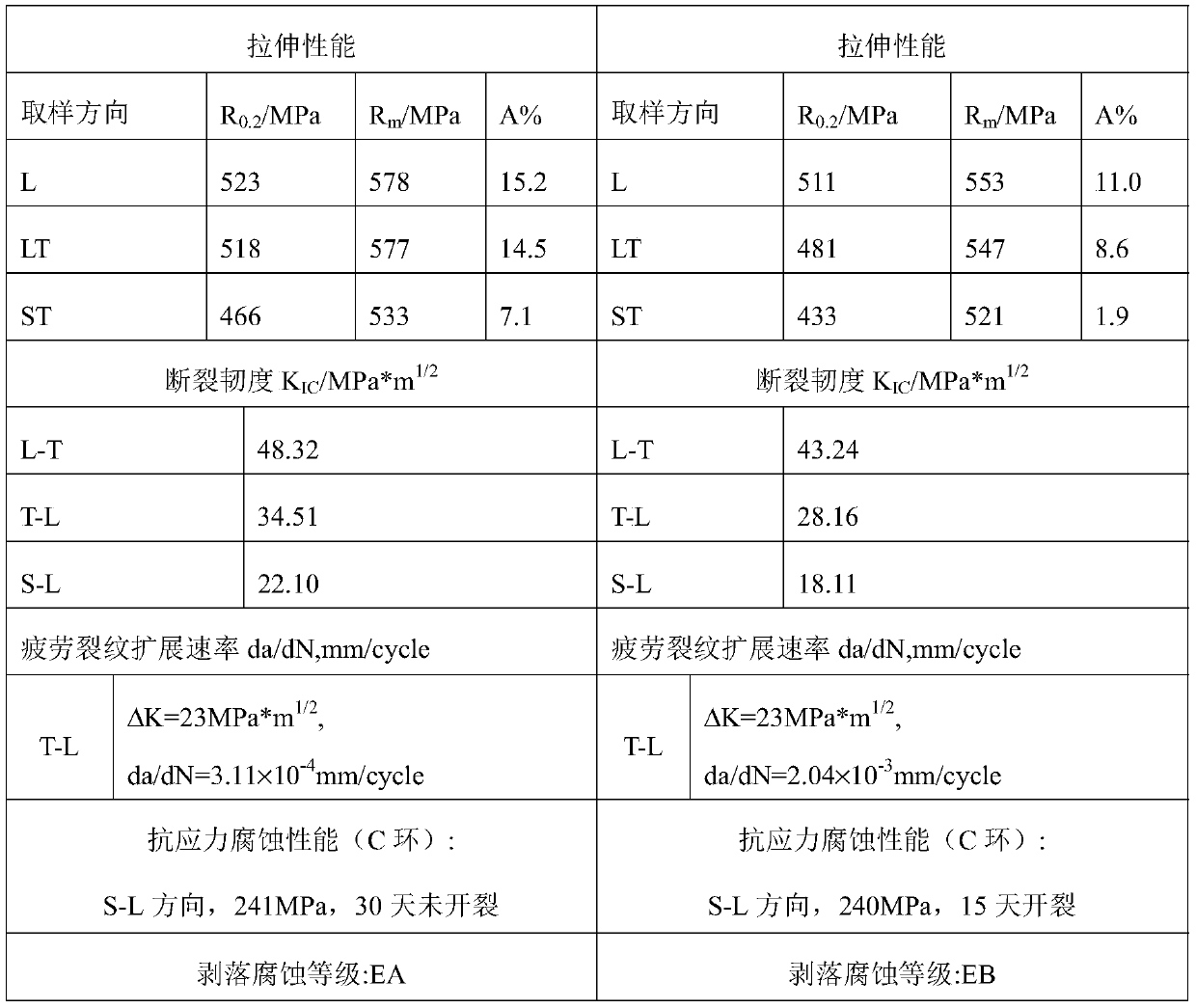

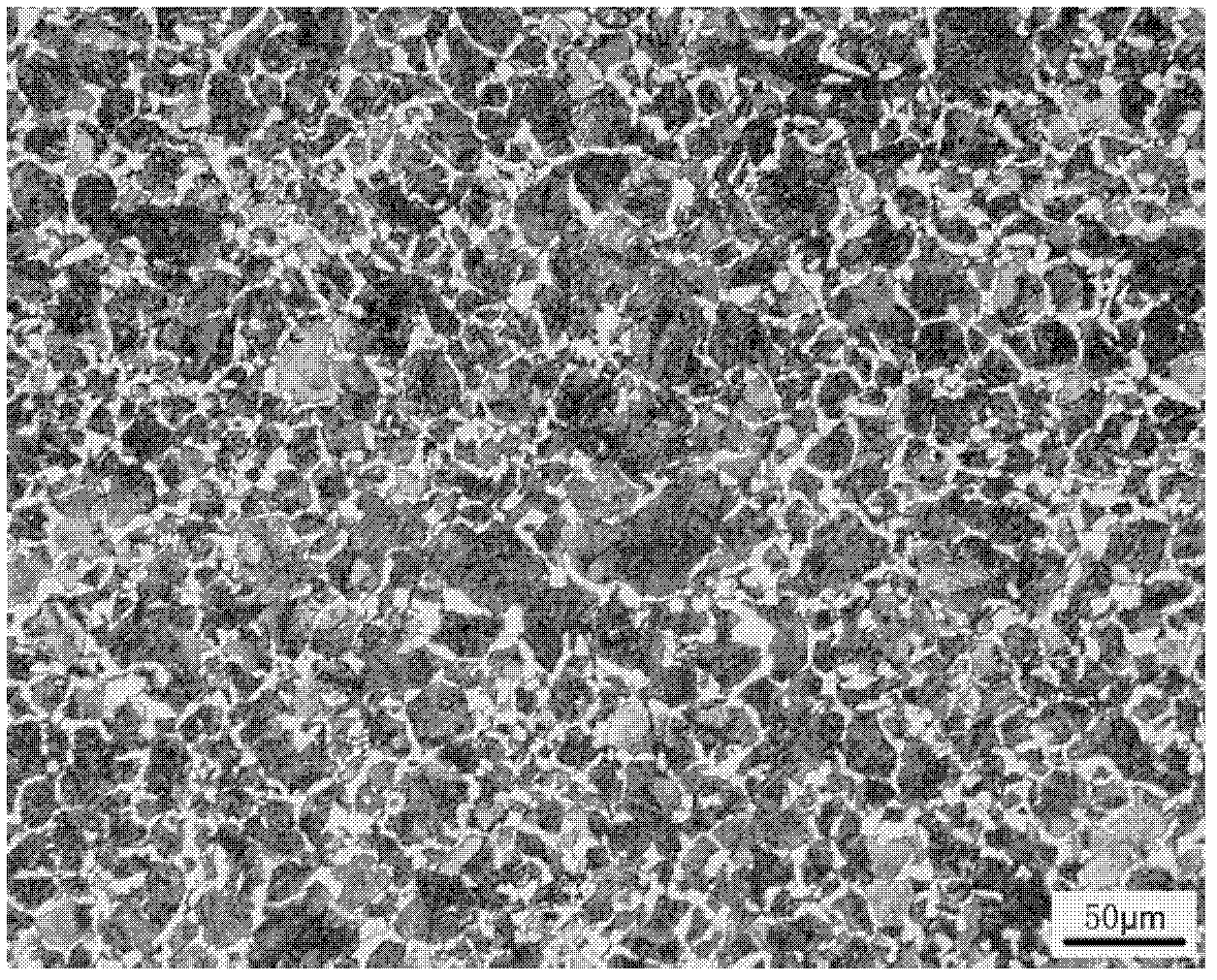

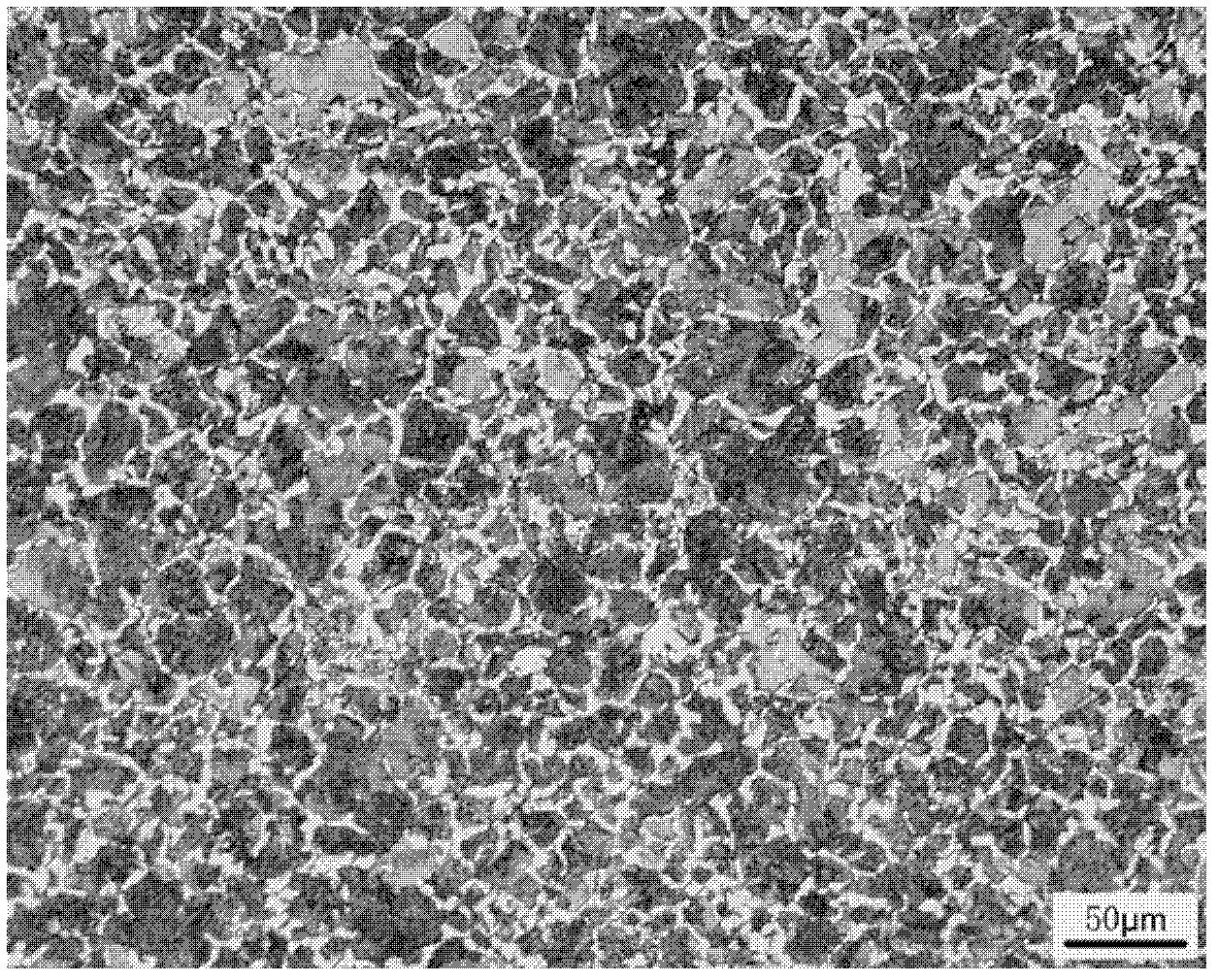

Preparation process for improving comprehensive performance of aluminum-lithium alloy product

The invention relates to the technical field of aluminum alloy thermal deformation and heat treatment, and in particular relates to a preparation process for improving the comprehensive performance ofan aluminum-lithium alloy product. The preparation process comprises the following steps that after a hot rolled plate / a hot forging completed forge piece is subjected to solution and quenching treatment, heat preservation is carried out for a period of time at a certain temperature, rolling treatment of certain deformation is carried out, and then secondary solution and quenching temperature, cold deformation and artificial aging treatment are carried out; after the solution and quenching temperature is carried out, medium-temperature heating and heat preservation are carried out; and a certain deformation energy storage is introduced in subsequent medium-temperature rolling deformation rolling, so that the plate is re-crystallized to a certain degree in the secondary solution and quenching temperature, the horizontal grain boundary among grains in the hot rolled plate is eliminated, a part of " nested " morphology is formed, improvement is achieved from two aspects of grain boundarymorphology and interface " purity ", and the comprehensive performance of an alloy is improved.

Owner:AVIC BEIJING INST OF AERONAUTICAL MATERIALS

Hot beverage container

InactiveUS7475792B2Easy to cleanIncrease temperatureDomestic cooling apparatusLighting and heating apparatusEngineeringCooling pipe

Owner:HANSEN DAVID SCOTT

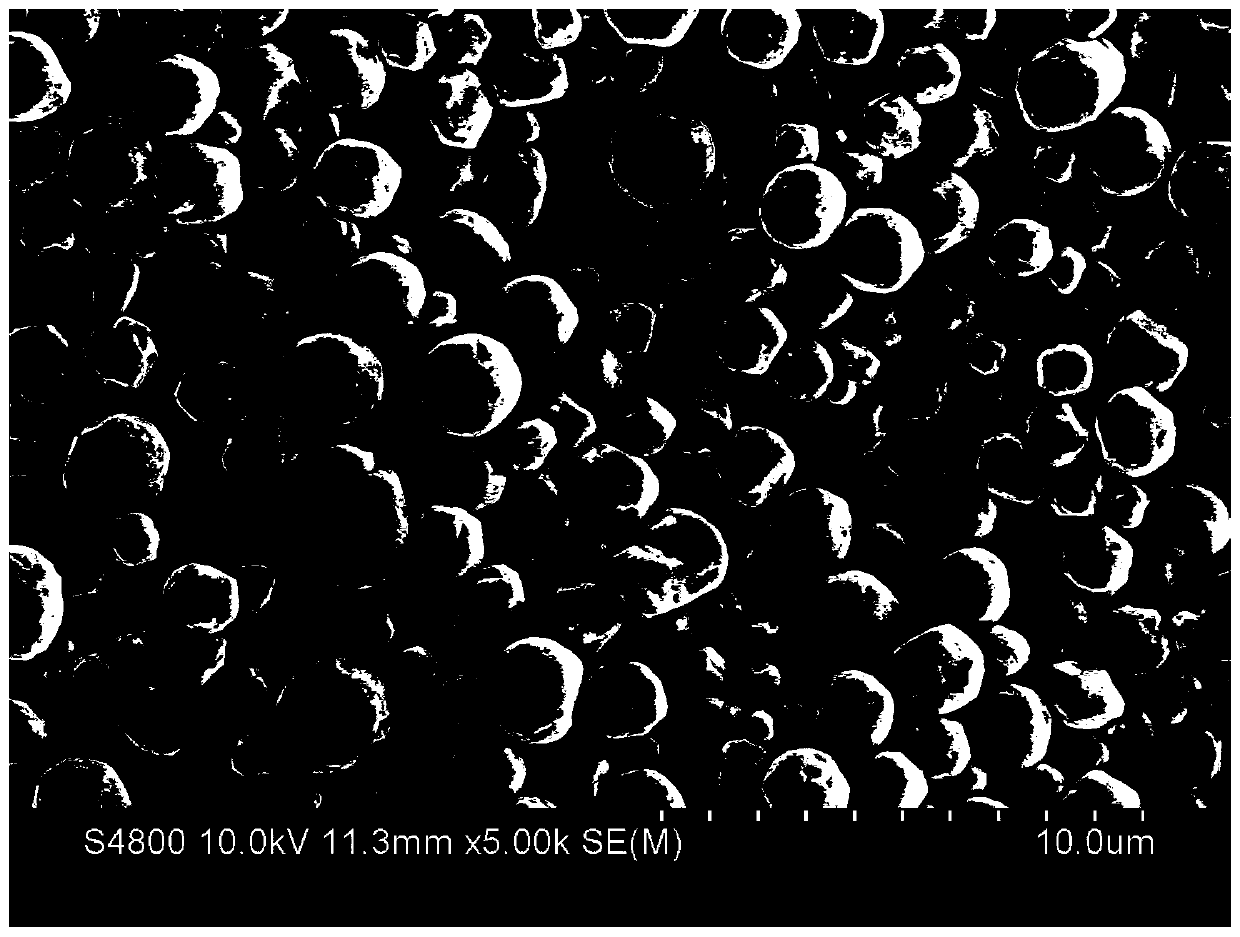

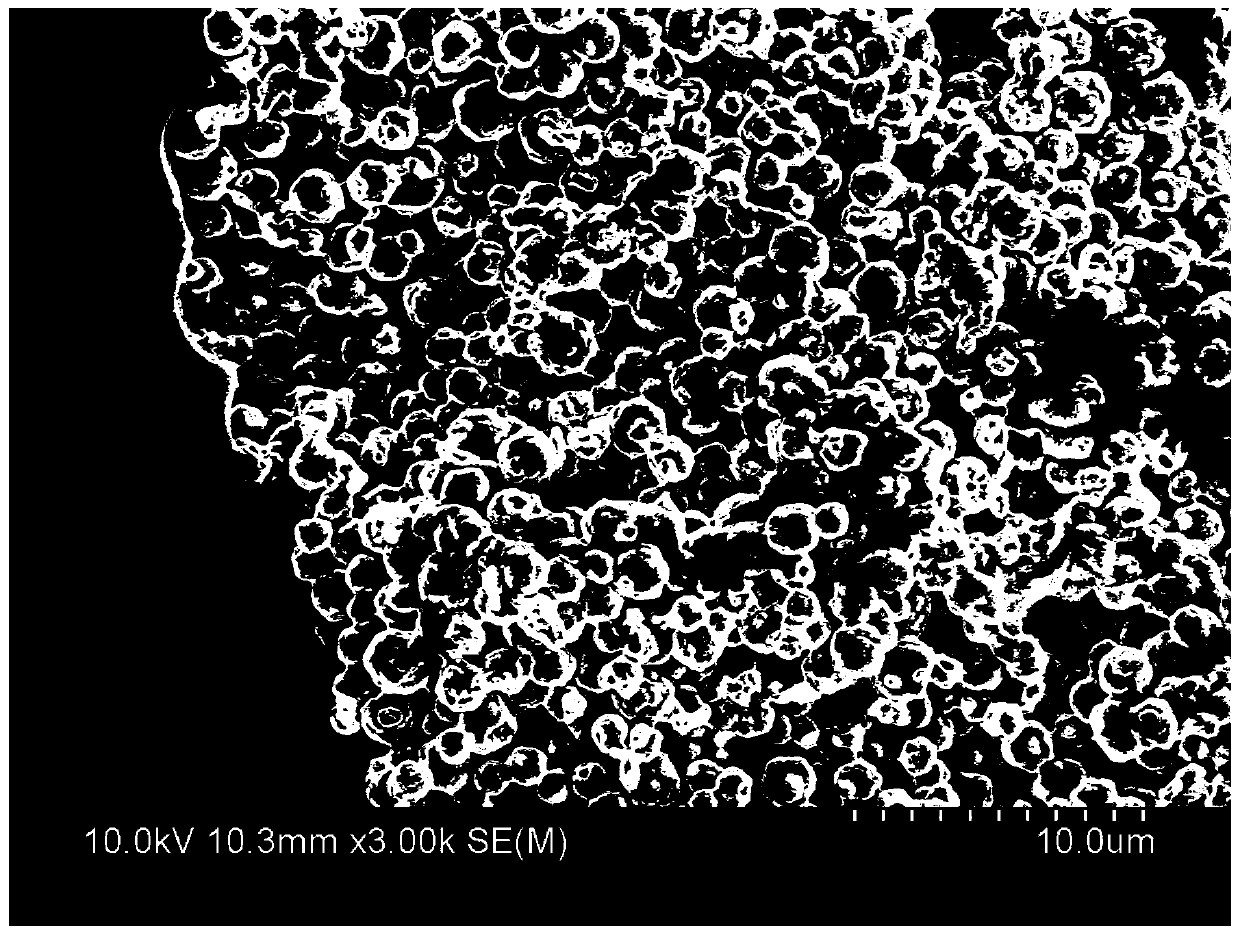

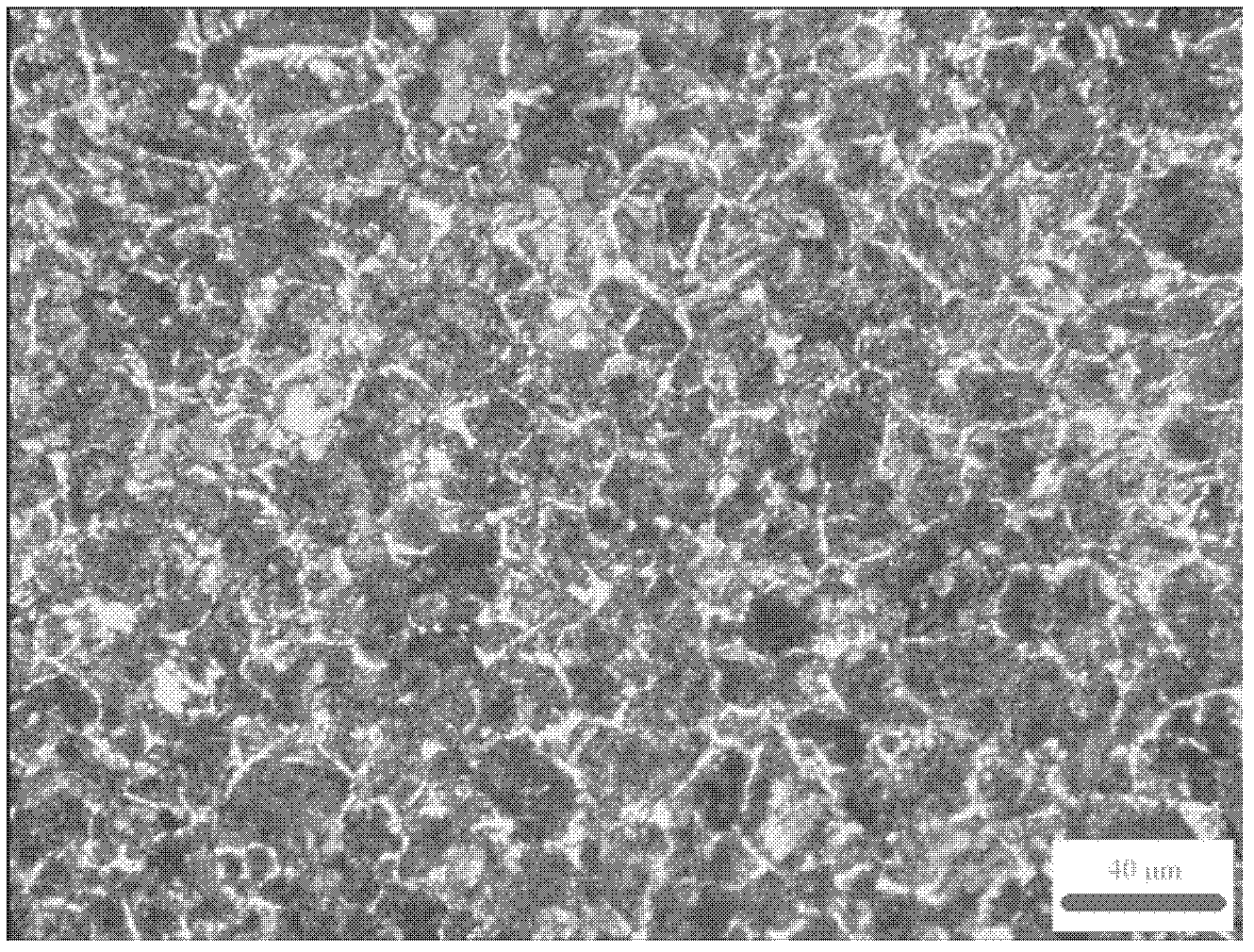

Preparation method of spheroidal silver powder

InactiveCN110666184AImprove liquidityGood filling effectTransportation and packagingMetal-working apparatusMetallurgyChemical modification

The invention relates to a preparation method of spheroidal silver powder. The method comprises the following steps: step 1, preparing a solution; step 2, performing reduction reaction; step 3, chemically modifying silver powder; step 4, performing silver powder surface treatment; and step 5, sieving and testing the silver powder. The silver powder prepared by the method has an average particle diameter D50 of 1.4-1.8 microns and a tap density of 6.0-6.5 g / cm3, and the spheroidal silver powder with holes inside can give consideration to filling performance and sintering activity.

Owner:苏州银瑞光电材料科技有限公司

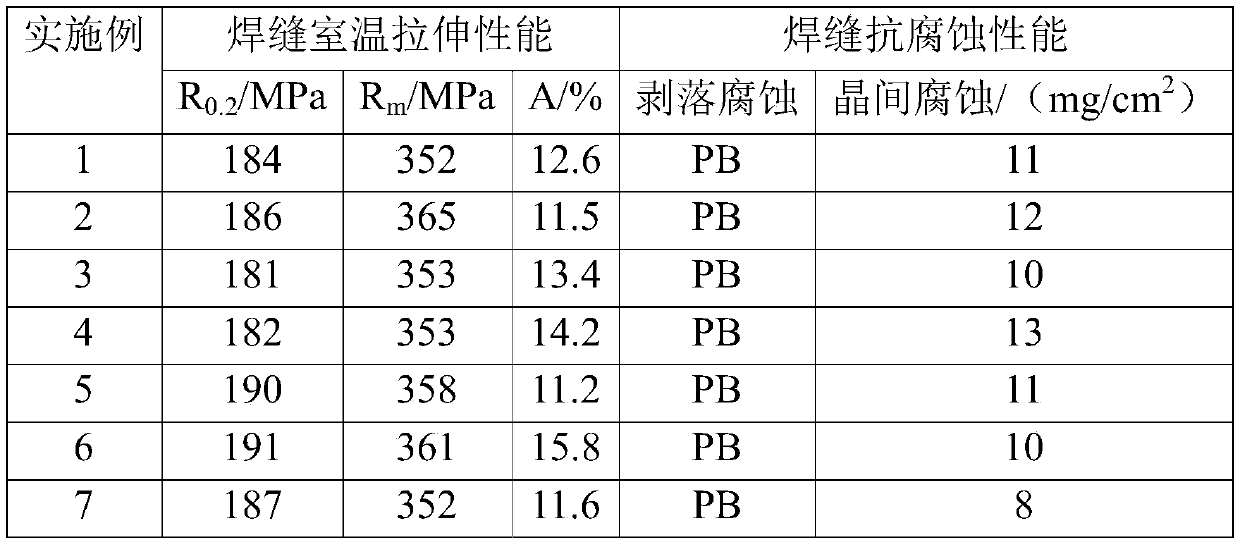

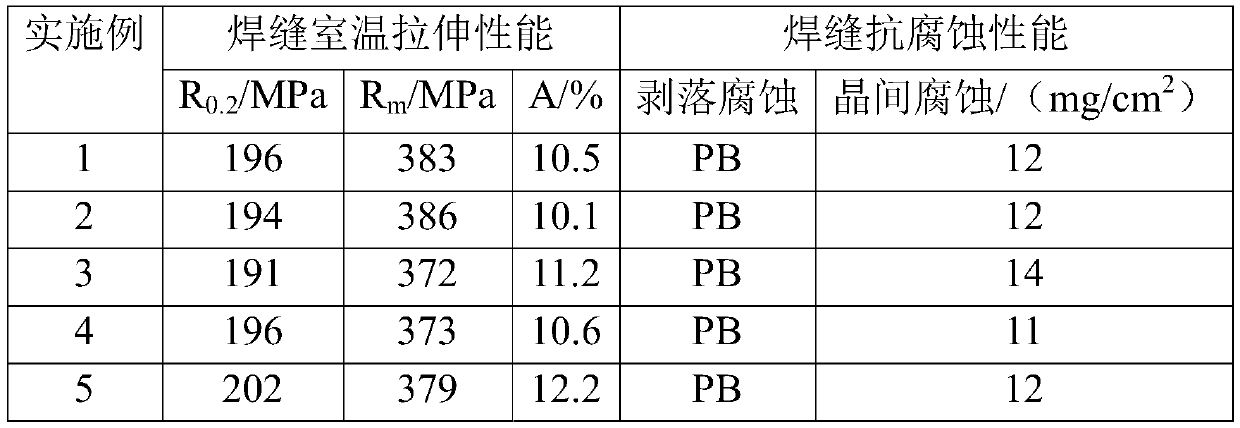

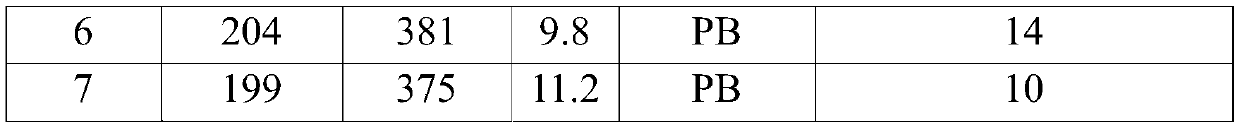

High-strength and corrosion-resistant Al-Mg-Zr aluminum alloy welding stick and preparation method thereof

ActiveCN109955003AHigh strengthGood formabilityWelding/cutting media/materialsSoldering mediaZincUltimate tensile strength

The invention discloses a high-strength and corrosion-resistant Al-Mg-Zr aluminum alloy welding stick and a preparation method thereof. The proportion of alloy elements in an Al-Mg-Zr alloy is controlled in an optimized manner, and meanwhile, powder preparation, hot isostatic pressing, extrusion, continuous extrusion and drawing processes are adopted for preparing the welding stick with the fine crystalline grains, uniform structure and the good comprehensive performance. The novel alloy welding stick has the good formability and the low hot cracking tendency in the TIG or MIG welding formingprocess, a welding joint has the high strength and excellent corrosion resistance, the welding stick can be used for welding corrosion-resistant Al-Mg series alloys and high-strength Al-Zr-Mg series alloys, welding requirements of all-aluminum ship and warship bodies and armor protection decks are met, and the application prospects are broad.

Owner:AVIC BEIJING INST OF AERONAUTICAL MATERIALS

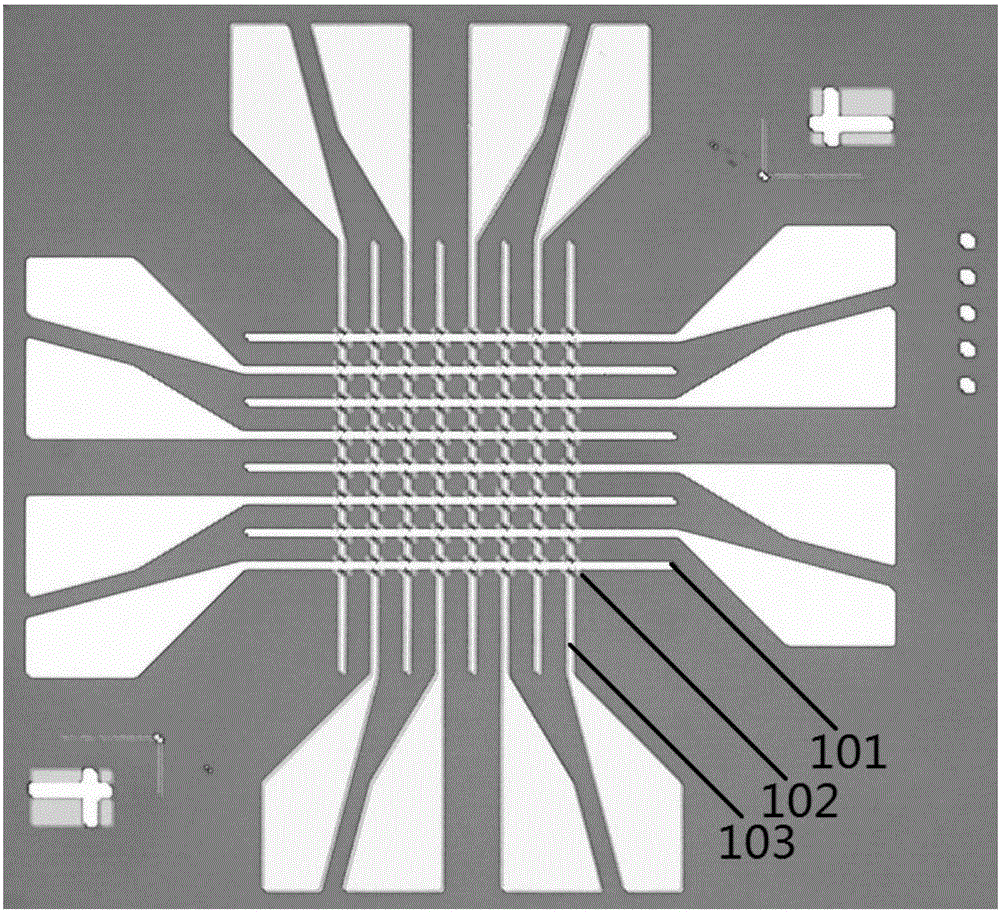

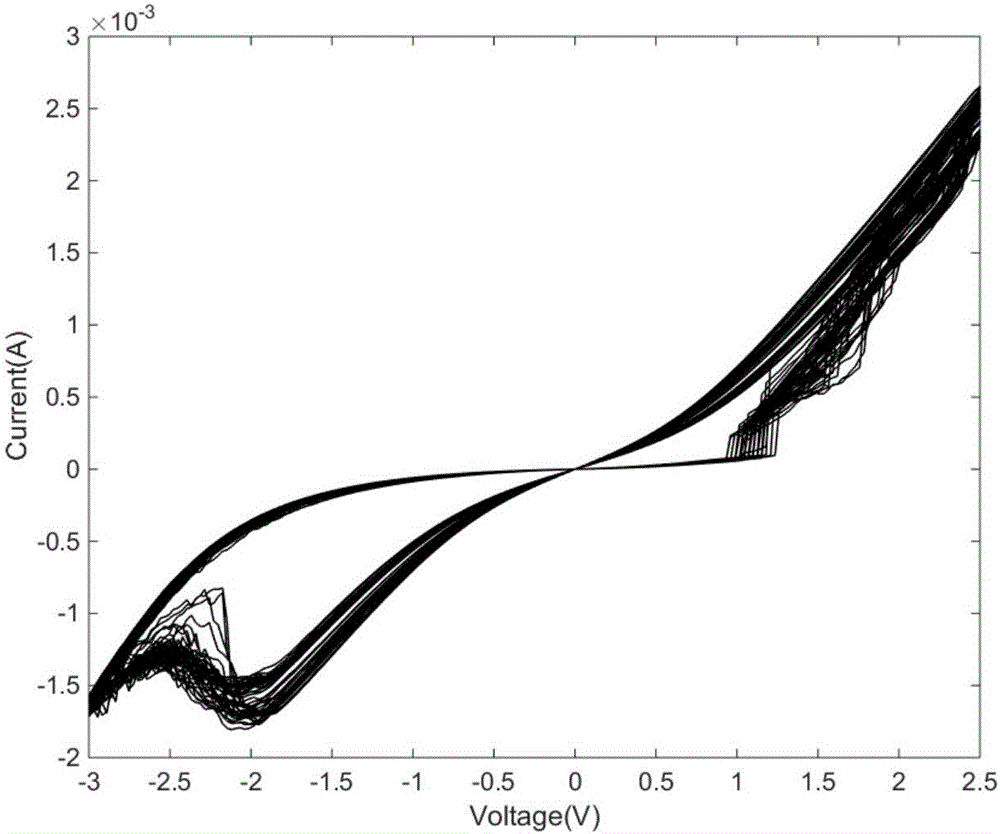

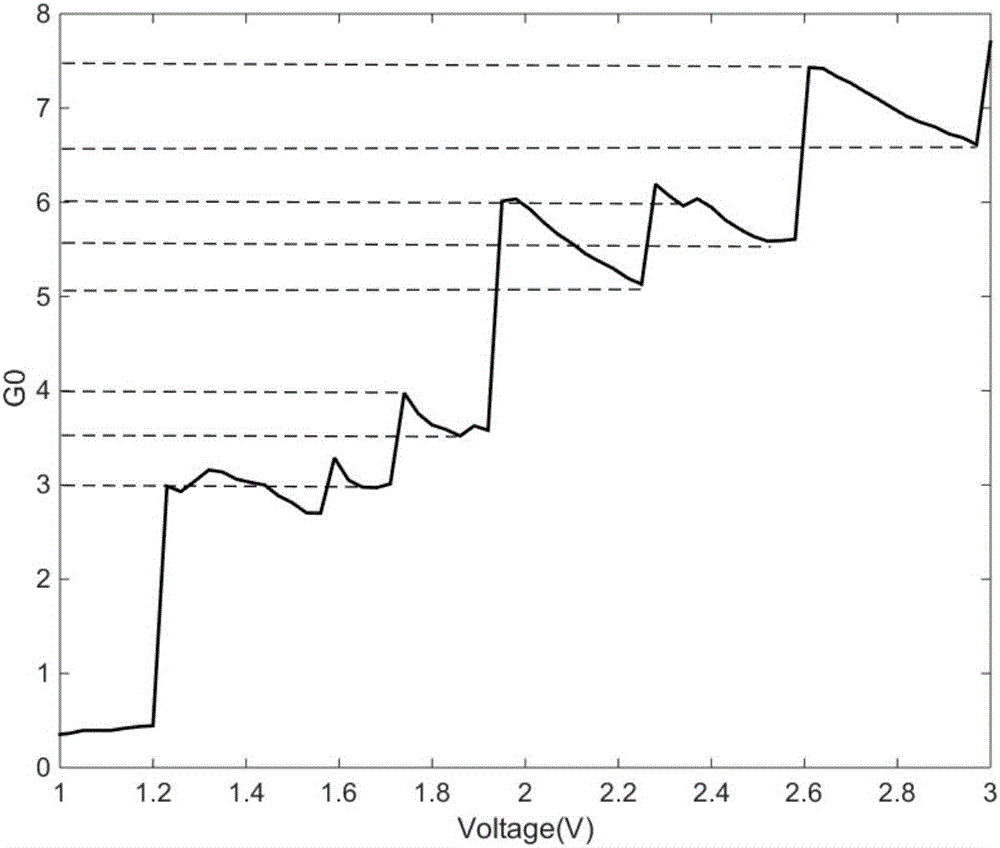

Quantum conductance effect based memristor and preparation and modulation method and application thereof

The invention discloses a quantum conductance effect based memristor and a preparation and modulation method and application thereof. The memristor includes an upper electrode, a function layer and a lower electrode and has an MIM crossbar structure. Through regulating the proportion of argon and oxygen, function layer material having different thicknesses and oxygen vacancy is prepared. During modulation, conductive fiber states of the function layer are regulated accurately by adopting a voltage scanning or pulse scanning method and the size of the conductive fibers is controlled within an atomic scale, so that discontinuous conducting behaviors in a number which is the integral multiple of a unit conducting value are obtained and conducting quantization of the memristor is realized. Through exacting different quantum states of the memristor, resistance corresponding to the different quantum states is taken as different impedance for device storage, so that multi-value storage is realized. Besides, a function of the memristor of simulating nerve cell synapsis is implemented. The memristor eliminates influence of impedance drifting caused by dispersion change of conductance states on device application and realizes the quantum storage device with smaller working current, higher storage density, faster reading speed and no loss after power failure.

Owner:HUAZHONG UNIV OF SCI & TECH

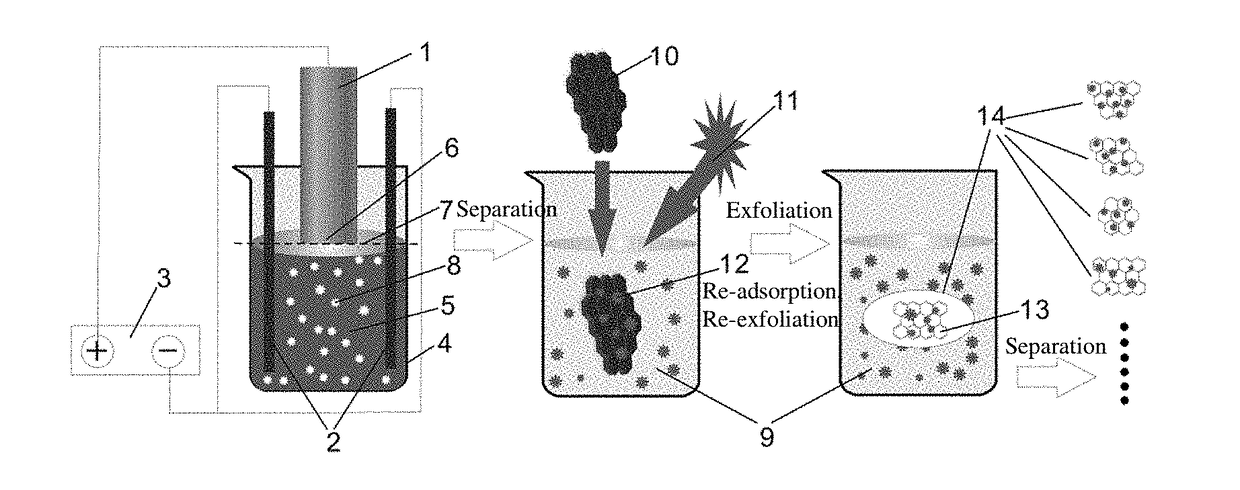

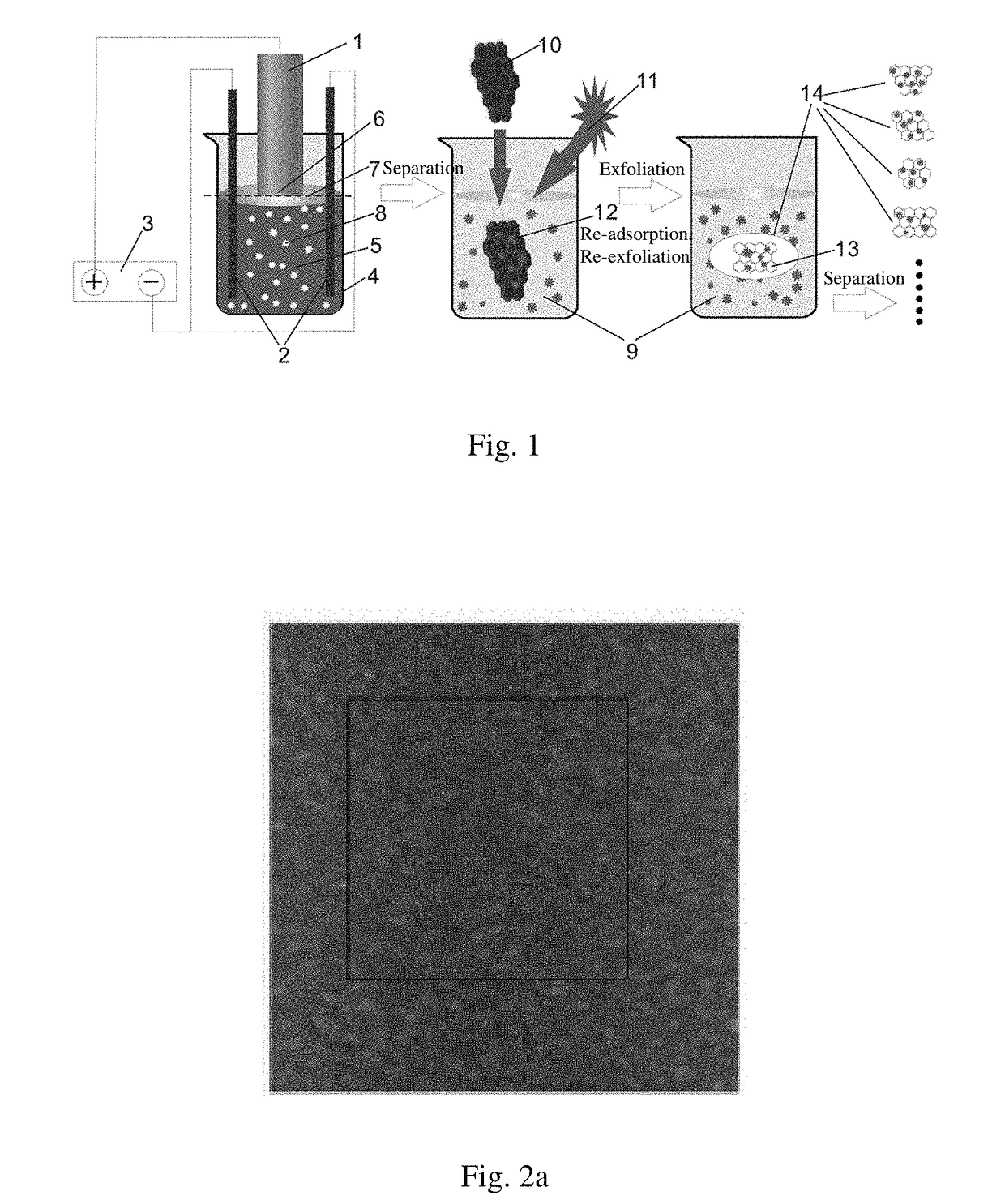

Graphene oxide quantum dot, material composed of same and graphene-like structure, and preparation method therefor

ActiveUS20180186645A1Effectively suppresses refoldingGreat dispersing and cutting abilityMaterial nanotechnologyElectrolysis componentsQuantum dotCvd graphene

Graphene oxide quantum dots (GOQDs) a composite nanomaterial formed by the GOQDs with graphene and / or graphene-like structure(s), and methods for preparing them are provided. The method for preparing GOQDs comprises providing a carbon-based 3D bulk material having a graphite layer structure as an anode, positioning an end face of the material in contact and parallel with the liquid surface of an electrolyte solution, and intermittently or continuously cutting and exfoliating graphite layers at the end face by electrochemical oxidation to obtain GOQDs. The method for preparing the composite nanomaterial comprises adding powder comprising graphite and / or graphite-like layer structure(s) to a solution of GOQDs; under an assistant mechanical action of high shearing force, subjecting the GOQDs adsorbed onto the graphite and / or graphite-like layer structure(s) in the solution to a cycle of exfoliation, re-adsorption, and re-exfoliation, to obtain a composite nanomaterial formed by quasi-zero and / or quasi-two dimensional graphene and / or graphene-like structure(s) and GOQDs.

Owner:XU HAIBO

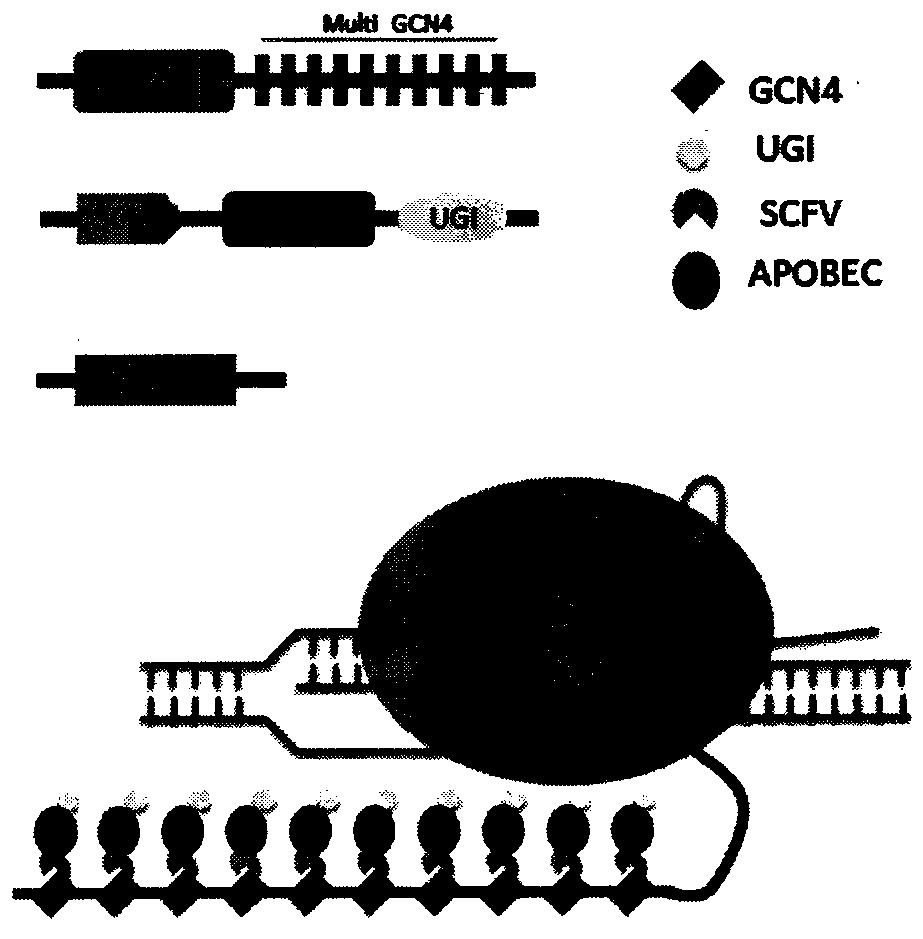

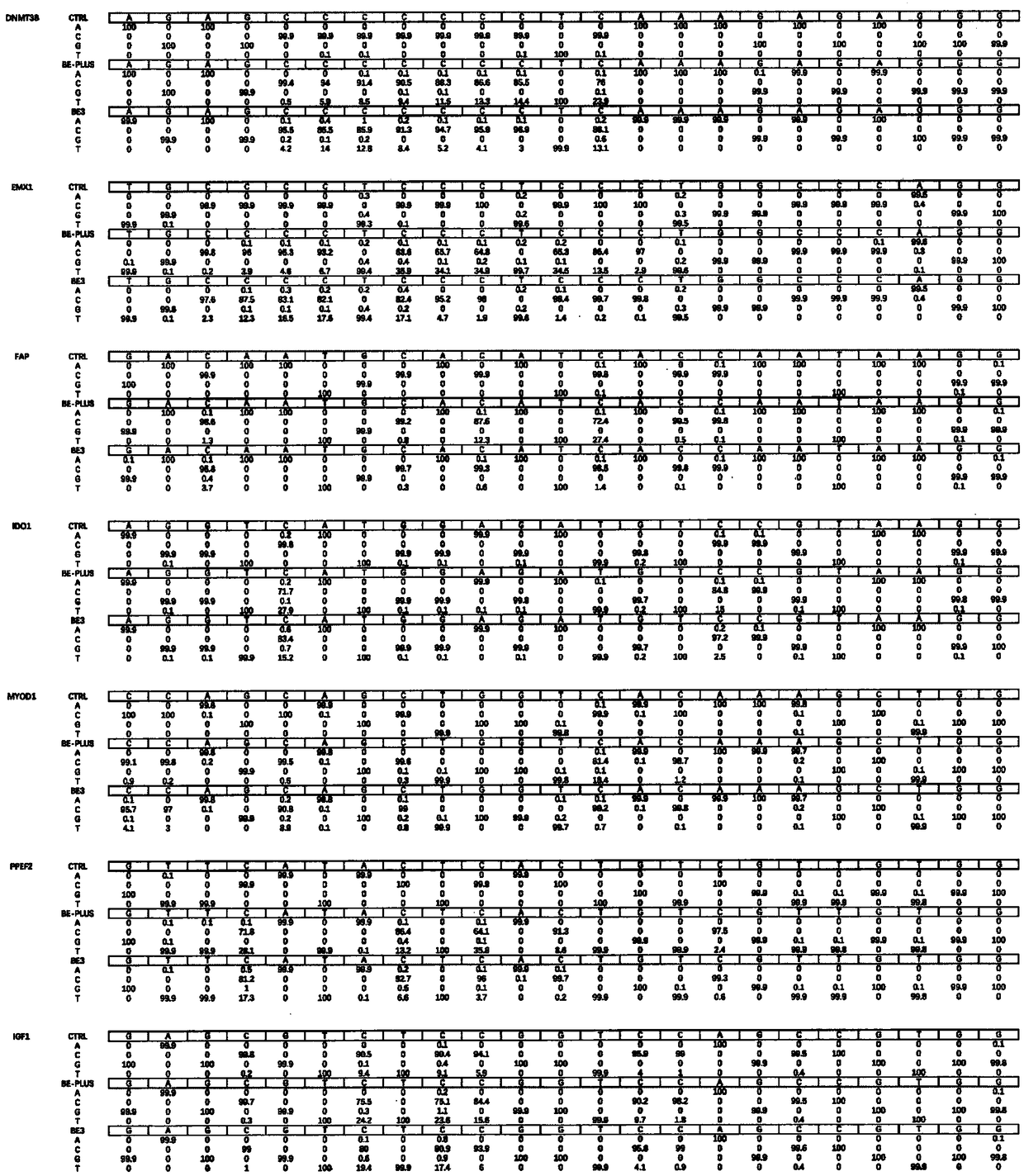

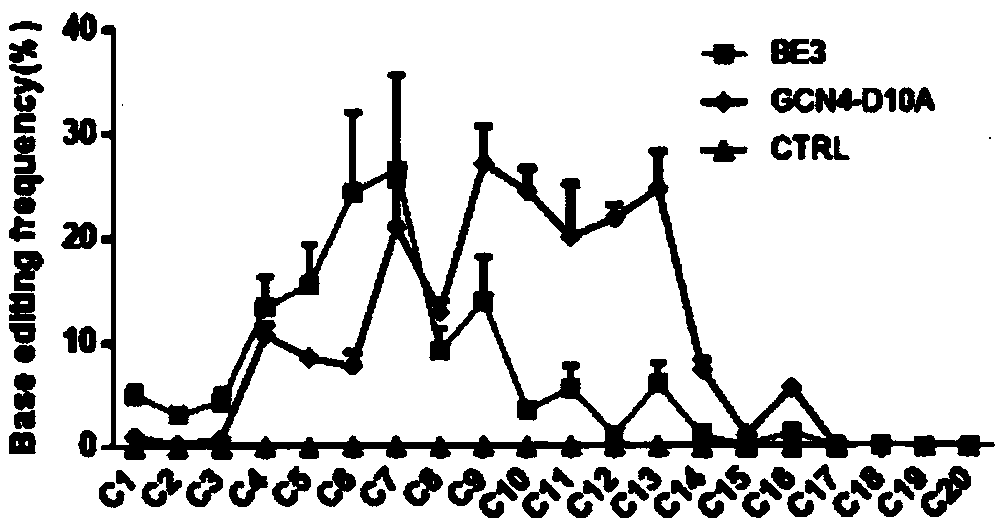

Base editing tool and application thereof

ActiveCN108715861AIncrease windowImprove accuracyVectorsVector-based foreign material introductionCytosine deaminaseSingle-Chain Antibodies

The invention provides a base editing tool and application thereof. The base editing tool is characterized by comprising GCN4-D10A, a scFv-APOBEC-UGI vector or a scFv-APOBEC-UGI-GB1 vector, and sgRNAat target specific sites, wherein the GCN4-D10A is formed by connecting multi-copied GCN4 to D10A-Cas9; the scFv-APOBEC-UGI vector is formed by connecting cytosine deaminase APOBEC and uracil glycosylase inhibitors UGI to a single-chain antibody scFv; the scFv-APOBEC-UGI-GB1 vector is formed by connecting the cytosine deaminase APOBEC and uracil glycosylase inhibitors UGI and a thermal stability domain GB1 for preventing multimerization to the single-chain antibody scFv. Compared with a commonly used base editing tool, the base editing tool disclosed by the invention has the advantages that the base editing windows are obviously increased, and the application range of base editing in genome is further widened.

Owner:SHANGHAI TECH UNIV

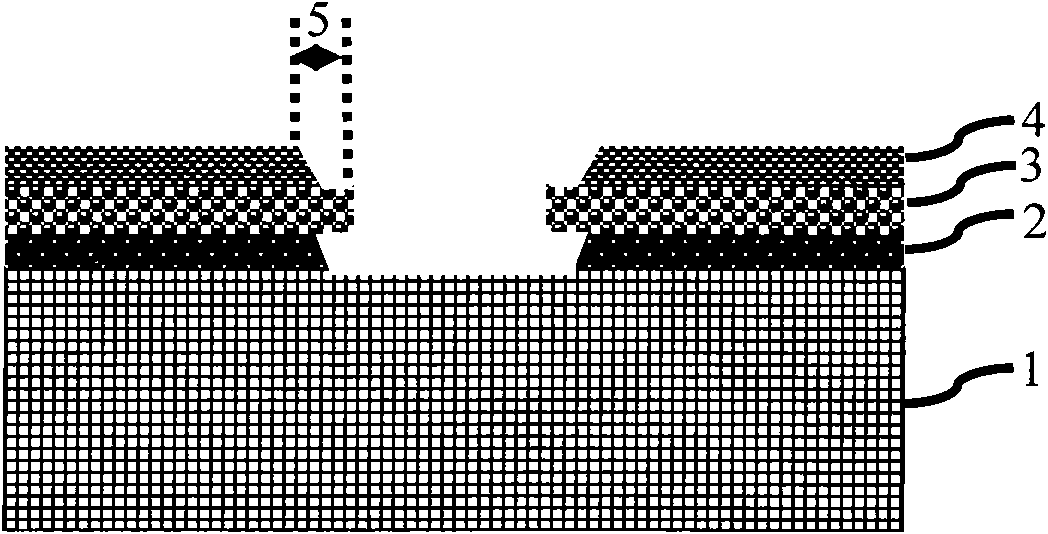

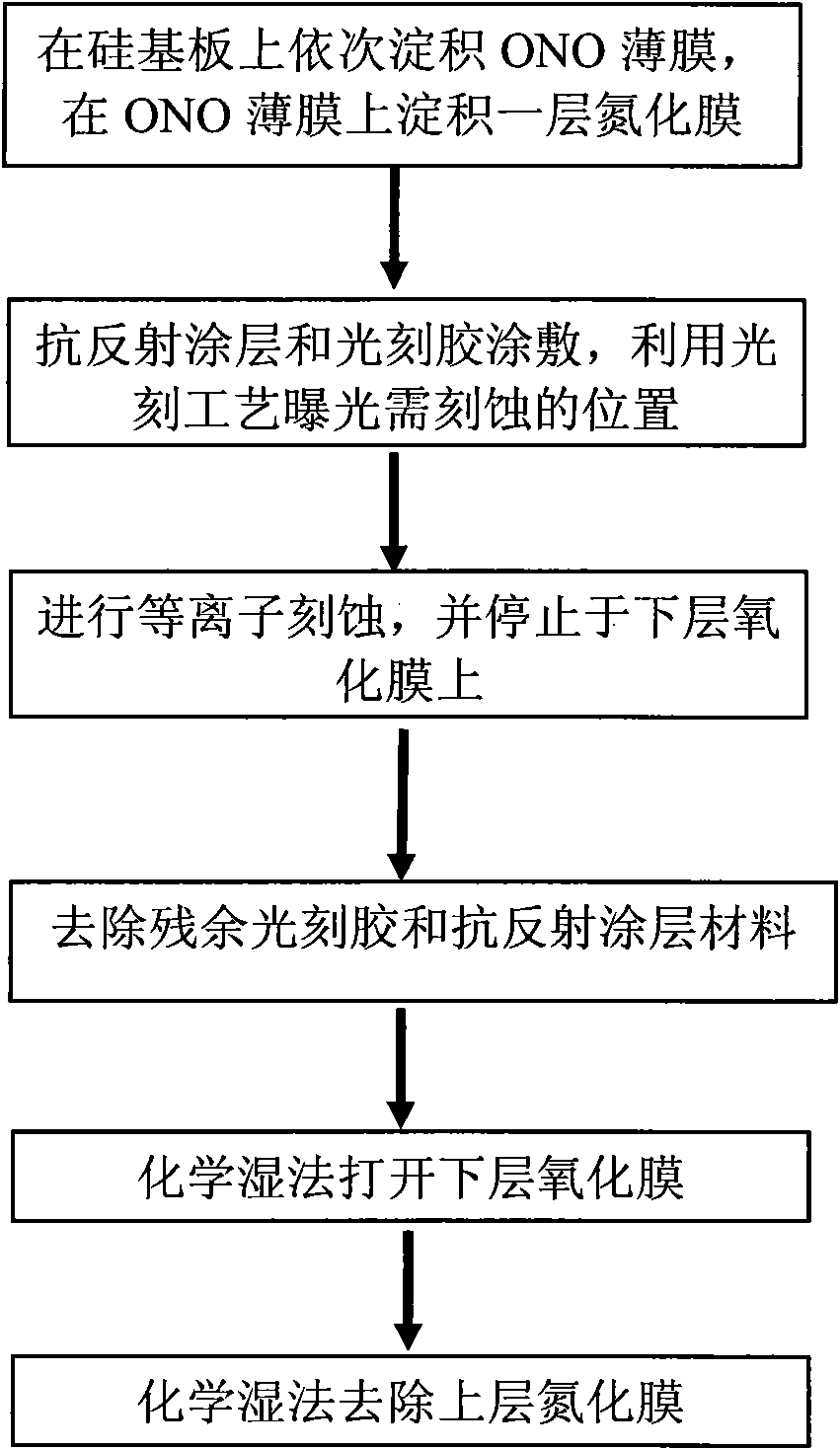

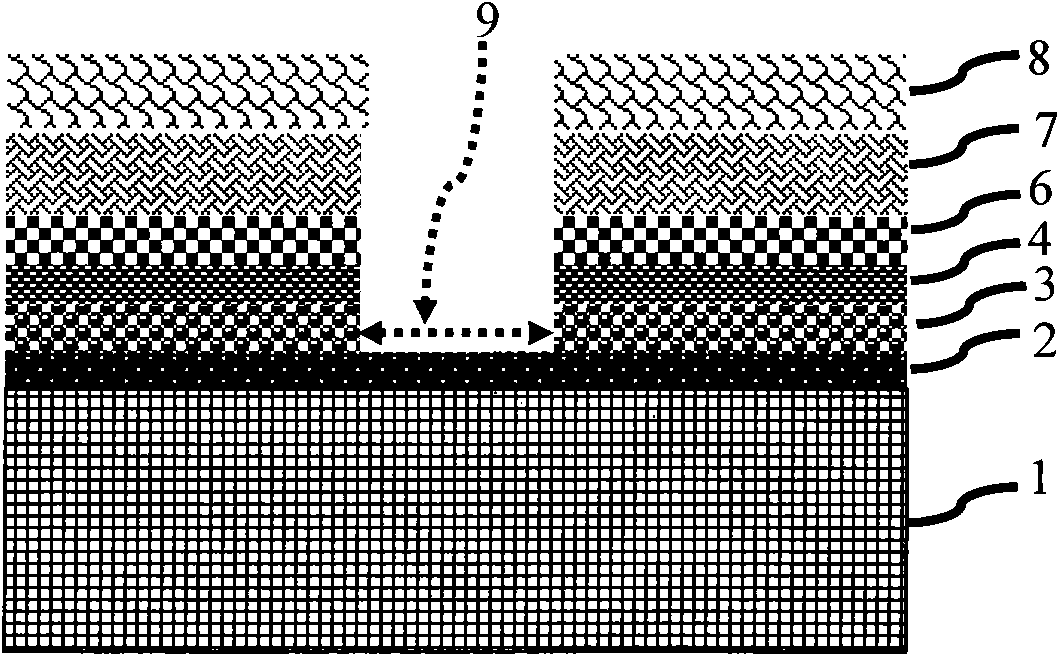

Method for producing ONO structure

InactiveCN101567312AEliminate strippingEnsure etch uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesNitric oxideNitride

The invention discloses a method for producing an ONO structure, comprising the following steps: (1) depositing a lower-layer oxide film, a middle-layer nitric-oxide film and an upper-layer oxide film on a silicon substrate in sequence to form an ONO thin film, and then depositing a nitride film on the formed ONO thin film; (2) coating an anti-reflection coating and photoresist on the nitride film, and then using a photoetching technique to expose a position to be etched; (3) carrying out plasma etching at the position to be etched, and stopping on the lower-layer oxide film; (4) removing the residual photoresist and the anti-reflection coating; (5) further using a wet etching technique to etch the lower-layer oxide film; and (6) removing the residual nitride film by the wet etching technique to form the ONO structure. The structure can solve the problem of peeling off the photoresist, ensure uniformity of etching and effectively control side etching.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

Surface correction structure and correction method of semiconductor structure

ActiveCN109524312AImprove yieldImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureCorrection method

The application discloses a surface correction structure and correction method of a semiconductor structure. The surface correction structure comprises a back film and a stress layer adjacent to the back film. The back film is arranged on the surface of the semiconductor structure and is adjacent to the surface of the semiconductor structure. According to the correction structure, a flat surface is provided for the follow-up cover layer and the correction structure is suitable for surface warping with various directivity, so that the yield and reliability of the semiconductor device are improved.

Owner:YANGTZE MEMORY TECH CO LTD

Method for producing Nb-containing high-speed train wheel steel

InactiveCN102534396AHigh strengthImproves the toughness of steel under high-strength conditionsMetallic materialsPearlite

The invention relates to a method for producing Nb-containing high-speed train wheel steel, and belongs to the field of metal materials. The wheel steel comprises the following components in percentage by weight: 0.40 to 0.70 percent of C, 0.70 to 0.80 percent of Mn, 0.30 to 0.60 percent of Si, 0.015 to 0.110 percent of Nb, 0.20 to 0.35 percent of Cr, less than or equal to 0.020 percent of P, less than or equal to 0.015 percent of S and the balance of Fe and inevitable elements. The method comprises the following steps of: smelting, forging to obtain a steel billet, performing normalization and heat preservation at the temperature of between 850 and 900 DEG C for 1 hour, performing air cooling or water spray cooling to room temperature, and ensuring that cooling speed is controlled in therange of 1 to 15 DEG C / s and a room temperature structure is ferrite and pearlite. The high-speed train wheel steel produced by the method has the tensile strength of 740 to 900MPa, the yield strength of 450 to 570MPa, the breaking elongation of 15 to 25 percent and the low temperature (-20 DEG C) impact work (Akv) of 15 to 20J, and a uniform structure with 10 to 25 percent of ferrite can be obtained at room temperature. The Nb-containing high-speed train wheel steel has mechanical properties of high strength and toughness, and overcomes the defect of a low toughness value of the conventionalhigh and medium carbon wheel steel.

Owner:UNIV OF SCI & TECH BEIJING

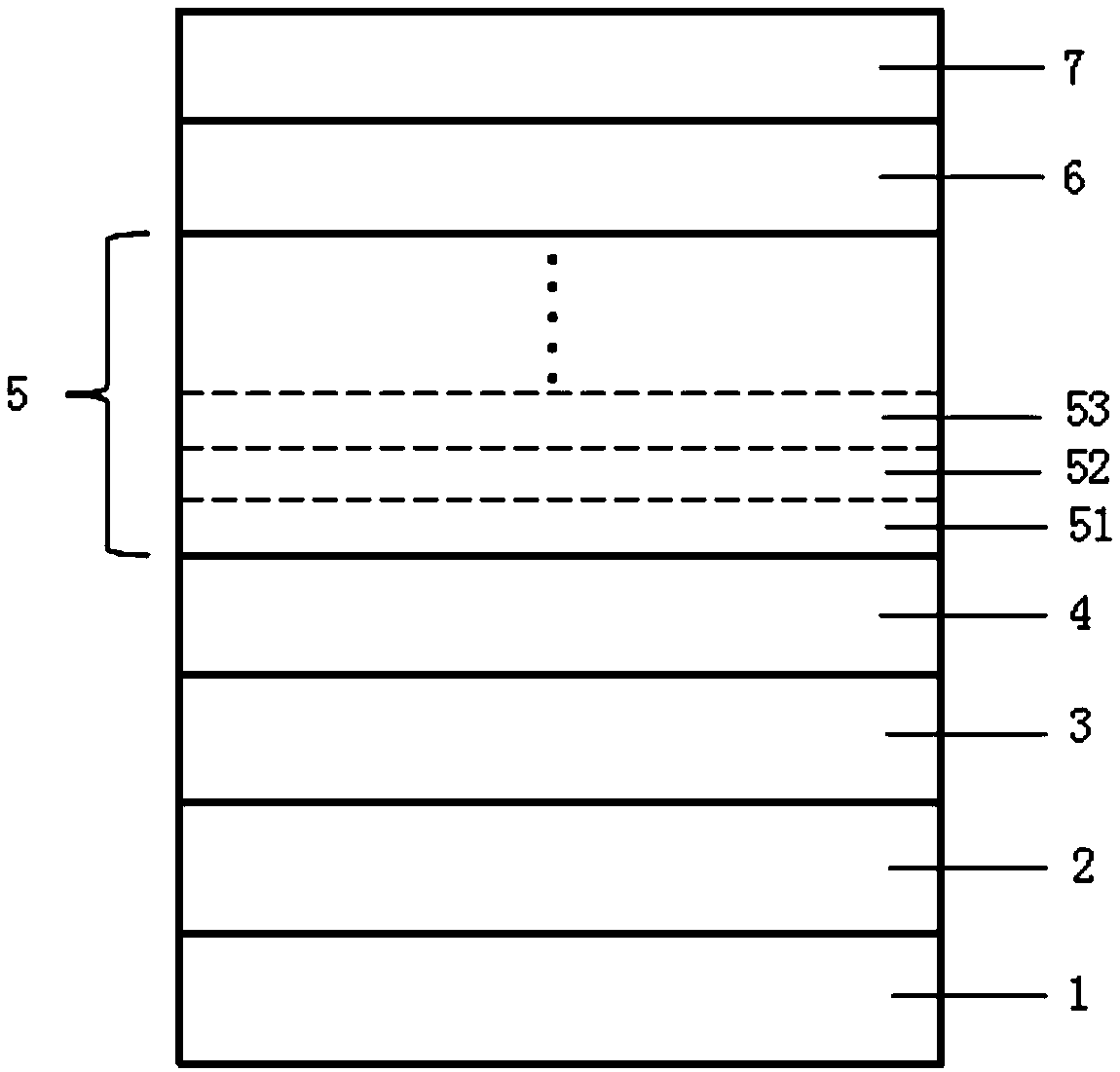

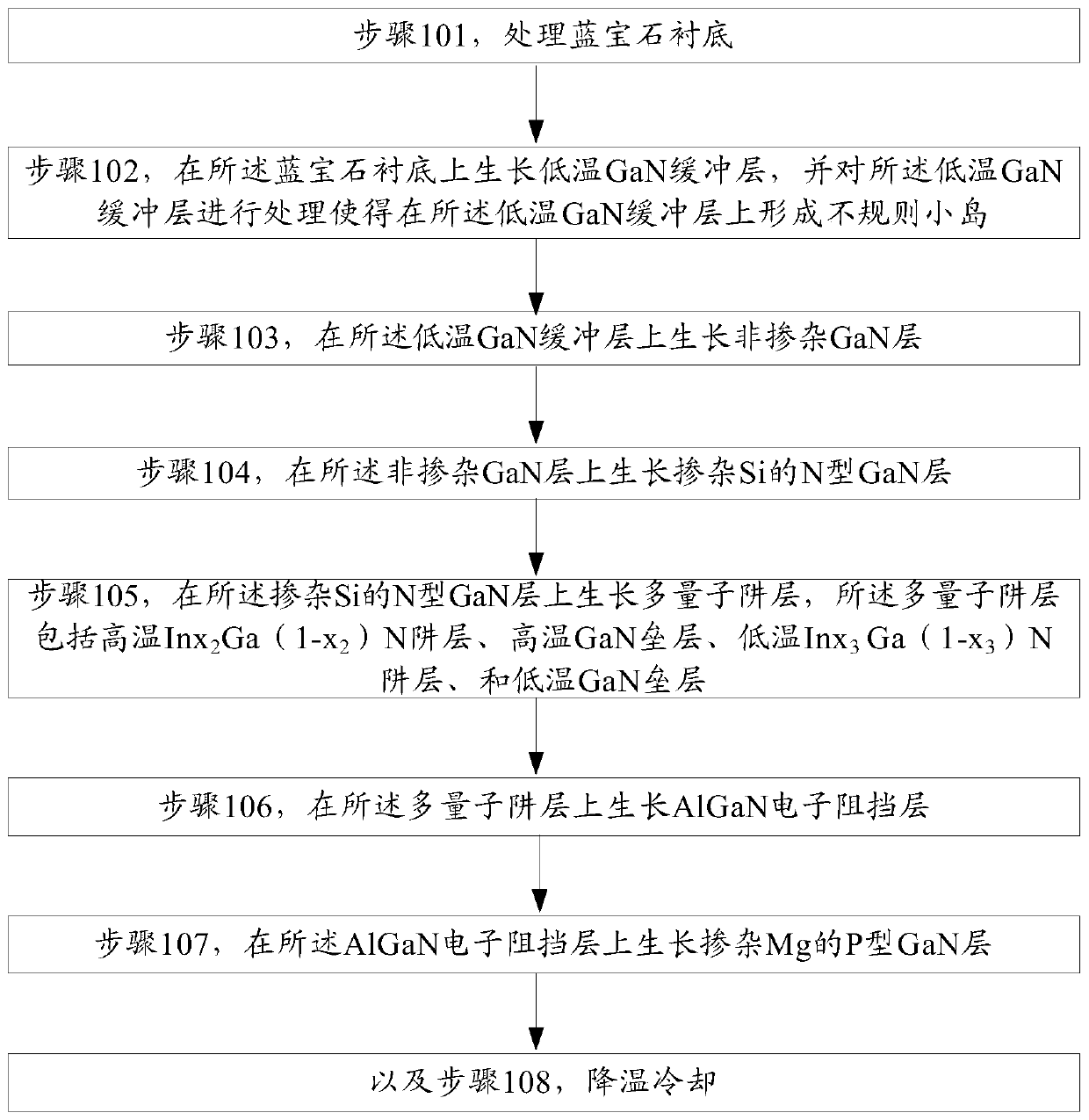

Growth method for epitaxial structure of LED

ActiveCN109411573ASolve quality problemsSolve efficiency problemsSemiconductor/solid-state device manufacturingSemiconductor devicesQuantum wellBiology

The invention discloses a growth method for an epitaxial structure of an LED. The method sequentially comprises the following steps of treating a substrate, growing a low temperature buffer layer GaN,growing a non-doped GaN layer, growing an Si-doped N-type GaN layer, growing a multi-quantum-well layer, growing an AlGaN electronic barrier layer, growing an Mg-doped P-type GaN layer and cooling, wherein growing the multi-quantum-well layer sequentially comprises the following steps of pretreating, growing an Iny1Ga(1-yL)N layer, growing an Iny2Ga(1-y2)N layer, carrying out high-temperature treatment and growing a GaN layer. The method solves the problems that the growth quality of a quantum well is poor and the radiative recombination efficiency of the quantum well is low in an existing epitaxial growth method for the LED, so that the luminous efficiency of the LED is improved, the warping of an epitaxial wafer is reduced, and the yield of products is improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

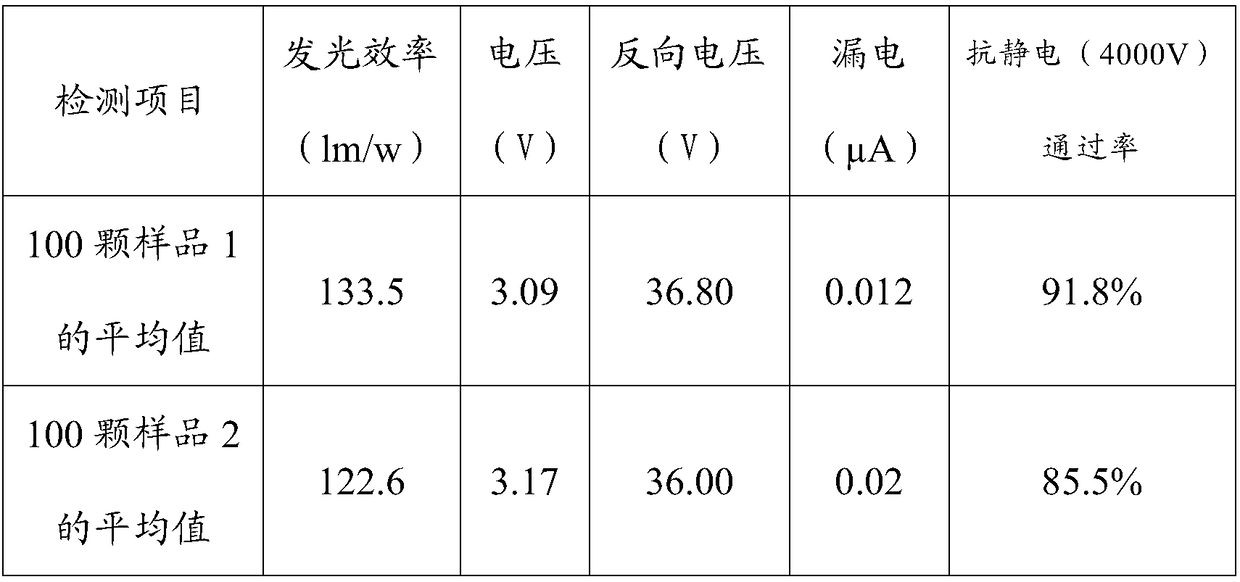

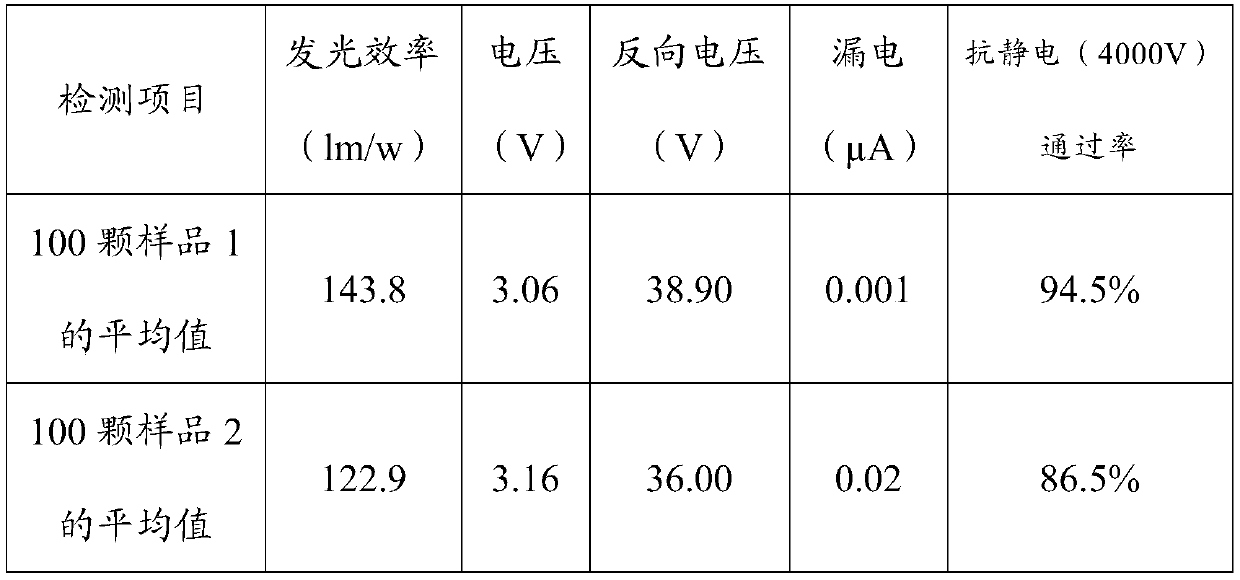

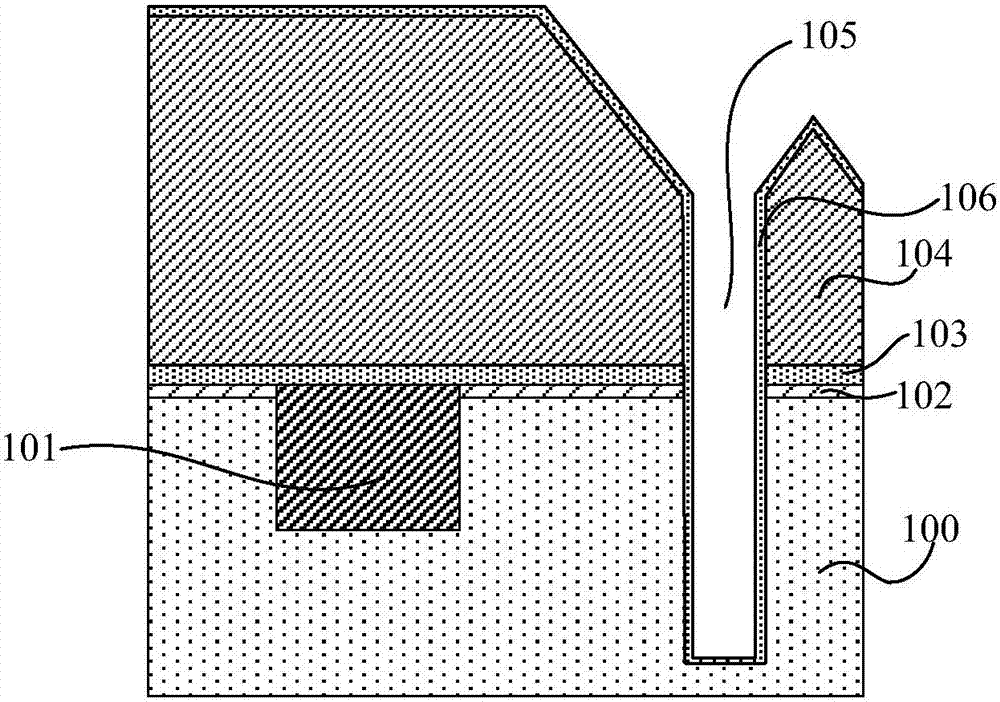

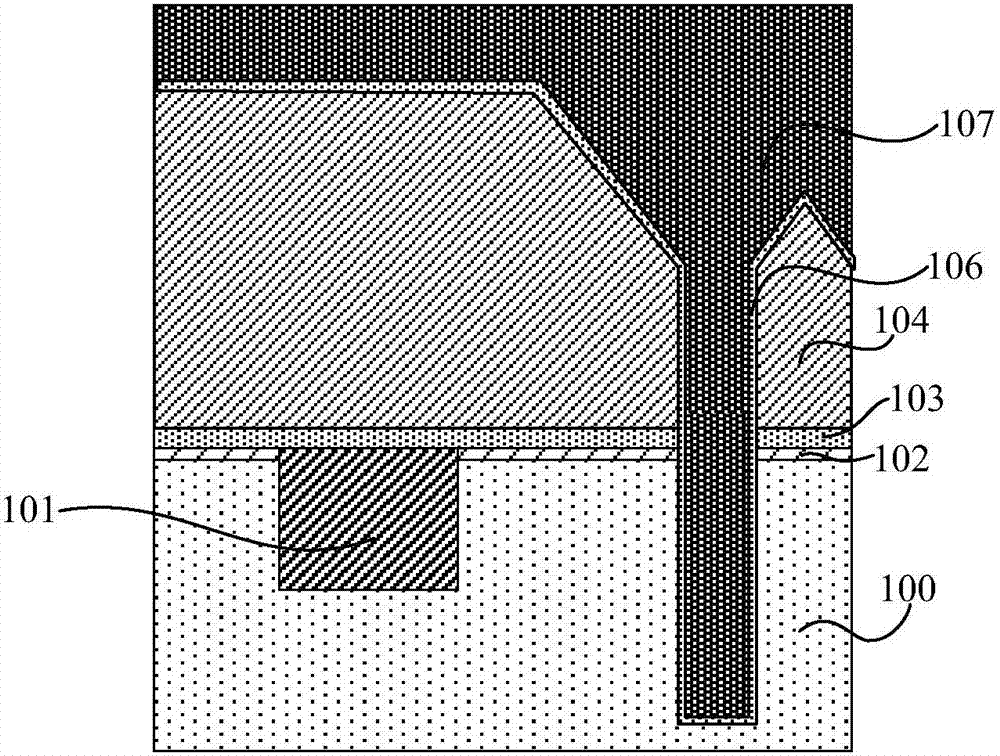

LED epitaxial structure growth method

ActiveCN109860345AIncrease brightnessImprove leakageSemiconductor devicesQuantum wellOptoelectronics

The invention discloses an LED epitaxial structure growth method. The method comprises steps: a sapphire substrate is processed; a low-temperature GaN buffer layer grows on the sapphire substrate, thelow-temperature GaN buffer layer is processed, and an irregular island is formed on the low-temperature GaN buffer layer; an undoped GaN layer grows on the low-temperature GaN buffer layer; a Si-doped N-type GaN layer grows on the undoped GaN layer; a multi-quantum well layer grows on the Si-doped N-type GaN layer; an AlGaN electron blocking layer grows on the multi-quantum well layer; a Mg-dopedP-type GaN layer grows on the AlGaN electron blocking layer; and temperature reduction and cooling are carried out. According to the growth method disclosed in the invention, the light emitting efficiency of the LED can be effectively enhanced, warpage of the epitaxial wafer can be reduced, the qualified rate of the GaN epitaxial wafer is improved, the surface of the epitaxial layer becomes flat,and the appearance is better.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

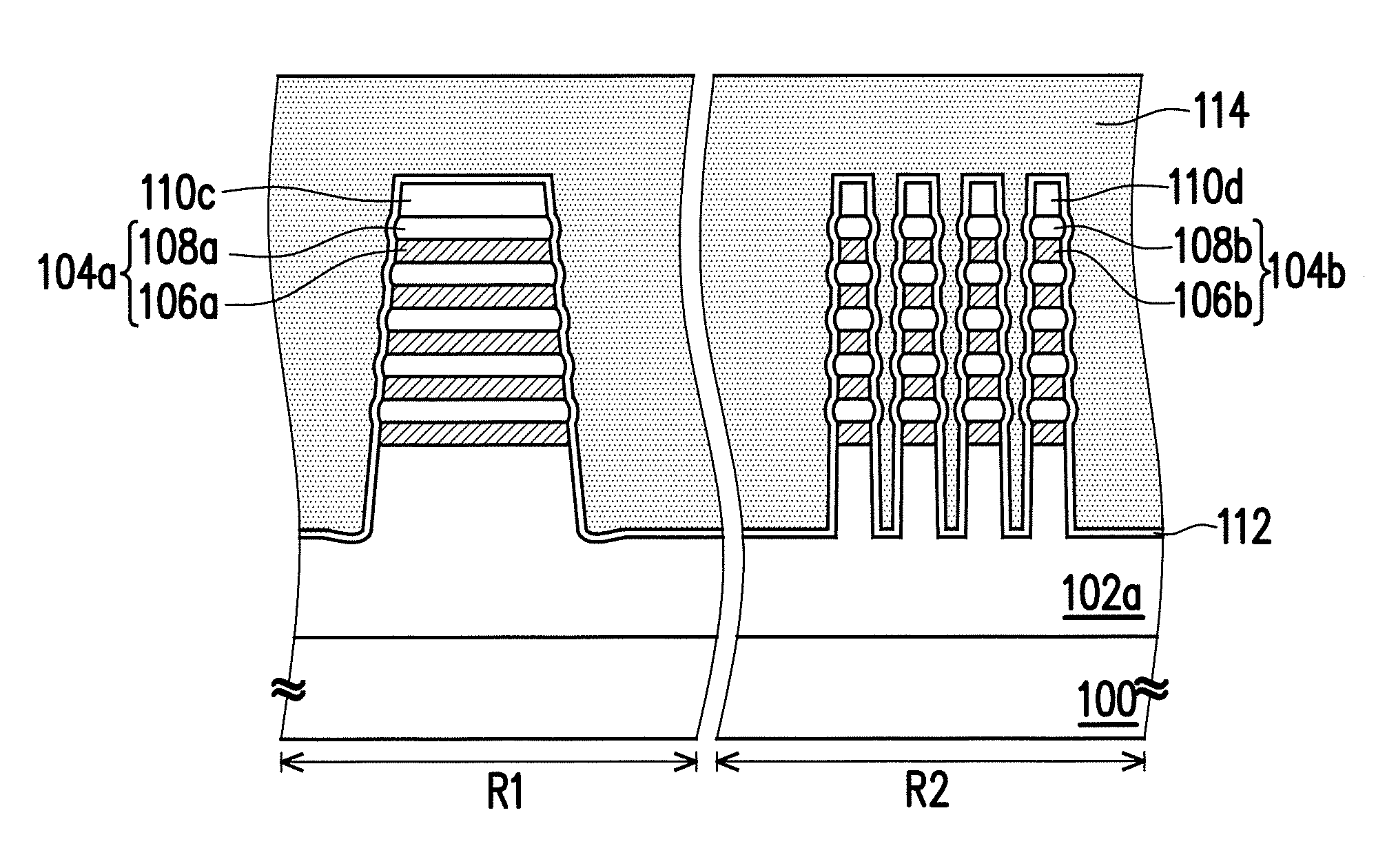

Manufacturing method of semiconductor device

ActiveCN107425018AExpanding the removal process windowIncrease windowSolid-state devicesRadiation controlled devicesCapacitanceDielectric layer

The invention provides a manufacturing method of a semiconductor device, and relates to the technical field of semiconductors. The method comprises the steps that a semiconductor substrate is provided, a first dielectric layer is formed on the surface of the semiconductor substrate, and a patterned mask layer is formed on the first dielectric layer; a deep trench arranged in the semiconductor substrate is formed; a second dielectric layer is formed on the bottom part and the side wall of the deep trench; a first polysilicon layer is formed through deposition to fill in the deep trench; the first time of etching is performed to etch and remove partial first polysilicon layer, wherein the top surface of the remaining first polysilicon layer is higher than the top surface of the first dielectric layer and lower than the top surface of the mask layer; the mask layer is removed; the second time of etching is performed to etch and remove the first polysilicon layer; and the top polar plate of the deep trench capacitor is formed. According to the method, etching damage to other film layers or materials which are arranged at the external side of the deep trench and have the same material with that of the mask layer in the removing process of the mask layer can be effectively avoided and the window of the mask layer removing process can be expanded.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

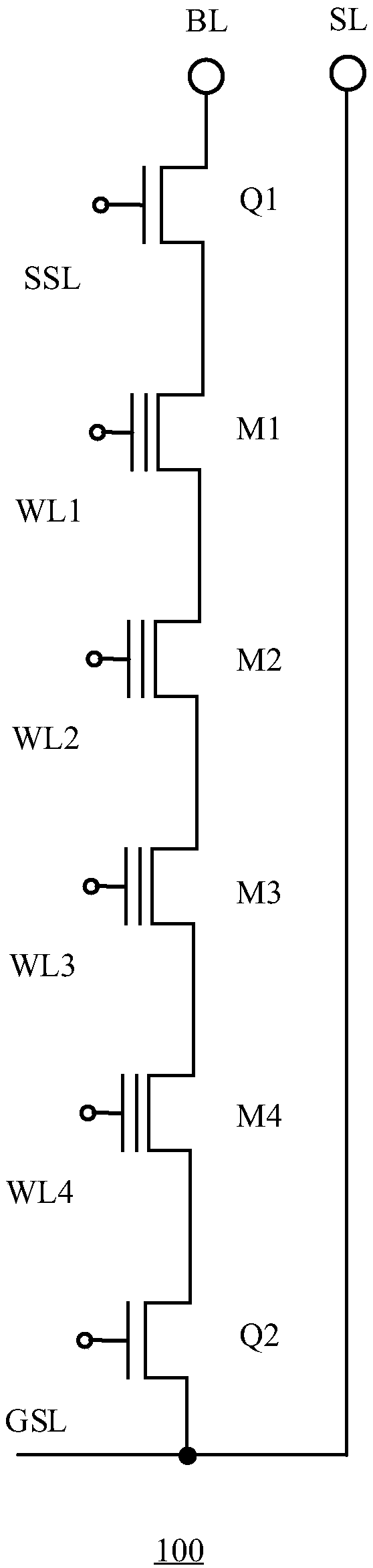

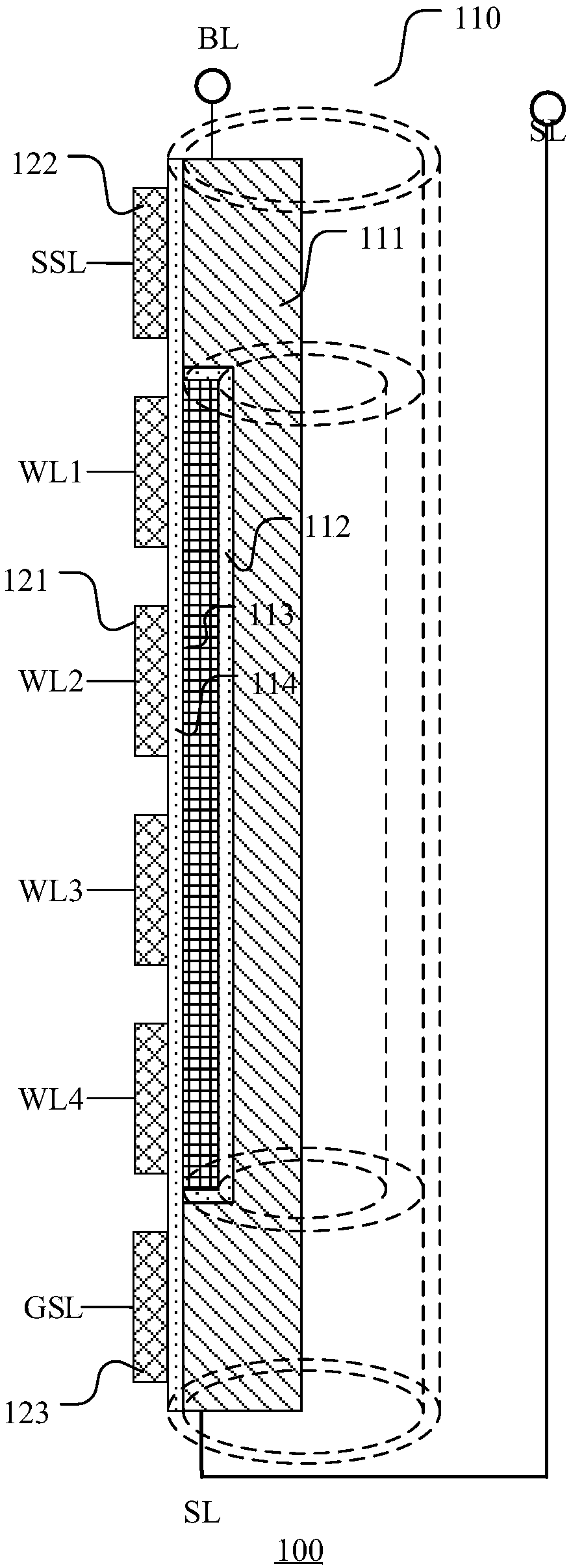

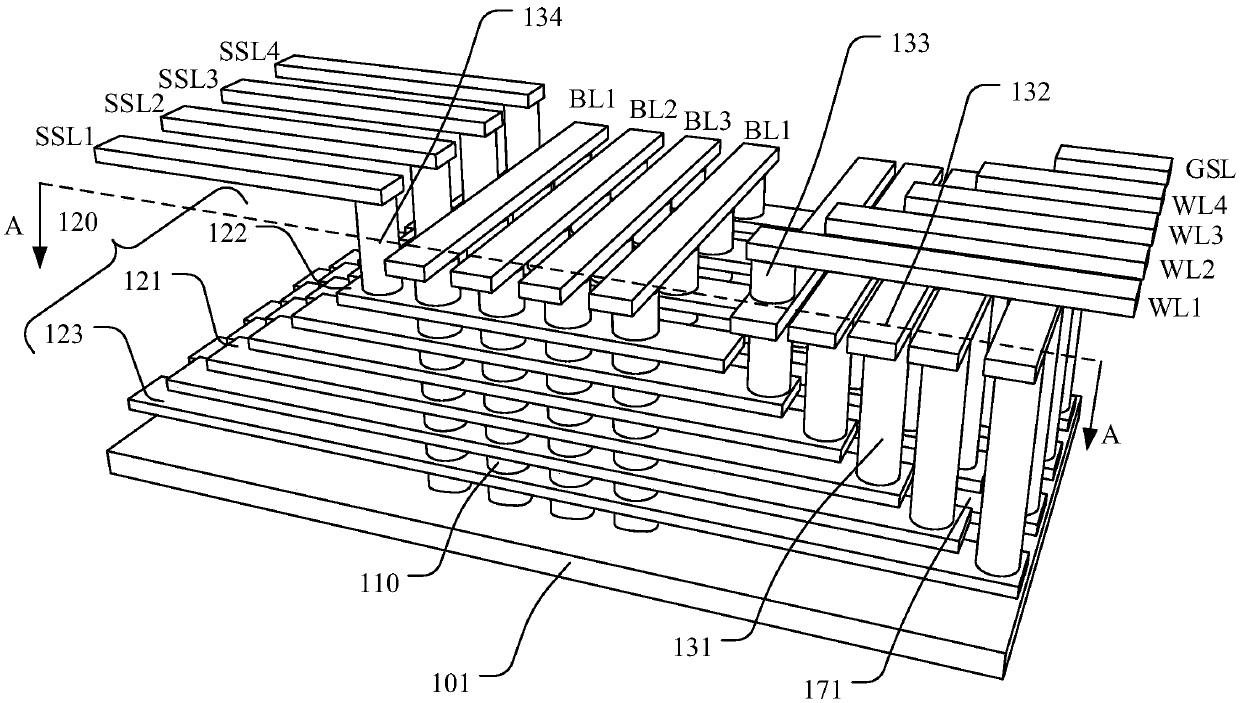

Memory device and method of manufacturing the same

ActiveUS20160284808A1Enlarge regionImproving a sub-trench defectSolid-state devicesSemiconductor devicesEngineering

Owner:MACRONIX INT CO LTD

Technological method for planarization of radio frequency LDMOS polysilicon channel

InactiveCN102522336ALower on-resistanceIncrease windowSemiconductor/solid-state device manufacturingLDMOSMetal silicide

The invention discloses a technological method for planarization of a radio frequency LDMOS polysilicon channel. After polysilicon deposition is carried out, in order to carry out planarization processing on a surface of a polysilicon channel, the method is implemented by the following steps that: (1), a bottom organic antireflective layer is coated; (2), etchback is carried out on the bottom organic antireflective layer; (3), main etching is carried out on the polysilicon to remove polysilicon that is outside the channel; and (4), over etching is carried out on the polysilicon to enable the polysilicon surface inside the channel to be planarized. According to the method provided in the invention, before the etchback of the polysilicon, the bottom organic antireflective layer is coated to carry out planarization; and a dry etching technology with a low selection ratio is utilized to carry out etchback, so that roughness drop of the polysilicon surface inside the channel is reduced; therefore, continuous metal silicide can be formed; and objectives that conductive resistance of the RF LDMOS is reduced and a subsequent technological window is increased can be achieved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Etching method

ActiveCN105609415AFlexible angle adjustmentImprove performanceSemiconductor/solid-state device manufacturingApplication areasSemiconductor

The invention discloses a novel dry etching method, which comprises the following steps: forming a to-be-etched layer on a semiconductor substrate; forming a masking material on the to-be-etched layer; carrying out dry etching on the masking material and the to-be-etched layer; simultaneously carrying out lateral etching (parallel to the surface of the substrate) of a masking layer and longitudinal etching (vertical to the surface of the substrate) of the to-be-etched layer; and obtaining the inclination angle (the included angle between a slope surface and the surface of the substrate) of the corresponding etched slope surface by accurately controlling the speed ratio. The method can flexibly adjust the inclination angle of the etched slope surface within a large range (0-90 degrees), and especially has advantages in the field of the application with a small inclination angle (smaller than 20 degrees) of the etched slope surface in comparison with a conventional etching method.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

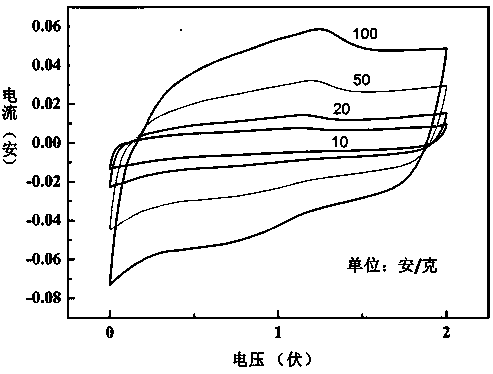

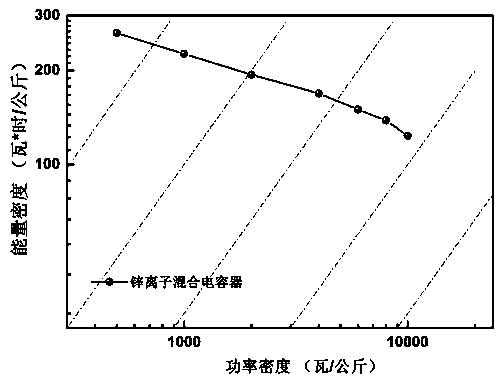

Method for constructing zinc ion hybrid capacitor

InactiveCN109524248ARich sourcesSimple equipment requirementsHybrid capacitor electrolytesHybrid capacitor electrodesHigh concentrationHigh energy

The invention discloses a method for constructing a zinc ion hybrid capacitor. The method comprises: 1) preparing a high-concentration salt electrolyte base aqueous solution by water and potassium acetate or sodium perchlorate; 2) adding a zinc salt to the electrolyte basic aqueous solution, and preparing a composite salt electrolyte; 3) coating a metal electrode piece with a high-specific-surfacethree-dimensional activated carbon material to obtain a three-dimensional activated carbon positive electrode; 4) successively assembling the zinc sheet, a diaphragm added with the composite salt electrolyte, and the three-dimensional activated carbon positive electrode into the zinc ion hybrid capacitor. The zinc ion hybrid capacitor has high energy density and power density, and has excellent performance. Since the used electrolyte is a water system, the zinc ion hybrid capacitor has excellent safety performance.

Owner:LANZHOU INST OF CHEM PHYSICS CHINESE ACAD OF SCI

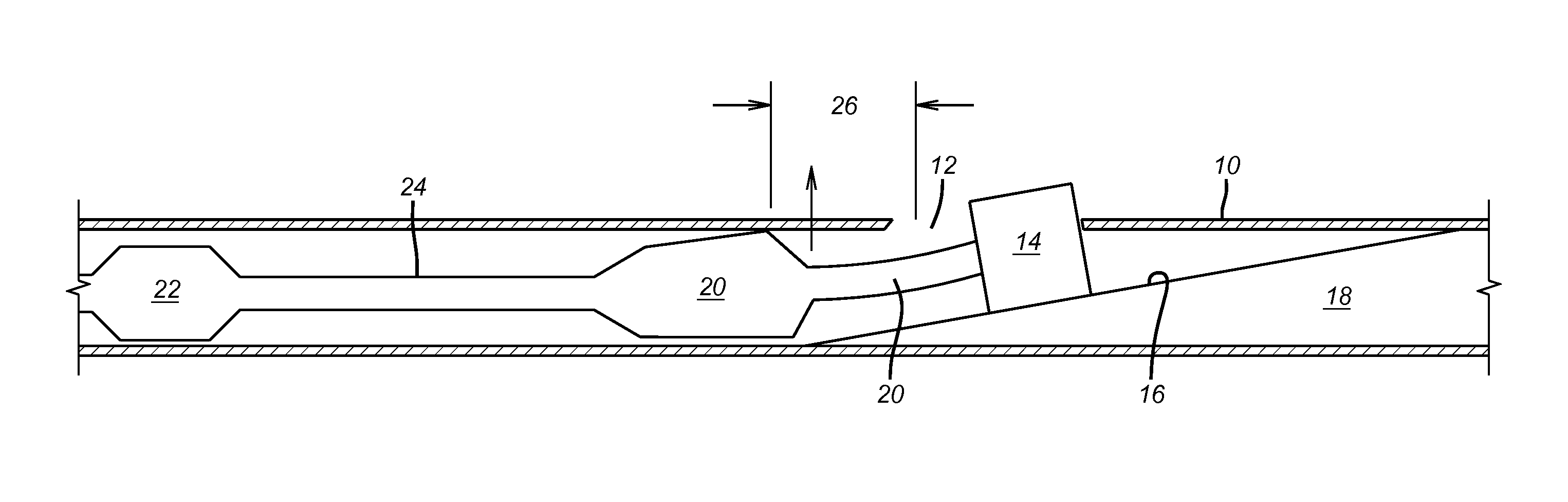

Lower Mill Spaced Cutting Ring Structure

ActiveUS20150152702A1Increase contact stressIncrease windowDrill bitsFluid removalStructural engineering

The cutting structure on the lower mill is arrayed in rows that are preferably parallel. The cutting structure in each row is made sharper and more durable than prior designs with the objective of cutting the window higher than where the window mill started the window. The use of the rows increases the contact stress of the inserts on the casing inside wall because at any given time fewer and sharper inserts are cutting the casing wall to lengthen the window. As a row wears down the next row takes over to continue the cutting where the previous row was active and to further penetrate the casing wall. The cutout angle can also increase as this occurs. As a result a decreased insert density results in more effective casing wall cutting to extend the window to allow larger tools to exit into the window off the whipstock.

Owner:BAKER HUGHES INC

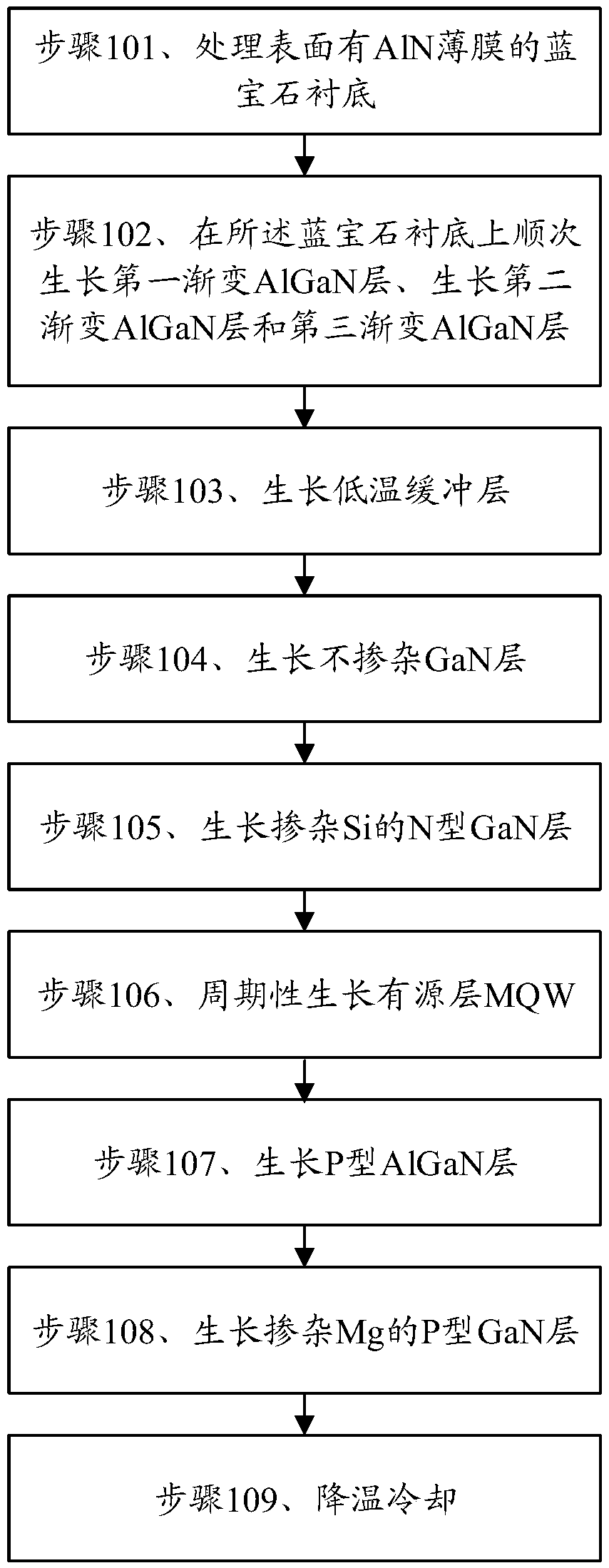

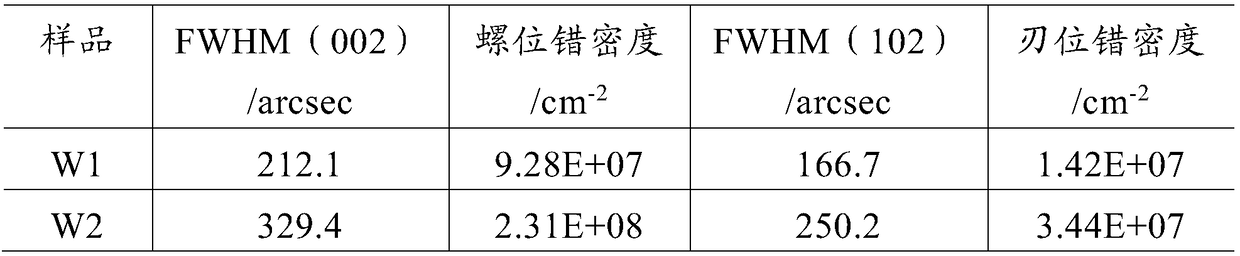

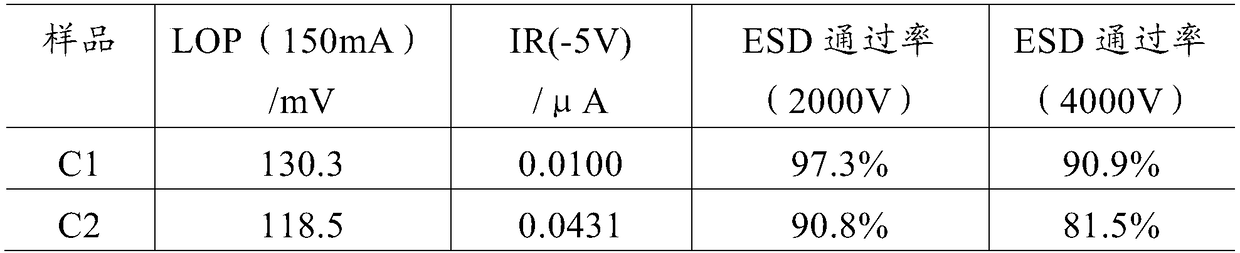

LED epitaxial wafer growth method

ActiveCN109300854AEvenly filledImprove uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsActive layer

The present invention discloses an LED epitaxial wafer growth method. The method comprises the steps of: arranging a sapphire substrate of an AlN film at a processing surface, growing a first gradualchange AlGaN layer, a second gradual change AlGaN layer and a third gradual change AlGaN layer in order on the sapphire substrate, growing a low-temperature buffer layer, an un-doped GaN layer and a Si-doped N-type GaN layer, periodically growing an active layer MQW, growing a P-type AlGaN layer, growing a Mg-doped P-type GaN layer, and performing cooling. The first gradual change AlGaN layer, thesecond gradual change AlGaN layer and the third gradual change AlGaN layer are grown to reduce the dislocation density, improve the crystalline quality, reduce the warping of an epitaxial wafer, improve the percent of pass of the GaN epitaxial wafer and improve the LED luminous efficiency. The gradual change AlGaN layers are subjected to annealing processing to allow the whole surface of the epitaxial wafer to be smoother, allow the surface hexagonal defects and the hollow pits to be fewer and allow the whole appearance to be better.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

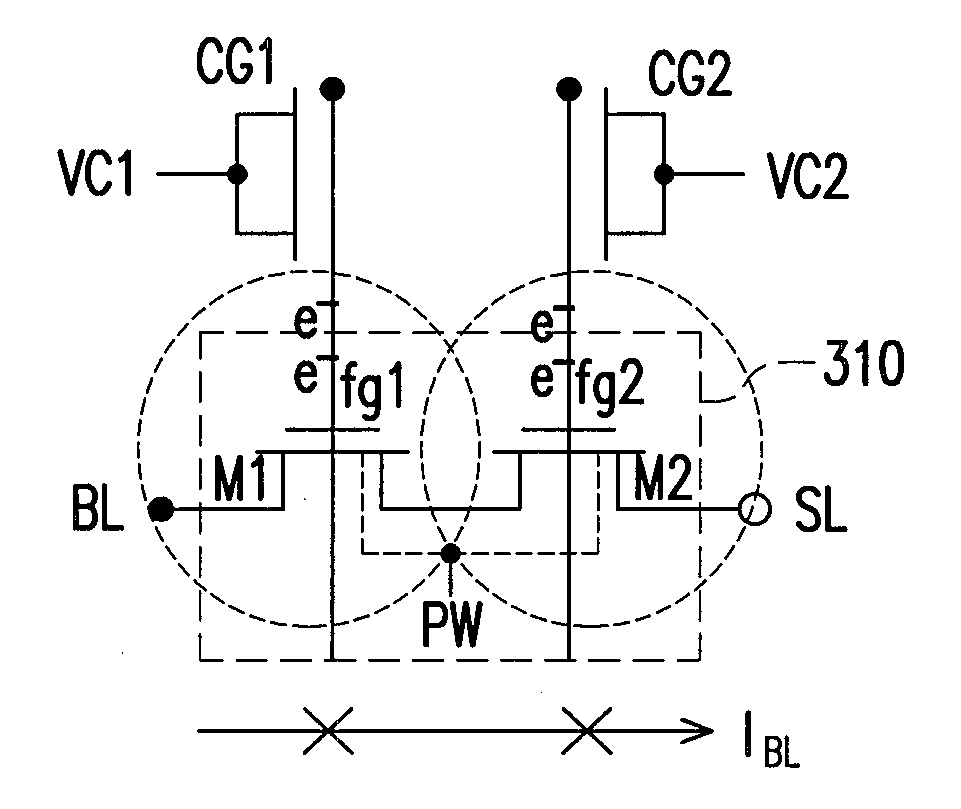

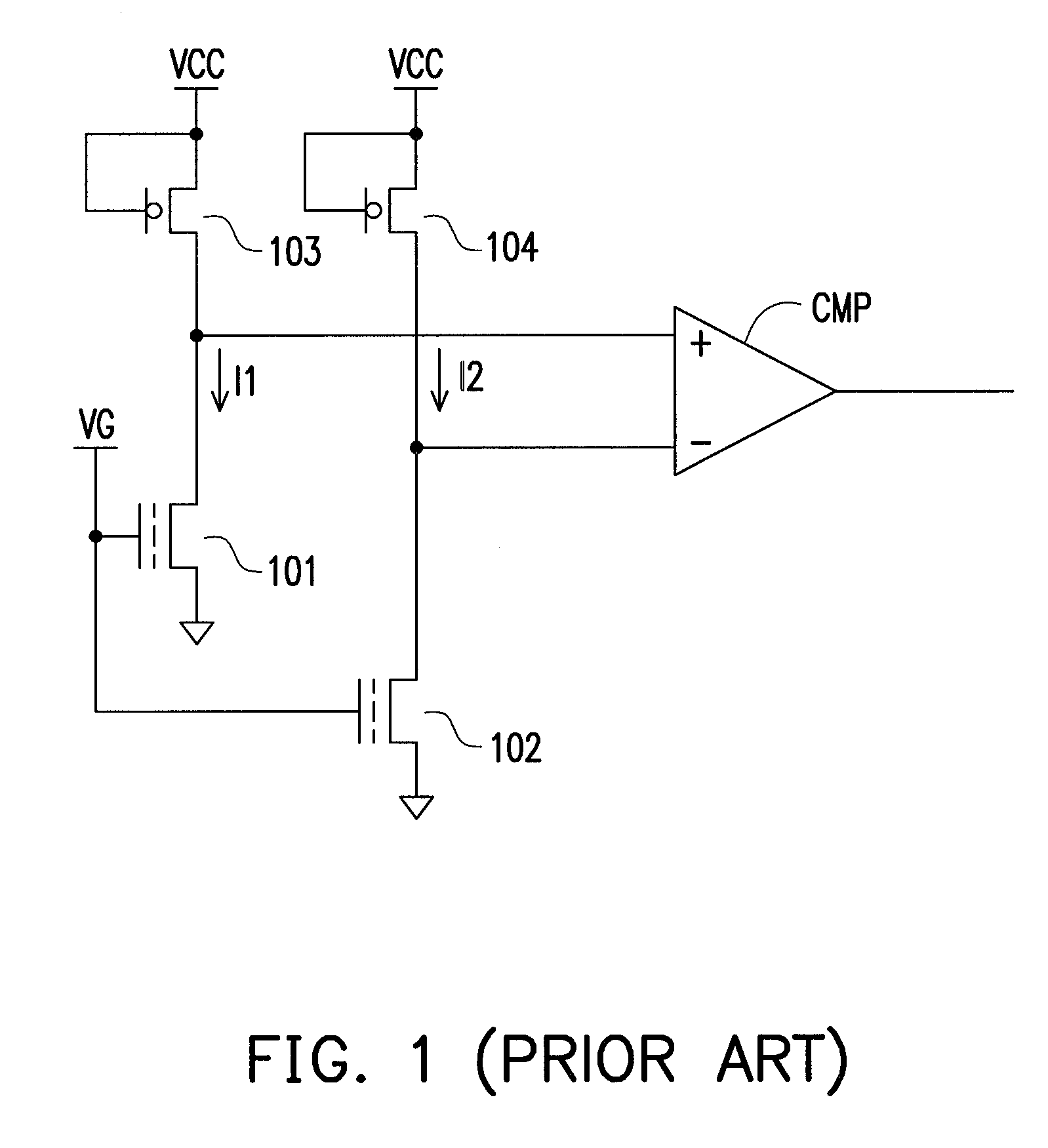

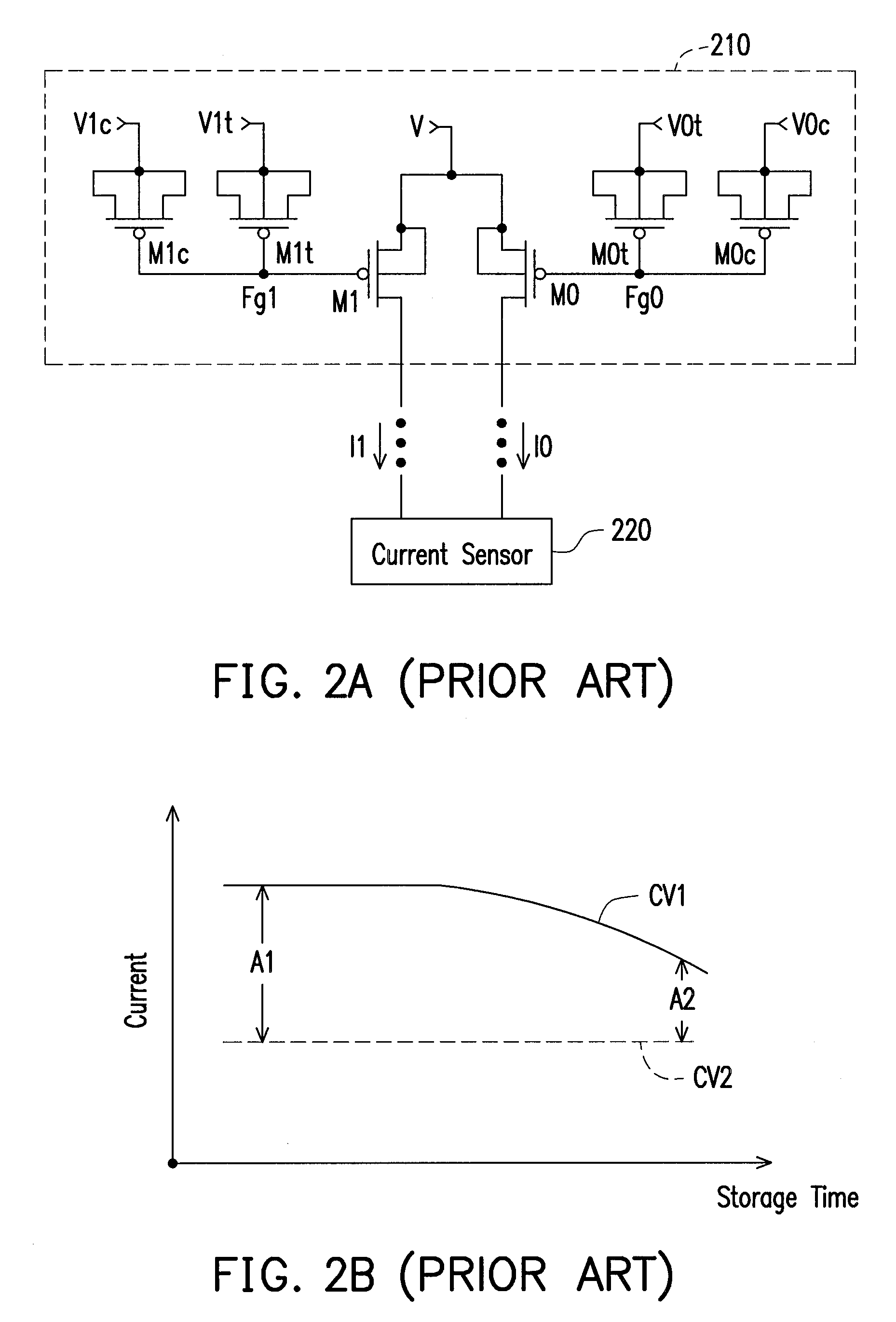

Non-volatile memory unit cell with improved sensing margin and reliability

ActiveUS20120273860A1Improve sensing marginWiden the memory windowTransistorSolid-state devicesCouplingEngineering

An only-one-polysilicon layer non-volatile memory unit cell includes a first P-type transistor, a second P-type transistor, a N-type transistor pair, a first and second coupling capacitors is provided. The N-type transistor pair has a third transistor and a fourth transistor that are connected. The third transistor and the fourth transistor have a first floating polysilicon gate and a second floating polysilicon gate to serve as charge storage mediums, respectively. One end of the second coupling capacitor is connected to the gate of the second transistor and is coupled to the second floating polysilicon gate, the other end of the second coupling capacitor receives a second control voltage. One end of the second coupling capacitor is connected to the gate of the second transistor and is coupled to the second floating polysilicon gate, the other end of the second coupling capacitor receives a second control voltage.

Owner:EMEMORY TECH INC

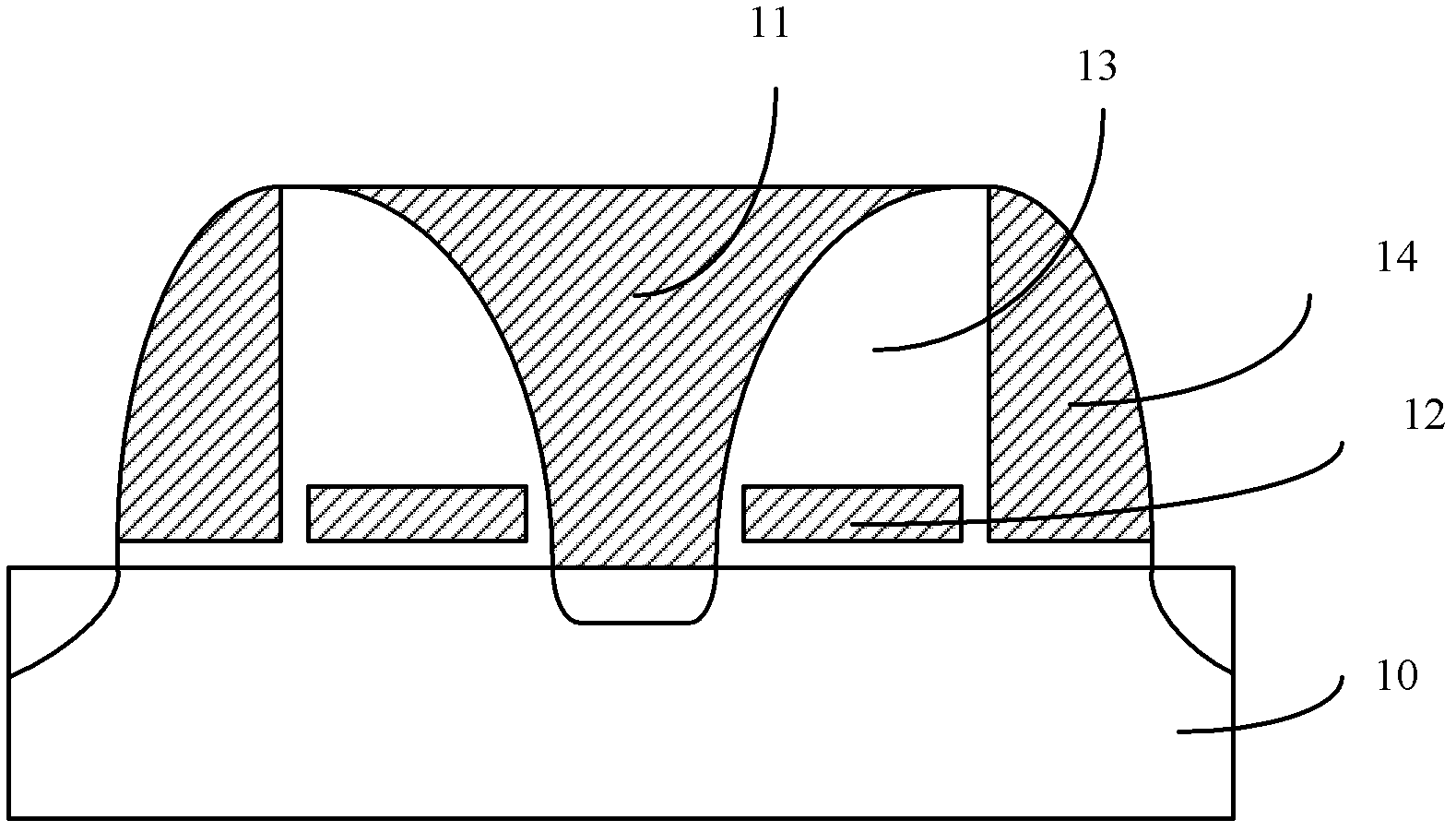

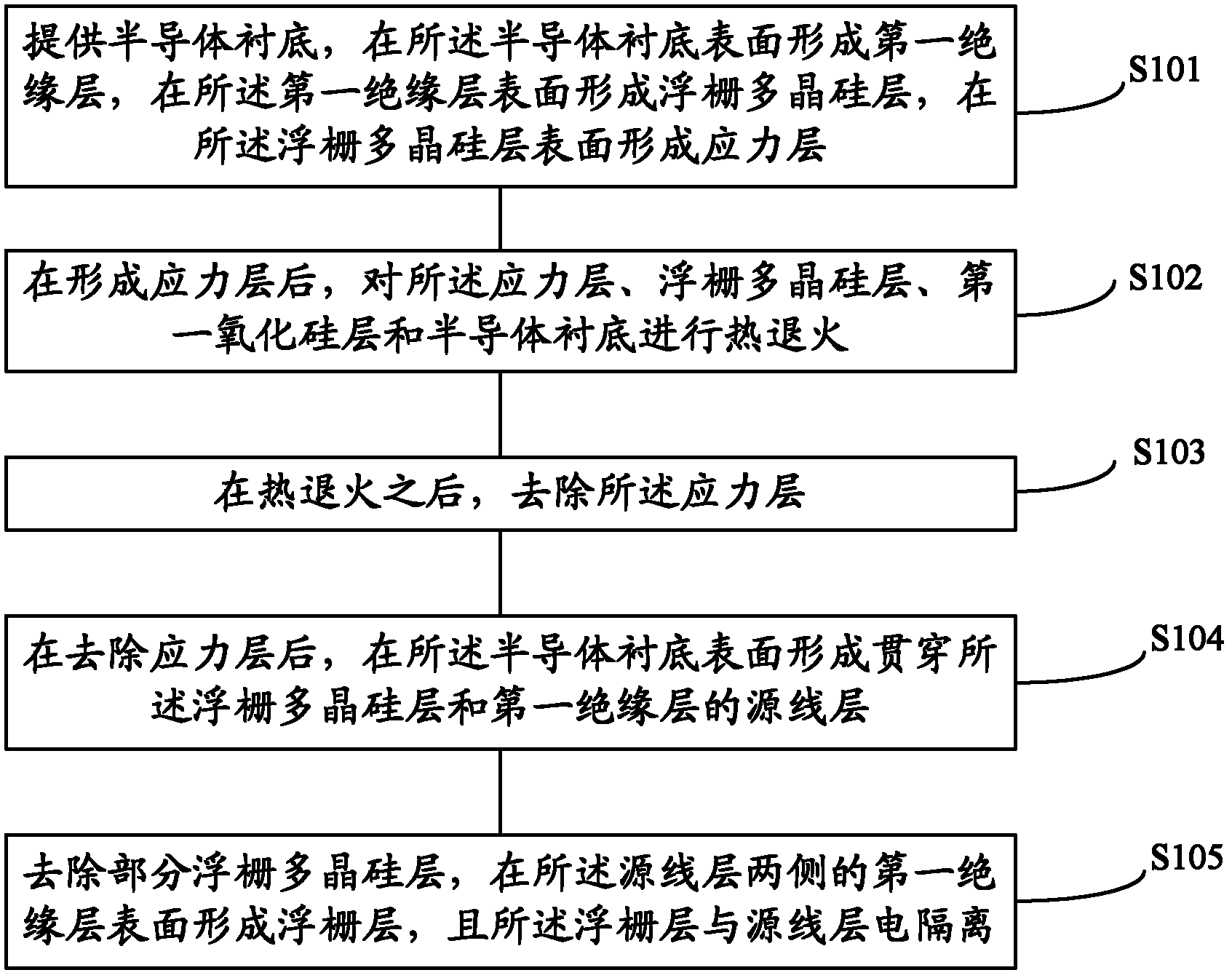

Forming method for memory cell of flash memory

ActiveCN102637647ASmall sizeImprove mobilitySemiconductor/solid-state device manufacturingCharge carrier mobilitySemiconductor

The invention discloses a forming method for a memory cell of a flash memory. The forming method comprises the steps of: providing a semiconductor substrate; forming a first insulating layer on the surface of the semiconductor substrate; forming a floating gate polycrystalline silicon layer on the surface of the first insulating layer; forming a stress layer on the surface of the floating gate polycrystalline silicon layer; after the forming of the stress layer, conducting thermal annealing on the stress layer, the floating gate polycrystalline silicon layer, the first insulating layer and the semiconductor substrate; after thermal annealing, removing the stress layer; after the removal of the stress layer, forming a source line layer passing through the floating gate polycrystalline silicon layer and the first insulating layer on the surface of the semiconductor substrate; and removing part of the floating gate polycrystalline silicon layer and forming a floating gate layer on the surface of the first insulating layer on two sides of the source line layer, wherein the floating gate layer is electrically isolated from the source line layer. The forming method for the memory cell of the flash memory can retain stress inside the floating gate layer, thereby enhancing the channel carrier mobility of the memory cell of the flash memory and reducing the size of the memory cell of the flash memory simultaneously when improving the data retention.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

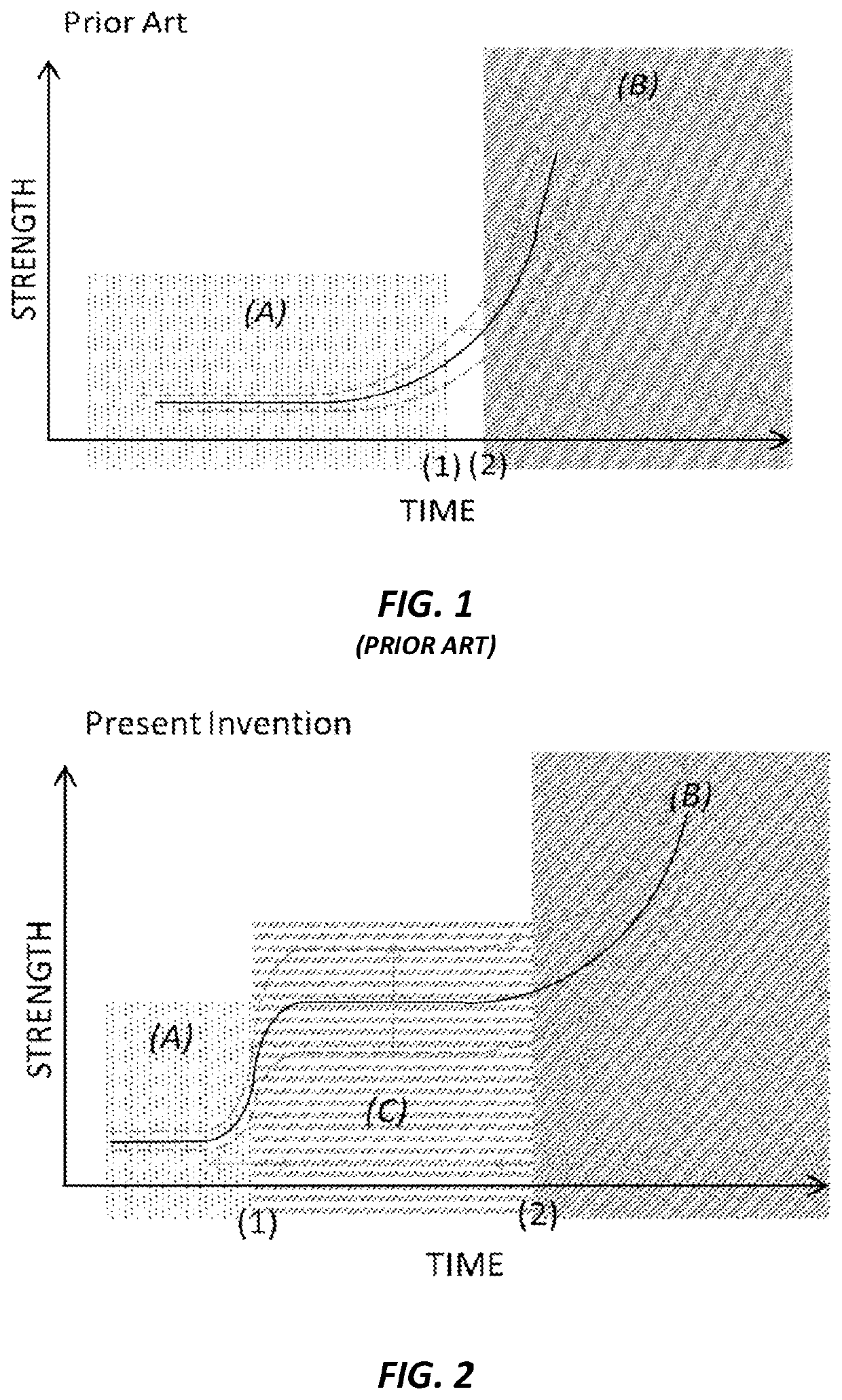

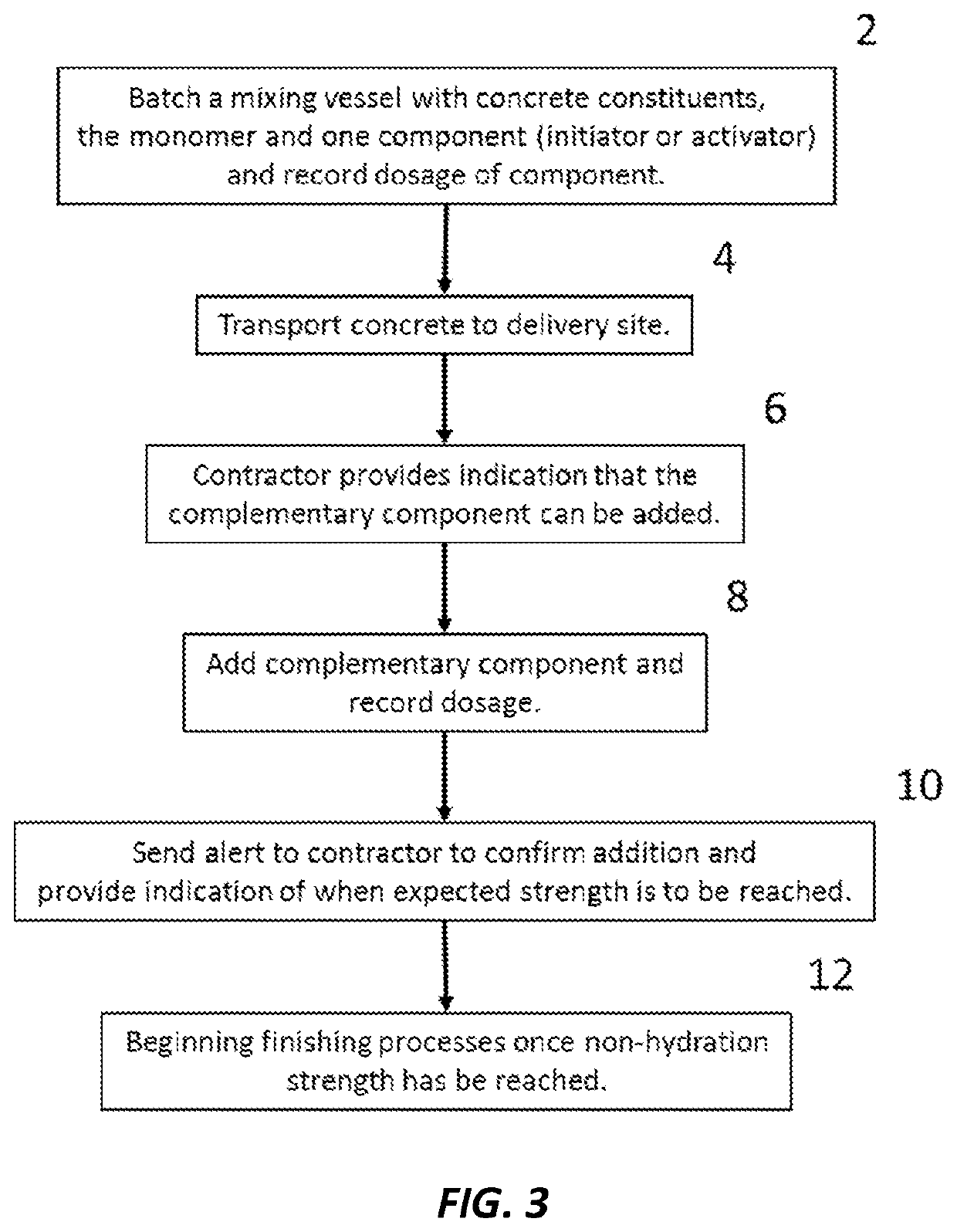

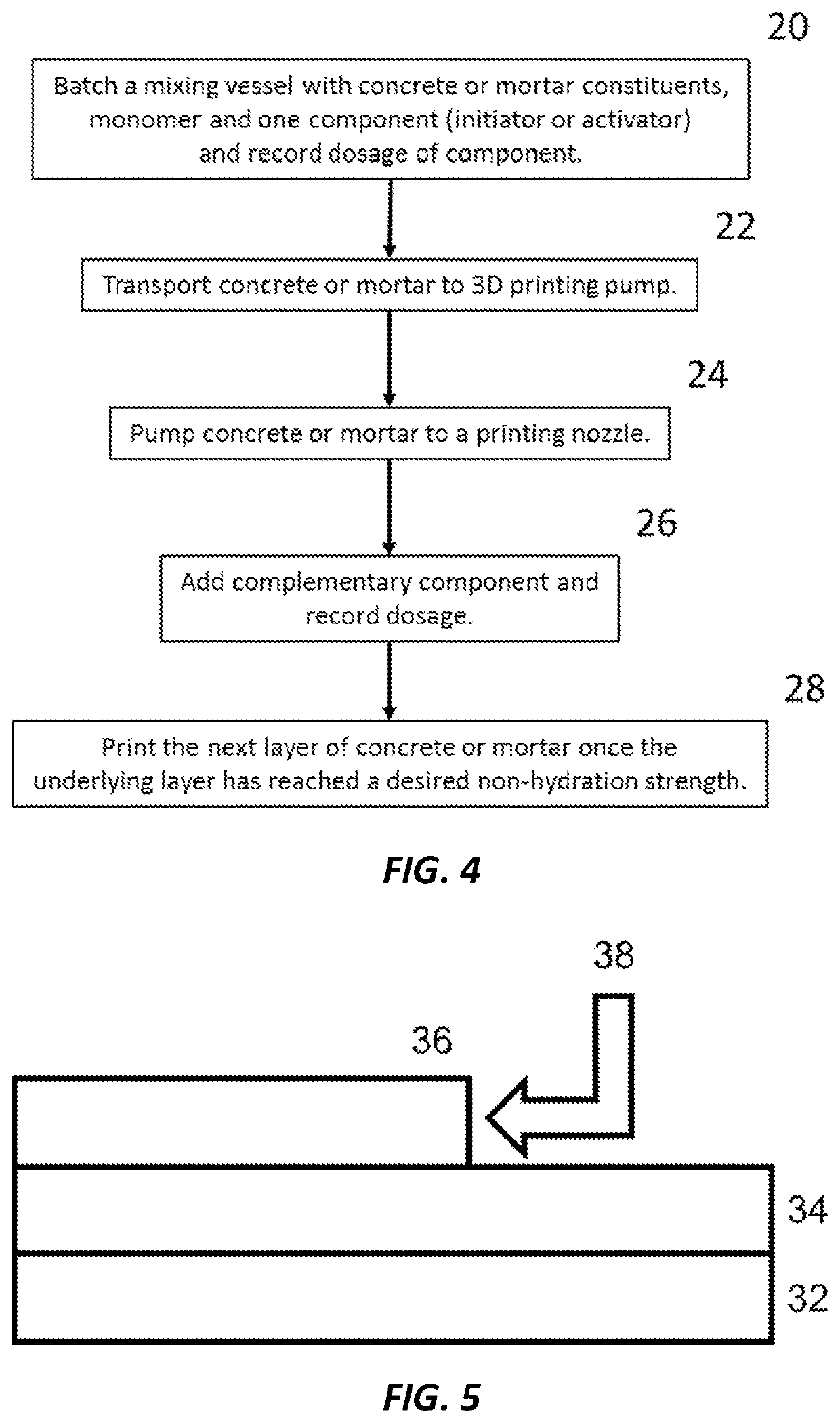

Non-hydration strength in cementitious compositions

PendingUS20210355031A1Increase windowHigh strengthAdditive manufacturing apparatusCement mixing apparatusHydration reactionPolymer science

Described are compositions and methods for controlled strength development in a hydratable cementitious material, and more particularly to the use of polymerizable monomer components, which are initiated and activated by a redox pair which are mixed in controlled fashion, for enhancing non-hydration strength within the matrix of the plastic hydratable cementitious material before setting of the cementitious material begins. Exemplary applications include minimizing pressures on formwork for high fluid ready-mix applications, enhancing support and bonding properties for integrated concrete slab work and other sequential applications, or facilitating speedy 3D printing applications, among other unique possibilities.

Owner:GCP APPL TECH INC

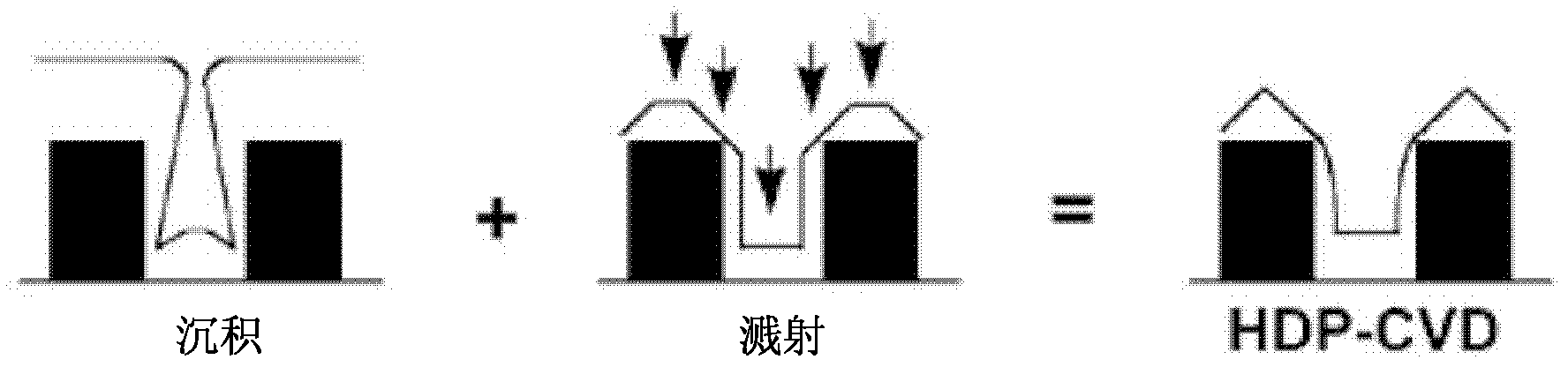

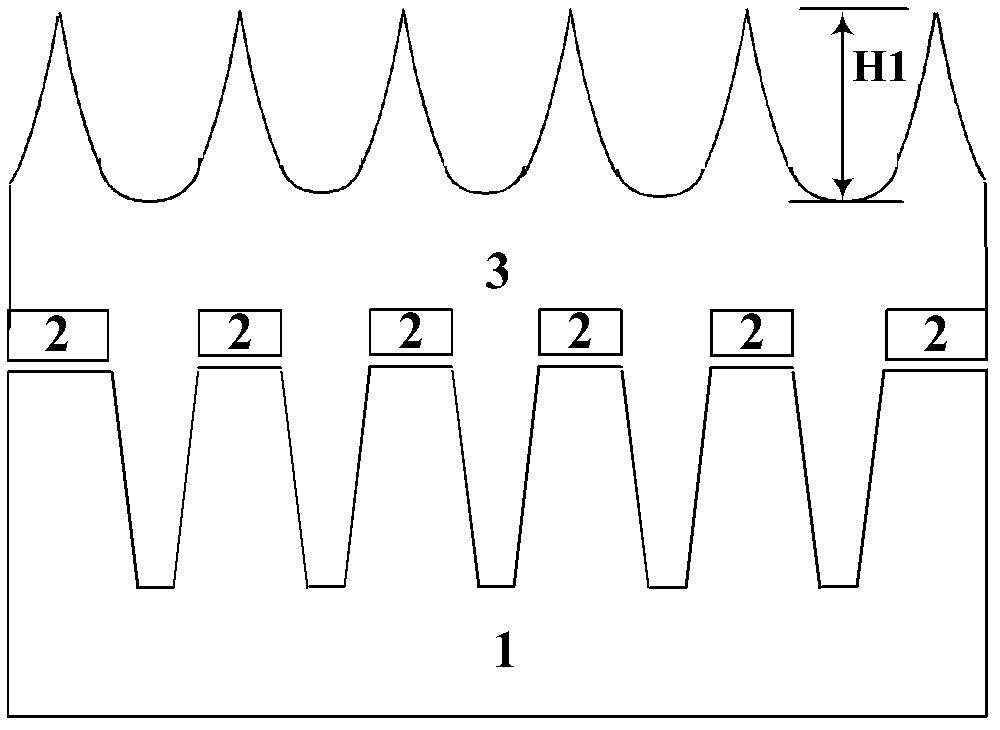

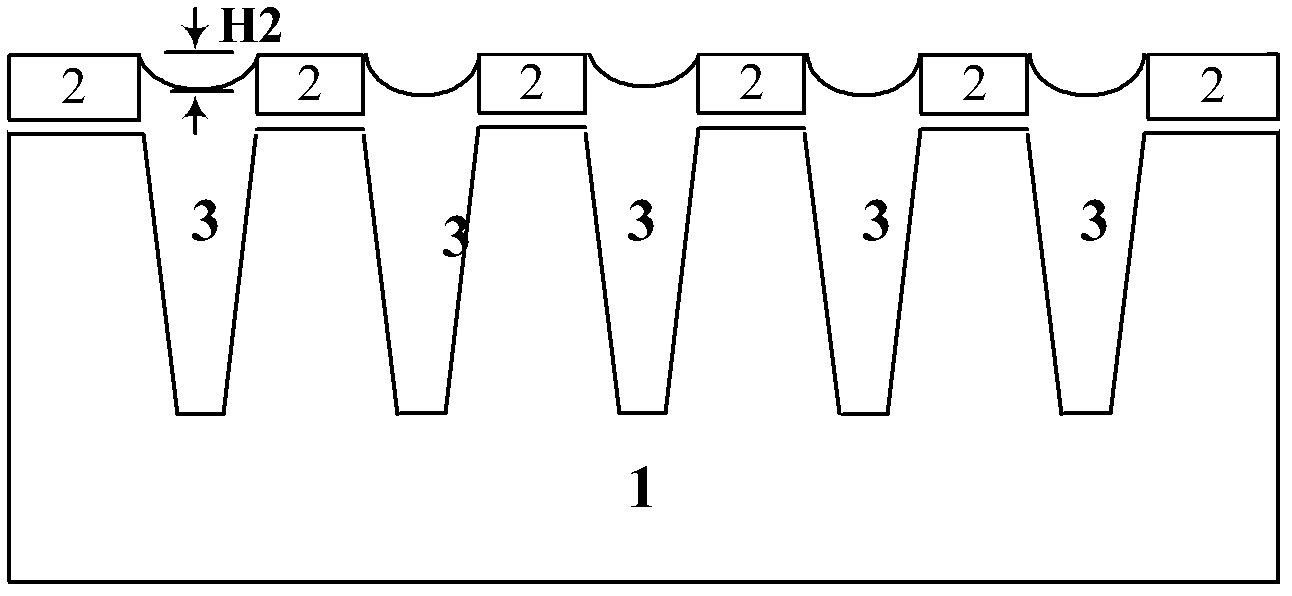

Process for improving isolating oxide chemical mechanical planarization (CMP) uniformity

ActiveCN102969238AImprove planarization uniformityImprove uniformitySemiconductor/solid-state device manufacturingHigh densityEngineering

The invention discloses a process for improving isolating oxide CMP uniformity. The process comprises the steps of forming a cushion layer on a substrate, and forming isolating oxide layers on the cushion layer and in the substrate; forming first covering layers on isolating oxide layers, wherein the height difference between tops of first covering layers is equal to or lager than that between tops of isolating oxide layers; forming second covering layers on first covering layers, wherein the height difference between tops of second covering layers is smaller than that between tops of first covering layers and / or that between tops of isolating oxide layers; and conducting CMP treatment on second covering layers, first covering layers and isolating oxide layers sequentially till the cushion layer is exposed. According to the process, integration is conducted in a process chamber of high-density plasma (HDP) depositions, no additional process step is required, the filling effect can be guaranteed at the same time when height differences are effectively reduced, and dishing defects in the CMP process can be reduced or avoided, so that the planarization uniformity of the CMP process can be improved, and the window of the CMP process can be expanded.

Owner:BEIJING YANDONG MICROELECTRONICS