Technological method for planarization of radio frequency LDMOS polysilicon channel

A process method and polysilicon technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of discontinuous metal silicide and increase in on-resistance, and achieve the advantages of increasing the window and reducing the on-resistance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] In order to have a more specific understanding of the technical content, characteristics and effects of the present invention, now in conjunction with the illustrated embodiment, the details are as follows:

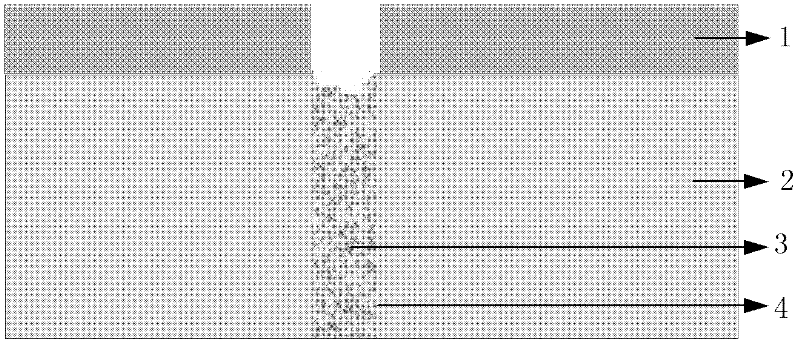

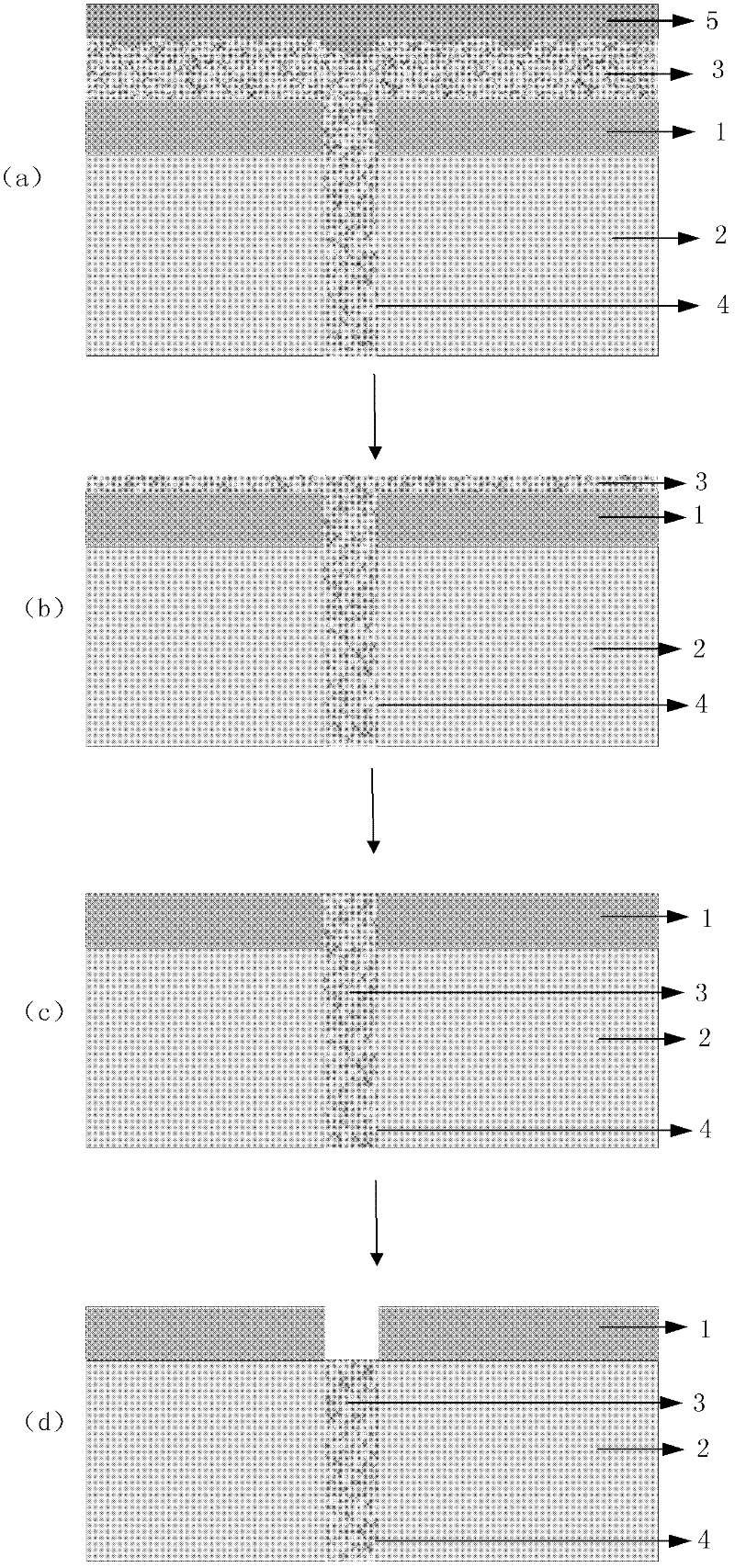

[0022] see image 3 As shown, the radio frequency LDMOS polysilicon channel planarization process method of this embodiment, after the polysilicon 3 is deposited, according to the following steps, the surface of the polysilicon 3 in the channel 4 is planarized:

[0023] In step 1, a bottom organic anti-reflection layer 5 is evenly coated on the polysilicon 3 by using the fluidity of organic matter, as shown in Figure 3 (a).

[0024] The coating thickness is greater than the sum of the drop caused by the uneven surface of the polysilicon 3 and the depression at the top of the polysilicon 3 in the channel 4 . Since the maximum drop on the surface of the polysilicon 3 can reach 1500 angstroms, the thickness of the coated bottom organic anti-reflective layer 5 should ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More