Forming method for memory cell of flash memory

A technology of storage unit and flash memory, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc. It can solve the problems of unfavorable development needs of flash memory miniaturization, insignificant performance improvement of flash memory, and large storage unit size, etc., to achieve programming Effects related to improved reading efficiency, reduced size, and improved retention

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

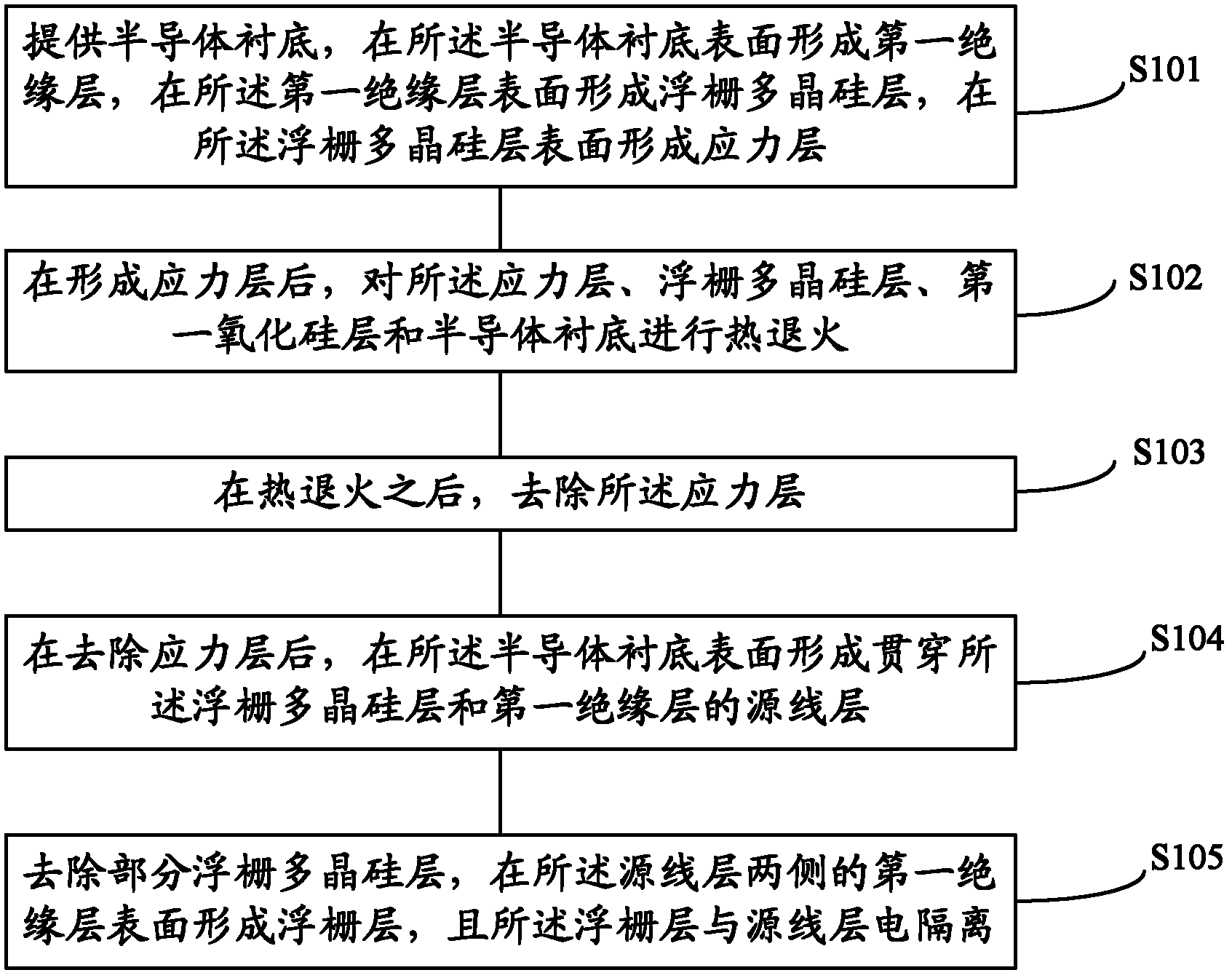

[0043] As described in the background technology, the memory cell of the flash memory covered with the stress layer in the prior art does not greatly improve the carrier mobility, and the data retention is low, resulting in little improvement in the performance of the flash memory; moreover, the stress layer covered will Enlarging the size of the storage unit of the flash memory is not conducive to the miniaturization development requirements of the flash memory.

[0044] The inventors of the present invention have found through research that the increase in carrier mobility is not so great because the stress provided by the stress layer can only be conducted to the channel region of the semiconductor substrate through the source line layer and the control gate layer, so The stress conducted into the channel region is small, and the carrier mobility is not greatly improved; and the covered stress layer will occupy space, making the size of the memory cell of the flash memory la...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More